# **1996 Communications Products Data Book**

5

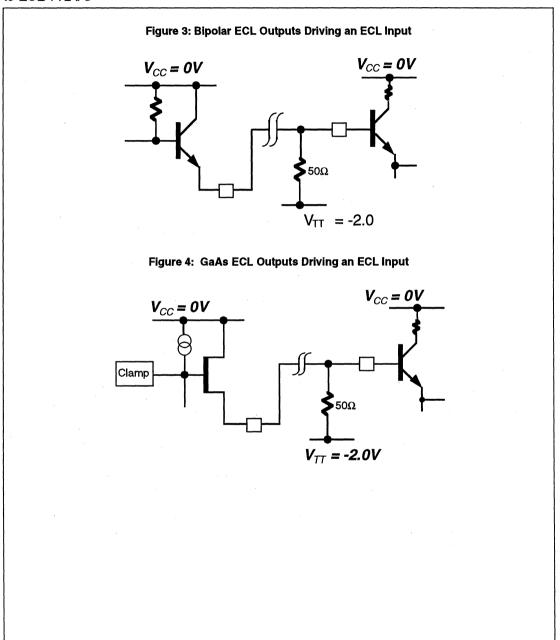

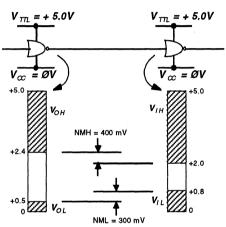

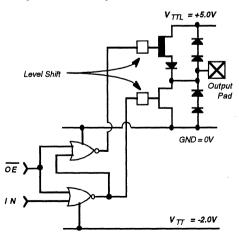

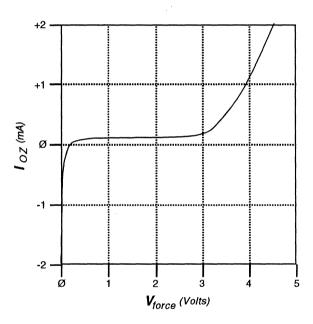

ж г.

r x X

**Communications Products**

# 1996 Communications Products Data Book

Vitesse Semiconductor Corporation reserves the right to make changes in its products or specifications or other information at any time without prior notice. Thus, the reader is cautioned to confirm that data sheets and other information in this publication are current before placing orders. The company assumes no responsibility for any circuitry described other than circuitry entirely embodied in a Vitesse product.

#### Trademarks

Vitesse, FURY, FX, GLX, VIPER and SCFX are trademarks of Vitesse Semiconductor Corporation Mentor is a trademark of Mentor Graphics Corporation LASAR is a trademark of Teradyne, Inc. Synopsys® and Design Compiler® are registered trademarks of Synopsys, Inc. Verilog and Valid are registered trademarks of Cadence Design Systems, Inc. The X Window System is a trademark of the Massachusetts Institute of Technology Postscript® is a trademark of Adobe Systems Macintosh is a trademark of Apple Computer, Inc. IBM is a trademark of International Business Machines Corp. Sun Workstation is a registered trandemark of Sun Microsystems, Inc. Apollo is a registered trademark of HP/Apollo Computer, Inc. Pentium<sup>™</sup> is a trademark of Intel Corporation

All other trademarks or registered trademarks mentioned herein remain the property of their respective companies.

VITESSE Semiconductor Corporation 741 Calle Plano Camarillo, CA 93012 Phone: (805) 388-3700 Fax: (805) 987-5896

Copyright ® Vitesse Semiconductor Corporation 1996 All rights reserved. Printed in U.S.A.

> G54010-0-0594 3M August 1996

۷

® VITESSE 1996 Communications Product Data Book

General

# Table of Contents

# **GENERAL INFORMATION**

| Introduction                                   | xxi   |

|------------------------------------------------|-------|

| Document Designations                          | xxiii |

| Vitesse U.S. Sales Offices                     |       |

| Vitesse European Sales Office                  |       |

| U.S. Representative Offices                    |       |

| International Representatives and Distributors |       |

# DATACOMMUNICATIONS

| Fibre Channel Product Summary | 1 |

|-------------------------------|---|

| Fibre Channel Overview        |   |

| Transmitter/Receiver Overview | 7 |

#### VSC7105/VSC7106

| Features                                   | 9  |

|--------------------------------------------|----|

| General Description                        | 9  |

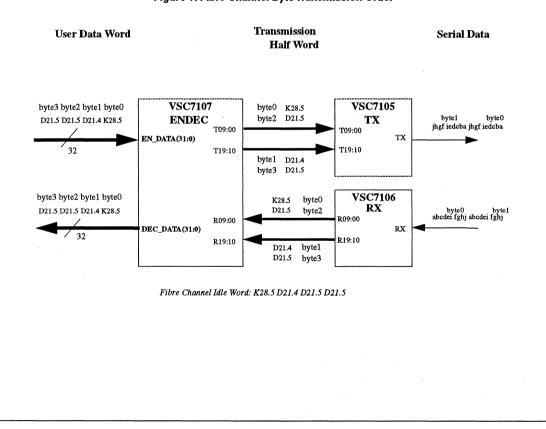

| System Block Diagram                       | 9  |

| VSC7105 Transmitter Functional Description | 10 |

| VSC7106 Receiver Functional Description    |    |

| Absolute Maximum Ratings                   |    |

| Recommended Operating Conditions           | 24 |

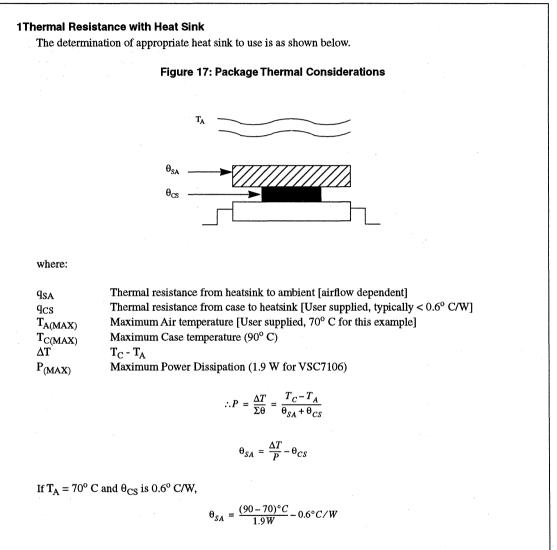

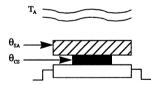

| Package Thermal Characteristics            | 31 |

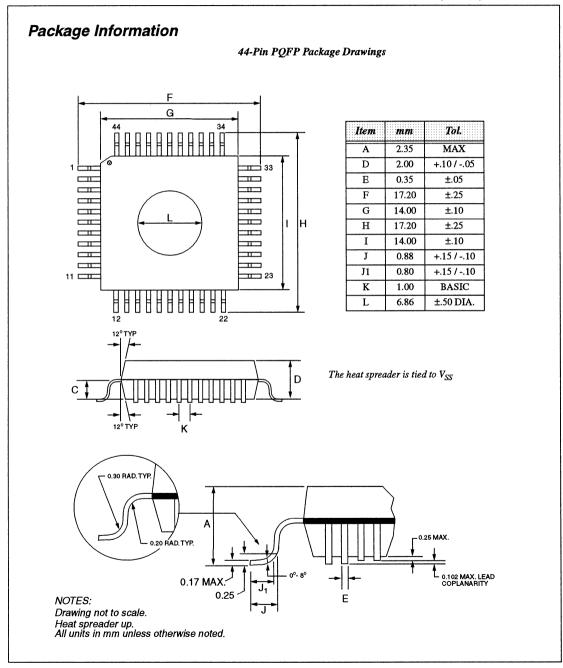

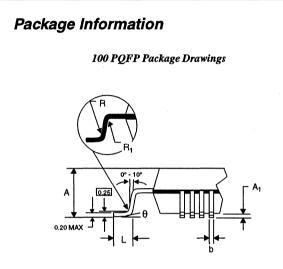

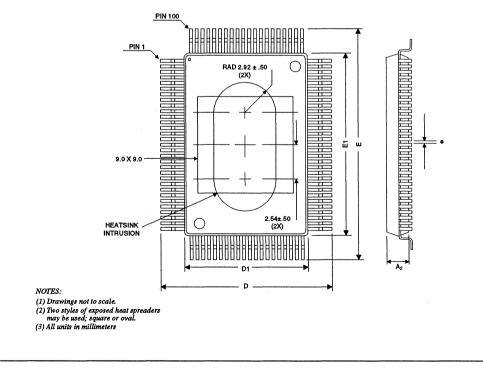

| Package Information                        | 33 |

| Ordering Information                       | 34 |

|                                            |    |

### VSC7107

| Features                             | 35 |

|--------------------------------------|----|

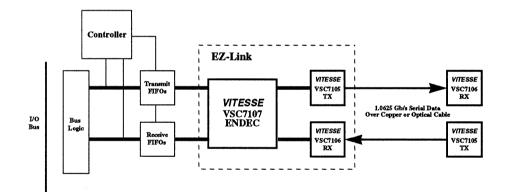

| System Block Diagram                 | 35 |

| General Description                  | 35 |

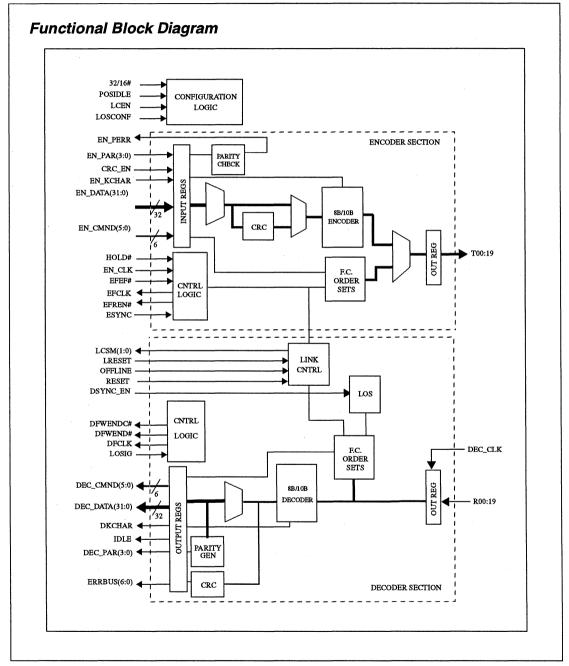

| Functional Description               |    |

| Functional Block Diagram             |    |

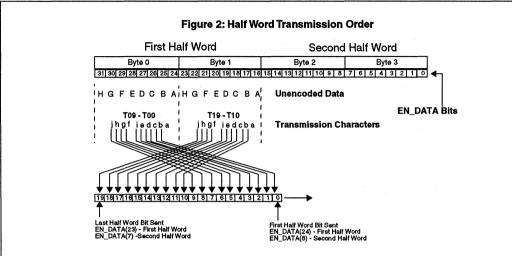

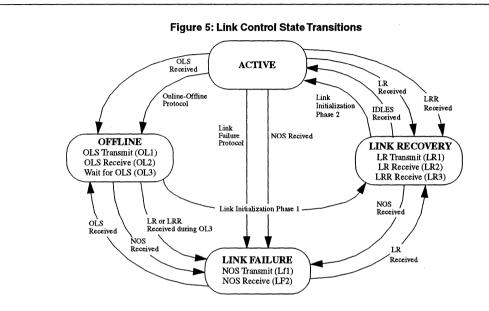

| Fibre Channel Transmission Protocols | 42 |

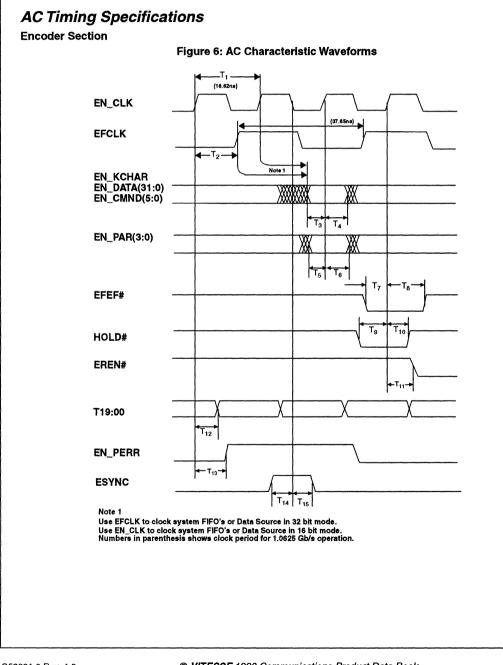

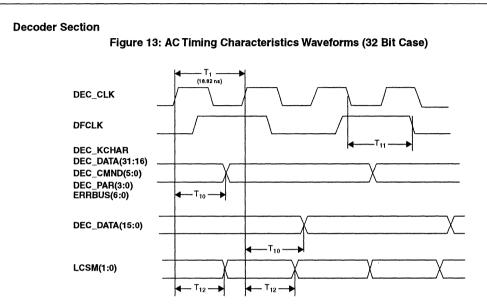

| AC Timing Specifications             | 57 |

| Electrical Specifications            |    |

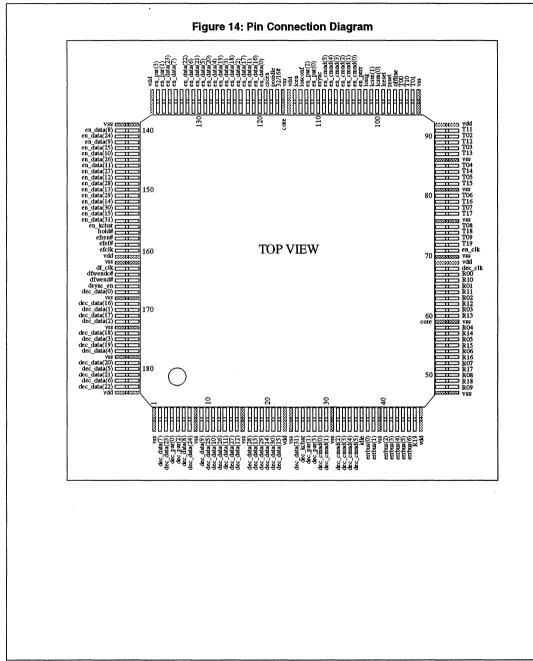

| Pin Description Tables               | 64 |

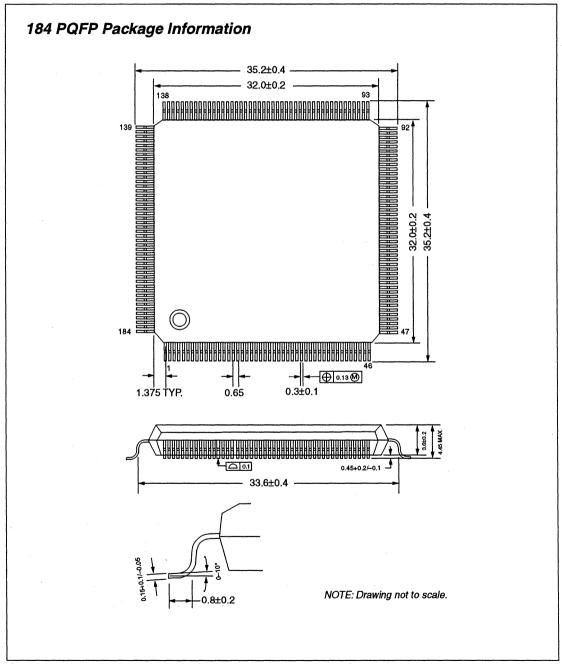

| Package Information                  | 66 |

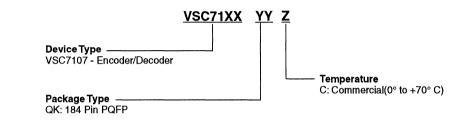

| Ordering Information                 | 67 |

# Table of Contents

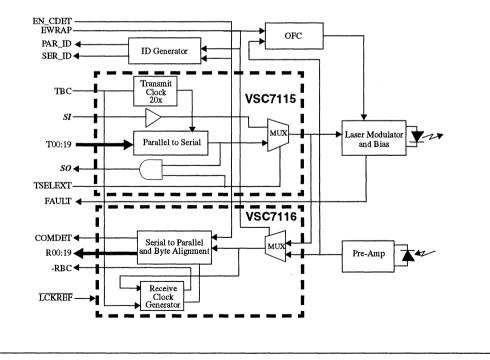

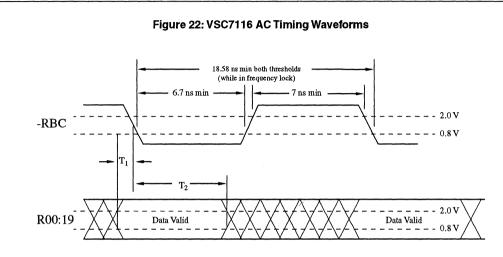

| VSC7115/VSC7116                            |    |

|--------------------------------------------|----|

| Features                                   | 69 |

| General Description                        |    |

| Gigabaud Link Module Block Diagram         | 69 |

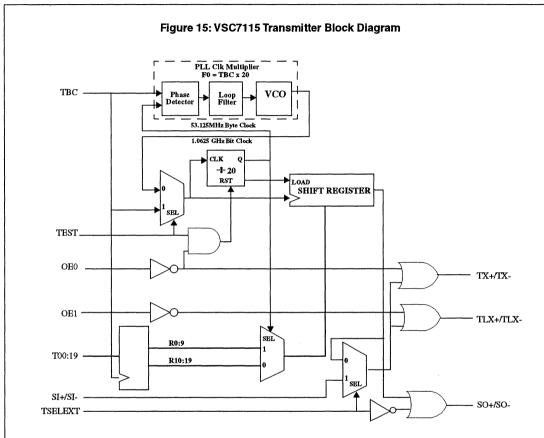

| VSC7115 Transmitter Functional Description | 70 |

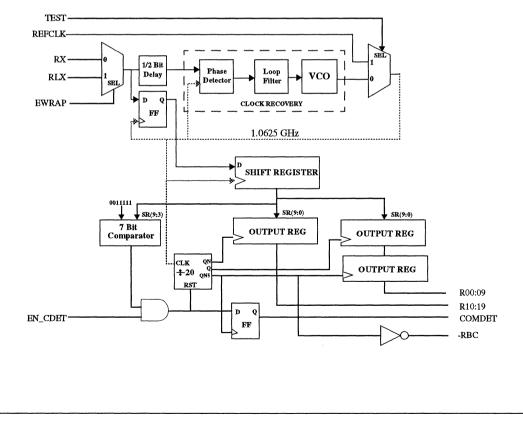

| VSC7116 Receiver Functional Description    | 72 |

| Absolute Maximum Ratings                   | 78 |

| Recommended Operating Conditions           | 78 |

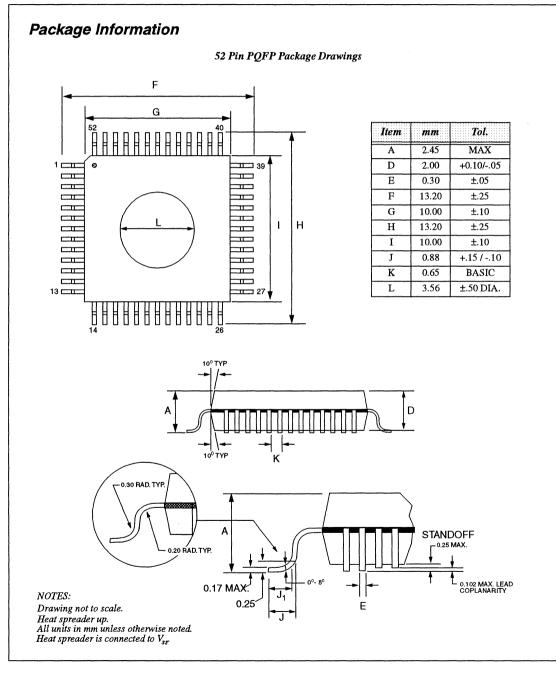

| Package Information                        | 83 |

| Ordering Information                       | 84 |

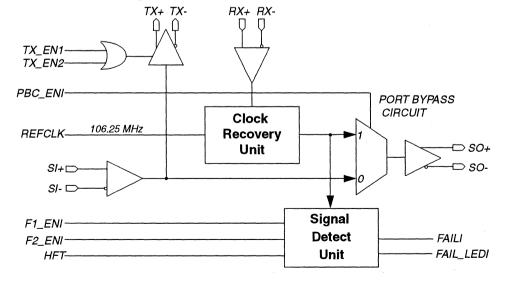

| VSC7120                                    |    |

| Features                                   |    |

| General Description                        |    |

| VSC7120 Block Diagram                      |    |

| Functional Description                     |    |

| Repeater Mode                              |    |

| Hub Mode                                   |    |

| Signal Detect Unit Behavior                | 91 |

| AC Characteristics                         |    |

| DC Characteristics                         | 93 |

| Absolute Maximum Ratings                   | 94 |

| Recommended Operating Conditions           | 94 |

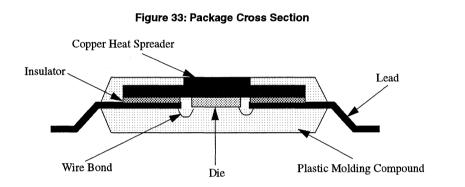

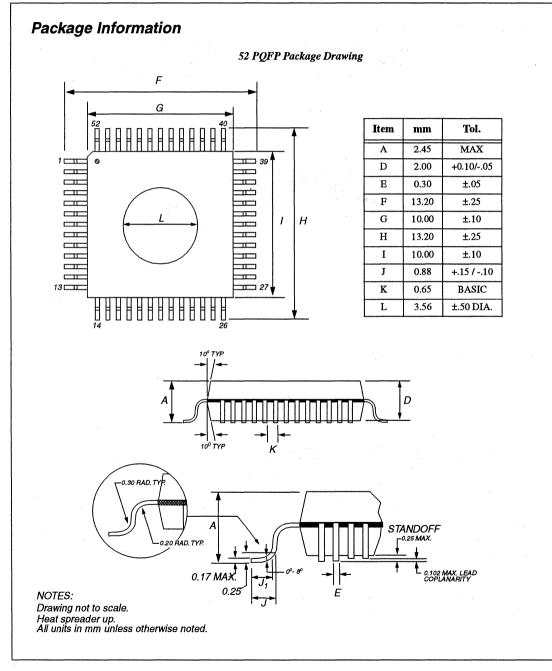

| Package Thermal Characteristics            |    |

| Package Information                        |    |

| Ordering Information                       | 99 |

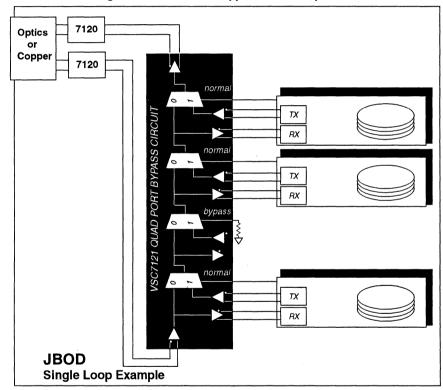

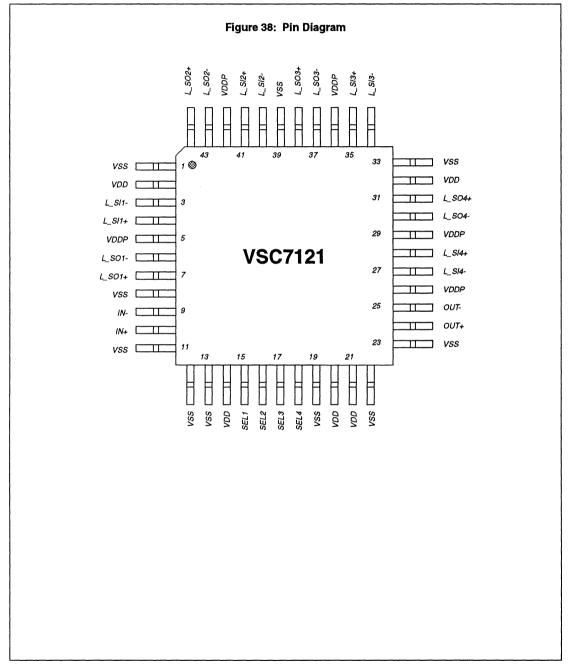

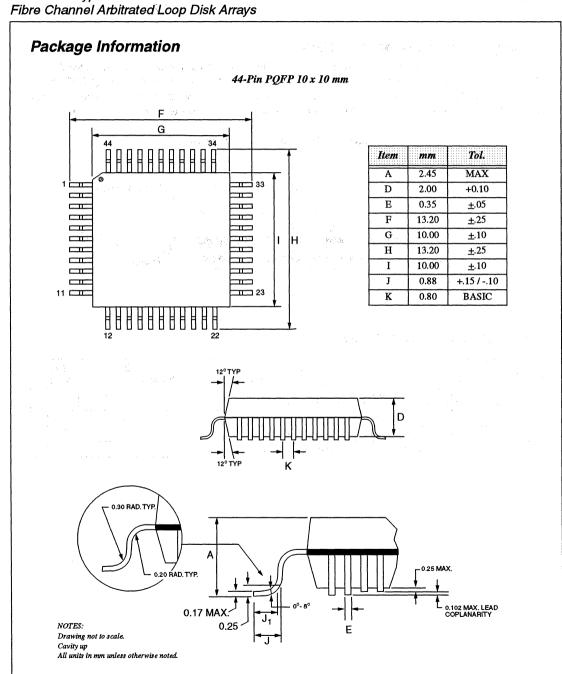

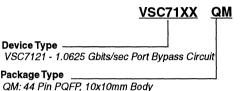

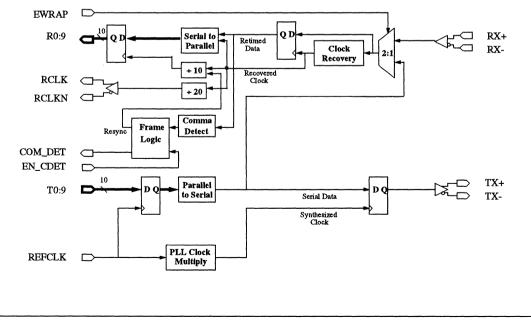

#### VSC7121

1996 Communications Products Data Book

| Features                         |  |

|----------------------------------|--|

| General Description              |  |

| 7121 Block Diagram               |  |

| Absolute Maximum Ratings         |  |

| Recommended Operating Conditions |  |

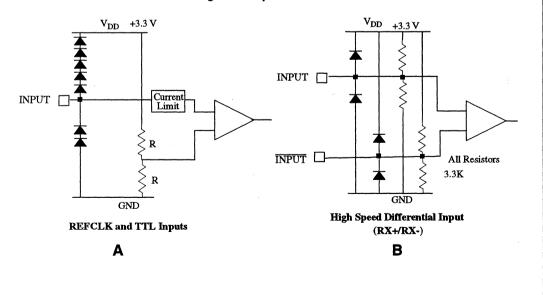

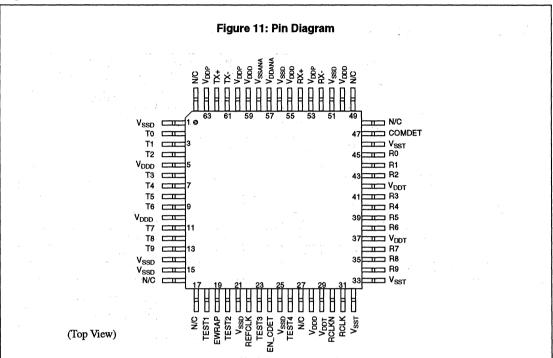

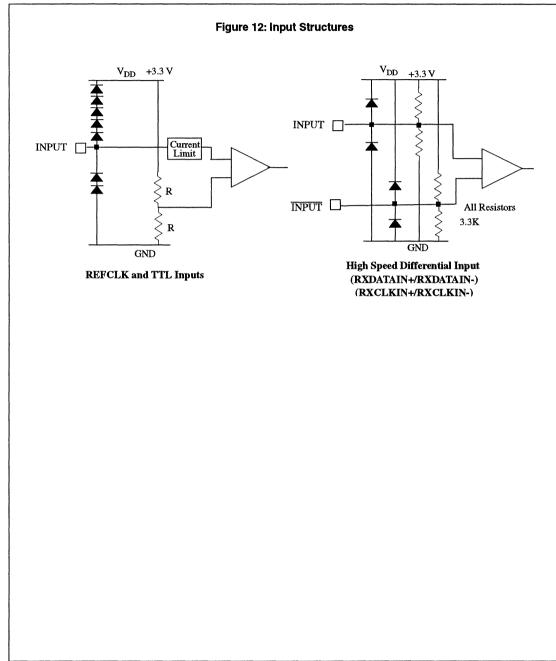

| Input Structures                 |  |

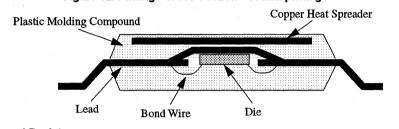

| Package Thermal Characteristics  |  |

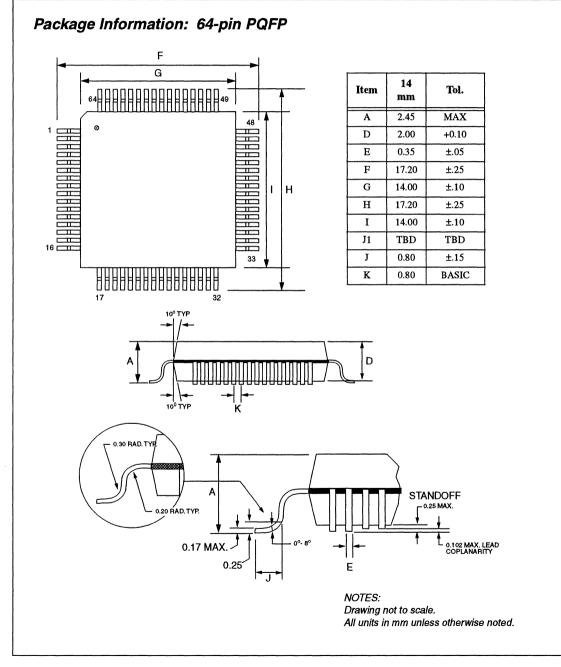

| Package Information              |  |

| Ordering Information             |  |

| -                                |  |

# Table of Contents

| VSC7125                          |     |

|----------------------------------|-----|

| Features                         |     |

| General Description              |     |

| Block Diagram                    |     |

| Functional Description           | 114 |

| Absolute Maximum Ratings         |     |

| Recommended Operating Conditions |     |

| DC Characteristics               |     |

| Thermal Considerations           |     |

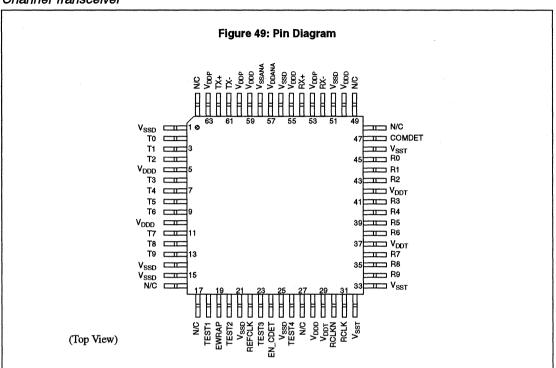

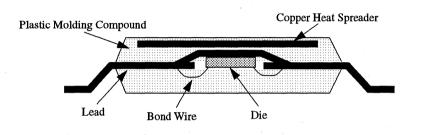

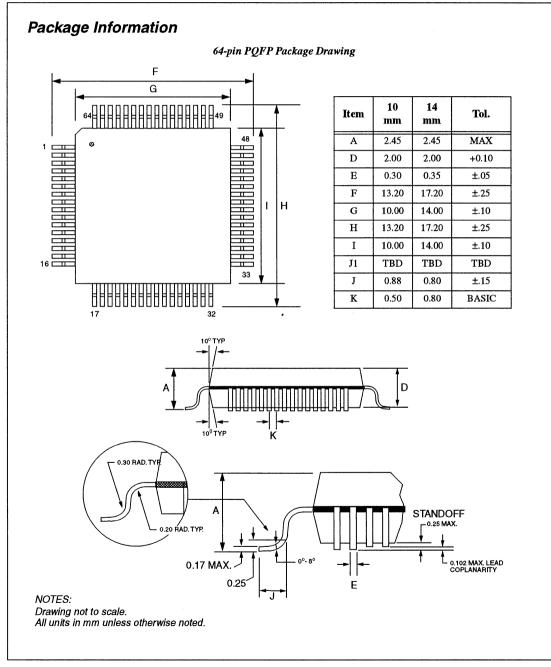

| Package Information              | 127 |

| Ordering Information             |     |

#### VSC7126

| Features              | 129 |

|-----------------------|-----|

| General Description   | 129 |

| VSC7126 Block Diagram | 129 |

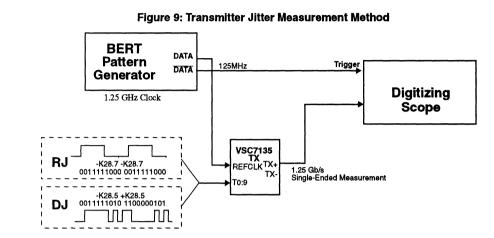

#### VSC7135

| Features                         | 131 |

|----------------------------------|-----|

| General Description              | 131 |

| Functional Description           |     |

| Absolute Maximum Ratings         |     |

| Recommended Operating Conditions |     |

| DC Characteristics               |     |

| Thermal Considerations           |     |

| Package Information              | 145 |

| Ordering Information             |     |

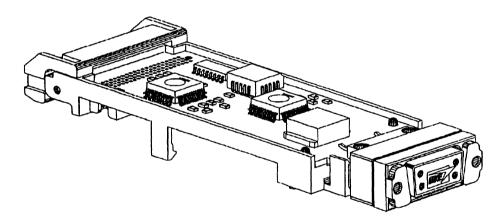

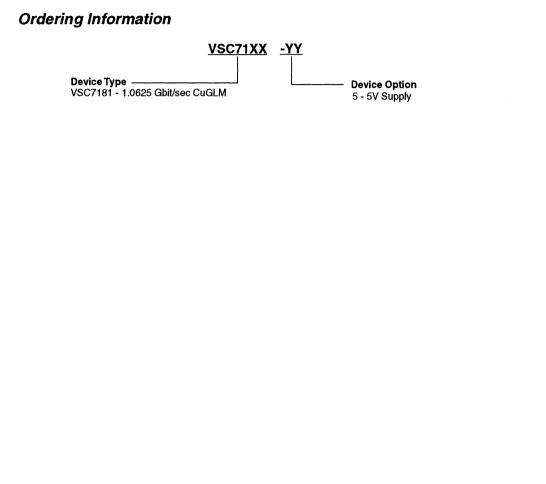

# VSC7181

| Features                         | 147 |

|----------------------------------|-----|

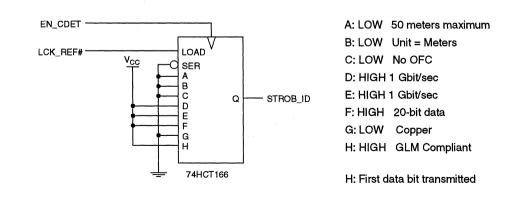

| Copper GLM Module                | 147 |

| General Description              | 147 |

| Functional Description           |     |

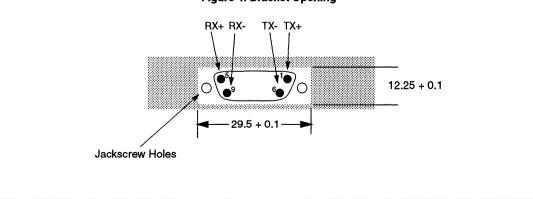

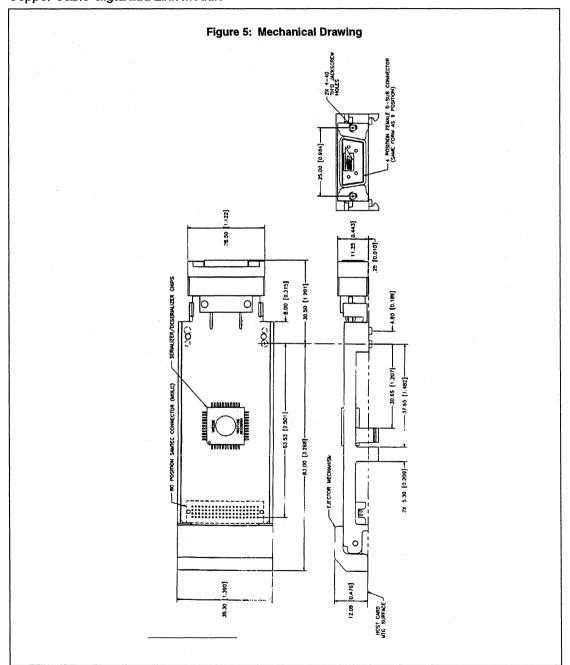

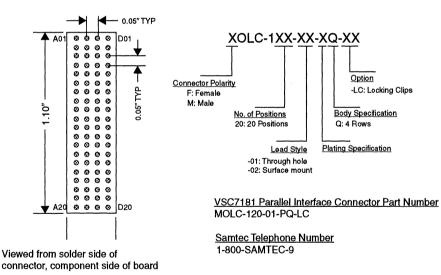

| Physical Description             | 151 |

| Electrical Interface             |     |

| Absolute Maximum Ratings         |     |

| Recommended Operating Conditions |     |

| Ordering Information             |     |

| 6                                |     |

# 1996 Communications Products Data Book

# Table of Contents

| Contents/Benefits    |     |

|----------------------|-----|

| General Description  |     |

| CuGLM Evaluation Kit |     |

| Order Information    | 164 |

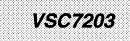

#### VSC7201A

| Features                           | 165 |

|------------------------------------|-----|

| Introduction                       |     |

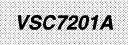

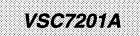

| VSC7201A - Block Diagram           |     |

| Terms and Conventions              |     |

| Quick Signal Pin Reference         |     |

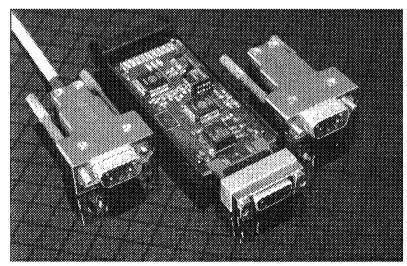

| SCI Overview                       |     |

| Node Interface Bus (NIBus)         |     |

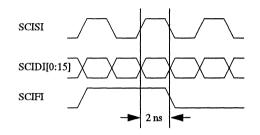

| SCI High Speed Link Signals        |     |

| Latency                            |     |

| Performance Counters               |     |

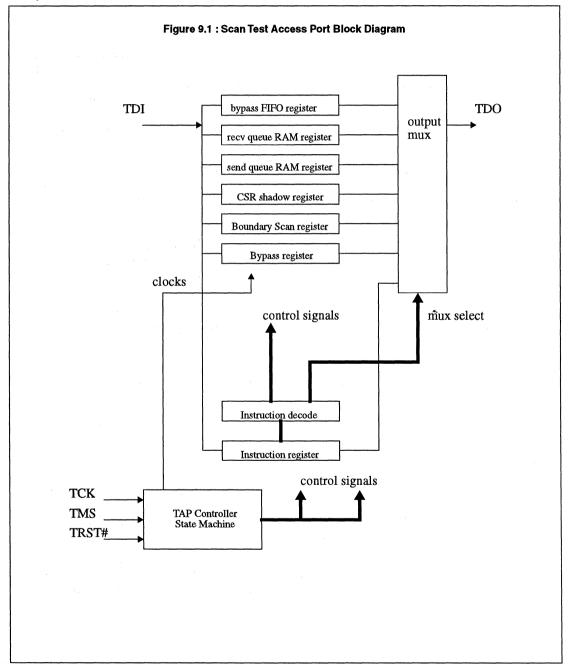

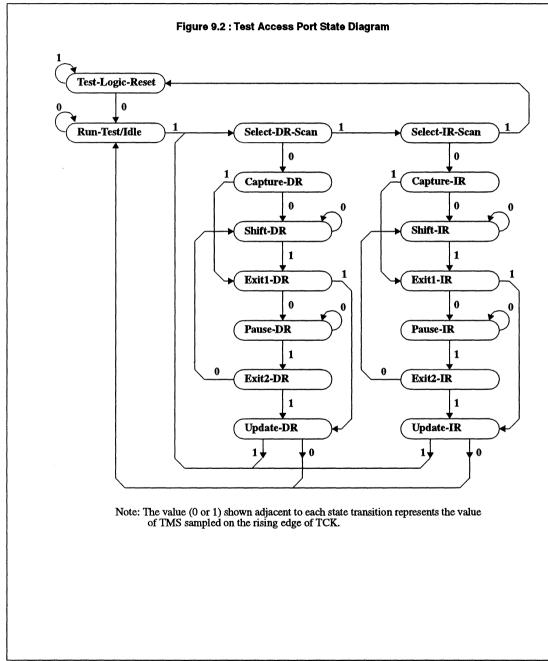

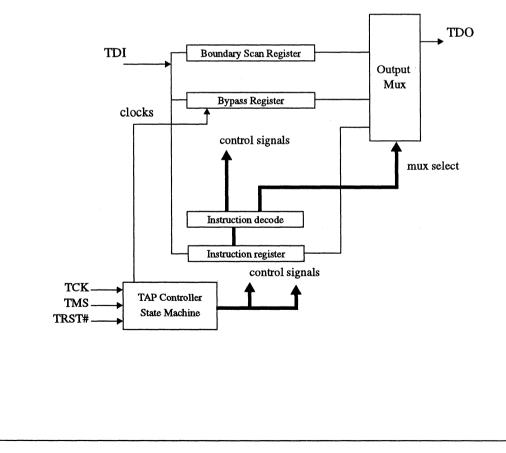

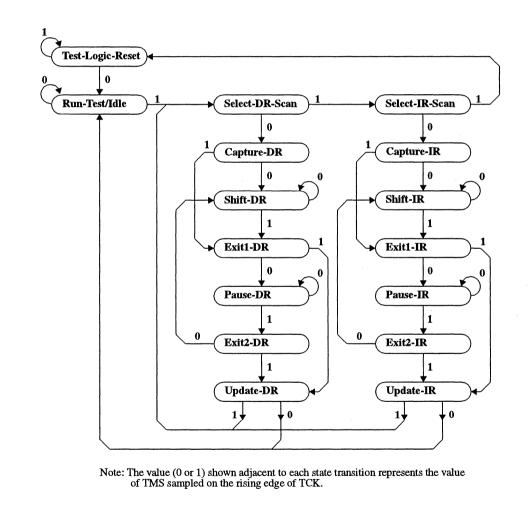

| Test Access Port                   |     |

| Internal Scan Test and Diagnostics |     |

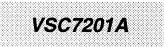

| Electrical Specifications          |     |

| Package Pin Description            |     |

| Signal Pin Description             |     |

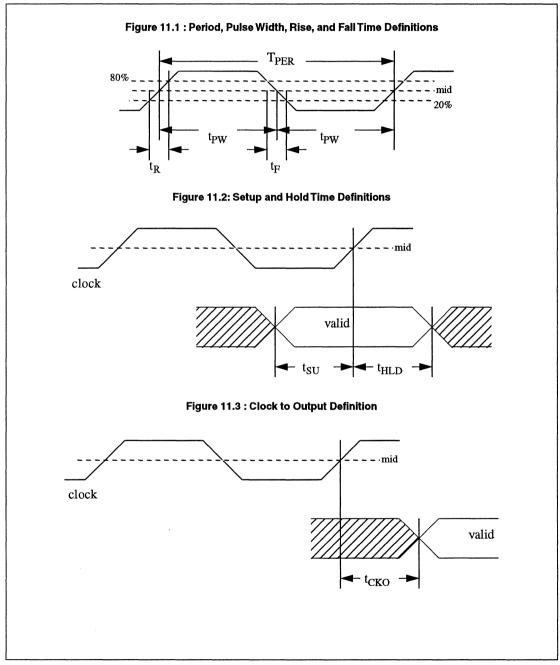

| Mechanical Specifications          |     |

| Thermal Specifications             |     |

| Ordering Information               |     |

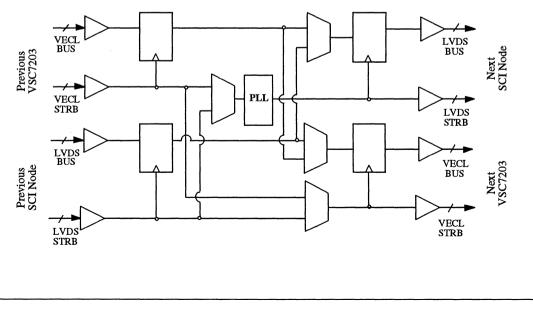

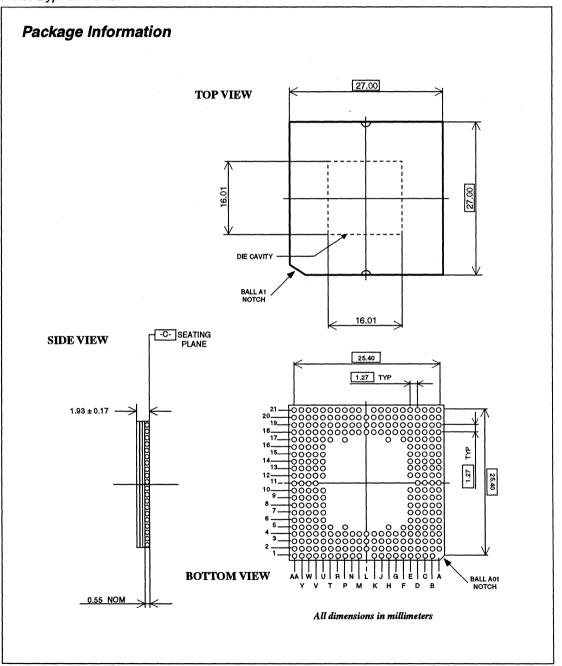

### VSC7203

| Features                         |     |

|----------------------------------|-----|

| Introduction                     |     |

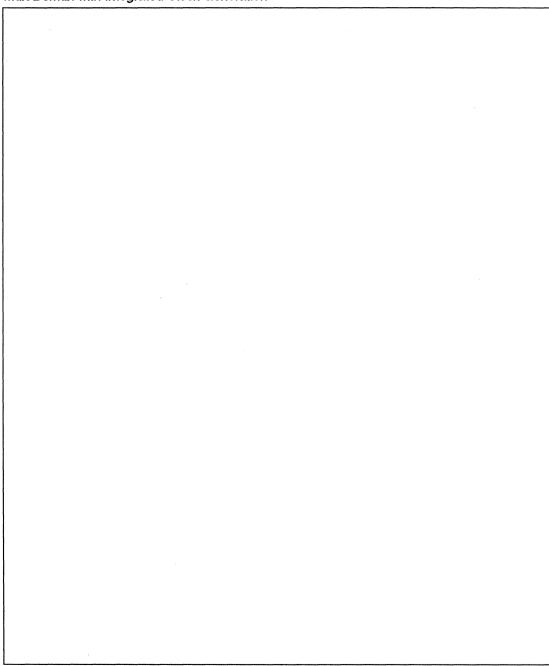

| VSC7203 Functional Block Diagram | 261 |

| Functional Description           |     |

| JTAG                             |     |

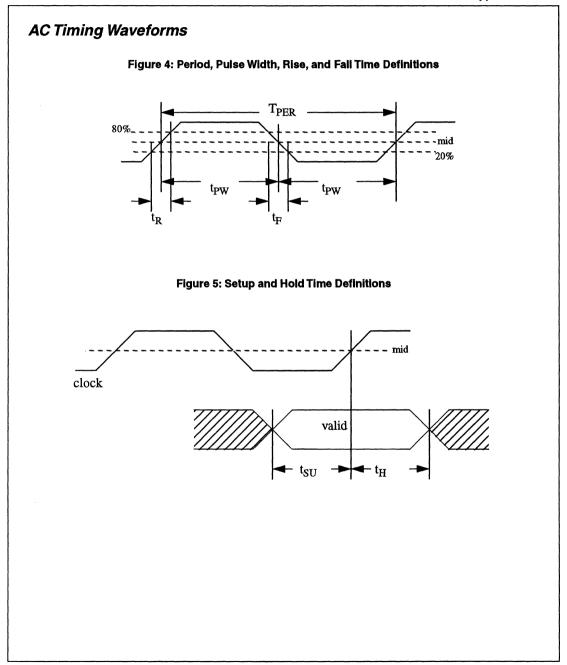

| AC Characteristics               |     |

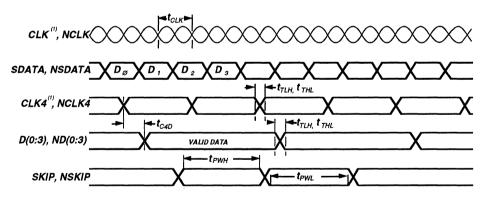

| AC Timing Waveforms              |     |

| DC Characteristics               |     |

| Absolute Maximum Ratings         |     |

| Recommended Operating Conditions |     |

| Package Pin Description          |     |

| Package Pinout [by Pin Number]   |     |

| Package Pinout [by Signal Name]  | 277 |

|                                  |     |

General

# Table of Contents

| VSC7203 continued                              |  |

|------------------------------------------------|--|

| Package Information                            |  |

| Ordering Information                           |  |

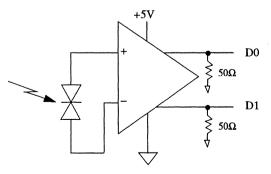

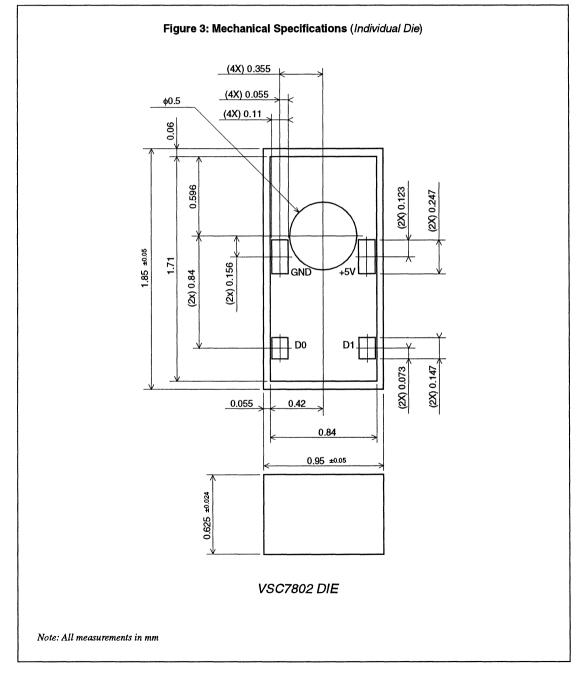

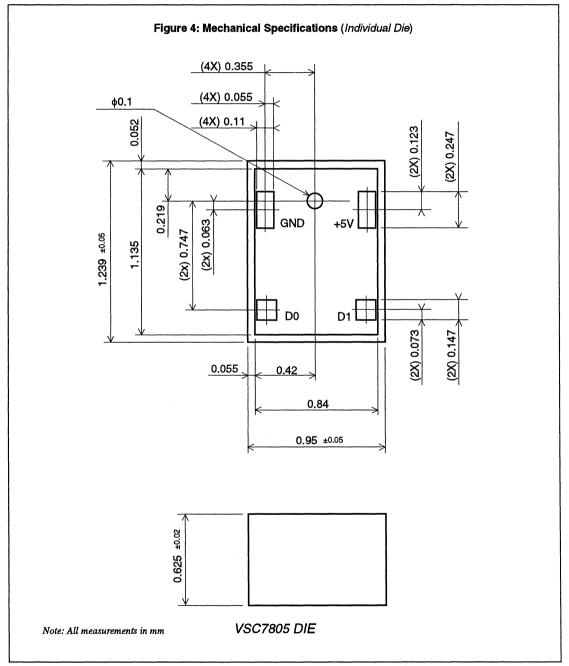

| VSC7802 and VSC7805                            |  |

| Features                                       |  |

| General Description                            |  |

| VSC7802/7805 Block Diagram                     |  |

| Electro-Optical Specifications                 |  |

| Absolute Maximum Ratings                       |  |

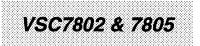

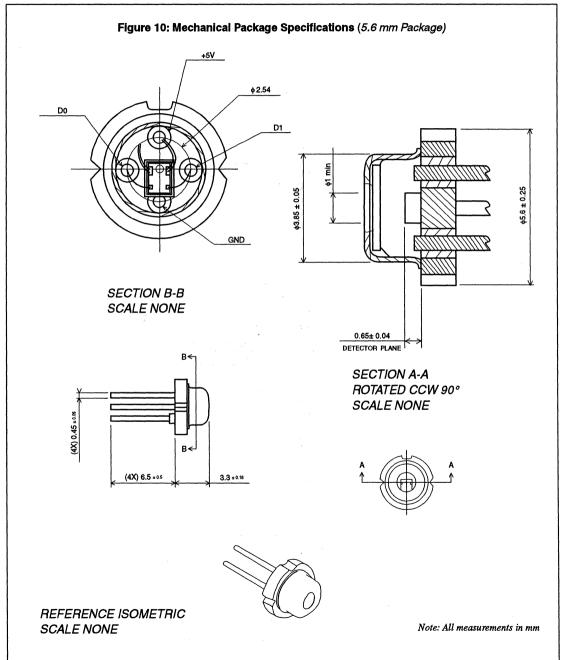

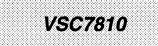

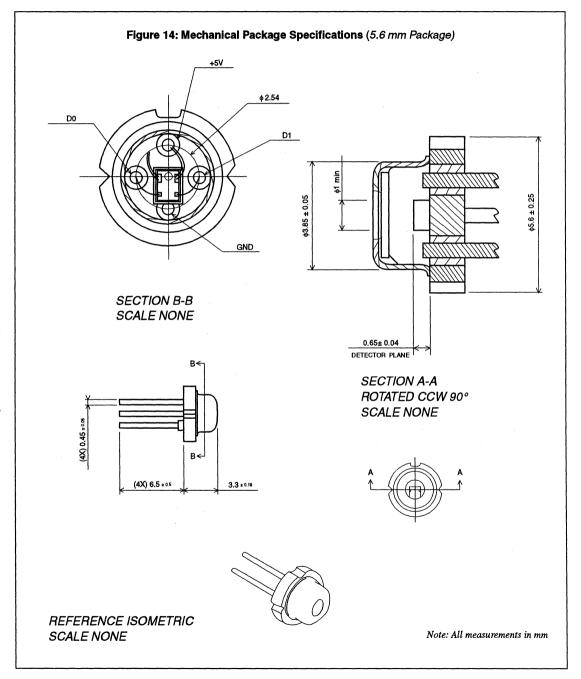

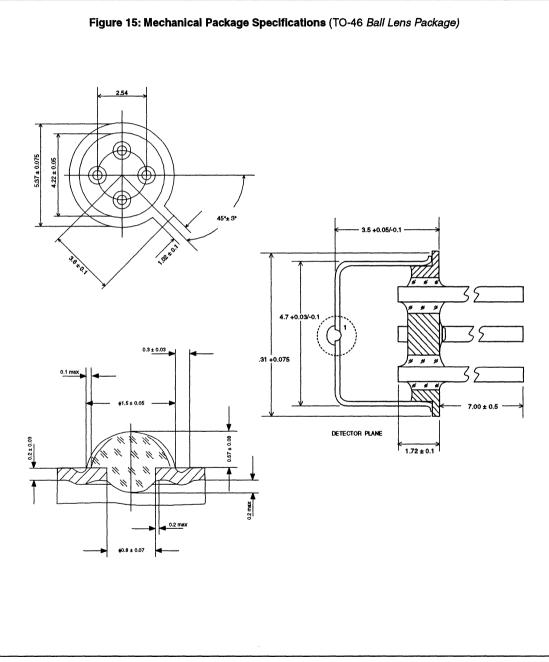

| Mechanical Package Specifications              |  |

| Ordering Information                           |  |

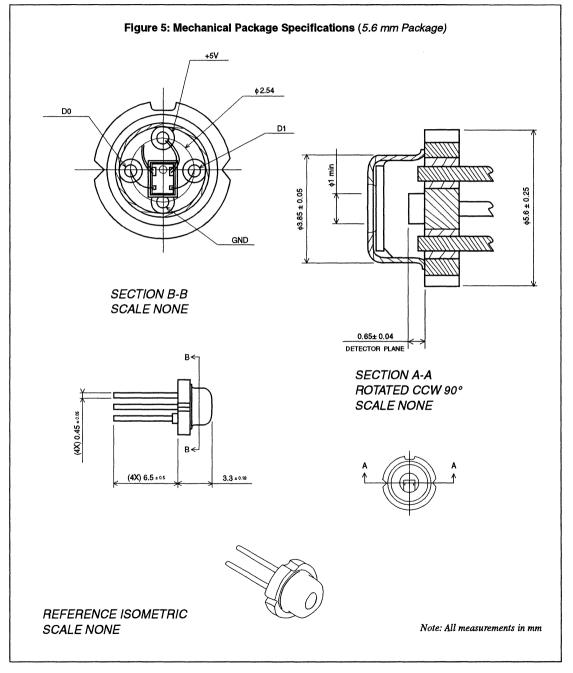

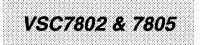

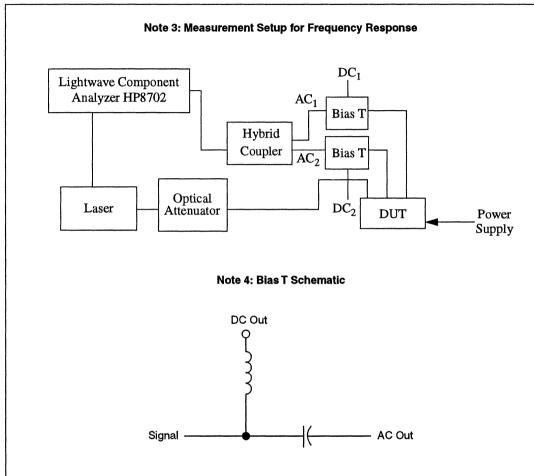

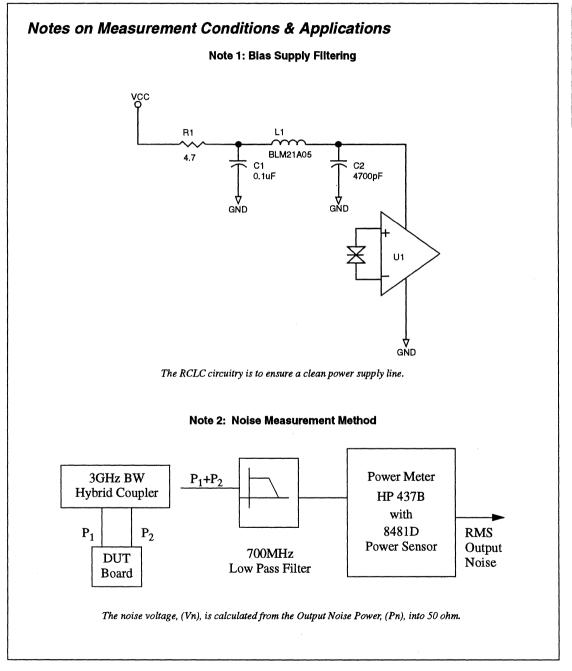

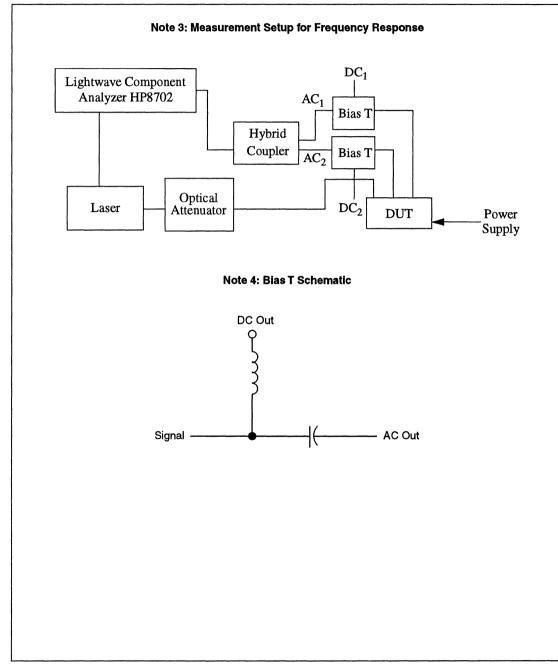

| Notes on Measurement Conditions & Applications |  |

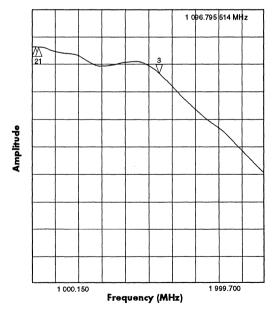

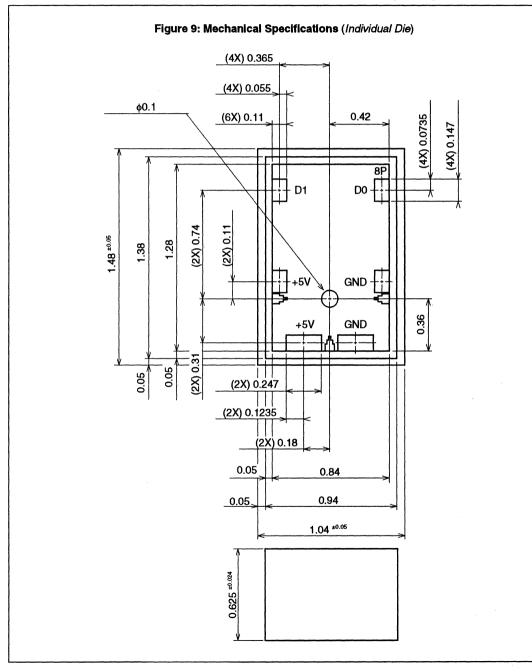

# VSC7810

| Features                                       | .295 |

|------------------------------------------------|------|

| General Description                            | .295 |

| VSC7810 Block Diagram                          |      |

| Electro-Optical Specifications                 |      |

| Absolute Maximum Ratings                       |      |

| Mechanical Package Specifications              |      |

| Ordering Information                           |      |

| Notes on Measurement Conditions & Applications |      |

# Transmitter/Receiver Design Guide

| Introduction                                |  |

|---------------------------------------------|--|

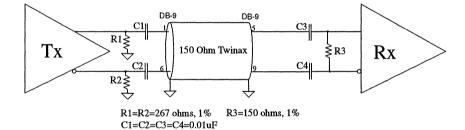

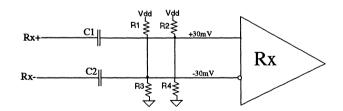

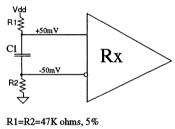

| System Interfacing                          |  |

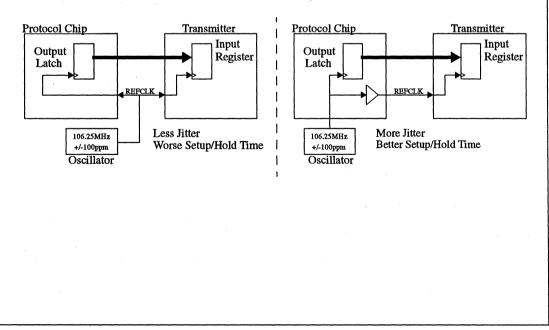

| Clock Generation                            |  |

| High Speed Signal Termination               |  |

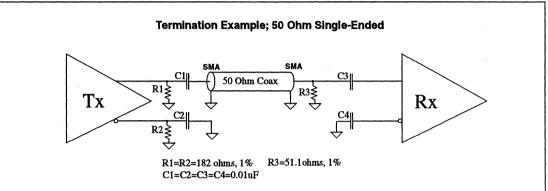

| Single-Ended, 50 Ohm Termination            |  |

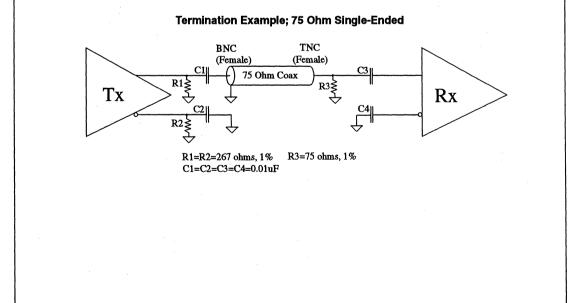

| Single Ended, 75 Ohm Termination            |  |

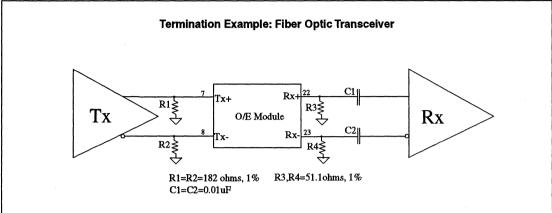

| Fiber Optic Module Termination              |  |

| Preventing Oscillations                     |  |

| Unused Inputs                               |  |

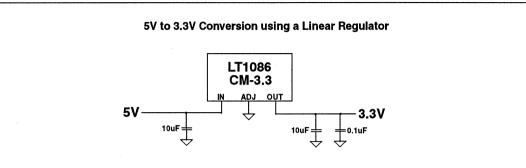

| Power Supply Considerations                 |  |

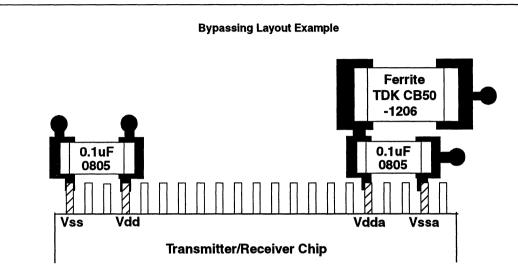

| Bypassing                                   |  |

| Layout Considerations                       |  |

| High Speed Serial I/O Layout Considerations |  |

| Conclusion                                  |  |

| Component Supplier List                     |  |

|                                             |  |

# Table of Contents

| TELECOMMUNICATIONS                            |

|-----------------------------------------------|

| Telecommunications Product Summary            |

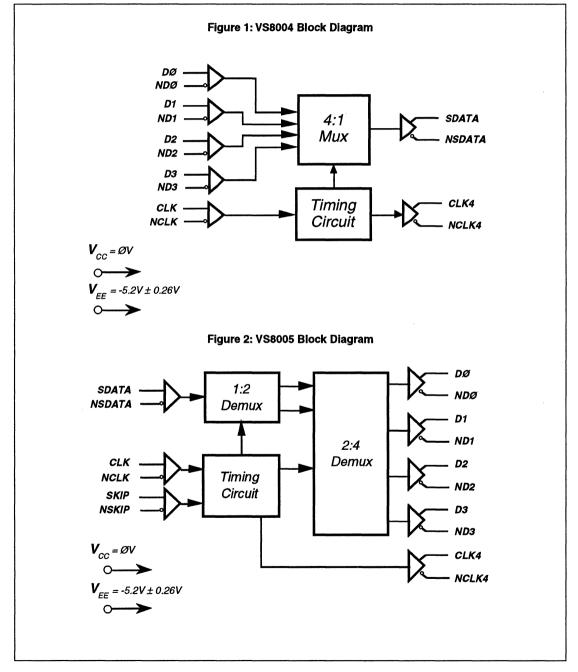

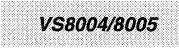

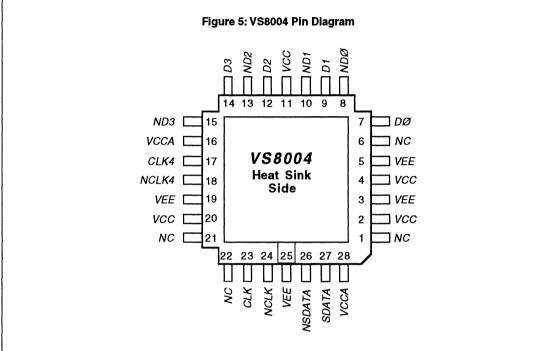

| VS8004/VS8005                                 |

| Features                                      |

| Functional Description                        |

| VS8004                                        |

| VS8005                                        |

| SKIP Signal                                   |

| Applications                                  |

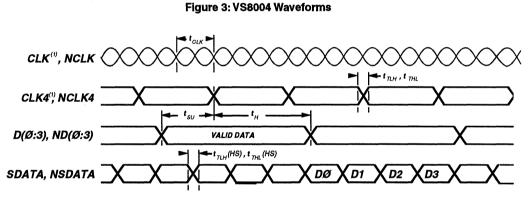

| VS8004 AC Characteristics                     |

| VS8005 AC Characteristics                     |

| Absolute Maximum Ratings                      |

| Recommended Operating Conditions              |

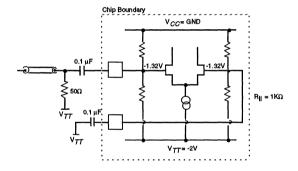

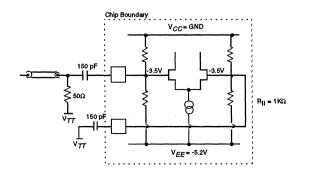

| DC Characteristics                            |

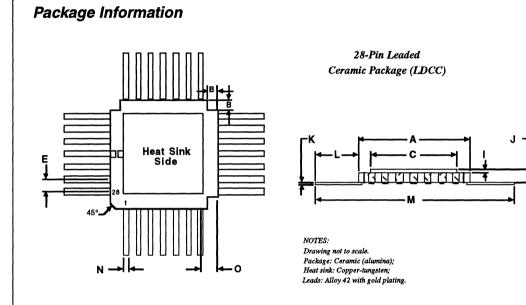

| Package Information                           |

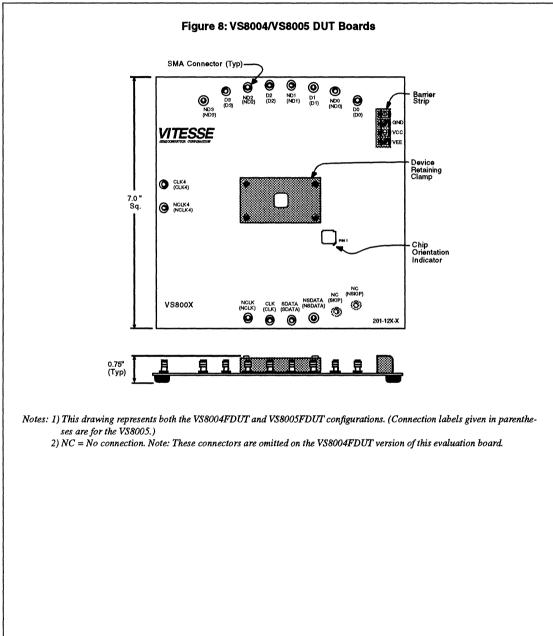

| DUT Boards                                    |

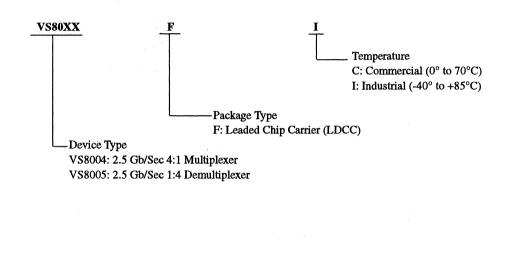

| Ordering Information                          |

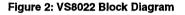

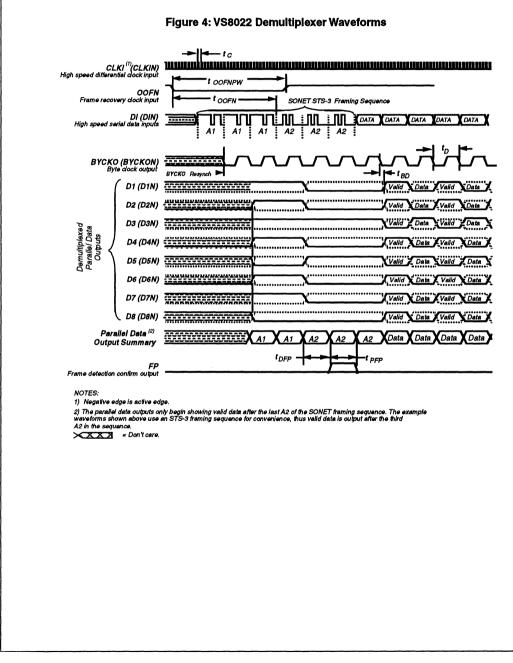

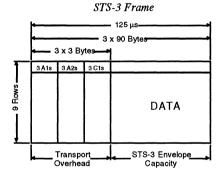

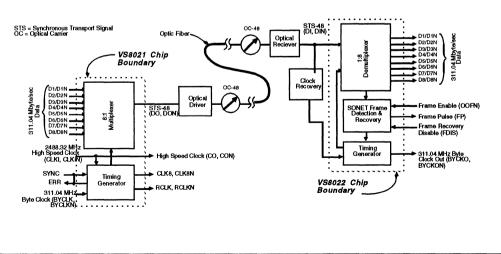

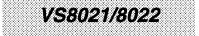

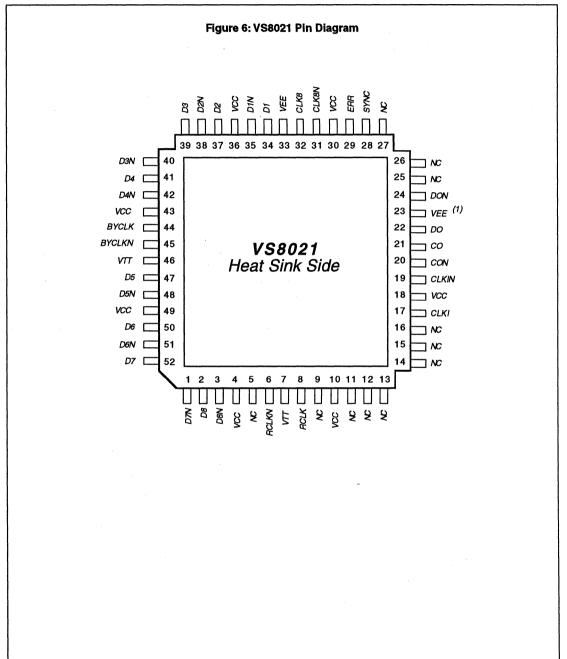

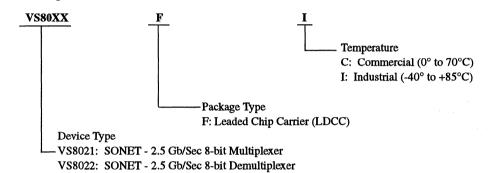

| VS8021/VS8022                                 |

| Features                                      |

| Functional Description                        |

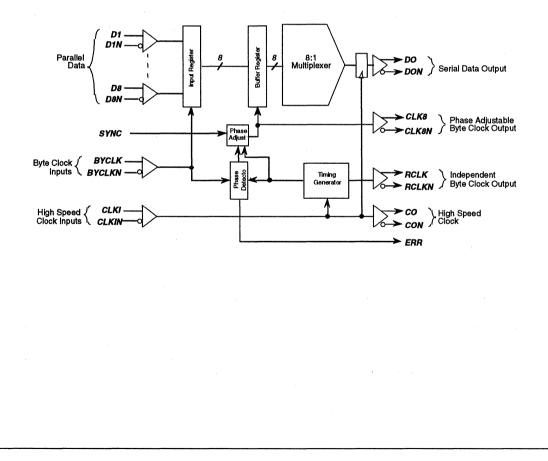

| VS8021                                        |

| VS8022                                        |

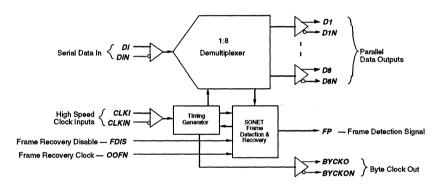

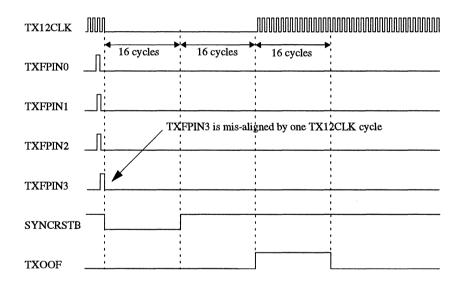

| VS8021 Multiplexer AC Characteristics         |

| VS8022 Demultiplexer AC Characteristics       |

| VS8022 SONET Frame Recovery and Detection     |

| Absolute Maximum Ratings                      |

| Recommended Operating Conditions              |

| DC Characteristics                            |

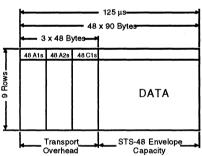

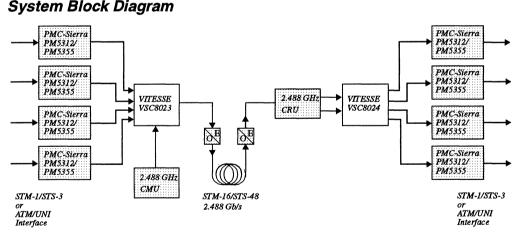

| Example Application: STS-48 SONET System Link |

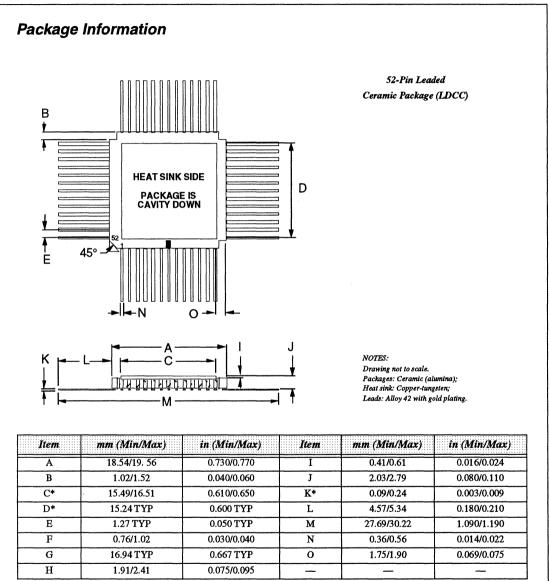

| Package Information                           |

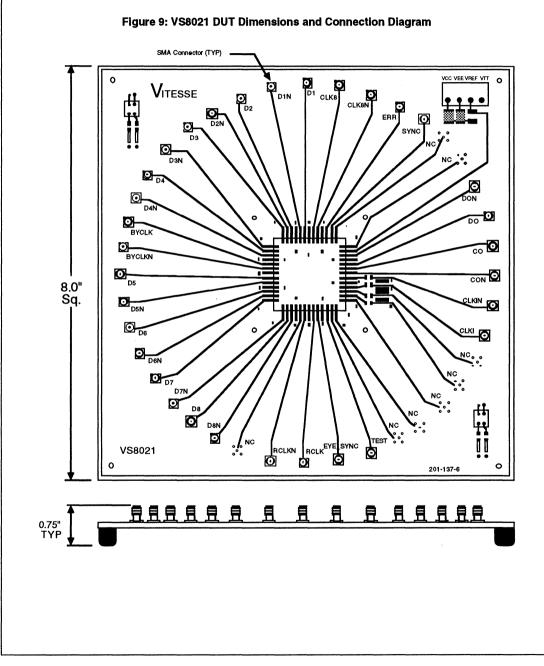

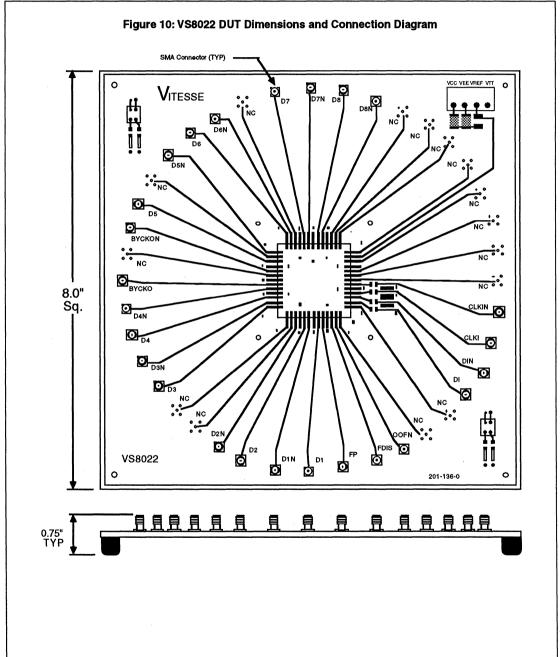

| DUT Boards                                    |

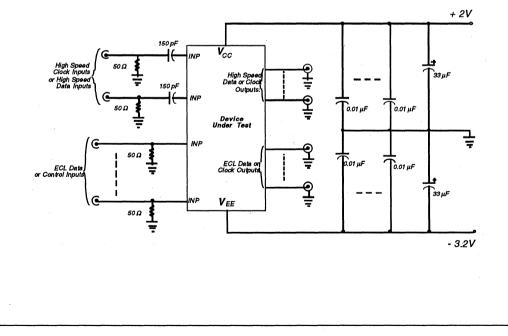

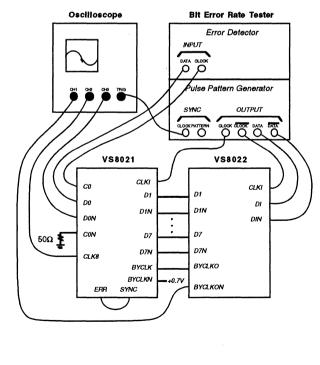

| DUT Test Setup                                |

General

# Table of Contents

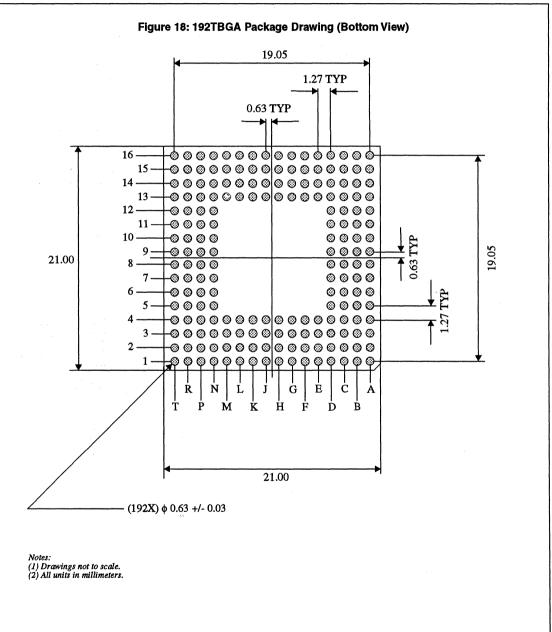

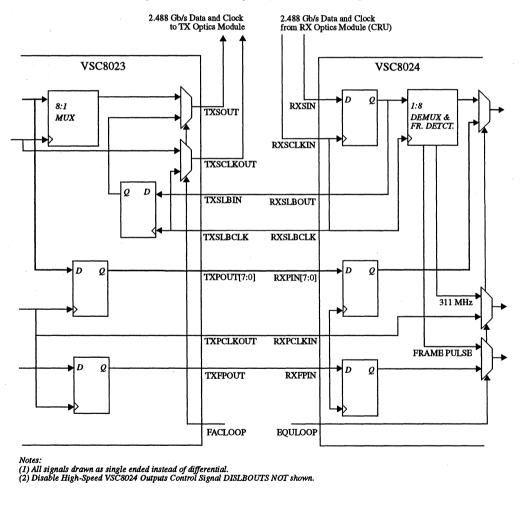

#### VSC8023/VSC8024

| Features                          | 359 |

|-----------------------------------|-----|

| System Block Diagram              |     |

| General Description               |     |

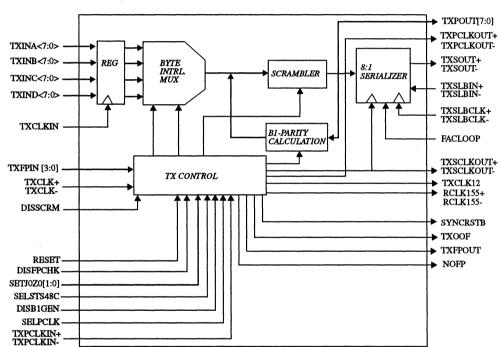

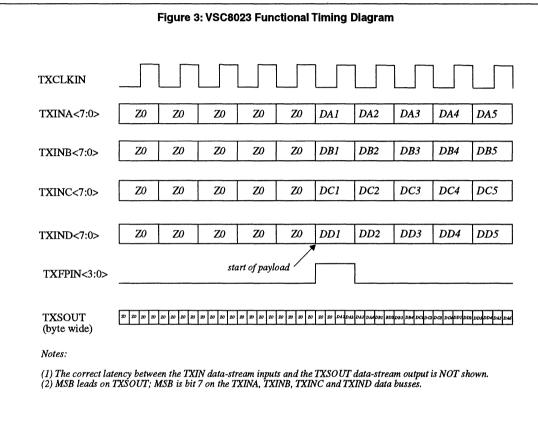

| VSC8023 Functional Description    |     |

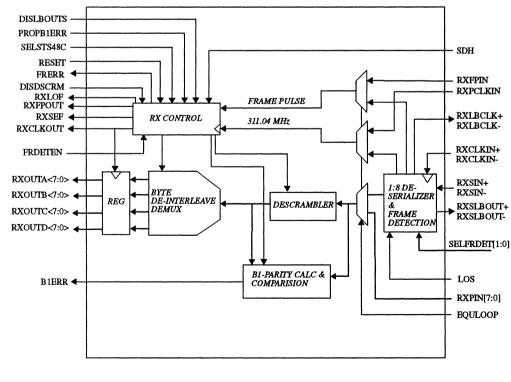

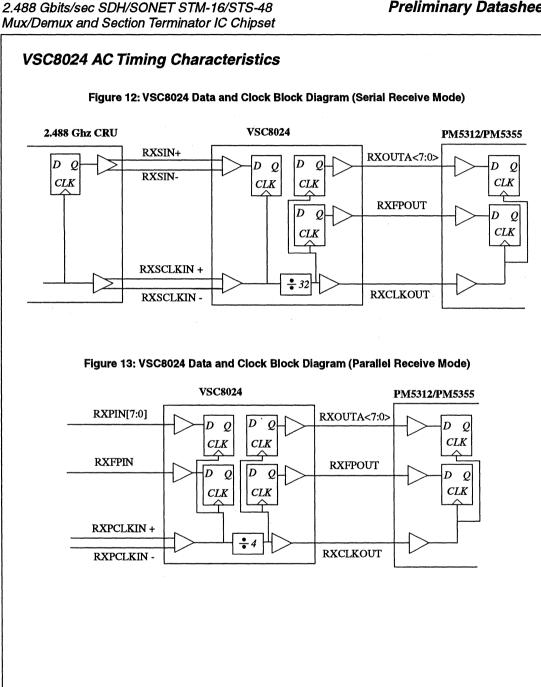

| VSC8024 Functional Description    |     |

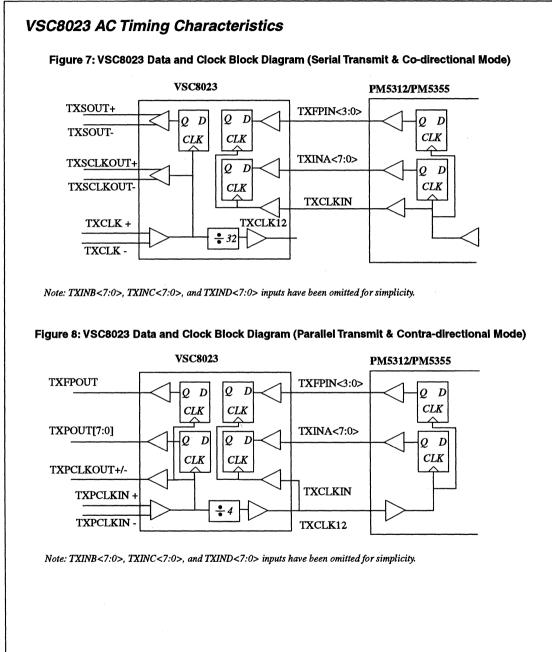

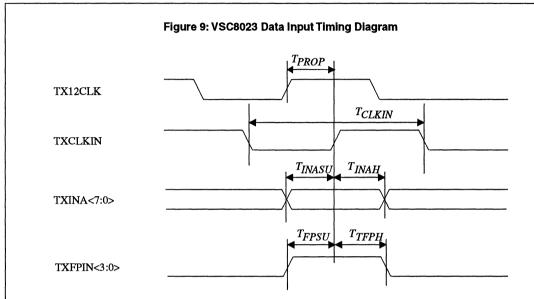

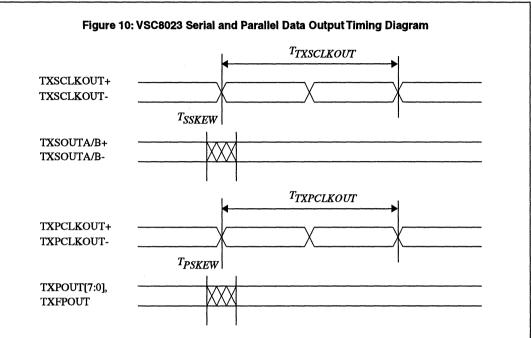

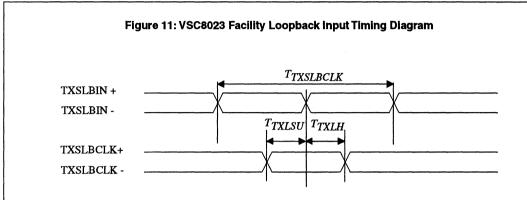

| VSC8023 AC Timing Characteristics |     |

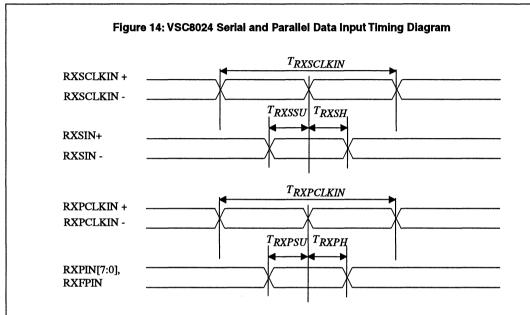

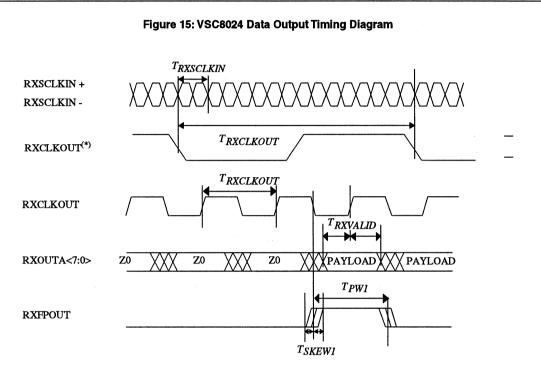

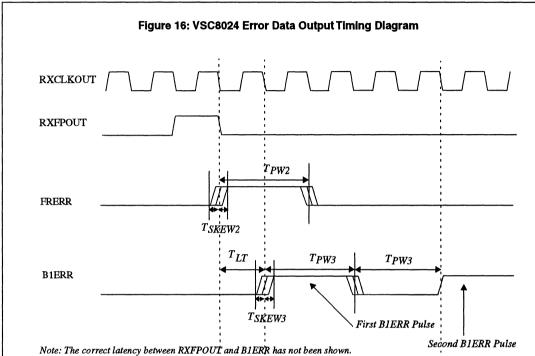

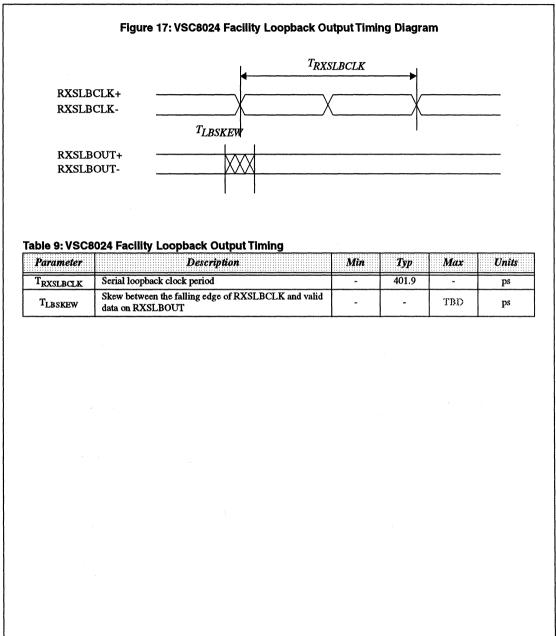

| VSC8024 AC Timing Characteristics |     |

| Absolute Maximum Ratings          |     |

| Recommended Operating Conditions  |     |

| ESD Ratings                       |     |

| DC Characteristics                |     |

| Power Dissipation                 |     |

| VSC8023 Package Pin Description   |     |

| VSC8024 Package Pin Description   |     |

| Application Notes                 |     |

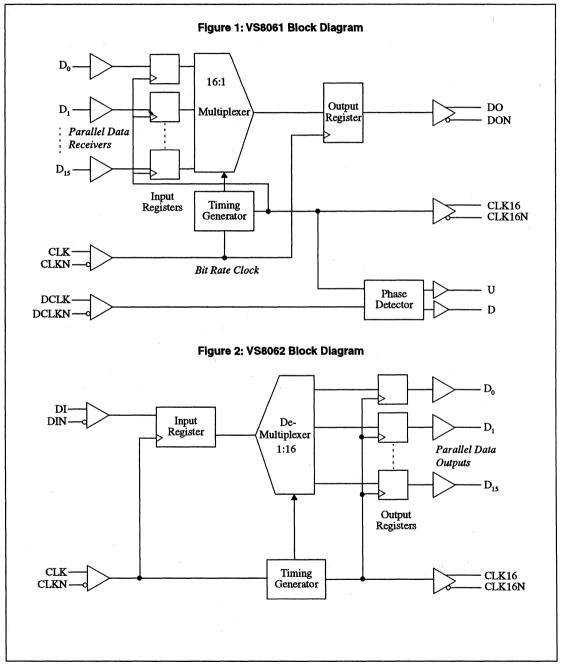

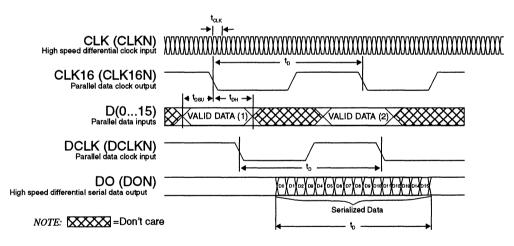

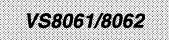

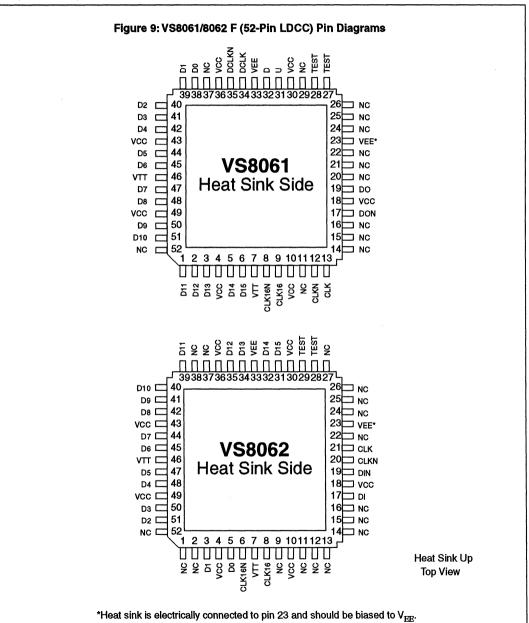

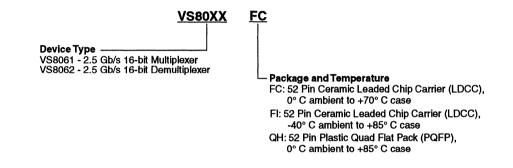

#### VS8061/VS8062

| Features                                |     |

|-----------------------------------------|-----|

| Functional Description                  |     |

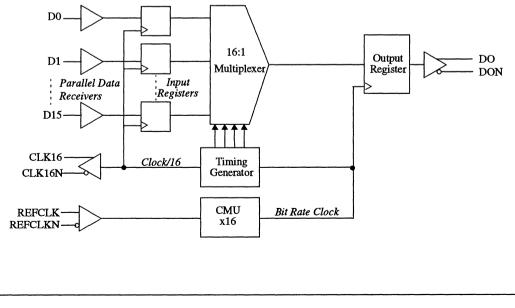

| VS8061 Multiplexer                      |     |

| VS8062 Demultiplexer                    |     |

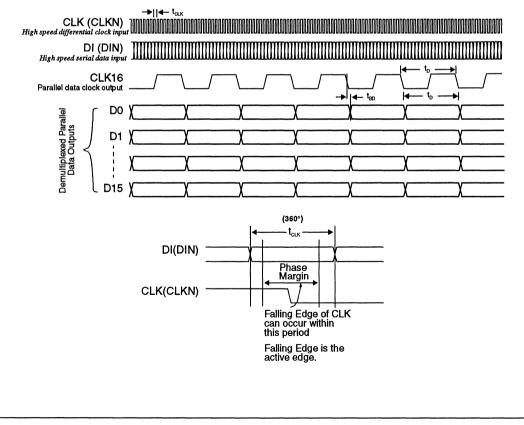

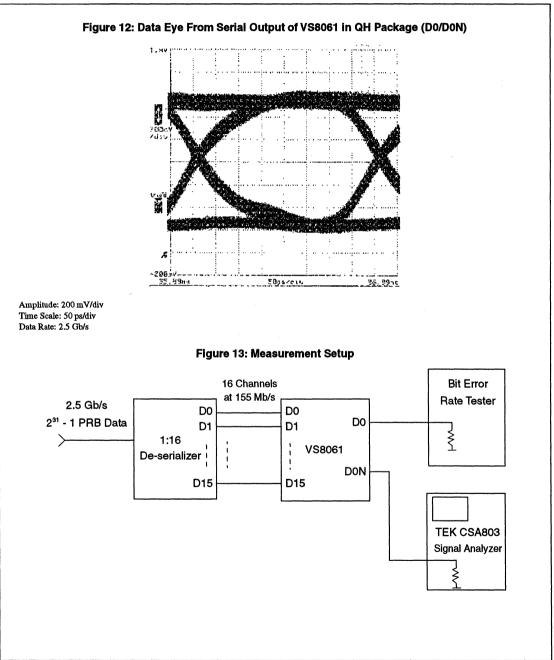

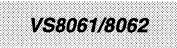

| VS8061 Multiplexer AC Characteristics   | 387 |

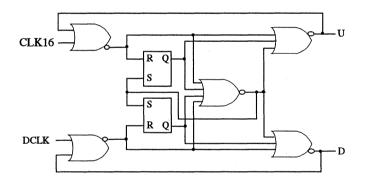

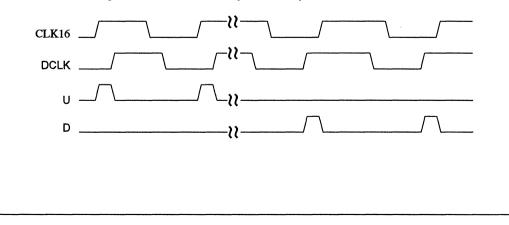

| VS8061 Phase Detector Logic Diagram     |     |

| VS8062 Demultiplexer AC Characteristics | 389 |

| Absolute Maximum Ratings                |     |

| Recommended Operating Conditions        |     |

| ESD Ratings                             |     |

| DC Characteristics                      |     |

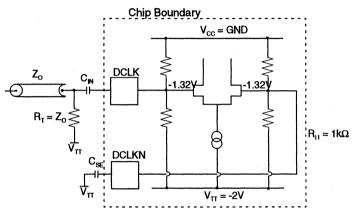

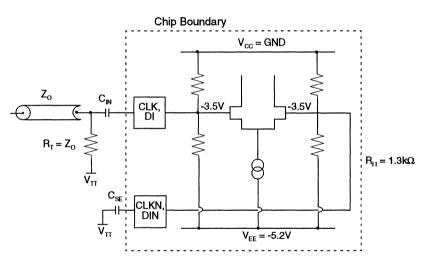

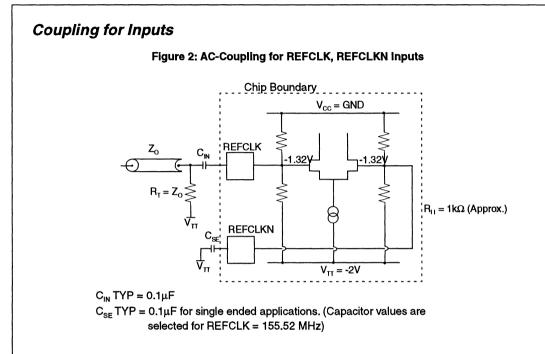

| Coupling for Inputs                     |     |

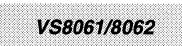

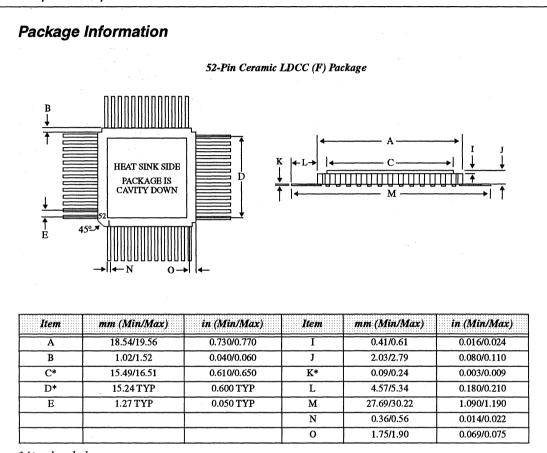

| Package Information                     |     |

| Thermal Considerations                  |     |

| Ordering Information                    | 403 |

|                                         |     |

# 1996 Communications Products Data Book

# Table of Contents

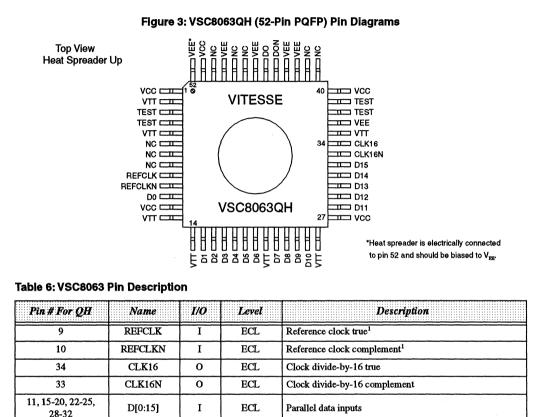

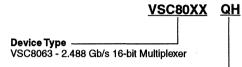

| VSC8063                          |     |

|----------------------------------|-----|

| Features                         | 405 |

| Functional Description           |     |

| VSC8063 Block Diagram            | 405 |

| Absolute Maximum Ratings         |     |

| Recommended Operating Conditions |     |

| DC Characteristics               |     |

| Coupling for Inputs              |     |

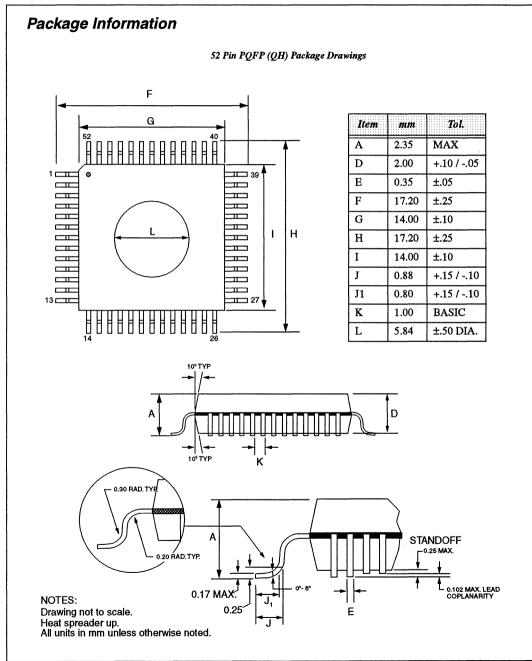

| Package Information              |     |

| Thermal Considerations           |     |

| Ordering Information             | 414 |

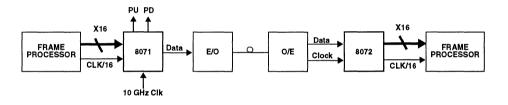

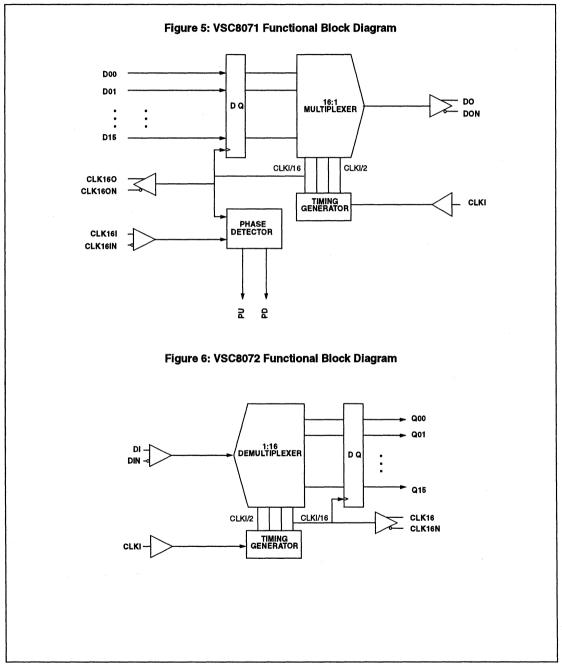

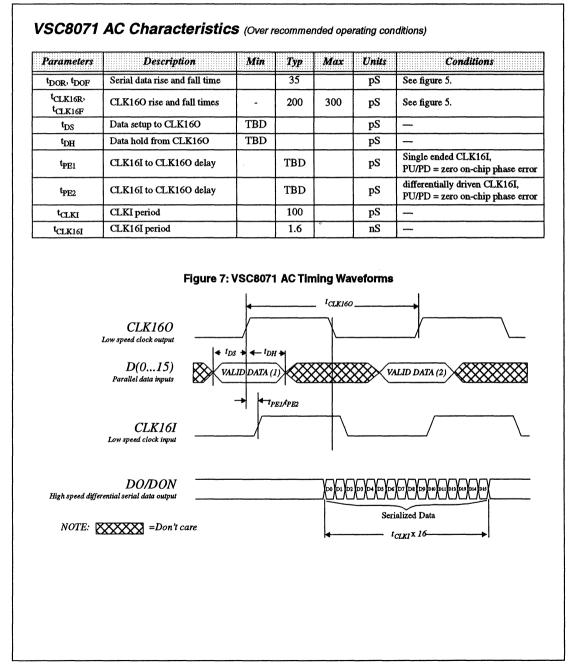

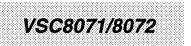

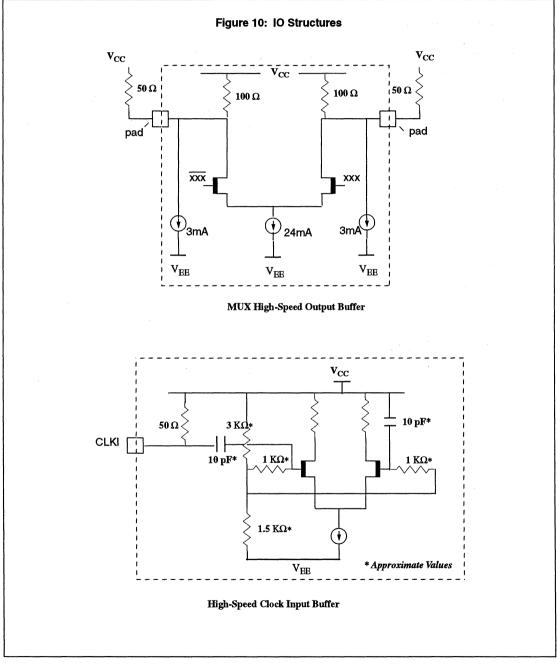

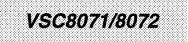

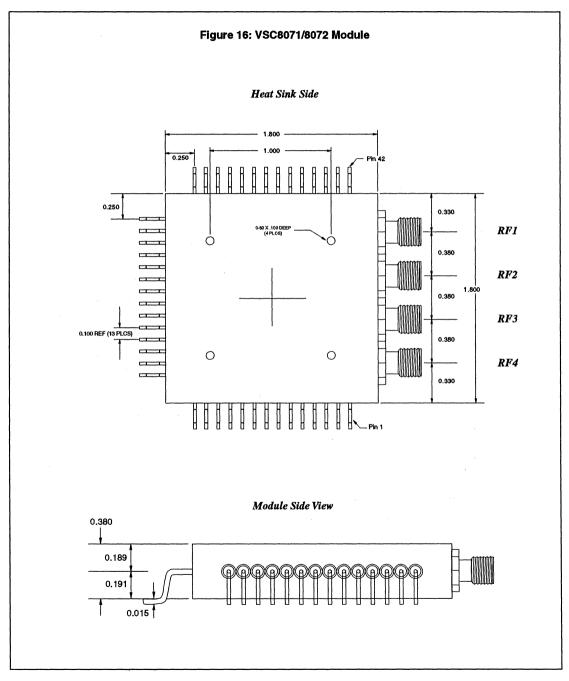

#### VSC8071/VSC8072

| Features                         | 415 |

|----------------------------------|-----|

| Typical System Block Diagram     | 415 |

| General Description              | 415 |

| VSC8071 AC Characteristics       | 417 |

| VSC8072 AC Characteristics       | 418 |

| DC Characteristics               | 420 |

| Absolute Maximum Ratings         | 421 |

| Recommended Operating Conditions | 421 |

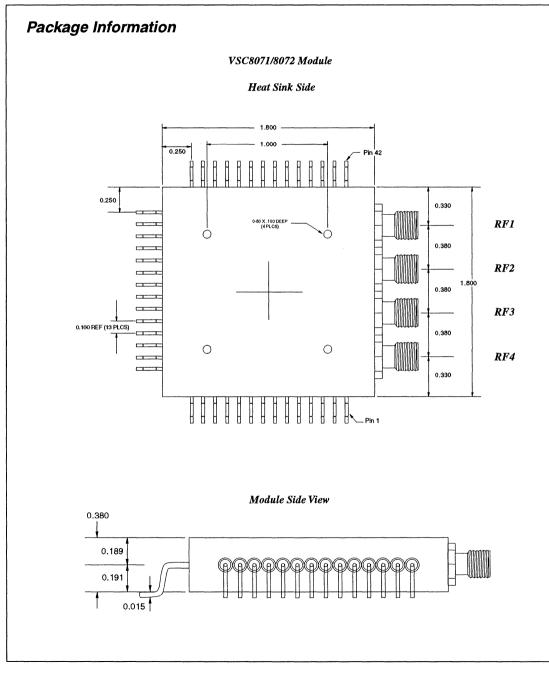

| Package Information              |     |

| Ordering Information             |     |

| -                                |     |

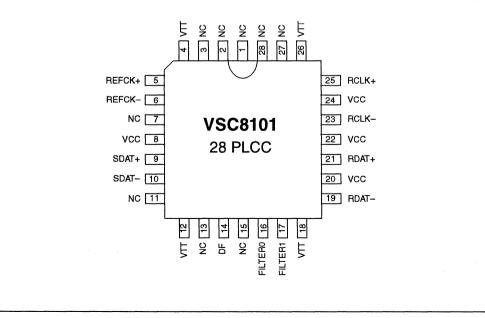

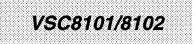

# VSC8101/VSC8102

| 9 |

|---|

| 9 |

| 1 |

| 2 |

| 2 |

| 3 |

| 4 |

| 9 |

| 1 |

| 2 |

|   |

# Table of Contents

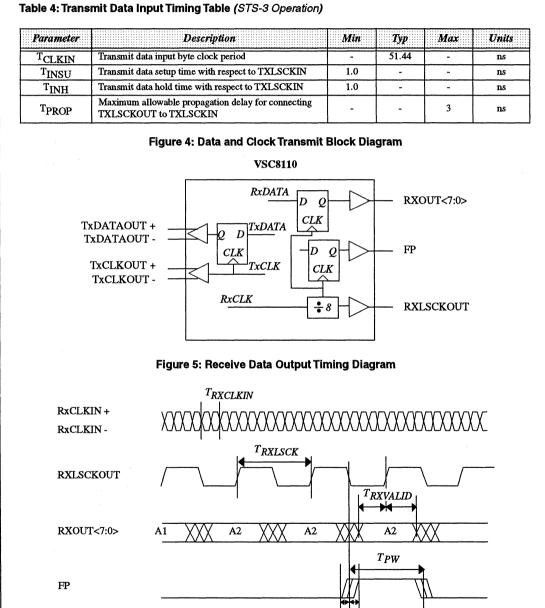

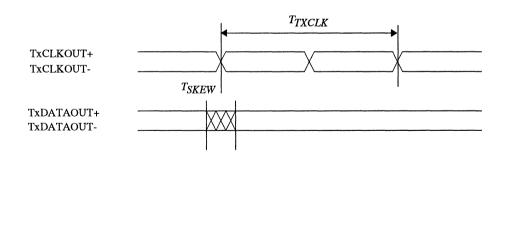

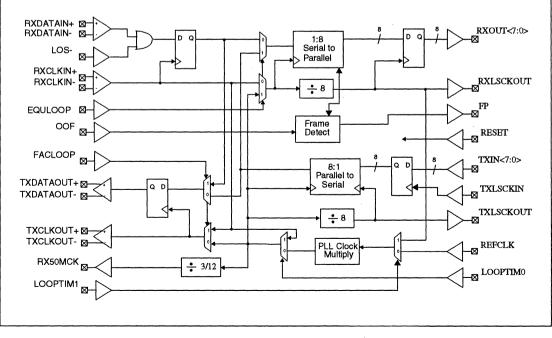

| VSC8110                          |     |

|----------------------------------|-----|

| Features                         |     |

| General Description              |     |

| Functional Description           |     |

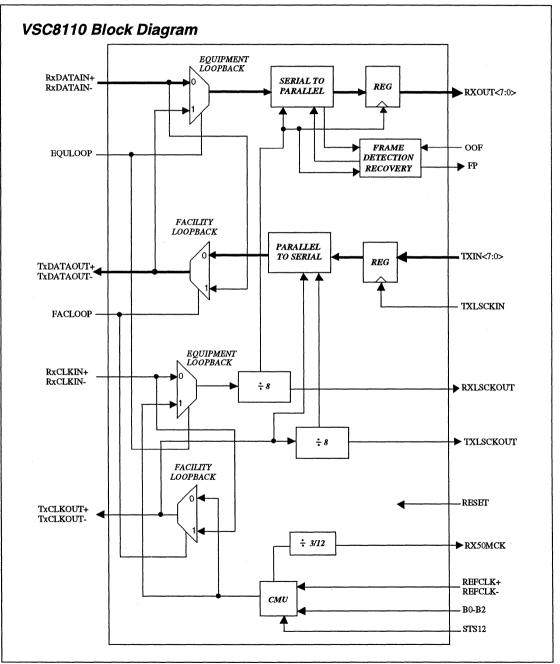

| VSC8110 Block Diagram            |     |

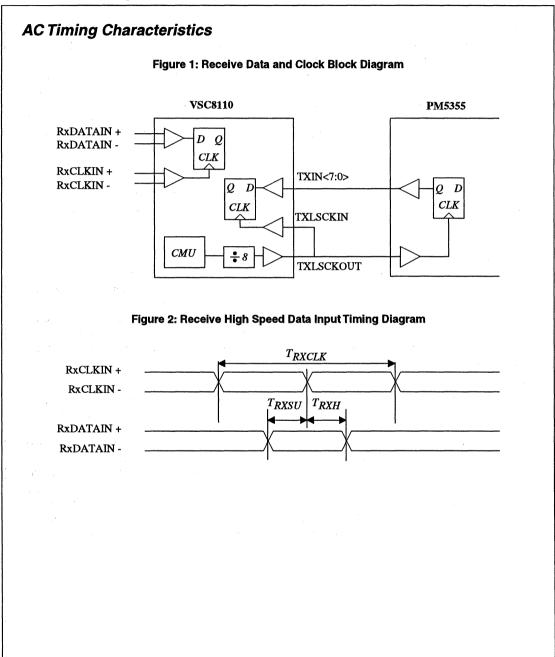

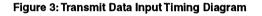

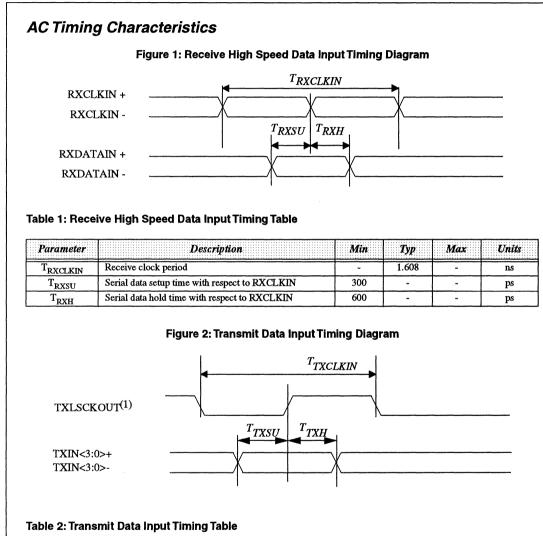

| AC Timing Characteristics        |     |

| Data Latency                     | 450 |

| Absolute Maximum Ratings         |     |

| Recommended Operating Conditions | 451 |

| ESD Ratings                      |     |

| DC Characteristics               | 452 |

| Power Dissipation                | 453 |

| Clock Multiplier Unit            | 453 |

| Package Pin Description          | 454 |

| Package Thermal Characteristics  | 457 |

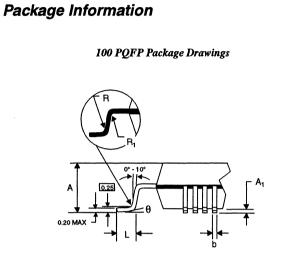

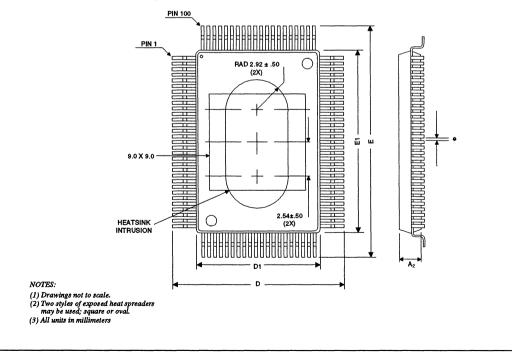

| Package Information              | 458 |

| Ordering Information             | 459 |

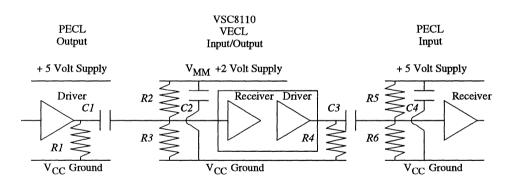

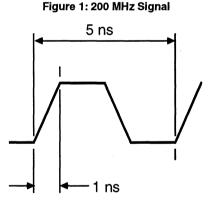

| Application Notes                | 460 |

# VSC8110EV

| Features                           |  |

|------------------------------------|--|

| General Description                |  |

| VSC8110 Evaluation Board           |  |

| VSC8110 Evaluation Board Operation |  |

# VSC8111

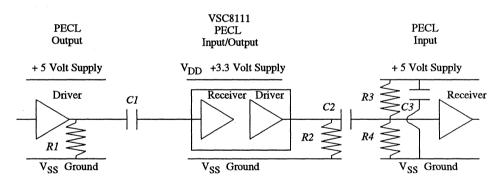

| Features                         | 467 |

|----------------------------------|-----|

| General Description              | 467 |

| VSC8111 Block Diagram            | 467 |

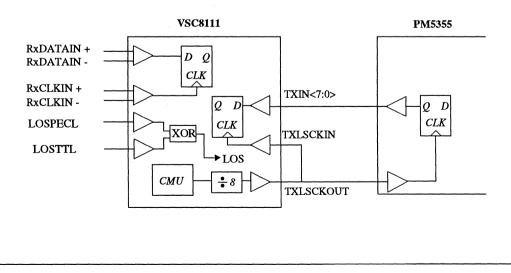

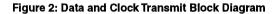

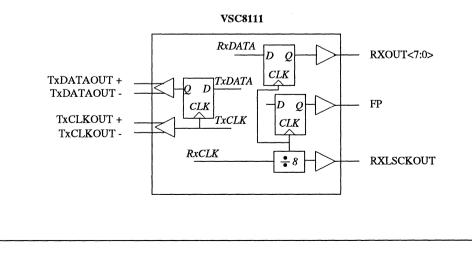

| Functional Description           | 468 |

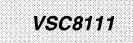

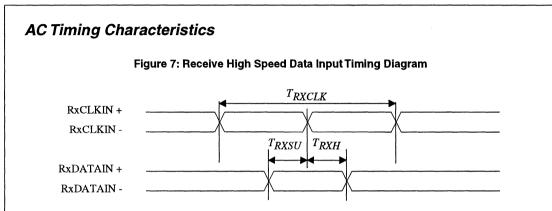

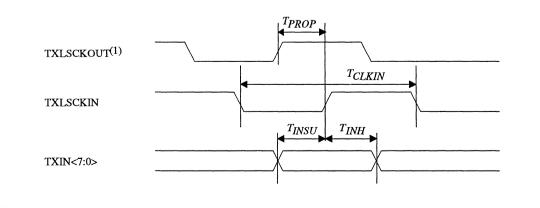

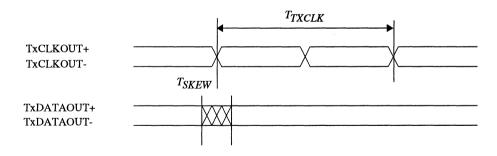

| AC Timing Characteristics        |     |

| Data Latency                     |     |

| Absolute Maximum Ratings         | 477 |

| Recommended Operating Conditions | 477 |

| DC Characteristics               | 478 |

| Power Dissipation                |     |

| Clock Multiplier Unit            | 479 |

| Package Pin Description          |     |

| Package Information              |     |

| Package Thermal Characteristics  |     |

# 1996 Communications Products Data Book

# Table of Contents

| VSC8111 continued                |     |

|----------------------------------|-----|

| Ordering Information             | 486 |

| Application Notes                |     |

|                                  |     |

| VSC8112                          |     |

| Features                         |     |

| General Description              |     |

| VSC8112 Block Diagram            |     |

| Functional Description           |     |

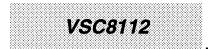

| AC Timing Characteristics        |     |

| DC Characteristics               |     |

| Power Dissipation                |     |

| Clock Multiplier Unit            |     |

| Data Latency                     |     |

| Absolute Maximum Ratings         |     |

| Recommended Operating Conditions |     |

| ESD Ratings                      |     |

| Package Pin Description          |     |

| Package Thermal Characteristics  |     |

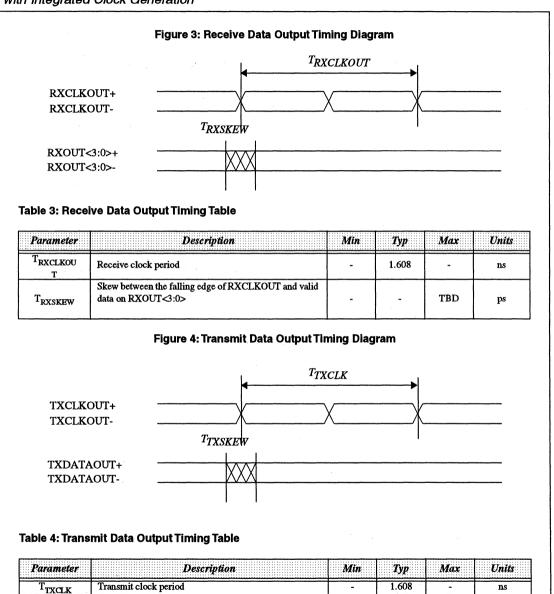

| Package Information              |     |

| Ordering Information             |     |

| Application Notes                |     |

# VSC864A-2

| Features                         | 505 |

|----------------------------------|-----|

| General Description              | 505 |

| Functional Description           | 505 |

| Absolute Maximum Ratings         |     |

| Recommended Operating Conditions | 507 |

| AC Characteristics               | 508 |

| AC Timing Waveforms              | 509 |

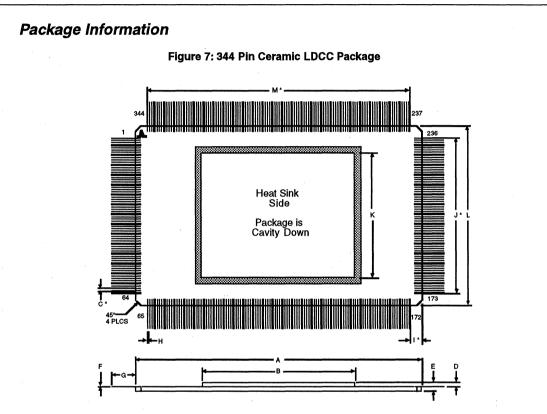

| Package Information              | 514 |

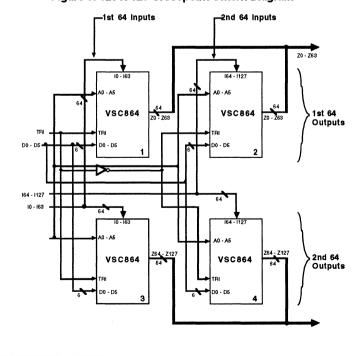

| Expandability                    | 515 |

| Ordering Information             |     |

| -                                |     |

# Table of Contents

# PACKAGING

| Introduction                                                | 517 |

|-------------------------------------------------------------|-----|

| Trim and Form Equipment                                     |     |

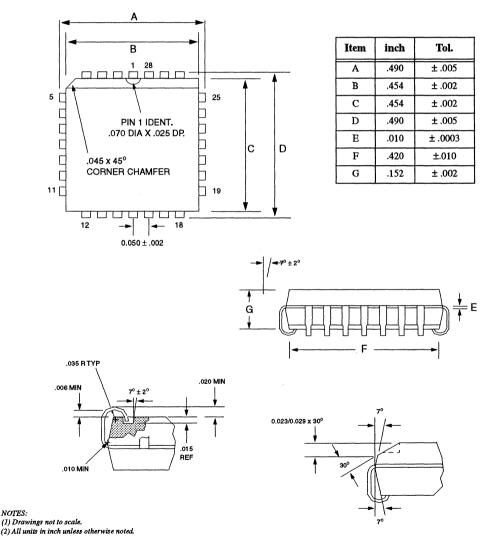

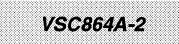

| 28 Pin Ceramic LDCC Package Dimensions                      |     |

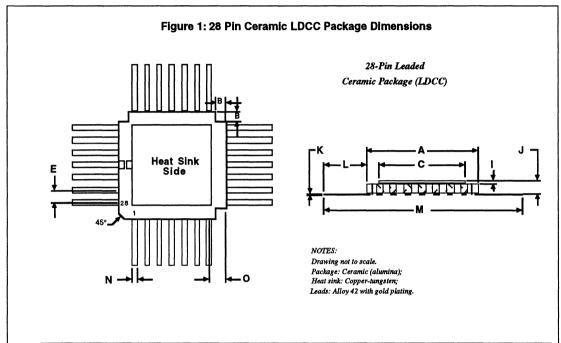

| 28 PLCC Package Dimensions (JEDEC Format)                   |     |

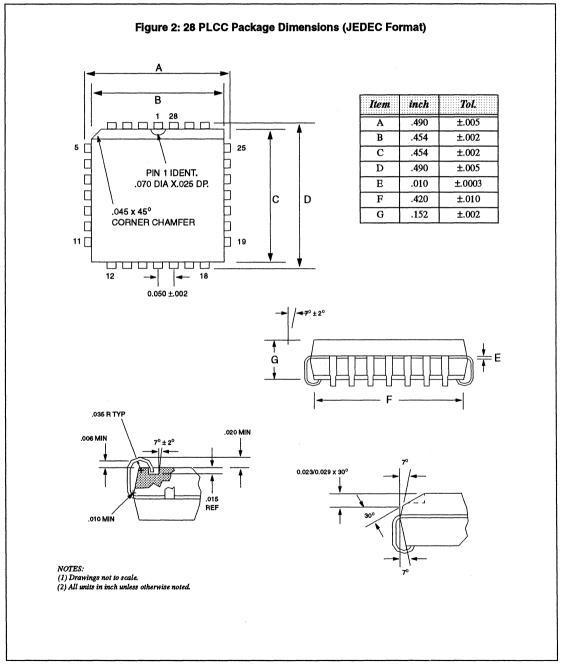

| 44 Pin PQFP Package Dimensions                              |     |

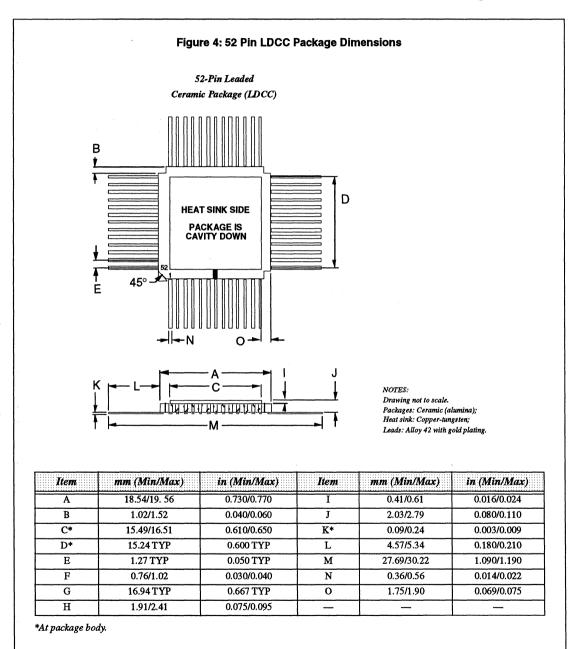

| 52 Pin LDCC Package Dimensions                              |     |

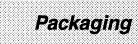

| 52 Pin PQFP Package Dimensions                              |     |

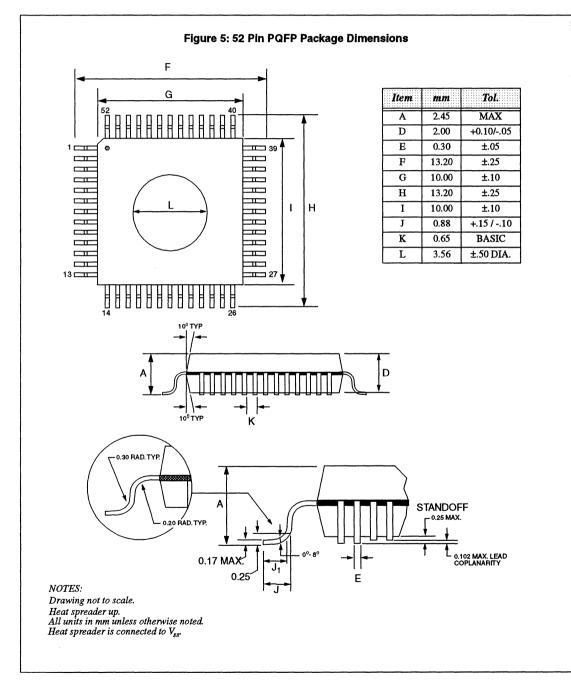

| 64 Pin PQFP Package Dimensions                              |     |

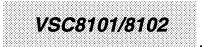

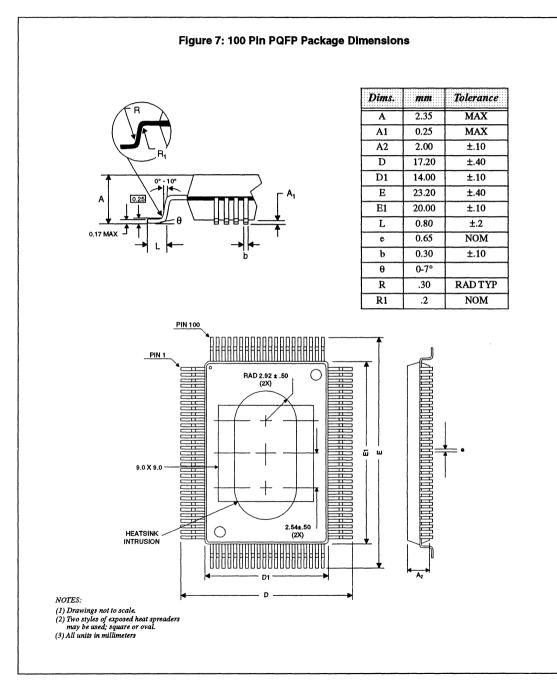

| 100 Pin PQFP Package Dimensions                             |     |

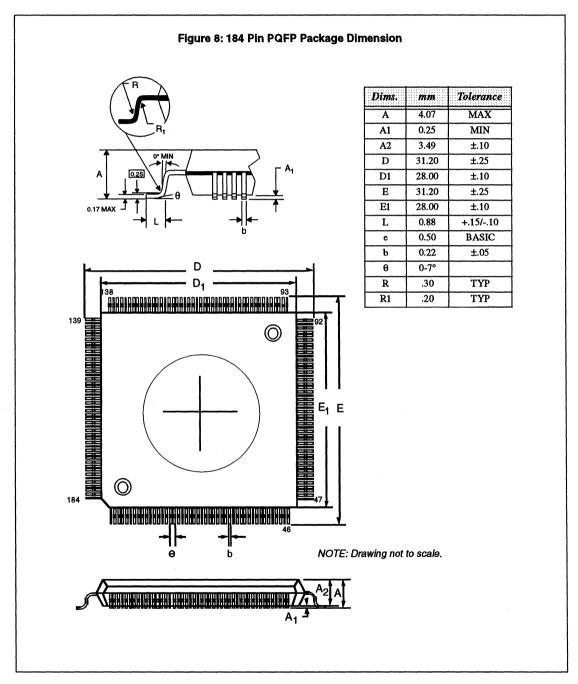

| 184 Pin PQFP Package Dimensions                             |     |

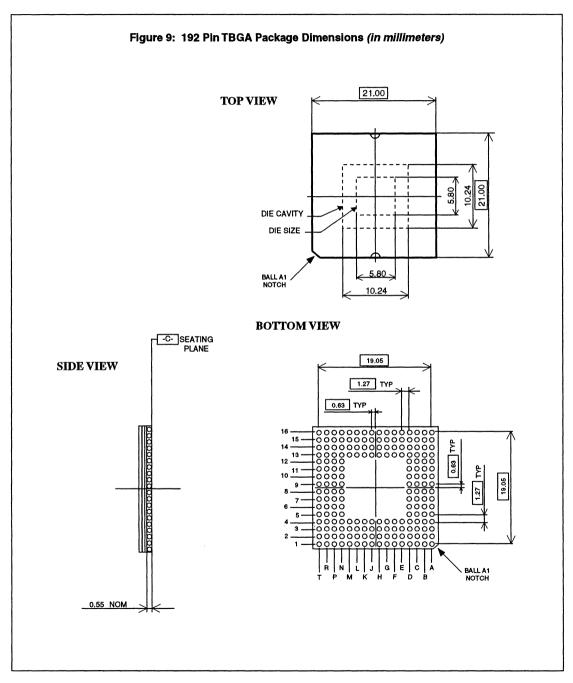

| 192 Pin TBGA Package Dimensions                             |     |

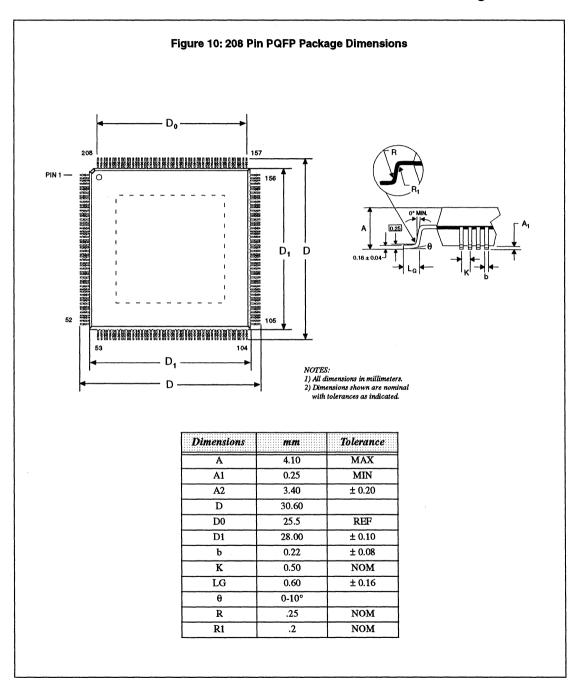

| 208 Pin PQFP Package Dimensions                             |     |

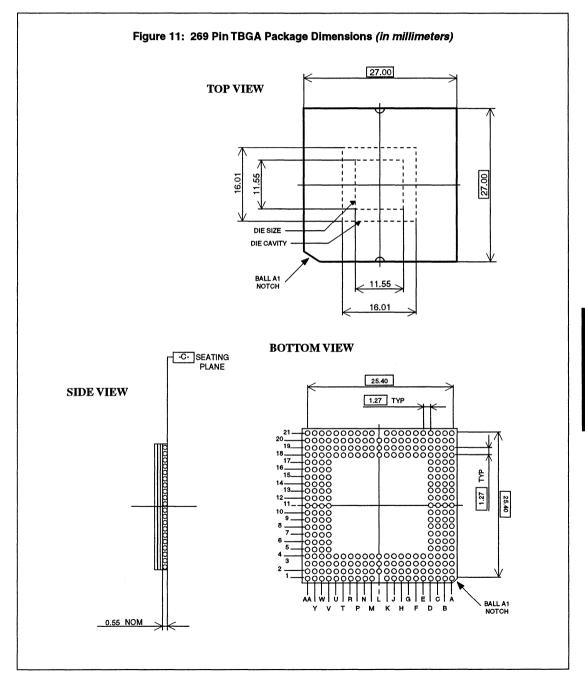

| 269 Pin TBGA Package Dimensions                             |     |

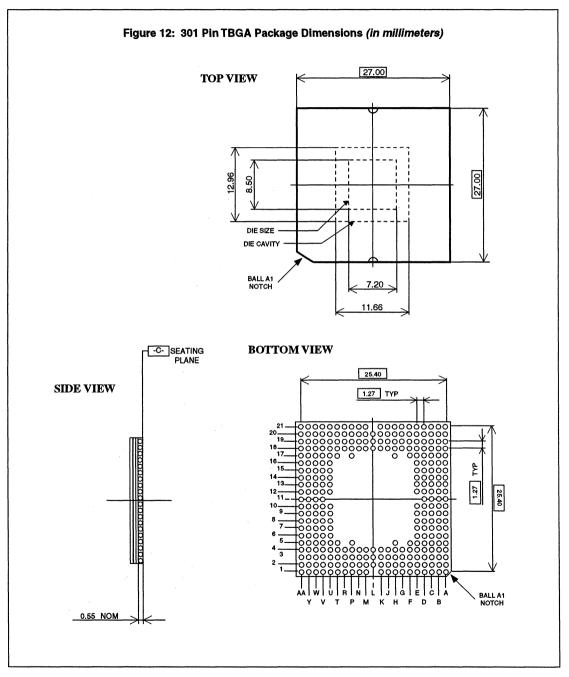

| 301 Pin TBGA Package Dimensions                             |     |

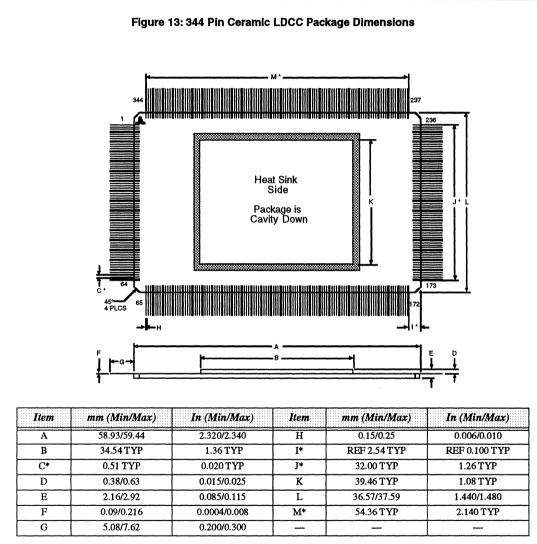

| 344 Pin Ceramic LDCC Package Dimensions                     |     |

| Mechanical Package Specifications (5.6 mm Package)          |     |

| Mechanical Package Specifications (TO-46 Ball Lens Package) |     |

| VSC8071/VSC8072 Module                                      |     |

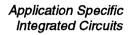

# ASICS

| ASIC Product Summary | 535 |

|----------------------|-----|

| ASICs Overview       | 537 |

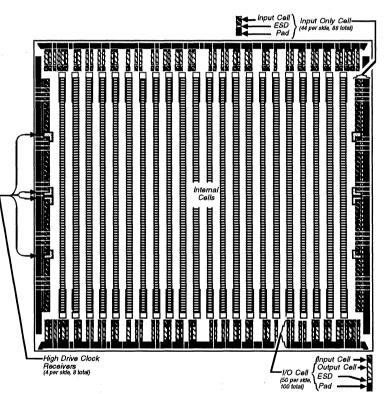

### GLX, FX, SCFX Masterslice Arrays

| Features          | 541 |

|-------------------|-----|

| Description       | 541 |

| Masterslice Array |     |

# **GLX** Arrays

| Features                |  |

|-------------------------|--|

| Description             |  |

| Array Specific Features |  |

# FX Arrays

| Features                |     |

|-------------------------|-----|

| Description             |     |

| Array Specific Features | 545 |

# 1996 Communications Products Data Book

# Table of Contents

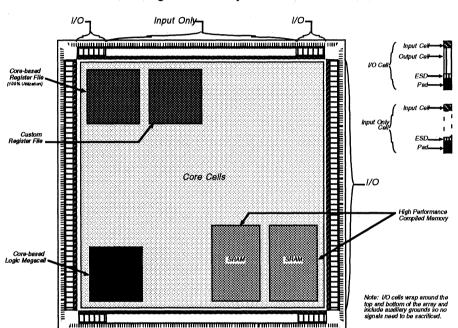

| VIPER Arrays                                                              |

|---------------------------------------------------------------------------|

| Features                                                                  |

| Description                                                               |

| Array Specific Features                                                   |

|                                                                           |

| SCFX Arrays                                                               |

| Features                                                                  |

| Description                                                               |

| Array Specific Features                                                   |

|                                                                           |

| FURY Arrays                                                               |

| Features                                                                  |

| Description                                                               |

| Array Specific Features                                                   |

| Allay Specific Features                                                   |

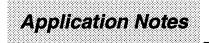

| APPLICATION NOTES                                                         |

|                                                                           |

| Application Note 1 "Printed Circuit Board Considerations"                 |

| Introduction                                                              |

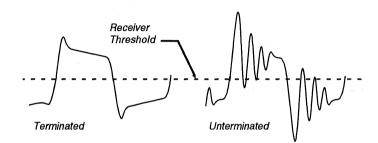

| Why Are Properly Terminated Transmission Lines Needed?                    |

| Transmission Line Theory                                                  |

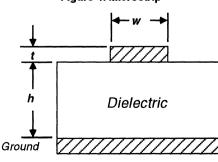

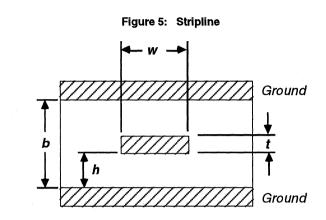

| Practical Transmission Lines                                              |

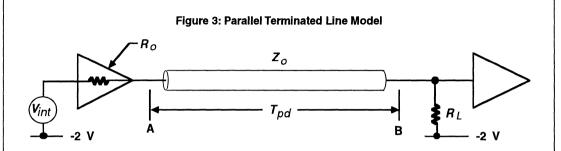

| Parallel Terminated Lines                                                 |

| Power Distribution                                                        |

|                                                                           |

| Application Note 2 "Interfacing GaAs Products to ECL/TTL"                 |

| Introduction                                                              |

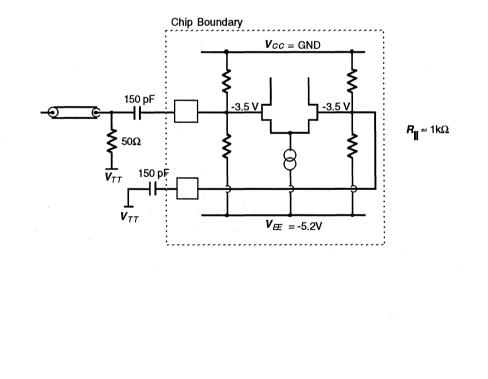

| ECL I/O                                                                   |

| TTL I/O                                                                   |

| DC Specifications                                                         |

| Absolute Maximum Ratings                                                  |

| Recommended Operating Condition                                           |

| 1 5                                                                       |

| Application Note 4 "Generation of a -2 Volt Supply from a +5 Volt Supply" |

| Description                                                               |

| Flyback Converter Configuration                                           |

|                                                                           |

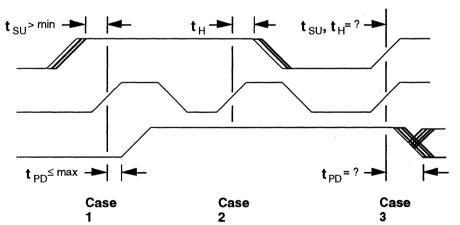

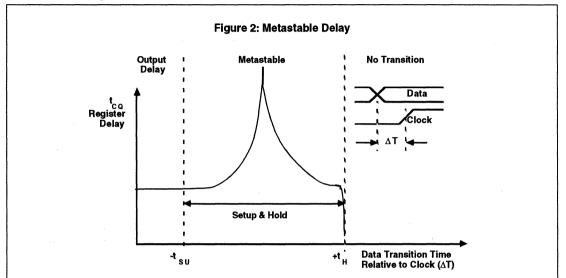

| Application Note 6 "Metastable Behavior of GaAs DCFL Registers"           |

| Introduction                                                              |

| Metastability Theory                                                      |

|                                                                           |

General

# Table of Contents

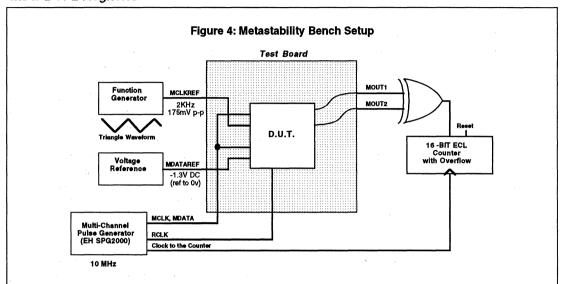

| Metastability Characterization                                               |          |

|------------------------------------------------------------------------------|----------|

| Test Setup                                                                   |          |

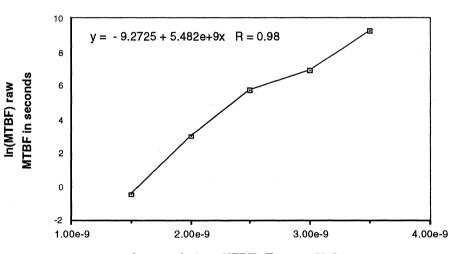

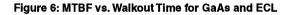

| Test Results                                                                 |          |

| Synchronizer Applications                                                    |          |

| Conclusions                                                                  |          |

|                                                                              |          |

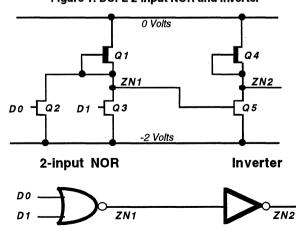

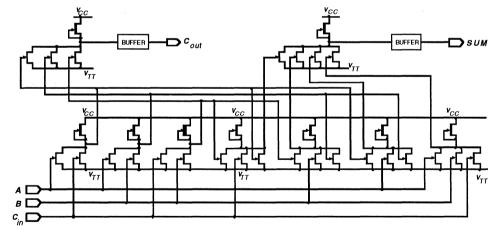

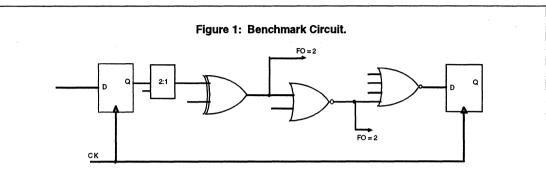

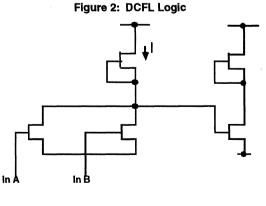

| Application Note 7 "GaAs DCFL ASIC Design"                                   |          |

| Introduction                                                                 |          |

| What is Direct-Coupled FET Logic?                                            |          |

| Buffering Tradeoffs                                                          |          |

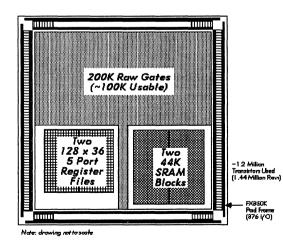

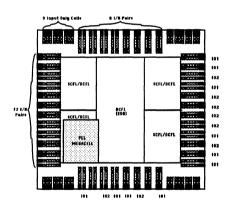

| FURY Gate Array Architecture                                                 |          |

| FX Array Architecture                                                        |          |

| System Considerations                                                        |          |

| Conclusion                                                                   |          |

|                                                                              |          |

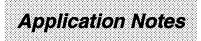

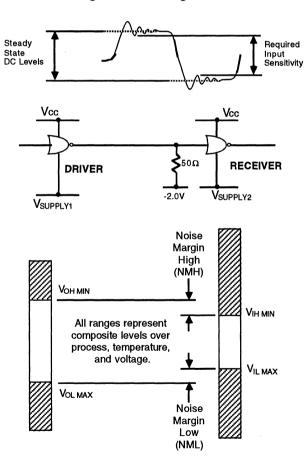

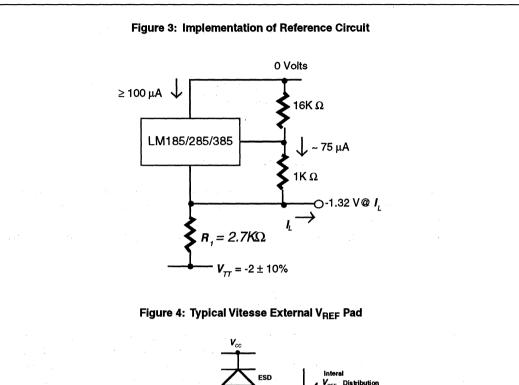

| Application Note 8 "Generating an External ECL Input Reference"              |          |

| Introduction                                                                 |          |

| Reference Circuit Description                                                |          |

|                                                                              |          |

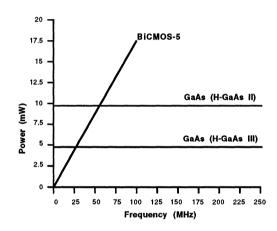

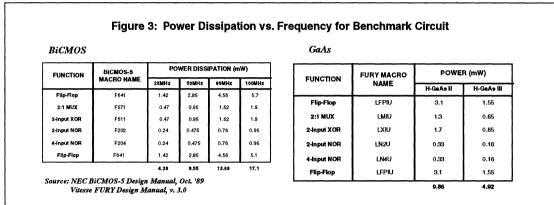

| Application Note 10 "Power Dissipation: BiCMOS vs GaAs"                      |          |

| Introduction                                                                 |          |

| Power Calculations for BiCMOS                                                | 591      |

| Power Calculation for DCFL GaAs Circuits                                     |          |

| Benchmark Circuit                                                            |          |

| Conclusion                                                                   |          |

|                                                                              |          |

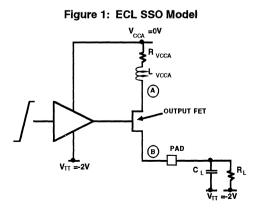

| Application Note 11 "The Effects of Simultaneously Switching Outputs in GaAs | Devices" |

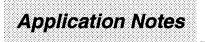

| Introduction                                                                 | 597      |

| Statement of Problem                                                         | 597      |

| Electrical Effects of Output Switching: A Basic Model                        | 597      |

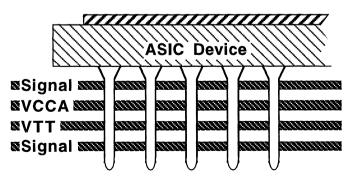

| ASIC Device and Package Features to Alleviate SSO Problems                   |          |

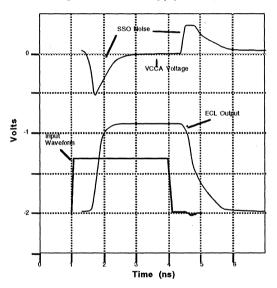

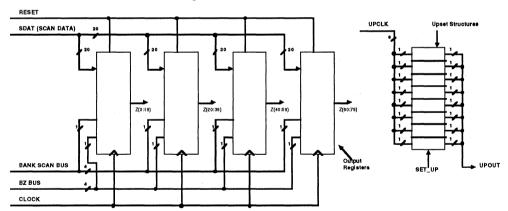

| SSO Test Chip Description                                                    |          |

| SSO Test Results                                                             | 600      |

| Simultaneous Switching Noise                                                 | 600      |

| System Design Recommendations for Minimizing SSO Effects                     | 601      |

|                                                                              |          |

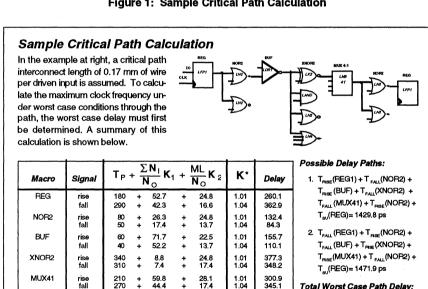

| Application Note 13 "Calculating Path Delays in FX Gate Arrays"              |          |

| Introduction                                                                 |          |

| Delay Equation                                                               | 603      |

| Sample Critical Path Calculation                                             |          |

| -                                                                            |          |

# Table of Contents

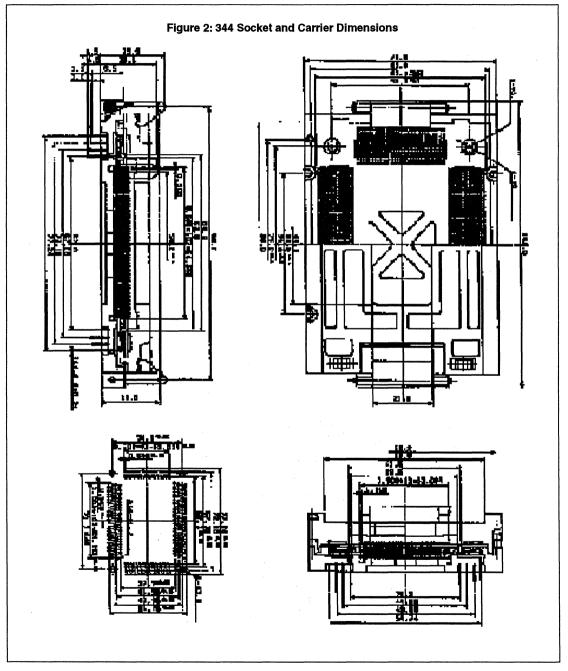

| Application Note 14 "Working With the 344 Pin LDCC Package"                 |

|-----------------------------------------------------------------------------|

| Introduction                                                                |

| Procedures for Attachment to a Printed Circuit Board                        |

| Package Thermal Properties                                                  |

| Trim And Form Equipment                                                     |

| Conclusion                                                                  |

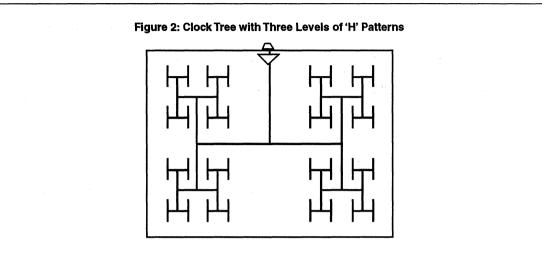

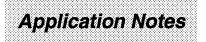

| Application Note 17 "Implementing the Fixed Clock Tree in FX Gate Arrays"   |

| Introduction                                                                |

| Background                                                                  |

| Clock Tree Architectures                                                    |

| Vitesse Clock Trees                                                         |

| CAD Interface                                                               |

| Custom Masterslices                                                         |

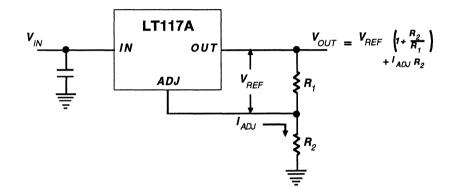

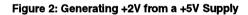

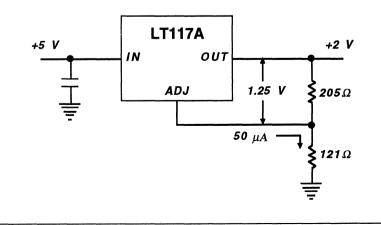

| Application Note 18 "Generation of +2V or +3.3V Supplies from a +5V Supply" |

| Generating +2V or +3.3V with the LT117A                                     |

| Generating +2V from a +5V Supply                                            |

| Generating +3.3V from a +5V Supply                                          |

| Protection Diodes                                                           |

| Application Note 20 "Plastic Packaging Moisture Sensitivity Levels"         |

| Levels of Moisture Sensitivity                                              |

| Handling of Devices at Customer Site                                        |

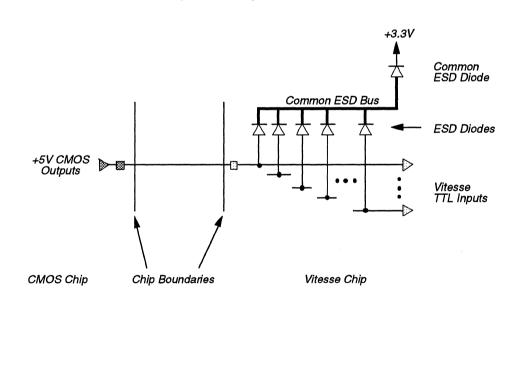

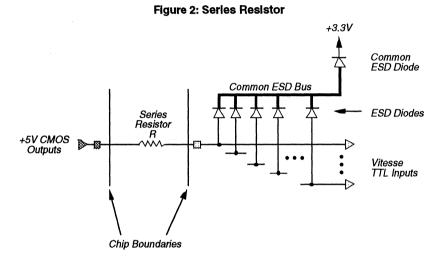

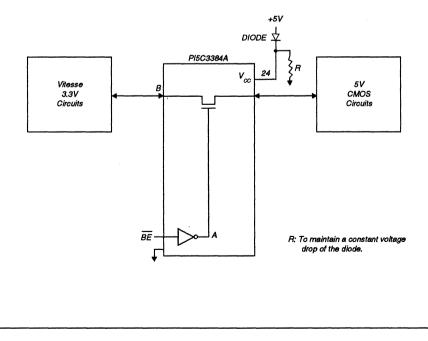

| Application Note 22 "Interfacing Vitesse +3.3V TTL with +5V CMOS"           |

| Introduction                                                                |

| Solution #1, Series Resistor                                                |

| Solution #2 Bus Switch                                                      |

| Conclusion                                                                  |

|                                                                             |

| Application Note 24 "Information Sources for Fibre Channel"                 |

| Summary of Information Sources for Fibre Channel                            |

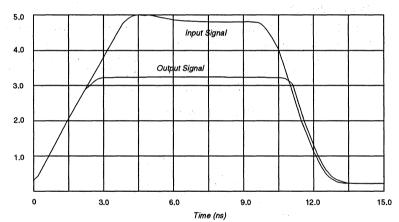

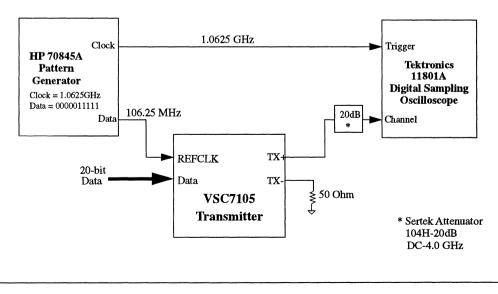

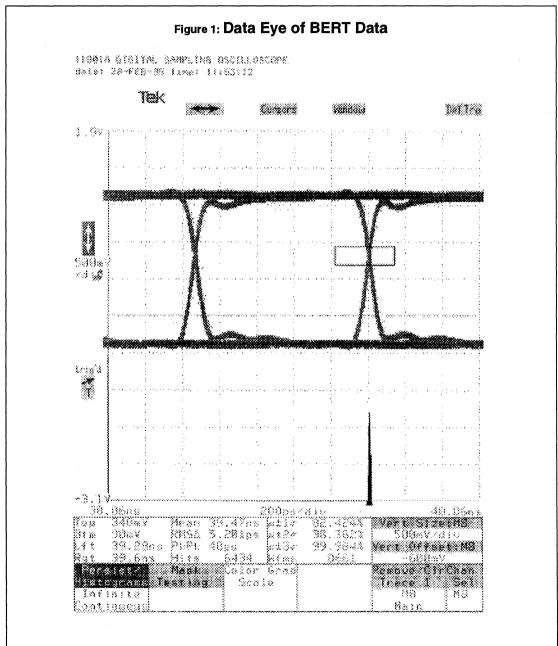

| Application Note 25 "Measuring Eye Diagrams on the VSC7105 Transmitter"     |

| Eye Diagram Test Setup                                                      |

| Data Eye of BERT Data                                                       |

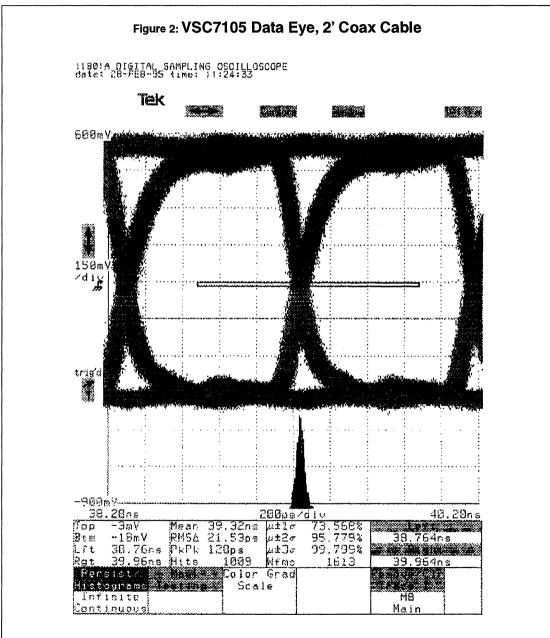

| VSC7105 Data Eye, 2' Coax Cable                                             |

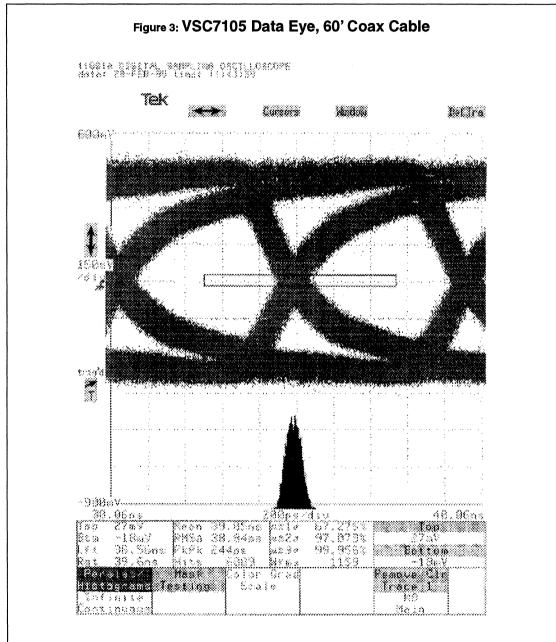

| VSC7105 Data Eye, 60' Coax Cable                                            |

# VITESSE

# Introduction

This 1996 Communications Product Data Book contains the latest information on the entire range of communications products and services from Vitesse Semiconductor Corporation. We are pleased to present you with this compilation of information in one convenient source. This book includes complete product data sheets and product previews for Vitesse communication devices. Supplementary information regarding packaging and applications is also included.

Vitesse Semiconductor Corporation is a proven leader in the design and manufacture of high performance, mixed signal, digital LSI and VLSI GaAs ICs. The company, which was founded in 1984, has developed a revolutionary process, allowing it to deliver affordable, very large scale (VLSI) gallium arsenide (GaAs) ICs.

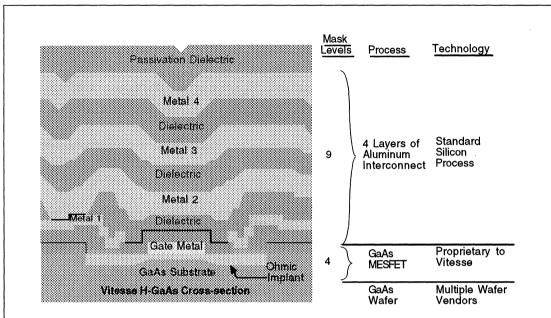

The key to success for Vitesse has been the development of mixed signal devices and the unique H-GaAs manufacturing technology. Rather than developing a process based on existing GaAs microwave transistor technology, Vitesse chose to develop an entirely new process based on proven silicon MOS manufacturing methods. This strategy solved two major problems which had prevented GaAs ICs from receiving wide acceptance: low complexity and high cost. The result is a high yielding, proprietary process which produces circuits with a speed-power product unmatched by any other IC manufacturing technology.

The markets for Vitesse's products include applications such as computers, communications, automated test equipment, instrumentation, and general military/aerospace. In order to compete in these markets, Vitesse chose to make its products look and feel exactly like silicon products, but with significant improvements in speed, complexity, and reduced power dissipation. The combination of GaAs performance and silicon MOS manufacturing techniques is the key Vitesse advantage. The results are families of IC products that set new performance standards at prices competitive with high performance silicon products.

Vitesse is committed to providing the highest performance integrated circuits in the world. The Vitesse manufacturing process has been designed to realize this objective with a combination of process innovations

#### Introduction

and proven MOS manufacturing techniques. The distinguishing features of the Vitesse process are: 1) excellent transistor electrical parameter control, 2) unprecedented manufacturing yields on VLSI complexity GaAs circuits, and 3) process simplicity and fast cycle time.

Vitesse has pioneered the now well-accepted concept of designing GaAs products that are compatible with existing silicon technologies. Input/output levels and power supplies found in TTL, ECL and CMOS are standard in the entire family of Vitesse products.

#### Datacommunications

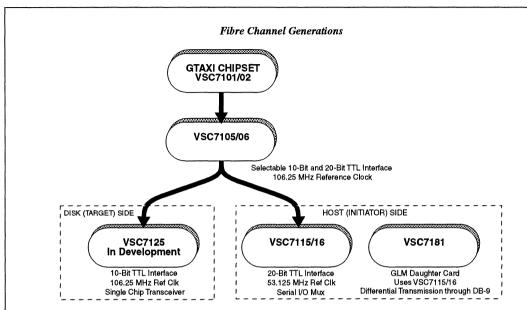

In 1992 Vitesse introduced the G-TAXI chipset, the first generation general purpose serial link for both Fibre Channel and proprietary protocols at baud rates up to 1.25 Gb/s. This first generation chipset included a 32/40 bit TTL system interface bus, ANSI 8B/10B encoding and decoding, and completely integrated on-chip PLL clock generation and clock and data recovery circuitry.

In 1993 the second generation Fibre Channel products were introduced. The +3.3 volt supply VSC7105 and VSC7106 transmitter and receiver chipset and the VSC7107 CMOS encoder/decoder offered the functionality of the G-TAXI chipset at one half the power.

In 1995 Vitesse minimizes power in Fibre Channel designs with the introduction of the VSC7125 Fibre Channel Transceiver. Constructed using the H-GaAs IV process, this device is a single chip fully integrated Fibre Channel transceiver designed for high volume applications. The VSC7125 is the product of extensive experience in high speed PLL based clock generation, and clock and data recovery, coupled with the exceptional speed-power capabilities of the Vitesse H-GaAs IV process. In three generations, Vitesse has lowered the power required for the transmitter and receiver functions from 6.5 W to 650 mW, and package requirements from two ceramic packages to a single 10 mm PQFP.

#### Telecommunications

Vitesse's VS8000 family of telecommunications ICs address the needs of the newest generation of telecommunications systems incorporating data rates up to 10 Gb/s. These standard multiplexer/demultiplexer chipsets are suitable for proprietary or Synchronous Optical Network (SONET) STS-3 through STS-192 applications and are available in 4, 8 and 16 channel configurations. These products feature very low power dissipation and ECL compatibility.

In addition to the VS8000 family of multiplexer/demultiplexer chipsets, Vitesse offers a family of crosspoint switches which are ideal for high speed telecommunications data distribution, computer network and multiprocessor switching, video switching, and test equipment.

### ASICs

Summary information on Vitesse ASIC products is included herein as well. Detailed specifications on Vitesse's complete line of ASICs are available in a separate ASIC Product Data Book. Contact your local Vitesse Sales office or Vitesse headquarters at (805) 388-3700 to obtain a copy of this data book.

1996 Communications

Products Data Book

# Introduction

# **Document Designations**

#### **Product Preview**

This is usually a one-page document describing a product to give customers a general idea of the product's functionality and use.

#### **Target Specification**

This document contains information about a proposed product during its design phase of development and is subject to change without notice at any time. All features and specifications are design goals only. Please contact Vitesse Semiconductor to obtain the latest product status and most recent version of this specification.

#### **Advanced Product Information**

This document contains information about a new product during its fabrication or early sampling phase of development. The information in this document is based on design targets, simulation results or early prototype test results. Characteristic data and other specifications are subject to change without notice.

#### **Preliminary Data Sheet**

This document contains information about a product during its preproduction phase of development. The information in this document is based on test results and initial product characterization. Characteristic data and other specifications are subject to change without notice

#### **Data Sheet**

This data sheet evolves from the Preliminary data sheet. It is a result of test information collected from fully characterized devices. This is a document used for a product which is mature enough to be considered "In Production". All specs are mature and verified by testing on multiple lots or product characterization.

Vitesse Semiconductor Corporation reserves the right to make changes in its products' specifications or other information at any time without prior notice. Therefore the reader is cautioned to confirm that the datasheet is current prior to placing any orders. The company assumes no responsibility for any circuitry described other that circuitry entirely embodied in a Vitesse product.

Introduction

# Vitesse U.S. Sales Offices

#### **Corporate Headquarters**

741 Calle Plano Camarillo, CA 93012 TEL: (805) 388-7501 FAX: (805) 388-7565

#### National Sales Office

488 Schooley's Mt. Rd. Hastings Commons, Bldg. 1B Hackettstown, NJ 07840 TEL: (908) 979-0990 FAX: (908) 979-0992

#### Northwestern Sales Office

470 Mercury Drive Sunnyvale, CA 94086 TEL: (408) 730-3657 FAX: (408) 245-9406

#### **Corporate International Office**

6994 El Camino Real , #205A La Costa, CA 92009 TEL: (619) 431-0085 FAX: (619) 431-0714

#### North Central Sales Office

108 Rosedale Towers 1700 West Highway 36 St. Paul, MN 55113 TEL: (612) 639-1460 FAX: (612) 639-1469

#### Northeastern Sales Office

70 Walnut Street Wellesley, MA 02181 TEL: (617) 239-8075 FAX: (617) 239-8069

#### South Central Sales Office

833 East Arapaho #112 Richardson, TX 75081 TEL: (214) 669-9797 FAX: (214) 669-2266

#### Southwestern Sales Office

10850 Wilshire Blvd., Ste. 820 Los Angeles, CA 90024 TEL: (310) 441-1864 FAX: (310) 441-1784

# Vitesse European Sales Office

#### Strategy Center

10, rue des Gaudines 78105 Saint Germain en Laye, France TEL: 011-33-1-3975-6310 FAX: 011-33-1-3975-2062

1996 Communications

Products Data Book

# 1996 Communications Products Data Book

# **General Information**

# U.S. Representative Offices

#### Advanced Technical Marketing, Inc.

4900 SW Griffith Drive, #155 Beaverton, OR 97005 TEL: (503) 643-8307 FAX: (503) 643-4364

8521 154th Avenue NE Redmond, WA 98052 TEL: (206) 869-7636 FAX: (206) 869-9841

#### Assoc. Electronic Marketing, Inc.

11520 St. Charles Rock Rd. #131 Bridgeton, MO 63044 TEL: 314/298/9900 FAX: 314/298-8660

4001 Shady Oak Drive Marion, IA 52302 TEL: 319/377-1129 FAX :319/377-1539

9716 Rosehill Lenexa, KS 66215 TEL: 913/888-0022 FAX: 913/888-4848

#### Avtek, Associates

10632 Little Patuxent Pkwy #435 Columbia, MD 21044 TEL: (410) 740-5100 FAX: (410) 740-5103

#### **Eagle Technical Sales**

1801 G Hicks Road Rolling Meadows, IL 60008 TEL: (847) 991-0700 FAX: (847) 991-0714

#### Fahrner-Miller Associates, Inc.

1885 De La Cruz Blvd., #200 Santa Clara, CA 95050 TEL: (408) 727-9800 FAX: (408) 496-6952

5110 Reservation Road Placerville, CA 95667 TEL: (916) 677-5838 FAX: (916) 677-6226

#### **Giesting & Associates**

2854 Blue Rock Road P.O. Box 39398 Cincinnati, Ohio 45239 TEL: (513) 385-1105 FAX: (513) 385-5069

34441 Eight Mile Rd Suite 1B Livonia, MI 48152 TEL: (810) 478-8106 FAX: (810) 477-6908

339 Arrowhead Springs Lane Versailles, KY 40383 TEL: (606) 873-2330 FAX: (606) 873-6233

370 Ridgepoint Drive Carmel, IN 46032 TEL: (317) 844-5222 FAX: (317) 844-5861

471 Walnut Street Pittsburgh, PA 15238 TEL: (412) 828 3553 FAX: (412) 828-6160

1996 Communications

Products Data Book

# **General Information**

#### Integrated Technology, Inc.

182 Main Street Salem, NH 03079 TEL: (603) 898-6333 FAX: (603) 898-6895

#### Leading Concept Technologies

3700 Campus Drive, #104 Newport Beach, CA 92660 TEL: (714) 851-0654 FAX: (714) 851-1004

#### Parallax Sales, Inc.

734 Walt Whitman Road Melville, NY 11747 TEL: (516) 351-1000 FAX: (516) 351-1606

#### SC Cubed

4300 North Miller Road, #103 Scottsdale, AZ 85251 TEL: (602) 946-6321 FAX: (602) 946-0028

6390 Greenwich Dr. #180 San Diego, CA 92122 TEL: (619) 546-3730 FAX: (619) 546-3731

#### S-J Associates, Inc

15 Coventry Lane Naugatuck, CT 06770 TEL: (203) 723-4707 FAX: (203) 723-1629

#### Technology Representatives, Inc.

17311 Dallas Pkwy, Ste. 140 Dallas, TX 75248 TEL: (214) 713-9027 FAX: (214) 931-6159

#### Thorson Rocky Mountain, Inc.

7108 "D" South Alton Way, Suite A Englewood, CO 80112 TEL: (303) 773-6300 FAX: (303) 773-6302

5505 South 900 East, Suite #140 Salt Lake City, UT 84117 TEL: (801) 264-9665 FAX: (801) 264-9881

#### **Tronex Vision & Technology Solutions**

PO Box 1225 1004 Howell Court Duluth, GA 30136 TEL: (770) 476-5494 FAX: (770) 476-4423

5840 Faringdon Place Raleigh, NC 27609 TEL: (919) 954-7000 FAX: (919) 790-8200

4039 Abingdon Road Charlotte, NC 28211 TEL: (704) 362-1066 FAX: (704) 362-1064

652 Johnston Street S.E. Decatur, AL 35601 . TEL: (205) 355-2120 FAX: (205) 355-7717

# International Representatives and Distributors

1996 Communications Products Data Book

#### **AUSTRALIA & NEW ZEALAND**

#### Logic 4 Australasia

50 King William Road Goodwood S. Australia 5034 TEL: 011-61-8-373-2811 FAX: 011-61-8-373-2286

Unit 6, 23-25 Wadhurst Dug Boronia, Vic. 3155, Australia TEL: 011-61-3-887-3800 FAX: 011-61-3-887-3811

#### CANADA

#### J-Squared Technologies, Inc.

300 March Road #501 Kanata, Ontario K2K 2E2 (Ottawa) TEL: 613/592-9540 FAX: 613/592-7051

3395 American Drive Bldg 306 #2 Mississauga, Ontario L4V 1T4 (Toronto) TEL: 905/672-2030 FAX: 905/672-2047

100 Alexis Nihon, Ste.960 Ville St. Laurent, Quebec H4M 2P5 (Montreal) TEL: 514/747-1211 FAX: 514/747-9824

#### FRANCE

#### MISIL Technologies 2 Rue De La Couture

B.P. Silic 301 Rungis Cedex, France 94588 TEL: 011-33 1 45 60 0021 FAX: 011 33 1 45 60 0186

#### GERMANY

#### Hy-Line GmbH

Inselkamnerstrasse 10 82008 Unterhaching, Germany TEL: 011-49-89-614-50340 FAX: 011-49-89-614-50350

#### ISRAEL

#### AST (Advanced Semiconductor Technology)

47/7 Golomb Street Herzlia, Israel 46305 TEL: 011-972-9-583355 FAX: 011-972-9-505525

#### JAPAN

#### H.Y. Associates Co., Ltd.

3-1-10, Sekimachikita, Nerima-Ku Tokyo 177 Japan TEL: 011-81-33-929-7111 FAX: 011-81-33-928-0301

# KOREA

#### Beaver International, Inc.

3601 Deauville Court Calabasas, CA 91302 TEL: (818) 591-0356 FAX: (818) 591-0753

#### SINGAPORE - HQ

#### Serial System (Singapore)

11Jalan Mesin #06-00 Standard Industrial Building Singapore 1336 TEL: 011-65-2800-200 FAX: 011-65-286-1812/286-6723

#### SWEDEN

#### IE Komponenter AB

Box 113, S-161 11 Bromma, Sweden TEL: 011-46-880-4685 FAX: 011-46-826-2286

### TAIWAN

1996 Communications

Products Data Book

#### Tamarack Microelectronics

16 Fl, No.1, Fu-Hsing N. Road Taipei, Taiwan R.O.C. TEL: 011-886-02-772-7400 FAX: 011-886-02-776-0545

#### UNITED KINGDOM

#### Broadband Technology 2000 Ltd.

Unit 2 Grafton Street High Wycombe Buckinghamshire HP123AJ, UK TEL: 011-44-149-447-4800 FAX: 011-44-149-444-3100

# **Product Summary**

| Product Family | Description                                                                                                                                                                                       | Features                                                                                                                                                                                                                                                                                                            |

|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VSC7105/7106   | 1.0625 Gbit/sec ANSI X3T11 compatible<br>Fibre Channel transmitter and receiver<br>chipset. Suitable for both copper and optical<br>link applications.                                            | VSC7105<br>1.0625 Gbit/sec Fibre Channel Transmitter<br>Integrated PLL for Clock Multiplication<br>VSC7106<br>1.0625 Gbit/sec Fibre Channel Receiver<br>Integrated PLL-Based Clock Recovery Unit<br>Both<br>106MHz Reference Clock<br>Selectable 10-bit or 20-bit TTL Parallel Data Interface<br>Single 3.3V Supply |

| VSC7107        | Fibre Channel ENDEC with FC-1 link<br>functions and FC-2 framing assistance<br>functions. Suitable for custom Fibre Channel<br>links to sustain up to 200 MByte/sec duplex<br>data communication. | 8B/10B Encoding<br>32-Bit Synchronous FIFO Data Interface<br>CRC Calculation and Checking<br>Fibre Channel Ordered Sets Framing Assist with<br>CMND Bus<br>Automatic IDLE Generation<br>Link Error Reporting                                                                                                        |

| VSC7115/7116   | 1.0625 Gbit/sec ANSI X3T11 compatible<br>Fibre Channel transmitter and receiver<br>chipset. GLM compatible interface.                                                                             | VSC7115<br>1.0625 Gbit/sec Fibre Channel Transmitter<br>Integrated PLL for Clock Multiplication<br>VSC7116<br>1.0625 Gbit/sec Fibre Channel Receiver<br>Integrated PLL-Based Clock Recovery Unit<br>Both<br>53 MHz Reference Clock<br>20-bit TTL Compatible Parallel Data Interface<br>Single 3.3V Supply           |

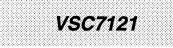

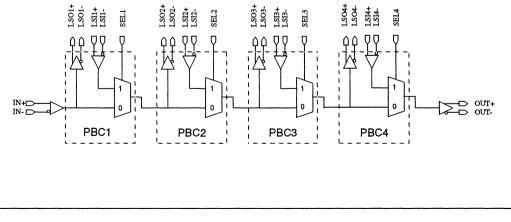

| VSC7120        | 1.0625 Gbit/sec Fibre Channel Repeater for<br>use in disk arrays and FC-AL Hubs.                                                                                                                  | Integrated PLL-Based Clock Recovery Unit<br>Embedded Port Bypass Circuit<br>Signal Detect Unit for Invalid 8B/10B Characters and<br>Oscillation Detection                                                                                                                                                           |

| VSC7121        | Quad Port Bypass Circuit cascaded for use in<br>Fibre Channel Arbitrated Loop disk arrays.                                                                                                        | Up to 1.0625 Gbit/sec Operation<br>Four Port Bypass Circuits<br>Low Power Consumption<br>Low Jitter Accumulation<br>Cascadable for Larger Loops                                                                                                                                                                     |

| VSC7125        | 1.0625 Gbit/sec ANSI X3T11 10-Bit Fibre<br>Channel transceiver.                                                                                                                                   | 10-bit Study Group TTL Compatible Parallel Interface<br>Integrated Clock Multiplier and Clock Recovery Unit.<br>106 MHz Reference Clock and Transmit Byte Clock<br>Single 3.3V Supply<br>650 mW Power                                                                                                               |

| VSC7126        | 1.0625 Gbit/sec ANSI 20-bit Fibre Channel<br>Transceiver.                                                                                                                                         | GLM Compatible Single Chip Transceiver<br>53 MHz Reference Clock<br>Single 3.3V Supply<br>750 mW Power                                                                                                                                                                                                              |

# **Product Summary**

| Product Family                | Description                                                                           | Features                                                                                                                                                                                                                                                                                                                                                                                                                              |

|-------------------------------|---------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VSC7135                       | 1.25 Gbit/sec Transceiver for Gigabit<br>Ethernet.                                    | Single Chip Transceiver<br>125 MHz Reference Clock<br>Single 3.3V Supply<br>780 mW Power                                                                                                                                                                                                                                                                                                                                              |

| VSC7181                       | 1.0625 Gbit/sec ANSI X3T11 and FCSI<br>GLM compliant copper gigabaud link<br>module.  | 1.0625 Gbit/sec Copper GLM Daughtercard<br>ANSI Standard 9-pin D-Shell Serial Connector<br>20-bit TTL Compatible Parallel Interface<br>80-pin Samtec Parallel Connector<br>Single 5V Supply                                                                                                                                                                                                                                           |

| VSC7181EV                     | 1.0625 Gbit/sec Fibre Channel Copper<br>Gigabaud Link Module Evaluation Kit.          | Easy to Use Kit Containing:<br>Two (2) VSC7181 CuGLM<br>One (1) 5m Gore Fibre Channel Duplex Cable<br>Assembly with DB-9 Connector<br>One (1) Female Loopback Adaptor<br>One (1) Male Loopback Adaptor                                                                                                                                                                                                                                |

| VSC7201A                      | 1 GByte/Sec SCI Compliant Link Controller.                                            | Conforms to IEEE SCI Standards: IEEE Standard<br>1596-1992<br>Sends and Receives SCI Data in 2ns for 1GByte/s<br>Data Rate<br>High Speed Link Interface Conforms to Low Voltage<br>Differential I/O Standard (IEEE P1596.3)<br>64-bit Bi-Directional GTL System Interface<br>+3.3V and +2V Power Supplies Required<br>269 Tape Ball Grid Array Package (TBGA - 50<br>mil centers)<br>IEEE Std 1149.1 Test Access Port for Diagnostics |

| VSC7203                       | 1 GByte/s SCI Compliant Switch Node<br>Bypass Circuit.                                | 2-port Switch Capable of Passing SCI Packets<br>Multiplexers Allow Bypassing Around any Port for<br>Faulty Node Isolation<br>Sends and Receives SCI Symbols every 2ns for 1<br>GByte/s Data Rate per Port<br>+3.3V and +2V Power Supplies<br>301 BGA Package (50 mil spacing, 27mm/side)<br>IEEE Std 1149.1 Test Access Port for Diagnostic and<br>Boundary Scan                                                                      |

| VSC7802<br>VSC7805<br>VSC7810 | Fibre Channel short-wave optical detectors with integrated transimpedance amplifiers. | Three Products Supporting 266, 531, and 1063 Mbit/sec<br>Data Rates.<br>770 - 850nm Detectors<br>Integrated AGC                                                                                                                                                                                                                                                                                                                       |

# Fibre Channel Overview

Fibre Channel is an emerging standard for high speed, serial data communication developed by the ANSI X3T11 Technical Committee consisting of a wide breadth of the electronics industry including representatives from optical components, electrical connectors, semiconductor components, disk drive, computer systems, and network systems companies.

Fibre Channel's heritage draws from the experience of the SCSI, ESCON, HIPPI, and FDDI standards community as all were part of the original ANSI X3T9 Technical Committee. Fibre Channel provides a unifying networked, high performance I/O channel by which SCSI, IP, ESCON, and other protocols may be mapped into one interconnect to tie together supercomputers, mainframes, servers, workstations, and peripherals.

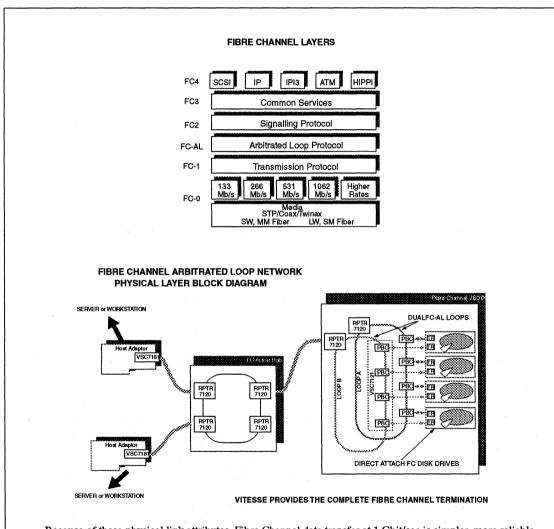

Fibre Channel is a layered transport protocol. It incorporates a physical layer transport definition (FC-0 and FC-1) and a framing and flow control definition (FC-2) with a common services layer (FC-3) and an upper layer for multi-protocol mapping onto Fibre Channel (FC-4). Refer to Fibre Channel Layers diagram.

Fibre Channel's strengths are many. Two unique strengths that differentiates Fibre Channel from other serial interconnects lies in its robust physical layer (FC-0 and FC-1) and it's support of a low-cost, arbitrated loop topology (FC-AL).

Fibre Channel's robust physical layer is based on the use of serial, point to point connections and the use of the 8B/10B encoding scheme developed and patented by IBM and licensed for use by Fibre Channel developers.

Serial, point to point links minimizes the transmission line problems and clock to data skew issues associated with data transfers over multi-drop busses at high data rates.

The 8B/10B encoding is a dc-balanced, run-length limited code which simplifies and cost-reduces Gbit/sec serial links with only a 20% encoding overhead. The dc-balanced code provides greater noise margins on copper links by minimizing the effects of baseline wander. The run-length limited code constrains the spectral content on the data link. This minimizes issues such as intersymbol interference and line coupling with capacitors or transformers, thus simplifying line fault detection to a digital rather than an analog problem.

# Fibre Channel Overview

Because of these physical link attributes, Fibre Channel data transfer at 1 Gbit/sec is simpler, more reliable, with a bit error rate less than  $10^{-12}$ , and lower in cost than other serial interconnects.

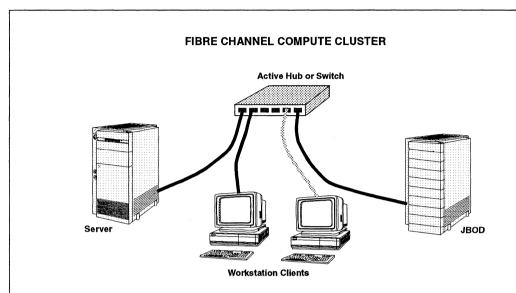

Fibre Channel's Arbitrated Loop topology retains the cost-effectiveness and user-friendliness of a multidrop bus interconnect like ethernet and SCSI. Data rates of 1 Gbit/sec and above are permitted on copper cables over moderate distances (50meters) and on optical cables over long distance (10km). Most importantly, FC-AL does not require expensive switches and may use simple active hubs instead for reliable connectivity.

These attributes of Fibre Channel coupled with its reliable transport and flow control protocol (FC-2) and its flexible upper-layer protocol mapping (FC-4) has prompted Fibre Channel's adoption as a storage peripheral

Datacommunications Products

# Fibre Channel Overview

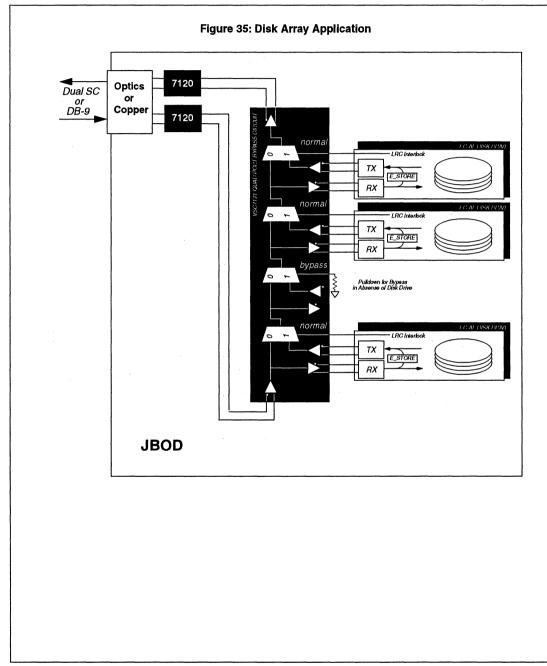

interconnect not only as a connection between RAID (Redundant Array of Independent Disks) and servers, but also on individual disk drives with embedded RAID which increases performance and capacity of RAID and JBOD (Just a Bunch Of Disks) systems. High performance peripherals interconnected to servers and clients through 1 Gbit/sec Fibre Channel provide scalable, fault tolerant compute clusters and legacy LAN performance is enhanced through the use of Fibre Channel's Gbit/sec reliable transmission for a network backbone. High speed, remote data acquisition for imaging is made possible with Fibre Channel as well.

Vitesse Semiconductor has developed the most complete physical layer product offering through a family of industry compliant Fibre Channel transmitters and receivers along with Gbit/sec repeaters and bypass circuits. A physical layer block diagram, of an Arbitrated Loop cluster of Fibre Channel disk drives in a JBOD, interconnected to workstations with an active hub, is shown on the previous page. Additionally, Vitesse is working with the ANSI technical committee to ensure reliability and interoperability of GBit/sec interconnects.

Vitesse also offers protocol products enabling the construction of custom Fibre Channel ports for such custom applications as data acquisition, RAID controllers, network backbones, and print server controllers. These products are summarized in the Product Summary.

# Datacommunications Products

# Fibre Channel Overview

### Transmitter/Receiver Overview

Fibre Channel transmitters and receivers implements the ANSI X3T11 Fibre Channel FC-0 layer minus the media and the optical drivers. These circuits are also referred to as Serializers and Deserializers respectively or SERDES collectively. SERDES more accurately describes the chip's function as they perform the task of serializing from and deserializing to parallel data for serial transmission.

Vitesse Semiconductor was the first to produce 1.0625 Gbit/sec transmitters and receivers predating industry standardization and our products have evolved with the Fibre Channel industry. This is why Vitesse has several similar products.

Two industry standardization efforts are significant. The first is the Gigabaud Link Module (GLM) profile established by Hewlett Packard, IBM, and Sun Microsystems as one of the profiles produced by the Fibre Channel Systems Initiative. The GLM specification's intent was to specify interchangeable daughtercard "modules" which contain all the high frequency circuits and board layouts. This will simplify the FC port design to a 53MHz TTL design and permit user speed and media selectability while ensuring multiple sources. Thus the GLM specification documents a 20-bit, 53MHz TTL timing interface as well as a physical definition. The GLM timing interface is reflected in the Vitesse VSC7115/16 product and the physical and electrical profile is implemented in the Vitesse VSC7181 product.

The second significant industry document is the 10-Bit Interface Specification which is a Technical Report published by the ANSI X3T11 Technical Committee. The driving force behind this effort is to define a lower pin count interface requested by the HDD (hard disk drive) industry due to the defacto standardization on dualported Fibre Channel disk drives. Reducing the I/O to 10-bit from 20-bit reduces a dual ported disk controller's pin count by 40 signals. This interface is implemented in the Vitesse VSC7125 product. Facets of the 10-Bit Interface Specification are taken from the VSC7105/06 product which predates both the GLM and 10-Bit Specification. diagram showing the Vitesse Transmitter and receiver product offering is shown above.

# Datacommunications Products

# Transmitter/Receiver Overview

1.0625 Gbit/sec Transmitter/Receiver Chipset for Fibre Channel or Proprietary Serial Links

## Features

- ANSI X3T11 Fibre Channel Compatible at 1.0625 Gbit/s

- On-chip Fully Monolithic Clock Recovery and Clock Multiplication Circuits Require No External Components

- On Chip Clock Multiplication Relieves System of High Speed Clock Generation

- Single +3.3V Supply Operation

- Dual Receiver Serial Inputs and Transmitter Outputs for Loopback and Multiple Link Applications

- Selectable 10 or 20 bit TTL Compatible Parallel Interface

- High Sensitivity Differential Receiver Suitable for both Coaxial and Optical Link Applications

## **General Description**

The VSC7105/VSC7106 chipset is compatible with the ANSI X3T11 Fibre Channel Standard. Fibre Channel is a high speed communication channel standardized by ANSI for mapping upper layer protocols (ULP) such as SCSI, IP, and HIPPI. Fibre Channel can then provide a channel over which concurrent communication of all ULP's may exist on a single interconnect between workstations, mainframes, and supercomputers, and for connection to mass storage devices and other peripherals. The Fibre Channel physical layer is also ideal for building cost effective, very high speed point-to-point communications links.

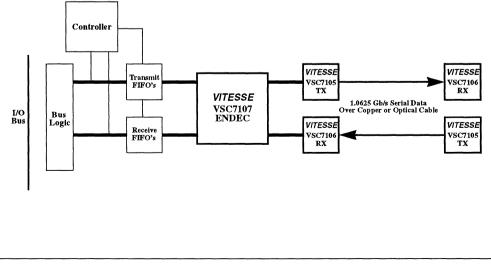

This chipset implements the Fibre Channel electrical transceiver physical layer for 1.0625 Gb/s operation. At 1.0625 Gb/s, Fibre Channel delivers 100 MByte/s of data bandwidth over a single cable. This bandwidth equals or exceeds most bus bandwidths. This chipset performs the high speed serialization and de-serialization function that makes bus-bandwidth, serial communication possible. This chipset can drive electrical cables directly or interface with optical modules.

## System Block Diagram

1.0625 Gbit/sec Transmitter/Receiver Chipset for Fibre Channel or Proprietary Serial Links

VSC7105/7106

#### VSC7105 Transmitter Functional Description

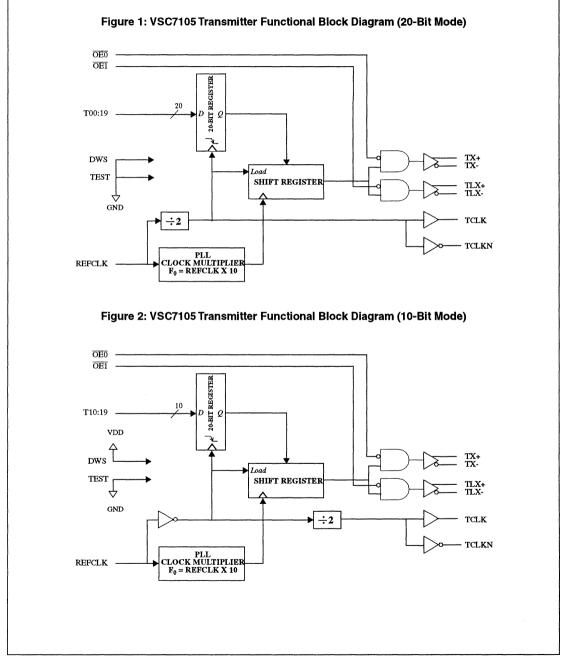

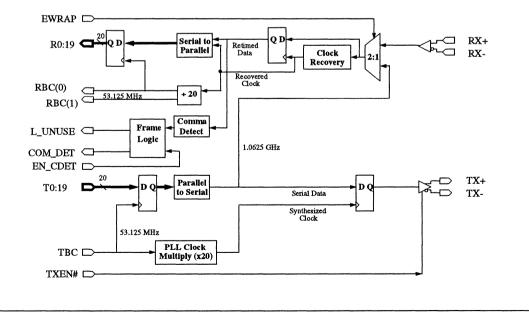

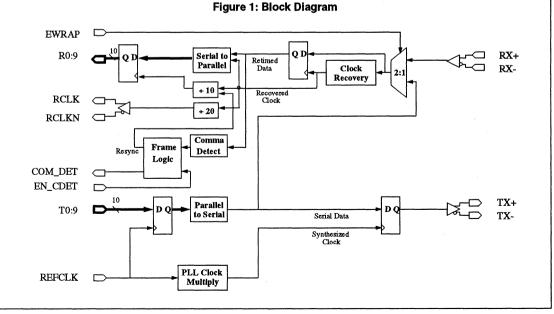

The VSC7105 is an ANSI X3T11 compatible Fibre Channel (FC) transmitter designed to work at the FC baud rate of 1.0625 Gb/s. The VSC7105 performs the serialization of parallel data and simplifies system design by performing clock multiplication from the parallel data clock. The VSC7105 has two modes of operation: 10-bit and 20-bit. The functional block diagrams for the 20-bit and 10-bit modes are shown in Figure 1 and Figure 2 respectively.

The VSC7105 accepts 8B/10B encoded TTL input data as one or two parallel 10 bit characters which are clocked into the device at 1/10 or 1/20 of the baud rate. User data should be encoded for transmission using the 8B/10B block code described in the Fibre Channel specification or any other equivalent coding scheme with a transition density of 40% or greater and a maximum run length of 6 consecutive 1's or 0's. The VSC7105 serializes the input data and transmits it at a baud rate of 10 times the frequency of the REFCLK input. The device includes a phase locked loop-based clock multiplier that generates the baud clock. This PLL is fully monolithic, and requires no external components.

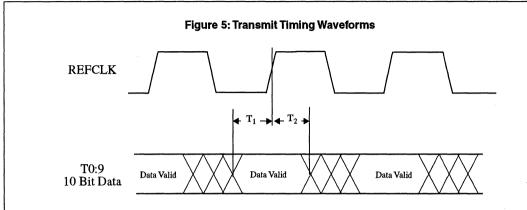

The parallel input port timing is derived from the REFCLK input. REFCLK is internally divided by two, and driven off chip as complementary TTL outputs: TCLK and TCLKN. In 20-bit mode, the VSC7105 loads parallel data on the falling edge of TCLK. TCLK thus provides a convenient means to clock the data source. For 10 bit mode, the VSC7105 loads parallel data on the rising edge of REFCLK. The rising edge of REFCLK corresponds to the falling edges of both TCLK and TCLKN. The system designer may either use the rising edge of REFCLK or the falling edges of TCLK and TCLKN to clock the data source. Only data on T10:19 are used in 10-bit mode. The width of the input data bus is controlled by the DWS (Data Width Select) input. A logic LOW on this input places the VSC7105 in 20-bit mode and a logic HIGH places the VSC7105 in 10-bit mode.

Output Enable controls are provided for each of the serial output ports.  $\overline{OE0}$  controls the primary outputs, TX, while  $\overline{OE1}$  controls the secondary outputs, TLX. When an  $\overline{OE}$  control is brought HIGH, the respective output is forced to a logical HIGH state. For example, a logical HIGH on the TX differential outputs will cause TX-to be LOW and TX+ to be HIGH. The secondary outputs can be used as a local loopback for system testing.

A three-level TEST signal is provided to facilitate functional testing and to select NRZ or NRZI data format. When TEST is left floating, REFCLK replaces the PLL-generated internal clock. For normal operation using the PLL-generated bit clock in Fibre Channel compliant mode which uses NRZ formatting, the TEST pin is tied to GND. For normal operation using NRZI formatting, the TEST pin is tied  $V_{DD}$ .

VSC7105/7106

#### 1.0625 Gbit/sec Transmitter/Receiver Chipset for Fibre Channel or Proprietary Serial Links

#### 1.0625 Gbit/sec Transmitter/Receiver Chipset for Fibre Channel or Proprietary Serial Links

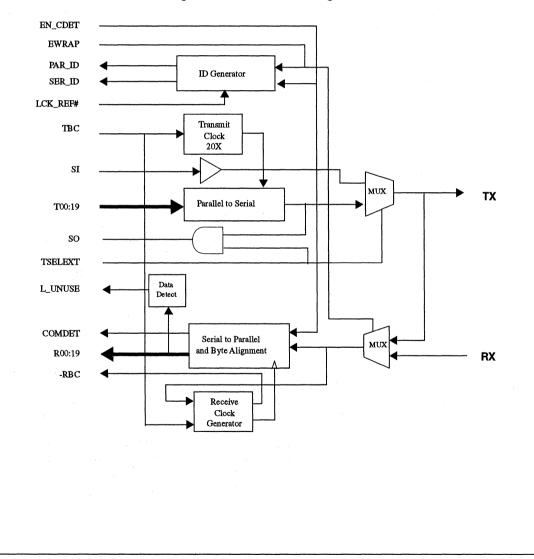

#### **Transmission Character Interface**

VSC7105/7106

In Fibre Channel, an encoded byte is 10 bits and is referred to as a transmission character. A Fibre Channel word is 32 bits which is encoded into a transmission word of 40 bits. The 20 bit interface on the VSC7105 corresponds to a half transmission word. This document uses character and half-word to refer to transmission character and half transmission word respectively. Hence the VSC7105 has a selectable transmission character or half transmission word Fibre Channel interface. The bit ordering and its relationship to Fibre Channel bit position is shown in Figure 3 for the VSC7105. In 20-bit mode, T00 is transmitted first and in 10-bit mode, T10 is transmitted first.

| Parallel Data<br>Bits  | 1 9    | 1 | 17 | 1 6      | 1<br>5 | 1 4     | 13       | 1                | 1        | 1<br>0 | 09 | 08 | 07      | 06 | 0 | 04 | 0                | 02 | 0 | 0    |

|------------------------|--------|---|----|----------|--------|---------|----------|------------------|----------|--------|----|----|---------|----|---|----|------------------|----|---|------|

|                        | ļ́.    |   | ·  | <u> </u> | ļ      |         | <u> </u> |                  | <u> </u> |        | Ļ  |    | · · · · | ļ  |   |    | ļ                |    |   | ļ    |

| 8B/10B Bit<br>Position | j      | h | g  | f        | i      | e       | đ        | c                | b        | a      | j  | h  | g       | f  | i | e  | d                | c  | b | a    |

|                        | Î      |   |    |          | 1      | First I |          | Bit Tra<br>it Mo |          | ted    |    |    |         |    | F |    | ata Bi<br>20-Bit |    |   | ed 🕇 |

| Last Data Bit Transn   | vitted |   |    |          |        |         |          |                  |          |        |    |    |         |    |   |    |                  |    |   |      |

Figure 3: Transmission Order and Mapping to Fibre Channel Character

## VSC7106 Receiver Functional Description

The VSC7106 is an ANSI compatible Fibre Channel (FC) receiver designed to work at the FC baud rate of 1.0625 Gb/s. The VSC7106 accepts differential high speed serial inputs, extracts the clock and retimes the data from the serial bit stream. The serial bit stream should be 8B/10B encoded data produced by a FC compatible transmitter, or any other source with a transition density of 40% or greater and a maximum run length of 6 consecutive 1's or 0's. The retimed serial bit stream is converted into either a 10 or 20-bit parallel output word. The VSC7106 provides Fibre Channel SYNC character recognition and data word alignment. The VSC7106 has internal PLL-based clock recovery circuitry which requires no external components.

Serial data is received on the RX, RLX pins as determined by LPEN. The PLL clock recovery circuit will lock to the data stream if the clock to be recovered is within 1.0% of the expected data rate. The expected data rate is 10 times the REFCLK frequency. For example if the REFCLK used is 106.25MHz, then the incoming serial baud rate must be 1.0625 Gigabaud  $\pm 1.0\%$ .

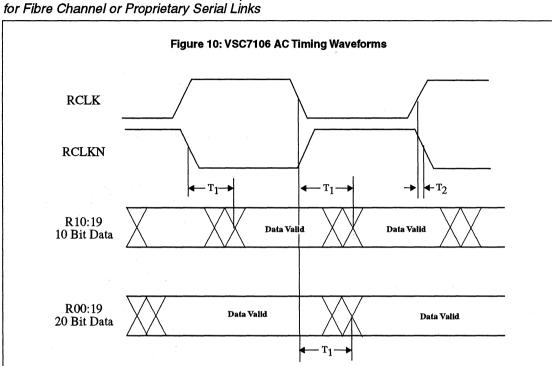

The VSC7106 provides complementary TTL recovered clock, RCLK and RCLKN, which is at one twentieth of the serial baud rate. This clock is generated by dividing down the high-speed clock which is phase locked to the serial data. If serial input data is not present, or does not meet the required transition density or baud rate, the RCLK frequency will be within +/-1.5% of half of the REFCLK.. The serial data is retimed by the internal high-speed clock, and deserialized. Parallel data is loaded into the output register on the falling edge of RCLK in 20-bit mode or on the falling edges of RCLK and RCLKN in 10 bit mode. The width of the output field can be 10 or 20-bit, under the control of the DWS (Data Width Select) pin. A logic LOW on this input causes the parallel data to be presented 20-bit wide. A logic HIGH causes a single 10-bit character to be presented on

1.0625 Gbit/sec Transmitter/Receiver Chipset for Fibre Channel or Proprietary Serial Links

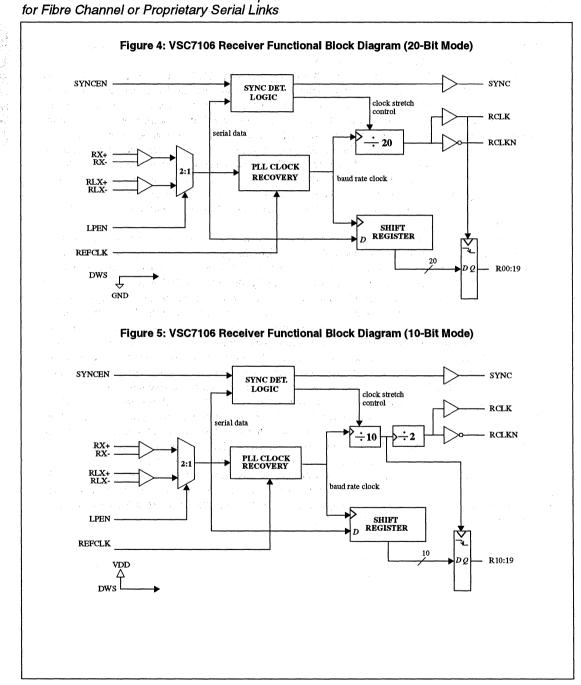

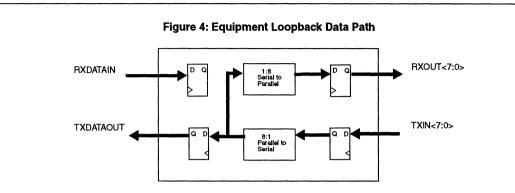

R10:19. R00:09 are held HIGH in this mode. The functional block diagrams for operation in 20-bit or 10-bit modes are shown in Figure 4 and Figure 5 respectively.

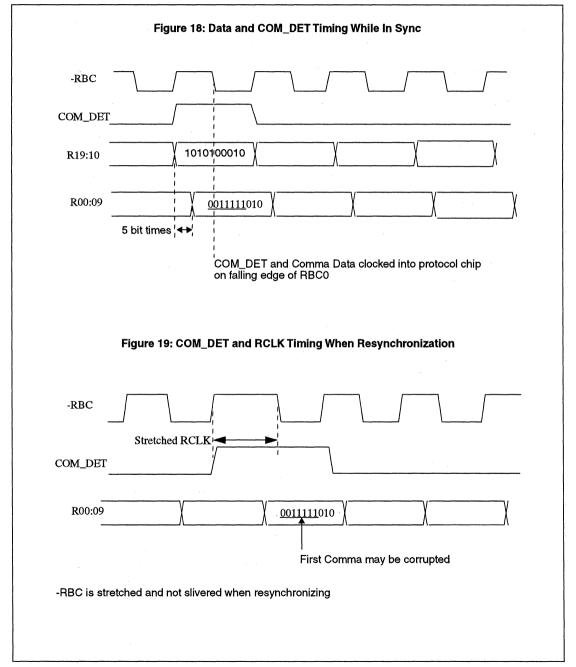

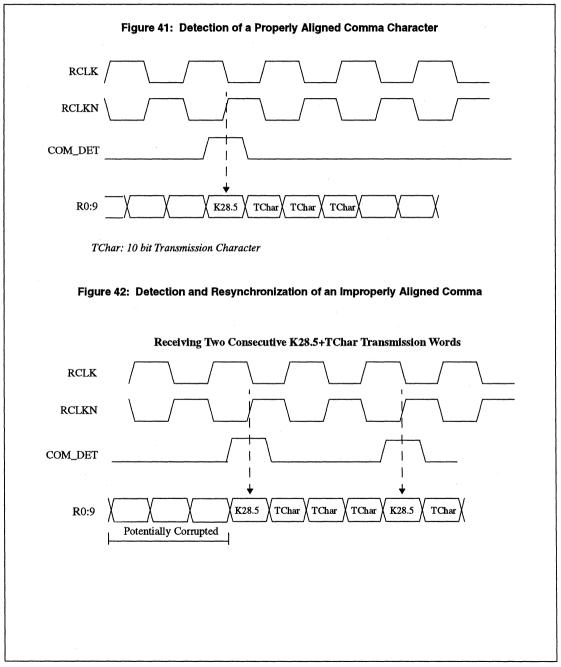

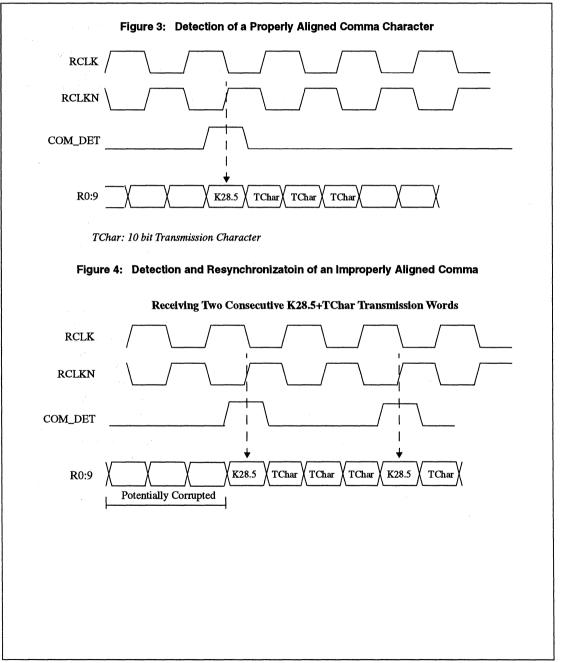

Word synchronization is enabled in the VSC7106 by tying the SYNCEN pin to  $V_{DD}$ . When synchronization is enabled, the VSC7106 constantly examines the serial data for the presence of the Fibre Channel "Sync" character. This pattern is "0011111010" and is referred to as a K28.5 character with negative beginning disparity. The K28.5 character is not a normal data character, but a special character defined specifically for synchronization by Fibre Channel. Improper alignment occurs when a K28.5 straddles a 10 bit boundary or when a K28.5 is in the wrong 10-bit position of a half-word. When an improperly aligned sync character is encountered in 20-bit mode, the internal divider which produces RCLK and RCLKN is stalled in such a manner that the sync character is aligned in the R00:09 output field. This results in proper character and half-word alignment. In 10-bit mode, proper alignment is established when the K28.5 does not straddle a 10-bit character boundary, and appears in a character that is clocked out on the falling edge of RCLKN. Half-word synchronization is still relevant in 10-bit mode.

When the parallel data alignment changes in response to a sync pattern, some data which would have been presented on the parallel output port will be lost. The detection of the sync character is pipelined. Depending on the required new output phase, the sync character itself may be destroyed by the synchronization operation. Nonetheless, data following the sync character will be correctly aligned. Thus if downstream logic requires detection of the sync character (for example, to accomplish ordered set alignment) then more than one sync character must be transmitted in order to guarantee that one will be forwarded out of the VSC7106 incorrupt-ible. Fibre Channel compliant systems requires the receipt of a minimum of three ordered sets for word synchronization. Ordered sets are special Fibre Channel transmission words that have the K28.5 sync character as the first character received. The first of these ordered sets will cause resynchronization in the VSC7106. The subsequent two ordered sets will be correctly aligned when they are received. In systems where synchronization is undesired, tying SYNCEN to GND will disable the sync function, and the data will be unframed.

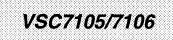

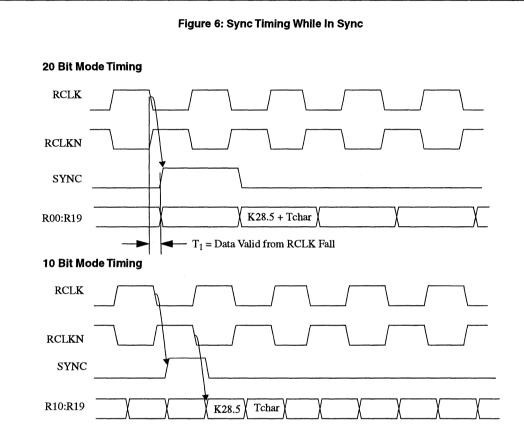

On encountering a sync pattern, a pulse is generated on the SYNC output to inform the user that realignment of the parallel data field may have occurred. The SYNC pulse is presented one cycle in advance of the actual K28.5 character, and has a duration equal to the data. When operating the VSC7106 in 20-bit mode, the SYNC pulse spans one period of RCLK. In 10-bit mode, the pulse is HIGH for half of an RCLK period. Functional waveforms for synchronization in both modes are given in Figure 6 and Figure 7. Figure 6 shows the case when a sync character is detected and no phase adjustment is necessary. It illustrates the position of the SYNC pulse in relation to the sync character. Figure 7 shows the case where the K28.5 is detected, but out of alignment and a change in RCLK and the output data is required. Note that the VSC7106 always stretches the RCLK so it will never create a clock sliver on resynchronization.

# VSC7105/7106

1.0625 Gbit/sec Transmitter/Receiver Chipset

Data Sheet

#### 1.0625 Gbit/sec Transmitter/Receiver Chipset for Fibre Channel or Proprietary Serial Links

TChar: 10 bit Transmission Character

1.0625 Gbit/sec Transmitter/Receiver Chipset for Fibre Channel or Proprietary Serial Links

VSC7105/7106

Data Sheet

#### 1.0625 Gbit/sec Transmitter/Receiver Chipset for Fibre Channel or Proprietary Serial Links

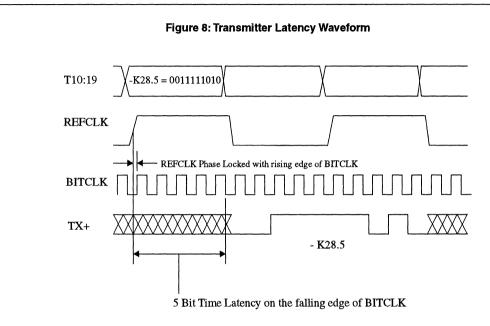

#### Table 1: Data Latency

| VSC7105 Parallel to Serial Latency (10-Bit Mode) | 5 Bit Times  |

|--------------------------------------------------|--------------|

| VSC7105 Parallel to Serial Latency (20-Bit Mode) | 5 Bit Times  |

| VSC7106 Serial to Parallel Latency (10-Bit Mode) | 26 Bit Times |

| VSC7106 Serial to Parallel Latency (20-Bit Mode) | 46 Bit Times |

# 1.0625 Gbit/sec Transmitter/Receiver Chipset for Fibre Channel or Proprietary Serial Links

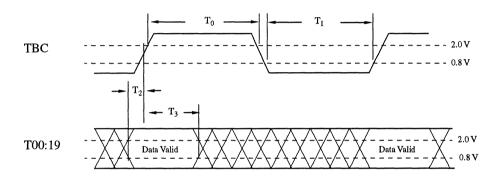

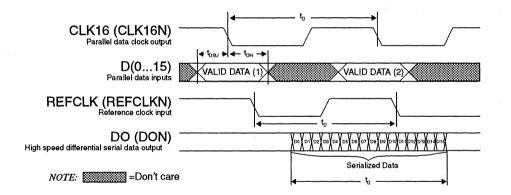

# Figure 9: VSC7105 Timing Waveforms REFCLK - T<sub>0</sub>-← <sup>T</sup>1-← T<sub>6</sub> ←T0→ TCLK TCLKN T<sub>2</sub> -Т3-T10:19 Data Valid Data Valid Data Valid 10 Bit Data T4т5 -T-T-4 T00:19 Data Valid 20 Bit Data - T4-T5+

Data Sheet

#### 1.0625 Gbit/sec Transmitter/Receiver Chipset for Fibre Channel or Proprietary Serial Links

#### Table 2: VSC7105 AC Characteristics

| Parameters                         | Description                                      | Min | Max  | Units | Conditions                                                                        |

|------------------------------------|--------------------------------------------------|-----|------|-------|-----------------------------------------------------------------------------------|

| T <sub>0</sub>                     | REFCLK rise to TCLK fall<br>and TCLKN rise       | 1.0 | 4.0  | ns    | _                                                                                 |

| T <sub>1</sub>                     | REFCLK rise to TCLK rise<br>and TCLKN fall       | 1.0 | 4.0  | ns    |                                                                                   |

| T <sub>2</sub>                     | Data setup w.r.t. REFCLK                         | 1.0 | -    | ns    | —                                                                                 |

| T <sub>3</sub>                     | Data hold w.r.t. REFCLK                          | 5.0 |      | ns    | -                                                                                 |

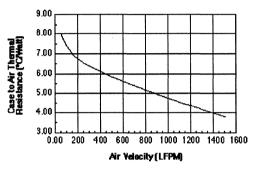

| T <sub>4</sub>                     | Data setup w.r.t. TCLK/<br>TCLKN                 | 5.0 |      | ns    | Derived from Data setup to REFCLK and<br>REFCLK to TCLK/TCLKN delay               |