# System Programming Manual

VX900 Series

All-in-One System Processor

Preliminary Revision 1.41 October 4, 2011

VIA TECHNOLOGIES, INC.

### **Copyright Notice:**

Copyright © 2009-2011 VIA Technologies Incorporated. All Rights Reserved. No part of this document may be reproduced, transmitted, transcribed, stored in a retrieval system or translated into any language, in any form or by any means, electronic, mechanical, magnetic, optical, chemical, manual or otherwise without the prior written permission of VIA Technologies Incorporated. The material in this document is for information only and is subject to change without notice. VIA Technologies Incorporated reserves the right to make changes in the product design without reservation and without notice to its users.

### **Trademark Notices:**

VX900, VX900M, VX900H, VX900MH may only be used to identify products of VIA Technologies.

C7<sup>®</sup> is a registered trademark of VIA Technologies.

Nano™ is a registered trademark of VIA Technologies.

Windows <sup>®</sup>, Windows Vista <sup>®</sup> are registered trademarks of Microsoft Corp.

PCI™ and PCI Express™ are trademarks of the PCI Special Interest Group.

DVI is a trademark of Digital Display Working Group (DDWG).

HDMI is a trademark of HDMI Licensing, LLC.

DisplayPort<sup>™</sup> is a trademark of Video Electronics Standards Association (VESA).

VESA™ is a trademark of the Video Electronics Standards Association.

All trademarks are the properties of their respective owners.

### **Disclaimer Notice:**

No license is granted, implied or otherwise, under any patent or patent rights of VIA Technologies, Inc. VIA Technologies makes no warranties, implied or otherwise, in regard to this document and to the products described in this document. VIA Technologies assumes no responsibility for any errors in this document. Furthermore, VIA Technologies assumes no responsibility for the use or misuse of the information in this document and for any patent infringements that may arise from the use of this document. The information and product specifications within this document are subject to change at any time, without notice and without obligation to notify any person of such change.

### Offices:

VIA Technologies Incorporated USA Office: 940 Mission Court Fremont, CA 94539 USA Tel: (510) 683-3300

Fax: (510) 683-3301 or (510) 687-4654

Home Page: http://www.viatech.com

VIA Technologies Incorporated Taiwan Office: 1F, 531, Zhongzheng Rd., Xindian Dist., New Taipei City 231, Taiwan ROC

Tel: (886-2) 2218-5452 Fax: (886-2) 2218-5453

Home page: <a href="http://www.via.com.tw">http://www.via.com.tw</a>

# **REVISION HISTORY**

| <b>Document Release</b> | Date     | Revision                                                                 | Initials |

|-------------------------|----------|--------------------------------------------------------------------------|----------|

| 1.0                     | 9/10/10  | Initial public release                                                   | JW       |

| 1.01                    | 11/25/10 | Updated the base address in the descripton of "Bus Master IDE I/O Space" | JW       |

| 1.1                     | 3/9/11   | Updated bit descriptions of:                                             | JW       |

|                         |          | SATA_EPHY index Rx24[7:5], Rx34[7:5];                                    |          |

|                         |          | D16F4 Rx5B-5A[15:12];                                                    |          |

|                         |          | D17F0 Rx94[1:0], Rx97[2] and Rx9F[7];                                    |          |

|                         |          | PMIO Rx26[2], Rx6F[4]                                                    |          |

| 1.2                     | 3/14/11  | Updated D17F0 Rx46[7] and Rx47[7]                                        | EY       |

| 1.3                     | 4/18/11  | Updated FSB support up to 1066Mhz for VX900                              | EY       |

|                         |          | Updated D0F7 Rx76[7]                                                     |          |

| 1.4                     | 8/4/11   | Modify D17F0 Rx95[0] and PMIO Rx20[14]                                   | DA       |

| 1.41                    | 10/4/11  | Updated D20F0 Rx3D description                                           | JW       |

# TABLE OF CONTENTS

| REVISION HISTORY                                                                                                             | l        |

|------------------------------------------------------------------------------------------------------------------------------|----------|

| TABLE OF CONTENTS                                                                                                            | П        |

| LIST OF TABLES                                                                                                               | VIII     |

| LIST OF FIGURES                                                                                                              | IX       |

| REGISTER OVERVIEW                                                                                                            | 1        |

| REGISTER DOCUMENT INTRODUCTION                                                                                               | 1        |

| MODULE AND REGISTER SCOPE DEFINITIONS                                                                                        | 2        |

| Register Scope Map Within Modules                                                                                            |          |

| Attribute Definition                                                                                                         | 4        |

| PCI CONFIGURATION SPACE I/O                                                                                                  | 5        |

| NORTH MODULE IRQ AND APIC CONTROL                                                                                            | 6        |

| PCIE LINK DECLARATION DESCRIPTION                                                                                            | 6        |

| IRQ AND INTERRUPT ASSIGNMENT TABLE                                                                                           | 6        |

| APIC REGISTER I/O  Memory Mapped I/O APIC Registers  Indexed I/O APIC Registers                                              | 7        |

| DEVICE 0 FUNCTION 0 (D0F0): HOST CONTROLLER                                                                                  | 11       |

| PCI CONFIGURATION SPACE                                                                                                      | 11       |

| Header Registers (00-3Fh)                                                                                                    | 18       |

| DEVICE 0 FUNCTION 1 (D0F1): ERROR REPORTING                                                                                  |          |

| PCI CONFIGURATION SPACE  Header Registers (00-3Fh)  Host Bus Error Report (40-6Fh)                                           | 25       |

| DEVICE 0 FUNCTION 2 (D0F2): CPU BUS CONTROLLER (V4IF)                                                                        | 31       |

| PCI CONFIGURATION SPACE                                                                                                      | 31       |

| Header Registers (00-3Fh)                                                                                                    | 38       |

| DRAMC Interface Control (53-56h)CPU Bus Interface Control (57-5Ch)                                                           | 44<br>48 |

| DRAMC Interface Control (5D-5Fh)                                                                                             | 54<br>55 |

| CPU Bus AGTL+ I/O Driving Control (70–7Dh)  Output Beat Time Control for HA and HD (7E-8Fh)  DRAM Interface Control (90–91h) | 65       |

| Power Management Related Control (92-95h)                                             |     |

|---------------------------------------------------------------------------------------|-----|

| CPU Bus Interface Control (96-9Fh)                                                    | 77  |

| AGTL Physical Control (A0–A2h)                                                        |     |

| Output and Input Timing Adjustment for AGTL+ I/O Trace Delay (A3-FFh)                 | 83  |

| DEVICE 0 FUNCTION 3 (D0F3): DRAM BUS CONTROL                                          | 101 |

| PCI CONFIGURATION SPACE                                                               |     |

| Header Registers (00–3Fh)                                                             | 105 |

| DRAM Rank (Row) Beginning / Ending Address (40–4Fh)                                   | 110 |

| MA Map / Command Rate (50–53h)                                                        |     |

| Physical-to-Virtual Rank Mapping (54–57h)                                             |     |

| Virtual Rank Interleave Address Select / Enable (58–5Fh)                              |     |

| DRAMC Pipeline Control (60–64h)                                                       |     |

| DRAM Queue / Arbitration (65–67h)                                                     |     |

| DRAM Page Control (68–69h)                                                            |     |

| DRAM Miscellaneous Control (6A-6Fh)                                                   |     |

| DRAM Signal Timing Control (70–7Fh)                                                   |     |

| Shadow RAM Control (80–83h)                                                           |     |

| DRAM Tost Pottorn Control (9C 9Eb)                                                    |     |

| DRAM Test Pattern Control (8C-8Fh)                                                    |     |

| DRAM ODT Control (9C-9Fh)                                                             |     |

| UMA/GMINT Registers (A0–AFh)                                                          |     |

| VDIF/VMINT Registers (B0–BFh)                                                         |     |

| DRAM Timing Parameters (C0-CBh)                                                       |     |

| DRAM MRS for Initialization (CC-CFh)                                                  |     |

| DDR2/DDR3 – I/O Pad Termination and Driving Control (D0–DFh)                          |     |

| DRAM Driving Control (E0–EBh)                                                         |     |

| DRAM Signal Timing Control (EC-EFh)                                                   |     |

| DRAM Memory Remap (F0-FFh)                                                            |     |

| DEVICE 0 FUNCTION 4 (D0F4): POWER MANAGEMENT AND CHIP TESTING CONTROL                 |     |

| PCI Configurations                                                                    |     |

| Header Registers (00-3Fh)                                                             |     |

| Test Mode Registers (40-7Fh)                                                          |     |

| Power Management Control (80–FFh)                                                     |     |

| DEVICE 0 FUNCTION 5 (D0F5): APIC AND CENTRAL TRAFFIC CONTROL                          |     |

| PCI CONFIGURATION SPACE                                                               | 249 |

| 1 01 001/11001411101/511102                                                           |     |

| Header Registers (00–3Fh)                                                             |     |

| Central Traffic - Downstream Control (60–7Fh)                                         |     |

| Central Traffic - Downstream Control (00–711)                                         |     |

| PCIe Message Controller and Power Management (A0–FFh)                                 |     |

| DEVICE 0 FUNCTION 6 (D0F6): SCRATCH REGISTERS                                         |     |

| PCI CONFIGURATION SPACE                                                               |     |

|                                                                                       |     |

| Header Registers (00–3Fh)                                                             |     |

| BIOS Scratch Registers (40-FFh)                                                       |     |

| DEVICE 0 FUNCTION 7 (D0F7): NORTH-SOUTH MODULE INTERFACE CONTROL                      |     |

| PCI CONFIGURATION SPACE                                                               |     |

| Header Registers (00-3Fh)                                                             |     |

| North-South Module Interface Control (40–6Fh)                                         |     |

|                                                                                       |     |

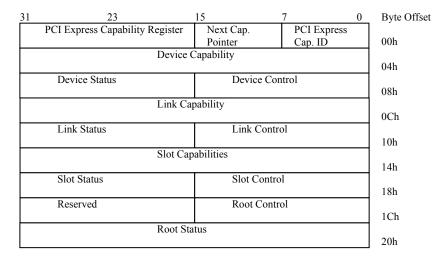

| DEVICE 3 FUNCTION 0-3 (D3F0-3): PCI EXPRESS ROOT PORT 0-3 (PCI-TO-PCI VIRTUAL BRIDGE) | 292 |

| PCI CONFIGURATION SPACE                                                             | 292 |

|-------------------------------------------------------------------------------------|-----|

| Header Registers (00-3Fh)                                                           | 294 |

| PCI Express Capability Registers (40-9Fh)                                           |     |

| PCI Power Management Capability Structure Registers (A0-AFh)                        | 324 |

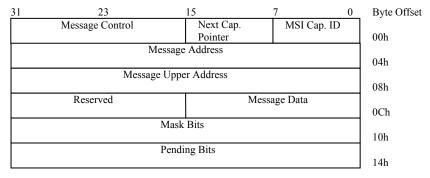

| PCI Message Signal Interrupt (MSI) Capability Structure Registers (B0-DFh)          | 326 |

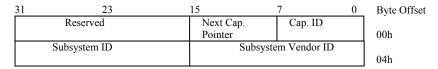

| Subsystem ID and Subsystem Vendor ID Capability Structure Registers (E0-FFh)        | 328 |

| DEVICE 3 FUNCTION 0 (D3F0-3) – PCI EXPRESS ROOT PORT EXTENDED SPACE                 | 329 |

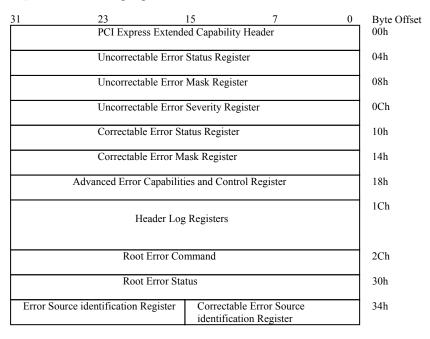

| Advanced Error Reporting Capability (100-137h)                                      |     |

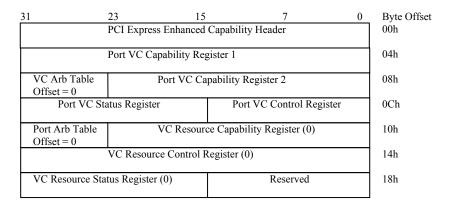

| Virtual Channel Capability (140-167h)                                               |     |

| VC0 Resource (150-15Bh)                                                             |     |

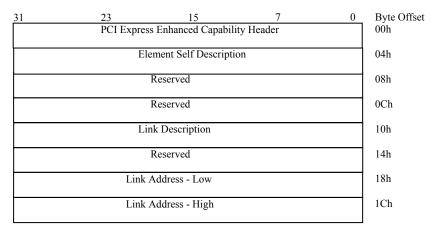

| PCI Express Root Complex Link Declaration Capability (170-18Bh)                     |     |

| PCI Express Transaction Layer Registers (1A0-1A8h)                                  | 347 |

| PCI Express Data Link Layer Registers (1B0-1B9h)                                    |     |

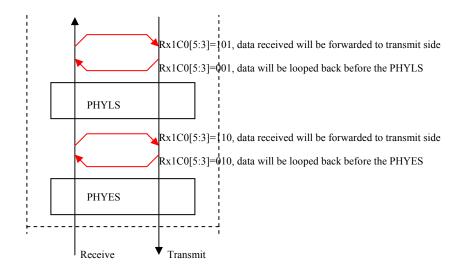

| PCI Express Physical Layer Logical Sub-Block Registers (1C0-1CFh)                   |     |

| PCI Express Power Management Module Registers (1D0-1D7h)                            |     |

| PCI Express Message Controller Related Registers (1D8-1DFh)                         |     |

| PCI Express Link Management Registers (1E0-1E9h)                                    |     |

| PCI Express Electrical PHY Test Registers (1F0-1F9h)                                | 375 |

| DEVICE 3 FUNCTION 4 (D3F4) – PCI EXPRESS PHYSICAL LAYER ELECTRICAL SUB-BLOCK        | 384 |

| PCI CONFIGURATION SPACE                                                             | 384 |

| Header Registers (00–3Fh)                                                           | 384 |

| PCI Express Physical Layer Electrical Sub-block Registers (40-FFh)                  | 390 |

| PCI EXPRESS ROOT COMPLEX REGISTER BLOCK                                             | 416 |

| RCRB-H MMIO                                                                         | 416 |

| Virtual Channel (VC) Capability (000-03Fh)                                          |     |

| Root Complex Link Declaration Enhanced Capability (040-04Fh)                        |     |

| Link Entry for PE0 (050-05Fh)                                                       |     |

| Link Entry for PE1 (060-06Fh)                                                       |     |

| Link Entry for PE2 (070-07Fh)                                                       |     |

| Link Entry for PE3 (080-08Fh)                                                       |     |

| Link Entry for HDAC (090-1FFh)                                                      |     |

| Port Arbitration Timer (200-20Fii) – Not Support                                    |     |

| Port Arbitration Timer for VC1 (220-22Fh) – Not support                             |     |

| Host Side Upstream Arbitration Timers (230-23Fh)                                    |     |

| DRAM Side Upstream Arbitration Timers (240-25Fh)                                    |     |

| SLI / Host Arbitration Timers (260-26Fh) - Not support                              |     |

| P2P Arbitration Timer of PCIe (270-27Fh)                                            | 428 |

| SOUTH MODULE LEGACY CONTROL                                                         | 430 |

| LEGACY I/O PORTS                                                                    | 430 |

| Keyboard Controller I/O Registers                                                   | 432 |

| DMA Controller I/O Registers                                                        | 436 |

| DMA Controller Shadow Registers                                                     |     |

| Interrupt Controller I/O Registers                                                  |     |

| Interrupt Controller I/O Shadow Registers                                           |     |

| Timer / Counter I/O Registers                                                       |     |

| CMOS / RTC I/O Registers                                                            |     |

| Keyboard / Mouse Wakeup Index / Data Registers<br>Keyboard / Mouse Wakeup Registers |     |

| •                                                                                   |     |

| MEMORY MAPPED I/O APIC REGISTERS                                                    |     |

| Indexed I/O APIC Registers                                                          |     |

| DEVICE 10 FUNCTION 0-3 (D10F0-F3): PCI UART PORT 0-3                                | 449 |

| PCI UART PCI CONFIGURATION SPACE                                                          | 449 |

|-------------------------------------------------------------------------------------------|-----|

| Header Registers (00-3Fh)                                                                 |     |

| PCI UART Host Controller MMIO Registers (PCI UART-MMIO)                                   |     |

| PCI UART Host Controller Legacy Registers (00-0Fh)                                        |     |

| PCI UART Host Controller HP/DMA Registers (10-7Fh)                                        | 460 |

| DEVICE 11 FUNCTION 0 (D11F0): USB DEVICE                                                  | 467 |

| PCI CONFIGURATION SPACE                                                                   | 467 |

| Header Registers (00-3Fh)                                                                 |     |

| USB PHY And MAC Control (40-7Fh)                                                          |     |

| VIA USB DEVICE MEMORY-MAPPED I/O REGISTERS (USBD-MMIO)                                    | 478 |

| VIA USB Communication Capability and Shadow Registers (00-0Fh)                            | 478 |

| VIA USB Device Controller Operational Registers (10-1Fh)                                  | 479 |

| VIA USB Device Endpoint Controller Operational Registers (20-2Fh)                         | 482 |

| VIA USB Device Endpoint Transfer Descriptor Registers (30-11Fh)                           |     |

| DEVICE 12 FUNCTION 0 (D12F0): SDIO HOST CONTROLLER                                        | 505 |

| PCI CONFIGURATION SPACE                                                                   | 505 |

| Header Registers (00-3Fh)                                                                 |     |

| SDIO PCI Device Specific Registers (40-FFh)                                               |     |

| SDIO MMIO SPACE                                                                           |     |

| SDIO Host Standard Registers (00-FFh)                                                     | 513 |

| DEVICE 13 FUNCTION 0 (D13F0): MULTIPLE MEMORY CARD CONTROLLER                             |     |

| PCI CONFIGURATION SPACE                                                                   |     |

| Header Registers (00-3Fh)PCI Card Reader – Specific Configuration Registers (40-FFh)      |     |

| MMIO SPACE                                                                                |     |

| xDC MMIO Registers (00-FFh)                                                               |     |

| SDC MMIO Registers (00-FFh)                                                               |     |

| Data DMA Control Registers (00-FFh)                                                       | 550 |

| CICH DMA Control Registers (00-FFh)                                                       | 552 |

| PCI Control Registers (00-FFh)                                                            | 555 |

| DEVICE 15 FUNCTION 0 (D15F0): SERIAL ATA CONTROLLER                                       | 557 |

| PCI CONFIGURATION SPACE                                                                   | 559 |

| Header Registers (00-3Fh)                                                                 |     |

| SATA Registers (40-54h)                                                                   |     |

| SATA (Primary Channel) Link Control Registers (55-56h)                                    |     |

| SATA HIT Control Registers (57-5En)  SATA Hot Plug and RAMBIST Status Registers (5F-63h)  |     |

| SATA EPHY Control Register (64-77h) – For Index Register                                  |     |

| Miscellaneous Registers (78-7Fh)                                                          |     |

| SATA Transport Control Registers (80-9Fh)                                                 |     |

| SATA SCR (Status and Control) Registers (A0-AFh)<br>Legacy / Back Door Registers (B0-FFh) |     |

| SATA EPHY INDEX REGISTER (SATA-EPHYC)                                                     | 589 |

| SATA EPHY Control Registers (00-3Fh)                                                      | 589 |

| BUS MASTER IDE I/O SPACE (IDE-IO)                                                         | 597 |

| Bus Master Controller (00-0Fh)                                                            | 597 |

| DEVICE 16 FUNCTION 0-3 (D16F0-F3): USB 1.1 UHCI PORTS 0-7                                 | 598 |

|                                                                                           |     |

| PCI CONFIGURATION SPACE                                                                               | 598 |

|-------------------------------------------------------------------------------------------------------|-----|

| Header Registers (00-3Fh)USB 1.1-Specific Configuration Registers (40-FFh)                            |     |

| USB 1.1 I/O SPACE (USB 1.1-IO)                                                                        |     |

| USB 1.1 I/O Registers (00-13h)                                                                        |     |

| DEVICE 16 FUNCTION 4 (D16F4): USB 2.0 EHCI                                                            |     |

| PCI CONFIGURATION SPACE                                                                               | 609 |

| Header Registers (00-3Fh)                                                                             |     |

| USB 2.0-Specific Configuration Registers (40-FFh)                                                     |     |

| EHCI USB 2.0 MEMORY MAPPED I/O REGISTERS                                                              |     |

| EHCI Capabilities (00-0Bh)                                                                            |     |

| Host Controller Operations (10-9Fh)                                                                   |     |

| Debug Port Controller Operational Registers (A0-B3h)                                                  |     |

| DEVICE 17 FUNCTION 0 (D17F0): BUS CONTROL AND POWER MANAGEMENT                                        | 633 |

| PCI CONFIGURATION SPACE                                                                               | 633 |

| Header Registers (00-3Fh)                                                                             | 633 |

| ISA Bus Control (40-49h)                                                                              |     |

| LPC Firmware Memory Control (4A-4Bh)                                                                  |     |

| Miscellaneous Control (4C-4Fh)                                                                        |     |

| Function Control (50-51h)                                                                             |     |

| Serial IRQ, LPC and PC / PCI DMA Control (52-53h)                                                     |     |

| GPIO and Miscellaneous Control (58-5Bh)                                                               |     |

| Programmable Chip Select (PCS) Control (5C-67h)                                                       |     |

| High Precision Event Timers (HPET) (68-6Bh)                                                           |     |

| ISA Decoding Control (6C-73h)                                                                         | 653 |

| PCI I/O Cycle Control (74-7Fh)                                                                        |     |

| Power Management-Specific Configuration Registers (80-AFh)                                            |     |

| PCI UART Control Registers (B0-FFh)                                                                   |     |

| System Management Bus-Specific Configuration Registers (D0-E7h)                                       |     |

| MMIO SPACE REGISTERS                                                                                  |     |

|                                                                                                       |     |

| Control Registers (000-009h)                                                                          |     |

|                                                                                                       |     |

| POWER MANAGEMENT IO SPACE                                                                             | 679 |

| ACPI IO Space Registers (PMIO 00-0Fh)Processor Power Management Registers (PMIO 10-1Fh)               |     |

| General Purpose Power Management Registers (PMIO 10-1Fn)                                              |     |

| IO Trap Registers (PMIO 54-6Fh)                                                                       |     |

| POWER MANAGEMENT MEMORY MAPPED IO SPACE                                                               |     |

| Watchdog Timer Memory Base (PM-MMIO 00-07h)                                                           |     |

| SYSTEM MANAGEMENT IO SPACE                                                                            |     |

| System Management Bus I/O Space Registers (SMIO 00-0Fh)                                               |     |

|                                                                                                       |     |

| CEC MMIO REGISTERS (CONSUMER ELECTRONICS CONTROLLER REGISTERS) CEC Controller MMIO Registers (00-FFh) |     |

| HPET MMIO SPACE                                                                                       |     |

| HPET MMIO Control Registers (00-148h)                                                                 |     |

|                                                                                                       |     |

| SPI BUS 0 MMIO REGISTER SPACE                                                                         |     |

| MMIO Register (00-87h)                                                                                |     |

| DEVICE 17 FUNCTION 7 (D17F7): SOUTH-NORTH MODULE INTERFACE CONTROL                                    | 728 |

| PCI CONFIGURATION SPACE                                               | 728 |

|-----------------------------------------------------------------------|-----|

| Header Registers (00-3Fh)                                             |     |

| South -North Module Interface Control (40-5F)                         | 731 |

| DRAM Configuration (60h)                                              |     |

| Shadow RAM Control (61-6Fh)                                           |     |

| Conventional PCI Bus Control (70-7Fh)                                 |     |

| CCA Related Control (80-CFh)                                          |     |

| HDAC Control (D0-DFh)                                                 |     |

| Dynamic Clock Control (E0-E3h)                                        |     |

| DRAM Above 4G Support (E4-FFh)                                        | 744 |

| DEVICE 19 FUNCTION 0 (D19F0): PCI TO PCI BRIDGE                       | 745 |

| PCI CONFIGURATION SPACE                                               | 745 |

| Header Registers (00-3Fh)                                             | 745 |

| PCI Device-Specific Registers (40-FFh)                                | 750 |

| DEVICE 20 FUNCTION 0 (D20F0): HIGH DEFINITION AUDIO CONTROLLER (HDAC) | 751 |

| PCI CONFIGURATION SPACE                                               | 751 |

| Header Registers (00-3Fh)                                             | 751 |

| HDAC Device-Specific Configuration (40-FFh)                           | 755 |

| HDAC PCI EXTENDED CONFIGURATION SPACE                                 |     |

| HDAC PCI Extended Configuration (100-260h)                            | 759 |

| HIGH DEFINITION AUDIO CONTROLLER MEMORY MAPPED I/O SPACE (HDAC-MMIO)  | 762 |

| Global Capabilities and Control (00-1Bh)                              |     |

| Reserved Registers (1C-1Fh)                                           |     |

| Interrupt Control (20-27h)                                            |     |

| Reserved Registers (28-2Fh)                                           |     |

| Synchronization Control (30-3Bh)                                      |     |

| Reserved Registers (3C-3Fh)                                           |     |

| HDAC CORB (Command Output Ring Buffer) Control (40-4Fh)               |     |

| HDAC RIRB (Response Input Ring Buffer) Control (50-5Fh)               |     |

| HDAC Immediate Command Control (60-69h)                               |     |

| Reserved Registers (6A-6Fh)                                           |     |

| DMA Position Base Address (70-77h)                                    |     |

| Reserved Registers (78-7Fh)                                           |     |

| HDAC Stream Descriptors (80-17Fh)                                     |     |

| Reserved Registers (180-202Fh)                                        |     |

| Alias Registers (2030-2167h)                                          | 779 |

# LIST OF TABLES

| TABLE 1. VX900M AND VX900 FEATURE COMPARISON TABLE                                           |            |

|----------------------------------------------------------------------------------------------|------------|

| TABLE 2. MEMORY MAPPED I/O APIC REGISTERS SUMMARY TABLE                                      | 7          |

| TABLE 3. I/O REDIRECTION TABLE                                                               | 9          |

| TABLE 4. DEFINITIONS OF REQUEST SIGNALS FOR P4 BUS PROTOCOL                                  | 32         |

| TABLE 5. TRANSACTION TYPES DEFINED BY HREQA# AND HREQB# SIGNALS                              | 33         |

| TABLE 6. DATA TRANSFER BURST ORDER                                                           | 33         |

| TABLE 7. RX50 DYNAMIC DEFER SNOOP STALL TABLE                                                | 39         |

| TABLE 8. RX51 THE CPU BUS CONTROLLER'S RESPONSE FOR DIFFERENT CYCLES AT DIFFERENT            |            |

| REGISTER SETTINGS                                                                            | 41         |

| TABLE 9. DRAM WRITE RETIRE POLICY                                                            | 42         |

| TABLE 10. ENABLING OF FAST TRDY FEATURE                                                      |            |

| TABLE 11. DRAM WRITE RETIRE POLICY ADJUSTMENTS IN HOSTBW PERIOD AND DRAMBW PERIOI            | ) 52       |

| TABLE 12. COMPLETE DRAM SUPPORTING MODE                                                      | 102        |

| TABLE 13. RX50 NUMBER OF BITS FOR BANK / ROW / COLUMN ADDRESS SUPPORTED FOR DIFFEREN         | JT MA      |

| MAP TYPE                                                                                     | 112        |

| TABLE 14. RX52 BANK ADDRESS SELECTIONS                                                       | 114        |

| TABLE 15. RX53 BANK ADDRESS SELECTIONS                                                       |            |

| TABLE 16. RX61 WRITE MERGING OPTIONS WITH RX62[7:4] =A AND RX62[3:0] =B                      | 122        |

| TABLE 17. RX6B A TYPICAL MA MAPPING FOR A MRS COMMAND                                        |            |

| TABLE 18. RX6E.1 DRAM DATA BURST ORDER FOR DDR2 (RX6C[7] = 0)                                |            |

| TABLE 19. RX6E.2 DRAM DATA BURST ORDER FOR DDR3 (RX6C[7] = 1)                                | 132        |

| TABLE 20. RX78.1: DETAIL REGISTER DESCRIPTIONS FOR RX78                                      | 144        |

| TABLE 21. RX84.1 ON BOARD DECODING FOR RX84[0]                                               |            |

| TABLE 22. RX9C.1 MODTO ASSERTION LOGIC FOR DDR3 AND DDR2 SYSTEM                              |            |

| TABLE 23. RX9E.1 SUGGESTED SETTING FOR RX9E[5:4], RX9F[1:0,5:4,7:6] FOR DDR2/DDR3 AT DIFFERE | ENT        |

| FREQUENCY                                                                                    | 160        |

| FREQUENCYTABLE 24. RXAA: THE CLOCK BEHAVIOR OF THE PCIE'S PLL ON DIFFERENT REGISTERS SETTING |            |

| SPECIFIED AT RXAA[3:0]                                                                       |            |

| TABLE 25. RX90.1: BITS DEFINITION FOR RX91-90H                                               | 268        |

| TABLE 26. RX90.2: PANEL TYPE SELECTION                                                       |            |

| TABLE 27. RX92.1: BITS DEFINITION FOR RX93-92H                                               |            |

| TABLE 28. PCIE LANE CONFIGURATION OF THIS CHIP                                               |            |

| TABLE 29. RX70. DE-EMPHASIS VALUE FOR THE TRANSMITTING CIRCUIT                               |            |

| TABLE 30. PHYLS_STATE_PE0-3_[7:0] MAPPING                                                    |            |

| TABLE 31. TUNING FUNCTION BIST EVENT SELECTION FOR GEN 1                                     | 404        |

| TABLE 32. TUNING FUNCTION BIST EVENT SELECTION FOR GEN 2                                     |            |

| TABLE 33. SYSTEM I/O PORTS MAP                                                               |            |

| TABLE 34. KEYBOARD CONTROLLER COMMAND CODES                                                  |            |

| TABLE 35. CMOS REGISTER SUMMARY                                                              |            |

| TABLE 36. I/O REDIRECTION TABLE                                                              |            |

| TABLE 37. PCI UART DEBUG PIN SELECTION SCHEME                                                |            |

| TABLE 38. PCI UART HIGH BAUD RATE CONTROL                                                    |            |

| TABLE 39. DETERMINATION OF TRANSFER TYPE                                                     |            |

| TABLE 40. PCI CARD READER-SPECIFIC MMIO REGISTERS                                            |            |

| TABLE 41. COMMAND TYPE FIELD ENCODINGS                                                       |            |

| TABLE 42. RX58[1]                                                                            |            |

| TABLE 43. PNP IRQ ROUTING TABLE                                                              |            |

| TABLE 44. INTERNAL APIC, PCI DEVICES IRQ ROUTING TABLE                                       |            |

| TABLE 45. HPET IRQ ROUTING TABLE                                                             |            |

| TABLE 46. C3 LATENCY CONFIGURATION TABLE                                                     |            |

| TABLE 47, C4 LATENCY CONFIGURATION TABLE                                                     | 672<br>673 |

# **LIST OF FIGURES**

| FIGURE 1. SYSTEM BLOCK DIAGRAM FOR D0F0                                                                                             |                       |

|-------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| FIGURE 2. REGISTER LEVEL BLOCK DIAGRAM FOR D0F0                                                                                     |                       |

| FIGURE 3. SYSTEM BLOCK DIAGRAM FOR D0F1                                                                                             |                       |

| FIGURE 4. REGISTER LEVEL BLOCK DIAGRAM FOR D0F1                                                                                     | 24                    |

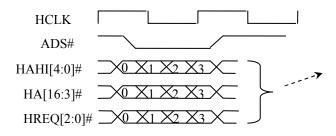

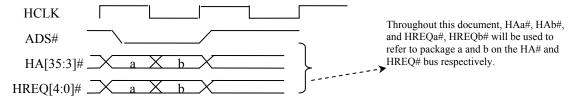

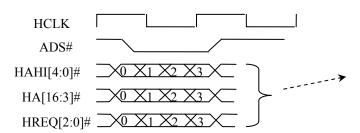

| FIGURE 5. RX60.1 VIA'S V4 BUS ADDRESS CONVEYING MECHANISM – 4X SAMPLING                                                             | 29                    |

| FIGURE 6. SYSTEM BLOCK DIAGRAM FOR D0F2                                                                                             | 31                    |

| FIGURE 7. INTEL'S P4 BUS ADDRESS CONVEYING MECHANISM – 2X SAMPLING                                                                  | 32                    |

| FIGURE 8. VIA'S V4 BUS ADDRESS CONVEYING MECHANISM – 4X SAMPLING                                                                    |                       |

| FIGURE 9. A TYPICAL BEHAVIOR OF HOSTBW AND DRAMBW WHEN RX5F[2] AND RX5F[1] ARE BOT                                                  | H                     |

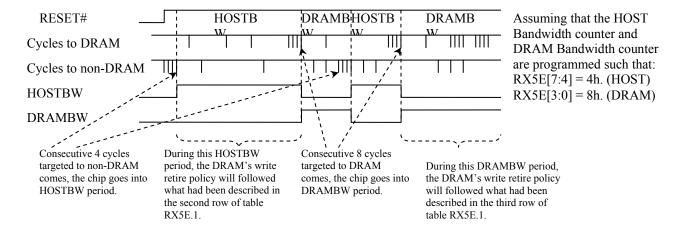

| PROGRAMMED TO 1                                                                                                                     | 52                    |

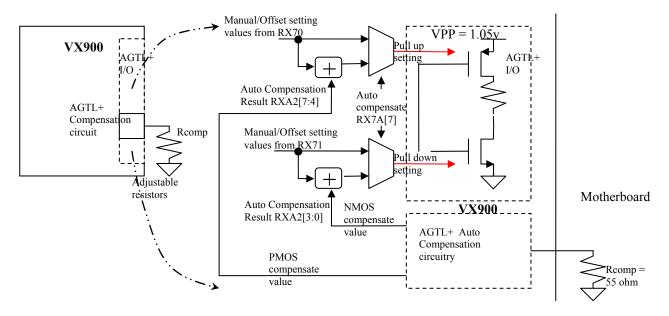

| PROGRAMMED TO 1FIGURE 10. PULL UP AND PULL DOWN RESISTANCE REGISTER CONTROL ON THE AGTL+ I/O – USE                                  | HA AS                 |

| AN EXAMPLE                                                                                                                          | 57                    |

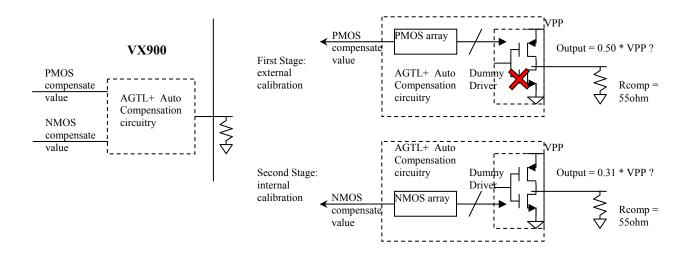

| FIGURE 11. CALIBRATION PROCESS FOR THE AGTL+ AUTO COMPENSATION CIRCUITRY                                                            | 57                    |

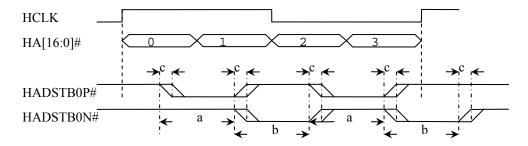

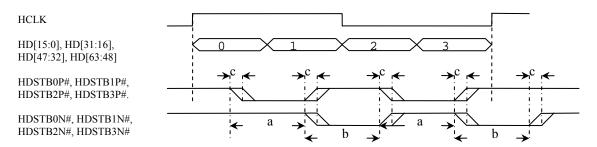

| FIGURE 12. TIMING RELATIONSHIP FOR THE ADDRESS AND ADDRESS STROBE ON THE V4 BUS                                                     | 65                    |

| FIGURE 13. TIMING RELATIONSHIP FOR THE DATA AND DATA STROBE ON THE V4 BUS                                                           | 67                    |

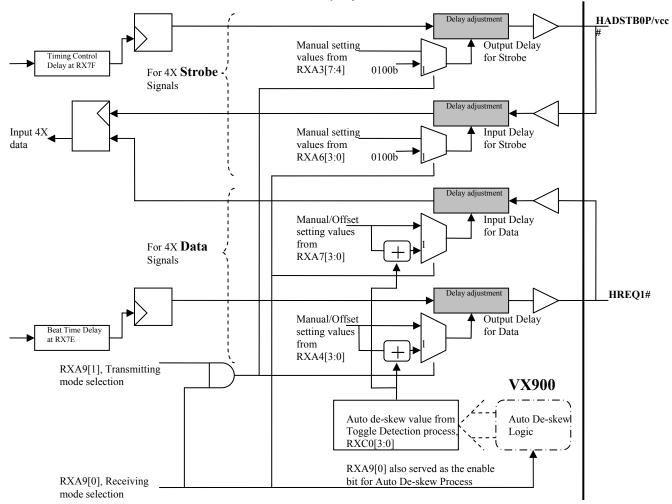

| FIGURE 14. STRUCTURE OF OUTPUT AND INPUT DELAY ADJUSTMENT FOR STROBE AND HA/HD SIG                                                  | GNALS                 |

|                                                                                                                                     |                       |

| FIGURE 15. SYSTEM BLOCK DIAGRAM FOR D0F3                                                                                            | 101                   |

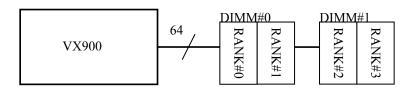

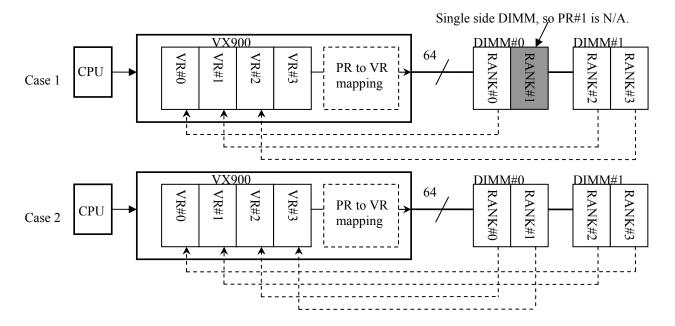

| FIGURE 16. VX900 SERIES DRAM SUPPORTING SCHEMES                                                                                     | 102                   |

| FIGURE 17. EXAMPLES OF PHYSICAL RANK (PR) TO VIRTUAL RANK (VR) MAPPING                                                              |                       |

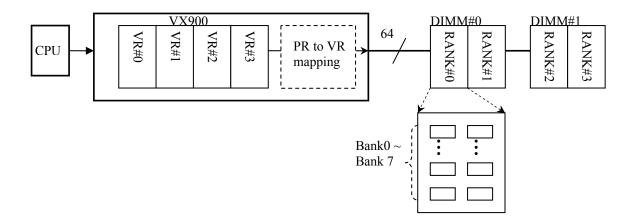

| FIGURE 18. BANK STRUCTURE IN THE DRAM DIMM                                                                                          | 104                   |

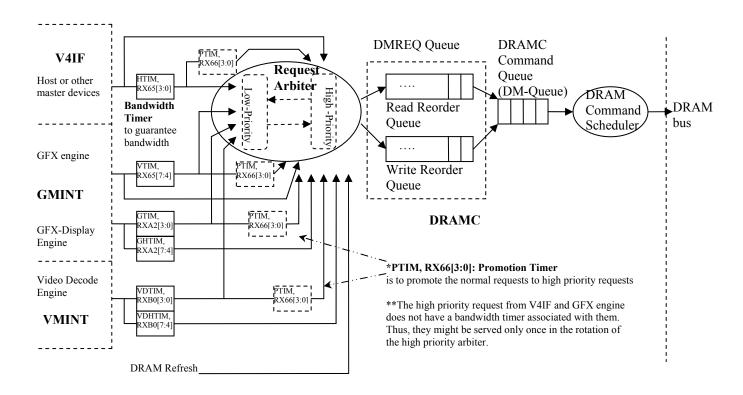

| FIGURE 19. RX61.1 THE STRUCTURE OF THE REQUEST ARBITER, REQUEST QUEUES AND THE COM                                                  |                       |

| SCHEDULER IN DRAMC                                                                                                                  | 122                   |

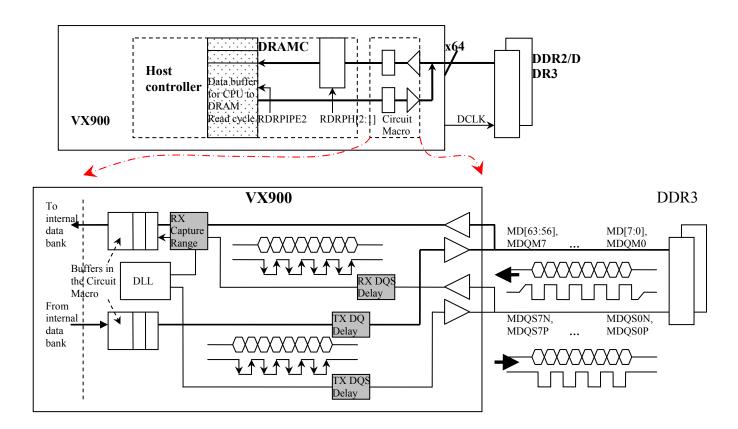

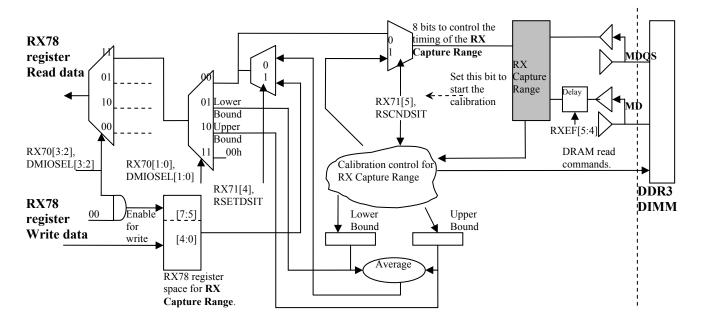

| FIGURE 20. RX70.1 TIMING CONTROL FOR THE DDR3 I/O RECEIVING AND TRANSMITTING                                                        |                       |

| FIGURE 21. RX70.2 AND RX78 RELATED STRUCTURE WHEN RX70[3:2] = 11B, WHICH IS TO CONTROL                                              | THE                   |

| SETTING OF RX CAPTURE RANGE                                                                                                         |                       |

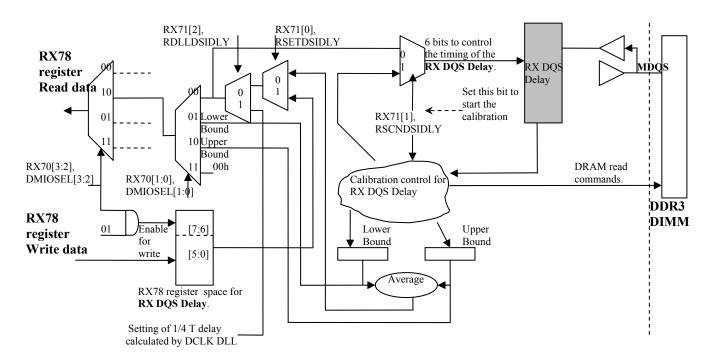

| FIGURE 22. RX70.3 AND RX78 RELATED STRUCTURE WHEN RX70[3:2] = 10B, WHICH IS TO CONTROL                                              | THE                   |

| SETTING OF RY DOS DELAY                                                                                                             | 136                   |

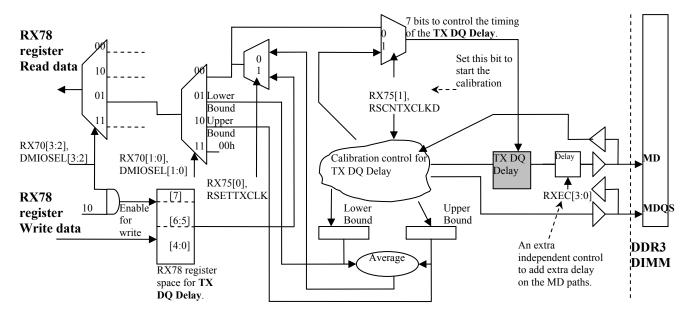

| SETTING OF RX DQS DELAYFIGURE 23. RX70.4 AND RX78 RELATED STRUCTURE WHEN RX70[3:2] = 01B, WHICH IS TO CONTROL                       | THE                   |

| SETTING OF TX DQ DELAY                                                                                                              |                       |

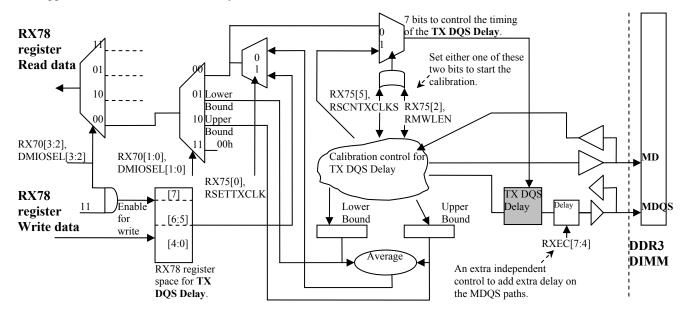

| FIGURE 24. RX70.5 AND RX78 RELATED STRUCTURE WHEN RX70[3:2] = 00B, WHICH IS TO CONTROL                                              | 150<br>THE            |

| SETTING OF TX DQS DELAY                                                                                                             |                       |

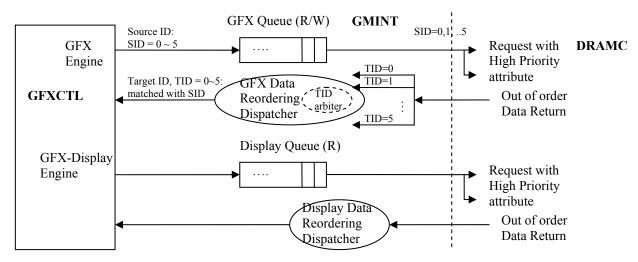

| FIGURE 25. RXA3.1 STRUCTURE OF REQUESTS AND DATA RETURN HANDLING UNITS OF THE GMIN                                                  | 1 <i>57</i><br>IT 163 |

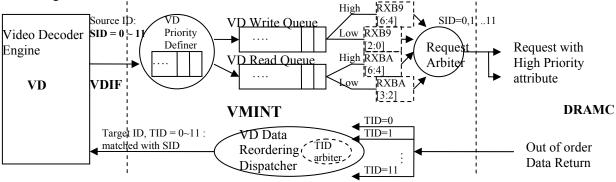

| FIGURE 26. RXB1.1 STRUCTURE OF REQUESTS AND DATA RETURN HANDLING UNITS OF THE VMIN                                                  |                       |

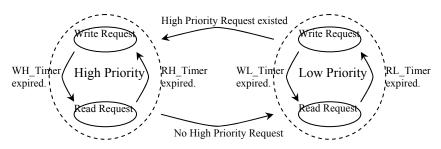

| FIGURE 27. RXB1.2. THE OWNERSHIP SHIFTING FOR THE REQUEST ARBITER                                                                   |                       |

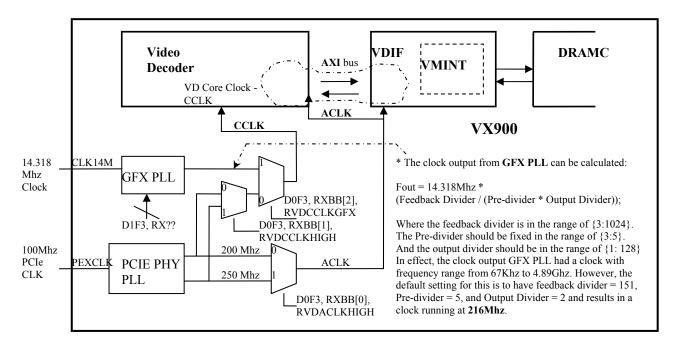

| FIGURE 28. RXBB.1 CLOCKING SCHEME OPTIONS USED FOR VIDEO DECODER                                                                    |                       |

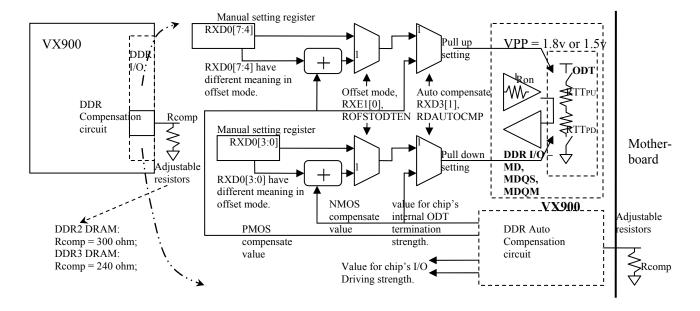

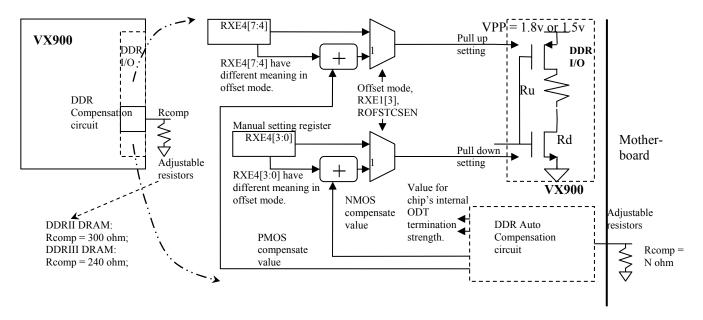

| FIGURE 29. RXD0.1 PULL-UP AND PULL-DOWN RESISTANCE REGISTER CONTROL FOR INTERNAL O                                                  |                       |

| TERMINATION STRENGTHTERMINATION STRENGTH                                                                                            |                       |

| FIGURE 30. RXD0.2 PULL-UP AND PULL-DOWN RESISTANCE REGISTER CONTROL FOR DRIVING                                                     | 103                   |

| STRENGTH OF MCS[3:0]#                                                                                                               | 196                   |

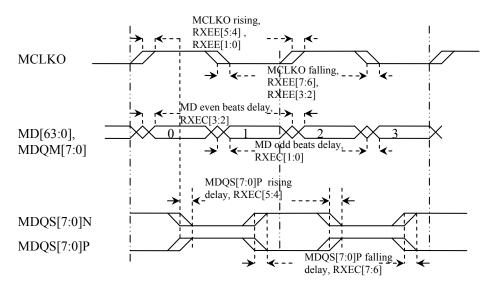

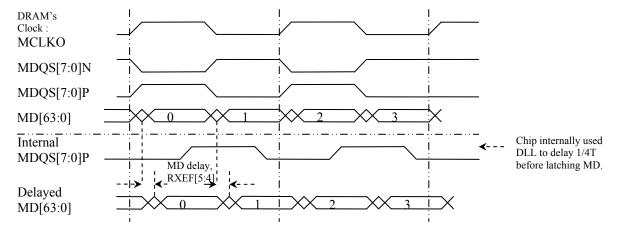

| FIGURE 31. RXEC.1 OUTPUT DELAY TIMING CONTROL FOR MD, MDQM, MDQS AND MCLKO                                                          |                       |

| FIGURE 32. RXEF.1 INPUT DELAY TIMING CONTROL FOR MDFIGURE 32. RXEF.1 INPUT DELAY TIMING CONTROL FOR MD                              |                       |

| FIGURE 32. RXEF.1 INPUT DELAY TIMING CONTROL FOR MDFIGURE 33. SYSTEM BLOCK DIAGRAM FOR D0F4                                         |                       |

| FIGURE 34. REGISTER LEVEL BLOCK DIAGRAM FOR D0F4                                                                                    |                       |

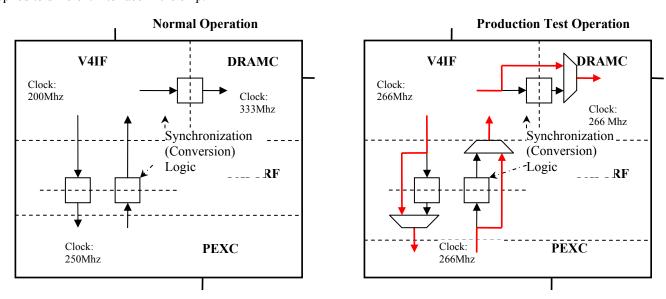

| FIGURE 34. REGISTER LEVEL BLOCK DIAGRAM FOR DUF4FIGURE 35. RX44.1 ASYNCHRONOUS CIRCUIT & BYPASSING LOGIC FOR CHIP PRODUCTION TEST M | 209<br>40DE           |

|                                                                                                                                     |                       |

| EICHDE 27 DV00 1 DVNAMIC CLOCK CTOD EFATIDE. LICE VAIE AC AN EVAMBLE                                                                |                       |

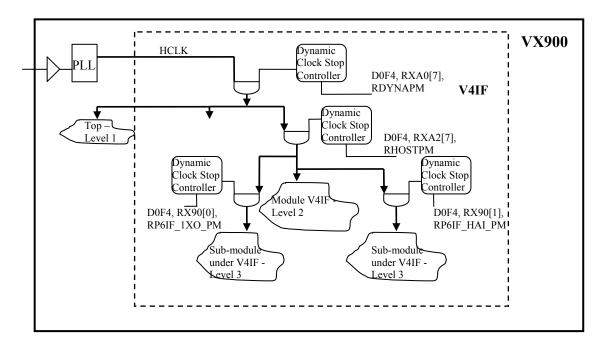

| FIGURE 36. RX80.1 DYNAMIC CLOCK STOP FEATURE - USE V4IF AS AN EXAMPLE                                                               |                       |

| FIGURE 37. SYSTEM BLOCK DIAGRAM FOR D0F5                                                                                            |                       |

| FIGURE 38. REGISTER LEVEL BLOCK DIAGRAM FOR D0F5                                                                                    |                       |

| FIGURE 39. RX88.1 FLOW CONTROL FOR VIDEO DECODER'S DATA IN BETWEEN VD AND PXPTRF                                                    |                       |

| FIGURE 40. SYSTEM BLOCK DIAGRAM FOR D0F6                                                                                            |                       |

| FIGURE 41. REGISTER LEVEL BLOCK DIAGRAM FOR D0F6                                                                                    |                       |

| FIGURE 42. SYSTEM BLOCK DIAGRAM FOR D0F7                                                                                            |                       |

| FIGURE 43. REGISTER LEVEL BLOCK DIAGRAM FOR D0F7                                                                                    | 285                   |

| 2 |

|---|

| 3 |

| 4 |

| 6 |

| 8 |

| 9 |

| 8 |

| 3 |

| 9 |

| 7 |

|   |

### **REGISTER OVERVIEW**

### **Register Document Introduction**

This document includes the registers for VIA VX900 Series. Please refer to Table 1 for the specification differences of VX900 Series products.

VX900 Series is an all-in-one system processor that integrates functional modules of the traditional North Module and South Module, plus 3D/2D and Video Processors, Video Decoding Accelerator and controller for external display interface. The register set is partitioned into two blocks: System Processor and Graphics and Video Module; of which, processor related registers are described in this **System Programming Manual** while graphics and video registers are described in the **Graphics Programming Guide**.

Table 1. VX900M and VX900 Feature Comparison Table

| Product Model   | VX900M<br>VX900MH *    | VX900<br>VX900H *  |

|-----------------|------------------------|--------------------|

| FSB Speed (MHz) | 400-800                | 400-1066           |

| Memory Type     | Single channel         | Single channel     |

|                 | DDR2 667               | DDR2 800           |

|                 | DDR3 800               | DDR3 1066          |

| PCI Express     | 3 ports: 3*1           | 4 ports: 1*8 + 3*1 |

|                 | Gen1 (1.1)             | Gen2 (1.1 / 2.0)   |

| Video Interface | LVDS – single channel  |                    |

| HDMI – 1 port   |                        | 1 port             |

|                 | Display Port – 2 ports |                    |

| Video Decoding  | HD capable BD capable  |                    |

| Core Voltage    | 1.0V 1.2V              |                    |

Note: VX900H and VX900MH are with HDCP capability supported, while VX900 and VX900M are not.

### **Module and Register Scope Definitions**

### **Module Name Abbreviations**

**NM:** North Module. It contains functional modules of the traditional North Bridge chip. **SM:** South Module. It contains functional modules of the traditional South Bridge chip.

**NSMIC:** North-South Module Interface Control **SNMIC:** South-North Module Interface Control

PM: Power Management

**HDAC:** High Definition Audio Controller

### **Register Scope Map Within Modules**

To specifically identify every function, the following abbreviations will be applied in subsequent sections.

| Abbreviation of<br>Register Space /<br>Module Name | Register Space           | Function                                            |

|----------------------------------------------------|--------------------------|-----------------------------------------------------|

| North Module                                       |                          |                                                     |

| D0F0                                               | PCI Device 0, Function 0 | GFX Access and Debugging Control                    |

| D0F1                                               | PCI Device 0, Function 1 | Error Reporting                                     |

| D0F2                                               | PCI Device 0, Function 2 | Host Bus Control                                    |

| D0F3                                               | PCI Device 0, Function 3 | DRAM Bus Control                                    |

| D0F4                                               | PCI Device 0, Function 4 | Power Management and Chip Testing Control           |

| D0F5                                               | PCI Device 0, Function 5 | Central Traffic Control and APIC                    |

| D0F6                                               | PCI Device 0, Function 6 | Scratch Registers                                   |

| D0F7                                               | PCI Device 0, Function 7 | North-South Module Interface Control <b>NSMIC</b> > |

| D3F0                                               | PCI Device 3, Function 0 | PCI Express Root Port 0 – x8, x4, x2, x1            |

| D3F1                                               | PCI Device 3, Function 1 | PCI Express Root Port 1 – x2,x1                     |

| D3F2                                               | PCI Device 3, Function 2 | PCI Express Root Port 2 – x1                        |

| D3F3                                               | PCI Device 3, Function 3 | PCI Express Root Port 3 – x1                        |

| D3F4                                               | PCI Device 3, Function 4 | PCI Express EPHY Block                              |

| RCRBH                                              | Memory Space             | PCI Express Root Complex Register Block for Host    |

| Abbreviation of  | Register Space              | Function                                                    |

|------------------|-----------------------------|-------------------------------------------------------------|

| Register Space / | <b>.</b>                    |                                                             |

| Module Name      |                             |                                                             |

|                  | Sout                        | h Module                                                    |

| D10F0~F3         | PCI Device 10, Function 0~3 | PCI UART Ports 0-3 Registers                                |

| D11F0            | PCI Device 11, Function 0   | USB Mass Storage Device                                     |

| USBD-MMIO        | Memory Space                | USB Device Memory Mapped I/O Space Registers                |

| D12F0            | PCI Device 12, Function 0   | SDIO Host Controller                                        |

| SDIO-MMIO        | Memory Space                | SDIO Memory Mapped I/O Space Registers                      |

| D13F0            | PCI Device 13, Function 0   | Card Reader Controller                                      |

| xDC-MMIO         | Memory Space                | Extreme Digital-Picture Controller Memory Mapped I/O        |

| SDC-MMIO         | Memory Space                | Security Digital Controller Memory Mapped I/O Space         |

| Data DMA-MMIO    | Memory Space                | Data DMA Memory Mapped I/O Space Registers                  |

| CICH DMA-MMIO    | Memory Space                | CICH DMA Memory Mapped I/O Space Registers                  |

| PCI Control-MMIO | Memory Space                | PCI Control Memory Mapped I/O Space Registers               |

| D15F0            | PCI Device 15, Function 0   | Serial ATA Controller                                       |

| D16F0            | PCI Device 16, Function 0   | USB 1.1 UHCI Ports 0-1                                      |

| D16F1            | PCI Device 16, Function 1   | USB 1.1 UHCI Ports 2-3                                      |

| D16F2            | PCI Device 16, Function 2   | USB 1.1 UHCI Ports 4-5                                      |

| D16F3            | PCI Device 16, Function 3   | USB 1.1 UHCI Ports 6-7                                      |

| USB 1.1-IO       | IO Space                    | USB 1.1 I/O Space Registers                                 |

| D16F4            | PCI Device 16, Function 4   | USB 2.0 EHCI Controller, Ports 0-5                          |

| USB 2.0-MMIO     | Memory Space                | EHCI USB 2.0 Memory Mapped I/O Space Registers              |

| D17F0            | PCI Device 17, Function 0   | Bus and Power Management Control                            |

| PMIO             | IO Space                    | ACPI I/O Registers                                          |

| PM-MMIO          | Memory Space                | Power Management Memory Mapped I/O Space                    |

| SMIO             | IO Space                    | System Management Bus I/O Space Registers                   |

| CEC              | MMIO Space                  | Consumer Electronics Controller                             |

| HPET             | Memory Space                | HPET Memory Mapped I/O Space Registers                      |

| SPI-MMIO         | Memory Space                | Special Peripheral Interface Memory Mapped I/O Space        |

| SPI0-MMIO        | Memory Space                | SPI Bus 0 Memory Mapped I/O Space Registers                 |

| D17F7            | PCI Device 17, Function 7   | South-North Module Interface Control <b><snmic></snmic></b> |

| D19F0            | PCI Device 19, Function 0   | PCI-to-PCI Bridge                                           |

| D20F0 / HDAC     | PCI Device 20, Function 0   | High Definition Audio Controller                            |

| HDAC-MMIO        | Memory Space                | HDAC Memory Mapped I/O Space Registers                      |

### **Register Table Format**

In the register descriptions, column "Default" indicates the power-on default value of register bit(s), while column "Attribute" indicates access type of register bit.

### **Attribute Definition**

### **Basic Attributes**

**RO:** Read Only.

**WO:** Write Only. (register value can not be read by the software)

**RW:** Read / Write.

**RW1:** Write Once then Read Only after that. **RW1C:** Read / Write of "1" clears bit to zero.

Sticky Attributes: adding a "S" in tail to indicate a sticky register, which means that register will not be set or altered by hot reset.

ROS: Sticky-Read-Only.

WOS: Sticky-Write-Only.

RWS: Sticky-Read/Write.

RW1S: Sticky-Write-Once.

RW1CS: Sticky-Write-1-to-Clear.

### **Special Default Value Definitions**

**Dip**: means the default value is set by dip switch or strapping. **HwInit**: Hardware initialized; bit default value is set by hardware.

**ROMSIP:** The default value with ROMSIP attribute is loaded from preset ROM when chipset resets.

Default Value: 0000 0000h

Default Value: 0000 0000h

### **PCI Configuration Space I/O**

All north bridge's PCI space registers are addressed via the following configuration mechanism:

### Mechanism #1

These ports respond only to double-word accesses. Byte or word accesses will be passed on unchanged.

### **I/O Port Address: CFB-CF8h**

### **PCI Configuration Address**

| Bit   | Attribute | Default | Description                                                                           |

|-------|-----------|---------|---------------------------------------------------------------------------------------|

| 31    | RW        | 0       | Configuration Space Enable                                                            |

|       |           |         | 0: Disabled                                                                           |

|       |           |         | 1: Convert configuration data port writes to configuration cycles on the PCI bus      |

| 30:24 | RO        | 0       | Reserved (always reads 0)                                                             |

| 23:16 | RW        | 0       | PCI Bus Number                                                                        |

|       |           |         | Used to choose a specific PCI bus in the system                                       |

| 15:11 | RW        | 0       | Device Number                                                                         |

|       |           |         | Used to choose a specific device in the system                                        |

| 10:8  | RW        | 0       | Function Number                                                                       |

|       |           |         | Used to choose a specific function if the selected device supports multiple functions |

| 7:2   | RW        | 0       | Register Number (also called the "Offset")                                            |

|       |           |         | Used to select a specific DWORD in the configuration space                            |

| 1:0   | RW        | 0       | Fixed (always reads 0)                                                                |

### **I/O Port Address: CFF-CFCh**

### **PCI Configuration Data**

| I | Bit  | Attribute | Default | Description            |

|---|------|-----------|---------|------------------------|

| Ī | 31:0 | RW        | 0       | PCI Configuration Data |

Note: Refer to PCI Bus Specification Version 2.3 for further details on operation of the above configuration registers.

# NORTH MODULE IRQ AND APIC CONTROL

## **PCIE Link Declaration Description**

|                 | PE0(D3F0) | PE1(D3F1) | PE2(D3F2) | PE3(D3F3) |

|-----------------|-----------|-----------|-----------|-----------|

| Device number   | 03        | 03        | 03        | 03        |

| Component ID    | 01        | 01        | 01        | 01        |

| Function number | 0         | 1         | 2         | 3         |

| Port number     | 1         | 2         | 3         | 4         |

## **IRQ** and Interrupt Assignment Table

| Internal IRQ# | Device Interrupt         |

|---------------|--------------------------|

| IRQ0          | INTA_PE0                 |

| IRQ1          | INTB_PE0                 |

| IRQ2          | INTC_PE0                 |

| IRQ3          | INTD_PE0 or MSGC_INT_PE0 |

| IRQ4          | INTA_PE1                 |

| IRQ5          | INTB_PE1                 |

| IRQ6          | INTC_PE1                 |

| IRQ7          | INTD_PE1 or MSGC_INT_PE1 |

| IRQ8          | INTA_PE2                 |

| IRQ9          | INTB_PE2                 |

| IRQ10         | INTC_PE2                 |

| IRQ11         | INTD_PE2 or MSGC_INT_PE2 |

| IRQ12         | INTA_PE3                 |

| IRQ13         | INTB_PE3                 |

| IRQ14         | INTC_PE3                 |

| IRQ15         | INTD_PE3 or MSGC_INT_PE3 |

| IRQ16         | USINTA                   |

| IRQ17         | USINTB                   |

| IRQ18         | Reserved                 |

| IRQ19         | Reserved                 |

| IRQ20         | Reserved                 |

| IRQ21         | Reserved                 |

| IRQ22         | Reserved                 |

| IRQ23         | Reserved                 |

### **APIC Register I/O**

### Memory Mapped I/O APIC Registers

The IO APIC registers are accessed by an indirect addressing scheme using Index Registers and Data Registers that are mapped into memory space.

Table 2. Memory Mapped I/O APIC Registers Summary Table

| Memory Address | Function               | Size   |

|----------------|------------------------|--------|

| FECxyz00       | APIC Index             | 8 bit  |

| FECxyz10       | APIC Data              | 32 bit |

| FECxyz20       | APIC IRQ Pin Assertion | 8 bit  |

| FECxyz40       | APIC EOI               | 8 bit  |

Please reference D0F5 Rx40[3:0] and Rx41[7:0] for the control  $x,\,y,\,z$

### Memory Address: FECxyz00h

APIC Index Default Value: 0000 0000h

| Bit  | Attribut | Default | Description                             |

|------|----------|---------|-----------------------------------------|

| 31:8 | RO       | 0       | Reserved                                |

| 7:0  | RW       | 0       | I/O APIC Index                          |

|      |          |         | 8-bit pointer to the I/O APIC register. |

### Memory Address: FECxyz10h

APIC Data Default Value: 0000 0000h

| Bit  | Attribut | Default | Description                                                                                                                                 |

|------|----------|---------|---------------------------------------------------------------------------------------------------------------------------------------------|

| 31:0 | RW       | 0       | I/O APIC Data This is a 32-bit register for the data to be read or written to the I/O APIC indirect register pointed by the Index Register. |

### Memory Address: FECxyz20h

APIC IRQ Pin Assertion Default Value: nnh

| Bit | Attribut | Default | Description                                                                                                  |

|-----|----------|---------|--------------------------------------------------------------------------------------------------------------|

| 7:5 | RO       | 0       | Reserved                                                                                                     |

| 4:0 | WO       | nnh     | IRQ Number                                                                                                   |

|     |          |         | Bit[4:0] written to this register contain the IRQ number for this interrupt. The only valid values are 0-23. |

### Memory Address: FECxyz40h

APIC EOI Default Value: nnh

| Bit | Attribut | Default | Description                                                                                                                        |

|-----|----------|---------|------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | WO       | nnh     | Redirection Entry Clear                                                                                                            |

|     |          |         | When a write is issued to this register, the I/O APIC will check this field and compare it with the vector field for each entry in |

|     |          |         | the I/O Redirection Table. When a match is found, the "Remote_IRR" bit for that I/O Redirection Entry will be cleared.             |

### **Indexed I/O APIC Registers**

For index registers setting, please refer to Memory Address FECxyz00h (APIC Index) and FECxyz10 (APIC Data).

### Index: 00h I/O APIC Identification Default Value: 0000 0000h

| Bit   | Attribut | Default | Description                                                 |

|-------|----------|---------|-------------------------------------------------------------|

| 31:28 | RO       | 0       | Reserved                                                    |

| 27:24 | RW       | 0       | I/O APIC Identification                                     |

|       |          |         | Software must program this value before using the I/O APIC. |

| 23:0  | RO       | 0       | Reserved                                                    |

### Index: 01h

I/O APIC Version Default Value: 0017 8003h

| Bit   | Attribut | Default | Description                                                                                                                       |

|-------|----------|---------|-----------------------------------------------------------------------------------------------------------------------------------|

| 31:24 | RO       | 0       | Reserved                                                                                                                          |

| 23:16 | RO       | 17h     | Maximum Redirection Entry                                                                                                         |

|       |          |         | This value is equal to the number of interrupt input pins for the I/O APIC minus one. For this I/O APIC, the value is 17h.        |

| 15    | RO       | 1b      | PCI IRQ                                                                                                                           |

|       |          |         | This bit is set to 1 to indicate that this version of the I/O APIC implements the IRQ Assertion register and that PCI devices are |

|       |          |         | allowed to write to it to cause interrupt.                                                                                        |

| 14:8  | RO       | 0       | Reserved                                                                                                                          |

| 7:0   | RO       | 03h     | APIC Version                                                                                                                      |

|       |          |         | The implementation version for this I/O APIC is 03h.                                                                              |

### Index: 02h

**I/O APIC** Arbitration Default Value: 0000 0000h

| Bit   | Attribut | Default | Description             |

|-------|----------|---------|-------------------------|

| 31:28 | RO       | 0       | Reserved                |

| 27:24 | RO       | 0       | I/O APIC Arbitration ID |

| 23:0  | RO       | 0       | Reserved                |

### Index: 03h

**Boot Configuration** Default Value: 0000 0000h

| Bit  | Attribut | Default | Description                                                  |

|------|----------|---------|--------------------------------------------------------------|

| 31:1 | RO       | 0       | Reserved                                                     |

| 0    | RW       | 0       | Delivery Type                                                |

|      |          |         | 0: Interrupt Delivery Mechanism is via the APIC Serial Bus.  |

|      |          |         | 1: Interrupt Delivery Mechanism is a Front-side Bus Message. |

Index: 10-3Fh

### **I/O Redirection Table**

There are 24 64-bit I/O Redirection Table entry registers. Each register is a dedicated entry for each interrupt input signal.

**Table 3. I/O Redirection Table**

| Index  | Function                          |

|--------|-----------------------------------|

| 11-10h | I/O APIC Redirection – APIC IRQ0  |

| 13-12h | I/O APIC Redirection – APIC IRQ1  |

| 15-14h | I/O APIC Redirection – APIC IRQ2  |

| 17-16h | I/O APIC Redirection – APIC IRQ3  |

| 19-18h | I/O APIC Redirection – APIC IRQ4  |

| 1B-1Ah | I/O APIC Redirection – APIC IRQ5  |

| 1C-1Dh | I/O APIC Redirection – APIC IRQ6  |

| 1E-1Fh | I/O APIC Redirection – APIC IRQ7  |

| 21-20h | I/O APIC Redirection – APIC IRQ8  |

| 23-22h | I/O APIC Redirection – APIC IRQ9  |

| 25-24h | I/O APIC Redirection – APIC IRQ10 |

| 27-26h | I/O APIC Redirection – APIC IRQ11 |

| 29-28h | I/O APIC Redirection – APIC IRQ12 |

| 2B-2Ah | I/O APIC Redirection – APIC IRQ13 |

| 2D-2Ch | I/O APIC Redirection – APIC IRQ14 |

| 2F-2Eh | I/O APIC Redirection – APIC IRQ15 |

| 31-30h | I/O APIC Redirection – APIC IRQ16 |

| 33-32h | I/O APIC Redirection – APIC IRQ17 |

| 35-34h | I/O APIC Redirection – APIC IRQ18 |

| 37-36h | I/O APIC Redirection – APIC IRQ19 |

| 39-38h | I/O APIC Redirection – APIC IRQ20 |

| 3B-3Ah | I/O APIC Redirection – APIC IRQ21 |

| 3D-3Ch | I/O APIC Redirection – APIC IRQ22 |

| 3F-3Eh | I/O APIC Redirection – APIC IRQ23 |

### I/O Redirection Entry

### Default Value: nnn1 nnnn nnnn nnnnh

| Bit   | Attribut | Default | Description                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

|-------|----------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 63:56 | RW       | nnh     | Destination Field In Physical Mode (bit-11=0), bits [59:56] contain an APIC ID. In Logical Mode (bit-11=1), bits [63:56] of the Destination Field specify the logical destination address.                                                                                                                                                                                                                                     |  |  |

|       |          |         | Destination Mode IOREDTBLx[11] Logical Destination Address  0: Physical Mode IOREDTBLx[59:56] = APIC ID  1: Logical Mode IOREDTBLx[63:56] = Set of  processors                                                                                                                                                                                                                                                                 |  |  |

| 55:17 | RO       | 0       | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

| 16    | RW       | 0       | Interrupt Mask 0: Not Mask 1: Masked                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

| 15    | RW       | 0       | Trigger Mode Indicates the type of signal on the interrupt pin that triggers an interrupt.  0: Edge Sensitive  1: Level Sensitive                                                                                                                                                                                                                                                                                              |  |  |

| 14    | RO       | 0       | Remote Interrupt Request Register (IRR)  This bit is used for level triggered interrupts. Its meaning is undefined for edge triggered interrupts. For level triggered interrupts, this bit is set to 1 when local APIC(s) accept the level interrupt sent by the IOAPIC.  0: EOI message with a matching interrupt vector is received from a local APIC  1: Level sensitive interrupt sent by IOAPIC accepted by local APIC(s) |  |  |

| 13    | RW       | 0       | Interrupt Input Pin Polarity Specifies the polarity of the interrupt signal.  0: High active  1: Low active                                                                                                                                                                                                                                                                                                                    |  |  |

| 12    | RO       | 0       | Delivery Status  Contains the current status of the delivery of this interrupt.  0: Idle (there is currently no activity for this interrupt.)  1: Send Pending (the interrupt has been injected but its delivery is temporarily held either because the APIC bus is busy or because the receiving APIC unit can not currently accept the interrupt.)                                                                           |  |  |

| 11    | RW       | 0       | Destination Mode Determines the interpretation of the Destination field. 0: Physical Mode  1: Logical Mode                                                                                                                                                                                                                                                                                                                     |  |  |

| 10:8  | RW       | 000Ь    | Delivery Mode Specify how the APICs listed in the destination field should act upon reception of this signal.  000: Fixed 001: Lowest Priority 010: SMI 011: Reserved 100: NMI 101: INIT 110: Reserved 111: ExtINT                                                                                                                                                                                                             |  |  |

| 7:0   | RW       | nnh     | Interrupt Vector Contain the interrupt vector for this interrupt. Vector values range from 10h to FEh.                                                                                                                                                                                                                                                                                                                         |  |  |

# **DEVICE 0 FUNCTION 0 (D0F0): HOST CONTROLLER**

### **PCI Configuration Space**

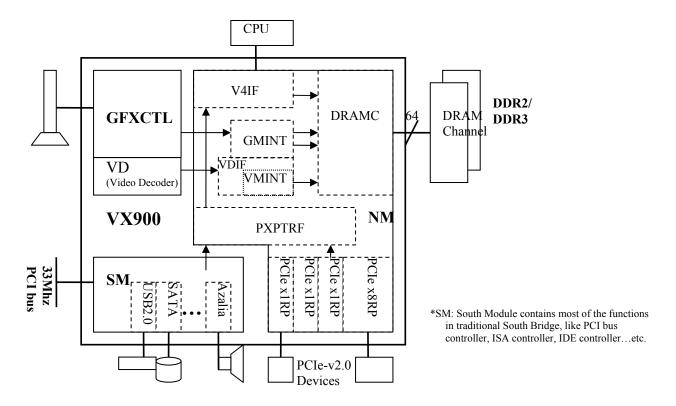

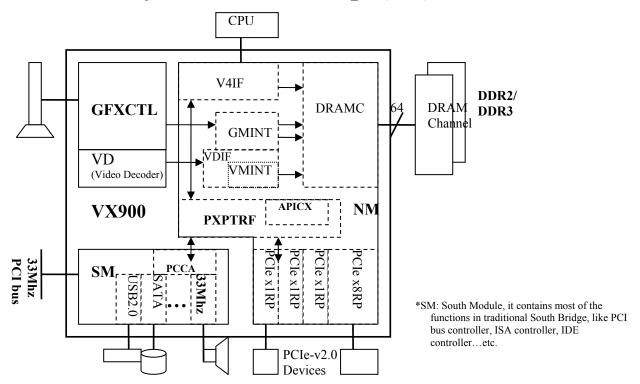

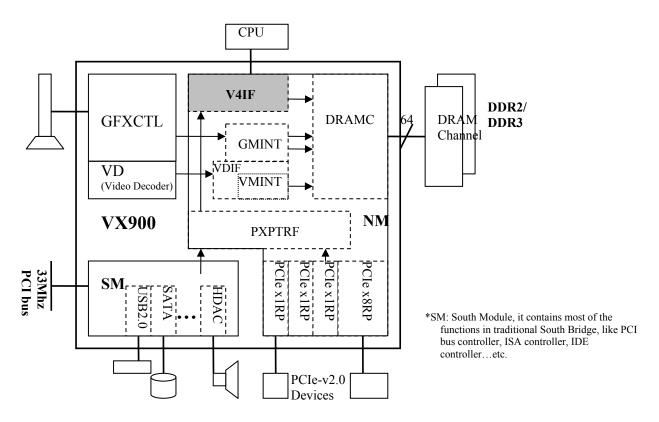

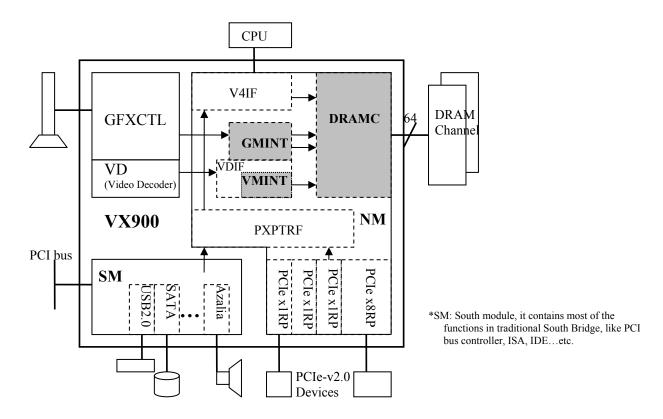

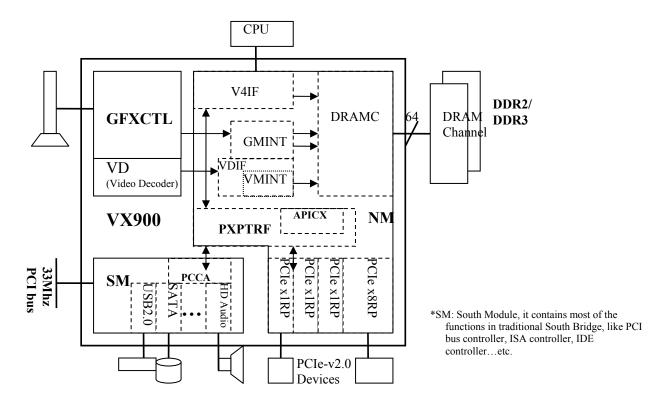

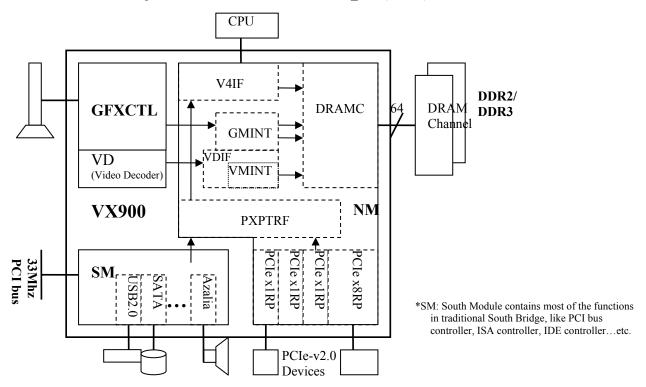

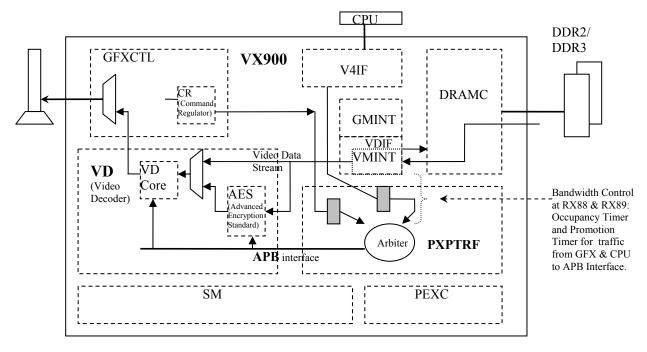

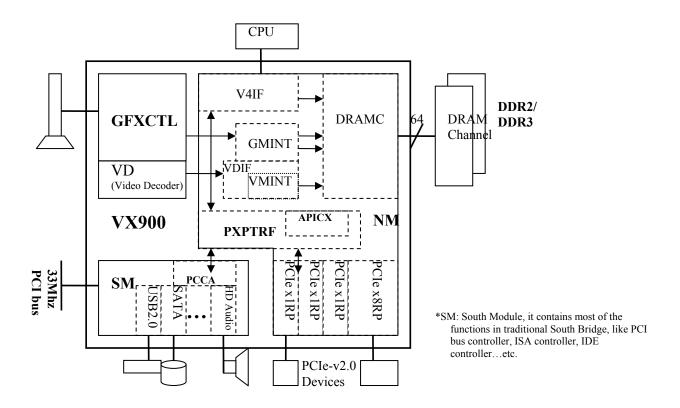

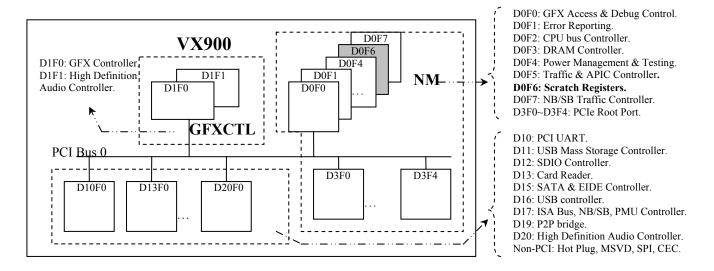

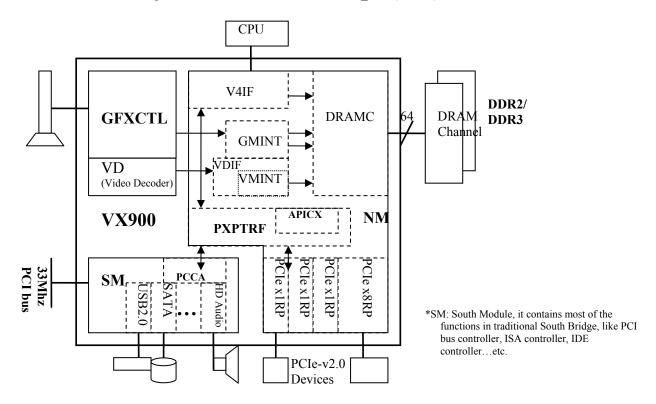

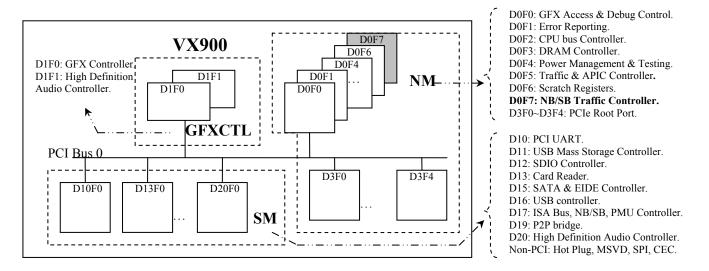

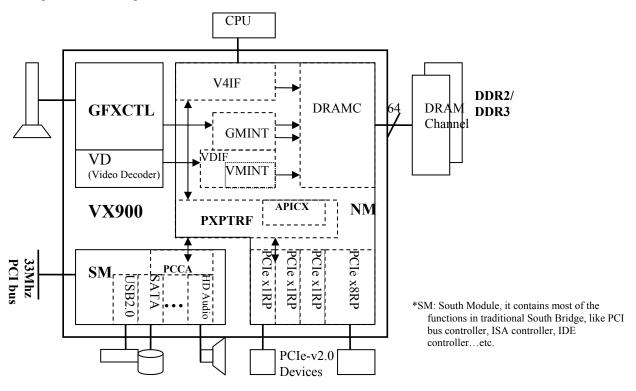

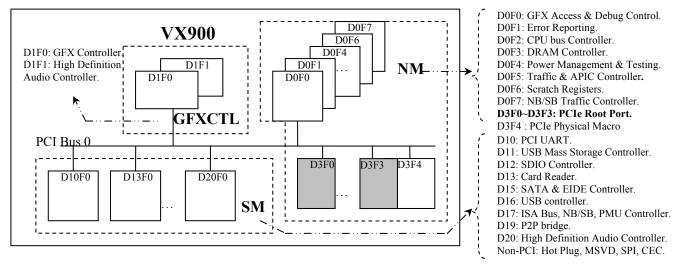

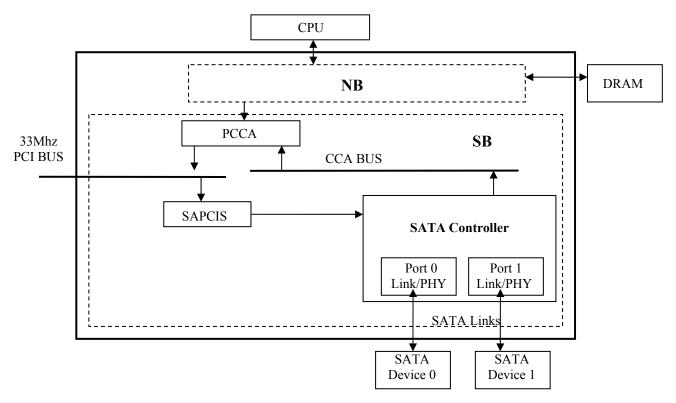

The VX900 Series integrates the functions of conventional chipset North Bridge, South Bridge and the Graphics Controller (GFXCTL) into one single chip. The traditional functions of North Bridge is included in the North Module (NM) of this chip; while the functions of traditional South Bridge, like PCI bus controller and ISA controller, are included in the South Module (SM) of this chip, as shown in Figure 1 below.

Device 0 Function 0 is a Host Bridge. All registers in this function are located in PCI configuration space and should be programmed using PCI configuration mechanism 1 through I/O registers CF8 / CFC with bus number 0, device number 0 and function number 0. For example: I/O write CF8h, with the data having the following format.

| Bit-31 | Bits [30:24] | Bits [23:16] | Bits [15:11]     | Bits [10:8]        | Bits [7: 2]        | Bit-1                | Bit-0 |

|--------|--------------|--------------|------------------|--------------------|--------------------|----------------------|-------|

| Enable | Reserved     | Bus Number   | Device<br>Number | Function<br>Number | Register<br>Number | 0                    | 0     |

| 1      | 000_0000     | 0000_0000    | 0_0000           | 000                | RX v               | alue with bit[1:0] = | = 00b |

And then I/O read CFCh, to get the data or I/O write CFCh, written\_data (32 bits).

Figure 1. System Block Diagram for D0F0

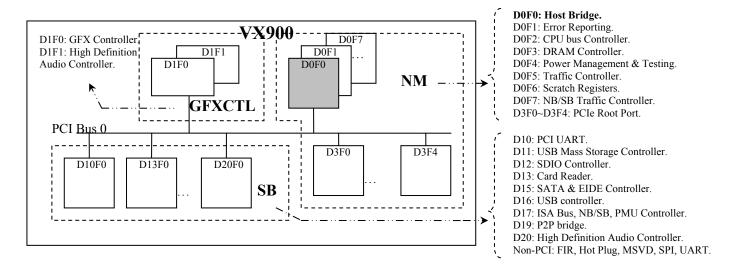

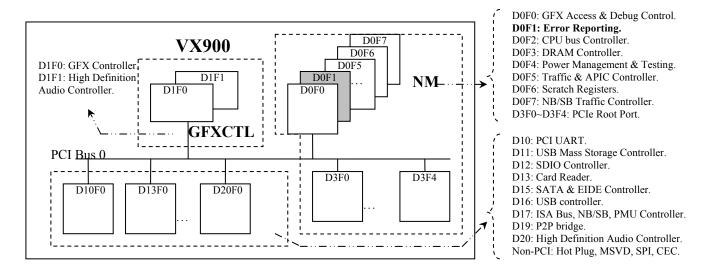

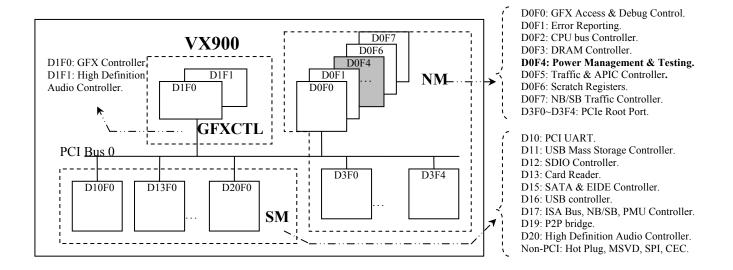

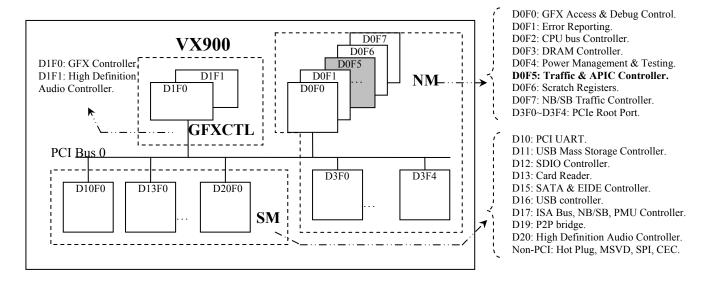

Figure 2. Register Level Block Diagram for D0F0

The registers in this function are accessibility control for internal modules, debugging selections, and other miscellaneous controls. Please refer to the shadow block in Figure 2 for the register level location of this function in the whole chip.