# Linear Integrated Circuits DATABOOK

mm

Sug

## INTRODUCTION

Unitrode Integrated Circuits Corporation is a recognized leader in the development and manufacture of high performance circuits for power management. The company provides significant IC products for switching power supplies, motor drives and special function circuits, optimized for smart-power applications.

We are committed to the creation of new and innovative circuits to serve unique and valuable functions. To achieve this goal, we take a totally integrated approach to definition, development and production. Design and process engineers work together, often directly with customers, so that users can maximize their impact on product development.

Unitrode's state-of-the art manufacturing facility in Merrimack, New Hampshire, has been awarded JAN Microcircuit Certification. The facility includes 65,000 square feet dedicated to engineering, wafer fabrication, assembly and testing. Volume assembly operations take place at other facilities in the United States and the Far East.

We are also committed to objectives of the Unitrode Corporation described in its Mission Statement:

"We will continuously improve our techniques for understanding the needs of our customers and fulfilling their high value-added requirements. We will deliver quality products of superior performance. They will be supplied on time and at a fair price. By matching our capabilities and customer needs, we will best achieve our profit-growth objective."

It is this approach, carried out by dedicated personnel working in the most modern facilities, that makes the Unitrode difference — that makes it possible for us to offer the best in cost-performance integrated circuits.

This databook describes our current IC product lines. We welcome your inquiries about these devices, or about the development of new ones to meet your specific needs.

Unitrode Corporation makes no representation that the use or interconnection of the circuits described herein will not infringe on existing or future patent rights, nor do the descriptions contained herein imply the granting of licenses to make, use or sell equipment constructed in accordance therewith.

© 1987, by Unitrode Corporation. All rights reserved. This book, or any part or parts thereof, must not be reproduced in any form without permission of the copyright owner.

NOTE: The information presented in this section is believed to be accurate and reliable. However, no responsibility is assumed by Unitrode Corporation for its use.

Doorbell,<sup>®</sup> Sensistor,<sup>®</sup> and Magnum<sup>®</sup> are registered trademarks of Unitrode Corporation

BISYN<sup>™</sup> is a trademark of Unitrode Corporation

MULTIWATT® is a registered trademark of SGS Corporation

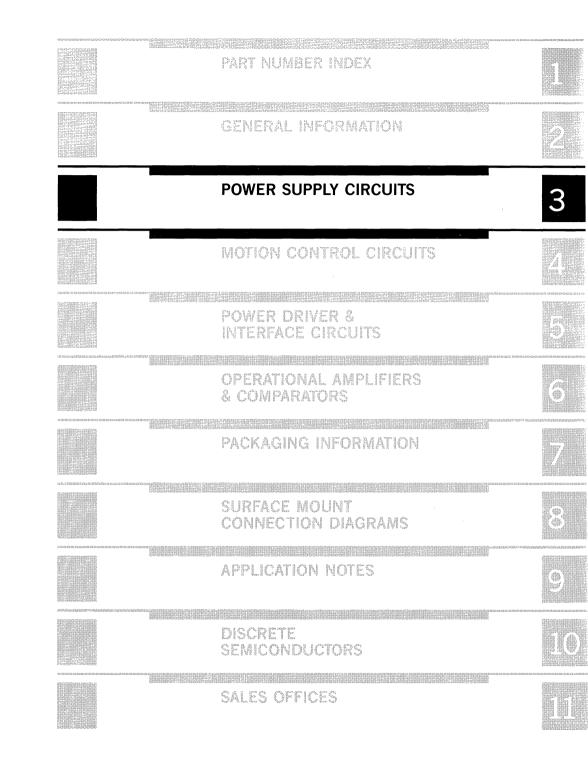

| PART NUMBER INDEX                       | 1  |

|-----------------------------------------|----|

| GENERAL INFORMATION                     | 2  |

| POWER SUPPLY CIRCUITS                   | 3  |

| MOTION CONTROL CIRCUITS                 | 4  |

| POWER DRIVER &<br>INTERFACE CIRCUITS    | 5  |

| OPERATIONAL AMPLIFIERS<br>& COMPARATORS | 6  |

| PACKAGING INFORMATION                   | 7  |

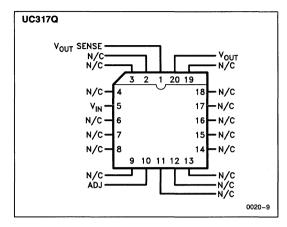

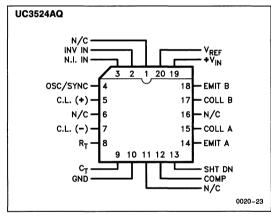

| SURFACE MOUNT<br>CONNECTION DIAGRAMS    | 8  |

| APPLICATION NOTES                       | 9  |

| DISCRETE<br>SEMICONDUCTORS              | 10 |

| SALES OFFICES                           | 11 |

©Copyright 1987 Unitrode Integrated Circuits, Merrimack, NH. All rights reserved.

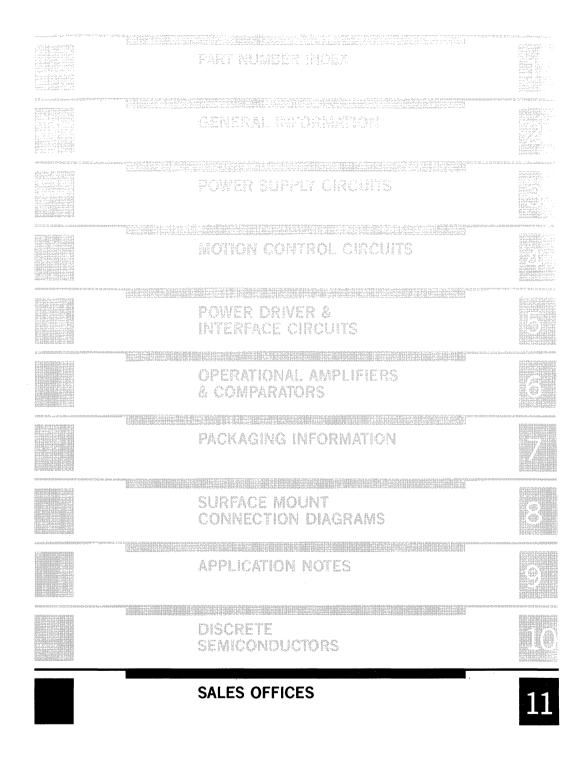

## **TABLE OF CONTENTS**

| Sec | tion                                                                                                              | Page           |

|-----|-------------------------------------------------------------------------------------------------------------------|----------------|

| 1   | PART NUMBER INDEX                                                                                                 | . 1-3          |

| 2   | GENERAL INFORMATION<br>Quality Statement<br>Process Flow Chart<br>Package Cross Reference<br>Ordering Information | . 2-4<br>. 2-5 |

| 3   | POWER SUPPLY CIRCUITS<br>Selection Guide<br>Datasheets                                                            |                |

| 4   | MOTION CONTROL CIRCUITS<br>Selection Guide<br>Datasheets                                                          |                |

| 5   | POWER DRIVER & INTERFACE CIRCUITS<br>Selection Guide<br>Datasheets                                                |                |

| 6   | OPERATIONAL AMPLIFIERS & COMPARATORS<br>Selection Guide<br>Datasheets                                             |                |

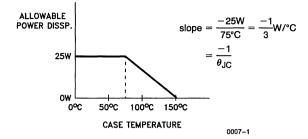

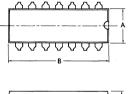

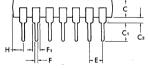

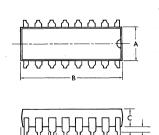

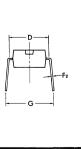

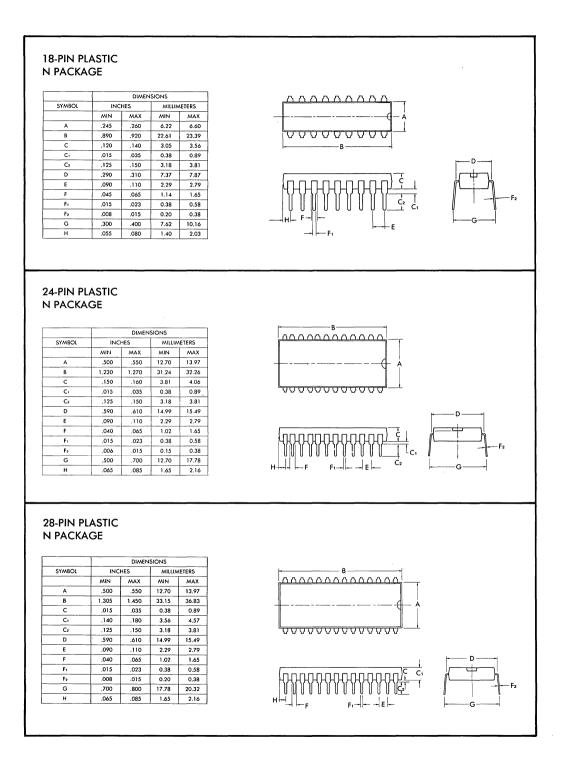

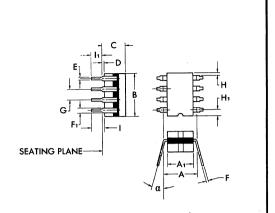

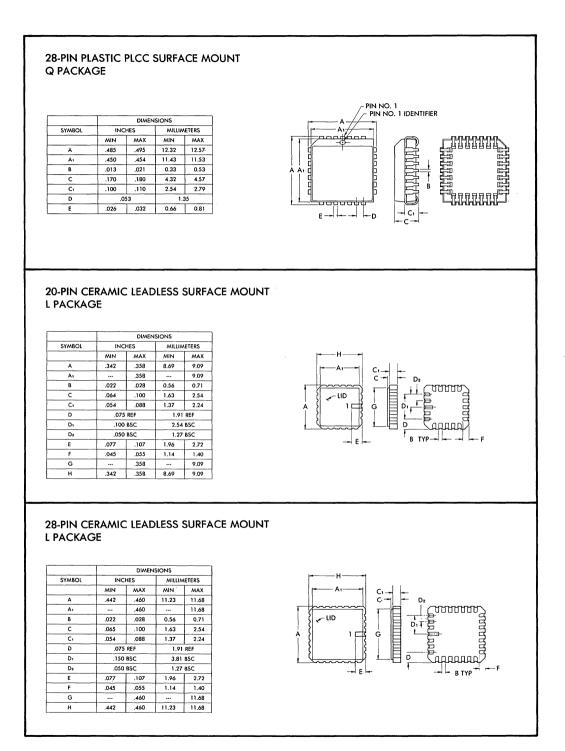

| 7   | PACKAGING INFORMATION<br>Device Thermal Management<br>Index<br>Mechanical Drawings                                | . 7-7          |

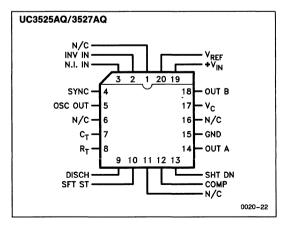

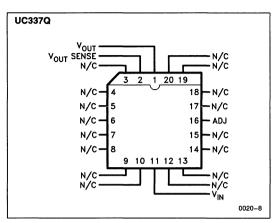

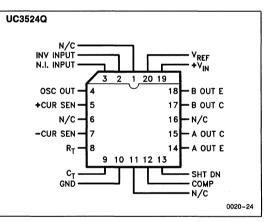

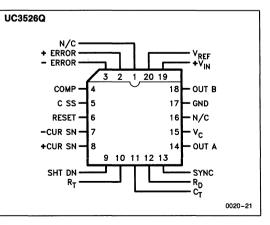

| 8   | SURFACE MOUNT CONNECTION DIAGRAMS                                                                                 | . 8-3          |

| 9   | APPLICATION NOTES<br>Table of Contents<br>Application Notes                                                       |                |

| 10  | DISCRETE SEMICONDUCTORS                                                                                           | 10-3           |

| 11  | SALES OFFICES                                                                                                     | 11-3           |

## PART NUMBER INDEX

| PAGE         | PART NUMBER         | DESCRIPTION                                              | PAGE | PART NUMBER   | DESCRIPTION                                      |

|--------------|---------------------|----------------------------------------------------------|------|---------------|--------------------------------------------------|

| 4-5          | L292V               | 2A; 35V, H-Bridge;                                       | 3-26 | UC493AJ       | 40V; 200mA; Precision                            |

| -12          | L293BN              | 15 Pin Power Tab<br>1A; 35V; 4 Channel                   | 3-26 | UC493AN       | PWM; Ceramic Dip<br>40V; 200mA; Precision        |

|              |                     | Push-Pull Driver;                                        |      |               | PWM; Plastic Dip                                 |

| 4-12         | L293D               | "Batwing" Plastic Dip<br>1A; 35V; 4 Channel              | 3-26 | UC494ACJ      | 40V; 200mA; Precision<br>PWM; Ceramic Dip        |

|              |                     | Driver With Diodes;<br>"Batwing Plastic Package"         | 3-26 | UC494ACN      | 40V; 200mA; Precision<br>PWM; Plastic Dip        |

| 5-5          | L295V               | 2.5A; 45V; Dual PWM                                      | 3-26 | UC494AJ       | 40V; 200mA; Precision                            |

|              |                     | Solenoid Driver;<br>15 Pin Power Tab                     | 3-26 | UC494AN       | PWM; Ceramic Dip<br>40V; 200mA; Precision        |

| 3-7          | L296V               | 4A; 40V; High Current<br>Switching Regulator;            | 3-26 | UC495ACJ      | PWM; Plastic Dip<br>40V; 200mA; Precision        |

|              |                     | 15 Pin Power Tab                                         |      |               | PWM; Ceramic Dip                                 |

| 4-16         | L298V               | Dual Full Bridge Driver;<br>15 Pin Power Tab             | 3-26 | UC495ACN      | 40V; 200mA; Precision<br>PWM: Plastic Dip        |

| 4-20         | L298DV              | Dual Full Bridge                                         | 3-26 | UC495AJ       | 40V; 200mA; Precision                            |

|              |                     | Driver With Diodes;<br>15 Pin Power Tab                  | 3-26 | UC495AN       | PWM; Ceramic Dip<br>40V; 200mA; Precision        |

| 3-15<br>*    | UC117K<br>UC120-05K | 1.5A; TO-3; Pos. Adj. Reg.<br>1.0A; -5V; TO-3;           | 3-26 | UC495BCJ      | PWM; Plastic Dip<br>Precision PWM w/Buffered     |

|              |                     | Precision Fixed Reg.                                     |      |               | Output; Ceramic Dip                              |

| *            | UC120-12K           | 1.0A; -12V; TO-3;<br>Precision Fixed Reg.                | 3-26 | UC495BCN      | Precision PWM w/Buffered<br>Output; Plastic Dip  |

| *            | UC120-15K           | 1.0A; -15V; TO-3;                                        | 3-26 | UC495BJ       | Precision PWM w/Buffered                         |

| 3-19         | UC137K              | Precision Fixed Reg.<br>1.5A; TO-3; Neg. Adj. Reg.       | 3-26 | UC495BN       | Output; Ceramic Dip<br>Precision PWM w/Buffered  |

| *            | UC140-05K           | 1.0A; +5V; TO-3;<br>Precision Fixed Reg.                 | 6-15 | UC542J        | Output; Plastic Dip<br>High Slew Rate Op-Amp;    |

| *            | UC140-12K           | 1.0A; +12V; TO-3;                                        |      |               | Čeramic Dip                                      |

| *            | UC140-15K           | Precision Fixed Reg.<br>1.0A; +15V; TO-3;                | 4-24 | UC1517J       | Bilevel Stepper Drive<br>Circuit: Ceramic Dip    |

| 2 2 2        |                     | Precision Fixed Reg.                                     | 3-30 | UC1524AJ      | 60V; 200mA; Precision                            |

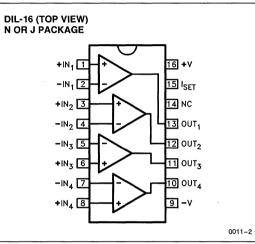

| 3-22<br>6-11 | UC150K<br>UC161J    | 3.0A; TO-3; Pos. Adj. Reg.<br>Quad Comparator;           | 3-34 | UC1524J       | PWM; Ceramic Dip<br>40V; 100mA; PWM;             |

| 6-11         | UC161J/883          | Ceramic Dip<br>Quad Comparator;                          | 3-39 | UC1525AJ      | Ceramic Dip<br>40V; 500mA; Precision             |

|              |                     | Ceramic Dip                                              |      |               | PWM; Ceramic Dip                                 |

| 5-9          | UC195H,K            | Smart Power Transistor;<br>TO-3; TO-5                    | 3-46 | UC1526AJ      | Advanced Ceramic Dip<br>High Performance PWM     |

| 3-15<br>3-19 | UC217K<br>UC237K    | 1.5A; TO-3; Pos. Adj. Reg.<br>1.5A; TO-3; Neg. Adj. Reg. | 3-46 | UC1526AJ/883B | Advanced Ceramic Dip                             |

| 3-22         | UC250K              | 3.0A; TO-3; Pos. Adj. Reg.                               | 3-52 | UC1526J       | High Performance PWM<br>High Performance         |

| 5-9          | UC295H,K            | Smart Power Transistor;<br>TO-3; TO-5                    | 3-39 | UC1527AJ      | PWM; Ceramic Dip<br>40V; 500mA; Precision        |

| 3-15         | UC317K              | 1.5A; TO-3; Pos. Adj. Reg.                               |      |               | PWM; Ceramic Dip                                 |

| 3-15<br>*    | UC317T<br>UC320-05K | 1.5A; TO-220; Pos. Adj. Reg.<br>1A; -5V; TO-3;           | 3-58 | UC1543J       | Power Supply Supervisory<br>Circuit; Ceramic Dip |

| aje          | UC320-12K           | Precision Fixed Reg.<br>1A; -12V; TO-3;                  | 3-58 | UC1544J       | Power Supply Supervisory                         |

|              |                     | Precision Fixed Reg.                                     | 4-30 | UC1610J       | Circuit; Ceramic Dip<br>Dual Schottky Diode      |

| *            | UC320-15K           | 1A; -15V; TO-3;<br>Precision Fixed Reg.                  |      |               | Bridge; 8-Pin;<br>Ceramic Dip                    |

| 3-19         | UC337K              | 1.5A; TO-3; Neg. Adj. Reg.                               | 3-62 | UC1611J       | Schottky Array;                                  |

| 3-19<br>*    | UC337T<br>UC340-05K | 1.5A; TO-220; Neg. Adj. Reg.<br>1A; +5V; TO-3;           | 4-32 | UC1633J       | Ceramic Dip<br>Phase Locked Controller;          |

| *            | UC340-12K           | Precision Fixed Reg.<br>1A; +12V; TO-3;                  |      |               | Ceramic Dip                                      |

|              |                     | Precision Fixed Reg.                                     | 4-39 | UC1634J       | Phase Locked Controller;<br>Ceramic Dip          |

| *            | UC340-15K           | 1A; +15V; TO-3;<br>Precision Fixed Reg.                  | 4-42 | UC1637J       | 500mA; 40V; PWM DC Serve<br>Motor Control Chip;  |

| 3-22         |                     | 3A; TO-3; Pos. Adj. Reg.                                 |      |               | Ceramic Dip                                      |

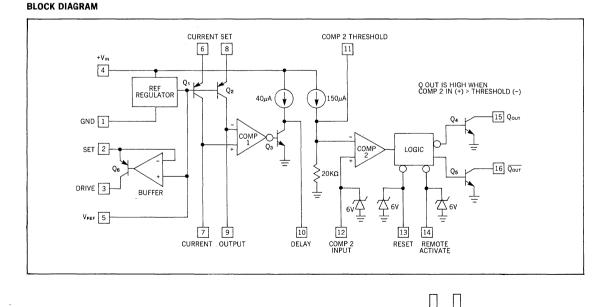

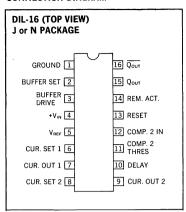

| 5-9          | UC395H,K            | Smart Power Transistor;<br>TO-3; TO-5                    | 5-14 | UC1704J       | Bridge Transducer Switch;<br>-25°C to +125°C:    |

| -26          | UC493ACJ            | 40V; 200mA; Precision<br>PWM; Ceramic Dip                |      |               | Ceramic Dip                                      |

| 8-26         | UC493ACN            | 40V; 200mA; Precision                                    |      |               |                                                  |

|              |                     | PWM; Plastic Dip                                         |      |               |                                                  |

## PART NUMBER INDEX

| PAGE         | PART NUMBER        | DESCRIPTION                                                      | PAGE | PART NUMBER | DESCRIPTION                                                     |

|--------------|--------------------|------------------------------------------------------------------|------|-------------|-----------------------------------------------------------------|

| 5-18         | UC1705J            | Low Cost High Speed                                              | 3-39 | UC2525AN    | 40V; 500mA; Precision                                           |

| 5-21         | UC1706J            | Driver; Ceramic Dip<br>Dual Output Driver;<br>Ceramic Dip        | 3-46 | UC2526AJ    | PWM; Plastic Dip<br>Advanced High<br>Performance PWM;           |

| 5-25         | UC1707J            | Dual Uncommitted Power                                           |      |             | Ceramic Dip                                                     |

| 5-25         | UC1707J/883        | Drivers; Ceramic Dip<br>Dual Uncommitted Power                   | 3-46 | UC2526AN    | Advanced High<br>Performance PWM;                               |

| 4-50         | UC1717J            | Drivers; Ceramic Dip<br>1A; 40V; Stepper Motor<br>Drive Circuit; | 3-52 | UC2526J     | Plastic Dip<br>High Performance PWM;<br>Ceramic Dip             |

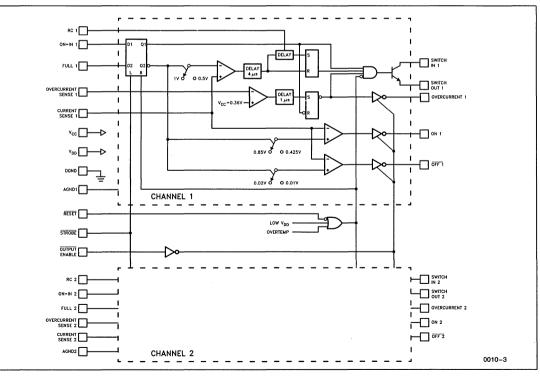

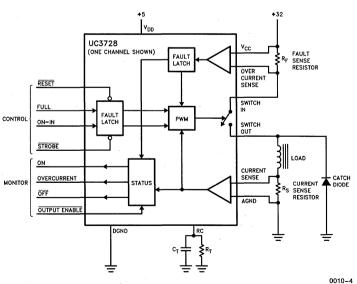

| 5-31         | UC1728P            | Ceramic Dip<br>Dual Smart Switch;                                | 3-52 | UC2526N     | High Performance<br>PWM; Plastic Dip                            |

| 3-64         | UC1730J            | Power Ceramic Dip<br>Temperature & Airflow                       | 3-39 | UC2527AJ    | 40V; 500mA; Precision<br>PWM; Ceramic Dip                       |

| ļ            |                    | Sensor; Ceramic Dip                                              | 3-39 | UC2527AN    | 40V; 500mA; Precision                                           |

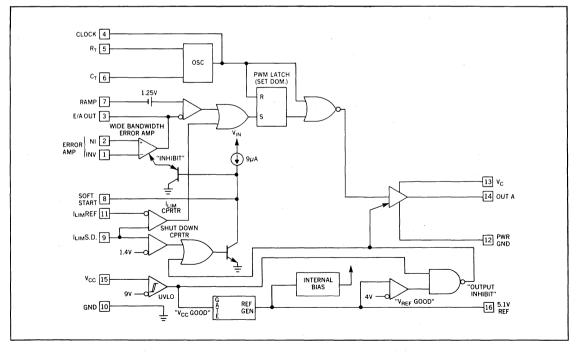

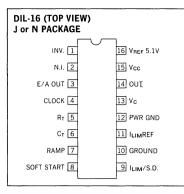

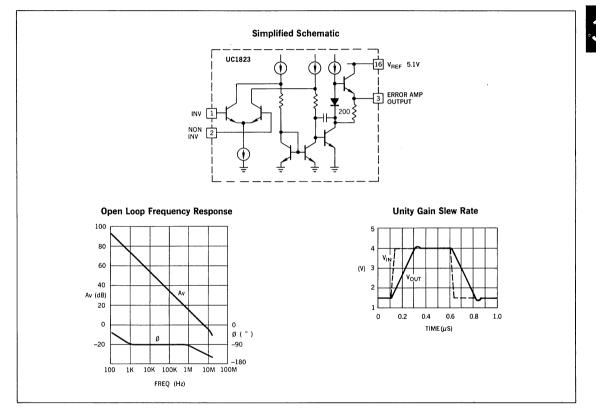

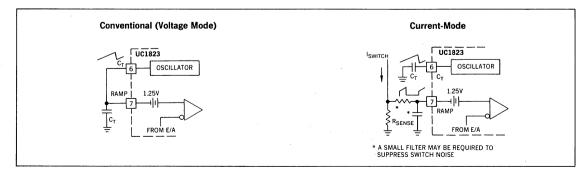

| 3-68         | UC1823J/883B       | Single Output 1MHz<br>PWM; Ceramic Dip                           | 3-58 | UC2543J     | PWM; Plastic Dip<br>Power Supply Supervisory                    |

| 3-74         | UC1825J            | Dual Output 1MHz<br>PWM; Ceramic Dip                             | 3-58 | UC2543N     | Circuit; Ceramic Dip<br>Power Supply Supervisory                |

| 3-74         | UC1825J/883B       | Ultra High Frequency<br>PWM; Ceramic Dip                         | 3-58 | UC2544J     | Circuit; Plastic Dip<br>Power Supply Supervisory                |

| 3-81         | UC1834J            | High Efficiency<br>Linear Regulator;                             | 3-58 | UC2544N     | Circuit; Ceramic Dip<br>Power Supply Supervisory                |

| 3-85         | UC1835J            | Ceramic Dip<br>Low Cost, High                                    | 4-32 | UC2633J     | Circuit; Plastic Dip<br>Phase Locked Controller;<br>Ceramic Dip |

| 2.05         | 11010261           | Efficiency Regulator;<br>Ceramic Dip                             | 4-32 | UC2633N     | Phase Locked Controller;<br>Plastic Dip                         |

| 3-85         | UC1836J            | Adjustable High<br>Efficiency Regulator;                         | 4-39 | UC2634J     | Phase Locked Controller;<br>Ceramic Dip                         |

| 3-88         | UC1838J            | Ceramic Dip<br>Magnetic Amplifier                                | 4-39 | UC2634N     | Phase Locked Controller;<br>Plastic Dip                         |

| 2 01         | 11019401           | Control Circuit;<br>Ceramic Dip                                  | 4-42 | UC2637J     | 500mA; 40V; PWM DC Servo<br>Motor Control Chip;                 |

| 3-91<br>3-99 | UC1840J            | 40V; 200mA; PWM<br>Controller; Ceramic Dip                       | 4-42 | UC2637N     | Ceramic Dip<br>500mA; 40V; PWM DC Servo                         |

| 3-99         | UC1841J<br>UC1842J | Programmable, Off-line<br>PWM; Ceramic Dip                       | 4-42 | 00203/11    | Motor Control Chip;<br>Plastic Dip                              |

| 3-107        |                    | Low Cost Current Mode<br>PWM; Ceramic Dip                        | 3-64 | UC2730J     | Temperature and<br>Airflow Sensor;                              |

|              | UC1843J            | Low Cost Current Mode<br>PWM, Ceramic Dip                        | 3-64 | UC2730N     | Ceramic Dip<br>Temperature and                                  |

| 3-107        | UC1843J/883B       | Low Cost Current Mode<br>PWM; Ceramic Dip                        | 5-04 | 0027301     | Airflow Sensor;<br>Plastic Dip                                  |

| 3-107        | UC1844J            | Low Cost Current Mode<br>PWM; Ceramic Dip                        | 3-64 | UC2730T     | Temperature and<br>Airflow Sensor;                              |

| 3-107        | UC1845J            | Low Cost Current Mode<br>PWM; Ceramic Dip                        | 0.00 |             | TO-220                                                          |

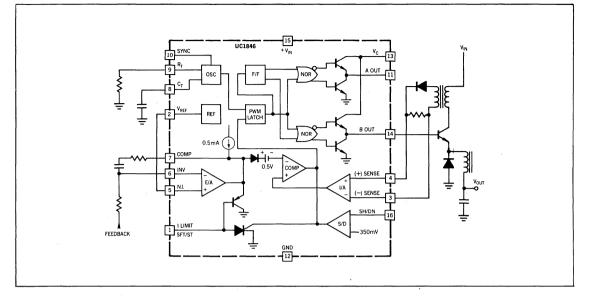

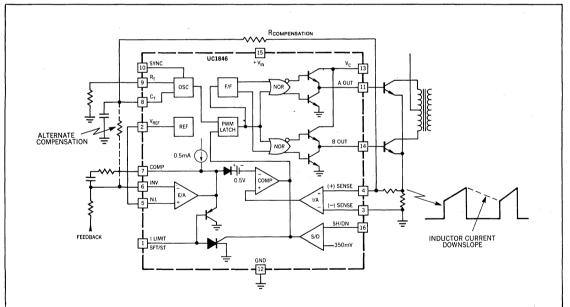

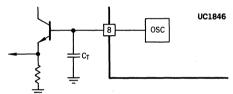

| 3-113        | UC1846J            | Current Mode PWM;<br>Ceramic Dip                                 | 3-68 | UC2823J     | Single Output 1MHz<br>PWM; Ceramic Dip                          |

| 3-113        | UC1847J            | Current Mode PWM;<br>Ceramic Dip                                 | 3-68 | UC2823N     | Single Output 1MHz<br>PWM; Plastic Dip                          |

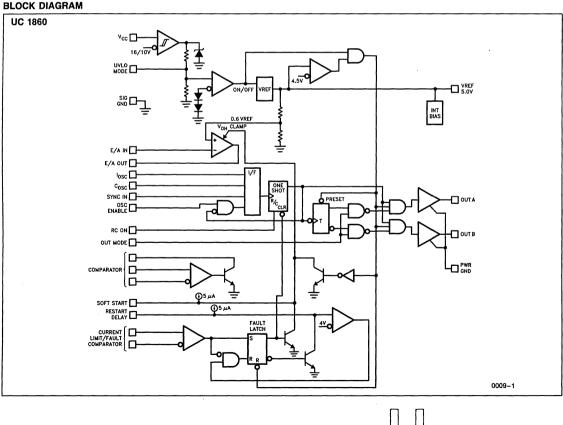

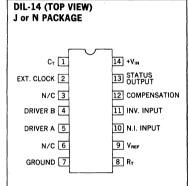

| 3-121        | UC1860J            | Resonant Mode Controller;<br>Ceramic Dip                         | 3-74 | UC2825J     | Dual Output 1MHz<br>PWM; Ceramic Dip                            |

| 3-122        | UC1901J            | Isolated Feedback<br>Generator; Ceramic Dip                      | 3-74 | UC2825N     | Dual Output 1MHz<br>PWM; Plastic Dip                            |

| 3-126        | UC1903J            | Triple Voltage and Line<br>Monitor; Ceramic Dip                  | 3-81 | UC2834J     | High Efficiency Linear<br>Regulator; Ceramic Dip                |

| 3-30         | UC2524AJ           | 60V; 200mA; Precision<br>PWM; Ceramic Dip                        | 3-81 | UC2834N     | High Efficiency Linear<br>Regulator; Plastic Dip                |

| 3-30         | UC2524AN           | 60V; 200mA; Precision<br>PWM; Plastic Dip                        | 3-85 | UC2835J     | Low Cost, High<br>Efficiency Regulator;                         |

| 3-34         | UC2524J            | 40V; 100mA; PWM;<br>Ceramic Dip                                  | 3-85 | UC2835N     | Ceramic Dip<br>Low Cost, High                                   |

| 3-34         | UC2524N            | 40V; 100mA; PWM;<br>Plastic Dip                                  |      |             | Efficiency Regulator;<br>Plastic Dip                            |

| 3-39         | UC2525AJ           | 40V; 500mA; Precision<br>PWM; Ceramic Dip                        | 3-85 | UC2836J     | Adjustable High<br>Efficiency Regulator;<br>Ceramic Dip         |

## PART NUMBER INDEX

1

| PAGE           | PART NUMBER        | DESCRIPTION                                                               | PAGE | PART NUMBER | DESCRIPTION                                                              |

|----------------|--------------------|---------------------------------------------------------------------------|------|-------------|--------------------------------------------------------------------------|

| 3-85           | UC2836N            | Adjustable High<br>Efficiency Regulator;                                  | 3-30 | UC3524AN    | 50V; 200mA; Precision<br>PWM; Plastic Dip                                |

| 2.00           |                    | Plastic Dip                                                               | 3-34 | UC3524J     | 40V; 100mA; PWM;                                                         |

| 3-88           | UC2838J            | Magnetic Amplifier<br>Control Circuit;<br>Ceramic Din                     | 3-34 | UC3524N     | Ceramic Dip<br>40V; 100mA; PWM;                                          |

| 3-88           | UC2838N            | Ceramic Dip<br>Magnetic Amplifier<br>Control Circuit;                     | 3-39 | UC3525AJ    | Plastic Dip<br>40V; 500mA; Precision<br>PWM; Ceramic Dip                 |

| 3-91           | UC2840J            | Plastic Dip<br>40V; 200mA; PWM                                            | 3-39 | UC3525AN    | 40V; 500mA; Precision<br>PWM; Plastic Dip                                |

| 3-91           | UC2840N            | Controller; Ceramic Dip<br>40V; 200mA; PWM                                | 3-46 | UC3526AJ    | Advanced High<br>Performance PWM;                                        |

| 3-99           | UC2841J            | Controller; Plastic Dip<br>Programmable, Off-line                         | 3-46 | UC3526AN    | Ceramic Dip<br>Advanced High                                             |

| 3-99           | UC2841J            | PWM; Ceramic Dip<br>Programmable, Off-line                                |      |             | Performance PWM;<br>Plastic Dip                                          |

| 3-107          | UC2841N<br>UC2842J | Programmable, Off-line<br>PWM; Plastic Dip<br>Low Cost Current Mode       | 3-52 | UC3526J     | Plastic Dip<br>High Performance<br>PWM; Ceramic Dip                      |

| 3-107          | UC2842J<br>UC2842N | PWM; Ceramic Dip<br>Low Cost Current Mode                                 | 3-52 | UC3526N     | PWM; Ceramic Dip<br>High Performance<br>PWM; Plastic Dip                 |

| 3-107          | UC2842N<br>UC2843J | Low Cost Current Mode<br>PWM; Plastic Dip<br>Low Cost Current Mode        | 3-39 | UC3527AJ    | 40V; 500mA; Precision                                                    |

| 3-107<br>3-107 | UC2843J<br>UC2843N | Low Cost Current Mode<br>PWM; Ceramic Dip<br>Economy PWM;                 | 3-39 | UC3527AN    | PWM; Ceramic Dip<br>40V; 500mA; Precision<br>PWM; Plastic Dip            |

| 3-107<br>3-107 | UC2843N<br>UC2844J | Economy PWM;<br>Plastic Dip<br>Low Cost Current Mode                      | 3-58 | UC3543J     | Power Supply Supervisory                                                 |

|                |                    | PWM; Ceramic Dip                                                          | 3-58 | UC3543N     | Circuit; Ceramic Dip<br>Power Supply Supervisory<br>Circuit: Plastic Dip |

| 3-107          | UC2844N            | Low Cost Current Mode<br>PWM; Plastic Dip                                 | 3-58 | UC3544J     | Circuit; Plastic Dip<br>Power Supply Supervisory                         |

| 3-107          | UC2845J            | Low Cost Current Mode<br>PWM; Ceramic Dip                                 | 3-58 | UC3544N     | Circuit; Ceramic Dip<br>Power Supply Supervisory                         |

| 3-107          | UC2845N            | Low Cost Current Mode<br>PWM; Plastic Dip                                 | 4-30 | UC3610J     | Circuit; Plastic Dip<br>Dual Schottky Diode                              |

| 3-113          | UC2846J            | Current Mode PWM;<br>Ceramic Dip                                          | 4-30 | UC3610N     | Bridge; Ceramic Dip<br>Dual Schottky Diode                               |

| 3-113          | UC2846N            | Current Mode PWM;<br>Plastic Dip                                          | 3-62 | UC3611J     | Bridge; Plastic Dip<br>Schottky Array;                                   |

| 3-113          | UC2847J            | Current Mode PWM;<br>Ceramic Dip                                          | 3-62 | UC3611N     | Ceramic Dip<br>Schottky Array;                                           |

| 3-113          | UC2847N            | Current Mode PWM;<br>Plastic Dip                                          | 4-61 | UC3620V     | Plastic Dip<br>3-Phase DC Motor                                          |

| 3-121          | UC2860J            | Resonant Mode Controller;<br>Ceramic Dip                                  | 4-66 | UC3622V     | Controller; Power SIP<br>Switchmode Brushless                            |

| 3-121          | UC2860N            | Resonant Mode Controller;<br>Plastic Dip                                  |      |             | DC Motor Driver;<br>15-Pin Power Tab                                     |

| 3-122          | UC2901J            | Isolated Feedback<br>Generator; Ceramic Dip                               | * .  | UC3623V     | Low Noise Brushless<br>DC Motor Driver;                                  |

| 3-122          | UC2901N            | Isolated Feedback                                                         |      | 1103633     | 15 Pin Power Tab                                                         |

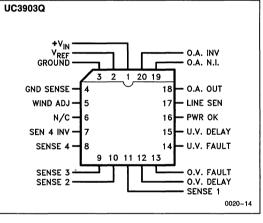

| 3-126          | UC2903J            | Generator; Plastic Dip<br>Triple Voltage and Line<br>Monitor: Caramic Dip | 4-32 | UC3633J     | Phase Locked Controller;<br>Ceramic Dip<br>Phase Locked Controller;      |

| 3-126          | UC2903N            | Monitor; Ceramic Dip<br>Triple Voltage and Line                           | 4-32 | UC3633N     | Phase Locked Controller;<br>Plastic Dip                                  |

| 3-133          | UC2906J            | Monitor; Plastic Dip<br>Lead Acid Battery                                 | 4-39 | UC3634J     | Phase Locked Controller;<br>Ceramic Dip                                  |

| 3-133          | UC2906N            | Charger; Ceramic<br>Lead Acid Battery                                     | 4-39 | UC3634N     | Phase Locked Controller;<br>Plastic Dip                                  |

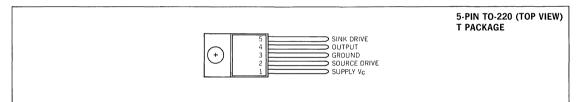

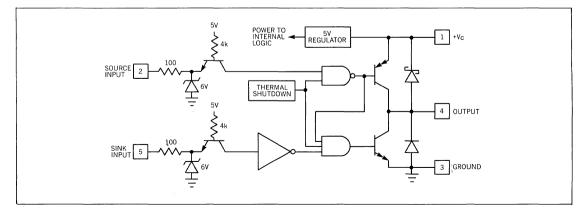

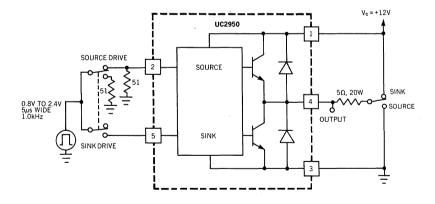

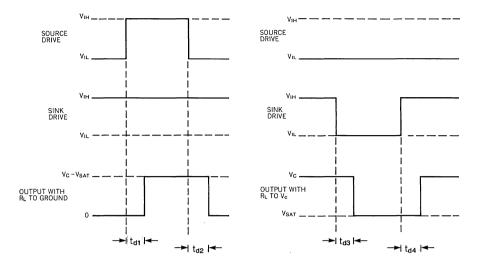

| 5-33           | UC2950T            | Charger; Plastic<br>Half Bridge, Bipolar                                  | 4-42 | UC3637J     | 500mA; 40V; PWM DC Serve<br>Motor Control Chip;                          |

| -33            | UC29501            | Switch; 5-Pin TO-220<br>Monolithic Power                                  | 4-4Ż | 1036375     | Ceramic Dip                                                              |

| 0              | 0001/04            | Monolithic Power<br>Amplifier<br>15-Pin Power Tab                         | 4-42 | UC3637N     | 500mA; 40V; PWM DC Serve<br>Motor Control Chip;<br>Plastic Din           |

| -24            | UC3517J            | Bilevel Stepper Drive                                                     | 4-70 | UC3657V     | Plastic Dip<br>Triple Half Bridge                                        |

| -24            | UC3517N            | Circuit; Ceramic Dip<br>Bilevel Stepper Drive                             | -    |             | Power Driver;<br>15-Pin Power Tab                                        |

| -30            | UC3524AJ           | Circuit; Plastic Dip<br>50V; 200mA; Precision                             | 5-14 | UC3704J     | Bridge Transducer Switch;<br>0°C to +70°C; Ceramic Di                    |

|                |                    | PWM; Ceramic Dip                                                          | 5-14 | UC3704N     | Bridge Transducer Switch;<br>0°C to +70°C: Plastic Dip                   |

## PART NUMBER INDEX

| PAGE | PART NUMBER | DESCRIPTION                                                      | PAGE  | PART NUMBER | DESCRIPTION                                                    |

|------|-------------|------------------------------------------------------------------|-------|-------------|----------------------------------------------------------------|

| 5-18 | UC3705J     | High Speed Power                                                 | 3-99  | UC3841J     | Programmable, Off-line                                         |

| 5-18 | UC3705N     | Driver; Ceramic Dip<br>High Speed Power                          | 3-99  | UC3841N     | PWM; Ceramic Dip<br>Programmable, Off-line<br>PWM; Plastic Dip |

| 5-18 | UC3705T     | Driver; Plastic Dip<br>Low Cost High Speed                       | 3-107 | UC3842J     | Low Cost Current Mode                                          |

| 5-21 | UC3706J     | Driver; 5-Pin TO-220<br>Dual Output Driver;                      | 3-107 | UC3842N     | PWM; Ceramic Dip<br>Low Cost Current Mode                      |

| 5-21 | UC3706N     | Ceramic Dip<br>Dual Output Driver;                               | 3-107 | UC3843J     | PWM; Plastic Dip<br>Low Cost Current Mode                      |

| 5-25 | UC3707J     | Plastic Dip<br>Dual Uncommitted Power                            | 3-107 | UC3843N     | PWM; Ceramic Dip<br>Low Cost Current Mode                      |

| 5-25 | UC3707N     | Drivers; Ceramic Dip<br>Dual Uncommitted Power                   | 3-107 | UC3844J     | PWM; Plastic Dip<br>Low Cost Current Mode                      |

| 4-74 | UC3717AN    | Drivers; Plastic Dip<br>Stepper Motor Drive                      | 3-107 | UC3844N     | PWM; Ceramic Dip<br>Low Cost Current Mode<br>PWM; Plastic Dip  |

| 4-50 | UC3717J     | Circuit; Plastic Dip<br>1A; 40V; Stepper Motor<br>Drive Circuit: | 3-107 | UC3845J     | Low Cost Current Mode<br>PWM; Ceramic Dip                      |

| 4-50 | UC3717N     | Ceramic Dip                                                      | 3-107 | UC3845N     | Low Cost Current Mode<br>PWM; Plastic Dip                      |

| 4-50 | 0037171     | 1A;40V; Stepper Motor<br>Drive Circuit;<br>Plastic Dip           | 3-113 | UC3846J     | Current Mode PWM;<br>Ceramic Dip                               |

| 5-36 | UC3720V     | Smart Power Switch;<br>15 Pin Power Tab                          | 3-113 | UC3846N     | Current Mode PWM;<br>Plastic Dip                               |

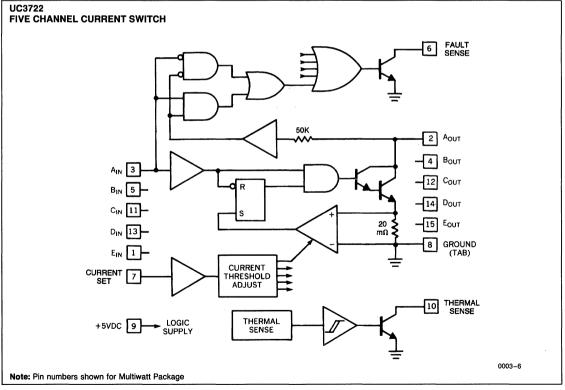

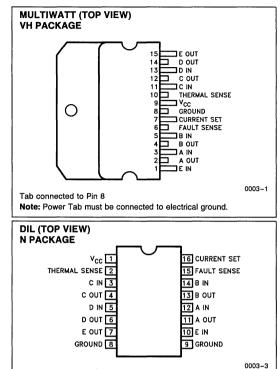

| 5-40 | UC3722V     | Five Channel Power Tab<br>15 Pin Power Tab                       | 3-113 | UC3847J     | Current Mode PWM;<br>Ceramic Dip                               |

| 5-31 | UC3728N     | Dual Smart Switch;<br>Plastic Dip                                | 3-113 | UC3847N     | Current Mode PWM;<br>Plastic Dip                               |

| 5-31 | UC3728L     | Dual Smart Switch<br>Ceramic Surface Mount                       | 3-140 | UC3850J     | Switching Power Supply<br>Control Sys.;                        |

| 3-64 | UC3730J     | Temperature & Airflow<br>Sensor; Ceramic Dip                     | 3-140 | UC3850N     | Ceramic Pkg.<br>Switching Power Supply                         |

| 3-64 | UC3730N     | Temperature & Airflow<br>Sensor; Plastic Dip                     |       |             | Control Sys.;<br>Plastic Pkg.                                  |

| 3-64 | UC3730T     | Temperature & Airflow<br>Sensor; T0-220                          | 3-121 | UC3860J     | Resonant Mode Controller;<br>Ceramic Dip                       |

| 3-68 | UC3823J     | Single Output 1MHz<br>PWM; Ceramic Dip                           | 3-121 | UC3860N     | Resonant Mode Controller;<br>Plastic Dip                       |

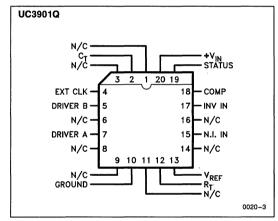

| 3-68 | UC3823N     | Single Output 1MHz<br>PWM; Plastic Dip                           | 3-122 | UC3901J     | Isolated Feedback<br>Generator; Ceramic Dip                    |

| 3-74 | UC3825J     | Dual Output 1MHz<br>PWM; Ceramic Dip                             | 3-122 | UC3901N     | Isolated Feedback<br>Generator; Plastic Dip                    |

| 3-74 | UC3825N     | Dual Output 1MHz<br>PWM; Plastic Dip                             | 3-126 | UC3903J     | Triple Voltage and Line<br>Monitor; Ceramic Dip                |

| 3-81 | UC3834J     | High Efficiency Linear<br>Regulator; Ceramic Dip                 | 3-126 | UC3903N     | Triple Voltage and Line<br>Monitor; Plastic Dip                |

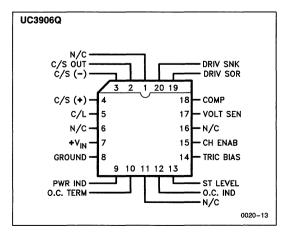

| 3-81 | UC3834N     | High Efficiency Linear<br>Regulator; Plastic Dip                 | 3-133 | UC3906J     | Lead Acid Battery<br>Charger; Ceramic                          |

| 3-85 | UC3835J     | Low Cost, High<br>Efficiency Regulator;                          | 3-133 | UC3906N     | Lead Acid Battery<br>Charger; Plastic                          |

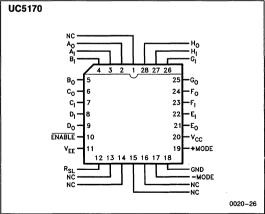

| 3-85 | UC3835N     | Ceramic Dip<br>Low Cost, High                                    | 5-44  | UC5170N     | Octal Single Ended<br>Driver; Plastic Dip                      |

| -    |             | Efficiency Regulator;<br>Plastic Dip                             | 5-44  | UC5170Q     | Octal Single Ended<br>Driver; PLCC                             |

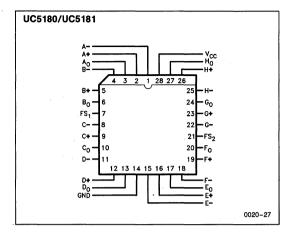

| 3-85 | UC3836J     | Adjustable High Efficiency<br>Regulator; Ceramic Dip             | 5-48  | UC5180N     | Octal Line Receiver;<br>Plastic Dip                            |

| 3-85 | UC3836N     | Adjustable High Efficiency<br>Regulator; Plastic Dip             | 5-48  | UC5180Q     | Octal Line Receiver;<br>PLCC                                   |

| 3-88 | UC3838J     | Magnetic Amplifier<br>Control Circuit;                           | 5-48  | UC5181N     | Octal Line Receiver;<br>Plastic Dip                            |

| 3-88 | UC3838N     | Ceramic Dip<br>Magnetic Amplifier                                | 5-48  | UC5181Q     | Octal Line Receiver;<br>PLCC                                   |

|      |             | Control Circuit;<br>Plastic Dip                                  | 3-144 | UC7805ACK   | 1A; +5V; TO-3;<br>Precision Fixed Reg.                         |

| 3-91 | UC3840J     | 40V; 200mÅ; PWM<br>Controller; Ceramic Dip                       | 3-144 | UC7805ACT   | 1A; +5V; TO-220;<br>Precision Fixed Reg.                       |

| 3-91 | UC3840N     | 40V; 200mA; PWM<br>Controller; Plastic Dip                       | 3-144 | UC7805AK    | 1A; +5V; TO-3;<br>Precision Fixed Reg.                         |

| PAGE           | PART NUMBER          | DESCRIPTION                                               | PAGE | PART NUMBER | DESCRIPTION |

|----------------|----------------------|-----------------------------------------------------------|------|-------------|-------------|

| 3-144          | UC7805CK             | 1A; +5V; TO-3; Fixed Reg.                                 |      |             |             |

| 3-144          | UC7805CT             | 1A; +5V; TO-220; Fixed Reg.                               |      |             |             |

| 3-144          | UC7805K              | 1A; +5V; TO-3; Fixed Reg.                                 |      |             |             |

| 3-144          | UC7812ACK            | 1A; +12V; TO-3;<br>Precision Fixed Reg.                   |      |             |             |

| 3-144          | UC7812ACT            | 1A; +12V; TO-220;                                         |      |             |             |

| 3-144          | UC7812AK             | Precision Fixed Reg.<br>1A; +12V; TO-3;                   |      |             |             |

| 2 1 4 4        | 110701001            | Precision Fixed Reg.                                      |      |             |             |

| 3-144<br>3-144 | UC7812CK<br>UC7812CT | 1A; +12V; TO-3; Fixed Reg.<br>1A; +12V; TO-220 Fixed Reg. |      |             |             |

| 3-144          | UC7812K              | 1A; +12V; TO-220 Fixed Reg.                               |      |             |             |

| 3-144          | UC7815ACK            | 1A; +15V; TO-3;                                           |      |             |             |

|                |                      | Precision Fixed Reg.                                      |      |             |             |

| 3-144          | UC7815ACT            | 1A; +15V; TO-220;                                         |      |             |             |

| 3-144          | UC7815AK             | Precision Fixed Reg.<br>1A; +15V; TO-3;                   |      |             |             |

| C 117          |                      | Precision Fixed Reg.                                      |      |             |             |

| 3-144          | UC7815CK             | 1A; +15V; TO-3; Fixed Reg.                                |      |             |             |

| 3-144          | UC7815CT             | 1A; +15V; TO-220; Fixed Reg.                              |      |             |             |

| 3-144          |                      | 1A; +15V; TO-3; Fixed Reg.                                |      |             |             |

| 3-149          | UC7905ACK            | 1A; -5V; TO-3;<br>Precision Fixed Reg.                    |      |             |             |

| 3-149          | UC7905ACT            | 1A; -5V; TO-220;                                          |      |             |             |

|                |                      | Precision Fixed Reg.                                      |      |             |             |

| 3-149          | UC7905AK             | 1A; -5V; TO-3;                                            |      |             |             |

| 3-149          | UC7905СК             | Precision Fixed Reg.<br>1A; -5V; TO-3; Fixed Reg.         |      |             |             |

| 3-149          | UC7905CT             | 1A; -5V; TO-220; Fixed Reg.                               |      |             |             |

| 3-149          | UC7905K              | 1A; -5V; TO-3; Fixed Reg.                                 |      |             |             |

| 3-149          | UC7912ACK            | 1A; -12V; TO-3;                                           |      |             |             |

| 2 1 4 0        | U07010ACT            | Precision Fixed Reg.                                      |      |             |             |

| 3-149          | UC7912ACT            | 1A; -12V; TO-220;<br>Precision Fixed Reg.                 |      |             |             |

| 3-149          | UC7912AK             | 1A; -12V; TO-3;                                           |      |             |             |

|                |                      | Precision Fixed Reg.                                      |      |             |             |

| 3-149          | UC7912CK             | 1A; -12V; TO-3; Fixed Reg.                                |      |             |             |

| 3-149          | UC7912CT             | 1A; -12V; TO-220 Fixed Reg.                               |      |             |             |

| 3-149          | UC7912K<br>UC7915ACK | 1A; -12V; TO-3; Fixed Reg.<br>1A; -15V; TO-3;             |      |             |             |

|                | 007913ACK            | Precision Fixed Reg.                                      |      |             |             |

| 3-149          | UC7915ACT            | 1A; -15V; TO-220;                                         |      |             |             |

|                |                      | Precision Fixed Reg.                                      |      |             |             |

| 3-149          | UC7915AK             | 1A; -15V; TO-3;<br>Precision Fixed Pog                    |      |             |             |

| 3-149          | UC7915CK             | Precision Fixed Reg.<br>1A; -15V; TO-3; Fixed Reg.        |      |             |             |

| 3-149          | UC7915CT             | 1A; -15V; TO-220; Fixed Reg.                              |      |             |             |

| 3-149          | UC7915K              | 1A; -15V; TO-3; Fixed Reg.                                |      |             |             |

|                |                      | OP AMPS                                                   |      |             |             |

| 6-4            | UCOP01J              | High Speed Op-Amp;                                        |      |             |             |

| 6-4            | UCOP01GJ             | Ceramic Dip<br>High Speed Op-Amp;                         |      |             |             |

| 0-4            | 00010103             | Ceramic Dip                                               |      |             |             |

| 6-4            | UCOP01CN             | High Speed Op-Amp;                                        |      |             |             |

| 6 1            |                      | Plastic Dip                                               |      |             |             |

| 6-4            | UCOP01HN             | High Speed Op-Amp;<br>Plastic Dip                         |      |             |             |

| 6-8            | UCOP02J              | High Speed Op-Amp;                                        |      |             |             |

|                |                      | Ceramic Dip                                               |      |             |             |

| 6-8            | UCOP02AJ             | High Speed Op-Amp;                                        |      |             |             |

| 6-8            | UCOP02BJ             | Ceramic Dip<br>High Speed Op-Amp;                         |      |             |             |

|                |                      | Ceramic Dip                                               | 1    |             |             |

| 6-8            | UCOP02CN             | High Speed Op-Amp;                                        |      |             |             |

| 6 9            |                      | Plastic Dip                                               |      |             |             |

| 6-8            | UCOP02DN             | High Speed Op-Amp;<br>Plastic Dip                         |      |             |             |

| 6-8            | UCOP02EN             | High Speed Op-Amp;                                        |      |             |             |

|                |                      | Plastic Dip                                               |      |             |             |

.

## QUALITY STATEMENT

To become the recognized leader in the areas of quality and reliability, Unitrode Integrated Circuits Corporation has established and will continue to maintain high standards of design and workmanship that equal or surpass those sustained within our industry.

Further, it is our intent to consistently demonstrate quality conformance through professional leadership, technological commitment, and dedicated human resource.

To this end, Unitrode Integrated Circuits will continue to assure ongoing customer satisfaction.

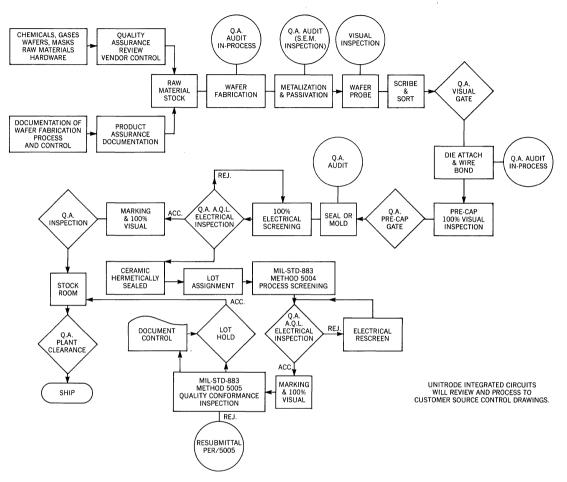

## UNITRODE INTEGRATED CIRCUITS PROCESS FLOW

| UNITRODE ASSEMBLY<br>PACKAGE CODE | ASSEMBLY LOCATION<br>CLASS B PRODUCT |

|-----------------------------------|--------------------------------------|

| К                                 | Korea                                |

| В                                 | Thailand                             |

| Р                                 | Philippines — S.D.P.I.               |

| Т                                 | Philippines — Telefunken             |

| I                                 | U.S.A. — Indy                        |

| Р                                 | Singapore                            |

## PACKAGE CROSS REFERENCE

|                           | PLASTIC | CERAMIC | MULTIWATT® | PLCC | LCC | SOIC  | то-з  | С<br>ТО-220 |

|---------------------------|---------|---------|------------|------|-----|-------|-------|-------------|

| UNITRODE                  | N       | L       | v          | Q    | L   | D     | к     | Т           |

| Linear<br>Tech            | N, N8   | J, J8   | -          | -    | L   | 5, 58 | к     | т           |

| Integrated<br>Power       | N       | J, L    | -          | -    | L   | D     | к     | т           |

| SGS                       | B, N, P |         | v          | -    |     | _     | к     | -           |

| Silicon<br>General        | M, N    | J, Y    | -          | —    | L   | -     | к     | Р           |

| Texas<br>Instru-<br>ments | P, N    | J, JG   | -          | FN   | FC  | D, DW | к     | кс          |

| Signetics                 | N       | F       | -          |      | -   | D     | _     | U           |

| National                  | N       | J       | -          | _    |     | _     | K, KC | Т           |

| Motorola                  | P       | U       | _          | FN   |     | D     | K, KC | т           |

| Fairchild                 | Т, Р    | D, R    | -          |      | L   | —     | к     | U           |

| Sprague                   | A, M, B | R       | —          | E    |     | L     | v     | т           |

2

## **ORDERING INFORMATION**

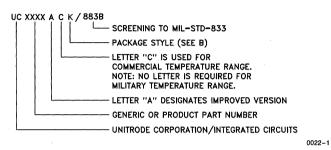

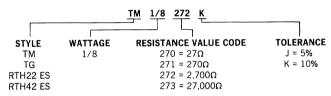

### A. PART NUMBER DESIGNATORS

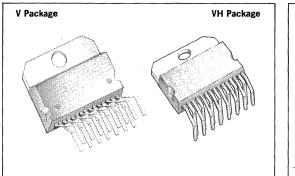

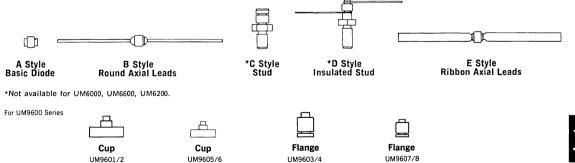

#### **B. PACKAGE SUFFIXES**

| LETTER<br>DESIGNATOR | PACKAGE TYPE              |

|----------------------|---------------------------|

| N                    | -Plastic Molded DIP       |

| J                    | -Glass-Sealed Ceramic DIP |

| S                    | Side-Braized Ceramic DIP  |

| D                    | -SO Surface Mount         |

| L                    | -Ceramic Leadless         |

|                      | Chip Carrier              |

| Q                    | -Plastic Molded Quad PLCC |

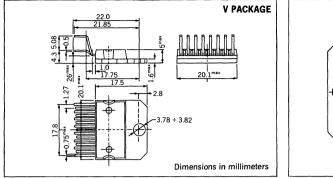

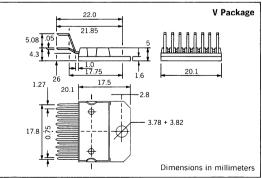

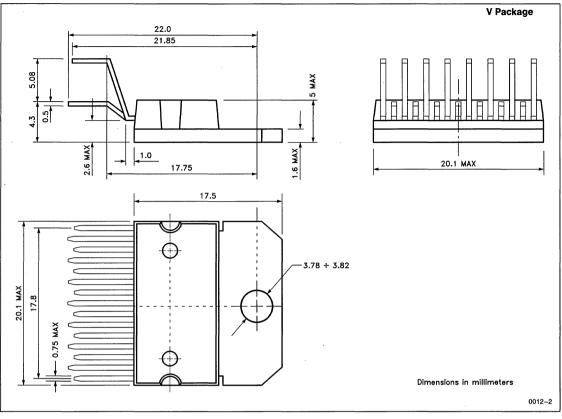

| V                    | -Multiwatt® Vertical      |

|                      | Mount                     |

| . VH                 | Multiwatt® Horizontal     |

|                      | Mount                     |

| н                    | —TO-5 Metal Can           |

| К                    | -TO-3 Steel-Base Power    |

| т                    | -TO-220 Plastic Power     |

| P                    | -Ceramic Power            |

#### **JAN Part Numbering System**

| J                                                                                                     | M38510/                        | 117                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 04                        | В                                  | Y                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | С                                                                              |

|-------------------------------------------------------------------------------------------------------|--------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|

| JAN Designator<br>Cannot be marked<br>with "J" unless<br>qualified on Part I or<br>Part II of the QPL | General<br>Procurement<br>Spec | Refers to Detail Spec         101       Op Amps         102       Voltage Regulators         103       Comparators         104       Interface         105       733         106       Voltage Followers         107       Positive Fixed         Voltage Regulators       108         108       Transistor Arrays         109       Timers         110       Quad Op Amps         112       Voltage Comparator         113       D to A Converter         114       Bi-Fet Op Amps         115       Negative Adjustable         Voltage Regulators         117       Positive Adjustable         Voltage Regulators         118       Negative Adjustable         Voltage Regulators         118       Negative Adjustable         Voltage Regulators         119       Bi-Fet Op Amps | Defines<br>Device<br>Type | Processing<br>Level<br>S<br>B<br>C | Package Type<br>A 14-lead $\frac{1}{4} \times \frac{1}{4}$ Flatpak<br>B 14-lead $\frac{1}{4} \times \frac{1}{4}$ Flatpak<br>C 14-lead $\frac{1}{4} \times \frac{3}{4}$ Dip<br>D 14-lead $\frac{1}{4} \times \frac{3}{6}$ Flatpak<br>E 16-lead $\frac{1}{4} \times \frac{3}{6}$ Flatpak<br>G 8-lead Can<br>H 10-lead $\frac{1}{4} \times \frac{1}{4}$ Flatpak<br>I 10-lead $\frac{1}{4} \times \frac{1}{4}$ Flatpak<br>I 10-lead $\frac{1}{4} \times \frac{1}{4}$ Flatpak<br>J 24-lead $\frac{3}{6} \times \frac{5}{6}$ Flatpak<br>P 8-lead Can<br>Y 2-lead Can<br>Y 2-lead TO-3 Can<br>Z 24-lead $\frac{1}{4} \times \frac{3}{6}$ Flatpak | Lead Finish<br>A Hot Solder Dip<br>B Tin Plate<br>C Gold Plate<br>X Any Finish |

.

## PRODUCT SELECTION GUIDE

### Switching Regulator Control ICs

Note: Most series available screened to /883B Rev. C.

|                                                                                                              |    |          |     |                 | 1         | /    |               | PE                      | RF  | ORMANC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | EC   | НА     | RA       | СТЕ          | RIS     | STIC   | CS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |             |                           |

|--------------------------------------------------------------------------------------------------------------|----|----------|-----|-----------------|-----------|------|---------------|-------------------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|--------|----------|--------------|---------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|---------------------------|

|                                                                                                              |    |          |     | ,               | Γ         | Γ.   | Γ,            |                         | Ζ   | /                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | /    | /      |          |              | Γ,      | Γ,     | Contracting Contra | Mode /      |                           |

|                                                                                                              |    |          |     | /               | /         | /    | /             | Outon to Chronic Andrew | /   | and a start of the | /    | Cilla. | <u>ş</u> | /            | /       | /      | Contraction Contraction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | <i>\$</i> / | \$                        |

|                                                                                                              |    | Koll Pac | 1   | Du. Slar erence | 2/        | /    | Shubu De Lock | in and                  |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Ę    | °,     | /        | Son Pole Out | 5/3     | /      | o o o                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | à           | Contraction of the second |

|                                                                                                              |    | 1.       | 20/ | erence          | 1         | 1    | 3/            | Output Current          | 142 | 10/ 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | eque | /      | 3/       | 20           | 10/     | cille  | S Son                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 3.          | 11 510                    |

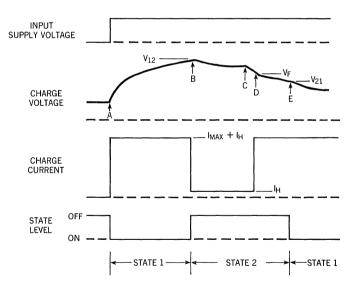

|                                                                                                              | 1  | 00 A.    | 8   | See.            | Und Lolon | -Nor | 13            | Com In                  | · / | A COMPANY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | ,    | 0,00   | 14       | 100          | and and | olden? | the bie of                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 1           | and and a contraction     |