LSI Products Division TRW Electronic Components Group

LSI Products Division TRW Electronic Components Group P.O. Box 2472 La Jolla, CA 92038

©TRW Inc. 1985. TRW is the name and mark of TRW Inc.

LSI Products Division TRW Electronic Components Group

,

Introduction Product Indexes Advance Information A/D Converters Evaluation Boards D/A Converters Multipliers Multiplier-Accumulators Special Function Products Memory/Storage Products Reliability Package Information Glossary Ordering Information Application Notes And Reprints (Listings)

LSI Products Division TRW Electronic Components Group

### Introduction

Product Indexes Advance Information A/D Converters Evaluation Boards D/A Converters Multipliers Multipliers Special Function Products Special Function Products Memory/Storage Products Reliability Package Information Glossary Ordering Information Application Notes And Reprints (Listings)

LSI Products Division TRW Electronic Components Group

### **Challenging the Future**

As the world leader of high-speed data acquisition and digital signal processing components, TRW LSI Products has made a commitment to the future. In the early 1960s, TRW developed TTL and pioneered the evolution of Integrated Circuit and VLSI technologies. Today TRW LSI is conducting research to create new products and set high-performance standards in the design, development and manufacture of components. 1-micron technology is now the standard used at TRW in both bipolar and CMOS processes. This represents a major breakthrough in IC manufacturing, producing faster and more cost-effective products.

As system technologies change and grow, the group of dedicated employees at TRW LSI Products has committed the future to setting even higher standards in order to provide the customer with better, more reliable, and more useful products. TRW LSI Products currently offers a diverse line of DSP components, including: multipliers, multiplier-accumulators, A/D and D/A converters, shift registers, floating point processors, and others. The use of innovative designs and state-of-the-art manufacturing processes has resulted in product quality that is unsurpassed in the industry. Each device receives thorough testing, and passes stringent quality control requirements. TRW LSI's components have been proven in many applications, ranging from telecommunications and broadcasting to oil and space exploration, medical electronics and underwater surveillance.

TRW LSI Products prides itself in its responsiveness to customers' requirements and needs. As world technological advances intensify, the most modern research techniques are applied to real-life situations in order to produce devices designed to improve system reliability while reducing circuit cost, size and power requirements.

Our superior products meet all of your specific needs. Follow us as we develop components that will require less space, less energy consumption and less design effort for your system. Follow us as we challenge the future.

|          | ۷ | L            | S   | ī  |

|----------|---|--------------|-----|----|

|          | D | A            | T   | A  |

|          | B | 0            | 0   | К  |

|          |   |              |     |    |

|          |   | ين.<br>منابع |     |    |

| N. W.    |   |              | A   |    |

|          |   |              |     | S  |

| <b>F</b> |   | A            | X   | Č, |

|          | 4 | X            |     | X  |

|          | ß | X            |     |    |

|          |   |              | Par |    |

### Introduction Product Indexes

Advance Information AID Converters Evaluation Boards D/A Converters Multipliers Multiplier-Accumulators Special Function Products Memory/Storage Products Namory/Storage Products Reliability Package Information Glossary Ordering Information Application Notes And Reprints (Listings)

.

### **Product Index (Family)**

| A/D Converters |                | Catalog Page Number |

|----------------|----------------|---------------------|

| TDC1001        | 8-Bit, 2.5MSPS | D 5                 |

| TDC1002        | 8-Bit, 1.0MSPS | D 5                 |

| TDC1007        | 8-Bit, 20MSPS  | D 15                |

| TDC1014        | 6-Bit, 25MSPS  | D 27                |

| TDC1019        | 9-Bit, 15MSPS  | D 37                |

| TDC1019-1      | 9-Bit, 18MSPS  | D 37                |

| TDC1021        | 4-Bit, 25MSPS  | D 49                |

| TDC1025        | 8-Bit, 50MSPS  | D 59                |

| TDC1027        | 7–Bit, 18MSPS  | D 75                |

| TDC1029        | 6-Bit, 100MSPS | D 85                |

| TDC1044        | 4-Bit, 25MSPS  | D 97                |

| TDC1046        | 6-Bit, 25MSPS  | D 107               |

| TDC1047        | 7-Bit, 20MSPS  | D 117               |

| TDC1048        | 8-Bit, 20MSPS  | D 127               |

| TDC1147        | 7-Bit, 15MSPS  | D 139               |

#### **Evaluation Boards**

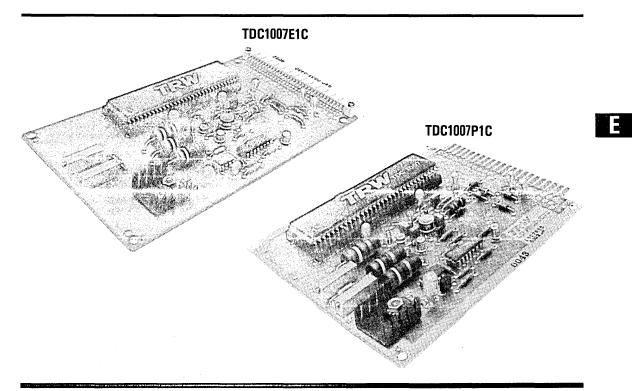

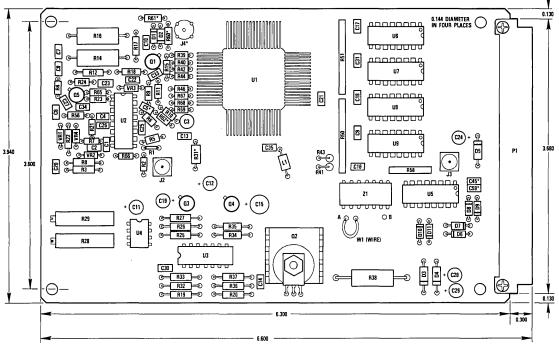

| TDC1007E1C/P1C | 8-Bit, 20MSPS  | E 5  |

|----------------|----------------|------|

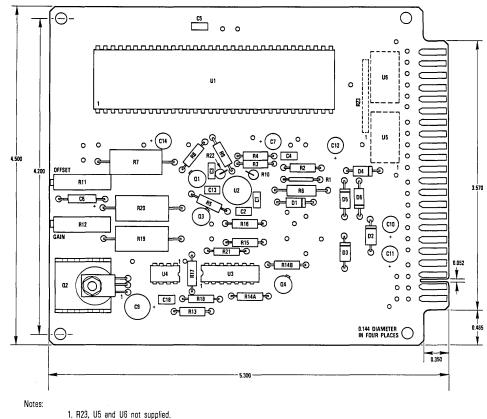

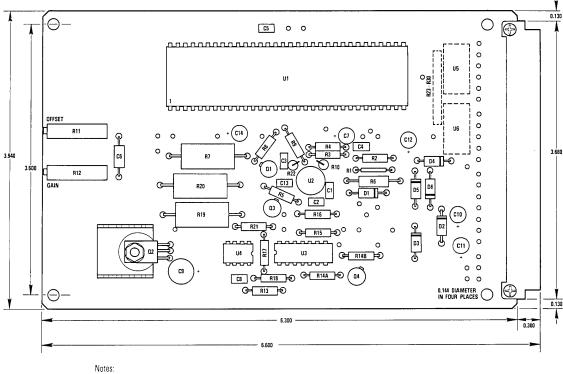

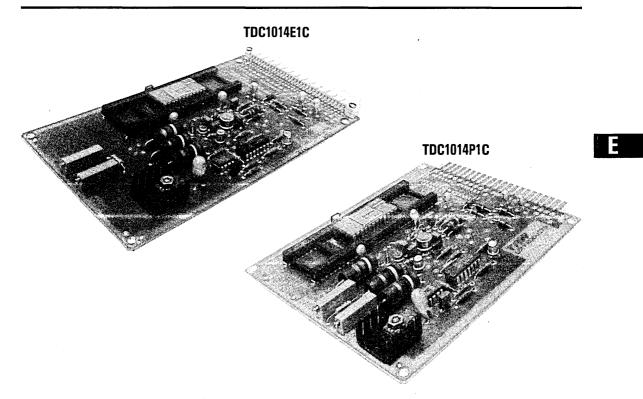

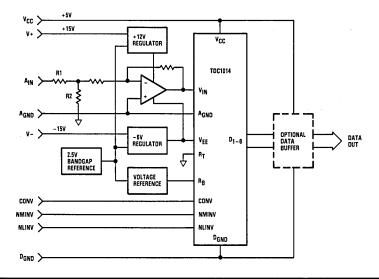

| TDC1014E1C/P1C | 6-Bit, 25MSPS  | E 21 |

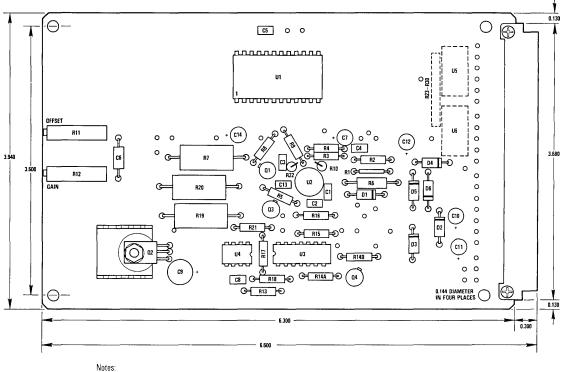

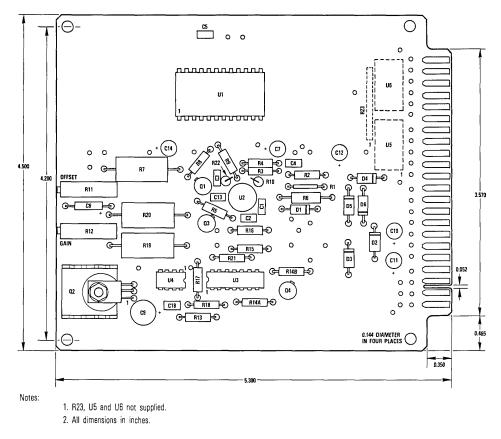

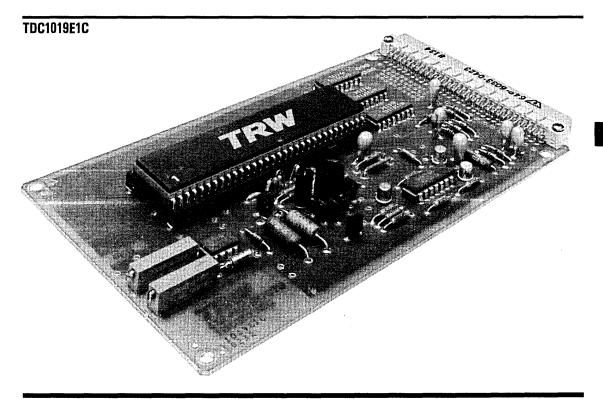

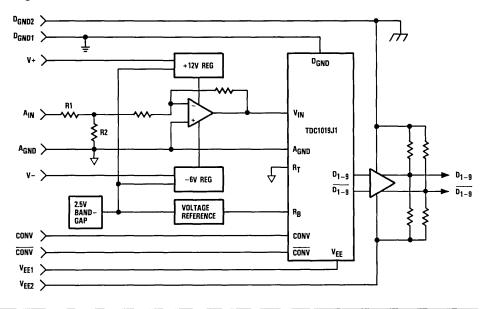

| TDC1019E1C     | 9-Bit, 15MSPS  | E 35 |

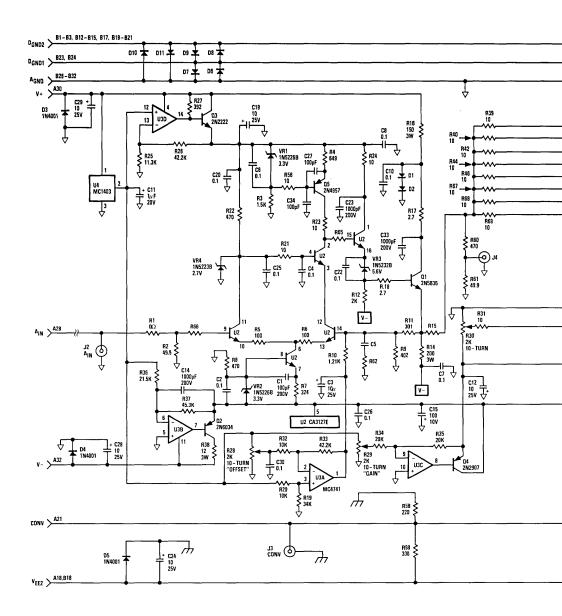

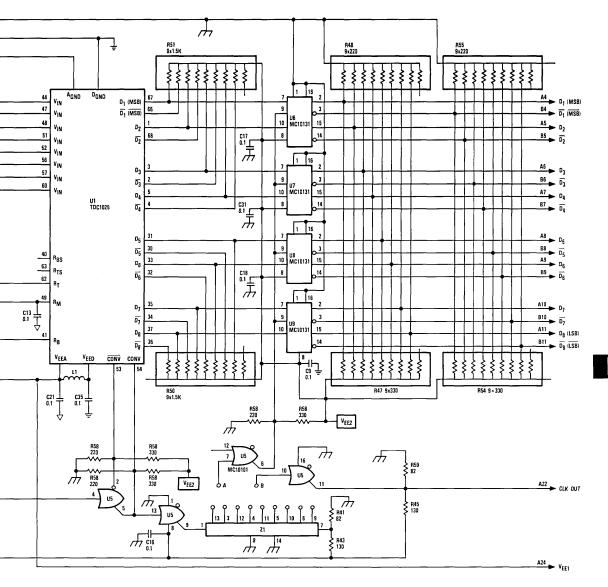

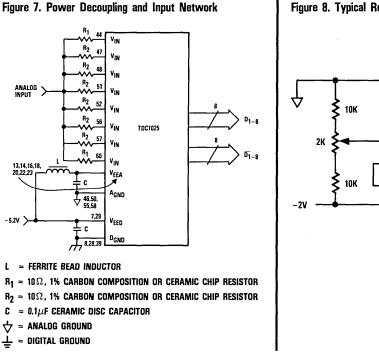

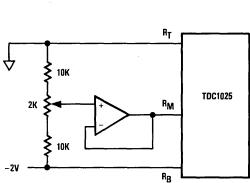

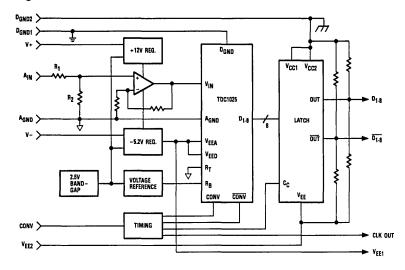

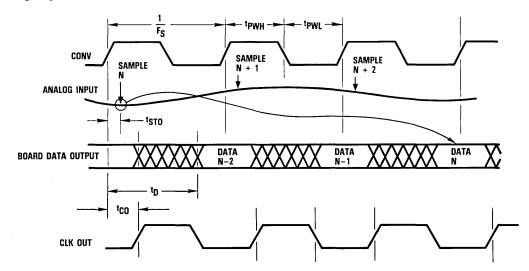

| TDC1025E1C     | 8-Bit, 50MSPS  | E 49 |

| TDC1029E1C     | 6-Bit, 100MSPS | E 61 |

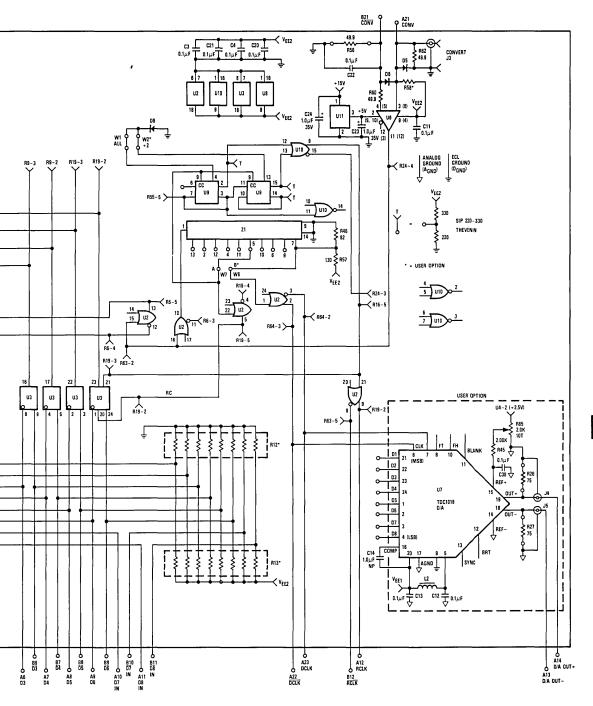

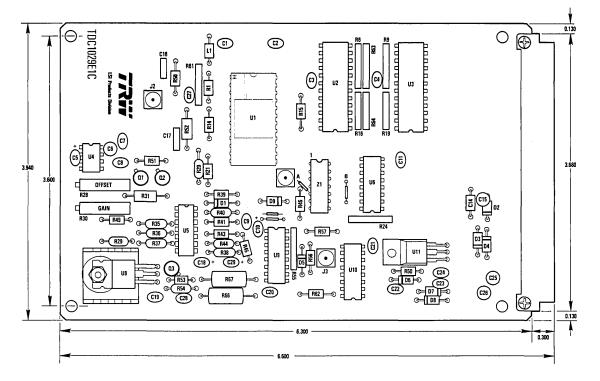

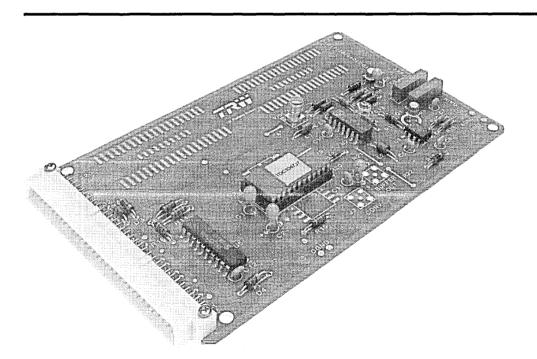

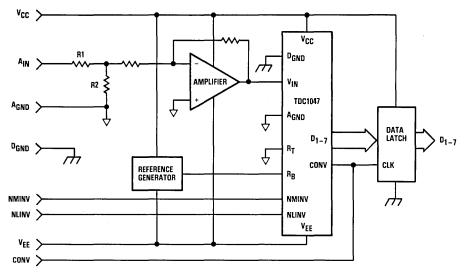

| TDC1047E1C     | 7-Bit, 20MSPS  | E 73 |

| TDC1048E1C     | 8-Bit, 20MSPS  | E 83 |

|                |                |      |

#### **D/A Converters**

| Diri Constituto |                |      |

|-----------------|----------------|------|

| TDC1016-8       | 8-Bit, 20MSPS  | F 5  |

| TDC1016-9       | 9-Bit, 20MSPS  | F 5  |

| TDC1016-10      | 10-Bit, 20MSPS | F 5  |

| TDC1018         | 8-Bit, 125MSPS | F 17 |

| TDC1034         | 4-Bit, 125MSPS | F 31 |

#### Multipliers

| MPY008H   | 8 x 8 Bit, 90ns Cycle Time      | G 5  |

|-----------|---------------------------------|------|

| MPY008H-1 | 8 x 8 Bit, 65ns Cycle Time      | G 5  |

| MPY08HU   | 8 x 8 Bit, 90ns Cycle Time      | G 15 |

| MPY08HU-1 | 8 x 8 Bit, 65ns Cycle Time      | G 15 |

| MPY012H   | 12 x 12 Bit, 115ns Cycle Time   | G 25 |

| MPY112K   | 12 x 12 Bit, 50ns Cycle Time    | G 39 |

| MPY016H   | 16 x 16 Bit, 145ns Cycle Time   | G 49 |

| MPY016K   | 16 x 16 Bit, 45ns Cycle Time    | G 63 |

| MPY016K-1 | 16 x 16 Bit, 40ns Cycle Time    | G 63 |

| TMC216H   | 16 x 16, 145ns Cycle Time, CMOS | G 77 |

|           |                                 |      |

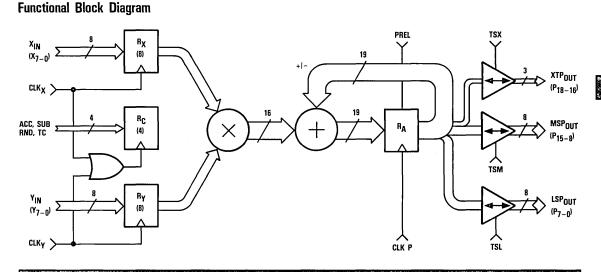

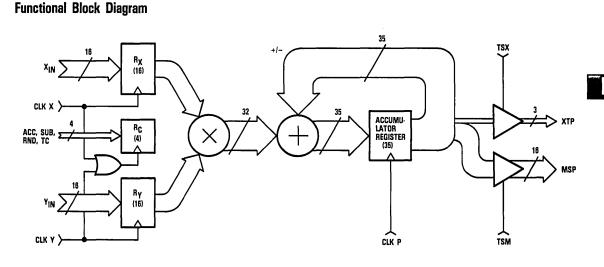

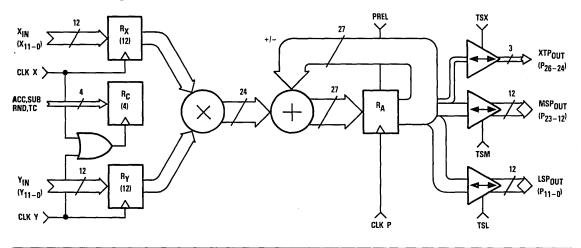

#### Multiplier - Accumulators

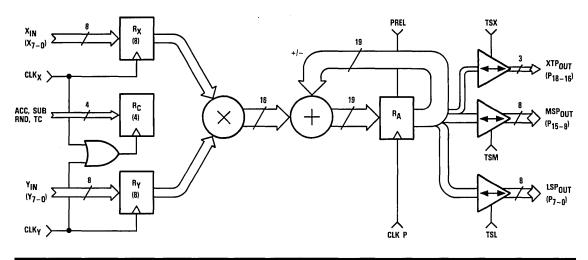

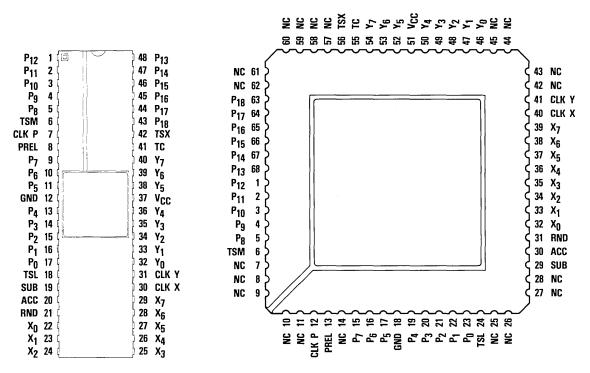

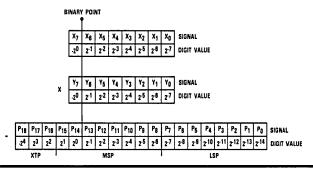

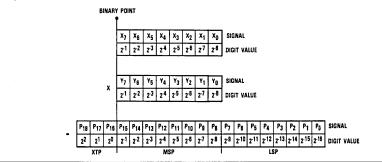

| 8 x 8 Bit, 100ns Cycle Time, 19-Bit Output         | H 5                                                                                                                                                                                                                                                           |

|----------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

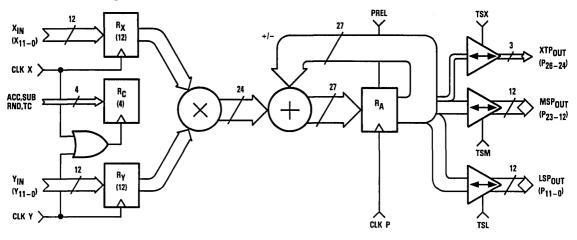

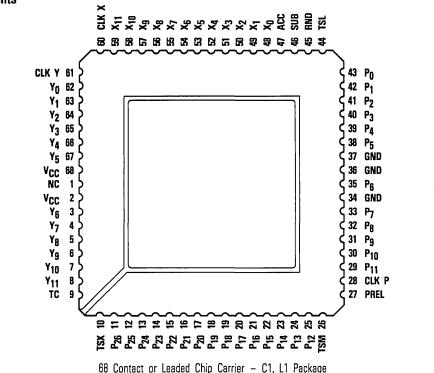

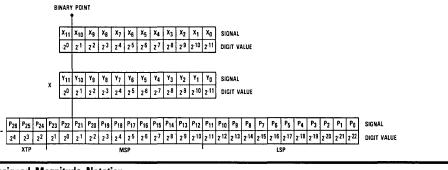

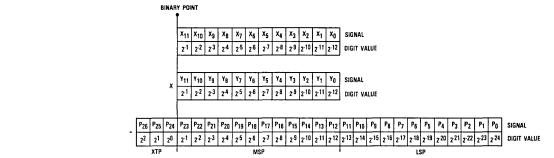

| 12 x 12 Bit, 135ns Cycle Time, 27-Bit Output       | H 17                                                                                                                                                                                                                                                          |

| 16 x 16 Bit, 165ns Cycle Time, 35-Bit Output       | H 29                                                                                                                                                                                                                                                          |

| 16 x 16 Bit, 100ns Cycle Time, 19-Bit Output       | H 41                                                                                                                                                                                                                                                          |

| 12 x 12 Bit, 135ns Cycle Time, 27-Bit Output, CMOS | H 53                                                                                                                                                                                                                                                          |

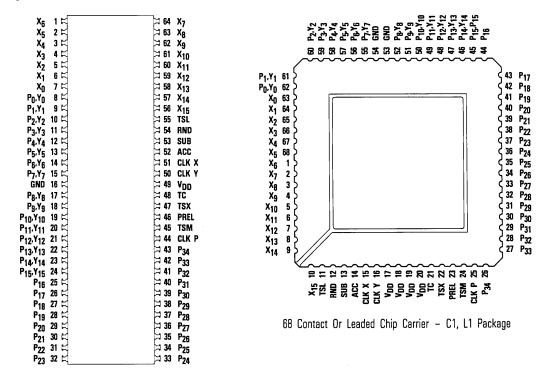

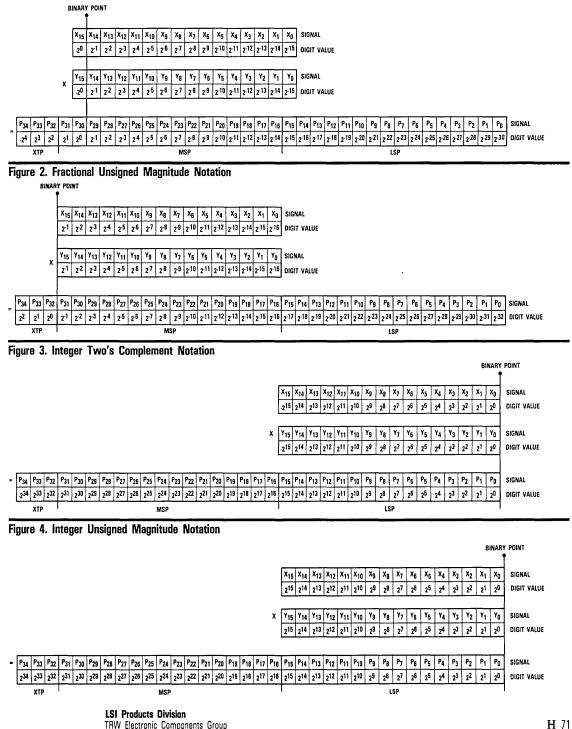

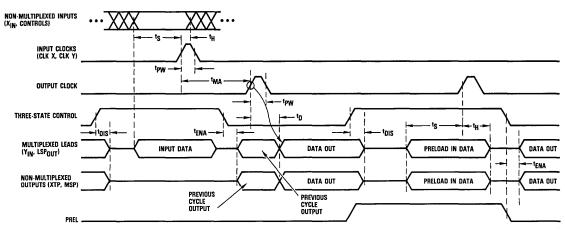

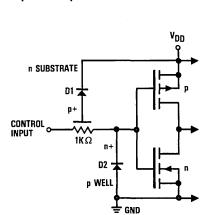

| 16 x 16 Bit, 160ns Cycle Time, CMOS                | H 65                                                                                                                                                                                                                                                          |

| 16 x 16 Bit, 100ns Cycle Time, CMOS                | H 77                                                                                                                                                                                                                                                          |

|                                                    | 12 x 12 Bit, 135ns Cycle Time, 27-Bit Output         16 x 16 Bit, 165ns Cycle Time, 35-Bit Output         16 x 16 Bit, 100ns Cycle Time, 19-Bit Output         12 x 12 Bit, 135ns Cycle Time, 27-Bit Output, CMOS         16 x 16 Bit, 160ns Cycle Time, CMOS |

#### **Special Functions**

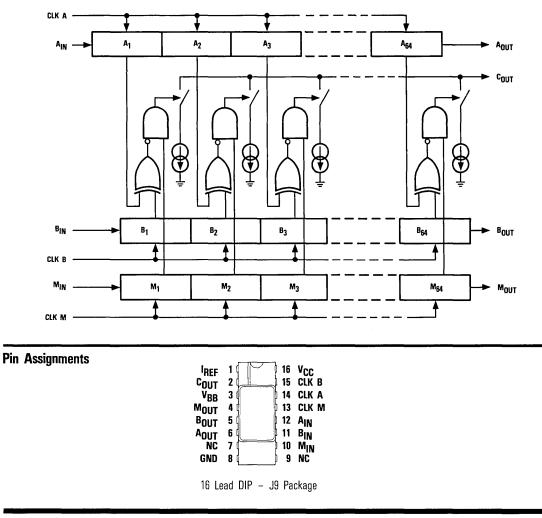

| TDC1004 | 64 x 1 Bit, 10MHz, Digital Correlator, Analog Output  | I 5  |

|---------|-------------------------------------------------------|------|

| TDC1022 | 22-Bit, 10MHz, Floating Point Arithmetic Unit         | I 13 |

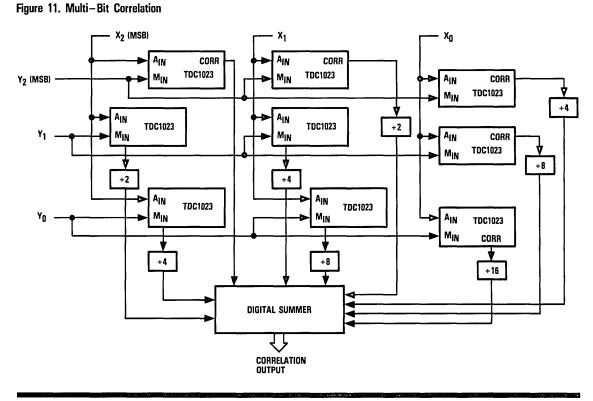

| TDC1023 | 64 x 1 Bit, 15MHz, Digital Correlator, Digital Output | I 29 |

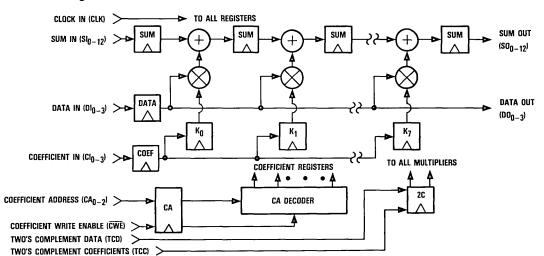

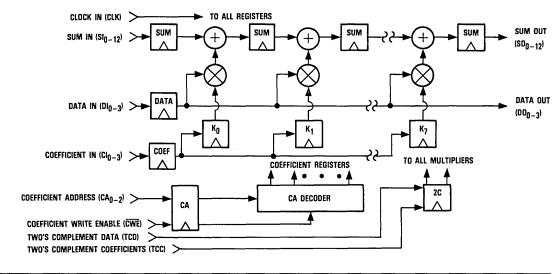

| TDC1028 | 4 x 4 x 8 Bit, 10MHz, Digital Filter (FIR)            | I 43 |

#### Memory/Storage Products

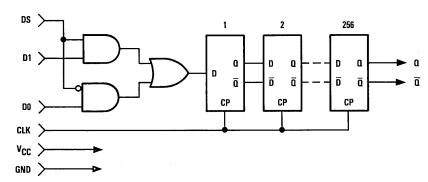

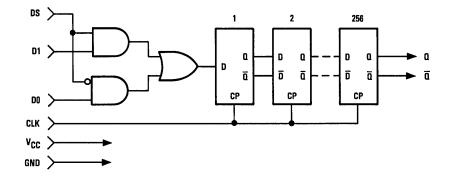

| TDC1005 | 64 x 2 Bit, 25MHz, Shift Register            | J 5  |

|---------|----------------------------------------------|------|

| TDC1006 | 256 x 1 Bit, 25MHz, Shift Register           | J 11 |

| TDC1011 | 8-Bit, 18MHz, Variable Length Shift Register | J 17 |

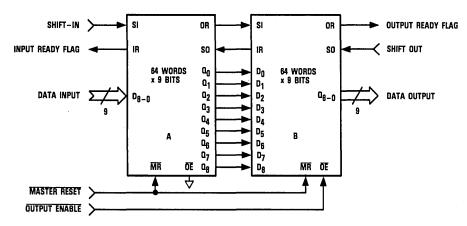

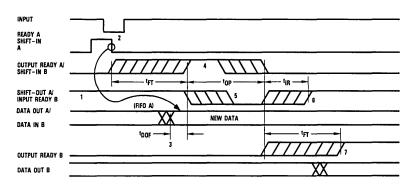

| TDC1030 | 64 x 9, 15MHz, First-In First-Out Memory     | J 25 |

See pages C 3-C 25 for information on our future products.

| Numerical Order |                                                        | Catalog Page Number |

|-----------------|--------------------------------------------------------|---------------------|

| MPY008H         | 8 x 8 Bit Multiplier, 90ns Cycle Time                  | G 5                 |

| MPY008H - 1     | 8 x 8 Bit Multiplier, 65ns Cycle Time                  | G 5                 |

| MPY08HU         | 8 x 8 Bit Multiplier, 90ns Cycle Time                  | G 15                |

| MPY08HU-1       | 8 x 8 Bit Multiplier, 65ns Cycle Time                  | G 15                |

| MPY012H         | 12 x 12 Bit Multiplier, 115ns Cycle Time               | G 25                |

| MPY016H         | 16 x 16 Bit Multiplier, 145ns Cycle Time               | G 49                |

| MPY016K         | 16 x 16 Bit Multiplier, 45ns Cycle Time                | G 63                |

| MPY016K-1       | 16 x 16 Bit Multiplier, 40ns Cycle Time                | G 63                |

| MPY112K         | 12 x 12 Bit Multiplier, 50ns Cycle Time                | G 39                |

|                 |                                                        |                     |

| TDC1001         | 8-Bit A/D Converter, 2.5MSPS, Successive Approximation | D 5                 |

| TDC1002         | 8-Bit A/D Converter, 1.0MSPS, Successive Approximation | D 5                 |

| TDC1004         | 64 x 1 Bit Digital Correlator, 10MHz, Analog Output    | I 5                 |

| TDC1005         | 64 x 2 Bit Shift Register, 25MHz                       | J 5                 |

| TDC1006         | 256 x 1 Bit Shift Register, 25MHz                      | J 11                |

| TDC1007         | 8-Bit A/D Converter, 20MSPS                            | D 15                |

| TDC1007E1C      | 8-Bit Evaluation Board, 20MSPS                         | E 5                 |

| TDC1008         | 8 x 8 Bit Multiplier-Accumulator, 100ns Cycle Time     | H 5                 |

| TDC1009         | 12 x 12 Bit Multiplier-Accumulator, 135ns Cycle Time   | H 17                |

| TDC1010         | 16 x 16 Bit Multiplier-Accumulator, 165ns Cycle Time   | H 29                |

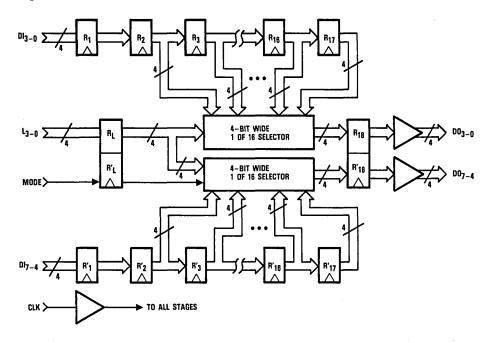

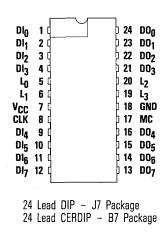

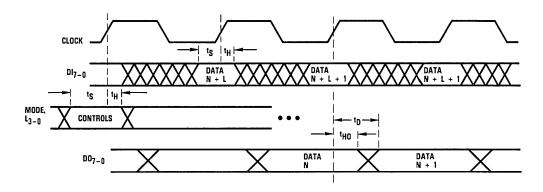

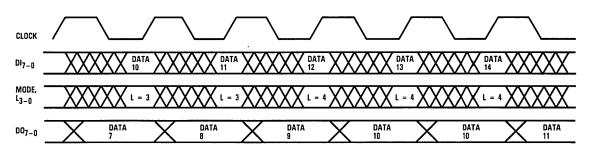

| TDC1011         | 8-Bit Variable Length Shift Register, 18MHz            | J 17                |

| TDC1014         | 6-Bit A/D Converter, 25MSPS                            | D 27                |

| TDC1014E1C      | 6-Bit Evaluation Board, 25MSPS                         | E 21                |

| TDC1016-8       | 8-Bit D/A Converter, 20MSPS                            | F 5                 |

| TDC1016-9       | 9-Bit D/A Converter, 20MSPS                            | F 5                 |

| TDC1016-10      | 10-Bit D/A Converter, 20MSPS                           | F 5                 |

| TDC1018         | 8-Bit D/A Converter, 125MSPS                           | F 17                |

| TDC1019         | 9-Bit A/D Converter, 15MSPS                            | D 37                |

| TDC1019-1       | 9-Bit A/D Converter, 18MSPS                            | D 37                |

| TDC1019E1C      | 9-Bit Evaluation Board, 15MSPS                         | E 35                |

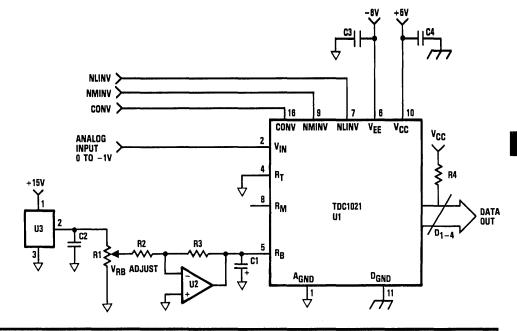

| TDC1021         | 4-Bit, A/D Converter, 25MSPS                           | D 49                |

| TDC1022         | 22-Bit Floating Point Arithmetic Unit, 10MHz           | I 13                |

| TDC1023         | 64 x 1 Bit Digital Correlator, 15MHz, Digital Output   | I 29                |

| TDC1025         | 8-Bit A/D Converter, 50MSPS                            | D 59                |

| TDC1025E1C      | 8-Bit Evaluation Board, 50MSPS                         | E 49                |

| TDC1027         | 7-Bit A/D Converter, 18MSPS                            | D 75                |

| TDC1028         | 4 x 4 x 8 Bit Digital Filter (FIR), 10MHz              | I 43                |

| TDC1029         | 6-Bit A/D Converter, 100MSPS                           | D 85                |

| TDC1029E1C      | 6-Bit Evaluation Board, 100MSPS                        | E 61                |

| TDC1030         | 64 x 9 Bit First-In First-Out Memory, 15MHz            | J 25                |

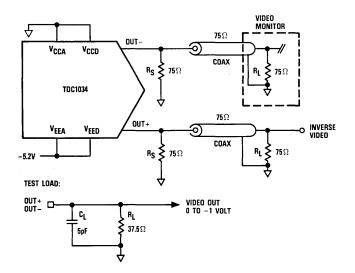

| TDC1034         | 4-Bit D/A Converter, 125MSPS                           | F 31                |

| TDC1043         | 16 x 16 Bit Multiplier-Accumulator, 100ns Cycle Time   | H 41                |

| TDC1044         | 4-Bit A/D Converter, 25MSPS                            | D 97                |

| TDC1046         | 6-Bit A/D Converter, 25MSPS                            | D 107               |

| TDC1047         | 7-Bit A/D Converter, 20MSPS                            | D 117               |

| TDC1047E1C      | 7-Bit Evaluation Board, 20MSPS                         | E 73                |

| TDC1048         | 8-Bit A/D Converter, 20MSPS, Low Power                 | D 127               |

| TDC1048E1C      | 8-Bit Evaluation Board, 20MSPS                         | E 83                |

| TDC1147         | 7-Bit A/D Converter, 15MSPS                            | D 139               |

| TMC2009 | 12 x 12 Bit CMOS Multiplier-Accumulator, 135ns Cycle Time | H 53 |

|---------|-----------------------------------------------------------|------|

| TMC2010 | 16 x 16 Bit CMOS Multiplier-Accumulator, 160ns Cycle Time | H 65 |

| TMC2110 | 16 x 16 Bit CMOS Multiplier-Accumulator, 100ns Cycle Time | H 77 |

| TMC216H | 16 x 16 Bit CMOS Multiplier, 145ns Cycle Time             | G 77 |

See pages C 3-C 25 for information on our future products.

### Introduction Product Indexes Advance Information A/D Converters Evaluation Boards D/A Converters Multipliers Multipliers Multiplier-Accumulators Special Function Products Memory/Storage Products Reliability Package Information Glossary Ordering Information Application Notes And Reprints (Listings)

**C** 1

### **TDC1033** Advance Information

### **Floating Point Registered Arithmetic/Logic Unit**

22-bit (with 16-bit compatibility mode)

The TRW TDC1033 is a monolithic integrated circuit arithmetic/logic unit with an on-chip register file. It operates on numbers represented in two formats: 16-bit fixed point two's complement and 22-bit floating point. The 22-bit floating point format has a 16-bit two's complement significand and a 6-bit two's complement exponent giving full 16-bit precision over a 384dB dynamic range.

In the 16-bit fixed point mode, the TDC1033 is function and microcode compatible with an array of four industry standard 2901-bit slice processors including the 2902 carry-look-ahead chip. The 22-bit floating point arithmetic functions are parallel to the fixed-point arithmetic functions providing an easy way for the designer to upgrade system performance without reprogramming microcode.

Either saturation or wrap-around treatment of overflow and underflow conditions may be selected for floating point operation.

To retain compatibility with the 2901-bit slice processors, there is a single data input port and a single data output port; these ports are fully TTL compatible. All data inputs and outputs are registered. The data outputs are three-state to allow use on a bus. The 2901's internal dual-port RAM has been retained and widened to 22 bits. Likewise, the internal bus paths are 22 bits wide. Twenty-seven pins are used to supply instructions, controls and addresses to the TDC1033. It operates at up to 6 million operations/second (6MHz clock).

#### Features

- Microprogrammable (Replaces Four 2901-Bit Slice Units) In Fixed Point Mode

- Eases Upgrade Of Systems To Floating Point

- Full 16-Bit Precision Over Wide Dynamic Range

- Two's Complement Fixed And Floating Point Operation

- User-Selectable Saturation Limiting Or Wrap-Around Overflow Handling

- Three-State TTL Outputs

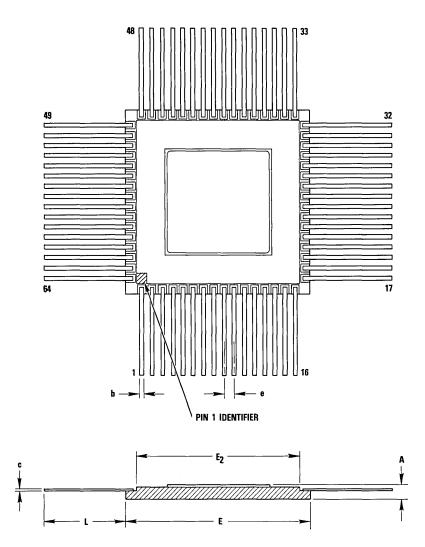

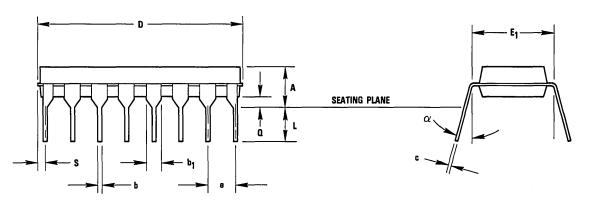

- Available In 84 Lead Pin Grid Array Or Leadless Chip Carrier

#### **Applications**

- Fast Fourier Transformers

- Digital Filters

- · Geometric Transformations For Image Processing And Computer Graphics

- Array Processors

- High-Speed Controllers

- Arithmetic Element Module (With TDC1042 Multiplier)

#### Simplified Block Diagram

Point

R XNOR S

#### Instructions

Phone: (619) 457-1000

TWX: 910-335-1571

Telex: 697-957

| Floating Point  | Fixed Poi |

|-----------------|-----------|

| R + S           | R + S     |

| S – R           | S – R     |

| R – S           | R – S     |

| Normalize R + S | R OR A    |

| Denormalize R   | R AND S   |

|                 | R AND S   |

|                 | R XOR S   |

Flags SIGN Significand Overflow ZERO Exponent Overflow Significand Carry Out

©TBW Inc. 1985 40G01200 Rev. B-5/85 Printed in the U.S.A.

TRii

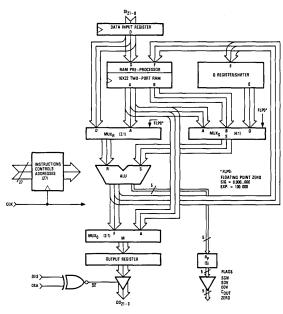

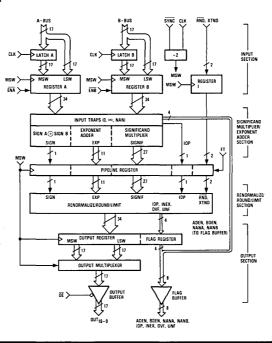

#### **Functional Block Diagram**

LSI Products Division TRW Electronic Components Group

The TDC1033 consists of five functional sections:

- 1. The Source Multiplexers For The ALU

- 2. The Arithmetic/Logic Unit (ALU) Itself

- 3. The Two-Port RAM (Register File) And RAM Shifter

#### **Source Multiplexers**

The source multiplexers select which inputs will be applied to the ALU Section. The operation of these multiplexers is controlled by three microcode instruction bits,  $I_2 - I_0$ .

The R multiplexer is a one-of-three data selector which applies to either:

- 1. The present data input to the chip

- The RAM "A" output (i.e., the word in register file "A" selected by the A Address, ADA<sub>3</sub>-ADA<sub>0</sub>) or

- 3. A floating point zero

to the "A" input port of the ALU Section.

The S multiplexer is a one-of-four data selector which applies either:

- 1. The RAM "A" output (as defined above)

- The RAM "B" output (i.e., the word in register file "B" selected by the B Address, ADB<sub>3</sub>-ADB<sub>0</sub>)

- 3. The Q register output or

- 4. A floating point zero

to the "B" input port of the ALU Section.

#### Arithmetic/Logic Unit

The ALU receives two numbers, denoted R and S, from the source multiplexers. It then performs one of eight fixed point operations, or one of five floating point operations on those quantities. The output of the ALU is bused to the RAM shifter, the Q register shifter and the output multiplexer. The ALU is controlled by eight registered inputs  $(A_3 - A_0)$ , Carry In (CIN), Round (RND), Scale (SCA) and Limit (LMT).

The ALU consists of four blocks:

- 1. The Denormalize Section

- 2. The Adder/Logic Section

- 3. The Renormalize Section

- 4. The Round/Scale/Limit Section

- LSI Products Division TRW Electronic Components Group

- 4. The Q Register And Shifter

- 5. The Output Multiplexer

The Denormalize and Renormalize sections are enabled in the floating point mode and disabled in the fixed point mode. The Denormalize Section compares the two operands' exponents and shifts the significand of the smaller by the difference between the exponents. In floating point mode, the Adder/Logic Section operates on the significand of the result. In fixed-point mode, the Adder/Logic Section operates on the selected 16-bit operands as directed by the control inputs to the device with no denormalization. The Renormalize Section performs the necessary shifts to remove redundant sign bits adjusting the exponent as required. The flags SGN (Significand SiGN), SOV (Significand OVerflow), EOV (Exponent OVerflow), ZERO (zero significand) and COUT (significand Carry OUT) are generated in the Renormalize Section. Note that while the significand flags are active in the fixed point mode, the EOV flag will not be active in the fixed point mode. In floating point mode only, the Round/Scale/Limit Section adjusts the result according to its controls. These controls and their effects are: RND (add a ONE to the bit position just below the LSB), SCA (subtract one from the exponent effectively, divide the result by two) and LMT (force the output to the maximum representable magnitude on overflow and force the output to floating point zero on underflow).

#### RAM

The RAM is a two-port 16-deep by 22-bit wide register file. The RAM preprocessor allows one of the following to be loaded into RAM:

- 1. The input data register contents

- 2. The full 22 bits of the current ALU output

- 3. Half the value of the significand of the current ALU output (sign-extended, but retaining the same exponent)

- Twice the value of the significand of the current ALU output (with the same exponent)

Controls  $DC_4-DC_0$  select which preprocessor function is to be performed. Two data words ("A" and "B", selected by the appropriate address bits) can be accessed from the RAM during one machine cycle. The RAM Write Enable (WE) is

strobed by the rising edge of the chip mester clock except in the NOP and  ${\rm Q}$  register write cases.

There are four instructions which control the loading of the RAM:

- 1. NOP (No OPeration)

- 2. Load F

- 3. Load F/2

- 4. Load 2F

(What is loaded into the RAM is the value selected by the RAM preprocessor.)

In the Load F/2 case, a one-bit right shift of the significand is performed and the Most Significant Bit (MSB) is loaded from one of four sources:

- 1. One

- 2. Zero

- 3. MSB of F (two's complement sign extension)

- 4. LSB of F (for rotation)

In the Load 2F case, a one-bit left shift of the significand is performed and the Least Significant Bit (LSB) is loaded from one of four sources:

- 1. One

- 2. Zero

- 3. MSB of F for 16-bit word rotation

- Q shifter significand MSB (used for 32-bit word shift or rotation)

#### **Q** Register/Shifter

The Q register/shifter is a 22-bit register which is reloaded each clock cycle with either the previous ALU output value (this is used for performing accumulation, division, etc.) or variously shifted versions of its own present contents. The control signals to this section are  $DC_4-DC_0$  and the DIVide control (DIV). There are nine Q register functions:

- 1. Load current ALU output. Load significand and hold exponent if DIV = 0

- Shift significand right one place and shift a zero into the MSB

- 3. Shift significand right one place and shift the significand LSB of the ALU output into the MSB

- 4. Shift significand right one place and sign extend

- Shift significand left one place and shift a zero into the LSB of the significand

- 6. Shift significand left one place and force ALU significand MSB into the LSB of the significand

- 7. Rotate Q register contents left (MSB into LSB)

- 8. Rotate Q register contents right (LSB into MSB)

- 9. NOP (no operation-i.e., hold current Q register contents)

Use of the  $\Omega$  register is especially advantageous in double-precision fixed point calculations. Note that the exponent field is UNAFFECTED by any  $\Omega$  register shift.

#### **Output Multiplexer**

The output multiplexer is a one-of-two data selector which applies either the ALU output or the RAM "A" output to the output register. The selection is internally decoded from control signals  $DC_4-DC_{\Omega}$ .

**TDC1042** Advance Information

#### **Floating Point Multiplier**

22-bit (with 16-bit fixed point compatibility mode)

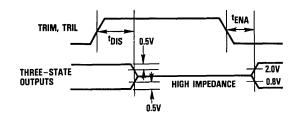

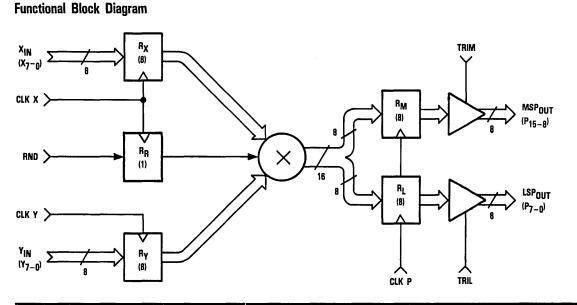

The TRW TDC1042 is a monolithic integrated circuit multiplier which operates on numbers represented in a 22-bit floating point format or in a 16-bit fixed point format. The floating point format has a 16-bit two's complement significand and a 6-bit two's complement exponent giving full 16-bit precision over a 384dB dynamic range. Either saturation or wrap-around treatment of overflow conditions may be selected.

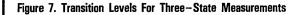

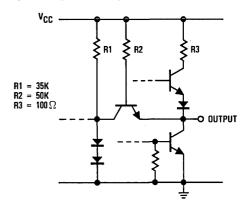

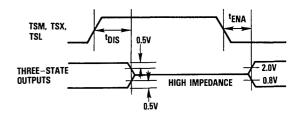

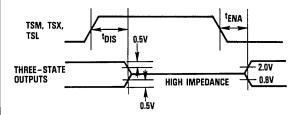

Each of the two inputs and the output has its own fully TTL compatible port providing high-speed (non-multiplexed) I/O. All data inputs and outputs are registered as well as the three instruction inputs and one of the control inputs. The data outputs are three-state to allow use on a bus.

Two internal registers and a source-selection multiplexer on the multiplicand ("B") input allow efficient implementation of complex multiplication. An internal pipeline register can be enabled to reach a data throughput rate of 10MHz (guaranteed over temperature and supply voltage variations). The device can provide a new product every 100 nanoseconds. The non-pipelined "feedthrough" mode permits 6MHz operation without the extra stage of pipeline latency.

#### Features

- Microprogrammable

- Full 16-Bit Precision Over Wide Dynamic Range

- Two's Complement Fixed Or Floating Point Multiplication

- Selectable Pipelining

- User-Selectable Saturation Limiting Or Wrap-Around Overflow Handling

- Fully Parallel I/O Structure

- Fixed Point Operation Available

- Three-State TTL Outputs

- Available In 84 Lead Pin Grid Array Or Leadless Chip Carrier

#### Applications

- Fast Fourier Transformers

- Digital Filters

- Companion Multiplier For ALU In Microprogrammed Signal Processors

- Coprocessor To TDC1033 Registered Arithmetic Logic Unit

- Geometric Transformations For Image Processing And Computer Graphics

LSI Products Division TRW Electronic Components Group P.O. Box 2472 La Jolla, CA 92038 Phone: (619) 457 - 1000 Telex: 697 - 957 TWX: 910 - 335 - 1571 ©TRW Inc. 1985 40G01201 Rev. B-5/85 Printed in the U.S.A.

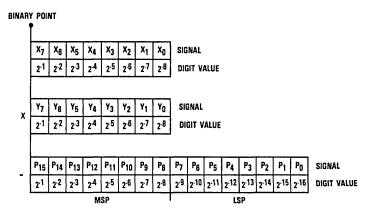

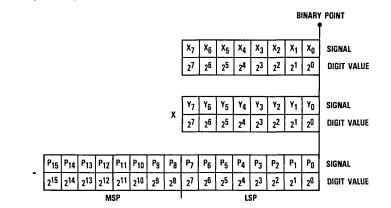

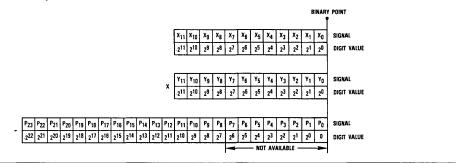

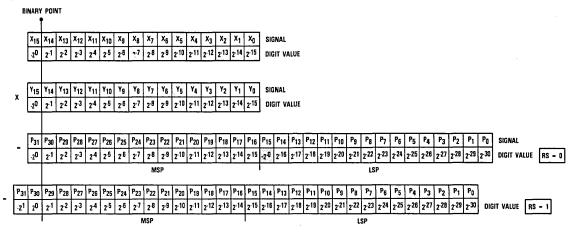

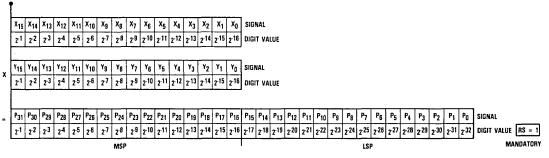

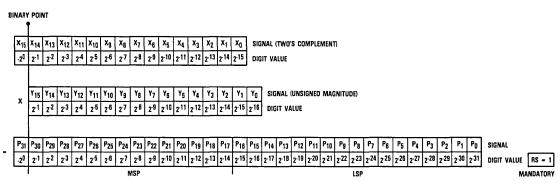

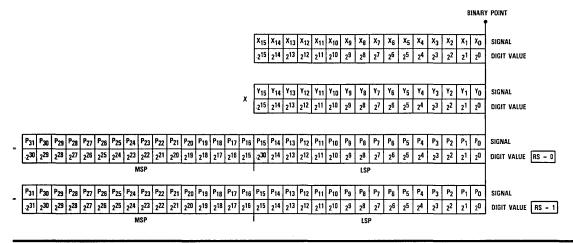

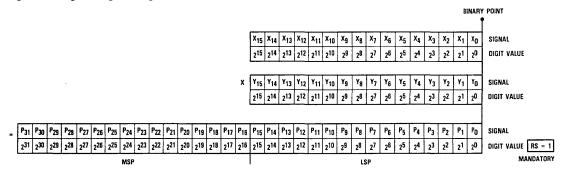

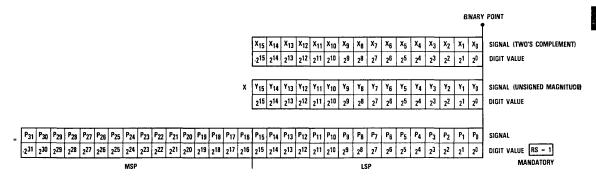

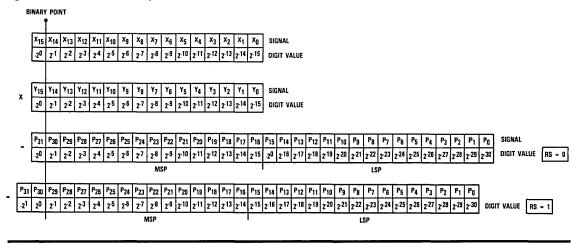

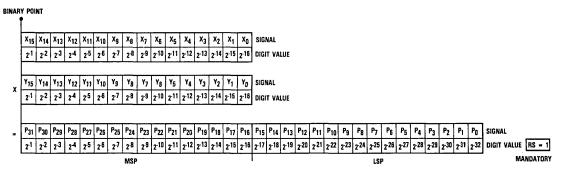

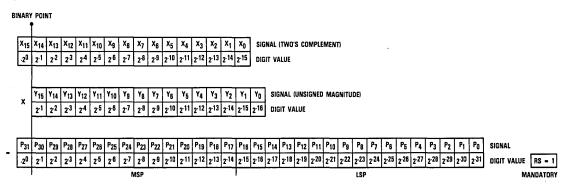

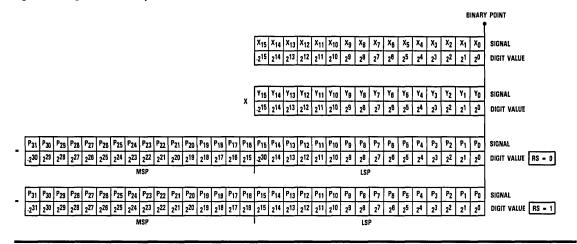

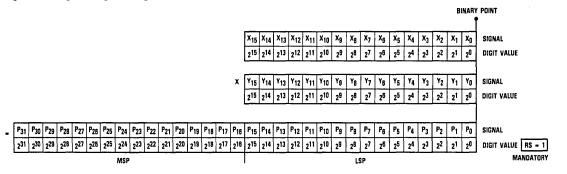

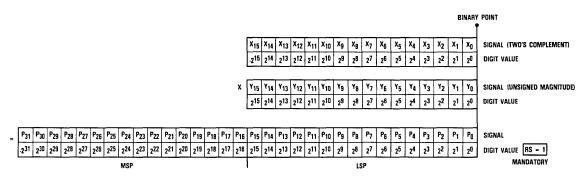

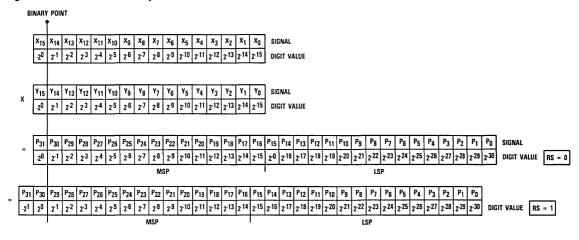

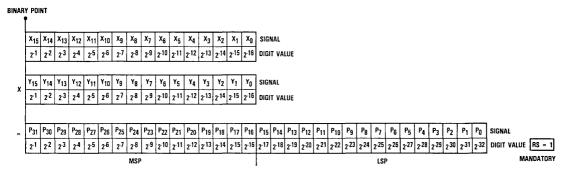

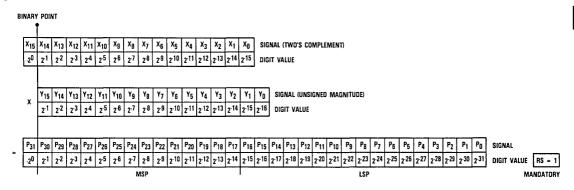

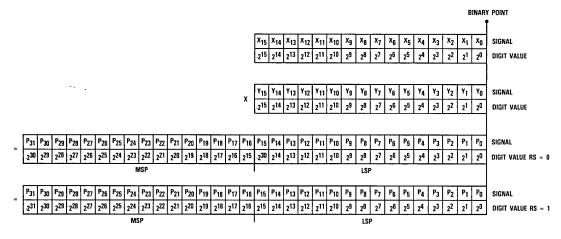

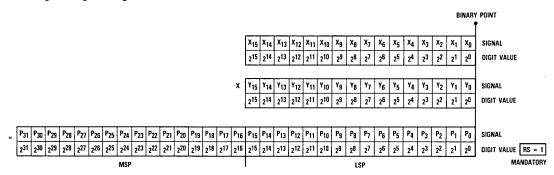

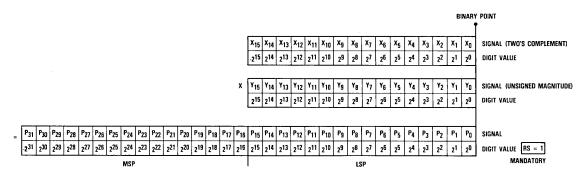

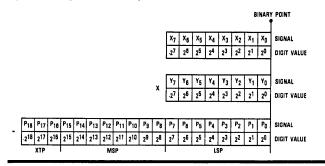

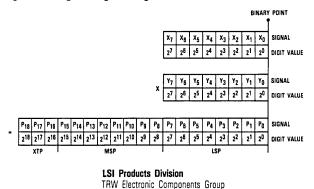

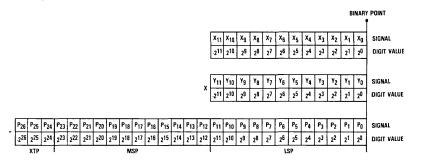

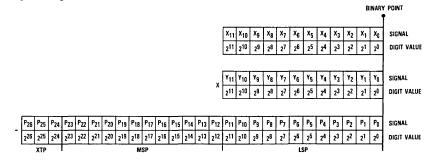

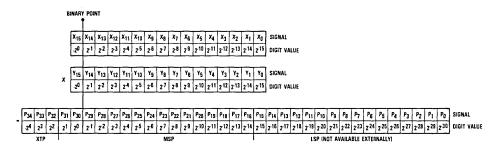

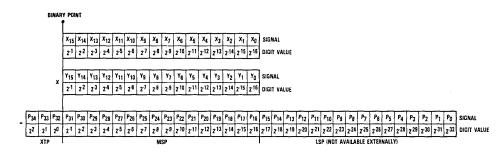

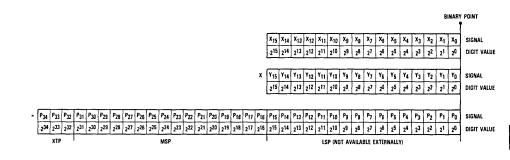

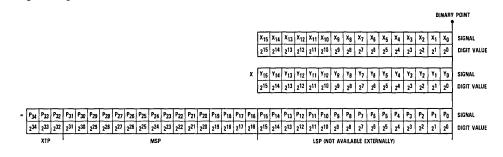

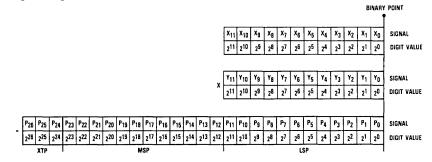

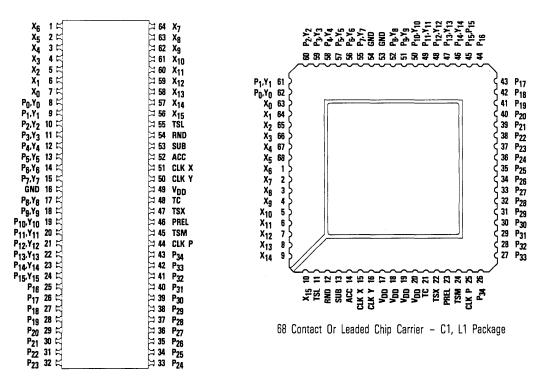

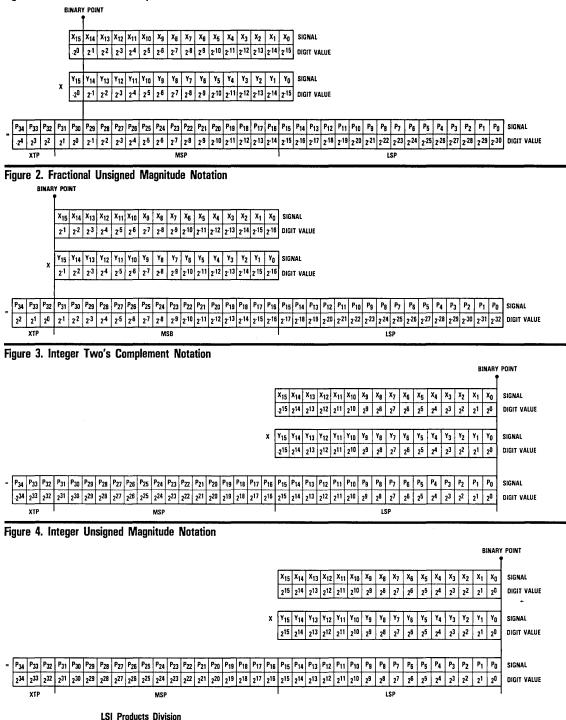

#### **Floating Point Data Format**

#### Input, Output with MSP Selected

#### Exponent

The exponent is represented by bits  $D_{16}$  through  $D_{21}$ . It is a two's complement integer with  $D_{21}$  the two's complement sign bit. The exponent ranges from -32 to 31.

Exponent =

$$D_{21} \times (-2^5) + \sum_{n=16}^{20} D_n \times 2^{(n-16)}$$

#### Zero

Zero is represented as follows:

Significand = 0.000 0000 0000 0000 Exponent = 100 000

#### Significand

The significand (sometimes referred to as the MANTISSA) is represented by bits  $D_{15}$  through  $D_0$ . It is a fractional two's complement number with 16-bit precision:  $D_{15}$  is the two's complement sign bit. The significand ranges from  $(1-2^{-15})$  to -1.

Significand =  $D_{15} \times (-1) + \sum_{n=0}^{14} D_n \times 2^{(n-15)}$

#### **Output with LSP Selected**

The exponent field is duplicated. The significand field (D<sub>15</sub> – D<sub>0</sub>) carries binary weighting from 2<sup>-16</sup> through 2<sup>-31</sup>, respectively. Thus, the significand is  $\sum_{n=0}^{15}$  D<sub>n</sub> x 2<sup>(n-31)</sup> when the LSP is output. The two LSBs (2<sup>-30</sup> and 2<sup>-31</sup>) are zero-filled as required by internal significand shifting.

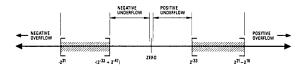

#### **Representable Floating Point (FLP) Number Range**

Normalized Floating Point Range: A normalized floating point number is one for which the first two bits of the significand (D<sub>15</sub> and D<sub>14</sub>) are different, that is  $D_{15} \oplus D_{14} = 1$ .

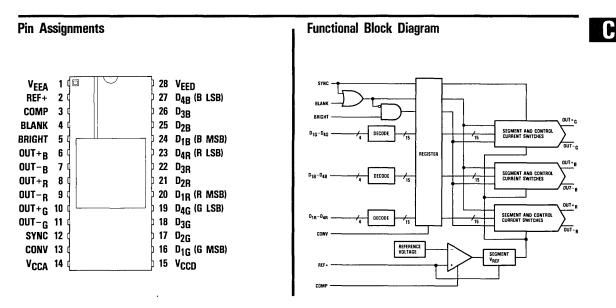

**TDC1334** Advance Information

#### **Digital-To-Analog Converter** Triple 4-bit, 100MSPS

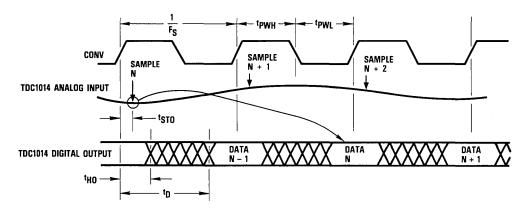

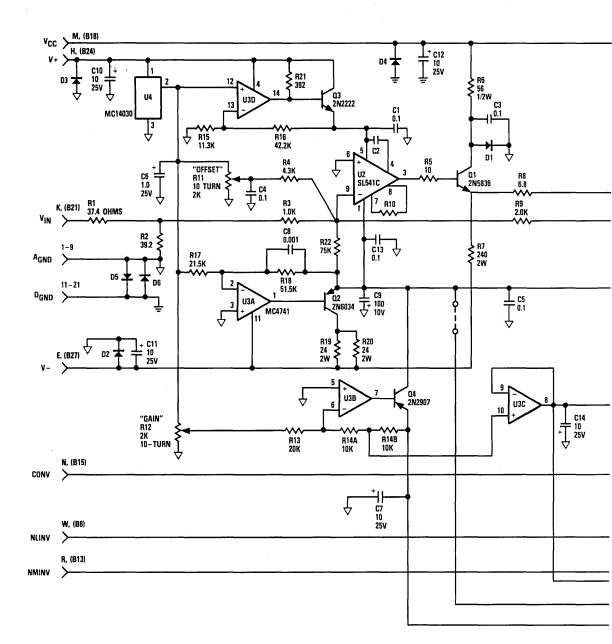

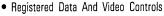

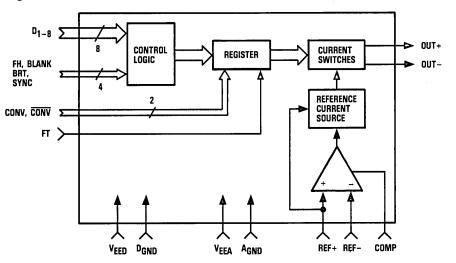

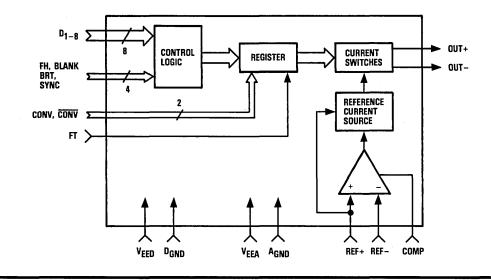

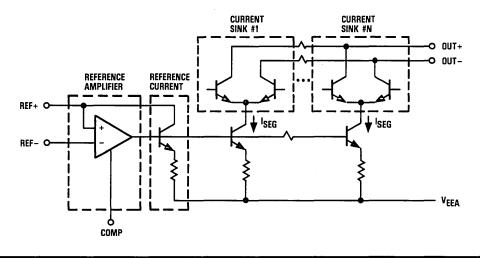

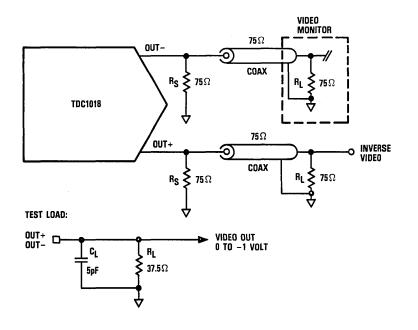

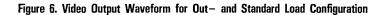

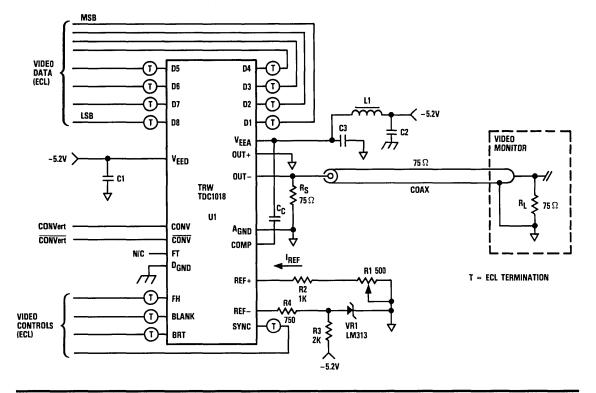

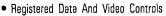

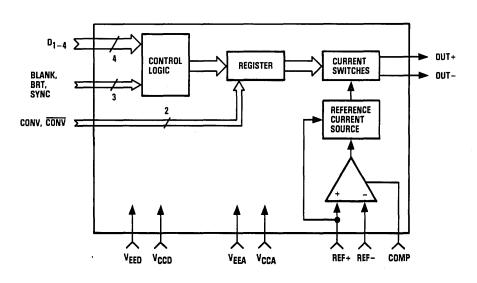

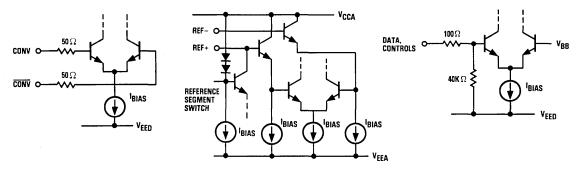

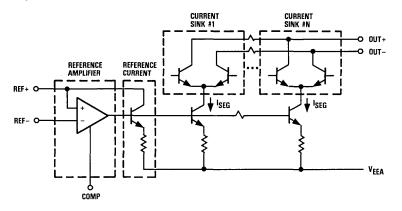

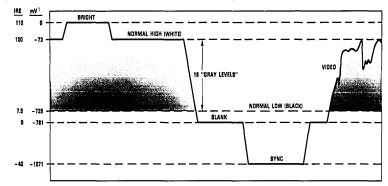

The TRW TDC1334 consists of three separate 4-bit D/A converters on a single monolithic integrated circuit. The TDC1334 has been designed for high-speed operation and is compatible with ECL logic families. All data and control inputs to the device are registered on the rising edge of the clock (CONV) input.

A single on-chip band-gap voltage source is used as the reference for all three D/A converters and a single external resistor determines gain of the TDC1334. Video controls, Sync and Blank, are included on the TDC1334 for accurately setting D/A output levels during synchronization and CRT blanking intervals. A brightness enhancement control, Bright, is used for emphasizing portions of a CRT display and cursor identification.

Each of the three D/A converters has two complementary current output terminals that can drive 75 0hm lines. The device has been designed to minimize digital feedthrough and for optimum printed circuit board layout. Analog and digital

grounds have been kept separate for maximum flexibility in system grounding.

#### **Features**

- Complete, Monolithic, "Graphics Ready"

- Three Identical 4-Bit D/A Converters

- Registered Data Inputs

- Registered Sync, Blank, And Bright Controls

- On-Board Reference

- Linearity Error Less Than 1/8 LSB

- 100MSPS Operation

- ECL Compatible Inputs

- Complementary Current Outputs

- Single -5.2 Volt Power Supply Required

- Can Be Operated In TTL Systems

- Available In A 28 Lead Ceramic DIP

LSI Products Division TRW Electronic Components Group P.O. Box 2472 La Jolla, CA 92038 Phone: (619) 457–1000 Telex: 697–957 TWX: 910–335–1571 ©TRW Inc. 1985 40G02018 Rev. A-1/85 Printed in the U.S.A.

# **7***RW*

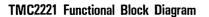

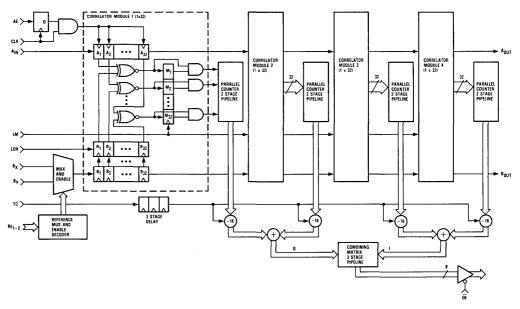

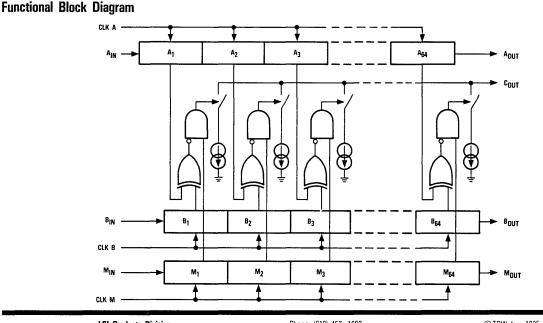

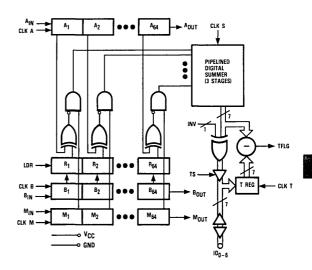

# CMOS Programmable Digital Output Correlators

4 x 32 Bit, 20MHz 1 x 128 Bit, 20MHz

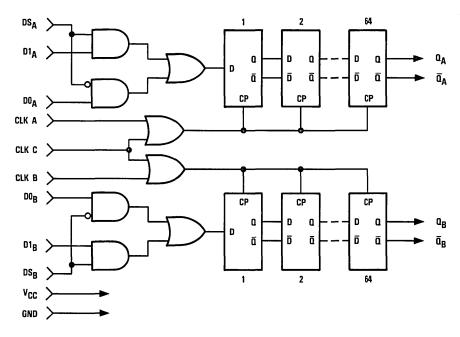

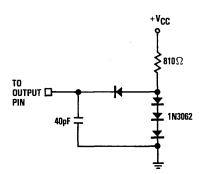

The TMC2220 is a high-speed digital CMOS correlator divided into four separate 1 x 32 bit correlator modules. The four module correlation scores are weighted and combined according to user programming. Possible configurations include a single 4 x 32 bit, 2 x 64 bit, or 1 x 128 and a pair of separate 1 x 64, or 2 x 32 correlators. In addition, a bit-by-bit masking capability within each module provides total word length flexibility. Each 32-bit module consists of a serial reference shift register, a parallel reference holding latch, a serial data shift register, a masking latch and a parallel counter.

A decoder controls the four two-input reference multiplexers and reference register enables to choose one of eight reference loading schemes. For each of the correlator modules, the reference word is serially shifted into the B register through one of the two multiplexed ports. By clocking the R latch, the reference residing in B is parallel-loaded into R. This allows the user to preload a new reference word into the B register while correlation is being performed between the data and present reference. The four A data registers can be loaded individually or simultaneously with the use of the independent data clock enables. The masking function is defined with the LM control; loading a zero into a cell of the latch will mask the corresponding correlation bit. When the mask latch is in the transparent mode (LM held HIGH), all 32 correlation bits are active.

During the correlation process, the latched reference and data words are continually compared bit-for-bit by exclusive-NOR circuits and ANDed with the latched mask function. Each exclusive-NOR bit contributes one bit to the parallel counter – all bits with a zero in the mask latch have no effect. The output represents the number of positions which match at any one time between the A data register and R reference latch. The module correlation score can be selected by the user as unipolar (0 to 32) or bipolar (-16 to +16) with the TC control.

A 3-bit instruction determines the weighting factor for each of the correlator modules. The weighted outputs are combined

into pairs and are available as two independent correlations, Q and I, through the 10-bit main output port and the 8-bit auxiliary port. A programmable matrix combines the Q and I outputs to obtain three additional functions through the main port: Q+I, Q+I/2, and a Max (|Q|, |I|) + 1/2 MIN (|Q|, |I|) approximation for the magnitude quantity SQRT ( $I^2 + Q^2$ ). To simplify interface timing, the programming controls are synchronous, and are appropriately delayed to accommodate the pipelining through the weighting and recombining circuitry.

The TMC2221 combines four 1 x 32 correlator modules in series for a fixed single channel configuration. The reduced complexity and package size of the TMC2221 are ideal for those applications requiring less versatility than the TMC2220. By making use of the masking function, any size single channel length of up to 128 is possible.

With the TMC2221, the reference word is serially loaded through the single two-input multiplexed reference port of the first correlator module. Although the configuration is fixed, the reference loading process and basic operation for each module are similar to those of the TMC2220. The outputs are summed with equal weighting, and the result is output through the single 8-bit port.

#### Features

- 20MHz Correlation Rate

- Single +5V Power Supply

- Low Power CMOS Process Technology

- Three-State TTL Compatible Outputs

- Data Bit Masking Capability

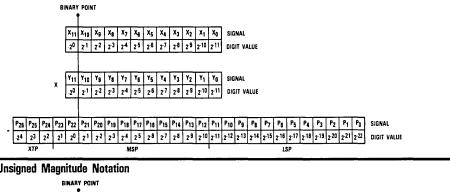

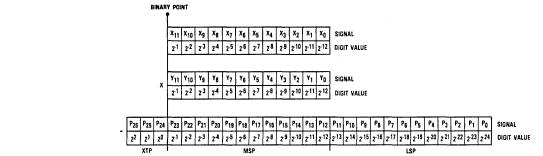

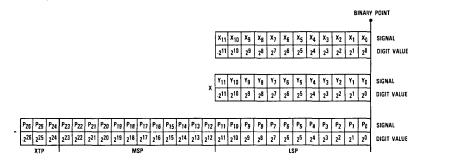

- Two's Complement Or Unsigned Magnitude Correlation Score

- TMC2220 Provides User Programmable Reference Multiplexing, Module Weighting Factors And Recombining Circuitry for 256 Different Correlation Modes.

- Multibit Correlation With TMC2220 Allows for Improved Detection Accuracy In Noisy Environments

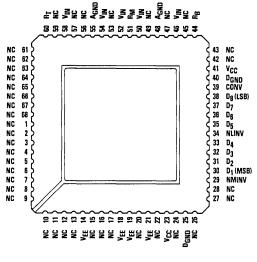

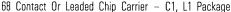

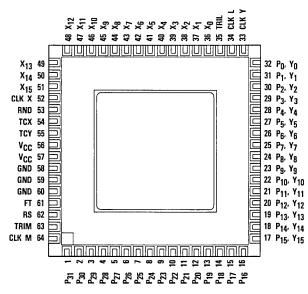

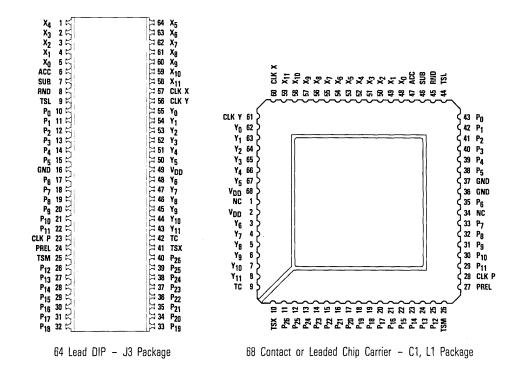

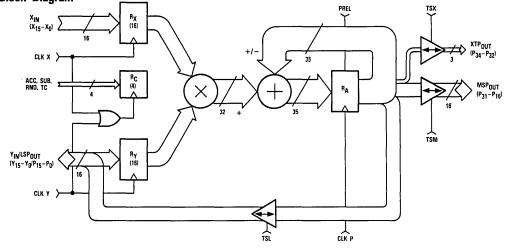

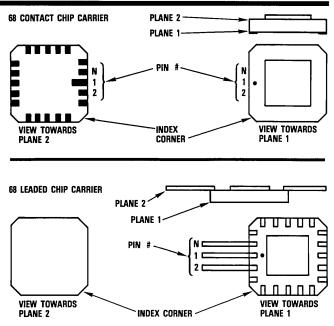

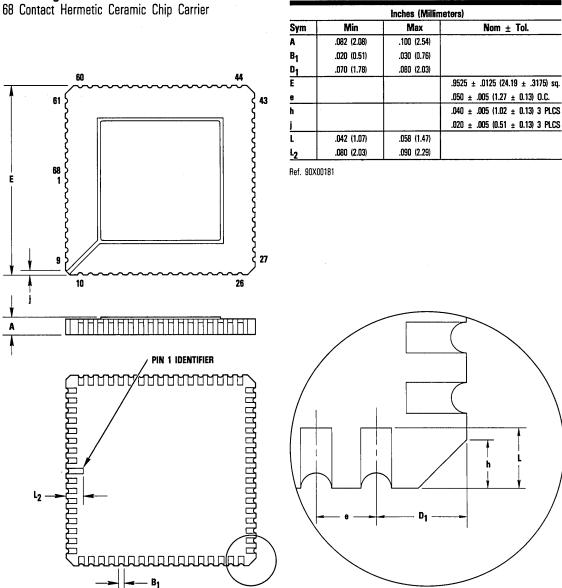

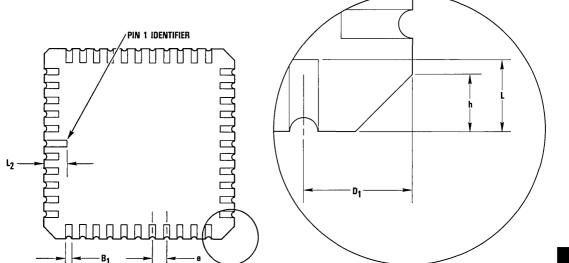

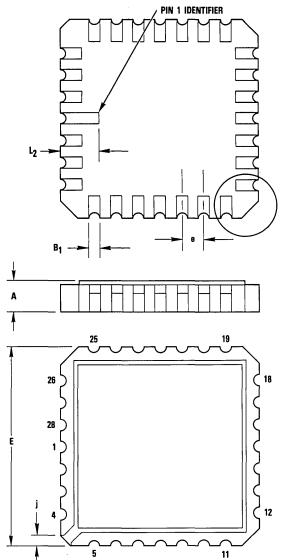

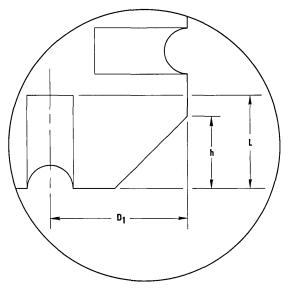

- TMC2220 Available In A 64 Lead Ceramic DIP, 68 Contact Chip Carrier, Or 68 Leaded Chip Carrier

- TMC2221 Package Size Reduced With Fixed Single Channel Configuration (1 x 1 Through 1 x 128)

- TMC2221 Available In A 28 Lead Ceramic DIP, 28 Lead CERDIP, Or 28 Contact Chip Carrier

#### **Applications**

- Signal Detection

- Radar Signature Recognition

- Secure Communications

- Robotics

Decoder

Inputs

W2 W1 W0

0

1

0

1

0 0 0

0 0 1

0 1

0 1

1 0

1 0

1 1 0

1 1 1

#### Module Weighting Factor Programming

**Internal Channel**

Configuration

TMC2220

T

I<sub>c</sub> + I<sub>d</sub>

$3I_c + I_d$

$4I_c + I_d$

I<sub>c</sub>

$3I_{c} + 2I_{d}$

41<sub>c</sub> + 21<sub>d</sub>

51<sub>c</sub> + 21<sub>d</sub>

ď

۵

$0_a + 0_b$

$30_a + 0_b$

40<sub>a</sub> + 0<sub>b</sub>

$30_a + 20_b$

$40_a + 20_b$

$50_a + 20_b$

Q,

Qh

| • | Automatic | Testing | Equipment |

|---|-----------|---------|-----------|

|---|-----------|---------|-----------|

- Electro-Optical Navigation

- Pattern And Character Recognition

**Reference Multiplex and Enable Programming**

#### **Module Reference** Port Selected Decoder TMC2220 TMC2221 Inputs RE2 RE1 REn<sup>1</sup> a b c d а Ō 0 0 0000 0 1 0 0 0 X 0 0 0 0 0 0 Y X invalid 1 0 0 Y Y 0 1 1 XXXX Х 1 0 0 YXXX 1 0 1 Y YXYX 1 1 0 1 1 YYYY 1

Note: The LSB of the decoder,  $RE_0$ , is not used on the TMC2221.

LSI Products Division TRW Electronic Components Group

### TMC2220/TMC2221

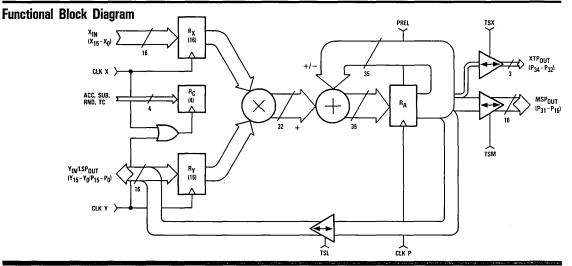

#### TMC2220 Functional Block Diagram

LSI Products Division TRW Electronic Components Group C

LSI Products Division TRW Electronic Components Group

Ň

••••••

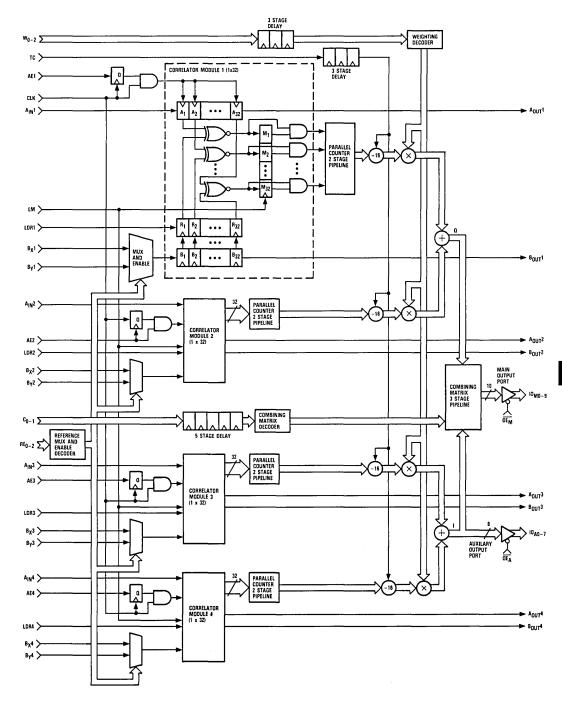

### **TMC2243** Advance Information

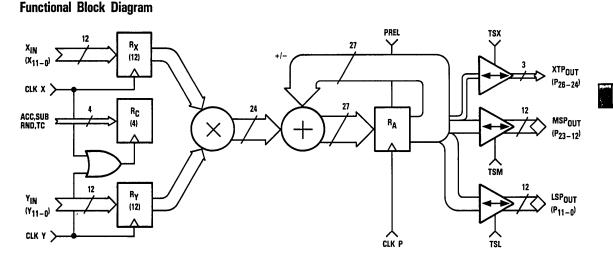

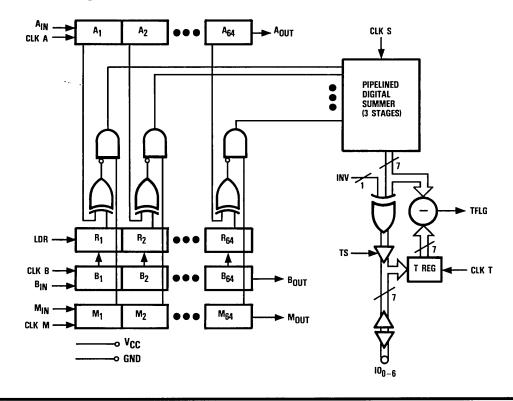

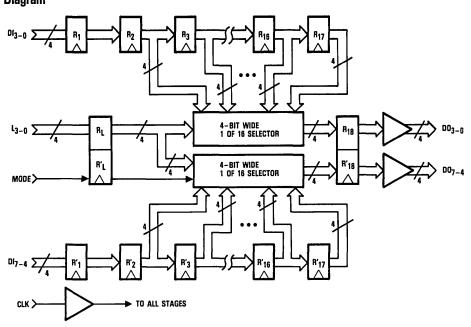

#### **Systolic FIR Filter Module** 10-bit, 20MHz

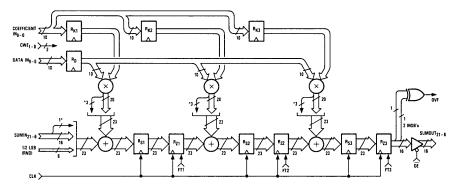

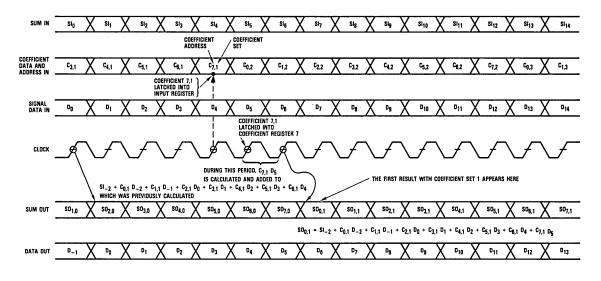

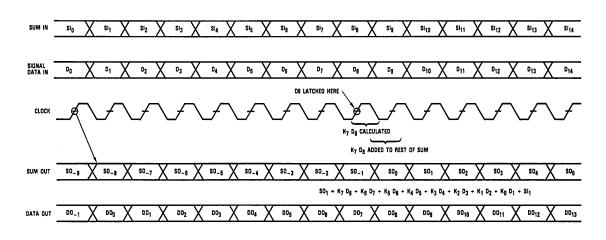

The TRW TMC2243 is a three-stage, 10-bit systolic FIR filter module. This device is fully expandable and is specifically configured to support video signal processing requirements. The TMC2243 comprises three 10-bit multiply and add (MAD) cells, each with special "feedthrough registers" which support zero coefficient taps. These registers are ordinarily in transparent mode; enabling them will insert a zero coefficient tap into the filter. On each clock cycle, a 2-bit coefficient write enable control allows any one of the three coefficients to be modified using the data at the coefficient input bus. Adaptive filtering is facilitated by this programmability.

The function SUMOUT(n) = SUMIN(n-3) + D(n-4)K1 + D(n-3)K2 + D(n-2)K3 is performed by the device, the basic computation of a FIR filter. The data, D(i), and the coefficients, K(i), are 10-bit two's complement numbers. The SUMIN and SUMOUT buses are 16 bits wide to allow for word growth. The 16-bit incoming sum (SUMIN<sub>21-6</sub>) is sign-extended by one bit, yielding a 17-bit two's complement number. Additionally, 1/2 LSB rounding is implemented by appending 100000, thereby expanding the data to 23 bits. In order to minimize rounding and overflow errors, the internal summation paths are 23 bits. An overflow flag indicates when two's complement overflow beyond the representable number range has occurred. The TMC2243 is built with TRW's OMICRON-C<sup>TM</sup> 1-micron CMOS process. The device operates at a clock rate of 20MHz (50ns) in order to support video speed applications.

#### Features

- 20MHz Guaranteed Clock Rate Over Standard Temperature Range (0° to 70°C)

- Systolic Architecture Allows For Expansion

- Efficient Implementation Of Zero Coefficient Taps

- Wide Internal Summation Paths For Overflow Protection

- Programmable Coefficients

- All Inputs And Outputs Registered

- Three-State Outputs

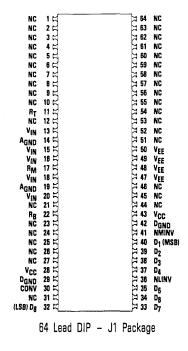

- Available In 64 Lead DIP

#### **Applications**

- FIR Filters

- Adaptive Filters

- One And Two Dimensional Convolution

- Video Processing

H

#### TMC2243 Functional Block Diagram

Note:

1. \*The MSB is duplicated, thereby sign-extending.

LSI Products Division TRW Electronic Components Group P.O. Box 2472 La Jolla, CA 92038 Phone: (619) 457–1000 Telex: 697–957 TWX: 910–335–1571 ©TRW Inc. 1985 40G02174 Rev. A-2/85 Printed in the U.S.A.

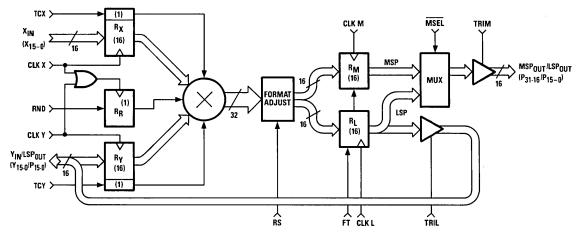

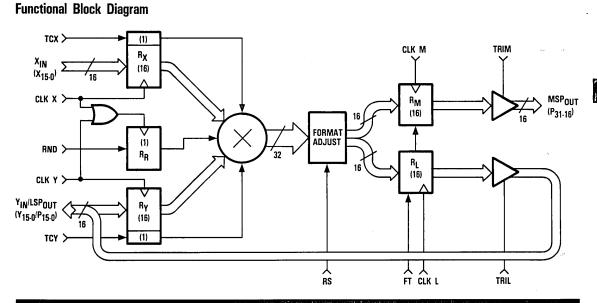

# **Floating Point Arithmetic Unit** 32/34 bits, 125ns

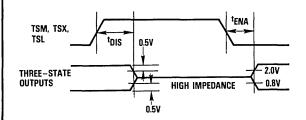

The TRW TMC3200 is a 32/34-bit floating point arithmetic unit. It performs operations on floating point numbers in either IEEE standard 32-bit or an extended 34-bit format, and also accommodates a 24-bit two's complement integer (fixed point) format. Full conversion flexibility between the three data formats is available. The TMC3200 is built with TRW's OMICRON-C<sup>TM</sup> 1-micron CMOS process. With a cycle time of 125ns, the throughput rate of the TMC3200 is 8Mflops (Million floating point operations per second).

All data and instructions are registered. The input operands are selected from the input bus, floating point zero, and the accumulate path. The input operands each enter on 17-bit buses at alternate rising edges of the double-speed chip master clock (16MHz). The 8-bit instruction register latches inputs which control the operand selection, the ALU instruction, the data format and the rounding method. Renormalizing, rounding, and limiting logic are provided to ensure proper handling of special cases and correct output data formatting. The result is output as two words on successive chip master clock cycles, and it emerges through a 17-bit three-state output port.

#### Features

- 8Mflop Throughput Rate (125ns Pipelined Cycle Time)

- IEEE Standard 754 Draft 10.0 32-Bit Or Extended 34-Bit Floating Point Data Format

- Integer Two's Complement 24-Bit (Fixed Point) Data Format

- Full Conversion Between All Data Formats

- Flexible Data Source Selection

- Internal Accumulator Feedback Path

- Selection Of Unbiased Round-To-Nearest And Round-Toward-Zero

- Automatic Limiting For Overflow/Underflow Cases

- All Inputs And Outputs TTL Compatible

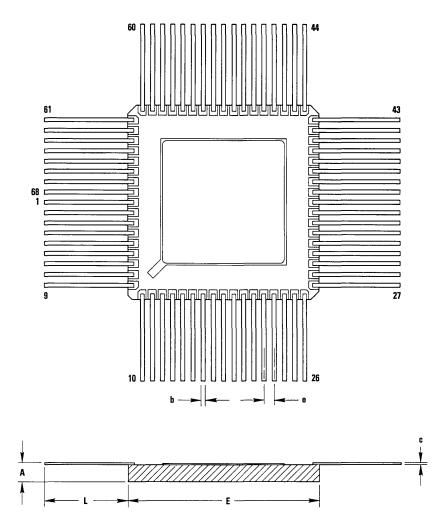

- Available In 84 Contact Chip Carrier or 88 Pin Grid Array

#### Applications

- Matrix Operations And Geometric Transforms

- ALU In Microprogrammed Array Processors

- · Graphics And Image Processing

- Floating Point Digital Filters And FFTs

- Radar And Sonar Signal Processors

- Use With 16-Bit Machines (Arithmetic Processors)

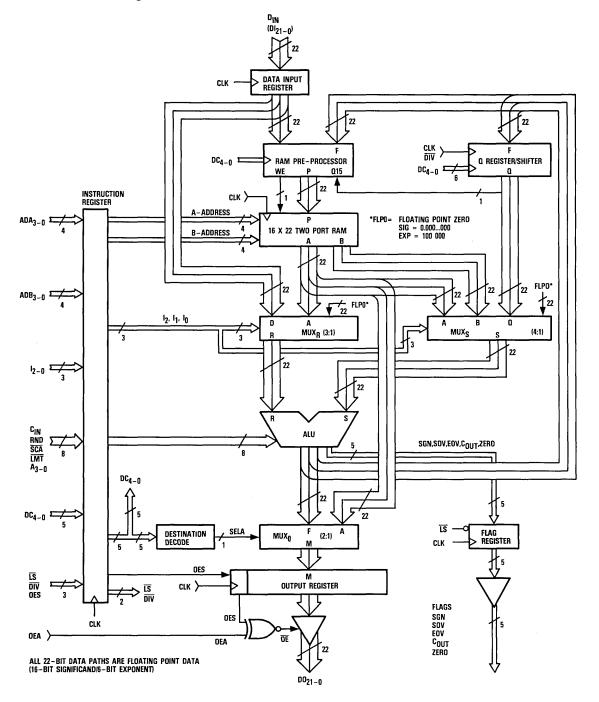

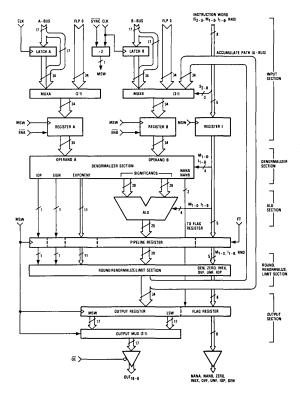

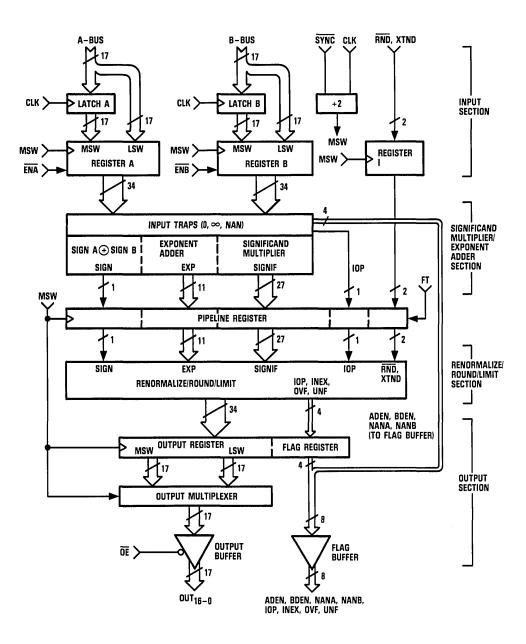

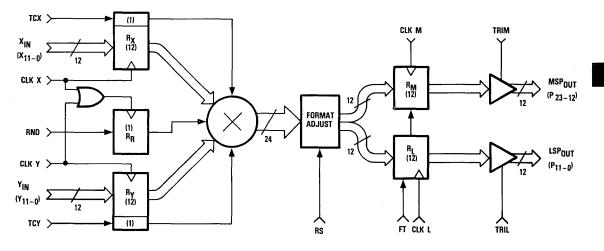

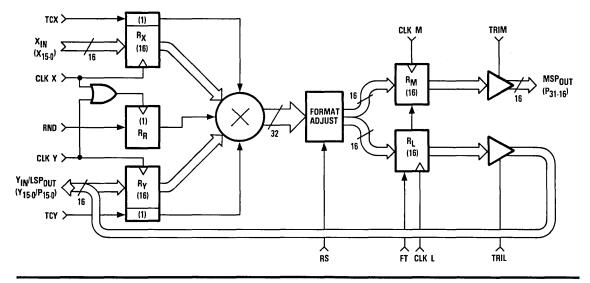

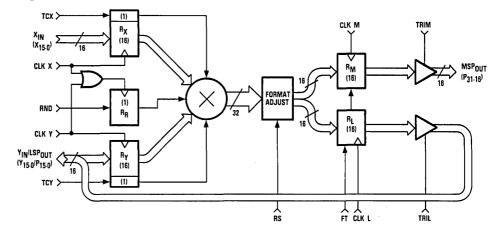

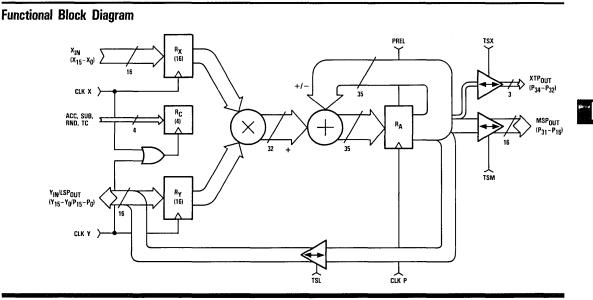

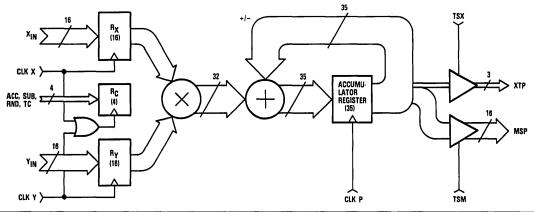

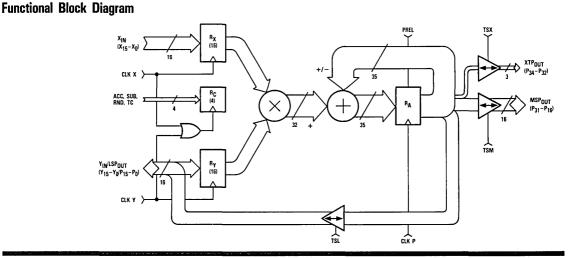

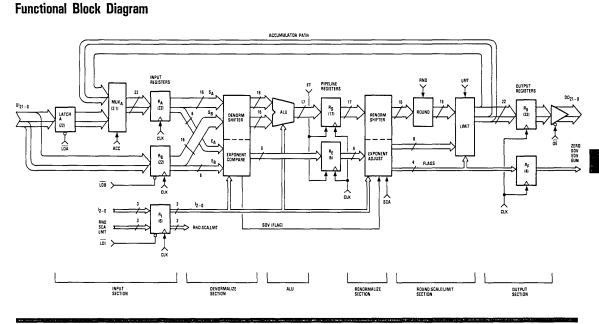

#### TMC3200 Functional Block Diagram

C

LSI Products Division TRW Electronic Components Group P.O. Box 2472 La Jolla, CA 92038 Phone: (619) 457–1000 Telex: 697–957 TWX: 910–335–1571 ©TRW Inc. 1985 40G02175 Rev. A-2/85 Printed in the U.S.A.

#### **Functional Block Diagram**

LSI Products Division TRW Electronic Components Group

### TMC3200

#### **Functional Description**

The TMC3200 is functionally divided into five sections: the input section, the denormalizer, the ALU, the round/renormalize/limit section, and the output section.

#### Input Section

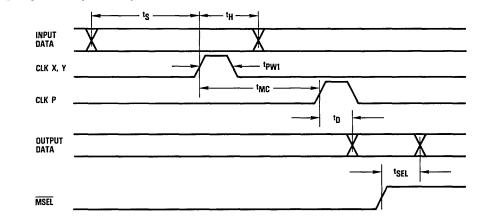

The input section accepts the A and B operands, along with the 8-bit instruction word. The instruction is decoded in this section, determining the action of the A and B source multiplexers, the ALU operation, the rounding mode, and data format of the operands. The chip master clock (CLK) is divided by two, generating the Most Significant Word (MSW) signal, which is used internally for I/O multiplexing and is also available as an output flag.

The A and B operands each enter on their respective 17-bit input buses. Input preload registers clocked by the 16MHz chip master clock latch in the data on the input buses at the rising edge of CLK. Provided the enable controls for the operand registers (ENA and ENB) are LOW, the data present at the preload registers and the data present at the input bus are simultaneously loaded into the operand registers at the rising edge of internal signal MSW. This means that the preload registers need to have the MSW loaded with the rising edge of CLK one cycle before the MSW signal goes HIGH, and the LSW must be present at the input bus when signal MSW goes HIGH. The SYNChronization control (SYNC) aligns the MSW signal with the chip master clock. The MSW and LSW of the incoming operands must be present at the input bus on alternate cycles of CLK.

The operand registers are loaded with every other cycle of the master clock. Note that the preload register is strobed every cycle of CLK, though its contents are loaded into the operand registers only on alternate cycles of CLK.

The 8-bit instruction word is loaded into the instruction register at the rising edge of CLK, so it must be input at the same time as the MSW of the operands with which it is associated. The instruction word must be held through both load cycles (MSW and LSW input) of the data to which it applies. The instruction word is divided into four fields: one to control the operand source multiplexers ( $S_{2-0}$ ), one to select the data format ( $M_{1-0}$ ), one to control the arithmetic operation performed ( $OP_{1-0}$ ), and one to control the rounding method (RND). The A operand can be selected from two possible sources: the A input bus or a hardwired floating point

zero. The B operand can be selected from three possible sources: the B input bus, the accumulator feedback path, or a floating point zero. The input and output data formats may be selected from 32-bit floating point, 34-bit floating point, or 24-bit integer (fixed point). The input and output formats may differ. The arithmetic operation performed is selected from A+B, A-B, B-A, -A-B, and CONVB (convert B to different data format). The rounding method is either IEEE (unbiased) round-to-nearest, or IEEE round-toward-zero (truncation).

#### **Denormalizer Section**

This section prepares the operands for the ALU by denormalizing the operand with the smaller exponent. This section also expands the exponent field to 11 bits and the significand field to 28 bits. This is done to accommodate the calculation of intermediate results to the precision required by the IEEE 32-bit and the extended 34-bit data formats. Since integers require no denormalization, this section is bypassed when integers are input.

The denormalizer section consists of an exponent comparator, a sign processor, zero-detectors, a denormalizing barrel shifter, and the subtraction inverter. The denormalizer generates floating point numbers with identical exponents (if possible) which can be directly added by the ALU. Input traps identify special cases which require separate treatment.

The exponent comparator detects the special IEEE trap conditions of zero (-512 in the 34-bit format) and 255 (511 in the 34-bit format), identifies the larger exponent, and calculates the absolute difference between the two exponents. The magnitude of the difference between the two exponents determines the amount of shift performed by the denormalizing barrel shifter.

The denormalizing barrel shifter can right-shift the significand of the operand having the smaller exponent as required, up to 25 places (after which the significand field becomes zero, with the "sticky bit" set). The amount of right-shift is equal to the difference between the exponents, as computed by the exponent comparator. Guard, round, and sticky bits are generated as specified in the IEEE standard. The MSBs of the shifted significand are zero-filled as they are downshifted. A no-shift capability handles the cases of equal operand exponents and integer operands. H

The sign processor and the subtraction inverter handle the signs of the operands and support subtraction, respectively. The operands entering the ALU are modified as needed to ensure that a positive fraction field results; the appropriate sign is computed and appended.

#### **ALU** Section

The outputs of the denormalizer section are the larger incoming exponent, various status flags, sign information, and the two 28-bit significands. The ALU handles the 28-bit significands and the sign information. Input to this section is "preconditioned" so that it can perform either "A + B" or "A - B." The arithmetic follows the standard IEEE 32-bit, extended 34-bit, or integer rules, as appropriate. The ALU output is a 28-bit significand field.

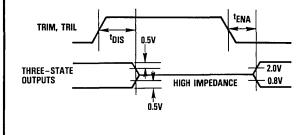

The ALU output, the exponent, the sign information, the Invalid OPeration (IOP) flag, and five instruction bits are the inputs to the 46-bit pipeline register. This register may be enabled by bringing the FeedThrough (FT) control LOW. When FT=1, the pipeline register is transparent.

#### **Round/Renormalize/Limit Section**

The TMC3200 supports IEEE standards for "unbiased rounding toward nearest" when rounding is enabled ( $\overline{\text{RND}}$  is LOW). When  $\overline{\text{RND}}$  is HIGH, the TMC3200 truncates the result. The rounding adder is directly after the pipeline register and operates on the result generated by the ALU. The rounded result is the input to the renormalizer.

The renormalizer is able to shift right one bit, shift left up to 25 bits, or not shift at all, based on the state of the overflow bit and the other bits of the significand. If the overflow bit is set, the data is right-shifted to renormalize the number. If the overflow bit is not set, the number may be normalized already, in which case, no shift is required. In the event the number is not already normalized, the significand is left-shifted enough places to place a "1" in the (hidden) bit position immediately below the overflow bit. The direction and number of places shifted is noted and this information is used to adjust the exponent. The renormalizing shifter also provides the status flag "inexact result." The renormalize section also contains an exponent adder which modifies the exponent passed to it by the denormalizer (the larger of the two operand exponents). The exponent is decremented by one for each left shift which was required for the renormalization of the significand. In the event of a right shift, the exponent is incremented by one, and the exponent remains the same in the case of no shift. This exponent is examined for overflow or underflow of the output data format. There are two cases in which the renormalizer is

disabled: when converting floating point to integer and when converting from 34-bit to 32-bit IEEE denormalized format.

The limiter uses the flags and the value of the exponent in order to replace overflowing numbers with a signed infinity or full-scale positive or negative integers as appropriate, underflowing numbers are replaced with zero. Invalid operations (infinity minus infinity or NaN plus any number) trigger NaN output. In cases other than described above, the limiter will output the result of the renormalizer unchanged.

#### **Output Section**

The output section contains the feedback accumulate path (U path), the 42-bit output register (34-bit output data, 8 flags), the output multiplexer, and the output buffers.

The U path is a 34-bit feedback path to the input section of the TMC3200 which feeds into the B operand multiplexed register. This bus carries the output of the limiter section back so that a 34-bit representation of the result being clocked into the output register is available simultaneously at the input of the B operand register, meeting the setup requirements of this register.

The output register is clocked by the MSW signal, which runs at half the rate of the system clock. The contents of this register will be the 34-bit output from the limit section, along with the flags (ZERO, DENormalized result, OVerFlow, UNderFlow, INEXact result, NAN in A, NAN in B, Invalid OPeration).

The flags are valid for the duration for which a result is held in the output register, except for the NANA and NANB flags. These flags are set when their particular input operand is a NAN and will remain set until a new legal operand is loaded. These flags are based on the operands only; ALU results flushed to NANs do not set the NAN flags. The remaining flags become valid with their corresponding results and remain as long as the associated result is in the output register. Since the flags are not three-stated, they are independent of the  $\overline{\text{OE}}$ control.

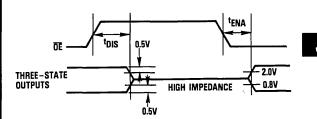

The output multiplexer selects either the most or least significant word of the result and presents it at the inputs of the output buffers. The output multiplexer is controlled by the signal MSW, selecting the most significant word when MSW is HIGH, the least significant word when MSW is LOW. The output buffers are three-stated. When Output Enable ( $\overline{OE}$ ) is LOW, the buffers drive the output bus, when  $\overline{OE}$  is HIGH, the drivers are in the high-impedance state.

### **TMC3201** Advance Information

# **Floating Point Multiplier** 32/34 bits, 125ns

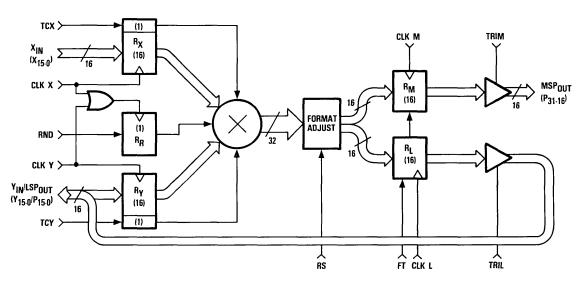

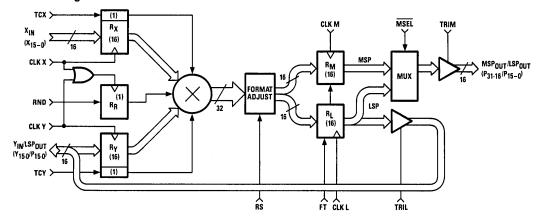

The TRW TMC3201 is a 32/34-bit floating point multiplier. It multiplies numbers in either IEEE standard 32-bit or extended 34-bit floating point formats. The TMC3201 is built with TRW's OMICRON-C<sup>TM</sup> 1-micron CMOS process. With a cycle time of 125ns, the throughput rate of the TMC3201 is 8Mflops (Million floating point operations per second).

The data, controls, and status flags are registered. The input operands each enter on 17-bit buses at alternate rising edges of the double-speed chip master clock (16MHz). The instruction register latches in controls for rounding mode and data format. Renormalizing, rounding, and limiting logic are provided to ensure proper handling of special cases and proper formatting of the output data. The result is output as two words on successive chip master clock cycles, and it emerges through a 17-bit three-state output port.

#### Features

- 8Mflop Throughput Rate (125ns Pipelined Cycle Time)

- IEEE Standard 754 Draft 10.0 32-Bit Or Extended 34-Bit Floating Point Data Format

- Selection Of Unbiased Round-To-Nearest And Round-Toward-Zero

- Automatic Limiting For Overflow/Underflow Cases

- All Inputs And Outputs TTL Compatible

- Available In 84 Contact Chip Carrier Or 88 Pin Grid Array

#### Applications

- Matrix Operations And Geometric Transforms

- ALU In Microprogrammed Array Processors

- Graphics And Image Processing

- Floating Point Digital Filters And FFTs

- Radar And Sonar Signal Processors

- Use With 16-Bit Machines (Arithmetic Processor)

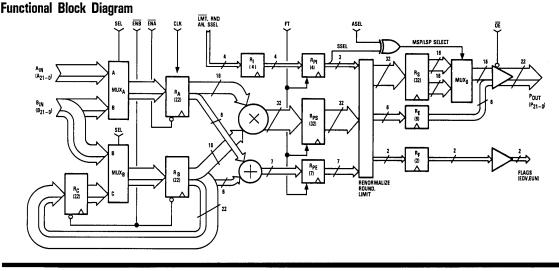

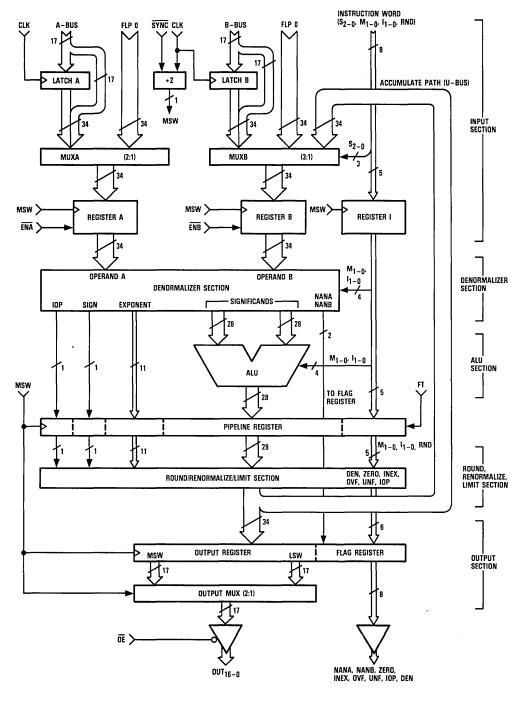

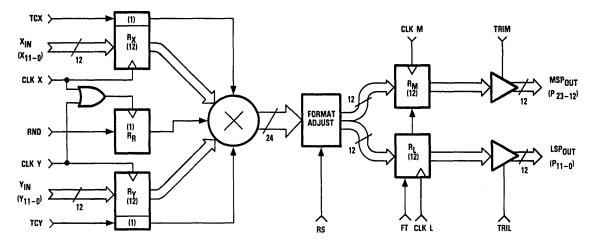

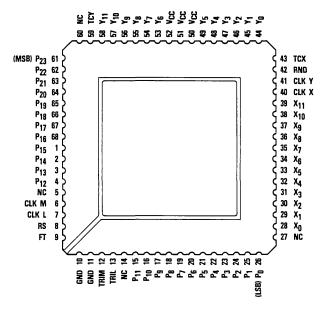

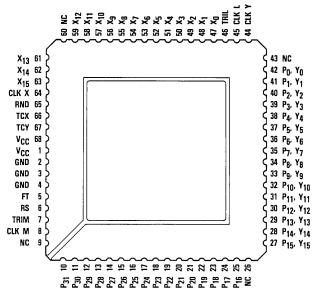

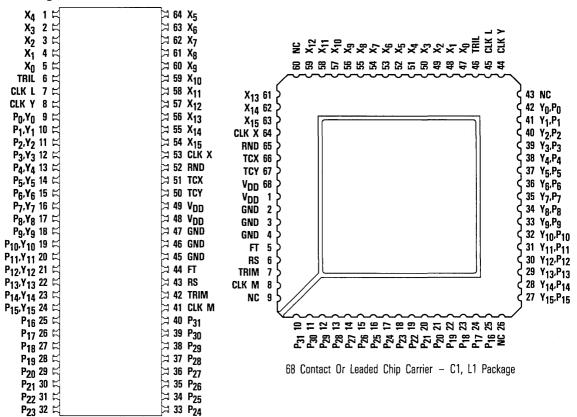

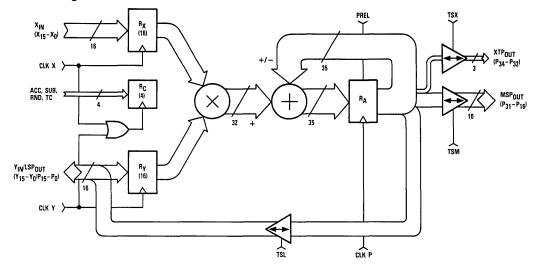

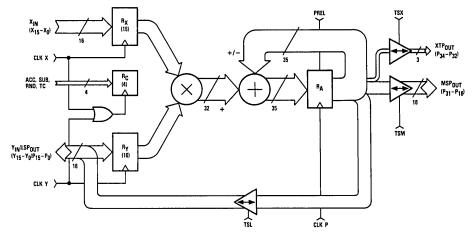

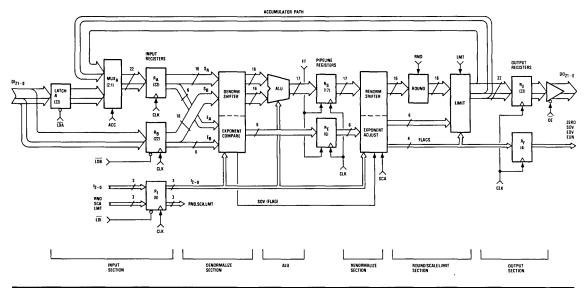

#### **TMC3201 Functional Block Diagram**

LSI Products Division TRW Electronic Components Group P.O. Box 2472 La Jolla, CA 92038 Phone: (619) 457–1000 Telex: 697–957 TWX: 910–335–1571 © TRW Inc. 1985 40G02176 Rev. A-2/85 Printed in the U.S.A.

7Riii

## **Functional Block Diagram**

#### **Functional Description**

The TMC3201 is functionally divided into four sections: the input section, the significand multiplier/exponent adder, the renormalize/round/limit section, and the output section.

#### **Input Section**

The input section accepts the A and B operands, along with the 2-bit instruction word. The instruction is decoded in this section, determining the rounding mode and data format of the operands. The chip master clock (CLK) is divided by two, generating the Most Significant Word (MSW) signal, which is used internally for I/O multiplexing and is also available as an output flag.

The A and B operands each enter on their respective 17-bit input buses. Input preload registers clocked by the 16MHz chip master clock latch in the data on the input buses at the rising edge of CLK. Provided the enable controls for the operand registers (ENA and ENB) are LOW, the data present at the preload registers and the data present at the input bus are simultaneously loaded into the operand registers at the rising edge of internal signal MSW. This means that the preload registers need to have the MSW loaded with the rising edge of CLK one cycle before the MSW signal goes HIGH, and the LSW must be present at the input bus when signal MSW goes HIGH. The SYNChronization control (SYNC) aligns the MSW signal with the chip master clock. The MSW and LSW of the incoming operands must be present at the input bus on alternate cycles of CLK. The operand registers are loaded with every other cycle of the master clock. Note that the preload register is strobed every cycle of CLK, though its contents are loaded into the operand registers only on alternate cycles of CLK.

During the input operation, the inputs A and B are tested for the special cases of infinity, zero, NaNs, and denormalized numbers. Internal flags which identify these cases are generated. If NaNs are found, NANA or NANB flag is set immediately; these internal flags are also available as output signals. In this event, the product output will be the product NaN and the Invalid OPeration (IOP) flag will be set. Multiplication of zero x infinity also triggers a NaN output and sets the IOP flag. The TMC3201 is not able to process denormalized operands, and in the event of denormalized incoming operands, the appropriate ADEN or BDEN flags are set. The product output in this case will be zero.

#### Significand Multiplier/Exponent Adder

Floating point multiplication involves multiplication of the significand fields and addition of the exponent fields. The

24 x 24 bit multiplier generates the most significant 26 bits of the product, along with a "sticky bit" which is the logical OR of the low order 22 bits of the binary product. The 23 bits of the input fractional fields are input along with the implicit "hidden bit" (assumed to be a "1"). The 24-bit numbers are multiplied, though only the high order 26 bits are output. The output of the significand multiplier is a 27-bit number consisting of the overflow bit, the "hidden bit," the 23 bits of the fractional output, a guard bit, and a "sticky bit." This output is latched by the pipeline register which follows the multiplier array.

The exponents in floating point multiplication are added. The A and B exponent fields are added, generating an 11-bit nonbiased two's complement product exponent. This result is passed to the pipeline registers, and the exponent adjust section performs further processing before final output.

The 27-bit significand and the 11-bit exponent are the inputs to the pipeline register, along with the instructions, the Invalid OPeration flag (IOP), and the sign information. This 42-bit word is latched into the pipeline register on the rising edge of the signal MSW, provided that the FeedThrough control (FT) is LOW.

#### **Renormalize/Round/Limit Section**

The significand emerging from the pipeline register is tested for overflow. The significand field overflow bit is the MSB of the 27-bit significand, and if it is a "1," an overflow has occurred. This is compensated for by a right shift of one bit with an associated increment of the exponent by one. After the shift (if one was required), the overflow and hidden bits are no longer needed, hence they are dropped from the significand field. The renormalized significand is passed to the rounding adder.

If the  $\overline{\text{RND}}$  control is LOW, the TMC3201 will round-to-nearest, according to IEEE standard rules. If  $\overline{\text{RND}}$  is HIGH, the TMC3201 will truncate (IEEE round-toward-zero). Note that there is exactly one case where rounding can generate an overflowed result. In this case, the product is right-shifted and the exponent is incremented by one. The rounded product is output as a 23-bit number, with the "hidden bit" now guaranteed to be a "1." The exponent emerging from the pipeline register is an 11-bit doubly biased exponent. The extra IEEE bias of decimal 127 is subtracted from the "raw exponent" and any increments necessary due to right-shifting of the significand field are made. This 12-bit exponent is checked for values of greater than or equal to 255 decimal (for IEEE 32-bit format) or 511 (for extended 34-bit format). These conditions signify an overflow. Underflow has occurred if the exponent is less than or equal to zero (IEEE 32-bit) or -512 (extended 34-bit). The ten LSBs of the exponent and the rounded significand enter the limit section.

The limiter forces the significand and exponent fields to clean signed infinities, clean zero, or the TMC3201 NaN if appropriate. Overflow cases are forced to the signed infinities, underflow and zero cases are forced to a clean zero, and invalid operation cases are forced to the NaN. Additionally, the two status flags, OVerFlow (OVF) and UNderFlow (UNF), are generated for output in this section. The output of this section is a 34-bit field, interpreted as either IEEE 32-bit or extended 34-bit data. The output of the limit section goes directly to the product register.

### **Output Section**

The output section contains the 38-bit output register (34-bit output data, 4 flags), the output multiplexer, and the output buffers. The output register is clocked by the MSW signal, which runs at half the rate of the system clock. The contents of this register will be the 34-bit output from the limit section, along with the flags. The flags are valid for the duration for which a result is held in the output register. except for the NANA, NANB, ADEN, and BDEN flags. These flags are set when their particular input operand is a NAN or denormalized, respectively, and will remain set until a new legal operand is loaded. These flags are based on the operands only; results flushed to NANs (for example, zero x infinity) do not set the NAN flags. The remaining flags become valid with their corresponding results and remain as long as the associated result is in the output register. Since the flags are not three-stated, they are independent of the OE control.

The output multiplexer selects either the most or least significant word of the result and presents it at the inputs of the output buffers. The output multiplexer is controlled by the signal MSW, selecting the most significant word when MSW is HIGH, the least significant word when MSW is LOW. The output buffers are three-stated. When Output Enable ( $\overline{OE}$ ) is LOW, the buffers drive the output bus, when  $\overline{OE}$  is HIGH, the drivers are in the high-impedance state.

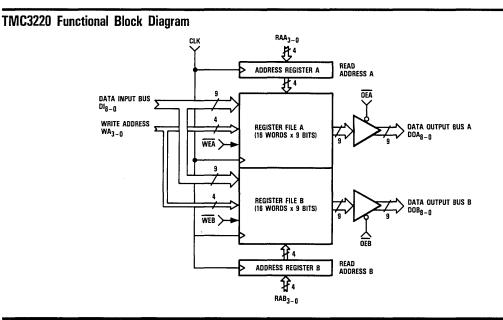

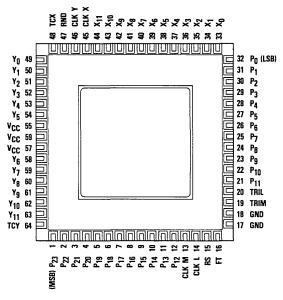

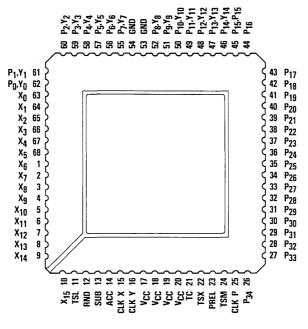

## **TMC3220** Advance Information

## Three Port Register File

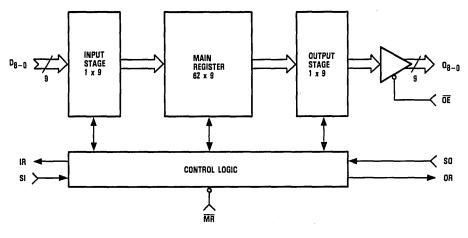

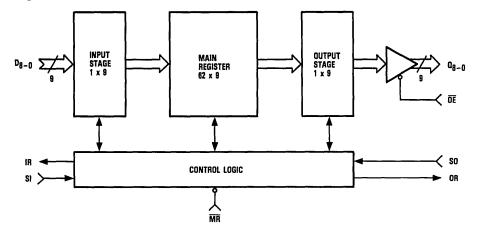

16 words x 9 bits, 20MHz

The TRW TMC3220 is a 16-word x 9-bit three port register file with two independent read ports and one write port. Internally, the device comprises two separate cores of 16-word x 9-bit dual port RAMs. Separate write enables, along with a single 4-bit write address allow either or both core RAMs to receive a given input data word. On each clock cycle, the two 4-bit read addresses can each access any of the 16 words of memory. Ordinarily, the two write enables are tied together, and the TMC3220 functions as a 16-word x 9-bit three port RAM. Separating the write enables causes the device to function as two independent two port RAMs.

The TMC3220 is specifically designed to operate with the TMC3200/3201 families of floating point devices, providing scratch memory and programmable interconnection supporting a variety of applications. The TMC3220 is built with TRW's OMICRON-C<sup>TM</sup> 1-micron CMOS process and will operate at a guaranteed clock rate of 20MHz. The clock rate of the TMC3220 also makes it suitable for video speed applications.

## Features

- $\bullet$  Guaranteed 20MHz Clock Rate Over Standard Temperature Range 10° to 70°C)

- Configured For Use With 32/34 Bit Floating Point Family

- Two Fully Independent Read Ports

- · Separate Write Enables

- Easily Cascadable In Word Size And Number of Words

- Low Power Consumption CMOS Process

- Three-State Outputs

- Available In 48 Lead DIP or 44 Contact Chip Carrier

## Applications

- Cache Memory For High-Speed Processors

- Graphics And Image Processors

- High-Speed Program Memory And Controllers

- Storage For Video Processors

Phone: (619) 457–1000 Telex: 697–957 TWX: 910–335–1571 © TRW Inc. 1985 40G02179 Rev. A-2/85 Printed in the U.S.A. LSI Products Division TRW Electronic Components Group

| ۷ | L   | S            | I            |

|---|-----|--------------|--------------|

| D | A   | T            | A            |

| B | 0   | 0            | К            |

|   |     |              |              |

|   | 7   |              |              |

|   |     | A            | A            |

|   | 6   | S            |              |

| 4 | S   | $\mathbf{X}$ | $\mathbf{X}$ |

| 6 | Ś   |              | S            |

| X | 100 |              |              |

|   | D   | D A          | D A T        |

Introduction Product Indexes Advance Information A/D Converters Evaluation Boards D/A Converters Nultipliers Nultipliers Nultiplier-Accumulators Special Function Products Nomery/Storage Products Nomery/Storage Products Neinchility Package Information Giventry Ordering Information Application Notes And Reprints (Listings) A/D Converters

.

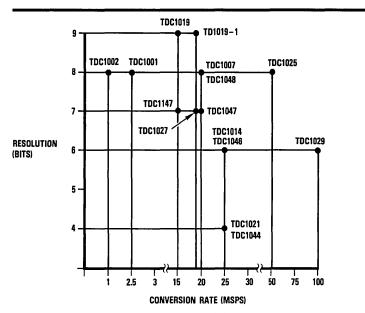

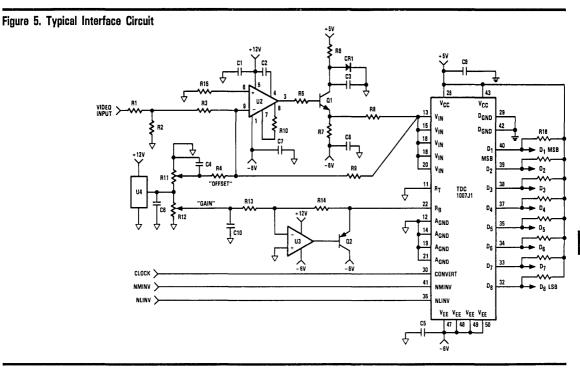

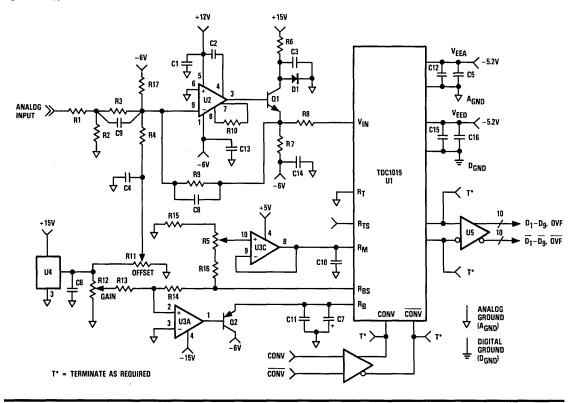

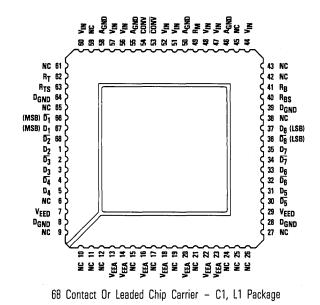

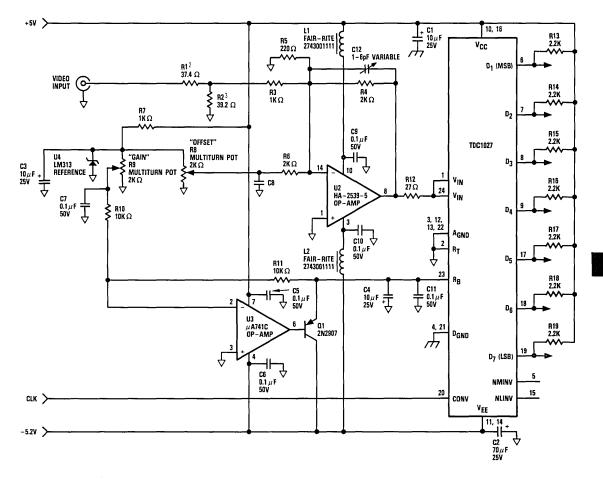

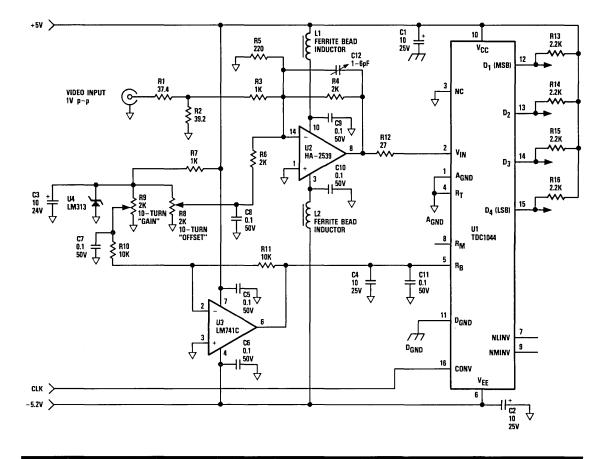

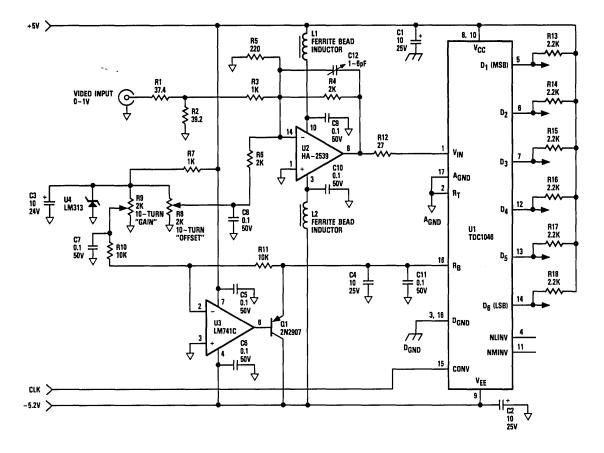

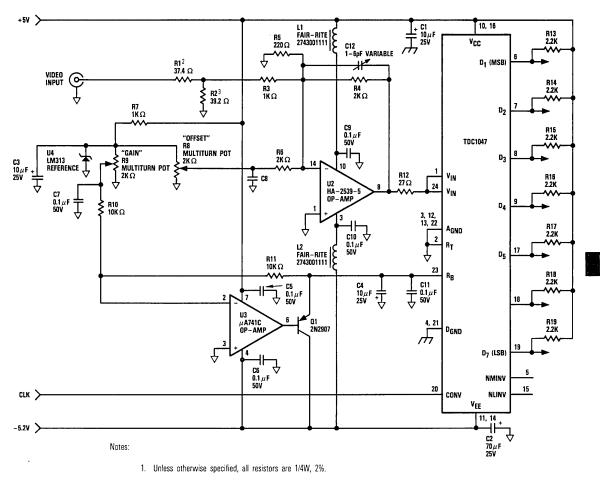

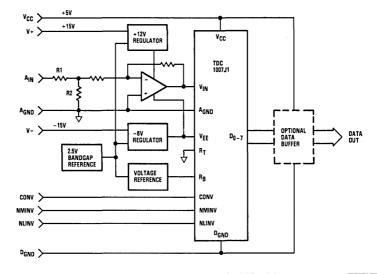

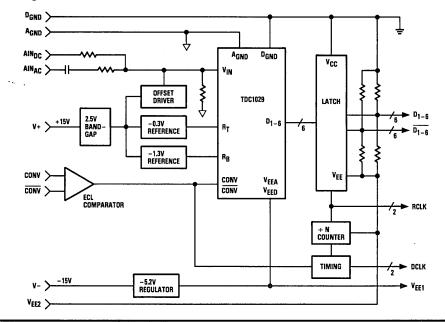

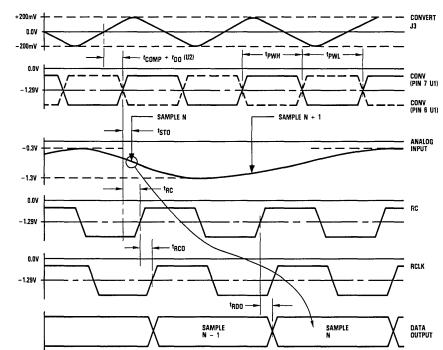

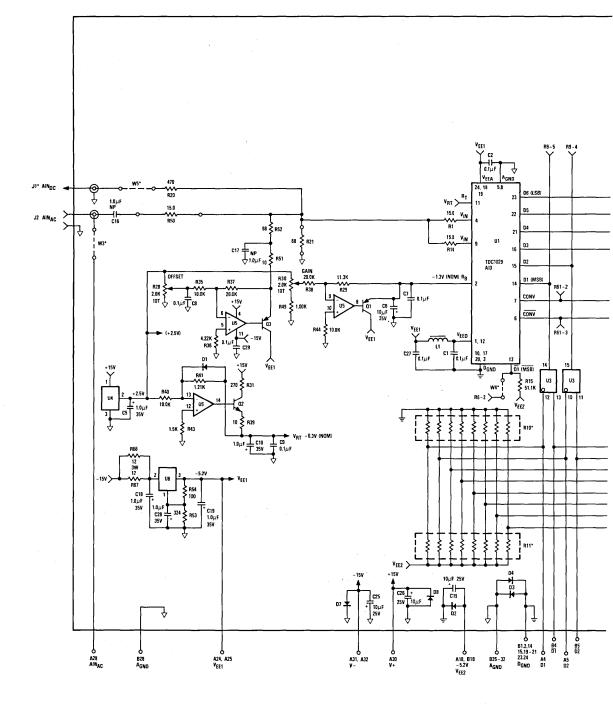

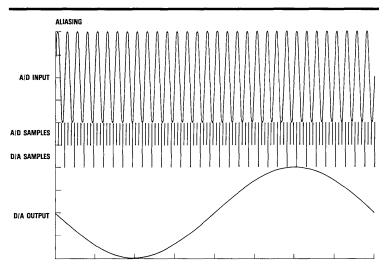

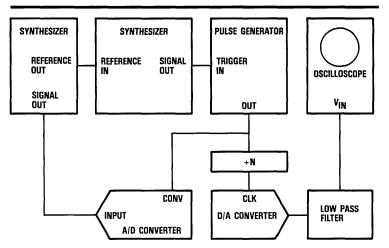

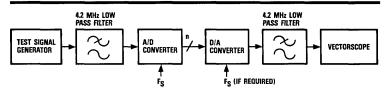

TRW LSI's line of monolithic highspeed analog-to-digital (A/D) converters consists primarily of devices that employ parallel "flash" architecture. The exceptions are the TDC1001 and TDC1002 successive approximation A/D converters. The entire line of A/D converters covers resolutions from four to nine bits and conversion rates from 1 to 100MSPS. All of these devices are built with TRW's proven 3D (triple-diffused) bipolar technology which provides significant advantages in performance, size, power, and reliability. Many products are now available manufactured with TRW's new OMICRON-B<sup>™</sup> 1-micron process.

TRW LSI Products pioneered the development of monolithic high-speed A/D converters by introducing the TDC1007 in 1977. This device is an 8-bit 20MSPS A/D converter which has become an industry standard in video, radar, and imaging applications. The development of fine lithography techniques has yielded faster, more accurate, and less expensive A/D converters. Most of TRW LSI's A/D converters are available with an evaluation board which contains all peripheral circuitry necessary for quick and convenient operation of the device.

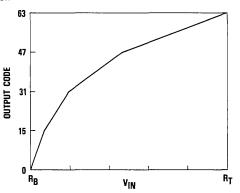

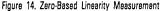

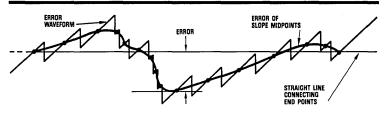

Figure 1. Resolution vs. Conversion Rate For TRW-LSI A/D Converters.

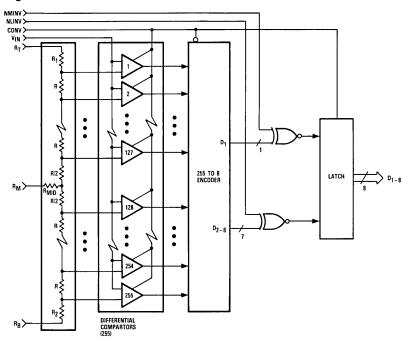

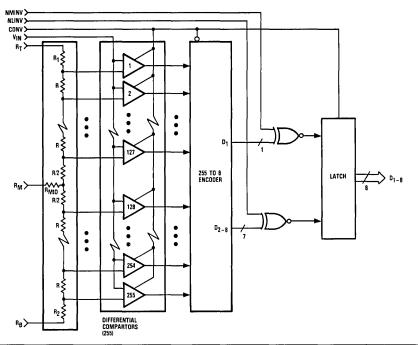

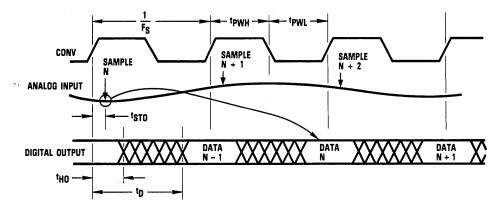

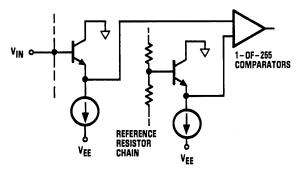

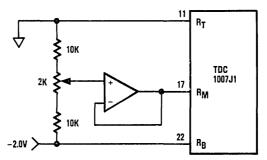

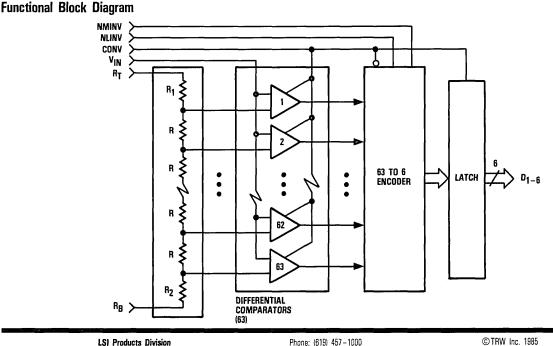

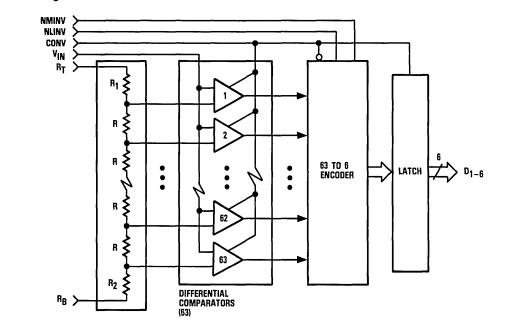

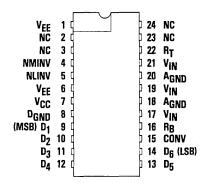

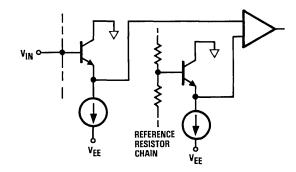

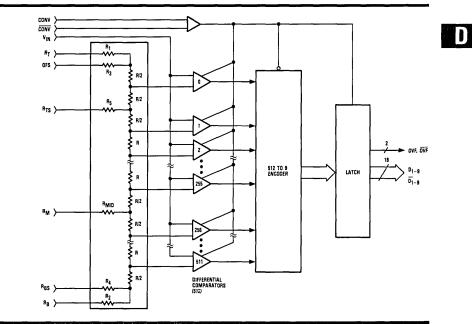

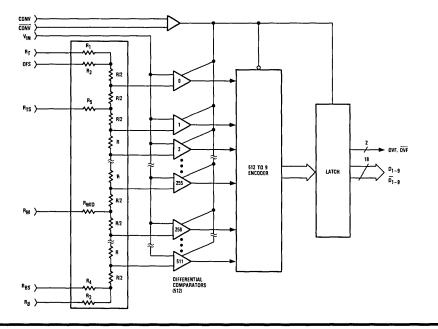

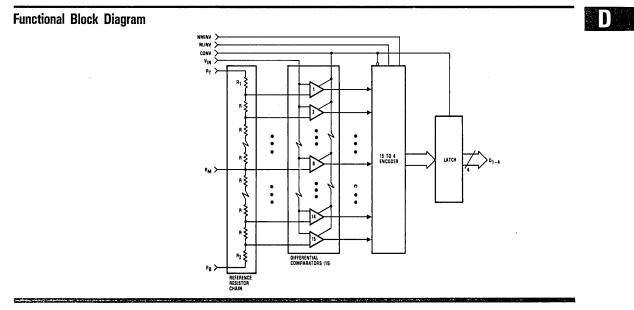

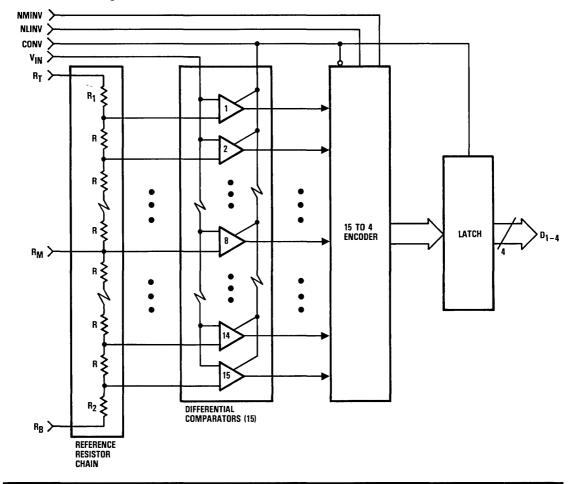

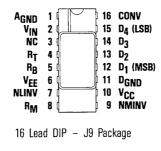

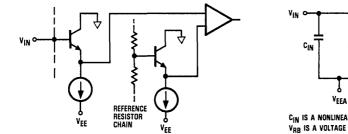

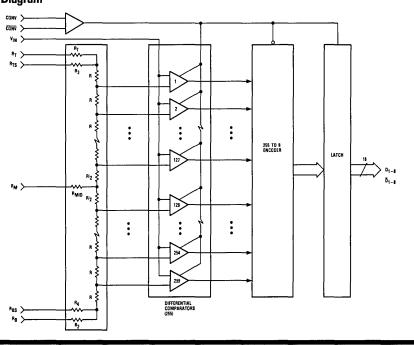

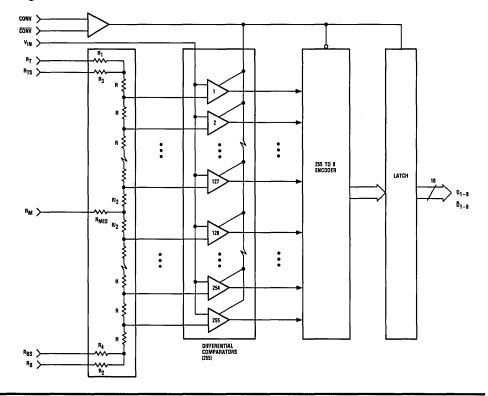

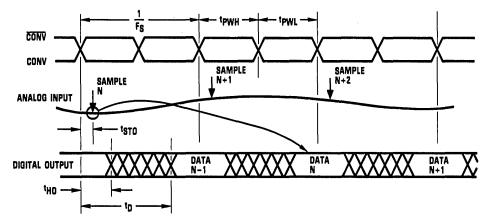

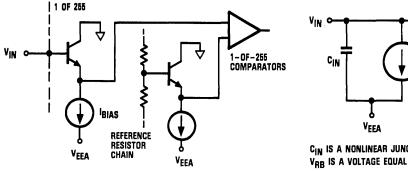

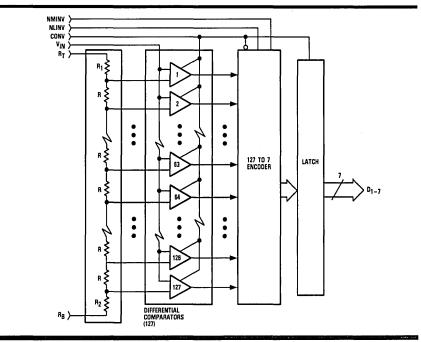

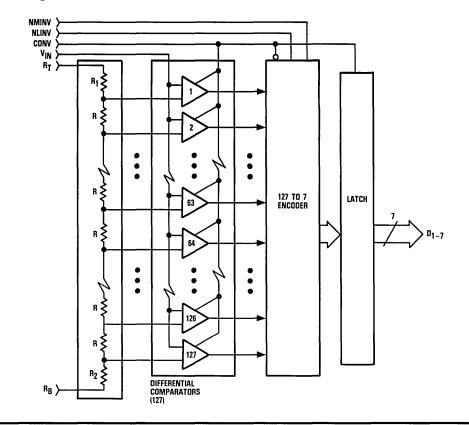

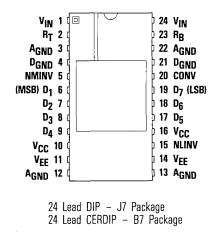

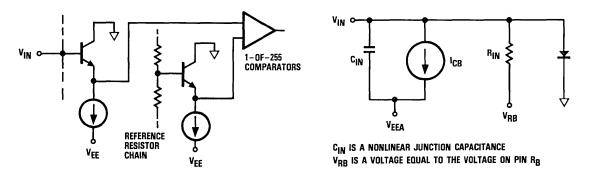

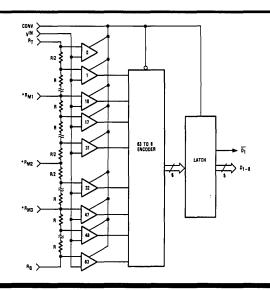

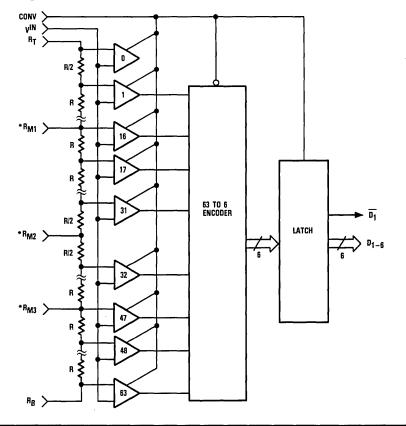

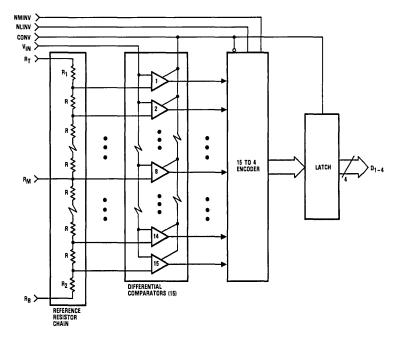

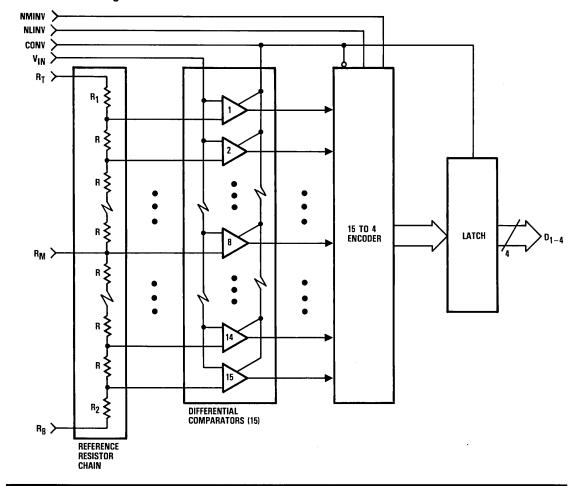

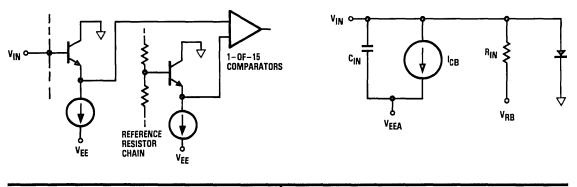

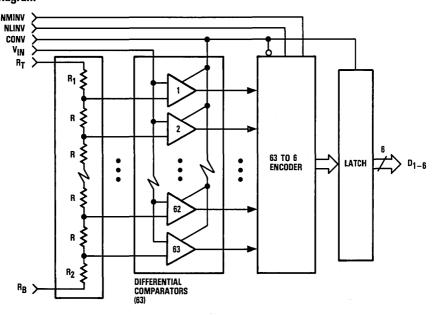

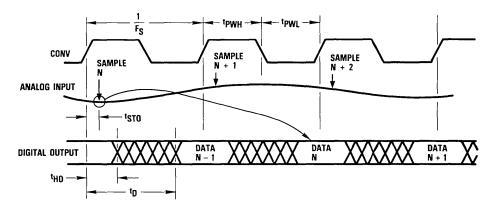

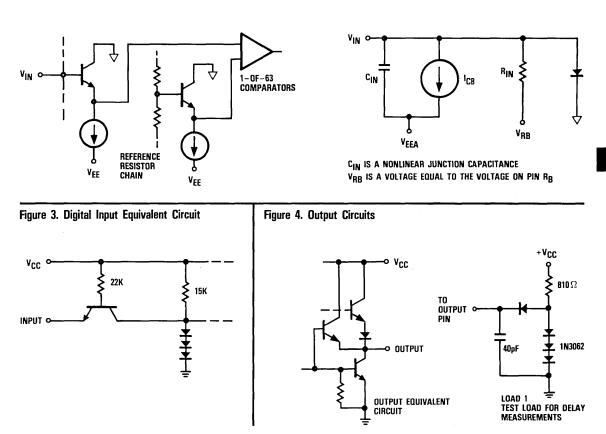

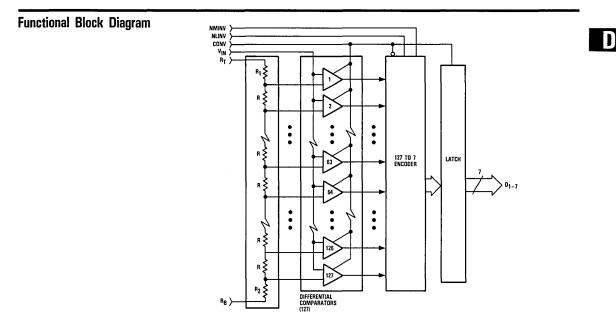

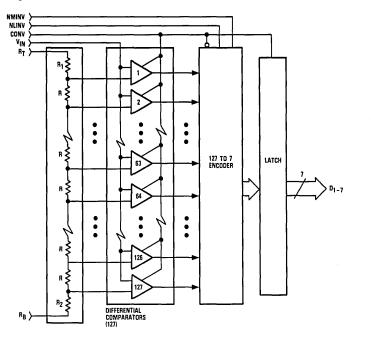

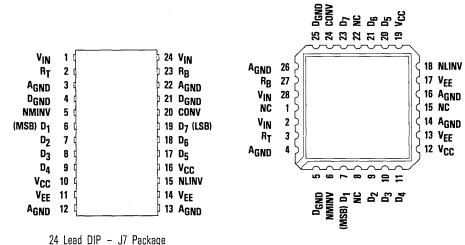

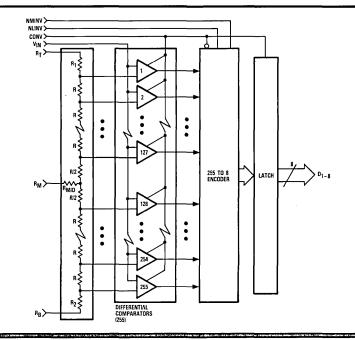

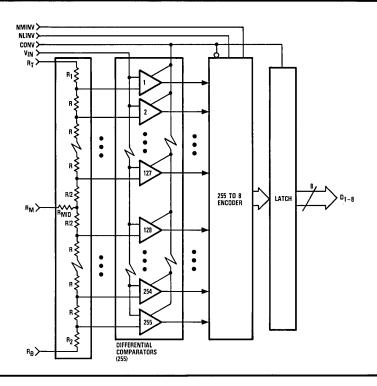

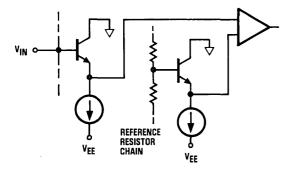

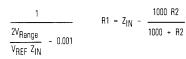

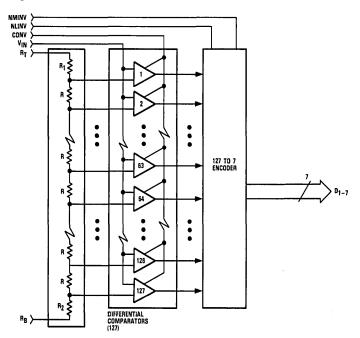

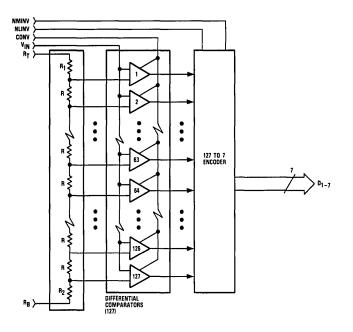

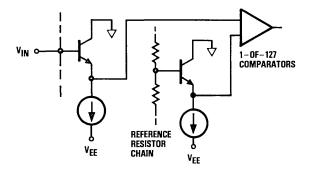

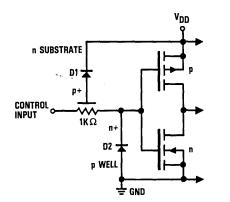

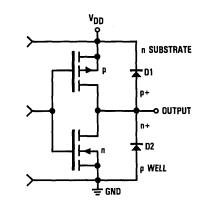

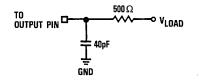

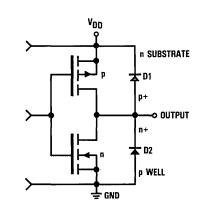

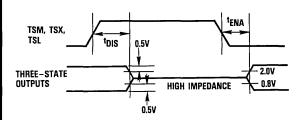

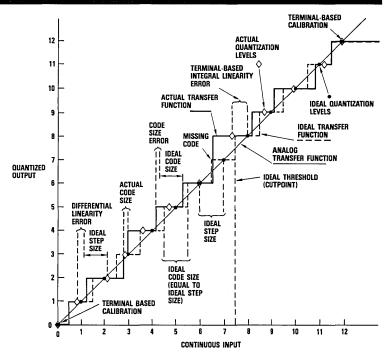

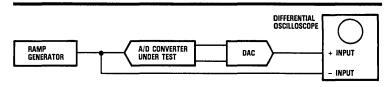

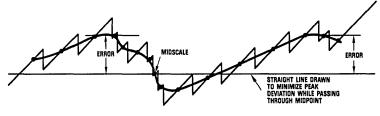

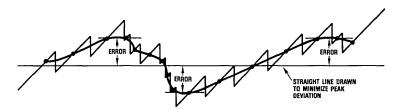

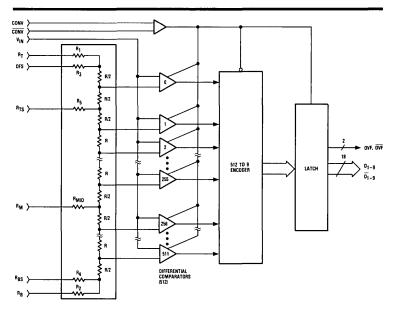

#### "Flash" A/D Converters

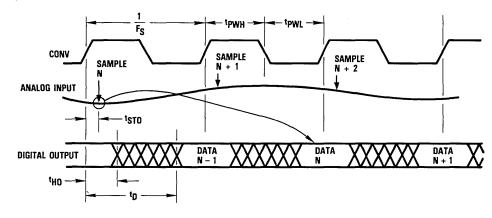

"Flash" A/D converters have three major functional sections: the comparator array, encoding logic, and output data latches. The input voltage to the A/D is compared with  $(2^N)$ -1 separate reference voltage points which differ from adjacent points by a voltage equivalent to one Least Significant Bit (LSB). N is the number of data outputs, or the resolution of the A/D converter in bits. The comparator reference voltage points are tapped from a reference resistor chain which is driven by an external reference voltage source.

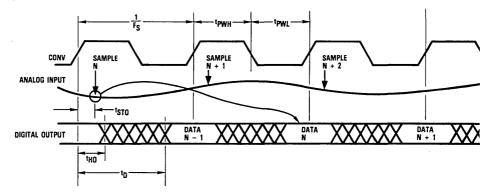

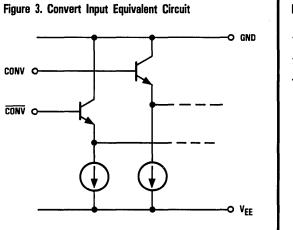

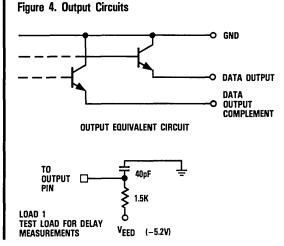

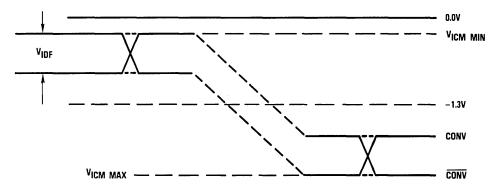

The outputs from the  $(2^N)$ -1 comparators form a code sometimes referred to as a "thermometer" code (all comparators referred to voltages more positive than the input signal will be off, and those referred to voltages more negative then the input signal will be on). The "thermometer" code from the comparator array is then encoded into an N-bit binary word. The conversion operation is controlled by a single CONVert (clock) signal which latches the N-bit results from the encoding logic. The output latches of the converter hold data valid while the conversion is taking place and are updated by the CONVert signal. Some converters have additional data controls which allow data formatting of straight binary, inverse binary, two's complement, or inverse two's complement notation.

#### Successive Approximation A/D Converters

Successive approximation A/D converters have three major functional sections: the comparator, D/A converter, and successive approximation register (SAR). The comparator compares the unknown input voltage to the output of the internal D/A. Successive approximation is an iterative process during which the SAR stores data from the comparator and presents new data to the D/A converter. At the end of the process, the data in the SAR drives the D/A converter to a level which is within 1/2 LSB of the unknown input voltage. At this time, the SAR data is the binary equivalent of the unknown input voltage.

Once the iterative process has terminated, the SAR data is latched in an output register and a "BUSY" signal will change state indicating that new output data is available.

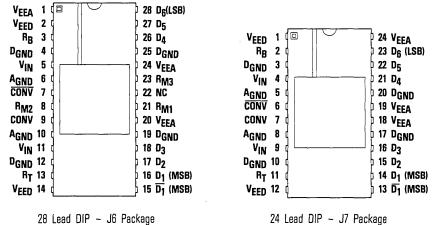

|           | Resolution | Conversion<br>Rate <sup>1</sup> | Power<br>Dissipation |                      |                                    |

|-----------|------------|---------------------------------|----------------------|----------------------|------------------------------------|

| Product   | Bits       | (MSPS)                          | (Watts)              | Package              | Notes                              |

| TDC1001   | 8          | 2.5                             | 0.7                  | J8                   | Successive approximation           |

| TDC1002   | 8          | 1.0                             | 0.7                  | JB                   | Successive approximation           |

| TDC1007   | 8          | 20                              | 2.7                  | J1, C1, L1<br>E1, P1 | Evaluation boards                  |

| TDC1014   | 6          | 25                              | 1.1                  | J7, B7<br>E1, P1     | Evaluation boards                  |

| TDC1019   | 9          | 15                              | 4.7                  | J1, C1, L1<br>E1     | ECL compatible<br>Evaluation board |

| TDC1019-1 | 9          | 18                              | 4.7                  | J1, C1, L1           | Speed selected version             |

| TDC1021   | 4          | 25                              | 0.6                  | J9                   |                                    |

| TDC1025   | 8          | 50                              | 3.9                  | C1, L1<br>E1         | ECL compatible<br>Evaluation board |

| TDC1027   | 7          | 18                              | 1.8                  | J7, B7               |                                    |

| TDC1029   | 6          | 100                             | 2.1                  | J7, J6<br>E1         | ECL compatible<br>Evaluation board |

| TDC1044   | 4          | 25                              | 0.4                  | J9, N9               |                                    |

| TDC1046   | 6          | 25                              | 0.8                  | J8, B8               |                                    |

| TDC1047   | 7          | 20                              | 1.1                  | J7, B7, C3<br>E1     | Evaluation Board                   |

| TDC1048   | 8          | 20                              | 1.6                  | J6, C3, B6<br>E1     | Evaluation board                   |

| TDC1147   | 7          | 15                              | 1.1                  | J7, B7, C3           |                                    |

Note: 1. Guaranteed, Worst Case,  $T_A = 0^{\circ}C$  to 70°C.

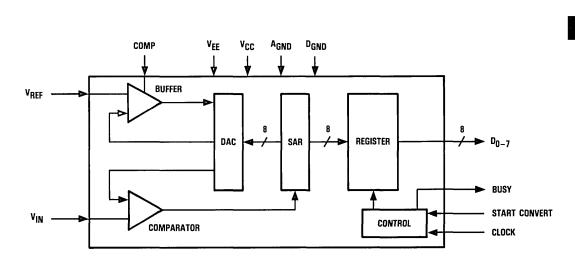

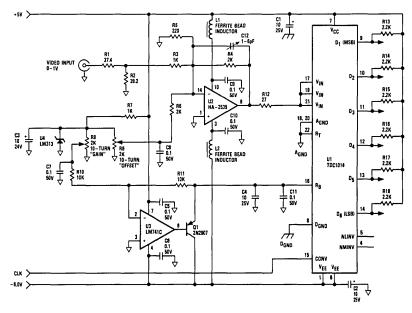

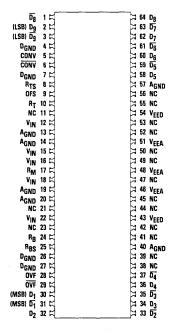

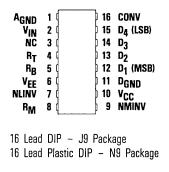

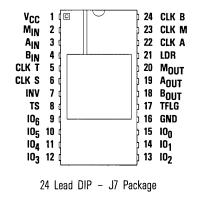

# **TDC1001** (400ns) **TDC1002** (1µsec)

## Successive Approximation A/D Converters

8-bit, 2.5MSPS, 1MSPS

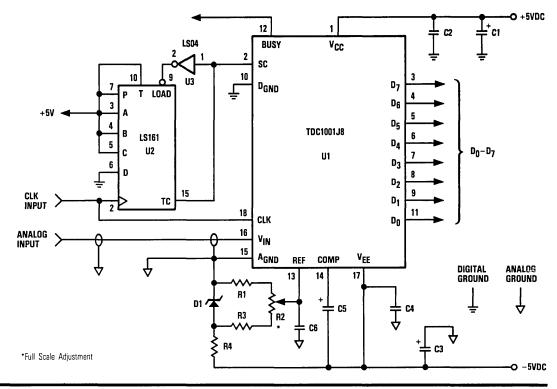

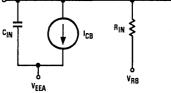

The TRW TDC1001 and TDC1002 analog-to-digital converters are high-speed, 8-bit successive approximation devices. These bipolar, monolithic converters offer significant advantages in size, cost, and performance, as well as high reliability and low-power consumption.

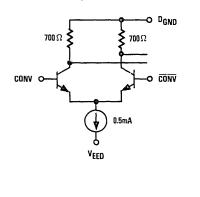

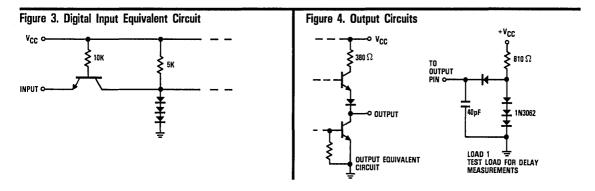

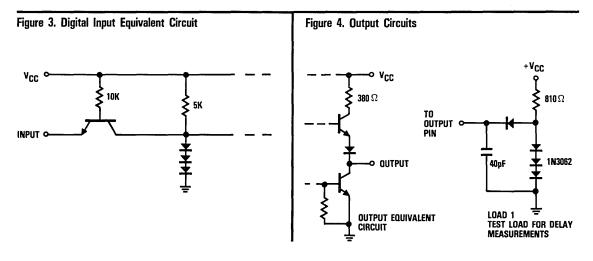

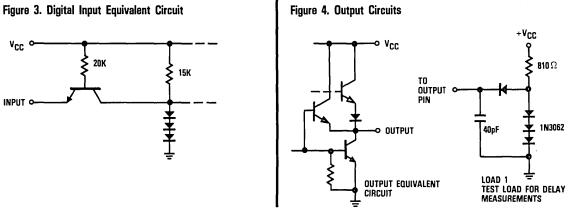

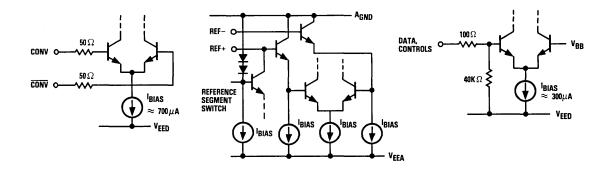

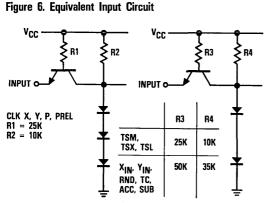

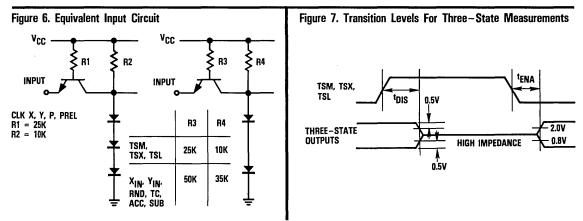

All digital interfaces are TTL compatible. A single +5VDC supply is required by the digital circuitry while -5VDC is required by the analog portion of the device. The analog and digital ground planes are internally isolated.

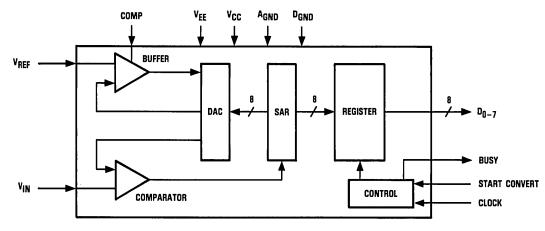

The TDC1001 and TDC1002 consist of a comparator, reference buffer, 8-bit D/A converter, successive approximation register, output register, and control circuitry.

## **Features**

- 8-Bit Resolution

- Binary Output Coding

- TTL Compatible

- ±1/2 LSB Linearity

- Parallel Output Register

- 600mW Power Dissipation

- Available In 18 Lead DIP

## Applications

- Microprocessor Systems

- Numerical Control Interface

- Data Acquisition Systems

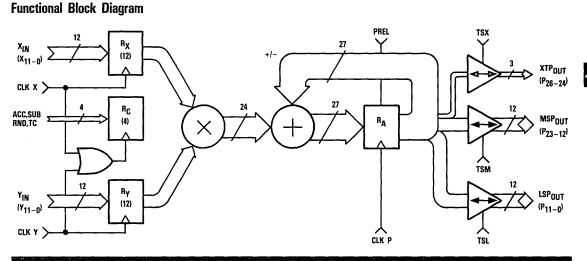

## **Functional Block Diagram**

LSI Products Division TRW Electronic Components Group P.O. Box 2472 La Jolla, CA 92038 Phone: (619) 457-1000 Telex: 697-957 TWX: 910-335-1571 ©TRW Inc. 1985 40G00272 Rev. F-1/85 Printed in the U.S.A.

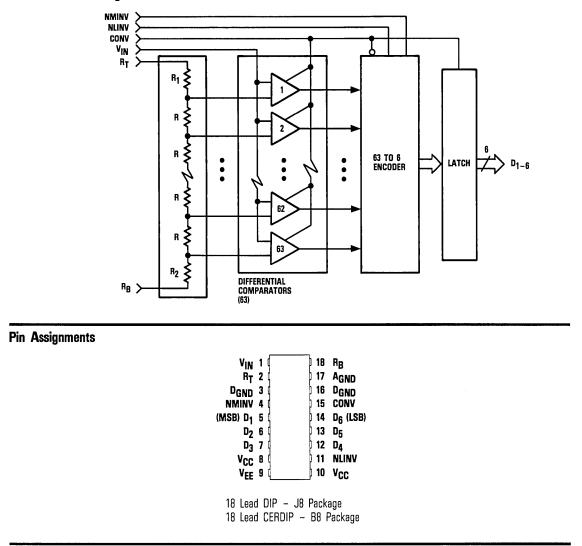

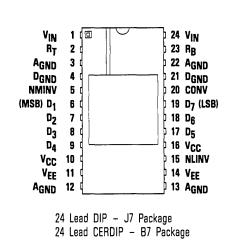

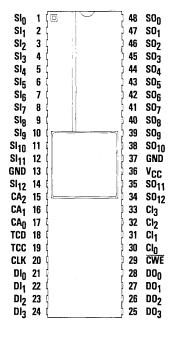

## TDC1001/1002

## **Functional Block Diagram**

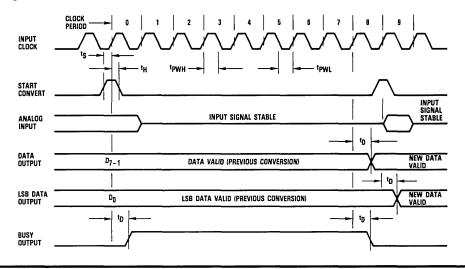

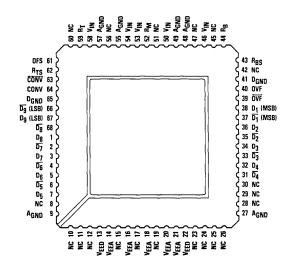

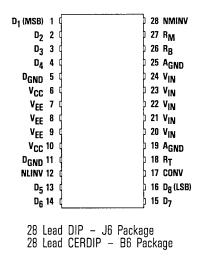

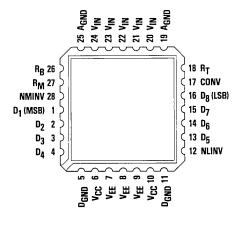

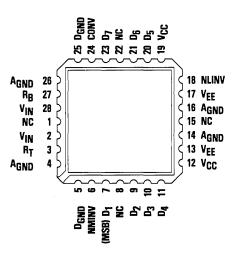

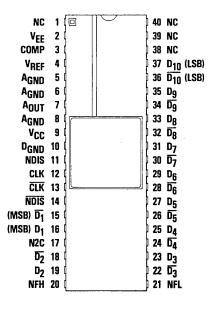

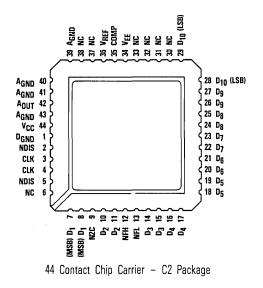

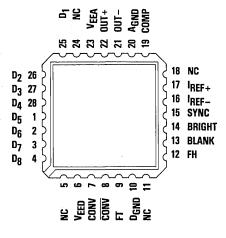

## **Pin Assignments**

18 Lead DIP - J8 Package

## **Functional Description**

### **General Information**

The TDC1001 and TDC1002 consist of six functional sections: comparator for the analog input, reference buffer, 8-bit D/A converter (DAC), successive approximation register (SAR), output

register, and control circuitry. The SAR and comparator will sequentially compare the analog input to the DAC output. The conversion process requires nine clock cycles.

#### Power

The TDC1001 and TDC1002 operate from separate analog and digital power supplies. Analog power ( $V_{EE}$ ) is -5.0VDC and digital power ( $V_{CC}$ ) is +5.0VDC. All power and ground pins must be connected.

Separate decoupling for each supply is recommended. The return for I<sub>EE</sub>, the current drawn from the V<sub>EE</sub> supply, is A<sub>GND</sub>. The return for I<sub>CC</sub>, the current drawn from the V<sub>CC</sub> supply, is D<sub>GND</sub>.

| Name             | Function               | Value   | J8 Package |

|------------------|------------------------|---------|------------|

| /EE              | Analog Supply Voltage  | -5.0VDC | Pin 17     |

| V <sub>CC</sub>  | Digital Supply Voltage | +5.0VDC | Pin 1      |

| Agnd             | Analog Ground          | 0.0VDC  | Pin 15     |

| D <sub>GND</sub> | Digital Ground         | 0.0VDC  | Pin 10     |

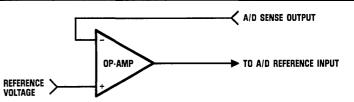

#### Reference

The TDC1001 and 1002 accept a nominal input reference voltage of -0.5VDC. The voltage should be supplied by a precision voltage reference, as the accuracy of this voltage will

have a significant effect on the overall accuracy of the system. The reference voltage input pin should be bypassed to  $A_{GND}$  as close as possible to the device terminal.

| Name             | Function                | Value   | J8 Package |

|------------------|-------------------------|---------|------------|

| V <sub>REF</sub> | Reference Voltage Input | -0.5VDC | Pin 13     |

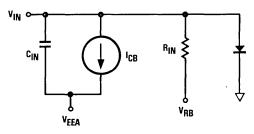

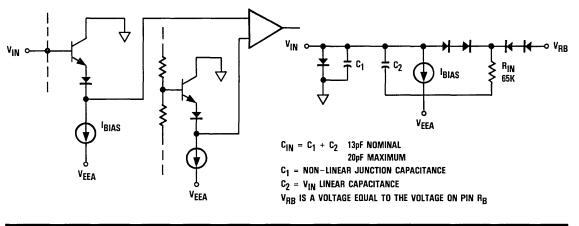

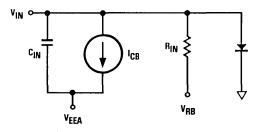

### Analog Input

The analog input range of the device is set by the reference voltage. This is nominally -0.5VDC with an absolute tolerance of  $\pm 0.1VDC$ . Since the device is a successive approximation

type A/D converter, a sample-and-hold circuit may be required in some applications.

| Name            | Function     | Value      | J8 Package |

|-----------------|--------------|------------|------------|

| v <sub>IN</sub> | Analog Input | 0 to -0.5V | Pin 16     |

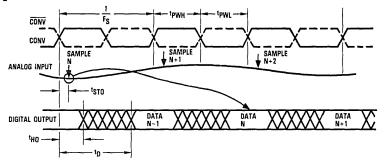

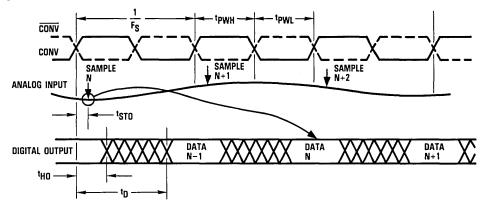

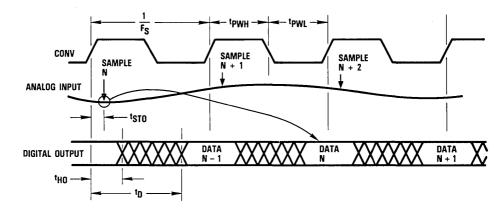

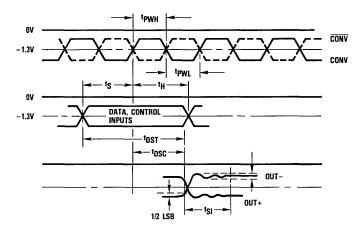

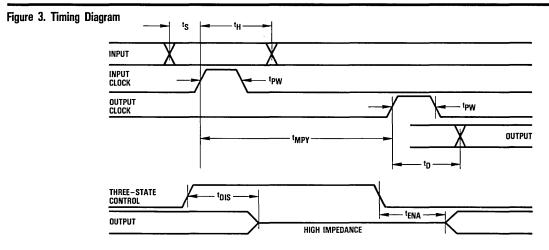

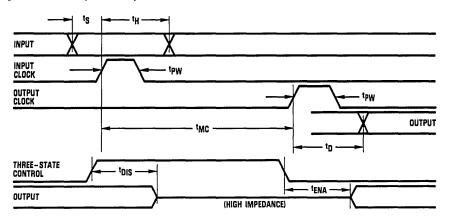

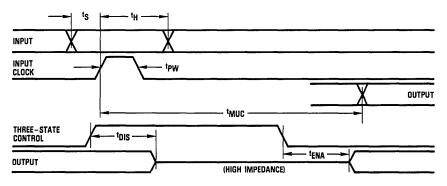

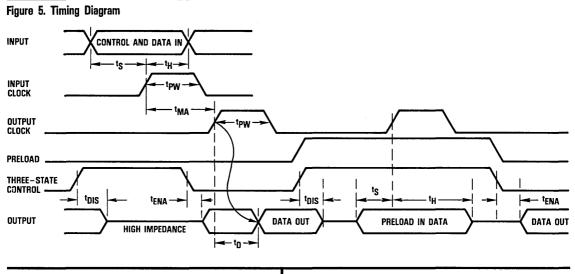

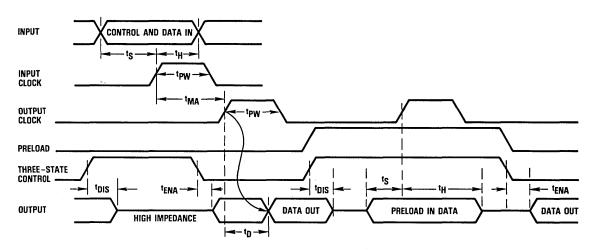

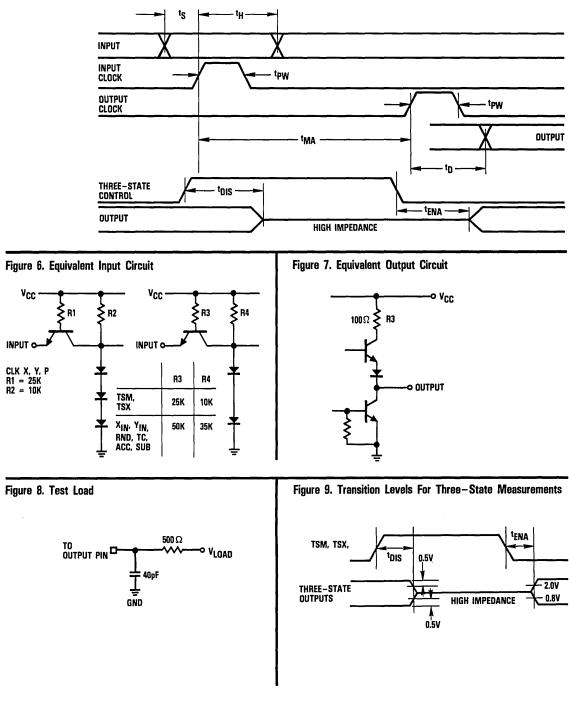

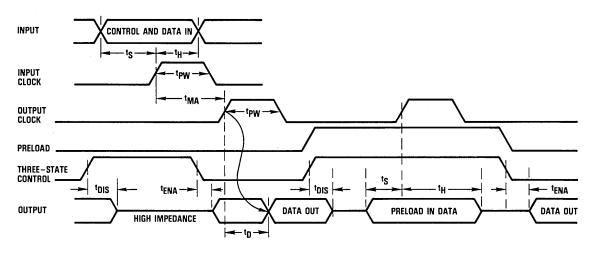

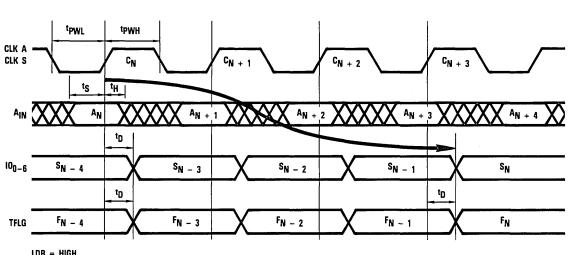

#### **Conversion Timing Description**

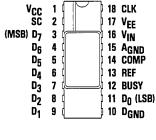

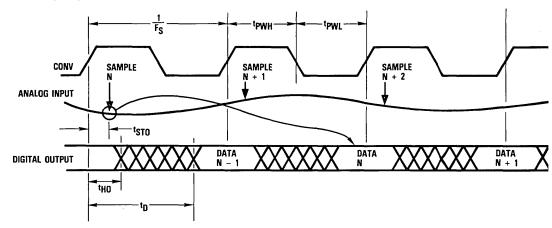

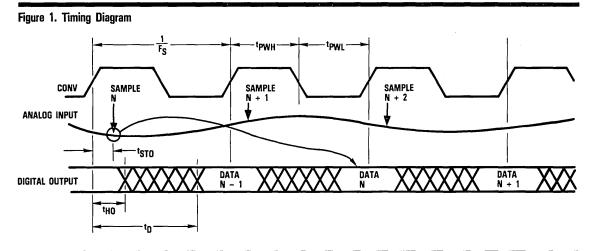

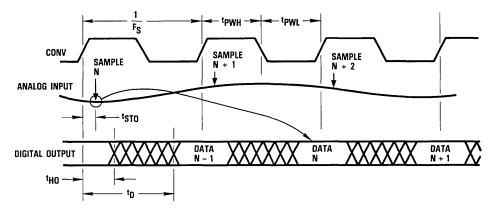

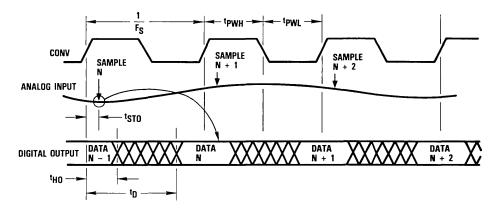

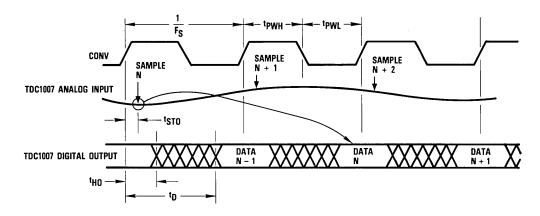

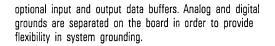

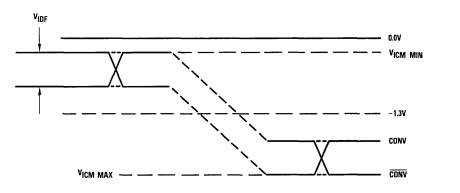

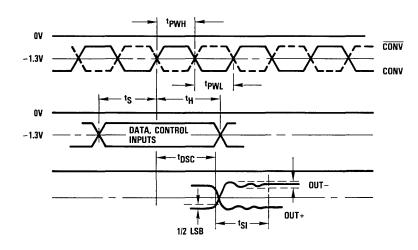

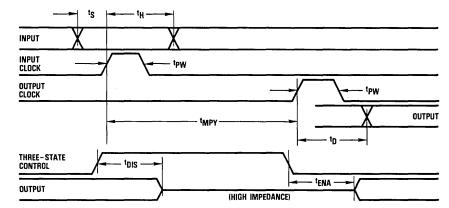

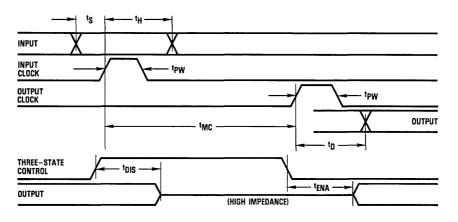

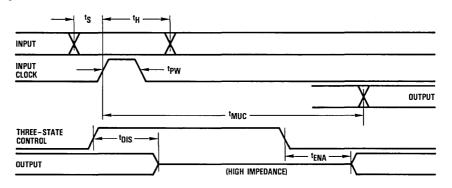

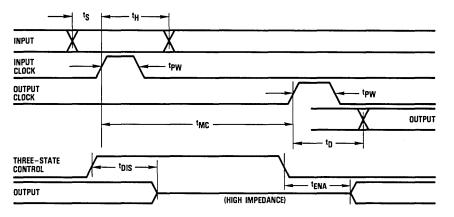

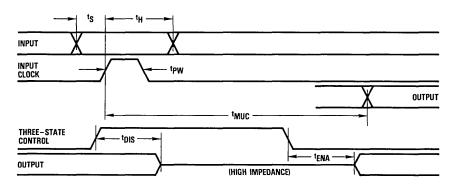

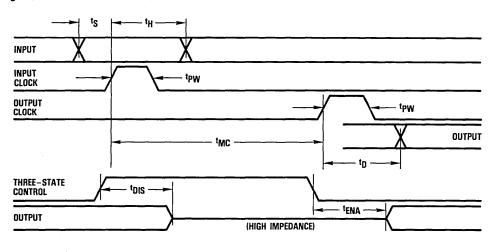

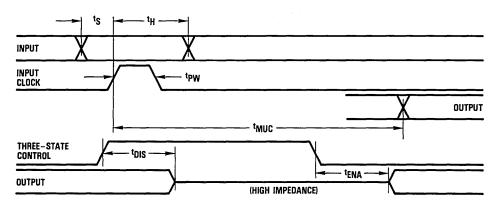

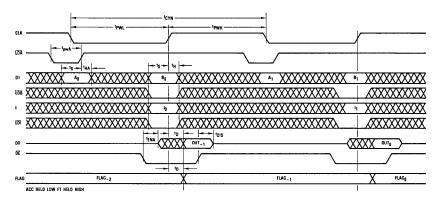

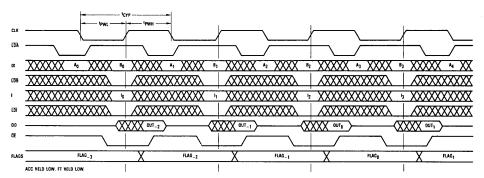

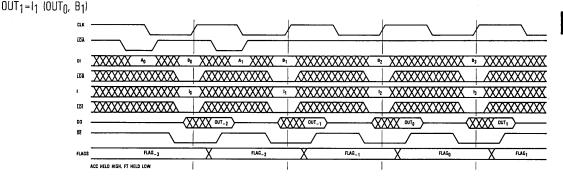

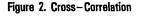

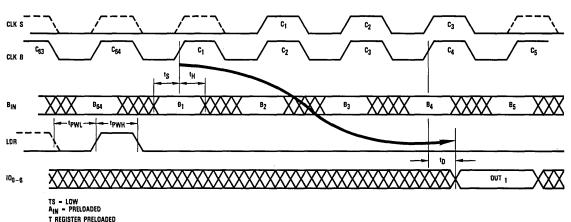

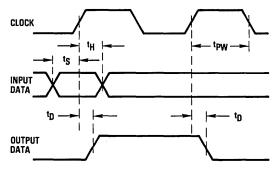

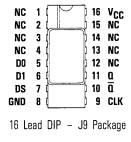

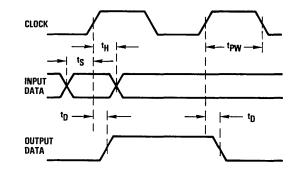

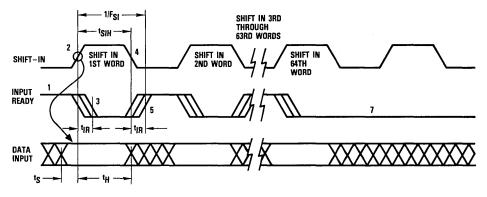

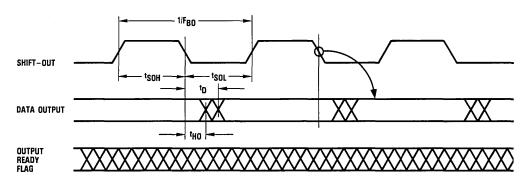

The timing sequence of the TDC1001 and 1002 is typical of successive approximation converters. Nine clock cycles are required for each conversion. Start Convert must transition from LOW to HIGH a minimum of t<sub>S</sub> prior to the leading edge of the first convert pulse, and must remain HIGH a minimum of t<sub>H</sub> after the edge.

This first cycle clears the BUSY flag and prepares the device for a new conversion. The following eight clock cycles convert each data bit (MSB first, LSB last). During these eight clock cycles, the analog input must be held stable (to within 1/2 LSB). At  $t_D$  nanoseconds after the rising edge of the eighth clock pulse, the seven most significant bits are valid (and the BUSY signal goes LOW). At  $t_D$  nanoseconds after the conversion is completed.

| Name  | Function            | Value | J8 Package |

|-------|---------------------|-------|------------|

| SC    | Start Convert Input | TTL   | Pin 2      |

| BUSY  | Busy Flag Output    | TTL   | Pin 12     |

| CLOCK | Convert Clock Input | TTL   | Pin 18     |

D

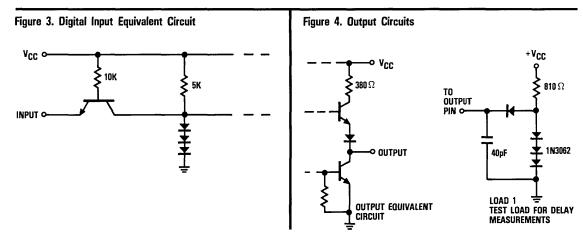

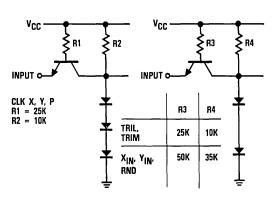

#### **Data Outputs**

The outputs of the TDC1001 and 1002 are TTL compatible and capable of driving four low-power Schottky TTL (54/74 LS) unit loads or the equivalent. The outputs hold the previous

data a minimum time (tp) after the rising edge of Start Convert (SC).

| Name           | Function   | Value | J8 Package |

|----------------|------------|-------|------------|

| D <sub>7</sub> | MSB Output | TTL   | Pin 3      |

| D <sub>6</sub> |            | TTL   | Pin 4      |

| D <sub>5</sub> |            | TTL   | Pin 5      |

| D <sub>4</sub> |            | ΠL    | Pin 6      |

| D3             |            | TTL   | Pin 7      |

| D <sub>2</sub> |            | TTL   | Pin 8      |

| D <sub>1</sub> |            | TTL   | Pin 9      |

| Do             | LSB Output | TTL   | Pin 11     |

#### **Compensation Pin**

The COMPensation pin (COMP), is provided for external compensation of the internal reference amplifier.

The compensation capacitor must be connected between this pin and  $V_{EE}.$  A tantalum capacitor greater than  $10\mu F$  is recommended for proper operation.

| Name | Description      | Value  | J8 Package |

|------|------------------|--------|------------|

| COMP | Compensation Pin | >10µ F | Pin 14     |

#### **Output Coding**

An analog input voltage of 0.0V will produce a digital output code of all zeros; an analog input voltage of -0.50V will produce a digital output code of all ones.

## TDC1001/1002

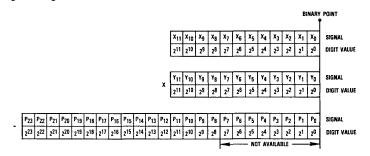

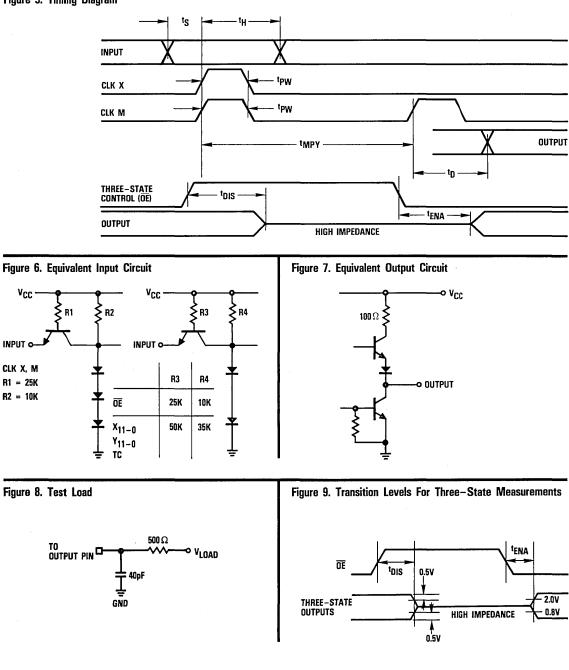

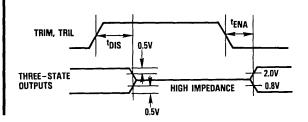

Figure 1. Timing Diagram

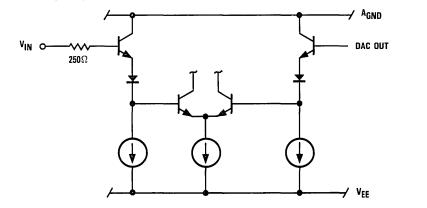

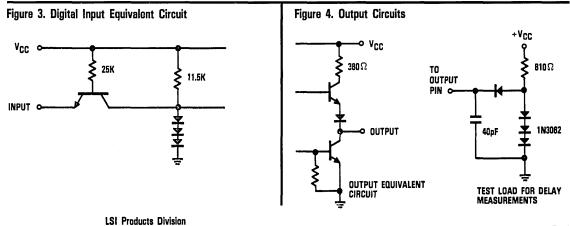

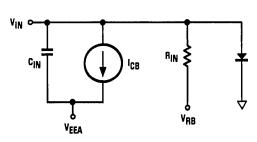

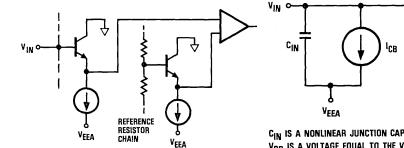

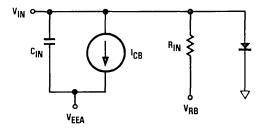

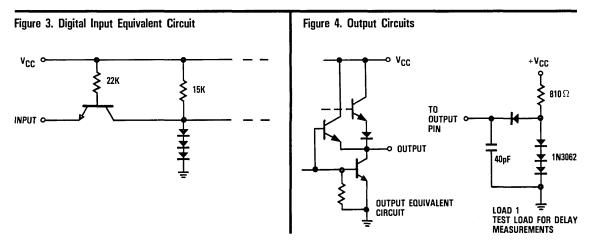

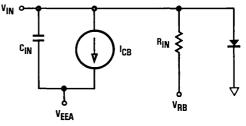

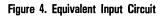

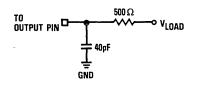

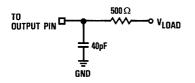

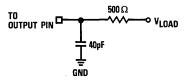

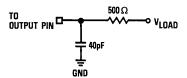

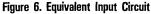

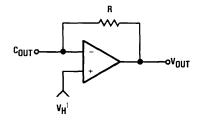

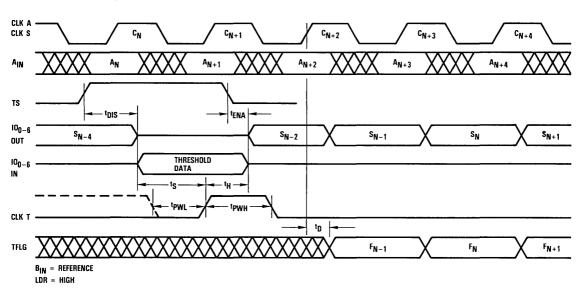

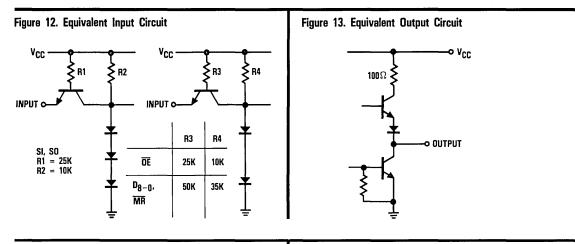

#### Figure 2. Simplified Analog Input Equivalent Circuit

D

## TDC1001/1002

Absolute maximum ratings (beyond which the device will be damaged)<sup>1</sup>

| Supply Voltag | 8                                                                                                                                                                                                  |                                 |

|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|

|               | V <sub>CC</sub> (measured to D <sub>GND</sub> )                                                                                                                                                    | 0 to +6.0V                      |

|               | VEE (measured to AGND)                                                                                                                                                                             | 0 to -6.0V                      |