# High-Performance FIFO Memories

# Designer's Handbook

# High-Performance FIFO Memories

1996

1996

Advanced System Logic Products

| General Information                | 1 |

|------------------------------------|---|

| Product Overview                   | 2 |

| Specific Application Reports       | 3 |

| Power Considerations               | 4 |

| Mechanical and Thermal Information | 5 |

| Device Models                      | 6 |

| Quality and Reliability Assurance  | 7 |

# High-Performance FIFO Memories Designer's Handbook

#### IMPORTANT NOTICE

Texas Instruments (TI) reserves the right to make changes to its products or to discontinue any semiconductor product or service without notice, and advises its customers to obtain the latest version of relevant information to verify, before placing orders, that the information being relied on is current.

TI warrants performance of its semiconductor products and related software to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

Certain applications using semiconductor products may involve potential risks of death, personal injury, or severe property or environmental damage ("Critical Applications").

TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, INTENDED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT APPLICATIONS, DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS.

Inclusion of TI products in such applications is understood to be fully at the risk of the customer. Use of TI products in such applications requires the written approval of an appropriate TI officer. Questions concerning potential risk applications should be directed to TI through a local SC sales office.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards should be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance, customer product design, software performance, or infringement of patents or services described herein. Nor does TI warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used.

Copyright © 1996, Texas Instruments Incorporated

Printed in U.S.A. by Custom Printing Company Owensville, Missouri

#### INTRODUCTION

The Texas Instruments (TI) High-Performance FIFO Memories Designer's Handbook has been created to provide users and potential users of TI's FIFOs with a comprehensive collection of information and data used as a reference guide during the design-in process. In a much broader sense, the designer's handbook also is a means to further the overall understanding and awareness of TI's FIFOs and their many applications.

The contents of the handbook complement the information contained in the 1996 High-Performance FIFO Memories Data Book, literature number SCAD003C. In addition to an expanded series of FIFO application notes, the handbook also contains information that is useful to the designer, such as sample power-dissipation calculations, mechanical packaging data, thermal-resistance data, and quality/reliability assurance information. Section 6, *Device Models*, includes lists of available VHDL [VHSIC (very high-speed integrated circuits) hardware-description language] models and logic-modeling behavior models.

This designer's handbook is organized into seven major sections: *General Information* (section 1), *Product Overview* (section 2), *Specific Application Reports* (section 3), *Power Considerations* (section 4), *Mechanical and Thermal Information* (section 5), *Device Models* (section 6), and *Quality and Reliability Assurance* (section 7).

Section 1 contains a glossary of symbols, terms, and definitions that are used throughout the handbook. These symbols, terms, and definitions are presented in accordance with those currently agreed upon by the JEDEC Council of the Electronic Industries Association.

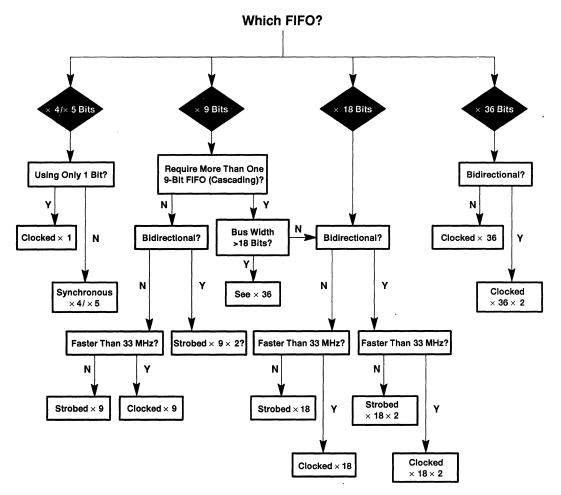

Section 2 provides an overview of TI's FIFO products. The summary charts in this section allow quick reference of key FIFO parameters, such as architecture, organization, speed sort, maximum clock frequency, and available packaging options. The features associated with TI's advanced application-specific FIFOs are summarized in this section. Section 2 also includes a flow chart that can be used as an aid in selecting a FIFO architecture based on a known bus width.

Section 3 provides a comprehensive set of FIFO application reports. The application reports are organized into subsections based on the subject matter of each report. The subsections are *FIFO Performance and Reliability*, *FIFO Features*, and *FIFO Applications*.

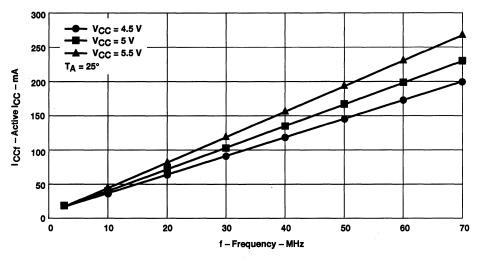

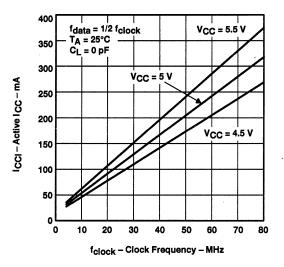

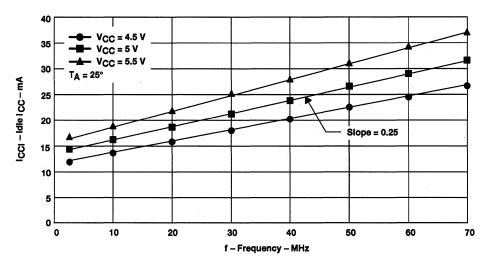

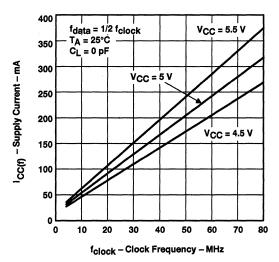

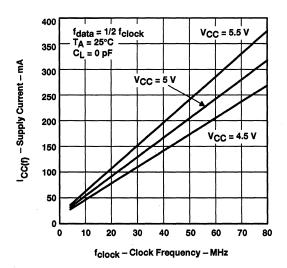

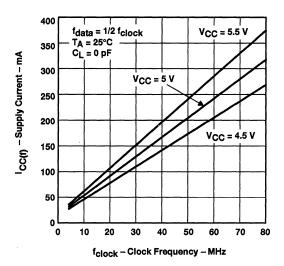

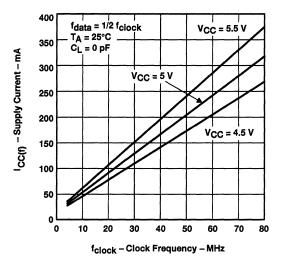

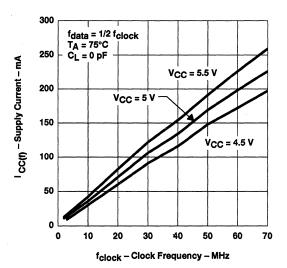

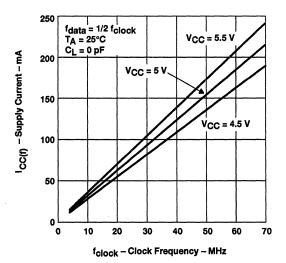

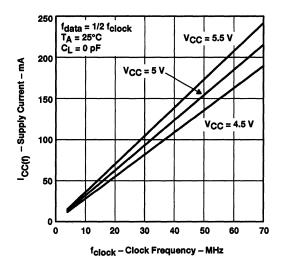

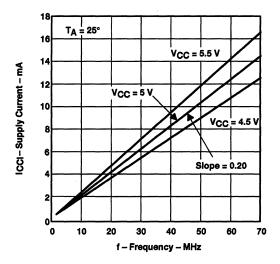

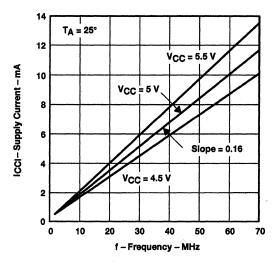

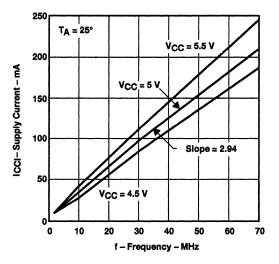

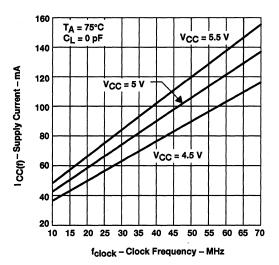

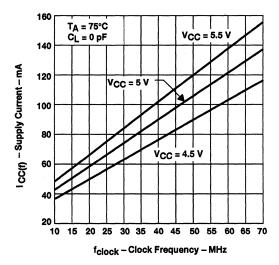

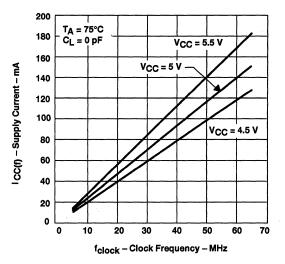

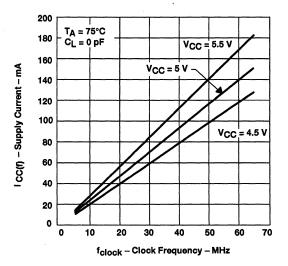

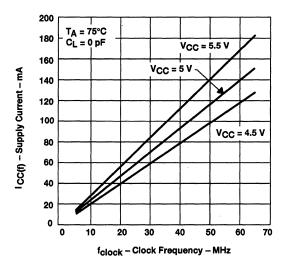

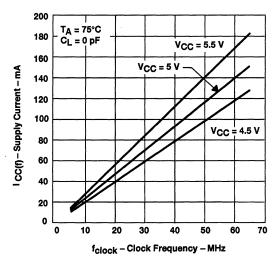

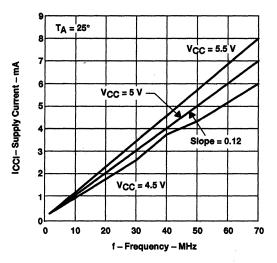

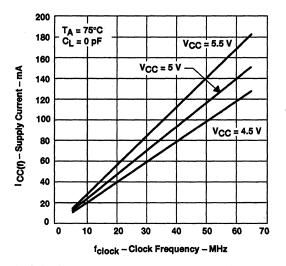

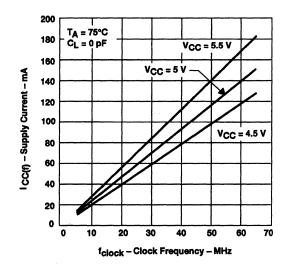

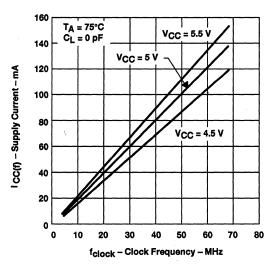

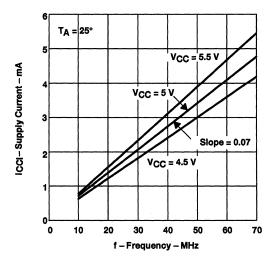

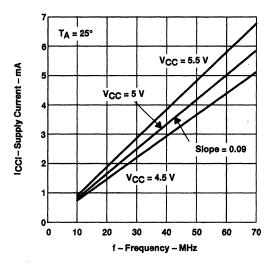

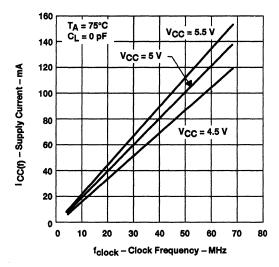

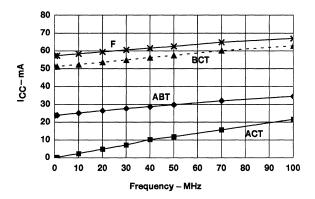

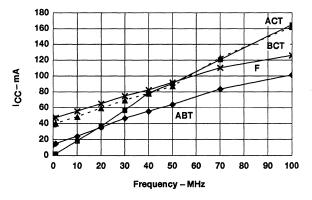

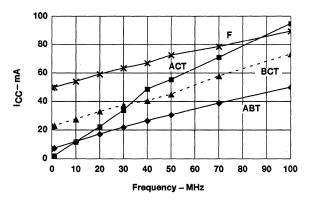

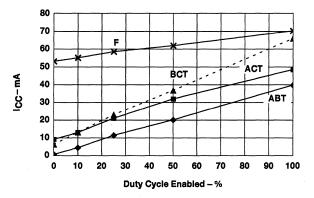

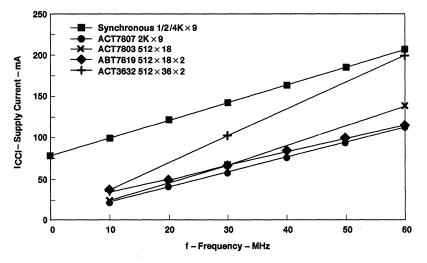

Section 4 provides typical power characteristics in the form of active supply current versus frequency for each of TI's advanced FIFOs. Plots of idle supply current versus frequency also are given for a select number of FIFOs. In addition to this data, sample power-dissipation calculations are performed for a representative set of FIFOs. The application report in this section is used as a guideline for these calculations. Calculations and equations are provided for CMOS FIFOs and Advanced BiCMOS Technology (ABT) FIFOs.

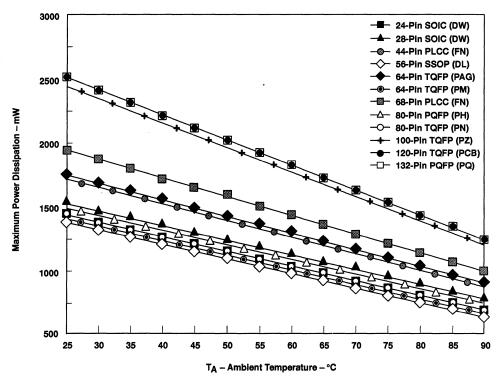

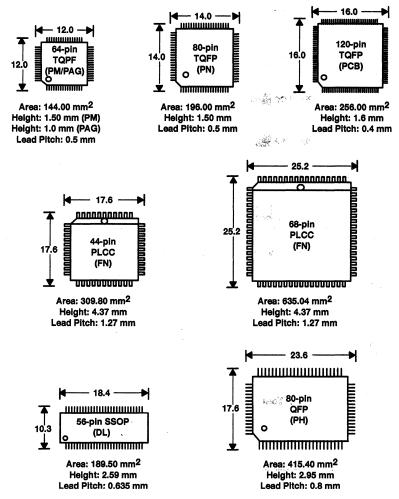

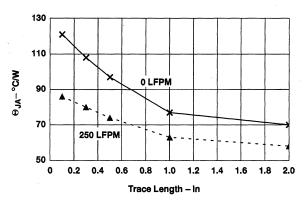

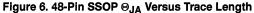

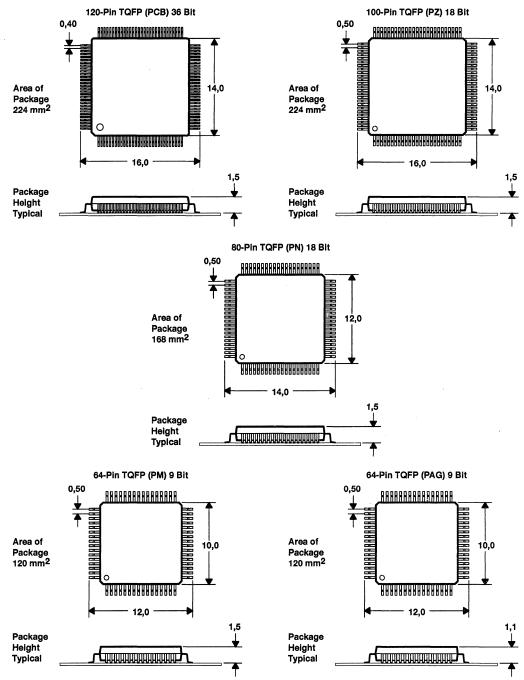

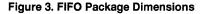

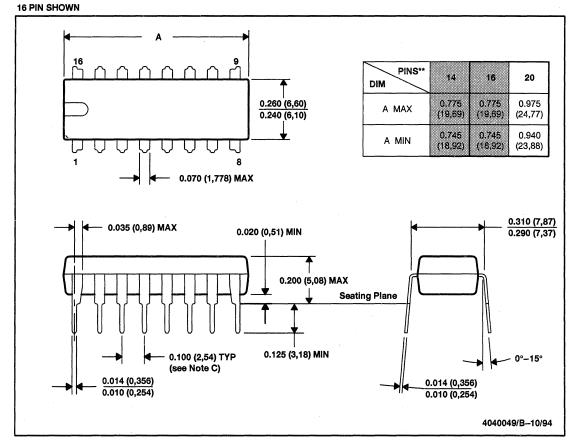

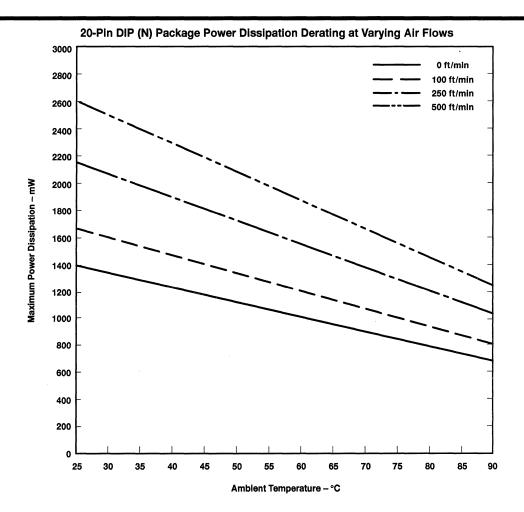

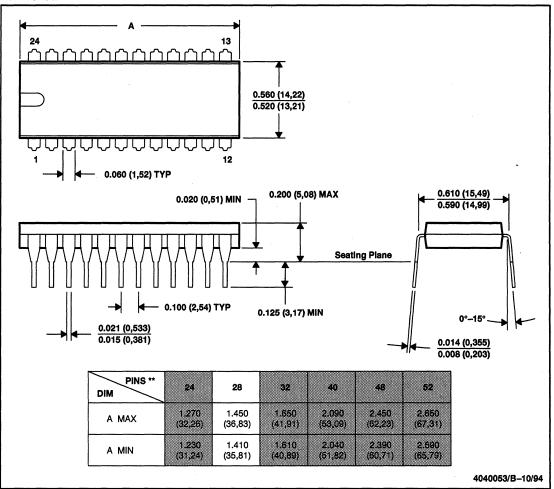

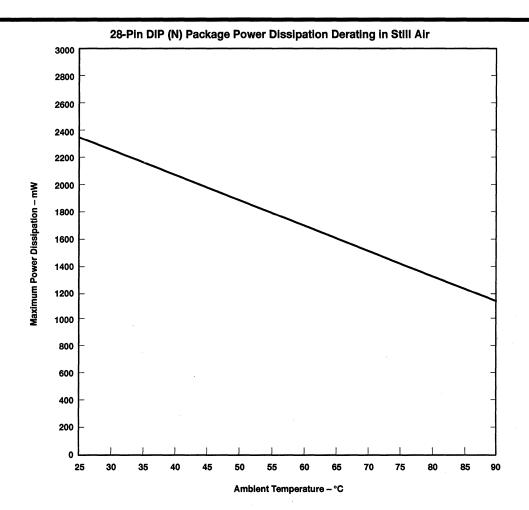

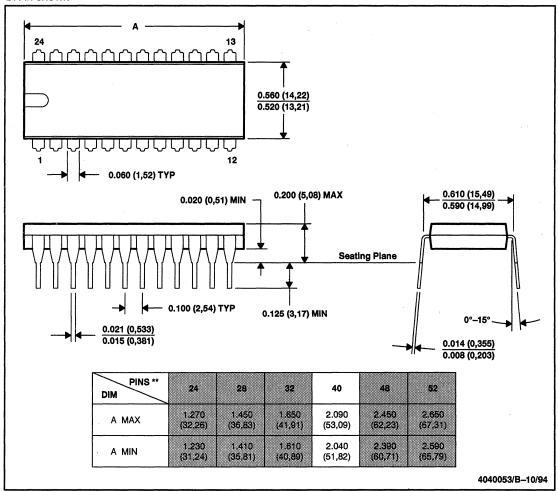

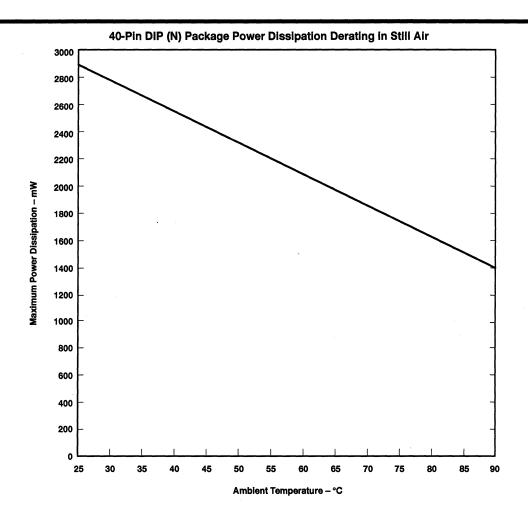

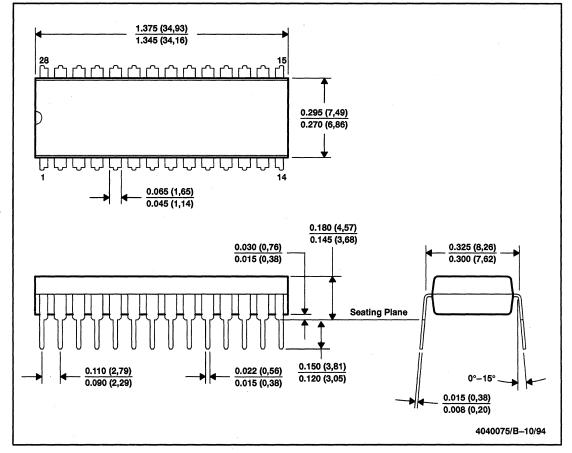

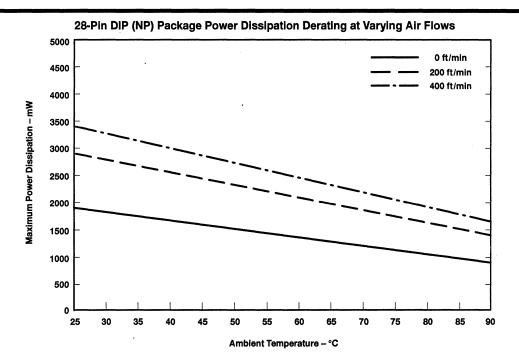

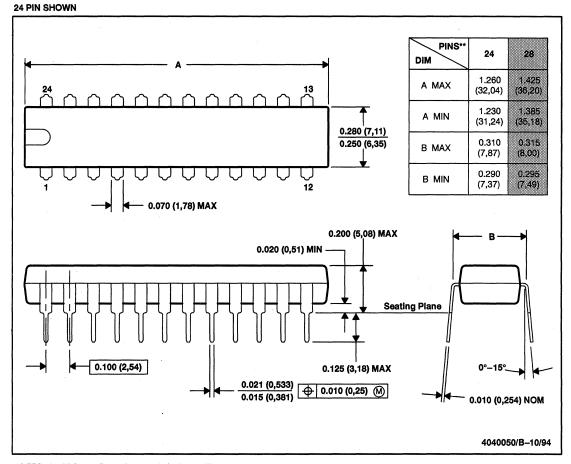

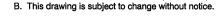

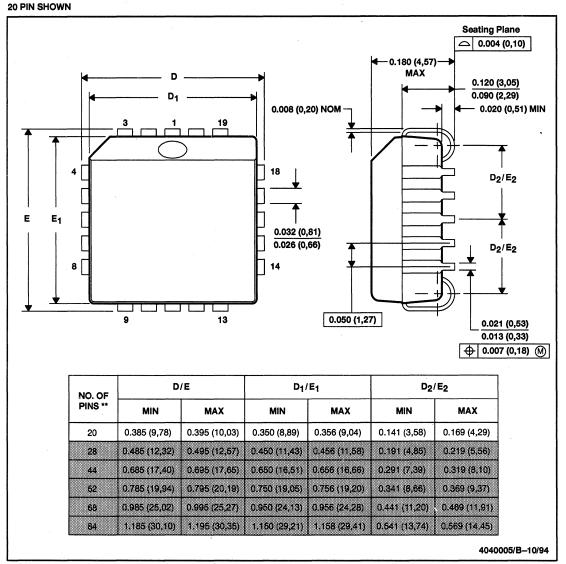

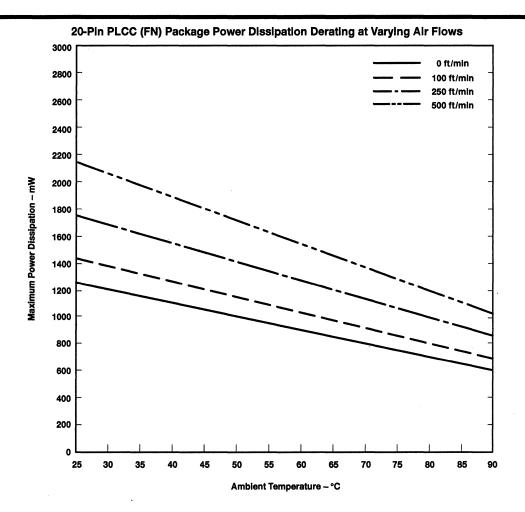

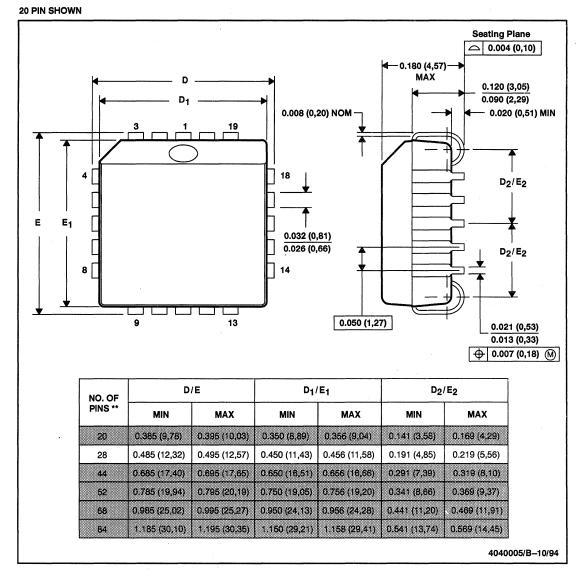

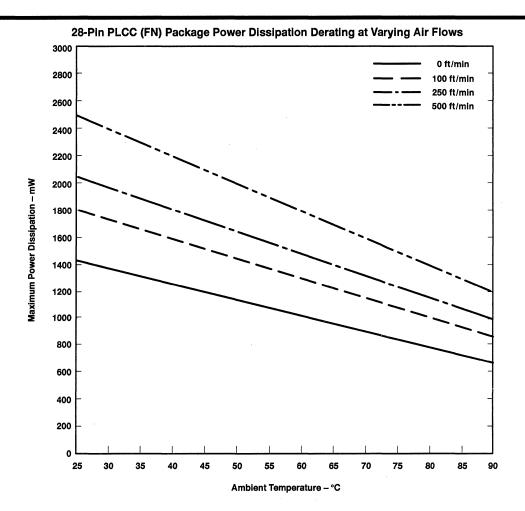

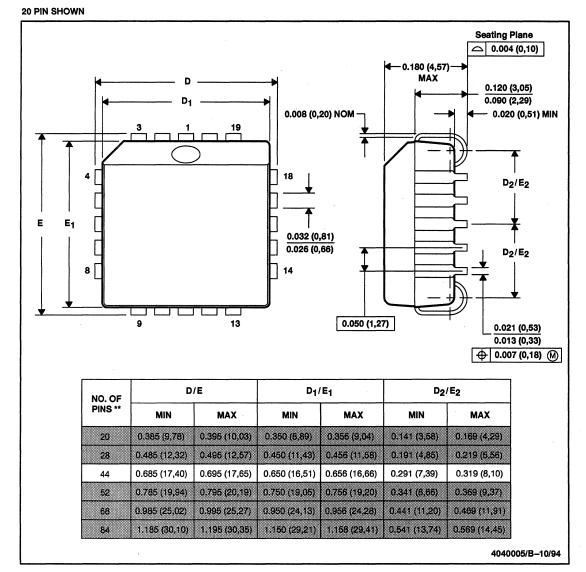

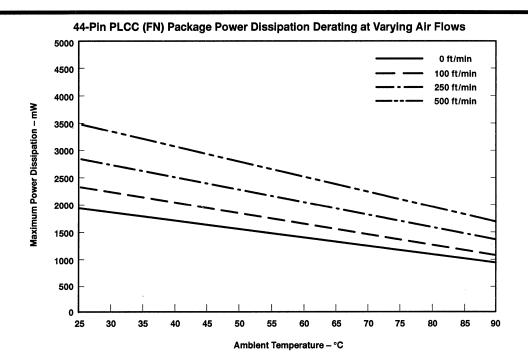

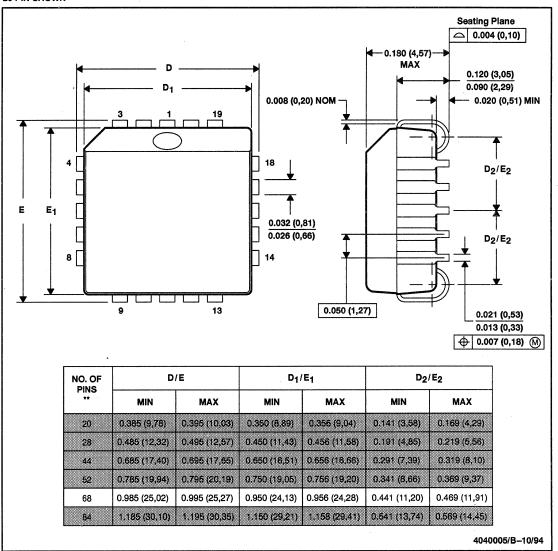

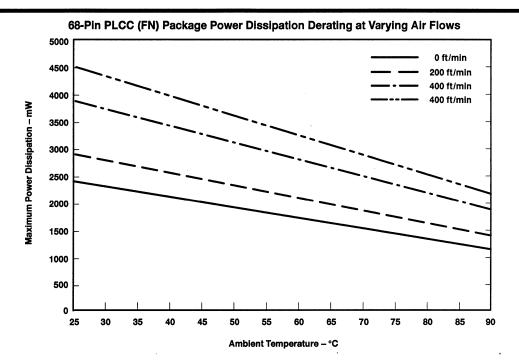

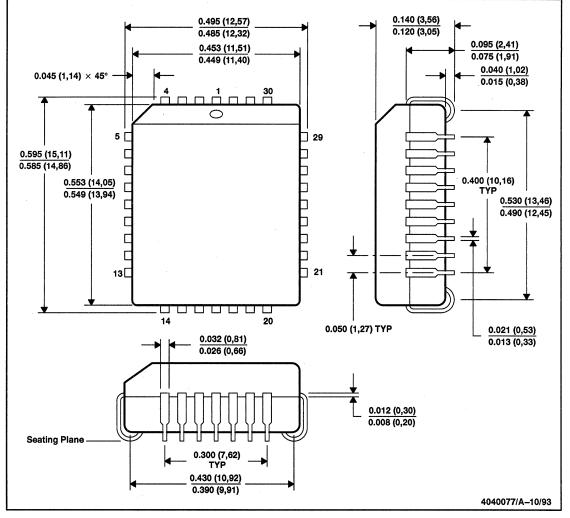

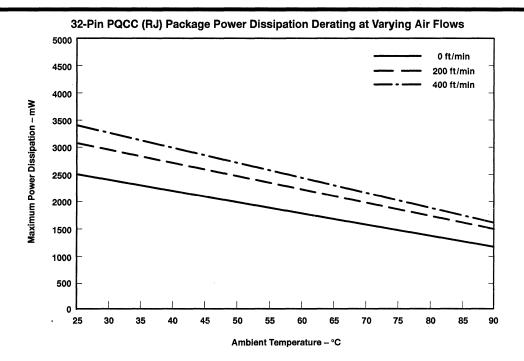

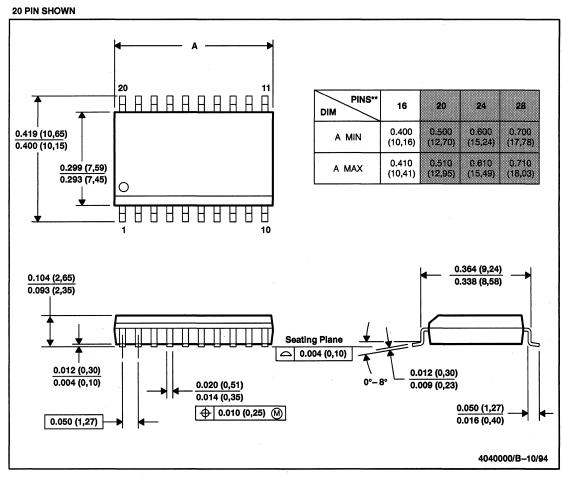

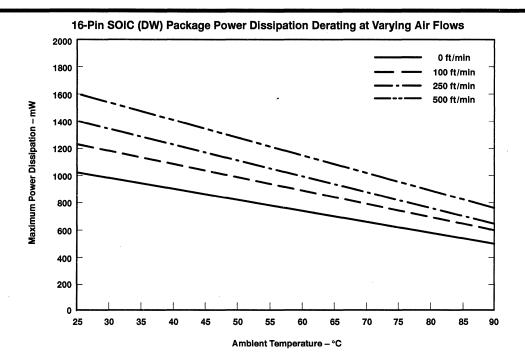

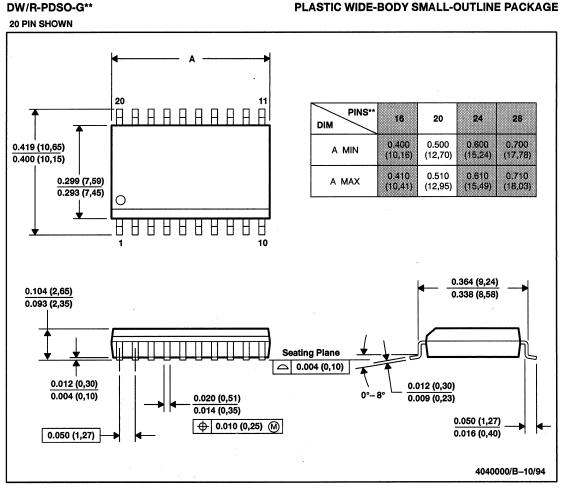

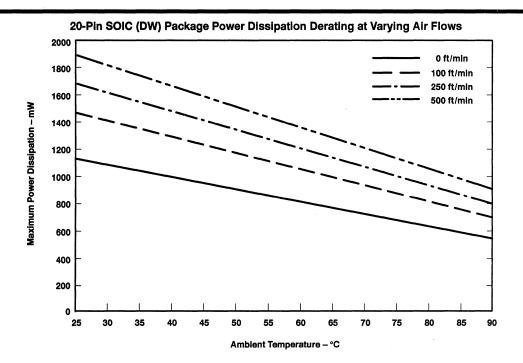

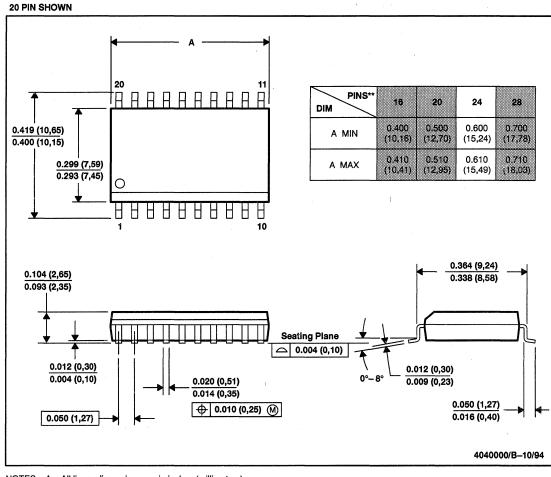

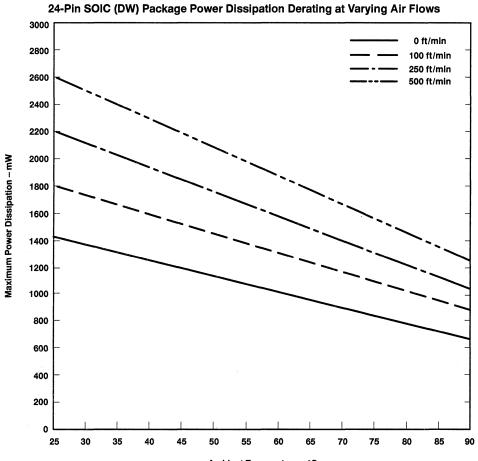

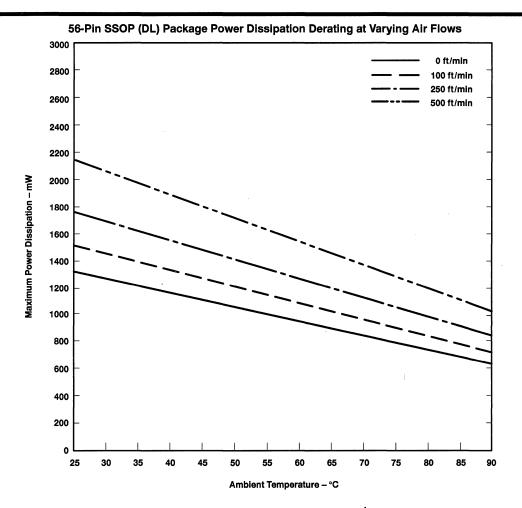

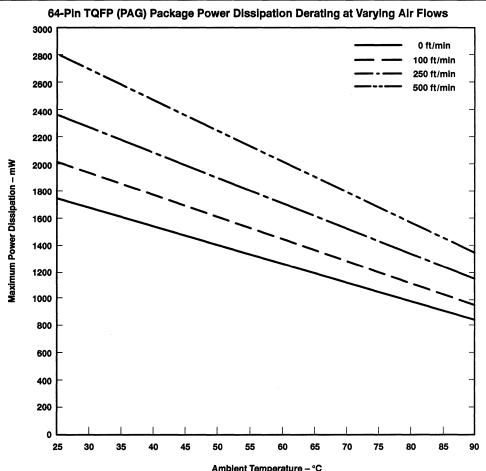

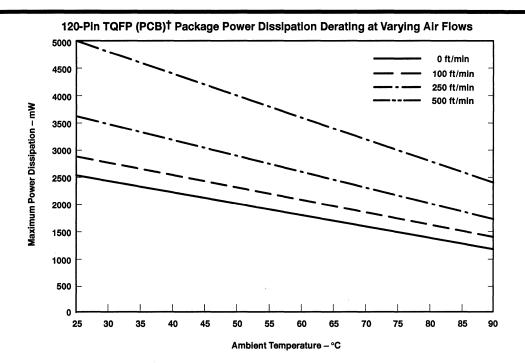

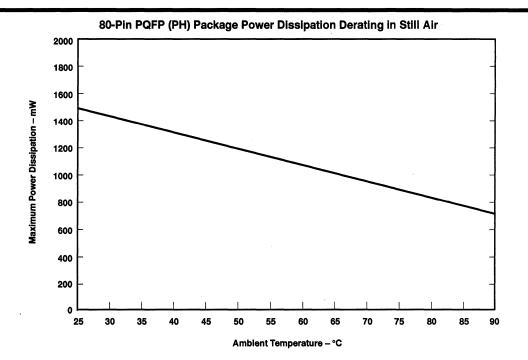

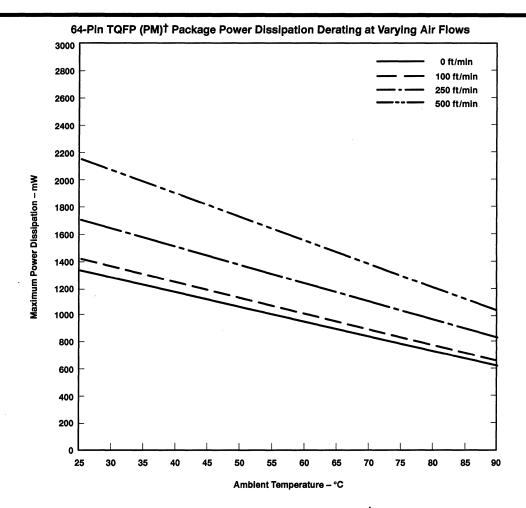

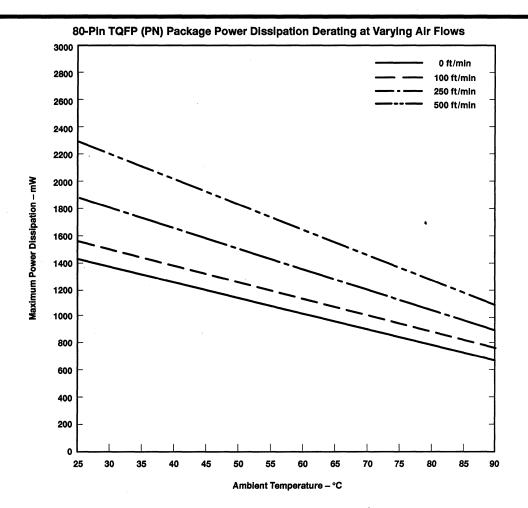

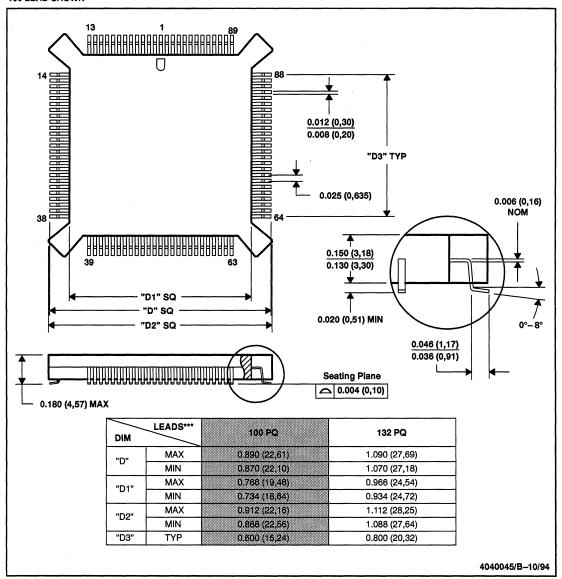

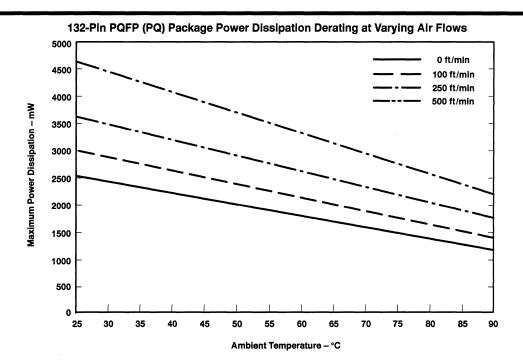

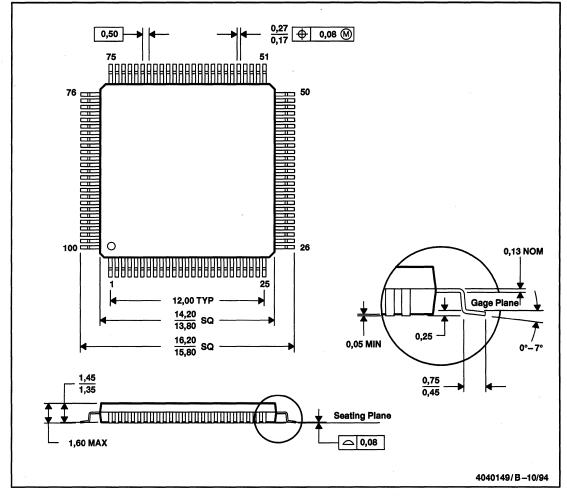

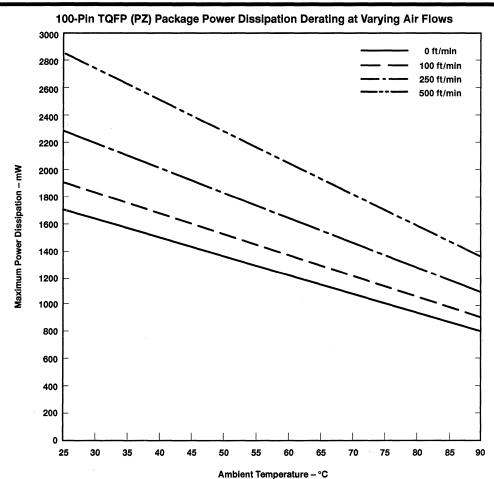

Section 5 contains mechanical drawings for each FIFO packaging option. The official JEDEC descriptor is used to identify each package type. These drawings typically include the following dimensions: lead pitch (tip to tip), body width and length, shoulder-to-shoulder insertion width, lead width, thickness, and angles, and package maximum height, and stand-off clearances from seating plane to bottom of the package. Included with the mechanical data is thermal data for each FIFO packaging option. Thermal resistance values for varying conditions and power-dissipation derating curves for varying air flows are

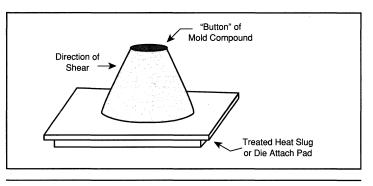

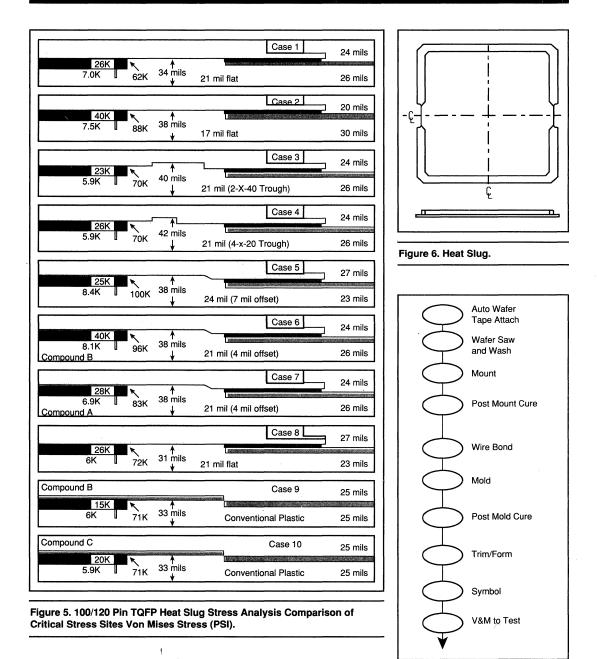

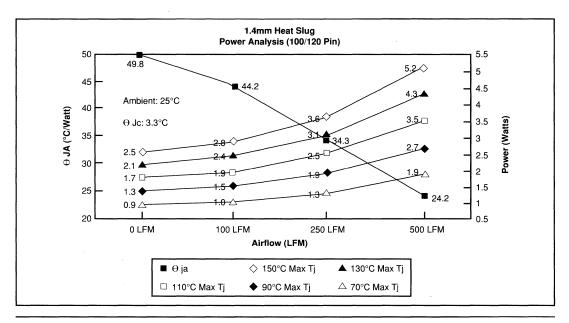

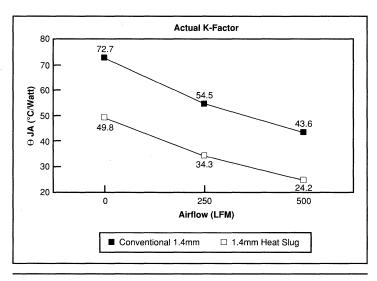

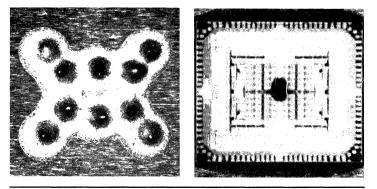

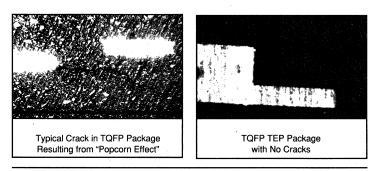

presented for each package type. Several application reports and papers also are included in this section to provide further detail regarding overall thermal considerations and thermal-resistance measurements, including the design and development of the thermally enhanced thin quad flat package (TQFP).

Section 6 contains a list of the behavioral models currently available from TI. All speed sorts of the devices under consideration are included in the models. VHDL models of FIFO devices included in this section may be obtained by calling the Advanced System Logic hotline at 903-868-5202.

Section 7 addresses the issue of quality and reliability assurance for TI's FIFO products. Concepts such as the qualification of products and processes, quality and reliability assurance in integrated-circuit design, and quality and reliability monitoring are discussed.

For further information on TI's FIFO products or applications, please contact the Advanced System Logic hotline at 903-868-5202. For information on TI's military FIFO devices, contact military Advanced System Logic marketing at 915-561-7289.

| Contents |  |

|----------|--|

|----------|--|

•

| Glossary                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Section 2 – Prod                                                                                                                                                                                                                                                                                                                                       | luct Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Advanced Cloc<br>Advanced Strot<br>Advanced Appli<br>Advanced Appli<br>Synchronous M<br>Asynchronous I<br>FIFO Functiona                                                                                                                                                                                                                               | ngs         2-3           ked FIFOs         2-5           bed FIFOs         2-5           ication-Specific Clocked FIFOs         2-6           ication-Specific FIFO Features         2-6           lature FIFOs         2-6           Mature FIFOs         2-7           lity         2-7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                                                                                                                                                                                                                                                                                                        | Chart                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Section 3 – Spec                                                                                                                                                                                                                                                                                                                                       | cific Application Reports 3–1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

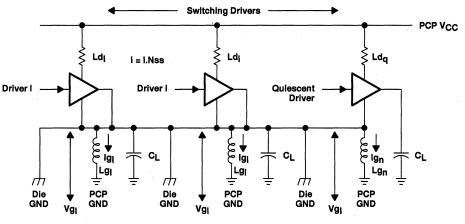

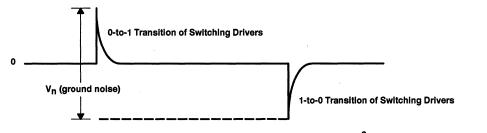

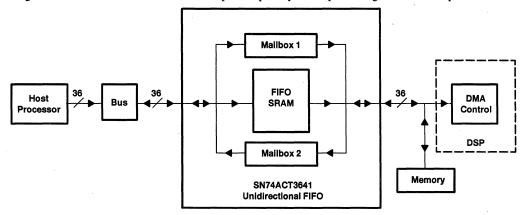

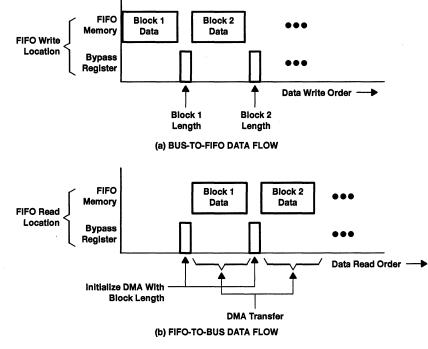

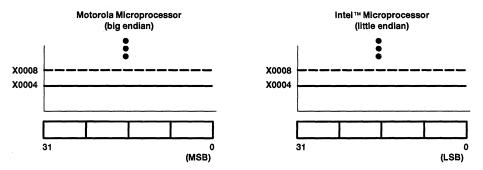

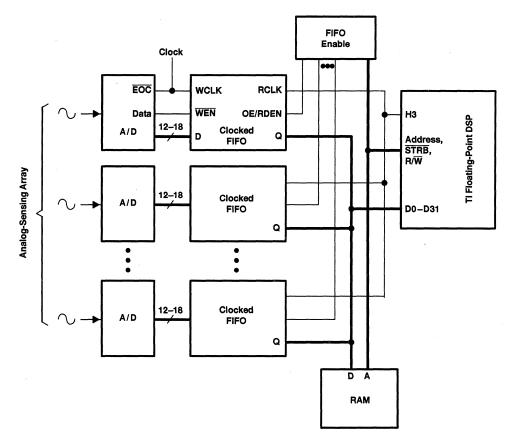

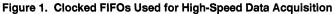

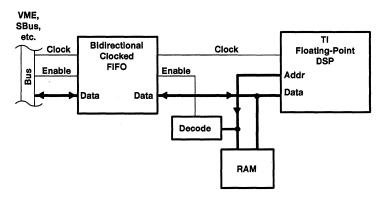

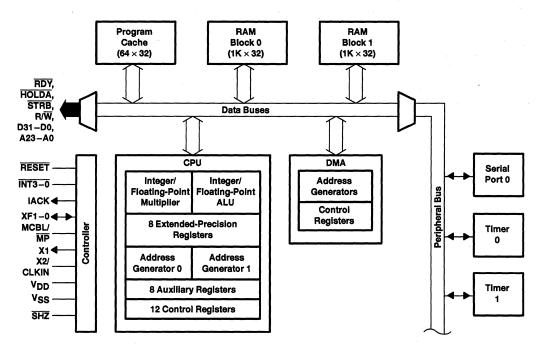

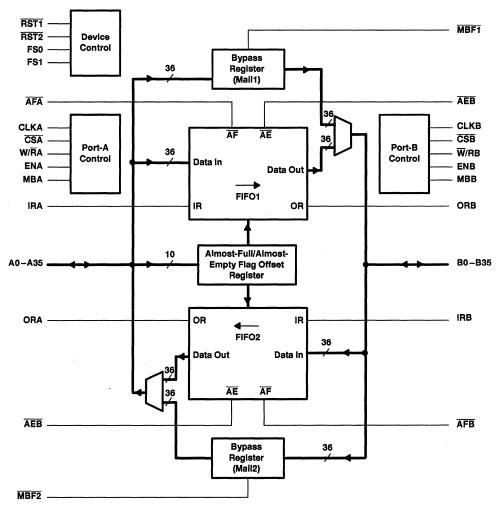

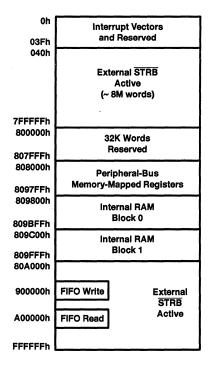

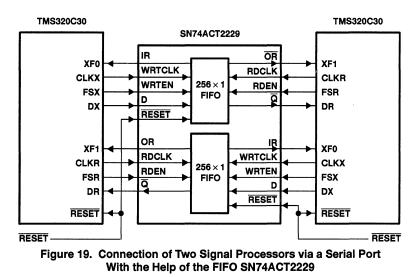

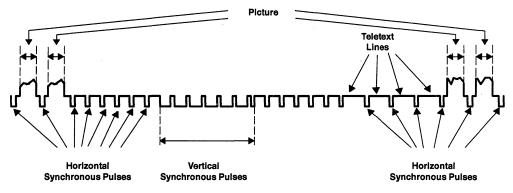

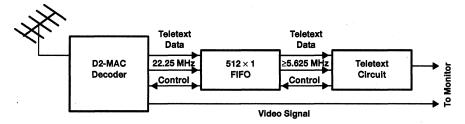

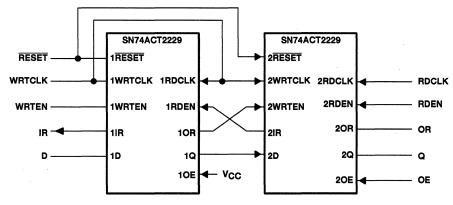

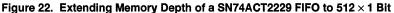

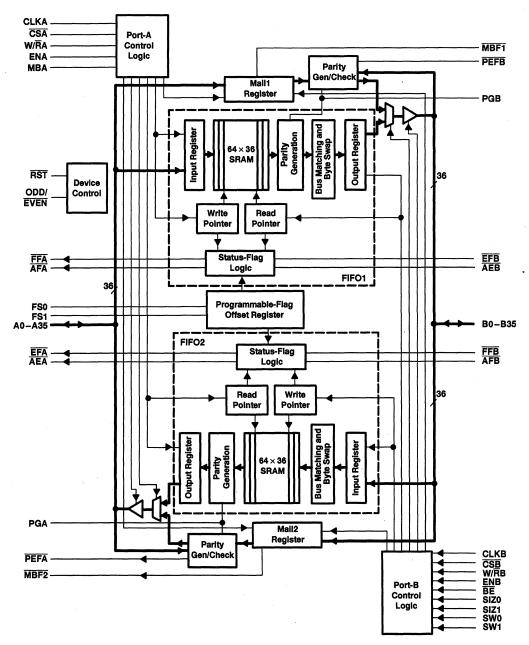

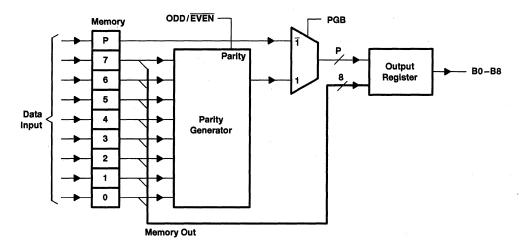

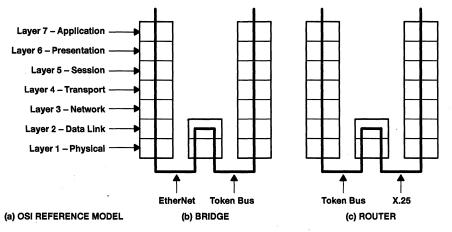

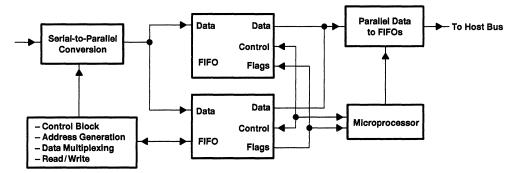

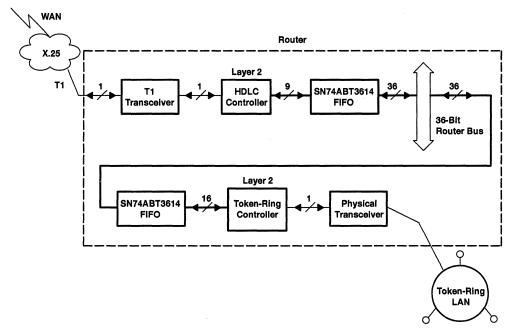

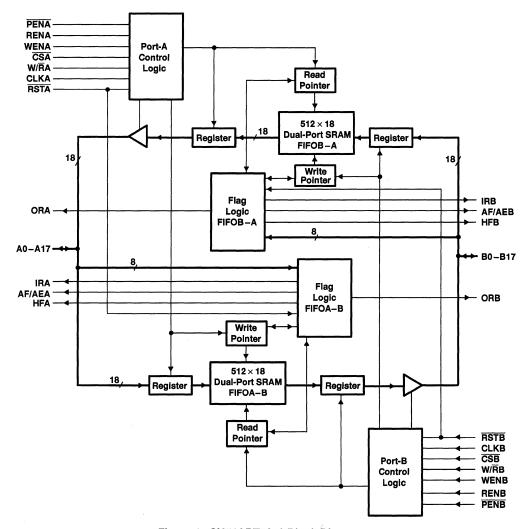

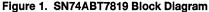

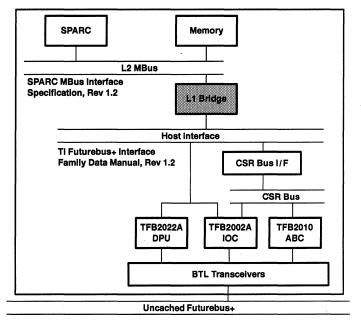

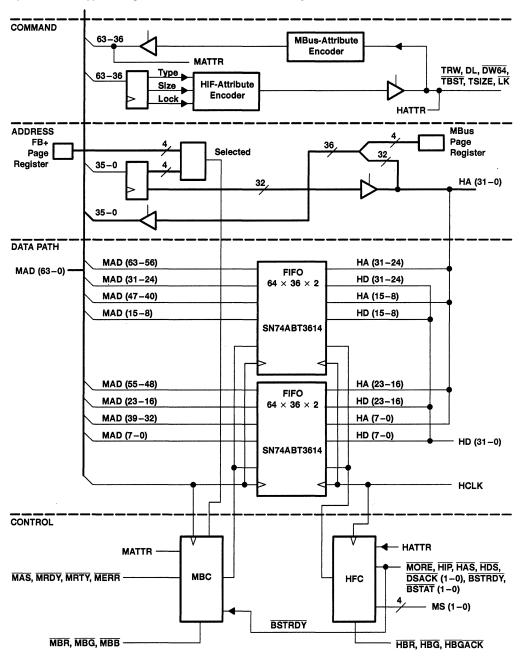

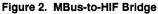

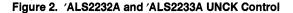

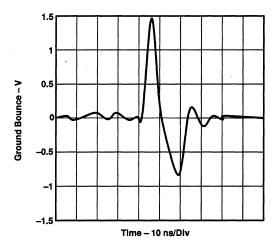

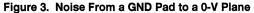

| Metastability Pe<br>FIFO Memories<br>Simultaneous-S<br>FIFO Solutions<br>FIFO Features<br>FIFO Patented<br>for FIR Filter<br>FIFO Mailbox-B<br>Advanced Bus-<br>Parity-Generate<br>for High-Ban<br>FIFO Applications .<br>Multiple-Queue<br>Interfacing TI C<br>FIFOs With a W<br>Internetworking<br>High-Speed, Hig<br>SPARC MBus-ti<br>1K × 9 × 2 As | and Reliability       3-3         aerformance of Clocked FIFOs       3-5         solution to Reduce FIFO Metastability       3-17         Switching Noise Analysis for Texas Instruments FIFO Products       3-23         for Increasing Clock Rates and Data Widths       3-41         Synchronous Retransmit: Programmable DSP-Interface Application         ing       3-53         Sypass Registers: Using Bypass Registers to Initialize DMA Control       3-65         Matching/Byte-Swapping Features for Internetworking FIFO Applications       3-75         a and Parity-Check Features       3-87         dwidth-Computing FIFO Applications       3-97         locked FIFOs With TI Floating-Point Digital Signal Processors       3-121         /ord Width of One Bit       3-141         the SN74ABT3614       3-161         gh-Drive SN74ABT7819 FIFO       3-181         o-Futurebus+ Bridge Using the Texas Instruments Futurebus+ Chipset       3-193         ynchronous FIFOS SN74ACT2235 and SN74ACT2236       3-207         SN74ALS2232A and SN74ALS2233A       3-217 |

| Section 4 – Powe                                                                                                                                                                                                                                                                                                                                       | er Considerations 4–1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Introduction<br>Key Power-Diss                                                                                                                                                                                                                                                                                                                         | 4-3           sipation Equations for ACT FIFOs         4-5           sipation Equations for ABT FIFOs         4-6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Application Report                                                                                                                                                                                                                                                                                                                                     | ion Calculations for TI FIFO Products                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

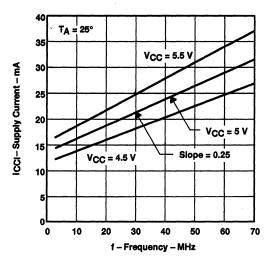

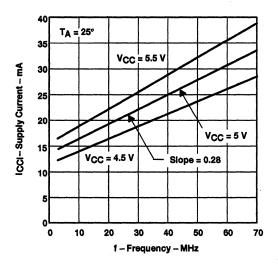

| Sample Power-<br>Power Characte<br>SN74ACT22<br>Versus Cl<br>SN74ACT22                                                                                                                                                                                                                                                                                 | 4-31           Dissipation Calculations for SN74ACT229           4-33           eristics           4-34           26 and SN74ACT2228 Single FIFO Supply Current           lock Frequency           4-34           27 and SN74ACT2229 Single FIFO Supply Current           lock Frequency           4-34           27 and SN74ACT2229 Single FIFO Supply Current           lock Frequency           4-34                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

## Section 4 – Power Considerations (Continued)

| 36-Bit Clocked FIFOs                                                                       |

|--------------------------------------------------------------------------------------------|

| Sample Power-Dissipation Calculations for SN74ABT3613                                      |

| Power Characteristics                                                                      |

| SN74ABT3611 Supply Current Versus Clock Frequency                                          |

| SN74ABT3612 Supply Current Versus Clock Frequency                                          |

| SN74ABT3613 Supply Current Versus Clock Frequency                                          |

| SN74ABT3614 Supply Current Versus Clock Frequency                                          |

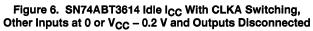

| SN74ABT3614 Idle Current With CLKA Switching, Other Inputs at 0 or V <sub>CC</sub> – 0.2 V |

| and Outputs Disconnected                                                                   |

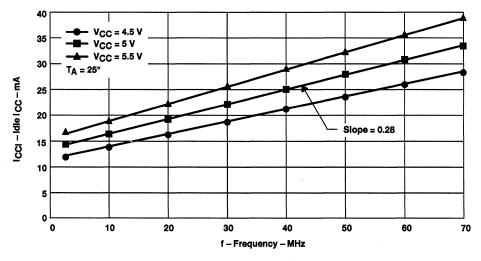

| SN74ABT3614 Idle Current With CLKB Switching, Other Inputs at 0 or $V_{CC}$ – 0.2 V        |

| and Outputs Disconnected                                                                   |

| Sample Power-Dissipation Calculations for SN74ACT3641                                      |

| Power Characteristics                                                                      |

| SN74ACT3632 Supply Current Versus Clock Frequency                                          |

| SN74ACT3638 Supply Current Versus Clock Frequency                                          |

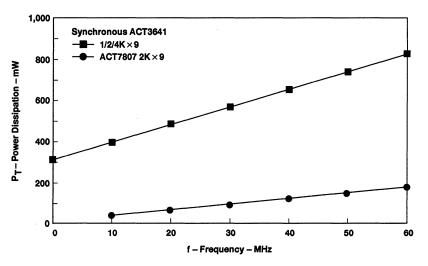

| SN74ACT3631 and SN74ACT3641 Supply Current Versus Clock Frequency                          |

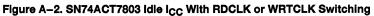

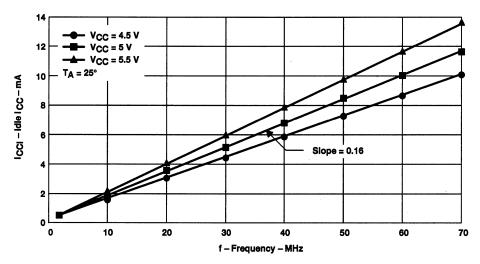

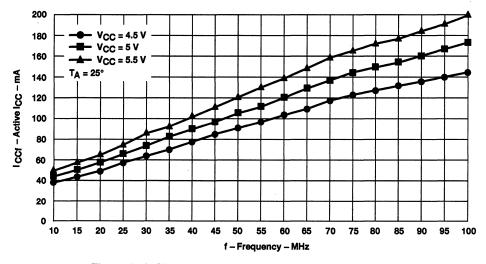

| SN74ACT3641 Idle Current With CLKA Switching                                               |

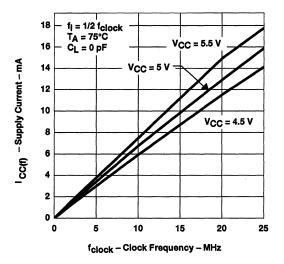

| SN74ACT3641 Idle Current With CLKB Switching                                               |

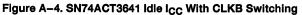

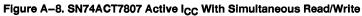

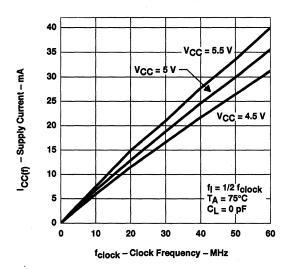

| SN74ACT3641 Active Current With CLKA and CLKB Switching,                                   |

| Simultaneous Read/Write and CLKB as Data Output                                            |

| 18-Bit Clocked/Strobed FIFOs                                                               |

| Sample Power-Dissipation Calculations for SN74ABT7819                                      |

| Power Characteristics                                                                      |

| SN74ABT7819 Supply Current Versus Clock Frequency                                          |

| SN74ABT7820 Supply Current Versus Clock Frequency                                          |

| Sample Power-Dissipation Calculations for SN74ACT7803                                      |

| Power Characteristics                                                                      |

| SN74ACT7804 Supply Current Versus Clock Frequency                                          |

| SN74ACT7806 Supply Current Versus Clock Frequency                                          |

| SN74ACT7814 Supply Current Versus Clock Frequency                                          |

| SN74ACT7803 Supply Current Versus Clock Frequency                                          |

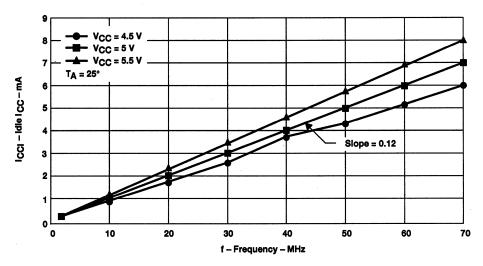

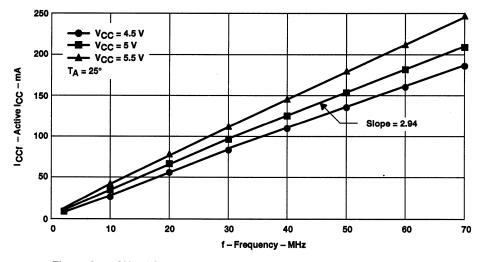

| SN74ACT7803 Idle Current With RDCLK or WRTCLK Switching                                    |

| SN74ACT7805 Supply Current Versus Clock Frequency                                          |

| SN74ACT7813 Supply Current Versus Clock Frequency                                          |

| 9-Bit Clocked/Strobed FIFOs                                                                |

| Sample Power-Dissipation Calculations for SN74ACT7807                                      |

| Power Characteristics                                                                      |

| SN74ACT7807 Supply Current Versus Frequency                                                |

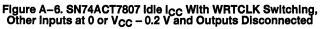

| SN74ACT7807 Idle Current With WRTCLK Switching,                                            |

| Other Inputs at 0 or $V_{CC}$ – 0.2 V and Outputs Disconnected                             |

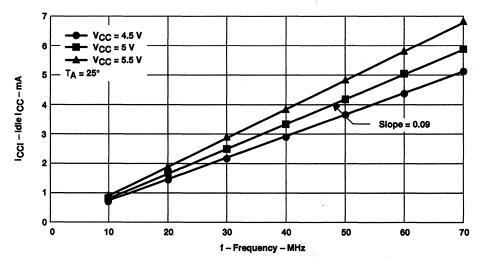

| SN74ACT7807 Idle Current With RDCLK Switching,                                             |

| Other Inputs at 0 or $V_{CC}$ – 0.2 V and Outputs Disconnected                             |

| SN74ACT7808 Supply Current Versus Frequency                                                |

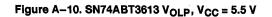

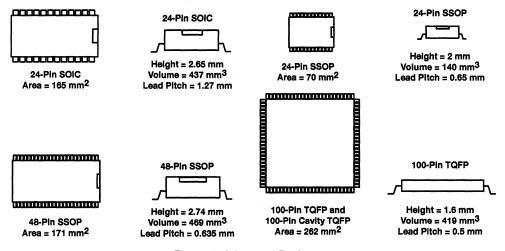

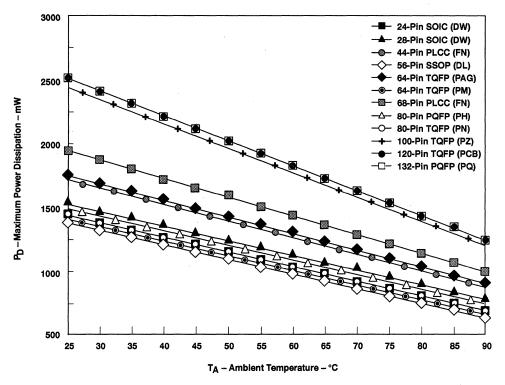

| Section 5 – Mechanical and Thermal Information                                             |

| Comparison Summary of Advanced Packaging Derating Curves (in Still Air)                    |

| Introduction                                                                               |

| Application Reports/Papers                                                                 |

| FIFO Surface-Mount Package Information                                                     |

| FIFO Memories: Fine-Pitch Surface-Mount Manufacturability                                  |

| Package Thermal Considerations                                                             |

| K-Factor Test-Board Design Impact on Thermal-Impedance Measurements                        |

| More Power in Less Space: A Thermal Enhancement Solution for Thin Packages                 |

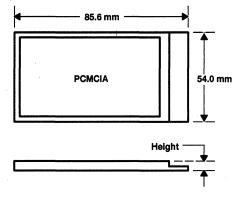

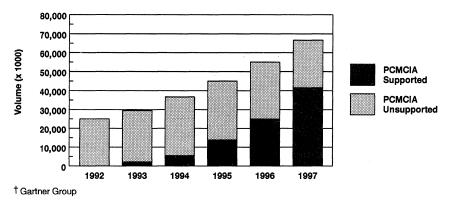

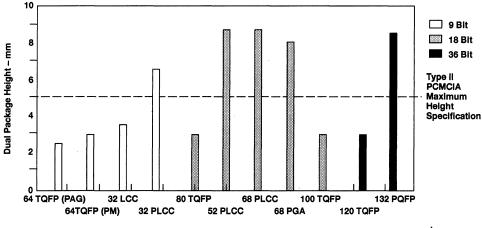

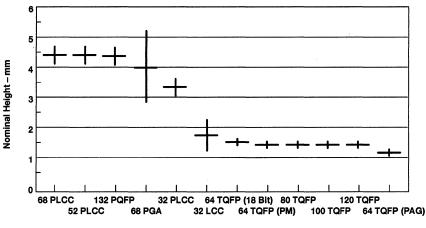

| FIFO Surface-Mount Packages for PCMCIA Applications                                        |

# Section 5 – Mechanical and Thermal Information (Continued)

| Package Outlines and Thermal Data                              |

|----------------------------------------------------------------|

| Introduction                                                   |

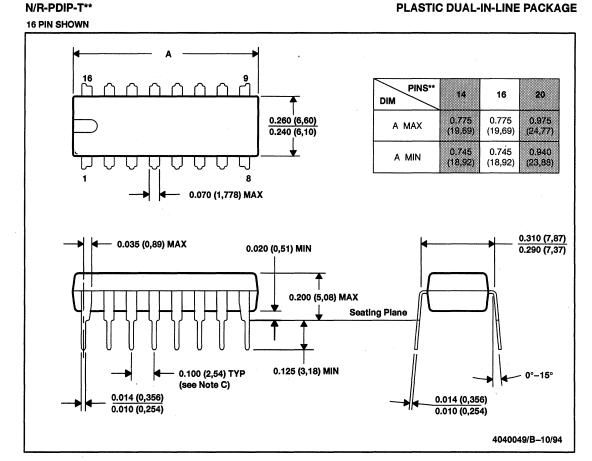

| Plastic Dual-In-Line Package (PDIP)                            |

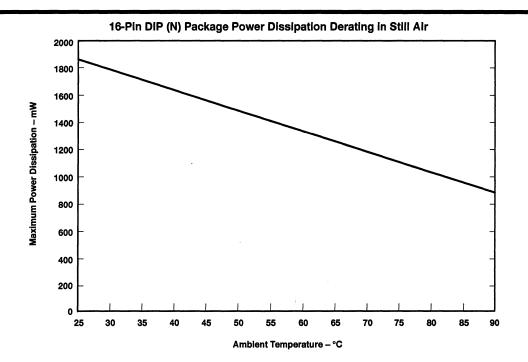

| N/R-PDIP-T16 (16-Pin DIP)                                      |

| N/R-PDIP-T20 (20-Pin DIP)5-86                                  |

| N/R-PDIP-T28 (28-Pin DIP-600 mil)5–88                          |

| N/R-PDIP-T40 (40-Pin DIP)5–90                                  |

| NP/R-PDIP-T28 (28-Pin DIP-300 mil)                             |

| NT/R-PDIP-T24 (24-Pin DIP)5–94                                 |

| Plastic J-Leaded Chip Carrier (PQCC)                           |

| FN/S-PQCC-J20 (20-Pin PLCC)                                    |

| FN/S-PQCC-J28 (28-Pin PLCC)                                    |

| FN/S-PQCC-J44 (44-Pin PLCC)                                    |

| FN/S-PQCC-J68 (68-Pin PLCC)                                    |

| RJ/R-PQCC-J32 (32-Pin PLCC)                                    |

| Plastic Wide-Body Small-Outline Package (PDSO)                 |

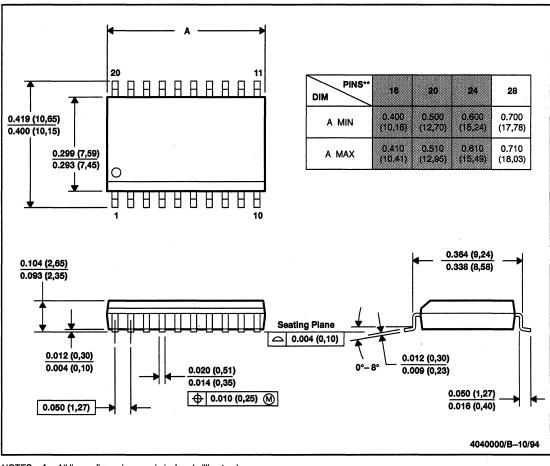

| DW/R-PDSO-G16 (16-Pin SOIC)                                    |

| DW/R-PDSO-G20 (20-Pin SOIC)                                    |

| DW/R-PDSO-G24 (24-Pin SOIC)                                    |

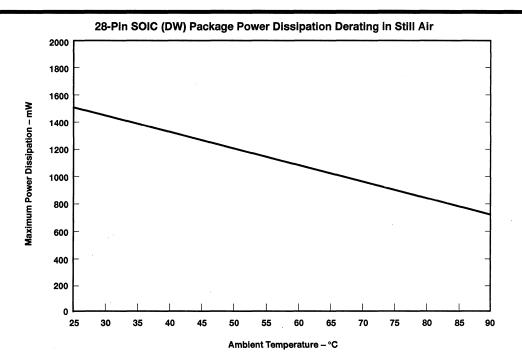

| DW/R-PDSO-G28 (28-Pin SOIC)                                    |

| Plastic Small-Outline Package (PDSO)                           |

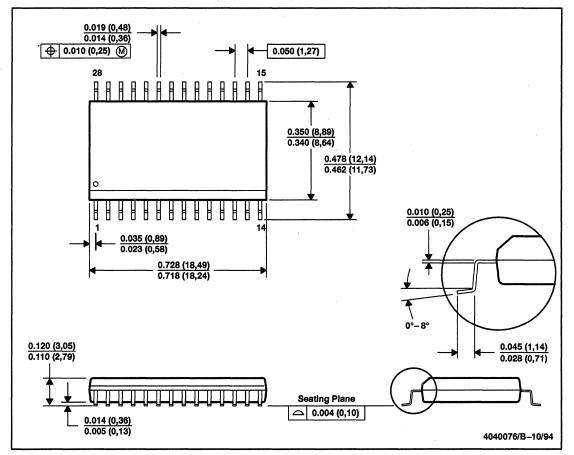

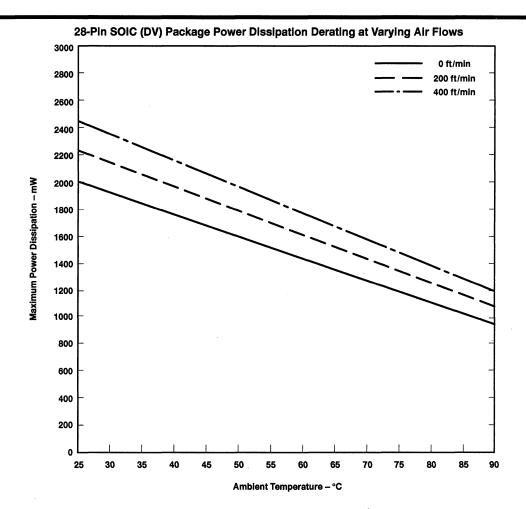

| DV/R-PDSO-G28 (28-Pin SOIC)                                    |

| Plastic Shrink Small-Outline Package (PDSO)                    |

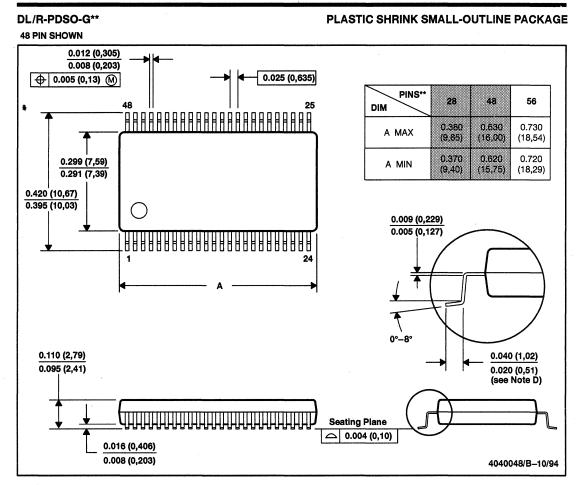

| DL/R-PDSO-G56 (56-Pin SSOP)                                    |

| Plastic Quad Flatpack (PQFP)                                   |

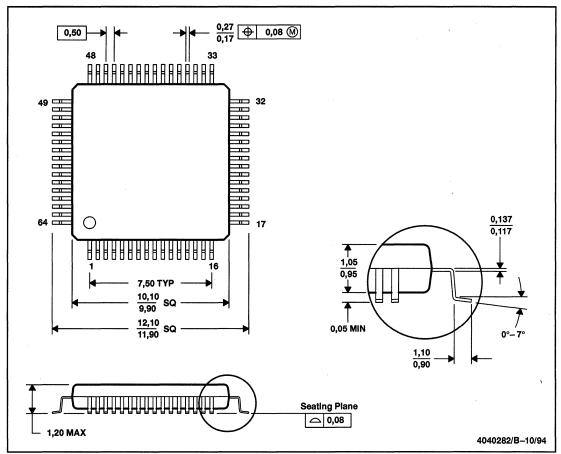

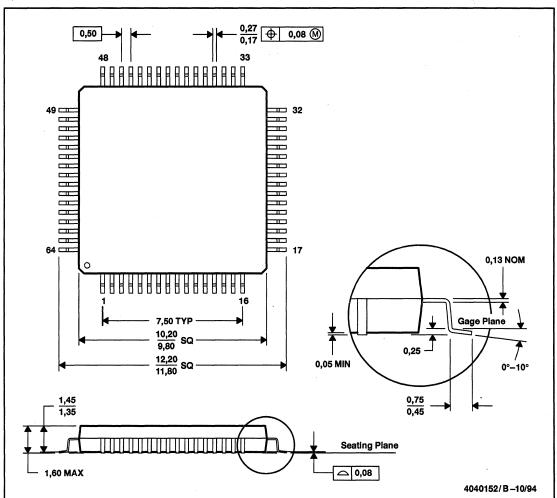

| PAG/S-PQFP-G64 (64-Pin TQFP)                                   |

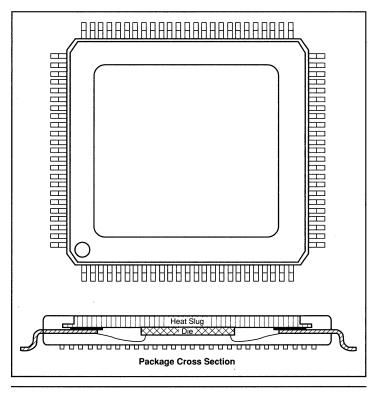

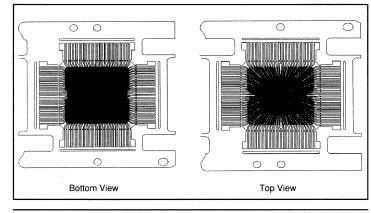

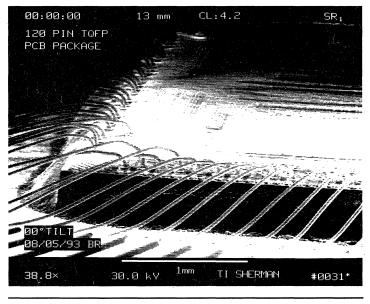

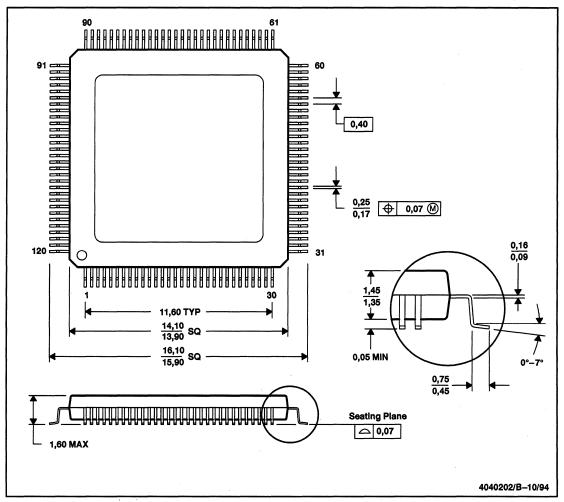

| PCB/S-PQFP-G120 (120-Pin TQFP)                                 |

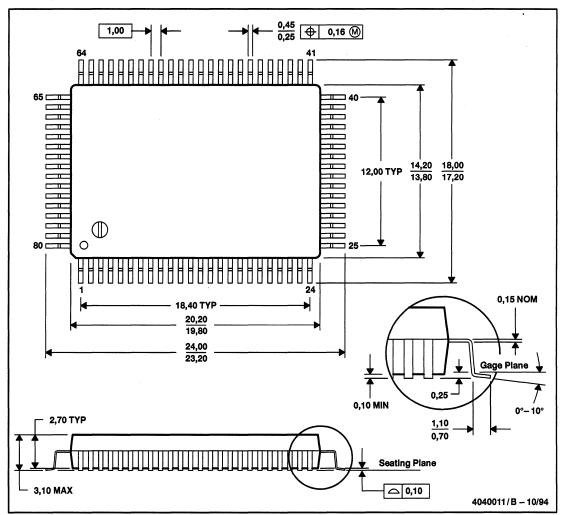

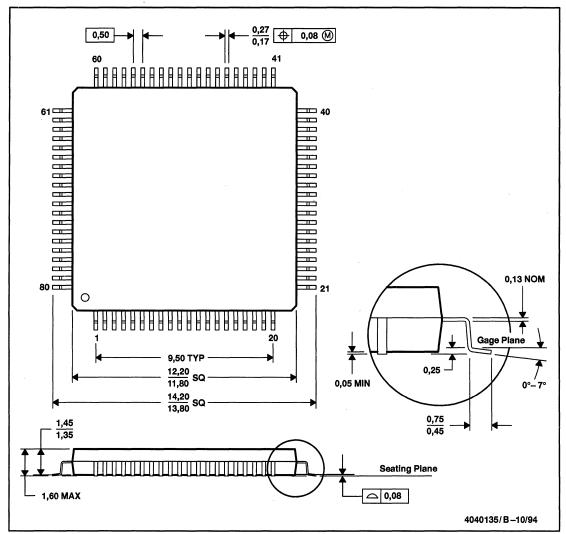

| PH/R-PQFP-G80 (80-Pin TQFP)                                    |

| PM/S-PQFP-G64 (64-Pin TQFP)                                    |

| PN/S-PQFP-G80 (80-Pin TQFP)                                    |

| PQ/S-PQFP-G132 (132-Pin TQFP)                                  |

| PZ/S-PQFP-G100 (100-Pin TQFP)                                  |

|                                                                |

| Section 6 – Device Models                                      |

| VHDL Models                                                    |

| Logic-Modeling Behavioral Models                               |

| Section 7 – Quality and Reliability Assurance                  |

|                                                                |

| Qualification of Products and Processes                        |

| Introduction                                                   |

| Quality and Reliability Assurance in Integrated-Circuit Design |

| General Quality and Reliability Rules                          |

| Process-Specific Design Rules                                  |

| Methodology-Oriented Design Rules                              |

| Change Control                                                 |

| Giungo Control                                                 |

ix

#

| Quality and Reliability Monitoring          |  |

|---------------------------------------------|--|

| Environmental Laboratory                    |  |

| Methods of Measuring Component Reliability  |  |

| Failure-Rate Calculations for FIFO Products |  |

| Qualification Data for FIFO Products        |  |

| Life-Test and ESD-Characterization Data     |  |

х

| General Information                | 1 |

|------------------------------------|---|

| Product Overview                   | 2 |

| Specific Application Reports       | 3 |

| Power Considerations               | 4 |

| Mechanical and Thermal Information | 5 |

| Device Models                      | 6 |

| Quality and Reliability Assurance  | 7 |

Í–2

#### INTRODUCTION

These symbols, terms, and definitions are in accordance with those currently agreed upon by the JEDEC Council of the Electronic Industries Association (EIA) for use in the USA and by the International Electrotechnical Commission (IEC) for international use.

#### operating conditions and characteristics (in sequence by letter symbols)

| Input capacitance<br>The internal capacitance at an input of the device                                                                                                                                                                                                                              |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Output capacitance<br>The internal capacitance at an output of the device                                                                                                                                                                                                                            |

| Power dissipation capacitance                                                                                                                                                                                                                                                                        |

| Used to determine the no-load dynamic power dissipation per logic function (see individual circuit pages):<br>$P_D = C_{pd} V_{CC}^2 f + I_{CC} V_{CC}$ .                                                                                                                                            |

| Maximum clock frequency                                                                                                                                                                                                                                                                              |

| The highest rate at which the clock input of a bistable circuit can be driven through its required sequence while maintaining stable transitions of logic level at the output with input conditions established that should cause changes of output logic level in accordance with the specification |

| Supply current                                                                                                                                                                                                                                                                                       |

| The current into* the V <sub>CC</sub> supply terminal of an integrated circuit                                                                                                                                                                                                                       |

| Supply current change                                                                                                                                                                                                                                                                                |

| The increase in supply current for each input that is at one of the specified TTL voltage levels rather than 0 or $V_{CC}$                                                                                                                                                                           |

| Output high-leakage current                                                                                                                                                                                                                                                                          |

| The maximum leakage current into the collector of the pulldown-output transistor when the output is high and the output forcing condition $V_0 = 5.5 \text{ V}$                                                                                                                                      |

| Input-hold current                                                                                                                                                                                                                                                                                   |

| Input current that holds the input at the previous state when the driving device goes to a high-impedance state                                                                                                                                                                                      |

| High-level input current                                                                                                                                                                                                                                                                             |

| The current into* an input when a high-level voltage is applied to that input                                                                                                                                                                                                                        |

| Low-level input current                                                                                                                                                                                                                                                                              |

| The current into* an input when a low-level voltage is applied to that input                                                                                                                                                                                                                         |

| Input/output power-off leakage current                                                                                                                                                                                                                                                               |

| The maximum leakage current into/out of the input/output transistors when forcing the input/output to 4.5 V and $V_{CC} = 0$                                                                                                                                                                         |

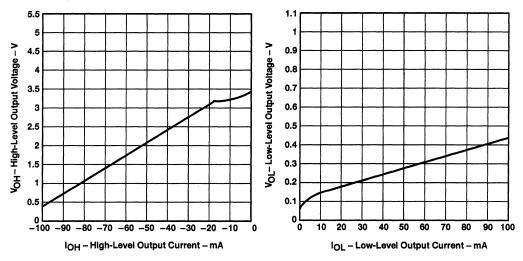

| High-level output current                                                                                                                                                                                                                                                                            |

| The current into* an output with input conditions applied that, according to the product specification, establishes a high level at the output                                                                                                                                                       |

| Low-level output current                                                                                                                                                                                                                                                                             |

| The current into* an output with input conditions applied that, according to the product specification, establishes a low level at the output                                                                                                                                                        |

|                                                                                                                                                                                                                                                                                                      |

\*Current out of a terminal is given as a negative value.

# GLOSSARY SYMBOLS, TERMS, AND DEFINITIONS

| loz              | Off-state (high-impedance-state) output current (of a 3-state output)                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

|                  |                                                                                                                                                                                                                       | rent flowing into* an output having 3-state capability with input conditions established that, ig to the product specification, establishes the high-impedance state at the output                                                                                                                                             |  |  |  |

| $R_{\Theta JA}$  | Junctio                                                                                                                                                                                                               | n-to-ambient thermal resistance                                                                                                                                                                                                                                                                                                |  |  |  |

|                  | The ther                                                                                                                                                                                                              | mal resistance from the semiconductor junction(s) to the ambient                                                                                                                                                                                                                                                               |  |  |  |

| $R_{\Theta JC}$  | Junctio                                                                                                                                                                                                               | n-to-case thermal resistance                                                                                                                                                                                                                                                                                                   |  |  |  |

|                  | The ther                                                                                                                                                                                                              | mal resistance from the semiconductor junction(s) to a stated location on the case                                                                                                                                                                                                                                             |  |  |  |

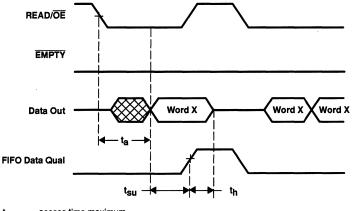

| ta               | Access                                                                                                                                                                                                                | time                                                                                                                                                                                                                                                                                                                           |  |  |  |

|                  | The time<br>at an out                                                                                                                                                                                                 | interval between the application of a specified input pulse and the availability of valid signals tput                                                                                                                                                                                                                         |  |  |  |

| t <sub>c</sub>   | Clock c                                                                                                                                                                                                               | ycle time                                                                                                                                                                                                                                                                                                                      |  |  |  |

|                  | Clock cy                                                                                                                                                                                                              | cle time is 1/f <sub>max</sub> .                                                                                                                                                                                                                                                                                               |  |  |  |

| t <sub>dis</sub> | Disable                                                                                                                                                                                                               | time (of a 3-state or open-collector output)                                                                                                                                                                                                                                                                                   |  |  |  |

|                  |                                                                                                                                                                                                                       | pagation time between the specified reference points on the input and output voltage waveforms<br>output changing from either of the defined active levels (high or low) to a high-impedance (off)                                                                                                                             |  |  |  |

|                  | NOTE:                                                                                                                                                                                                                 | For 3-state outputs, $t_{dis} = t_{PHZ}$ or $t_{PLZ}$ . Open-collector outputs change only if they are low at the time of disabling, so $t_{dis} = t_{PLH}$ .                                                                                                                                                                  |  |  |  |

| t <sub>en</sub>  | Enable                                                                                                                                                                                                                | time (of a 3-state or open-collector output)                                                                                                                                                                                                                                                                                   |  |  |  |

|                  | The propagation time between the specified reference points on the input and output voltage waveforms with the output changing from a high-impedance (off) state to either of the defined active levels (high or low) |                                                                                                                                                                                                                                                                                                                                |  |  |  |

|                  | NOTE:                                                                                                                                                                                                                 | In the case of memories, this is the access time from an enable input (e.g., $\overline{OE}$ ). For 3-state outputs, t <sub>en</sub> = t <sub>PZH</sub> or t <sub>PZL</sub> . Open-collector outputs change only if they are responding to data that would cause the output to go low, so t <sub>en</sub> = t <sub>PHL</sub> . |  |  |  |

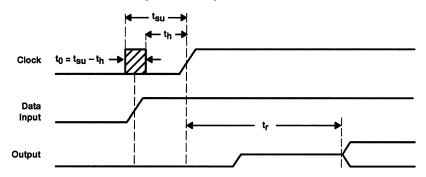

| th               | Hold tim                                                                                                                                                                                                              | 10                                                                                                                                                                                                                                                                                                                             |  |  |  |

|                  |                                                                                                                                                                                                                       | interval during which a signal is retained at a specified input terminal after an active transition t another specified input terminal                                                                                                                                                                                         |  |  |  |

|                  | NOTES:                                                                                                                                                                                                                | 1. The hold time is the actual time interval between two signal events and is determined by the system in which the digital circuit operates. A minimum value is specified that is the shortest interval for which correct operation of the digital circuit is to be expected.                                                 |  |  |  |

|                  |                                                                                                                                                                                                                       | 2. The hold time may have a negative value, in which case, the minimum limit defines the longest interval (between the release of the signal and the active transition) for which correct operation of the digital circuit is to be expected.                                                                                  |  |  |  |

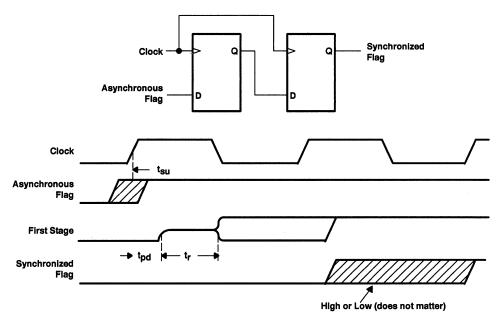

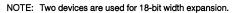

| t <sub>pd</sub>  | Propaga                                                                                                                                                                                                               | ation delay time                                                                                                                                                                                                                                                                                                               |  |  |  |

| •                | The time<br>output cl                                                                                                                                                                                                 | between the specified reference points on the input and output voltage waveforms with the hanging from one defined level (high or low) to the other defined level ( $t_{pd} = t_{PHL}$ or $t_{PLH}$ )                                                                                                                          |  |  |  |

| t <sub>PHL</sub> | Propaga                                                                                                                                                                                                               | ation delay time, high-to-low level output                                                                                                                                                                                                                                                                                     |  |  |  |

|                  |                                                                                                                                                                                                                       | be between the specified reference points on the input and output voltage waveforms with the hanging from the defined high level to the defined low level                                                                                                                                                                      |  |  |  |

| t <sub>PHZ</sub> | Disable                                                                                                                                                                                                               | time (of a 3-state output) from high level                                                                                                                                                                                                                                                                                     |  |  |  |

|                  |                                                                                                                                                                                                                       | interval between the specified reference points on the input and the output voltage waveforms 3-state output changing from the defined high level to the high-impedance (off) state                                                                                                                                            |  |  |  |

| •••              |                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                |  |  |  |

\*Current out of a terminal is given as a negative value.

#### tPLH Propagation delay time, low-to-high level output

The time between the specified reference points on the input and output voltage waveforms with the output changing from the defined low level to the defined high level

#### tpLZ Disable time (of a 3-state output) from low level

The time interval between the specified reference points on the input and the output voltage waveforms with the 3-state output changing from the defined low level to the high-impedance (off) state

#### t<sub>PZH</sub> Enable time (of a 3-state output) to high level

The time interval between the specified reference points on the input and output voltage waveforms with the 3-state output changing from the high-impedance (off) state to the defined high level

#### tpzL Enable time (of a 3-state output) to low level

The time interval between the specified reference points on the input and output voltage waveforms with the 3-state output changing from the high-impedance (off) state to the defined low level

#### t<sub>su</sub> Setup time

The time interval between the application of a signal at a specified input terminal and a subsequent active transition at another specified input terminal

NOTES: 1. The setup time is the actual time interval between two signal events and is determined by the system in which the digital circuit operates. A minimum value is specified that is the shortest interval for which correct operation of the digital circuit is to be expected.

2. The setup time may have a negative value, in which case, the minimum limit defines the longest interval (between the active transition and the application of the other signal) for which correct operation of the digital circuit is to be expected.

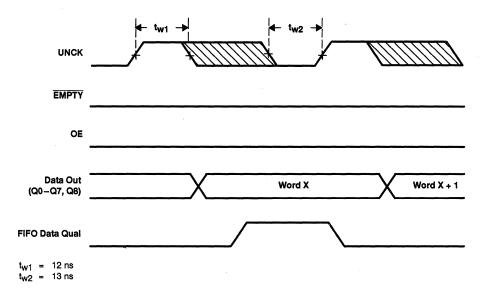

#### tw Pulse duration (width)

The time interval between specified reference points on the leading and trailing edges of the pulse waveform

#### VIH High-level input voltage

An input voltage within the more positive (less negative) of the two ranges of values used to represent the binary variables

NOTE: A minimum is specified that is the least-positive value of high-level input voltage for which operation of the logic element within specification limits is to be expected.

#### VIL Low-level input voltage

An input voltage within the less positive (more negative) of the two ranges of values used to represent the binary variables

NOTE: A maximum is specified that is the most-positive value of low-level input voltage for which operation of the logic element within specification limits is to be expected.

#### V<sub>OH</sub> High-level output voltage

The voltage at an output terminal with input conditions applied that, according to product specification, establishes a high level at the output

#### V<sub>OL</sub> Low-level output voltage

The voltage at an output terminal with input conditions applied that, according to product specification, establishes a low level at the output

#### V<sub>IT+</sub> Positive-going input threshold level

The voltage level at a transition-operated input that causes operation of the logic element, according to specification, as the input voltage rises from a level below the negative-going threshold voltage,  $V_{IT-}$

## GLOSSARY SYMBOLS, TERMS, AND DEFINITIONS

#### V<sub>IT</sub>... Negative-going input threshold level

The voltage level at a transition-operated input that causes operation of the logic element, according to specification, as the input voltage falls from a level above the positive-going threshold voltage, V<sub>IT+</sub>

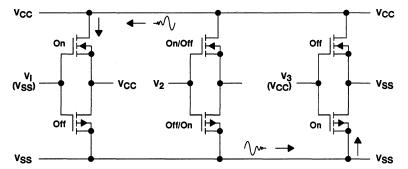

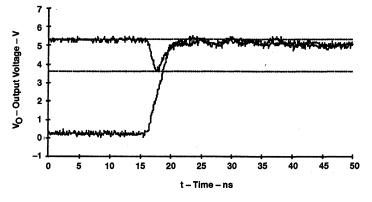

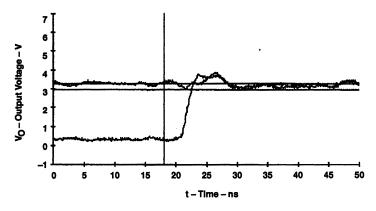

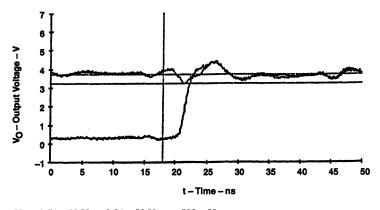

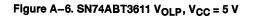

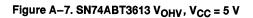

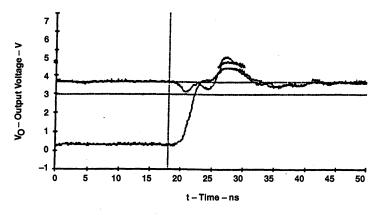

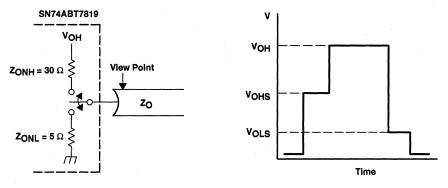

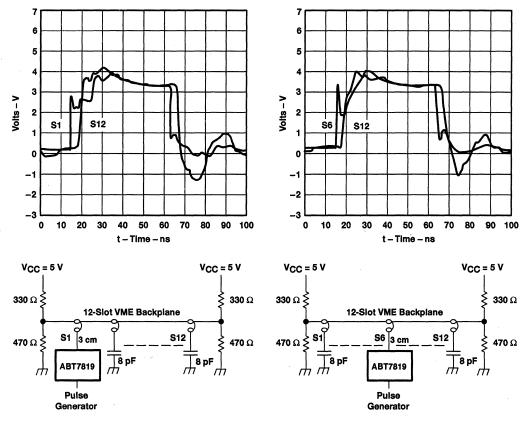

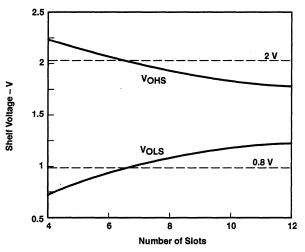

VOHV

High-level output voltage change during simultaneous switching

The minimum (valley) voltage induced on a quiescent high-level output during switching of other outputs

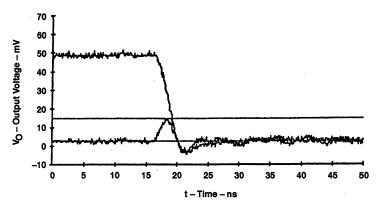

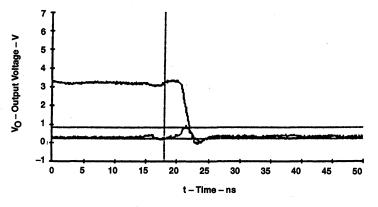

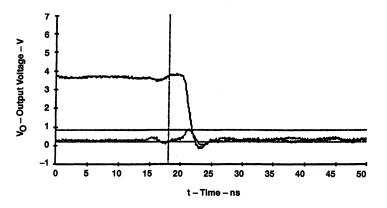

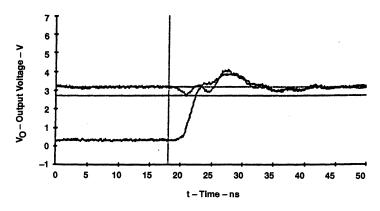

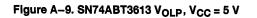

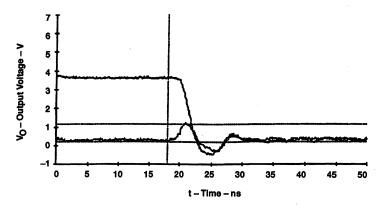

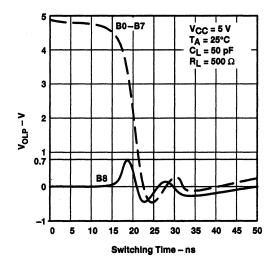

VOLP

Low-level output voltage change during simultaneous switching

The maximum (peak) voltage induced on a quiescent low-level output during switching of other outputs

#### definitions

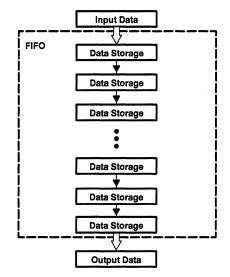

#### asynchronous FIFO

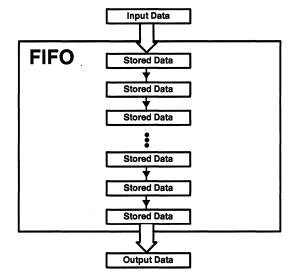

Data writes are initiated by a low-level pulse on the write-enable input when the full flag is not asserted. Likewise, data reads are initiated by a low-level pulse on the read-enable input when the empty flag is not asserted. The empty and full flags are not synchronized to a particular clock and reflect the instantaneous comparison of the read and write pointers.

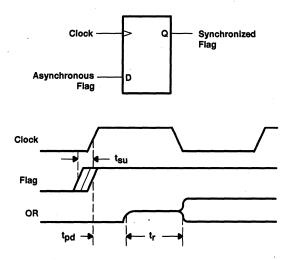

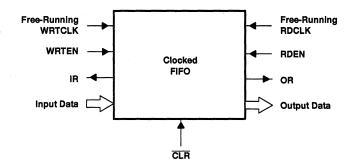

#### clocked FIFO

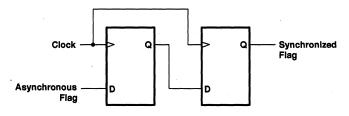

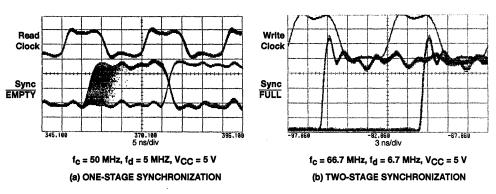

Data is written by a low-to-high transition of a write clock when write-enable inputs are asserted and the input-ready flag is not asserted. Likewise, data is read by a low-to-high transition of a read clock when read-enable inputs are asserted and the output-ready flag is asserted. The input-ready flag is multistaged synchronized to the write clock and the output-ready flag is multistaged synchronized to the read clock, improving metastability.

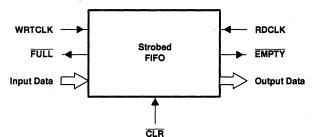

#### strobed FIFO

Data is written on a low-to-high transition on the load-clock input when the full flag is not asserted. Likewise, data is read on a low-to-high transition on the unload-clock input when the empty-flag is not asserted. The empty and full flags are not synchronized to a particular clock and reflect the instantaneous comparison of the read and write pointers.

#### synchronous FIFO

The term synchronous refers to a port-control method and does not imply that data writes and reads must be synchronous to one another. Data is written by a low-to-high transition of a write clock when write-enable inputs are asserted and the full flag is not asserted. Likewise, data is read by a low-to-high transition of a read clock when read-enable inputs are asserted and the empty flag is not asserted. The empty flag is single-staged synchronized to the read clock and the full flag is single-staged synchronized to the write clock.

| General Information                | 1 |

|------------------------------------|---|

| Product Overview                   | 2 |

| Specific Application Reports       | 3 |

| Power Considerations               | 4 |

| Mechanical and Thermal Information | 5 |

| Device Models                      | 6 |

| Quality and Reliability Assurance  | 7 |

**2** Product Overview

2–2

# FIFO Product Offerings

# Page

| Advanced Clocked FIFOs                      | 2-5 |

|---------------------------------------------|-----|

| Advanced Strobed FIFOs                      | 2-5 |

| Advanced Application-Specific Clocked FIFOs | 2-6 |

| Advanced Application-Specific FIFO Features | 2-6 |

| Synchronous Mature FIFOs                    | 2-6 |

| Asynchronous Mature FIFOs                   | 2–7 |

| FIFO Functionality                          | 2-8 |

. . .

2--4

## **FIFO PRODUCT OFFERINGS**

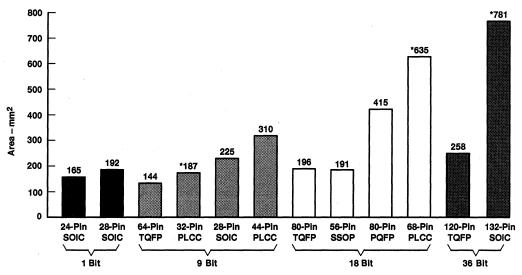

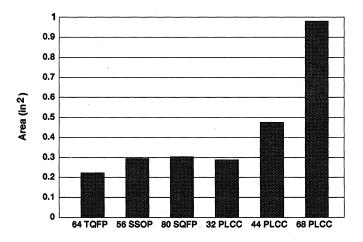

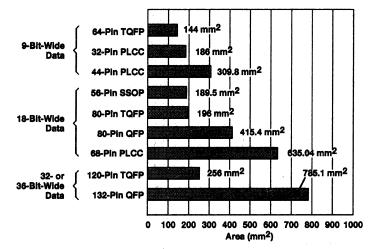

| DEVICE                                       | ORGANIZATION                    | SPEED SORT<br>t <sub>C</sub> (ns) | MAXIMUM<br>FREQUENCY<br>(MHz) | ACCESS<br>TIME (ns) | IOH/IOL<br>(mA) | PACKAGE                                  | PITCH<br>(mm) | AREA<br>(mm <sup>2</sup> ) |

|----------------------------------------------|---------------------------------|-----------------------------------|-------------------------------|---------------------|-----------------|------------------------------------------|---------------|----------------------------|

| SN74ACT7884<br>SN74ACT7882<br>SN74ACT7881    | 4K × 18<br>2K × 18<br>1K × 18   | -15, -20,-30                      | 67, 50, 33                    | 11, 13, 18          | 8/16            | 80-pin TQFP (PN)<br>68-pin PLCC (FN)     | 0.5<br>1.27   | 196<br>310                 |

| SN74ACT7811                                  | 1K × 18                         | -15, -18, -20,<br>-25             | 40, 35, 29, 17                | 15, 18,<br>20, 25   | 8/16            | 80-pin TQFP (PN)<br>68-pin PLCC (FN)     | 0.5<br>1.27   | 196<br>310                 |

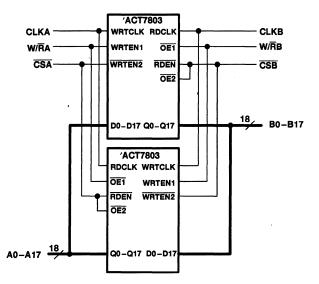

| SN74ACT7803<br>SN74ACT7805<br>SN74ACT7813    | 512 × 18<br>256 × 18<br>64 × 18 | -15, -20, -25,<br>-40             | 67, 50, 40, 30                | 12, 13,<br>15, 20   | 8/16            | 56-pin SSOP (DL)                         | 0.635         | 191                        |

| SN74ACT7807                                  | 2K × 9                          | -15, -20, -25,<br>-40             | 67, 50, 40, 25                | 12, 13,<br>18, 25   | 8/16            | 64-pin TQFP (PM/PAG)<br>44-pin PLCC (FN) | 0.5<br>1.27   | 144<br>310                 |

| SN74ABT7819                                  | 512 × 18 × 2                    | -12, -15, -20,<br>-30             | 80, 67, 50, 33                | 9, 10, 12,<br>14    | 12/24           | 80-pin TQFP (PN)<br>80-pin PQFP (PH)     | 0.5<br>0.8    | 196<br>432                 |

| SN74ALVC7803<br>SN74ALVC7805<br>SN74ALVC7813 | 512 × 18<br>256 × 18<br>64 × 18 | -20, -25,-40                      | 25, 40, 50                    | 13, 15, 20          | 8/16            | 56-pin SSOP (DL)                         | 0.635         | 191                        |

#### Advanced Clocked FIFOs

#### **Advanced Strobed FIFOs**

| DEVICE                                       | ORGANIZATION                    | SPEED SORT<br>t <sub>C</sub> (ns) | MAXIMUM<br>FREQUENCY<br>(MHz) | ACCESS<br>TIME (ns) | IOH/IOL<br>(mA) | PACKAGE                                  | PITCH<br>(mm) | AREA<br>(mm <sup>2</sup> ) |

|----------------------------------------------|---------------------------------|-----------------------------------|-------------------------------|---------------------|-----------------|------------------------------------------|---------------|----------------------------|

| SN74ACT7802                                  | 1K × 18                         | -25, -40, -60                     | 40, 25, 17                    | 30, 35, 45          | 8/16            | 80-pin TQFP (PN)<br>68-pin PLCC (FN)     | 0.5<br>1.27   | 196<br>635                 |

| SN74ACT2235<br>SN74ACT2236                   | 1K × 9 × 2                      | -20, -30, -40,<br>-60             | 50, 33, 25, 17                | 25, 25,<br>35, 45   | 8/16            | 64-pin TQFP (PM/PAG)<br>44-pin PLCC (FN) | 0.5<br>1.27   | 144<br>310                 |

| SN74ACT7804<br>SN74ACT7806<br>SN74ACT7814    | 512 × 18<br>256 × 18<br>64 × 18 | -20, -25, -40                     | 50, 40, 25                    | 15, 18, 20          | 8/16            | 56-pin SSOP (DL)                         | 0.635         | 191                        |

| SN74ACT7808                                  | <sup>.</sup> 2K × 9             | -20, -25, -30,<br>-40             | 50, 40, 33, 25                | 15, 18,<br>20, 22   | 8/16            | 64-pin TQFP (PM/PAG)<br>44-pin PLCC (FN) | 0.5<br>1.27   | 196<br>635                 |

| SN74ABT7820                                  | 512 × 18 × 2                    | -15, -20, -25,<br>-40             | 67, 50, 40, 33                | 12, 14,<br>15, 17   | 12/24           | 80-pin TQFP (PN)<br>80-pin PQFP (PH)     | 0.5<br>0.8    | 196<br>432                 |

| SN74ALVC7804<br>SN74ALVC7806<br>SN74ALVC7814 | 512 × 18<br>256 × 18<br>64 × 18 | -20, -25,-40                      | 25, 40, 50                    | 13, 15, 20          | 8/16            | 56-pin SSOP (DL)                         | 0.635         | 191                        |

## FIFO PRODUCT OFFERINGS

| DEVICE                                    | ORGANIZATION                                                                                             | SPEED SORT<br>t <sub>c</sub> (ns) | MAXIMUM<br>FREQUENCY<br>(MHz) | ACCESS<br>TIME (ns) | IOH/IOL<br>(mA) | PACKAGE                                 | PITCH<br>(mm) | AREA<br>(mm <sup>2</sup> ) |

|-------------------------------------------|----------------------------------------------------------------------------------------------------------|-----------------------------------|-------------------------------|---------------------|-----------------|-----------------------------------------|---------------|----------------------------|

| SN74ACT2226<br>SN74ACT2228                | 64 × 1<br>256 × 1                                                                                        |                                   | 22                            | 20                  | 8/16            | 24-pin SOIC (DW)                        | 1.27          | 165                        |

| SN74ACT2227<br>SN74ACT2229                | 64 × 1<br>256 × 1                                                                                        |                                   | 60                            | 9                   | 8/16            | 28-pin SOIC (DW)                        | 1.27          | 192                        |

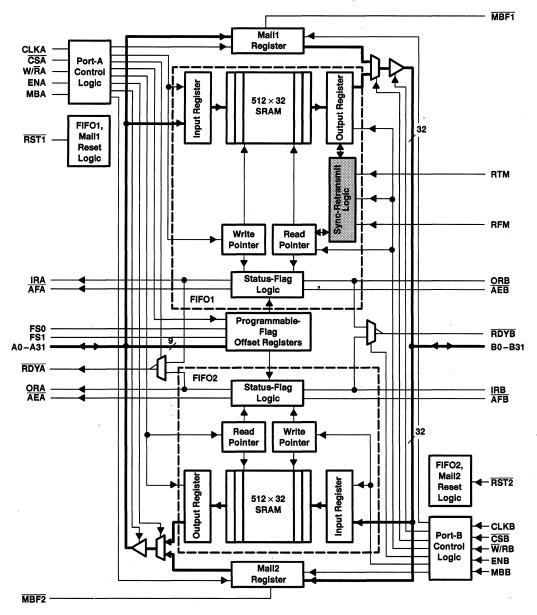

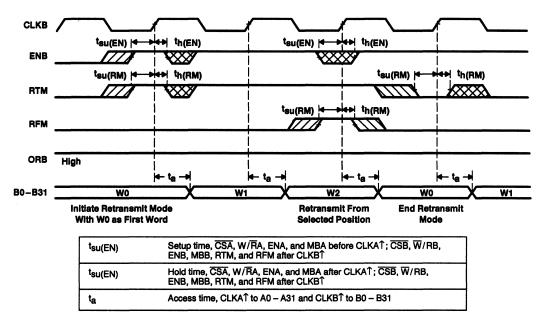

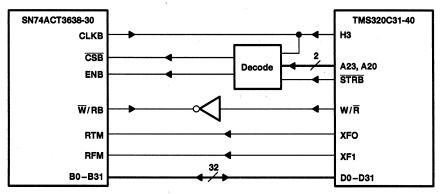

| SN74ACT3638                               | 512 × 32 × 2                                                                                             | -15, -20, -30                     | 67, 50, 33                    | 11, 13, 15          | 4/8             | 120-pin TQFP (PCB)<br>132-pin PQFP (PQ) | 0.4<br>0.635  | 256<br>781                 |

| SN74ACT3622<br>SN74ACT3632<br>SN74ACT3642 | $\begin{array}{c} 256 \times 36 \times 2 \\ 512 \times 36 \times 2 \\ 1K \times 36 \times 2 \end{array}$ | -15, -20, -30                     | 67, 50, 33                    | 11, 13, 15          | 4/8             | 120-pin TQFP (PCB)<br>132-pin PQFP (PQ) | 0.4<br>0.635  | 256<br>781                 |

| SN74ACT3631<br>SN74ACT3641<br>SN74ACT3651 | 512 × 36<br>1K × 36<br>2K × 36                                                                           | -15, -20, -30                     | 67, 50, 33                    | 11, 13, 15          | 4/8             | 120-pin TQFP (PCB)<br>132-pin PQFP (PQ) | 0.4<br>0.635  | 256<br>781                 |

| SN74ABT3611<br>SN74ABT3613                | 64 × 36<br>64 × 36                                                                                       | -15, -20, -30                     | 67, 50, 33                    | 10, 12, 15          | 4/8             | 120-pin TQFP (PCB)<br>132-pin PQFP (PQ) | 0.4<br>0.635  | 256<br>781                 |

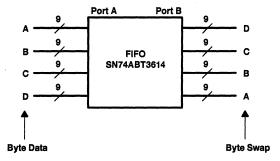

| SN74ABT3612<br>SN74ABT3614                | $\begin{array}{c} 64 \times 36 \times 2 \\ 64 \times 36 \times 2 \end{array}$                            | -15, -20, -30                     | 67, 50, 33                    | 10, 12, 15          | 4/8             | 120-pin TQFP (PCB)<br>132-pin PQFP (PQ) | 0.4<br>0.635  | 256<br>781                 |

#### Advanced Application-Specific Clocked FIFOs

## Advanced Application-Specific FIFO Features

| TELECOMMUNIC                                             | TELECOMMUNICATIONS FIFOs                                                                                                                                           |  |  |  |  |  |  |  |  |  |

|----------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|--|

| SN74ACT2226<br>SN74ACT2228<br>SN74ACT2227<br>SN74ACT2229 | Dual independent FIFO with separate output enables, separate I /O, separate resets, characterized to industrial temperature specification: $-40^{\circ}$ C to 85°C |  |  |  |  |  |  |  |  |  |

| DIGITAL-SIGNAL-PROCESSING FIFOs                          |                                                                                                                                                                    |  |  |  |  |  |  |  |  |  |

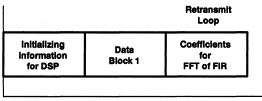

| SN74ACT3638<br>SN74ACT3631<br>SN74ACT3641<br>SN74ACT3651 | Microprocessor interface-control logic, synchronous retransmit capability, mailbox-bypass registers for each FIFO                                                  |  |  |  |  |  |  |  |  |  |

| SN74ACT3622<br>SN74ACT3632<br>SN74ACT3642                | Microprocessor interface-control logic, mailbox-bypass registers for each FIFO                                                                                     |  |  |  |  |  |  |  |  |  |

| HIGH-BANDWIDT                                            | TH COMPUTING FIFOs                                                                                                                                                 |  |  |  |  |  |  |  |  |  |

| SN74ABT3611<br>SN74ABT3612                               | Microprocessor interface-control logic, parity generation and parity check,<br>mailbox-bypass registers for each FIFO                                              |  |  |  |  |  |  |  |  |  |

| INTERNETWORK                                             | ING FIFOs                                                                                                                                                          |  |  |  |  |  |  |  |  |  |

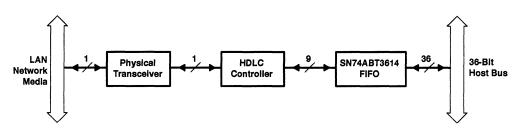

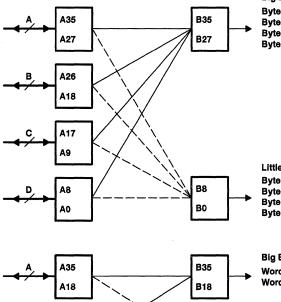

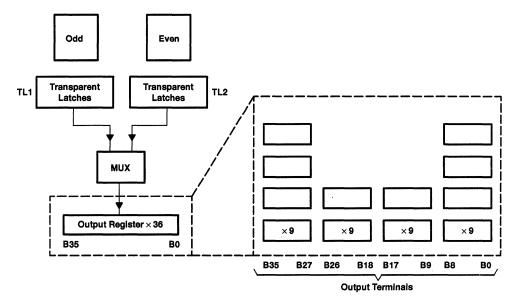

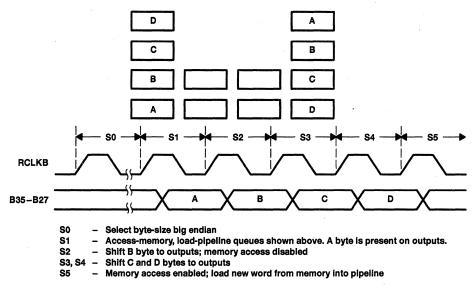

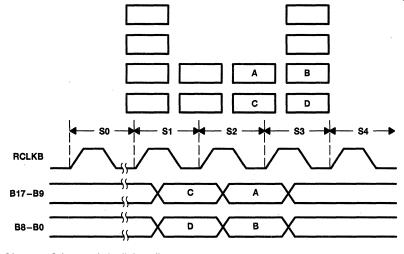

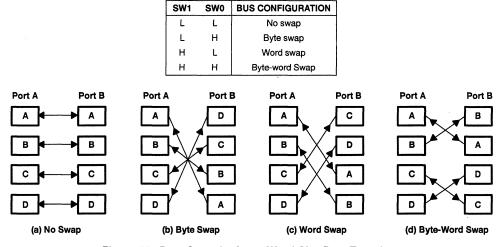

| SN74ABT3613<br>SN74ABT3614                               | Microprocessor interface-control logic, parity generation and parity check, bus<br>matching and byte swapping, mailbox-bypass registers for each FIFO              |  |  |  |  |  |  |  |  |  |

#### Synchronous Mature FIFOs

| DEVICE                                                           | ORGANIZATION                          | SPEED SORT<br>t <sub>C</sub> (ns) | MAXIMUM<br>FREQUENCY<br>(MHz) | ACCESS<br>TIME (ns) | PACKAGE          |

|------------------------------------------------------------------|---------------------------------------|-----------------------------------|-------------------------------|---------------------|------------------|

| SN74ACT72211L<br>SN74ACT72221L<br>SN74ACT72231L<br>SN74ACT72241L | 512 × 9<br>1K × 9<br>2K × 9<br>4K × 9 | -15, -20, -25,<br>-50             | 67, 50, 40, 20                | 10, 12,<br>15, 25   | 32-pin PLCC (RJ) |

# **FIFO PRODUCT OFFERINGS**

| DEVICE                                          | ORGANIZATION                | SPEED SORT<br>t <sub>C</sub> (ns) | MAXIMUM<br>FREQUENCY<br>(MHz) | ACCESS<br>TIME (ns) | PACKAGE                                                |  |  |

|-------------------------------------------------|-----------------------------|-----------------------------------|-------------------------------|---------------------|--------------------------------------------------------|--|--|

| SN74ACT7200L                                    | 256 × 9                     | -15, -25, -50                     | 67, 40, 20                    | 10, 12, 20          |                                                        |  |  |

| SN74ACT7201LA<br>SN74ACT7201LA<br>SN74ACT7202LA | 512 $	imes$ 9, 1K $	imes$ 9 | -15, -25, -35,<br>-50             | 67, 50, 40, 20                | 10, 12,<br>15, 25   | 28-pin DIP (NP)<br>28-pin SOIC (DV)                    |  |  |

| SN74ACT7203L<br>SN74ACT7204L                    | 2K × 9                      | -15, -25, -50                     | 67, 40, 20                    | 10, 12, 20          | 32-pin PLCC (RJ)                                       |  |  |

| 3N74AG17204L                                    | 4K × 9                      | -15, -25, -50                     | 07, 40, 20                    | 10, 12, 20          |                                                        |  |  |

| SN74ACT7205L                                    | 8K × 9                      | -15, -25, -50                     | 67, 40, 20                    | 10, 12, 20          | 28-pin DIP (NP)                                        |  |  |

| SN74ACT7206                                     | 16K × 9                     | -15, -25, -50                     | 67, 40, 20                    | 10, 12, 20          | 32-pin PLCC (RJ)                                       |  |  |

| SN74ALS2238                                     | 32 × 9 × 2                  |                                   | 40                            |                     | 40-pin DIP (N)<br>44-pin PLCC (FN)                     |  |  |

| SN74ALS2233A                                    | 64 × 9                      |                                   | 40                            |                     | 28-pin DIP (N)<br>44-pin PLCC (FN)                     |  |  |

| SN74ALS2232A                                    | 64 × 8                      |                                   | 40                            |                     | 24-pin DIP (NT)<br>28-pin PLCC (FN)                    |  |  |

| SN74ALS235                                      | 64 × 5                      | -                                 | 25                            |                     | 20-pin DIP (N)<br>20-pin SOIC (DW)                     |  |  |

| SN74ALS233                                      | 16 × 5                      |                                   | 30                            |                     | 20-pin DIP (N)<br>20-pin SOIC (DW)                     |  |  |

| SN74ALS232B                                     | 16 × 4                      |                                   | 30                            |                     | 16-pin DIP (N)<br>16-pin SOIC (DW)<br>20-pin PLCC (FN) |  |  |

| SN74ALS229B                                     | 16 × 5                      |                                   | 30                            |                     | 20-pin PLCC (FN)<br>20-pin DIP (N)<br>20-pin SOIC (DW) |  |  |

| SN74S225                                        | 16 × 5                      |                                   | 10                            |                     | 20-pin DIP (N)                                         |  |  |

## Asynchronous Mature FIFOs

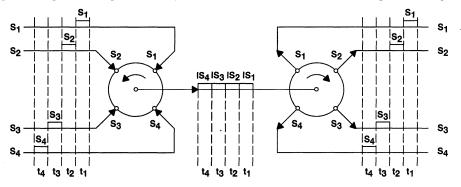

PRODUCT OVERVIEW

| <b>FIFO</b> | Funct | tionality |

|-------------|-------|-----------|

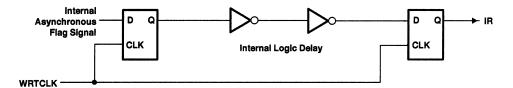

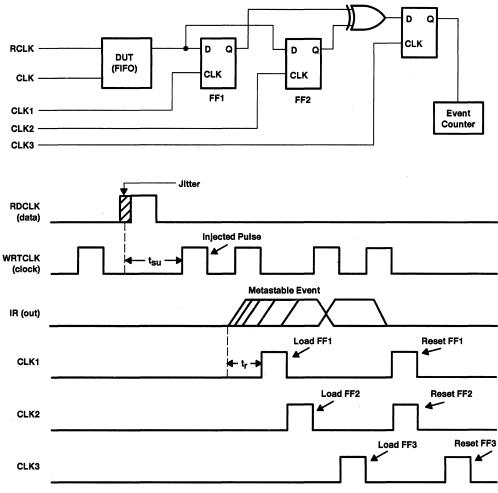

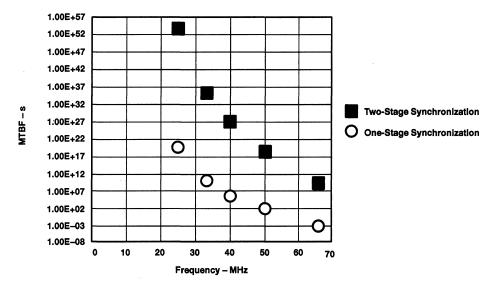

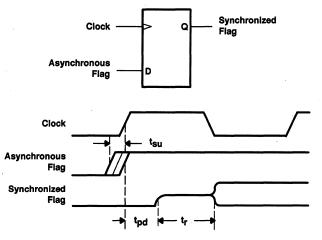

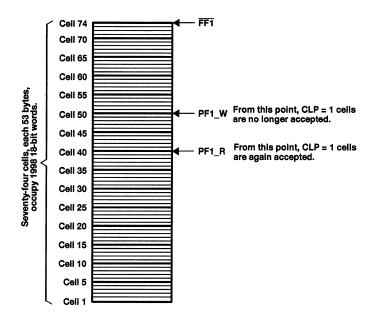

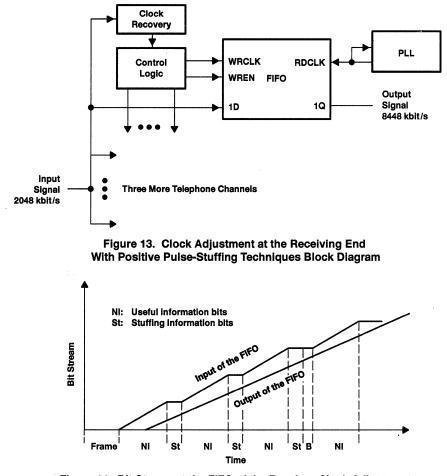

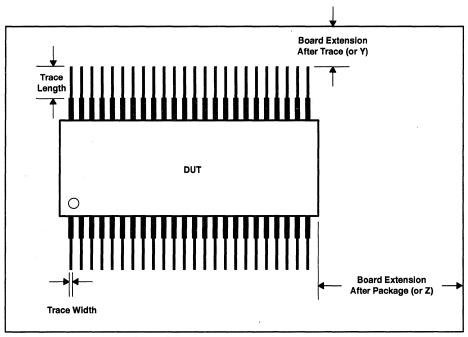

|-------------|-------|-----------|