# High-speed CMOS Logic Data Book

1983

Silicon-gate Complementary MOS

| GENERAL INFORMATION          |

|------------------------------|

| RATINGS AND CHARACTERISTICS  |

| DESCRIPTIVE INFORMATION      |

| EXPLANATION OF LOGIC SYMBOLS |

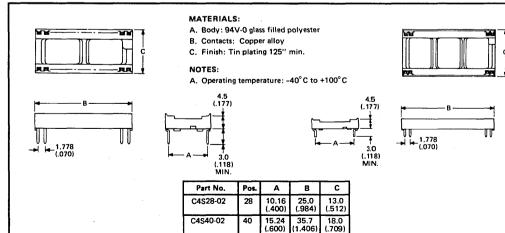

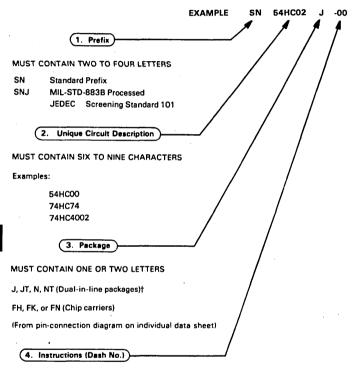

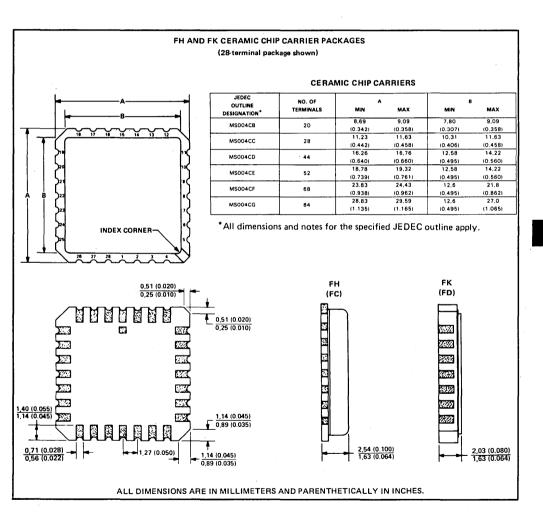

**ORDERING INSTRUCTIONS AND MECHANICAL DATA**

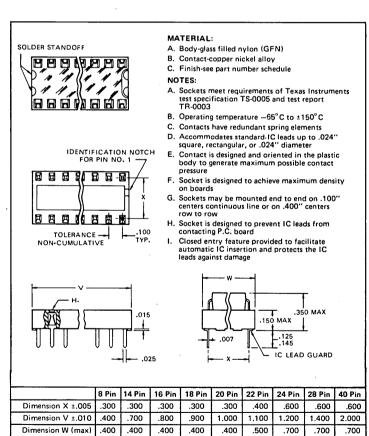

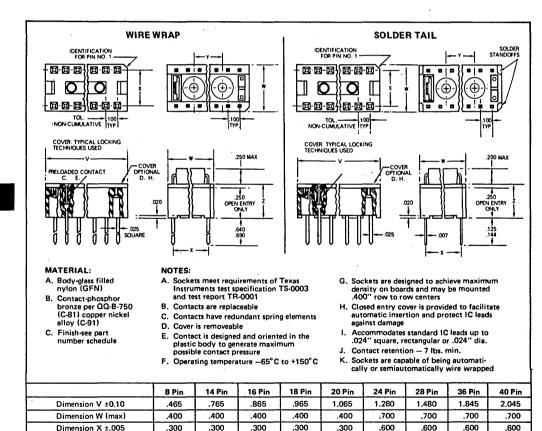

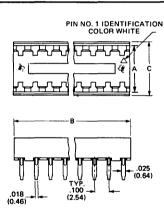

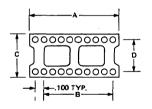

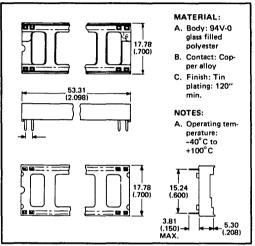

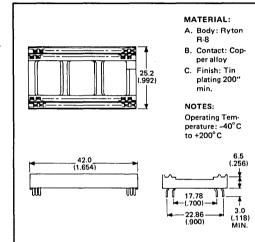

IC SOCKETS

# TI Sales Offices

ALABAMA: Huntsville, 500 Wynn Drive, Suite 514. Huntsville, AL 35805, (205) 837-7530.

ARIZONA: Phoenix, P.O. Box 35160, 8102 N. 23rd Ave., Suite A, Phoenix, AZ 85021, (602) 995-1007.

CALIFORNIA: El Segundo, 831 S. Douglas St., El Segundo, CA 90245, (213) 973-2571; Irvine, 17891 Cartwight Rd., trvine, CA 92714, (714) 660-1200; Sacramento, 1900 Point West Way, Suite 171, Sacramento, CA 95815, (916) 929-1521; West Way, Suite 1/1, Sacramento, CA 95815, (910) 929-1521; San Diego, 4333 View Ridge Ave., Suite B., San Diego, CA 92123, (714) 278-9600; Santa Clara, 5353 Betsy Ross Dr., Santa Clara, CA 95054, (408) 980-9000; Woodland Hills, 21220 Erwin Sc., Woodland Hills, CA 91367, (213) 704-7759.

COLORADO: Denver, 9725 E. Hampden St., Suite 301, Denver, CO 80231, (303) 695-2800.

CONNECTICUT: Wallingford, 9 Barnes Industrial Park Rd., Barnes Industrial Park, Wallingford, CT 06492, (203) 269-0074.

FLORIDA: Clearwater, 2280 U.S. Hwy. 19 N., Suite 232, Clearwater, FL 33515, (813) 796-1926; Ft. Lauderdale, 2765 N.W. 62nd St., Ft. Lauderdale, FL 33309, (305) 973-8502; Maitland, 2601 Maitland Center Parkway, Maitland, FL 32751, (305) 646-9600.

GEORGIA: Atlanta, 3300 Northeast Expy., Building 9, Atlanta, GA 30341, (404) 452-4600.

ILLINOIS: Arlington Heights, 515 W. Algonquin, Arlington Heights, IL 60005, (312) 640-2934.

INDIANA: Ft. Wayne, 2020 Inwood Dr., Ft. Wayne, IN 46805, (219) 424-5174; Indianapolis, 2346 S. Lynhurst, Suite J-400, Indianapolis, IN 46241, (317) 248-8555.

IOWA: Cedar Rapids, 373 Collins Rd. NE, Suite 200, Cedar Rapids, IA 52402, (319) 395-9550.

MARYLAND: Baltimore, 1 Rutherford Pl., 7133 Rutherford Rd., Baltimore, MD 21207, (301) 944-8600.

MASSACHUSETTS: Waltham, 504 Totten Pond Rd., Waltham, MA 02154, (617) 890-7400.

MICHIGAN: Farmington Hills, 33737 W. 12 Mile Rd., Farmington Hills, MI 48018, (313) 553-1500.

MINNESOTA: Edina, 7625 Parklawn, Edina, MN 55435, (612) 830-1600

MISSOURI: Kansas City, 8080 Ward Pkwy., Kansas City, MO 64114, (816) 523-2500; St. Louis, 11861 Westline Industrial Drive, St. Louis, MO 63141, (314) 569-7600.

NEW JERSEY: Clark, 292 Terminal Ave. West, Clark, NJ

NEW MEXICO: Albuquerque, 5907 Alice NSE, Suite E., Albuquerque, NM 87110, (505) 265-8491.

NEW YORK: East Syracuse, 6700 Old Collamer Rd., East Syracuse, NY 13057, (315) 463-9291; Endicott, 112 Nanticoke Ave., P.O. Box 6818, Endicort, NY 13760, (607) 754-3900; Melville, I Huntington Quadrangle, Suite 3ClO, P.O. Box 2936. Melville, NY 11747, (516) 454-6602, Poughkeepsie, 201 Suuth Ave., Poughkeepsie, NY 12601, (914) 473-2900; Rochester, 1210 Jefferson Rd., Rochester, NY 14623, (716) 424-3400. NEW YORK: East Syracuse, 6700 Old Collamer Rd., East

NORTH CAROLINA: Charlotte, 8 Woodlawn Green, Woodlawn Rd., Charlotte, NC 28210, (704) 527-0930; Raleigh, 3000 Highwoods Blvd., Suite 118, Raleigh, NC 27625, (919) 876-2725.

OHIO: Beachwood, 23408 Commerce Park Rd., Beachword, OH 44122, (216) 464-6100; Dayton, Kingsley Bldg., 4124 Linden Ave., Dayton, OH 45432, (513) 258-3877.

OKLAHOMA: Tulsa, 3105 E. Skelly Dr., Suite 110, Tulsa, OK 74105, (918) 749-9547.

OREGON: Beaverton, 6700 SW 105th St., Suite 110, Beaverton, OR 97005, (503) 643-6758.

PENNSYLVANIA: Ft. Washington, 575 Virginia Dr., Ft Washington, PA 19034, (215) 643-6450; Coraopolis, PA 15108, 420 Rouser Rd., 3 Airport Office PK, (412) 771-8550.

TENNESSEE: Johnson City, P.O. Drawer 1255, Erwin Hwy., Johnson City, TN 37601, (615) 461-2191.

TEXAS: Austin, 12501 Research Blvd.; P.O. Box 2909, Austin, TX 78723, (512) 250-7655; Dallas, P.O. Box 1087, Adstri, TX 76127, (312) 230-7633; Datass, F.O. Exx Vo.C., Richardson, TX 75080; Houston, 9100 Southwest Frwy., Suite 237, Houston, TX 77036, (713) 778-6592; San Antonio, 1000 Central Park South, San Antonio, TX 78232, (512) 496-1779.

UTAH: Salt Lake City, 3672 West 2100 South, Salt Lake City, UT 84120, (801) 973-6310.

VIRGINIA: Fairfax, 3001 Prosperity, Fairfax, VA 22031, (703) 849-1400; Midlothian, 13711 Sutter's Mill Circle, Midlothian, VA 23113, (804) 744-1007.

WISCONSIN: Brookfield, 205 Bishops Way, Suite 214, Brookfield, WI 53005, (414) 784-3040.

WASHINGTON: Redmond, 2723 152nd Ave., N.E. Bldg 6, Redmond, WA 98052, (206) 881-3080.

CANADA: Ottawa, 416 Mac Laren St., Ottawa, Canaua, K2POMS, (613) 233-1177. Richmond Hill, 280 Centre St. E., Richmond Hill L40C Haran, Canada, (416) 884-9181; St. Laurent, Ville St. Laurent Quebec, 9460 Trans Canada Hwy. St. Laurent, Quebec, Canada H4S1R7, (514) 334-3635.

# TI Distributors

ALABAMA: Hall-Mark (205) 837-8700.

ARIZONA: Phoenix, Kierulff (602) 243-4101; Marshall (602) 968-6181; Wyle (602) 249-2232; Tucson, Kierulff (602)

CALIFORNIA: Los Angeles/Orange County, Arrow (213) 701-7500, (714) 851-8961; JACO (714) 540-5602, (213) 998-2200; Kerolff (213) 729-525, (714) 731-7311, Marshall (213) 999-5001, (213) 868-0141, (714) 556-6402, R.V. Watherfund (714) 613-6900, (213) 889-3541, (714) 623-1261; Wyle (213) 122-8100, (714) 641-611; San Diego, Arrow (619) 563-6800, Kerolff (619) 7278-7212, Marshall (109) 728-8400. R.V. Weatherford (619) 695-1700; Wyle (619) 565-9171; San Francisco Bay Area, Arrow (408) 745-6600; Kierulff (415) 968-6292; Marshall (408) 732-1100; Wyle (408) 727-2500; inta Barbara, R.V. Weatherford (805) 465-8551

COLORADO: Arrow (303) 758-2100: Kierulff (303) 790-4444; Wyle (303) 457-9953

CONNECTICUT: Arrow (203) 265-7741; Diplomat (203) 797-9674; Kierulif (203) 265-1115; Marshall (203) 265-3822; Milgray (203) 795-0714.

FLORIDA: Ft. Lauderdale, Arrow (305) 973-8502; Diplomat (305) 971-7160; Half-Mark (305) 971-9280; Kierulif (305) 952-6950; Orlando, Arrow (305) 725-1480; Diplomat (305) 725-4520; Half-Mark (305) 855-4020; Milgray (305) 647-5747; Tampa, Diplomat (812) 443-341; Kierulif (813) 376-1966.

GEORGIA: Arrow (404) 449-8252; Hall-Mark (404) 447-8000; Kierulff (404) 447-5252; Marshall (404) 923-5750.

ILLINOIS: Arrow (312) 397-3440; Diplomat (312) 595-1000; Hall-Mark (312) 860-3800; Kierulff (312) 640-0200; Newark (312) 638-4411.

INDIANA: Indianapolis, Arrow (317) 243-9353; Graham (317) 634-8202; Ft. Wayne, Graham (219) 423-3422.

KANSAS: Kansas City, Component Specialties (913) 492-3555; Hall-Mark (913) 888-4747; Wichita, LCOMP (316) 265,9507

MARYLAND: Arrow (301) 247-5200; Diplomat (301) 995-1226; Hall-Mark (301) 796-9300; Kierulff (301) 247-5020; Milgray (301) 468-6400.

MASSACHUSETTS: Arrow (617) 933-8130; Diplomat (617) 429-4120; Kierulff (617) 667-8331; Marshall (617) 272-8200; Time (617) 935-8080.

MICHIGAN: Detroit, Arrow (313) 971-8200; Newark (313) 967-0600; Grand Rapids, Newark (616) 243-0912.

MINNESOTA: Arrow (612) 830-1800; Hall-Mark (612) 854-3223; Kierulff (612) 941-7500.

MISSOURI: Kansas City, LCOMP (816) 221-2400; St. Louis, Arrow (314) 567-6888; Hall-Mark (314) 291-5350; Kierulff (314) 739-0855.

NEW HAMPSHIRE: Arrow (603) 668-6968.

NEW JERSEY: Arrow (201) 575-5300, (609) 235-1900; Diplomar (201) 785-1830; General Radio (609) 964-8560; Hall-Mark (201) 575-4415, (609) 424-0880; JACO (201) 778-4722; Kierulif (201) 575-6750; Marshall (201) 340-1900; Milgray (609) 983-5010.

NEW MEXICO: Arrow (505) 243-4566; International Electronics (505) 345-8127.

NEW YORK: Long Island, Arrow (516) 231-1000, Diplumar (516) 434-6400, Hall-Mark (516) 737-0600, JACO (516) 273-5500, Marchall (516) 273-244, Milgray (516) 456-500, (800) 645-3986; Hall-Mark (516) 737-2600; Rochester, Armw (716) 275-0300, Marshall (716) 257-5000, Marshall (716) 257-6760, Rochester Radio Supply (716) 456-7800, Syracuse, Armw (315) 652-1000. Diplumar (315) 652-5000, Marshall (707) 74-3100.

NORTH CAROLINA: Arrow (919) 876-3132, (919) 725-8711; Hall-Mark (919) 872-0712; Kierulff (919) 852-6261.

OHIO: Cincinnati, Graham (513) 772-1661; Hall-Mark (513) 563-5980; Cleveland, Arrow (216) 248-3990; Hall-Mark (216) 473-2907; Kierulff (216) 587-6558; Columbus, Hall-Mark (614) 473-2907; Nieruit (210) 367-6538; Columbus, Hall-Ma 846-1882; Dayton, Arrow (513) 435-5563; ESCO (513) 226-1133: Marshall (513) 236-8088.

OKLAHOMA: Component Specialties (918) 664-2820; Hall-Mark (918) 665-3200; Kierulff (918) 252-7537.

OREGON: Kierulff (503) 641-9150; Wyle (503) 640-6000.

PENNSYLVANIA: Arrow (412) 856-7000, (215) 928-1800; General Radio (215) 922-7037; Hall-Mark (215) 355-7300.

TEXAS: Austin, Arrow (512) 835-4180; Component Specialties (512) 837-8922; Hall-Mark (512) 258-8848; Kienliff (512) 835-2090; Dallas, Arrow (214) 386-7500; Component Specialties (214) 357-6511; Hall-Mark (214) 341-1147. al Electronics (214) 233-9323; Kierulff (214) International Electronics (219) 232-3925; Kierulff (214) 343-2400; El Paso, International Electronics (915) 778-9761; Houston, Arriw (713) 491-4100; Component Specialties (713) 771-7217; Hall-Mark (713) 781-6100; Harrison Equipment (713) 879-2600; Kierulff (713) 530-7030.

UTAH: Diplomat (801) 486-4134; Kierulff (801) 973-6913; Wyle (801) 974-9953.

WASHINGTON: Arrow (206) 643-4800; Kierulff (206) 575-4420; Wyle (206) 453-8300.

WISCONSIN: Arrow (414) 764-6600; Hall-Mark (414) 761-3000; Kierulff (414) 784-8160.

CANADA: Calgary, Future (403) 259-6408: Varah (403) 230-1235; Hamilton, Varah (416) 561-9311; Montreal, CESCO (511) 735-531; Future (514) 944-7710; Ottawa, CESCO (613) 216-6905; Future (613) 820-8313; Quebec City, CESCO (418) 674-7213; Toronto, CESCO (4616) 661-0202; Puture (416) 635-553; Vancouver, Future (604) 435-545; Varah (604) 631-7211; Winningey, Varah (204) 435-690; BA

# High-Speed CMOS Logic Data Book

# IMPORTANT NOTICE

Texas Instruments reserves the right to make changes at any time in order to improve design and to supply the best product possible.

Texas Instruments assumes no responsibility for infringement of patents or rights of others based on Texas Instruments applications assistance or product specifications, since TI does not possess full access to data concerning the use or applications of customer's products. TI also assumes no responsibility for customer product designs.

ISBN 0-89512-114-X Library of Congress No. 82-074480

# HIGH-SPEED CMOS LOGIC DATA BOOK

Texas Instruments is pleased to announce the SN74HC family of high-speed CMOS logic circuits. This versatile new family promises to be the product family of choice for many new logic systems, offering a unique combination of high-speed, low-power dissipation, high noise immunity, wide fanout capability, extended supply voltage range, and high reliability.

This data book describes the initial product line scheduled for introduction during 1983. Included are pinout and package information, logic symbols, maximum ratings and dc electrical characteristics. At the time of this edition, JEDEC recommendations for ac performance have not been finalized, consequently the timing requirements and switching characteristics for each device have been left blank. However, as each new family member is released, TI will publish the corresponding ac parameters, which may be obtained from your nearest TI field sales office or your local authorized TI distributor. Later editions of this data book will contain complete ac specifications.

# TI Worldwide Sales Offices

ALABAMA: Huntsville, 500 Wynn Drive, Suite 514, Huntsville, AL 35805, (205) 837-7530.

ARIZONA: Phoenix, P.O. Box 35160, 8102 N. 23rd Ave., Suite A, Phoenix, AZ 85021, (602) 995-1007.

CALIFORNIA: El Segundo, 831 S. Douglas St., El Segundo, CA 90245, (213) 973-2571; Irvine, 17891 Cartwripht Rd., Plrine, CA 9714, (714) 660-1200; Sacramento, 1900 Point West Way, Suite 171, Sacramento, CA 95815, (916) 929-1521; San Diego, 433 View Ridge Ave., Suite B., San Diego, CA 91213, (714) 278-9600; Santa Clara, 5151 Betty Ross Dr., Santa Clara, CA 95054, (408) 980-9000, Woodland Hills, 21220 Ewin St., Woodland Hills, 247279.

COLORADO: Denver, 9725 E. Hampden St., Suite 301, Denver, CO 80231, (303) 695-2800.

CONNECTICUT: Wallingford, 9 Barnes Industrial Park Rd., Barnes Industrial Park, Wallingford, CT 06492, (203) 269-0074.

FLORIDA: Clearwater, 2280 U.S. Hwy. 19 N., Suite 232, Clearwater, Fl. 33515, (813) 796-1926; Fr. Lauderdale, 2765 N.W. 62nd St., Fr. Lauderdale, Fl. 33309, 3059 973-8502; Maitland, 2601 Maitland Center Parkway, Maitland, Fl. 32751, 305) 646-9605.

GEORGIA: Atlanta, 3300 Northeast Expy., Building 9, Atlanta, GA 30341, (404) 452-4600.

ILLINOIS: Arlington Heights, 515 W. Algonquin, Arlington Heights, IL 60005, (312) 640-2934.

INDIANA: Ft. Wayne, 2020 Inwood Dr., Ft. Wayne, IN 46805, (219) 424-5174; Indianapolis, 2346 S. Lynhurst, Suite J-400, Indianapolis, IN 46241, (317) 248-8555.

IOWA: Cedar Rapids, 373 Collins Rd. NE, Suite 200, Cedar Rapids, IA 52402, (319) 395-9550.

MARYLAND: Baltimore, 1 Rutherford Pl., 7133 Rutherford Rd., Baltimore, MD 21207, (301) 944-8600.

MASSACHUSETTS: Waltham, 504 Totten Pond Rd., Waltham, MA 02154, (617) 890-7400.

MICHIGAN: Farmington Hills, 33737 W. 12 Mile Rd., Farmington Hills, MI 48018, (313) 553-1500.

MINNESOTA: Edina, 7625 Parklawn, Edina, MN 55435, (612) 830-1600.

MISSOURI: Kansas City, 8080 Ward Pkwy., Kansas City, MO 64114, (816) 523-2500; St. Louis, 11861 Westline Industrial Drive, St. Louis, MO 63141, (314) 569-7600.

NEW JERSEY: Clark, 292 Terminal Ave. West, Clark, NJ 07066, (201) 574-9800.

NEW MEXICO: Albuquerque, 5907 Alice NSE, Suite E., Albuquerque, NM 8711C, (505) 265-8491.

NEW YORK: East Syracuse, 6700 Old Collamer Rd., East Syracuse, NY 19357, (315) 463-9291; Endicott, 112 Nanticoke Ave., P.O. Box 618, Endicott, NY 13760, (607) 754-3900; Melville, 1 Huntington Quadrangle, Suite 3ClO, P.O. Box 2936, Melville, NY 11747, (516) 454-6600; Poughkeepsie, 201 South Ave., Poughkeepsie, NY 12601, (914) 473-2900; Rochester, 1210 Jefferson Rd., Rochester, NY 14623, (716) 424-5400.

NORTH CAROLINA: Charlotte, 8 Woodlawn Green, Woodlawn Rd., Charlotte, NC 28210, (704) 527-0930; Raleigh, 3000 Highwoods Blvd., Suite 118, Raleigh, NC 27625, (919) 876-2725.

OHIO: Beachwood, 23408 Commerce Park Rd., Beachwood, OH 44122, (216) 464-6100; Dayton, Kingsley Bldg., 4124 Linden Ave., Dayton, OH 45432, (513) 258-3877.

OKLAHOMA: Tulsa, 3105 E. Skelly Dr., Suite 110, Tulsa, OK 74105, (918) 749-9547.

OREGON: Beaverton, 6700 SW 105th St., Suite 110, Beaverton, OR 97005, (503) 643-6758.

PENNSYLVANIA: Ft. Washington, 575 Virginia Dr., Ft. Washington, PA 19034, (215) 643-6450; Coraopolis, PA 15108, 420 Rouser Rd., 3 Airport Office PK, (412) 771-8550.

TENNESSEE: Johnson City, P.O. Drawer 1255, Erwin Hwy., Johnson City, TN 37601, (615) 461-2191.

TEXAS: Austin, 12501 Research Blvd., P.O. Box 2909, Austin, TX 78723, (512) 250-7655; Dallas, P.O. Box 1087, Richardson, TX 75000; Houston, 9100 Southwest Fruy, Suite 237, Houston, TX 77036, (713) 778-6592; San Antonio, 1000 Central Park South, San Antonio, TX 78232, (512) 496-1779.

UTAH: Salt Lake City, 3672 West 2100 South, Salt Lake City, UT 84120, (801) 973-6310.

VIRGINIA: Fairfax, 3001 Prosperity, Fairfax, VA 22031, (703) 849-1400; Midlothian, 13711 Sutter's Mill Circle, Midlothian, VA 23113, (804) 744-1007.

WISCONSIN: Brookfield, 205 Bishops Way, Suite 214, Brookfield, WI 53005, (414) 784-3040.

WASHINGTON: Redmond, 2723 152nd Ave., N.E. Bldg 6, Redmond, WA 98052, (206) 881-3080.

CANADA: Ottawa, 436 Mac Laren St., Ottawa, Canada, K2POM8, (613) 233-1177: Richmond Hill, 280 Centre St. E., Richmond Hill (4C1B), Ontario, Canada, (4)6) 884-9181; St. Laurent, Ville St. Laurent Quebec, 9460 Trans Canada Hwy., St. Laurent, Quebec, Canada H491,R7, (514) 334-3635.

ARGENTINA, Texas Instruments Argentina S.A.I.C.F: Esmeralda 130, 15th Floor, 1035 Buenos Aires, Argentina, 394-2963.

AUSTRALIA (& NEW ZEALAND), Texas Instruments Australia Ltd.: Unit 1A, 9 Byfield St., North Ryde (Svdney), New South Wale, Australia 131, Q + 887-1122; 5th Flaor, 418 St. Kilda Road, Mellyourne, Victoria, Australia 3004, 01+267-4677; 717 Philip Highway, Elizabeth, South Australia 5112, Q8+255-2066.

AUSTRIA, Texas Instruments Ges.m.b.H.: Industriestrabe B/16, A-2345 Brunn/Gebirge, 2236-846210.

BELGIUM, Texas Instruments N.V. Belgium S.A.: Mercure Centre, Rakerstraar 100, Rue de la Fusee, 1130 Brussels, Belgium, 02/720.80.00.

BRAZIL, Texas Instruments Electronicos do Brasil Ltda.: Av. Faria Lima, 2003, 20 0 Andar — Pinheiros, Cep-01451 Sao Paulo, Brazil, 815-6166.

DENMARK, Texas Instruments A/S, Marielundvej 46E, DK-2730 Herley, Denmark, 2 - 91 74 00.

FINLAND, Texas Instruments Finland OY: PL 56, 00510 Helsinki 51, Finland, (90) 7013133.

FRANCE, Texas Instruments France: Headquarters and Prod. Plant, BP 05, 06270 Villeneuve-Loubet, (93) 20-01-01; Parts Office, BP 67 8-10 Avenue Mortane-Saulnier, Fâll41 Veliny-Villacoublay, (1) 946-97-12; Lyon Sales Office, L'Oree D'Ecully, Battemen B, Chemin de Forestiere, 6910 Ecully, Edwinson B, Chemin de Forestiere, 6910 Ecully, Edwinson Color, (88) 12-12-12-06, Remos. 23-25 Rue du Putra Mauger. 51100 Rennes, (99) 79-54-81; Toulouse Sales Office, Le Petipole — 2, Chemin du Pigeonnier de la Cepter. 31100 Toulouse, (61) 44-18-19, Marseille Sales Office, Noilly Paradis — 140 Rue Paradis, 13006 Marseille, (91) 37-25-30.

GERMANY, Texas Instruments Deutschland GmbH: Haggerty-strase I, D-8050 Freising, 68161-801; Kurfuerstendams 195190, D-1000 Berlin 15, 030-8827305; III. Hagen 43/Kibbelstrase, D-4300 Essen, 0201-24250; Frankfurter Allee 6-8, D-6236 Eschbern 1, 68196-48174; Hamburger Strasse II, D-2000 Hamburg 76, 040-2201154, Kirchborstestrases 2, D-3000 Hamburg 15, 0511-048021; Arabellastrases 15, D-8000 Misenchen 81, 089-92341; Maybachstrasse II, D-7302 Oscribilern 2/Nellingen, 0711-1300.

HONG KONG (+ PEOPLES REPUBLIC OF CHINA), Texas Instruments Asia Ltd.: 8th Floor, World Shipping Ctr., Harbour City, 7 Canton Rd., Kowloon, Hong Kong, 3+722-1223.

IRELAND, Texas Instruments (Ireland) Limited: 25 St. Stephens Green, Dublin 2, Eire, 01 609222.

ITALY, Texas Instruments Semiconduttori Italia Spa: Viale Delle Scienze, I. (2015 Cittaducale (Reiet), Italy, 0746 694.1; Via Salara Kh. 24 (Talazo: Coman), Mortercondu Scalo Cologno Monesee (Milano), 02 (53)524; Corso Svitzera, 185, 1010 Torton, Linky, 01 (74548; Via.) J. Borzic, 6, 45100 Bologna, Italy, 051 53581; Via Nazareth, 7, 35100 Padowa, Italy, 024 50550; Via Nazareth, 7, 35100 Padowa,

JAPAN, Texas Instruments Asia Ltd.: 4F Aoyama Fuji Bldg., 6-12, Kita Aoyama 3-Chome, Minato-ku, Tokyo, Japan 107, 03-498-2111, Cokas Branch, 5F, Nissho lwai Bldg., 30 Imabsahi, 3-Chome, Higashi-ku, Osaka, Japan 541, 06-204-1881; Nagoya Branch, 7F Danii Toyota West Bldg., 10-27, Meieki 4-Chome, Nakamura-ku, Nagoya, Japan 450, 052-583-8691.

KOREA, Texas Instruments Supply Co.: Room 201, Kwangpxong Bldg., 24-1, Hwayand-Dong, Sung dong-ku, 133 Seoul, Korea, 02 + 464-6274/5.

MEXICO, Texas Instruments de Mexico S.A.: Poniente 116, No. 489, Colonia Vallejo, Mexico, D.F. 02300, 567-9200.

MIDDLE EAST, Texas Instruments: No. 13, 1st Floor Mannai Bldg., Diplomatic Area, Manama, P.O. Box 26335, Bahrain, Arabian Gulf, 973 - 27 46 81.

NETHERLANDS, Texas Instruments Holland B.V., P.O. Box 12995, (Bullewijk) 1100 AZ Amsterdam, Zuid-Oost, Holland (020) 5602911.

NORWAY, Texas Instruments Norway A/S: Kr. Augustsgt. 13, Oslo I, Norway, (2) 20 60 40.

PHILIPPINES, Texas Instruments Asia Ltd.: 14th Floor, Ba-Lepanto Bidg., 8747 Paseo de Roxas, Makati, Metro Manila, Philippines, 882465.

PORTUGAL, Texas Instruments Equipamento Electronico (Portugal), Lda.: Rua Eng. Frederico Ulrich, 2650 Moreira Da Maia, 4470 Maia, Portugal, 2-9481003.

SCOTLAND, Texas Instruments Limited: 126-128 George Street, Edinburgh, Scotland, EH1 2AN, 031 226 2691.

SINGAPORE (+ INDIA, INDONESIA, MALAYSIA, THAILAND), Texas Instruments Asia Ltd.: P.O. Box 138, Unit #02-08, Block 6, Kolam Ayer Industrial Est., Lorong Bakar Batu, Singapore 1344, Republic of Singapore, 747-2255.

SPAIN, Texas Instruments Espana, S.A.: C/Jose Lazaro Galdiano No. 6, Madrid 16, 1/458.14.58.

SWEDEN, Texas Instruments International Trade Corporation (Sverigefilialen): Box 39103, 10054 Stockholm, Sweden, 08 - 735480

SWITZERLAND, Texas Instruments, Inc. Riedstrasse 6, CH-8953 Dietikon (Zuerich) Switzerland, 1-740 2220.

TAIWAN, Texas Instruments Supply Co.: 10th Floor, Fu-Shing Bldg., 71 Sung-Kiang Road, Taipei, Taiwan, Republic of China, 02 + 521-9321.

UNITED KINGDOM, Texas Instruments Limited: Manton Lane, Bedford, MK41 PA, England, 0234 67466; 186 High Street, Slugh, SLI 1LD, England, 0753 35545; St. James House, Wellington Road North, Stockport, SK4 2RT, England, 051 442 8448.

# **GENERAL INFORMATION**

| Alphanumeric Index                | 1 -: |

|-----------------------------------|------|

| Glossary                          | 1 -  |

| Functional Index/Selection Guide  | 1 -  |

| Explanation of Function Tables1   | -1:  |

| Parameter Measurement Information | -14  |

| TYPE    |         | RATINGS AND DESCRIP CHARACTERISTICS* INFORMA |      | TYPE    |             | SS AND<br>ERISTICS* | DESCRIPTIVE<br>INFORMATION |  |

|---------|---------|----------------------------------------------|------|---------|-------------|---------------------|----------------------------|--|

| NUMBERS | TABLE   | PAGE                                         | PAGE | NUMBERS | TABLE       | PAGE                | PAGE                       |  |

| 'HC00   | 1       | 2-3                                          | 3-2  | 'HC173  | 191         | 2-5                 | 3-80                       |  |

| 'HC02   | 1       | 2-3                                          | 3-3  | 'HC174  | IV          | 2-6                 | 3-82                       |  |

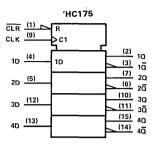

| 'HCO4   | 1       | 2-3                                          | 3-4  | 'HC175  | H           | 2-4                 | 3-82                       |  |

| 'HC08   | ł       | 2-3                                          | 3-5  | 'HC189  | 181         | 2-5                 | 3-84                       |  |

| 'HC10   | 1       | 2-3                                          | 3-6  | 'HC190  | IV          | 2-6                 | 3-87                       |  |

| 'HC11   | 1       | 2-3                                          | 3-7  | 'HC191  | IV ·        | 2-6                 | 3-87                       |  |

| 'HC14   | I       | 2-3                                          | 3-8  | 'HC192  | · IV        | 2-6                 | 3-91                       |  |

| 'HC20   | ı       | 2-3                                          | 3-9  | 'HC193  | ١V          | 2-6                 | 3-91                       |  |

| 'HC21   | i       | 2-3                                          | 3-10 | 'HC194  | IV          | 2-6                 | 3-95                       |  |

| 'HC27   | J       | 2-3                                          | 3-11 | 'HC195  | IV          | 2-6                 | 3-98                       |  |

| 'HC30   | l       | 2-3                                          | 3-12 | 'HC221  | IV          | 2-6                 | 3-100                      |  |

| 'HC32   | ı       | 2-3                                          | 3-13 | 'HC240  | III         | 2-5                 | 3-102                      |  |

| 'HC36   | 1       | 2-3                                          | 3-14 | 'HC241  | 111         | 2-5                 | 3-102                      |  |

| 'HC42   | í٧      | 2-6                                          | 3-15 | 'HC242  | IR          | 2-5                 | 3-104                      |  |

| 'HC51   | ı       | 2-3                                          | 3-17 | 'HC243  | Ш           | 2-5                 | 3-104                      |  |

| 'HC73   | II      | 2-4                                          | 3-18 | 'HC244  | 111         | 2-5                 | 3-106                      |  |

| 'HC74   | 11      | 2-4                                          | 3-20 | 'HC245  | 111         | 2-5                 | 3-108                      |  |

| 'HC75   | 11      | 2-4                                          | 3-22 | 'HC251  | 131         | 2-5                 | 3-110                      |  |

| 'HC76   | 11      | 2-4                                          | 3-24 | 'HC253  | - 111       | 2-5                 | 3-112                      |  |

| 'HC77   | II      | 2-4                                          | 3-26 | 'HC257  | Ш           | 2-5                 | 3-114                      |  |

| 'HC78   | li .    | 2-4                                          | 3-28 | 'HC258  | 111         | 2-5                 | 3-114                      |  |

| 'HC85   | IV      | 2-6                                          | 3-30 | 'HC259  | IV          | 2-6                 | 3-116                      |  |

| 'HC86   | ı       | 2-3                                          | 3-32 | 'HC266  | I           | 2-3                 | 3-118                      |  |

| 'HC107  | II      | 2-4                                          | 3-34 | 'HC273  | IV          | 2-6                 | 3-119                      |  |

| 'HC109  | H       | 2-4                                          | 3-36 | 'HC280  | IV          | 2-6                 | 3-121                      |  |

| 'HC112  | II      | 2-4                                          | 3-38 | 'HC299  | III .       | 2-5                 | 3-123                      |  |

| 'HC113  | II      | 2-4                                          | 3-40 | 'HC323  | III         | 2-5                 | 3-126                      |  |

| 'HC114  | П       | 2-4                                          | 3-42 | 'HC352  | 111         | 2-5                 | 3-129                      |  |

| 'HC123  | IV      | 2-6                                          | 3-44 | 'HC353  | 111         | 2-5                 | 3-131                      |  |

| 'HC132  | 1       | 2-3                                          | 3-46 | 'HC354  | III         | 2-5                 | 3-133                      |  |

| 'HC133  | l       | 2-3                                          | 3-47 | 'HC356  | 111         | 2-5                 | 3-136                      |  |

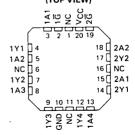

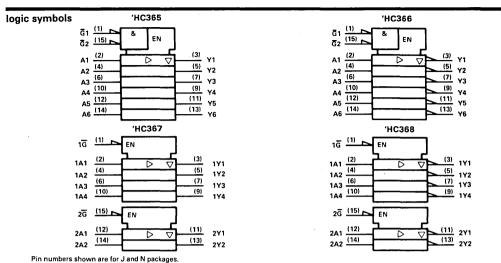

| 'HC137  | IV      | 2-6                                          | 3-48 | 'HC365  | III<br>     | 2-5                 | 3-139                      |  |

| 'HC138  | IV      | 2-6                                          | 3-50 | 'HC366  | 111         | 2-5                 | 3-139                      |  |

| 'HC139  | IV      | 2-6                                          | 3-52 | 'HC367  | <b>i</b> II | 2-5                 | 3-139                      |  |

| 'HC147  | IV      | 2-6                                          | 3-54 | 'HC368  | 111         | 2-5                 | 3-139                      |  |

| 'HC151  | 111     | 2-5                                          | 3-56 | 'HC373  | 111         | 2-5                 | 3-141                      |  |

| 'HC152  | III<br> | 2-5                                          | 3-58 | 'HC374  | 111         | 2-5 `               | 3-143                      |  |

| 'HC153  | III     | 2-5                                          | 3-60 | 'HC377  | IV<br>      | 2-6                 | 3-145                      |  |

| 'HC154  | IV      | 2-6                                          | 3-62 | 'HC378  | IV<br>      | 2-6                 | 3-145                      |  |

| 'HC157  | III<br> | 2-5                                          | 3-64 | 'HC379  | ï           | 2-4                 | 3-145                      |  |

| 'HC158  | III     | 2-5                                          | 3-64 | 'HC386  | <br>        | 2-3                 | 3-148                      |  |

| 'HC160  | IV      | 2-6                                          | 3-66 | 'HC390  | IV<br>nv    | 2-6                 | 3-149                      |  |

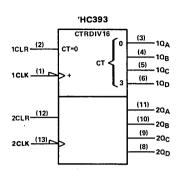

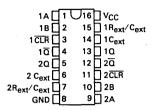

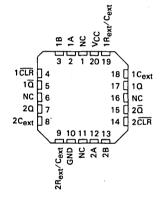

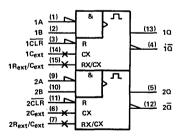

| 'HC161  | IV      | 2-6                                          | 3-66 | 'HC393  | IV.         | 2-6                 | 3-149                      |  |

| 'HC162  | IV      | 2-6                                          | 3-66 | 'HC423  | IV .        | 2-6                 | 3-152                      |  |

| 'HC163  | IV      | 2-6                                          | 3-66 | 'HC490  | . IV        | 2-6                 | 3-154                      |  |

| 'HC164  | IV      | 2-6                                          | 3-72 | 'HC533  | 111         | 2-5                 | 3-156                      |  |

| 'HC165  | IV      | 2-6                                          | 3-74 | 'HC534  | )))         | 2-5                 | 3-158                      |  |

| 'HC166  | IV      | 2-6                                          | 3-77 | 'HC563  | Ш           | 2-5                 | 3-160                      |  |

<sup>\*</sup>See these pages for absolute maximum ratings, recommended operating conditions, and electrical characteristics.

# TEXAS INSTRUMENTS

<sup>†</sup>See these pages for description, pin assignments, timing requirements, and switching characteristics.

# **ALPHANUMERIC INDEX**

|         |                              | GS AND<br>ERISTICS* | DESCRIPTIVE INFORMATION† | TYPE    |      | GS AND<br>ERISTICS* | DESCRIPTIVE INFORMATION† |

|---------|------------------------------|---------------------|--------------------------|---------|------|---------------------|--------------------------|

| NUMBERS | BERS TABLE PAGE PAGE NUMBERS | NUMBERS             | TABLE                    | PAGE    | PAGE |                     |                          |

| 'HC564  | III                          | 2-5                 | 3-162                    | 'HC648  | Ш    | 2-5                 | 3-186                    |

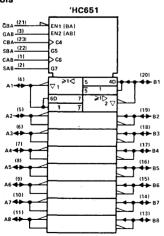

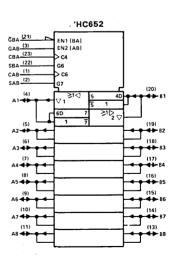

| 'HC573  | 111                          | 2-5                 | 3-164                    | 'HC651  | 111  | 2-5                 | 3-190                    |

| 'HC574  | 111                          | 2-5                 | 3-166                    | 'HC652  | Ш    | 2-5                 | 3-190                    |

| 'HC590  | Ш                            | 2-5                 | 3-168                    | 'HC688  | iV   | 2-6                 | 3-194                    |

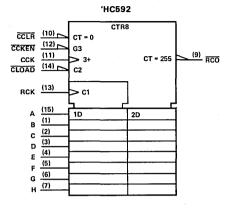

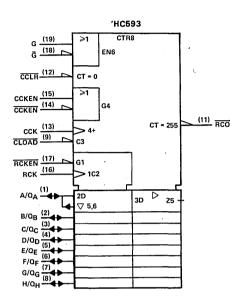

| 'HC592  | IV                           | 2-6                 | 3-170                    | 'HC4002 | 1    | 2-3                 | 3-196                    |

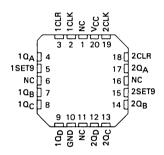

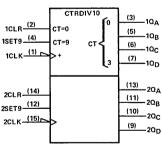

| 'HC593  | 111                          | 2-5                 | 3-170                    | 'HC4017 | IV   | 2-6                 | 3-197                    |

| 'HC594  | 111                          | 2-5                 | 3-173                    | 'HC4020 | iV   | 2-6                 | 3-199                    |

| 'HC595  | Ш                            | 2-5                 | 3-175                    | 'HC4040 | IV   | 2-6                 | 3-201                    |

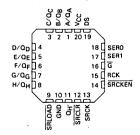

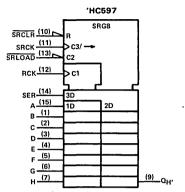

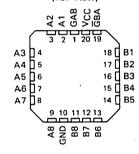

| 'HC597  | IV                           | 2-6                 | 3-177                    | 'HC4060 | IV   | 2-6                 | 3-203                    |

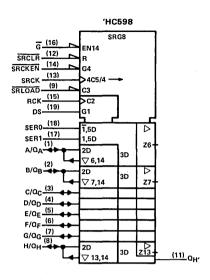

| 'HC598  | 111                          | 2-5                 | 3-177                    | 'HC4075 | 1    | 2-3                 | 3-205                    |

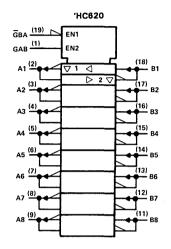

| 'HC620  | Ш                            | 2-5                 | 3-180                    | 'HC4078 | 1    | 2-3                 | 3-206                    |

| 'HC623  | Ш                            | 2-5                 | 3-180                    | 'HC4511 | IV   | 2-6                 | 3-207                    |

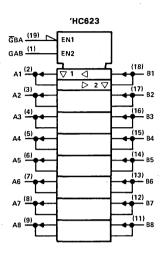

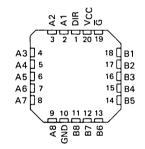

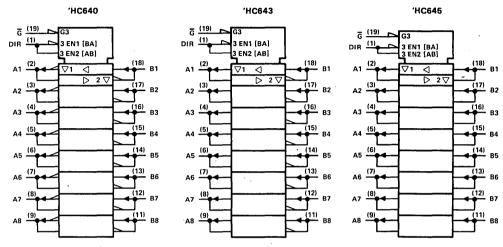

| 'HC640  | 181                          | 2-5                 | 3-183                    | 'HC4514 | IV   | 2-6                 | 3-209                    |

| 'HC643  | ui                           | 2-5                 | 3-183                    | 'HC4515 | IV   | 2-6                 | 3-209                    |

| 'HC645  | III                          | 2-5                 | 3-183                    | 'HC4538 | IV   | 2-6                 | 3-212                    |

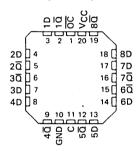

| 'HC646  | 111                          | 2-5                 | 3-186                    | 'HC4724 | IV   | 2-6                 | 3-214                    |

<sup>\*</sup>See these pages for absolute maximum ratings, recommended operating conditions, and electrical characteristics.

<sup>†</sup>See these pages for description, pin assignments, timing requirements, and switching characteristics.

# GLOSSARY SYMBOLS, TERMS, AND DEFINITIONS

#### INTRODUCTION

These symbols, terms, and definitions are in accordance with those currently agreed upon by the JEDEC Council of the Electronic Industries Association (EIA) for use in the USA and by the International Electrotechnical Commission (IEC) for international use.

#### OPERATING CONDITIONS AND CHARACTERISTICS (IN SEQUENCE BY LETTER SYMBOLS)

# Cpd Power dissipation capacitance

Used to determine the no-load dynamic power dissipation per logic function (See individual circuit pages):  $P_D = C_{old} \ V_{CC^2} \ f + I_{CC} \ V_{CC}$ .

# f<sub>max</sub> Maximum clock frequency

The highest rate at which the clock input of a bistable circuit can be driven through its required sequence while maintaining stable transitions of logic level at the output with input conditions established that should cause changes of output logic level in accordance with the specification.

# ICC Supply current

The current into\* the VCC supply terminal of an integrated circuit.

# IJH High-level input current

The current into\* an input when a high-level voltage is applied to that input.

# IIL Low-level input current

The current into\* an input when a low-level voltage is applied to that input.

## IOH High-level output current

The current into\* an output with input conditions applied that, according to the product specification, will establish a high level at the output.

## IOL Low-level output current

The current into\* an output with input conditions applied that, according to the product specification, will establish a low level at the output.

#### Ins Short-circuit output current

The current into\* an output when that output is short-circuited to ground (or other specified potential) with input conditions applied to establish the output logic level farthest from ground potential (or other specified potential).

# IOZ Off-state (high-impedance-state) output current (of a three-state output)

The current flowing into\* an output having three-state capability with input conditions established that, according to the production specification, will establish the high-impedance state at the output.

## VIH High-level input voltage

An input voltage within the more positive (less negative) of the two ranges of values used to represent the binary variables.

E: A minimum is specified that is the least-positive value of high-level input voltage for which operation of the logic element within specification limits is guaranteed.

<sup>\*</sup> Current out of a terminal is given as a negative value.

# GLOSSARY SYMBOLS, TERMS, AND DEFINITIONS

# VIL Low-level input voltage

An input voltage level within the less positive (more negative) of the two ranges of values used to represent the binary variables.

NOTE: A minimum is specified that is the most-positive value of low-level input voltage for which operation of the logic element within specification limits is guaranteed.

# VOH High-level output voltage

The voltage at an output terminal with input conditions applied that, according to product specification, will establish a high level at the output.

# VOL Low-level output voltage

The voltage at an output terminal with input conditions applied that, according to product specification, will establish a low level at the output:

# V<sub>T+</sub> Positive-going threshold level

The voltage level at a transition-operated input that causes operation of the logic element according to specification as the input voltage rises from a level below the negative-going threshold voltage, V<sub>T</sub>...

# /T... Negative-going threshold level

The voltage level at a transition-operated input that causes operation of the logic element according to specification as the input voltage falls from a level above the positive-going threshold voltage, V<sub>T+</sub>.

## a Access time

The time interval between the application of a specified input pulse and the availability of valid signals at an output.

# tdis Disable time (of a three-state output)

The time interval between the specified reference points on the input and output voltage waveforms, with the three-state output changing from either of the defined active levels (high or low) to a high-impedance (off) state. (tdis = tpHz or tpt z).

# ten Enable time (of a three-state output)

The time interval between the specified reference points on the input and output voltage waveforms, with the three-state output changing from a high-impedance (off) state to either of the defined active levels (high or low). ( $t_{en} = tpzH$  or tpzL).

#### t<sub>h</sub> Hold time

The time interval during which a signal is retained at a specified input terminal after an active transition occurs at another specified input terminal.

- NOTES: 1. The hold time is the actual time interval between two signal events and is determined by the system in which the digital circuit operates. A minimum value is specified that is the shortest interval for which correct operation of the digital circuit is guaranteed.

- The hold time may have a negative value in which case the minimum limit defines the longest interval (between the release of the signal and the active transition) for which correct operation of the digital circuit is guaranteed.

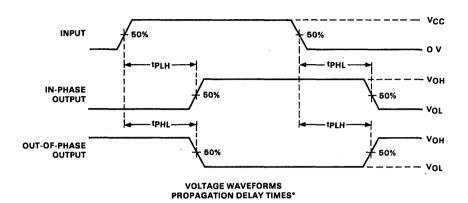

# tpd Propagation delay time

The time between the specified reference points on the input and output voltage waveforms with the output changing from one defined level (high or low) to the other defined level. (tod = tpHL or tpLH).

# tphL Propagation delay time, high-to-low level output

The time between the specified reference points on the input and output voltage waveforms with the output changing from the defined high level to the defined low level.

# tpHZ Disable time (of a three-state output) from high level

The time interval between the specified reference points on the input and the output voltage waveforms with the three-state output changing from the defined high level to a high-impedance (off) state.

The time between the specified reference points on the input and output voltage waveforms with the output changing from the defined low level to the defined high level.

Disable time (of a three-state output) from low level tpi7

> The time interval between the specified reference points on the input and output voltage waveforms with the three-state output changing from the defined low level to a high-impedance (off) state.

Enable time (of a three-state output) to high level **tPZH**

> The time interval between the specified reference points on the input and output voltage waveforms with the three-state output changing from a high-impedance (off) state to the defined high level.

**tPZL** Enable time (of a three-state output) to low level

> The time interval between the specified reference points on the input and output voltage waveforms with the three-state output changing from a high-impedance (off) state to the defined low level.

ter Sense recovery time

> The time interval needed to switch a memory from a write mode to a read mode and to obtain valid data signals at the output.

Setup time tsu

> The time interval between the application of a signal at a specified input terminal and a subsequent active transition at another specified input terminal.

> NOTES: 1. The setup time is the actual time interval between two signal events and is determined by the system in which the digital circuit operates. A minimum value is specified that is the shortest interval for which correct operation of the digital circuit is guaranteed.

The setup time may have a negative value in which case the minimum limit defines the longest interval (between the active transition and the application of the other signal) for which correct operation of the digital circuit is guaranteed.

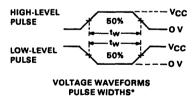

Pulse duration (width) tw

The time interval between specified reference points on the leading and trailing edges of the pulse waveform.

Texas Instruments

INCORPORATED

# 1.

# **FUNCTIONAL INDEX/SELECTION GUIDE**

| FUNCTIONS                                                      | PAGE |

|----------------------------------------------------------------|------|

| AND/NAND Gates and Inverters                                   | 1-8  |

| OR/NOR/EXCLUSIVE-OR and A-O-I Gates                            | 1-8  |

| Schmitt-trigger NAND Gates and Inverters                       | 1-8  |

| Bus Drivers and Transceivers with 3-State Outputs              | 1-8  |

| Dual J-K Flip-flops                                            | 1-9  |

| D-Type Flip-flops                                              | 1-9  |

| Latches and Registers                                          | 1-9  |

| Monostable Multivibrators                                      | 1-9  |

| Shift Registers                                                | 1-10 |

| Asynchronous Counters                                          | 1-10 |

| Synchronous Counters                                           | 1-10 |

| Comparators, Parity Generators/Checkers, and Priority Encoders | 1-10 |

| Data Selectors/Multiplexers                                    | 1-11 |

| Decoders/Demultiplexers                                        | 1-11 |

| Display Decoders/Drivers                                       | 1-11 |

| Random-Access Memories (RAM's)                                 |      |

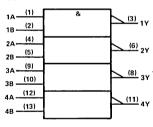

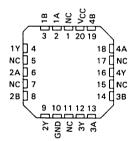

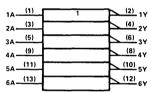

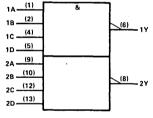

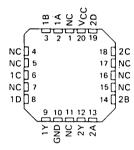

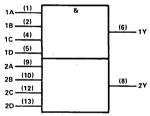

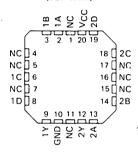

# AND, NAND GATES AND INVERTERS

(for Maximum Ratings and Electrical Characteristics See Table I, Page 2-3)

| DESCRIPTION               | DEVICE<br>TYPE | DESCRIPTIVE INFORMATION |

|---------------------------|----------------|-------------------------|

| Hex Inverters             | 'HC04          | 3-4                     |

| Quad 2-Input NAND Gates   | 'HC00          | 3-2                     |

| Quad 2-Input AND Gates    | 'HC08          | 3-5                     |

| Triple 3-Input NAND Gates | 'HC10          | 3-6                     |

| Triple 3-Input AND Gates  | 'HC11          | 3-7                     |

| Dual 4-Input NAND Gates   | 'HC20          | 3-9                     |

| Dual 4-Input AND Gates    | 'HC21          | 3-10                    |

| 8-Input NAND Gate         | 'HC30          | 3-12                    |

| 13-Input NAND Gate        | 'HC133         | 3-47                    |

# **SCHMITT-TRIGGER GATES AND INVERTERS**

(for Maximum Ratings and Electrical Characteristics See Table I,

| ray                     | 10 2-31        |                         |

|-------------------------|----------------|-------------------------|

| DESCRIPTION             | DEVICE<br>TYPE | DESCRIPTIVE INFORMATION |

| Hex Inverters           | 'HC14          | 3-8                     |

| Quad 2-Input NAND Gates | 'HC132         | 3-46                    |

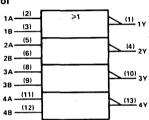

# OR, NOR, EXCLUSIVE-OR, AND AND-OR-INVERT GATES

(for Maximum Ratings and Electrical Characteristics See Table I,

Page 2.3)

| Page 2-3)                 |         |             |  |  |  |  |  |

|---------------------------|---------|-------------|--|--|--|--|--|

| DESCRIPTION               | DEVICE  | DESCRIPTIVE |  |  |  |  |  |

| DESCRIPTION               | TYPE    | INFORMATION |  |  |  |  |  |

| Quad 2-Input NOR Gates    | 'HC02   | 3-3         |  |  |  |  |  |

| Guad 2-Input NON Gates    | 'HC36   | 3-14        |  |  |  |  |  |

| Quad 2-Input OR Gates     | 'HC32   | 3-13        |  |  |  |  |  |

| Quad 2-Input EXCLUSIVE-   | 'HC266  | 3-118       |  |  |  |  |  |

| NOR Gates                 | HC200   | 3-110       |  |  |  |  |  |

| Quad 2-Input EXCLUSIVE-OR | 'HC86   | 3-32        |  |  |  |  |  |

| Gates                     | 'HC386  | 3-148       |  |  |  |  |  |

| Dual 2-Wide 2-Input A-O-I | 'HC51   | 3-17        |  |  |  |  |  |

| Gates                     | псэт    | 3-17        |  |  |  |  |  |

| Triple 3-Input NOR Gates  | 'HC27   | 3-11        |  |  |  |  |  |

| Triple 3-Input OR Gates   | 'HC4075 | 3-205       |  |  |  |  |  |

| Dual 4-Input NOR Gates    | 'HC4002 | 3-196       |  |  |  |  |  |

| 8-Input NOR Gate          | 'HC4078 | 3-206       |  |  |  |  |  |

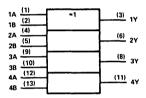

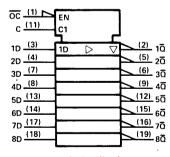

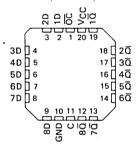

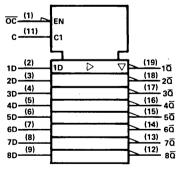

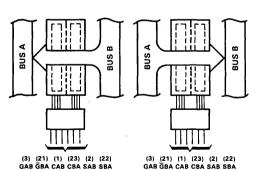

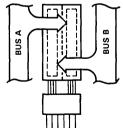

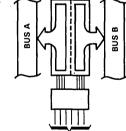

## **BUS DRIVERS AND TRANSCEIVERS WITH 3-STATE OUTPUTS**

(for Maximum Ratings and Electrical Characteristics See Table III, Page 2-5)

| DESCRIPTION                 | OUTPUT DATA        | CONTROL INPUTS        | DEVICE | DESCRIPTIVE |

|-----------------------------|--------------------|-----------------------|--------|-------------|

|                             |                    |                       | TYPE   | INFORMATION |

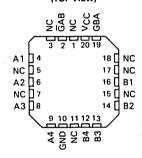

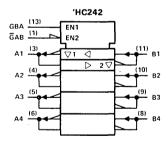

| Quad Bus Transceivers       | Inverting          | Independent Enables   | 'HC242 | 3-104       |

| Quau bus Hanscelvers        | True               | for A and B Buses     | 'HC243 | 3-104       |

|                             | True               | Common Enables        | 'HC365 | T           |

| Hex Bus Drivers/Receivers   | Inverting          | Common Enables        | 'HC366 | 2 400       |

| nex bus Drivers/ Receivers  | True               | Commented Franklin    | 'HC367 | 3-139       |

|                             | Inverting          | Symmetrical Enables   | 'HC368 |             |

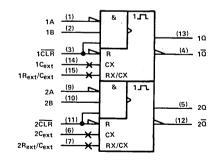

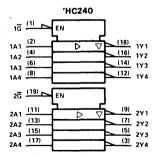

|                             | Inverting          | Symmetrical Enables   | 'HC240 | 3-102       |

| Octal Bus Drivers/Receivers | True               | Complementary Enables | 'HC241 | 3-102       |

|                             | True               | Symmetrical Enables   | 'HC244 | 3-106       |

|                             | Inverting          | Independent Enables   | 'HC620 | 2 100       |

|                             | True               | for A and B Buses     | 'HC623 | 3-180       |

| Octal Bus Transceivers      | Inverting          |                       | 'HC640 |             |

| Octal Bus Transceivers      | True and Inverting | Enable and            | 'HC643 | 3-183       |

|                             | T                  | Direction Control     | 'HC645 | 7           |

|                             | True               |                       | 'HC245 | 3-108       |

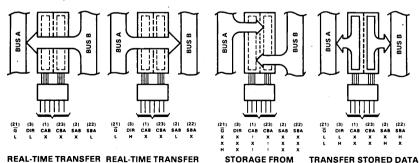

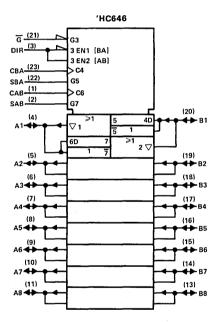

|                             | True               | Enable and            | 'HC646 | 2 106       |

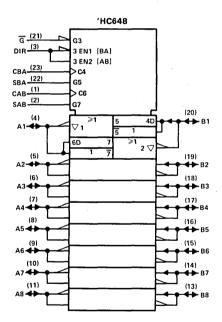

| Octal Bus Transceivers      | Inverting          | Direction Control     | 'HC648 | 3-186       |

| with Registers              | Inverting          | Independent Enables   | 'HC651 | 2 400       |

|                             | True               | for A and B Buses     | 'HC652 | 3-190       |

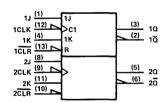

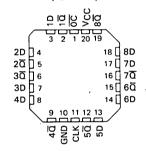

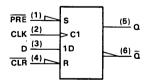

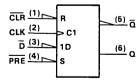

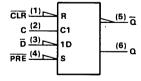

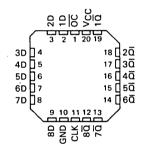

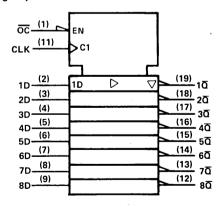

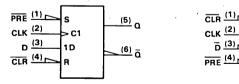

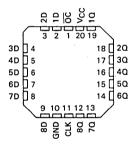

# **D-TYPE FLIP-FLOPS**

| DESCRIPTION                 | ОИТРИТ          | OTHER               | DEVICE               | RATINGS AND CHARACTERISTICS |       | DESCRIPTIVE |      |

|-----------------------------|-----------------|---------------------|----------------------|-----------------------------|-------|-------------|------|

| DESCRIPTION                 | CONFIGUATION    | FEATURES            | TYPE                 | TABLE                       | PAGE  | INFORMATION |      |

| Dual D-type Flip-flops with | C               | Independent         | 'HC74                |                             |       | 3-20        |      |

| Preset and Clear            | Complementary   | Clocks              | HC/4                 | l                           |       | 3-20        |      |

| Quad D-Type Flip-flops with | C               | Common Clear        | 'HC175               | "                           | "   2 | 2-4         | 3-82 |

| Common Clocks               | Complementary   | Output Enable       | 'HC379               |                             |       | 3-145       |      |

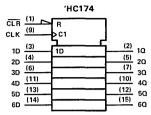

| Hex D-Type Flip-flops with  | 0               | Common Clear        | 'HC174               |                             | 2.0   | 3-82        |      |

| Common Clocks               | Q only          | Output Enable       | 'HC378               |                             |       | 0.0         | 2-6  |

|                             | Q only          | Common Clear        | 'HC273               | IV 2-6                      | 3-119 |             |      |

|                             | Q only          | Output Enable       | 'HC377               | 1                           |       | 3-145       |      |

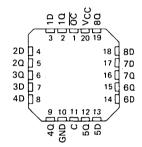

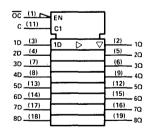

| Octal D-type Flip-flops     | 2 64-4- 0       | 0                   | 'HC374               |                             |       | 3-143       |      |

| with Common Clocks          | 3-State, Q only | Output Control      | utput Control 'HC574 | ]<br>-<br>-                 | 2-5   | 3-166       |      |

|                             | 3-State, Q only | ly Output Control — | 'HC534               |                             |       | 3-158       |      |

|                             | 3-State, Clonly |                     | 'HC564               |                             |       | 3-162       |      |

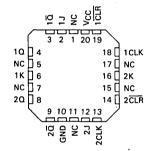

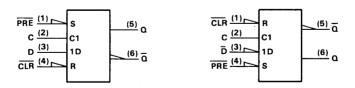

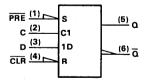

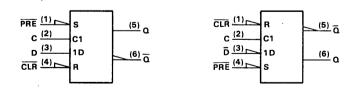

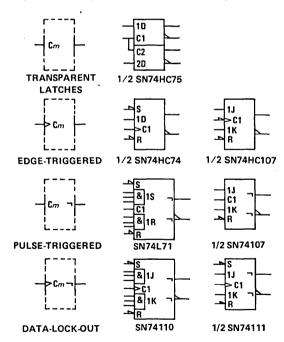

# **DUAL J-K FLIP-FLOPS**

(for Maximum Ratings and Electrical Characteristics See Table II, Page 2-4)

| DESCRIPTION                     | DEVICE | DESCRIPTIVE |  |

|---------------------------------|--------|-------------|--|

| DESCRIPTION                     | TYPE   | INFORMATION |  |

| Dual J-K Flip-flops with Clear  | 'HC73  | 3-18        |  |

| Dual 3-K Flip-liops With Clear  | 'HC107 | 3-34        |  |

| Dual J-K Flip-flops with Preset | 'HC113 | 3-40        |  |

| Dual J-K Flip-flops with        | 'HC78  | 3-28        |  |

| Preset, Common Clock, and       |        |             |  |

| Common Clear                    | 'HC114 | 3-42        |  |

| Dual J-K Flip-flops with Preset | 'HC76  | 3-24        |  |

| and Clear                       | 'HC112 | 3-38        |  |

| Dual J-K Flip-flops with Preset | 'HC109 | 3-36        |  |

| and Clear                       | 110109 | 3-30        |  |

# **LATCHES AND REGISTERS**

| DESCRIPTION               | OUTPUTS         | DEVICE  | RATINGS AND<br>CHARACTERISTICS |      | DESCRIPTIVE |

|---------------------------|-----------------|---------|--------------------------------|------|-------------|

|                           |                 | TYPE    | TABLE                          | PAGE | INFORMATION |

| 0 -10 1                   | Complementary   | 'HC75   |                                | 3-22 |             |

| Quad D-type Latches       | Q only          | 'HC77   | u ,                            | 2-4  | 3-26        |

| Quad D-type Registers     | Q only, 3-state | 'HC173  |                                |      | 3-80        |

|                           | 0 1 - 2         | 'HC373  | 'HC573 III 2                   |      | 3-141       |

| 0                         | Q only, 3-state | 'HC573  |                                | 2.5  | 3-164       |

| Octal D-Type Latches      | Ōl 2            | 'HC533  |                                | 2-5  | 3-156       |

|                           | Q only, 3-state | 'HC563  |                                |      | 3-160       |

| 0.00                      |                 | 'HC4724 | IV                             |      | 3-214       |

| 8-Bit Addressable Latches | Q only          | 'HC259  |                                | 2-6  | 3-116       |

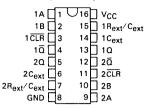

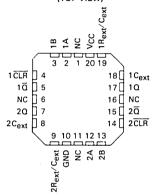

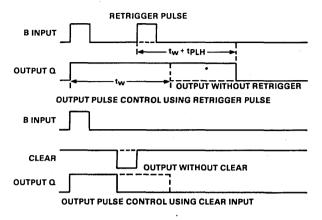

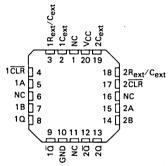

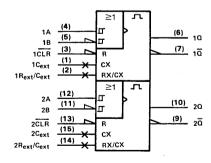

# **MONOSTABLE MULTIVIBRATORS**

(for Maximum Ratings and Electrical Characteristics See Table IV, Page 2-4)

| DESCRIPTION                    | FE            | DEVICE<br>TYPE              | DESCRIPTIVE INFORMATION |       |

|--------------------------------|---------------|-----------------------------|-------------------------|-------|

| Dual Monostable Multivibrators |               |                             | 'HC221                  | 3-100 |

| with Direct Clear, Postive     |               |                             | 'HC123                  | 3-44  |

| and Negative Inputs, and       | Retriggerable | 14011                       | 'HC423                  | 3-152 |

| complementary Outputs          |               | Will not trigger from clear | 'HC4538                 | 3-212 |

# TEXAS INSTRUMENTS

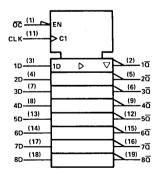

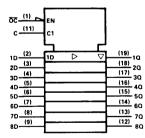

| SH | IFT | RE | GI | STE | <b>-RS</b> |

|----|-----|----|----|-----|------------|

| DESCRIPTION                                             | INDUTE                                               | INPUTS OUTPUTS                       |        | RATINGS AND CHARACTERISTIC |      | DESCRIPTIVE |  |

|---------------------------------------------------------|------------------------------------------------------|--------------------------------------|--------|----------------------------|------|-------------|--|

| DESCRIPTION                                             | INPUIS                                               | OUIPUIS                              | TYPE   | TABLE                      | PAGE | INFORMATION |  |

| 4-Bit Shift Register with Clear                         | J-K/Parallel                                         | Parallel                             | 'HC195 |                            |      | 3-98        |  |

| 4-Bit Bidirectional Shift<br>Registers with Clear       | Serial/Parallel                                      | Parallel                             | 'HC194 |                            |      | 3-95        |  |

|                                                         | Serial/Parallel, Clock<br>Inhibit, Shift/Load        | 2 Serial                             | 'HC165 | C165 IV 2-6                |      | 3-74        |  |

| 8-Bit Shift Registers                                   | 2 Serial, Clear                                      | Parallel                             | 'HC164 |                            |      | 3-72        |  |

| -                                                       | Serial/Parallel, Clear,<br>Clock Inhibit, Shift/Load | Serial                               | 'HC166 |                            |      | 3-77        |  |

| 8-Bit Shift Registers with                              | Serial/Parallel                                      | Serial                               | 'HC597 |                            |      | 3-177       |  |

| Input Registers                                         | Serial/Parallel                                      | 3-state Parallel<br>(MultiplexedI/O) | 'HC598 |                            |      | 3-177       |  |

| 8-Bit Bidirectional Shift<br>Registers with Storage and | Serial/Parallel                                      | 3-state Parallel                     | 'HC299 | 111                        | 2-5  | 3-123       |  |

| Multiplexed 3-State I/O                                 | Serial/ Farallel                                     |                                      | 'HC323 | •••                        |      | 3-126       |  |

| 8-Bit Shift Registers with                              | Serial                                               | Parallel                             | 'HC594 |                            |      | 3-173       |  |

| Output Registers                                        | Serial                                               | 3-State Parallel                     | 'HC595 |                            |      | 3-175       |  |

# SYNCHRONOUS COUNTERS

| DESCRIPTION                          | FEATURES      |                            | TYPE    | RATINGS AND<br>CHARACTERISTICS |      | DESCRIPTIVE |

|--------------------------------------|---------------|----------------------------|---------|--------------------------------|------|-------------|

|                                      |               |                            |         | TABLE                          | PAGE | -           |

| Daniel                               | Async Clear   | 0                          | 'HC160  | ,                              |      | 3-66        |

| Decade                               | Sync Clear    | Sync Load                  | 'HC162  |                                |      | 3-66        |

| Decede He (Dece                      | Clock Inhibit | A 1 d                      | 'HC190  |                                |      | 3-87        |

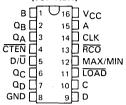

| Decade Up/Down                       | Async Clear   | Async Load                 | 'HC192  |                                |      | 3-91        |

| Divide-by-10<br>Johnson Counter      | Async Clear   |                            | 'HC4017 |                                | 2-6  | 3-197       |

| A Dia Dinama                         | Async Clear   |                            | 'HC161  | IV                             | 2-6  | 3-66        |

| 4-Bit Binary                         | Sync Clear    | Sync Load                  | 'HC163  |                                |      | 3-66        |

| 4 Bis Bissey Us (Davis               | Clock Inhibit | Asses I and                | 'HC191  |                                |      | 3-87        |

| 4-Bit Binary Up/Down                 | Async Clear   | - Async Load               | 'HC193  |                                | ľ    | 3-91        |

| 0.03.03                              |               |                            | 'HC592  | •                              |      | 3-170       |

| 8-Bit Binary with<br>Input Registers | Sync Clear    | Multiplexed<br>3-state I/O | 'HC593  |                                | 2-5  | 3-170       |

| 8-Bit Binary with Output Registers   | Sync Clear    | 3-state Outputs            | 'HC590  | (1)                            | 2-5  | 3-168       |

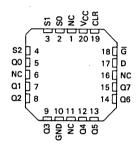

# ASYNCHRONOUS (RIPPLE CLOCK) COUNTERS (for Maximum Ratings and Electrical Characteristics See Table IV, Page 2-6)

| DESCRIPTION                     | FEATURES           | DEVICE<br>TYPE | DESCRIPTIVE INFORMATION |

|---------------------------------|--------------------|----------------|-------------------------|

| 12-Bit Binary<br>Counters       |                    | 'HC4040        | 3-201                   |

| 14-Bit Binary                   |                    | 'HC4020        | 3-199                   |

| Counters -                      | On-chip Oscillator | 'HC4060        | 3-203                   |

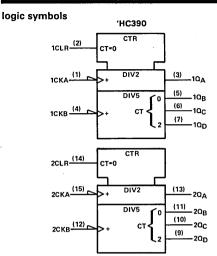

| Dual Decade                     | Bi-quinary or BCD  | 'HC390         | 3-149                   |

| Counters                        | Set-to-9 Input     | 'HC490         | 3-154                   |

| Dual 4-Bit Bi-<br>nary Counters |                    | 'HC393         | 3-149                   |

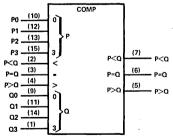

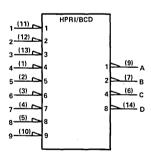

# COMPARATORS, PARITY GENERATORS/ CHECKERS, AND PRIORITY ENCODERS

(for Maximum Ratings and Electrical Characteristics See Table IV, Page 2-6)

| DESCRIPTION                                       | DEVICE<br>TYPE | DESCRIPTIVE INFORMATION |

|---------------------------------------------------|----------------|-------------------------|

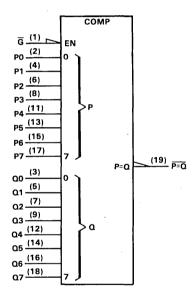

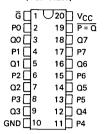

| 4-Bit Magnitude Comparators                       | 'HC85          | 3-30                    |

| 8-Bit Magnitude Comparators                       | 'HC688         | 3-194                   |

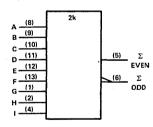

| 9-Bit Odd/Even Parity<br>Generator/Checker        | 'HC280         | 3-121                   |

| 10-Line Decimal to 4-Line<br>BCD Priority Encoder | 'HC147         | 3-54                    |

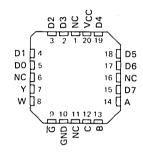

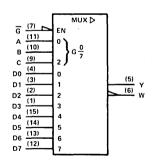

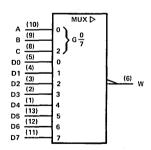

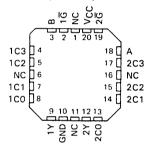

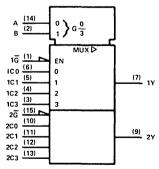

# **DATA SELECTORS/MULTIPLEXERS**

(for Maximum Ratings and Electrical Characteristics See Table III, Page 2-5)

| DESCRIPTION           | INPUTS                         | OUTPUTS                | DEVICE<br>TYPE | DESCRIPTIVE INFORMATION |

|-----------------------|--------------------------------|------------------------|----------------|-------------------------|

|                       |                                | Inverting              | 'HC152         | 3-58                    |

|                       | Enable                         | Complementary          | 'HC151         | 3-56                    |

| 8-Line-to-1-Line      | Enable                         | Complementary, 3-state | 'HC251         | 3-110                   |

| 8-Line-to-1-Line      | Transparent<br>Latches, Enable | Complementary 3-state  | 'HC354         | 3-133                   |

|                       | Registers, Enable              | 3-state                | 'HC356         | 3-136                   |

|                       |                                | True, 3-state          | 'HC253         | 3-112                   |

| Dual 4-line-to-1-Line | Independent                    | Inverting, 3-state     | 'HC353         | 3-131                   |

| Duai 4-iine-to-1-Line | Enables                        | True                   | 'HC153         | 3-60                    |

|                       |                                | Inverting              | 'HC352         | 3-129                   |

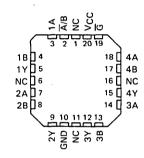

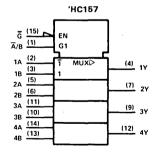

|                       |                                | True                   | 'HC157         | 3-64                    |

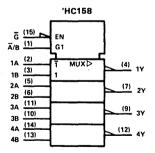

| Quad 2-Line-to-1-Line | Common Enable                  | Inverting              | 'HC158         | 3-64                    |

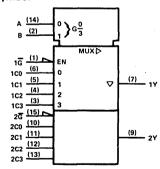

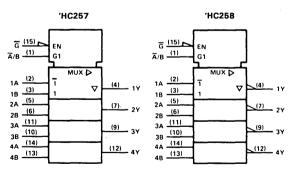

|                       | Common Enable                  | True, 3-state          | 'HC257         | 3-114                   |

|                       | 1                              | Inverting, 3-state     | 'HC258         | 3-114                   |

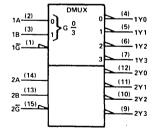

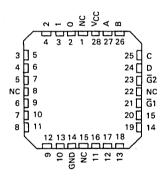

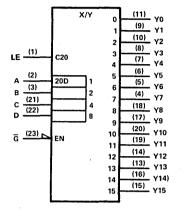

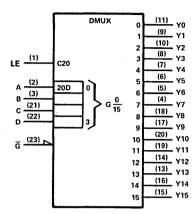

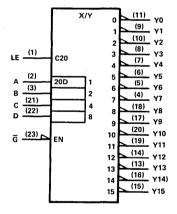

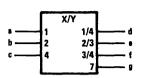

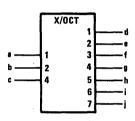

# **DECODERS/DEMULTIPLEXERS**

(for Maximum Ratings and Electrical Characteristics See Table IV, Page 2-6)

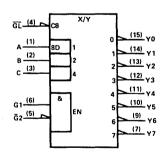

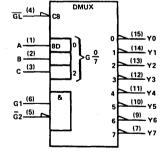

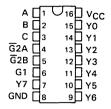

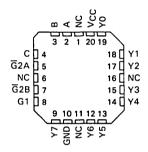

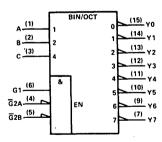

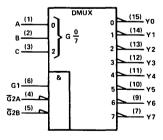

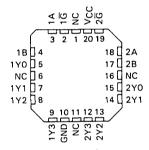

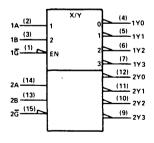

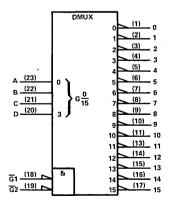

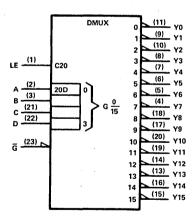

DEVICE DESCRIPTIVE DESCRIPTION **FEATURES** TYPE INFORMATION 2 Enables 'HC154 3-62 4-Line-to-16-Line Input latches, 'HC4514 3-209 Output Enable 'HC4515 3-209 4-Line-to-10-Line. HC42 3-15 BCD-to-Decimal 3 Enables 'HC138 3-50 3-Line-to-8-Line 3 Enables, Ad-'HC137 3-48 dress Latches

'HC139

3-52

Independent

Enables

Dual 2-Line-

to-4-Line

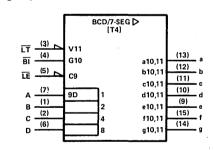

# **DISPLAY DECODERS/DRIVERS**

| DESCRIPTION                       | DEVICE<br>TYPE | RATING<br>CHARACT |      | DESCRIPTIVE<br>INFORMATION |  |

|-----------------------------------|----------------|-------------------|------|----------------------------|--|

|                                   |                | TABLE             | PAGE | iidi Olimarioit            |  |

| BCD-to-7-Segment Decoders/Drivers | 'HC4511        | N/                | 2-6  | 3-207                      |  |

| with Input Latches                | HC4511         | IV                | 2-0  | 3-207                      |  |

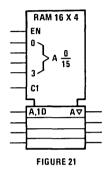

# **RANDOM ACCESS MEMORIES**

| DESCRIPTION | ORGANIZATION | FEATURES        | DEVICE | RATINGS AND<br>CHARACTERISTICS |      | DESCRIPTIVE  |

|-------------|--------------|-----------------|--------|--------------------------------|------|--------------|

|             |              |                 | ITFE   | TABLE                          | PAGE | IN ON MATION |

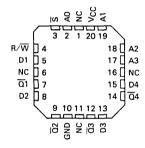

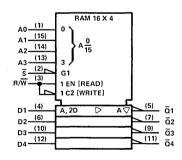

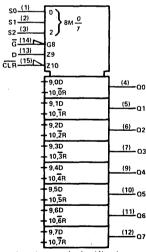

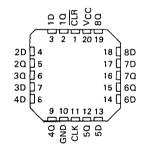

| 64-Bit      | 16 x 4       | 3-state Outputs | 'HC189 | HI                             | 2-5  | 3-84         |

# **EXPLANATION OF FUNCTION TABLES**

The following symbols are now being used in function tables on TI data sheets:

H = high level (steady state)

= low level (steady state)

† = transition from low to high level

= transition from high to low level

X = irrelevant (any input, including transitions)

Z = off (high-impedance) state of a 3-state output

a..h = the level of steady-state inputs at inputs A through H respectively

Qo = level of Q before the indicated steady-state input conditions were established

$\overline{Q}_{Q}$  = complement of  $Q_{Q}$  or level of  $\overline{Q}$  before the indicated steady-state input conditions were established

$Q_n$  = level of Q before the most recent active transition indicated by  $\dagger$  or  $\downarrow$

= one high-level pulse = one low-level pulse

TOGGLE = each output changes to the complement of its previous level on each active transition indicated by † or ↓.

If, in the input columns, a row contains only the symbols H, L, and/or X, this means the indicated output is valid whenever the input configuration is achieved and regardless of the sequence in which it is achieved. The output persists so long as the input configuration is maintained.

Ш

# **EXPLANATION OF FUNCTION TABLES**

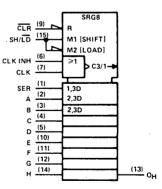

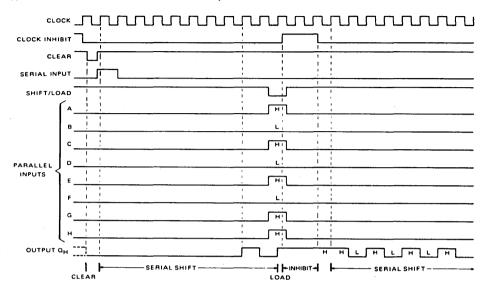

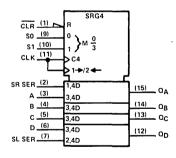

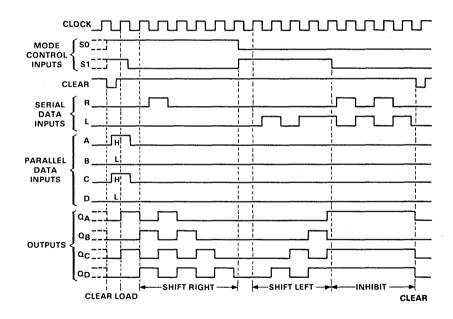

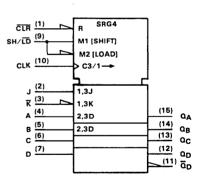

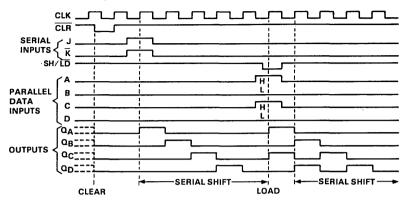

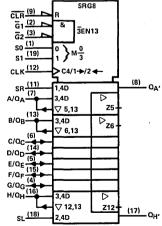

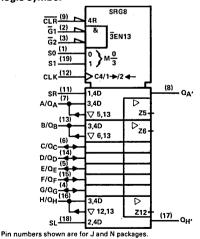

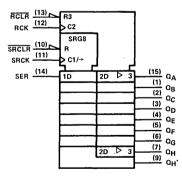

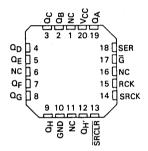

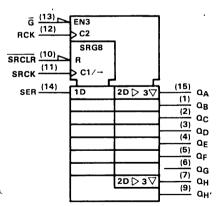

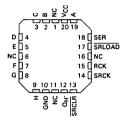

Among the most complex function tables in this book are those of the shift registers. These embody most of the symbols used in any of the function tables, plus more. Below is the function table of a 4-bit bidirectional universal shift register, e.g., type SN74HC194.

#### FUNCTION TARIF

| INPUTS |      |     |        |      |        |   |          | OUT | PUTS |                |          |               |          |

|--------|------|-----|--------|------|--------|---|----------|-----|------|----------------|----------|---------------|----------|

| 01540  | MODE |     | OI OOK | SE   | SERIAL |   | PARALLEL |     | 0.   | 0-             | 0-       |               |          |

| CLEAR  | S1   | \$0 | CLOCK  | LEFT | RIGHT  | A | В        | С   | D    | Q <sub>A</sub> | αВ       | αc            | σD       |

| L      | X    | Х   | X      | ×    | X      | X | X        | Х   | X    | L              | L        | L             | L        |

| н      | ×    | Х   | L      | ×    | ×      | х | X        | х   | Х    | QAO            | $Q_{BO}$ | $a_{co}$      | $Q_{DO}$ |

| н      | н    | Н   | 1      | ×    | X      | a | b        | С   | d    | а              | b        | С             | d        |

| Н      | L    | Н   | t      | ×    | н      | х | X        | Х   | х    | Н              | $Q_{An}$ | $Q_{Bn}$      | $Q_{Cn}$ |

| н      | L    | Н   | 1      | ×    | L      | х | Х        | Х   | Х    | L              | $Q_{An}$ | $Q_{Bn}$      | $Q_{Cn}$ |

| Н      | н    | L   | 1      | н    | X      | х | Х        | Х   | Х    | $\alpha_{Bn}$  | $Q_{Cn}$ | $\alpha_{Dn}$ | н        |

| Н      | н    | L   | 1      | L    | x      | х | Х        | Х   | Х    | QBn            | $Q_{Cn}$ | $Q_{Dn}$      | L        |

| н      | L    | L   | x      | x    | х      | х | х        | х   | Х    | QAD            | QBn      | QCn           | QDO      |

The first line of the table represents a synchronous clearing of the register and says that if clear is low, all four outputs will be reset low regardless of the other inputs. In the following lines, clear is inactive (high) and so has no effect.

The second line shows that so long as the clock input remains low (while clear is high), no other input has any effect and the outputs maintain the levels they assumed before the steady-state combination of clear high and clock low was established. Since on other lines of the table only the rising transition of the clock is shown to be active, the second line implicitly shows that no further change in the outputs will occur while the clock remains high or on the high-to-low transition of the clock,

The third line of the table represents synchronous parallel loading of the register and says that if S1 and S0 are both high then, without regard to the serial input, the data entered at A will be at output  $Q_A$ , data entered at B will be at  $Q_B$ , and so forth, following a low-to-high clock transition.

The fourth and fifth lines represent the loading of high- and low-level data, respectively, from the shift-right serial input and the shifting of previously entered data one bit; data previously at  $Q_B$  is now at  $Q_B$ , the previous levels of  $Q_B$  and  $Q_C$  are now at Qc and Qp respectively, and the data previously at Qp is no longer in the register. This entry of serial data and shift takes place on the low-to-high transition of the clock when S1 is low and S0 is high and the levels at inputs A through D have no effect.

The sixth and seventh lines represent the loading of high- and low-level data, respectively, from the shift-left serial input and the shifting of previously entered data one bit; data previously at  $Q_B$  is now at  $Q_A$ , the previous levels of  $Q_C$  and  $Q_D$  are now at QB and QC, respectively, and the data previously at QA is no longer in the register. This entry of serial data and shift takes place on the low-to-high transition of the clock when S1 is high and S0 is low and the levels at inputs A through D have no effect.

The last line shows that as long as both mode inputs are low, no other input has any effect and, as in the second line, the outputs maintain the levels they assumed before the steady-state combination of clear high and both mode inputs low was established.

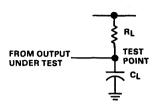

#### **TOTEM POLE OUTPUTS**

|         | PARAMETER              | R <sub>L</sub> ‡ | CL†‡   |

|---------|------------------------|------------------|--------|

| tpLH or | Standard outputs       | ∞                | 50 pF  |

| tPHL    | High-current outputs § | •                | 150 pF |

<sup>†</sup>C<sub>L</sub> includes probe and test fixture capacitance.

‡These values apply only when alternative values (R<sub>I</sub> = 2 k $\Omega$ , C<sub>I</sub> = 15 pF) are not specified in the column heading in switching characteristics.

§High-current outputs are indicated by the ▷ in the logic symbol.

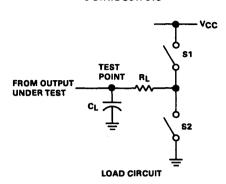

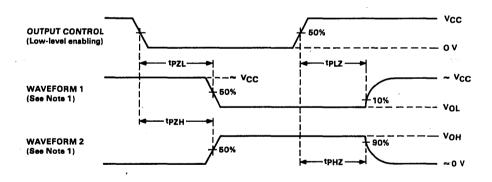

# 3-STATE OUTPUTS

| PARAMETER    | R <sub>L</sub> ‡ | CL†‡  | S <sub>1</sub> | S <sub>2</sub> |

|--------------|------------------|-------|----------------|----------------|

| tPZH         | 1 κΩ             | F - F | OPEN           | CLOSED         |

| tPZL         | - ' K.           | 5 pF  | CLOSED         | OPEN           |

| tPHZ         | 1.10             | 50 -F | OPEN           | CLOSED         |

| tPLZ         | 1 kΩ   50 pF     |       | CLOSED         | OPEN           |

| tPLH or tPHL |                  | 75 pF | CLOSED         | OPEN           |

<sup>†</sup>C<sub>L</sub> includes probe and test fixture capacitance. These values apply only when alternative values (R<sub>L</sub> = 667Ω, C<sub>L</sub> = 45 pF) are not specified in the column heading in switching characteristics.

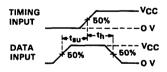

**VOLTAGE WAVEFORMS** SETUP AND HOLD TIMES\*

<sup>\*</sup> In the examples above, the phase relationships between inputs and outputs have been chosen arbitrarily. All input pulses are supplied by generators having the following characteristics: PRR  $\leq$  1 MHz,  $Z_{out} \approx 50\Omega$ ,  $t_f = 6$  ns.  $t_f = 6$  ns.

# PARAMETER MEASUREMENT INFORMATION

VOLTAGE WAVEFORMS

ENABLE AND DISABLE TIMES, THREE-STATE OUTPUTS\*

Note: 1. Waveform 1 is for an output with internal conditions such that the output is low except when disabled by the output control.

Waveform 2 is for an output with internal conditions such that the output is high except when disabled by the output control.

In the examples above, the phase relationships between inputs and outputs have been chosen arbitrarily.

All input pulses are supplied by generators having the following characteristics: PRR ≤ 1 MHz, Z<sub>out</sub> ≈ 50 Ω, t<sub>f</sub> = 6 ns, t<sub>f</sub> = 6 ns.

# THIS PAGE INTENTIONALLY LEFT BLANK

# Ratings and Characteristics

# **ATTENTION**

These devices contain circuits to protect the inputs and outputs against damage due to high static voltages or electrostatic fields; however, it is advised that precautions be taken to avoid application of any voltage higher than maximum-rated voltages to these high-impedance circuits.

Unused inputs must always be connected to an appropriate logic voltage level, preferably either  $V_{\hbox{\footnotesize{CC}}}$  or ground.

# SPECIFICATIONS FOR SSI CIRCUITS

D2684, DECEMBER 1982

absolute maximum ratings over operating free-air temperature ranget

| Supply voltage range, VCC                                                             | 0.5 to 7 V              |

|---------------------------------------------------------------------------------------|-------------------------|

| Input diode current, $I_{IK}(V_I < -0.5 \text{ V or } V_I > V_{CC} + 0.5 \text{ V})$  | ±20 mA                  |

| Output diode current, $I_{OK}(V_O < -0.5 \text{ V or } V_O > V_{CC} + 0.5 \text{ V})$ | ±20 mA                  |

| Continuous output current (-0.5 V < V <sub>O</sub> < V <sub>CC</sub> + 0.5 V)         | ±25 mA                  |

| Continuous current through VCC or GND pins                                            | ±50 mA                  |

| Lead temperature 1,6 mm (1/16 in) from case: J package for 60 seconds                 | 300°C                   |

| N package for 10 seconds                                                              | 260°C                   |

| Storage temperature range                                                             | 65°C to 150°C           |

| resses beyond those listed under "Absolute Maximum Ratings" may cause permanent dama  | ge to the device. These |

†Str are stress ratings only and functional operation of the device at these or any other conditions beyond those indicated under "Recommended Operating Conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

# recommended operating conditions

|                                         |                         |      | SN54H | C'                    |      | SN74H | 2'                    |      |

|-----------------------------------------|-------------------------|------|-------|-----------------------|------|-------|-----------------------|------|

|                                         |                         | MIN  | NOM   | MAX                   | MIN  | NOM   | MAX                   | UNIT |

| V <sub>CC</sub> Supply voltage          |                         | 2    | 5     | 6                     | 2    | 5     | 6                     | V    |

|                                         | V <sub>CC</sub> = 4.5 V | 3.15 |       |                       | 3.15 |       |                       |      |

| VIH High-level input voltage            | V <sub>CC</sub> = 5 V   | 3.50 |       |                       | 3.50 |       |                       | V    |

|                                         | V <sub>CC</sub> = 5.5 V | 3.85 |       |                       | 3.85 |       |                       |      |

|                                         | V <sub>CC</sub> = 4.5 V | 0    |       | 0.9                   | 0    |       | 0.9                   |      |

| V <sub>IL</sub> Low-level input voltage | V <sub>CC</sub> = 5 V   | 0    |       | 1.0                   | 0    |       | 1.0                   | V    |

|                                         | V <sub>CC</sub> = 5.5 V | 0    |       | 1.1                   | 0    |       | 1.1                   |      |

| V <sub>I</sub> Input voltage            |                         | -0.5 |       | V <sub>CC</sub> + 0.5 | -0.5 |       | V <sub>CC</sub> + 0.5 | ٧    |

| VO Output voltage                       |                         | -0.5 |       | V <sub>CC</sub> + 0.5 | -0.5 |       | V <sub>CC</sub> + 0.5 | V    |

| IOH High-level output current           |                         |      |       | -4                    |      |       | -4                    | mA   |

| IOL Low-level output current            |                         |      |       | 3.4                   |      |       | 4                     | mA   |

| Input transition (rise and fa           | II) times               | 0    |       | 500                   | 0    |       | 500                   |      |

| tt (except Schmitt-trigger inp          | uts)                    | 0    |       | 500                   | ٥    |       | 500                   | ns   |

| TA Operating free-air tempera           | ture                    | -55  |       | 125                   | -40  |       | 85                    | °C   |

electrical characteristics, VCC = 5 V ± 10%,

over recommended operating free-air temperature range (unless otherwise noted)

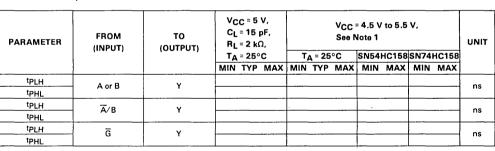

|                     |                                                                                    |                          | T                    | = 25°C |      | SN541                | HC' | SN741                | HC' |      |

|---------------------|------------------------------------------------------------------------------------|--------------------------|----------------------|--------|------|----------------------|-----|----------------------|-----|------|

| PARAMETER           | TEST CONDITIONS                                                                    |                          | MIN                  | TYP‡   | MAX  | MIN                  | MAX | MIN                  | MAX | UNIT |

|                     | V <sub>I</sub> = V <sub>IH</sub> or V <sub>IL</sub> , '<br>I <sub>OH</sub> = -4mA  | V <sub>CC</sub> = 4.5 V, | 3.86                 |        |      | 3.56                 |     | 3.70                 | -   |      |