The Engineering Staff of TEXAS INSTRUMENTS INCORPORATED Semiconductor Group

# **Second Edition**

**FEBRUARY 1976**

# TABLE OF CONTENTS

| 1. | ARC | CHITECTURE                                           |

|----|-----|------------------------------------------------------|

|    | 1.1 | Introduction                                         |

|    | 1.2 | The Stack                                            |

|    | 1.3 | Registers                                            |

|    | 1.4 | The Arithmetic Unit                                  |

|    | 1.5 | Status and Control                                   |

|    | 1.6 | I/O Operations                                       |

|    | 1.7 | Instruction Timing                                   |

| 2. | тмз | S 8080 INSTRUCTION SET                               |

|    | 2.1 | Instruction Formats                                  |

|    | 2.2 | Instruction Set Description                          |

|    |     | 2.2.1 Instruction Symbols                            |

|    |     | 2.2.2 Accumulator Group Instructions                 |

|    |     | 2.2.3 Input/Output Instructions                      |

|    |     | 2.2.4 Machine Instructions                           |

|    |     | 2.2.5 Program Counter and Stack Control Instructions |

|    |     | 2.2.6 Register Group Instructions                    |

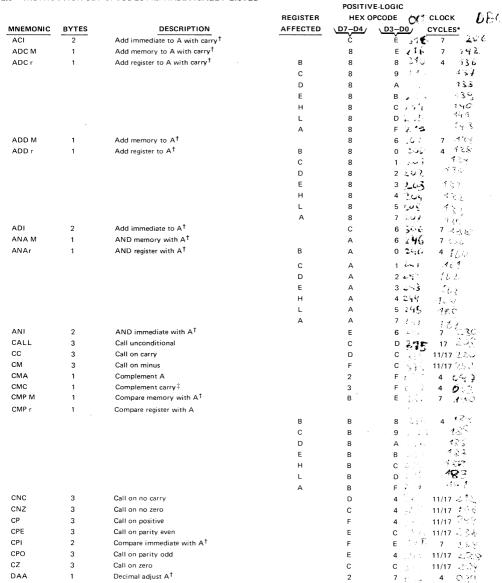

|    | 2.3 | Instruction Set Opcodes Alphabetically Listed        |

| 3. | тмз | S 8080 ELECTRICAL AND MECHANICAL SPECIFICATIONS      |

|    | 3.1 | Absolute Maximum Ratings                             |

|    | 3.2 | Recommended Operating Conditions                     |

|    | 3.3 | Electrical Characteristics                           |

|    | 3.4 | Timing Requirements                                  |

|    | 3.5 | Switching Characteristics                            |

|    | 3.6 | Terminal Assignments                                 |

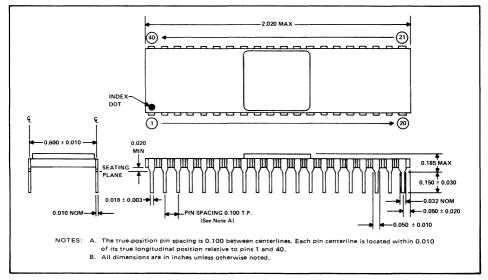

|    | 3.7 | Mechanical Data                                      |

|    |     |                                                      |

# LIST OF ILLUSTRATIONS

| Figure 1 | TMS 8080 Functional Block Diagram |  |  |  |  |  |  |  |  |  |  |  |  | 2  |

|----------|-----------------------------------|--|--|--|--|--|--|--|--|--|--|--|--|----|

| Figure 2 | Voltage Waveforms                 |  |  |  |  |  |  |  |  |  |  |  |  | 19 |

Information contained in this publication is believed to be accurate and reliable. However, responsibility is assumed neither for its use nor for any infringement of patents or rights of others that may result from its use. No license is granted by implication or otherwise under any patent or patent right of Texas Instruments or others.

> Copyright © 1975 Texas Instruments Incorporated

> > 1

# TMS 8080 MICROPROCESSOR

# 1. ARCHITECTURE

# 1.1 INTRODUCTION

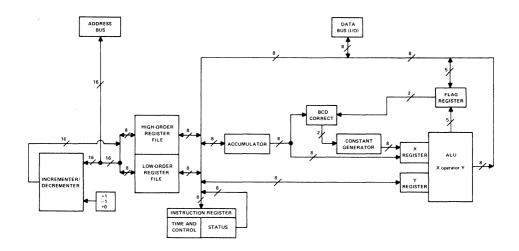

The TMS 8080 is an 8-bit parallel central processing unit (CPU) fabricated on a single chip using a high-speed N-channel silicon-gate process. (See Figure 1). A complete microcomputer system with a  $2\mu$ s instruction cycle can be formed by interfacing this circuit with any appropriate memory. Separate 8-bit data and 16-bit address buses simplify the interface and allow direct addressing of 65,536 bytes of memory. Up to 256 input and 256 output ports are also provided with direct addressing. Control signals are brought directly out of the processor and all signals, excluding clocks, are TTL compatible.

# 1.2 THE STACK

The TMS 8080 incorporates a stack architecture in which a portion of external memory is used as a pushdown stack for storing data from working registers and internal machine status. A 16-bit stack pointer (SP) is provided to facilitate stack location in the memory and to allow almost unlimited interrupt handling capability. The CALL and RST (restart) instructions use the SP to store the program counter (PC) into the stack. The RET (return) instruction uses the SP to acquire the previous PC value. Additional instructions allow data from registers and flags to be saved in the stack.

#### 1.3 REGISTERS

The TMS 8080 has three categories of registers: general registers, program control registers, and internal registers. The general registers and program control registers are listed in Table 1. The internal registers are not accessible by the programmer. They include the instruction register, which holds the present instruction, and several temporary storage registers to hold internal data or latch input and output addresses and data.

FIGURE 1-TMS 8080 FUNCTIONAL BLOCK DIAGRAM

#### 1.4 THE ARITHMETIC UNIT

Arithmetic operations are performed in an 8-bit parallel arithmetic unit that has both binary and decimal capabilities. Four testable internal flag bits are provided to facilitate program control, and a fifth flag is used for decimal corrections. Table 2 defines these flags and their operation. Decimal corrections are performed with the DAA instruction. The DAA corrects the result of binary arithmetic operation on BCD data as shown in Table 3.

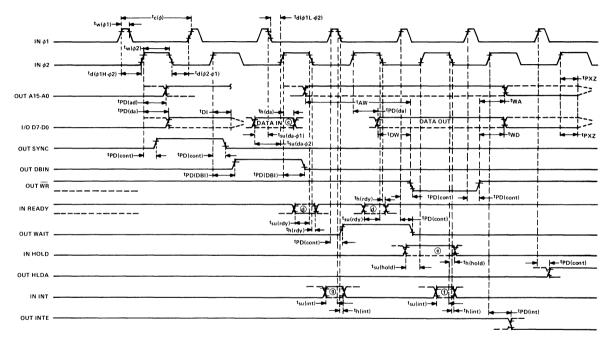

#### 1.5 STATUS AND CONTROL

Two types of status are provided by the TMS8080. Certain status is indicated by dedicated control lines. Additional status is transmitted on the data bus during the beginning of each instruction cycle (machine cycle). Table 4 indicates the pin functions of the TMS8080. Table 5 defines the status information that is presented during the beginning of each machine cycle (SYNC time) on the data bus.

### 1.6 I/O OPERATIONS

Input/output operations (I/O) are performed using the IN and OUT instructions. The second byte of these instructions indicates the device address (256 device addresse). When an IN instruction is executed, the input device address appears in duplicate on A7 through A0 and A15 through A8, along with WO and INP status on the data bus. The addressed input device then puts its input data on the data bus for entry into the accumulator. When an OUT instruction is executed, the same operation occurs except that the data bus has OUT status and then has output data.

Direct memory access channels (DMA) can be OR-tied directly with the data and address buses through the use of the HOLD and HLDA (hold acknowledge) controls. When a HOLD request is accepted by the CPU, HLDA goes high, the address and data lines are forced to a high-impedance or "floating" condition, and the CPU stops until the HOLD request is removed.

Interfacing with different speed memories is easily accomplished by use of the WAIT and READY pins. During each machine cycle, the CPU polls the READY input and enters a wait condition until the READY line becomes true. When the WAIT output pin is high, it indicates that the CPU has entered the wait state.

Designing interrupt driven systems is simplified through the use of vectored interrupts. At the end of each instruction, the CPU polls the INT input to determine if an interrupt request is being made. This action does not occur if the CPU is in the HOLD state or if interrupts are disabled. The INTE output indicates if the interrupt logic is enabled (INTE is high). When a request is honored, the INTA status bit becomes high, and an RST instruction may be inserted to force the CPU to jump to one of eight possible locations. Enabling or disabling interrupts is controlled by special instructions (El or DI). The interrupt input is automatically disabled when an interrupt request is accepted or when a RESET signal is received.

# 1.7 INSTRUCTION TIMING

The execution time of the instructions varies depending on the operation required and the number of memory references needed. A machine cycle is defined to be a memory referencing operation and is either 3, 4, or 5 state times long. A state time (designated S) is a full cycle of clocks  $\phi$ 1 and  $\phi$ 2. (NOTE: The exception to this rule is the DAD instruction, which consists of 1 memory reference in 10 state times). The first machine cycle (designated M1) is either 4 or 5 state times long and is the "instruction fetch" cycle with the program counter appearing on the address bus. The CPU then continues with as many M cycles as necessary to complete the execution of the instruction (up to a maximum of 5). Thus the instruction execution time varies from 4 state times (several including ADDr) to 18 (XTHL). The WAIT or HOLD conditions may affect the execution time since they can be used to control the machine (for example to "single step") and the HALT instruction forces the CPU to stop until an interrupt. In the event of an interrupt, the PC will not be incremented during the next M1 and an RST instruction are beinserted.

### TABLE 1 TMS 8080 REGISTERS

| NAME            | DESIGNATOR | LENGTH | PURPOSE                                                   |

|-----------------|------------|--------|-----------------------------------------------------------|

| Accumulator     | A 8        |        | Used for arithmetic, logical, and I/O operations          |

| B Register      | B          | 8      | General or most significant 8 bits of double register BC  |

| C Register      | C          | 8      | General or least significant 8 bits of double register BC |

| D Register      | D          | 8      | General or most significant 8 bits of double register DE  |

| E Register      | E          | 8      | General or least significant 8 bits of double register DE |

| H Register      | н          | 8      | General or most significant 8 bits of double register HL  |

| L Register      | L          | . 8    | General or least significant 8 bits of double register HL |

| Program Counter | PC         | 16     | Contains address of next byte to be fetched               |

| Stack Pointer   | SP         | 16     | Contains address of the last byte of data saved in        |

|                 |            |        | the memory stack                                          |

| Flag Register   | F          | 5      | Five flags (C, Z, S, P, C1)                               |

NOTE: Registers B and C may be used together as a single 16-bit register, likewise, D and E, and H and L.

# TABLE 2

#### FLAG DESCRIPTIONS

| SYMBOL | TESTABLE | DESCRIPTION                                                                                                                                                                           |

|--------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| C      | YES      | C is the carry/borrow out of the MSB (most significant bit) of the ALU (Arithment Logic Unit). A TRUE condition (C = 1) indicates overflow for addition or underflow for subtraction. |

| z      | YES      | A TRUE condition (Z = 1) indicates that the output of the ALU is equal to zero.                                                                                                       |

| S      | YES      | A TRUE condition (S = 1) indicates that the MSB of the ALU output is equal to a one (1).                                                                                              |

| Р      | YES      | A TRUE condition (P = 1) indicates that the output of the ALU has even parity (the number of bits equal to one is even).                                                              |

| C1     | NO       | C1 is the carry out of the fourth bit of the ALU (TRUE condition). C1 is used only for BCD correction with the DAA instruction.                                                       |

# TABLE 3 FUNCTION OF THE DAA INSTRUCTION

Assume the accumulator (A) contains two BCD digits, X and Y

|   | ACCUM          | ULAT  | OR                            | ACCUMULATOR |       |    |                               |  |  |  |  |

|---|----------------|-------|-------------------------------|-------------|-------|----|-------------------------------|--|--|--|--|

|   | BEFO           | RE DA | А                             | AFTER DAA   |       |    |                               |  |  |  |  |

| С | $A_7\ldotsA_4$ | C1    | A <sub>3</sub> A <sub>0</sub> | С           | A7 A4 | C1 | A <sub>3</sub> A <sub>0</sub> |  |  |  |  |

| 0 | X < 10         | 0     | Y < 10                        | 0           | ×     | 0  | Y                             |  |  |  |  |

| 0 | X < 10         | 1     | Y < 10                        | 0           | ×     | 0  | Y + 6                         |  |  |  |  |

| 0 | X < 9          | 0     | Y ≥ 10                        | 0           | X + 1 | 1  | Y + 6                         |  |  |  |  |

| 1 | X < 10         | 0     | ' Y < 10                      | 1           | X + 6 | 0  | Y                             |  |  |  |  |

| 1 | X < 10         | 1     | Y < 10                        | 1           | X + 6 | 0  | Y + 6                         |  |  |  |  |

| 1 | X < 10         | 0     | Y ≥ 10                        | 1           | X + 7 | 1  | Y + 6                         |  |  |  |  |

| 0 | X ≥ 10         | 0     | Y < 10                        | 1           | X + 6 | 0  | Y                             |  |  |  |  |

| 0 | X ≥ 10         | 1     | Y < 10                        | 1           | X + 6 | 0  | Y + 6                         |  |  |  |  |

| 0 | X ≥ 9          | 0     | Y ≥ 10                        | 1           | X + 7 | 1  | Y + 6                         |  |  |  |  |

NOTE: The corrections shown in Table 3 are sufficient for addition. For subtraction, the programmer must account for the borrow condition that can occur and give erroneous results. The most straight forward method is to set A = 99<sub>16</sub> and carry = 1. Then add the minuend to A after subtracting the subtrahend from A.

| TMS 8080 PIN DEFINITIONS |          |            |                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |  |

|--------------------------|----------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| SIGNATURE                | PIN      | 1/0        | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |  |

| A15 (MSB)                | 36       | OUT        | A15 through A0 comprise the address bus. True memory or I/O device addresses appear on                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |  |

| A14                      | 39       | OUT        | this 3-state bus during the first state time of each instruction cycle.                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |  |

| A13                      | 38       | OUT        |                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |  |

| A12                      | 37       | OUT        |                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |  |

| A11                      | 40       | OUT        |                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |  |

| A10                      | 1        | OUT        |                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |  |

| A9                       | 35       | OUT        |                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |  |

| A8                       | 34       | OUT        |                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |  |

| A7<br>A6                 | 33<br>32 | OUT        |                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |  |

| A0<br>A5                 | 31       | OUT<br>OUT |                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |  |

| A4                       | 30       | OUT        |                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |  |

| A3                       | 29       | OUT        |                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |  |

| A2                       | 27       | OUT        |                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |  |

| A1                       | 26       | OUT        |                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |  |

| A0 (LSB)                 | 25       | OUT        |                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |  |

| D7 (MSB)                 | 6        | IN/OUT     |                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |  |

| D6                       | 5        | IN/OUT     | D7 through D0 comprise the bidirectional 3-state data bus. Memory, status, or I/O data is                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |  |

| D5                       | 4        | IN/OUT     | transferred on this bus.                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |  |

| D4                       | 3        | IN/OUT     |                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |  |

| D3                       | 7        | IN/OUT     |                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |  |

| D2                       | 8        | IN/OUT     |                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |  |

| D1                       | 9        | IN/OUT     |                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |  |

| D0 (LSB)                 | 10       | IN/OUT     |                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |  |

| V <sub>SS</sub>          | 2        |            | Ground reference                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |  |

| V <sub>BB</sub>          | 11       |            | Supply voltage (-5 V nominal)                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |  |

| vcc                      | 20       |            | Supply voltage (5 V nominal)                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |  |

| VDD                      | 28       |            | Supply voltage (12 V nominal)                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |  |

| φ1                       | 22       | IN         | Phase 1 clock.                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |  |

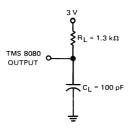

| φ2                       | 15       | IN         | Phase 2 clock. See page 19 for $\phi$ 1 and $\phi$ 2 timing.                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |  |

| RESET                    | 12       | IN         | Reset. When active (high) for a minimum of 3 clock cycles, the RESET input causes the<br>TMS 8080 to be reset. PC is cleared, interrupts are disabled, and after RESET, instruction<br>execution starts at memory location 0. To prevent a lockup condition, a HALT instruction<br>must not be used in location 0.                                           |  |  |  |  |  |  |  |

| HOLD                     | 13       | IN         | Hold signal. When active (high) HOLD causes the TMS 8080 to enter a hold state and float<br>(put the 3-state address and data bus in a high-impedance state). The chip acknowledges<br>entering the hold state with the HLDA signal and will not accept interrupts until it leaves<br>the hold state.                                                        |  |  |  |  |  |  |  |

| INT                      | 14       | IN         | Interrupt request. When active (high) INT indicates to the TMS8080 that an interrupt is being requested. The TMS8080 polls INT during a HALT or at the end of an instruction. The request will be accepted except when INTE is low or the CPU is in the HOLD condition.                                                                                      |  |  |  |  |  |  |  |

| INTE                     | 16       | OUT        | Interrupts enabled. INTE indicates that an interrupt will be accepted by the TMS 8080<br>unless it is in the hold state. INTE is set to a high logic level by the EI (Enable Interrupt)<br>instruction and reset to a low logic level by the DI (Disable Interrupt) instruction. INTE is<br>also reset when an interrupt is accepted and by a high on RESET. |  |  |  |  |  |  |  |

| DBIN                     | 17       | ОUT        | Data bus in. DBIN indicates whether the data bus is in an input or an output mode.<br>(high = input, low = output).                                                                                                                                                                                                                                          |  |  |  |  |  |  |  |

#### TABLE 4 TMS 8080 PIN DEFINITIONS

### TABLE 4 (CONTINUED)

| SIGNATURE | PIN | 1/0 | DESCRIPTION                                                                                                                                                                                                                        |  |  |  |  |  |  |

|-----------|-----|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| WR        | 18  | ουτ | Write. When active (low) $\overline{\rm WR}$ indicates a write operation on the data bus to memory or to an I/O port.                                                                                                              |  |  |  |  |  |  |

| SYNC      | 19  | OUT | Synchronizing control line. When active (high) SYNC indicates the beginning of each machine cycle of the TMS8080. Status information is also present on the data bus durin SYNC for external latches.                              |  |  |  |  |  |  |

| HLDA      | 21  | оυт | Hold acknowledge. When active (high) HLDA indicates that the TMS8080 is in a hold state.                                                                                                                                           |  |  |  |  |  |  |

| READY     | 23  | IN  | Ready control line. An active (high) level indicates to the TMS 8080 that an external device<br>has completed the transfer of data to or from the data bus. READY is used in conjunction<br>with WAIT for different memory speeds. |  |  |  |  |  |  |

| WAIT      | 24  | OUT | Wait status. When active (high) WAIT indicates that the TMS8080 has entered a wait state pending a READY signal from memory.                                                                                                       |  |  |  |  |  |  |

## TABLE 5 TMS 8080 STATUS

| SIGNATURE | DATA BUS BIT | DESCRIPTION                                                                                                               |

|-----------|--------------|---------------------------------------------------------------------------------------------------------------------------|

| INTA      | D0           | Interrupt acknowledge.                                                                                                    |

| wo        | D1           | Indicates that current machine cycle will be a read (input) (high = read) or a write (output)<br>(low = write) operation. |

| STACK     | D2           | Indicates that address is stack address from the SP.                                                                      |

| HLTA      | D3           | HALT instruction acknowledge.                                                                                             |

| OUT       | D4           | Indicates that the address bus has an output device address and the data bus has output data.                             |

| M1        | D5           | Indicates instruction acquisition for first byte.                                                                         |

| INP       | D6           | Indicates address bus has address of input device.                                                                        |

| MEMR      | D7           | Indicates that data bus will be used for memory read data.                                                                |

# 2. TMS 8080 INSTRUCTION SET

#### 2.1 INSTRUCTION FORMATS

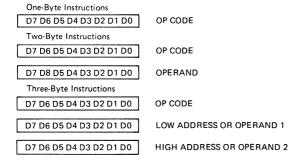

TMS 8080 instructions are either one, two, or three bytes long and are stored as binary integers in successive memory locations in the format shown below.

# 2.2 INSTRUCTION SET DESCRIPTION

Operations resulting from the execution of TMS 8080 instructions are described in this section. The flags that are affected by each instruction are given after the description.

# 2.2.1 INSTRUCTION SYMBOLS

| SYMBOL    |                       | DESCRIPTION                     |               |

|-----------|-----------------------|---------------------------------|---------------|

| <b2></b2> | Second byte of instr  | ruction                         |               |

| <b3></b3> | Third byte of instru  | ction                           |               |

| ra        | Register #            | <u>#</u>                        | Register Name |

|           | 000                   | -                               | В             |

|           | 001                   |                                 | С             |

|           | 010                   |                                 | D             |

|           | 011                   |                                 | E             |

|           | 100                   |                                 | н             |

|           | 101                   |                                 | L             |

|           | 111                   |                                 | А             |

| ۲b        | Register #            | <b>#</b>                        | Register Name |

|           | 00                    | _                               | BC            |

|           | 01                    |                                 | DE            |

|           | 10                    |                                 | HL            |

|           | 11                    |                                 | SP            |

| rc        | Register #            | <u><u></u></u>                  | Register Name |

|           | 0                     |                                 | BC            |

|           | 1                     |                                 | DE            |

| ۲d        | Register #            | <u><u></u></u>                  | Register Name |

|           | 00                    |                                 | BC            |

|           | 01                    |                                 | DE            |

|           | 10                    |                                 | HL            |

| rdL ·     | Least significant 8 b |                                 |               |

| rdH       | Most significant 8 bi |                                 |               |

| f         | i lugo                | rue condition                   |               |

|           | Zero (Z)              | Result is zero                  |               |

|           | Carry (C)             | Carry/borrow out of MSB is o    | one           |

|           | Parity (P)            | Parity of result is even        |               |

|           | Sign (S)              | MSB of result is one            |               |

|           | Carry 1(C1)           | Carry out of fourth bit is one  |               |

| M         |                       | ined by registers H and L       |               |

| ()        | Contents of specifie  | •                               |               |

| []        |                       | contained in specified register |               |

| ÷         | Is transferred to     |                                 |               |

|           | Exchange              |                                 |               |

| Am        | Bit m of A register ( | accumulator)                    |               |

| {}<br>}   | Flags affected        |                                 |               |

| b2        | Single byte immedia   |                                 |               |

| b3b2      | Double byte immed     |                                 |               |

| (nnn)8    | (nnn) is an octal (ba | se 8) number                    |               |

# 2.2.2 ACCUMULATOR GROUP INSTRUCTIONS

|          |                |       | M CYCLES/ |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|----------|----------------|-------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MNEMONIC | OPERANDS       | BYTES | STATES    | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| ACI      | b2             | 2     | 2/7       | (A) $\leftarrow$ (A) + $<\!\!\mathrm{b_2}\!\!>\!\!+\!(\mathrm{carry}),$ add the second byte of the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|          |                |       |           | instruction and the contents of the carry flag to register A and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|          |                |       |           | place in A. {C,Z,S,P,C1}                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| ADC      | м              | 1     | 2/7       | (A) ← (A) + (M) + (carry). { C,Z,S,P,C1 }                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| ADC      | ra             | 1     | 1/4       | $(A) \leftarrow (A) + (r_a) + (carry) + (C,Z,S,P,C1)$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| ADD      | м              | 1     | 2/7       | (A) $\leftarrow$ (A) + (M), add the contents of M to register A and place in                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|          |                |       |           | A. {C,Z,S,P,C1}                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| ADD      | ra             | 1     | 1/4       | $(A) \leftarrow (A) + (r_a) \cdot \{C, Z, S, P, C1\}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| ADI      | b2             | 2     | 2/7       | $(A) \leftarrow (A) + \langle b_2 \rangle$ . $\{C, Z, S, P, C1\}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| ANA      | м              | 1     | 2/7       | (A) $\leftarrow$ (A) AND (M), take the logical AND of M and register A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|          |                |       |           | and place in A. The carry flag will be reset low. {C,Z,S,P,C1}                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| ANA      | ra             | 1     | 1/4       | (A) $\leftarrow$ (A) AND (r <sub>a</sub> ). {C,Z,S,P,C1}                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| ANI      | b2             | 2     | 2/7       | (A) $\leftarrow$ (A) AND $<$ b <sub>2</sub> >. {C,Z,S,P,C1}                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| CMA      |                | 1     | 1/4       | (A) $\leftarrow$ (A), complement A.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| CMC      |                | 1     | 1/4       | $(carry) \leftarrow (carry)$ , complement the carry flag. $\{C\}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| CMP      | М              | 1     | 2/7       | (A) – (M), compare the contents of M to register A and set the $(A - A - A) = (A - A)$ |

|          |                |       |           | flags accordingly, { C,Z,S,P,C1 }<br>(A) = (M) Z = 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |