# **MOS/LSI** from Texas Instruments

(t)

# MOS/LSI from Texas Instruments

October 1970

# index

|                                                            |     |   | 1     |

|------------------------------------------------------------|-----|---|-------|

| PRELIMINARY INFORMATION                                    |     |   | 3     |

| MOS/LSI NUMBERING SYSTEM                                   |     |   | 4     |

| MOS/LSI PACKAGING                                          |     |   | 5     |

| MOS/LSI SYSTEM COMPATIBILITY                               |     |   |       |

| SHIFT REGISTERS.                                           |     |   | . 15  |

| TMS3000LR, TMS3001LR DUAL STATIC SHIFT REGISTERS           |     |   | . 20  |

| TMS3002LR DUAL 50-BIT SHIFT REGISTER                       |     |   | . 27  |

| TMS3003LR DUAL 100-BIT SHIFT REGISTER                      |     |   | . 27  |

| TMS3012JR DUAL 128-BIT ACCUMULATOR                         |     |   |       |

| TMS3028LR DUAL 128-BIT SHIFT REGISTER                      |     |   | . 34  |

| TMS3016LR DUAL 16-BIT STATIC SHIFT REGISTER                |     |   | . 39  |

| TMS3026JC 6-BIT SERIAL IN PARALLEL OUT SHIFT REGISTER      |     |   | . 45  |

| TMS3101LC DUAL 100-BIT STATIC SHIFT REGISTER               |     |   | . 49  |

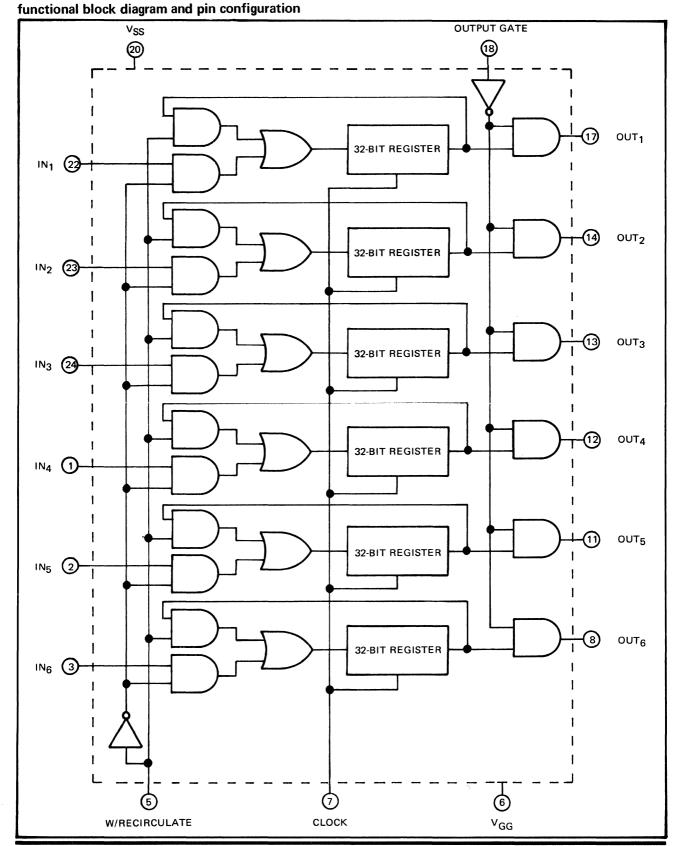

| TMS3112JC HEX 32-BIT STATIC SHIFT REGISTER                 |     |   | . 54  |

| TMS3304LR TRIPLE 66-BIT DYNAMIC SHIFT REGISTER             |     |   | . 60  |

| TMS3305LR TRIPLE 64-BIT DYNAMIC SHIFT REGISTER             |     |   | . 60  |

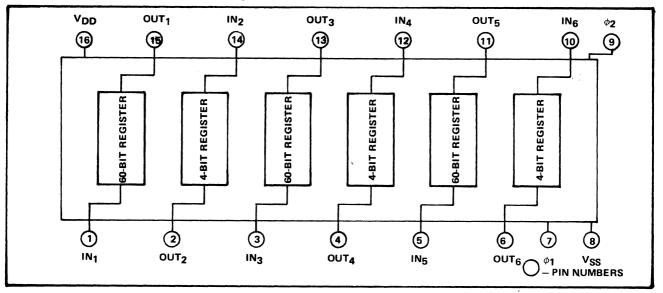

| TMS3309JC TWIN 512-BIT DYNAMIC SHIFT REGISTER/ACCUMULATOR  |     |   |       |

| TMS3314JR TRIPLE (60 + 4) DYNAMIC SHIFT REGISTER           |     |   | . 72  |

| TMS3401LC 512-BIT DYNAMIC SHIFT REGISTER                   |     |   |       |

| TMS3406LR DUAL 100-BIT DYNAMIC SHIFT REGISTER              |     |   |       |

|                                                            |     |   |       |

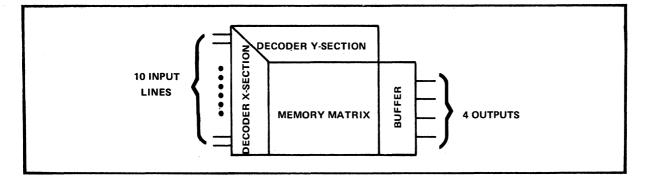

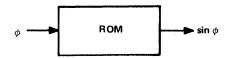

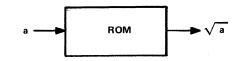

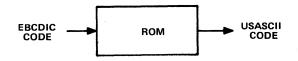

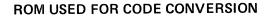

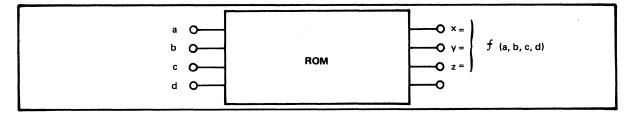

| READ ONLY MEMORIES                                         |     |   | . 88  |

| CUSTOM BIT PATTERN                                         |     |   |       |

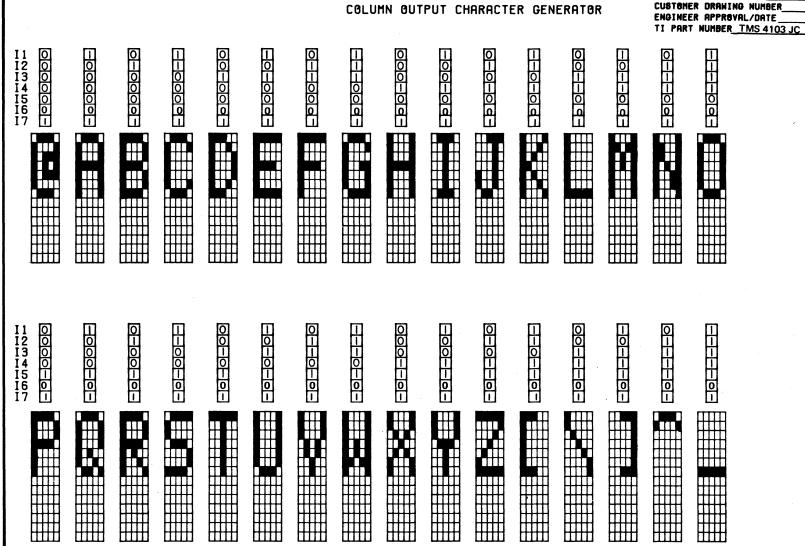

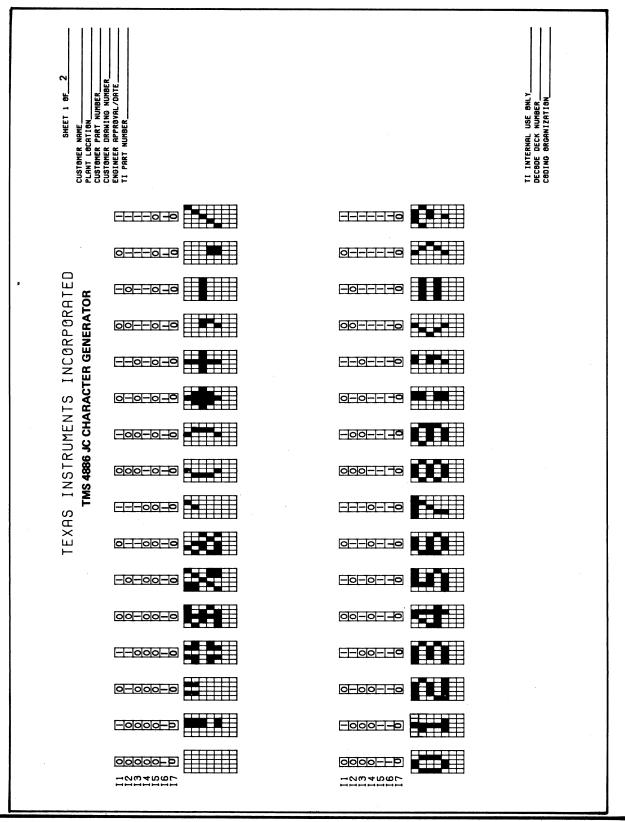

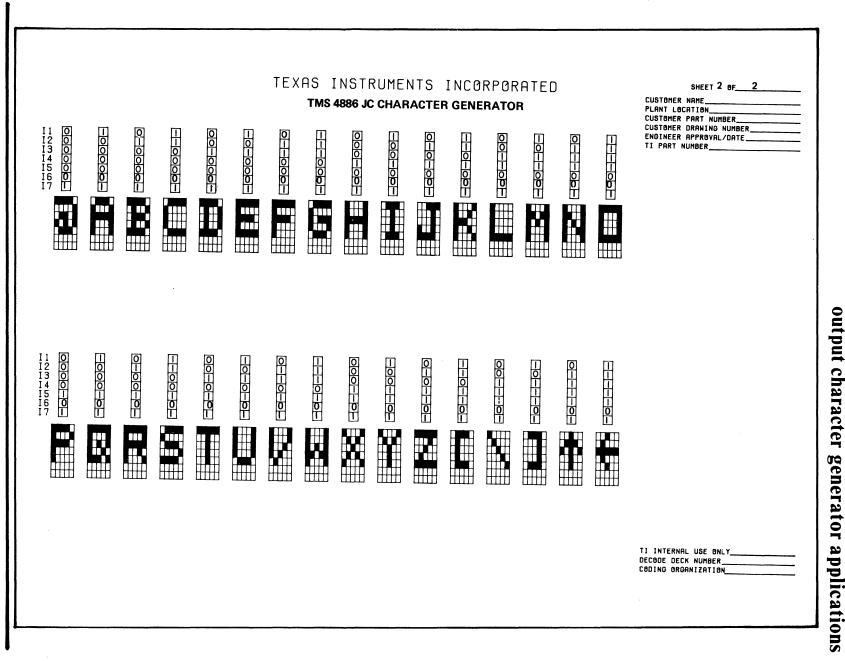

| TMS2400JC ROW OUTPUT CHARACTER GENERATOR                   |     |   |       |

| TMS2600JC 2048-BIT STATIC READ-ONLY MEMORY                 |     |   |       |

| TMS2800JC 1024-BIT STATIC READ-ONLY MEMORY                 |     |   |       |

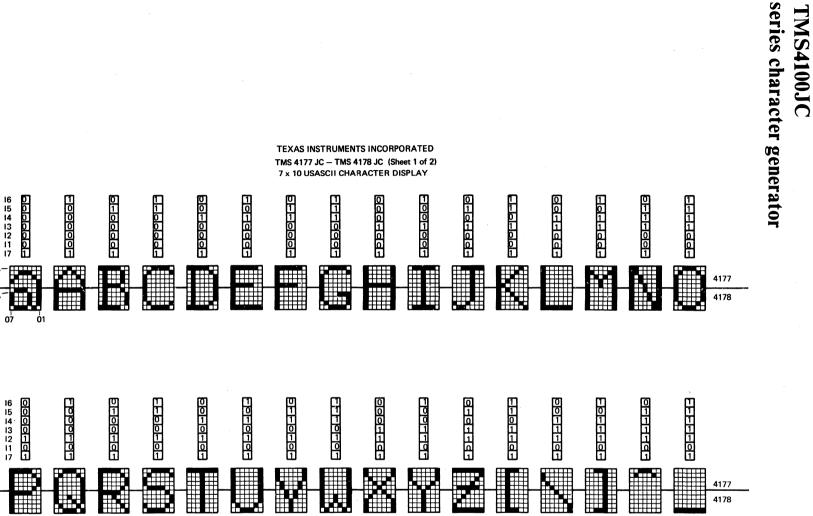

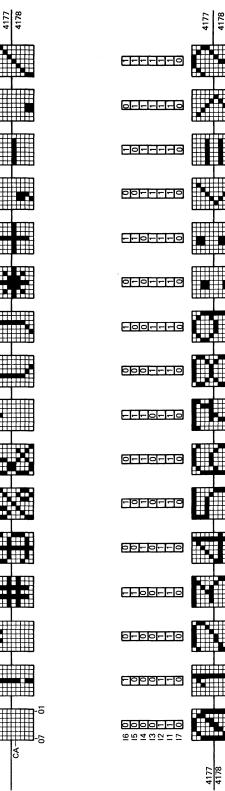

| TMS4100JC SERIES CHARACTER GENERATOR                       |     |   |       |

| TMS4300JC 4096-BIT STATIC READ-ONLY MEMORY                 |     |   |       |

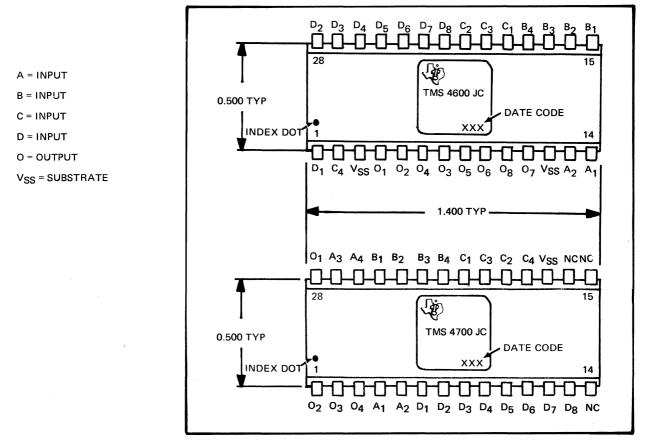

| TMS4500JC, TMS4600JC, TMS4700JC 2048-BIT HIGH SPEED STATIC |     | • |       |

| READ-ONLY MEMORIES                                         |     |   | . 139 |

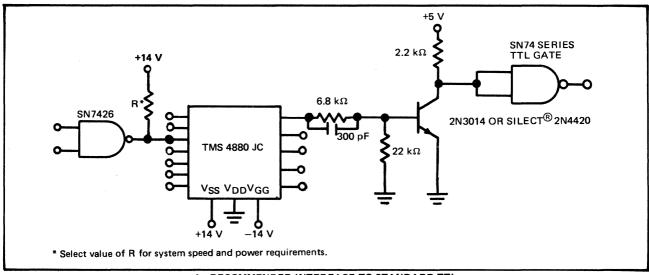

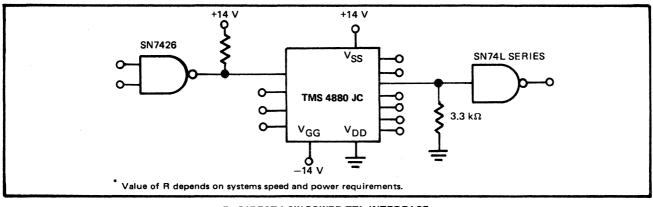

| TMS4880JC STATIC READ-ONLY MEMORY FOR PARALLEL OUTPUT      |     |   |       |

| CHARACTER GENERATOR APPLICATIONS                           |     |   | . 145 |

|                                                            |     | - |       |

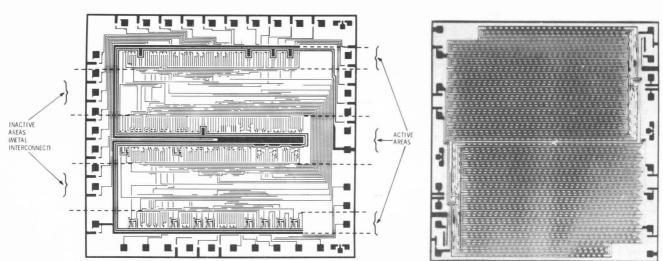

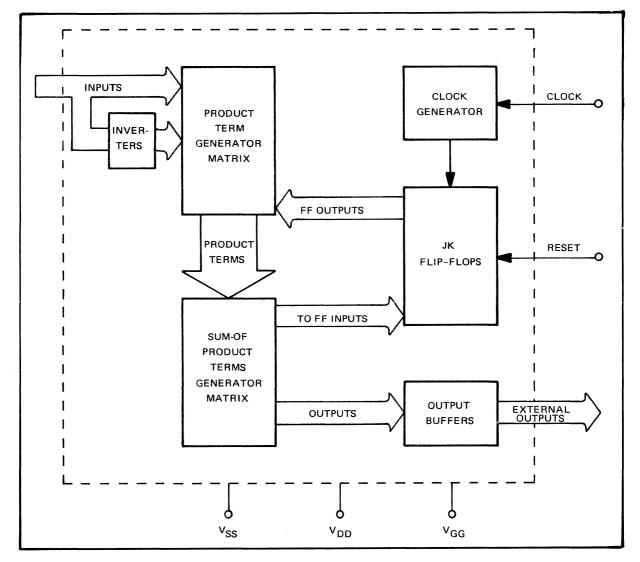

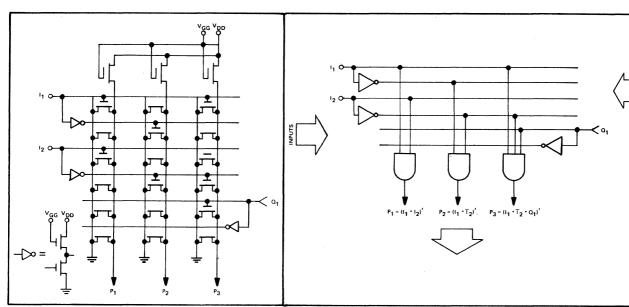

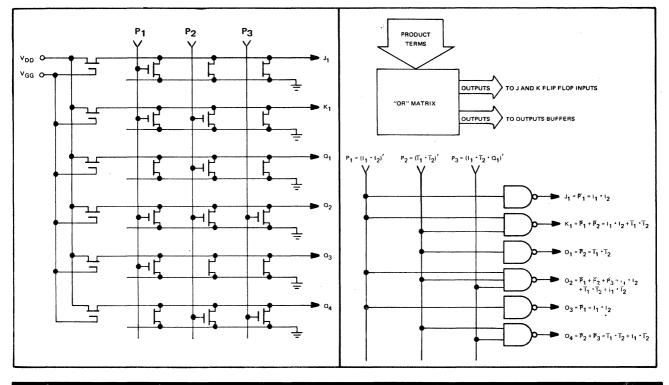

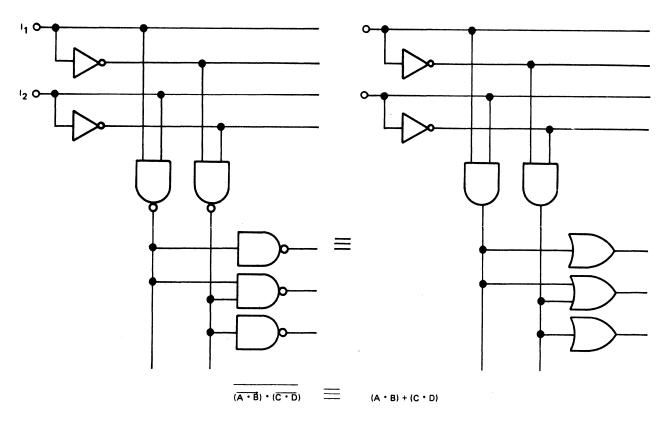

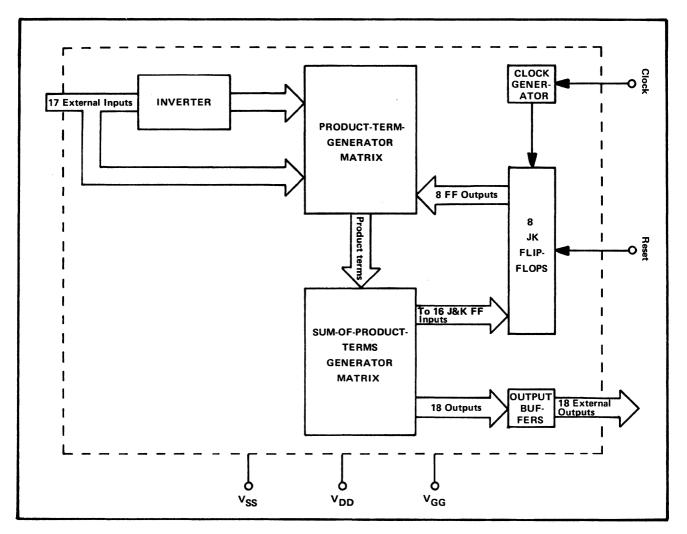

| PROGRAMMABLE LOGIC ARRAYS                                  |     |   | . 152 |

| TMS2000JC, TMS2200JC PROGRAMMABLE LOGIC ARRAYS             |     |   | . 158 |

|                                                            |     |   |       |

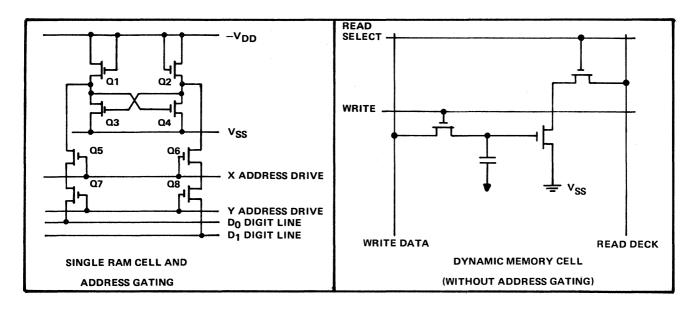

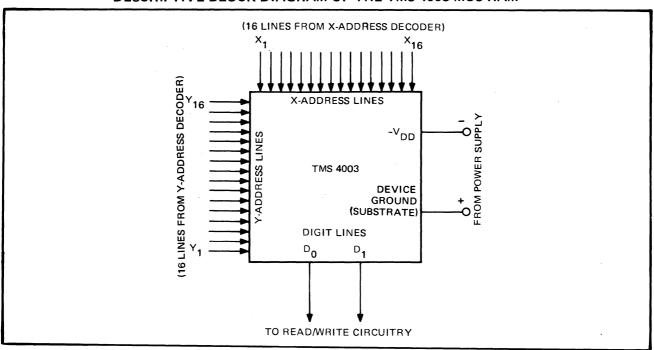

| RANDOM ACCESS MEMORIES                                     |     |   | . 167 |

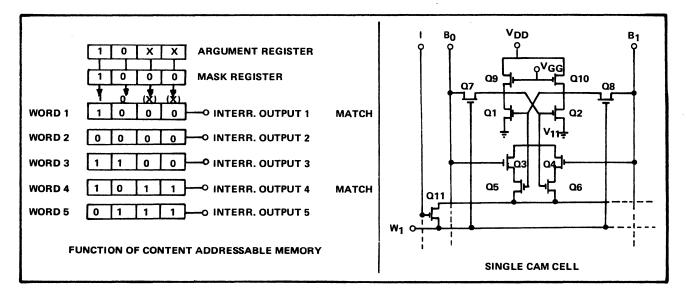

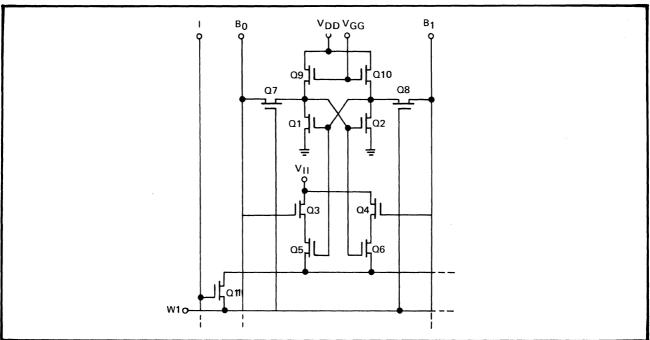

| TMS4000JC HIGH-SPEED CONTENT-ADDRESSABLE MEMORY            |     |   |       |

| TMS4003JR 256-BIT RANDOM-ACCESS MEMORY                     |     |   |       |

|                                                            |     |   |       |

| SPECIAL PURPOSE DEVICES                                    |     |   | . 186 |

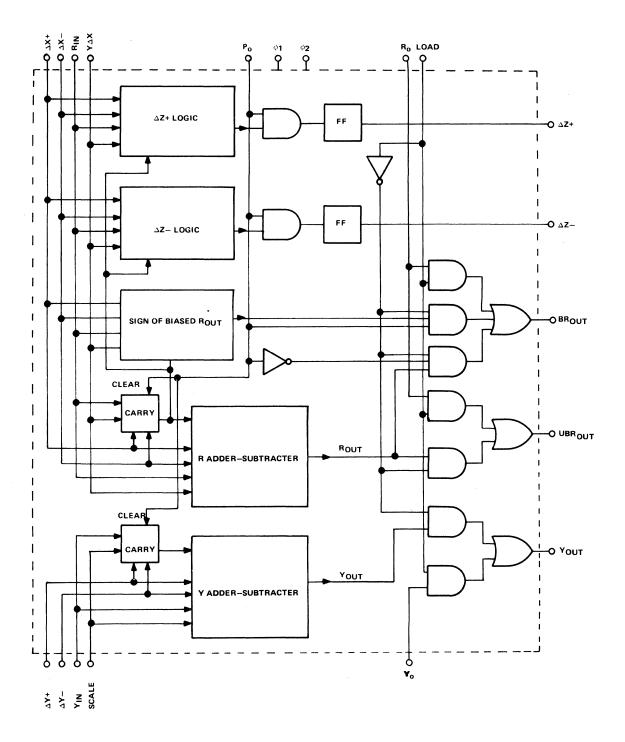

| TMS5700JC DIGITAL DIFFERENTIAL ANALYZER ELEMENT            |     |   |       |

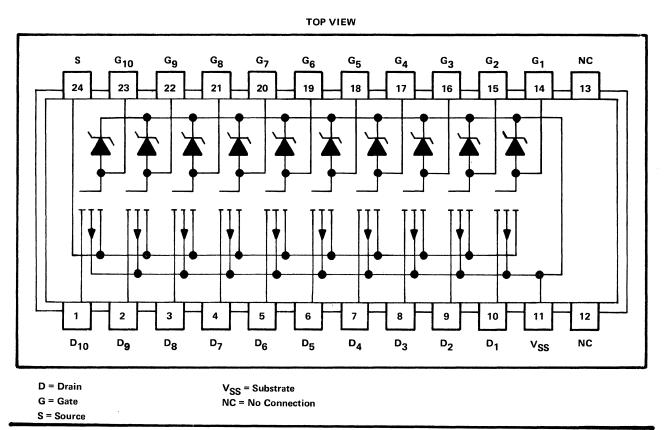

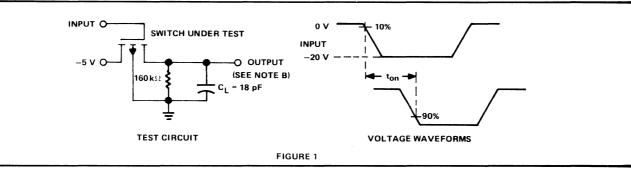

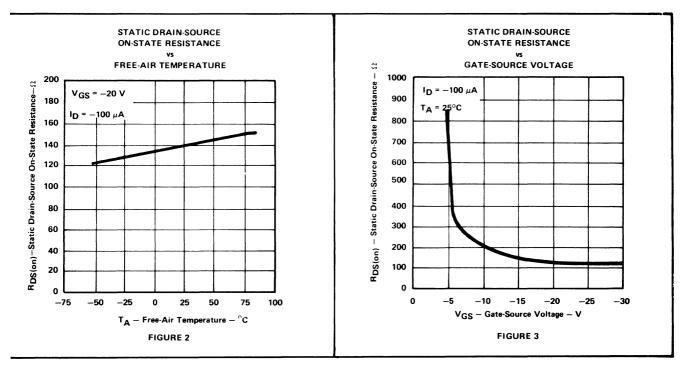

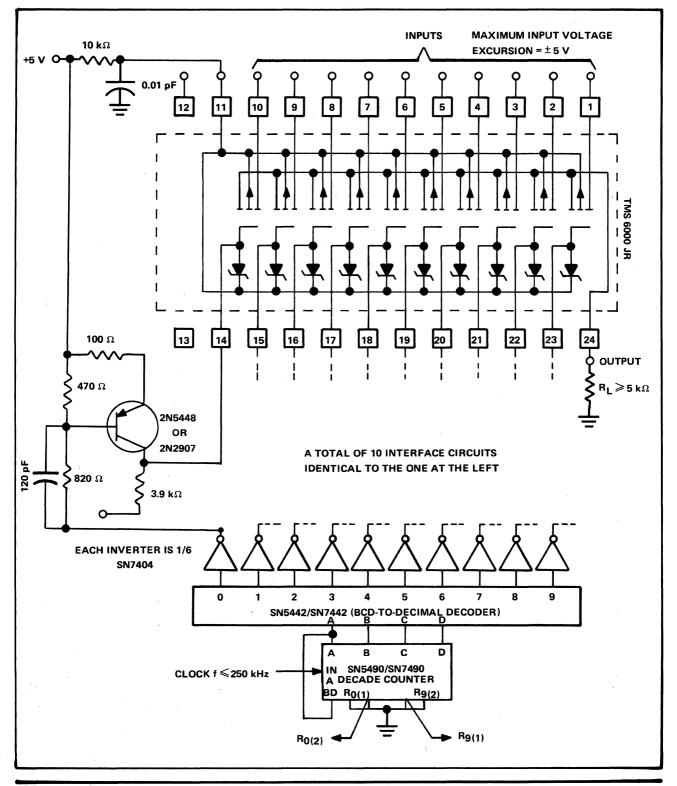

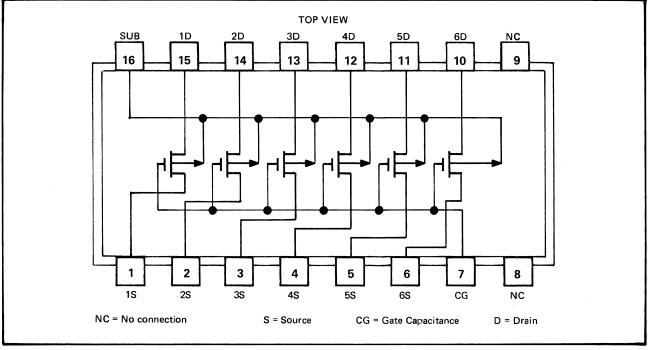

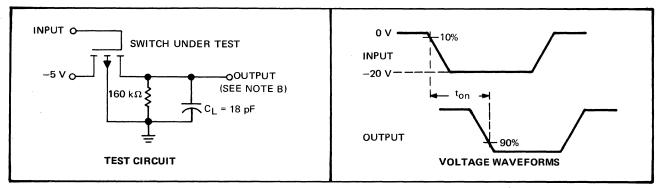

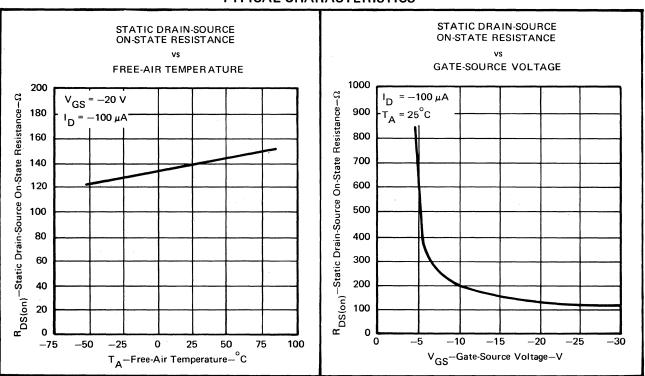

| TMS6000JR COMMON-SOURCE 10-CHANNEL ANALOG                  |     | - |       |

| SWITCH FOR HIGH SPEED MULTIPLEX APPLICATION                |     |   | . 191 |

| TMS6002JR SIX-CHANNEL ANALOG SWITCH                        |     |   |       |

| TMS6005JR, TMS6009JR SIX-CHANNEL ANALOG SWITCHES           |     |   |       |

| TMS3802LS SIX-STAGE FREQUENCY DIVIDER                      |     |   |       |

|                                                            | • • | • | . 200 |

|                                                            |     | - | . 206 |

|                                                            |     | • |       |

i

### introduction

#### MOS . . . . . . . an innovative technology

Many types of equipment previously not suitable for electronic control can now take full advantage of the latest electronic technology. Equipment costs can be kept low, and equipment size can be easily reduced. MOS (Metal Oxide Silicon) circuits are ideal for digital applications including timers and counters, data transmission and switching equipment, recorders, calculators, controls and computer equipment. MOS is also applicable for analog applications such as telemetry and test equipment.

MOS technology can be applied to hundreds of types of equipment at costs usually lower than other technologies with significant improvements in reliability.

The introduction of MOS/LSI into new classes of equipments is possible since the basic MOS device combines the best attributes of the pentode vacuum tube with all of the advantages of the transistor. MOS devices are high input impedance small, simple to fabricate, and they consume little power; consequently, they offer the highest complexity of large scale integrated circuits.

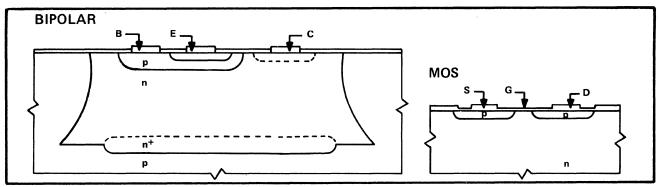

COMPARISON OF TRANSISTOR CROSS SECTIONS

#### WHAT IS MOS?

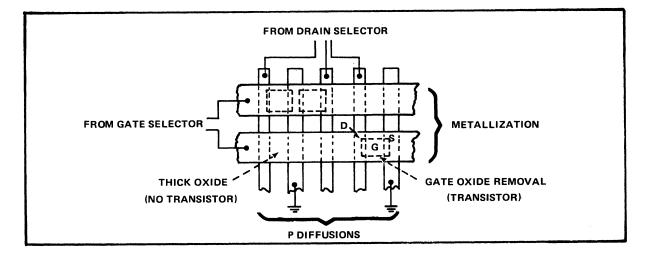

Only one-third of the process steps are needed for MOS ICs as for the standard double diffused bipolar IC. But the most significant feature is the large number of semiconductor circuit elements that can be put on a small chip. This high circuit density means large scale integration, and permits TI to put up to 5,000 devices on a silicon chip only 150 x 150 mils square. Each transistor in the MOS/LSI array requires as little as 1 square mils of chip area, a great reduction over the bipolar transistors requiring 49 to 50 square mils.

## introduction

Natural advantages of MOS/LSI include:

- increased circuit complexity per package

- lower cost per circuit function

- fewer parts to assemble and inspect

- fewer subsystems to test

- lower power drain per function

- a choice of standard or custom products to meet specific application requirements.

From the design standpoint, MOS/LSI is a two dimension layout rather than a three dimension. Mathematically you can predict its operation easier, and these mathematical models lend themselves to Computer Aided Design analysis. So the circuit can be laid out and its operation checked before it's built.

With its many applications and its simple fabrication, MOS/LSI is definitely headed for growth and expansion. It is probably the most important electronic innovation since the integrated circuit was developed by TI in 1958.

Preliminary information only is available on some of the products included in this catalog. This is indicated by the following statement on the first page of the specification.

The material herein is believed to be accurate and reliable; however, some parameters specified are derived from evaluation units and may change after full characterization.

This means that a full characterization of the products on which we supply only preliminary information is in process, but has not yet been completed.

The information contained has been obtained through a thorough engineering evaluation of a large number of units over a period of time. Production units are fully final tested to meet the specifications. All products included in this catalog are in volume production at the present time. A full characterization is in process. Due to the high level of complexity of MOS/LSI a full characterization requires much more time than SSI or MSI integrated circuits. You may design any of these devices into your equipment with full confidence.

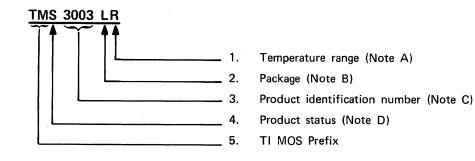

## mos/lsi numbering system

#### **TEXAS INSTRUMENTS MOS/LSI DEVICE NUMBERING SYSTEM**

Electrical characteristics presented in this catalog, unless otherwise noted, apply for circuit type(s) listed in the page heading, regardless of package. Factory orders for circuits described in this catalog should include the complete part type numbers listed on each page.

#### MOS NUMBERING SYSTEM

#### NOTE A **Temprature Range**

- С  $-25^{\circ}$ C to  $+85^{\circ}$ C (commercial)

- -55°C to +125°C (military) Μ

- $-55^{\circ}$ C to  $+85^{\circ}$ C (reduced military) R

- Special range (as designated by customer) S

#### NOTE B

#### Package

- F Flat package

- Ceramic dual-in-line J

- Ν Plastic dual-in-line

- TO-5 type L

- υ Unencapsulated (beam lead, etc.)

#### NOTE C

NOTE D

#### **Product Identification Number**

Part number unique to each type of device

#### **Product Status**

- S Standard devices

- Х Prototype (all new designs)

- С Custom design

- Т High reliability

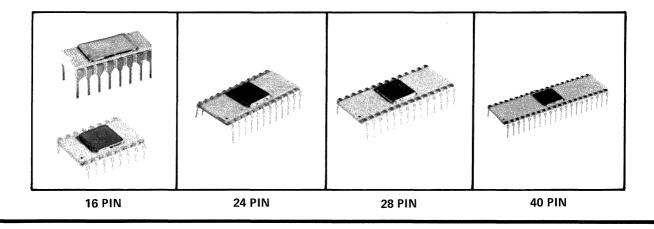

Due to the high complexity of MOS/LSI, TI has had to innovate in the packaging area. The packages selected by TI are standards of the industry. Accessories for these packages are readily available.

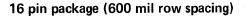

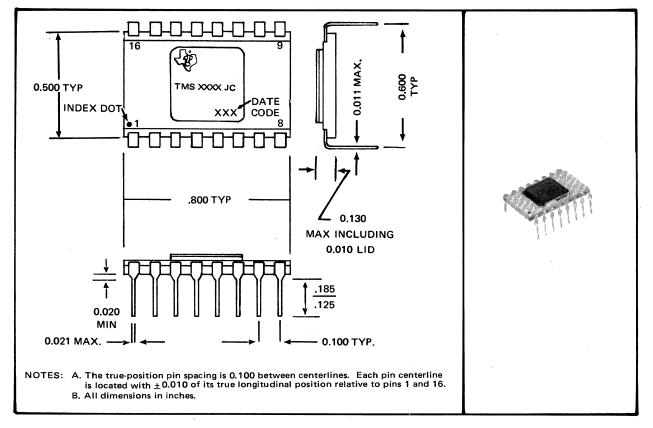

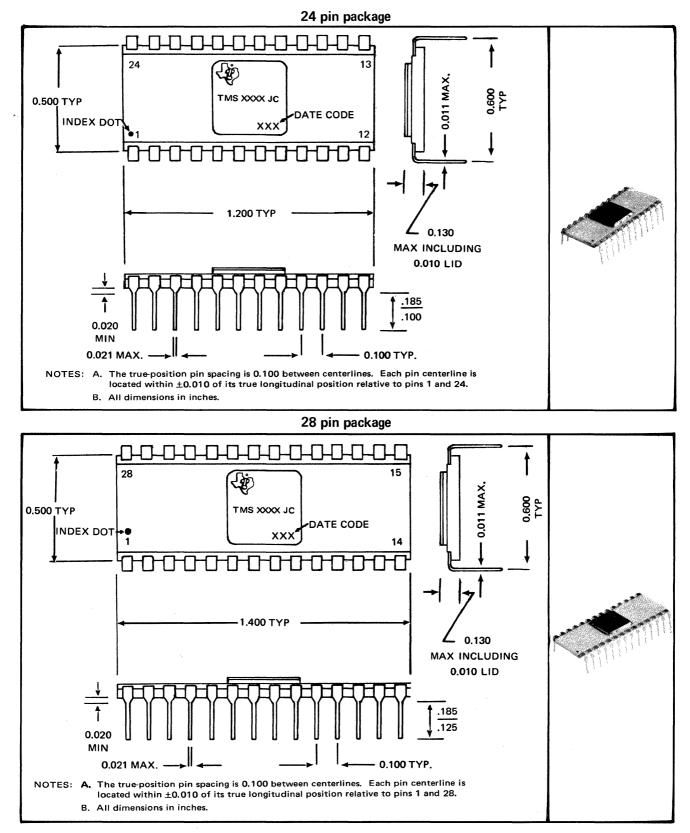

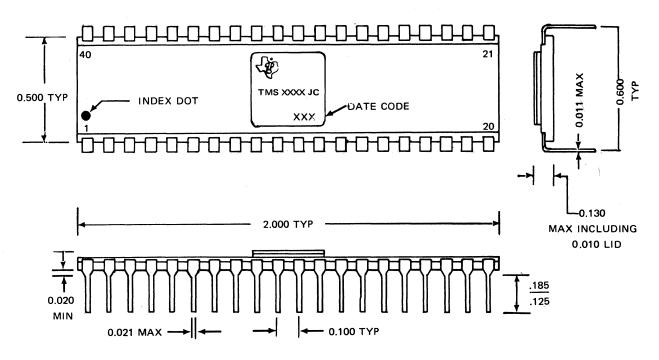

#### 1) Dual-in-line package

#### a) Pin-to-pin spacing

A pin-to-pin spacing of 100 mils has been selected for all dual-in-line packages.

#### b) Row-to-row spacing

Two spacings are used, 300 mils and 600 mils.

#### c) Ceramic dual-in-line package types

TI uses several hermetically sealed ceramic dual-in-line packages. These packages consist of a ceramic base, gold plated cap and gold plated lids.

The following packages are presently in use:

|                      | 16 PIN | 24 PIN | 28 PIN | 40 PIN |

|----------------------|--------|--------|--------|--------|

| 300 mil between rows | х      |        |        |        |

| 600 mil between rows | х      | х      | х      | х      |

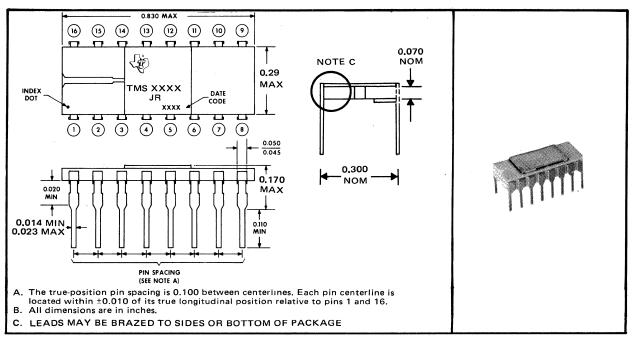

#### 16 pin package (300 mil row spacing)

40 pin package

- NOTES: 1. A true-position pin spacing is 0.100 between centerlines. Each pin centerline is located within  $\pm 0.010$  of its true longitudinal position relative to pins (1) and (40)

- 2. All dimensions in inches.

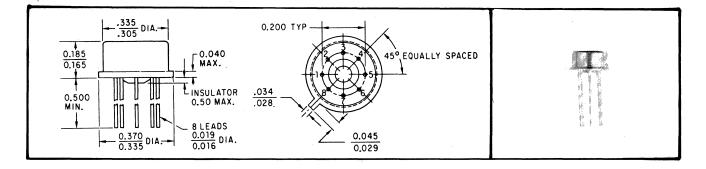

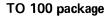

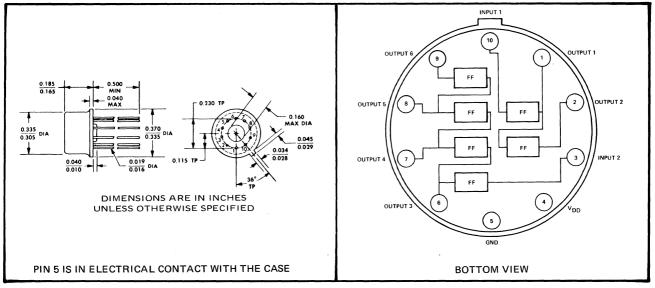

#### 2) 'TO' type packages

For devices such as shift registers requiring few inputs and outputs TI uses two 'TO' type packages.

#### TO 99 package

#### 3) Manufacturing information

#### a) Alloying

Alloying is performed under inert atmosphere. A silicon gold eutectic is formed during the alloying operation.

#### b) Bonding

Thermal compression bonding is used. Typical bond strength is 5 grams. Bond strength is monitored on a lot to lot basis. Any bond strength of less than 2½ grams causes rejection of the entire lot of devices.

#### c) Sealing

TI uses a low temperature gold tin brazing to seal ceramic packages.

TO type packages are welded.

Glass leaks are eliminated by using an etheylene glycol solution heated to +150°C.

Fine leak elimination is performed through mass spectrometer techniques.

All MOS/LSI devices produced by TI are capable of withstanding 5 x  $10^{-7}$  PPM fine leak inspection, and may be screened to 5 x  $10^{-8}$  PPM fine leak if desired by the customer for special applications.

#### d) Shock and Vibration

All packages are capable of withstanding a shock of 3,000 Gs.

All devices are capable of passing a 20,000 G acceleration (centrifuge) test in the Y axis.

Pin strength is measured by a pin shearing test. All pins are able to withstand the application of a force of 6 pounds at  $45^{\circ}$  in the peel off direction.

#### **MOS/LSI SYSTEM COMPATIBILITY**

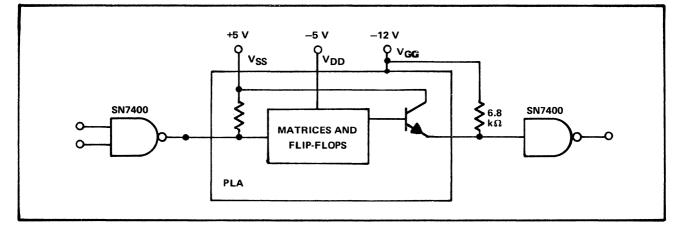

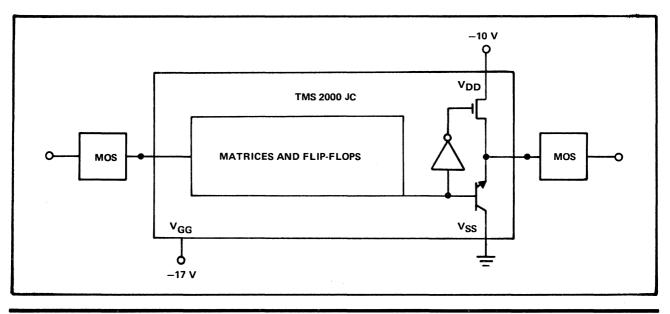

MOS/LSI circuits have in the past few years conclusively proven their value to system designers. Most designs presently under consideration use both MOS/LSI and bipolar technologies in order to take full advantage of the low cost and high packaging density of MOS/LSI, as well as the flexibility of bipolar techniques for low complexity functions. With present MOS/LSI devices the task of the designer has been greatly simplified. Present MOS devices do not require separate interface circuits between MOS and MOS circuits or between bipolar and MOS circuits. MOS/MOS and MOS/Bipolar compatibility is demonstrated in each of the data sheets included in this catalog. The following information is general and applicable to all TI MOS/LSI devices.

#### 1) POWER SUPPLIES

Two manufacturing technologies are common in MOS/LSI and prevalent in the industry: High Threshold MOS and Low Threshold MOS. The power supply requirements generally are:

|                | V <sub>SS</sub> | V <sub>DD</sub> | V <sub>GG</sub> |

|----------------|-----------------|-----------------|-----------------|

| High Threshold | 0               | -12 V           | _24 V           |

| Low Threshold  | 0               | —5 V            | –17 V           |

Where

$V_{SS}$  is the substrate supply  $V_{DD}$  is the drain supply  $V_{GG}$  is the gate supply

The drain supply will draw most of the current. Some circuits are designed to use only one power supply (saturated logic).  $V_{DD}$  and  $V_{GG}$  are then common.

To use MOS in a system it is often convenient to translate all the power supply voltages by a certain voltage. The common arrangement is:

|                | V <sub>SS</sub> | v <sub>DD</sub> | V <sub>GG</sub> |

|----------------|-----------------|-----------------|-----------------|

| High Threshold | +12 V           | 0 V             | –12 V           |

| Low Threshold  | +5 V            | 0 V             | —12 V           |

NOTE: Some high threshold devices are specified at V<sub>GG</sub> = -28 V and V<sub>DD</sub> = -14 V.

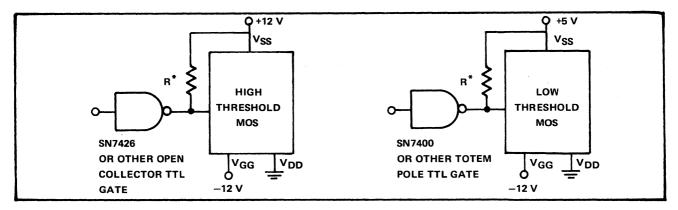

#### 2) COMPATIBILITY

Referencing all voltages to  $V_{SS}$  the input swing on most MOS circuits is as follows:

|                | High Level  | Low level       |

|----------------|-------------|-----------------|

| High Threshold | 0 to -3 V   | –9 V to –24 V   |

| Low Threshold  | 0 to -1.5 V | -4.2 V to -17 V |

Relating to the translated power supplies as above this becomes:

|                 | High Threshold | Low Threshold  |  |  |  |  |  |

|-----------------|----------------|----------------|--|--|--|--|--|

| V <sub>SS</sub> | +12 V          | +5 V           |  |  |  |  |  |

| V <sub>DD</sub> | 0 V            | 0 V .          |  |  |  |  |  |

| V <sub>GG</sub> | -12 V          | –12 V          |  |  |  |  |  |

| High level      | +9 V to +12 V  | +3.5 V to +5 V |  |  |  |  |  |

| Low level       | +3 V to -12 V  | 0.8 V to -12 V |  |  |  |  |  |

In all cases the input of the MOS circuit will look like a very high impedance. The input compatibility is easily achieved.

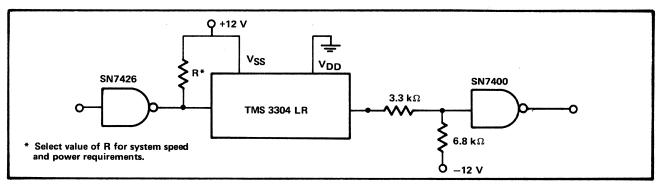

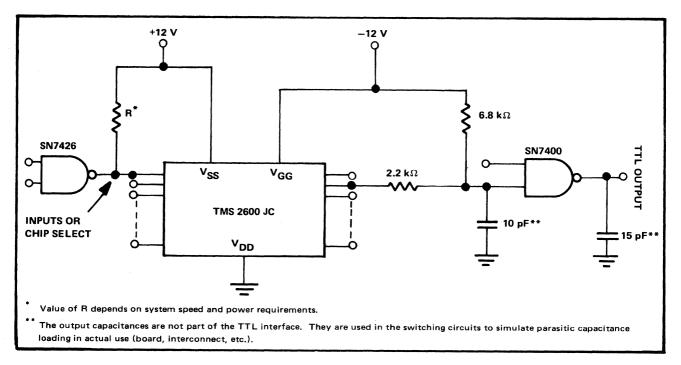

The value of the R\* resistor varies depending on speed-power requirements. In many cases this resistor is diffused on the MOS chip. For low threshold MOS this resistor assures that the worst case TTL output (2.4 V) is pulled up to at least 3.5 V for proper MOS circuit operation.

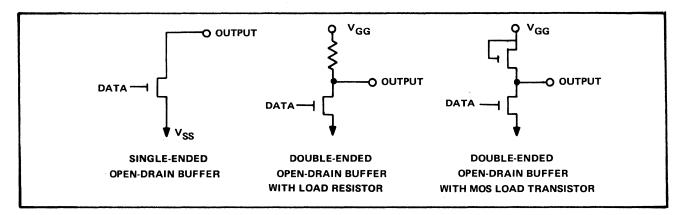

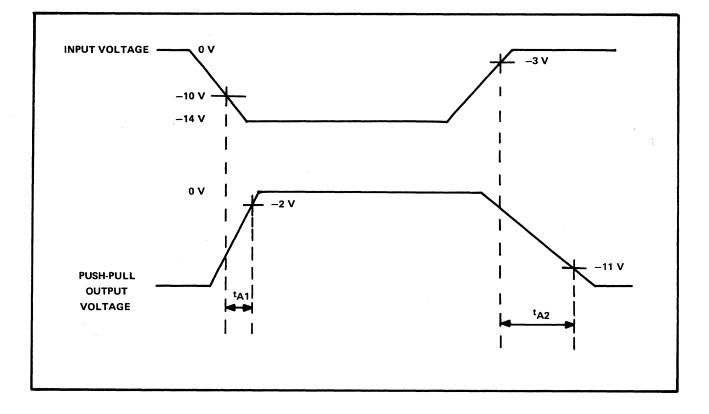

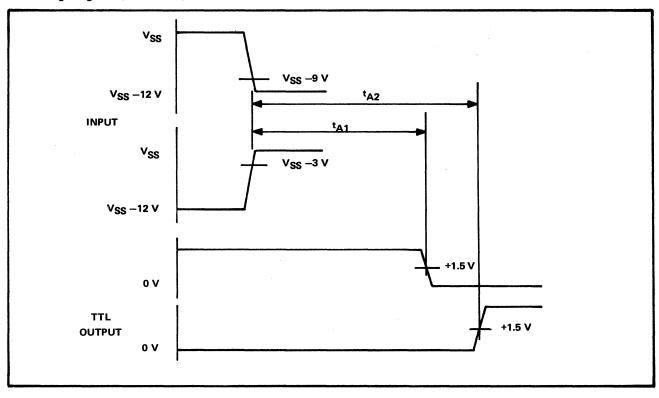

#### 3) OUTPUT COMPATIBILITY

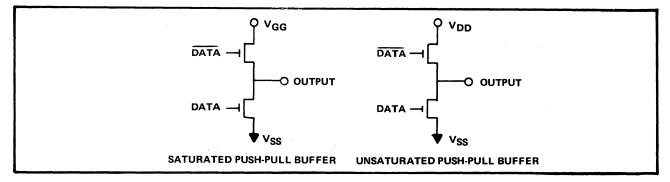

Two types of buffers are commonly used on MOS devices:

Single-ended open-drain buffer

Push-pull buffer

#### a) Single-ended open-drain

The buffer is simply a current switch. In the "off" state the impedance of the buffer is extremely large while in the "on" state it is typically under  $1 k\Omega$ . A discrete resistor or an MOS transistor may be used as a load with a single-ended open-drain buffer. This resistor may be internal to the MOS circuit.

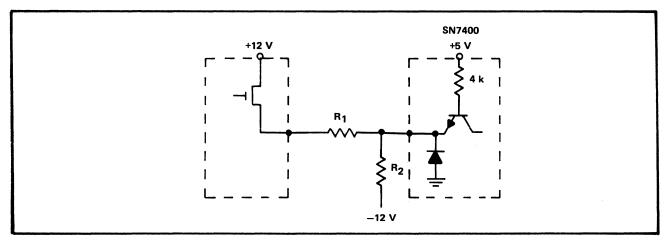

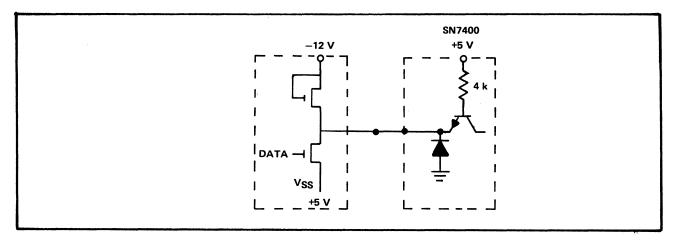

In every case compatibility with MOS is easily achieved. For instance a single-ended buffer with high threshold MOS:

$R_2$  provides the necessary current sink for the TTL input,  $R_1$  limits the positive excursion to +5 V. If used for low threshold MOS,  $V_{SS}$  is translated up to +5 V instead of +12 V and  $R_1$  can be eliminated. If  $R_2$  is on the chip no external components are necessary.

#### b) Push-pull buffer

Two types are common

The unsaturated push-pull buffer is the most commonly used for low threshold circuits. It permits direct TTL compatibility without external components.

#### 4) CLOCKS

Depending on the type of circuit there are different clock requirements:

No clocks - Static RAM's, ROM's, etc.

1 clock – with other clocks generated internally

2 clocks - most shift registers

4 clocks - very high speed low power dissipation shift registers

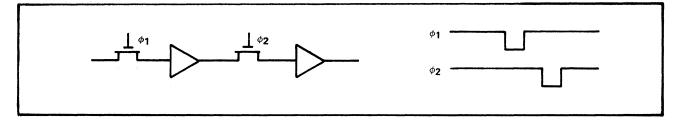

#### a) One external clock

An internal circuit generates the clocks from a single outside clock signal. The outside clock signal has the same swing as the data input signal and the compatibility is identical (see preceeding paragraph 3).

Single clock low threshold MOS circuits will accept a TTL clock without adding additional components.

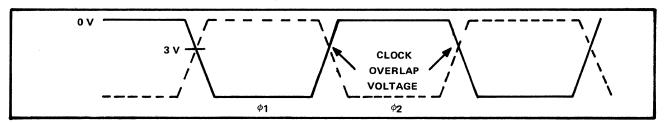

#### b) Two or four clocks

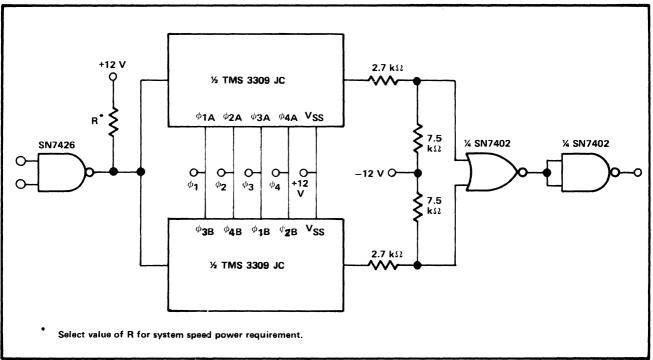

The clock signals must swing between  $V_{SS}$  and  $V_{GG}$ . To go from a single TTL level clock to a multiple MOS level clock two circuits are required: 1) a clock generator to generate the necessary clock pulses, and 2) a clock driver to bring the clock levels to the required values. In most cases only one clock circuit is needed for an entire MOS/LSI system.

In all digital equipment there is a need to temporarily store and transfer data. MOS shift registers are ideally suited for these applications, because they can economically store very large amounts of information.

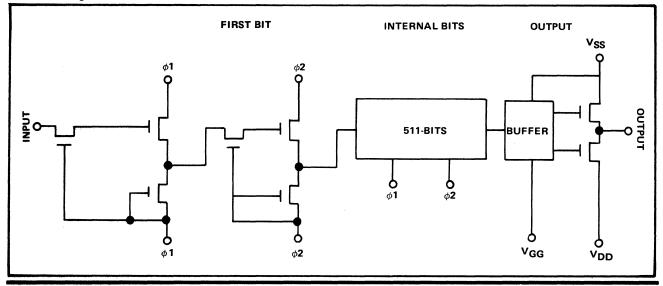

#### **Basic Configuration**

MOS shift registers can be supplied in the following configurations:

Serial-in/Serial-out Parallel-in/Serial-out Serial-in/Parallel-out

The serial-in/serial-out configuration is by far the most popular.

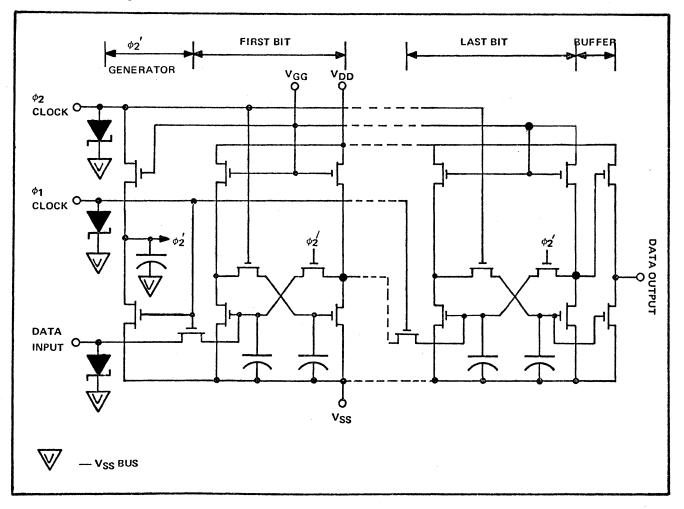

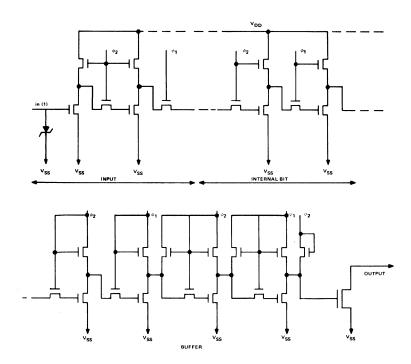

An MOS shift register will be able to store N bits. Each bit is stored on a basic cell consisting of two MOS inverters and of timing devices.

#### Static or Dynamic?

In a static shift register storage element the two inverters are connected to form a latch. The data can be stored indefinitely. There is no minimum frequency of operation.

Dynamic shift registers use two independent inverters (not cross-coupled). The data is temporarily stored on a capacitor inherent to an MOS device. The device can not be operated below a certain clock frequency, or the data storage will be lost.

Dynamic shift registers are faster than static registers and dissipate much less power. They are not as flexible to use in a system.

#### **Static Shift Registers**

A static shift register uses two static MOS inverters. Three phases (clocks) are necessary to operate a static shift register. The third phase clock is always generated internally. The third phase times the feedback loop. The second clock phase is often generated internally.

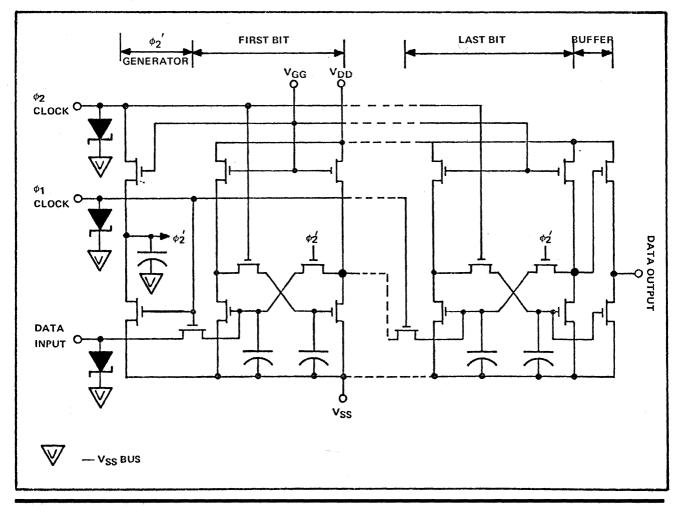

Basic cell of static shift register and  $\phi$ 3 internal generation

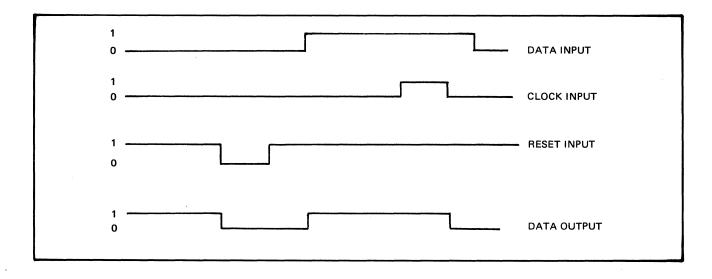

Timing diagram for a static shift register

Static shift registers operate in the 0 to 2 MHz clock range. They are extremely flexible and data can be held indefinitely, as long as power is supplied.

#### **Dynamic Shift Registers**

Dynamic shift registers use either two or four phases (clocks). These phases can be generated on the chip or be supplied externally. Two-phase shift registers can be classified as ratio and ratioless circuits.

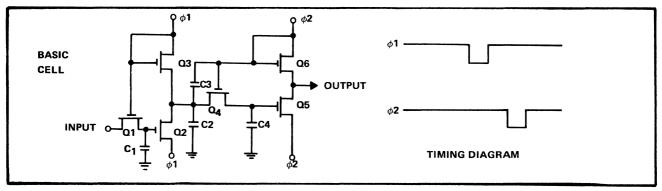

The two phase ratio type shift register consists of two simple dynamic inverters and of timing devices.

Basic cell for a dynamic shift register

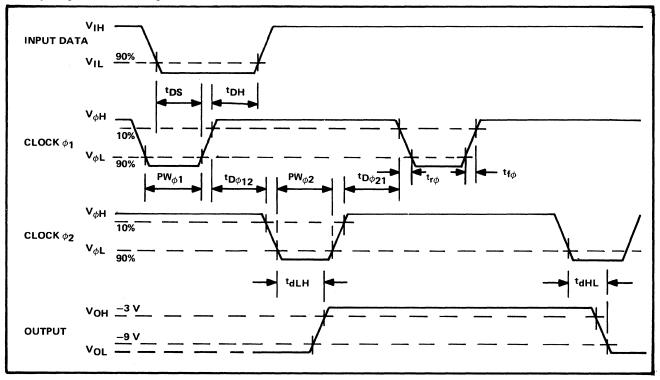

Timing diagram for a 2 phase dynamic shift register

When  $\phi_1$  is at a logic level 1 (low) the capacitance C<sub>1</sub> charges at the inverse of the data input. Data is transferred out when  $\phi_2$  goes to 1.

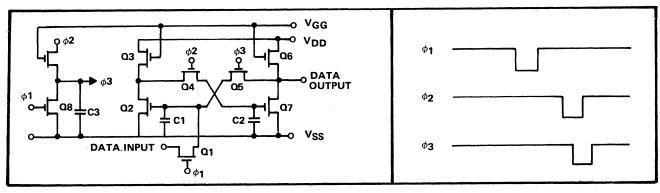

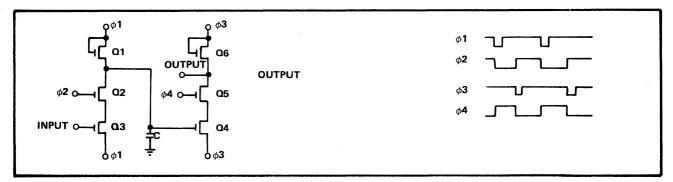

The two phase ratioless dynamic shift register has been designed to decrease the power dissipation and the chip area. In a ratio type circuit current flows through the inverter when the clock and data input are simultaneously at a logic 1. There must be a certain minimum ratio between the size of the two MOS transistors in the inverters (typically >5:1). This will take more chip area than in a ratioless shift register. In a ratioless shift register the MOS devices used are usually of identical size.

2 phase ratioless dynamic shift register

The 2 Phase 'Ratioless' Dynamic Shift Register uses identical transistors throughout and can therefore work at higher clock rates since the precharging paths are of lower impedance than those in the ratio circuit. When  $\phi_1$  goes to '1' C<sub>2</sub> charges to '1' via Q<sub>3</sub> and C<sub>1</sub> charges to the Data Input level via Q<sub>1</sub>. When  $\phi_1$  returns to '0' transistor Q<sub>2</sub> turns ON if the INPUT level was a '1' and discharges C<sub>2</sub>. For a '0' input Q<sub>2</sub> stays OFF and C<sub>2</sub> is not discharged. Now  $\phi_2$  goes to a '1' and turns on Q<sub>4</sub> so that C<sub>2</sub> shares any charge it has with C<sub>4</sub>. C<sub>3</sub> is used to compensate for the loss of potential across C<sub>2</sub> by introducing a small extra charge on the negative edge of  $\phi_2$ . It does not introduce enough to destroy a logic '0' on C<sub>2</sub>. When  $\phi_2$  returns to a '0' the charge on C<sub>4</sub> transfers the Data Input level to the OUTPUT.

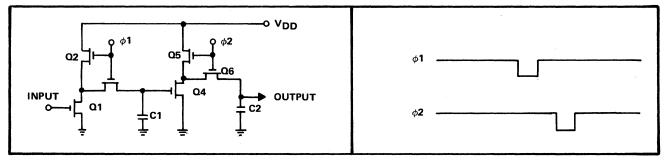

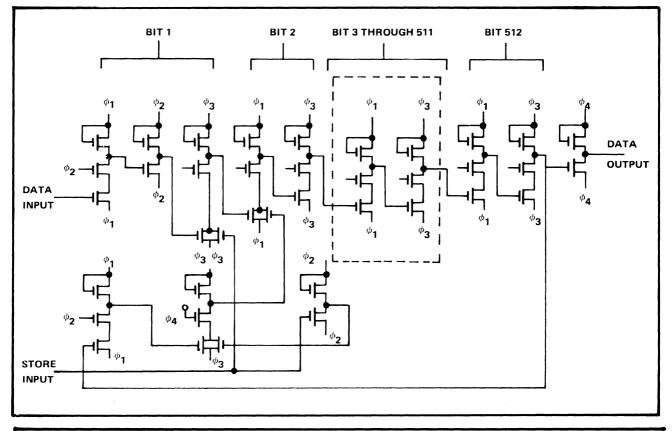

Four phase shift registers are used for very high density circuits operated at very high speed.

4 phase shift register basic cell and timing diagram

In the basic 4 Phase Dynamic Shift Register C is precharged via  $Q_1$  during  $\phi_1$ . After  $\phi_1$ ,  $\phi_2$  holds  $Q_2$ ON so C takes a level which is the inverse of the input. The process is repeated by the SLAVE section  $Q_4 - Q_6$  so that the INPUT level is transferred to the OUTPUT after  $\phi_3$  and during  $\phi_4$ . The stage uses similar transistors throughout giving high package density. Power dissipation is low, speed can be high but a relatively complex clock drive circuit is required.

|             | CLOCK | LOGIC   | POWER SUPPLY | FREQUENCY       | NUMBER OF BITS        |

|-------------|-------|---------|--------------|-----------------|-----------------------|

| TMS 3000 LR | 2     | Static  | +14 V14 V    | 0 – 1 MHz       | 2 × 25                |

| TMS 3001 LR | 2     | Static  | +14 V14 V    | 0 — 1 MHz       | 2 x 32                |

| TMS 3002 LR | 2     | Static  | +14 V14 V    | 0 — 1 MHz       | 2 × 50                |

| TMS 3003 LR | 2     | Static  | +14 V14 V    | 0 — 1 MHz       | 2 x 100               |

| TMS 3012 JR | 1     | Static  | +14 V14 V    | 0 — 1 MHz       | 2 x 128 (Accumulator) |

| TMS 3016 LR | 2     | Static  | +14 V14 V    | 0 — 1 MHz       | 2 x 16                |

| TMS 3026 JC | 1     | Static  | +14 V14 V    | 0 – 250 KHz     | 6 bit SIPO            |

| TMS 3028 LR | 1     | Static  | +14 V14 V    | 0 – 1 MHz       | 2 x 128               |

| TMS 3101 LC | 2     | Static  | +5 V – –12 V | 0 – 2.5 MZ      | 2 x 100               |

| TMS 3112 JC | 1     | Static  | +5 V12 V     | 0 – 1 MZ        | 6 × 32                |

| TMS 3304 LR | 2     | Dynamic | +14 V14 V    | 10 KHz – 5 MHz  | 3 × 66                |

| TMS 3305 LR | 2     | Dynamic | +14 V14 V    | 10 KHz – 5 MHz  | 3 × 64                |

| TMS 3309 LR | 4     | Dynamic | +12 V12 V    | 10 KHz – 10 MHz | 2 x 512               |

| TMS 3314 JC | 2     | Dynamic | +14 V14 V    | 10 KHz – 2 MHz  | 3 (60 +4)             |

| TMS 3401 LC | 2     | Dynamic | +5 V – –12 V | 20 KHz – 5 MHz  | 1 x 512               |

| TMS 3406 LR | 2     | Dynamic | +5 V – –12 V | 10 KHz – 2 MHz  | 2 x 100               |

#### **MOS Shift Registers from TI**

#### Applications

Main applications of MOS shift registers are refresh memories, scratch pad memories, data handling, and delay lines.

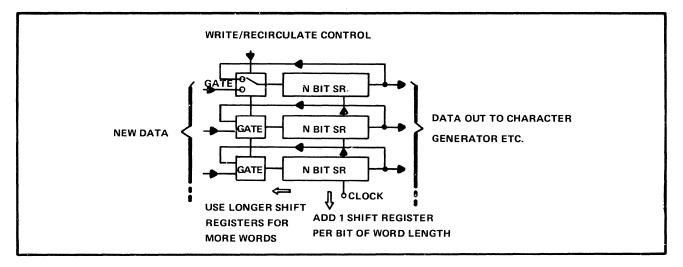

Any N-bit shift register can be used as a Refresh Memory by returning outputs to inputs as shown. A particular bit of information is available at the output every

N seconds.

This is particularly useful for renewing fading displays such as CRT character generator systems. New data is written in via a 2-way input gate circuit.

Shift registers used as refresh memory

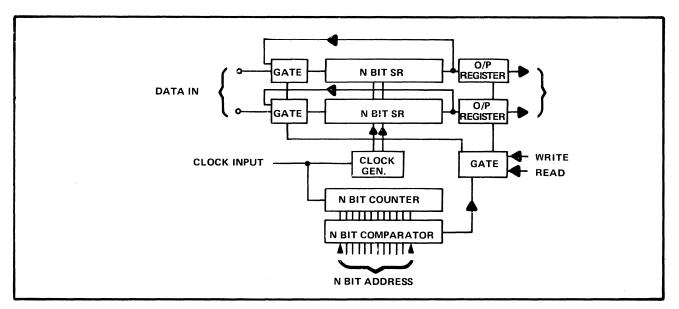

By adding an address counter and comparator in the Refresh Memory it becomes a 'Scratch Pad' memory. Data can be written in and read out of any point specified by the input address code. An output register is necessary to store the required output data and to provide a 1 bit delay so that the 'Read' address is the same as the 'Write' address since there is a 1 bit delay between output and input.

Shift registers used as scratch pad memory

#### FEATURING

- Static logic

- DC to 1 MHz operation

- Low power dissipation

- Push-pull output buffers

- TTL compatible

#### description

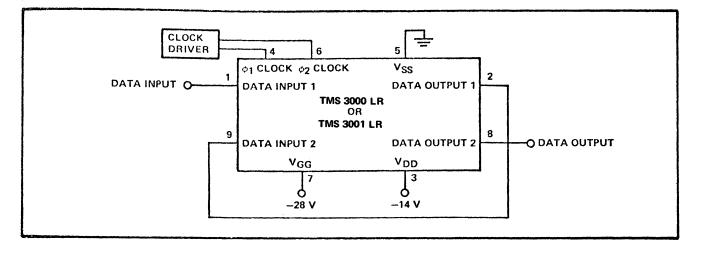

The TMS 3000 LR and TMS 3001 LR are dual static shift registers. Each device contains two d-c to 1 MHz shift registers with independent input and output terminals and common clocks and power. MOS thick-oxide technology is used to fabricate cross-coupled flip-flops for each register bit so that data can be stored indefinitely. The transistors in the device are the P-channel enhancement-mode type. All input leads have zener network protection and all outputs contain low output impedance, non-inverting push-pull output buffers.

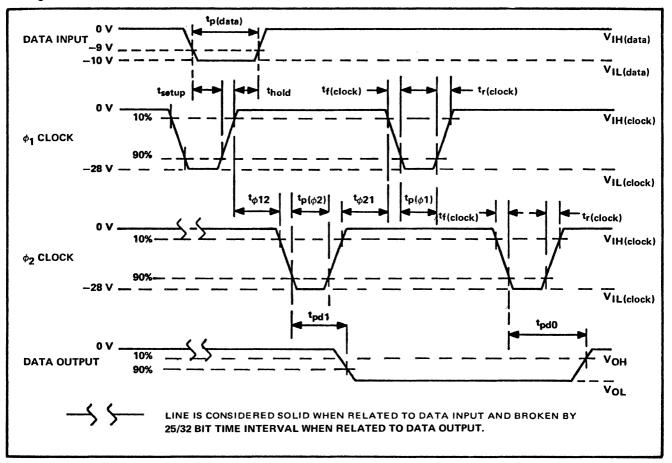

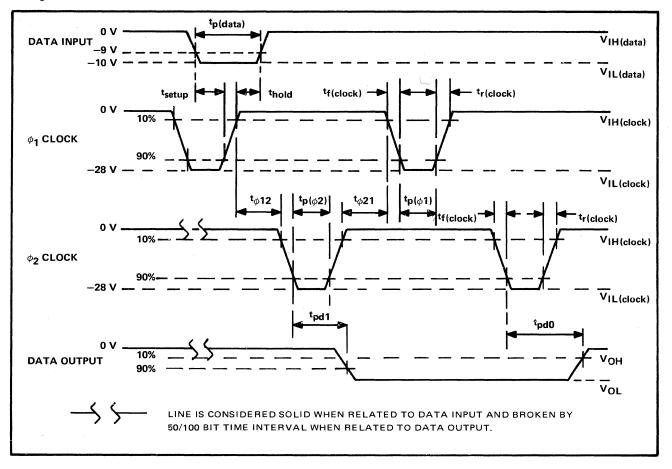

Two power supply levels and two clocks are required for operation with a third clock generated internally. Data is transferred into the register when the  $\phi_1$  clock is pulsed to logic 1. Data is shifted when the  $\phi_1$  clock is returned to logic 0 and the  $\phi_2$  clock is pulsed to logic 1. Output data appears on the logic 0 to logic 1 transition of the  $\phi_2$  clock. For long term storage, the  $\phi_1$  clock must be held at logic 0 and the  $\phi_2$  clock at logic 1.

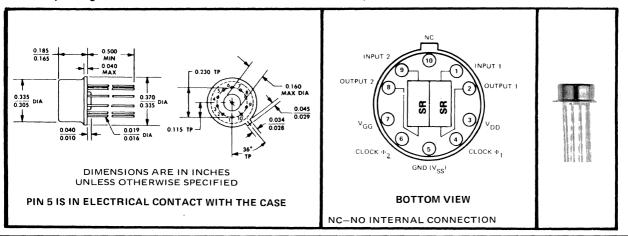

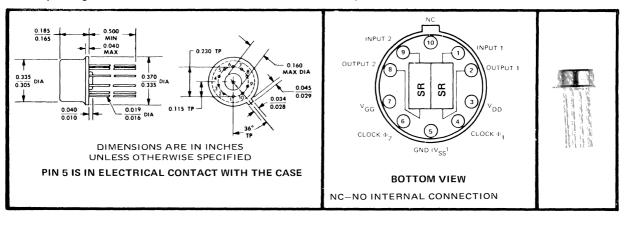

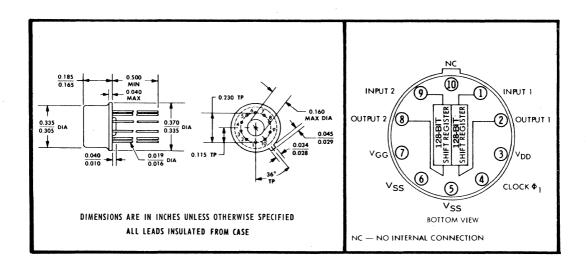

#### mechanical data and pin configuration

The package outline is the same as JEDEC TO-100 except for diameter of standoff.

#### logic definition

Negative logic is assumed

- a) Logic 1 = most negative voltage

- b) Logic 0 = most positive voltage

#### absolute maximum ratings over operating free-air temperature range (unless otherwise noted)

| Supply voltage V <sub>DD</sub> range (See Note 1)                         |                                                                                                  |  |  |  |  |  |  |  |

|---------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| Supply voltage V <sub>GG</sub> range (See Note 1)                         | $-30$ V to 0.3 V                                                                                 |  |  |  |  |  |  |  |

| Phase one clock input voltage V <sub>ø1</sub> range (See Note 1)          | $-30$ V to 0.3 V                                                                                 |  |  |  |  |  |  |  |

| Phase two clock input voltage $V_{\phi 2}^{\phi}$ range (See Note 1)      |                                                                                                  |  |  |  |  |  |  |  |

| Data input voltage V <sub>1</sub> range (See Note 1)                      |                                                                                                  |  |  |  |  |  |  |  |

| Power dissipation                                                         | 450 mW                                                                                           |  |  |  |  |  |  |  |

| Operating free-air temperature range                                      | $-55^{\circ}$ C to $85^{\circ}$ C                                                                |  |  |  |  |  |  |  |

| Storage temperature range                                                 | $\cdot$ $\cdot$ $\cdot$ $\cdot$ $\cdot$ $\cdot$ $\cdot$ $\cdot$ $-55^{\circ}C$ to $150^{\circ}C$ |  |  |  |  |  |  |  |

| 5.1. There uplies a value are with respect to notwork around terminal Man |                                                                                                  |  |  |  |  |  |  |  |

NOTE 1. These voltage values are with respect to network ground terminal,  $\mathsf{V}_{\mbox{SS}}.$

#### recommended operating conditions

| CHARACTERISTICS                                                                                        | MIN        | NOM | MAX | UNITS |

|--------------------------------------------------------------------------------------------------------|------------|-----|-----|-------|

| Supply voltage VDD                                                                                     | -12        | -14 | -15 | V     |

| Supply voltage V <sub>GG</sub>                                                                         | -24        | -28 | -29 | V     |

| Logic 0 data input voltage V <sub>i(0)</sub> (See Note 2)                                              | 0.3        | 0   | -2  | V     |

| Logic 1 data input voltage V <sub>i(1)</sub> (See Note 2)                                              | 9          | -14 | -29 | V     |

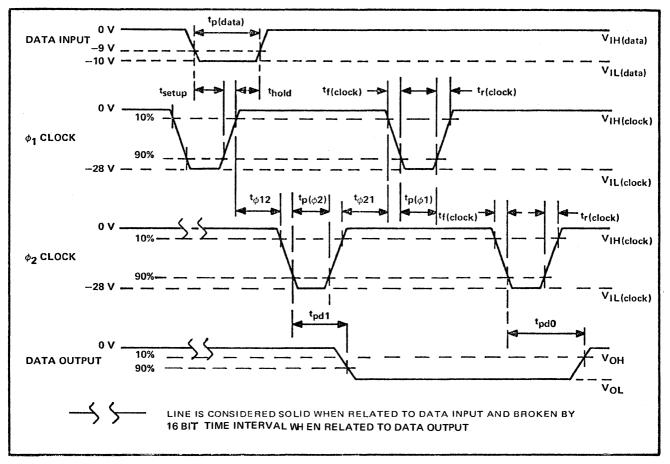

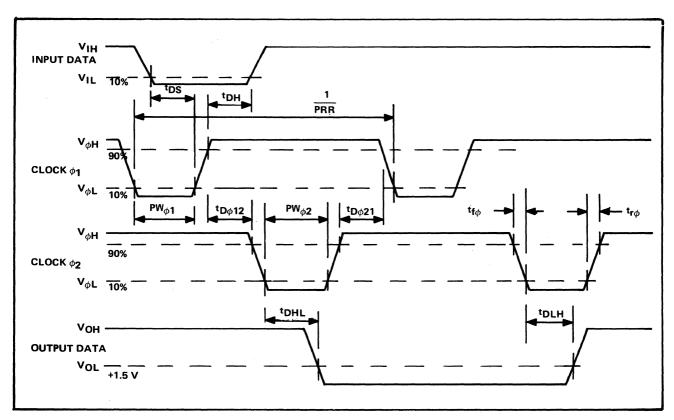

| Width of data pulse, t <sub>p(data)</sub> (See voltage waveforms)                                      | 0.4†       |     |     | μs    |

| Data setup time, t <sub>setup</sub> (See voltage waveforms and Note 3)                                 | 100        |     |     | ns    |

| Data hold time, thold (See voltage waveforms and Note 4)                                               | 20         |     |     | ns    |

| Logic 0 clock input voltage V $_{ m 00(clock)}$ (See Notes 2 and 5)                                    | 0.3        | 0   | -2  | V     |

| Logic 1 clock input voltage V $_{\phi1(	ext{clock})}$ (See Notes 2 and 5)                              | -24        | -28 | -29 | V     |

| Rise time of clock pulse, tr(clock) (See voltage waveforms)                                            | <b>Q</b> . |     | 5   | μs    |

| Fall time of clock pulse, tf(clock) (See voltage waveforms)                                            |            |     | 5   | μs    |

| $\phi_1$ clock pulse width, t $_{p(\phi_1)}$ (See voltage waveforms)                                   | 0.3†       |     | 10† | μs    |

| $\phi_2$ clock pulse width, tp( $\phi_2$ ) (See voltage waveforms)                                     | 0.4†       |     | ∞t  | μs    |

| Time interval from $\phi_1$ clock to $\phi_2$ clock input pulse, t $_{\phi12}$ (See voltage waveforms) | 0.01       |     | 10  | μs    |

| Time interval from $\phi_2$ clock to $\phi_1$ clock input pulse, $t_{\phi 21}$ (See voltage waveforms) | 0.01       |     | 10  | μs    |

| Clock repetition rate                                                                                  | 0          |     | 1   | MHz   |

NOTES: 2. These voltage values are with respect to network ground terminal,  $V_{SS}$ .

- 3. Setup time is the interval immediately preceeding the positive-going edge of the phase 1 clock pulse during which interval the data to be recognized must be maintained at the input to ensure its recognition.

- 4. Hold time is the interval immediately following the positive-going edge of the phase 1 clock pulse during which interval the data to be recognized must be maintained at the input to ensure its recognition.

- 5. The two clock pulses must never be simultaneously more than 3 volts more negative than  $V_{\mbox{SS}}$ .

$^{\dagger}\,$  These values are at V  $_{DD}$  = -14 V, V  $_{GG}$  = -28 V, and T  $_{A}$  =  $25^{\circ}C.$

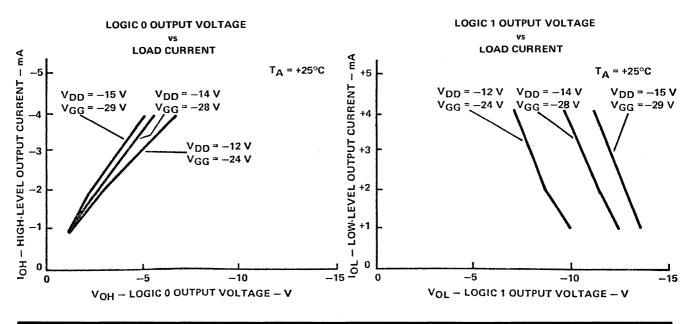

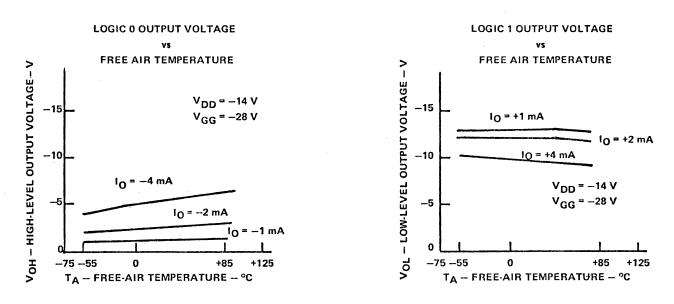

electrical characteristics over operating free-air temperature range (unless otherwise noted)

|                   | PARAMETER                                                 | TEST CONDITION                                    | NS <sup>†</sup> MIN | түр‡  | MAX  | UNITS |

|-------------------|-----------------------------------------------------------|---------------------------------------------------|---------------------|-------|------|-------|

| μL                | Logic 1 input current into data input                     | V <sub>I</sub> = -20 V                            |                     |       | 0.5  | μA    |

| <sup>η</sup> ι(φ) | Logic 1 input current into either<br>clock input          | $V_{\phi} = -28 V V_{GG}$                         | = 0 V               |       | 50   | μA    |

| Vou               | Logic 0 output voltage                                    | I <sub>O</sub> = 0 mA<br>I <sub>O</sub> = -2.0 mA |                     |       | -1   | v     |

| Vон               | Logic o output vonage                                     |                                                   |                     | -2.6  | 5    | v     |

| VOL               | Logic 1 output voltage                                    | IO = 0 mA                                         | -12                 |       |      | V     |

| VUL               | Logic Fourput vontage                                     | I <sub>O</sub> = 1.0 mA                           | -11                 | -11.6 |      | v     |

| ROH               | Output resistance, logic 0                                | I <sub>O</sub> = -2.0 mA                          |                     |       | 2.5  | kΩ    |

| ROL               | Output resistance, logic 1                                | l <sub>O</sub> = 1.0 mA                           |                     |       | 3    | kΩ    |

| IDD               | Supply current from VDD terminal*                         | TMS 3000 L                                        | R                   | -14   | -20  | mA    |

| .00               |                                                           | TMS 3001 LR                                       |                     | -16   | -24  | mA    |

| IGG               | Supply current from V <sub>GG</sub> terminal <sup>*</sup> | TMS 3000 LR                                       |                     | -2    | -3.5 | mA    |

| ·GG               |                                                           | TMS 3001 L                                        | R                   | -2    | -3.5 | mA    |

| f <sub>max</sub>  | Maximum clock frequency                                   |                                                   | 1                   |       |      | MHz   |

<sup>†</sup> Unless otherwise noted, voltages are as shown in the nominal column of the recommended operating conditions (nominal operating voltages).

<sup>†</sup> All typical values are at  $T_A = 25^{\circ}C$ .

\* Current into a terminal is a positive value.

## switching characteristics, V\_{DD} = -14 V, V\_{GG} = -28 V, R<sub>L</sub> = 10 m $\Omega$ , C<sub>L</sub> = 20 pF, T<sub>A</sub> = 25°C

|                     | PARAMETER TEST CONDITIONS                                               |                                                       | TEST CONDITIONS            |    | ТҮР      | MAX      | UNITS    |

|---------------------|-------------------------------------------------------------------------|-------------------------------------------------------|----------------------------|----|----------|----------|----------|

| <sup>t</sup> pd0    | Propagation delay time to high level from $\phi_2$ clock to data output | See voltage waveforms                                 |                            |    | 325      | 475      | ns       |

| <sup>t</sup> pd1    | Propagation delay time to low level from $\phi_2$ clock to data output  | See voltage waveforms                                 |                            |    | 325      | 475      | ns       |

| C <sub>in(¢1)</sub> | Capacitance of $\phi_1$ clock input                                     | $V_{I} = 0 V,$<br>$V_{I(\phi 2)} = 0 V,$<br>f = 1 MHz | TMS 3000 LR<br>TMS 3001 LR |    | 8<br>11  | 12<br>15 | pF<br>pF |

| C <sub>in(¢2)</sub> | Capacitance of $\phi_2$ clock input $^*$                                | $V_1 = 0 V,$<br>$V_{1(\phi_1)} = 0 V,$<br>f = 1 MHz   | TMS 3000 LR<br>TMS 3001 LR |    | 15<br>20 | 20<br>30 | pF<br>pF |

| C <sub>in</sub>     | Capacitance of data input                                               | Vi = 0,                                               | f = 1 MHz                  | 1. | 5        | 7        | pF       |

\*  $c_{in(\phi_2)}$  includes the capacitance of the internal  $\phi_2$  clock.

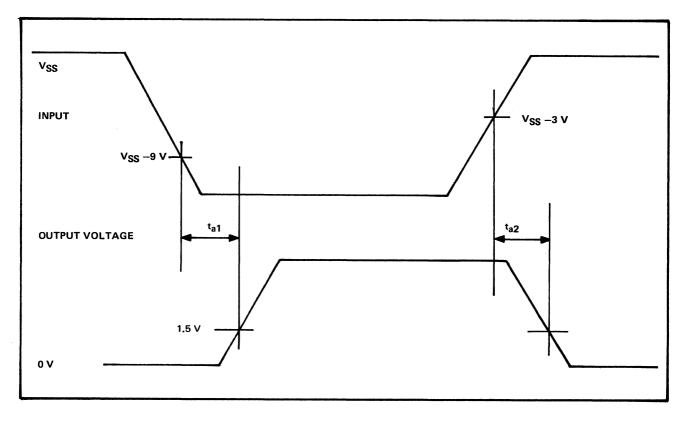

voltage waveforms

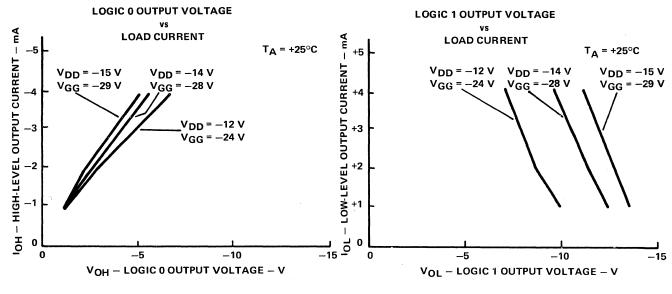

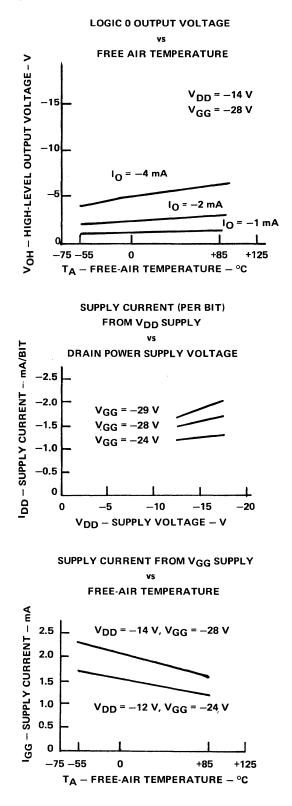

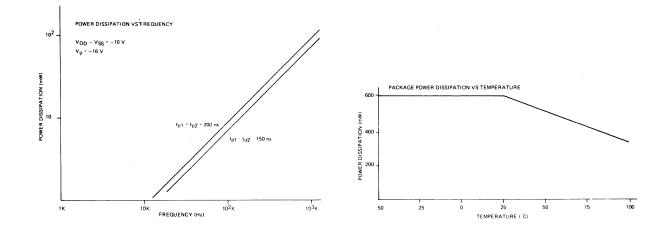

typical characteristics

typical characteristics (continued)

#### typical application data

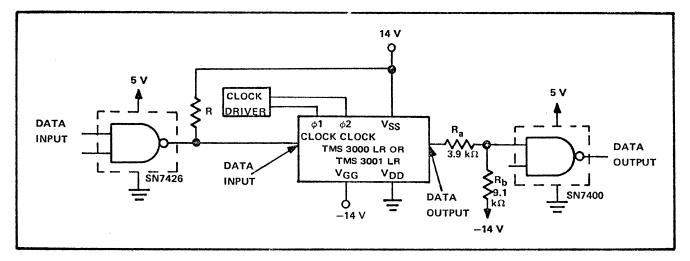

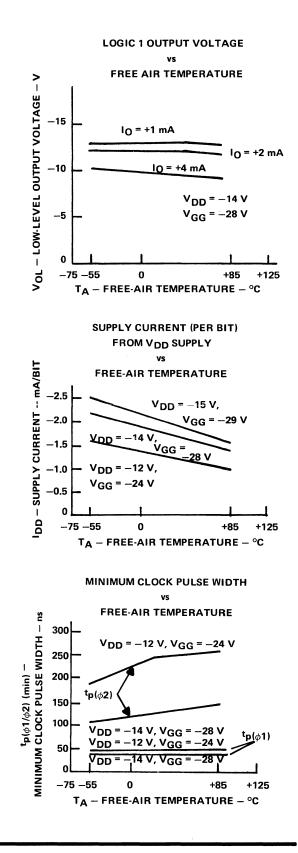

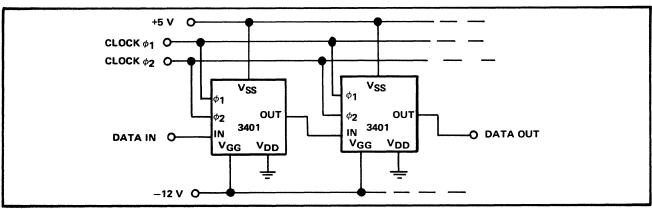

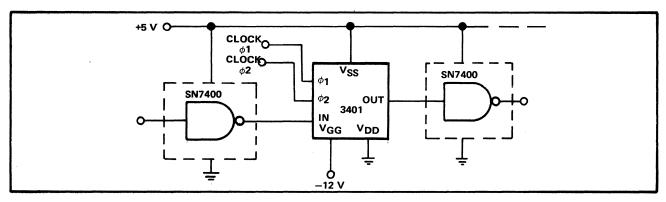

#### 1) MOS/TTL interface

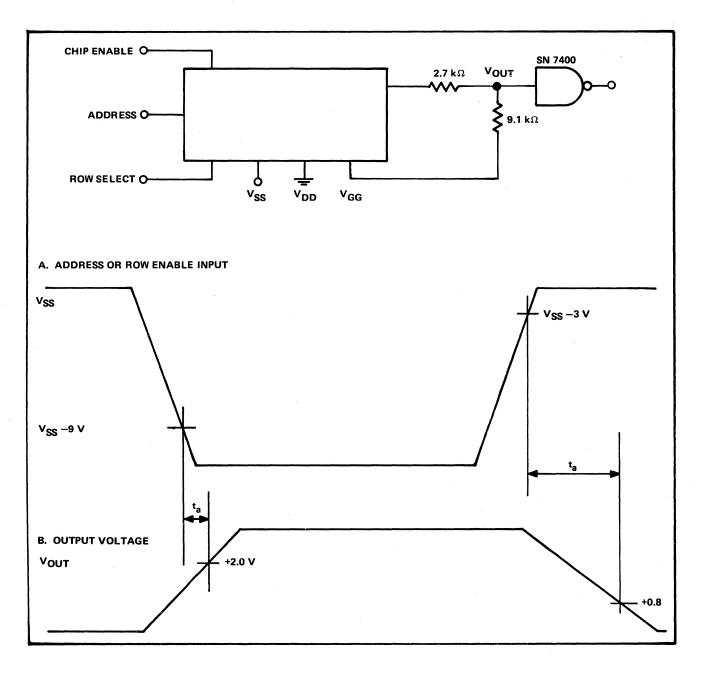

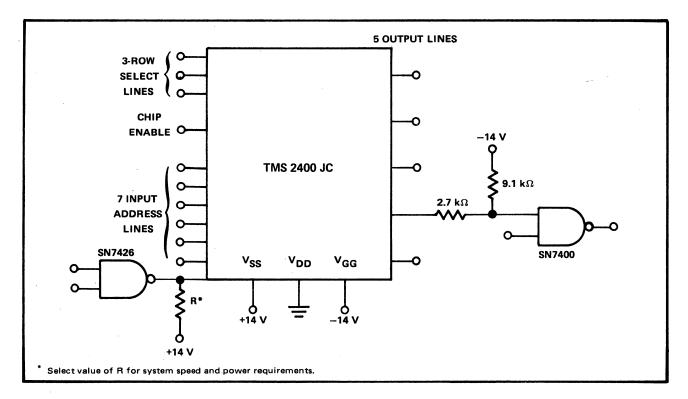

With proper supply voltages, interfacing can be achieved with only three resistors. A typical MOS/ TTL interface is shown below.

An input pull-up resistor is required to provide the necessary input voltage swing. The value of this resistor (R) depends on the actual circuit requirements – values as low as 1 k $\Omega$  can be used for high-speed operation while values as high as 15 k $\Omega$  can be used when low power consumption is important rather than high-speed.

At the output interface, the 9.1 k $\Omega$  resistor sinks the 1.6 mA of TTL-gate current when 0 volts is required on the TTL input. When 3 volts is required on the TTL input, the MOS output device supplies current from 14 volts, through the 3.9 k $\Omega$  resistor and the 9.1 k $\Omega$  resistor to -14 volts. The 3.9 k $\Omega$  resistor limits the voltage at the TTL gate input to 5 volts maximum.

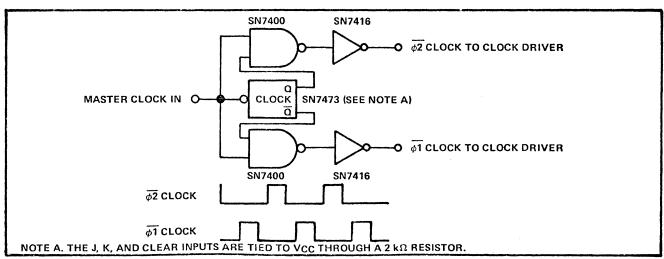

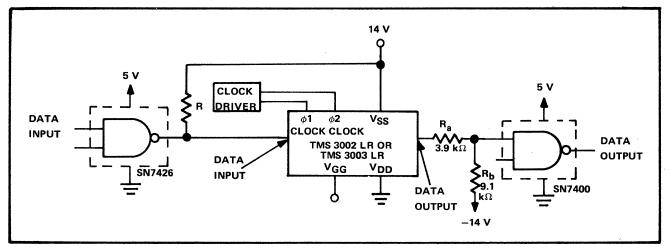

#### 2) Two-phase clock generator

#### expansion to single 50- or 64-bit register

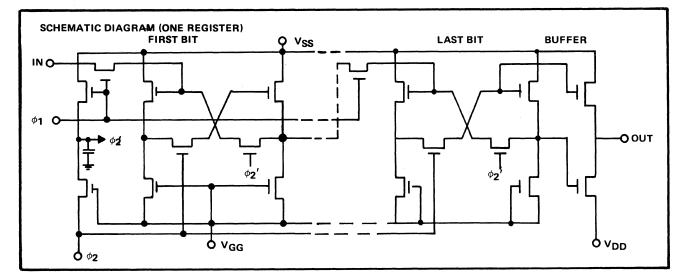

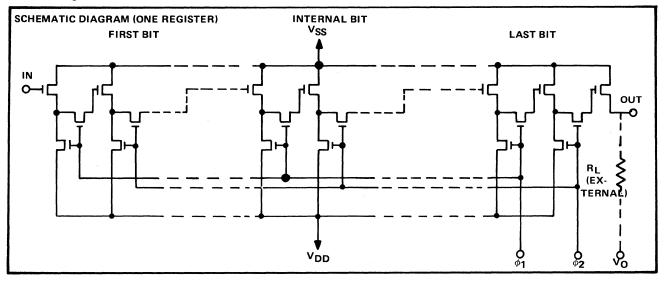

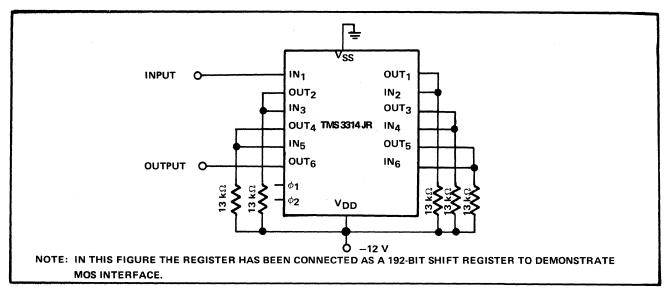

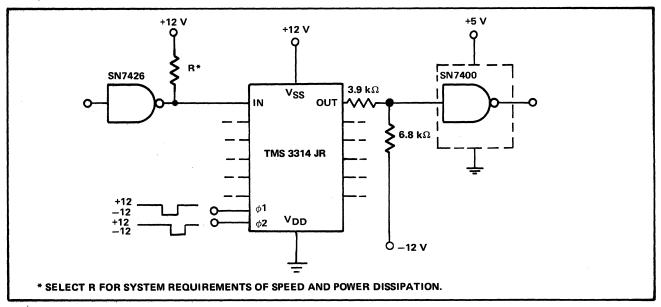

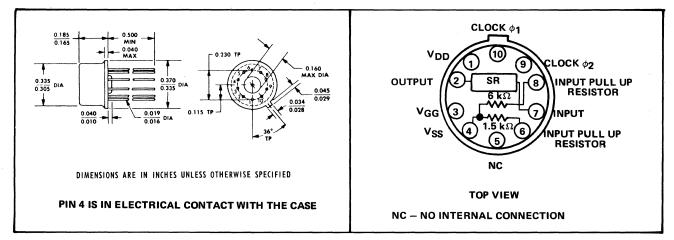

schematic (each register)

#### FEATURING

- Static logic

- DC to 1 MHz operation

- Low power dissipation

- Push-pull output buffers

- TTL compatible

#### description

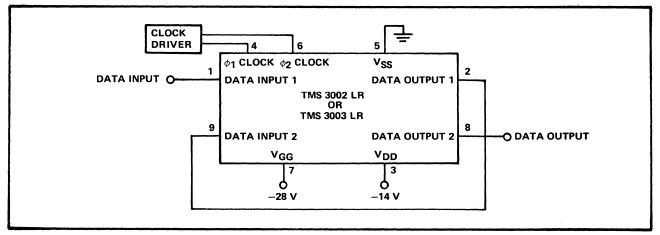

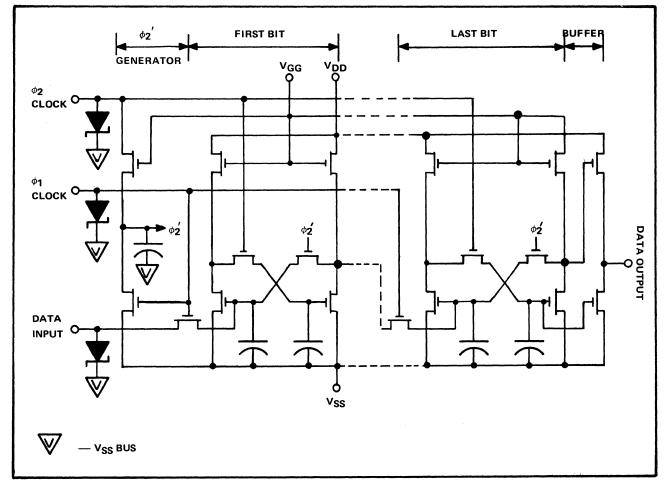

The TMS 3002 LR and TMS 3003 LR are dual static shift registers. Each device contains two d-c to 1 MHz shift registers with independent input and output terminals and common clocks and power. MOS thick oxide technology is used to fabricate cross coupled flip-flops for each register bit so that data can be stored indefinitely. The transistors in the device are the P-channel enhancement-mode type. All input leads have zener network protection and all outputs contain low output impedance non-inverting push-pull output buffers.

Two power supply levels and two clocks are required for operation with a third clock generated internally. Data is transferred into the register when the  $\phi_1$  clock is pulsed to logic 1. Data is shifted when the  $\phi_1$  clock is returned to logic 0 and the  $\phi_2$  clock is pulsed to logic 1. Output data appears on the logic 0 to logic 1 transition of the  $\phi_2$  clock. For long term storage, the  $\phi_1$  clock must be held at logic 0 and the  $\phi_2$  clock at logic 1.

#### mechanical data and pin configuration

The package outline is the same as JEDEC TO-100 except for diameter of standoff.

#### logic definition

Negative logic is assumed

- a) Logic 1 = most negative voltage

- b) Logic 0 = most positive voltage

#### absolute maximum ratings over operating free-air temperature range (unless otherwise noted)

| • • •                                                         |   |   |   |       |   |   |   |   |   |                |

|---------------------------------------------------------------|---|---|---|-------|---|---|---|---|---|----------------|

| Supply voltage V <sub>DD</sub> range (See Note 1)             | • |   |   | •     |   |   | • |   |   | -30 V to 0.3 V |

| Supply voltage V <sub>GG</sub> range (See Note 1)             | • | • |   | •     |   |   |   |   | • | -30 V to 0.3 V |

| Phase one clock input voltage $V_{\phi 1}$ range (See Note 1) | • |   |   | •     |   |   | • |   |   | -30 V to 0.3 V |

| Phase two clock input voltage $V_{\phi 2}$ range (See Note 1) |   |   |   | •     |   | • |   |   |   | -30 V to 0.3 V |

| Data input voltage V <sub>1</sub> range (See Note 1)          |   |   | • | •     |   |   |   | • |   | -30 V to 0.3 V |

| Power dissipation                                             |   |   |   |       |   |   |   |   |   | 450 mW         |

| Operating free-air temperature range                          | • |   |   | •     |   |   |   |   |   | –55°C to 85°C  |

| Storage temperature range                                     |   |   |   | • . • | • |   |   |   |   | –55°C to 150°C |

|                                                               |   |   |   |       |   |   |   |   |   |                |

NOTE 1. These voltage values are with respect to network ground terminal,  $\rm V_{SS}.$

#### recommended operating conditions

| CHARACTERISTICS                                                                                       | MIN  | NOM | МАХ | UNITS |

|-------------------------------------------------------------------------------------------------------|------|-----|-----|-------|

| Supply voltage VDD                                                                                    | -12  | -14 | -15 | v     |

| Supply voltage V <sub>GG</sub>                                                                        | -24  | -28 | -29 | v     |

| Logic 0 data input voltage V <sub>i(0)</sub> (See Note 2)                                             | 0.3  | 0   | -2  | v     |

| Logic 1 data input voltage V <sub>i(1)</sub> (See Note 2)                                             | -9   | -14 | 29  | V     |

| Width of data pulse, t <sub>p(data)</sub> (See voltage waveforms)                                     | 0.4† |     |     | μs    |

| Data setup time, t <sub>setup</sub> (See voltage waveforms and Note 3)                                | 100  |     |     | ns    |

| Data hold time, thold (See voltage waveforms and Note 4)                                              | 20   |     |     | ns    |

| Logic 0 clock input voltage V $_{\phi 0(clock)}$ (See Notes 2 and 5)                                  | 0.3  | 0   | 2   | V     |

| Logic 1 clock input voltage $V_{\phi 1(clock)}$ (See Notes 2 and 5)                                   | -24  | -28 | -29 | v     |

| Rise time of clock pulse, t <sub>r(clock)</sub> (See voltage waveforms)                               |      | 0   | 5   | μs    |

| Fall time of clock pulse, t <sub>f(clock)</sub> (See voltage waveforms)                               |      |     | 5   | μs    |

| $\phi_1$ clock pulse width, t <sub>p(<math>\phi</math>1)</sub> (See voltage waveforms)                | 0.3† |     | 10† | μs    |

| $\phi_2$ clock pulse width, t <sub>p(<math>\phi_2</math>)</sub> (See voltage waveforms)               | 0.4† |     | ∞†  | μs    |

| Time interval from $\phi_1$ clock to $\phi_2$ clock input pulse, $t_{\phi12}$ (See voltage waveforms) | 0.01 |     | 10  | μs    |

| Time interval from $\phi_2$ clock to $\phi_1$ clock input pulse, $t_{\phi21}$ (See voltage waveforms) | 0.01 |     | 10  | μs    |

| Clock repetition rate                                                                                 | 0    |     | 1   | MHz   |

NOTES: 2. These voltage values are with respect to network ground terminal, V<sub>SS</sub>.

3. Setup time is the interval immediately preceeding the positive going edge of the phase 1 clock pulse during which interval the data to be recognized must be maintained at the input to ensure its recognition.

4. Hold time is the interval immediately following the positive-going edge of the phase 1 clock pulse during which interval the data to be recognized must be maintained at the input to ensure its recognition.

5. The two clock pulses must never be simultaneously more than 3 volts more negative than  $V_{SS}$ .

$^{\dagger}$  These values are at V\_DD = -14 V, V\_GG = -28 V, and T\_A =  $25^{\circ}\text{C}.$

electrical characteristics over operating free-air temperature range (unless otherwise noted)

|                    | PARAMETER                                        | TEST CONDITIONS <sup>†</sup>  | MIN | түр‡  | MAX | UNITS |

|--------------------|--------------------------------------------------|-------------------------------|-----|-------|-----|-------|

| μL                 | Logic 1 input current into data input            | $V_{I} = -20 V$               |     |       | 0.5 | μA    |

| <sup> </sup> ΙL(φ) | Logic 0 input current into either clock<br>input | $V_{I} = -28 V, V_{GG} = 0 V$ |     |       | 50  | μΑ    |

| V <sub>OH</sub>    | Logic 0 output voltage                           | 1 <sub>O</sub> = 0 mA         |     |       | -1  | V     |

|                    |                                                  | l <sub>O</sub> = -2.0 mA      |     | -2.6  | -5  | V     |

| Ve                 | Logic 1 output voltage                           | I <sub>O</sub> = 0 mA         | -12 |       |     | V     |

| VOL                |                                                  | I <sub>O</sub> = 1.0 mA       | -11 | -11.6 |     | V     |

| ROH                | Output resistance, logic 0                       | I <sub>O</sub> = -2.0 mA      |     |       | 2.5 | kΩ    |

| ROL                | Output resistance, logic 1                       | I <sub>O</sub> = 1.0 mA       |     |       | 3   | kΩ    |

|                    | Supply current from V <sub>DD</sub> terminal∮    | TMS 3002 LR                   |     | -8.5  | -15 | mA    |

| DD                 |                                                  | TMS 3003 LR                   |     | -16   | -26 | mA    |

|                    | Supply current from V <sub>GG</sub> terminal∮    | TMS 3002 LR                   |     | -2    | -3  | mA    |

| IGG                |                                                  | TMS 3003 LR                   |     | -2    | -3  | mA    |

| f <sub>max</sub>   | Maximum clock frequency                          |                               | 1   |       |     | MHz   |

<sup>†</sup> Unless otherwise noted, voltages are as shown in the nominal column of the recommended operating conditions (nominal operating voltages).

<sup>†</sup> All typical values are at  $T_A = 25^{\circ}C$ .

$\oint$  Current into a terminal is a positive value.

# switching characteristics, V<sub>DD</sub> = -14 V, V<sub>GG</sub> = -28 V, R<sub>L</sub> = 10 m $\Omega$ , C<sub>L</sub> = 20 pF, T<sub>A</sub> = 25°C

|                     | PARAMETER TEST CONDITIONS                                               |                                                                  | MIN                        | ТҮР | MAX      | UNIT     |          |

|---------------------|-------------------------------------------------------------------------|------------------------------------------------------------------|----------------------------|-----|----------|----------|----------|

| <sup>t</sup> pdo    | Propagation delay time to high level from $\phi_2$ clock to data output | See voltage wave                                                 |                            | 250 | 400      | ns       |          |

| <sup>t</sup> pd1    | Propagation delay time to low level from $\phi_2$ clock                 | See voltage waveforms                                            |                            |     | 250      | 350      | ns       |

| C <sub>in(φ1)</sub> | Capacitance of $\phi_1$ clock input                                     | V <sub>I</sub> = 0 V,<br>V <sub>I (φ2)</sub> = 0 V,<br>f = 1 MHz | TMS 3002 LR<br>TMS 3003 LR |     | 18<br>28 | 23<br>33 | pF<br>pF |

| C <sub>in(φ2)</sub> | Capacitance of $\phi_2$ clock input <sup>*</sup>                        | V <sub>I</sub> = 0 V,<br>V <sub>I (φ1)</sub> = 0 V,<br>f = 1 MHz | TMS 3002 LR<br>TMS 3003 LR |     | 30<br>53 | 35<br>60 | pF<br>pF |

| C <sub>in</sub>     | Capacitance of data input                                               | V <sub>1</sub> = 0,                                              | f = 1 MHz                  |     | 5        | 7        | pF       |

$C_{in(\phi_2)}$  includes the capacitance of the internal  $\phi'_2$  clock.

voltage waveforms

#### typical characteristics (continued)

# TMS3002LR - dual 50-bit shift register TMS3003LR - dual 100-bit shift register

### typical application data

### 1) MOS/TTL interface

With proper supply voltages, interfacing can be achieved with only three resistors. A typical MOS/TTL interface is shown below.

An input pull-up resistor is required to provide the necessary input voltage swing. The value of this resistor (R) depends on the actual circuit requirements – values as low as 1 k $\Omega$  can be used for high-speed operation while values as high as 15 k $\Omega$  can be used when low power consumption is important rather than high-speed.

At the output interface, the 9.1 k $\Omega$  resistor sinks the 1.6 mA of TTL-gate current when 0 volts is required on the TTL input. When 3 volts is required on the TTL input, the MOS output device supplies current from 14 volts, through the 3.9 k $\Omega$  resistor and the 9.1 k $\Omega$  resistor to -14 volts. The 3.9 k $\Omega$  resistor limits the voltage at the TTL gate input to 5 volts maximum.

### 2) Two-phase clock generator

### TMS3002LR - dual 50-bit shift register TMS3003LR - dual 100-bit shift register

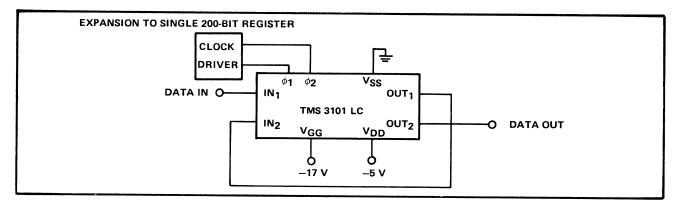

expansion to single 100- or 200-bit register

schematic (each register)

# TMS3012JR – dual 128-bit accumulator TMS3028LR – dual 128-bit shift register

preliminary information

### FEATURING

- 256 bits of storage

- Single clock phase

- Static logic

- TTL compatible

- DC to 1 MHz operation

- Push-pull output buffers

- 16-Pin hermetic ceramic dual-in-line package (TMS 3012 JR)

- Recirculating control logic (TMS 3012 JR)

### description

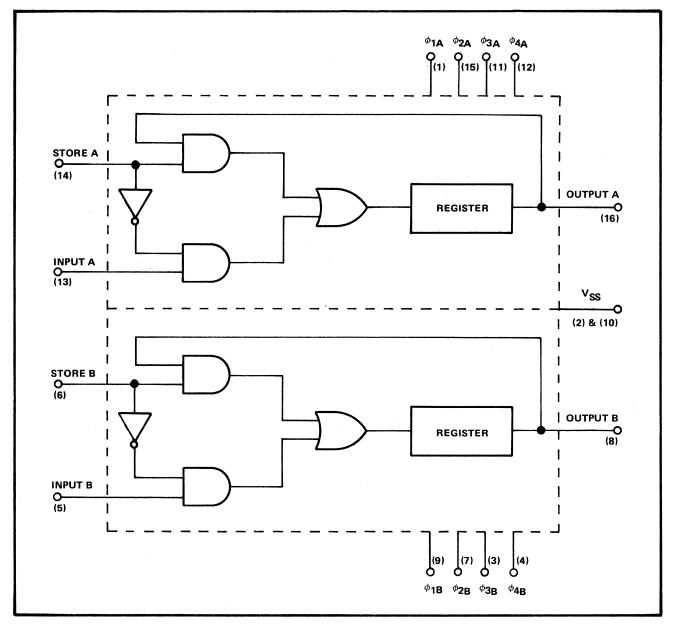

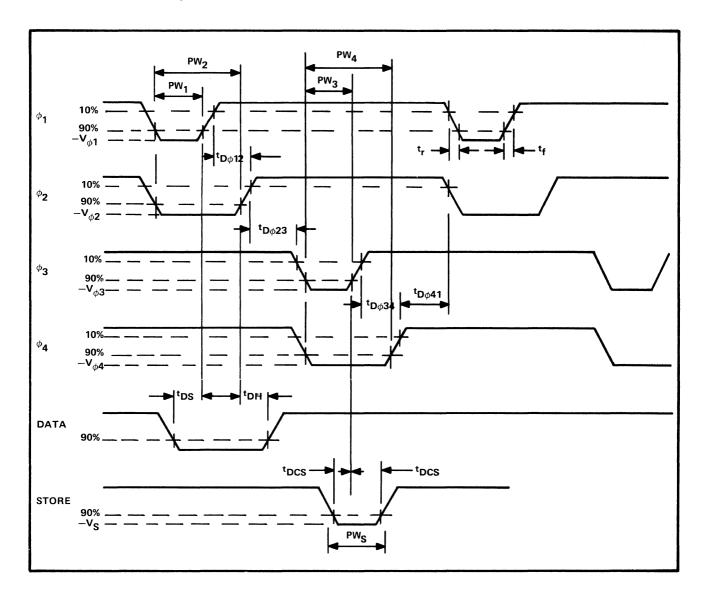

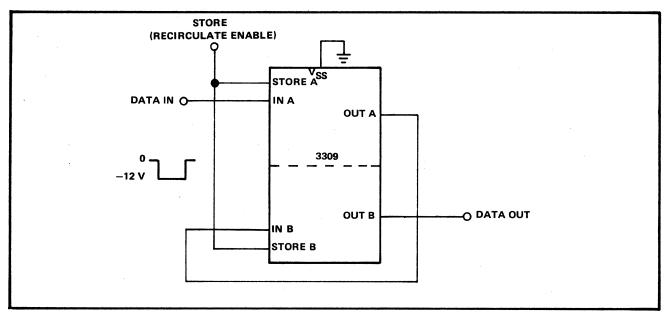

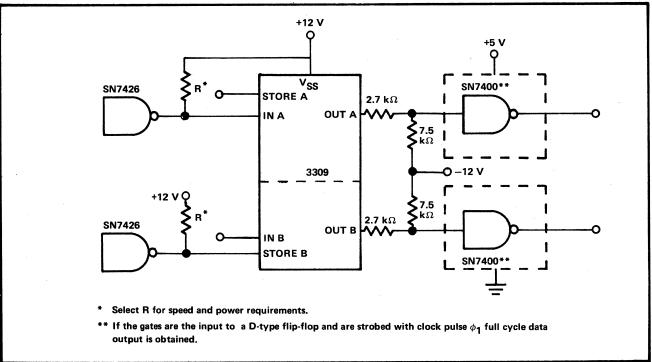

The TMS 3012 JR consists of two separate 128-bit static shift registers with independent input and output terminals and logic, within the circuit, for loading and recirculating information. Two power supplies and one external clock are required for operation. Three clocks are generated internally. Cross-coupled flip-flops are used to implement each bit of delay and enable data to be stored indefinitely between two clock pulses. The entire device is constructed on a single monolithic chip using thick-oxide techniques and MOS P-channel enhancement-mode transistors.

The TMS 3028 LR is identical to the TMS 3012 JR except for the fact that recirculate logic is not included on the chip and that the device is mounted in a TO-100 package instead of a ceramic dual-inline package.

#### operation

Transferring data into the register and shifting the data in the register are accomplished when the  $\phi_{IN}$  clock is at a logic 1; for long-term data storage, the  $\phi_{IN}$  clock must be held at logic 0. Output appears on the positive-going edge of the  $\phi_{IN}$  clock pulse.

#### logic definition

Negative logic is assumed

- a) Logic 1 = most negative voltage

- b) Logic 0 = most positive voltage

### TMS3012JR-dual 128-bit accumulator TMS3028LR-dual 128-bit shift register

TMS 3012 JR RECIRCULATE INPUT A | RECIRCULATE CONTROL A | 3 OUTPUT A 5 **REGISTER A** INPUT A 2 RECIRCULATE INPUT B 14 RECIRCULATE OUTPUT B 12 REGISTER B 1 INPUT B (15) 1 L CLOCK  $\phi_{IN}$ V<sub>GG</sub> VSS VDD 9 6) (11) 7 X DENOTES PIN NUMBER (x)

functional diagram and pin breakout

### absolute maximum ratings over operating free-air temperature range (unless otherwise noted)

| Supply voltage V <sub>DD</sub> range <sup>*</sup>      |   |  |  |   |  |  |  |  |  | - |   | -30 V to 0.3 V                  |

|--------------------------------------------------------|---|--|--|---|--|--|--|--|--|---|---|---------------------------------|

| Supply voltage V <sub>GG</sub> range <sup>*</sup>      | • |  |  |   |  |  |  |  |  |   |   | -30 V to 0.3 V                  |

| Clock and data input voltage ranges*                   | • |  |  | • |  |  |  |  |  |   |   | -30 V to 0.5 V                  |

| Operating free-air temperature range                   |   |  |  |   |  |  |  |  |  |   |   | $-55^{\circ}C$ to $85^{\circ}C$ |

| Storage temperature range                              |   |  |  |   |  |  |  |  |  |   | - | –55°C to 150°C                  |

| se voltage values are with respect to substrate termin |   |  |  |   |  |  |  |  |  |   |   |                                 |

\* These voltage values are with respect to substrate terminal.

### recommended operating conditions

| CHARACTERISTICS                                                         | MIN | NOM | MAX | UNITS |

|-------------------------------------------------------------------------|-----|-----|-----|-------|

| Supply voltage V <sub>DD</sub>                                          | -13 | -14 | -15 | v     |

| Supply voltage V <sub>GG</sub>                                          | -27 | -28 | -29 | v     |

| Width of data pulse, t <sub>(data)</sub> (See voltage waveforms)        | 0.4 |     | 10  | μs    |

| Width of clock pulses: tp (Logic 1)<br>See voltage waveforms            | 0.3 |     | ∞   | μs    |

| t <sub>p</sub> (Logic 0)                                                | 0.6 |     | 5   | μs    |

| Rise time of clock pulse, t <sub>r(clock)</sub> (See voltage waveforms) |     |     | 5   | μs    |

| Fall time of clock pulse, tf(clock) (See voltage waveforms)             |     |     | 1   | μs    |

| Clock repetition rate                                                   | 0   |     | 1   | MHz   |

- CONTINUED -

# TMS3012JR-dual 128-bit accumulator TMS3028LR-dual 128-bit shift register

### recommended operating conditions (continued)

| CH                   | IARACTERISTICS                                                                | MIN | NOM | MAX | UNITS |

|----------------------|-------------------------------------------------------------------------------|-----|-----|-----|-------|

| V <sub>in(1)</sub> * | Data/Recirculate Control Logic 1 voltage                                      | -9  | -14 | -15 | v     |

| V <sub>in(0)</sub> * | Data/Recirculate Control Logic 0 voltage                                      | 0   | 0   | -2  | v     |

| $V_{in(1)\phi}^*$    | Logic 1 clock input voltage                                                   | -9  | -14 | -15 | v     |

| $V_{in(0)\phi}^*$    | Logic 0 clock input voltage                                                   | 0   | 0   | -2  | v     |

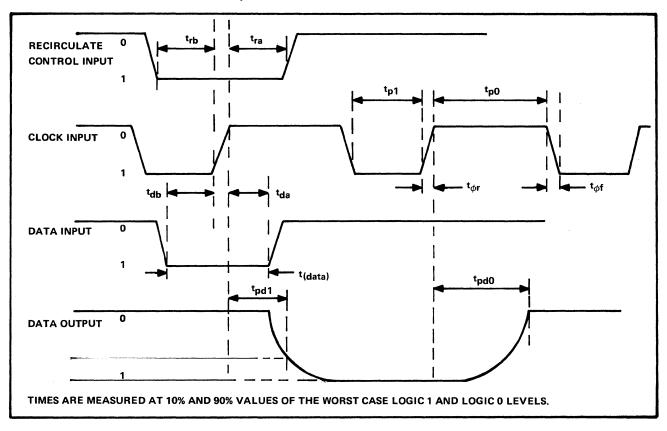

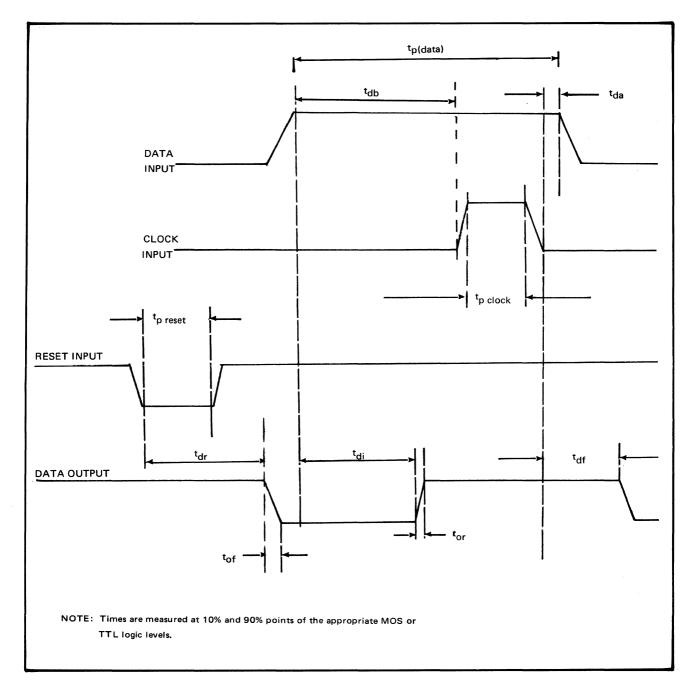

| Data chang           | e time before clock change to 0 (t <sub>db</sub> )                            | 0.2 |     |     | μs    |

| Data chang           | e time after clock change to 0 (t <sub>da</sub> )                             | 0.2 |     |     | μs    |

| Recirculate          | control change time before clock change to 0 ( $t_{\text{rb}}$ ) (See Note 2) | 0.3 |     |     | μs    |

| Recirculate          | control change time after clock change to 0 $(t_{ra})$ (See Note 2)           | 0.3 |     |     | μs    |

NOTES: 1. All voltages are with respect to VSS.

2. TMS 3012 JR only.

To ensure correct data loading, the input should reach the desired level at least time  $t_{db}$  before the clock goes to logic 0, and should remain at that level for a time  $t_{da}$  after the clock has changed to 0. Similarly, the recirculate control input should not change state for a period  $t_{rb}$  before and  $t_{ra}$  after the clock change from logic 1 to logic 0.

#### electrical characteristics at nominal operating conditions and 25°C

| PA                  | ARAMETER                                     | TEST CONDITIONS <sup>†</sup>              | MIN | TYP <sup>†</sup> | MAX  | UNITS |

|---------------------|----------------------------------------------|-------------------------------------------|-----|------------------|------|-------|

| V <sub>out(1)</sub> | Logic 1 output voltage                       | $R_L = 10 k\Omega$ to $V_{SS}$            | -11 | -13              |      | v     |

| V <sub>out(0)</sub> | Logic 0 output voltage                       | R <sub>L</sub> = 10 kΩ to V <sub>SS</sub> |     | -0.3             | -1   | v     |

| lin(1)              | Data input, leakage current                  | V <sub>in</sub> = -20 V                   |     |                  | -0.5 | μA    |

| l <sub>in(1)φ</sub> | Clock input, leakage current                 | $V_{in\phi} = -20 V, V_{GG} = 0$          |     |                  | 0.5  | μA    |

| Zout                | Output impedance to ground                   | V <sub>out</sub> = 0 to1 V                |     | 0.7              | 1.5  | kΩ    |

| IDD                 | Supply current into V <sub>DD</sub> terminal | $V_{DD} = -15 V$ , $V_{GG} = -29 V$       |     | -23              | -30  | mA    |

| IGG                 | Supply current into VGG terminal             | $V_{DD} = -15 V$ , $V_{GG} = -29 V$       |     | -3               | -5.5 | mA    |

$^\dagger\,$  Unless otherwise noted, R  $_L$  = 10 k  $\Omega,$  and C  $_L$  = 10 pF.

<sup>†</sup> All other pins are at  $V_{SS}$

### dynamic electrical characteristics, $V_{DD}$ = -14 V, $V_{GG}$ = -28 V, $T_A$ = 25°C

| F                | PARAMETER                                                                | TEST CONDITIONS                                                    | MIN | ТҮР | MAX | UNITS |

|------------------|--------------------------------------------------------------------------|--------------------------------------------------------------------|-----|-----|-----|-------|

| <sup>t</sup> pd1 | Propagation delay time to logic 1 level from clock $\phi$ to data output | $R_{L}$ = 10 k $\Omega$ to ground, $C_{L}$ = 10 pF                 |     | 500 | 700 | ns    |

| <sup>t</sup> pd0 | Propgation delay time to logic O level from clock $\phi$ to data output  | $R_L = 10 \text{ k}\Omega$ to ground, $C_L = 10 \text{ pF}$        |     | 400 | 600 | ns    |

| C <sub>in</sub>  | Capacitance of data input                                                | <sup>°</sup> V <sub>in</sub> = 0, f = 1 MHz, T <sub>A</sub> = 25°C |     | 3   | 5   | pF    |

| C <sub>inφ</sub> | Capacitance of clock input                                               | V <sub>inφ</sub> = 0, f = 1 MHz, T <sub>A</sub> = 25°C             |     | 5   | 7   | pF    |

### TMS3012JR-dual 128-bit accumulator TMS3028LR-dual 128-bit shift register

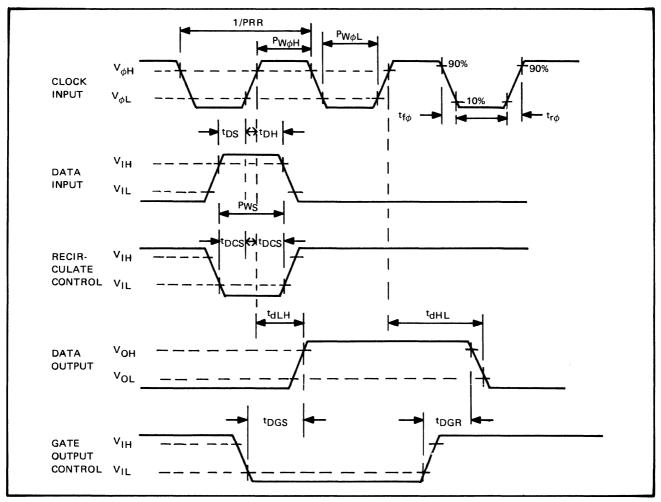

voltage waveforms (TMS 3012 LR only)

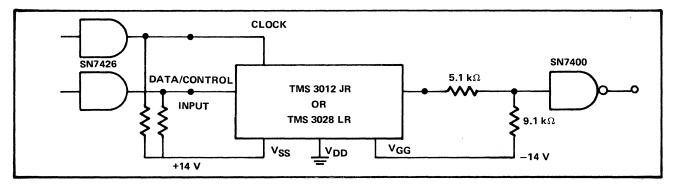

### interface circuits

a) TTL/DTL

### b) MOS

No external components are required.

### TMS3012JR – dual 128-bit accumulator TMS3028LR – dual 128-bit shift register

### mechanical data

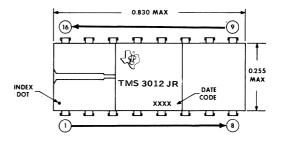

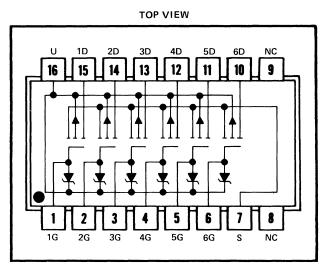

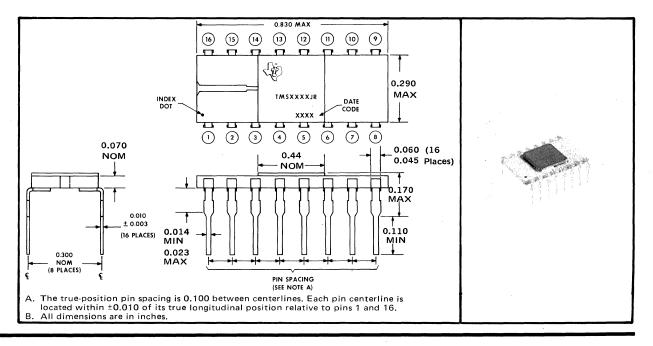

The TMS 3012 JR is mounted in a 16-pin hermetically sealed dual-in-line package consisting of a ceramic base, gold-plated cap, and gold-plated leads. The package is designed for insertion in mountinghole rows on 0.300-inch centers.

A. The true-position pin spacing is 0.100 between centerlines. Each pin centerline is located within  $\pm 0.010$  of its true longitudinal position relative to pins 1 and (16)

B. All dimensions are in inches.

| PIN NO. | FUNCTION              | PIN NO. | FUNCTION              |

|---------|-----------------------|---------|-----------------------|

| 1       | No connection         | 9       | Clock $\phi$          |

| 2       | Input A               | 10      | No connection         |

| 3       | Recirculate Input A   | 11      | V <sub>GG</sub>       |

| 4       | Recirculate Control A | 12      | Output B              |

| 5       | Output A              | 13      | Recirculate Control B |

| 6       | V <sub>DD</sub>       | 14      | Recirculate Input B   |

| 7       | V <sub>SS</sub>       | 15      | Input B               |

| 8       | No connection         | 16      | No connection         |

|         |                       |         |                       |

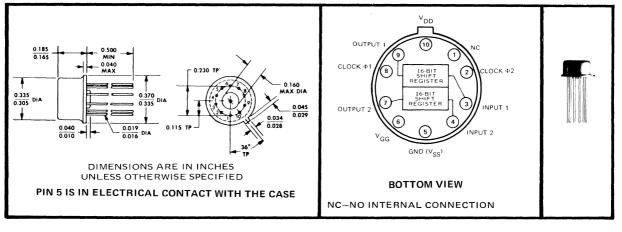

The TMS 3028 LR package outline is same as JEDEC TO-100 except for diameter of standoff.

### FEATURING

- Static logic

- DC to 1 MHz operation

- Low power dissipation

- Push-pull output buffers

- TTL compatible

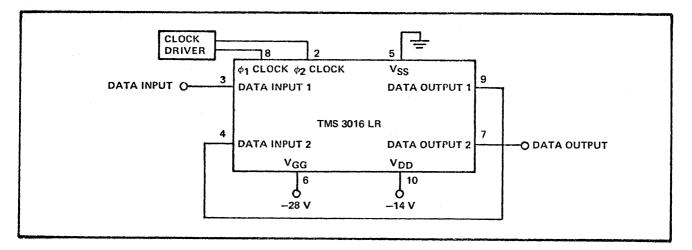

### description

The TMS 3016 LR is a dual static shift register. This device contains two d-c to 1 MHz shift registers with independent input and output terminals and common clocks and power. MOS thick-oxide technology is used to fabricate cross-coupled flip-flops for each register bit so that data can be stored indefinitely. The transistors in the device are the P-channel enhancement-mode type. All input leads have zener network protection and all outputs contain low output impedance, non-inverting push-pull output buffers.

Two power supply levels and two clocks are required for operation with a third clock generated internally. Data is transferred into the register when the  $\phi_1$  clock is pulsed to logic 1. Data is shifted when the  $\phi_1$  clock is returned to logic 0 and the  $\phi_2$  clock is pulsed to logic 1. Output data appears on the logic 0 to logic 1 transition of the  $\phi_2$  clock. For long term storage, the  $\phi_1$  clock must be held at a logic 0 and the  $\phi_2$  clock at a logic 1.

#### mechanical data and pin configuration

The package outline is the same as JEDEC TO-100 except for diameter of standoff.

### logic definition

Negative logic is assumed

- a) Logic 1 = most negative voltage

- b) Logic 0 = most positive voltage

#### absolute maximum ratings over operating free-air temperature range (unless otherwise noted)

| Supply voltage V <sub>DD</sub> range (See Note 1)             |  |

|---------------------------------------------------------------|--|

| Supply voltage $V_{GG}$ range (See Note 1)                    |  |

| Phase one clock input voltage $V_{\phi 1}$ range (See Note 1) |  |

| Phase two clock input voltage $V_{\phi 2}$ range (See Note 1) |  |

| Data input voltage V <sub>1</sub> range (See Note 1)          |  |

| Power dissipation                                             |  |

| Operating free-air temperature range                          |  |

| Storage temperature range                                     |  |

NOTE 1. These voltage values are with respect to network ground terminal,  $V_{\mbox{SS}}$ .

### recommended operating conditions

| CHARACTERISTICS                                                                                       | MIN  | NOM | MAX | UNITS |

|-------------------------------------------------------------------------------------------------------|------|-----|-----|-------|

| Supply voltage VDD                                                                                    | -12  | -14 | -15 | V     |

| Supply voltage V <sub>GG</sub>                                                                        | -24  | -28 | 29  | v     |

| Logic 0 data input voltage V <sub>i(0)</sub> (See Note 2)                                             | 0.3  | 0   | -2  | v     |

| Logic 1 data input voltage V <sub>i(1)</sub> (See Notes 2)                                            | -9   | -14 | -29 | v     |

| Width of data pulse, t <sub>p(data)</sub> (See voltage waveforms)                                     | 0.4† |     |     | μs    |

| Data setup time, t <sub>setup</sub> (See voltage waveforms and Note 3)                                | 100  |     |     | ns    |

| Data hold time, thold (See voltage waveforms and Note 4)                                              | 20   |     |     | ns    |

| Logic 0 clock input voltage V_{\phi0(clock)} (See Notes 2 and 5)                                      | 0.3  | 0   | -2  | v     |

| Logic 1 clock input voltage V $_{\phi 1(	ext{clock})}$ (See Notes 2 and 5)                            | -24  | 28  | 29  | v     |

| Rise time of clock pulse, t <sub>r(clock)</sub> (See voltage waveforms)                               |      | 0   | 5   | μs    |

| Fall time of clock pulse, tf(clock) (See voltage waveforms)                                           |      |     | 5   | μs    |

| $\phi_1$ clock pulse width, $t_{p(\phi1)}$ (See voltage waveforms)                                    | 0.3† |     | 10† | μs    |

| $\phi_2$ clock pulse width, $t_{p(\phi2)}$ (See voltage waveforms)                                    | 0.4† |     | ∞†  | μs    |

| Time interval from $\phi_1$ clock to $\phi_2$ clock input pulse, $t_{\phi12}$ (See voltage waveforms) | 0.01 |     | 10  | μs    |

| Time interval from $\phi_2$ clock to $\phi_1$ clock input pulse, $t_{\phi21}$ (See voltage waveforms) | 0.01 |     | 10  | μs    |

| Clock repetition rate                                                                                 | 0    |     | 1   | MHz   |

NOTES: 2. These voltage values are with respect to network ground terminal,  $\mathsf{V}_{SS}.$

3. Setup time is the interval immediately preceeding the positive-going edge of the phase 1 clock pulse during which interval the data to be recognized must be maintained at the input to ensure its recognition.

4. Hold time is the interval immediately following the positive-going edge of the phase 1 clock pulse during which interval the data to be recognized must be maintained at the input to ensure its recognition.

5. The two clock pulses must never be simultaneously more than 3 volts more negative than  $\mathsf{V}_{SS}.$

$^{\dagger}$  These values are at V\_DD = -14 V, V\_GG = -28 V, and T\_A =  $25^{o}C.$

### electrical characteristics over operating free-air temperature range (unless otherwise noted)

|                    | PARAMETER                                     | TEST CONDITIONS                     | MIN | түр†  | МАХ                                                    | UNITS |

|--------------------|-----------------------------------------------|-------------------------------------|-----|-------|--------------------------------------------------------|-------|

| 46                 | Logic 1 input current into data input         | V <sub>I</sub> = -29 V              |     |       | 0.5                                                    | μΑ    |

| <sup> </sup> ΙL(φ) | Logic 0 input current into either clock input | $V_{\phi} = -29 V$ , $V_{GG} = 0 V$ |     |       | 50                                                     | μA    |

| Vau                |                                               | I <sub>O</sub> = 0 mA               |     |       | $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$ | v     |

| VOH                | OH Logic 0 output voltage                     | 1 <sub>O</sub> = -2.0 mA            |     | -2.6  | -5                                                     | V     |

| Max                |                                               | I <sub>O</sub> = 0 mA               | -12 |       |                                                        | v     |

| VOL                | Logic 1 output voltage                        | I <sub>O</sub> = 1.0 mA             | -11 | -11.6 |                                                        | v     |

| ROH                | Output resistance, logic 0                    | I <sub>O</sub> = -2.0 mA            |     |       | 2.5                                                    | kΩ    |

| ROL                | Output resistance, logic 1                    | I <sub>O</sub> = -1.0 mA            |     |       | 3                                                      | kΩ    |

| IDD                | Supply current from VDD terminal*             |                                     |     | -8    | -12                                                    | mA    |

| IGG                | Supply current from VGG terminal*             |                                     |     | -16   | -25                                                    | mA    |

| fmax               | Maximum clock frequency                       |                                     | 1   |       |                                                        | MHz   |

<sup>†</sup> Unless otherwise noted, voltages are as shown in the nominal column of the recommended operating conditions (nominal operating voltages).

<sup>†</sup> All typical values are at  $T_A = 25^{\circ}$ C.

\* Current into a terminal is a positive value.

# switching characteristics, V<sub>DD</sub> = -14 V, V<sub>GG</sub> = -28 V, R<sub>L</sub> = 10 m $\Omega$ , C<sub>L</sub> = 20 pF, T<sub>A</sub> = 25°C

|                     | PARAMETER                                                               | TEST CONDITIONS                                              | MIN | түр | MAX | UNITS |

|---------------------|-------------------------------------------------------------------------|--------------------------------------------------------------|-----|-----|-----|-------|

| <sup>t</sup> pd0    | Propagation delay time to high level from $\phi_2$ clock to data output | See voltage waveforms                                        |     | 250 | 400 | ns    |

| <sup>t</sup> pd1    | Propagation delay time to low level from $\phi_2$ clock to data output  | See voltage waveforms                                        |     | 250 | 350 | ns    |

| C <sub>in(φ1)</sub> | Capacitance of $\phi_1$ clock input                                     | V <sub>I</sub> = 0 V, V <sub>I(φ2)</sub> = 0 V,<br>f = 1 MHz |     | 6   | 10  | pF    |

| C <sub>in(φ2)</sub> | Capacitance of $\phi_2$ clock input*                                    | V <sub>I</sub> = 0 V, V <sub>I(φ1)</sub> = 0 V,<br>f = 1 MHz |     | 15  | 20  | pF    |

| C <sub>in</sub>     | Capacitance of data input                                               | V <sub>I</sub> = 0, f = 1 MHz                                |     | 2   | 14  | pF    |

\*  $C_{in(\phi_2)}$  includes the capacitance of the internal  $\phi_2$  clock.

voltage waveforms

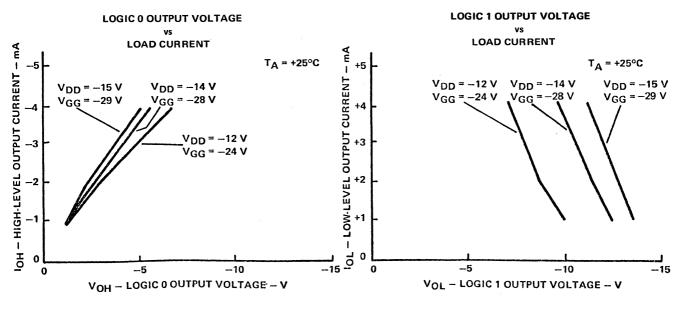

typical characteristics

### typical applications data

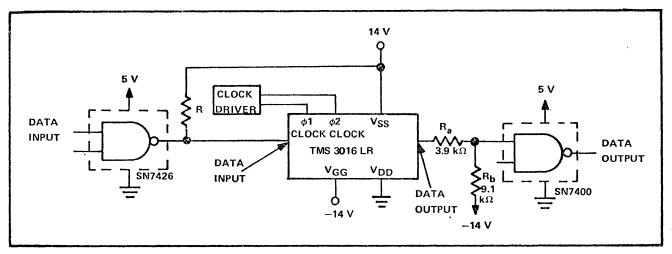

### 1) MOS/TTL interface

With proper supply voltages, interfacing can be achieved with only three resistors. A typical MOS/TTL interface is shown below.

An input pull-up resistor is required to provide the necessary input voltage swing. The value of this resistor (R) depends on the actual circuit requirements – values as low as  $1 \text{ k}\Omega$  can be used for high-speed operation while values as high as  $15 \text{ k}\Omega$  can be used when low power consumption is important rather than high-speed.

At the output interface, the 9.1 k $\Omega$  resistor sinks the 1.6 mA of TTL-gate current when 0 volts is required on the TTL input. When 3 volts is required on the TTL input, the MOS output device supplies current from 14 volts, through the 3.9 k $\Omega$  resistor and the 9.1 k $\Omega$  resistor to -14 volts. The 3.9 k $\Omega$  resistor limits the voltage at the TTL gate input to 5 volts maximum.

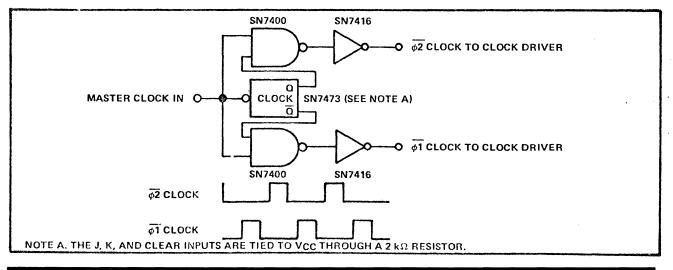

### 2) Two-phase clock generator

expansion to single 32 register

### schematic (each register)

preliminary information

### FEATURING

- Static operation

- Single clock

- Single power supply

- TTL compatible

- Complementary parallel outputs

- Single ended output buffers

- 16-pin ceramic dual-in-line packages

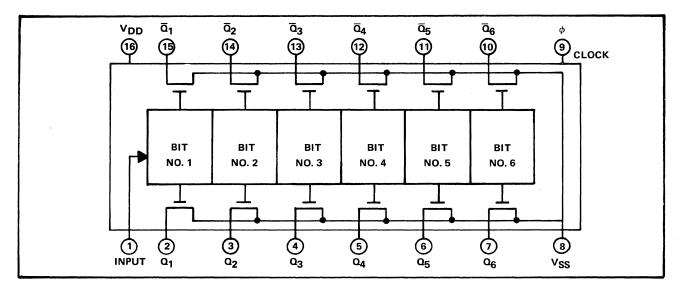

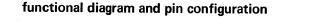

### description

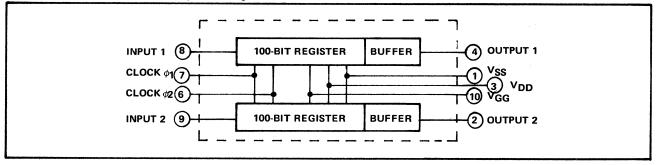

The TMS 3026 JC is a 6-bit serial-input parallel-output static shift register, constructed on a single monolithic chip with MOS p-channel enhancement-mode transistors. Both true and complement are available at the parallel outputs. Each output has an unclocked single-ended output buffer. The output level is determined by different external load resistors and load power supply. One power supply, one clock, and ground are required for operation. Cross-coupled flip-flops are used to implement each bit of delay, enabling data to be stored indefinitely when the clock is grounded.

### logic definition

Negative logic is assumed:

- a) Logic 1 = most negative voltage

- b) Logic 0 = most positive voltage

#### operation

Both transferring data into the register and shifting the data in the register are accomplished when the clock is at a logical 1. For long-term data storage, the clock must be held at logical 0. Output data appears on the positive-going edge of the clock pulse.

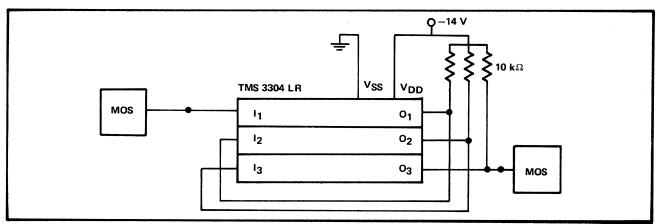

functional diagram and pin configuration

absolute maximum ratings (over operating free-air temperature range unless otherwise noted)

| Supply voltage V <sub>DD</sub> range (See note) |     |     | . $-30$ V to 0.3 V |

|-------------------------------------------------|-----|-----|--------------------|

| Clock and data input voltage ranges (See note)  | ••• |     | . $-30$ V to 0.3 V |

| Operating free-air temperature range            |     |     | . −25°C to 85°C    |

| Storage temperature range                       |     | • • | –55°C to 150°C     |

NOTE: These voltage values are with respect to network  $\mathsf{V}_{SS}$  terminal.

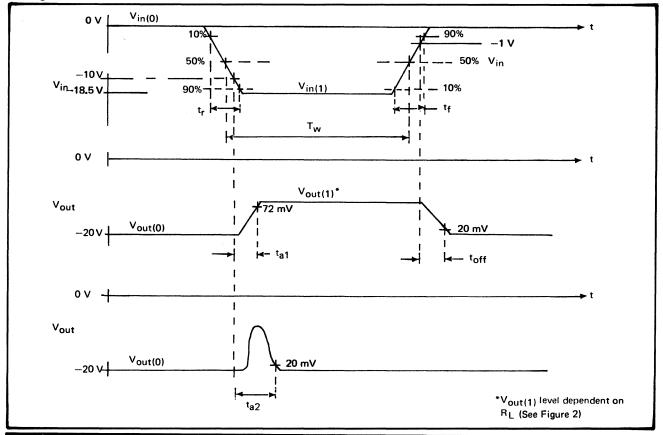

#### recommended operating conditions

| CHARACTERISTICS                                                         | MIN  | NOM | МАХ  | UNITS |

|-------------------------------------------------------------------------|------|-----|------|-------|

| Logical 1 data input voltage Vin(1)                                     | -10  | -12 | -29  | v     |

| Logic 0 data input voltage Vin(0)                                       | +0.3 | 0   | -3   | v     |

| Logic 1 clock input voltage ${\sf V}_{\sf in(1)\phi}$                   | -10  | -12 | -29  | v     |

| Logic 0 clock input voltage ${\sf V}_{\sf in}(0)\phi$                   | +0.3 | 0   | -3   | · v   |

| Width of data pulse, t <sub>p(data)</sub> (See Voltage Waveforms)       | 1    |     |      | μs    |

| Rise time of clock pulse, t <sub>r(clock)</sub> (See Voltage Waveforms) |      |     | 50   | μs    |

| Fall time of clock pulse, t <sub>f(clock)</sub> (See Voltage Waveforms) |      |     | 50   | μs    |

| Clock repetition rate                                                   | 0    |     | 0.25 | MHz   |

| Width of clock pulses, $t_{p(clock \phi)}$ (See Voltage Waveforms)      | 1    |     |      | μs    |

| Supply voltage VDD                                                      | -23  | -24 | -29  | V     |

### electrical characteristics (at nominal operating conditions and 25°C unless otherwise noted)

| PARAMETER           |                                 | TEST CONDITIONS         | MIN | ТҮР | МАХ   | UNITS |

|---------------------|---------------------------------|-------------------------|-----|-----|-------|-------|

| V <sub>out(1)</sub> | Logic 1 output voltage (Note 1) |                         |     | 24  |       | v     |

| V <sub>out(0)</sub> | Logic 0 output voltage          | I <sub>out</sub> = 1 mA |     | 0.7 | 1.2   | v     |

| V <sub>out(0)</sub> | Logic 0 output voltage          | l <sub>out</sub> = 2 mA |     | 2   | 4     | v     |

| lin                 | Input leakage current           | V <sub>in</sub> = -29 V |     |     | 0.5   | μA    |

| $I_{in}(\phi)$      | Clock leakage current           | $V_{in\phi} = -29 V$    |     |     | 0.5   | μA    |

| IDD                 | Supply current                  |                         |     | 1.2 | 2.0   | mA    |

| f                   | Operating frequency             |                         | 0   |     | 0.250 | KHz   |

NOTE 1: For a logic 1 the MOS single-ended buffer is "off" and the output voltage is determined by the external load resistor and power supply voltage.

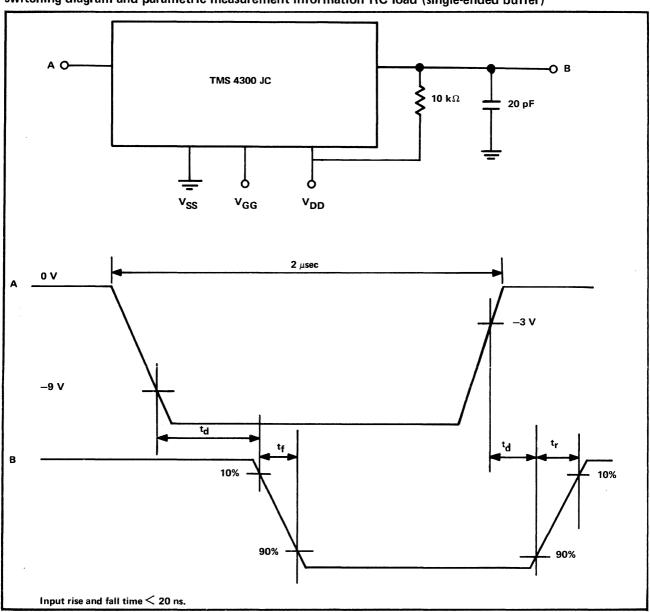

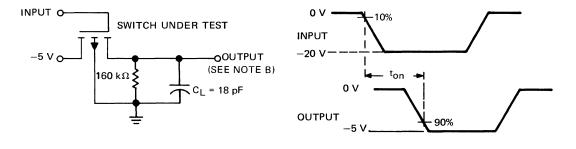

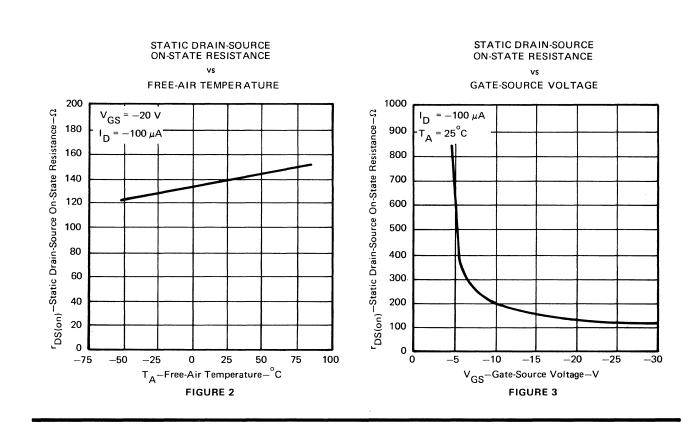

### dynamic electrical characteristics (at nominal operating conditions and 25°C unless otherwise noted)

|                  | PARAMETER                                                                   | TEST CONDITIONS                                     | MIN | ТҮР | MAX | UNITS |

|------------------|-----------------------------------------------------------------------------|-----------------------------------------------------|-----|-----|-----|-------|

| <sup>t</sup> pd1 | Propagation delay time to logic 1<br>level from clock $\phi$ to data output | See Voltage Waveforms                               |     | 2   | 4   | μs    |

| <sup>t</sup> pd0 | Propagation delay time to logic 0 level from clock $\phi$ to data output    | See Voltage Waveforms                               |     | 1   | 2   | μs    |

| C <sub>in</sub>  | Capacitance of data input                                                   | $V_{in} = 0,$ $T_A = 25^{\circ}C,$<br>f = 1 MHz     |     | 3.0 | 5.0 | pF    |

| C <sub>inø</sub> | Capacitance of the clock input                                              | $V_{in\phi} = 0,$ $T_A = 25^{\circ}C,$<br>f = 1 MHz |     | 3.0 | 5.0 | pF    |

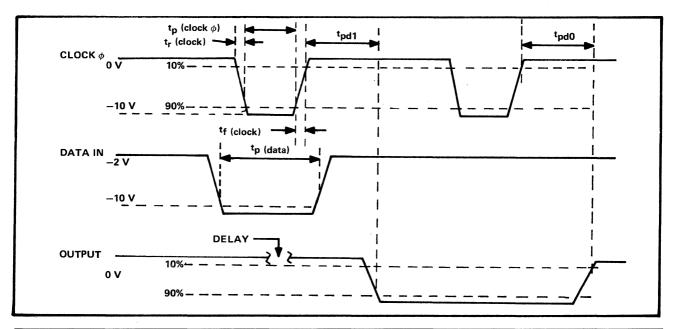

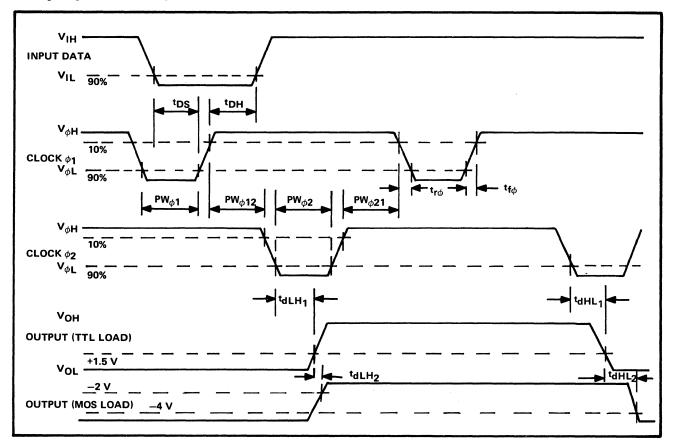

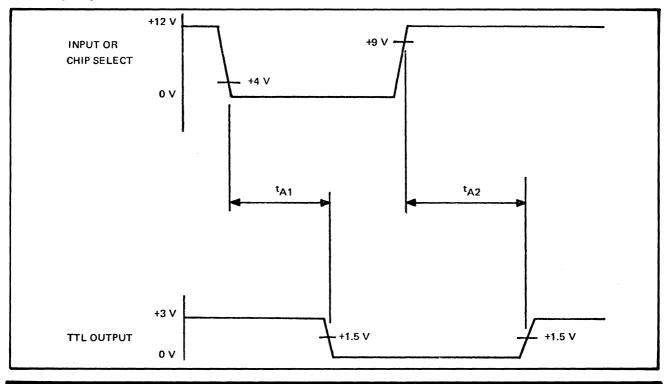

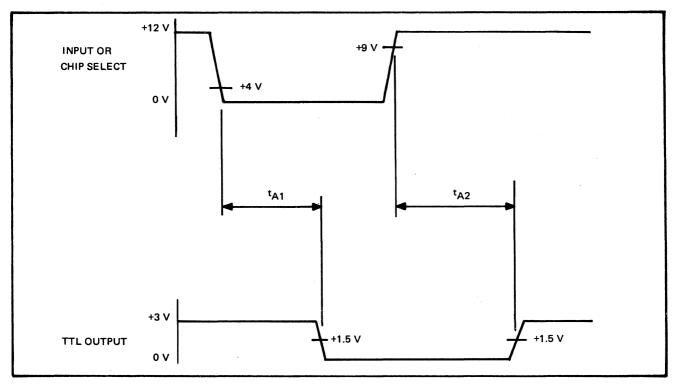

#### voltage waveforms

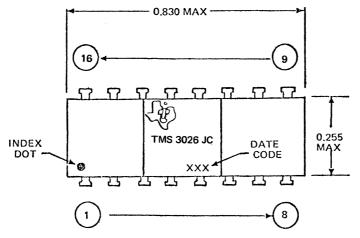

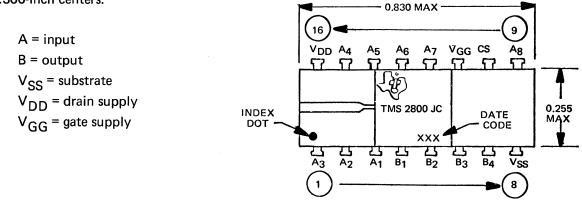

### mechanical data

The TMS 3026 JC is mounted in a 16-lead, hermetically sealed, dual-in-line package consisting of a ceramic base, gold-plated cap, and gold-plated leads. The package is intended for insertion in 0.024  $\pm$  0.002-inch-diameter mounting holes, which are spaced 0.300 inches between row centerlines.

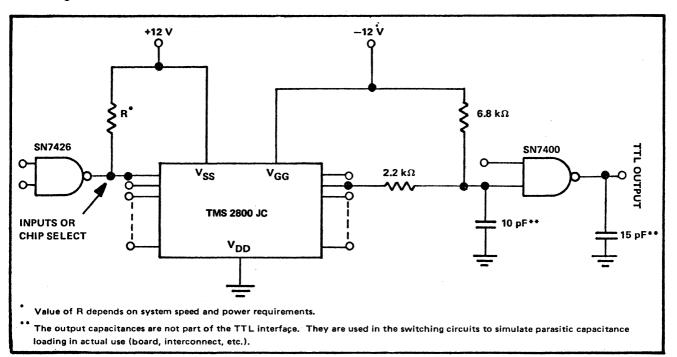

#### interface

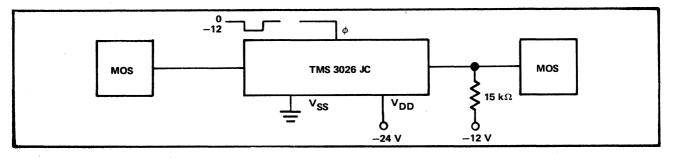

### a) MOS interface

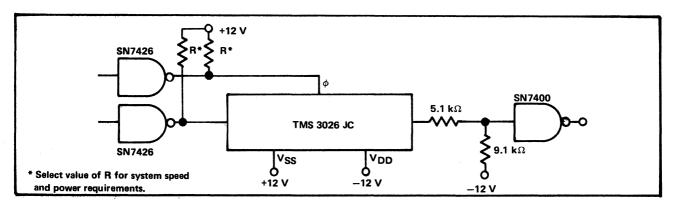

### b) TTL interface

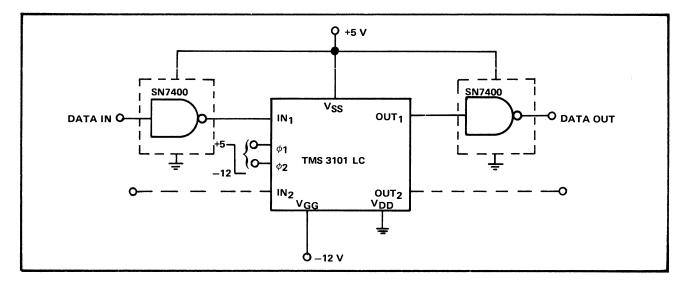

preliminary information

#### FEATURING

- DC to 2.5 MHz operation

- Low power dissipation

- Direct interface with DTL/TTL

- Static operation

- Push-pull output buffer

- Low threshold technology

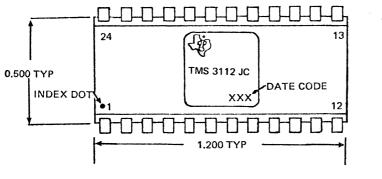

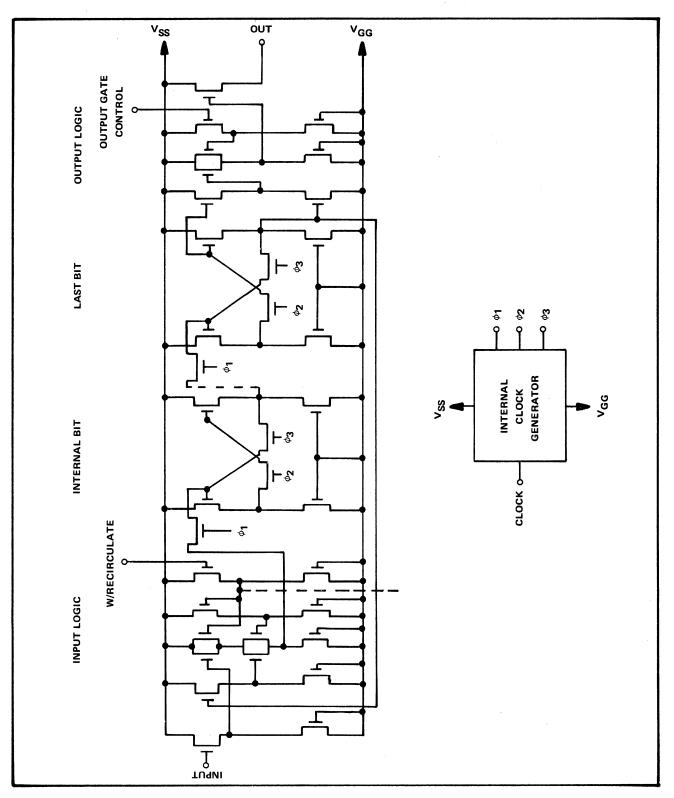

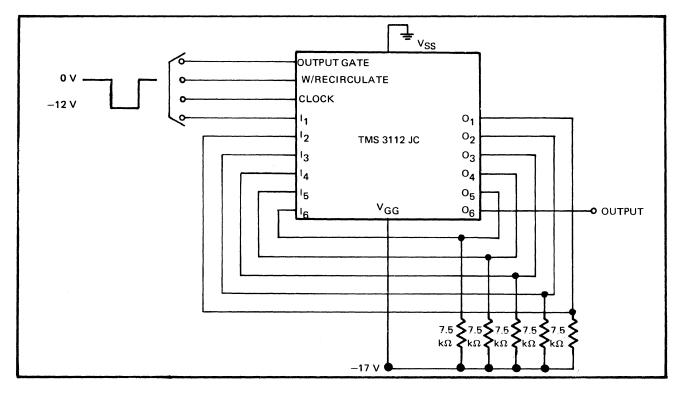

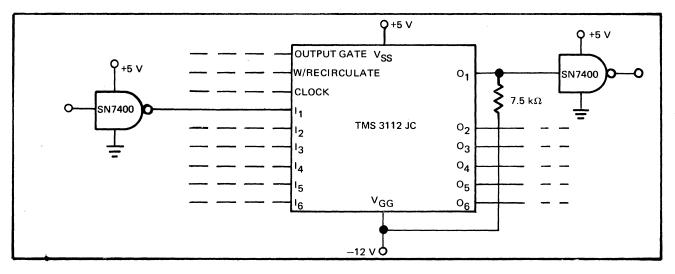

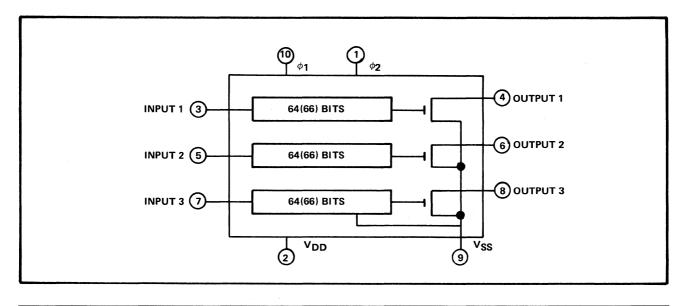

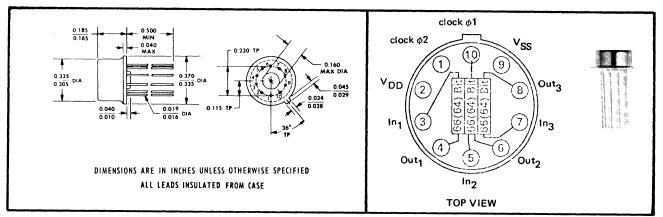

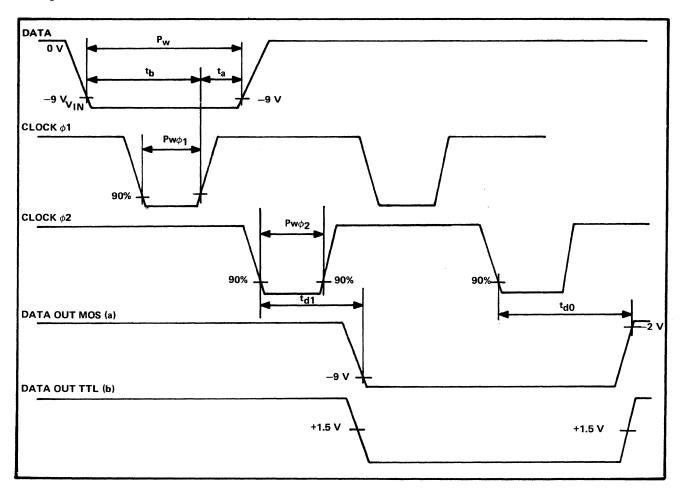

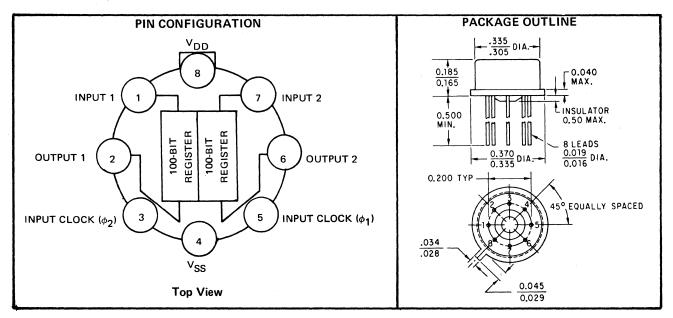

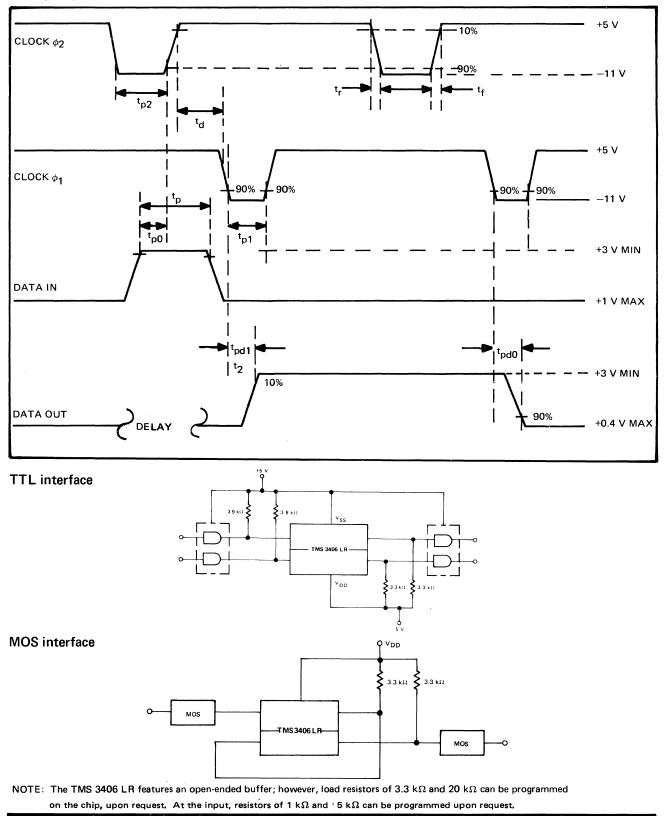

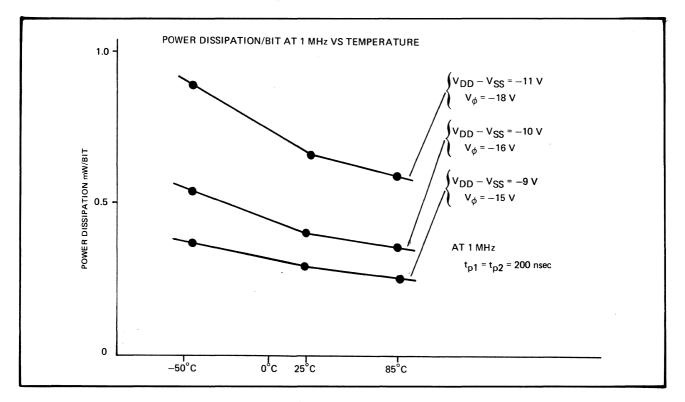

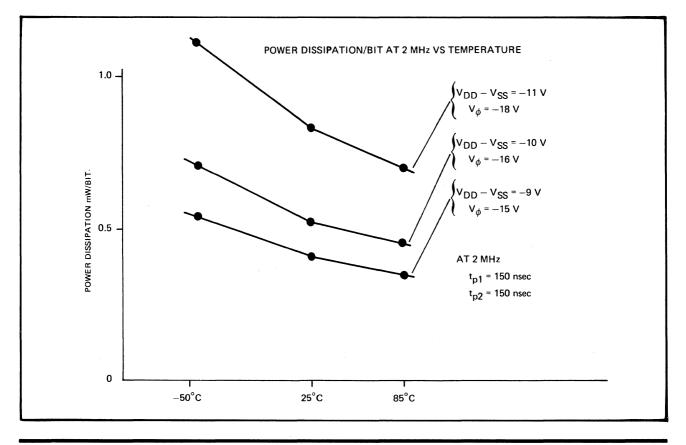

### description