The Engineering Staff of TEXAS INSTRUMENTS INCORPORATED Semiconductor Group

DEZEMBER 1977

**TEXAS INSTRUMENTS**

Information contained in this publication is believed to be accurate and reliable. However, responsibility is assumed neither for its use nor for any infringement of patents or rights of others that may result from its use. No license is granted by implication or otherwise under any patent or patent right of Texas Instruments or others.

Copyright<sup>©</sup> 1977 Texas Instruments Incorporated

## TABLE OF CONTENTS

|                                                                                       | Page |

|---------------------------------------------------------------------------------------|------|

| 1. SUMMARY SCHOTTKY TTL MEMORIES                                                      | 2    |

| TTL PROM Data Manual Series 54S/74S                                                   | 3    |

| <ul> <li>SN54S330, SN54S331, SN74S330, SN74S331 : FPLA</li> </ul>                     |      |

| • SN74S225 : FIFO                                                                     |      |

|                                                                                       |      |

| 2. MOS EPROMS                                                                         |      |

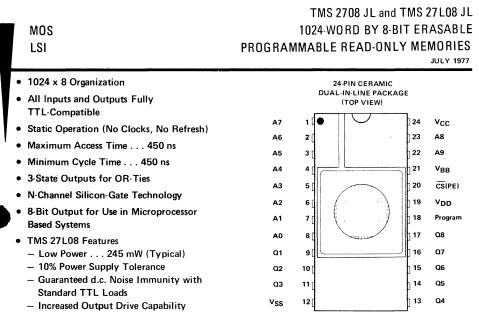

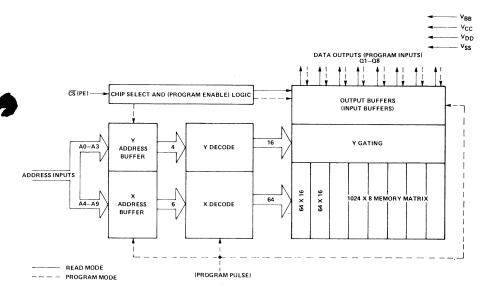

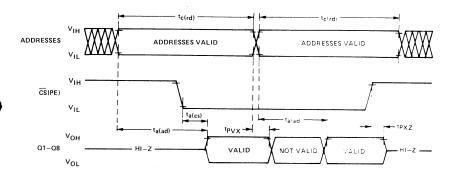

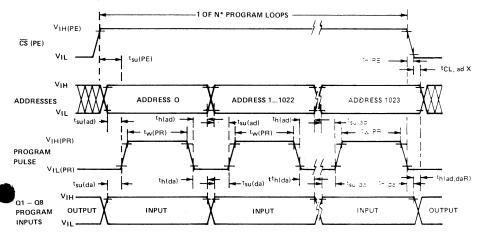

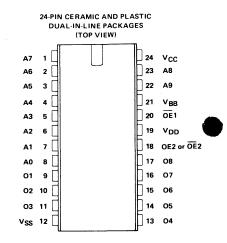

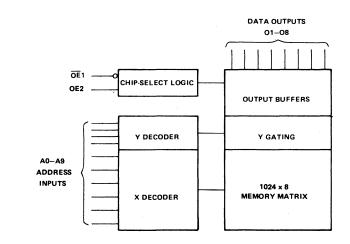

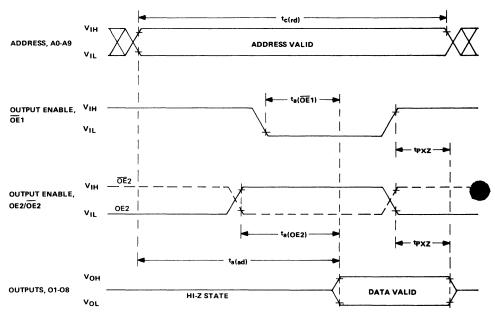

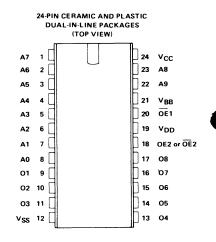

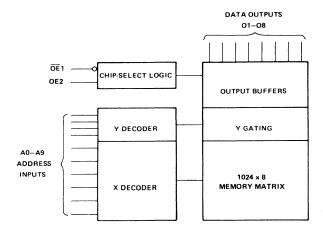

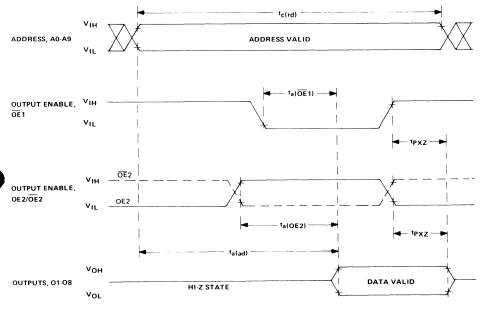

| <ul> <li>TMS2708JL and TMS27L08JL : 1024 x 8 Bit EPROM</li> </ul>                     | 27   |

| TMS2716JL : 2048 x 8 Bit EPROM                                                        | 33   |

| 3. MOS ROMS                                                                           |      |

| • TMS4700JL, NL : 1024 x 8 Bit ROM                                                    | 40   |

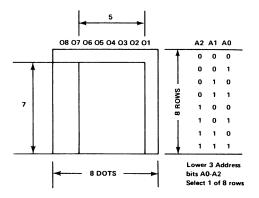

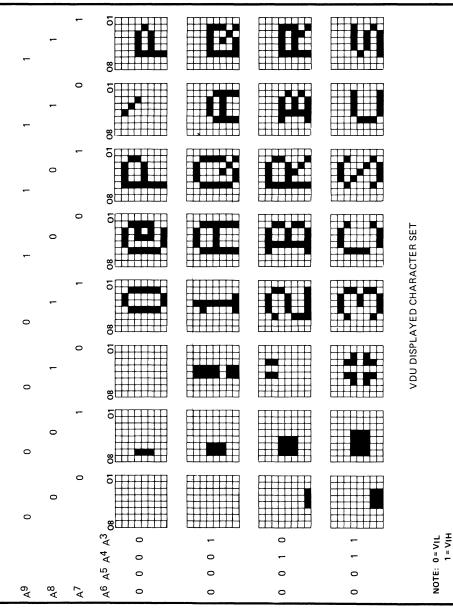

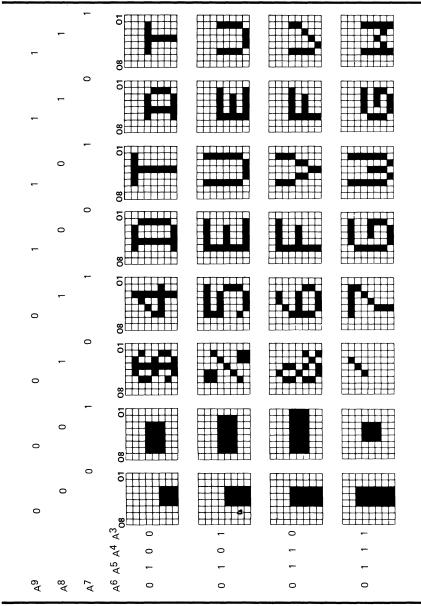

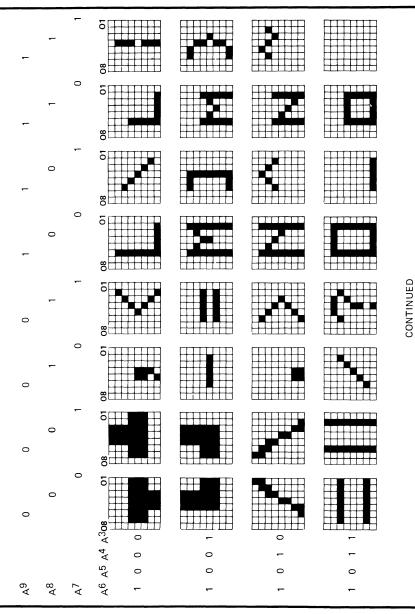

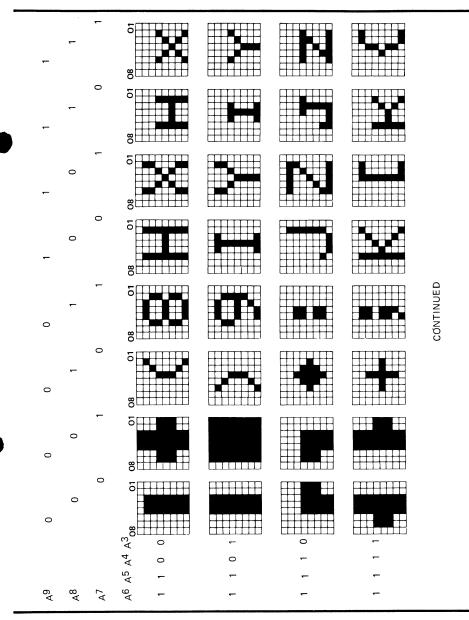

| TMS4710JL, NL : 1024 x 8 Bit Character Generator                                      | 44   |

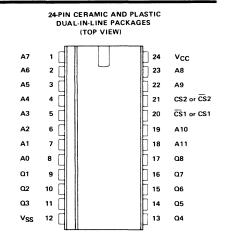

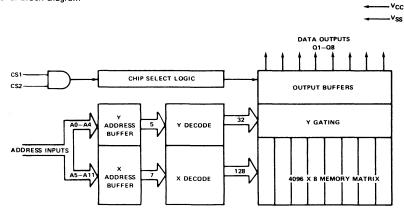

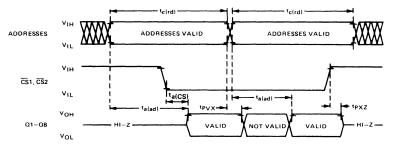

| • TMS4732JL, NL : 4096 x 8 Bit ROM                                                    | 52   |

| 4. STATIC MOS RAMS                                                                    |      |

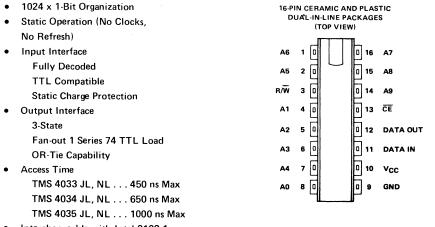

| <ul> <li>TMS4033JL, NL, TMS4034JL, NL, TMS4035JL, NL : 1024 x 1 Bit RAM</li> </ul>    | 56   |

| TMS4036JL, NL, TMS4036-1JL, NL, TMS4036-2JL, NL : 64 x 8 Bit RAM                      |      |

| <ul> <li>TMS4039JL, NL, TMS4039-1JL, NL, TMS4039-2JL, NL : 256 x 4 Bit RAM</li> </ul> |      |

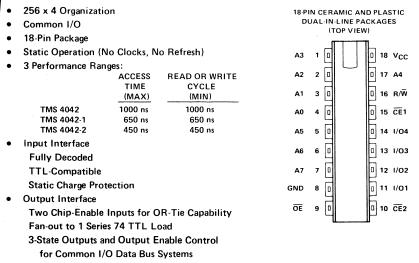

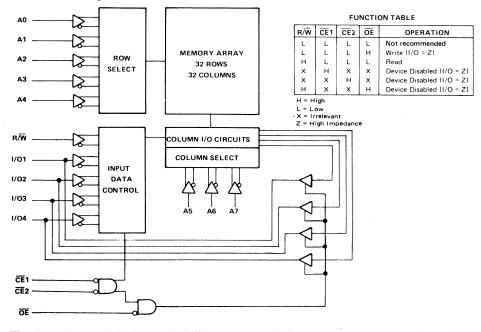

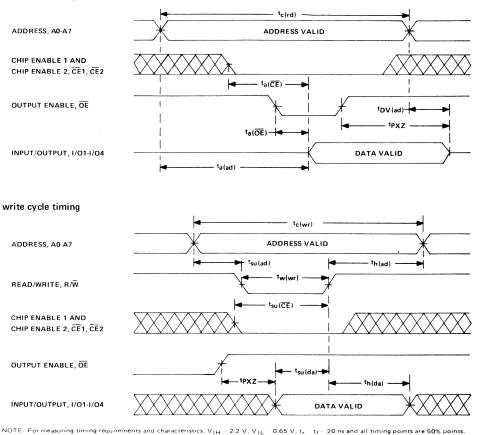

| • TMS4042JL, NL, TMS4042-1JL, NL, TMS4042-2JL, NL : 256 x 4 Bit RAM                   | 68   |

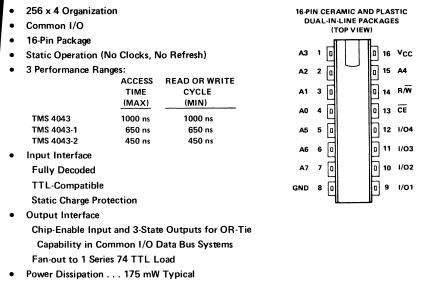

| <ul> <li>TMS4043JL, NL, TMS4043-1JL, NL, TMS4043-2JL, NL : 256 x 4 Bit RAM</li> </ul> | 72   |

| <ul> <li>TMS4044, -45, -30, -25, -20, -15JL, NL : 4096 x 1 Bit RAM</li> </ul>         |      |

| <ul> <li>TMS4046, -45, -30, -25, -20, -15JL, NL : 4096 x 1 Bit RAM</li> </ul>         |      |

| <ul> <li>TMS4045, -45, -30, -25, -20, -15JL, NL : 1024 x 4 Bit RAM</li> </ul>         |      |

| • TMS4047, -45, -30, -25, -20, -15JL, NL : 1024 x 4 Bit RAM                           |      |

| 5. DYNAMIC MOS RAMS                                                                   |      |

| TMS4027-15, TMS4027-20, TMS4027-25JL, NL : 4096 x 1 Bit RAM                           |      |

| • TMS4051JL, NL, TMS4051-1JL, NL : 4096 x 1 Bit RAM                                   |      |

| <ul> <li>TMS4116-15JL, TMS4116-20JL, TMS4116-25JL : 16384 x 1 Bit RAM</li> </ul>      |      |

| • TMS4070JL, TMS4070-1JL, TMS4070-2JL                                                 | 109  |

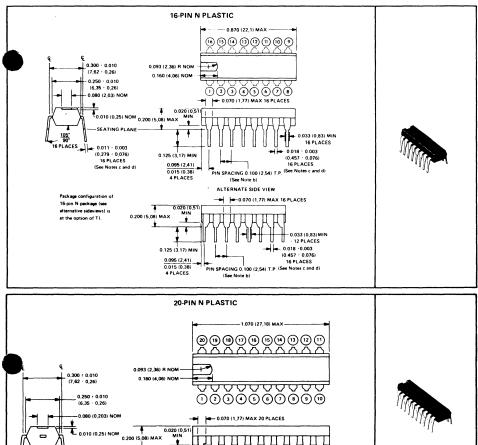

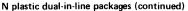

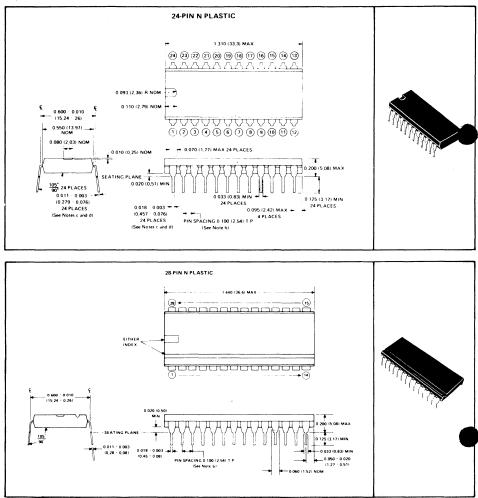

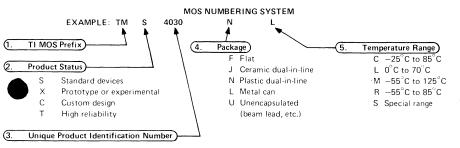

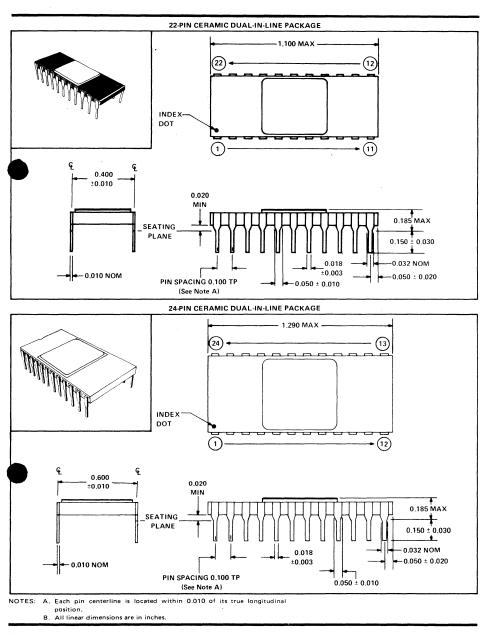

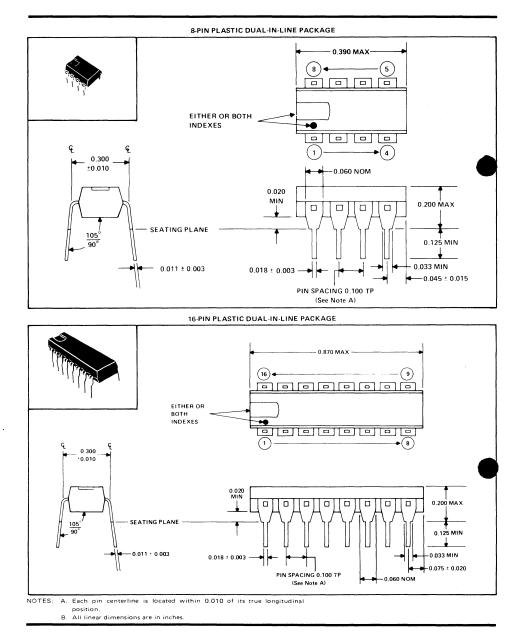

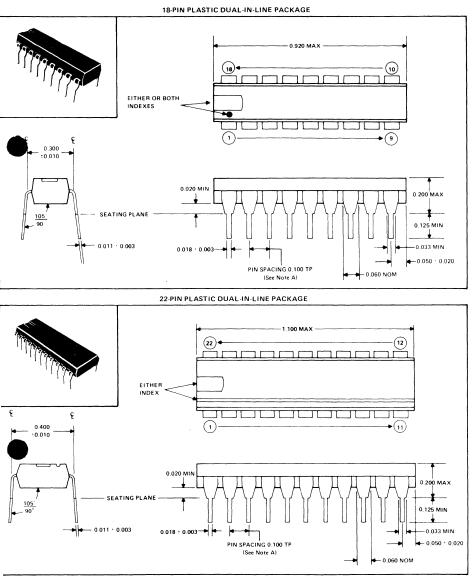

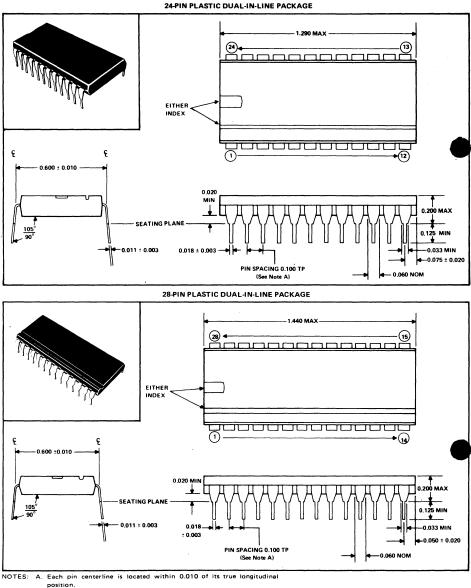

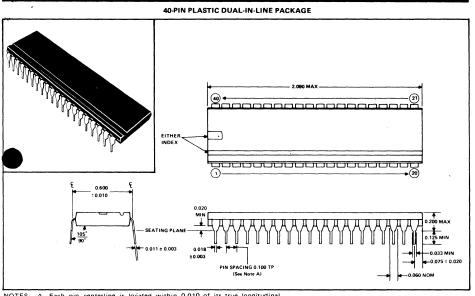

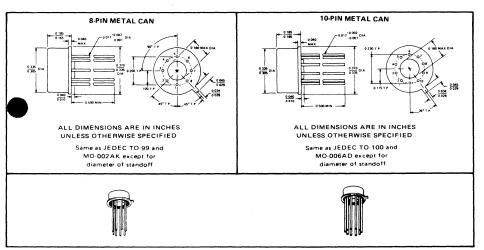

| 6. MECHANICAL SPECIFICATIONS                                                          |      |

| TTL Integrated Circuits Mechanical Data                                               |      |

| MOS LSI Mechanical Data                                                               | 112  |

|                                                                                       |      |

### 1

## FIELD PROGRAMMABLE READ-ONLY MEMORY (PROM) LINE SUMMARY (SEE PAGE

## MASK-PROGRAMMED READ-ONLY MEMORY (ROM) LINE SUMMARY

| TYPE NUMBER    | (BACKACES)     | TYPE OF                                                                                                          | BIT SIZE                   | TYPICAL PER            | RFORMANCE            | SEE  |        |  |

|----------------|----------------|------------------------------------------------------------------------------------------------------------------|----------------------------|------------------------|----------------------|------|--------|--|

| -55°C to 125°C | 0° to 70°C     | OUTPUT(S)                                                                                                        | (ORGANIZATION)             | ADDRESS<br>ACCESS TIME | POWER<br>DISSIPATION | PAGE |        |  |

| SN5488A(J, W)  | SN7488A(J, N)  | Open-Collector         256 Bits         26 ns         320 mV           (32 W x 8 B)         26 ns         320 mV | 26 ns 320                  |                        | Deen-Collector 26 ns |      | 320 mW |  |

| SN54187(J, W)  | SN74187(J, N)  | Open-Collector                                                                                                   | 1024 Bits<br>(256 W x 4 B) | 40 ns                  | 460 mW               | 2    |        |  |

| SN54S270(J)    | SN74S270(J, N) | Open-Collector                                                                                                   | 2048 Bits                  | 45                     | 505                  |      |        |  |

| SN54S370(J)    | SN74S370(J, N) | 3-State                                                                                                          | (512 W x 4 B)              | 45 ns                  | 525 mW               | 7    |        |  |

| SN54S271(J)    | SN74S271(J, N) | Open-Collector                                                                                                   | 2048 Bits                  |                        |                      |      |        |  |

| SN54S371(J)    | SN74S371(J, N) | 3-State                                                                                                          | (256 W × 8 B)              | 45 ns                  | 525 mW               |      |        |  |

## READ/WRITE MEMORY (RAM) LINE SUMMARY

| SEE               | FORMANCE    | TYPICAL PER | OUTPUT         | BIT SIZE       |                  | TYPE NUMBER      |

|-------------------|-------------|-------------|----------------|----------------|------------------|------------------|

| PAGE              | POWER       | ADDRESS     | CONFIGURATION  | (ORGANIZATION) | 0°C to 70°C      | -55°C to 125°C   |

| 1.405             | DISSIPATION | ACCESS TIME | CONTRONTION    | (oneanization) |                  | 00 0 10 120 0    |

| 15                | 375 mW      | 25 ns       | Three-state    | , 64 bits      | SN 74S189(J, N)  | SN54S189(J, W)   |

| 15                | 375 mw      | 20 ns       | Open-Collector | (16 W × 4B)    | SN74S289(J, N)   | SN54S289(J, W)   |

| 1                 | 500 mW      | 25 ns       |                |                | SN74S200A(J, N)  | SN54S200A(J, W)  |

|                   | 275 mW      | 25          | Three-State    |                | SN74LS200A(J, N) | SN54LS200A(J, W) |

| 19                | 275/100* mW | 35 ns       |                | 256 bits       | SN74LS202(J, N)  | SN54LS202(J, W)  |

| - ' <sup>19</sup> | 500 mW      | 25 ns       |                | (256 W × 1B)   | SN74S300A(J, N)  | SN54S300A(J, W)  |

| 7                 | 275 mW      | 35 ns       | Open-Collector |                | SN74LS300A(J, N) | SN54LS300A(J, W) |

| 7                 | 275/100* mW | 35 ns       |                |                | SN74LS302(J, N)  | SN54LS302(J, W)  |

|                   | 550 mW      | 30 ns       |                |                | SN74S214A(J, N)  |                  |

| 7                 | 550 mW      | 40 ns       | Three-State    |                | SN74S214(J, N)   | SN54S214(J)      |

| 7                 | 200 mW      | 65 ns       |                |                | SN74LS214(J, N)  | SN54LS214(J)     |

| 7 ~               | 200/100*mW  | 75 ns       |                | 1024 bits      | SN74LS215(J,N)   | SN54LS215(J)     |

| - 25              | 550 mW      | 30 ns       |                | (1024 W × 1B)  | SN74S314A(J, N)  |                  |

| 1                 | 550 mW      | 40 ns       |                |                | SN74S314(J, N)   | SN54S314(J)      |

| 7                 | 200 mW      | 75 ns       | Open-Collector |                | SN74LS314(J, N)  | SN54LS314(J)     |

| 7                 | 200/100 mW  | 75 ns       |                |                | SN74S314(J, N)   | SN54LS315(J)     |

|                   | 600 mW      | 40 ns       |                |                | SN74S207(J, N)   | SN54S207(J)      |

| 7 🗲               | 200 mW      | 75 ns       | -              | 1024 bits      | SN74LS207(J, N)  | SN54LS207(J)     |

|                   | 600 mW      | 40 ns       | Three-State    | (256 W × 4B)   | SN74S208(J,N)    | SN54S208(J)      |

|                   | 200 mW      | 75 ns       |                |                | SN74LS208(J,N)   | SN54LS208(J)     |

| 1 27              |             | 75          | Three-State    | 4096 bits      | SN745400(J, N)   | SN54S400(J)      |

| 37                | 500 mW      | 75 ns       | Open-Collector | (4096 W x 1B)  | SN74S401(J, N)   | SN54S401(J)      |

## FIRST-IN/FIRST-OUT (FIFO) MEMORY

|                          | 017 0175                                         | TYPICAL PERFORMANCE |               |         |             |      |  |  |

|--------------------------|--------------------------------------------------|---------------------|---------------|---------|-------------|------|--|--|

|                          | YPE NUMBER BIT SIZE<br>(PACKAGES) (ORGANIZATION) |                     | RATES         | FALL    | POWER       | PAGE |  |  |

| (PACKAGES) (ORGANIZATION | (ORGANIZATION)                                   | INPUT               | OUTPUT        | THROUGH | DISSIPATION | PAGE |  |  |

| SN74S225(J, N)           | 80 bits<br>(16 W x 5B)                           | d-c to 10 MHz       | d-c to 10 MHz | 215 ns  | 400 mW      | 39   |  |  |

\*Powered down

# SCHOTTKY<sup>†</sup> PROM'S

- Titanium-Tungsten (Ti-W) Fuse Links for Fast, Low-Voltage, Reliable Programming

- All Schottky-Clamped PROM's Offer: Fast Chip Select to Simplify System Decode Choice of Three-State or Open-Collector Outputs P-N-P Inputs for Reduced Loading on System Buffers/Drivers

- Full Decoding and Chip Select Simplify System Design

- Applications Include: Microprogramming/Firmware Loaders Code Converters/Character Generators Translators/Emulators Address Mapping/Look-Up Tables

|                | R (PACKAGES)                                | BIT SIZE       | OUTPUT         | TYPICAL PER            | RFORMANCE |  |

|----------------|---------------------------------------------|----------------|----------------|------------------------|-----------|--|

| -55°C to 125°C | 0°C to 70°C                                 | (ORGANIZATION) | CONFIGURATION  | ADDRESS<br>ACCESS TIME | POWER     |  |

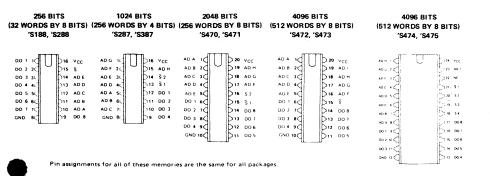

| 64S188(J, W)   | SN74S188(J, N)                              | 256 bits       | open-collector | 95                     |           |  |

| SN54S288(J, W) | SN74S288(J, N)                              | (32 W × 8 B)   | three-state    | 25 ns                  | 400 mW    |  |

| SN54S287(J, W) | SN74S287(J, N)                              | 1024 bits      | three-state    | 10                     |           |  |

| SN54S387(J, W) | SN74S387(J, N)                              | (256 W x 4 B)  | open-collector | 42 ns                  | 500 mW    |  |

| SN54S470(J)    | SN74S470(J, N)                              | 2048 bits      | open-collector | 50                     |           |  |

| SN54S471(J)    | SN74S471(J, N)                              | (256 W × 8 B)  | three-state    | 50 ns                  | 550 mW    |  |

| SN54S472(J)    | SN74S472(J, N)                              | 4096 bits      | three-state    |                        |           |  |

| SN54S473(J)    | SN74S473(J, N)                              | (512 W x 8 B)  | open-collector | 55 ns                  | 600 mW    |  |

| SN54S474(J, W) | SN74S474(J, N)                              | 4096 bits      | three-state    |                        |           |  |

| SN54S475(J, W) | 4\$475(J, W) \$N74\$475(J, N) (512 W x 8 B) |                | open-collector | 55 ns                  | 600 mW    |  |

### description

These monolithic TTL programmable read-only memories (PROM's) feature titanium-tungsten (Ti-W) fuse links with each link designed to program in one millisecond or less. These PROM's offer considerable flexibility for upgrading existing designs or improving new designs as they feature full Schottky clamping for improved performance, low-current MOS-compatible p-n-p inputs, choice of bus-driving three-state or open-collector outputs, and improved chip-select access times.

The high-complexity 2048- and 4096-bit 20-pin PROM's can be used to significantly improve system density for fixed memories as all are offered in a dual-in-line package having pin-row spacings of 0.300 inch.

TEXAS INSTRUMENTS

# SERIES 54S/74S PROGRAMMABLE READ-ONLY MEMORIES

### description (continued)

Data can be electronically programmed, as desired, at any bit location in accordance with the programming procedure specified. All PROM's, except the 'S287 and 'S387, are supplied with a low-logic-level output condition stored at each bit location. The programming procedure open-circuits Ti-W metal links, which reverses the stored logic level at selected locations. The procedure is irreversible; once altered, the output for that bit location is permanently programmed. Outputs never having been altered may later be programmed to supply the opposite output level. Operation of the unit within the recommended operating conditions will not alter the memory content.

Active level(s) at the chip-select input(s) enables all of the outputs. An inactive level at any chip-select input causes all outputs to be off.

The three-state output offers the convenience of an open-collector output with the speed of a totem-pole output; it can be bus-connected to other similar outputs yet it retains the fast rise time characteristic of the TTL totem-pole output. The open-collector output offers the capability of direct interface with a data line having a passive pull-up.

absolute maximum ratings over operating free-air temperature range (unless otherwise noted)

| Supply voltage (see Note 1)           |                 | <br> | 7V             |

|---------------------------------------|-----------------|------|----------------|

| Input voltage                         |                 | <br> | 5.5 V          |

| Off-state output voltage              |                 | <br> | 5.5 V          |

| Operating free-air temperature range: | SN54S' Circuits | <br> | –55°C to 125°C |

|                                       | SN74S' Circuits | <br> | 0°C to 70°C    |

| Storage temperature range             |                 | <br> | –65°C to 150°C |

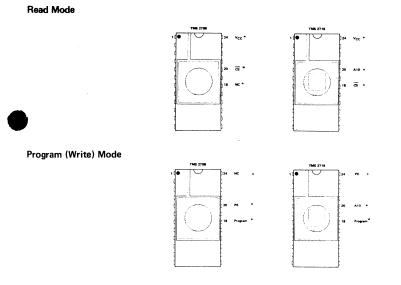

recommended conditions for programming

|                                                                           |                             | SN5              | 4S', SN | 745' |     |

|---------------------------------------------------------------------------|-----------------------------|------------------|---------|------|-----|

|                                                                           |                             | MIN              | NOM     | MAX  |     |

| Supply voltage, V <sub>CC</sub> (see Note 1)                              | Steady state                | 4.75             | 5       | 5.75 |     |

| Supply voltage, VCC (see Note 1)                                          | Program pulse               | 10               | 10.5    | 11†  |     |

| Input voltage                                                             | High level, V <sub>1H</sub> | 2.4              |         | 5    | v   |

|                                                                           | Low level, VIL              | 0                |         | 0.5  | 1 * |

| Termination of all outputs except the one to be programmed                |                             | See load circuit |         |      |     |

| remination of an outputs except the one to be programmed                  |                             | (Figure 1)       |         |      |     |

| Voltage applied to output to be programmed, VO(pr) (see Note 2)           |                             | 0                | 0.25    | 0.3  | V   |

| Duration of V <sub>CC</sub> programming pulse Y (see Figure 2 and Note 3) |                             | 0.9              | 1       | 10   | ms  |

| Programming duty cycle                                                    |                             |                  | 25      | 35   | %   |

| Free-air temperature                                                      |                             | 0                |         | 55   | °C  |

<sup>†</sup>Absolute maximum ratings.

NOTES: 1. Voltage values are with respect to network ground terminal. The supply-voltage rating does not apply during programming. 2. The 'S188, 'S288, 'S470, 'S471, 'S472, 'S473, 'S474, and 'S475 are supplied with all bit locations containing a low logic level, and

The 'S188, 'S288, 'S470, 'S471, 'S472, 'S473, 'S474, and 'S475 are supplied with all bit locations containing a low logic level, and programming a bit changes the output of the bit to high logic level. The 'S287 and 'S387 are supplied with all bit outputs at a high logic level, and programming a bit changes it to a low logic level.

3. Programming is guaranteed if the pulse applied is 0.9 ms long.

### step-by-step programming procedure

- 1. Apply steady-state supply voltage ( $V_{CC} = 5 V$ ) and address the word to be programmed.

- 2. Verify that the bit location needs to be programmed. If not, proceed to the next bit.

- 3. If the bit requires programming, disable the outputs by applying a high-logic-level voltage to the chip-select input(s).

- 4. Only one bit location is programmed at a time. Connect each output not being programmed to 5 V through 3.9 kΩ and apply the voltage specified in the table to the output to be programmed. Maximum current out of the programming output supply during programming is 150 mA.

- 5. Step V<sub>CC</sub> to 10.5 V nominal. Maximum supply current required during programming is 750 mA.

- Apply a low-logic-level voltage to the chip-select input(s). This should occur between 10 µs and 1 ms after V<sub>CC</sub> has reached its 10.5-V level. See programming sequence of Figure 2.

- 7. After the X pulse time (1 ms) is reached, a high logic level is applied to the chip-select inputs to disable the outputs.

- 8. Within 10  $\mu$ s to 1 ms after the chip-select input(s) reach a high logic level, V<sub>CC</sub> should be stepped down to 5 V at which level verification can be accomplished.

- The chip-select input(s) may be taken to a low logic level (to permit program verification) 10 μs or more after V<sub>CC</sub> reaches its steady-state value of 5 V.

- 10. At a Y pulse duty cycle of 35% or less, repeat steps 1 through 8 for each output where it is desired to program a bit.

NOTE: Only one programming attempt per bit is recommended.

LOAD CIRCUIT FOR EACH OUTPUT NOT BEING PROGRAMMED OR FOR PROGRAM VERIFICATION FIGURE 1

FIGURE 2-VOLTAGE WAVEFORMS FOR PROGRAMMING

# SERIES 54S/74S **PROGRAMMABLE READ-ONLY MEMORIES WITH 3-STATE OUTPUTS**

### recommended operating conditions

|                                                |            | 'S287, 'S471 |   |      | <b>'S288</b> |     |      | 'S472, 'S474 |     |      |    |

|------------------------------------------------|------------|--------------|---|------|--------------|-----|------|--------------|-----|------|----|

|                                                |            | MIN NOM MAX  |   | MIN  | NOM          | MAX | MIN  | NOM          | MAX | UNIT |    |

|                                                | Series 54S | 4.5          | 5 | 5.5  | 4.5          | 5   | 5.5  | 4.5          | 5   | 5.5  |    |

| Supply voltage, V <sub>CC</sub>                | Series 74S | 4.75         | 5 | 5.25 | 4.75         | 5   | 5.25 | 4.75         | 5   | 5.25 | v  |

|                                                | Series 54S |              |   | -2   |              |     | -2   |              |     | -2   |    |

| High-level output current, IOH                 | Series 74S |              |   | -6.5 |              |     | -6.5 |              |     | -6.5 | mA |

| Low-level output current, IOL                  | •          |              |   | 16   |              |     | 20   |              |     | 12   | mA |

| Operating free-air temperature, T <sub>A</sub> | Series 54S | -55          |   | 125♦ | -55          |     | 125  | -55          |     | 125  | °c |

|                                                | Series 74S | 0            |   | 70   | 0            |     | 70   | 0            |     | 70   |    |

## electrical characteristics over recommended operating free-air temperature range (unless otherwise noted)

|        |                                                         | 7507 00101                                           | vouat                                           |     | SN54S     |            |     | SN745     |            |      |

|--------|---------------------------------------------------------|------------------------------------------------------|-------------------------------------------------|-----|-----------|------------|-----|-----------|------------|------|

|        | PARAMETER                                               | TEST CONDIT                                          | IONS                                            | MIN | TYP‡      | MAX        | MIN | TYP‡      | MAX        | UNIT |

| VIH    | High-level input voltage                                |                                                      |                                                 | 2   |           |            | 2   |           |            | V    |

| VIL    | Low-level input voltage                                 |                                                      |                                                 |     |           | 0.8        |     |           | 0.8        | V    |

| VIK    | Input clamp voltage                                     | V <sub>CC</sub> = MIN,                               | l₁ = −18 mA                                     |     |           | -1.2       |     |           | -1.2       | v    |

| ∨он    | High-level output voltage                               | · V <sub>CC</sub> = MIN,<br>V <sub>IL</sub> = 0.8 V, | V <sub>IH</sub> = 2 V,<br>I <sub>OH</sub> = MAX | 2.4 | 3.4       |            | 2.4 | 3.2       |            | v    |

| VOL    | Low-level output voltage                                | V <sub>CC</sub> = MIN,<br>V <sub>IL</sub> = 0.8 V,   | V <sub>IH</sub> = 2 V,<br>I <sub>OL</sub> = MAX |     |           | 0.5        |     |           | 0.5        | v    |

| lozн · | Off-state output current,<br>high-level voltage applied | V <sub>CC</sub> = MAX,<br>V <sub>O</sub> = 2.4 V     | V <sub>IH</sub> = 2 V,                          |     |           | 50         |     |           | 50         | μA   |

| IOZL   | Off-state output current,<br>low-level voltage applied  | V <sub>CC</sub> = MAX,<br>V <sub>O</sub> = 0.5 V     | V <sub>IH</sub> = 2 V,                          |     |           | -50        |     |           | 50         | μA   |

| 4      | Input current at maximum<br>input voltage               | V <sub>CC</sub> = MAX,                               | V <sub>1</sub> = 5.5 V                          |     |           | 1          |     |           | 1          | mA   |

| Чн     | High-level input current                                | V <sub>CC</sub> = MAX,                               | VI = 2.7 V                                      |     |           | 25         |     |           | 25         | μA   |

| կլ     | Low-level input current                                 | V <sub>CC</sub> = MAX,                               | V <sub>I</sub> = 0.5 V                          |     |           | -250       |     |           | -250       | μA   |

| los    | Short-circuit output current §                          | V <sub>CC</sub> = MAX                                |                                                 | -30 |           | -100       | -30 |           | -100       | mA   |

|        | Supply suggest                                          | V <sub>CC</sub> = MAX,<br>Chip select(s) at 0 V,     | 'S287<br>'S288                                  |     | 100<br>80 | 135<br>110 |     | 100<br>80 | 135<br>110 | mA   |

| ICC    | Supply current                                          | Outputs open,                                        | 'S471                                           |     | 110       | 155        |     | 110       | 155        |      |

|        |                                                         | See Note 4                                           | 'S472, 'S474                                    |     | 120       | 155        |     | 120       | 155        |      |

### switching characteristics over recommended ranges of TA and VCC (unless otherwise noted)

| ТҮРЕ               | TEST CONDITIONS     | `t <sub>a(ad)</sub> (ns)<br>Access time from<br>address |     | Access t | ;) (ns)<br>ime from<br>enable time) | tp <sub>XZ</sub> (ns)<br>Disable time from<br>high or low ley |    |  |

|--------------------|---------------------|---------------------------------------------------------|-----|----------|-------------------------------------|---------------------------------------------------------------|----|--|

|                    |                     | TYP‡                                                    | MAX | TYP‡     | MAX                                 | TYP‡                                                          | MA |  |

| SN54S287           |                     | 42                                                      | 75  | 15       | 40                                  | 12                                                            | 40 |  |

| SN74S287           |                     | 42                                                      | 65  | 15       | 35                                  | 12                                                            | 35 |  |

| SN54S288           | CL = 30 pF for      | 25                                                      | 50  | 12       | 30                                  | 8                                                             | 30 |  |

| SN74S288           | ta(ad) and ta(S)    | 25                                                      | 40  | 12       | 25                                  | 8                                                             | 20 |  |

| SN54S471           | 5 pF for tPXZ;      | 50                                                      | 80  | 20       | 40                                  | 15                                                            | 35 |  |

| SN74S471           | $R_L = 300 \Omega;$ | 50                                                      | 70  | 20       | 35                                  | 15                                                            | 30 |  |

| SN54S472, SN54S474 | See Figure 4        | 55                                                      | 85  | 20       | 45                                  | 15                                                            | 40 |  |

| SN74S472, SN74S474 | 1                   | 55                                                      | 75  | 20       | 40                                  | 15                                                            | 35 |  |

<sup>1</sup>For conditions shown as MIN or MAX, use the appropriate value specified under recommended operating conditions. <sup>‡</sup>AII typical values are at V<sub>CC</sub> = 5 V, T<sub>A</sub> = 25<sup>6</sup>C. <sup>§</sup>Not more than one output should be shorted at a time and duration of the short-circuit should not exceed one second. <sup>♦</sup>An SN545287 in the W package operating at free-air temperatures above 108°C requires a heat sink that provides a thermal resistance from case-to-free-air, R<sub>BCA</sub>, of not more than 42°C/W. NOTE 4: The typical values of I<sub>CC</sub> shown are with all outputs low.

### recommended operating conditions

|                                                |            | ʻS188     |     | 'S387, 'S470 |      |     | 'S473, 'S475 |      |     |      |    |

|------------------------------------------------|------------|-----------|-----|--------------|------|-----|--------------|------|-----|------|----|

|                                                |            | MIN NOM M | MAX | MIN          | NOM  | MAX | MIN          | NOM  | MAX | UNIT |    |

| Supply voltage, V <sub>CC</sub>                | Series 54S | 4.5       | 5   | 5.5          | 4.5  | 5   | 5.5          | 4.5  | 5   | 5.5  |    |

|                                                | Series 74S | 4.75      | 5   | 5.25         | 4.75 | 5   | 5.25         | 4.75 | 5   | 5.25 |    |

| High-level output voltage, VOH                 |            |           |     | 5.5          |      |     | 5.5          |      |     | 5.5  | V  |

| Low-level output current, IOL                  |            |           |     | 20           |      |     | 16           |      |     | 12   | mA |

| Operating free-air temperature, T <sub>A</sub> | Series 54S | -55       |     | 125          | -55  |     | 125♦         | -55  |     | 125  |    |

|                                                | Series 74S | 0         |     | 70           | 0.   |     | 70           | 0    |     | 70   | C  |

## octrical characteristics over recommended operating free-air temperature range (unless otherwise noted)

|     | PARAMETER                              | TEST CONDI                                       | TIONS <sup>†</sup>      | MIN | түр‡ | MAX  | UNIT |

|-----|----------------------------------------|--------------------------------------------------|-------------------------|-----|------|------|------|

| VIH | High-level input voltage               |                                                  |                         | 2   |      |      | V    |

| VIL | Low-level input voltage                |                                                  |                         |     |      | 0.8  | V    |

| VIK | Input clamp voltage                    | V <sub>CC</sub> = MIN,                           | I <sub>I</sub> = -18 mA |     |      | 1.2  | V    |

| юн  | High-level output current              | V <sub>CC</sub> = MIN,<br>V <sub>IH</sub> = 2 V, | V <sub>OH</sub> = 2.4 V |     |      | 50   | μA   |

| юн  | ingnievel output current               | VIH = 2.0,<br>VIL = 0.8 V                        | V <sub>OH</sub> = 5.5 V |     |      | 100  |      |

| VOL | OI Low-level output voltage            | V <sub>CC</sub> = MIN,                           | V <sub>IH</sub> = 2 V,  |     |      | 0.5  | v    |

| VOL |                                        | V <sub>IL</sub> = 0.8 V,                         | IOL = MAX               | 0.  |      |      | V    |

| ų – | Input current at maximum input voltage | V <sub>CC</sub> = MAX,                           | V <sub>1</sub> = 5.5 V  |     |      | 1    | mA   |

| Чн  | High-level input current               | V <sub>CC</sub> = MAX,                           | V <sub>1</sub> = 2.7 V  |     |      | 25   | μA   |

| μL  | Low-level input current                | V <sub>CC</sub> = MAX,                           | V <sub>I</sub> = 0.5 V  |     |      | -250 | μA   |

|     |                                        | V <sub>CC</sub> = MAX,                           | 'S188                   |     | 80   | 110  |      |

|     | C                                      | Chip select(s) at 0 V,                           | 'S387 '                 |     | 100  | 135  | 1.   |

| lcc | Supply current                         | Outputs open,                                    | 'S470                   |     | 110  | 155  | mA   |

|     |                                        | See Note 4                                       | 'S473; 'S475            |     | 120  | 155  | 1    |

## switching characteristics over recommended ranges of TA and VCC (unless otherwise noted)

| TYPE               | TEST CONDITIONS          |      | ) (ns)<br>ime from<br>iress | Access t | 5) (ns)<br>ime from<br>(enable time) | Propagation<br>Iow-to-high | H (ns)<br>n delay time,<br>I-level output<br>ct (disable time) |

|--------------------|--------------------------|------|-----------------------------|----------|--------------------------------------|----------------------------|----------------------------------------------------------------|

|                    |                          | TYP‡ | MAX                         | TYP‡     | MAX                                  | TYP‡                       | MAX                                                            |

| N54S188            |                          | 25   | 50                          | 12       | 30                                   | 12                         | 30                                                             |

| CN74S188           |                          | 25   | 40                          | 12       | 25                                   | 12                         | 25                                                             |

| SN54S387           | С <sub>L</sub> = 30 рF,  | 42   | 75                          | 15       | 40                                   | 15                         | 40                                                             |

| SN74S387           | R <sub>L1</sub> = 300 Ω, | 42   | 65                          | 15       | 35                                   | 15                         | 35                                                             |

| SN54S470           | R <sub>L2</sub> = 600 Ω, | 50   | 80                          | 20       | 40                                   | 15                         | 35                                                             |

| SN74S470           | See Figure 3             | 50   | 70                          | 20       | · 35                                 | 15                         | 30                                                             |

| SN54S473, SN54S475 |                          | 55   | 85                          | 20       | 45                                   | 15                         | 40                                                             |

| SN74S473, SN74S475 |                          | 55   | 75                          | 20       | 40                                   | 15                         | 35                                                             |

<sup>†</sup>For conditions shown as MIN or MAX, use the appropriate value specified under recommended operating conditions.

‡All typical values are at  $V_{CC} = 5 V$ ,  $T_A = 25^{\circ}C$ .

ΦAn SN54S387 in the W package operating at free-air temperatures above 108°C requires a heat sink that provides a thermal resistance from case-to-free-air, R<sub>θCA</sub>, of not more than 42°C/W.

NOTE 4: The typical values of ICC shown are with all outputs low.

# SERIES 54S/74S PROGRAMMABLE READ-ONLY MEMORIES

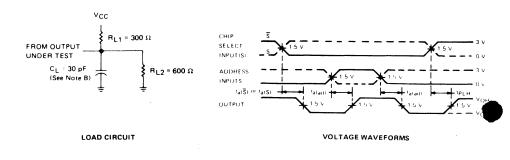

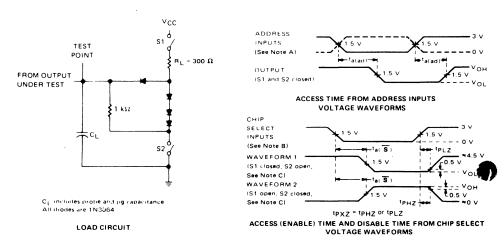

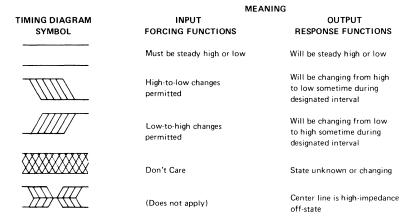

## PARAMETER MEASUREMENT INFORMATION

NOTES:

- A. The input pulse generator has the following characteristics:  $Z_{out} \approx 50 \ \Omega$ , PRR  $\leq 1 \ MHz$ , t<sub>r</sub>  $\leq 2.5 \ ns$ , and t<sub>f</sub>  $\leq 2.5 \ ns$ .

- B. CL includes probe and jig capacitance.

- C. The pulse generator is connected to the input under test. The other inputs, memory content permitting, are connected so that the input will switch the output under test.

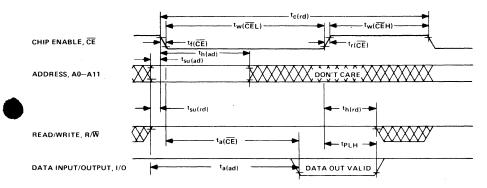

### FIGURE 3 - SWITCHING TIMES OF 'S188, 'S470, 'S387, 'S473, AND 'S475

- NOTES: A. When measuring access times from address inputs, the chip-select input(s) is(are) low.

- B. When measuring access and disable times from chip-select input(s), the address inputs are steady-state.

- C. Waveform 1 is for the output with internal conditions such that the output is low except when disabled. Waveform 2 is for the output with internal conditions such that the output is high except when disabled.

- D. Input waveforms are supplied by pulse generators having the following characteristics:  $t_{\rm f} \le 2.5$  ns,  $t_{\rm f} \le 2.5$  ns, PRR  $\le 1$  MHz, and  $Z_{\rm Out} \approx 50 \ \Omega$ .

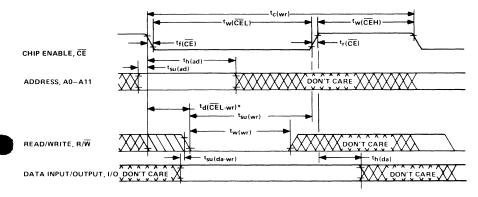

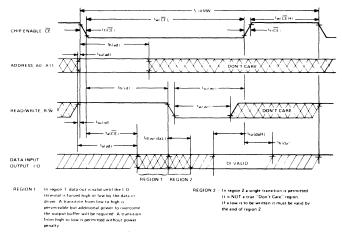

FIGURE 4 - SWITCHING TIMES OF 'S287, 'S288, 'S471, 'S472, AND 'S474

# SCHOTTKY† TTL

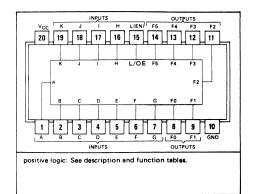

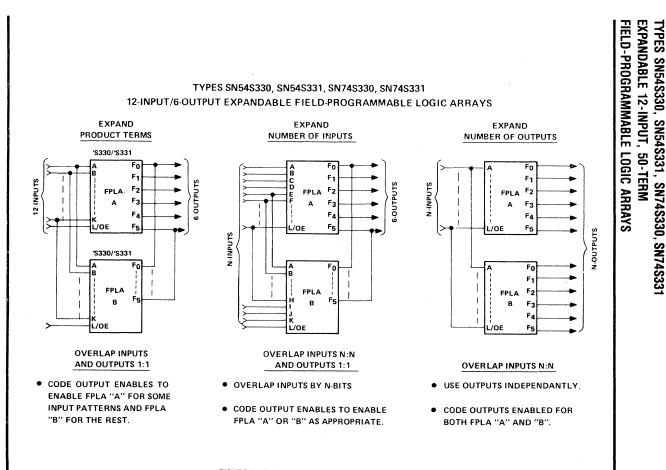

## TYPES SN54S330, SN54S331, SN74S330, SN74S331 EXPANDABLE 12-INPUT, 50-TERM FIELD-PROGRAMMABLE LOGIC ARRAYS DECEMBER 1976

- Field-Programmable Logic Array Organized 12-Inputs/50-Product Terms/6-Outputs

- Programmable Options Include:

- Active High or Low Inputs/Outputs

- Choice of Dedicated Enable Input or Automatic Enable by True Product Terms

- Number of Inputs, Outputs, and Product Terms are Expandable

- High Density 20-Pin Package

- Full Schottky Clamping for High-Performance:

- 35 ns Typical Data Delay Time

- 20 ns Typical Enable Time

- Reliable TI-W Fuse Links for Fast, Low-Voltage Programming

SN54S330, SN54S331 . . . J PACKAGE SN74S330, SN74S331 . . . J OR N PACKAGE

• Choice of 3-State ('S330) or 2.5 kΩ Passive-Pullup ('S331) Outputs

### description

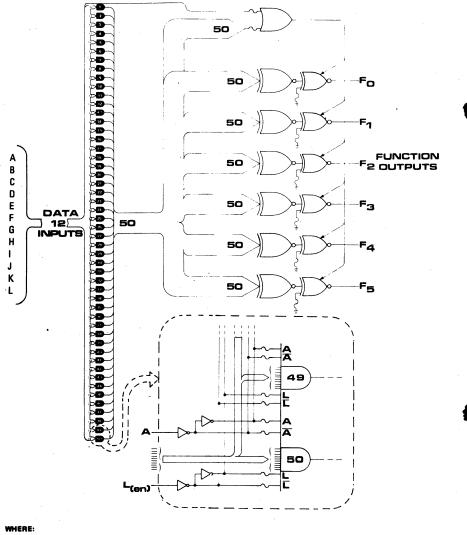

These high-performance, Schottky-clamped 12-input, 6-output logic arrays can be field programmed to provide 50 product terms derived from the 12 inputs and sum the 50 products onto 6-output lines. They feature a programmable option which permits the FPLA outputs to be automatically enabled by a true product term or, to dedicate during programming, input (L/OE) to serve as an output enable (OE). Either option makes the FPLA expandable with respect to product terms.

For every product term, 12 input variables can be programmed as high or low. Logic flexibility is further enhanced by the feature that the six outputs can be programmed individually to be active high or low.

The SN54S/74S330 is implemented with bus-driving 3-state outputs and can be connected directly to similar outputs in a bus-organized system. The SN54S/74S331 is implemented with a 2.5 k $\Omega$  passive pull-up resistor on each output meaning that:

- The output can be combined with other similar or open-collector outputs to perform the logical wire-AND or a simple enable/disable function.

- b. The series SN74S' outputs are also rated to source 250  $\mu$ A of current at V<sub>OH</sub> = 3.7 minimum for direct interface with MOS input thresholds.

The TI-W fuse links, used in the 'S330/'S331, feature the same low-voltage programming characteristics and proven reliability which Texas Instruments PROM's have demonstrated over a number of years.

F1 = F0, F1, F2, F3, F4, or F5

(ABC ..... L); = 12 PROGRAMMABLE INPUTS (H = TRUE OR L = TRUE) FOR EACH OF 50 PRODUCT TERMS

# **TEXAS INSTRUMENTS**

### absolute maximum ratings over operating free-air temperature range (unless otherwise noted)

| Supply voltage, V <sub>CC</sub> (see Note 1) . |                    |               |

|------------------------------------------------|--------------------|---------------|

| Input voltage                                  |                    | 5.5 V         |

|                                                |                    | 5.5 V         |

| Operating free-air temperature range:          |                    | I             |

|                                                | SN74S330, SN74S331 | I 0°C to 70°C |

| Storage temperature range                      |                    |               |

NOTE 1: Voltage values are with respect to network ground terminal.

### recommended operating conditions

|                                    |                       | SN54S | 330, SN | 54\$331 | SN74S | 330, SN | 74\$331 | UNIT |

|------------------------------------|-----------------------|-------|---------|---------|-------|---------|---------|------|

|                                    |                       | MIN   | NOM     | MAX     | MIN   | NOM     | MAX     | UNIT |

| Supply voltage, V <sub>CC</sub>    |                       | 4.5   | 5       | 5.5     | 4.75  | 5       | 5.25    | V    |

|                                    | 'S330 (T-S)           |       |         | -2      |       |         | -6.5    |      |

| High-level output current, IOH     | 'S331 (2.5 kΩ Pullup) |       |         | -0.2    |       |         | -0.25   | mA   |

| Operating free-air temperature, TA |                       | -55   |         | 125     | 0     |         | 70      | °C   |

### electrical characteristics over recommended operating free-air temperature range (unless otherwise noted)

|      | PARAMETER                                              |              | TEST CON                                           | DUTIONOT                                          | SN54S | 330, SN | 54\$331 | SN74S | 330, SN | 74\$331 |      |

|------|--------------------------------------------------------|--------------|----------------------------------------------------|---------------------------------------------------|-------|---------|---------|-------|---------|---------|------|

|      | PARAMETER                                              |              | TEST CON                                           | DITIONS                                           | MIN   | TYPT    | MAX     | MIN   | TYP     | MAX     | UNIT |

| VIH  | High-level input voltage                               |              |                                                    |                                                   | 2     |         |         | 2     |         |         | v    |

| VIL  | Low-level input voltage                                |              |                                                    |                                                   |       |         | 0.8     |       |         | 0.8     | V    |

| VIK  | Input clamp voltage                                    |              | V <sub>CC</sub> = MIN,                             | lj =18 mA                                         |       |         | -1.2    |       |         | -1.2    | V    |

| ∨он  | High-level output voltage                              | ʻS330        | $V_{CC} = MIN,$<br>$V_{IH} = 2 V$                  | IOH = MAX                                         | 2.4   | 3.4     |         | 2.4   | 3.1     |         | ٧.   |

| чон  | Thigh tever output voltage                             | ʻS331        | VIL = 0.8 V                                        | IOH = MAX                                         | 3.7   | 4.5     |         | 3.7   | 4,4     |         | ۷.   |

| VOL  | Low-level output voltage                               |              | V <sub>CC</sub> = MIN,<br>V <sub>IL</sub> = 0.8 V, | V <sub>IH</sub> = 2 V,<br>I <sub>OL</sub> = 20 mA |       |         | 0.5     |       |         | 0.5     | v    |

| 10ZH | Off-state output current,                              | <b>'S330</b> | VCC = MAX                                          | V0 = 2.4V                                         |       |         | 50      |       |         | 50      |      |

| loff | high-level voltage applied                             | 'S331        | VCC - WAA                                          | V <sub>O</sub> = 2.4V                             |       |         | 50      |       |         | 50      | μA   |

| IOZL | Off-state output current,<br>low-level voltage applied | ʻS330        | V <sub>CC</sub> = MAX,                             | V <sub>O</sub> = 0.5 V                            |       |         | -50     |       |         | 50      | μA   |

| 1    | Input current at maximum<br>input voltage              |              | V <sub>CC</sub> = MAX,                             | V <sub>I</sub> = 5.5 V                            |       |         | 1       |       |         | 1       | mA   |

| Чн   | High-level input current                               |              | V <sub>CC</sub> = MAX,                             | VI = 2.7 V                                        |       |         | 50      |       |         | 50      | μA   |

| ЧL   | Low-level input current                                |              | V <sub>CC</sub> = MAX,                             | Vi = 0.5 V                                        |       |         | -0.25   |       |         | -0.25   | mA   |

| los  | Short-circuit output                                   | 'S330        | VCC = MAX                                          |                                                   | -30   |         | -100    | -30   |         | 100     |      |

| os   | current§                                               | 'S331        |                                                    |                                                   | -1.4  |         | -4.4    | -1.4  |         | -4.4    | mA   |

| 100  | Supply current                                         | <b>'S330</b> | V <sub>CC</sub> = MAX,                             | See Note 2                                        |       | 110     |         |       | 110     |         | mA   |

| lcc  | Supply current                                         | '\$331       | VCC - WAA,                                         | See NOTE 2                                        |       | 122     |         |       | 122     |         | INA  |

<sup>†</sup>For conditions shown as MIN or MAX, use the appropriate value specified under recommended operating conditions.

All typical values are at  $V_{CC}$  = 5 V,  $T_A = 25^{\circ}C$ . Not more than one output of the 'S330 should be shorted at a time.

OTE 2: ICC is measured with all outputs open and all inputs grounded.

## switching characteristics, $V_{CC}$ = 5 V, $T_A$ = 25°C

| PARAMETER        | FROM      | то           | TEST CONDITIONS | MIN | TYP | MAX | UNIT |

|------------------|-----------|--------------|-----------------|-----|-----|-----|------|

| <sup>t</sup> PLH | Any input | Any output   |                 |     | 35  |     | ns   |

| <sup>t</sup> PHL |           |              | CL = 30 pF      |     | 35  |     | 113  |

| <sup>t</sup> ZL  | Enable    | Any output   | ο[ - 30 μ;      |     | 15  |     | ns   |

| <sup>t</sup> ZH  |           |              |                 |     | 15  |     |      |

| tHZ              | Enable    | Any output   | CL = 5 pF       |     | 15  |     | ns   |

| tLZ              | Lindoit   | , any output | 9L 9 P          |     | 15  |     |      |

### programming the FPLA

The 'S330 and 'S331 are fabricated to include reliable low-voltage programmable Ti-W fuse links which have identical fusing characteristics with those used in TI's PROM's. The conditions recommended for programming the FPLA are virtually identical to those used for TI's PROM's; however, the AND-OR combinational logic performed by an FPLA requires that sequential programming be employed which establishes the AND term including the data/enable L/OE input before the OR term. Programming the automatic enable feature active, the true/false logic level of the outputs, and the data/enable input (L/OE) can be accomplished before or after the AND and OR matrices are established.

### recommended conditions for programming

|                                      |                                                | MIN  | NOM  | MAX  | UNIT |

|--------------------------------------|------------------------------------------------|------|------|------|------|

| Supply voltage, VCC (see Note 1)     |                                                | 4.75 | 5    | 5.75 | V.   |

| Program pulse voltage, V (pr) (see N | lote 1)                                        | 10   | 10.5 | 11†  | 2    |

| Program pulse rise time              |                                                |      | 100  |      | ٦s   |

|                                      | High level, VIH                                | 2.4  |      | 5    | v    |

| Input voltage (see Note 1)           | Low level, VIL                                 | 0    |      | 0.5  | v    |

| Voltage applied to output for OR p   | programming, V <sub>O(pr)</sub> (see Figure D) | 0    | 0.25 | 0.3  | V    |

| Duration of programming pulse Y      | see Figures A, C, D, and Note 2)               | 0.9  | 1    | 20   | ms   |

| Programming duty cycle               |                                                |      | 25   | 35   | %    |

| Free-air temperature                 |                                                | 0    |      | 55   | °c   |

<sup>†</sup>Absolute maximum ratings,

NOTES: 1. Voltage values are with respect to the GND terminal.

2. Programming is guaranteed if the pulse applied is 0.9ms long. Typically, programming occurs in 1 ms.

### programming the true/false logic level of the outputs

The FPLA is supplied with internal conditions established such that when a programmed AND or  $\overline{\text{AND}}$  input term is true the associated function output (F<sub>n</sub>) will be at a high logic level voltage, V<sub>OH</sub>.

Programming the output to provide a low logic level voltage ( $V_{OL}$ ) when the programmed input term is true can be accomplished by using AND/AND terms 50 through 55 shown in Table I and fusing the desired outputs using the step-by-step procedure.

| AD | DRES | APPL | IED T | O OUT | PUTS | PRODUCT TERM | PROGRAMS                             |

|----|------|------|-------|-------|------|--------------|--------------------------------------|

| F5 | F4   | F3   | F2    | F1    | Fo   | ADDRESSED    | PRUGRAMS                             |

| н  | н    | L    | L     | н     | L    | 50           | Output F5 true low                   |

| н  | н    | L    | L     | н     | н    | 51           | Output F <sub>4</sub> true low       |

| н  | н    | L    | н     | L     | Ł    | 52           | Output F3 true low                   |

| н  | н    | L    | н     | L     | н    | 53           | Output F <sub>2</sub> true low       |

| н  | н    | L    | н     | н     | L    | 54           | Output F1 true low                   |

| н  | н    | L    | н     | н     | н    | 55           | Output F <sub>0</sub> true low       |

| н  | н    | н    | L     | L     | L    | 56           | L/OE input into logical product term |

| н  | н    | н    | L     | L     | н    | 57           | Automatic output enable active       |

TABLE I - ADDRESSES FOR PROGRAMMING OUTPUT LEVELS AND ENABLES

Programming can be verified before AND-OR programming by applying V<sub>CC</sub> = 5 V and measuring V<sub>OL</sub>  $\leq$  0.5 V at the programmed output(s). After programming this test can be made by applying the input conditions which correspond to each term programmed to result in an active low-level output.

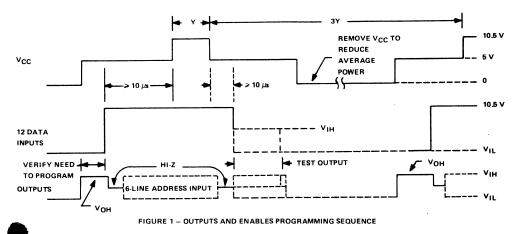

### step-by-step programming procedure for outputs and enables

- Apply steady-state supply voltage (V<sub>CC</sub> = 5 V) and disable the outputs by applying 10.5 volts to the 12 data inputs. See Figure 1.

- 2. Verify that the fuse link needs to be programmed. If not, proceed to the next term.

- Only one fuse link is programmed at a time. Address the term to be programmed by applying VIH and VIL to the outputs in accordance with Table I.

- 4. Step VCC to 10.5 V nominal. Maximum supply current required during programming is 750 mA.

- After the Y pulse time (1 ms) is reached, V<sub>CC</sub> should be stepped down to 5V at which level verification can be accomplished.

- The data inputs may be taken to logic levels (to permit program verification) 10 μs or more after V<sub>CC</sub> reaches its steady-state value of 5 V.

- 7. At a Y pulse duty cycle of 35% or less, repeat steps 1 through 6 for each function to be programmed.

NOTES 3: V<sub>CC</sub> should be removed between program-pulses to reduce dissipation and chip temperatures. See Figure 1.

### programming the L(en) input

The L/OE input must be programmed either to function as a dedicated enable or to function as the 12th data input.

If it is to become the 12th data input a single fuse, at term 562 (see Table I), should be programmed in accordance with steps 1 through 4 above; then, input L is programmed logically into each AND/AND product term.

If input L/OE is to function as a dedicated output enable, term 562 is not fused: however, both AND/AND fuse links at each of the 50 product term addresses must be fused as outlined below creating a "don't care" for input L. This causes the input to become an overriding output enable/disable for the package.

### programming the automatic disable to be inactive

The '\$330 and '\$331 are supplied with fuse links completing a circuit which automatically disables the six outputs (highimpedance (Z) for '\$330, high (H) for '\$331) for any product term which is purely "don't care"; i.e., not decoded by the AND matrix. Fusing one link inactivates the automatic output enabling circuit resulting in the six outputs being enabled for any input term, even "don't care".

The automatic disable fuse is programmed inactive by addressing term 57<sub>2</sub> (see Table I) and fusing in accordance with the step-by-step procedure above.

### programming the AND/AND product terms

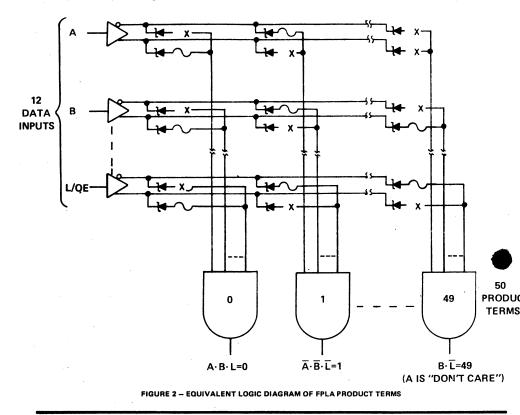

Each of the 50 product terms are capable of being programmed to decode a 12-wide term consisting of any combination of active (true) high, active (true) low, or don't care (H or L) input conditions at each of the 12 lines. This capability implemented by providing AND/NAND decode input gates each having a pair of associated fusible links which can be programmed to inactivate the unused decode level. Both decode levels can be removed resulting in a "don't care" input. The equivalent logic diagram showing the fusible links is shown in Figure 2.

**TEXAS INSTRUMENTS**

A particular pattern is assumed to have been programmed into the AND/ $\overline{\text{AND}}$  fuse matrix with fused links opened at the locations marked with an "X". The resultant product terms are enumerated for the outputs of each product-term AND gate.

Product terms programmed into the AND/AND matrix will be used to select the term for programming the OR (summing) matrix. Redundant product terms will select two sum terms in the OR matrix, and overlapping product terms may select two or more sum terms. Reliable programming can be accomplished if redundant product terms are avoided and overlapping product terms are made unique for programming.

Redundant product terms are defined as being absolutely equal; i.e., ABCDEFG≡ABCDEFG. Use of apparently redundant terms is possible if the term does not use all inputs as the remaining inputs can be utilized to create unique terms for programming purposes by expansion:

Example:

### ABCDEFGH≡ABCEDFGH

After programming the OR matrix, the product terms can be readdressed and the H input can be programmed "don't care".

Overlapping terms are defined as two or more product terms in which the lesser product term can be addressed as a result of the application of a larger product term.

### Examples:

ABCDEFG ← This large product term AB DE G ← also addresses these small terms A CD F ←

The small terms can be made unique for programming by simply expanding to non-redundant inputs.

ABCDEFG - Large term

AB DEFG Small terms made unique by expanding (one fuse link each)

After programming the OR matrix, the product terms can be shortened by readdressing each and programming the added inputs to a "don't care". The AND/AND matrix is programmed one fuse at a time by addressing the term in accordance with Table II and fusing the input while applying the logic level desired to be active. See Figure 3.

### TABLE II -- ADDRESSES FOR PROGRAMMING PRODUCT TERMS

| ADD | RESS | APPLI | ED TO | OUTP | UTS | PRODUCT   |

|-----|------|-------|-------|------|-----|-----------|

| F5  | F4   | F3    | F2    | Fo   | F1  | ADDRESSED |

| L   | L    | L     | L     | L    | L   | 0         |

| L   | L    | L     | L     | L    | н   | 1         |

| L   | L    | L     | L     | н    | L   | 2         |

| L   | L    | L     | L     | н    | н   | 3         |

|     |      |       |       |      |     |           |

|     |      |       |       |      |     | •         |

| н   | н    |       | ,     |      |     | 48        |

| -11 |      | Ľ     | L     | L    | L . |           |

| н   | н    | L     | L     | L    | н   | 49        |

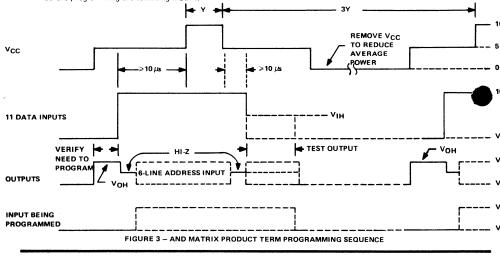

### step-by-step programming procedure for AND matrix

- Apply steady-state supply (V<sub>CC</sub> = 5 V) and disable the outputs by applying 10.5 volts to the 12 data inputs. See Figure 3.

- 2. Verify that the fuse link needs to be programmed. If not, proceed to the next term.

- Only one fuse link is programmed at a time. Address the term to be programmed by applying V<sub>IH</sub> and V<sub>IL</sub> to the outputs in accordance with Table II.

- 4. Apply the level to be true at the input to be programmed.

- 5. Step V<sub>CC</sub> to 10.5 V nominal. Maximum supply current required during programming is 750 mA.

- After the Y pulse time (1 ms) is reached, V<sub>CC</sub> should be stepped down to 5 V at which level verification can be accomplished.

- The data inputs may be taken to logic levels (to permit program verification) 10 μs or more after V<sub>CC</sub> reaches its steady-state value of 5 V.

- 8. At a Y pulse duty cycle of 35% or less, repeat steps 1 through 7 for each input to be programmed.

NOTES: 4. V<sub>CC</sub> should be removed between program-pulses to reduce dissipation and chip temperatures. See Figure 3.

5. If the input just programmed is to be a "don't care" and is not being used to expand the product term repeat steps 4 and 5 with the opposite logic level applied to the input. Before changing the product term address, program all inputs (A through L/OE for this product term including all "don't cares".

6. If input L/OE is to be used as a dedicated package enable it must be programmed as a "don't care" by fusing both links at each of the 50 product term locations.

The OR (summing) matrix for each product term can be programmed immediately upon completion of the 12-wide AND/AND term associated with it; or, the entire AND/AND term matrix can be programmed for all 50 product terms before programming the summing matrix.

### programming the OR (summing) matrix

Product term(s) programmed into the AND/ $\overline{\text{AND}}$  matrix can now be selected to provide a true logic level output. The true logic level output at F<sub>0</sub> through F<sub>5</sub> will be high if the output polarity fuses are intact, or F<sub>0</sub> through F<sub>5</sub> will be low if the output polarity fuses have been programmed, or a combination of highs and lows if some of the output polarity fuses have been programmed.

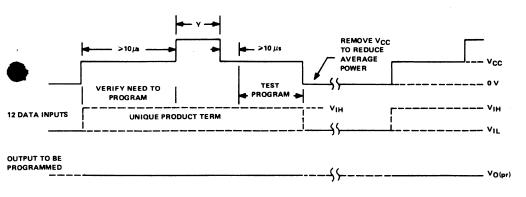

### step-by-step programming procedure for OR matrix

Programming the OR matrix consists of fusing (one at a time) those outputs (F<sub>0</sub> through F<sub>5</sub>) which are desired to be false in the addressed product term. The procedure is:

- 1. Apply steady-state supply voltage (V<sub>CC</sub> = 5 V) and apply the unique product term. See Figure 4.

- 2. Verify that the fuse link needs to be programmed. If not, proceed to the next fuse link.

- Only one fuse link is programmed at a time. Enable the term to be programmed by applying VO(pr) to the first output to be false in the product term.

- 4. Step V<sub>CC</sub> to 10.5 V nominal. Maximum supply current required during programming is 750 mA.

- 5. After the Y pulse time (1 ms) is reached, VCC should be stepped down to 5 V at which level verification can be accomplished.

- 6. Program verification can occur 10 µs or more after V<sub>CC</sub> reaches its steady-state value of 5 V.

- 7. At a Y pulse duty cycle of 35% or less repeat steps 1 through 6 for each output to be programmed false for the active product term.

- NOTES: 7. V<sub>CC</sub> should be removed between program pulses to reduce dissipation and chip temperatures. See Figure 1.

- If product terms were expanded to make then unique for programming purposes the product terms can be addressed and the added inputs can be removed by programming them to a "don't care" (fuse the remaining links).

FIGURE 4 - OR TERM PROGRAMMING SEQUENCE

Texas Instruments

Texas Instruments

FIGURE 5 - EXPANDING THE 'S330, 'S331 FPLA

## APPLICATIONS

The FPLA is efficiently suited for generating the sum of product terms which are normally required to implement:

- Memory mapping/supplemental functions

- Random logic or function generators

- Sequential controllers

- Status decoders or result interpreters

- Priority encoders

### MEMORY CONTROL/SUPPLEMENTAL FUNCTIONS

The FPLA is ideally suited for implementing a wide variety of functions with respect to the control and/or supplementing of system memory capabilities. Some are:

- Memory mapping

- Microprogram control

- Memory patch

- PROM extension

The wide input capability of the 'S330/'S331 FPLA makes it ideal for decoding either a current memory address or a variety of status lines and generate a unique system control function.

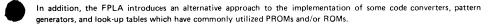

## MEMORY MAPPING/MICROPROGRAM CONTROL (See Figure 6)

These similar control functions utilize FPLAs which decode the assigned (mapped) addresses to accomplish system memory management; and/or, the FPLAs decode the current system address/status and implement the hardwired jump, branch-to-subroutine, or starting address in the microprogram control memory.

FIGURE 6 - MEMORY MAPPING/MICROPROGRAM CONTROL

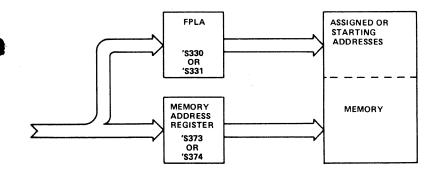

### MEMORY PATCH/PROM EXTENSION (See Figures 7 and 8)

These supplemental functions are cost-effective solutions for enhancing or upgrading existing memory systems or designs. Either the patch or extension can be used to correct existing deficiencies, to prioritize improved control over existing functions, or to extend the existing capabilities. Priority and source select can be programmed into the FPLA.

FIGURE 7 - MEMORY PATCH

### **DIGITAL SEQUENTIAL CONTROLLERS (See Figure 9)**

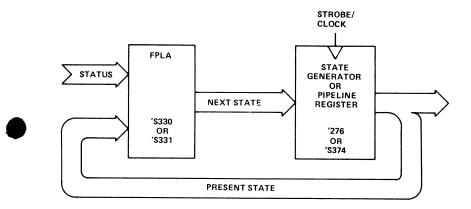

This broad category of functions range from simple stand-alone machine controllers to the microprogram sequencing of any size computer or machine. The identifiable common denominator being that a sequential controller decodes a present state and generates the next state. Contrasted to a data processor or computer which generates information from operating on a word of data, the sequential controller generates information on a bit-by-bit basis.

Sequences generated can range from simple counting schemes to arbitrary bit-by-bit generation of any unique output states.

This application shows how the FPLA can simplify the implementation of a sequential controller. When the combinatorial logic of the FPLA is combined with the flexibility and synchronization of standard flip-flops in feed-back loop, the full capability to generate a next state functional directive can be decoded from the present state the outputs of the flip flops (present state) in conjunction with the status inputs.

## STATUS DECODERS/RESULT INTERPRETERS

This broad category of functions, generally described as the elements which monitor the execution results of present instructions in sequential machines, can provide the decision-making hardware needed to both determine that the present operation is complete and simultaneously generate the next starting address or state. The actual configuration varies widely, but one popular method is to configure the FPLA similar to that shown for memory mapping.

### FIGURE 9 - SEQUENTIAL CONTROLLER

## PRIORITY ENCODERS

The unique properties of the FPLA's capability to be programmed for decoding a number of product terms in virtaully any combination provides the user with the flexibility of identifying and implementing virtually any prioritized scheme. This option is normally available in any use shown for the 'S330/'S331.

### RANDOM LOGIC OR FUNCTION GENERATORS

The 'S330/'S331 FPLAs provide the system designer with the options of reducing package count and/or system design time. Random gate logic can potentially be replaced at a package ratio of 12.5-to-1 up to 50-to-1 depending on the particular system needs. Function generators can be programmed directly into the FPLA from simple truth tables. In addition to reducing design and production start-up time, this technique can reduce the direct and indirect costs associated with logic and package minimization processes.

# SCHOTTKY† TTL MEMORY

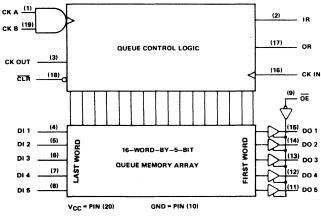

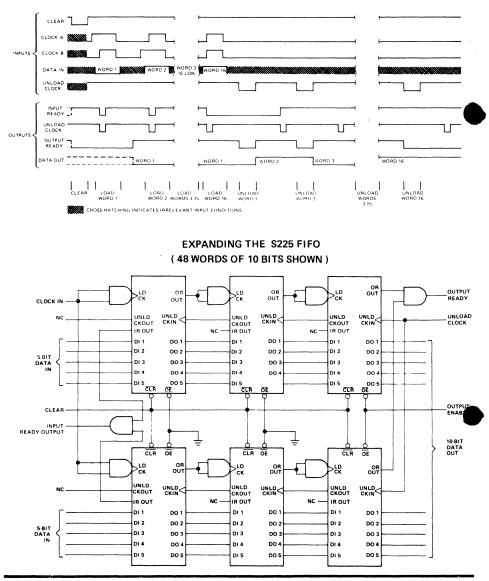

# TYPE SN74S225 16 x 5 ASYNCHRONOUS FIRST-IN/FIRST-OUT MEMORY

SEPTEMBER 1976

- Independent Synchronous Inputs and Outputs

- Organized as 16-Words of 5 Bits

- DC to 10 MHz Data Rate

- 3-State Data Outputs

- 20-Pin, 300-mil, High Density Package

### description

This 80-bit active-element memory is a monolithic, Schottky-clamped transistor-transistor logic (STTL) array organized as 16 words of five-bits each. The 'S225 can easily be expanded to 16N-words of 5N-bits in length and features a single enable control for all 3-state data outputs.

#### Pin assignments are same for all packages

### operation

A FIFO is a memory storage device which allows data to be written into and/or read from its array at independent data rates. The 'S225 is a FIFO which will process data at any desired clock rate from DC to 10 MHz. The data is processed in a parallel format, word by word.

Reading or writing is done independently utilizing separate synchronous data clocks. Data may be written into the array on the low-to-high transition of either load clock input. Data may be read out of the array on the low-to-high transition of the unload clock input (normally high). When writing data into the FIFO one of the load clock inputs must be held high while the other strobes in the data. This arrangement allows either load clock to function as an inhibit for the other.

Status of the 'S225 is provided by three outputs. Input ready monitors the status of the last word location and signifies when the memory is full. This output is high whenever the memory is available to accept any data. The unload clock output also monitors the last word location. This output generates a low-logic-level pulse (synchronized to the interclock pulse) when the location is vacant. The third status output, output ready, is high when the first word location contains valid data and unload clock input is high. When unload clock input is low, output ready will be low. The first word location is defined as the location from which data is provided to the outputs.

The data outputs are noninverted with respect to the data inputs and are three-state with a common control input, output enable. When output enable is low, the data outputs are enabled to function as totem-pole outputs. A high-logic-level forces each data output to a high-impedance state while all other inputs and outputs remain active.

The clear input invalidates all data stored in the memory array by clearing the control logic and setting output ready to a low-logic-level on the high-to-low transition of a low-active pulse. The data outputs do not change as a result of the clear input; however, the output ready at a low-logic-level signifies invalid data.

## FUNCTION TABLES

Table 1 - Input Functions

| Input   | Pin | Description        |

|---------|-----|--------------------|

| СКА     | 1   | Load Clock A       |

| DI1-DI5 | 4.8 | Data Inputs        |

| ŌĒ      | 9   | Output Enable      |

| CK IN   | 16  | Unload Clock Input |

| ČLR     | 18  | Clear              |

| СК В    | 19  | Load Clock B       |

| GND     | 10  | Ground pin         |

| Vcc     | 20  | Supply Voltage     |

#### Table 2 - Output Functions

| Output      | Pin     | Description         |

|-------------|---------|---------------------|

| IR          | 2       | Input Ready         |

| CK OUT      | 3       | Unload Clock Output |

| DO 5 - DO 1 | 11 - 15 | Data Outputs        |

| OR          | 17      | Output Ready        |

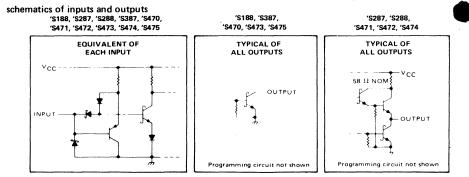

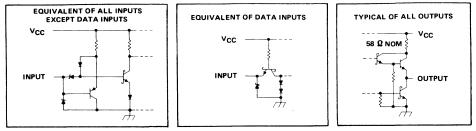

### sohematics of inputs and outputs

functional block diagram

### absolute maximum ratings over operating free-air temperature range (unless otherwise noted)

| Supply Voltage, VCC (see Note  | 1)     |    |  |  |  |  |  |  |  |  |  |  |     |     |      | 7V   |

|--------------------------------|--------|----|--|--|--|--|--|--|--|--|--|--|-----|-----|------|------|

| Input Voltage                  |        |    |  |  |  |  |  |  |  |  |  |  | •   |     |      | 5.5V |

| Off-State Output Voltage       |        |    |  |  |  |  |  |  |  |  |  |  |     |     |      | 5.5V |

| Operating Free-Air Temperature | e Rang | je |  |  |  |  |  |  |  |  |  |  | 0   | °C  | to   | 70°C |

| Storage Temperature Range      |        |    |  |  |  |  |  |  |  |  |  |  | 65° | C t | o 1! | 50°C |

|                                |        |    |  |  |  |  |  |  |  |  |  |  |     |     |      |      |

NOTE 1: All voltage values are with respect to network ground terminal.

### recommended operating conditions

|                                          |                                                      | MIN  | NOM | MAX  | UNIT     |

|------------------------------------------|------------------------------------------------------|------|-----|------|----------|

| Supply Voltage, V <sub>CC</sub>          |                                                      | 4.75 | 5   | 5.25 | V        |

|                                          | All Outputs Except Data                              |      |     | -3.2 | mA       |

| High-level output current, IOH           | Data Outputs                                         |      |     | -6.5 | <u> </u> |

|                                          | All Outputs Except Data                              |      |     | 8    | mA       |

| Low-level output current, IOL            | Data Outputs                                         |      |     | 16   |          |

|                                          | Load Clock A or B, tw (high)                         | 25   |     |      |          |

| Pulse Width                              | Unload Clock Input, tw (low)                         | 7    |     |      | ns       |

|                                          | Clear, t <sub>w</sub> (low)                          | 40   |     |      |          |

| Setup Time                               | Data to Load Clock, t <sub>SU</sub> (DIi) See Note 2 | -15† |     |      | ns       |

|                                          | Clear Release to Load Clock, t <sub>su</sub>         | 25†  |     |      | 1        |

| Hold Time, Data from Load Clock, th(Dli) |                                                      | 70†  |     |      | ns       |

| Operating free-air temperature, TA       |                                                      | 0    |     | 70   | °c       |

NOTE 2: Data must be setup within 15 ns after the load clock positive transition.

$\dagger \equiv$  The arrow indicates that the low-to-high transition of the load clock is used for reference.

### electrical characteristics over recommended operating free-air temperature range (unless otherwise noted)

|                  | PARAMETER                                            |                                      | TEST CON                                           | DITIONS                                          | MIN | TYP‡ | MAX      | UNIT | 1 |

|------------------|------------------------------------------------------|--------------------------------------|----------------------------------------------------|--------------------------------------------------|-----|------|----------|------|---|

| VIH              | High-level input voltage                             |                                      |                                                    |                                                  | 2   |      |          | v    | ] |

| VIL              | Low-level input voltage                              |                                      |                                                    |                                                  |     |      | 0.8      | V    | ] |

| VIK              | Input clamp voltage                                  |                                      | V <sub>CC</sub> = MIN,                             | lj = -18 mA                                      |     |      | -1.2     | V    | 1 |

| ∨он              | High-level output voltage                            |                                      | V <sub>CC</sub> = MIN,<br>V <sub>IL</sub> = 0.8 V, | V <sub>IH</sub> = 2 V,<br>I <sub>OH</sub> = MAX  | 2.4 | 2.9  |          | v    | ] |

| VOL              | Low-level output voltage                             |                                      | V <sub>CC</sub> = MIN,<br>V <sub>IL</sub> = 0.8 V, | V <sub>IH</sub> = 2 V,<br>I <sub>OL</sub> = MAX  |     | 0.35 | 0.50     | v    |   |

| lozн             | Off-state output current, high-level voltage applied |                                      | V <sub>CC</sub> = MAX,<br>V <sub>IL</sub> = 0.8 V, | V <sub>IH</sub> = 2 V,<br>V <sub>O</sub> = 2.4 V |     |      | 50       | μΑ   | ſ |

| <sup>I</sup> OZL | Off-state output current, low-level voltage applied  |                                      | V <sub>CC</sub> = MAX,<br>V <sub>IL</sub> ≈ 0.8 V, | V <sub>IH</sub> ≖ 2 V,<br>V <sub>O</sub> = 0.5 V |     |      | -50      | μΑ   | Τ |

| 1                | Input current at maximum input voltage               |                                      | VCC = MAX,                                         | V <sub>1</sub> = 5.5 V                           |     |      | 1        | mA   | 1 |

| ЧΗ               | High-level input current                             | Data In<br>All Inputs Except Data In | V <sub>CC</sub> = MAX,                             | V <sub>I</sub> = 2.7 V                           |     |      | 40<br>25 | μA   | 1 |

| 1                | 1 tt                                                 | Data In                              |                                                    | N - 05 M                                         |     |      | -1       | mA   | 1 |

| 41               | Low-level input current                              | All Inputs Except Data In            | V <sub>CC</sub> ≈ MAX,                             | V <sub>I</sub> = 0.5 V                           |     |      | -250     | μA   | ] |

| los              | Short-circuit output current §                       |                                      | V <sub>CC</sub> = MAX                              |                                                  | -30 |      | -100     | mA   | ] |

| Icc              | Supply Current                                       |                                      | V <sub>CC</sub> = MAX,                             | See Note 3                                       |     | 80   | 120      | mA   | 1 |

<sup>†</sup> For conditions shown as MIN or MAX use the appropriate value specified under recommended operating conditions.

‡All typical values are at  $V_{CC} = 5 \text{ V}$ ,  $T_A = 25^{\circ} \text{ C}$ . § Duration of the short circuit should not exceed one second.

NOTE 3: ICC is measured with all inputs grounded and the output open.

# switching characteristics over recommended operating ranges of TA and VCC (unless otherwise noted)

| PARAMETERS        | FROM   | то     | TEST                                | MIN | түр‡ | мах | UNIT |

|-------------------|--------|--------|-------------------------------------|-----|------|-----|------|

| f <sub>max</sub>  | СК А   |        | C <sub>L</sub> = 30 pF,             | 10  | 20   |     | MHz  |

| fmax              | СК В   |        | $R_{\rm L} = 300 \ \Omega,$         | 10  | 20   |     | MHz  |

| fmax              | CK IN  |        | See Note 4                          | 10  | 20   |     | MHz  |

| tw                | CK OUT |        |                                     | 7   | 14   |     | ns   |

| <sup>t</sup> PLZ  | ŌĒ     | DOi    | C <sub>L</sub> = 5 pF,              |     |      | 40  |      |

| <sup>t</sup> PHZ  | UL     | 501    | R <sub>L1</sub> = 300 Ω, See Note 4 |     |      | 40  | ns   |

| <sup>t</sup> PLH  | CK IN  | DOi    |                                     |     | 50   | 75  |      |

| <sup>t</sup> PHL  | CK IN  | 501    |                                     |     | 50   | 75  | ns   |

|                   | CK A   |        |                                     |     |      |     |      |