# TMS34061 User's Guide

# 1. Introduction

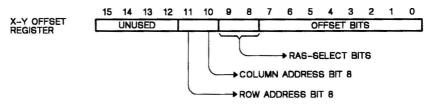

The TMS34061 Video System Controller (VSC) is a high-performance NMOS device that controls the video display and the dynamic memory of a bit-mapped graphics system. Although primarily designed to provide control of multiport Video RAMs (VRAMs), such as the TMS4161 and 256K video RAMs, the TMS34061 is also compatible with conventional 64K and 256K DRAMs and easily configures to a variety of CPUs. The sync and blanking signals necessary to interface to a raster-scan CRT display are generated by the TMS34061, which is the only device currently available that combines VRAM and DRAM control and CRT control on a single chip.

The principal role of the VSC is to provide an external processor with virtually unlimited access to video memory, eliminating delays caused by conflicts with display update functions. Using the TMS34061, the system CPU is relieved of the burden of controlling the system memory, refreshing video memory, and reloading VRAM internal shift registers for bit-mapped displays.

Highly programmable, the TMS34061 supports a broad range of raster-scan display systems with various resolutions and scan rates. Some of the major functions of the TMS34061 VSC are:

- Generates all control signals necessary to control VRAM devices, as well as those necessary to control conventional 64K and 256K DRAMs.

- Generates the video synchronization and blanking signals necessary to control a CRT monitor.

- Accommodates processor data paths of arbitrary width. The TMS34061 works equally well with 8-, 16-, 20-, and 32-bit processors.

- Supports both interlaced and non-interlaced displays of essentially any display resolution (from 256 to greater than 4096 pixels per line).

- Automatically generates the special display-update cycles required by VRAM memories to maintain the CRT display.

- X-Y indirect addressing improves the performance of graphics primitives as well as supporting host processors with limited addressing range.

- Automatically performs periodic DRAM refresh cycles necessary to maintain data stored in the VRAMs, as well as in conventional 64K and 256K DRAMs.

- Universally programmable interface and READY/WAIT logic provides for efficient communication with all leading microprocessors as well as high-speed bit slice processors.

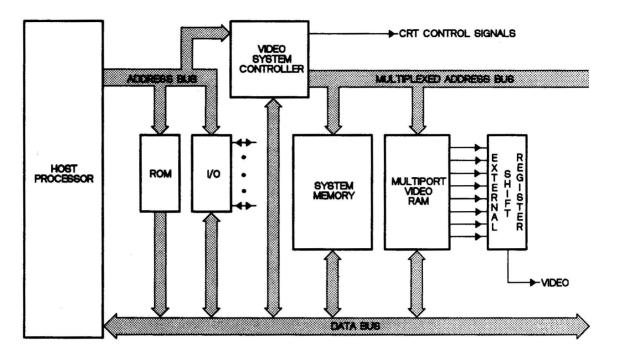

The block diagram of a typical system using the TMS34061 with the TMS4161 VRAM is shown in Figure 1-1.

Figure 1-1. Block Diagram of Typical TMS34061 VSC System

# **1.1 Typical Applications**

- Business and Personal Computer Systems

- Bit-Mapped Terminals

- CAD/CAM/CAE Workstations

- Instrumentation

- Printers (Laser)

- Plotters

# 1.2 Key Features

- Virtually constant availability of the memory to the host processor, since display access and dynamic RAM refresh require less than 6% of the total memory bandwidth.

- Controls bidirectional data transfer in the TMS4161 VRAM's internal shift register; from shift register to memory and from memory to shift register.

- Each TMS34061 can directly drive up to 64 VRAM or DRAM devices and can control more than 64 with external hardware.

- Provides shift-register reload for the TMS4161's internal shift register at a completely user-programmable rate.

- Generates user-programmable control signals (horizontal sync, vertical sync, and blanking) which support a broad range of raster-scan display systems with varying resolutions and scan rates.

- Provides dynamic RAM refreshing for VRAM and system DRAM at user-selectable rates.

- Synchronizes to an external sync source, allowing images to be superimposed on externally generated sources.

- Separate video and system clocks allow the video system and the host processor to run asynchronously.

# 2. Pinout and Signal Descriptions

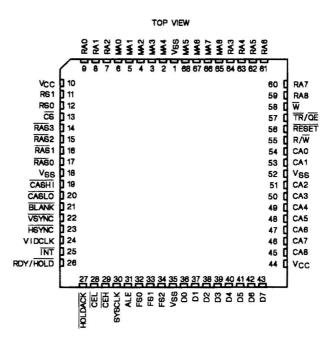

The pin number assignments and signal names for the TMS34061 are given in Figure 2-1. A description of each signal is given in Table 2-1.

Figure 2-1. TMS34061 Pin Assignments and Signal Names

The TMS34061 comes in a 68-terminal, J-leaded chip carrier plastic (PLCC) pack-age.

| SIGNAL   | PIN              | I/O | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|----------|------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MA8-MA0  | 65-68,<br>2-6    | Ο   | Memory Address 8-0.<br>The nine memory address outputs are multiplexed address<br>lines designed to interface directly to TMS4161 VRAMs,<br>as well as conventional DRAMs. The TMS34061 multi-<br>plexes up to nine row and nine column address bits over<br>these lines. A 256K DRAM that requires nine bits of row<br>and column addresses utilizes all nine outputs. A 64K<br>DRAM requires only eight bits of row and column addresses<br>and therefore utilizes only eight outputs (MA7-MA0). MA0<br>is the LSB.                                                                                                                                                                                                                                                                                                         |

| RA8-RA0  | 59-64,<br>7-9    | 1   | Row Address 8-0.<br>These nine address inputs are mutiplexed to memory<br>address pins MA8-MA0 during row address time when a<br>host-direct memory access cycle is executed. On host-ini-<br>tiated shift-register-transfer cycles, these inputs are multi-<br>plexed on MA8-MA0 during column address time. While<br>ALE is high and no internal cycle is taking place, the<br>MA8-MA0 outputs follow the RA8-RA0 inputs, which are<br>latched by the high-to-low transition of ALE. RA0 is the<br>LSB.                                                                                                                                                                                                                                                                                                                     |

| CA8-CA0  | 45-51,<br>53, 54 | I   | Column Address 8-0.<br>These nine address inputs are multiplexed to memory<br>address pins MA8-MA0 during column address time when<br>a host-initiated memory cycle is performed. When the host<br>accesses a TMS34061 internal register, the code input on<br>CA6-CA2 determines which register is selected, and the<br>value input on CA1 selects the upper or lower byte of the<br>register. During an X-Y address cycle, the value input on<br>CA4-CA1 determines the manner in which the X-Y address<br>stored within the TMS34061 is incremented or decremented<br>following completion of the cycle. On host-initiated shift-<br>register-transfer cycles, these inputs are multiplexed on<br>MA8-MA0 during column address time. These inputs are<br>latched by the high-to-low transition of ALE. CA0 is the<br>LSB. |

| RS1, RS0 | 11, 12           | I   | Row Address Strobe Selects 1 and 0.<br>During host-direct cycles and shift register transfer cycles,<br>these two pins determine which of the four row address<br>strobes RAS3-RAS0 is driven active low. RS1-RS0 are<br>latched by the trailing edge of ALE. If extended RAS mode<br>is enabled, these inputs are ignored.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| СЕН      | 29               | I   | Column Address Enable High Byte.<br>When active low, this signal enables the CASHI output<br>during a host-direct memory cycle or a host-initiated shift-<br>register-transfer cycle.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

Table 2-1. TMS34061 Signal Descriptions

| SIGNAL   | PIN   | I/O | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|----------|-------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CEL      | 28    | I   | Column Address Enable Low Byte.<br>When active low, this signal enables the CASLO output<br>during a host-direct memory cycle or a host-initated shift-<br>register-transfer cycle. CEL also strobes data into the<br>internal registers during register write cycles and enables<br>register data onto D7-D0 during register read cycles.                                                                                                                                                                                                                                                                                                                                                                                                           |

| ALE      | 31    | Ι   | Address Latch Enable.<br>The high-to-low transition of ALE latches the $\overline{CS}$ ,<br>RA8-RA0, CA8-CA0, RS1-RS0, and FS2-FS0 inputs, and<br>is interpreted by the TMS34061 as a command from the<br>host to initiate the cycle specified by the values latched at<br>these inputs. ALE must be synchronous with SYSCLK and<br>must meet setup and hold times specified with regard to<br>each low-to-high SYSCLK transition.                                                                                                                                                                                                                                                                                                                   |

| R∕₩      | 55    | I   | Read/Write.<br>During a memory cycle initiated by the host, $R/\overline{W}$ determines the direction of the data transfer (high for read, low for write) and determines the state of the $\overline{W}$ signal output from the TMS34061 to the memory. By appropriately controlling the state of the $R/\overline{W}$ input, the system is allowed to execute the following cycles: read, write, early write, or read-modify write. Similarly, during an access of an internal register by the host, $R/\overline{W}$ indicates whether the data is transferred to or from the register. At the beginning of the register access cycle, $R/\overline{W}$ is required to be valid prior to the high-to-low transition on the $\overline{CEL}$ input. |

| ĪNT      | 25    | 0   | Interrupt Request Low.<br>This output indicates that an interrupt condition previously<br>enabled by the host processor has occurred. INT will remain<br>active until the host processor initiates a read of the status<br>register. The TMS34061 can be programmed to generate<br>an interrupt at the start of a particular scan line in each<br>vertical field and also when either a DRAM-refresh error or<br>display-update error has occurred.                                                                                                                                                                                                                                                                                                  |

| D7-D0    | 43-36 | I/O | Data Bus Pins 7-0.<br>The host accesses the internal registers of the TMS34061<br>through this eight-bit bi-directional data bus. Each register<br>within the TMS34061 that is host accessible must be<br>accessed one byte at a time via D7-D0. D0 is the LSB.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| RDY/HOLD | 26    | 0   | Ready or Hold.<br>The operation and timing of RDY/HOLD is configured by<br>several control bits contained in Control Register 2 and also<br>by the state of the HOLDACK input at the end of reset. With<br>the TMS34061 configured in the Wait or Ready mode, the<br>RDY/HOLD pin remains in high impedance until the host<br>requests a memory cycle. In Hold/Hold-Acknowledge<br>mode, this pin is always driven low.                                                                                                                                                                                                                                                                                                                              |

| Table 2-1. TMS34061 Signal Descriptions (Continued | Table 2-1. | TMS34061 | Signal | Descriptions | (Continued |

|----------------------------------------------------|------------|----------|--------|--------------|------------|

|----------------------------------------------------|------------|----------|--------|--------------|------------|

| SIGNAL    | PIN   | 1/0 | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|-----------|-------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| HOLDACK   | 27    | I   | Hold Acknowledge.<br>When the TMS34061 is configured in<br>Hold/Hold-Acknowledge mode, the host responds to the<br>TMS34061's hold request issuing a handshaking signal by<br>driving HOLDACK low. The TMS34061 can perform an<br>internally requested cycle (display update or DRAM refresh)<br>in this mode only when a handshaking acknowledgment<br>has been received. The HOLDACK pin is also used to dictate<br>active level of the TMS34061's RDY/HOLD pin at system<br>powerup. The input level of the HOLDACK pin just prior to<br>the end of reset determines if the RDY/HOLD output is<br>initially configured as active high or active low. If HOLDACK<br>is high at the end of reset and the TMS34061 remains in<br>Ready or Wait mode, the RDY/HOLD output is active low<br>(a low signifies "ready," while a high signifies "not ready").<br>The meaning of the high and low levels of RDY/HOLD is<br>reversed if HOLDACK is low at the end of reset. However,<br>if the TMS34061 is in the Hold/Hold-Acknowledge mode,<br>the meaning of the HOLDACK level at the end of reset. |

| <u>CS</u> | 13    | I   | Chip Select.<br>This input operates as a master chip select. Before any<br>host-initiated access involving the TMS34061 can begin,<br>CS must be active low. This includes access of both<br>TMS34061 internal registers and the memory system<br>controlled by the TMS34061.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| FS2-FS0   | 34-32 | I   | Function Select 2-0.<br>The three-bit function select code input on FS2-FS0 indi-<br>cates the type of cycle requested by the host processor.<br>All cycles initiated by the host begin on the falling edge of<br>ALE.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| SYSCLK    | 30    | I   | System Clock.<br>SYSCLK is the system clock input used to generate the<br>timing of signals output to the memory and the timing of<br>the INT and the RDY/HOLD signals output to the host. All<br>host interface signals input to the TMS34061 must be<br>synchronous to SYSCLK.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| RESET     | 56    | I   | Reset.<br>An active low RESET places the TMS34061 in a known<br>initial state. While RESET is low, the internal registers are<br>forced to their default values, and all VRAM control outputs<br>are forced to their inactive levels. RESET should be driven<br>low when power is first applied and remain low for at least<br>1 ms. After RESET is brought inactive high, the host should<br>wait 1 ms before accessing TMS34061 or the memory it<br>controls. This time is required to allow the TMS34061 to<br>perform at least eight RAS-only VRAM (or DRAM) refresh<br>cycles, thus bringing the VRAMs (or DRAMs) up to their<br>current initial state, as described in the specifications for the<br>TMS4161 VRAM and the TMS4164 DRAM. After the<br>required time has elapsed, the registers internal to the<br>TMS34061 should be loaded with the values appropriate<br>to the application.                                                                                                                                                                                             |

| Table 2-1. TMS34061 Signal Descriptions | (Continued) |

|-----------------------------------------|-------------|

|-----------------------------------------|-------------|

| SIGNAL    | PIN   | I/O | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-----------|-------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RAS3-RAS0 | 14-17 | 0   | Row Address Strobe 3-0.<br>These active-low outputs are designed to drive the RAS<br>inputs on both the TMS4161 VRAM and conventional<br>DRAMs. During a host-direct memory or shift-register-<br>transfer cycle, RAS3-RAS0 are controlled by the RS1-RS0<br>inputs in default-mode operation. The two-bit code input<br>on RS1-RS0 determines which of the four RAS outputs is<br>driven active low during the cycle. Alternately, bits B1-B0<br>of Control Register 2 can be used to replace the values on<br>RS1-RS0 when the extended RAS mode is selected.<br>Furthermore, the RAS overrides can be set in Control<br>Register 2, forcing the corresponding RAS output to be<br>active on host-direct memory and shift-register-transfer<br>cycles and internal X-Y cycles. During a DRAM refresh<br>cycle, all four RAS outputs are driven active low in the<br>default mode of operation. If B7 of Control Register 1 is<br>set to 1, only one RAS output will be active at one time.<br>In this mode the active RAS output is determined by the<br>value in the Display Address register. |

| CASHI     | 19    | 0   | Column Address Strobe High Byte.<br>This active low output is designed to directly drive the CAS<br>inputs on both the TMS4161 VRAM and conventional<br>DRAMs. During memory cycles initiated by the host, CASHI<br>becomes active only after the CEH input is driven active low.<br>In 16-bit systems CASHI is typically used to enable a read<br>or write to the high byte (eight MSBs) of the memory data<br>bus. CASHI is driven low during internally-requested<br>display-update cycles, and remains inactive during VRAM<br>refresh cycles.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| CASLO     | 20    | 0   | Column Address Strobe Low Byte.<br>The operation of CASLO is similar to that of CASHI, as<br>described above, except that CASLO is enabled by an active<br>low on CEL rather than CEH. In 16-bit systems, CASLO is<br>typically used to enable the low byte (eight LSBs) of the<br>memory data bus. CASLO is driven active low during<br>internally-requested display-update cycles and remains<br>active high during VRAM refresh cycles.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| W         | 58    | 0   | Write Control.<br>This signal is used to drive the $\overline{W}$ inputs to both the TMS4161 VRAM and conventional DRAMs. $\overline{W}$ follows the R/ $\overline{W}$ pin on host-direct memory cycles. On host-initiated shift-register-transfer cycles, the state of $\overline{W}$ is determined by the FS0 code. During internally-initiated display-update cycles, $\overline{W}$ is driven low if a write is indicated by bit B6 in Control Register 1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

Table 2-1. TMS34061 Signal Descriptions (Continued)

| SIGNAL          | PIN              | I/O | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|-----------------|------------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TR/QE           | 57               | 0   | Shift Register Transfer and Output Enable.<br>The $\overline{TR}/\overline{QE}$ output can directly drive the $\overline{TR}/\overline{QE}$ inputs on<br>the TMS4161 VRAM. The signals used to enable shift-re-<br>gister transfer cycles and VRAM output buffers during read<br>cycles are multiplexed over this single pin.                                                                                                                                                            |

| BLANK           | 21               | 0   | Video Blanking.<br>The BLANK output controls the blanking input on a CRT<br>monitor. BLANK is driven active low during both horizontal<br>and vertical blanking intervals. This output is TTL-compa-<br>tible. The entire screen is blanked immediately following<br>reset, and the active portions of the screen are unblanked<br>only after control bit 13 in Control Register 2 is set.                                                                                               |

| HSYNC           | 23               | Ι/Ο | Horizontal Sync.<br>HSYNC generates the horizontal sync pulses used to control<br>a CRT monitor. It operates as an output except when the<br>External Sync mode is enabled. HSYNC is driven active low<br>during horizontal sync intervals whose timing is determined<br>by the values programmed in the TMS34061's horizontal<br>timing registers. In External Sync mode, HSYNC is an input<br>and an active low on HSYNC resets the Horizontal counter<br>register to zero.            |

| VSYNC           | 22               | 1/0 | Vertical Sync.<br>VSYNC generates the vertical sync pulses used to control a<br>CRT monitor and operates as an output except when the<br>external sync mode is enabled. VSYNC is driven active low<br>during vertical sync intervals whose timing is determined<br>by the values programmed in the TMS34061's vertical<br>timing registers. In External Sync mode, VSYNC is an input,<br>and an active low on VSYNC resets the vertical counter<br>register to zero.                     |

| VIDCLK          | 24               | 1   | Video Clock.<br>The video input clock drives the logic within the TMS34061<br>chip that is responsible for generating the timing for the<br>sync and blanking signals. VIDCLK also drives the logic<br>responsible for generating internal requests for display-up-<br>date and VRAM refresh cycles. Typically, VIDCLK is<br>harmonically related to the dot (or pixel) clock used to<br>stream video data from the external shift registers in the<br>memory system to the CRT monitor. |

| Vcc             | 10, 44           |     | +5 volt supply input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| V <sub>SS</sub> | 1, 18,<br>35, 52 |     | Ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Table 2-1 | TMS34061  | Signal | Descriptions | (Concluded) |

|-----------|-----------|--------|--------------|-------------|

|           | 11100-001 | o.a.u. | Descriptions | (conoradoa) |

# 3. Architecture

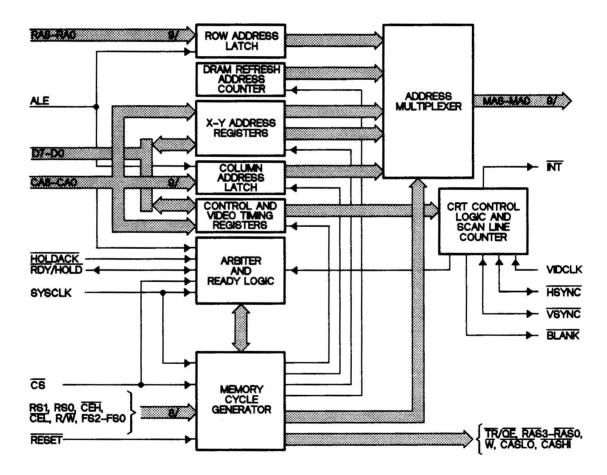

The TMS34061 consists of ten basic functional blocks (see Figure 3-1):

- Address multiplexer

- Row address latches

- Column address latches

- DRAM refresh counters

- X-Y address registers (internal)

- Status, control, video timing, display update registers, and scan line counter (internal)

- Arbiter

- Memory cycle generator

- CRT control

- Universal host interface and ready logic

Figure 3-1. TMS34061 Internal Architecture Block Diagram

# 3.1 Address Multiplexer

The address multiplexer provides the Multiport VRAM array with row and column addresses at the proper times. Its inputs come from the host system, X-Y indirect address register, the display address register, and the DRAM refresh address counter. The specific source of the address is controlled by the arbiter, and the RA or CA portion of the address is controlled by the memory cycle generator. The 9-bit MA address outputs provide 18 multiplexed address signals. The address multiplexer can directly drive inputs for up to 64 TMS4161 Multiport VRAM devices or conventional dynamic RAM devices of up to 256K bits.

# 3.2 Row and Column Address Latches

The address latches allow the TMS34061 to be used without external latches in systems that multiplex address and data on the same bus. The row latches are transparent, which means that while Address Latch Enable (ALE) is high, the outputs MA0-MA8 follow the address input on RA0-RA8 (assuming an internal cycle is not in progress). The falling edge of ALE internally latches the row and column inputs from the host before being multiplexed to the Memory Address Outputs.

# 3.3 DRAM Refresh Counters

The TMS34061 has a 9-bit refresh counter which can be programmed to perform a varying number of DRAM refresh cycles per horizontal line. The refresh burst length is determined by bits B14-B12 in Control Register 1. These three bits select from zero to seven refresh cycles per horizontal line. During a refresh cycle, the refresh address counter outputs a 9-bit row address on the MA0-MA8 pins during the row address time.

# 3.4 Internal Registers

#### Note:

Section 4 discusses all internal registers in greater detail.

# 3.4.1 X-Y Address Registers

X-Y addressing capability is especially useful when the linear addressing range of the host is too limited to provide proper access to all pixels on the screen. The contents of the X-Y registers replace the RAO-RA8 and CAO-CA8 inputs as the source for the MAO-MA8 memory address outputs when an X-Y operation is selected. A 4-bit code on the inputs CA4-CA1 of the TMS34061 during X-Y cycles determines how the address is adjusted on completion of the X-Y operation (see Section 4.4 for details). X-Y capability relieves the host from calculating the address of the next pixel to be modified.

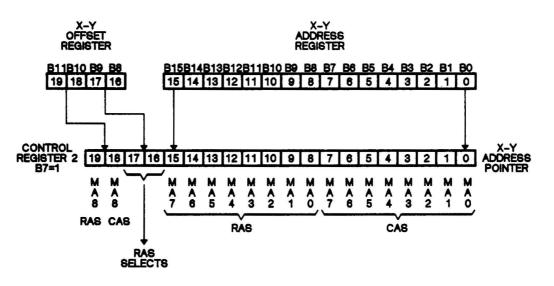

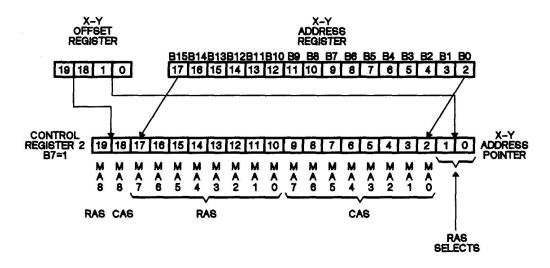

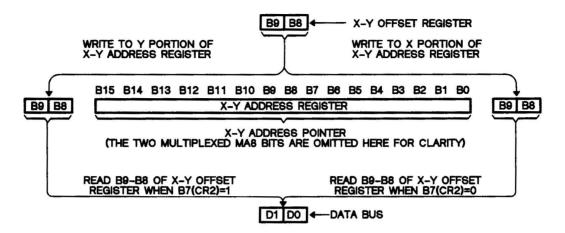

X-Y Address Register The X-Y Address Register contains 16 host-accessible bits that eventually become part of the 20-bit X-Y Address Pointer. Various graphic memory configurations can be tailored by the eight combinations of programmable X(LSB) and Y(MSB) boundaries.

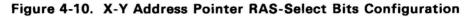

- X-Y Offset Register The 16-bit X-Y Offset Register utilizes only 11 bits, B10-B0. Bits B7-B0 define boundaries between the X and Y portions of the X-Y Address Register. The B8-B9 expansion bits determine which of the four row address strobes (RAS 3-RAS 0) will be active during the X-Y indirect cycle. B11 (row address bit) and B10 (column address bit) are multiplexed on MA8 output.

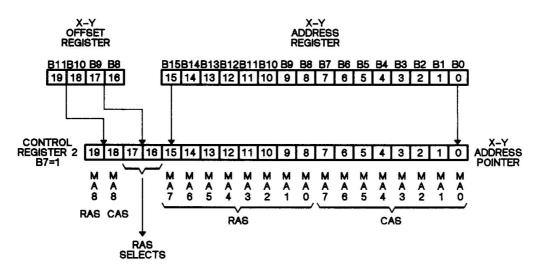

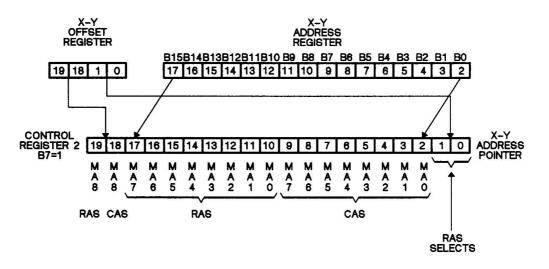

- X-Y Address Pointer The TMS34061 has a 20-bit X-Y Address Pointer constructed from all 16 bits of the X-Y Address Register and 4 bits of the X-Y Offset Register. Two of the four bits of the X-Y Offset Register control the RAS 0-RAS 3 outputs. These two bits can be programmed (via B7 of Control Register 2) to be the least significant bits or the most significant bits of the X-Y address. Figure 3-2 and Figure 3-3 show how the 20-bit X-Y Address Pointer Register is constructed from the X-Y Address Register and the X-Y Offset Register and how it is output on the TMS34061's memory bus. Bits B17-B0 of the X-Y Address Pointer effectively form an 18-bit counter, each bit adjusted by the X-Y adjustment codes. Bits B19-B18 are not modified by the X-Y adjustment codes.

Figure 3-2. X-Y Address Pointer Register Construction

Figure 3-3. X-Y Address Pointer Register Output

#### 3.4.2 Control Registers 1 and 2

The TMS34061 has two 16-bit host-programmable internal Control Registers which dictate TMS34061 operation. Each register may be read from and written to by the host. Video functions governed by the Control Registers include DRAM refresh frequencies, display-update timing cycles, and configuration of video timing functions. Enabling of interrupt requests and some host interface signals are also controlled by these registers.

#### 3.4.3 Status Register

The Status Register is responsible for three conditions within the TMS34061 that may require host interrupts. This three-bit register can be read from but not written to by the host. After reading the register, all bits are reset to zero. Each register bit represents the status of one of three different conditions (logic "high" in the bit indicates the condition has been detected). When detection has occurred, the TMS34061 sends an interrupt request by driving INT active low. If interrupts are enabled, two interrupt enable bits in Control Register 1 determine which interrupt sources are able to set the interrupt output.

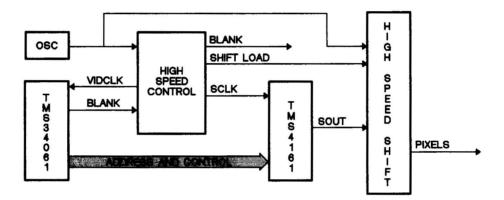

# 3.4.4 Video Timing Registers

Horizontal and vertical sync and blanking interval timing is controlled by ten Video Timing registers. Four timing registers along with a horizontal counter generate horizontal timing signals, while four timing registers coupled with a video counter are responsible for the vertical timing signals. Another register, the Vertical Interrupt, sends an interrupt request to the host when a specified scan line is reached. The following registers comprise the Video Timing section:

- Horizontal End Sync

- Horizontal End Blank

- Horizontal Start Blank

- Horizontal Total

- Horizontal Counter

- Vertical End Sync

- Vertical End Blank

- Vertical Start Blank

- Vertical Total

- Vertical Counter

- Vertical Interrupt

#### 3.4.5 Display Update Registers

The video information, which the CRT receives for a specific scan line, is transferred during the horizontal blanking interval immediately preceding that line. This transfer is accomplished by means of a display-update cycle, which the TMS34061 performs automatically. The data is first moved from a specific row in VRAM to a shift register internal to VRAM. The contents of this shift register are output during the horizontal active period. The three display update registers then program the address output during each display update cycle.

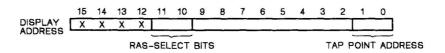

| Displaγ Address        | This 12-bit register stores the address of the data to<br>be output on the next display update cycle. Bits 9-2<br>are output on MA7-MA0 as the row address; MA8 is<br>driven low during this time. Bits 1 and 0 are output on<br>MA7-MA6 as the column address; MA8 and MA5-<br>MA0 are driven low during this time. In the default<br>mode operation, all four RAS strobes are active during<br>a display-upeate cycle, and bits B11-B10 have no<br>effect on the RAS strobes. When the display-update<br>RAS-mode bit (B7 in Control Register 1) is set to one,<br>the active RAS strobe during a display-update cycle is<br>selected by bits B11-B10. |

|------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Display Address Update | The four-bit Display Address Update Register may be                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

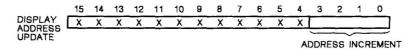

- Display Address Update The four-bit Display Address Update Register may be read from or written to by the host. The data stored in this register control how the address is incremented after an update cycle has completed. The four LSBs of the Display Updatae Register are added to the Display Address Register to create the address output for the next display-update cycle.

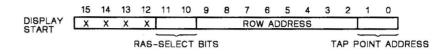

- **Display Start** This 12-bit register may be read from or written to by the host. The Display Start Register specifies the memory location which is displayed at the upper left of the screen. At the beginning of each vertical blanking

interval, the contents stored in this register are loaded into the Display Address Register.

# 3.5 Arbiter

The arbiter determines whether the host processor, the video shift-register reload logic, or the dynamic RAM refresh logic can access the memory. Since the display and refresh functions of the TMS34061 normally use less than 6% of the available memory cycles, the arbiter usually grants memory access to the host. When a conflict arises, the arbiter grants priority as follows:

- 1) Any cycle in progress

- 2) A display-update cycle (internally granted request)

- 3) A DRAM refresh cycle that has been delayed for more than ½ horizontal line

- 4) Any host-requested cycle

- 5) DRAM-refresh cycle

Three modes can inform the host processor of an internal cycle:

- Synchronous Ready mode

- Wait mode

- Hold/Hold Acknowledge mode

These modes determine the TMS34061's response to the host's request for a memory cycle and to conflicting requests for memory cycles. In all modes of operation, the TMS34061 reports its inability to execute the requested display and refresh cycles by setting bit 2 of the Status Register to one. The TMS34061's host operating mode is selected by B11 and B12 of Control Register 2.

# 3.5.1 READY/WAIT Operating Modes

#### Synchronous Ready In the Synchronous Ready Mode, the TMS34061 responds to each host request for a memory cycle by bringing RDY/HOLD to its inactive level from a highimpedance state. When N SYSCLK transitions occur (where N is the value set by bits B10-B8 of Control Register 2) after CASHI or CASLO becomes active in a host-requested memory cycle, the RDY/HOLD pin switches to the active ready state. Bit B14 in Control Register 2 allows the RDY/HOLD pin to trigger off RASO-RAS3 instead of CASLO or CASHI. The active level of the RDY/HOLD pin is determined by the state of the HOLDACK pin at the end of Reset. If HOLDACK is low at the end of Reset, the RDY/HOLD pin will be active low when the TMS34061 is not ready. If HOLDACK is high, the RDY/HOLD pin will be active high when the TMS34061 is not ready.

Wait The Wait Mode is similar to the Ready Mode, except that the READY/HOLD line becomes active WAIT only if the host is requested to wait for the completion of its requested memory cycle. If the host system requests access during an internally-requested cycle, WAIT immediately goes to the active state. It remains there until the completion of the internal cycle, 1½ SYSCLK periods before RAS0-RAS3 goes active during execution of the host requested cycle.

Hold/Hold Acknowledge This mode of operation is intended for use with host systems which do not allow wait states once a memory-access cycle has been initiated. In the Hold/Hold Acknowledge mode, the TMS34061 tests the state of the HOLDACK pin to determine if the system is in a hold condition when it is time for a shift register transfer or refresh cycle. If HOLDACK is low, the TMS34061 requests a hold state by bringing RDY/HOLD from a high-impedance state to its active level. The TMS34061 then waits for the HOLDACK input to go low before initiating the shift-register transfer and refresh cycles. Once HOLD has been granted, HOLDACK can be removed only after HOLD has returned to its active high state. It is important to note that in this mode of operation the TMS34061 must be granted the hold state prior to the end of the horizontal blanking interval. If it is not, the error flag in the status register is set and the update cycle may be missed.

# 3.6 Memory Cycle Generator

The Memory Cycle Generator processes the various memory cycles as requested by the arbiter and provides the external memory array with the RAS,  $\overline{CAS}$ ,  $\overline{TR}/\overline{OE}$ , and  $\overline{W}$  signals. It controls the multiplexer during all of its cycles so that the address and control line setup and hold requirements are met. The cycles generated by the memory cycle generator are listed below.

- Host-requested cycles

- Host-direct random access

- Host-indirect X-Y random access

- Memory-to-shift register transfer

- Shift register-to-memory transfer

- Delayed host-requested cycles

- Internally-requested memory-to-shift register transfer

- Internally-requested refresh cycle.

# 3.7 CRT Control

The TMS34061 generates the HSYNC, VSYNC, and BLANK signals used to drive a CRT monitor in a bit-mapped graphics system. These signals are synchronous to the Video Input Clock (VIDCLK). HSYNC, VSYNC, and BLANK are programmed through eight host-accessible video timing registers, which are easily configured to accommodate a variety of display resolutions and CRT monitors in either interlaced or non-interlaced modes. Two additional registers, clocked by VIDCLK, maintain the current horizontal and vertical counts. The values in these two counters are compared with the values in the eight video timing registers to determine the limits of the sync

and blanking intervals. The TMS34061 can be configured to accept HSYNC and VSYNC as inputs allowing synchronization to an external video source.

# 4. Programmable Registers

This section explains the addressing and programming of the TMS34061's registers.

- Default register values after reset

- CPU interface registers

- Status Register

- Control Registers 1 and 2

- Vertical Interrupt Register

- CRT Control Registers

- Display-Update Registers

- Video Timing Registers

- X-Y Address Pointer

- X-Y Address Register

- X-Y Offset Register

The TMS34061 contains 18 programmable registers. Each register is nominally 16 bits wide and can be written to and read from by the host processor through an 8-bit data path one byte at a time. Other registers internal to the TMS34061 are inaccessible to the host processor; these are also discussed in this section. The bit-numbering convention to be used for all registers is shown in Figure 4-1.

The host processor accesses the programmable registers within the VSC by means of special read and write cycles. A register-access cycle is selected by setting the function-select input pins FS2-FS0 to one of two 3-bit codes, either 000 or 010. One of 18 registers is selected by the 5-bit register address input on column-address input pins CA6-CA2, as indicated in Figure 4-2. Binary codes 00000 through 10001 are valid register addresses. Codes 10010 through 11111 are reserved. The high or low byte of the register is selected by the value input on CA1. If CA1 is zero, the register low byte is selected; otherwise, the register high byte is selected. In Figure 4-2, the active bits in each 16-bit register location are indicated by the letter "A." The unimplemented bits, indicated as "X," are always read as zeroes.

| 15  | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0   |

|-----|----|----|----|----|----|---|---|---|---|---|---|---|---|---|-----|

|     |    |    |    |    |    |   |   |   |   |   |   |   |   |   |     |

| MSB |    |    |    |    |    |   |   |   |   |   |   |   |   |   | LSB |

Figure 4-1. Register Bit-Numbering Convention

| INP                                                                                                                                                                                                                                                                                                                                         | UT PIN VALUES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                   |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| C C C C C C<br>A A A A A<br>6 5 4 3 2                                                                                                                                                                                                                                                                                                       | UPPER LOWER<br>BYTE BYTE<br>(CA1=1) (CA1=0)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | REGISTER NAME                                                                                                                                                                                                                                                                                                                                                                                                     |

| 0   0   0   0   1     0   0   0   0   1   1     0   0   0   1   1   0     0   0   0   1   1   0     0   0   0   1   1   0     0   0   1   1   0   1   1     0   1   0   0   1   1   0     0   1   0   0   1   1   0     0   1   0   0   1   1   0     0   1   1   0   0   1   1     0   1   1   0   0   0   1     1   0   0   0   1   1   1 | ICINITATION     ICINITATION       XXXXAAAA     AAAAAAAA       XXXXAAAA     AAAAAAAAA       XXXXAAAA     AAAAAAAA       XXXXAAAA     AAAAAAAAA       XXXXAAAA     AAAAAAAAA       XXXXAAAA     AAAAAAAA       XXXXAAAA     AAAAAAAA       XXXXAAAA     AAAAAAAAA       AAAAAAAAA     AAAAAAAAA       XXXXAAAA     AAAAAAAAA       XXXXAAAA | HORIZONTAL END SYNC<br>HORIZONTAL END BLANK<br>HORIZONTAL START BLANK<br>HORIZONTAL TOTAL<br>VERTICAL END SYNC<br>VERTICAL END BLANK<br>VERTICAL START BLANK<br>VERTICAL TOTAL<br>DISPLAY START<br>UERTICAL INTERRUPT<br>CONTROL REGISTER 1<br>CONTROL REGISTER 2<br>STATUS REGISTER<br>X-Y OFFSET REGISTER<br>X-Y OFFSET REGISTER<br>X-Y ADDRESS REGISTER<br>DISPLAY ADDRESS REGISTER<br>VERTICAL COUNT REGISTER |

|                                                                                                                                                                                                                                                                                                                                             | $ \begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 01<br>02<br>03<br>04<br>05<br>06                                                                                                                                                                                                                                                                                                                                                                                  |

NOTE: "A" = ACTIVE REGISTER BIT, "X" = BIT NOT IMPLEMENTED.

# 4.1 Default Register Values After Reset

Host-accessible registers are set to the values indicated in Table 4-1 immediately following reset.

B14-B12 of Control Register 1, the Refresh Burst Length bits, are all set to ones immediately after reset. This configures the TMS34061 to the maximum number of DRAM-refresh cycles per horizontal scan line. The video timing registers are also set to non-zero default values. This is necessary because of the manner in which the scheduling of DRAM-refresh cycles is tied to the video timing. The row address output from the VSC during the first DRAM-refresh cycle following reset will be all zeros.

The three wait-state limit bits, B10-B8 of Control Register 2, contain the binary code 110 (decimal 6) immediately following reset. This configures the VSC to insert a delay of six SYSCLK edges into each cycle initiated by the host processor.

| REGISTER NAME            | VAL  | UE AF | TER R | ESET |

|--------------------------|------|-------|-------|------|

| Horizontal End Sync      | xxxx | 0000  | 0001  | 0000 |

| Horizontal End Blank     | xxxx | 0000  | 0010  | 0000 |

| Horizontal Start Blank   | xxxx | 0001  | 1111  | 0000 |

| Horizontal Total         | xxxx | 0010  | 0000  | 0000 |

| Vertical End Sync        | xxxx | 0000  | 0000  | 0100 |

| Vertical End Blank       | xxxx | 0000  | 0001  | 0000 |

| Vertical Start Blank     | xxxx | 0000  | 1111  | 0000 |

| Vertical Total           | xxxx | 0001  | 0000  | 0000 |

| Display Update Register  | xxxx | xxxx  | xxxx  | 0000 |

| Display Start Register   | xxxx | 0000  | 0000  | 0000 |

| Vertical Interrupt       | xxxx | 0000  | 0000  | 0000 |

| Control Register 1       | x111 | 0000  | 000x  | 0000 |

| Control Register 2       | x000 | 0110  | 0000  | 0000 |

| Status Register          | xxxx | xxxx  | xxxx  | x000 |

| X-Y Offset Register      | xxxx | 0000  | 0001  | 0x00 |

| X-Y Address Register     | 0000 | 0000  | 0000  | 0000 |

| Display Address Register | xxxx | 0000  | 0000  | 0000 |

| Vertical Counter         | xxxx | 0000  | 0000  | 0000 |

Table 4-1. Host-Accessible Registers After Reset

Note: Bits indicated as "x" are not implemented and are always read as zeros.

Host-inaccessible registers are set to the values indicated below, immediately following reset.

Table 4-2. Host-Inaccessible Registers After Reset

| REGISTER NAME         | VALUE AFTER RESET |      |      |      |  |  |

|-----------------------|-------------------|------|------|------|--|--|

| Horizontal Counter    | xxxx              | 0000 | 0000 | 0000 |  |  |

| Refresh Address       | xxxx              | xxx0 | 0000 | 0000 |  |  |

| Refresh Burst Counter | xxxx              | xxxx | xxxx | x111 |  |  |

| Scan Line Counter     | xxxx              | xxxx | xxxx | 0000 |  |  |

Note: Bits indicated as "x" are not implemented.

#### 4.2 CPU Interface Registers

The TMS34061 VSC contains two directly-accessible control registers, a status register, and an interrupt register that are programmed by the host processor to configure the operation of the VSC. The functions controlled by these registers include:

- The behavior of host interface signals

- The timing of display-update cycles

- Enabling of interrupt requests

- Frequency of DRAM-refresh cycles

- Configuration of video timing functions

- Interrupt control

Control Registers 1 and 2 are both 16-bit registers. Both may be read from and written to by the host processor. The functions assigned to the individual bits within these registers are indicated in the following definitions. The bit-numbering convention shown in Figure 4-1 is used. Control Registers 1 and 2 are forced to the default values indicated in Table 4-1 during reset.

#### 4.2.1 Control Register 1

| B15           | B14-B12                    | B11                         | B10                             | B9                  | B8                         | 87     | B6                             | B5 | B4            | B3-B0                  |

|---------------|----------------------------|-----------------------------|---------------------------------|---------------------|----------------------------|--------|--------------------------------|----|---------------|------------------------|

| RESERVED<br>0 | REFRESH<br>BURST<br>LENGTH | ERROR<br>NTERRUPT<br>ENABLE | VERTICAL<br>INTERRUPT<br>ENABLE | INTERLACE<br>ENABLE | EXTERNAL<br>SYNC<br>ENABLE | UPUNIC | DISPLAY<br>UPDATE<br>DIRECTION |    | RESERVED<br>0 | LINE<br>COUNT<br>LIMIT |

Figure 4-3. Control Register 1

#### Bits Function

#### B3-B0 Line Count Limit.

The Line Count Limit determines the number of horizontal lines that are counted by the Scan Line Counter before a display-update cycle is granted. The Scan Line Counter repeatedly cycles from zero to the limit value specified in bits B3-B0, incrementing at the end of each horizontal scan line and comparing the count to the value stored in bits B3-B0. When equal, a display-update cycle is granted on that horizontal line during the blanking interval and the Scan Line Counter is zeroed. When the line count limit is set to zero, display-update cycles occur on every scan line.

| <b>B</b> 3 | B2 | B1 | <b>B</b> 0 | PERFORM DISPLAY UPDATE      |

|------------|----|----|------------|-----------------------------|

| 0          | 0  | 0  | 0          | After each scan line        |

| 0          | 0  | 0  | 1          | After every other scan line |

| 0<br>0     | 0  | 1  | 0          | After every 3rd scan line   |

| 0          | 0  | 1  | 1          | After every 4th scan line   |

| 0          | 1  | 0  | 0          | After every 5th scan line   |

| 0          | 1  | 0  | 1          | After every 6th scan line   |

| 0          | 1  | 1  | 0          | After every 7th scan line   |

| :          | :  | 1  | :          |                             |

| :          | 1  | 1  |            | :                           |

| 1          | 1  | 1  | 1          | After every 16th scan line  |

- **B4** Reserved - always 0. **B5** Display Update Inhibit. When B5 is one, display-update cycles are inhibited and do not occur. When B5 is zero, display-update cycles are enabled. B5 overrides all other display update parameters. **B6 Display Update Direction.** When B6 is one, display-update cycles transfer data from the shift register to the memory cell array of each TMS4161 Multiport VRAM. When B6 is zero, displayupdate cycles transfer data from the memory cell array to the shift register. **B7** Display-Update RAS Mode. When B7 is zero, all four row address strobe pins, RAS3-RAS0, are active during a display-update cycle. When B7 is one, only one of the four strobes is active during a display-update cycle. The active strobe is selected by the value contained in the two MSBs (bits B11-B10) of the Display Address Register. **B8** External Sync Enable. When B8 is zero, the external video sync mode is disabled. This turns the HSYNC and VSYNC into outputs, and horizontal and vertical sync and vertical timing is generated within the TMS34061. When B8 is one, external sync mode is enabled. The HSYNC and VSYNC pins are now configured as inputs and the VSC locks on to the externally-generated sync signals. **B9** Interlace Enable. When B9 is zero, the VSC is configured for non-interlaced scan. When B9 is one, the VSC is configured for interlaced scan. **B10** Vertical Interrupt Enable. When B10 is zero, the setting of the Vertical Interrupt Flag in the Status Register does not cause an interrupt request to the host processor. When B10 is one, the interrupt request is enabled. B11 Error Interrupt Enable. When B11 is zero, the setting of an error interrupt flag in the Status Register does not cause the TMS34061 to send an interrupt request to the host processor. When B11 is one, the setting of either display or refresh error interrupt flag causes an interrupt request.

- B14-B12Refresh Burst Length.<br/>B14-B12 contains a three-bit binary number specifying the number of DRAM-refresh<br/>cycles generated per horizontal scan line. If the number is specified as zero, no<br/>DRAM-refresh cycles occur. The encoding of these bits is indicated below:

| B14 | B13 | B12 | REFRESH BURST LENGTH   |

|-----|-----|-----|------------------------|

| 0   | 0   | 0   | No DRAM-refresh cycles |

| 0   | 0   | 1   | 1 cycle per scan line  |

| 0   | 1   | 0   | 2 cycles per scan line |

| 0   | 1   | 1   | 3 cycles per scan line |

| 1   | 0   | 0   | 4 cycles per scan line |

| 1   | 0   | 1   | 5 cycles per scan line |

| 1   | 1   | 0   | 6 cycles per scan line |

| 1   | 1   | 1   | 7 cycles per scan line |

B15 Reserved – always 0. When read, B15 returns a zero.

#### Note:

When programming the TMS34061 in External Sync Enable mode (B8 in Control Register 1 is set to one), the lower byte of Control Register 1 (bits B7-B0) has logic in this path to prevent the non-host-accessible memory controller timing register from being updated asynchronously. The contents of the lower byte of Control Register 1 are transferred to the memory controller timing register on the Start of Blank interval internal to the TMS34061. Therefore, when external sync is being input, a front porch interval (BLANK output active low before the sync input is active low) is necessary for the lower byte of Control Register 1 to be transferred to the memory controller. The contents of the lower byte of Control Register 1 are updated immediately, but the transfer to the memory controller timing register occurs only during this Start of Blank interval.

#### 4.2.2 Control Register 2

| B15           | B14              | B13                        | B12-B11                    | B10-B8                 | B7                                  | B6 | B5B2             | B1-B0                     |

|---------------|------------------|----------------------------|----------------------------|------------------------|-------------------------------------|----|------------------|---------------------------|

| RESERVED<br>0 | RAG/CAS<br>READY | BLANK<br>ENTIRE<br>DISPLAY | RDY/HOLD<br>MODE<br>SELECT | WAIT<br>STATE<br>LIMIT | X-Y ADDR.<br>POINTER<br>RAS<br>MODE |    | RAS<br>OVERRIDES | EXTENDED<br>RAS<br>SELECT |

Figure 4-4. Control Register 2

#### Bits Function

**B1-B0** Extended RAS Select Bits. When bit B6 of Control Register 2 is **one**, the two-bit value in B1-B0 replaces the value input on the RS1-RS0 inputs during a host-direct or shift-register transfer cycle and determines which of the four RAS outputs is driven active-low during the cycle. The encoding of B1-B0 is as follows:

| B1 | <b>B0</b> | ACTIVE STROBE |

|----|-----------|---------------|

| 0  | 0         | RAS0          |

| 0  | 1         | RAS1          |

| 1  | 0         | RAS2          |

| 1  | 1         | RAS3          |

#### B5-B2 RAS Overrides.

Each of the four RAS-override bits, B5-B2, is dedicated to one of the four RAS outputs, RAS3 to RAS0. When an override bit is set to **one**, the corresponding RAS output is forced to its active-low level during the following four types of cycles:

- Host-direct write,

- X-Y-indirect write,

- Shift-register write,

- Shift-register read cycles.

When an override bit is **zero**, the corresponding RAS output is controlled by other means. Namely, during host-direct write cycles, RS1-RS0 or B1-B0 are used to select one of four row address strobes to be activated, and during X-Y-indirect write cycles, the RAS-select bits from either the two MSBs or the two LSBs of the X-Y Address Pointer are used. In other words, the four RAS-override enables are logically-ORed with the result of the decode of the two designated RAS-select bits. The RAS-override bits never affect host-direct read cycles, X-Y indirect read cycles, or cycles initiated internally by the VSC. The individual RAS-override enables are assigned as follows:

| BIT | FUNCTION          |

|-----|-------------------|

| B2  | Force RASO active |

| B3  | Force RAS1 active |

| B4  | Force RAS2 active |

| B5  | Force RAS3 active |

|     |                   |

B6 Extended RAS Mode.

When B6 is zero, the values input on the RS1-RS0 pins select one of the four RAS outputs during a host-direct or shift-register transfer cycle. When B6 is one, the two-bit code in B1-B0 selects one of the strobes.

- B7 X-Y Address Pointer RAS Mode. When B7 is one, bits B8-B9 of the X-Y Offset Register become the two MSBs in the X-Y Address Pointer which selects one of the four RAS outputs during a X-Yindirect cycle. When B7 is zero, these two X-Y Offset Register bits become the LSBs which enable one of the four RAS outputs.

- **B10-B8** Wait State Limit. The 3-bit code in B10-B8 determines the number of wait states inserted into cycles initiated by the host processor. A wait state is a delay of one-half of a SYSCLK clock period inserted into a cycle to increase its duration. The cycle is delayed by post-poning the ready signal to the host processor. B10-B8 are encoded as follows:

| B10 | <b>B9</b> | <b>B</b> 8 | INSERT DELAY OF |

|-----|-----------|------------|-----------------|

| 0   | 0         | 0          | 0 wait states   |

| 0   | 0         | 1          | 1 wait state    |

| 0   | 1         | 0          | 2 wait states   |

| 0   | 1         | 1          | 3 wait states   |

| 1   | 0         | 0          | 4 wait states   |

| 1   | 0         | 1          | 5 wait states   |

| 1   | 1         | 0          | 6 wait states   |

| 1   | 1         | 1          | 7 wait states   |

B12-B11 RDY/HOLD Mode Select.

The RDY/HOLD output is configured by B12-B11 to operate as a "ready," "wait," or "hold" signal to accommodate the interfacing requirements of a variety of host processors. B12-B11 are encoded as follows:

| B12 | B11 | MODE SELECTED |

|-----|-----|---------------|

| 0   | 0   | Ready signal  |

| 0   | 1   | Wait signal   |

| 1   | 0   | Hold signal   |

| 1   | 1   | Reserved      |

B13 Screen Enable. When B13 is zero, the BLANK driven output is active-low continuously. When B13 is one, the BLANK output is driven low only during horizontal and vertical blanking intervals.

- B14 RAS/CAS Ready Enable When B14 is zero, CASLO or CASHI enables the ready timing. When B14 is a one, RAS3-RAS0 enables the ready timing.

- B15 Reserved always 0.

#### 4.2.3 Status Register

The Status Register contains three bits, each representing a particular internal condition. A bit value of one indicates presence of the corresponding condition described in Table 4-3. When one of the bits is set and the corresponding interrupt-enable bit in Control Register 1 is set to a one, the TMS34061 sends an interrupt request to the host processor by driving the INT output to its active-low level. The Status Register can be read, but not written to, by the host processor. A read of the Status Register will cause all of the bits to be reset to zero, thereby clearing the interrupt request, if one has been active.

In all modes of operation, the VSC sets an error flag to alert the host processor that it cannot complete an internally-requested cycle. For example, if a display-update cycle requested at the beginning of a horizontal blanking interval is not completed by the time the horizontal blanking interval ends, bit 1 of the Status Register is set to one. If the Error Interrupt Enable bit in Control Register 1 is also one, the VSC sends an interrupt request to the host processor. Similarly, if all DRAM-refresh cycles scheduled to occur during a scan line have not been completed by the start of the next horizontal blanking interval, bit 2 of the Status Register is set to one. Again, this causes the TMS34061 to send an interrupt request to the host processor if the

Error Interrupt Enable bit is one. When the host processor reads the Status Register, all three bits are cleared, thereby removing the interrupt request.

| BIT | FUNCTION                                                                                                                                                                       |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| В0  | Vertical Interrupt. A one in this bit indicates that the vertical interrupt condition has occurred.                                                                            |

| B1  | Display Error. A one in this bit Indicates that the TMS34061 was unable to perform a display-update cycle requested during the horizontal blanking interval.                   |

| B2  | Refresh Error. A one in this bit indicates that the TMS34061 was unable execute the designated number of cycles before the beginning of the next horizontal blanking interval. |

Table 4-3. Status Register Bit Definitions

#### 4.2.4 Vertical Interrupt Register

The contents of the 12-bit Vertical Interrupt Register are compared to the Vertical Counter. If these are equal and the vertical interrupt is enabled, then at the end of the current scan line the VSC sends an interrupt request to the host processor by driving the  $\overline{INT}$  pin active low. The high-to-low transition of  $\overline{INT}$  occurs one to two SYSCLK periods from the start of horizontal sync.  $\overline{INT}$  then remains active low until the host processor responds by reading the Status Register. An active RESET signal forces the Vertical Interrupt Register to >000. The contents of this register may be read or written to by the host processor.

# 4.3 CRT Control Registers

# 4.3.1 Display-Update Registers

The TMS34061 is designed to work with the TMS4161 Multiport VRAM, which contains both a 256-by-256 memory cell array and a 256-bit shift register whose contents are shifted out serially and transmitted to the CRT monitor. A typical bit-mapped graphics system may contain 16, 32, or more TMS4161 VRAMs. The video data to be transmitted to the CRT monitor during an active scan line is transferred from a selected row within the memory cell array to the shift register during the horizontal blanking interval preceding the scan line. The transfer (by means of a display-update cycle) is performed automatically by the VSC. The address output during each display-update cycle is programmed through the three Display-Update Registers shown in Figure 4-5, Figure 4-6, and Figure 4-7: Display Address, Display Address Update, and Display Address Start Registers. A fourth register, the Scan Line Counter, is used to count the number of horizontal scan lines output between successive display-update cycles.