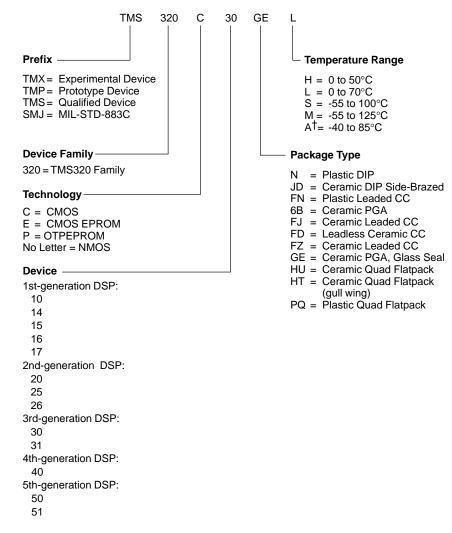

### TMS320C3x User's Guide

2558539-9721 revision J October 1994

# **TMS320C3x**

# User's Guide

1994

**Digital Signal Processing Products**

**9**94

#### **IMPORTANT NOTICE**

Texas Instruments (TI) reserves the right to make changes to its products or to discontinue any semiconductor product or service without notice, and advises its customers to obtain the latest version of relevant information to verify, before placing orders, that the information being relied on is current.

TI warrants performance of its semiconductor products and related software to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

Certain applications using semiconductor products may involve potential risks of death, personal injury, or severe property or environmental damage ("Critical Applications").

TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, INTENDED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT APPLICATIONS, DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS.

Inclusion of TI products in such applications is understood to be fully at the risk of the customer. Use of TI products in such applications requires the written approval of an appropriate TI officer. Questions concerning potential risk applications should be directed to TI through a local SC sales office.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards should be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance, customer product design, software performance, or infringement of patents or services described herein. Nor does TI warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used.

Copyright © 1994, Texas Instruments Incorporated

### Preface

### **Read This First**

#### About This Manual

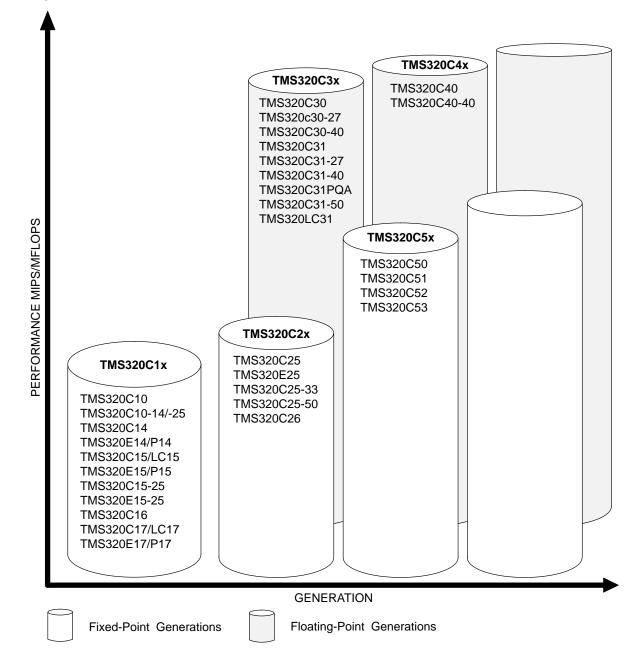

This user's guide serves as a reference book for the TMS320C3x generation of digital signal processors, which includes the TMS320C30, TMS320C30-27, TMS320C30-40, TMS320C31, TMS320C31-27, TMS320C31-40, TMS320C31-50, TMS320LC31, and TMS320C31PQA. Throughout the book, all references to 'C3x refer collectively to 'C30 and 'C31, and the TMS320C30 and TMS320C31 refer to all speed variations unless an exception is noted. This document provides information to assist managers and hardware/software engineers in application development.

#### How to Use This Book

This revision of the TMS320C3x User's Guide incorporates the following changes:

- Updated reference list of publications

- Improved description of repeat modes and interrupts in Chapter 6

- Description of power management modes in Chapter 6

- Improved description of serial ports and DMA coprocessor in Chapter 8

- Description of power management instructions in Chapter 10

- Description of low-power-mode interrupt interface in Chapter 12

- More detailed information on MPSD emulator interface, signal timings, and connections between emulator and target system

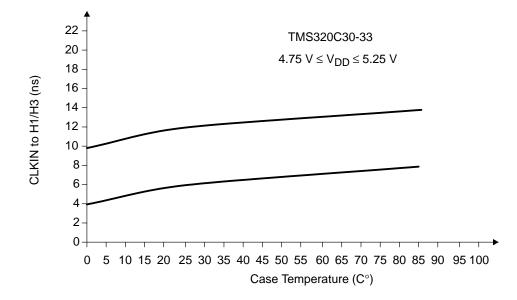

- Current timing specification in Chapter 13

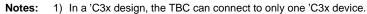

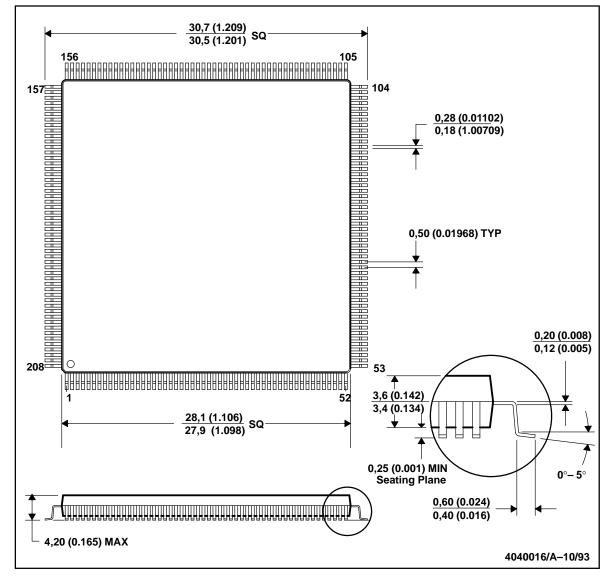

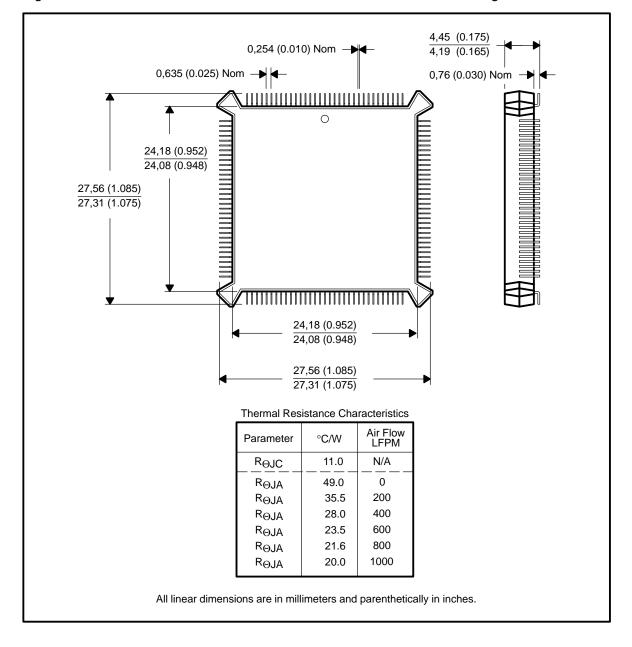

- TMS320C30PPM pinout, mechanical drawing, and timings in Chapter 13

- Development support description and device/tool part numbers in Appendix B

- Data sheet for current military versions of the 'C3x in Appendix E

Read This First

#### Notational Conventions

This document uses the following conventions:

Program listings, program examples, interactive displays, filenames, and symbol names are shown in a special font. Examples use a bold version of the special font for emphasis. Here is a sample program listing:

| 0014 | 0006 |      | .even  |    |   |

|------|------|------|--------|----|---|

| 0013 | 0005 | 0006 | .field | б, | 3 |

| 0012 | 0005 | 0003 | .field | 3, | 4 |

| 0011 | 0005 | 0001 | .field | 1, | 2 |

In syntax descriptions, the instruction, command, or directive is in a **bold** face font and parameters are in *italics*. Portions of a syntax that are in **bold face** should be entered as shown; portions of a syntax that are in *italics* describe the type of information that should be entered. Here is an example of a directive syntax:

.asect "section name", address

**.asect** is the directive. This directive has two parameters, indicated by *section name* and *address*. When you use .asect, the first parameter must be an actual section name, enclosed in double quotes; the second parameter must be an address.

❑ Square brackets ([ and ] ) identify an optional parameter. If you use an optional parameter, you specify the information within the brackets; you don't enter the brackets themselves. Here's an example of an instruction that has an optional parameter:

LALK 16-bit constant [, shift]

The **LALK** instruction has two parameters. The first parameter, *16-bit constant*, is required. The second parameter, *shift*, is optional. As this syntax shows, if you use the optional second parameter, you must precede it with a comma.

Square brackets are also used as part of the pathname specification for VMS pathnames; in this case, the brackets are actually part of the pathname (they are not optional).

□ Braces ( { and } ) indicate a list. The symbol | (read as *or*) separates items within the list. Here's an example of a list:

{ \* | \*+ | \*- }

This provides three choices: \*, \*+, or \*-.

Unless the list is enclosed in square brackets, you must choose one item from the list.

Some directives can have a varying number of parameters. For example, the .byte directive can have up to 100 parameters. The syntax for this directive is

**.byte** value<sub>1</sub> [, ... , value<sub>n</sub>]

This syntax shows that .byte must have at least one value parameter, but you have the option of supplying additional value parameters separated by commas.

#### Information About Cautions

This book may contain cautions and warnings.

A caution describes a situation that could potentially cause your system to behave unexpectedly.

| This is what a caution looks like. |  |

|------------------------------------|--|

|                                    |  |

|                                    |  |

The information in a caution is provided for your information. Please read each caution carefully.

#### **Related Documentation From Texas Instruments**

The following books describe the TMS320 floating-point devices and related support tools. To obtain a copy of any of these TI documents, call the Texas Instruments Literature Response Center at (800) 477–8924. When ordering, please identify the book by its title and literature number.

- **TMS320 Floating-Point DSP Assembly Language Tools User's Guide** (literature number SPRU035) describes the assembly language tools (assembler, linker, and other tools used to develop assembly language code), assembler directives, macros, common object file format, and symbolic debugging directives for the 'C3x and 'C4x generations of devices.

- **TMS320 Floating-Point DSP Optimizing C Compiler User's Guide** (literature number SPRU034) describes the TMS320 floating-point C compiler. This C compiler accepts ANSI standard C source code and produces TMS320 assembly language source code for the 'C3x and 'C4x generations of devices.

- **TMS320C3x C Source Debugger** (literature number SPRU053) describes the 'C3x debugger for the emulator, evaluation module, and simulator. This book discusses various aspects of the debugger interface, including window management, command entry, code execution, data management, and breakpoints. It also includes a tutorial that introduces basic debugger functionality.

- TMS320 Family Development Support Reference Guide (literature number SPRU011) describes the TMS320 family of digital signal processors and the various products that support it. This includes code-generation tools (compilers, assemblers, linkers, etc.) and system integration and debug tools (simulators, emulators, evaluation modules, etc.). This book also lists related documentation, outlines seminars and the university program, and provides factory repair and exchange information.

- **TMS320 Third-Party Support Reference Guide** (literature number SPRU052) alphabetically lists over 100 third parties who supply various products that serve the family of TMS320 digital signal processors, including software and hardware development tools, speech recognition, image processing, noise cancellation, modems, etc.

#### References

The publications in the following reference list contain useful information regarding functions, operations, and applications of digital signal processing (DSP). These books also provide other references to many useful technical papers. The reference list is organized into categories of general DSP, speech, image processing, and digital control theory and is alphabetized by author.

#### General Digital Signal Processing:

Antoniou, Andreas, *Digital Filters: Analysis and Design*. New York, NY: McGraw-Hill Company, Inc., 1979.

Bateman, A., and Yates, W., *Digital Signal Processing Design*. Salt Lake City, Utah: W. H. Freeman and Company, 1990.

Brigham, E. Oran, *The Fast Fourier Transform.* Englewood Cliffs, NJ: Prentice-Hall, Inc., 1974.

Burrus, C.S., and Parks, T.W., *DFT/FFT and Convolution Algorithms*. New York, NY: John Wiley and Sons, Inc., 1984.

Chassaing, R., and Horning, D., *Digital Signal Processing with the TMS320C25.* New York, NY: John Wiley and Sons, Inc., 1990.

*Digital Signal Processing Applications with the TMS320 Family, Vol. I.* Texas Instruments, 1986; Prentice-Hall, Inc., 1987. *Digital Signal Processing Applications with the TMS320 Family, Vol. II.* Texas Instruments, 1990; Prentice-Hall, Inc., 1990.

*Digital Signal Processing Applications with the TMS320 Family, Vol. III.* Texas Instruments, 1990; Prentice-Hall, Inc., 1990.

Gold, Bernard, and Rader, C.M., *Digital Processing of Signals*. New York, NY: McGraw-Hill Company, Inc., 1969.

Hamming, R.W., *Digital Filters*. Englewood Cliffs, NJ: Prentice-Hall, Inc., 1977.

Hutchins, B., and Parks, T., *A Digital Signal Processing Laboratory Using the TMS320C25*. Englewood Cliffs, NJ: Prentice-Hall, Inc., 1990.

IEEE ASSP DSP Committee (Editor), *Programs for Digital Signal Processing*. New York, NY: IEEE Press, 1979.

Jackson, Leland B., *Digital Filters and Signal Processing.* Hingham, MA: Kluwer Academic Publishers, 1986.

Jones, D.L., and Parks, T.W., *A Digital Signal Processing Laboratory Using the TMS32010.* Englewood Cliffs, NJ: Prentice-Hall, Inc., 1987.

Lim, Jae, and Oppenheim, Alan V. (Editors), *Advanced Topics in Signal Processing*. Englewood Cliffs, NJ: Prentice-Hall, Inc., 1988.

Morris, L. Robert, *Digital Signal Processing Software*. Ottawa, Canada: Carleton University, 1983.

Oppenheim, Alan V. (Editor), *Applications of Digital Signal Processing*. Englewood Cliffs, NJ: Prentice-Hall, Inc., 1978.

Oppenheim, Alan V., and Schafer, R.W., *Digital Signal Processing.* Englewood Cliffs, NJ: Prentice-Hall, Inc., 1975.

Oppenheim, Alan V., and Schafer, R.W., *Discrete-Time Signal Processing.* Englewood Cliffs, NJ: Prentice-Hall, Inc., 1989.

Oppenheim, Alan V., and Willsky, A.N., with Young, I.T., *Signals and Systems*. Englewood Cliffs, NJ: Prentice-Hall, Inc., 1983.

Parks, T.W., and Burrus, C.S., *Digital Filter Design.* New York, NY: John Wiley and Sons, Inc., 1987.

Rabiner, Lawrence R., and Gold, Bernard, *Theory and Application of Digital Signal Processing*. Englewood Cliffs, NJ: Prentice-Hall, Inc., 1975.

Treichler, J.R., Johnson, Jr., C.R., and Larimore, M.G., *Theory and Design of Adaptive Filters*. New York, NY: John Wiley and Sons, Inc., 1987.

#### Speech:

Gray, A.H., and Markel, J.D., *Linear Prediction of Speech*. New York, NY: Springer-Verlag, 1976.

Jayant, N.S., and Noll, Peter, *Digital Coding of Waveforms*. Englewood Cliffs, NJ: Prentice-Hall, Inc., 1984.

Papamichalis, Panos, *Practical Approaches to Speech Coding.* Englewood Cliffs, NJ: Prentice-Hall, Inc., 1987.

Parsons, Thomas., *Voice and Speech Processing.* New York, NY: McGraw Hill Company, Inc., 1987.

Rabiner, Lawrence R., and Schafer, R.W., *Digital Processing of Speech Signals.* Englewood Cliffs, NJ: Prentice-Hall, Inc., 1978.

Shaughnessy, Douglas., *Speech Communication.* Reading, MA: Addison-Wesley, 1987.

#### Image Processing:

Andrews, H.C., and Hunt, B.R., *Digital Image Restoration*. Englewood Cliffs, NJ: Prentice-Hall, Inc., 1977.

Gonzales, Rafael C., and Wintz, Paul, *Digital Image Processing.* Reading, MA: Addison-Wesley Publishing Company, Inc., 1977.

Pratt, William K., *Digital Image Processing*. New York, NY: John Wiley and Sons, 1978.

#### Multirate DSP:

Crochiere, R.E., and Rabiner, L.R., *Multirate Digital Signal Processing*. Englewood Cliffs, NJ: Prentice-Hall, Inc., 1983.

Vaidyanathan, P.P., *Multirate Systems and Filter Banks*. Englewood Cliffs, NJ: Prentice-Hall, Inc.

#### Digital Control Theory:

Dote, Y., *Servo Motor and Motion Control Using Digital Signal Processors*. Englewood Cliffs, NJ: Prentice-Hall, Inc., 1990.

Jacquot, R., *Modern Digital Control Systems.* New York, NY: Marcel Dekker, Inc., 1981.

Katz, P., *Digital Control Using Microprocessors*. Englewood Cliffs, NJ: Prentice-Hall, Inc., 1981.

Kuo, B.C., *Digital Control Systems.* New York, NY: Holt, Reinholt and Winston, Inc., 1980.

Moroney, P., *Issues in the Implementation of Digital Feedback Compensators.* Cambridge, MA: The MIT Press, 1983.

Phillips, C., and Nagle, H., *Digital Control System Analysis and Design.* Englewood Cliffs, NJ: Prentice-Hall, Inc., 1984.

#### Adaptive Signal Processing:

Haykin, S., *Adaptive Filter Theory.* Englewood Cliffs, NJ: Prentice-Hall, Inc., 1991.

Widrow, B., and Stearns, S.D. *Adaptive Signal Processing.* Englewood Cliffs, NJ: Prentice-Hall, Inc., 1985.

#### Array Signal Processing:

Haykin, S., Justice, J.H., Owsley, N.L., Yen, J.L., and Kak, A.C. *Array Signal Processing.* Englewood Cliffs, NJ: Prentice-Hall, Inc., 1985.

Hudson, J.E. *Adaptive Array Principles.* New York, NY: John Wiley and Sons, 1981.

Monzingo, R.A., and Miller, J.W. *Introduction to Adaptive Arrays.* New York, NY: John Wiley and Sons, 1980.

#### If You Need Assistance. . .

| If you want to                                                     | Do this                                                                                                                                                                                                                      |

|--------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Order Texas Instruments documentation                              | Call the TI Literature Response Center: (800) 477–8924                                                                                                                                                                       |

| Ask questions about product operation or report suspected problems | Call the DSP hotline:<br>(713) 274–2320<br>FAX: (713) 274–2324<br>Electronic Mail: 4389750@mcimail.com.<br>European fax line: +33–1–3070–1032                                                                                |

| Report mistakes in this document<br>or any other TI documentation  | Fill out and return the reader response card at<br>the end of this book, or send your comments to:<br>Texas Instruments Incorporated<br>Technical Publications Manager, MS 702<br>P.O. Box 1443<br>Houston, Texas 77251–1443 |

#### Trademarks

ABEL is a registered trademark of Data I/O Corporation. CodeView, MS, MS-DOS, MS-Windows, and Presentation Manager are trademarks of Microsoft Corp. DEC, Digital DX, Ultrix, VAX, and VMS and are trademarks of Digital Equipment Corp. HPGL is a registered trademark of Hewlett-Packard Co. Macintosh and MPW are trademarks of Apple Computer Corp. Micro Channel, OS/2, PC-DOS, and PGA are trademarks of IBM Corp. SPARC, Sun 3, Sun 4, Sun Workstation, SunView, and SunWindows are trademarks of Sun Microsystems, Inc.

UNIX is a registered trademark of UNIX Systems Laboratories, Inc.

х

### Contents

| 1 | A ger |          | <b>1-1</b> scription of the TMS320C30 and TMS320C31, their key features, and typical                 |

|---|-------|----------|------------------------------------------------------------------------------------------------------|

|   | 1.1   | Genera   | I Description                                                                                        |

|   | 1.2   |          | 0C30 Key Features 1-6                                                                                |

|   | 1.3   |          | 0C31 Key Features                                                                                    |

|   | 1.4   |          | Applications 1-10                                                                                    |

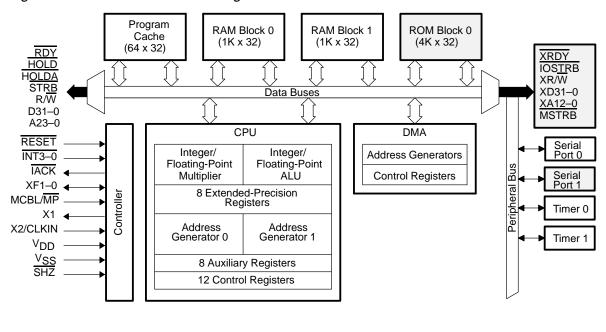

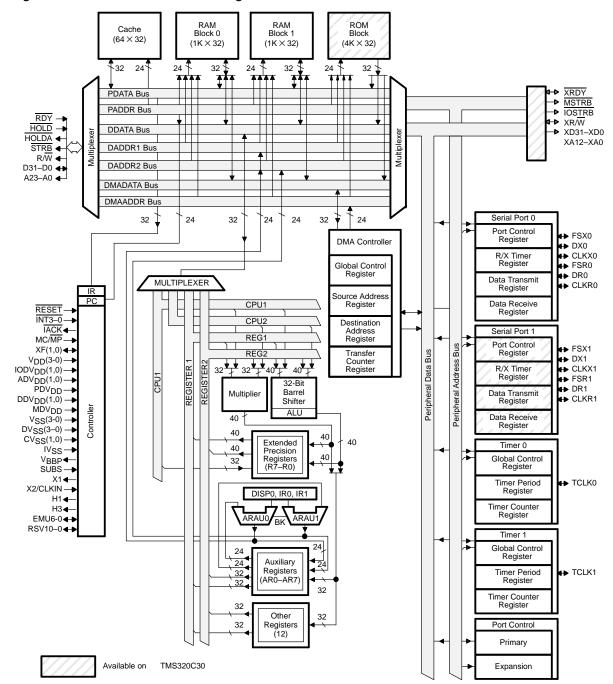

| 2 | TMS3  | 320C3x   | Architecture                                                                                         |

|   |       |          | ock diagram, TMS320C3x design description, hardware components, device<br>I instruction set summary. |

|   | 2.1   | Archite  | ctural Overview                                                                                      |

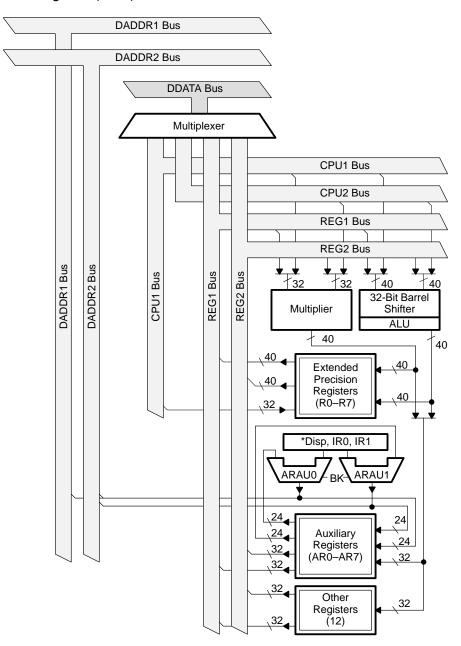

|   | 2.2   | Central  | Processing Unit (CPU) 2-4                                                                            |

|   |       | 2.2.1    | Multiplier                                                                                           |

|   |       | 2.2.2    | Arithmetic Logic Unit (ALU)                                                                          |

|   |       | 2.2.3    | Auxiliary Register Arithmetic Units (ARAUs)                                                          |

|   |       | 2.2.4    | CPU Register File 2-7                                                                                |

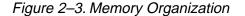

|   | 2.3   | Memor    | y Organization                                                                                       |

|   |       | 2.3.1    | RAM, ROM, and Cache                                                                                  |

|   |       | 2.3.2    | Memory Maps                                                                                          |

|   |       | 2.3.3    | Memory Addressing Modes                                                                              |

|   | 2.4   | Instruct | ion Set Summary                                                                                      |

|   | 2.5   |          | Bus Operation                                                                                        |

|   | 2.6   |          | I Instruction Set Summary                                                                            |

|   | 2.7   |          | al Bus Operation 2-26                                                                                |

|   |       | 2.7.1    | External Interrupts 2-26                                                                             |

|   |       | 2.7.2    | Interlocked-Instruction Signaling                                                                    |

|   | 2.8   | Periphe  | erals                                                                                                |

|   |       | 2.8.1    | Timers                                                                                               |

|   |       | 2.8.2    | Serial Ports                                                                                         |

|   | 2.9   | Direct I | Memory Access (DMA)                                                                                  |

|   | 2.10  |          | 0C30 and TMS320C31 Differences 2-30                                                                  |

|   | -     | 2.10.1   | Data/Program Bus Differences                                                                         |

|   |       |          | Serial-Port Differences                                                                              |

|   |       | 2.10.3   | Reserved Memory Locations 2-30                                                                       |

|   |       |          | •                                                                                                    |

|   | 2.11  | 2.10.5<br>2.10.6 | Effects on the IF and IE Interrupt Registers       2         User Program/Data ROM       2         Development Considerations       2         Integration       2 | 2-31<br>2-31 |

|---|-------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|

| 3 | Desci | ription of       | r <b>s, Memory, and Cache</b><br>f the registers in the CPU register file. Includes memory maps and explains<br>che architecture, algorithm, and control bits.    |              |

|   | 3.1   |                  | egister File                                                                                                                                                      | 3-2          |

|   | 0.1   | 3.1.1            | Extended-Precision Registers (R7–R0)                                                                                                                              |              |

|   |       | 3.1.2            | Auxiliary Registers (AR7–AR0)                                                                                                                                     |              |

|   |       | 3.1.3            | Data-Page Pointer (DP)                                                                                                                                            |              |

|   |       | 3.1.4            | Index Registers (IR0, IR1)                                                                                                                                        |              |

|   |       | 3.1.5            | Block Size Register (BK)                                                                                                                                          |              |

|   |       | 3.1.6            | System Stack Pointer (SP)                                                                                                                                         | 3-4          |

|   |       | 3.1.7            | Status Register (ST)                                                                                                                                              |              |

|   |       | 3.1.8            | CPU/DMA Interrupt Enable Register (IE)                                                                                                                            |              |

|   |       | 3.1.9            | CPU Interrupt Flag Register (IF)                                                                                                                                  |              |

|   |       | 3.1.10           | I/O Flags Register (IOF)                                                                                                                                          |              |

|   |       | 3.1.11           | Repeat-Count (RC) and Block-Repeat Registers (RS, RE)                                                                                                             |              |

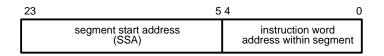

|   |       | 3.1.12           | Program Counter (PC)                                                                                                                                              |              |

|   | 3.2   |                  | Reserved Bits and Compatibility                                                                                                                                   |              |

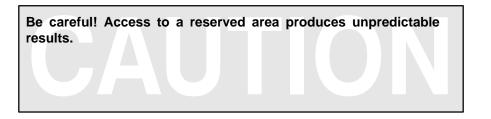

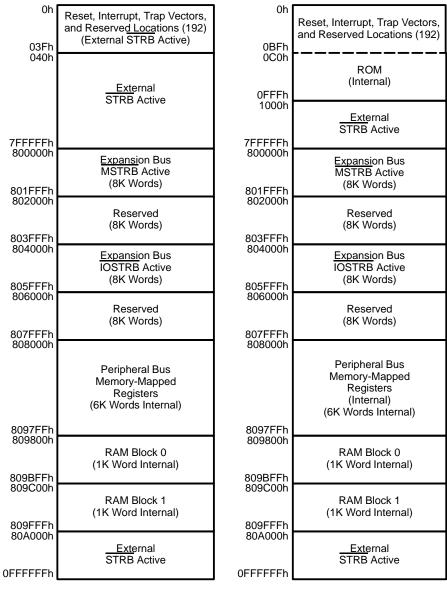

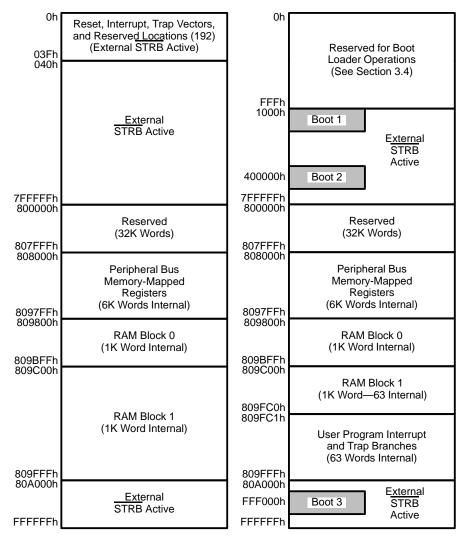

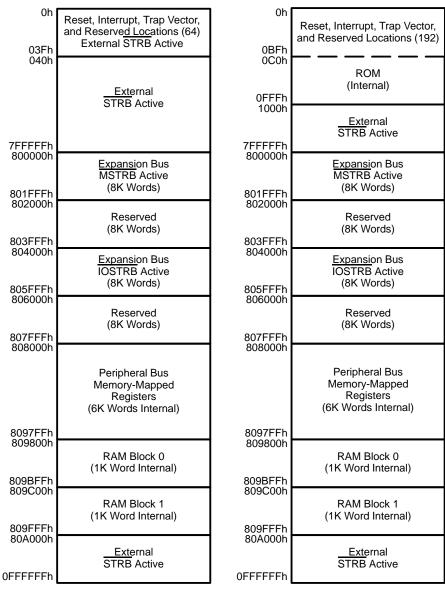

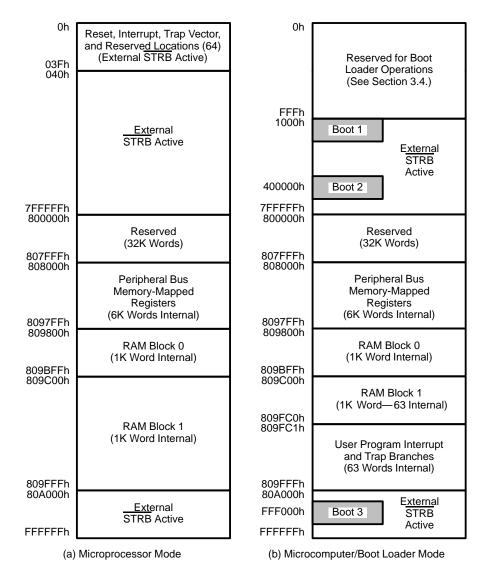

|   | 3.2   | 3.2.1            | TMS320C3x Memory Maps                                                                                                                                             |              |

|   |       | 3.2.1            | TMS320C31 Memory Maps                                                                                                                                             |              |

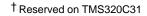

|   |       | 3.2.2            | Reset/Interrupt/Trap Vector Map                                                                                                                                   |              |

|   |       | 3.2.4            | Peripheral Bus Map                                                                                                                                                |              |

|   | 3.3   |                  | tion Cache                                                                                                                                                        |              |

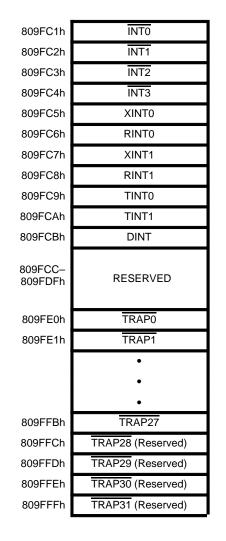

|   | 0.0   | 3.3.1            | Cache Architecture                                                                                                                                                |              |

|   |       | 3.3.2            | Cache Algorithm                                                                                                                                                   |              |

|   |       | 3.3.3            | Cache Control Bits                                                                                                                                                |              |

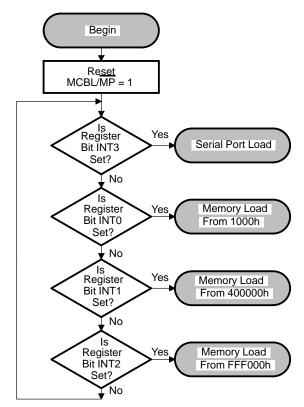

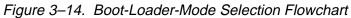

|   | 3.4   | Using t          | he TMS320C31 Boot Loader                                                                                                                                          | 3-26         |

|   |       | 3.4.1            | Boot-Loader Operations                                                                                                                                            | 3-26         |

|   |       | 3.4.2            | Invoking the Boot Loader                                                                                                                                          | 3-26         |

|   |       | 3.4.3            | Mode Selection                                                                                                                                                    |              |

|   |       | 3.4.4            | External Memory Loading                                                                                                                                           |              |

|   |       | 3.4.5            | Examples of External Memory Loads                                                                                                                                 |              |

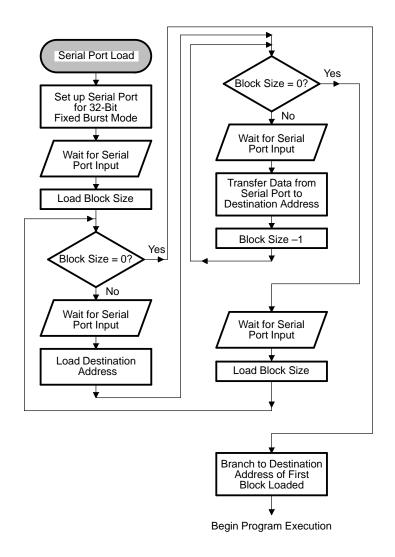

|   |       | 3.4.6            | Serial-Port Loading                                                                                                                                               |              |

|   |       | 3.4.7            | Interrupt and Trap-Vector Mapping                                                                                                                                 |              |

|   |       | 3.4.8            | Precautions                                                                                                                                                       |              |

| 4 |       |                  | and Floating-Point Operation                                                                                                                                      |              |

|   |       |                  | of signed and unsigned integer and floating-point formats. Discussion of multiplication, addition, subtraction, normalization, rounding, and conversions.         | :            |

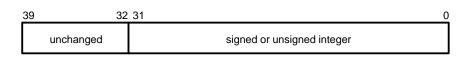

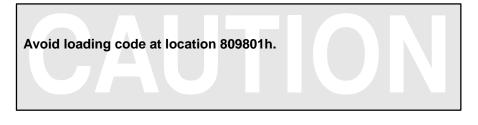

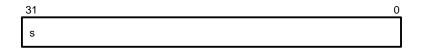

|   | 4.1   | Integer          | Formats                                                                                                                                                           | 4-2          |

|   |       | 4.1.1            | Short-Integer Format                                                                                                                                              | 4-2          |

|   |       | 4.1.2            | Single-Precision Integer Format                                                                                                                                   | 4-2          |

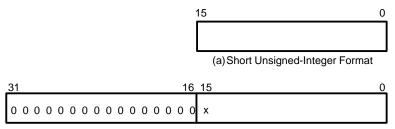

|   | 4.2   | -         | ed-Integer Formats                                                            |     |

|---|-------|-----------|-------------------------------------------------------------------------------|-----|

|   |       | 4.2.1     | Short Unsigned-Integer Format                                                 |     |

|   |       | 4.2.2     | Single-Precision Unsigned-Integer Format                                      |     |

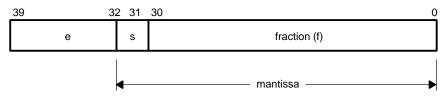

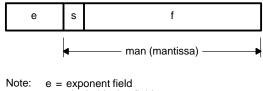

|   | 4.3   |           | g-Point Formats                                                               |     |

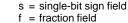

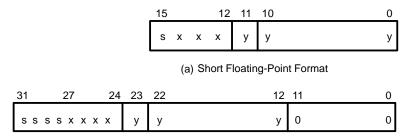

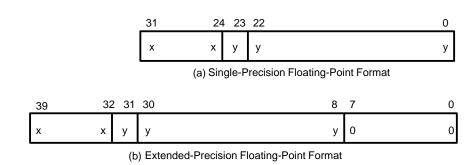

|   |       | 4.3.1     | Short Floating-Point Format                                                   |     |

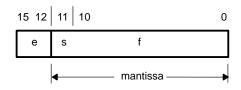

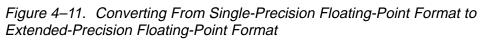

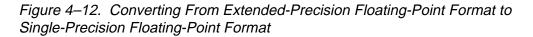

|   |       | 4.3.2     | Single-Precision Floating-Point Format                                        |     |

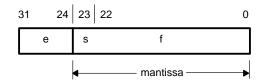

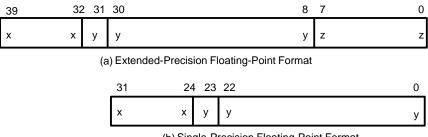

|   |       | 4.3.3     | Extended-Precision Floating-Point Format                                      |     |

|   |       | 4.3.4     | Conversion Between Floating-Point Formats                                     | 4-8 |

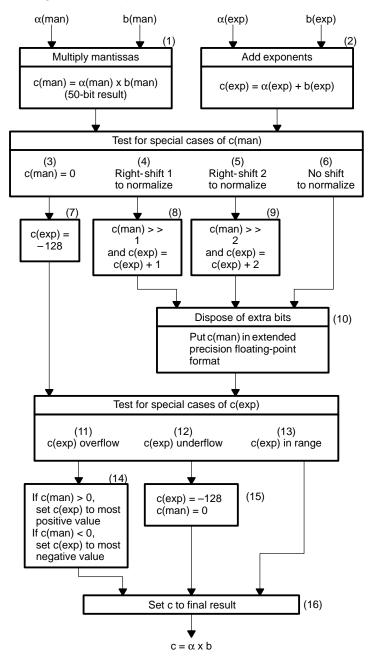

|   | 4.4   | Floating  | g-Point Multiplication                                                        | -10 |

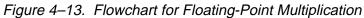

|   | 4.5   | Floating  | g-Point Addition and Subtraction 4                                            | -14 |

|   | 4.6   | Norma     | ization Using the NORM Instruction 4                                          | -18 |

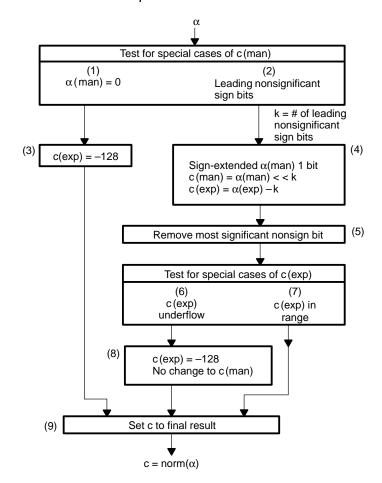

|   | 4.7   | Roundi    | ng: The RND Instruction 4                                                     | -20 |

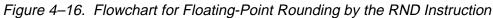

|   | 4.8   | Floating  | g-Point-to-Integer Conversion 4                                               | -22 |

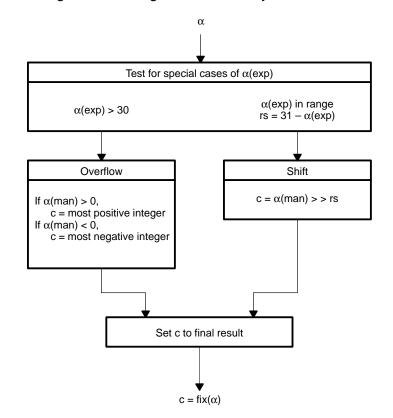

|   | 4.9   | Integer   | -to-Floating-Point Conversion 4                                               | -24 |

| 5 | Addro | essing    |                                                                               | 5-1 |

|   | Opera | ation, en | coding, and implementation of addressing modes. Format descriptions. System   |     |

|   | stack | manage    | ement.                                                                        |     |

|   | 5.1   | Types of  | of Addressing                                                                 |     |

|   |       | 5.1.1     | Register Addressing                                                           |     |

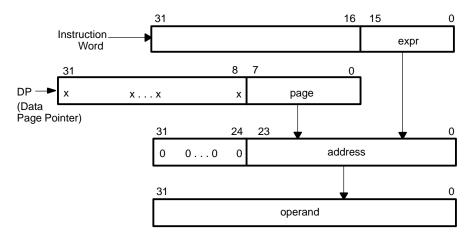

|   |       | 5.1.2     | Direct Addressing                                                             | 5-4 |

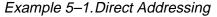

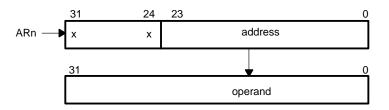

|   |       | 5.1.3     | Indirect Addressing                                                           | 5-5 |

|   |       | 5.1.4     | Short-Immediate Addressing 5                                                  | -16 |

|   |       | 5.1.5     | Long-Immediate Addressing 5                                                   | -17 |

|   |       | 5.1.6     | PC-Relative Addressing 5                                                      | -17 |

|   | 5.2   | Groups    | of Addressing Modes                                                           | -19 |

|   |       | 5.2.1     | General Addressing Modes 5                                                    | -19 |

|   |       | 5.2.2     | Three-Operand Addressing Modes 5                                              | -20 |

|   |       | 5.2.3     | Parallel Addressing Modes 5                                                   | -21 |

|   |       | 5.2.4     | Conditional-Branch Addressing Modes 5                                         | -23 |

|   | 5.3   | Circula   | r Addressing                                                                  | -24 |

|   | 5.4   | Bit-Rev   | versed Addressing                                                             | -29 |

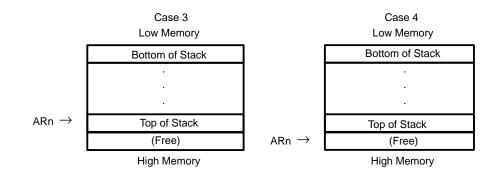

|   | 5.5   |           | and User Stack Management 5                                                   |     |

|   |       | 5.5.1     | System Stack Pointer 5                                                        |     |

|   |       | 5.5.2     | Stacks                                                                        |     |

|   |       | 5.5.3     | Queues                                                                        |     |

| 6 | Prog  | ram Flov  | w Control                                                                     | 6-1 |

| - | Softw |           | trol of program flow with repeat modes and branching. Interlocked operations. |     |

|   | 6.1   | Repeat    | Modes                                                                         | 6-2 |

|   |       | 6.1.1     | Repeat-Mode Control Bits                                                      |     |

|   |       | 6.1.2     | Repeat-Mode Operation                                                         |     |

|   |       | 6.1.3     | RPTB Instruction                                                              |     |

|   |       |           |                                                                               |     |

Contents xiii

#### Contents

|   |                                                                                  | 6.1.4                                                                                                                                                                                         | RPTS Instruction                                                                                                                                                                                                                                                                                                                                                                                                                                                | 6-5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|---|----------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   |                                                                                  | 6.1.5                                                                                                                                                                                         | Repeat-Mode Restrictions                                                                                                                                                                                                                                                                                                                                                                                                                                        | 6-6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|   |                                                                                  | 6.1.6                                                                                                                                                                                         | RC Register Value After Repeat Mode Completes                                                                                                                                                                                                                                                                                                                                                                                                                   | 6-6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|   |                                                                                  | 6.1.7                                                                                                                                                                                         | Nested Block Repeats                                                                                                                                                                                                                                                                                                                                                                                                                                            | 6-7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|   | 6.2                                                                              | Delaye                                                                                                                                                                                        | d Branches                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 6-8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

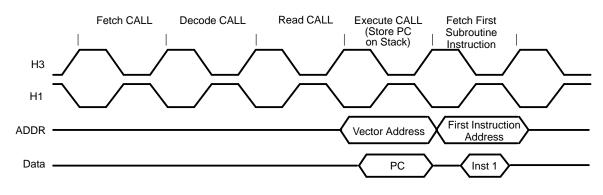

|   | 6.3                                                                              | Calls, 7                                                                                                                                                                                      | Traps, and Returns                                                                                                                                                                                                                                                                                                                                                                                                                                              | . 6-10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|   | 6.4                                                                              | Interloc                                                                                                                                                                                      | cked Operations                                                                                                                                                                                                                                                                                                                                                                                                                                                 | . 6-12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|   | 6.5                                                                              | Reset (                                                                                                                                                                                       | Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                       | . 6-18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|   | 6.6                                                                              | Interrup                                                                                                                                                                                      | pts                                                                                                                                                                                                                                                                                                                                                                                                                                                             | . 6-23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|   |                                                                                  | 6.6.1                                                                                                                                                                                         | Interrupt Vector Table                                                                                                                                                                                                                                                                                                                                                                                                                                          | . 6-23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|   |                                                                                  | 6.6.2                                                                                                                                                                                         | Interrupt Prioritization                                                                                                                                                                                                                                                                                                                                                                                                                                        | . 6-25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|   |                                                                                  | 6.6.3                                                                                                                                                                                         | Interrupt Control Bits                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|   |                                                                                  | 6.6.4                                                                                                                                                                                         | Interrupt Processing                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|   |                                                                                  | 6.6.5                                                                                                                                                                                         | CPU Interrupt Latency                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|   |                                                                                  | 6.6.6                                                                                                                                                                                         | CPU/DMA Interaction                                                                                                                                                                                                                                                                                                                                                                                                                                             | . 6-30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|   |                                                                                  | 6.6.7                                                                                                                                                                                         | TMS320C3x Interrupt Considerations                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|   |                                                                                  | 6.6.8                                                                                                                                                                                         | TMS320C30 Interrupt Considerations                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|   |                                                                                  | 6.6.9                                                                                                                                                                                         | Prioritization and Control                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|   | 6.7                                                                              |                                                                                                                                                                                               | 20LC31 Power Management Modes                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|   |                                                                                  | 6.7.1                                                                                                                                                                                         | IDLE2                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|   |                                                                                  | 6.7.2                                                                                                                                                                                         | LOPOWER                                                                                                                                                                                                                                                                                                                                                                                                                                                         | . 6-38                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|   |                                                                                  |                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|   |                                                                                  | ammabl<br>Externa<br>7.1.1<br>7.1.2<br>Externa                                                                                                                                                | of primary and expansion interfaces. External interface timing diagrar<br>le wait-states and bank switching.<br>al Interface Control Registers<br>Primary-Bus Control Register<br>Expansion-Bus Control Register<br>al Interface Timing<br>Primary-Bus Cycles                                                                                                                                                                                                   | 7-2<br>7-3<br>7-5<br>7-6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

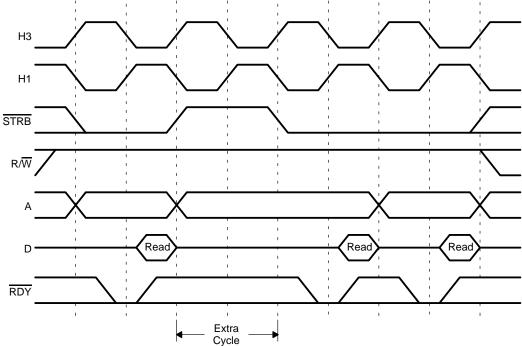

|   | Progr<br>7.1                                                                     | ammabl<br>Externa<br>7.1.1<br>7.1.2<br>Externa<br>7.2.1                                                                                                                                       | le wait-states and bank switching.<br>al Interface Control Registers<br>Primary-Bus Control Register<br>Expansion-Bus Control Register<br>al Interface Timing<br>Primary-Bus Cycles                                                                                                                                                                                                                                                                             | 7-2<br>7-3<br>7-5<br>7-6<br>7-6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

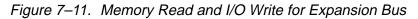

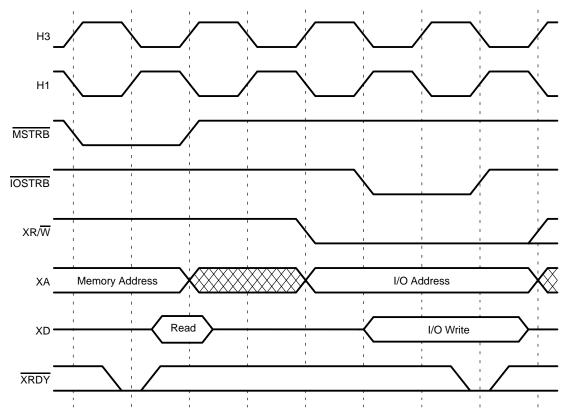

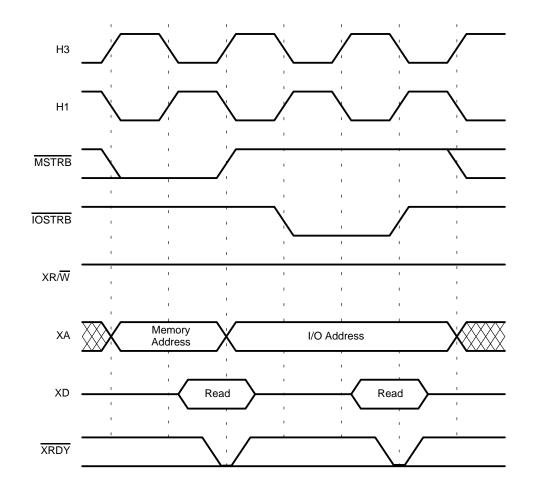

|   | Progr.<br>7.1<br>7.2                                                             | ammabl<br>Externa<br>7.1.1<br>7.1.2<br>Externa<br>7.2.1<br>7.2.2                                                                                                                              | le wait-states and bank switching.<br>al Interface Control Register<br>Primary-Bus Control Register<br>Expansion-Bus Control Register<br>al Interface Timing<br>Primary-Bus Cycles<br>Expansion-Bus I/O Cycles                                                                                                                                                                                                                                                  | 7-2<br>7-3<br>7-5<br>7-6<br>7-6<br>7-11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

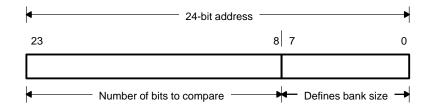

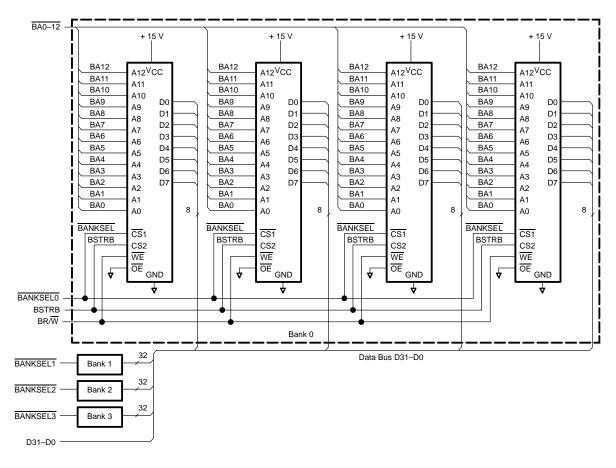

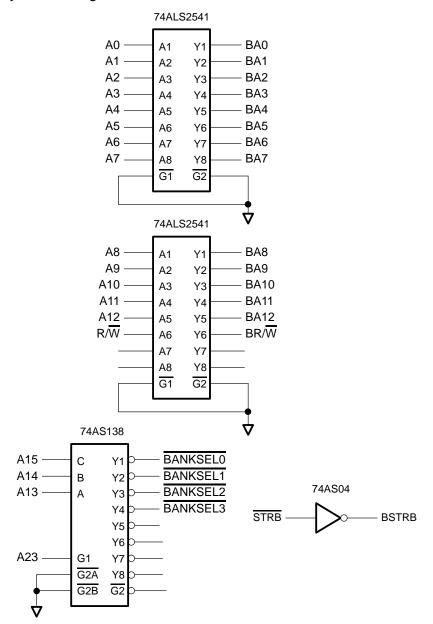

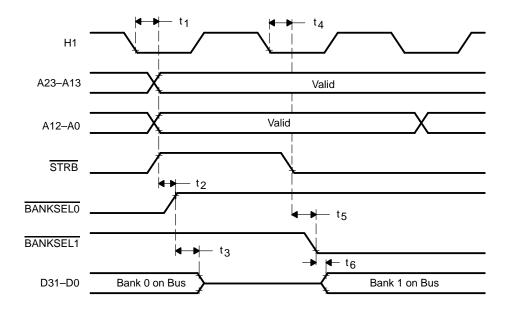

|   | Progr<br>7.1                                                                     | Ammable<br>Externa<br>7.1.1<br>7.1.2<br>Externa<br>7.2.1<br>7.2.2<br>Program                                                                                                                  | le wait-states and bank switching.<br>al Interface Control Registers<br>Primary-Bus Control Register<br>Expansion-Bus Control Register<br>al Interface Timing<br>Primary-Bus Cycles<br>Expansion-Bus I/O Cycles<br>mmable Wait States                                                                                                                                                                                                                           | 7-2<br>7-3<br>7-5<br>7-6<br>7-6<br>7-11<br>7-28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

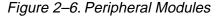

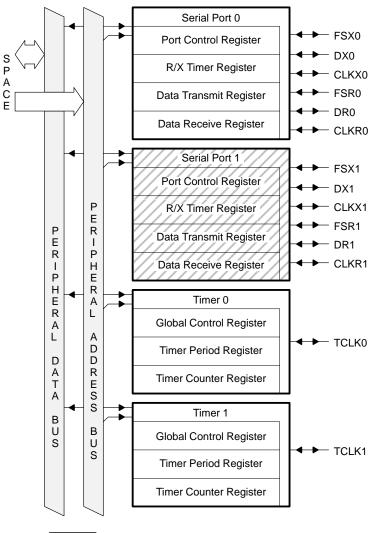

| 8 | Progr.<br>7.1<br>7.2<br>7.3<br>7.4<br>Perip                                      | Externa<br>7.1.1<br>7.1.2<br>Externa<br>7.2.1<br>7.2.2<br>Program<br>Program<br>herals.                                                                                                       | le wait-states and bank switching.<br>al Interface Control Register<br>Primary-Bus Control Register<br>Expansion-Bus Control Register<br>al Interface Timing<br>Primary-Bus Cycles<br>Expansion-Bus I/O Cycles                                                                                                                                                                                                                                                  | 7-2<br>7-3<br>7-5<br>7-6<br>7-6<br>7-11<br>7-28<br>7-30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 8 | Progr.<br>7.1<br>7.2<br>7.3<br>7.4<br>Perip                                      | Externa<br>7.1.1<br>7.1.2<br>Externa<br>7.2.1<br>7.2.2<br>Prograd<br>Prograd<br>herals .                                                                                                      | le wait-states and bank switching.<br>al Interface Control Registers<br>Primary-Bus Control Register<br>Expansion-Bus Control Register<br>al Interface Timing<br>Primary-Bus Cycles<br>Expansion-Bus I/O Cycles<br>mmable Wait States<br>mmable Bank Switching                                                                                                                                                                                                  | 7-2<br>7-3<br>7-6<br>7-6<br>7-6<br>7-6<br>7-30<br>8-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 8 | Progr.<br>7.1<br>7.2<br>7.3<br>7.4<br><b>Perip</b><br><i>Descr</i>               | Externa<br>7.1.1<br>7.1.2<br>Externa<br>7.2.1<br>7.2.2<br>Prograd<br>Prograd<br>herals .                                                                                                      | le wait-states and bank switching.<br>al Interface Control Register<br>Primary-Bus Control Register<br>Expansion-Bus Control Register<br>al Interface Timing<br>Primary-Bus Cycles<br>Expansion-Bus I/O Cycles<br>mmable Wait States<br>mmable Bank Switching                                                                                                                                                                                                   | 7-2<br>7-3<br>7-5<br>7-6<br>7-6<br>7-6<br>7-30<br>8-1<br>8-2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 8 | Progr.<br>7.1<br>7.2<br>7.3<br>7.4<br><b>Perip</b><br><i>Descr</i>               | Externa<br>7.1.1<br>7.1.2<br>Externa<br>7.2.1<br>7.2.2<br>Prograd<br>Prograd<br>herals .<br>ription of                                                                                        | le wait-states and bank switching.<br>al Interface Control Register                                                                                                                                                                                                                                                                                                                                                                                             | 7-2<br>7-3<br>7-5<br>7-6<br>7-6<br>7-6<br>7-6<br>7-6<br>7-30<br>7-30<br>8-2<br>8-2<br>8-3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

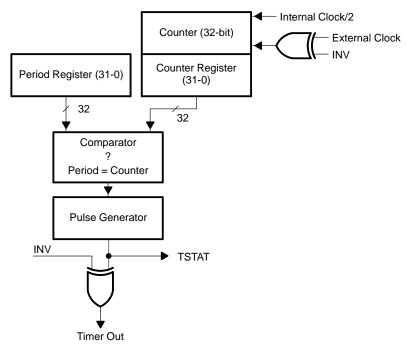

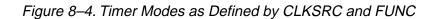

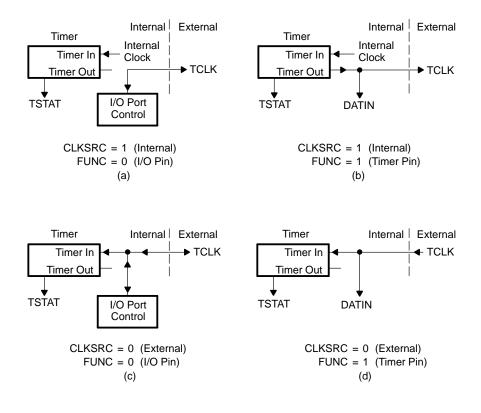

| 8 | Progr.<br>7.1<br>7.2<br>7.3<br>7.4<br><b>Perip</b><br><i>Descr</i>               | Ammable<br>Externa<br>7.1.1<br>7.1.2<br>Externa<br>7.2.1<br>7.2.2<br>Program<br>Program<br>herals .<br>ription of<br>Timers<br>8.1.1<br>8.1.2<br>8.1.3                                        | le wait-states and bank switching.<br>al Interface Control Registers<br>Primary-Bus Control Register<br>Expansion-Bus Control Register<br>al Interface Timing<br>Primary-Bus Cycles<br>Expansion-Bus I/O Cycles<br>mmable Wait States<br>mmable Bank Switching<br>f the DMA controller, timers, and serial ports.<br>Timer Global-Control Register<br>Timer Period and Counter Registers<br>Timer Pulse Generation                                              | 7-2<br>7-3<br>7-5<br>7-6<br>7-6<br>7-6<br>7-6<br>7-6<br>7-6<br>7-6<br>7-6<br>7-6<br>7-6<br>7-6<br>7-6<br>7-6<br>7-6<br>7-6<br>7-6<br>7-6<br>7-6<br>7-6<br>7-6<br>7-6<br>7-6<br>7-6<br>7-6<br>7-6<br>7-6<br>7-6<br>7-6<br>7-6<br>7-6<br>7-6<br>7-6<br>7-6<br>7-8<br>7-8<br>7-8<br>7-8<br>7-8<br>7-8<br>7-8<br>7-8<br>7-8<br>7-8<br>7-8<br>7-8<br>7-8<br>7-8<br>7-8<br>7-8<br>7-8<br>7-8<br>7-8<br>7-8<br>7-8<br>7-8<br>7-8<br>7-8<br>7-8<br>7-8<br>7-8<br>7-8<br>7-8<br>7-8<br>7-8<br>7-8<br>7-8<br>7-8<br>7-8<br>8-1<br>8-3<br>8-8<br>8-8<br>8-8<br>8-8<br>8-8<br>8-8<br>8-8<br>8-8 |

| 8 | Progr.<br>7.1<br>7.2<br>7.3<br>7.4<br><b>Perip</b><br><i>Descr</i>               | Ammable<br>Externa<br>7.1.1<br>7.1.2<br>Externa<br>7.2.1<br>7.2.2<br>Program<br>Program<br>herals .<br>ription of<br>Timers<br>8.1.1<br>8.1.2<br>8.1.3<br>8.1.4                               | le wait-states and bank switching.<br>al Interface Control Registers<br>Primary-Bus Control Register<br>Expansion-Bus Control Register<br>al Interface Timing<br>Primary-Bus Cycles<br>Expansion-Bus I/O Cycles<br>mmable Wait States<br>mmable Bank Switching<br>f the DMA controller, timers, and serial ports.<br>Timer Global-Control Register<br>Timer Period and Counter Registers<br>Timer Pulse Generation<br>Timer Operation Modes                     | 7-2<br>7-3<br>7-5<br>7-6<br>7-6<br>7-6<br>7-30<br>7-30<br>8-1<br>8-2<br>8-3<br>8-8<br>8-8<br>8-8<br>8-10                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 8 | Progr.<br>7.1<br>7.2<br>7.3<br>7.4<br><b>Perip</b><br><i>Descr</i>               | ammable<br>Externa<br>7.1.1<br>7.1.2<br>Externa<br>7.2.1<br>7.2.2<br>Prograd<br>Prograd<br>herals .<br>fiption of<br>Timers<br>8.1.1<br>8.1.2<br>8.1.3<br>8.1.4<br>8.1.5                      | le wait-states and bank switching.<br>al Interface Control Registers<br>Primary-Bus Control Register<br>Expansion-Bus Control Register<br>al Interface Timing<br>Primary-Bus Cycles<br>Expansion-Bus I/O Cycles<br>mmable Wait States<br>mmable Bank Switching<br>f the DMA controller, timers, and serial ports.<br>Timer Global-Control Register<br>Timer Period and Counter Registers<br>Timer Pulse Generation<br>Timer Operation Modes<br>Timer Interrupts | 7-2<br>7-3<br>7-5<br>7-6<br>7-6<br>7-6<br>7-6<br>7-30<br>7-30<br>8-1<br>8-2<br>8-3<br>8-8<br>8-8<br>8-8<br>8-8<br>8-10<br>8-11                                                                                                                                                                                                                                                                                                                                                                                                                                                      |