| SECTION I    | PAGE<br>3<br>5-9<br>10-12 | <br> | INDEX<br>PART NUMBER<br>FUNCTIONAL<br>CROSS REFERENCE                                             |              |

|--------------|---------------------------|------|---------------------------------------------------------------------------------------------------|--------------|

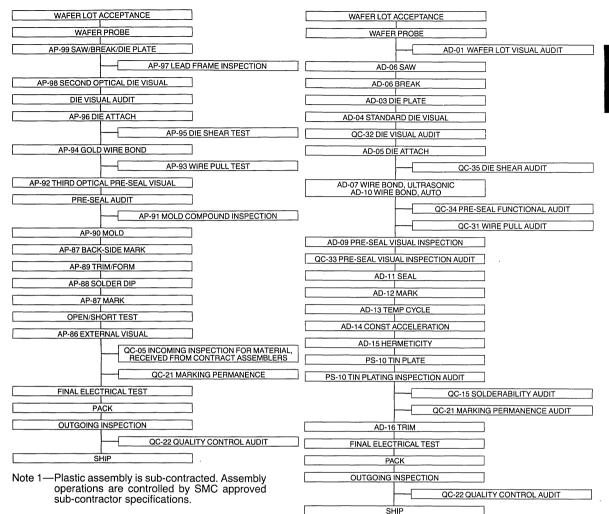

| SECTION II   | 17-24                     |      | GENERAL INFORMATION<br>INTRODUCTION<br>CUSTOM CAPABILITIES<br>QUALITY ASSURANCE & QUALITY CONTROL |              |

| SECTION III  | 33-262                    |      | DATA COMMUNICATION PRODUCTS                                                                       |              |

| SECTION IV   | 263-290                   |      | BAUD RATE GENERATOR                                                                               |              |

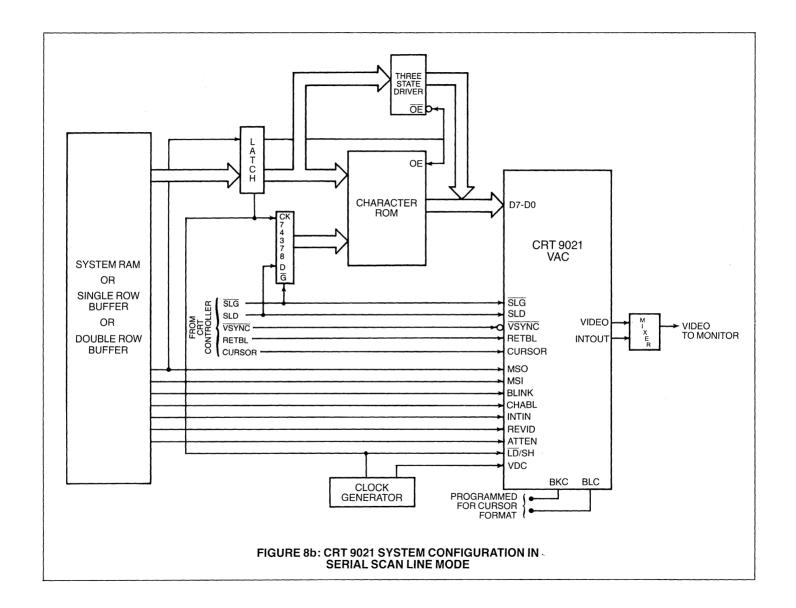

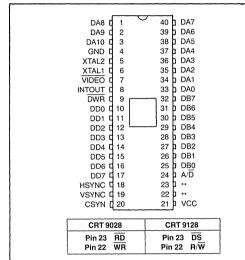

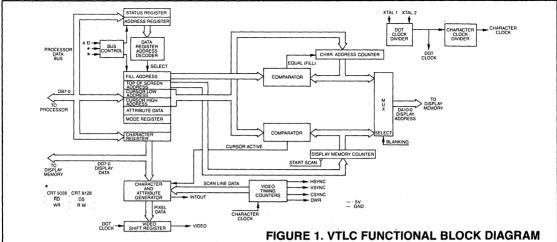

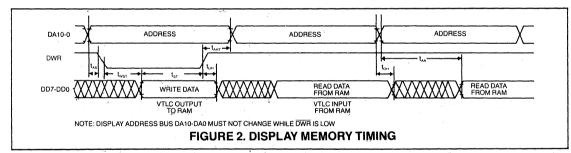

| SECTION V    | 291-456                   | •••• | CRT DISPLAY                                                                                       | ABLE         |

| SECTION VI   | 457-662                   |      | FLOPPY DISK/HARD DISK                                                                             | of<br>Itents |

| SECTION VII  | 663-678                   | •••• | KEYBOARD ENCODER                                                                                  |              |

| SECTION VIII | 679-688                   | •••• | SHIFT REGISTER                                                                                    |              |

| SECTION IX   | 689-734                   |      | MICROPROCESSOR PRODUCTS                                                                           |              |

| SECTION X    | 735-742                   |      | ORDERING INFORMATION                                                                              |              |

TA ( CON

## PART NUMBER INDEX

| PART NUMBER | PAGE | PART NUMBER   | PAGE |

|-------------|------|---------------|------|

| COM 1553A   | 35   | CRT 5057      | 293  |

| COM 1553B   | 51   | CRT 7004      | 303  |

| COM 1671    | 67   | CRT 7220      | 309  |

| COM 1863    | 83   | CRT 8002      | 333  |

| COM 2017    | 91   | CRT 8002H     | 347  |

| COM 2502    | 91   | CRT 8021      | 355  |

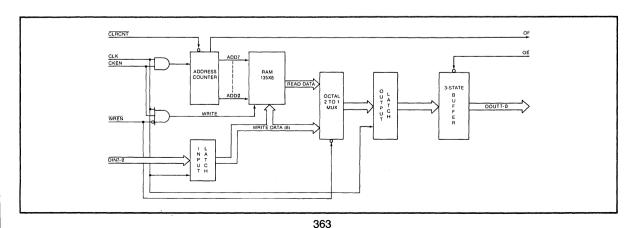

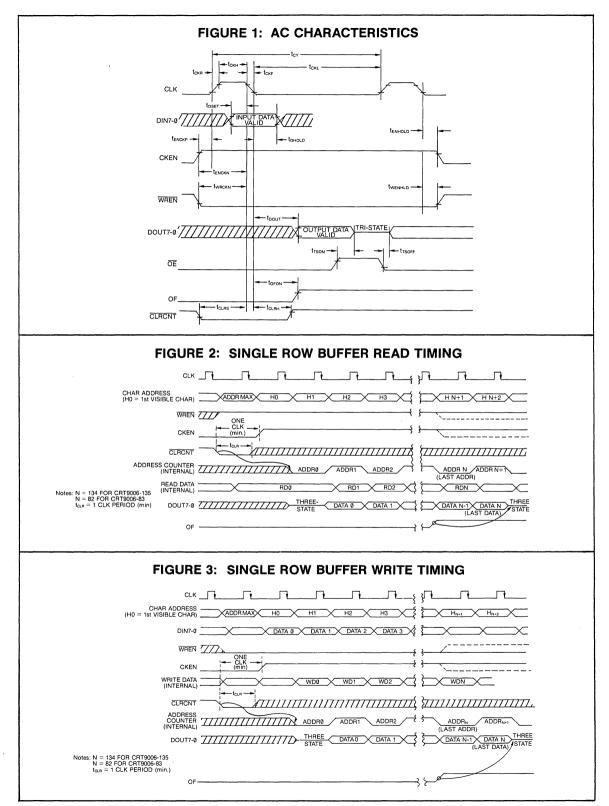

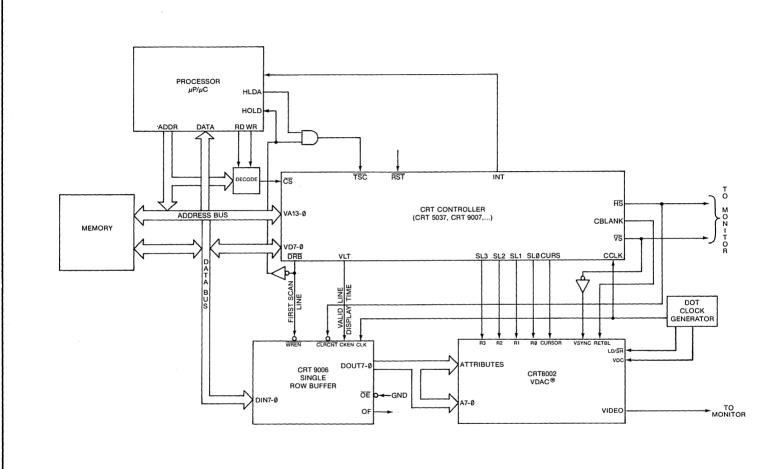

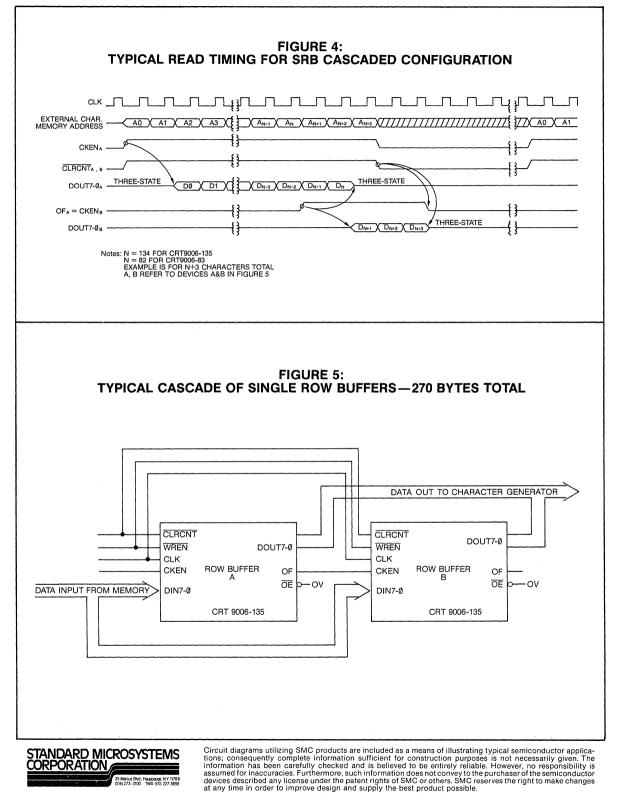

| COM 2601    | 99   | CRT 9006      | 363  |

| COM 2651    | 107  | CRT 9007      | 369  |

| COM 2661    | 119  | CRT 9021      | 389  |

| COM 5016/T  | 265  | CRT 9028      | 401  |

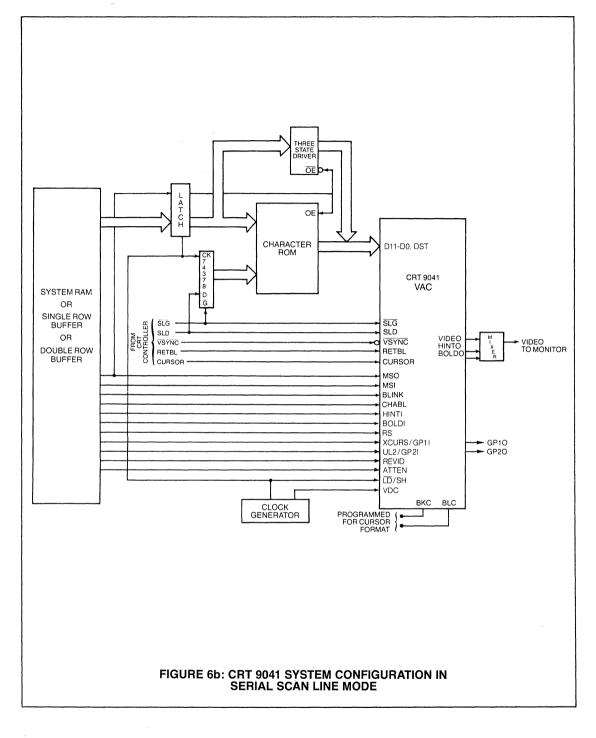

| COM 5025    | 131  | CRT 9041      | 417  |

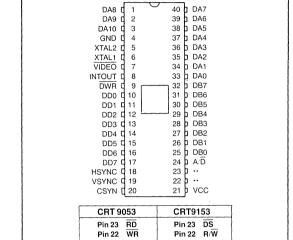

| COM 5026/T  | 267  | CRT 9053      | 433  |

| COM 5036/T  | 265  | CRT 9128      | 401  |

| COM 5046/T  | 267  | CRT 9153      | 433  |

| COM 52C50   | 143  | CRT 9212      | 449  |

| COM 7210    | 145  | CRT 97C11     | 455  |

| COM 78808   | 157  | FDC 765A      | 459  |

| COM 8004    | 173  | FDC 1791      | 477  |

| COM 8017    | 179  | FDC 1793      | 477  |

| COM 8018    | 83   | FDC 1795      | 477  |

| COM 8046/T  | 273  | FDC 1797      | 477  |

| COM 8116/T  | 275  | FDC 7265      | 459  |

| COM 81C17   | 187  | FDC 72C65     | 475  |

| COM 8126/T  | 277  | FDC 72C66     | 475  |

| COM 8136/T  | 275  | FDC 9216/B    | 493  |

| COM 8146/T  | 277  | FDC 9229T/BT  | 497  |

| COM 8156/T  | 285  | FDC 92C36/B   | 505  |

| COM 81C66/T | 289  | FDC 9238/B/BT | 509  |

| COM 8251A   | 189  | FDC 9239/B/BT | 513  |

| COM 8502    | 179  | FDC 92C49     | 521  |

| COM 9004    | 205  | FDC 9266      | 523  |

| COM 9026    | 213  | FDC 9267      | 539  |

| COM 9032    | 229  | FDC 9268      | 555  |

| COM 9046    | 235  | FDC 9791      | 557  |

| COM 90C56   | 239  | FDC 9793      | 557  |

| COM 90C57   | 241  | FDC 9795      | 557  |

| COM 9064    | 243  | FDC 9797      | 557  |

| CRT 5027    | 293  | HDC 1100-01   | 573  |

| CRT 5037    | 293  | HDC 1100-12   | 577  |

| CRT 5047    | 301  | HDC 1100-03   | 581  |

|             |      |               |      |

SECTION I

| PART NUMBER | PAGE | PART NUMBER | PAGE |

|-------------|------|-------------|------|

| HDC 1100-04 | 585  | KR 9600     | 665  |

| HDC 1100-05 | 589  | KR 9601     | 665  |

| HDC 7261    | 593  | KR 9602     | 665  |

| HDC 9223    | 595  | MPU 800     | 691  |

| HDC 9224    | 599  | MPU 810A    | 715  |

| HDC 9225    | 635  | MPU 830     | 727  |

| HDC 9226    | 647  | MPU 831     | 727  |

| HDC 9227    | 655  | SR 5015     | 681  |

| HYC 9058    | 251  | SR 5017     | 685  |

| HYC 9068    | 257  | SR 5018     | 685  |

| HYC 9078    | 261  |             |      |

# FUNCTIONAL INDEX

## **Data Communication Products**

| Part<br>Number         | Name                                 | Description                                                                                                                                                   | Max<br>Baud Rate               | Power<br>Supplies | Package           | Page    |

|------------------------|--------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|-------------------|-------------------|---------|

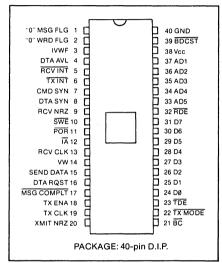

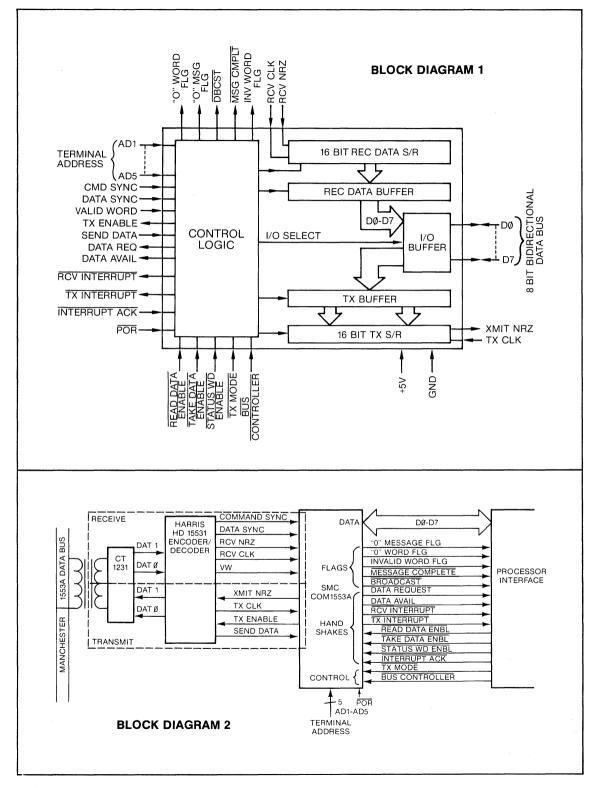

| COM 1553A              | MIL-STD-<br>1553A<br>Controller      | MIL-STD-1553A Manchester Interface<br>Controller                                                                                                              | 1 MB                           | +5                | 40 DIP/<br>44SMT  | 35-50   |

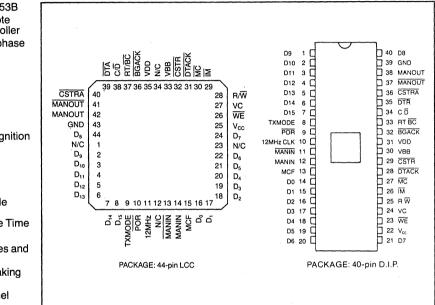

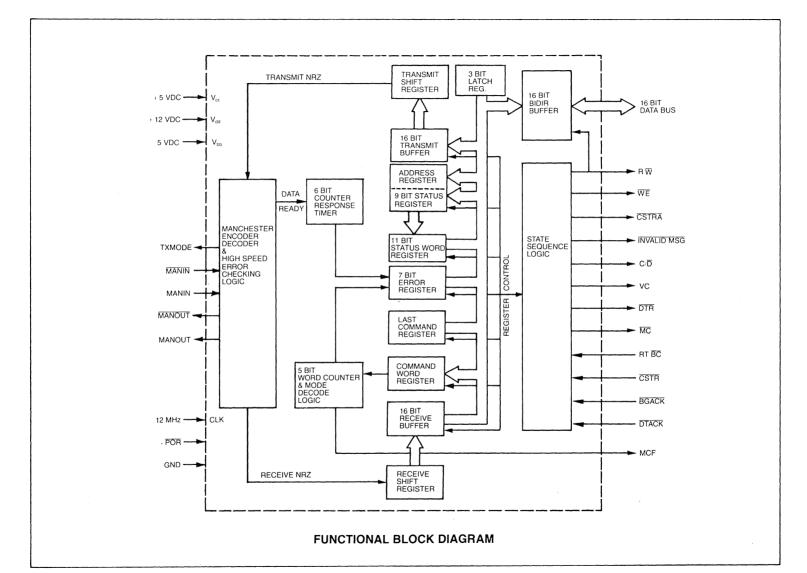

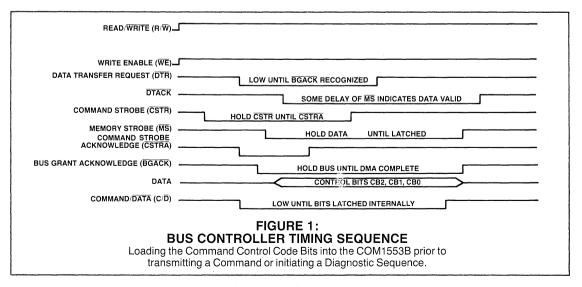

| COM 1553B              | MIL-STD-<br>1553B<br>Controller      | MIL-STD-1553B Manchester Interface<br>Bus Controller/Remote Terminal                                                                                          | 1 MB                           | +5, -5, +12       | 40 DIP/<br>44SMT  | 51-66   |

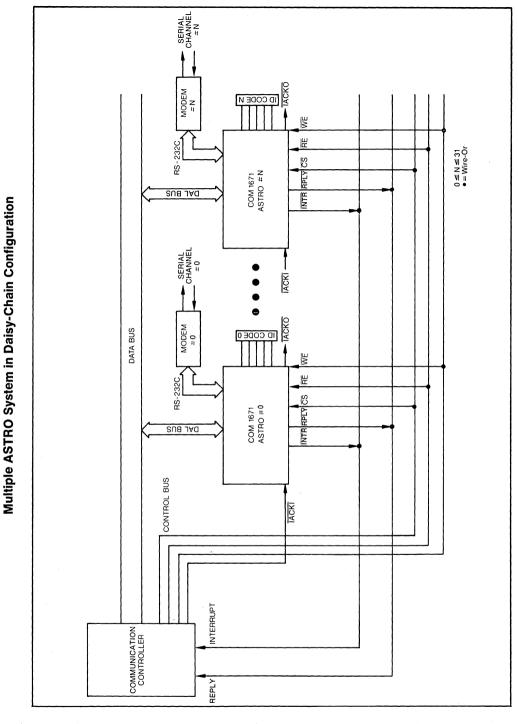

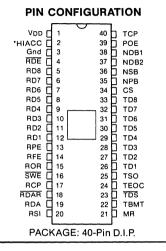

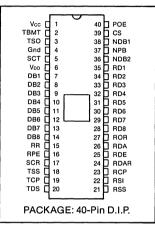

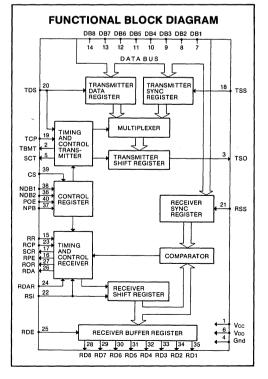

| COM 1671               | ASTRO                                | Asynchronous/Synchronous<br>Transmitter/Receiver, Full Duplex, 5-8<br>data bit, 1X or 32X clock                                                               | 1 MB                           | +5, -5, +12       | 40 DIP            | 67-82   |

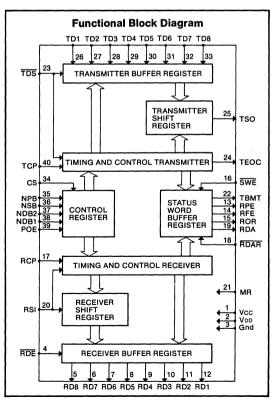

| COM 1863               | UART                                 | Universal Asynchronous Receiver/<br>Transmitter, Full Duplex, 5-8 data bit,<br>1, 1¼, 2 stop bit, enhanced distortion<br>margin                               | 62.5 KB                        | +5                | 40 DIP            | 83-90   |

| COM 2017               | UART                                 | Universal Asynchronous Receiver/<br>Transmitter, Full Duplex, 5-8 data bit,<br>1, 1½, 2 stop bit (use 8017 for new designs)                                   | 25 KB                          | +5, -12           | 40 DIP            | 91-98   |

| COM 2502               | UART                                 | Universal Asynchronous Receiver/<br>Transmitter, Full Duplex, 5-8 data bit,<br>1, 2 stop bit (use 8502 for new designs)                                       | 25 KB                          | +5, -12           | 40 DIP            | 91-98   |

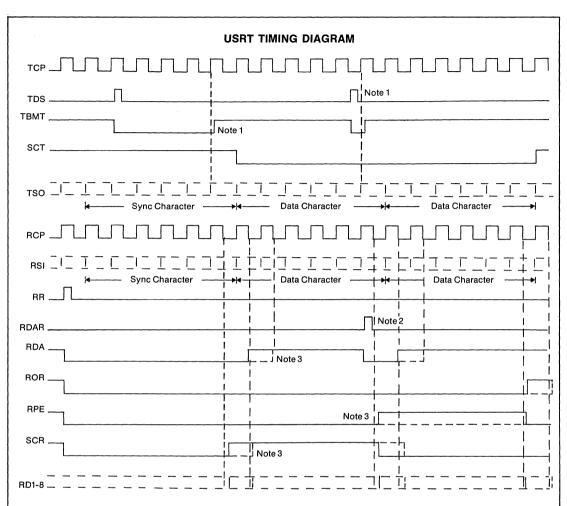

| COM 2601               | USRT                                 | Universal Synchronous Receiver/<br>Transmitter, STR, BSC, Bi-sync<br>compatible                                                                               | 250 KB                         | +5, -12           | 40 DIP            | 99-106  |

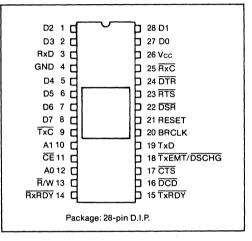

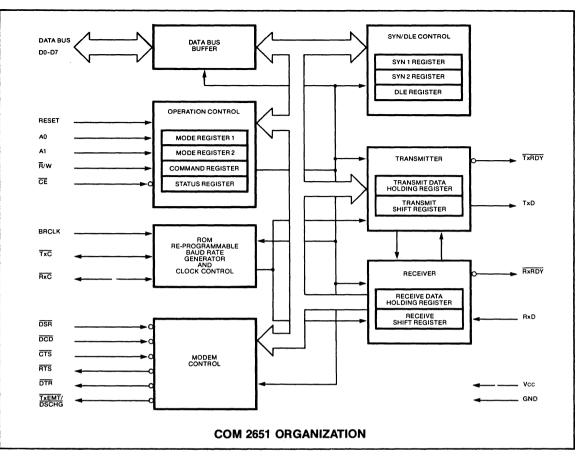

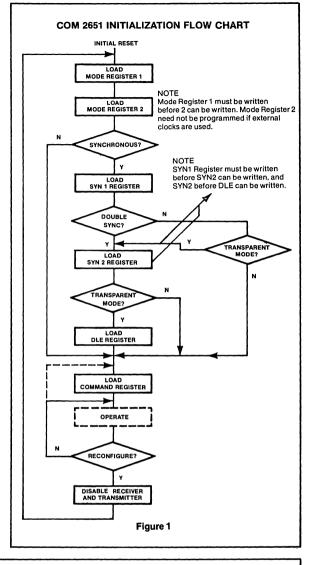

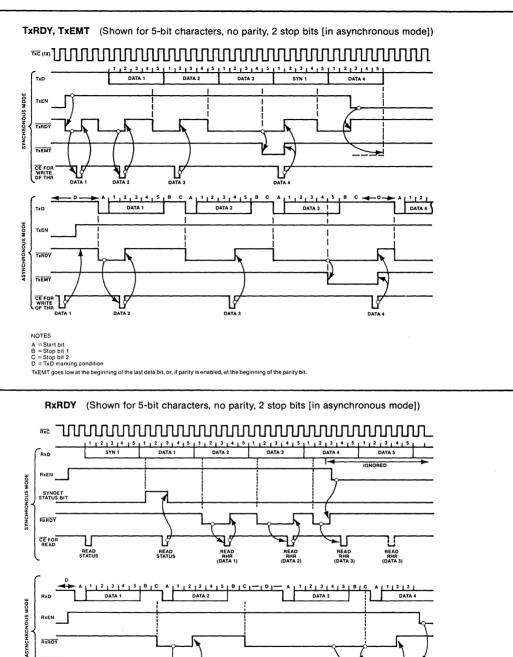

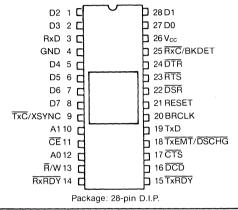

| COM 2651               | USART/PCI                            | Universal Synchronous/Asynchronous<br>Receiver/Transmitter, Programmable<br>Communication Interface, Internal<br>Baud Rate Generator, 1X, 16X, 64X clock      | 1 MB                           | +5                | 28 DIP/<br>28 SMT | 107-118 |

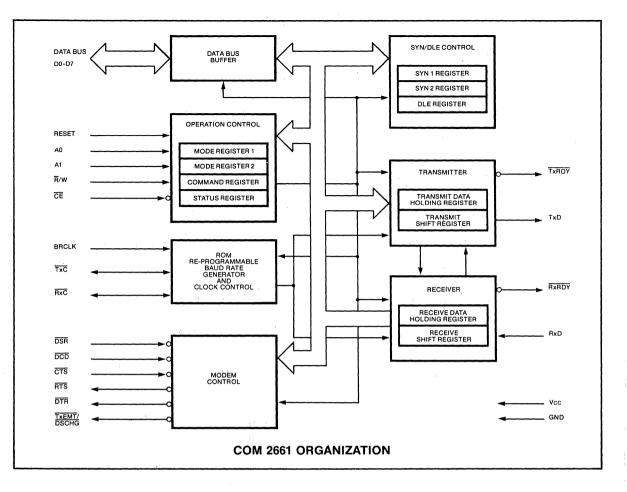

| COM 2661-1<br>-2<br>-3 | USART/EPCI                           | Universal Synchronous/Asynchronous<br>Receiver/Transmitter, Programmable<br>Communication Interface, Internal<br>Baud Rate Generator, 1X, 16X, 64X clock      | 1 MB                           | +5                | 28 DIP/<br>28 SMT | 119-130 |

| COM 5025               | Multi-Protocol<br>USYNRT             | SDLC, HDLC, ADCCP, Bi-sync, DDCMP<br>compatible, automatic bit stuffing/<br>stripping, frame detection/generation,<br>CRC generation/checking, sync detection | 1.5 MB                         | +5, +12           | 40 DIP            | 131-142 |

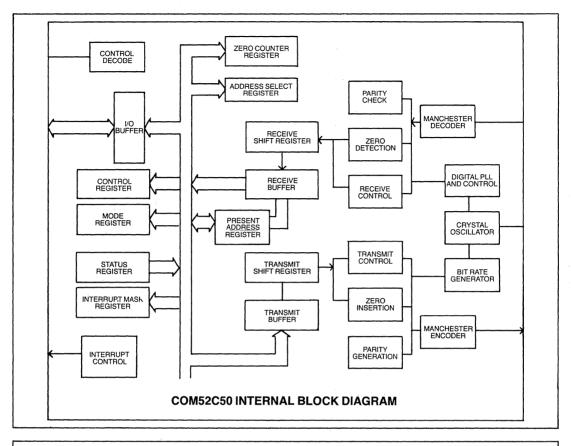

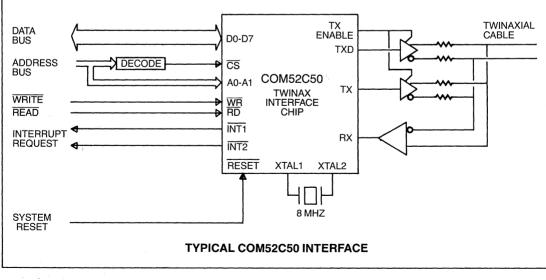

| COM 52C50              | TWINAX                               | Interface Controller for IBM System/<br>34, 36, 38 designated TWINAX or<br>5250 environment, CMOS                                                             | 1 MB                           | +5                | 28 DIP/<br>28 SMT | 143-144 |

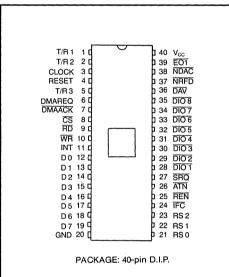

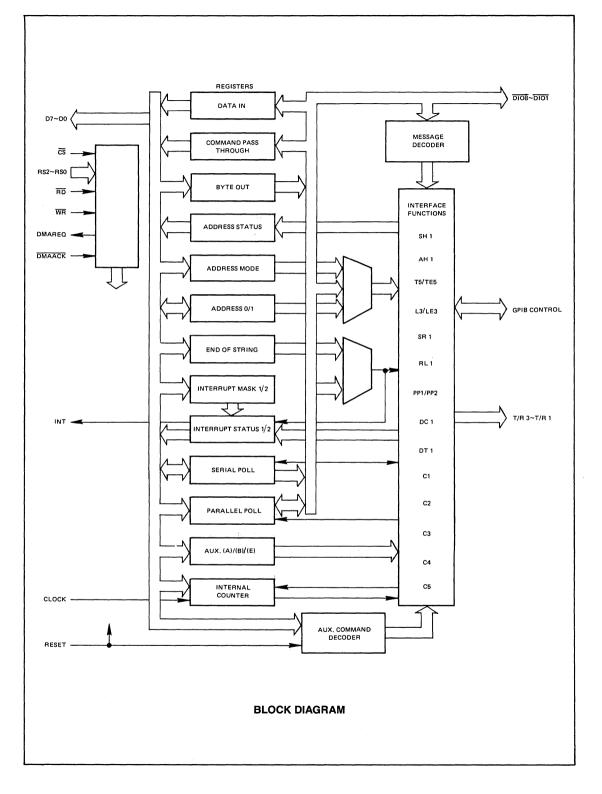

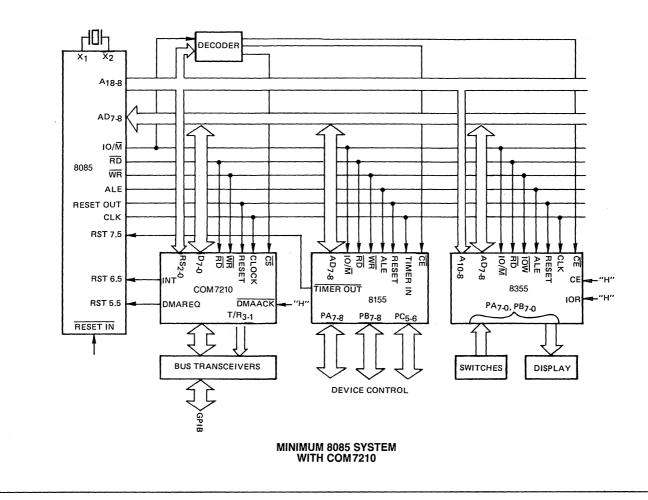

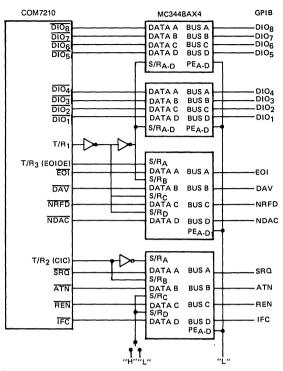

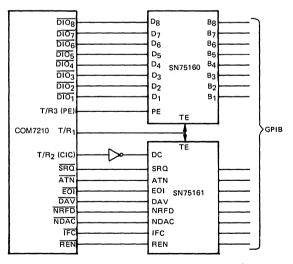

| COM 7210               | GPIB<br>Interface                    | Intelligent Interface Controller<br>for GPIB (IEEE-488-1978)                                                                                                  | 8 MHz                          | +5                | 40 DIP            | 145-156 |

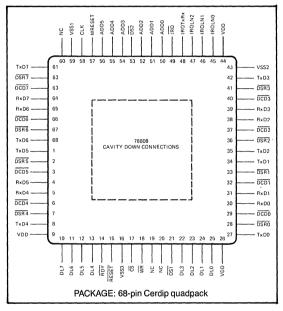

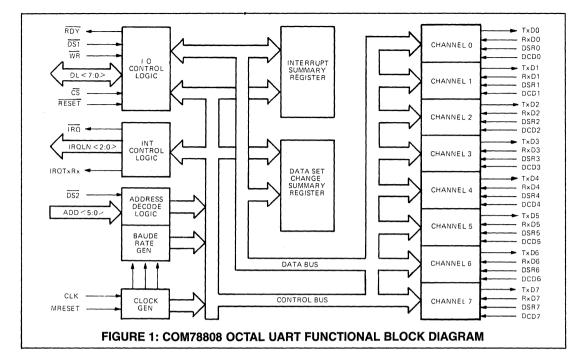

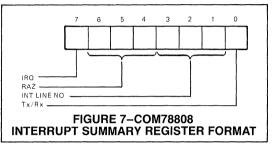

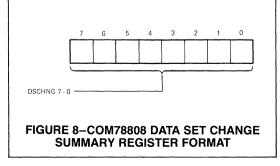

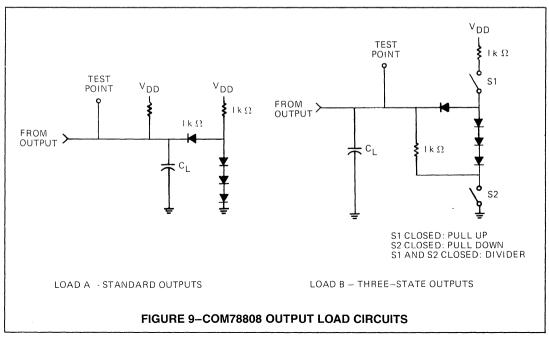

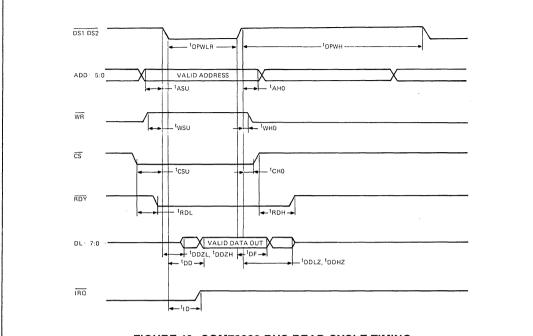

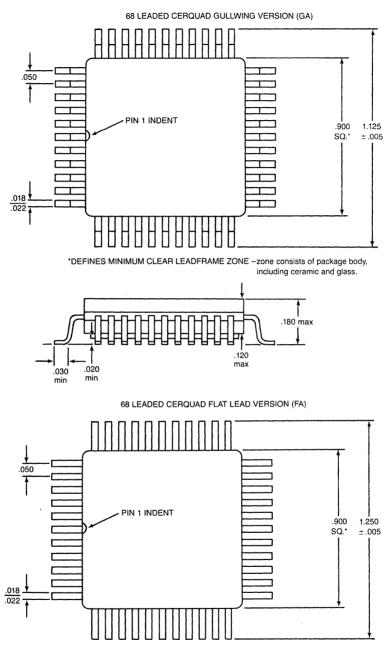

| COM 78808              | OCTAL UART                           | 8 UART's, 8 Baud Rate Generators plus<br>control logic and modem signals all<br>on a single chip                                                              | 19.2 KB                        | +5                | 68 CERDIP<br>LCC  | 157-172 |

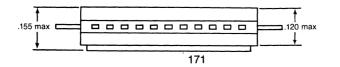

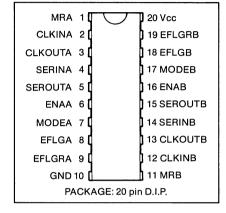

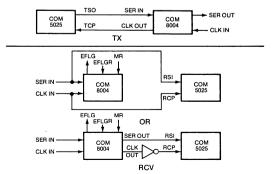

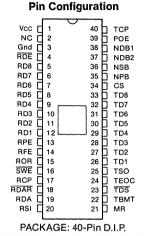

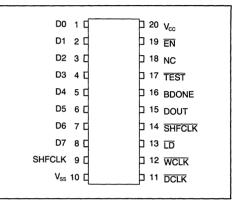

| COM 8004               | 32 Bit CRC<br>Generator/<br>Checker  | Companion device to COM 5025<br>Dual 32 bit CRC Generator/Checker                                                                                             | 2.0 MB                         | +5                | 20 DIP            | 173-178 |

| COM 8017               | UART                                 | Universal Asynchronous Receiver/<br>Transmitter, Full Duplex, 5-8 data bit,<br>1, 1½, 2 stop bit (compatible with<br>COM 2017)                                | 40 KB                          | +5                | 40 DIP            | 179-186 |

| COM 8018               | UART                                 | Universal Asynchronous Receiver/<br>Transmitter, Full Duplex, 5-8 data bit,<br>1, 1½, 2 stop bit, enhanced distortion,<br>margin                              | 62.5 KB                        | +5                | 40 DIP            | 83-90   |

| COM 81C17              | UART                                 | Universal Asynchronous Receiver/<br>Transmitter, Full Duplex with built-in<br>Baud Rate Generator, CMOS                                                       | 19.5 KB                        | +5                | 20 DIP/<br>28 SMT | 187-188 |

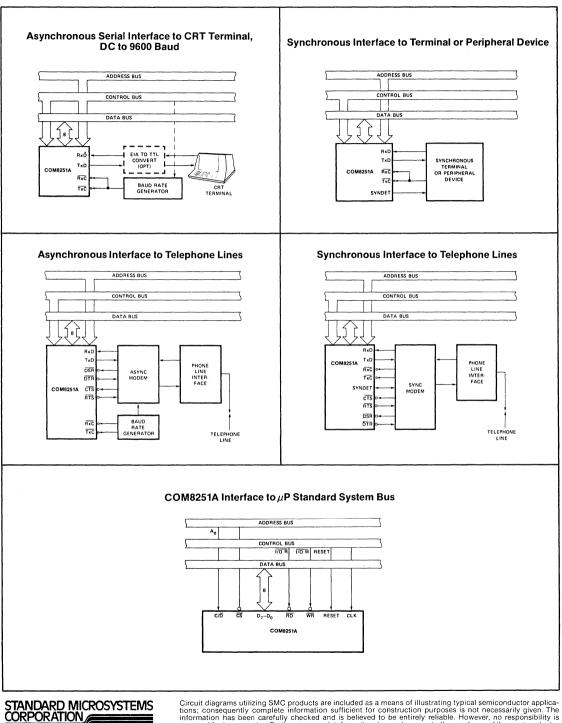

| COM 8251A              | USART                                | Universal Synchronous/Asynchronous<br>Receiver/Transmitter, Full Duplex,<br>5-8 data bit, 1, $1/2$ , 2 stop bit                                               | 64 KB (sync)<br>9.6 KB (async) | +5                | 28 DIP            | 189-204 |

| COM 8502               | UART                                 | Universal Asynchronous Receiver/<br>Transmitter, Full Duplex, 5-8 data bit,<br>1, 2 stop bit (compatible with COM 2502)                                       | 40 KB                          | +5                | 40 DIP            | 179-186 |

| COM 9004               | IBM 3270<br>Receiver/<br>Transmitter | IBM 3274 Compatible Receiver/<br>Transmitter for COAX type "A" protocol<br>(use COM 9064 for new designs)                                                     | 2.36 MB                        | +5, ±12           | 40 DIP/<br>44 SMT | 205-212 |

## Data Communication Products CONT.

| Part<br>Number           | Name                         | Description                                                                                                           | Max<br>Baud Rate | Power<br>Supplies | Package           | Page    |

|--------------------------|------------------------------|-----------------------------------------------------------------------------------------------------------------------|------------------|-------------------|-------------------|---------|

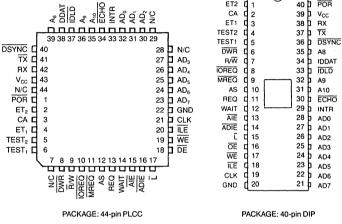

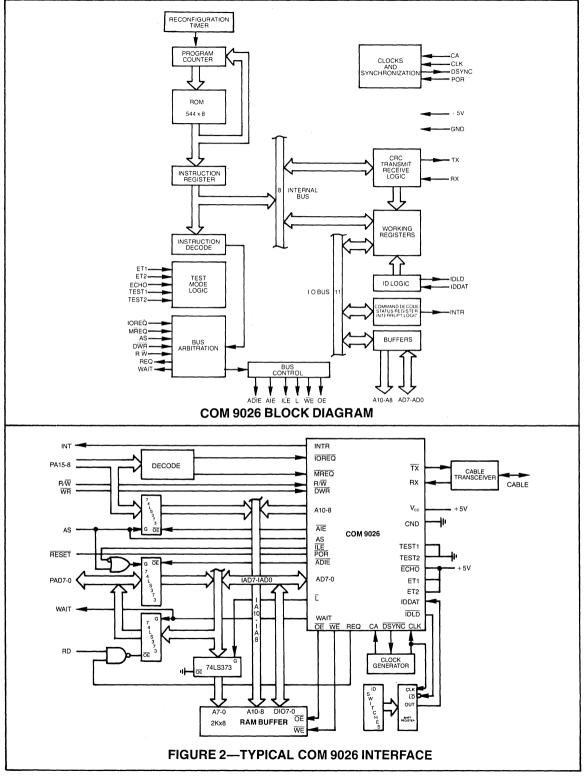

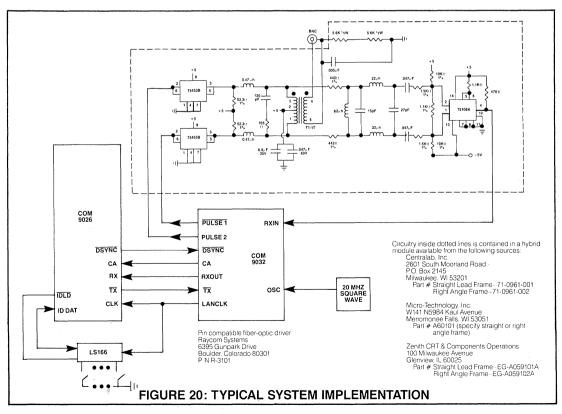

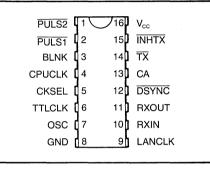

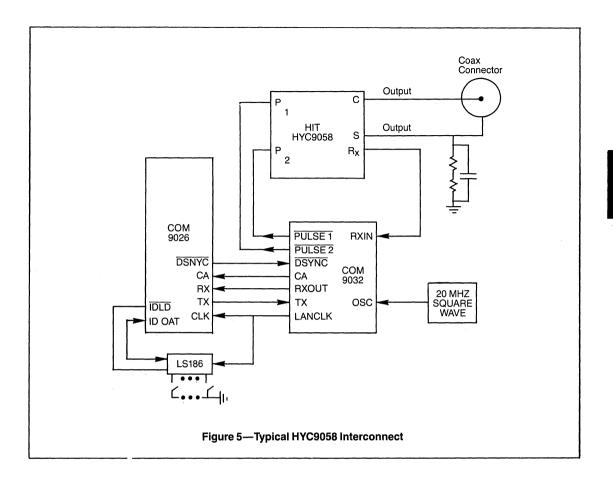

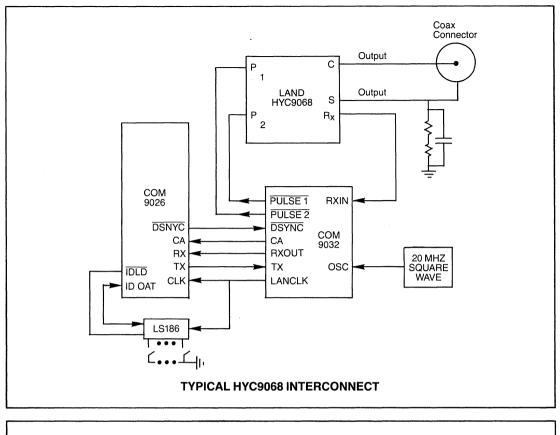

| COM 9026                 | LANC                         | Local Area Network Controller for token<br>pass systems                                                               | 2.5 MB           | +5                | 40 DIP/<br>44 SMT | 213-228 |

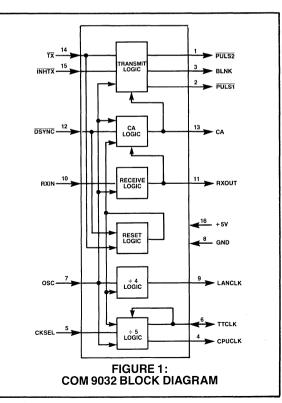

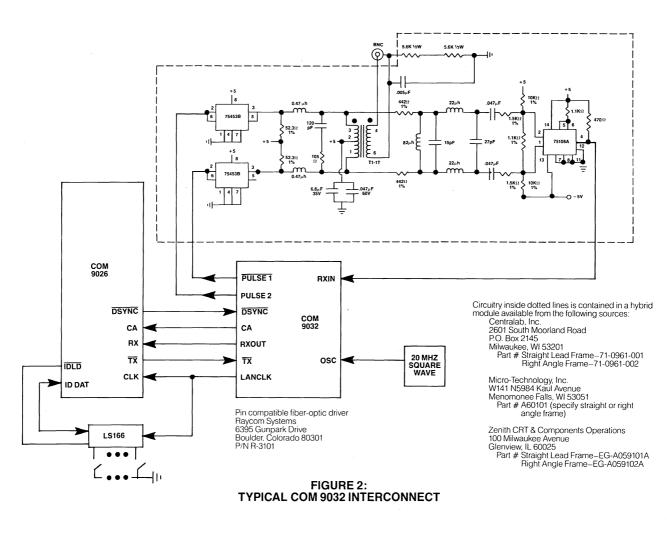

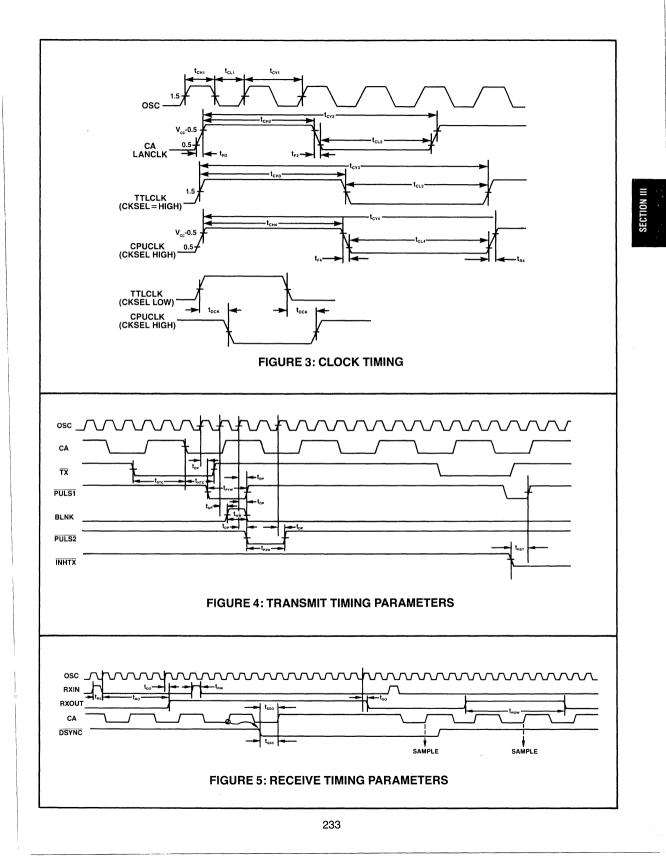

| COM 9032                 | LANT                         | Local Area Network Transceiver                                                                                        | 2.5 MB           | +5                | 16 DIP            | 229-234 |

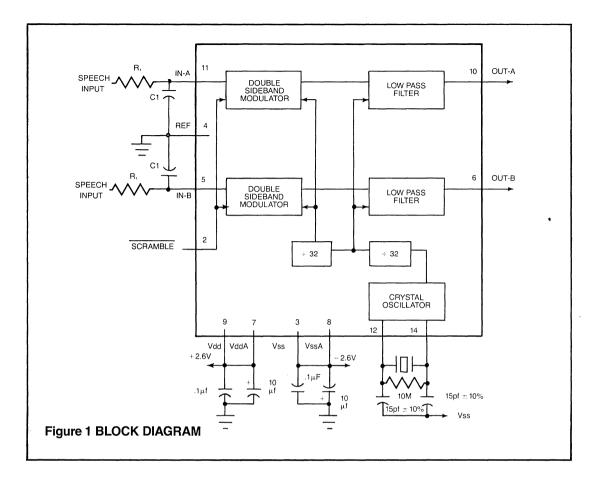

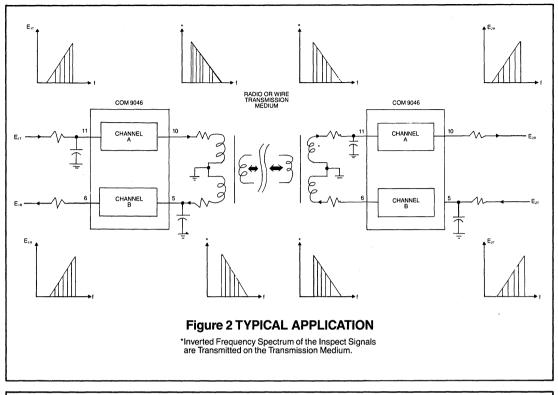

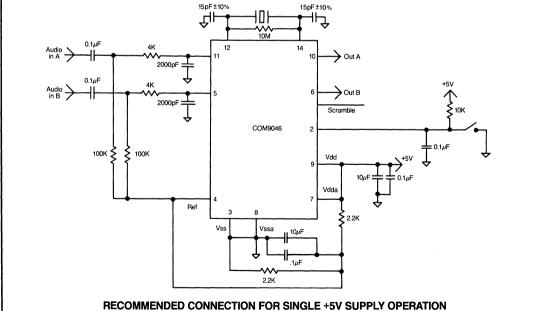

| COM 9046                 | SSBSS                        | Single Side Band Speech Scrambler,<br>Low Power, Full Duplex, uses 3.58 MHz<br>TV burst crystal                       | NA               | ±2.6              | 14 DIP            | 235-238 |

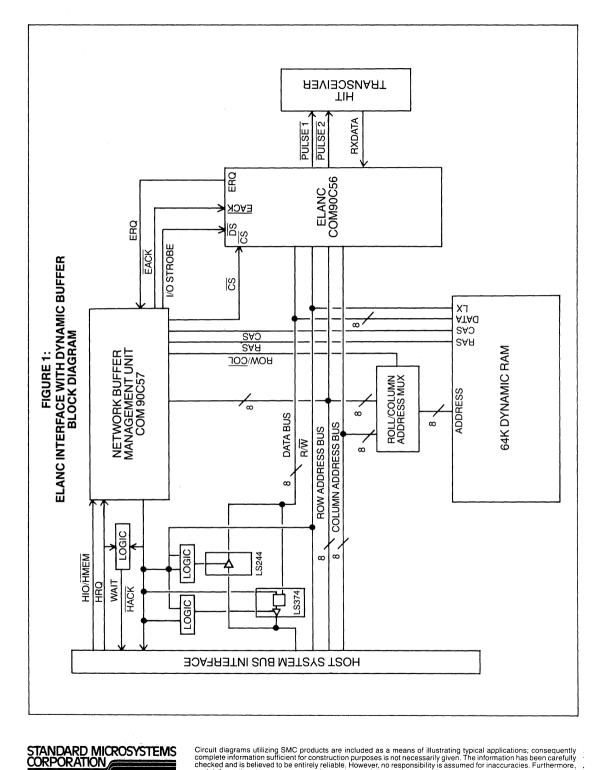

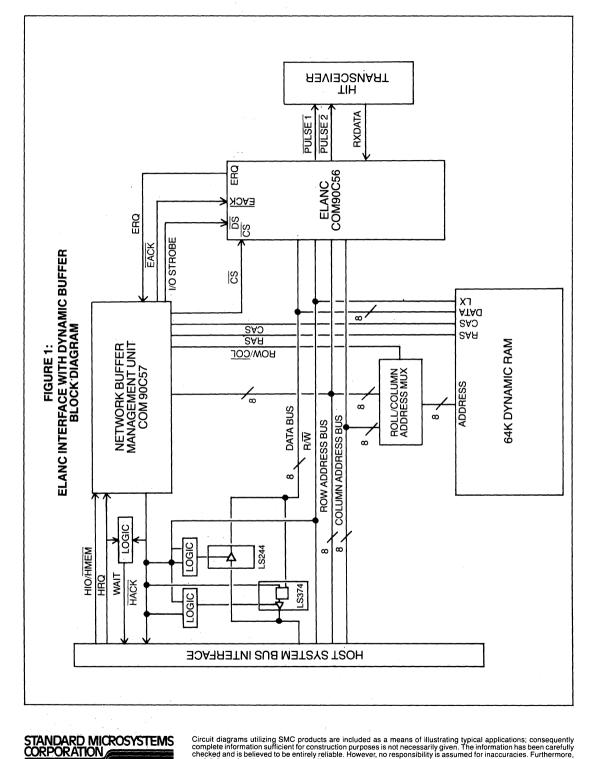

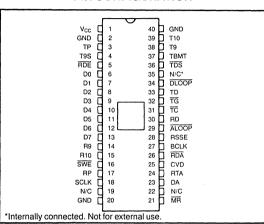

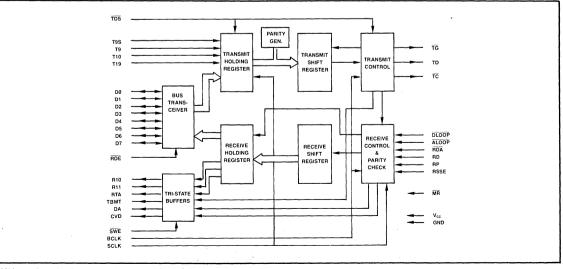

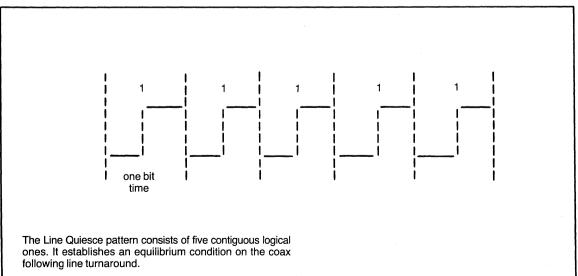

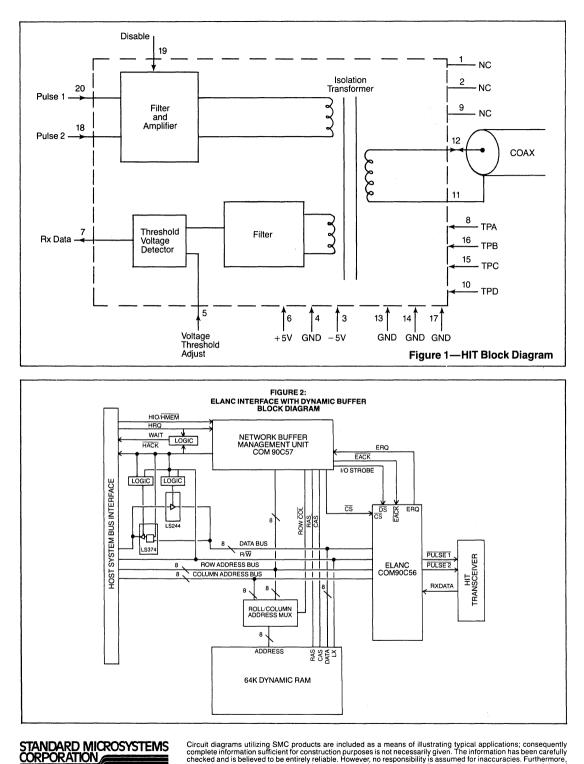

| COM 90C56(2)             | ELANC                        | CMOS Enhanced Local Area Network<br>Controller, with high throughput,<br>network management and network<br>diagnostic | 5 MBps           | +5                | 48 PLCC           | 239-240 |

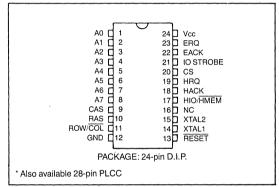

| COM 90C57 <sup>(2)</sup> | NBMU                         | CMOS Network Buffer Management<br>Unit, to simplify interface of ELANC<br>with dynamic RAM's                          | 5 Mps            | +5                | 24 DIP/<br>28 SMT | 241-242 |

| COM 9064                 | IBM 3270                     | IBM 3270 COAX type "A" controller<br>+5V only version of COM 9004                                                     | 2.36 MB          | +5                | 40 DIP/<br>44 SMT | 243-250 |

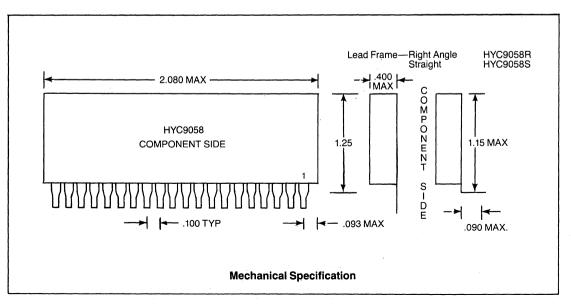

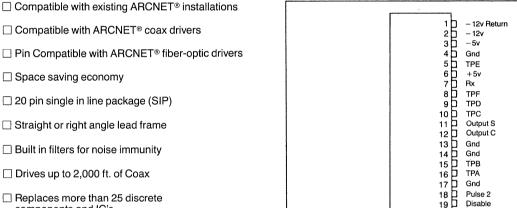

| HYC 9058                 | +5V only version of COM 9004 |                                                                                                                       | 2.5 MBps         | +5                | 20 SIP            | 251-256 |

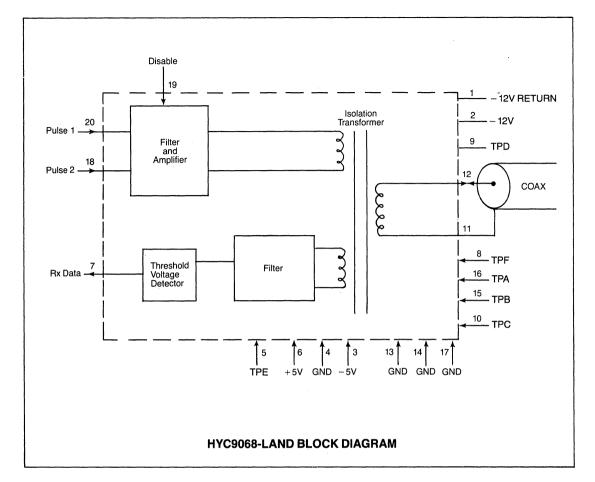

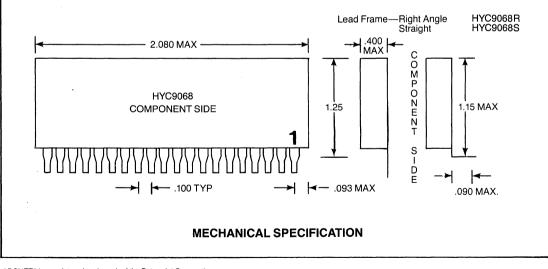

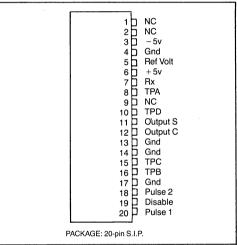

| HYC 9068                 | LAND                         | Local Area Network Driver with $(93 \ \Omega)$ line matching impedance for ARCNET networks                            | 2.5 MBps         | +5                | 20 SIP            | 257-260 |

| HYC 9078(2)              | HIT 2                        | High Impedance Transceiver for Local<br>Area Networks for operation at 5MHz                                           | 5 MBps           | +5                | 20 SIP            | 261-262 |

(2)For future release

#### TIMING CONTROLLERS

| Part<br>Number           | Description                                                                                                 | Features                                                                                                          | Display<br>Format                                                                              | Max<br>Clock                         | Power<br>Supplies | Package | Page    |

|--------------------------|-------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|--------------------------------------|-------------------|---------|---------|

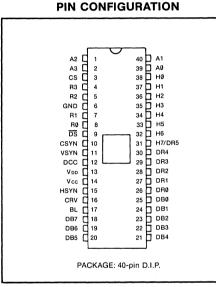

| CRT 5027                 |                                                                                                             |                                                                                                                   | Programmable                                                                                   | 4MHz                                 | +5, +12           | 40 DIP  | 293-300 |

| CRT 5037                 | Provides all of the                                                                                         | Balanced beam interlace                                                                                           | Programmable                                                                                   | 4MHz                                 | +5, +12           | 40 DIP  | 293-300 |

| CRT 5047                 | timing and control for<br>interlaced and non-<br>interlaced CRT display                                     | Fixed format                                                                                                      | 80 column<br>24 row                                                                            | 4MHZ                                 | +5, +12           | 40 DIP  | 301-302 |

| CRT 5057                 |                                                                                                             | Line-lock                                                                                                         | Programmable                                                                                   | 4MHz                                 | +5, +12           | 40 DIP  | 293-300 |

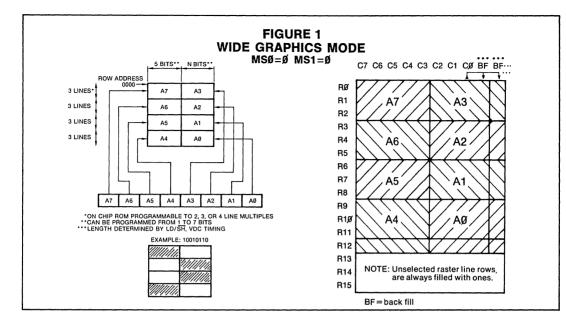

| CRT 7220A,<br>-1, -2     | Graphics Display<br>Controller                                                                              | Intelligent graphics<br>display controller                                                                        | 1024 x 1024 Pixel                                                                              | 6, 7, 8<br>MHz                       | +5                | 40 DIP  | 309-332 |

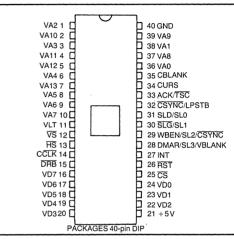

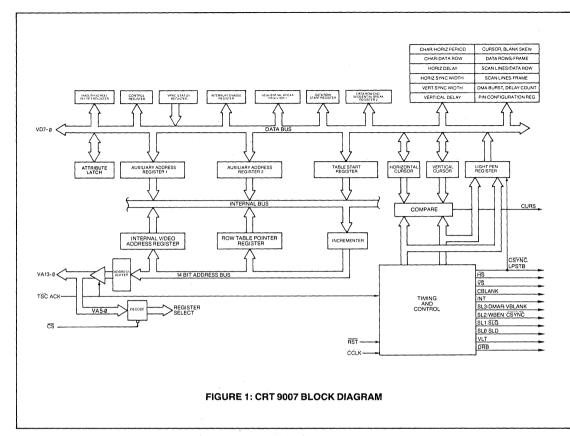

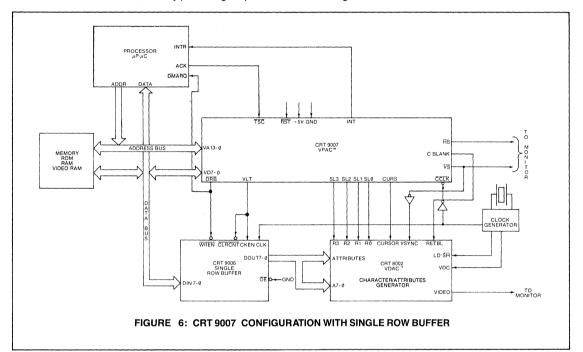

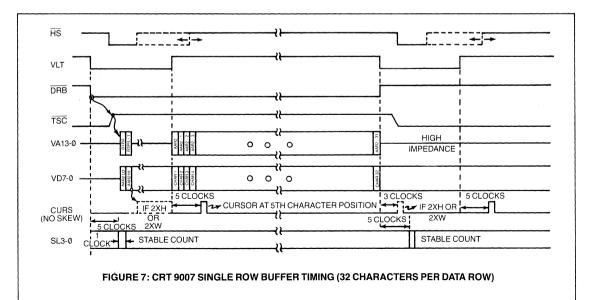

| CRT 9007A,<br>B, C       | CRT video processor<br>and controller                                                                       | Sequential or row-<br>table driven memory<br>programmable DMA                                                     | Programmable                                                                                   | A-3.7 MHz<br>B-3.33 MHz<br>C-2.5 MHz | +5                | 40 DIP  | 369-388 |

| CRT 97C11 <sup>(2)</sup> | 3rd generation CRT<br>controller which<br>allows manipulation<br>of independent win-<br>dow areas on screen | Control of window size<br>and position, window<br>attributes, prog cursor,<br>max of 127 windows,<br>DRAM refresh | Up to 16K pixels<br>vertical and 1KxN<br>(N = display<br>memory width) in<br>horizontal pixels | TBD                                  | +5                | 68 PLCC | 455-456 |

#### VIDEO TERMINAL LOGIC CONTROLLERS

| Part<br>Number       | Description                                                                                                             | Features                                                                                  | Display<br>Format                                                            | Attributes                                                                                                                        | Max<br>Clock | Power<br>Supply | Package | Page    |

|----------------------|-------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|--------------|-----------------|---------|---------|

| CRT 9028/<br>9128(1) | bute control for                                                                                                        | Separate display<br>memory eliminates                                                     |                                                                              | Tagged attri-<br>butes: reverse<br>video, blank,<br>blink, under-<br>line, intensity<br>and wide/thin<br>graphics.                |              |                 |         | 401-416 |

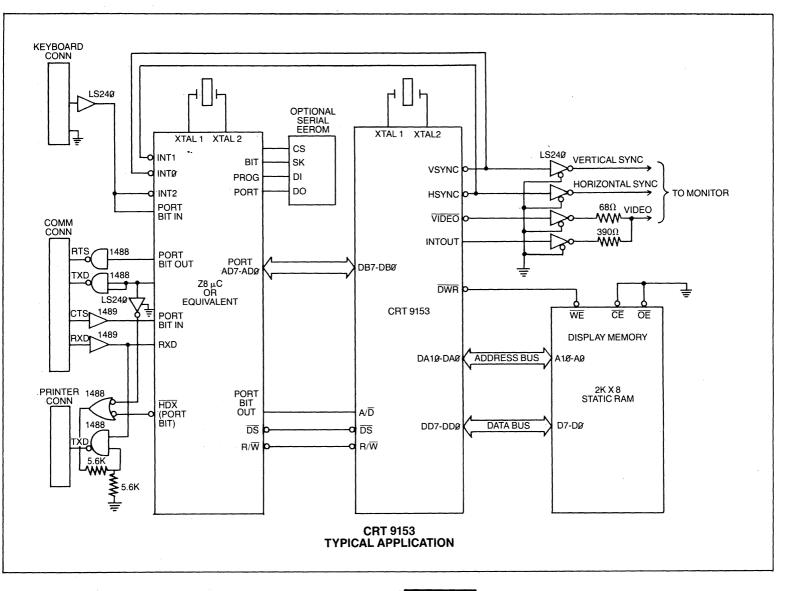

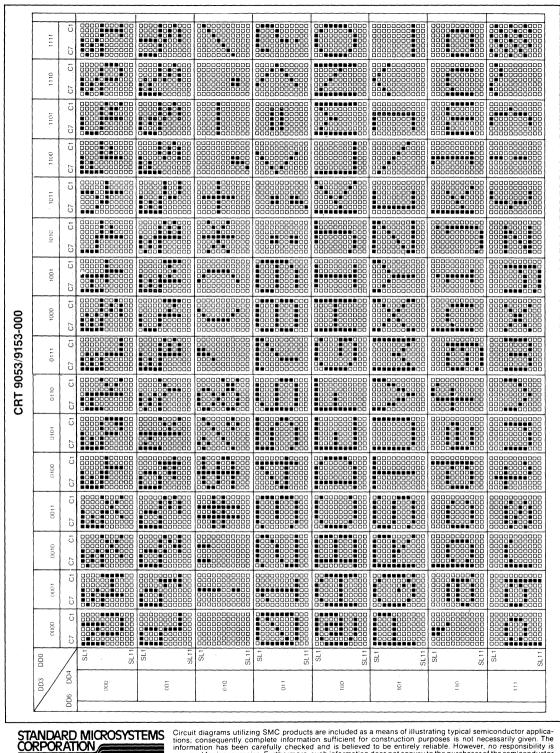

| CRT 9053/<br>9153(1) | alphanumeric and<br>graphics display. Two<br>types of processor<br>interface signals<br>differentiate the<br>two parts. | contention, smooth<br>scroll, status row,<br>on-board clock, and<br>video shift register. | Mask pro-<br>grammable,<br>7x11 charac-<br>ter font, 9x13<br>character cell. | Embedded or<br>tagged attri-<br>butes: reverse<br>video, blank,<br>blink, under-<br>line, intensity<br>and wide/thin<br>graphics. |              |                 | 40 DIP  | 433-448 |

<sup>(1)</sup>May be custom mask programmed

(2)For future release

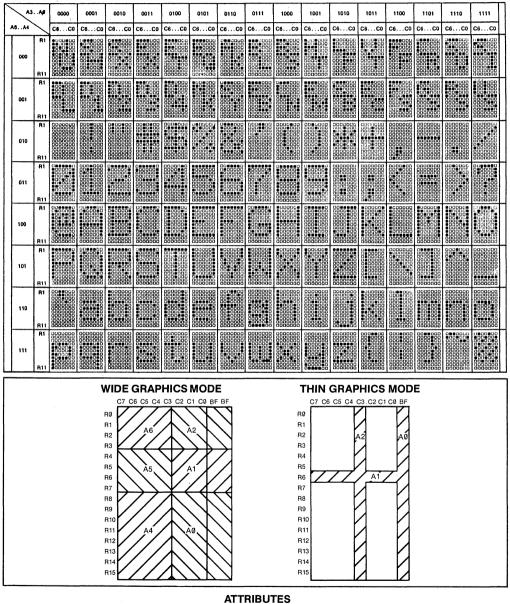

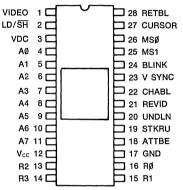

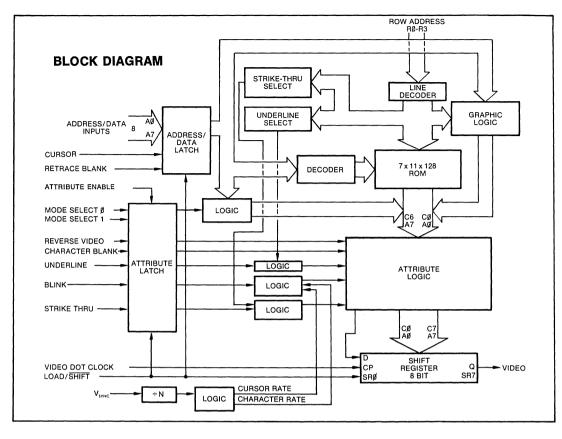

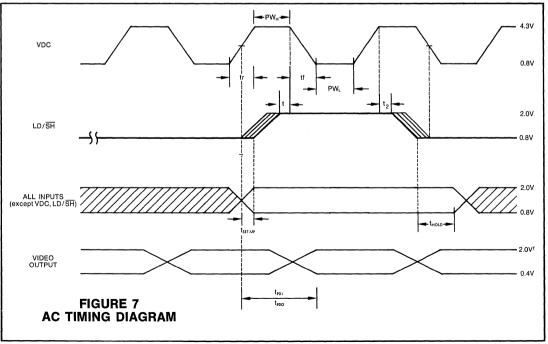

#### CHARACTER GENERATORS

| Part<br>Number | Description                                                        | Max<br>Frequency | Power Supply | Package | Page    |

|----------------|--------------------------------------------------------------------|------------------|--------------|---------|---------|

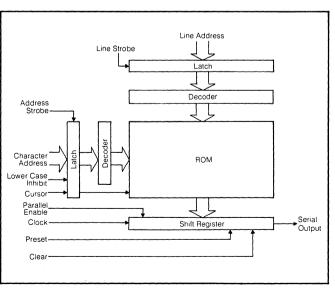

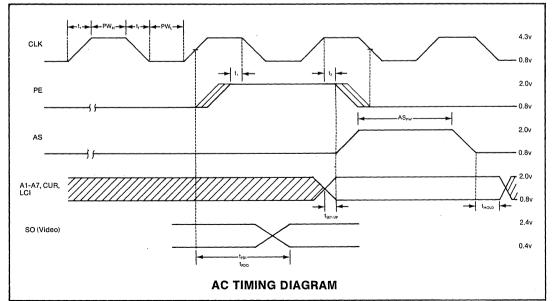

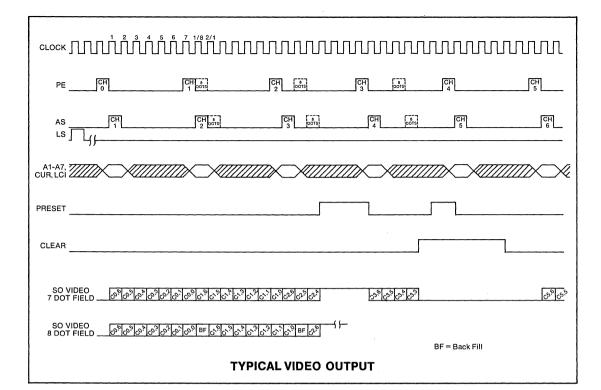

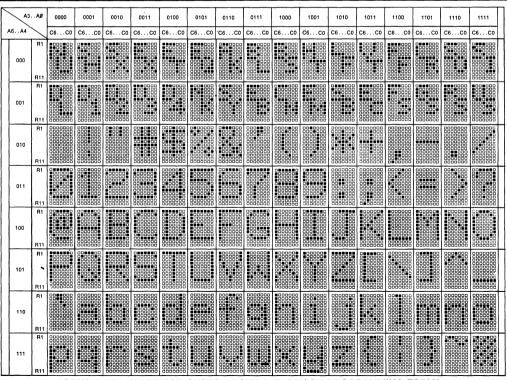

| CRT 7004A(1.4) |                                                                    | 20 MHz           |              |         |         |

| CRT 7004B(1,4) | 7 x 11 x 128 character generator,<br>latches, video shift register | 15 MHz           | +5           | 24 DIP  | 303-308 |

| CRT 7004C(1,4) | Taucites, video stillt register                                    | 10 MHz           |              |         |         |

#### **ROW BUFFER**

| Part<br>Number | Description                                                                 | Max<br>Row Length | Power Supply | Package | Page    |

|----------------|-----------------------------------------------------------------------------|-------------------|--------------|---------|---------|

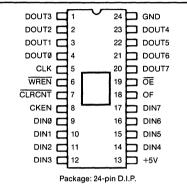

| CRT 9006-83    | 8 bit wide serial cascadable single row                                     | 83 characters     | +5           | 24 DIP  | 363-368 |

| CRT 9006-135   | buffer memory for CRT or printer                                            | 135 characters    | +5           | 24 DIP  | 303-308 |

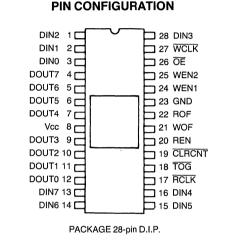

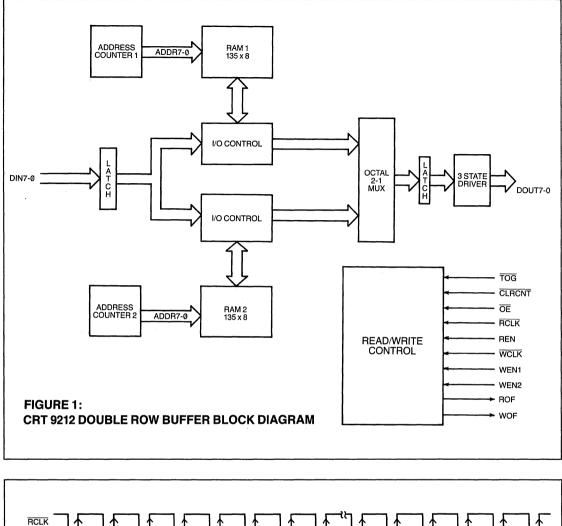

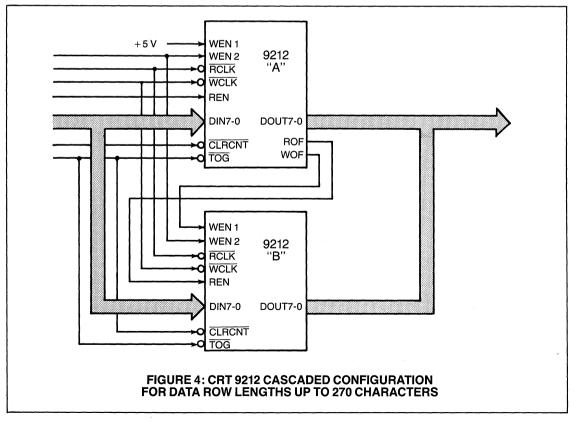

| CRT 9212       | 8 bit wide serial cascadable double row<br>buffer memory for CRT or printer | 135 characters    | +5           | 28 DIP  | 449-454 |

#### **VDAC**<sup>~</sup> **DISPLAY CONTROLLERS**

| Part<br>Number             | Description                                                                                                                                                 | Display                                  | Attributes                  | Max<br>Clock | Power<br>Supplies | Package | Page    |         |

|----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|-----------------------------|--------------|-------------------|---------|---------|---------|

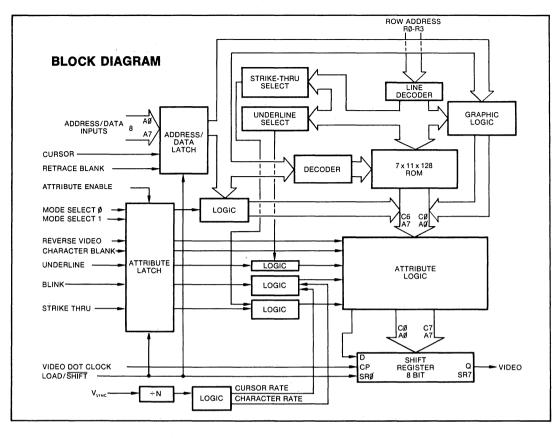

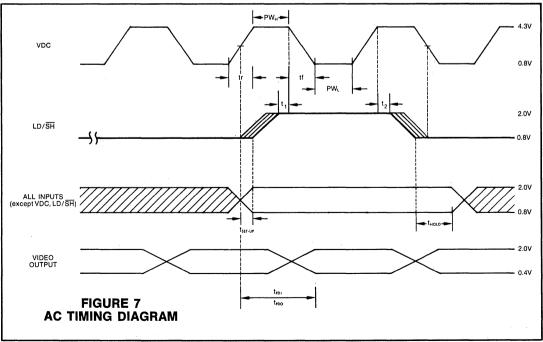

| CRT 8002H                  | Provides complete                                                                                                                                           | 7x11 dot matrix,                         | Reverse video               | 25 MHz       |                   |         | 347-354 |         |

| CRT 8002A(1,3)             | display and attri-<br>butes control for<br>alphanumeric and<br>graphic display.<br>Consists of 7 x 11 x 128<br>character generator,<br>video shift register | for thin graphics,<br>and on-chip cursor | blank<br>blink<br>underline | 20 MHz       |                   | v       | •       | 333-346 |

| CRT 8002B <sup>(1,3)</sup> |                                                                                                                                                             |                                          | strike-thru                 | +5<br>15 MHz | 28 DIP            | 333-346 |         |         |

| CRT 8002C(1,3)             | latches, graphics and attributes circuits.                                                                                                                  |                                          |                             | 10 MHz       |                   |         | 333-346 |         |

#### VIDEO ATTRIBUTES CONTROLLERS

| Part<br>Number  | Description                                                                                                                                  | Display                                                                                                      | Attributes                                                          | Max<br>Clock                       | Power<br>Supply | Package | Page    |

|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|------------------------------------|-----------------|---------|---------|

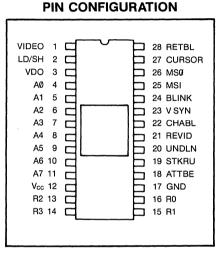

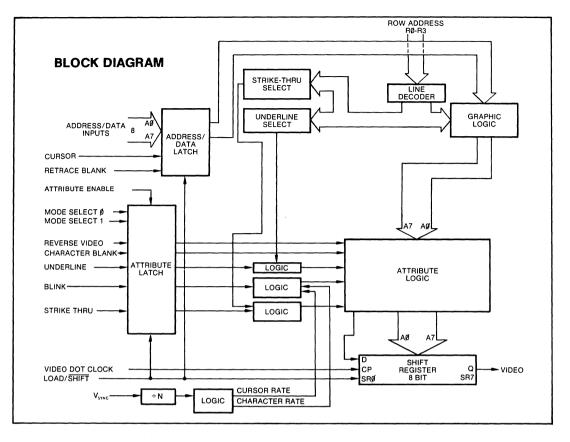

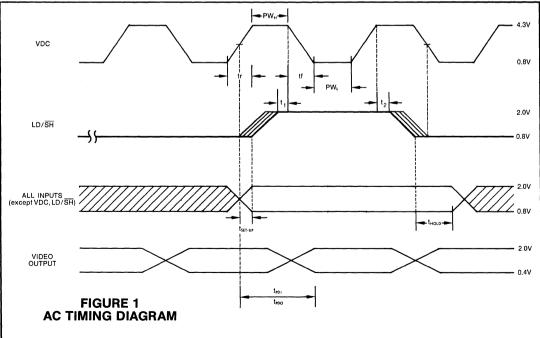

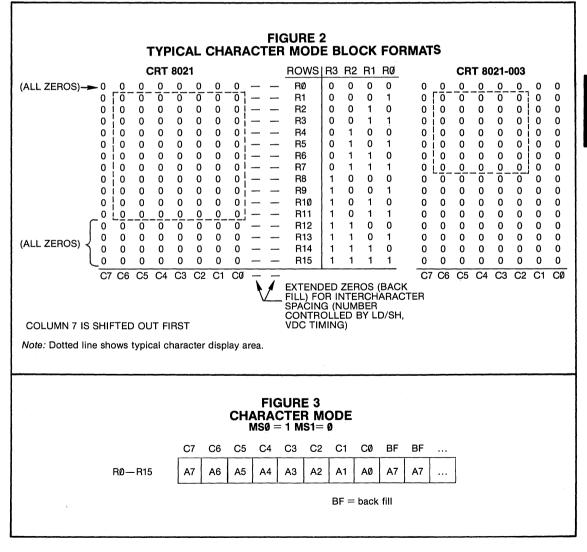

| CRT 8021        | Provides attributes<br>and graphics control<br>for CRT video<br>displays         Alphanumeric, wid<br>graphics, thin graph<br>on-chip cursor |                                                                                                              | Reverse video,<br>blank, blink<br>underline,<br>strike-thru         | 20 MHz                             | +5              | 28 DIP  | 355-362 |

| CRT 9021B       |                                                                                                                                              |                                                                                                              | Reverse video,<br>blank, blink<br>underline,<br>intensity           | 28.5 MHz                           | +5              | 28 DIP  | 389-400 |

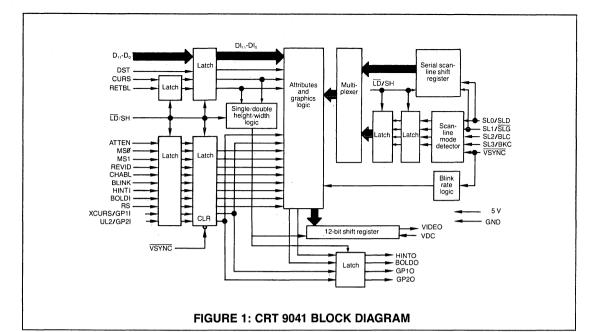

| CRT 9041A, B, C | Provides attributes and<br>graphics control for CRT<br>video displays. Full<br>VT100 <sup>®</sup> and VT220 <sup>®</sup><br>compatible       | Alphanumeric, wide<br>and thin graphics, 4<br>cursor modes, double<br>height/width, 12 bit<br>shift register | Reverse video,<br>blink, blank,<br>underline, 4<br>intensity levels | A-33 MHz<br>B-30 MHz<br>C-28.5 MHz | +5              | 40 DIP  | 417-432 |

<sup>(1)</sup>May be custom mask programmed

<sup>(3)</sup>Also available as CRT8002A, B, C-001 Katakana CRT8002A, B, C-003, -018 5 x 7 dot matrix

(4)Also available as CRT7004A, B, C -003 5 x 7 dot matrix

VT100 and VT220 are registered trademarks of Digital Equipment Corp.

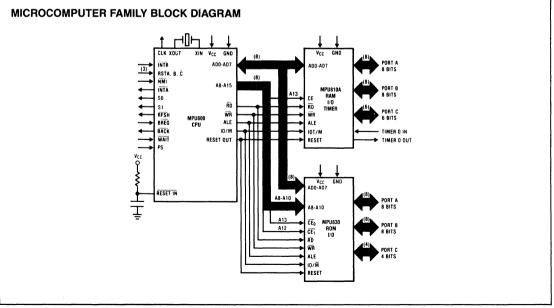

## Microprocessor Products

| Part<br>Number | Description    | Size  | Process | Speed   | Power<br>Supplies | Package | Page    |

|----------------|----------------|-------|---------|---------|-------------------|---------|---------|

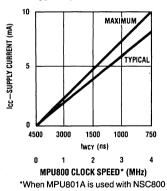

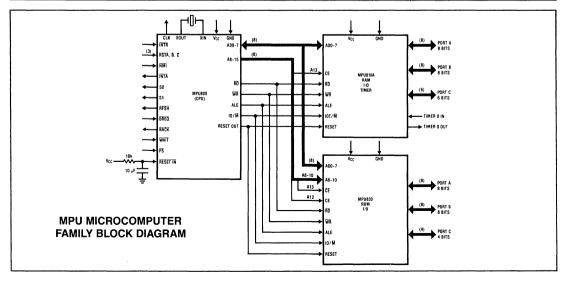

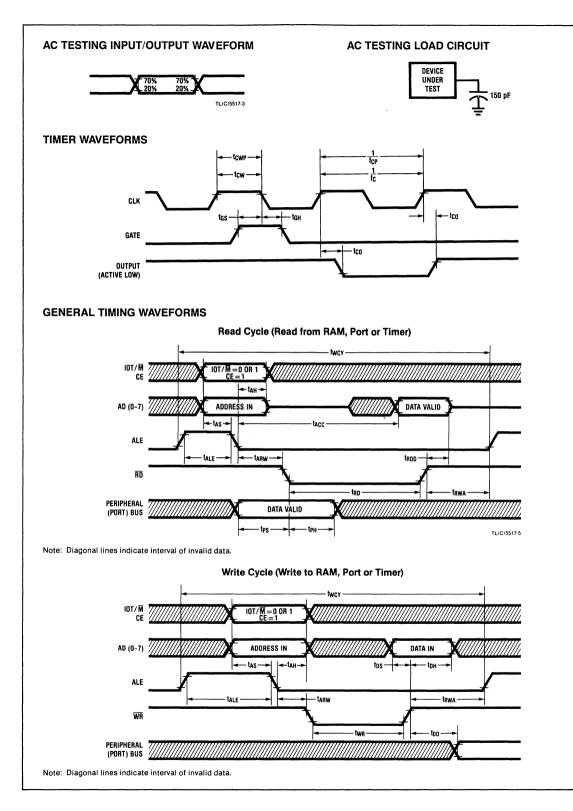

| MPU800         | Microprocessor | 8 Bit | CMOS    | 2.5 MHz | 5V                | 40 DIP  | 691-714 |

| MPU800-1       | Microprocessor | 8 Bit | CMOS    | 1.0 MHz | 5V                | 40 DIP  | 691-714 |

| MPU800-4       | Microprocessor | 8 Bit | CMOS    | 4.0 MHz | 57                | 40 DIP  | 691-714 |

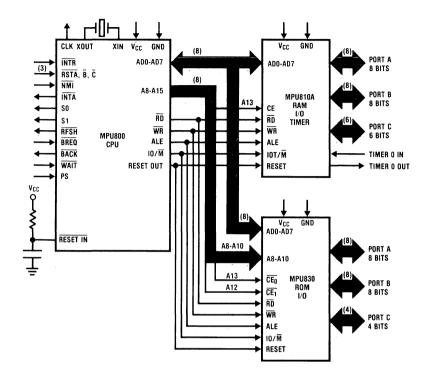

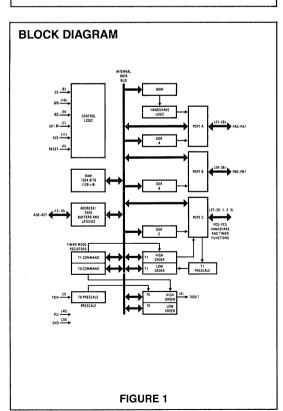

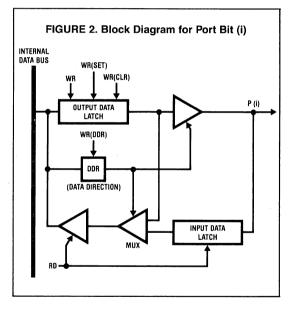

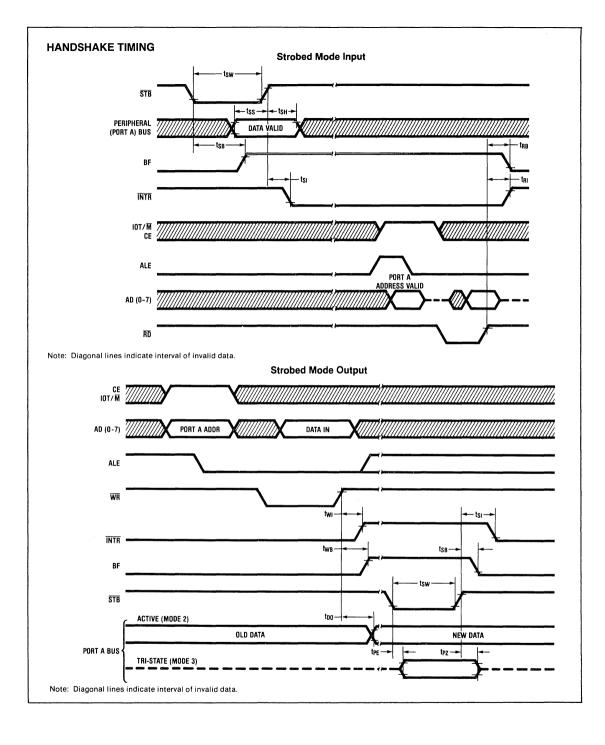

| MPU810A        | RAM-I/O-Timer  | 8 Bit | CMOS    | 2.5 MHz | 57                | 40 DIP  | 715-726 |

| MPU810A-1      | RAM-I/O-Timer  | 8 Bit | CMOS    | 1.0 MHz | 57                | 40 DIP  | 715-726 |

| MPU810A-4      | RAM-I/O-Timer  | 8 Bit | CMOS    | 4.0 MHz | 57                | 40 DIP  | 715-726 |

| MPU830         | ROM-I/O        | 8 Bit | CMOS    | 2.5 MHz | 5V                | 40 DIP  | 727-734 |

| MPU830-1       | ROM-I/O        | 8 Bit | CMOS    | 1.0 MHz | 5V                | 40 DIP  | 727-734 |

| MPU830-4       | ROM-I/O        | 8 Bit | CMOS    | 4.0 MHz | 5V                | 40 DIP  | 727-734 |

| MPU831         | I/O            | 8 Bit | CMOS    | 2.5 MHz | 57                | 40 DIP  | 727-734 |

| MPU831         | I/O            | 8 Bit | CMOS    | 1.0 MHz | 57                | 40 DIP  | 727-734 |

| MPU831-4       | I/O            | 8 Bit | CMOS    | 4.0 MHz | 57                | 40 DIP  | 727-734 |

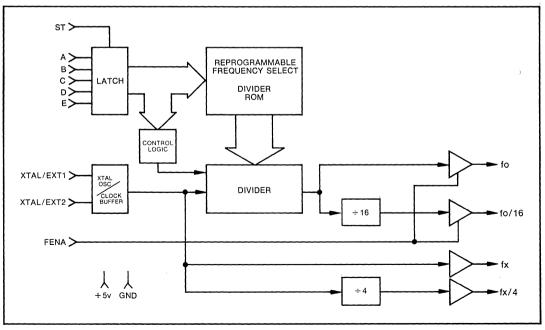

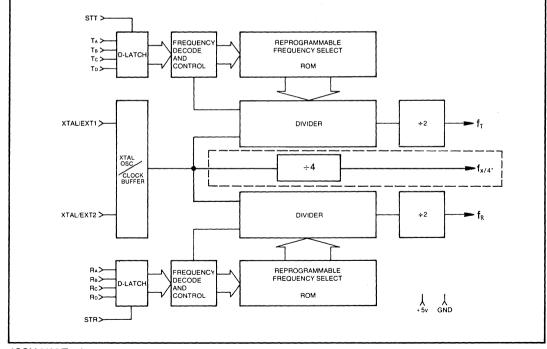

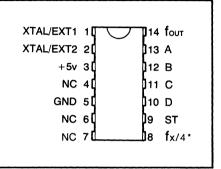

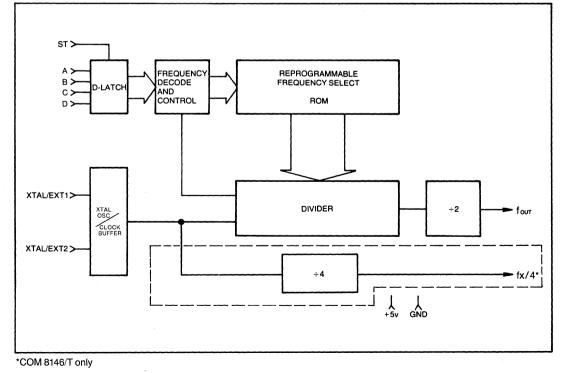

## **Baud Rate Generator**

| Part<br>Number            | Description                | Features                                                                                                              | Power<br>Supplies | Package | Page    |

|---------------------------|----------------------------|-----------------------------------------------------------------------------------------------------------------------|-------------------|---------|---------|

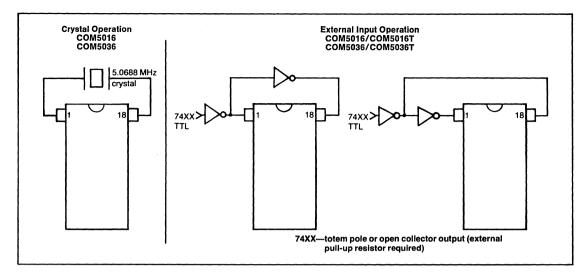

| COM 5016                  | Dual Baud Rate Generator   | On-chip oscillator or external frequency input (use 8116 for new designs)                                             | +5, +12           | 18 DIP  | 265-266 |

| COM 5016T(1)              | Dual Baud Rate Generator   | External frequency input                                                                                              | +5, +12           | 18 DIP  | 265-266 |

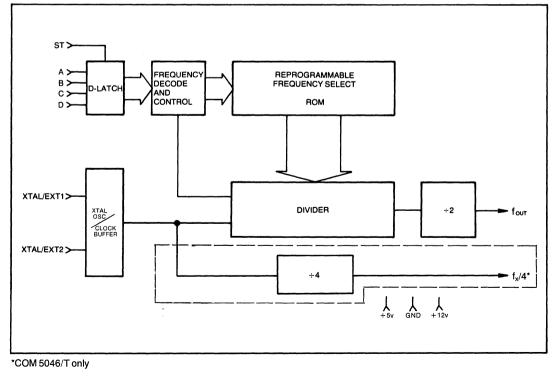

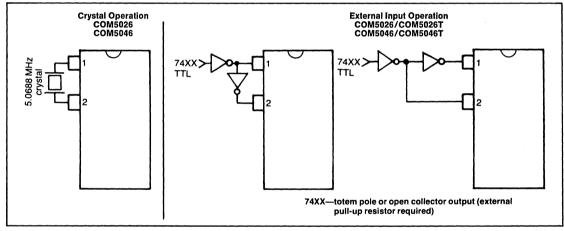

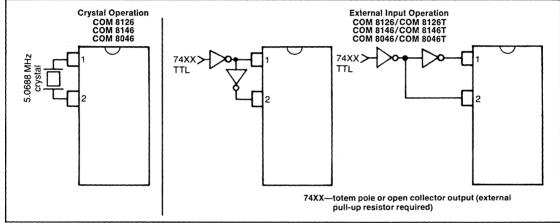

| COM 5026                  | Single Baud Rate Generator | On-chip oscillator or external frequency input (use 8126 for new designs)                                             | +5, +12           | 14 DIP  | 267-272 |

| COM 5026T(1)              | Single Baud Rate Generator | External frequency input                                                                                              | +5, +12           | 14 DIP  | 267-272 |

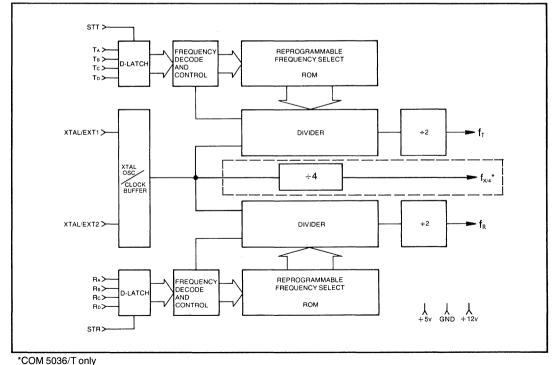

| COM 5036                  | Dual Baud Rate Generator   | COM 5016 with additional output of<br>input frequency ÷ 4 (use 8136 or 81C36<br>for new designs)                      | +5, +12           | 18 DIP  | 265-266 |

| COM 5036T <sup>(1)</sup>  | Dual Baud Rate Generator   | COM 5016T with additional output of input frequency ÷ 4                                                               | +5, +12           | 18 DIP  | 265-266 |

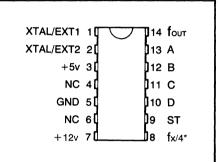

| COM 5046                  | Single Baud Rate Generator | COM 5026 with additional output of<br>input frequency ÷ 4 (use 8146 for<br>new designs)                               | +5, +12           | 14 DIP  | 267-272 |

| COM 5046T <sup>(1)</sup>  | Single Baud Rate Generator | COM 5026T with additional output of<br>input frequency ÷ 4                                                            | +5, +12           | 14 DIP  | 267-272 |

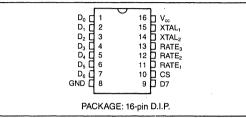

| COM 8046                  | Single Baud Rate Generator | 32 baud rates; 1X, 16X, 32X clock outputs;<br>single +5 volt supply                                                   | +5                | 16 DIP  | 273-274 |

| COM 8046T(1)              | Single Baud Rate Generator | COM 8046 with external frequency<br>input only                                                                        | +5                | 16 DIP  | 273-274 |

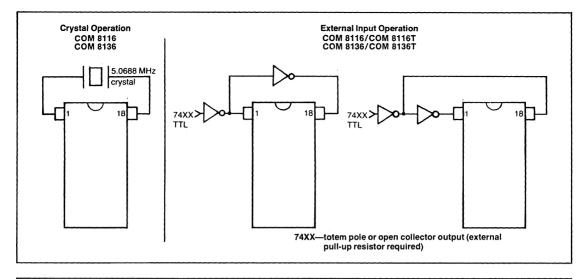

| COM 8116                  | Dual Baud Rate Generator   | Single + 5 volt version of COM 5016                                                                                   | +5                | 18 DIP  | 275-276 |

| COM 8116T(1)              | Dual Baud Rate Generator   | Single + 5 volt version of COM 5016T                                                                                  | +5                | 18 DIP  | 275-276 |

| COM 8126                  | Single Baud Rate Generator | Single + 5 volt version of COM 5026                                                                                   | +5                | 14 DIP  | 277-284 |

| COM 8126T(1)              | Single Baud Rate Generator | Single + 5 volt version of COM 5026T                                                                                  | +5                | 14 DIP  | 277-284 |

| COM 8136                  | Dual Baud Rate Generator   | Single + 5 volt version of COM 5036                                                                                   | +5                | 18 DIP  | 275-276 |

| COM 8136T(1)              | Dual Baud Rate Generator   | Single + 5 volt version of COM 5036T                                                                                  | +5                | 18 DIP  | 275-276 |

| COM 8146                  | Single Baud Rate Generator | Single + 5 volt version of COM 5046                                                                                   | +5                | 14 DIP  | 277-284 |

| COM 8146T(1)              | Single Baud Rate Generator | Single + 5 volt version of COM 5046T                                                                                  | +5                | 14 DIP  | 277-284 |

| COM 8156                  | Dual Baud Rate Generator   | High-frequency clock input version of<br>COM 8116 with additional outputs of<br>input frequency $\div$ 2 and $\div$ 8 | +5                | 18 DIP  | 285-288 |

| COM 8156T <sup>(1)</sup>  | Dual Baud Rate Generator   | External clock input version of<br>COM 8156                                                                           | +5                | 18 DIP  | 285-288 |

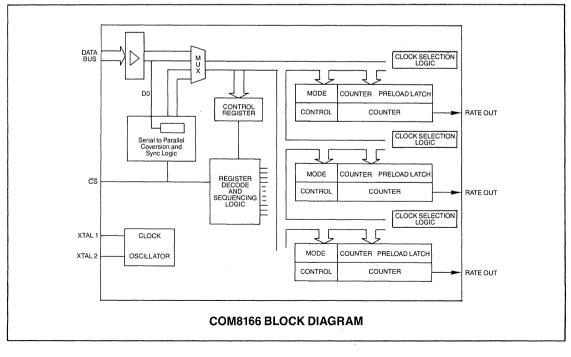

| COM 81C66(2)              | Timer/Clock Generator      | CMOS User Programmable Clock and Timer                                                                                | +5                | 16 DIP  | 289-290 |

| COM 81C66T <sup>(2)</sup> | Timer/Clock Generator      | External Frequency Input version<br>of COM 8166T                                                                      | +5                | 16 DIP  | 289-290 |

<sup>(1)</sup>May be custom mask programmed <sup>(2)</sup>For future release

# Keyboard Encoder

| Part<br>Number            | No. of<br>Keys | Modes | Features                                                                 | St<br>Suffix                | andard Fonts<br>Description | Power<br>Supplies | Package           | Page    |

|---------------------------|----------------|-------|--------------------------------------------------------------------------|-----------------------------|-----------------------------|-------------------|-------------------|---------|

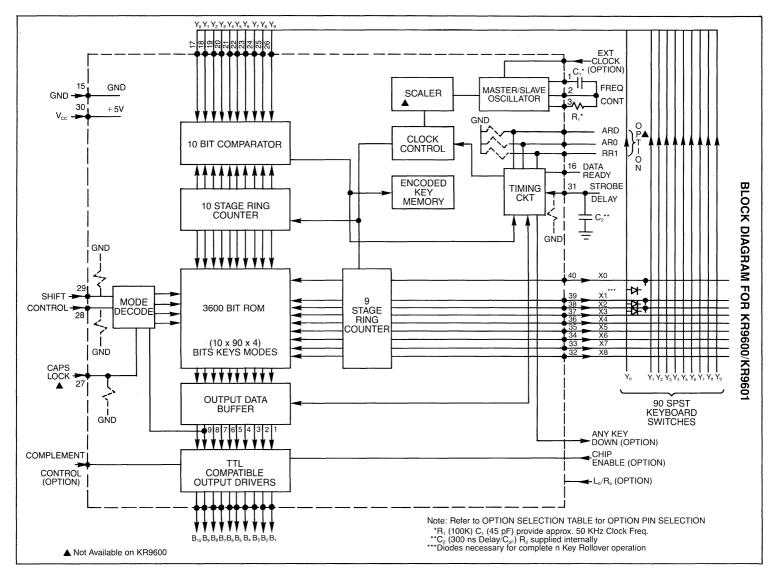

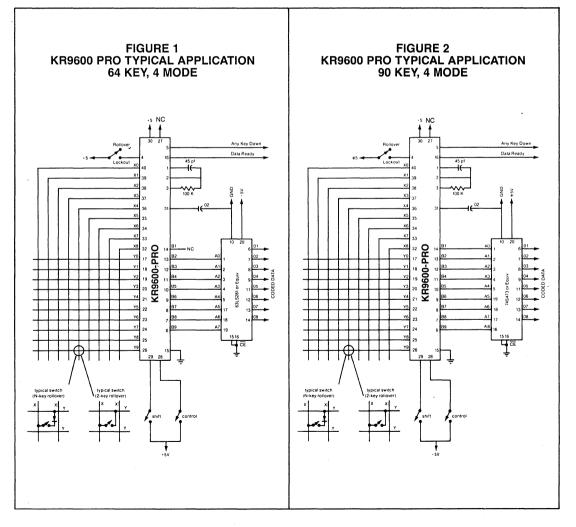

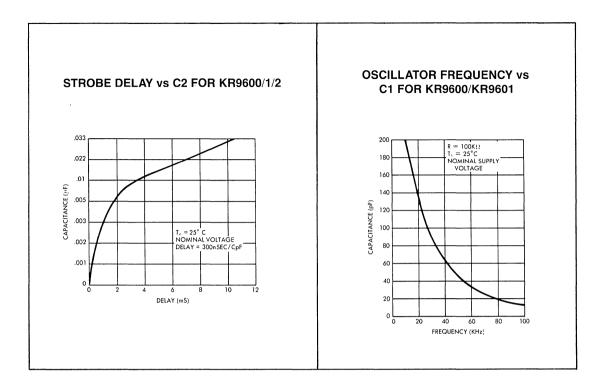

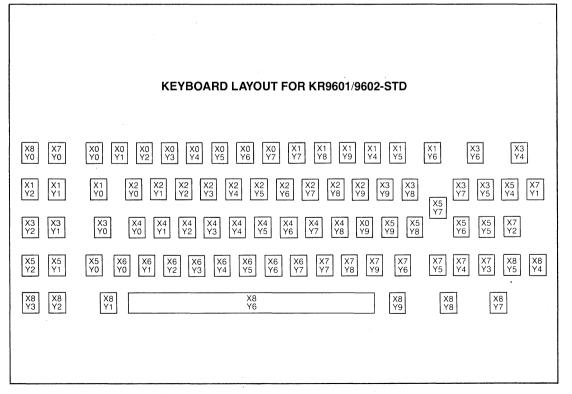

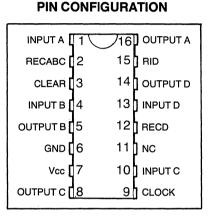

| KR-9600 XX <sup>(1)</sup> | 90             | 4     | 2 or N Key<br>Rollover                                                   | -PRO<br>-STD                | Binary Sequential<br>ASCII  | +5                | 40 DIP/<br>44 SMT | 665-678 |

| KR-9601 XX <sup>(1)</sup> | 90             | 4     | 2 or N Key<br>Rollover,<br>caps-lock, -012 <sup>(1)</sup><br>auto-repeat | -STD<br>-012 <sup>(2)</sup> | Binary Sequential<br>ASCII  | +5                | 40 DIP/<br>44 SMT | 665-678 |

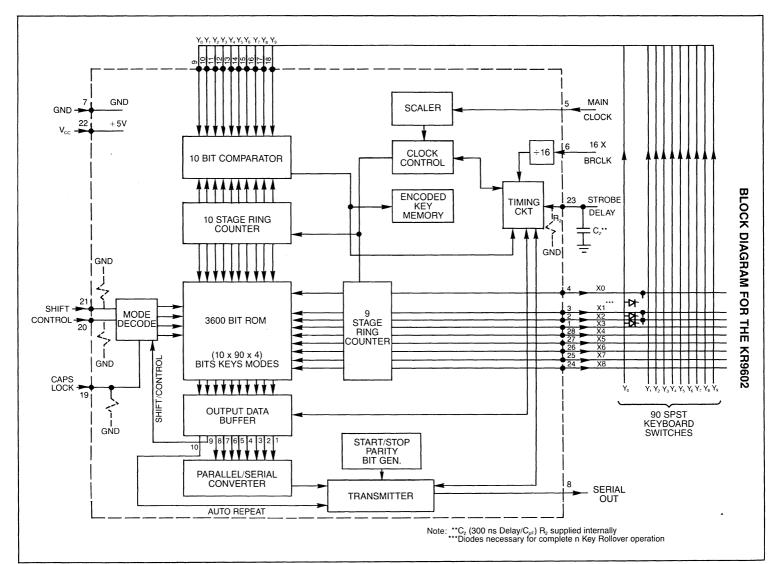

| KR-9602 XX <sup>(1)</sup> | 90             | 4     | 2 or N Key<br>Rollover,<br>caps-lock,<br>auto-repeat,<br>serial output   | -STD<br>-005 <sup>(2)</sup> | Binary Sequential<br>ASCII  | +5                | 28 DIP/<br>28 SMT | 665-678 |

${}^{(1)}\ensuremath{\text{May}}$  be custom mask programmed  ${}^{(2)}\ensuremath{\text{For}}$  future release

# Smmmmm Floppy Disk/Hard Disk

| Part<br>Number     | Description                                                                                                                 | Sector/<br>Format | Density        | Data<br>Bus | Side/Head<br>Select Output | Power<br>Supplies | Package            | Page    |

|--------------------|-----------------------------------------------------------------------------------------------------------------------------|-------------------|----------------|-------------|----------------------------|-------------------|--------------------|---------|

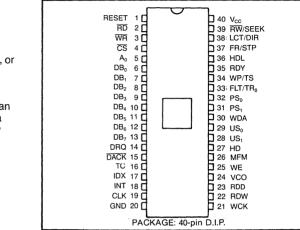

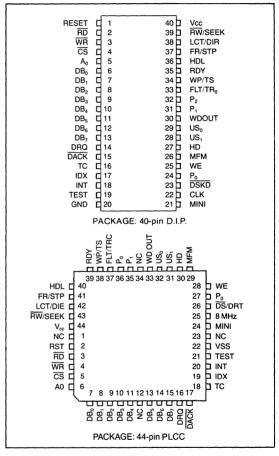

| FDC765A/765-2      | Floppy Disk Controller/Formatter                                                                                            | Soft              | Double         | True        | Yes                        | +5                | 40 DIP             | 459-474 |

| FDC7265            | Micro Floppy Disk<br>Controller/Formatter                                                                                   | Soft              | Double         | True        | Yes                        | +5                | 40 DIP             | 459-474 |

| FDC72C65           | CMOS Floppy Disk<br>Controller/Formatter                                                                                    | Soft              | Double         | True        | Yes                        | +5                | 40 DIP/<br>44 PLCC | 475-476 |

| FDC72C66           | CMOS Micro Floppy Disk<br>Controller/Formatter                                                                              | Soft              | Double         | True        | Yes                        | +5                | 40 DIP/<br>44 PLCC | 475-476 |

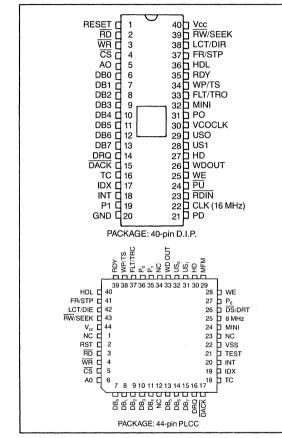

| FDC9266            | Floppy Disk Controller/Formatter<br>with data separator, and<br>write precompensation generator                             | Soft              | Double         | True        | Yes                        | +5                | 40 DIP/<br>44 PLCC | 523-538 |

| FDC9267            | Floppy Disk Controller/Formatter<br>with high performance analog<br>data separator and write pre-<br>compensation generator | Soft              | Double<br>Quad | True        | Yes                        | +5                | 40 DIP/<br>44 PLCC | 539-554 |

| FDC9268            | Enhanced Floppy Disk Controller/<br>Formatter with Data Separator and<br>Write Precompensation Generator                    | Soft              | Double<br>Quad | True        | Yes                        | +5                | 40 DIP/<br>44 PLCC | 555-556 |

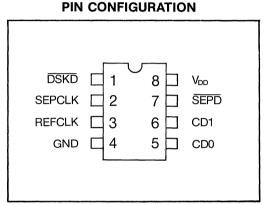

| FDC9216/B          | Floppy Disk Data Separator                                                                                                  | Soft/Hard         | Double         | NA          | NA                         | +5                | 8 DIP              | 493-496 |

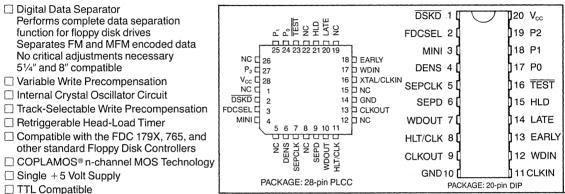

| FDC9229T/BT        | Floppy Disk Data Separator,<br>Head Load Timer, Write<br>Precompensation Generator                                          | Soft/Hard         | Double         | NA          | NA                         | +5                | 20 DIP/<br>28 PLCC | 497-504 |

| FDC92C36/B         | Enhanced CMOS Floppy Disk<br>Data Separator                                                                                 | Soft/Hard         | Double<br>Quad | NA          | NA                         | +5                | 8 DIP              | 505-508 |

| FDC9238/B/BT/T     | Enhanced CMOS Floppy Disk<br>Data Separator and<br>Clock Generator                                                          | Soft/Hard         | Double<br>Quad | NA          | NA                         | +5                | 14 DIP             | 509-512 |

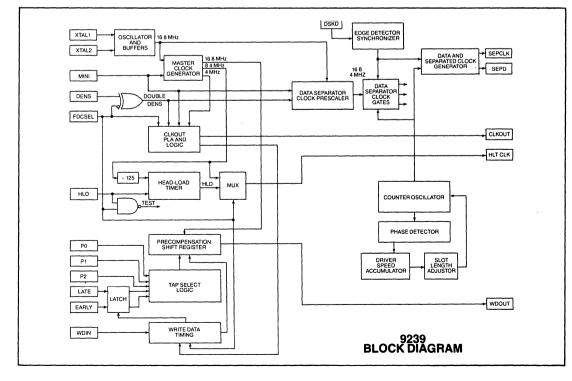

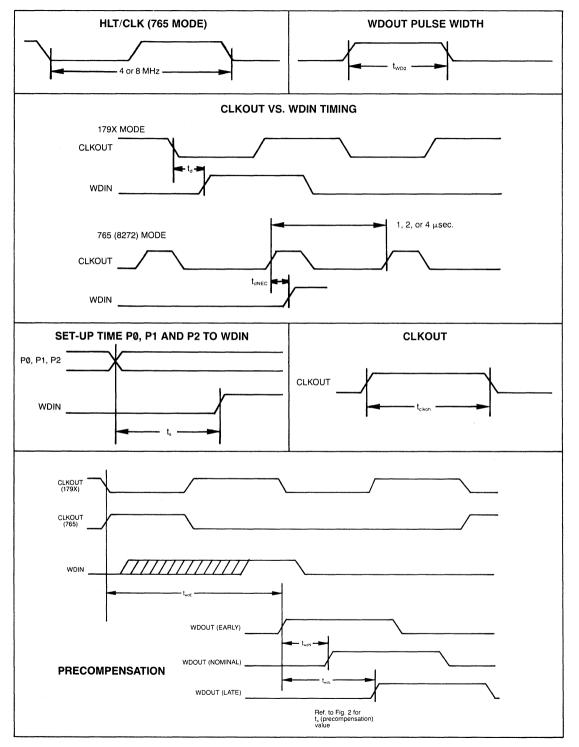

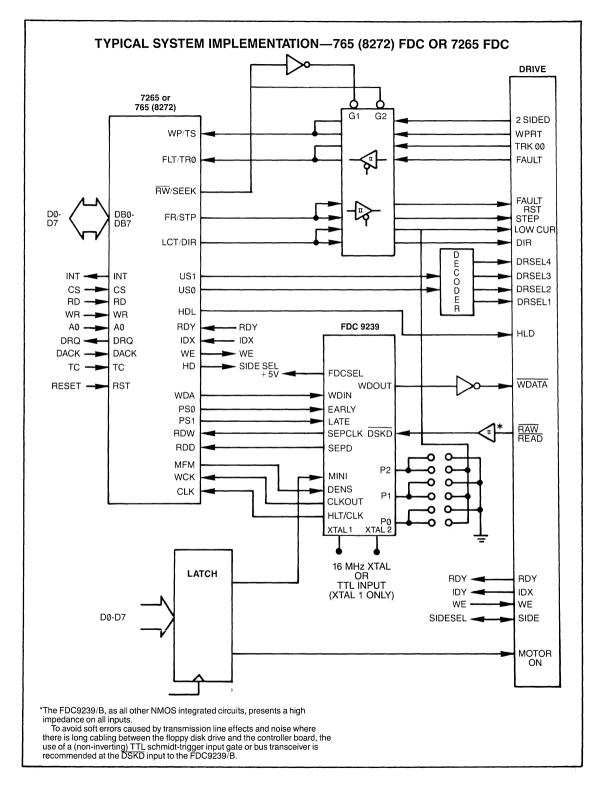

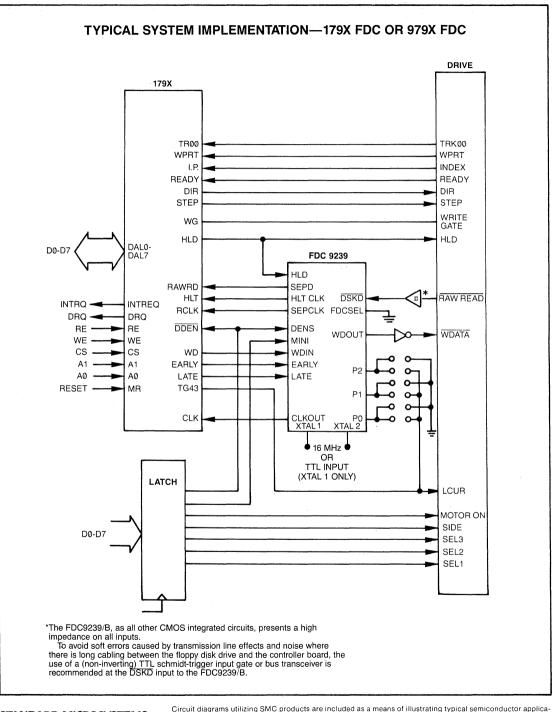

| FDC9239B/BT/T      | Enhanced CMOS Floppy Disk Data<br>Separator, Head Load Timer,<br>Write Precompensation Generator                            | Soft/Hard         | Double<br>Quad | NA          | NA                         | +5                | 20 DIP/<br>28 PLCC | 513-520 |

| FDC92C49           | Analog CMOS Floppy Disk Data<br>Separator, Head Load Timer,<br>Write Precompensation Generator                              | Soft/Hard         | Double<br>Quad | NA          | NA                         | +5                | 24 DIP/<br>28 PLCC | 521-522 |

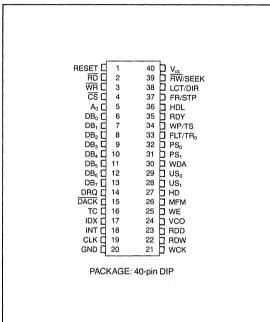

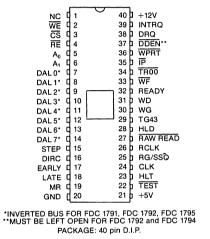

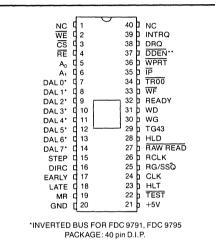

| FDC1791            | Floppy Disk Controller/Formatter                                                                                            | Soft              | Double         | Inverted    | . No                       | +5, +12           | 40 DIP             | 477-492 |

| FDC1793            | Floppy Disk Controller/Formatter                                                                                            | Soft              | Double         | True        | No                         | +5, +12           | 40 DIP             | 477-492 |

| FDC1795            | Floppy Disk Controller/Formatter                                                                                            | Soft              | Double         | Inverted    | Yes                        | +5, +12           | 40 DIP             | 477-492 |

| FDC1797            | Floppy Disk Controller/Formatter                                                                                            | Soft              | Double         | True        | Yes                        | +5, +12           | 40 DIP             | 477-492 |

| FDC9791            | Floppy Disk Controller/Formatter                                                                                            | Soft              | Double         | Inverted    |                            | +5                | 40 DIP             | 557-572 |

| FDC9793            | Floppy Disk Controller/Formatter                                                                                            | Soft              | Double         | True        | No                         | +5                | 40 DIP             | 557-572 |

| FDC9795            | Floppy Disk Controller/Formatter                                                                                            | Soft              | Double         | Inverted    |                            | +5                | 40 DIP             | 557-572 |

| FDC9797            | Floppy Disk Controller/Formatter                                                                                            | Soft              | Double         | True        | Yes                        | +5                | 40 DIP             | 557-572 |

| HDC1100-XX         | Hard Disk Controller                                                                                                        | Soft              | Double         | True        | NA                         | +5                | 20 DIP             | 573-592 |

| HDC7261<br>HDC9223 | Hard Disk Controller (ST506/SMD)                                                                                            | Soft/Hard         | Double         | True        | Yes                        | +5                | 40 DIP             | 593-594 |

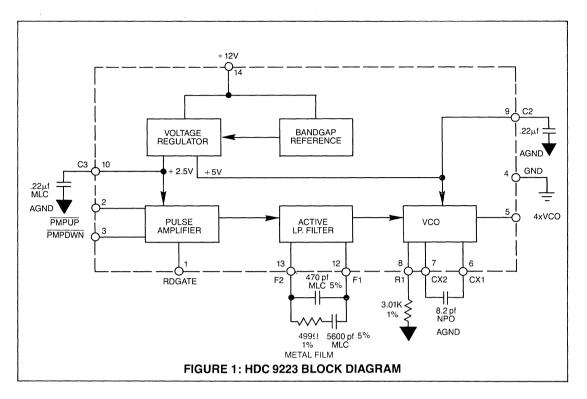

| HDC9223            | Analog Data Separator Support<br>Circuit                                                                                    | Soft              | Double         | NA          | NA                         | +12               | 14 DIP             | 595-598 |

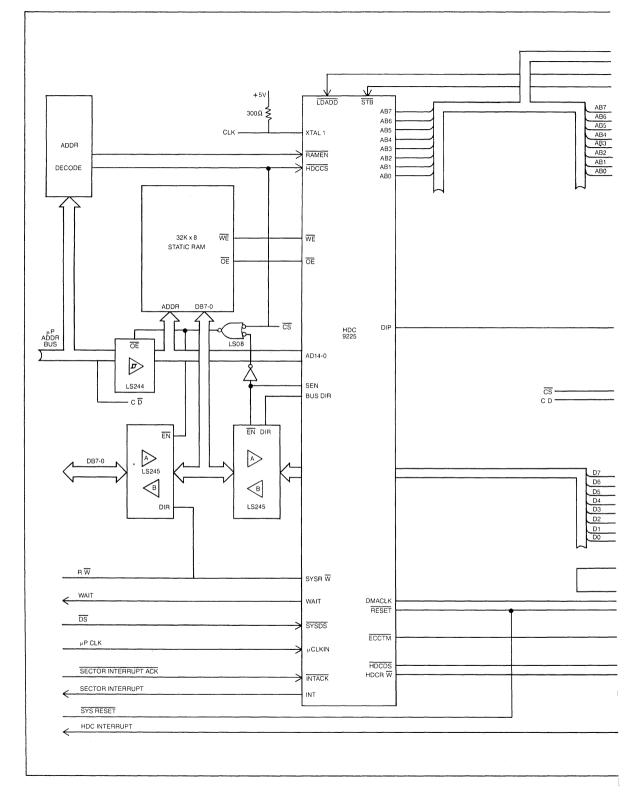

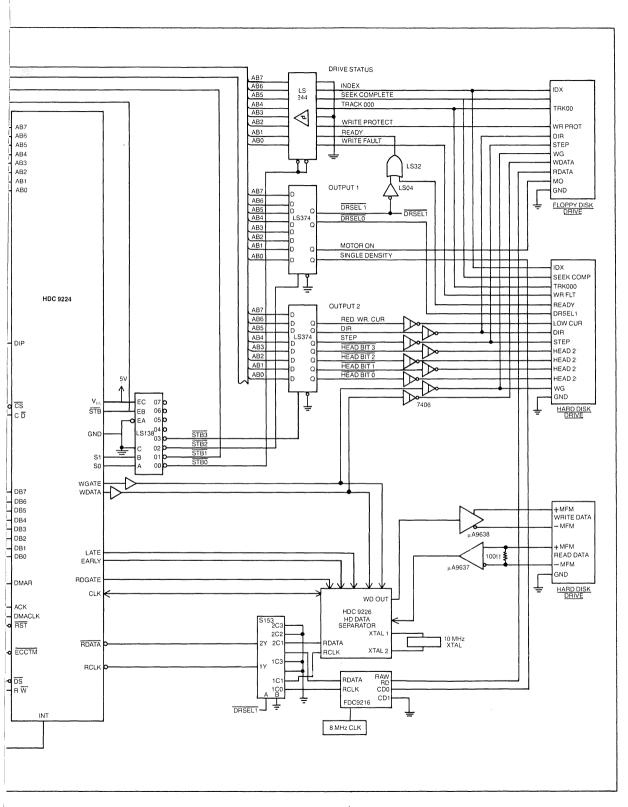

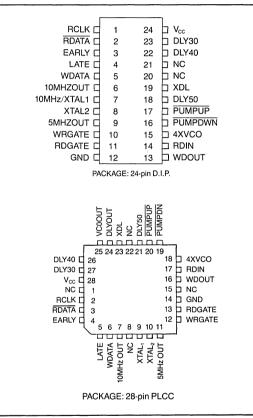

| HDC9224            | Hard/Floppy Disk Controller<br>Up to 4 drives with tape back-up                                                             | Soft<br>(ST-506)  | Double         | True        | Yes                        | +5                | 40 DIP/<br>44 PLCC | 599-634 |

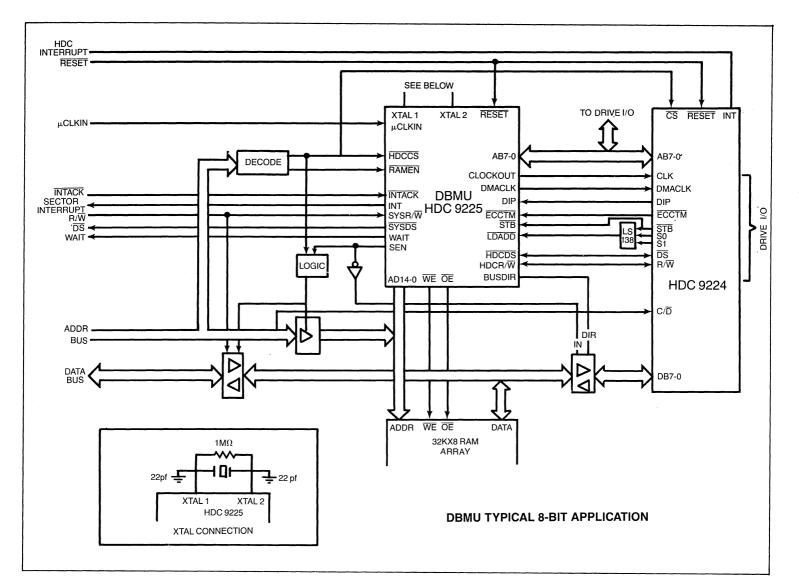

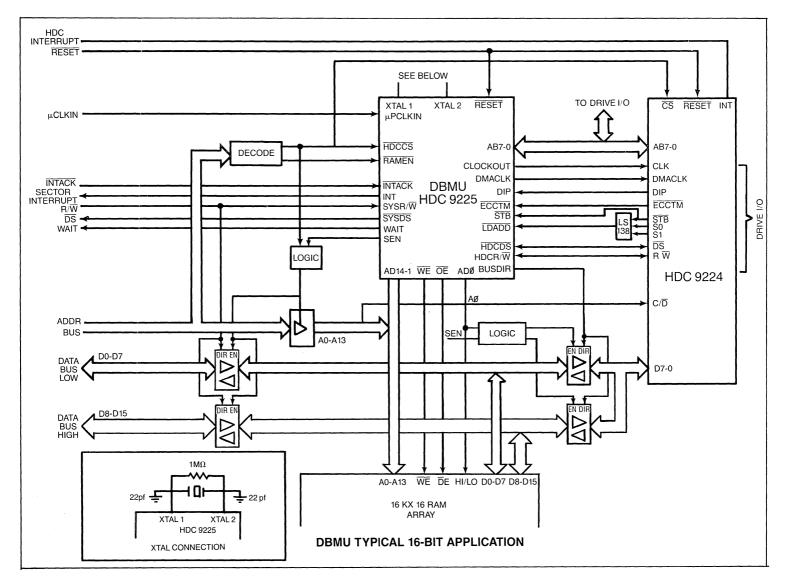

| HDC9225            | Disk Buffer Management Unit                                                                                                 | ST-506            | Double         | True        | NA                         | +5                | 48 DIP             | 635-646 |

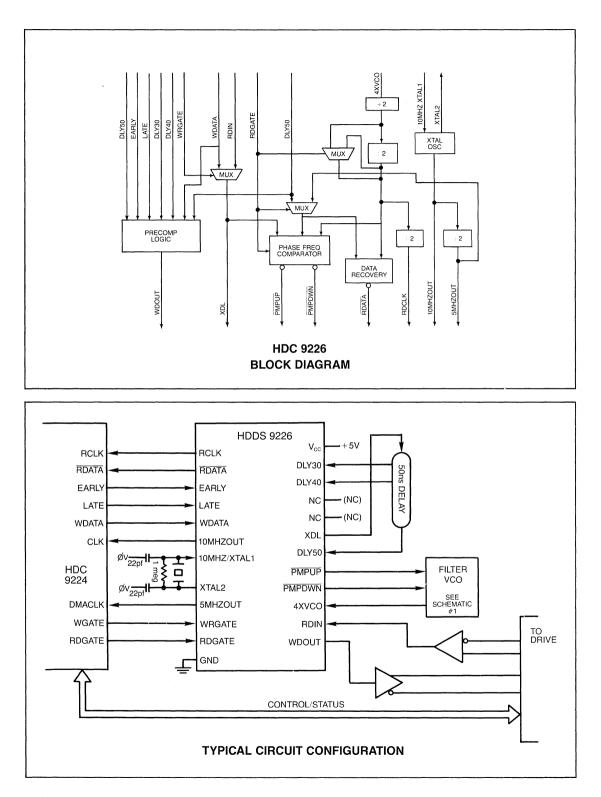

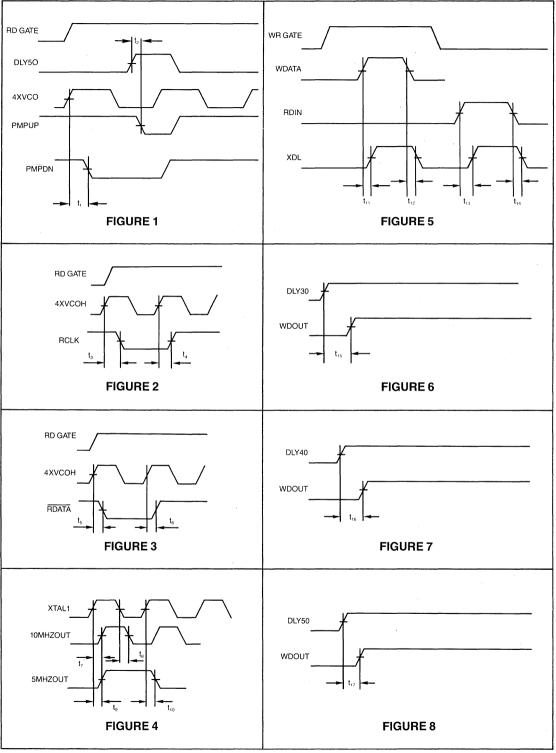

| HDC9226            | Hard Disk Data Separator                                                                                                    | ST-506            | Double         | NA          | NA                         | +5                | 24 DIP/<br>28 PLCC | 647-654 |

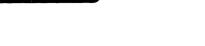

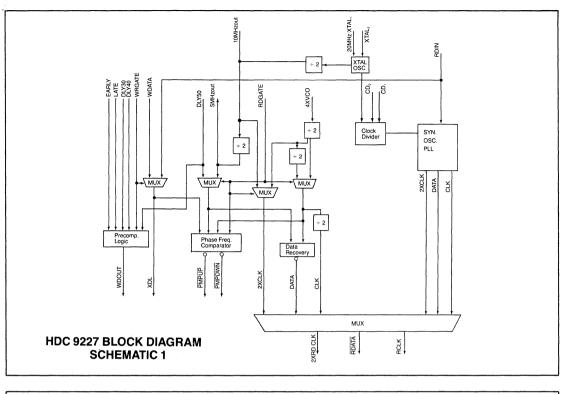

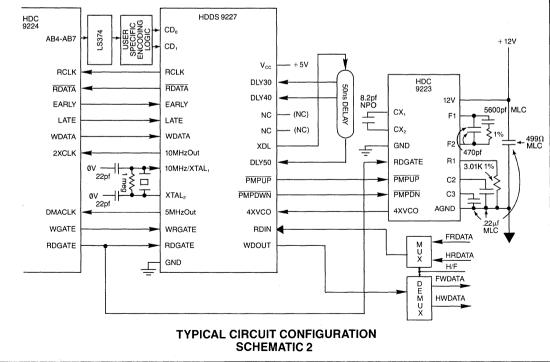

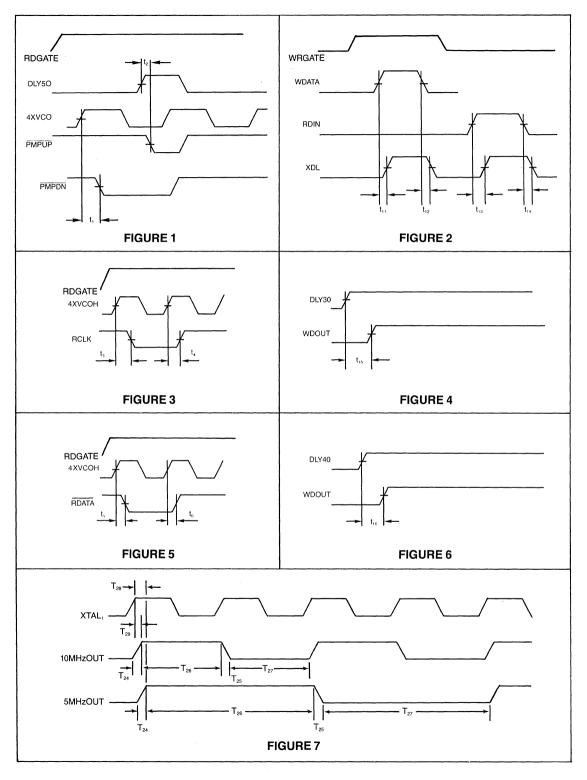

| HDC9227            | High Performance Hard Disk And<br>Floppy Disk Data Separators                                                               | Soft<br>(ST-506)  | Double<br>Quad | NA          | NA                         | +5                | 28 DIP             | 655-662 |

# Shift Register

| Part<br>Number      | Description                                            | Feature                              | Max<br>Clock Freq. | Power<br>Supply | Package | Page    |

|---------------------|--------------------------------------------------------|--------------------------------------|--------------------|-----------------|---------|---------|

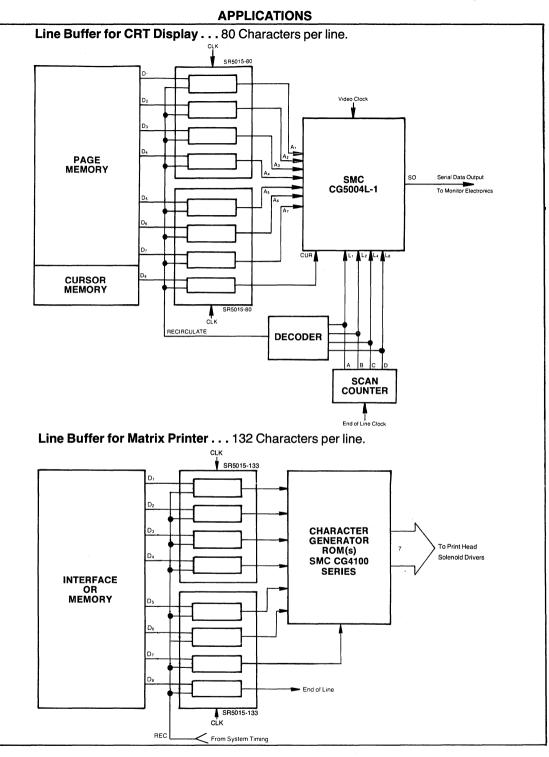

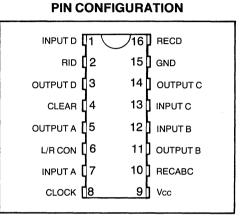

| SR 5015-80, 81, 133 | Quad Static Shift Register<br>Mask Programmable Length | Load, Recirculate,<br>Shift Controls | 1 MHz              | +5              | 16 DIP  | 681-684 |

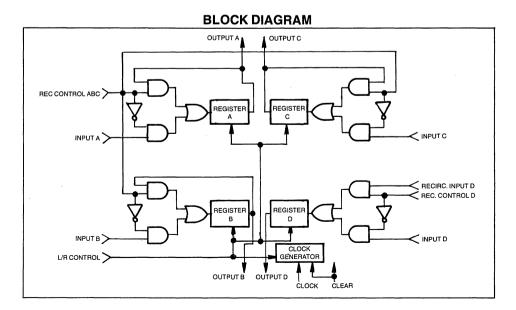

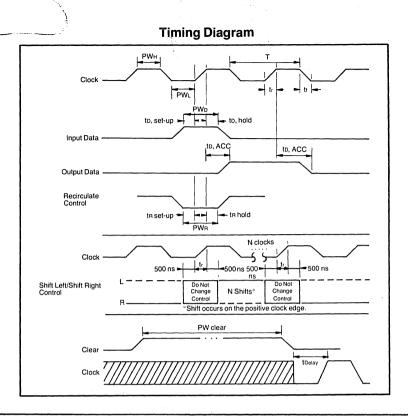

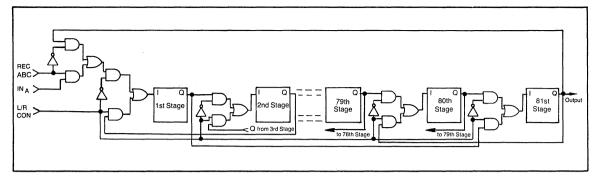

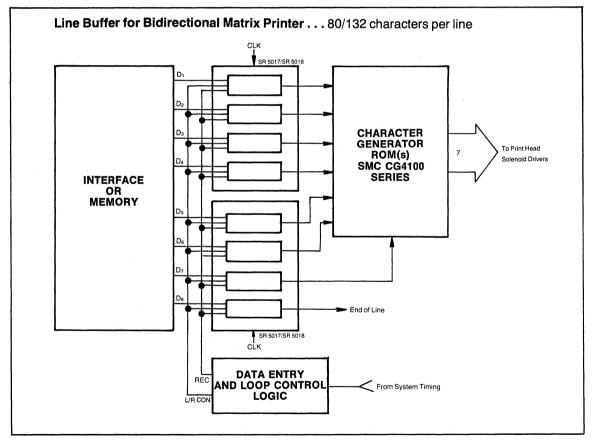

| SR 5017             | Quad 133 Bit                                           | Shift Left/Shift                     |                    |                 |         |         |

| SR 5018             | Quad 81 Bit                                            | Right, Recirculate<br>Controls       | 1 MHz              | +5              | 16 DIP  | 685-688 |

## **SMC CROSS**

| Description                                | SMC<br>Part #                | AMI       | AMD  | Fairchild           | General<br>Instrument | Harris             | Intel    |

|--------------------------------------------|------------------------------|-----------|------|---------------------|-----------------------|--------------------|----------|

| UART (11/2 SB)**                           | COM2017                      | S1883*    | _    | _                   | AY 5-1013A            | _                  |          |

| UART (1, 2 SB)**                           | COM2502                      |           |      |                     | AY 5-1013             | -                  |          |

| UART (n-Channel)**                         | COM8017                      | S6850*    | —    | F6850*              | AY 3-1015             | HM6402*            | -        |

| UART (n-Channel)**                         | COM8502                      | _         |      |                     | AY 3-1015             | HM6403*            |          |

| UART (n-Channel)*                          | COM1863                      | S1602*    | _    | _                   | —                     | —                  | _        |

| USRT                                       | COM2601                      | S2350*    | _    | -                   |                       | _                  | -        |

| ASTRO                                      | COM1671                      | _         |      |                     |                       | _                  |          |

| PCI                                        | COM2651                      |           | _    | _                   |                       |                    | _        |

| EPCI                                       | COM2661                      |           |      |                     | AY2661                |                    |          |

| USART                                      | COM8251A                     |           | 8251 |                     | _                     |                    | 8251A    |

| Multi-Protocc<br>USYNRT                    | COM5025                      | S6852*    |      | F3846*<br>F3856*    | _                     |                    |          |

| IEEE-488                                   | COM7210                      |           |      | F68488*<br>96LS488* |                       |                    | 8291/92* |

| COAX I/F Circuit                           | COM9004/<br>COM9064          |           | _    | _                   | _                     | —                  | _        |

| LAN Controller                             | COM9026                      | _         |      |                     | -                     |                    |          |

| Dual Baud Rate Gen.                        | COM5016/36/<br>COM8116/36    |           | _    |                     | AY5-8116/36           | _                  | _        |

| Single Baud Rate Gen.                      | COM5026/46/<br>COM8126/46    | _         |      | F4702*              | _                     | HD4702*<br>HD6405* | _        |

| 90 Key KB Encoder                          | KR9600/01/02                 |           |      |                     | AY 5-3600*            | _                  |          |

| CRT Controller                             | CRT5037                      |           |      |                     | -                     |                    | 8275     |

| Character Generator                        | CRT7004                      | S8564*    | _    |                     |                       | _                  |          |

| Character Generator/<br>Display Controller | CRT8002                      |           |      |                     |                       | _                  | _        |

| Graphics Controller                        | CRT7220/<br>CRT7220A         | =         | _    | Ξ                   | =                     | =                  | 82720    |

| Video Processor and<br>Controller          | CRT9007                      |           | —    | -                   | -                     | _                  |          |

| Video Attributes<br>Controller             | CRT9041                      | —         | _    | _                   | _                     | _                  | -        |

| Video Terminal Logic<br>Controller         | CRT9028/9128<br>CRT9053/9153 | _         | _    | _                   | _                     | _                  | _        |

| Shift Register                             | SR5015                       | S2182/3/5 |      | _                   | _                     | _                  | _        |

| CMOS Microprocessor                        | MPU800                       | _         | —    | _                   |                       |                    | -        |

| CMOS RAM-I/O-Timer                         | MPU810A                      |           | _    |                     |                       |                    | -        |

| CMOS ROM-I/O                               | MPU830                       | _         |      |                     |                       | —                  |          |

| CMOS Input/Output                          | MPU831                       | —         | _    | _                   | _                     | —                  | -        |

| Octal UART                                 | COM78808                     | —         |      | _                   | _                     | _                  | —        |

\*Functional equivalent.

\*\*Most UART'S are interchangeable; consult the factory for detailed information on interchangeability.

## **REFERENCE GUIDE**

| Motorola            | National   | NEC                 | Signetics | Solid<br>State<br>Scientific | DEC   | Texas<br>Instruments | Western<br>Digital |

|---------------------|------------|---------------------|-----------|------------------------------|-------|----------------------|--------------------|

|                     | MM5303*    | —                   | —         | —                            |       | TMS6011              | TR1602             |

|                     | —          | -                   | 2536*     | _                            | —     | _                    | TR1402             |

| MC6850*             | NSC858*    | _                   | —         | SCR1854*                     | —     | —                    | —                  |

| _                   | _          | _                   | —         |                              |       | —                    | TR1983*            |

|                     |            | -                   | —         | _                            |       | _                    | TR1863             |

|                     | —          | _                   | —         |                              |       |                      | _                  |

| _                   | INS1671    | —                   | _         | _                            | -     | —                    | UC1671             |

|                     | INS2651    | -                   | 2651      | _                            | _     | —                    |                    |

| MC2661*             | -          | -                   | 2661      | _                            | —     | —                    | —                  |

| -                   | INS8251    | μPD8251A            | _         | _                            | —     | —                    | TR1983*            |

| 2652*               | 6852*      | _                   | 2652      | SND5025                      | _     | —                    | SD1933*            |

| MC6BB488*           |            | μPD7210             | _         |                              | _     | TMS9914*             | WD9914*            |

|                     | DP8340/41* |                     | _         |                              |       | _                    | _                  |

|                     | _          | -                   | _         | _                            | —     | _                    | WD2840*            |

| _                   | _          | -                   | -         | _                            |       | —                    | BR1941<br>BR1943/4 |

| MC14411*            | MM307*     |                     | -         |                              | _     | _                    | _                  |

| —                   | MM5740*    | —                   | —         |                              |       | TMS5001              | —                  |

| MC6845*             | DP8350*    | —                   | _         | SND5027<br>SND5037           | _     | TMS9927              | —                  |

| MCM66700*<br>MC6570 | DM8678*    | _                   | 2609      | _                            | _     | _                    | _                  |

|                     |            |                     | _         | SND8002                      | _     | _                    | _                  |

| =                   | =          | μPD7220<br>μPD7220A | _         | =                            | =     | _                    | =                  |

| _                   | —          | -                   | SCN2674*  |                              | _     | _                    |                    |

| —                   | —          | _                   | SCN2675*  |                              |       | _                    | _                  |

| <u> </u>            | NS455*     | _                   |           |                              | —     | _                    | —                  |

|                     | 5024*      |                     | 2532*     |                              | _     | TMS3113*<br>TMS3114* |                    |

|                     | NSC800     | _                   | _         |                              |       | _                    |                    |

|                     | NSC810A    |                     | ·         |                              | _     | _                    | _                  |

|                     | NSC830     |                     | _         |                              |       |                      | -                  |

| _                   | NSC831     | _                   | -         |                              | _     |                      | _                  |

| _                   | ·          | _                   | _         | _                            | 78808 | _                    | _                  |

11

## FLOPPY DISK/HARD DISK

| Description                 | SMC<br>Part # | Fujitsu | NEC       | Western<br>Digital | intei | Siemens   | Rockwell |

|-----------------------------|---------------|---------|-----------|--------------------|-------|-----------|----------|

| Floppy Disk Controller      | FDC1791-02    | MB8876  | _         | FD1791-02          |       | SAB-1791  | —        |

| Floppy Disk Controller      | FDC1792-02    | _       |           | FD1792-02          |       |           | —        |

| Floppy Disk Controller      | FDC1793-02    | M8877   | _         | FD1793-02          | _     | SAB-1793  | _        |

| Floppy Disk Controller      | FDC1794-02    | _       | -         | FD1794-02          | _     | _         | _        |

| Floppy Disk Controller      | FDC1795-02    |         | -         | FD1795-02          |       | SAB-1795  | -        |

| Floppy Disk Controller      | FDC1797-02    |         | _         | FD1797-02          |       | SAB-1797  |          |

| Floppy Disk Controller      | FDC9791       | MB8876* |           | FD1791-02*         |       | SAB-1791* |          |

| Floppy Disk Controller      | FDC9793       | M8877*  |           | FD1793-02*         |       | SAB-1793* |          |

| Floppy Disk Controller      | FDC9795       |         | _         | FD1795-02*         |       | SAB-1795* |          |

| Floppy Disk Controller      | FDC9797       |         | _         | FD1797-02*         | _     | SAB-1797* | _        |

| Floppy Disk Controller      | FDC765A       | _       | μPD765A   | _                  | 8272A | _         | 765A     |

| Microfloppy Disk Controller | FDC7265       |         | μPD7265   | _                  |       | _         | _        |

| Floppy Disk Controller      | FDC765A-2     | _       | μPD765A-2 |                    | —     | -         | _        |

| Floppy Disk Controller      | FDC72C65      | _       | μPD72065C | — .                |       |           | _        |

| Microfloppy Disk Controller | FDC72C66      | _       | μPD72066C | _                  |       |           | —        |

| Floppy Disk Data Separator  | FDC9216       |         | _ ·       | FD9216             | _     | -         | —        |

| Floppy Disk Data Separator  | FDC92C36      |         |           | FD92C32            |       | -         | _        |

| Hard Disk Controller        | FDC7261A      | -       | μPD7261A  | _                  | _     | —         | —        |

| Hard Disk Controller        | HDC1100-XX    |         | -         | WD1100-X           | —     |           |          |

| Universal Disk Controller   | HDC9224       | -       | μPD7260** | — .                | _     | -         | -        |

\*SMC part will replace cited device with no changes required. \*\*Functional Equivalent.

## Innovation in Microelectronic Technology is the Key to Growth at Standard Microsystems.

Since its inception, Standard Microsystems has been a leader in creating new technology for metal oxide semiconductor large scale integrated (MOS/LSI) and very large scale integrated (MOS/VLSI) circuits.

Standard Microsystems' COPLAMOS® silicon gate n-channel process, licensed to over 15 prominent semiconductor companies, is the defacto standard for high speed, high density integrated circuits.

COPLAMOS<sup>®</sup> utilizes a self-aligned, field-doped, locally oxidized structure to eliminate parasitic currents and shunt capacitance, allowing the tight packing of circuitry essential for VLSI, yet with performance rivaling that of bipolar technologies.

In addition, on-chip generation of substrate bias, also pioneered by Standard Microsystems, when added to the COPLAMOS® technology, results in the ability to design dense, high-speed, low-power n-channel MOS integrated circuits through the use of one external power supply voltage.

Another Standard Microsystems' innovation is the CLASP® process. CLASP® provides a fast turnaround, easily programmable semi-custom LSI technology through the use of ion implantation to define either an active or passive device in the matrix of a memory or logic array. This step is accomplished after all wafer manufacturing steps are performed including metalization and final passivation layer formation. Thus, the wafer can be tested and stored until customer needs dictate the application, a huge saving in turnaround time and inventory costs.

These innovations in both process and circuit technology have received widespread industry recognition. In fact, many of the world's most prominent semiconductor companies have been granted patent and patent/technology licenses covering various aspects of these technologies. The companies include Texas Instruments, IBM, General Motors, ITT, Western Electric, Mostek, Hitachi, Fujitsu, National Semiconductor, Mitsubishi, NEC, AT&T, Data General, and Oki Electric, among others.

Over the past few years, scientists and engineers at Standard Microsystems have been developing a technology to significantly reduce the sheet resistivity of the gate material used in MOS, dramatically decreasing internal time constants in MOS devices.

This technology replaces the polycrystalline silicon normally used in n-channel MOS devices with an alternate material, titanium disilicide. This has enabled Standard Microsystems to become the first semiconductor manufacturer to market and sell MOS/VLSI circuits which employ a metal silicide to replace the conventional doped polycrystalline silicon layer.

Standard Microsystems is continuing its technological leadership with the introduction of new products utilizing advanced low power n-well and p-well CMOS processes.

## We've Established a Position as the Industry Leader in Microprocessor Peripheral Products with a Steady String of Industry "Firsts".

Innovation at Standard Microsystems extends far beyond new processes. Standard Microsystems has established a position as the industry leader in microprocessor peripheral products with a steady string of industry "firsts".

Standard Microsystems has continually recognized the need for communication controllers to handle the latest data communication protocols. As a result, Standard Microsystems has introduced many new products in the area of data communications. Among these are the COM2601, the first synchronous receiver/ transmitter for bi-sync protocols, and the COM5025, the first multiprotocol receiver/transmitter for all standard bit and byte oriented synchronous protocols, including SDLC, HDLC, ADCCP, bi-sync, and DDCMP.

Recognizing the office automation requirement for distributed processing via local area networks, SMC was the first to sell a monolithic VLSI circuit for Local Area Network Control, the industry standard COM9026, a complete controller for token-passing LAN systems. Other areas pioneered by SMC, with the introduction of unique monolithic controllers, include two important IBM families of computers with large installed bases and very high growth rate. The COM9064 is the first single controller for the IBM 3270 Coax Type "A" protocol, while the COM52C50 is the

first and only single chip controller for the IBM System/3x that is commercially available in the market.

SMC also has a first in the area of military standards with the COM1553B controller. This device integrates all the functions necessary to implement the MIL-STD-1553B communication protocol adopted as a standard by the three branches of the military in the U.S.

These data communications firsts offer designers cost effective solutions to the problems of connecting small computers to each other and to Mainframes.

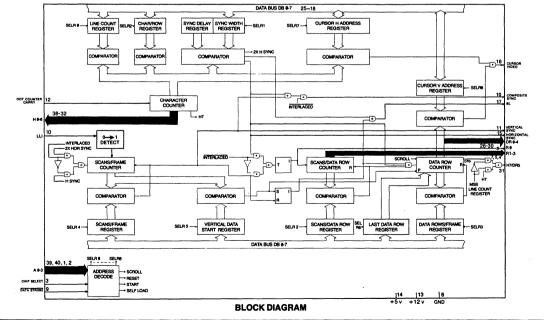

In another area, CRT display systems have traditionally required a great deal of support circuitry for the complex timing, refresh and control functions.

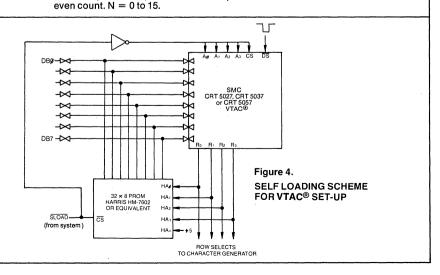

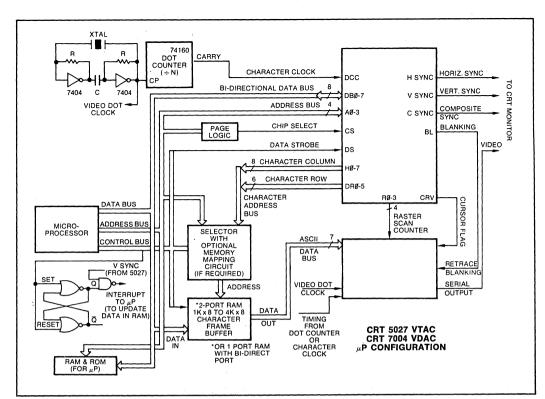

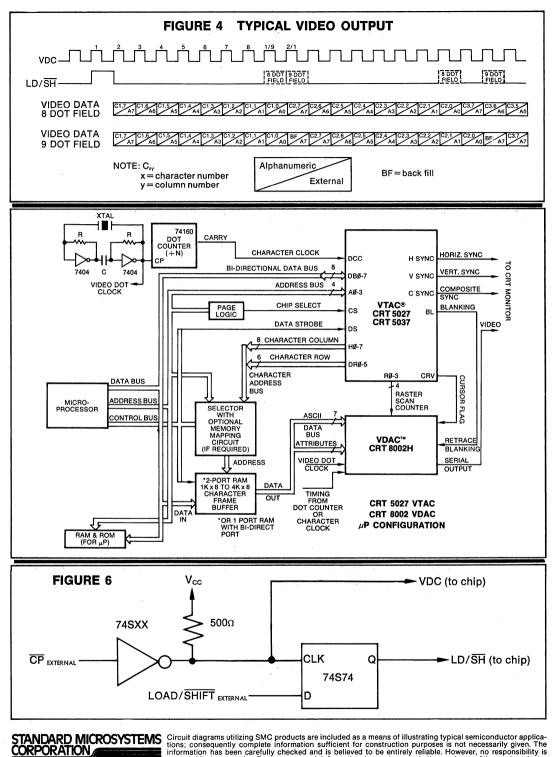

This need led the engineers at Standard Microsystems to develop the CRT5027 Video Timer and Controller (VTAC®), the first CRT controller to provide all of these functions on a single chip. The display, graphics and attributes control functions were then all combined for the first time in the CRT8002 Video Display Attributes Controller (VDAC®).

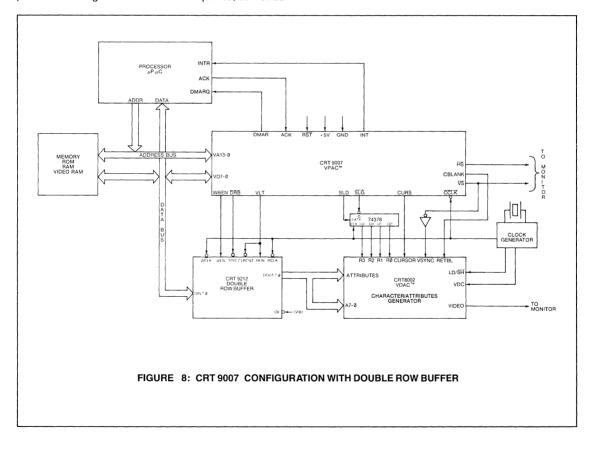

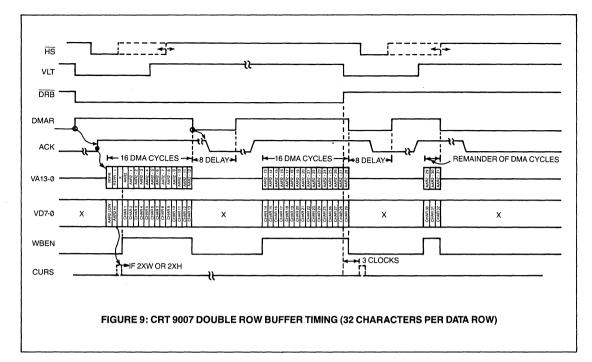

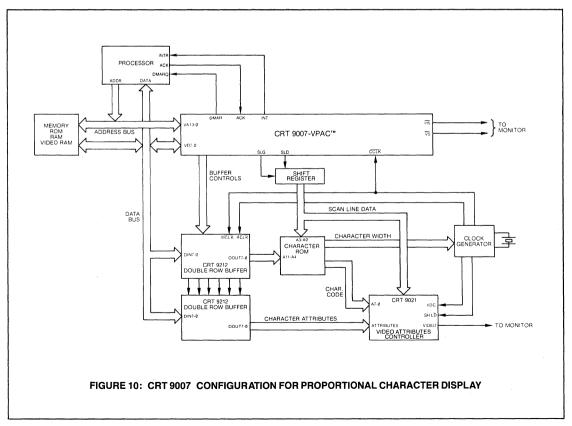

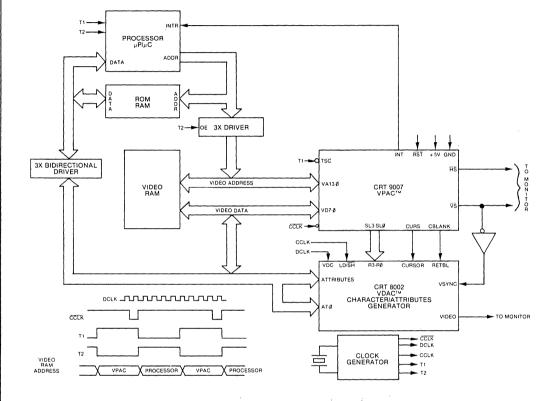

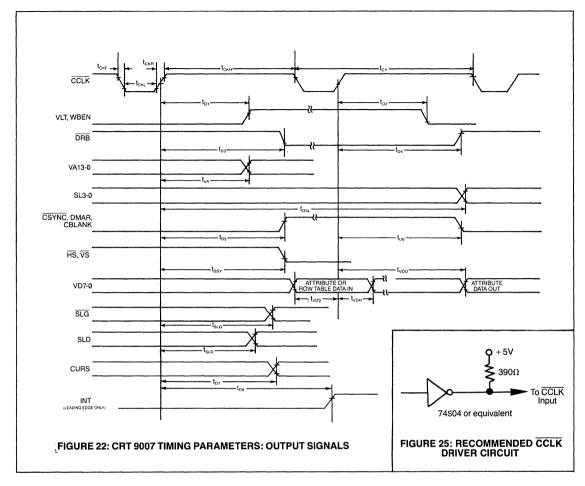

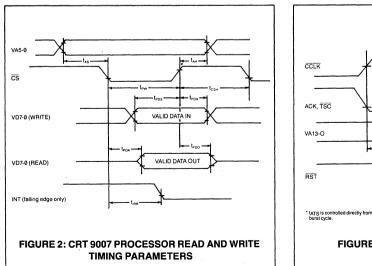

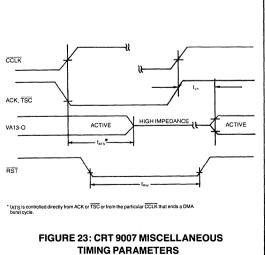

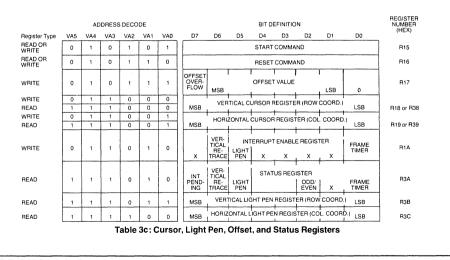

Another major achievement has been the development of the "next generation" Video Processor And Controller (VPAC®), the CRT9007. Besides replacing up to 80 SSI and MSI TTL devices, the VPAC® is the first CRT controller to provide a hardware solution to many of the software problems of CRT Video Controller design. The CRT9007 is the basis of a complete high performance, low cost, CRT control family, which includes single and double row buffers, and a variety of Video Attribute Controllers utilizing the COPLAMOS® technology to run from 20 MHz to 33 MHz. The various elements of the VPAC® family can be selected to provide the optimal video control solution from low to high end systems.

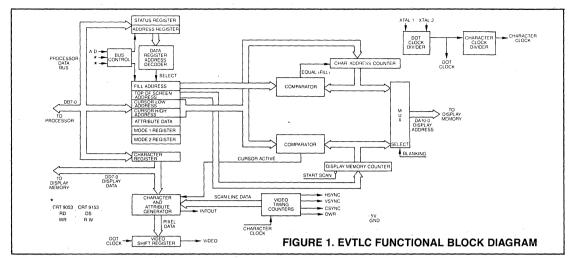

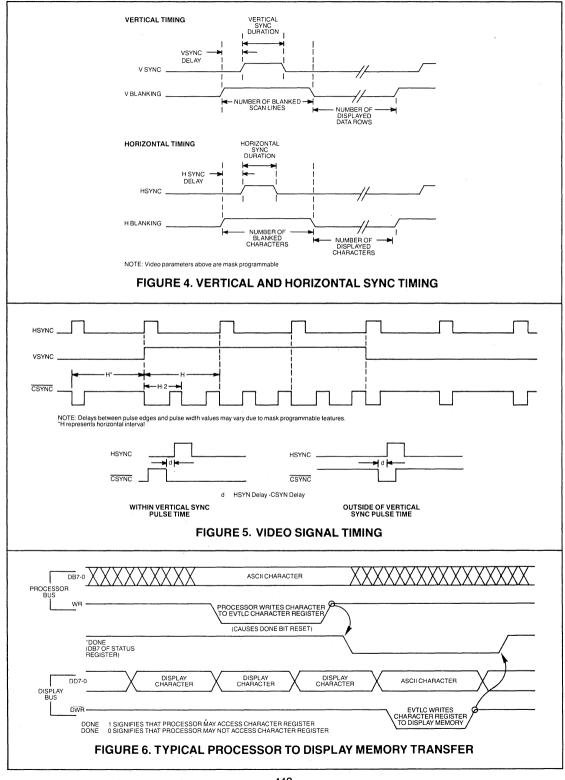

Most recently, the CRT9028 VTLC and CRT9053 EVTLC have integrated the entire video and attribute control functions, as well as the character generator, all on one VLSI circuit. A complete terminal can be built using these devices with just the inclusion of a RAM and microprocessor.

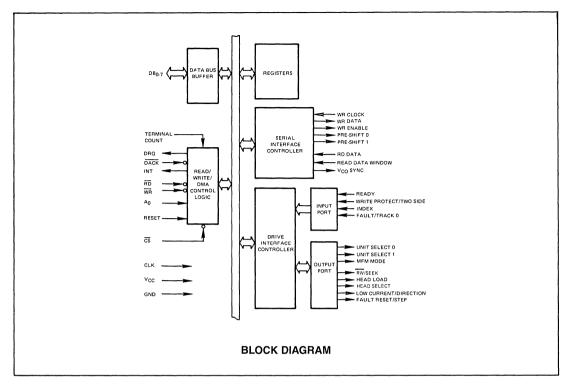

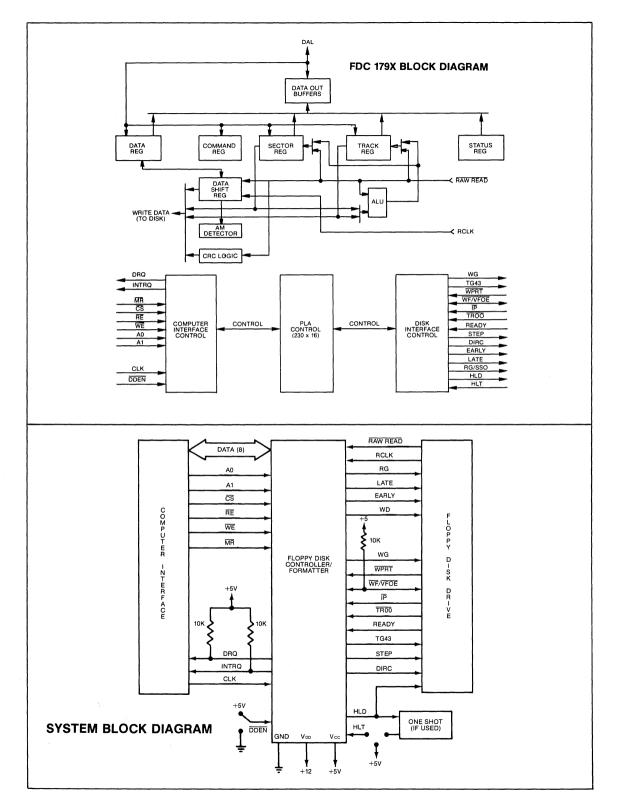

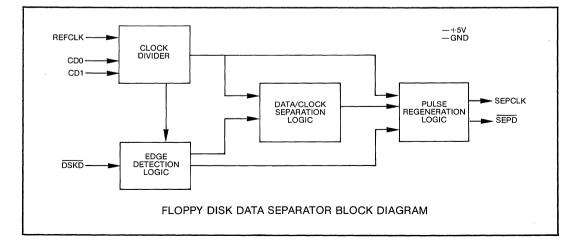

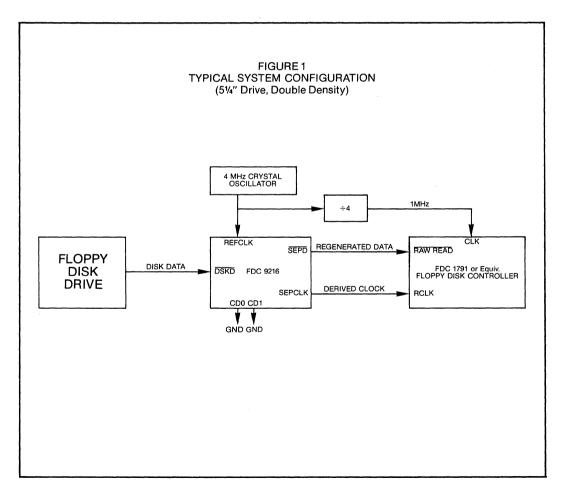

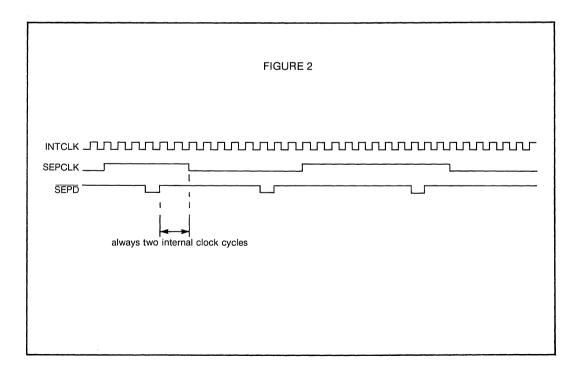

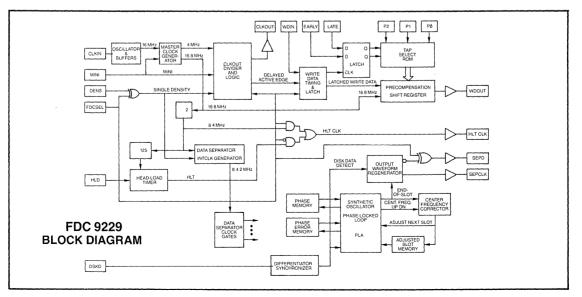

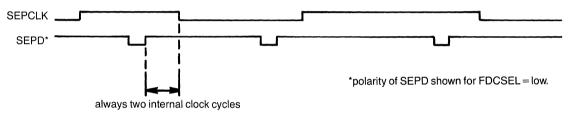

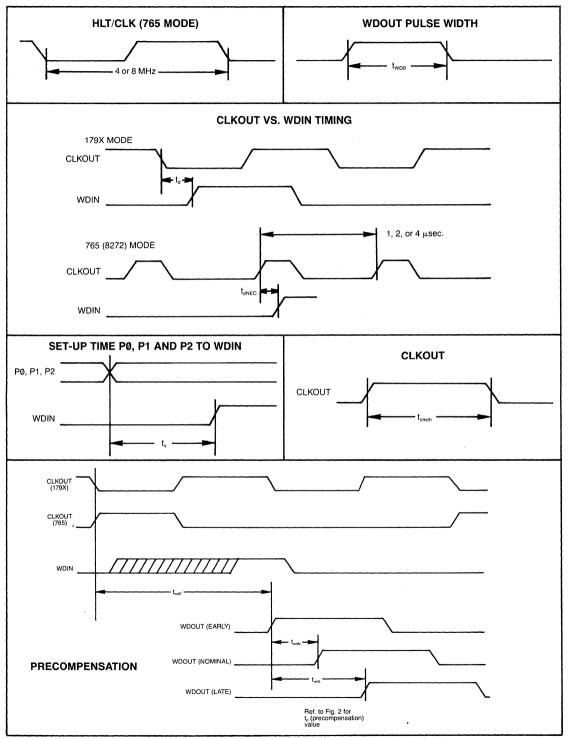

Standard Microsystems has spearheaded many developments in the rotating memory area as well. Extracting the actual stored data and clock signals from the distorted and jittery signal provided by a floppy disk drive has historically required not only a large number of analog components, but finicky production line adjustments. Both of these problems are solved by SMC products. The FDC9216 Floppy Disk Data Separator provides a revolutionary single chip solution to the data separation problem in a single 8 pin mini-dip package. Utilizing both long-term and short-term timing correctors, the FDC9216 requires absolutely no external components or adjustments. The FDC9229 Floppy Disk Interface Circuit provides, in addition to the digital data separator, a clock generator, precom-

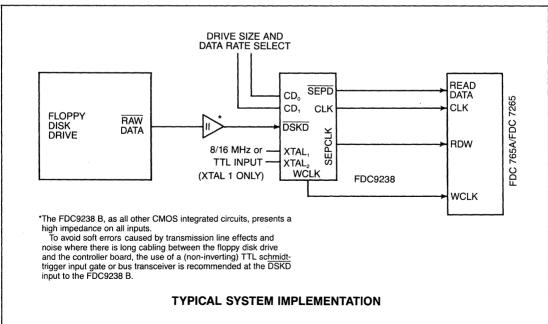

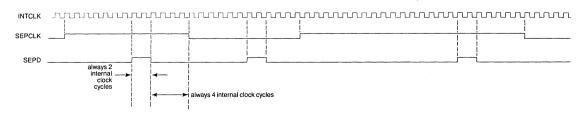

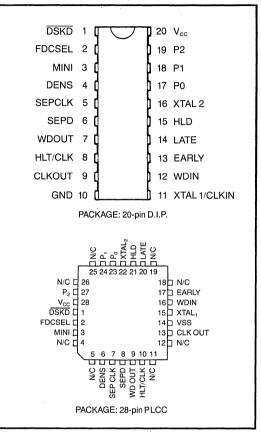

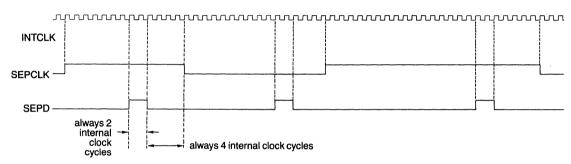

pensation generator, and head load timer. The new FDC9236 and FDC9239 provide even higher resolution data acquisition with the additional benefit of low power CMOS technology. The FDC9236 and FDC9239 are pin for pin replacements for the FDC9216 and FDC9229. SMC's FDC9238 offers high resolution, CMOS technology, and FDC765 compatibility, all in a 14 pin package.

Along with these data separators, Standard Microsystems offers a broad line of floppy disk controllers, including the FDC9266, FDC9267, and FDC9268, which combine the industry standard FDC765A Floppy Disk Controller with a choice of SMC Data Separator/Precompensation Generators, all on one chip. The FDC9266, FDC9267, and FDC9268 provide the highest level of integration in floppy disk control circuits.

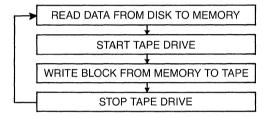

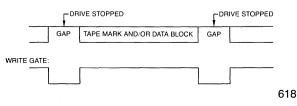

The HDC9224 Universal Disk Controller is the first IC to control not only hard disks, but also floppy disks and the tape drives used to back up the disks, as well. In addition, it offers user transparent error detection and correction for up to four 16 head drives.

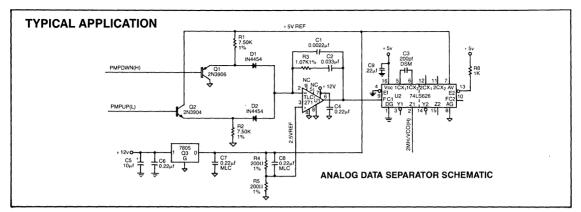

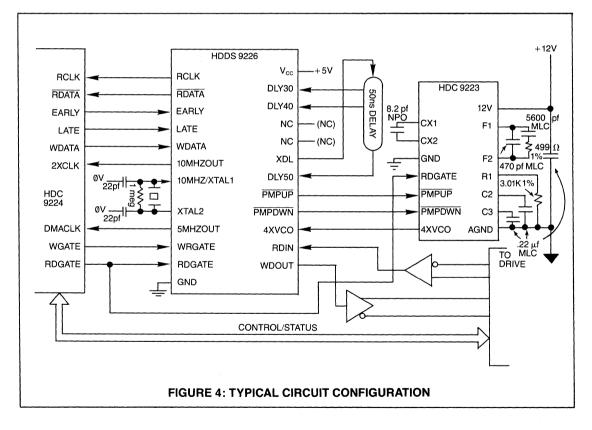

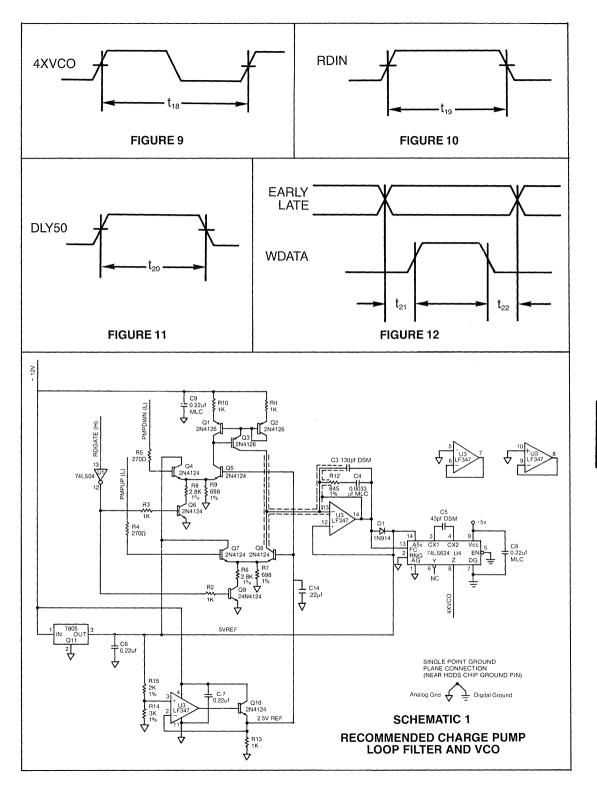

Hard disk drives suffer from the same signal distortion and jitter as floppy disk drives. SMC provides a choice of Hard Disk Data Separators to solve this problem. The HDC9226 enhances the HDC9224 by providing hard disk data separation with a soft error rate as low or lower than that of the drive itself. The HDC9227 Dual Data Separator includes both a Hard Disk Data Separator and a high resolution Floppy Disk Data Separator on a single chip. Designed for use with either the HDC9226 or HDC9227, the HDC9223 Analog Data Separator Support chip includes all the active analog circuit components needed to form a phase locked loop for performing hard disk data separation.

The HDC9225, when used with the HDC9224, greatly reduces the total number of IC's required by a hard disk control system, while permitting low cost RAMs to be used in a dual-ported configuration to improve system performance.

Achievements like these help keep Standard Microsystems' custom and standard products in the forefront of technology, with increased speeds and densities and a lower cost per function.

### Improvements in Processing and Manufacturing Keep Pace with Advances in Semiconductors.

With the phenomenal growth of the electronics industry, innovation is, of course, highly desirable. But, if the products are to perform as designed, they also have to be reliable.

That's why at Standard Microsystems we take every means to insure the utmost quality and dependability. Consequently, "state-of-the-art" applies not only to our products, but to the way we manufacture them.

In wafer fabrication, the latest equipment and techniques are employed. In addition to conventional processing equipment, we use ion implantation technology extensively. We also use plasma reactors for much of our etching and stripping operations to maintain tight tolerances on process parameters. Perkin Elmer scanning projection printers and TRE mask steppers assure that the critical photolithographic requirements of the latest small geometry processes are met.

Standard Microsystems' commitment to excellence is further demonstrated in the use of the latest Fairchild, Megatest and Genrad testers. Our full service capability lets us make full use of the technologies we develop. We can produce any quantity of semiconductors customers may require. What's more, we can provide our customers with the fast delivery times that they require in today's increasingly competitive environment.

## Custom MOS. A Small Revolution with a Large Impact.

Remarkable advances in semiconductor technology, combined with the availability of quality, low-cost electronics, continue to open new markets for products incorporating micro-electronic components.

Today, metal-oxide semiconductor/large scale integrated (MOS/LSI) circuits are integral components in computers and computer peripherals, automobiles, televisions, electrical appliances, data communications, bank terminals, telephones and a host of other significant applications.

With further applications for large scale integrated and very large scale integrated (VLSI) circuits being discovered every day, one thing is certain. They will have a profound effect on our lifestyle.

### Custom Commitment.

Custom Products has its own management, marketing, and engineering team that is fully dedicated to developing and producing standard cell semicustom and full custom products.

Custom MOS/LSI is a major portion of our business. A sizable portion of all our revenue is a direct result of our custom MOS/LSI projects.

Over the years, Standard Microsystems has developed custom circuits for a wide variety of applications: Computers and computer peripherals, telecommunications and data communications, garage door openers and burglar alarms, electronic toys and games, musical instruments and more. Both over-theair and cable T.V. systems have made use of our custom circuits. One company's line of word processing equipment makes almost exclusive use of our custom LSI.

As a company committed to serve the custom marketplace, Standard Microsystems has developed the resources and established procedures for MOS/LSI and MOS/VLSI circuit development that enables the company to respond rapidly to growing customer needs.

### The Custom Option.

Standard Microsystems offers two custom design alternatives: fully crafted custom

design and cell library based designs. Where reduction of chip size for lowest production pricing in high volume is the dominant factor, the fully crafted design method will provide the best solution. However, development costs and development time will be greatest. Where quick turnaround and reduction of engineering costs are dominant factors then use of our cell library design approach will be the better alternative.

Regardless of the design approach, a custom circuit will provide—

#### Lowest Overall Cost.

The overall cost savings realized with custom MOS/VLSI circuitry can be substantial, especially when high-volume production is encountered.

Savings are effected in several ways. Because custom designed circuits contain only necessary components, the cost of unused circuitry on standard microprocessors or integrated circuits is eliminated. Costs for troubleshooting, repair and warranty claims are reduced. In addition, custom MOS can be more economical over SSI and MSI when purchase, inventory and assembly costs are considered. Also, when a system contains a large amount of SSI and MSI, its custom counterpart can significantly reduce power consumption.

#### Lowest Parts Count.

There are many applications where a singlepackage custom LSI or VLSI circuit can outperform a microprocessor and its ROM and RAM circuits while reducing costs. A custom LSI unit can rapidly execute repetitive functions using high speed logic. A microprocessor needs time-consuming algorithms to do the same thing.

#### Highest Reliability.

Higher reliability is achieved, especially when replacing circuits that contain significant amounts of SSI and MSI. Fewer parts and solder points reduce the failure rate and raise the reliability. This means low MTTR (mean time to repair), which translates into lower maintenance costs and higher customer satisfaction.

#### Minimum Size, Weight, Power Dissipation.

The size and complexity of printed circuit boards are greatly reduced when using a custom circuit. The custom circuit results in a most compact package, specifically designed to perform only the necessary tasks utilizing minimum power and space.

#### Unique Proprietary Features.

Proprietary design is another major benefit. It protects your design from would-be copiers because it makes testing and support difficult. This, coupled with the complexity of custom semiconductor fabrication, makes duplicating your custom circuit far less probable.

### A Complete Cell Library Design System for Semicustom LSI/VLSI.

#### An idea whose time has come.

To prosper, if not survive, in today's fast-paced electronics industry, you must differentiate your products from the competition.

This means designing in more features, higher reliability and lower power consumption, while reducing size to a minimum. Of course, your next-generation products should also cost less than their predecessors.

i-ull custom CMOS LSI/VLSI is one way to achieve these goals, but that approach has definite limitations. For example, long development times can upset scheduled product introductions and high development costs can significantly erode profit margins.

Fortunately, the availability of powerful workstations and a new generation of CAD software tools has created a viable alternative: Semicustom LSI/VLSI.

Now, Standard Microsystems Corporation is offering you a complete semicustom design system that combines the advantages of full custom CMOS with rapid turnaround, low cost and virtually guaranteed first-time success.

We call our new system Customation<sup>™</sup>. It is a "standard cell" design approach that uses a database of proven building blocks and a family of state-of-the-art software tools which enable the engineer to both perform the design and verify it with the utmost speed and precision.

A typical Customation™ design sequence involves the use of a progression of software design tools, with the output of one serving as the input for the next. Although the designer is constantly monitoring this process, he is not actually "in line". Therefore, problems due to human error are virtually eliminated and you're assured that first silicon is working silicon.

The result? You get the semicustom ICs you need quickly and your development and production costs are reduced.

## Bringing Process, Software and Hardware Together.

#### Process technology you can count on.

For over a decade, Standard Microsystems has been at the leading edge of n-channel, silicon-gate process technology. Our patented COPLAMOS® process is used throughout the world and is one of the most widely licensed processes in the semiconductor industry.

Now we've channeled our expertise into a production-proven 3-micron, silicon-gate CMOS process that's compatible with the design rules of several other major semiconductor manufacturers, including NCR Corporation, our contractual alternate source. It's the cornerstone of our Customation™ design system.

#### A large, proven cell library.

The Customation<sup>™</sup> cell library includes more than 180 cells. Most emulate 74LS logic functions, so your design engineers are already familiar with them. The design system stores the cell layouts, logical models and performance characteristics of each cell in its database. You can feel confident about the performance of these cells, too. They are thoroughly characterized and have been used successfully in numerous applications.

Standard Microsystems is dedicated to incorporating more complex macrocells and supercells into the library. These currently encompass such functions as ROMs, RAMs, and core microprocessors and, in the future, will include data communications functions as well as computer peripheral controllers developed at SMC.

#### Industry-standard software.

Customation<sup>™</sup> gives you a complete and integrated set of software tools for design, simulation, modeling, checking, and verification test pattern generation.

CUSTOMATION™ is a trademark of Standard Microsystems Corporation COPLAMOS® is a registered trademark of Standard Microsystems Corporation.

SECTION II

Whenever possible, we've utilized "industrystandard" software that provides a wellproven package of design aids which many of your engineers may already be comfortable using. It can also be licensed through Standard Microsystems.

#### A turnkey workstation.

Standard Microsystems offers a complete turnkey workstation design system that you can use at your own facility. This system, along with SMC's utility software, is optimally configured for semicustom design, combining high performance and ease of operation. We are also constantly enhancing our software to support other workstations and mainframes. Workstations can be acquired directly from the manufacturer or through special arrangement with SMC.

Much of our software already runs on VAX computers. We are currently porting our cell library and software onto several other popular workstations. Please check with us on the status support for your preferred workstation.

### A Design Partnership.

#### Comprehensive training.

Even if you've never had IC design experience, Standard Microsystems can quickly teach you to create cell-based ICs using Customation™.

At our plant on Long Island, we conduct classes for all skill levels, tailoring our instruction to your particular needs and experience level. We cover all phases of design, and you'll work on an actual Customation™ workstation to get hands-on experience and sharpen your design technique. You'll complete the training session ready to produce usable designs utilizing Customation™.

#### Do your design work at your place or ours.

A major benefit of Customation<sup>™</sup> is the control it gives you over your design. You work at your own pace—at your own facility, if you wish—verifying the logic through simulation at each step of the way.

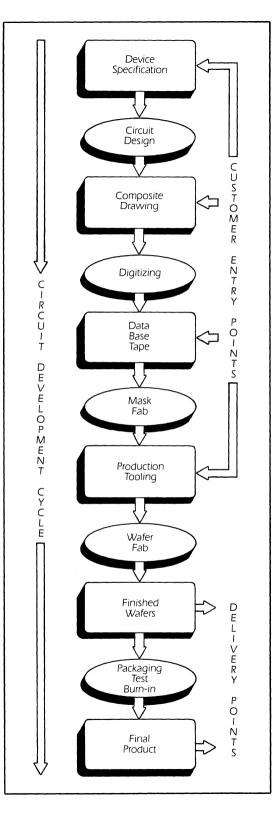

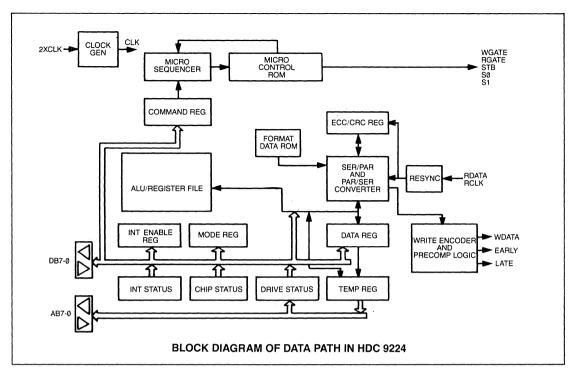

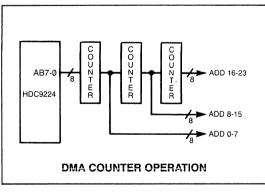

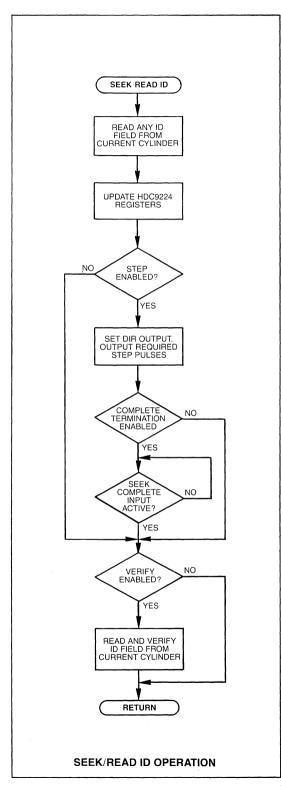

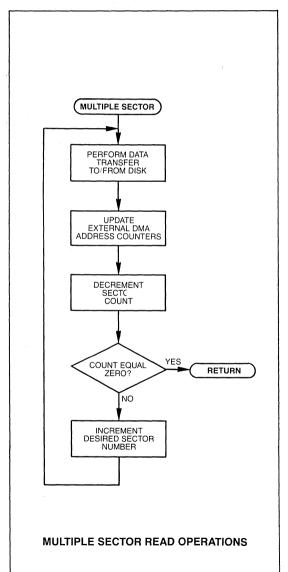

We provide everything you need to perform the design from schematic capture through logic simulation and timing analysis.