# LOAD-COMPENSATED DTL INTEGRATED CIRCUIT

## TYPES ZAO1A AND ZAO2A SINGLE AND DUAL NAND/NOR GATES

## ONE OR TWO DIODE-TRANSISTOR LOGIC CIRCUITS IN A SINGLE CHIP OF SILICON

- Low Power-Speed Product 60 pico-watt-sec

- Operates From Single Power Supply

- Typical Propagation Delay Time 12 nsec

- Typical Power Dissipation 5mw

- High Fan-Out-5 at -55 to 70°C

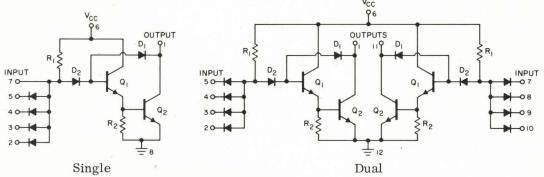

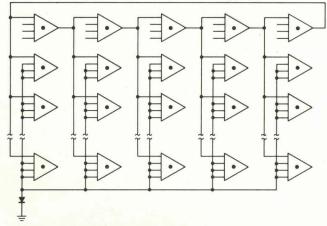

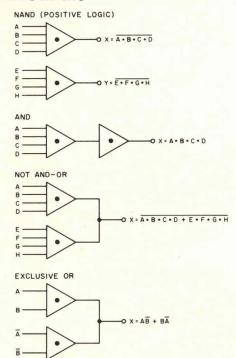

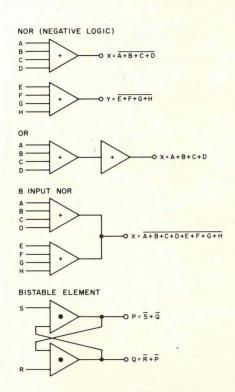

#### CIRCUIT DIAGRAMS

The logic operation of this circuit is identical with conventional DTL. The unique emitter-follower diode-clamp arrangement provides high-speed switching, high gain and low-power operation.

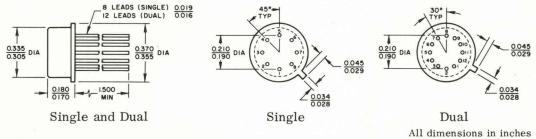

## MECHANICAL DATA

Single gate in modified 8-lead TO-5 package Dual gate in modified 12-lead TO-5 package (both available in flat package by July 1963)

Pin 8 (single) and pin 12 (dual) are in electrical contact with the case.

## PRODUCT CONDITIONING

Long life and mechanical reliability are ensured by subjecting <u>each unit</u> to the following tests:

- High Temperature Storage: 72 hours at 200°C

- Thermal Shock: +200°C to -65°C for 5 Cycles

- 30,000G Centrifuge in the Y<sub>1</sub> Plane

- Helium and Gross Leak Tests for Hermeticity

- Post-Bake Clean-Up to Assure Solderability

1140 West Evelyn Avenue Sunnyvale, California (408) 245-1000

## OPERATIONAL CHARACTERISTICS AT VCC=4v

| Characteristic                                                                                                                                      | Min | Тур            | Max            | Unit                 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------|-----|----------------|----------------|----------------------|

| Fan-in at -55 to +70°C                                                                                                                              |     |                | 4 <sup>†</sup> |                      |

| Fan-out at<br>$T_A = 70^{\circ}C$ , $\Delta V = 0.1 \text{ v (see Note 1)}$                                                                         |     |                | 5              |                      |

| Worst-Case DC Stability, ΔV, at 70°C<br>Fan-out = 5                                                                                                 | 100 |                |                | mv                   |

| Power Dissipation per Gate at 25°C (see Note 2)                                                                                                     |     | 5              |                | mw                   |

| Average Propagation Delay per Gate (see pp. 3,4), When Fan-in = 1 and Fan-out = 1, at $T_A = +25^{\circ}C$ $T_A = -55^{\circ}C$ $T_A = 70^{\circ}C$ |     | 12<br>14<br>14 | 15             | nsec<br>nsec<br>nsec |

<sup>†</sup> Diode array available for single gate to improve fan-in.

## ABSOLUTE MAXIMUM RATINGS AT 25° C

| Power Supply Voltage, V <sub>CC</sub> |   |  |  |  |  |  |  |  |     | 6 v       |

|---------------------------------------|---|--|--|--|--|--|--|--|-----|-----------|

| Gate Input Voltage                    |   |  |  |  |  |  |  |  |     | 6 v       |

| Gate Output Voltage (Input Grounded)  |   |  |  |  |  |  |  |  |     |           |

| Operating Temperature Range           |   |  |  |  |  |  |  |  | -55 | to +70°C  |

| Storage Temperature Range             | - |  |  |  |  |  |  |  | -55 | to +200°C |

## STATIC CHARACTERISTICS (WORST-CASE) VCC=4v

(See opposite page for test conditions)

|                     | Characteristic                                                                                      | Т             | Unit  |       |        |  |

|---------------------|-----------------------------------------------------------------------------------------------------|---------------|-------|-------|--------|--|

|                     | Characteristic                                                                                      | -55°C         | +25°C | +70°C | Onic   |  |

| I <sub>OFF</sub>    | Maximum Output Current with Gate OFF                                                                | 5*            | 10*   | 20*   | μа     |  |

| I <sub>R(max)</sub> | Maximum Reverse Current<br>per Input Diode                                                          | 0.05*         | 0.10* | 0.30* | μа     |  |

| I i(max)            | Maximum Input Current with Gate OFF (Max Load Presented to Driving Stage), with $V_i = V_F$ -100 mv | 1.15*         | 1.30* | 1.35* | ma     |  |

| V <sub>F</sub>      | Maximum Voltage at any<br>Input that will Ensure<br>Turn-OFF (Max False Voltage)                    | 1.38*         | 1.14* | 0.95* | v      |  |

| V <sub>o(max)</sub> | Maximum Output Voltage When Fully Loaded at: Fan-out = 5 Fan-out = 25                               | 1.02<br>1.30* | 0.94* | 0.85* | v<br>v |  |

| $V_T$               | Minimum Input Voltage that<br>will Ensure Turn-ON<br>(Minimum True Voltage)<br>Fan-out = 5          | 2.00          | 1.78  | 1.62  | v      |  |

| ΔV                  | DC Stability Margin (V <sub>F</sub> - V <sub>o</sub> )<br>Fan-out = 5                               | 0.36*         | 0.20* | 0.10* | v      |  |

<sup>\*</sup>Characteristics so designated are tested on every unit

#### Notes:

- 1. This is the maximum fan-out permissible for worst-case logic design with a 4 v power supply when the d-c stability  $\Delta V$  margin is 0.1 v.

- Power dissipation is defined as power supply voltage times average current drawn per gate. (See test circuit, p. 3).

## MEASUREMENT OF STATIC CHARACTERISTICS

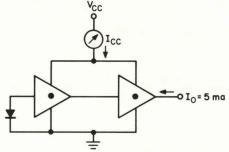

Power Dissipation Test Circuit

Power dissipation per gate =  $\frac{V_{CC} \times I_{CC}}{2}$ As measured above, the power dissipation is the average between the OFF stage and typically loaded ON stage and is equivalent to a 50% duty cycle for a single gate.

#### TEST CONDITIONS

| Characteristic to be      | Set or Measure<br>e.g., to Detern<br>V <sub>o</sub> at 4 v, Mea | Other                              |                         |                                     |                                                 |

|---------------------------|-----------------------------------------------------------------|------------------------------------|-------------------------|-------------------------------------|-------------------------------------------------|

| Determined                | I <sub>i</sub><br>Input<br>Current                              | V <sub>i</sub><br>Input<br>Voltage | I。<br>Output<br>Current | V <sub>o</sub><br>Output<br>Voltage | Conditions                                      |

| $ m V_{F}$                |                                                                 | Measure                            | I *                     | 4 v                                 | Free inputs connected to $V_{CC}$               |

| I <sub>i(max)</sub>       | Measure                                                         | V <sub>F</sub> * -100 mv           | ×                       | 4 v                                 | Free inputs connected to V <sub>CC</sub>        |

| I <sub>R(max)</sub>       | Measure                                                         | 4 v                                |                         |                                     | Open circuit<br>output<br>One input<br>grounded |

| Vo(max)                   | F.I. $\left[I_{OFF}^* + {}_*\right]$<br>(F.O 1) $I_{R(max)}$    |                                    | F.O. x I * i(max)       | Measure                             |                                                 |

| $\mathbf{V}_{\mathrm{T}}$ | I <sub>OFF</sub> + (F.O1) I <sub>R(max)</sub> *                 | Measure                            | F.O. x I* i(max)        |                                     | Free inputs<br>open                             |

$$F.I. = fan-in$$

## MEASUREMENT OF DYNAMIC CHARACTERISTICS

Test Circuit for Propagation Delay/Fan-out Measurements

Waveform propagated through two stages. Average propagation delay per stage

$$t_{d(avg)} = \frac{t_{d1} + t_{d2}}{4}$$

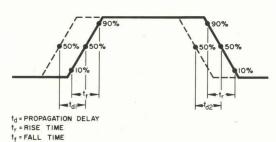

Waveforms and Time Delays

<sup>\*</sup> Definitions and values for temperatures from -55 to +  $70^{\circ}$ C obtained from table on opposite page.

## DYNAMIC CHARACTERISTICS

|                           | FAN-OUT |               |                          |      |  |  |  |  |  |

|---------------------------|---------|---------------|--------------------------|------|--|--|--|--|--|

| TIME                      | i       | (FREE INPUTS) | (FREE INPUTS) HELD FALSE | UNIT |  |  |  |  |  |

| tr<br>(O-I<br>(TRANSIENT) | 10      | 18            | 30                       | nsec |  |  |  |  |  |

| (TRANSIENT)               | 5       | 20            | 20                       | nsec |  |  |  |  |  |

Typical Rise and Fall Times  $V_{CC} = 4 \text{ volts, } + 25^{\circ}C$

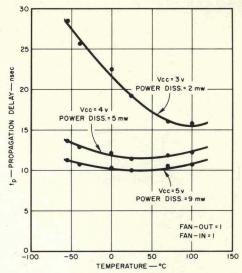

Typical Propagation Delay vs. Voltage and Temp

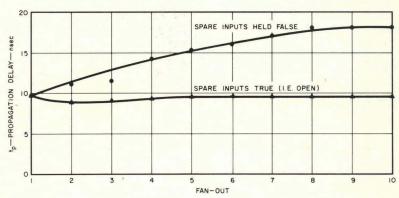

Effect of Loading on Propagation Delay

## LOGIC DIAGRAMS

Printed in USA May 1, 1963