Siliconix

# Analog Switches and Their Applications

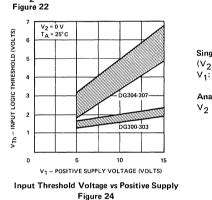

alog Switches and Their Applications

E

# Analog Switches and Their Applications

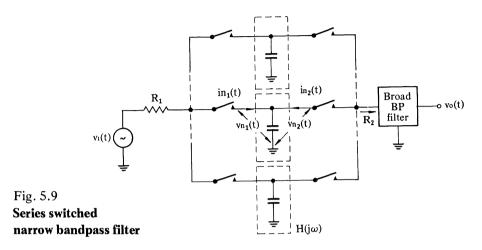

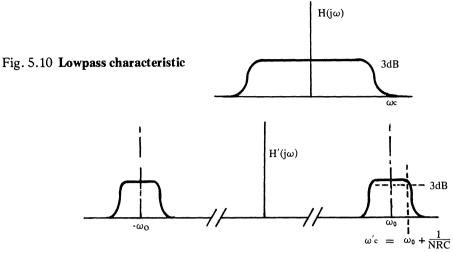

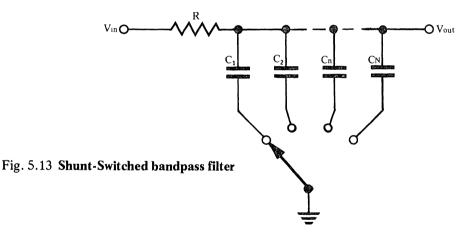

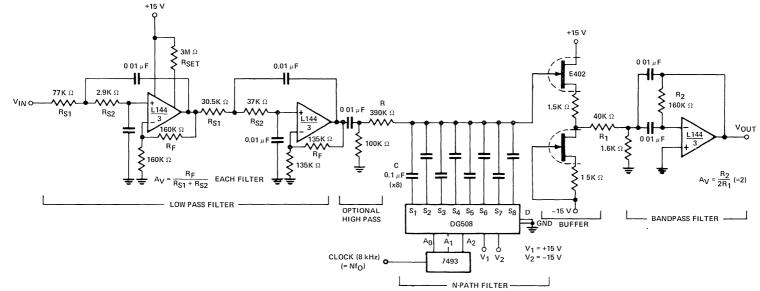

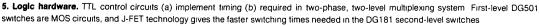

Copyright © by Siliconix incorporated. All Rights Reserved. Printed in the U.S.A. This book, or parts thereof, may not be reproduced in any form without permission from Siliconix incorporated.

Information contained in this book is believed to be accurate and reliable. However, we cannot accept responsibility for its use, nor for any infringement of patents or rights of others which may result from its use. Publication of this information does not imply any authority or license for the use of any patented feature.

Siliconix incorporated, 1976

## Preface

An abundance of literature is available on discrete semiconductor devices and integrated circuits, wherein the applications emphasis is mainly on linear and digital circuitry. Furthermore, most written information on sample-and-hold circuits, analog-to-digital and digital-to-analog converters, multiplexers and N-Channel filters tend to concentrate on systems considerations. Comparatively little has been written on the subject which bridges the linear and digital fields, namely analog switching and the effects that analog switches have on system performance.

The object of this book is to introduce the reader to FET analog switches and familiarize him with the way that the switch control or driver circuit affects switch performance. By developing an understanding of the circuit combinations that can be used for analog switching, the reader is then able to analyze the effects on system performance. With this objective in mind the contents are divided into seven chapters.

With the exception of chapters one and seven, all chapters are subdivided into two major sections. The first subsection is a theoretical discussion of analog switches. The second subsection is practical application circuits.

Chapter one is an introduction to the FET as a switch, the second chapter describes various driver circuits and their interaction with FET switches. The next four chapters are devoted to describing the performance of Analog Switches in four different fields of signal handling. Chapter seven contains a collection of applications material written by Siliconix personnel.

## **CONTENTS**

Page

### Chapter 1 Introduction to FET Switches

#### THEORETICAL DISCUSSION

| 1.1  | Introduction 1-1                                                  |

|------|-------------------------------------------------------------------|

| 1.2  | Comparison of Electromechanical<br>and Semiconductor Switches 1-1 |

| 1.3  | Elementary Semiconductor                                          |

|      | Theory 1-5                                                        |

| 1.4  | The p-n Junction 1-6                                              |

| 1.5  | The Bipolar Transistor 1-8                                        |

| 1.6  | The Field Effect Transistor 1-9                                   |

| 1.7  | Junction FETs 1-10                                                |

| 1.8  | MOSFETs 1-15                                                      |

| 1.9  | The FET as a Switch 1-18                                          |

| 1.10 | Summary1-32                                                       |

|      |                                                                   |

#### Chapter 2 Switch and Driver Circuits Page

#### THEORETICAL DISCUSSION

| 2.1 | Introduction                |

|-----|-----------------------------|

| 2.2 | Types of FET Switches 2-1   |

| 2.3 | Driver Circuits 2-3         |

| 2.4 | Interface Circuits          |

| 2.5 | General Comments on Driver  |

|     | Gates2-18                   |

| 2.6 | Sources of Error 2-21       |

| 2.7 | Noise Immunity 2-37         |

| 2.8 | Choosing the Optimum Driver |

|     | Gate                        |

|     |                             |

#### PRACTICAL APPLICATIONS

| 2.9  | Application Circuits 2-48 |

|------|---------------------------|

| 2.10 | References                |

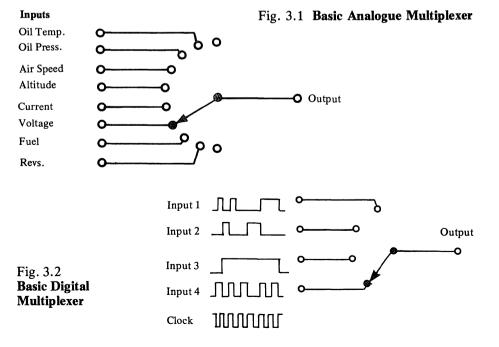

| Chapter | - 3 Multiplexing                                           | Page |

|---------|------------------------------------------------------------|------|

| THE     | ORETICAL DISCUSSION                                        |      |

| 3.1     | Introduction                                               | 3-1  |

| 3.2     | Factors Affecting System                                   |      |

|         | Performance                                                | 3-2  |

| 3.3     | Considerations of Multiplexer                              | ~ ~  |

|         | Errors                                                     |      |

| 3.4     | FET Multiplexer Performance                                | 3-11 |

| 3.5     | Principal Applications Areas of<br>Multiplexers            | 3-24 |

| 3.6     | Primary Requirements of Analog<br>Switches as Multiplexers | 3-25 |

| 3.7     | Analog Signal Characteristics 3                            |      |

| 3.8     | Techniques Used in Multiplexing 3                          | 3-27 |

| 3.9     | Supermultiplexing                                          | 3-29 |

| 3.10    | Examples of Multiplexer<br>Applications                    | 3-34 |

| 3.11    | Conclusions                                                |      |

| PRAG    | CTICAL APPLICATIONS                                        |      |

| 3.12 | Application Circuits | 39 |

|------|----------------------|----|

| 3.13 | References           | 10 |

#### Chapter 4 Sample-and-Hold Circuits Page

#### THEORETICAL DISCUSSION

| 4.1 | Introduction                   | 4-1  |

|-----|--------------------------------|------|

| 4.2 | Basic Sample-and-Hold Circuits | 4-1  |

| 4.3 | Types of Circuits              | 4-4  |

| 4.4 | Sources of Error               | 4-11 |

| 4.5 | Methods for Reducing Errors    | 4-14 |

| 4.6 | Miscellaneous Applications of    |

|-----|----------------------------------|

|     | IC Switches and Multiplexers in  |

|     | Sample-and-Hold Applications4-20 |

| 4.7 | Low Level Sample-and-Hold        |

#### PRACTICAL APPLICATIONS

| 4.8 | Application Circuits 4-37 |

|-----|---------------------------|

| 4.9 | References                |

Page

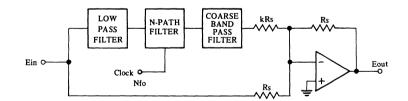

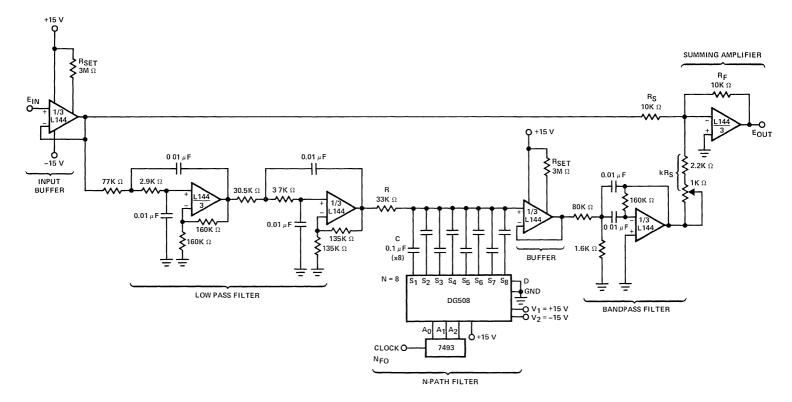

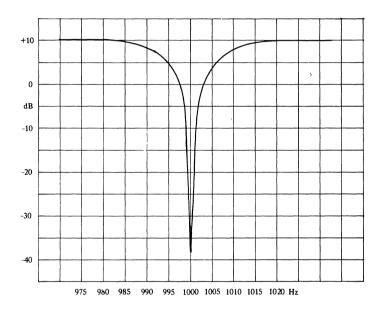

#### Chapter 5 N-path Filters

#### THEORETICAL DISCUSSION

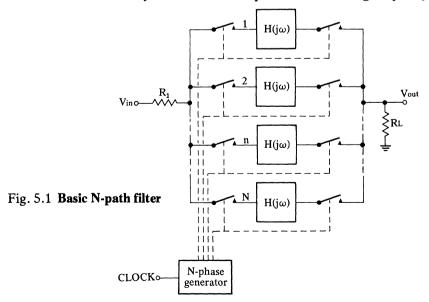

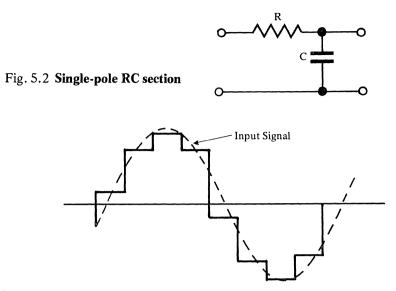

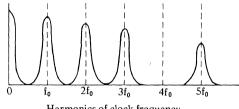

| 5.1 | Introduction                   | 5-1  |

|-----|--------------------------------|------|

| 5.2 | Basic N-path Filter            | 5-2  |

| 5.3 | Analysis                       | 5-4  |

| 5.4 | Bandpass Filter Analysis       | 5-8  |

| 5.5 | Shunt Switched Bandpass Filter | 5-12 |

#### PRACTICAL APPLICATIONS

| 5.6 | Applications 5 | -12 |

|-----|----------------|-----|

| 5.7 | Summary        | -21 |

| 5.8 | References     | -21 |

#### Chapter 6 Signal Conversion Using

| Analog Switches | Page |

|-----------------|------|

|-----------------|------|

#### THEORETICAL DISCUSSION

| 6.1 | Introduction           | 6-1  |

|-----|------------------------|------|

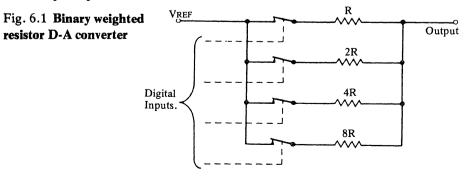

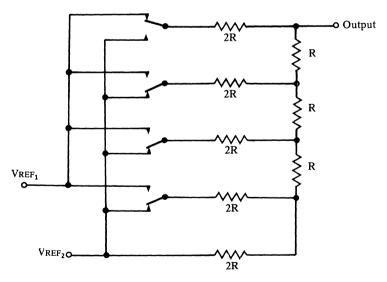

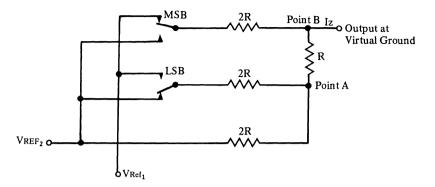

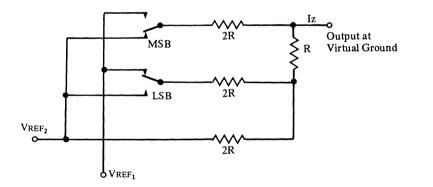

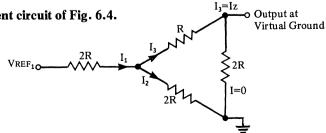

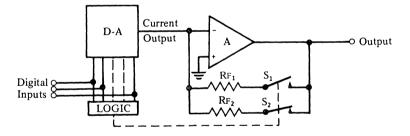

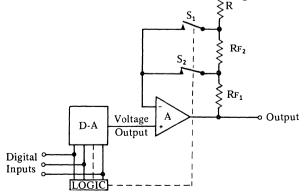

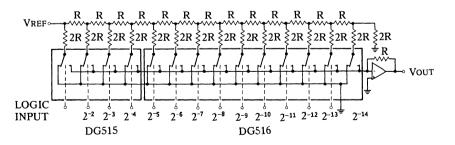

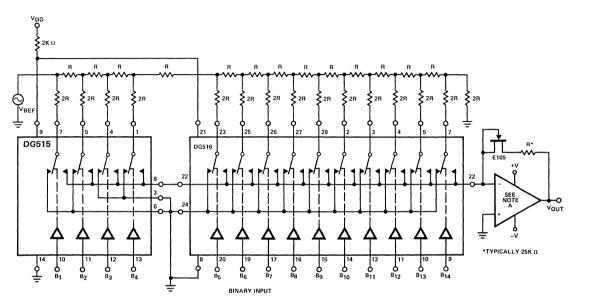

| 6.2 | D-to-A Converters      | 6-1  |

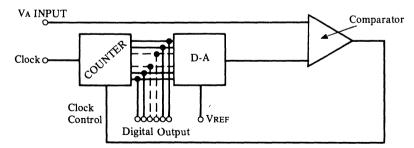

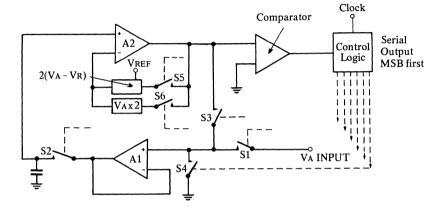

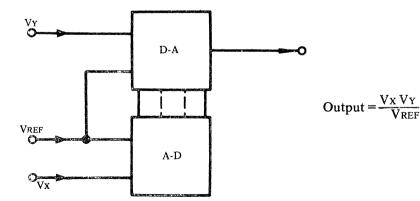

| 6.3 | A-to-D Converters      | 6-4  |

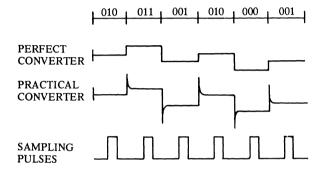

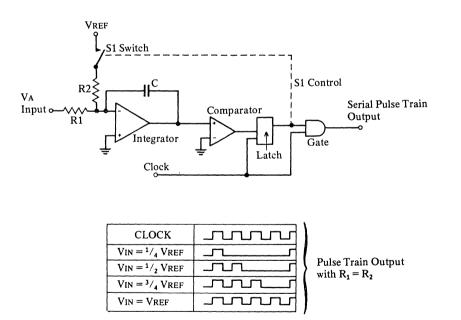

| 6.4 | Deglitching            | 6-6  |

| 6.5 | Coding                 | 6-6  |

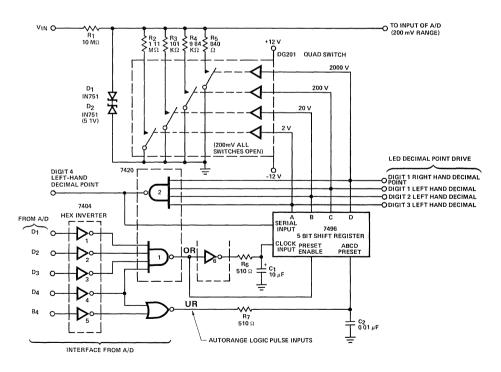

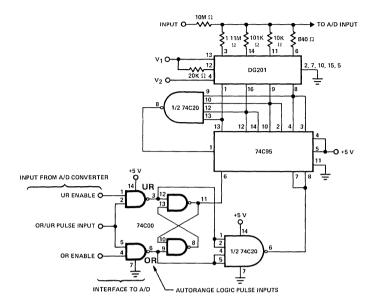

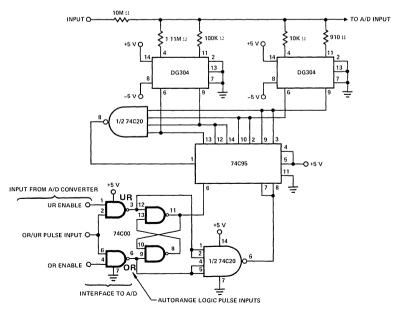

| 6.6 | Ranging                | 6-7  |

| 6.7 | Multiplying Conversion | 6-8  |

| 6.8 | Delta-Sigma Modulation | 6-9  |

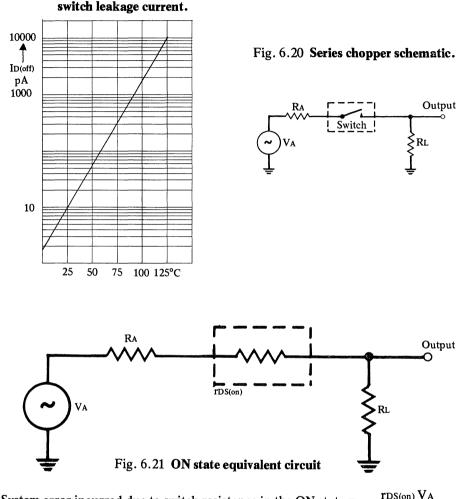

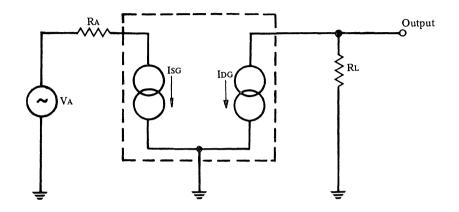

| 6.9 | Switch Parameters      | 6-10 |

| 6.10                   | Advantages Gained by the<br>Use of FET Switches                |  |

|------------------------|----------------------------------------------------------------|--|

| 6.11                   | Summary of A-D and D-A<br>Conversion Applications 6-14         |  |

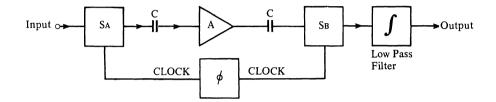

| 6.12                   | Chopping                                                       |  |

| 6.13                   | Performance and Selection of<br>FET Switches for Choppers 6-15 |  |

| 6.14                   | Summary of Chopping<br>Applications                            |  |

| PRACTICAL APPLICATIONS |                                                                |  |

####

#### Chapter 7 Applications Information Page

| 7.1     | FETs as Analog Switches (AN72-2)                                             |

|---------|------------------------------------------------------------------------------|

| 7.2     | IC Multiplexer Increases Analog<br>Switching Speeds (AN73-2)                 |

| 7.3     | Switching High-Frequency Signals<br>with FET Integrated Circuits<br>(AN73-3) |

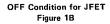

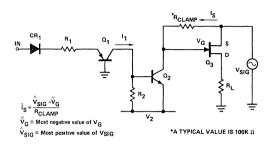

| 7.4     | Driver Circuits for the JFET<br>Analog Switch (AN73-5)7-27                   |

| 7.5     | An Introduction To FETs<br>(AN73-7)7-37                                      |

| 7.6     | Analog Switches in Sample-and-<br>Hold Circuits (AN74-2)7-57                 |

| 7.7     | CMOS Analog Switches (AN75-1)7-63                                            |

| 7.8     | DG300 Series Analog Switch<br>Applications (AN76-6)                          |

| 7.9     | Multiplexer Adds Efficiency to 32-Channel Telephone System                   |

| 7.10    | (TA73-1)7-93<br>Designing with Monolithic FET                                |

|         | Switches (TA73-2)                                                            |

| Annendi | x I 8-1                                                                      |

| Index   |                                                                              |

|         | fices                                                                        |

|         |                                                                              |

## Introduction to FET Switches CHAPTER

Switch and Driver Circuits CHAPTER

Multiplexing CHAPTER 3

Sample-and-Hold Circuits CHAPTER 4

N-path Filters CHAPTER 5

Signal Conversion using Analog Switches CHAPTER

Applications Information <sup>CHAPTER</sup><sub>7</sub>

### Chapter 1

## **Introduction to FET Switches**

#### 1.1 INTRODUCTION

One of the most common control elements in electrical circuitry is the simple ON-OFF switch. This has evolved over the years from the manually operated circuit breaker of the early experimenters to the multiswitch integrated circuit of today. In every application, the function of the switch remains the same, viz. to isolate or connect two sections of an electrical circuit.

Until the advent of the thermionic valve, switching action was effected almost exclusively by the manual or electromechanical opening and closing of metal contacts. The operation of mechanical switches is easily understood and they require a very simple form of maintenance. However, with today's increasing demands of modern circuits, it has become evident that electromechanical switches alone cannot meet all requirements and that there are applications in which only electronic types are viable. By far the most popular of these is the semiconductor switch.

In recent years, semiconductor switches have made inroads into application areas that hitherto have been exclusively the domain of electromechanical devices. Solid-state switches are now used in sample-and-hold circuits; multiplexers; high power switching; chopper circuits etc., whereas in the past some form of electromechanical switch would have been used.

#### 1.2 COMPARISON OF ELECTROMECHANICAL AND SEMICONDUCTOR SWITCHES

#### 1.2.1 General

The types of electromechanical and semiconductor switches available are many and varied, each having some advantages and some disadvantages. The choice between a mechanical and semiconductor switch usually depends upon the application. The performance and major switching parameters of both types are compared in the following sections.

#### 1.2.2 **ON Resistance**

Most electromechanical switches initially have very low ON-resistance, typically tens of milliohms. During their lifetime, however, wear at the switch contact surfaces can increase this resistance value by a factor of a hundred or more. Semiconductor switches have higher ON resistance but their resistance is constant over the switch lifetime. Field effect transistors are available with ON resistances of less than 2 ohms and some high power bipolar transistors can have collector-emitter saturation resistances of less than 100 milliohms. If the application required a switch with near zero ON resistance, the main contender would then be the electromechanical type, but if a constant ON resistance over the switch lifetime is of prime importance, then the semiconductor switch is far more preferable.

#### 1.2.3 **OFF Isolation**

The maximum OFF resistance of electromechanical switches is limited by surface conduction along the package. This resistance is reduced considerably in moist environments or through careless handling. Nevertheless, extremely high OFF resistance is possible, and with specially treated reed switches this can be as high as  $10^{12}$  ohms. The OFF resistance of semiconductor switches can have the same order of magnitude. The value of the semiconductor switch leakage current is roughly proportional to the square root of the voltage across the junction, and it increases with increasing temperature. Values of junction leakages can be less than one picoamp at 25°C for low power field effect transistor switches.

#### 1.2.4 Switching Speed

Semiconductor switches comprise no moving parts, hence their switching speed is not limited by contact inertia. Consequently, switching times of nano-seconds are easily attainable and maximum switching rates are often in excess of  $10^6$  operations per second. By comparison electromechanical switches are slow indeed. Even the fastest of reed switches have turn-on/turn-off times measured in milliseconds, and maximum switching rates rarely exceed a few hundred operations per second.

#### 1.2.5 Maximum ON Current

Power dissipation ratings limit the maximum currents that semiconductor devices are able to switch: collector currents of up to 100 amperes are possible with bipolars, while the largest field effect transistors at present have maximum drain currents in the region of 10 amperes. High power switches, with forced cooling, can conduct currents of up to 1000 amperes. Some electromechanical switches are capable of conducting currents of many thousands of amperes, but switching such high currents with these devices causes severe arcing and burning of contact faces. Electromechanical switches capable of conducting thousands of amperes are therefore normally switched when the load current is zero.

#### 1.2.6 Maximum OFF Voltage

For electromechanical switches the maximum OFF voltage is limited by the voltage breakdown of the insulating dielectric. For large switches, with wide contact spacing, the maximum OFF voltage can be many hundreds of thousands of volts. The smaller electromechanical devices, reed switches, miniature relays etc. are capable of switching several hundreds of volts.

Operation of semiconductor switches relies on p-n junction action. Consequently the reverse biased breakdown voltage of the junction sets a limit to the maximum voltage that can be switched. Some thyristor devices have breakdown voltages as high as 1000 volts, while bipolar and field effect transistors can have maximum switching voltages in the region of 200 volts. It must be stressed that this is more than adequate to meet the needs of most semiconductor systems which normally run off supplies of less than 50 volts.

#### 1.2.7 Minimum Analogue Voltage

The minimum analogue voltage switchable is determined by the total error signal contributed by the switch. One source of error in electromechanical devices is the

thermal EMF generated across the moving contacts. This can be tens of microvolts. A much larger error, prevalent in dry reed relays, results from the dynamic noise generated by contact bounce. This can be as high as 500 microvolts peak-to-peak initially, decaying to tens of microvolts after a few milliseconds.

Bipolar semiconductor switches require a finite collector-emitter voltage to maintain conduction. This voltage which is seldom less than a few millivolts, appears as an offset and severely limits the minimum value of analogue voltage that can be switched.

Field effect transistors have no such offset and are used extensively in low voltage switching applications. The thermal EMFs generated in field effect transistors are virtually zero, owing to their near symmetrical structure. Factors affecting the low level analogue switching voltage capability of FETS are switching transient breakthrough into the channel from the gate, and thermal noise due to the channel ON resistance. Both these topics are considered in detail in Chapters 2 and 3.

#### 1.2.8 Drive Signals

Compatibility with existing circuits is an important consideration when deciding on a switch type. If, as is frequently the case, there is some degree of involvement with computers or other electronic systems which require standard logic control signals, then switching systems which respond to the same type of logic signals are desirable. The voltage levels required to operate electromechanical switches normally vary between 1 and 250 volts and most require a driving power greater than 50mW. Since logic driving circuits are limited in their power handling capability, this necessarily means that electromechanical switches usually require some form of interfacing with their logic control elements. Most semiconductor switches, owing to their lower drive power requirements, are directly compatible with transistor logic systems.

#### 1.2.9 Switching Life

Since electromechanical switches comprise some moving parts, their operating life is affected by mechanical wear; in particular, wear at the contact surfaces. This can lead to an increase in ON resistance and the eventual welding together of the contacts. Figures for operating life times or switching cycles are difficult to assess since they depend on operating conditions. A dry reed relay switching at the rate of 100Hz would perform  $10^8$  switching operations in only 300 hours which is approximately the minimum expected lifetime of the relay.

This figure would be greatly reduced if the relay were switching into an inductive or capacitive load. Inductive loads produce arcing at the switch contacts because of the back EMF induced when the switch is opened. Capacitive loads accelerate contact wear due to current surges when the switch turns on. The switching life of a semiconductor device is not limited by mechanical wear and provided it is operated within its maximum specified ratings it can continue to switch almost indefinitely. For example, the mean time before failure (MTBF) of semiconductor devices is usually well in excess of 100,000 hours. Consequently, a semiconductor switch operating at 10<sup>6</sup> Hz could perform in excess of 3.6 x 10<sup>14</sup> cycles during its operating life.

#### 1.2.10 Reliability

In many applications the ability of a device to survive in adverse environments is most important. Military and space equipments need to withstand extremes of temperature, pressure, mechanical shock etc. without impairing operation. In general, semiconductor devices exhibit greater resistance to adverse environments than electromechanical types. Semiconductors are less susceptible to damage or change of state through shock, vibrations or high accelerations and do not suffer from sticking contacts due to freezing at very low temperatures. Their electrical characteristics are dependent on temperature and are somewhat prone to change when subjected to high energy radiation. However, this does not prevent their use in military equipment requiring an operating temperature range of  $-55^{\circ}$ C to  $125^{\circ}$ C, or in satellite applications with the attendant high radiation environment.

#### 1.2.11 System Size

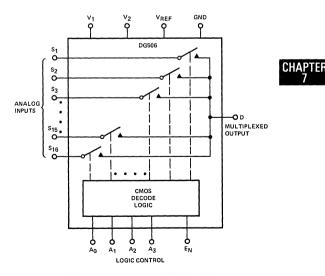

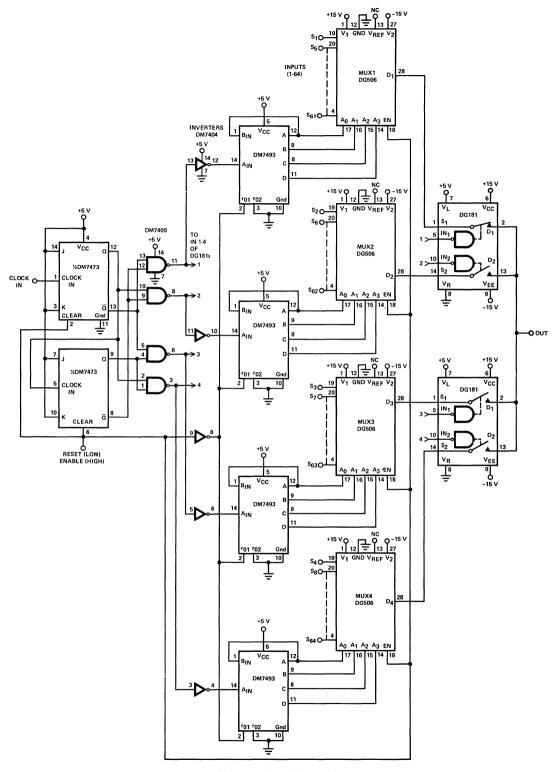

Size, power consumption and weight of components become increasingly important as systems grow more complex. In this respect, the semiconductor switch has distinct advantages over its electromechanical counter part. The use of integrated circuits and modern fabrication techniques enable multiple switches to be contained in a single robust package. The Siliconix DG506, for example, has 16 switches with their binary decode circuitry in a 28 pin package measuring only 1.4 inches x 0.6 inches. An equivalent system using relays would be considerably more bulky.

#### 1.2.12 System Costs

Total system costs should take into account not only the initial capital outlay but also factors such as maintenance costs, personnel training and the secondary costs resulting from system failures.

Switch for switch, the costs for electromechanical and semiconductor types are comparable, but as circuit complexity increases the cost per switch for semiconductor systems using integrated circuits falls, giving them a considerable price advantage over electromechanical types. Costly equipment down-time is also greatly reduced with semiconductor systems due to their higher reliability and longer lifetimes.

#### 1.3 ELEMENTARY SEMICONDUCTOR THEORY

It is relevant at this stage to present a brief description of semiconductors and their application as switches.

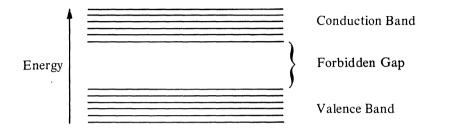

Quantum mechanics shows that electrons in a solid can be represented as occupying discrete energy bands which are separated from each other by forbidden energy gaps.

CHAPTER

#### Fig. 1.1 Comparative energy levels

Fig. 1.1 represents the two outermost bands of any atom, the valence band and the conduction band, separated by a forbidden energy gap. It is the availability of electrons in the conduction band which determines the conductivity of a solid. Conduction can only occur if electrons arrive in the conduction band from the valence band. For this to happen, the electrons must receive sufficient energy to enable them to 'jump' the forbidden energy gap between the two bands.

If the forbidden energy band is wide, and prevents electrons appearing in the conduction band, the material is an insulator. Electrons will move from the valence to conduction band if sufficient energy is imparted to them. The application of a high electric field will do this. Thus, for all insulators, there is a specific voltage at which their insulating properties break down. In metals, the valence and conduction bands overlap with the result that electrons are freely available in the conduction band and can be persuaded to move between atoms when only a small voltage is applied. Thus, metals are good conductors of electricity.

In certain materials, the thermal energy imparted to some electrons at ambient temperatures is sufficient to enable them to cross the forbidden energy gap. For these materials there is a finite probability of electrons appearing in the conduction band. Therefore these materials will exhibit slight electrical conductivity which increases with increasing temperature. Such materials are referred to as semiconductors. Although many semiconducting materials exist, the two most widely used are silicon and germanium, with silicon being the more common of the two at present.

The width of the forbidden energy gap in pure silicon is of the order of 1.1 electron-volts at room temperature; the average thermal energy of the valence electrons is 0.025 electron-volts; thus, the probability of electrons appearing in the conduction band is small and the conductivity is very low. Conductivity can be increased if certain impurities are added to the semiconductor.

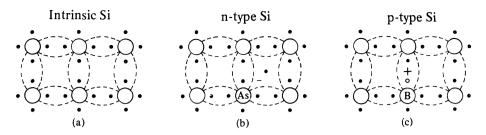

Fig. 1.2 Schematic crystal structure of intrinsic and doped silicon.

Both silicon and germanium have a valency of 4. This means that a pure or intrinsic semiconductor will have a crystal structure as in Fig. 1.2a. Each silicon atom binds with its neighbouring atom to produce a stable configuration of eight valence electrons associated with each nucleus. If an impurity atom, such as arsenic with a valency of 5 is introduced into the crystal structure (Fig. 1.2b), then a free electron results from the binding of the valence electrons. This electron can be easily elevated to the conduction band and, therefore, contribute to electrical conduction. The arsenic atom can be said to have donated a free electron to the semiconductor and for this reason the impurity atom is known as a donor atom. Obviously the greater the concentration of donor atoms, the greater will be the number of free electrons and the greater the conductivity. Semiconductors treated with donor impurities are known as **n** type. The existence of the free electrons does not constitute a net negative charge in the structure as associated with it is a localised positive charge on the arsenic atom. This positive charge also contributes to electric current but to a lesser extent. To distinguish between the two types of charge carriers in n type semiconductors, the free electrons are known as majority carriers and the positive charges as minority carriers.

If a trivalent impurity, such as boron or indium is introduced, the binding of the valence electrons results in a **space** or **hole** in the valence band (Fig. 1.2c). An electron from a neighbouring atom will move to fill the hole thereby causing a hole to appear in its place. The result is that a hole behaves similarly to a free electron but with a positive charge. It will contribute to electric current since a movement of holes in one direction is effectively the same as a movement of electrons in the opposite direction. Impurity atoms of this type are known as acceptor atoms and a semiconductor so treated is called  $\mathbf{p}$  type. In a  $\mathbf{p}$  type semiconductor, the **holes** are the majority carriers and the electrons are the minority carriers.

The process of adding impurities to semiconductors is known as doping. Impurity atoms may be either diffused into the pure semiconductor at high temperature or injected into the crystal structure using Ion Implantation techniques.

#### 1.4 **P-N JUNCTION**

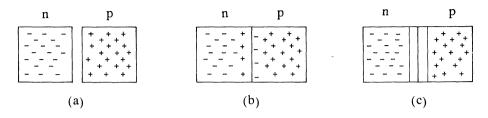

If **n** and **p** type semiconductors are joined, then at the junction the free electrons of the **n** type and the holes of the **p** type will be mutually attracted and will drift towards each other (Fig. 1.3b). Some will cross the junction producing a potential drop which tends to prevent any further flow of charge carriers across the junction. This results in regions deficient in majority charge carriers on both sides of the junction. These regions act as insulating regions and are known as depletion layers (Fig. 1.3c).

#### Fig. 1.3 Showing formation of a depletion layer at a p-n junction.

If a voltage supply is now applied to the junction with the negative terminal to the  $\mathbf{n}$  type and the positive to the  $\mathbf{p}$  type, it will oppose the inherent potential barrier already existing at the junction. If the applied voltage is greater than the potential barrier, it will cause more carriers to cross the junction and an electric current results. In this arrangement, the junction is said to be forward biased. If the voltage is applied with opposite polarity, then effectively the charge carriers in the  $\mathbf{n}$  and  $\mathbf{p}$  regions will be attracted away from the junction, resulting in an increase in the width of the depletion layer with an increase in potential drop across the junction which exactly opposes the applied voltage. Thus, very little current can flow and the junction is said to be reverse biased.

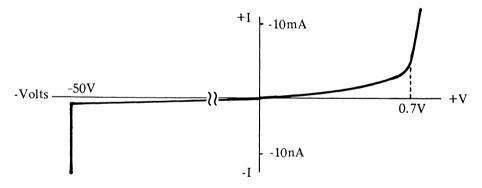

Fig. 1.4 V/I characteristic for silicon p-n junction.

A junction of **n** and **p** type semiconductors performs the function of a rectifying diode as shown by the voltage/current characteristic of Fig. 1.4. This reverse bias current is temperature dependent; its value for silicon approximately doubles for every  $10^{\circ}$ C increase in temperature. Other factors affecting the reverse current are dopant concentrations and junction area. The value is typically of the order of 1 nanoamp at 10 volts, but can be less than 1 picoamp. The reverse current increases sharply when the reverse voltage becomes sufficiently high. This is due to avalanche breakdown across the junction and to a large extent is dependent upon dopant concentration. A decrease in dopant concentration will result in an increased breakdown voltage. Breakdown voltages can be in excess of 1000V.

For a junction that consists of n and p conducting regions separated by an insulating depletion layer, there is associated with it a particular value of capacitance. This capacitance normally degrades the performance of semiconductor devices and efforts are usually directed at keeping the capacitance to a minimum. Factors affecting the value of junction capacitance are applied voltage, junction area, and impurity concentration. As the reverse bias voltage increases, so the width of the depletion layer increases thus reducing the capacitance.

A reduction in impurity concentration produces an increase in the depletion layer width for a given reverse bias voltage, and consequently a reduction in capacitance. Minimum junction capacitance is aimed for in most products, but varactor diodes make use of this voltage dependent characteristic and are designed for specific capacitance/voltage sensitivities. Values of junction capacitances can vary from less than 1 pico farad to greater than 10 nano Farads.

#### 1.5 **THE BIPOLAR TRANSISTOR**

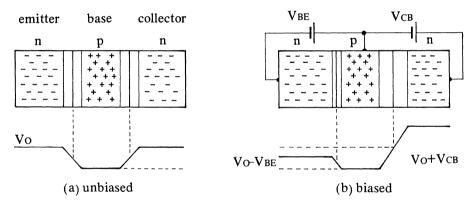

If a second p-n junction is added in close proximity to the first, a three terminal n-p-n or p-n-p device is produced. Such a device is the basis of a bipolar transistor. An n-p-n type bipolar schematic structure is shown in Fig. 1.5.

#### Fig. 1.5 Bipolar schematic structure

Fig. 1.5a shows the structure and potential distribution when no external voltages are applied. Under this condition the potential steps on each side of the centre or base region are equal and there is no net charge transfer across the junctions.

If external voltages are applied as in Fig. 1.5b, the base-emitter junction will be forward biased and the base-collector junction reverse biased. There will be a reduction in the base-emitter potential barrier and electrons will be injected into the base region from the emitter. These would normally recombine with holes in the base region, but if the width of the depletion layer of the reverse biased collector-base junction extends sufficiently into the base region, most of the electrons will be swept across to the collector where they recombine with holes to form collector current.

For a basic understanding of how the device operates, consider positive or negative charges (positive for a p-type emitter, negative for an n-type) flowing

from the emitter into the base region. A fraction x (say) of these recombine with charges of opposite polarity in the base region and so gives rise to base current. The remaining (1-x) fraction of charges reaches the collector-base depletion region across which they are accelerated into the collector. The algebraic sum of collector and base currents is equal to the emitter current YIE). The ratio of collector to base currents is (1-x)IE: xIE; that is, (1-x): x. For a given bipolar transistor, x is practically constant at constant temperature, and for normal bipolar action is «1. Current amplification can therefore be effected: a small increase in base current results in a much larger increase in collector current.

For high current gain performance, the number of electrons arriving at the collector from the emitter must be maximised. Therefore, the collector-base depletion layer must be made wider by lightly doping the base, and the base thickness made as small as possible. The number of electrons emitted is maximised by heavily doping the emitter with respect to the base, which inherently results in a low base-emitter breakdown voltage. The collector is lightly doped near the junction but heavily doped at the point where metal contact is made to it, and sometimes in the regions away from the junction, to reduce saturation resistance. This gives the desired low contact resistance. It is implicit in the foregoing discussion that a bipolar will function with the collector and emitter interchanged. This is so, but only with a low inverse current gain and lower operating voltages.

#### 1.6 THE FIELD EFFECT TRANSISTOR

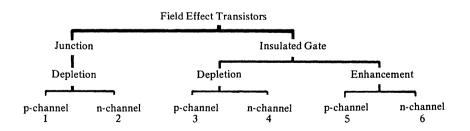

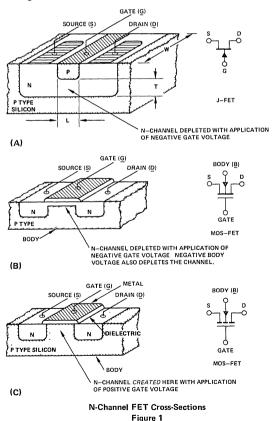

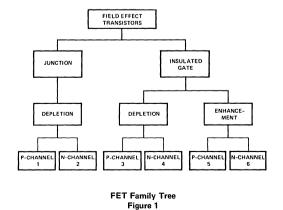

Bipolar transistors are often termed minority carrier transistors by virtue of the minority carrier current through the base. However, the field effect transistor (FET) relies on majority carrier current for its operation. A FET consists essentially of an electrically conducting channel (either n- or p- type) whose conductivity may be controlled by applying a voltage to a controlling gate terminal. There are two distinct branches of the FET family—the JUNCTION FET and the INSULATED GATE FET, with further subdivisions as shown in Fig. 1.6. The two types will be reviewed in detail.

#### 1.7 JUNCTION FETS

#### 1.7.1 General Layout and Characteristics

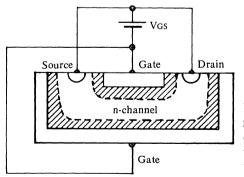

The JFET consists of a channel of n- or p- type semiconductor embedded in a semiconductor region of opposite polarity.

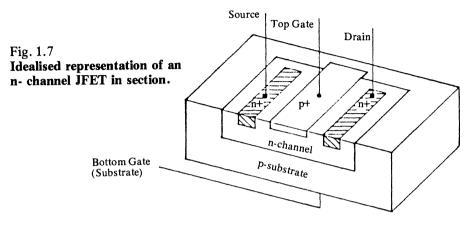

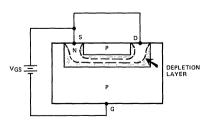

Fig. 1.7 shows an idealized n-channel JFET where the p-type region is the controlling gate and the n-type channel has electrical connections made at both ends (Source and Drain). Electrical connection to the gate is made at either the substrate or top gate contact. The controlling gate is isolated from the conducting channel by virtue of the reverse biased p-n junction. To understand how the JFET works, one must consider its operation under two distinct bias conditions.

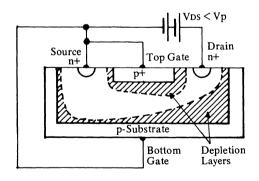

Fig. 1.8b n-channel FET working in saturation region. n-channel is almost cut off between Drain and Source. (Only channel depletion regions are shown). Fig. 1.8a **n-channel JFET working below saturation.** n-type conducting channel existing between Source and Drain. (Only channel depletion regions are shown).

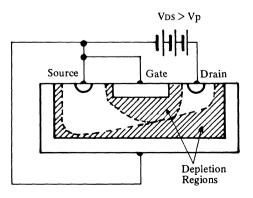

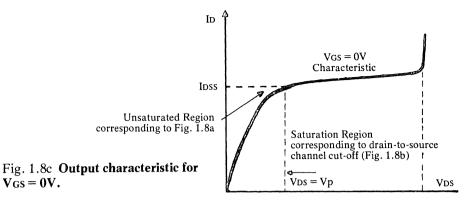

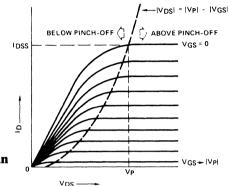

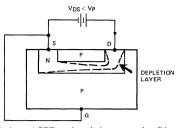

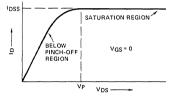

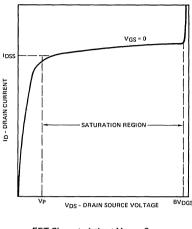

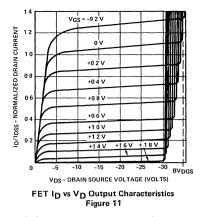

Fig. 1.8a illustrates the idealized cross sectional diagram of an n-channel JFET with a positive voltage VDS applied between drain and source, and with the gate shorted to the source. Since the drain is positive with respect to source and gate, the drain-gate junction will always be reverse biased and practically no gate current will flow. A depletion region will form over the whole p-n junction area and this will be physically greatest at the high field regions between the drain and gate. The existence of the depletion region reduces the effective channel width and thereby increases the channel resistance. An increase in the value of VDs increases the width of the depletion region. This results in a reduction of the channel cross-section and an increase in channel resistance. Above a certain VDs value, the channel will no longer exhibit a resistive characteristic but reaches a state of saturation Fig. 1.8b where the channel current changes very little for a large change in VDS. The JFET is then said to be saturated. This saturation current is given the symbol IDSS which is an abbreviation for the drain to source current with the gate short-circuited. The ID/VDS characteristic at VGS = 0V is shown in Fig. 1.8c. Initially ID increases almost linearly with VDs until the depletion region begins to 'pinch-off' the channel, and the curve flattens out at the IDSS value. The value of VDS at which this takes place is termed the 'pinch-off' voltage and is given the symbol Vp.

Fig. 1.9

**n-channel JFET showing channel depletion layer** when drain-source voltage VDs=0V and VGs=negative voltage.

Consider the case of Fig. 1.9 where VDS = 0V and a negative gate-source voltage (-VGS) is applied. The depletion region is controlled mainly by the gate-source voltage VGS: the depletion region widens as VGS becomes more negative and

consequently the channel resistance increases. Therefore, for values of VDs at or near to zero volts, the drain-source resistance is controlled by VGs. As VGs increases, the channel resistance increases until a voltage VGs(off) is reached, at which level the channel is completely 'pinched-off' and no drain current allowed to flow. This value of VGs(off) is equal in magnitude but opposite in polarity to Vp, and is usually referred to as the 'Gate Pinch-off' Voltage'. It also is given the symbol Vp.

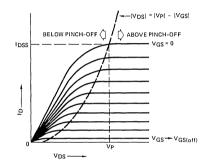

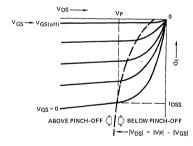

Fig. 1.10 Family of output characteristics for an n-channel JFET.

A combination of VDs and VGs bias conditions results in a family of characteristics (Fig. 1.10). From this it is seen that there are two important modes of operation for a JFET, namely:

1) Operation to the left of the pinch-off voltage locus. This is known as the unsaturated or triode region where ID is governed by both VDs and VGs. As will be seen later, the triode region is most important when the JFET is used as an analogue switch.

2) Operating to the right of the pinch-off voltage locus. Here the JFET is in the saturated or pentode region and ID is controlled almost entirely by VGS. In this region, the JFET is most useful as a voltage amplifier.

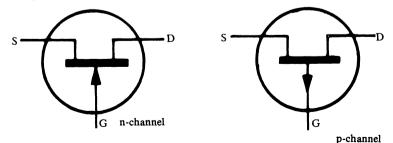

The operation of a p-channel JFET is similar to the n-type except that voltage polarities and current directions are reversed. The symbols for both n and p channels are shown in Fig. 1.11. The arrows on the gate show the polarity of the gate-channel junction.

#### Fig. 1.11 Symbols for Junction FETs

The application of a negative voltage to the gate of an n-channel JFET increases the depth to which the depletion layer extends into the channel, and so reduces the conductivity of the channel. A small positive voltage on the gate has the opposite effect. If the gate-to-channel voltage were sufficient to forward bias the p-n junction (approximately 0.6 volts) a significant current would flow from the gate (p-region) into the channel (n-region). For this reason, the n-channel JFET is normally operated with the gate at a negative voltage with respect to the channel. The JFET is therefore considered to be a DEPLETION mode device.

The foregoing applies equally to the p-channel JFET except that the voltage polarities are reversed.

#### 1.7.2 **JFET Fabrication**

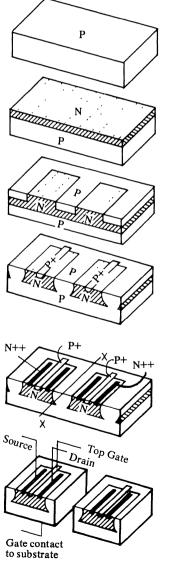

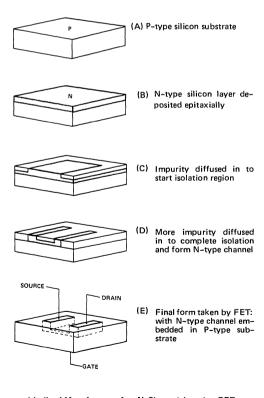

Junction FETs are usually manufactured using silicon planar technology. Figs. 1.12a—f illustrate the processing steps for fabricating an idealized n-channel\_JFET.

Fig. 1.12

a) **p**-type silicon wafer (substrate)

- b) **n**-type silicon epitaxial layer grown on to **p**-substrate.

- c) **p**-type acceptor impurity diffused in, to start isolation region.

- d) p+ impurity diffused in, to form top gate. Simultaneously, p region diffuses to complete isolation between the n islands.

- e) **n**++ type impurity diffused into **n**type channel to form Drain and Source contacts. Physical isolation of each FET is achieved by scribing and breaking wafer along x-x axis

- f) Formation of discrete n-channel FETS after 'scribing and breaking' procedure. Since the edges of the p+ regions of the top gate are diffused into the p-substrate, electrical contact is made to the top gate, via the p-substrate.

The process begins with a mono-crystalline substrate of p-type silicon in the form of a circular wafer  $1^{1}/_{2}$  inches to 3 inches in diameter and approximately 0.010 inches thick. A thin layer of n-type silicon is then grown epitaxially on top of the substrate (Fig. 1.12b). The epitaxial process used to form the drain-source channel allows a fine control on dopant concentration and film thickness, important factors if consistent device performance is to be achieved.

A film of silicon dioxide is grown on the surface of the epitaxial layer. A photo-resistive material is applied to the oxide and the wafer is subsequently exposed to ultra violet light through a mask. Chemical solutions are then used to etch away the unexposed photo-resist and then the silicon dioxide. The photoresist that remains is then removed. An acceptor type impurity is diffused through the pattern in the oxide mask (Fig. 1.12c) to begin the formation of the isolation regions. Further oxide films are grown and subsequently selectively etched; another acceptor type diffusion is performed to produce the top p-type gate, and simultaneously complete the isolation of each n-type island on the substrate (Fig. 1.12d). By a similar process, a donor impurity is diffused into the n type islands to form the n++ Drains and Sources. Aluminium is then deposited on to the n++ diffusion regions to form the drain and source contacts. In most cases, the gate contact could be made via the substrate (Fig. 1.12f). The majority of devices have drain and source symmetry that allows complete electrical interchangeability of these two terminals. Depending on the type of FET and wafer size, more than 15,000 FETS can be fabricated on one wafer.

#### 1.7.3 Assembly and Test

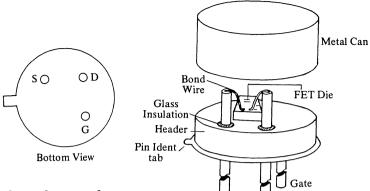

The same general processing and assembly techniques are applicable to both junction and MOS FET devices. The wafers are inspected visually for any obvious defects such as mask misalignment, poor metallisation etc. and then 100% probe tested on major electrical parameters. Any reject FET dice on the wafer are automatically ink marked by the probe tester. The impurities diffused into the back of the wafer during fabrication are removed by back lapping which also reduces the wafer to a convenient thickness. The wafer is then scribed and broken into individual die (Fig. 1.12e). Next, the dice are subjected to a further visual inspection prior to assembly. A typical discrete FET package is illustrated in Fig. 1.13. Here a JFET die is shown mounted on to a metal header. The die is eutectically bonded on to the header which is in electrical contact with one of the three external leads. In this instance, the backgate on the FET is used to make contact with the gate lead. The other two leads are embedded in glass that insulates them from each other and the header body. Attached to these leads are aluminium or gold wires to make connections to the source and drain terminals of the die.

Source

Drain

CHAPTER

#### Fig. 1.13 Typical metal can package.

The header assembly is visually inspected and any defective devices rejected. Finally, the metal can is welded to the header in a dry nitrogen environment to form a hermetic seal. Other package options are available, including dualin-line and flat pack types. Encapsulating materials most commonly used are metal-ceramic, plastic, or epoxy resin. Devices are available with a variety of process and screening options in accordance with military, industrial or consumer reliability specifications. Screening for high reliability devices usually includes a burn-in to eliminate infant mortality failures. Each device is tested on major electrical parameters. The good devices are then marked with the part number, manufacturer's symbol and the date of manufacture. Before leaving the plant each batch is sample tested to ensure conformance with specifications.

#### 1.8 MOSFETS

The MOSFET or metal-oxide-semiconductor FET uses a film of high purity dielectric such as silicon dioxide or silicon nitride to insulate the gate from the channel. Due to the insulation properties of the MOS gate, both positive and negative gate voltages may be applied to unprotected MOSFETs (see Section 1.8.2). Four forms of MOSFET are possible:

- a) n- Channel Depletion c) n- Channel Enhancement

- b) p- Channel Depletion d) p- Channel Enhancement

#### 1.8.1 **Depletion MOSFETS**

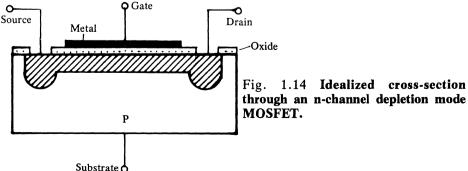

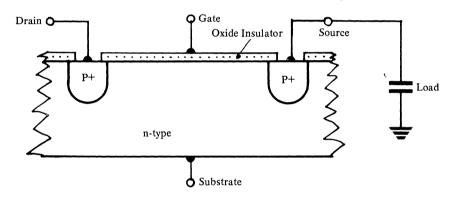

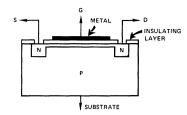

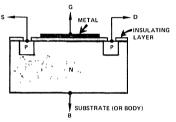

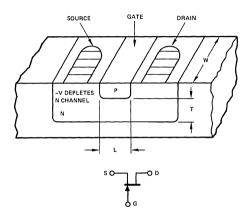

Fig. 1.14 shows the basic cross-section of an n-channel depletion mode MOSFET.

In early MOSFETs, the formation of an n-channel relied upon the charge induced by the oxide impurities at the oxide-semiconductor interface. The repeatability, therefore, was not good. Present day MOSFETs are fabricated by much cleaner and repeatable processing. The introduction of an additional n-type region between n+ type source and drain forms the initial channel. This is enhanced or depleted according to the gate voltage applied.

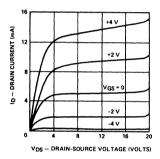

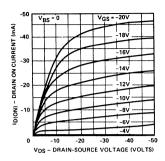

In operation, a negative gate voltage must be applied to turn the channel off and in this sense the device behaves exactly as an n channel JFET. However, if a positive voltage is applied to the gate, additional negative charges will be attracted to the oxide/semiconductor interface thus increasing the channel conductivity. The device can therefore be operated in both depletion and enhancement mode. Fig. 1.15 shows the family of output characteristics for a typical n channel depletion MOSFET.

Fig. 1.15 Family of output characteristics for the Siliconix 2N3631 n-channel depletion MOSFET.

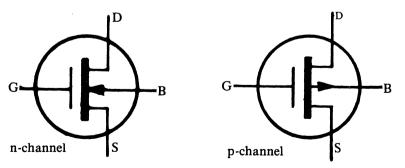

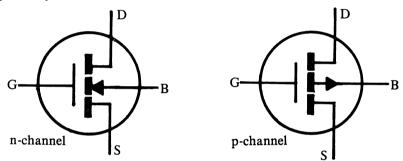

The manufacture of p-channel depletion types is possible if very clean processes are used but they are not available commercially in large quantities. The symbols for depletion MOSFETS are shown in Fig. 1.16.

#### Fig. 1.16 Symbols for depletion MOSFETS

#### 1.8.2 Enhancement MOSFETS

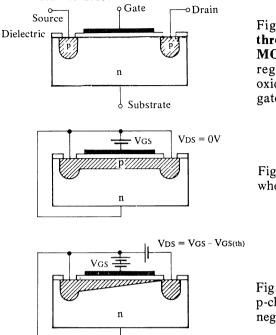

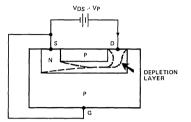

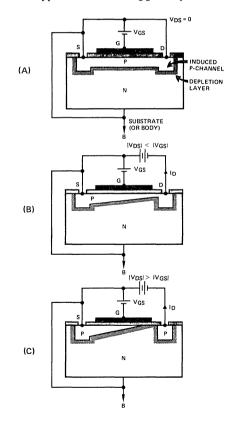

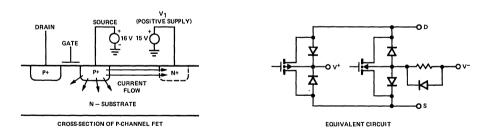

Enhancement MOSFETS are normally OFF devices requiring the application of either a negative (for p-channel MOS) or positive (for n-channel) gate voltage before channel conduction is possible. The operation of a p-channel enhancement MOSFET is illustrated in Figs. 1.17 to 1.19.

Fig. 1.17 Idealised cross-section through a p-channel enhancement MOSFET showing negative charge region existing at the oxide/semiconductor interface with no gate voltage applied.

Fig. 1.18 showing induced p-channel when  $V_{GS} \gg V_{GS(th)}$  ( $V_{DS} = 0V$ ).

CHAPTER

Fig. 1.19 showing the pinch-off of the p-channel as drain voltage increases negatively with respect to the substrate.

The device consists of an n-type substrate into which a p-type impurity is diffused to form separate sources and drains. The metal gate is insulated from the substrate by an oxide layer. As in the depletion MOSFET, free electrons are inherently attracted to the oxide/semiconductor interface to form an n-type layer, which has a higher concentration of negative charge carriers than the surrounding n-type substrate Fig. 1.17. When the gate-to-source voltage is zero, virtually no current can flow from source to drain or from drain to source as there is a reverse biased junction in each direction. Therefore, the device is normally OFF. If a negative gate-to-source voltage is applied, positive charges are attracted to the oxide/semiconductor interface where they recombine with free electrons. Increasing the gate voltage negatively causes more charge carriers to recombine until a voltage VGs(th) is reached, at which all the free electrons at the semiconductor/insulator surface have recombined. Any further increase in gate voltage produces a p-type layer beneath the gate thus forming a conducting channel between the source and drain (Fig. 1.18) whose conductivity increases with increasing VGs. If a negative drain voltage is applied with respect to the source, the drain-gate differential voltage will now be reduced and consequently the channel narrows toward the drain. When  $V_{DS}-V_{GS} = V_{GS(th)}$  the channel will be pinched off (Fig. 1.19) at the drain.

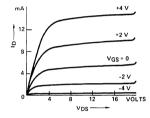

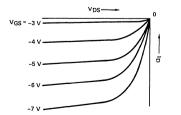

Any further increase in VDs would have little effect on the value of channel unless VGs were increased which would then require a greater VDs for pinch-off current. Fig. 1.20 shows a family of output characteristics for a typical p-channel enhancement MOSFET.

Fig. 1.20 Family of output characteristics for the Siliconix 3N163 p-channel enhancement of MOSFET.

The design and operation of an n-channel enhancement MOSFET is similar to the p-channel enhancement MOS but voltage polarities are reversed.

Fig. 1.21 symbols for enhancement MOSFETs

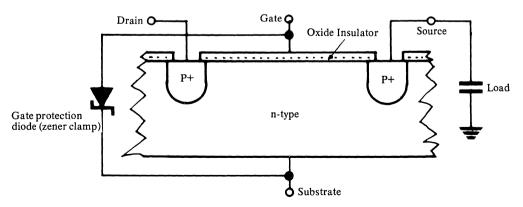

The extremely high gate-to-channel resistances in excess of 10<sup>15</sup> ohms present a problem when handling MOSFETs. Electrostatic charge build-up at the gate can cause the gate-channel capacitance to charge up to voltages which can be in excess of the gate-to-channel dielectric breakdown. Permanent damage to the dielectric can therefore occur. To protect the gate dielectric, many MOSFETS are manufactured with an integrated zener clamp, which consists of a p-n junction, between the gate and substrate. The zener breakdown voltage is designed to be less than that of the gate dielectric but sufficiently high to prevent limitation of the operating voltage.

Since the zener diode is reverse biased during normal operation, the gate leakage current is almost completely determined by the diode leakage current. Dielectric leakage current is a minor factor in comparison. A protected MOSFET has inherently a much higher gate leakage current than an unprotected MOSFET.

#### 1.9 THE FET AS A SWITCH

The high OFF-to-ON resistance ratio of field effect transistors makes them ideal components for use in switching applications. This section covers the major switching parameters of FETs and indicates the degree of performance achievable with commercially available devices.

#### 1.9.1 **ON Resistance**

Switching applications usually require ON resistances to be as small as possible. The ON resistance of field effect transistors depends on the concentration and mobility of the charge carriers in the channel and the physical size of the conducting channel. n-channel devices have lower ON resistance than p-channel devices of similar channel dimensions because of the higher carrier mobility in ntype material.

Since the MOSFET has an extremely thin induced channel, it tends to have a higher ON resistance than a junction FET of similar size. Even so, the geometry of a conventional p-channel MOSFET can be tailored to give low ON resistance as in the case of the Siliconix 3N167 for which rDs(ON) is a maximum of 20 ohms. The DG515 integrated circuit contains a 6.25 ohm NMOS switch. The new MOSPOWER devices which utilise VMOS technology have resistances of less than 2 ohms.

#### 1.9.1.1 Junction FET ON Resistance

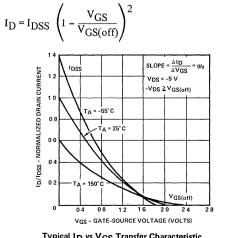

For a junction FET operating in its saturation region, its output characteristic may be approximated by the quadratic function given in equation 1.1

$$I_{D} = I_{DSS} \left( 1 - \frac{V_{GS}}{V_{p}} \right)^{2} \qquad \text{eqn. 1.1}$$

In the saturation region, the value of ID is essentially independent of VDs and the device has a very high dynamic resistance  $\frac{dVDs}{dID}$

For the same FET operating in the non-saturated (triode) region, the output characteristic is given by equation 1.2

$$I_{D} = \frac{V_{DS}}{V_{p}} I_{DSS} \left[ 2 \left( 1 - \frac{V_{GS}}{V_{p}} \right) - \frac{V_{DS}}{V_{p}} \right]$$

eqn. 1.2

From equation 1.2, the channel resistance rDs in the triode region is found to be:

$$r_{DS} = \frac{V_{DS}}{I_D} = \frac{V_p^2}{2I_{DSS}(V_p - V_{GS} - \frac{V_{DS}}{2})} eqn 1.3$$

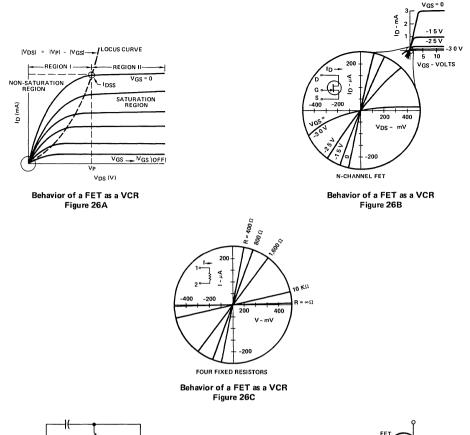

In the triode region, a junction FET behaves as a resistor whose value is dependent upon VGs and VDs. Indeed for very low values of drain-to-source voltage, ID is almost linear with VDs, for a given VGs. For this reason JFETs are widely used as voltage controlled resistors. Over a wider range of drain-to-source voltage, rDs will also depend on VDs; the ID/VDs relationship becomes non-linear as VDs increases. This limits the useful range of VDs. However, techniques exist which employ feedback between drain and gate to reduce the rDs non-linearity and to extend the dynamic range of VDs.

1-19

A junction FET operating under reverse biased gate-source conditions, exhibits minimum channel resistance rDs when both VGs and VDs are zero. Under these conditions an n-channel FET with a Vp of 5V and an IDss of 100mA would, from equation 1.3, exhibit an rDs(ON) of 25 ohms. Such a FET would have an active area of about 0.15 square millimetres. To reduce ON resistance, one option is to increase the active area; for example, the Siliconix U290 n-channel JFET has an ON resistance of less than 2.5 ohms and has an active area of the order of 1 square millimetre.

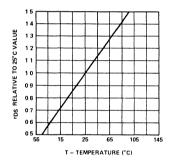

The channel resistance of FETs is temperature dependent. This is due to two effects: a) charge carrier mobility reduces with increasing temperature and so tends to increase channel resistance, and b) the width of the gate-to-channel depletion region decreases with increasing temperature, tending to decrease the resistance. For low values of VGs, the decrease in carrier mobility is the dominant factor and under these conditions junction FETs exhibit a positive temperature coefficient of resistance of about 0.7% per °C (Fig. 1.22).

Fig. 1.22 ON Resistance vs. Ambient Temperature for a typical n-channel JFET.

As the gate-source voltage approaches the V<sub>GS(off)</sub> value, the percentage increase in channel resistance as the temperature increases is balanced by a decrease in resistance due to the decreasing width of the gate-to-channel depletion area. Thus, junction FETs can be biased to a point at which the resistance has a zero temperature coefficient, as illustrated for a p-channel JFET in Fig. 1.23.

Fig. 1.23 rDs VS. VGs and Temperature for a pchannel JFET.

#### 1.9.1.2. MOSFET ON-Resistance

Equation 1.4 is an approximation for the drain current flowing in a MOSFET when operated well into the saturation region. i.e.  $|V_{DS}| > |V_{GS}| - |V_{GS(th)}|$

$$ID = \frac{\beta}{2} (VGS - VGS(th))^2 \qquad \text{eqn. 1.4}$$

In this region, VDs has little effect and ID is almost entirely controlled by VGs. The device constant  $\beta$  is a function of the geometry of the MOSFET and is given as

$$\beta = \mu \quad \frac{e_0 \quad W}{To \ L} \qquad \text{eqn. 1.5}$$

where  $e_0$  = dielectric constant

$\mu$  = mobility of charge carriers

L = channel length from source to drain

W = channel width

To = thickness of gate dielectric.

In the unsaturated (triode) region, the drain current is approximated by Equation 1.6

$$I_{D} = \beta \left\{ V_{DS} \left[ V_{GS} - V_{GS(th)} \right] - \frac{V_{DS}^{2}}{2} \right\}$$

eqn. 1.6

Thus the ON resistance is given by:

$$r_{DS} = \frac{V_{DS}}{I_D} \approx \left\{ \beta \left( \left[ V_{GS} - V_{GS(th)} \right] - \frac{|V_{DS}|}{2} \right) \right\}^{-1} \qquad \text{eqn. 1.7}$$

For n-channel and p-channel enhancement MOSFETS, VGs(th) is positive and negative respectively, whereas for depletion MOSFETS reverse polarities apply.

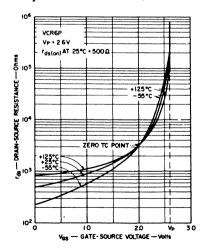

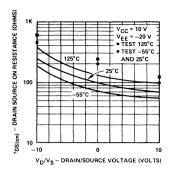

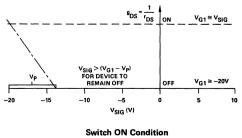

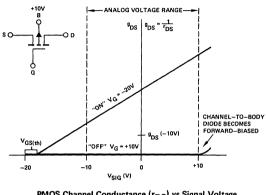

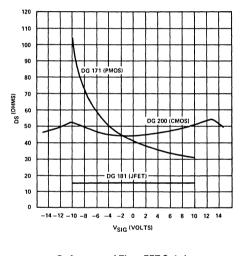

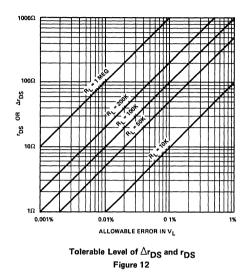

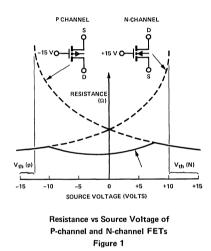

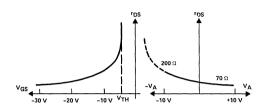

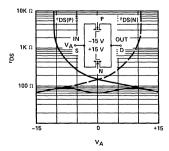

As with junction FETS, the rDs of a MOSFET is dependent not only on VGs but also upon VDs, the minimum ON resistance occurring when |VGS - VDS| is a maximum. Therefore, if MOS devices are used in switching circuits that have fixed gate voltages applied in the ON state, the channel resistance will be modulated by any variation in the analogue signal voltage. Fig. 1.24 illustrates how rDs varies with analogue signal for a typical p-channel enhancement MOSFET.

CHAPTER

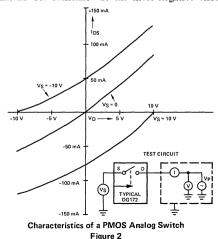

Clearly for p-channel devices, the minimum ON resistance is achieved when the analogue signal is at its most positive value, Fig. 1.24 shows that the resistance can vary by a factor of 3:1 over the analogue range -10V to +10V.

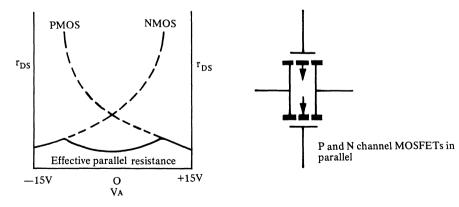

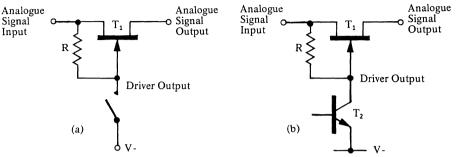

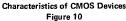

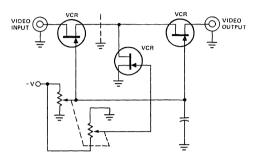

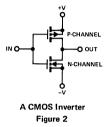

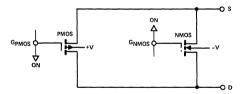

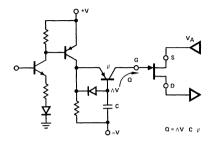

For those applications in which this variation in rDs is unacceptably high, a junction FET having a constant ON resistance over the analogue range, would be more suitable. Alternatively, use could be made of n-channel and p-channel MOSFETs connected in parallel. A negative going analogue signal which causes an increase in the rDs of the p-channel MOS, simultaneously causes a decrease in the rDs of the n-channel MOS. Such complementary MOSFET arrangements are used extensively in integrated circuits.

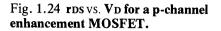

The effects of temperature on channel resistance are similar in both MOS and junction FETs. An increase in temperature causes a reduction in the channel carrier mobility, and a reduction in the threshold voltage. The net effect is that MOSFET channel resistance exhibits a positive temperature coefficient of about 0.4% per °C for high values of VGs. This coefficient falls with VGs until a zero temperature coefficient point is reached (see Fig. 1.25).

Fig. 1.25 rDS(on) VS. VGS and Temperature for Siliconix 3N167 p-channel enhancement MOSFET.

#### 1.9.2 Isolation

Both MOS and junction FETs exhibit extremely high OFF resistance. For most FETs this is greater than 10<sup>10</sup> ohms and in some FETs can exceed 10<sup>13</sup> ohms. In FET applications, the leakage currents Is(OFF) and ID(OFF) are a better measure of the OFF performance of a switch.

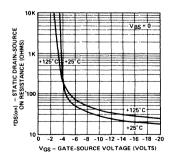

a) Junction FET Leakage Currents

Fig. 1.26 represents an n-channel JFET in the OFF state. The total drain current ID(OFF) is the sum of the drain-gate junction leakage IDG, and the current IDs(OFF) flowing to the source through the high resistance of the OFF channel. The resistance comprises that of the depletion region, shunted by the package header resistance. Most metal-can headers have pin-to-pin resistances of greater than 3 x  $10^{13}$  ohms and the FET depletion region resistance can be in excess of  $10^{13}$  ohms. IDs(OFF) in most applications is therefore just a few picoamps. The leakage currents IDG and IsG will obey the p-n junction leakage relationship of equation 1.8.

$$I = Io\left[\left(\exp\left(\frac{Ve}{1 kT}\right) - 1\right] \qquad \text{eqn. 1.8}$$

снарт

where V is the applied junction voltage, e is the electronic charge (e = 1.602 x  $10^{-19}$ C), T is absolute temperature, k is Boltzmann's constant (k = 1.38 x  $10^{-23} \text{ j/}^{0}$ K), and Io is the reverse saturation current. Thus for small applied junction voltages the leakage currents will increase exponentially with V, but for values of V »  $\frac{\text{kT}}{\text{e}}$  the leakage tends towards the reverse saturation current Io; this then

increases approximately as the square root of the applied voltage.

The temperature dependence of Io for silicon is given by the approximation Equation 1.9

$$Io = AT \exp \left(-\frac{1.12e}{2kT}\right) eqn. 1.9$$

where A is a constant.

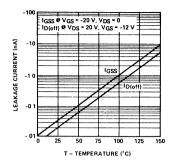

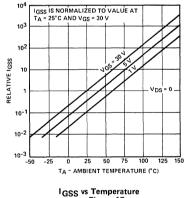

Equation 1.9 indicates that Io doubles for approximately every 10°C rise in temperature. In practice, the leakage current increases at a slightly lower rate, as indicated by the graph of Fig. 1.27 which shows the gate-to-channel leakage currents IGSS and ID(OFF) versus temperature for a typical n-channel JFET switch.

Fig. 1.27 Leakage Current vs. Ambient Temperature for an n-channel JFET.

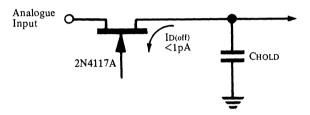

Junction FETs are available with specified maximum OFF leakages ranging from nanoamps to less than one picoamp at 25°C. This wide range is due to the variation in the geometry and processing of different types. Low leakage FETS usually have the smallest geometry. For example, the Siliconix 2N4338 n-channel JFET has a maximum ID(OFF) of 50 picoamps at 25°C with VDG = -20 volts and VGs = -5 volts, and has an active area of about 0.02 square millimetres. The Siliconix U290 has a maximum ID(OFF) of 1nA at 25°C with VDS = 5 volts, VGS = -10 volts and an active area of about 1 square millimetre.

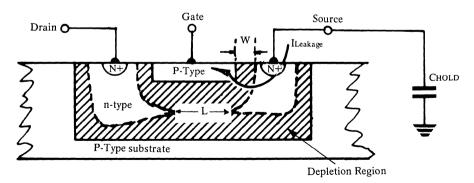

#### b) MOSFET Leakage Currents

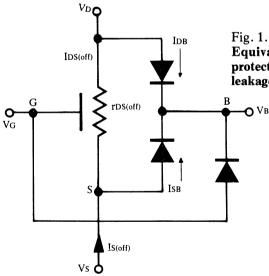

Fig. 1.28 Equivalent circuit of a p-channel protected MOSFET showing the OFF leakage paths.

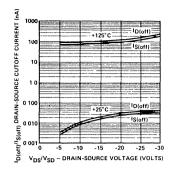

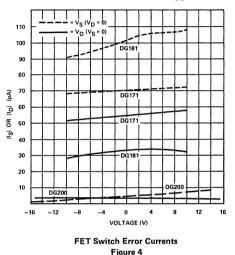

The extremely high gate-to-channel resistance isolates any direct leakage paths from the channel into the gate. However, leakage paths exist from the source and drain (also from the gate in protected devices) into the substrate via the reverse biased junctions (Fig. 1.28). The leakage values are of the same order as those for junction FETs and have similar characteristics although the OFF leakages Is(OFF) and ID(OFF) show a greater dependence upon VDS.

Fig. 1.29 Variation of OFF leakages with applied voltage and temperature for the Siliconix 3N167 p-channel enhancement MOSFET.

#### 1.9.3 Offset Voltage

Unlike the bipolar transistor which exhibits a significant VCE offset voltage, the VDS offset for a FET in the ON state is usually negligible. All bipolar transistors have inherent potential barriers at the base-emitter base-collector junctions (Fig. 1.5) and these must be offset by a small VCE voltage before conduction can occur. This offset voltage is rarely less than 10 millivolts making bipolar transistors unsuitable for switching applications involving low voltage analogue signals.

FET offset voltage results from thermoelectric EMFs generated between source and drain, also from the product of the gate leakage current and the ON resistance. In most applications, these are negligible.

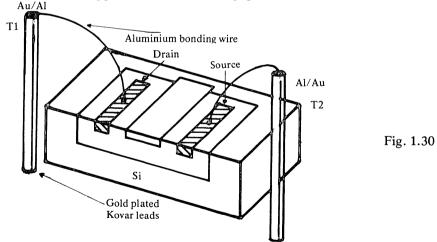

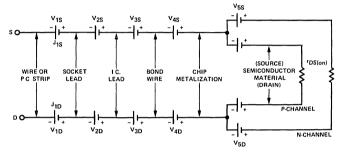

The sources of thermoelectric EMFs for a FET are shown in Fig. 1.30. If, through localised heating on the chip, or through heat applied from external sources via the leads, a temperature gradient of  $T_1$ - $T_2$  is developed between drain and source, then the total thermal offset voltage will be:

$\begin{bmatrix} Thermoelectric coefficient + Thermoelectric coefficient \\ Gold/Aluminium & Aluminium/Silicon \end{bmatrix} x (T_1 - T_2).$

The thermoelectric coefficient for the aluminium-silicon junction is about 0.4 millivolts /°C, while for the gold-aluminium junction it is much less at 0.004

millivolts /°C. If it is assumed that the package leads are at constant temperature, any contribution from the gold—Kovar junction can be eliminated. Hence, the thermoelectric offset for FETs is about  $0.4 \text{ mV/}^{\circ}C$ .

Usually for discrete FETS, due to the small size of the chip and symmetry in the drain-source layout, the  $T_1$  and  $T_2$  temperatures are nearly equal and the thermoelectric offset is very small—of the order of a few microvolts.

On a large integrated circuit some parts of the chip will dissipate more heat than others. It is therefore imperative when designing the layout to ensure that drain and source are both in areas which are subjected to the same amount of local heating. Thermoelectric EMFs also exist in bipolar transistors but these are negligible compared with the barrier offset. The offset voltage resulting from gate leakage current for an n-channel JFET is illustrated in Fig. 1.31.

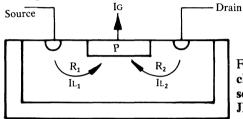

Fig. 1.31a Gate leakage current x channel resistance adds to the drain source offset voltage for an n-channel JFET.

The gate leakage IG comprises leakage currents from the source and drain,  $IL_1$  and  $IL_2$  respectively. These leakage currents flow to the gate via sections of the channel with bulk resistances  $R_1$  and  $R_2$ . Thus the offset due to gate leakage is  $(R_1 \times IL_1) - (R_2 \times IL_2)$ . At room temperature, this voltage will be extremely small, of the order of 1 nano volt but since leakage currents increase with temperature, this offset voltage can be several microvolts at 150°C. A similar situation exists with MOSFETS, although the leakage is now from the source and drain to the substrate.

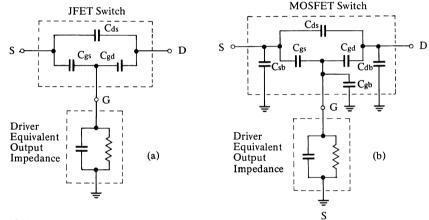

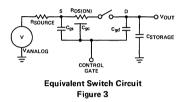

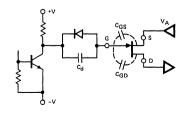

#### 1.9.4 FET Capacitances

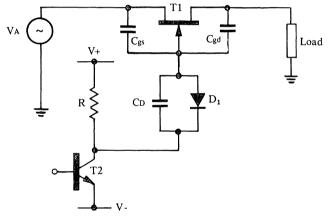

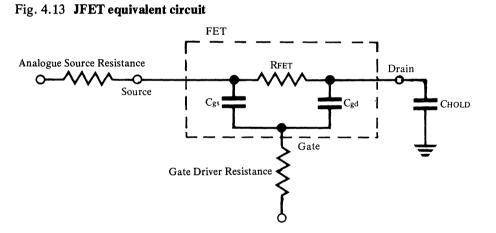

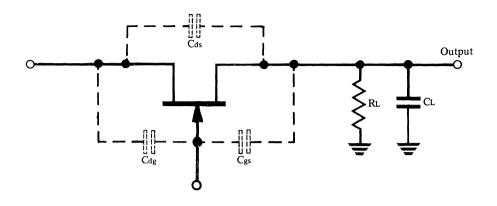

As mentioned in Section 1.4 all p-n junctions exhibit a value of capacitance which is dependent upon the area and depth of the depletion region. For field effect transistors there is a distributed capacitance between the gate and the channel whose value is determined by the FET geometry, the dopant levels, and the applied voltages. The gate-to-channel capacitance can be considered as two lumped capacitors, the gate-to-source capacitance (Cgs) and the gate-to-drain capacitance (Cgd). There is also a drain-to-source capacitance (Cds) which is largely the header capacitance but this is small (« 1.0 pico Farads) compared with the others and can usually be neglected.

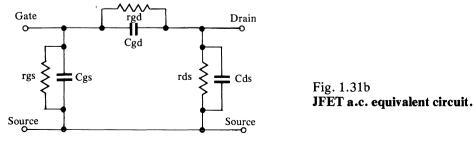

An equivalent circuit of a junction FET is shown in Fig. 1.31b.

The junction capacitances are shown shunted by reverse biased junction resistances, rgs and rgd. These resistances are of such high values that for most purposes they may be ignored and the gate impedance considered as purely capacitive.

Most FET data sheets quote junction capacitances with relation to input and output, that is, Ciss and Crss. The input capacitance Ciss is defined as the capacitance between gate and source when the drain is a.c. short circuited to the source. Analysis of Fig. 1.31 shows that Ciss is defined by equation 1.10.

$$C_{iss} = C_{gs} + C_{gd} \qquad \text{eqn. 1.10}$$

The output capacitance  $C_{oss}$  is the capacitance measured between drain and source with the gate shorted to the source. Thus  $C_{oss}$  is given by equation 1.11.

$$C_{oss} = C_{ds} + C_{gd} \qquad eqn. 1.11$$

Since  $C_{ds}$  is «  $C_{gd}$ , then  $C_{oss} \cong C_{gd} \cong C_{rss}$ . An alternative symbol for  $C_{gd}$  is  $C_{rss}$  which refers to the 'reverse' capacitance and is usually quoted in data sheets in preference to  $C_{gd}$  or  $C_{oss}$ .

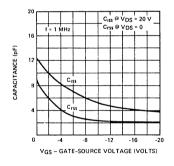

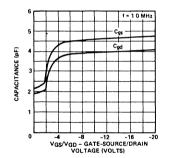

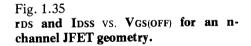

For a p-n step junction, the capacitance is inversely proportional to the square root of the applied voltage and the variations of C<sub>iss</sub> and C<sub>rss</sub> for a typical n-channel JFET are given in Fig. 1.32.

#### Fig. 1.32 Common Source Capacitances vs. Gate-Source Voltage.

Junction capacitance varies only slightly with temperature, there being a slight increase with increasing temperature due to a decrease in the junction barrier potential. The barrier potential varies by about -2.2 millivolts per °C. Thus, as VGs increases, the temperature dependence becomes less pronounced. The physical size of the FET is a major factor in determining the value of its junction capacitances. The typical curves given in Fig. 1.32 relate to the Siliconix 2N4391 JFET which has an active area of about 0.15 square millimitres. The curves indicate a maximum Ciss of 12 pico Farads. For the Siliconix U290 n-channel JFET which has an active area of about 1 square millimetre, the typical maximum value of Ciss is 160 pico Farads.

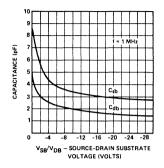

In the case of MOSFETS, channel-to-body junction capacitance must also be considered. This can be treated in a similar manner to the gate capacitance of a JFET. For simplicity, this is considered as two lumped capacitances  $C_{db}$  and  $C_{sb}$ . Fig. 1.33 shows the variation of  $C_{db}$  and  $C_{sb}$  for a typical p-channel enhancement MOSFET.

CHAPTER

1 10

Fig. 1.33 Typical Substrate Capacitance vs. Voltage for the Siliconix M103 pchannel enhancement MOSFET.

MOS gate capacitance is a minimum when the device is OFF. When the device turns ON, the carrier concentration in the channel increases with a subsequent increase in gate-channel capacitance. Fig. 1.34 illustrates the sharp increase in Cgs and Cgd that occur when the gate-source voltage is close to VGS(th) for an enhancement MOSFET

Fig. 1.34 Typical Gate Capacitance vs. Voltage for the Siliconix M113 p-channel enhancement MOSFET.

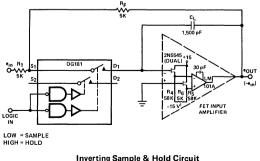

In switching applications the interelectrode capacitances should be kept as small as possible to minimise charge feed through of the gate signal into the channel. Since the channel turn-on switching time is largely determined by the gate capacitance, a low value of interelectrode capacitance is therefore required for fast switching times. Low capacitance is generally achieved by using smaller geometry FETs. This usually implies that the value of ON resistance is likely to increase. The following table of Siliconix n-channel JFETs illustrates the compromise which must be made between capacitance and rDs.

| Device | rDS(ON) max. | Ciss max. | Crss max. |

|--------|--------------|-----------|-----------|

| 2N5432 | 5 ohms       | 30pF      | 15pF      |

| 2N4391 | 30 ohms      | 14pF      | 3.5pF     |

| 2N3966 | 220 ohms     | 6pF       | 1.5pF     |

Direct comparisons of the respective switching speeds are difficult to make because they are defined for specific circuit configurations and for specific values of load resistance values. However, as an indication of performance attainable, switching times of the Siliconix 2N4391 are given below

| Device | td(max) | tr(max) | toff(max) | tf(max) | RL       |

|--------|---------|---------|-----------|---------|----------|

| 2N4391 | 15ns    | 5ns     | 20ns      | 15ns    | 830 ohms |

where  $t_d = turn$ -on delay.  $t_r = rise$  time.  $t_{off} = turn$ -off delay.  $t_f = fall$  time.  $R_L = load$  resistance.

### 1.9.5 Pinch-Off Voltage (Vp) and Threshold Voltage (VGS(th))

#### 1.9.5.1 Pinch-off Voltage

In Section 1.7 the pinch-off voltage Vp of a junction FET was defined as the drain-to-gate voltage at which the channel begins to pinch-off. This voltage is largely determined by the depth of the channel and by the impurity concentration in the channel. Junction FETs of a given geometry are manufactured to various Vp ranges by controlling the depth of the gate diffusion into the channel.

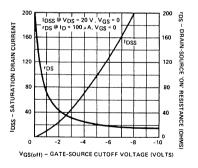

A knowledge of Vp is important since most of the other parameters may be predicted from it. In particular, both IDSS and rDS(ON) are functions of Vp. The expression 'begins to pinch-off'' is an inexact definition and it becomes difficult to specify and test for Vp as a drain-to-gate voltage. For this reason, JFET data sheets specify VGS(OFF) which has the same magnitude but opposite polarity to the pinch-off voltage. VGS(OFF) is the gate-to-source voltage required to turn OFF the FET and is specified for a particular value of drain voltage and current. Fig. 1.35 shows the values of IDSS and rDS(ON) plotted against VGS(OFF) for a typical nchannel JFET geometry.

Measurements show that IDSS is approximately proportional to  $(Vp)^{1.5}$  and that rDS is approximately proportional to  $(Vp)^{-0.5}$ .

Pinch-off voltage shows a slight increase with temperature. The voltage Vp, consists of the pinch-off potential Wo between gate and channel and the junction barrier potential  $\psi$  (equation 1.12)

$$Vp = Wo - \psi$$

eqn. 1.12

#### 1-29

## CHAPTER

Wo is constant with temperature, its value being determined by the charge carrier concentration and the square of the channel depth. The junction barrier potential decreases by about 2.2 millivolts  $/^{\circ}C$ , so Vp will increase at the same rate.

#### 1.9.5.2 Threshold Voltage

The threshold voltage of MOS devices depends upon the work functions between the metal gate-dielectric-semiconductor interfaces, also on the thickness and permittivity of the dielectric. Silicon MOS switches with silicon dioxide as the dielectric are manufactured using either high or low threshold processes, the basic difference between the two processes being in the choice of the silicon crystal orientation. The high threshold PMOS process uses a '111' orientation ntype substrate and has a threshold voltage of about 4 volts. For low threshold a '100' orientation is used giving a VGS(th) of about 2 volts.

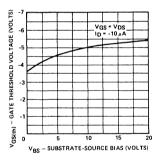

If enhancement MOSFETS are used for analogue switching, a low threshold voltage is desirable to minimise the gate voltage excursion required. Thus, even with the low threshold processes, a minimum VGs of 2 to 3 volts is required to turn the switch ON. This can be a disadvantage for applications involving low analogue signals, as considerable errors can be introduced by charge coupling through the gate-channel capacitance. FETS with a low VGS(th) (or Vp) are therefore preferable for such applications. The substrate bias has a considerable effect on the value of VGS(th) for, if the substrate-channel junction reverse bias is increased, a higher gate voltage is required to maintain conduction, Fig. 1.36.

Fig. 1.36 Gate Threshold Voltage vs. Substrate Bias for the Siliconix M103 pchannel enhancement MOSFET.

Increasing temperature causes a reduction in VGS(th) by about 4 millivolts /°C for the high threshold process and about 2.7 milivolts /°C for low threshold devices. In addition, if the manufacturing process is not clean, a significant shift in VGS(th) can occur if the device is operated at high temperatures for any length of time. This shift is the result of a migration of impurity ions in the oxide which occurs at elevated temperature and under the influence of applied voltages. When the device returns to a normal working temperature the redistribution of charges in the gate oxide results in a change of threshold voltage. The impurities are normally positively charged sodium ions so that if the gate in a PMOS device is maintained at a negative voltage and at high temperature, the ions will be attracted away from the oxide/semiconductor interface with a consequent reduction in threshold voltage. The magnitude of the shift in VGS(th) due to this mechanism depends on time, temperature, impurity concentration and gate bias voltage.

#### 1.9.6 Saturation Current IDss

A knowledge of the maximum drain current that a FET can conduct is important in analogue switch applications. Ideally, an analogue switch should have constant ON resistance over the full signal range, so that for normal purposes the drain current should be considerably less than the saturation drain current. Also in applications involving sample-and-hold circuits the capacitor charging rate can be affected by the IDSS value.

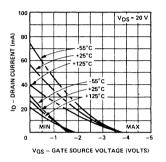

Equation 1.1 showed how the drain saturation current of an n-channel JFET varied with gate-source voltage for a given Vp and IDSS, and this is illustrated graphically in Fig. 1.37.

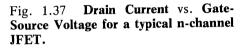

It can be seen in Fig. 1.37 that IDSS falls considerably with increasing temperature. This is due to a reduction in the channel carrier mobility. Junction FETS are presently available with IDSS values ranging from a few milliamperes to over 1 ampere. For MOSFETS the drain saturation current was given by equation 1.4 and a typical example is illustrated in Fig. 1.38.

Fig. 1.38 Drain Saturation Current vs. VGs for a typical p-channel enhancement MOSFET.

Since MOSFETS can operate in enhancement mode, the maximum drain saturation current is usually limited by the maximum power dissipation or gate breakdown voltages of the device.

#### 1.9.7 Breakdown Voltage

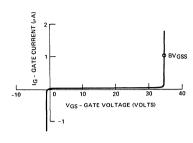

The maximum analogue signal which may be switched is limited by the gate-tochannel breakdown voltage or the drain-to-source breakdown voltage. In junction FETS breakdown results from avalanche multiplication of carriers in the depletion region. On JFET data sheets this breakdown voltage is given the

#### 1-31

### CHAPTER

symbol BVGss, that is, the breakdown between gate and source with the source and drain electrically short ciruited. Typical gate-to-channel breakdown voltages for junction FETs are in the range 30-100 volts, although for the Siliconix U328 n-channel JFET, BVGss is a minimum of -275 volts. The gate dielectric of MOSFETS usually has a breakdown voltage in excess of 100 volts. However, avalanche breakdown between the channel and body restricts the maximum drain-to-source voltage. The minimum drain-to source breakdown BVDss for MOSFETS is usually of the order of 30 volts. For high breakdown geometries, such as the Siliconix M119 p-channel enhancement MOSFET, minimum BVDss is -75 volts.

For 'protected' MOSFETS, the maximum analogue signal is also limited by the breakdown voltage of the gate-to-body diode BVGBS. If this value is exceeded by the analogue-to-gate voltage, current will flow from the channel into the gate via the substrate. Data Sheets for most protected MOSFETS specify minimum values of BVGBS in the range 30-40 volts although the Siliconix M119 has a minimum BVGBS of -80 volts.

#### 1.10 SUMMARY

This chapter has considered, in broad terms, the basic family of field effect transistors and their performance as analogue switches. The following chapter will deal with the wider range of integrated circuits and hybrids, including FET switches, drivers and driver-gate combinations which are presently available.

Introduction to FET Switches CHAPTER

Switch and Driver Circuits CHAPTER

Multiplexing CHAPTER 3

Sample-and-Hold Circuits 4

N-path Filters CHAPTER 5

Signal Conversion using Analog Switches CHAPTER

Applications Information CHAPTER 7

## Chapter 2

# **Switch and Driver Circuits**

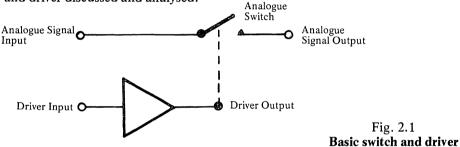

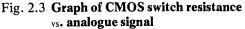

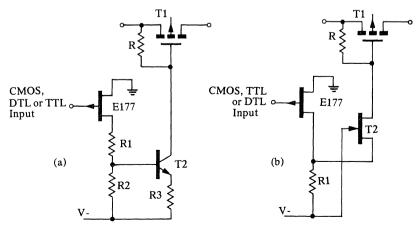

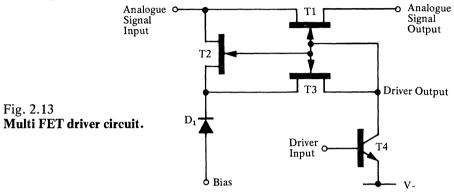

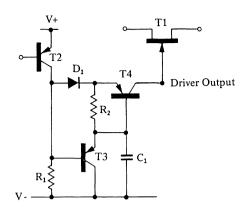

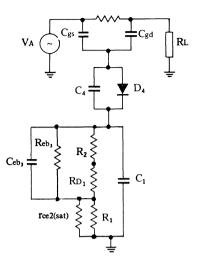

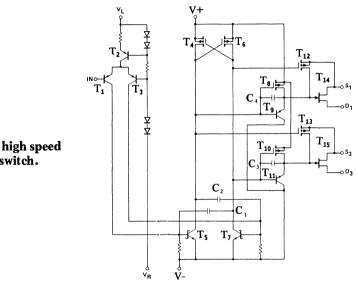

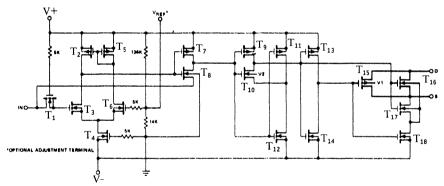

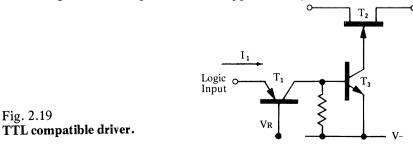

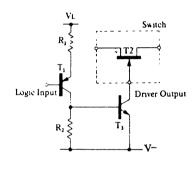

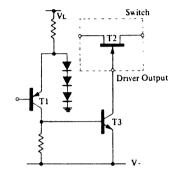

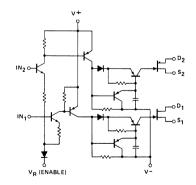

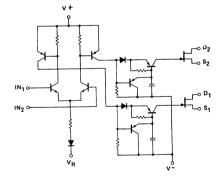

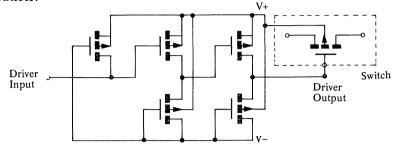

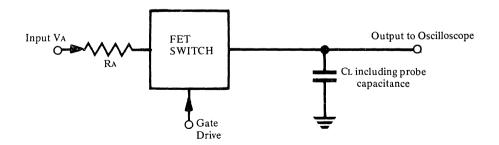

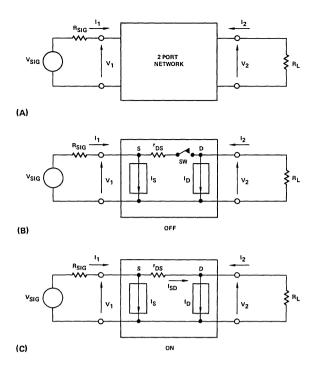

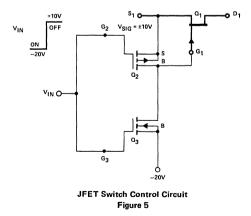

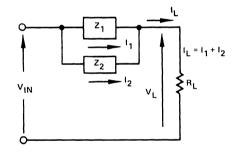

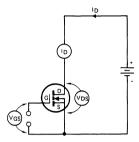

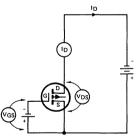

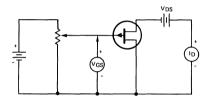

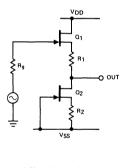

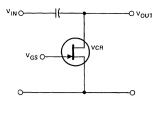

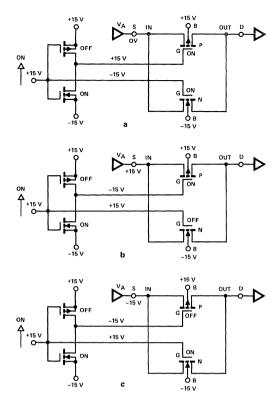

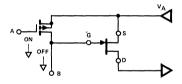

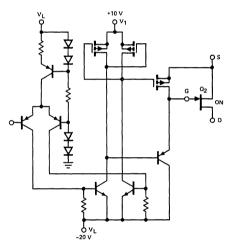

2.1 In the previous chapter it was shown that FETs have many of the characterisitics that are desirable of a good switch. However, a switch has to be controlled; it has to be driven OFF or ON. The basic arrangement of any switch is shown in Fig. 2.1. In a rotary mechanical switch the driver is the spindle, in a relay the driver is a coil, and in a solid-state switch the driver is usually a semiconductor circuit. The driver circuit makes a significant contribution to the overall performance of the switch or gate.

Innumerable circuits have been designed to drive FET switches (*Ref. 2.1 & 2.2*) and about 10 of these have been adopted as industry standards. The mode of operation of these circuits will be described and the interaction between switch and driver discussed and analysed.

Although the analogue signal input and output terminals of the FET switch will frequently be referred to in the ensuing chapter as the source and drain, it will be on the understanding that the source and drain are interchangeable, because the majority of switching FETs are bilateral and symmetrical.

#### 2.2 **TYPES OF FET SWITCHES.**

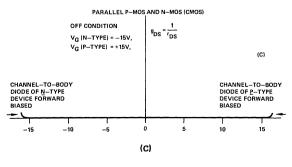

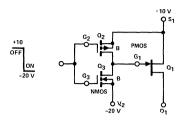

Before investigating the various types of driver circuits, the prime differences between JFET, PMOS (or NMOS) and CMOS which form the three families of FET switches should be stressed.

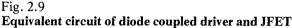

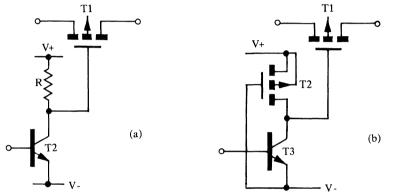

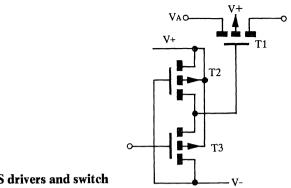

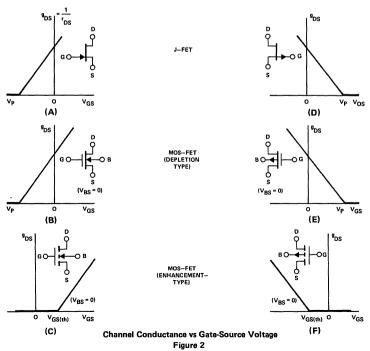

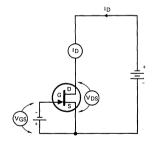

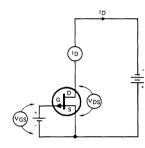

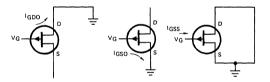

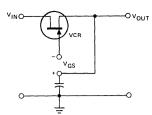

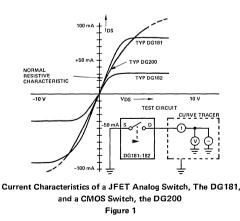

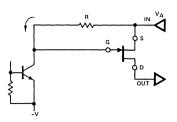

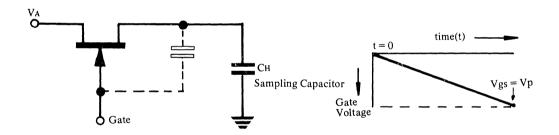

- 2.2.1 JFET The p- or n- channel JFET switch is a depletion mode device. To maintain it in the ON state the value of VGs should be at or near zero volts. To implement the ON state, the gate-and-source or gate-and-drain can be connected together through a resistor, or the gate-to-channel diode can be slightly forward biased by the leakage current of a diode placed in the gate circuit. In either case, the VGs will remain at or near zero volts for all d.c. levels of analogue signal. Consequently, the resistance of the FET is kept constant and equal to rDs(on) for all values of analogue signal.

- 2.2.2 **MOSFET** To maintain an n- or p- channel MOSFET switch in the ON state, the gate is usually held at some reference voltage which ensures that the V<sub>GS</sub>

CHAPTER

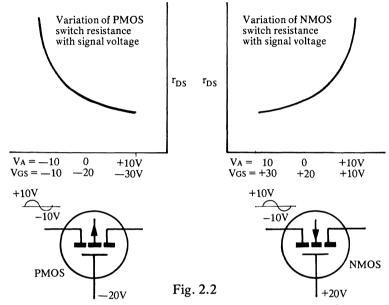

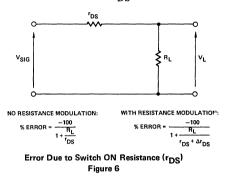

exceeds the threshold voltage of the MOSFET even when the analogue signal (VA) is at the extremes of its dynamic range, hence keeping the MOSFET on for all values of VA. However, since the rDs of a MOSFET is related to VGs by equation 1.7, the rDs will vary as the analogue signal voltage level varies (Fig. 2.2).

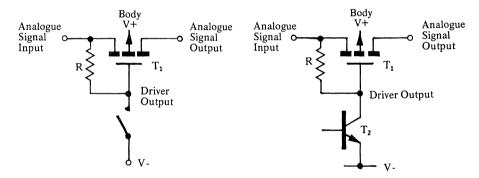

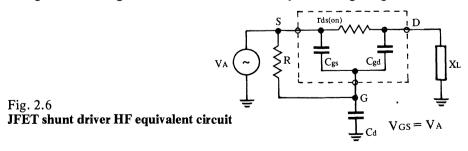

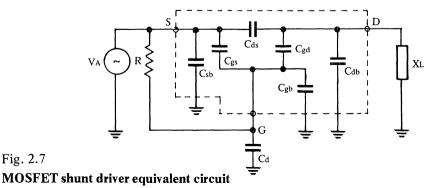

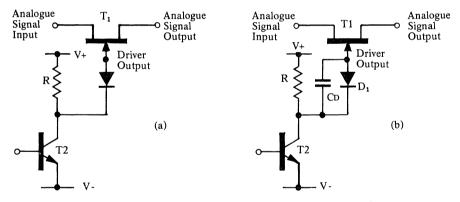

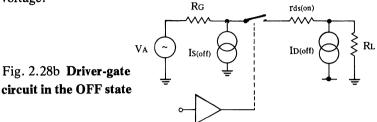

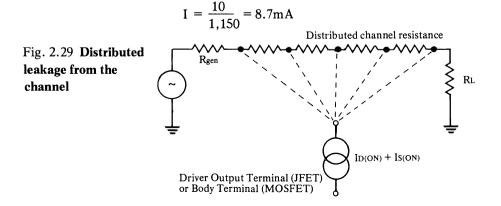

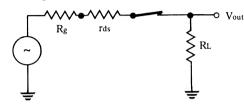

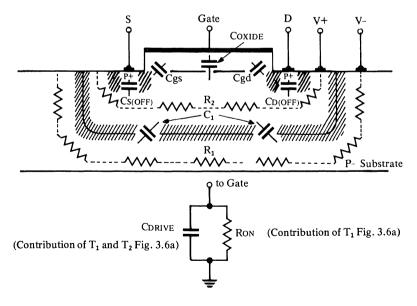

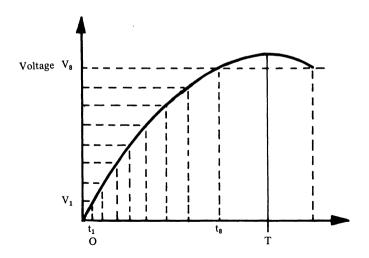

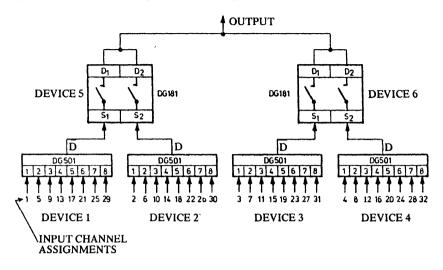

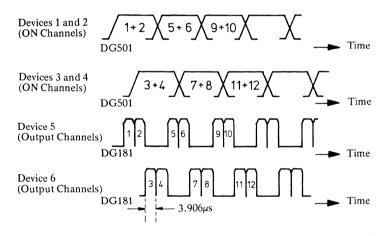

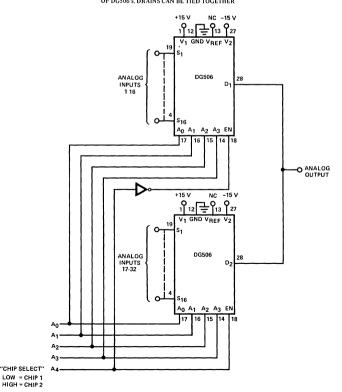

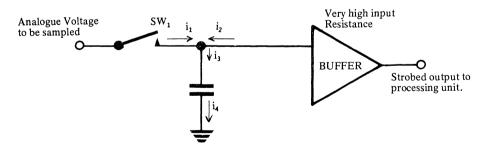

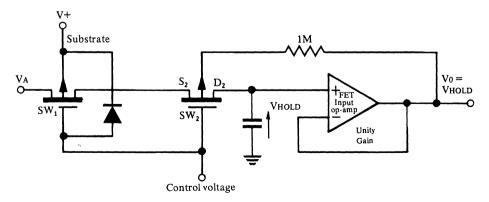

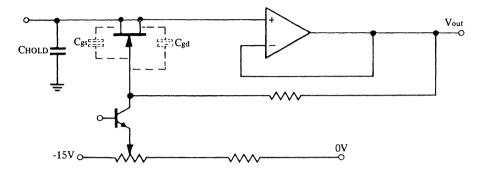

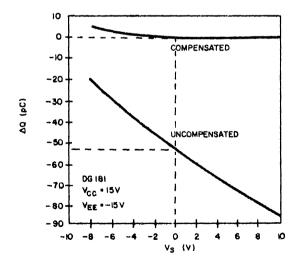

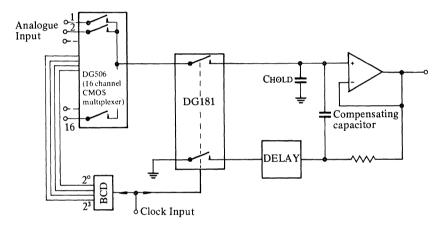

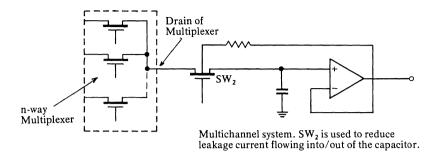

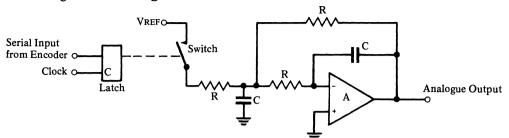

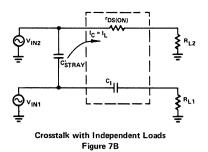

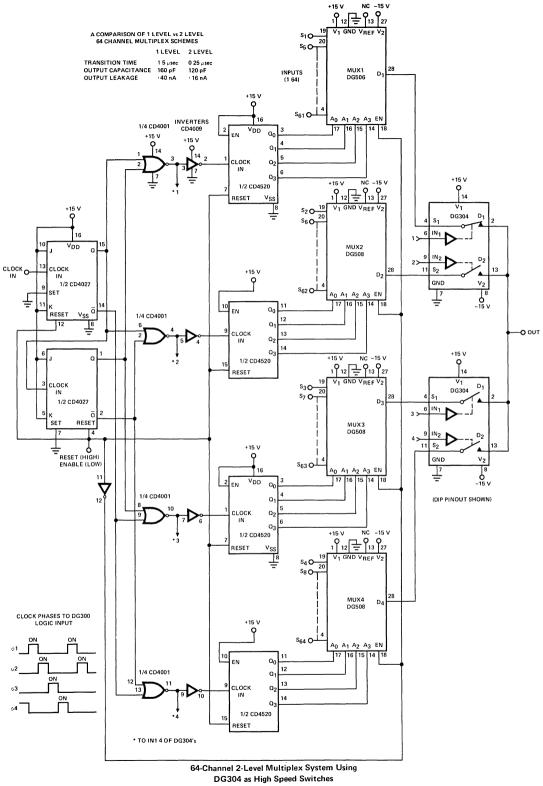

The variation in ON resistance of the P and NMOS transistor with analogue signal is a serious limitation in some applications since it can cause distortion of the analogue output signal. This can be minimised if the load resistance is high compared with the switch resistance.