# Signetics

Integrated Fuse Logic 1981

## FOREWORD

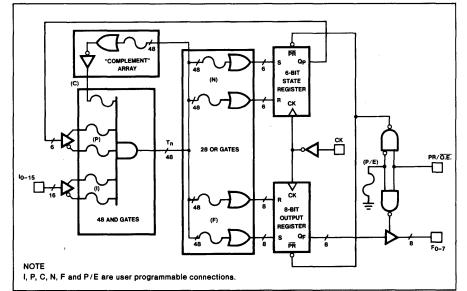

Signetics Integrated Fuse Logic elements combine into single-chip dense arrays of gates, buffers, and flip-flops interconnected via fusible Ni-Cr links. IFL, in effect, lifts circuit connections from the printed circuit board and integrates them on chip where they can be selectively blown by the user with standard PROM programming equipment.

The flexible architecture of Signetics IFL elements allows a "firmware" approach to the synthesis of complex logic functions which result in distinct design advantages. Specifically, most random logic designs using discrete TTL elements can be condensed into fewer IC packages, dramatically reducing overall system cost. Also, since IFL devices can be customized or edited in the field without retooling, your products can benefit from shorter development cycles, custom design flexibility, and quick recovery from design errors.

With the ability to manipulate a flexible logic system quick to debug and adapt to changes in architecture, you gain a competitive edge, not only by compacting in a system more functions, speed, and cost advantages, but by getting your products to the market ahead of your competitors.

## **Revised November 1981**

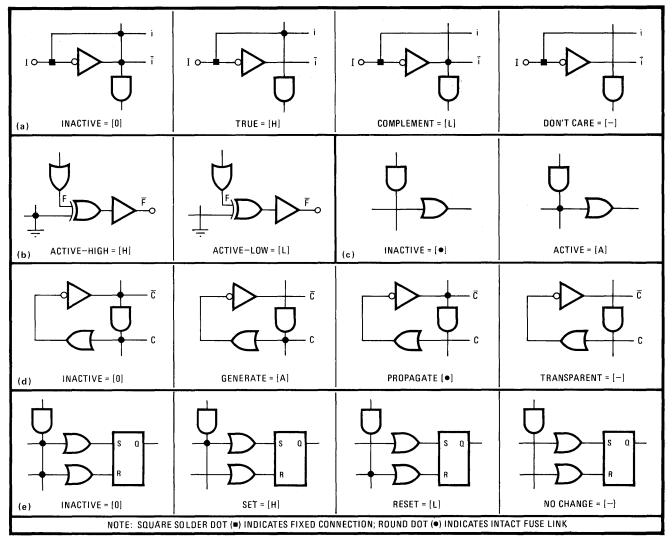

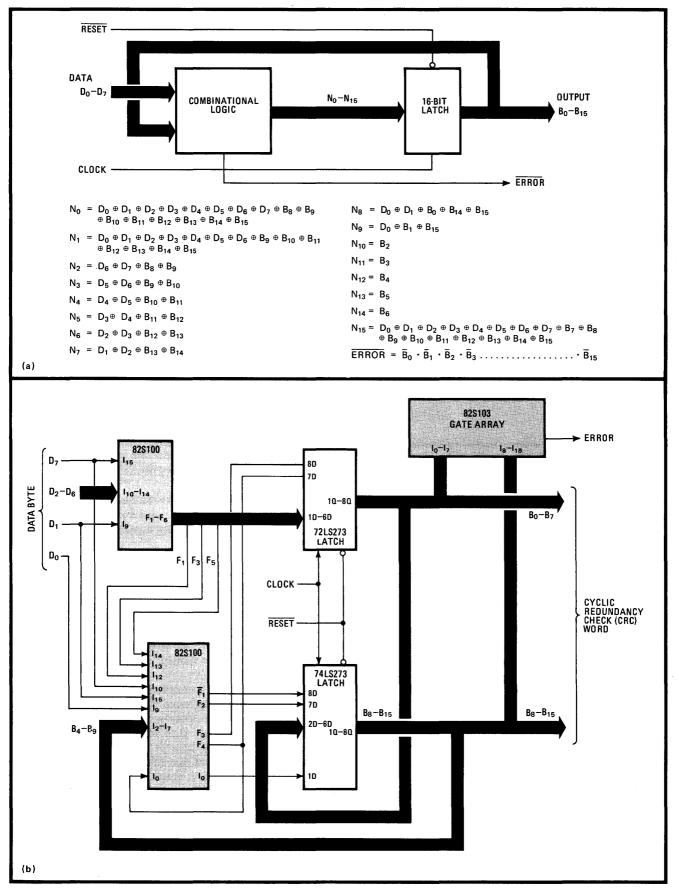

1

# Contents

| Integrated Fuse Logic Series 28 Data Specifications |    |

|-----------------------------------------------------|----|

| 82S100/101 – FPLA                                   | 3  |

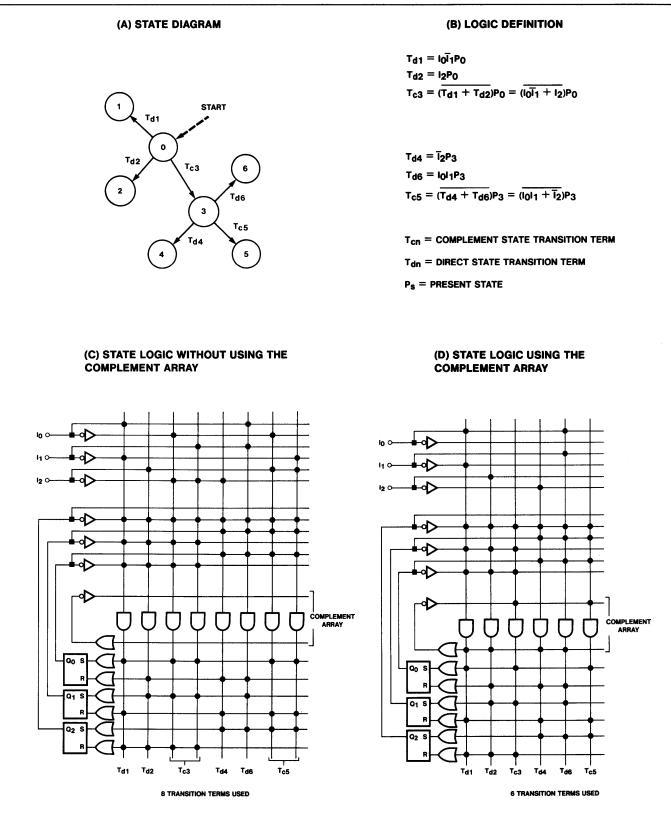

| 82S102/103-FPGA                                     | 15 |

| 82S104/105-FPLS                                     | 23 |

| 82S106/107-FPRP                                     | 45 |

| Integrated Fuse Logic Series 20 Data Specifications |

|-----------------------------------------------------|

| 82S150/151 – FPGA 57                                |

| 82S152/153-FPLA 63                                  |

| 82S154-159-FPLS                                     |

#### **Technical Article**

- "Field Programmable Arrays:

#### **DEFINITION OF TERMS**

| Data Sheet Identification     | Product Status                | Definition                                                                                                                                                                                                                                                     |

|-------------------------------|-------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Preview                       | Formative or<br>In Design     | This data sheet contains the design<br>specifications for product develop-<br>ment. Specifications may change in<br>any manner without notice.                                                                                                                 |

| Advance Information           | Sampling or<br>Pre-Production | This data sheet contains advance<br>information and specifications are<br>subject to change without notice.                                                                                                                                                    |

| Preliminary                   | First<br>Production           | This data sheet contains preliminary<br>data and supplementary data will be<br>published at a later date. Signetics<br>reserves the right to make changes<br>at any time without notice in order<br>to improve design and supply the<br>best possible product. |

| No<br>Identification<br>Noted | Full<br>Production            | This data sheet contains final<br>specifications. Signetics reserves<br>the right to make changes at any<br>time without notice in order to im-<br>prove design and supply the best<br>possible product.                                                       |

<sup>©</sup> Copyright 1981 Signetics Corporation

## FIELD PROGRAMMABLE LOGIC ARRAY (16X48X8) 825100 (T.S.)/825101 (O.C.)

#### DESCRIPTION

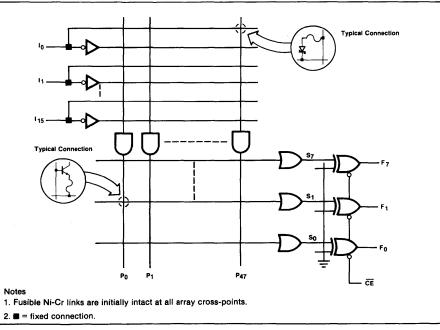

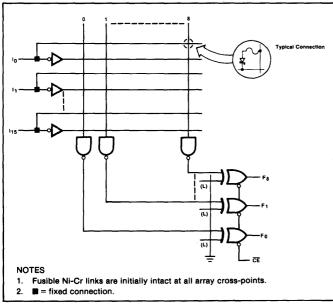

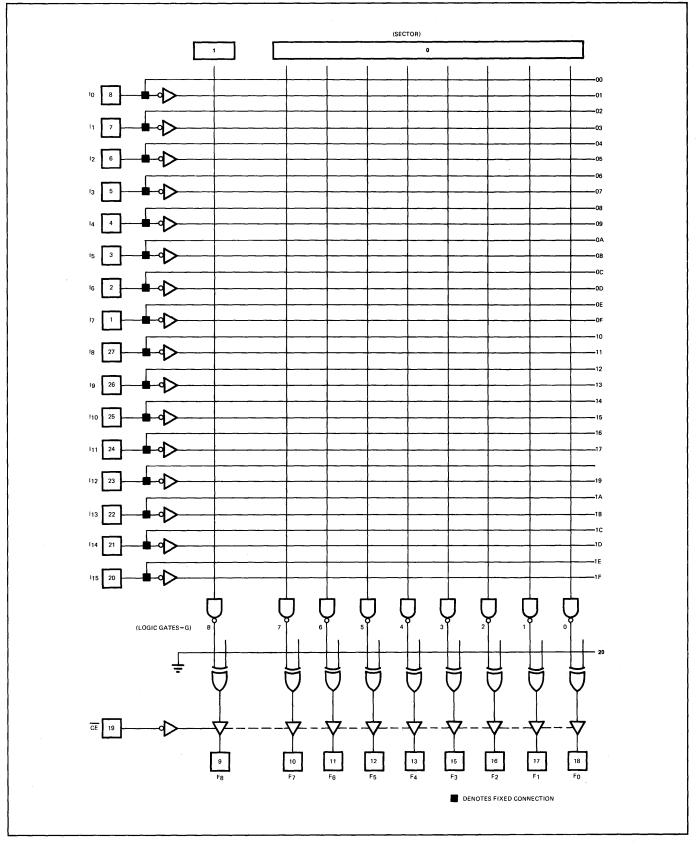

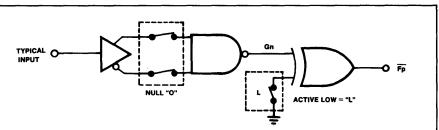

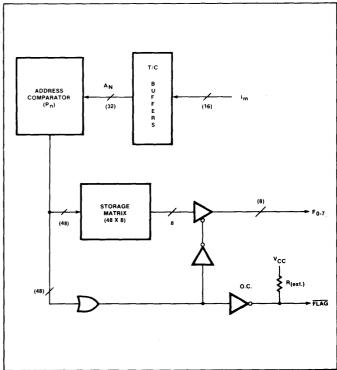

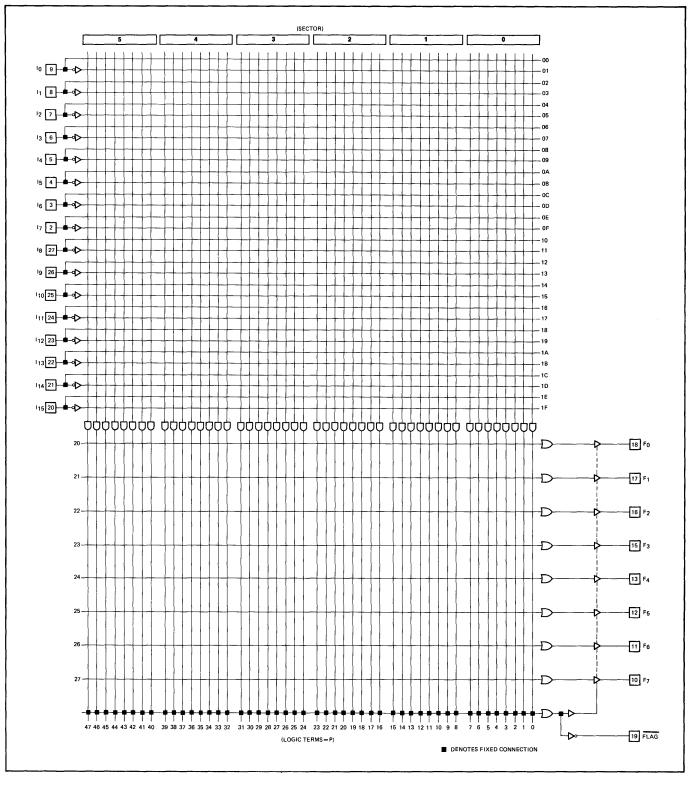

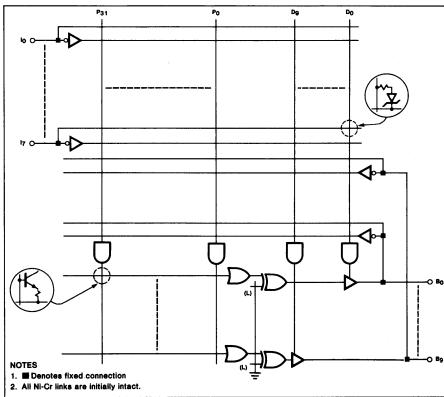

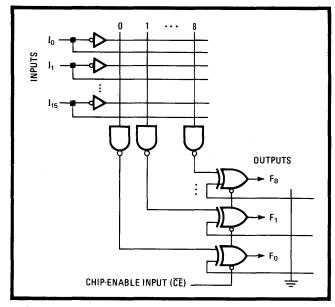

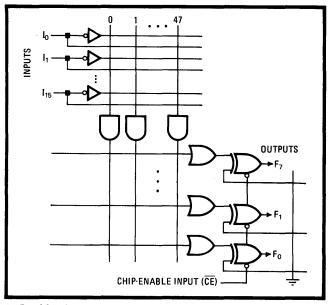

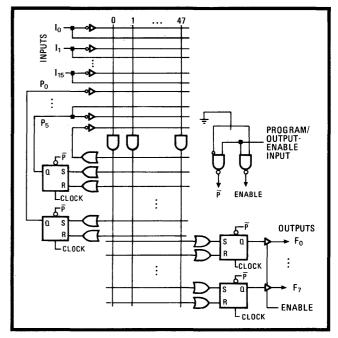

The 82S100 (tri-state outputs) and the 82S101 (open collector outputs) are Bipolar Programmable Logic Arrays, containing 48 product terms (AND terms), and 8 sum terms (OR terms). Each OR term controls an output function which can be programmed either true active-high (Fp), or true active-low ( $\overline{F_p}$ ). The true state of each output function is activated by any logical combination of 16-input variables, or their complements, up to 48 terms. Both devices are field programmable, which means that custom patterns are immediately available by following the fusing procedure outlined in this data sheet.

The 82S100 and 82S101 are fully TTL compatible, and include chip-enable control for expansion of input variables, and output inhibit. They feature either open collector or tri-state outputs for ease of expansion of product terms and application in busorganized systems.

Both devices are available in commercial and military temperature ranges. For the commercial temperature range (0°C to +75°C) specify N82S100/101, F or N, and for the military temperature range (-55°C to +125°C) specify S82S100/101, F or G, I, R.

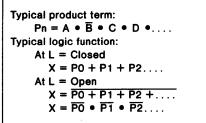

#### LOGIC FUNCTION

Typical Product Term:  $P_0 = I_0 \bullet I_1 \bullet I_2 \bullet I_5 \bullet I_{13}$

Typical Output Functions: @  $\overline{CE} = 0$ :  $F_0 = (P_0 + P_1 + P_2)$  @ L = Closed  $F_0 = (\overline{P_0} + \overline{P_1} + \overline{P_2})$  @ L = Open

NOTE

For each of the 8 outputs, either the function Fp (active-high) or  $\overline{F}_p$  (active low) is available, but not both. The required function polarity is programmed via link (L).

#### **FEATURES**

- Field programmable (Ni-Cr link)

- Input variables: 16

- Output functions: 8

- Product terms: 48

- Address access time: S82S100/101—80ns Max N82S100/101—50ns Max

- Power dissipation: 600mW typ

Input loading:

- S82S100/101: -150μA Max N82S100/101: -100μA Max

- Chip enable input

Output option:

- 82S100: Tri-state 82S101: Open collector

- Output disable function: Tri-state — Hi-Z Open collector — Hi

#### **APPLICATIONS**

- CRT display systems

- Random logic

- Code conversion

- Peripheral controllers

- Function generators

- Look-up and decision tables

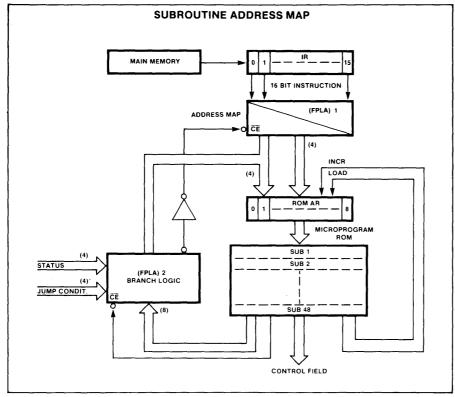

- Microprogramming

- Address mapping

- Character generators

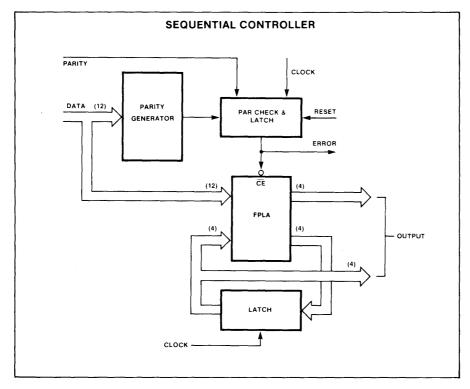

- Sequential controllers

- Data security encoders

- Fault detectors

- Frequency synthesizers

#### INTEGRATED FUSE LOGIC SERIES 28

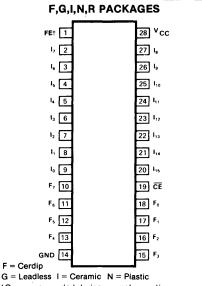

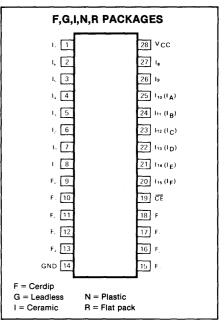

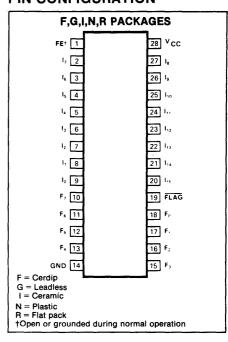

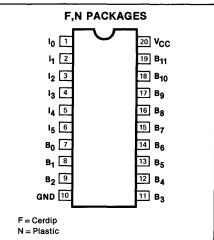

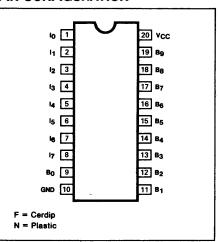

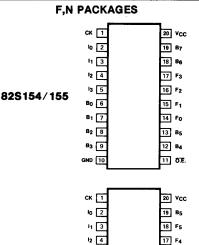

#### **PIN CONFIGURATION**

†Open or grounded during normal operation

#### **TRUTH TABLE**

| MODE                 | Pn   | ĊĒ | Sr<br>f(Pn) | Fp | Fp   |

|----------------------|------|----|-------------|----|------|

| Disabled<br>(82S101) | x    | 1  | ~           | 1  | 1    |

| Disabled<br>(82S100) | bled |    |             |    | Hi-Z |

|                      | 1    | 0  | Yes         | 1  | 0    |

| Read                 | 0    | 0  |             | 0  | 1    |

| neau                 | х    | 0  | No          | 0  | 1    |

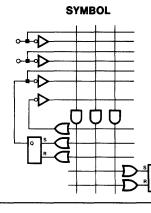

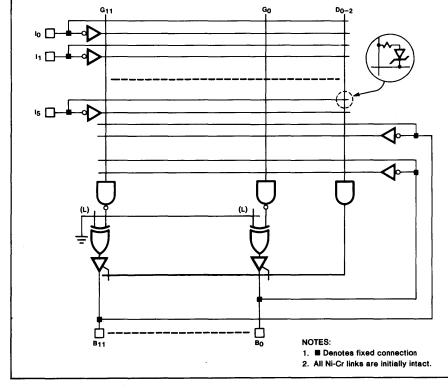

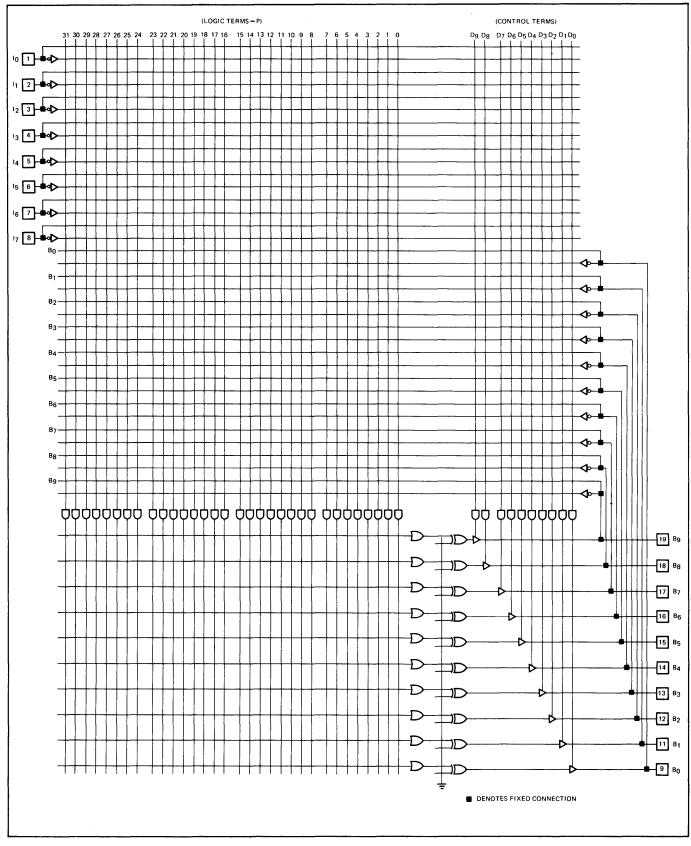

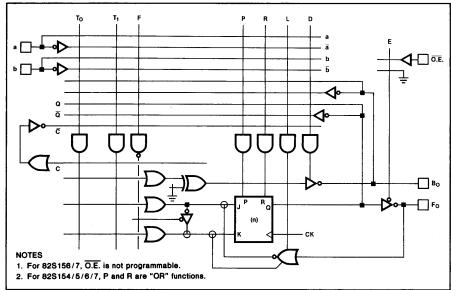

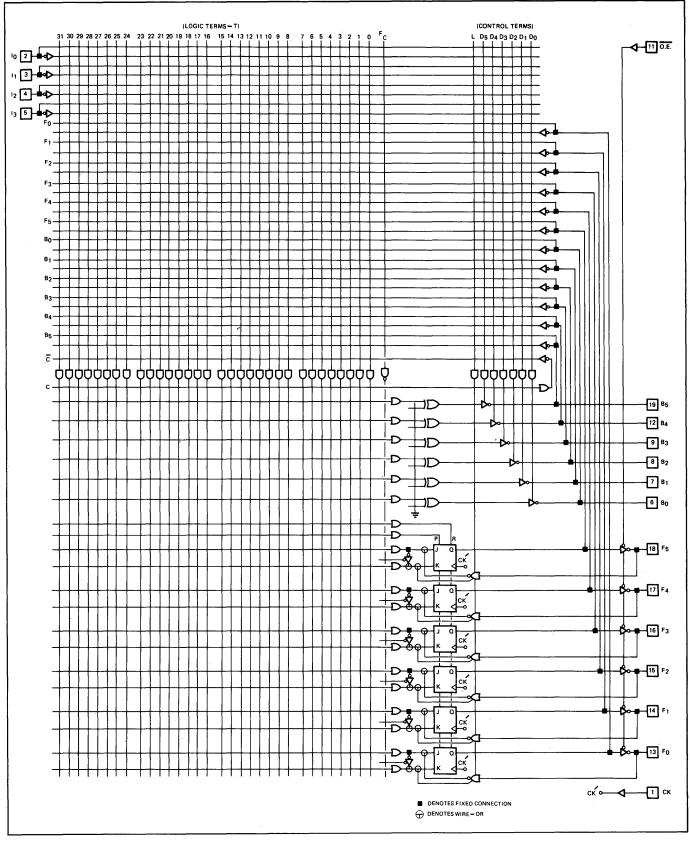

#### LOGIC DIAGRAM

#### JUNE 1981

# INTEGRATED FUSE LOGIC

#### SERIES 28

82S100 (T.S.)82S101 (O.C.)

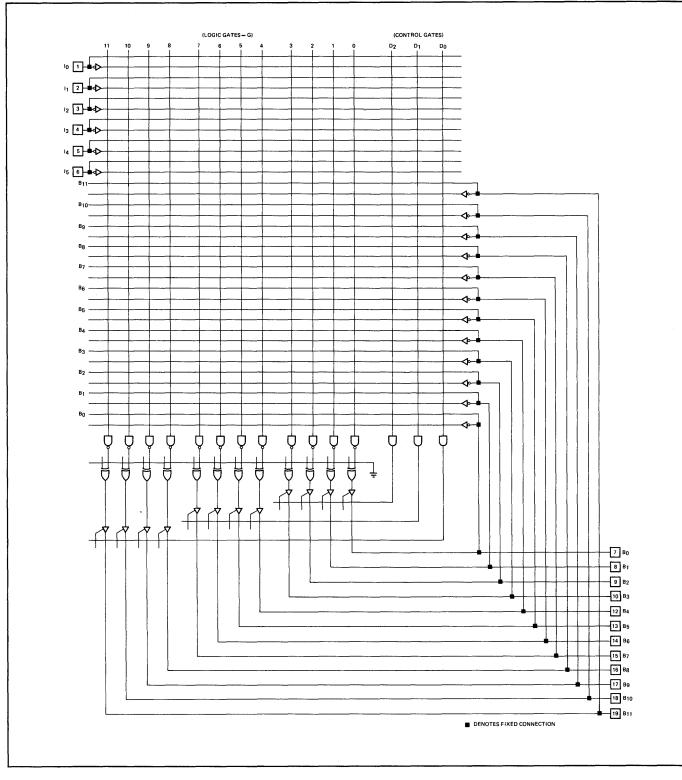

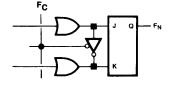

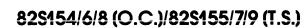

#### FPLA LOGIC DIAGRAM

**BIPOLAR MEMORY DIVISION**

# 825100 (T.S.)/825101 (O.C.)

**SERIES 28**

Maximum

junction Maximum ambient

Allowable thermal rise ambient

to junction

MAY 1981

150° C

75° C

75° C

# FIELD PROGRAMMABLE LOGIC ARRAY (16X48X8)

#### ABSOLUTE MAXIMUM RATINGS1

| DADAI                                   | METER                                                                                                                    | RA              |                                   |                                     |

|-----------------------------------------|--------------------------------------------------------------------------------------------------------------------------|-----------------|-----------------------------------|-------------------------------------|

|                                         | "EICN                                                                                                                    | Min             | Max                               | UNIT                                |

| Vcc<br>Vin<br>Vout<br>Iin<br>Iout<br>Ta | Supply voltage<br>Input voltage<br>Output voltage<br>Input currents<br>Output currents<br>Temperature range<br>Operating | -30             | +7<br>+5.5<br>+5.5<br>+30<br>+100 | Vdc<br>Vdc<br>Vdc<br>mA<br>mA<br>°C |

| Tstg                                    | N82S100/101<br>S82S100/101<br>Storage                                                                                    | 0<br>-55<br>-65 | +75<br>+125<br>+150               |                                     |

| THERMAL RATINGS |               |                      |  |  |  |  |  |  |  |  |  |

|-----------------|---------------|----------------------|--|--|--|--|--|--|--|--|--|

| TEMPERATURE     | MILI-<br>TARY | COM-<br>MER-<br>CIAL |  |  |  |  |  |  |  |  |  |

|                 |               |                      |  |  |  |  |  |  |  |  |  |

175° C

125° C

50° C

INTEGRATED FUSE LOGIC

####

|                               |                                                                                 |                                                                                                                              | N8  | 2\$100/      | 101                    | S82 | 2S100/       | 101                    |                |

|-------------------------------|---------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|-----|--------------|------------------------|-----|--------------|------------------------|----------------|

|                               | PARAMETER                                                                       | TEST CONDITIONS                                                                                                              | Min | Typ2         | Max                    | Min | Typż         | Max                    | UNI            |

| ViH<br>ViL<br>ViC             | Input voltage <sup>3</sup><br>High<br>Low<br>Clamp <sup>3,4</sup>               | $V_{CC} = Max$ $V_{CC} = Min$ $V_{CC} = Min. I_{IN} = -18mA$                                                                 | 2   | -0.8         | 0.85                   | 2   | -0.8         | 0.8<br>-1.2            | V              |

| V <sub>ОН</sub><br><b>Vо∟</b> | Output voltage<br>High (82S100)3,5<br>Low3,6                                    | $V_{CC} = Min$ $I_{OH} = -2mA$ $I_{OL} = 9.6mA$                                                                              | 2.4 | 0.35         | 0.45                   | 2.4 | 0.35         | 0.50                   | V              |

| hн<br>hL                      | Input current<br>High<br>Low                                                    | $V_{1N} = 5.5V$<br>$V_{1N} = 0.45V$                                                                                          |     | <1<br>-10    | 25<br>-100             |     | <1<br>-10    | 50<br>-150             | μA             |

| Iolk<br>Io(off)<br>Ios        | Output current<br>Leakage7<br>Hi-Z state (82S100)7<br>Short circuit (82S100)4,8 | $\overline{CE} = High, V_{CC} = Max$ $V_{OUT} = 5.5V$ $V_{OUT} = 5.5V$ $V_{OUT} = 0.45V$ $\overline{CE} = Low, V_{OUT} = 0V$ | -20 | 1<br>1<br>-1 | 40<br>40<br>-40<br>-70 | -15 | 1<br>1<br>-1 | 60<br>60<br>-60<br>-85 | μΑ<br>μΑ<br>mA |

| Icc                           | V <sub>CC</sub> supply current <sup>9</sup>                                     | V <sub>CC</sub> = Max                                                                                                        |     | 120          | 170                    |     | 120          | 180                    | mA             |

| Cin<br>Cout                   | Capacitance <sup>7</sup><br>Input<br>Output                                     | $\overline{CE} = High, V_{CC} = 5.0V$ $V_{IN} = 2.0V$ $V_{OUT} = 2.0V$                                                       |     | 8<br>17      |                        |     | 8<br>17      |                        | pF             |

####

S82S100/101: -55°C  $\leq T_A \leq$  +125°C, 4.5V  $\leq V_{CC} \leq$  5.5V

|                 |                                           |                  |                      | NE  | 325100/1 | 01       | Sa  | 2\$100/1         | 01       |      |

|-----------------|-------------------------------------------|------------------|----------------------|-----|----------|----------|-----|------------------|----------|------|

| P/              | ARAMETER                                  | то               | FROM                 | Min | Typ2     | Max      | Min | Typ <sup>2</sup> | Max      | UNIT |

| Tia<br>Tce      | Progagation delay<br>Input<br>Chip enable | Output<br>Output | Input<br>Chip enable |     | 35<br>15 | 50<br>30 |     | 35<br>15         | 80<br>50 | ns   |

| T <sub>CD</sub> | Disable time<br>Chip disable              | Output           | Chip enable          |     | 15       | 30       |     | 15               | 50       | ns   |

NOTES on following page.

**SERIES 28**

INTEGRATED FUSE LOGIC

MAY 1981

#### NOTES

- Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only, and functional operation of the device at these or any other conditions above those indicated in the operation of the device specifications is not implied.

- 2. All voltage values are at  $V_{CC} = 5V$ ,  $T_A = 25^{\circ}C$ .

- 3. All voltage values are with respect to network ground terminal.

- 4. Test one at a time.

- 5. Measured with  $V_{IL}$  applied to  $\overline{CE}$  and a logic high stored.

- 6. Measured with a programmed logic condition for which the output test is at a low logic level. Output

- sink current is applied thru a resistor to V<sub>CC</sub>. 7. Measured with V<sub>III</sub> applied to CE

- Measured with V<sub>IH</sub> applied to CE.

Duration of short circuit should not exceed

- 8. Duration of short circuit should not exceed 1 second.

- 9. Icc is measured with the chip enable input grounded, all other inputs at 4.5V and the outputs open.

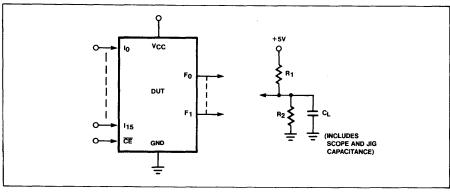

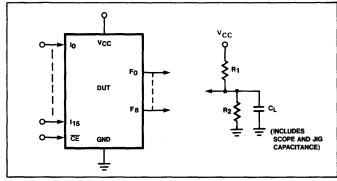

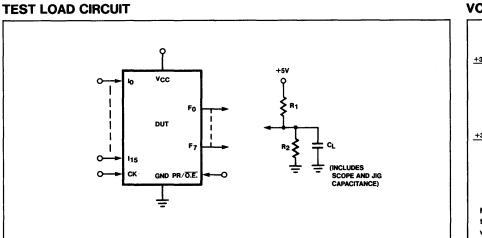

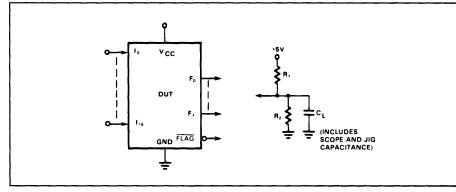

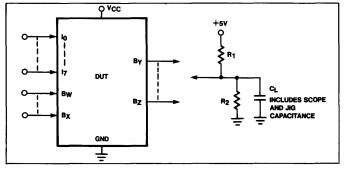

#### **TEST LOAD CIRCUIT**

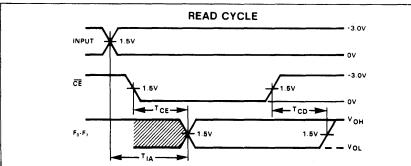

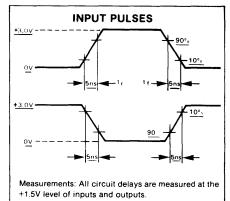

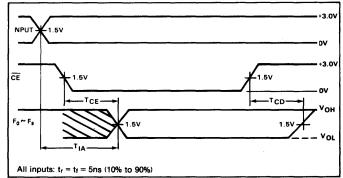

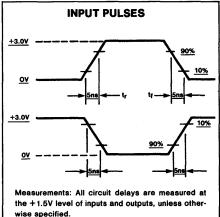

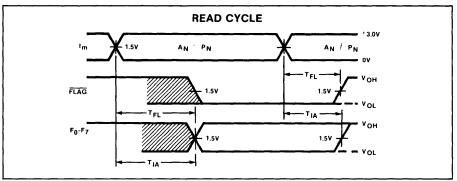

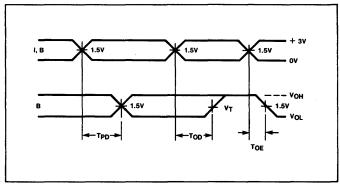

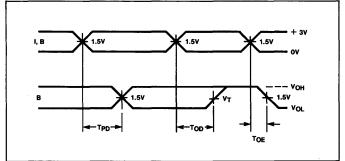

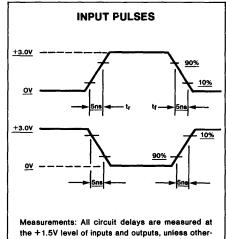

#### TIMING DIAGRAM

#### TIMING DEFINITIONS

- TCE Delay between beginning of Chip Enable low (with Input valid) and when Data Output becomes valid.

- TCD Delay between when Chip Enable becomes high and Data Output is in off state (Hi-Z or high).

- T<sub>IA</sub> Delay between beginning of valid Input (with Chip Enable low) and when Data Output becomes valid.

#### **VIRGIN DEVICE**

6

The 82S100/101 are shipped in an unprogrammed state, characterized by:

- 1. All internal Ni-Cr links are intact.

- Each product term (P-term) contains both true and complement values of every input variable I<sub>m</sub> (P-terms always logically "false").

- The "OR" Matrix contains all 48-P-terms.

The polarity of each output is set to active high (Fp function).

- 5. All outputs are at a low logic level.

#### RECOMMENDED PROGRAMMING PROCEDURE

To program each of 8 Boolean logic functions of 16 true or complement variables, including up to 48 P-terms, follow the Program/Verify procedures for the "AND" matrix, "OR" matrix, and output polarity outlined below. To maximize recovery from programming errors, leave all links in unused device areas intact.

#### SET-UP

Terminate all device outputs with a 10K resistor to +5V. Set GND (pin 14) to 0V.

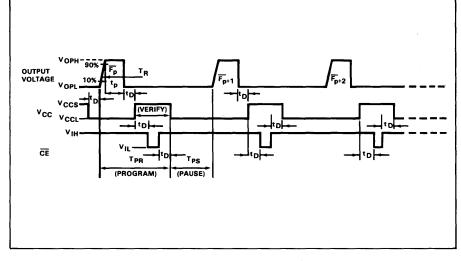

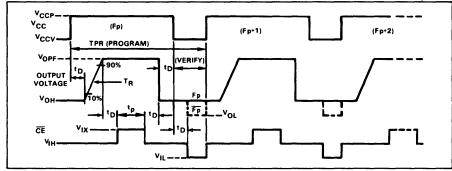

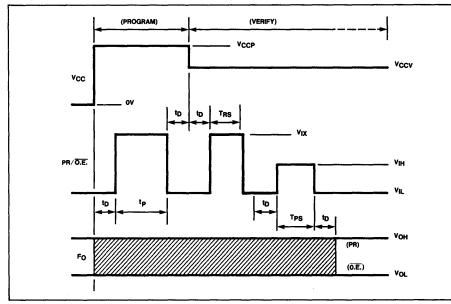

#### **VOLTAGE WAVEFORM**

#### **Output Polarity**

# PROGRAM ACTIVE LOW (Fp FUNCTION)

Program output polarity before programing "AND" matrix and "OR" matrix. Program 1 output at the time. (L) links of unused outputs are not required to be fused.

- 1. Set FE (pin 1) to VFEL.

- 2. Set Vcc (pin 28) to VccL.

- 3. Set  $\overline{CE}$  (pin 19), and I<sub>0</sub> through I<sub>15</sub> to V<sub>IH</sub>. 4. Apply V<sub>OPH</sub> to the appropriate output,

- and remove after a period t<sub>p</sub>.

- 5. Repeat step 4 to program other outputs.

#### VERIFY OUTPUT POLARITY

- 1. Set FE (pin 1) to V<sub>FEL</sub>; set V<sub>CC</sub> (pin 28) to V<sub>CCS</sub>.

- Enable the chip by setting CE (pin 19) to VIL.

- 3. Address a non-existent P-term by applying V<sub>IH</sub> to all inputs I<sub>0</sub> through I<sub>15</sub>.

- 4. Verify output polarity by sensing the logic state of outputs F<sub>0</sub> through F<sub>7</sub>. All outputs at a high logic level are programmed active low (F<sub>p</sub> function), while all outputs at a low logic level are programmed active high ( $\overline{F_p}$  function).

- 5. Return VCC to VCCP or VCCL.

#### MAY 1981

# INTEGRATED FUSE LOGIC SERIES 28

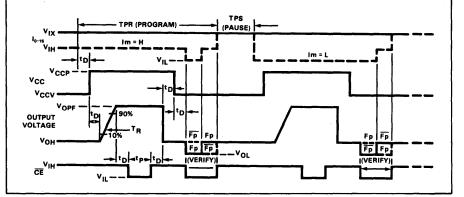

### "AND" Matrix

#### PROGRAM INPUT VARIABLE

Program one input at the time and one Pterm at the time. All input variable links of unused P-terms are not required to be fused. However, unused input variables must be programmed as Don't Care for all programmed P-terms.

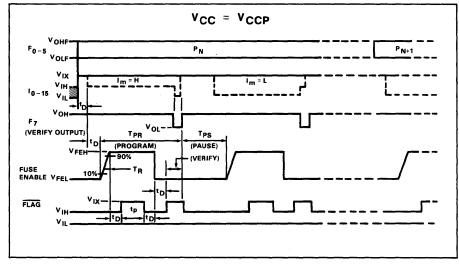

- 1. Set FE (pin 1) to V<sub>FEL</sub>, and V<sub>CC</sub> (pin 28) to V<sub>CCP</sub>.

- 2. Disable all device outputs by setting  $\overrightarrow{CE}$  (pin 19) to V<sub>IH</sub>.

- Disable all input variables by applying V<sub>IX</sub> to inputs I<sub>0</sub> through I<sub>15</sub>.

- Address the P-term to be programmed (No. 0 through 47) by forcing the corresponding binary code on outputs F<sub>0</sub> through F<sub>5</sub> with F<sub>0</sub> as LSB. Use standard TTL logic levels V<sub>OHF</sub> and V<sub>OLF</sub>.

- 5a. If the P-term contains neither  $I_0$  nor  $\overline{I_0}$ (input is a Don't Care), fuse both  $I_0$  and  $\overline{I_0}$  links by executing both steps 5b and 5c, before continuing with step 7.

- $\begin{array}{l} 5\,b\ .\ If the\ P-term\ contains\ I_0,\ set\ to\ fuse\ the} \\ \hline I_0\ link\ by\ lowering\ the\ input\ voltage\ at} \\ I_0\ from\ V_{IX}\ to\ V_{IH}.\ Execute\ step\ 6. \end{array}$

- 5 c. If the P-term contains  $\overline{I_0}$ , set to fuse the I<sub>0</sub> link by lowering the input voltage at I<sub>0</sub> from V<sub>IX</sub> to V<sub>IL</sub>. Execute step 6.

- 6 a . After t<sub>D</sub> delay, raise FE (pin 1) from V<sub>FEL</sub> to V<sub>FEH</sub>.

- 6 b. After t<sub>D</sub> delay, pulse the  $\overline{CE}$  input from V<sub>IH</sub> to V<sub>IX</sub> for a period t<sub>p</sub>.

- 6 c. After t<sub>D</sub> delay, return FE input to V<sub>FEL</sub>.

- Disable programmed input by returning I<sub>0</sub> to V<sub>IX</sub>.

- 8. Repeat steps 5 through 7 for all other input variables.

- 9. Repeat steps 4 through 8 for all other Pterms.

- 10. Remove  $V_{\text{IX}}$  from all input variables.

#### VERIFY INPUT VARIABLE

- 1. Set FE (pin 1) to V<sub>FEL</sub>; set V<sub>CC</sub> (pin 28) to V<sub>CCP</sub>.

- 2. Enable  $F_7$  output by setting  $\overline{CE}$  to  $V_{IX}$ .

- 3. Disable all input variables by applying V<sub>IX</sub> to inputs I<sub>0</sub> through I<sub>15</sub>.

- Address the P-term to be verified (No. 0 through 47) by forcing the corresponding binary code on outputs F<sub>0</sub> through F<sub>5</sub>.

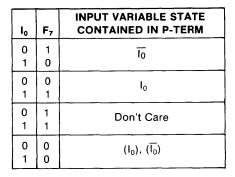

- 5. Interrogate input variable I<sub>0</sub> as follows:

- A. Lower the input voltage at  $I_0$  from  $V_{IX}$  to  $V_{IH}$ , and sense the logic state of output F<sub>7</sub>.

- B. Lower the input voltage at  $I_0$  from V<sub>IH</sub> to V<sub>IL</sub>, and sense the logic state output F<sub>7</sub>.

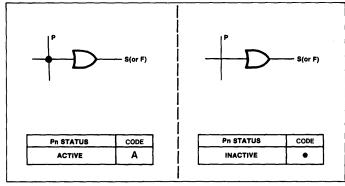

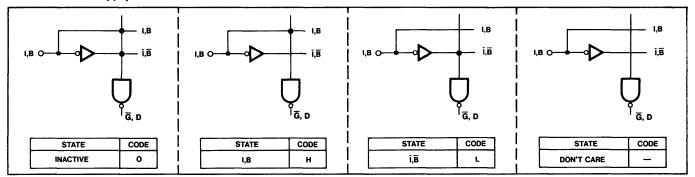

The state of  $I_0$  contained in the P-term is determined in accordance with the following truth table:

Note that 2 tests are required to uniquely determine the state of the input variable contained in the P-term.

- 6. Disable verified input by returning I<sub>0</sub> to Vix.

- 7. Repeat steps 5 and 6 for all other input variables.

- 8. Repeat steps 4 through 7 for all other P-terms.

- 9. Remove VIX from all input variables.

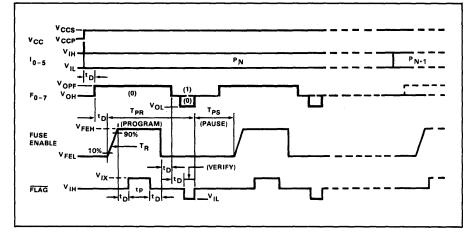

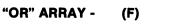

#### "OR" MATRIX PROGRAM PRODUCT TERM

Program one output at the time for one P-term at the time. All  $P_n$  links in the "OR" matrix corresponding to unused outputs and unused P-terms are not required to be fused.

- 1. Set FE (pin 1) to VFEL.

- 2. Disable the chip by setting  $\overline{CE}$  (pin 19) to V<sub>IH</sub>.

- 3. After t<sub>D</sub> delay, set V<sub>CC</sub> (pin 28) to V<sub>CCS</sub>, and inputs I<sub>6</sub> through I<sub>15</sub> to V<sub>IH</sub>, V<sub>IL</sub>, or V<sub>IX</sub>.

- Address the P-term to be programmed (No. 0 through 47) by applying the corresponding binary code to input

variables I<sub>0</sub> through I<sub>5</sub>, with I<sub>0</sub> as LSB.

5a. If the P-term is contained in output function F<sub>0</sub> (F<sub>0</sub> = 1 or F<sub>0</sub> = 0), got to step 6, (fusing cycle not required).

82S100 (T.S.)82S101 (O.C.)

- 5b. If the P-term is **not** contained in output function  $F_0$  ( $F_0 = 0$  or  $\overline{F_0} = 1$ ), set to fuse the  $P_n$  link by forcing output  $F_0$  to VOPF.

- 6a. After t<sub>D</sub> delay, raise FE (pin 1) from VFEL to VFEH.

- 6b. After t<sub>D</sub> delay, pulse the  $\overline{CE}$  input from  $V_{IH}$  to  $V_{IX}$  for a period t<sub>p</sub>.

- After t<sub>D</sub> delay, return FE input to VFEL.

After t<sub>D</sub> delay, remove V<sub>OPF</sub> from output F<sub>0</sub>.

- Repeat steps 5 and 6 for all other output functions.

- 8. Repeat steps 4 through 7 for all other P-terms.

- 9. Remove V<sub>CCS</sub> from V<sub>CC</sub>.

#### VERIFY PRODUCT TERM

- 1. Set FE (pin 1) to V<sub>FEL</sub>.

- 2. Disable the chip by setting  $\overline{CE}$  (pin 19) to VIH.

- 3. After  $t_D$  delay, set  $V_{CC}$  (pin 28) to  $V_{CCS}$ , and inputs  $I_0$  through  $I_{15}$  to  $V_{IH}$ ,  $V_{IL}$ , or  $V_{IX}$ .

- Address the P-term to be verified (No. 0 through 47) by applying the corresponding binary code to input variables I<sub>0</sub> through I<sub>5</sub>.

- 5. After t<sub>D</sub> delay, enable the chip by setting  $\overline{CE}$  (pin 19) to V<sub>IL</sub>.

- To determine the status of the P<sub>n</sub> link in the "OR" matrix for each output function F<sub>p</sub> or F<sub>p</sub>, sense the state of outputs F<sub>0</sub> through F<sub>7</sub>. The status of the link is given by the following truth table:

| OUTP                | UT                 |                  |

|---------------------|--------------------|------------------|

| Active High<br>(Fp) | Active Low<br>(Fp) | P-TERM LINK      |

| <br>0<br>1          | 1<br>0             | Fused<br>Present |

- Repeat steps 4 through 6 for all other Pterms.

- 8. Remove V<sub>CCS</sub> from V<sub>CC</sub>.

# INTEGRATED FUSE LOGIC

MAY 1981

SERIES 28

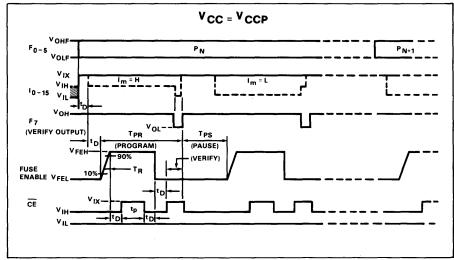

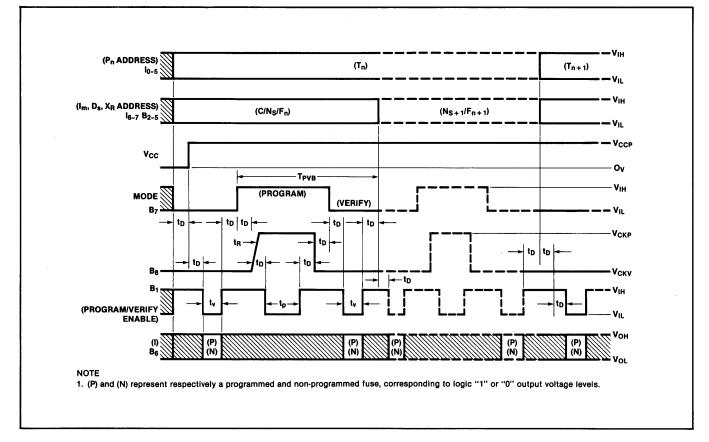

#### OUTPUT POLARITY PROGRAM-VERIFY SEQUENCE (TYPICAL)

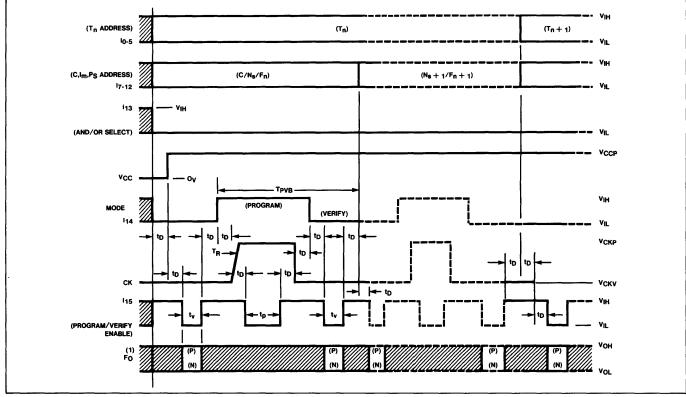

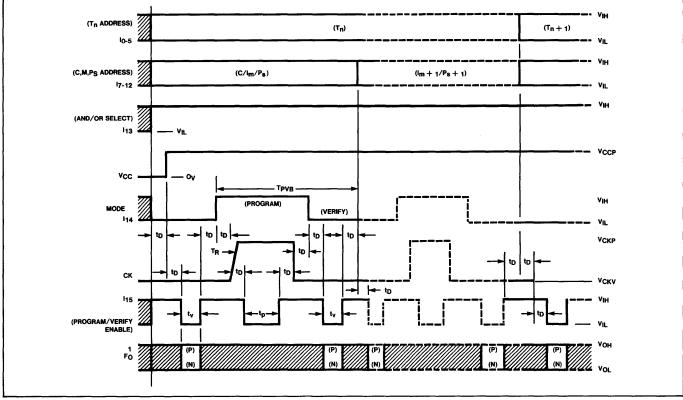

#### "AND" MATRIX PROGRAM-VERIFY SEQUENCE (TYPICAL)

#### "OR" MATRIX PROGRAM-VERIFY SEQUENCE (TYPICAL)

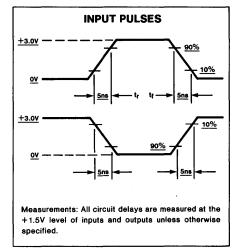

#### **PROGRAMMING SYSTEM SPECIFICATIONS**<sup>1</sup> ( $T_A = +25^{\circ}C$ )

|                 | PARAMETER                                                                                | TEST CONDITIONS                                             |           |             |              |         |  |

|-----------------|------------------------------------------------------------------------------------------|-------------------------------------------------------------|-----------|-------------|--------------|---------|--|

|                 | PARAMETER                                                                                | TEST CONDITIONS                                             | Min       | Тур         | Max          |         |  |

| Vccs            | V <sub>CC</sub> supply (program/verify<br>"OR", verify output polarity) <sup>2</sup>     | I <sub>CCS</sub> = 550mA, min,<br>Transient or steady state | 8.25      | 8.5         | 8.75         | V       |  |

| VccL<br>Iccs    | V <sub>CC</sub> supply (program output polarity)<br>I <sub>CC</sub> limit (program "OR") | $V_{CCS} = +8.5 \pm .25V$                                   | 0<br>550  | 0.4         | 0.8<br>1,000 | V<br>m/ |  |

| Voph<br>Vopl    | Output voltage<br>Program output polarity <sup>3</sup><br>Idle                           | I <sub>ОРН</sub> = 300 ± 25mA                               | 16.0<br>0 | 17.0<br>0.4 | 18.0<br>0.8  | v       |  |

| Іорн            | Output current limit (Program output polarity)                                           | $V_{OPH} = +17 \pm 1V$                                      | 275       | 300         | 325          | m       |  |

| Vi∺<br>Vi∟      | Input voltage<br>High<br>Low                                                             |                                                             | 2.4<br>0  | 0.4         | 5.5<br>0.8   | V       |  |

| կը<br>կլ        | Input current<br>High<br>Low                                                             | $V_{IH} = +5.5V$<br>$V_{IL} = 0V$                           |           | -           | 50<br>-500   | μ       |  |

| Vohf<br>Volf    | Forced output voltage<br>High<br>Low                                                     |                                                             | 2.4<br>0  | 0.4         | 5.5<br>0.8   | V       |  |

| IOHF<br>IOLF    | Output current<br>High<br>Low                                                            | $V_{OHF} = +5.5V$<br>$V_{OLF} = 0V$                         |           |             | 100<br>-1    | μ/<br>m |  |

| Vix             | CE program enable level                                                                  |                                                             | 9.5       | 10          | 10.5         | V       |  |

| lix1            | Input variables current                                                                  | $V_{IX} = +10V$                                             |           |             | 10           | m       |  |

| lix2            | CE input current                                                                         | $V_{IX} = +10V$                                             |           |             | 10           | m       |  |

| VFEH            | FE supply (program)3                                                                     | $I_{FEH} = 300 \pm 25 mA$ ,<br>Transient or steady state    | 16.0      | 17.0        | 18.0         |         |  |

| VFEL            | FE supply (idle)                                                                         | $I_{FEL} = -1mA$ , max                                      | 1.25      | 1.5         | 1.75         | l v     |  |

| IFEH            | FE supply current limit                                                                  | $V_{\text{FEH}} = +17 \pm 1V$                               | 275       | 300         | 325          | m       |  |

| VCCP            | Vcc supply (program/verify "AND")                                                        | I <sub>CCP</sub> = 550mA, min,<br>Transient or steady state | 4.75      | 5.0         | 5.25         | V       |  |

| ICCP            | I <sub>CC</sub> limit (program "AND")                                                    | $V_{CCP} = +5.0 \pm .25V$                                   | 550       | [           | 1,000        | m       |  |

| VOPF            | Forced output (program)                                                                  |                                                             | 9.5       | 10          | 10.5         | l v     |  |

| IOPF            | Output current (program)                                                                 |                                                             |           |             | 10           | m       |  |

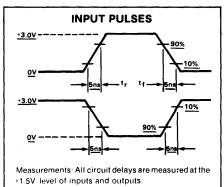

| TR              | Output pulse rise time                                                                   | 10% to 90%                                                  | 10        |             | 50           | μ       |  |

| tP              | CE programming pulse width                                                               |                                                             | 0.3       | 0.4         | 0.5          | m       |  |

| tD              | Pulse sequence delay                                                                     |                                                             | 10        | ]           | ]            | μ       |  |

| T <sub>PR</sub> | Programming time                                                                         |                                                             |           | 0.6         |              | [ m     |  |

| TPR<br>TPR + T  |                                                                                          |                                                             |           |             | 50           | 9       |  |

| FL              | Fusing attempts per link                                                                 |                                                             |           |             | 2            | су      |  |

| Vs              | Verify threshold4                                                                        |                                                             | 1.4       | 1.5         | 1.6          | \\      |  |

NOTES

1. These are specifications which a Programming System must satisy in order to be qualified by Signetics.

2. Bypass V<sub>CC</sub> to GND with a 0.01µf capacitor to reduce voltage spikes.

3. Care should be taken to ensure that the voltage is maintained during the entire fusing cycle. The recommended supply is a constant current source clamped at the specified voltage limit.

Vs is the sensing threshold of the FPLA output voltage for a programmed link. It normally constitutes

the reference voltage applied to a comparator circuit to verify a successful fusing attempt.

These are new limits resulting from device improvements, and which supersede, but do not obsolete the performance requirements of previously manufactured programming equipment.

# 82S100 (T.S.)82S101 (O.C.) INTEGRATED FUSE LOGIC

SERIES 28

9

# 825100 (T.S.)825101 (O.C.)

#### INTEGRATED FUSE LOGIC SERIES 28

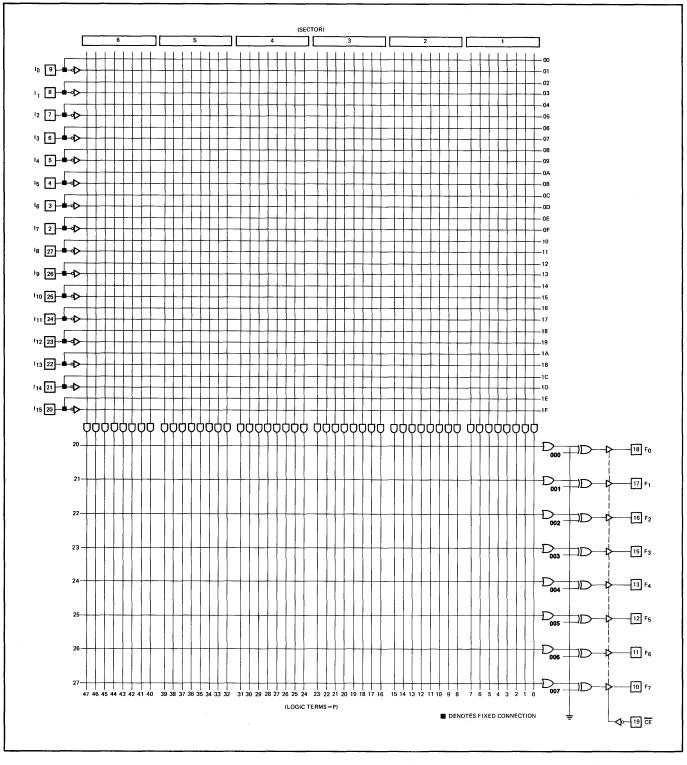

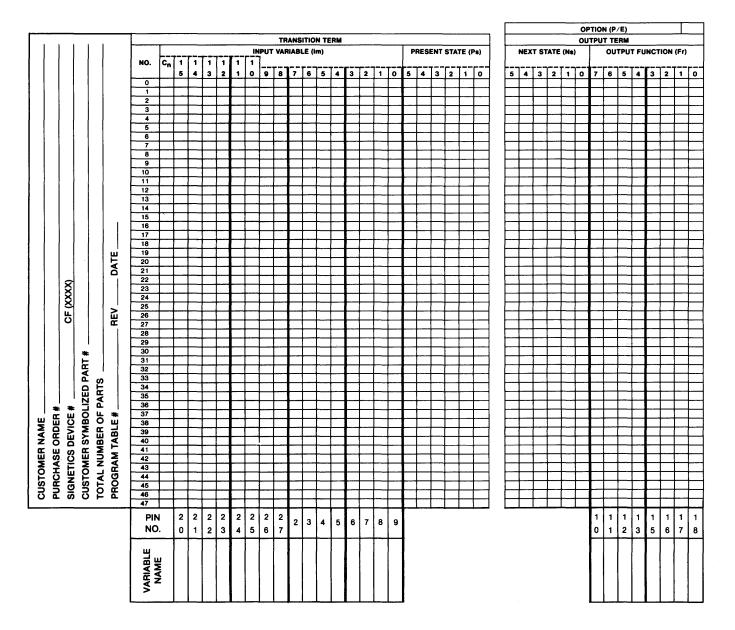

#### LOGIC PROGRAMMING

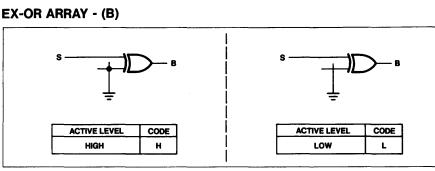

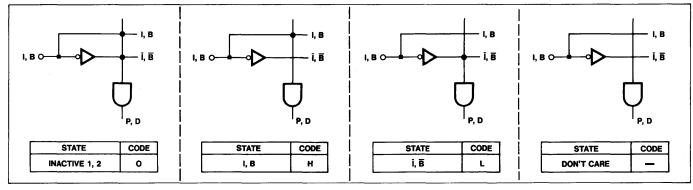

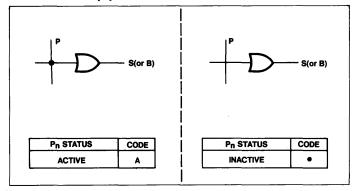

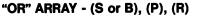

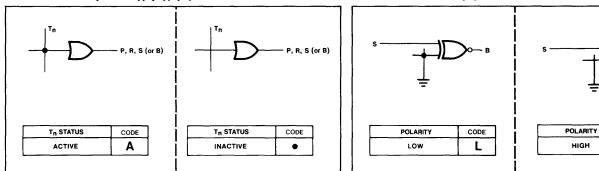

EX-OR ARRAY-(F)

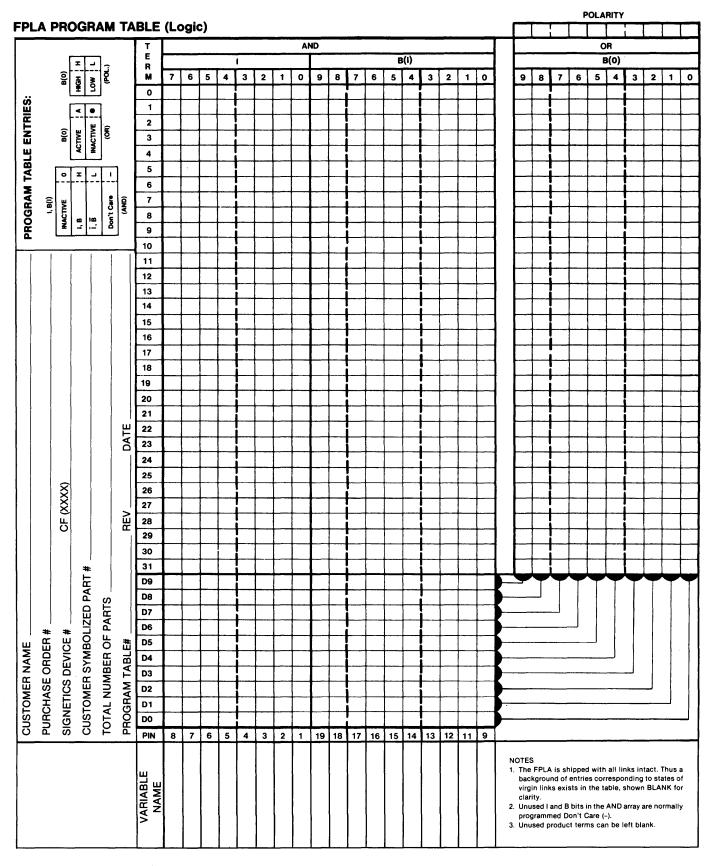

The FPLA can be programmed by means of Logic programming equipment.

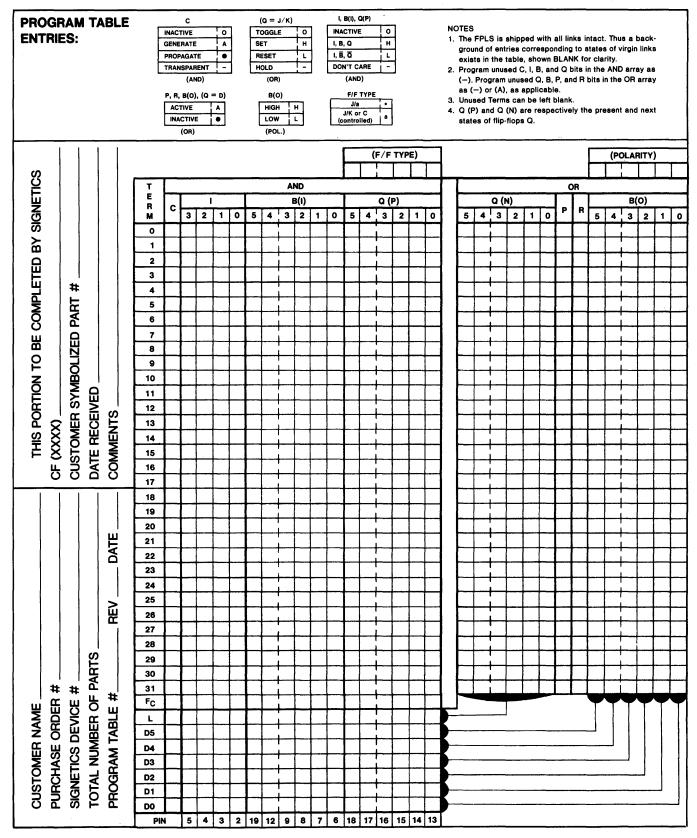

With Logic programming, the AND/OR/EX-OR gate input connections necessary to implement the desired logic function are coded directly from logic equations using the Program Table on the following page.

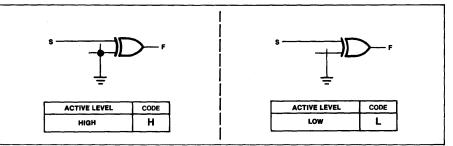

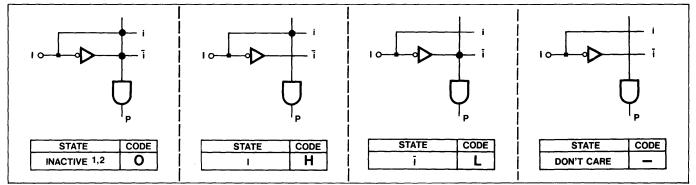

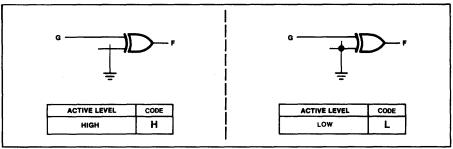

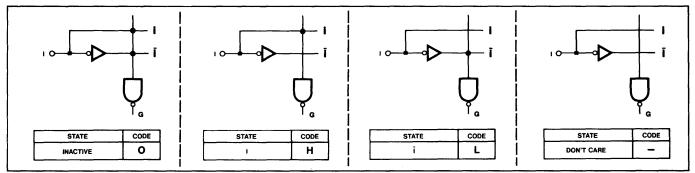

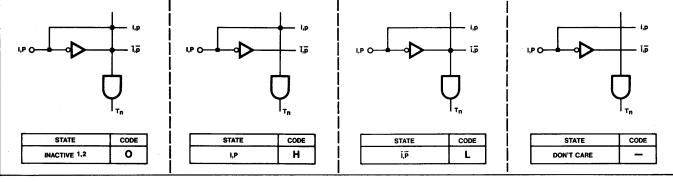

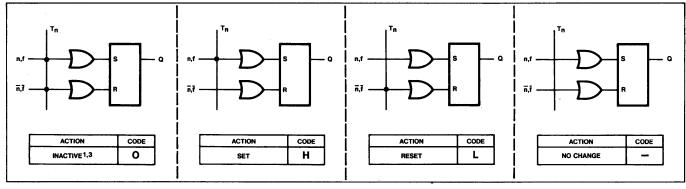

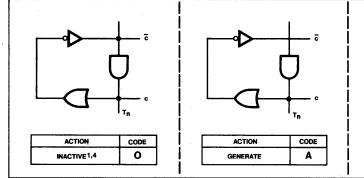

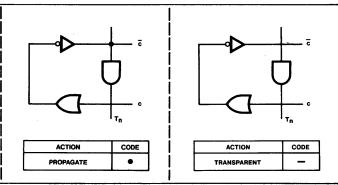

In this Table the logic state or action of variables I, P, and F, associated with each Sum Term S<sub>r</sub>, is assigned a symbol which results in the proper fusing pattern of corresponding link pairs, defined as follows:

#### "AND" ARRAY - (I)

#### "OR" ARRAY - (F)

#### NOTES

1. This is the initial unprogrammed state of all link pairs. It is normally associated with all unused (inactive) AND gates Pn.

2. Any gate Pn will be unconditionally inhibited if any one of its (I) link pairs is left intact.

#### FPLA PROGRAM TABLE (Logic)

**BIPOLAR MEMORY DIVISION**

| Γ                     |                     | [                                      |                            |                       |                                                                                             |                  |          |          |          |           |   |          |          | СТ       |   |          |          |   |          |          |          |          |                 |          |          | ACT      |          | LE          | VEL      | 1   |                                                |

|-----------------------|---------------------|----------------------------------------|----------------------------|-----------------------|---------------------------------------------------------------------------------------------|------------------|----------|----------|----------|-----------|---|----------|----------|----------|---|----------|----------|---|----------|----------|----------|----------|-----------------|----------|----------|----------|----------|-------------|----------|-----|------------------------------------------------|

|                       | اب_ ا               |                                        | [                          |                       | uts<br>uts                                                                                  |                  |          |          |          |           |   |          |          |          |   |          |          |   |          | 6        |          |          | , <del></del> - | <u> </u> |          | <u> </u> |          |             |          |     |                                                |

|                       | N                   | Active<br>Low                          |                            |                       | e e                                                                                         | NO               | 1        | 1        | 1        | 1         | 1 | 1        | ]        |          |   |          |          |   |          |          |          |          |                 |          | ου       | ITPI     | JT F     | UN          | сті      | 2N1 |                                                |

|                       | ш                   | Active                                 | -                          |                       | d on<br>ed c                                                                                |                  | 5        | 4        | 3        | 2         | 1 | 0        | 9        | 8        | 7 | 6        | 5        | 4 | 3        | 2        | 1        | 0        |                 | 7        | 6        | 5        | 4        | З           |          | Γī  | ] [                                            |

| 1                     | OUTPUT ACTIVE LEVEL |                                        | 1                          |                       | <ol> <li>Polarity programmed once only</li> <li>Enter (H) for all unused outputs</li> </ol> | 0                | †        | †        | t        | $\square$ |   | <u> </u> | 1        |          |   | <b>†</b> |          |   | <u> </u> | <u> </u> | <u>†</u> | <u> </u> |                 |          |          | Ť        |          | Ť           |          | ⊢   | Ť                                              |

|                       | E                   |                                        |                            |                       | allu                                                                                        | 1                | 1        | 1        | †        | -         |   |          | 1        |          |   |          | 1        |   |          | -        |          |          |                 |          |          | +        |          |             | <u> </u> | -   |                                                |

|                       | A                   |                                        | Γ                          |                       | prog                                                                                        | 2                | 1        | Ī        | Ť        |           |   |          | 1        | 1        |   |          | 1        |   |          |          |          |          |                 |          |          | <b></b>  |          |             |          |     | 1                                              |

| 1                     | 5                   |                                        |                            |                       | ≩Ĵ                                                                                          | 3                | T        |          | Ι        |           |   |          |          |          |   |          |          |   |          |          |          |          |                 |          |          |          |          |             |          |     |                                                |

|                       | ГР                  | Active<br>High                         | II                         | ES                    | olar<br>nter                                                                                | 4                |          |          |          |           |   |          | 1        |          |   |          |          |   |          |          |          |          |                 |          |          |          |          |             |          |     | 1                                              |

|                       | 2                   | Active<br>High                         | 1-                         | NOTES                 | сш                                                                                          | 5                |          | L        | ļ        |           |   |          |          |          |   |          |          |   |          |          |          |          |                 |          |          |          |          |             |          |     |                                                |

|                       | 0                   |                                        |                            | Z                     | - 0                                                                                         | 6                | <u> </u> | <u> </u> | L        |           |   | ļ        | L        |          |   |          |          |   |          |          |          | [        | ĺ               |          |          | [        |          |             |          |     | L                                              |

| 1                     |                     |                                        | +                          | –                     |                                                                                             | 7                |          |          |          |           |   | -        |          | <u> </u> |   |          |          |   |          |          | -        | -        | -               |          |          |          |          |             |          |     | <u> </u>                                       |

|                       |                     | ₽ ot                                   |                            |                       | rms                                                                                         | 8                | +        | +        | <u> </u> |           |   |          |          | <b> </b> |   | <u> </u> |          |   |          | <u> </u> | <u> </u> |          |                 |          |          | <u> </u> |          |             |          |     | <u> </u>                                       |

| ß                     |                     | 2 11                                   | Ð                          |                       | P-te                                                                                        | 10               | +        | ÷        | <u> </u> |           |   |          | -        | <u> </u> |   |          | <u> </u> |   |          |          |          |          | ł               |          |          |          |          |             |          |     | <u> </u>                                       |

| Ē                     | z                   | ern<br>htii                            | • (period)                 |                       | lari                                                                                        | 11               | +        | <u>+</u> | +        |           |   |          | +        | <u> </u> |   |          |          |   |          |          |          |          | ŀ               |          | ——       |          | ┼──      |             |          |     | ├                                              |

| Ξ                     | 12                  | Ser                                    | l g                        |                       | t po                                                                                        | , 12             | +        | +        | <u> </u> | +         |   | <u> </u> | <u> </u> |          |   |          |          |   |          |          | <u> </u> |          | · }             |          | <b>—</b> |          | <u> </u> |             |          |     | $\vdash$                                       |

| lμ                    | 15                  | Prod. Term Not<br>Present in Fp        | •                          |                       | utpu<br>Jts c                                                                               | 13               | +        | †        | <b>†</b> | <b>†</b>  |   | <b> </b> | t        |          |   |          |          |   |          | <u> </u> | +        | -        | ŀ               |          |          |          |          |             |          |     | 1                                              |

| 2                     | 3                   | <u>م</u> ۳                             |                            |                       | ht of                                                                                       | 14               | +        | †        | †        |           |   |          | t        |          |   |          |          |   |          |          | <u> </u> |          | ŀ               |          |          |          |          |             |          |     |                                                |

| Ā                     | E                   |                                        | $t \rightarrow t$          | 1                     | oi<br>pidol                                                                                 | 15               | 1        | 1        | 1        |           |   |          |          |          |   |          | 1        |   |          |          | t –      |          | ł               |          |          |          | 1        | <b>I</b> '' |          | -   | <u>† – – – – – – – – – – – – – – – – – – –</u> |

| Σ                     | OUTPUT FUNCTION     | د                                      |                            |                       | nde<br>1USE                                                                                 | 16               | 1        | [        |          |           |   |          |          |          |   |          |          |   |          |          |          |          | f               |          |          |          |          |             |          |     | [                                              |

| Į₹                    | 빌                   | ern<br>P F                             |                            |                       | epe<br>ir ur                                                                                | 17               |          |          |          |           |   |          |          |          |   | -        |          |   |          |          |          |          | ľ               |          |          |          |          |             |          |     |                                                |

| PROGRAM TABLE ENTRIES | Ы                   | Prod. Term<br>Present in Fp            | ∢                          |                       | Entries independent of output polarity<br>Enter (A) for unused outputs of used P-terms      | 18               |          |          |          |           |   |          |          |          |   |          |          |   |          |          |          |          | Ī               |          |          |          |          |             |          |     |                                                |

| Ř                     |                     | od                                     |                            | i.                    | er (/                                                                                       | 19               |          |          |          |           |   |          |          |          |   |          |          |   |          |          |          |          | F               |          |          |          |          |             |          |     |                                                |

|                       |                     | م ج                                    |                            | NOTES'                | ыщ                                                                                          | 20               |          | ļ        | L        |           |   |          |          | <u> </u> |   |          |          |   |          |          |          |          |                 |          |          |          |          |             |          |     |                                                |

|                       |                     |                                        |                            | ž                     | - 0                                                                                         | 21               | <b> </b> | <b> </b> |          |           |   |          |          | <u> </u> |   |          | -        |   |          |          | ļ        |          | ŀ               |          |          |          |          |             | <b> </b> |     | ļ                                              |

|                       |                     |                                        |                            | Γ                     |                                                                                             | 22               |          | <b> </b> | ļ        |           |   | ļ        |          |          |   |          |          |   |          |          | ļ        |          | ł               |          |          |          |          | ·           |          |     | <u> </u>                                       |

|                       | li                  | Don't Care                             | 12                         |                       | -                                                                                           | 23<br>24         |          | <u> </u> |          |           |   |          |          |          |   |          |          |   |          |          |          |          | -               |          |          |          |          | _           | <u> </u> |     | <u> </u>                                       |

| 1                     | ω                   | Ö                                      | - (dash)                   |                       | rsec                                                                                        | 24               | +        |          |          |           |   |          | -        |          |   |          |          |   |          |          | ļ        | -        | ⊦               |          |          |          |          |             |          |     |                                                |

|                       | Ы                   | ,<br>L                                 | 0                          |                       | of                                                                                          | 26               | +        | $\vdash$ |          |           |   |          |          |          |   |          |          |   |          |          |          |          | ŀ               |          |          |          |          |             |          |     |                                                |

|                       | I¥<br>∭             | ă                                      |                            |                       | puts                                                                                        | 27               | 1        |          | <u>+</u> |           |   |          | -        |          |   |          |          |   |          |          | ł        |          | ŀ               |          |          |          |          | -           |          |     |                                                |

|                       | INPUT VARIABLE      |                                        |                            |                       | Enter (-) for unused inputs of used<br>P-terms                                              | 28               | +        |          |          |           |   |          |          |          |   |          |          |   |          |          | $\vdash$ |          | ŀ               |          |          |          |          |             | <u> </u> | -   | <u> </u>                                       |

|                       | F                   | E                                      |                            |                       | esn                                                                                         | 29               | 1        | +        |          |           |   |          |          |          |   | -        |          |   |          |          | +        |          | h               |          |          |          | t        |             |          |     | t                                              |

|                       | 2                   | 12                                     |                            |                       | 'n                                                                                          | 30               |          |          |          |           |   |          |          |          |   |          |          |   |          |          |          |          | ſ               |          |          |          |          |             |          |     |                                                |

|                       | Ī.                  |                                        | ļ                          | {                     | s -) fo                                                                                     | 31               |          |          |          |           |   |          |          |          |   |          |          |   |          |          |          |          | ľ               |          |          |          |          |             |          |     |                                                |

|                       |                     | ~                                      | -                          | NOTE                  | Enter (-)<br>P-terms                                                                        | 32               |          |          |          |           |   |          |          |          |   |          |          |   |          |          |          |          |                 |          |          |          |          |             |          |     |                                                |

| ļ                     |                     | <u></u>                                | I                          | ž                     | <u>5</u> 4                                                                                  | 33               |          |          |          |           |   |          |          |          |   |          |          |   |          |          |          |          |                 |          |          |          |          |             |          |     |                                                |

| 1                     |                     |                                        |                            |                       |                                                                                             | 34               |          |          |          |           |   |          |          |          |   |          |          |   |          |          |          |          |                 |          |          |          |          |             |          |     |                                                |

| ⊢                     |                     |                                        | L                          |                       |                                                                                             | 35               |          |          |          |           |   |          | L        |          |   |          | _        |   |          |          |          |          | ŀ               |          |          |          | L        |             |          |     |                                                |

|                       |                     |                                        |                            |                       |                                                                                             | 36               | <b> </b> | L        |          |           |   |          |          |          |   |          |          |   |          |          |          |          | ł               |          |          |          |          |             |          |     | -                                              |

|                       |                     |                                        |                            |                       |                                                                                             | 37               | <b> </b> |          |          |           |   |          |          |          |   |          |          |   |          |          |          |          | ł               |          | -        |          |          | -           |          | -   |                                                |

|                       |                     |                                        |                            |                       | ш                                                                                           | 38<br>39         | ł        |          |          |           |   |          |          |          |   |          |          |   |          |          |          |          | ⊢               |          |          |          |          |             |          |     |                                                |

| 1                     |                     | XX                                     |                            |                       | DATE                                                                                        | 40               | <u> </u> |          |          |           |   |          |          |          |   |          |          |   |          |          |          |          | ┝               |          |          |          |          |             |          |     | -                                              |

|                       |                     | X                                      |                            |                       | <u> </u>                                                                                    | 40               | †        |          |          |           |   |          |          |          |   |          |          |   | $\vdash$ |          |          |          | ┢               | _        |          | -        |          |             | +        |     | 1                                              |

| 1                     |                     | CF (X)                                 |                            |                       |                                                                                             | 42               |          |          |          |           |   |          |          |          |   |          |          |   |          |          |          |          | ŀ               |          |          |          |          |             | +        |     | $\mathbf{t}$                                   |

|                       |                     | 0                                      |                            |                       |                                                                                             | 43               |          |          |          |           |   |          |          |          |   |          |          |   |          |          |          |          | t               |          |          |          |          |             |          |     |                                                |

| ł                     |                     |                                        |                            |                       | REV                                                                                         | 44               |          |          |          |           |   |          |          |          |   |          |          |   |          |          |          |          |                 |          |          |          |          |             |          |     |                                                |

|                       |                     |                                        | -                          |                       | æ                                                                                           | 45               |          |          |          |           |   |          |          |          |   |          |          |   |          |          |          |          | Ē               |          |          |          |          |             |          |     |                                                |

|                       |                     |                                        | ŧ                          |                       |                                                                                             | 46               | 1        |          |          |           |   |          |          |          |   |          |          |   |          |          |          |          | Γ               |          |          |          |          |             |          |     |                                                |

| 1                     |                     |                                        | AH                         | ļ                     |                                                                                             | 47               |          |          |          |           |   |          |          |          |   |          |          |   |          |          |          |          | T               |          |          |          |          |             |          |     |                                                |

|                       |                     |                                        | 9                          | TS                    |                                                                                             |                  |          |          |          | -         |   | <u> </u> |          |          |   | _        |          | - |          | _        | -        |          | ħ               |          |          |          |          |             |          |     |                                                |

|                       |                     |                                        | ZEI                        | AB                    |                                                                                             | PIN<br>NO.       | 2        | 2<br>1   | 2        | 2         | 2 | 2<br>5   | 2        | 2        | 2 | 3        | 4        | 5 | 6        | 7        | 8        | 9        |                 | 1        | 1        | 1        | 1        | 1<br>5      | 1        |     | 1                                              |

| ŀ                     | :                   | #<br>₩<br>₩                            | SOLI;                      | F P.                  | *                                                                                           | NU.              | 0        | -        | 2        | 3         | 4 | 5        | 6        | 7        |   |          |          |   |          |          |          |          | ┟               | 0        | 1        | 2        | 3        | 5           | 6        | 7   | 8                                              |

|                       | CUSTOMER NAME       | PURCHASE ORDER #<br>SIGNETICS DEVICE # | CUSTOMER SYMBOLIZED PART # | TOTAL NUMBER OF PARTS | PROGRAM TABLE #                                                                             | VARIABLE<br>NAME |          |          |          |           |   |          |          |          |   |          |          |   |          |          |          |          |                 |          |          |          |          |             |          |     |                                                |

# 82\$100 (T.S.)82\$101 (O.C.)

#### INTEGRATED FUSE LOGIC SERIES 28

## 82S100 (T.S.)82S101 (O.C.)

#### INTEGRATED FUSE LOGIC SERIES 28

#### **TWX TAPE CODING**

The FPLA Program Table can be sent to Signetics in ASCII code format via airmail using any type of 8-level tape (paper, mylar, fanfold, etc.), or via TWX: just dial (910) 3399283, tell the operator to turn the paper puncher on, and acknowledge. At the end of transmission instruct the operator to send tape to Signetics Order Entry.

A number of Program Tables can be se-

quentially assembled on a continuous tape as follows, however limit tape length to a roll of 1.75 inch inside diameter, and 4.25 inch outside diameter:

|  | MAIN | 25<br>(C/R)<br>MIN. | SUB<br>HEADING<br>(1) | 25<br>RUBOUTS<br>MIN. | PROGRAM TABLE<br>DATA (1) | 25<br>(C/R)<br>MIN. | SUB<br>HEADING<br>(N) | 25<br>RUBOUTS<br>MIN. | PROGRAM TABLE |

|--|------|---------------------|-----------------------|-----------------------|---------------------------|---------------------|-----------------------|-----------------------|---------------|

|--|------|---------------------|-----------------------|-----------------------|---------------------------|---------------------|-----------------------|-----------------------|---------------|

A. The MAIN HEADING at the beginning of tape includes the following information, with each entry preceded by a (\$) character, whether used or not:

| 1. Customer Name   | 4. Purchase Order No        |

|--------------------|-----------------------------|

| 2. Customer TWX No | 5. Number of Program Tables |

| 3. Date            | 6. Total Number of Parts    |

B. Each SUB HEADING should contain specific information pertinent to each Program Table as follows, with each entry preceded by a (\$) character, whether used or not:

| 1. Signetics Device No. | 4. Date                        |

|-------------------------|--------------------------------|

| 2. Program Table No     | 5. Customer Symbolized Part No |

| 3. Revision             | 6. Number of Parts             |

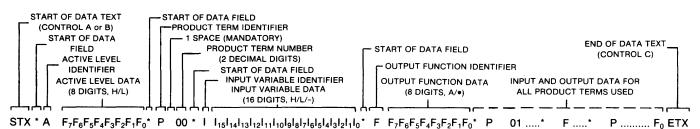

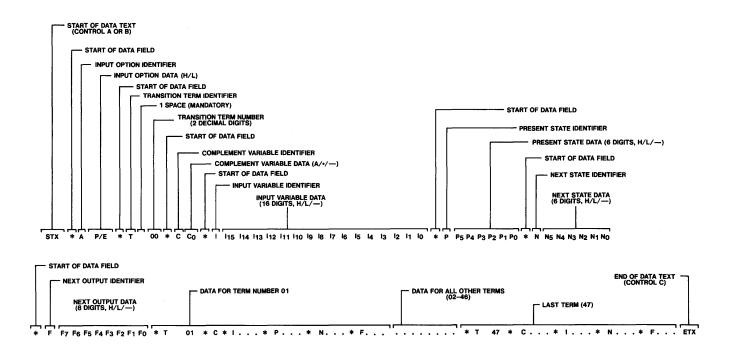

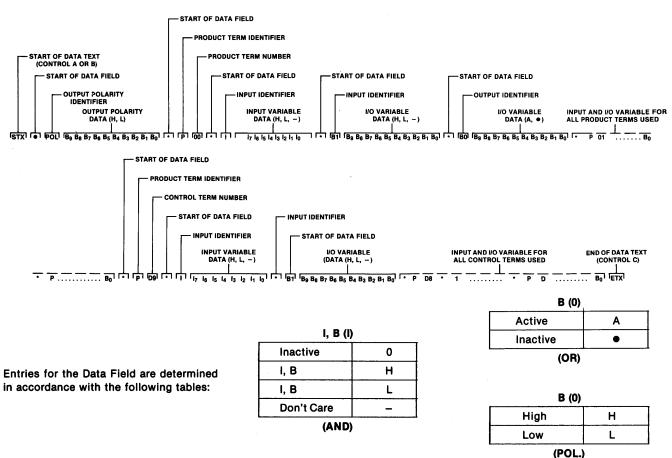

C. Program Table data blocks in Logic format are initiated with an STX character, and terminated with an ETX character. The body of the data consists of Output Active Level, Product Term, and Output Function information separated by appropriate identifiers in accordance with the following sequence:

Entries for the 3 Data Fields are determined in accordance with the following Table:

| OUTPUT FUNCTION |                            |                                   |          |  |

|-----------------|----------------------------|-----------------------------------|----------|--|

|                 | roduct terr<br>resent in F | Product term not<br>present in Fp |          |  |

| -               | A                          | ·                                 | (period) |  |

NOTES

NOTE

Enter (---) for unused inputs of used P-terms.

Entries independent of output polarity.

Enter (A) for unused outputs of used P-terms.

NOTES

1. Polarity programmed once only.

Active high

н

**OUTPUT ACTIVE LEVEL**

Active low

L

2. Enter (H) for all unused outputs.

Although the Product Term data are shown entered in sequence, this is not necessary. It is possible to input only one Product Term, if desired. Unused Product Terms require no entry. ETX signalling end of Program Table may occur with less than the maximum number of Product Terms entered.

NOTES

- Corrections to any entry can be made by backspace and rubout. However, limit consecutive rubouts to less than 25.

- Terms can be re-entered any number of times. The last entry for a particular P-Term will be interpreted as valid data.

- To facilitate an orderly Teletype print out, carriage returns, line feeds, spaces, rubouts etc. may be interspersed between data groups.

- Comments are allowed between data fields, provided that an asterisk (\*) is not used in any Heading or Comment entry.

# 82S100 (T.S.)82S101 (O.C.)

# INTEGRATED FUSE LOGIC SERIES 28

MAY 1981

#### **TYPICAL APPLICATIONS**

# Signetics

#### MAY 1981

# 82S102 (O.C.)/82S103 (T.S.)

#### DESCRIPTION

The 82S102 and 82S103 are Bipolar programmable AND/NAND gate array, containing 9 gates sharing 16 common inputs. On-chip input buffers enable the user to individually program for each gate either the True ( $I_m$ ), Complement ( $\overline{I_m}$ ), or Don't Care (X) logic state of each input. In addition, the polarity of each gate output is individually programmable to implement either AND or NAND logic functions.

Alternately, if desired, OR/NOR logic functions can also be realized by programming for each gate the complement of its input variables, and output (DeMorgan theorem).

Both devices are field-programmable, which means that custom patterns are immediately available by following the fusing procedure outlined in this data sheet.

The 82S102 and 82S103 include chipenable control for output strobing and inhibit. They feature either open collector or tri-state outputs for ease of expansion of input variables and application in busorganized systems.

Both devices are available in the commercial and military temperature ranges. For the commercial range (0° C to  $+75^{\circ}$  C) specify N82S102/103, F or N, and for the military range (-55° C to +125° C) specify S82S102/103, F, G, I, and R.

#### FEATURES

- Field programmable (Ni-Cr link)

- 16 input variables

- 9 output functions

- Chip enable input

- I/O propagation delay: N82S102/103: 35ns max S82S102/103: 50ns max

- Power dissipation: 600mW typ

Input loading: N82S102/103: -100μA max

- S82S102/103: -150μA max Output options:

- 82S102: Open collector 82S103: Tri-state

- Output disable function: 82S102: Hi 82S103: Hi-Z

- Fully TTL compatible

#### **APPLICATIONS**

- Random logic

- Address decoders

- Code detectors

- Peripheral selectors

- Fault monitors

- Machine state decoders

#### INTEGRATED FUSE LOGIC SERIES 28

#### **PIN CONFIGURATION**

#### LOGIC FUNCTION

Typical Output Functions @  $\overline{CE} = 0$ :

$\begin{array}{l} \text{At } L = \text{Open:} \\ F_0 = (I_0 \bullet I_1 \bullet I_2 \bullet \ldots \bullet \overline{Im}) \\ \text{At } L = \text{Closed:} \end{array}$

NOTES

For each of the 9 outputs, either the function Fp (active high) or  $\overline{Fp}$  (active low) is available but not both. The required function polarity is programmed via link (L).

#### LOGIC DIAGRAM

#### ABSOLUTE MAXIMUM RATINGS

|      | PARAMETER          | RATING      | UNIT |

|------|--------------------|-------------|------|

| Vcc  | Supply voltage     | +7          | Vdc  |

| Vin  | Input voltage      | +5.5        | Vdc  |

|      | Output voltage     |             | Vdc  |

| Voн  | High (82S102)      | +5.5        |      |

| Vo   | Off-state (82S103) | +5.5        |      |

| lin  | Input current      | ±30         | mA   |

| lout | Output current     | +100        | mA   |

|      | Temperature range  |             | °C   |

| TA   | Operating          |             |      |

|      | N82S102/103        | 0 to +75    |      |

|      | S82S102/103        | -55 to +125 |      |

| Tstg | Storage            | -65 to +150 |      |

# 82S102 (O.C.)/82S103 (T.S.)

#### INTEGRATED FUSE LOGIC SERIES 28

JUNE 1981

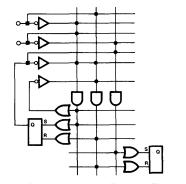

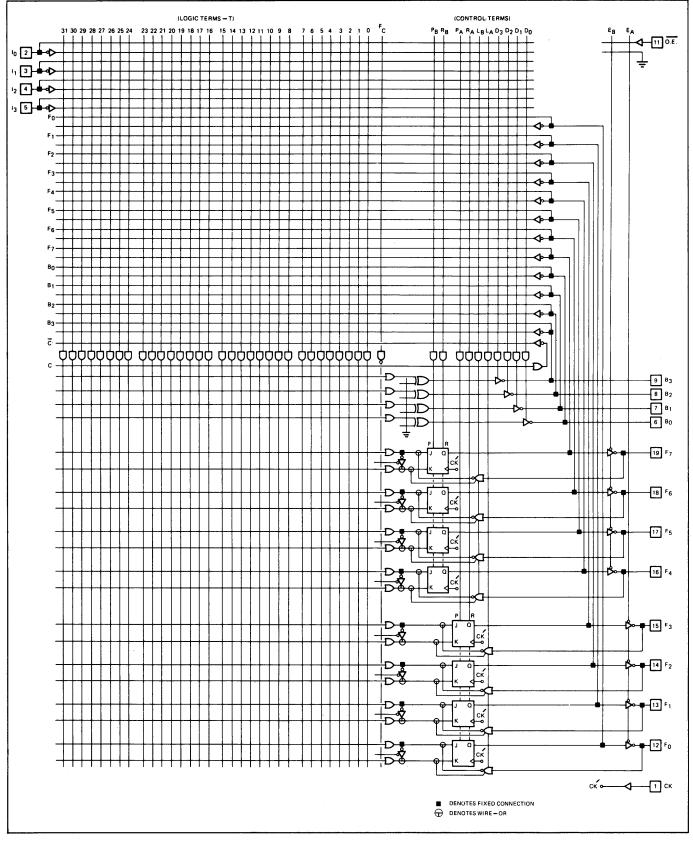

#### FPGA LOGIC DIAGRAM

# 82\$102 (O.C.)/82\$103 (T.S.)

#### INTEGRATED FUSE LOGIC **SERIES 28**

#### DC ELECTRICAL CHARACTERISTICS N82S102/103: $0^{\circ}C \le T_A \le +75^{\circ}C$ , $4.75V \le V_{CC} \le 5.25V$ S82S102/103: $-55^{\circ}C \le T_{A} \le +125^{\circ}C$ , $4.5V \le V_{CC} \le 5.5V$

|                        | PADAMETED                                                                                | TEST CONDITIONS                                                                   | N   | B2S102/1         | 03                     | S   | UNIT         |                        |                |

|------------------------|------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|-----|------------------|------------------------|-----|--------------|------------------------|----------------|

|                        | PARAMETER1                                                                               | TEST CONDITIONS                                                                   | Min | Typ <sup>2</sup> | Max                    | Min | Typ2         | Max                    |                |

| VIL<br>VIH             | Input voltage<br>Low <sup>1</sup><br>High <sup>1</sup>                                   | V <sub>CC</sub> = Min<br>V <sub>CC</sub> = Max                                    | 2.0 |                  | 0.85                   | 2.0 |              | 0.8                    | V              |

| Vic                    | Clamp <sup>1,3</sup>                                                                     | $V_{CC} = Min, I_{IN} = -18mA$                                                    |     | -0.8             | -1.2                   |     | -0.8         | -1.2                   |                |

| Vol<br>Voн             | Output voltage<br>Low <sup>1,4</sup><br>High (82S103)1,5                                 | V <sub>CC</sub> = Min<br>I <sub>OL</sub> = 9.6mA<br>I <sub>OH</sub> = -2mA        | 2.4 | 0.35             | 0.45                   | 2.4 | 0.35         | 0.50                   | V              |

| hц<br>hн               | Input current<br>Low<br>High                                                             | V <sub>IN</sub> = 0.45V<br>V <sub>IN</sub> = 5.5V                                 | ľ   | -10<br><1        | -100<br>25             |     | -10<br><1    | -150<br>50             | μA             |

| Iolk<br>Io(off)<br>Ios | Output current<br>Leakage (82S102)6<br>Hi-Z state (82S103)6<br>Short circuit (82S103)3,7 | $V_{CC} = Max$ $V_{OUT} = 5.5V$ $V_{OUT} = 5.5V$ $V_{OUT} = 0.45V$ $V_{OUT} = 0V$ | -20 | 1<br>1<br>-1     | 40<br>40<br>-40<br>-70 | -15 | 1<br>1<br>-1 | 60<br>60<br>-60<br>-85 | μΑ<br>μΑ<br>mA |

| lcc                    | V <sub>CC</sub> supply current <sup>8</sup>                                              | V <sub>CC</sub> = Max                                                             |     | 120              | 170                    |     | 120          | 180                    | mA             |

| Cin<br>Cout            | Capacitance<br>Input<br>Output <sup>6</sup>                                              | $V_{CC} = 5.0V$ $V_{IN} = 2.0V$ $V_{OUT} = 2.0V$                                  |     | 8<br>15          |                        |     | 8<br>15      |                        | pF             |

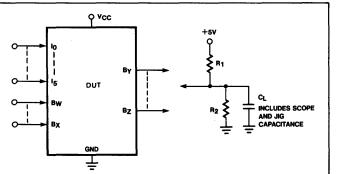

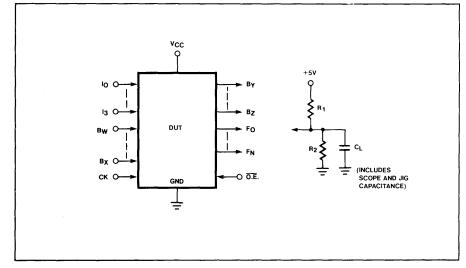

#### AC ELECTRICAL CHARACTERISTICS $R_1 = 470\Omega, R_2 = 1k\Omega, C_L = 30pF$

N82S102/103:  $0^{\circ}C \le T_{A} \le +75^{\circ}C$ ,  $4.75V \le V_{CC} \le 5.25V$

S82S102/103:  $-55^{\circ}C \le T_{A} \le +125^{\circ}C, 4.5V \le V_{CC} \le 5.5V$

|            |                                           |                  |                      | N82S102/103 |          |          | S82S103/103 |                  |          |      |

|------------|-------------------------------------------|------------------|----------------------|-------------|----------|----------|-------------|------------------|----------|------|

| PARAMETER  |                                           | TO FROM          |                      | Min         | Typ2     | Max      | Min         | Typ <sup>2</sup> | Max      | UNIT |

| TIA<br>TCE | Progagation delay<br>Input<br>Chip enable | Output<br>Output | Input<br>Chip enable |             | 20<br>15 | 35<br>30 |             | 20<br>15         | 55<br>45 | ns   |

| TCD        | Disable time<br>Chip disable              | Output           | Chip enable          |             | 15       | 30       |             | 15               | 45       | ns   |

NOTES

All typical values are at V<sub>CC</sub> = 5V, T<sub>A</sub> = 25°C. 2.

3. Test each output one at a time.

4. Measured with a programmed logic condition for which the output under test is at a low logic level.

Output sink current is supplied through a resistor to Vcc.

5. Measured with  $V_{IL}$  applied to  $\overline{CE}$  and a logic high at the output.

6. Measured with VIH applied to CE.

7. Duration of short circuit should not exceed 1 second.

8. Icc is measured with the chip enable input grounded, all other inputs at 4.5V and the outputs open.

#### **TEST LOAD CIRCUIT**

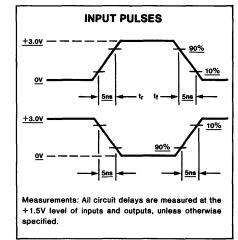

#### **VOLTAGE WAVEFORM**

<sup>1.</sup> All voltage values are with respect to network ground terminal.

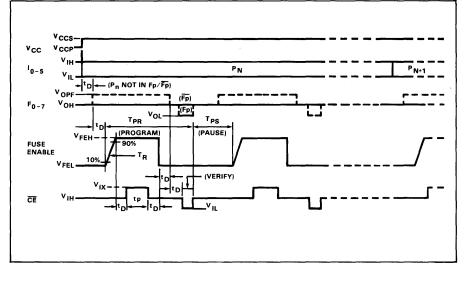

#### OUTPUT POLARITY PROGRAM-VERIFY SEQUENCE (TYPICAL)

#### INPUT MATRIX PROGRAM-VERIFY SEQUENCE (TYPICAL)

#### **VIRGIN DEVICE**

The 82S102/103 are shipped in an unprogrammed state, characterized by:

- 1. All internal Ni-Cr links are intact.

- Each gate contains both true and complement values of every input variable Im (logic Null state).

- 3. The polarity of each output is set to active low ( $\overline{F_P}$  function).

- 4. All outputs are at a high logic level.

#### RECOMMENDED PROGRAMMING PROCEDURE

To program each of 9 Boolean logic functions of 16 True, Complement, or Don't Care input variables follow the program/verify procedures for the Input Matrix and Output Polarity outlined below. To maximize recovery from programming errors, leave all links of unused gates intact.

#### SET-UP

Terminate all device outputs with a 10K $\Omega$  resistor to +5V.

#### **Output Polarity**

#### **PROGRAM ACTIVE HIGH (Fp FUNCTION)**

Program output polarity before programming inputs (for convenience). Program one output at a time. (L) links of unused outputs are not required to be fused.

- 1 . Set GND (pin 14) to 0V, and V<sub>CC</sub> (pin 28) to V<sub>CCV</sub>.

- 2. Disable all device outputs by setting CE (pin 19) to VIH.

- 3 . Disable all input variables by applying  $V_{1X}$  to inputs  $I_0$  through  $I_{15}$ .

- A.Raise V<sub>CC</sub> (pin 28) from V<sub>CCV</sub> to V<sub>CCP</sub>.

- B After t<sub>D</sub> delay, force output to be programmed to V<sub>OPF</sub>.

- C.After t<sub>D</sub> delay, pulse the CE input from V<sub>IH</sub> to V<sub>IX</sub> for a period t<sub>p</sub>.

- D.After to delay, remove VOPF voltage source from output being programmed.

- E . After t<sub>D</sub> delay, return  $V_{CC}$  (pin 28) to  $V_{CCV}$ , and verify.

- F. Repeat steps A through E for any other output.

#### VERIFY OUTPUT POLARITY

- 1 . Set GND (pin 14) to 0V, and  $V_{CC}$  (pin 28) to  $V_{CCV}.$

- 2. Disable all input variables by applying  $V_{IX}$  to inputs  $I_0$  through  $I_{15}. \label{eq:VIX}$

- A .After t<sub>D</sub> delay, set the  $\overline{CE}$  input to V<sub>IL</sub>.

- B. Verify output polarity by sensing the logic state of outputs  $F_0$  through  $F_8$ . All outputs at a low logic level are programmed active low ( $F_p$  function), while all outputs at a high logic level are programmed active high ( $F_p$  function).

## 82S102 (O.C.)/82S103 (T.S.)

# INTEGRATED FUSE LOGIC SERIES 28

#### Input Matrix PROGRAM INPUT VARIABLE

Program one input at a time for one gate at a time. Input variable links of unused gates are not required to be fused. However, unused input variables must be programmed at Don't Care for all used gates.

- 1. Set GND (pin 14) to 0V, and  $V_{CC}$  (pin 28) to  $V_{CCV}.$

- 2. Disable all device outputs by setting  $\overline{CE}$  (pin 19) to V<sub>IH</sub>.

- Disable all input variables by applying V<sub>IX</sub> to inputs I<sub>0</sub> through I<sub>15</sub>.

- A-1.If a gate contains nether  $I_0$  nor  $\overline{I_0}$  (input is a Don't Care), fuse both links by executing both steps A-2 and A-3, before continuing with step C.

- A-2.If a gate contains I<sub>0</sub>, set to fuse link by lowering the input voltage at I<sub>0</sub> from V<sub>IX</sub> to V<sub>IL</sub>. Execute step B.

- A-3.If a gate contains  $\overline{I_0}$ , set to fuse link by lowering the input voltage at I<sub>0</sub> from V<sub>IX</sub> to V<sub>IL</sub>. Execute step B.

- B-1.After t<sub>D</sub> delay, raise V<sub>CC</sub> from V<sub>CCV</sub> to V<sub>CCP</sub>.

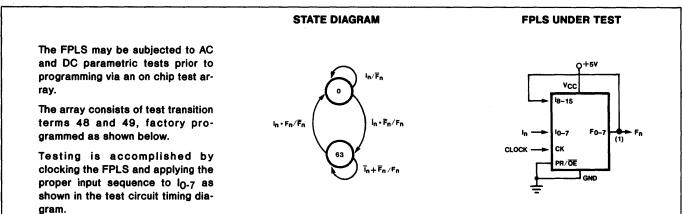

- B-2.After t<sub>D</sub> delay, force output of gate to be programmed to V<sub>OPF</sub>.