### TABLE OF CONTENTS

| 8228      | 4096-Bit Bipolar ROM (1024x4 ROM)                                    | 3  |

|-----------|----------------------------------------------------------------------|----|

| 82509     | 576-Bit Bipolar RAM (64x9)                                           | 5  |

| 82S10     | 1024x1 Bit Bipolar RAM (Open Collector)                              | 9  |

| 82S11     | 1024x1 Bit Bipolar RAM (Tri-State)                                   | 9  |

| 82S12     | High Speed Multiport Memory (8x4 Multiport RAM)                      | 13 |

| 82S16     | 256-Bit Bipolar RAM (256x1 RAM)–Tri-State                            | 15 |

| 82S17     | 256-Bit Bipolar RAM (256x1 RAM)–Open Collector                       | 15 |

| 82S21     | 64-Bit Bipolar High Speed Write-While-Read RAM (32x2 RAM)            | 19 |

| 82\$23    | 256-Bit Bipolar Programmable ROM (32x8 ROM)–Open Collector           | 22 |

| 82S25     | 64-Bit Bipolar Scratch Pad Memory (16x4 RAM)                         | 27 |

| 82S27     | 1024-Bit Bipolar Programmable ROM (256x4 PROM)                       | 31 |

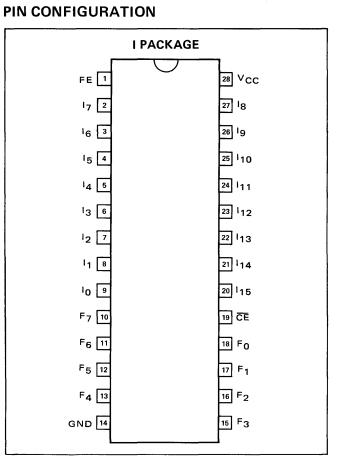

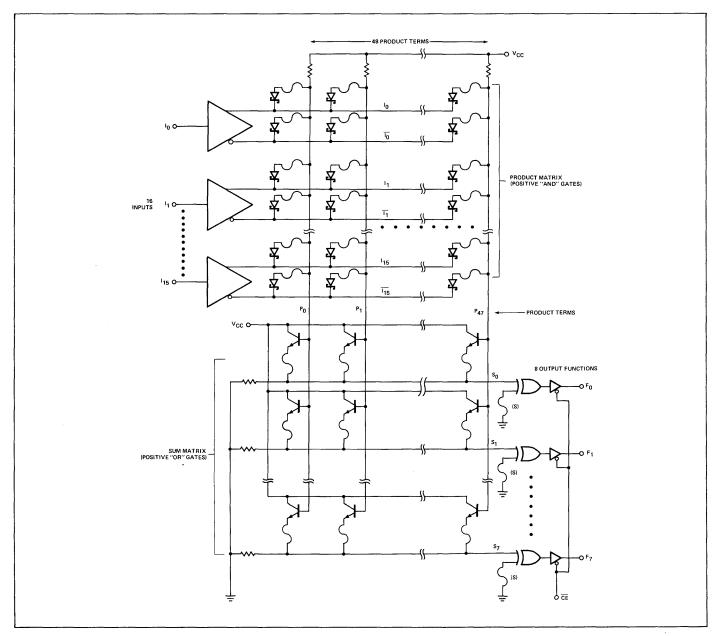

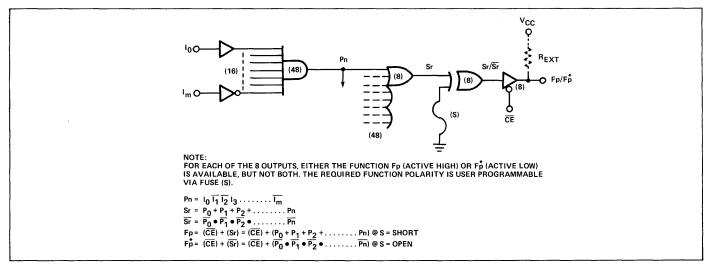

| 82S100    | Bipolar Field-Programmable Logic Array (16x8x48 FPLA)-Tri-State      | 36 |

| 82S101    | Bipolar Field-Programmable Logic Array (16x8x48 FPLA)–Open Collector | 36 |

| 82S112    | High Speed Multiport Memory (8x4 Multiport RAM)                      | 13 |

| 82S114    | 2048-Bit Bipolar ROM (256x8 PROM)                                    | 41 |

| 82S115    | 4096-Bit Bipolar ROM (512x8 PROM)                                    | 41 |

| 82S116    | 256-Bit Bipolar RAM (256x1 RAM)—Tri-State                            | 47 |

| 82S117    | 256-Bit Bipolar RAM (256x1 RAM)-Open Collector                       | 47 |

| 82S123    | 256-Bit Bipolar Programmable ROM (32x8 ROM)-Tri-State                | 22 |

| 82S126    | 1024-Bit Bipolar Programmable ROM (256x4 PROM)                       | 51 |

| 82S129    | 1024-Bit Bipolar Programmable ROM (256x4 PROM)                       | 51 |

| 82S130    | 2048-Bit Bipolar Programmable ROM (512x4 PROM)                       | 56 |

| 82S131    | 2048-Bit Bipolar Programmable ROM (512x4 PROM)                       | 56 |

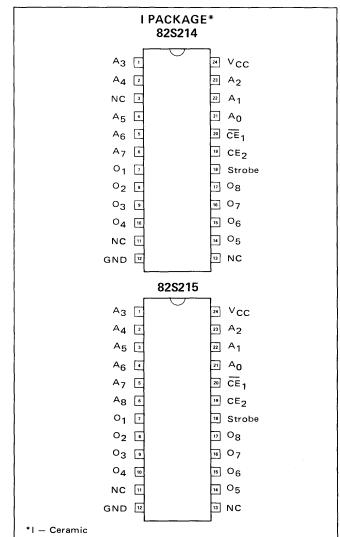

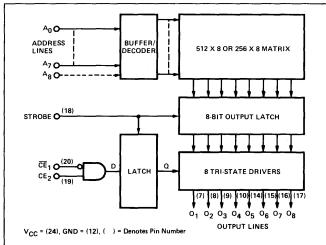

| 82S214    | 2048-Bit Bipolar ROM (256x8 ROM)                                     | 61 |

| 82S215    | 4096-Bit Bipolar ROM (512x8 ROM)                                     | 61 |

| 82S226    | 1024-Bit Bipolar Read Only Memory (256x4 ROM)                        | 64 |

| 82S229    | 1024-Bit Bipolar Read Only Memory (256x4 ROM)                        | 64 |

| 82S230    | 2048-Bit Bipolar ROM (512x4 ROM)                                     | 67 |

| 82S231    | 2048-Bit Bipolar ROM (512x4 ROM)                                     | 67 |

| 54/74S200 | TTL 256x1 RAM (Tri-State)                                            | 70 |

| 54/74S201 | TTL 256x1 RAM (Tri-State)                                            | 70 |

| 54/74S301 | TTL 256x1 RAM (Open Collector)                                       | 70 |

| 3101A     | 64-Bit Bipolar Scratch Pad Memory (16x4 RAM)                         | 74 |

| 10139     | ECL High Performance 256-PROM                                        | 78 |

| 93415A    | 1024x1 Bit Bipolar RAM (Open Collector)                              | 82 |

| 93425A    | 1024x1 Bit Bipolar RAM (Tri-State)                                   | 82 |

|           | Package Information                                                  | 86 |

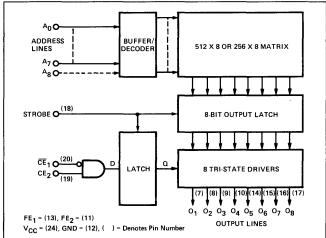

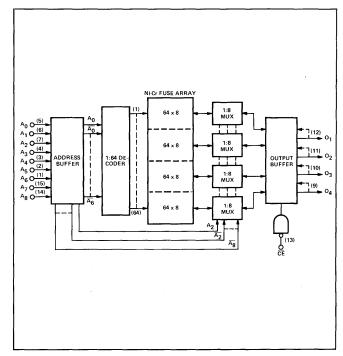

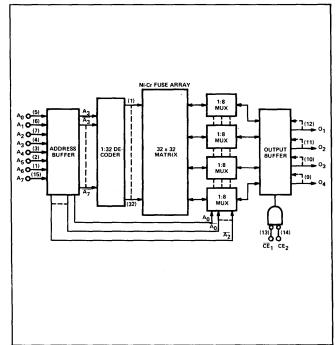

#### DESCRIPTION

The 8228 is a 4096 Bit Bipolar Read Only Memory organized as 1024 words by 4 bits per word. Available in a 16 pin dual in-line package, the 8228 can provide very high bit packing density by replacing four standard 256X4 ROMS.

The 8228 is fully TTL compatible and includes on-the-chip decoding. Typical access time is 50ns with a power consumption of only .125mW per bit.

The standard 8228 ROM pattern is the USASCII Row Character Generator code; however, custom patterns are also available. The standard pattern is specified as the N8228I - CB162, while custom circuits are identified as N8228I - CXXX. A truth table/order blank is included on page 4-46 for ordering custom patterns.

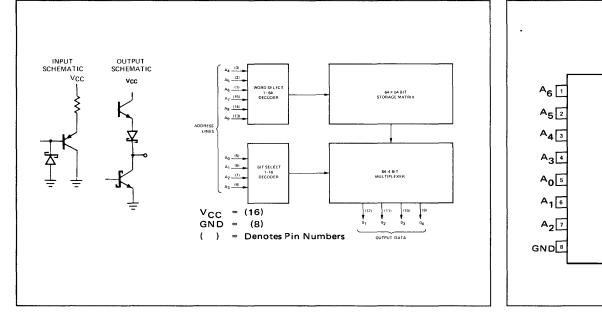

### **BLOCK DIAGRAM**

### DIGITAL 8000 SERIES TTL/MEMORY

See page 4-35 for CB162 Pattern and USASCII Row Character Generator.

### **FEATURES**

- BUFFERED ADDRESS LINES

- ON THE CHIP DECODING

- TOTEM POLE OUTPUTS

- DIODE PROTECTED INPUTS

- 16 PIN PACKAGE (1/3 SIZE OF 24 PIN PACKAGE)

APPLICATIONS MICROPROGRAMMING HARDWIRED ALGORITHMS CHARACTER RECOGNITION CHARACTER GENERATION CONTROL STORE

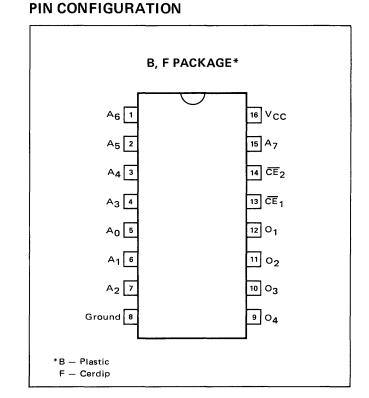

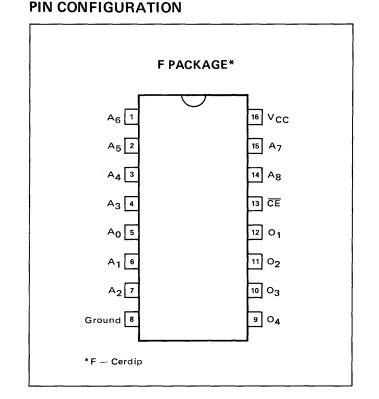

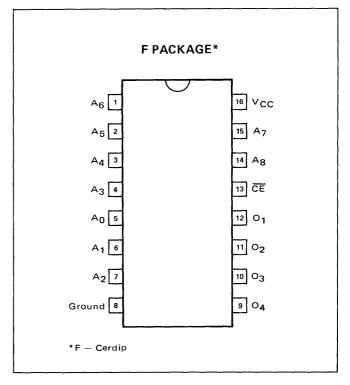

#### **PIN CONFIGURATION**

<sup>16</sup> Vcc

15 A7

14 A8

13 Ag

12 O1

11 02

10 O3

, O4

### **ELECTRICAL CHARACTERISTICS** $0^{\circ}C \le T_A \le 75^{\circ}C$ ; $4.75 \lor \lor V_{CC} \le 5.25 \lor$

| CHARACTERISTICS              |      | LI   | MITS |       |                             |       |

|------------------------------|------|------|------|-------|-----------------------------|-------|

|                              | MIN. | TYP. | MAX. | UNITS | TEST CONDITIONS             | NOTES |

| "0" Output Voltage           |      |      | 0.5  | v     | l <sub>out</sub> = 11.2 mA  |       |

| "1" Output Voltage           | 2.7  |      |      | v     | $i_{out} = -1.0 \text{ mA}$ |       |

| "0" Input Current            |      | -10  | -400 | μA    | V <sub>in</sub> = 0.45V     |       |

| "1" Input Current            |      | 1    | 25   | μA    | V <sub>in</sub> = 5.5V      |       |

| Input Voltage                |      |      |      |       |                             |       |

| "0" Level (V <sub>IL</sub> ) |      |      | .85  | V     |                             |       |

| "1" Level (VIH)              | 2.0  |      |      | v     |                             |       |

### ELECTRICAL CHARACTERISTICS (Cont'd)

|                              |      | LI   | MITS |       |                         |       |

|------------------------------|------|------|------|-------|-------------------------|-------|

| CHARACTERISTICS              | MIN. | TYP. | MAX. | UNITS | TEST CONDITIONS         | NOTES |

| Input Clamp Voltage          | -1.2 |      |      | V     | l <sub>in</sub> = -18mA |       |

| Power Consumption            |      | 140  | 170  | mA    | 01 to 03 = "0"          |       |

| Output Short Circuit Current | -20  |      | -70  | mA    | VOUT = 0 Volts          |       |

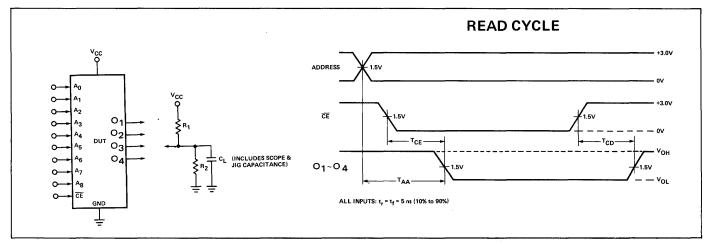

### SWITCHING CHARACTERISTICS $0 \le T_A \le 75^{\circ}$ C, 4.75 $\le V_{CC} \le 5.25$ V

| CHARACTERISTICS               |      | L    | IMITS |       | TEST CONDITIONS | NOTES |

|-------------------------------|------|------|-------|-------|-----------------|-------|

|                               | MIN. | TYP. | MAX.  | UNITS | TEST CONDITIONS | NOTES |

| Access Time-Address to Output |      | 50   | 70    | ns    |                 | 5     |

NOTES

1. Positive current is defined as into the terminal referenced.

2. No more than one output should be grounded at the same time.

3. Manufacturer reserves the right to make design and process changes and improvements.

Applied voltages must not exceed 6.0V. Input currents must not exceed ±30mA. Output currents must not exceed ±100mA. Storage temperature must be between -60°C to +150°C.

5. Rise and fall time for this test must be less than 5ns. Input amplitudes are 2.8V and all measurements are made at 1.5V.

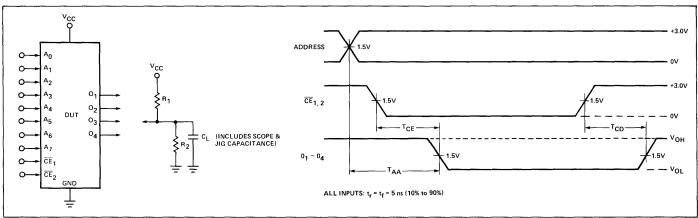

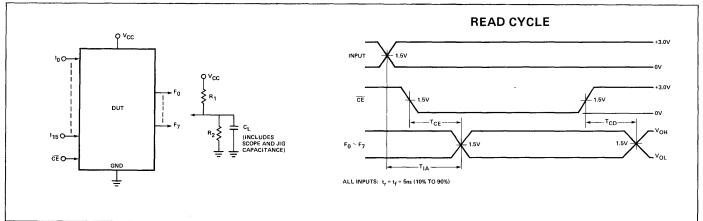

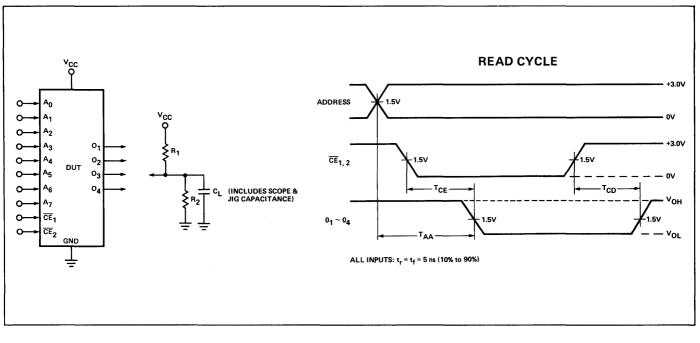

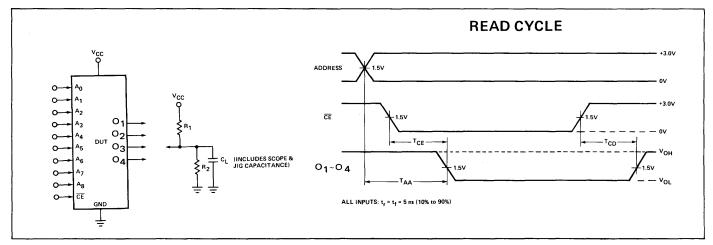

### AC TEST FIGURE AND WAVEFORM

# 576-BIT BIPOLAR RAM (64x9) 82509

### **JUNE 1975**

### DIGITAL 8000 SERIES TTL/MEMORY

### DESCRIPTION

The 82S09 is a 576-Bit, Schottky clamped TTL, random access memory, organized as 64X9. This organization allows byte manipulation of data, including parity. Where parity is not monitored, the ninth bit can be used as a flag or status indicator for each word stored. With a typical access time of 30ns, it is ideal for scratch-pad, push-down stacks, buffer memories, and other internal memory applications in which cost and performance requirements dictate a wide data path in favor of word depth.

The 82S09 is fully TTL compatible, and features open collector outputs, chip enable input, and a very low current PNP input structure to enhance memory expansion.

During WRITE operation, the logic state of the device output follows the complement of the data input being written. This feature allows faster execution of WRITE-READ cycles, enhancing the performance of systems utilizing indirect addressing modes, and/or requiring immediate verification following a WRITE cycle.

The 82S09 is available in the commercial and military temperature ranges. For the commercial temperature range (0°C to +75°C) specify N82S09, I. For the military temperature range (-55°C to +125°C) specify S82S09, I.

### **FEATURES**

- ORGANIZATION 64 X 9

- ADDRESS ACCESS TIME: S82S09 - 80ns, MAXIMUM N82S09 - 45ns, MAXIMUM

- WRITE CYCLE TIME: S82S09 - 70ns, MAXIMUM N82S09 - 45ns, MAXIMUM

- POWER DISSIPATION 1.3mW/BIT TYPICAL

- INPUT LOADING: S82S09 - (-150µA) MAXIMUM N82S09 - (-100µA) MAXIMUM

- OUTPUT FOLLOWS COMPLEMENT OF DATA INPUT **DURING WRITE**

- ON-CHIP ADDRESS DECODING

- OPEN COLLECTOR OUTPUTS

- CHIP ENABLE FOR WORD EXPANSION

- BYTE I/O MANIPULATION, INCLUDING PARITY

APPLICATIONS **BUFFER MEMORY** CONTROL REGISTER **FIFO MEMORY** PUSH DOWN STACK SCRATCH PAD

#### **TRUTH TABLE**

| MODE      | CE | WE | ١ <sub>N</sub> | 0 <sub>N</sub>               |

|-----------|----|----|----------------|------------------------------|

| READ      | 0  | 1  | х              | Complement<br>of Data Stored |

| WRITE "0" | 0  | 0  | 0              | 1                            |

| WRITE "1" | 0  | 0  | 1              | 0                            |

| DISABLED  | 1  | х  | х              | 11                           |

X = Don't care.

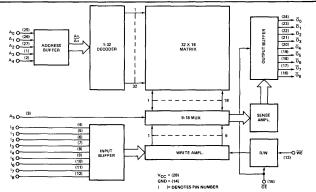

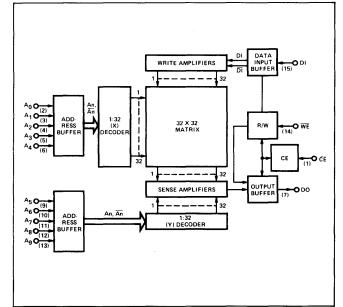

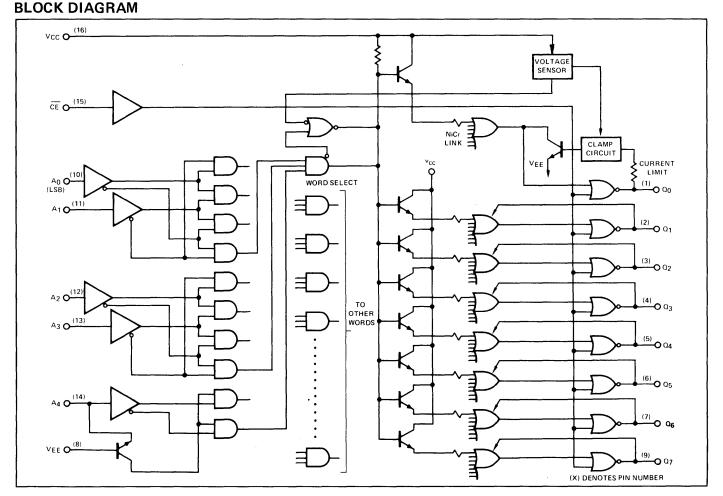

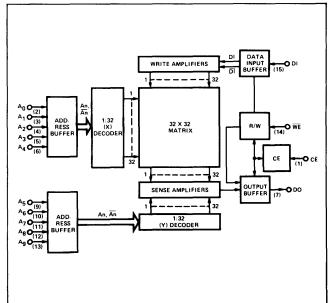

### **BLOCK DIAGRAM**

### **ABSOLUTE MAXIMUM RATINGS**

|                  | PARAMETER <sup>1</sup>                              | RATING                                                                      | UNIT     |

|------------------|-----------------------------------------------------|-----------------------------------------------------------------------------|----------|

| V <sub>CC</sub>  | Power Supply Voltage                                | +7                                                                          | Vdc      |

| V <sub>in</sub>  | Input Voltage                                       | +5.5                                                                        | Vdc      |

| V <sub>OH</sub>  | High Level Output Voltage (82S10)                   | +5.5                                                                        | Vdc      |

| TA               | Operating Temperature Range<br>(N82S09)<br>(S82S09) | 0 <sup>°</sup> to +75 <sup>°</sup><br>−55 <sup>°</sup> to +125 <sup>°</sup> | °C<br>°C |

| T <sub>stg</sub> | Storage Temperature Range                           | $-65^{\circ}$ to $+150^{\circ}$                                             | °C       |

### **ELECTRICAL CHARACTERISTICS**<sup>7</sup>

## $\begin{array}{lll} S82S09 & -55^{\circ}C \leqslant T_{A} \leqslant +125^{\circ}C, \, 4.5V \leqslant V_{CC} \leqslant 5.5 \\ N82S09 & 0^{\circ}C \leqslant T_{A} \leqslant +75^{\circ}C, \, 4.75V \leqslant V_{CC} \leqslant 5.25 \end{array}$

|                  |                                |                                                             |     | S82S09           | ······ |     | N82S09           |      | [ <u>_</u> |

|------------------|--------------------------------|-------------------------------------------------------------|-----|------------------|--------|-----|------------------|------|------------|

|                  | PARAMETER <sup>1</sup>         | TEST CONDITIONS                                             | MIN | TYP <sup>2</sup> | МАХ    | MIN | TYP <sup>2</sup> | MAX  | UNIT       |

| VIL              | Low Level Input Voltage        | V <sub>CC</sub> = MIN                                       |     |                  | .80    |     |                  | .85  | v          |

| VIH              | High Level Input Voltage       | V <sub>CC</sub> = MAX                                       | 2.2 |                  |        | 2.0 |                  |      | v          |

| V <sub>IC</sub>  | Input Clamp Voltage            | V <sub>CC</sub> = MIN, I <sub>IN</sub> = -12mA<br>(Note 5)  |     | -1.0             | -1.5   |     | -1.0             | -1.5 | V          |

| V <sub>OL</sub>  | Low Level Output Voltage       | V <sub>CC</sub> = MIN, I <sub>OL</sub> = 6.4mA<br>(Note 6)  |     | 0.35             | 0.50   |     | 0.35             | 0.5  | V          |

| I <sub>OLK</sub> | Output Leakage Current         | V <sub>CC</sub> = MAX, V <sub>OUT</sub> = 5.5V<br>(Note 4)  |     | 1                | 60     |     | 1                | 40   | μΑ         |

| L <sub>IL</sub>  | Low Level Input Current        | V <sub>IN</sub> = 0.45V                                     |     | -10              | - 150  |     | - 10             | -100 | μA         |

| Чн               | High Level Input Current       | V <sub>IN</sub> = 5.5V                                      |     | 1                | 40     |     | 1                | 25   | μA         |

| Icc              | V <sub>CC</sub> Supply Current | V <sub>CC</sub> = MAX (Note 3)                              |     | 150              | 200    |     | 150              | 190  | mA         |

| C <sub>IN</sub>  | Input Capacitance              | V <sub>CC</sub> = 5.0V, V <sub>IN</sub> = 2.0V              |     | 5                |        |     | 5                |      | pF         |

| С <sub>ОИТ</sub> | Output Capacitance             | V <sub>CC</sub> = 5.0V, V <sub>OUT</sub> = 2.0V<br>(Note 4) |     | 8                |        |     | 8                |      | pF         |

NOTES:

1. All voltage values are with respect to network ground terminal.

2. All typical values are at  $V_{CC} = 5V$ ,  $T_A = 25^{\circ}C$ .

3. ICC is measured with the write enable and memory enable input grounded, all other inputs at 4.5V, and the outputs open.

4. Measured with  $V_{IH}$  applied to  $\overline{CE}$ .

5. Test each input one at the time.

6. Measured with the logic "0" stored. Output sink current is supplied through a resistor to  $V_{CC}$ .

7. The Operating Ambient Temperature Ranges are guaranteed with transverse air flow exceeding 400 linear feet per minute and a two minute warm-up.

|                  |                                    | TEST CONDITIONS                     |     | S82S09           |     |     | N82S09                    |     | LINIT |

|------------------|------------------------------------|-------------------------------------|-----|------------------|-----|-----|---------------------------|-----|-------|

|                  | PARAMETER                          | TEST CONDITIONS                     | MIN | TYP <sup>1</sup> | MAX | MIN | TYP <sup>1</sup>          | MAX | UNIT  |

| Propaga          | ation Delays                       |                                     |     |                  |     |     | • · · · · · · · · · · · · |     |       |

| T <sub>AA</sub>  | Address Access Time                |                                     |     | 30               | 80  |     | 30                        | 45  | ns    |

| T <sub>CE</sub>  | Chip Enable Access Time            |                                     |     | 15               | 50  | }   | 15                        | 30  | ns    |

| т <sub>ср</sub>  | Chip Enable Output Disable<br>Time |                                     |     | 15               | 50  |     | 15                        | 30  | ns    |

|                  |                                    |                                     |     |                  |     |     |                           |     |       |

| Write S          | et-up Times                        | $C_L = 30 pF$                       |     |                  |     |     |                           |     |       |

| T <sub>WSA</sub> | Address to Write Enable            | $R_1 = 600\Omega$ $R_2 = 900\Omega$ | 10  | 0                |     | 5   | 0                         |     | ns    |

| T <sub>WSD</sub> | Data In to Write Enable            | _                                   | 50  | 25               |     | 35  | 25                        |     | ns    |

| Twsc             | CE to Write Enable                 |                                     | 10  | 0                |     | 5   | 0                         |     | ns    |

| Write H          | lold Times                         |                                     |     |                  |     |     |                           |     |       |

| Т <sub>WHA</sub> | Address to Write Enable            |                                     | 10  | 0                |     | 5   | 0                         | i.  | ns    |

| Т <sub>WHD</sub> | Data In to Write Enable            |                                     | 5   | 0                |     | 5   | 0                         |     | ns    |

| т <sub>wнс</sub> | CE to Write Enable                 |                                     | 10  | 0                |     | 5   | 0                         |     | ns    |

| Т <sub>WP</sub>  | Write Enable Pulse Width (Note 2)  |                                     | 50  | 25               |     | 35  | 25                        |     | ns    |

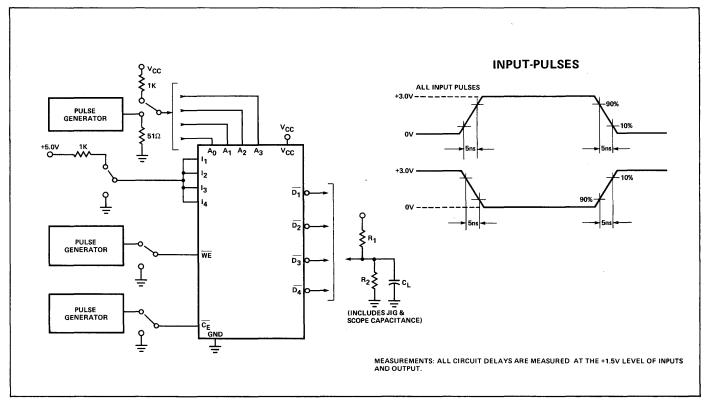

### SWITCHING CHARACTERISTICS<sup>3</sup>

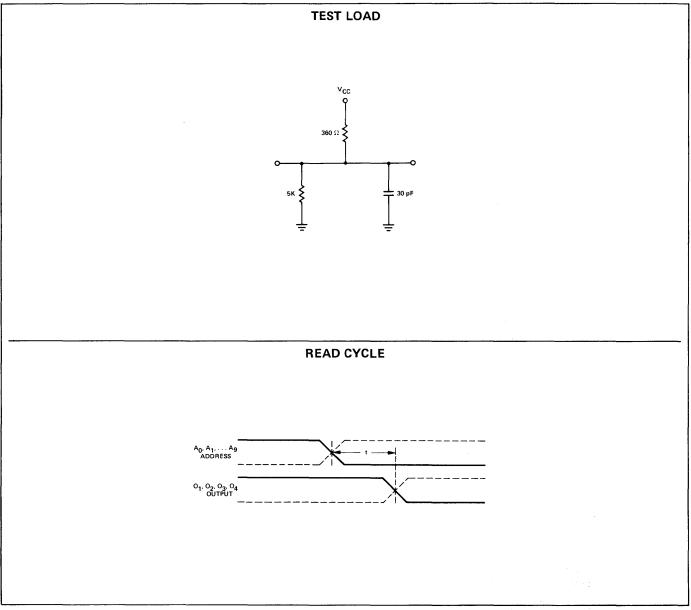

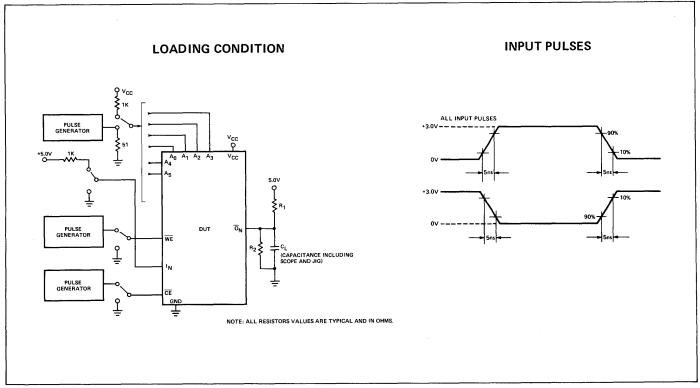

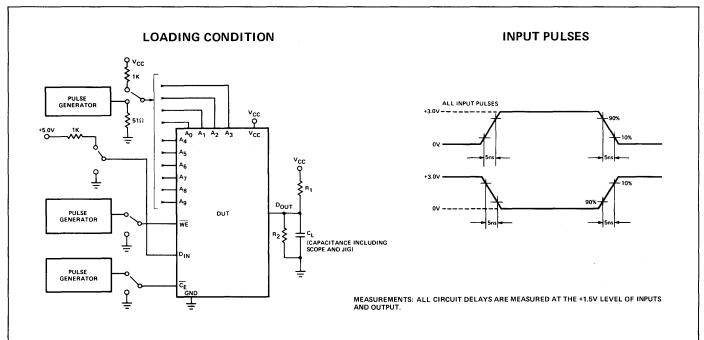

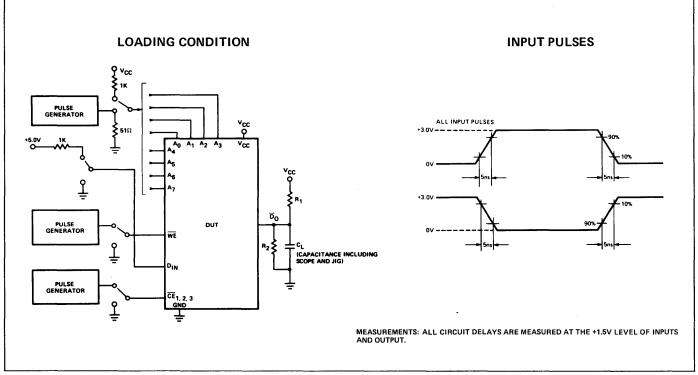

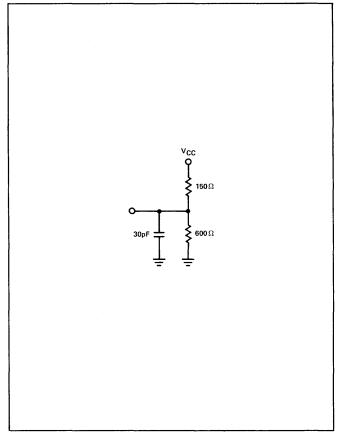

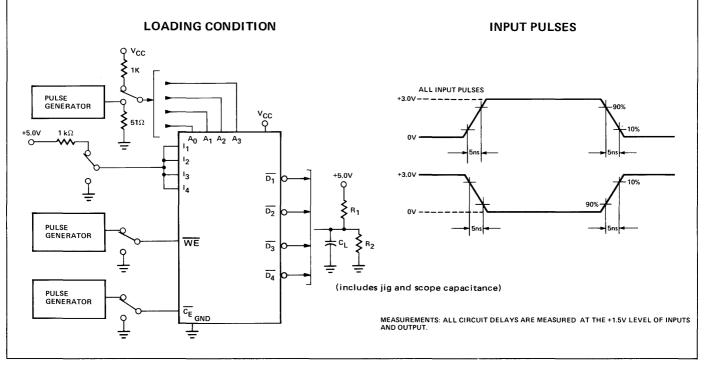

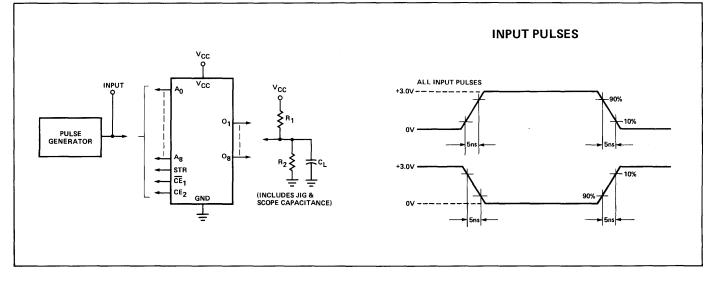

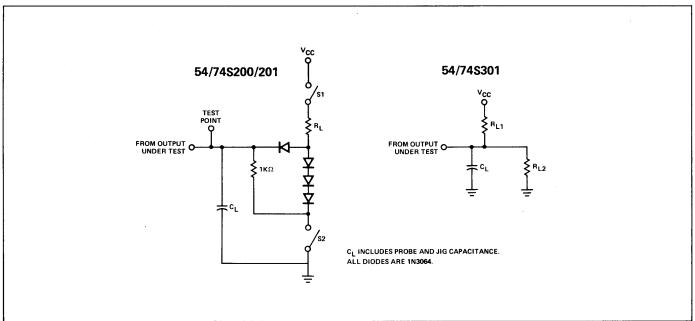

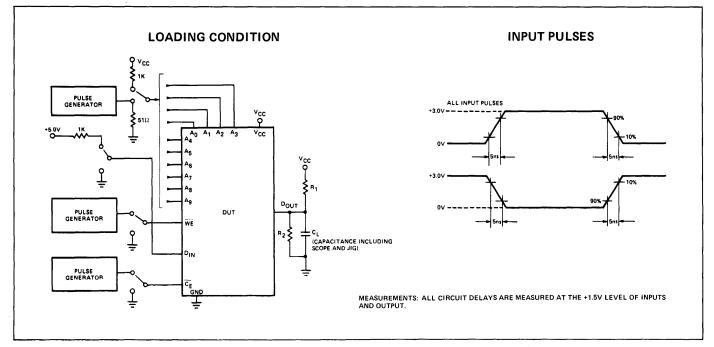

### AC TEST LOAD

NOTES:

- 1. Typical values are at  $V_{CC}$  = +5.0V, and  $T_A$  = +25°C. 2. Minimum required to guarantee a WRITE into the slowest bit.

3. The Operating Ambient Temperature Ranges are guaranteed with transverse air flow exceeding 400 linear feet per minute and a two minute warm-up.

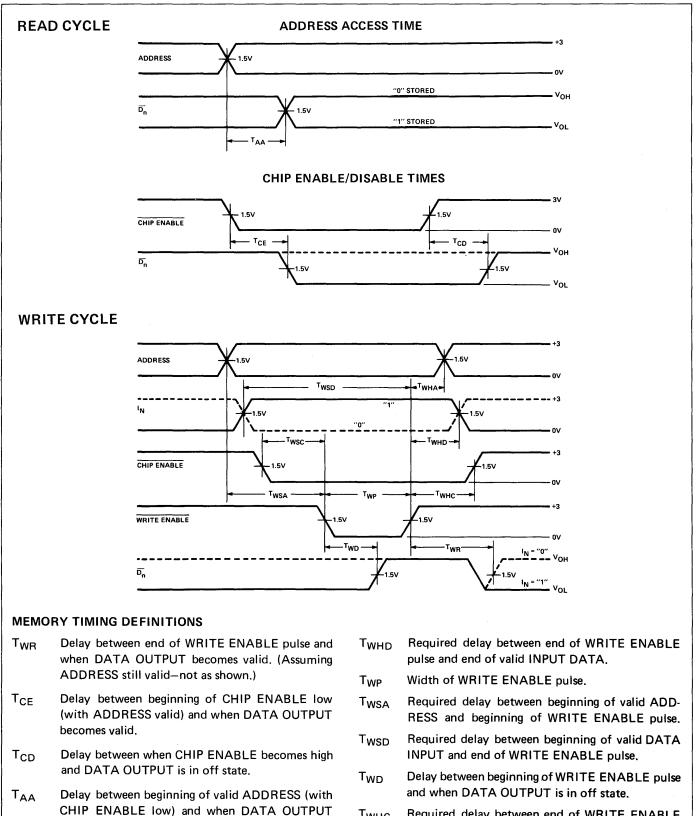

### SWITCHING PARAMETERS MEASUREMENT INFORMATION

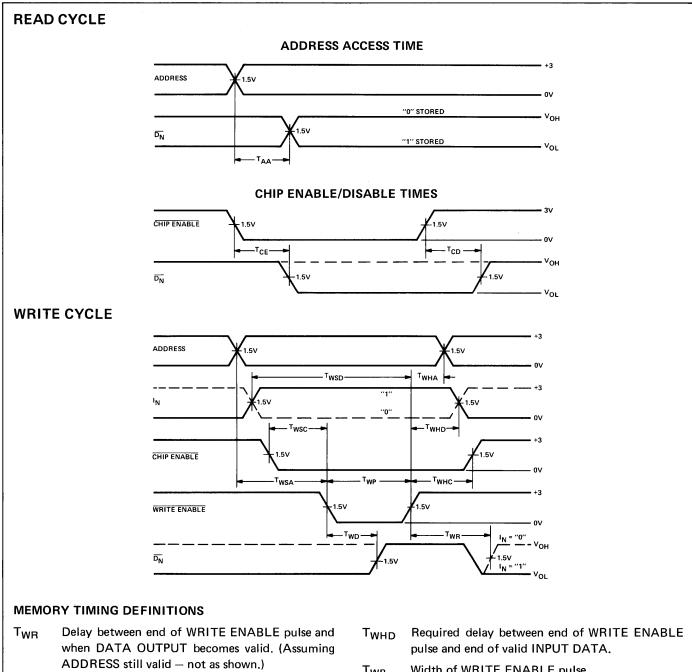

pulse and end of valid INPUT DATA.

T<sub>WHA</sub> Required delay between end of WRITE ENABLE pulse and end of valid ADDRESS.

### 1024x1 BIT BIPOLAR RAM OPEN COLLECTOR (82S10) TRI-STATE (8211) 82S11

### FEBURARY 1975 DIGITAL 8000 SERIES TTL/MEMORY

### DESCRIPTION

The 82S10/11 is a high speed 1024-bit random access memory organized as 1024 words X 1 bit. With a typical access time of 30ns, it is ideal for cache buffer applications and for systems requiring very high speed main memory.

Both the 82S10 and 82S11 require a single +5 volts power supply and feature very low current PNP input structures. They are fully TTL compatible, and include on-chip decoding and a chip enable input for ease of memory expansion. They feature either Open Collector or Tri-State outputs for optimization of word expansion in bussed organizations.

Both 82S10 and 82S11 devices are available in the commercial and military temperature ranges. For the commercial temperature range (0°C to +75°C) specify N82S10/11, I. For the military temperature range (-55°C to +125°C) specify S82S10/11, I.

### **FEATURES**

- ORGANIZATION 1024 X 1

- ADDRESS ACCESS TIME: S82S10/11 – 70ns, MAXIMUM N82S10/11 – 45ns, MAXIMUM

- WRITE CYCLE TIME: S82S10/11 – 75ns, MAXIMUM N82S10/11 – 45ns, MAXIMUM

- POWER DISSIPATION 0.5mW/BIT, TYPICAL

- INPUT LOADING: S82S10/11 – (-150μA) MAXIMUM N82S10/11 – (-100μA) MAXIMUM

- ON-CHIP ADDRESS DECODING

- OUTPUT OPTIONS: 82S10 – OPEN COLLECTOR 82S11 – TRI-STATE

- NON-INVERTING OUTPUT

- BLANKED OUTPUT DURING WRITE

- 16 PIN CERAMIC PACKAGE

### APPLICATIONS

HIGH SPEED MAIN FRAME CACHE MEMORY BUFFER STORAGE WRITABLE CONTROL STORE

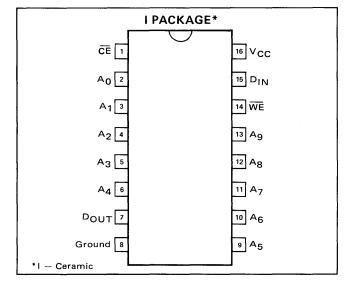

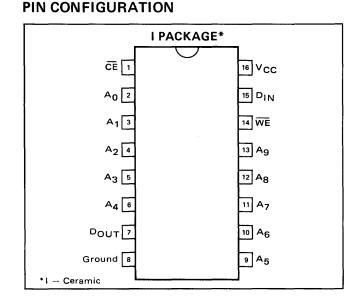

### PIN CONFIGURATION

### **TRUTH TABLE**

| MODE      | CE | WE | DIN   | Do     | DUT    |

|-----------|----|----|-------|--------|--------|

|           |    |    | - 114 | 82S10  | 82511  |

| READ      | 0  | 1  | Х     | STORED | STORED |

|           |    |    |       | DATA   | DATA   |

| WRITE "0" | 0  | 0  | 0     | 1      | High-Z |

| WRITE "1" | 0  | 0  | 1     | 1      | High-Z |

| DISABLED  | 1  | Х  | Х     | 1      | High-Z |

X = Don't care.

### **BLOCK DIAGRAM**

### **ABSOLUTE MAXIMUM RATINGS**

|                  | PARAMETER <sup>1</sup>                                    | RAMETER <sup>1</sup> RATING     |          |  |  |

|------------------|-----------------------------------------------------------|---------------------------------|----------|--|--|

| V <sub>CC</sub>  | Power Supply Voltage                                      | +7                              | Vdc      |  |  |

| V <sub>in</sub>  | Input Voltage                                             | +5.5                            | Vdc      |  |  |

| V <sub>он</sub>  | High Level Output Voltage (82S10)                         | +5.5                            | Vdc      |  |  |

| Vo               | Off-State Output Voltage (82S11)                          | +5.5                            | Vdc      |  |  |

| T <sub>A</sub>   | Operating Temperature Range<br>(N82S10/11)<br>(S82S10/11) | 0° to +75°<br>−55° to +125°     | °C<br>°C |  |  |

| T <sub>stg</sub> | Storage Temperature Range                                 | $-65^{\circ}$ to $+150^{\circ}$ | °C       |  |  |

### **ELECTRICAL CHARACTERISTICS**<sup>9</sup>

S82S10/11 -55°C ≤T<sub>A</sub> ≤+125°C, 4.5V ≤V<sub>CC</sub> ≤5.5 N82S10/11 0°C ≤T<sub>A</sub> ≤+75°C, 4.75V ≤V<sub>CC</sub> ≤5.25

|                  |                                         | TEST CONDITIONS                                               | s   | 82S10/1          | 1    | N   | 82S10/1          | 1     |          |

|------------------|-----------------------------------------|---------------------------------------------------------------|-----|------------------|------|-----|------------------|-------|----------|

|                  | PARAMETER                               | TEST CONDITIONS                                               | MIN | TYP <sup>2</sup> | MAX  | MIN | TYP <sup>2</sup> | MAX   | UNIT     |

| VIL              | Low Level Input Voltage                 | V <sub>CC</sub> = MIN (Note 1)                                |     |                  | .80  |     |                  | .85   | V        |

| Vін              | High Level Input Voltage                | V <sub>CC</sub> = MAX (Note 1)                                | 2.1 |                  |      | 2.1 |                  |       | v        |

| V <sub>IC</sub>  | Input Clamp Voltage                     | V <sub>CC</sub> = MIN, I <sub>IN</sub> = -12mA<br>(Note 1, 7) |     | -1.0             | -1.5 | -   | -1.0             | -1.5  | V        |

| Vol              | Low Level Output Voltage                | V <sub>CC</sub> = MIN, I <sub>OL</sub> = 16mA<br>(Note 1, 8)  |     | 0.35             | 0.50 |     | 0.35             | 0.45  | V        |

| V <sub>ОН</sub>  | High Level Output<br>Voltage (82S11)    | V <sub>CC</sub> = MIN, I <sub>OH</sub> = -2mA<br>(Note 1, 5)  | 2.4 |                  |      | 2.4 |                  |       | V        |

| I <sub>OLK</sub> | Output Leakage Current<br>(82S10)       | V <sub>CC</sub> = MAX, V <sub>OUT</sub> = 5.5V<br>(Note 6)    |     | 1                | 60   |     | 1                | 40    | μΑ       |

| IO(OFF)          |                                         | V <sub>CC</sub> = MAX, V <sub>OUT</sub> = 5.5V                |     | 1                | 100  |     | 1                | 60    | μA       |

|                  | Current (82S11)                         | V <sub>CC</sub> = MAX, V <sub>OUT</sub> = 0.45V<br>(Note 6)   |     | -1               | -100 |     | -1               | -60   | μΑ       |

| ł₁∟              | Low Level Input Current                 | V <sub>IN</sub> = 0.45V                                       |     | -10              | -150 |     | -10              | -100  | μA       |

| ιн               | High Level Input Current                | V <sub>IN</sub> = 5.5V                                        |     | 1                | 40   |     | 1                | 25    | μA       |

| I <sub>OS</sub>  | Short Circuit Output<br>Current (82S11) | V <sub>CC</sub> = MAX, V <sub>OUT</sub> = 0V<br>(Note 3)      | -20 |                  | -100 | -20 |                  | - 100 | mA       |

| Icc              | V <sub>CC</sub> Supply Current          | $V_{CC} = MAX$ (Note 4)                                       |     | 120              | 155  |     | 120              | 155   | mA       |

|                  |                                         | 0 < T <sub>A</sub> <25°C<br>T <sub>A</sub> ≥25°C              |     | 95               | 130  |     | 95               | 130   | mA<br>mA |

|                  |                                         | T <sub>A</sub> ≤0°C                                           |     |                  | 170  |     |                  | 170   | mA       |

| C <sub>IN</sub>  | Input Capacitance                       | V <sub>CC</sub> = 5.0V, V <sub>IN</sub> = 2.0V                |     | 4                |      |     | 4                |       | pF       |

| Cout             | Output Capacitance                      | V <sub>CC</sub> = 5.0V, V <sub>OUT</sub> = 2.0V               |     | 7                |      |     | 7                |       | pF       |

NOTES:

1. All voltage values are with respect to network ground terminal.

2. All typical values are at  $V_{CC} = 5V$ ,  $T_A = 25^{\circ}C$ .

3. Duration of the short-circuit should not exceed one second.

4. I<sub>CC</sub> is measured with the write enable and memory enable inputs grounded, all other inputs at 4.5V, and the output open.

5. Measured with  $V_{1L}$  applied to  $\overline{CE}$  and a logic "1" stored.

6. Measured with  $V_{1H}$  applied to  $\overline{CE}$ .

7. Test each input one at the time.

9. The Operating Ambient Temperature Ranges are guaranteed with transverse air flow exceeding 400 linear feet per minute and a two minute warm-up. Typical thermal resistance values of the package at maximum temperature are:

$\phi_{\mathsf{JA}}$  Junction to Ambient at 400 fpm air flow – 50° C/Watt

$\phi_{\mathsf{JA}}$  Junction to Ambient – still air – 90° C/Watt

$\phi_{JA}$  Junction to Case – 20° C/Watt

<sup>8.</sup> Measured with a logic "0" stored. Output sink current is supplied through a resistor to  $V_{CC}$ .

### SIGNETICS 1024 X 1 BIT BIPOLAR RAM = 82S10/11

### SWITCHING CHARACTERISTICS<sup>3</sup>

|                  |                                        |                                     | S   | 82S10/1          | 1   | N   | 82S10/1                 | 1   |      |

|------------------|----------------------------------------|-------------------------------------|-----|------------------|-----|-----|-------------------------|-----|------|

|                  | PARAMETER                              | TEST CONDITIONS                     | MIN | TYP <sup>1</sup> | MAX | MIN | <b>TYP</b> <sup>1</sup> | MAX | UNIT |

| Propaga          | ation Delays                           |                                     |     |                  |     |     |                         |     |      |

| T <sub>AA</sub>  | Address Access Time                    |                                     |     | 30               | 70  |     | 30                      | 45  | ns   |

| TCE              | Chip Enable Access Time                |                                     |     | 15               | 45  |     | 15                      | 30  | ns   |

| т <sub>ср</sub>  | Chip Enable Output Disable<br>Time     |                                     |     | 15               | 45  |     | 15                      | 30  | ns   |

| T <sub>WD</sub>  | Write Enable to Output<br>Disable Time |                                     |     | 20               | 45  |     | 20                      | 30  | ns   |

| Twr              | Write Recovery Time                    |                                     |     | 20               | 45  |     | 20                      | 30  | ns   |

| Write S          | et-up Times                            | C <sub>L</sub> = 30pF               |     |                  |     |     |                         |     |      |

| T <sub>WSA</sub> | Address to Write Enable                | $R_1 = 270\Omega$ $R_2 = 600\Omega$ | 15  | 0                |     | 5   | 0                       |     | ns   |

| T <sub>WSD</sub> | Data In to Write Enable                |                                     | 55  | 35               |     | 40  | 35                      |     | ns   |

| Twsc             | CE to Write Enable                     |                                     | 5   | 0                | :   | 5   | 0                       |     | ns   |

| Write H          | lold Times                             |                                     |     |                  |     |     |                         |     |      |

| T <sub>WHA</sub> | Address to Write Enable                |                                     | 10  | 0                | :   | 5   | 0                       |     | ns   |

| T <sub>WHD</sub> | Data In to Write Enable                |                                     | 5   | 0                |     | 5   | 0                       |     | ns   |

| т <sub>wнс</sub> | CE to Write Enable                     |                                     | 5   | 0                |     | 5   | 0                       |     | ns   |

| T <sub>WP</sub>  | Write Enable Pulse Width (Note 2)      |                                     | 50  | 25               |     | 35  | 25                      |     | ns   |

### AC TEST LOAD

NOTES:

- 1. Typical values are at  $V_{CC}$  = +5.0V, and  $T_A$  = +25°C. 2. Minimum required to guarantee a WRITE into the slowest bit.

- 3. The Operating Ambient Temperature Ranges are guaranteed with transverse air flow exceeding 400 linear feet per minute and a two minute warm-up. Typical thermal resistance values of the package at maximum temperature are:

- $heta_{

m JA}$  Junction to Ambient at 400 fpm air flow 50 $^{\circ}$  C/Watt

- $\theta_{JA}$  Junction to Ambient still air 90° C/Watt  $\theta_{JA}$  Junction to Case 20° C/Watt

### SWITCHING PARAMETERS MEASUREMENT INFORMATION

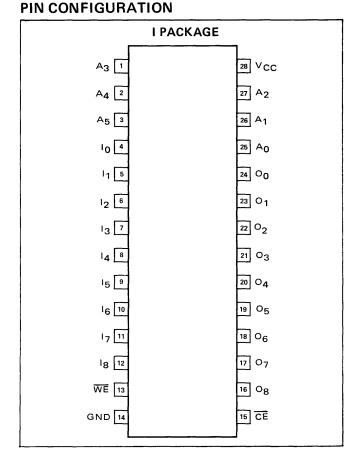

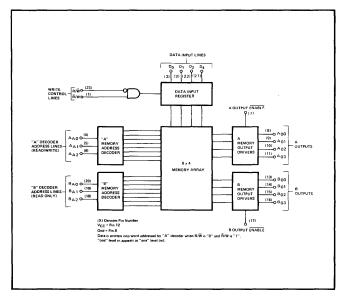

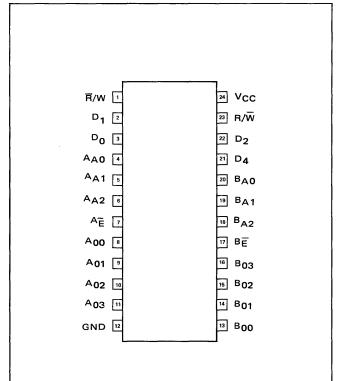

### HIGH SPEED MULTIPORT MEMORY (8x4 MULTIPORT RAM) 82S112

### DIGITAL 8000 SERIES TTL/MEMORY

### DESCRIPTION

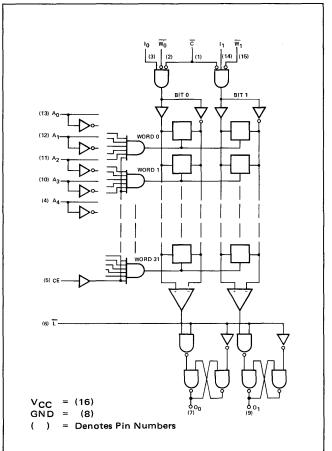

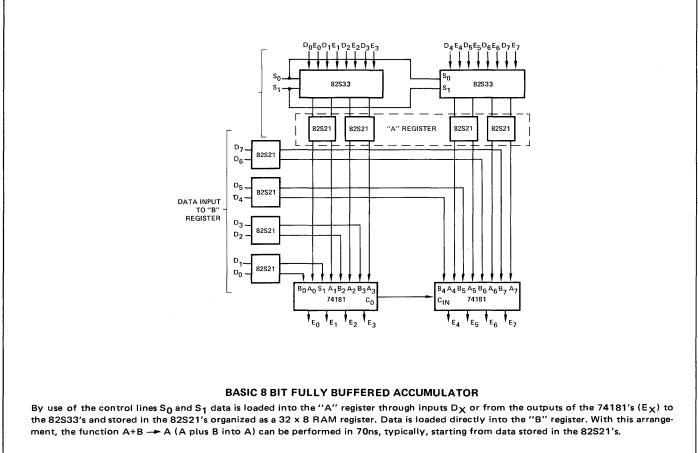

The 82S12/112 is a Schottky TTL 32 bit multiport memory organized in 8 words of 4 bits each. The device is ideally suited for high speed accumulators and buffer memories.

Stored data is addressed through 2 independent sets of 3-input decoders, and read out when the corresponding output enable line is low. Two separate word locations can, therefore, be read at the same time by enabling both the A and B output drivers. In addition, data can be read and written at the same time by utilizing the "A" address to specify the location of the word to be written, and the "B" address to specify the word to be read.

The 82S12/112 can be used in larger memory arrays since it includes all the control logic required to disable the chip and the outputs are open-collector devices suitable for "Wire-ORing."

### **FEATURES**

- LOW CURRENT INPUT BUFFERS (-25µA TYPICAL)

- SEPARATE INPUT DECODERS FOR EACH WORD

- SEPARATE OUTPUT ENABLE LINES FOR EACH WORD

- OPEN COLLECTOR (82S12) OR TRI-STATE (82S112) OUTPUTS

- 2 WRITE ENABLE LINES

- FAST ACCESS (20 ns TYPICAL)

- USEFUL 8 × 4 ORGANIZATION

- TTL COMPATIBLE

- NON INVERTING DATA LINES

### **BLOCK DIAGRAM**

#### **APPLICATIONS**

SCRATCH PAD MEMORY BUFFER MEMORY ACCUMULATOR REGISTER GENERAL REGISTER

#### **PIN CONFIGURATION**

### TRUTH TABLE

| Ē∕w        | R/W | A<br>OUTPUT | B<br>OUTPUT | MODE                | Ουτ     | PUTS    |

|------------|-----|-------------|-------------|---------------------|---------|---------|

| <b>n/w</b> | n/w |             |             | MODE                | Α       | В       |

|            |     | ENABLE      | ENABLE      |                     | ~       | D       |

| 0          | x   | 1           | 1           | Outputs<br>Disabled | "1"     | "1"     |

| 0          | X   | 1           | 0           | Read                | "1"     | Data    |

| 0          | X   | 0           | 1           | Read                | Data    | "1"     |

| 0          | ×   | 0           | 0           | Read                | Data    | Data    |

| 1          | 1   | 1           | 1           | Read                | "1"     | "1"     |

| 1          | 1   | 1           | 0           | Read                | "1"     | Data    |

| 1          | 1   | 0           | 1           | Read                | Data    | "1"     |

| 1          | 1   | 0           | 0           | Read                | Data    | Data    |

| 1          | 0   | 1           | 1           | Write               | "1"     | "1"     |

| 1          | 0   | 1           | 0           | Write               | "1"     | Data    |

|            |     |             |             |                     |         | "B"     |

|            |     |             |             |                     |         | Address |

| 1          | 0   | 0           | 1           | Write               | Data    | "1"     |

|            |     |             |             |                     | Being   |         |

|            |     |             |             |                     | Written |         |

| 1          | 0   | 0           | 0           | Write               | Data    | Data    |

|            |     |             |             |                     | Being   | "B"     |

|            |     |             |             |                     | Written | Address |

### **OBJECTIVE ELECTRICAL SPECIFICATIONS** $0^{\circ}C \le T_{A} \le 75^{\circ}C$ ; -4.75 V $\le V_{CC} \le 5.25$ V.

| CHARACTERISTICS            |                | LIMITS  |         |       |                              |  |  |

|----------------------------|----------------|---------|---------|-------|------------------------------|--|--|

| CHARACTERISTICS            | MIN.           | TYP.    | MAX.    | UNITS | TEST CONDITIONS              |  |  |

| Input "0" Current          |                |         | -250    | μA    | V <sub>in</sub> = 0.45 V     |  |  |

| Input "1" Current          |                |         | 25      | μA    | V <sub>in</sub> = 5.5 V      |  |  |

| Input "0" Threshold Voltag | e              |         | 0.85    | V     |                              |  |  |

| Input "1" Threshold Voltag | e 2.0          |         |         | V     |                              |  |  |

| Input Clamp Voltage        | -1.2           |         |         | V     | l <sub>in</sub> = –18 mA     |  |  |

| Output "0" Current         | 16             |         |         | mA    | V <sub>out</sub> = 0.5 V     |  |  |

| Output "0" Current         | 9.6            |         |         |       | $V_{out} = 0.45 V$           |  |  |

| Output "1" Voltage (825112 | 2) 2.6         |         |         | Volts | $I_{out} = -3.2 \text{ mA}$  |  |  |

| Output Off Current (82S12) |                |         | 40      | μA    | V <sub>out</sub> ≤ 5.5 V     |  |  |

| Output Off Current (82S112 | 2) —40         |         | +40     | μA    | $0.45 \le V_{out} \le 5.5 V$ |  |  |

| Power Consumption          |                | 110/550 | 160/840 | mA/mW | Outputs Enabled              |  |  |

| Write Pulse Width          | 「1             | 15      | 30      | ns    | $T_A = 25^{\circ}C$ Only     |  |  |

| Г                          | 1              |         | 45      | ns    | 0°C ≤ T <sub>A</sub> ≤ 75°C  |  |  |

| Address Set Up Time        | 2              | 10      |         | ns    | A                            |  |  |

| Address Hold Time          | <sup>7</sup> 3 | 0       |         | ns    |                              |  |  |

| Data Input Hold Time 1     | 4              | 15      |         | ns    |                              |  |  |

| Write Access Time          | 5              | 30      |         | ns    |                              |  |  |

| Data Input Set Up Time     | 6              | 5       |         | ns    |                              |  |  |

| Output Enable Time         | 7              | 10      | 20      | ns    |                              |  |  |

| Output Disable Time        | 8              | 10      | 20      | ns    |                              |  |  |

| Address Access Time        | 9              | 20      | 30      | ns    |                              |  |  |

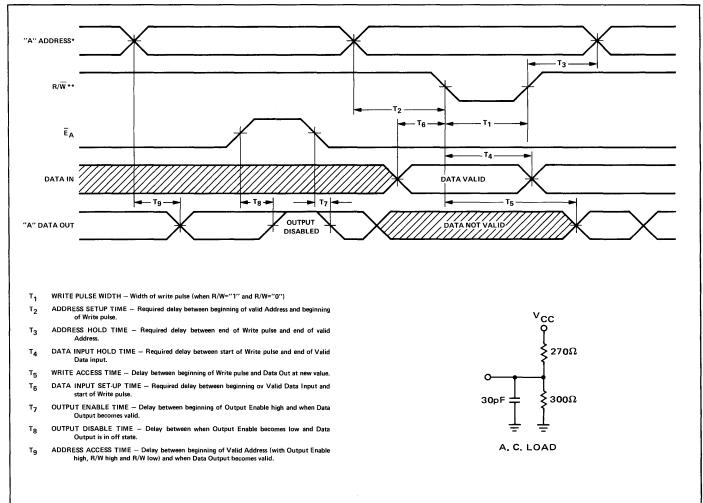

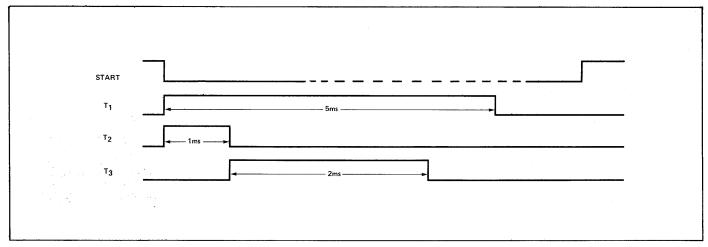

### **TIMING DIAGRAM**

NOTES

\*"B" Address functions identically in read mode. No write mode through B address decoder. \*\*R/W input is either the reverse of R/W or held high.

Outputs can be disabled during write cycle to penetrate a known output state during write.

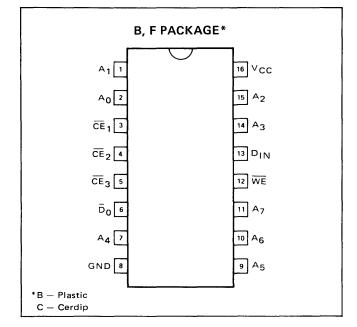

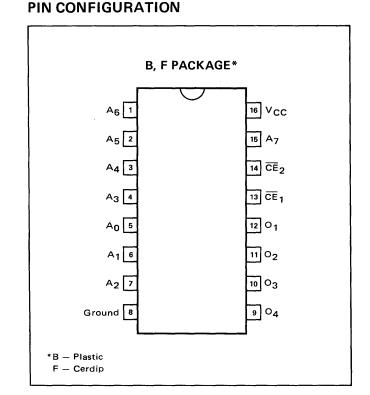

### 256-BIT BIPOLAR RAM (256x1 RAM) (82S16 TRI-STATE) (82S17 OPEN COLLECTOR) 82S17

### FEBRUARY 1975 DIGITAL 8000 SERIES TTL/MEMORY

### DESCRIPTION

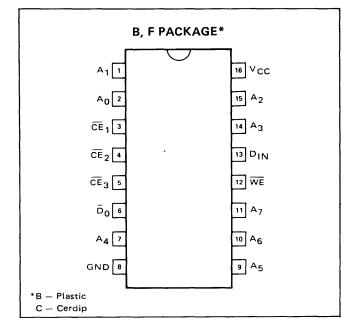

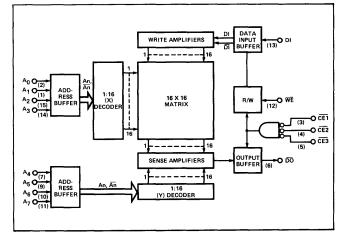

The 82S16 and 82S17 are Schottky clamped TTL, read/ write memory arrays organized as 256 words of one bit each. They feature either open collector or tri-state output options for optimization of word expansion in bussed organizations. Memory expansion is further enhanced by full on-chip address decoding, 3 chip enable inputs and PNP input transistors which reduce input loading to  $25\mu$ A for a "1" level, and  $-250\mu$ A (S82S16/17) or  $-100\mu$ A (N82S16/17) for a "0" level.

During WRITE operation, the logical state of the output of both devices follows the complement of the data input being written. This feature allows faster execution of WRITE-READ cycles, enhancing the performance of systems utilizing indirect addressing modes, and/or requiring immediate verification following a WRITE cycle.

Both devices have fast read access and write cycle times, and thus are ideally suited in high-speed memory applications such as "Cache", buffers, scratch pads, writable control stores, etc.

Both 82S16 and 82S17 devices are available in the commercial and military temperature ranges. For the commercial temperature range ( $0^{\circ}$ C to +75 $^{\circ}$ C) specify N82S16/17, B or F. For the military temperature range (-55 $^{\circ}$ C to +125 $^{\circ}$ C) specify S82S16/17, F only.

### **FEATURES**

- ORGANIZATION 256 X 1

- ADDRESS ACCESS TIME: S82S16, S82S17 – 70ns, MAXIMUM N82S16, N82S17 – 50ns, MAXIMUM

- WRITE CYCLE TIME: S82S16, S82S17 – 70ns, MAXIMUM N82S16, N82S17 – 55ns, MAXIMUM

- POWER DISSIPATION 1.5mW/BIT TYPICAL

- INPUT LOADING: S82S16, S82S17 – (-250μA) MAXIMUM N82S16, N82S17 – (-100μA) MAXIMUM

- OUTPUT FOLLOWS COMPLEMENT OF DATA INPUT DURING WRITE

- ON-CHIP ADDRESS DECODING

- 16 PIN CERAMIC DIP

- OUTPUT OPTION: TRI-STATE – 82S16 OPEN COLLECTOR – 82S17

### APPLICATIONS

BUFFER MEMORY WRITABLE CONTROL STORE MEMORY MAPPING PUSH DOWN STACK SCRATCH PAD

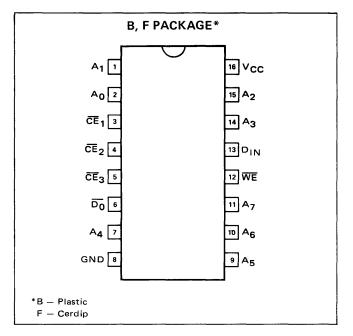

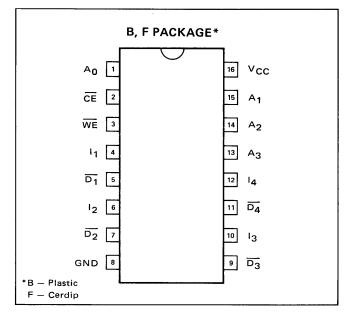

### PIN CONFIGURATION

#### **TRUTH TABLE**

|   |           |     |    |     | DO             | υT             |

|---|-----------|-----|----|-----|----------------|----------------|

|   | MODE      | CE* | WE | DIN | 82S16          | 82S17          |

|   | READ      | 0   | 1  | х   | STORED<br>DATA | STORED<br>DATA |

|   | WRITE "0" | 0   | 0  | 0   | 1              | 1              |

|   | WRITE "1" | 0   | 0  | 1   | 0              | 0              |

|   | DISABLED  | 1   | Х  | Х   | High-Z         | 1              |

| - | WRITE "1" | Ŭ   | 0  | 1   | 1<br>0         |                |

\*"'0" = All  $\overline{CE}$  inputs low; "1" = one or more  $\overline{CE}$  inputs high. X = Don't care.

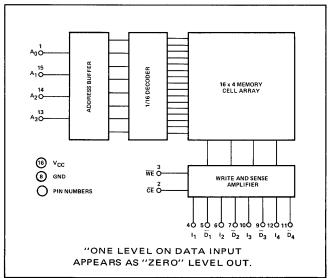

### **BLOCK DIAGRAM**

### **ABSOLUTE MAXIMUM RATINGS**

|                  | PARAMETER                                             | RATING                                                 | UNIT    |

|------------------|-------------------------------------------------------|--------------------------------------------------------|---------|

| V <sub>CC</sub>  | Power Supply Voltage                                  | +7                                                     | Vdc     |

| V <sub>IN</sub>  | Input Voltage                                         | +5.5                                                   | Vdc     |

| V <sub>OUT</sub> | High Level Output Voltage (82S17)                     | +5.5                                                   | Vdc     |

| Vo               | Off-State Output Voltage (82S16)                      | +5.5                                                   | Vdc     |

| T <sub>A</sub>   | Operating Temperature Range<br>S82S16/17<br>N82S16/17 | $-55^{\circ}$ to $+125^{\circ}$<br>0° to $+75^{\circ}$ | °c<br>℃ |

| T <sub>stg</sub> | Storage Temperature Range                             | $-65^{\circ}$ to $+150^{\circ}$                        | °C      |

### **ELECTRICAL CHARACTERISTICS**

|                     |                                              |                                                             | N   | 32S16/           | 17   | SE  | 82816/1          | 17   |      |       |

|---------------------|----------------------------------------------|-------------------------------------------------------------|-----|------------------|------|-----|------------------|------|------|-------|

|                     | PARAMETER                                    | TEST CONDITIONS                                             | MIN | TYP <sup>2</sup> | MAX  | MIN | TYP <sup>2</sup> | MAX  | UNIT | NOTES |

| VIH                 | High-Level Input Voltage                     | V <sub>CC</sub> = MAX                                       | 2.0 |                  |      | 2.0 |                  |      | V    | 1     |

| V <sub>IL</sub>     | Low-Level Input Voltage                      | V <sub>CC</sub> = MIN                                       |     |                  | 0.85 |     |                  | 0.8  | V    | 1     |

| V <sub>IC</sub>     | Input Clamp Voltage                          | V <sub>CC</sub> = MIN, I <sub>IN</sub> = -12mA              |     | -1.0             | -1.5 |     | -1.0             | -1.5 | V    | 1, 8  |

| V <sub>OH</sub>     | High-Level Output<br>Voltage (82S16)         | V <sub>CC</sub> = MIN, I <sub>OH</sub> = -3.2mA             | 2.6 |                  |      | 2.4 |                  |      | V    | 1, 6  |

| V <sub>OL</sub>     | Low-Level Output<br>Voltage                  | V <sub>CC</sub> = MIN, I <sub>OL</sub> = 16mA               |     | 0.35             | 0.45 |     | 0.35             | 0.5  | V    | 1, 7  |

| I <sub>OLK</sub>    | Output Leakage Current<br>(82S17)            | V <sub>OUT</sub> = 5.5V                                     |     | 1                | 40   |     | 1                | 40   | μA   | 5     |

| I <sub>O(OFF)</sub> | Hi-Z State Output                            | V <sub>OUT</sub> = 5.5V                                     |     | 1                | 40   |     | 1                | 50   | μA   | 5     |

|                     | Current (82S16)                              | V <sub>OUT</sub> = 0.45V                                    | ]   | -1               | -40  |     | -1               | -50  | μA   | 5     |

| I <sub>IH</sub>     | High-Level Input Current                     | V <sub>CC</sub> = MAX, V <sub>IN</sub> = 5.5V               |     | 1                | 25   |     | 1                | 25   | μA   | 8     |

| ЧL                  | Low-Level Input Current                      | V <sub>CC</sub> = MAX, V <sub>IN</sub> = 0.45V              |     | -10              | -100 |     | - 10             | -250 | μA   | 8     |

| I <sub>OS</sub>     | Short-Circuit Output<br>Current (82S16)      | $V_{CC} = MAX, V_O = 0V$                                    | -20 |                  | -70  | -20 |                  | -70  | mA   | 3     |

| Icc                 | V <sub>CC</sub> Supply Current<br>(82S16/17) | V <sub>CC</sub> = MAX                                       |     | 80               | 115  |     | 80               | 120  | mA   | 4     |

|                     | V <sub>CC</sub> Supply Current<br>(82S16/17) | V <sub>CC</sub> = MAX, T <sub>A</sub> = +125 <sup>°</sup> C |     |                  |      |     |                  | 99   | mA   | 4     |

| C <sub>IN</sub>     | Input Capacitance                            | $V_{IN} = 2.0V$ $V_{IN} = 5.0V$                             |     | 5                |      |     | 5                |      | pF   |       |

| C <sub>OUT</sub>    | Output Capacitance                           | $V_{OUT} = 2.0V$ $V_{CC} = 5.0V$                            |     | 8                |      |     | 8                |      | pF   |       |

NOTES:

1. All voltage values are with respect to network ground terminal.

2. All typical values are at  $V_{CC} = 5V$ ,  $T_A = +25^{\circ}C$ .

3. Duration of the short-circuit should not exceed one second.

4. ICC is measured with the write enable and memory enable inputs grounded, all other inputs at 4.5V, and the output open.

5. Measured with  $V_{IH}$  applied to  $\overline{CE1}$ ,  $\overline{CE2}$  and  $\overline{CE3}$ .

Measured with a logic "O" stored and V<sub>IL</sub> applied to CE<sub>1</sub>, CE<sub>2</sub> and CE<sub>3</sub>.

Measured with a logic "1" stored. Output sink current is supplied through a resistor to V<sub>CC</sub>.

8. Test each input one at the time.

### SIGNETICS 256-BIT BIPOLAR RAM (256 X 1 RAM) = 82S16, 82S17

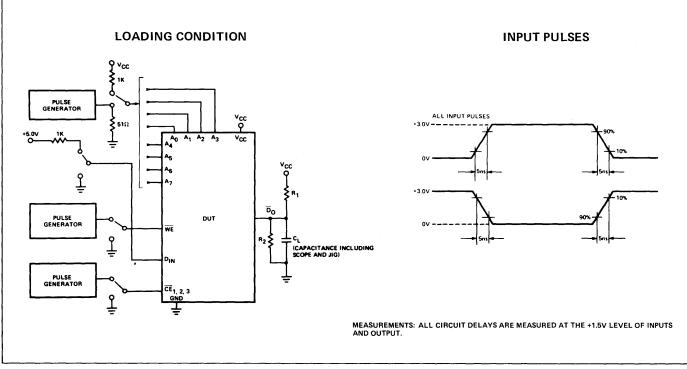

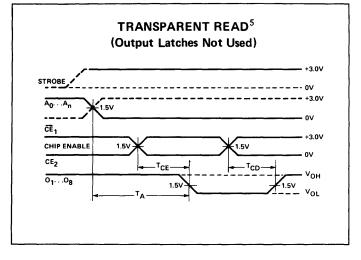

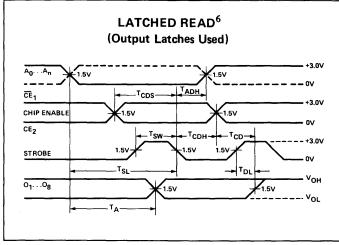

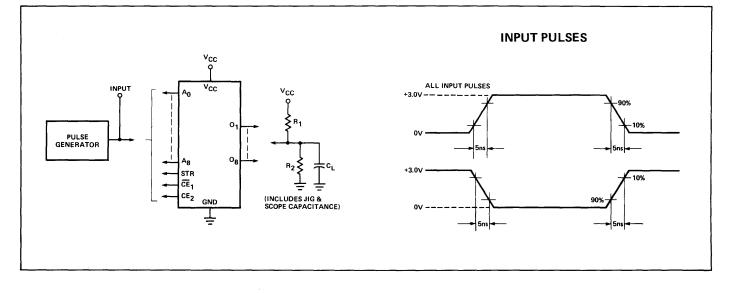

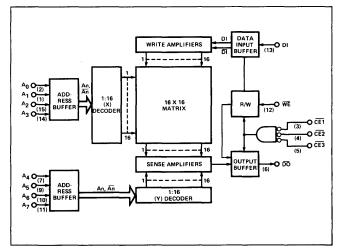

### SWITCHING CHARACTERISTICS

|                  |                                      |                                                  | 5   | 82516/1          | 7                                       | N                                     | 82S16/1          | 7                                     | UNIT |

|------------------|--------------------------------------|--------------------------------------------------|-----|------------------|-----------------------------------------|---------------------------------------|------------------|---------------------------------------|------|

|                  | PARAMETER                            | TEST CONDITIONS                                  | MIN | TYP <sup>1</sup> | MAX                                     | MIN                                   | TYP <sup>1</sup> | МАХ                                   |      |

| Propaga          | ation Delay                          |                                                  |     |                  |                                         |                                       |                  |                                       |      |

| T <sub>AA</sub>  | Address Access Time                  |                                                  |     | 40               | 70                                      |                                       | 40               | 50                                    | ns   |

| T <sub>CE</sub>  | Chip Enable Access Time              | $R_1 = 270\Omega$ $R_2 = 600\Omega$ $C_L = 30pF$ |     | 30               | 40                                      |                                       | 30               | 40                                    | ns   |

| Т <sub>СD</sub>  | Chip Enable Output Disable<br>Time   |                                                  |     | 30               | 40                                      |                                       | 30               | 40                                    | ns   |

| T <sub>WD</sub>  | Write Enable to Output<br>Valid Time |                                                  |     | 30               | 55                                      |                                       | 30               | 40                                    | ns   |

| Write S          | et-up Times                          |                                                  |     |                  | • · · · · · · · · · · · · · · · · · · · | · · · · · · · · · · · · · · · · · · · |                  | • • • • • • • • • • • • • • • • • • • | •••• |

| T <sub>WSA</sub> | Address to Write Enable              | $R_1 = 270\Omega$                                | 20  | 5                |                                         | 20                                    | 5                |                                       | ns   |

| T <sub>WSD</sub> | Data In to Write Enable              | $R_2 = 600\Omega$                                | 50  | 40               |                                         | 40                                    | 30               |                                       | ns   |

| Twsc             | CE to Write Enable                   | C <sub>L</sub> = 30pF                            | 10  | 0                |                                         | 10                                    | 0                |                                       | ns   |

| Write H          | lold Times                           |                                                  |     | •                | •                                       |                                       |                  |                                       |      |

| TWHA             | Address to Write Enable              | $R_1 = 270\Omega$                                | 10  | 0                |                                         | 5                                     | 0                |                                       | ns   |

| Т <sub>WHD</sub> | Data In to Write Enable              | $R_2 = 600\Omega$                                | 10  | 0                |                                         | 5                                     | 0                |                                       | ns   |

| т <sub>wнc</sub> | CE to Write Enable                   | C <sub>L</sub> = 30pF                            | 10  | 0                |                                         | 5                                     | 0                |                                       | ns   |

| T <sub>WP</sub>  | Write Enable Pulse Width             | Note 2                                           | 40  | 20               |                                         | 30                                    | 15               | l                                     | ns   |

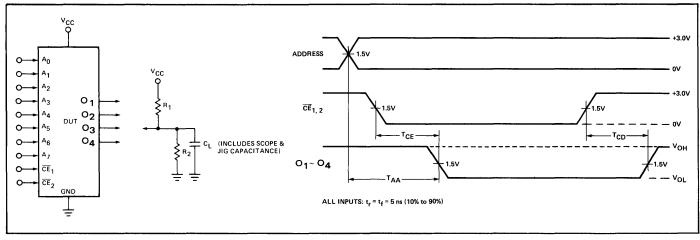

### AC TEST LOAD

NOTES:

- 1. Typical values are at V<sub>CC</sub> = +5.0V, and T<sub>A</sub> = +25 $^{\circ}$ C.

- 2. Minimum required to guarantee a WRITE into the slowest bit.

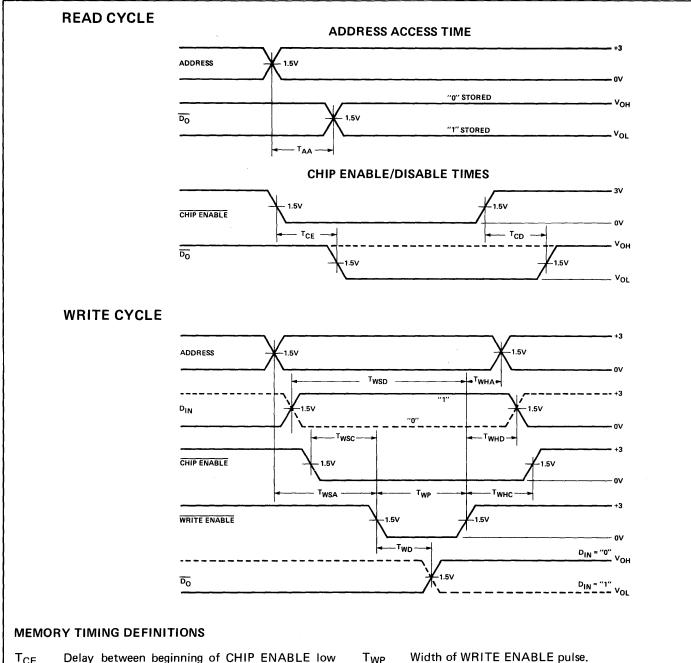

### SWITCHING PARAMETERS MEASUREMENT INFORMATION

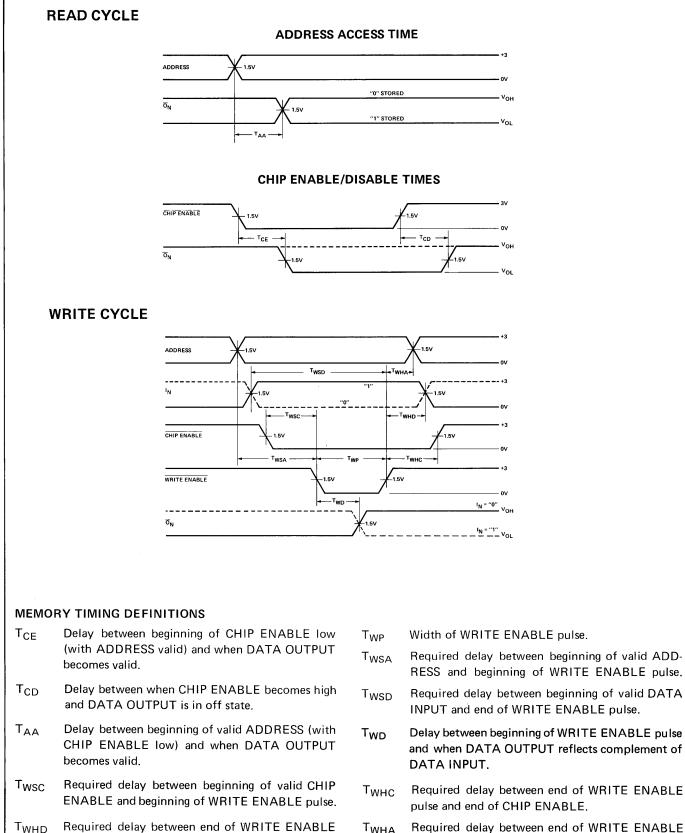

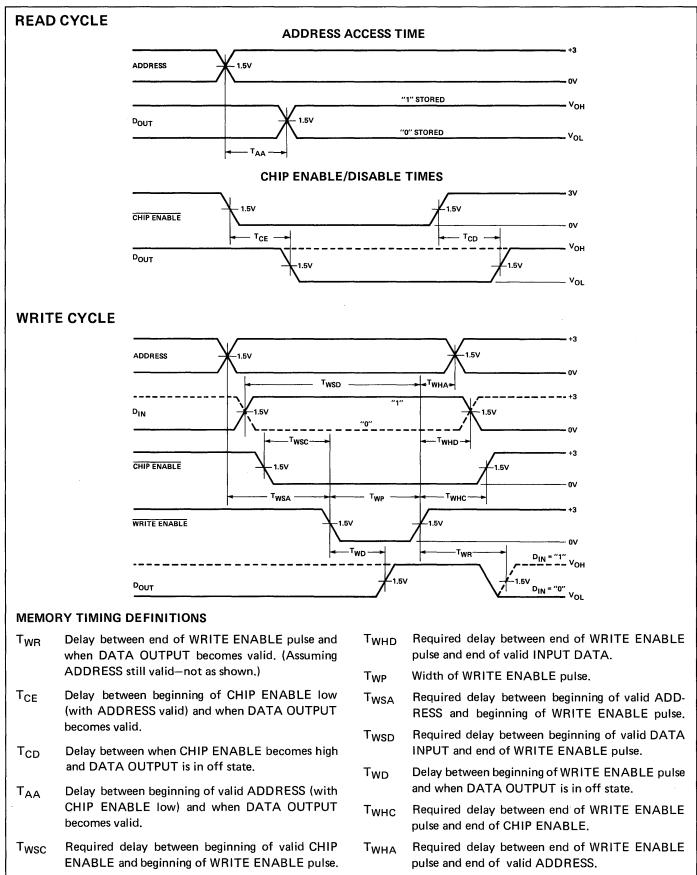

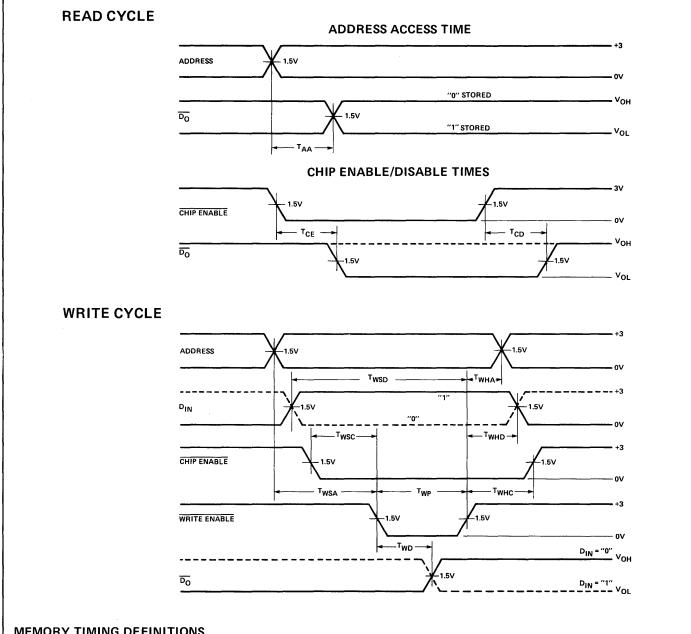

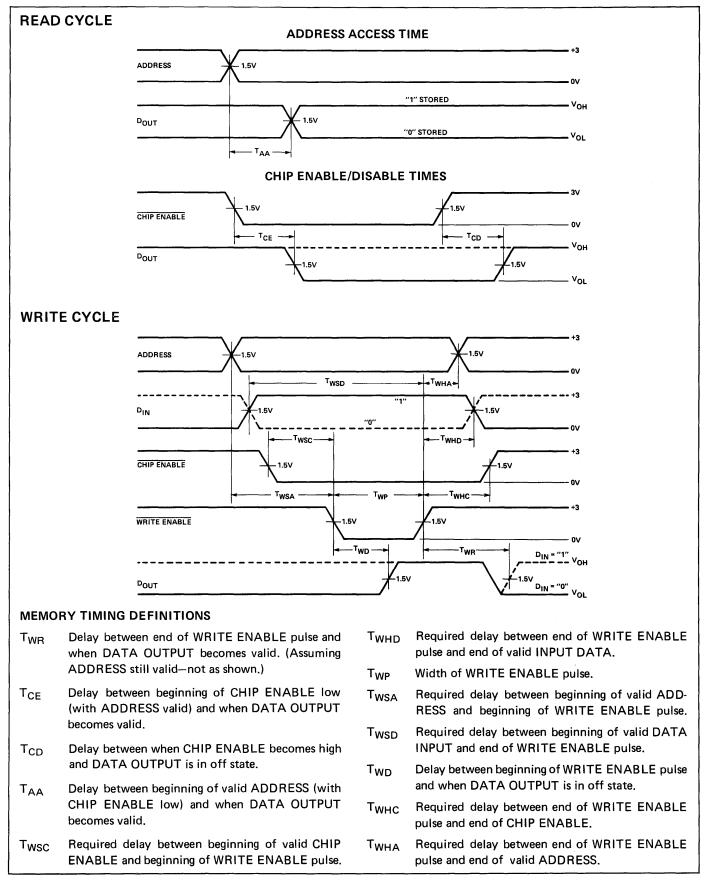

### MEMORY TIMING DEFINITIONS

- TCE Delay between beginning of CHIP ENABLE low (with ADDRESS valid) and when DATA OUTPUT becomes valid.

- Delay between when CHIP ENABLE becomes high T<sub>CD</sub> and DATA OUTPUT is in off state.

- Delay between beginning of valid ADDRESS (with TAA CHIP ENABLE low) and when DATA OUTPUT becomes valid.

- Required delay between beginning of valid CHIP Twsc ENABLE and beginning of WRITE ENABLE pulse.

- Required delay between end of WRITE ENABLE TWHD pulse and end of valid INPUT DATA.

- T<sub>WP</sub> Width of WRITE ENABLE pulse.

- Required delay between beginning of valid ADD-T<sub>WSA</sub> RESS and beginning of WRITE ENABLE pulse.

- Required delay between beginning of valid DATA TWSD INPUT and end of WRITE ENABLE pulse.

- $\mathsf{T}_{\mathsf{WD}}$ Delay between beginning of WRITE ENABLE pulse and when DATA OUTPUT reflects complement of DATA INPUT.

- Required delay between end of WRITE ENABLE Тинс pulse and end of CHIP ENABLE.

- Required delay between end of WRITE ENABLE TWHA pulse and end of valid ADDRESS.

### 64-BIT BIPOLAR HIGH SPEED WRITE-WHILE-READ RAM (32x2 RAM)

### DESCRIPTION

The 82S21 is a TTL 64 bit Write-While-Read Random Access Memory organized in 32 words of 2 bits each. The 82S21 is ideally suited for high speed buffers and as the memory element in high speed accumulators.

Words are selected through a 5 input decoder when the Read-Write enable input, CE is at logic "1".  $\overline{W_0}$  and  $\overline{W_1}$  are the write inputs for bit 0 and bit 1 of the word selected.  $\overline{C}$  is the write control input. When  $\overline{W_X}$  and  $\overline{C}$  are both at logic "0" data on the  $I_0$  and  $I_1$  data lines are written into the addressed word. The read function is enabled when either  $\overline{W_X}$  or  $\overline{C}$  is at logic "1".

An internal latch is on the chip to provide the Write-While-Read capability. When the latch control line,  $\overline{L}$ , is logic "1" and data is being read from the 82S21, the latch is effectively bypassed. The data at the output will be that of the addressed word. When  $\overline{L}$  goes from a logic "1" to logic "0" the outputs are latched and will remain latched regardless of the state of any other address or control line. When  $\overline{L}$  goes from "0" to "1" the outputs unlatch and the outputs will be that of the present address word.

#### **FEATURES**

- BUFFERED ADDRESS LINES

- ON CHIP LATCHES

- ON CHIP DECODING

- BIT MASKING CONTROL LINES

- ENABLE CONTROL LINE

- OPEN COLLECTOR OUTPUTS WITH 40mA CAPABILITY

- PROTECTED INPUTS

- VERY HIGH SPEEDS (25ns TYP)

#### TRUTH TABLE

| CE | C | $\overline{w_0}$ | W1 | ī | Mode                       | Outputs                                                                                                             |

|----|---|------------------|----|---|----------------------------|---------------------------------------------------------------------------------------------------------------------|

| X  | Х | X                | Х  | 0 | Output Hold                | Data from last addressed word when CE = "1"                                                                         |

| 0  | x | x                | X  | 1 | Read & Write Disabled      | Disabled logic "1"                                                                                                  |

| 1  | 1 | x                | X  | X | Read                       | Data stored in addressed word                                                                                       |

| 1  | 0 | 1                | 1  | x | Read                       | Data stored in addressed word                                                                                       |

| 1  | 0 | 0                | 0  | 0 | Write Data                 | Data from last word address when L went from<br>"1" to "0"                                                          |

| 1  | 0 | 0                | 0  | 1 | Write Data                 | Data being written into memory                                                                                      |

| 1  | 0 | 0                | 1  | × | Write Data into Bit 0 Only | If $\overline{L}$ = 0: Data from last word address when L went from "1" to "0"                                      |

| 1  | 0 | 1                | 0  | x | Write Data into Bit 1 Only | If $\overline{L} = 1$ : Data being written into the selected bit location<br>and stored in other addressed location |

### DIGITAL 8000 SERIES TTL/MEMORY

#### **APPLICATIONS**

SCRATCH PAD MEMORY BUFFER MEMORY ACCUMULATOR REGISTER CONTROL STORE

#### LOGIC DIAGRAM

### SIGNETICS 64-BIT HIGH SPEED WRITE-WHILE-READ ROM = 82S21

### **ELECTRICAL CHARACTERISTICS** $0^{\circ}C \le T_A \le 75^{\circ}C$ ; 4.75V $\le V_{CC} \le 5.25V$

|                                      |      | LIN  | AITS    |       |                         |       |

|--------------------------------------|------|------|---------|-------|-------------------------|-------|

| CHARACTERISTICS                      | MIN. | TYP. | MAX.    | UNITS | TEST CONDITIONS         | NOTES |

| "0" Output Voltage                   |      |      | .45     | v     | V <sub>out</sub> = 32mA |       |

| "1" Output Leakage Current           |      |      | 40      | μA    | V <sub>out</sub> = 5.5V |       |

| "0" Input Current (All Inputs)       |      |      | -1.6    | mA    | V <sub>in</sub> = 0.45∨ |       |

| "1" Input Current (All Inputs)       |      |      | 25      | μA    | V <sub>in</sub> = 5.5V  |       |

| Input "O" Voltage (V <sub>IL</sub> ) |      |      | 0.85    | v     |                         |       |

| Input "1" Voltage (V <sub>IH</sub> ) | 2.0  |      |         | v     |                         |       |

| Power Consumption                    |      |      | 130/683 | mA/mW |                         |       |

| Input Clamp Voltage                  | -1.2 |      |         | v     | I <sub>in</sub> = -18mA | i     |

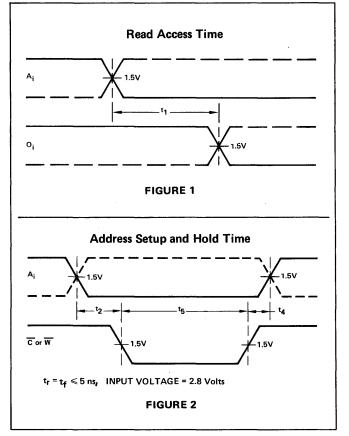

### SWITCHING CHARACTERISTICS $0 \le T_A \le 75^{\circ}$ C, 4.75 $\le V_{CC} \le 5.25$ V

|                                    |                |      | LIŇ  | IITS |       |                 |       |  |

|------------------------------------|----------------|------|------|------|-------|-----------------|-------|--|

| CHARACTERISTICS                    |                | MIN. | TYP. | MAX. | UNITS | TEST CONDITIONS | NOTES |  |

| Read Access Time Address to Output | t1             |      | 25   | 50   | ns    |                 |       |  |

| Address Set-Up Time                | t2             |      | 8    | 15   | ns    |                 |       |  |

| Data Set-Up Time                   | t3             |      | 15   | 20   | ns    |                 |       |  |

| Address Hold Time                  | t4             |      |      | 0    | ns    |                 |       |  |

| Control or Write Pulse Width       | t5             |      | 15   | 20   | ns    |                 |       |  |

| Write Access Time                  | <sup>t</sup> 6 |      | 20   | 25   | ns    |                 |       |  |

| Address to Latch Set-Up Time       | t7             |      | 25   | 50   | ns    |                 |       |  |

| Latch Address to Address Hold Time | t8             |      | 7    | 10   | ns    |                 |       |  |

| Delatch Access Time                | tg             | ļ    | 15   | 25   | ns    |                 |       |  |

| Data Hold Time                     | t10            |      | 0    | 5    | ns    |                 |       |  |

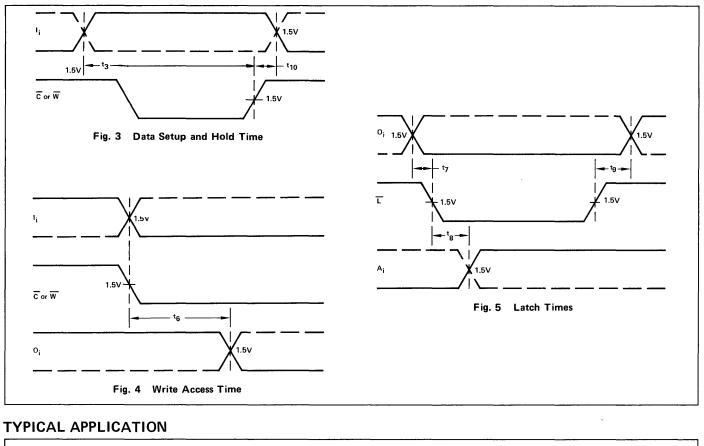

### **AC WAVEFORM**

### SIGNETICS 64-BIT HIGH SPEED WRITE-WHILE-READ ROM = 82S21

### **AC WAVEFORMS**

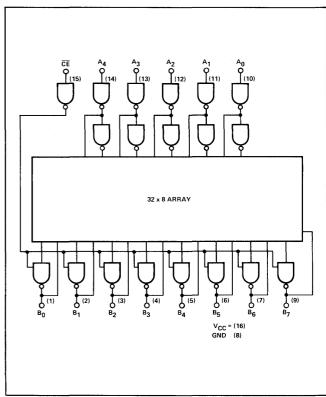

### 256-BIT BIPOLAR PROGRAMMABLE ROM (32x8 ROM) | (82S23 OPEN COLLECTOR) (82S123 TRI-STATE)

### FEBRUARY 1975 DIGITAL 8000 SERIES TTL/MEMORY

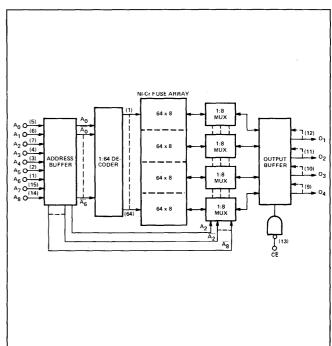

### DESCRIPTION

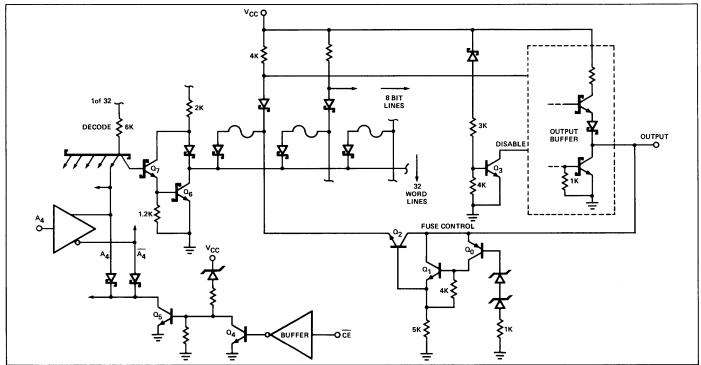

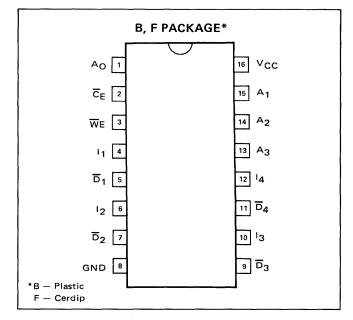

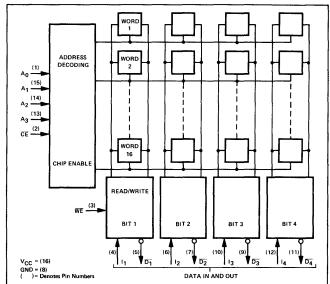

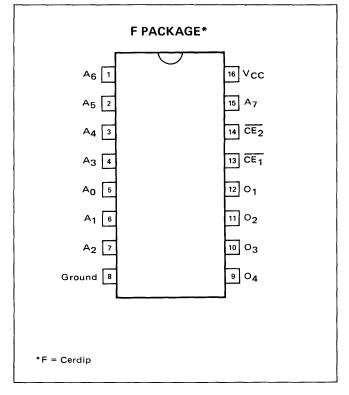

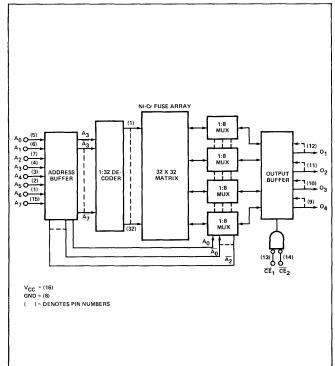

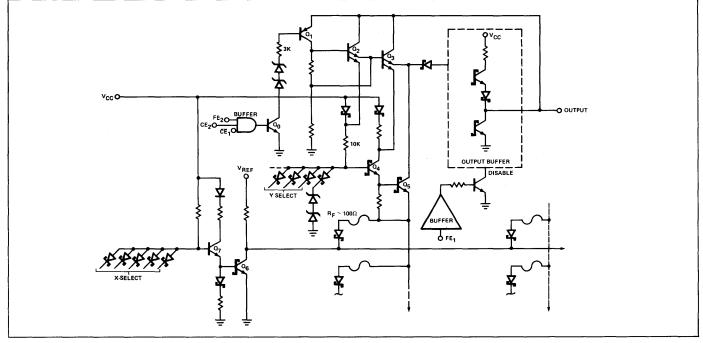

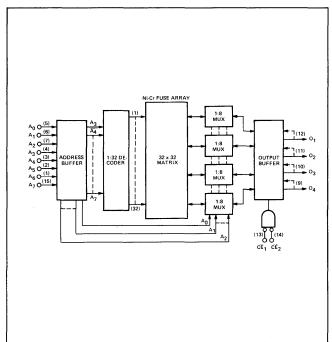

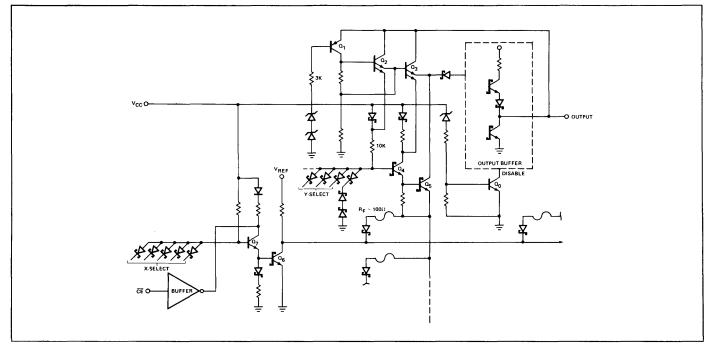

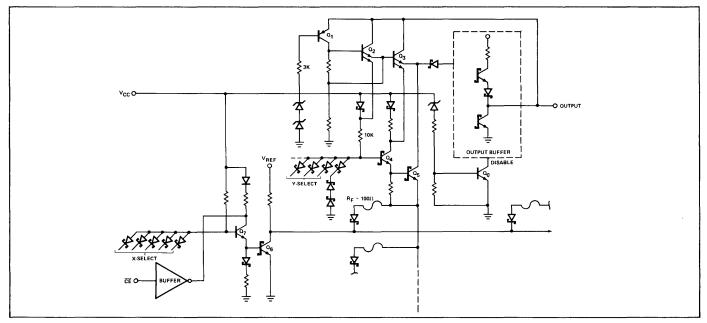

The 82S23 (Open Collector Outputs) and the 82S123 (Tri-State Outputs) are Bipolar 256-Bit Read Only Memories, organized as 32 words by 8 bits per word. They are Field-Programmable, which means that custom patterns are immediately available by following the fusing procedure given in this data sheet. The standard 82S23 and 82S123 devices are supplied with all outputs at logical "0". Outputs are programmed to a logic "1" level at any specified address by fusing a Ni-Cr link matrix.

The 82S23 and 82S123 are fully TTL compatible, and include on-chip decoding and one chip enable input for ease of memory expansion. They feature either Open Collector or Tri-State outputs for optimization of word expansion in bussed organizations.

Both 82S23 and 82S123 devices are available in the commercial and military temperature ranges. For the commercial temperature range ( $0^{\circ}$ C to +75 $^{\circ}$ C) specify N82S23/123, B or F. For the military temperature range (-55 $^{\circ}$ C to +125 $^{\circ}$ C) specify S82S23/123, F only.

### **FEATURES**

- ORGANIZATION 32 X 8

- ADDRESS ACCESS TIME: S82S23/S82S123 – 65ns, MAXIMUM N82S23/N82S123 – 50ns, MAXIMUM

- POWER DISSIPATION 1.3mW/BIT TYPICAL

- INPUT LOADING: S82S23/123 – (-150μA) MAXIMUM N82S23/123 – (-100μA) MAXIMUM

- ON-CHIP ADDRESS DECODING

- OUTPUT OPTION: OPEN COLLECTOR – 82S23 TRI-STATE – 82S123

- NO SEPARATE "FUSING" PINS

- UNPROGRAMMED OUTPUTS ARE "0" LEVEL

- 16-PIN CERAMIC DIP

### APPLICATIONS

PROTOTYPING/VOLUME PRODUCTION SEQUENTIAL CONTROLLERS FORMAT CONVERSION HARDWIRED ALGORITHMS RANDOM LOGIC CODE CONVERSION

**82S23**

82S123

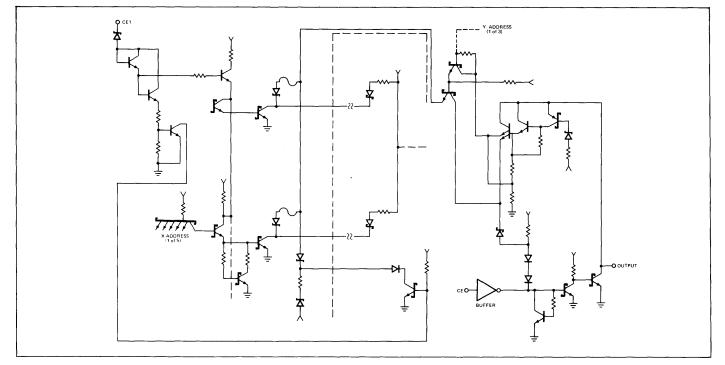

### LOGIC DIAGRAM

### **ABSOLUTE MAXIMUM RATINGS**

|                  | PARAMETER                                                   | RATING                          | UNIT     |

|------------------|-------------------------------------------------------------|---------------------------------|----------|

| V <sub>CC</sub>  | Power Supply Voltage                                        | +7                              | Vdc      |

| V <sub>IN</sub>  | Input Voltage                                               | +5.5                            | Vdc      |

| V <sub>OH</sub>  | High Level Output Voltage (82S23)                           | +5.5                            | Vdc      |

| vo               | Off-State Output Voltage (82S123)                           | +5.5                            | Vdc      |

| Τ <sub>Α</sub>   | Operating Temperature Range<br>(N82S23/123)<br>(S82S23/123) | 0° to +75°<br>-55° to +125°     | ວ°<br>ວ° |

| T <sub>stg</sub> | Storage Temperature Range                                   | $-65^{\circ}$ to $+150^{\circ}$ | °C       |

| · · · · · · ·       |                                          | TEST CONDITIONS                                                                      | S82S | 23/882 | S123      | N829 | S23/N82 | S123      |          |

|---------------------|------------------------------------------|--------------------------------------------------------------------------------------|------|--------|-----------|------|---------|-----------|----------|

|                     | PARAMETER                                | TEST CONDITIONS <sup>1</sup>                                                         | MIN  | ТҮР    | MAX       | MIN  | ТҮР     | MAX       | UNIT     |

| V <sub>OL</sub>     | "0" Output Voltage                       | I <sub>OUT</sub> = 16mA                                                              |      |        | 0.5       |      |         | 0.45      | v        |

| I <sub>OLK</sub>    | Output Leakage Current<br>(82S23)        | <u>CE</u> = "1", V <sub>OUT</sub> = 5.5V                                             |      |        | 50        |      |         | 40        | μA       |

| I <sub>O(OFF)</sub> | Hi-Z State Output Current<br>(82S123)    | <u>CE</u> = "1", V <sub>OUT</sub> = 5.5V<br><u>CE</u> = "1", V <sub>OUT</sub> = 0.5V |      |        | 50<br>-50 |      |         | 40<br>-40 | μΑ<br>μΑ |

| V <sub>OH</sub>     | "1" Output Voltage<br>(82S123)           | CE = "0", I <sub>OUT</sub> = -2mA,<br>"1" STORED                                     | 2.4  |        |           | 2.4  |         |           | V        |

| C <sub>IN</sub>     | Input Capacitance                        | V <sub>CC</sub> = 5.0V, V <sub>IN</sub> = 2.0V                                       |      | 5      |           |      | 5       |           | pF       |

| С <sub>ОИТ</sub>    | Output Capacitance                       | V <sub>CC</sub> = 5.0V, V <sub>OUT</sub> = 2.0V                                      |      | 8      |           |      | 8       |           | pF       |

| I <sub>IL</sub>     | "0" Input Current                        | V <sub>IN</sub> = 0.45V                                                              |      |        | - 150     |      |         | -100      | μA       |

| Чн                  | "1" Input Current                        | V <sub>IN</sub> = 5.5V                                                               |      |        | 50        |      |         | 50        | μA       |

| VIL                 | "0" Level Input Voltage                  |                                                                                      |      |        | 0.8       |      |         | 0.85      | V        |

| VIH                 | "1" Level Input Voltage                  |                                                                                      | 2.0  |        |           | 2.0  |         |           | v        |

| I <sub>CC</sub>     | V <sub>CC</sub> Supply Current           |                                                                                      |      | 65     | 85        |      | 65      | 77        | mA       |

| V <sub>IC</sub>     | Input Clamp Voltage                      | I <sub>N</sub> = - 18mA                                                              |      | -0.8   | -1.2      |      | -0.8    | -1.2      | v        |

| I <sub>OS</sub>     | Output Short Circuit Current<br>(82S123) | V <sub>OUT</sub> = 0V                                                                | -20  |        | - 100     | -20  |         | -90       | mA       |

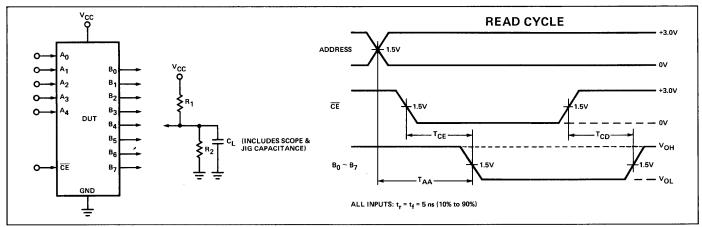

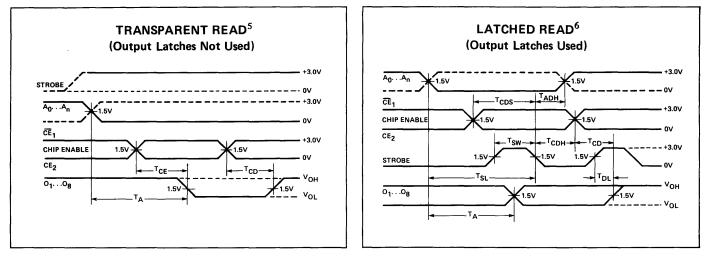

### SWITCHING CHARACTERISTICS

| PARAMETER                              | TEST CONDITIONS <sup>1</sup> | S825 | 23/8828          | 5123 | N82S | 23/N82S          | 123 |      |

|----------------------------------------|------------------------------|------|------------------|------|------|------------------|-----|------|

| FARAMETER                              | TEST CONDITIONS              | MIN  | TYP <sup>2</sup> | MAX  | MIN  | TYP <sup>2</sup> | MAX | UNIT |

| Propagation Delay                      |                              |      |                  |      |      |                  |     | •    |

| T <sub>AA</sub> Address to Output      | C <sub>L</sub> = 30pF        |      | 35               | 65   |      | 35               | 50  | ns   |

| T <sub>CD</sub> Chip Disable to Output | $R_1 = 270\Omega$            |      | 25               | 40   |      | 25               | 35  | ns   |

| T <sub>CE</sub> Chip Enable to Output  | $R_2 = 600\Omega$            |      | 25               | 40   |      | 25               | 35  | ns   |

NOTES:

1. Positive current is defined as into the terminal referenced.

2. Typical values are at  $V_{CC}$  = 5.0V,  $T_A$  = +25°C.

### SIGNETICS 256-BIT BIPOLAR PROGRAMMABLE ROM (32 X 8 PROM) = 82S23, 82S123

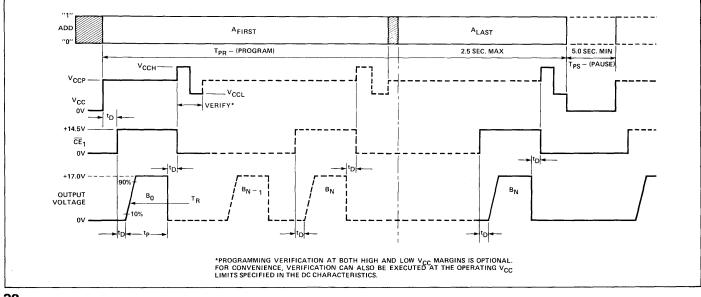

|                               |                            | TEST CONDITIONS                                              |      | LIMITS |      |      |

|-------------------------------|----------------------------|--------------------------------------------------------------|------|--------|------|------|

| PARAMETER                     |                            | TEST CONDITIONS                                              | MIN  | ТҮР    | MAX  | UNIT |

| Power Su                      | pply Voltage               |                                                              | •    |        |      |      |

| V <sub>CCP</sub> <sup>1</sup> | To Program                 | I <sub>CCP</sub> = 250 ± 50mA<br>(Transient or steady state) | 9.5  | 10.0   | 10.5 | V    |

| V <sub>CCH</sub>              | Upper Verify Limit         |                                                              | 5.3  | 5.5    | 5.7  | v    |

| V <sub>CCL</sub>              | Lower Verify Limit         |                                                              | 4.3  | 4.5    | 4.7  | v    |

| V <sub>S</sub> <sup>3</sup>   | Verify Threshold           |                                                              | 0.9  | 1.0    | 1.1  | V    |

| I <sub>CCP</sub>              | Programming Supply Current | $V_{CCP} = +10.0 \pm 0.5 V$                                  | 200  | 250    | 300  | mA   |

| Input Vol                     | Itage                      | · · · · · · · · · · · · · · · · · · ·                        |      |        | •    |      |

| V <sub>IH</sub>               | Logical "1"                |                                                              | 2.4  |        | 5.5  | V    |

| VIL                           | Logical "0"                |                                                              | 0    | 0.4    | 0.8  | V    |

| Input Cur                     | rrent                      |                                                              |      |        |      | •    |

| I <sub>IH</sub>               | Logical "1"                | V <sub>IH</sub> = +5.5V                                      |      |        | 50   | μA   |

| կլ                            | Logical "O"                | V <sub>1L</sub> = +0.4V                                      |      |        | -500 | μΑ   |

| V <sub>OUT</sub> <sup>2</sup> | Output Programming Voltage | I <sub>OUT</sub> = 65 ± 3mA<br>(Transient or steady state)   | 15.0 | 15.5   | 16.0 | V    |

| Ιουτ                          | Output Programming Current | V <sub>OUT</sub> = +15.5 ± 0.5V                              | 62   | 65     | 68   | mA   |

| т <sub>в</sub>                | Output Pulse Rise Time     |                                                              | 10   |        | 50   | μs   |

| tp                            | CE Programming Pulse Width |                                                              | 1    |        | 2    | ms   |

| t <sub>V</sub>                | Verify Delay               |                                                              | 50   |        |      | μs   |

| t <sub>D</sub>                | Pulse Sequence Delay       |                                                              | 10   |        |      | μs   |

| T <sub>PR</sub>               | Programming Time           | $V_{CC} = V_{CCP}$                                           |      |        | 2.5  | sec  |

| T <sub>PS</sub>               | Programming Pause          | V <sub>CC</sub> = 0V                                         | 5    |        |      | sec  |

| T <sub>PR</sub> <sup>4</sup>  | Programming Duty Cycle     |                                                              |      |        | 33   | %    |

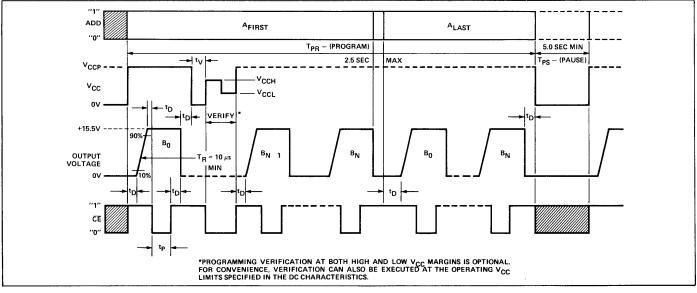

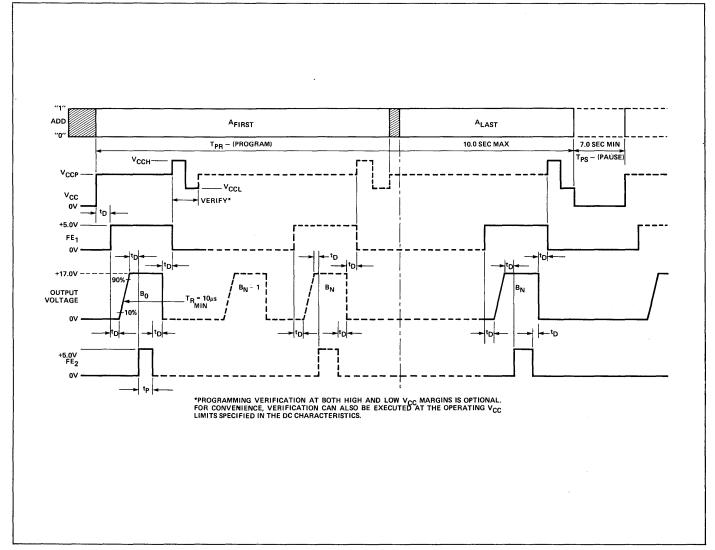

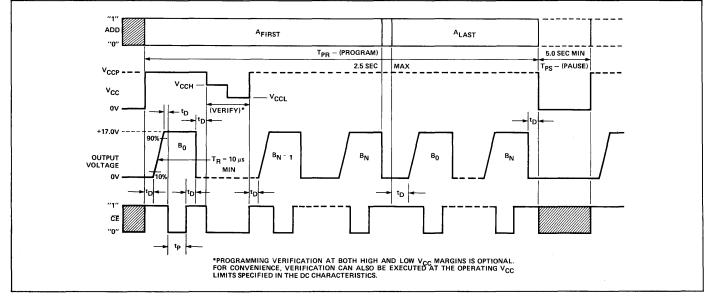

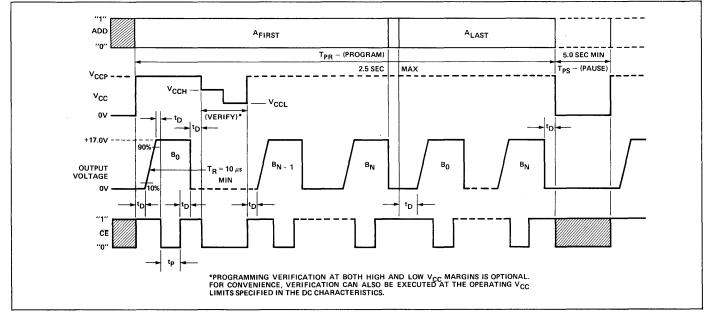

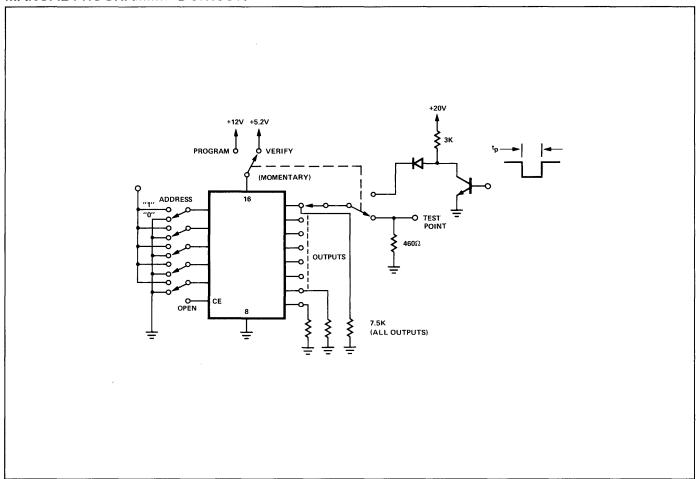

#### **PROGRAMMING SPECIFICATIONS** (Testing of these limits may cause programming of device.) $T_A = +25^{\circ}C$

### **PROGRAMMING PROCEDURE**

- 1. Terminate all device outputs with a 10K  $\!\Omega$  resistor to VCC.

- 2. Select the Address to be programmed, and raise V<sub>CC</sub> to  $V_{CCP} = +10 \pm 0.5V$ .

- 3. After 10 $\mu$ s delay, apply IOUT = 65 ± 3mA to the output to be programmed. Program one output at a time.

- 4. After  $10\mu s$  delay, pulse the  $\overline{CE}$  input to logic "0" for 1 to 2 ms.

- 5. After  $10\mu$ s delay, remove IOUT from the programmed output.

- 6. After 10µs delay, return V<sub>CC</sub> to 0V.

NOTES:

- 1. Bypass  $V_{\mbox{CC}}$  to GND with a  $0.01\mu\mbox{F}$  capacitor to reduce voltage spikes.

- 2. Care should be taken to insure that +15.5 ± 0.5V output voltage is maintained during the entire fusing cycle. The recommended supply is a constant current source clamped at the specified voltage limit.

7. To verify programming, after 50µs delay, raise V<sub>CC</sub>

to V<sub>CCH</sub> = +5.5  $\pm$  .2V, and apply a logic "0" level

to the CE input. The programmed output should remain

in the "1" state. Again, lower VCC to VCCL = +4.5

$\pm$  .2V, and verify that the programmed output remains

8. Raise V<sub>CC</sub> to V<sub>CCP</sub> = +10  $\pm$  0.5V and repeat steps 3

9. After  $10\mu$ s delay, repeat steps 2 through 8 to program

through 7 to program other bits at the same address.

in the "1" state.

all other address locations.

- 3. V<sub>S</sub> is the sensing threshold of the PROM output voltage for a programmed bit. It normally constitutes the reference voltage applied to a comparator circuit to verify a successful fusing attempt.

- Continuous fusing for an unlimited time is also allowed, provided that a 33% duty cycle is maintained. This may be accomplished by following each Program-Verify cycle with a Rest period (V<sub>CC</sub> = 0V) of 4ms.

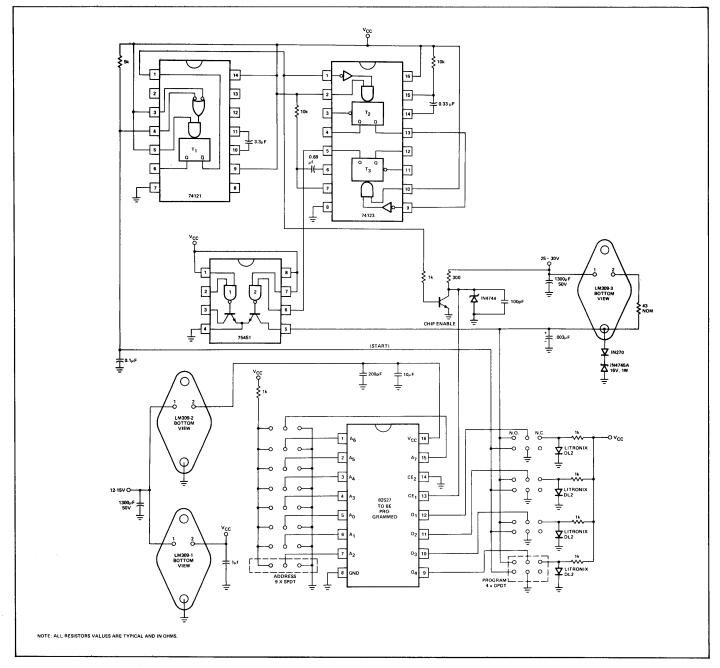

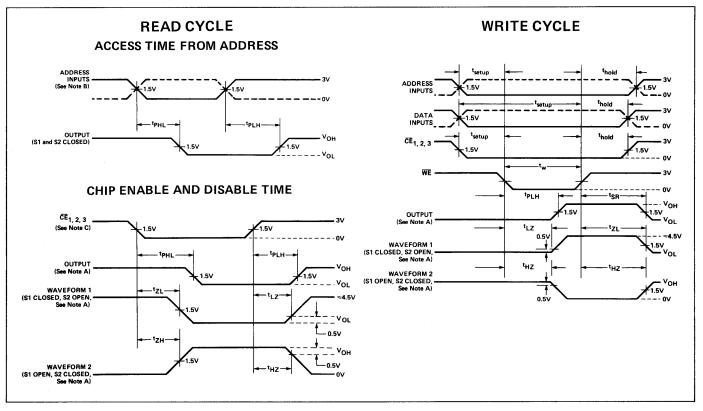

### AC TEST FIGURE AND WAVEFORM

### **TYPICAL FUSING PATH**

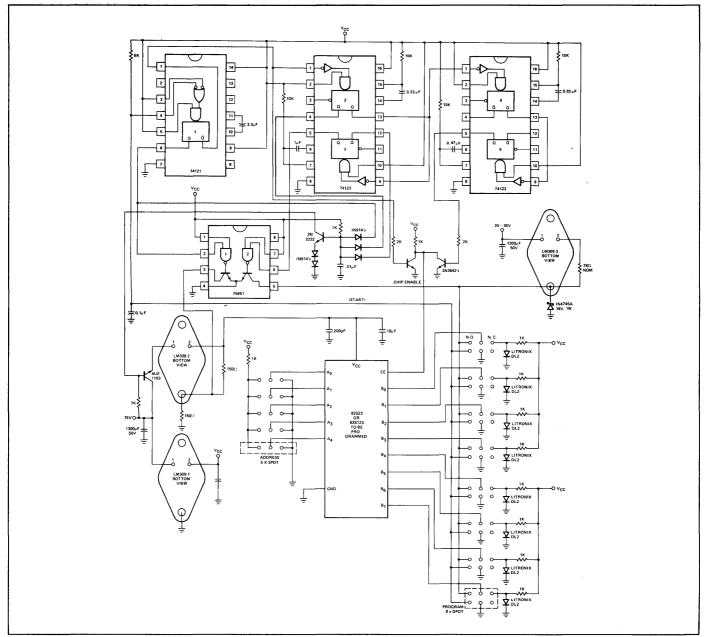

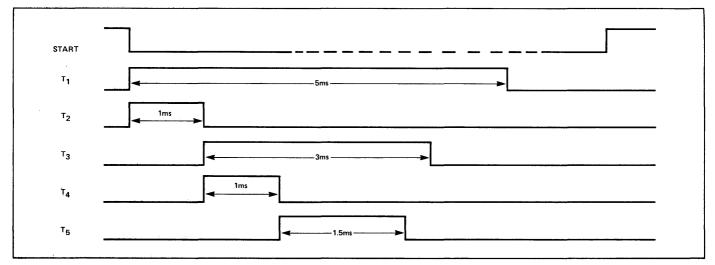

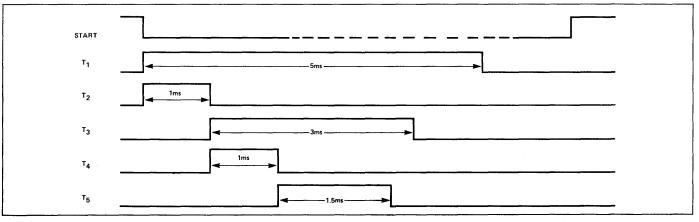

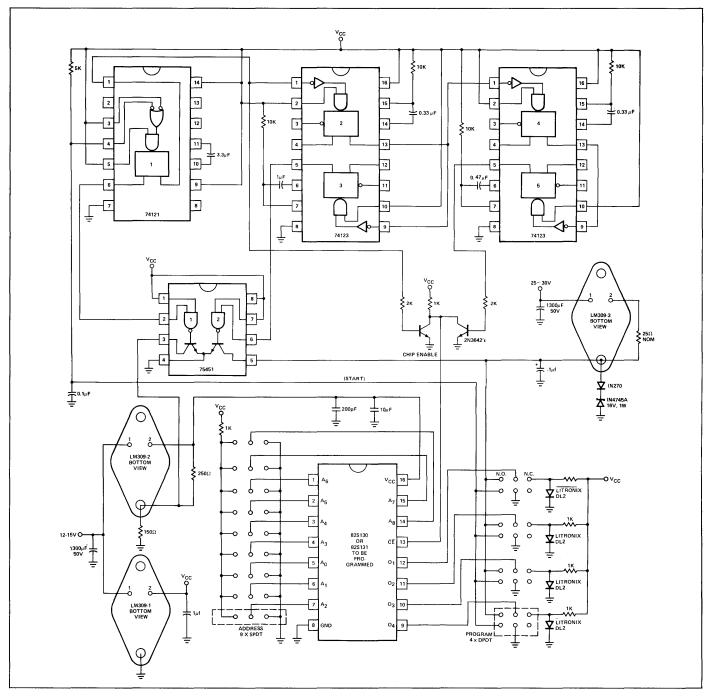

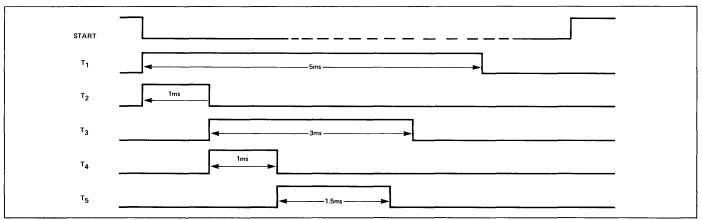

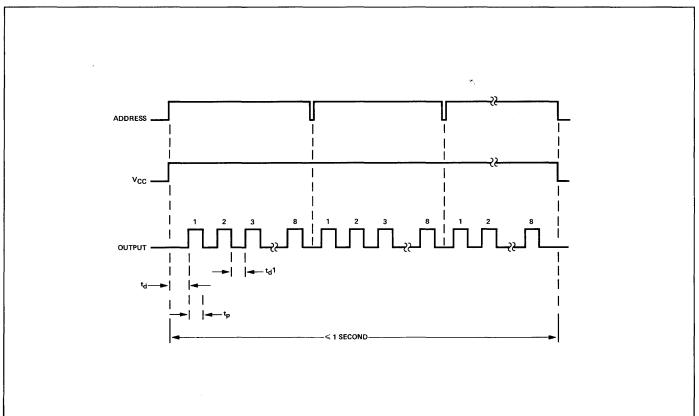

### **TYPICAL PROGRAMMING SEQUENCE**

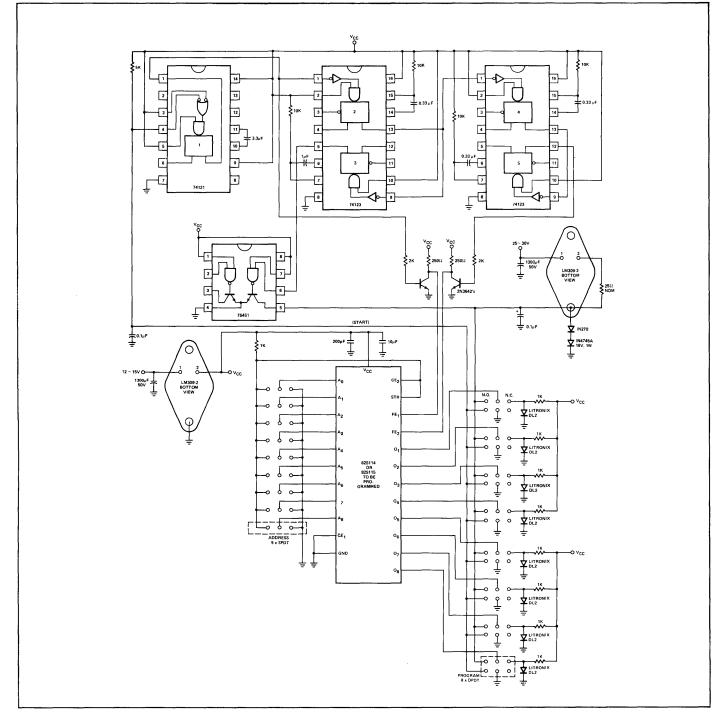

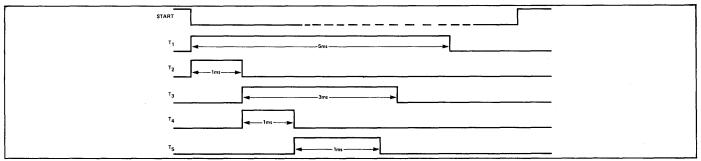

### SIGNETICS 256-BIT BIPOLAR PROGRAMMABLE ROM (32 X 8 PROM) = 82S23, 82S123

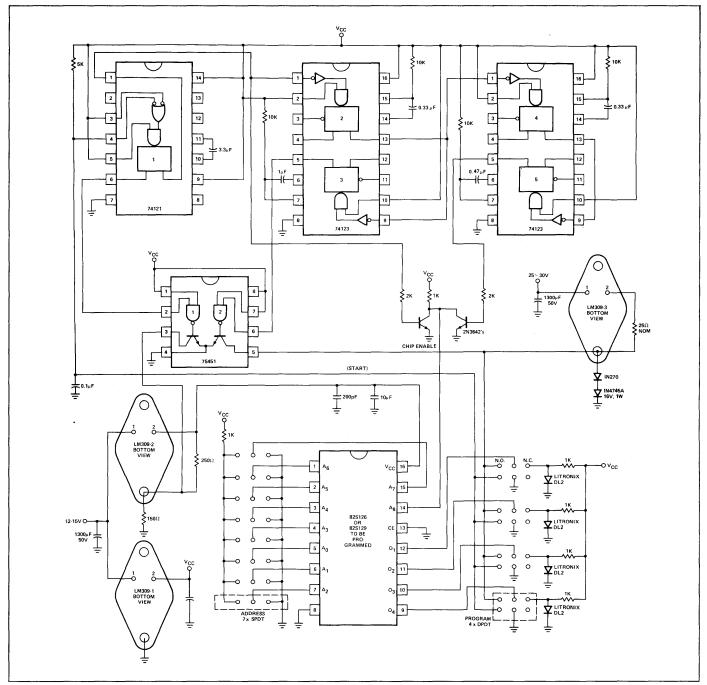

### MANUAL PROGRAMMER

### TIMING SEQUENCE

26

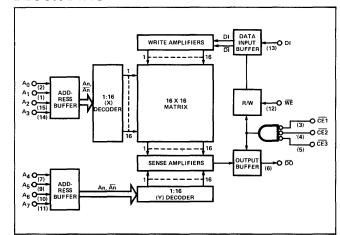

### 64-BIT BIPOLAR SCRATCH PAD MEMORY (16x4 RAM) 82S25

### FEBRUARY 1975 DIGITAL 8000 SERIES TTL/MEMORY

### DESCRIPTION

The 82S25 is a 64-bit, Schottky clamped TTL, Read-Write Random Access Memory ideal for use in scratch pad and high-speed buffer memory applications.

The 82S25 is a fully decoded memory array organized as 16 words of 4 bits each, with separate input and output lines. It features PNP inputs, one chip enable line, and open collector outputs for ease of memory expansion.

The outputs of the 82S25 assume a logic "1" state during write. This allows both memory inputs and outputs to share a common bus for minimizing interconnections, and more effective utilization of common I/O circuitry.

The 82S25 is available in the commercial and military temperature ranges. For the commercial temperature range ( $0^{\circ}$ C to +75 $^{\circ}$ C) specify N82S25, B or F. For the military temperature range (-55 $^{\circ}$ C to +125 $^{\circ}$ C) specify S82S25, F only.

### **FEATURES**

- ORGANIZATION 16 X 4

- ADDRESS ACCESS TIME: S82S25 – 60ns, MAXIMUM N82S25 – 50ns, MAXIMUM

- WRITE CYCLE TIME: S82S25 – 50ns, MAXIMUM N82S25 – 35ns, MAXIMUM

- POWER DISSIPATION 6.25mW/BIT, TYPICAL

- INPUT LOADING: S82S25 – (-150μA) MAXIMUM N82S25 – (-100μA) MAXIMUM

- OUTPUT BLANKING DURING WRITE

- ON-CHIP ADDRESS DECODING

- OPEN COLLECTOR OUTPUTS

- 16 PIN CERAMIC DIP

### APPLICATIONS

SCRATCH PAD MEMORY BUFFER MEMORY PUSH DOWN STACKS CONTROL STORE

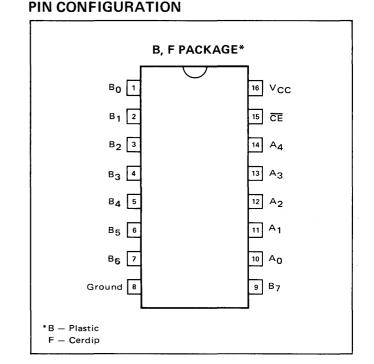

### PIN CONFIGURATION

### **TRUTH TABLE**

| MODE      | ĈĒ | WĒ | In | Dn                           |

|-----------|----|----|----|------------------------------|

| Read      | 0  | 1  | х  | Complement<br>of data stored |

| Write "O" | 0  | 0  | 0  | 1                            |

| Write "1" | 0  | 0  | 1  | 1                            |

| Disabled  | 1  | Х  | х  | 1                            |

X = Don't care.

### **BLOCK DIAGRAM**

### **ABSOLUTE MAXIMUM RATINGS**

|                  | PARAMETER <sup>1</sup>                              | RATING                          | UNIT     |

|------------------|-----------------------------------------------------|---------------------------------|----------|

| V <sub>CC</sub>  | Power Supply Voltage                                | +7                              | Vdc      |

| V <sub>in</sub>  | Input Voltage                                       | +5.5                            | Vdc      |

| V <sub>он</sub>  | High Level Output Voltage                           | +5.5                            | Vdc      |

| Τ <sub>Α</sub>   | Operating Temperature Range<br>(N82S25)<br>(S82S25) | 0° to +75°<br>-55° to +125°     | °C<br>°C |

| T <sub>stg</sub> | Storage Temperature Range                           | $-65^{\circ}$ to $+150^{\circ}$ | °c       |

# $\begin{array}{l} \textbf{ELECTRICAL CHARACTERISTICS} \quad \begin{array}{l} S82S25 & -55^{\circ}C \leqslant T_{A} \leqslant +125^{\circ}C, \ 4.5V \leqslant V_{CC} \leqslant 5.5V \\ N82S25 & 0^{\circ}C \leqslant T_{A} \leqslant +75^{\circ}C, \ 4.75V \leqslant V_{CC} \leqslant 5.25V \end{array}$

|                  |                         | TECT CONDITIONS                                                        | S   | 82S25 <sup>1,2</sup> | 2,3  | N82S25 <sup>1,2,3</sup> |                          |      |      |  |

|------------------|-------------------------|------------------------------------------------------------------------|-----|----------------------|------|-------------------------|--------------------------|------|------|--|

|                  | PARAMETER               | TEST CONDITIONS                                                        | MIN | TYP <sup>8</sup> MAX |      | MIN                     | MIN TYP <sup>8</sup> MAX |      | UNIT |  |

| I <sub>IL</sub>  | "0" Input Current       | V <sub>IN</sub> = 0.45V                                                |     | -10                  | -150 |                         | -10                      | -100 | μA   |  |

| ін               | "1" Input Current       | V <sub>IN</sub> = 5.5V                                                 |     |                      | 25   |                         |                          | 10   | μA   |  |

| VIL              | "0" Level Input Voltage | V <sub>CC</sub> = MIN                                                  |     |                      | .80  |                         |                          | .85  | v    |  |

| V <sub>IH</sub>  | "1" Level Input Voltage | V <sub>CC</sub> = MAX                                                  | 2.0 |                      | i    | 2.0                     |                          |      | V    |  |

| VIC              | Input Clamp Voltage     | I <sub>IN</sub> = -12mA, V <sub>CC</sub> = MIN<br>(Note 6)             |     | -1.0                 | -1.5 |                         | -1.0                     | -1.5 | V    |  |