# SIEMENS

# ICs for Communications Databook 1990/91

# **ICs for Communications**

Data Book 1990/91

#### Published by Siemens Integrated Circuit Division 2191 Laurelwood Rd., Santa Clara, CA 95054

For the circuits, descriptions, and tables indicated no responsibility is assumed as far as patents or other rights of third parties are concerned.

The information describes the type of component and shall not be considered as assured characteristics.

Terms of delivery and rights to change design reserved.

For questions on technology, delivery, and prices please contact the Offices of Siemens Components.

# Table of ContentsSummary of TypesGeneral Information

**ICs for Digital Exchange Systems**

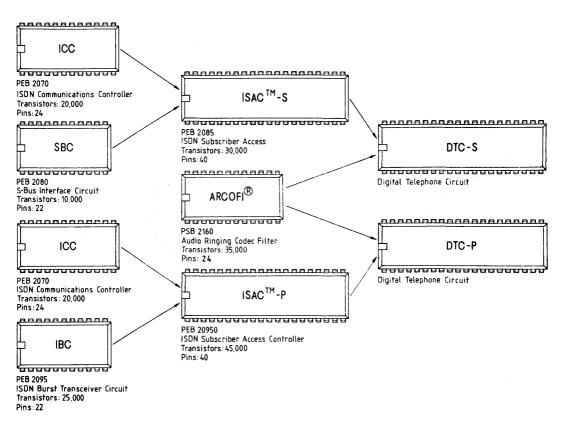

**ICs for ISDN Exchange Systems**

**ICs for ISDN Terminals**

**Support Tools**

**ICs for Data Communication**

**Package Outlines**

**Siemens Sales Office Listings**

# Table of Contents Summary of Types

# Contents

| Summary of Types                         | Page |

|------------------------------------------|------|

| 1. Types in alphanumerical order         | 9    |

| 2. Types in application-oriented order   | 12   |

| General Information                      |      |

| 1. Type designation code for ICs         | 17   |

| 2. Mounting instructions                 |      |

| 3. Processing guidelines for ICs         | 20   |

| 4. Data classification                   | 23   |

| 5. Quality assurance                     | 24   |

| 6. Summary of the most important symbols | 28   |

| Technical Data                           | 31   |

| Package Outlines                         | .727 |

| Siemens Sales Office Listings            | .743 |

# 1.1 Types in Alphanumerical Order

|            | Туре       | Ordering Code | Function                                     | Page |

|------------|------------|---------------|----------------------------------------------|------|

| S          | PEB 2025-P | Q67100-H6038  | ISDN Exchange Power Controller (IEPC)        | 227  |

|            | PEB 2035-C | Q67100-H8358  | Advanced CMOS Frame Aligner (ACFA)           | 44   |

| S          | PEB 2035-N | Q67100-H8684  | Advanced CMOS Frame Aligner (ACFA)           | 44   |

|            | PEB 2035-P | Q67100-H8359  | Advanced CMOS Frame Aligner (ACFA)           | 44   |

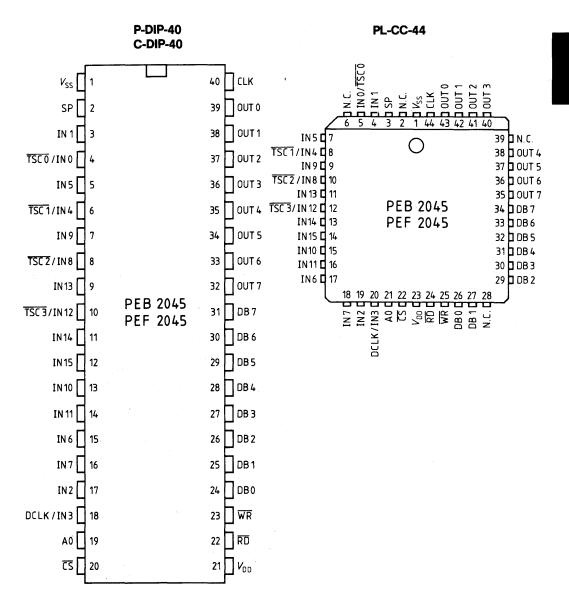

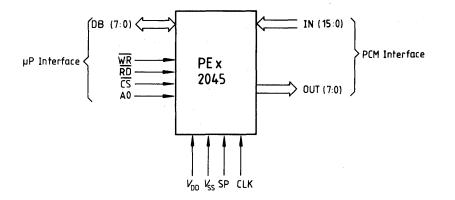

|            | PEB 2045-C | Q67100-H8323  | Memory Time Switch CMOS (MTSC)               | 90   |

| S          | PEB 2045-N | Q67100-H8602  | Memory Time Switch CMOS (MTSC)               | 90   |

|            | PEB 2045-P | Q67100-H8322  | Memory Time Switch CMOS (MTSC)               | 90   |

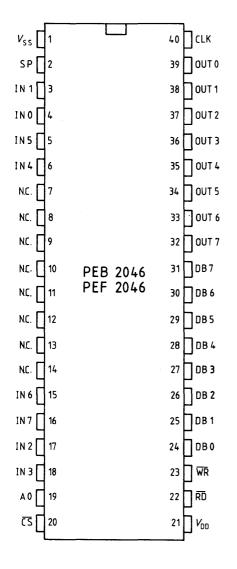

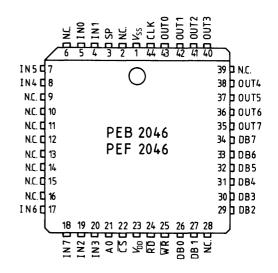

|            | PEB 2046-C | Q67100-H6103  | Memory Time Switch Small (MTSS)              | 119  |

| S          | PEB 2046-N | Q67100-H6104  | Memory Time Switch Small (MTSS)              | 119  |

|            | PEB 2046-P | Q67100-H6105  | Memory Time Switch Small (MTSS)              | 119  |

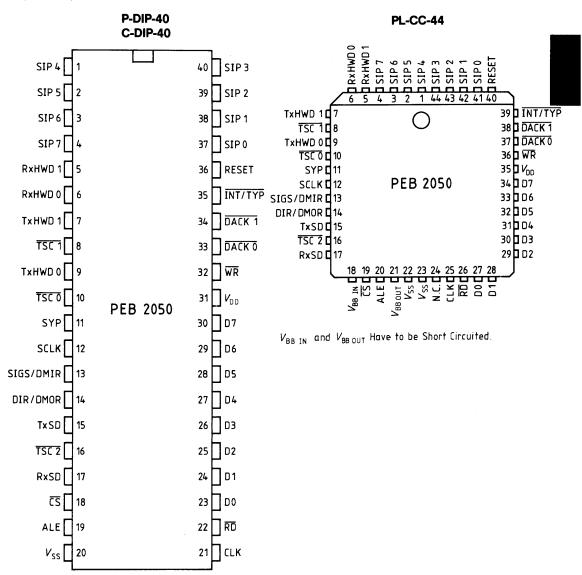

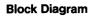

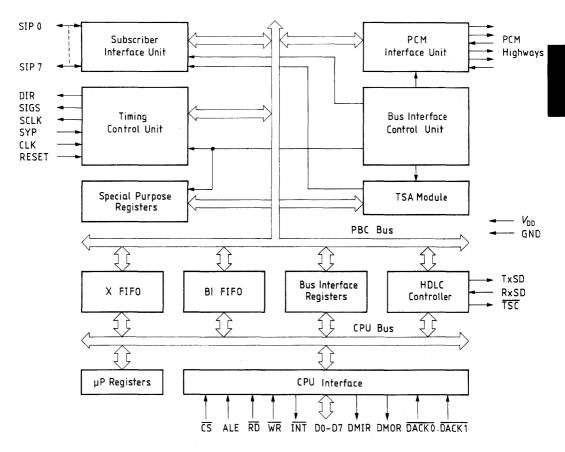

|            | PEB 2050-C | Q67100-Z157   | Peripheral Board Controller (PBC)            | 136  |

| S          | PEB 2050-N | Q67100-H8392  | Peripheral Board Controller (PBC)            | 136  |

|            | PEB 2050-P | Q67100-H3032  | Peripheral Board Controller (PBC)            | 136  |

| V          | PEB 2052-C | Q67100-H6059  | PCM Interface Controller (PIC)               | 154  |

| <b>'</b> S | PEB 2052-N | Q67100-H6060  | PCM Interface Controller (PIC)               | 154  |

| V          | PEB 2052-P | Q67100-H6061  | PCM Interface Controller (PIC)               | 154  |

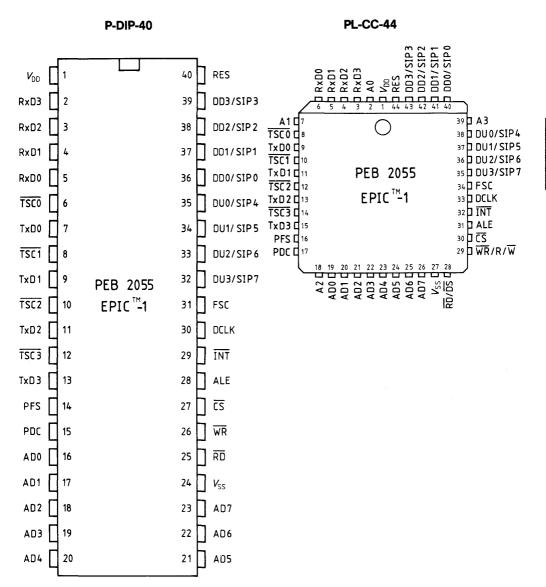

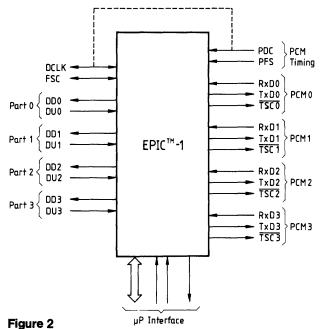

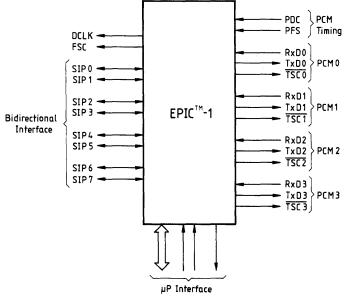

| V          | PEB 2055-C | Q67100-H6034  | Extended PCM Interface Controller (EPICTM-1) | 242  |

| 'S         | PEB 2055-N | Q67100-H6035  | Extended PCM Interface Controller (EPICTM-1) | 242  |

| V          | PEB 2055-P | Q67100-H6036  | Extended PCM Interface Controller (EPICTM-1) | 242  |

| V          | PEB 2056-C | Q67100-H6117  | Extended PCM Interface Controller (EPICTM-2) | 274  |

| 'S         | PEB 2056-N | Q67100-H6116  | Extended PCM Interface Controller (EPICTM-2) | 274  |

| V          | PEB 2056-P | Q67100-H6115  | Extended PCM Interface Controller (EPIC™-2)  | 274  |

| S          | PEB 2060-N | Q67100-H8393  | Signal Processing Codec Filter (SICOFI®)     | 167  |

|            | PEB 2060-P | Q67100-Z170   | Signal Processing Codec Filter (SICOFI®)     | 167  |

|            | PEB 2070-C | Q67100-H8328  | ISDN Communications Controller (ICC)         | 276  |

| S          | PEB 2070-N | Q67100-H8394  | ISDN Communications Controller (ICC)         | 276  |

|            | PEB 2070-P | Q67100-H2953  | ISDN Communications Controller (ICC)         | 276  |

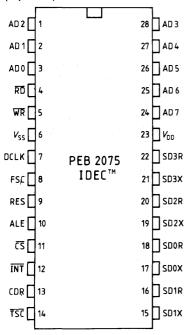

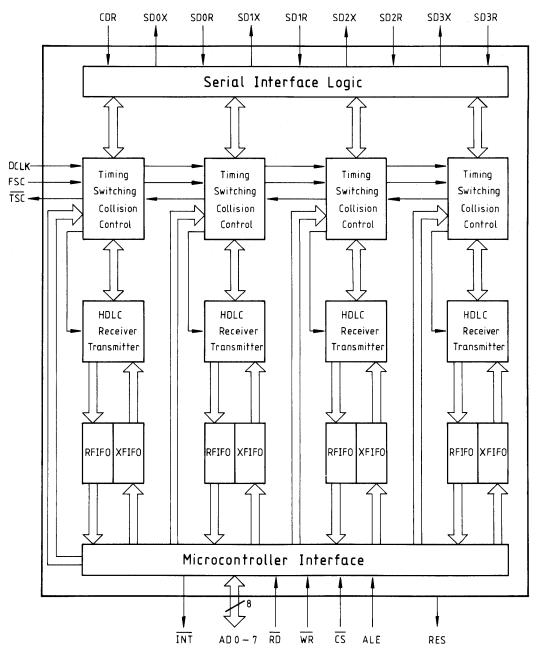

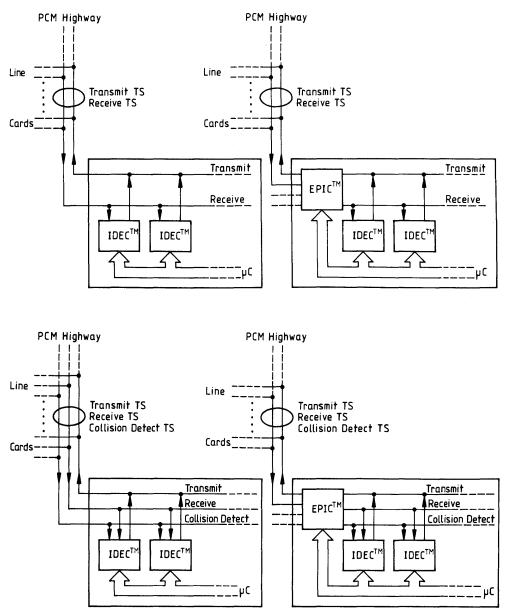

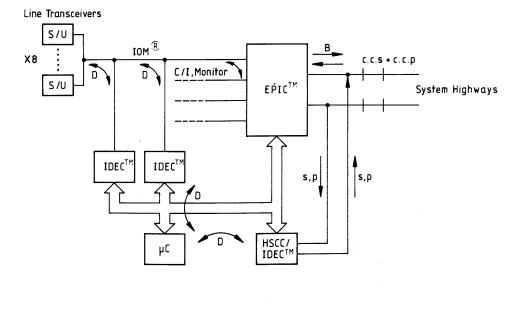

| 'S         | PEB 2075-N | Q67100-H8683  | ISDN D-Channel Exchange Controller (IDEC)    | 316  |

| V          | PEB 2075-P | Q67100-H8682  | ISDN D-Channel Exchange Controller (IDEC)    | 316  |

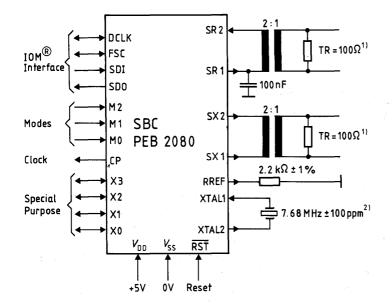

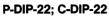

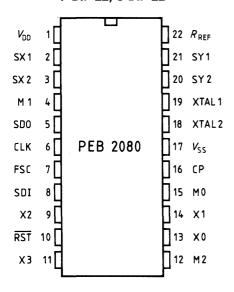

|            | PEB 2080-C | Q67100-H8329  | S-Bus Interface Circuit (SBC)                | 339  |

| S          | PEB 2080-N | Q67100-H8395  | S-Bus Interface Circuit (SBC)                | 339  |

|            | PEB 2080-P | Q67100-H2954  | S-us Interface Circuit (SBC)                 | 339  |

| S          | PEB 2081-N | Q67100-H6093  | S/T Bus Interface Circuit Extended (SBCX)    | 381  |

|            | PEB 2081-P | Q67100-H6091  | S/T Bus Interface Circuit Extended (SBCX)    | 381  |

▼= New Type S=Surface Mounted Device (SMD) SICOFI®, IOM®, ARCOFI®, ISAC™-S, ITAC™, IPAT™, ISAC™-P, EPIC™ are registered trademarks of Siemens AG

| Туре          | Ordering Code | Function                                     | Page |

|---------------|---------------|----------------------------------------------|------|

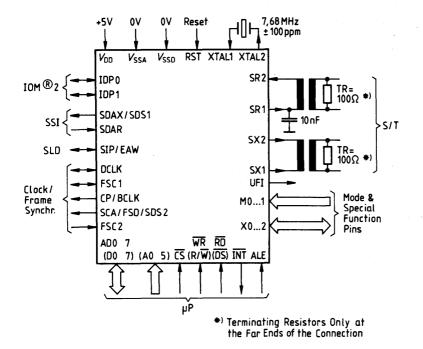

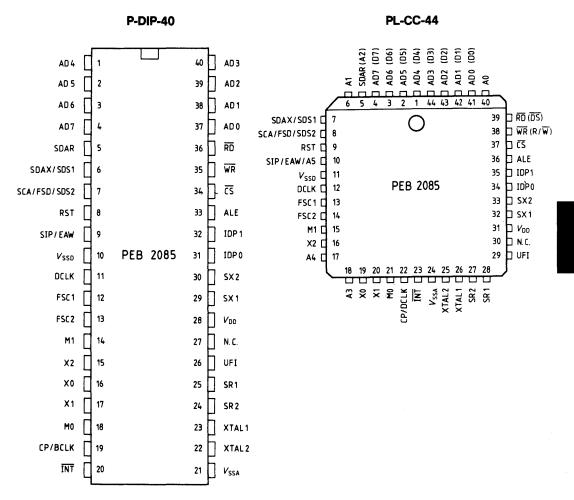

| S PEB 2085-N  | Q67100-H8399  | ISDN Subscriber Access Controller (ISAC™-S)  | 495  |

| PEB 2085-P    | Q67100-H8401  | ISDN Subscriber Access Controller (ISACTM-S) | 495  |

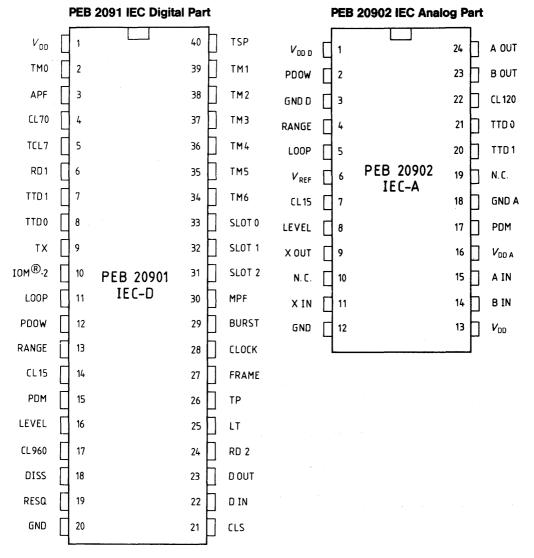

| PEB 20901-C   | Q67100-C8679  | ISDN Echo-Cancellation Circuit (IEC-T)       | 415  |

| S PEB 20901-N | Q67100-H6113  | ISDN Echo-Cancellation Circuit (IEC-T)       | 415  |

| ▼ PEB 20901-P | Q67100-H8678  | ISDN Echo-Cancellation Circuit (IEC-T)       | 415  |

| PEB 20902-C   | Q67100-H8680  | ISDN Echo-Cancellation Circuit (IEC-T)       | 415  |

| S PEB 20902-N | Q67100-H6114  | ISDN Echo-Cancellation Circuit (IEC-T)       | 415  |

| PEB 20902-P   | Q67100-H8681  | ISDN Echo-Cancellation Circuit (IEC-T)       | 415  |

| ▼ PEB 2091-C  | Q67100-H6063  | ISDN Echo-Cancellation Circuit (IEC-Q)       | 442  |

| S PEB 2091-N  | Q67100-H6119  | ISDN Echo-Cancellation Circuit (IEC-Q)       | 442  |

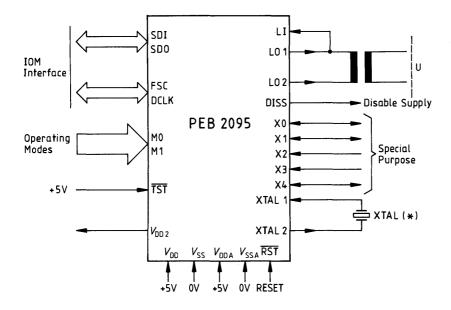

| PEB 2095-C    | Q67100-H8398  | ISDN Burst Transceiver Circuit (IBC)         | 459  |

| S PEB 2095-N  | Q67100-H8396  | ISDN Burst Transceiver Circuit (IBC)         | 459  |

| PEB 2095-P    | Q67100-H8397  | ISDN Burst Transceiver Circuit (IBC)         | 459  |

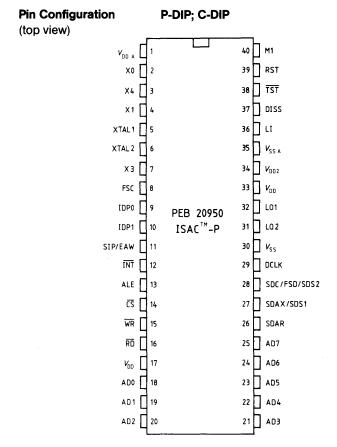

| ▼ PEB 20950-C | Q67100-H8613  | ISDN Subscriber Access Controller (ISAC™-P)  | 485  |

| S PEB 20950-N | Q67100-H8614  | ISDN Subscriber Access Controller (ISAC™-P)  | 485  |

| ▼ PEB 20950-P | Q67100-H8550  | ISDN Subscriber Access Controller (ISAC™-P)  | 485  |

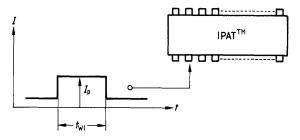

| PEB 2235-C    | Q67100-H8604  | ISDN Primary Access Transceiver (IPAT™)      | 70   |

| S PEB 2235-N  | Q67100-H8685  | ISDN Primary Access Transceiver (IPAT™)      | 70   |

| PEB 2235-P    | Q67100-H8603  | ISDN Primary Access Transceiver (IPAT™)      | 70   |

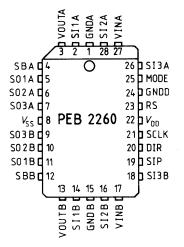

| S PEB 2260-N  | Q67100-H6067  | Dual Channel Codec Filter (SICOFI®-2)        | 198  |

| ▼ PEF 2045-C  | Q67100-H6054  | Memory Time Switch CMOS (MTSC)               | 90   |

| S PEF 2045-N  | Q67100-H6055  | Memory Time Switch CMOS (MTSC)               | 90   |

| ▼ PEF 2045-P  | Q67100-H6056  | Memory Time Switch CMOS (MTSC)               | 90   |

| ▼ PEF 2046-C  | Q67100-H6106  | Memory Time Switch (MTSS)                    | 119  |

| S PEF 2046-N  | Q67000-H6107  | Memory Time Switch (MTSS)                    | 119  |

| ▼ PEF 2046-P  | Q67100-H6108  | Memory Time Switch (MTSS)                    | 119  |

| S PSB 2110-N  | Q67100-H8644  | ISDN Terminal Adapter Circuit (ITAC™)        | 594  |

| PSB 2110-P    | Q67100-H8643  | ISDN Terminal Adapter Circuit (ITAC™)        | 594  |

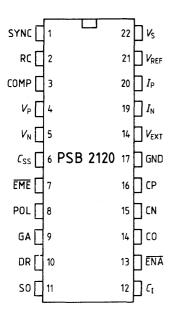

| PSB 2120-P    | Q67100-H8645  | ISDN Remote Power Controller (IRPC)          | 596  |

| PSB 2121-P    | Q67100-H8646  | General Purpose Power Controller (GPPC)      | 613  |

| ▼ PSB 2121-T  | Q67100-H6032  | General Purpose Power Controller (GPPC)      | 613  |

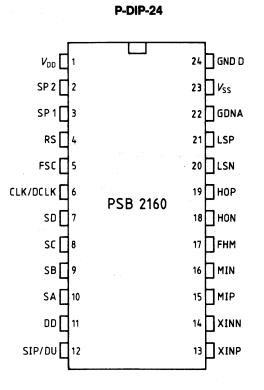

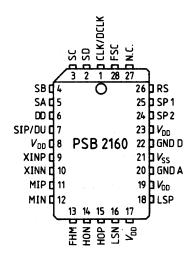

| S PSB 2160-N  | Q67100-H6031  | Audio Ringing Codec Filter (ARCOFI®)         | 557  |

| PSB 2160-P    | Q67100-H8503  | Audio Ringing Codec Filter (ARCOFI®)         | 557  |

| SAB 82520-C   | Q67100-H8830  | High-Level Serial Communications             |      |

|               |               | Controller (HSCC)                            | 658  |

| S SAB 82520-N | Q67100-H8400  | High-Level Serial Communications             |      |

|               |               | Controller (HSCC)                            | 658  |

| SAB 82520-P   | Q67100-H8014  | High-Level Serial Communications             |      |

|               |               | Controller (HSCC)                            | 658  |

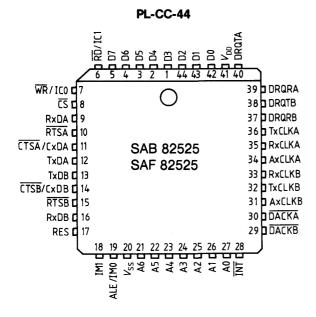

| S SAB 82525-N | Q67100-H8590  | High-Level Serial Communications             |      |

|               |               | Controller Extended (HSCX)                   | 672  |

| Туре           | Ordering Code | Function                                                       | Page |

|----------------|---------------|----------------------------------------------------------------|------|

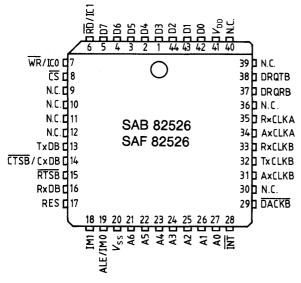

| S SAB 82526-N  | Q67100-H6111  | High-Level Serial Communications<br>Controller Extended (HSCX) | 672  |

| SAF 82520-C    | Q67100-H8325  | High-Level Serial Communications Controller (HSCC)             | 658  |

| S SAF 82520-N  | Q67100-H8610  | High-Level Serial Communications<br>Controller (HSCC)          | 658  |

| SAF 82520-P    | Q67100-H8512  | High-Level Serial Communications<br>Controller (HSCC)          | 658  |

| S SAF 82525-N  | Q67100-H6057  | High-Level Serial Communications<br>Controller (HSCC)          |      |

| 'S SAF 82526-N | Q67100-H6129  | High-Level Serial Communications<br>Controller (HSCC)          |      |

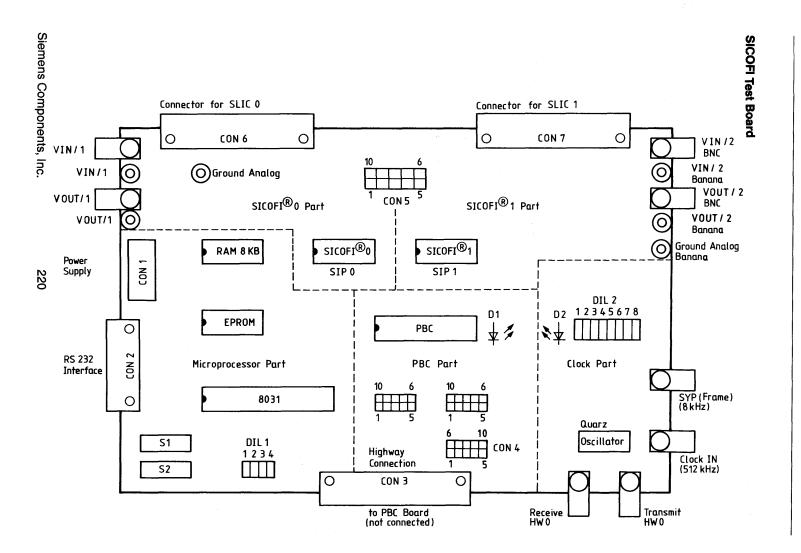

| STU 2050       | Q67100-Z166   | PBC User Board                                                 | 214  |

| STU 2060       | Q67100-H3238  | SICOFI® User Board                                             | 217  |

| STUT 2060      | Q67100-H6058  | SICOFI® Test Board                                             | 219  |

# **1.2 Types in Application-Oriented Order**

#### ICs for Digital Exchange System

| PEB 2035-C        | Advanced CMOS Frame Aligner (ACFA)                       | . 44                                                                                                             |

|-------------------|----------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|

| S PEB 2035-N      | Advanced CMOS Frame Aligner (ACFA)                       | . 44                                                                                                             |

| PEB 2035-P        | Advanced CMOS Frame Aligner (ACFA)                       | . 44                                                                                                             |

| PEB 2235-C        | ISDN Primary Access Transceiver (IPAT™)                  | . 70                                                                                                             |

| S PEB 2235-N      | ISDN Primary Access Transceiver (IPAT™)                  | . 70                                                                                                             |

| PEB 2235-P        | ISDN Primary Access Transceiver (IPAT™)                  | . 70                                                                                                             |

| PEB 2045-C        | Memory Time Switch CMOS (MTSC)                           | . 90                                                                                                             |

| S PEB 2045-N      | Memory Time Switch CMOS (MTSC)                           | . 90                                                                                                             |

| PEB 2045-P        | Memory Time Switch CMOS (MTSC)                           | . 90                                                                                                             |

| ▼ PEF 2045-C      | Memory Time Switch CMOS (MTSC)                           | . 90                                                                                                             |

| ▼S PEF 2045-N     | Memory Time Switch CMOS (MTSC)                           | . 90                                                                                                             |

| ▼ PEF 2045-P      | Memory Time Switch CMOS (MTSC)                           | . 90                                                                                                             |

| ▼ PEB 2046-C      | Memory Time Switch Small (MTSS)                          | . 119                                                                                                            |

| ▼S PEB 2046-N     | Memory Time Switch Small (MTSS)                          | . 119                                                                                                            |

| ▼ PEB 2046-P      | Memory Time Switch Small (MTSS)                          | . 119                                                                                                            |

| ▼ PEF 2046-C      | Memory Time Switch Small (MTSS)                          | . 119                                                                                                            |

| ▼S PEF 2046-N     | Memory Time Switch Small (MTSS)                          | . 119                                                                                                            |

| ▼ PEF 2046-P      | Memory Time Switch Small (MTSS)                          | . 119                                                                                                            |

| PEB 2050-C        | Peripheral Board Controller (PBC)                        | . 136                                                                                                            |

| S PEB 2050-N      | Peripheral Board Controller (PBC)                        |                                                                                                                  |

| PEB 2050-P        | Peripheral Board Controller (PBC)                        | . 136                                                                                                            |

| ▼ PEB 2052-C      | PCM Interface Controller (PIC)                           | . 154                                                                                                            |

| ▼S PEB 2052-N     | PCM Interface Controller (PIC)                           | . 154                                                                                                            |

| ▼ PEB 2052-P      | PCM Interface Controller (PIC)                           | . 154                                                                                                            |

| S PEB 2060-N      | Signal Processing Codec Filter (SICOFI®)                 |                                                                                                                  |

| PEB 2060-P        | Signal Processing Codec Filter (SICOFI®)                 | . 167                                                                                                            |

| ▼S PEB 2260-N     | Dual Channel Codec Filter (SICOFI®)                      | . 198                                                                                                            |

| STU 2050          | PBC User Board                                           | . 214                                                                                                            |

| STU 2060          | SICOFI® User Board                                       | . 217                                                                                                            |

| STUT 2060         | SICOFI® Test Board                                       | . 219                                                                                                            |

| ICs for ISDN Exch | anga Svetame                                             |                                                                                                                  |

|                   | ange Systems                                             |                                                                                                                  |

| PEB 2025-P        | ISDN Exchange Power Controller (IEPC)                    |                                                                                                                  |

| PEB 2055-C        | Extended PCM Interface Controller (EPIC™-1)              | CT-111121 GERE PROF PM 1 GERESSEE                                                                                |

| ▼S PEB 2055-N     | Extended PCM Interface Controller (EPICTM-1)             | <                                                                                                                |

| ▼ PEB 2055-P      | Extended PCM Interface Controller (EPIC™-1)              |                                                                                                                  |

| ▼ PEB 2056-C      | Extended PCM Interface Controller (EPIC <sup>™</sup> -2) | . 274                                                                                                            |

|                   |                                                          | and the second |

Extended PCM Interface Controller (EPICTM-2) ..... 274 ▼S PEB 2056-N **PEB 2056-P** Extended PCM Interface Controller (EPIC™-2) .....

Siemens Components, Inc.

Page

274

## ICs for ISDN Exchange System (cont'd)

| . 276<br>. 276<br>. 276<br>. 316<br>. 316<br>. 339 |

|----------------------------------------------------|

| . 276<br>. <b>316</b><br>. 316                     |

| . <b>316</b><br>. 316                              |

|                                                    |

|                                                    |

| . 339                                              |

| . 339                                              |

| . 339                                              |

| . 381                                              |

| . 381                                              |

| . 415                                              |

| . 415                                              |

| . 415                                              |

| . 415                                              |

| . 415                                              |

| . 415                                              |

| . 442                                              |

| . 442                                              |

| . 459                                              |

| . 459                                              |

| . 459                                              |

| . 485                                              |

| . 485                                              |

|                                                    |

|                                                    |

Page

#### ICs for ISDN Terminals

| S  | PEB 2085-N | ISDN Subscriber Access Controller (ISAC™-S) | 495 |

|----|------------|---------------------------------------------|-----|

|    | PEB 2085-P | ISDN Subscriber Access Controller (ISAC™-S) | 495 |

| S  | PSB 2160-N | Audio Ringing Codec Filter (ARCOFI®)        | 557 |

|    | PSB 2160-P | Audio Ringing Codec Filter (ARCOFI®)        | 557 |

| S  | PSB 2110-N | ISDN Terminal Adapter Circuit (ITAC™)       | 594 |

|    | PSB 2110-P | ISDN Terminal Adapter Circuit (ITAC™)       | 594 |

|    | PSB 2120-P | ISDN Remote Power Controller (IRPC)         | 596 |

|    | PSB 2121-P | General Purpose Power Controller (GPPC)     | 613 |

| ▼S | PSB 2121-T | General Purpose Power Controller (GPPC)     | 613 |

| Advance Information |                                       |     |

|---------------------|---------------------------------------|-----|

| PSB 79C30E          | Digital Subscriber Controller (DSC/E) | 592 |

|                     |                                       |     |

| Support Tools       |                                       |     |

| SIPB 5000           | ISDN PC Development System            | 625 |

|          | ICs for Data C | Communication                                               | Page |

|----------|----------------|-------------------------------------------------------------|------|

|          | SAB 82520-C    | High-Level Serial Communications Controller (HSCC)          | 658  |

|          | SAB 82520-N    | High-Level Serial Communications Controller (HSCC)          | 658  |

|          | SAB 82520-P    | High-Level Serial Communications Controller (HSCC)          | 658  |

| V        | SAF 82520-C    | High-Level Serial Communications Controller (HSCC)          | 658  |

| V        | SAF 82520-N    | High-Level Serial Communications Controller (HSCC)          | 658  |

| V        | SAF 82520-P    | High-Level Serial Communications Controller (HSCC)          | 658  |

| V        | SAB 82525-N    | High-Level Serial Communications Controller Extended (HSCX) | 672  |

| V        | SAB 82526-N    | High-Level Serial Communications Controller Extended (HSCX) | 672  |

| V        | SAF 82525-N    | High-Level Serial Communications Controller Extended (HSCX) | 672  |

| <b>V</b> | SAF 82526-N    | High-Level Serial Communications Controller Extended (HSCX) | 672  |

# Advance Information

| SAB 79C401 | Integrated Data Protocol Controller (IDPC) | 724 |

|------------|--------------------------------------------|-----|

|            |                                            |     |

# **General Information**

#### 1. Type-Designation Code for ICs

IC type designations are based on the European Pro Electron system. The code system is explained in the Pro Electron brochure D 15\*), edition 1988.

\*) Available from Pro Electron, Avenue Louise, 430 (B.12) B-1050 Brussels, Belgium.

#### 2. Mounting Instructions

#### **Plastic and Ceramic Packages**

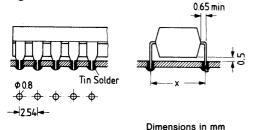

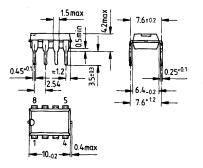

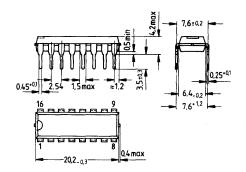

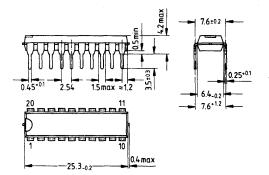

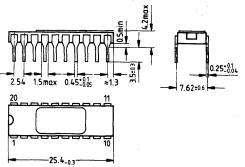

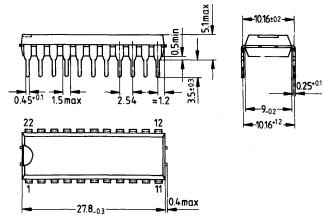

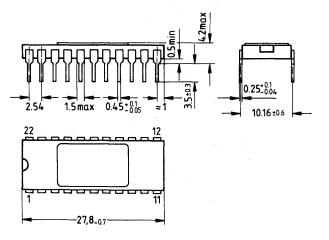

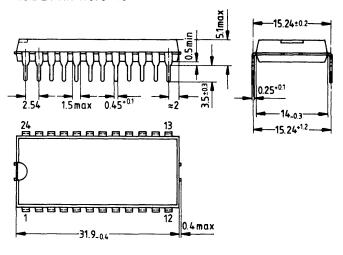

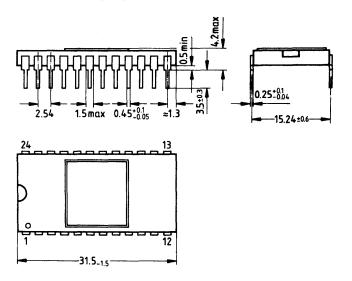

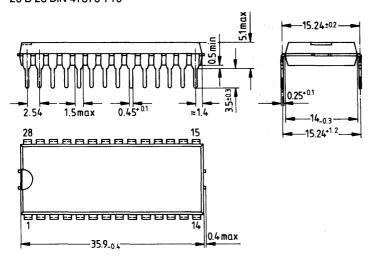

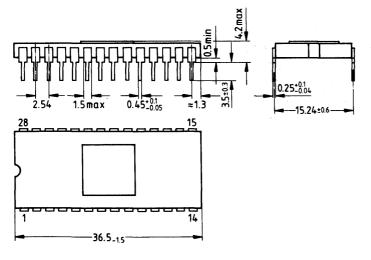

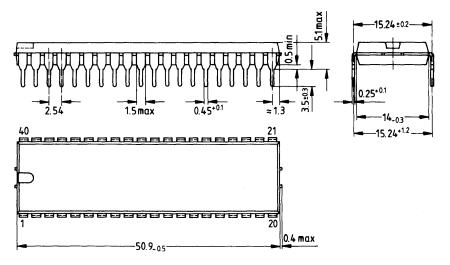

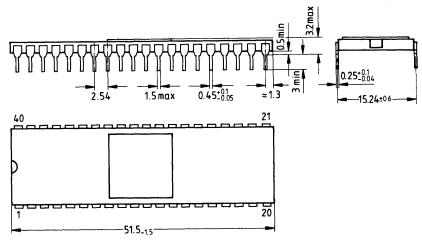

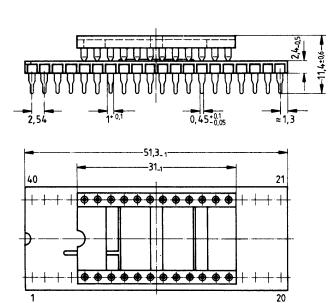

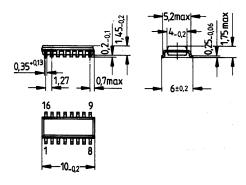

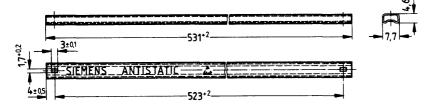

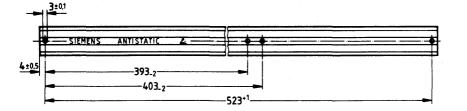

The pins of the cases are bent downwards by an angle of  $90^{\circ}$  and fit into holes with a diameter of between 0.7 and 0.9 mm spaced 2.54 mm apart. The dimension x is given in the corresponding drawing.

The bottom of the package will not touch the PC board after insertion because the pins have shoulders just below the package (see figure 1).

After insertion of the package into the PC board it is advisable to bend the ends of two pins at an angle of approx. 30° to the board so that the package does not have to be pressed down during soldering. The packages are soldered on that side of the PCB facing away from the package.

The maximum permissible soldering temperature is 350 °C (max. 3 s) for manual soldering and 260 °C (max. 10 s) for dip soldering and wave soldering.

#### Figure 1

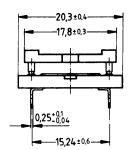

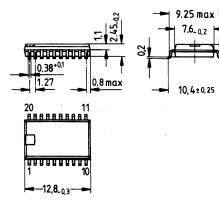

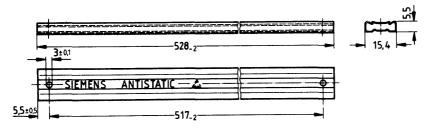

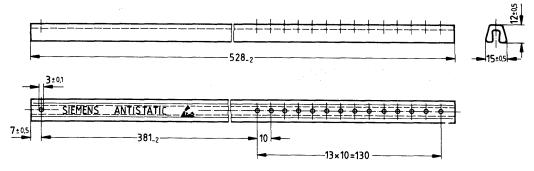

# Plastic Packages (P-DSO and PL-CC) for Surface Mounting (SMD)

| Iron soldering:        | soldering temperature 350 °C for max. 3 s;<br>minimum distance between package and soldering point 1.5 mm<br>package temperature max. 150 °C; no mechanical stress on<br>the pins |

|------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Vapor phase soldering: | soldering temperature 215 °C, max. soldering time 40 s, 2 x.                                                                                                                      |

| Wave soldering:        | soldering temperature 260 °C, max. soldering time 8 s.<br>(pins and package are dipped into the tin bath)                                                                         |

#### Storage, Pretreatment for Processing of ICs in PL-CC Packages

The components are to be stored in a dry place. For soldering methods which may lead to a thermal shock stress (e.g. vapor phase soldering) it is recommended to dry the ICs in PL-CC package at 125 °C for a period of 24 hours.

#### Other Points to Note

Ensure that no current is able to flow between the solder bath or soldering iron and the PCB. It is advisable to ground the pins that are to be soldered as well as the solder bath or soldering iron.

When they are being prepared and inserted in a PCB, circuits should be protected against static charging. Under no circumstances may the components be removed or inserted whilst the operating voltage is switched on.

The increase in chip temperature during the soldering process results in a temporary increase in electrostatic sensitivity of integrated circuits. Special precautions should therefore be taken against line transients, e.g. through the switching of inductances on magnetic chutes, etc.

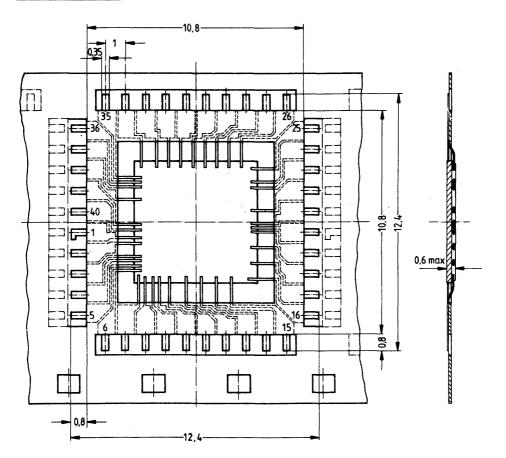

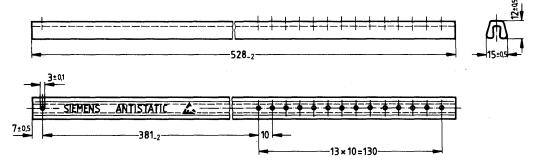

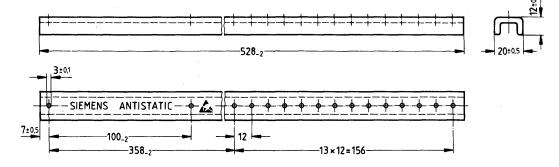

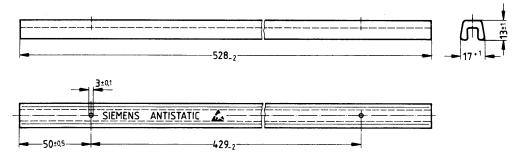

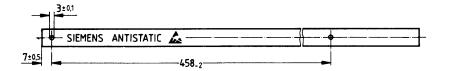

#### MIKROPACK (SMD)

MIKROPACK components are delivered on film reels.

#### **Mounting Suggestions**

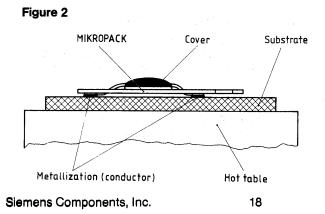

- a) We recommend vapor phase soldering: soldering temperature 215 °C, soldering time max. 40 s.

- b) For prototypes and small quantities (up to approximately 50.0 items/y), the hot table soldering method can also be used (figure 2).

#### **Required Equipment and Accessories**

- cutting device

- hot table, temperature regulated (e.g. Weld-Equip, Unitek)

- stereo microscope (e.g. Wild, Zeiss, magnification 6...40 times)

- substrate material: epoxy resin; hard paper; ceramic (thick thin film)

#### **Soldering Data**

- soldering temperature: 210 °C max.

- solder coating on substrate: Pb/Sn (e.g. 60/40) wave-tinned or electrodeposited

- soldering time: approx. 10 s

- flux: e.g. colophony, dissolved in alcohol

- cleaning agents (as required): e.g. Freon TP-35, TE, TF

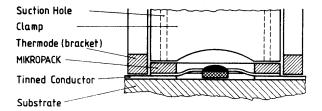

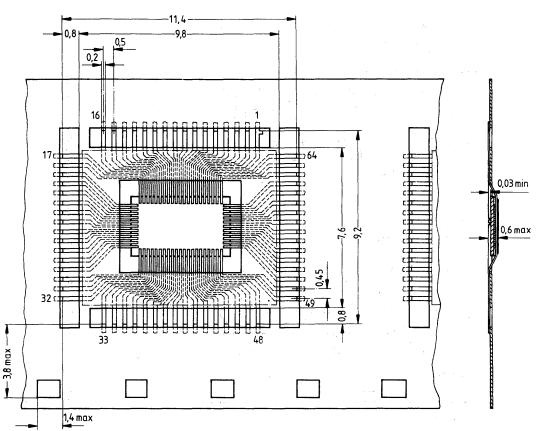

- c) For large quantities (e.g. more than 50.0 items/y) thermode soldering is also suitable (figure 3).

#### Figure 3

#### **Required Equipment**

- soldering equipment (e.g. Weld-Equip, Farco, Jade)

- substrate material: epoxy resin; hard paper; flexible materials, e.g. polyamide

#### **Soldering Data**

- soldering temperature: 220 °C max.

- solder coating on the substrate: Pb/Sn (e.g. 60/40), wave-tinned or electrodeposited

- soldering time: approx. 10 s

- flux: e.g. colophony dissolved in alcohol

- cleaning agents (as required); e.g. Freon TP-35, TE, TF

#### 3. Processing Guidelines for ICs

Integrated circuits (ICs) are electrostatic-sensitive (ESS) devices. The demand for greater packing density has led to smaller structures on semiconductor chips, with the result that today every IC, whether bipolar, MOS, or CMOS, has to be protected against electrostatics.

MOS and CMOS devices generally have integrated protective circuits and it is virtually impossible for them to be destroyed by purely static electricity. On the other hand, there is acute danger from electrostatic discharges (ESD).

Of the multitude of possible sources of discharge, charged devices should be mentioned in addition to charged persons. Low-resistive discharges can produce peak powers amounting to kilowatts.

For the protection of devices the following principles should be observed:

- a) Reduction of charging voltage, below 200 V if possible.

Means which are effective here are an increase in relative humidity to ≥60% and the replacement of highly charging plastics by antistatic materials.

- b) With every kind of contact with the device pins a charge equalization is to be expected. This should always be highly resistive (ideally  $R = 10^6$  to  $10^9 \Omega$ ).

All in all this means that ICs call for special handling, because uncontrolled charges, voltages from ungrounded equipment or persons, surge voltage spikes and similar influences can destroy a device. Even if devices have protective circuits (e.g. protective diodes) on their inputs, the following guidelines for their handling should nevertheless be observed.

#### Identification

The packing of ESS devices is provided with the following label by the manufacturer:

#### Scope

The guidelines apply to the storage, transport, testing, and processing of all kinds of ICs, equipped and soldered circuit boards that comprise such components.

#### Handling of Devices

1. ICs must be left in their containers until they are processed.

- 2. ICs may only be handled at specially equipped work stations. These stations must have work surfaces covered with a conductive material of the order of  $10^6$  to  $10^9 \Omega$ /cm.

- 3. With humidity of > 50% a coat of pure cotton is sufficient. In the case of chargeable synthetic fibers the clothing should be worn close-fitting. The wrist strap must be worn snugly on the skin and be grounded across a resistor of 50 to 100 k $\Omega$ .

- 4. If conductive floors,  $R = 5 \times 10^4$  to  $10^7 \Omega$  are provided, further protection can be achieved by using so-called MOS chairs and shoes with a conductive sole  $(R \approx 10^5 \text{ to } 10^7 \Omega)$ .

- 5. All transport containers for ESS devices and assembled circuits boards must first be brought to the same potential by being placed on the work surface or touched by the operator before the individual devices may be handled. The potential equalization should be across a resistor of  $10^6$  to  $10^8 \Omega$ .

- 6. When loading machines and production devices it should be noted that the devices come out of the transport magazine charged and can be damaged if they touch metal, e.g. machine parts.

Example 1) conductive (black) tubes.

The devices may be destroyes in the tube by charged persons or come out of the tube charged if this is emptied by a charged person.

Conductive tubes may only be handled at ESS work stations (high-resistance work-station and person grounding).

Example 2) anti-static (transparent) tubes.

The devices cannot be destroyed in the tube by charged persons (there may be a rare exception in the case of custom ICs with unprotected gate pins). The devices can be engangered as in 1) when the tube is emptied if the latter, especially at low humidity, is no longer sufficiently anti-static after a long period of storage (> 1 year).

In both cases damage can be avoided by discharging the devices across a grounded adapter of high-resistance material ( $\approx 10^6$  to  $10^8 \Omega$ /cm) between the tube and the machine.

The use of metal tubes – especially of anodized aluminium – is not advisable because of the danger of low-resistance device discharge.

#### Storage

ESS devices should only be stored in identified locations provided for the purpose. During storage the devices should remain in the packing in which they are supplied. The storage temperature should not exceed  $60 \,^{\circ}$ C.

#### Transport

ESS devices in approved packing tubes should only be transported in suitable containers of conductive or longterm anti-static-treated plastic or possibly unvarnished wood. Containers of both high-charging plastic or very low-resistance materials are unsuitable.

Transfer cars and their rollers should exhibit adequate electrical conductivity ( $R < 10^6 \Omega$ ). Sliding contacts and grounding chains will not reliably eliminate charges.

#### Incoming Inspection

In incoming inspection the above guidelines should be observed. Otherwise any right to refund or replacement if devices fail inspection may be lost.

#### Material and Mounting

1. The drive belts of machines used for the processing of the devices, in as much as they come into contact with them (e.g. bending and cutting machines, conveyor belts), should be treated with anti-static spray (e.g. anti-static spray 100 from Kontakt-chemie). It is better, however, to avoid the contact completely.

- 2. If ESS devices have to be soldered or desoldered manually, soldering irons with thyristor control may not be used. Siemens EMI-suppression capacitors of the type B 81711-B31...-B36 have proven very effective against line transients.

- 3. Circuit boards fitted and soldered with ESS devices are always to be considered as endangered.

#### **Electrical Tests and Application Circuit**

- 1. The devices should be processed with observation of these guidelines. Before assembled and soldered circuit boards are tested, remove any shorting rings.

- 2. The sockets or integrated circuits must not be conducting any voltage when individual devices or assembled circuit boards are inserted or withdrawn, unless works' specifications state otherwise. Ensure that the test devices and power supplies do not produce any voltage spikes, either when being turned on and off in normal operation or if the power fuse blows or other fuses respond.

- 3. When supplying bipolar integrated circuits with current, the negative voltage  $(-V_s \text{ or GND})$  has first to be connected. In general, an interruption of this potential during operation is not permissible.

- 4. Signal voltages may only be applied to the inputs of ICs when or better after the supply voltage is turned on. They must be disconnected when or better before the supply voltage is turned off.

- Power supplied of integrated circuits are to be blocked as near as possible at the supply terminals of the IC. With bipolar ICs it is recommended to use a low-inductance electrolytic capacitor or at least a paralleled cermaic capacitor of 100 nF to 470 nF for example.

Using ICs with high output currents, the necessary value of the electrolytic capacitor must be adapted to the test or application circuit. Transient behavior and dynamic output resistance of the power supplied, line inductances in the supply and load circuit and in particular inductive loads or motors have to be considered. When switching off line inductances of inductive loads, the stored power has to be consumed externally, unless otherwise specified (e.g. by an electrolytic capacitor, diodes, Z diodes or the power supply). Also a switching off the supply voltage prior to the load rejection should be taken into account.

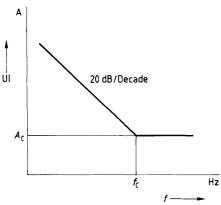

- 6. ICs with low-pass character of the output stages (e.g. PNP drivers or PNP/NPN end stages), normally need an additional external compensation at the output. This applies particularly to complex loads. The output of AF power amplifiers is compensated by the Boucherot element. In individual cases, bridge circuits only need a capacitance for bypassing the load. Depending on the application it is, however, also recommended to connect one capacitor from each output to ground.

- 7. Observe any notes and instructions in the respective data books.

#### Packing of Assembled PC Boards or Flatpack Units

The packing material should exhibit low volume conductivity:  $10^5 \ \Omega/cm < \rho < 10^{10} \ \Omega/cm$ .

In most cases – especially with humidity of > 40% – this requirement is fulfilled by simple corrugated board. Better protection is obtained with bags of conductive poly-ethylene foam (e.g. RCAS 1200 from Richmond of Redlands, California).

One should always ensure that boards cannot touch.

In special cases it may be necessary to provide protection against strong electric fields, such as can be generated by conveyor belts for example. For this purpose a sheath of aluminium foil is recommended, although direct contact between the film and the PCB must be avoided. Cardboard boxes with an aluminium-foil lining, such as those used for shipping our devices, are available from Laber of Munich.

#### Ultrasonic Cleaning of ICs

The following recommendation applies to plastic packages. For cavity packages (metal and also ceramic) separate regulations have to be observed.

Freon and isopropyl alcohol (trade name: propanol) can be used as solvents. These solvents can also be used for plastic packages because they do not eat into the plastic material.

An ultrasonic bath in double halfwave operation is advisable because of the low component stress.

The ultrasonic limits are as follows:

| sound frequency            | f | > 40 kHz                       |

|----------------------------|---|--------------------------------|

| exposure                   | t | < 2 min                        |

| alternating sound pressure | р | < 29 kPa                       |

| sound power                | Ν | < 0.5 W/cm <sup>2</sup> /liter |

#### 4. Data Classification

#### **Maximum Ratings**

Maximum ratings are absolute ratings; exceeding any one of these values may cause irreversible damage to the integrated circuit.

#### Characteristics

The listed characteristics are ensured over the operating range of the integrated circuit. Typical charateristics specify mean values expected over the production spread. If not otherwise specified, typical characteristics apply at  $T_A = 25$  °C and the given supply voltage.

#### **Operating Range**

In the operating range the functions given in the circuit description are fulfilled.

#### 5. Quality Assurance

The high quality and reliability of integrated circuits from Siemens are the results of carefully managed design and production which is systematically checked and controlled at each stage.

The procedures are subject to a quality assurance system; full details are given in the brochure "Quality Assurance – Integrated Circuits".

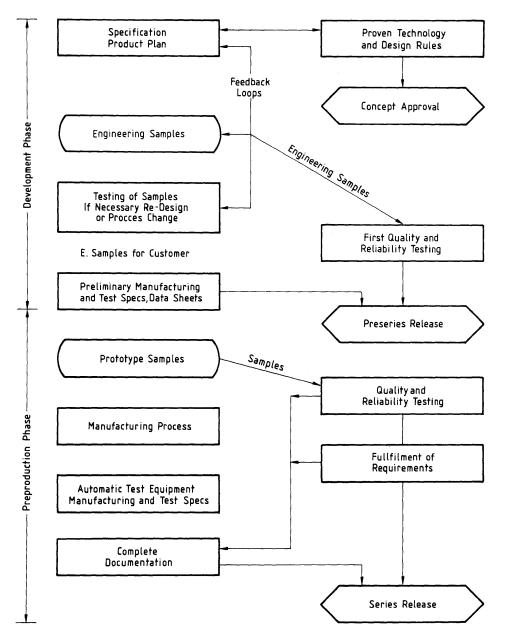

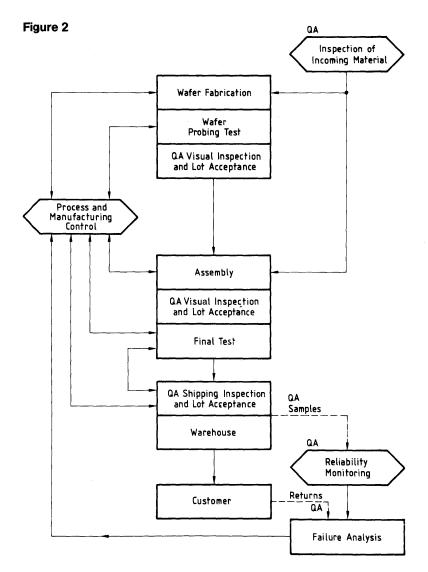

**Figure 1 and 2** show the most important stages of QA system. Quality assurance (QA) department independent of production and development are responsible for the selected measures, acceptance procedures and information feedback loops. Operating QA departments have stat-of-the-art test and measuring equipment at is disposal, work according to approved methods of statistical quality control, and provided with facilities for accelerate life and are environmental tests used for both qualification and routine monitoring tests.

The latest methods and equipment for preparation and analysis are employed to achieve continuity of quality and reliability.

#### Conformance

Each integrated circuit is subjected to a final test at the end of the production process. These are carried out by computer-controlled, automatic test systems because hundreds of thousands of operating conditions as well as a large number of static and dynamic parameters have to be considered. Moreover, the test systems are extremely reliable and reproducible. The quality assurance department carries out a final check in the form of a lot-by-lot sampling inspection to additionally ensure this minimum percent defectives as well as the acceptable quality level (AQL). Sampling inspection is performed in accordance with the inspection plans of DIN 40080, as well as of the identical MIL-STD-105 or IEC 410.

# **General Information**

Figure 1

# **General Information**

#### Reliability

#### Measures Taken during Development

The reliability of ICs is already considerably influenced at the development stage. Siemens has, therefore, fixed certain design standards for the development of circuit and layout, e.g. specifying minimum width and spacing of conductive layers on a chip, dimensions and electrical parameters of protective circuits for electrostatic charge, etc. An examination with the aid of carefully arranged programs operated on large-scale computers, guarantees the immediate identification and elimination of unintentional violations of these designs standards.

#### In-Process Control during Production

The manufacturing of integrated circuits comprises several hundred production steps. As each step is to be executed with utmost accuracy, the in-process control is of outstanding importance. Some processes require more than a hundred different test measures. The tests have been arranged such that the individual process steps can be reproduced continuously.

The decreasing failure rates reflect the never ending effort in this direction; in the course of the years they have been reduced considerably despite an immense rise in IC complexity.

#### **Reliability Monitoring**

The general course of the IC failure rate versus time is shown by a so-called "bathtub" curve. The failure rate has its peak during the first few operating hours (early failure period). After the early failure period has decayed, the "constant" failure rate period starts during which the failures may occur at an approximately uniform rate. This period ends with a repeated rise of the curve during the wear-out failure period. For ICs, however, the latter period usually lies far beyond the service life specified for the individual equipment.

Reliability tests for ICs are usually desctructive examinations. They are, therefore, carried out with samples. Most failure mechanisms can be accelerated by means of higher temperatures. Due to the temperature dependence of the failure mechanisms, it is possible to simultane future operational behavior within a short time by applying high temperatures; this is called life test.

The acceleration factor *B* for the life test can be obtained from the Arrhenius equation

$$B = \exp \left(\frac{E_A}{k} \left(\frac{1}{T_1} - \frac{1}{T_2}\right)\right)$$

where  $T_2$  is the temperature at which the life test is performed,  $T_1$  is the assumed operating temperature, and k is the Boltzmann constant.

Important for factor *B* is the activation energy  $E_A$ . It lies between 0.3 and 1.3 eV and differs considerably for the individual failure mechanisms.

For all Siemens ICs, the reliability data from life tests is converted to an operating temperature of  $T_A = 40$  °C, assuming an average activation energy of 0.4 eV. The acceleration factor for life tests at 125 °C is thus 24, compared with operational behavior. This method considers also failure mechanisms with low activation energy, i.e. which are only slightly accelerated by the temperature effect.

Various reliability tests are periodically performed with IC types that are representative of a certain production line – this is described in the brochure "Quality Assurance-Integrated Circuits". Such tests are e.g. humidity test at 85°C and 85% relative humidity, pressure cooker test, as well as life tests up to 1000 hours and more. Test results are available in the form of summary reports.

# 6. Summary of the Most Important Symbols

|                         | e meet impertant eymbole             |

|-------------------------|--------------------------------------|

| b i                     | Pulse duration                       |

| В                       | Current gain                         |

| B                       | Bandwidth                            |

| BI                      | Input of output amplifier            |

| BO                      | Output of output amplifier           |

| С                       | Capacitance                          |

| C <sub>I</sub>          | Input capacitance                    |

| CICLK                   | Input capacitance of the clock input |

| CL                      | Load capacitance                     |

| D                       | Data input                           |

| DO                      | Data output                          |

| E                       | Enable                               |

| F,                      | Input load factor                    |

| , Fo                    | Output load factor                   |

| F <sub>OH</sub>         | Output load factor, H signal         |

| F <sub>OL</sub>         | Output load factor, L signal         |

| f,                      | Input frequency                      |

| $f_{\rm CL}, f_{\Phi}$  | Clock frequency                      |

| f                       | Maximum counter frequency            |

| I <sub>DD</sub>         | Drain supply current                 |

| I,                      | Input current                        |

| I <sub>H</sub>          | H-input current                      |

|                         | L-input current                      |

| I                       | Input                                |

| I1                      | Input 1                              |

| 12                      | Input 2                              |

| Ι                       | Input bias current                   |

| I <sub>oo</sub>         | Output offset current                |

| I <sub>o</sub>          | Short-circuit output current         |

| I <sub>OH</sub>         | H-output current                     |

| I <sub>OL</sub>         | L-output current                     |

| I <sub>SH</sub>         | H-supply current                     |

| I <sub>SL</sub>         | L-supply current                     |

| MO                      | Mixer output                         |

| 0 <sub>s</sub> , GND    | Ground, earth                        |

| P <sub>tot</sub>        | Total power consumption              |

| Po                      | Output power                         |

| CLK                     | Clock                                |

| 0                       | Output                               |

| $\overline{\mathbf{O}}$ | Output, inverted                     |

| ~                       |                                      |

| $R_{G}$ Generator resistance $R_{I}$ Input resistance $R_{CL}$ Collector load resistance $R_{L}$ Load resistance $R_{L}$ Load resistance $R_{P}$ Adjustmente resistance $R_{thJA}$ Therminal resistance (Junction to ambient) $R_{OH}$ H-output resistance $R_{OL}$ L-output resistance at output $T_A$ Ambient temperature $T_{case}$ Case temperature $T_{case}$ Case temperature $T_{case}$ Case temperature $T_{case}$ Delay time of the HL transition of the output signal $t_{DHLO}$ Delay time of the LH transition of the output signal $t_{DLH}$ Delay time of the LH transition of the output signal $t_{DLH}$ Delay time time $t_{H}$ Hold time $t_{I}$ Input pulse duration $t_{n+1}$ Bit time after clock pulse $t_{P}$ Average signal propagation time $t_{SVD}$ Delay time $t_{CLKY}$ Clock period $t_{PR}$ Reset pulse duration $t_{PS}$ Average signal propagation time (set, reset input) $t_{PS}$ Set pulse duration $t_{PS}$ Set pulse duration $t_{RR}$ Reset pulse duration $t_{RR}$ Reset pulse duration $t_{RR}$ Reset pulse duration $t_{RR}$ Key debounce time $t_{SS}$ Set pulse duration $t_{RR}$ Reset pulse duration $t_{RR}$ Reset pulse duration $t_{RR}$ Signal transition time (f                                                                           | R                   | Resistance                                           |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|------------------------------------------------------|

| $\begin{array}{llllllllllllllllllllllllllllllllllll$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | R <sub>G</sub>      | Generator resistance                                 |

| $R_L$ Load resistance $R_P$ Adjustmente resistance $R_{thJA}$ Therminal resistance (Junction to ambient) $R_{OH}$ H-output resistance $R_{OL}$ L-output resistance $R_O$ Load resistance at output $T_A$ Ambient temperature $T_{asse}$ Case temperature $T_{casse}$ Case temperature $T_1$ Junction temperature $T_C$ Temperature coefficient $t_d$ Pulse delay time $t_{DLHO}$ Delay time of the LL transition of the output signal $t_{DLHO}$ Delay time of the LH transition of the output signal $t_{DLHO}$ Delay time of the LH transition of the output signal $t_{DLHO}$ Delay time of the LH transition of the output signal $t_{DLHO}$ Delay time of the LH transition of the output signal $t_{DLH}$ Delay time of the LH transition of the output signal $t_{DLH}$ Delay time of the Clock pulse $t_{n+1}$ Bit time after clock pulse $t_{n+1}$ Bit time after clock pulse $t_{p}$ Average signal propagation time $t_{SVD}$ Delay time $t_{cLKY}$ Clock period $t_{PHLR,S}$ Signal propagation time (set, reset input) $t_{pS}$ Average signal propagation time (set, reset input) $t_{pS}$ Average signal propagation time (set, reset input) $t_{pS}$ Set pulse duration $t_{p}$ Key debounce time $t_{p}$ Key depression period $t_{p}$ Counting pulse duration $t_{p}$ Setup | R                   | Input resistance                                     |

| $R_p$ Adjustmente resistance $R_{thuA}$ Therminal resistance (Junction to ambient) $R_{OH}$ H-output resistance $R_{OL}$ L-output resistance $R_{OL}$ L-output resistance $R_{OL}$ L-output resistance $R_{O}$ Load resistance at output $T_A$ Ambient temperature $T_{atg}$ Storage temperature $T_{case}$ Case temperature $T_{case}$ Case temperature $TC$ Temperature coefficient $t_d$ Pulse delay time $t_{DLHO}$ Delay time of the HL transition of the output signal $t_{DLHO}$ Delay time of the LH transition of the output signal $t_{DLH}$ Delay time of the Clock pulse $t_{n+1}$ Bit time before clock pulse $t_{n+1}$ Bit time before clock pulse $t_{pP}$ Average signal propagation time $t_{SVD}$ Delay time $t_{pR}$ Signal propagation time (from H to L) $t_{PR,S}$ Average signal propagation time (set, reset input) $t_{pS}$ Set pulse duration $t_d$ Key debounce time $t_p$ Key depression period $t_{pC}$ Counting pulse duration $t_{r}$ Recovery time $t_s$ Setup time $t_o$ Output pulse duration $t_{rL}$ Recovery time $t_s$ Setup time $t_{pO}$ Output pulse duration $t_{rL}$ Recovery time $t_{s}$ Setup time $t_{o}$ Output pulse duration $t_{rLH}$ S                                                                                                    | R <sub>CL</sub>     | Collector load resistance                            |

| $R_{tht,JA}$ Therminal resistance (Junction to ambient) $R_{OH}$ H-output resistance $R_{OL}$ L-output resistance $R_{OL}$ L-output resistance $R_{O}$ Load resistance at output $T_A$ Ambient temperature $T_{atg}$ Storage temperature $T_{case}$ Case temperature $T_{case}$ Case temperature $TC$ Temperature coefficient $t_d$ Pulse delay time $t_{DLO}$ Delay time of the HL transition of the output signal $t_{DLHO}$ Delay time of the LH transition of the output signal $t_{DLHO}$ Delay time $t_{H}$ Hold time $t_{H}$ Bit time before clock pulse $t_{n+1}$ Bit time after clock pulse $t_{n+1}$ Bit time after clock pulse $t_{PP}$ Average signal propagation time $t_{SVD}$ Delay time $t_{CLKY}$ Clock period $t_{PHLR,S}$ Signal propagation time (from H to L) $t_{PR,S}$ Average signal propagation time (set, reset input) $t_{PS}$ Set pulse duration $t_{d}$ Key depression period $t_{pC}$ Counting pulse duration $t_{q}$ Recovery time $t_{s}$ Setup time $t_{O}$ Output pulse duration $t_{TLH}$ Signal transition time (from H to L) $t_{PR,S}$ Setup time $t_{O}$ Output pulse duration $t_{T+1}$ Signal transition time (from H to L) $t_{T+1}$ Signal transition time (from H to L) $t_{T+1$                                                                  | $R_{L}$             | Load resistance                                      |

| $R_{OH}$ H-output resistance $R_{OL}$ L-output resistance $R_O$ Load resistance at output $T_A$ Ambient temperature $T_{stg}$ Storage temperature $T_{case}$ Case temperature $T_{case}$ Case temperature $T_{case}$ Case temperature $TC$ Temperature coefficient $t_d$ Pulse delay time $t_{DHL O$ Delay time of the HL transition of the output signal $t_{DLH}$ Delay time of the LH transition of the output signal $t_{DLH}$ Delay time of the LH transition of the output signal $t_{DLH}$ Delay time of the LH transition of the output signal $t_{DLH}$ Delay time $t_{H}$ Hold time $t_1$ Input pulse duration $t_n$ Bit time before clock pulse $t_{n+1}$ Bit time after clock pulse $t_{n+1}$ Bit time after clock pulse $t_{p}$ Average signal propagation time $t_{SVD}$ Delay time $t_{CLKY}$ Clock period $t_{PHLR,S}$ Signal propagation time (set, reset input) $t_{pR}$ Reset pulse duration $t_{pR}$ Reset pulse duration $t_{pR}$ Counting pulse duration $t_{p}$ Key depression period $t_{pC}$ Counting pulse duration $t_{p}$ Recovery time $t_{s}$ Setup time $t_{o}$ Output pulse duration $t_{r}$ Recovery time $t_{s}$ Setup time $t_{o}$ Output pulse duration $t_{ri$                                                                                           | R <sub>P</sub>      | Adjustmente resistance                               |

| $R_{OH}$ H-output resistance $R_{OL}$ L-output resistance $R_O$ Load resistance at output $T_A$ Ambient temperature $T_{stg}$ Storage temperature $T_{case}$ Case temperature $T_{case}$ Case temperature $T_{case}$ Case temperature $T_case$ Case temperature coefficient $t_d$ Pulse delay time $t_{DHL O$ Delay time of the HL transition of the output signal $t_{DLH O$ Delay time of the LH transition of the output signal $t_{DLH O$ Delay time of the LH transition of the output signal $t_{DLH O$ Delay time of the LH transition of the output signal $t_{DLH O$ Delay time $t_{H}$ Hold time $t_{H}$ Bit time after clock pulse $t_{n+1}$ Bit time after clock pulse $t_{n+1}$ Signal propagation time (from H to L) $t_{PP}$ Average signal propagation time (set, reset input) $t_{PQ}$ Pair-delay time $t_{PR,S}$ Set pulse duration $t_{pR}$ Reset pulse duration $t_{p}$ Key depression period $t_{pC}$ Counting pulse duration $t_{T}$ Transmission time – $t_r$ rise time, $t_l$ fall time $t_r$ Recovery time $t_s$ Setup time $t_{LH}$ Signal transition time (from H to L) $t_{THL}$ Signal transition time (from H to L) $t_{THL}$ Signal transition time (from H to L)                                                                                              | R <sub>thJA</sub>   | Therminal resistance (Junction to ambient)           |

| $\begin{array}{llllllllllllllllllllllllllllllllllll$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                     | H-output resistance                                  |

| $\begin{array}{llllllllllllllllllllllllllllllllllll$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | R <sub>OL</sub>     | L-output resistance                                  |

| $T_{stg}$ Storage temperature $T_{case}$ Case temperature $T_j$ Junction temperature $TC$ Temperature coefficient $t_d$ Pulse delay time $t_{DHL O}$ Delay time of the HL transition of the output signal $t_{DLH O}$ Delay time of the LH transition of the output signal $t_{DLH O}$ Delay time of the LH transition of the output signal $t_{DLH O}$ Delay time of the LH transition of the output signal $t_{DLH O}$ Delay time $t_{H}$ Hold time $t_{I}$ Input pulse duration $t_n$ Bit time before clock pulse $t_{n+1}$ Bit time after clock pulse $t_{n+1}$ Bit time after clock pulse $t_{r+1}$ Bit genal propagation time $t_{SVD}$ Delay time $t_{CLKY}$ Clock period $t_{PHL}$ Signal propagation time (from H to L) $t_{PHL}$ Signal propagation time (set, reset input) $t_{pD}$ Pair-delay time $t_{pR}$ Average signal propagation time (set, reset input) $t_{pS}$ Set pulse duration $t_{d}$ Key depression period $t_{pC}$ Counting pulse duration $t_{T}$ Transmission time – $t_r$ rise time, $t_r$ fall time $t_r$ Recovery time $t_s$ Setup time $t_O$ Output pulse duration $t_{TLH}$ Signal transition time (from H to L) $t_{TLH}$ Signal transition time (from H to L)                                                                                             |                     | Load resistance at output                            |

| $T_{case}$ Case temperature $T_j$ Junction temperature $TC$ Temperature coefficient $t_d$ Pulse delay time $t_{DHL O}$ Delay time of the HL transition of the output signal $t_{DLH O}$ Delay time of the LH transition of the output signal $t_{DLH O}$ Delay time of the LH transition of the output signal $t_{DLH}$ Delay time $t_{H}$ Hold time $t_{I}$ Input pulse duration $t_n$ Bit time before clock pulse $t_{n+1}$ Bit time after clock pulse $t_{P}$ Average signal propagation time $t_{SVD}$ Delay time $t_{CLKY}$ Clock period $t_{PHL}$ Signal propagation time (from H to L) $t_{PR}$ Reset pulse duration $t_{PR}$ Average signal propagation time (set, reset input) $t_{PS}$ Set pulse duration $t_{pR}$ Reset pulse duration $t_{q}$ Key debounce time $t_p$ Key depression period $t_{pC}$ Counting pulse duration $t_{T}$ Transmission time - $t_r$ rise time, $t_r$ fall time $t_r$ Recovery time $t_s$ Setup time $t_O$ Output pulse duration $t_{TLH}$ Signal transition time (from H to L) $t_{TLH}$ Signal transition time (from H to L)                                                                                                                                                                                                                          | T <sub>A</sub>      | Ambient temperature                                  |

| $T_{case}$ Case temperature $T_j$ Junction temperature $TC$ Temperature coefficient $t_d$ Pulse delay time $t_{DHL O}$ Delay time of the HL transition of the output signal $t_{DLH O}$ Delay time of the LH transition of the output signal $t_{DLH O}$ Delay time of the LH transition of the output signal $t_{DLH}$ Delay time $t_{H}$ Hold time $t_{I}$ Input pulse duration $t_n$ Bit time before clock pulse $t_{n+1}$ Bit time after clock pulse $t_{P}$ Average signal propagation time $t_{SVD}$ Delay time $t_{CLKY}$ Clock period $t_{PHL}$ Signal propagation time (from H to L) $t_{PR}$ Reset pulse duration $t_{PR}$ Average signal propagation time (set, reset input) $t_{PS}$ Set pulse duration $t_{pR}$ Reset pulse duration $t_{q}$ Key debounce time $t_p$ Key depression period $t_{pC}$ Counting pulse duration $t_{T}$ Transmission time - $t_r$ rise time, $t_r$ fall time $t_r$ Recovery time $t_s$ Setup time $t_O$ Output pulse duration $t_{TLH}$ Signal transition time (from H to L) $t_{TLH}$ Signal transition time (from H to L)                                                                                                                                                                                                                          | T <sub>sta</sub>    | Storage temperature                                  |

| $T_j$ Junction temperature $TC$ Temperature coefficient $t_d$ Pulse delay time $t_{DHL O}$ Delay time of the HL transition of the output signal $t_{DLH O}$ Delay time of the LH transition of the output signal $t_{DLH O}$ Delay time $t_{H}$ Hold time $t_{I}$ Input pulse duration $t_n$ Bit time before clock pulse $t_{n+1}$ Bit time after clock pulse $t_{p}$ Average signal propagation time $t_{SVD}$ Delay time $t_{CLKY}$ Clock period $t_{PHLR,S}$ Signal propagation time (from H to L) $t_{PR}$ Reset pulse duration $t_{pR}$ Reset pulse duration $t_{pR}$ Key debounce time $t_p$ Key depression period $t_{pC}$ Counting pulse duration $t_{T}$ Transmission time – $t_r$ rise time, $t_r$ fall time $t_r$ Recovery time $t_s$ Setup time $t_o$ Output pulse duration $t_{T}$ Recovery time $t_s$ Setup time $t_o$ Output pulse duration $t_{T}$ Recovery time $t_s$ Setup time $t_o$ Output pulse duration $t_{TLH}$ Signal transition time (from H to L) $t_{TLH}$ Signal transition time (from L to H)                                                                                                                                                                                                                                                                   | -                   | Case temperature                                     |

| $t_d$ Pulse delay time $t_{DHL O}$ Delay time of the HL transition of the output signal $t_{DLH O}$ Delay time of the LH transition of the output signal $t_{DLH}$ Delay time $t_{LH}$ Hold time $t_{H}$ Hold time $t_{I}$ Input pulse duration $t_n$ Bit time before clock pulse $t_{n+1}$ Bit time after clock pulse $t_{p}$ Average signal propagation time $t_{SYD}$ Delay time $t_{CLKY}$ Clock period $t_{PHL}$ Signal propagation time (from H to L) $t_{PHLR,S}$ Signal propagation time (set, reset input) $t_{pR}$ Reset pulse duration $t_{pR}$ Reset pulse duration $t_{pR}$ Set pulse duration $t_{pR}$ Key debounce time $t_p$ Key depression period $t_p$ Recovery time $t_s$ Set pulse duration $t_r$ Recovery time $t_s$ Setup time $t_0$ Output pulse duration $t_{T}$ Transmission time – $t_r$ rise time, $t_r$ fall time $t_r$ Recovery time $t_s$ Setup time $t_0$ Output pulse duration $t_{TLH}$ Signal transition time (from H to L) $t_{TLH}$ Signal transition time (from L to H)                                                                                                                                                                                                                                                                                  |                     | Junction temperature                                 |

| $t_{DHL O}$ Delay time of the HL transition of the output signal $t_{DLH O}$ Delay time of the LH transition of the output signal $t_{DLH}$ Delay time $t_{H}$ Hold time $t_{I}$ Input pulse duration $t_n$ Bit time before clock pulse $t_{n+1}$ Bit time after clock pulse $t_{p}$ Average signal propagation time $t_{SYD}$ Delay time $t_{CLKY}$ Clock period $t_{PHL}$ Signal propagation time (from H to L) $t_{PHLR,S}$ Signal propagation time (set, reset input) $t_{pR}$ Reset pulse duration $t_{pR}$ Average signal propagation time (set, reset input) $t_{pS}$ Set pulse duration $t_{qC}$ Counting pulse duration $t_{r}$ Reset pulse duration $t_{r}$ Recovery time $t_r$ Recovery time $t_r$ Recovery time $t_r$ Setup time $t_r$ Setup time $t_r$ Recovery time $t_r$ Setup time $t_r$ Signal transition time (from H to L) $t_{TLH}$ Signal transition time (from L to H)                                                                                                                                                                                                       | ŤC                  | Temperature coefficient                              |

| $t_{DLH O}$ Delay time of the LH transition of the output signal $t_{DLH}$ Delay time $t_{LH}$ Hold time $t_{H}$ Hold time $t_{I}$ Input pulse duration $t_{n}$ Bit time before clock pulse $t_{n+1}$ Bit time after clock pulse $t_{r+1}$ Bit time after clock pulse $t_{r+1}$ Bit time after clock pulse $t_{r+1}$ Bit time after clock pulse $t_{n+1}$ Bit time after clock pulse $t_{p}$ Average signal propagation time (from H to L) $t_{PLLR,S}$ Signal propagation time (set, reset input) $t_{pS}$ Set pulse duration $t_{pR}$ Reset pulse duration $t_{pC}$ Counting pulse duration $t_{pC}$ Counting pulse duration $t_{r}$ Recovery time $t_{s}$ Setup time $t_{o}$ Output pulse duration $t_{THL}$ Signal transition time (from H to L) $t_{TLH}$ Signal transition time (from L to H)                                                                                                                                                                                   | t <sub>d</sub>      | Pulse delay time                                     |

| $t_{DLH O}$ Delay time of the LH transition of the output signal $t_{DLH}$ Delay time $t_{H}$ Hold time $t_{I}$ Input pulse duration $t_{n}$ Bit time before clock pulse $t_{n+1}$ Bit time after clock pulse $t_{r+1}$ Signal propagation time $t_{SYD}$ Delay time $t_{CLKY}$ Clock period $t_{PHL}$ Signal propagation time (from H to L) $t_{PHL}$ Signal propagation time (set, reset input) $t_{PD}$ Pair-delay time $t_{pR}$ Reset pulse duration $t_{pR}$ Average signal propagation time (set, reset input) $t_{pS}$ Set pulse duration $t_d$ Key depression period $t_{pC}$ Counting pulse duration $t_{T}$ Transmission time – $t_r$ rise time, $t_r$ fall time $t_r$ Recovery time $t_s$ Setup time $t_0$ Output pulse duration $t_{THL}$ Signal transition time (from H to L) $t_{THL}$ Signal transition time (from L to H)                                                                                                                                                                                                                                                            | t <sub>DHL O</sub>  | Delay time of the HL transition of the output signal |

| thickHold time $t_{\rm H}$ Input pulse duration $t_{\rm n}$ Bit time before clock pulse $t_{\rm n+1}$ Bit time after clock pulse $t_{\rm p}$ Average signal propagation time $t_{\rm SYD}$ Delay time $t_{\rm CLKY}$ Clock period $t_{\rm PHL}$ Signal propagation time (from H to L) $t_{\rm PHL}$ Signal propagation time (set, reset input) $t_{\rm PHL}$ Signal propagation time (set, reset input) $t_{\rm pR}$ Reset pulse duration $t_{\rm pR}$ Reset pulse duration $t_{\rm qd}$ Key debounce time $t_{\rm p}$ Key depression period $t_{\rm pC}$ Counting pulse duration $t_{\rm r}$ Recovery time $t_{\rm s}$ Setup time $t_{\rm r}$ Recovery time $t_{\rm s}$ Setup time $t_{\rm r}$ Signal transition time (from H to L) $t_{\rm THL}$ Signal transition time (from L to H)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                     | Delay time of the LH transition of the output signal |

| $t_1$ Input pulse duration $t_n$ Bit time before clock pulse $t_{n+1}$ Bit time after clock pulse $t_p$ Average signal propagation time $t_{SYD}$ Delay time $t_{CLKY}$ Clock period $t_{PHL}$ Signal propagation time (from H to L) $t_{PHL}$ Signal propagation time (set, reset input) $t_{PD}$ Pair-delay time $t_{PR}$ Reset pulse duration $t_{PR,S}$ Average signal propagation time (set, reset input) $t_{pS}$ Set pulse duration $t_d$ Key debounce time $t_p$ Key depression period $t_p$ Counting pulse duration $t_r$ Recovery time $t_s$ Setup time $t_r$ Recovery time $t_s$ Setup time $t_r$ Signal transition time (from H to L) $t_{TLH}$ Signal transition time (from L to H)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | t <sub>DLH</sub>    | Delay time                                           |

| $t_n$ Bit time before clock pulse $t_{n+1}$ Bit time after clock pulse $t_{n+1}$ Bit time after clock pulse $t_{p}$ Average signal propagation time $t_{SYD}$ Delay time $t_{CLKY}$ Clock period $t_{PHL}$ Signal propagation time (from H to L) $t_{PHLR,S}$ Signal propagation time (set, reset input) $t_{PD}$ Pair-delay time $t_{pR}$ Reset pulse duration $t_{pR,S}$ Average signal propagation time (set, reset input) $t_{pS}$ Set pulse duration $t_d$ Key debounce time $t_p$ Key depression period $t_{pC}$ Counting pulse duration $t_T$ Transmission time – $t_r$ rise time, $t_r$ fall time $t_r$ Recovery time $t_s$ Setup time $t_0$ Output pulse duration $t_{THL}$ Signal transition time (from H to L) $t_{TLH}$ Signal transition time (from L to H)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | t <sub>H</sub>      | Hold time                                            |

| $t_{n+1}$ Bit time after clock pulse $t_p$ Average signal propagation time $t_{SYD}$ Delay time $t_{CLKY}$ Clock period $t_{PHL}$ Signal propagation time (from H to L) $t_{PHLR,S}$ Signal propagation time (set, reset input) $t_{PD}$ Pair-delay time $t_{pR}$ Reset pulse duration $t_{PR,S}$ Average signal propagation time (set, reset input) $t_{pS}$ Set pulse duration $t_{d}$ Key debounce time $t_p$ Key depression period $t_{pC}$ Counting pulse duration $t_r$ Recovery time $t_s$ Setup time $t_o$ Output pulse duration $t_{TLH}$ Signal transition time (from H to L)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | t <sub>i</sub>      | Input pulse duration                                 |

| $t_P$ Average signal propagation time $t_{SYD}$ Delay time $t_{CLKY}$ Clock period $t_{PHL}$ Signal propagation time (from H to L) $t_{PHLR,S}$ Signal propagation time (set, reset input) $t_{PD}$ Pair-delay time $t_{pR}$ Reset pulse duration $t_{PR,S}$ Set pulse duration $t_{d}$ Key debounce time $t_p$ Key depression period $t_pC$ Counting pulse duration $t_r$ Recovery time $t_s$ Set pulse duration $t_r$ Gounting pulse duration $t_r$ Recovery time $t_s$ Set pulse duration $t_r$ Recovery time $t_s$ Set pulse duration $t_r$ Recovery time $t_s$ Set pulse duration $t_{TLH}$ Signal transition time (from H to L) $t_{TLH}$ Signal transition time (from L to H)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | t <sub>n</sub>      | Bit time before clock pulse                          |

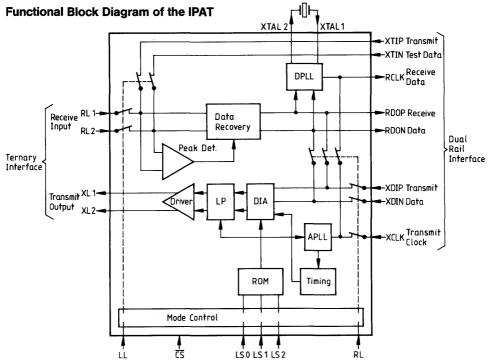

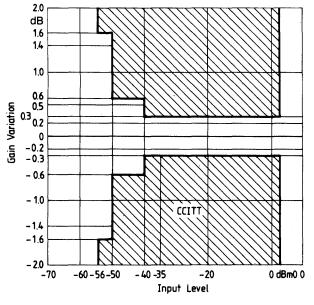

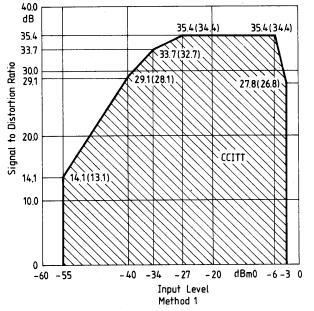

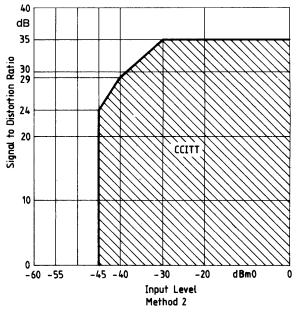

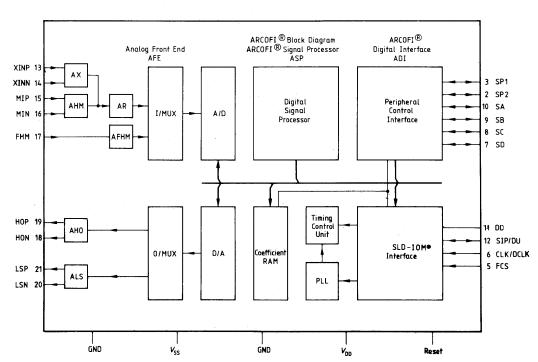

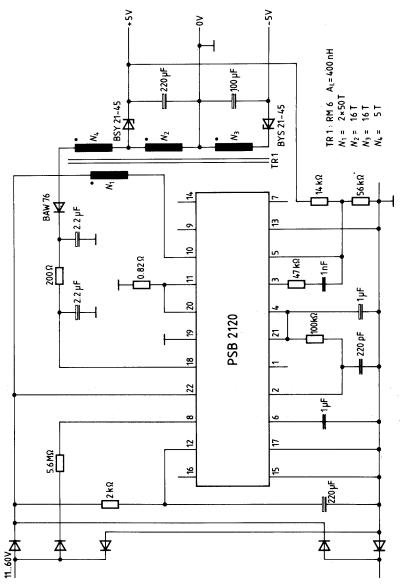

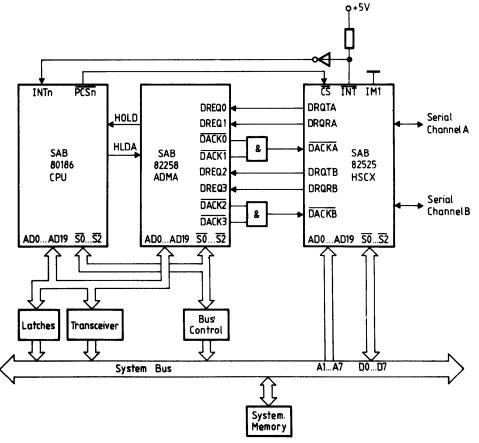

| $t_P$ Average signal propagation time $t_{SYD}$ Delay time $t_{CLKY}$ Clock period $t_{PHL}$ Signal propagation time (from H to L) $t_{PHLR,S}$ Signal propagation time (set, reset input) $t_{PD}$ Pair-delay time $t_{pR}$ Reset pulse duration $t_{PR,S}$ Set pulse duration $t_{d}$ Key debounce time $t_p$ Key depression period $t_pC$ Counting pulse duration $t_r$ Recovery time $t_s$ Set pulse duration $t_r$ Gounting pulse duration $t_r$ Recovery time $t_s$ Set pulse duration $t_r$ Recovery time $t_s$ Set pulse duration $t_r$ Recovery time $t_s$ Set pulse duration $t_{TLH}$ Signal transition time (from H to L) $t_{TLH}$ Signal transition time (from L to H)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | t <sub>n+1</sub>    | Bit time after clock pulse                           |