SIEMENS

# Consumer IC

Data Book 1987/88

**Consumer IC**

1987/88

Contents

$\bigcirc$

Summary of Types Cross Reference Guide

**General Information**

**Technical Data**

**Package Outlines**

**Siemens Sales Offices**

## **Consumer IC**

Data Book 1987/88

フ

Contents

## **Table of Contents**

$\supset$

| 1   | Summary of Types                         | Page |

|-----|------------------------------------------|------|

| 1.1 | Types in alphanumerical order            | 11   |

| 1.2 | Types by application order               | . 13 |

| 2   | General Information                      |      |

| 2.1 | Type Designation Code                    | 21   |

| 2.2 | Mounting Instructions                    | 21   |

| 2.3 | Processing Guidelines for ICs            | 25   |

| 2.4 | Data Classification                      | 28   |

| 2.5 | Quality Assurance                        | 28   |

| 2.6 | Summary of terms and symbols             | 33   |

| 3   | Technical Data                           | 37   |

| 4   | Package Outlines                         | 927  |

| 5   | Listing of Siemens Sales and Rep Offices | 945  |

- .

Summary of Types

## Summary of Types

## 1.1 Types in Alphanumerical Order

#### Page

| HKZ 101                | Hall-effect vane switch         | 37  |

|------------------------|---------------------------------|-----|

| S 041 P                | FM IF amplifier and demodulator | 43  |

| S 042 P                | Mixer                           | 49  |

| S 178 A                | Video pulse generator           | 55  |

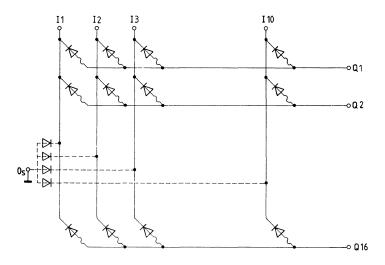

| S 353                  | Programmable diode matrix       | 65  |

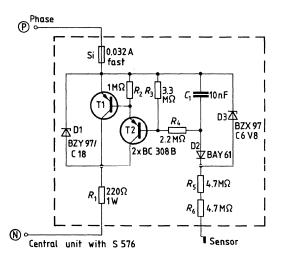

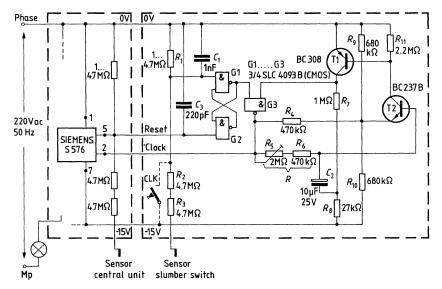

| S 576 A                | Electronic dimmer               | 71  |

| S 576 B                | Electronic dimmer               | 71  |

| S 576 C                | Electronic dimmer               | 71  |

| S 576 D                | Electronic switch               | 71  |

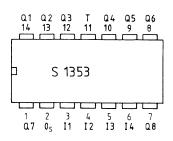

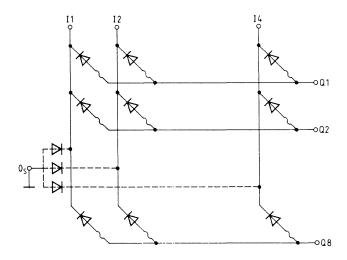

| S 1353                 | Programmable diode matrix       | 65  |

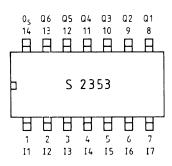

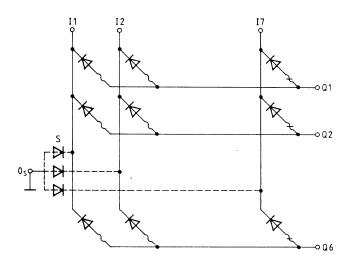

| S 2353                 | Programmable diode matrix       | 65  |

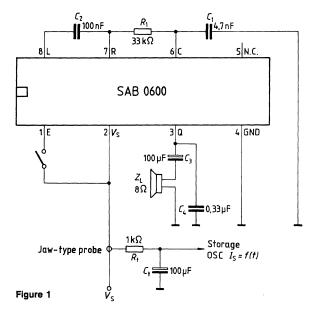

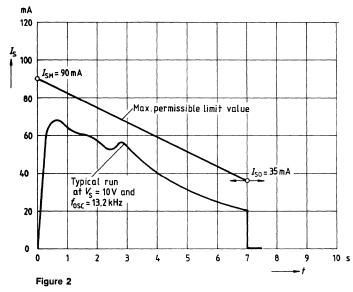

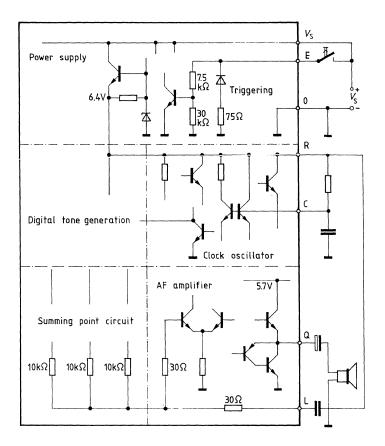

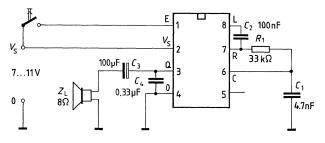

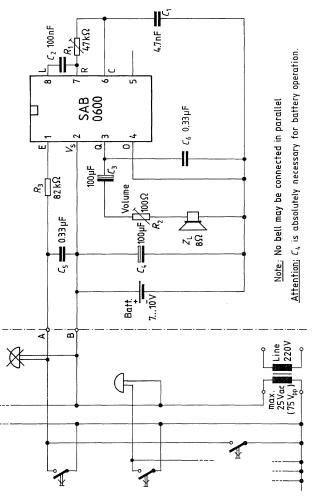

| SAB 0600               | Three tone chime                |     |

| SAB 0601               | Single tone chime               |     |

| SAB 0601               | Dual tone chime                 |     |

|                        |                                 | 81  |

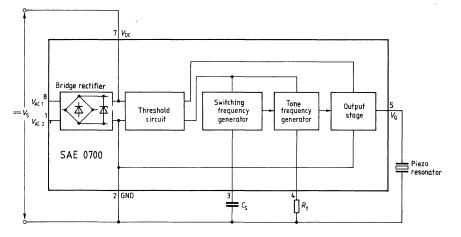

| SAE 0700               | Audible signal device           |     |

| SDA 0808A;B            | 8 bit/15 μs ADC                 |     |

| SDA 2008               | IR transmitter                  |     |

| SDA 2040               | Microcontroller (4k ROM).       |     |

| SDA 2060               | Microcontroller (6k ROM).       |     |

| SDA 2080               | Microcontroller (8k ROM)        |     |

| SDA 2082               | Microcontroller                 |     |

| SDA 2110               | Microcontroller                 |     |

| SDA 2112-2             | Video PLL                       |     |

| SDA 2120               | 120 MHz radio PLL               | 165 |

| SDA 2131               | Static LED driver               | 179 |

| SDA 2208-2             | IR transmitter                  | 185 |

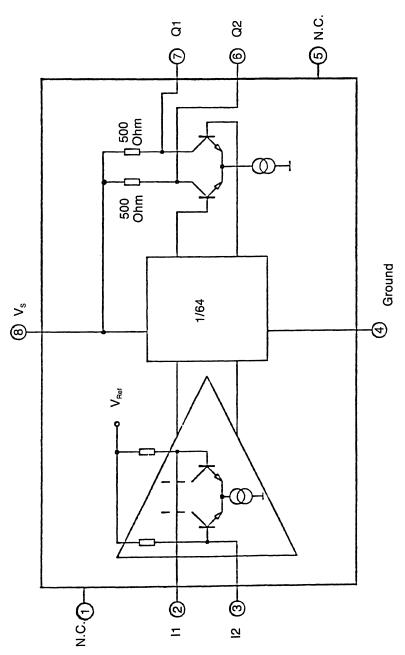

| SDA 2211               | Prescaler 1:64                  | 195 |

| SDA 2506               | 128 x 8 EEPROM                  | 201 |

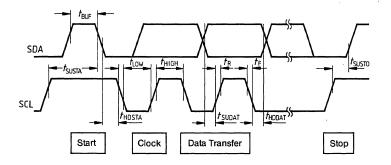

| SDA 2516               | 128 x 8 EEPROM IIC bus          | 207 |

| SDA 2526               | 256 x 8 EEPROM IIC bus          | 213 |

| SDA 3112               | Video PLL.                      |     |

| SDA 3202               | 1.3 GHz Video PLL IIC bus       |     |

| SDA 3203               | 1.3 GHz Video PLL               |     |

| SDA 4212               | Prescaler 1:64/256              |     |

| SDA 5200 N             | 6 bit A/D converter             |     |

| SDA 5200 S             | 6 bit A/D converter             |     |

| SDA 6020               | 6 bit A/D converter             |     |

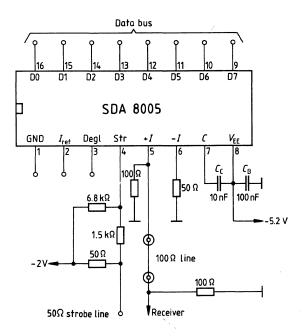

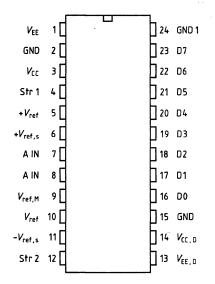

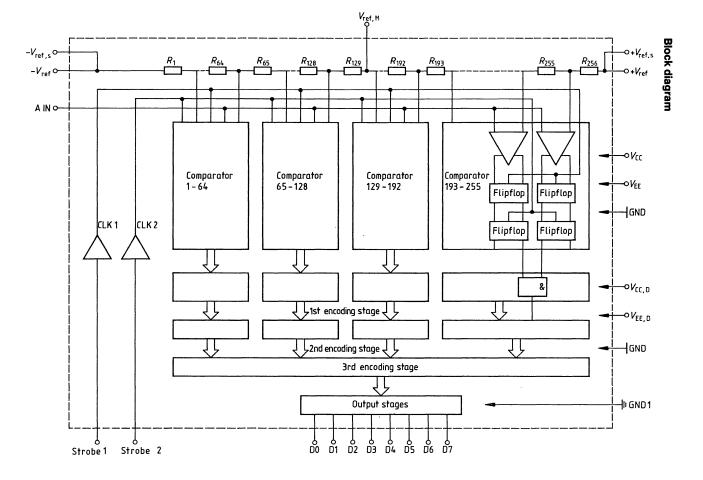

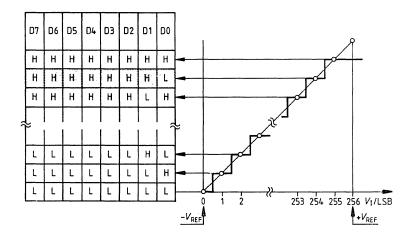

| SDA 8005               | 8 bit D/A converter             |     |

| SDA 8010               | 8 bit A/D converter             |     |

| SLE 5001               | IR transmitter                  |     |

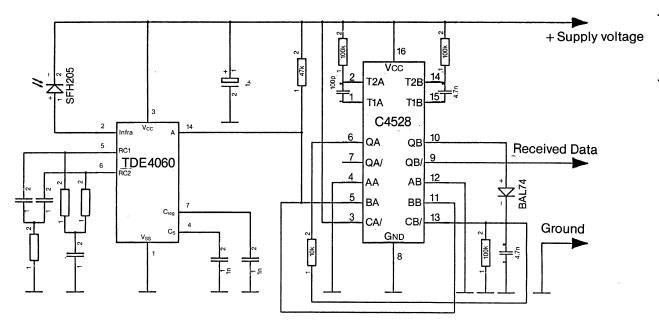

| SLE 5002               | IR receiver                     |     |

| TBA 120 S              | FM IF amplifier & demodulator.  |     |

| TBA 120 S              | FM IF amplifier & demodulator   |     |

| TBA 120 T<br>TBA 120 U |                                 |     |

|                        | FM IF amplifier & demodulator   |     |

| TBB 042 G              | Mixer                           |     |

| TBB 200                | PLL frequency synthesizer       | 343 |

## Page

| TBB 469                | FM receiver                  | . 359 |

|------------------------|------------------------------|-------|

| TBB 1469               | FM receiver                  |       |

| TBB 2469 G             | FM receiver                  | . 369 |

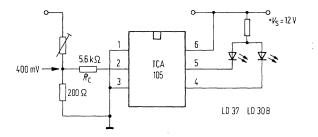

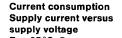

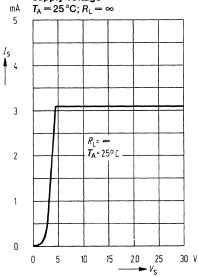

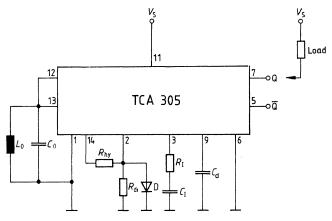

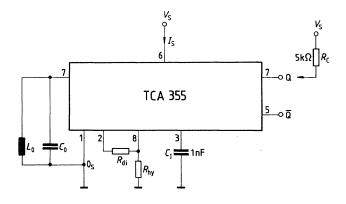

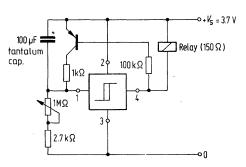

| TCA 105 B;G            | Threshold switch             | . 373 |

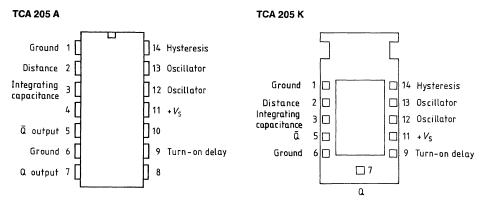

| TCA 205 A              | Proximity switch             |       |

| TCA 205 K              | Proximity switch             |       |

| TCA 305 A;G            | Proximity switch             |       |

| TCA 355 B;G            | Proximity switch             |       |

| TCA 345 A              | Threshold switch             |       |

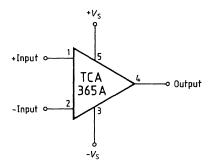

| TCA 365 A              | Power op amp                 |       |

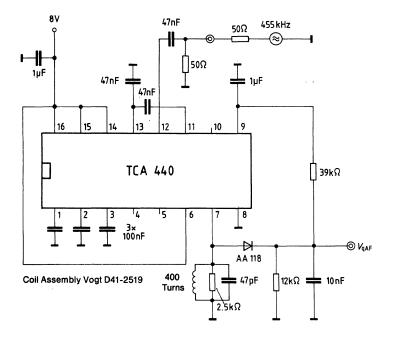

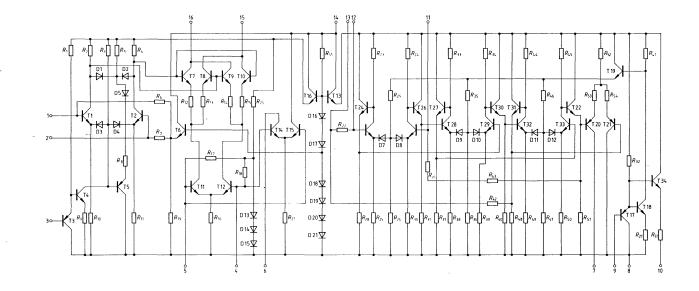

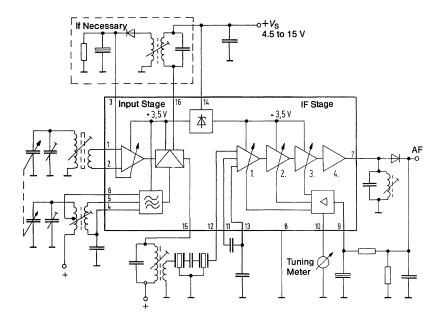

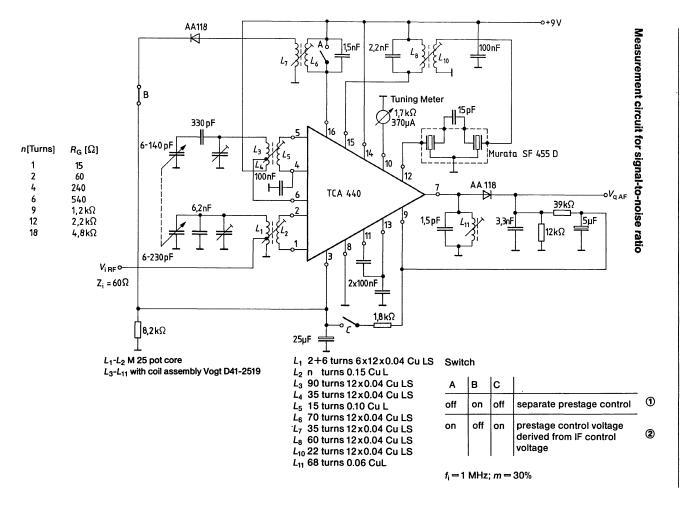

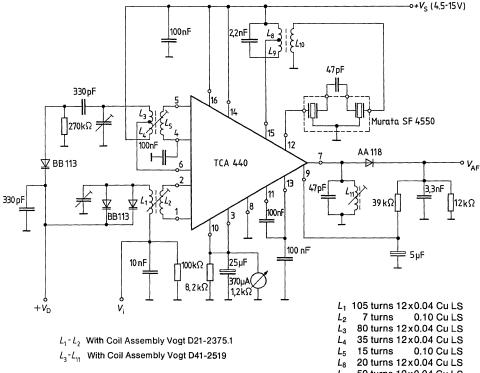

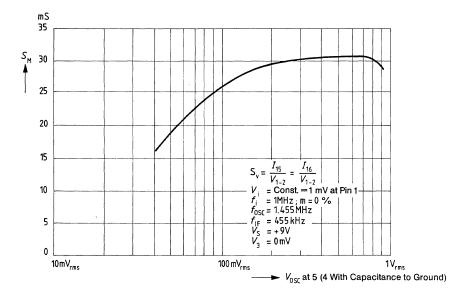

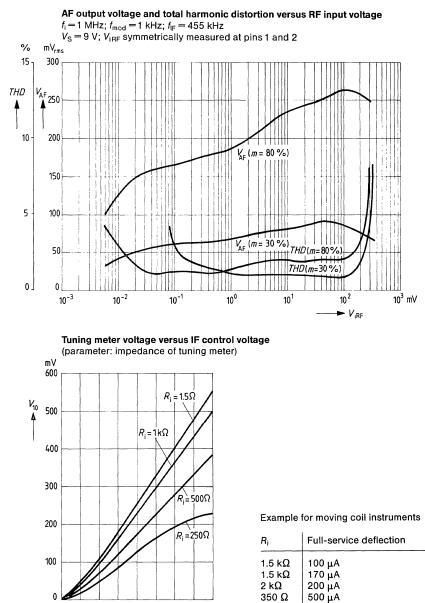

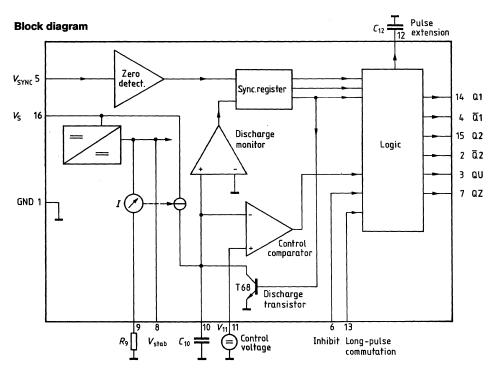

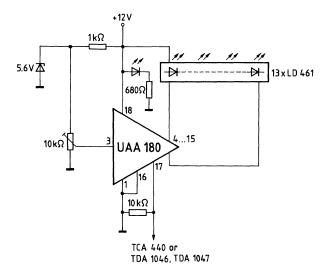

| TCA 440                | AM receiver                  |       |

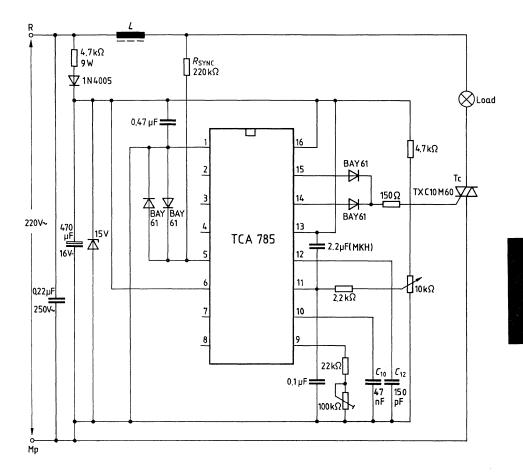

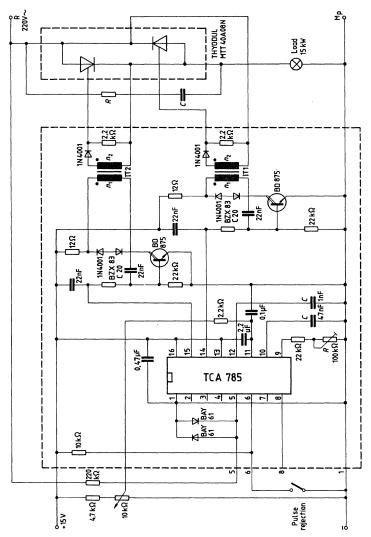

| TCA 785                | Phase controller             |       |

| TCA 955                | Speed controller             |       |

| TCA 965                | Window discriminator         |       |

| TCA 1365               | Power op amp                 |       |

| TCA 1560               | Stepper motor driver         |       |

| TCA 1561               | Stepper motor driver         |       |

| TCA 2365               | Dual power op amp            |       |

| TCA 4500 A             | FM stereo decoder            |       |

| TCA 4500 A<br>TCA 4511 | FM PLL stereo decoder        |       |

| TDA 1037               | Audio power amp              |       |

| TDA 1037<br>TDA 4001   | Addio power amp              |       |

|                        |                              |       |

| TDA 4010               | AM receiver                  |       |

| TDA 4050 B             | IR preamplifier              |       |

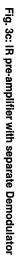

| TDA 4060               | IR preamplifier              |       |

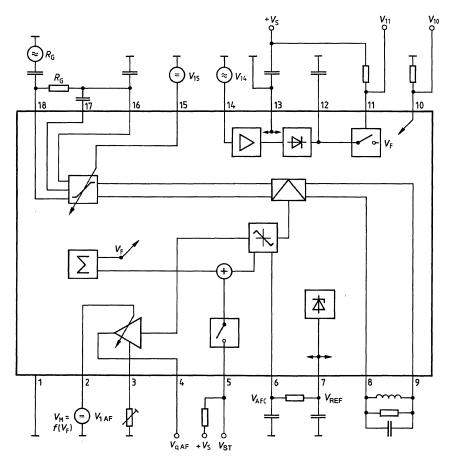

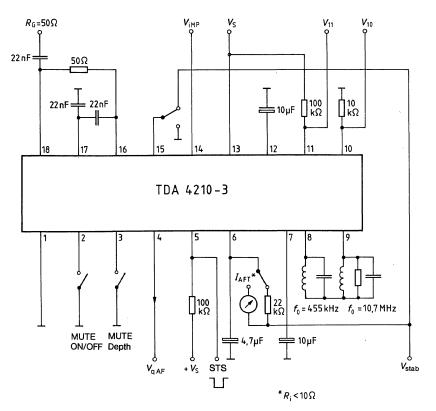

| TDA 4210-3             | FM IF for car radios.        |       |

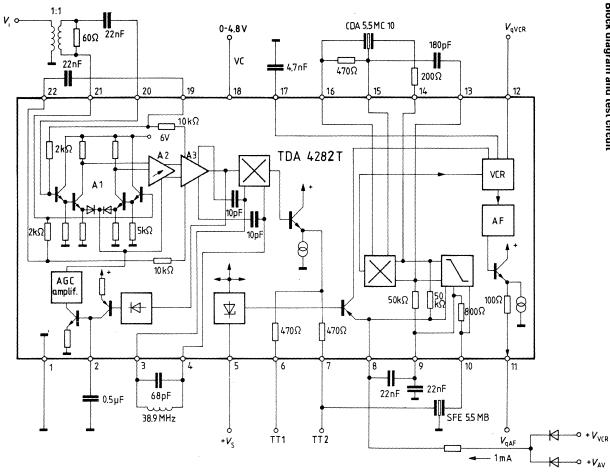

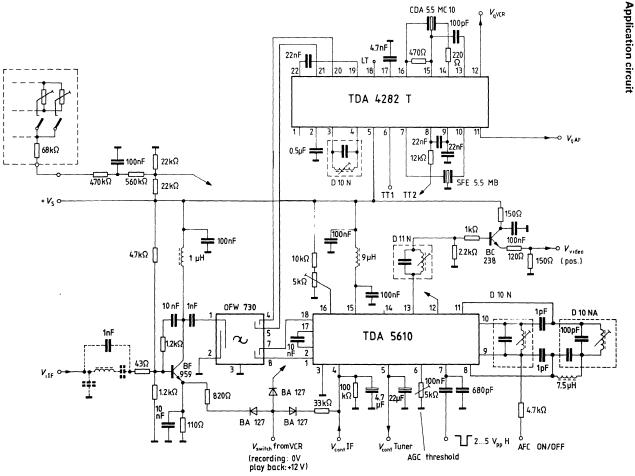

| TDA 4282 T             | Quasi parallel IF            |       |

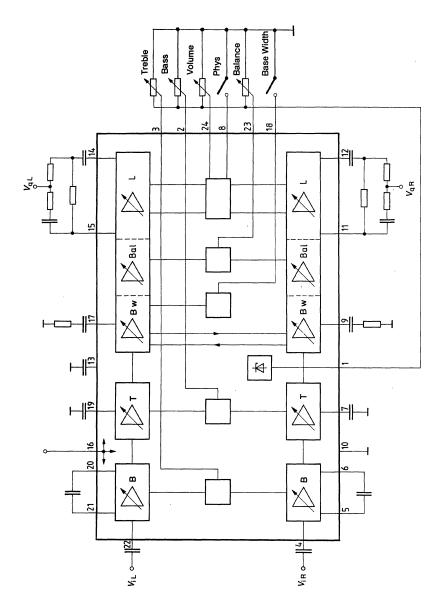

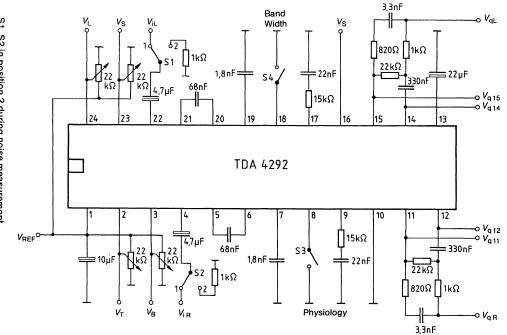

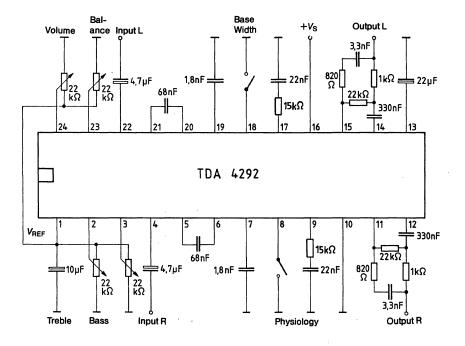

| TDA 4292               | DC stereo tone control       |       |

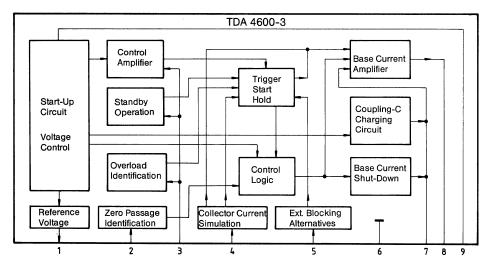

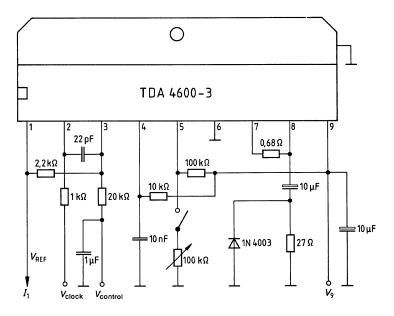

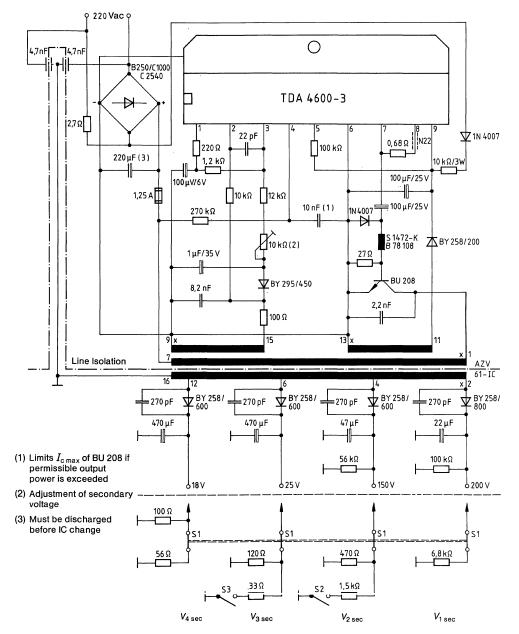

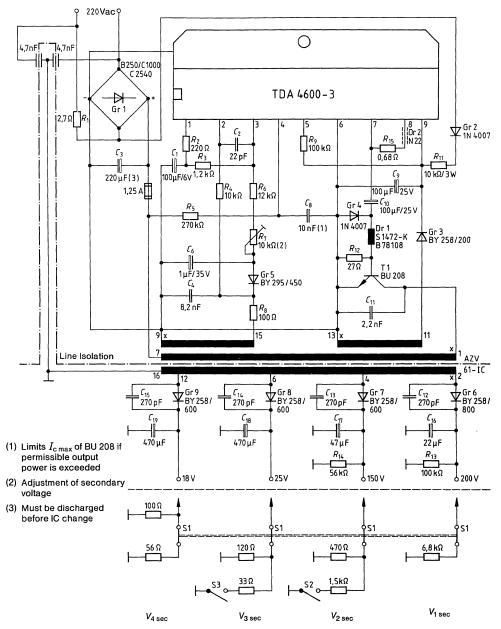

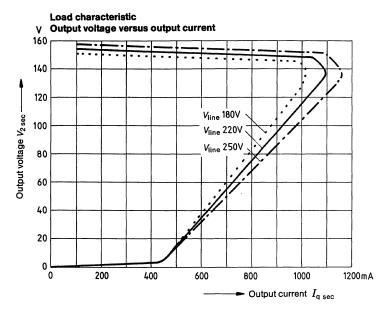

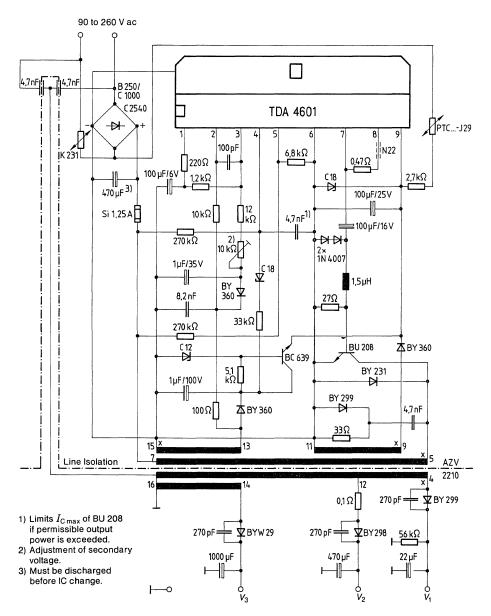

| TDA 4600-3             | SMPS controller              |       |

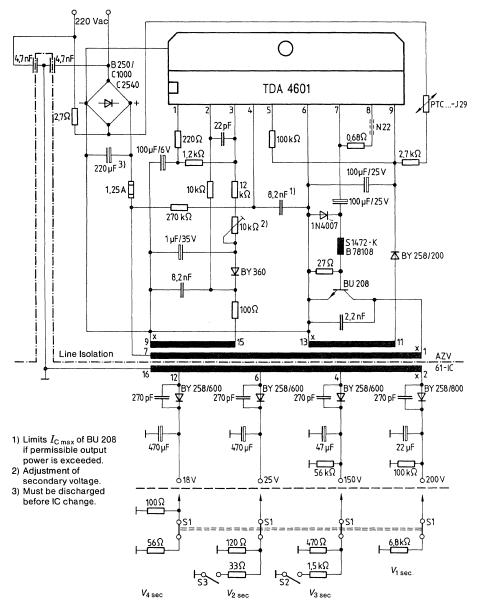

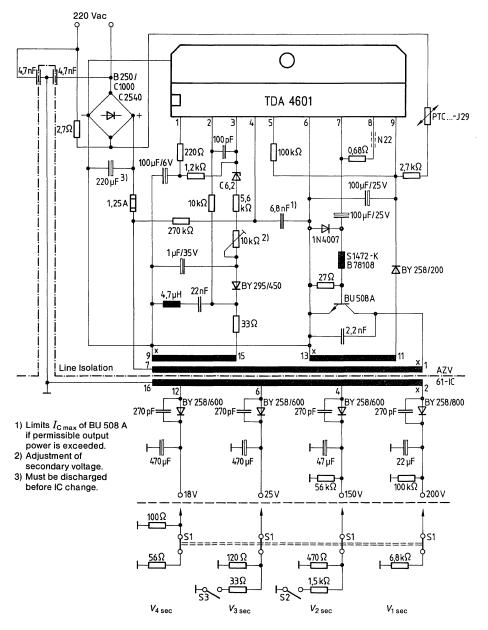

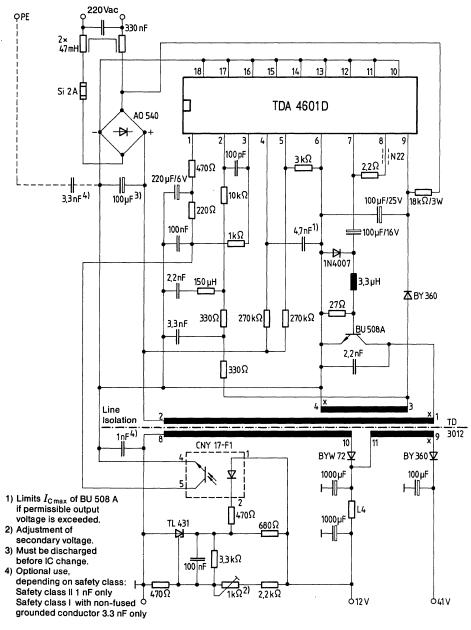

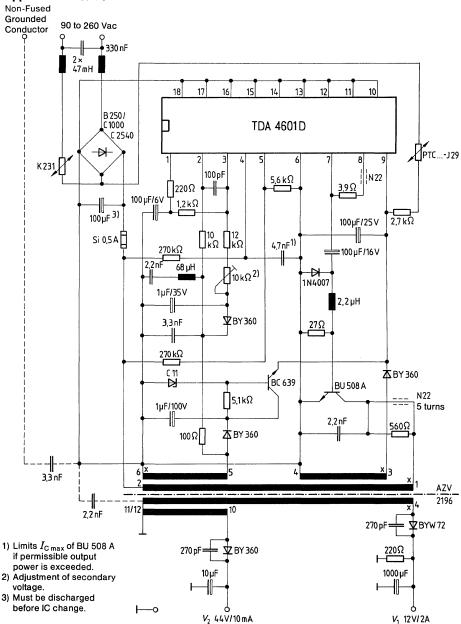

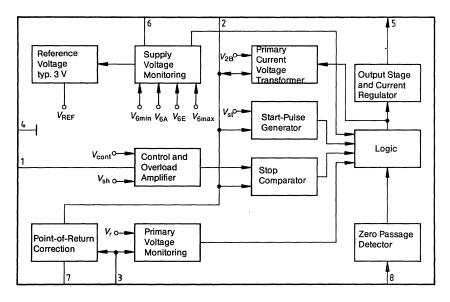

| TDA 4601 ;D            | SMPS controller              |       |

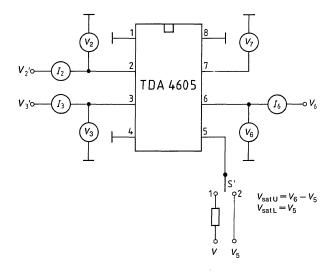

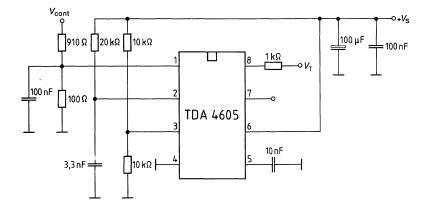

| TDA 4605               | SMPS controller              |       |

| TDA 4814               | Sinewave controller          |       |

| TDA 4918A              | Push-pull SMPS controller    |       |

| TDA 4919G              | Single-ended SMPS            |       |

| TDA 4930               | Audio power amp 2 x 10W      |       |

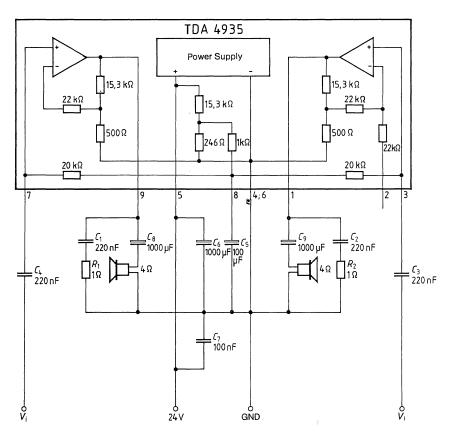

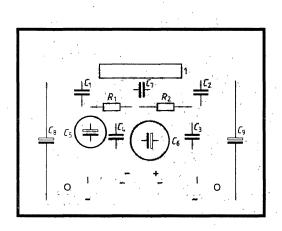

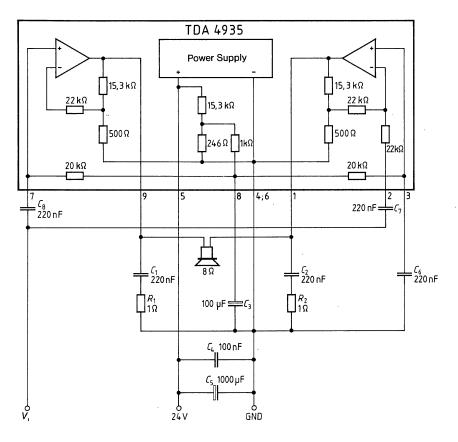

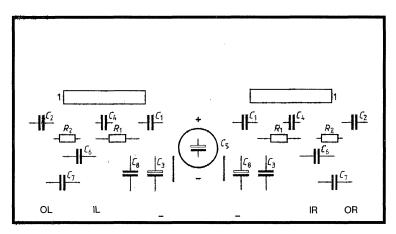

| TDA 4935               | Audio power amp 2 x 15W      |       |

| TDA 5400-2             | Video IF w/AFC               |       |

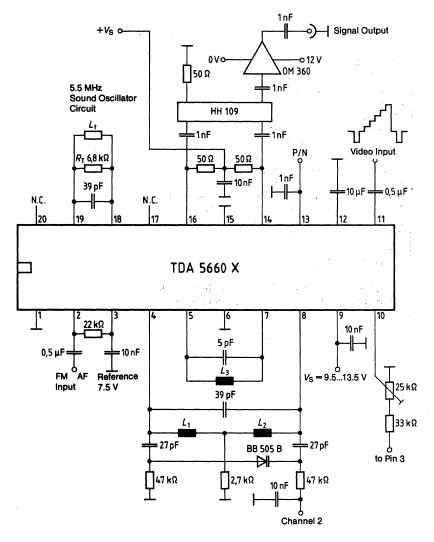

| TDA 5660 P             | VHF/UHF modulator            | . 705 |

| TDA 5660 X             | TDA 5660P in SO-20 package   | .749  |

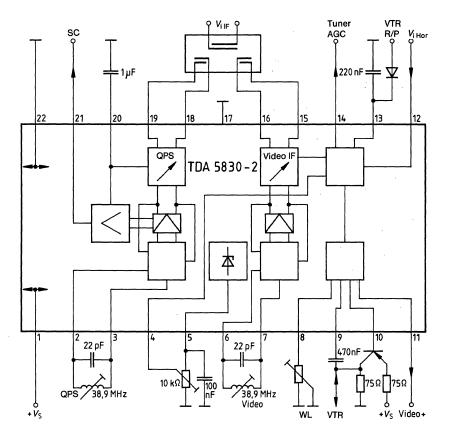

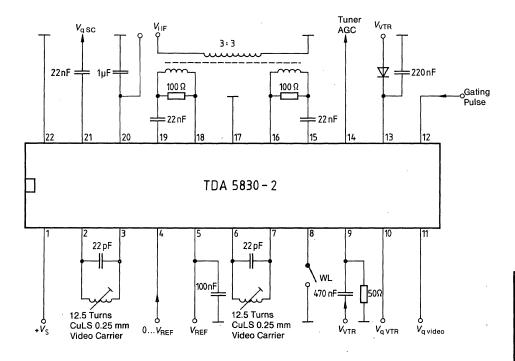

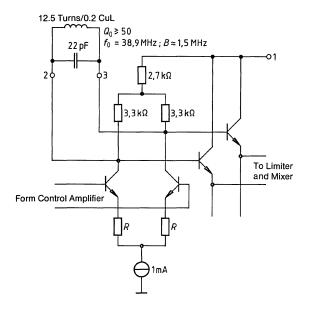

| TDA 5830-2             | Video IF & Q-P sound         | . 759 |

| TDA 5835               | Video IF & Q-P w/AFC         | .775  |

| TDA 5850               | Video switch                 |       |

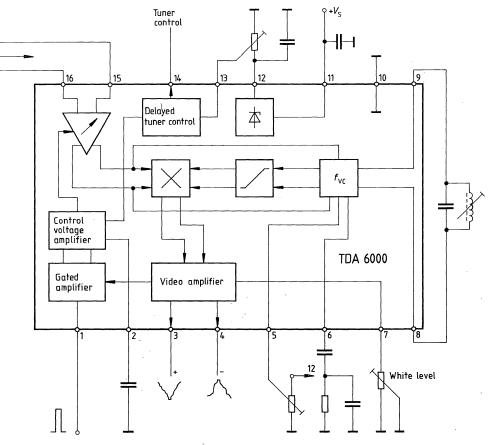

| TDA 6000               | Video IF w/synch demodulator | . 795 |

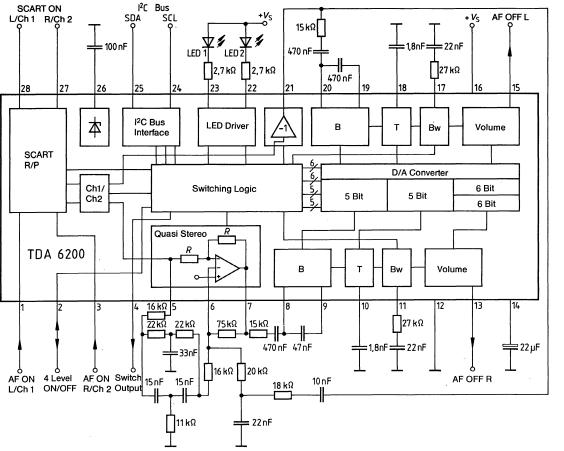

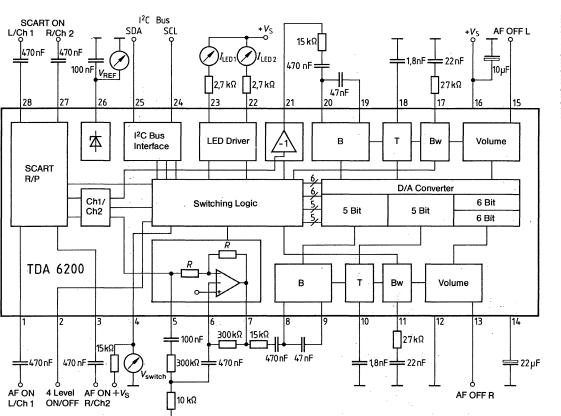

| TDA 6200               | Sound control, IIC bus       |       |

.....

## **Summary of Types**

#### Page

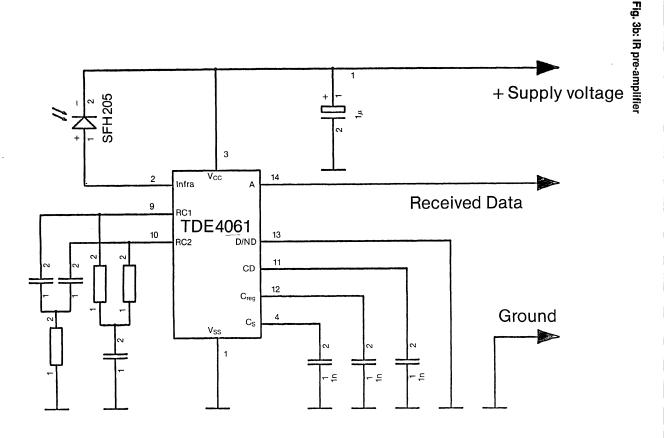

| TDE 4060     | IR Preamp                  | ••• |

|--------------|----------------------------|-----|

| TDE 4061     | IR Preamp w/demodulator    | • • |

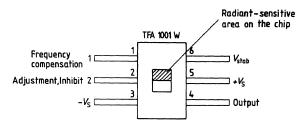

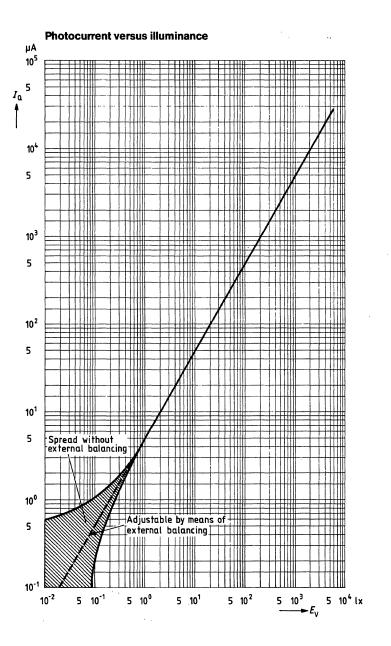

| TFA 1001 W   | Photodiode w/amplifier     |     |

| TLB 4902 F   | Hall-effect switch         |     |

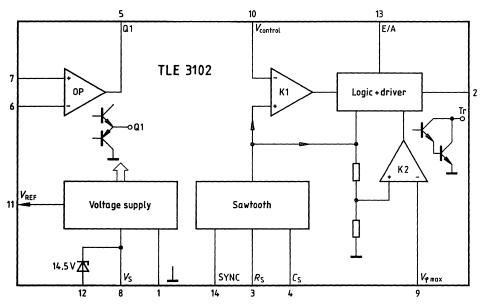

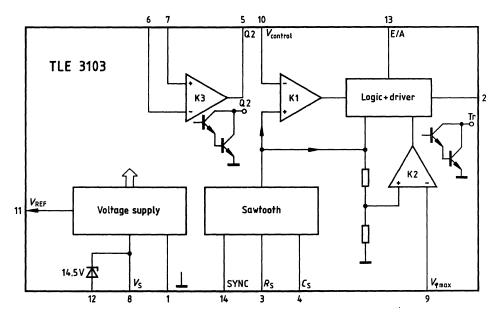

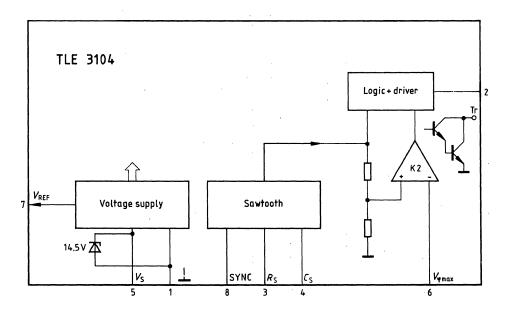

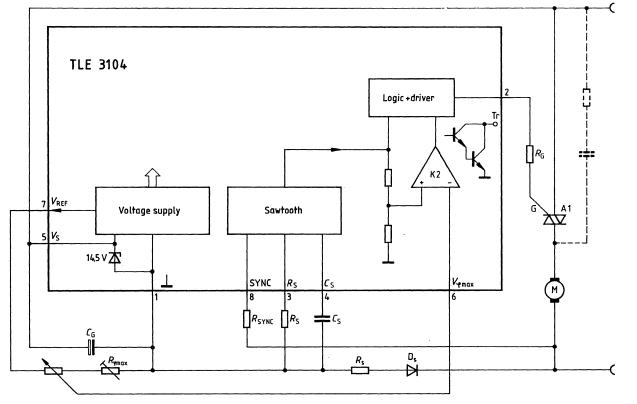

| TLE 3101     | Phase controller           |     |

| TLE 3102     | Phase controller           |     |

| TLE 3103     | Phase controller           |     |

| TLE 3104     | Phase controller           |     |

| TLE 4201 A   | DC motor driver            |     |

| TLE 4201 S   | DC motor driver            |     |

| TLE 4901 F;K | Hall-effect switch         |     |

| TLE 4903 F   | Hall-effect switch         |     |

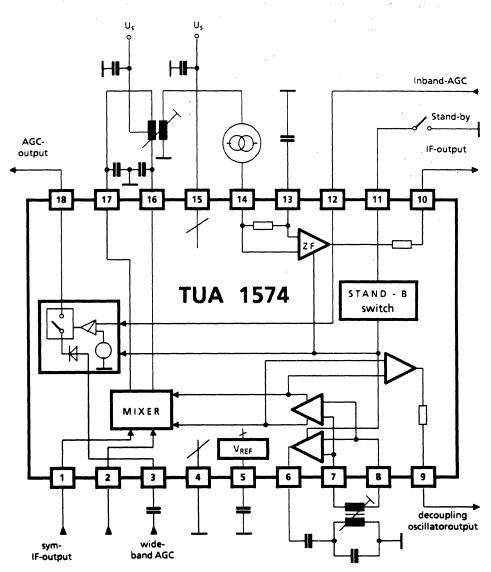

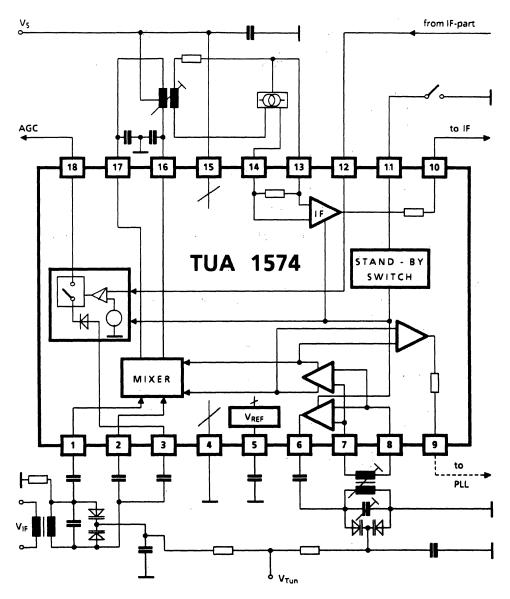

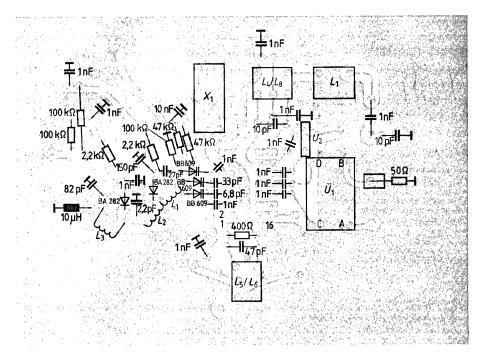

| TUA 1574     | FM tuner IC                |     |

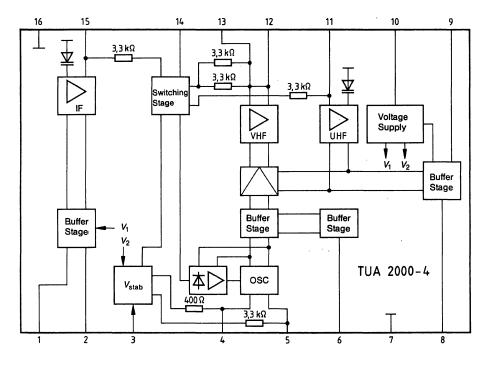

| TUA 2000-4   | VHF tuner IC 400 MHz       |     |

| TUA 2005     | VHF tuner IC 700 MHz       |     |

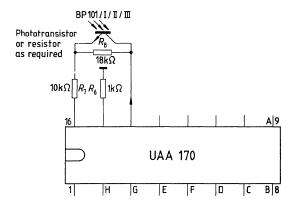

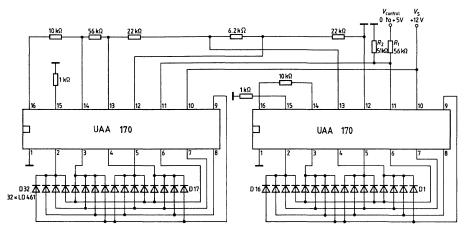

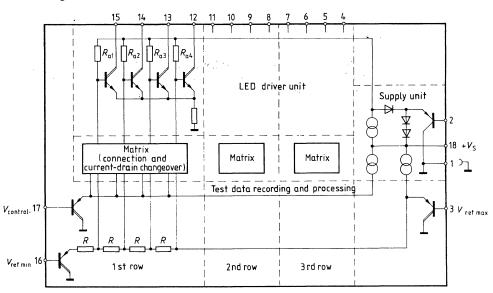

| UAA 170      | LED driver for dot display |     |

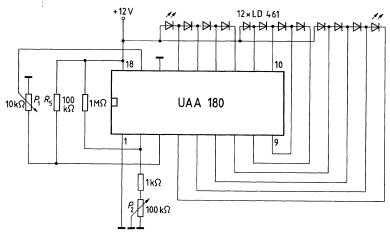

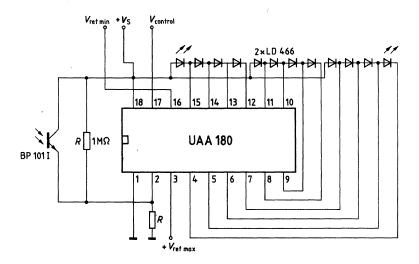

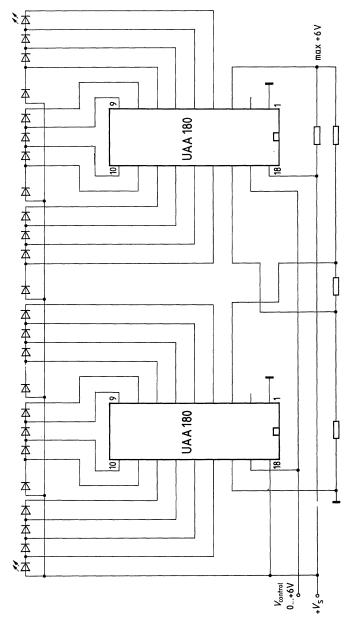

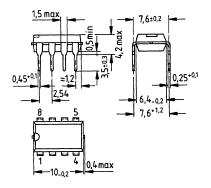

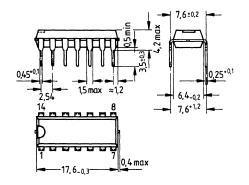

| UAA 180      | LED driver for bar display |     |

#### 1.2 Applications Order

#### **1.2.1 ICs for Industrial Applications**

#### Power Operational Amplifiers

| TCA 365 A   | Power op amp      |

|-------------|-------------------|

|             | Power op amp      |

| TCA 2365 ;A | Dual power op amp |

#### **Threshold Switches**

| TCA 105 B;G | Threshold switch     | 373 |

|-------------|----------------------|-----|

| TCA 345 A   | Threshold switch     | 393 |

| TCA 965     | Window discriminator | 447 |

#### Switched Mode Power Supply

| TDA 4600-3  | SMPS controller        | . 573 |

|-------------|------------------------|-------|

| TDA 4061; D | SMPS controller        | . 589 |

| TDA 4605    | SMPS controller        | . 615 |

| TDA 4814    | Sinewave controller    | .635  |

| TDA 4918 A  | Push-pull SMPS control | .647  |

| TDA 4919 G  | Single-ended SMPS      | . 659 |

#### Page

#### **Control of Thyristors and Triacs**

| TCA 785     | Phase controller  | 425 |

|-------------|-------------------|-----|

| TLE 3101    | Phase controller  | 833 |

| TLE 3102    | Phase controller  | 845 |

| TLE 3103    | Phase controller  | 847 |

| TLE 3104    | Phase controller  | 848 |

| S 576 A;B;C | Electronic dimmer | 71  |

| S 576 D     | Electronic switch | 71  |

#### Data Converters

| SDA 0808 A;I | B 8 bit/15 μs ADC   | 95  |

|--------------|---------------------|-----|

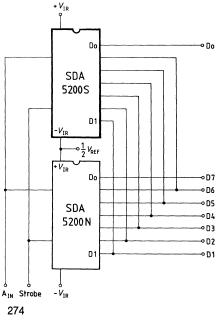

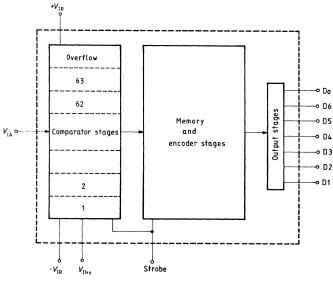

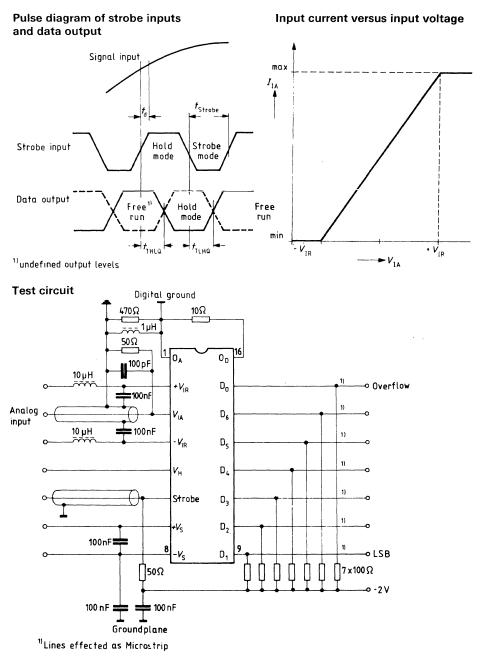

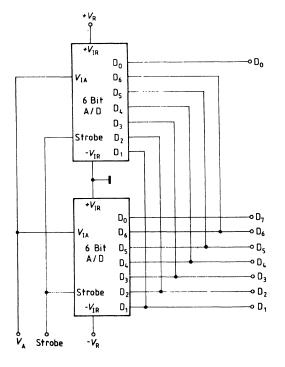

| SDA 5200 N   | 6 bit A/D converter | 263 |

| SDA 5200 S   | 6 bit A/D converter | 269 |

| SDA 6020     | 6 bit A/D converter | 275 |

| SDA 8005     | 8 bit D/A converter | 281 |

| SDA 8010     | 8 bit A/D converter | 293 |

#### Audible Signal Devices

| SAB 0600 | Three tone chime      | 81 |

|----------|-----------------------|----|

| SAB 0601 | Single tone chime     | 81 |

| SAB 0602 | Dual tone chime       | 81 |

| SAE 0700 | Audible signal device | 89 |

#### IC's for Radio Communications

| TBB 042 G  | Mixer                     |

|------------|---------------------------|

| TBB 200 ;G | PLL frequency synthesizer |

| TBB 469    | FM receiver               |

| TBB 1469   | FM receiver               |

| TBB 2469 G | FM receiver               |

| S 353      | Programmable diode matrix |

| S 1353     | Programmable diode matrix |

| S 2353     | Programmable diode matrix |

#### **DC Motor Control**

| TCA 955 ;K   | Speed controller     | 441 |

|--------------|----------------------|-----|

| TLE 4201 A;S | DC motor driver      | 353 |

| TCA 1560     | Stepper motor driver | 469 |

| TCA 1561     | Stepper motor driver | 469 |

## Summary of Types

-

Page

#### Sensors, Hall-Effect, Proximity Switches

| TFA 1001 W  | Photodiode w/amplifier  | 815 |

|-------------|-------------------------|-----|

| TLB 4902 F  | Hall-effect switch      | 827 |

| TLE 4901 F  | Hall-effect switch      | 863 |

| TLE 4903 F  | Hall-effect switch      | 869 |

| HKZ 101     | Hall-effect vane switch |     |

| TCA 205 A;K | Proximity switch        |     |

| TCA 305 A;B | Proximity switch        | 385 |

#### **Miscellaneous Industrial**

| SLE 5001    | IR Key transmitter       |

|-------------|--------------------------|

|             | IR Key receiver          |

| S 178 A     | Video pulse generator 55 |

| TDE 4060/61 | IR Preamplifier          |

#### 1.2.2 IC's for Entertainment Applications

#### TV Tuners

| TUA 2000-4 | VHF tuner IC 400 MHz | . 881 |

|------------|----------------------|-------|

| TUA 2005   | VHF tuner IC 700 MHz | . 899 |

#### **IR Remote Control**

| SDA 2008   | IR | transmitter  |

|------------|----|--------------|

| SDA 2208-2 | IR | transmitter  |

| TDA 4050 B | IR | preamplifier |

| TDA 4060   | IR | preamplifier |

#### Prescalers

| SDA 2211 | Prescaler 1:64     | . 195 |

|----------|--------------------|-------|

| SDA 4212 | Prescaler 1:64/256 | 255   |

#### Video PPĽs

| SDA 2112-2 | Video PLL                 |

|------------|---------------------------|

| SDA 3112   | Video PLL                 |

| SDA 3202   | 1.3 GHz video PLL IIC bus |

| SDA 3203   | 1.3 GHz video PLL         |

#### Page

#### Single Chip Microcomputer

| SDA 2040 | Microcontroller (4k ROM) | 121 |

|----------|--------------------------|-----|

| SDA 2060 | Microcontroller (6k ROM) | 121 |

| SDA 2080 | Microcontroller (8k ROM) | 121 |

| SDA 2082 | Microcontroller          | 131 |

| SDA 2110 | Microcontroller          | 145 |

#### **Nonvolatile Memories**

| SDA 2506 | 128 x 8 EEPROM         | 201 |

|----------|------------------------|-----|

| SDA 2516 | 128 x 8 EEPROM IIC bus | 207 |

| SDA 2526 | 256 x 8 EEPROM IIC bus | 213 |

#### **Display Drivers**

| SDA 2131 | Static LED driver          | 79 |

|----------|----------------------------|----|

| UAA 170  | LED driver for dot display | 11 |

| UAA 180  | LED driver for bar display | 19 |

#### Video Sound IF

| TDA 4282 T | Quasi parallel IF              | 53        |

|------------|--------------------------------|-----------|

|            | Video IF w/AFC                 |           |

| TDA 5830-2 | Video IF & Q-P sound           | 59        |

| TDA 5835   | Video IF & Q-P w/AFC           | 75        |

| TDA 5850   | Video switch                   | <b>91</b> |

| TDA 6000   | Video IF w/synch demodulator75 | 95        |

#### **Miscellaneous Entertainment**

| TDA 5660 P | VHF/UHF modulator705 | j |

|------------|----------------------|---|

| TDA 5660 X | VHF/UHF modulator749 | ) |

#### **SMPS Control**

| TDA 4600-3  | SMPS controller   | 3 |

|-------------|-------------------|---|

| TDA 4601 ;D | SMPS controller   | 9 |

| TDA 4605    | SMPS controller61 | 5 |

#### **Radio Tuners**

| S 042 P  | Mixer             | 49  |

|----------|-------------------|-----|

| TUA 1574 | FM tuner IC       | 875 |

| SDA 2120 | 120 MHz radio PLL | 165 |

## Summary of Types

$\sim$

Page

#### Radio IF

| S 041 P              | FM IF amplifier & demodulator 43 |

|----------------------|----------------------------------|

| TCA 440              | AM receiver                      |

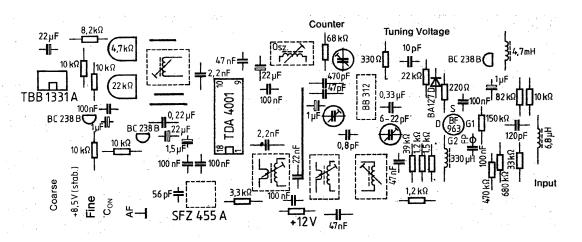

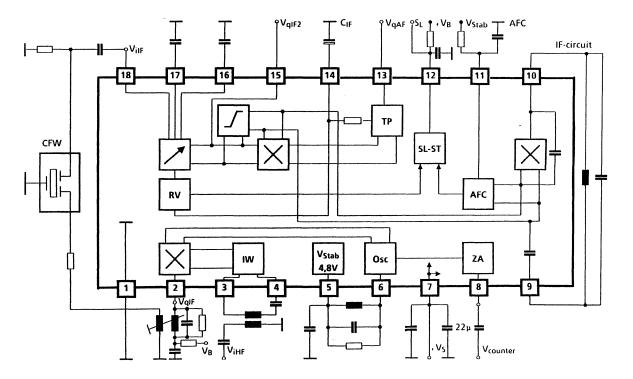

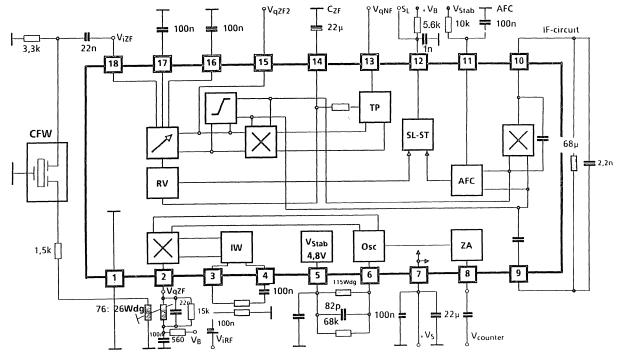

| TDA 4001             | AM receiver                      |

| TDA 4010             | AM receiver                      |

| TDA 4210-3           | FM IF for car radios541          |

| FM Stere             | o Decoders                       |

| TCA 4500 A           | FM Stereo decoder                |

| TCA 4511             | FM PLL stereo decoder            |

| Audio Po             | wer Amplifiers                   |

| TDA 1037             |                                  |

|                      | Audio power amplifier            |

| TDA 4930             | Audio power amplifier            |

|                      |                                  |

| TDA 4930<br>TDA 4935 | Audio power amplifier 2 x 10W    |

## **General Information**

-----

-

#### 2.1 Type-designation code for ICs

IC type designations are based on the European Pro Electron system. The code system is explained in the Pro Electron brochure D 15\*), edition 1985.

\*) Available from Pro Electron, Avenue Louise, 430 (B.12) B-1060 Brussels, Belgium

#### 2.2 Mounting instructions

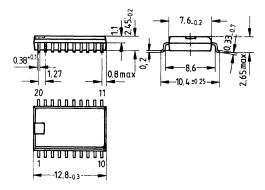

#### 2.2.1 Plastic package

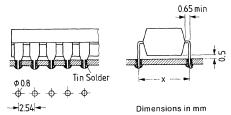

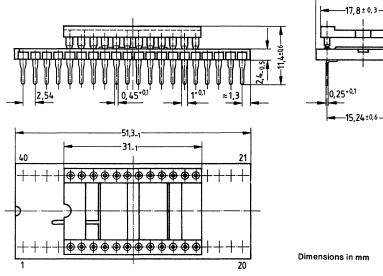

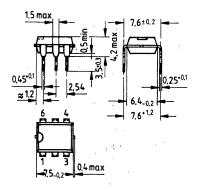

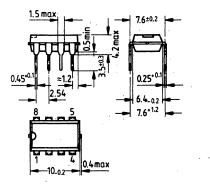

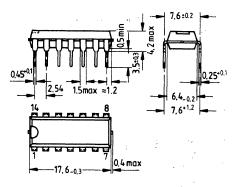

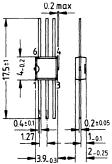

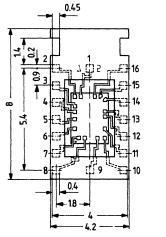

The pins of the cases are bent downwards by an angle of  $90^{\circ}$  and fit into holes with a diameter of between 0.7 and 0.9 mm spaced 2.54 mm apart. The dimension x is given in the corresponding drawing.

The bottom of the package will not touch the PC board after insertion because the pins have shoulders just below the package (see figure 1).

After insertion of the package into the PC board it is advisable to bend the ends of two pins at an angle of approx.  $30^{\circ}$  to the board so that the package does not have to be pressed down during soldering. Plastic packages are soldered on that side of the PCB facing away from the package.

The maximum permissible soldering temperature is  $300 \,^{\circ}$ C (max. 5 s) for manual soldering and  $260 \,^{\circ}$ C (max. 10 s) for dip soldering and wave soldering.

Figure 1

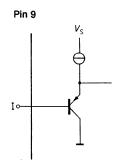

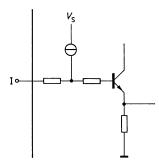

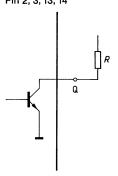

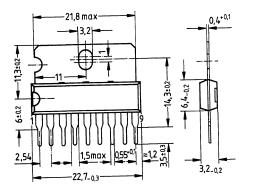

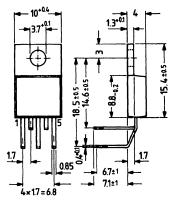

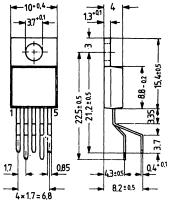

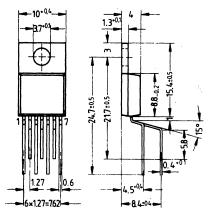

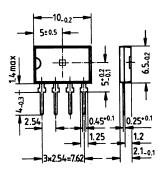

#### 2.2.2 Power package with 5, 7, or 9 pins

Power packages generally have wider pins than stated in paragraph 2.2.1, meaning that the hole diameter on the PCB must be between 1.1 and 1.8 mm. If the pins are bent, there should be no stress between the pins and the package. The minimum distance between the package and the bending point is 2 mm.

Refer to paragraph 2.2.1 for soldering temperatures.

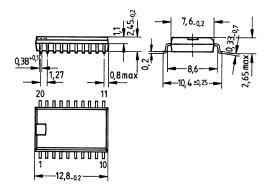

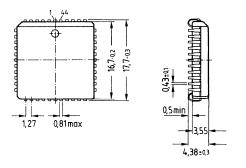

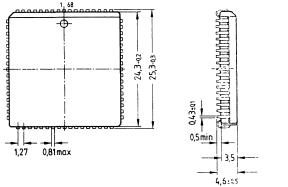

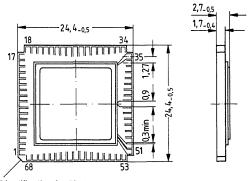

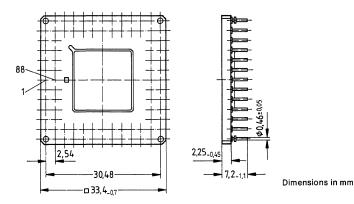

#### 2.2.3 Plastic packages (SO and PLCC) for surface mounting (SMD)

Iron soldering: soldering temperature 300 °C for max. 5 s; minimum distance between package and soldering point 1.5 mm package temperature max. 150 °C; no mechanical stress on the pins

Vapor phase soldering: soldering temperature 215 °C, max. soldering time 30 s

Wave soldering: (pins and package are dipped into the tin bath)

soldering temperature 260 °C, max. soldering time 3 s.

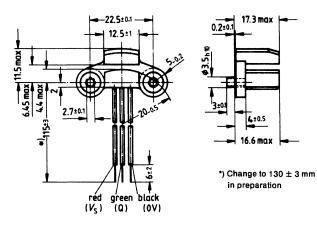

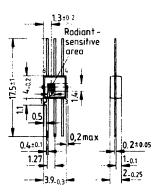

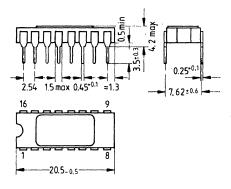

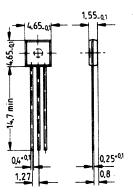

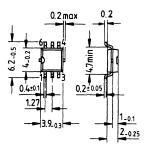

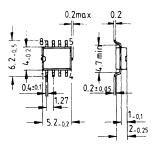

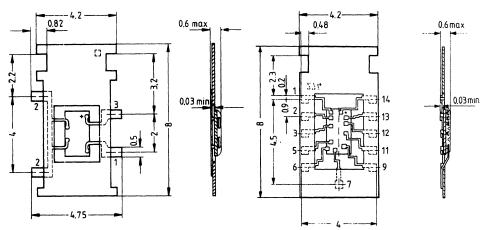

#### 2.2.4 5 H 8 DIN 41873 and similar packages

The package may be mounted in any position. The ends of the pins may be kinked up to a distance of 1.5 mm from the bottom of the package to suit the hole spacing **(fig. 2).**

Pins that are too long should be clipped before soldering.

Iron or dip soldering may be employed.

Maximum soldering duration for dip soldering at 250 °C bath temperature  $t_{max} = 5$  s at 300 °C bath temperature  $t_{max} = 4$  s for iron soldering at 250 °C iron temperature  $t_{max} = 15$  s

at 300 °C iron temperature  $t_{max} = 12 \text{ s}$

at 350 °C iron temperature  $t_{max} = 8 s$

Dimensions in mm

Figure 2

#### 2.2.5 Other points to note

Ensure that no current is able to flow between the solder bath or soldering iron and the PCB. It is advisable to ground the pins that are to be soldered as well as the solder bath or soldering iron.

When they are being prepared and inserted in a PCB, circuits should be protected against static charging. Under no circumstances may the components be removed or inserted whilst the operating voltage is switched on.

The increase in chip temperature during the soldering process results in a temporary increase in electrostatic sensitivity of integrated circuits. Special precautions should therefore be taken against line transients, e.g. through the switching of inductances on magnetic chutes, etc.

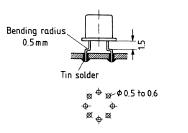

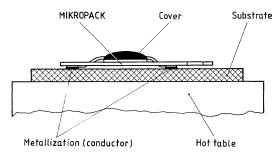

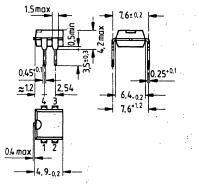

#### 2.2.6 MIKROPACK (SMD)

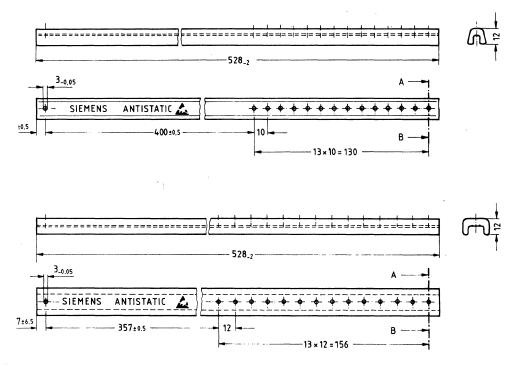

MIKROPACK components are delivered on film reels.

#### **Mounting suggestions**

- a) We recommend vapor phase soldering: soldering temperature 215 °C, soldering time max. 30 s

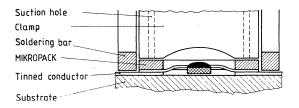

- b) For prototypes and small quantities (up to approximately 50.0 items/y), the hot table soldering method can also be used (fig. 3).

#### Figure 3

#### **Required equipment and accessories**

- cutting device

- hot table, temperature regulated (e.g. Weld-Equip, Unitek)

- stereo microscope (e.g. Wild, Zeiss, magnification 6 · · · 40 times)

- substrate material: epoxy resin; hard paper; ceramic (thick thin film)

#### Soldering data

- soldering temperature: 210 °C max.

- solder coating on substrate: Pb/Sn (e.g. 60/40) wave-tinned or electrodeposited

- soldering time: approx. 10 s

- flux: e.g. colophony, dissolved in alcohol

- cleaning agents (as required): e.g. Freon TP-35, TE, TF

c) For large quantities (e.g. more than 50.0 items/y) bar soldering is also suitable.

Figure 4

#### **Required equipment**

- soldering equipment (e.g. Weld-Equip, Farco, Jade)

- substrate material: epoxy resin; hard paper; flexible materials, e.g. polyamide

#### Soldering data

- soldering temperature: 210 °C max.

- solder coating on the substrate: Pb/Sn (e.g. 60/40), wave-tinned or electrodeposited

- soldering time: approx. 2 s

- flux: e.g. colophony dissolved in alcohol

- cleaning agents (as required): e.g. Freon TP-35, TE, TF

## **General Information**

#### 2.3 Processing guidelines for ICs

Integrated circuits (ICs) are electrostatic-sensitive (ESS) devices. The requirement for greater packing density has led to increasingly small structures on semiconductor chips, with the result that today every IC, whether bipolar, MOS, or CMOS, has to be protected against electrostatics.

MOS and CMOS devices generally have integrated protective circuits and it is hardly possible any more for them to be destroyed by purely static electricity. On the other hand, there is acute danger from electrostatic discharges (ESD).

Of the multitude of possible sources of discharge, charged devices should be mentioned in addition to charged persons. With low-resistive discharges it is possible for peak power amounting to kilowatts to be produced.

For the protection of devices the following principles should be observed:

- a) Reduction of charging voltage, below 200 V if possible. Means which are effective here are an increase in relative humidity to  $\geq 60\%$ and the replacement of highly charging plastics by antistatic materials.

- b) With every kind of contact with the device pins a charge equalization is to be expected. This should always be highly resistive (ideally  $R = 10^6$  to  $10^8 \Omega$ ).

All in all this means that ICs call for special handling, because uncontrolled charges, voltages from ungrounded equipment or persons, surge voltage spikes and similar influences can destroy a device. Even if devices have protective circuits (e.g. protective diodes) on their inputs, the following guidelines for their handling should nevertheless be observed.

#### 2.3.1 Identification

The packing of ESS devices is provided with the following label by the manufacturer:

#### 2.3.2 Scope

The guidelines apply to the storage, transport, testing, and processing of all kinds of ICs, equipped and soldered circuit boards that comprise such components.

#### 2.3.3 Handling of devices

- 1. ICs must be left in their containers until they are processed.

- 2. ICs may only be handled at specially equipped work stations. These stations must have work surfaces covered with a conductive material of the order of  $10^6$  to  $10^9 \Omega$ /cm.

- 3. With humidity of >50% a coat of pure cotton is sufficient. In the case of chargeable synthetic fibers the clothing should be worn close-fitting. The wrist strap must be worn snugly on the skin and be grounded across a resistor of 50 to 100 k $\Omega$ .

- 4. If conductive floors,  $R = 5 \times 10^4$  to  $10^7 \Omega$  are provided, further protection can be achieved by using so-called MOS chairs and shoes with a conductive sole ( $R \approx 10^5$  to  $10^7 \Omega$ ).

- 5. All transport containers for ESS devices and assembled circuit boards must first be brought to the same potential by being placed on the work surface or touched by the operator before the individual devices may be handled. The potential equalization should be across a resistor of  $10^6$  to  $10^8 \Omega$ .

- 6. When loading machines and production devices it should be noted that the devices come out of the transport magazine charged and can be damaged if they touch metal, e.g. machine parts.

Example 1) conductive (black) tubes.

The devices may be destroyed in the tube by charged persons or come out of the tube charged if this is emptied by a charged person.

Conductive tubes may only be handled at ESS work stations (high-resistance work-station and person grounding).

Example 2) anti-static (transparent) tubes.

The devices cannot be destroyed by charged persons in the tube (there may be a rare exception in the case of custom ICs with unprotected gate pins). The devices can be endangered as in 1) when the tube is emptied if the latter, especially at low humidity, is no longer sufficiently anti-static after a long period of storage (> 1 year).

In both cases damage can be avoided by discharging the devices across a grounded adapter of high-resistance material ( $\approx 10^6$  to  $10^8 \Omega$ /cm) between the tube and the machine.

The use of metal tubes – especially of anodized aluminum – is not advisable because of the danger of low-resistance device discharge.

#### 2.3.4 Storage

ESS devices should only be stored in identified locations provided for the purpose. During storage the devices should remain in the packing in which they are supplied. The storage temperature should not exceed  $60 \,^{\circ}$ C.

#### 2.3.5 Transport

ESS devices in approved packing tubes should only be transported in suitable containers of conductive or longterm anti-static-treated plastic or possibly unvarnished wood. Containers of high-charging plastic or very low-resistance materials are in like manner unsuitable.

Transfer cars and their rollers should exhibit adequate electrical conductivity ( $R < 10^6 \Omega$ ). Sliding contacts and grounding chains will not reliably eliminate charges.

#### 2.3.6 Incoming inspection

In incoming inspection the above guidelines should be observed. Otherwise any right to refund or replacement if devices fail inspection may be lost.

#### 2.3.7 Material and mounting

- The drive belts of machines used for the processing of the devices, in as much as they come into contact with them (e.g. bending and cutting machines, conveyor belts), should be treated with anti-static spray (e.g. anti-static spray 100 from Kontaktchemie). It is better, however, to avoid the contact completely.

- If ESS devices have to be soldered or desoldered manually, soldering irons with thyristor control may not be used. Siemens EMI-suppression capacitors of the type B 81711-B31...-B36 have proven very effective against line transients.

- Circuit boards fitted and soldered with ESS devices are always to be considered as endangered.

#### 2.3.8 Electrical tests

- 1. The devices should be processed with observation of these guidelines. Before assembled and soldered circuit boards are tested, remove any shorting rings.

- 2. Test sockets must not be conducting any voltage when individual devices or assembled circuit boards are inserted or withdrawn, unless works' specifications state otherwise. Ensure that the test devices do not produce any voltage spikes, either when being turned on and off in normal operation or if the power fuse blows or other fuses respond.

- 3. Signal voltages may only be applied to the inputs of ICs when or after the supply voltage is turned on. They must be disconnected before or when the supply voltage is turned off.

- 4. Observe any notes and instructions in the respective data books.

#### 2.3.9 Packing of assembled PC boards or flatpack units

The packing material should exhibit low volume conductivity:  $10^5 \ \Omega/cm < \rho < 10^{10} \ \Omega/cm$ .

In most cases – especially with humidity of >40% – this requirement is fulfilled by simple corrugated board. Better protection is obtained with bags of conductive polyethylene foam (e.g. RCAS 1200 from Richmond of Redlands, California).

One should always ensure that boards cannot touch.

In special cases it may be necessary to provide protection against strong electric fields, such as can be generated by conveyor belts for example. For this purpose a sheath of aluminum foil is recommended, although direct contact between the film and the PCB must be avoided. Cardboard boxes with an aluminum-foil lining, such as those used for shipping our devices, are available from Laber of Munich.

#### 2.3.10 Ultrasonic cleaning of ICs

The following recommendation applies to plastic packages. For cavity packages (metal and also ceramic) separate regulations have to be observed.

Freon and isopropyl alcohol (trade name: propanol) can be used as solvents. These solvents can also be used for plastic packages because they do not eat into the plastic material.

An ultrasonic bath in double halfwave operation is advisable because of the low component stress.

The ultrasonic limits are as follows:

| sound frequency            | f | >40 kHz                       |

|----------------------------|---|-------------------------------|

| exposure                   | t | <2 min                        |

| alternating sound pressure | р | <0.29 bar                     |

| sound power                | Ν | <0.5 W/cm <sup>2</sup> /liter |

#### 2.4 Data classification

#### **Maximum ratings**

Maximum ratings are absolute ratings; exceeding only one of these values may cause irreversible damage to the integrated circuit.

#### Characteristics

The listed characteristics are ensured over the operating range of the integrated circuit. Typical characteristics specify mean values expected over the production spread. If not otherwise specified, typical characteristics will apply at  $T_A = 25$  °C and for the given supply voltage.

#### **Operating range**

In the operating range the functions given in the circuit description will be fulfilled.

#### 2.5 Quality Assurance

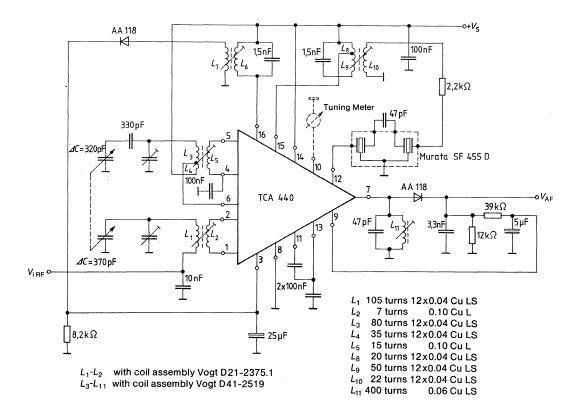

#### 2.5.1 Quality Assurance System

The high quality and reliability of integrated circuits from Siemens is the result of a carefully arranged production which is systematically checked and controlled at each production stage.

The procedures are subject to a quality assurance system; full details are given in the brochure 'Siemens Quality Assurance System – Integrated Circuits' (SQS-IC).

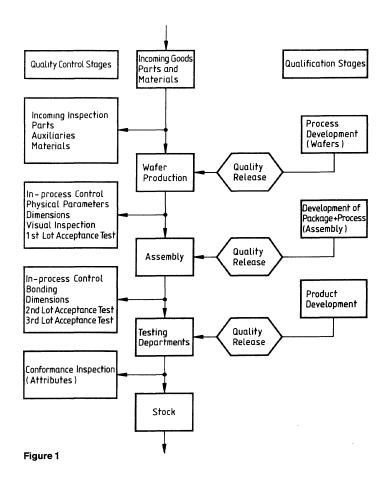

**Figure 1** shows the most important stages of the "SQS-IC". A quality assurance (QA) department which is independent of production and development, is responsible for the selected control measures, acceptance procedures, and information feedback loops. This department has state-of-the-art test and measuring equipment at its disposal, works according to approved methods of statistical quality control, and is provided with facilities for accelerated life and environmental tests used for both qualification and routine monitoring tests.

The latest methods and equipment for preparation and analysis are employed to achieve continuity of quality and reliability.

#### 2.5.2 Conformance

Each integrated circuit is subjected to a final test at the end of the production process. These tests are carried out by computer-controlled, automatic test systems because hundreds of thousands of operating conditions as well as a large number of static and dynamic parameters have to be considered. Moreover, the test systems are extremely reliable and reproducible. The quality assurance department carries out a final check in the form of a lot-by-lot sampling inspection to additionally ensure this minimum percent defectives as well as the acceptable quality level (AQL). Sampling inspection is performed in accordance with the inspection plans of DIN 40080, as well as of the identical MIL-STD-105 or IEC 410.

The table shows the results of such sampling inspections performed with hundreds of thousands of ICs during 1985. These results correspond to the average outgoing quality (AOQ), and are specified as defectives per million (DPM).

|                                  | AOQ<br>(DPM) | Sum of<br>electrical<br>defectives<br>AOQ<br>(DPM) | Sum of<br>mechanical<br>defectives<br>AOQ<br>(DPM) |

|----------------------------------|--------------|----------------------------------------------------|----------------------------------------------------|

| SSI/MSI<br>≤1000 gate functions  | 40 ···       | 200                                                | 100                                                |

| LSI/VLSI<br>≥1000 gate functions | 120          | 400                                                | 200                                                |

#### 2.5.3 Reliability

#### 2.5.3.1 Measures Taken during Development

The reliability of ICs is already considerably influenced at the development stage. Siemens has, therefore, fixed certain design standards for the development of circuit and layout, specifying e.g. minimum width and spacing of conductive layers on a chip, dimensions and electrical parameters of protective circuits for electrostatic charge, etc. An examination with the aid of carefully arranged programs operated on large-scale computers, guarantees the immediate identification and elimination of unintentional violations of these design standards.

#### 2.5.3.2 In-Process Control during Production

The manufacturing of integrated circuits comprises several hundred production steps. As each step is to be executed with utmost accuracy, the in-process control is of outstanding importance. Some processes require more than a hundred different test measures. The tests have been arranged such that the individual process steps can be reproduced continuously. The decreasing failure rates reflect the never ending effort in this direction; in the course of the years they have been reduced considerably despite an immense rise in the IC's complexity.

So in 1985 the typical random failure rates estimated for accelerated life tests with almost 2 million ICs of all complexities are found to be around 80 fit.

#### 2.5.3.3 Reliability Monitoring

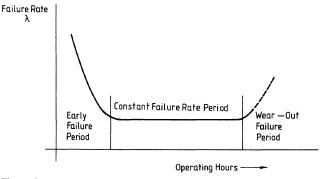

The general course of the IC's failure rate versus time is shown by a so-called "bathtub" curve (figure 2). The failure rate has its peak during the first few operating hours (early failure period). After the early failure period has decayed, the "constant" failure rate period starts during which the failures may occur at an approximately uniform rate. This period ends with a repeated rise of the curve during the wear-out failure period. For ICs, however, the latter period usually lies far beyond the service life specified for the individual equipment.

#### Figure 2

Reliability tests for ICs are usually destructive examinations. They are, therefore, carried out with samples. Most failure mechanisms can be accelerated by means of higher temperatures. Due to the temperature dependence of the failure mechanisms, it is possible to simulate future operational behavior within a short time by applying high temperatures; this is called life test.

The acceleration factor B for the life test can be obtained from the Arrhenius equation

$$B = \exp\left(\frac{E_{A}}{k_{1}}\left(\frac{1}{T_{1}}-\frac{1}{T_{2}}\right)\right)$$

where  $T_2$  is the temperature at which the life test is performed,  $T_1$  is the assumed operating temperature, and k is the Boltzmann constant.

Important for factor *B* is the activation energy  $E_A$ . It lies between 0.3 and 1.3 eV and differs considerably for individual failure mechanisms.

For all Siemens ICs, the reliability data from life tests is converted to an operating temperature of  $T_A = 40$  °C, assuming an average activation energy of 0.4 eV. The acceleration factor for life tests at 125 °C is thus 24, compared with operational behavior. This method considers also failure mechanisms with low activation energy, i.e. which are only slightly accelerated by the temperature effect.

Various reliability tests are periodically performed with IC types that are representative of a certain production line – this is described in the brochure "SQS-IC". Such tests are e.g. humidity test at 85°C and 85% relative humidity, pressure cooker test, as well as life tests up to 1000 hours and more. Test results are available in the form of summary reports. ----

#### 2.6 Summary of terms and symbols in alphabetical order

|                                 | y or torino and oynibolo in alphaboli |

|---------------------------------|---------------------------------------|

| A, B                            | Indices for limit value               |

| AC                              | Alternating current                   |

| AF                              | Audio frequency                       |

| AM                              | Amplitude modulation                  |

| B                               | Bandwidth                             |

| -                               |                                       |

| С                               | Capacitance                           |

| C <sub>i</sub> , C <sub>l</sub> | Input capacitance                     |

| C <sub>CLK</sub> , Cø           | Clock capacitor                       |

| CLK                             | Clock                                 |

| DC                              | Direct current                        |

| D                               | Differential                          |

| f                               | Frequency                             |

| Δf                              | Frequency deviation                   |

| FM                              | Frequency modulation                  |

| f <sub>i</sub> , f <sub>l</sub> | Input frequency                       |

| $f_q, f_Q$                      | Output frequency                      |

| G                               | Gain                                  |

| G                               | giga (10 <sup>9</sup> )               |

| GND                             | Ground                                |

| Hy                              | Hysteresis                            |

| Hz                              | Cycles per second (Hertz)             |

| i. I                            | Input                                 |

| I, I                            | Current                               |

|                                 | Current consumption                   |

| I <sub>S</sub><br>IF            | •                                     |

|                                 | Intermediate frequency                |

| k                               | kilo (10 <sup>3</sup> )               |

| ĸ                               | Kelvin                                |

| L                               | Inductance                            |

| m                               | Milli $(10^{-3})$                     |

| м                               | Mega (10 <sup>6</sup> )               |

| m                               | Modulation factor                     |

| MW                              | Medium wave                           |

| N, n                            | Noise                                 |

| 0                               | Offset                                |

| OSC                             | Oscillator                            |

| P, P <sub>V</sub>               | Power dissipation                     |

| P <sub>tot</sub>                | Max. perm. power dissipation          |

| рр                              | Peak-to-peak                          |

| q, Q                            | Output                                |

| Q, Q <sub>B</sub>               | Q-factor                              |

| -, -, B<br>R                    | Resistance                            |

| R <sub>th JC</sub>              | Thermal resistance (junction-case)    |

| R <sub>th SC</sub>              | Thermal resistance (system-case)      |

|                                 | Thermal resistance (system-air)       |

| R <sub>th SA</sub><br>RF        | Radio frequency                       |

|                                 | naulo nequency                        |

| <u>S + N</u><br>N               | Signal-to-noise ratio            |

|---------------------------------|----------------------------------|

| т                               | Cycle time                       |

| Т                               | Temperature                      |

| тс                              | Temperature coefficient          |

| t                               | Time                             |

| TA                              | Ambient temperature in operation |

| T <sub>stq</sub>                | Storage temperature              |

| Tj                              | Junction temperature             |

| t <sub>H</sub>                  | Hold time                        |

| t <sub>i</sub>                  | Input pulse duration             |

| t <sub>n</sub>                  | Instant prior to clock pulse     |

| t <sub>n+1</sub>                | Instant after clock pulse        |

| t <sub>P</sub>                  | Average pulse transit time       |

| t <sub>pd</sub>                 | Pulse delay time                 |

| t <sub>P HL</sub>               | HL pulse transit time            |

| t <sub>P LH</sub>               | LH pulse transit time            |

| t <sub>pl</sub>                 | Input pulse duration             |

| t <sub>p Q</sub>                | Output pulse duration            |

| t <sub>p R</sub>                | Reset pulse duration             |

| t <sub>pS</sub>                 | Set pulse duration               |

| t <sub>p CLK</sub>              | Clock pulse duration             |

| t <sub>pZ</sub>                 | Count pulse duration             |

| t <sub>s</sub>                  | Set-up time                      |

| t <sub>T</sub>                  | Signal transition time           |

| t <sub>t</sub>                  | Dead time                        |

| t <sub>Q</sub>                  | Output pulse duration            |

| t <sub>T HL</sub>               | HL transition time               |

| t <sub>T LH</sub>               | LH transition time               |

| THD                             | Total harmonic distortion        |

| V                               | Volt                             |

| V, v                            | Voltage, general                 |

| V <sub>Hy</sub>                 | Hysteresis voltage               |

| V <sub>i</sub> , V <sub>I</sub> | Input voltage<br>Output voltage  |

| V <sub>q</sub> , V <sub>Q</sub> | Reverse voltage                  |

| V <sub>R</sub>                  | Supply voltage                   |

| V <sub>S</sub><br>W             | Watt                             |

|                                 | Impedance                        |

| Z<br>Z                          | Zener                            |

| <b>~</b>                        | 20101                            |

## **Technical Data**

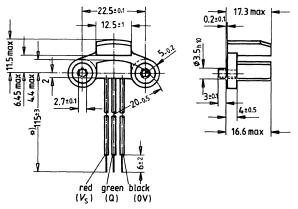

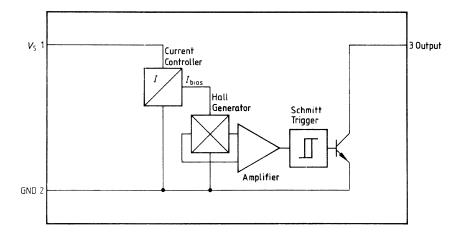

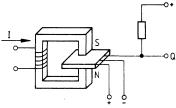

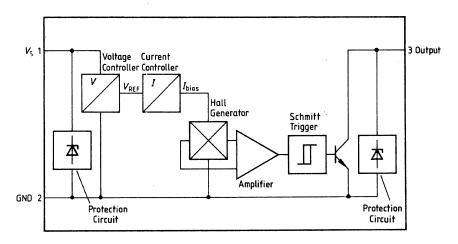

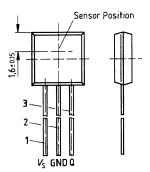

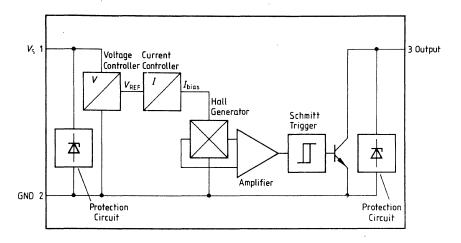

The Hall-effect vane switch HKZ 101 is a contactless switch consisting of a monolithic integrated Hall-effect circuit and a special magnetic circuit hermetically sealed in a plastic package. The switch is actuated by a shoft-iron vane which is passed through the air gap between magnet and Hall sensor.

The main application field is in cars, i.e. as a breakerless trigger in electronic ignition systems. Numerous industrial applications can be found in control engineering, especially in those areas where switches must operate maintenance-free under harsh environmetal conditions (e.g. rpm sensor, limit switch, position sensor, speed measurement, shaft encoder, scanning of coding disks, etc.).

#### Features

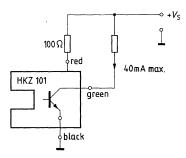

- Contactless switch with open collector output (40 mA)

- Static switching

- High switching frequency

- Hermetically sealed with plastic

- Unaffected by dirt, light, vibration

- Large temperature and voltage range

- Integrated overvoltage protection

- High interference immunity

#### Special package

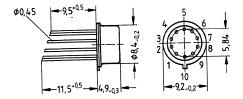

\*)Change to 130±3mm in preparation

#### Function

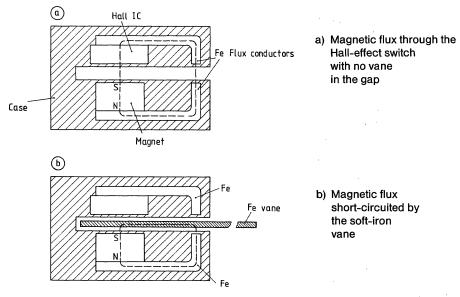

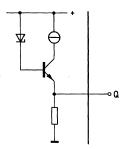

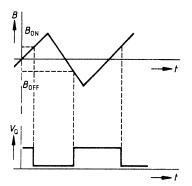

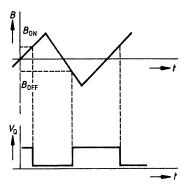

The Hall-effect switch is actuated by a soft-iron vane that passes through the air gap between magnet and Hall-effect sensor. The vane short-circuits the magnetic flux before the Hall-effect sensor, as shown in figure 1. The open collector output is conductive (LOW) when the vane is outside the air gap, and blocks (HIGH) when the vane is introduced into the air gap. The output remains HIGH as long as the vane remains in the air gap. This static function does not require a minimum operating frequency. The output signal shape is independent of the operating frequency.

The circuit features integrated overvoltage protection against most of the voltage peaks occurring in automotive and industrial applications. The output stage has a Schmitt trigger characteristic. Most electronic circuits can be driven directly due to the open collector output current of max. 40 mA.

**Principle of operation**

Figure 1

#### Mechanical characteristics

The Hall-effect vane switch is hermetically sealed in a special plastic, so that it can also be used under harsh environmental conditions. The package is waterproof, vibration-resistant and resistant to gasoline, oil and salt. Two tubular rivets are incorporated in the package to mount the sensor on its carrier plate. The circuit has three flexible leads for power supply and output.

#### **Application notes**

· · · · ·

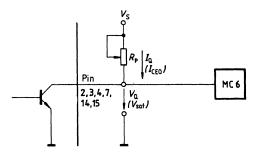

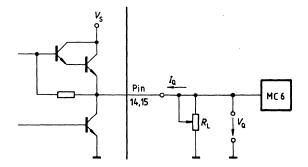

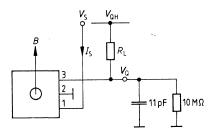

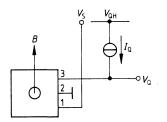

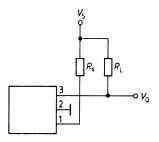

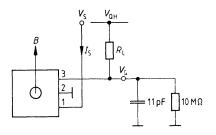

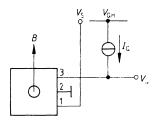

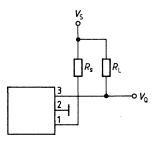

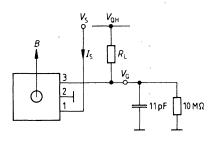

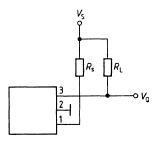

The output current of the "open collector" must be limited to the maximum permissible value by a load resistor adapted to the application.

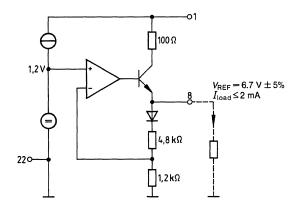

For optimum efficiency of the integrated overvoltage protection, it is suggested that a resistor of approx. 100  $\Omega$  be provided in the component's power supply to limit the current.

| Maximum ratings                                                                                                                                                                                                                                  |                                                                                                                                                        | Test conditions                                                                              | Lower<br>limit B                             | Upper<br>limit A                                       |                                            |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|----------------------------------------------|--------------------------------------------------------|--------------------------------------------|

| Supply voltage<br>Output voltage in OFF-state<br>Inverse supply current<br>(limited externally)<br>Output current<br>Inverse output current<br>Ambient temperature<br>during operation<br>Storage temperature<br>Thermal resistance (system-air) | V <sub>S</sub><br>V <sub>Q</sub><br>-I <sub>S</sub><br>I <sub>Q</sub><br>-I <sub>Q</sub><br>T <sub>amb</sub><br>T <sub>stg</sub><br>R <sub>th SA</sub> | $T_{amb} = 25 ^{\circ}C$<br>$T_{amb} \le 80 ^{\circ}C$<br>$t \le 1 \text{h}$<br>without vane | -1.2<br>-0.8<br>-40<br>-40                   | 24<br>30<br>30<br>200<br>40<br>30<br>135<br>150<br>170 | V<br>V<br>W<br>MA<br>MA<br>°C<br>°C<br>K/W |

| Operating range                                                                                                                                                                                                                                  |                                                                                                                                                        |                                                                                              |                                              |                                                        |                                            |

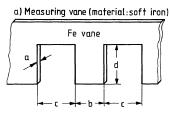

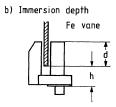

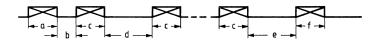

| Ambient temperature<br>Supply voltage<br>Vane <sup>1</sup> ): thickness<br>width<br>gap length<br>immersion depth<br>gap height                                                                                                                  | T <sub>amb</sub><br>V <sub>S</sub><br>a<br>b<br>c<br>h<br>d                                                                                            |                                                                                              | -40<br>4.5<br>0.5<br>8<br>8<br>4.6<br>17.3-h | 130<br>24<br>9                                         | °C<br>V<br>mm<br>mm<br>mm<br>mm            |

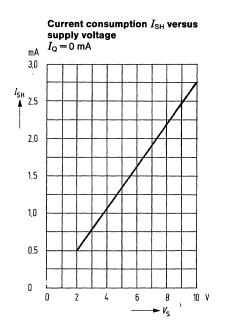

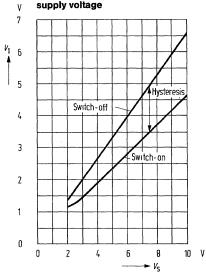

| Characteristics<br>$V_{\rm S} = 5$ V to 18 V;<br>$T_{\rm amb} = -30$ °C to 130 °C |                                       | Test conditions                                                                                                                               | Lower<br>limit B | Upper<br>limit A |                |

|-----------------------------------------------------------------------------------|---------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|------------------|------------------|----------------|

| Output saturation voltage                                                         | V <sub>Q sat</sub>                    | without vane<br>$I_Q = 40 \text{ mA}$<br>$T_{amb} = -30 \text{ to } 110 ^{\circ}\text{C}$<br>$T_{amb} = 110 \text{ to } 130 ^{\circ}\text{C}$ |                  | 0.4              | v              |

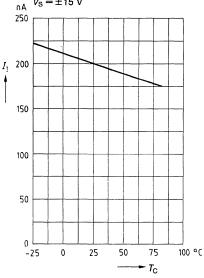

| Output reverse current<br>Supply current<br>Delay time                            | $I_{QR}$<br>$I_S$<br>$t_{LH}, t_{HL}$ | with vane<br>without vane<br>$I_Q = 40 \text{ mA}$                                                                                            |                  | 10<br>12<br>1    | μA<br>mA<br>μs |

| Overvoltage protection                                                            |                                       |                                                                                                                                               |                  |                  |                |

| – Supply voltage (V <sub>S</sub> )<br>– Output (V <sub>Q</sub> )                  | V <sub>SZ</sub><br>V <sub>S0</sub>    | $I_{\rm S}$ = 16 mA<br>$I_{\rm S}$ = 16 mA                                                                                                    | 32<br>32         | 42<br>42         | v<br>v         |

#### Switching point characteristics

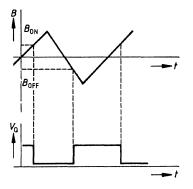

#### Definitions

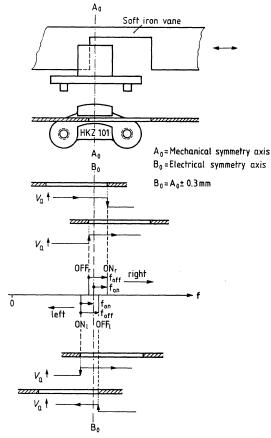

In most applications, the switching point is set exactly by mechanical adjustment, thus compensating all mechanical tolerances in the system including the scatter of the Hall-effect vane switch. For the function of the device in operation, only the deviations of those characteristics depending on temperature and operating voltage are important.

The characteristic values of the switching points are, therefore, not directly referred to the mechanical dimensions of the vane switch, but to an electrically defined symmetry  $B_0$  according to formula 1):

1)

$$B_0 = (ON_{left} + OFF_{left} + ON_{right} + OFF_{right})$$

: 4

$B_0 = A_0 \pm 0.3 \text{ mm}$

The definition of the operate and release points is shown in figure 2.

Operate point  $f_{ON}$  is obtained by subtracting the measured ON operate value from the reference point  $B_0$ :

2)  $f_{ON} = ON_{right} - B_0 = B_0 - ON_{left}$

The release point  $f_{\text{OFF}}$  is calculated from the difference between the appropriate ON and OFF points:

3)  $f_{OFF} = ON_{right} - OFF_{right} = OFF_{left} - ON_{left}$

$f_{ON 0}$  and  $f_{OFF 0}$  are the switching points measured for the individual component under normal conditions ( $V_{S} = 12$  V,  $T_{amb} = 25$  °C) within the characteristic device deviation

The deviations of the operate and release points are defined according to 4):

4)  $\Delta f_{ON} = f_{ON} - f_{ON0}$  $\Delta f_{OFF} = f_{OFF} - f_{OFF0}$

# Switching point definitions

41

# Mechanical measurement conditions

Figure 3

#### Switching point characteristics

Vane: a = 0.75 mm, b = 8 mm, c = 10 mm Position: center of air gap  $V_s = 5$  V to 18 V

|               |                    | Test conditions                                               | Lower<br>limit B | typ   | Upper<br>limit A |    |

|---------------|--------------------|---------------------------------------------------------------|------------------|-------|------------------|----|

| HKZ 101       |                    |                                                               | 1                |       |                  |    |

| Operate point | fono               | $V_{\rm S} = 12 \text{ V}, T_{\rm amb} = 25 ^{\circ}\text{C}$ | 0.85             | 1.45  | 2.05             | mm |

| Deviations    | $\Delta f_{ON}$    | $T_{\rm amb} = -30$ to 25 °C                                  | -0.4             | +0.15 | +0.7             | mm |

|               |                    | $T_{\rm amb} = 25$ to 80 °C                                   | -0.2             | +0.15 | +0.4             | mm |

|               |                    | $T_{\rm amb} = 80 \text{ to } 130 ^{\circ}\text{C}$           | -0.4             | +0.2  | +0.7             | mm |

| Release point | f <sub>OFF 0</sub> | $V_{\rm S} = 12 \text{ V}, T_{\rm amb} = 25 ^{\circ}\text{C}$ | 1.54             | 2.54  | 3.54             | mm |

| Deviations    | $\Delta f_{OFF}$   | $T_{\rm amb} = -30$ to 25 °C                                  | -0.8             | +0.3  | 1.4              | mm |

|               |                    | $T_{\rm amb} = 25$ to 80 °C                                   | -0.4             | +0.3  | 0.8              | mm |

|               |                    | $T_{amb} = 80 \text{ to } 130 ^{\circ}\text{C}$               | -0.8             | +0.4  | 1.4              | mm |

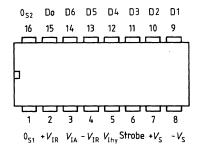

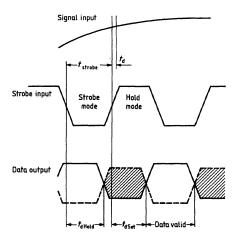

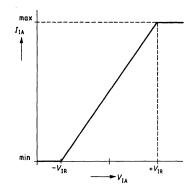

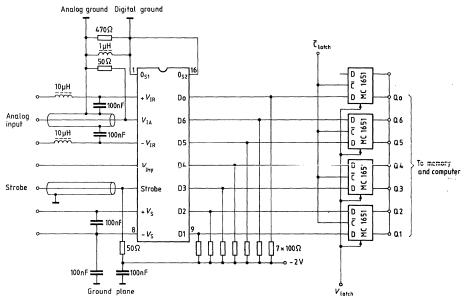

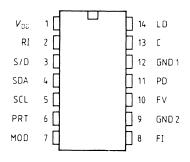

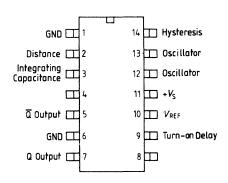

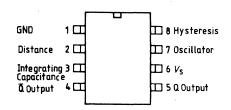

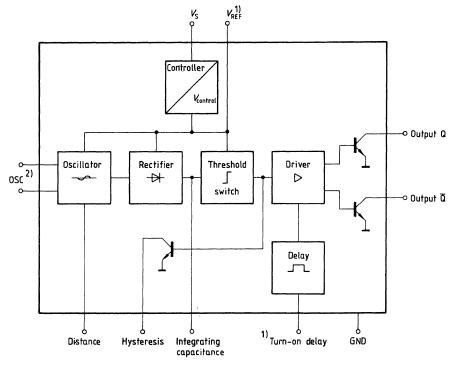

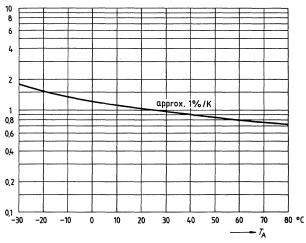

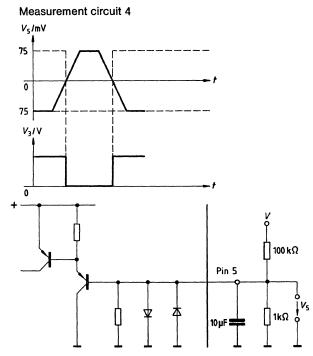

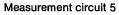

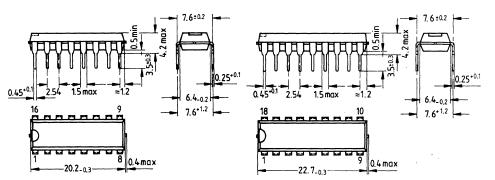

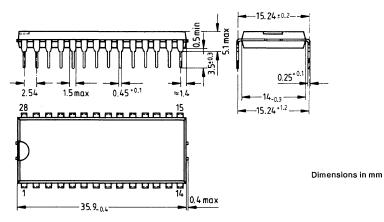

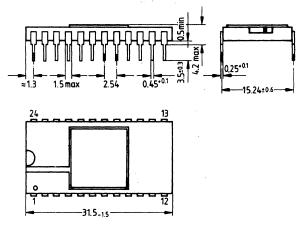

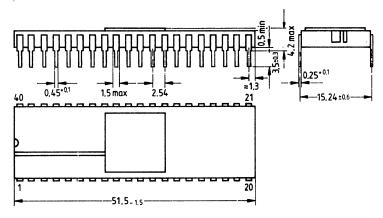

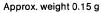

#### DIP 16

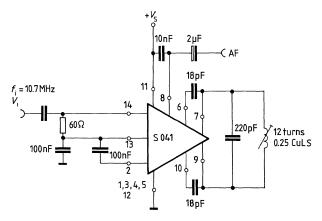

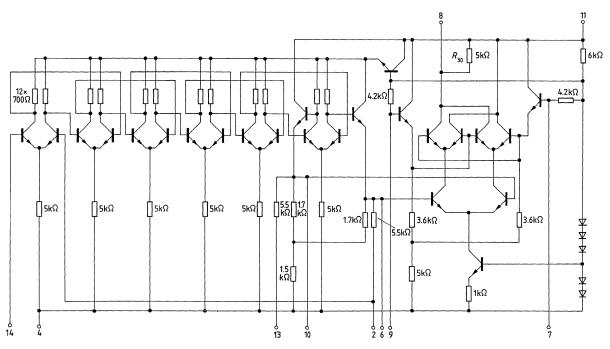

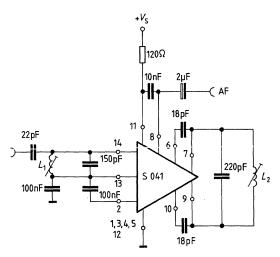

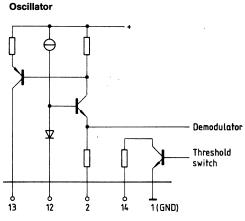

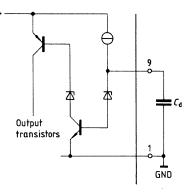

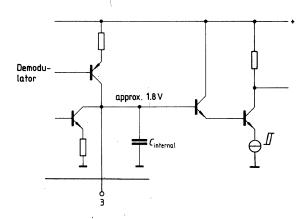

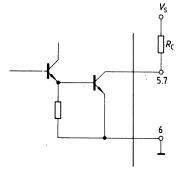

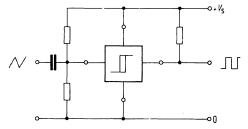

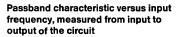

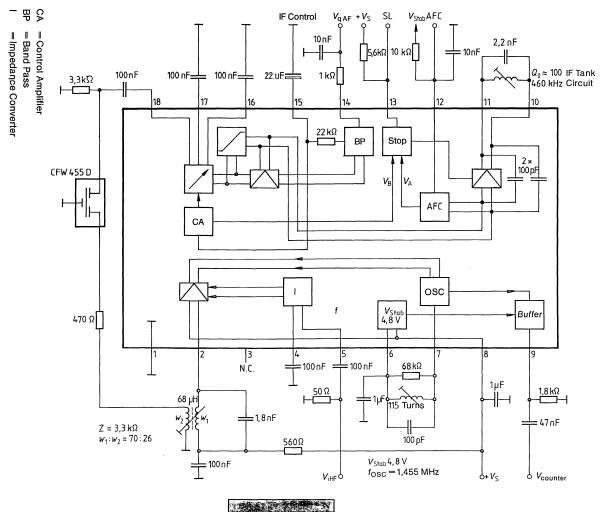

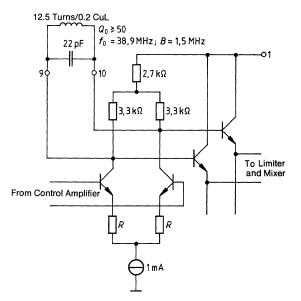

S 041 P is a symmetrical, six-stage amplifier with symmetrical coincidence demodulator for amplifying, limiting, and demodulating frequency-modulated signals. The IC is particularly suited for sets where low current consumption is of importance, or where major supply fluctuations occur.

The pin configuration corresponds to the well-known TBA 120. Pin 5 of S 041 P, however, is not connected internally. These types are especially suited for applications in narrow-band FM systems (455 kHz) and in conventional or standard FM IF systems (10.7 MHz).

#### Features

Topart.

- Good limiting properties

- Wide voltage range

- Low current consumption

- Few external components

| Maximum ratings                                                      |         |                                                      |                                 |                |

|----------------------------------------------------------------------|---------|------------------------------------------------------|---------------------------------|----------------|

| Supply voltage<br>Junction temperature<br>Storage temperature range  |         | Vs<br>Tj<br>T <sub>stg</sub>                         | 15<br>150<br>—40 to 125         | v<br>°C<br>°C  |

| Thermal resistance (system-air)                                      | S 041 P | R <sub>th SA</sub>                                   | 90                              | κ/w            |

| Operating range                                                      |         |                                                      |                                 |                |

| Supply voltage range<br>Frequency range<br>Ambient temperature range |         | V <sub>S</sub><br>f <sub>i</sub><br>T <sub>amb</sub> | 4 to 15<br>0 to 35<br>−25 to 85 | V<br>MHz<br>°C |

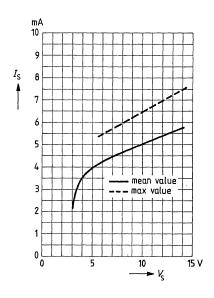

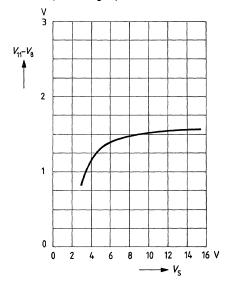

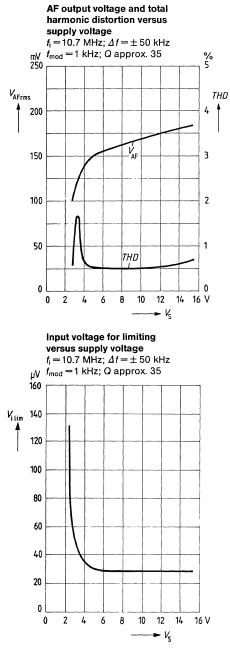

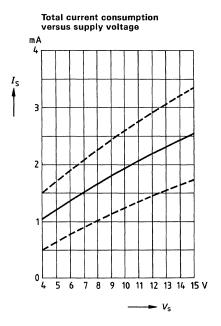

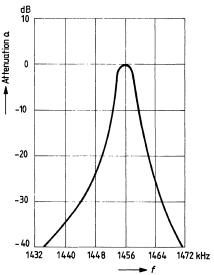

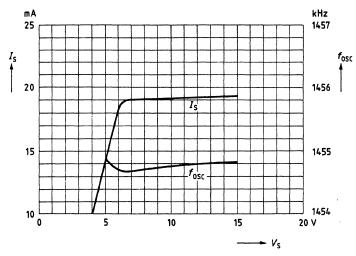

|                                                                                                                                                            |                                                        | min        | typ            | max | 1 P            |

|------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|------------|----------------|-----|----------------|

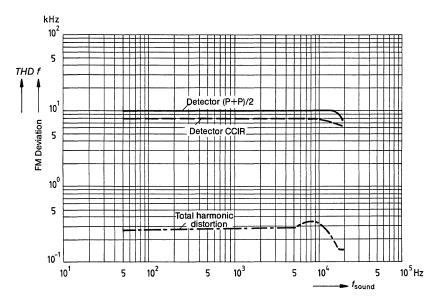

| Current consumption<br>AF output voltage<br>( $f_i = 10.7 \text{ MHz}$ , $\Delta f = \pm 50 \text{ kHz}$ , $V_i = 10 \text{ mV}$ )                         | I <sub>S</sub><br>V <sub>q rms</sub>                   | 4.0<br>100 | 5.4<br>170     | 6.8 | mA<br>mV       |

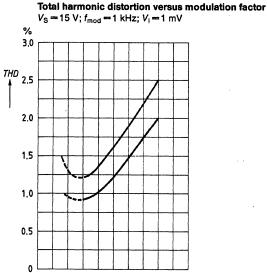

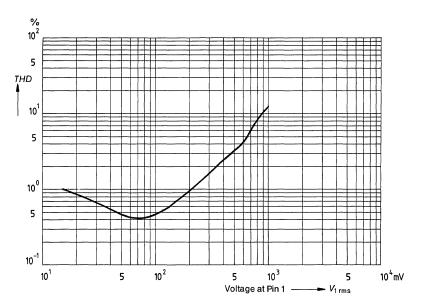

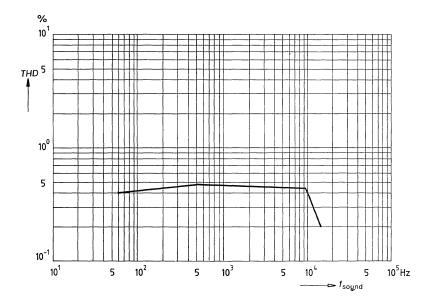

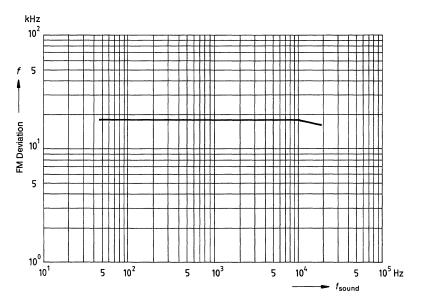

| Total harmonic distortion<br>( $f_i = 10.7 \text{ MHz}$ , $\Delta f = \pm 50 \text{ kHz}$ , $V_i = 10 \text{ mV}$ )                                        | THD                                                    |            | 0.55           | 1.0 | %              |

| Deviation of AF output voltage<br>( $V_{\rm S}$ = 15 V $\rightarrow$ 4 V, $f_{\rm i}$ = 10.7 MHz,<br>$\Delta f$ = ± 50 kHz)                                | ∆Vq                                                    |            | 1.5            |     | dB             |

| Input voltage for limiting $(f_i = 10.7 \text{ MHz}, \Delta f = \pm 50 \text{ kHz})$                                                                       | V <sub>i lim</sub>                                     |            | 30             | 60  | μV             |

| IF voltage gain (f <sub>i</sub> = 10.7 MHz)<br>IF output voltage for limiting                                                                              | Gν                                                     |            | 68             |     | dB             |

| (each output)                                                                                                                                              | Vqpp                                                   |            | 130            |     | mV             |

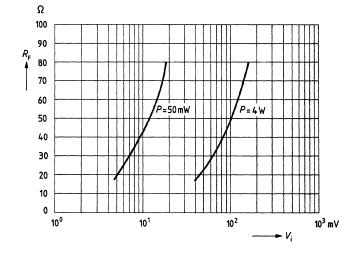

| Input impedance $f_i = 10.7 \text{ MHz}$<br>$f_i = 455 \text{ kHz}$                                                                                        | $Z_i$<br>$Z_i$                                         |            | 20/2<br>50/4   |     | kΩ/pF<br>kΩ/pF |

| Output resistance (pin 8)<br>Voltage drop at AF ballast resistance<br>AM suppression<br>( $V_i = 10 \text{ mV}, \Delta f = \pm 50 \text{ kHz}, m = 30\%$ ) | R <sub>q</sub><br>V <sub>11-8</sub><br>a <sub>AM</sub> | 3.5        | 5<br>1.5<br>60 | 8.5 | kΩ<br>V<br>dB  |

|                                                                                                                                                            |                                                        |            |                |     |                |

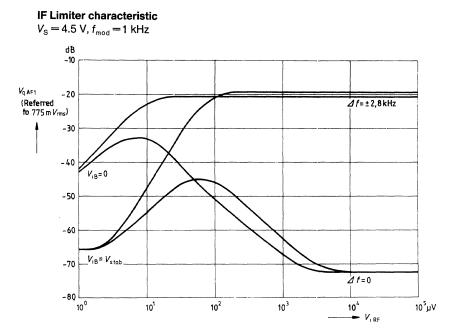

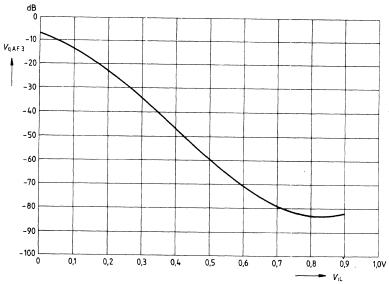

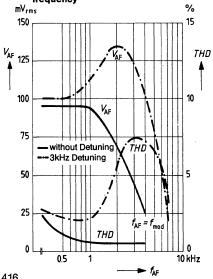

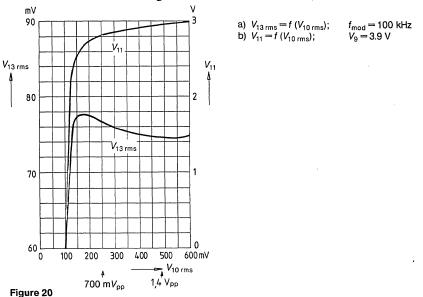

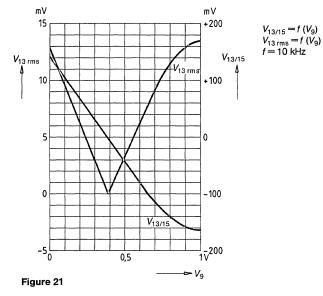

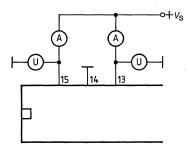

# Characteristics ( $V_{\rm S} = 12$ V, Q approx. 35, $f_{\rm mod} = 1$ kHz, $T_{\rm amb} = 25$ °C)

All connections mentioned in the index refer to S 041 P (e.g.  $V_{11}$ )

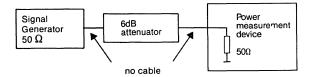

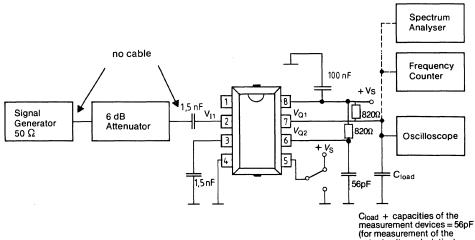

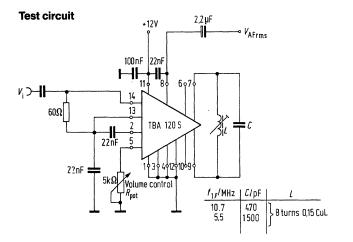

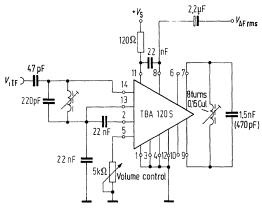

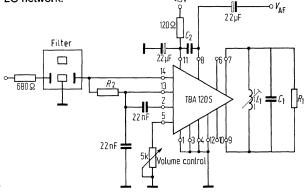

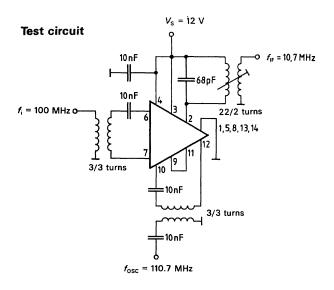

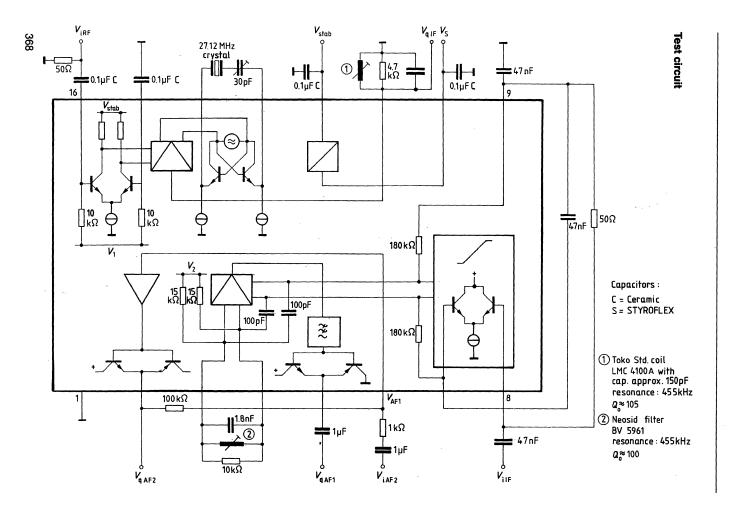

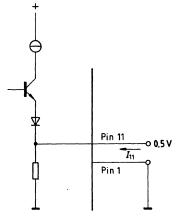

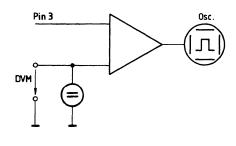

## Test circuit

44

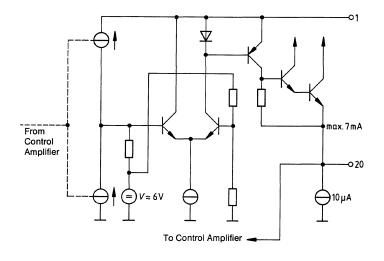

# Circuit diagram

(

ú

45

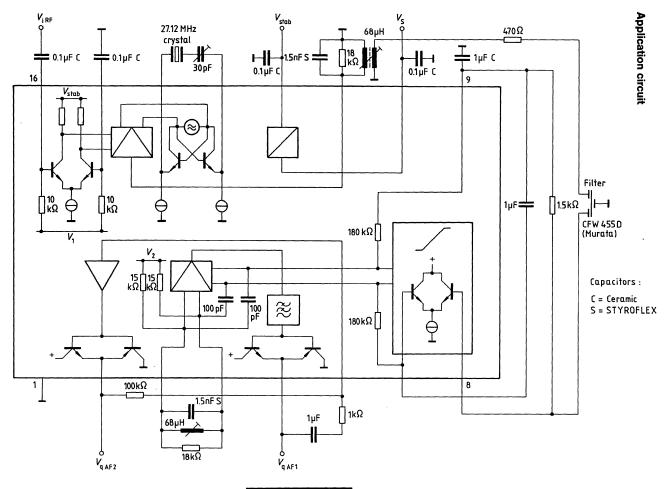

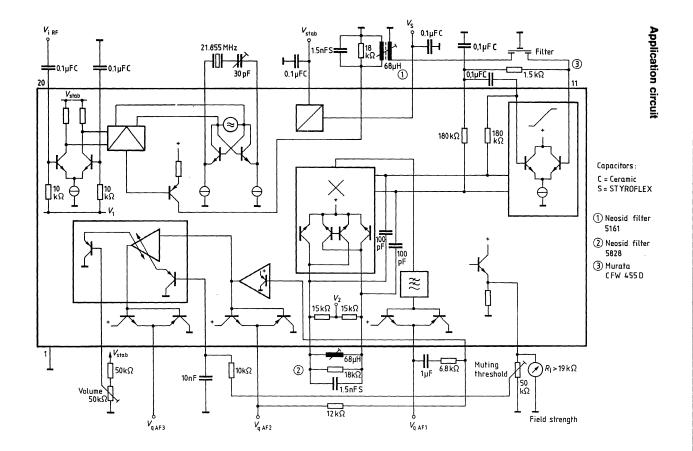

Application circuit for 10.7 MHz (FM IF) and 455 kHz (narrow-band FM)

Data in parentheses for 455 kHz (narrow-band FM)

| Coils                                        | 10.7 MHz | 455 kHz                                                                             |

|----------------------------------------------|----------|-------------------------------------------------------------------------------------|

| L <sub>1</sub><br>L <sub>2</sub><br>Coil set |          | 71.5 turns/12 x 0,04 CuLS<br>71.5 turns/12 x 0.04 CuLS<br>D 41–2393 of Messrs. Vogt |

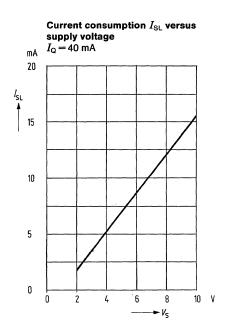

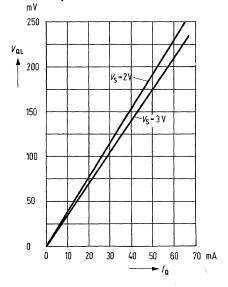

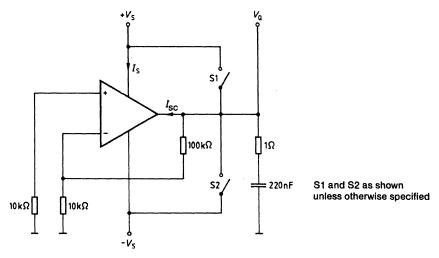

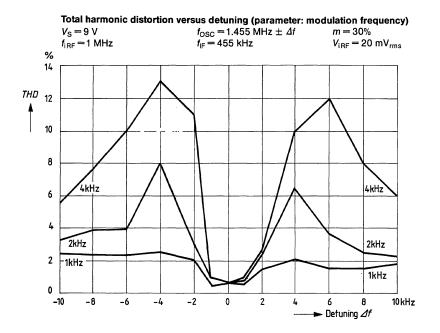

# Current consumption versus supply voltage

Sec. 10

DC output voltage difference versus supply voltage (without signal)

mV

300

200

100

0

50

AFrms

тно ~' a²

40

► Q factor

V<sub>AF,rms</sub>

N . . . .

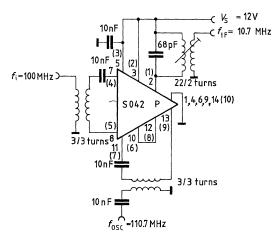

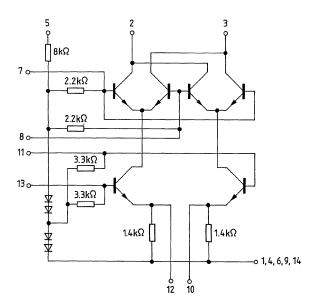

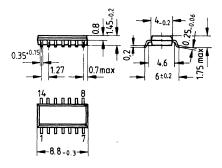

#### DIP 14

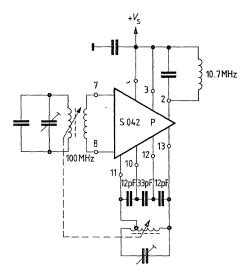

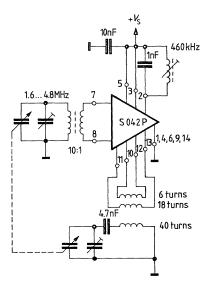

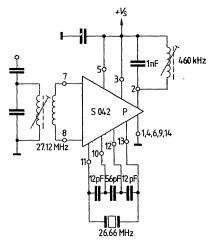

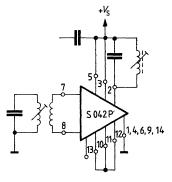

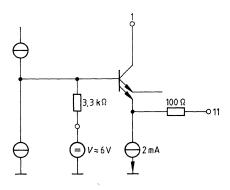

Symmetrical mixer for frequencies up to 200 MHz. It can be driven by an external source or by the built-in oscillator. The input signals are suppressed at the outputs. In addition to the usual mixer applications in receivers, converters, and demodulators for AM and FM, the S 042 P can also be used as electronic polarity switches, multipliers, etc.

#### Features

- Versatile application

- Wide range of supply voltage

- Few external components

- High conversion transconductance

- Low noise figure

| Maximum ratings                                                      |                                          |                         |               |

|----------------------------------------------------------------------|------------------------------------------|-------------------------|---------------|

| Supply voltage<br>Junction temperature<br>Storage temperature range  | V <sub>S</sub><br>Tj<br>T <sub>stg</sub> | 15<br>150<br>-40 to 125 | v<br>°C<br>°C |

| Thermal resistance (system-air) S 042 P:                             | R <sub>th SA</sub>                       | 90                      | K/W           |

| Operating range<br>Supply voltage range<br>Ambient temperature range | Vs<br>7 <sub>amb</sub>                   | 4 to 15<br>             | V<br>°C       |

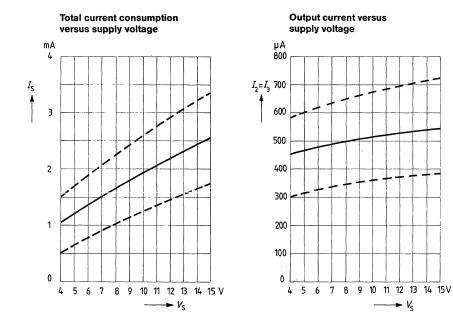

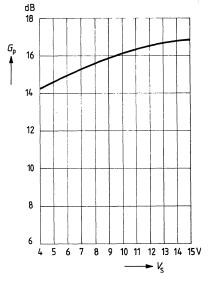

# Characteristics ( $V_{\rm S} = 12$ V, $T_{\rm amb} = 25$ °C)

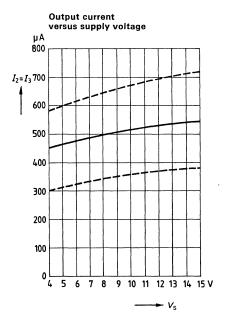

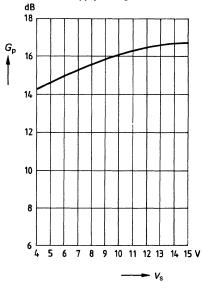

|                                                                                                | min                                                                                 | typ                                                                                                                                                                                              | max                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                         |

|------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $I_{S} = I_{2} + I_{3} + I_{5}$ $I_{2} = I_{3}$ $I_{3} - I_{2}$ $I_{5}$ $G_{p}$ $V_{2}, V_{3}$ | 1.4<br>0.36<br>60<br>0.7<br>14<br>25                                                | 2.15<br>0.52<br>1.1<br>16.5                                                                                                                                                                      | 2.9<br>0.68<br>60<br>1.6                                                                                                                                                                                                                       | mA<br>mA<br>mA<br>dB<br>V                                                                                                                                                                                                               |

| $C_{2-M}, C_{3-M}$ $S = \frac{I_2}{V_7 - V_8} = \frac{I_3}{V_7 - V_8}$ NE                      |                                                                                     | 6<br>5                                                                                                                                                                                           |                                                                                                                                                                                                                                                | pF<br>mS<br>dB                                                                                                                                                                                                                          |

|                                                                                                | $I_{3}-I_{2}$ $I_{5}$ $G_{p}$ $V_{2}, V_{3}$ $C_{2-M}, C_{3-M}$ $S = I_{2}$ $I_{3}$ | $\begin{bmatrix} I_{3} - I_{2} & & -60 \\ I_{5} & & 0.7 \\ G_{p} & & 14 \end{bmatrix}$ $V_{2}, V_{3} & & 25$ $C_{2-M}, C_{3-M} \\ S = \frac{I_{2}}{V_{7} - V_{R}} = \frac{I_{3}}{V_{7} - V_{R}}$ | $\begin{bmatrix} I_3 - I_2 \\ I_5 \\ G_p \end{bmatrix} \xrightarrow{-60} 0.7 \\ 14 \\ 16.5 \\ V_2, V_3 \\ S = \frac{I_2}{V_7 - V_8} = \frac{I_3}{V_7 - V_8} \end{bmatrix} \xrightarrow{-60} 6 \\ 5 \\ 5 \\ 5 \\ 5 \\ 5 \\ 5 \\ 5 \\ 5 \\ 5 \\$ | $\begin{bmatrix} I_3 - I_2 & & & -60 \\ I_5 & & & 0.7 \\ G_p & & & 14 \\ V_2, V_3 & & & 25 \\ C_{2-M}, C_{3-M} \\ S = \frac{I_2}{V_7 - V_8} = \frac{I_3}{V_7 - V_8} \end{bmatrix} \begin{bmatrix} 60 \\ 1.6 \\ 6 \\ 5 \\ \end{bmatrix}$ |

All connections mentioned in the index refer to S 042 P (e.g.  $I_2$ )

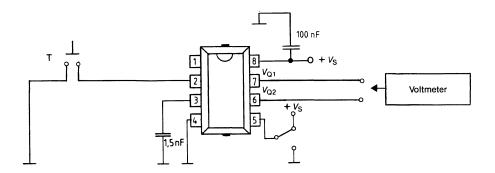

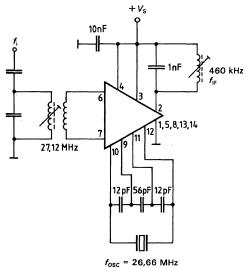

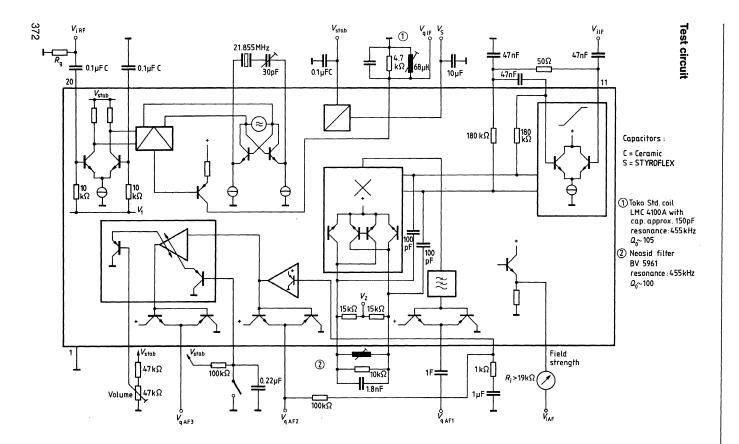

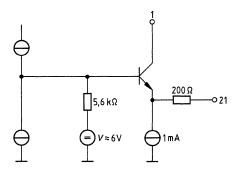

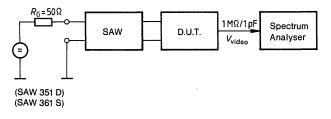

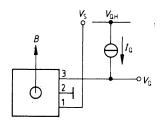

#### **Test circuit**

Connections in parentheses apply to S 042E

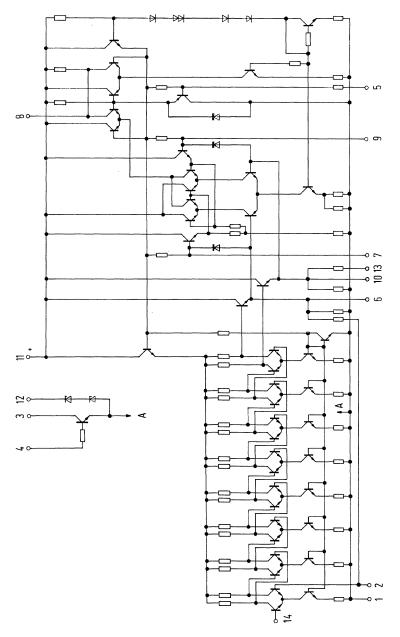

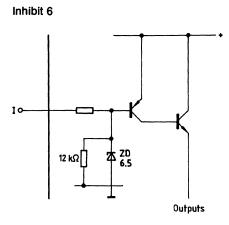

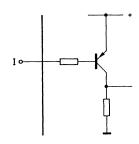

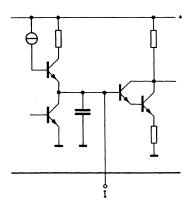

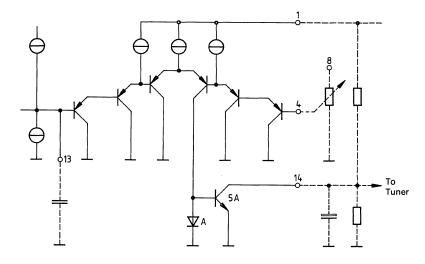

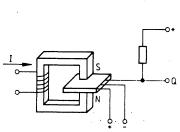

#### Circuit diagram

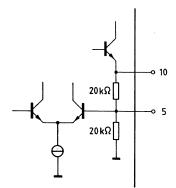

A galvanic connection between pins 7 and 8 and pins 11 and 13 through coupling windings is recommended.

Between pins 10 and 14 (ground) and between pins 12 and 14, one resistance each of at least 220  $\Omega$  may be connected to increase the currents and thus the conversion transconductance. Pins 10 and 12 may be connected through any impedance. In case of a direct connection between pins 10 and 12, the resistance from this pin to 14 may be at least 100  $\Omega$ . Depending on the layout, a capacitor (10 to 50 pF) may be required between pins 7 and 8 to prevent oscillations in the VHF band.

Power gain versus supply voltage

#### **Application circuits**

5

VHF mixer with inductive tuning

Mixer for short-wave application in self-oscillating operation

Mixer for remote control receivers without oscillator

For overtone crystals an adequate inductance is recommended between pins 10 and 12 to avoid oscillations to the fundamental tone.

Differential amplifier with internal neutralization, also suited for use as limiter for frequencies up to 50 MHz or at higher currents up to 100 MHz

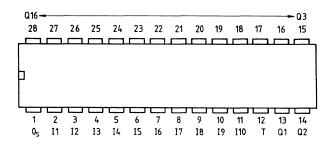

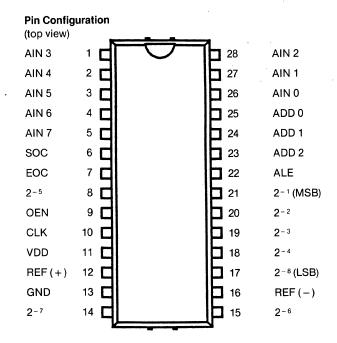

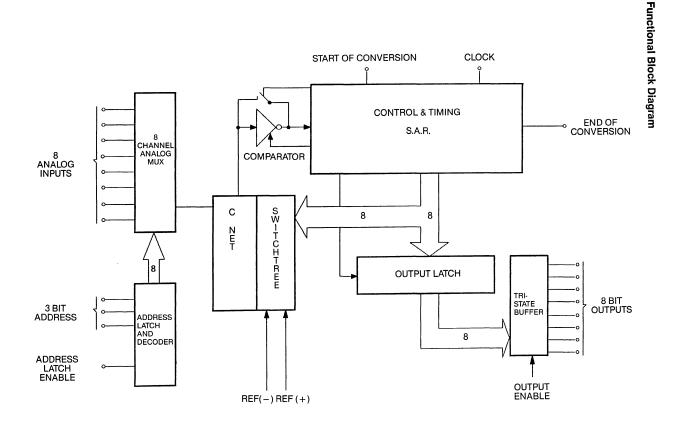

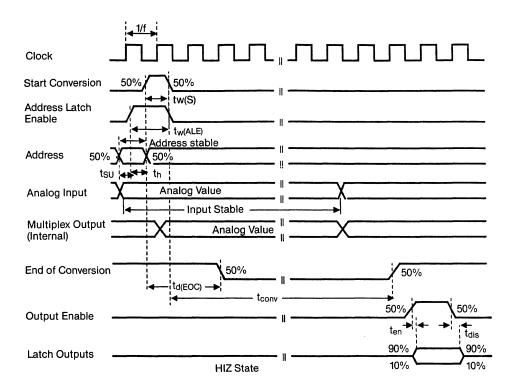

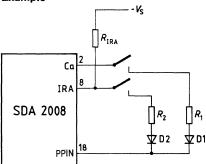

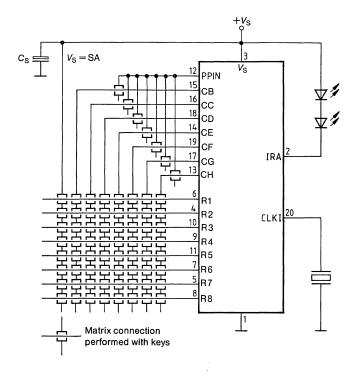

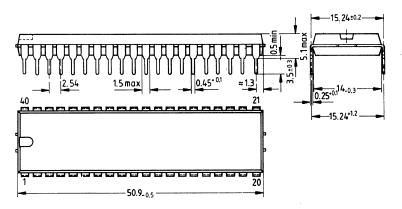

#### **DIP 28**

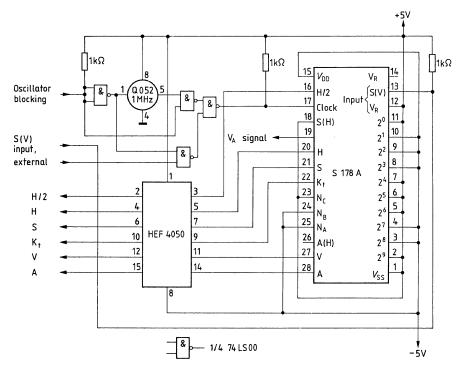

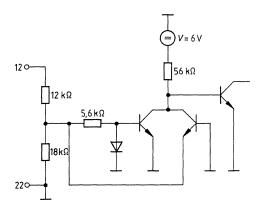

The S 178 A is an MOS circuit using p-channel metal-gate-technology with enhancement and depletion transistors, featuring the following technical characteristics:

The **video pulse generator** produces the sync, control, and erase signals required for the control of cameras, mixers, and other equipment.

The following signals are generated:

- Gating signal A

- Sync signal S

- Horizontal pulse H

- Vertical pulse V

- Terminal pulse K<sub>t</sub>

- Horizontal gating pulse A (H)

- Double line frequency  $H_{2}$ half vertical frequency  $V_{R}$   $\rightarrow$   $H_{2} + V_{R}$  signal with external signal mixing

- Vidicon gating signal V<sub>A</sub>

#### Features

All pulses are derived digitally from an input frequency corresponding to a pulse scheme, with a duty cycle of 1:1.

Pulse width according to latest CCIR and EIA standards.

The following 6 pulse schemes have been programmed permanently (by 3-bit coding and line number coding):

525 lines (60 Hz) required input frequency 1.008 MHz

625 lines (50 Hz) required input frequency 1.000 MHz

735 lines (60 Hz) required input frequency 1.4112 MHz

875 lines (50 Hz) required input frequency 1.400 MHz

1023 lines (60 Hz) required input frequency 1.96416 MHz

1249 lines (50 Hz) required input frequency 1.9984 MHz

Deviating from the above, any line number between 512 and 1535 lines may be programmed.

It should be noted, however, that a frame frequency of 50 Hz (partial picture duration 20 ms) or 60 Hz (16.66) is achieved.

Within the operating frequency it is, however, possible to mix any standard position with any line number.

The following relation applies:

Input frequency  $f_{\rm I} = 64$ : line period H

= 32: line number Z x frame frequency  $f_{\rm fr}$

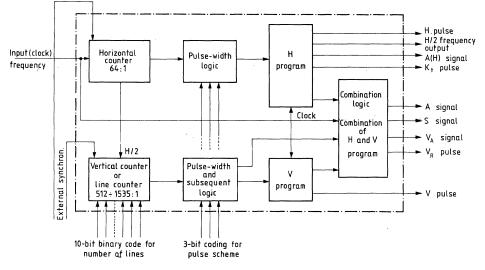

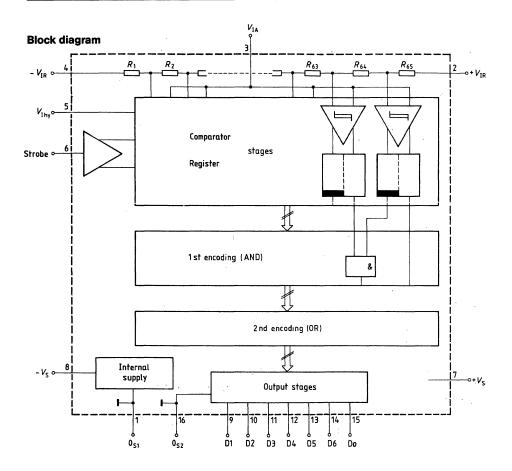

#### **Block diagram**

| Maximum ratings                                         |                  | Lower<br>limit B | Upper<br>limit A |     |

|---------------------------------------------------------|------------------|------------------|------------------|-----|

| Supply voltage ) referred                               | V <sub>DD</sub>  | -12              | 0.3              | v   |

| Voltage at all inputs $\int$ to $V_{SS} = 0$ V          | VI               | -20              | 0.3              | V   |

| Input current                                           | $I_{\rm I}$      |                  | 100              | μΑ  |

| $(V_{\rm I} = 0.3 \text{ V}; V_{\rm SS} = 0 \text{ V})$ |                  |                  |                  |     |

| Output current                                          | I <sub>QH</sub>  |                  | -100             | μA  |

|                                                         | IQL              |                  | 2                | mA  |

| Junction temperature                                    | T.               |                  | 125              | l°C |

| Storage temperature                                     | T <sub>stq</sub> | -55              | 125              | °C  |

| Ambient temperature during operation                    | $T_{amb}$        | -25              | 75               | °C  |

.....

| <b>Characteristics</b> $T_{amb} = 25 ^{\circ}\text{C}$                       |                                                      | Test conditions                                                                     | Lower<br>limit B                         | typ      | Upper<br>limit A                         |              |

|------------------------------------------------------------------------------|------------------------------------------------------|-------------------------------------------------------------------------------------|------------------------------------------|----------|------------------------------------------|--------------|

| Supply voltage<br>Supply current                                             | $-V_{\rm DD}$<br>$I_{\rm DD}$                        |                                                                                     | 9.5                                      | 10<br>60 | 10.5<br>70                               | V<br>mA      |

| Inputs                                                                       |                                                      | direct control<br>with TTL output<br>level                                          |                                          |          |                                          |              |

| H input voltage<br>L input voltage                                           | V <sub>IH</sub><br>V <sub>IL</sub>                   |                                                                                     | V <sub>SS</sub> -1.5<br>-V <sub>DD</sub> |          | V <sub>SS</sub><br>-V <sub>DD</sub> +5.5 | v<br>v       |

| Outputs                                                                      |                                                      | when loaded<br>with one TTL input                                                   | -                                        |          |                                          |              |

| H output voltage<br>L output voltage                                         | V <sub>QH</sub><br>V <sub>QL</sub>                   | $I_{QH} = -40 \ \mu A$<br>$I_{QL} = 1.6 \ m A$<br>when loaded with<br>2 LPS inputs: | V <sub>SS</sub> -2.6<br>TTL GND-0.7      |          | TTL GND+0.4                              | v<br>v       |

| H output voltage<br>L output voltage                                         | V <sub>QH</sub><br>V <sub>QL</sub>                   | $I_{QH} = -40 \ \mu A$<br>$I_{QL} = 0.8 \ m A$<br>for capacitive<br>load only:      | V <sub>SS</sub> -2.6<br>LPS GND-0.7      |          | LPS GND+0.4                              | v<br>v       |

| H output voltage<br>L output voltage<br>Signal transition time<br>of outputs | V <sub>QH</sub><br>V <sub>QL</sub><br>t <sub>T</sub> | when loaded with<br>2 LPS inputs                                                    | V <sub>SS</sub> -2.6<br>V <sub>DD</sub>  |          | V <sub>DD</sub> +1<br>100                | V<br>V<br>ns |

| Input frequency<br>Propagation delay time                                    | f <sub>CLK</sub><br>t <sub>P</sub>                   | clock slope –<br>signal output                                                      | 1<br>0.2                                 |          | 2<br>0.4                                 | MHz<br>μs    |

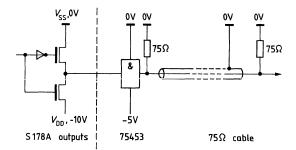

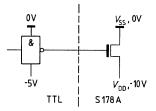

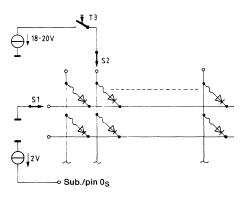

#### Interface to 75 $\Omega$ cable

A driver stage is required as the pulse generator outputs can be loaded with one TTL input, each. The circuit is to be designed according to the diagram below.

As a driver stage for the 75  $\Omega$  coaxial cable, the TTL circuit 75453 (maximum output current 300 mA; pulse delay 11 ns) is recommended.

#### Programming list for line number coding

| Pin number   | 2              | 3              | 4      | 5                     | 6          | 7      | 8                     | 9                     | 10             | 11         | 25             | 24             | 23 |

|--------------|----------------|----------------|--------|-----------------------|------------|--------|-----------------------|-----------------------|----------------|------------|----------------|----------------|----|

| Line number  | 2 <sup>9</sup> | 2 <sup>8</sup> | 27     | <b>2</b> <sup>6</sup> | <b>2</b> ⁵ | 2⁴     | <b>2</b> <sup>3</sup> | <b>2</b> <sup>2</sup> | 2 <sup>1</sup> | <b>2</b> º | N <sub>A</sub> | N <sub>B</sub> | Nc |

| 525<br>524   | H<br>H         | L<br>L         | L<br>L | L<br>L                | L<br>L     | L<br>L | н<br>н                | H<br>L                | L<br>H         | H<br>L     | L              | L              | L  |

| 625<br>624   | H<br>H         | L<br>L         | L<br>L | н<br>н                | H<br>H     | H<br>L | L<br>H                | L<br>H                | L<br>H         | H<br>L     | L              | L              | н  |

| 735<br>734   | H<br>H         | L<br>L         | н<br>Н | н<br>Н                | L<br>L     | H<br>H | H<br>H                | н<br>Н                | H<br>L         | H<br>L     | L              | н              | L  |

| 875<br>874   | H<br>H         | н<br>Н         | L<br>L | н<br>Н                | H<br>H     | L<br>L | H<br>H                | L<br>L                | Ĥ<br>L         | H<br>L     | L              | н              | н  |

| 1023<br>1022 | н              | H<br>H         | H<br>H | н<br>Н                | H<br>H     | H<br>H | н<br>Н                | н<br>Н                | H<br>L         | H<br>L     | н              | L              | L  |

| 1249<br>1248 | L<br>L         | L<br>L         | H<br>H | H<br>H                | H<br>L     | L<br>H | L<br>H                | L<br>H                | L<br>H         | H<br>L     | н              | Ĺ              | н  |

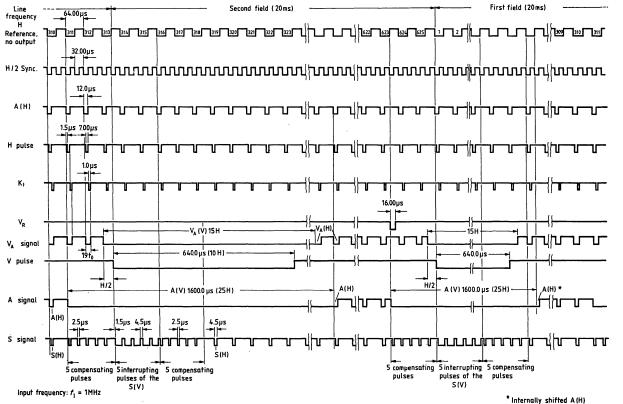

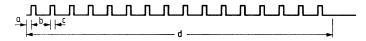

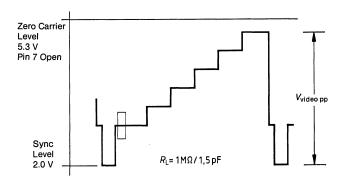

Pulse scheme for 625 lines

S 178 A

59

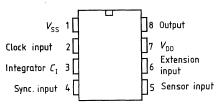

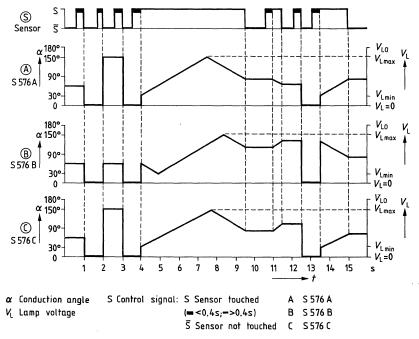

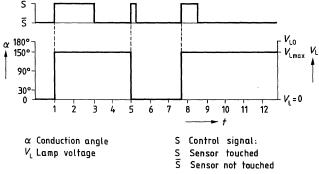

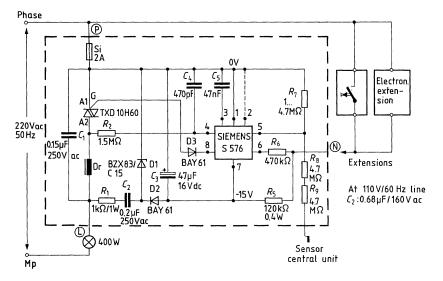

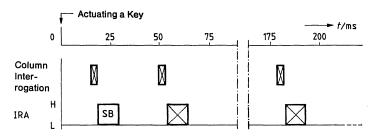

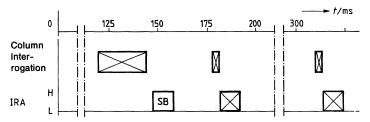

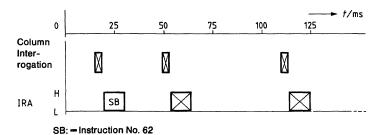

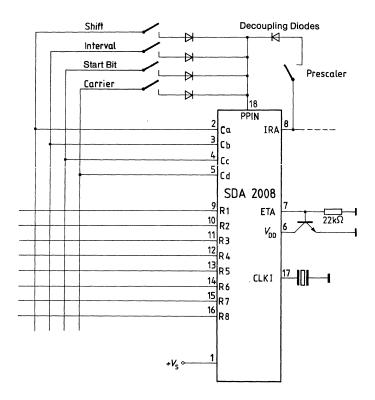

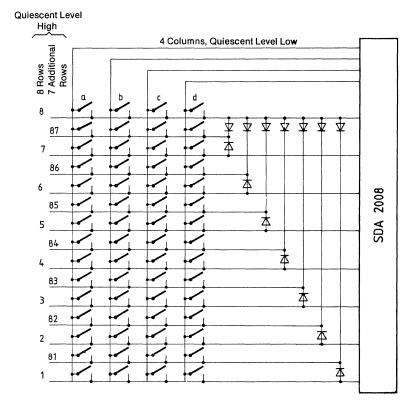

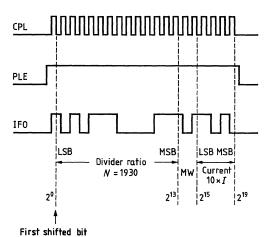

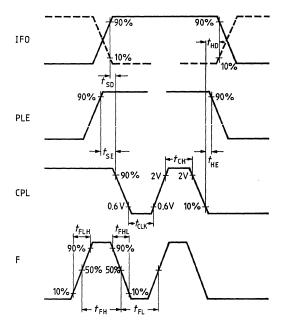

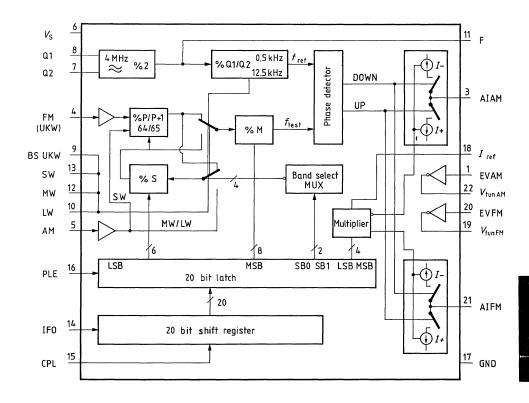

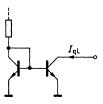

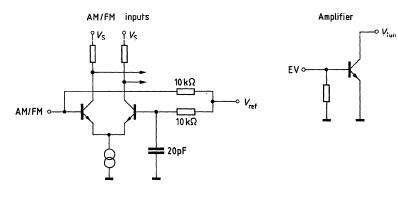

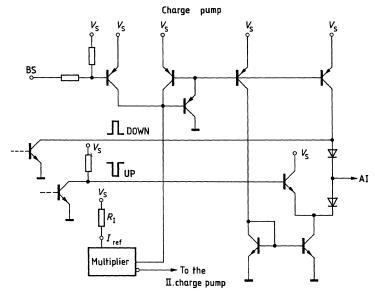

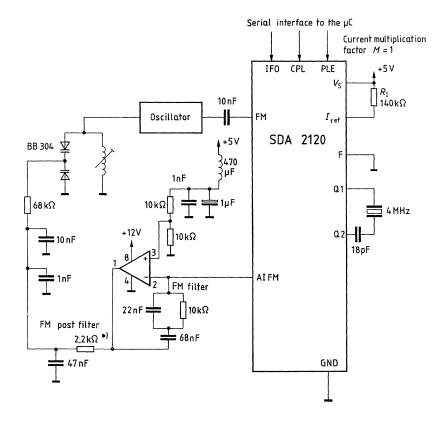

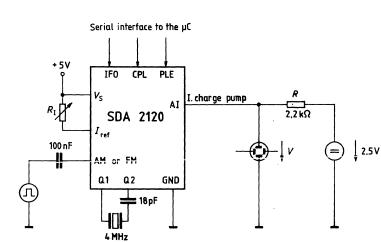

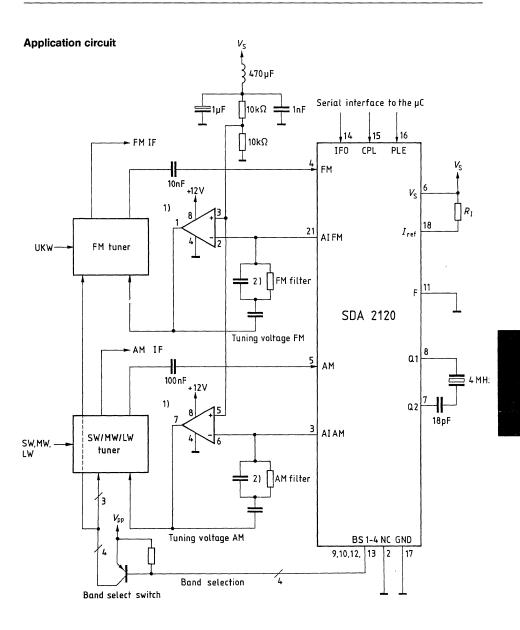

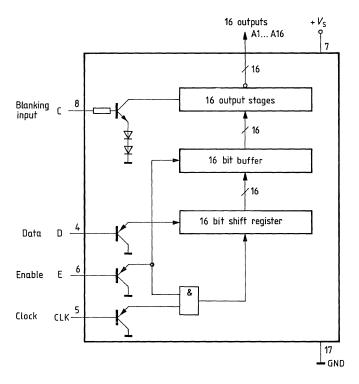

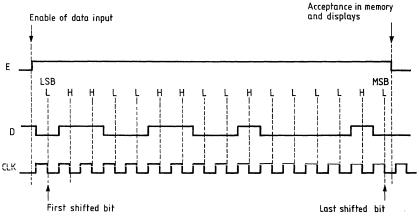

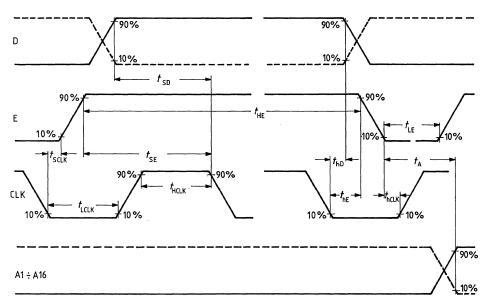

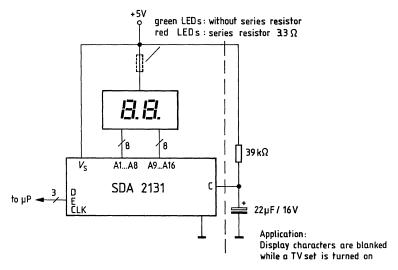

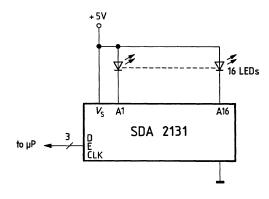

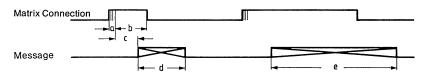

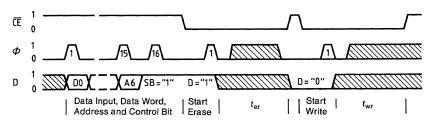

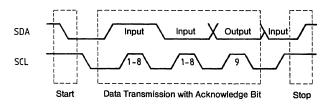

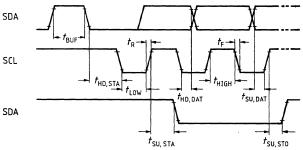

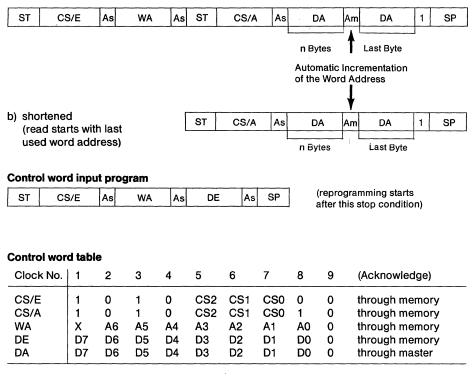

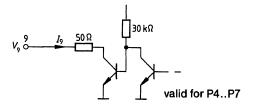

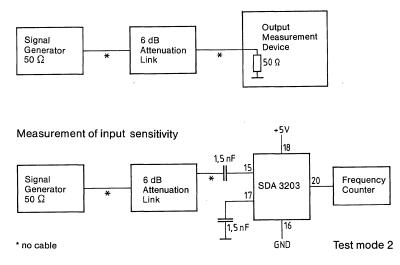

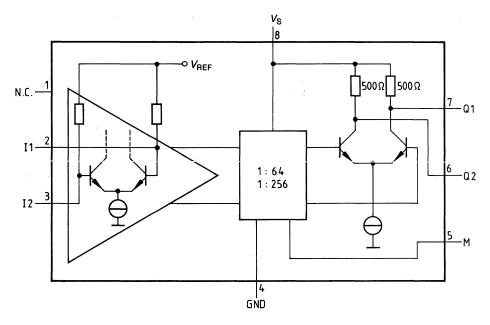

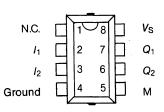

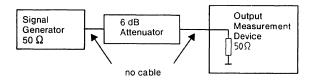

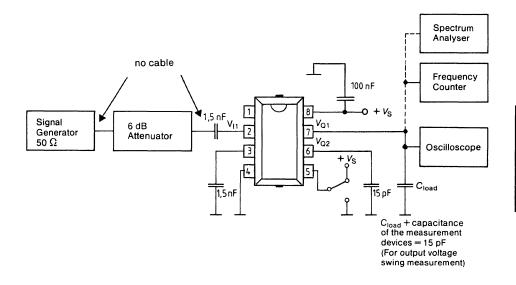

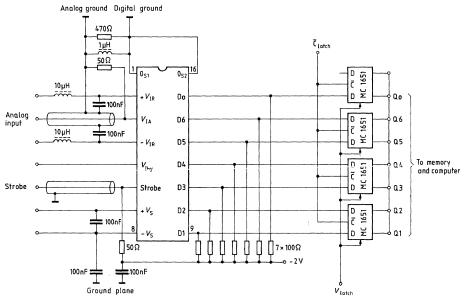

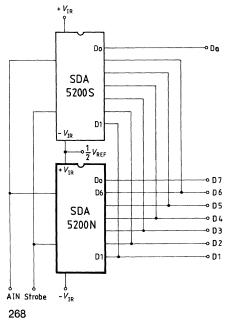

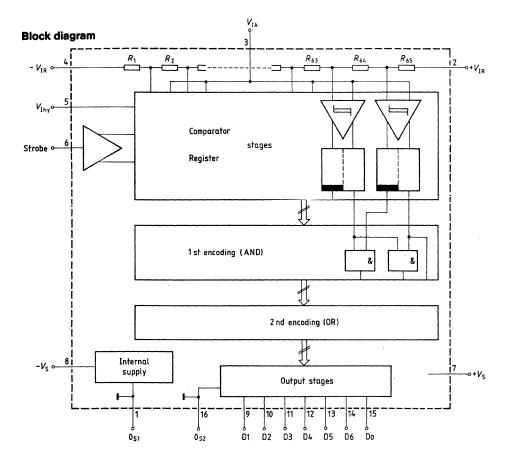

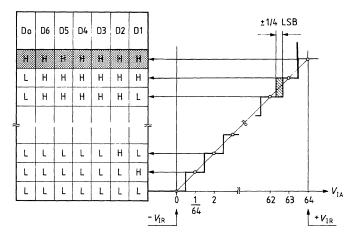

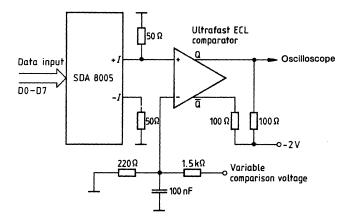

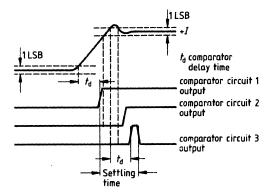

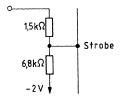

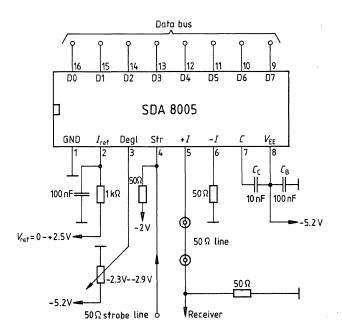

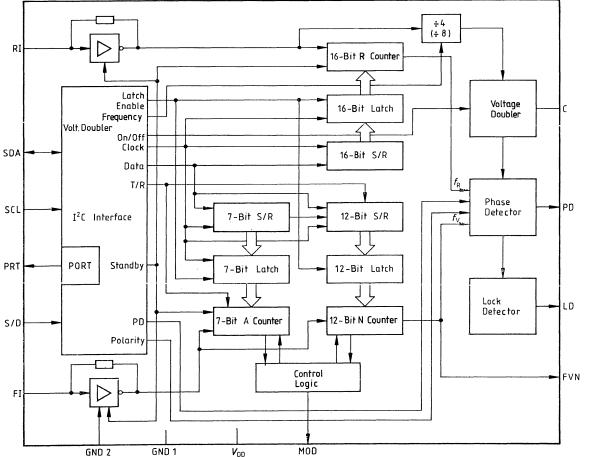

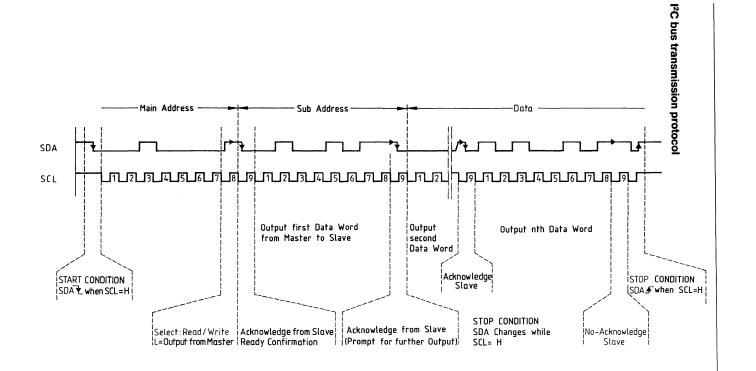

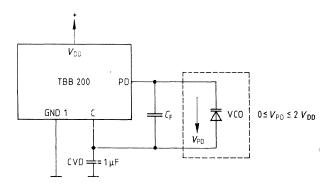

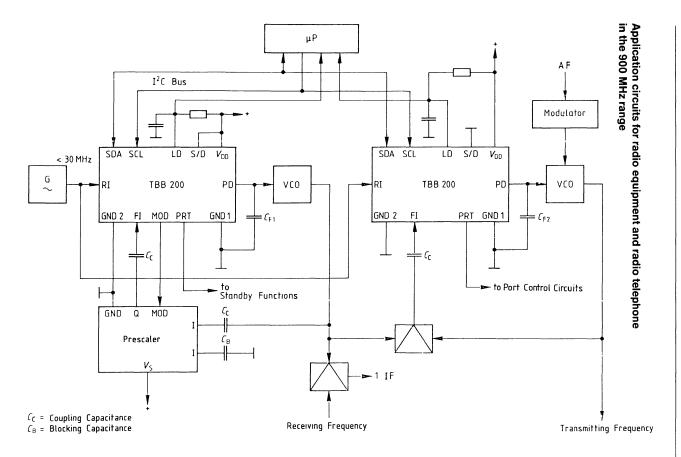

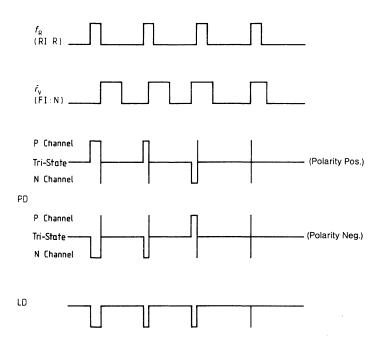

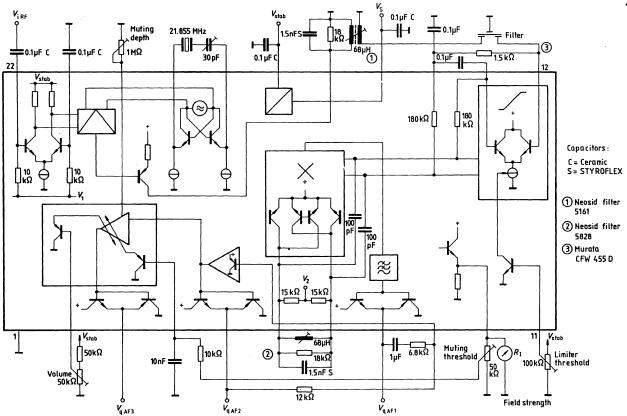

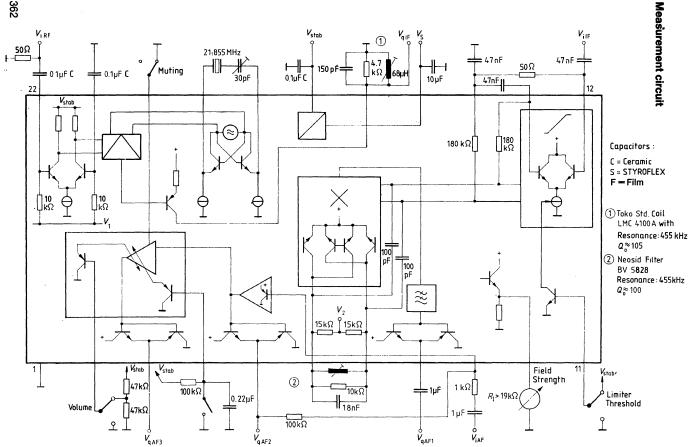

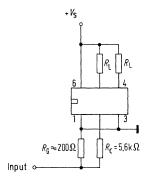

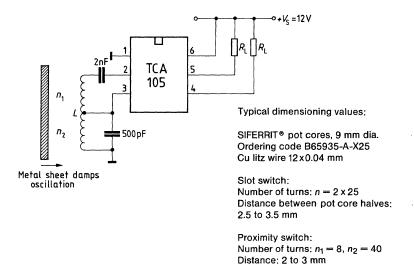

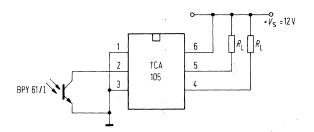

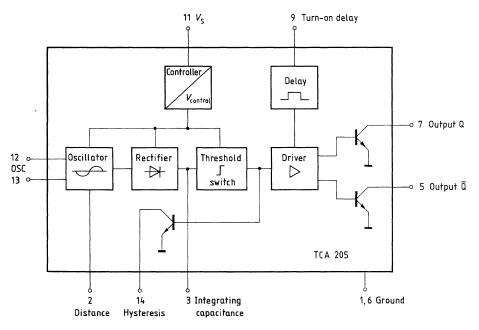

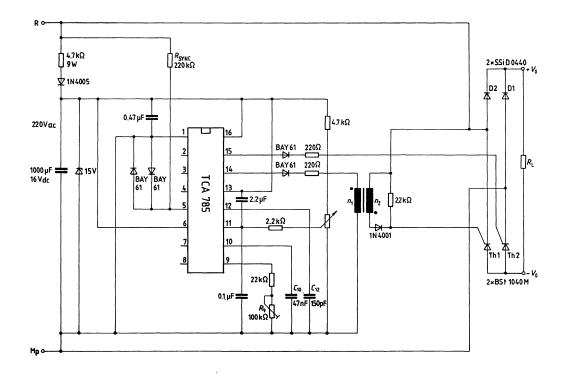

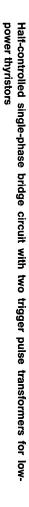

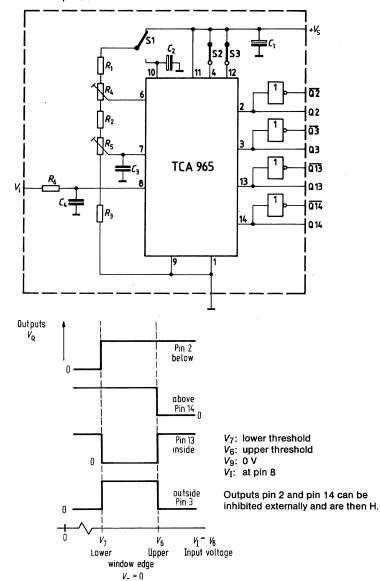

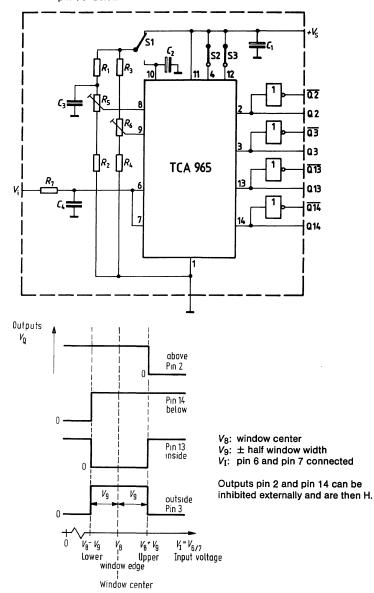

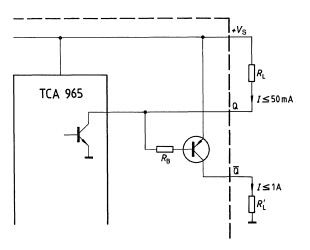

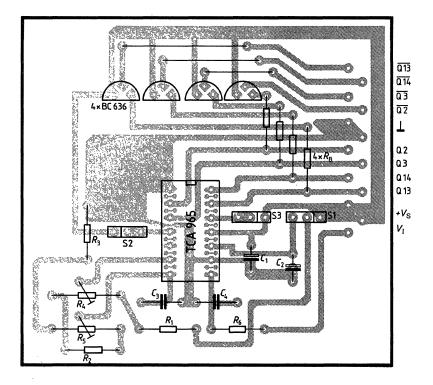

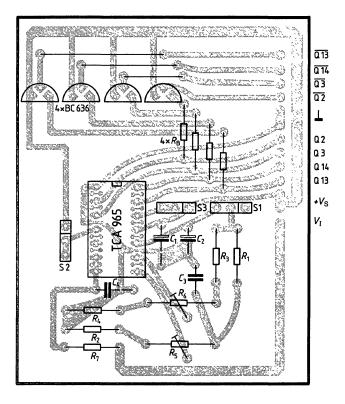

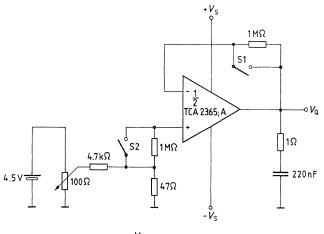

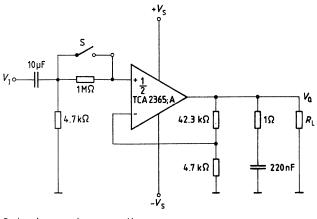

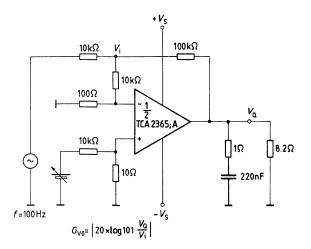

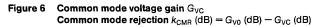

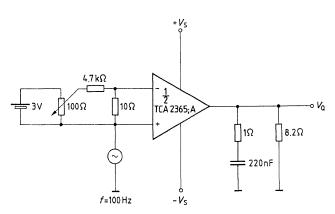

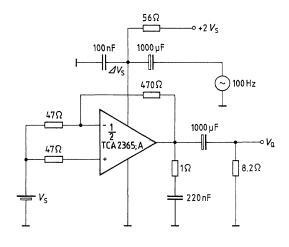

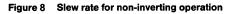

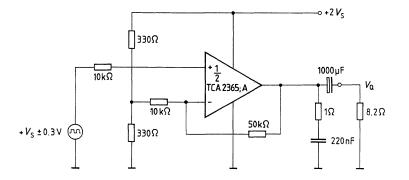

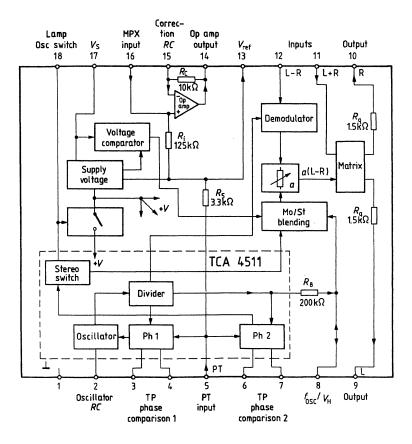

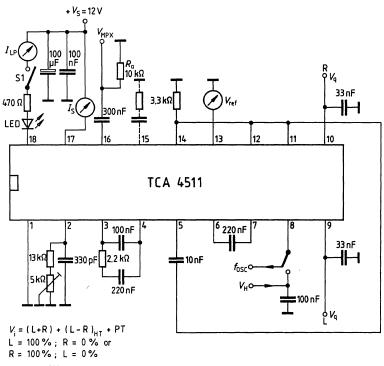

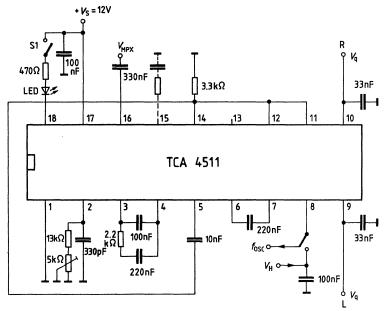

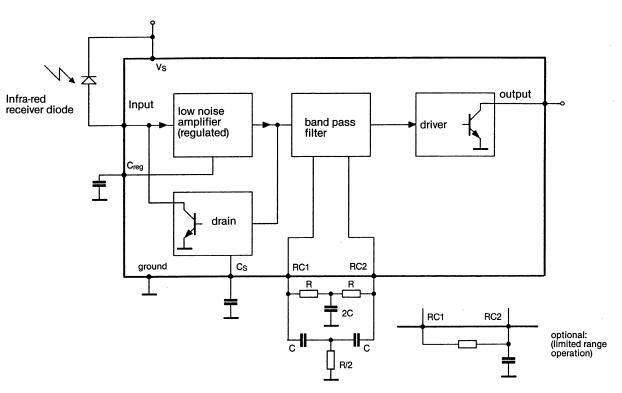

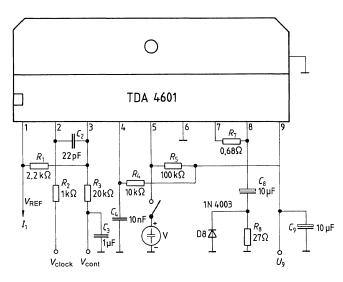

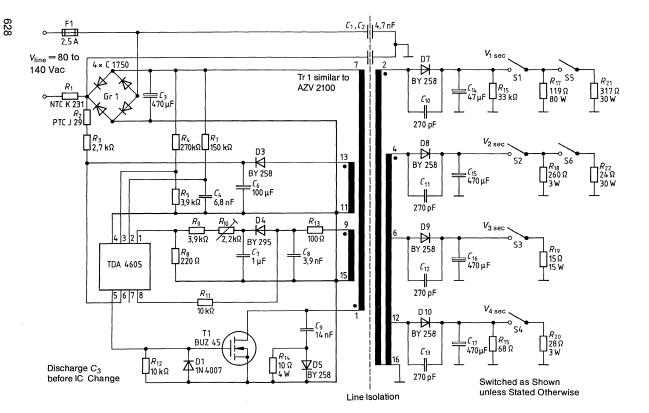

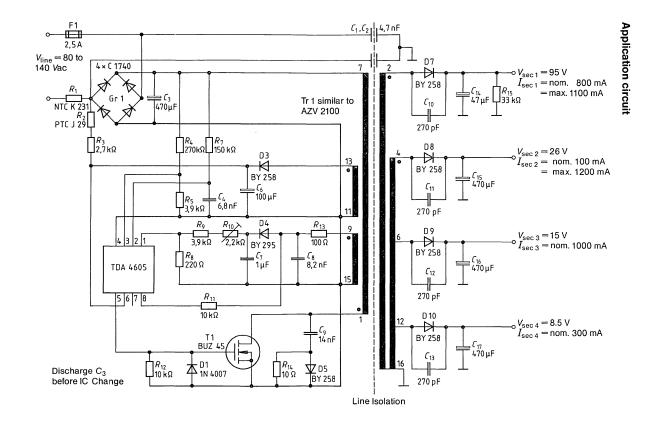

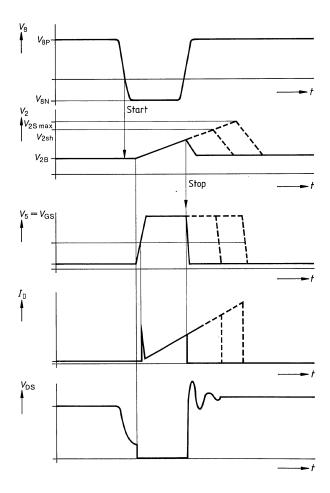

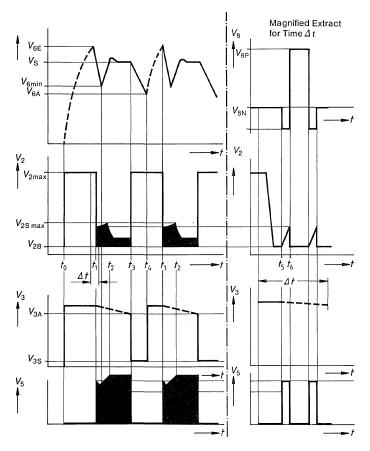

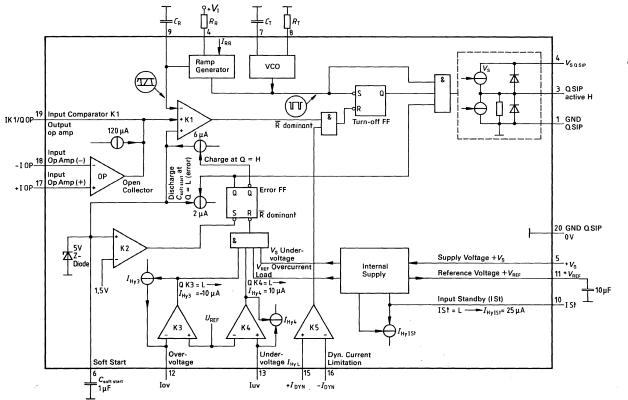

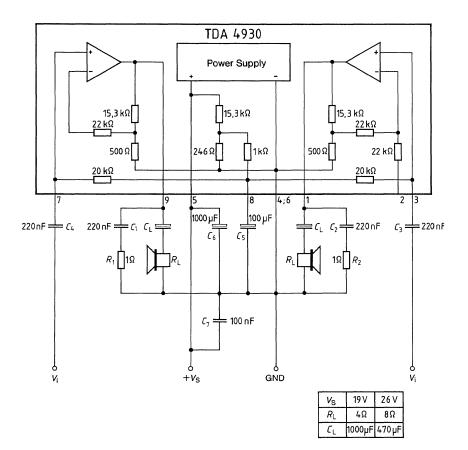

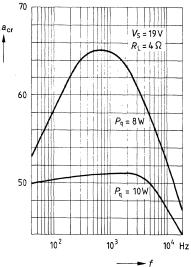

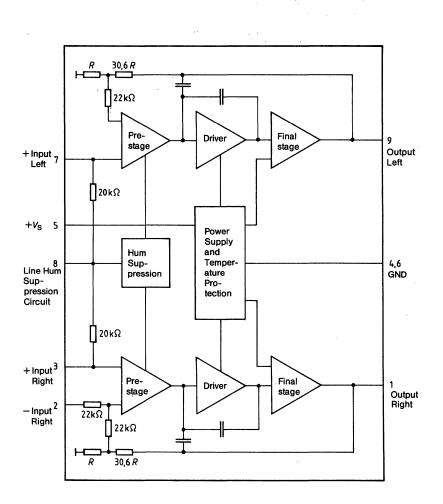

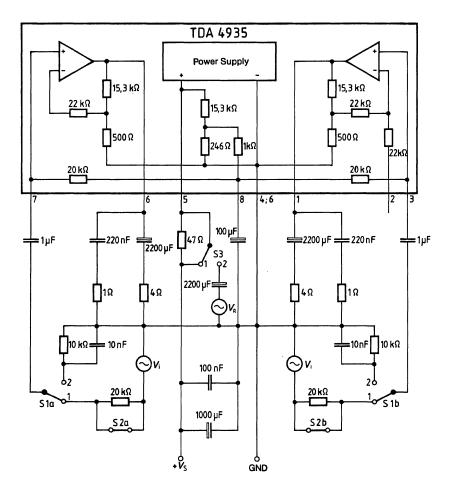

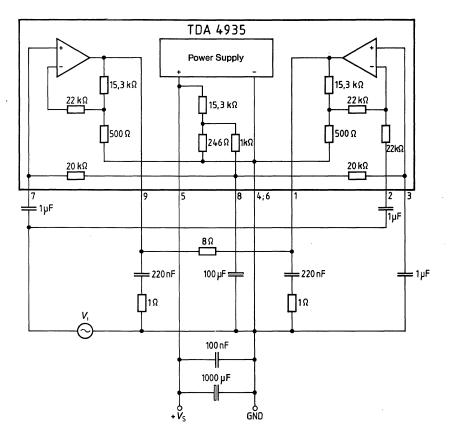

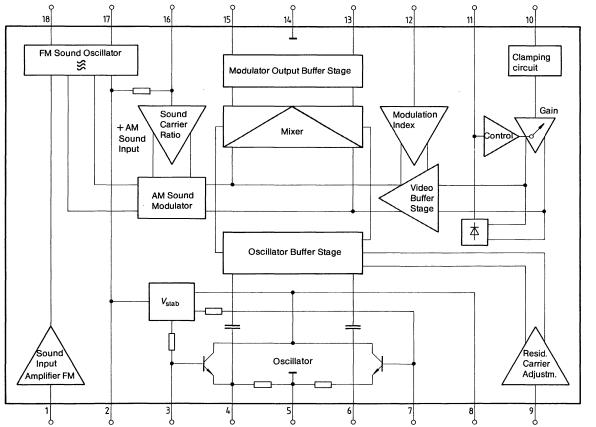

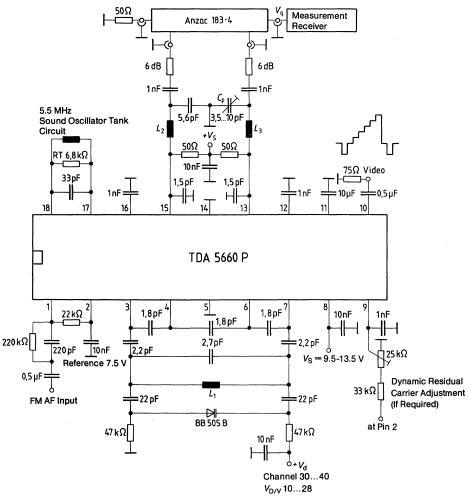

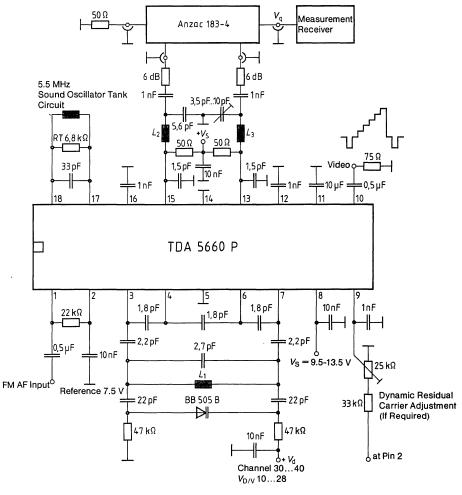

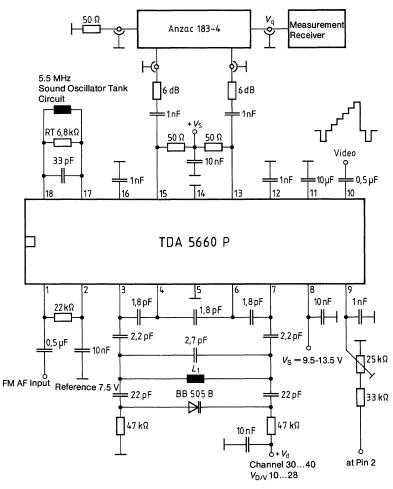

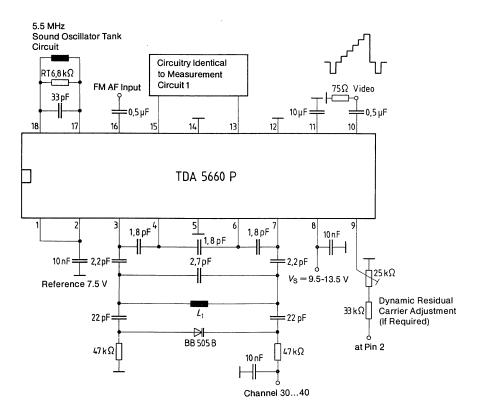

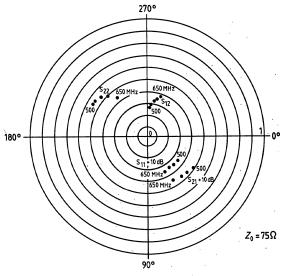

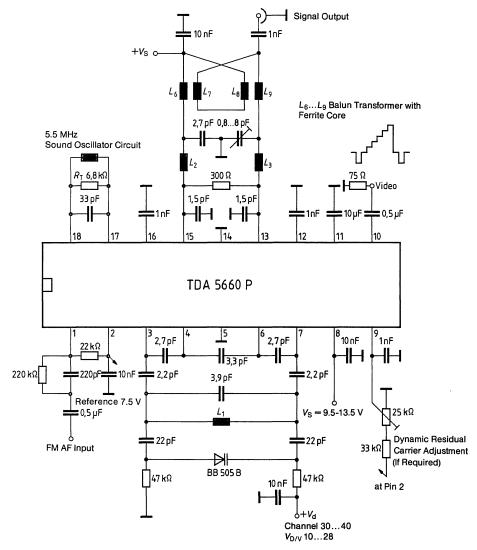

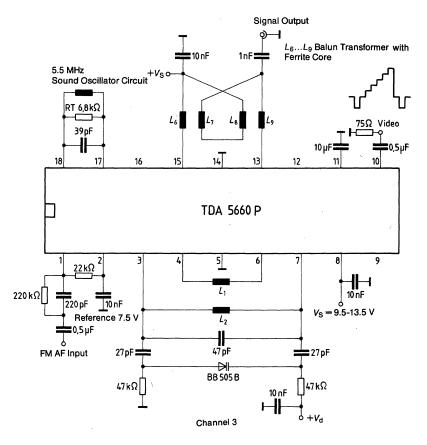

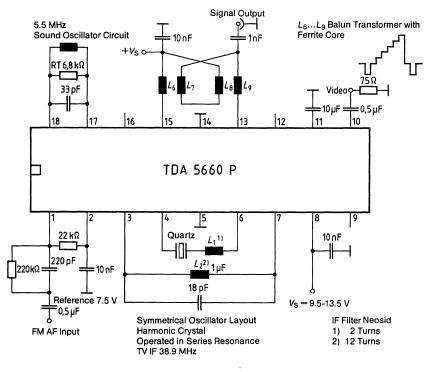

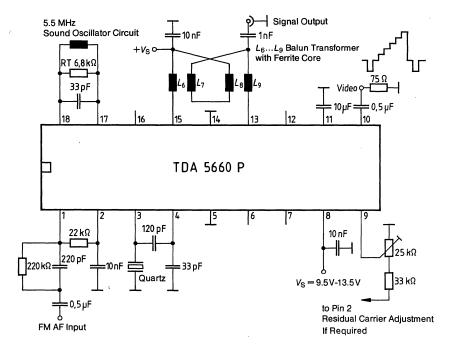

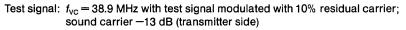

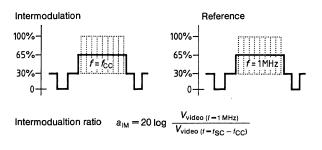

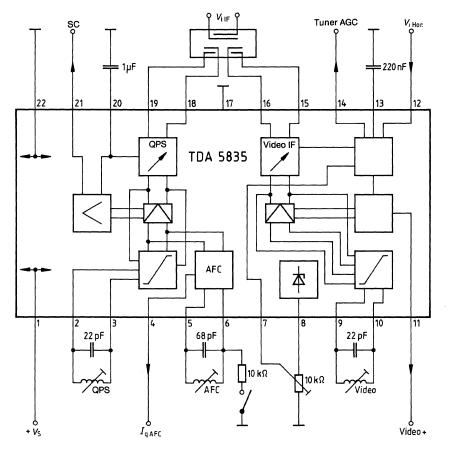

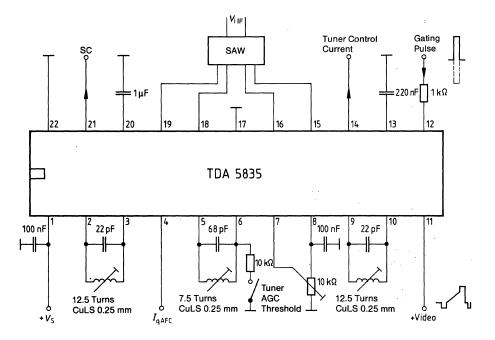

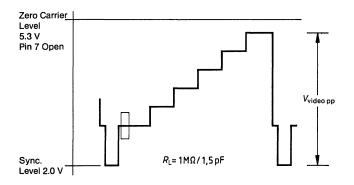

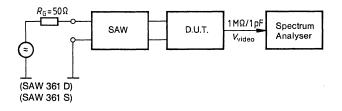

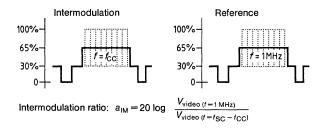

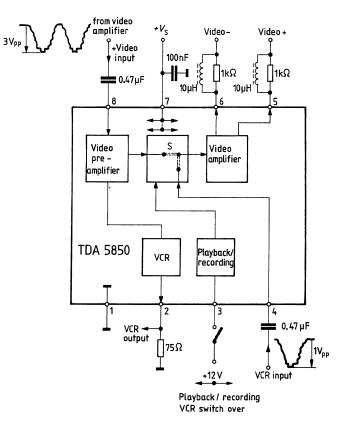

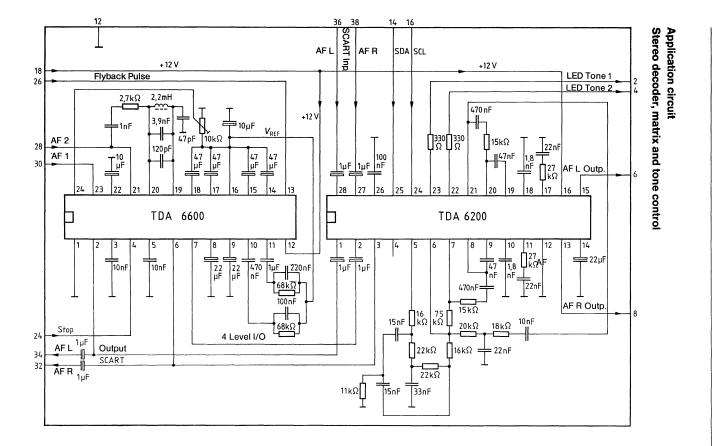

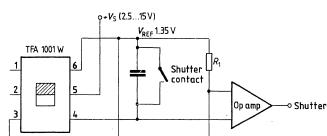

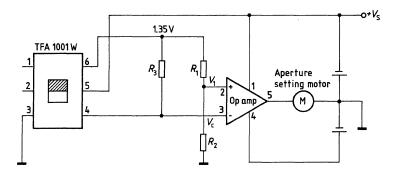

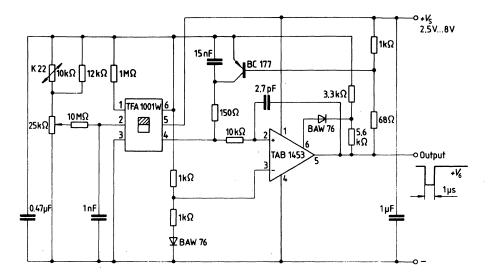

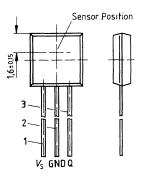

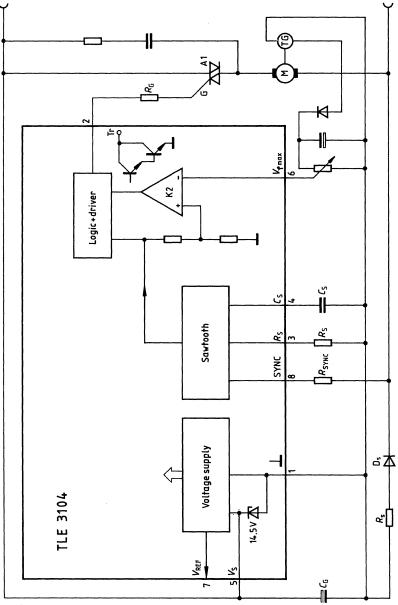

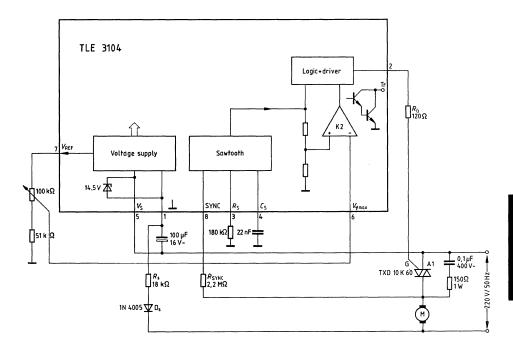

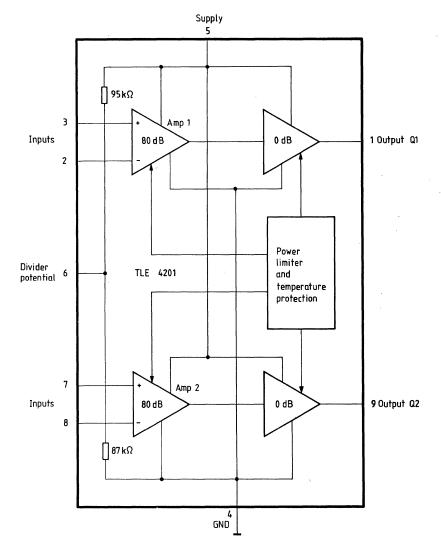

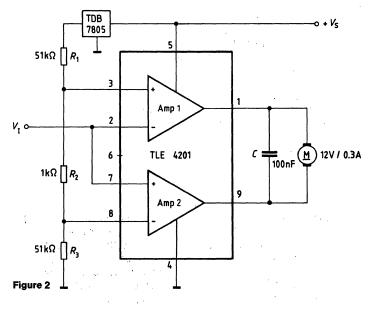

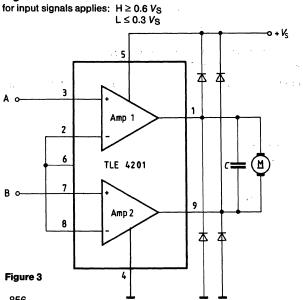

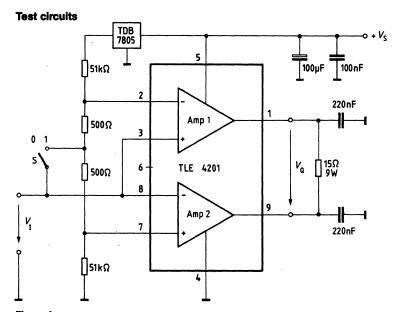

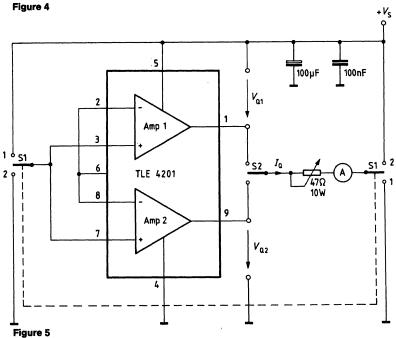

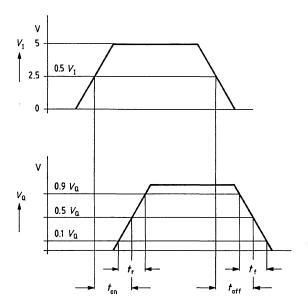

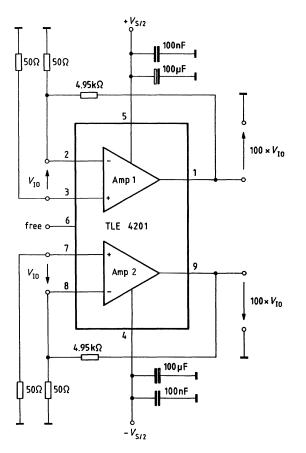

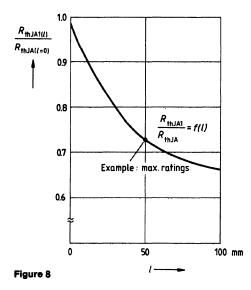

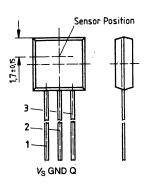

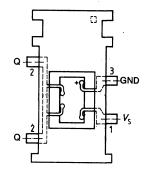

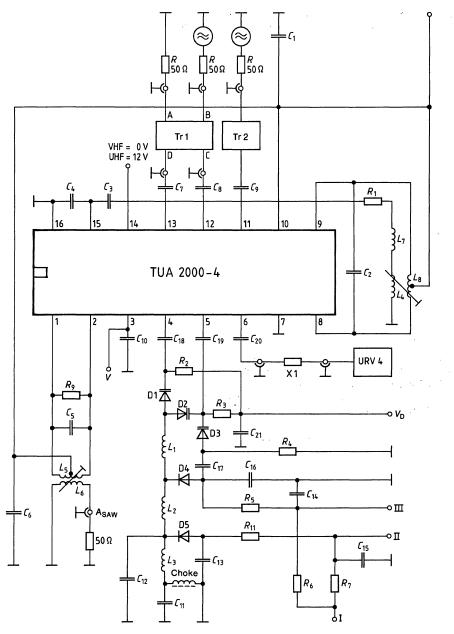

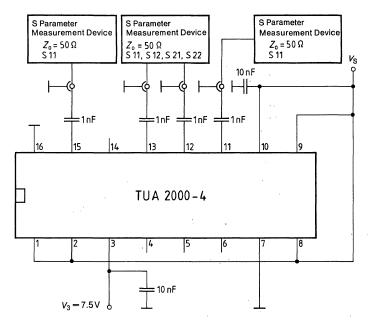

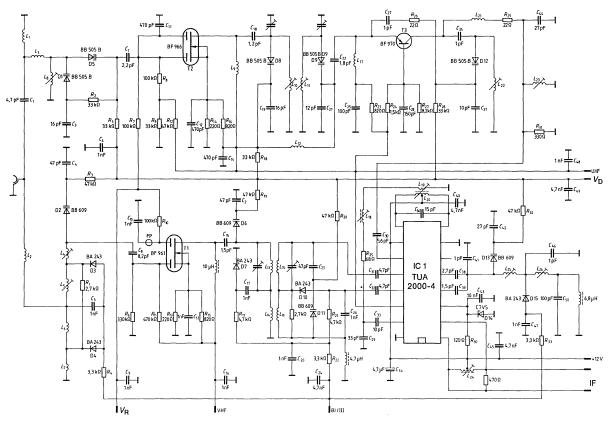

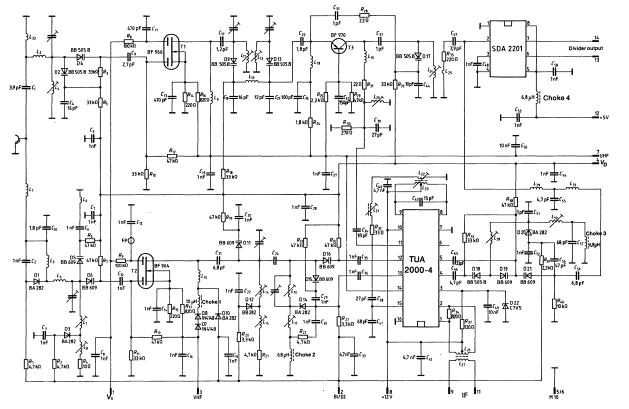

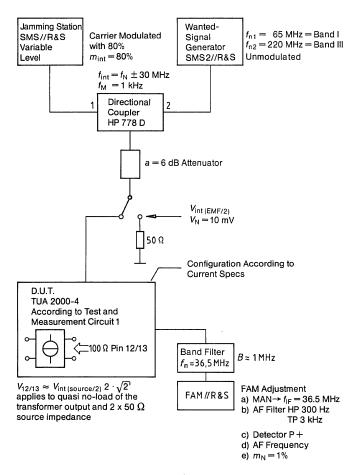

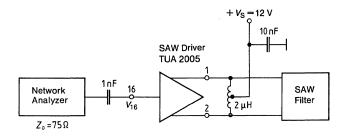

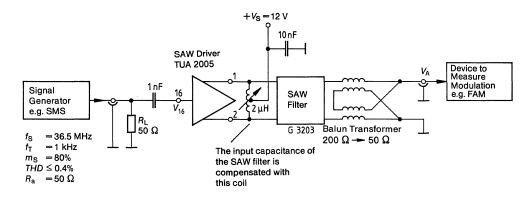

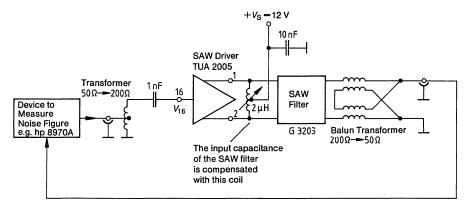

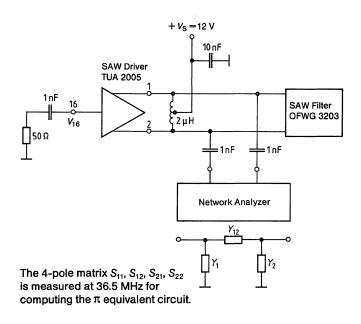

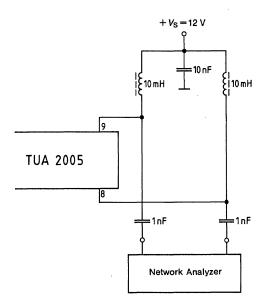

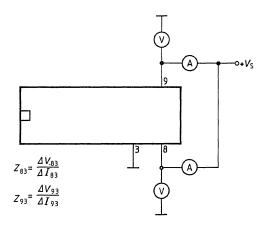

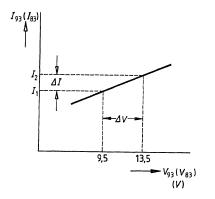

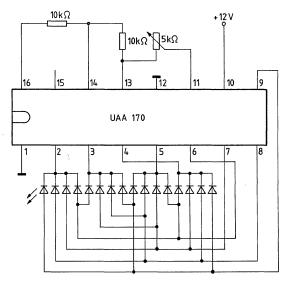

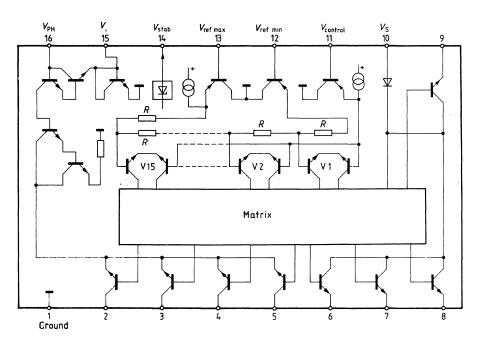

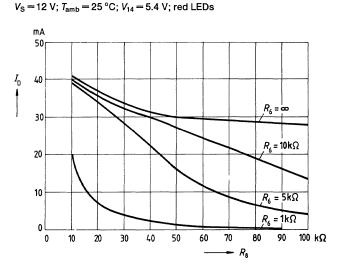

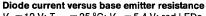

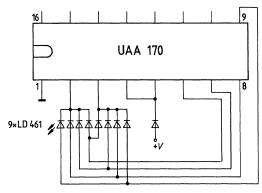

| Pin<br>No. |                                                | 525<br>f = 1.0<br>$t_0 = 0.4$ |      |                          | 625<br>f = 1.0<br>$t_0 = 0.1$ |    | Hz                       | 735<br>f = 1.4<br>$t_0 = 0.3$ |       |                          | 875<br>f = 1.40<br>$t_0 = 0.3$ |     |                   |        | 1023<br>f = 1.96416  MHz<br>$t_0 = 0.25456 \mu \text{s}$ |                  |       | 1249<br>f = 1.9984  MHz<br>$t_0 = 0.2502 \mu\text{s}$ |                          |  |