# SIEMENS

# Industrial IC Data Book 1985

Microprocessors ■ Microcontrollers ■ Peripherals ■ Support Memory ■ Telecom ■ Data Converters ■ SMPS Controllers **Table of Contents**

**General Information**

Summary of Types

Microcontroller and Microprocessor Components

**Peripheral and Support Components**

**Memory Components**

**Telecom Components**

**Data Conversion Components**

Switched Mode Power Supply (SMPS) Components

Integrated Circuits for Consumer Applications

. .

.

# SIEMENS

# Industrial IC Data Book 1985

. . . . .

.

## **Table of Contents**

## Page

| 1.  | General Information       |                                                        |     |

|-----|---------------------------|--------------------------------------------------------|-----|

| 1.1 | Type designation code     | for ICs                                                | 15  |

| 1.2 |                           |                                                        |     |

| 1.3 | Processing guidelines f   | or ICs                                                 | 16  |

|     | Identification            |                                                        |     |

|     | Scope                     |                                                        |     |

|     | Handling of devices       |                                                        |     |

|     | Storage                   |                                                        |     |

|     | Transport                 |                                                        |     |

|     | Incoming inspection       |                                                        |     |

|     | Material and mounting     |                                                        |     |

|     | Electrical tests          |                                                        |     |

|     | Packaging of assemble     | d PC boards or flat pack units                         |     |

|     | Ultrasonic cleaning of I  | •                                                      |     |

| 1.4 |                           | ental ratings                                          | 19  |

|     | Maximum ratings           | 0                                                      |     |

|     | Electrical characteristic | S                                                      |     |

|     | Operating data            |                                                        |     |

| 1.5 |                           |                                                        | 20  |

|     | Package dimensions        |                                                        |     |

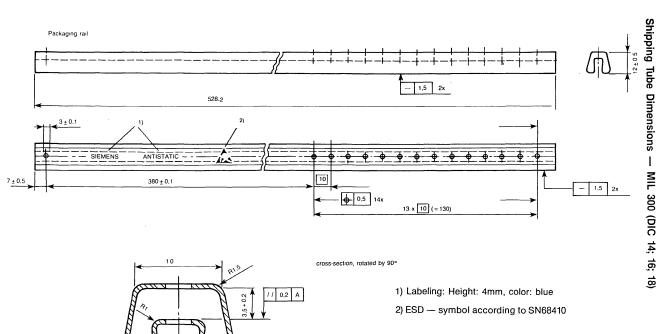

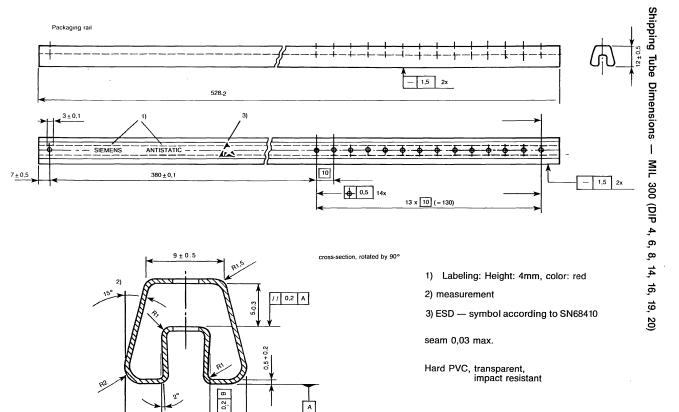

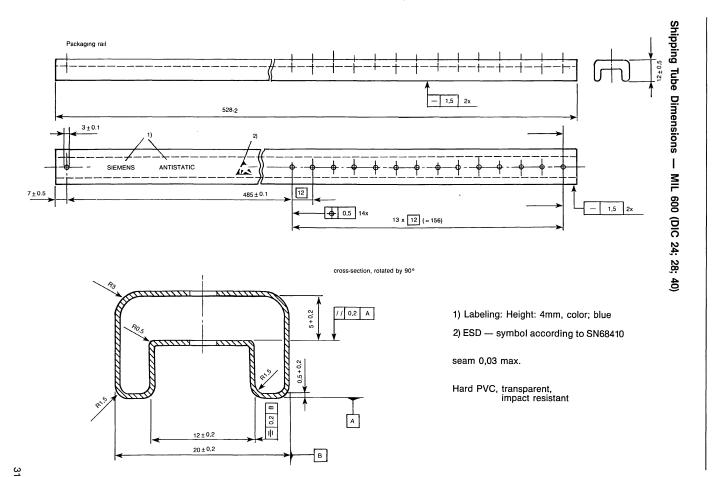

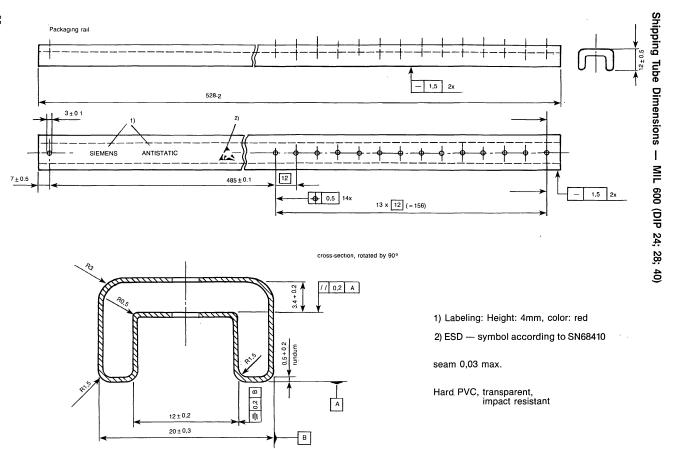

|     | Shipping tube dimensio    | ons                                                    |     |

| 1.6 |                           |                                                        | 33  |

|     | Quality assurance syste   |                                                        |     |

|     | Quality specifications    |                                                        |     |

|     | Quality conformance       |                                                        |     |

|     | Reliability               |                                                        |     |

| 1.7 | Thermal coefficients      |                                                        | 40  |

| 2.  | Summary of Types          |                                                        |     |

| 2.1 | Component selection a     | uide                                                   | 43  |

|     | genipenent cerection g    |                                                        |     |

| 3.  | Microcontroller and M     | icroprocessor Components                               |     |

|     | SAB 8031/8051             | 8-bit single chip microcomputer                        | 49  |

|     | SAB 8031/8051-EXT         | 8-bit single chip microcomputer with extended          |     |

|     |                           | temperature range                                      |     |

|     | SAB 8031A/8051A           | 8-bit single chip microcomputer                        | 81  |

|     | SAB 8031A/8051A-EXT       | 8-bit single chip microcomputer with extended          |     |

|     |                           | temperature range                                      | 99  |

|     | SAB 8032A/8052A           | 8-bit single chip microcomputer                        | 117 |

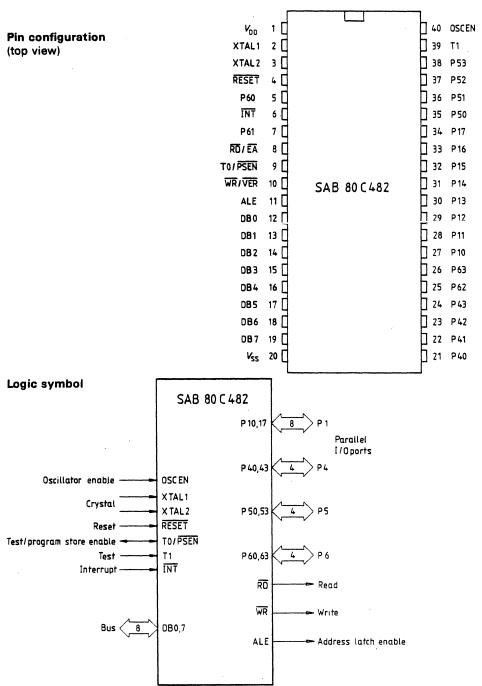

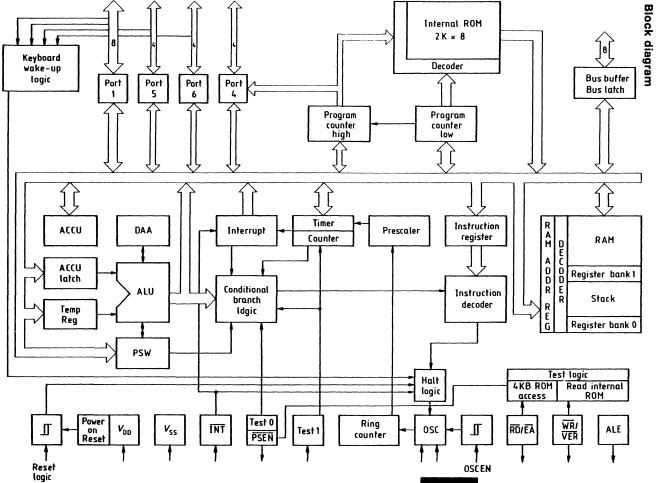

|     | SAB 80C482                | 8-bit single chip CMOS microcomputer                   | 133 |

|     | SAB 8086                  | 16-bit microprocessor                                  | 161 |

|     | SAB 8088                  | 16-bit microprocessor with 8-bit data bus interface    | 199 |

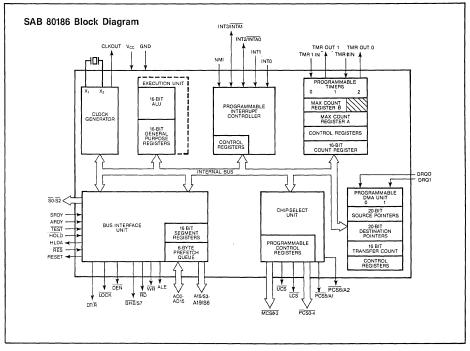

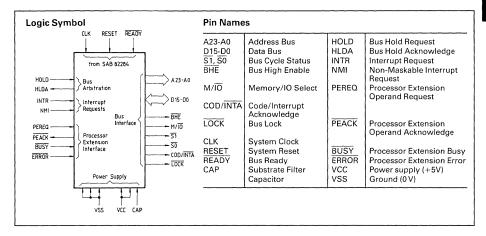

|     | SAB 80186                 | High integration 16-bit microprocessor                 | 229 |

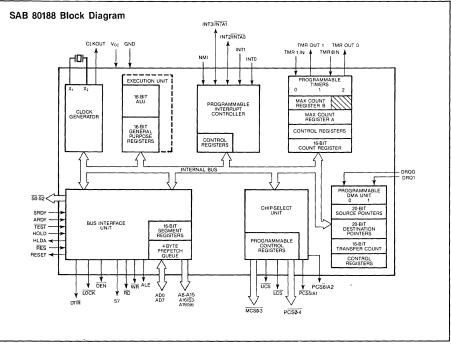

|     | SAB 80188                 | High integration 16-bit microprocessor with 8-bit data |     |

|     |                           | bus interface                                          | 231 |

|     | SAB 80286                 | High performance 16-bit microprocessor with memory     |     |

|     |                           | management and protection                              | 233 |

## 4. Peripheral and Support Components

,

### Page

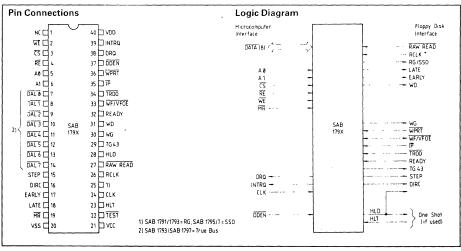

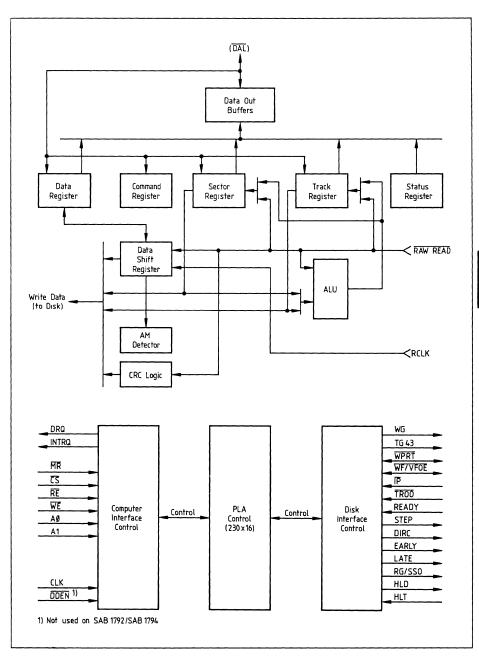

| SAB 1791/93/95/97 | Floppy disk formatter/controller                    |

|-------------------|-----------------------------------------------------|

| SAB 2793A/97A     | Floppy disk formatter/controller                    |

| SAB 8237A         | High performance programmable DMA controller 353    |

| SAB 8256A         | Programmable multifunction UART (MUART)             |

| SAB 8259A         | Programmable interrupt controller                   |

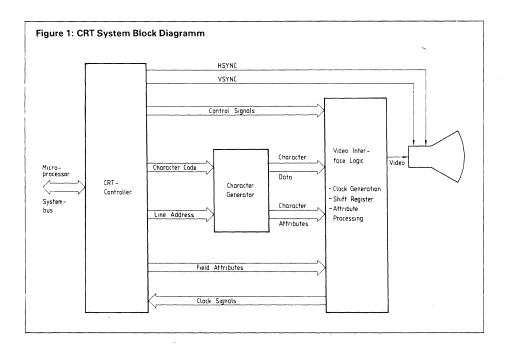

| SAB 8275          | Programmable CRT controller 405                     |

| SAB 8276          | Small system CRT controller                         |

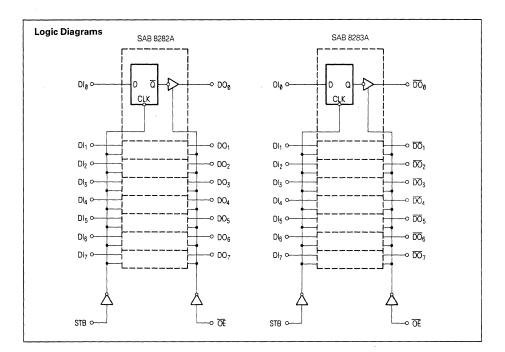

| SAB 8282A/8283A   | Octal latch                                         |

| SAB 8284B         | Clock generator and driver for SAB 8086             |

|                   | family processors465                                |

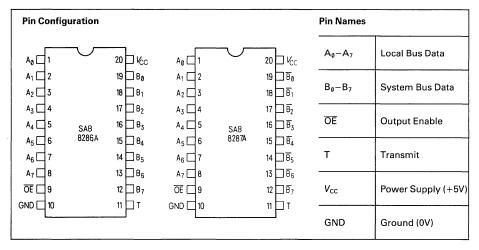

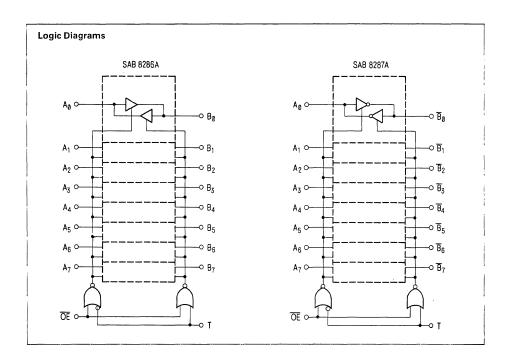

| SAB 8286A/8287A   | Octal bus transceiver                               |

| SAB 8288A         | Bus controller for SAB 8086 family processors 485   |

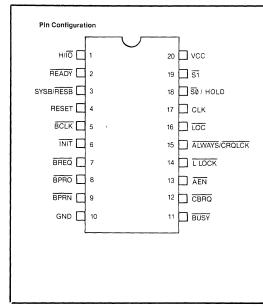

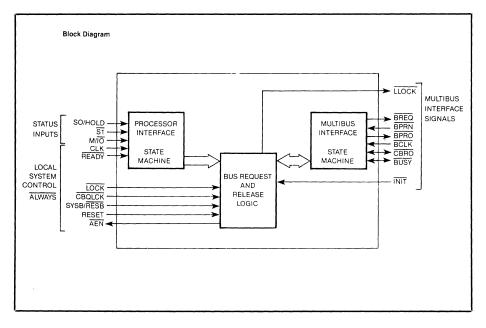

| SAB 8289          | Bus arbiter for SAB 8086 family processors          |

| SAB 82258         | Advanced DMA controller for 8 or 16-bit systems 507 |

| SAB 82284         | Clock generator and ready interface for SAB 80286   |

|                   | family processors                                   |

| SAB 82288         | Bus controller for SAB 80286 family processors567   |

| SAB 82289         | Bus arbiter for SAB 80286 family processors         |

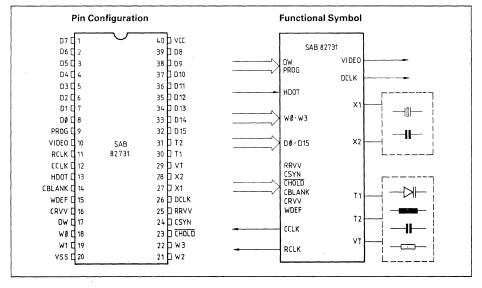

| SAB 82731         | Dot rate generator                                  |

|                   |                                                     |

## 5. Memory Components

| SAB 81C50/81C51 | CMOS static ram; 256 X 8-bit with multiplex bus<br>interface |

|-----------------|--------------------------------------------------------------|

| 0.10 01050      |                                                              |

| SAB 81C52       | CMOS static ram; 256 X 8-bit with multiplex bus              |

|                 | interface                                                    |

| HYB 4164        | Dynamic ram; 65, 536 X 1-bit639                              |

| HYB 41256       | Dynamic ram; 262, 144 X 1-bit                                |

| HYB 41257       | Dynamic ram; 262, 144 X 1-bit with nibble mode 669           |

|                 |                                                              |

### 6. Telecom Components

| PEB 2030        | Frame alignment circuit                         |

|-----------------|-------------------------------------------------|

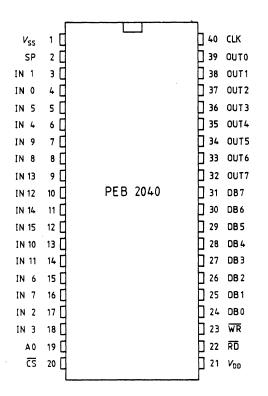

| PEB 2040        | Memory time switch                              |

| PEB 2050        | Peripheral board controller                     |

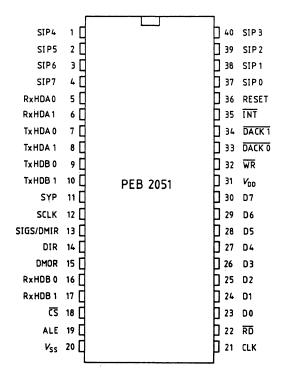

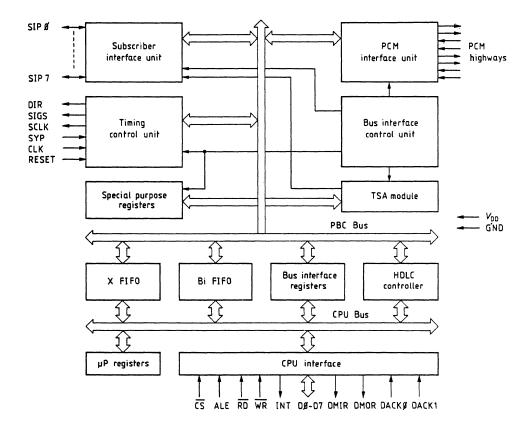

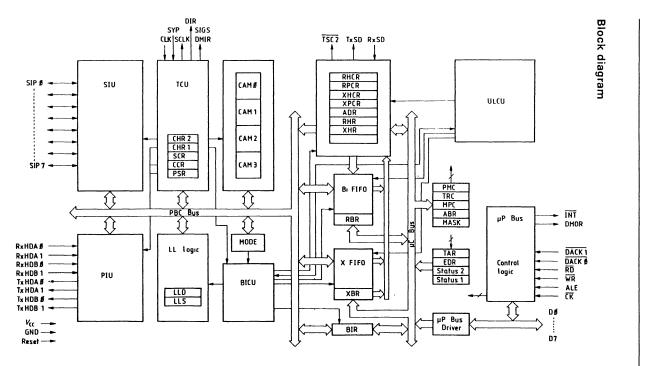

| PEB 2051        | Peripheral board controller733                  |

| PEB 2060        | Programmable digital signal processing          |

|                 | CODEC-FILTER                                    |

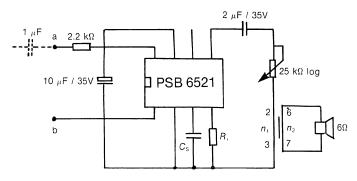

| PSB 6520        | Tone ringer                                     |

| PSB 6521        | Tone ringer                                     |

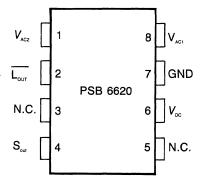

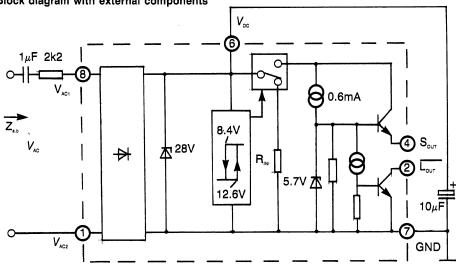

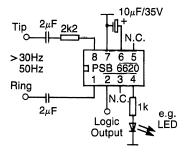

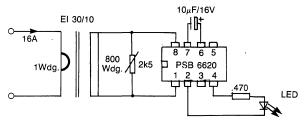

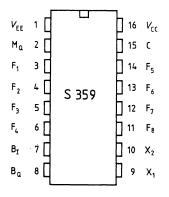

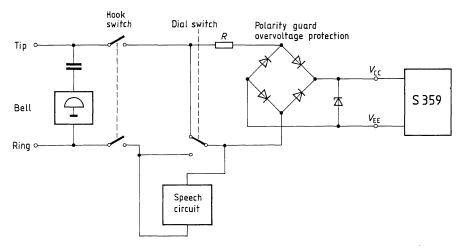

| PSB 6620        | Ring detector                                   |

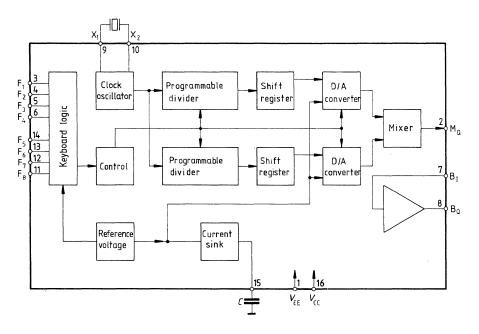

| PSB 8590        | DTMF generator/dialer                           |

| PSB 8591        | DTMF generator/dialer                           |

| PSB 8592        | DTMF generator/dialer                           |

| SAB 80C482      | 8-bit single chip CMOS microcomputer            |

| SAB 81C50/81C51 | CMOS static ram; 256 X 8-bit with multiplex bus |

|                 | interface                                       |

## Page

| SAB 81C52 | CMOS static ram; 256 X 8-bit with multiplex bus |

|-----------|-------------------------------------------------|

|           | interface                                       |

| PSB 7510  | CMOS LCD controller853                          |

## 7. Data Conversion Components

| SDA 5200N | 6-bit flash A/D converter      | . 875 |

|-----------|--------------------------------|-------|

| SDA 5200S | 6-bit flash A/D converter      | . 881 |

| SDA 6020  | 6-bit flash A/D converter      | . 887 |

| SDA 8005  | 8-bit high speed D/A converter | . 893 |

| SDA 8010  | 8-bit flash A/D converter      | . 905 |

## 8. Switched Mode Power Supply (SMPS) Components

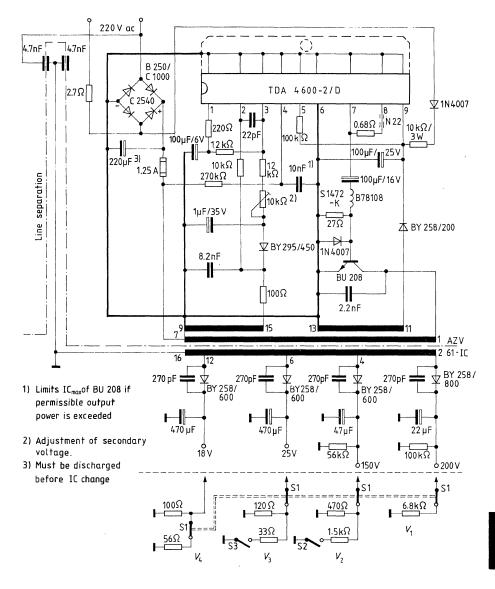

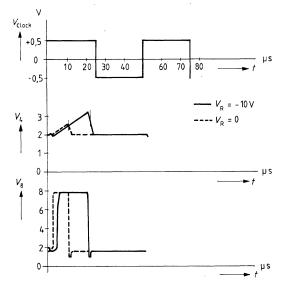

| TDA 4600-2/4600-2D | Control IC for switched mode power supplies |

|--------------------|---------------------------------------------|

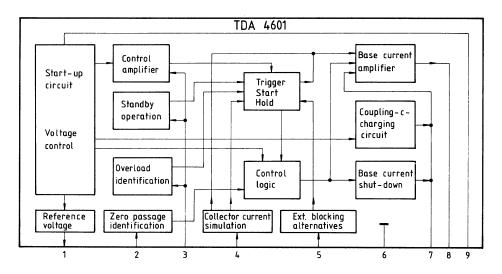

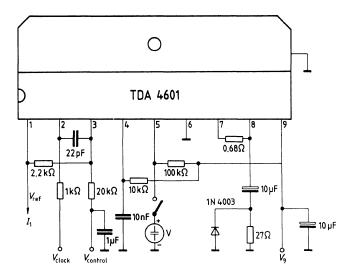

| TDA 4601/4601D     | Control IC for switched mode power supplies |

| TDA 4700/4700A     | Control IC for switched mode power supplies |

| TDA 4714A/4714B    | Control IC for switched mode power supplies |

| TDA 4716A/4716B    | Control IC for switched mode power supplies |

| TDA 4718/4718A     | Control IC for switched mode power supplies |

## 9. Integrated Circuits for Consumer Applications

| 9.1     | VHF/UHF Video Modulator IC                                                           | * |

|---------|--------------------------------------------------------------------------------------|---|

| 9.2     | Video IF ICs                                                                         | * |

| 9.3     | Video Single Pole Double Throw Switch IC                                             | * |

| 9.4     | Quasiparallel Sound (Split Sound) Amplifier                                          | * |

| 9.5     | Video IF/Quasiparallel Sound (Split Sound) Combo ICs                                 | * |

| 9.6     | TV Stereo/Dual Sound (German Standard) and Matrix IC                                 | * |

| 9.7     | ICs for Switched Mode Power Supplies<br>TDA 4600-2, TDA 4600-2D, TDA 4601, TDA 4601D | * |

| 9.8     | IC for Pin Cushion Correction in CRT Applications                                    | * |

| *See Co | nsumer Data Book or contact your local Siemens Representative.                       |   |

## **Table of Contents**

## Page

| 9.9            | Programmable Multistandard Sync Pulse Generator* * S 178A                                                                           |

|----------------|-------------------------------------------------------------------------------------------------------------------------------------|

| 9.10           | High Frequency Prescalers       *         SDA 2211, SDA 2311, SDA 4042, S 89, SDA 4211                                              |

| 9.11           | Phase Locked Loop (PLL) Devices       *         SDA 2112-2, SDA 3002, SDA 3112, SDA 3202, SDA 3203                                  |

| 9.12           | Application Oriented Single Chip Microcomputers* * SDA 2010, SDA 2011, SDA 2030, SDA 2110, SDA 3010, SDA 3110, SAB 80215, SAB 80315 |

| 9.13           | IR Transmitter ICs, Preamplifiers, Receivers                                                                                        |

| 9.14           | Non Volatile Memories*<br>SDA 2116, SDA 2216                                                                                        |

| 9.15           | Display Drivers and Controllers       *         SDA 2131, SDA 2005, UAA 170, UAA 180, SDA 2014                                      |

| 9.16           | Audio Control ICs *<br>TDA 4290-2S, TDA 4292, TDA 6200                                                                              |

| 9.17           | AF Power Amplifiers                                                                                                                 |

| 9.18           | Tuner/Mixer ICs/FM Receivers         *           TUA 2000-4, S 042P, TBB 469, TBB 1469, TBB 2469         *                          |

| 9.19           | FM IF Amplifiers with Demodulator                                                                                                   |

| 9.20           | AM IF Amplifiers with Demodulator                                                                                                   |

| 9.21           | AM/FM-IF Combination IC *<br>TDA 4100, TDA 4110X                                                                                    |

| 9.22           | PLL for AM/FM Receivers*<br>SDA 2120, S 187B                                                                                        |

| 9.23           | FM Stereo Decoders                                                                                                                  |

| *See Coi<br>10 | nsumer Data Book or contact your local Siemens Representative.                                                                      |

## **Table of Contents**

## Page

| 9.24 | Photoelectric Devices * TFA 1001W                                                                                     |

|------|-----------------------------------------------------------------------------------------------------------------------|

| 9.25 | Timer ICs                                                                                                             |

| 9.26 | Phase Control ICs                                                                                                     |

| 9.27 | DC Motor Control                                                                                                      |

| 9.28 | Window Discriminator ICs * TCA 965                                                                                    |

| 9.29 | Threshold Switches                                                                                                    |

| 9.30 | Programmable Diode Matrix*<br>S 353, S 1353, S 2353                                                                   |

| 9.31 | Audible Signal Devices**<br>SAB 0600, SAB 0601, SAB 0602, SAB 0700                                                    |

| 9.32 | Sensor ICs, Proximity Switches, Hall Effect Devices*<br>TCA 305A/G, TCA 355B/G, HKZ 101, HKZ 101S, TLE 4903, SAS 231W |

\*See Consumer Data Book or contact your local Siemens Representative.

## **General Information**

#### 1.1 Type Designation Code For ICs

The IC type designations are based on the European code system of Pro Electron.\* The code system is explained in the Pro Electron brochure D 15, 1982 edition, which can be obtained from:

> Pro Electron Boulevard de Waterloo 103 1000 Brussels, Belgium

\*Some exceptions exist.

### 1.2 Mounting Instructions

#### Plastic Package With 8, 14, 16, 18, 20, 22, 24, 28, or 40 Pins

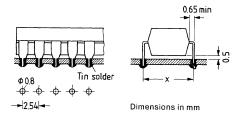

The pins are bent downwards in a  $90^{\circ}$  angle and fit into holes with a diameter of between 0.7 and 0.9 mm spaced 2.54 mm apart. The dimension x(see figure below) is given in the mechanical dimension drawings for the various packages.

The bottom of the package will not touch the PC board after insertion because the pins have shoulders just below the package (see figure below).

After the package is inserted into the PC board, it is advisable to bend the ends of two pins at an angle of approx. 30° to the board so that the package does not have to be pressed down during soldering. Plastic packages are soldered on that side of the PCB facing away from the package.

The maximum permissable soldering temperature is 265°C (max. 10 s) for manual soldering and 240°C (max 4 s) for dip soldering.

Figure 1

#### **Power Package With 9 Pins**

Power packages generally have wider pins than standard plastic packages; meaning the hole diameter on the PCB must be between 1.1 and 1.8 mm. If the pins are bent, there should be no stress between the pins and the package. The minimum distance between the package and the bending point is 2 mm.

The soldering temperatures for power packages are the same as for plastic packages.

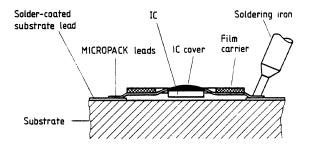

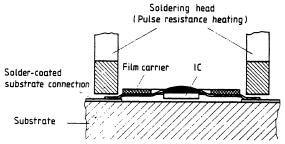

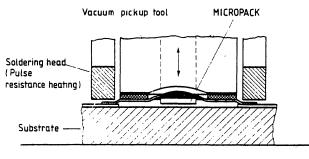

#### **Micropack Packages**

Mounting instructions for components available in a micropack are found within the Data Sheet.

#### Precautions

Ensure that no current is able to flow between the solder bath or soldering iron and the PCB. It is advisable to ground the pins that are to be soldered as well as the solder bath or soldering iron.

When they are being prepared and inserted in a PCB, integrated circuits should be protected against static charging. Under no circumstances may the components be removed or inserted while the operating voltage is switched on.

The increase in chip temperature during the soldering process results in a temporary increase in electrostatic sensitivity of integrated circuits. Special precautions should therefore be taken against line transients, e.g. through the switching of inductive loads.

#### 1.3 Processing Guidelines For ICs

Integrated circuits (ICs) are electrostatic-sensitive (ESS) devices. The requirement for greater packing density has led to increasingly small structures on semiconductor chips, with the result that today every IC, whether bipolar, MOS, or CMOS, has to be protected against electrostatics.

MOS and CMOS devices generally have integrated protective circuits and it is hardly possible any more for them to be destroyed by purely static electricity. On the other hand, there is acute danger from electrostatic discharges (ESD).

Of the multitude of possible sources of discharge, charged devices should be mentioned in addition to charged persons. With low-resistance discharges, it is possible for peak power amounting to kilowatts to be produced.

For the protection of devices, the following principles should be observed:

- a) Reduction of charging voltage, below 200 V if possible. Means which are effective here are an increase in relative humidty to  $\geq 60\%$  and the replacement of highly charging plastics by antistatic materials.

- b) With every kind of contact with the device pins a charge equalization is to be expected. This should always be highly resistive (ideally  $R = 10^6$  to  $10^8$  ohms).

All in all this means that ICs call for special handling, because uncontrolled charges, voltages from ungrounded equipment or persons, surge voltage spikes and similar influences, can destroy a device. Even if devices have protective circuits (e.g. protective diodes) on their inputs, the following guidelines for their handling should nevertheless be observed.

#### Identification

The packing of ESS devices is provided with the following label by the manufacturer.

#### Scope

The guidelines apply to the storage, transport, testing, and processing of all kinds of ICs, as well as equipment and soldered circuit boards that contain such components.

#### Handling of Devices

- 1. ICs must be left in their containers until they are processed.

- ICs may only be handled at specially equipped work stations. These stations must have work surfaces covered with a conductive material of the order of 10<sup>6</sup> to 10<sup>9</sup> ohms to ground.

- 3. With humidity of > 50% pure cotton clothing is sufficient. In the case of chargeable synthetic fibers, the clothing should be worn close-fitting. A wrist strap grounded across a resistor of 5 x  $10^4$  to  $10^5$  ohms must be worn snugly on the skin.

- 4. If conductive floors,  $R = 5 \times 10^4$  to  $10^7$  ohms are provided, further protection can be achieved by using so-called MOS chairs and shoes with a conductive sole ( $R = 10^5$  to  $10^7$  ohms).

- 5. All transport containers for ESS devices and assembled circuit boards must first be brought to the same potential by being placed on the work surface or touched by the operator before the individual devices may be handled. The potential equalization should be accross a resistor of 10<sup>6</sup> to 10<sup>8</sup> ohms.

- 6. When loading machines and production devices, it should be noted that the devices come out of the transport magazine charged and can be damaged if they touch metal, e.g. machine parts.

- Example 1) conductive (black) tubes.

The devices may be destroyed in the tube by charged persons or come out of the tube charged if this is emptied by a charged person. Conductive tubes may only be handled at ESS work stations (highresistance work-station and person grounded).

Example 2) anti-static (transparent) tubes.

The devices cannot be destroyed by charged persons in the tube (there may be a rare exception in the case of custom ICs with unprotected gate pins). The devices can be endangered as in 1) when the tube is emptied if the tube, especially at low humidity, is no longer sufficiently anti-static after a long period of storage (> 1 year).

In both cases, damage can be avoided by discharging the devices across a grounded adapter of high-resistance material ( $= 10^{\circ}$  to  $10^{\circ}$  ohms) between the tube and the machine.

The use of metal tubes — especially of anodized aluminum — is not advisable because of the danger of low-resistance device discharge.

#### Storage

ESS devices should only be stored in identified locations provided for the purpose. During storage, the devices should remain in the packing in which they are supplied. The storage temperature should not exceed 60°C.

#### Transport

ESS devices in approved packing tubes should only be transported in suitable containers of conductive or longterm anti-static-treated plastic or possibly unvarnished wood. Containers of high-charging plastic or very low-resistance materials are in like manner unsuitable. Transfer cars and their rollers should exhibit adequate electrical resistance ( $R < 10^6$  ohms). Sliding contacts and grounding chains will not reliably eliminate charges.

#### Incoming Inspection

At incoming inspection, the above guidelines should be observed. Otherwise any right to refund or replacement if devices fail inspection may be lost.

#### Material and Mounting

- 1. The drive belts of machines used for the processing of the devices (e.g. bending and cutting machines, conveyor belts), should be treated with anti-static spray (e.g. anti-static spray 100 from Kontaktchemie).

- If ESS devices have to be soldered or desoldered manually, soldering irons with thyristor control should not be used. Siemens EMI-suppression capacitors of the type B 81711-B31...-B36 are recommended to protect against line transients.

- 3. Circuit boards fitted and soldered with ESS devices are always to be considered electrostatically sensitive.

#### **Electrical Tests**

- 1. The devices should be processed with observation of these guidelines. Before assembled and soldered circuit boards are tested, remove any shorting rings.

- Test receptacles must not have voltage applied when individual devices or assembled circuit boards are inserted or withdrawn, unless specifications state otherwise. Ensure that the testers do not produce any voltage spikes, either when being turned on and off in normal operation or if the power fuse blows or other fuses respond.

- 3. Signal voltages may only be applied to the inputs of ICs when or after the supply voltage is turned on. They must be disconnected before or when the supply voltage is turned off.

- 4. Observe any notes and instructions in the respective data books.

#### Packing Of Assembled PC Boards or Flatpack Units

The packing material should exhibit low volume conductivity:  $10^5$  ohm-cm  $< \rho < 10^{10}$  ohm-cm.

In most cases — especially with humidity of > 40% — this requirement is fulfilled by simple corrugated board. Better protection is obtained with bags of conductive polyethylene foam (e.g. RCAS 1200 from Richmond of Redlands, CA).

One should always ensure that boards cannot touch.

In special cases, it may be necessary to provide protection against strong electric fields, such as can be generated by conveyor belts for example. For this purpose, a sheath of aluminum foil is recommended, although direct contact between the foil and the PCB must be avoided. Cardboard boxes with an aluminum-foil lining, such as those used for shipping Siemens devices, are available from Laber of Munich.

#### **Ultrasonic Cleaning Of ICs**

The following recommendation applies to plastic packages. For cavity packages (metal and also ceramic), separate regulations have to be observed.

Freon and isopropyl alcohol (trade name: propanol) can be used as solvents. These solvents can also be used for plastic packages because they do not eat into the plastic material.

An ultrasonic bath in double halfwave operation is advisable because of the low component stress.

## 1.4 Electrical And Environmental Ratings

#### **Maximum Ratings**

The maximum ratings are absolute limits. The IC may be destroyed if only a single one of these values is exceeded.

#### **Electrical Characteristics**

The electrical characteristics include the guaranteed tolerances of the values maintained by an IC for the specified operating range.

The typical characteristics are mean values that can be expected on the basis of the production. Unless otherwise specified, the typical characteristics apply to  $T_{amb} = 25$  °C and the given supply voltage.

#### Operating Data

The functions stated in the circuit description are fulfilled within the range of the operating data.

1.5 Mechanical Dimensions Package Dimensions

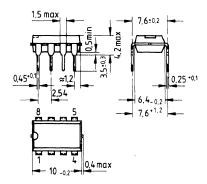

Plastic plug-in package 20 A 8 DIN 41866 8 pins, DIP

Approx. weight 0.7 g

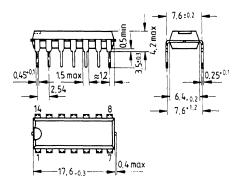

Plastic plug-in package 20 A 14 DIN 41866 14 pins, DIP

Approx. weight 1.1 g

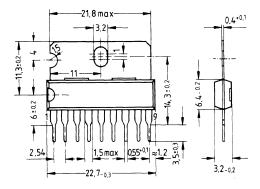

Plastic power package, with cooling fin and 9 pins, SIP (TDA 4601)

Approx. weight 1.9 g

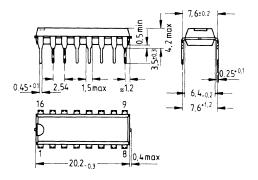

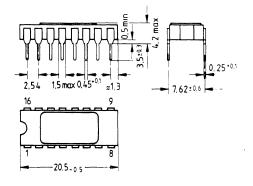

Plastic plug-in package 20 A 16 DIN 41866, 16 pins, DIP

Approx. weight 1.2 g

Ceramic package, 16 pins, DIC

Approx. weight 1.4 g

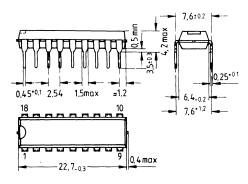

Plastic plug-in package 20 A 18 DIN 41866, 18 pins, DIP

Approx. weight 1.3 g

Ceramic package, 18 pins, DIC

Approx. weight 2.7 g

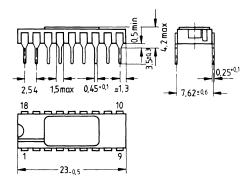

Plastic plug-in package 20 A 20 DIN 41866, 20 pins, DIP

Approx. weight 1.5 g

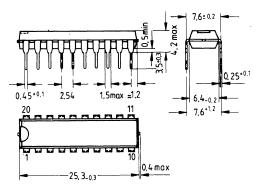

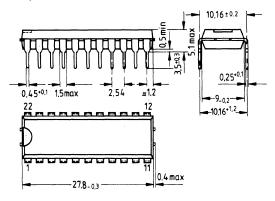

Plastic plug-in package 20 D 22 DIN 41866, 22 pins, DIP

Approx. weight 2.1 g

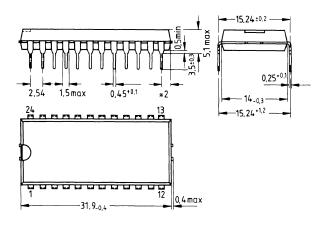

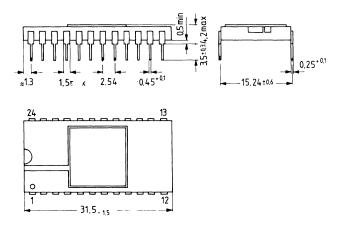

Plastic plug-in package 20 B 24 DIN 41866, 24 pins, DIP

Approx. weight 2.5 g

Ceramic package, 24 pins, DIC

Approx. weight 3 g

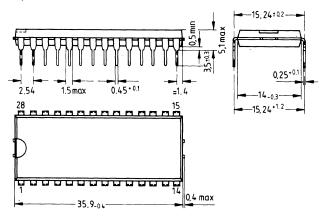

Plastic plug-in package 20 B 28 DIN 41866, 28 pins, DIP

Approx. weight 3 g

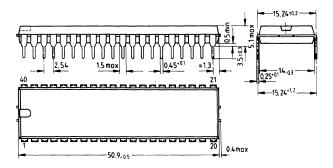

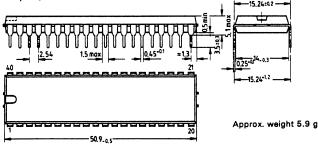

Plastic plug-in package 20B 40 DIN 41866, 40 pins, DIP

Approx. weight 5.9 g

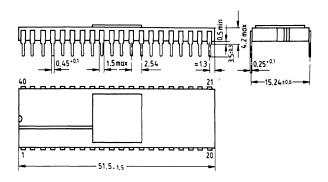

Ceramic package, 40 pins, DIC (SAB 8086)

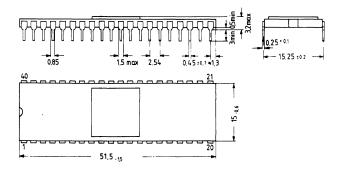

Ceramic package, 40 pins, DIC

Approx. weight 5.9 g

•

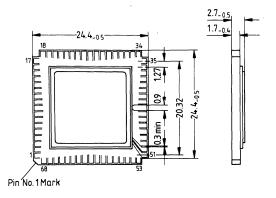

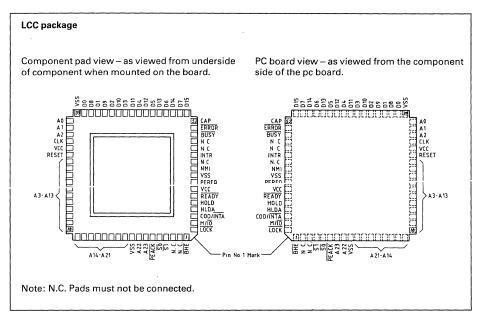

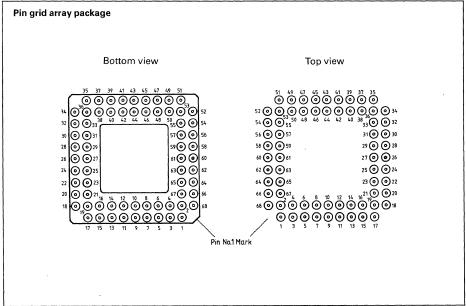

Ceramic package, 68 pins, LCC

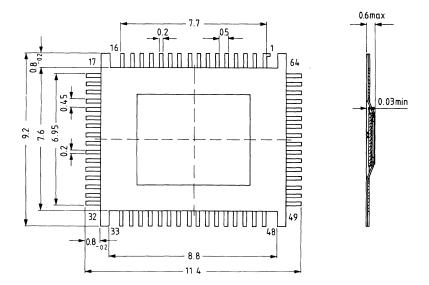

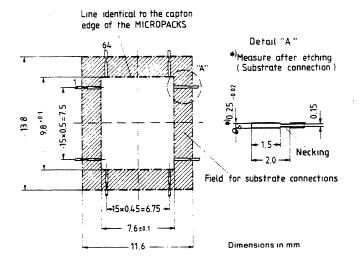

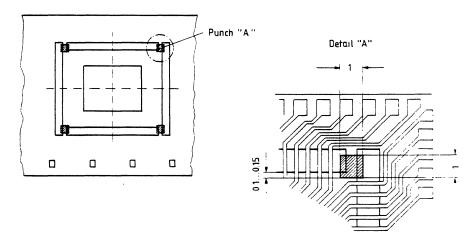

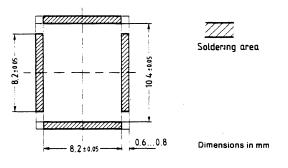

MICROPACK, 64 connections

+ 0.2

0,5

в

A

₹ 0,2 B

4,5

6-0,2 15

#### seam 0,03 max.

Hard PVC, transparent, impact resistant

29

22

Α

в

4

5,5-0,5 15±0,3

م ہو۔ میں د د انہو مہ

32

General Information

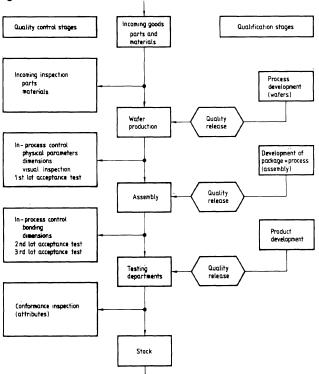

## 1.6 Quality And Reliability

## **Quality Assurance System**

The high quality and reliability of integrated circuits from Siemens is the result of a carefully arranged production which is systematically checked and controlled at each production stage.

The procedures are subject to a quality assurance system; full details are given in the brochure "Siemens Quality Assurance System-Integrated Circuits" (SQS-IC).

Figure 1 shows the most important stages of the "SQS-IC". A quality assurance (QA) department which is independent of production and development, is responsible for the selected control measures, acceptance procedures, and information feedback loops. This department has state-of-the-art test and measuring equipment at its disposal, works according to approved methods of statistical quality control, and is provided with facilities for accelerated life and environmental tests used for both qualification and routine monitoring tests.

The latest methods and equipment for preparation and analysis are employed to achieve a continuous development of quality and reliability.

#### **Quality Specifications**

The delivery quality of integrated circuits is specified as follows:

- 1. Maximum ratings and tolerance limits of the characteristics.

- Sampling inspection, AQL values (acceptable quality level) Inspection by attributes<sup>1)</sup> is based on the identical sampling inspection plans DIN 40080, (or) MIL-STD-105, inspection level II, normal inspection, or IEC 410.

A delivery lot for which the defect percentage for a certain characteristic is equal or less than the specified AQL value, will most probably (more than 95%) be accepted in the appropriate sampling inspection.

The average defect percentage of delivered products lies, in general, clearly below the AQL value and is known as the average outgoing quality (AOQ). Only the number of defective units is evaluated in the sampling inspection.

#### 3. Defects

A defect exists if a component characteristic does not correspond to the specifications in the data sheet.

The defects are classified as total defects, defects in the electrical features, and defects in the mechanical features. Unless otherwise agreed upon, the AQL values in section 5 apply to the various defect types.

#### 4. Classification of defects

| Total defect:                                            | <ul> <li>open contact or short circuit within a specified<br/>temperature range</li> <li>no marking, or wrong type and/or direction of<br/>marking</li> </ul>                |

|----------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                          | <ul> <li>wrong marking of pin 1</li> <li>mixed with wrong versions/types</li> <li>components not aligned within one rail/tube</li> <li>broken package and/or pins</li> </ul> |

| Defects in the<br>electrical features:<br>Defects in the | - exceeding electrical specification limits                                                                                                                                  |

| mechanical features:                                     | <ul> <li>defects on the package surface</li> <li>type marking hard to identify</li> <li>bent pins</li> <li>wrong dimensions</li> </ul>                                       |

1) Inspection for a characteristic for which only two mutually exclusive properties are specified (good/bad).

### 5. AQL table

|                                          | AQL values |        |

|------------------------------------------|------------|--------|

| Defect type                              | Bipolar IC | MOS IC |

| Total defect (mechanical and electrical) | 0.1        | 0.25   |

| Defect in the electrical features        | 0.4        | 0.4    |

| Defect in the mechanical features        | 0.4        | 0.4    |

| AOL value 1.5 applies to switching times |            |        |

AQL value 1.5 applies to switching times

#### 6. Incoming inspection

The tests carries out by the manufacturer are intended to render expensive incoming inspection by the user unnecessary. If the user, however, wants to carry out such inspections, we recommend the use of a sampling inspection plan as described in section 7. The test method used must be agreed upon between customer and supplier.

The following information is required to adjust a possible claim:

test circuit, sample size, number of defective items found, sample of evidence, packing list.

|            | AQL value |                |                   |   |      |   |     |   |             |    |    |    |        |    |        |    |    |    |          |                  |       |

|------------|-----------|----------------|-------------------|---|------|---|-----|---|-------------|----|----|----|--------|----|--------|----|----|----|----------|------------------|-------|

| Lot size   |           | Sample<br>size | 0.06              | 5 | 0.10 | 0 | .15 | 0 | .25         | 0. | 40 | 0. | 65     | 1. | .0     | 1. | 5  | 2. | 5        | 4.0              | 6.5   |

|            |           |                | AF                | 1 | AR   | A | R   | A | R           | A  | R  | A  | R      | A  | R      | A  | R  | A  | R        | AR               | AR    |

| 2 to       | 8         | 2              |                   |   |      |   |     |   |             |    | }  |    |        |    |        |    |    |    |          |                  | 0_1   |

| 9 to       | 15        | 3              |                   |   |      |   |     |   |             |    |    |    |        |    |        |    |    |    | L        | ₩<br>0_1         |       |

| 16 to      | 25        | 5              |                   |   |      |   |     |   |             |    |    |    |        |    |        | v  | 7  | 0  | ♥<br>1   |                  |       |

| 26 to      | 50        | 8              |                   |   |      |   |     |   |             |    |    |    |        |    |        | 0  |    | 4  | 4        |                  | 1 2   |

| 51 to      | 90        | 13             |                   |   |      |   |     |   |             |    |    |    | 7      | 0  | 7<br>1 |    |    |    | -        | 1 <sup>♥</sup> 2 | 23    |

| 91 to      | 150       | 20             |                   |   |      |   |     |   |             | V  | 7  | 0  | 7<br>1 | -  |        |    | 7  | 1  | 2        | 23               | 34    |

| 151 to     | 280       | 32             |                   |   |      |   |     |   |             | 0  |    | 4  | à      |    |        | 1  | 2  | 2  | 3        | 34               | 56    |

| 281 to     | 500       | 50             |                   |   |      |   |     | 0 | ¥<br>1<br>▲ |    | Ī  |    |        | 1  | 2      | 2  | 3  | 3  | 4        | 56               | 78    |

| 501 to     | 1200      | 80             |                   |   | V    | 0 | 7   |   |             |    | 7  | 1  | 2      | 2  | 3      | 3  | 4  | 5  | 6        | 78               | 10 11 |

| 1201 to    | 3200      | 125            |                   |   | 0_1  |   | 4   |   |             | 1  | 2  | 2  | 3      | 3  | 4      | 5  | 6  | 7  | 8        | 10 11            | 14 15 |

| 3201 to 1  | 0000      | 200            | 0 <b>√</b> 1      |   | T    |   |     | 1 | ₹<br>2      | 2  | 3  | 3  | 4      | 5  | 6      | 7  | 8  | 10 | 11       | 14 15            | 21 22 |

| 10001 to 3 | 5000      | 315            | T                 |   | V    | 1 | 2   | 2 | 3           | 3  | 4  | 5  | 6      | 7  | 8      | 10 | 11 | 14 | 15       | 21 22            |       |

| 35001-15   | 50000     | 500            |                   |   | 12   | 2 | 3   | 3 | 4           | 5  | 6  | 7  | 8      | 10 | 11     | 14 | 15 | 21 | 22       | 4                |       |

| 150001-50  | 00000     | 800            | <b>▼</b><br>  1 2 | 2 | 23   | 3 | 4   | 5 | 6           | 7  | 8  | 10 | 11     | 14 | 15     | 21 | 22 |    | <b>A</b> |                  |       |

| 500001 and | dmore     | 1250           | 2 3               | 3 | 34   | 5 | 6   | 7 | 8           | 10 | 11 | 14 | 15     | 21 | 22     |    | •  |    |          |                  |       |

### 7. Sampling inspection plan for normal inspection

in accordance with DIN 40080 or MIL-Std-105 D, inspection level II, or IEC410

- A = Acceptance number, i.e. the maximum number of defective sample units up to which the lot is accepted.

- B = Rejection number, i.e. the number of defective sample units which must at least be found for the lot to be rejected.

### Additional requirement

As the combination Acceptance 0 and Rejection 1 has a low degree of significance, the next larger size should be sampled.

### Quality Conformance

Each integrated circuit is subject to a final test at the end of the production process. Those tests are carried out by computer-controlled, automatic test systems because hundred of thousands of operating conditions as well as many static and dynamic parameters are to be considered. Moreover, the test systems are extremely reliable and reproducible. The quality assurance department carries out a final check in the form of a lot-by-lot sampling inspection to additionally ensure this minimum failure rate as well as the acceptable quality level (AQL). Sampling inspection is performed in accordance with the inspection plans of DIN 40080, as well as of the identical MIL-STD-105 or IEC 410.

The table below shows the results of such sampling inspections performed with hundred of thousands of ICs in 1984. Those results correspond to the average outgoing quality (AOQ), and are specified as defectives per million.

|                                   | Total<br>defects | Sum of<br>electrical<br>defects | Sum of<br>mechanical<br>defects |

|-----------------------------------|------------------|---------------------------------|---------------------------------|

|                                   | AOQ<br>(dpm)     | AOQ<br>(dpm)                    | AOQ<br>(dpm)                    |

| SSI/MSI<br>≤ 1000 gate functions  | 60               | 300                             | 500                             |

| LSI/VLSI<br>≥ 1000 gate functions | 400              | 800                             | 600                             |

Due to the low failure rate, the user generally need not perform an incoming inspection.

### Reliability

### Measures taken during development

The reliability of ICs is already considerably influenced at the development stage. Siemens has, therefore, fixed certain design standards for the development of circuit and layout, specifying e.g. minimum width and spacing of conductive layers on a chip, dimensions and electrical parameters of protective circuits for electrostatic charge, etc. An examination with the aid of carefully arranged programs operated on large-scale computers, guarantees the immediate identification and elimination of unintentional offenses against those design standards.

### In-process control during production

The manufacturing of integrated circuits comprises several hundred production steps. As each step is to be executed with utmost accuracy, the in-process control is of outstanding importance. Some processes require more than a hundred different test measures. The tests have been arranged such that the individual process steps can be reproduced continuously.

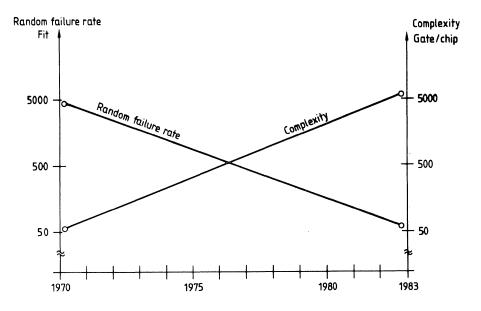

The decreasing failure rates reflect the never ending effort in this direction; in the course of years they have been reduced considerably despite an immense rise in the IC's complexity.

### **General Information**

### Figure 2

Figure 2 shows the general course of the failure rate for digital MOS ICs in fit for the years 1970 to 1983. The increasing complexity as regards gate functions/chip is also specified.

#### **Reliability monitoring**

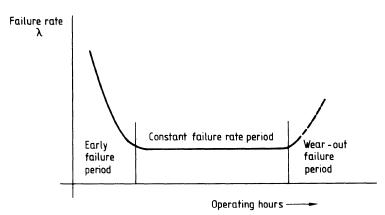

The general course of the IC's failure rate versus time is shown by a so-called "bathtub" curve (figure 3). The failure rate has its peak during the first few operating hours (early failure period). After the early failure period has decayed, the "constant" failure rate period starts during which the failures may occur at an approximately uniform rate. This period ends with a repeated rise of the curve during the wear-out failure period. For IC's, however, the latter period lies usually far beyond the service life specified for the individual equipment.

### **General Information**

#### Figure 3

Reliability tests for ICs are usually destructive examinations. They are, therefore, carried out with samples. Most failure mechanisms can be accelerated by means of higher temperatures. Due to the temperature dependence of the failure mechanisms, it is possible to simulate a future operational behavior within a short time by applying high temperatures; this is called life test.

The acceleration factor B for the life test can be obtained from the Arrhenius Equation

$$B = \exp \left[ \left( \frac{EA}{k} \right) \left( \frac{T_2 - T_1}{T_1 T_2} \right) \right]$$

where  $T_2$  is the temperature at which the life test is performed,  $T_1$  is the assumed operating temperature, and k is the Boltzmann constant.

Important for factor B is the activation energy  $E_{A^*}$ . It lies between 0.3 and 1.3 eV and differs considerably for individual failure mechanisms.

For all Siemens ICs, the reliability data from life tests is converted to an operating temperature of  $T_{amb} = 40$  °C, assuming an average activation energy of 0.4 eV. The acceleration factor for life tests is thus 24, compared with operational behavior. This method considers also failure mechanisms with low activation energy, i.e. which are only slightly accelerated by the temperature effect.

Various reliability tests are periodically performed with IC types that are representative of a certain production line-this is described in the brochure "SQS-IC". Such tests are e.g. humidity test at 85°C and 85% relative humidity, pressure cooker test, as well as life tests up to 1000 hours and more. Test results are available in the form of summary reports.

### 1.7 Thermal Coefficients Plastic Packages

| Type/ | Mounting Area | Chip Size | R <sub>thSA</sub> |

|-------|---------------|-----------|-------------------|

| Pins  | mm x mm       | mm²       | °K/W              |

| DIL 8 | 2.0 x 3.0     | 4         | 108               |

| 14    | 2.0 x 3.6 N   | 4/5       | 79/77             |

|       | 3.5 x 4.2 N   | 4/7/12    | 72/67/62          |

| 16    | 2.0 x 3.6     | 4/5       | 77/75             |

|       | 3.5 x 5.0     | 4/7/15    | 71/65/59          |

|       | 3.5 x 6.5     | 8         | 63                |

|       | 3.7 x 10.2    | 25        | 60                |

| 18    | 2.8 x 3.6     | 4/7       | 70/65             |

|       | 3.5 x 5.5     | 4/7/15    | 66/60/55          |

| 20    | 3.8 x 5.5 N   | 7/17      | 65/60             |

|       | 4.0 x 7.8     | 18        | 56                |

| 22    | 4.5 x 5.5     | 7/21      | 56/47             |

| 24    | 4.2 x 5.2     | 7/18      | 55/52             |

|       | 6.2 x 7.2     | 7/30/40   | 49/45/44          |

| 28    | 4.2 x 5.2     | 7/18      | 51/48             |

|       | 6.0 x 7.5     | 7/30/40   | 45/41/40          |

| 40    | 6.0 x 7.5     | 7/30/40   | 43/39/38          |

N = new package, S = special package according to package catalogue

### Ceramic multi-layer packages

N = new package, S = special package according to package catalogue.

#### Plastic power package

| Type/ | Mounting Area          | Chip Size | R <sub>thSA</sub> | R <sub>thSC</sub> |  |

|-------|------------------------|-----------|-------------------|-------------------|--|

| Pins  | mm x mm                | mm²       | ⁰K/W              | °K/W              |  |

| SIL 9 | 2.5 x 3.4<br>3.4 x 4.3 | 4.7<br>7  | 60<br>60          | 2.2<br>2.2        |  |

N = new package, S = special package according to package catalogue.

Summary of Types

|     | Siemens Part No.         | Function Page                                                                                 |

|-----|--------------------------|-----------------------------------------------------------------------------------------------|

| 2.1 | Component Selection      | Guide                                                                                         |

|     | Microcontroller and M    | licroprocessor Components                                                                     |

|     | SAB 8031-P               | 8-bit single chip microcomputer without internal                                              |

|     |                          | ROM, 12 MHz 49                                                                                |

|     | SAB 8031-10-P            | 8-bit single chip microcomputer without internal                                              |

|     | SAB 8031-T40/85-P        | ROM, 10 MHz                                                                                   |

|     |                          | ROM, 10 MHz, -40°C to +85°C temp. range                                                       |

|     | SAB 8031-T40/110-P       | 8-bit single chip microcomputer without internal                                              |

|     |                          | ROM, 8 MHz, -40°C to +110°C                                                                   |

|     |                          | temp. range                                                                                   |

|     | SAB 8031A-P              | 8-bit single chip microcomputer without internal                                              |

|     | SAB 8031A-15-P           | ROM, 12 MHz                                                                                   |

|     | 0AD 0001A-10-1           | ROM, 15 MHz                                                                                   |

|     | SAB 8031A-T40/85-P       | 8-bit single chip microcomputer without internal                                              |

|     |                          | ROM, 12 MHz, -40 °C to +85 °C temp. range 99                                                  |

|     | SAB 8031A-T40/110-P      |                                                                                               |

|     | 045 0000 B               | ROM, 10 MHz, -40°C to + 110°C temp. range 99                                                  |

|     | SAB 8032A-P              | 8-bit single chip microcomputer without internal                                              |

|     | SAB 8051-P               | ROM, 12 MHz, (enhanced SAB 8031A-P) 117<br>8-bit single chip microcomputer with internal mask |

|     | 040 0001-1               | programmed ROM, 12 MHz 49                                                                     |

|     | SAB 8051-10-P            | 8-bit single chip microcomputer with internal mask                                            |

|     |                          | programmed ROM, 10 MHz 49                                                                     |

|     | SAB 8051-T40/85-P        | 8-bit single chip microcomputer with internal mask                                            |

|     |                          | programmed ROM, 10 MHz, -40 °C to +85 °C                                                      |

|     | SAB 8051-T-40/110-P      | temp. range                                                                                   |

|     | SAD 8031-1-40/110-F      | programmed ROM, 8 MHz, -40°C to +110°C                                                        |

|     |                          | temp. range                                                                                   |

|     | SAB 8051A-P              | 8-bit single chip microcomputer with internal mask                                            |

|     |                          | programmed ROM, 12 MHz 81                                                                     |

|     | SAB 8051A-15-P           | 8-bit single chip microcomputer with internal mask                                            |

|     |                          | programmed ROM, 15 MHz                                                                        |

|     | SAB 8051A-T40/85-P       | 8-bit single chip microcomputer with internal mask<br>programmed ROM, 12 MHz, -40°C to +85°C  |

|     |                          | temp. range                                                                                   |

|     | SAB 8051A-T40/110-P      | 8-bit single chip microcomputer with internal mask                                            |

|     |                          | programmed ROM, 10 MHz, -40 °C to +110 °C                                                     |

|     |                          | temp. range                                                                                   |

|     | SAB 8052A-P              | 8-bit single chip microcomputer with internal mask                                            |

|     |                          | programmed ROM, 12 MHz, (enhanced SAB 8051A-P) 117                                            |

|     | SAB 8086-P<br>SAB 8086-C | 16-bit microprocessor, 5 MHz       161         16-bit microprocessor, 5 MHz       161         |

|     |                          | 10-bit microprocessor, 5 winz                                                                 |

| SAB 8086-1-P       16-bit microprocessor, 10 MHz       161         SAB 8086-2-P       16-bit microprocessor, 8 MHz       161         SAB 8086-2-C       16-bit microprocessor, 8 MHz       161         SAB 8088-P       16-bit microprocessor, with 8-bit data bus<br>interface, 5 MHz       199         SAB 8088-P       16-bit microprocessor, with 8-bit data bus<br>interface, 8 MHz       199         SAB 80186-C       High integration 16-bit microprocessor, 8 MHz       229         SAB 80186-C       High integration 16-bit microprocessor, 8 MHz       221         SAB 80286-6-C       High performance 16-bit microprocessor, 8 MHz, LCC.233       SAB 80286-6C         SAB 80286-6-C       High performance 16-bit microprocessor, 6 MHz, PGA.233       SAB 80286-6C         SAB 80286-6-C       High performance 16-bit microprocessor, 6 MHz, PGA.233       SAB 80286-6C         SAB 80286-CG       High performance 16-bit microprocessor, 6 MHz, PGA.233       SAB 80286-6C         SAB 1791-02-P       Floppy disk controller with non-inverted data bus       .299         SAB 1791-02-P       Floppy disk controller with non-inverted data bus       .299         SAB 1797-02-P       Floppy disk controller with non-inverted data bus,<br>built in data separator and write precompen-<br>sation logic       .255         SAB 2797A-02-P       Floppy disk controller with non-inverted data bus,<br>side select output <t< th=""><th></th><th>Siemens Part No.</th><th>Function</th><th>Page</th></t<>                                |   | Siemens Part No.       | Function                                           | Page  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|------------------------|----------------------------------------------------|-------|

| SAB 8086-1-C       16-bit microprocessor, 10 MHz       161         SAB 8086-2-C       16-bit microprocessor, 8 MHz       161         SAB 8086-2-C       16-bit microprocessor, 8 MHz       199         SAB 8088-2-P       16-bit microprocessor, with 8-bit data bus<br>interface, 5 MHz       199         SAB 80186-C       High integration 16-bit microprocessor, 8 MHz       221         SAB 80186-C       High integration 16-bit microprocessor, 8 MHz       231         SAB 80286-C       High performance 16-bit microprocessor, 6 MHz, LCC. 233       SAB 80286-CG         SAB 80286-C       High performance 16-bit microprocessor, 6 MHz, LCC. 233         SAB 80286-CG       High performance 16-bit microprocessor, 6 MHz, LCC. 233         SAB 80286-CG       High performance 16-bit microprocessor, 6 MHz, PGA. 233         SAB 80286-CG       High performance 16-bit microprocessor, 6 MHz, PGA. 233         SAB 80286-CG       High performance 16-bit microprocessor, 6 MHz, PGA. 233         SAB 1791-02-P       Floppy disk controller with non-inverted data bus       299         SAB 1793-02-P       Floppy disk controller with non-inverted data bus       299         SAB 1797-02-P       Floppy disk controller with non-inverted data bus, built in data separator and write precompensation logic       325         SAB 8237A-9       Floppy disk controller with non-inverted data bus, side select output, and bu                                                                                                             |   | SAB 8086-1-P           | 16-bit microprocessor, 10 MHz                      | . 161 |

| SAB 8086-2-P       16-bit microprocessor, 8 MHz       161         SAB 8086-2-C       16-bit microprocessor, 8 MHz       161         SAB 8088-P       16-bit microprocessor, with 8-bit data bus<br>interface, 5 MHz       199         SAB 8088-2-P       16-bit microprocessor, with 8-bit data bus<br>interface, 8 MHz       199         SAB 80186-C       High integration 16-bit microprocessor, 8 MHz       229         SAB 80286-C       High performance 16-bit microprocessor, 8 MHz       231         SAB 80286-C       High performance 16-bit microprocessor, 6 MHz, LCC. 233         SAB 80286-CG       High performance 16-bit microprocessor, 6 MHz, PGA.233         SAB 80286-CG       High performance 16-bit microprocessor, 6 MHz, PGA.233         SAB 80286-CG       High performance 16-bit microprocessor, 6 MHz, PGA.233         SAB 80286-CG       High performance 16-bit microprocessor, 6 MHz, PGA.233         SAB 80286-CG       High performance 16-bit microprocessor, 6 MHz, PGA.233         SAB 80286-CG       High performance 16-bit microprocessor, 6 MHz, PGA.233         SAB 1791-02-P       Floppy disk controller with non-inverted data bus       299         SAB 1791-02-P       Floppy disk controller with non-inverted data bus,<br>and side select output       299         SAB 1797-02-P       Floppy disk controller with non-inverted data bus,<br>built in data separator and write precompen-<br>sation logic       325                                                                                        |   | SAB 8086-1-C           |                                                    |       |

| SAB 8086-2-C       16-bit microprocessor, 8 MHz       161         SAB 8088-P       16-bit microprocessor with 8-bit data bus<br>interface, 5 MHz       199         SAB 8088-2-P       16-bit microprocessor, with 8-bit data bus<br>interface, 8 MHz       199         SAB 80186-C       High integration 16-bit microprocessor, 8 MHz       229         SAB 80286-C       High performance 16-bit microprocessor, 8 MHz, LCC.233         SAB 80286-C       High performance 16-bit microprocessor, 6 MHz, LCC.233         SAB 80286-C       High performance 16-bit microprocessor, 6 MHz, LCC.233         SAB 80286-C       High performance 16-bit microprocessor, 6 MHz, PGA.233         SAB 80286-C       High performance 16-bit microprocessor, 6 MHz, PGA.233         SAB 80286-C       High performance 16-bit microprocessor, 6 MHz, PGA.233         SAB 80286-C       High performance 16-bit microprocessor, 6 MHz, PGA.233         SAB 80286-C       High performance 16-bit microprocessor, 6 MHz, PGA.233         SAB 80286-C       High performance 16-bit microprocessor, 6 MHz, PGA.233         SAB 80286-C       High performance 16-bit microprocessor, 6 MHz, PGA.233         SAB 1795-02-P       Floppy disk controller with non-inverted data bus       299         SAB 1795-02-P       Floppy disk controller with non-inverted data bus, built in data separator and write precompensation logic       229         SAB 2793-02-P                                                                                                      |   | SAB 8086-2-P           | •                                                  |       |

| SAB 8088-P       16-bit microprocessor with 8-bit data bus<br>interface, 5 MHz       199         SAB 8088-2-P       16-bit microprocessor, with 8-bit data bus<br>interface, 8 MHz       199         SAB 80186-C       High integration 16-bit microprocessor, 8 MHz       229         SAB 80188-C       High integration 16-bit microprocessor, 8 MHz       231         SAB 80286-C       High performance 16-bit microprocessor, 8 MHz, LCC. 233         SAB 80286-C       High performance 16-bit microprocessor, 6 MHz, LCC. 233         SAB 80286-CG       High performance 16-bit microprocessor, 6 MHz, LCC. 233         SAB 80286-CG       High performance 16-bit microprocessor, 6 MHz, PGA. 233         SAB 80286-CG       High performance 16-bit microprocessor, 6 MHz, PGA. 233         SAB 80286-CG       High performance 16-bit microprocessor, 6 MHz, PGA. 233         SAB 80286-CG       High performance 16-bit microprocessor, 6 MHz, PGA. 233         SAB 80286-CG       High performance 16-bit microprocessor, 8 MHz, PGA. 233         SAB 1791-02-P       Floppy disk controller with non-inverted data bus       299         SAB 1795-02-P       Floppy disk controller with non-inverted data bus       299         SAB 1797-02-P       Floppy disk controller with non-inverted data bus, built in data separator and write precompensation logic       325         SAB 2797A-02-P       Floppy disk controller with non-inverted data bus, side sel                                                                               |   | SAB 8086-2-C           |                                                    |       |

| interface, 5 MHz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |   | SAB 8088-P             |                                                    |       |

| interface, 8 MHz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |   |                        | •                                                  | . 199 |

| SAB 80186-C       High integration 16-bit microprocessor, 8 MHz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |   | SAB 8088-2-P           | 16-bit microprocessor, with 8-bit data bus         |       |

| SAB 80188-CHigh integration 16-bit microprocessor with 8-bit<br>data bus interface, 8 MHz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |   |                        | interface, 8 MHz                                   | . 199 |

| data bus interface, 8 MHz231SAB 80286-CHigh performance 16-bit microprocessor, 8 MHz, LCC .233SAB 80286-CGHigh performance 16-bit microprocessor, 6 MHz, PGA .233SAB 802482-P8-bit single chip CMOS microcomputer with internal<br>mask programmed ROM, 3 MHz (80C48 with special<br>features)Peripheral and Support Components133SAB 1791-02-PFloppy disk controller with non-inverted data busSAB 1793-02-PFloppy disk controller with non-inverted data busSAB 1795-02-PFloppy disk controller with non-inverted data busand side select output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |   | SAB 80186-C            | High integration 16-bit microprocessor, 8 MHz      | . 229 |

| data bus interface, 8 MHz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |   | SAB 80188-C            | High integration 16-bit microprocessor with 8-bit  |       |

| SAB 80286-6-CHigh performance 16-bit microprocessor, 6 MHz, LCC. 233SAB 80286-CGHigh performance 16-bit microprocessor, 8 MHz, PGA. 233SAB 80286-6-CGHigh performance 16-bit microprocessor, 6 MHz, PGA. 233SAB 80286-6-CGHigh performance 16-bit microprocessor, 6 MHz, PGA. 233SAB 802482-P8-bit single chip CMOS microcomputer with internal mask programmed ROM, 3 MHz (80C48 with special features)mask programmed ROM, 3 MHz (80C48 with special features)133Peripheral and Support Components299SAB 1791-02-PFloppy disk controller with non-inverted data bus299SAB 1795-02-PFloppy disk controller with non-inverted data bus299SAB 1797-02-PFloppy disk controller with non-inverted data bus299SAB 2793A-02-PFloppy disk controller with non-inverted data bus, built in data separator and write precompensation logic229SAB 2797A-02-PFloppy disk controller with non-inverted data bus, side select output, and built in data separator and write precompensation logic325SAB 8237A-5-P8-bit high performance programmable DMA controller, 5 MHz353SAB 8256A-PProgrammable multi-function component with timers/counters, an interrupt controller, baud rate generator, serial and parallel ports (faster version of the SAB 8256A)369SAB 8259AProgrammable interrupt controller, 5 MHz369SAB 8259A-2-PProgrammable interrupt controller, 5 MHz369SAB 8259A-2-PProgrammable interrupt controller, 5 MHz369SAB 8259A-2-PProgrammable interrupt controller, 5 MHz369SAB 8259A-2-P <td< td=""><td></td><td></td><td></td><td>.231</td></td<>        |   |                        |                                                    | .231  |

| SAB 80286-CGHigh performance 16-bit microprocessor, 8 MHz, PGA. 233SAB 80286-6-CGHigh performance 16-bit microprocessor, 6 MHz, PGA. 233SAB 80C482-P8-bit single chip CMOS microcomputer with internal<br>mask programmed ROM, 3 MHz (80C48 with special<br>features).133Peripheral and Support ComponentsSAB 1791-02-PFloppy disk controller with inverted data busSAB 1795-02-PFloppy disk controller with non-inverted data bus299SAB 1797-02-PFloppy disk controller with non-inverted data busand side select output299SAB 2793A-02-PFloppy disk controller with non-inverted data bus<br>and side select output299SAB 2793A-02-PFloppy disk controller with non-inverted data bus,<br>built in data separator and write precompen-<br>sation logic325SAB 2797A-02-PSAB 2797A-02-PFloppy disk controller with non-inverted data bus,<br>built in data separator and write precompen-<br>sation logic325SAB 8237A-PSAB 8237A-P8-bit high performance programmable DMA<br>controller, 3 MHzSAB 8237A-S-P8-bit high performance programmable DMA<br>controller, 5 MHzSAB 8256A-PProgrammable multi-function component with<br>timers/counters, an interrupt controller, baud rate<br>generator, serial and parallel portsSAB 8256A-2-PProgrammable multi-function component with<br>timers/counters, an interrupt controller, baud rate,<br>generator, serial and parallel ports (faster<br>version of the SAB 8256A)SAB 8259AProgrammable interrupt controller, 5 MHzSAB 8259AProgrammable interrupt controller, 6 MHzSA                                    |   | SAB 80286-C            | High performance 16-bit microprocessor, 8 MHz, LCC | . 233 |

| SAB 80286-CGHigh performance 16-bit microprocessor, 8 MHz, PGA. 233SAB 80286-6-CGHigh performance 16-bit microprocessor, 6 MHz, PGA. 233SAB 80C482-P8-bit single chip CMOS microcomputer with internal<br>mask programmed ROM, 3 MHz (80C48 with special<br>features).133Peripheral and Support ComponentsSAB 1791-02-PFloppy disk controller with inverted data busSAB 1795-02-PFloppy disk controller with non-inverted data bus99SAB 1795-02-PFloppy disk controller with non-inverted data busand side select output299SAB 1797-02-PFloppy disk controller with non-inverted data bus<br>and side select output299SAB 2793A-02-PFloppy disk controller with non-inverted data bus,<br>built in data separator and write precompen-<br>sation logic310SAB 8237A-P8-bit high performance programmable DMA<br>controller, 3 MHzSAB 8256A-PProgrammable multi-function component with<br>timers/counters, an interrupt controller, bud rate<br>generator, serial and parallel portsSAB 8256A-2-PSAB 8256A-2-PProgrammable multi-function component with<br>timers/counters, an interrupt controller, bud rate<br>generator, serial and parallel portsSAB 8259AProgrammable interrupt controller, 5 MHzSAB 8259AProgrammable interrupt controller, 6 MHzSAB 8259ASAB 8259AProgrammable interrupt controller, 6 MHzSAB 8259AProgrammable interrupt controller, 7 MHzSAB 8259ASAB 8259ASAB 8259A <td></td> <td>SAB 80286-6-C</td> <td>High performance 16-bit microprocessor, 6 MHz, LCC</td> <td>. 233</td>                                                      |   | SAB 80286-6-C          | High performance 16-bit microprocessor, 6 MHz, LCC | . 233 |

| SAB 80286-6-CGHigh performance 16-bit microprocessor, 6 MHz, PGA. 233SAB 80C482-P8-bit single chip CMOS microcomputer with internal<br>mask programmed ROM, 3 MHz (80C48 with special<br>features).Peripheral and Support Components133SAB 1791-02-PFloppy disk controller with inverted data busSAB 1795-02-PFloppy disk controller with non-inverted data busSAB 1797-02-PFloppy disk controller with non-inverted data busSAB 1797-02-PFloppy disk controller with non-inverted data busSAB 2793A-02-PFloppy disk controller with non-inverted data bus,<br>built in data separator and write precompen-<br>sation logicSAB 2797A-02-PFloppy disk controller with non-inverted data bus,<br>built in data separator and write precompen-<br>sation logicSAB 8237A-P8-bit high performance programmable DMA<br>controller, 3 MHzSAB 8237A-P8-bit high performance programmable DMA<br>controller, 5 MHzSAB 8256A-PProgrammable multi-function component with<br>timers/counters, an interrupt controller, baud rate<br>generator, serial and parallel portsSAB 8259AProgrammable interrupt controller, 5 MHzSAB 8259AProgrammable interrupt controller, 5 MHzSAB 8259AProgrammable interrupt controller, 5 MHzSAB 8259AProgrammable interrupt controller, 6 MHzSAB 8259AProgrammable interrupt controller, 8 MHz <td></td> <td></td> <td></td> <td></td> |   |                        |                                                    |       |

| SAB 80C482-P8-bit single chip CMOS microcomputer with internal<br>mask programmed ROM, 3 MHz (80C48 with special<br>features)Peripheral and Support Components133SAB 1791-02-PFloppy disk controller with inverted data bus299SAB 1793-02-PFloppy disk controller with non-inverted data bus299SAB 1797-02-PFloppy disk controller with non-inverted data bus<br>and side select output299SAB 2793A-02-PFloppy disk controller with non-inverted data bus<br>and side select output299SAB 2793A-02-PFloppy disk controller with non-inverted data bus,<br>built in data separator and write precompen-<br>sation logic325SAB 8237A-PFloppy disk controller with non-inverted data bus,<br>side select output, and built in data separator and<br>write precompensation logic325SAB 8237A-P8-bit high performance programmable DMA<br>controller, 3 MHz353SAB 8256A-PProgrammable multi-function component with<br>timers/counters, an interrupt controller, baud rate<br>generator, serial and parallel ports369SAB 8259AProgrammable multi-function component with<br>timers/counters, an interrupt controller, 5 MHz369SAB 8259A-2-PProgrammable interrupt controller, 6 MHz395SAB 825                                                                               |   |                        |                                                    |       |

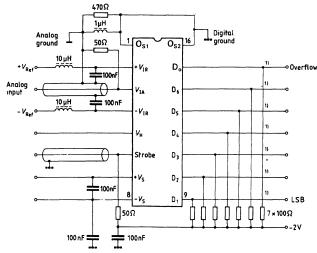

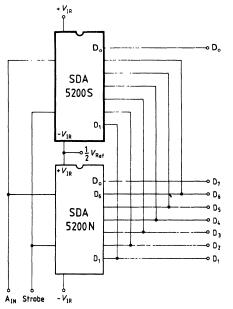

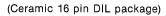

| mask programmed ROM, 3 MHz (80C48 with special<br>features)133Peripheral and Support Components133SAB 1791-02-PFloppy disk controller with inverted data bus299SAB 1793-02-PFloppy disk controller with non-inverted data bus299SAB 1795-02-PFloppy disk controller with inverted data bus and<br>side select output299SAB 1797-02-PFloppy disk controller with non-inverted data bus<br>and side select output299SAB 2793A-02-PFloppy disk controller with non-inverted data bus,<br>built in data separator and write precompen-<br>sation logic325SAB 2797A-02-PFloppy disk controller with non-inverted data bus,<br>side select output, and built in data separator and<br>write precompensation logic325SAB 8237A-P8-bit high performance programmable DMA<br>controller, 3 MHz353SAB 8237A-P8-bit high performance programmable DMA<br>controller, 5 MHz353SAB 8256A-PProgrammable multi-function component with<br>timers/counters, an interrupt controller, baud rate<br>generator, serial and parallel ports369SAB 8259AProgrammable interrupt controller, 5 MHz369SAB 8259A-2-PProgrammable interrupt controller, 5 MHz369SAB 8259A-2-PProgrammable interrupt controller, 5 MHz395SAB 8259A-2-PProgrammable interrupt controller, 6 MHz395SAB 8259A-2-PProgrammable interrupt controller, 6 MHz395SAB 8259A-2-PProgrammable interrupt controller, 7 MHz395SAB 8259A-2-PProgrammable interrupt controller, 8 MHz395SAB                                                                                                                               |   |                        |                                                    |       |