UPDATED

### **GENERAL INFORMATION – 1**

**PSEUDO-STATIC RAMs – 2**

STATIC RAMs – 3

MASK-PROGRAMMABLE ROMs - 4

**FIFO MEMORIES – 5**

**APPLICATION NOTES & CONFERENCE PAPERS – 6**

PACKAGING – 7

### NOTICE

The specifications contained within this Sharp Memory Data Book are current as of the publication date.

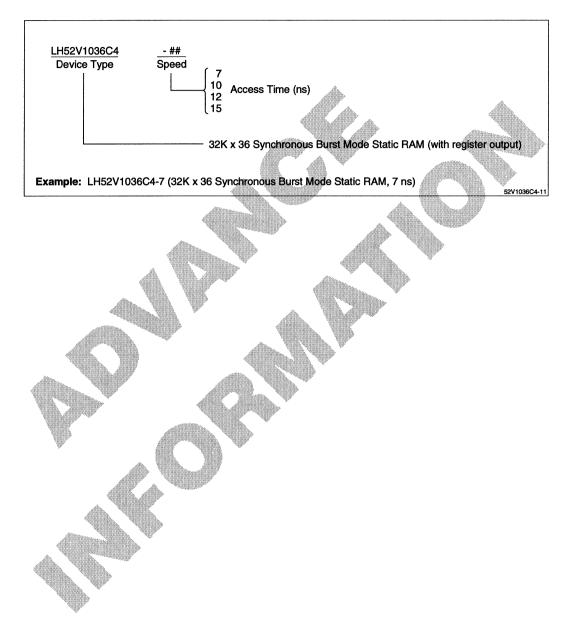

**CLASSIFICATION \*** DESCRIPTION Product Preview Contains information about a device that is in the planning stage or the soon to be in-development stage. Advance Information Contains information about a device that is in development. Includes design specifications for device development. Preliminary Contains information for device soon to be, or recently, released to production. No label is used for this Contains information about a device that is in full classification. production.

The product data provided is classified and labeled as follows:

\* Note: occasionally certain product data information may be classified and labeled differently than the main classification label. For example, a main label may be 'Preliminary,' but the 15 ns version of that part may be labeled 'Advance Information.'

The Sharp Memory Data Book is the proprietary product of Sharp and is copyrighted, with all rights reserved. Under the copyright laws, no part of this publication may be reproduced or transmitted in any form or by any means, electronic or mechanical, for any purpose, in whole or in part, without the express written permission of Sharp. Express written permission is also required before any use of this publication may be made by a third party.

Sharp reserves the right to make changes in the circuitry or specifications described herein at any time without notice in order to improve design or reliability. The information in this Memory Data Book has been carefully checked to be accurate, however, Sharp makes no warranty for any errors which may appear in this document. Contact Sharp to obtain the latest version of device specifications before placing your order.

Sharp makes no representations that circuitry described herein is free from infringement of patent or other rights of third parties which may result from its use. No license is granted by implication under any patent rights or other rights of Sharp Corporation.

© SHARP Corporation, 1994. Printed and bound in the U.S.A.

### PREFACE

As we become more and more an information-oriented society, memory products have come to play a major role in both home and office equipment. On the one hand, computer-related services are growing ever more sophisticated and diverse; on the other, they are becoming much more accessible to each of us in our daily lives. Along with this increase in the importance of the information processing in our lives, we are faced with a growing demand for memory products using the most advanced technology.

To keep pace with this rapid progress, we at Sharp will continue to direct our efforts at understanding the crucial trends of the moment in this area and supply our customers with products that truly meet their needs. In short, to contribute to a better life for all of us in this age of expanding technology.

Sharp has developed a wide range of memory units including PSRAMs, SRAMs, Mask-Programmable ROMs, and FIFO Memories for use in numerous areas of application. Sharp memory units are used extensively in personal computers, advanced office automation and measuring control equipment, video games, as well as in character processing and dictionary ROMs.

This data book has been especially compiled for the use of our customers. Listed here is the entire range of memory products developed and manufactured by Sharp, with detailed explanations of their many functions and outstanding features. We hope that you find this book useful in determining which Sharp products are best suited to your needs. Please contact us directly if you have any further questions.

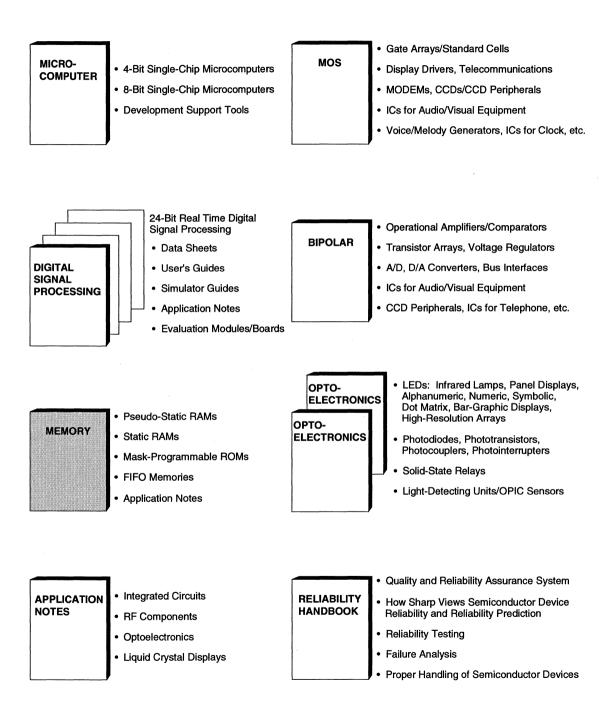

### SHARP'S INTEGRATED CIRCUIT DOCUMENTATION

### TABLE OF CONTENTS

| SECTION |                                          | PAGE  |

|---------|------------------------------------------|-------|

| 1       | GENERAL INFORMATION                      | 1-1   |

|         | Alphanumeric Index                       | 1-1   |

|         | Product Lineup                           | 1-2   |

|         | Quality Assurance                        | 1-10  |

|         | Timing Diagram Conventions               | 1-24  |

| 2       | PSEUDO-STATIC RAMs                       | 2-1   |

|         | Pseudo-Static RAM Cross Reference        | 2-41  |

| 3       | STATIC RAMs                              | 3-1   |

|         | Static RAM Cross Reference               | 3-195 |

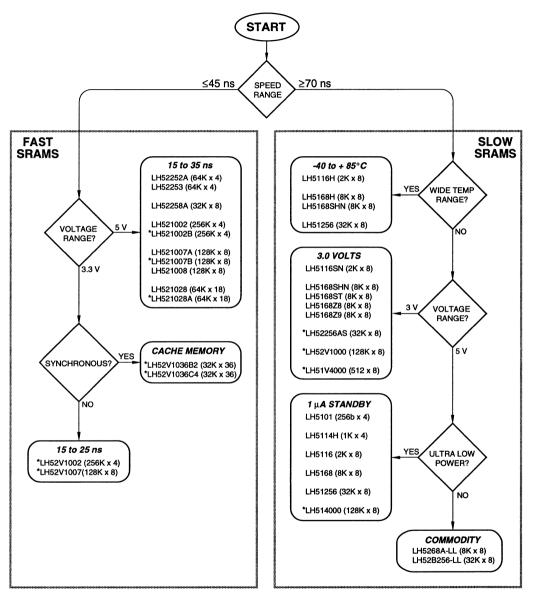

|         | Choosing a Sharp Static RAM              | 3-198 |

| 4       | MASK-PROGRAMMABLE ROMs                   | 4-1   |

| 5       | FIFO MEMORIES                            |       |

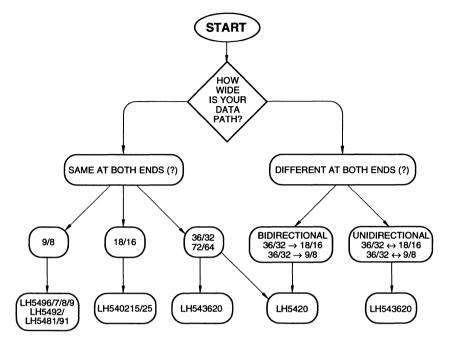

|         | The Sharp Way to Choose a FIFO           | 5-1   |

|         | FIFO Cross Reference                     | 5-306 |

| 6       | APPLICATION NOTES &<br>CONFERENCE PAPERS | 6-1   |

| 7       | PACKAGING                                |       |

|         | Package Selection Summary                | 7-1   |

### **GENERAL INFORMATION – 1**

**PSEUDO-STATIC RAMs – 2**

STATIC RAMs – 3

MASK-PROGRAMMABLE ROMs – 4

**FIFO MEMORIES – 5**

**APPLICATION NOTES & CONFERENCE PAPERS – 6**

PACKAGING – 7

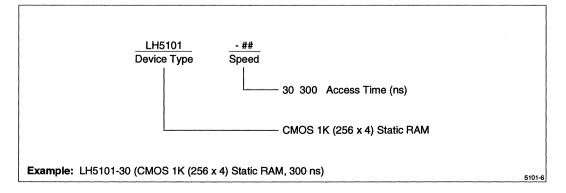

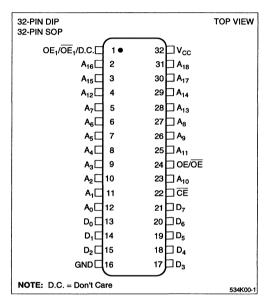

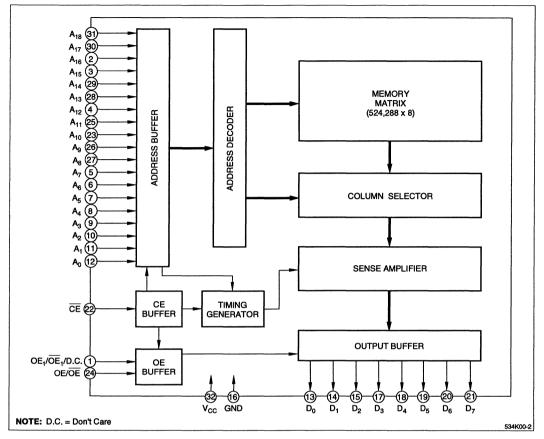

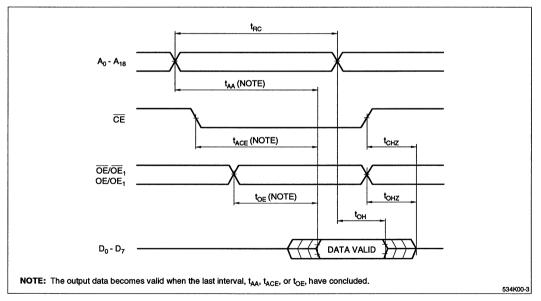

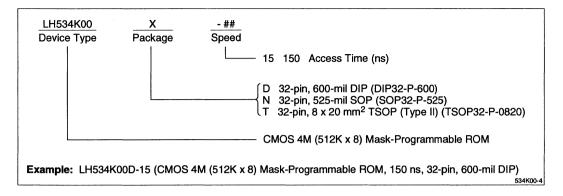

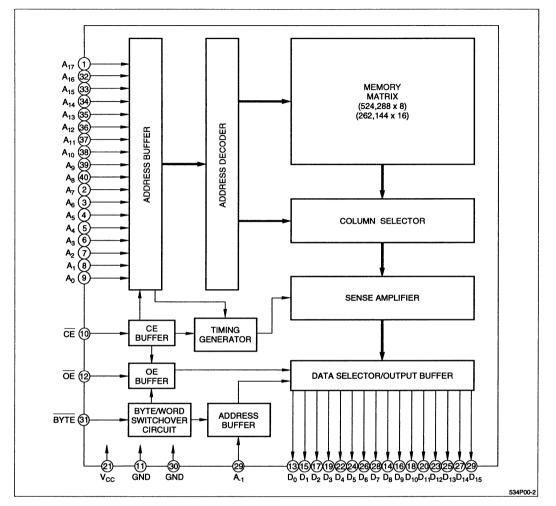

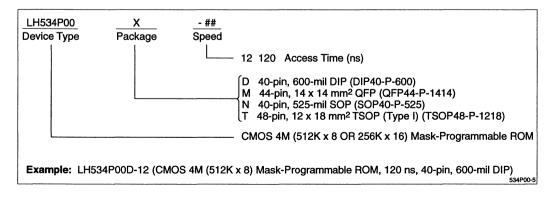

4-56

#### **PSEUDO-STATIC RAMs Density Organization** LH5P832 256K 32K × 8 2-1 LH5P864 512K 2-8 64K × 8 LH5P8128 1M 128K × 8 2-17 LH5P8129 1M 128K × 8 2-29 Pseudo-Static RAM Cross Reference 2-41 STATIC RAMs LH5101 1K $256 \times 4$ 3-1 LH5114 4K $1K \times 4$ 3-7 16K LH5116/H $2K \times 8$ 3-13 LH5116S 16K $2K \times 8$ 3-21 LH5118/H 16K 2K × 8 3-28 LH5168/H 64K $8K \times 8$ 3-36 LH5168SH 64K $8K \times 8$ 3-45 LH5168ST 64K 8K × 8 3-53 LH5168Z8 64K 8K × 8 (3 V) 3-61 LH5168Z9 64K 8K × 8 (3 V) 3-69 LH5268A 64K 8K × 8 3-77 LH51256L 256K 32K × 8 3-85 LH52B256 256K 32K × 8 3-92 LH52252A 256K 64K × 4 3-101 LH52253 256K $64K \times 4$ 3-108 256K LH52258A 32K × 8 3-115 LH521002 1M 256K × 4 3-123 LH521007A 1M 128K × 8 3-131 LH521008 1M 128K × 8 3-139 LH521028 1.125M 64K × 18 3-147 LH52V1036B2 1.125M $32K \times 36$ 3-162 LH52V1036C4 1.125M $32K \times 36$ 3-178 Static RAM Cross Reference 3-195 MASK-PROGRAMMABLE ROMs LH53259 256K $32K \times 8$ 4-1 512K 4-5 LH53515 64K × 8 128K × 8 LH53H0900 1M 4-9 LH530800A 1M 128K × 8 4-13 LH530800A-Y 1M 128K × 8 4-17 LH531000B 1M 128K × 8 4-20 LH532000B 2M 256K × 8/128K × 16 4-24 2M $256K \times 8/128K \times 16$ 4-30 LH532000B-S 4-36 LH532100B 2M 256K × 8 LH53H4000/ 4M 512K × 8/256K × 16 4-40 LH53H4100 512K × 8 LH534K00 4M 512K × 8 4-41 4M 4-46 LH534P00 512K × 8/256K × 16 LH534R00 4M 512K × 8 4-51

#### MASK-PROGRAMMABLE ROMs (cont'd) Density Organization LH534000B 4M 512K × 8/256K × 16

| EI IOO IOOOD                       |               | OTER X OFECORY TO              |       |  |  |  |

|------------------------------------|---------------|--------------------------------|-------|--|--|--|

| LH534000B-S                        | 4M            | 512K × 8/256K × 16             | 4-62  |  |  |  |

| LH534100B                          | 4M            | 512K × 8                       | 4-68  |  |  |  |

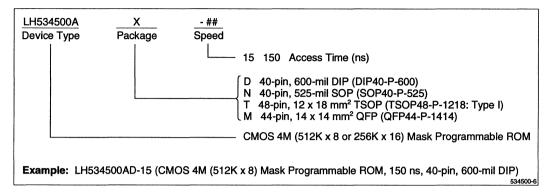

| LH534500A                          | 4M            | $512K \times 8/256K \times 16$ | 4-73  |  |  |  |

| LH534600A                          | 4M            | $512K \times 8/256K \times 16$ | 4-79  |  |  |  |

| LH538P00A                          | 8M            | $1M \times 8/512K \times 16$   | 4-84  |  |  |  |

| LH538R00A                          | 8M            | 1M × 8                         | 4-90  |  |  |  |

| LH538000-S                         | 8M            | $1M \times 8/512K \times 16$   | 4-95  |  |  |  |

| LH538300B                          | 8M            | 1M × 8                         | 4-101 |  |  |  |

| LH538500B                          | 8M            | $1M \times 8/512K \times 16$   | 4-106 |  |  |  |

| LH538600                           | 8M            | $1M \times 8/512K \times 16$   | 4-113 |  |  |  |

| LH5316500C                         | 16M           | $2M \times 8/1M \times 16$     | 4-120 |  |  |  |

| LH5316501                          | 16M           | $2M \times 8/1M \times 16$     | 4-126 |  |  |  |

| LH5332500                          | 32M           | $4M \times 8/2M \times 16$     | 4-131 |  |  |  |

| FIFO MEMORIES                      |               |                                |       |  |  |  |

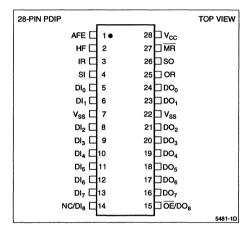

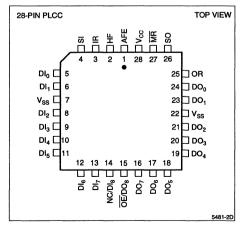

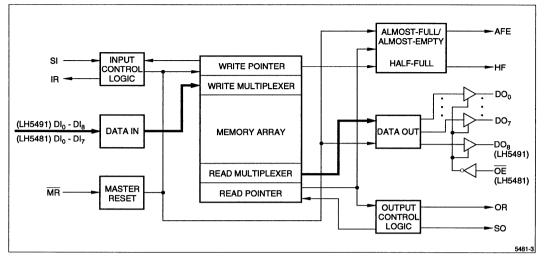

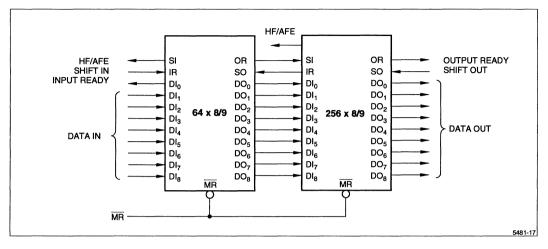

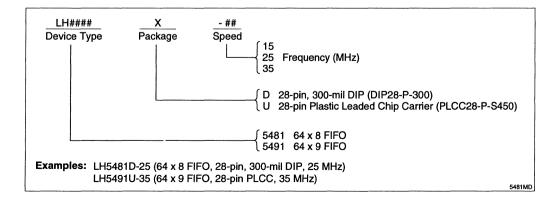

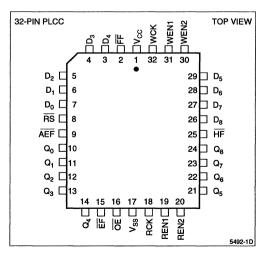

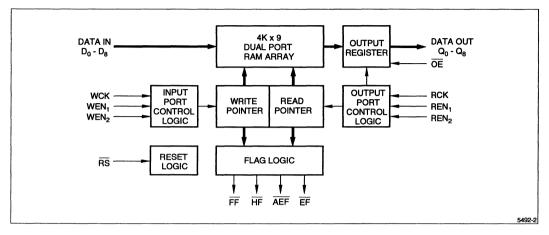

| LH5481/91                          | 0.5K          | 64 × 8/64 × 9                  | 5-2   |  |  |  |

| LH5492                             | 36K           | 4K × 9                         | 5-16  |  |  |  |

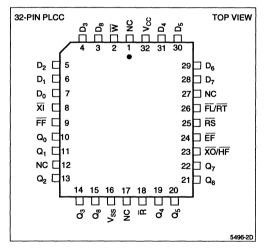

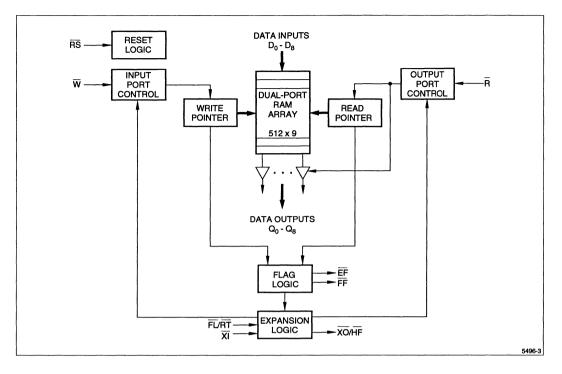

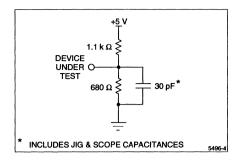

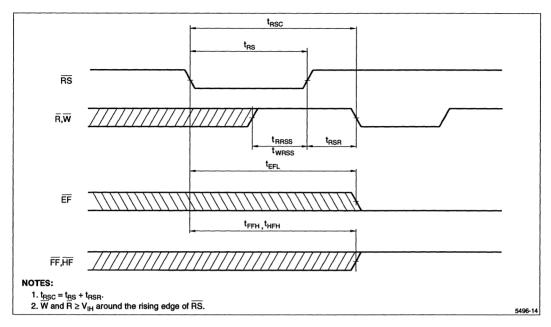

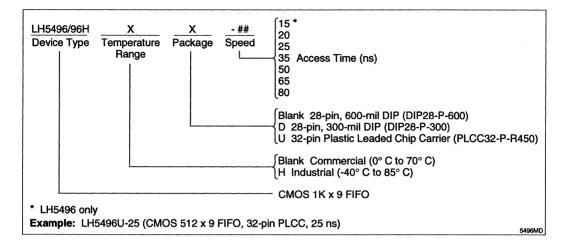

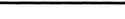

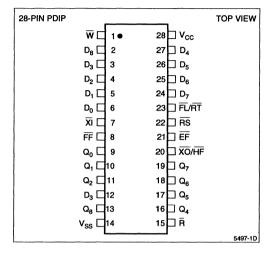

| LH5496/96H                         | 4.5K          | 512 × 9                        | 5-34  |  |  |  |

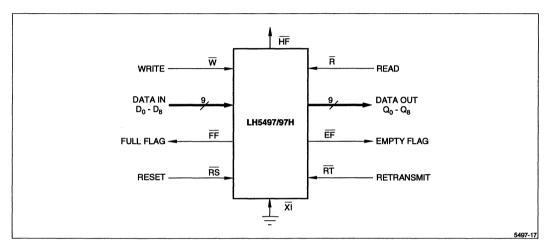

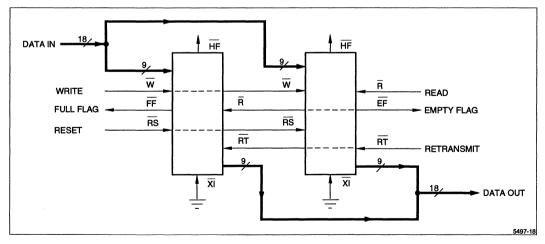

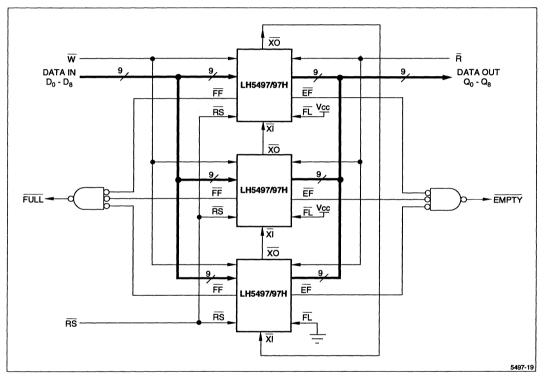

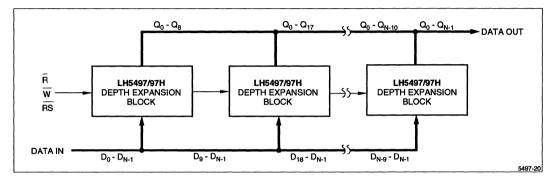

| LH5497/97H                         | 9K            | 1K × 9                         | 5-49  |  |  |  |

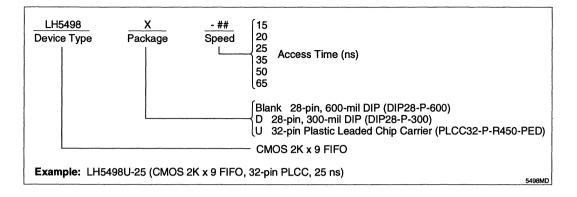

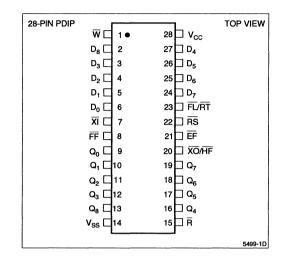

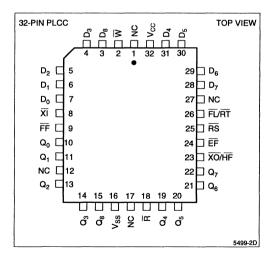

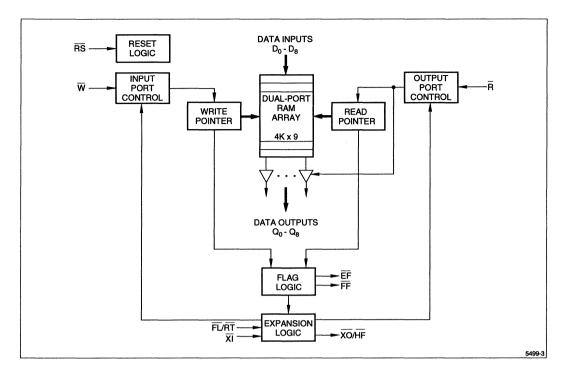

| LH5498                             | 18K           | 2K × 9                         | 5-64  |  |  |  |

| LH5499                             | 36K           | 4K × 9                         | 5-79  |  |  |  |

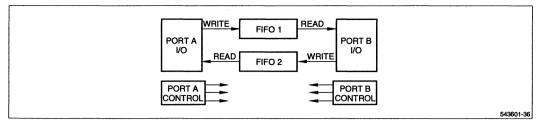

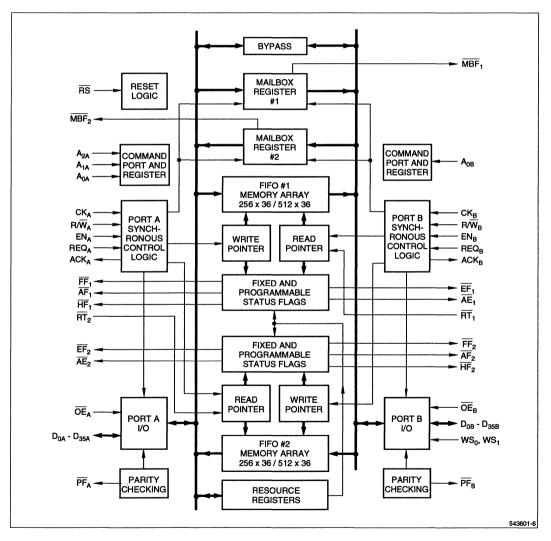

| LH5420                             | 18K           | 256 × 36 × 2                   | 5-94  |  |  |  |

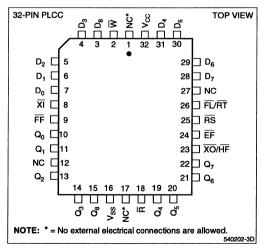

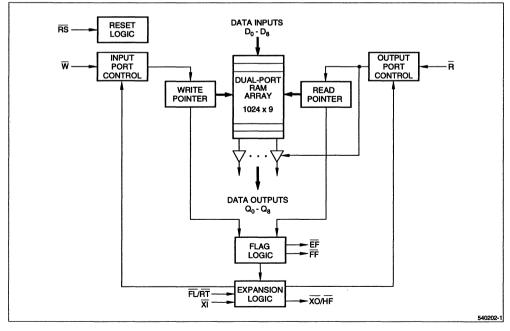

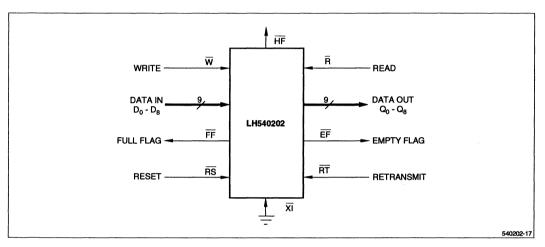

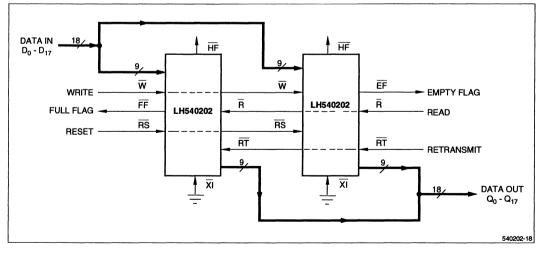

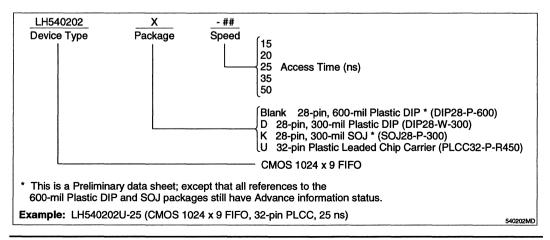

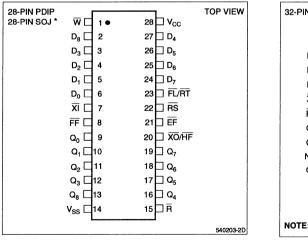

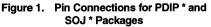

| LH540202                           | 9K            | 1K × 9                         | 5-129 |  |  |  |

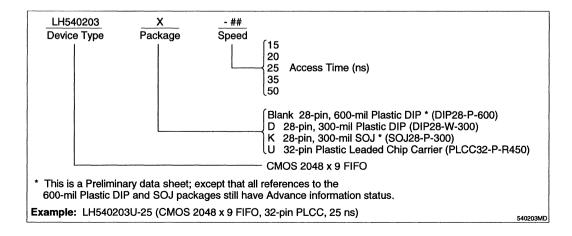

| LH540203                           | 18K           | 2K × 9                         | 5-145 |  |  |  |

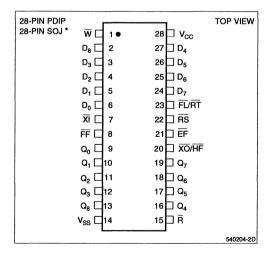

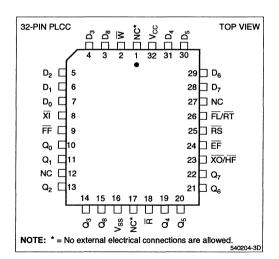

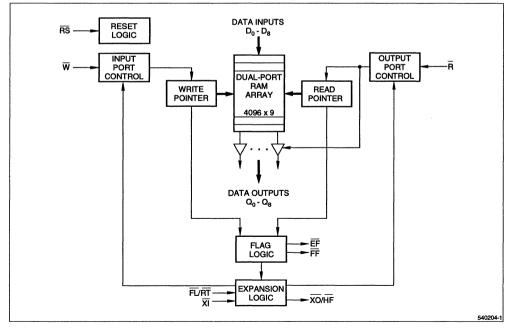

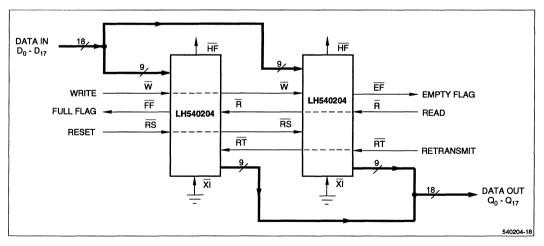

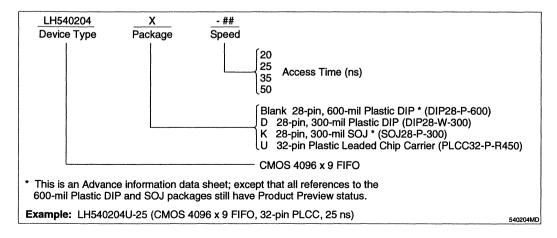

| LH540204                           | 36K           | 4K × 9                         | 5-161 |  |  |  |

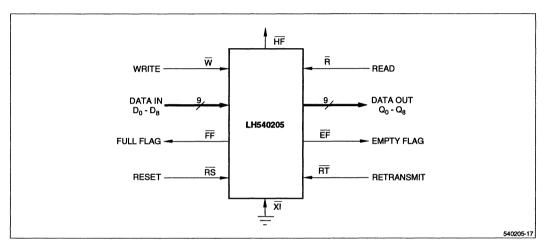

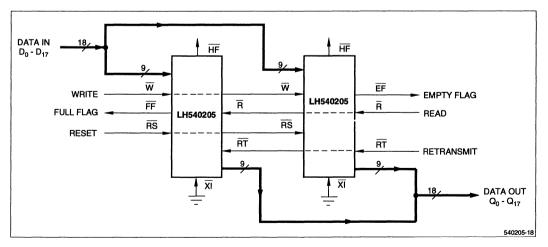

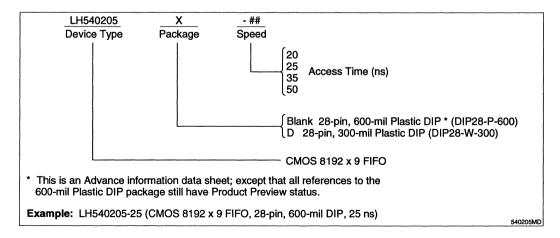

| LH540205                           | 72K           | 8K × 9                         | 5-177 |  |  |  |

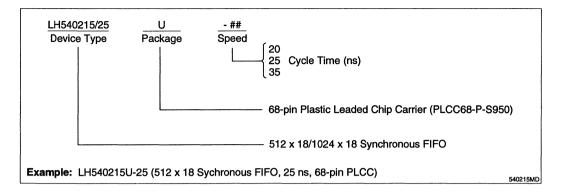

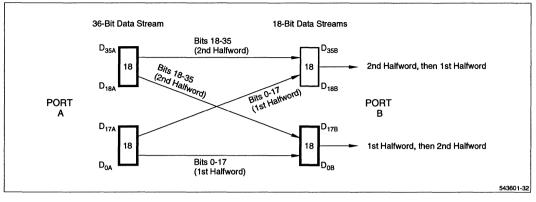

| LH540215/25                        | 9K/18K        | 512 × 18/1K × 18               | 5-193 |  |  |  |

| LH543601/11                        | 18K/36K       | 256 × 36 × 2/                  |       |  |  |  |

|                                    |               | 512 × 36 × 2                   | 5-231 |  |  |  |

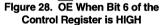

| LH543620                           | 36K           | 1K × 36                        | 5-271 |  |  |  |

| FIFO Cross Ref                     | erence        |                                | 5-306 |  |  |  |

| APPLICATION NO                     | OTES & CO     | ONFERENCE PAPERS               |       |  |  |  |

| Pseudo-Static R                    |               |                                |       |  |  |  |

| Pseudo-Static F                    |               |                                | 6-1   |  |  |  |

| FIFO Memories                      | FIFO Memories |                                |       |  |  |  |

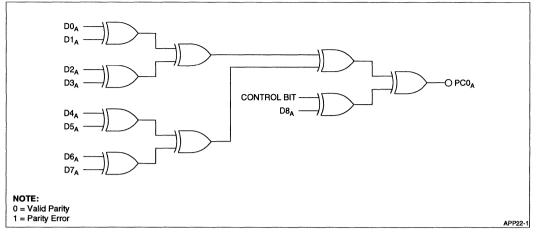

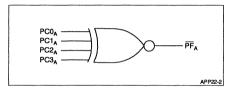

| Parity Checking                    |               |                                | 6-5   |  |  |  |

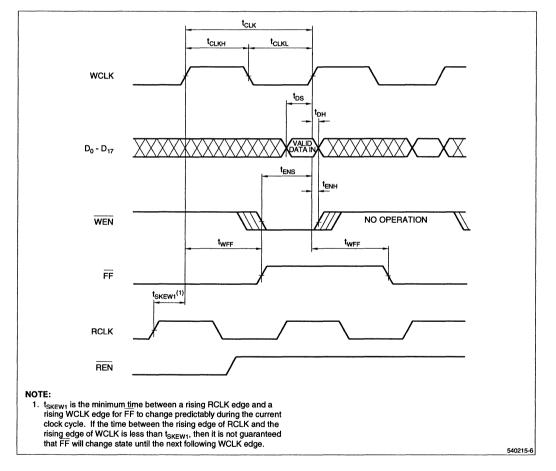

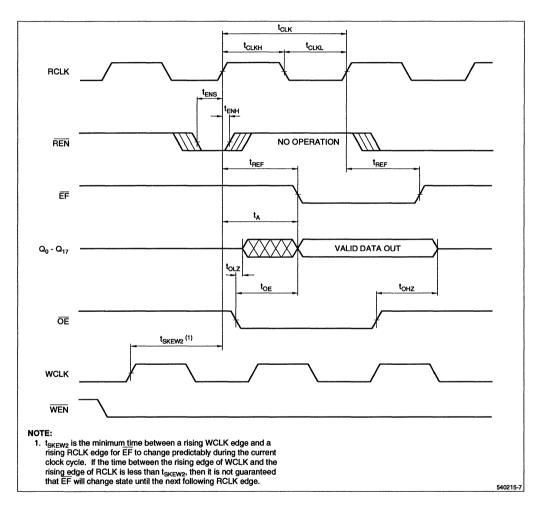

| FIFO Flag Timing: Marching To      |               |                                |       |  |  |  |

| Two Different Drummers 6-8         |               |                                |       |  |  |  |

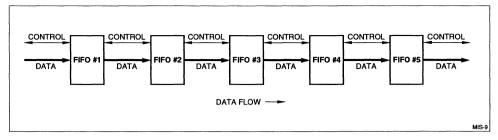

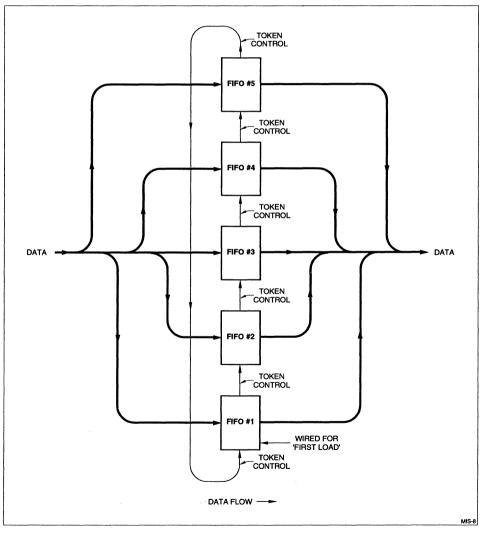

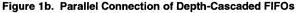

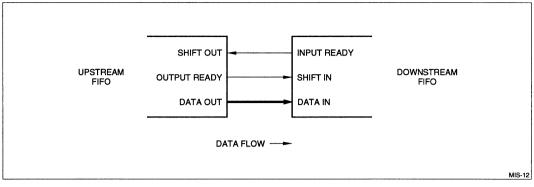

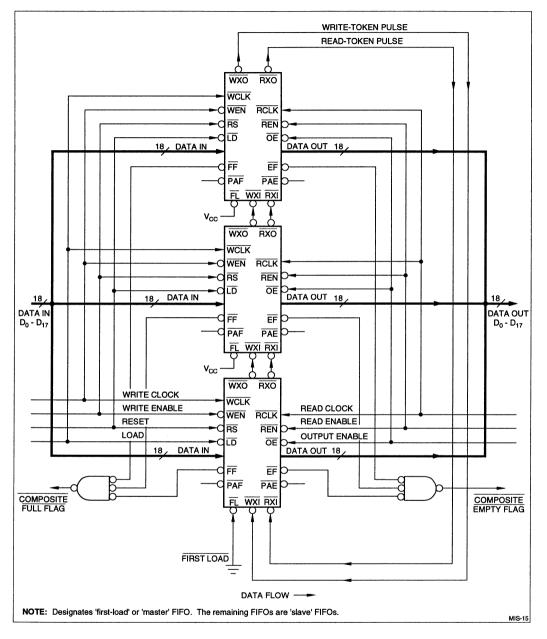

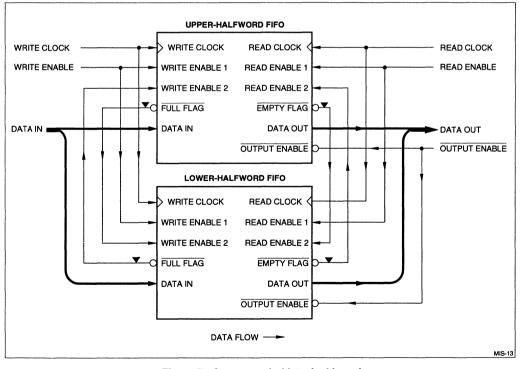

| Different Stroke<br>FIFOs of Varie |               | Cascade and Parallel           | 6-16  |  |  |  |

|                                    |               |                                | 0-10  |  |  |  |

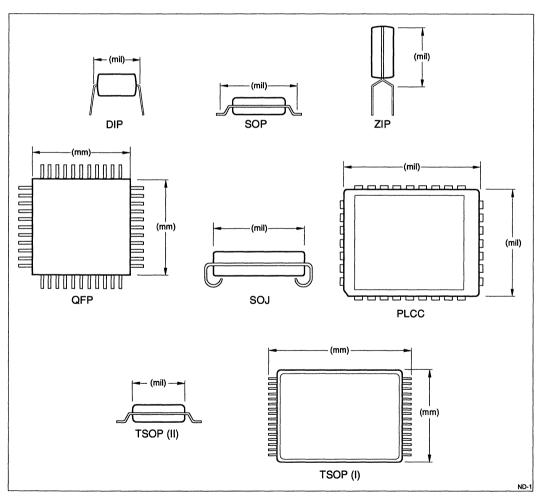

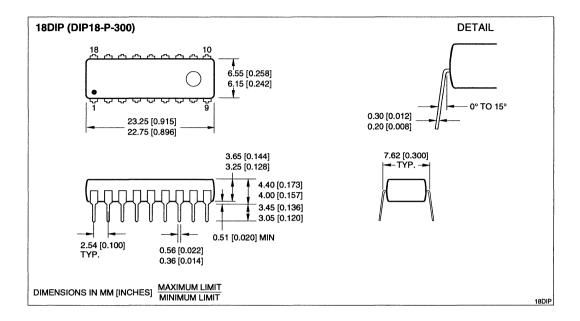

#### PACKAGING

| Package Selections: Static RAMs            | 7-1 |

|--------------------------------------------|-----|

| Package Selections: Mask-Programmable ROMs | 7-2 |

| Package Selections: FIFO Memories          | 7-3 |

| PSEU | DENSITY<br>256K<br>20 512K | ORGAN- MODI<br>IZATION NUMB<br>32K x 8 LH5P6<br>64K x 8 LH5P6<br>128K x 8 LH5P8<br>128K x 8 LH5P8 | ER 50 60 7/<br>332 | TIMES (ns<br>0 80 100 1     |                            | CYCLE TIMES (ns)<br>00 110 130 140 150                     |                   | PACKAGE S<br>DIP SOP SOJ D<br>28 28 2<br>32 32 32 32 32 32 32 32 32 32 32 32 32 3 |  |

|------|----------------------------|---------------------------------------------------------------------------------------------------|--------------------|-----------------------------|----------------------------|------------------------------------------------------------|-------------------|-----------------------------------------------------------------------------------|--|

|      | CAPACITY                   | CONFIG-<br>URATION<br>(WORDS x BITS)                                                              | MODEL NO.          | ACCESS<br>TIME (ns)<br>MAX. | CYCLE<br>TIME (ns)<br>MIN. | POWER<br>CONSUMPTION<br>OPERATING/<br>STANDBY<br>(mW) MAX. | OPERATING<br>MODE | PACKAGE                                                                           |  |

|      | 256K                       | 32,768 x 8                                                                                        | LH5P832            | 100<br>120                  | 160<br>190                 | 357.5/16.5<br>303/16.5                                     | PSEUDO<br>SRAM    | 28DIP/<br>28SK-DIP/<br>28SOP                                                      |  |

|      | 512K                       | 65,536 x 8                                                                                        | LH5P864            | 80                          | 140                        | 440/5.5                                                    | PSEUDO<br>SRAM    | 32 SOP                                                                            |  |

|      |                            |                                                                                                   |                    | 60                          | 100                        | 572/5.5                                                    |                   |                                                                                   |  |

|      |                            |                                                                                                   | LH5P8128           | 80                          | 130                        | 440/5.5                                                    |                   |                                                                                   |  |

|      | 1M                         | 131,072 x 8                                                                                       |                    | 100                         | 160                        | 358/5.5                                                    | PSEUDO<br>SRAM    | 32DIP/<br>32SOP/                                                                  |  |

|      |                            |                                                                                                   |                    | 60                          | 100                        | 572/5.5                                                    | Griam             | 32TSOP <sup>3</sup>                                                               |  |

|      |                            |                                                                                                   | LH5P8129           | 80                          | 130                        | 385/5.5                                                    |                   |                                                                                   |  |

|      |                            |                                                                                                   |                    | 100                         | 160                        | 358/5.5                                                    |                   |                                                                                   |  |

### **PSEUDO STATIC RAMs**

#### NOTES:

= Not available.

- Operating frequency or access/cycle time parts that are either available now or soon to be available. Contact your Sharp representative for availability.

1. <u>CS</u> Control 2. CE Control 3. TSOP(I) 4. TSOP(II) - Consult factory for availability.

MD-7A

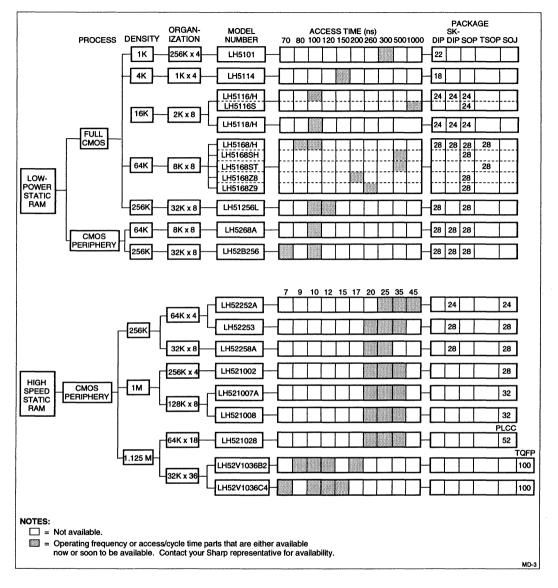

### **STATIC RAMs**

### STATIC RAMs

| PROCESS   | DENSITY | ORGANIZATION<br>(WORDS × BITS) | MODEL NO.             | ACCESS<br>TIME (ns)<br>MAX. | CYCLE<br>TIME<br>(ns) MiN. | POWER<br>CONSUMPTION<br>OPERATING/<br>STANDBY<br>(mW/µW) MAX. | PACKAGE                            |

|-----------|---------|--------------------------------|-----------------------|-----------------------------|----------------------------|---------------------------------------------------------------|------------------------------------|

| FULL CMOS | 1K      | 256 × 4                        | LH5101                | 300                         | 300                        | 137.5/55                                                      | 22DIP                              |

|           | 4K      | 1,024 × 4                      | LH5114                | 150                         | 150                        | 110/27.5                                                      | 18DIP                              |

|           | 16K     | 2,048 × 8                      | LH5116                | 100                         | 100                        | 220/5.5                                                       | 24DIP/24SOP/24SK-DIP               |

|           |         |                                | LH5116H 1             | 100                         | 100                        | 220/5.5                                                       |                                    |

|           |         |                                | LH5116S 4             | 1000                        | 1000                       | 33/3.3                                                        | 24SOP                              |

|           |         |                                | LH5118                | 100                         | 100                        | 220/5.5                                                       | 24DIP/24SOP/24SK-DIP               |

|           |         |                                | LH5118H 1             | 100                         | 100                        | 220/5.5                                                       |                                    |

|           | 64K     | 8,192 × 8                      | LH5168                | 100                         | 100                        | 248/5.5                                                       | 28DIP/28SOP/28SK-DIP/<br>28TSOP(I) |

| 1         |         |                                | LH5168H <sup>1</sup>  | 100                         | 100                        | 275/16.5                                                      | 28DIP/28SOP/28SK-DIP               |

|           |         |                                | LH5168SH 1, 4         | 500                         | 500                        | 60/9 (3V)                                                     | 28SOP                              |

|           |         |                                | LH5168ST              | 500                         | 500                        | 60/3 (3V)                                                     | 28TSOP(I)                          |

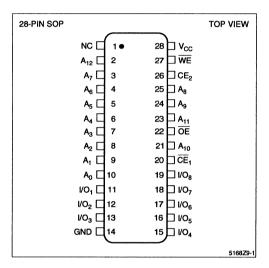

|           |         |                                | LH5168Z8              | 200                         | 200                        | 60/3 (3V)                                                     | 28SOP                              |

|           |         |                                | LH5168Z9              | 260                         | 260                        | 60/3 (3V)                                                     | 28SOP                              |

|           | 256K    | 32,768 × 8                     | LH51256L <sup>1</sup> | 100                         | 100                        | 248/27.5                                                      | 28DIP/28SOP                        |

|           |         | 4                              |                       | 120                         | 120                        |                                                               |                                    |

| CMOS      | 64K     | 8,192 × 8                      | LH5268A               | 100                         | 100                        | 220/220                                                       | 28DIP/28SK-DIP/28SOP               |

| PERIPHERY | 256K    | 65,536 × 4                     | LH52252A              | 25                          | 25                         | 825/5500                                                      | 24SK-DIP/24SOJ                     |

|           |         |                                |                       | 35                          | 35                         | 660/5500                                                      |                                    |

|           |         |                                |                       | 45                          | 45                         | 550/5500                                                      |                                    |

|           |         |                                | LH52253               | 20                          | 20                         | 800/5500                                                      | 28SK-DIP/28SOJ                     |

|           |         |                                |                       | 25                          | 25                         | 745/5500                                                      |                                    |

|           |         |                                |                       | 35                          | 35                         | 745/5500                                                      |                                    |

|           |         | 32,768 × 8                     | LH52B256              | 70                          | 70                         | 440/550                                                       | 28DIP/28SOP/28SK-DIP/              |

|           |         |                                |                       | 100                         | 100                        | 385/550                                                       | 28TSOP(I)                          |

|           |         |                                | LH52258A              | 20                          | 20                         | 825/5500                                                      | 28SK-DIP/28SOJ                     |

| -         |         |                                |                       | 25                          | 25                         | 745/5500                                                      |                                    |

|           | 1M      | 262,144 × 4                    | LH521002              | 20                          | 20                         | 715/11000                                                     | 28SOJ                              |

|           |         |                                |                       | 25                          | 25                         | 660/11000                                                     |                                    |

|           |         | 101 070 0                      | 111501000             | 35                          | 35                         | 550/11000                                                     | 32SOJ                              |

|           |         | 131,072 × 8                    | LH521008              | 20                          | 20                         | 825/11000<br>770/11000                                        | 32500                              |

|           |         |                                |                       | 25<br>35                    | 25                         | 660/11000                                                     |                                    |

|           |         |                                | LH521007A             | 20                          | 20                         | 770/27500                                                     | 32SOJ                              |

|           |         |                                | L102 100/A            | 20                          | 20                         | 688/27500                                                     | 02000                              |

|           |         |                                |                       | 35                          | 35                         | 633/27500                                                     |                                    |

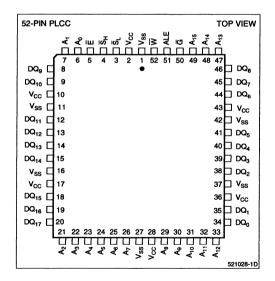

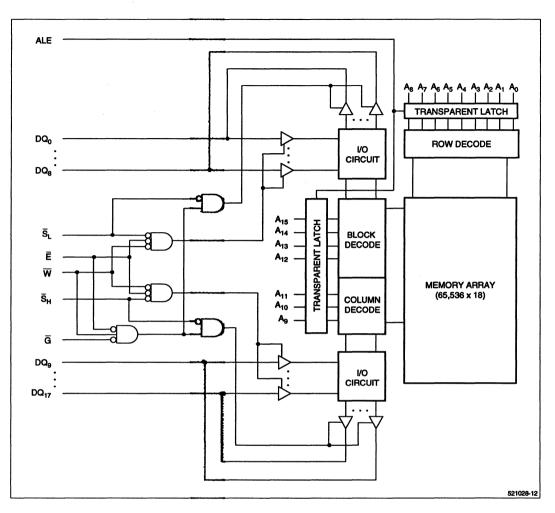

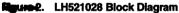

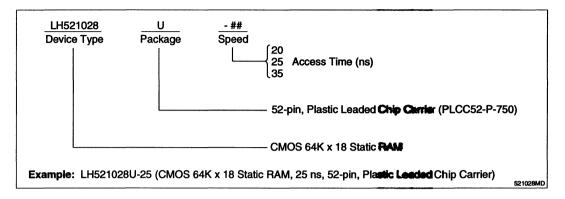

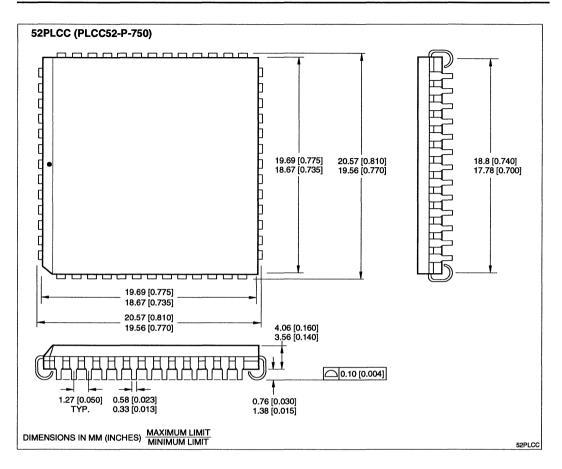

| ł         | 1.125M  | 65,536 × 18                    | LH521028              | 20                          | 20                         | 1650/275000                                                   | 52PLCC                             |

|           |         | 00,000 × 10                    | 2.02.020              | 25                          | 25                         | 1650/275000                                                   | 52. 200                            |

|           |         |                                |                       | 35                          | 35                         | 1650/275000                                                   |                                    |

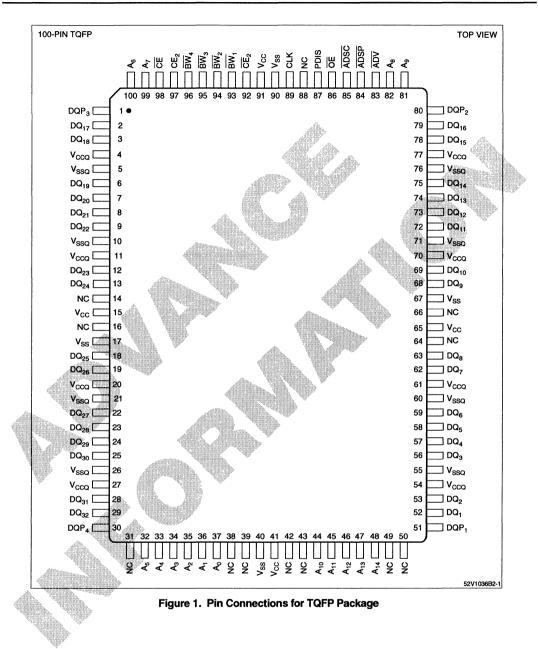

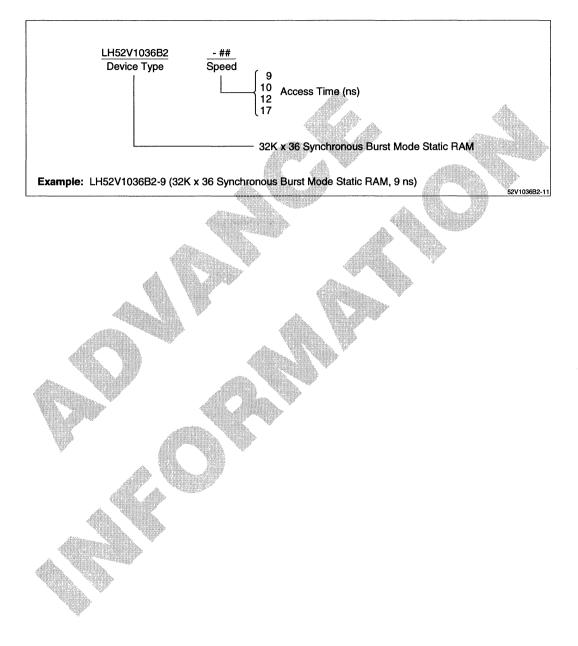

|           |         | 32,768 × 36                    | LH52V1036B2           | 9                           | 15                         | 866/295                                                       | 100TQFP                            |

|           | J 32,   |                                |                       | 10                          | 15                         | 866/295                                                       |                                    |

|           |         |                                |                       | 12                          | 20                         | 728/243                                                       |                                    |

|           |         |                                |                       | 17                          | 25                         | 624/208                                                       |                                    |

|           |         |                                | LH52V1036C4           | 7                           | 15                         | 866/295                                                       |                                    |

|           |         |                                |                       | 10                          | 20                         | 728/243                                                       |                                    |

|           |         |                                |                       | 12                          | 25                         | 624/208                                                       |                                    |

|           |         |                                |                       | 15                          | 30                         | 572/191                                                       |                                    |

#### NOTES:

1. T<sub>OPR</sub> = -40 to +85°C

2. T TSOP (Type I) Forward bend TR TSOP (Type I) Reverse bend

3. Supply Voltage (V) =  $3 \pm 10\%$

4. Supply Voltage (V) = 2.5 to 5.5

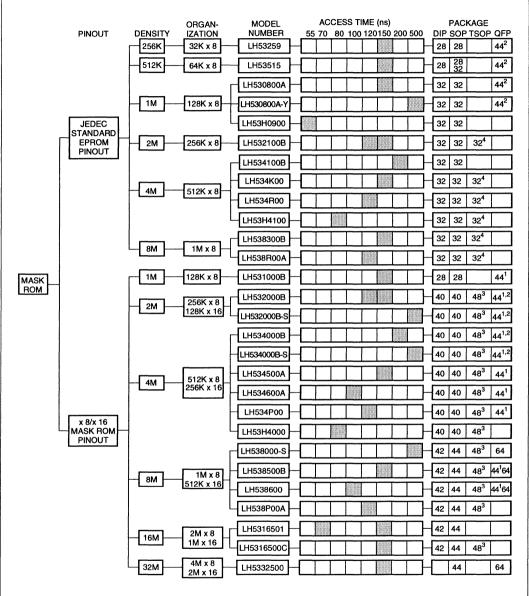

### **MASK-PROGRAMMABLE ROMs**

#### NOTES:

= Not available.

- Operating frequency or access/cycle time parts that are either available

- now or soon to be available. Contact your Sharp representative for availability. LH5XXX: CMOS

1 14 14 14 mm<sup>2</sup> - - -

- 1. 14 x 14 mm<sup>2</sup> package

- 2. QFP also available in 10 x 10 mm<sup>2</sup> package

- 3. TSOP (Type I)

4. TSOP (Type II)

MD-5

### MASK-PROGRAMMABLE ROMs

| DENSITY | ORGANIZATION<br>(WORDS × BITS)  | MODEL NO.   | USERS NO. | ACCESS TIME<br>(ns) MAX.<br>CYCLE TIME<br>(ns) MIN. | POWER<br>CONSUMPTION<br>(mW) MAX. | PACKAGE                             |

|---------|---------------------------------|-------------|-----------|-----------------------------------------------------|-----------------------------------|-------------------------------------|

| 256K    | 32,768 × 8                      | LH53259     | LH5359XX  | 150                                                 | 110                               | 28DIP/28SOP/44QFP 2                 |

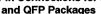

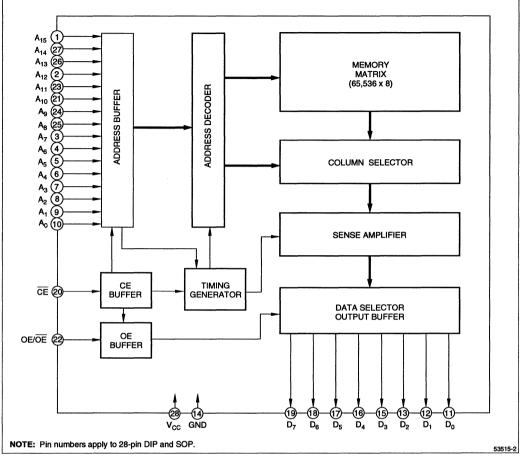

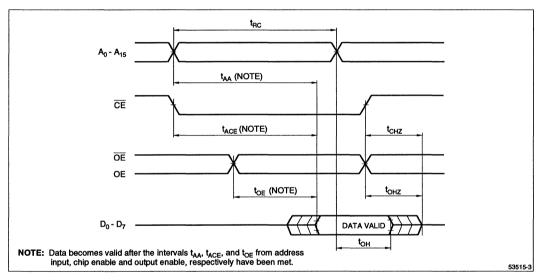

| 512K    | 65,536 × 8                      | LH53515     | LH5315XX  | 150                                                 | 195                               | 28DIP/28SOP/44QFP 2/32SOP           |

| 1M      | 131,072 × 8                     | LH53H0900   | LH5H09XX  | 55                                                  | 660                               | 32DIP/32SOP                         |

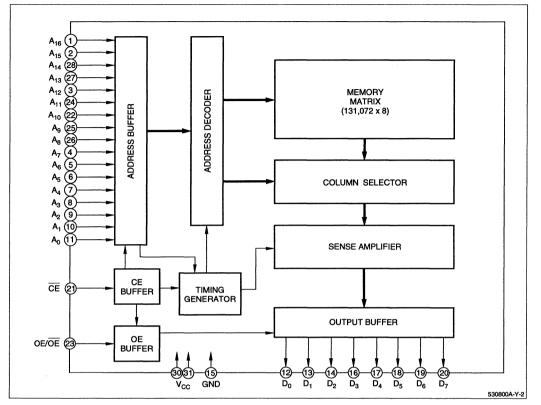

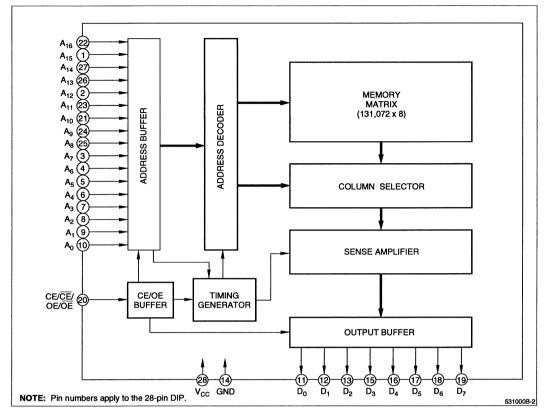

|         |                                 | LH530800A   | LH531HXX  | 150                                                 | 195                               | 32DIP/32SOP/44QFP 2                 |

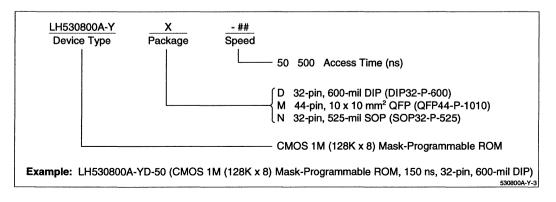

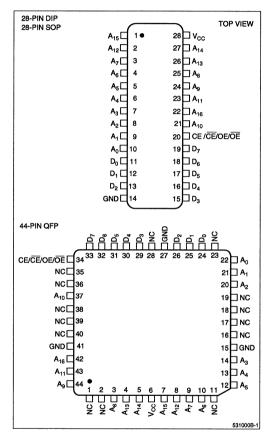

|         |                                 | LH530800A-Y | LH531YXX  | 500                                                 | 193                               | 32DIP/32SOP/44QFP 2                 |

|         |                                 | LH531000B   | LH531GXX  | 150                                                 | 195                               | 28DIP/28SOP/44QFP 1                 |

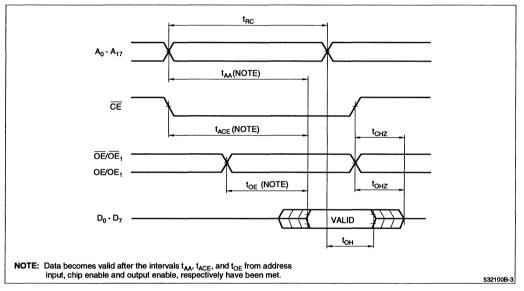

| 2M      | 262,144 × 8                     | LH532100B   | LH532HXX  | 120/150                                             | 275                               | 32DIP/32SOP/32TSOP(II)              |

|         | 262,144 × 8                     | LH532000B   | LH532GXX  | 120/150                                             | 275                               | 40DIP/40SOP/44QFP 1,2 /48TSOP(I)    |

|         | 131,072 × 16                    | LH532000B-S | LH532SXX  | 500                                                 | 225/275                           | 40DIP/40SOP/44QFP 1,2 /48TSOP(I)    |

| 4M      | 524,288 × 8                     | LH53H4100   | LH5H41XX  | 80                                                  | 550                               | 32DIP/32SOP/32TSOP(II)              |

|         |                                 | LH534K00    | LH534KXX  | 150                                                 | 330                               | 32DIP/32SOP/32TSOP(II)              |

|         |                                 | LH534R00    | LH534RXX  | 120                                                 | 358                               | 32DIP/32SOP/32TSOP(II)              |

|         |                                 | LH534100B   | LH534HXX  | 200                                                 | 275                               | 32DIP/32SOP                         |

|         | 524,288 × 8                     | LH53H4000   | LH5H40XX  | 80                                                  | 550                               | 40DIP/40SOP/48TSOP(I)               |

|         | 262,144 × 16                    | LH534P00    | LH534PXX  | 120                                                 | 358                               | 40DIP/40SOP/44QFP 1/48TSOP(I)       |

|         |                                 | LH534600A   | LH534UXX  | 100                                                 | 550                               | 40DIP/40SOP/44QFP 1/48TSOP(I)       |

|         |                                 | LH534500A   | LH534FXX  | 150                                                 | 275                               | 40DIP/40SOP/44QFP 1 /48TSOP(I)      |

|         |                                 | LH534000B   | LH534GXX  | 200                                                 | 275                               | 40DIP/40SOP/44QFP 1.2 /48TSOP(I)    |

|         |                                 | LH534000B-S | LH534SXX  | 500                                                 | 225/275                           | 40DIP/40SOP/44QFP 1,2 /48TSOP(I)    |

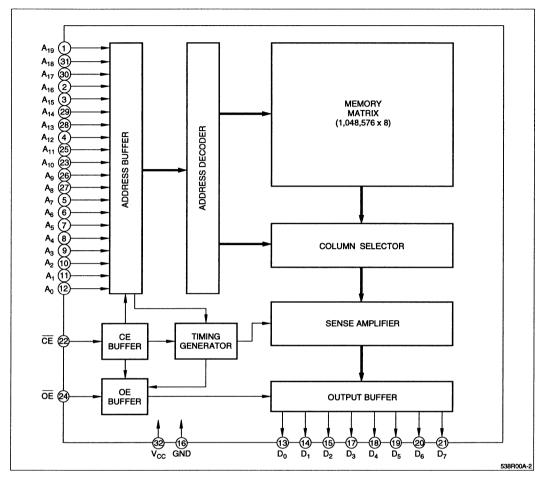

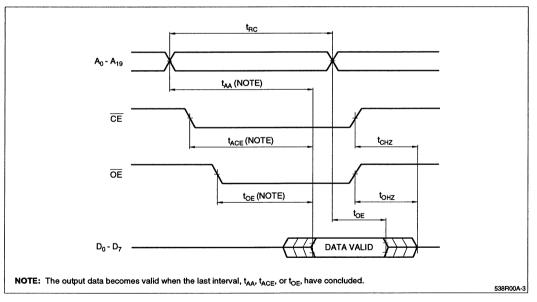

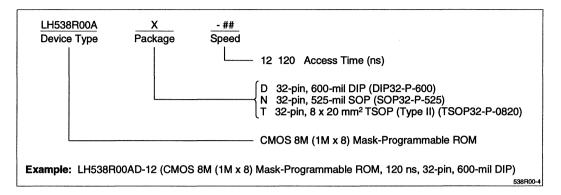

| 8M      | 1,048,576 × 8                   | LH538R00A   | LH538HXX  | 120                                                 | 330                               | 32DIP/32SOP/32TSOP(II)              |

|         |                                 | LH538300B   | LH5383XX  | 150                                                 | 275                               | 32DIP/32SOP/32TSOP(11)              |

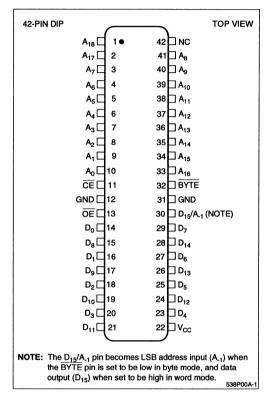

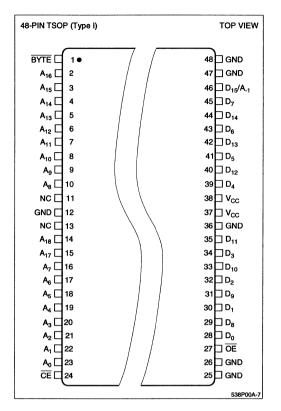

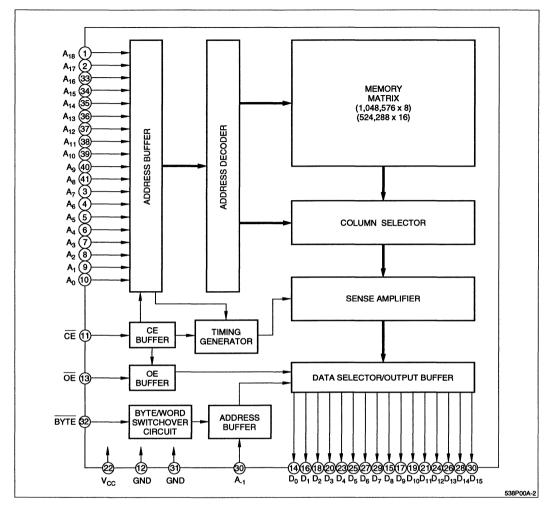

|         | 1,048,576 × 8                   | LH538P00A   | LH538PXX  | 120                                                 | 330                               | 42DIP/44SOP/48TSOP(I)               |

|         | 524,288 × 16                    | LH538000-S  | LH538SXX  | 500                                                 | 225/275                           | 42DIP/44SOP/48TSOP(I)/64QFP         |

|         |                                 | LH538500B   | LH5385XX  | 150                                                 | 275                               | 42DIP/44SOP/44QFP 1/64QFP/48TSOP(I) |

|         |                                 | LH538600    | LH5386XX  | 100                                                 | 385                               | 42DIP/44SOP/44QFP 1/64QFP/48TSOP(I) |

| 16M     | 2,097,152 × 8                   | LH5316500C  | LH5370XX  | 150                                                 | 275                               | 42DIP/44SOP/48TSOP(I)               |

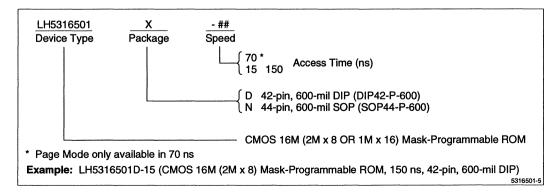

|         | 1,048,576 × 16                  | LH5316501   | LH5371XX  | 150/70 <sup>3</sup>                                 | 385                               | 42DIP/44SOP                         |

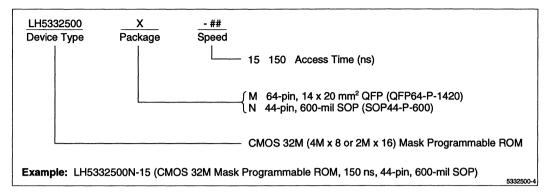

| 32M     | 4,194,304 × 8<br>2,097,152 × 16 | LH5332500   | LH5355XX  | 150                                                 | 275                               | 44SOP/64QFP                         |

NOTES:

1.  $14 \times 14 \text{ mm}^2$  package

2. QFP also available in  $10 \times 10 \text{ mm}^2$  package

3. Page Mode only available in 70 ns

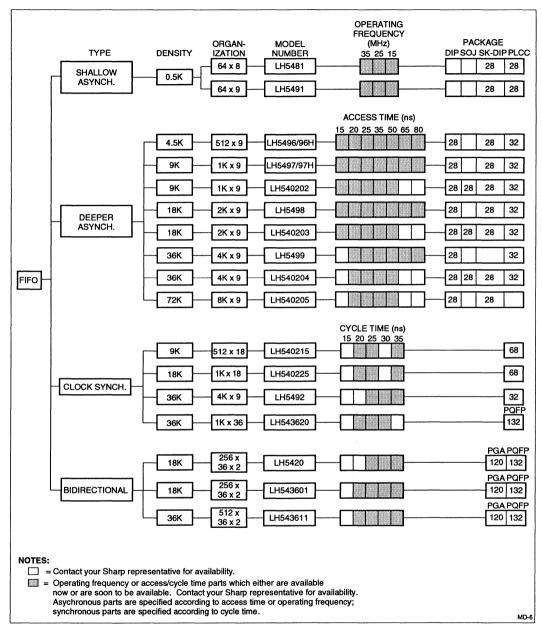

### **FIFO MEMORIES**

### **FIFO MEMORIES**

| DENSITY | ORGANIZATION<br>(WORDS × BITS) | MODEL NO.   | OPERATING<br>FREQUENCY<br>(MHz) | ACCESS<br>TIME<br>(ns) MAX. | CYCLE<br>TIME<br>(ns) MIN. | POWER<br>CONSUMPTION<br>(mW) MAX.<br>ACTIVE/<br>STANDBY | PACKAGE                         |

|---------|--------------------------------|-------------|---------------------------------|-----------------------------|----------------------------|---------------------------------------------------------|---------------------------------|

| 0.5K    | 64 × 8                         | LH5481      | 15                              | 26                          | 67                         | 248/                                                    | 28SK-DIP/28PLCC                 |

|         |                                |             | 25                              | 22                          | 40                         |                                                         |                                 |

|         |                                |             | 35                              | 20                          | 28                         |                                                         |                                 |

|         | 64 × 9                         | LH5491      | 15                              | 26                          | 67                         | 248/                                                    | 28SK-DIP/28PLCC                 |

|         |                                |             | 25                              | 22                          | 40                         |                                                         |                                 |

|         |                                |             | 35                              | 20                          | 28                         |                                                         |                                 |

| 4.5K    | 512 × 9                        | LH5496      | 40                              | 15                          | 25                         | 550/28                                                  | 28SK-DIP/28DIP/32PLCC           |

|         |                                | LH5496/96H  | 33                              | 20                          | 30                         |                                                         |                                 |

|         |                                |             | 28                              | 25                          | 35                         |                                                         |                                 |

|         |                                |             | 22                              | 35                          | 45                         |                                                         |                                 |

|         |                                |             | 15                              | 50                          | 65                         |                                                         |                                 |

|         |                                |             | 12                              | 65                          | 80                         |                                                         |                                 |

|         |                                |             | 10                              | 80                          | 100                        |                                                         |                                 |

| 9K      | 1,024 × 9                      | LH5497      | 40                              | 15                          | 25                         | 550/28                                                  | 28SK-DIP/28DIP/32PLCC           |

|         |                                | LH5497/97H  | 33                              | 20                          | 30                         |                                                         |                                 |

|         |                                |             | 28                              | 25                          | 35                         |                                                         |                                 |

|         |                                |             | 22                              | 35                          | 45                         | _                                                       |                                 |

|         |                                |             | 15                              | 50                          | 65                         |                                                         |                                 |

|         |                                |             | 12                              | 65                          | 80                         |                                                         |                                 |

|         |                                |             | 10                              | 80                          | 100                        |                                                         |                                 |

|         |                                | LH540202 *  | 40                              | 15                          | 25                         | 550/28                                                  | 285K-DIP/28DIP/28SOJ/<br>32PLCC |

|         |                                |             | 33                              | 20                          | 30                         |                                                         |                                 |

|         |                                |             | 28                              | 25                          | 35                         |                                                         |                                 |

|         |                                |             | 22                              | 35                          | 45                         |                                                         |                                 |

|         |                                |             | 15                              | 50                          | 65                         |                                                         |                                 |

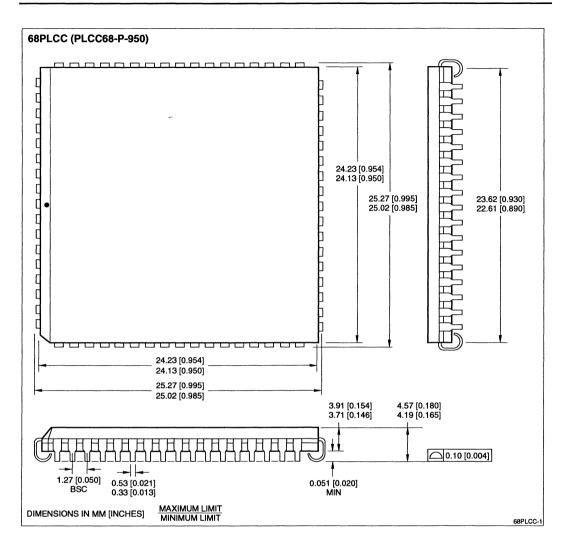

|         | 512 × 18                       | LH540215 *  | 50                              | 12                          | 20                         | 550/28                                                  | 68PLCC                          |

|         |                                |             | 40                              | 15                          | 25                         |                                                         |                                 |

| 1011    |                                |             | 28                              | 20                          | 35                         |                                                         |                                 |

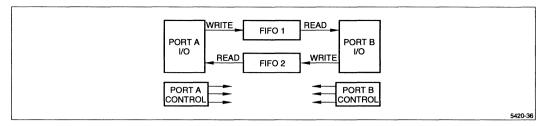

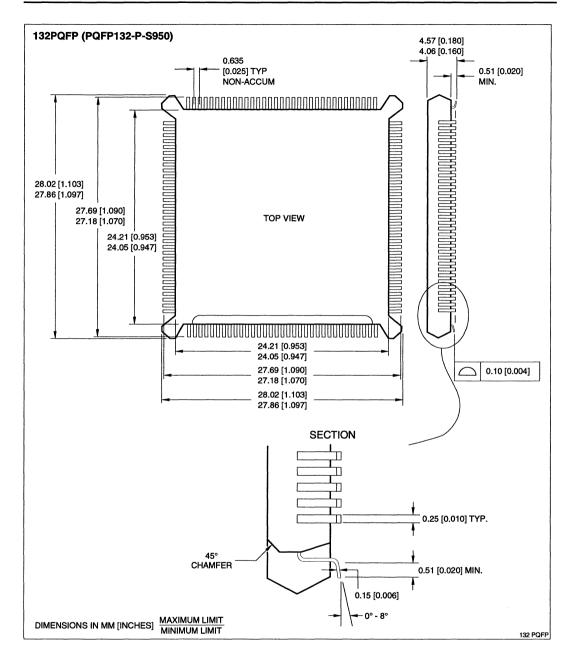

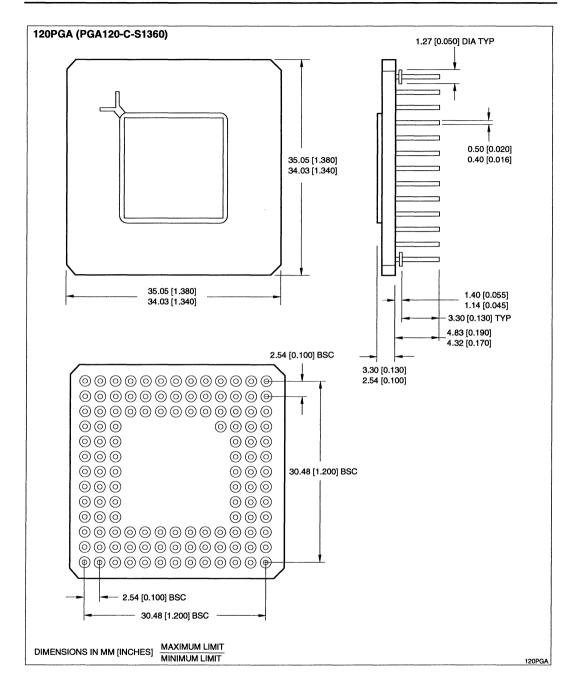

| 18K     | $256 \times 36 \times 2$       | LH5420      | 40                              | 15                          | 25                         | 1540/                                                   | 120PGA/132PQFP                  |

|         |                                |             | 33                              | 20                          | 30                         |                                                         |                                 |

|         | -                              | 111540004 + | 28                              | 25                          | 35                         | 1540/                                                   | 400004/000000                   |

|         |                                | LH543601 *  | 50<br>40                        | 12<br>15                    | 20                         | 1540/                                                   | 120PGA/132PQFP                  |

|         |                                |             | 33                              | 15                          | 25<br>30                   | -                                                       |                                 |

|         |                                |             | 28                              | 21                          | 30<br>35                   |                                                         |                                 |

|         | 2.048 × 0                      | LH5498      | 40                              | 15                          | 33<br>25                   | 550/28                                                  | 28SK-DIP/28DIP/32PLCC           |

|         | 2,048 × 9                      | LU3490      | 33                              | 20                          | 25<br>30                   | 55U/20                                                  | 2031-017/20017/322200           |

|         |                                |             | 28                              | 20                          | 30                         |                                                         |                                 |

|         |                                |             | 28                              | 25<br>35                    | 45                         |                                                         |                                 |

|         |                                |             | 15                              | 35<br>50                    | 45<br>65                   |                                                         |                                 |

|         |                                |             |                                 |                             |                            |                                                         |                                 |

|         |                                | 12          | 65                              | 80<br>100                   |                            |                                                         |                                 |

Primary parameter for speed-grade specification. \* Contact your Sharp representative for availability.

### FIFO MEMORIES (cont'd)

| DENSITY | ORGANIZATION<br>(WORDS × BITS) | MODEL NO.  | OPERATING<br>FREQUENCY<br>(MHz) | ACCESS<br>TIME<br>(ns) MAX. | CYCLE<br>TIME<br>(ns) MiN. | POWER<br>CONSUMPTION<br>(mW) MAX.<br>ACTIVE/<br>STANDBY | PACKAGE               |

|---------|--------------------------------|------------|---------------------------------|-----------------------------|----------------------------|---------------------------------------------------------|-----------------------|

| 18K     | 2,048 × 9                      | LH540203 * | 40                              | 15                          | 25                         | 550/28                                                  | 28SK-DIP/28DIP/28SOJ/ |

|         |                                |            | 33                              | 20                          | 30                         |                                                         | 32PLCC                |

|         |                                |            | 28                              | 25                          | 35                         |                                                         |                       |

|         |                                |            | 22                              | 35                          | 45                         |                                                         |                       |

|         |                                |            | 15                              | 50                          | 65                         |                                                         |                       |

|         | 1,024 × 18                     | LH540225 * | 50                              | 12                          | 20                         | 550/28                                                  | 68PLCC                |

|         |                                |            | 40                              | 15                          | 25                         |                                                         |                       |

|         |                                |            | 28                              | 20                          | 35                         |                                                         |                       |

|         |                                |            | 20                              | 25                          | 50                         |                                                         |                       |

| 36K     | 512 × 36 × 2                   | LH543611 * | 50                              | 12                          | 20                         | 1540/                                                   | 120PGA/132PQFP        |

|         |                                |            | 40                              | 15                          | 25                         |                                                         |                       |

|         |                                |            | 33                              | 18                          | 30                         |                                                         |                       |

|         |                                |            | 28                              | 21                          | 35                         |                                                         |                       |

|         | 4,096 × 9                      | LH5499     | 33                              | 20                          | 30                         | 605/44                                                  | 28DIP/32PLCC          |

|         |                                |            | 28                              | 25                          | 35                         |                                                         |                       |

|         |                                |            | 22                              | 35                          | 45                         |                                                         |                       |

|         | 1                              |            | 15                              | 50                          | 65                         |                                                         |                       |

|         |                                |            | 12                              | 65                          | 80                         |                                                         |                       |

|         |                                |            | 10                              | 80                          | 100                        |                                                         |                       |

|         |                                | LH540204 * | 33                              | 20                          | 30                         | 605/44                                                  | 28SK-DIP/28DIP/28SOJ/ |

|         |                                |            | 28                              | 25                          | 35                         |                                                         | 32PLCC                |

|         |                                |            | 22                              | 35                          | 45                         |                                                         |                       |

|         |                                |            | 15                              | 50                          | 65                         |                                                         |                       |

|         |                                | LH5492     | 40                              | 20                          | 25                         | 825/138                                                 | 32PLCC                |

|         |                                |            | 33                              | 22                          | 30                         |                                                         |                       |

|         |                                |            | 28                              | 25                          | 35                         |                                                         |                       |

|         | 1,024 × 36                     | LH543620 * | 50                              | 14                          | 20                         | TBD                                                     | 132PQFP               |

|         |                                |            | 40                              | 15                          | 25                         |                                                         |                       |

|         |                                |            | 33                              | 21                          | 30                         |                                                         |                       |

| 72K     | 8,192 × 9                      | LH540205 * | 33                              | 20                          | 30                         | 605/44                                                  | 28SK-DIP/28DIP        |

|         |                                |            | 28                              | 25                          | 35                         |                                                         |                       |

|         |                                |            | 22                              | 35                          | 45                         |                                                         |                       |

|         |                                |            | 15                              | 50                          | 65                         |                                                         |                       |

Primary parameter for speed-grade specification.

\* Contact your Sharp representative for availability.

### QUALITY ASSURANCE

#### **Quality Assurance System**

Sharp develops and produces a wide range of consumer and industrial-use semiconductor products.

In recent years, the applications of ICs have expanded significantly, into fields where extremely high levels of quality are critical.

In response, Sharp has implemented a total quality assurance system that encompasses the entire production process from planning to after-sales service. This system ensures that quality is a priority in the planning development and production and guarantees product reliability through rigorous reliability testing. We compiled the "Sharp Semiconductor Reliability Handbook, IC Edition" to introduce you to the results of some of our research and to our quality and reliability philosophy and programs. We hope that it is informative and that it will help Sharp customers develop and refine their quality and reliability assurance and control activities. We will introduce a part of this system here.

Sharp's quality and reliability assurance activities are based on the following guidelines:

- All personnel should participate in quality assurance by continually cultivating a higher level of quality awareness.

- In the design and development stages of new products, create reliable designs that consider reliability in every respect.

- Quality control in all production processes, all working environments, materials, equipment, and measuring devices should be carefully monitored to ensure quality and reliability from the very beginning of the production process.

- Confirm long-term reliability and obtain a thorough understanding of practical limits through reliability testing.

- Continually work to improve quality through application of data from process inspections, reliability testing, and market surveys.

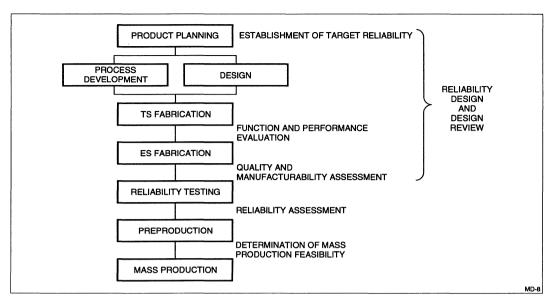

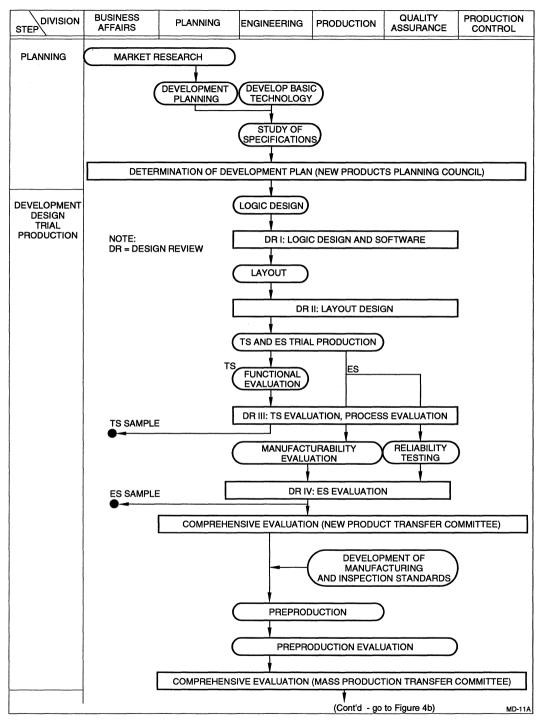

#### Quality Assurance During New Product Development

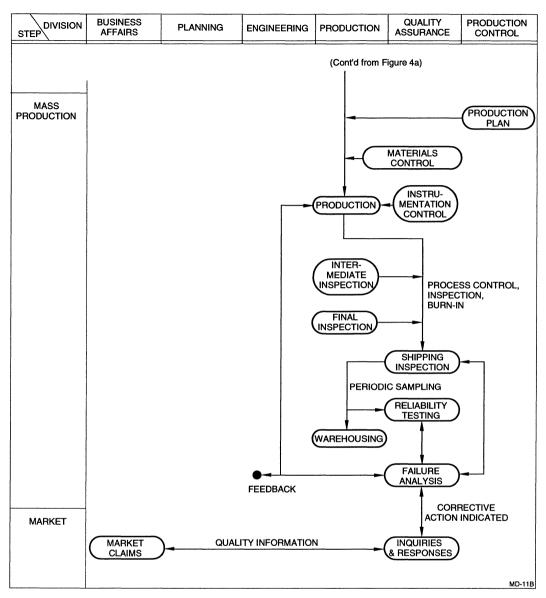

New product development *(Figure 1)* begins with an accurate grasp of the purpose, environment, and manners in which customers will use the product as well as the required reliability. A development plan is then drafted, clarifying the price, quantity, sales period and target reliability of the product to be manufactured.

Quality and reliability are built into the product from the beginning of the product cycle by introducing design review (DR) and reliability planning in the development and design stage. The first tasks undertaken in this stage are process development and circuitry design, by which a prototype, or technical sample (TS), is made. An evaluation of the technical sample is conducted, centering on the function and performance of the sample under conditions in which the final product will be used (TS evaluation).

Next, an engineering sample (ES) is made, based on the results of the TS evaluation, and it is subjected to ES evaluation. The ES evaluation consists of determining, under mass production conditions, whether the product functions and performs as intended during development and design. Reliability testing is also used to decide whether the engineering sample has the required degree of reliability.

In the final stage, the transfer of the product to mass production is discussed - based on the results of the TS and ES evaluations. Once TS and ES are accepted, preproduction begins. At this time, it is determined whether the quality and reliability obtained during development and design can be maintained, whether there are any discrepancies in the production process and what yields will be. The manufacturability of the product is determined, based on these results.

DR (Design Review) is performed to prevent faulty operation and to enhance the functions, usability, quality and reliability, upon completion of structural design, logic design, software design, circuit design, TS/ES evaluation and reliability tests.

Figure 1. New Product Development Steps

| PROCESS                                               | CHARACTERISTIC(S) CONTROLLED                                                                   | PURPOSE OF CONTROL                                                                                                       |

|-------------------------------------------------------|------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|

| V INCOMING<br>SILICON<br>WAFER<br>OXIDATION           | EXTERNAL APPEARANCE, DIMENSIONS,<br>SHEET RESISTIVITY                                          | REMOVE PRODUCTS HAVING<br>IMPROPER DIMENSIONS,<br>FLAWS AND CRYSTAL DEFECTS.<br>ENSURE PROPER SHEET<br>RESISTANCE VALUES |

|                                                       | EXTERNAL APPEARANCE, FILM<br>THICKNESS, SURFACE CLEANLINESS                                    | FIND PINHOLES, CHECK SURFACE<br>CLEANLINESS AND CONTROL<br>FILM THICKNESS                                                |

| UISUAL INSPECTION<br>MONITORING<br>O ION IMPLANTATION | DEVELOPABILITY, ETCHABILITY,<br>LINE WIDTH                                                     | CHECK FOR PROPER<br>DEVELOPMENT AND ETCHING.<br>CONTROL LINE WIDTH                                                       |

| FRAME C DICING                                        | ELECTRICAL CHARACTERISTICS,<br>MAJOR DEVICE CHARACTERISTICS                                    | REMOVE PRODUCTS HAVING<br>POOR ELECTRICAL CHARACTER-<br>ISTICS. ENSURE PROPER<br>DEVICE CHARACTERISTICS                  |

|                                                       | EXTERNAL APPEARANCE                                                                            | REMOVE CRACKED AND<br>CHIPPED ITEMS.                                                                                     |

|                                                       | EXTERNAL APPEARANCE<br>ADHESIVE STRENGTH                                                       | ENSURE QUALITY OF DIE<br>BONDS                                                                                           |

|                                                       | EXTERNAL APPEARANCE<br>TENSILE STRENGTH                                                        | CHECK POSITION AND SHAPE OF<br>BONDS. ENSURE PROPER WIRE<br>TENSILE STRENGTH                                             |

|                                                       | TEMPERATURE, TIME, STRESS<br>WIRE CONDUCTIVITY                                                 | ENSURE MOLDABILITY. ENSURE<br>PROPER WIRE CONFIGURATION                                                                  |

| STABILIZED BAKE                                       | INGREDIENTS, TEMPERATURE,<br>CONTAMINATION                                                     | MAINTAIN FINISH QUALITY                                                                                                  |

|                                                       | THICKNESS, UNIFORMITY<br>(SOLDERABILITY)<br>PLATED LAYER COMPOSITION<br>PLATED LAYER THICKNESS | REMOVE PRODUCTS HAVING<br>PLATING IRREGULARITIES.<br>MAINTAIN PLATING QUALITY                                            |

|                                                       | TEMPERATURE, TIME,<br>MARKING MATERIAL                                                         | MAINTAIN MARK QUALITY                                                                                                    |

| LEAD CUT<br>FORMING                                   | TOOLING SHARPNESS<br>TOOLING DIMENSIONS                                                        | PREVENT ABNORMAL STRESS ON<br>PLASTIC MOLD RESULTING IN<br>DAMAGE                                                        |

| Y                                                     |                                                                                                | MD-9                                                                                                                     |

|                                                       | a 2 Example of the Quelity Control P                                                           |                                                                                                                          |

Figure 2. Example of the Quality Control Process

### **Raw Materials Control**

The level of product quality and reliability is largely governed by the quality of the materials originally making up the production process and environment.

It is the responsibility of the vendor to execute the quality assurance of basic materials purchased by Sharp. Raw material quality assurance is conducted according to the following system:

- Initial selections of a raw material manufacturer.

- Quality qualification for each new material put into use (quality and reliability assessments of devices in which such new materials are used).

- Periodic quality consultations based on quality information obtained during mass production.

Acceptance inspections are carried out as necessary based on acceptance criteria derived from product specifications and approved drawings.

### Control of the Manufacturing Environment

Integrated circuit devices are manufactured in a clean room where there is minimal airborne particulates. The use of ultrapure water also aids cleanliness. Such conditions are necessary due to the adhesion of even small bits of foreign particles (0.1  $\mu$ m or less), no more than 1/5 - 1/10 the size of the smallest IC pattern, can result in defects later in the process.

Particulates not only affects chip yields, but can also have a lethal affect on the quality and reliablity of a device. Therefore, the cleanliness of every piece of equipment and facility in the plant as well as that of work clothes and work articles are controlled. Degree of cleanliness is usually expressed numerically as the number of particles over 0.5  $\mu$ m per cubic foot of air.

The degree of cleanliness maintained in Sharp clean rooms, where wafers come in direct contact with air, is Class 1. Temperature and humidity are maintained at constant levels by continuous computer-controlled monitoring (Table 1).

The ultrapure de-ionized (DI) water used in the wafer process is manufactured with an ultrapurification equipment, employing ion-exchange treatment, ultraviolet irradiation and ultrafiltration systems.

Table 1.

Clean Room Temperature & Humidity Standards

| Temperature | 24 ± 0.5°C |

|-------------|------------|

| Humidity    | 45 ± 5% RH |

## Control of Facilities and Instrumentation

Intregrated circuit device technology is experiencing rapid revolutionary change, and advances in IC production facilities and equipment are equally impressive.

Process automation is promoted by using the latest CIM (Computer Intregrated Manufacturing) system to create devices having stable quality and to reduce variance of characteristics. In addition, production facilities maintenance control, and precision control for various instrumentation devices are implemented by both daily and periodic spot inspections.

Facilities' control is conceptually based on Total Productive Maintenance (TPM), in which all concerned employees systematically participate in facilities maintenance activities. Sharp's goal is to create a highly skilled human resource through activities such as:

- operator-initiated maintenance;

- scheduled maintenance;

- corrective maintenance.

Control of instrumentation devices is in accordance with Japanese national standards. Regular calibration by overseeing public agencies also helps maintain a high level of accuracy in these devices.

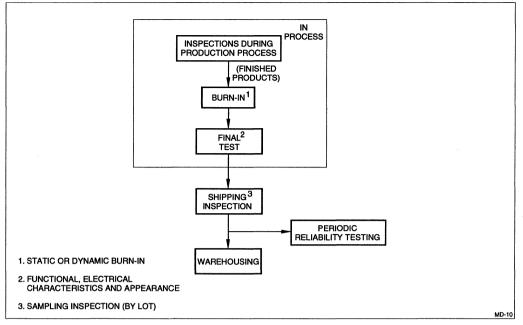

Figure 3. Product Inspection System

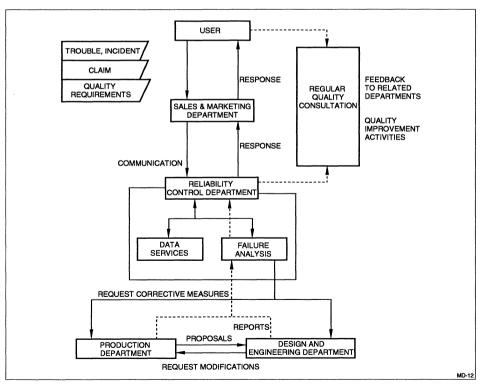

# Quality Control During the Production Process

Designed-in quality and reliability must be faithfully built into a device during production to manufacture consistently high-quality and high-reliability products.

Production Operations are therefore based on specific, established operational standards. Checks are performed at each process step to decide whether specific characteristics have been obtained and quality has been built in. Each process is monitored to ensure that defectives are not sent to the next process. This is done by rigorously carrying out various standardized controls, appropriate to each process, such as monitoring, visual inspections and sampling inspections.

Sharp strongly promotes the automation of production facilities and equipment. Sharp works to prevent quality problems before they occur and to stabilize quality. Operations that required human skills in the past are now automated. Computer Integrated Manufacturing (CIM) is being introduced into the wafer process. CIM is used to implement comprehensive production control, including conveyance within a process, equipment monitoring and progress control. CIM enables several types of process data to be processed together. Control charts and process capacity index (Cpk) are computed in real time for individual pieces of equipment. Even minute fluctuations in characteristics are fed back to improve control.

Reliability is also being assessed by periodic sampling. This test is a long-term reliability assessment, and the results are fed back to the related divisions.

While quality assurance tests and inspections are conducted for improving and maintaining quality, they also are used to predict the probable reliability a product will have in the marketplace. They provide a multi-faceted approach to ensuring product quality.

| Table 2.                      |

|-------------------------------|

| <b>Reliability Test Items</b> |

| CLASSIFICATION                     | TEST                            | PURPOSE & CONDITIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | REFERENCE<br>STANDARDS                                           |

|------------------------------------|---------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|

| Thermal<br>Environment<br>Tests    | Soldering Heat                  | To determine soldering heat resistance.<br><u>Standard test conditions:</u><br>Solder bath temperature: $260 \pm 5^{\circ}$ C<br>Time: $10 \pm 1$ sec.<br>Solder composition: Pb:Sn = 4:6                                                                                                                                                                                                                                                                                                                                                        | JIS C 7022: A-1<br>MIL-STD-750 C 2031<br>IEC Pub. 68 Test Tb     |

|                                    | Temperature Cycling             | To determine resistance to high and low temperatures<br>and to temperature changes between these extremes.<br>Standard test conditions:<br>$T_a = T_{stg}$ MIN ~ $T_{stg}$ MAX [gas environment]                                                                                                                                                                                                                                                                                                                                                 | JIS C 7022: A-4<br>MIL-STD-883 C 1010<br>IEC Pub. 68 Test Na, Nb |

|                                    | Thermal Shock                   | To determine resistance to sudden changes in temperature.<br><u>Standard test conditions:</u><br>$T_a = T_{stg MIN} \sim T_{stg MAX}$ [liquid environment]                                                                                                                                                                                                                                                                                                                                                                                       | JIS C 7022: A-3<br>MIL-STD-883 C 1011<br>IEC Pub. 68 Test Nc     |

| Mechanical<br>Environment<br>Tests | Variable Frequency<br>Vibration | To determine resistance to vibration during<br>transportation and use.<br><u>Standard test conditions:</u><br>Cycle: 100 ~ 2000 H <sub>z</sub> in 4 min.<br>Peak acceleration: 20 G<br>Orientation: four (4) times in each of the<br>orientations of $\pm X$ , $\pm Y$ and $\pm Z$                                                                                                                                                                                                                                                               | JIS C 7022: A-10<br>MIL-STD-883 C 2007<br>IEC Pub. 68 Test Fc    |

|                                    | Mechanical Shock                | To determine resistance to shocks during<br>transportation & use.<br><u>Standard test conditions:</u><br>Peak acceleration: 1500 G<br>Pulse duration: 0.5 ms<br>Orientation: three (3) pulses in each of the<br>orientations $\pm X$ , $\pm Y$ and $\pm Z$                                                                                                                                                                                                                                                                                       | JIS C 7022: A-7<br>MIL-STD-883 C 2002<br>IEC Pub. 68 Test Ea     |

|                                    | Constant Acceleration           | To determine resistance to constant acceleration.<br><u>Standard test conditions:</u><br>Stress level: 20,000 G,<br>Orientation: applied for one (1) min. in each<br>of the orientations $\pm X$ , $\pm Y$ and $\pm Z$                                                                                                                                                                                                                                                                                                                           | JIS C 7022: A-9<br>MIL-STD-883 C 2001<br>IEC Pub. 68 Test Ga     |

|                                    | Lead Integrity                  | To determine resistance to installation and handling<br>such as wiring.<br>(1) Tensile strength.<br>Standard test conditions:<br>A specified load is applied in a direction<br>parallel to the lead axis for 10 ± 1 sec.<br>(2) Bending strength.<br>Standard test conditions:<br>A specified load is applied to the tip of each<br>lead and the lead is bent once each through a<br>+ and - 90° arc and back. (The specified load<br>is determined by nominal cross section or nominal<br>section modulus.)<br>*TCP (tape carrier package): N/A | JIS C 7002: A-11<br>IEC Pub. 68 Test U                           |

### Table 2. (cont'd) Reliability Test Items

| CLASSIFICATION                     | TEST                                    | PURPOSE & CONDITIONS                                                                                                                                                                                                                                                                                                                                           | REFERENCE<br>STANDARDS                                      |

|------------------------------------|-----------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|

| Mechanical<br>Environment<br>Tests | Solderability                           | To determine the solderability of leads which are<br>connected by soldering.<br><u>Standard test conditions:</u><br>Solder bath temperature: $230 \pm 5$ °C,<br>Dip time: $5 \pm 0.5$ sec.<br>Solder composition: Pb:Sn = 4:6, used with<br>rosin flux.                                                                                                        | JIS C 7022: A-2<br>MIL-STD-883 C 2003                       |

|                                    | Seal (Hermeticity)                      | To determine the effectiveness of the seal of<br>hermetically sealed devices.<br>(1) Fine leak detection (helium): measured with a<br>helium detector after storage in an He atmosphere at<br>a prescribed pressure for a designated time period.<br>(2) Gross leak observation (bubbles): observation of<br>bubbles formed by a fluorocarbon or silicone oil. | JIS C 7022: A-6<br>MIL-STD-883 C 1014<br>IEC Pub. 68 Test Q |

|                                    |                                         | ·                                                                                                                                                                                                                                                                                                                                                              |                                                             |

| Life Tests                         | High Temperature<br>Operation           | To determine resistance to prolonged operating<br>stress, electrical and thermal.<br>Standard test conditions:<br>$T_a = T_{op MAX}$<br>Operating source voltage = Max. operating voltage                                                                                                                                                                      | JIS C 7022: B-1<br>MIL-STD-883 C 1005                       |

|                                    | High Temperature<br>Storage             | To determine resistance to prolonged high<br>temperature storage.<br><u>Standard test conditions:</u><br>T <sub>a</sub> = T <sub>stg MAX</sub>                                                                                                                                                                                                                 | JIS C 7022: B-3<br>MIL-STD-883 C 1008                       |

|                                    | Low Temperature<br>Storage              | To determine resistance to prolonged low temperature storage.<br><u>Standard test conditions:</u><br>$T_a = T_{stg MIN}$                                                                                                                                                                                                                                       | JIS C 7022: B-4<br>IEC Pub. 68 Test A                       |

|                                    | High Temperature/<br>High Humidity Bias | To determine resistance to prolonged temperature,<br>humidity and electrical stress.<br><u>Standard test conditions:</u><br>85°C, 85% RH<br>Applied voltage = V <sub>TYPICAL</sub>                                                                                                                                                                             | JIS C 7022: B-5<br>IEC Pub. 68 Test C                       |

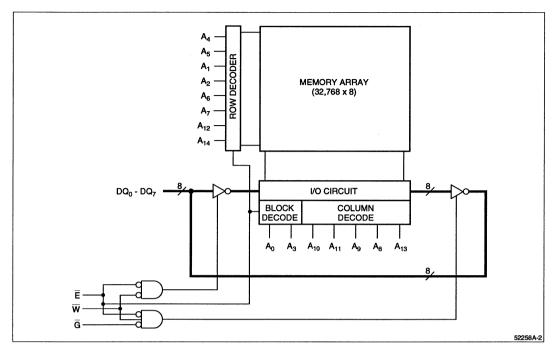

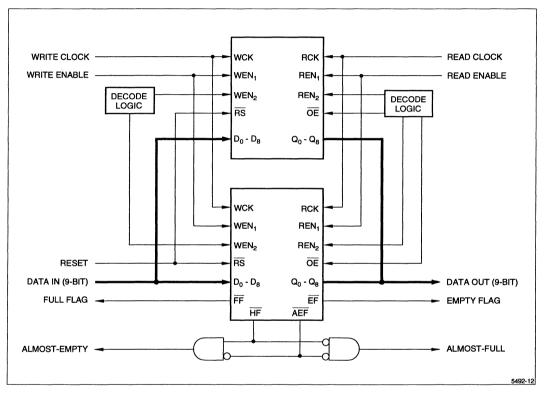

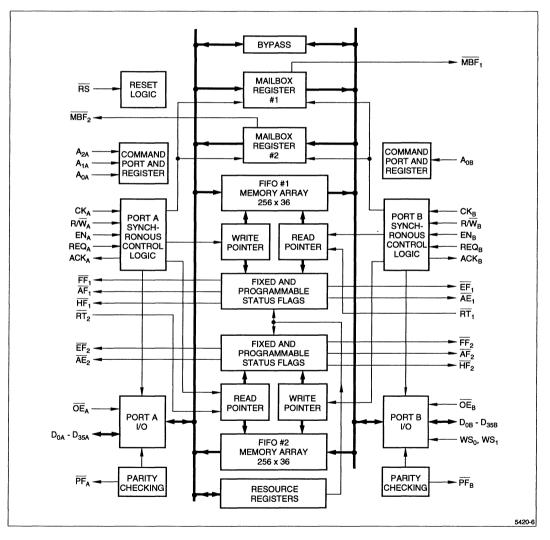

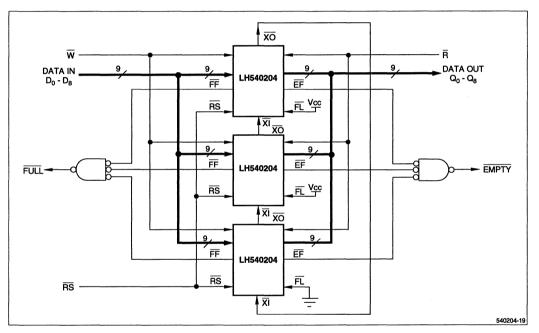

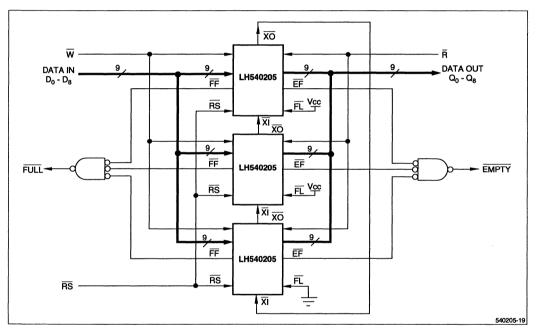

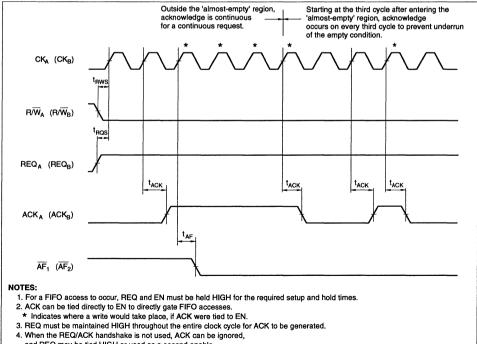

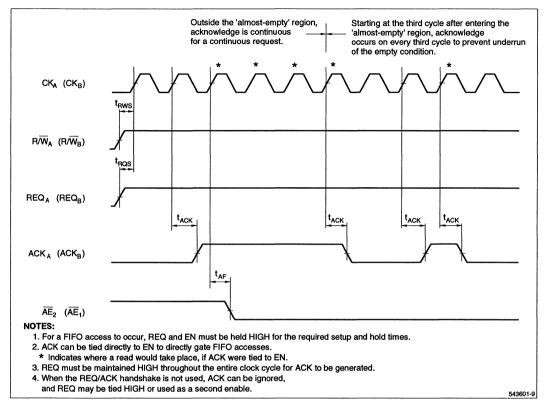

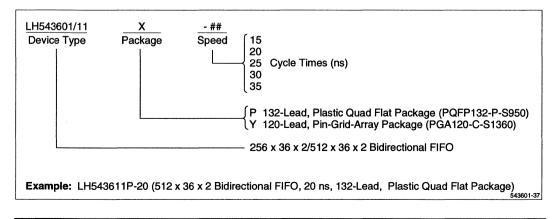

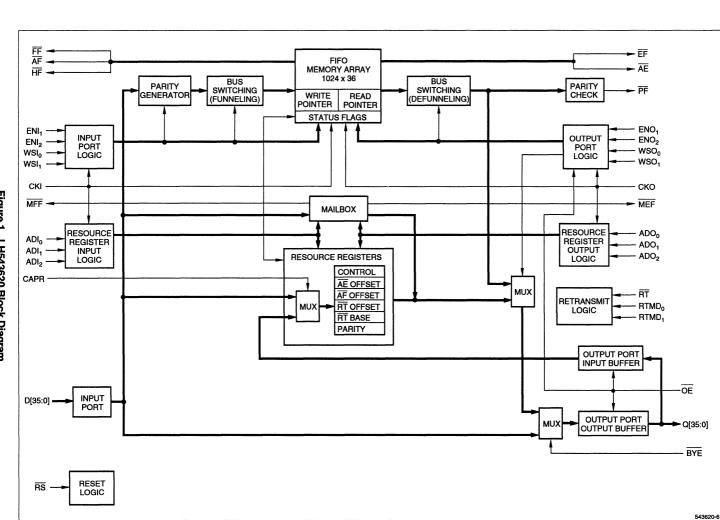

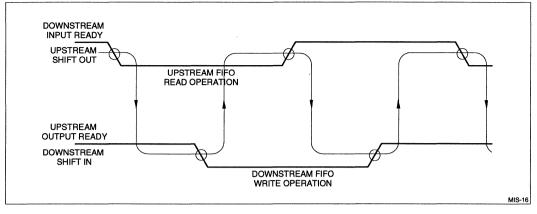

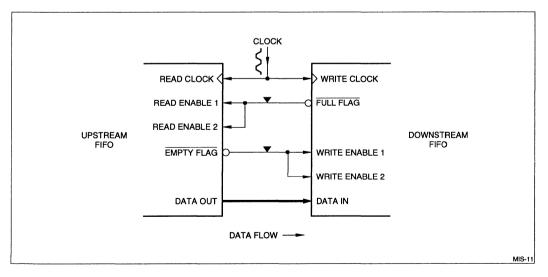

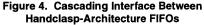

| CLASSIFICATION | TEST                                | PURPOSE & CONDITIONS                                                                                                                                                                                                                                                         | REFERENCE<br>STANDARDS               |