# EPROM AND FLASH MEMORY PRODUCTS

DATABOOK

1<sup>st</sup> EDITION

SGS-THOMSON MICROELECTRONICS

5

# EPROM and FLASH MEMORY PRODUCTS

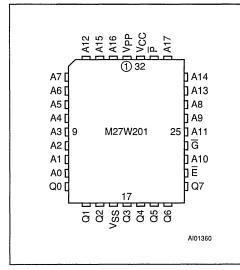

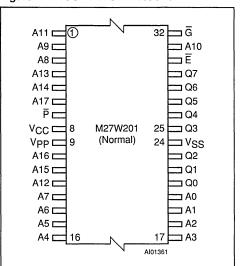

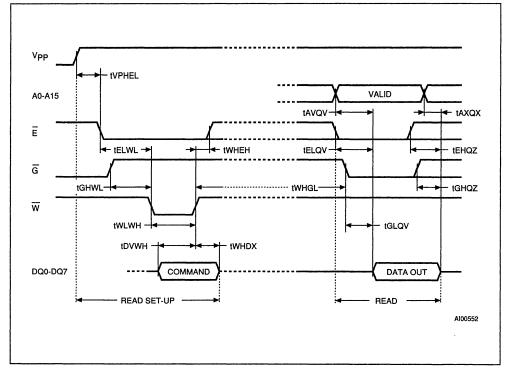

13.19

# DATABOOK

1<sup>st</sup> EDITION

**JUNE 1995**

#### USE IN LIFE SUPPORT DEVICES OR SYSTEMS MUST BE EXPRESSLY AUTHORIZED

SGS-THOMSON PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF SGS-THOMSON Microelectronics. As used herein:

- Life support devices or systems are those which (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform, when properly used in accordance with instructions for use provided with the product, can be reasonably expected to result in significant injury to the user.

- A critical component is any component of a life support device or system whose failure to perform can reasonably be expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

489

| <section-header></section-header> |      |     |

|-----------------------------------|------|-----|

| INTRODUCTION                      | Page | 5   |

| GENERAL INDEX                     |      | 8   |

| NMOS UV EPROM                     |      | 11  |

| UV EPROM and OTP MEMORY           |      | 69  |

| DUAL VOLTAGE FLASH MEMORY         |      | 341 |

| SINGLE VOLTAGE FLASH MEMORY       |      | 723 |

z.

# INTRODUCTION

SGS-THOMSON Microelectronics is a broad range semiconductor company. The product range includes memory products which satisfy the needs of a wide range of applications. They include

- Non-Volatile Memories: OTP Memories, UV EPROMs, FLASH Memories, Serial and Parallel EEPROMs and NVRAMs (battery backed SRAMs)

- Synchronous and Asynchronous Fast SRAMs

This databook provides comprehensive technical information on the OTP Memory, UV EPROM and FLASH Memory products.

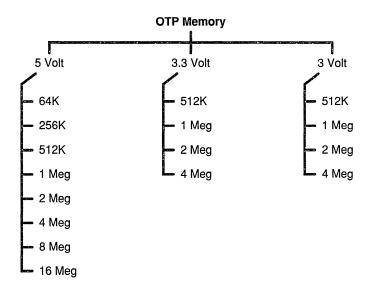

#### OTP Memories (One Time Programmable Memories).

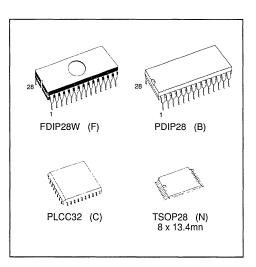

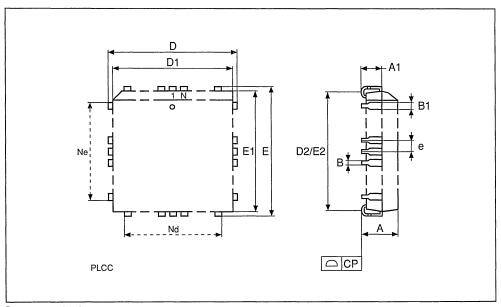

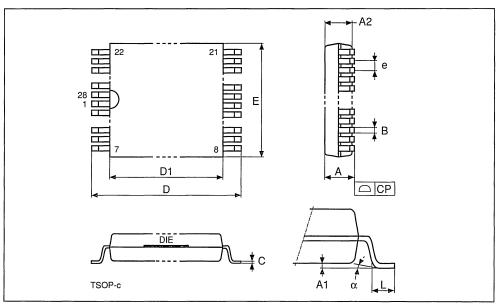

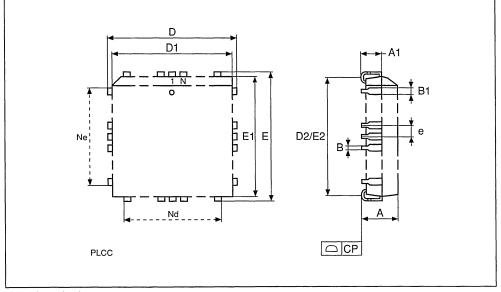

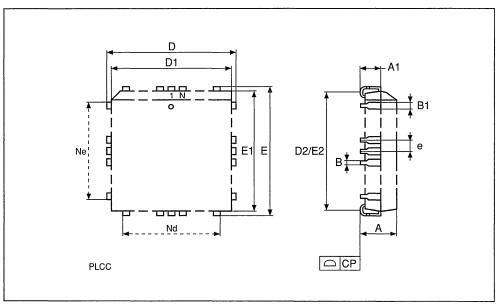

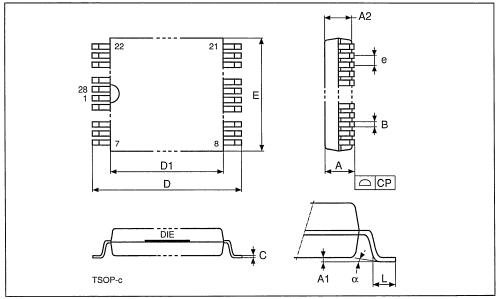

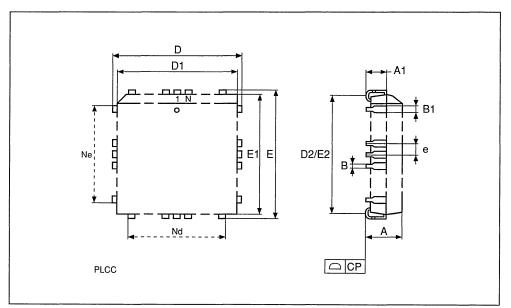

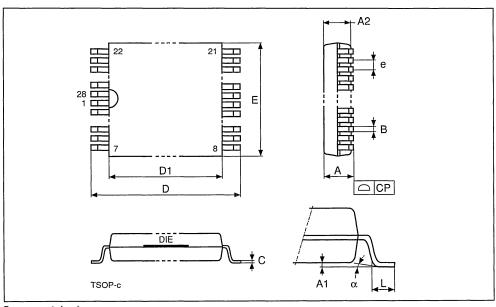

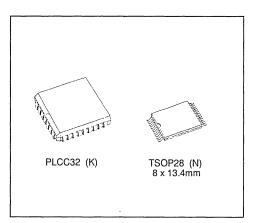

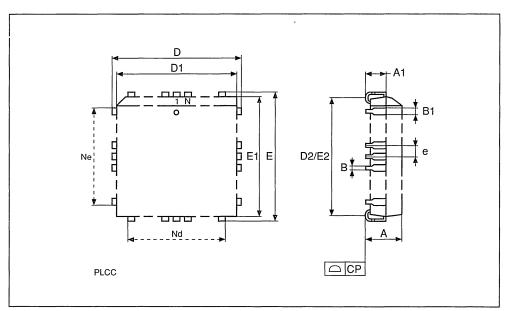

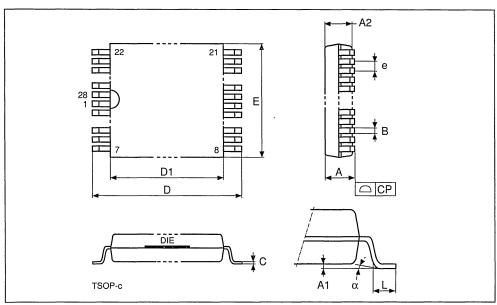

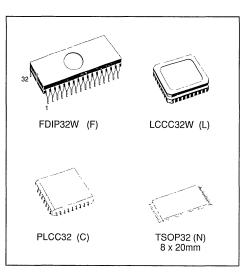

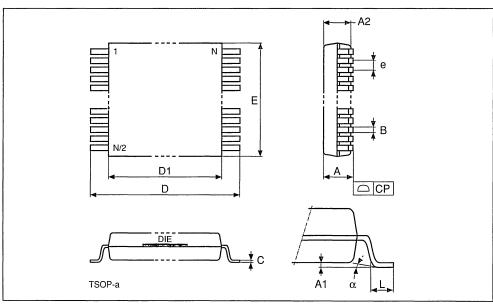

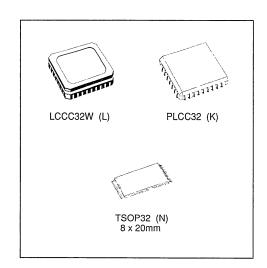

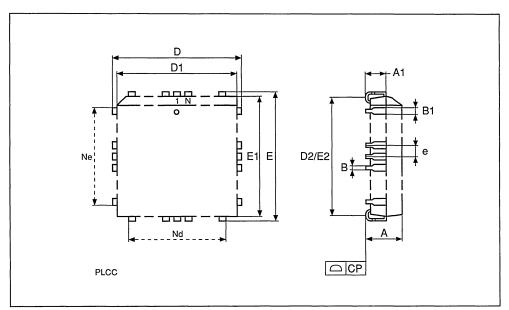

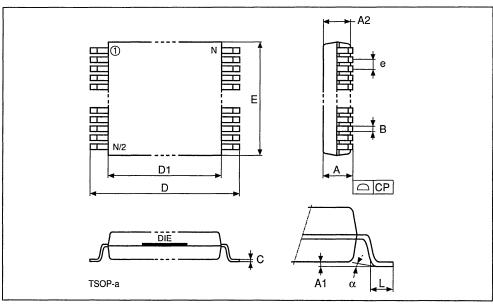

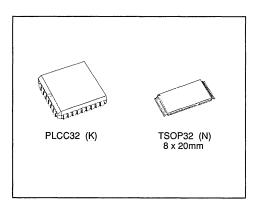

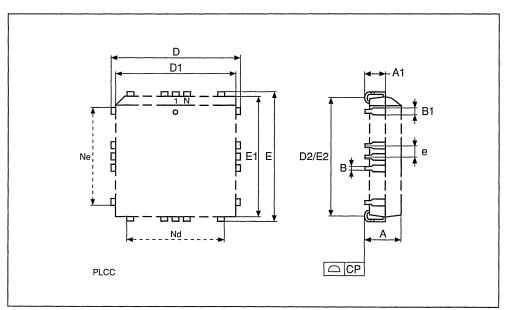

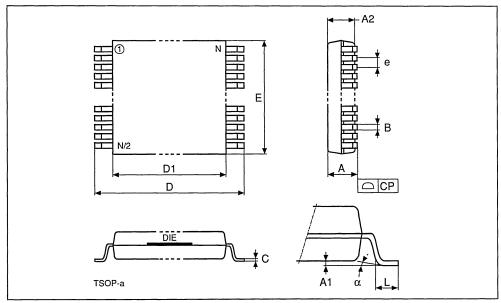

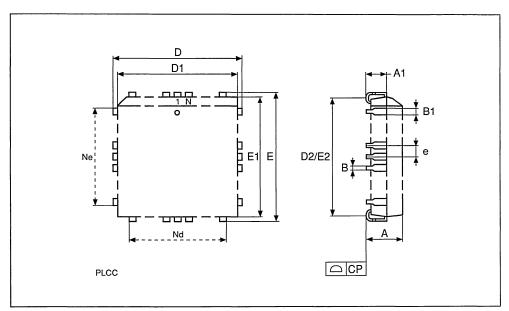

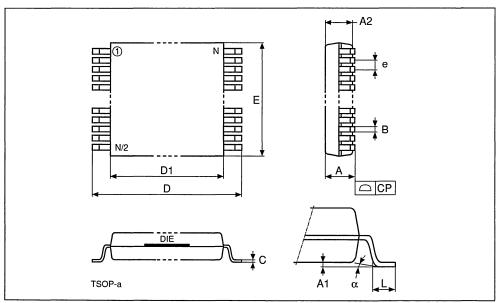

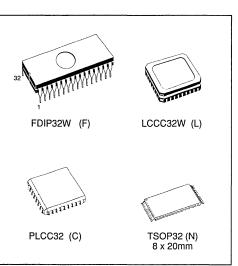

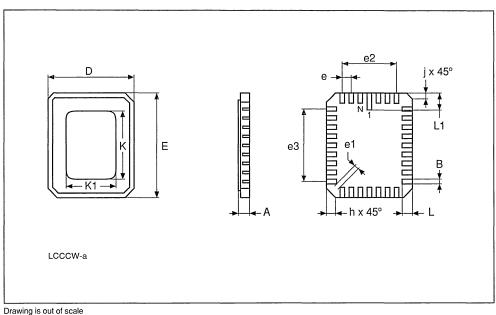

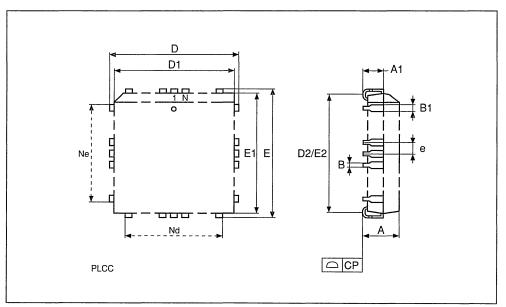

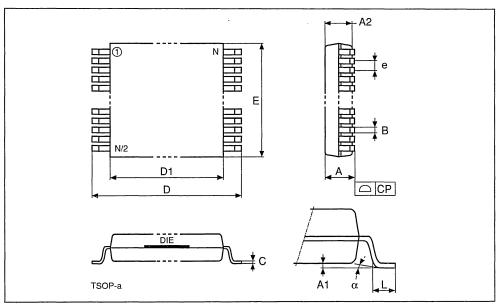

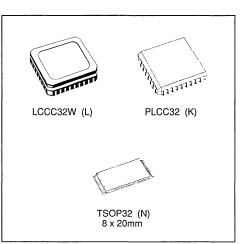

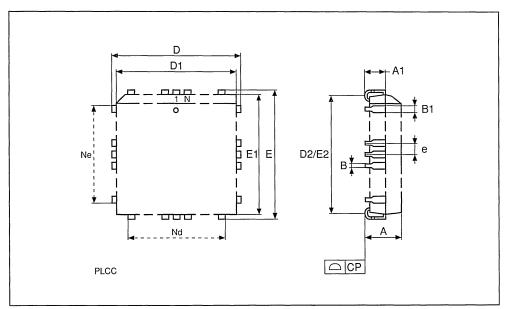

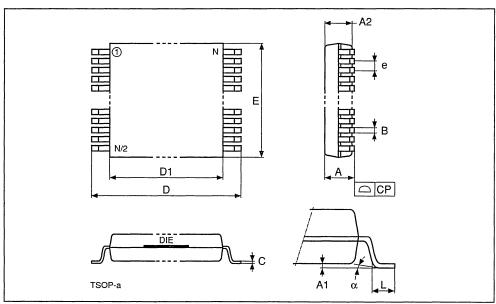

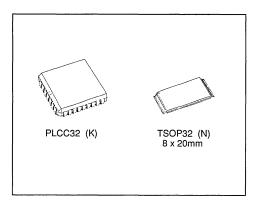

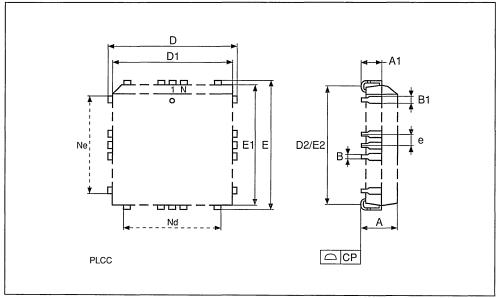

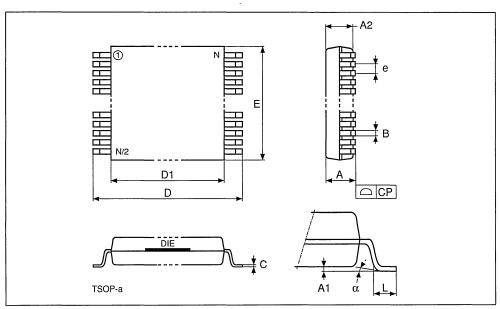

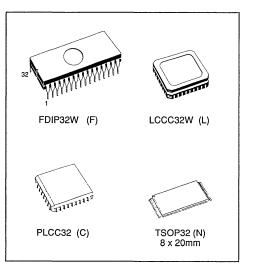

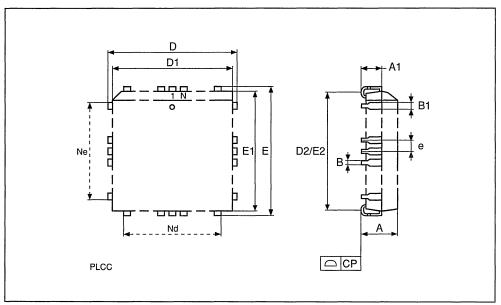

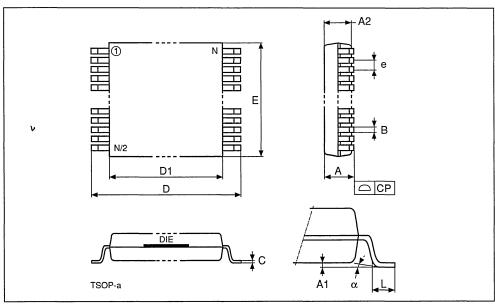

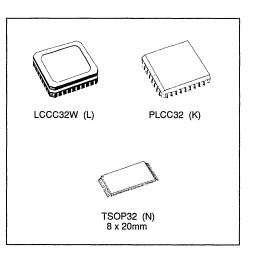

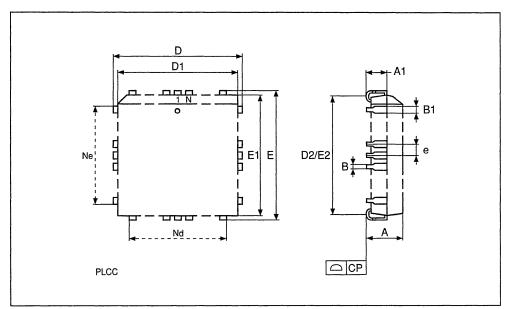

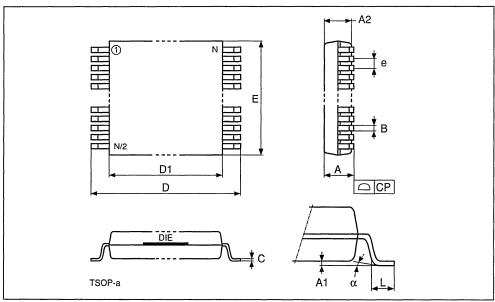

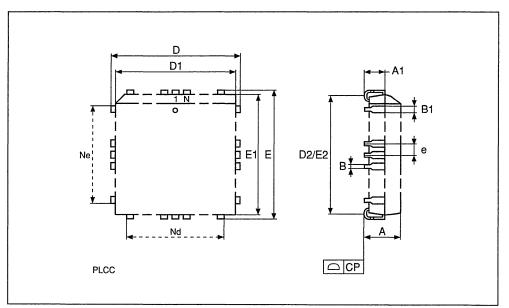

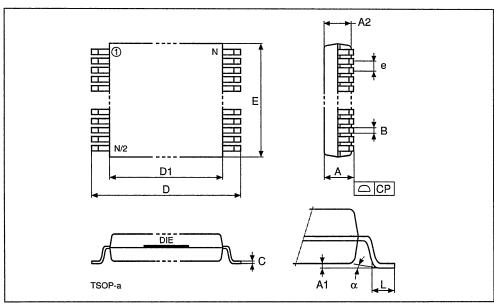

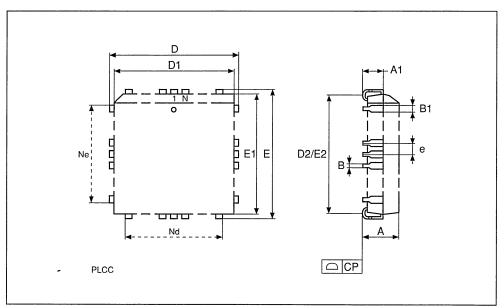

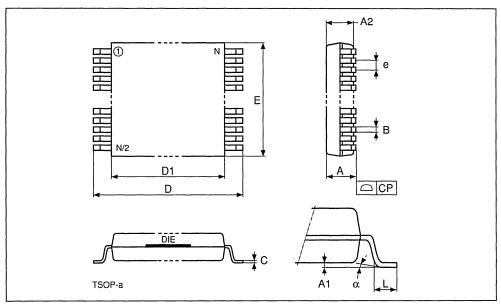

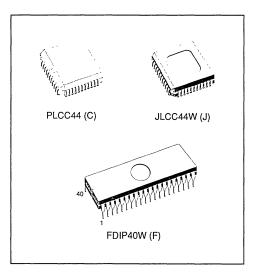

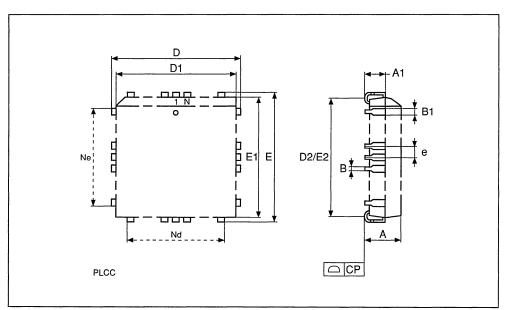

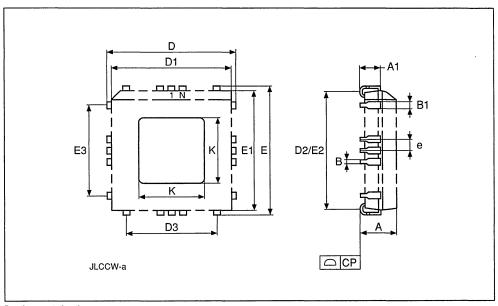

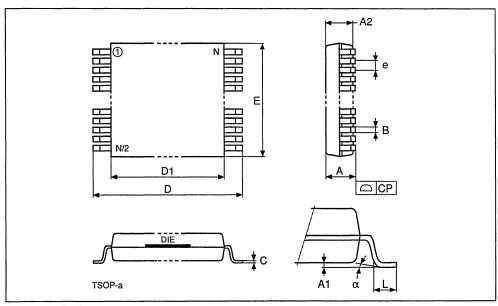

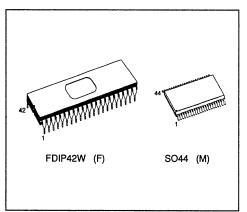

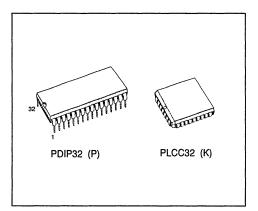

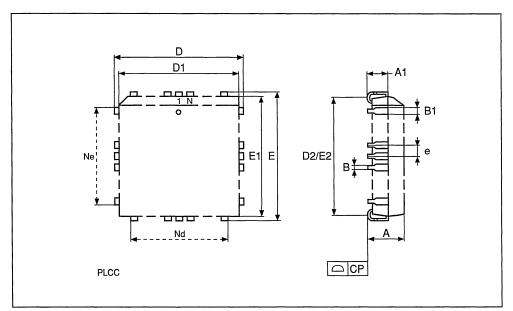

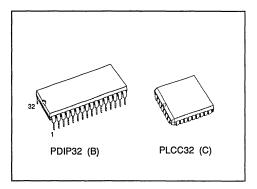

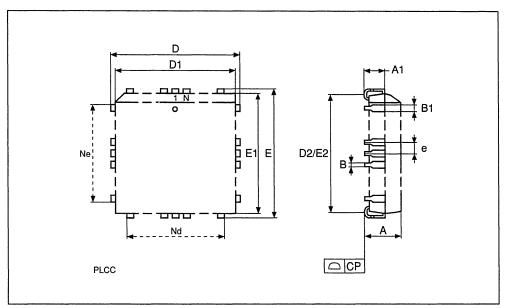

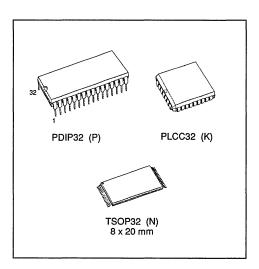

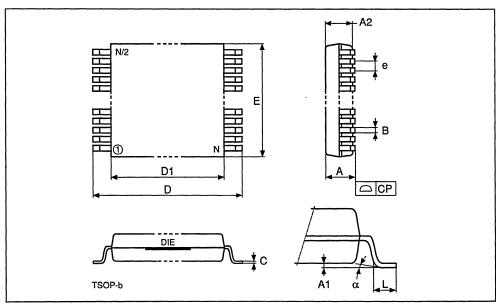

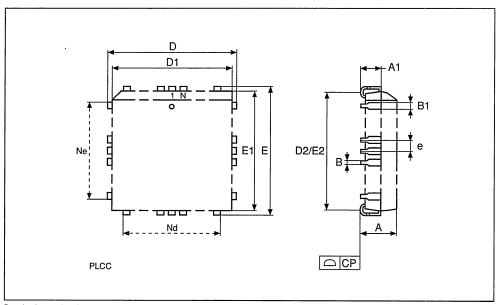

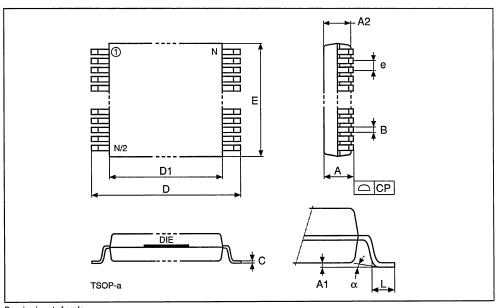

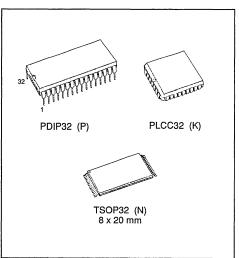

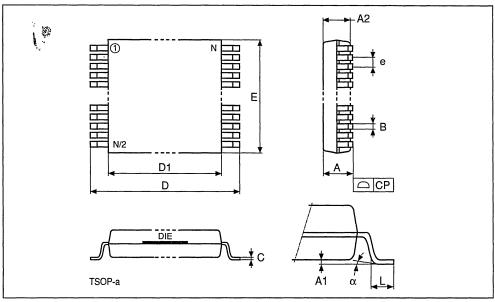

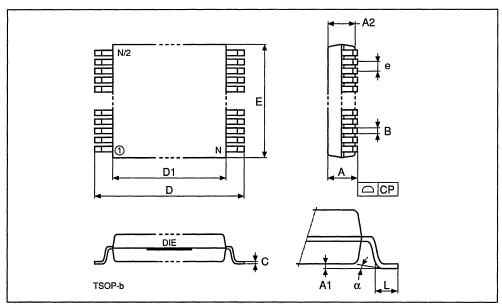

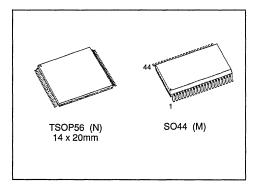

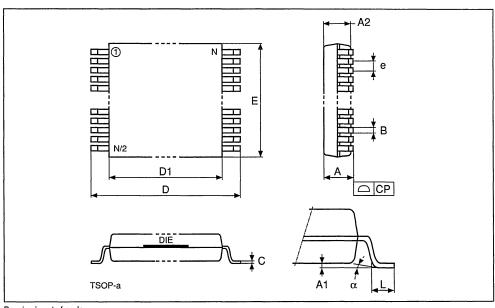

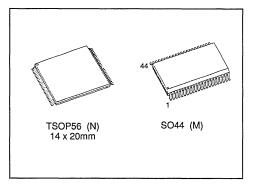

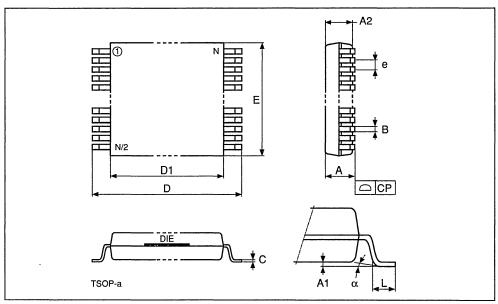

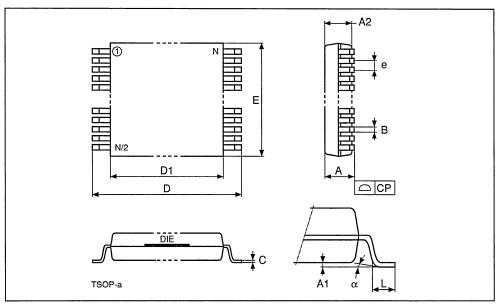

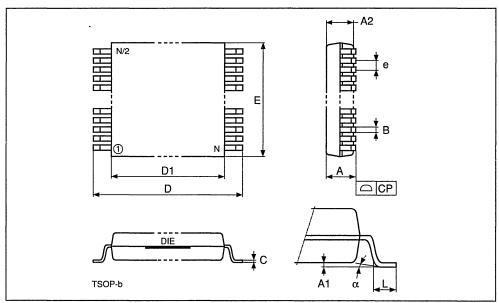

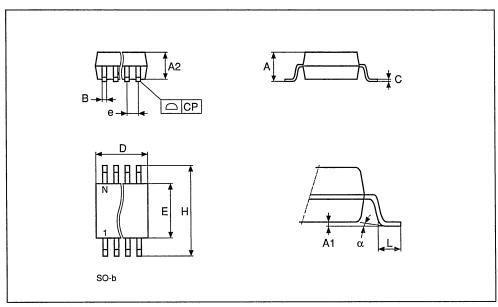

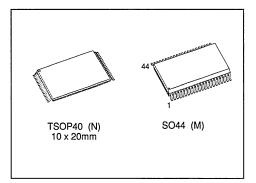

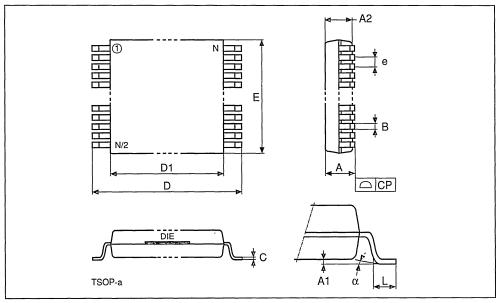

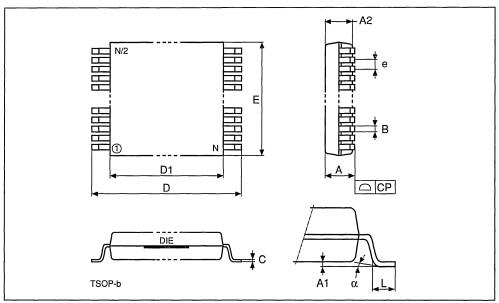

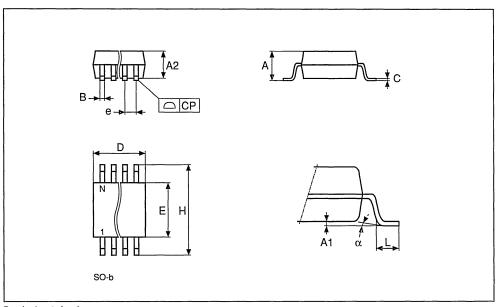

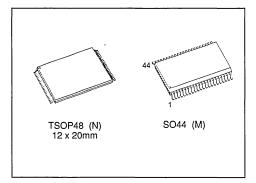

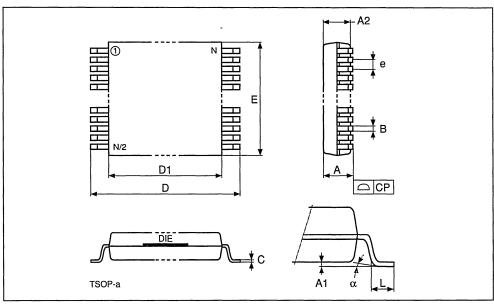

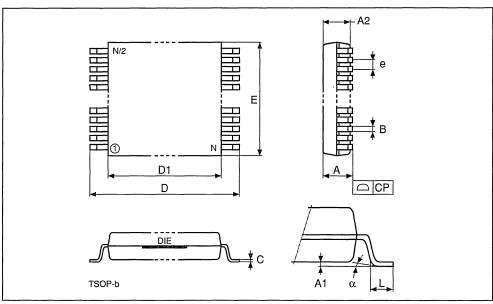

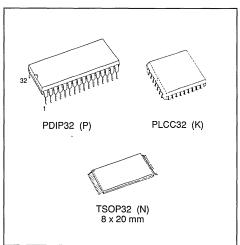

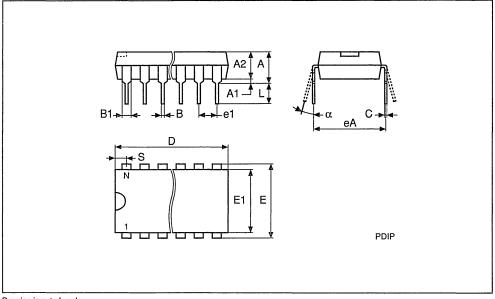

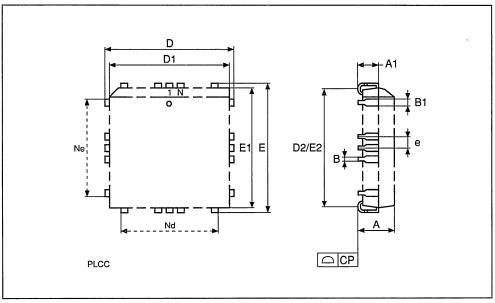

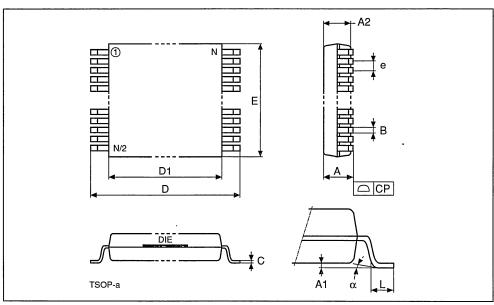

These devices are in many ways similar to UV EPROMs but are packaged in plastic packages, including both through hole mounting, Dual-In-Line Packages and surface mounting types. The surface mounting types include both the PLCC (Plastic Leaded Chip Carrier) and the TSOP (Thin Small Outline Package).

OTP Memories are not eraseable, but are programed one time only using the same programming techniques as for UV EPROMs. Memory densities range from 64K to 8 Megabits using modern CMOS technologies. New technologies allow operation down to supply voltages as low as 2.7 Volts, suitable for battery powered, portable applications.

OTP Memories often can be used to replace FLASH Memories, giving a significant saving in costs, when the memory content is stable and not likely to need re-programing during the system life. Like FLASH they offer the advantage over Mask ROMs of having their content programed at the final moment of equipment assembly, rather than weeks beforehand.

SGS-THOMSON

5

#### UV EPROMs (UV light eraseable Electrically Programmable Read Only Memories).

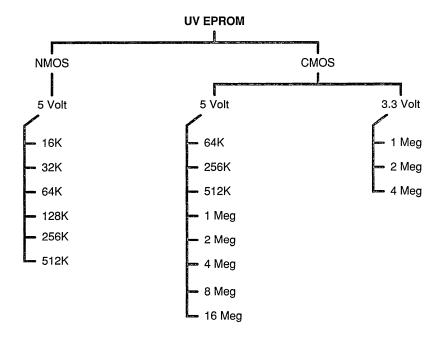

This is a family of EPROMs which can be electrically programed and erased by exposure to UV light through a quartz window in the package. SGS-THOMSON supports both the older NMOS ranges from 16K through 512K bits and the most modern CMOS technologies with products from 64K to 16 Megabit.

#### FLASH Memories (Electrically programmable and eraseable memories).

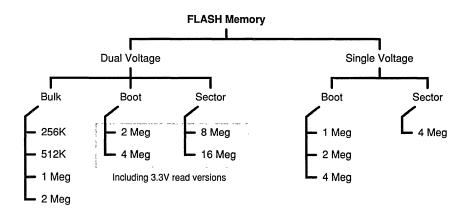

The FLASH Memory provides a new flexibility for the system designer by implementing both electrical programming, like the EPROM, and electrical erase. Erasure is in bulk, for the whole chip, or in blocks or sectors.

The FLASH Memory can be erased and re-programed in the equipment and finds applications wherever there is a requirement to change the contents of the non-volatile memory.

SGS-THOMSON has an extensive program of both process R & D and product design which results in many new products updates and introductions every year.

Please contact your nearest Sales Office to learn about new products that have been introduced since this databook was published.

# **GENERAL INDEX-**

| NMOS UV E | PROM                                                                                       | 11  |

|-----------|--------------------------------------------------------------------------------------------|-----|

| M2716     | NMOS 16K (2K x 8) UV EPROM                                                                 | 13  |

| M2732A    | NMOS 32K (4K x 8) UV EPROM                                                                 | 21  |

| M2764A    | NMOS 64K (8K x 8) UV EPROM                                                                 | 29  |

| M27128A   | NMOS 128K (16K x 8) UV EPROM                                                               | 39  |

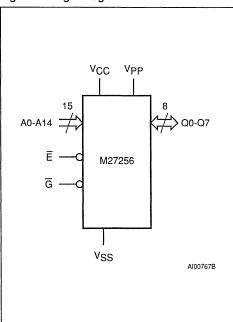

| M27256    | NMOS 256K (32K x 8) UV EPROM                                                               | 49  |

| M27512    | NMOS 512K (64K x 8) UV EPROM                                                               | 59  |

| CMOS UV E | PROM AND OTP MEMORY                                                                        | 69  |

| M27C64A   | 64K (8K x 8) UV EPROM AND OTP MEMORY                                                       | 71  |

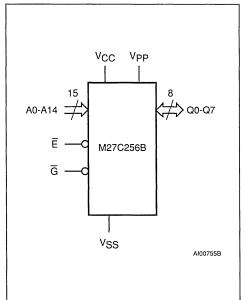

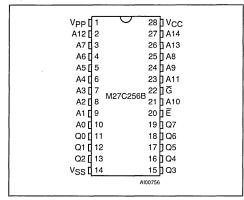

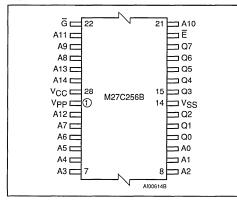

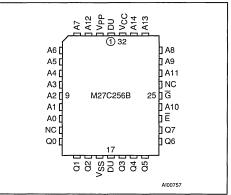

| M27C256B  | 256K (32K x 8) UV EPROM AND OTP MEMORY                                                     | 81  |

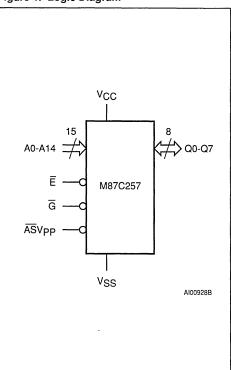

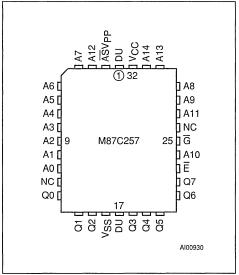

| M87C257   | ADDRESS LATCHED 256K (32K x 8) UV EPROM AND OTP MEMORY                                     | 93  |

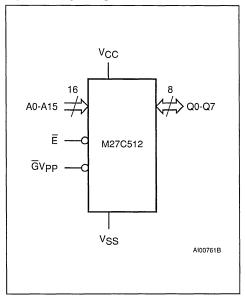

| M27C512   | 512K (64K x 8) UV EPROM AND OTP MEMORY                                                     | 105 |

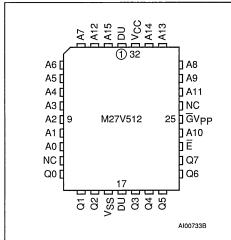

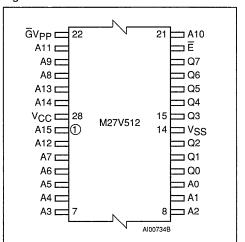

| M27V512   | LOW VOLTAGE 512K (64K x 8) OTP MEMORY                                                      | 119 |

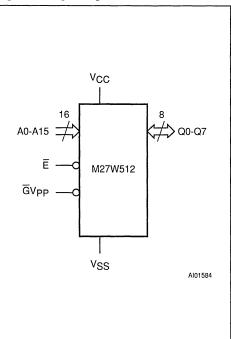

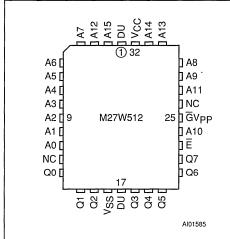

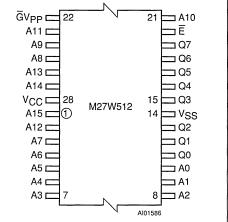

| M27W512   | VERY LOW VOLTAGE 512K (64K x 8) OTP MEMORY                                                 | 131 |

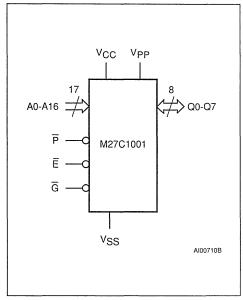

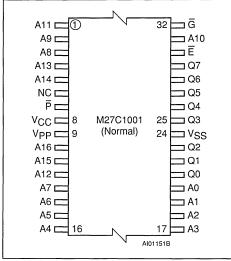

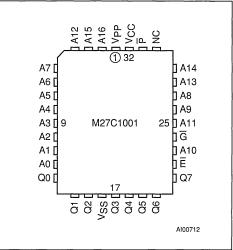

| M27C1001  | 1 MEGABIT (128K x 8) UV EPROM AND OTP MEMORY                                               | 143 |

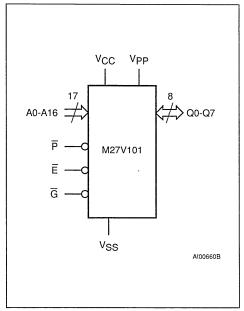

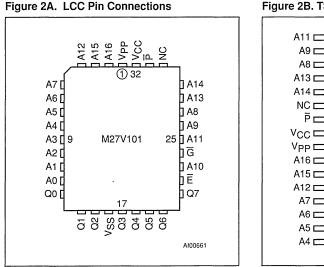

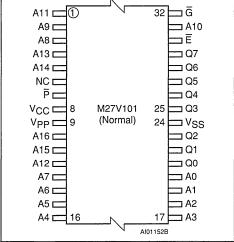

| M27V101   | LOW VOLTAGE 1 MEGABIT (128K x 8) UV EPROM AND OTP MEMORY                                   | 157 |

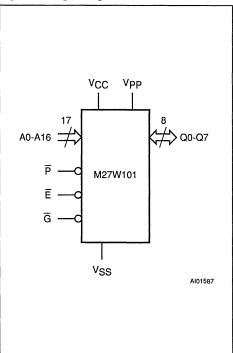

| M27W101   | VERY LOW VOLTAGE 1 MEGABIT (128K x 8) OTP MEMORY                                           | 169 |

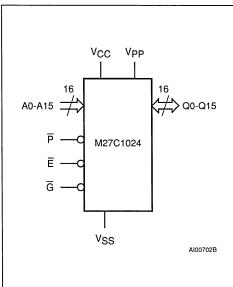

| M27C1024  | 1 MEGABIT (64K x 16) UV EPROM AND OTP MEMORY                                               | 181 |

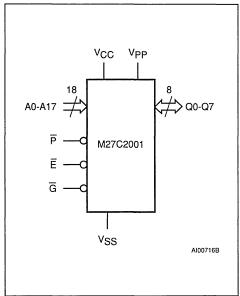

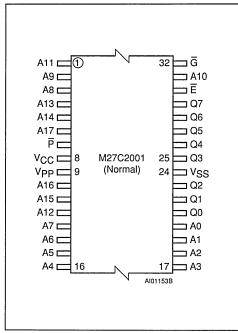

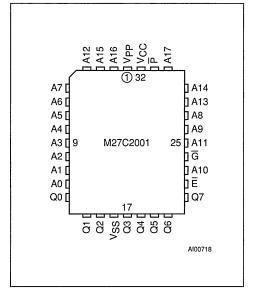

| M27C2001  | 2 MEGABIT (256K x 8) UV EPROM AND OTP MEMORY                                               | 193 |

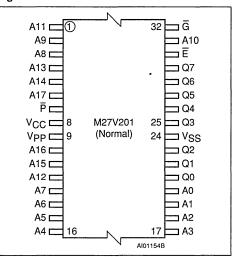

| M27V201   | LOW VOLTAGE 2 MEGABIT (256K x 8) UV EPROM AND OTP MEMORY                                   | 207 |

| M27W201   | VERY LOW VOLTAGE 2 MEGABIT (256K x 8) OTP MEMORY                                           | 219 |

| M27C4001  | 4 MEGABIT (512K x 8) UV EPROM AND OTP MEMORY                                               | 231 |

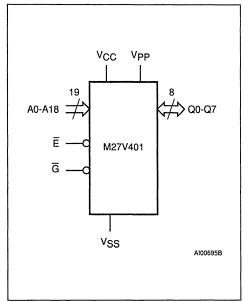

| M27V401   | LOW VOLTAGE 4 MEGABIT (512K x 8) UV EPROM AND OTP MEMORY                                   | 245 |

| M27W401   | VERY LOW VOLTAGE 4 MEGABIT (512K x 8) OTP MEMORY                                           | 257 |

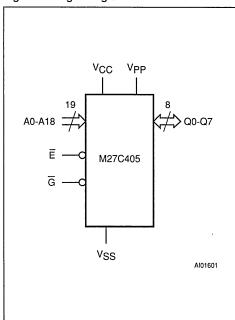

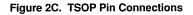

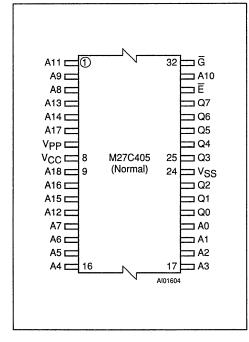

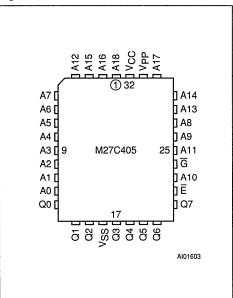

| M27C405   | 4 MEGABIT (512K x 8) OTP MEMORY<br>(pin compatible with Single Voltage 4Meg Flash M29F040) | 269 |

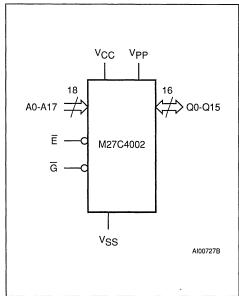

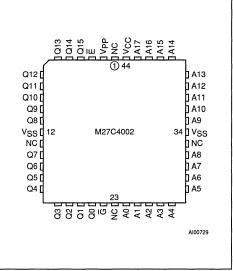

| M27C4002  | 4 MEGABIT (256K x 16) UV EPROM AND OTP MEMORY                                              | 283 |

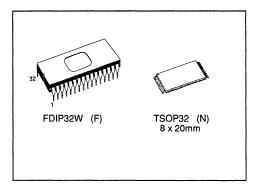

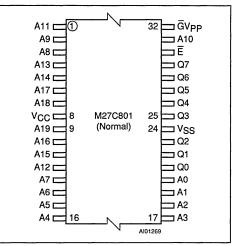

| M27C801   | 8 MEGABIT (1 MEG x 8) UV EPROM AND OTP MEMORY                                              | 295 |

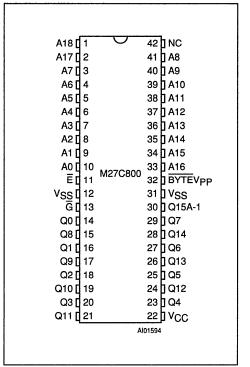

| M28C800   | 8 MEGABIT (1 MEG x 8 or 512K x 16) UV EPROM AND OTP MEMORY                                 | 307 |

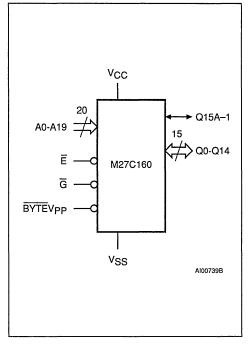

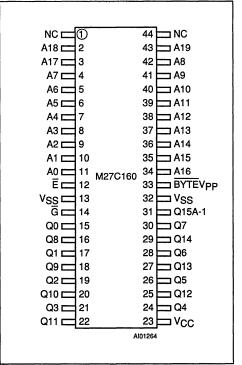

| M27C160   | 16 MEGABIT (2 MEG x 8 or 1 MEG x 16) UV EPROM AND OTP MEMORY                               | 319 |

| M27C160   | 16 MEGABIT (2 MEG x 8 or 1 MEG x 16) UV EPROM                                              | 329 |

|           |                                                                                            | 341 |

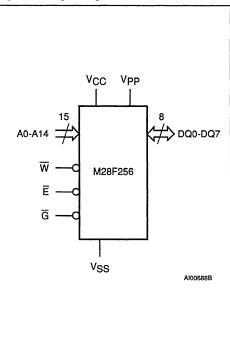

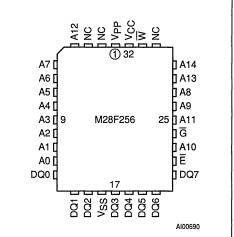

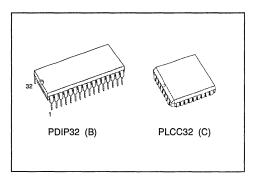

| M28F256   | 256K (32K x 8, CHIP ERASE) FLASH MEMORY                                                    | 343 |

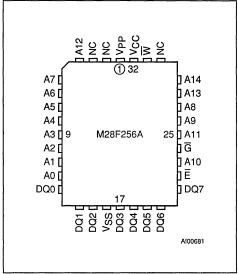

| M28F256A  | 256K (32K x 8, CHIP ERASE) FLASH MEMORY                                                    | 361 |

| M28F512   | 512K (64K x 8, CHIP ERASE) FLASH MEMORY                                                    | 379 |

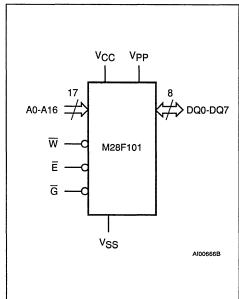

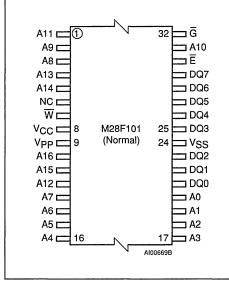

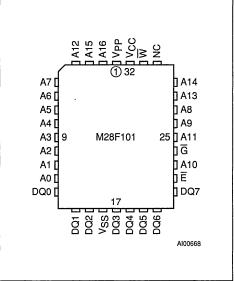

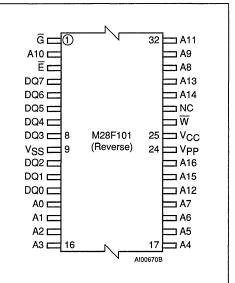

| M28F101   | 1 MEGABIT (128K x 8, CHIP ERASE) FLASH MEMORY                                              | 399 |

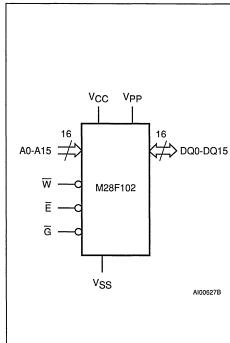

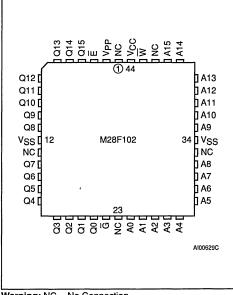

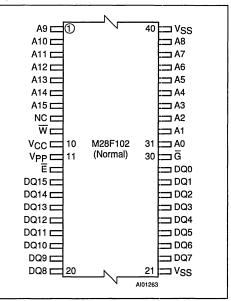

| M28F102   | 1 MEGABIT (64K x 16, CHIP ERASE) FLASH MEMORY                                              | 421 |

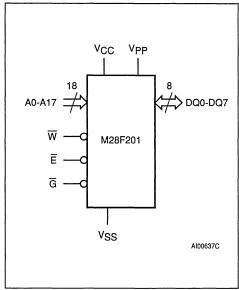

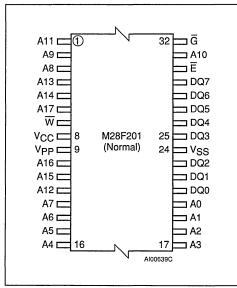

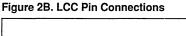

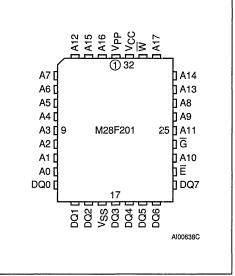

| M28F201   | 2 MEGABIT (256K x 8, CHIP ERASE) FLASH MEMORY                                              | 441 |

| M28V201   | LOW VOLTAGE 2 MEGABIT (256K x 8, CHIP ERASE) FLASH MEMORY                                  | 441 |

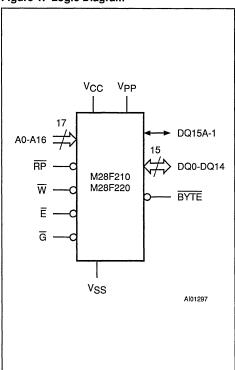

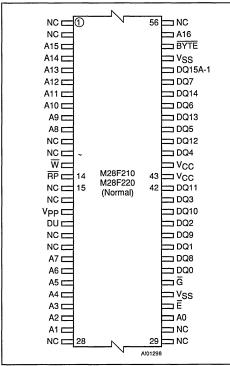

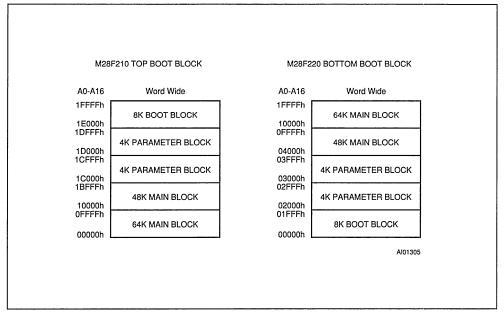

| M28F210   | 2 MEGABIT (x 8 or x 16, BLOCK ERASE) FLASH MEMORY                                          | 463 |

| M28F220   |                                                                                            | 463 |

| M28V210   | LOW VOLTAGE 2 MEGABIT (x 8 or x 16, BLOCK ERASE) FLASH MEMORY                              | 463 |

| M28V220   | LOW VOLTAGE 2 MEGABIT (x 8 or x 16, BLOCK ERASE) FLASH MEMORY                              | 463 |

#### DUAL VOLTAGE FLASH MEMORY (cont'd)

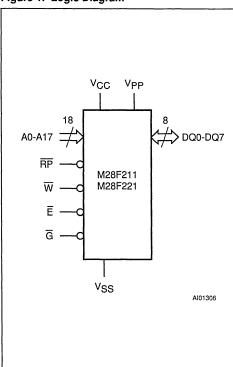

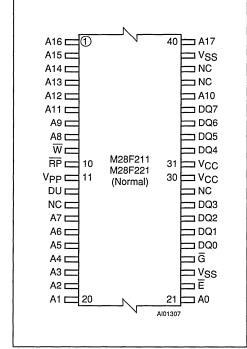

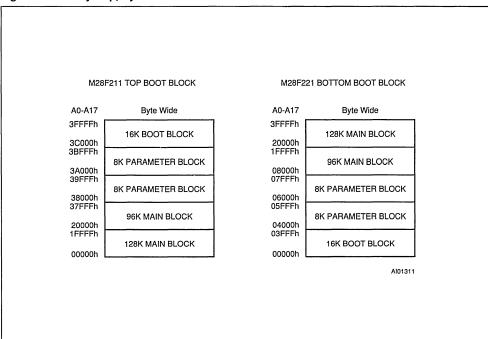

| M28F211   | 2 MEGABIT (x 8, BLOCK ERASE) FLASH MEMORY                               | 495 |

|-----------|-------------------------------------------------------------------------|-----|

| M28F221   | 2 MEGABIT (x 8, BLOCK ERASE) FLASH MEMORY                               | 495 |

| M28V211   | LOW VOLTAGE 2 MEGABIT (x 8, BLOCK ERASE) FLASH MEMORY                   | 495 |

| M28V221   | LOW VOLATGE 2 MEGABIT (x 8, BLOCK ERASE) FLASH MEMORY                   | 495 |

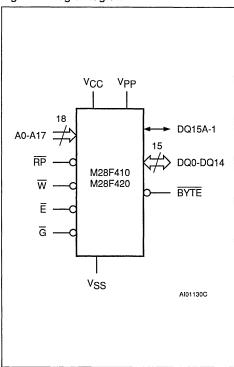

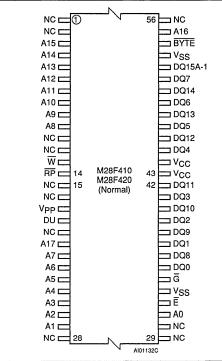

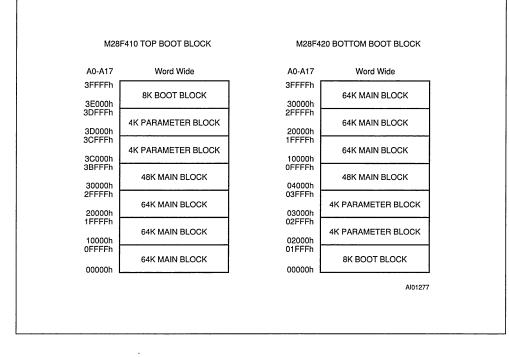

| M28F410   | 4 MEGABIT (x8 or x16, BLOCK ERASE) FLASH MEMORY                         | 523 |

| M28F420   | 4 MEGABIT (x8 or x16, BLOCK ERASE) FLASH MEMORY                         | 523 |

| M28V410   | LOW VOLTAGE 4 MEGABIT (x8 or x16, BLOCK ERASE) FLASH MEMORY             | 561 |

| M28V420   | LOW VOLTAGE 4 MEGABIT (x8 or x16, BLOCK ERASE) FLASH MEMORY             | 561 |

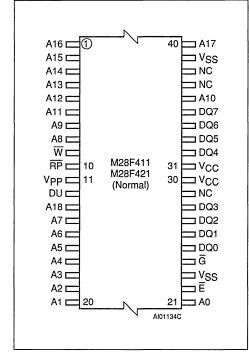

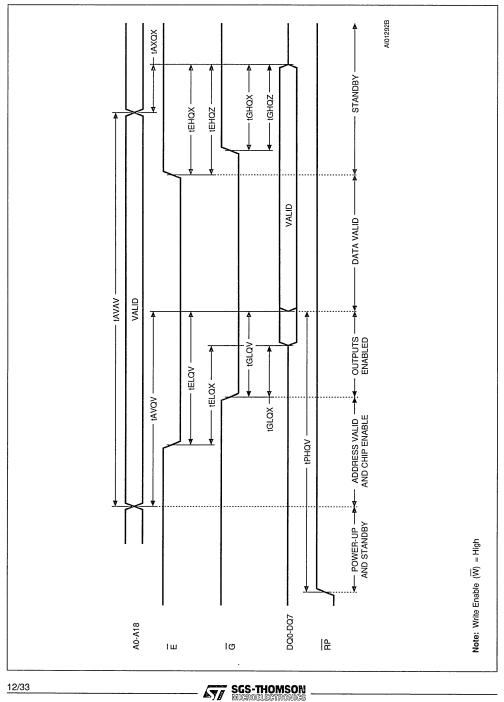

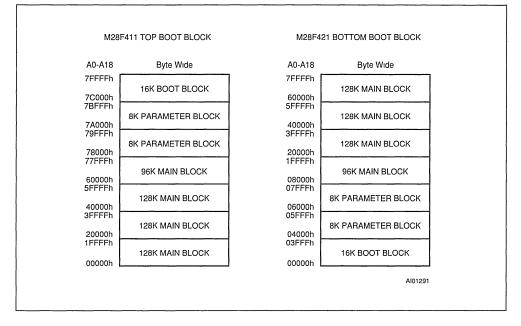

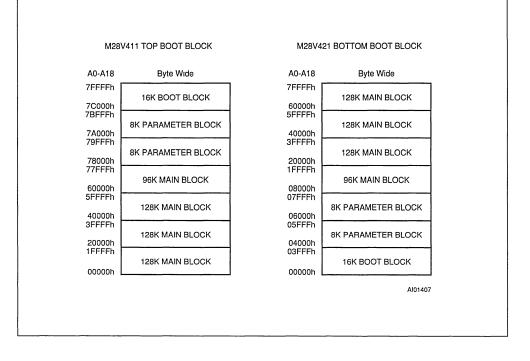

| M28F411   | 4 MEGABIT (x8, BLOCK ERASE) FLASH MEMORY                                | 587 |

| M28F421   | 4 MEGABIT (x8, BLOCK ERASE) FLASH MEMORY                                | 587 |

| M28V411   | LOW VOLTAGE 4 MEGABIT (x8, BLOCK ERASE) FLASH MEMORY                    | 621 |

| M28V421   | LOW VOLTAGE 4 MEGABIT (x8, BLOCK ERASE) FLASH MEMORY                    | 621 |

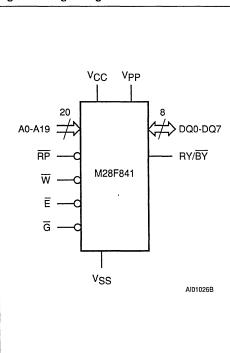

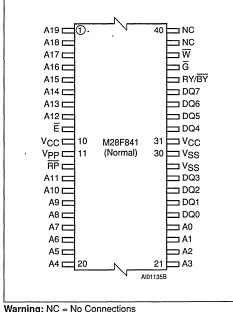

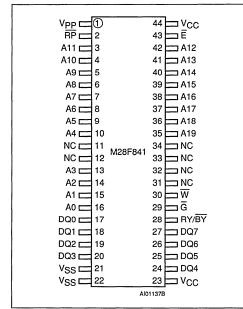

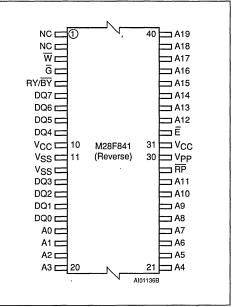

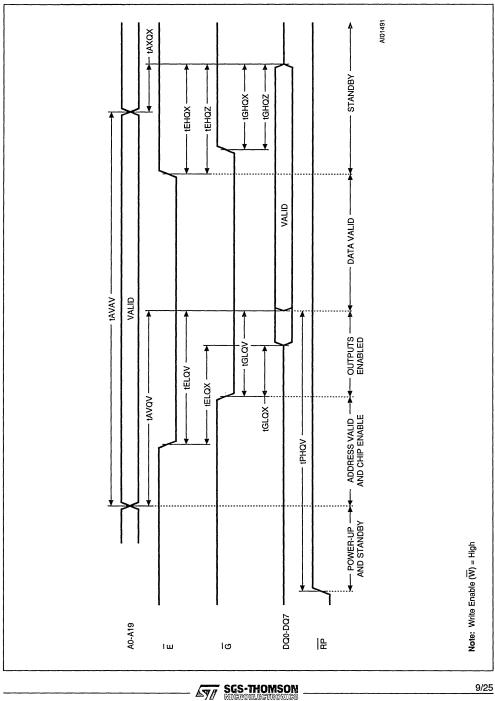

| M28F841   | 8 MEGABIT (1 MEG x 8, SECTOR ERASE) FLASH MEMORY                        | 645 |

| M28V841   | LOW VOLTAGE 8 MEGABIT (1 MEG x 8, SECTOR ERASE) FLASH MEMORY            | 671 |

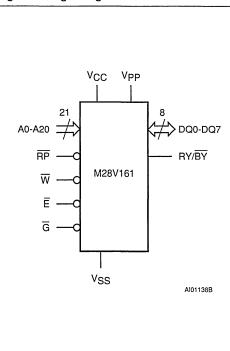

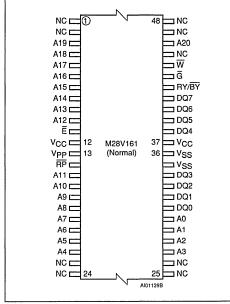

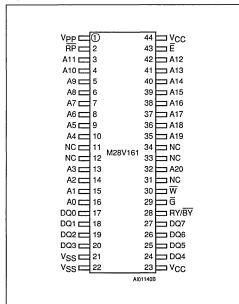

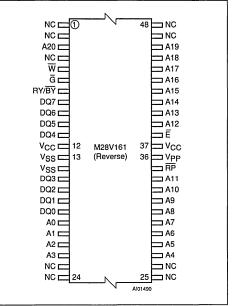

| M28V161   | LOW VOLTAGE 16 MEGABIT (2 MEG x 8, SECTOR ERASE) FLASH MEMORY $\ . \ .$ | 697 |

| SINGLE VC | LTAGE FLASH MEMORY                                                      | 723 |

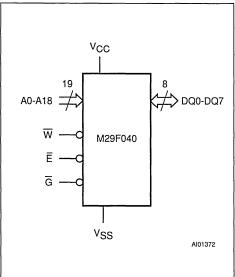

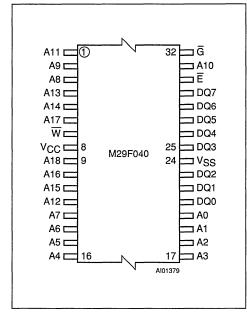

| M29F040   | SINGLE SUPPLY 4 MEGABIT (512K x 8, SECTOR ERASE) FLASH MEMORY           | 725 |

# **NMOS UV EPROM**

# M2716

# NMOS 16K (2K x 8) UV EPROM

- 2048 x 8 ORGANIZATION

- 525mW Max ACTIVE POWER, 132mW Max STANDBY POWER

- ACCESS TIME:

- M2716-1 is 350ns

- M2716 is 450ns

- SINGLE 5V SUPPLY VOLTAGE

- STATIC-NO CLOCKS REQUIRED

- INPUTS and OUTPUTS TTL COMPATIBLE DURING BOTH READ and PROGRAM MODES

- THREE-STATE OUTPUT with TIED-OR-CAPABILITY

- EXTENDED TEMPERATURE RANGE

- PROGRAMMING VOLTAGE: 25V

#### DESCRIPTION

The M2716 is a 16,384 bit UV erasable and electrically programmable memory EPROM, ideally suited for applications where fast turn around and pattern experimentation are important requirements.

The M2716 is housed in a 24 pin Window Ceramic Frit-Seal Dual-in-Line package. The transparent lid allows the user to expose the chip to ultraviolet light to erase the bit pattern. A new pattern can then be written to the device by following the programming procedure.

| Table | 1. | Signal | Names |

|-------|----|--------|-------|

|-------|----|--------|-------|

| A0 - A10        | Address Inputs        |

|-----------------|-----------------------|

| Q0 - Q7         | Data Outputs          |

| ĒP              | Chip Enable / Program |

| Ğ               | Output Enable         |

| VPP             | Program Supply        |

| Vcc             | Supply Voltage        |

| V <sub>SS</sub> | Ground                |

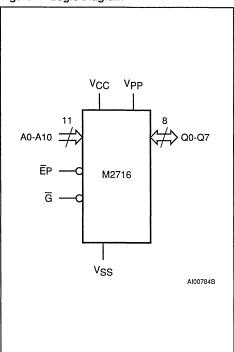

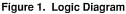

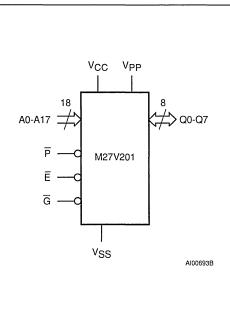

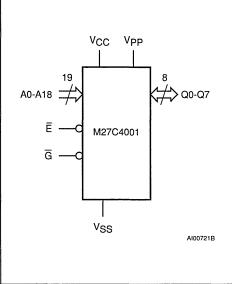

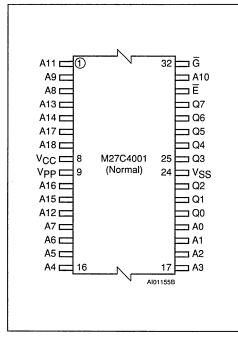

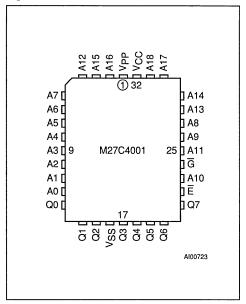

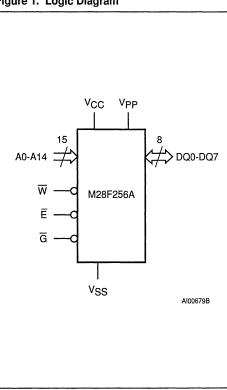

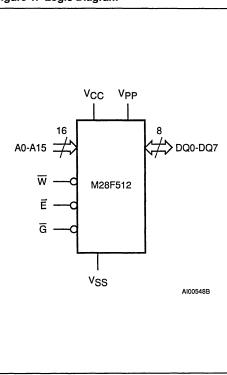

#### Figure 1. Logic Diagram

| Symbol            | Parameter                                        | Parameter          |                        | Unit |                      |    |

|-------------------|--------------------------------------------------|--------------------|------------------------|------|----------------------|----|

| TA                | Ambient Operating Temperature grade 1<br>grade 6 |                    |                        |      | 0 to 70<br>-40 to 85 | °C |

| T <sub>BIAS</sub> | Temperature Under Bias                           | grade 1<br>grade 6 | -10 to 80<br>-50 to 95 | °C   |                      |    |

| T <sub>STG</sub>  | Storage Temperature                              |                    | -65 to 125             | °C   |                      |    |

| Vcc               | Supply Voltage                                   |                    | -0.3 to 6              | v    |                      |    |

| VIO               | Input or Output Voltages                         |                    | -0.3 to 6              | V    |                      |    |

| V <sub>PP</sub>   | Program Supply                                   |                    | -0.3 to 26.5           | v    |                      |    |

| PD                | Power Dissipation                                |                    | 1.5                    | w    |                      |    |

Table 2. Absolute Maximum Ratings

Note: Except for the rating "Operating Temperature Range", stresses above those listed in the Table "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only and operation of the device at these or any other conditions above those indicated in the Operating sections of this specification is not implied. Exposure to Absolute Maximum Rating conditions for extended periods may affect device reliability. Refer also to the SGS-THOMSON SURE Program and other relevant quality documents.

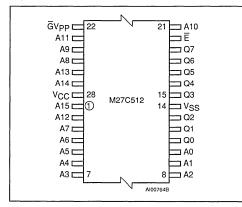

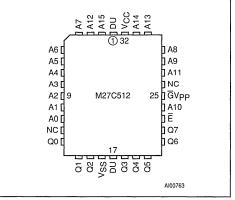

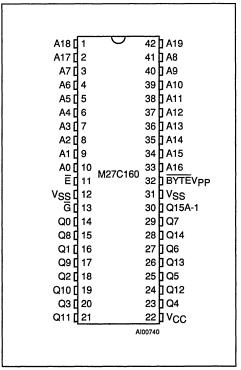

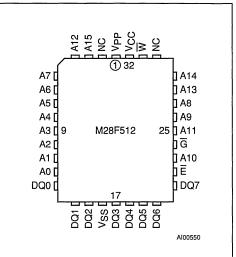

Figure 2. DIP Pin Connections

| A7 [<br>A6 [<br>A5 [<br>A4 [<br>A3 [<br>A2 [<br>A0 [<br>Q0 [<br>Q1 [<br>Q2 [<br>VSS [ | 2<br>3<br>4<br>5<br>6 M2716<br>7<br>8<br>9<br>10<br>11 | 24 ] V <sub>C</sub> C<br>23 ] A8<br>22 ] A9<br>21 ] V <sub>P</sub> P<br>20 ] G<br>19 ] A10<br>18 ] EP<br>17 ] Q7<br>16 ] Q6<br>15 ] Q5<br>14 ] Q4<br>13 ] Q3<br>Al00785 |

|---------------------------------------------------------------------------------------|--------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                       |                                                        | F                                                                                                                                                                       |

|                                                                                       |                                                        |                                                                                                                                                                         |

|                                                                                       |                                                        |                                                                                                                                                                         |

#### **DEVICE OPERATION**

The M2716 has 3 modes of operation in the normal system environment. These are shown in Table 3.

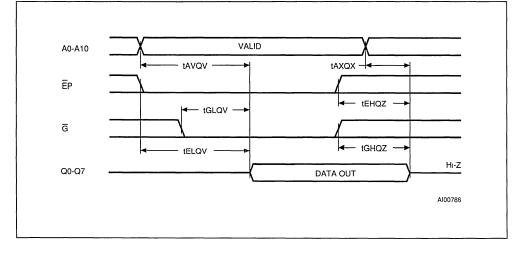

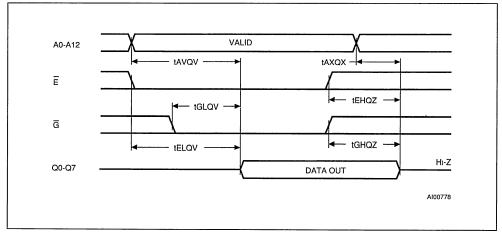

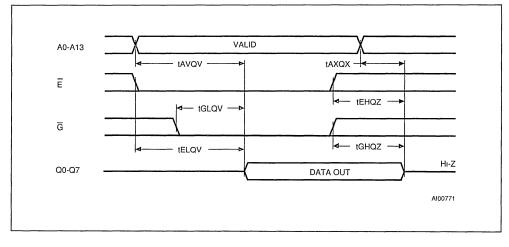

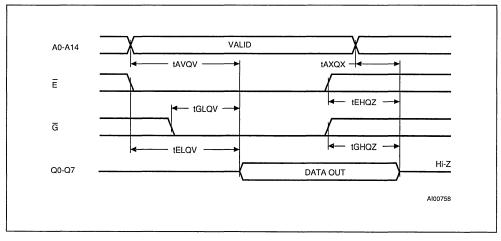

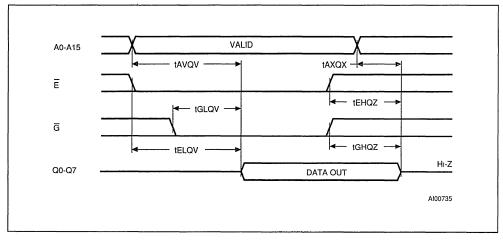

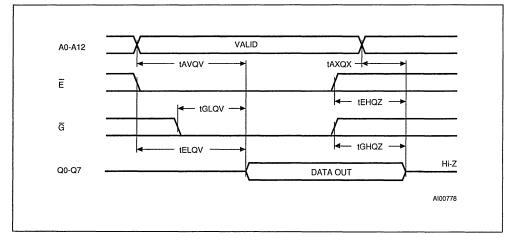

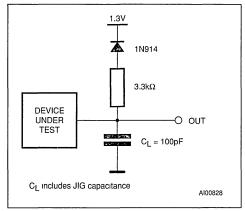

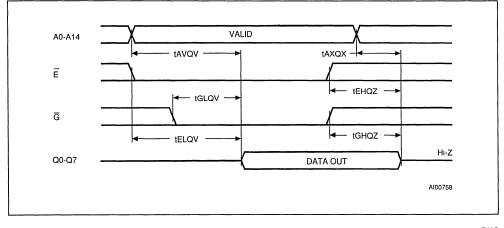

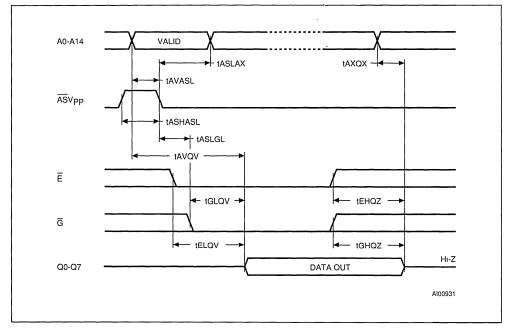

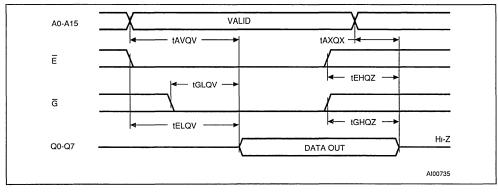

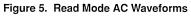

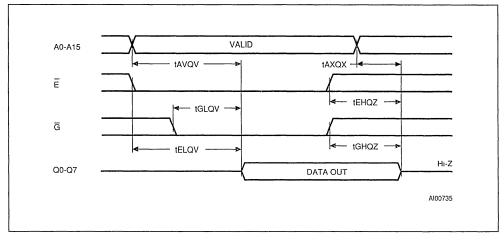

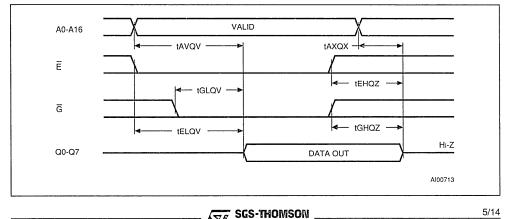

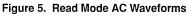

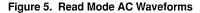

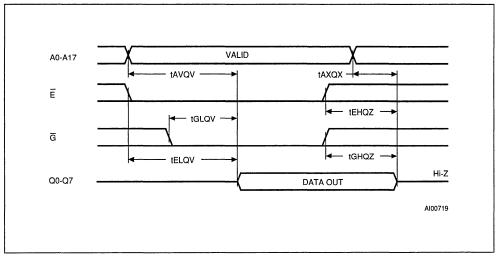

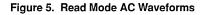

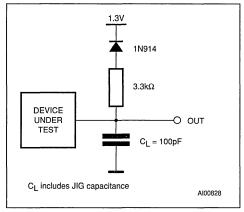

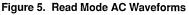

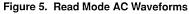

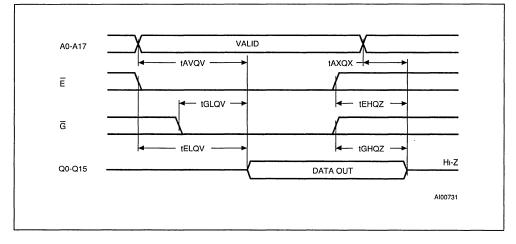

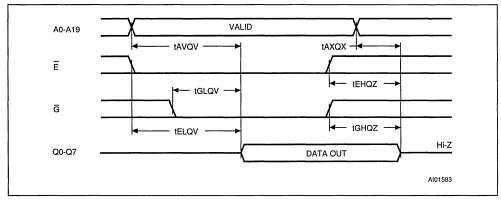

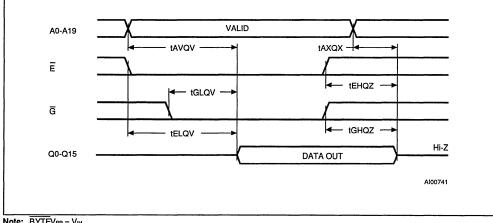

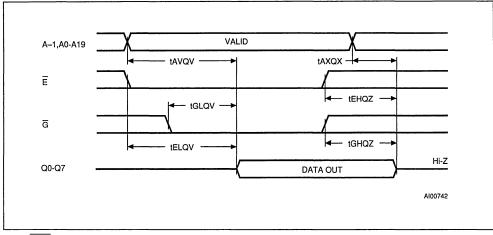

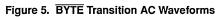

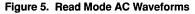

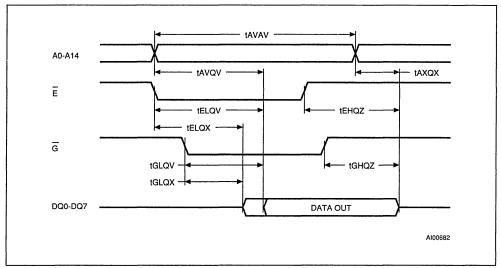

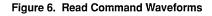

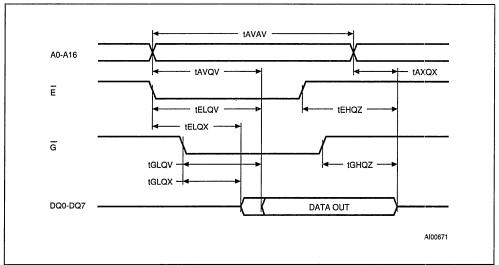

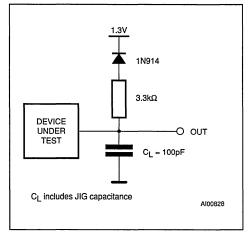

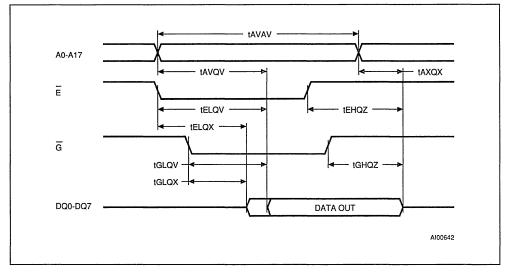

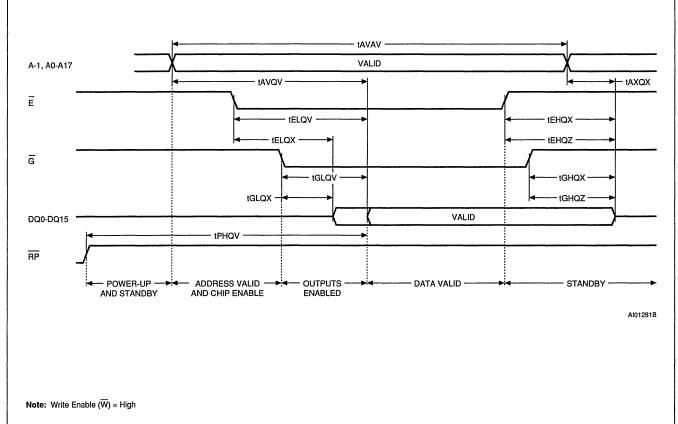

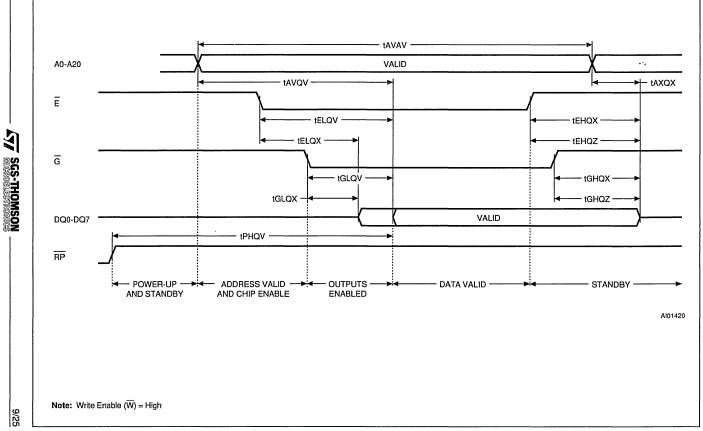

**Read Mode.** The M2716 read operation requires that  $\overline{G} = V_{IL}$ ,  $\overline{EP} = V_{IL}$  and that addresses A0-A10 have been stabilized. Valid data will appear on the output pins after time tAVQV, tGLQV or tELQV (see Switching Time Waveforms) depending on which is limiting.

**Deselect Mode**. The M2716 is deselected by making  $\overline{G} = V_{IH}$ . This mode is independent of  $\overline{EP}$  and the condition of the addresses. The outputs are Hi-Z when  $\overline{G} = V_{IH}$ . This allows tied-OR of 2 or more M2716's for memory expansion.

Standby Mode (Power Down). The M2716 may be powered down to the standby mode by making  $\overline{EP} = V_{IH}$ . This is independent of  $\overline{G}$  and automatically puts the outputs in the Hi-Z state. The power is reduced to 25% (132 mW max) of the normal operating power. V<sub>CC</sub> and V<sub>PP</sub> must be maintained at 5V. Access time at power up remains either t<sub>AVQV</sub> or t<sub>ELQV</sub> (see Switching Time Waveforms).

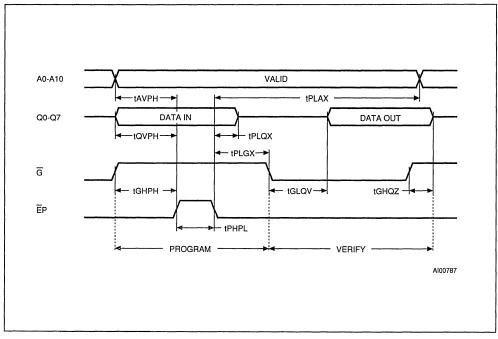

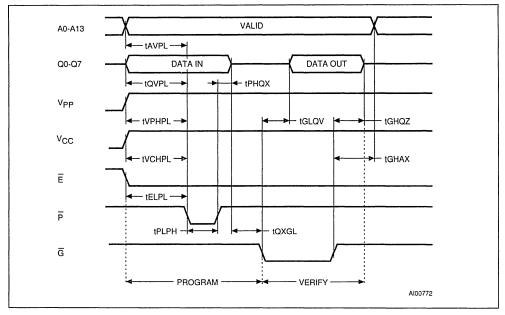

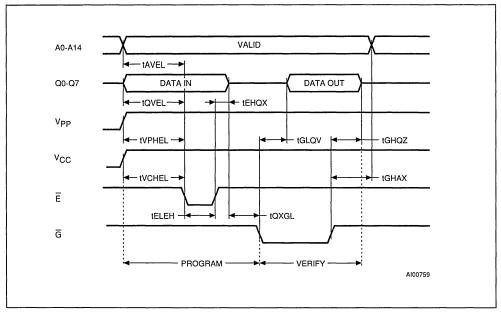

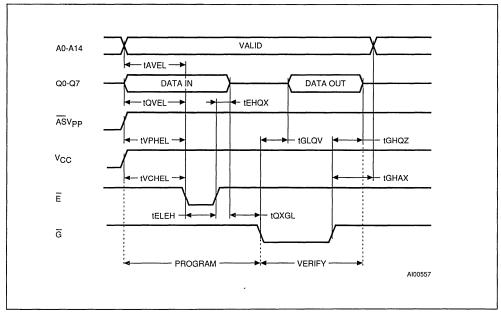

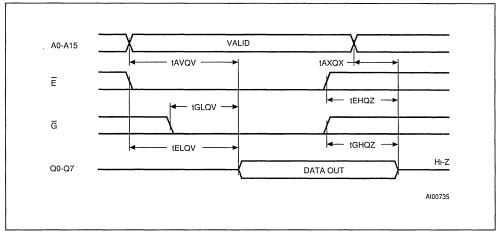

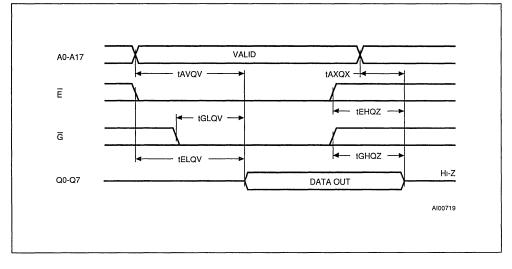

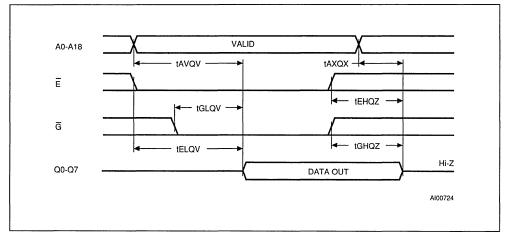

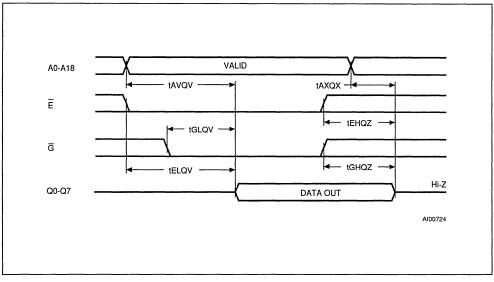

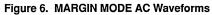

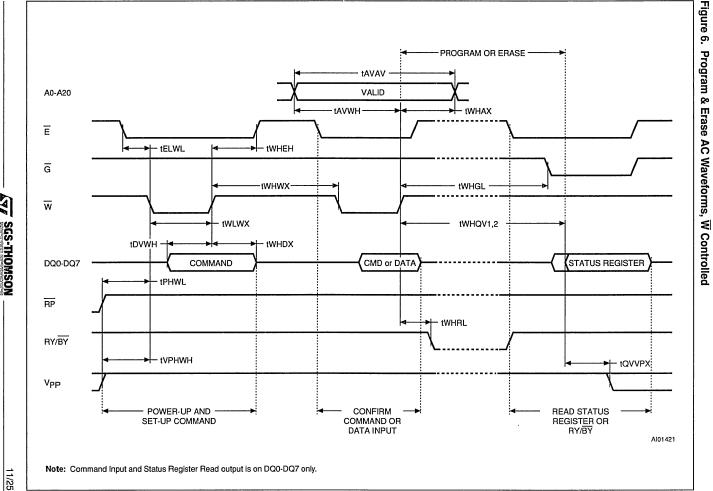

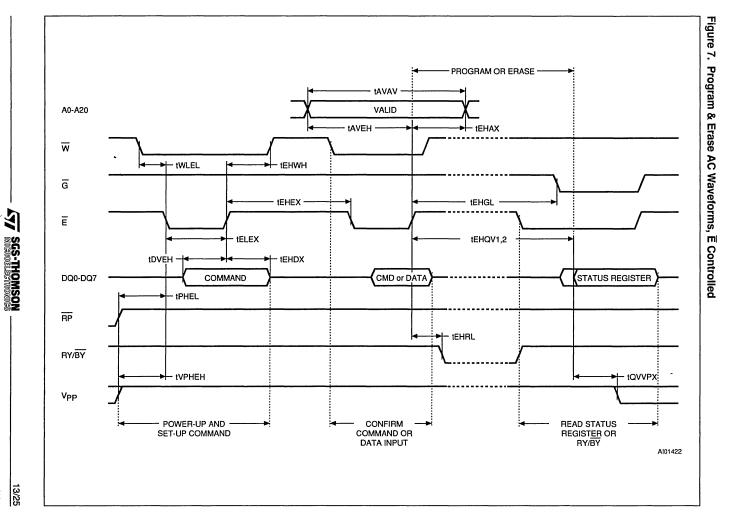

#### Programming

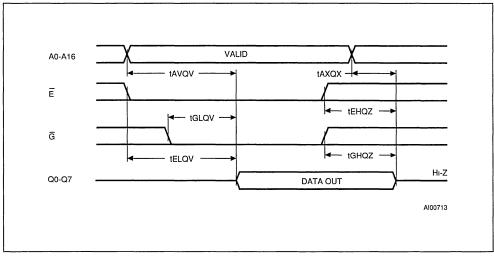

The M2716 is shipped from SGS-THOMSON completely erased. All bits will be at "1" level (output high) in this initial state and after any full erasure. Table 3 shows the 3 programming modes.

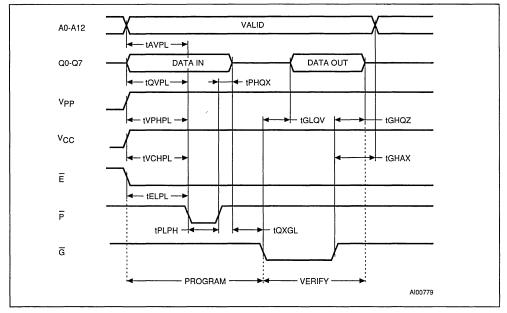

**Program Mode.** The M2716 is programmed by introducing "0"s into the desired locations. This is done 8 bits (a byte) at a time. Any individual address, sequential addresses, or addresses chosen at random may be programmed. Any or all of the 8 bits associated with an address location may be programmed with a single program pulse applied to the EP pin. All input voltage levels including the program pulse on chip enable are TTL compatible.

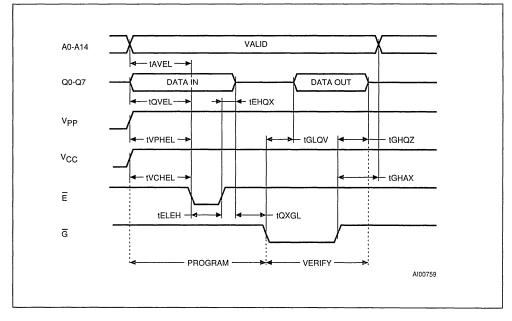

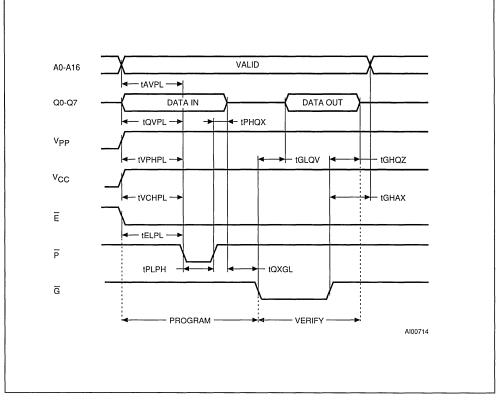

The programming sequence is: with V<sub>PP</sub> = 25V, V<sub>CC</sub> = 5V,  $\overline{G} = V_{IL}$  and  $\overline{EP} = V_{IL}$ , an address is selected and the desired data word is applied to the output pins (V<sub>IL</sub> = "0" and V<sub>IH</sub> = "1" for both address and data). After the address and data signals are stable the program pin is pulsed from V<sub>IL</sub> to V<sub>IH</sub> with a

#### DEVICE OPERATION (cont'd)

pulse width between 45ms and 55ms. Multiple pulses are not needed but will not cause device damage. No pins should be left open. A high level (V<sub>IH</sub> or higher) must not be maintained longer than  $t_{PHPL}$  (max) on the program pin during programming. M2716's may be programmed in parallel in this mode.

**Program Verify Mode.** The programming of the M2716 may be verified either one byte at a time during the programming (as shown in Figure 6) or by reading all of the bytes out at the end of the programming sequence. This can be done with  $V_{PP} = 25V$  or 5V in either case.  $V_{PP}$  must be at 5V for all operating modes and can be maintained at 25V for all programming modes.

**Program Inhibit Mode.** The program inhibit mode allows several M2716's to be programmed simultaneously with different data for each one by controlling which ones receive the program pulse. All similar inputs of the M2716 may be paralleled. Pulsing the program pin (from V<sub>IL</sub> to V<sub>I</sub>) will program a unit while inhibiting the program pulse to a unit will keep it from being programmed and keeping  $\overline{G} = V_{IH}$  will put its outputs in the Hi-Z state.

#### ERASURE OPERATION

The M2716 is erased by exposure to high intensity ultraviolet light through the transparent window. This exposure discharges the floating gate to its initial state through induced photo current. It is recommended that the M2716 be kept out of direct sunlight. The UV content of sunlight may cause a partial erasure of some bits in a relatively short period of time.

An ultraviolet source of 2537 Å yielding a total integrated dosage of 15 watt-seconds/cm<sup>2</sup> power rating is used. The M2716 to be erased should be placed 1 inch away from the lamp and no filters should be used.

An erasure system should be calibrated periodically. The erasure time is increased by the square of the distance (if the distance is doubled the erasure time goes up by a factor of 4). Lamps lose intensity as they age, it is therefore important to periodically check that the UV system is in good order.

This will ensure that the EPROMs are being completely erased. Incomplete erasure will cause symptoms that can be misleading. Programmers, components, and system designs have been erroneously suspected when incomplete erasure was the basic problem.

| Mode            | ĒP        | G               | V <sub>PP</sub> | Q0 - Q7  |

|-----------------|-----------|-----------------|-----------------|----------|

| Read            | VIL       | VIL             | Vcc             | Data Out |

| Program         | VIH Pulse | ViH             | V <sub>PP</sub> | Data In  |

| Verify          | ViL       | VIL             | VPP or VCC      | Data Out |

| Program Inhibit | VIL       | V <sub>IH</sub> | V <sub>PP</sub> | Hi-Z     |

| Deselect        | x         | VIH             | Vcc             | Hi-Z     |

| Standby         | VIH       | x               | Vcc             | Hi-Z     |

#### Table 3. Operating Modes

Note:  $X = V_{IH}$  or  $V_{IL}$ .

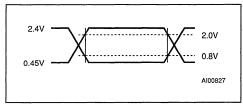

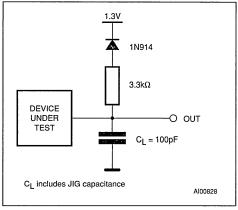

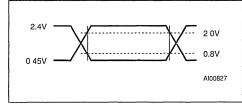

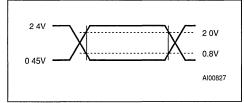

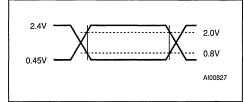

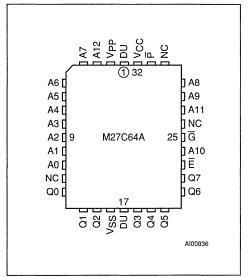

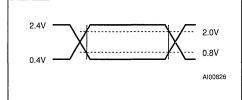

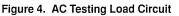

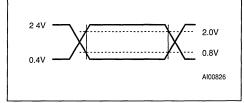

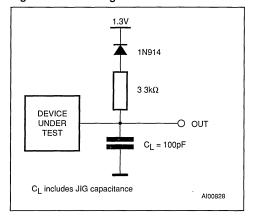

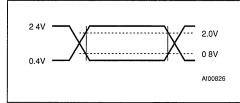

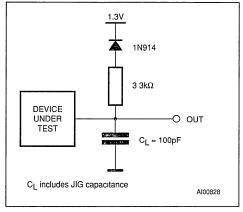

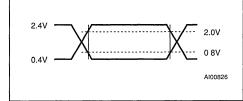

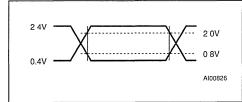

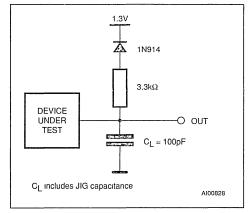

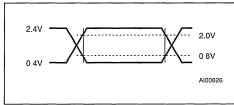

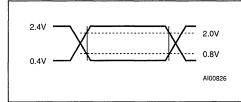

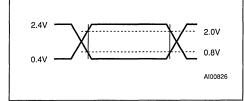

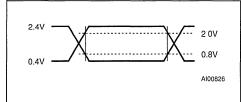

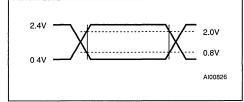

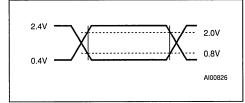

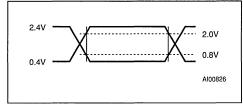

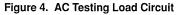

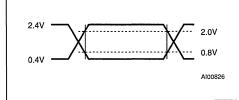

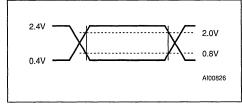

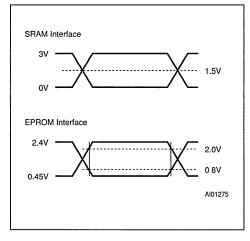

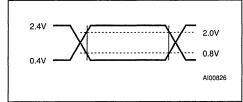

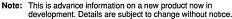

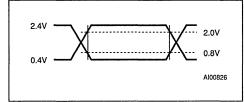

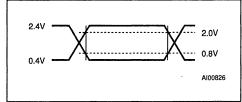

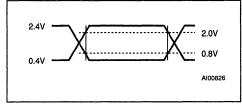

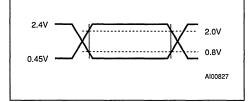

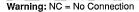

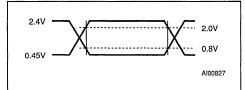

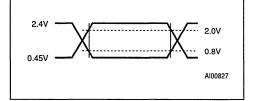

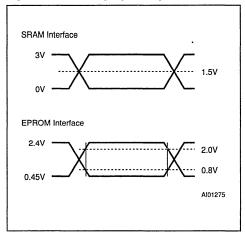

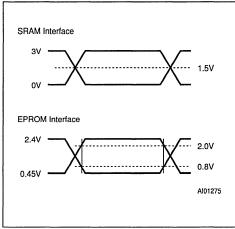

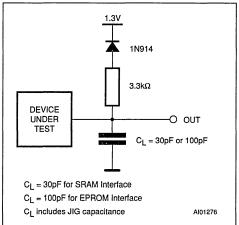

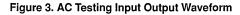

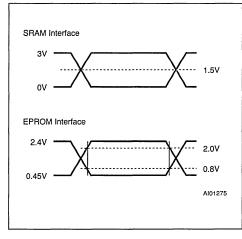

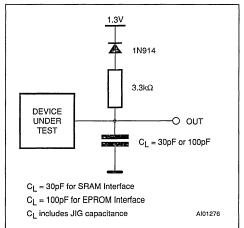

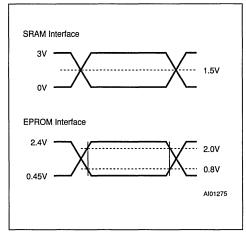

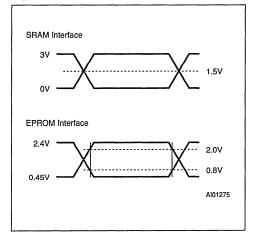

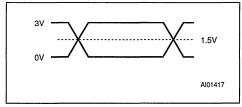

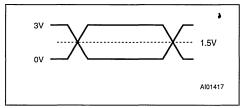

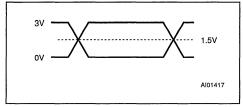

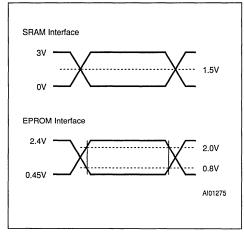

#### AC MEASUREMENT CONDITIONS

| Input Rise and Fall Times             | ≤ 20ns        |

|---------------------------------------|---------------|

| Input Pulse Voltages                  | 0.45V to 2.4V |

| Input and Output Timing Ref. Voltages | 0.8V to 2.0V  |

Note that Output Hi-Z is defined as the point where data is no longer driven.

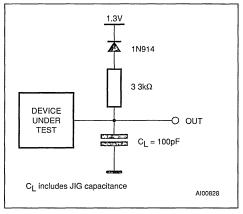

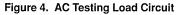

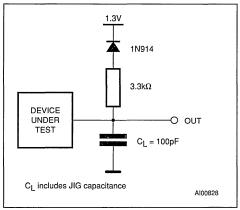

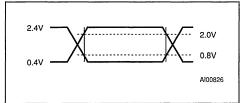

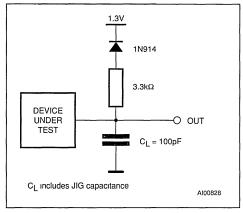

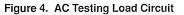

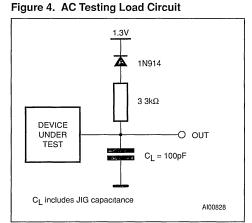

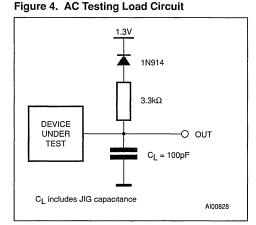

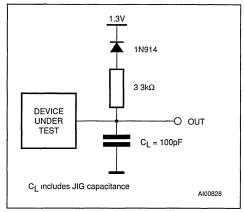

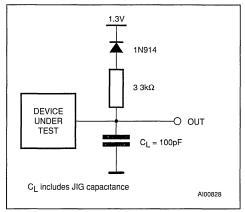

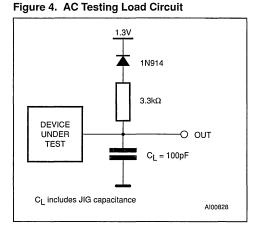

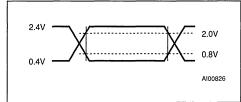

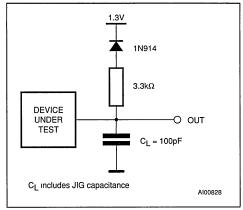

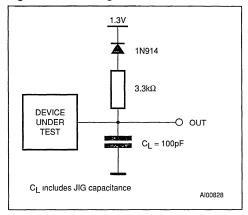

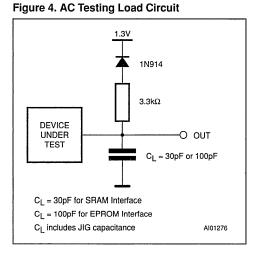

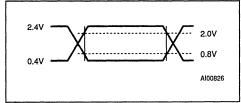

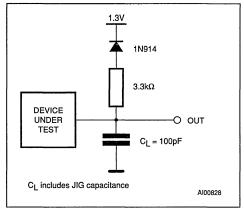

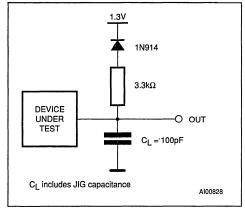

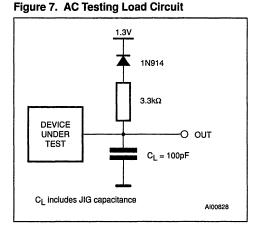

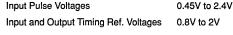

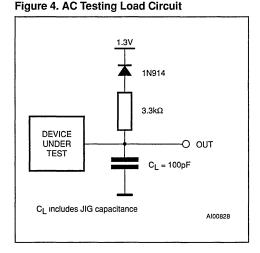

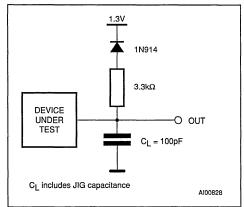

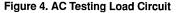

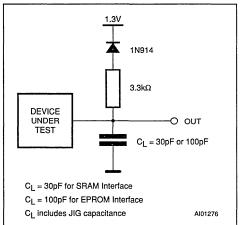

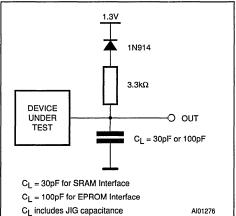

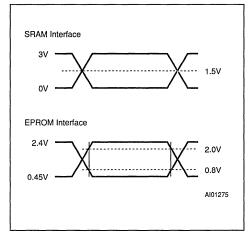

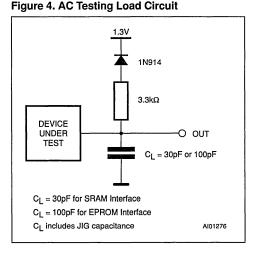

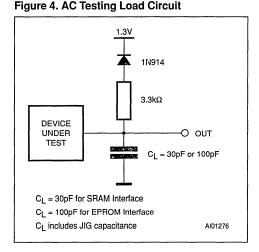

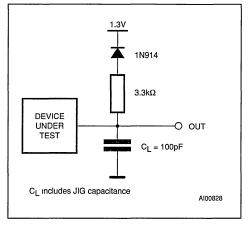

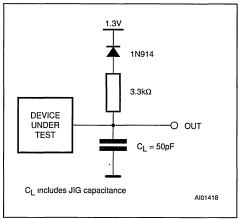

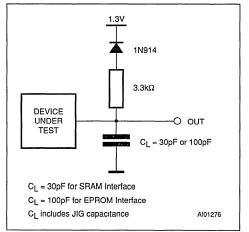

#### Figure 3. AC Testing Input Output Waveforms

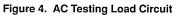

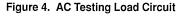

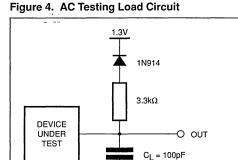

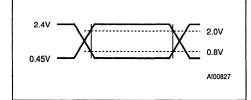

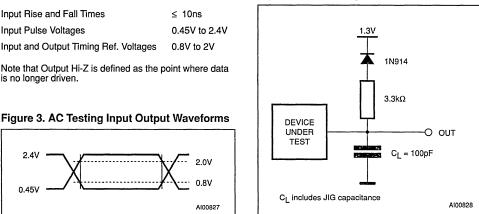

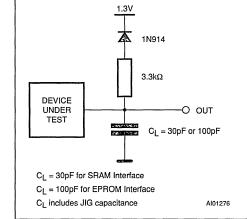

# $\begin{array}{c} 1.3V \\ \hline 1 N914 \\ \hline 3.3k\Omega \\ \hline 0 OUT \\ \hline C_L \text{ includes JIG capacitance} \\ \hline \\ A100828 \end{array}$

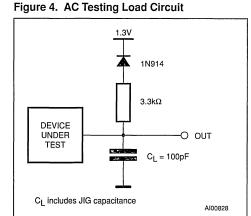

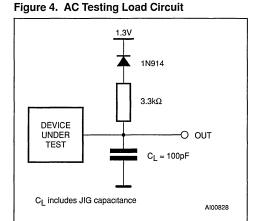

Figure 4. AC Testing Load Circuit

#### Table 4. Capacitance <sup>(1)</sup> ( $T_A = 25 \circ C$ , f = 1 MHz)

| Symbol          | Parameter          | Test Condition        | Min | Мах | Unit |

|-----------------|--------------------|-----------------------|-----|-----|------|

| C <sub>IN</sub> | Input Capacitance  | $V_{IN} = 0V$         |     | 6   | pF   |

| Соит            | Output Capacitance | V <sub>OUT</sub> = 0V |     | 12  | pF   |

Note: 1. Sampled only, not 100% tested.

#### Table 5. Read Mode DC Characteristics (1)

$(T_A = 0 \text{ to } 70 \text{ °C or } -40 \text{ to } 85 \text{ °C}; V_{CC} = 5V \pm 5\% \text{ or } 5V \pm 10\%; V_{PP} = V_{CC})$

| Symbol           | Parameter                | Test Condition                                            | ndition Min |                     | Unit |

|------------------|--------------------------|-----------------------------------------------------------|-------------|---------------------|------|

| lu               | Input Leakage Current    | $0 \le V_{IN} \le V_{CC}$                                 |             | ±10                 | μA   |

| ILO              | Output Leakage Current   | V <sub>OUT</sub> = V <sub>CC</sub> , EP = V <sub>CC</sub> |             | ±10                 | μΑ   |

| lcc              | Supply Current           | $\overline{E}P = V_{IL}, \overline{G} = V_{IL}$           |             | 100                 | mA   |

| I <sub>CC1</sub> | Supply Current (Standby) | $\overline{E}P = V_{IH}, \overline{G} = V_{IL}$           |             | 25                  | mA   |

| IPP              | Program Current          | VPP = V <sub>CC</sub>                                     |             | 5                   | mA   |

| VIL              | Input Low Voltage        |                                                           | -0.1        | 0.8                 | v    |

| VIH              | Input High Voltage       |                                                           | 2           | V <sub>CC</sub> + 1 | V    |

| Vol              | Output Low Voltage       | I <sub>OL</sub> = 2.1mA                                   |             | 0.45                | v    |

| V <sub>OH</sub>  | Output High Voltage      | I <sub>OH</sub> =400µА                                    | 2.4         |                     | v    |

Note: 1. Vcc must be applied simultaneously with or before VPP and removed simultaneously or after VPP.

#### Table 6. Read Mode AC Characteristics (1)

$(T_A = 0 \text{ to } 70 \text{ °C or } -40 \text{ to } 85 \text{ °C}; V_{CC} = 5V \pm 5\% \text{ or } 5V \pm 10\%; V_{PP} = V_{CC})$

|                                  |                 |                                         |                                                 |      | M2  | 716 |     |      |

|----------------------------------|-----------------|-----------------------------------------|-------------------------------------------------|------|-----|-----|-----|------|

| Symbol                           | Alt             | Parameter                               | Test Condition                                  | -1 b |     | bla | ink | Unit |

|                                  |                 |                                         |                                                 | Min  | Max | Min | Max |      |

| tavqv                            | tACC            | Address Valid to Output Valid           | $\overline{E}P = V_{IL}, \overline{G} = V_{IL}$ |      | 350 |     | 450 | ns   |

| tELQV                            | tce             | Chip Enable Low to Output Valid         | $\overline{G} = V_{1L}$                         |      | 350 |     | 450 | ns   |

| tGLQV                            | toe             | Output Enable Low to Output Valid       | ĒP = VIL                                        |      | 120 |     | 120 | ns   |

| t <sub>EHQZ</sub> (2)            | top             | Chip Enable High to Output Hi-Z         | $\overline{G} = V_{1L}$                         | 0    | 100 | 0   | 100 | ns   |

| t <sub>GHQZ</sub> <sup>(2)</sup> | t <sub>DF</sub> | Output Enable High to Output Hi-Z       | $\overline{E}P = V_{IL}$                        | 0    | 100 | 0   | 100 | ns   |

| taxox                            | tон             | Address Transition to Output Transition | $\overline{E}P = V_{IL}, \overline{G} = V_{IL}$ | 0    |     | 0   |     | ns   |

Notes: 1. Vcc must be applied simultaneously with or before VPP and removed simultaneously or after VPP. 2. Sampled only, not 100% tested.

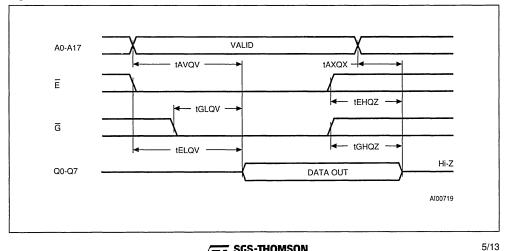

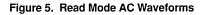

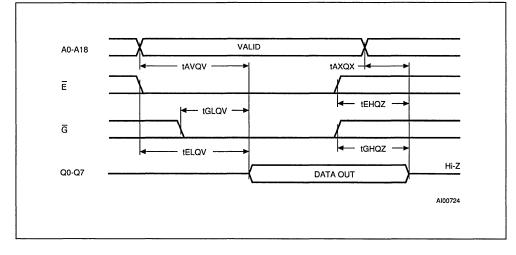

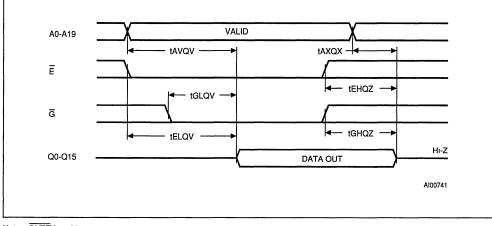

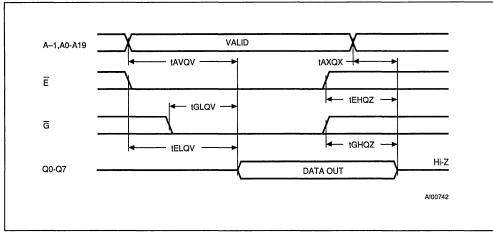

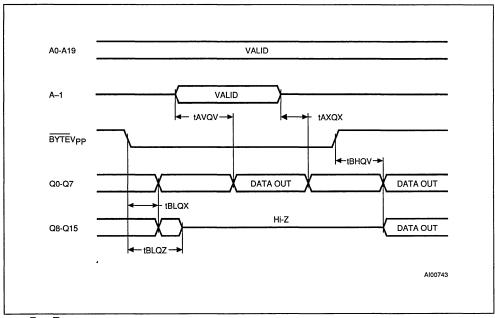

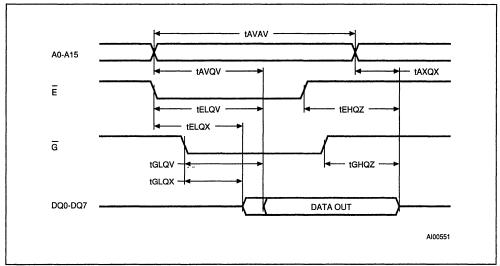

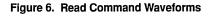

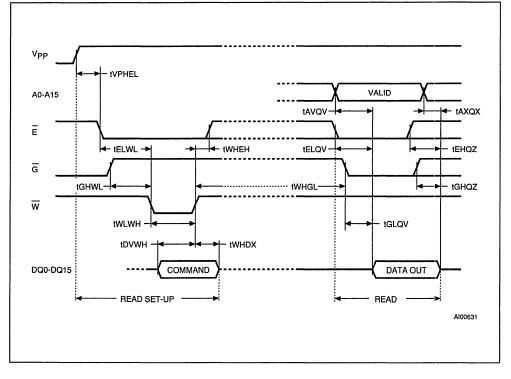

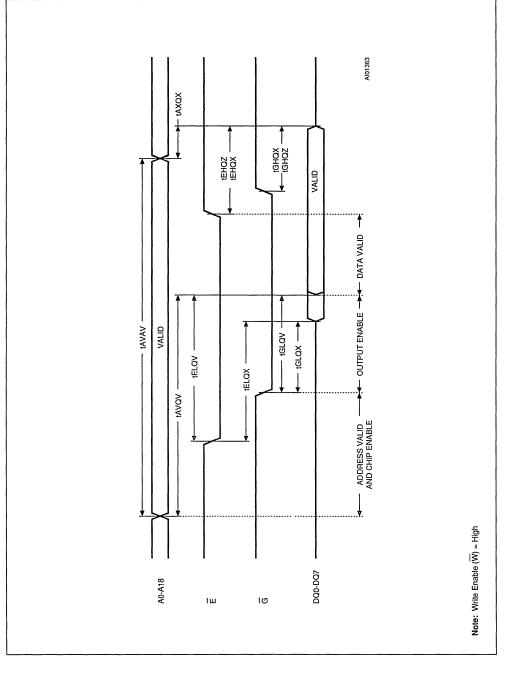

#### Figure 5. Read Mode AC Waveforms

# Table 7. Programming Mode DC Characteristics $^{(1)}$ (T\_A = 25 °C; V\_{CC} = 5V $\pm$ 5%; V\_{PP} = 25V $\pm$ 1V)

| Symbol | Parameter             | Test Condition                   | Min  | Max                 | Unit |

|--------|-----------------------|----------------------------------|------|---------------------|------|

| lu     | Input Leakage Current | $V_{IL} \leq V_{IN} \leq V_{IH}$ |      | ±10                 | μA   |

| lcc    | Supply Current        |                                  |      | 100                 | mA   |

| IPP    | Program Current       |                                  |      | 5                   | mA   |

| IPP1   | Program Current Pulse | EP = V <sub>IH</sub> Pulse       |      | 30                  | mA   |

| VIL    | Input Low Voltage     |                                  | -0.1 | 0.8                 | V    |

| VIH    | Input High Voltage    |                                  | 2    | V <sub>CC</sub> + 1 | V    |

Note: 1. Vcc must be applied simultaneously with or before VPP and removed simultaneously or after VPP.

# Table 8. Programming Mode AC Characteristics $^{(1)}$ (T\_A = 25 °C; V\_{CC} = 5V $\pm$ 5%; V\_{PP} = 25V $\pm$ 1V)

| Symbol            | Alt             | Parameter                                  | Test Condition          | Min | Max | Units |

|-------------------|-----------------|--------------------------------------------|-------------------------|-----|-----|-------|

| tavph             | tas             | Address Valid to Program High              | $\overline{G} = V_{IH}$ | 2   |     | μs    |

| t <sub>QVPH</sub> | t <sub>DS</sub> | Input Valid to Program High                | G = V <sub>IH</sub>     | 2   |     | μs    |

| t <sub>GHPH</sub> | tos             | Output Enable High to Program<br>High      |                         | 2   |     | μs    |

| tPL1PL2           | t <sub>PR</sub> | Program Pulse Rise Time                    |                         | 5   |     | ns    |

| tPH1PH2           | tPF             | Program Pulse Fall Time                    |                         | 5   |     | ns    |

| <b>t</b> PHPL     | t₽w             | Program Pulse Width                        |                         | 45  | 55  | ms    |

| <b>t</b> PLQX     | tон             | Program Low to Input Transition            |                         | 2   |     | μs    |

| t <sub>PLGX</sub> | tон             | Program Low to Output Enable<br>Transition |                         | 2   |     | μs    |

| tGLQV             | toe             | Output Enable to Output Valid              | ĒP = VIL                |     | 120 | ns    |

| t <sub>GHQZ</sub> | tDF             | Output Enable High to Output Hi-Z          |                         | 0   | 100 | ns    |

| tPLAX             | t <sub>АН</sub> | Program Low to Address Transition          |                         | 2   |     | μs    |

Notes: 1. V<sub>CC</sub> must be applied simultaneously with or before V<sub>PP</sub> and removed simultaneously or after V<sub>PP</sub>. 2. Sampled only, not 100% tested.

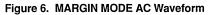

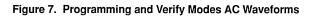

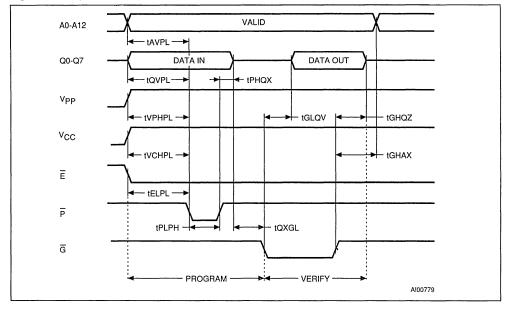

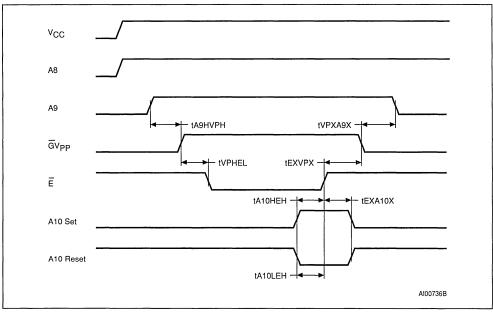

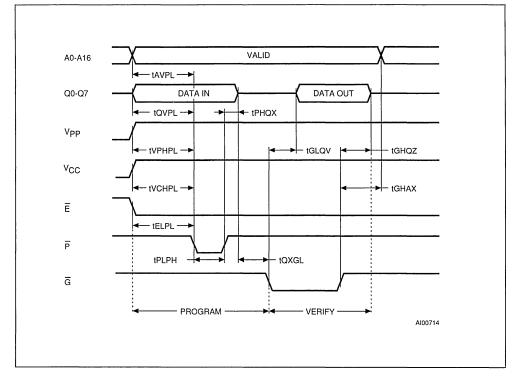

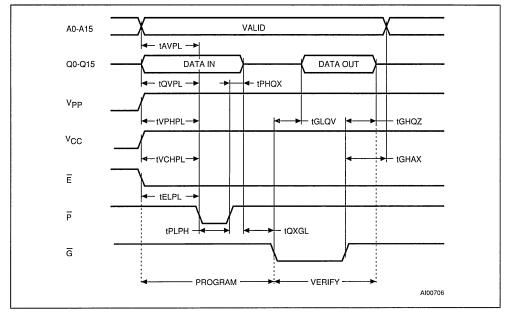

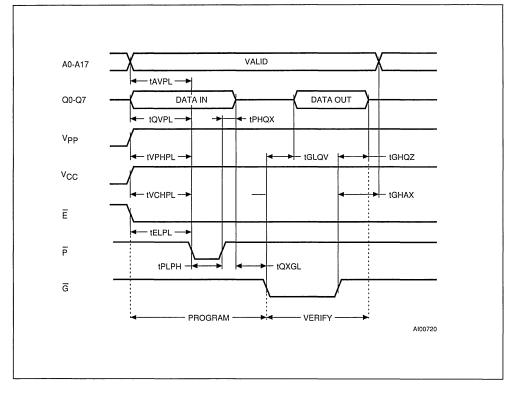

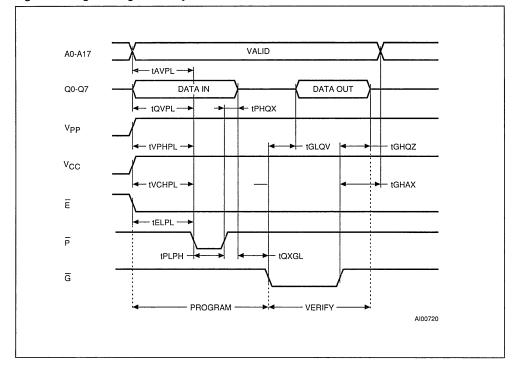

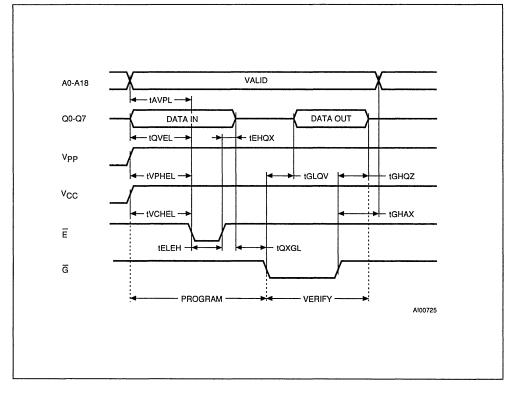

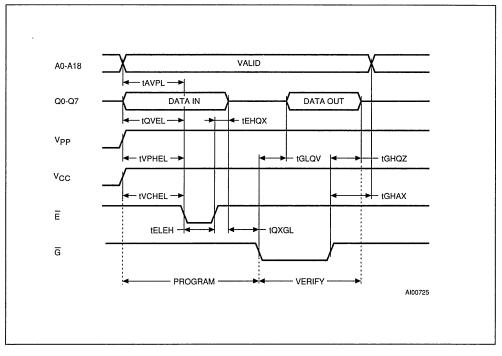

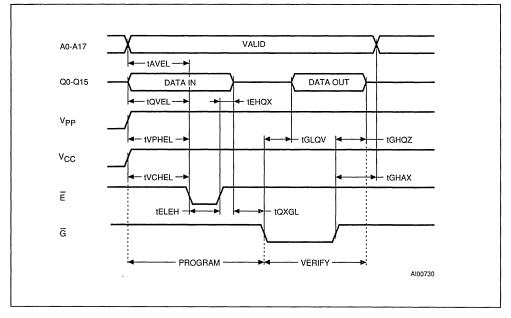

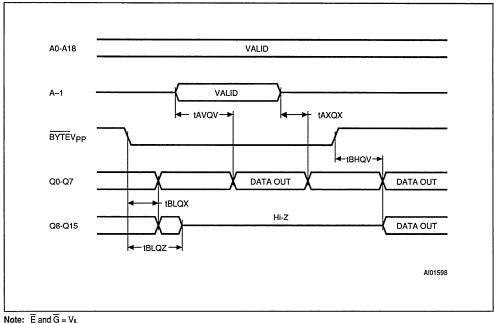

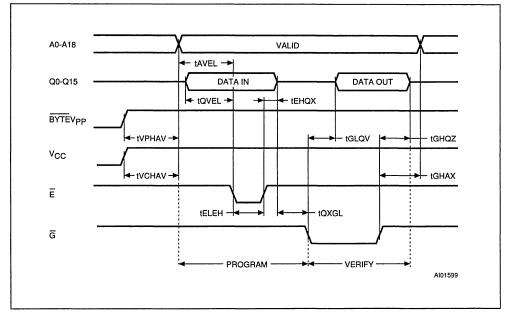

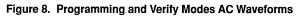

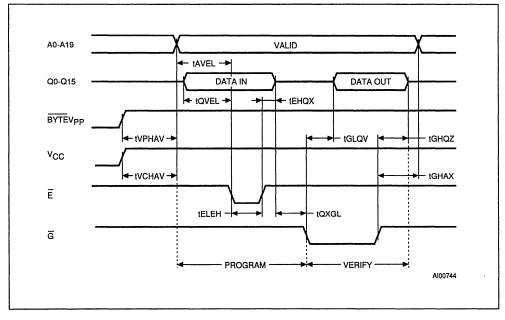

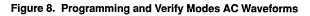

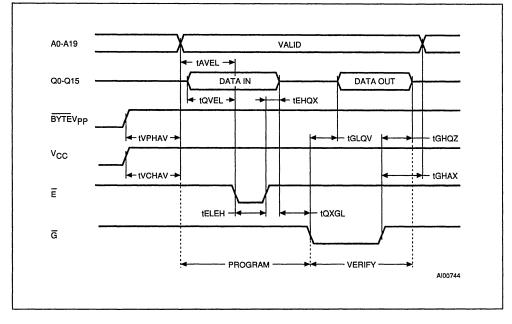

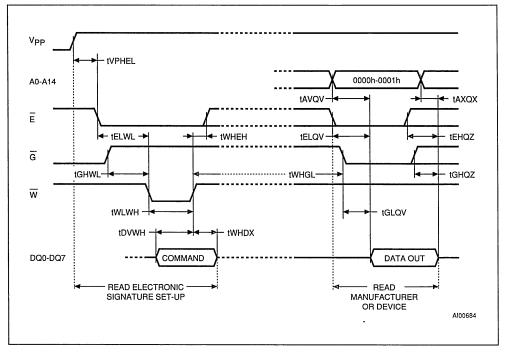

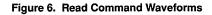

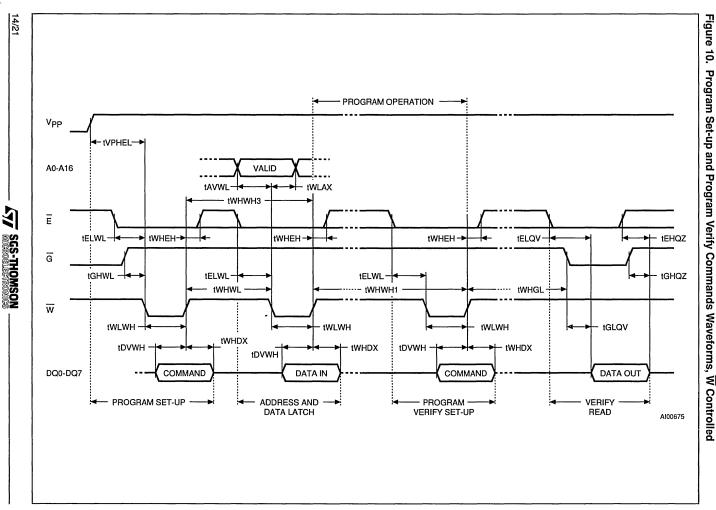

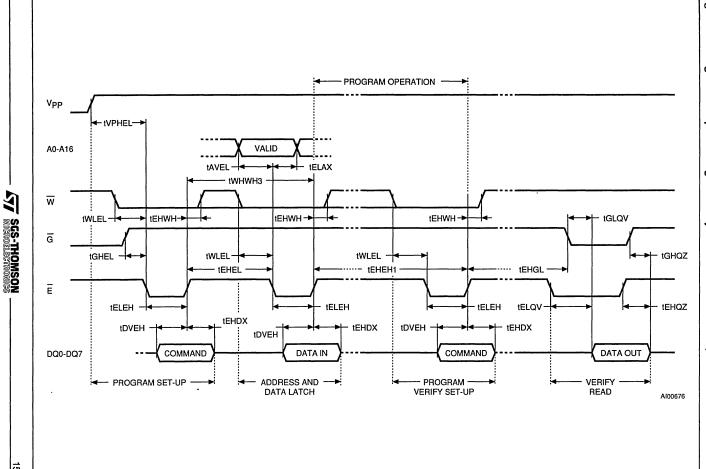

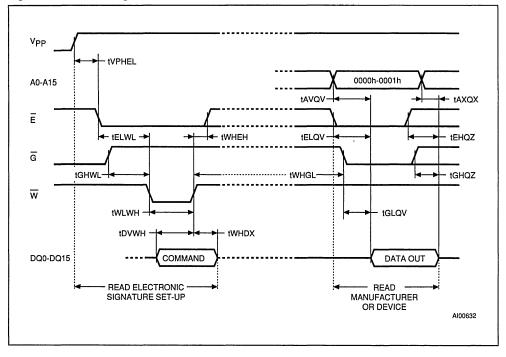

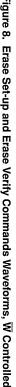

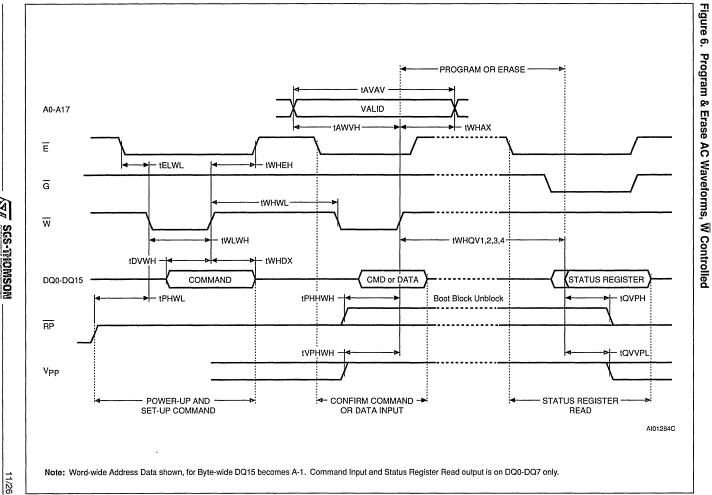

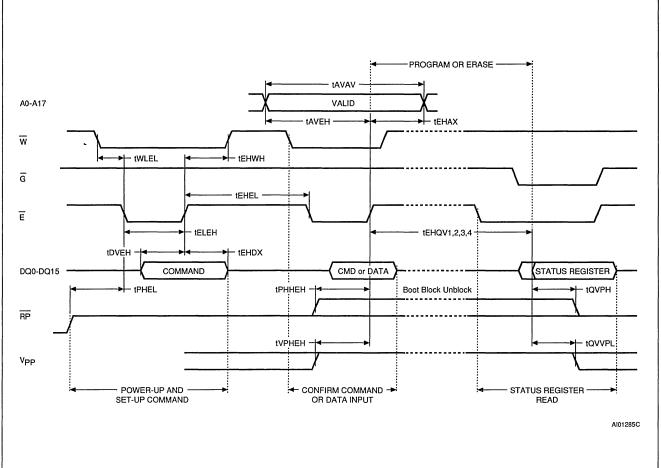

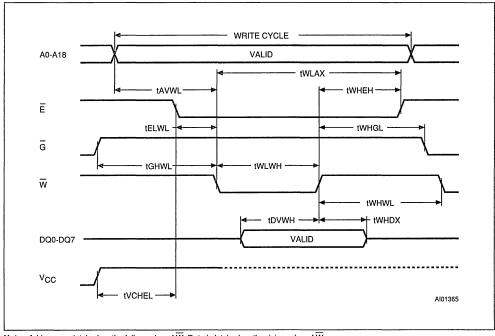

Figure 6. Programming and Verify Modes AC Waveforms

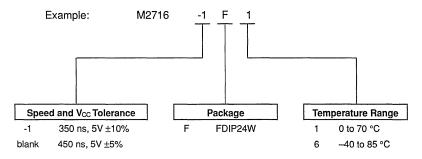

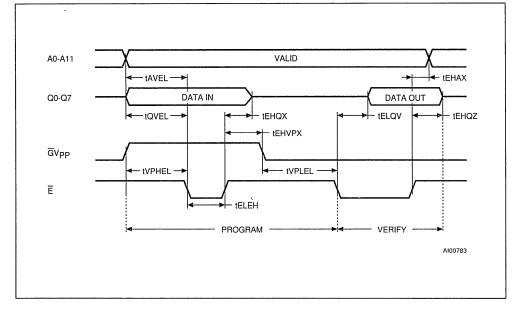

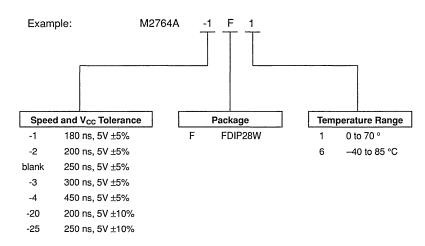

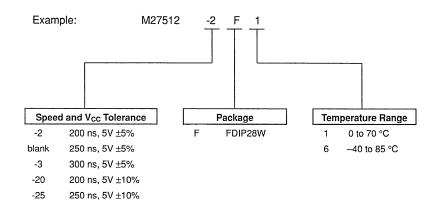

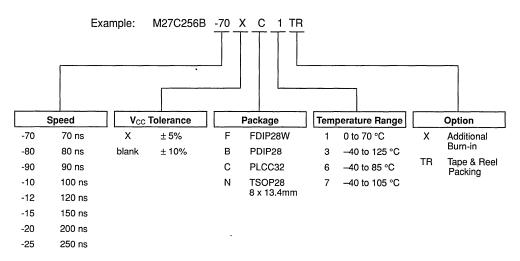

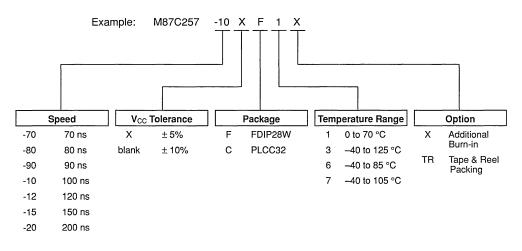

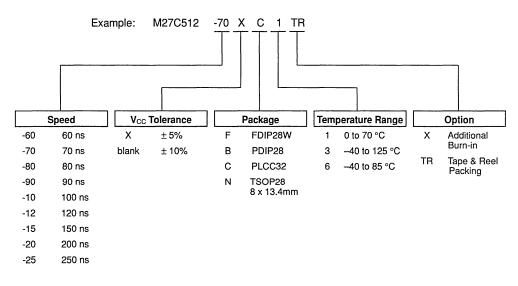

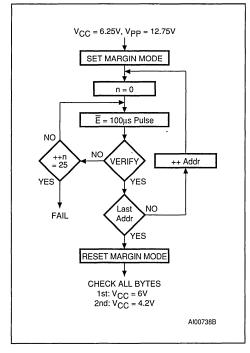

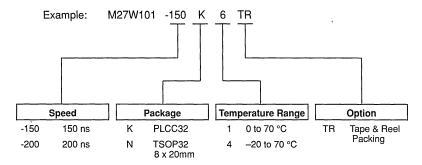

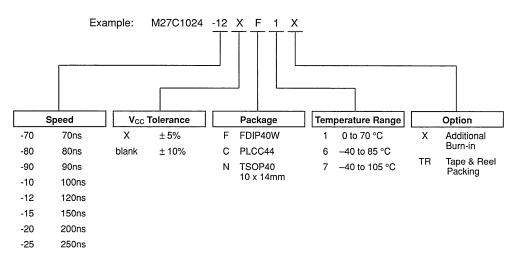

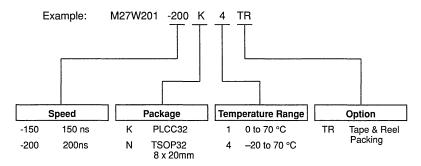

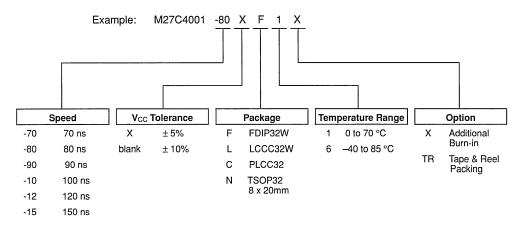

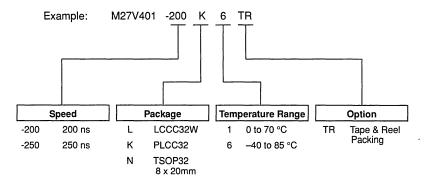

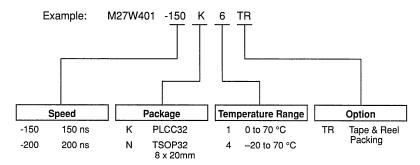

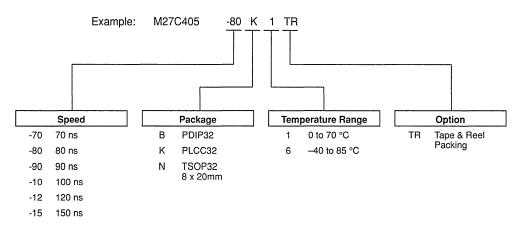

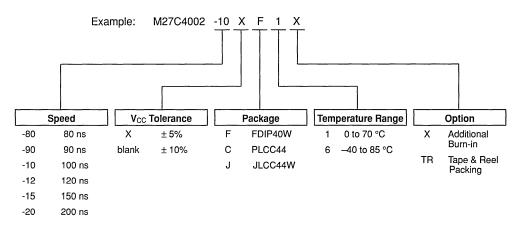

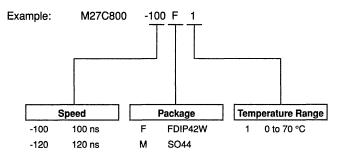

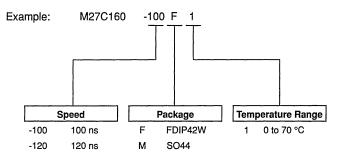

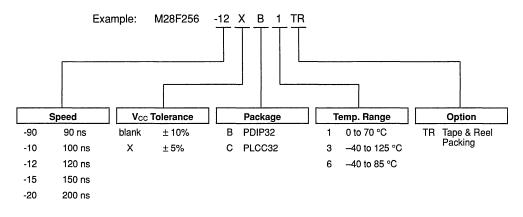

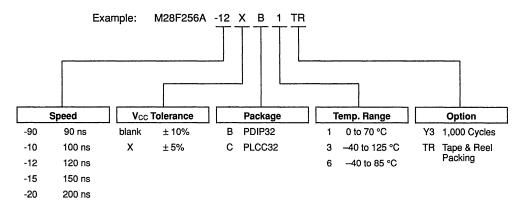

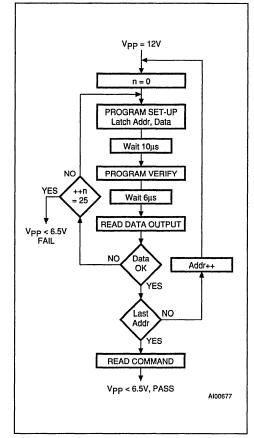

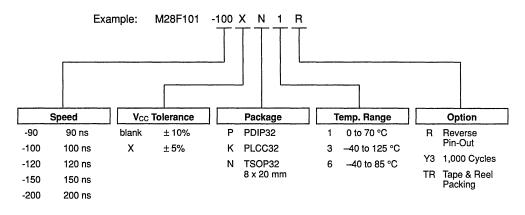

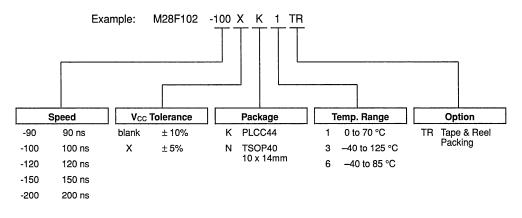

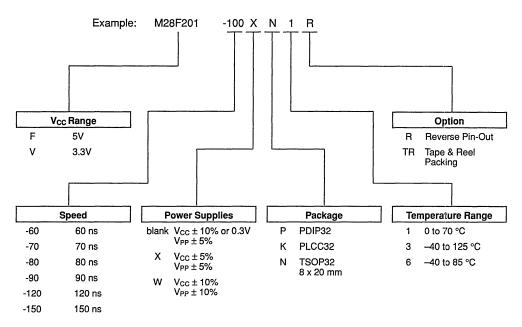

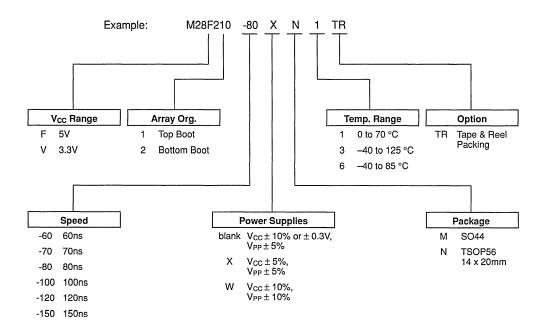

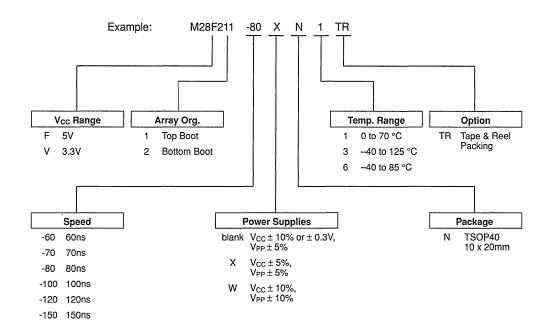

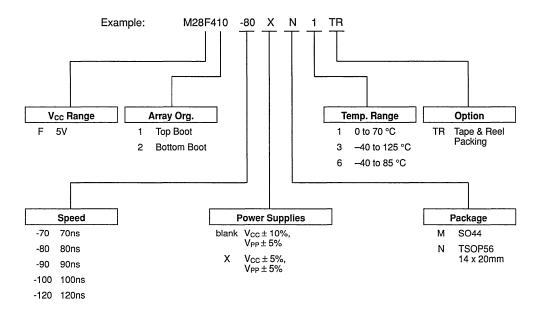

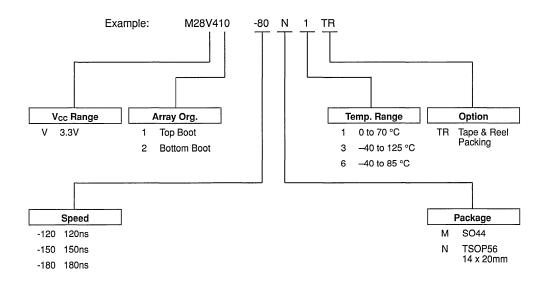

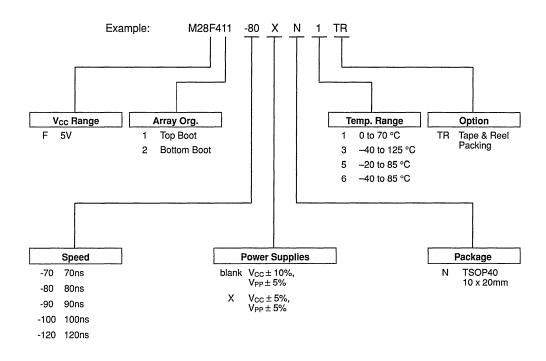

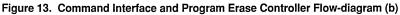

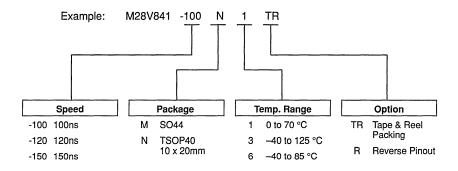

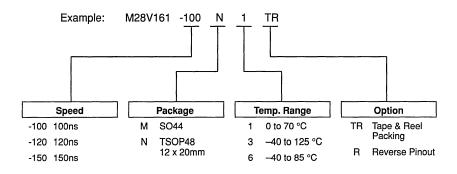

#### ORDERING INFORMATION SCHEME

For a list of available options (Speed,  $V_{CC}$  Tolerance, Package, etc...) refer to the current Memory Shortform catalogue.

For further information on any aspect of this device, please contact SGS-THOMSON Sales Office nearest to you.

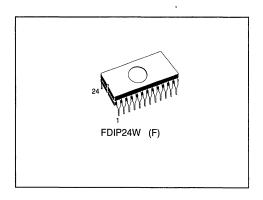

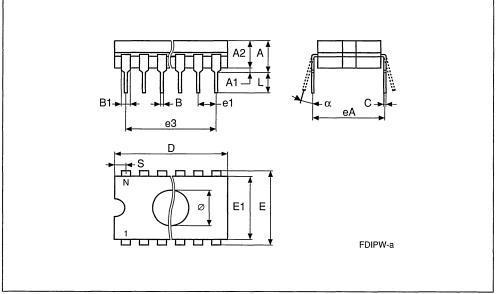

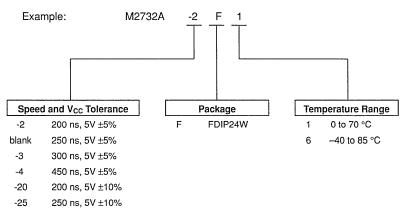

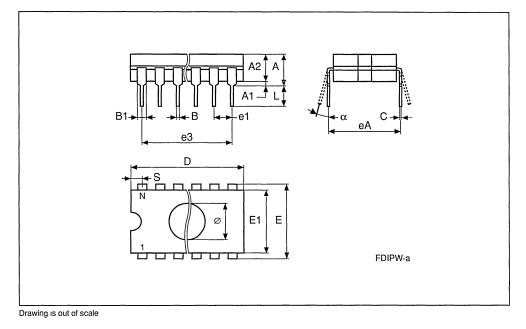

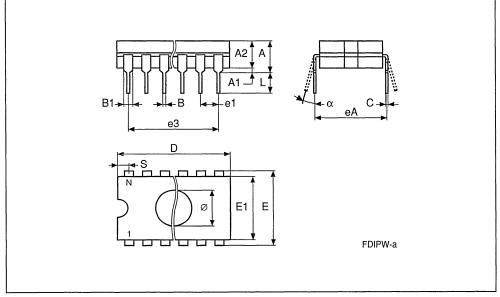

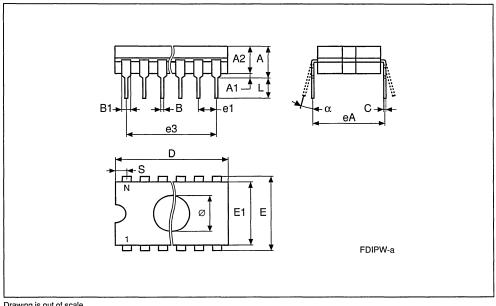

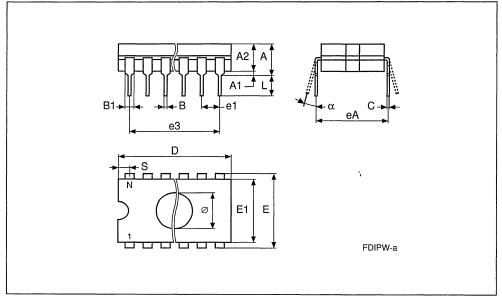

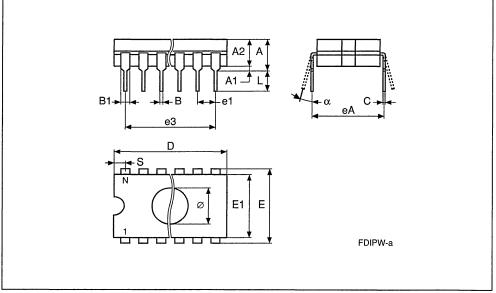

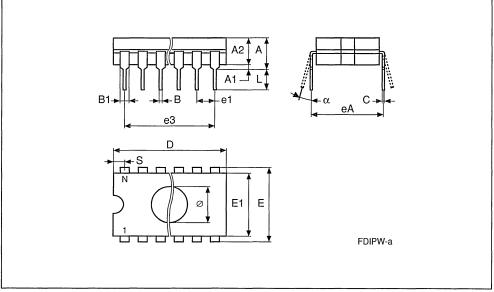

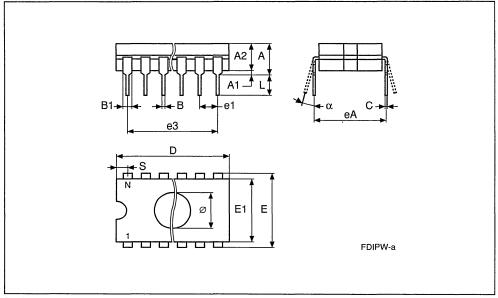

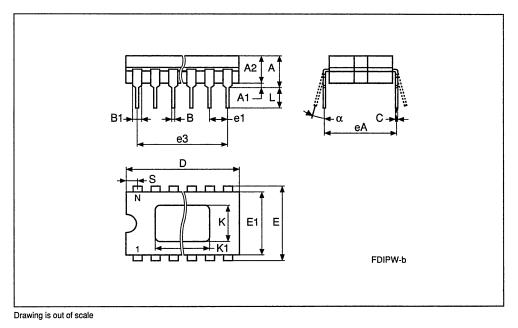

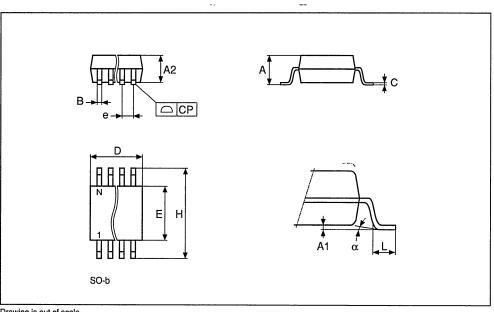

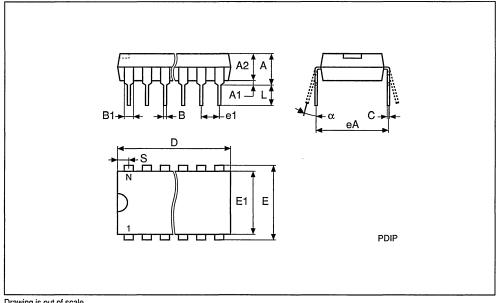

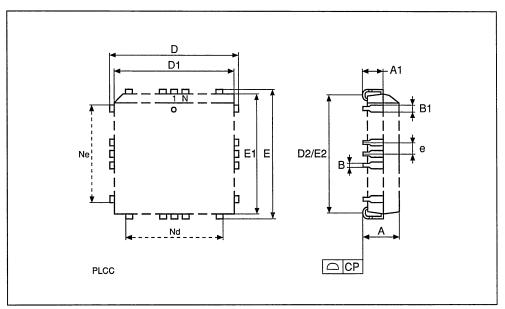

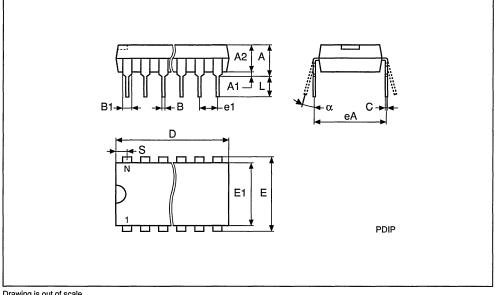

#### FDIP24W - 24 pin Ceramic Frit-seal DIP, with window

| Symb  |       | mm    |       |       | inches |       |

|-------|-------|-------|-------|-------|--------|-------|

| Gynno | Тур   | Min   | Max   | Тур   | Min    | Max   |

| А     |       |       | 5.71  |       |        | 0.225 |

| A1    |       | 0.50  | 1.78  | ,     | 0.020  | 0.070 |

| A2    |       | 3.90  | 5.08  |       | 0.154  | 0.200 |

| В     |       | 0.40  | 0.55  |       | 0.016  | 0.022 |

| B1    |       | 1.17  | 1.42  |       | 0.046  | 0.056 |

| С     |       | 0.22  | 0.31  |       | 0.009  | 0.012 |

| D     |       |       | 32.30 |       |        | 1.272 |

| E     |       | 15.40 | 15.80 |       | 0.606  | 0.622 |

| E1    |       | 13.05 | 13.36 |       | 0.514  | 0.526 |

| e1    | 2.54  | -     | -     | 0.100 | -      | _     |

| e3    | 27.94 | _     | -     | 1.100 | _      | -     |

| eA    |       | 16.17 | 18.32 |       | 0.637  | 0.721 |

| L     |       | 3.18  | 4.10  |       | 0.125  | 0.161 |

| S     |       | 1.52  | 2.49  |       | 0.060  | 0.098 |

| Ø     | 7.11  | _     | -     | 0.280 | -      | _     |

| α     |       | 4°    | 15°   | ,     | 4°     | 15°   |

| N     | 24 24 |       |       |       |        |       |

FDIP24W

Drawing is out of scale

# M2732A

## NMOS 32K (4K x 8) UV EPROM

- FAST ACCESS TIME: 200ns

- EXTENDED TEMPERATURE RANGE

- SINGLE 5V SUPPLY VOLTAGE

- LOW STANDBY CURRENT: 35mA max

- INPUTS and OUTPUTS TTL COMPATIBLE DURING READ and PROGRAM

- COMPLETELY STATIC

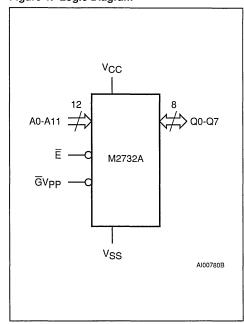

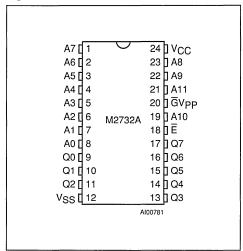

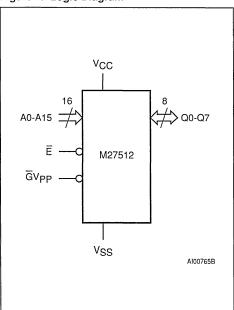

#### Figure 1. Logic Diagram

#### DESCRIPTION

The M2732A is a 32,768 bit UV erasable and electrically programmable memory EPROM. It is organized as 4,096 words by 8 bits. The M2732A with its single 5V power supply and with an access time of 200 ns, is ideal suited for applications where fast turn around and pattern experimentation one important requirements.

The M2732A is honsed in a 24 pin Window Ceramic Frit-Seal Dual-in-Line package. The transparent lid allows the user to expose the chip to ultraviolet light to erase the bit pattern. A new pattern can be then written to the clerice by following the programming procedure.

| Table | 1. | Signal | Names |

|-------|----|--------|-------|

|-------|----|--------|-------|

| A0 - A11             | Address Inputs                 |

|----------------------|--------------------------------|

| Q0 - Q7              | Data Outputs                   |

| Ē                    | Chip Enable                    |

| $\overline{G}V_{PP}$ | Output Enable / Program Supply |

| Vcc                  | Supply Voltage                 |

| V <sub>SS</sub>      | Ground                         |

Table 2. Absolute Maximum Ratings

| Symbol            | Parameter                     |                    | Value                  | Unit |

|-------------------|-------------------------------|--------------------|------------------------|------|

| T <sub>A</sub>    | Ambient Operating Temperature | grade 1<br>grade 6 | 0 to 70<br>40 to 85    | °C   |

| T <sub>BIAS</sub> | Temperature Under Bias        | grade 1<br>grade 6 | -10 to 80<br>-50 to 95 | °C   |

| T <sub>STG</sub>  | Storage Temperature           |                    | -65 to 125             | °C   |

| VIO               | Input or Output Voltages      |                    | –0.6 to 6              | V    |

| Vcc               | Supply Voltage                | _                  | -0.6 to 6              | V    |

| V <sub>PP</sub>   | Program Supply Voltage        |                    | -0.6 to 22             | V    |

Note: Except for the rating "Operating Temperature Range", stresses above those listed in the Table "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only and operation of the device at these or any other conditions above those indicated in the Operating sections of this specification is not implied. Exposure to Absolute Maximum Rating conditions for extended periods may affect device reliability. Refer also to the SGS-THOMSON SURE Program and other relevant quality documents

Figure 2. DIP Pin Connections

#### **DEVICE OPERATION**

The six modes of operation for the M2732A are listed in the Operating Modes Table. A single 5V power supply is required in the read mode. All inputs are TTL level except for  $V_{PP}$ .

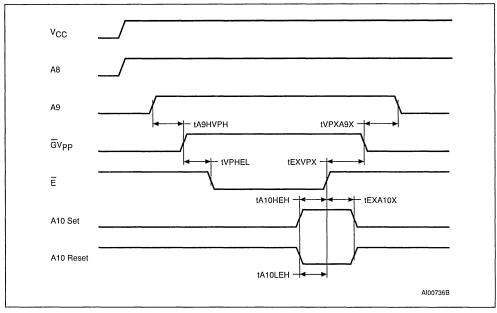

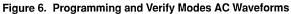

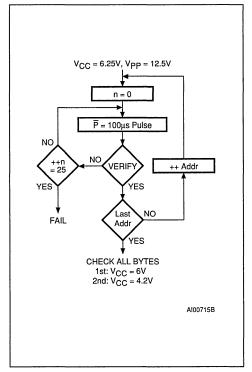

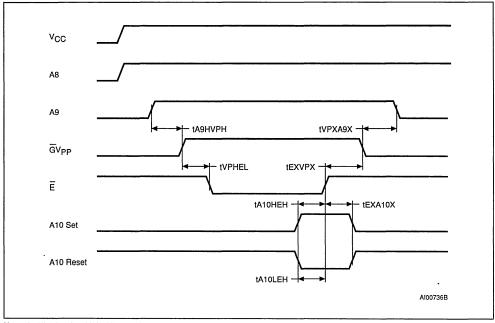

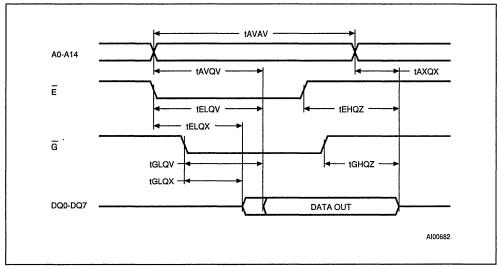

#### Read Mode

The M2732A has two control functions, both of which must be logically satisfied in order to obtain data at the outputs. Chip Enable ( $\overline{E}$ ) is the power control and should be used for device selection. Output Enable ( $\overline{G}$ ) is the output control and should

be used to gate data to the output pins, independent of device selection.

Assuming that the addresses are stable, address access time ( $t_{AVAQ}$ ) is equal to the delay from  $\overline{E}$  to output ( $t_{ELQV}$ ). Data is available at the outputs after the falling edge of  $\overline{G}$ , assuming that  $\overline{E}$  has been low and the addresses have been stable for at least  $t_{AVQV}$ - $t_{GLQV}$ .

#### Standby Mode

The M2732A has a standby mode which reduces the active power current by 70 %, from 125 mA to 35 mA. The M2732A is placed in the standby mode by applying a TTL high signal to  $\overline{E}$  input. When in standby mode, the outputs are in a high impedance state, independent of the  $\overline{G}V_{PP}$  input.

#### **Two Line Output Control**

Because M2732A's are usually used in larger memory arrays, this product features a 2 line control function which accommodates the use of multiple memory connection. The two line control function allows:

- a. the lowest possible memory power dissipation,

- b. complete assurance that output bus contention will not occur.

To most efficiently use these two control lines, it is recommended that  $\overline{E}$  be decoded and used as the primary device selecting function, while  $\overline{G}$  should be made a common connection to all devices in the array and connected to the READ line from the system control bus.

This ensures that all deselected memory devices are in their low power standby mode and that the output pins are only active when data is required from a particular memory device.

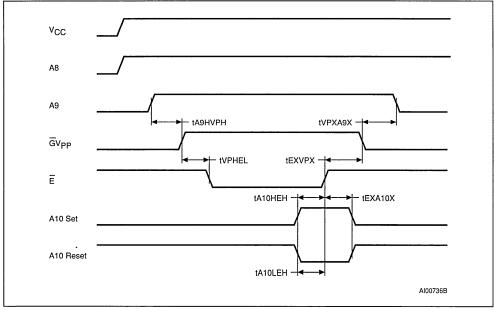

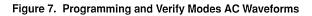

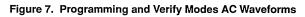

#### Programming

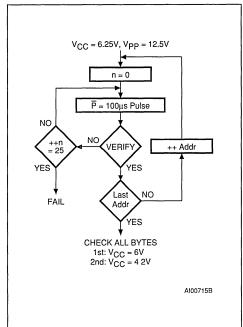

When delivered, and after each erasure, all bits of the M2732A are in the "1" state. Data is introduced by selectively programming "0's" into the desired bit locations. Although only "0's" will be programmed, both "1's" and "0's" can be presented in the data word. The only way to change a "0" to a "1" is by ultraviolet light erasure.

The M2732A is in the programming mode when the  $\overline{G}V_{PP}$  input is at 21V. A 0.1 $\mu$ F capacitor must be placed across  $\overline{G}V_{PP}$  and ground to suppress spurious voltage transients which may damage the device. The data to be programmed is applied, 8 bits in parallel, to the data output pins. The levels required for the address and data inputs are TTL.

When the address and data are stable, a 50ms, active low, TTL program pulse is applied to the  $\overline{E}$  input. A program pulse must be applied at each address location to be programmed. Any location can be programmed at any time - either individually, sequentially, or at random. The program pulse has a maximum width of 55ms. The M2732A must not be programmed with a DC signal applied to the  $\overline{E}$  input.

Programming of multiple M2732As in parallel with the same data can be easily accomplished due to the simplicity of the programming requirements. Inputs of the paralleled M2732As may be connected together when they are programmed with the same data. A low level TTL pulse applied to the  $\overline{E}$  input programs the paralleled 2732As.

#### Program Inhibit

Programming of multiple M2732As in parallel with different data is also easily accomplished. Except for  $\overline{E}$ , all like inputs (including  $\overline{G}V_{PP}$ ) of the parallel M2732As may be common. A TTL level program

pulse applied to a M2732A's  $\overline{E}$  input with  $\overline{G}V_{PP}$  at 21V will program that M2732A. A high level  $\overline{E}$  input inhibits the other M2732As from being programmed.

#### **Program Verify**

A verify should be performed on the programmed bits to determine that they were correctly programmed. The verify is carried out with  $\overline{G}V_{PP}$  and  $\overline{E}$  at  $V_{IL}.$

#### **ERASURE OPERATION**

The erasure characteristics of the M2732A are such that erasure begins when the cells are exposed to light with wavelengths shorter than approximately 4000 Å. It should be noted that sunlight and certain types of fluorescent lamps have wavelengths in the 3000-4000 Å range. Research shows that constant exposure to room level fluorescent lighting could erase a typical M2732A in approximately 3 years, while it would take approximately 1 week to cause erasure when exposed to the direct sunlight. If the M2732A is to be exposed to these types of lighting conditions for extended periods of time, it is suggested that opaque labels be put over the M2732A window to prevent unintentional erasure.

The recommended erasure procedure for the M2732A is exposure to shortwave ultraviolet light which has a wavelength of 2537 Å. The integrated dose (i.e. UV intensity x exposure time) for erasure should be a minimum of 15 W-sec/cm<sup>2</sup>. The erasure time with this dosage is approximately 15 to 20 minutes using an ultraviolet lamp with 12000  $\mu$ W/cm<sup>2</sup> power rating. The M2732A should be placed within 2.5 cm of the lamp tubes during erasure. Some lamps have a filter on their tubes which should be removed before erasure.

Table 3. Operating Modes

| Mode            | Ē         | GV <sub>PP</sub> | Vcc | Q0 - Q7  |

|-----------------|-----------|------------------|-----|----------|

| Read            | VIL       | VIL              | Vcc | Data Out |

| Program         | VIL Pulse | V <sub>PP</sub>  | Vcc | Data In  |

| Verify          | VIL       | VIL              | Vcc | Data Out |

| Program Inhibit | Vih       | V <sub>PP</sub>  | Vcc | Hi-Z     |

| Standby         | ViH       | х                | Vcc | Hi-Z     |

Note: X = VIH or VIL.

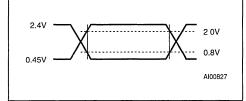

#### AC MEASUREMENT CONDITIONS

| Input Rise and Fall Times             | ≤ 20ns        |

|---------------------------------------|---------------|

| Input Pulse Voltages                  | 0.45V to 2.4V |

| Input and Output Timing Ref. Voltages | 0.8V to 2.0V  |

Note that Output Hi-Z is defined as the point where data is no longer driven.

#### Figure 3. AC Testing Input Output Waveforms

#### Table 4. Capacitance <sup>(1)</sup> ( $T_A = 25 \text{ °C}, f = 1 \text{ MHz}$ )

| Symbol           | Parameter                       | Test Condition        | Min | Max | Unit |

|------------------|---------------------------------|-----------------------|-----|-----|------|

| C <sub>IN</sub>  | Input Capacitance (except GVPP) | $V_{IN} = 0V$         |     | 6   | pF   |

| C <sub>IN1</sub> | Input Capacitance (GVPP)        | $V_{IN} = 0V$         |     | 20  | pF   |

| Cout             | Output Capacitance              | V <sub>OUT</sub> = 0V |     | 12  | pF   |

Note: 1. Sampled only, not 100% tested.

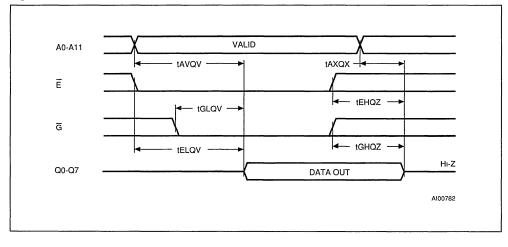

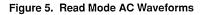

#### Figure 5. Read Mode AC Waveforms

67/

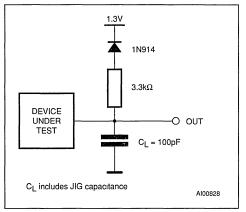

#### Figure 4. AC Testing Load Circuit

Table 5. Read Mode DC Characteristics  $^{(1)}$  (T<sub>A</sub> = 0 to 70 °C or –40 to 85 °C; V<sub>CC</sub> = 5V  $\pm$  5% or 5V  $\pm$  10%; V<sub>PP</sub> = V<sub>CC</sub>)

| Symbol          | Parameter                | Test Condition                                 | Va   | Value               |      |  |

|-----------------|--------------------------|------------------------------------------------|------|---------------------|------|--|

| Symbol          | ratallieter              | Test Condition                                 | Min  | Max                 | Unit |  |

| ۱ <sub>LI</sub> | Input Leakage Current    | $0 \le V_{IN} \le V_{CC}$                      |      | ±10                 | μA   |  |

| ILO             | Output Leakage Current   | V <sub>OUT</sub> = V <sub>CC</sub>             |      | ±10                 | μA   |  |

| lcc             | Supply Current           | $\overline{E} = V_{IL}, \overline{G} = V_{IL}$ |      | 125                 | mA   |  |

| Icc1            | Supply Current (Standby) | $\overline{E} = V_{IH}, \overline{G} = V_{IL}$ |      | 35                  | mA   |  |

| VIL             | Input Low Voltage        |                                                | -0.1 | 0.8                 | V    |  |

| VIH             | Input High Voltage       |                                                | 2    | V <sub>CC</sub> + 1 | V    |  |

| VOL             | Output Low Voltage       | I <sub>OL</sub> = 2.1mA                        |      | 0.45                | V    |  |

| V <sub>OH</sub> | Output High Voltage      | I <sub>OH</sub> =400µА                         | 2.4  |                     | V    |  |

Note: 1. Vcc must be applied simultaneously with or before VPP and removed simultaneously or after VPP.

#### Table 6. Read Mode AC Characteristics (1)

$(T_A = 0 \text{ to } 70 \text{ °C or } -40 \text{ to } 85 \text{ °C}; V_{CC} = 5V \pm 5\% \text{ or } 5V \pm 10\%; V_{PP} = V_{CC})$

|                                  |                 |                                            | Test                                                                     | M2732A |     |      |        |     |     |     |     |      |

|----------------------------------|-----------------|--------------------------------------------|--------------------------------------------------------------------------|--------|-----|------|--------|-----|-----|-----|-----|------|

| Symbol                           | Alt             | Parameter                                  | Condition                                                                | -2,    | -20 | blan | k, -25 | -   | 3   | -   | 4   | Unit |

|                                  |                 |                                            |                                                                          | Min    | Max | Min  | Max    | Min | Max | Min | Мах |      |

| tavov                            | tacc            | Address Valid to<br>Output Valid           | $\overline{\underline{E}} = V_{IL},$<br>$\overline{G} = V_{IL}$          |        | 200 |      | 250    |     | 300 |     | 450 | ns   |

| telav                            | t <sub>CE</sub> | Chip Enable Low to<br>Output Valid         | G = V <sub>IL</sub>                                                      |        | 200 |      | 250    |     | 300 |     | 450 | ns   |

| tglav                            | toe             | Output Enable Low to Output Valid          | $\overline{E} = V_{IL}$                                                  |        | 100 |      | 100    |     | 150 |     | 150 | ns   |

| t <sub>EHQZ</sub> <sup>(2)</sup> | tDF             | Chip Enable High to<br>Output Hi-Z         | G = V <sub>IL</sub>                                                      | 0      | 60  | 0    | 60     | 0   | 130 | 0   | 130 | ns   |

| t <sub>GHQZ</sub> <sup>(2)</sup> | tDF             | Output Enable High to Output Hi-Z          | Ē = V <sub>IL</sub>                                                      | 0      | 60  | 0    | 60     | 0   | 130 | 0   | 130 | ns   |

| taxox                            | tон             | Address Transition to<br>Output Transition | $\frac{\overline{E}}{\overline{G}} = V_{IL},$<br>$\overline{G} = V_{IL}$ | 0      |     | 0    |        | 0   |     | 0   |     | ns   |

Notes: 1. V<sub>CC</sub> must be applied simultaneously with or before V<sub>PP</sub> and removed simultaneously or after V<sub>PP</sub>. 2. Sampled only, not 100% tested.

# Table 7. Programming Mode DC Characteristics $^{(1)}$ (T\_A = 25 °C; V\_{CC} = 5V $\pm$ 5%; V\_{PP} = 21V $\pm$ 0.5V)

| Symbol | Parameter             | Test Condition                                 | Min  | Max                 | Units |

|--------|-----------------------|------------------------------------------------|------|---------------------|-------|

| ILI    | Input Leakage Current | $V_{1L} \leq V_{1N} \leq V_{1H}$               |      | ±10                 | μA    |

| lcc    | Supply Current        | $\overline{E} = V_{IL}, \overline{G} = V_{IL}$ |      | 125                 | mA    |

| IPP    | Program Current       | $\overline{E} = V_{IL}, \overline{G} = V_{PP}$ |      | 30                  | mA    |

| VIL    | Input Low Voltage     |                                                | -0.1 | 0.8                 | V     |

| VIH    | Input High Voltage    |                                                | 2    | V <sub>CC</sub> + 1 | V     |

| VOL    | Output Low Voltage    | I <sub>OL</sub> = 2.1mA                        |      | 0.45                | V     |

| VOH    | Output High Voltage   | I <sub>OH</sub> =400µА                         | 2.4  |                     | V     |

Note: 1. V<sub>CC</sub> must be applied simultaneously with or before V<sub>PP</sub> and removed simultaneously or after V<sub>PP</sub>

# Table 8. Programming Mode AC Characteristics $^{(1)}$ (T\_A = 25 °C; V\_{CC} = 5V $\pm$ 5%; V\_{PP} = 21V $\pm$ 0.5V)

| Symbol             | Alt              | Parameter                                         | Test Condition                                  | Min | Max | Units |

|--------------------|------------------|---------------------------------------------------|-------------------------------------------------|-----|-----|-------|

| tavel              | tas              | Address Valid to Chip Enable<br>Low               |                                                 | 2   |     | μs    |

| tavel              | t <sub>DS</sub>  | Input Valid to Chip Enable Low                    |                                                 | 2   |     | μs    |

| <b>t</b> VPHEL     | toes             | VPP High to Chip Enable Low                       |                                                 | 2   |     | μs    |

| tvpl1vpl2          | tPRT             | V <sub>PP</sub> Rise Time                         |                                                 | 50  |     | ns    |

| <b>t</b> ELEH      | t <sub>PW</sub>  | Chip Enable Program Pulse<br>Width                |                                                 | 45  | 55  | ms    |

| tEHQX              | t <sub>DH</sub>  | Chip Enable High to Input<br>Transition           |                                                 | 2   |     | μs    |

| t <sub>EHVPX</sub> | t <sub>OEH</sub> | Chip Enable High to V <sub>PP</sub><br>Transition |                                                 | 2   |     | μs    |

| tvplel             | tvR              | VPP Low to Chip Enable Low                        |                                                 | 2   |     | μs    |

| telqv              | t <sub>DV</sub>  | Chip Enable Low to Output<br>Valıd                | $\overline{E} = V_{IL},  \overline{G} = V_{IL}$ |     | 1   | μs    |

| t <sub>EHQZ</sub>  | t <sub>DF</sub>  | Chip Enable High to Output<br>Hi-Z                |                                                 | 0   | 130 | ns    |

| t <sub>EHAX</sub>  | t <sub>AH</sub>  | Chip Enable High to Address<br>Transition         |                                                 | 0   |     | ns    |

Note: 1. Vcc must be applied simultaneously with or before VPP and removed simultaneously or after VPP.

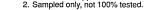

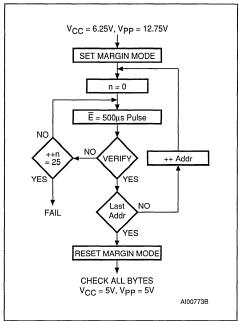

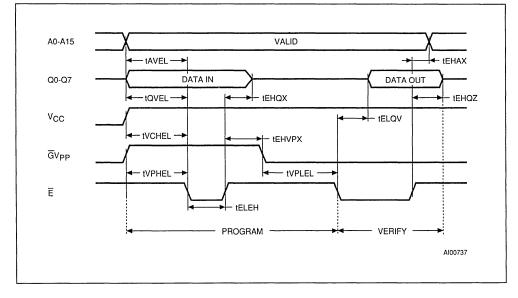

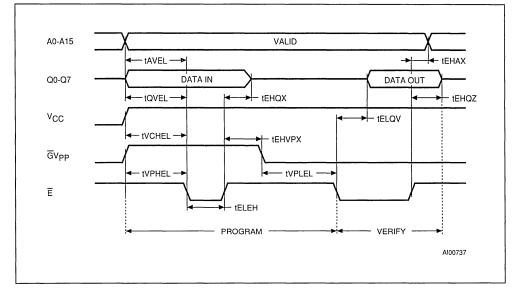

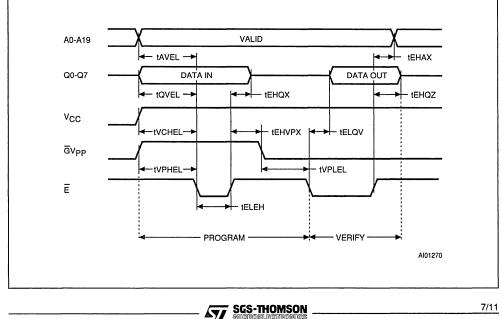

#### Figure 6. Programming and Verify Modes AC Waveforms

#### **ORDERING INFORMATION SCHEME**

For a list of available options (Speed,  $V_{CC}$  Tolerance, Package, etc...) refer to the current Memory Shortform catalogue.

For further information on any aspect of this device, please contact SGS-THOMSON Sales Office nearest to you.

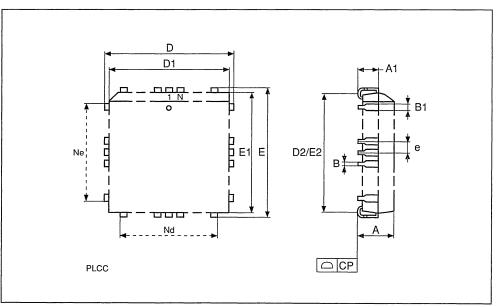

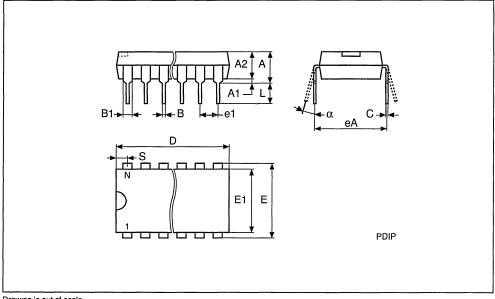

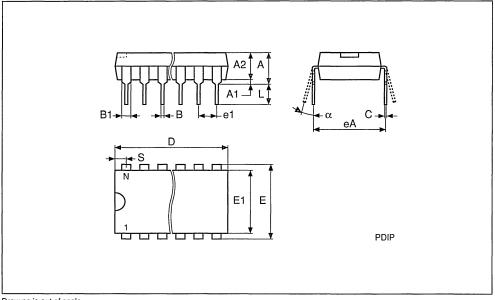

### FDIP24W - 24 pin Ceramic Frit-seal DIP, with window

| Symb  |       | mm    |       |       | inches |       |

|-------|-------|-------|-------|-------|--------|-------|

| Synno | Тур   | Min   | Max   | Тур   | Min    | Max   |

| A     |       |       | 5.71  |       |        | 0.225 |

| A1    |       | 0.50  | 1.78  |       | 0.020  | 0.070 |

| A2    |       | 3.90  | 5.08  |       | 0.154  | 0.200 |

| В     |       | 0.40  | 0.55  |       | 0.016  | 0.022 |

| B1    |       | 1.17  | 1.42  |       | 0.046  | 0.056 |

| С     |       | 0.22  | 0.31  |       | 0.009  | 0.012 |

| D     |       |       | 32.30 |       |        | 1.272 |

| E     |       | 15.40 | 15.80 |       | 0.606  | 0.622 |

| E1    |       | 13.05 | 13.36 |       | 0.514  | 0.526 |

| e1    | 2.54  | -     | -     | 0.100 | -      | _     |

| e3    | 27.94 | -     | _     | 1.100 | -      | -     |

| eA    |       | 16.17 | 18.32 |       | 0.637  | 0.721 |

| L     |       | 3.18  | 4.10  |       | 0.125  | 0.161 |

| S     |       | 1.52  | 2.49  |       | 0.060  | 0.098 |

| Ø     | 7.11  | -     | -     | 0.280 | -      | -     |

| α     |       | 4°    | 15°   |       | 4°     | 15°   |

| N     |       | 24    |       |       | 24     |       |

FDIP24W

Drawing is out of scale

# M2764A

# NMOS 64K (8K x 8) UV EPROM

- FAST ACCESS TIME: 180ns

- EXTENDED TEMPERATURE RANGE

- SINGLE 5V SUPPLY VOLTAGE

- LOW STANDBY CURRENT: 35mA max

- TTL COMPATIBLE DURING READ and PROGRAM

- FAST PROGRAMMING ALGORITHM

- ELECTRONIC SIGNATURE

- PROGRAMMING VOLTAGE: 12V

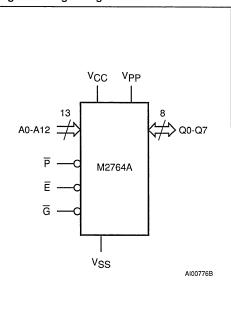

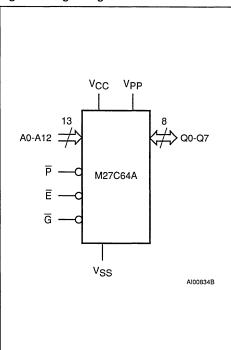

#### Figure 1. Logic Diagram

Table 1. Signal Names

The M2764A is a 65,536 bit UV erasable and electrically programmable memory EPROM. It is organized as 8,192 words by 8 bits.

The M27C64A is housed in a 28 pin Window Ceramic Frit-Seal Dual-in-Line package. The transparent lid allows the user to expose the chip to ultraviolet light to erase the bit pattern. A new pattern can then be written to the device by following the programming procedure.

| -               |                |

|-----------------|----------------|

| A0 - A12        | Address Inputs |

| Q0 - Q7         | Data Outputs   |

| Ē               | Chip Enable    |

| G               | Output Enable  |

| P               | Program        |

| V <sub>PP</sub> | Program Supply |

| Vcc             | Supply Voltage |

| V <sub>SS</sub> | Ground         |

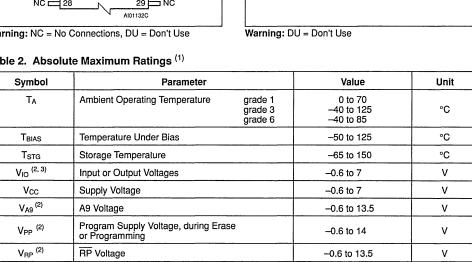

| Symbol            | Parameter                     |                    | Value                  | Unit |

|-------------------|-------------------------------|--------------------|------------------------|------|

| TA                | Ambient Operating Temperature | grade 1<br>grade 6 | 0 to 70<br>40 to 85    | °C   |

| T <sub>BIAS</sub> | Temperature Under Bias        | grade 1<br>grade 6 | -10 to 80<br>-50 to 95 | °C   |

| T <sub>STG</sub>  | Storage Temperature           |                    | 65 to 125              | °C   |

| Vio               | Input or Output Voltages      |                    | -0.6 to 6.5            | V    |

| Vcc               | Supply Voltage                |                    | -0.6 to 6.5            | v    |

| V <sub>A9</sub>   | A9 Voltage                    |                    | -0.6 to 13.5           | V    |

| V <sub>PP</sub>   | Program Supply                |                    | -0.6 to 14             | V    |

Table 2. Absolute Maximum Ratings

Note: Except for the rating "Operating Temperature Range", stresses above those listed in the Table "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only and operation of the device at these or any other conditions above those indicated in the Operating sections of this specification is not implied. Exposure to Absolute Maximum Rating conditions for extended periods may affect device reliability. Refer also to the SGS-THOMSON SURE Program and other relevant quality documents.

Figure 2. DIP Pin Connections

| VPP [ 1  | 28 ] V <sub>CC</sub> |

|----------|----------------------|

| A12 [ 2  | 27 ] P               |

| A7 [ 3   | 26 ] NC              |

| A6 [ 4   | 25 ] A8              |

| A5 [ 5   | 24 ] A9              |

| A4 [ 6   | 23 ] A11             |

| A3 [ 7   | 22 ] G               |

| A2 [ 8   | 21 ] A10             |

| A1 [ 9   | 20 ] E               |

| A0 [ 10  | 19 🛛 Q7              |

| Q0 [ 11  | 18 🗍 Q6              |

| Q1 [ 12  | 17 ] Q5              |

| Q2 [ 13  | 16 ] Q4              |

| Vss [ 14 | 15 ] Q3              |

|          | A100777              |

Warning: NC = No Connection.

#### **DEVICE OPERATION**

The seven modes of operations of the M2764A are listed in the Operating Modes table. A single 5V power supply is required in the read mode. All inputs are TTL levels except for VPP and 12V on A9 for Electronic Signature.

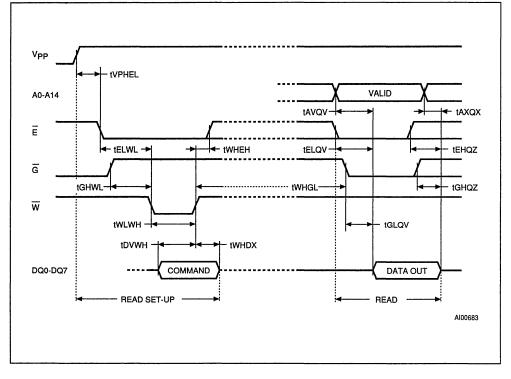

#### Read Mode

The M2764A has two control functions, both of which must be logically satisfied in order to obtain data at the outputs. Chip Enable (E) is the power control and should be used for device selection. Output Enable  $(\overline{G})$  is the output control and should be used to gate data to the output pins, independent of device selection.

Assuming that the addresses are stable, address access time  $(t_{AVQV})$  is equal to the delay from  $\overline{E}$  to output (tELQV). Data is available at the outputs after the falling edge of  $\overline{G}$ , assuming that  $\overline{E}$  has been low and the addresses have been stable for at least tavov-tgi ov.

#### Standby Mode

The M2764A has a standby mode which reduces the maximum active power current from 75mA to 35mA. The M2764A is placed in the standby mode by applying a TTL high signal to the E input. When in the standby mode, the outputs are in a high impedance state, independent of the  $\overline{G}$  input.

#### **Two Line Output Control**

Because EPROMs are usually used in larger memory arrays, the product features a 2 line control function which accommodates the use of multiple memory connection. The two line control function allows :

- a. the lowest possible memory power dissipation,

- b. complete assurance that output bus contention will not occur.

#### **DEVICE OPERATION** (cont'd)

For the most efficient use of these two control lines,  $\overline{E}$  should be decoded and used as the primary device selecting function, while  $\overline{G}$  should be made a common connection to all devices in the array and connected to the READ line from the system control bus.

This ensures that all deselected memory devices are in their low power standby mode and that the output pins are only active when data is desired from a particular memory device.

#### System Considerations

The power switching characteristics of fast EPROMs require careful decoupling of the devices. The supply current, lcc, has three segments that are of interest to the system designer: the standby current level, the active current level, and transient current peaks that are produced by the falling and rising edges of  $\overline{E}$ . The magnitude of the transient current peaks is dependent on the capacitive and inductive loading of the device at the output. The associated transient voltage peaks can be suppressed by complying with the two line output control and by properly selected decoupling capacitors. It is recommended that a 1 $\mu$ F ceramic capacitor be used on every device between V<sub>CC</sub> and V<sub>SS</sub>. This should be a high frequency capacitor

of low inherent inductance and should be placed as close to the device as possible. In addition, a  $4.7\mu$ F bulk electrolytic capacitor should be used between V<sub>CC</sub> and V<sub>SS</sub> for every eight devices. The bulk capacitor should be located near the power supply connection point. The purpose of the bulk capacitor is to overcome the voltage drop caused by the inductive effects of PCB traces.

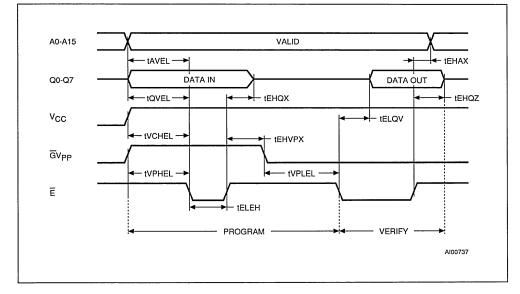

#### Programming

When delivered (and after each erasure for UV EPROM), all bits of the M2764A are in the "1" state. Data is introduced by selectively programming "0s" into the desired bit locations. Although only "0s" will be programmed, both "1s" and "0s" can be present in the data word. The only way to change a "0" to a "1" is by ultraviolet light erasure.

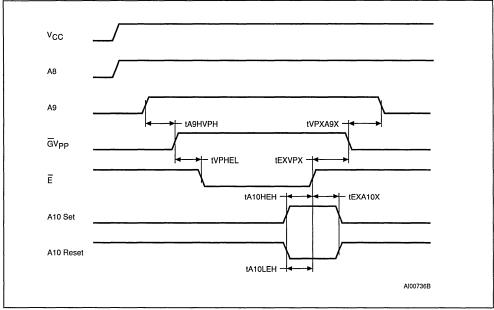

The M2764A is in the programming mode when  $V_{PP}$  input is at 12.5V and  $\vec{E}$  and  $\vec{P}$  are at TTL low. The data to be programmed is applied, 8 bits in parallel, to the data output pins. The levels required for the address and data inputs are TTL.

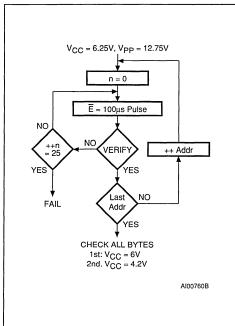

#### Fast Programming Algorithm

Fast Programming Algorithm rapidly programs M2764A EPROMs using an efficient and reliable method suited to the production programming environment. Programming reliability is also ensured as the incremental program margin of each byte is continually monitored to determine when it has

| Mode                 | Ē   | G               | P         | A9  | V <sub>PP</sub> | Q0 - Q7   |

|----------------------|-----|-----------------|-----------|-----|-----------------|-----------|

| Read                 | VIL | VIL             | VIH       | Х   | Vcc             | Data Out  |

| Output Disable       | VIL | V <sub>IH</sub> | VIH       | Х   | Vcc             | Hi-Z      |

| Program              | VIL | ViH             | VIL Pulse | Х   | V <sub>PP</sub> | Data In   |

| Verify               | VIL | VIL             | VIH       | Х   | V <sub>PP</sub> | Data Out  |

| Program Inhibit      | VIH | Х               | Х         | Х   | V <sub>PP</sub> | Hi-Z      |

| Standby              | VIH | х               | х         | x   | Vcc             | Hi-Z      |

| Electronic Signature | VIL | VIL             | VIH       | VID | Vcc             | Codes Out |

#### Table 3. Operating Modes

**Note:**  $X = V_{IH}$  or  $V_{IL}$ ,  $V_{ID} = 12V \pm 0.5\%$ .

#### Table 4. Electronic Signature

| Identifier          | A0  | Q7 | Q6 | Q5 | Q4 | Q3 | Q2 | Q1 | QÛ | Hex Data |

|---------------------|-----|----|----|----|----|----|----|----|----|----------|

| Manufacturer's Code | VIL | 0  | 0  | 1  | 0  | 0  | 0  | 0  | 0  | 20h      |

| Device Code         | VIH | 0  | 0  | 0  | 0  | 1  | 0  | 0  | 0  | 08h      |

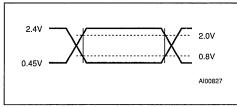

#### AC MEASUREMENT CONDITIONS

| Input Rise and Fall Times             | ≤ 20ns        |

|---------------------------------------|---------------|

| Input Pulse Voltages                  | 0.45V to 2.4V |

| Input and Output Timing Ref. Voltages | 0.8V to 2.0V  |

Note that Output Hi-Z is defined as the point where data is no longer driven.

#### Figure 3. AC Testing Input Output Waveforms

#### Table 5. Capacitance <sup>(1)</sup> (T<sub>A</sub> = 25 °C, f = 1 MHz )

| Symbol          | Parameter          | Test Condition        | Min | Max | Unit |

|-----------------|--------------------|-----------------------|-----|-----|------|

| C <sub>IN</sub> | Input Capacitance  | $V_{IN} = 0V$         |     | 6   | pF   |

| Cout            | Output Capacitance | V <sub>OUT</sub> = 0V |     | 12  | pF   |

Note: 1. Sampled only, not 100% tested.

#### Figure 5. Read Mode AC Waveforms

#### Table 6. Read Mode DC Characteristics <sup>(1)</sup>

$(T_A = 0 \text{ to } 70 \text{ °C or } -40 \text{ to } 85 \text{ °C}; V_{CC} = 5V \pm 5\% \text{ or } 5V \pm 10\%; V_{PP} = V_{CC})$

| Symbol          | Parameter                | Test Condition                                 | Min  | Max     | Unit |

|-----------------|--------------------------|------------------------------------------------|------|---------|------|

| lu              | Input Leakage Current    | $0 \le V_{IN} \le V_{CC}$                      |      | ±10     | μA   |

| ILO             | Output Leakage Current   | V <sub>OUT</sub> = V <sub>CC</sub>             |      | ±10     | μA   |

| lcc             | Supply Current           | $\overline{E} = V_{IL}, \overline{G} = V_{IL}$ |      | 75      | mA   |

| Icc1            | Supply Current (Standby) | Ē = V <sub>IH</sub>                            |      | 35      | mA   |

| Ірр             | Program Current          | $V_{PP} = V_{CC}$                              |      | 5       | mA   |

| VIL             | Input Low Voltage        |                                                | -0.1 | 0.8     | V    |

| V <sub>IH</sub> | Input High Voltage       |                                                | 2    | Vcc + 1 | v    |

| V <sub>OL</sub> | Output Low Voltage       | l <sub>OL</sub> = 2.1mA                        |      | 0.45    | V    |

| V <sub>OH</sub> | Output High Voltage      | I <sub>OH</sub> = –400µА                       | 2.4  |         | V    |

Note: 1. V<sub>CC</sub> must be applied simultaneously with or before V<sub>PP</sub> and removed simultaneously or after V<sub>PP</sub>.

#### Table 7A. Read Mode AC Characteristics (1)

$(T_A = 0 \text{ to } 70 \text{ °C or } -40 \text{ to } 85 \text{ °C}; V_{CC} = 5V \pm 5\% \text{ or } 5V \pm 10\%; V_{PP} = V_{CC})$

|                      |                 |                                         | Test                                                            |     |     | M27     | '64A |            |     |      |

|----------------------|-----------------|-----------------------------------------|-----------------------------------------------------------------|-----|-----|---------|------|------------|-----|------|

| Symbol               | Alt             | It Parameter                            | Condition                                                       | -   | 1   | -2, -20 |      | blank, -25 |     | Unit |

|                      |                 |                                         |                                                                 | Min | Max | Min     | Max  | Min        | Max |      |

| tavqv                | tacc            | Address Valid to<br>Output Valid        | $\overline{E} = V_{IL},$<br>$\overline{G} = V_{IL}$             |     | 180 |         | 200  |            | 250 | ns   |

| tELQV                | tce             | Chip Enable Low<br>to Output Valid      | $\overline{G} = V_{IL}$                                         |     | 180 |         | 200  |            | 250 | ns   |

| tglav                | toe             | Output Enable<br>Low to Output Valid    | $\overline{E} = V_{IL}$                                         |     | 65  |         | 75   |            | 100 | ns   |

| tehoz <sup>(2)</sup> | t <sub>DF</sub> | Chip Enable High<br>to Output Hi-Z      | G = VIL                                                         | 0   | 55  | 0       | 55   | 0          | 60  | ns   |

| tghaz <sup>(2)</sup> | t <sub>DF</sub> | Output Enable<br>High to Output HI-Z    | Ē = VIL                                                         | 0   | 55  | 0       | 55   | 0          | 60  | ns   |

| taxox                | tон             | Address Transition to Output Transition | $\overline{\underline{E}} = V_{1L},$<br>$\overline{G} = V_{1L}$ | 0   |     | 0       |      | 0          |     | ns   |

#### Table 7B. Read Mode AC Characteristics <sup>(1)</sup>

(T\_A = 0 to 70 °C or –40 to 85 °C; V\_{CC} = 5V  $\pm$  5% or 5V  $\pm$  10%; V\_{PP} = V\_{CC})

|                                  |                 |                                         | Teet                                                |     | M27 | 64A |     | Unit |

|----------------------------------|-----------------|-----------------------------------------|-----------------------------------------------------|-----|-----|-----|-----|------|

| Symbol /                         | Alt             | Parameter                               | Test<br>Condition                                   | -   | 3   | -   | 4   |      |

|                                  |                 |                                         |                                                     | Min | Max | Min | Max |      |

| tavqv                            | tacc            | Address Valid to<br>Output Valid        | $\overline{E} = V_{IL},$<br>$\overline{G} = V_{IL}$ |     | 300 |     | 450 | ns   |

| t <sub>ELQV</sub>                | tce             | Chip Enable Low<br>to Output Valid      | $\overline{G} = V_{IL}$                             |     | 300 |     | 450 | ns   |

| t <sub>GLQV</sub>                | t <sub>OE</sub> | Output Enable<br>Low to Output Valid    | $\overline{E} = V_{IL},$                            |     | 120 |     | 150 | ns   |

| t <sub>EHQZ</sub> <sup>(2)</sup> | tDF             | Chip Enable High<br>to Output Hi-Z      | $\overline{G} = V_{\text{IL}}$                      | 0   | 105 | 0   | 130 | ns   |

| t <sub>GHQZ</sub> <sup>(2)</sup> | t <sub>DF</sub> | Output Enable<br>High to Output Hi-Z    | Ē = VIL                                             | 0   | 105 | 0   | 130 | ns   |

| taxox                            | tон             | Address Transition to Output Transition | Ē=VIL,<br>G=VIL                                     | 0   |     | 0   |     | ns   |

Notes: 1. V<sub>CC</sub> must be applied simultaneously with or before V<sub>PP</sub> and removed simultaneously or after V<sub>PP</sub>. 2 Sampled only, not 100% tested.

#### Table 8. Programming Mode DC Characteristics (1)

$(T_A = 25 \text{ °C}; V_{CC} = 6V \pm 0.25V; V_{PP} = 12.5V \pm 0.3V)$

| Symbol | Parameter             | Test Condition                   | Min  | Max                 | Units |

|--------|-----------------------|----------------------------------|------|---------------------|-------|

| ILI    | Input Leakage Current | $V_{IL} \leq V_{IN} \leq V_{IH}$ |      | ±10                 | μA    |

| lcc    | Supply Current        |                                  |      | 75                  | mA    |

| Ірр    | Program Current       | Ē = ViL                          |      | 50                  | mA    |

| VIL    | Input Low Voltage     |                                  | -0.1 | 0.8                 | V     |

| VIH    | Input High Voltage    |                                  | 2    | V <sub>CC</sub> + 1 | v     |

| VoL    | Output Low Voltage    | I <sub>OL</sub> = 2.1mA          |      | 0.45                | v     |

| VOH    | Output High Voltage   | I <sub>OH</sub> = -400μA         | 2.4  |                     | V     |

| VA9    | A9 Voltage            |                                  | 11.5 | 12.5                | v     |

Note: 1. Vcc must be applied simultaneously with or before VPP and removed simultaneously or after VPP.

#### Table 9. Programming Mode AC Characteristics (1) $(T_A = 25 \text{ °C}; V_{CC} = 6V \pm 0.25V; V_{PP} = 12.5V \pm 0.3V)$

| Symbol                           | Alt              | Parameter                                   | Test Condition | Min  | Max   | Units |

|----------------------------------|------------------|---------------------------------------------|----------------|------|-------|-------|

| t <sub>AVPL</sub>                | tas              | Address Valid to Program Low                |                | 2    |       | μs    |

| tQVPL                            | tos              | Input Valid to Program Low                  |                | 2    |       | μs    |

| <b>t</b> VPHPL                   | tvps             | VPP High to Program Low                     |                | 2    |       | μs    |

| t <sub>VCHPL</sub>               | tvcs             | V <sub>CC</sub> High to Program Low         |                | 2    |       | μs    |

| <b>t</b> ELPL                    | tces             | Chip Enable Low to Program<br>Low           |                | 2    |       | μs    |

| t <sub>PLPH</sub>                | tpw              | Program Pulse Width (Initial)               | Note 2         | 0.95 | 1.05  | ms    |

| t <sub>PLPH</sub>                | topw             | Program Pulse Width<br>(Overprogram)        | Note 3         | 2.85 | 78.75 | ms    |

| tрнах                            | t <sub>DH</sub>  | Program High to Input<br>Transition         |                | 2    |       | μs    |

| taxgL                            | toes             | Input Transition to Output<br>Enable Low    |                | 2    |       | μs    |

| t <sub>GLQV</sub>                | toe              | Output Enable Low to Output Valid           |                |      | 150   | ns    |

| t <sub>GHQZ</sub> <sup>(4)</sup> | t <sub>DFP</sub> | Output Enable High to Output<br>Hi-Z        |                | 0    | 130   | ns    |

| t <sub>GHAX</sub>                | t <sub>AH</sub>  | Output Enable High to Address<br>Transition |                | 0    |       | ns    |

Notes: 1. V<sub>CC</sub> must be applied simultaneously with or before V<sub>PP</sub> and removed simultaneously or after V<sub>PP</sub>. 2. The Initial Program Pulse width tolerance is 1 ms  $\pm$  5%.

The length of the Over-program Pulse varies from 2.85 ms to 78.95 ms, depending of the multiplication value of the iteration counter.

Sampled only, not 100% tested.

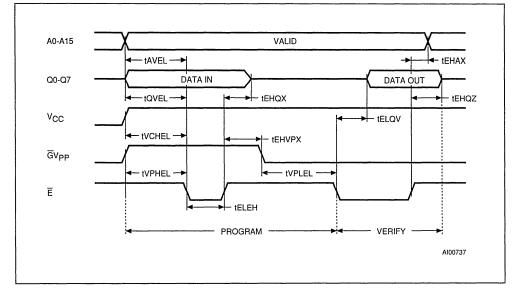

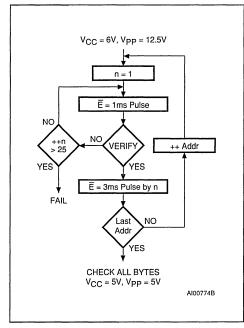

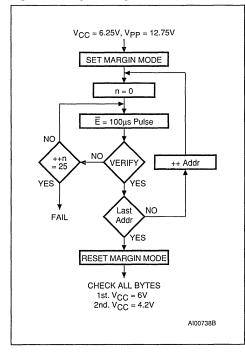

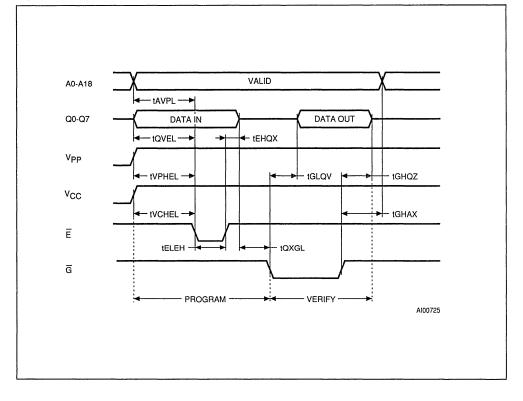

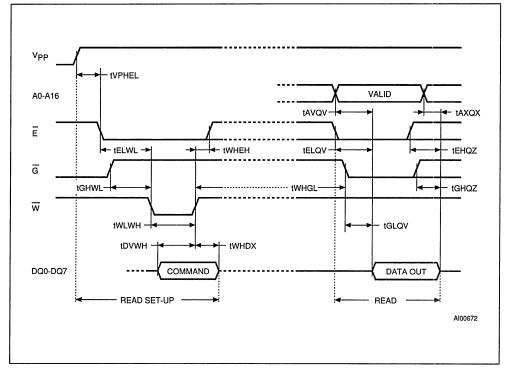

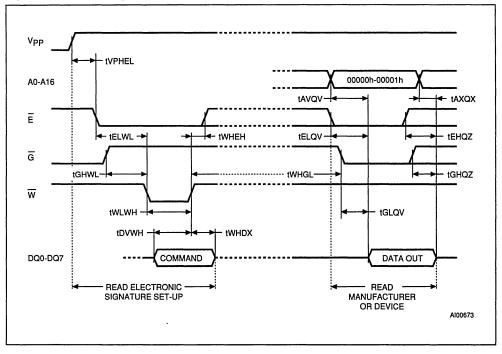

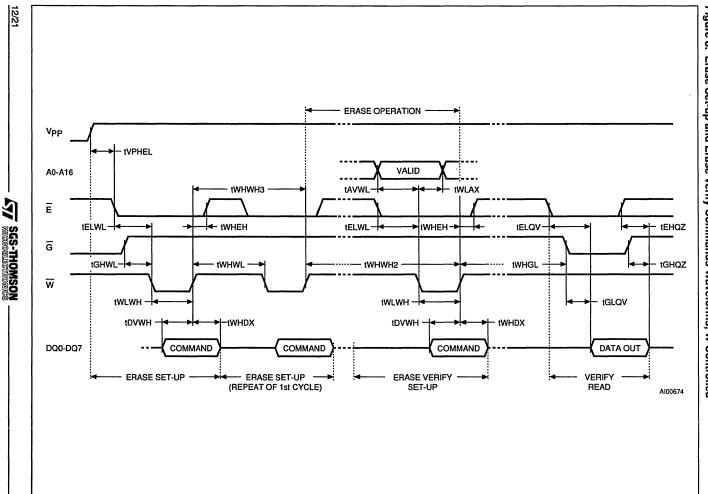

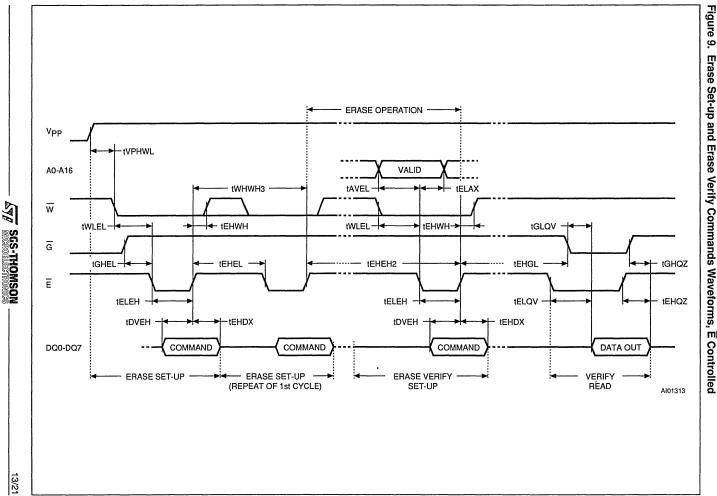

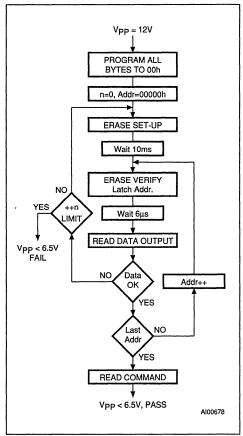

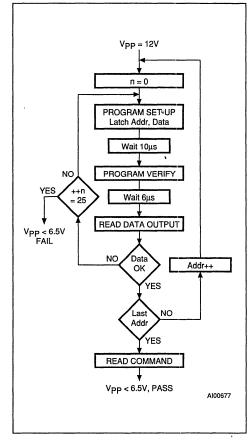

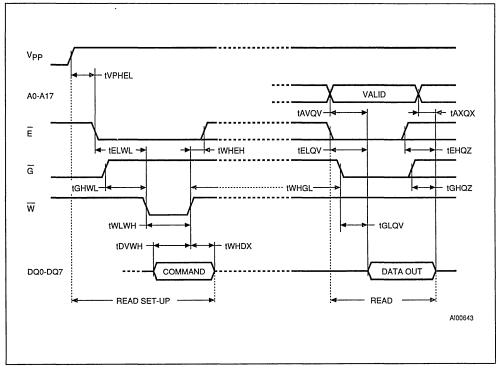

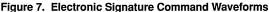

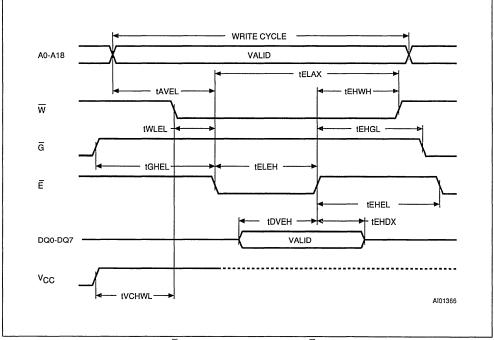

Figure 6. Programming and Verify Modes AC Waveforms

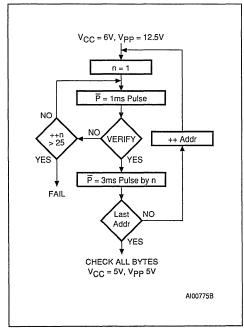

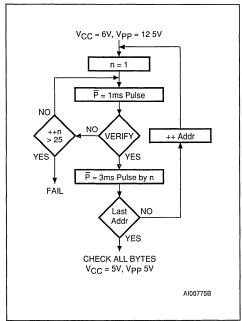

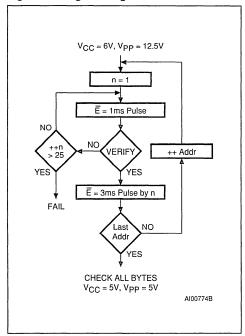

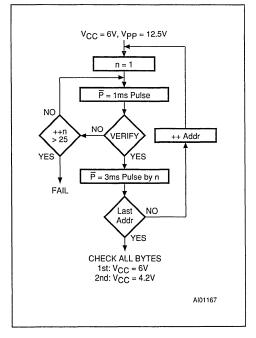

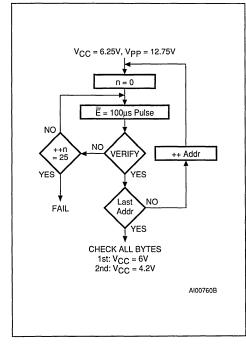

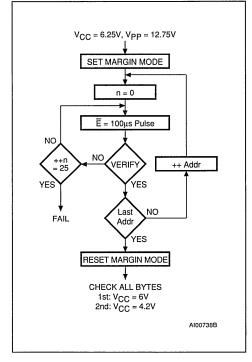

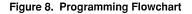

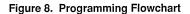

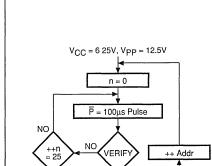

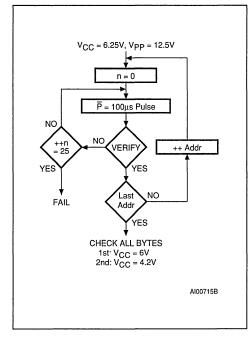

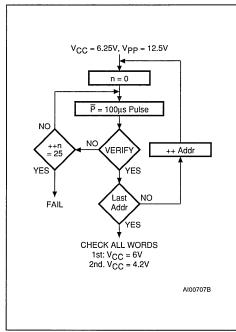

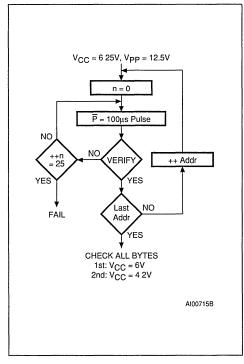

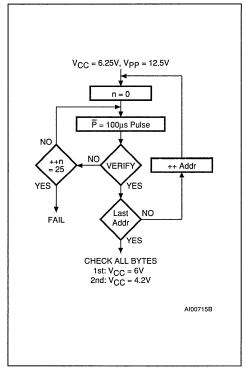

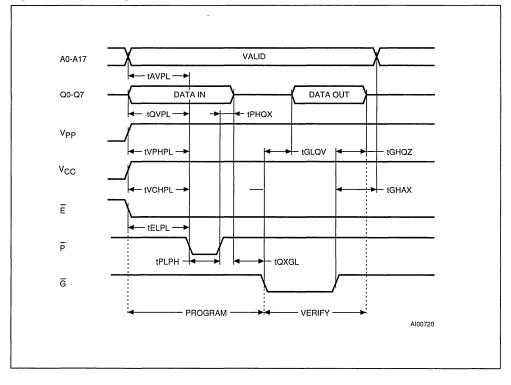

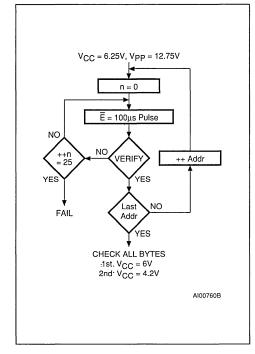

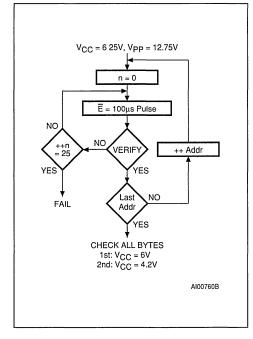

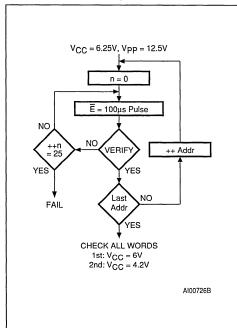

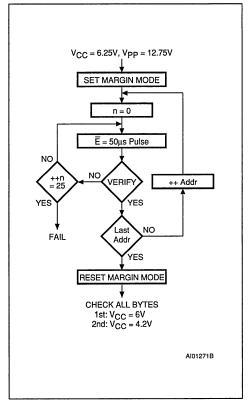

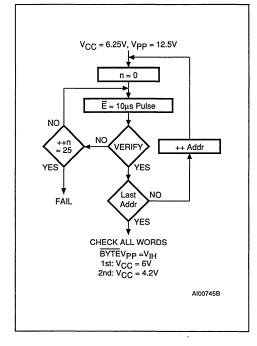

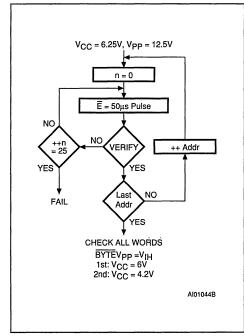

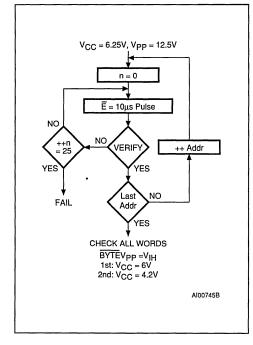

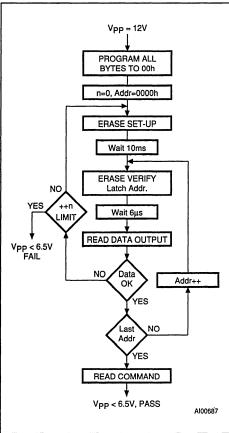

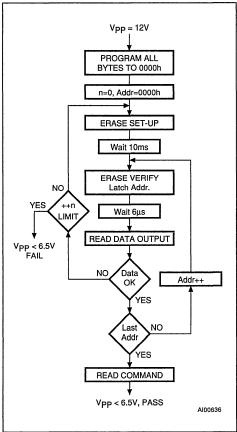

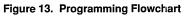

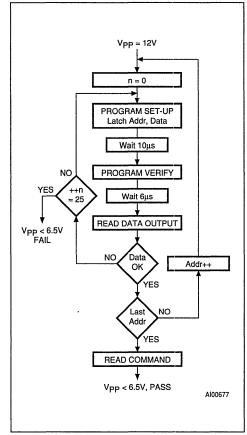

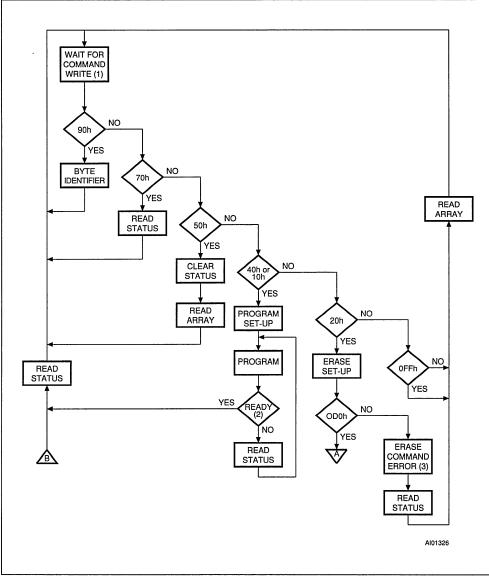

#### Figure 7. Fast Programming Flowchart

#### **DEVICE OPERATION** (cont'd)

been successfully programmed. A flowchart of the M2764A Fast Programming Algorithm is shown on the last page. The Fast Programming Algorithm utilizes two different pulse types: initial and over-program.

The duration of the initial  $\overline{P}$  pulse(s) is 1ms, which will then be followed by a longer overprogram pulse of length 3ms by n (n is equal to the number of the initial one millisecond pulses applied to a particular M2764A location), before a correct verify occurs. Up to 25 one-millisecond pulses per byte are provided for before the overprogram pulse is applied.

The entire sequence of program pulses and byte verifications is performed at  $V_{CC} = 6V$  and  $V_{PP} = 12.5V$ . When the Fast Programming cycle has been completed, all bytes should be compared to the original data with  $V_{CC} = 5V$  and  $V_{PP} = 5V$ .

#### **Program Inhibit**

Programming of multiple M2764A in parallel with different data is also easily accomplished. Except for E, all like inputs (including  $\overline{G}$ ) of the parallel M2764A may be common. A TTL low pulse applied to a M2764A's  $\overline{E}$  input, with V<sub>PP</sub> at 12.5V, will program that M2764A. A high level  $\overline{E}$  input inhibits the other M2764As from being programmed.

## **Program Verify**

A verify should be performed on the programmed bits to determine that they were correctly programmed. The verify is accomplished with  $\overline{G} = V_{IL}$ ,  $\overline{F} = V_{IL}$ ,  $\overline{P} = V_{IH}$  and  $V_{PP} = 12.5V$ .

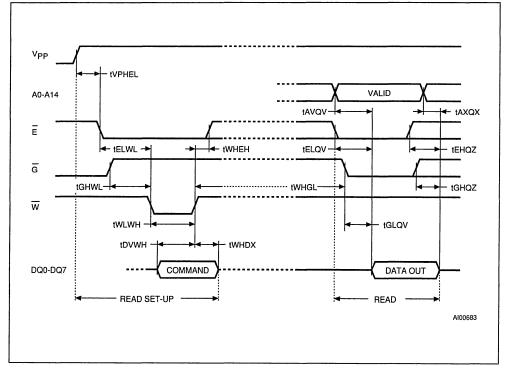

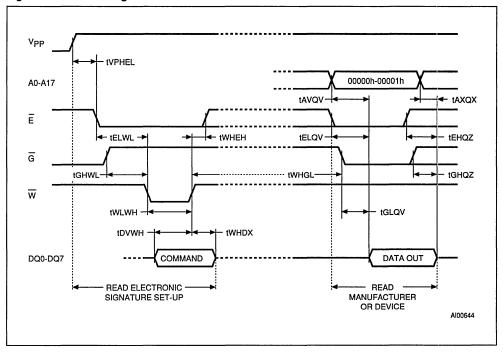

## **Electronic Signature**

The Electronic Signature mode allows the reading out of a binary code from an EPROM that will identify its manufacturer and type. This mode is intended for use by programming equipment to automatically match the device to be programmed with its corresponding programming algorithm. This mode is functional in the  $25^{\circ}C \pm 5^{\circ}C$  ambient temperature range that is required when programming the M2764A.

To activate this mode, the programming equipment must force 11.5V to 12.5V on address line A9 of the M2764A. Two identifier bytes may then be sequenced from the device outputs by toggling address line A0 from V<sub>IL</sub> to V<sub>IH</sub>. All other address lines must be held at V<sub>IL</sub> during Electronic Signature mode. Byte 0 (A0 = V<sub>IL</sub>) represents the manufacturer code and byte 1 (A0 = V<sub>IH</sub>) the device identifier code. For the SGS-THOMSON M2764A, these two identifier bytes are given below.

### ERASURE OPERATION (applies to UV EPPROM)

The erasure characteristic of the M2764A is such that erasure begins when the cells are exposed to light with wavelengths shorter than approximately 4000 Å. It should be noted that sunlight and some type of fluorescent lamps have wavelengths in the 3000-4000 A range. Research shows that constant exposure to room level fluorescent lighting could erase a typical M2764A in about 3 years, while it would take approximately 1 week to cause erasure when exposed to direct sunlight. If the M2764A is to be exposed to these types of lighting conditions for extended periods of time, it is suggested that opaque labels be put over the M2764A window to prevent unintentional erasure. The recommended erasure procedure for the M2764A is exposure to short wave ultraviolet light which has wavelength 2537 Å. The integrated dose (i.e. UV intensity x exposure time) for erasure should be a minimum of 15 W-sec/cm<sup>2</sup>. The erasure time with this dosage is approximately 15 to 20 minutes using an ultraviolet lamp with 12000 µW/cm<sup>2</sup> power rating. The M2764A should be placed within 2.5 cm (1 inch) of the lamp tubes during the erasure. Some lamps have a filter on their tubes which should be removed before erasure.

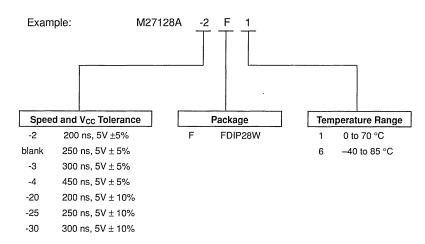

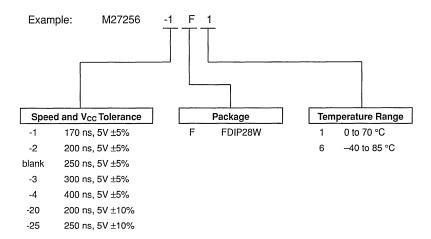

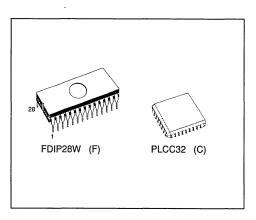

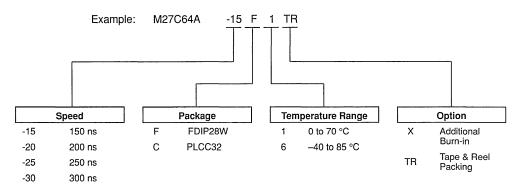

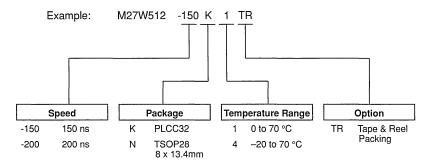

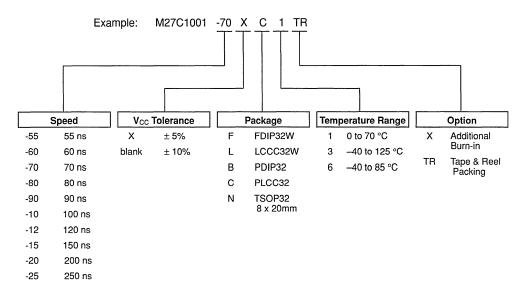

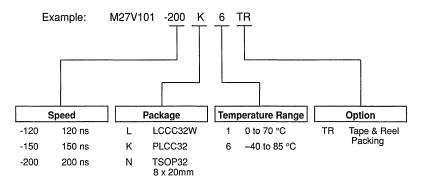

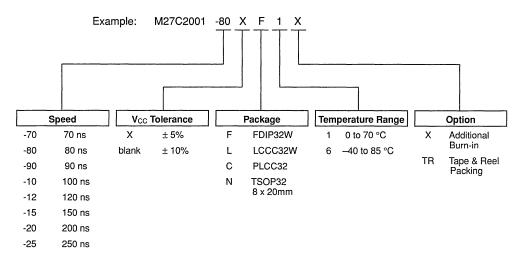

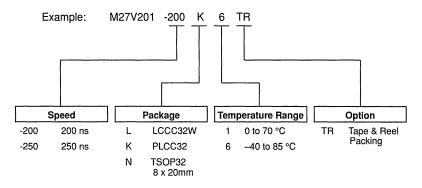

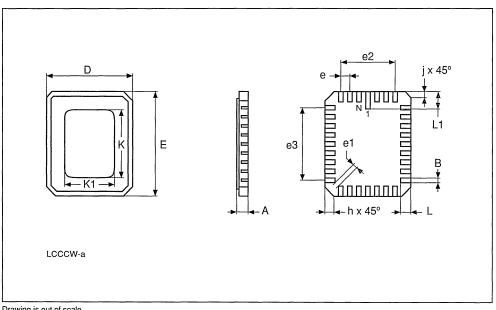

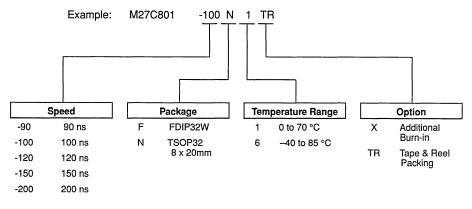

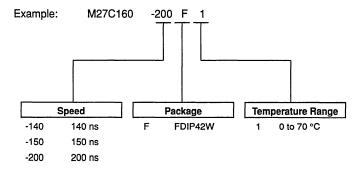

#### **ORDERING INFORMATION SCHEME**

For a list of available options (Speed, V<sub>CC</sub> Tolerance, Package, etc...) refer to the current Memory Shortform catalogue.

For further information on any aspect of this device, please contact SGS-THOMSON Sales Office nearest to you.

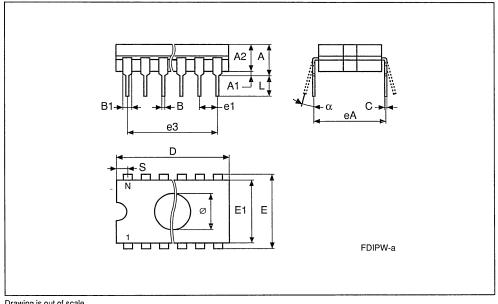

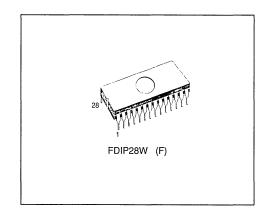

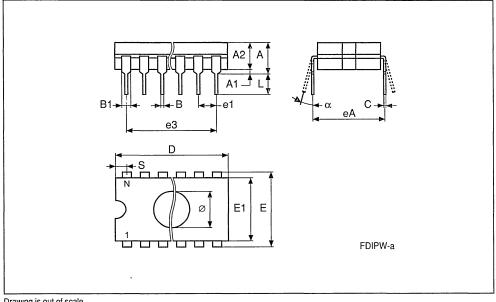

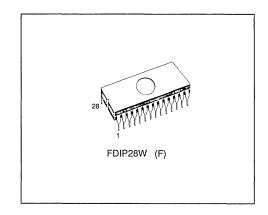

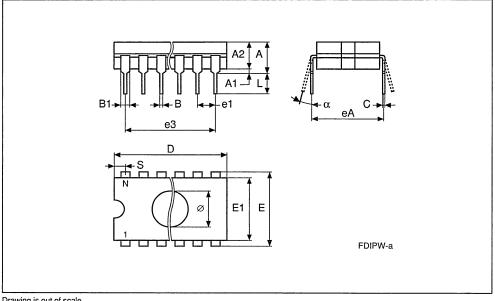

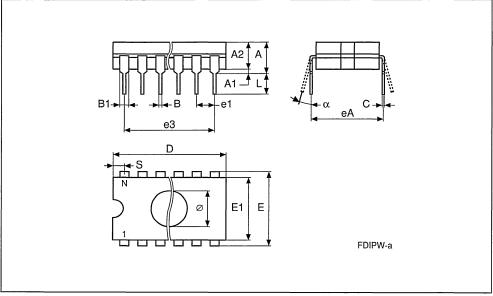

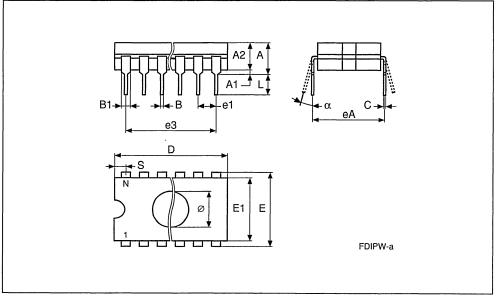

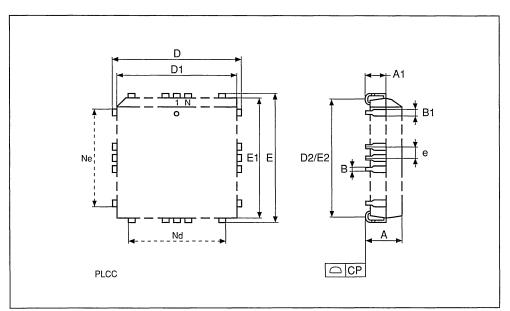

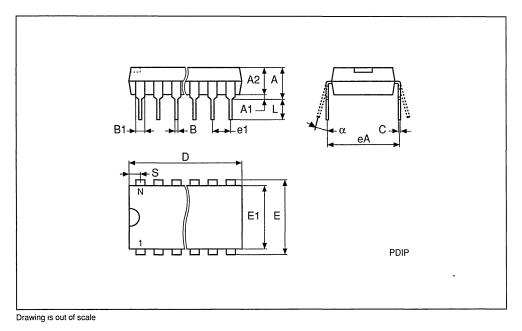

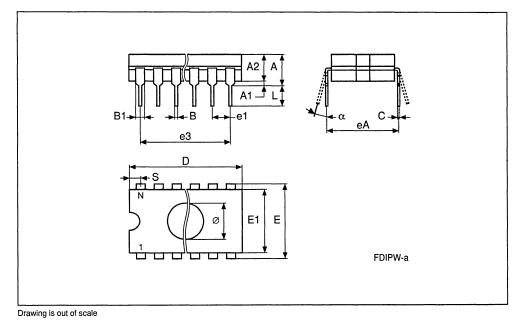

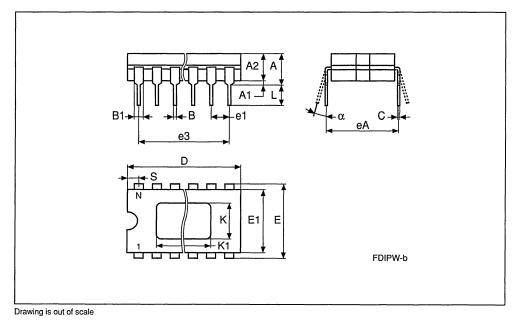

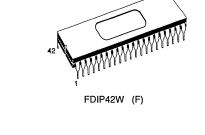

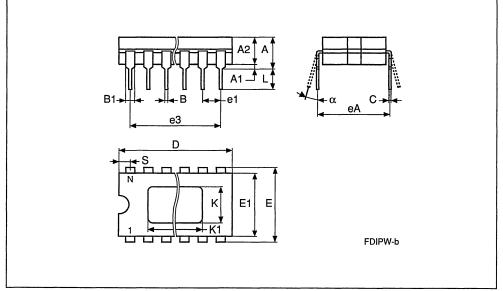

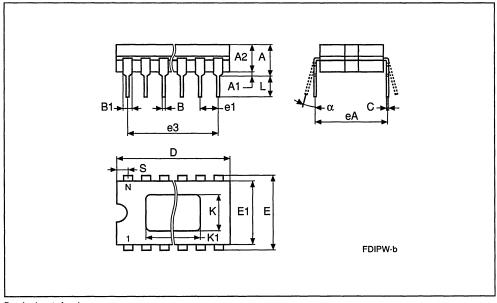

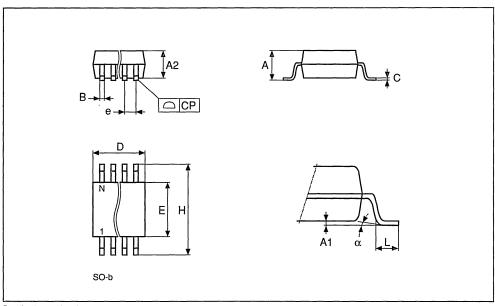

## FDIP28W - 28 pin Ceramic Frit-seal DIP, with window

| Symb  |       | mm    |                    |       | inches |       |

|-------|-------|-------|--------------------|-------|--------|-------|

| Synto | Тур   | Min   | Max                | Тур   | Min    | Max   |

| A     |       |       | 5.71               |       |        | 0.225 |

| A1    |       | 0.50  | 1.78               |       | 0.020  | 0.070 |

| A2    |       | 3.90  | 5.08               |       | 0.154  | 0.200 |

| В     |       | 0.40  | 0.55               |       | 0.016  | 0.022 |

| B1    |       | 1.17  | 1.42               |       | 0.046  | 0.056 |

| С     |       | 0.22  | 0.31               |       | 0.009  | 0.012 |

| D     |       |       | 38.10              |       |        | 1.500 |

| E     |       | 15.40 | 15.80              |       | 0.606  | 0.622 |

| E1    |       | 13.05 | <sup>.</sup> 13.36 |       | 0.514  | 0.526 |

| e1    | 2.54  | -     | -                  | 0.100 | -      | -     |

| e3    | 33.02 | -     | -                  | 1.300 | -      | -     |

| eA    |       | 16.17 | 18.32              |       | 0.637  | 0.721 |

| L     |       | 3.18  | 4.10               |       | 0.125  | 0.161 |

| S     |       | 1.52  | 2.49               |       | 0.060  | 0.098 |

| Ø     | 7.11  | -     | -                  | 0.280 | -      | -     |

| α     |       | 4°    | 15°                |       | 4°     | 15°   |

| N     |       | 28    |                    |       | 28     |       |

FDIP28W

Drawing is out of scale

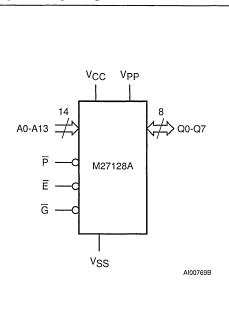

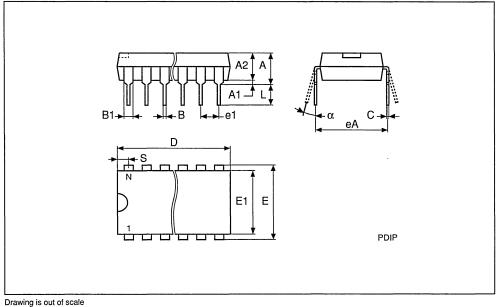

# M27128A

## NMOS 128K (16K x 8) UV EPROM

- FAST ACCESS TIME: 200ns

- EXTENDED TEMPERATURE RANGE

- SINGLE 5 V SUPPLY VOLTAGE

- LOW STANDBY CURRENT: 40mA max

- TTL COMPATIBLE DURING READ and PROGRAM

- FAST PROGRAMMING ALGORITHM

- ELECTRONIC SIGNATURE

- PROGRAMMING VOLTAGE: 12V

#### DESCRIPTION

Table 1. Signal Names

The M27128A is a 131,072 bit UV erasable and electrically programmable memory EPROM. It is organized as 16,384 words by 8 bits.