# **16 BIT MPUs & ASSOCIATED PERIPHERALS**

1<sup>st</sup> EDITION

HOMSON

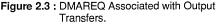

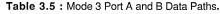

MICROELECTRONICS

000479

# 16 BIT MPUs & ASSOCIATED PERIPHERALS

DATABOOK

**1st EDITION**

**APRIL 1989**

#### USE IN LIFE SUPPORT MUST BE EXPRESSLY AUTHORIZED

SGS-THOMSON' PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF SGS-THOMSON Microelectronics. As used herein:

- Life support devices to systems are devices or systems which, are intended for surgical implant into the body to support or sustain life, and whose failure to perform, when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

| TABLE OF CONTENTS           |        |

|-----------------------------|--------|

|                             |        |

|                             |        |

| GENERAL INDEX               | Page 5 |

| PRODUCT GUIDE               | 7      |

| 68000 MICROPROCESSORS       | 11     |

| 68000 PERIPHERALS           | 171    |

| Z8500 UNIVERSAL PERIPHERALS |        |

|                             | 361    |

## GENERAL INDEX

#### Page

| PRODUCT GUIDE        | <br> | 7   |

|----------------------|------|-----|

| ALPHANUMERICAL INDEX | <br> | 8   |

|                      | <br> | . 9 |

| 68000 MICR | ROPROCESSORS |     | 1 |

|------------|--------------|-----|---|

| TS68000    |              | . 1 | 3 |

| TS68008    |              | 8   | 9 |

#### 68000 PERIPHERALS

| 68000 PERIPHERALS | 171 |

|-------------------|-----|

| TS68230           | 173 |

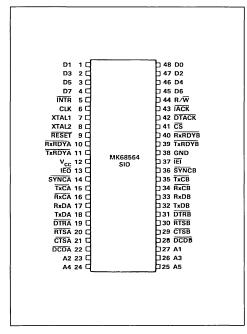

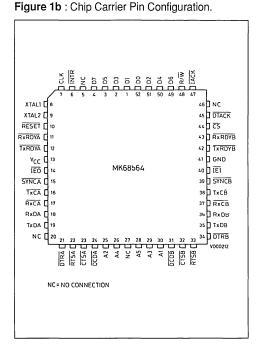

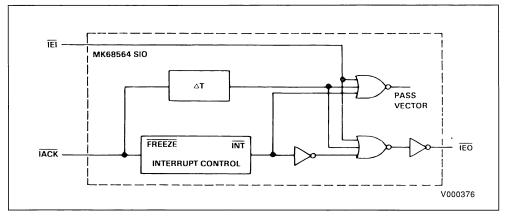

| MK68564           | 235 |

| MK68901           | 281 |

| TS68HC901         | 315 |

### Z8500 UNIVERSAL PERIPHERALS

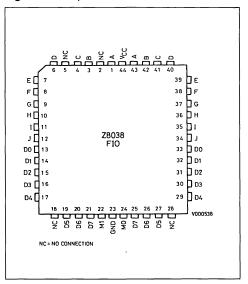

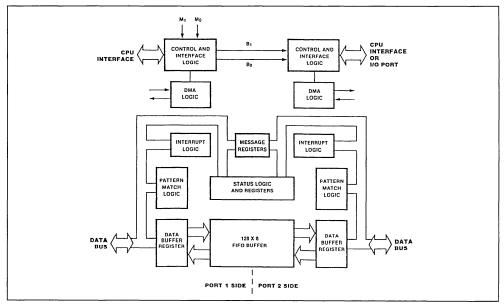

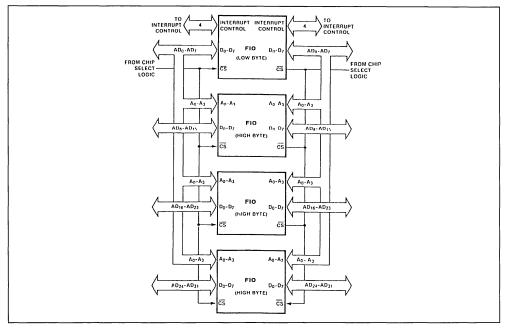

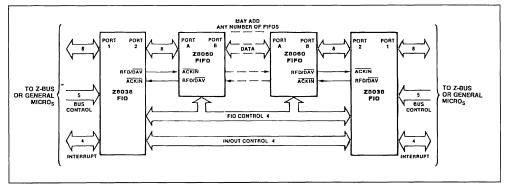

| Z8038 | 363 |

|-------|-----|

| Z8530 | 449 |

| Z8531 | 543 |

| Z8536 | 565 |

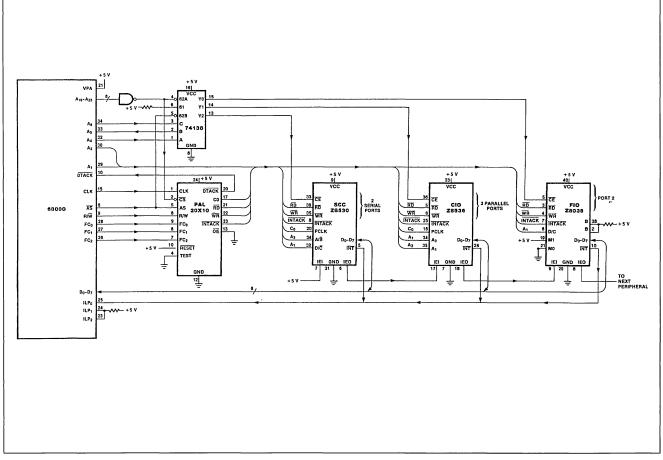

#### APPLICATION NOTE ..... . INTERFACING Z8500 UNIVERSAL PERIPHERALS TO THE TS68000 ..... 597

. •

# **PRODUCT GUIDE**

#### ALPHANUMERICAL INDEX

| Type<br>Number | Function                                      | Page<br>Number |

|----------------|-----------------------------------------------|----------------|

| MK68564        | Serial Input Output                           | 235            |

| MK68901        | Multi-Function Peripheral                     | 281            |

| TS68000        | 16/32-Bit Microprocessor                      | 13             |

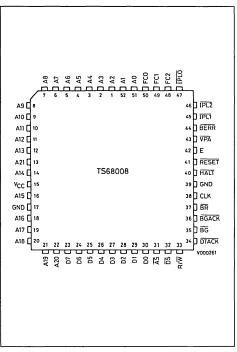

| TS68008        | 8/16-Bit Microprocessor with 8-Bit Data BUS   | 89             |

| TS68230        | Parallel Interface/Timer                      | 173            |

| TS68HC901      | CMOS Multifunction Peripheral                 | 315            |

| Z8038          | FIO/FIFO Input/Output Interface Unit          | 363            |

| Z8530          | Serial Communications Controller              | 449            |

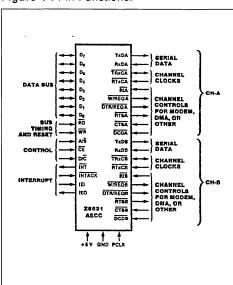

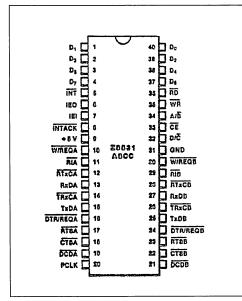

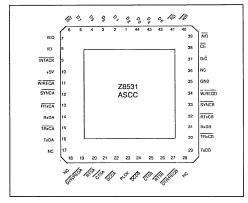

| Z8531          | Asynchronous Serial Communications Controller | 543            |

| Z8536          | Counter/Timer and Parallel I/O Unit           | 565            |

| Part. Number | Description                                                                                                                                      | Page |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------|------|

| TS68000      | 16/32-Bit Microprocessor, 16M Bytes, Direct Addressing, 56<br>Powerful Instructions, 14 Addressing Modes                                         | 13   |

| TS68008      | 8-Bit Version of the TS68000, 1M Bytes Direct Addressing, TS68000 Software Compatible                                                            | 89   |

| TS68230      | Parallel Interface Timer, up to 24 I/O Lines,<br>24-Bit Programmable Timer                                                                       | 173  |

| MK68564      | Dual Serial Input Output Controller, Asynchronous Synchronous<br>byte Oriented, Synchronous Bit Oriented Protocol,<br>up to 1.1M Bits per Second | 235  |

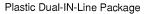

| MK68901      | Multi Function Peripheral, 8 I/O Lines, 16 Interrupt Sources,<br>Single Channel USART, Four 8-Bit Timers                                         | 281  |

| TS68HC901    | CMOS Version and Fully Compatible with the MK68901                                                                                               | 315  |

| Z8038        | FIFO Input Output Interface Unit, 128-Byte RAM Buffer,<br>Data Transactions Managing, 12 Operating Modes                                         | 363  |

| Z8530        | Serial Communication Controller, 2 Independent Channels,<br>Multiprotocol, up to 1M-Bit per Second                                               | 449  |

| Z8531        | Asynchronous Serial Communication Controller,<br>2 Independent Channels                                                                          | 543  |

| Z8536        | Counter/Timer and Parallel I/O Unit, Two 8-Bit Ports,<br>4-Bit Special Purpose Port, 16-Vector Interrupt Controller,<br>Three 16-Bit Timers      | 565  |

.

.

# 68000 MICROPROCESSORS

.

# TS68000

## HMOS 16/32-BIT MICROPROCESSOR

The TS68000 is the first implementation of the 68000 16/32 microprocessor architecture. The TS68000 has a 16-bit data bus and 24-bit address bus while the full architecture provides for 32-bit address and data buses. It is completely code-compatible with the TS68008 8-bit data bus implementation of the 68000 and is downward code-compatible with the TS68020 32-bit implementation of the architecture. Any user-mode programs written using the TS68000 instruction set will run unchanged on the TS68008 and TS68020. This is possible because the user programming model is identical for all three processors and the instruction sets are proper subsets of the complete architecture.

SGS-THOMSON MICROELECTRONICS

The resources available to the TS68000 user consist of the following :

- 16 32-bit data and address registers

- 16 megabyte direct addressing range

- 56 powerful instruction types

- Operations on five main data types

- Memory mapped I/O

- 14 addressing modes

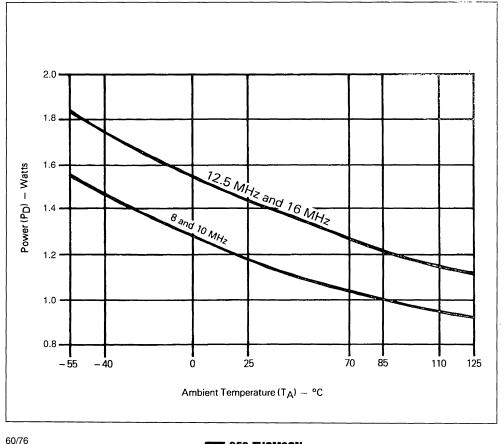

- 4 available versions : 8MHz, 10MHz, 12.5MHz and 16MHz

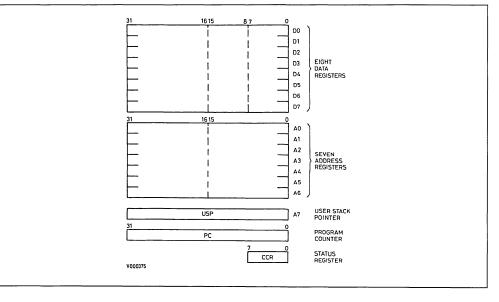

As shown in the user programming model, the TS68000 offers 16 32-bit registers and a 32-bit program counter. The first eight registers (D0-D7) are used as data registers for byte (8-bit), word (16-bit), and long word (32-bit) operations. The second set of seven registers (A0-A6) and the user stack pointer (USP) may be used as software stack pointers and base address registers. In addition, the registers may be used for word and long word operations. All of the 16 registers may be used as index registers.

#### PRELIMINARY INFORMATION

#### SECTION 1

#### INTRODUCTION

The TS68000 is the first implementation of the 68000 16/32 microprocessor architecture. The TS68000 has a 16-bit data bus and 24-bit address bus while the full architecture provides for 32-bit address an data buses. It is completely code-compatible with the TS68008 a-bit data bus implementation of the 68000 and is downward code-compatible with the TS68020 32-bit implementation of the architecture. Any user-mode programs written using the TS68008 and TS68020. This is possible because the user programming model is identical for all four processors and the instruction sets are proper subsets of the complete architecture.

The resources available to the TS68000 user consist of the following :

- 17 32-Bit Data and Address Registers

- 16 Megabyte Direct Addressing Range

- 56 Powerful Instruction Types

- Operations on Five Main Data Types

- Memory Mapped I/O

- 14 Addressing Modes

As shown in the user programming model (figure 1-1), the TS68000 offers 16 32-bit registers and a 32bit program counter. The first eight registers (D0-D7) are used as data registers for byte (8-bit), word (16bit), and long word (32-bit) operations. The second

Figure 1.1 : User Programming Model.

set of seven registers (A0-A6) and the user stack pointer (USP) may be used as software stack pointers and base address registers. In addition, the registers may be used for word and long word operations. All of the 16 registers may be used as index registers.

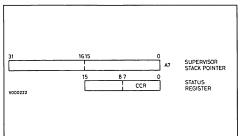

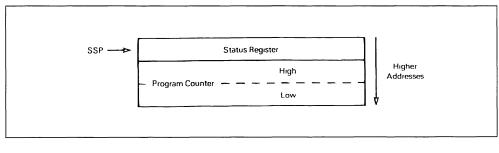

In supervisor mode, the upper byte of the status register and the supervisor stack pointer (SSP) are also available to the programmer. These registers are shown in figure 1-2.

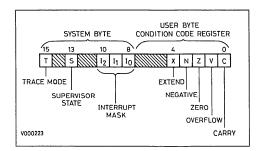

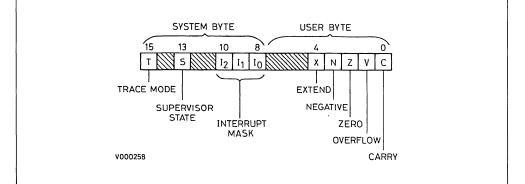

The status register (figure 1-3) contains the interrupt mask (eight levels available) as well as the condition codes : extend (X), negative (N), zero (Z), overflow (V), and carry (C). Additional status bits indicate that the processor is in a trace (T) mode and in a supervisor (S) or user state.

#### 1.1. DATA TYPES AND ADDRESSING MODES

Five basic data types are supported. These data types are :

- Bits

- BCD Digits (4 bits)

- Bytes (8 bits)

- Words (16 bits)

- Long Words (32 bits)

In addition, operations on other data types such as memory addresses, status word data, etc., are provided in the instruction set.

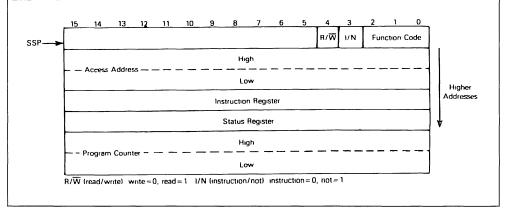

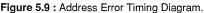

Figure 1.2 : Supervisor Programming Model Supplement.

#### Table 1.1 : Addressing Modes.

| Addressing Modes                                                                                                                                                                                    | Syntax                                                                      |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|

| Register Direct Addressing<br>Data Register Direct<br>Address Register Direct                                                                                                                       | Dn<br>An                                                                    |

| Absolute Data Addressing<br>Absolute Short<br>Absolute Long                                                                                                                                         | xxx W<br>xxx L                                                              |

| Program Counter Relative<br>Addressing<br>Relative with Offset<br>Relative with Index Offset                                                                                                        | d <sub>16</sub> (PC)<br>d <sub>8</sub> (PC, Xn)                             |

| Register Indirect Addressing<br>Register Indirect<br>Postincrement Register Indirect<br>Predecrement Register Indirect<br>Register Indirect with Offset<br>Indexed Register Indirect with<br>Offset | (An)<br>(An) +<br>– (An)<br>d <sub>16</sub> (An)<br>d <sub>8</sub> (An, Xn) |

| Immediate Data Addressing<br>Immediate<br>Quick Immediate                                                                                                                                           | #xxx<br>#1#8                                                                |

| Implied Addressing<br>Implied Register                                                                                                                                                              | SR USP SP PC                                                                |

Notes :

Dn = Data Register

An = Address Register

Xn = Address or Data Register used as Index Register

SR = Status Register

PC = Program Counter

SP = Stack Pointer USP = User Stack Pointer

() = Effective Address

() = Effective Address

$d_8 = 8$ -Bit Offset (displacement)  $d_{16} = 16$ -Bit Offset (displacement)

#XXX = Immediate Data

Figure 1.3 : Status Register.

The 14 address modes, shown in table 1.1, include six basic types :

- Register Direct

- Register Indirect

- Absolute

- Program Counter Relative

- Immediate

- Implied

Included in the register indirect addressing modes is the capability to do postincrementing, predecrementing, offsetting, and indexing. The program counter relative mode can also be modified via indexing and offsetting.

#### 1.2. INSTRUCTION SET OVERVIEW

The TS68000 instruction set is shown in table 1-2. Some additional instructions are variations, or subsets, of these and they appear in table 1-3. Special emphasis has been given to the instruction set's support of structured high-level languages to facilitate ease of programming. Each instruction, with few exceptions, operates on bytes, words, and long words and most instructions can use any of the 14 addressing modes. Combining instruction types, data types, and addressing modes, over 1000 useful instructions are provided. These instructions include signed and unsigned, multiply and divide, "quick" arithmetic operations, BCD arithmetic, and expanded operations (through traps).

| Table | 1.2 | : | Instruction | Set | Summary. |

|-------|-----|---|-------------|-----|----------|

|-------|-----|---|-------------|-----|----------|

| Mnemonic                                                        | Description                                                                                                                                                                                                         |

|-----------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ABCD                                                            | Add Decimal with Extend                                                                                                                                                                                             |

| ADD                                                             | Add                                                                                                                                                                                                                 |

| AND                                                             | Logical And                                                                                                                                                                                                         |

| ASL                                                             | Arithmetic Shift Left                                                                                                                                                                                               |

| ASR                                                             | Arithmetic Shift Right                                                                                                                                                                                              |

| Bcc                                                             | Branch Conditionally                                                                                                                                                                                                |

| BCHG                                                            | Bit Test and Change                                                                                                                                                                                                 |

| BCLR                                                            | Bit Test and Clear                                                                                                                                                                                                  |

| BRA                                                             | Branch always                                                                                                                                                                                                       |

| BSET                                                            | Bit Test and Set                                                                                                                                                                                                    |

| BSR                                                             | Branch to Subroutine                                                                                                                                                                                                |

| BTST                                                            | Bit Test                                                                                                                                                                                                            |

| CHK                                                             | Check Register against Bounds                                                                                                                                                                                       |

| CLR                                                             | Clear Operand                                                                                                                                                                                                       |

| CMP                                                             | Compare                                                                                                                                                                                                             |

| DBcc<br>DIVS<br>DIVU                                            | Test Condition, Decrement and<br>Branch<br>Signed Divide<br>Unsigned Divide                                                                                                                                         |

| EOR                                                             | Exclusive Or                                                                                                                                                                                                        |

| EXG                                                             | Exchange Registers                                                                                                                                                                                                  |

| EXT                                                             | Sign Extend                                                                                                                                                                                                         |

| JMP                                                             | Jump                                                                                                                                                                                                                |

| JSR                                                             | Jump to Subroutine                                                                                                                                                                                                  |

| LEA                                                             | Load Effective Address                                                                                                                                                                                              |

| LINK                                                            | Link Stack                                                                                                                                                                                                          |

| LSL                                                             | Logical Shift Left                                                                                                                                                                                                  |

| LSR                                                             | Logical Shift Right Left                                                                                                                                                                                            |

| MOVE                                                            | Move                                                                                                                                                                                                                |

| MULS                                                            | Signed Multiply                                                                                                                                                                                                     |

| MULU                                                            | Unsigned Mulitply                                                                                                                                                                                                   |

| NBCD                                                            | Negate Decimal with Extend                                                                                                                                                                                          |

| NEG                                                             | Negate                                                                                                                                                                                                              |

| NOP                                                             | No Operation                                                                                                                                                                                                        |

| NOT                                                             | One's Complement                                                                                                                                                                                                    |

| OR                                                              | Logical Or                                                                                                                                                                                                          |

| PEA                                                             | Push Effective Address                                                                                                                                                                                              |

| RESET<br>ROL<br>ROR<br>ROXL<br>ROXR<br>RTE<br>RTR<br>RTR<br>RTS | Reset External Devices<br>Rotate Left without Extend<br>Rotate Right without Extend<br>Rotate Left with Extend<br>Rotate Right with Extend<br>Return from Exception<br>Return and Restore<br>Return from Subroutine |

| SBCD                                                            | Subtract Decimal with Extend                                                                                                                                                                                        |

| Scc                                                             | Set Conditional                                                                                                                                                                                                     |

| STOP                                                            | Stop                                                                                                                                                                                                                |

| SUB                                                             | Subtract                                                                                                                                                                                                            |

| SWAP                                                            | Swap Data Register Halves                                                                                                                                                                                           |

| TAS                                                             | Test and Set Operand                                                                                                                                                                                                |

| TRAP                                                            | Trap                                                                                                                                                                                                                |

| TRAPV                                                           | Trap on Overflow                                                                                                                                                                                                    |

| TST                                                             | Test                                                                                                                                                                                                                |

| UNLK                                                            | Unlink                                                                                                                                                                                                              |

Table 1.3 : Variations of Instruction Types.

| Instruction<br>Type | Variation                                                                                        | Description                                                                                                                                                                                                                             |

|---------------------|--------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ADD                 | ADD<br>ADDA<br>ADDQ<br>ADDI<br>ADDX                                                              | Add<br>Add Address<br>Add Quick<br>Add Immediate<br>Add with Extend                                                                                                                                                                     |

| AND                 | AND<br>ANDI<br>ANDI to CCR<br>ANDI to SR                                                         | Logical And<br>And Immediate<br>And Immediate to<br>Condition Codes<br>And Immediate to<br>Status Register                                                                                                                              |

| СМР                 | CMP<br>CMPA<br>CMPM<br>CMPI                                                                      | Compare<br>Compare Address<br>Compare Memory<br>Compare Immediate                                                                                                                                                                       |

| EOR                 | EOR<br>EORI<br>EORI to CCR<br>EORI to SR                                                         | Exclusive Or<br>Exclusive Or Immediate<br>Exclusive Or Immediate<br>to Condition Codes<br>Exclusive Or Immediate<br>to Status Register                                                                                                  |

| MOVE                | MOVE<br>MOVEA<br>MOVEP<br>MOVEQ<br>MOVE from<br>SR<br>MOVE to SR<br>MOVE to SR<br>MOVE to<br>CCR | Move<br>Move Address<br>Move Multiple Registers<br>Move Peripheral Data<br>Move Quick<br>Move from Status<br>Register<br>Move to Status Register<br>Move to Status Register<br>Move to Condition<br>Codes<br>Move User Stack<br>Pointer |

| NEG                 | NEG<br>NEGX                                                                                      | Negate<br>Negate with Extend                                                                                                                                                                                                            |

| OR                  | OR<br>ORI<br>ORI to CCR<br>ORI to SR                                                             | Logical Or<br>Or Immediate<br>Or Immediate to<br>Condition Codes<br>Or Immediate to Status<br>Register                                                                                                                                  |

| SUB                 | SUB<br>SUBA<br>SUBI<br>SUBQ<br>SUBX                                                              | Subtract<br>Subtract Address<br>Subtract Immediate<br>Subtract Quick<br>Subtract with Extend                                                                                                                                            |

#### **SECTION 2**

# DATA ORGANIZATION AND ADDRESSING CAPABILITIES

This section contains a description of the registers and the data organization of the TS68000.

#### 2.1. OPERAND SIZE

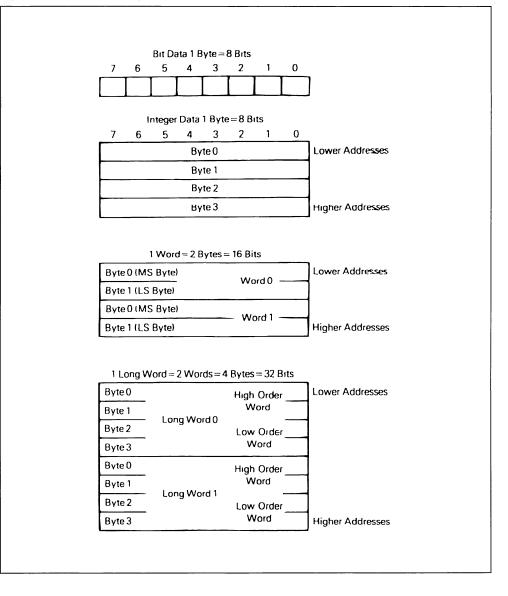

Operand sizes are defined as follows : a byte equals 8 bits, a word equals 16 bits, and a long word equals 32 bits. The operand size for each instruction is either explicitly encoded in the instruction or implicitly defined by the instruction operation. Implicit instructions support some subset of all three sizes.

#### 2.2. DATA ORGANIZATION IN REGISTERS

The eight data registers support data operands of 1, 8, 16, or 32 bits. The seven address registers together with the stack pointers support address operands of 32 bits.

2.2.1. DATA REGISTERS. Each data register is 32 bits wide. Byte operands occupy the low order 8 bits, word operands the low order 16 bits, and long word operands the entire 32 bits. The least significant bit is addressed as bit zero ; the most significant bit is addressed as bit 31.

When a data register is used as either a source or destination operand, only the appropriate low order portion is changed ; the remaining high order portion is neither used nor changed.

2.2.2. ADDRESS REGISTERS. Each address register and the stack pointer is 32 bits wide and holds a full 32-bit address. Address registers do not support the sized operands. Therefore, when an address register is used as a source operand, either the low order word or the entire long word operand is used depending upon the operation size. When an address register is used as the destination operand, the entire register is affected regardless of the operation size. If the operation size is word, any other operands are sign extended to 32 bits before the operation is performed.

#### 2.3. DATA ORGANIZATION IN MEMORY

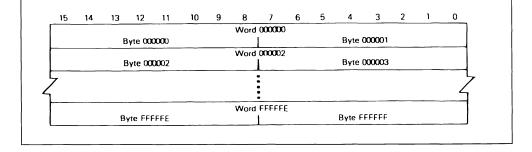

Bytes are individually addressable with the high order byte having an even address the same as the word, as shown in figure 2.1. The low order byte has an odd address that is one count higher than the word address. Instructions and multibyte data are accessed only on word (even byte) boundaries. If a long word datum is located at address n (n even), then the second word of that datum is located at address n + 2.

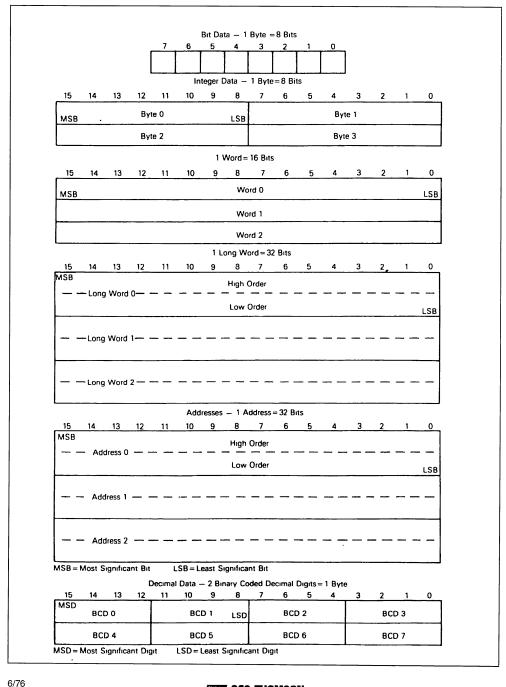

The data types supported by the TS68000 are : bit data, integer data of 8, 16, or 32 bits, 32-bit addresses and binary coded decimal data. Each of these data types is put in memory, as shown in figure 2.2. The numbers indicate the order in which the data would be accessed from the processor.

#### 2.4. ADDRESSING

Instructions for the TS68000 contain two kinds of information : the type of function to be performed and the location of the operand(s) on which to perform that function. The methods used to locate (address) the operand(s) are explained in the following paragraphs.

Instructions specify an operand location in one of three ways :

| Register Specification | -the number of the regis-<br>ter is given in the register<br>field of their instruction.                  |

|------------------------|-----------------------------------------------------------------------------------------------------------|

| Effective Address      | <ul> <li>use of the different effective<br/>addressing modes.</li> </ul>                                  |

| Implicit Reference     | <ul> <li>the definition of certain<br/>instructions implies the use<br/>of specific registers.</li> </ul> |

Figure 2.1 : Word Organization in Memory.

Figure 2.2 : Memory Data Organization.

#### 2.5. INSTRUCTION FORMAT

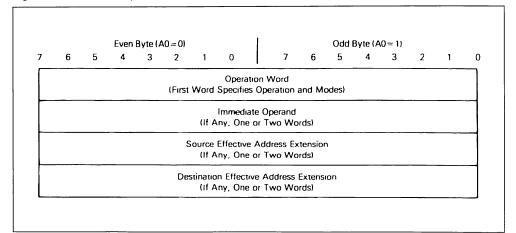

Instructions are from one to five words in length as shown in figure 2.3. The length of the instruction and the operation to be performed is specified by the first word of the instruction which is called the operation word. The remaining words further specify the operands. These words are either immediate operands or extensions to the effective address mode specified in the operation word.

#### 2.6. PROGRAM/DATA REFERENCES

The TS68000 separates memory references into two classes : program references and data references. Program references, as the name implies, are references to that section of memory that contains the program being executed. Data references refer to that section of memory that contains data. Operands reads are from the data space except in the case of the program counter relative addressing mode. All operand writes are to the data space.

#### 2.7. REGISTER SPECIFICATION

The register field within an instruction specifies the register to be used. Other fields within the instruction specify whether the register selected is an address or data register and how the register is to be used.

#### 2.8. EFFECTIVE ADDRESS

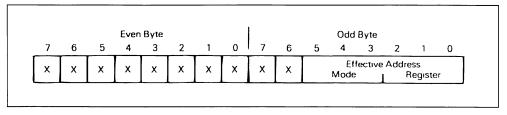

Most instructions specify the location of an operand by using the effective address field in the operation word. For example, figure 2.4 shows the general format of the single-effective-address instruction operation word. The effective address is composed of two 3-bit fields : the mode field and the register field. The value in the mode field selects the different address modes. The register field contains the number of a register.

The effective address field may require additional information to fully specify the operand. This additional information, called the effective address extension, is contained in the following word or words and is considered part of the instruction, as shown in figure 2.3. The effective address modes are grouped into three categories : register direct, memory addressing, and special.

2.8.1. REGISTER DIRECT MODES. These effective addressing modes specify that the operand is in one of 16 multifunction registers.

2.8.1.1. Data Register Direct.

The operand is in the data register specified by the effective address register field.

2.8.1.2. Address Register Direct.

The operand is in the address register specified by the effective address register field.

2.8.2. MEMORY ADDRESS MODES. These effective addressing modes specify that the operand is in memory and provide the specific address of the operand.

2.8.2.1. Address Register Indirect.

The address of the operand is in the address register specified by the register field. The reference is classified as a data reference with the exception of the jump and jump-to-subroutine instructions.

#### Figure 2.3 : Instruction Operation Word General Format.

| 15 | 14 | 13 | 12 | 11 | 10      | 9       | 8        | 7       | 6       | 5      | 4   | 3 | 2 | 1 | 0 |

|----|----|----|----|----|---------|---------|----------|---------|---------|--------|-----|---|---|---|---|

|    |    |    |    |    |         | (       | Operatio | on Wor  | d       |        |     |   |   |   |   |

|    |    |    |    | (F | irst W  | ord Sp  | ecities  | Operati | on and  | l Mode | -s) |   |   |   |   |

|    |    |    |    |    |         | Imn     | nediate  | Operar  | nd      |        |     |   |   |   |   |

|    |    |    |    |    | 0       |         |          | Two V   |         |        |     |   |   |   |   |

|    |    |    |    |    |         |         |          | Address |         |        |     |   |   |   |   |

|    |    |    |    |    |         |         |          | r Two ' |         |        |     |   |   |   |   |

|    |    |    |    |    |         |         |          |         |         |        |     |   |   |   |   |

|    |    |    |    | •  | Destina | ation E | ffective | e Addre | ss Exte | ension |     |   |   |   |   |

|    |    |    |    |    | ()      | f Any,  | One o    | r Two ۱ | Words)  |        |     |   |   |   |   |

Figure 2.4 : Single-Effective-Address Instruction Operation Word.

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4    | 3       | 2       | 1        |

|----|----|----|----|----|----|---|---|---|---|---|------|---------|---------|----------|

|    |    |    |    |    |    |   |   |   |   |   | Ef   | fective | e Addre | ss       |

| X  | х  | х  | х  | X  | х  | X | х | X | X |   | Mode |         | 1       | Register |

#### 2.8. EFFECTIVE ADDRESS (continued)

2.8.2.2. Address Register Indirect with Postincrement.

The address of the operand is in the address register specified by the register field. After the operand address is used, it is incremented by one, two, or four depending upon whether the size of the operand is byte, word, or long word. If the address register is the stack pointer and the operand size is byte, the address is incremented by two rather than one to keep the stack pointer on a word boundary. The reference is classified as a data reference.

2.8.2.3. Address Register Indirect with Predecrement.

The address of the operand is in the address register specified by the register field. Before the operand address is used, it is decremented by one, two, or four depending upon whether the operand size is byte, word, or long word. If the address register is the stack pointer and the operand size is byte, the address is decremented by two rather than one to keep the stack pointer on a word boundary. The reference is classified as a data reference.

2.8.2.4. Address Register Indirect with Displacement.

This addressing mode requires one word of extension. The address of the operand is the sum of the address in the address register and the sign-extended 16-bit displacement integer in the extension word. The reference is classified as a data reference with the exception of the jump and jump-to-subroutine instructions.

2.8.2.5. Address Register Indirect with Index.

This addressing mode requires one word of extension. The address of the operand is the sum of the address in the address register, the sign-extended displacement integer in the low order eight bits of the extension word, and the contents of the index register. The reference is classified as a data reference with the exception of the jump and jump-tosubroutine instructions.

2.8.3. SPECIAL ADDRESS MODES. The special address modes use the effective address register field to specify the special addressing mode instead of a register number.

2.8.3.1. Absolute Short Address.

This addressing mode requires one word of extension. The address of the operand is the extension word. The 16-bit address is sign extended before it is used. The reference is classified as a data reference with the exception of the jump and jump-tosubroutine instructions.

#### 2.8.3.2. Absolute Long Address.

This addressing mode requires two words of extension. The address of the operand is developed by the concatenation of the extension words. The high order part of the address is the first extension word ; the low order part of the address is the second extension word. The reference is classified as a data reference with the exception of the jump and jump-to-subroutine instructions.

2.8.3.3. Program Counter with Displacement.

This addressing mode requires one word of extension. The address of the operand is the sum of the address in the program counter and the sign-extended 16-bit displacement integer in the extension word. The value in the program counter is the address of the extension word. The reference is classified as a program reference.

2.8.3.4. Program Counter with Index.

This addressing mode requires one word of extension. The address is the sum of the address in the program counter, the sign-extended displacement integer in the lower eight bits of the extension word, and the contents of the index register. The value in the program counter is the address of the extension word. This reference is classified as a program reference.

2.8.3.5. Immediate Data.

This addressing mode requires either one or two words of extension depending on the size of the operation.

| Byte Operation      | <ul> <li>operand is low order byte<br/>of extension word</li> </ul>                                                                                                |

|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Word Operation      | -operand is extension word                                                                                                                                         |

| Long Word Operation | -operand is in the two ex-<br>tension words, high order<br>16 bits are in the first ex-<br>tension word, low order<br>16 bits are in the second<br>extension word. |

2.8.3.6. Implicit Reference.

Some instructions make implicit reference to the program counter (PC), the system stack pointer (SP), the supervisor stack pointer (SSP), the user stack pointer (USP), or the status register (SR). A selected set of instructions may reference the status register by means of the effective address field. These are :

| ANDI to CCR | EORI to SR | MOVE to CCR  |

|-------------|------------|--------------|

| ANDI to SR  | ORI to CCR | MOVE to SR   |

| EORI to CCR | ORI to SR  | MOVE from SR |

#### 2.9. EFFECTIVE ADDRESS ENCODING SUM-MARY

Table 2.1 is a summary of the effective addressing modes discussed in the previous paragraphs.

#### 2.10. SYSTEM STACK

The system stack is used implicitly by many instructions ; user stacks and queues may be created and maintained through the addressing modes. Address register seven (A7) is the system stack pointer (SP). The system stack pointer is either the supervisor stack pointer (SSP) or the user stack pointer (USP), depending on the state of the S bit in the status register. If the S bit indicates supervisor state, SSP is the active system stack pointer and the USP cannot be referenced as an address register. If the S bit indicates user state, the USP is the active system stack pointer, and the SSP cannot be referenced. Each system stack fills from high memory to low memory.

Table 2.1 : Effective Address Encoding Summary.

| Addrossing Mode                              | Mode | Deviator        |

|----------------------------------------------|------|-----------------|

| Addressing Mode                              | wode | Register        |

| Data Register Direct                         | 000  | Register Number |

| Address Register Direct                      | 001  | Register Number |

| Address Register Indirect                    | 010  | Register Number |

| Address Register Indirect with Postincrement | 011  | Register Number |

| Address Register Indirect with Predecrement  | 100  | Register Number |

| Address Register Indirect with Displacement  | 101  | Register Number |

| Address Register Indirect with Index         | 110  | Register Number |

| Absolute Short                               | 111  | 000             |

| Absolute Long                                | 111  | 001             |

| Program Counter with<br>Displacement         | 111  | 010             |

| Program Counter with<br>Index                | 111  | 011             |

| Immediate                                    | 111  | 100             |

#### **SECTION 3**

#### INSTRUCTION SET SUMMARY

This section contains an overview of the form and structure of the TS68000 instruction set. The instructions form a set of tools that include all the machine functions to perform the following operations :

Data Movement

Integer Arithmetic

Logical

Shift and Rotate

Bit Manipulation

**Binary Coded Decimal**

Program Control

System Control

The complete range of instruction capabilities combined with the flexible addressing modes described previously provide a very flexible base for program development.

#### 3.1. DATA MOVEMENT OPERATIONS

The basic method of data acquisition (transfer and storage) is provided by the move (MOVE) instruction. The move instruction and the effective addressing modes allow both address and data manipulation. Data move instructions allow byte, word, and long word operands to be transferred from memory to memory, memory to register, register to memory, and register to register. Address move instructions allow word and long word operand transfers and ensure that only legal address manipulations are executed. In addition to the general move instruction there are several special data movement instructions : move multiple registers (MOVEM), move peripheral data (MOVEP), exchange registers (EXG), load effective address (LEA), push effective address (PEA), link stack (LINK), unlink stack (UNLK), and move quick (MOVEQ). Table 3.1 is a summary of the data movement operations.

| Instruction | Operand<br>Size | Operation                                                                           |

|-------------|-----------------|-------------------------------------------------------------------------------------|

| EXG         | 32              | $R_X \leftrightarrow R_Y$                                                           |

| LEA         | 32              | EA ← An                                                                             |

| LINK        | -               | $\begin{array}{c} An \to (SP) \\ SP \to An \\ SP + Displacement \to SP \end{array}$ |

| MOVE        | 8, 16, 32       | $s \rightarrow d$                                                                   |

| MOVEM       | 16, 32          | $(EA) \rightarrow An, Dn$<br>An, Dn $\rightarrow EA$                                |

| Instruction | Operand<br>Size | Operation                                                                                                                     |

|-------------|-----------------|-------------------------------------------------------------------------------------------------------------------------------|

| MOVEP       | 16, 32          | $(EA) \rightarrow Dn$<br>$Dn \rightarrow (EA)$                                                                                |

| MOVEQ       | 8               | #xxx → Dn                                                                                                                     |

| PEA         | 32              | $EA \rightarrow - (SP)$                                                                                                       |

| SWAP        | 32              | Dn[31:16] ↔ Dn[15:0]                                                                                                          |

| UNLK        | -               | $\begin{array}{c} An \to Sp \\ (SP) + \to An \end{array}$                                                                     |

|             | estination      | <ul> <li>- () = indirect with predecrement</li> <li>() + = indirect with postdecrement</li> <li># = immediate data</li> </ul> |

#### 3.2. INTEGER ARITHMETIC OPERATIONS

The arithmetic operations include the four basic operations of add (ADD), subtract (SUB), multiply (MUL), and divide (DIV) as well as arithmetic compare (CMP), clear (CLR), and negate (NEG). The add and subtract instructions are available for both address and data operations, with data operations accepting all operand sizes. Address operations are limited to legal address size operands (16 or 32 bits). Data, address, and memory compare operations may be used on all sizes of data operands.

The multiply and divide operations are available for signed and unsigned operands using word multiply to produce a long word product, and a long word dividend with word divisor to produce a word quotient with a word remainder.

Multiprecision and mixed size arithmetic can be accomplished using a set of extended instructions. These instructions are : add extended (ADDX), subtract extended (SUBX), sign extend (EXT), and negate binary with extend (NEGX).

A test operand (TST) instruction that will set the condition codes as a result of a compare of the operand with zero is also available. Test and set (TAS) is a synchronization instruction useful in multiprocessor systems. Table 3.2 is a summary of the integer arithmetic operations.

Table 3.2 : Integer Arithmetic Operations.

|             | -                   |                                                                                                 |

|-------------|---------------------|-------------------------------------------------------------------------------------------------|

| Instruction | Operand<br>Size     | Operation                                                                                       |

| ADD         | 8, 16, 32<br>16, 32 | $\begin{array}{l} Dn+(EA)\toDn\\ (EA)+Dn\to(EA)\\ (EA)+\#xxx\to(EA)\\ An+(EA)\toAn \end{array}$ |

| ADDX        | 8, 26, 32<br>16, 32 | $Dx + Dy + X \rightarrow Dx$<br>- (Ax) + - (Ay)+ X $\rightarrow$ , (Ax)                         |

| CLR         | 8, 16, 32           | $O\toEA$                                                                                        |

| СМР         | 8, 16, 32<br>16, 32 | Dn – (EA)<br>(EA) – #xxx<br>(Ax) + – (Ay) –<br>An – (EA)                                        |

| DIVS        | 32 ÷ 16             | $Dn \div (EA) \rightarrow Dn$                                                                   |

| DIVU        | 32 ÷ 16             | $Dn \div (EA) \to Dn$                                                                           |

| EXT         | 8 → 16<br>16 → 32   | $(Dn)_8 \rightarrow Dn_{16}$ $(Dn)_{16} \rightarrow Dn_{32}$                                    |

| MULS        | 16 x 16 →<br>32     | $dN x (EA) \rightarrow Dn$                                                                      |

| MULU        | 16 x 16 →<br>32     | $dN \ge (EA) \rightarrow Dn$                                                                    |

| NEG         | 8, 16, 32           | $0 - (EA) \rightarrow (EA)$                                                                     |

| NEGX        | 8, 16, 32           | $O - (EA) - X \rightarrow (EA)$                                                                 |

| SUB         | 8, 16, 32<br>16, 32 | $\begin{array}{c} Dn+(EA)\toDn\\ (EA)+Dn\to(EA)\\ (EA)+\#xxx\to(EA)\\ An+(EA)\toAn \end{array}$ |

| SUBX        | 8, 16, 32           | $\frac{Dx - Dy - X \rightarrow Dx}{Dx - (Ax) - (Ay) - X \rightarrow (Ax)}$                      |

| TAS         | 8                   | [EA] – 0, 1 → EA [7]                                                                            |

| TST         | 8, 16, 32           | (EA) – 0                                                                                        |

Notes: [] = bit number

- () = indirect with predecrement

() + = indirect with postdecrement

# = immediate data

#### Table 3.4 : Shift and Rotate Operations.

#### 3.3. LOGICAL OPERATIONS

Logical operation instructions AND, OR, EOR, and NOT are available for all sizes of integer data operands. A similar set of immediate instructions (AN-DI, ORI, and EORI) provide these logical operations with all sizes of immediate data. Table 3.3 is a summary of the logical operations.

| Table 3.3 : Logical Oper |

|--------------------------|

|--------------------------|

| Instruction | Operand<br>Size                                                                                                         | Operation                                                                            |

|-------------|-------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|

| AND         | 8, 16, 32<br>$Dn\Lambda(EA) \rightarrow Dn$<br>$(EA)\Lambda Dn \rightarrow (EA)$<br>$(EA)\Lambda #xxx \rightarrow (EA)$ |                                                                                      |

| OR          | 8, 16, 32                                                                                                               | Dn v (EA) → Dn<br>(EA) v Dn → (EA)<br>(EA) v $\#xxx \rightarrow$ (EA)                |

| EOR         | 8, 16, 32                                                                                                               | $\begin{array}{l} (EA) \oplus Dy \to (EA) \\ (EA) \oplus \#xxx \to (EA) \end{array}$ |

| NOT         | 8, 16, 32                                                                                                               | $\sim$ (EA) $\rightarrow$ (EA)                                                       |

Notes: ~ = invert

# = immediate data  $\Lambda$  = logical AND

V = logical OR

⊕ = logical exclusive OR

#### 3.4. SHIFT AND ROTATE OPERATIONS

Shift operations in both directions are provided by the arithmetic instructions ASR and ASL and logical shift instructions LSR and LSL. The rotate instructions (with and without extend) available are ROXR, ROXL, ROR, and ROL. All shift and rotate operations can be performed in either registers or memory. Register shifts and rotates support all operand sizes and allow a shift count specified in a data register.

Memory shifts and rotates are for word operands only and allow only single-bit shifts or rotates.

Table 3.4 is a summary of the shift and rotate operations.

| Instruction | Operand Size | Operation   |

|-------------|--------------|-------------|

| ASL         | 8, 16, 32    | X/C • • • 0 |

| ASR         | 8, 16, 32    | → X/C       |

| LSL         | 8, 16, 32    |             |

| LSR         | 8, 16, 32    | 0 → X/C     |

| Instruction | Operand Size | Operation |

|-------------|--------------|-----------|

| ROL         | 8, 16, 32    |           |

| ROR         | 8, 16, 32    |           |

| ROXL        | 8, 16, 32    |           |

| ROXR        | 8, 16, 32    |           |

#### Table 3.4 : Shift and Rotate Operations (continued).

#### 3.5. BIT MANIPULATION OPERATIONS

Bit manipulation operations are accomplished using the following instructions : bit test (BTST), bit test and set (BSET), bit test and clear (BCLR), and bit test and change (BCHG). Table 3-5 is a summary of the bit manipulation operations (Z is bit 2 of the status register).

| Table 3.5 | : | Bit | Manipulation | Operations. |

|-----------|---|-----|--------------|-------------|

|-----------|---|-----|--------------|-------------|

| Instruction | Operand<br>Size | Operation                                                              |

|-------------|-----------------|------------------------------------------------------------------------|

| BTST        | 8, 32           | ~ bit of (EA) $\rightarrow$ Z                                          |

| BSET        | 8, 32           | ~ bit of (EA) $\rightarrow$ Z<br>1 $\rightarrow$ bit of EA             |

| BCLR        | 8, 32           | ~ bit of (EA) $\rightarrow$ Z<br>0 $\rightarrow$ bit of EA             |

| BCHG        | 8, 32           | ~ bit of (EA) $\rightarrow$ Z<br>~ bit of (EA) $\rightarrow$ bit of EA |

Note : ~ = Invert

#### 3.6. BINARY CODED DECIMAL OPERATIONS

Multiprecision arithmetic operations on binary coded decimal numbers are accomplished using the following instructions : add decimal with extend (ABCD), subtract decimal with extend (SBCD), and negate decimal with extend (NBCD). Table 3.6 is a summary of the binary coded decimal operations.

#### Table 3.6 : Binary Coded Decimal Operations.

| Instruction | Operand<br>Size | Operation                                                                                                                                                              |

|-------------|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ABCD        | 8               | $\begin{array}{r} Dx_{10} + Dy_{10} + X \to Dx \\ - (Ax)_{10} + - (Ay)_{10} + x \to (Ax) \end{array}$                                                                  |

| SBCD        | 8               | $\begin{array}{c} {\sf D} x_{10} - {\sf D} y_{10} - {\sf X} \to {\sf D} x\\ {\sf -} ({\sf A} x)_{10} - {\sf -} ({\sf A} y)_{10} - {\sf x} \to ({\sf A} x) \end{array}$ |

| NBCD        | 8               | $0 - (EA)_{10} - X \rightarrow (EA)$                                                                                                                                   |

Note :- ( ) = Indirect with predecrement

#### 3.7. PROGRAM CONTROL OPERATIONS

Program control operations are accomplished using a series of conditional and unconditional branch instructions and return instructions. These instructions are summarized in table 3.7.

The conditional instructions provide setting and branching for the following conditions :

CC - Carry Clear LS - Low or Same CS - Carry Set LT - Less Than EQ - Equal MI - Minus F - Never True NE - Not Equal PL - Plus GE - Greater or Equal T - Always True GT - Greater Than VC - no Overflow HI - Hiah VS - Overflow LE - Less or Equal

#### Table 3.7 : Program Control Operations.

| Instruction      | Operation                                                                                  |  |  |  |

|------------------|--------------------------------------------------------------------------------------------|--|--|--|

| Conditional      |                                                                                            |  |  |  |

| B <sub>CC</sub>  | Branch Conditionally (14 conditions)                                                       |  |  |  |

| DB <sub>CC</sub> | 8- and 16-bit Displacement<br>Test Condition, Decrement, and Branch<br>16-bit Displacement |  |  |  |

| Scc              | Set Byte Conditionally (16 condtions)                                                      |  |  |  |

| Unconditional    |                                                                                            |  |  |  |

| BRA              | Branch always<br>8 - and 16-bit Displacement                                               |  |  |  |

| BSR              | Branch to Subroutine<br>8- and 16-bit Displacement                                         |  |  |  |

| JMP              | Jump                                                                                       |  |  |  |

| JSR              | Jump to Subroutine                                                                         |  |  |  |

| Returns          |                                                                                            |  |  |  |

| RTR              | Return and Restore Condition Codes                                                         |  |  |  |

| RTS              | Return from Subroutine                                                                     |  |  |  |

#### 3.8. SYSTEM CONTROL OPERATIONS

System control operations are accomplished by using privileged instructions, trap generating in-

structions, and instructions that use or modify the status register. These instructions are summarized in table 3.8.

#### Table 3.8 : System Control Operations.

| Instruction                                                                                              | Operation                                                                                                                                                                                                                             |

|----------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Privileged<br>ANDI to SR<br>EORI to SR<br>MOVE EA to SR<br>MOVE USP<br>ORI to SR<br>RESET<br>RTE<br>STOP | Logical AND to Status Register<br>Logical EOR to Status Register<br>Load New Status Register<br>Move User Stack Pointer<br>Logical OR to Status Register<br>Reset External Devices<br>Return from Exception<br>Stop Program Execution |

| Trap Generating<br>CHK<br>TRAP<br>TRAPV                                                                  | Chek Data Register against Upper Bounds<br>Trap<br>Trap on Overflow                                                                                                                                                                   |

| Status Register<br>ANDI to CCR<br>EORI to CCR<br>MOVE EA to CCR<br>MOVE SR to EA<br>ORI to CCR           | Logical AND to Condition Codes<br>Logical EOR to Condtion Codes<br>Load New Condition Codes<br>Store Status Register<br>Logical OR to Condition Codes                                                                                 |

#### **SECTION 4**

## SIGNAL AND BUS OPERATION DESCRIPTION

This section contains a brief description of the input and output signals. A discussion of bus operation during the various machine cycles and operations is also given.

The terms **assertion** and **negation** will be used extensively. This is done to avoid confusion when dealing with a mixture of "active-low" and "active-high" signals. The term assert or assertion is used to indicate that a signal is active or true, independent of whether that level is represented by a high or low voltage. The term negate or negation is used to indicate that a signal is inactive or false.

#### 4.1. SIGNAL DESCRIPTION

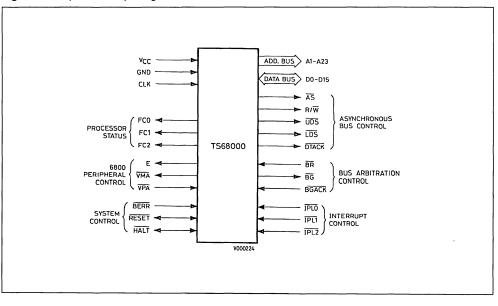

The input and output signals can be functionally organized into the groups shown in figure 4-1. The following paragraphs provide a brief description of the signals and a reference (if applicable) to other paragraphs that contain more detail about the function being performed.

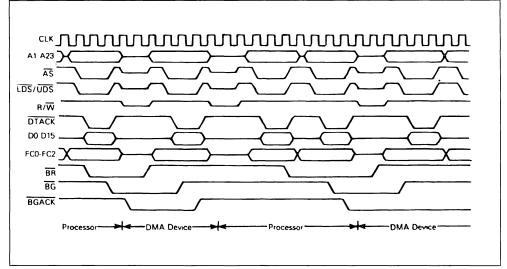

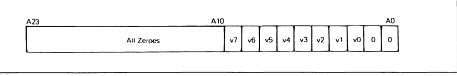

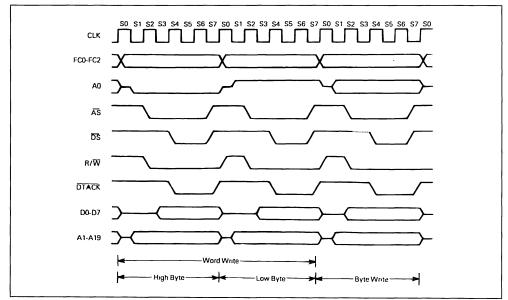

4.1.1. ADDRESS BUS (A1 through A23). This 23bit, unidirectional, three-state bus is capable of addressing 8 megawords of data. It provides the address for bus operation during all cycles except interrupt cycles. During interrupt cycles, address lines A1, A2, and A3 provide information about what level interrupt is being serviced while address lines A4 through A23 are all set to a logic high.

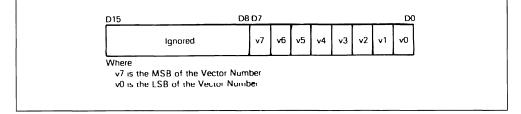

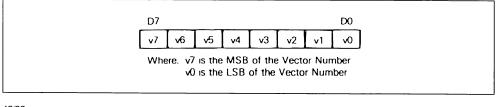

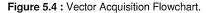

4.1.2. DATA BUS (D0 through D15). This 16-bit, bidirectional, three-state bus is the general purpose data path. It can transfer and accept data in either word or byte length. During an interrupt acknowledge cycle, the external device supplies the vector number on data lines D0-D7.

4.1.3. ASYNCHRONOUS BUS CONTROL. Asynchronous data transfers are handled using the following control signals : address strobe, read/write, upper and lower data strobes, and data transfer acknowledge. These signals are explained in the following paragraphs.

4.1.3.1. Address Strobe (AS).

This signal indicates that there is a valid address on the address bus.

4.1.3.2. Read/Write (R/W).

This signal defines the data bus transfer as a read or write cycle. The R/W signal also works in conjunction with the data strobes as explained in the following paragraph.

Figure 4.1 : Input and Output Signals.

4.1.3.3. Upper and Lower Data Strobe (UDS, LDS).

These signals control the flow of data on the data bus, as shown in table 4-1. When the R/W line is high, the processor will read from the data bus as indicated. When the R/W line is low, the processor will write to the data bus as shown.

4.1.3.4. Data Transfer Acknowledge (DTACK).

This input indicates that the data transfer is completed. When the processor recognizes DTACK during a read cycle, data is latched and the bus cycle terminated. When DTACK is recognized during a write cycle, the bus cycle is terminated. (Refer to 4.4 Asynchronous Versus Synchronous Operation).

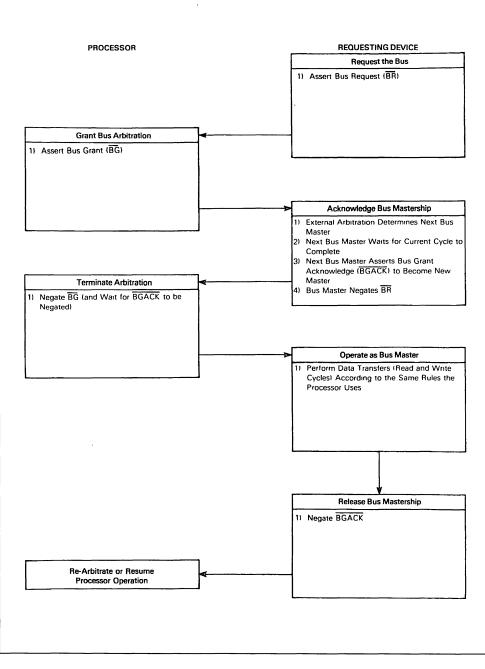

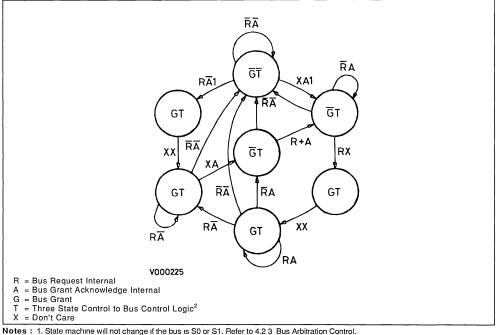

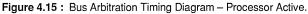

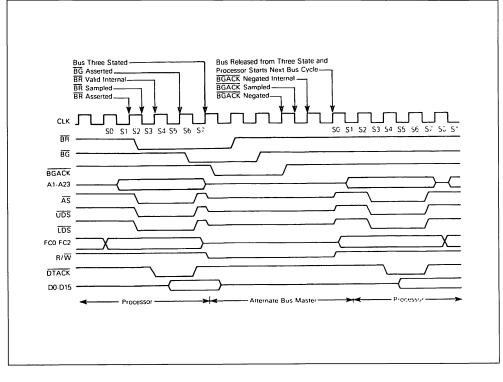

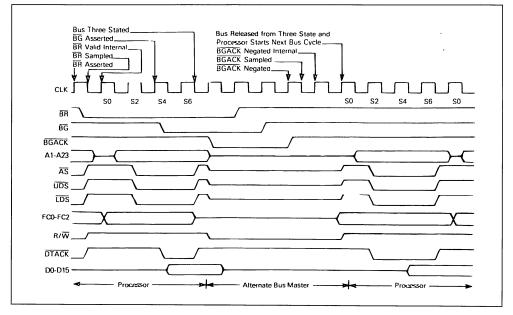

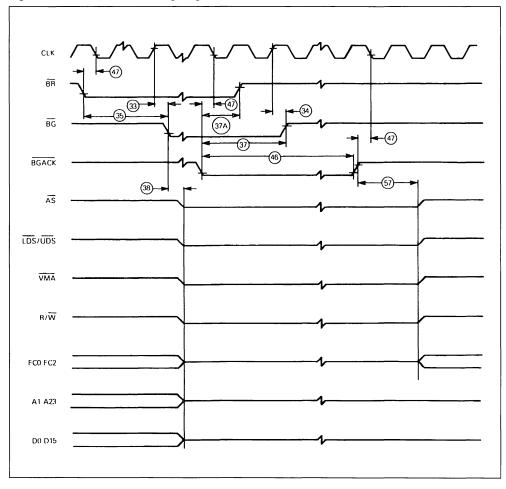

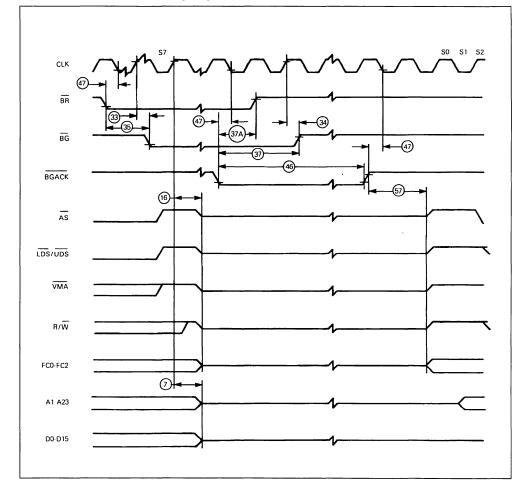

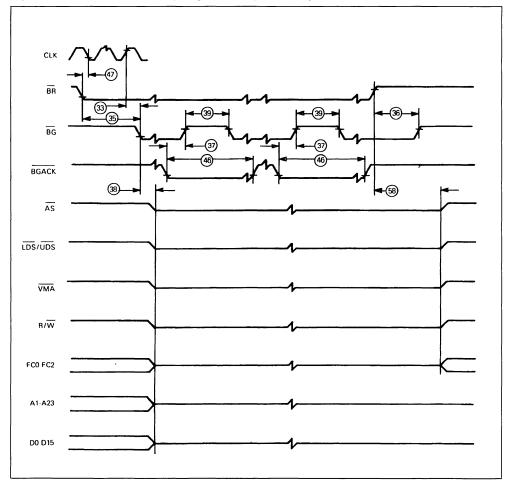

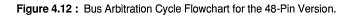

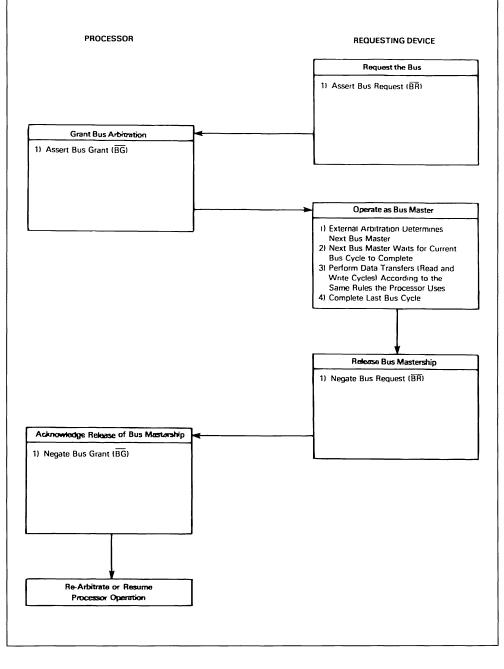

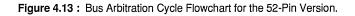

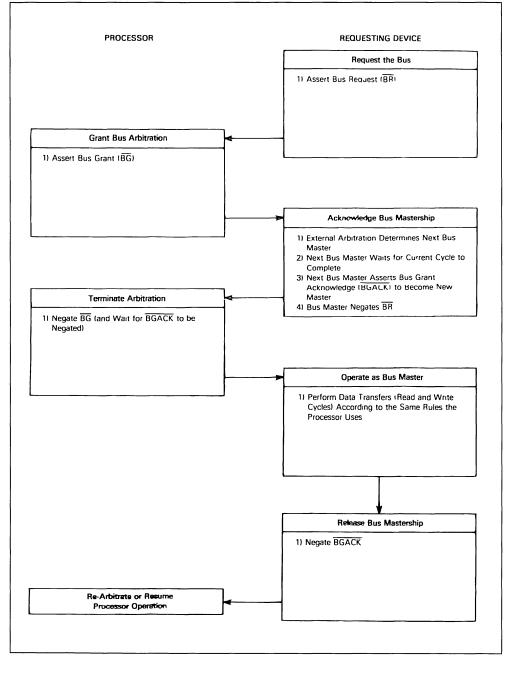

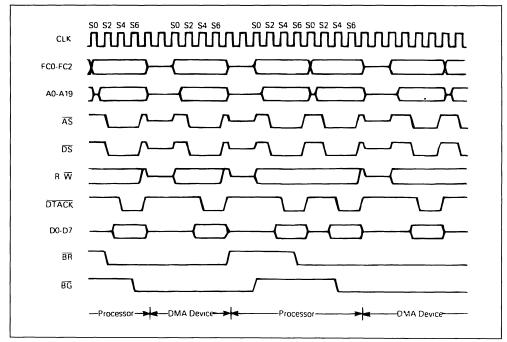

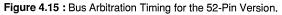

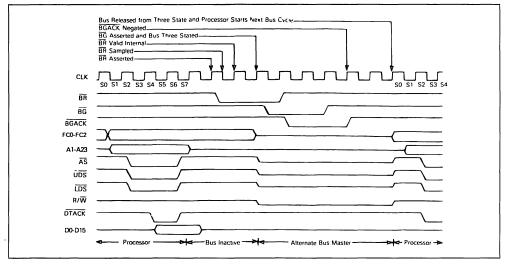

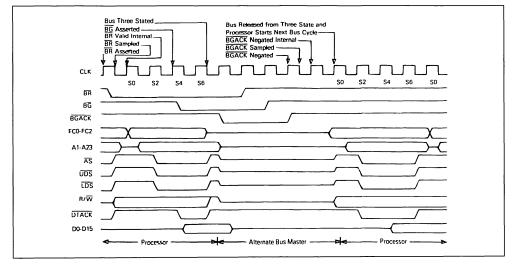

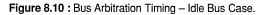

4.1.4. BUS ARBITRATION CONTROL. The three signals, bus request, bus grant, and bus grant acknowledge, form a bus arbitration circuit to determine which device will be the bus master device.

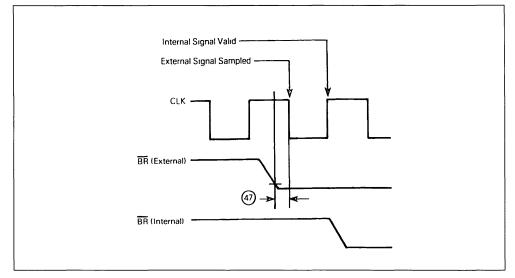

#### 4.1.4.1. Bus Request (BR).

This input is wire ORed with all other devices that could be bus masters. This input indicates to the processor that some other device desires to become the bus master.

#### 4.1.4.2. Bus Grant (BG).

This output indicates to all other potential bus master devices that the processor will release bus control at the end of the current bus cycle.

| Table 4.1 : Data Strobe C | ontrol of Data Bus. |

|---------------------------|---------------------|

|---------------------------|---------------------|

#### 4.1.4.3. Bus Grant Acknowledge (BGACK).

This input indicates that some other device has become the bus master. This signal should not be asserted until the following four conditions are met :

- 1. a bus grant has been received,

- 2. address strobe is inactive which indicates that the microprocessor is not using the bus,

- 3. data transfer acknowledge is inactive which indicates that neither memory nor peripherals are using the bus, and

- 4. bus grant acknowledge is inactive which indicates that no other device is still claiming bus mastership.

4.1.5. INTERRUPT CONTROL (IPL0, IPL1, IPL2). These input pins indicate the encoded priority level of the device requesting an interrupt. Level seven is the highest priority while level zero indicates that no interrupts are requested. Level seven cannot be masked. The least significant bit is given in IPL0 and the most significant bit is contained in IPL2. These lines must remain stable until the processor signals interrupt acknowledge (FC0-FC2 are all high) to insure that the interrupt is recognized.

4.1.6. SYSTEM CONTROL. The system control inputs are used to either reset or halt the processor and to indicate to the processor that bus errors have occurred. The three system control inputs are explained in the following paragraphs.

| UDS  | LDS  | R/W  | D8-D15                  | D0-D7                    |

|------|------|------|-------------------------|--------------------------|

| High | High | -    | No Valid Data           | No Valid Data            |

| Low  | Low  | High | Valid Data Bits<br>8-15 | Valid Data Bits<br>0-7   |

| High | Low  | High | No Valid Data           | Valid Data Bits<br>0-7   |

| Low  | High | High | Valid Data Bits<br>8-15 | No Valid Data            |

| Low  | Low  | Low  | Valid Data Bits<br>8-15 | Valid Data Bits<br>0-7   |

| High | Low  | Low  | Valid Data Bits<br>0-7* | Valid Data Bits<br>0-7   |

| Low  | High | Low  | Valid Data Bits<br>8-15 | Valid Data Bits<br>8-15* |

These conditions are a result of current implementation and may not appear on future devices.

#### TS68000

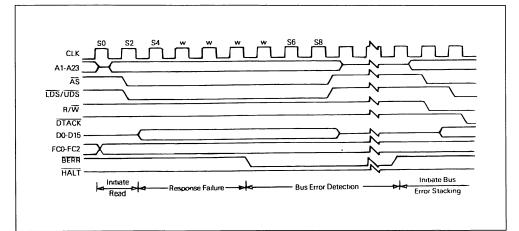

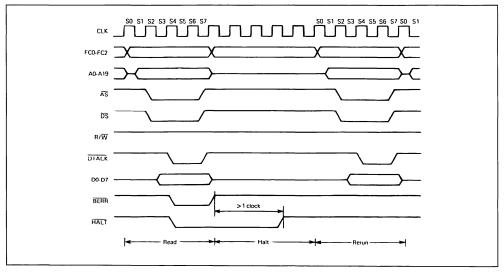

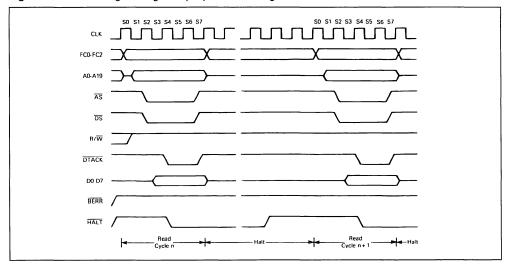

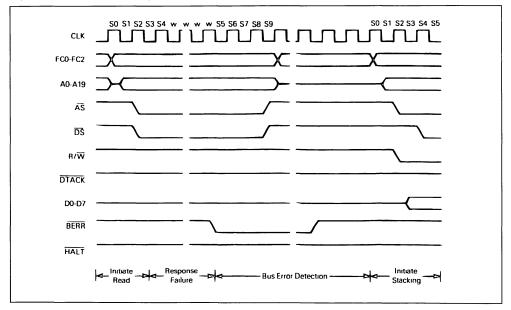

#### 4.1.6.1. Bus Error (BERR)

This input informs the processor that there is a problem with the cycle currently being executed. Problems may be a result of :

- 1. nonresponding devices,

- 2. interrupt vector number acquisition failure,

- 3. illegal access request as determined by a memory management unit, or

- 4. other application dependent errors.

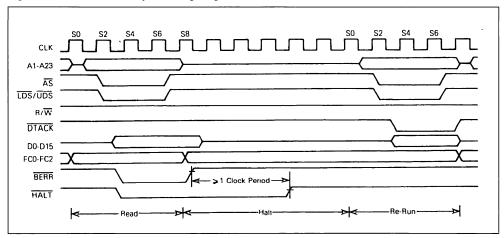

The bus error signal interacts with the halt signal to determine if the current bus cycle should be reexecuted or if exception processing should be performed.

Refer to **4.2.4. Bus Error and Halt Operation** for additional information about the interaction of the bus error and halt signals.

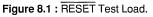

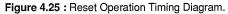

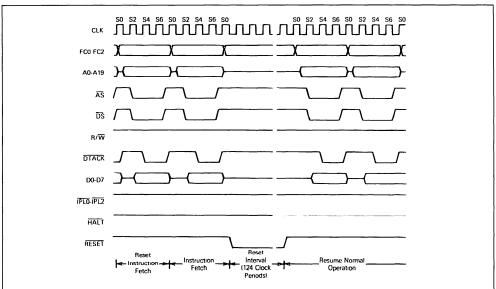

#### 4.1.6.2. Reset (RESET)

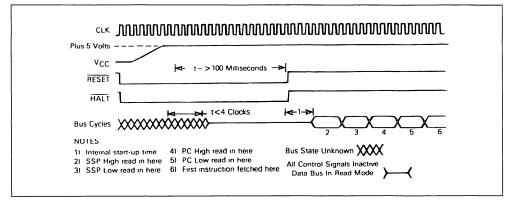

This bidirectional signal line acts to reset (start a system initialization sequence) the processor in response to an external reset <u>signal.</u> An internally generated reset (result of a RESET instruction) causes all external devices to be reset and the internal state of the processor is not affected. A total system reset (pro<u>cessor</u> and <u>external</u> devices) is the result of external HALT and RESET signals applied at the same time. Refer to **4.2.5. Reset Operation** for further information.

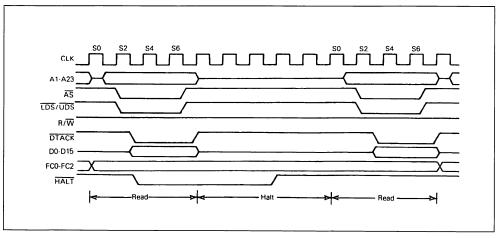

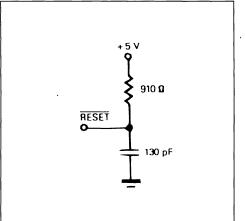

#### 4.1.6.3. Halt (HALT)

When this bidirectional line is driven by an external device, it will cause the processor to stop at the completion of the current bus cycle. When the processor has been halted using this input, all control signals are inactive and all three-state lines are put in their high-impedance state (refer to table 4.3). Refer to 4.2.4. Bus Error and Halt Operation for additional information about the interaction between the HALT and bus error signals.

When the processor has stopped executing instructions, such as in a double bus fault <u>condi</u>tion (refer to **4.2.4.4. Double Bus Faults**), the HALT line is driven by the processor to indicate to external devices that the processor has stopped.

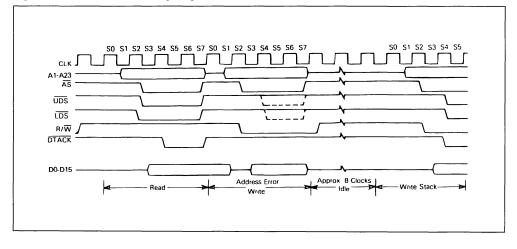

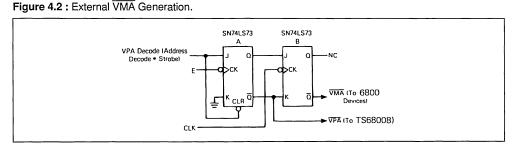

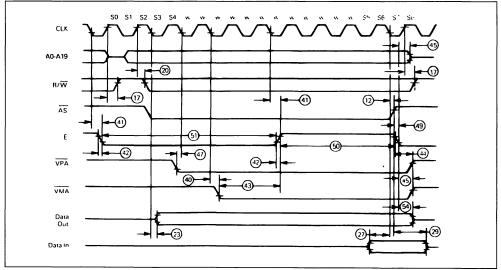

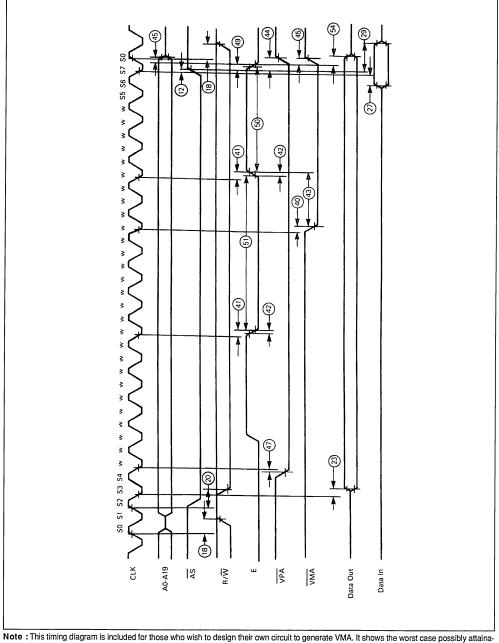

4.1.7. EF6800 PERIPHERAL CONTROL. These control signals are used to allow the interfacing of synchronous EF6800 peripheral devices with the

asynchronous TS68000. These signals are explained in the following paragraphs.

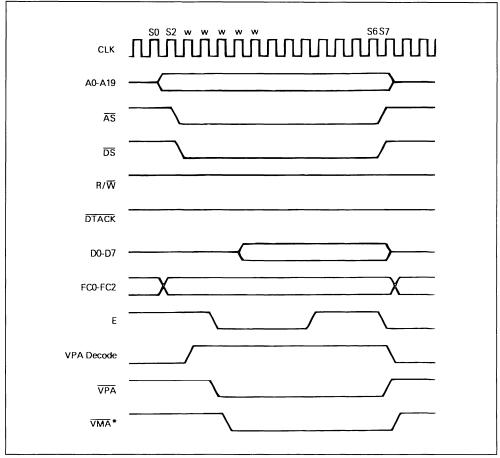

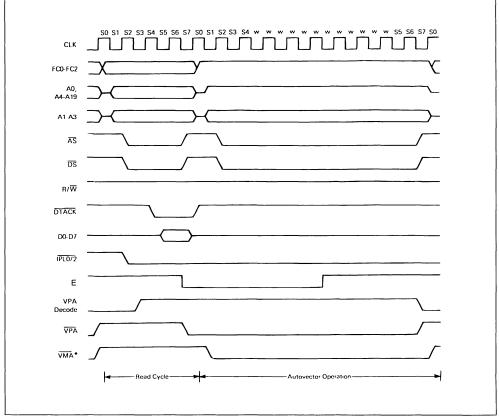

#### 4.1.7.1. Enable (E)

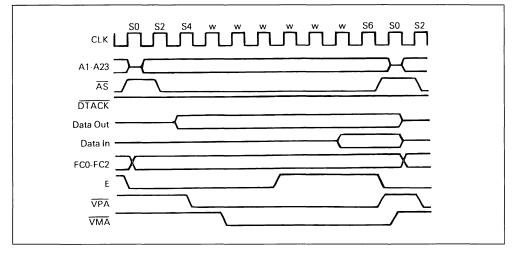

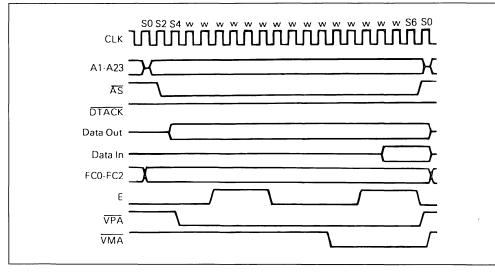

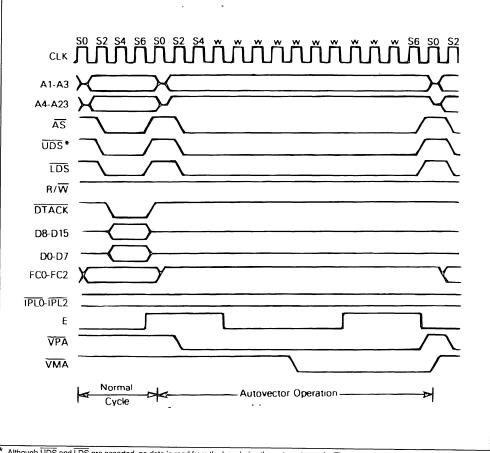

This signal is the standard enable signal common to all EF6800 type peripheral devices. The period for this output is ten TS68000 clock periods (six clocks low, four clocks high). Enable is generated by an internal ring counter which may come up in any state (i.e., at power on, it is impossible to guarantee phase relationship of E to CLK). E is a freerunning clock and runs regardless of the state of the bus on the MPU.

#### 4.1.7.2. Valid Peripheral Address (VPA)

This input indicates that the device or region addressed is an EF6800 Family device and that data transfer should be synchronized with the enable (E) signal. This input also indicates that the processor should use automatic vectoring for an interrupt. Refer to Section 6 Interface With Ef6800 Peripherals.

#### 4.1.7.3. Valid Memory Address (VMA)

This output is used to indicate to EF6800 peripheral devices that there is a valid address on the address bus and the processor is synchronized to enable. This <u>signal</u> only responds to a valid peripheral address (VPA) input which indicates that the peripheral is an EF6800 Family device.

4.1.8. PROCESSOR STATUS (FC0, FC1, FC2). These function code outputs indicate the state (user or supervisor) and the cycle type currently being executed, as shown in table 4.2. The information indicated by the function code outputs is valid whenever address strobe (AS) is active.

#### Table 4.2 : Function Code Outputs.

| Function Code output |      | output | Cycle Type            |  |

|----------------------|------|--------|-----------------------|--|

| FC2                  | FC1  | FC0    | Cycle Type            |  |

| Low                  | Low  | Low    | (undefined, reserved) |  |

| Low                  | Low  | High   | User Data             |  |

| Low                  | High | Low    | User Program          |  |

| Low                  | High | High   | (undefined, reserved) |  |

| High                 | Low  | Low    | (undefined, reserved) |  |

| High                 | Low  | High   | Supervisor Data       |  |

| High                 | High | Low    | Supervisor Program    |  |

| High                 | High | High   | Interrupt Acknowledge |  |

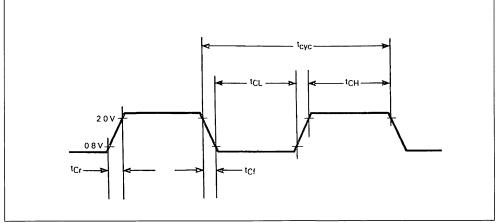

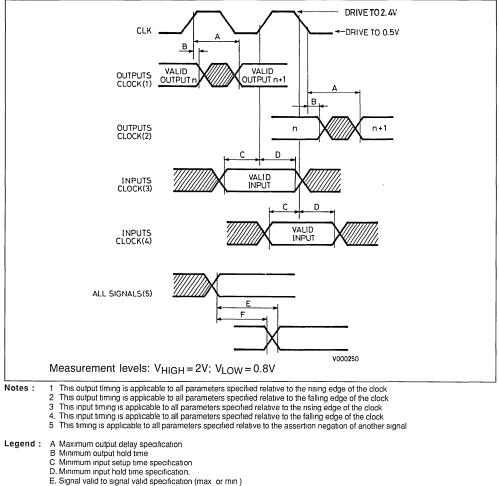

4.1.9. CLOCK (CLK). The clock input is a TTL-compatible signal that is internally buffered for development of the internal clocks needed by the processor. The clock input should not be gated off at any time and the clock signal must conform to minimum and maximum pulse width times.

4.1.10. SIGNAL SUMMARY. Table 4.3 is a summary of all the signals discussed in the previous paragraphs.

#### 4.2. BUS OPERATION

The following paragraphs explain control signal and bus operation during data transfers operations, bus arbitration, bus error and hait conditions, and reset operation.

4.2.1. DATA TRANSFER OPERATIONS. Transfer of data between devices involves the following leads.

- 1. address bus A1 through A23,

- 2. data bus D0 through D15, and

- 3. control signals.

The address and data buses are separate parallel buses to transfer data using an asynchronous bus structure. In all cycles, the bus master assumes responsibility for deskewing all signals it issues at both the start and end of a cycle. In addition, the bus master is responsible for deskewing the acknowledge and data signals from the slave device.

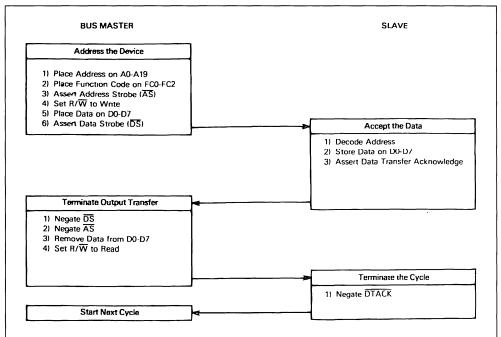

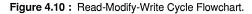

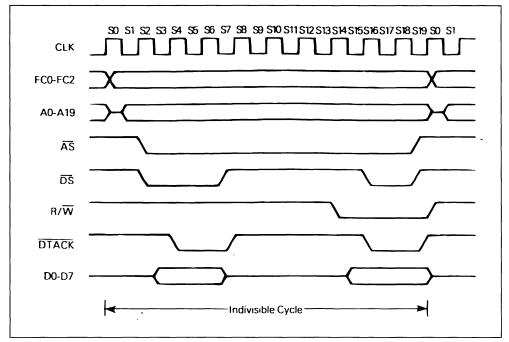

The following paragraphs explain the read, write, and read-modify-write cycles. The indivisible readmodify-write cycle is the method used by the TS68000 for interlocked multiprocessor communications.

| Signal Name                  | Nmemonic         | Input/output | Active State           | Hi              | Hi-Z            |  |

|------------------------------|------------------|--------------|------------------------|-----------------|-----------------|--|

| olghar Name                  | Milenome         |              | Active State           | On HALT         | On BGACK        |  |

| Address Bus                  | A1-A23           | Output       | High                   | Yes             | Yes             |  |

| Data Bus                     | D0-D15           | Input Output | High                   | Yes             | Yes             |  |

| Address Strobe               | AS               | Output       | Low                    | No              | Yes             |  |

| Read/write                   | R/W              | Output       | Read-high<br>Write-low | No              | Yes             |  |

| Upper and Lower Data Strobes | UDS, LDS         | Output       | Low                    | No              | Yes             |  |

| Data Transfer Acknowledge    | DTACK            | Input        | Low                    | No              | No              |  |

| Bus Request                  | BR               | Input        | Low                    | No              | No              |  |

| Bus Grant                    | BG               | Output       | low                    | No              | No              |  |

| Bus Grant Acknowledge        | BGACK            | Input        | Low                    | No              | No              |  |

| Interrupt Priority Level     | IPLO, IPL1, IPL2 | Input        | Low                    | No              | No              |  |

| Bus Error                    | BERR             | Input        | Low                    | No              | No              |  |

| Reset                        | RESET            | Input Output | Low                    | No <sub>1</sub> | No <sub>1</sub> |  |

| Halt                         | HALT             | Input Output | Low                    | No <sub>1</sub> | No <sub>1</sub> |  |

| Enable                       | E                | Output       | High                   | No              | No              |  |

| Valid Memory Address         | VMA              | Output       | Low                    | No              | Yes             |  |

| Valid Peripheral Address     | VPA              | Input        | Low                    | No              | No              |  |

| Function Code Output         | FC0, FC1, FC2    | Output       | High                   | No              | Yes             |  |

| Clock                        | CLK              | Input        | High                   | No              | No              |  |

| Power Input                  | V <sub>cc</sub>  | Input        | -                      | -               | -               |  |

| Ground                       | GND              | Input        | -                      | -               | -               |  |

Table 4.3 : Signal Summary.

Note: 1. Open drain

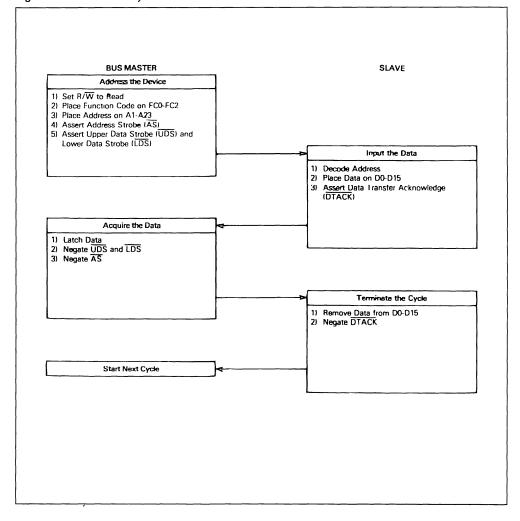

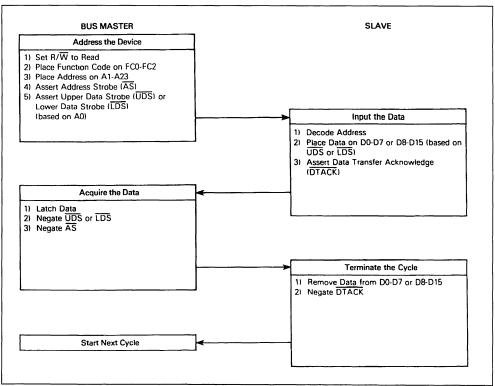

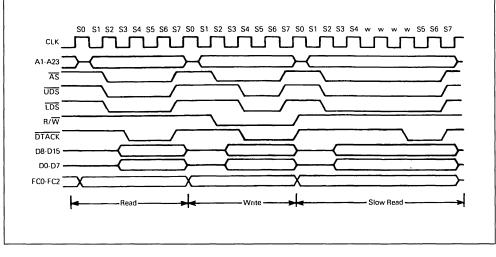

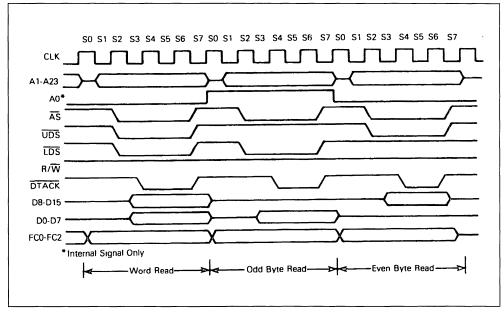

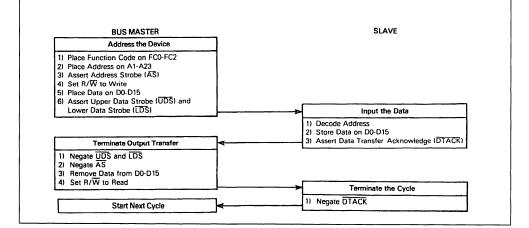

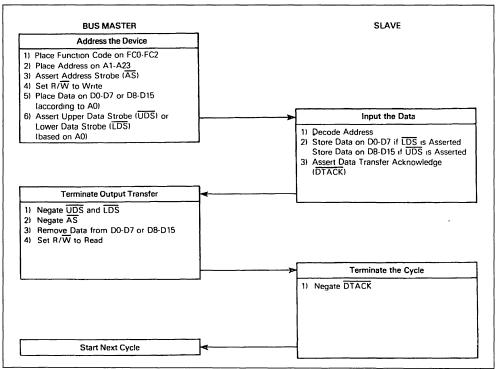

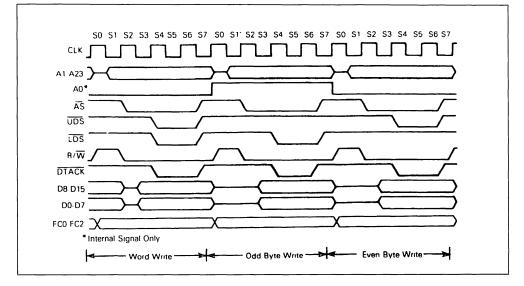

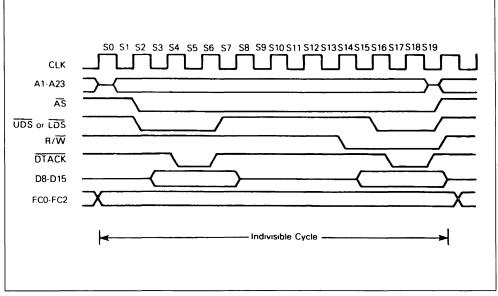

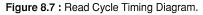

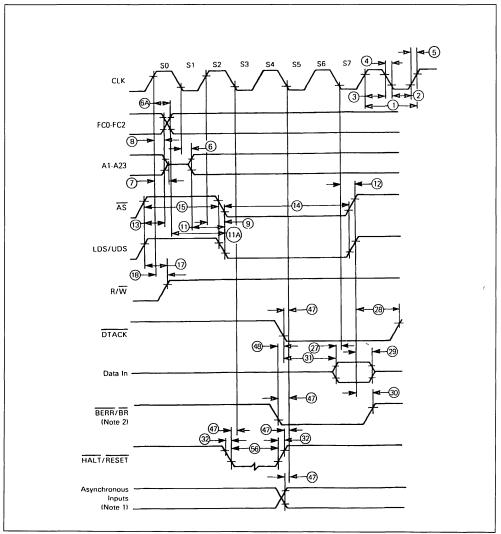

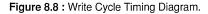

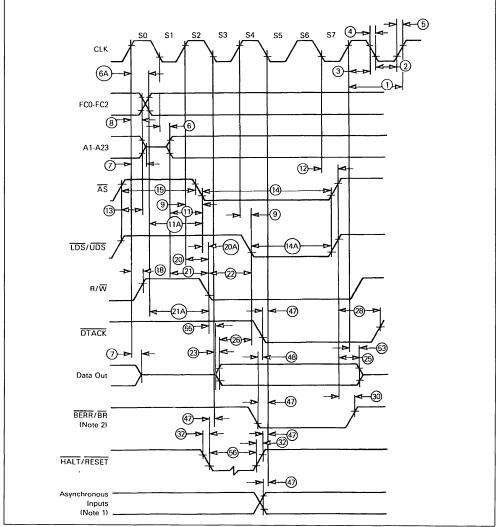

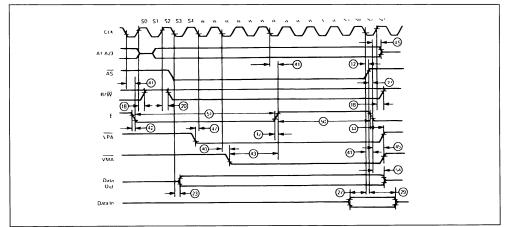

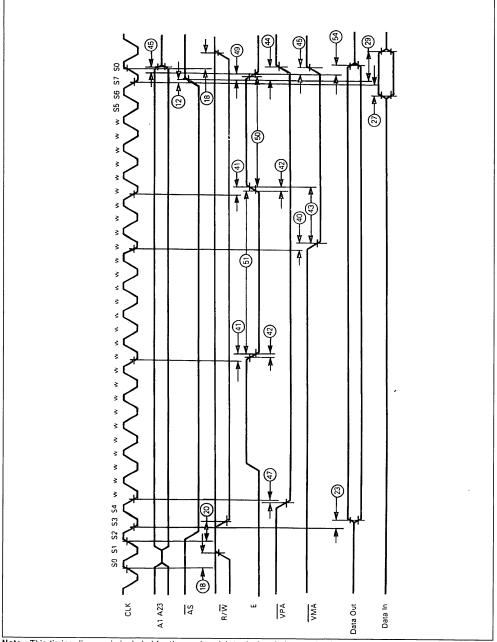

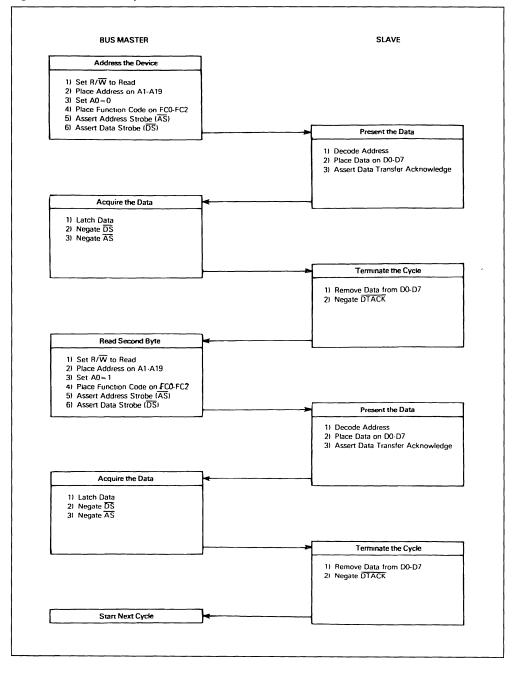

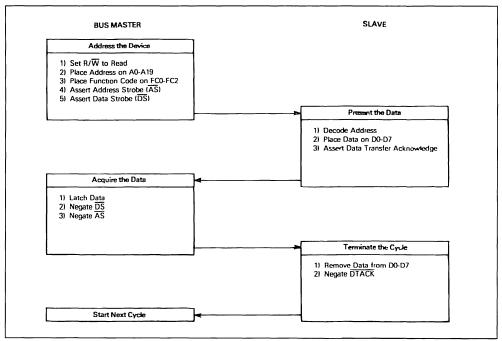

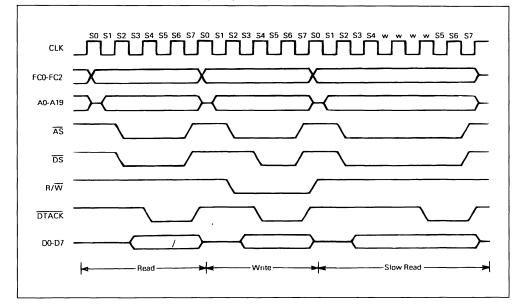

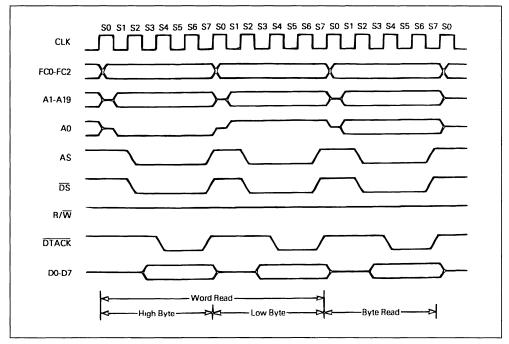

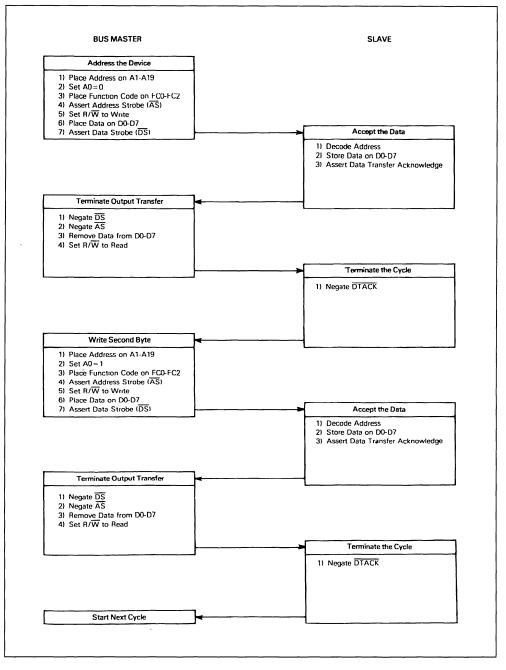

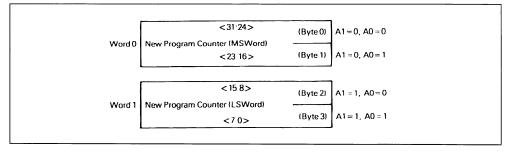

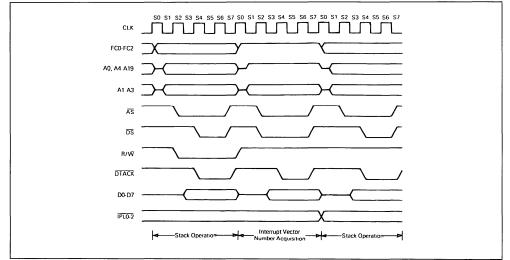

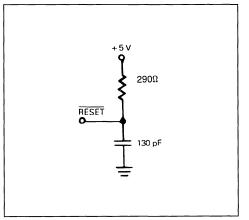

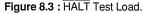

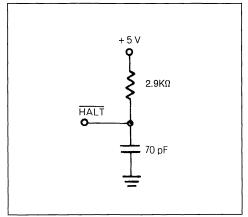

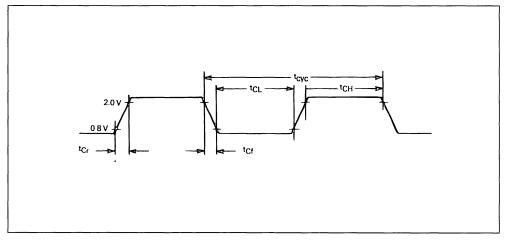

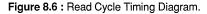

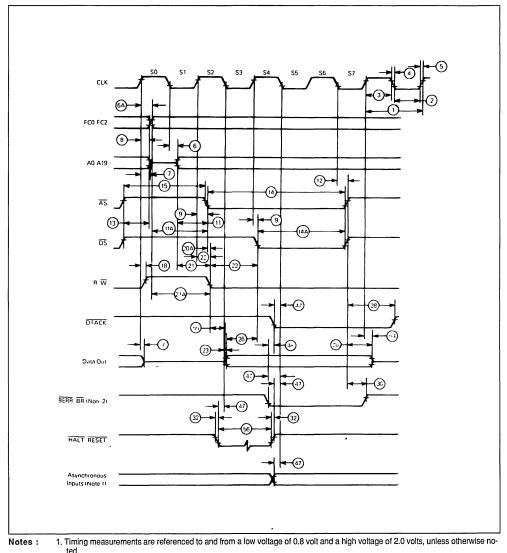

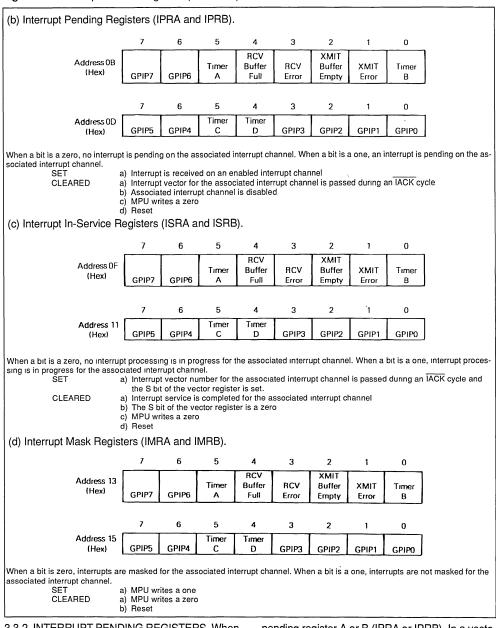

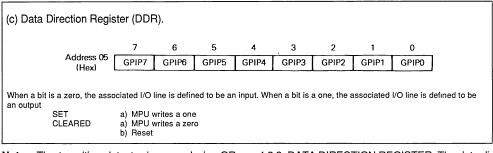

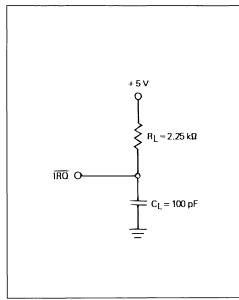

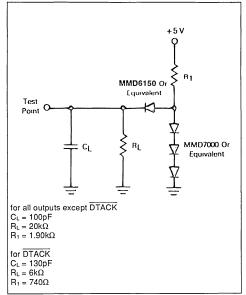

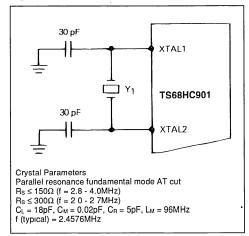

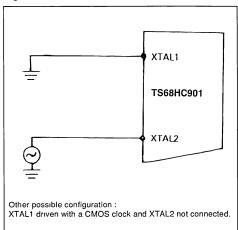

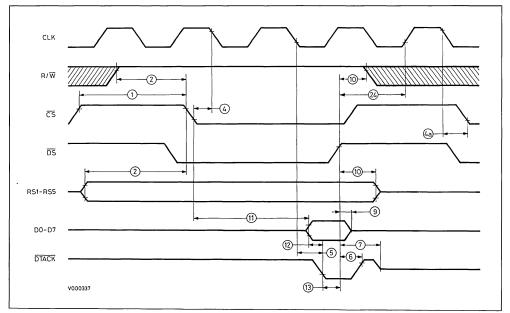

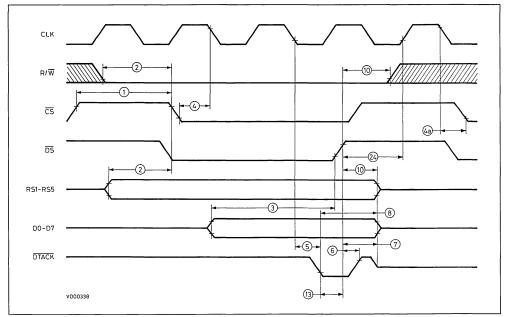

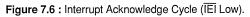

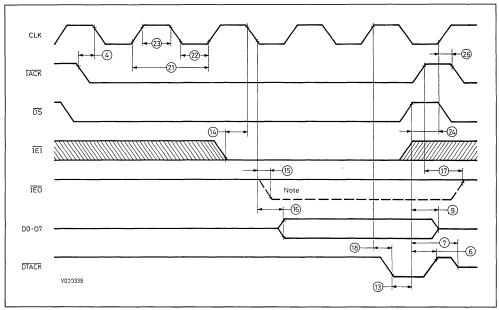

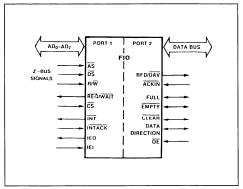

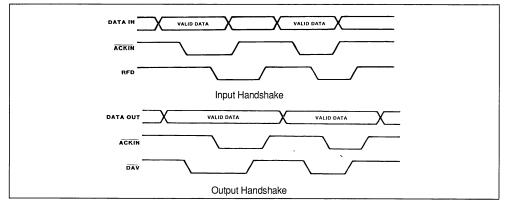

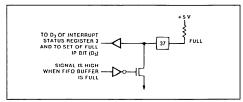

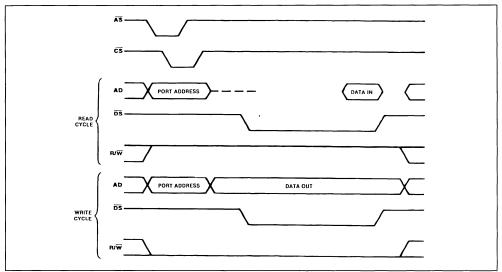

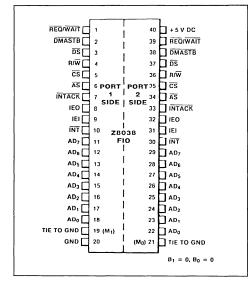

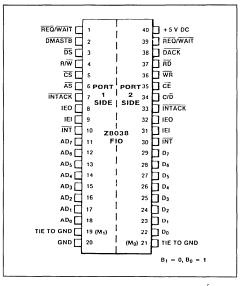

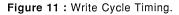

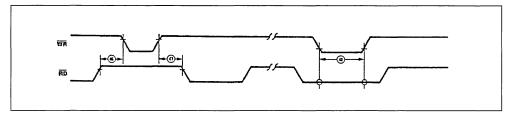

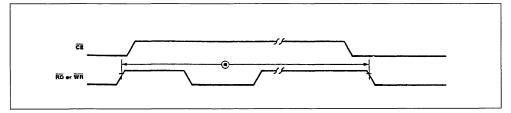

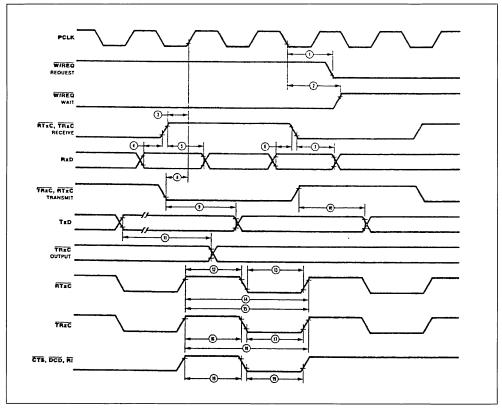

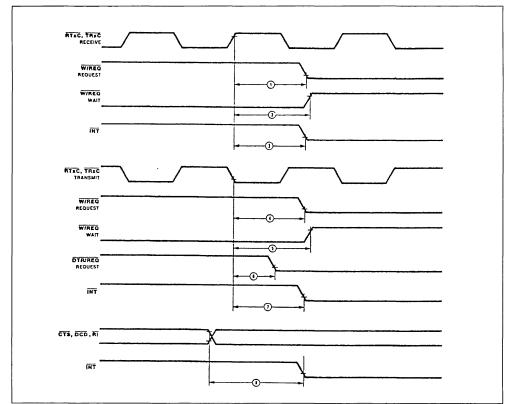

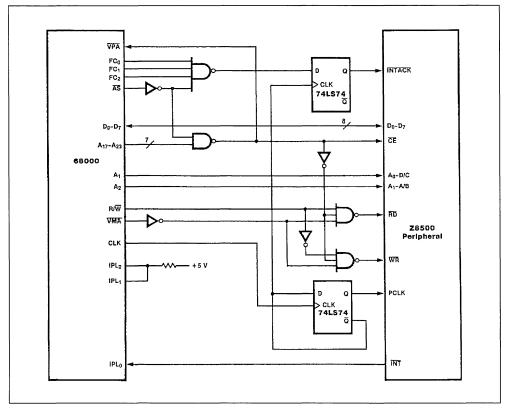

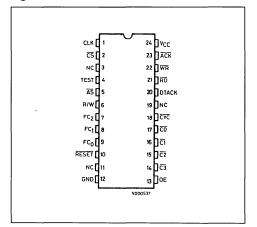

#### 4.2.1.1. Read Cycle