# MICROSYSTEMS

Microboards Development Systems Software

REA

RE/

RСЛ

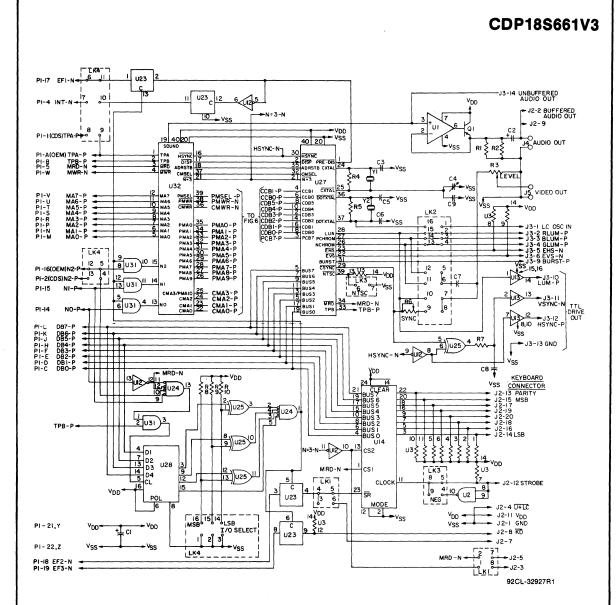

H/I

So d

SSD-270

MICROS

evelopment-Systems

croboards

Soi

ware

# **RCA Microsystems**

This DATABOOK contains complete technical information on the full line of Microboard computer systems and microprocessor development systems available from RCA Solid State Division. An Index to Products provides a complete listing of types.

The Index to Products is followed by a Product Classification Chart that groups systems according to product type and intended function.

Three separate data sections provide definitive ratings, performance specifications, and user information for (1) the CDP18S600 series of Microboard computer systems, (2) the CDP18S series of microprocessor development systems, and (3) software. Generally within each data section, the data pages for individual systems are grouped in alphanumerical sequence of type numbers. Because some devices are grouped together to show similarity of function, individual type numbers may be out of sequence. If you don't find the data on a specific type where you expect it to be, check the Index to Products.

The DATABOOK also contains selected application briefs and abstracts from application notes on RCA development systems.

## **Table of Contents**

|                                                                                | Page |

|--------------------------------------------------------------------------------|------|

| Index to Products                                                              | 3    |

| Product Classification Chart                                                   | 5    |

| Microboards                                                                    |      |

| Development Systems                                                            | 455  |

| Software                                                                       | 505  |

| Application Information                                                        |      |

| RCA Sales Offices, Manufacturers' Representatives, and Authorized Distributors | 565  |

Brussels • Buencs Aires • Hamburg • Madrid • Mexico City • Milan Montreal • Paris • Sao Paulo • Somerville NJ • Stockholm Sunbury on Thames • Taipei • Tokyo Information furnished by RCA is believed to be accurate and reliable. However, no responsibility is assumed by RCA for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent rights of RCA.

The data shown for some types are indicated as advance. Advance data are intended for engineering evaluation of types in the initial stages of design. The type designations and data are subject to change, unless otherwise arranged. No obligations are assumed for notice of change of future manufacture of these devices. For current information on the status of advance programs, please contact your local RCA sales office.

Copyright 1982 by RCA Corporation (All rights reserved under Pan-American Copyright Convention)

Trademark(s)®Registered Marca(s) Registrada(s)

Printed in USA/7-82

# Index to Products

| Type No.                   | Description                              | Page No    | Tech. Data<br>.File No. | т   |

|----------------------------|------------------------------------------|------------|-------------------------|-----|

| CDP18S005                  | COSMAC Develop-                          | 400        | DD100                   | С   |

|                            | ment System CDS II<br>COSMAC Develop-    | 469        | PD16C                   | с   |

|                            | ment System CDS III<br>COSMAC Develop-   |            | PD16C                   | с   |

| V3<br>CDP18S023,V3         | ment System IV                           | 472<br>428 | PD8                     | с   |

| CDP18S030A<br>CDP18S040V1, | Micromonitor                             | 479        | PD18D                   | c   |

| V3<br>CDP18S480,           | CRT Data Terminal                        | 484        | -                       | с   |

| V1, V2<br>CDP18S508        | PROM Programmer<br>UART Interface        | 486        | PD22B                   | с   |

| 000100510                  | Module<br>Byte I/O Medule                | 489        | PD19                    | _   |

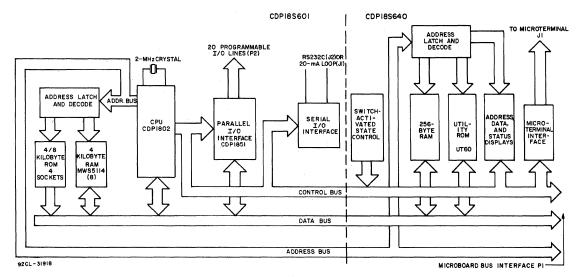

| CDP18S510<br>CDP18S601     | Byte I/O Module<br>Microboard Com-       | 492        | PD20                    | c   |

|                            | puter 4K RAM,<br>4/8K ROM                | 15         | MB-601                  | С   |

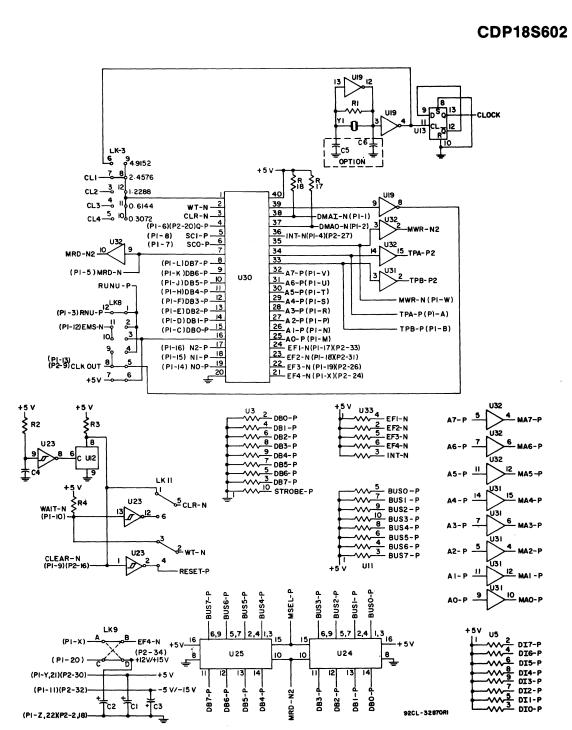

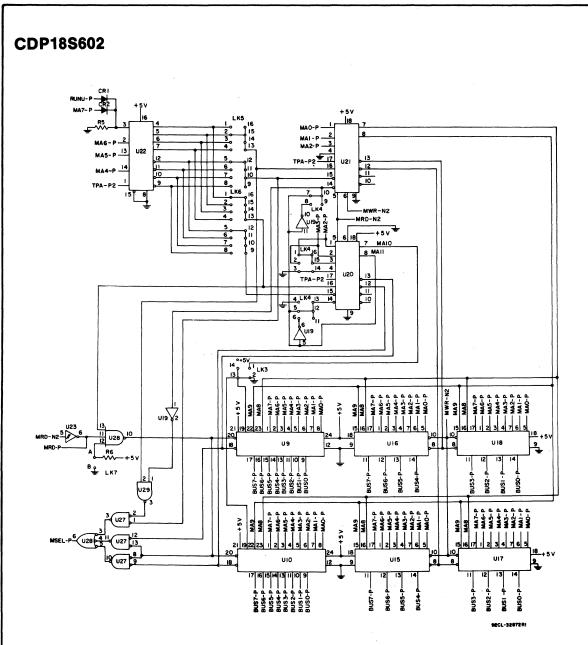

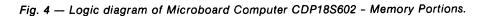

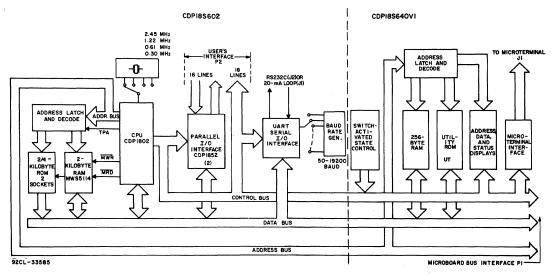

| CDP18S602                  | Microboard Com-<br>puter 2K RAM,         |            |                         | с   |

|                            | 2/4K ROM                                 | 28         | MB-602                  | С   |

| CDP18S603                  | Microboard Com-<br>puter 1K RAM.         |            |                         |     |

|                            | 4/8K ROM                                 | 43         | MB-603                  | с   |

| CDP18S604B                 | Microboard Com-<br>puter 1K RAM,         |            |                         |     |

|                            | 1/2/4K ROM/PROM                          | 56         | MB-604B                 | с   |

| CDP18S605                  | Microboard Com-                          |            |                         |     |

|                            | puter 2K RAM,<br>2/4K ROM/PROM           | 75         | MB-605                  | С   |

| CDP18S606                  | Microboard Com-<br>puter 4K RAM, 4/8K    |            |                         | с   |

|                            | ROM (CDP1805)                            | 90         | MB-606                  | с   |

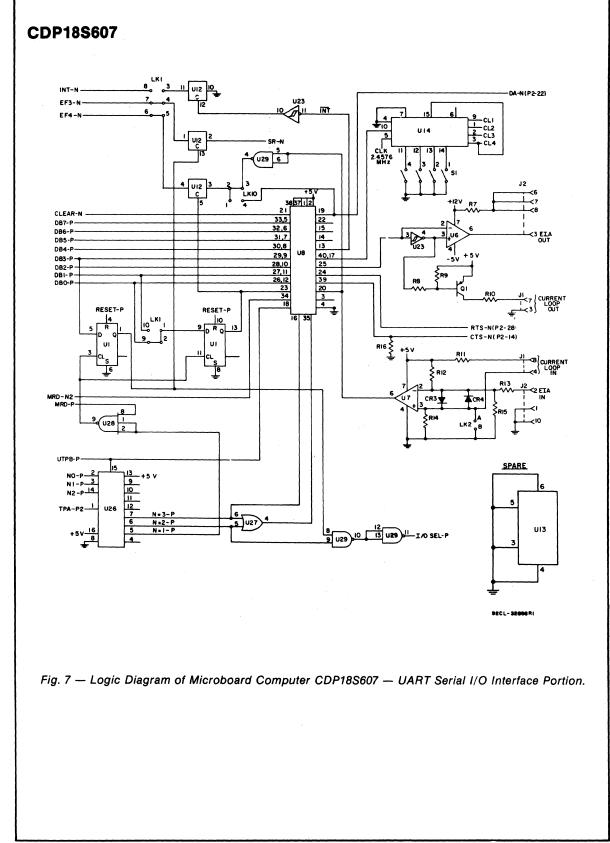

| CDP18S607                  | Microboard Com-<br>puter 2K RAM, 2/4K    |            |                         |     |

|                            | ROM (CDP1805)                            | 104        | MB-607                  | С   |

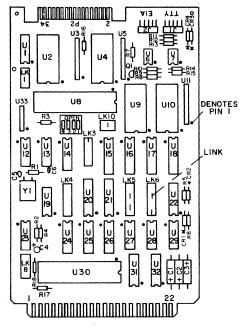

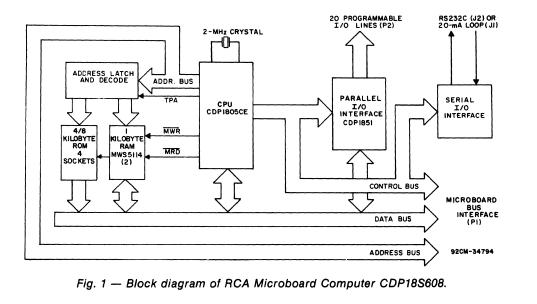

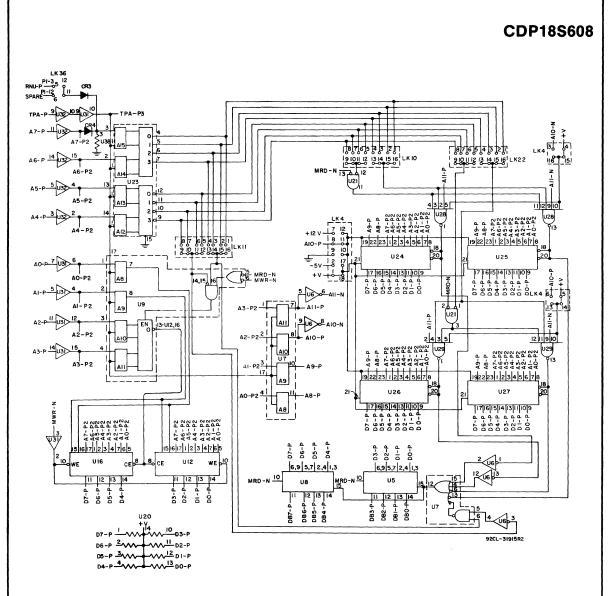

| CDP18S608                  | Microboard Com-                          |            |                         |     |

|                            | puter 1K RAM, 4/8K<br>ROM (CDP1805)      | 121        | MB-608                  | C   |

| CDP18S609                  | Microboard Com-                          |            |                         |     |

|                            | puter 1K RAM,<br>1/2/4K ROM              |            |                         | С   |

|                            | (CDP1805)                                | 136        | MB-609                  |     |

| CDP18S610                  | Microboard Com-                          |            |                         | C   |

|                            | puter 2K RAM, 2/4K<br>ROM (CDP1805)      | 155        | MB-610                  | с   |

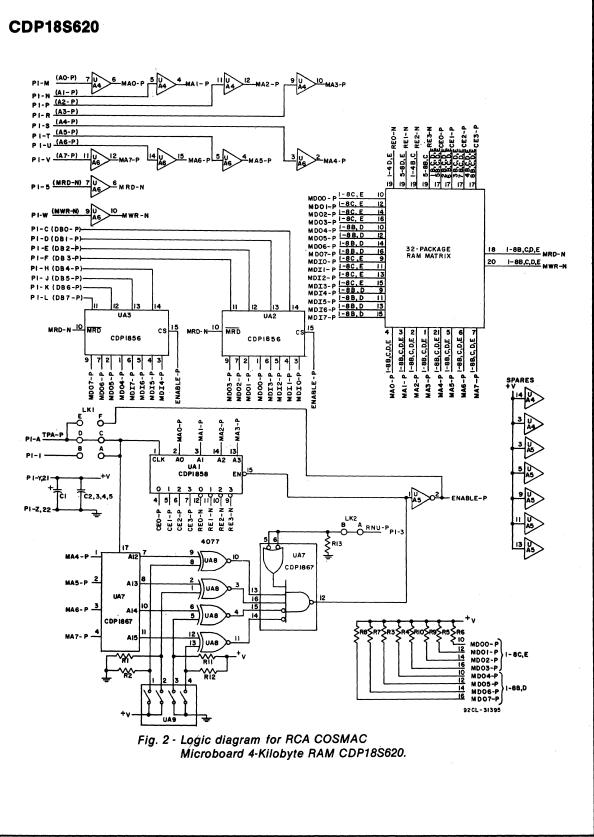

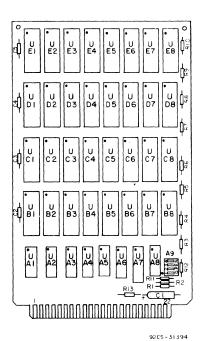

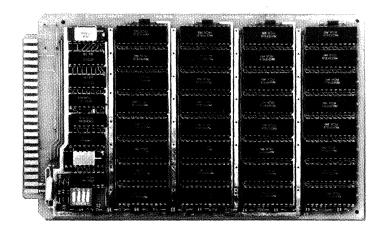

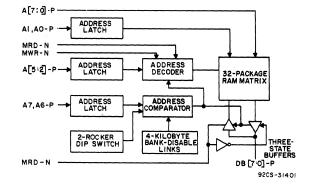

| CDP18S620                  | Microboard 4K RAM                        | 171        | MB-620                  |     |

| CDP18S621                  | Microboard 16K<br>RAM                    | 176        | MB-621                  | C   |

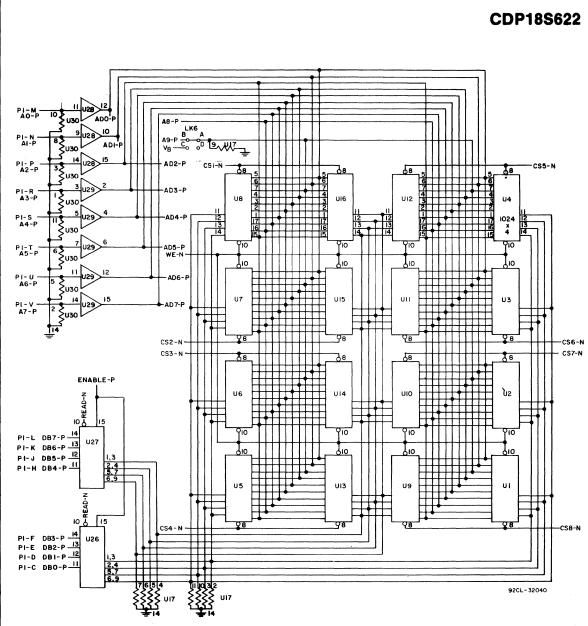

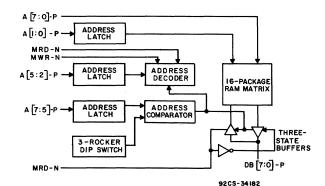

| CDP18S622                  | Microboard 8K RAM,                       |            |                         |     |

|                            | Battery-backup                           | 181        | MB-622                  | C   |

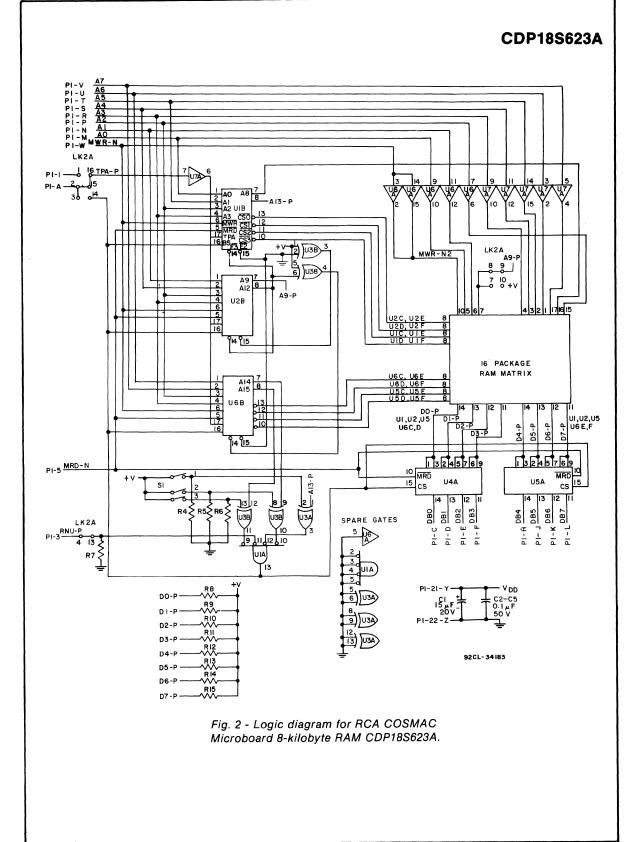

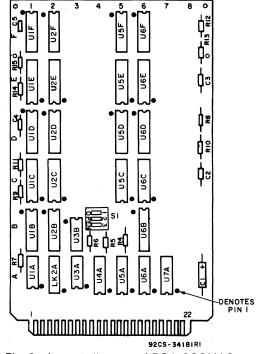

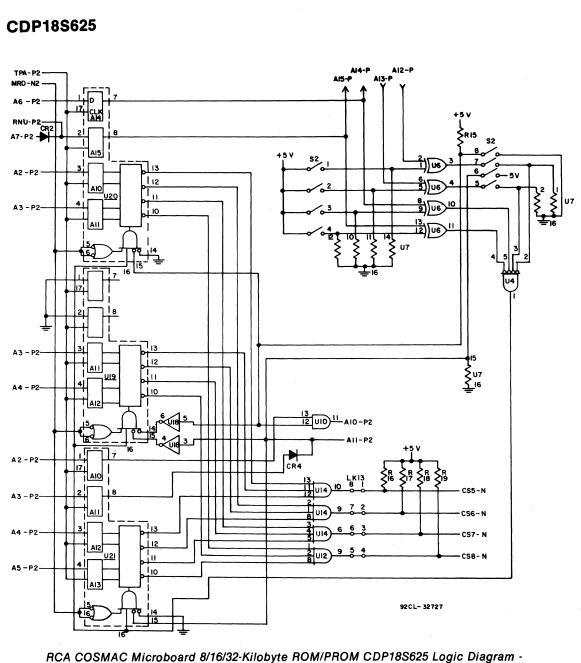

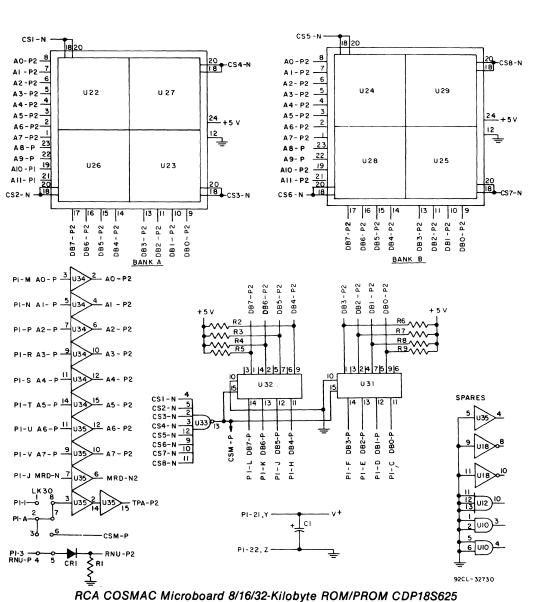

| CDP18S623A<br>CDP18S625    | Microboard 8K RAM<br>Microboard          | 190        | MB-623A                 | c   |

|                            | 8/16/32K                                 |            |                         |     |

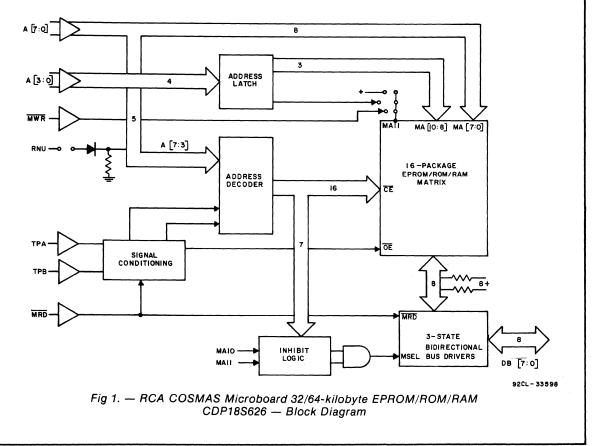

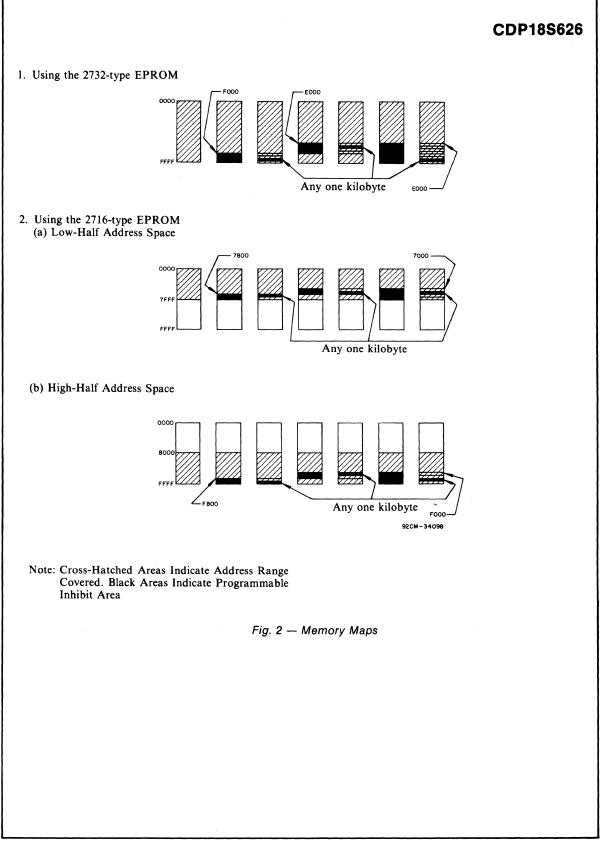

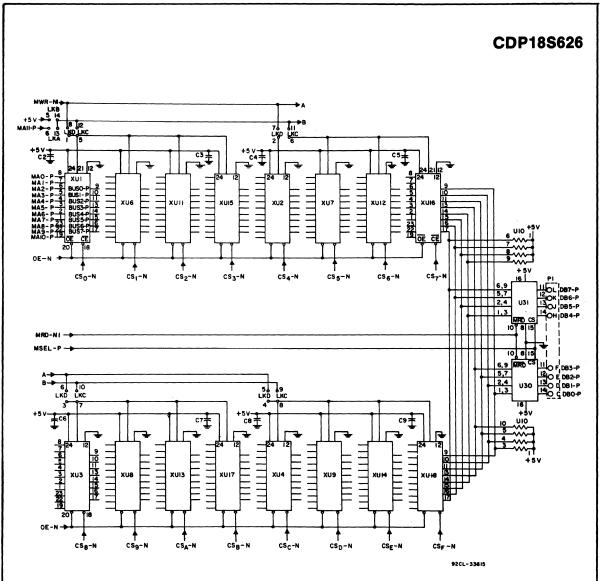

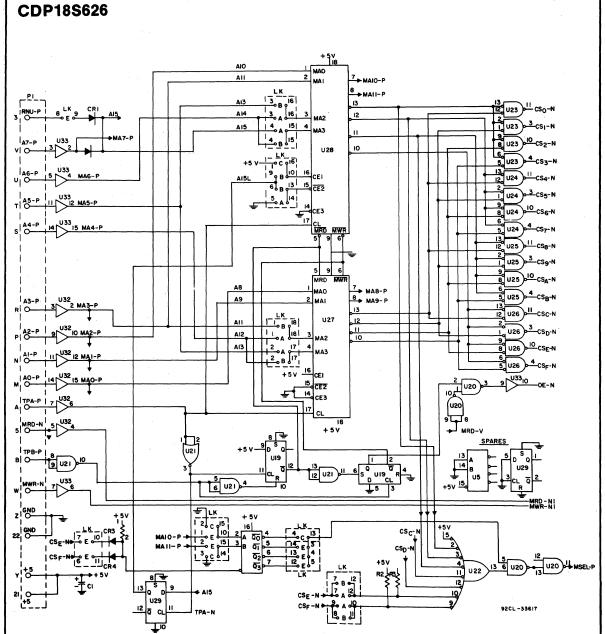

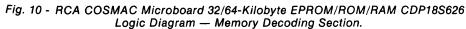

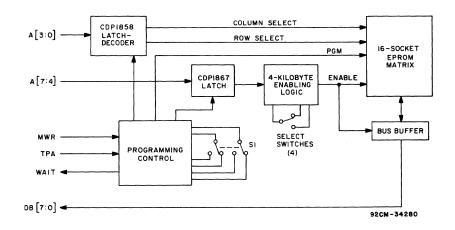

| CDP18S626                  | ROM/PROM<br>Microboard 32/64K            | 195        | MB-625                  | C   |

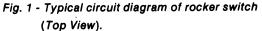

| CDP18S627                  | EPROM/ROM/RAM<br>Microboard 4K           | 207        | MB-626                  |     |

|                            | EPROM                                    | 229        | MB-627                  | C C |

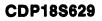

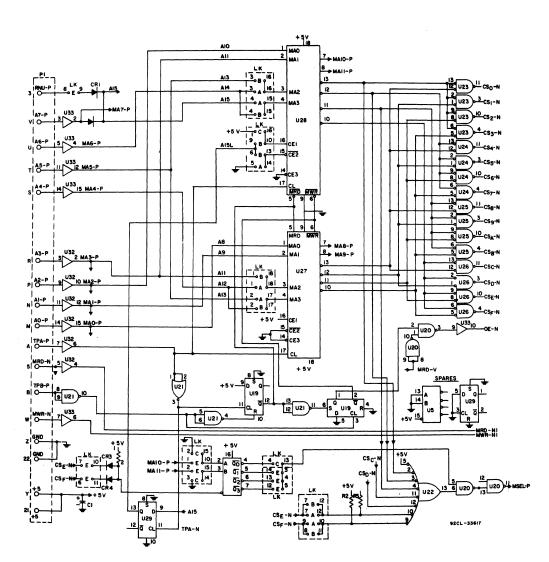

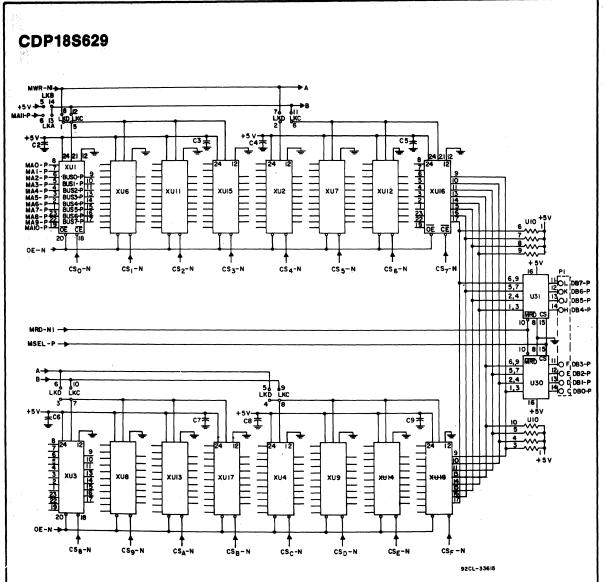

| CDP18S629                  | Microboard 32K                           | 237        | MB-629                  | С   |

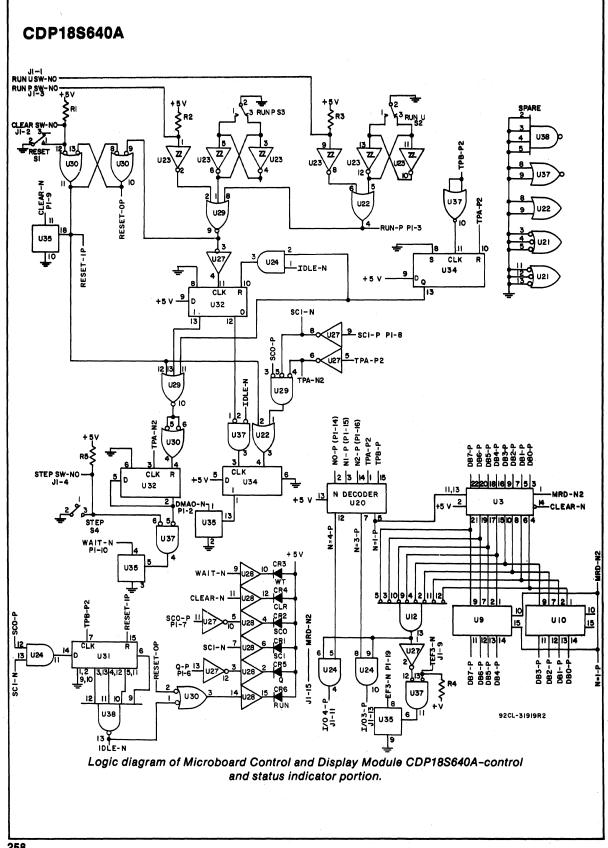

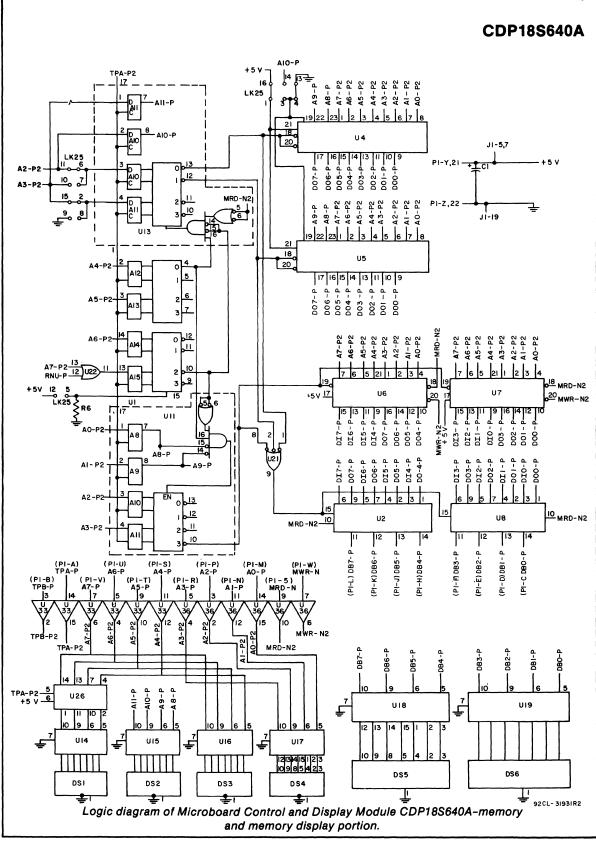

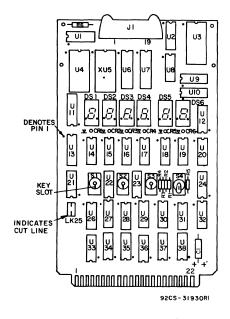

| CDP18S640A                 | Microboard Control                       | 207        |                         | ľ   |

| CDP18S640A1                | and Display Module<br>Microboard Control | 252        | MB-640A                 | с   |

|                            | and Display Module                       | 261        | MB-640A1                | ľ   |

|                            |                                          |            |                         | I   |

| Type No.           | Description                              | Page No. | Tech. Data<br>File No. |

|--------------------|------------------------------------------|----------|------------------------|

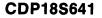

| CDP18S641          | Microboard UART                          | 270      | MB-641                 |

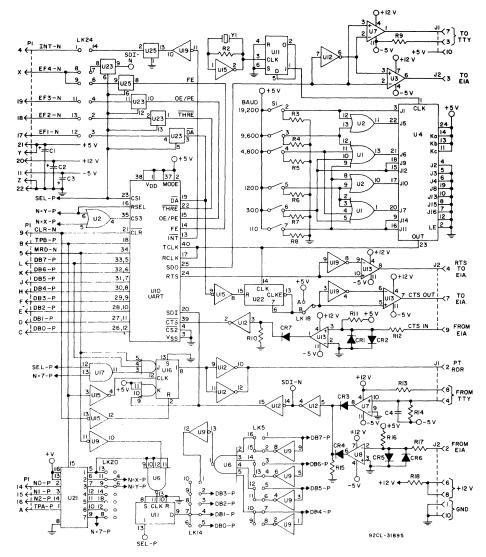

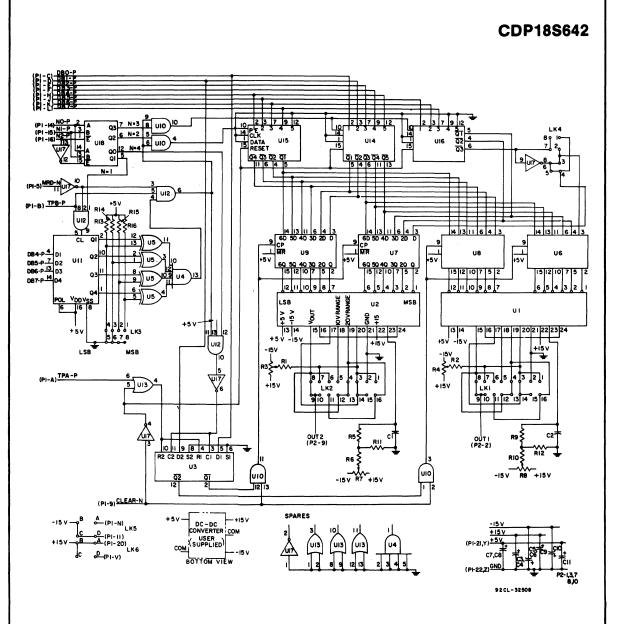

| CDP18S642          | Microboard D/A<br>Converter              | 270      | MB-641<br>MB-642       |

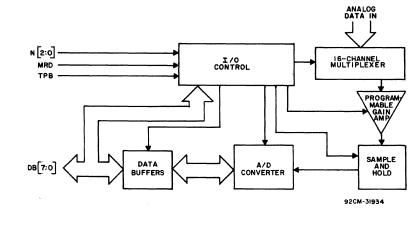

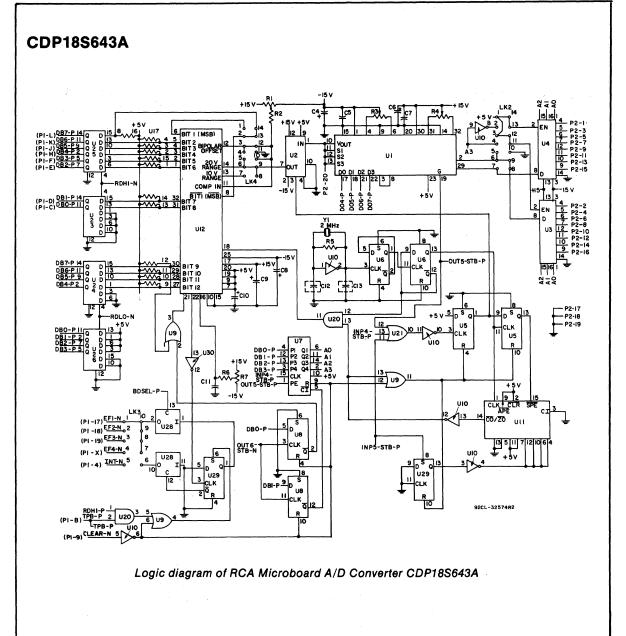

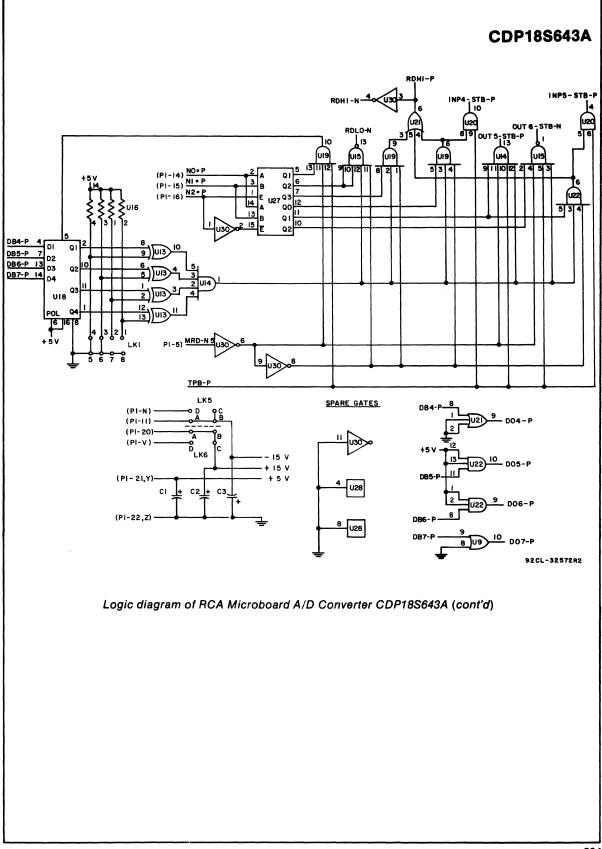

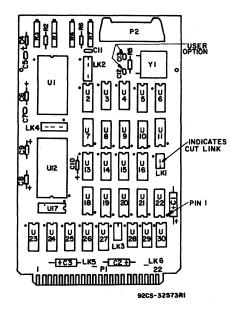

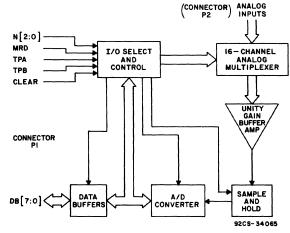

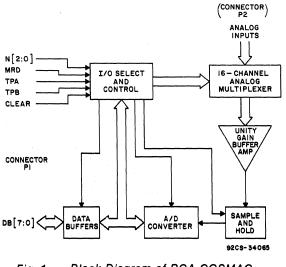

| CDP18S643A         | Microboard A/D                           |          |                        |

| CDP18S644          | Converter<br>Microboard A/D and          |          | MB-643A                |

| CDP18S646          | D/A Converter<br>Microboard Parallel     | 293      | MB-644                 |

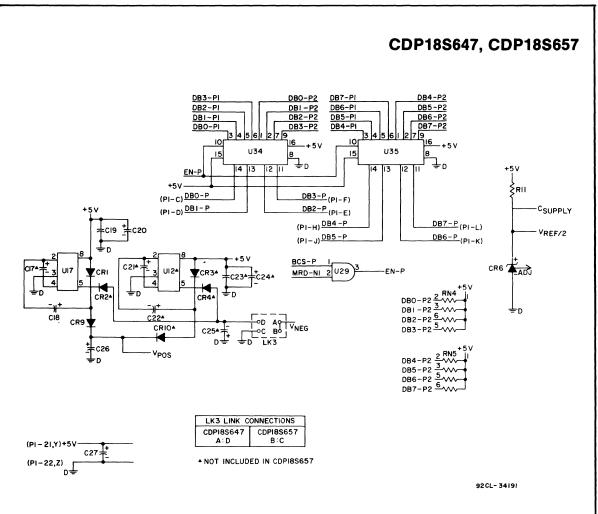

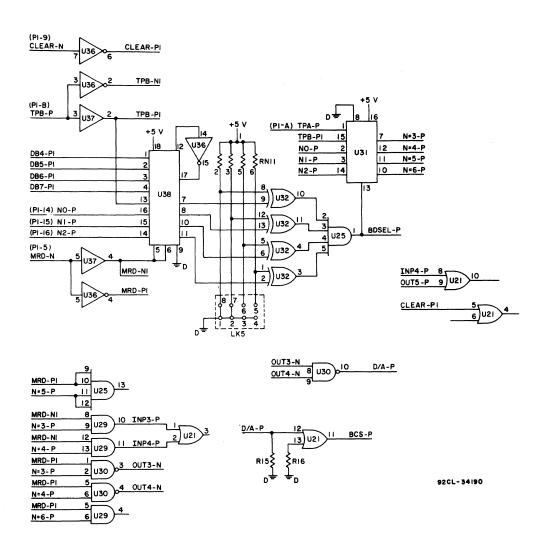

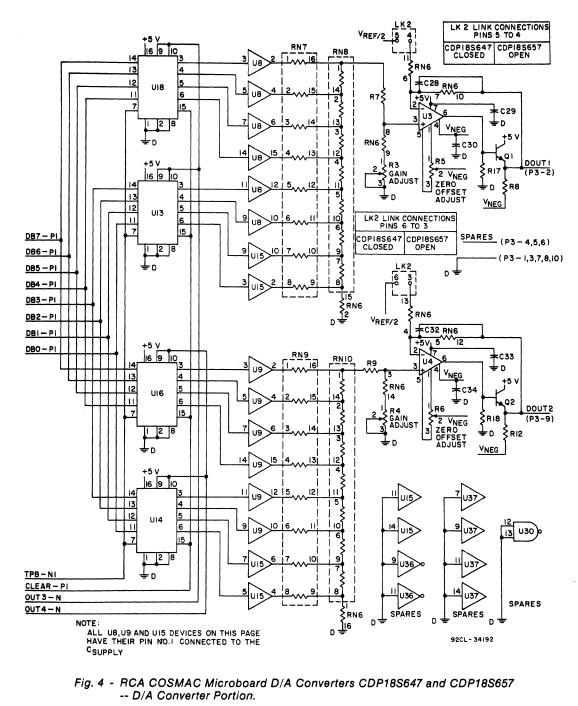

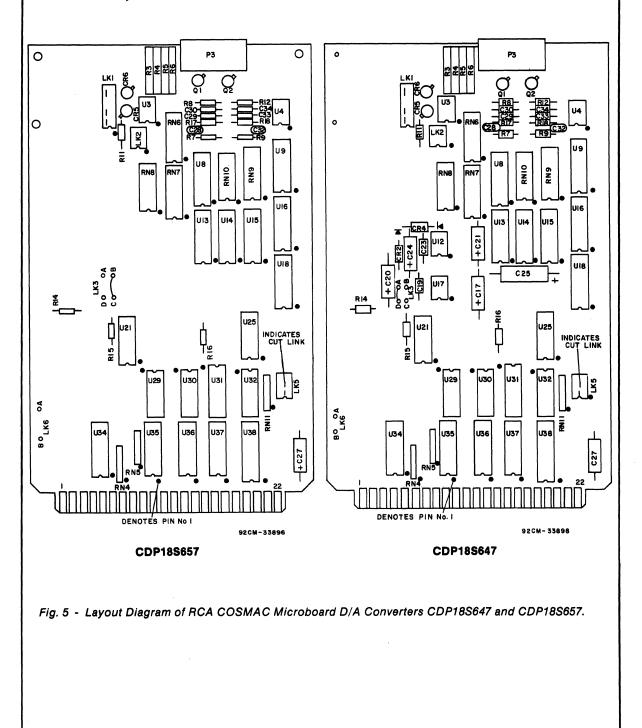

| CDP18S647          | I/O Module<br>Microboard D/A             | 308      | MB-646                 |

| CDP18S648          | Converter<br>Microboard A/D              | 319      | MB-647                 |

| CDP18S650          | Converter<br>Microboard Octal            | 330      | MB-648                 |

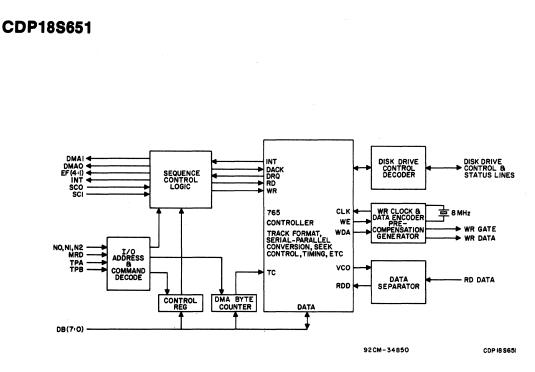

| CDP18S651          | Counter-Timer<br>Microboard Floppy       | 342      | _                      |

| CDP18S652          | Disk Controller<br>Microboard Memory     | 343      | -                      |

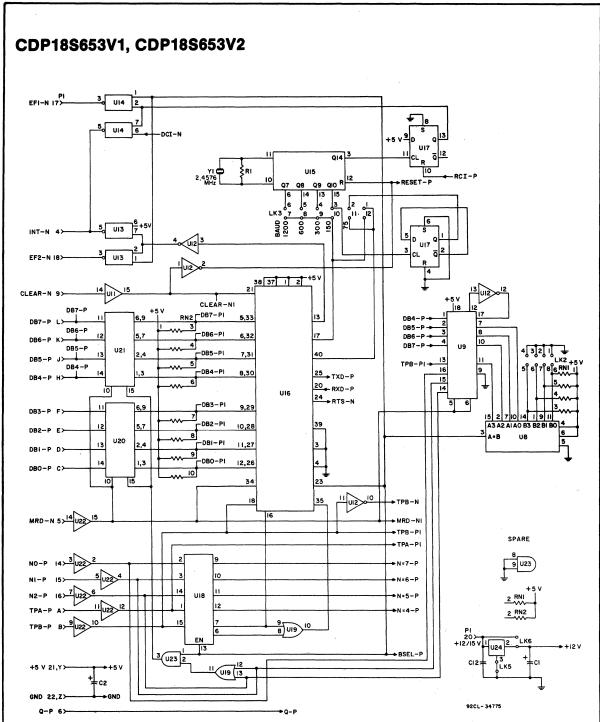

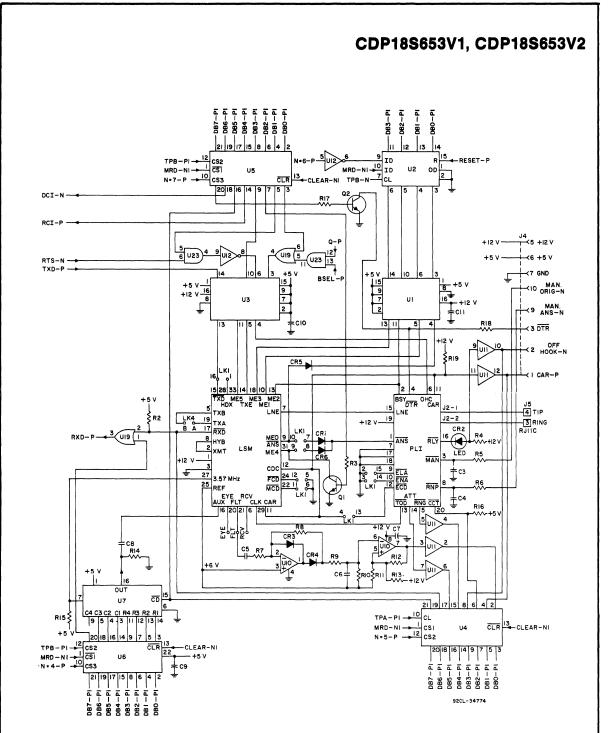

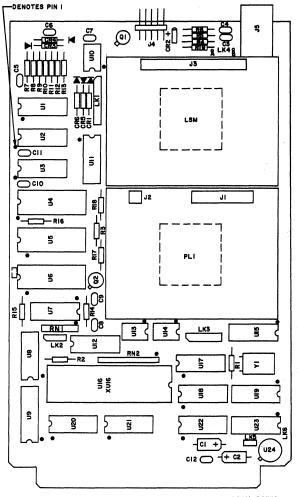

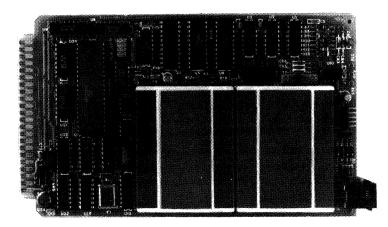

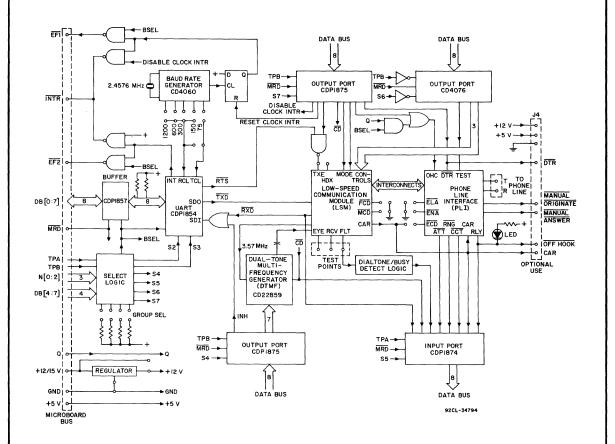

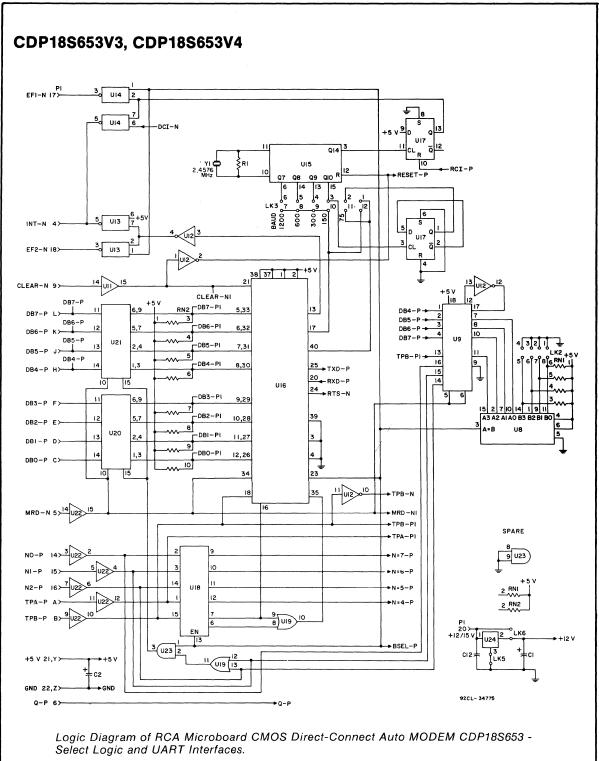

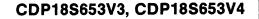

| CDP18S653V1.       | and Tape I/O<br>CMOS Direct-Con-         | 345      | -                      |

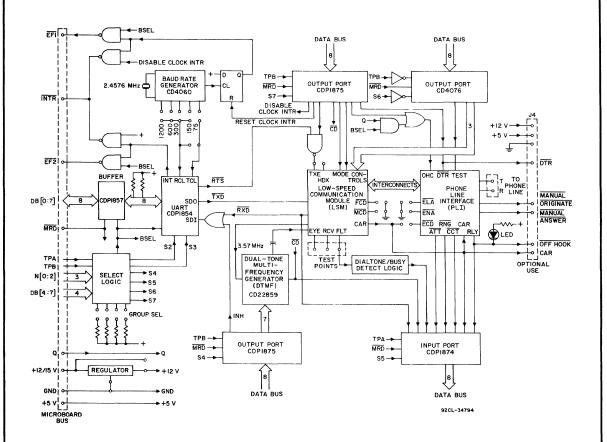

| V2                 | nect Auto MODEM<br>(Bell Compatible)     | 346      | MB-653V1,<br>V2        |

| CDP18S653V3,<br>V4 | CMOS Direct-Con-<br>nect Auto MODEM      | 353      | MB-653V3,              |

| CDP18S654          | (CCITT Compatible)<br>Microboard A/D and |          | V4                     |

| CDP18S657          | D/A Converter<br>Microboard D/A          | 293      | MB-644                 |

| CDP18S658          | Converter<br>Microboard A/D              | 319      | MB-647                 |

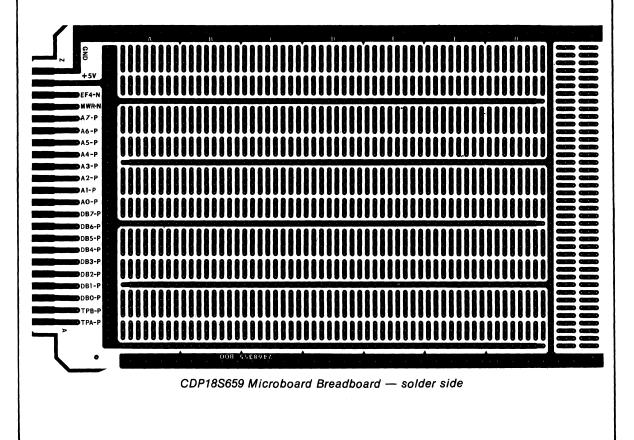

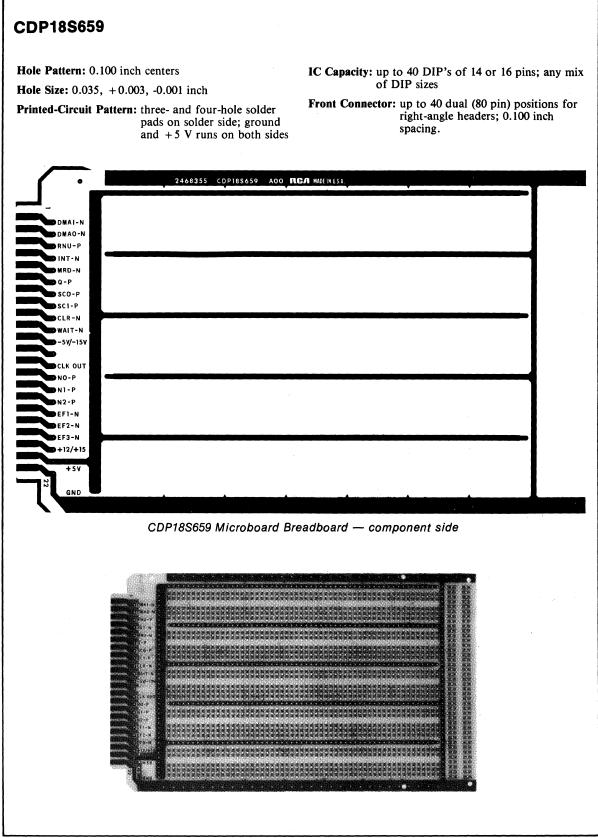

| CDP18S659          | Converter<br>Microboard Bread-           | 330      | MB-648                 |

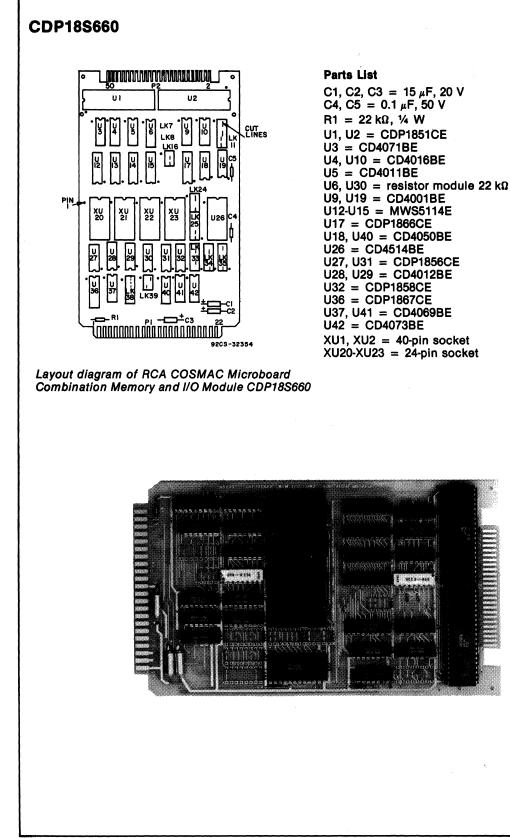

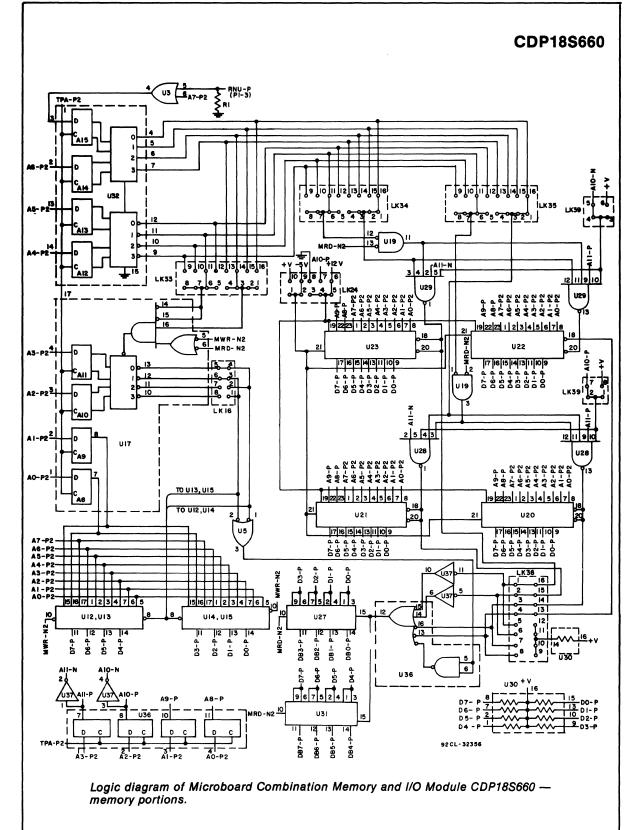

| CDP18S660          | board<br>Microboard Comb.                | 429      | MB-659                 |

|                    | Memory and I/O<br>Module                 | 361      | MB-660                 |

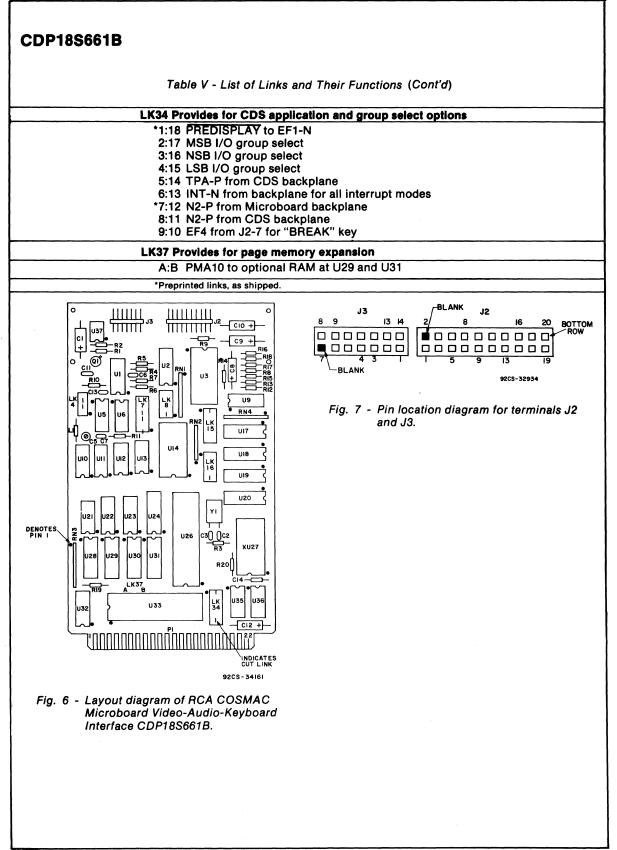

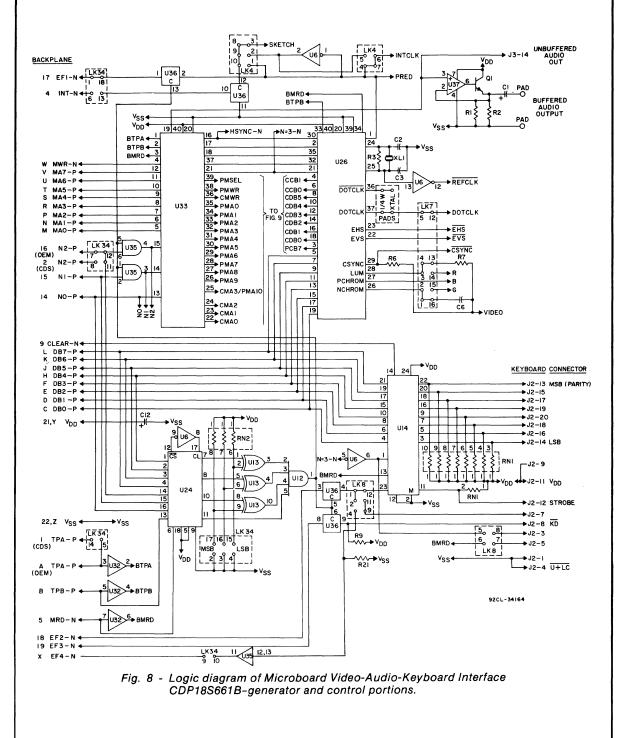

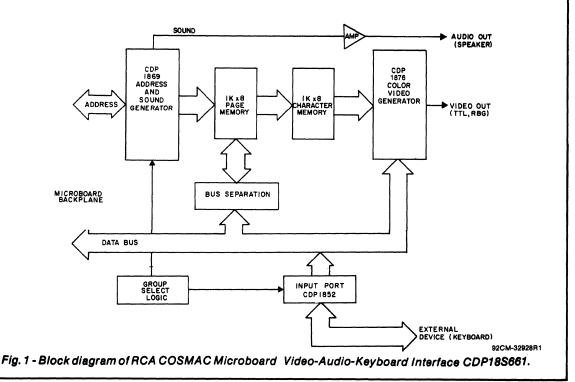

| CDP18S661B         | Microboard Video-<br>Audio-Keyboard      |          |                        |

| CDP18S661V3        | Interface (NTSC)<br>Microboard Video-    | 371      | MB-661B                |

| 227 10000140       | Audio-Keyboard<br>Interface (PAL)        | 385      | MB-661V3               |

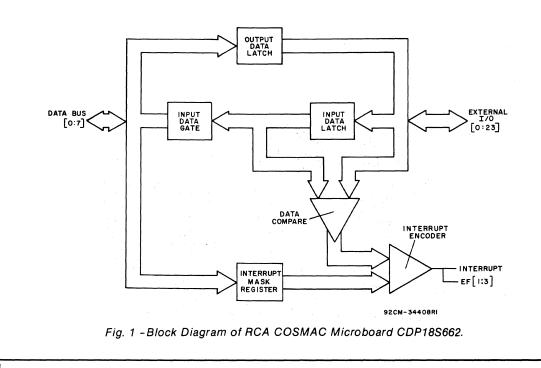

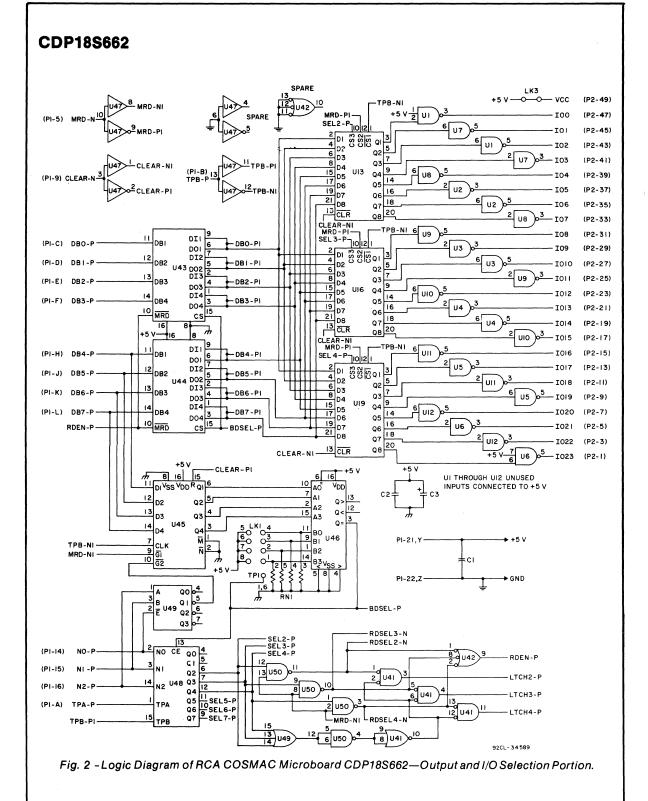

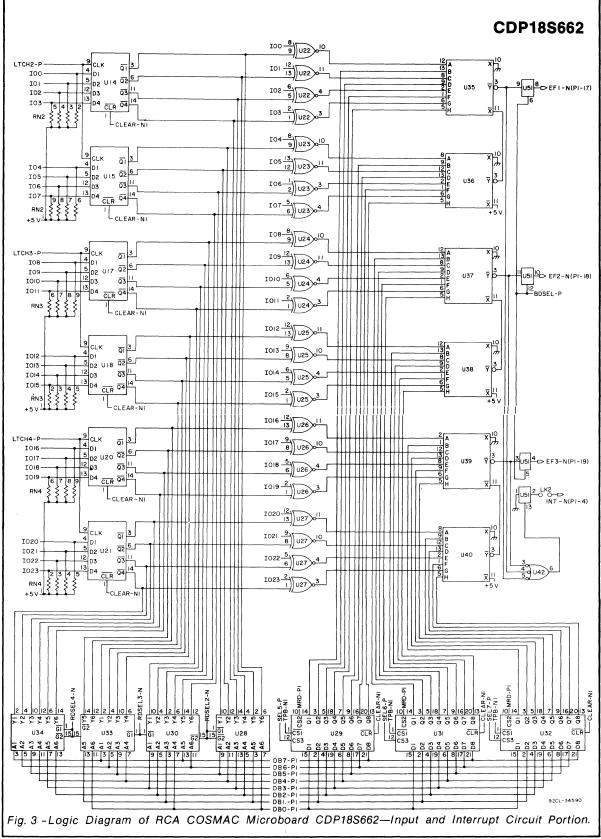

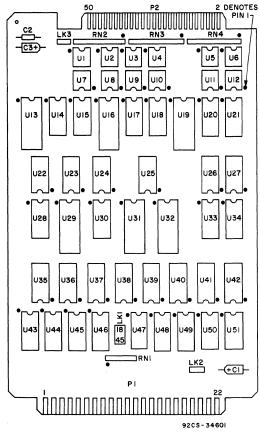

| CDP18S662          | PIO Opto 22 Module<br>Interface          |          | MB-662                 |

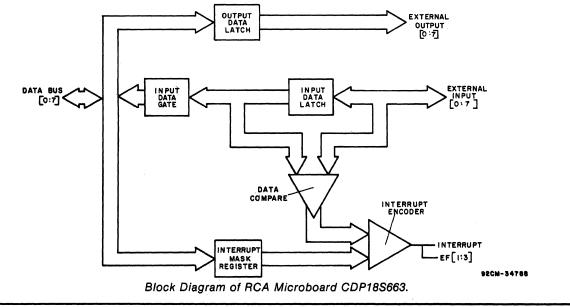

| CDP18S663          | Optically Isolated DC                    |          | 1910-002               |

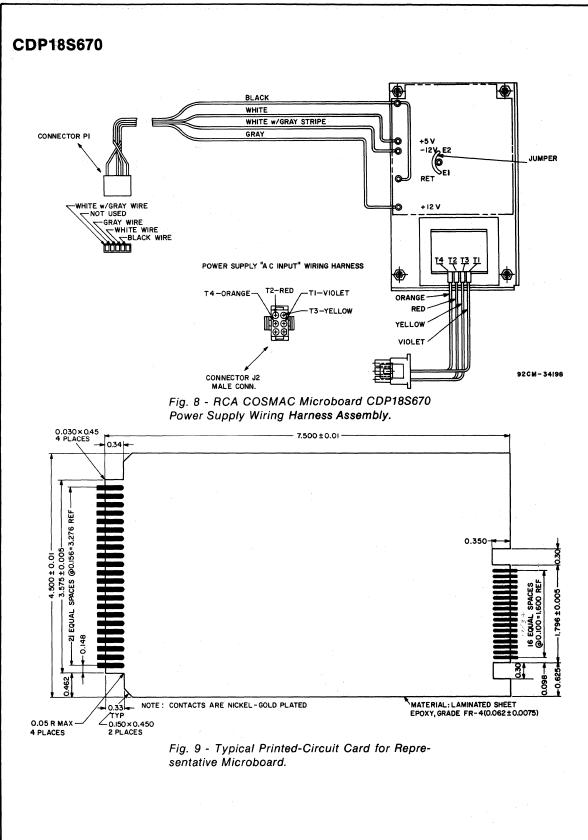

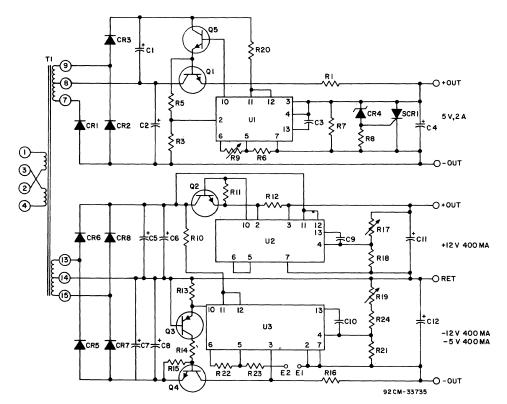

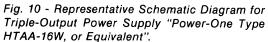

| CDP18S670          | Interface<br>Microboard 22-Card          | 401      | -                      |

| 00040000           | Chassis with Integral<br>Power Supply    | 431      | MB-670                 |

| CDP18S675          | Microboard 5-Card<br>Chassis             | 439      | MB-675                 |

| CDP18S676          | Microboard 5-Card<br>Chassis with Case   | 439      | MB-675                 |

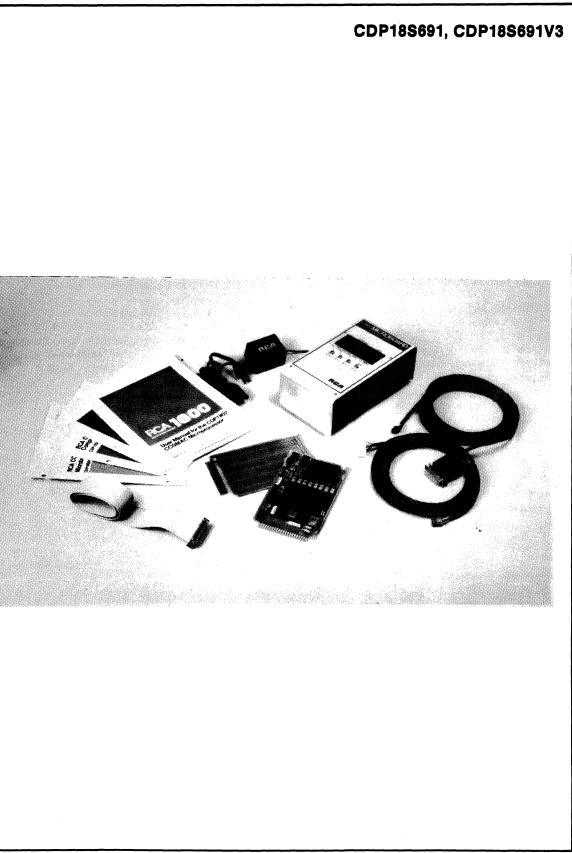

| CDP18S691,V3       | Microboard Proto-<br>typing System       |          |                        |

| CDP18S692,V3       | (CDP18S601)<br>Microboard Proto-         | 442      | MB-691                 |

|                    | typing System<br>(CDP18S602)             | 442      | MB-692                 |

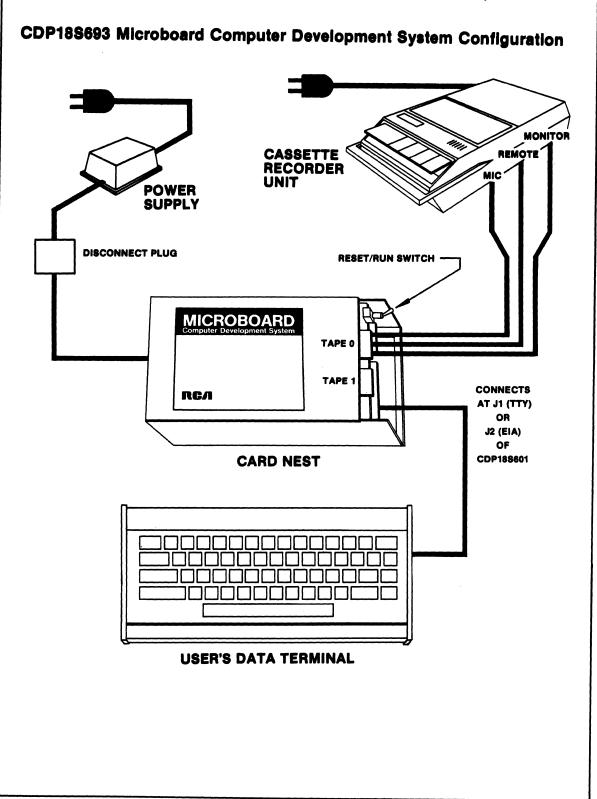

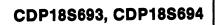

| CDP18S693          | Microboard Com-<br>puter Development     |          |                        |

| CDP18S694          | System (MCDS)<br>Microboard Com-         | 456      | PD13                   |

|                    | puter Development<br>System (MCDS)       | 456      | PD13                   |

# Index to Products

| Type No.   | Description          | Page No. | Tech. Data<br>File No. | Type No.        | Description         | Page No. | Tech. Data<br>File No. |

|------------|----------------------|----------|------------------------|-----------------|---------------------|----------|------------------------|

| CDP18S695  | Color Microboard     | •        |                        | CDP18S852       | Micro Concurrent    |          |                        |

|            | Computer Develop-    |          |                        |                 | PASCAL              |          |                        |

|            | ment System          | 464      | PD14                   |                 | Interpreter/Kernel  | 524      | PD44                   |

| CDP18S826, | Fixed-Point          |          |                        | CDP18S853       | Micro Concurrent    |          |                        |

| V1, V2     | Arithmetic           |          |                        |                 | PASCAL              |          |                        |

|            | Subroutines          | 531      | PD6                    |                 | Interpreter/Kernel  | 524      | PD44                   |

| CDP18S827  | Floating-Point       |          |                        | CDP18SUT60,     |                     |          |                        |

|            | Arithmetic           |          |                        | 61, 62          | Firmware            | 530      |                        |

|            | Subroutine           | 506      | PD7                    | CDPR582         | ROM-Based Fixed-    |          |                        |

| CDP18S831  | Micromonitor         |          |                        |                 | Point Binary        |          |                        |

|            | Operating System     |          |                        |                 | Arithmetic          | 531      | PD6                    |

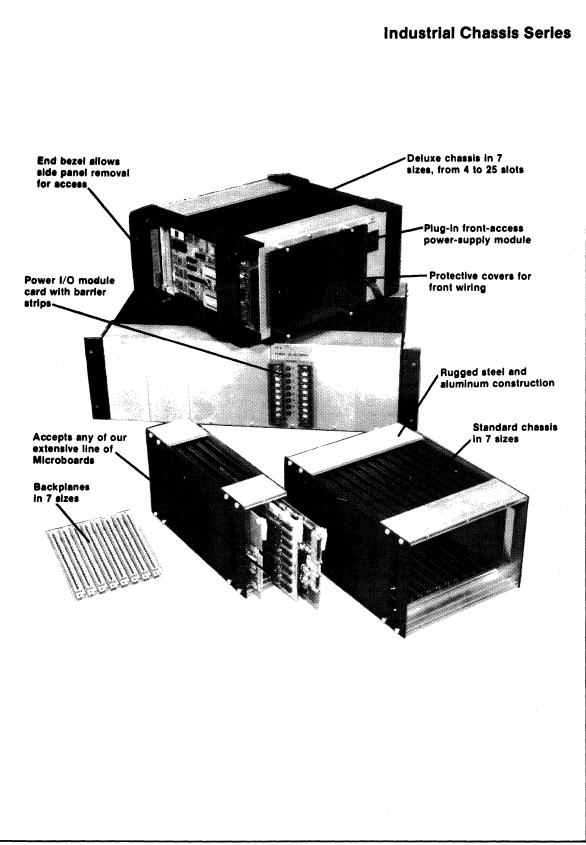

| CDP18S834  | (MOPS)<br>BASIC1     | 507      | PD31                   | Industrial Chas | sis Series:         |          |                        |

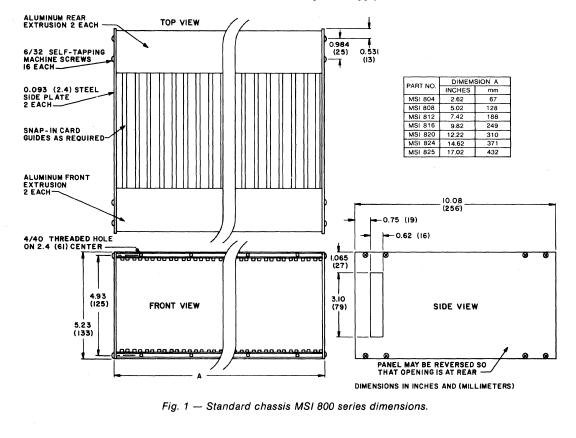

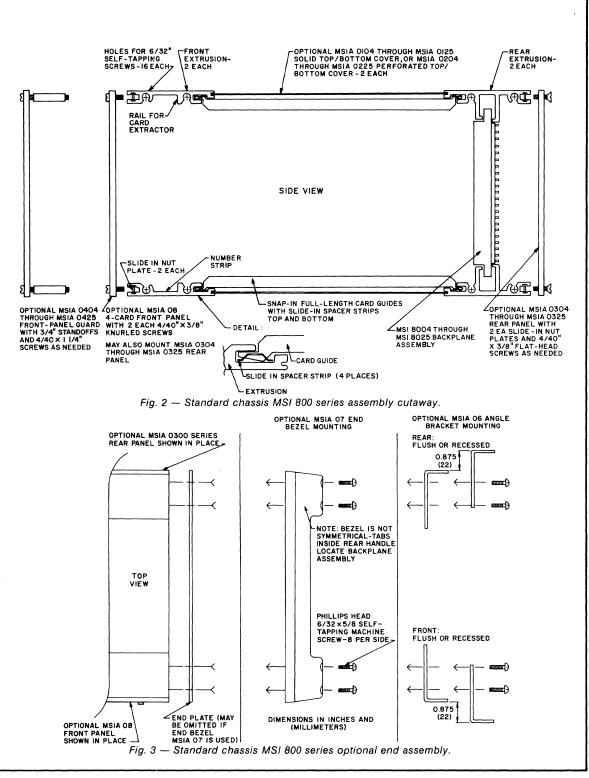

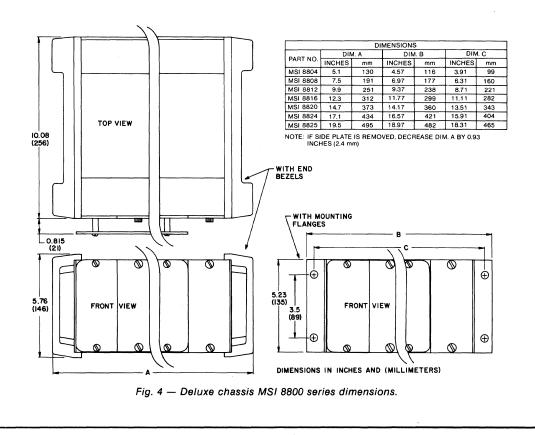

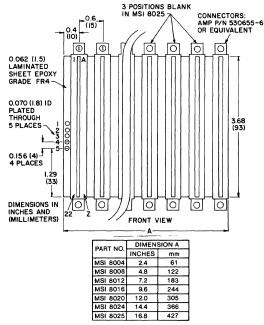

| CDP 165634 | Compiler/Interpreter | 511      | PD34                   | MSI 800 series  | Standard Industrial |          |                        |

| CDP18S835  | VIS Interpreter      | 514      | PD34                   |                 | Chassis Series      | 402      | МВ-8                   |

| CDP18S837  | CDOS Upgrade         | 514      | _                      | MSI 8000 series | Industrial Chassis  | 402      | WID 0                  |

| 001 100007 | Package (to CDS III) | 494      | PD37A                  |                 | Series Backplanes   |          |                        |

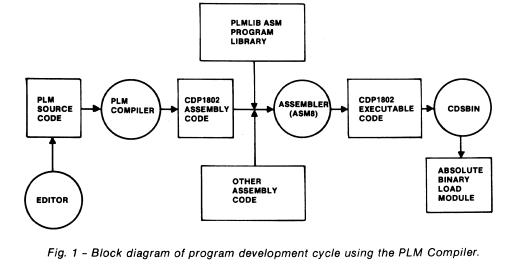

| CDP18S839  | PLM-1800 High-       | 707      | Dorn                   |                 | With Connectors     | 402      | MB-8                   |

| 021 100000 | Level-Language       |          |                        | MSI 8800 series | Deluxe Industrial   |          |                        |

|            | Compiler             | 515      | PD39                   |                 | Chassis Series      | 402      | MB-8                   |

| CDP18S840  | BASIC2 High-         |          |                        | MSIA series     | Industrial Chassis  |          |                        |

|            | Level-Language       |          |                        |                 | Accessories         | 402      | MB-8                   |

|            | Interpreter          | 518      | PD40                   |                 |                     |          |                        |

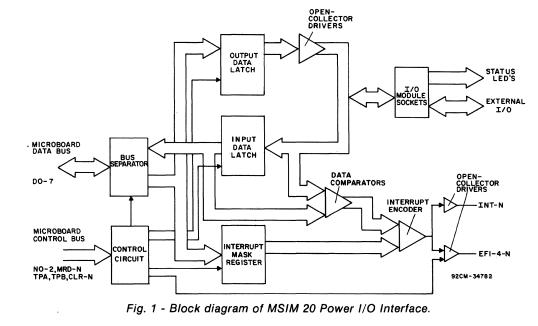

| CDP18S842  | Run-Time BASIC       |          |                        | MSIM 20         | Industrial Micro-   |          |                        |

|            | High-Level Language  | e        |                        |                 | board Power Inter-  |          |                        |

|            | Interpreter          | 521      |                        |                 | face Module         | 414      | MB-20                  |

| CDP18S843  | Assembler/Editor     |          |                        | MSIM 40, E      | Industrial Micro-   |          |                        |

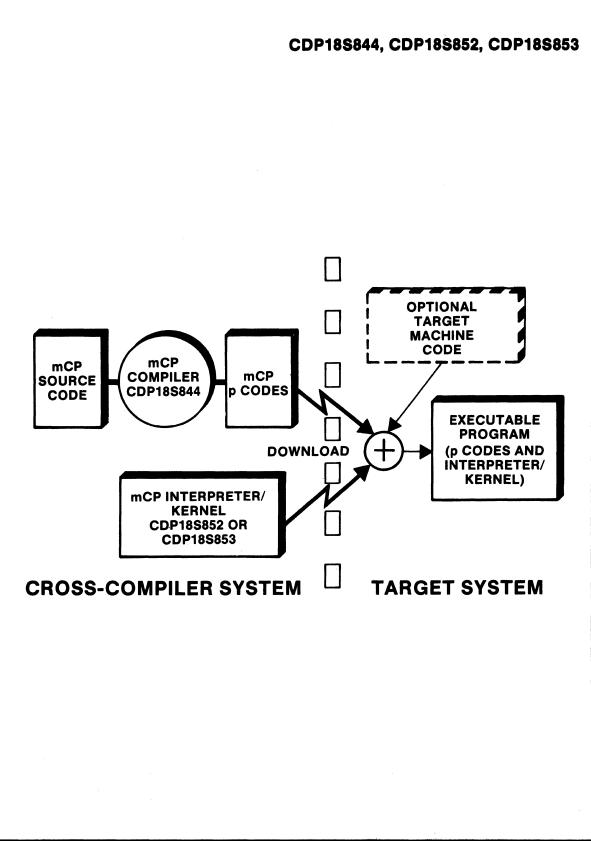

|            | Upgrade Firmware     | 523      | -                      | MSIM 41, E      | board Power         |          |                        |

| CDP18S844  | Micro Concurrent     |          |                        |                 | Supplies            | 426      |                        |

|            | PASCAL               |          |                        | MSIM 50         | Dual Floppy-Disk    |          |                        |

|            | Cross-Compiler       | 524      | PD44                   |                 | Drive Module        | 427      | -                      |

|            |                      |          |                        |                 |                     |          |                        |

4

# **Product Classification Chart** Microboard Computers

| CDP18S601<br>CDP18S602<br>CDP18S603<br>CDP18S604<br>CDP18S605 | 2 K RAM<br>3 1 K RAM<br>3 1 K RAM                         | A, 2/4K<br>A, 4/8K<br>A, 1/2/4 | ROM                                                 |                                                                  | CDP18S607 2K F<br>CDP18S608 1K F<br>CDP18S609 1K F                                                                   | RAM, 4/8<br>RAM, 2/4<br>RAM, 4/8<br>RAM, 1/2<br>RAM, 2/4 | 4K RO<br>3K RO<br>2/4K F | M<br>M<br>ROM/Pf |                           |

|---------------------------------------------------------------|-----------------------------------------------------------|--------------------------------|-----------------------------------------------------|------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|--------------------------|------------------|---------------------------|

| Microboard<br>Computer                                        | Clock<br>Frequency<br>(MHz)                               | RAM<br>(btyes)                 | ROM<br>(bytes)                                      | Serial<br>I/O Port                                               | I/O Lines                                                                                                            | Ctr.<br>Timer                                            | Po<br>V                  | wer*<br>  (mA)   | Temperature<br>Range (°C) |

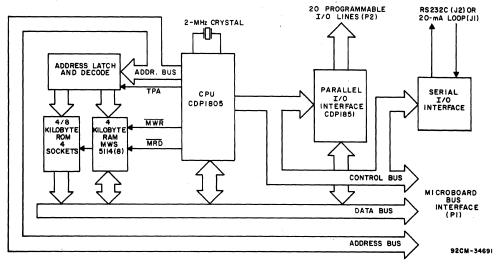

| CDP18S601<br>CPU:<br>CDP1802                                  | 2                                                         | 4K                             | 4K (CDP1834)<br>4K (2708)<br>4K (2758)<br>8K (2716) | Software-<br>driven;<br>Q output;<br>flag input                  | 25:<br>20 programmable<br>I/O (CDP1851);<br>4 flag inputs,<br>1 Q output                                             | _                                                        | + 5                      | 10               | -40 to +85                |

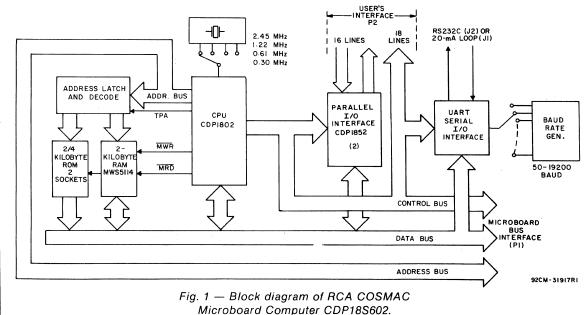

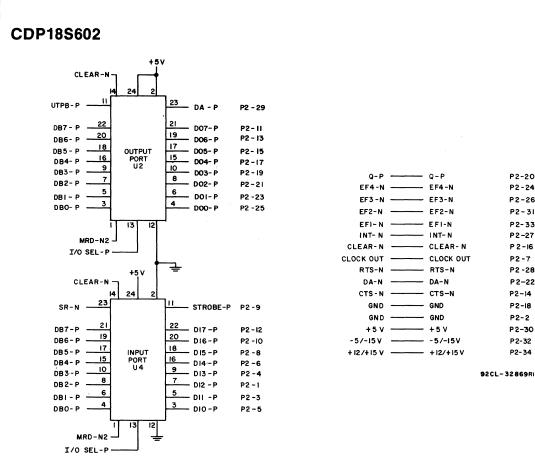

| CDP18S602<br>CPU:<br>CDP1802                                  | Selectable:<br>2.4576,<br>1.2288,<br>0.6144,<br>or 0.3072 | 2K                             | 2K (CDP1834)<br>2K (2758)<br>4K (2716)              | UART:<br>14 selectable<br>baud rates<br>from 50 to<br>19200 baud | 21:<br>8 inputs (CDP1852),<br>8 outputs (CDP1852),<br>4 flag inputs,<br>1 Q output                                   | _                                                        | + 5                      | 8                | -40 to +85                |

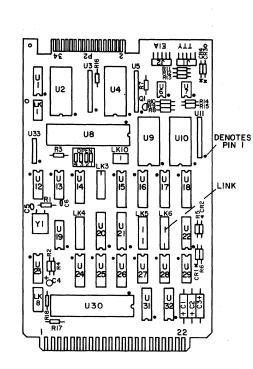

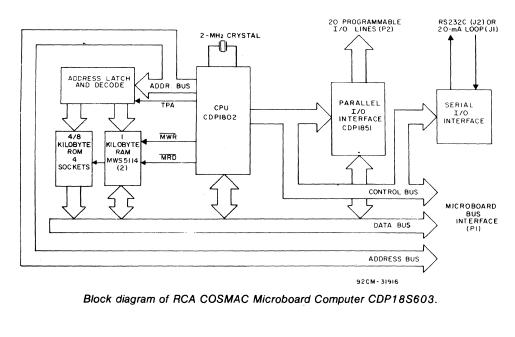

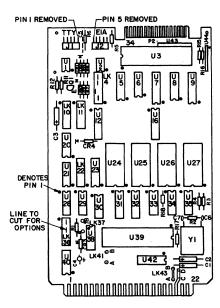

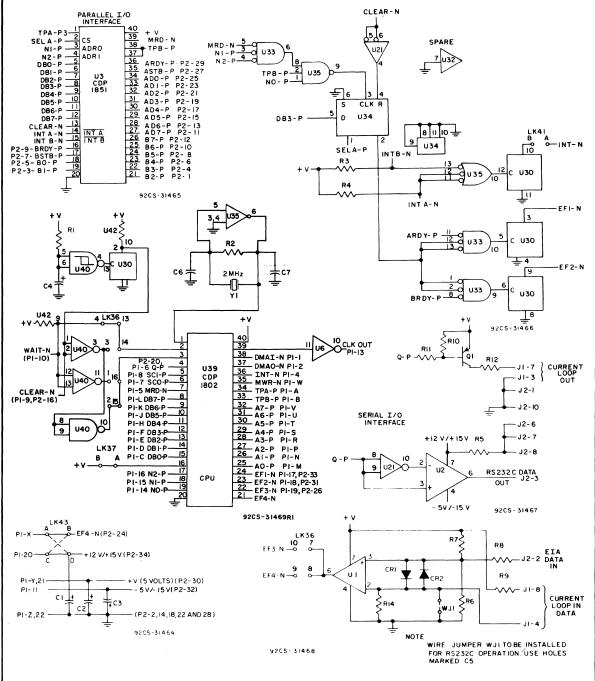

| CDP18S603<br>CPU:<br>CDP1802                                  | 2                                                         | 1K                             | 4K (CDP1834)<br>4K (2708)<br>4K (2758)<br>8K (2716) | Software-<br>driven;<br>Q output;<br>flag input                  | 25:<br>20 programmable<br>I/O (CDP1851);<br>4 flag inputs;<br>1 Q output                                             |                                                          | + 5                      | 7                | -40 to +85                |

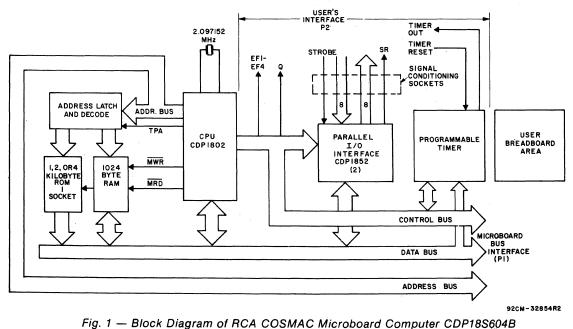

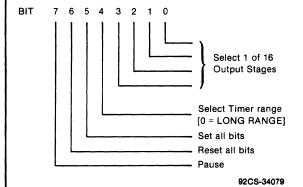

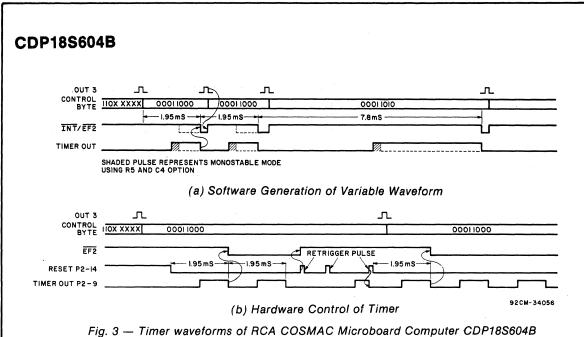

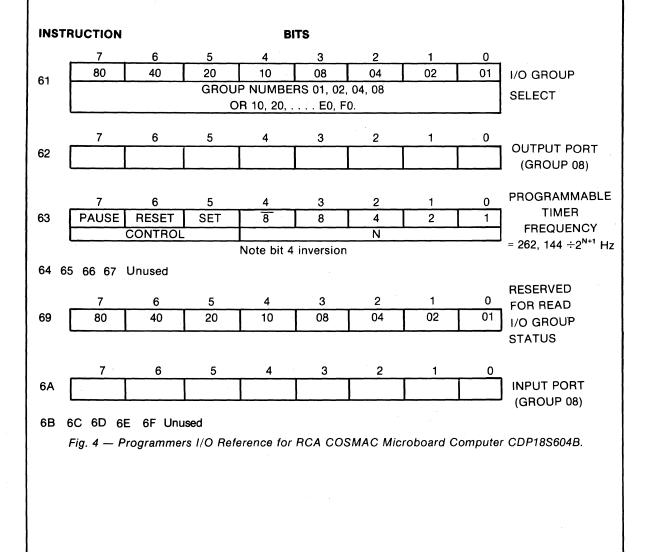

| CDP18S604B<br>CPU:<br>CDP1802                                 | 2.097152                                                  | 1K                             | 1K (CDP1834)<br>1K (2758)<br>2K (2716)<br>4K (2732) |                                                                  | 23:<br>8 inputs (CDP1852),<br>8 outputs (CDP1852),<br>4 flag inputs,<br>1 Q output<br>1 timer out<br>1 timer control | 1                                                        | + 5                      | 4                | -40 to +85                |

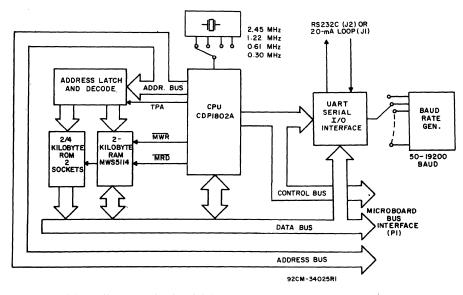

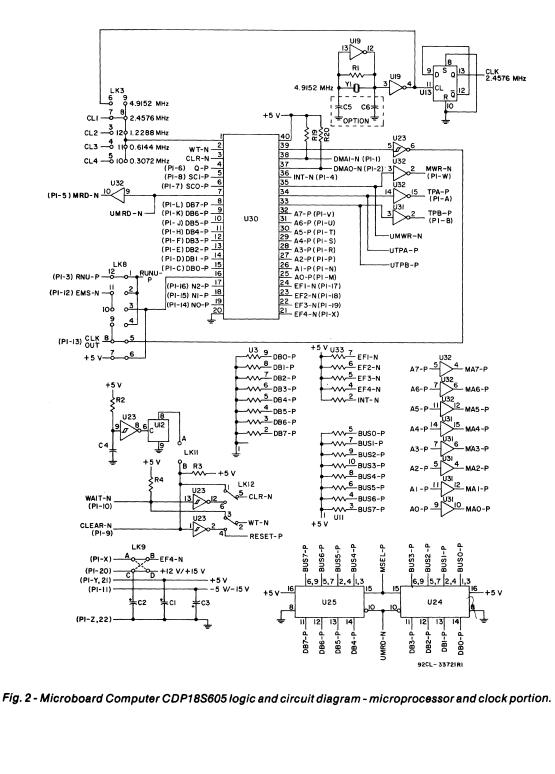

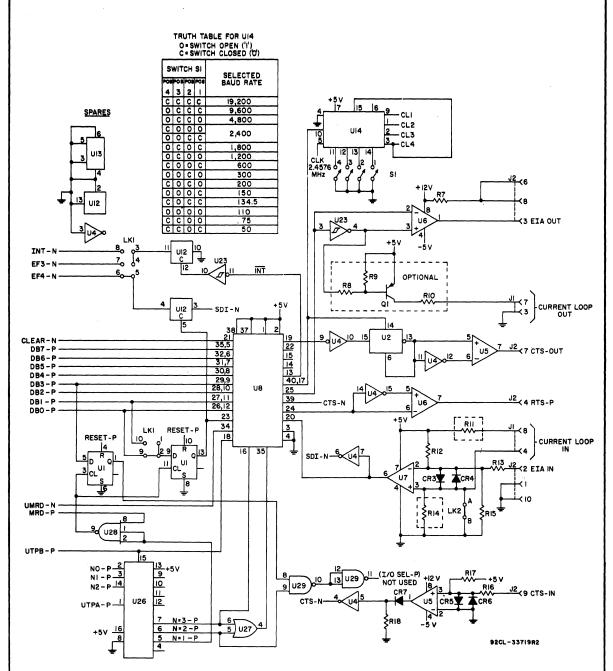

| CDP18S605<br>CPU:<br>CDP1802                                  | Selectable:<br>2.4576,<br>1.2288,<br>0.6144,<br>or 0.3072 | 2К                             | 2K (CDP1834)<br>2K (2758)<br>4K (2716)              | UART:<br>14 selectable<br>baud rates<br>from 50 to<br>19200 baud | _                                                                                                                    |                                                          | + 5                      | 8                | -40 to +85                |

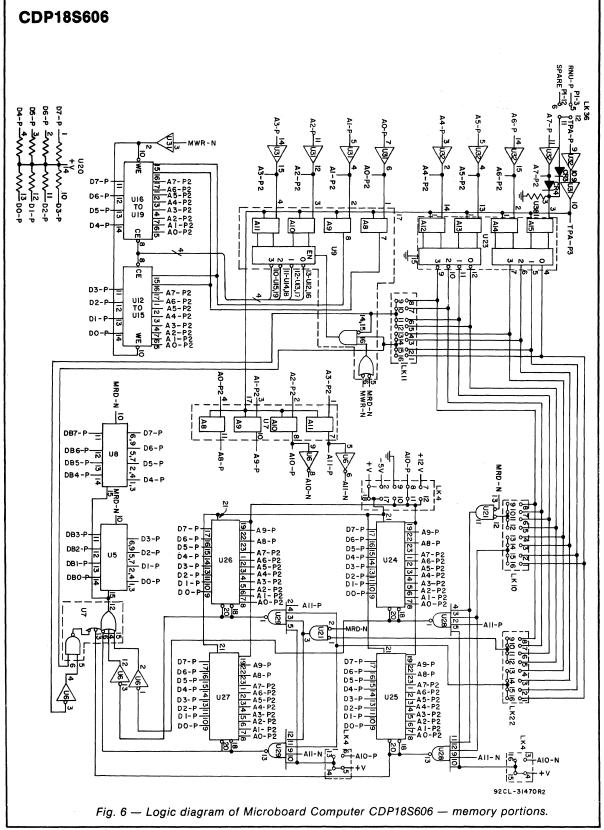

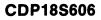

| CDP18S606<br>CPU:<br>CDP1805                                  | 2                                                         | 4К                             | 4K (CDP1834)<br>4K (2708)<br>4K (2758)<br>8K (2716) | Software-<br>driven;<br>Q output;<br>flag input                  | 25:<br>20 programmable<br>I/O (CDP1851);<br>4 flag inputs,<br>1 Q output                                             | 1                                                        | + 5                      | 10               | -40 to +85                |

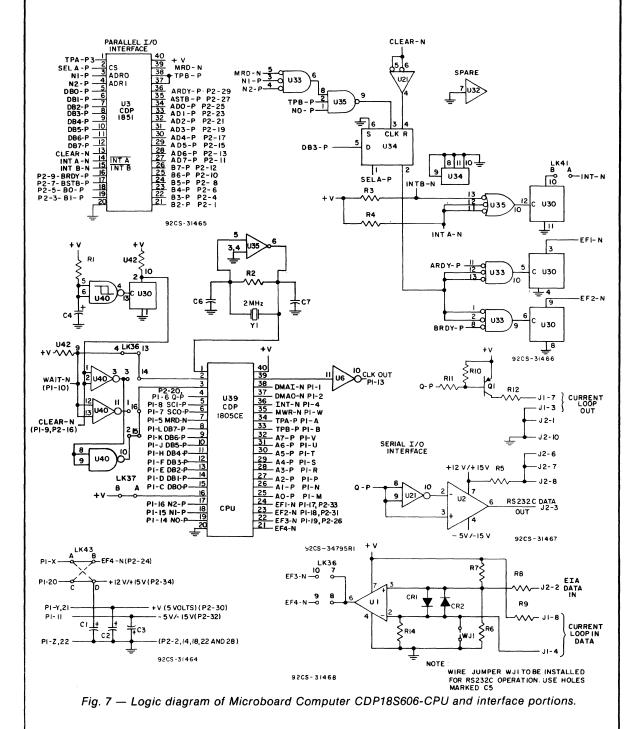

| CDP18S607<br>CPU:<br>CDP1805                                  | Selectable:<br>2.4576,<br>1.2288,<br>0.6144,<br>or 0.3072 | 2К                             | 2K (CDP1834)<br>2K (2758)<br>4K (2716)              | UART:<br>14 selectable<br>baud rates<br>from 50 to<br>19200 baud | 21:<br>8 inputs (CDP1852)<br>8 outputs (CDP1852)<br>4 flag inputs,<br>1 Q output                                     | 1                                                        | + 5                      | 8                | -40 to +85                |

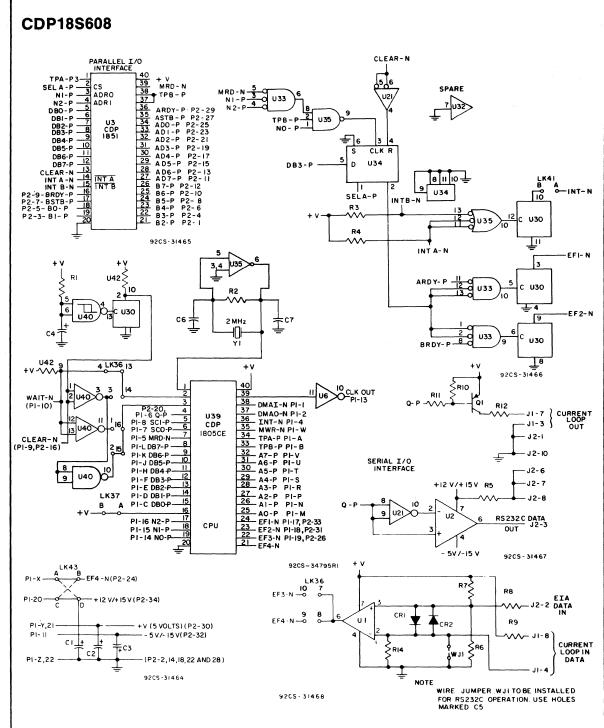

| CDP18S608<br>CPU:<br>CDP1805                                  | 2                                                         | 1K                             | 4K (CDP1834)<br>4K (2708)<br>4K (2758)<br>8K (2716) | Software-<br>driven;<br>Q output;<br>flag input                  | 25:<br>20 programmable<br>I/O (CDP1851);<br>4 flag inputs,<br>1 Q output                                             | 1                                                        | + 5                      | 7                | -40 to +85                |

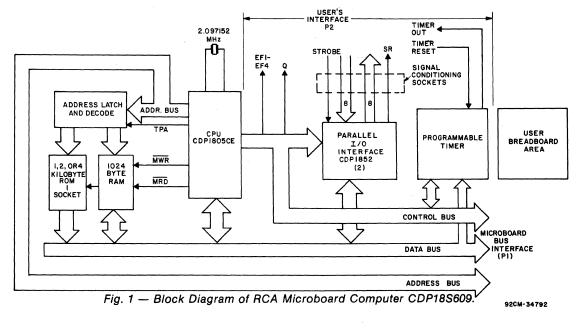

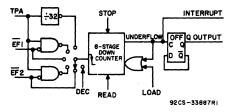

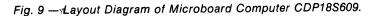

| CDP18S609<br>CPU:<br>CDP1805                                  | 2.097152                                                  | 1K                             | 1K (CDP1834)<br>1K (2758)<br>2K (2716)<br>4K (2732) |                                                                  | 23:<br>8 inputs (CDP1852),<br>8 outputs (CDP1852),<br>4 flag inputs,<br>1 Q output<br>1 timer out<br>1 timer control | 2                                                        | + 5                      | 4                | -40 to +85                |

| CDP18S610<br>CPU:<br>CDP1805                                  | Selectable:<br>2.4576,<br>1.2288,<br>0.6144,<br>or 0.3072 | 2K                             | 2K (CDP1834)<br>2K (2758)<br>4K (2716)              | UART:<br>14 selectable<br>baud rates<br>from 50 to<br>19200 baud | —                                                                                                                    | 1                                                        | + 5                      | 8                | -40 to +85                |

\*Typical values; running RS232C interface and no EPROM's. RS232C interface requires +12 to +15 V at 6 mA and -5 to -15V at 3 mA. Loop interface draws an additional 20 mA from the +5 V supply. CDP185604B and CDP185609 do not have RS232C or 20-mA interface.

# **Microboard Memories**

|            |                           | Page |           |                             | Page |

|------------|---------------------------|------|-----------|-----------------------------|------|

| CDP18S620  | Microboard 4-Kilobyte RAM | 171  | CDP18S625 | Microboard 8/16/32-Kilobyte |      |

| CDP18S621  | Microboard 16-Kilobyte    |      |           | ROM/PROM                    | 195  |

|            | RAM                       | 176  | CDP18S626 | Microboard 32/64-Kilobyte   |      |

| CDP18S622  | Microboard 8-Kilobyte     |      |           | EPROM/ROM/RAM               | 207  |

|            | Battery-Backup RAM        | 181  | CDP18S627 | Microboard 4-Kilobyte       |      |

| CDP18S623A | Microboard 8-Kilobyte RAM | 190  |           | EPROM                       | 229  |

|            | -                         |      | CDP18S629 | Microboard 32-Kilobyte      |      |

|            |                           |      |           | RAM                         | 237  |

|            | Memory          | 1         | Data                 | Po  | wer*             | Temperature |

|------------|-----------------|-----------|----------------------|-----|------------------|-------------|

| Microboard | Туре            | Bytes     | Rentention           | (V) | (mA)             | Range (°C)  |

| CDP18S620  | Static CMOS RAM | 4 K       | -                    | 5   | 4                | -40 to 85   |

| CDP18S621  | Static CMOS RAM | 16 K      | _                    | 5   | 6                | -40 to 85   |

| CDP18S622  | Static CMOS RAM | 8 K       | 96 h                 | 5   | 13'              | -40 to 70   |

| CDP18S623A | Static CMOS RAM | 8 K       | -                    | 5   | 6                | -40 to 85   |

| CDP18S625  | ROM/PROM        | 8/16/32 K | Permanent            | 5   | 10²              | -40 to 85   |

| CDP18S626  | ROM/EPROM, RAM  | 32/64 K   | Permanent<br>(ROM's) | 5   | 100 <sup>3</sup> | -40 to 706  |

| CDP18S627  | CMOS EPROM      | 4 K       | Permanent            | 5   | 8⁴               | -40 to 85   |

| CDP18S629  | Static CMOS RAM | 32 K      |                      | 5   | 275              | -40 to 85   |

Populated with sixteen CDP18U42 CMOS EPROM's

Populated with sixteen CDP18U42 CMOS EPROM's

Populated with sixteen 6116 CMOS RAM's

For operation at full temperature range the user should select ROM's or RAM's having suitable temperature specifications

# **Microboard Expansion Modules**

|            |                                                      | Page |             |                                                     | Page |

|------------|------------------------------------------------------|------|-------------|-----------------------------------------------------|------|

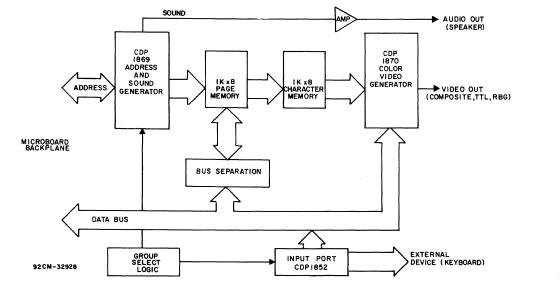

| CDP18S661B | Microboard Video-Audio-<br>Keyboard Interface (NTSC) | 371  | CDP18S661V3 | Microboard Video-Audio-<br>Keyboard Interface (PAL) | 385  |

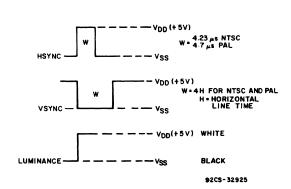

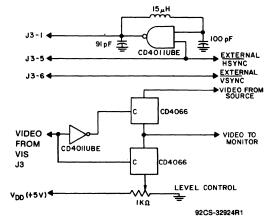

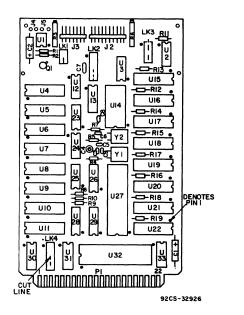

| Microboard  | Video<br>Signal | Dot<br>Matrix | Page N<br>Capacity | lemory<br>Address       | Characte<br>Capacity | r Memory<br>Address     | I/O<br>Addressing                                    | (V) | wer<br>  (mA) |

|-------------|-----------------|---------------|--------------------|-------------------------|----------------------|-------------------------|------------------------------------------------------|-----|---------------|

| CDP18S661B  | NTSC            | 6 x 8         | 1 K                | F800<br>through<br>FBFF | 1 K                  | F400<br>through<br>F7FF | Two-level group<br>select: 80-F0,<br>link selectable | 5   | 271           |

| CDP18S661V3 | PAL             | 6 x 9         | 1 K                | F800<br>through<br>FBFF | 1 K                  | F400<br>through<br>F7FF | Two-level group<br>select: 80-F0<br>link selectable  | 5   | 10'           |

# **Digital I/O Expansion Modules**

|             | 1                                                          | Page |              |                                     | Page |

|-------------|------------------------------------------------------------|------|--------------|-------------------------------------|------|

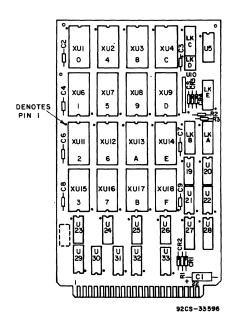

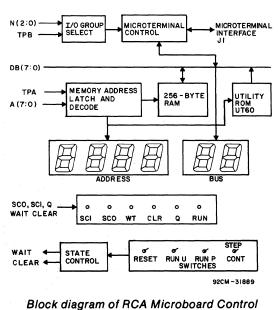

| CDP18S640A  | Microboard Control and Dis-<br>play Module (256-byte RAM;  | -    | CDP18S651    | Microboard Floppy Disk<br>Interface | 343  |

|             | 4 control switches; 6-digit<br>hex displays; 6 LED indica- |      | CDP18S652    | Microboard Memory and<br>Tape I/O   | 345  |

|             | tors; Utility runs software                                |      | CDP18S653V1, | ·                                   |      |

|             | UART)                                                      | 252  | V2           | Direct-Connect Auto                 |      |

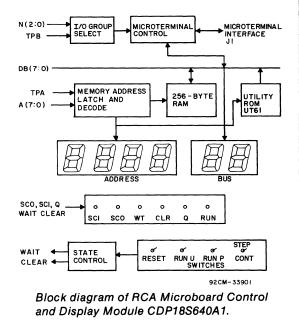

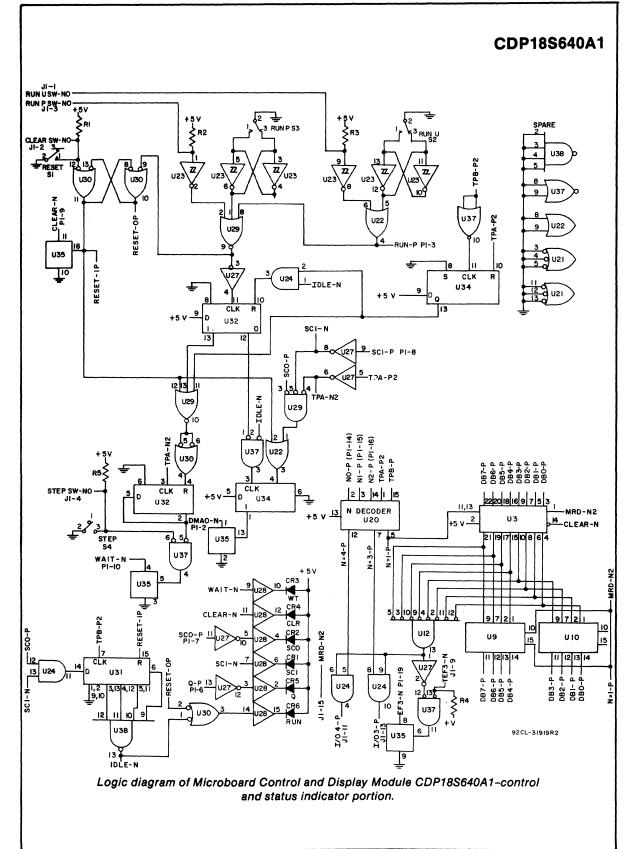

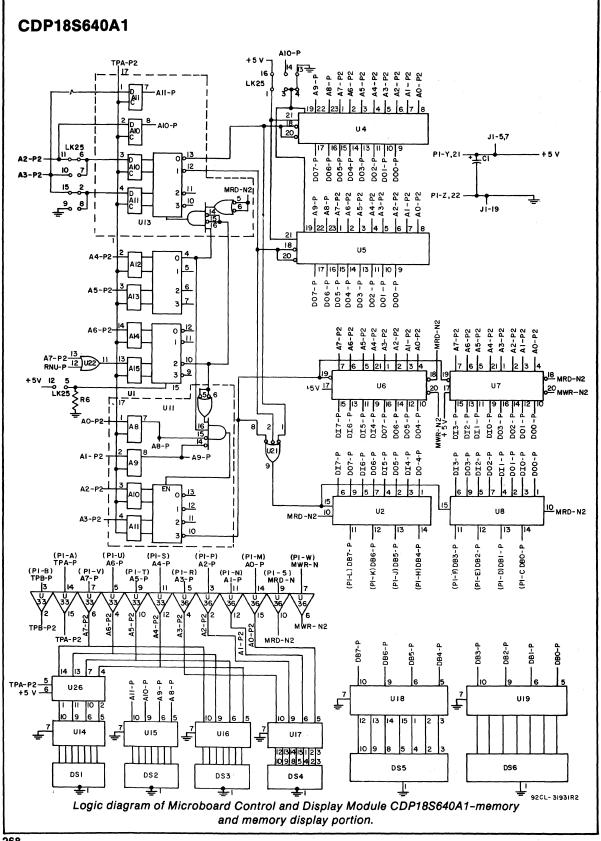

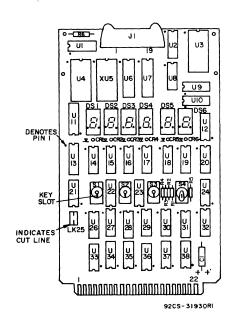

| CDP18S640A1 | Microboard Control and Dis-                                |      |              | Modems                              |      |

|             | play Module (256-byte RAM;                                 |      |              | (Bell Compatible)                   | 346  |

|             | 4 control switches; 6-digit                                |      | CDP18S653V3, |                                     |      |

|             | hex displays; 6 LED indica-<br>tors UART terminal inter-   |      | V4           | Direct-Connect Auto<br>Modems       |      |

|             | face; Utility runs hardware                                |      |              | (CCITT Compatible)                  | 353  |

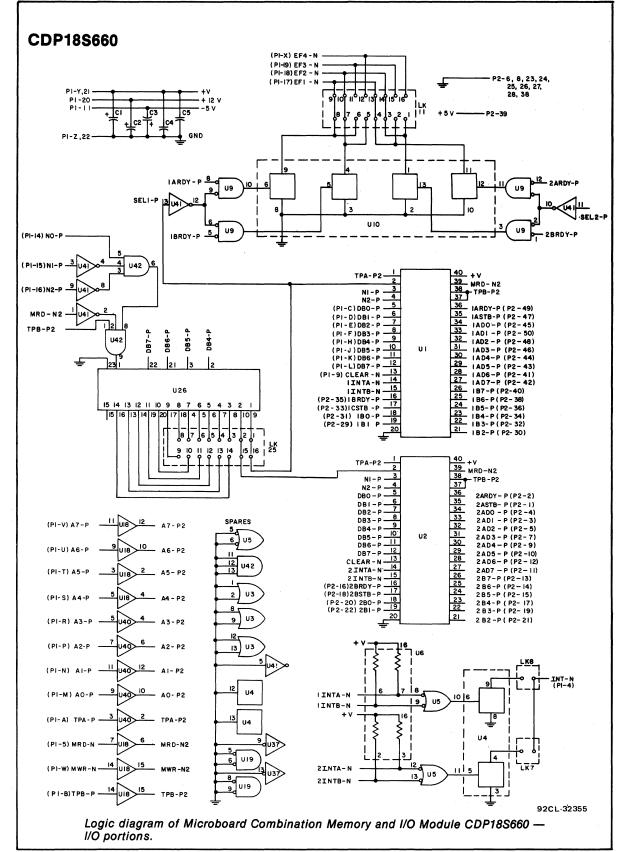

|             | UART)                                                      | 261  | CDP18S660    | Microboard Combination              |      |

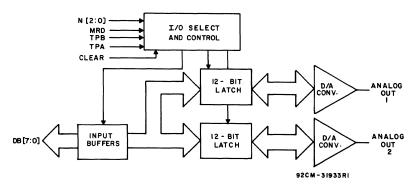

| CDP18S641   | Microboard UART Interface                                  | 270  | 021 100000   | Memory and I/O Module               | 361  |

| CDP18S646   | Microboard Parallel I/O                                    |      | CDP18S662    | PIO Opto 22 Module                  |      |

|             | Module                                                     | 308  | •==          | Interface                           | 394  |

| CDP18S650   | Microboard Counter/Timer                                   | 342  | CDP18S663    | Opto-Isolated PIO Module            | 401  |

|                                    | Serial I/O                                                             |                                                                           | Mer<br>RAM | nory<br>  ROM | Be       | ver*     | Temperature |

|------------------------------------|------------------------------------------------------------------------|---------------------------------------------------------------------------|------------|---------------|----------|----------|-------------|

| Microboard                         | Port                                                                   | I/O Lines                                                                 | (bytes)    | (bytes)       | (V)      | (mA)     | Range (°C)  |

| CDP18S640A                         | _                                                                      | 20 Lines<br>Interface for<br>Microterminal<br>CDP18S021                   | 256        | 1K<br>UT60    | 5        | 350      | 0 to 70     |

| CDP18S640A1                        | _                                                                      | 20 Lines<br>Interface for<br>Microterminal<br>CDP18S021                   | 256 ·      | 1K<br>UT61    | 5        | 350      | 0 to 70     |

| CDP18S641                          | UART: switch select-<br>able 110, 300, 1200, 4800,<br>9600, 19200 baud | _                                                                         |            |               | 5        | 2.011    | -40 to 85   |

| CDP18S646                          | _                                                                      | Three 8-bit out-<br>put ports; one<br>8-bit input port                    | —          | -             | 5        | 32       | -40 to 85   |

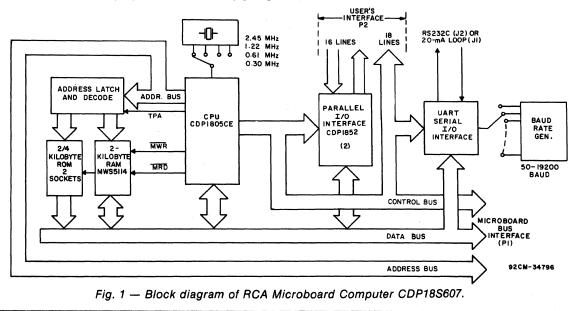

| CDP18S650                          | _                                                                      | 8 Counter-Timer<br>Modules; I/O lines<br>on 36-pin header                 | —          | -             | 5        | 10       | -40 to 85   |

| CDP18S651                          | _                                                                      | Handles most floppy disk<br>drives; Shugart Interface                     | -          |               | +5<br>-5 | 250<br>3 | 0 to 70     |

| CDP18S652                          | 2-cassette tape<br>I/O ports                                           | _                                                                         | 1 K        | 24 K          | 5        | 10       | 0 to 70     |

| CDP18S653V1, V3<br>CDP18S653V2, V4 | 300-baud modem<br>1200-baud modem                                      | _                                                                         | -          |               | 5,12     | 12,34    | -40 to 85   |

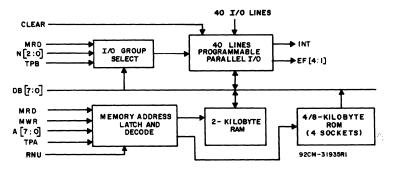

| CDP18S660                          |                                                                        | 40 programmable I/O<br>(2 CDP1851's) input, out-<br>put, or bidirectional | 2 K        | 8 K           | 5        | 8        | -40 to 85   |

| CDP18S662                          | _                                                                      | 24 bidirectional<br>parallel Opto 22<br>interface                         |            |               | 5        | 10       | -40 to 85   |

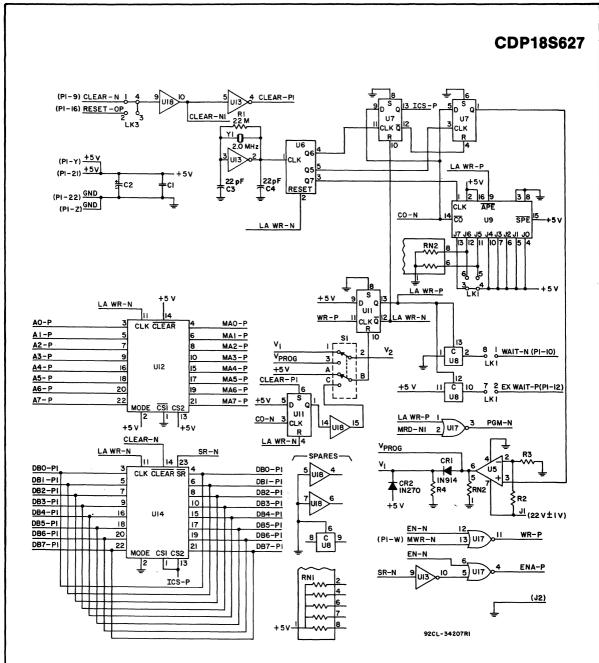

| CDP18S663                          | —                                                                      | 8 input, 8 output<br>optically isolated<br>DC lines                       | —          | -             | 5        | 85       | -40 to 85   |

\*Typical <sup>1</sup>Plus additional power required by data terminal <sup>2</sup>Disk drive and printer connected and reset.

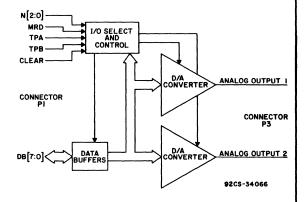

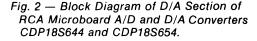

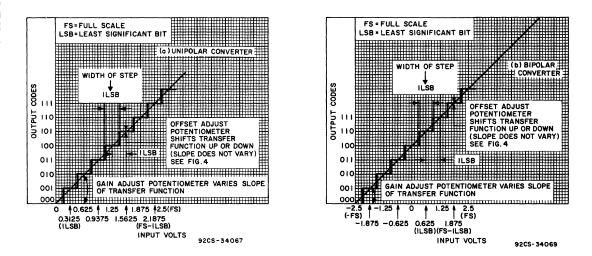

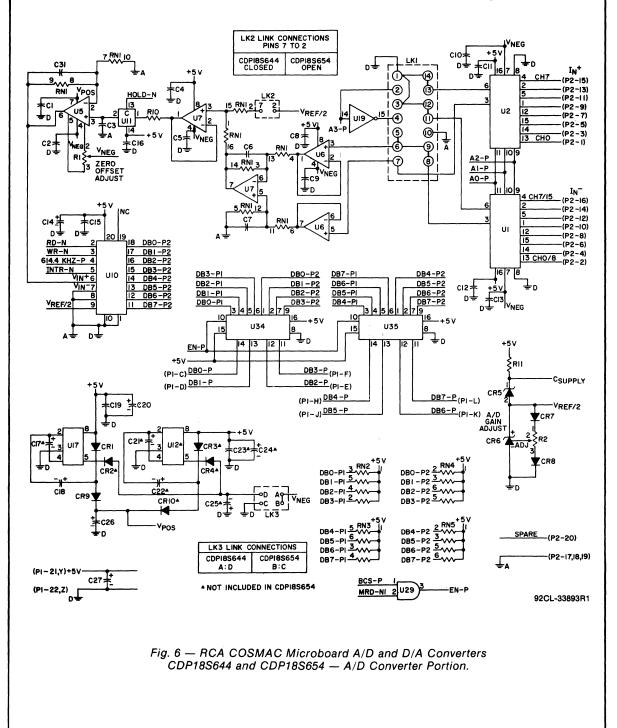

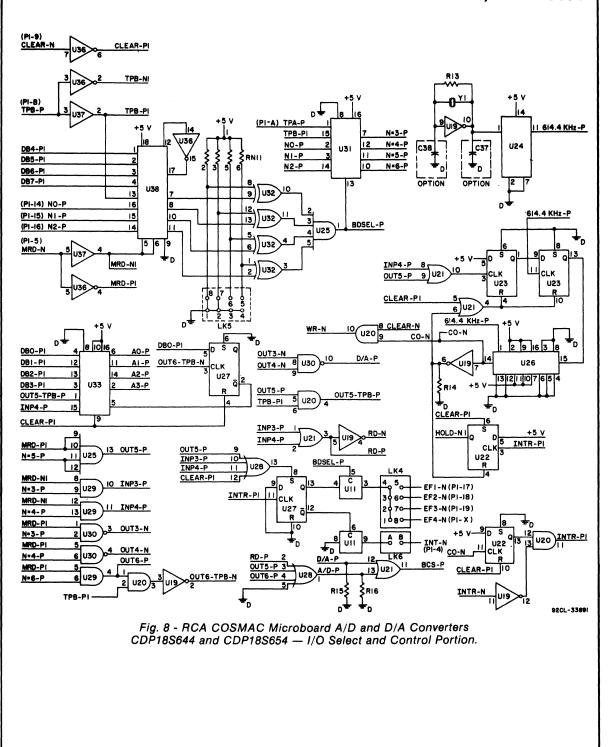

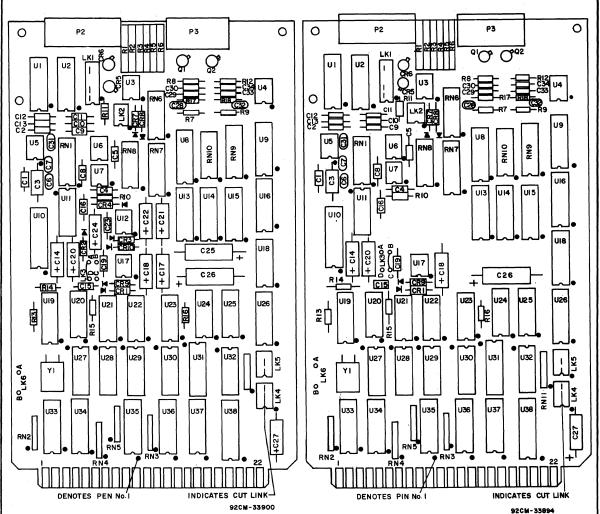

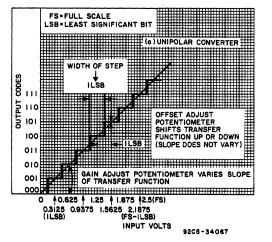

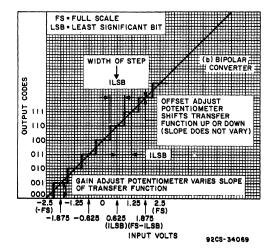

# **Microboard A/D and D/A Converters**

|            |                                  | Page |           |                                                | Page |

|------------|----------------------------------|------|-----------|------------------------------------------------|------|

| CDP18S642  | Microboard D/A Con-<br>verter    | 276  | CDP18S648 | Microboard A/D Con-<br>verter (8-bit bipolar)  | 330  |

| CDP18S643A | Microboard A/D Con-              |      | CDP18S654 | Microboard A/D and                             |      |

| CDP18S644  | verter<br>Microboard A/D and     | 283  |           | D/A Converter<br>(8-bit unipolar)              | 293  |

|            | D/A Converter<br>(8-bit bipolar) | 293  | CDP18S657 | Microboard D/A Con-<br>verter (8-bit unipolar) | 319  |

| CDP18S647  | Microboard D/A Con-              |      | CDP18S658 | Microboard A/D Con-                            |      |

|            | verter (8-bit bipolar)           | 319  |           | verter (8-bit unipolar)                        | 330  |

| Microboard | Version                              | Reso-<br>lution<br>(bits) | No. of<br>Channels | I/O<br>Voltage<br>Ranges (V)                       |          | racy at 2<br>significan<br>Gain |          | Settling (S) or<br>Conversion (C)<br>Time (µs) | Po<br>(V)        | wer⁰<br>(mA)   | Temperature<br>Range<br>(°C) |

|------------|--------------------------------------|---------------------------|--------------------|----------------------------------------------------|----------|---------------------------------|----------|------------------------------------------------|------------------|----------------|------------------------------|

| CDP18S642  | D/A²                                 | 12/8                      | 2                  | ±2.5, ±5,<br>or ± 10<br>0 to 2.5, 5, 10            | ±1⁄2     | ±½                              | ±½       | 5 (S)                                          | +5<br>+15<br>-15 | 26<br>50<br>50 | -25 to 85                    |

| CDP18S643A | A/D'                                 | 12/8                      | 8/16               | ±2.5, ±5, or ±10<br>0 to 2.5, 5, 10                | ±1⁄2     | ±1⁄2                            | ±½       | 105/275 (C)                                    | +5<br>+15<br>-15 | 85<br>50<br>50 | -25 to 85                    |

| CDP18S644  | A/D <sup>1</sup><br>D/A <sup>2</sup> | 8<br>8                    | 8/16<br>2          | $\pm 2.5$ , or 0 to 2.5<br>$\pm 2.5$ , or 0 to 2.5 | ±¾<br>±½ | ±¾<br>±½                        | ±¾<br>±½ | 215 (C)<br>15 (S)                              | +5               | 50             | -40 to 85                    |

| CDP18S647  | D/A <sup>2</sup>                     | 8                         | 2                  | ±2.5, or 0 to 2.5                                  | ±½       | ±½                              | ±½       | 15 (S)                                         | +5               | 22             | -40 to 85                    |

| CDP18S648  | A/D'                                 | 8                         | 8/16               | ±2.5, or 0 to 2.5                                  | ±¾       | ±¾                              | ±¾       | 215 (C)                                        | +5               | 40             | -40 to 85                    |

| CDP18S654  | A/D <sup>3</sup><br>D/A⁴             | 8<br>8                    | 8/16<br>2          | 0 to 2.5<br>0 to 2.5                               | ±¾<br>±½ | ±¾<br>±½                        | ±¾<br>±½ | 215 (C)<br>15 (S)                              | +5               | 15             | -40 to 85                    |

| CDP18S657  | D/A⁴                                 | 8                         | 2                  | 0 to 2.5                                           | ±1/2     | ±½                              | ±1/2     | 15 (S)                                         | +5               | 9              | -40 to 85                    |

| CDP18S658  | A/D <sup>3</sup>                     | 8                         | 8/16               | 0 to 2.5                                           | ±¾       | ±¾                              | ±¾       | 215 (C)                                        | +5               | 13             | -40 to 85                    |

<sup>o</sup>Typical <sup>1</sup>Binary or unipolar input <sup>2</sup>Binary or unipolar out <sup>3</sup>Unipolar input <sup>4</sup>Unipolar output <sup>5</sup>Microboards provide offset and gain adjustments permitting the user to null total system error

# **Microboard Industrial Chassis and Accessories**

|                |                                     | Page |                          |                       | Page |

|----------------|-------------------------------------|------|--------------------------|-----------------------|------|

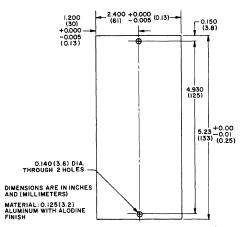

| Chassis        |                                     |      | MSIA 10                  | Cable conduit         | 402  |

| MSI 8000 serie | es Backplane with                   |      | MSIA 11                  | Card extractor        | 402  |

|                | connectors                          | 402  | Modules                  |                       |      |

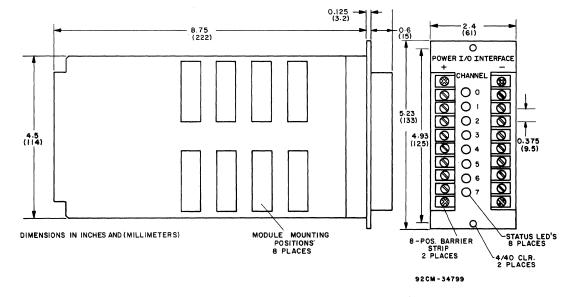

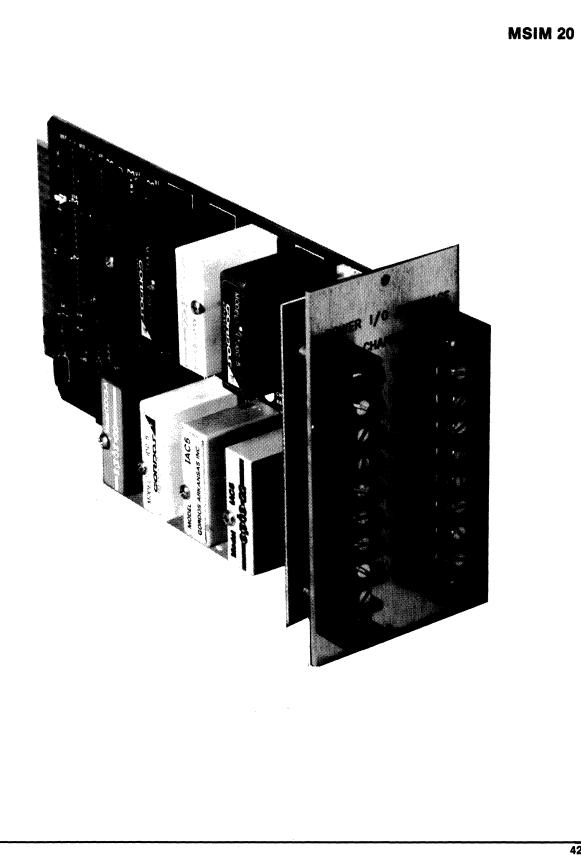

| MSI 800 series | Standard industrial                 |      | MSIM 20                  | Microboard I/O        |      |

|                | chassis                             | 402  | WISHWI 20                | module card           |      |

| MSI 8800 serie | es Deluxe industrial                |      |                          | , (mounts up to 8     |      |

|                | chassis                             | 402  |                          | industry standard     |      |

| Accessories    |                                     |      |                          | optically isolated    |      |

| MSIA 0100      | Solid top and bottom                |      |                          | power modules)        | 414  |

| series         | covers                              | 402  | MSIM 40, E               | Industrial microboard | 414  |

| MSIA 0200      |                                     | 402  | MSIM 40, E<br>MSIM 41. E |                       |      |

| series         | Perforated top and<br>bottom covers | 402  | WISTN 41, E              | power supplies        |      |

| MSIA 0300      |                                     |      |                          | (includes power cord, |      |

|                | Solid rear panels                   | 402  |                          | circuit breaker,      |      |

| series         |                                     |      |                          | switch, and power-on  |      |

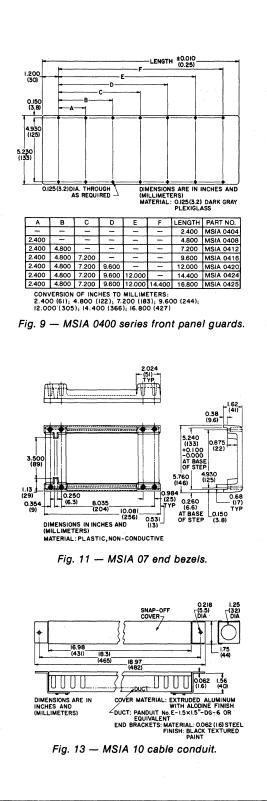

| MSIA 0400      | Front panel guards                  | 402  | MOIN FO                  | light)                | 426  |

| series         |                                     |      | MSIM 50                  | Micro floppy disk     |      |

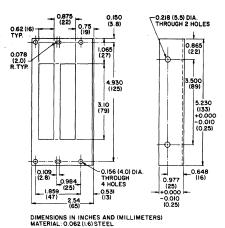

| MSIA 06        | Mounting angle                      |      |                          | drive module          |      |

|                | brackets                            | 402  |                          | (contains 2 disk      |      |

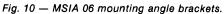

| MSIA 07        | End bezels (handles)                | 402  |                          | drives having storage |      |

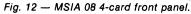

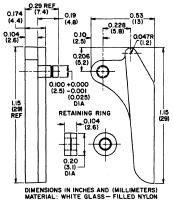

| MSIA 08        | Four-card front panel               | 402  |                          | capacity of 315 kilo- | 407  |

|                |                                     |      |                          | bytes each)           | 427  |

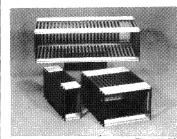

| No. of<br>Slots   | Standard<br>industrial<br>Chassis                                                                                                                                                                                                                                         | Deluxe<br>Industrial<br>Chassis                                                                                                                                                                                                                                                                                       | Backplanes<br>With Connector                                                                                 |

|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|

| 4                 | MSI 804                                                                                                                                                                                                                                                                   | MSI 8804                                                                                                                                                                                                                                                                                                              | MSI 8004                                                                                                     |

| 8                 | MSI 808                                                                                                                                                                                                                                                                   | MSI 8808                                                                                                                                                                                                                                                                                                              | MSI 8008                                                                                                     |

| 12                | MSI 812                                                                                                                                                                                                                                                                   | MSI 8812                                                                                                                                                                                                                                                                                                              | MSI 8012                                                                                                     |

| 16                | MSI 816                                                                                                                                                                                                                                                                   | MSI 8816                                                                                                                                                                                                                                                                                                              | MSI 8016                                                                                                     |

| 20                | MSI 820                                                                                                                                                                                                                                                                   | MSI 8820                                                                                                                                                                                                                                                                                                              | MSI 8020                                                                                                     |

| 24                | MSI 824                                                                                                                                                                                                                                                                   | MSI 8824                                                                                                                                                                                                                                                                                                              | MSI 8024                                                                                                     |

| 25                | MSI 825                                                                                                                                                                                                                                                                   | MSI 8825                                                                                                                                                                                                                                                                                                              | MSI 8025                                                                                                     |

| Features Include: | <ul> <li>Rugged steel and<br/>aluminum chassis</li> <li>44-pin, 0.156-inch pitch<br/>card connectors mounted<br/>on 6-inch centers</li> <li>Full-length card guides</li> <li>Card extractor rail</li> <li>Stick-on rubber feet</li> <li>Power-supply connector</li> </ul> | <ul> <li>All features of standard<br/>chassis plus —</li> <li>Slide-in solid top and<br/>bottom covers</li> <li>Screw-fastened front and<br/>rear panels</li> <li>Standoff mounted see-<br/>through front panel guard</li> <li>Two carrying handle/end<br/>bezels</li> <li>Two mounting angle<br/>brackets</li> </ul> | • Bare microboard<br>backplane/connector<br>assembly from Standard<br>chassis with power-supply<br>connector |

# Other Chassis, Accessories, and Prototyping Systems

|             |                                                             | Page |           |                                              | Page |

|-------------|-------------------------------------------------------------|------|-----------|----------------------------------------------|------|

| CDP18S023   | Power Converter (110 V ac, 60<br>Hz to 5 V dc 600 mA, reg.) | 428  | CDP18S691 | Microboard Prototyping<br>System (CDP18S601, |      |

| CDP18S023V3 | Power Converter (220 V ac, 50                               |      |           | CDP18S640, CDP18S659,                        |      |

|             | Hz to 5 V dc 600 mA, reg.)                                  | 428  |           | Chassis, Cables, Utility                     |      |

| CDP18S659   | Microboard Breadboard                                       | 429  |           | Program)                                     | 442  |

| CDP18S670   | Microboard 25-Card Chassis                                  |      | CDP18S692 | Microboard Prototyping                       |      |

|             | with Case and Power Supply                                  | 431  |           | System (CDP18S602,                           |      |

| CDP18S675   | Microboard 5-Card Chassis                                   | 439  |           | CDP18S640A1, CDP18S659,                      |      |

| CDP18S676   | Microboard 5-Card Chassis                                   |      |           | Chassis, Cables, Utility                     |      |

|             | with Case                                                   | 439  |           | Program)                                     | 448  |

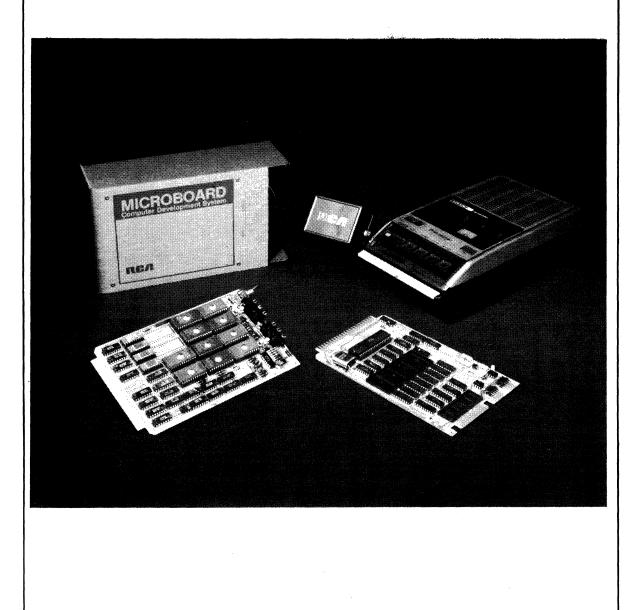

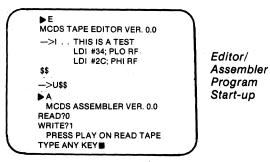

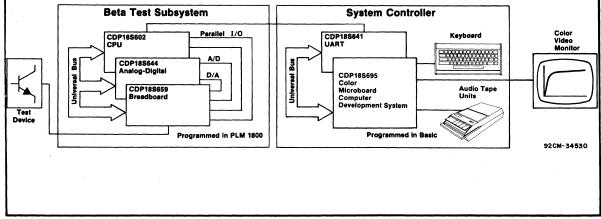

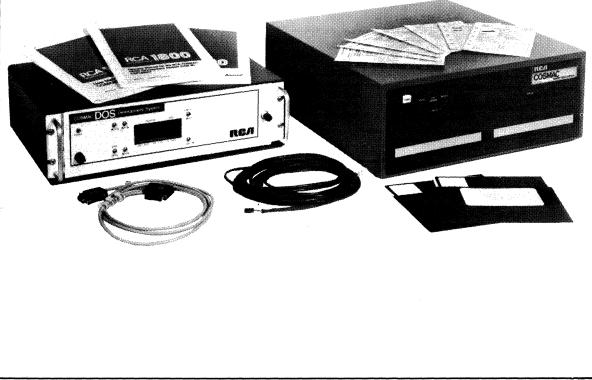

# Microboard Computer Development Systems (MCDS)

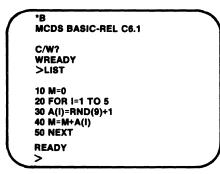

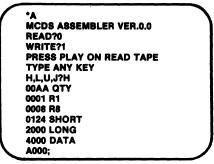

| CDP18S693 | MCDS with Floating-Point<br>BASIC3                                    | 456 | CDP18S695 | MCDS with Floating-Point<br>BASIC3 Resident              |

|-----------|-----------------------------------------------------------------------|-----|-----------|----------------------------------------------------------|

| CDP18S694 | MCDS with Floating-Point<br>BASIC3 Resident<br>Assembler/Editor, PROM |     |           | Assembler/Editor, PROM<br>Programmer, Color Enhanced 464 |

|           | Programmer                                                            | 456 |           |                                                          |

| MCDS Systems                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                               | DP1<br>694                            |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|---------------------------------------|--|

| System Includes:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                               |                                       |  |

| <ul> <li>CDP18S601 Computer</li> <li>CDP18S652 Memory and Tape I/O</li> <li>CDP18S661 Video/Audio Keyboard Interface</li> <li>Five-Card Chassis and Case</li> <li>ROM Monitor Program (2K)</li> <li>ROM-based BASIC3 Interpreter (12K) — development version</li> <li>Cassette I/O Unit for Memory Storage</li> <li>Dual Cassette I/O Unit for Memory Storage</li> <li>Resident ROM-based (6K) ASSEMBLER/EDITOR program</li> <li>CDP18S480 PROM Programmer Module</li> <li>VP601 Keyboard</li> <li>12-inch Color Monitor</li> </ul>                                               | X<br>X<br>X<br>X<br>X<br>X                                    | X X X X X X X X X X X X X X X X X X X |  |

| System Features:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                               |                                       |  |

| <ul> <li>Low Cost</li> <li>Resident ROM-based ASSEMBLER/EDITOR program</li> <li>Line editing</li> <li>Powerful 1802 I/O constructs in BASIC</li> <li>Full BASIC3 with floating point</li> <li>Cold/warm start</li> <li>6656 Multiple character variables (256x26)</li> <li>Resident ROM Monitor program</li> <li>Economical memory storage through audio tapes</li> <li>Terminal interface: 20-mA or RS232C serial with baud rates to 1200</li> <li>Expandable by use of Microboard modules</li> <li>PROM programmer software on cassette</li> <li>Color video display</li> </ul> | X<br>X<br>X<br>X<br>X<br>X<br>X<br>X<br>X<br>X<br>X<br>X<br>X |                                       |  |

| Power Requirements:           CDP18S693V1 110 V, 60 Hz         CDP18S693V3 220 V           CDP18S694V1 110 V, 60 Hz         CDP18S694V3 220 V           CDP18S695V1 110 V, 60 Hz         CDP18S694V3 220 V                                                                                                                                                                                                                                                                                                                                                                        |                                                               |                                       |  |

# **1800 Development Systems** High-Level Languages

|              |                                  | Page |

|--------------|----------------------------------|------|

| CDP18S005    | Development System CDS II        | 469  |

| CDP18S007V1  | DOS Development System           |      |

|              | 110 V, 60 Hz (Includes Floppy    |      |

|              | Disk System)                     | 469  |

| CDP18S007V3  | DOS Development System           |      |

|              | 220 V, 50 Hz (Includes Floppy    |      |

|              | Disk System)                     | 469  |

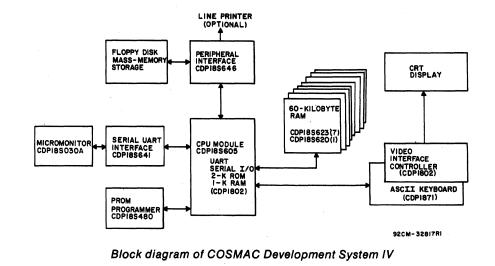

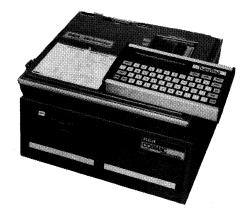

| CDP18S008V1  | Development System CDS IV        |      |

|              | 110 V, 60 Hz with Integral       |      |

|              | CRT Display, Keyboard,           |      |

|              | Central Processor, Full-         |      |

|              | Screen Editing                   | 472  |

| CDP18S008V3  | Development System CDS IV,       |      |

|              | 220 V, 50 Hz with Integral       |      |

|              | CRT Display, Keyboard,           |      |

|              | Central Processor, Full-         |      |

|              | Screen Editing                   | 472  |

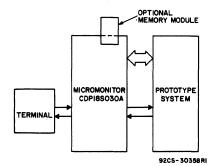

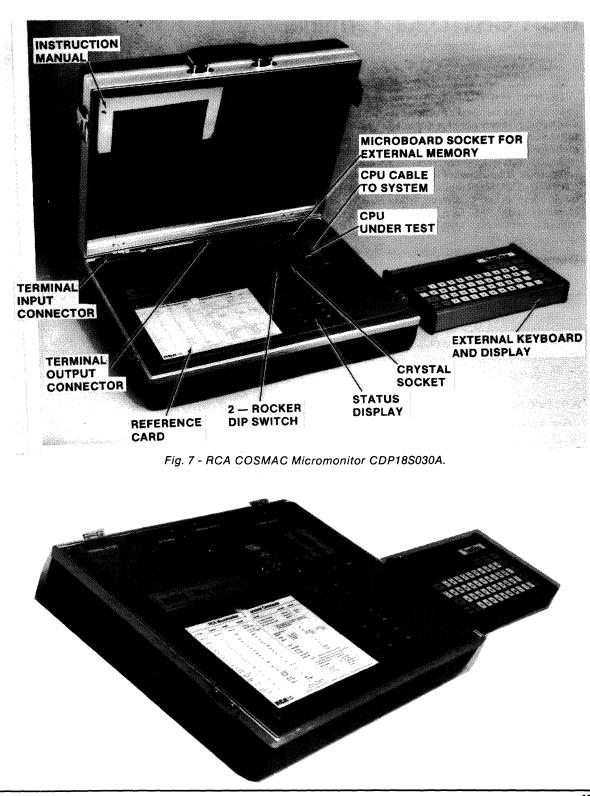

| CDP18S030A   | Micromonitor (Includes Built-    |      |

|              | In Keyboard and Display,         |      |

|              | Status Indicator Lights,         |      |

|              | Software Debugging               |      |

|              | Routines)                        | 479  |

| CDP18S040V1  | Video Terminal with Full-        |      |

|              | Screen Editing, 110 V, 60 Hz     | 484  |

| CDD185040V3  | Video Terminal with Full-        | 404  |

| CDF 10304013 | Screen Editing, 220 V, 50 Hz     | 484  |

| 000400400    | •. ,                             | 404  |

| CDP18S480    | PROM Programmer, includes        | 400  |

|              | software (disk-based)            | 486  |

| CDP18S480V1  | PROM Programmer, includes        |      |

|              | software (paper tape)            | 486  |

| CDP18S480V2  | <b>PROM Programmer, includes</b> |      |

|              | software (cassette tape)         | 486  |

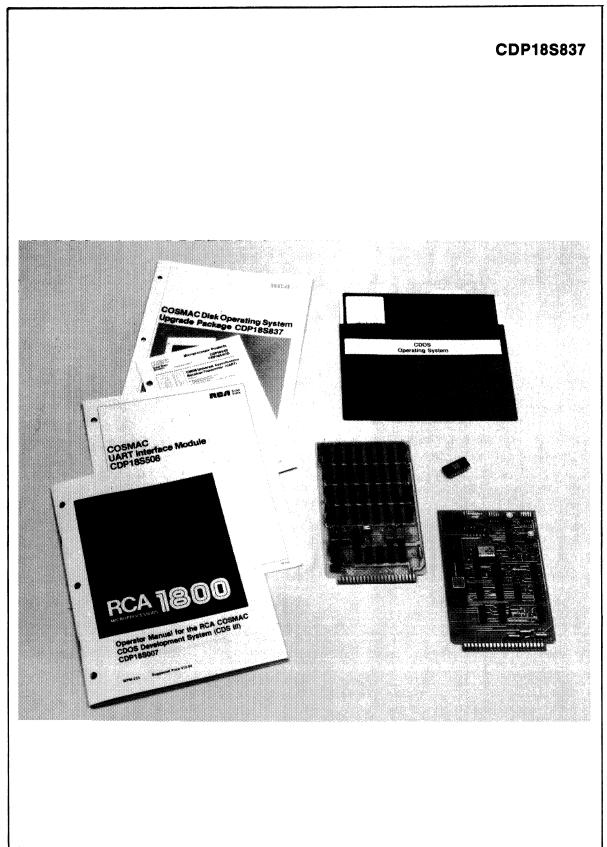

| CDP18S837    | Disk Operating System            |      |

|              | Upgrade Package (Upgrades        |      |

|              | CDP18S005 plus CDP18S805         |      |

|              | to CDP18S007)                    | 494  |

|              | -                                |      |

| , |           |                             | Page |

|---|-----------|-----------------------------|------|

| ) | CDP18S834 | BASIC1 Compiler/Interpreter | 511  |

|   | CDP18S839 | PLM 1800 Compiler           | 515  |

|   | CDP18S840 | BASIC2 Interpreter          | 518  |

| ) | CDP18S844 | Micro Concurrent PASCAL     |      |

|   |           | Compiler/Interpreter        | 524  |

|   | CDP18S852 | Micro Concurrent PASCAL     |      |

| ) |           | Interpreter/Kernel (8-Bit   |      |

|   |           | Systems)                    | 524  |

|   | CDP18S853 | Micro Concurrent PASCAL     |      |

|   |           | Interpreter/Kernel (16-Bit  |      |

|   |           |                             |      |

# **Additional Support Software**

Systems)

| CDP18S826   | Fixed-Point Binary Arithmetic |     |

|-------------|-------------------------------|-----|

|             | Subroutines (diskette)        | 531 |

| CDP18S826V1 | Fixed-Point Binary Arithmetic |     |

|             | Subroutines (paper tape)      | 531 |

| CDP18S826V2 | Fixed-Point Binary Arithmetic |     |

|             | Subroutines (cassette tape)   | 531 |

| CDP18S827   | Floating-Point Binary         |     |

|             | Arithmetic Subroutines        |     |

|             | (diskette)                    | 506 |

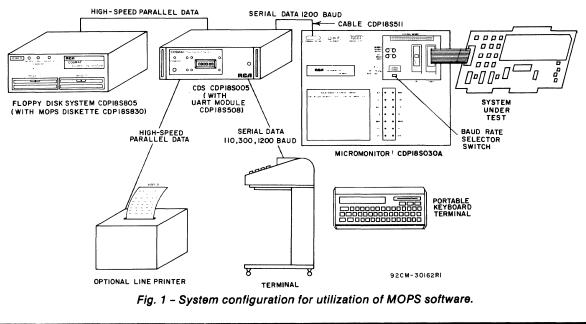

| CDP18S831   | Micromonitor Operator         |     |

|             | System (MOPS)                 | 507 |

| CDP18S835   | VIS Interpreter               | 514 |

|             |                               |     |

# **Additional Support Firmware**

| CDP18S842  | BASIC2/3 Run-Time                    |     |

|------------|--------------------------------------|-----|

|            | Interpreter ROM                      | 521 |

| CDP18S843  | MCDS Assembler/Editor ROM            | 523 |

| CDP18SUT60 | ROM-Based Utility Program            | 530 |

| CDP18SUT61 | ROM-Based Utility Program            | 530 |

| CDP18SUT62 | <b>ROM-Based Utility Program</b>     | 530 |

| CDPR582    | <b>ROM-Based Fixed-Point</b>         |     |

|            | <b>Binary Arithmetic Subroutines</b> | 531 |

524

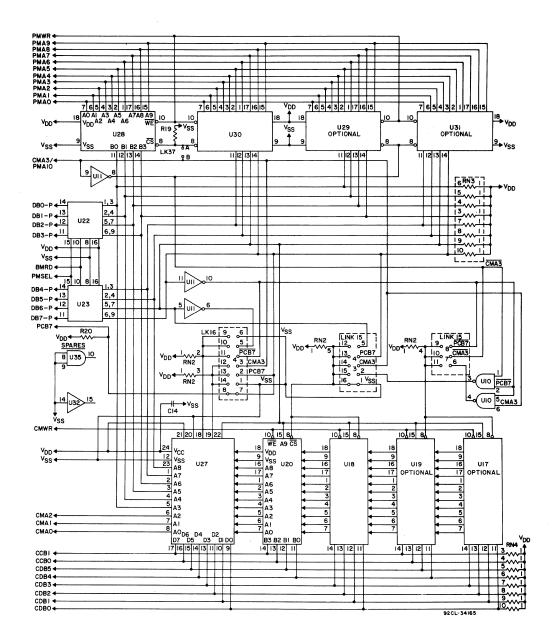

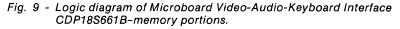

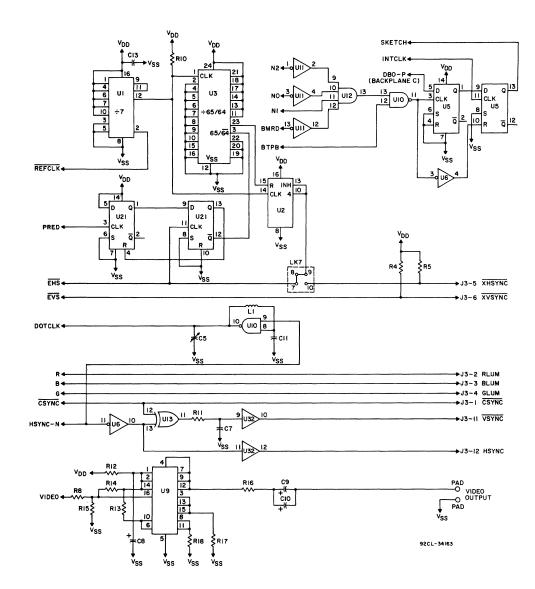

|  | 2. A state of the second se                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|--|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|  | $\left( \frac{\partial (x_{1})}{\partial x_{1}} + \frac{\partial (x_{2})}{\partial x_{1}} + \frac{\partial (x_{2})}{\partial x_{2}} + \frac$ |

|  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

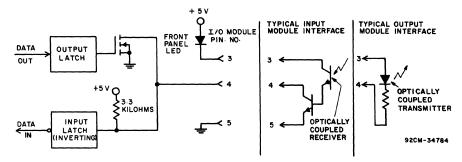

|  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |