Evaluation Kit Manual for the RCA CDP1802 COSMAC Microprocessor

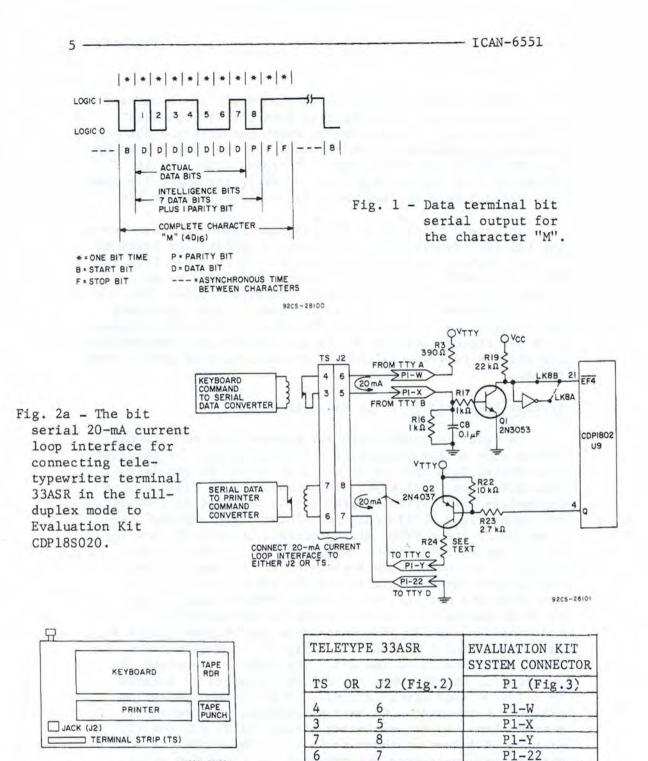

RCA| Solid State Division | Somervillo, NJ 08876

Copyright 1976 by RCA Corporation (All rights reserved under Pan-American Copyright Convention)

Printed in U.S.A. 9-76

Information furnished by RCA is believed to be accurate and reliable. However, no responsibility is assumed by RCA for its use, nor for any infringements of patents or other fights of - third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of RCA.

Trademark (s) Registered ® Marcais) Registrada(s)

# Table of Contents

| CDP18S020 Evaluation Assembly Instructions | Page 10 to 23     |

|--------------------------------------------|-------------------|

| Check-out Procedure                        | Page 24 to 29     |

| Troubleshooting Guide                      | Page 20 to 33     |

| Kit Design                                 | Page 34 to 56     |

| Kit Operation                              | Page 57 to 63     |

| UT4                                        | Page 64 to 87     |

| RCA File Number 945                        | Page 88 to 95     |

| RCA File Number 947                        | Page 96 to 103    |

| RCA File Number 936                        | -                 |

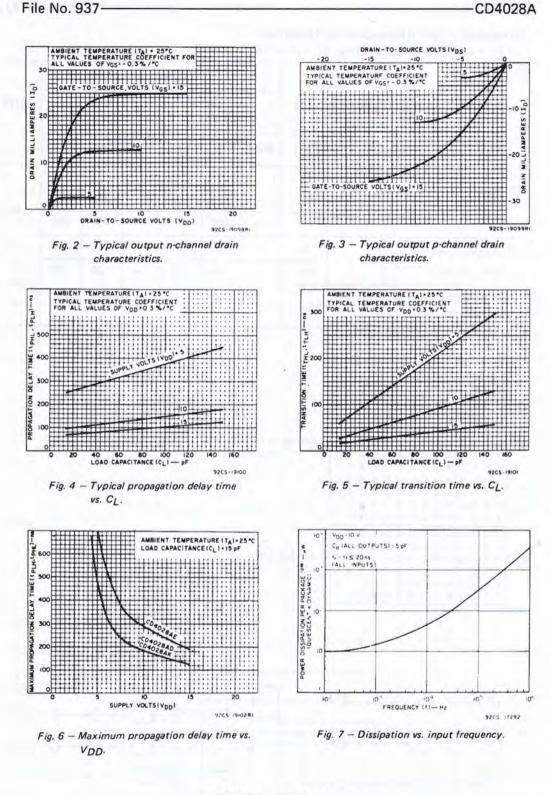

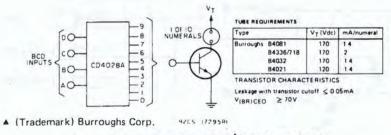

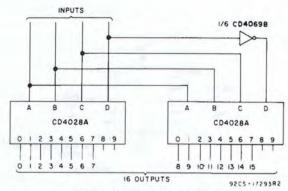

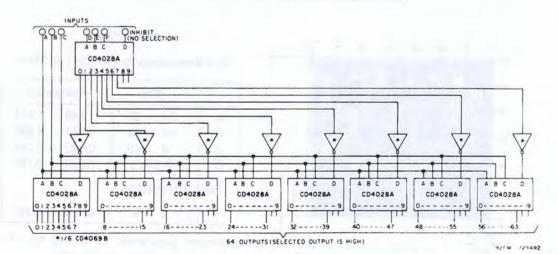

| RCA File Number 937                        | -                 |

| RCA File Number 926                        | -                 |

| RCA File Number 879                        | •                 |

| RCA File Number 858                        | -                 |

| RCA File Number 1023 (CDP1802)             | -                 |

| RCA File Number 1054 (CDP1822)             | -                 |

| (CDP 1831)                                 | -                 |

| (CDP 1832)                                 | . Page 176 to 179 |

| (CDP 1833)                                 | . Page 180 to 183 |

| (CDP 1834)                                 | . Page 184 to 187 |

| (CDP 1852)                                 |                   |

| (CDP 1854)                                 | . Page 192 to 205 |

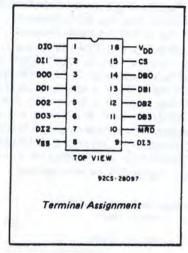

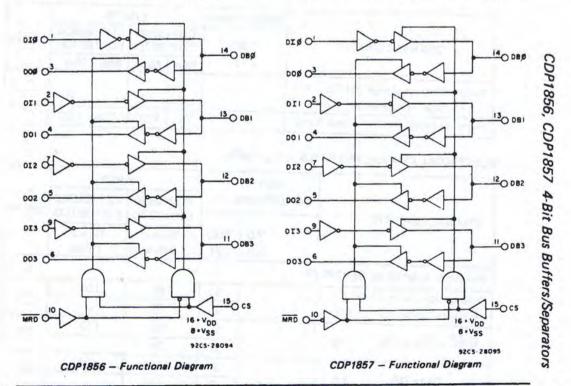

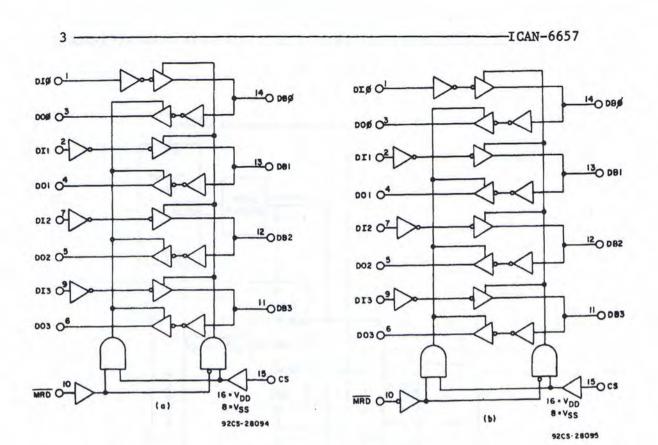

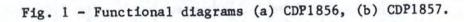

| (CDP 1856 – CDP1857)                       | . Page 206 to 211 |

| Application Notes (ICAN-6657)              | . Page 212 to 217 |

| (ICAN-6538)                                | . Page 218 to 225 |

| (ICAN-6543)                                | . Page 226 to 233 |

| (ICAN-6551)                                | . Page 234 to 249 |

| (ICAN-6632)                                | . Page 250 to 257 |

| (ICAN-6536)                                | . Page 258 to 265 |

| (ICAN-6637)                                | . Page 266 to 271 |

| (ICAN-6539)                                | . Page 272 to 275 |

| (ICAN-6540)                                | . Page 276 to 279 |

| (ICAN-6635)                                | . Page 280 to 287 |

| (ICAN-6547)                                | . Page 288 to 301 |

| Operating Considerations (1CE-402)         | . Page 302 to 307 |

| (ICAN- 6525)                               | . Page 308 to 315 |

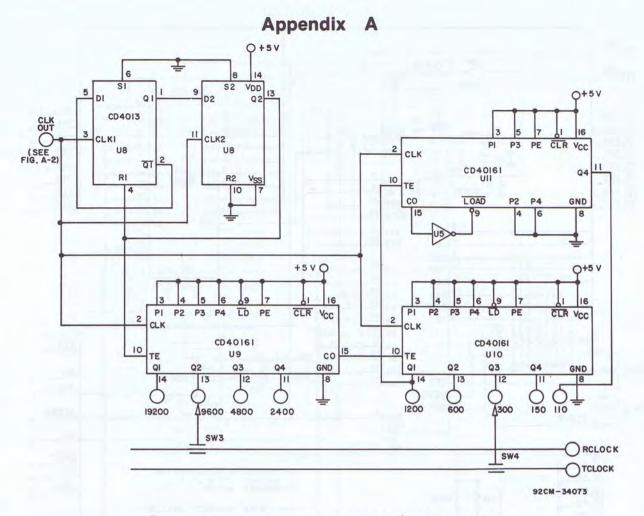

| Appendix A                                 | Page 316          |

| Appendix B                                 | . Page 317 to 318 |

| Appendix C                                 | Page 319          |

| Appendix D                                 | Page 320          |

| Appendix E (UT4 Instruction summary)       | . Page 321 to 322 |

| Appendix F                                 | . Page 323 to 324 |

| Appendix G                                 | . Page 325 to 326 |

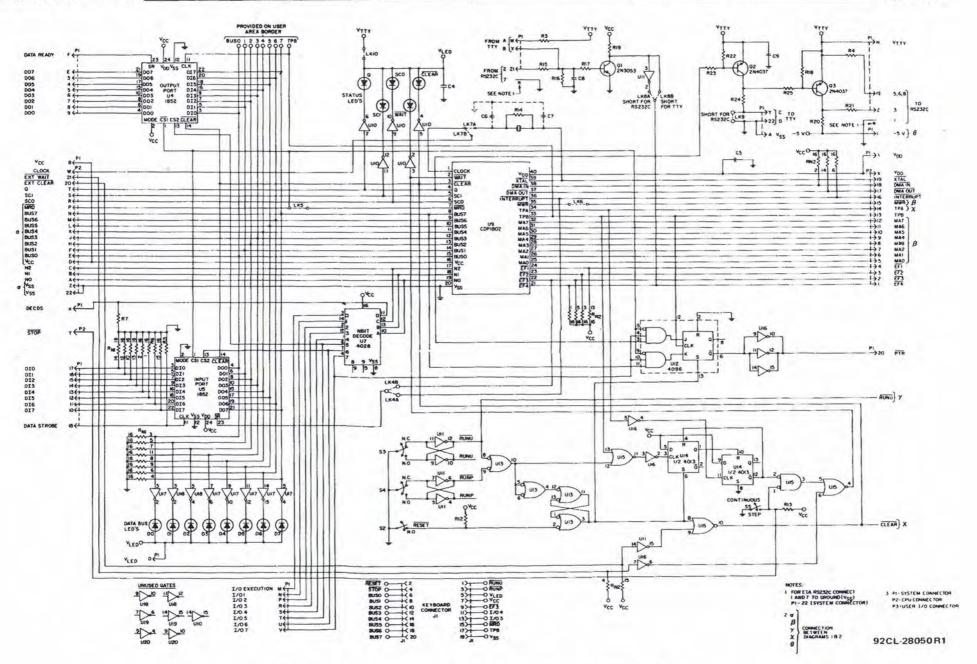

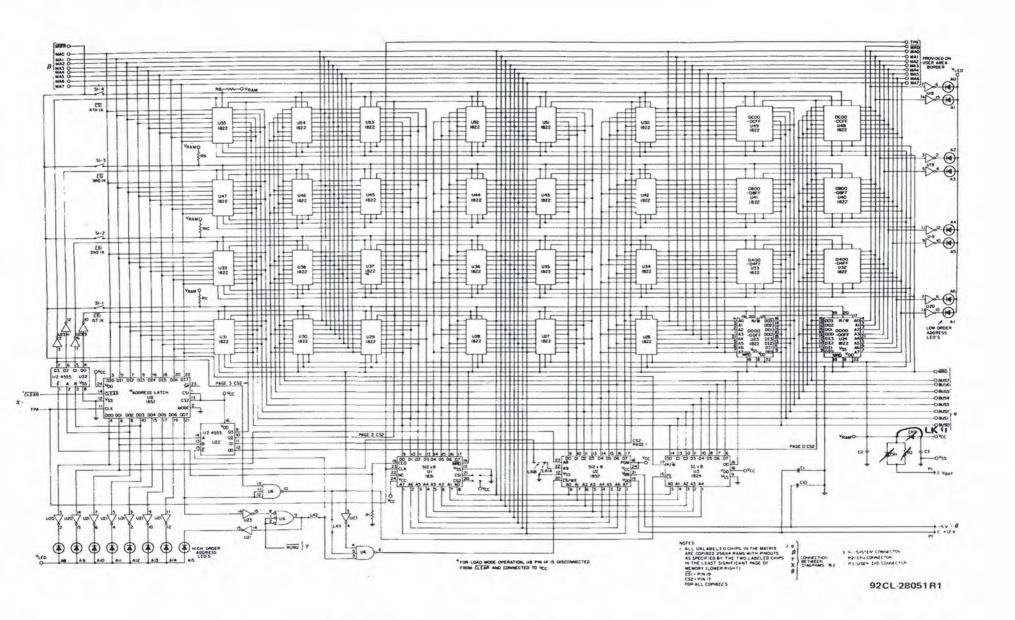

| Appendix H (CDP18S020 Schematic)           | . Page 327 to 329 |

| Appendix I                                 | Page 330          |

| Appendix J                                 | Page 331          |

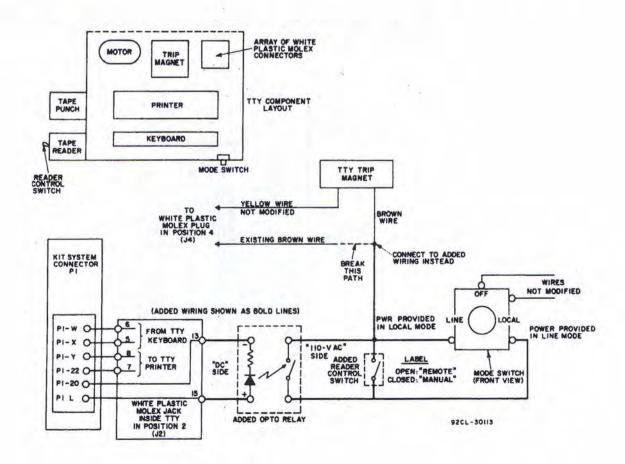

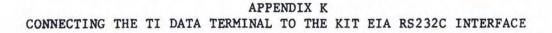

| Appendix K                                 | Page 332          |

| Appendix L                                 | . Page 333 to 337 |

| Tiny Basic                                 | . Page 338 to 371 |

| (ICAN-6991)                                | . Page 372 to 384 |

### EVALUATION KIT MANUAL FOR THE RCA CDP1802 COSMAC MICROPROCESSOR MPM-203

#### FOREWORD

The RCA CDP18S020 Evaluation Kit provides the key hardware and firmware elements for a computer system based on the RCA CDP1802 COSMAC Microprocessor. The kit is a useful, convenient evaluation tool intended to encourage and facilitate the application of the RCA 1800 series of microprocessors and associated components. With the hardware and firmware provided with this Kit, and augmented with an input/ output terminal and power supply, the user can readily prototype dedicated systems and evaluate software programs, components, and systems operation.

This Evaluation Kit Manual provides detailed information on the Kit, its components, its over-all configuration, and how it operates. The Manual tells how the Kit is assembled, how it can be used with various terminals, how to troubleshoot hardware, how the various systems are designed, how they operate, how to check out software, and how to make use of the resident firmware. In addition, a number of application notes are provided describing the I/O and control features, the memory systems available and their utilization, and the use of resident firmware for Read and Type routines.

As additional application notes are developed, they will be made available. Along with a careful study of this Manual, the user should refer to the following publications:

MPM-201 User Manual for the RCA CDP1802 COSMAC Microprocessor

MPM-206 Binary Arithmetic Subroutines for RCA COSMAC Microprocessors

Description

#### DESCRIPTION

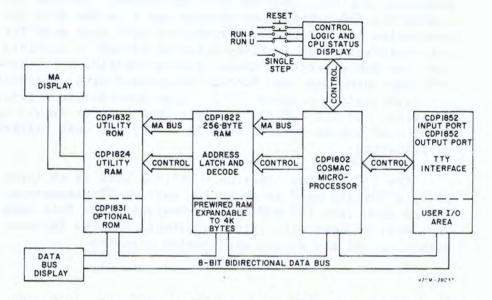

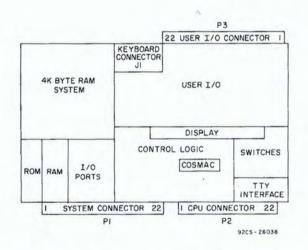

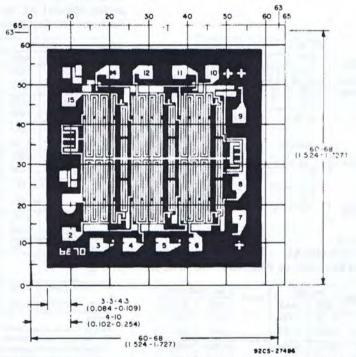

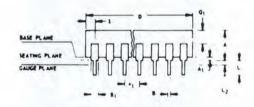

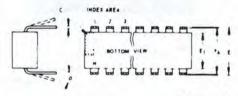

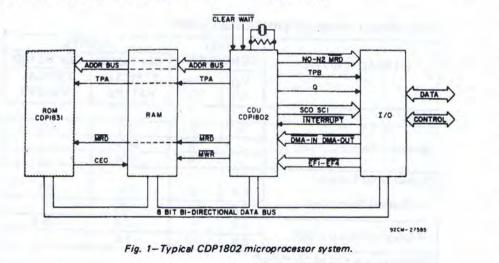

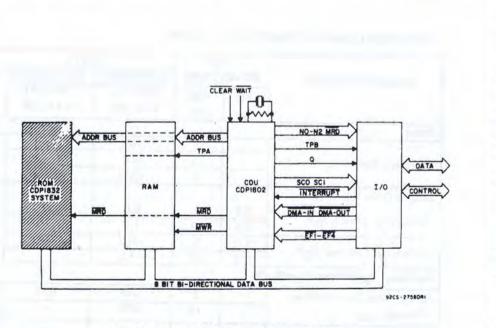

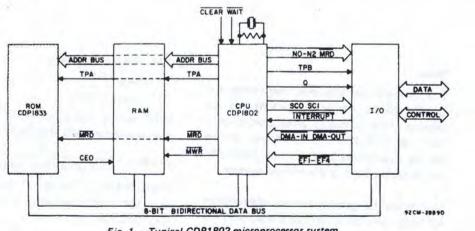

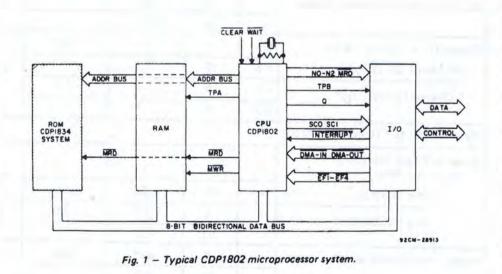

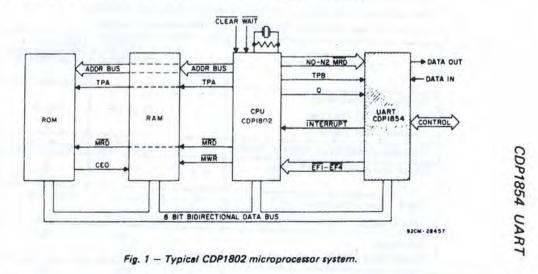

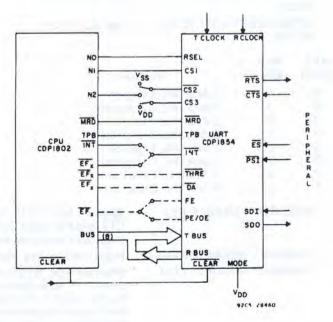

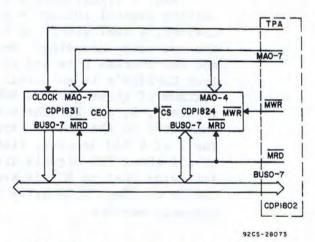

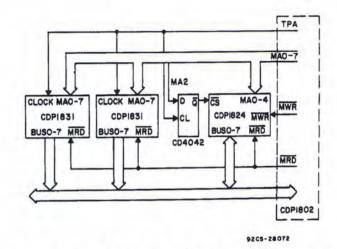

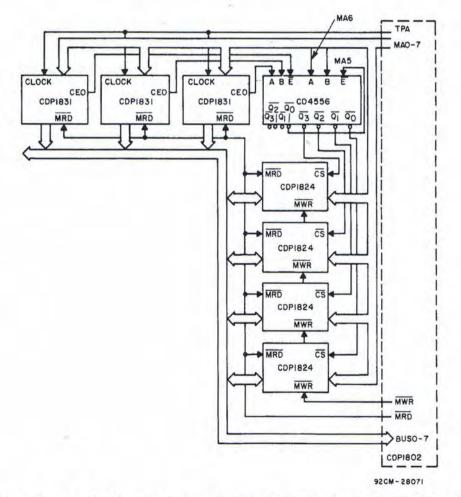

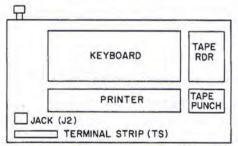

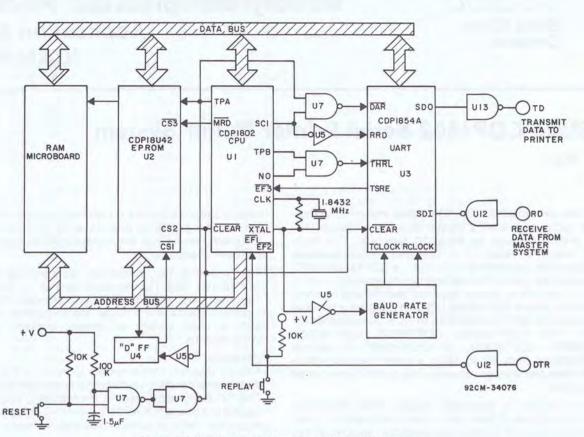

The CDP18S020 COSMAC Evaluation Kit is a complete microcomputer built around the CDP1802 microprocessor. All components including PC card are supplied for building a fully operational microprocessor system. A functional diagram of the Evaluation Kit is shown in Fig. 1-1 and Fig. 1-2 shows the topological layout of the PC card.

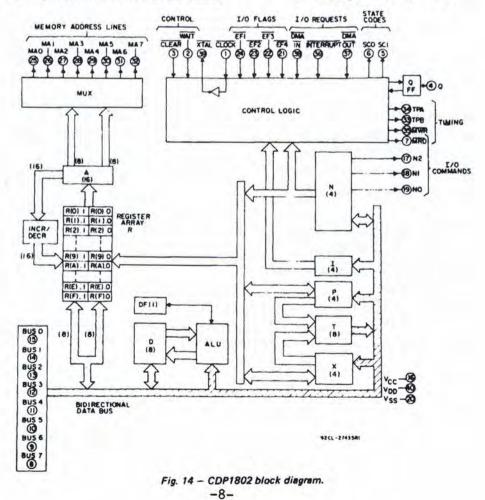

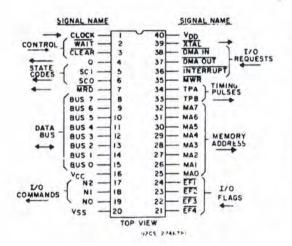

At the heart of the system is the CDP1802 COSMAC microprocessor. It is a single chip, 8-bit, static microprocessor fabricated in a self-aligned, silicon gate, CMOS technology. The CDP1802 offers all the advantages of CMOS technology including low power dissipation, single widerange power supply, full operating temperature range, high noise immunity, and single-phase clock. It combines a repertoire of 91 powerful instructions with the unique COSMAC architecture. This design maximizes performance with minimal memory usage. A comprehensive CDP1802 User Manual (MPM-201) and Data Sheet are provided with the Evaluation Kit to assist the user in understanding and applying the CDP1802 to his specific applications.

In addition to the CDP1802, the Evaluation Kit includes several other sections:

Clock and Control Display Memory 1/0

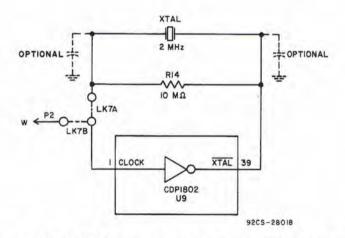

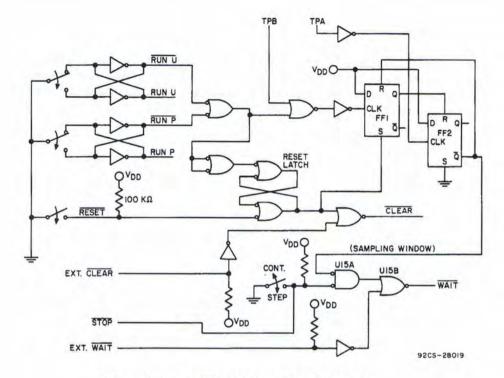

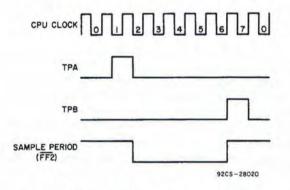

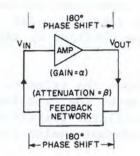

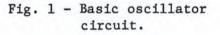

The <u>Clock and Control</u> section contains a crystal-controlled clock generator utilizing the CDP1802 on-chip oscillator, and control logic to interface the CPU with switches for Reset, Run Program, Run Utility, and Single-Step operations.

The <u>Display</u> section consists of interface circuits and LED's configured to display the 16-bit memory address bus (MA), 8-bit data bus (DB), and CPU status. A separate LED power supply connection is provided to permit low-power operation by disabling the LED displays.

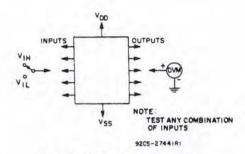

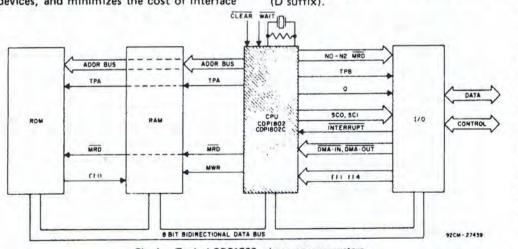

Fig. 1-1 - Functional diagram of CDP18S020 Evaluation Kit.

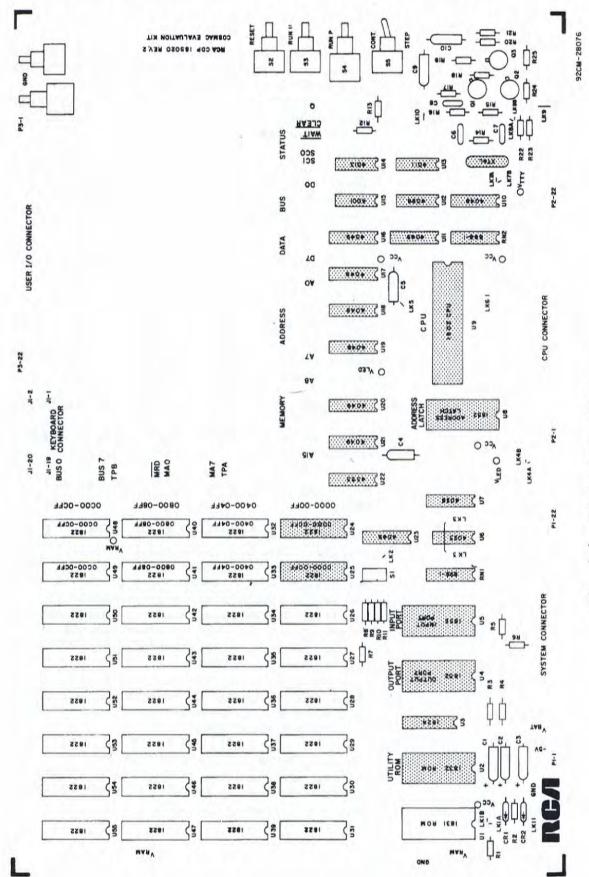

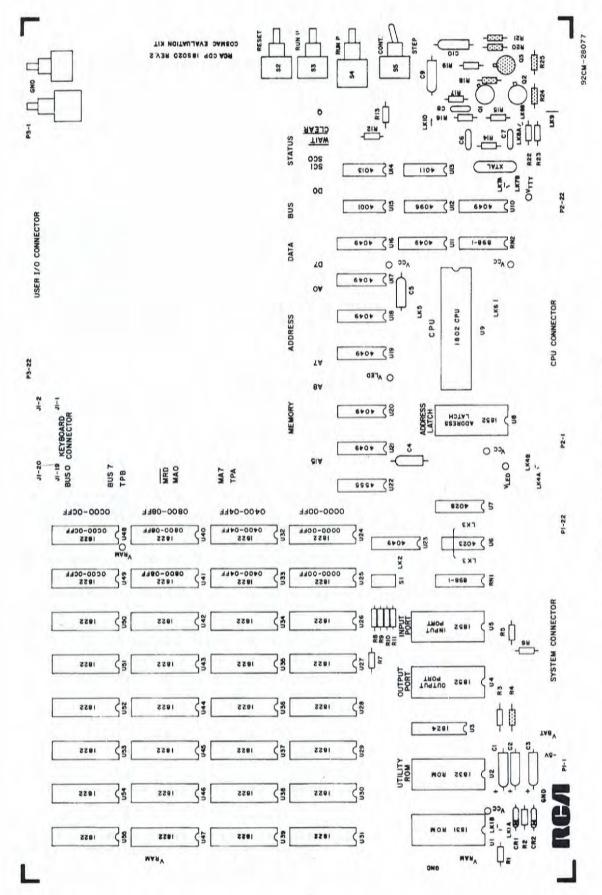

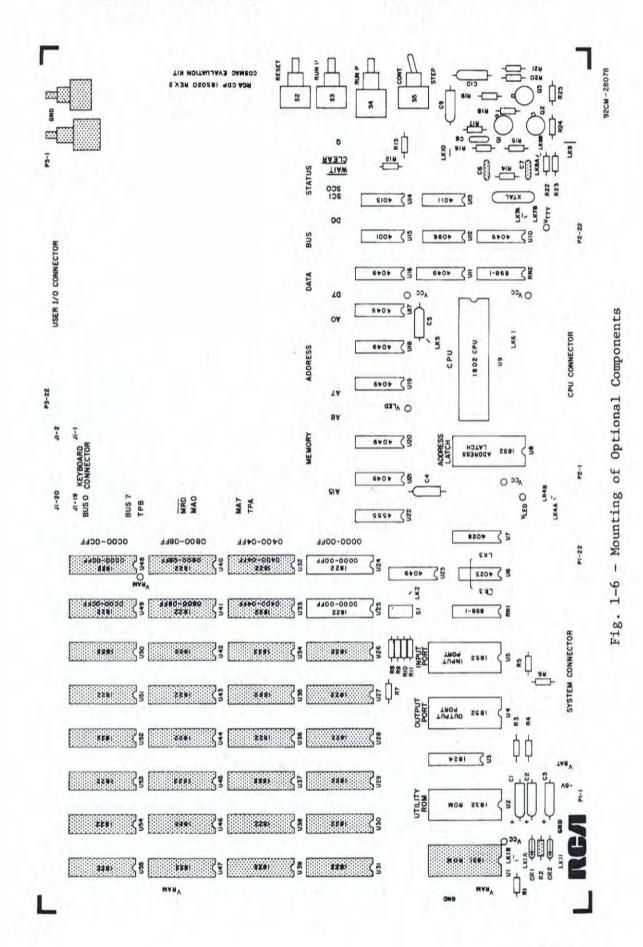

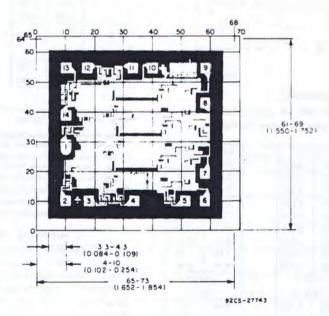

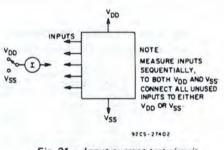

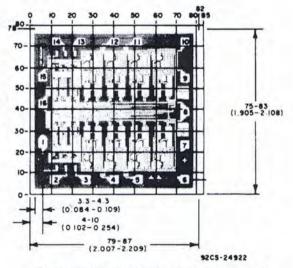

Fig. 1-2 - Topological layout of CDP18S020 Evaluation Kit from the component side.

Description

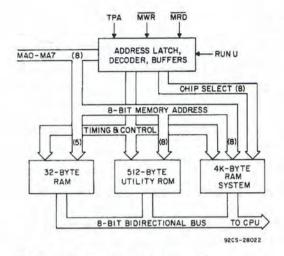

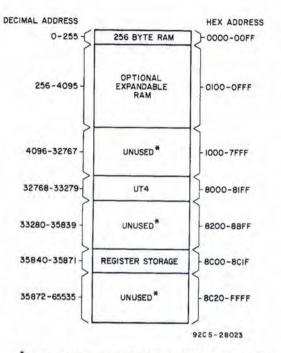

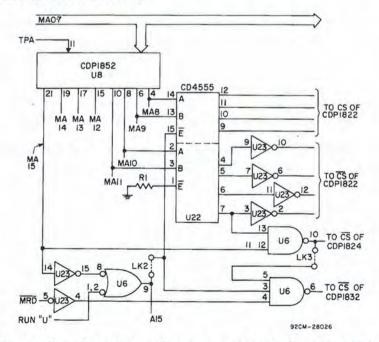

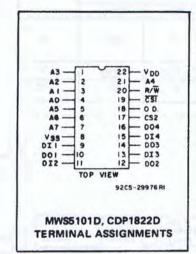

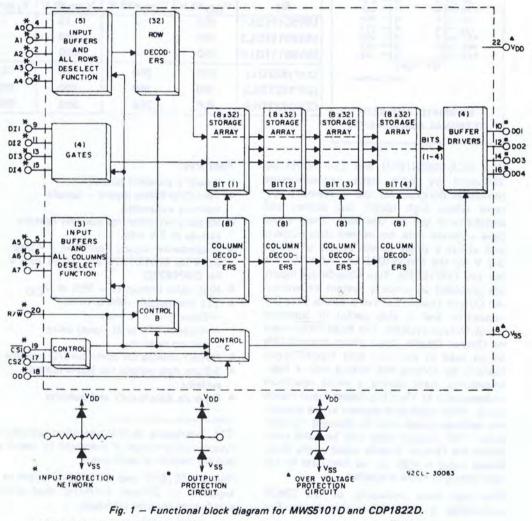

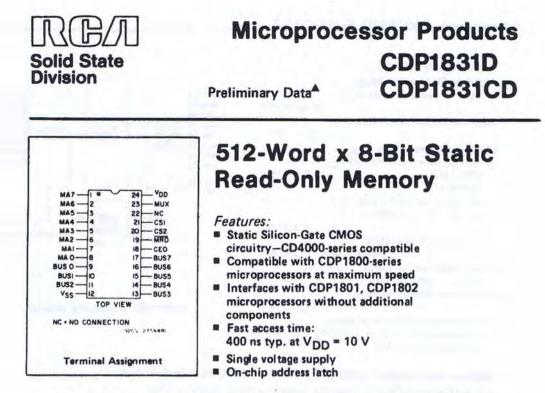

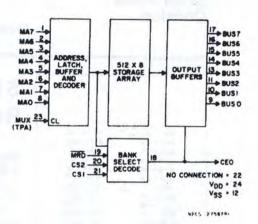

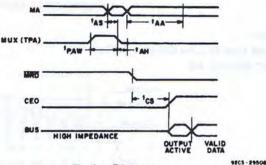

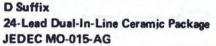

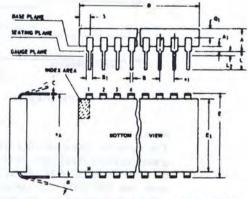

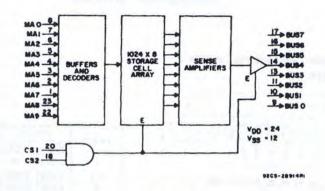

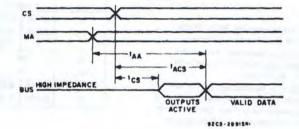

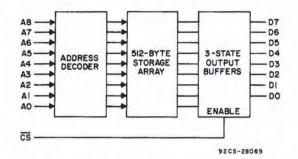

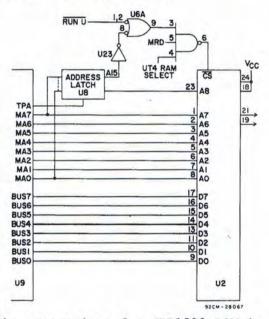

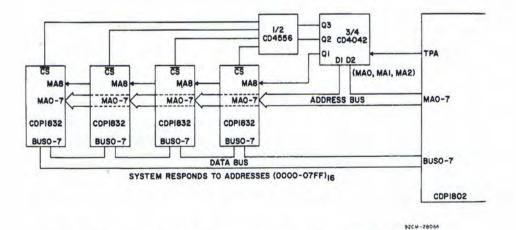

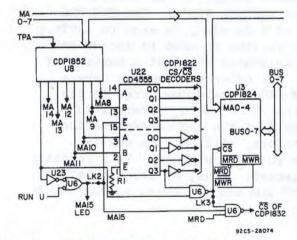

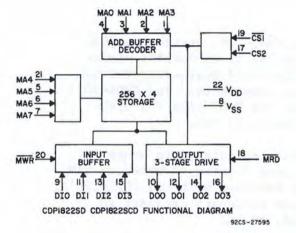

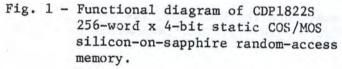

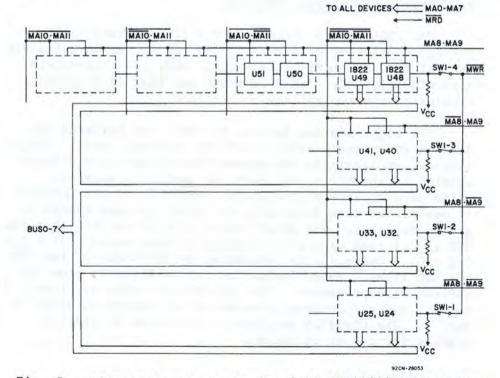

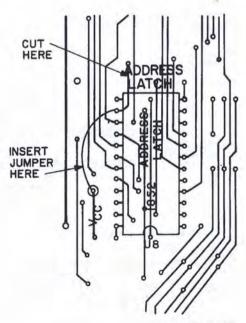

The <u>Memory</u> section is divided into RAM and ROM subsections. The RAM subsection contains a fully decoded, prewired, CDP1822-based 4K byte RAM system. Devices for populating 256 bytes of the system are provided with the Evaluation Kit CDP18S020. Provisions have been made for write-protection of 1-kilobyte blocks of RAM to simulate ROM. The ROM subsection consists of a CDPR512, a 512-byte CMOS ROM which has been factory programmed with resident software utility program (UT4). Also provided is a prewired location for the CDP1831 512-byte CMOS ROM for future expansion of memory or as a vehicle for custom mask pattern verification.

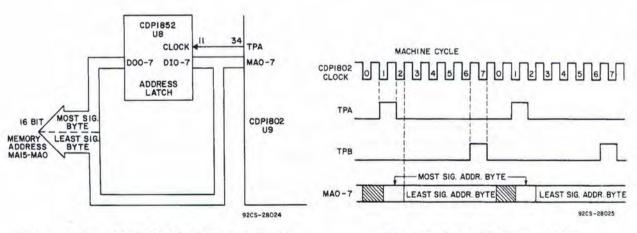

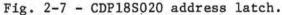

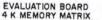

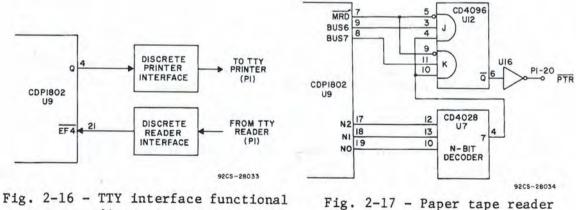

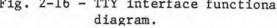

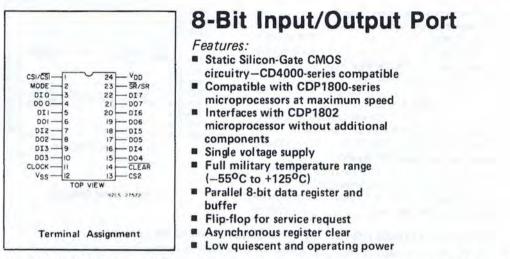

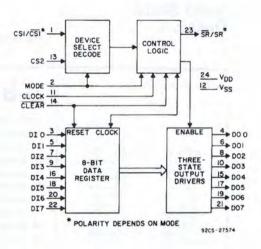

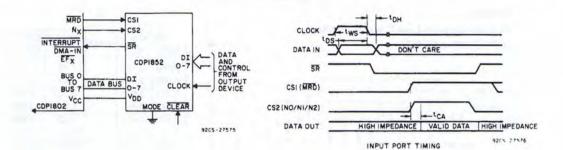

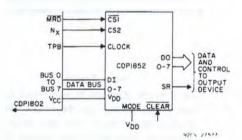

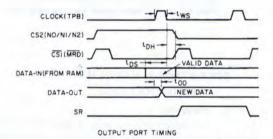

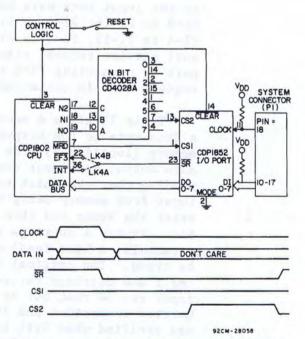

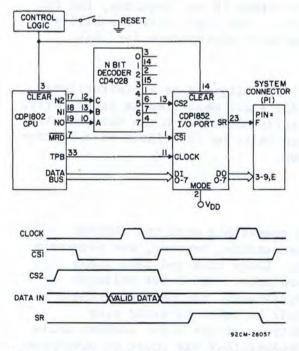

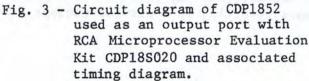

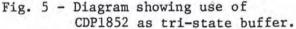

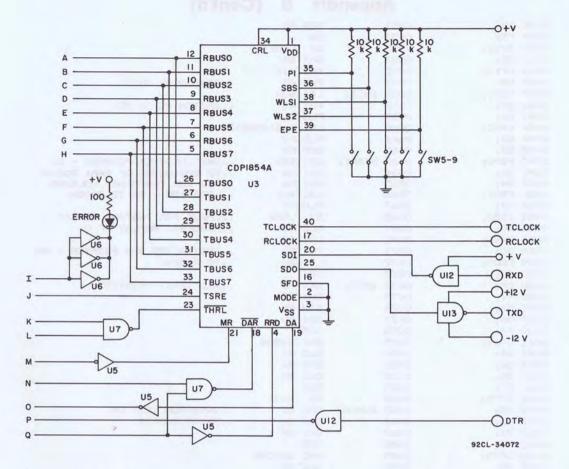

The I/O section contains a CDP1852 used as an input port, a CDP1852 used as an output port, a TTY interface, and an open area for adding user-designed I/O. This open area will be used with future application notes for construction of new device application circuits.

Kit Contents

# CDP18S020 EVALUATION KIT CONTENTS

The following items are supplied with the CDP18S020 Evaluation Kit:

- a) PC card prewired for CPU, RAM, ROM, Control, and Display.

- b) CDP1802 Microprocessor.

- c) 2 CDP1822 256x4 CMOS RAM's.

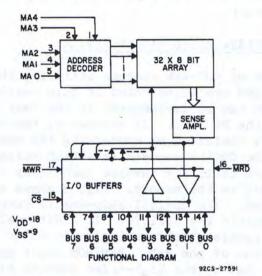

- d) CDP1824 32-byte CMOS RAM.

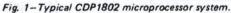

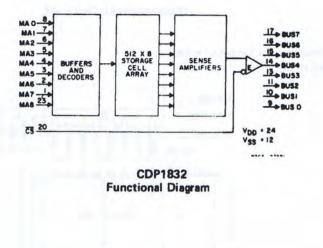

- e) CDP1832 512-byte CMOS ROM factory programmed with Utility Program UT4.

- f) 3 CDP1852 8-bit Input/Output Ports (1 used as address latch).

- g) Switches and standard CD4000 Series COS/MOS components for control.

- h) Discrete LED memory address bus, data bus, and CPU status display.

- i) Components for 20-mA TTY or RS232C interface.

- j) 2-MHz crystal.

- k) Miscellaneous hardware for mechanical assembly.

- 1) MPM-203, Evaluation Kit Manual for the RCA CDP1802 COSMAC Microprocessor.

- m) MPM-201, User Manual for the CDP1802 COSMAC Microprocessor.

- n) User registration card.

# CDP18S020 EVALUATION KIT SPECIFICATIONS

Specifications for the completed CDP18S020 Evaluation Kit are as follows:

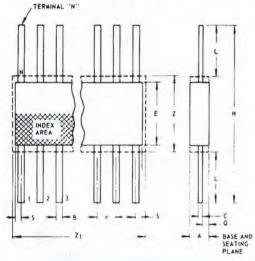

- a) PC card size : 14 x 9.7 x .062"

- b) Mating connectors : 44 pin, .156" spacing

- c) Power requirements (minimum configuration):  $V_{nD} = 5 V$ , 10 mA; 10 V, 20 mA

- $V_{\text{CC}} = 5 \text{ V}, 20 \text{ mA}; 10 \text{ V}, 40 \text{ mA}$   $V_{\text{LED}} = 5 \text{ V}, 600 \text{ mA}$  $V_{\text{TTV}} = 5 \text{ V}, 100 \text{ mA}$

- d) Operating speed: 2 MHz at  $V_{DD} = 4-12$  volts

- e) CPU: CDP1802 COSMAC microprocessor

- f) ROM: CDP1832, 512 bytes, factory programmed with UT4

- g) RAM: 2 CDP1822's, 256 bytes, expandable to 4K bytes

- CDP1824, 32 bytes (used by UT4)

- h) I/O: CDP1852 8-bit Input Port CDP1852 8-bit Output Port

- i) Data terminal interface: 20-mA current loop (TTY) or EIA RS232C (selectable)

- j) Display: 29 discrete LED's with separate supply

- k) Controls: RESET initializes CPU and control logic.

RUN U - initiates Utility Program (UT4) execution.

RUN P - initiates program execution CONTINUOUS/STEP - mode control.

#### ASSEMBLY INSTRUCTIONS

Your CDP18S020 COSMAC Evaluation Kit has been designed for minimum assembly time. The procedure consists of mounting and soldering the kit components and a minimal amount of discretionary wiring to configure the kit to your specific requirements. To assist you in the assembly operation, a step by step procedure is given below. Following this procedure and the use of good workmanship practices will assure successful completion of the assembly operation.

- Unpack the shipping carton, identify and sort all components, and check the contents against the parts list given in Table 1-I on the following page.

- Note: Prior to mounting on the PC card, all IC's should be kept in the conductive foam shipping carrier. The carrier keeps the IC leads shorted together and also protects the leads from physical damage.

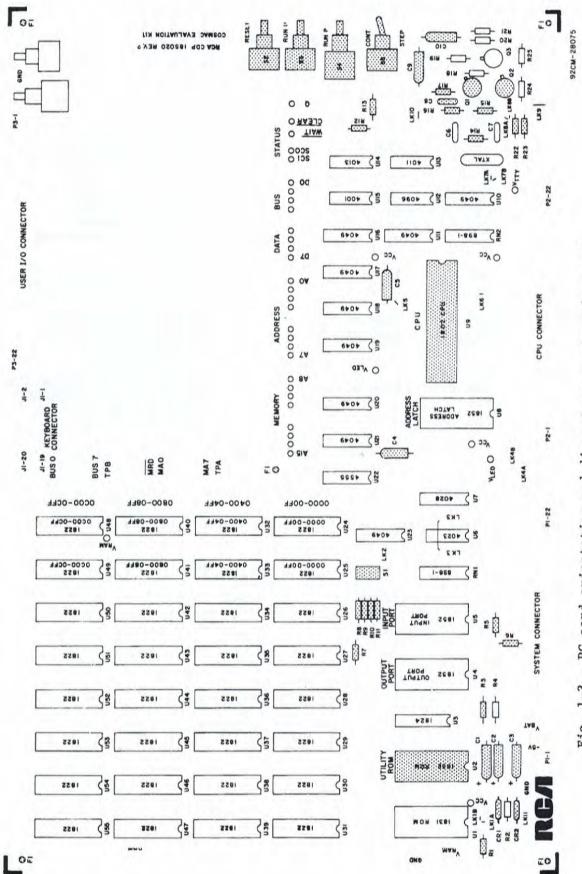

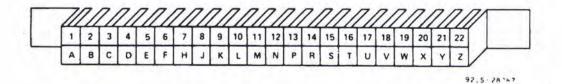

- 2. Orient the PC card as shown in Fig. 1-3. You are now looking at the component side of the card. All components will be mounted on this side and all soldering will be done on the reverse side. The component side of the PC card has silk-screened part numbers and location guides. It is recommended that you study the PC card and components and become familiar with the parts placement and nomenclature before beginning assembly.

- 3. General discrete component assembly instructions.

- a) When mounting components, bend the leads on the solder side of the PC card in the direction of the metal run - away from adjacent components or metal runs.

- b) When soldering components, preheat the connection and apply just enough solder to "wet" the connection. Avoid using excessive amounts of solder. Use only rosin-core solder.

Table 1-I - CDP18S020 parts 1ist.

| TYPE<br>NUMBER                            | CDP18S020<br>1.D.# | QTY.        | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-------------------------------------------|--------------------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CDP1802                                   | <b>U</b> 9         | 1           | COSMAC Microprocessor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| CDP1822                                   | U24,U25            | 2           | 256x4 Static RAM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| CDP1824                                   | U3                 | 1           | 32x8 Static RAM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| CDP1832                                   | U2                 | 1           | 512x8 Static ROM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

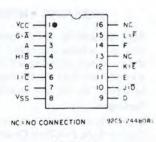

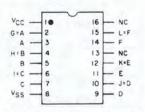

| CDP1852<br>CDP1852                        | U4,U5,U8           | 3           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| CDF1052                                   | 04,03,00           | 2           | 8-Bit Input/Output Port                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

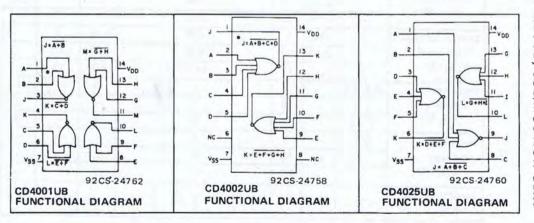

| CD4001                                    | U15                | 1           | Quad 2 Input NOR Gate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

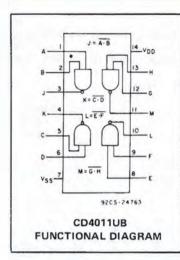

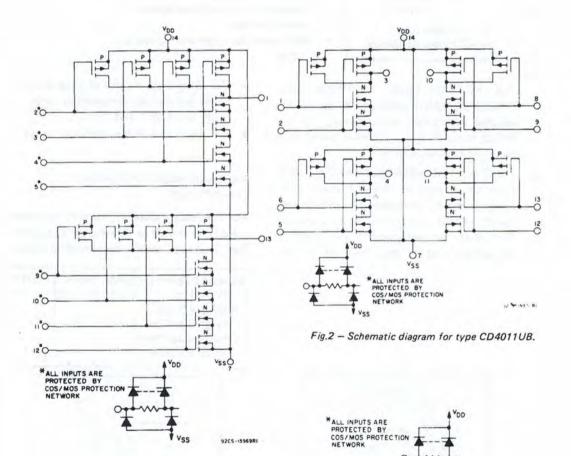

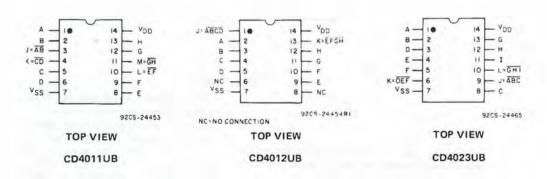

| CD4011                                    | U13                | 1           | Quad 2 Input NAND Gate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

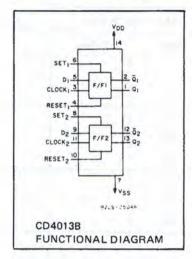

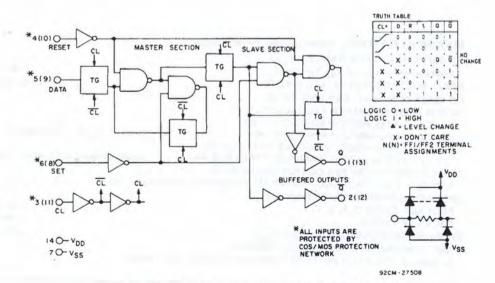

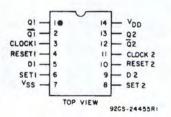

| CD4013                                    | U14                | 1           | Dual D Master-Slave<br>Flip-Flop                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

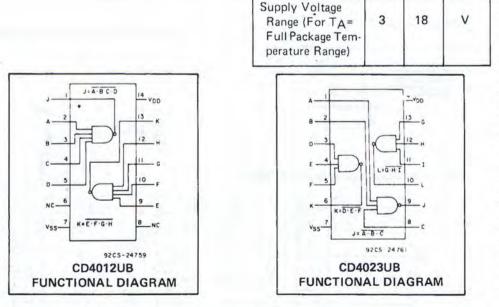

| CD4023                                    | U6                 | 1           | Triple 3-Input NAND Gate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

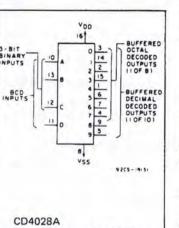

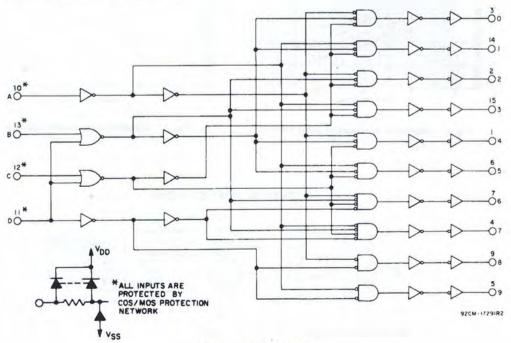

| CD4028                                    | U7                 | 1           | BCD-to-Decimal Decoder                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| CD4049                                    | U10,U11,U16        |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                           | thru U21, U23      | 9           | Hex Inverter Buffer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

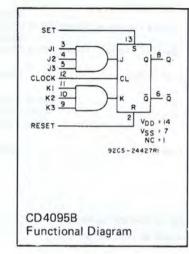

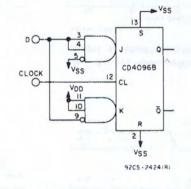

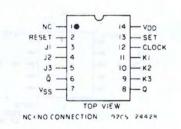

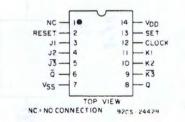

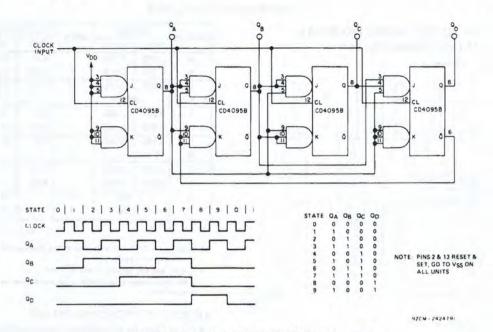

| CD4096                                    | U12                | 1           | Gated JK Master-Slave                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 001000                                    | UTH .              |             | Flip-Flop                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

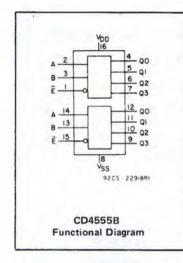

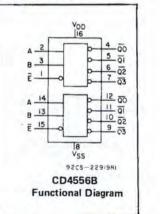

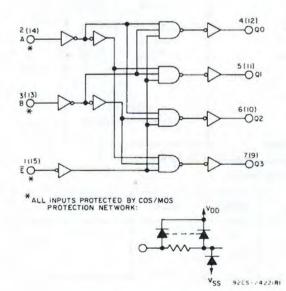

| CD4555                                    | U22                | 1           | Dual Binary 1 of 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 001000                                    |                    | -           | Decoder                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 76B04                                     | Sl                 | 1           | Quad SPST DIP Switch                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 8125                                      | S2,S3              | 2           | SPDT Pushbutton Switch                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 8225                                      | S4                 | 1           | DPDT Pushbutton Switch                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 7101                                      | S5                 | 1           | SPDT Toggle Switch                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

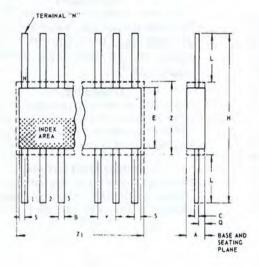

| 2N3053                                    | Q1                 | 1           | NPN Transistor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 2N4037                                    | Q2,Q3              | 2           | PNP Transistor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 2114037                                   | 42,45              | -           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| D1201F                                    | CR1,CR2            | .2          | Diode (1N4001 or equiv.)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 5082-4494                                 | LED's              | 29          | Red LED                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| T 310(C)                                  | C1 thru C5,C9,     | 7           | 15-Microfarad, 20-Volt                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                                           | C10                |             | Capacitor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

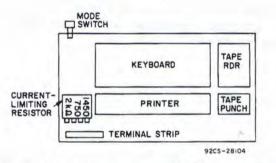

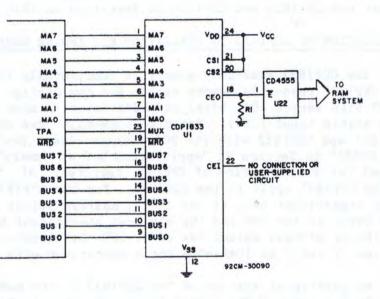

| CK05BX104                                 | C8                 | 1           | 0.1-Microfarad, 30-Volt<br>Capacitor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |