# GE Solid State Data Book

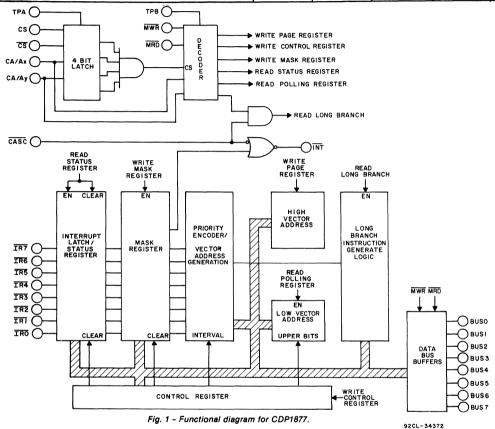

# RCA CMOS Microprocessors, Memories, and Peripherals

This DATABOOK contains detailed information on CMOS microprocessors, microcomputers, memories, and peripherals currently available from GE Solid State, a division of GE Corporation. GE Solid State is a consolidation of the strengths of three-broad-based semiconductor suppliers—GE Semiconductor, RCA Solid State and Intersil—that formerly operated as separate, independent organizations.

An Index to Products provides a complete listing of types. Following the Index to Products are several pages of general product information that include a Product Classification Chart that groups integrated circuits and systems according to product type and intended function; photographs showing available package options; a Product Overview that summarizes the basic features of each category of products; and a description of the Enhanced Product. The DATABOOK then includes a general discussion of Operating and Handling Considerations for CMOS Integrated Circuits.

Five separate data sections provide definitive ratings, electrical characteristics, and user information for the (1) 1800-Series Microprocessors and Microcomputers, (2) 6805-Series Microprocessors and Microcomputers, (3) CMOS Peripherals, (4) CMOS Random-Access Memories (RAMs), and (5) CMOS Read-Only Memories (ROMs). Within each data section, data pages for individual integrated circuits and systems are grouped in alphanumerical sequence by type numbers.

A section on CMOS LSI High-Reliability Devices provides a description of non-radiation-hardened CMOS LSI devices and radiation-hardened CMOS/SOS LSI RAMs with a list of devices available.

The DATABOOK also contains Dimensional Outlines of all packages in which memory/microprocessor products are supplied and a list of Application Notes on memory/microprocessor products.

#### **Table of Contents**

Guide to Products

1800-Series Microprocessors and Microcomputers

2

6805-Series Microprocessors and Microcomputers

3

CMOS Peripherals

4

Random-Access Memories (RAMs)

5

Read-Only Memories (ROMs) 6

High-Reliability Devices

7

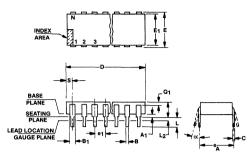

**Dimensional Outlines**

8

## **GE Solid State**

Somerville, NJ • Brussels • Paris • London • Munich • Hong Kong • Tokyo

GE/RCA/Intersil Semiconductors

Information furnished by RCA is believed to be accurate and reliable. However, no responsibility is assumed by GE or its affiliates for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent rights of GE, RCA or Intersil.

The device data shown for some types are indicated as product preview or advance information. **Product preview** data are intended for engineering evaluation of product under development. The type designations and data are subject to change or withdrawal, unless otherwise arranged. **Advance information data** are intended for guidance purposes in evaluating new product for equipment design. Such data are shown for types currently being designed for inclusion in our standard line of commercially available products. No obligations are assumed for notice of change of these devices. For current information on the status of product preview or advance information data programs, please contact your local GE sales office.

Copyright 1987 by GE Corporation (All rights reserved under Pan-American Copyright Convention)

Trademark(s) ®Registered Marca(s) Registrada(s)

Printed in USA/12-87

# **Guide to Products**

|                                       | PAGE |

|---------------------------------------|------|

| Index to Products                     | 4    |

| Production Classification Chart       | 5    |

| Packages and Ordering Information     | 6    |

| Product Overview                      | 8    |

| Enhanced Product                      | 9    |

| Operating and Handling Considerations | 11   |

# **Index to Products**

| Part         | Description                                                                                 | Page | File     |

|--------------|---------------------------------------------------------------------------------------------|------|----------|

| No.          |                                                                                             | No.  | No.      |

| CDM5332      | 4K x 8 ROM                                                                                  | 705  | 1366     |

| CDM5333      | 4K x 8 ROM                                                                                  | 705  | 1366     |

| CDM5364,A    | 8K x 8 ROM                                                                                  | 709  | 1467     |

| CDM5365      | 8K x 8 ROM                                                                                  | 714  | 1466     |

| CDM6116A     | 2K x 8 RAM                                                                                  | 636  | 1472     |

| CDM6264      | 8K x 8 RAM                                                                                  | 642  | 1505     |

| CDM53128     | 16K × 8 ROM                                                                                 | 718  | 1454     |

| CDM53256     | 32K × 8 ROM                                                                                 | 722  | 1453     |

| CDM62256     | 32 x 8 RAM                                                                                  | 648  | 1845     |

| CDP1802A,AC  | 8-Bit Microprocessor                                                                        | 17   | 1350     |

| CDP1802BC    | 8-Bit Microprocessor                                                                        | 39   | 1342     |

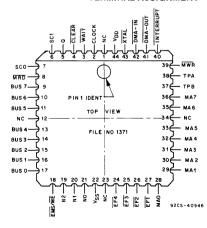

| CDP1804AC    | 8-Bit Microcomputer                                                                         | 60   | 1371     |

| CDP1805AC    | 8-Bit Microprocessor                                                                        | 85   | 1370     |

| CDP1806AC    | 8-Bit Microprocessor                                                                        | 85   | 1370     |

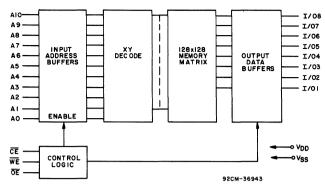

| CDP1822,C    | 256 x 4 RAM                                                                                 | 654  | 1074     |

| CDP1823,C    | 128 x 8 RAM                                                                                 | 660  | 1198     |

| CDP1824,C    | 32 x 8 RAM                                                                                  | 666  | 1103     |

| CDP1826C     | 64 x 8 RAM                                                                                  | 671  | 1311     |

| CDP1831,C    | 512 x 8 ROM                                                                                 | 726  | 1104     |

| CDP1832,C    | 512 x 8 ROM                                                                                 | 730  | 1145     |

| CDP1833,C,BC | 1K x 8 ROM                                                                                  | 734  | 1135     |

| CDP1834,C    | 1K x 8 ROM                                                                                  | 739  | 1143     |

| CDP1835C     | 2K x 8 ROM                                                                                  | 742  | 1267     |

| CDP1837C     | 4K x 8 ROM                                                                                  | 747  | 1381     |

| CDP1851,C    | Programmable I/O Interface  Byte-Wide I/O Port                                              | 363  | 1056     |

| CDP1852,C    |                                                                                             | 375  | 1166     |

| CDP1853,C    | 1 of 8 Decoder                                                                              | 383  | 1189     |

| CDP1854A,AC  |                                                                                             | 387  | 1193     |

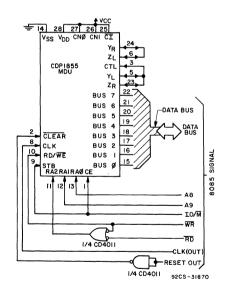

| CDP1855,C    | Programmable UART 8-Bit Programmable Multiply/Divide Unit                                   | 404  | 1053     |

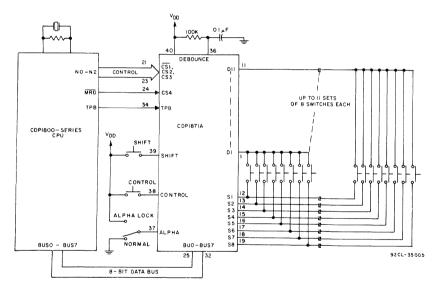

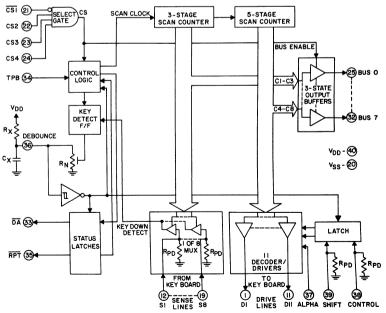

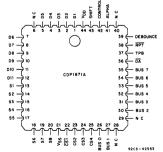

| CDP1871A,AC  | Keyboard Encoder, ASCIII Hex High-Speed 8-Bit Input Port                                    | 417  | 1374     |

| CDP1872C     |                                                                                             | 425  | 1255     |

| CDP1874C     | High-Speed 8-Bit Input Port                                                                 | 425  | 1255     |

| CDP1875C     | High-Speed 8-Bit Output Port Programmable Interrupt Controller (PIC)                        | 425  | 1255     |

| CDP1877,C    |                                                                                             | 430  | 1319     |

| CDP1878,C    | Dual-Timer Counter                                                                          | 439  | 1341     |

| CDP1879,C-1  | Real-Time Clock 6-Bit Latch & Decoder Memory Interface                                      | 452  | 1360     |

| CDP1881,C    |                                                                                             | 468  | 1367     |

| CDP1882,C    | 6-Bit Latch & Decoder Memory Interface                                                      | 468  | 1367     |

| CDP1883,C    | 7-Bit Latch & Decoder Memory Interface                                                      | 474  | 1507     |

| CDP6402,C    | Programmable UART                                                                           | 479  | 1328     |

| CDP65C51     | Asynchronous Communications Interface Adapter Asynchronous Communications Interface Adapter | 487  | 1470     |

| CDP65C51A    |                                                                                             | 503  | 1928     |

| CDP68EM05C4  | 8-Bit Microcomputer Piggyback Emulator                                                      | 351  | 1961     |

| CDP68EM05D2  | 8-Bit Microcomputer Piggyback Emulator                                                      | 355  | 1960     |

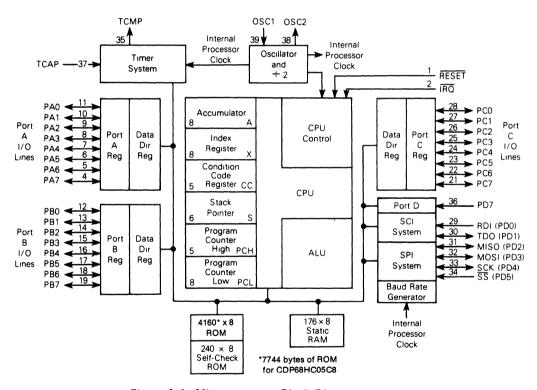

| CDP68HC05C4  | 8-Bit Microcomputer                                                                         | 111  | TSM-203A |

| CDP68HC05C8  | 8-Bit Microcomputer 8-Bit Microcomputer                                                     | 111  | TSM-203A |

| CDP68HC05D2  |                                                                                             | 193  | TSM-204A |

| CDP68HC05D2A | 8-Bit Microcomputer                                                                         | 240  | 2100     |

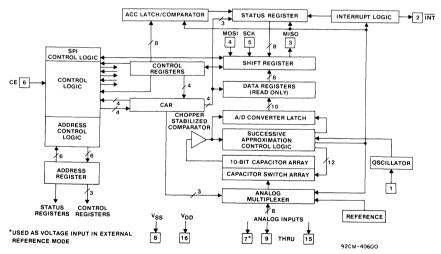

| CDP68HC68A2  | SPI A/D Converter                                                                           | 521  | 1963     |

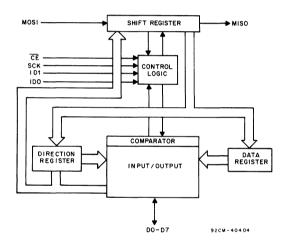

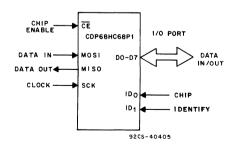

| CDP68HC68P1  | 8-Bit Single I/O Port                                                                       | 534  | 1858     |

| CDP68HC68R1  | SPI RAM 128 Bytes                                                                           | 679  | 1544     |

| CDP68HC68R2  | SPI RAM 256 Bytes                                                                           | 679  | 1544     |

| CDP68HC68T1  | SPI Real-Time Clock                                                                         | 542  | 1547     |

| CDP6805E2,C  | 8-Bit Microprocessor 8-Bit Microprocessor                                                   | 241  | 1363     |

| CDP6805E3,C  |                                                                                             | 274  | 1503     |

| CDP6805F2,C  | 8-Bit Microcomputer                                                                         | 307  | 1369     |

| CDP6805G2,C  | 8-Bit Microcomputer Real-Time Clock, MOTEL Bus                                              | 329  | 1364     |

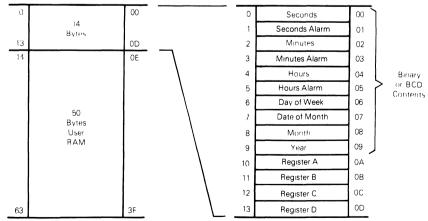

| CDP6818      |                                                                                             | 560  | 1375     |

| CDP6818A     | Real-Time Clock Plus RAM                                                                    | 579  | 2041     |

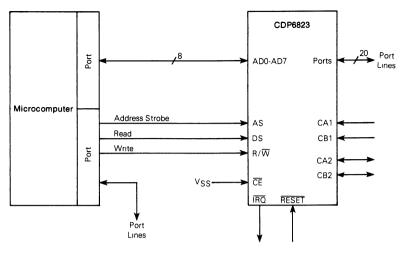

| CDP6823      | Parallel Interface                                                                          | 598  | 1377     |

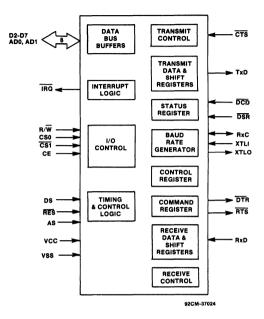

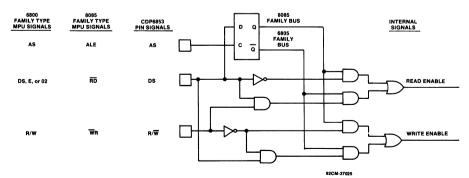

| CDP6853      | Asynchronous Communications Interface Adapter                                               | 612  | 1487     |

| MWS5101      | 256 x RAM                                                                                   | 686  | 1106     |

| MWS5101A     | 256 x 4 RAM                                                                                 | 692  | 1207     |

| MWS5114      | 1K x 4 RAM                                                                                  | 698  | 1325     |

|              |                                                                                             |      |          |

# **Product Classification Chart**

|                 |                               | Page |               |                              | Page |

|-----------------|-------------------------------|------|---------------|------------------------------|------|

| Part Number     | Description                   | No.  | Part Number   | Description                  | No.  |

| Microprocessors | s                             |      | Mask-Programi | nable ROMs                   |      |

| CDP1802A,AC     | 8-Bit                         | 17   | CDM5332       | 4K x 8                       | 705  |

| CDP1802BC       | 8-Bit                         | 39   | CDM5333       | 4K x 8                       | 705  |

| CDP1805AC       | 8-Bit with RAM and Counter/   | 85   | CDM5364,A     | 8K x 8                       | 709  |

|                 | Timer                         |      | CDM5365       | 8K x 8                       | 714  |

| CDP1806AC       | 8-Bit with RAM and Counter/   | 85   | CDM53128      | 16K x 8                      | 718  |

|                 | Timer                         |      | CDM53256      | 32K x 8                      | 722  |

| CDP6805E2,C     | 8-Bit with RAM I/O, Counter/  | 241  | CDP1831,C     | 512 x 8                      | 726  |

|                 | Timer                         |      | CDP1832,C     | 512 x 8                      | 730  |

| CDP6805E3,C     | 8-Bit with RAM, I/O, Counter/ | 274  | CDP1833,C,BC  | 1K x 8                       | 734  |

|                 | Timer                         |      | CDP1834,C     | 1K x 8                       | 739  |

|                 |                               |      | CDP1835C      | 2K x 8                       | 742  |

| Microcomputers  | •                             |      | CDP1837C      | 4K x 8                       | 747  |

| CDP1804AC       |                               | 00   |               |                              |      |

| CDP1804AC       | 8-Bit with RAM, ROM, Counter/ | 60   | Peripherals   |                              |      |

| CDP68HC05C4     | 8-Bit with RAM, ROM, I/O,     | 111  | CDP1851,C     | Programmable I/O Interface   | 363  |

| CDF06HC03C4     | Counter/Timer                 | 111  | CDP1851,C     | Byte-Wide I/O Port           | 375  |

| CDP68HC05C8     | 8-Bit with RAM, ROM, I/O,     | 111  | CDP1872C      | 8-Bit Input Port             | 425  |

| CDF0011C03C0    | Counter/Timer                 |      | CDP1874C      | 8-Bit Input Port             | 425  |

| CDP68HC05D2     | 8-Bit with RAM, ROM, I/O,     | 193  | CDP1875C      | 8-Bit Output Port            | 425  |

| CDF0011C03D2    | Counter/Timer                 | 130  | CDP68HC68P1   | 8-Bit Single I/O Port        | 534  |

| CDP68HC05D2A    |                               | 240  | CDP6823       | Parallel Interface           | 598  |

| ODI CONTOCODEN  | Counter/Timer                 | 240  | CDP1853,C     | 1 of 8 Decoder               | 383  |

| CDP6805F2,C     | 8-Bit with RAM, ROM, I/O      | 307  | CDP1881.C     | 6-Bit Latch & Decoder        | 468  |

| 05: 0000: 2,0   | Counter/Timer                 | 001  | CDP1882.C     | 6-Bit Latch & Decoder        | 468  |

| CDP6805G2,C     | 8-Bit with RAM, ROM, I/O      | 329  | CDP1883,C     | 7-Bit Latch & Decoder        | 474  |

| 0_1,00000,_,0   | Counter/Timer                 | 00   | CDP1854A.AC   | Programmable UART            | 387  |

|                 |                               |      | CDP6402,C     | Programmable UART            | 479  |

| Emulators       |                               |      | CDP65C51      | Asynchronous Communications  | 487  |

| CDP68EM05C4     | 8-Bit Microcomputer Piggyback | 351  |               | Interface Adapter            |      |

| CDP68EM05D2     | 8-Bit Microcomputer Piggyback | 355  | CDP65C51A     | Asynchronous Communications  | 503  |

|                 |                               |      |               | Interface Adapter            |      |

| D414            |                               |      | CDP6853       | Asynchronous Communications  | 612  |

| RAMs            |                               |      |               | Interface Adapter, (ACIA),   |      |

| CDP1822,C       | 256 x 4                       | 654  |               | MOTEL Bus                    |      |

| CDP1823,C       | 128 x 8                       | 660  | CDP1855,C     | 8-Bit Programmable Multiply/ | 404  |

| CDP1824,C       | 32 x 8                        | 666  |               | Divide Unit (MDU)            |      |

| CDP1826C        | 64 x 8                        | 671  | CDP1871A,AC   | Keyboard Encoder, ASCII Hex  | 417  |

| CDM6116A        | 2K x 8                        | 636  | CDP1878,C     | Dual Counter/Timer           | 439  |

| CDM6264         | 8K x 8                        | 642  | CDP1879,C-1   | Real-Time Clock              | 452  |

| CDM62256        | 32 x 8                        | 722  | CDP6818       | Real-Time Clock with RAM,    | 560  |

| MWS5101         | 256 x 4                       | 686  | 0000000       | MOTEL Bus                    |      |

| MWS5101A        | 256 x 4                       | 692  | CDP6818A      | Real-Time Clock Plus RAM     | 579  |

| M:WS5114        | 1K x 4                        | 698  | CDP68HC68T1   | SPI Real-Time Clock          | 542  |

| CDP68HC68R1     | SPI RAM 128-Bytes             | 679  | CDP1877,C     | Programmable Interrupt       | 430  |

| CDP68HC68R2     | SPI RAM 256-Bytes             | 679  | CDDcoucee40   | Controller                   | 504  |

|                 |                               |      | CDP68HC68A2   | SPI 10-Bit A/D Converter     | 521  |

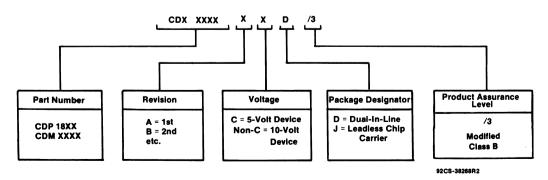

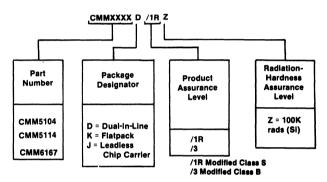

# **Package and Ordering Information**

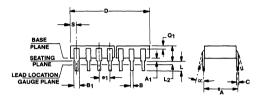

#### **Packages**

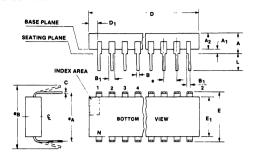

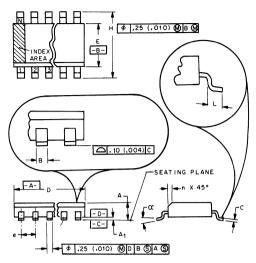

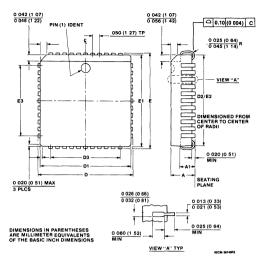

RCA CMOS microprocessor and memory integrated circuits are available in one or more of the following package styles and are identified by the Suffix Letters indicated: dual-inline side-brazed cerámic, dual-in-line plastic, small-outline plastic, plastic chip-carrier, and in chip form. The available package styles for any specific type are given in the technical data for that type.

D Suffix **Dual-In-Line Side-Brazed Ceramic Packages**

E Suffix Plastic Dual-In-Line Packages

8-, 16-, 18-, 20-, 22-, 24-, 28-, and 40-lead versions

M Suffix Small-Outline Plastic Package (SO)

16-, 18-, 22-, 24-, 28-, and 40-lead versions

16-, 20-, and 28-lead versions

Q Suffix Plastic Chip-Carrier

28- and 44-lead version

## **Ordering Information**

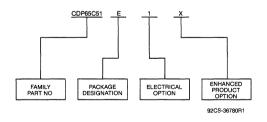

The RCA family packages and electrical options are identified by suffix letters indicated in the following chart. When ordering a Memory/Microprocessor device, it is important that the appropriate suffix letter be affixed to the type number of the device.

| Package/Option                                               | Suffix Letter |

|--------------------------------------------------------------|---------------|

| Dual-In-Line Side-Brazed Ceramic                             | D             |

| Dual-In-Line Plastic                                         | Ε             |

| Small-Outline Plastic (SOP)                                  | M             |

| Plastic Chip-Carrier                                         | Q             |

| Chip (when applicable)                                       | Н             |

| Enhanced Product Screening i.e., Burn-In - optional for D, E |               |

| package types                                                | X             |

| Electrical Option                                            | 1, 2, 4       |

For example, a CDP65C51-1 in a dual-in-line plastic package will be identified as the CDP65C51E1. A CDP65C51E1 with enhanced product screening option will be identified as the CDP65C51E1X.

# 1

# **Package and Ordering Information**

# Instructions for Submitting Data for ROM Patterns

#### **Data Format Options**

Data for RCA ROMs or microcomputers should be submitted in one of the following forms.

- Any industry-standard EPROM or ROM that is pin and polarity compatible with industry-standard 27XXX-series EPROMs.

- IBM PC 5¼-inch floppy diskette (data must be in Motorola "S" format)

- 3. GE worldwide electronic data transfer system

Regardless of the media on which the data is submitted, the entire address range of the ROM being requested must be covered, even if a portion of it is not being used. This restriction also applies to microcomputers. For example, a CDP5332 requires 4k bytes of EPROM, a CDP68HC05C4, 8K bytes.

#### Procedure for Submitting Data

- A. By EPROM, ROM or floppy diskette:

- Complete the application ROM and microcomputer information sheet. (Contact the nearest GE Solid State Sales Office for appropriate forms).

- 2. Submit the data as described above.

- Include a set of blank EPROMs that will cover the memory space of your ROM or microcomputer. These EPROMs will be returned to you.

- 4 When the EPROMs have been returned, confirm that the code is correct, and respond to GE Solid State by completing the ROM verification form. (Included with return of EPROM.)

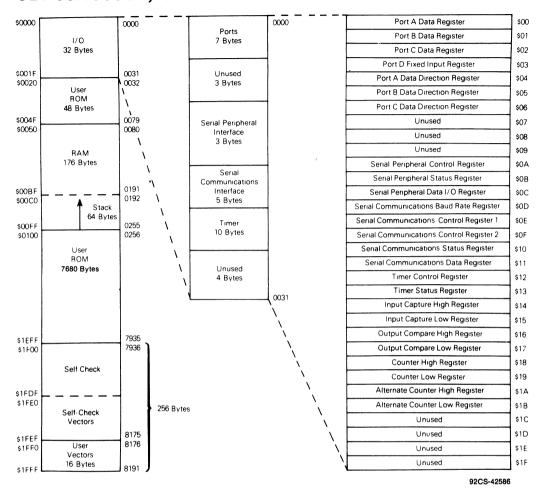

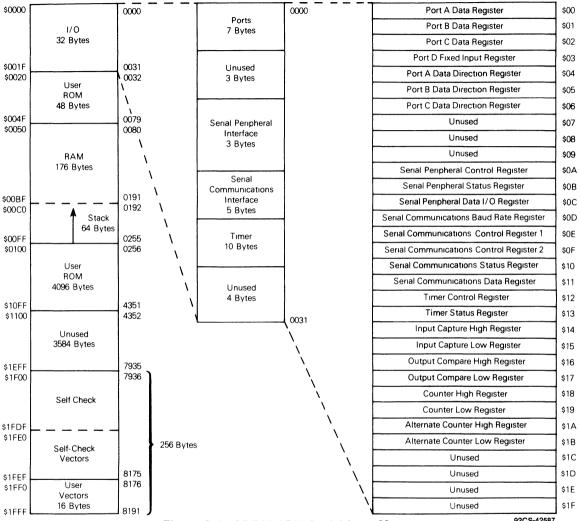

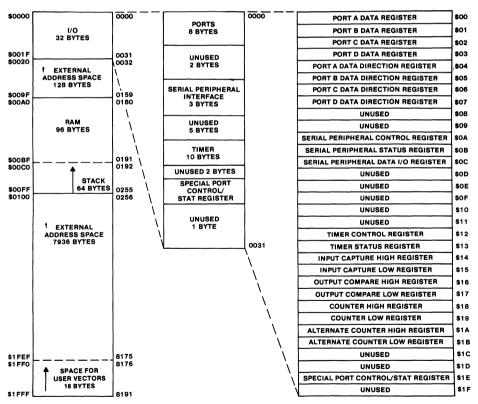

- NOTE-GE Solid State will add the latest self-check code in the memory areas of the Address map shown on the applicable data sheet on the CDP6805-series and CDP68HC05-series microcomputers. On all devices except the CDP6805F2, GE Solid State will assign a three-character variant code to the device and will add the ASCII equivalent of it to the ROM area. On the G2, this code is entered in locations 1FF2, 1FF3 and 1FF4; on the C4 in locations 1FF0, 1FF1, and 1FF2; and on the D2 in locations 1FE6, 1FF0, and 1FF1. GE Solid State also calculates a checksum byte of the entire ROM area, that is, the user ROM, selfcheck area, and the vector area. The checksum is the EXCLUIVE-OR of all the ROM bytes with hex FF. This byte is put in location 07F5 on the F2, 1FF5 on the G2, 1FF3 on the C4, and 1FE7 on the D2.

- B. By electronic data transfer:

Contact the nearest GE Solid State Sales Office for procedure.

#### **Product Overview**

An all CMOS line of microprocessor, microcomputer, memory, and peripheral integrated circuits for use in a broad range of diverse industrial, consumer, and military applications is available from GE Solid State. These devices offer the user all the advantages unique to CMOS technology, including:

- Low power drain makes CMOS integrated circuits a natural choice for battery-operated systems, battery backed-up systems, and systems in which heat dissipation is a prime consideration.

- High noise immunity and wide operating temperature range (up to -55°C to +125°C)\* — allows CMOS integrated circuits to be used in the most demanding industrial environments.

- Wide operating voltage range reduces the need for expensive regulated power supplies and there-by allows the design engineer greater freedom to concentrate on other aspects of system design.

#### **CDP1800 Series**

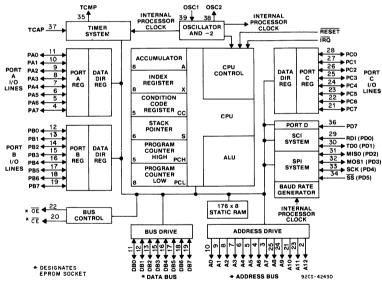

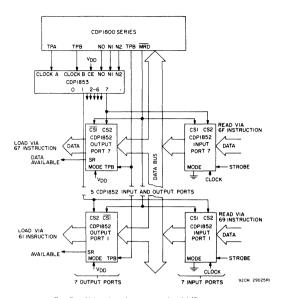

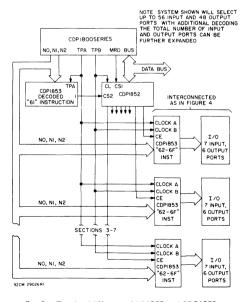

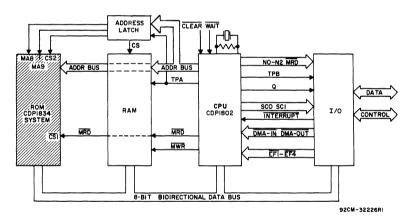

The RCA CDP1800 series offers a complete line of CMOS microprocessor, microcomputer and associated memory and peripheral devices. The heart of the series is the CDP1802A central processing unti (CPU). This unit, which features CMOS register-based architecture, offers 16 internal registers to facilitate data manipulation and to reduce the need for additional devices The need for external devices is even further reduced by use of on-chip clock, DMA, and single phase operation.

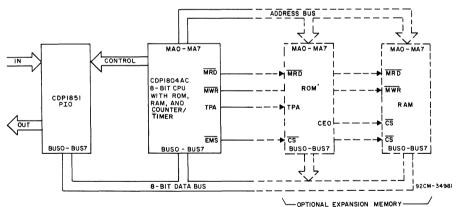

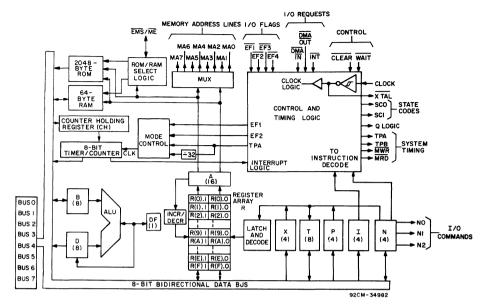

The CDP1804A microcomputer incorporates all the features of the CDP1802A augmented by additional hardware and increased performance capabilities. The additional on-chip hardware enhancements include 2-kilobytes of ROM, a 64-byte RAM array, and an 8-bit presettable down-counter. Thirty-two additional software instructions add subroutine call and return capability, enhance data transfer manipulation, control counter modes and interrupt arbitration and provide BCD arithmetic capability.

Also available, are two other 8-bit microprocessors that are functional and performance enhancements of the CDP1802A. The CDP1805A features an on-board RAM and Counter/Timer. The CDP1806A has all the features of the CDP1805A, but contains no on-board RAM.

The microprocessor and microcomputer devices use CMOS technology, designed on a single chip to maintain low power drain. They are intended for multi-system applications requiring general-purpose CPUs, large memory address space, and extensive external I/O for use with optimized peripherals.

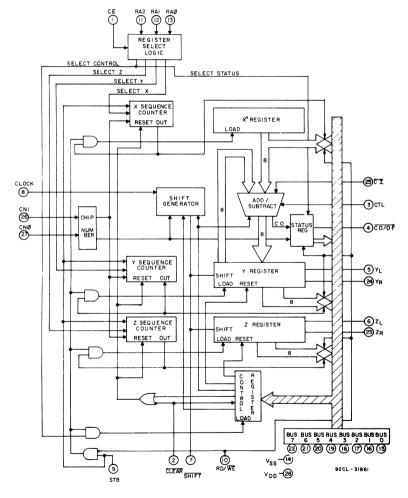

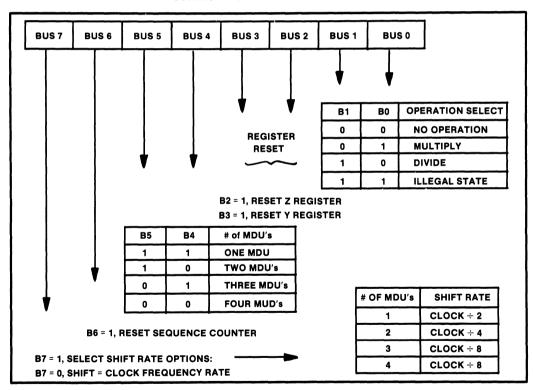

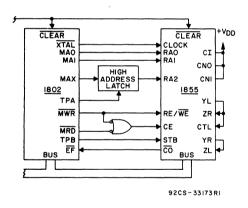

The RCA CDP1800-series memory/microprocessor product line offers the system designer exceptional flexibility in hardware/software tradeoffs In addition to microprocessor and microcomputers, this product line includes a hardware multiply/divide unit (MDU), a programmable I/O, keyboard interface circuits, latches and decoders, universal asynchronous receiver-transmitters (UARTs), and a broad complement of directly interfaceable random-access memories (RAMs) and read-only memories (ROMs).

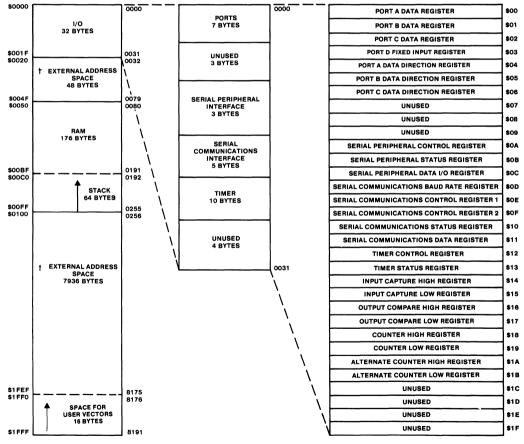

#### CDP6805 Series

The RCA CDP6805 family of CMOS microprocessors, microcomputers, and peripherals are primarily intended for single-

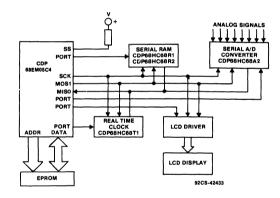

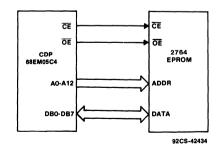

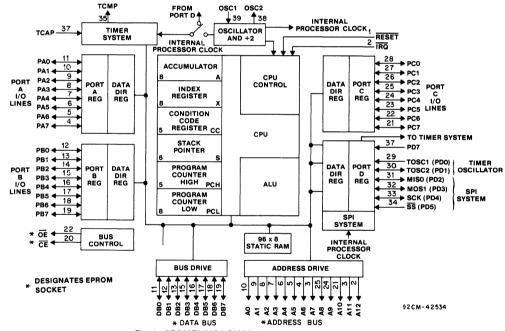

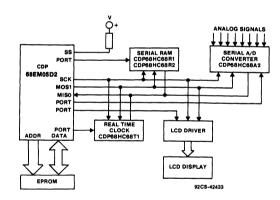

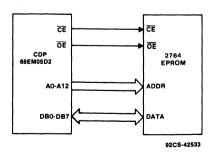

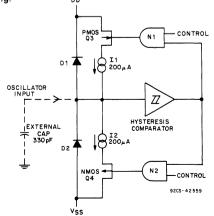

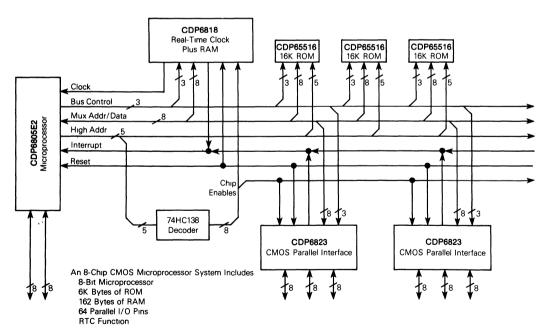

chip system applications requiring limited space, minimum memory, on-board I/O, and minimum external I/O. The series offers pin-for-pin replacements for Motorola's MC146805, and MC68HC05 series of microprocessors, microcomputers, and peripherals. This family of parts includes the CDP6805E2 and CDP6805E3 8-bit microprocessors, the CDP6805F2 8-bit microcomputer (1K ROM); the CDP6805G2 8-bit microcomputer (2K ROM); the CDP68HC05C4, CDP68HC05C8, and CDP68HC05D2 8-bit microcomputers featuring on-chip ROM, RAM, 16-bit timer, asynchronous serial communications interface (CDP68HC05C4, and CDP68HC05C8), synchronous serial peripheral interface, and 24 or 28 bidirectional I/O lines; the CDP68HC68T1 Serial Real-Time Clock/ RAM; the CDP68HC68R1 and CDP68HC68R2 Serial Peripheral Interface (SPI) RAMs; the CDP68HC68A2 10-bit A/D Converter; the CDP68HC68P1 Serial I/O Port: the CDP6818 Real-Time Clock plus RAM: and the CDP6823 Parallel Interface I/O. Also available is the CDP6853 Asynchronous Communications Interface Adapter which is a multiplexed-bus version of our CDP65C51 UART.

Additional types will be added as they become available.

#### General-Purpose Memories

In addition to the memories designed to interface directly with CDP1800-series microprocessors and microcomputers, a line of general-purpose memories is also available. These memories include industry-standard ROMs that can be mask-programmed to meet customer application requirements. These ROMs feature: low-power CMOS technology with high-noise immunity and full-temperature-range characteristics; space-efficient NAND stack memory cells providing small chip size for cost effectiveness; and JEDEC standard pin outs for interchangeability with industry-standard NMO ROMs and EPROMs.

The list of memories also includes fully static CMOS RAMs with densities up to 32K-bytes, low operating power, low standby current, and memory retention for 2-volt minimum standby battery voltage.

#### Memory/Microprocessor Surface-Mounted Packages

The RCA CMOS memory/microprocessor product line now includes standard CDP- and CDM-series chips in a new generation of IC miniaturized packages.

Microprocessors, microcomputers, memories, and peripherals are now offered in two versions of the surfacemounted-package configuration as follows:

- Small-outline package (SOP)

- Plastic chip-carrier (PCC)

The small-outline package (SOP) will be offered in 16-, 20-, 24- and 28-lead versions with 50-mil lead centers; the plastic chip-carrier (PCC) will be offered as 28- or 44-lead packages with 50-mil lead centers.

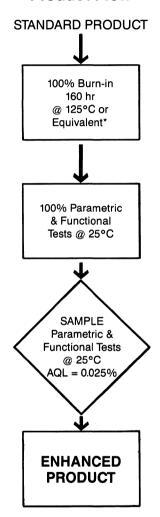

#### **Enhanced Product**

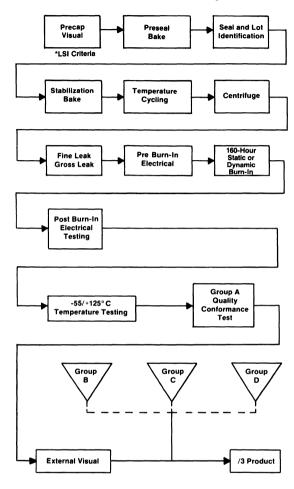

Most RCA memory/microprocessor parts are available with burn-in to enhance commercial reliability. This cost-effective approach is provided by the RCA Enhanced Product. Enhanced product is identified with the suffix "X", e.g., CDP1802ACEX.

<sup>\*</sup>Maximum Rating

# **Enhanced Product**

## **LSI Circuits**

| Burn-in Time*                                                                   | 160 Hours          |

|---------------------------------------------------------------------------------|--------------------|

| Temperature*                                                                    | 125°C              |

| Bias Voltage:<br>CDP1800 "C" Product<br>All Other<br>CDP1800 "Non-C"<br>Product | 7 V<br>6 V<br>11 V |

#### PRODUCT IDENTIFICATION

All enhanced product is identified by a suffix "x".

| Examples:  |             |

|------------|-------------|

| Standard   | Enhanced    |

| CDP1854ACE | CDP1854ACEX |

| CDP6805G2E | CDP6805G2EX |

<sup>\*</sup>Or equivalent means equivalent time-temperature/voltage resulting in the same activation energy.

#### **Product Flow**

# **Enhanced Product Application**

The need to achieve the enhanced reliability resulting from burn-in screening must be determined by careful analysis of system design and application.

How many IC's are incorporated into the total system? How many devices on each board?

Is the proper device being used for the application? What are the reliability goals?

What failure rates are being experienced without screening?

Cost-effectiveness of using enhanced CMOS can be determined by mutual analysis of the economic trade-offs made possible by the following features of the program:

- Available in both plastic and frit-seal ceramic packages.

- Offered on the industry's broadest line of circuit functions.

- 0.025% AQL cumulative.

- Reduction in PC board reworking through fewer line rejects.

- · Lower warranty requirements through the elimination of infant mortality failures.

- · Reduced incoming inspection cost by reduction or complete elimination of test procedures.

- · Reduction of system failures and related service expenses and customer complaints.

# **Enhanced Product Reliability Data**

FAILURE RATES IN PLASTIC DUAL-IN-LINE PACKAGES

|                     |                                |              |                        |                            | Failure                | Rate (FITs)*                  |

|---------------------|--------------------------------|--------------|------------------------|----------------------------|------------------------|-------------------------------|

| Product<br>Category | Device<br>Family               | Temp<br>(°C) | V <sub>DD</sub><br>(V) | Equivalent<br>Device Hrs.† | Standard<br>No Burn-In | Burn-In<br>(160 Hrs., 125°C)# |

| Memory/μP           |                                |              |                        |                            |                        |                               |

| C <sup>2</sup> L    | CDP1800                        | 85           | 7                      | $2.4 \times 10^{7}$        | 160                    | 67                            |

|                     | (RAM/ROM, I/O, $\mu$ P)        | 55           | 7                      | $4.6 \times 10^{8}$        | 8.3                    | 3.5                           |

| CMOSI               | CDP1800, CDP6805               | 85           | 6                      | $9.2 \times 10^{7}$        | 170                    | 71                            |

|                     | (RAM/ROM, $\mu$ COMP/ $\mu$ P) | 55           | 6                      | $1.8 \times 10^{9}$        | 8.8                    | 3.7                           |

| CMOS II             | ROMs Only                      | 85           | 6                      | $5.6 \times 10^{7}$        | 70                     | 29                            |

|                     | (64K, 128K, 256K)              | 55           | 6                      | $1.1 \times 10^9$          | 3.6                    | 1.5                           |

NOTES: \* FITs are the number of failures in 109 device hours. The failure rate is estimated at 60% upper confidence level. To convert the above data from FITs to %/1000 hours, multiply by 10-4.

† Equivalent device hours are extrapolated from accelerated test temperatures to the maximum 85°C rating and nominal use condition of 55°C, using a 1.0eV activation energy. Actual test temperatures ranged between 125°C-175°C.

#The difference in failure rate between standard and burned-in product is estimated from several sample studies.

# Operating and Handling Considerations RCA CMOS Integrated Circuits

This Note summarizes important operating recommendations and precautions which should be followed in the interest of maintaining the high standards of performance of solid-state devices.

The design flexibility provided by these devices makes possible their use in a broad range of applications and under many different operating conditions. When incorporating these devices in equipment, therefore, designers should anticipate the rare possibility of device failure and make certain that no safety hazard would result from such an occurrence.

#### **Absolute Maximum Ratings**

The published ratings of GE, RCA, and Intersil Solid-State Devices are based on the Absolute-Maximum Rating System, which is defined by the following Industry Standard (JEDEC) statement:

Absolute-Maximum Ratings are limiting values of operating and environmental conditions applicable to any electron device of a specified type as defined by its published data, and should not be exceeded under the worst probable conditions.

The device manufacturer chooses these values to provide acceptable serviceability of the device, taking no responsibility for equipment variations, environmental variations, and the effects of changes in operating conditions due to variations in device characteristics.

The equipment manufacturer should design so that initially and throughout life no absolute-maximum value for the intended service is exceeded with any device under the worst probable operating conditions with respect to supply voltage variation, equipment component variation, equipment control adjustment, load variation, signal variation, environmental conditions, and variations in device characteristics.

It is recommended that equipment manufacturers consult GE Solid State whenever device applications involve unusual electrical, mechanical or environmental operating conditions.

#### **GENERAL CONSIDERATIONS**

In general, with any application where devices are operated at voltages which may be dangerous to personnel, suitable precautionary measures should be taken to prevent direct contact with these devices.

The metal shells of some solid-state devices such as the TO-5-style package often used for integrated circuits usually has the substrate or most negative supply voltage connected to the case. Therefore, consideration should be given to the possibility of shock hazard if the shells are to operate at voltages appreciably above or below ground potential.

Devices should not be connected into or disconnected from circuits with the power on because high transient voltages may cause permanent damage to the devices.

In common with many electronic components, solid-state devices should be operated and tested in circuits which have reasonable values of current limiting resistance, or other forms of effective current overload protection. Failure to observe these precautions can cause excessive internal heating of the device and result in destruction and/or possible shattering of the enclosure.

The small size of most solid-state products provides obvious advantages to the designers of electronic equipment. However, it should be recognized that these compact devices

usually provide only relatively small insulation area between adjacent leads and the device package. When these devices are used in moist or contaminated atmospheres, therefore, supplemental protection must be provided to prevent the development of electrical conductive paths across the relatively small insulating surfaces.

#### Thermal Considerations

The maximum allowable power dissipation in a solid-state device is limited by the junction temperature. An important factor in assuring that the junction temperature remains below the specified maximum value is the ability of the associated thermal circuit to conduct heat away from the device.

When a solid-state device is operated in free air, without a heat sink, the steady-state thermal circuit is defined by the junction-to-free-air thermal resistance given in the published data for the device. Thermal considerations require that a free flow of air around the device is always present and that the power dissipation be maintained below the level which would cause the junction temperature to rise above the maximum rating at the worst-case ambient temperature.

#### **Electrostatic Voltage Discharge Considerations**

Electrostatic voltage discharge of sufficient energy can damage any solid-state device. These electrical potentials can be significantly reduced during handling or testing by following industry-accepted practices such as those used by GE Solid State. These include:

- properly grounded equipment, workstations, operators and handlers

- the use of air ionizers

- · control of ambient humidity

- device storage and transportation in a charge-dissipative medium such as "Eccosorb® LD26" or equivalent.

#### Mountina

Integrated circuits are normally supplied with tin-lead dipped leads to facilitate soldering into circuit boards.

When integrated circuits are welded onto printed-circuit boards or equipment, the presence of moisture between the closely spaced terminals can result in conductive paths that may impair device performance in high-impedance applications. It is therefore recommended that conformal coatings or potting be provided as an added measure of protection against moisture penetration.

In any method of mounting integrated circuits which involves bending or forming of the device leads, it is extremely important that the lead be supported and clamped between the bend and the package seal, and that bending be done with care to avoid damage to lead plating. In no case should the radius of the bend be less than the diameter of the lead, or in the case of rectangular leads, such as those used in RCA 14-lead and 16-lead flat-packages, less than the lead thickness. When solder-dipped leads are formed, they must be reflowed or redipped within 40 mils of the package body. It is also extremely important that the ends of the bent leads be straight to assure proper insertion through the holes in the printed-circuit board.

Many GE/RCA/Intersil semiconductor products are available in surface-mounted packages which enable the user to mount these devices directly on the surface of a circuit board. Unlike conventional dual-in-line (DIP) leaded packages which require through-holes for insertion, surface-mounted packages are soldered to a series of pads on a

•Trade Name: Emerson and Cumming, Inc.

# **Operating and Handling Considerations**

circuit board using a variety of acceptable techniques such as vapor phase or infrared reflow. This series of pads, commonly called a footprint, matches the lead or contact outline of the package(s) being used.

#### **Recommended Lead-Forming Practices**

#### **DIC Packages**

The leads on dual-in-line CERDIP or dual-in-line side-brazed packages are not intended to be bent or formed No further lead-forming is recommended.

#### Flat Packages

Flat packages including quad flat-packages are provided to users with the leads in a horizontal plane.

Since users form leads into many configurations, these relatively thin-leaded devices require a certain amount of care to avoid any handling which would affect the suitability of these leads

Taking guidance from MIL-STD 4544, the following is recommended when bending leads:

- a) the bend radius must exceed twice the lead thickness.

- Always start the bending 0.015 inches or more away from the device body to protect body-to-lead adherence, and body hermeticity.

- bend leads 85-degrees maximum to provide a strong fixed position condition.

- d) use roller-type die when forming gold-plated leads to minimize surface scouring.

- e) provide a minimum surface contact length of 2 times the lead width.

- f) leads should be cleaned of any bending tool lubricants to enhance solderability.

#### **Cleaning After Mounting**

A wide variety of chemicals and solvents is available for fluxing, degreasing, and flux removal. Care must be exercised in the selection of materials, such that from a reliability standpoint, there is no adverse effect on component life. A major contributor affecting device reliablity, is the chemical reaction of chloride with the aluminum metallization of the die. Eventually this etching process will result in electrical open circuits. The mechanism is defined as Electrolytic Metal Attack (EMA) and is accelerated in a mositure environment. Cleaning and fluxing compounds free of chloride will therefore maximize device life. Chloride is defined as the dissociated ion, which is soluble in water, as contrasted to the water insoluble organic chlorine of compounds such as perchloroethylene and trichloroethane. It is, of course, impractical to evaluate the long-term effect on semiconductor life of all chemicals which are marketed under a variety of brand names.

The choice of fluxes for electronic applications should be restricted to rosin types, R, RMA and RA and water soluble organic acid, OA, formulations. Inorganic acid fluxes should not be used as they can attack the internal metallization of the semiconductor. As stated above, it is further recommended, where applicable, that non-halide type fluxes be used for improved device reliability. Some examples of acceptable fluxes are:

A. Rosin Types (RA)

Alpha 711

Alpha 809 foam flux

Alpha 811 foam flux

Alpha 815 foam flux

Alpha TL33M halide free

Water soluble organic acid (OA) types, halide free Blackstone 1452 Kenco 183

Alpha 260HF and 265HF

Since circuit boards can fall into several categories, such as single sided, double sided with plated-through holes and densely populated multilayer types, it must be stressed that the manufacturer's recommendation be considered when choosing the proper flux for the process being used.

Flux cleaning and/or degreasing is necessary to assure that the final soldered assembly is free of contaminating soils. The choice of the cleaning system is relative to the soil being removed. Water-based cleaners are generally used to remove polar soils, such as rosin activators, organic acid residues, and finger salts. Solvent cleaners are chosen for removal of organic (non-polar) contaminants, which include rosins, oils, and greases. Cleaning methods can incorporate immersion (with or without ultrasonics), brushing, and spraying. The choice of cleaner should be based on affinity for the contaminant, ability to thoroughly wet the parts, and compatibility with components. It should also be safe to use.

Solvent cleaners are generally divided into two classes: chlorinated and fluorinated. These can be used for cleaning rosin-activated (RA) fluxes. The chlorinated solvents are more aggressive and care must be taken to assure there is no damage to components or substrate. This type solvent should not be used with silicone-encapsulated transistors as the solvent will tend to dissolve the plastic. The use of chlorinated solvents must be closely monitored because a breakdown to form acid components in the presence of moisture. The solvent should be checked regularly and discarded when acid levels exceed manufacturer's guidelines. Fluorinated solvents are normally blends of trifluorotrichloroethane with other solvents, such as: methanol, ethanol, isopropanol, acetone, methylene chloride, or chloroform. These solvents can be purchased under trade names as Freon TE, TE35, TP35, Frigen 113 TR-M, Haltron 113 MOM, and Flugene 113 MA. Fluorinated systems are milder acting and are used in vapor degreasing systems at the boiling point of the solvent mixture.

The solvents may be used for a maximum of 4 hours at 25°C or for a maximum of 1 hour at 50°C.

Rosin fluxes can be removed by either solvent or aqueous cleaners. The water systems contain an additive that reacts with the rosin acids to convert the acids to a water-soluble biodegradable soap. Water-soluble organic-acid fluxes may require the use of a neutralizer to accelerate the solubility of the acid residues and neutralize any residues that may remain. Alcohols are acceptable solvents for rosin-based flux removal; but because of flammability concerns, the fluorinated alcohol blends are preferred. Examples of suitable alcohols are methanol, isopropanol, and special denatured ethyl alcohols, such as SDA1, SDA30, SDA34, and SDA44.

If the completed assembly is to be encapsulated, the effect on the molded-plastic transistor must be studied from both a chemical and physical standpoint.

#### Handling

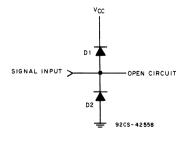

All CMOS gate inputs have a diode or resistor/diode gate protection network. All transmission gate inputs and all outputs have diode protection provided by inherent p-n

# **Operating and Handling Considerations**

junction diodes. These diode networks at input and output interface protect CMOS devices from gate-oxide failure in handling environments where static discharge is not excessive. In low-temperature, low-humidity environments, improper handling may result in device damage. It is recommended that ionizers be used in the handling and assembly areas to minimize damage from electrostatic discharge (ESD). See ICAN-6525, "Handling and Operating Considerations for MOS Integrated Circuits", for proper handling preedures.

#### Operating

#### **Unused Inputs**

All unused input leads must be connected to either the low rail ( $V_{SS}$ ,  $V_{EE}$ , or GND) or the high rail ( $V_{CC}$  or  $V_{DD}$ ), whichever is appropriate for the logic circuit involved. A floating input not only can result in faulty logic operation, but can cause the maximum-rated power dissipation to be exceeded and may result in damage to the device. Inputs to these types, which are mounted on printed-circuit boards that may temporarily become unterminated, should have a resistor to the high or low voltage supply rails A useful range of values for such resistors is from 10 kilohms to 1 megohm. Pins that are I/O must have a terminating resistor.

#### **Input Signals**

Signals shall not be applied to the inputs while the device power supply is off unless the input current is limited to a steady-state value of less than the absolute-maximum rating. Input currents of less than the maximum rating prevent device damage; however, proper operation may be impaired as a result of current flow through structural diode junctions.

#### **Output Short Circuits**

Shorting of outputs to the high or low supply rail can damage many of the higher-output-current CMOS types, such as the CD4007, CD4041, CD4049, and CD4050. In general, these types can all be safely shorted for supplies up to 5 volts, but will be damaged (depending on type) at higher power-supply voltages. For the CMOS HC/HCT/HCU types, outputs may be shorted to  $V_{\rm CC}$  (5 V  $\pm$  10%) for 1 second maximum and only one output at a time. For cases in which a short-circuit load, such as the base of a p-n-p or an n-p-n bipolar transistor, is directly driven, the device output characteristics given in the published data should be consulted to determine the requirements for a safe operation below the device maximum-rated output power.

For detailed CMOS IC operating and handling considerations, refer to Application Note ICAN-6525 "Handling and Operating Considerations for MOS Integrated Circuits."

#### **CMOS Power-Supply Distribution and Decoupling**

Power distribution should be a prime consideration in all

CMOS designs. Although DC power dissipation is very low, dynamic power (due to switching transients) can be high. High-voltage and/or low-temperature operation increase dynamic current transients.

A low-impedance power source and supply-to-ground capacitance bypass will significantly reduce noise generation on signal and power line to greatly enhance system reliability.

#### Decoupling

Higher speeds, faster edges and higher output-drive currents cause higher-frequency current transients to be imposed on ground and  $V_{\rm CC}$  rails of an IC. For LSI and high-speed families, consideration of power-supply distribution and decoupling become important. Before decoupling can be utilized for noise reduction, there must first be a good power-supply distribution network. A good ground connection system and capacitive decoupling must be employed. For details refer to Application Note ICAN-7329, "Power-Supply Distribution and Decoupling for CMOS High-Speed-Logic ICs."

#### **SOLID-STATE CHIPS**

When supplied in individual die form, solid-state chips, unlike packaged devices, are normally fragile and small in physical size, and therefore, require special-handling as follows:

- Chips must be stored under proper conditions to ensure that they are not subjected to a moist and/or contaminated atmosphere that could alter their electrical, physical, or mechanical characteristics. After the shipping container is opened, the chip must be stored under the following conditions:

- A. Storage temperature, 40°C

- B. Relative humidity, 50% max.

- C. Clean, dust-free environment

- The user must exercise proper care when handling chips to prevent even the slightest physical damage to the chip.

- The procedures used to reduce the possibility of electrostatic discharge in packaged devices also apply for solidstate chips.

- During mounting and lead bonding of chips, the user must use proper assembly techniques to obtain proper electrical, thermal, and mechanical performance.

- 5. After the chip has been mounted and bonded, any necessary procedure must be followed by the user to ensure that these non-hermetic chips are not subjected to moist or contaminated atmospheres which might cause the development of electrical conductive paths across the relatively small insulating surfaces. In addition, proper consideration must be given to the protection of these devices from other harmful environments which could conceivably adversely affect their proper performance.

# 1800-Series Microprocessors and Microcomputers

**Technical Data**

# Comparison of RCA CMOS CDP1800-Series Microprocessors and Microcomputers

| Features                                 | CDP1802A<br>CDP1802AC | CDP1802BC CDP1804AC |                   | CDP1805AC       | CDP1806AC       |  |  |  |

|------------------------------------------|-----------------------|---------------------|-------------------|-----------------|-----------------|--|--|--|

| Memory<br>Addressing (Bytes)             | 64k                   | 64k                 | 64k 64k           |                 | 64k             |  |  |  |

| On-Chip RAM (Bytes)                      | _                     | _                   | 64k               | 64k             | _               |  |  |  |

| On-chip ROM (Bytes)                      | _                     | _                   | 2k                | _               | _               |  |  |  |

| Max. Clock<br>Frequency (MHz)            | 3.2                   | 5                   | 5 5               |                 | 5               |  |  |  |

| nstruction Time 5/7.5 3                  |                       | 3.2/4.8             | 3.2/4.8 3.2/16    |                 | 3.2/16          |  |  |  |

| Timer/Counter Bits                       | _                     | _                   | _ 8               |                 | 8               |  |  |  |

| Prescalers                               | _                     | _                   | - ÷ 32            |                 | ÷ 32            |  |  |  |

| Bus Structure                            |                       | Non-m               | ultiplexed Addres | s Lines         |                 |  |  |  |

| Interrupts                               | <b>√</b>              | √                   | <b>√</b>          | √ √             | <b>√</b>        |  |  |  |

| Latched I/O Lines                        |                       |                     | Off-Chip          | •               |                 |  |  |  |

| Max. Operating Temp.<br>Temp. Range (°C) |                       |                     |                   |                 |                 |  |  |  |

| Package<br>No. of Pins                   | 40 D, E<br>44 Q       | 40 D, E<br>44 Q     | 40 D, E<br>—      | 40 D, E<br>44 Q | 40 D, E<br>44 Q |  |  |  |

| Serial Interface                         |                       | Q-Line              |                   |                 |                 |  |  |  |

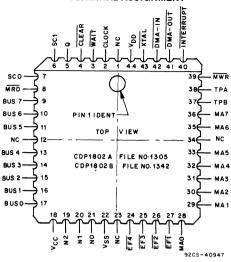

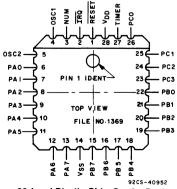

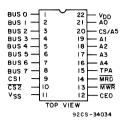

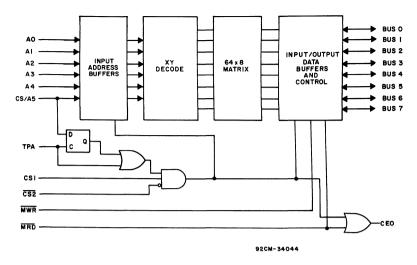

#### TERMINAL ASSIGNMENT

# **CMOS 8-Bit Microprocessor**

Features:

- Minimum instruction fetch-execute time of 5 μs or 7.5 μs at V<sub>DD</sub> = 5 V; 2.5 μs or 3.75 μs at V<sub>DD</sub> = 10 V

- Any combination of standard RAM and ROM up to 65,536 bytes

- Operates with slow memories, up to 1 µs access time at f<sub>CL</sub> = 4 MHz

- 8-bit parallel organization with bidirectional data bus and multiplexed address bus

- 16 x 16 matrix of registers for use as multiple program counters, data pointers, or data registers

- On-chip DMA, interrupt, and flag inputs

- Programmable single-bit output port

- 91 easy-to-use instructions

The RCA-CDP1802A LSI CMOS 8-bit register-oriented central-processing unit (CPU) is designed for use as a general-purpose computing or control element in a wide range of stored-program systems or products.

The CDP1802A includes all of the circuits required for fetching, interpreting, and executing instructions which have been stored in standard types of memories. Extensive input/output (I/O) control features are also provided to facilitate system design.

The 1800 series architecture is designed with emphasis on the total microcomputer system as an integral entity so that systems having maximum flexibility and minimum cost can be realized. The 1800 series CPU also provides a synchronous interface to memories and external controllers for I/O devices, and minimizes the cost of interface controllers. Further, the I/O interface is capable of supporting

devices operating in polled, interrupt-driven, or direct memory-access modes.

The CDP1802A and CDP1802AC are functionally identical. They differ in that the CDP1802A has a recommended operating voltage range of 4 to 10.5 volts, and the CDP1802AC a recommended operating voltage range of 4 to 6.5 volts.

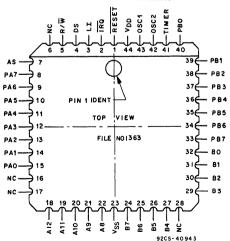

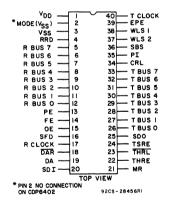

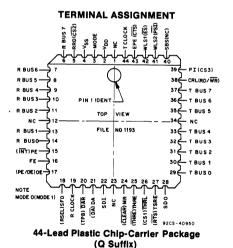

These types are supplied in 40-lead dual-in-line side-brazed ceramic packages (D suffix), 40-lead dual-in-line plastic packages (E suffix) and 44-lead plastic chip-carrier (PCC) package (Q suffix). The CDP1802AC is also available in chip form (H suffix).

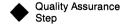

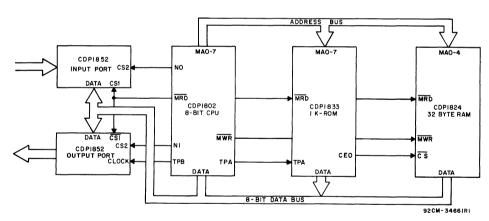

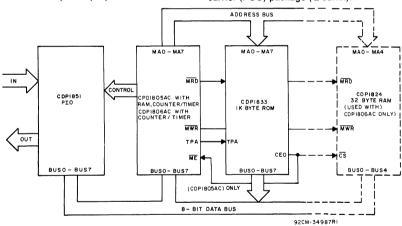

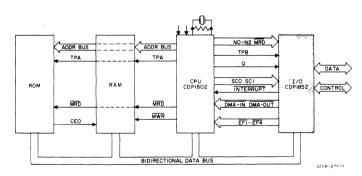

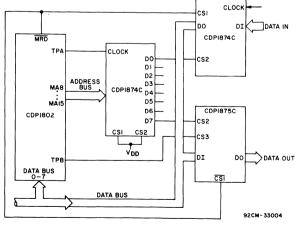

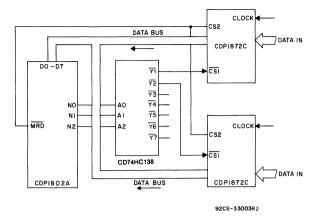

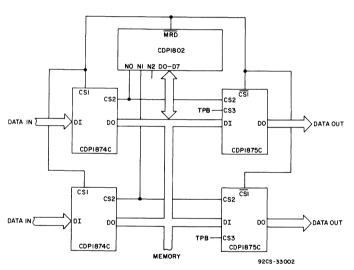

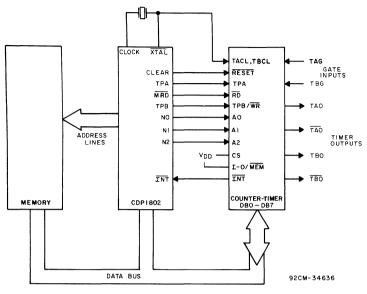

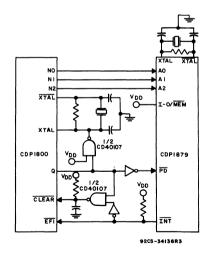

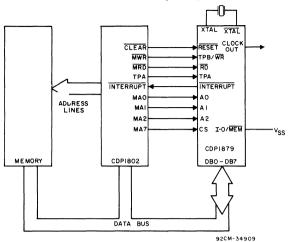

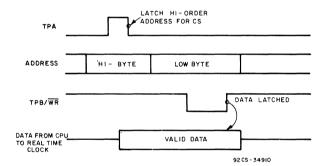

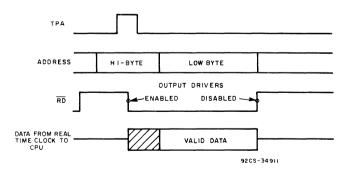

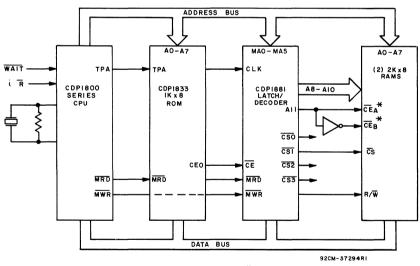

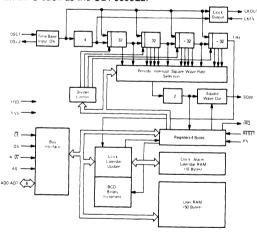

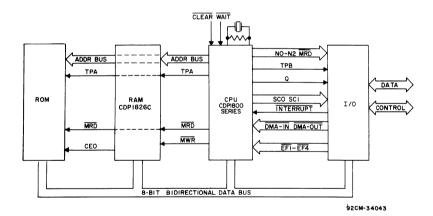

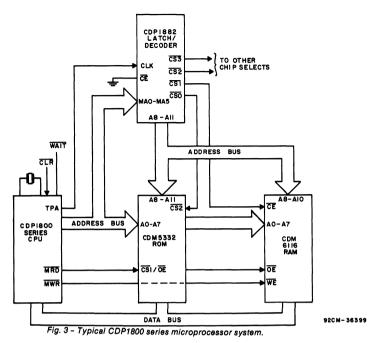

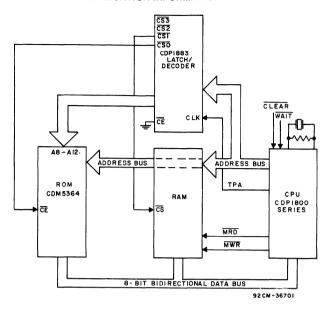

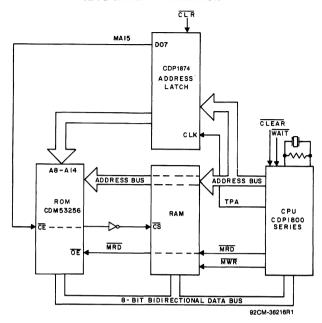

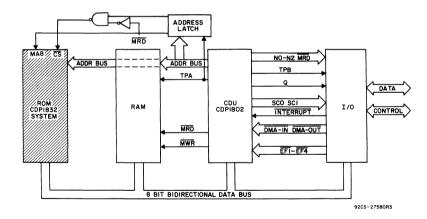

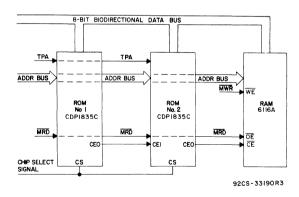

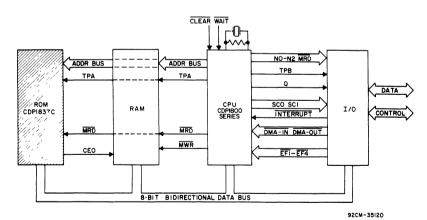

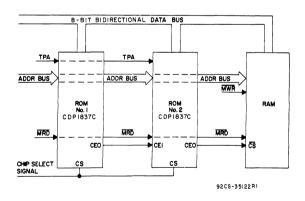

Fig. 1 - Typical CDP1802A small microprocessor system.

#### MAXIMUM RATINGS, Absolute-Maximum Values:

| DC SUPPLY-VOLTAGE RANGE, (V <sub>DD</sub> ).                                   |                                       |

|--------------------------------------------------------------------------------|---------------------------------------|

| (All voltages referenced to V <sub>SS</sub> terminal)                          |                                       |

| CDP1802A                                                                       | 0.5 to +11 V                          |

| CDP1802AC                                                                      | 0.5 to +7 V                           |

| INPUT VOLTAGE RANGE, ALL INPUTS                                                | 0.5 to V <sub>DD</sub> +0.5 V         |

| DC INPUT CURRENT, ANY ONE INPUT                                                | ±10 mA                                |

| POWER DISSIPATION PER PACKAGE (PD):                                            |                                       |

| For TA=-40 to +60°C (PACKAGE TYPE E)                                           | 500 mW                                |

| For T <sub>A</sub> =+60 to +85°C (PACKAGE TYPE E)                              | Derate Linearly at 12 mW/°C to 200 mW |

| For T <sub>A</sub> =-55 to +100°C (PACKAGE TYPE D)                             | 500 mW                                |

| For T <sub>A</sub> =+100 to +125°C (PACKAGE TYPE D)                            |                                       |

| For T <sub>A</sub> = -40°C to +85°C (PACKAGE TYPE Q) *                         |                                       |

| DEVICE DISSIPATION PER OUTPUT TRANSISTOR                                       |                                       |

| FOR TA=FULL PACKAGE-TEMPERATURE RANGE                                          | 100 mW                                |

| OPERATING-TEMPERATURE RANGE (TA)                                               |                                       |

| PACKAGE TYPE D                                                                 | 55 to +125°C                          |

| PACKAGE TYPE E and Q                                                           | 40 to +85°C                           |

| STORAGE TEMPERATURE RANGE (Tstg)                                               | 65 to +150°C                          |

| LEAD TEMPERATURE (DURING SOLDERING):                                           |                                       |

| At distance $1/16\pm1/32$ in $(1.59\pm0.79 \text{ mm})$ from case for 10 s max | +265°C                                |

<sup>\*</sup> Printed-circuit board mount: 57 mm x 57 mm minimum area x 1.6 mm thick G10 epoxy glass, or equivalent.

#### OPERATING CONDITIONS at TA=-40°C to +85°C

For maximum reliability, operating conditions should be selected so that operation is always within the following ranges:

|                                                                       | COND              | TIONS           |      |                 |      |                 |        |

|-----------------------------------------------------------------------|-------------------|-----------------|------|-----------------|------|-----------------|--------|

| CHARACTERISTIC                                                        | V <sub>CC</sub> 1 | V <sub>DD</sub> | CDP  | 1802A           | CDP1 | UNITS           |        |

|                                                                       | (V)               | (V)             | Min. | Max.            | Min. | Max.            |        |

| DC Operating Voltage<br>Range                                         | _                 | _               | 4    | 10.5            | 4    | 6.5             | V      |

| Input Voltage Range                                                   | _                 | _               | VSS  | V <sub>DD</sub> | Vss  | V <sub>DD</sub> | •      |

| Maximum Clock Input Rise or Fall Time, t <sub>r</sub> ,t <sub>f</sub> | 4 to 10.5         | 4 to 10.5       | _    | 1               | _    | 1               |        |

|                                                                       | 5                 | 5               | 5    | _               | 5    | _               |        |

| Minimum Instruction Time2                                             | 5                 | 10              | 4    | _               | _    | -               | μs     |

|                                                                       | 10                | 10              | 2.5  | _               | _    | _               |        |

| 14 ·                                                                  | 5                 | 5               | _    | 400             | _    | 400             | KBytes |

| Maximum DMA Transfer                                                  | 5                 | 10              | _    | 500             | _    | _               | per    |

| Rate                                                                  | 10                | 10              |      | 800             | _    | _               | second |

| Maximum Clock Input                                                   | 5                 | 5               | DC   | 3.2             | DC   | 3.2             |        |

| Frequency, f <sub>CL</sub> , Load                                     | 5                 | 10              | DC   | 4               |      |                 | MHz    |

| Capacitance (C <sub>L</sub> )=50 pF                                   | 10                | 10              | DC   | 6.4             | _    | <del>-</del>    |        |

<sup>1</sup>V<sub>CC</sub> must never exceed V<sub>DD</sub>.

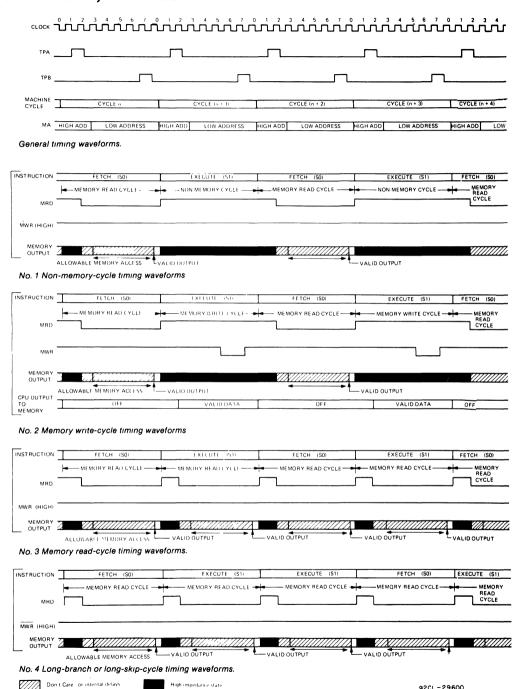

<sup>2</sup>Equals 2 machine cycles—one Fetch and one Execute operation for all instructions except Long Branch and Long Skip, which require 3 machine cycles—one Fetch and two Execute operations

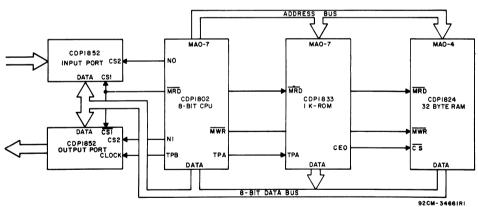

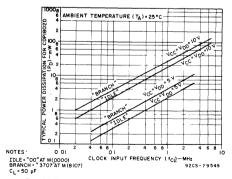

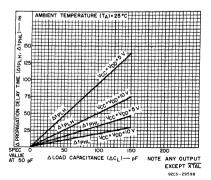

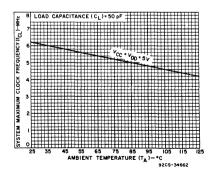

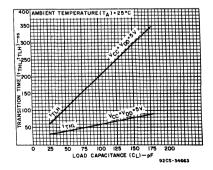

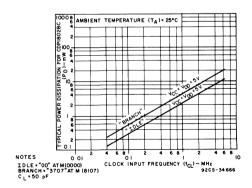

Fig. 2 - Typical maximum clock frequency as a function of temperature.

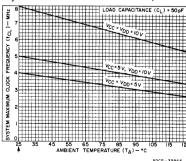

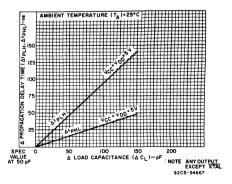

Fig. 3 - Typical transition time vs. load capacitance.

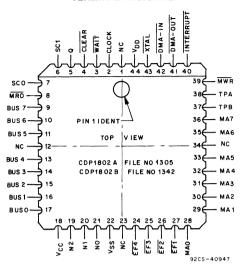

#### **TERMINAL ASSIGNMENT**

Plastic Chip-Carrier (PCC) Package

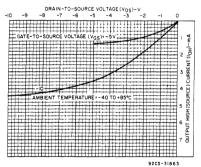

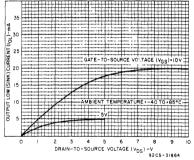

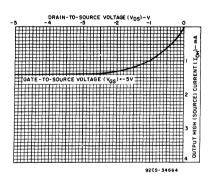

Fig. 4 · Minimum output high (source) current characteristics.

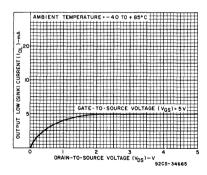

Fig. 5 - Minimum output low (sink) current characteristics.

Fig. 6 - Typical power dissipation as a function of clock frequency for BRANCH instruction and IDLE instruction

Fig 7 - Typical change in propagation delay as a function of a change in load capacitance.

STATIC ELECTRICAL CHARACTERISTICS at TA=-40 to +85° C, except as noted.

| OTATIO ELECTRICAL OF      |                 |          | ONDITION               | NS LIMITS         |       |          |           |           |       |          |       |

|---------------------------|-----------------|----------|------------------------|-------------------|-------|----------|-----------|-----------|-------|----------|-------|

| CHARACTERISTI             | С               | VOUT     | VIN                    | V <sub>CC</sub> , |       | DP1802/  | 4         | CDP1802AC |       |          | UNITS |

|                           |                 | (V)      | (V)                    | (V)               | Min.  | Typ.•    | Max.      | Min.      | Typ.  | Max.     |       |

| Quiescent Device Current  | IDD             | _        | _                      | 5<br>10           | _     | 0 1<br>1 | 50<br>200 | _         | 1     | 200<br>— | μΑ    |

| Output Low Drive (Sink)   |                 |          |                        |                   |       |          |           |           |       |          |       |

| Current                   | loL             | 0.4      | 0,5                    | 5                 | 1.1   | 2.2      | l –       | 1.1       | 2.2   | _        | mA    |

| (Except XTAL)             |                 | 0.5      | 0,10                   | 10                | 22    | 4.4      | _         | _         |       | _        | mA    |

| XTAL                      | lOL             | 0.4      | 5                      | 5                 | 170   | 350      | _         | 170       | 350   |          | μΑ    |

| Output High Drive (Source | :e)             |          |                        |                   |       |          |           |           |       |          |       |

| Current                   | ЮН              | 4.6      | 0,5                    | 5                 | -0 27 | -0 55    | _         | -0.27     | -0.55 |          | ^     |

| (Except XTAL)             |                 | 9.5      | 0,10                   | 10                | -0 55 | -1.1     |           |           |       |          | mA    |

| XTAL                      | ЮН              | 4.6      | 0                      | 5                 | -125  | -250     | _         | -125      | -250  | _        | μΑ    |

| Output Voltage            |                 | _        | 0,5                    | 5                 |       | 0        | 0.1       | _         | 0     | 0.1      |       |

| Low-Level                 | V <sub>OL</sub> | _        | 0,10                   | 10                |       | 0        | 0.1       | _         |       |          |       |

| Output Voltage            |                 | _        | 0,5                    | 5                 | 49    | 5        | _         | 4.9       | 5     | _        |       |

| High Level                | ۷он             | _        | 0,10                   | 10                | 9.9   | 10       | l –       | _         | _     | _        |       |

| Input Low Voltage         | VIL             | 0.5,4.5  | _                      | 5                 |       | _        | 1.5       | _         | _     | 1.5      |       |

|                           |                 | 0.5, 4.5 | _                      | 5,10              | _     | _        | 1         | <b>—</b>  |       |          | İ     |

|                           |                 | 1,9      | _                      | 10                |       | _        | 3         | _         |       | _        | V     |

| Input High Voltage        | $v_{IH}$        | 0.5,4.5  |                        | 5                 | 3.5   | _        | _         | 3.5       | _     | _        | Ì     |

|                           |                 | 0.5,4.5  | _                      | 5,10              | 4     |          |           | _         |       | _        |       |

|                           |                 | 1,9      |                        | 10                | 7     |          |           |           |       |          |       |

| CLEAR Input Voltage       | ٧н              |          |                        | 5                 | 0.4   | 0.5      |           | 0.4       | 0.5   |          |       |

| Schmitt Hysteresis        |                 |          |                        | 5,10              | 0.3   | 0.4      |           | _         |       |          |       |

|                           |                 |          |                        | 10                | 1.5   | 2        |           |           |       | _        |       |

| Input Leakage Current     | <sup>I</sup> IN | Any      | 0,5                    | 5                 |       | ±10-4    | ±1        | L –       | ±10-4 | ±1       |       |

| Input Loukago Gurrent     | 'IIN            | Input    | 0,10                   | 10                |       | ±10-4    | ±1        |           |       |          | μΑ    |

| 3-State Output Leakage    |                 | 0,5      | 0,5                    | 5                 |       | ±10-4    | ±1        | _         | ±10-4 | ±1       | "'    |

|                           | OUT             | 0,10     | 0,10                   | 10                |       | ±10-4    | ±1        | _         |       |          |       |

|                           | D1 <sup>Δ</sup> |          |                        |                   |       |          |           |           |       |          |       |

| f=3.2                     | MHz             |          | L                      | 5                 |       | 2        | 4         |           | 2     | 4        | mA    |

| Minimum Data Retention    |                 |          |                        |                   |       |          |           |           |       |          |       |

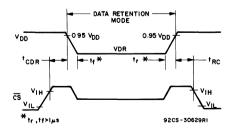

|                           | VDR             |          | $V_{DD}=V_{DR}$        |                   |       | 2        | 2.4       |           | 2     | 2.4      | V     |

| Data Retention Current    | <sup>I</sup> DR |          | V <sub>DD</sub> =2.4 V |                   | _     | 0.05     |           | _         | 0.5   |          | μΑ    |

| Input Capacitance         | CIN             |          |                        |                   | _     | 5        | 7.5       | _         | 5     | 7.5      | pF    |

| Output Capacitance C      | OUT             |          |                        |                   |       | 10       | 15        | -         | 10    | 15       | "     |

<sup>\*</sup>Typical values are for TA=25°C and nominal VDD

$\Delta$ Idle "00" at M(0000), C<sub>L</sub>=50 pF.

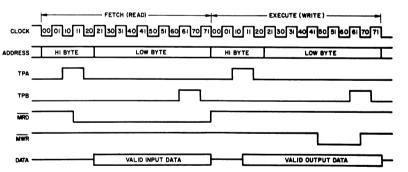

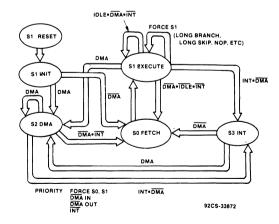

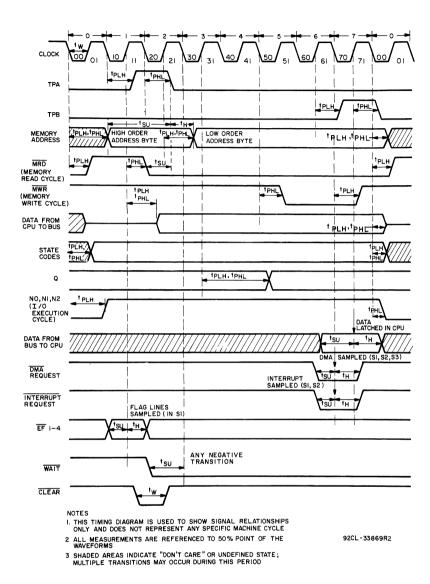

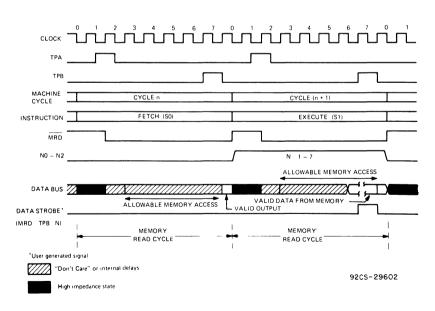

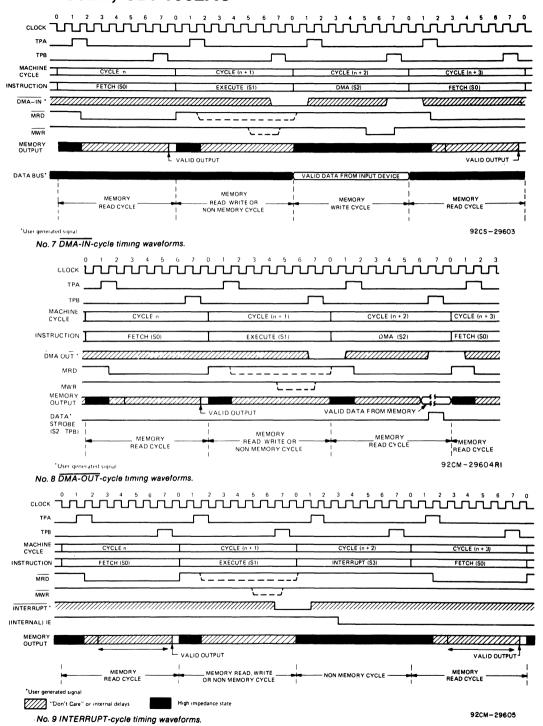

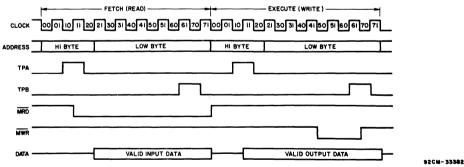

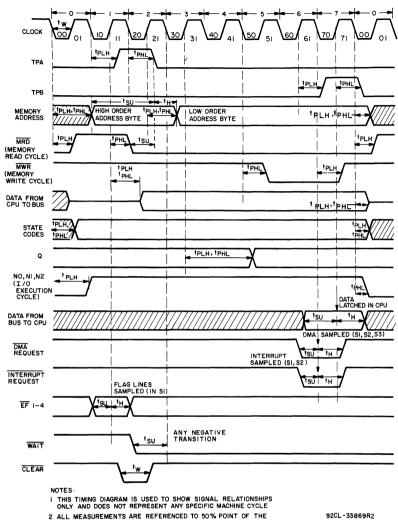

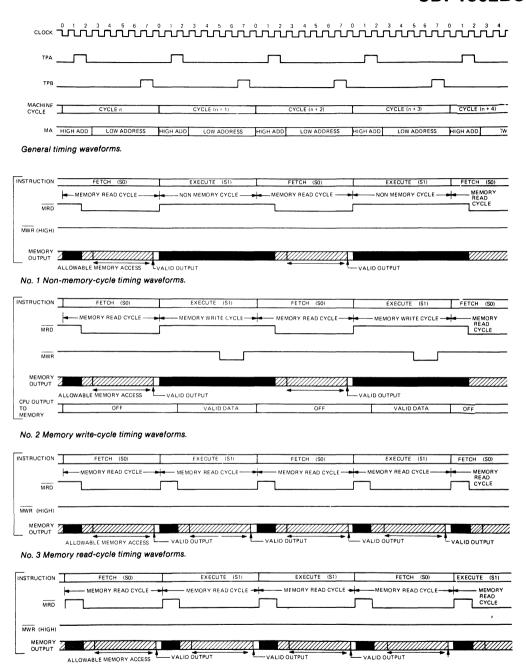

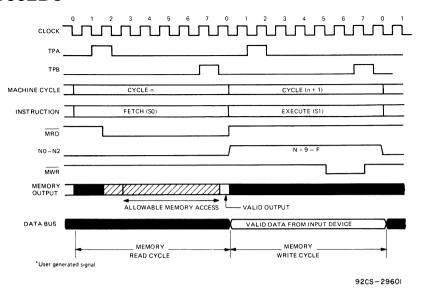

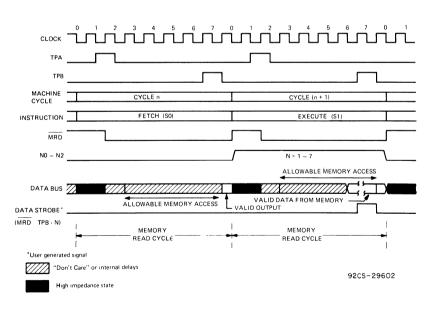

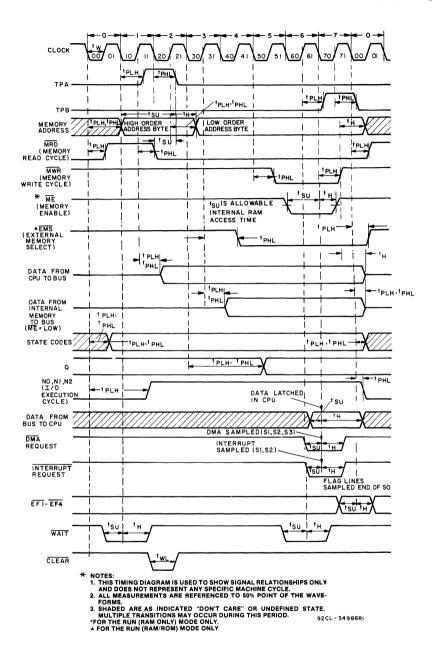

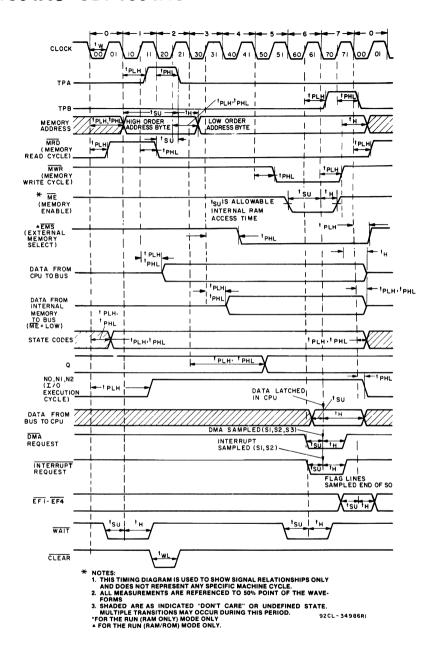

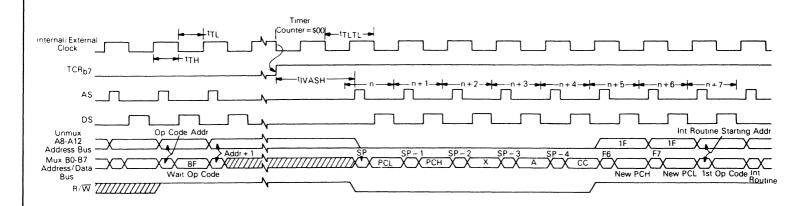

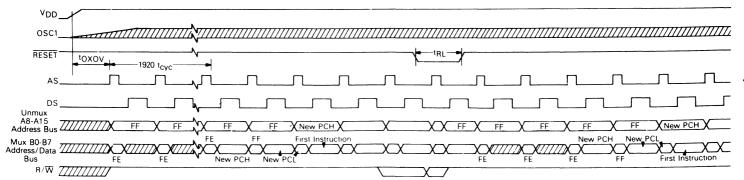

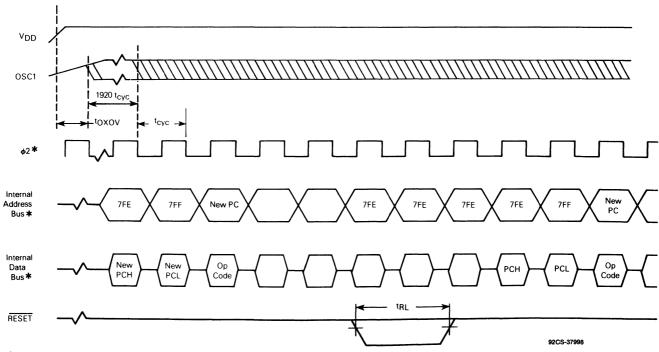

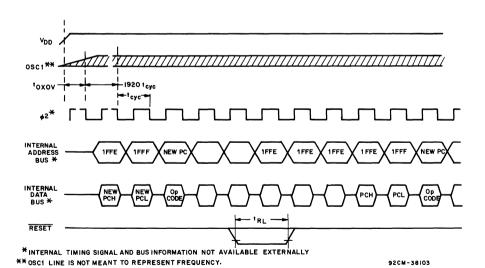

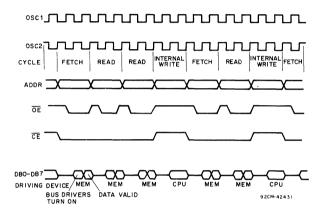

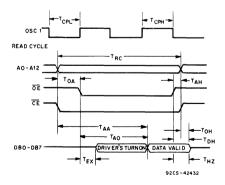

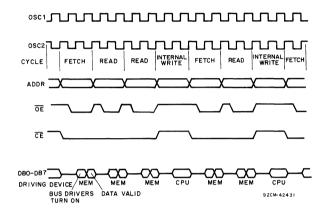

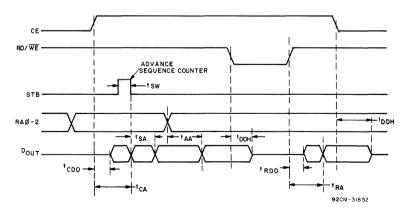

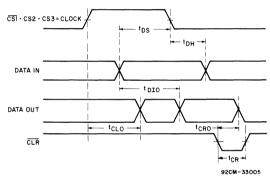

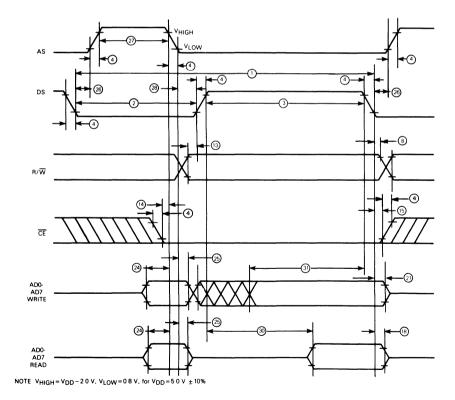

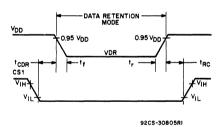

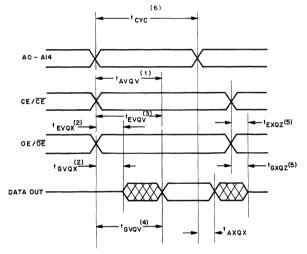

Fig. 9 - Basic dc timing waveforms, one instruction cycle.

#### SIGNAL DESCRIPTIONS

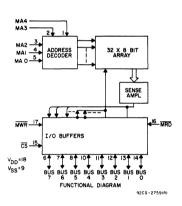

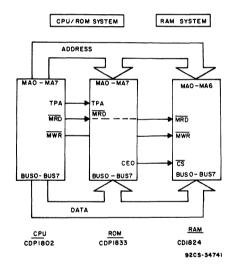

#### BUS 0 to BUS 7 (Data Bus):

8-bit bidirectional DATA BUS lines. These lines are used for transferring data between the memory, the microprocessor, and I/O devices.

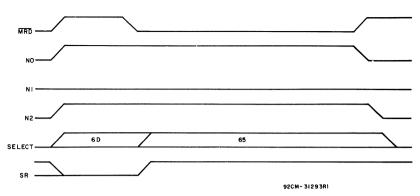

#### N0 to N2 (I/O) Lines):

Activated by an I/O instruction to signal the I/O control logic of a data transfer between memory and I/O interface. These lines can be used to issue command codes or device selection codes to the I/O devices (independently or combined with the memory byte on the data bus when an I/O instruction is being executed). The N bits are low at all times except when an I/O instruction is being executed. During this time their state is the same as the corresponding bits in the N register.

The direction of data flow is defined in the I/O instruction by bit N3 (internally) and is indicated by the level of the MRD signal.

MRD=V<sub>CC</sub>: Data from I/O to CPU and Memory

MRD=VSS: Data from Memory to I/O

#### EF1 to EF4 (4 Flags):

These inputs enable the I/O controllers to transfer status information to the processor. The levels can be tested by the conditional branch instructions. They can be used in conjunction with the INTERRUPT request line to establish interrupt priorities. These flags can also be used by I/O devices to "call the attention" of the processor, in which case the program must routinely test the status of these flag(s). The flag(s) are sampled at the beginning of every \$1 cycle.

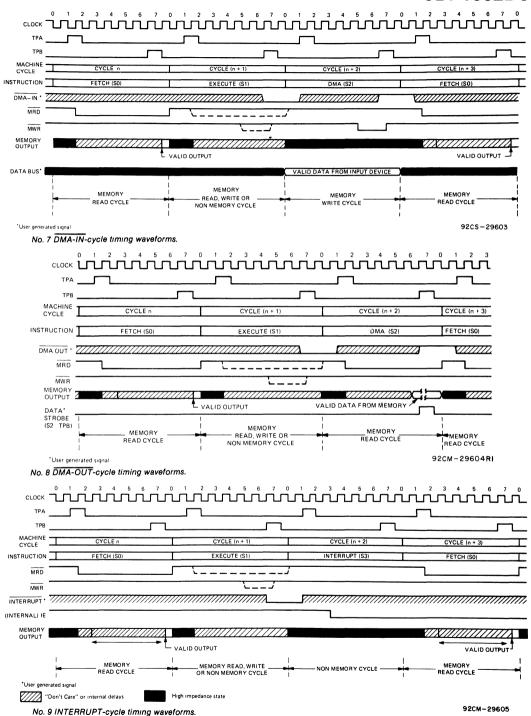

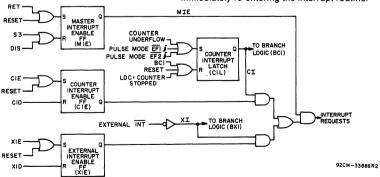

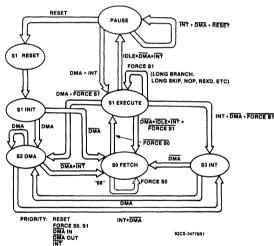

#### INTERRUPT, DMA-IN, DMA-OUT (3 I/O Requests)

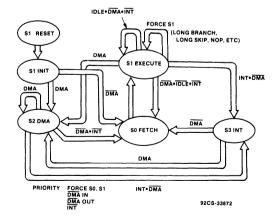

These inputs are sampled by the CDP1802A during the interval between the leading edge of TPB and the leading edge of TPA.

Interrupt Action: X and P are stored in T after executing current instruction; designator X is set to 2; designator P is set to 1; interrupt enable is reset to 0 (inhibit); and instruction execution is resumed. The interrupt action requires one machine cycle (S3).

**DMA Action:** Finish executing current instruction; R(0) points to memory area for data transfer; data is loaded into or read out of memory; and increment R(0).

Note: In the event of concurrent DMA and Interrupt requests, DMA-IN has priority followed by DMA-OUT and then Interrupt.

#### SC0, SC1, (2 State Code Lines):

These outputs indicate that the CPU is: 1) fetching an instruction, or 2) executing an instruction, or 3) processing a DMA request, or 4) acknowledging an interrupt request. The levels of state code are tabulated below. All states are valid at TPA. H=VCC, L=VSS.

| 0              | State Code Lines |     |  |  |  |

|----------------|------------------|-----|--|--|--|

| State Type     | SC1              | SC0 |  |  |  |

| S0 (Fetch)     | L.               | L   |  |  |  |

| S1 (Execute)   | L                | Н   |  |  |  |

| S2 (DMA)       | Н                | L   |  |  |  |

| S3 (Interrupt) | Н                | Н   |  |  |  |

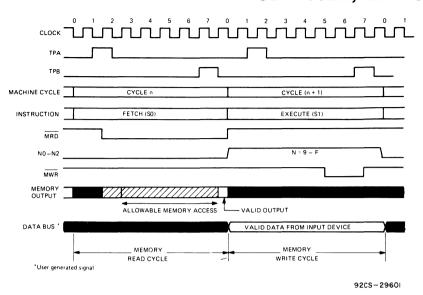

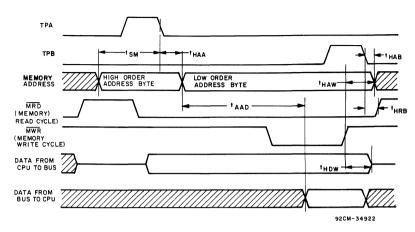

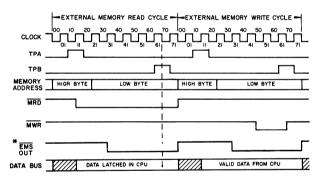

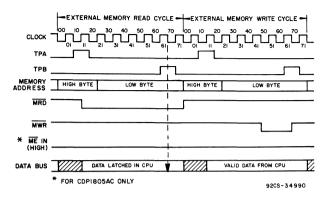

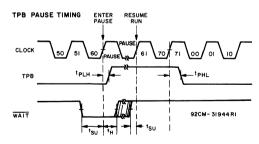

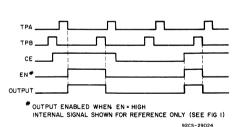

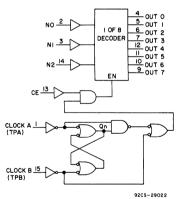

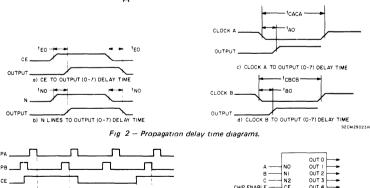

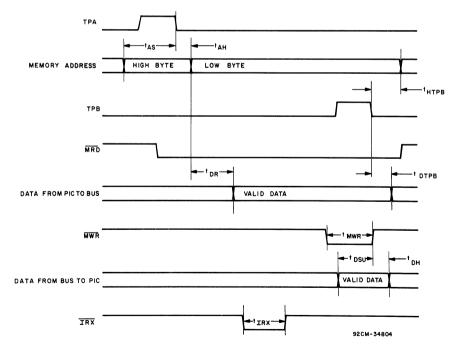

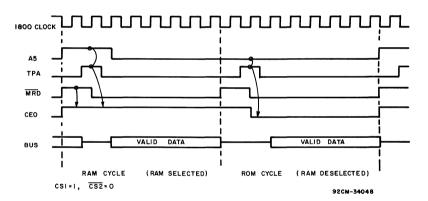

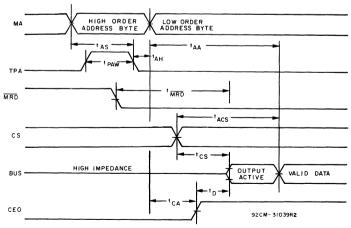

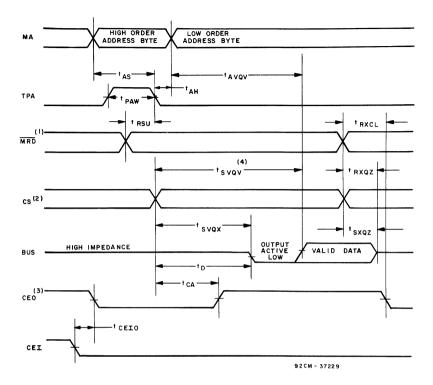

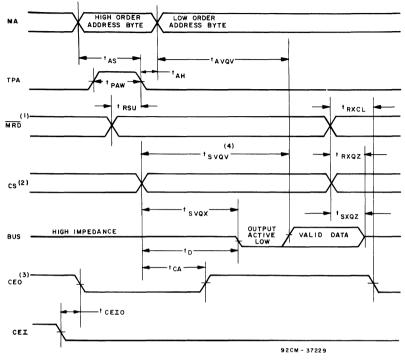

#### TPA, TPB (2 Timing Pulses):

Positive pulses that occur once in each machine cycle (TPB follows TPA). They are used by I/O controllers to interpret codes and to time interaction with the data bus. The trailing edge of TPA is used by the memory system to latch the higher-order byte of the 16-bit memory address. TPA is suppressed in IDLE when the CPU is in the load mode.

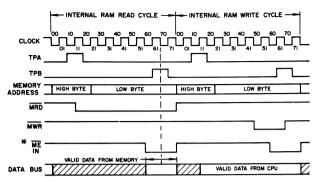

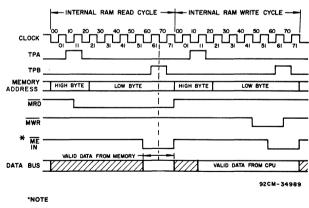

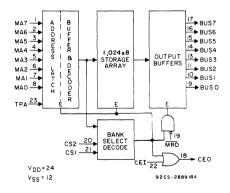

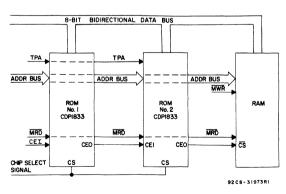

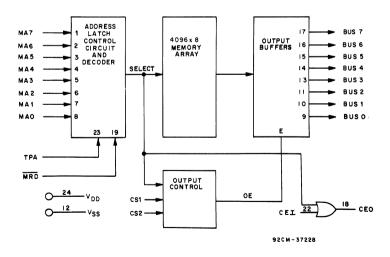

#### MA0 to MA7 (8 Memory Address Lines):

In each cycle, the higher-order byte of a 16-bit CPU memory address appears on the memory address lines MA0-7 first. Those bits required by the memory system can be strobed into external address latches by timing pulse TPA. The low-order byte of the 16-bit address appears on the address lines after the termination of TPA. Latching of all 8 higher-order address bits would permit a memory system of 64K bytes.

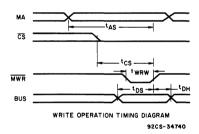

#### MWR (Write Pulse):

A negative pulse appearing in a memory-write cycle, after the address lines have stabilized.

#### MRD (Read Level):

A low level on MRD indicates a memory read cycle. It can be used to control three-state outputs from the addressed memory which may have a common data input and output bus. If a memory does not have a three-state high-impedance output, MRD is useful for driving memory/bus separator gates. It is also used to indicate the direction of data transfer during an I/O instruction. For additional information see Table I

#### o.

Single bit output from the CPU which can be set or reset under program control. During SEQ or REQ instruction execution, Q is set or reset between the trailing edge of TPA and the leading edge of TPB.

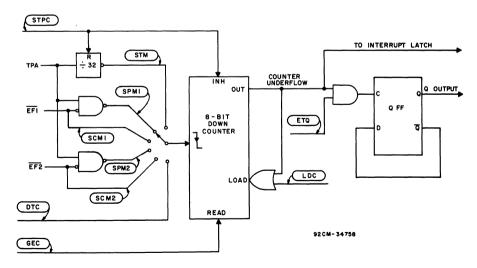

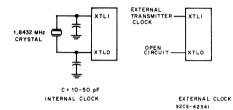

#### CLOCK:

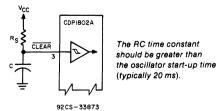

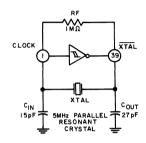

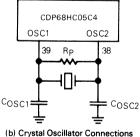

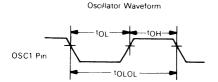

Input for externally generated single-phase clock. A typical clock frequency is 6.4 MHz at  $V_{CC} = V_{DD} = 10$  volts. The clock is counted down internally to 8 clock pulses per machine cycle.

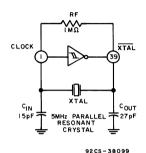

#### XTAL:

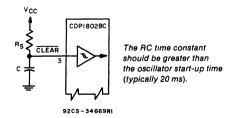

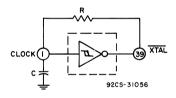

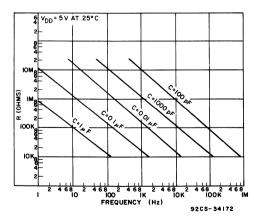

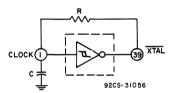

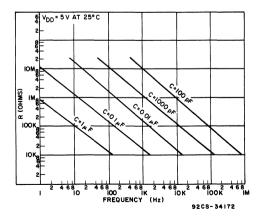

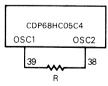

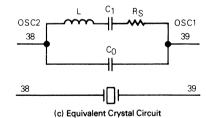

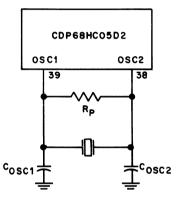

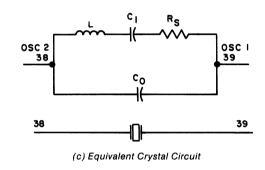

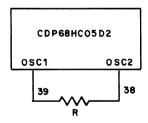

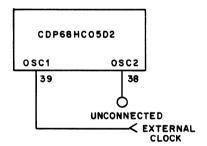

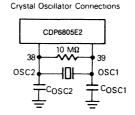

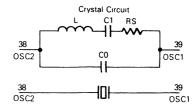

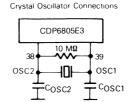

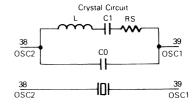

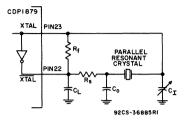

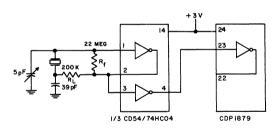

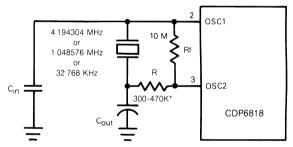

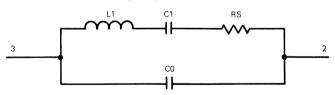

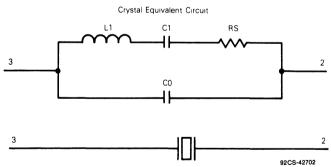

Connection to be used with clock input terminal, for an external crystal, if the on-chip oscillator is utilized. The crystal is connected between terminals 1 and 39 (CLOCK and XTAL) in parallel with a resistance (10 megohms typ.). Frequency trimming capacitors may be required at terminals 1 and 39. For additional information, see ICAN-6565.

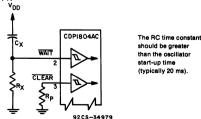

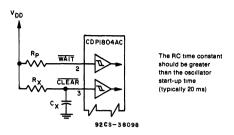

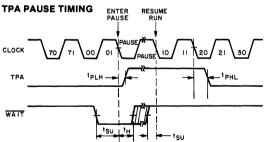

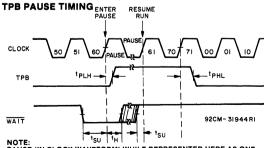

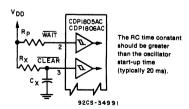

#### WAIT, CLEAR (2 Control Lines):

Provide four control modes as listed in the following truth table:

| CLEAR | WAIT | MODE  |

|-------|------|-------|

| L     | L    | LOAD  |

| L     | I    | RESET |

| Н     | L    | PAUSE |

| Н     | Н    | RUN   |

#### VDD, VSS, VCC (Power Levels):

The internal voltage supply VDD is isolated from the Input/Output voltage supply VCC so that the processor may operate at maximum speed while interfacing with peripheral devices operating at lower voltage. VCC must be less than or equal to VDD. All outputs swing from VSS to VCC. The recommended input voltage swing is VSS to VCC.

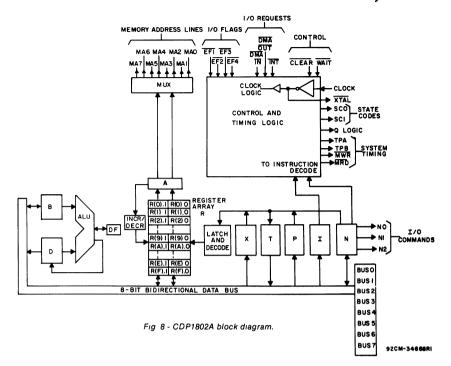

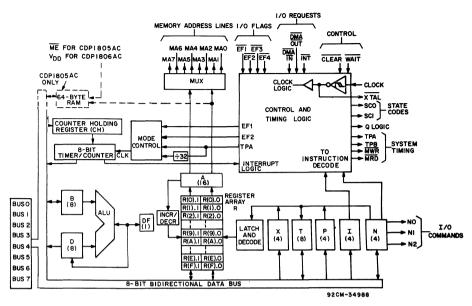

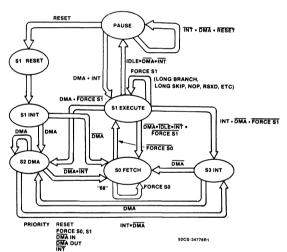

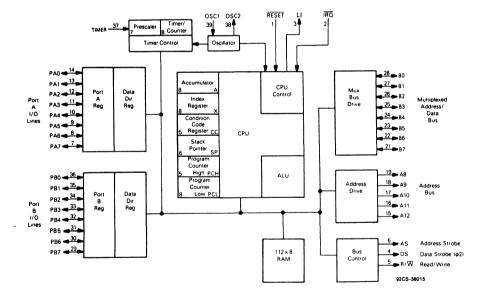

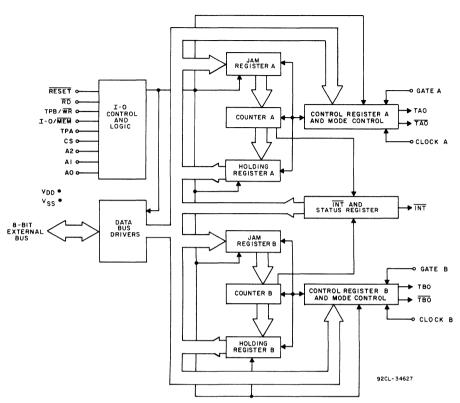

#### **ARCHITECTURE**

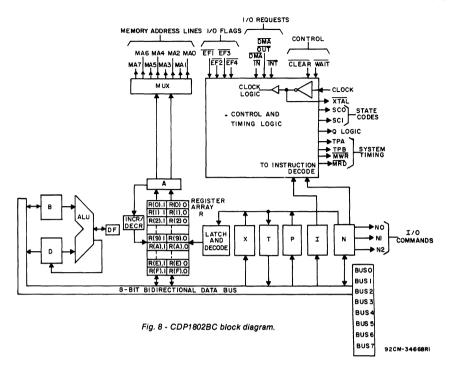

The CPU block diagram is shown in Fig. 8. The principal feature of this system is a register array (R) consisting of sixteen 16-bit scratchpad registers. Individual registers in the array (R) are designated (selected) by a 4-bit binary code from one of the 4-bit registers labeled N, P, and X. The contents of any register can be directed to any one of the following three paths:

- the external memory (multiplexed, higher-order byte first, on to 8 memory address lines);

- the D register (either of the two bytes can be gated to D):

- the increment/decrement circuit where it is increased or decreased by one and stored back in the selected 16-bit register.

The three paths, depending on the nature of the instruction, may operate independently or in various combinations in the same machine cycle.

With two exceptions, CPU instructions consist of two 8-clock-pulse machine cycles. The first cycle is the fetch cycle, and the second—and third if necessary—are execute cycles. During the fetch cycle the four bits in the P designator select one of the 16 registers R(P) as the current program counter. The selected register R(P) contains the address of the memory location from which the instruction is to be fetched. When the instruction is read out from the memory, the higher-order 4 bits of the instruction byte are loaded into the I register and the lower-order 4 bits into the N register. The content of the program counter is automatically incremented by one so that R(P) is now "pointing" to the next byte in the memory.

The X designator selects one of the 16 registers R(X) to "point" to the memory for an operand (or data) in certain ALU or I/O operations.

The N designator can perform the following five functions depending on the type of instruction fetched:

- designate one of the 16 registers in R to be acted upon during register operations;

- indicate to the I/O devices a command code or deviceselection code for peripherals;

- Indicate the specific operation to be executed during the ALU instructions, types of tests to be performed during the Branch instructions, or the specific operation required in a class of miscellaneous instructions (70-73 and 78-7B);

- indicate the value to be loaded into P to designate a new register to be used as the program counter R(P);

- indicate the value to be loaded into X to designate a new register to be used as data pointer R(X).

The registers in R can be assigned by a programmer in three different ways: as program counters, as data pointers, or as scratchpad locations (data registers) to hold two bytes of data.

#### **Program Counters**