# Product Description Guide: ICs for Bus Interface

# A NOTE ON 'LATCHUP' AND 'HOT INSERTION'

### PLX DEVICES ARE LATCHUP-FREE

CMOS devices have gained a reputation for having a tendency to latchup, especially when used in the electrically hostile environment of the backplane. Through special design techniques on the input and output buffers, PLX has been able to develop our CMOS devices in such a way that they are latchup-free under normal operating conditions i.e., when power ground are not shorted. The devices lack the parasitic current path, in both the inputs and outputs, necessary to initiate latchup.

- PLX inputs have very high impedance exhibiting only a very small leakage currents. The input transistor and ESAD structure do not have a conductive path between power and ground.

- PLX outputs have NMOS, not CMOS, buffers. The NMOS buffer does not contain a latchup path between power and ground. Inherently, NMOS gates have no parasitic latchup path.

### PLX DEVICES CAN FUNCTION IN 'HOT INSERTION' APPLICATIONS

Often, a design requirement exists for the board to be able to be inserted into and removed from the system while the system is powered up. This capability allows for easier debug and maintenance and is critical in "non-stop" applications. PLX devices are non-intrusive to their host board and to other boards in such a hot insertion application for three reasons:

- The devices have glitch free power up and power down characteristics. Spurious pulses from outputs are suppressed during ramp up or down.

- The devices' inputs and outputs, when powered down, appear as high impedance opens to the rest of the system. Other CMOS devices can have their inputs shorted to ground, a low impedance path which is hazardous since power and ground are shorted.

- The devices have no inherent latchup path under normal hot insertion procedures. A normal hot insertion procedure does not short power and ground under any conditions.

For more information on "latchup" and "hot insertion" please contact PLX and request a copy of our pamphlet entitled 'Interfacing To Backplane Buses Using CMOS Devices'.

### High Drive Current, Standard and Programmable ICs for Bus Interface

PLX Technology, Inc. designs and manufactures programmable logic devices (PLDs) and integrated circuits optimized for use in bus interface and other high drive current applications. Whether you use standard buses like VME, VME Subsystem Bus (VSB), Multibus<sup>™</sup>, Micro Channel<sup>™</sup> or a proprietary bus, PLX has the solution for you.

Choose from off-the-shelf ICs programmed for specific buses or programmable devices for custom requirements. Either way, you get a multitude of benefits:

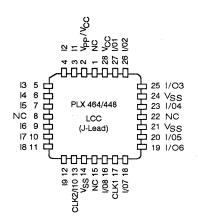

- Space-saving, 300-mil, 24-pin DIP or 28-pin LCC packages

- Integrated drivers up to 64mA, totem pole or open collector

- · Integrated input buffers

- Maximum integration of bus control logic

- Reduced chip count

- · Hot insertion capable and latchup-free design

- Metastable hardened circuitry

### PLX Gives You Comprehensive Design Assistance And Programming Support

Unique logic requirements can make your design task a difficult one. PLX understands the complexities of bus interface design and will help you find or create the right solution.

For example, first try one of our pre-programmed standard solution devices in your application. See how it performs. Then add capabilities by custom programming. This can be done for you by the willing experts at PLX or by you at your own premises. If you send or FAX a copy of the schematic or a block diagram of your application, PLX promises to save you time and design effort. If programming is required, chances are you have the programming tools you need. PLX programmable devices are supported by industry standards like ABEL<sup>™</sup> and CUPL<sup>™</sup> and the most popular models of programmers.

### **Bus Interface Kits Aid In The Design Task**

Design kits are available for your convenience. The enclosed Business Reply Cards describe the various Bus Interface Kits available from PLX Technology. Each kit is designed to give you the information and devices you need to find and implement the right bus interface solution for your application.

### How To Use This Guide

Look under the section appropriate to the bus your design uses to see features, a description and pinouts for PLX devices. If a programmable device is better suited to your design, there's a section describing PLX PLDs.

For information in greater detail call 1-800-759-3753, FAX PLX at (415) 960-0479 or complete one of the enclosed Business Reply Cards.

## Table Of Contents

|                         | Page |

|-------------------------|------|

| VME Bus                 | 2    |

| VME Subsystem Bus (VSB) | 8    |

| Multibus I™             | 12   |

| Multibus II™            | 14   |

| Micro Channel™          | 18   |

| Programmable Devices    | 19   |

|                         |      |

The PLX 448 and PLX 464 are protected by U.S. patent number 4,833,349

Micro Channel is registered trademark of IBM Corp.

Multibus I & II, PSB and ILBX are registered trademarks of Intel Corp.

NuBus is a trademark of Texas Instruments, Inc.

ABEL is a registered trademark of Data I/O Corp.

CUPL is registered trademark of Logical Devices, Inc.

## VMEbus

For VMEbus, PLX offers several devices which implement master control, slave control, interrupt handling and interrupt generation. These devices can be used together or as separate solutions according to your needs.

PLX's VME devices include:

- VME 1210/1220 Master Controllers: Slot 1 and Non-slot 1

- VME 2000 Slave Module Interface Device

- VME 3000/3010 Interrupt Generators (ROAK or RORA)

- VME 4000 Interrupt Handler

## VME 1210/1220 VME Master Controller with System Arbiter

### **Distinctive Features**

- VME 1210 provides two device chip set for slot 1 master bus controller and single level arbiter

- VME 1220 provides two device chip set for non-slot 1 master bus controller

- Integrates 48 mA and 64 mA VMEbus signals: AS\*, DS0\*, DS1\*, WRITE\*, BR\*, BBSY\*

- Integrates input hysteresis buffers

- Supports Release When Done (RWD) and Release On Request (ROR) protocols

- Supports address pipelining, block transfers, and early BBSY\* release

- Available in Commercial, Industrial, and Military temperature ranges

### Applications\_

- VMEbus masters residing in slot 1 boards (VME 1210)

- VMEbus masters residing in non-slot 1 boards (VME 1220)

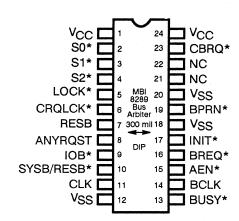

### Packages

### General Description

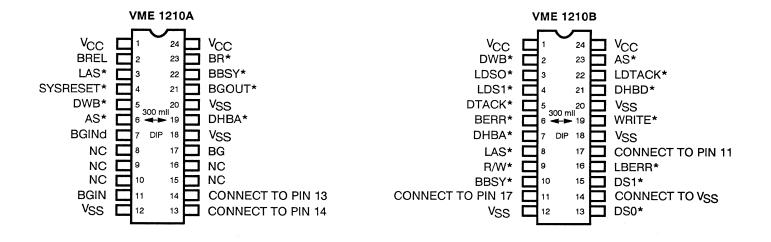

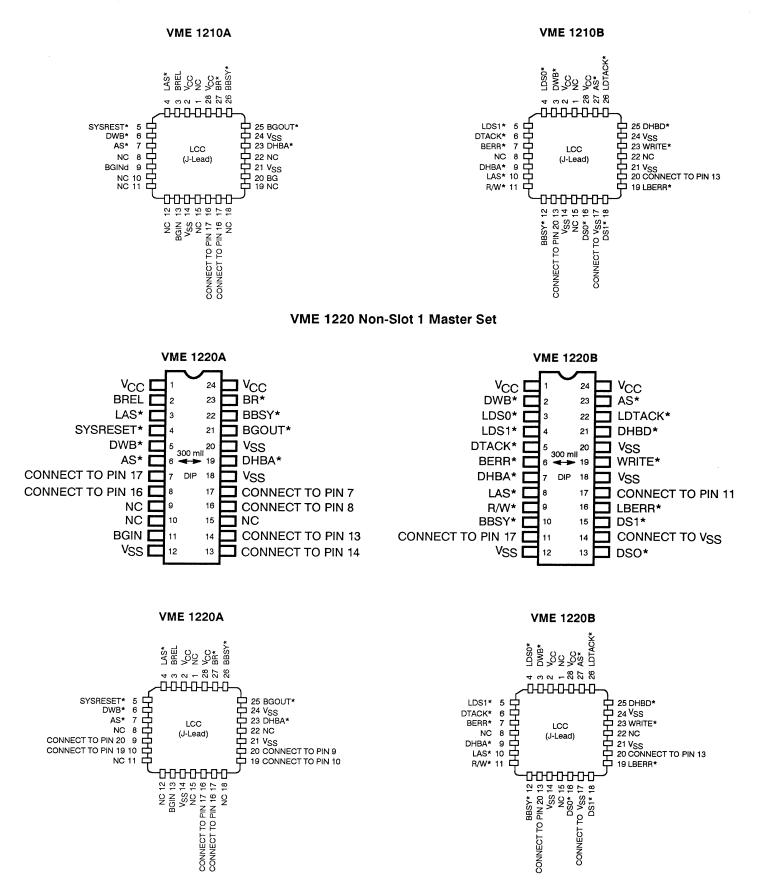

The VME 1210: The VME1210 is comprised of the VME 1210A and the VME 1210B for slot 1 applications. The devices are CMOS and packaged in 24 pin 300 mil wide DIPs or 28 pin J-type LCCs. The VME 1210A provides bus requesting, local arbitration, and single level system arbitration. The VME 1210B functions as the VMEbus controller. The requester initiates a VMEbus request from the local master's bus request for a data or interrupt cycle. The bus controller controls the bus after initiation of a bus cycle and relinquishes the bus at the end of the bus cycle. The bus controller supervises the handshaking between the local master CPU and the slave modules.

The VME 1220: The VME 1220 is comprised of the VME 1220A and the VME 1220B for non-slot 1 applications. The devices are CMOS and packaged in 24 pin 300 mil wide DIPs or 28 pin J-type LCCs. The VME 1220A provides bus requesting and local arbitration. The VME 1220B functions as the VMEbus controller. The requester initiates a VMEbus request from the local master's bus request for a data or interrupt cycle. The bus controller controls the bus after initiation of a bus cycle and relinquishes the bus at the end of the bus cycle. The bus controller supervises the handshaking between the local master CPU and the slave modules.

VME 1210 Slot 1 Master Set

### VME 1210 Slot 1 Master Set

### Pin Descriptions\_\_\_\_\_

### VME 1210A

| Pin #<br>LCC | Pin #<br>DIP | Signal    | Туре | Function                                                                 |

|--------------|--------------|-----------|------|--------------------------------------------------------------------------|

| 3            | 2            | BREL      | 1    | Active high; Bus release signal indicating<br>BBSY* can be released.     |

| 4            | 3            | LAS*      | Ι    | Active low; Address strobe from local master.                            |

| 5            | 4            | SYSRESET* | -    | Active low; VMEbus System Reset.                                         |

| 6            | 5            | DWB*      | 1    | Active low; Device wants bus, local master re-<br>quests control of bus. |

| 7            | 6            | AS*       | 1    | Active low; VMEbus Address Strobe.                                       |

| 9            | 7            | BGINd     | 1    | Active high; Delayed BG output via delay line.                           |

| 10           | 8            | NC        | 1    | No Connect.                                                              |

| 11           | 9            | NC        | Ι    | No Connect.                                                              |

| 12           | 10           | NC        | -    | No Connect.                                                              |

| 13           | 11           | BGIN      | -    | Active high; Inverted VMEbus Bus Grant in sig-<br>nal, BGIN*.            |

| 14. 21, 24   | 12, 18, 20   | Vss       |      | Chip Ground.                                                             |

| 16           | 13           | -         | 0    | Connect to pin 14 (DIP) or pin 17 (LCC).                                 |

| 17           | 14           | -         | 1    | Connect to pin 13 (DIP) or pin 16 (LCC).                                 |

| 18           | 15           | NC        | 0    | No Connect.                                                              |

| 19           | 16           | NC        | 0    | No Connect.                                                              |

| 20           | 17           | BG        | 0    | Active high; Bus grant output from arbiter.                              |

| 23           | 19           | DHBA*     | 0    | Active low; Device has bus address, address buffer enable.               |

| 25           | 21           | BGOUT*    | 0    | Active low; VMEbus Grant Out signal.                                     |

| 26           | 22           | BBSY*     | 1/0  | Active low; 48 mA open collector; VMEbus Bus<br>Busy signal.             |

| 27           | 23           | BR*       | 1/0  | Active low; 48 mA open collector, VMEbus Bus<br>Request signal.          |

| 2, 28        | 1, 24        | Vcc       |      | +5 V Chip Power.                                                         |

| 1, 8, 15, 22 | -            | NC        | -    | No Connect.                                                              |

### VME 1220A

| Pin #<br>LCC | Pin #<br>DIP | Signal    | Туре | Function                                                                 |

|--------------|--------------|-----------|------|--------------------------------------------------------------------------|

| 3            | 2            | BREL      | 1    | Active high; Bus release signal indicating<br>BBSY* can be released.     |

| 4            | 3            | LAS*      | 1    | Active low; Address strobe from local master.                            |

| 5            | 4            | SYSRESET* | -    | Active low; VMEbus System Reset.                                         |

| 6            | 5            | DWB*      | 1    | Active low; Device wants bus, local master re-<br>quests control of bus. |

| 7            | 6            | AS*       | 1    | Active low; VMEbus Address Strobe.                                       |

| 9            | 7            | -         |      | Connect to pin 17 (DIP) or pin 20 (LCC).                                 |

| 10           | 8            | -         | -    | Connect to pin 16 (DIP) or pin 19 (LCC).                                 |

| 11           | 9            | NC        | 1    | No Connect.                                                              |

| 12           | 10           | NC        | 1    | No Connect.                                                              |

| 13           | 11           | BGIN      | Ι    | Active high; Inverted VMEbus Bus Grant in sig-<br>nal, BGIN*.            |

| 14. 21, 24   | 12, 18, 20   | Vss       |      | Chip Ground.                                                             |

| 16           | 13           | -         | 0    | Connect to pin 14 (DIP) or pin 17 (LCC).                                 |

| 17           | 14           | -         | 1    | Connect to pin 13 (DIP) or pin 16 (LCC).                                 |

| 18           | 15           | NC        | 0    | No Connect.                                                              |

| 19           | 16           | -         | 0    | Connect to pin 8 (DIP) or pin 10 (LCC).                                  |

| 20           | 17           | -         | 0    | Connect to pin 7 (DIP) or pin 9 (LCC).                                   |

| 23           | 19           | DHBA*     | 0    | Active low; Device has bus address, address buffer enable.               |

| 25           | 21           | BGOUT*    | 0    | Active low; VMEbus Grant Out signal.                                     |

| 26           | 22           | BBSY*     | I/O  | Active low; 48 mA open collector; VMEbus Bus<br>Busy signal.             |

| 27           | 23           | BR*       | 0    | Active low; 48 mA open collector, VMEbus Bus<br>Request signal.          |

| 2, 28        | 1, 24        | Vcc       |      | +5 V Chip Power.                                                         |

| 1, 8, 15, 22 | -            | NC        | -    | No Connect.                                                              |

### VME 1210B and VME 1220B

| Pin #<br>LCC | Pin #<br>DIP | Signal          | Туре | Function                                                                                                                                                |

|--------------|--------------|-----------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3            | 2            | DWB*            | 1    | Active low; Device wants bus; local master<br>wants control of VMEbus.                                                                                  |

| 4            | 3            | LDS0*           |      | Active low; Lower data strobe from local mas-<br>ter.                                                                                                   |

| 5            | 4            | LDS1*           | 1    | Active low; Upper data strobe from local mas-<br>ter.                                                                                                   |

| 6            | 5            | DTACK*          | I    | Active low, VMEbus Data Transfer Acknowl-<br>edge, data is valid during a read cycle or data<br>has been accepted from the bus during a write<br>cycle. |

| 7            | 6            | BERR*           | 1    | Active low; VMEbus Error signal.                                                                                                                        |

| 9            | 7            | DHBA*           | 1    | Active low; Device has bus address, address buffer enable.                                                                                              |

| 10           | 8            | LAS*            | 1    | Active low; Address strobe from local master.                                                                                                           |

| 11           | 9            | R/W*            | 1    | Active high/low; Read or write cycle from local master.                                                                                                 |

| 12           | 10           | BBSY*           | I    | Active low; VMEbus Busy, local master controls bus.                                                                                                     |

| 13           | 11           | -               | 1    | Connect to pin 17 (DIP) or pin 20 (LCC).                                                                                                                |

| 14. 21, 24   | 12, 18, 20   | V <sub>SS</sub> |      | Chip Ground.                                                                                                                                            |

| 16           | 13           | DS0*            | 0    | Active low; 64 mA VMEbus lower Data Strobe signal, indicates valid data on bus.                                                                         |

| 17           | 14           |                 | 1    | Connect to V <sub>SS</sub> .                                                                                                                            |

| 18           | 15           | DS1*            | 0    | Active low; 64 mA VMEbus upper Data Strobe<br>signal, indicates valid data on bus.                                                                      |

| 19           | 16           | LBERR*          | 0    | Active low; Open collector signal, bus error to<br>local master.                                                                                        |

| 20           | 17           |                 | 0    | Connect to pin 11 (DIP) or pin 13 (LCC).                                                                                                                |

| 23           | 19           | WRITE*          | 0    | Active low; 48 mA VMEbus Write signal, indi-<br>cates bus read or write cycle.                                                                          |

| 25           | 21           | DHBD*           | 0    | Active low; Device has bus data, data buffer en-<br>able.                                                                                               |

| 26           | 22           | LDTACK*         | 0    | Active low; Open collector signal, data ac-<br>knowledge to local master.                                                                               |

| 27           | 23           | AS*             | 0    | Active low; 64 mA VMEbus Address Strobe sig-<br>nal, indicates valid address on bus.                                                                    |

| 2, 28        | 1, 24        | Vcc             |      | + 5 V Chip Power.                                                                                                                                       |

| 1, 8, 15, 22 | -            | NC              |      | No Connect.                                                                                                                                             |

### VME 1210/1220 General Information

|                                         | Commercial<br>0°C to +70°C                                            | Industrial<br>-40°C to +85°C                                          | Military<br>-55°C to +125°C                                           |  |  |  |

|-----------------------------------------|-----------------------------------------------------------------------|-----------------------------------------------------------------------|-----------------------------------------------------------------------|--|--|--|

| Package Type                            | 24 pin 300 mil DIP<br>28 pin J-Lead LCC                               | 24 pin 300 mil DIP<br>28 pin J-Lead LCC                               | 24 pin 300 mil DiP<br>28 pin J-Lead LCC                               |  |  |  |

| Package<br>Material                     | Plastic<br>Ceramic                                                    | Ceramic                                                               | Ceramic                                                               |  |  |  |

| High Drive<br>Current Outputs<br>(I OL) | To VMEbus spec<br>(Up to 64 mA, Open<br>Collector or Three-<br>state) | To VMEbus spec<br>(Up to 64 mA, Open<br>Collector or Three-<br>state) | To VMEbus spec<br>(Up to 64 mA, Open<br>Collector or Three-<br>state) |  |  |  |

### VME 2000 VMEbus Slave Module Interface Device

### Distinctive Features

- Provides logic, high current drive and buffers for slave module to VMEbus interface in 300 mil 24 pin DIP or 28 pin LCC package

- Supports Address Pipelining and Block Move Transfers

- Slave module selection in any VMEbus address space

- Drives 48 mA VMEbus DTACK\* and BERR\* signals

- Input Hysteresis filters bus noise

- Available in Commercial, Industrial, and Military temperature ranges

### Applications

Bus interface circuitry for VMEbus slave modules such as memories or I/O devices

### Pin Descriptions\_

### VME 2000

| 28 Pin<br>LCC | 24 Pin<br>DIP | Signal  | Туре | Function                                                                                                                                                                      |

|---------------|---------------|---------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2             | 1             | Vcc     | -    | 5 V Power Supply                                                                                                                                                              |

| 3             | 2             | SU      |      | Active high; supervisor/user; when high, super-<br>visor only transfers, when low, supervisor or<br>non-supervisor modes (user)                                               |

| 4             | 3             | AM2     | 1    | Address modifier bit 2, for address size, cycle type.                                                                                                                         |

| 5             | 4             | BC      | 1    | BERR* control, when high VME 2000 asserts<br>BERR* if non-supervisor accesses are at-<br>tempted when device is supervisor mode only,<br>when low, BERR* control is disabled. |

| 6             | 5             | IACK*   |      | Interrupt Acknowledge, denotes interrupt com-<br>mand.                                                                                                                        |

| 7             | 6             | AS*     | I    | Active low; Address Strobe, indicates valid ad-<br>dress on bus.                                                                                                              |

| 9             | 7             | ACK*    |      | Active low, Data Acknowledge, local slave<br>strobes ACK* to Indicate data is available or<br>accepted during read or write.                                                  |

| 10            | 8             | ADEN*   |      | Active low, Address Enable, enable output<br>from Address decoder.                                                                                                            |

| 11            | 9             | DS0*    |      | Active low, Data Strobe 0.                                                                                                                                                    |

| 12            | 10            | DS1*    |      | Active low, Data Strobe 1, Data strobes indi-<br>cate how many bytes are being transferred and<br>indicate valid data on bus.                                                 |

| 13            | 11            | ERR*    | 1    | Local Error.                                                                                                                                                                  |

| 14            | 12            | Vss     |      | Chip Ground.                                                                                                                                                                  |

| 16            | 13            | BERR*   | 1/0  | Active low, Bus Error, indicates data transfer was not complete. 48 mA open collector.                                                                                        |

| 17            | 14            |         | 1    | Tie to GND.                                                                                                                                                                   |

| 18            | 15            | DTACK*  | 1/0  | Active low, Data Transfer Acknowledge, hand-<br>shake to master indicating data is available or<br>accepted during read or write, 48 mA open col-<br>lector                   |

| 19            | 16            | MODSEL* | 0    | Active low, Module Select, the local slave mod-<br>ule is selected if ADEN* in enabled and AM<br>codes match.                                                                 |

| 20            | 17            | DIEN*   | 0    | Active low, Data One enable, upper case data byte enable.                                                                                                                     |

| 21            | 18            | Vss     | -    | Chip Ground.                                                                                                                                                                  |

| 23            | 19            | DOEN*   | 0    | Active low, Data Zero Enable, lower case data<br>byte enable.                                                                                                                 |

| 24            | 20            | Vss     | -    | Chip Ground.                                                                                                                                                                  |

| 25            | 21            | DS*     | 0    | Active low, D0EN* or D1EN* active enables DS*.                                                                                                                                |

| 26            | 22            | INTACK* | I    | Active low, Interrupt Acknowledge, from local<br>slave's Interrupt generator. When low, Indi-<br>cates Interrupt cycle for this slave and enables<br>MODSEL*.                 |

| 27            | 23            | NC      | I    | No Connect.                                                                                                                                                                   |

| 28            | 24            | Vcc     | -    | 5 V Power Supply                                                                                                                                                              |

| 1, 8, 15, 22  | -             | NC      | -    | No Connect.                                                                                                                                                                   |

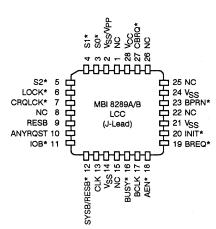

### **General Description**

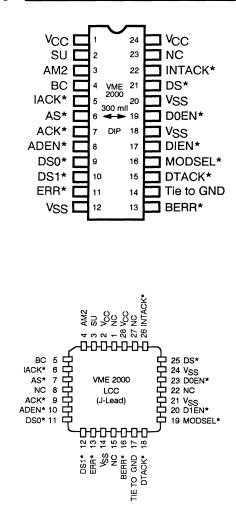

The VME 2000 is a CMOS device which incorporates most of the logic required to interface a slave module, such as a memory or an I/O device, to the VMEbus. It is packaged in a compact 24 pin 300 mil wide DIP or 28 pin LCC. In a VMEbus system, the slave responds to a master and transfers data to and from a master. The protocols of the VME 2000 meet the VMEbus IEEE 1014 timing requirements. The devices buffers and drives the VMEbus signals to the IEEE 1014 electrical specifications.

The VME 2000 supports address pipelining and block move data transfers. This part will function with any type of master module that meets the VMEbus specifications.

### Packages

### VME 2000 General Information

|                                                     | Commercial                                                            | Industrial                                                            | Military                                                              |

|-----------------------------------------------------|-----------------------------------------------------------------------|-----------------------------------------------------------------------|-----------------------------------------------------------------------|

|                                                     | 0°C to +70°C                                                          | −40°C to +85°C                                                        | -55°C to +125°C                                                       |

| Package Type                                        | 24 pin 300 mil DIP                                                    | 24 pin 300 mil DIP                                                    | 24 pin 300 mil DIP                                                    |

|                                                     | 28 pin J-Lead LCC                                                     | 28 pin J-Lead LCC                                                     | 28 pin J-Lead LCC                                                     |

| Package<br>Material                                 | Plastic<br>Ceramic                                                    | Ceramic                                                               | Ceramic                                                               |

| High Drive<br>Current Outputs<br>(I <sub>OL</sub> ) | To VMEbus spec<br>(Up to 48 mA, Open<br>Collector or Three-<br>state) | To VMEbus spec<br>(Up to 48 mA, Open<br>Collector or Three-<br>state) | To VMEbus spec<br>(Up to 48 mA, Open<br>Collector or Three-<br>state) |

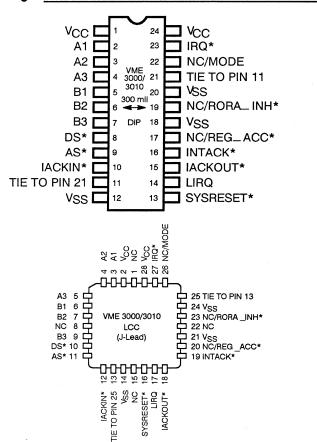

## VME 3000/3010 VMEbus Interrupt Generator

### Distinctive Features

- Provides random logic and high current drive for VMEbus interrupt generator in 300 mil 24 pin DIP or 28 pin LCC package

- IRQ\* can be connected to any single interrupt request level

- Includes interrupter arbitration logic

- Drives 48 mA IRQ\* signal

- Input hysteresis filters bus noise

- VME 3000 provides Release on Acknowledge operation

- VME 3010 provides Release on Register Access or Release on Acknowledge operation

- Available in Commercial, Industrial, and Military temperature ranges

### **Pin Descriptions**

| 28 Pin<br>LCC | 24 Pin<br>DIP | Signal         | Туре | Function                                                                                                                                                                                                                                                                                                                                                                       |

|---------------|---------------|----------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2             | 1             | Vcc            | -    | 5 V Power Supply                                                                                                                                                                                                                                                                                                                                                               |

| 3             | 2             | A <sub>1</sub> | 1    | Active high, Address bit 1; VME address bit.                                                                                                                                                                                                                                                                                                                                   |

| 4             | 3             | A <sub>2</sub> | 1    | Active high, Address bit 2; VME address bit.                                                                                                                                                                                                                                                                                                                                   |

| 5             | 4             | A3             | 1    | Active high, Address bit 3; VME address bit.                                                                                                                                                                                                                                                                                                                                   |

| 6             | 5             | B1             | 1    | Active high, Encode level bit 1; Encode bit fo<br>IRQ* priority level.                                                                                                                                                                                                                                                                                                         |

| 7             | 6             | <sup>B</sup> 2 | 1    | Active high, Encode level bit 2; Encode bit fo<br>IRQ* priority level.                                                                                                                                                                                                                                                                                                         |

| 9             | 7             | <sup>B</sup> 3 | 1    | Active high, Encode level bit 3; Encode bit fo<br>IRQ* priority level.                                                                                                                                                                                                                                                                                                         |

| 10            | 8             | DS*            | 1    | Active low, Data Strobe; DS0* for interrupt vec tor size.                                                                                                                                                                                                                                                                                                                      |

| 11            | 9             | AS*            | 1    | Active low, VMEbus Address Strobe; Indicates valid address.                                                                                                                                                                                                                                                                                                                    |

| 12            | 10            | IACKIN*        | 1    | Active low, Interrupt Acknowledge In; VMEbus<br>IACK* dalsy chain Input.                                                                                                                                                                                                                                                                                                       |

| 13            | 11            |                |      | Tie to pin 21 (DIP) or 25 (LCC).                                                                                                                                                                                                                                                                                                                                               |

| 14            | 12            | VSS            | -    | Chip Ground.                                                                                                                                                                                                                                                                                                                                                                   |

| 16            | 13            | SYSRESET*      |      | Active low, System Reset; VMEbus System<br>Reset.<br>Active high, Local Interrupt Request; Interrup                                                                                                                                                                                                                                                                            |

| 17            | 14            | LIRQ           | 1    | Request from local slave.                                                                                                                                                                                                                                                                                                                                                      |

| 18            | 15            | IACKOUT*       | 0    | Active low, Interrupt Acknowledge Out; IACK <sup>3</sup><br>dalsy chain output if interrupt cycle does no<br>belong to local slave.                                                                                                                                                                                                                                            |

| 19            | 16            | INTACK*        | 0    | Active low, Interrupt Acknowledge; VME 3000<br>generates INTACK* If interrupt cycle belongs<br>to local slave.                                                                                                                                                                                                                                                                 |

| 20            | 17            | NC/REG_ACC*    | I    | No connect on VME 3000. Register accessed<br>input on VME 3010. Input used only in RORA<br>mode. Indicates when the STATUS/ID register<br>on the slave has been read to complete the<br>RORA interrupt handling process. Assertion of<br>this input causes IRQ* to be negated. Tie to<br>GND if using VME 3010 ion ROAK mode.                                                  |

| 21            | 18            | VSS            |      | Chip Ground.                                                                                                                                                                                                                                                                                                                                                                   |

| 23            | 19            | NC/RORA_INH*   | 1    | No connect on VME 3000. LIRQ inhibit input to<br>VME 3010, input used only in RORA mode. Indi-<br>cates when the 2 µsec window after the<br>STATUS/ID register has been read is up. This<br>window causes LIRQ from the slave to be ig-<br>nored. When this input is negated, LIRQ will be<br>sampled again by the VME 3010. The to GND if<br>using the VME 3010 in ROAK mode. |

| 24            | 20            | Vss            | -    | Chip Ground.                                                                                                                                                                                                                                                                                                                                                                   |

| 25            | 21            |                | 0    | Tie to pin 11 (DIP) or pin 13 (LCC).                                                                                                                                                                                                                                                                                                                                           |

| 26            | 22            | NC/MODE        | Ι    | No connect on VME 3000. Mode input to VME<br>3010. Indicates VME 3010 mode of operation<br>tle to GND to operated VME 3010 in ROAk<br>mode: tle to VCC to operate VME 3010 in ROAk<br>mode.                                                                                                                                                                                    |

| 27            | 23            | IRQ*           | 0    | Active low, Interrupt Request; Interrupt request<br>can be connected to any priority level, 48 mA<br>OC.                                                                                                                                                                                                                                                                       |

| 28            | 24            | Vcc            | -    | 5 V Power Supply                                                                                                                                                                                                                                                                                                                                                               |

| 1, 8,         | -             | NC             |      | No Connect.                                                                                                                                                                                                                                                                                                                                                                    |

### Applications

Single level interrupt generator logic for VMEbus slave modules generating an 8 bit interrupt vector

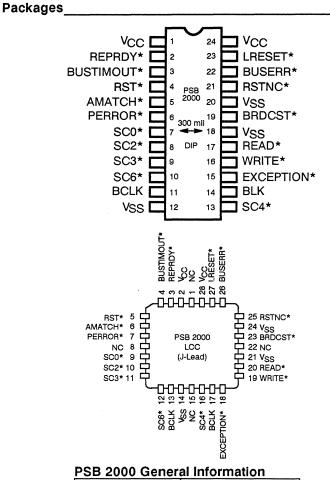

### **General Description**

The VME 3000/3010 is a CMOS single level interrupt generator for the VMEbus which is packaged in a compact 24 pin 300 mil wide DIP or 28 pin LCC. The protocols of the VME 3000/3010 meet the VMEbus IEEE 1014 timing requirements. The device buffers and drives the VMEbus signals to the IEEE1014 electrical specifications.

The VME 3000/3010 will respond to an interrupt cycle when it receives IACKIN\* fom the daisy chain. It arbitrates between IACKIN\* and the interrupt request signal, compares priority levels and generates an interrupt acknowledge or IACKOUT\* depending on which is appropriate.

The VME 3000 provides the Release on Acknowledge interrupter operation, while the VME 3010 provides both Release on Acknowledge and Release on Register Access.

This part will function with any interrupt handler and master module which meets the Rev. C.1 VMEbus specification.

### Packages

### VME 3000/3010 General Information

|                                                     | Commercial                                                            | Industrial                                                            | Military                                                              |

|-----------------------------------------------------|-----------------------------------------------------------------------|-----------------------------------------------------------------------|-----------------------------------------------------------------------|

|                                                     | 0°C to +70°C                                                          | -40°C to +85°C                                                        | −55°C to  + 125°C                                                     |

| Package Type                                        | 24 pin 300 mil DIP                                                    | 24 pin 300 mii DIP                                                    | 24 pin 300 mil DIP                                                    |

|                                                     | 28 pin J-Lead LCC                                                     | 28 pin J-Lead LCC                                                     | 28 pin J-Lead LCC                                                     |

| Package<br>Material                                 | Plastic<br>Ceramic                                                    | Ceramic                                                               | Ceramic                                                               |

| High Drive<br>Current Outputs<br>(I <sub>OL</sub> ) | To VMEbus spec<br>(Up to 48 mA, Open<br>Collector or Three-<br>state) | To VMEbus spec<br>(Up to 48 mA, Open<br>Collector or Three-<br>state) | To VMEbus spec<br>(Up to 48 mA, Open<br>Collector or Three-<br>state) |

Note: OC is Open Collector

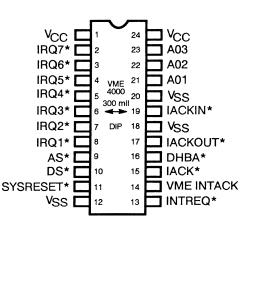

## VME 4000 VMEbus Interrupt Handler

### **Distinctive Features**

- Provides random logic and open collector drive for VMEbus interrupt handling in 300 mil 24 pin DIP or 28 pin LCC

- Monitors all seven interrupt levels

- Includes IACK-daisy chain driver for slot 1 configurations

- Directly drives open collector IACK\* signal

- Works with PLX VME 1200 Master Controller or any other master controller that meets IEEE 1014

- Input hysteresis filters bus noise eliminating need for external buffers

- Available in Commercial, Industrial and Military temperature ranges

### Applications

Interrupt handler logic for VMEbus interrupts on master modules

### Pin Descriptions

| VME 4         | 000           |           |      |                                                                                                                                                                |

|---------------|---------------|-----------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 28-Pin<br>LCC | 24-Pin<br>DIP | Signal    | Туре | Function                                                                                                                                                       |

| 3             | 2             | IRQ7*     | 1    | Active low; VMEbus Interrupt Request level 7.                                                                                                                  |

| 4             | 3             | IRQ6*     | 1    | Active low; VMEbus Interrupt Request level 6.                                                                                                                  |

| 5             | 4             | IRQ5*     | 1    | Active low; VMEbus Interrupt Request level 5.                                                                                                                  |

| 6             | 5             | IRQ4*     | I    | Active low; VMEbus Interrupt Request level 4.                                                                                                                  |

| 7             | 6             | IRQ3*     | 1    | Active low; VMEbus Interrupt Request level 3.                                                                                                                  |

| 9             | 7             | IRQ2*     | 1    | Active low; VMEbus Interrupt Request level 2.                                                                                                                  |

| 10            | 8             | IRQ1*     | 1    | Active low; VMEbus Interrupt Request level 1.                                                                                                                  |

| 11            | 9             | AS*       | 1    | Active low; Data Address Strobe. Used in slot 1<br>IACK-dalsy chain configurations only, other-<br>wise should be tied high.                                   |

| 12            | 10            | DS*       | I    | Active low; Logical AND of VMEbus Data<br>Strobe DSO* and DS1*. Used in slot 1 IACK-<br>dalsy chain configurations only, otherwise<br>should be tied high.     |

| 13            | 11            | SYSRESET* | 1    | Active low; VMEbus system reset.                                                                                                                               |

| 14. 21, 24    | 12, 18, 20    | VSS       |      | Chip Ground.                                                                                                                                                   |

| 16            | 13            | INTREQ*   | 0    | Active low, open collector, VMEbus interrupt re-<br>quest to local master (local interrupt)                                                                    |

| 17            | 14            | VMEINTACK | 1    | Active high; VMEbus interrupt acknowledge<br>from local master (IPL decode logic) to VME<br>4000.                                                              |

| 18            | 15            | IACK*     | 0    | Active Low, open collector; Interrupt Acknowl-<br>edge. Indicates Interrupt acknowledge cycle<br>occurring on VMEbus.                                          |

| 19            | 16            | DHBA*     | 1    | Active Low; Device has bus address. Indicates<br>local master has control of the VME address<br>bus.                                                           |

| 20            | 17            | IACKOUT*  | 0    | Active low; Interrupt Acknowledge Out. IACK-<br>dalsy chain driver output. Used in slot 1 con-<br>figurations only, otherwise should be left un-<br>connected. |

| 23            | 19            | IACKIN*   | 0    | Active low; Interrupt Acknowledge In. Input to<br>IACK-daisy chain driver. Used in slot 1 configu-<br>rations only, otherwise should be tied high.             |

| 25            | 21            | A01*      | 0    | Active high; Local master's address bus bit 1.                                                                                                                 |

| 26            | 22            | A02*      | 0    | Active high; Local master's address bus bit 2.                                                                                                                 |

| 27            | 23            | A03*      |      | Active high; Local master's address bus bit 3.                                                                                                                 |

| 2, 28         | 1, 24         | Vcc       | -    | + 5 V Chip Power.                                                                                                                                              |

| 1, 8, 15, 22  |               | NC        | -    | No Connect.                                                                                                                                                    |

### VME 4000 General Information

|                                                     | Commercial         | Industrial         | Military           |

|-----------------------------------------------------|--------------------|--------------------|--------------------|

|                                                     | 0°C to +70°C       | -40°C to +85°C     | -55°C to +125°C    |

| Package Type                                        | 24 pin 300 mil DIP | 24 pin 300 mil DIP | 24 pin 300 mil DIP |

|                                                     | 28 pin J-Lead LCC  | 28 pin J-Lead LCC  | 28 pin J-Lead LCC  |

| Package<br>Material                                 | Plastic<br>Ceramic | Ceramic            | Ceramic            |

| High Drive<br>Current Outputs<br>(I <sub>OL</sub> ) | To VMEbus spec     | To VMEbus spec     | To VMEbus spec     |

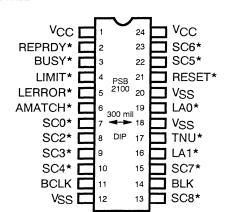

### **General Description**

The VME 4000 is a CMOS seven level interrupt handler for VMEbus interrupts which is packaged in a compact 24 pin 300 mil wide DIP or 28 pin LCC. The VME 4000 meets the VMEbus IEEE 1014 timing and electrical requirements.

The VME 4000 will generate an interrupt request to the local master (via a local interrupt handler) when any of its seven VMEbus interrupt requests inputs is asserted. Once the master generates an interrupt acknowledge back to the VME 4000, it participates in a VMEbus interrupt acknowledge cycle by driving the appropriate interrupt level code onto the address bus as well as asserting IACK\* on the bus.

If the VME 4000 is configured to be a slot 1 interrupt handler, it can provide the IACK-daisy chain driver function. The assertion of IACK\* on the bus will cause the VME 4000 to drive IACKOUT\* during the interrupt acknowledge cycle.

### Packages

## VSB Bus

VME Subsystem Bus (VSB) can be used in conjunction with the VMEbus to provide dedicated local memory or other subsystem functions. PLX offers single and multiple-master module interface devices plus a controller for slave applications:

- VSB 1400 Master Controller for Multimaster Systems

- VSB 1200 Master Controller for Single Master Systems

- VSB 2000 Controller for Slave Applications

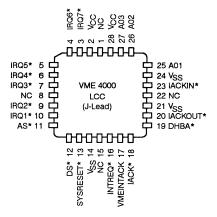

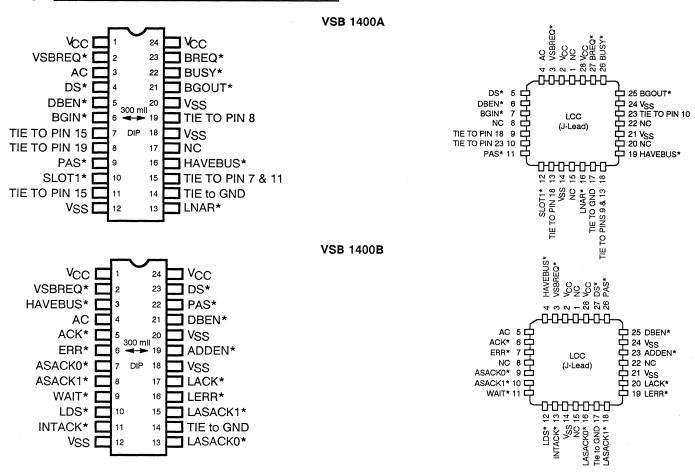

## VSB 1400 VSB Master Module Interface Device

### **Distinctive Features**

- · Bus interface circuitry for multi-master VSB systems

- VSB master chip contains

- Single level arbiter

- Bus requester

- Bus controller

- Supports vectored interrupt acknowledge cycle

- Supports the following performance enhancing options

- Block moves

- Early Bus Busy release

- Drives 48mA VSB bus signals: BREQ\*, DS\*, BUSY\*, PAS\*

- Input hysteresis allows device to monitor VSB signals without additional input buffers

- Available in Commercial, Industrial and Military temperature ranges

### Applications

Bus interface circuitry for slot1 or non slot1 VSB master module in multi-master VSB systems

### General Description

The VSB 1400 is a CMOS device which incorporates the protocol logic, drivers and buffers required to interface a master, typically a CPU, to the VSB (VME Subsystem Bus). It is packaged in compact 24 pin, 300 mil wide DIP or 28 pin LCC.

The VSB 1400 contains a VSB bus requester, controller and arbiter. The requester portion of the device asserts a VSB bus request in response to a request from the local master. The controller portion of the VSB 1400 supervises all the handshaking between the local master and the slaves. The VSB 1400 is designed to function in a multi-master VSB system, and can reside in any slot.

The protocols in the VSB 1400 are fully asynchronous.

This device is designed to function with any type of slave device or circuitry which meets the VSB specifications.

### Packages\_

### Pin Descriptions\_\_\_\_\_

### VSB 1400A

| Pin<br>LCC     | Pin<br>DIP | Signal   | I/O | Function                                                                                    |

|----------------|------------|----------|-----|---------------------------------------------------------------------------------------------|

| 2              | 1          | Vcc      | -   | 5V supply.                                                                                  |

| 3              | 2          | VSBREQ*  | 1   | Active low; Local master wants the bus.                                                     |

| 4              | 3          | AC       | I   | Active high; indicates to master when address por-<br>tion of VSB cycle is complete.        |

| 5              | 4          | DS*      | 1   | Active low; Indicates valid data on bus.                                                    |

| 6              | 5          | DBEN*    | Ι   | Active low; Data buffer enable                                                              |

| 7              | 6          | BGIN*    | -   | Active low; Bus Grant In from dalsy chain or bus re-<br>quest input for slot1 applications. |

| 9              | 7          |          | 1   | Tie to pin 15 (DIP) or pin 18 (LCC).                                                        |

| 10             | 8          |          | I   | Tie to pin 19 (DIP) or pin 23 (LCC).                                                        |

| 11             | 9          | PAS*     | Ι   | Active low; Indicates valid address on bus.                                                 |

| 12             | 10         | SLOT1*   | 1   | Active high; Enables system arbiter for slot 1 mas-<br>ters.                                |

| 13             | 11         |          |     | Tie to pin 15 (DIP) or pin 18 (LCC).                                                        |

| 14             | 12         | VSS      | -   | Chip Ground                                                                                 |

| 16             | 13         | LNAR*    | 0   | Active low; indicates to local master that single or block transfer cycle is complete.      |

| 17             | 14         |          | 1   | Tle to Ground                                                                               |

| 18             | 15         |          | 0   | Tie to pins 7 and 11 (DIP) or pins 9 and 13 (LCC).                                          |

| 19             | 16         | HAVEBUS* | 0   | Active low; Indicates to local master that it owns the bus and enables the strobes.         |

| 20             | 17         | NC       | -   | No Connect                                                                                  |

| 21             | 18         | Vss      |     | Chip Ground                                                                                 |

| 23             | 19         |          | 0   | Tie to pin 8 (DIP) or pin 10 (LCC).                                                         |

| 24             | 20         | VSS      | -   | Chip Ground                                                                                 |

| 25             | 21         | BGOUT*   | 0   | Active low; Bus Grant output to the daisy chain.                                            |

| 26             | 22         | BUSY*    | 0   | Active low; Indicates local master controls the bus, 48mA OC.                               |

| 27             | 23         | BREQ*    | 0   | Active low; Bus request, 48mA OC.                                                           |

| 28             | 24         | Vcc      | -   | 5V supply.                                                                                  |

| 1, 8<br>15, 22 |            | NC       | -   | No Connect                                                                                  |

| 28-Pin<br>LCC  | 24-Pin<br>DIP | Signal   | 1/0 | Function                                                                                                                                                                  |

|----------------|---------------|----------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2              | 1             | Vcc      | -   | 5V supply.                                                                                                                                                                |

| 3              | 2             | VSBREQ*  | 1   | Active low; Local master wants the bus.                                                                                                                                   |

| 4              | 3             | HAVEBUS* | 1   | Active low; Indicates to local master that it owns the bus and enables the strobes.                                                                                       |

| 5              | 4             | AC       | 1   | Active high; indicates to master when address po<br>tion of VSB cycle is complete.                                                                                        |

| 6              | 5             | ACK*     | 1   | Active low; Data valid or has been accepted.                                                                                                                              |

| 7              | 6             | ERR*     | 1   | Active low; Bus error or timeout has occurred.                                                                                                                            |

| 9              | 7             | ASACK0*  | -   | Active low; Byte size information and addre<br>transfer acknowledge.                                                                                                      |

| 10             | 8             | ASACK1*  | I   | Active low; Byte size information and addre<br>transfer acknowledge.                                                                                                      |

| 11             | 9             | WAIT*    | 1   | Active low; VSB cycle extension or hold.                                                                                                                                  |

| 12             | 10            | LDS*     | 1   | Active low; local master data strobe.                                                                                                                                     |

| 13             | 11            | INTACK*  |     | Active low; Interrupt Acknowledge Input, Indicate<br>that a vectored interrupt acknowledge cycle is b<br>ing initiated by the local master. If not used, must in<br>high. |

| 14             | 12            | Vss      | -   | Chip Ground                                                                                                                                                               |

| 16             | 13            | LASACK0* | 0   | Active low; Byte size information and addre<br>transfer acknowledge to local master.                                                                                      |

| 17             | 14            |          | Ι   | Tie to Ground                                                                                                                                                             |

| 18             | 15            | LASACK1* | 0   | Active low; Byte size information and addre<br>transfer acknowledge to local master.                                                                                      |

| 19             | 16            | LERR*    | 0   | Active low; Bus error or timeout to local master.                                                                                                                         |

| 20             | 17            | LACK*    | 0   | Active low; Data validation or acceptance to loc master.                                                                                                                  |

| 21             | 18            | VSS      | _   | Chip Ground                                                                                                                                                               |

| 23             | 19            | ADDEN*   | 0   | Active low; Address buffer enable.                                                                                                                                        |

| 24             | 20            | VSS      | -   | Chip Ground                                                                                                                                                               |

| 25             | 21            | DBEN*    | 0   | Active low; Data buffer enable.                                                                                                                                           |

| 26             | 22            | PAS*     | 1/0 | Active low; indicates valid address on bus, 48m<br>OC.                                                                                                                    |

| 27             | 23            | DS*      | 1/0 | Active low; Indicates valid data on bus 48mA OC                                                                                                                           |

| 28             | 24            | Vcc      | -   | 5V supply.                                                                                                                                                                |

| 1, 8<br>15, 22 |               | NC       | -   | No Connect                                                                                                                                                                |

### VSB 1400 General Information (Two Chip Set)

|                                                     | Commercial                                                           | Industrial                                                           | Military                                                             |

|-----------------------------------------------------|----------------------------------------------------------------------|----------------------------------------------------------------------|----------------------------------------------------------------------|

|                                                     | 0°C to +70°C                                                         | -40°C to +85°C                                                       | -55°C to  + 125°C                                                    |

| Package Type                                        | 24 pln 300 mil DIP                                                   | 24 pin 300 mil DIP                                                   | 24 pin 300 mil DIP                                                   |

|                                                     | 28 pln J-Lead LCC                                                    | 28 pin J-Lead LCC                                                    | 28 pin J-Lead LCC                                                    |

| Package<br>Material                                 | Plastic<br>Ceramic                                                   | Ceramic                                                              | Ceramic                                                              |

| High Drive<br>Current Outputs<br>( <sup>I</sup> OL) | To VSB bus spec<br>(Up to 48mA Open<br>Collector or Three-<br>state) | To VSB bus spec<br>(Up to 48mA Open<br>Collector or Three-<br>state) | To VSB bus spec<br>(Up to 48mA Open<br>Collector or Three-<br>state) |

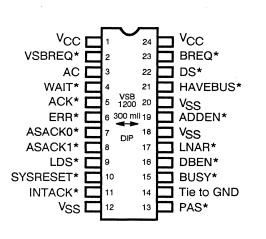

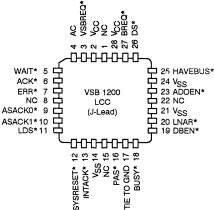

### **VSB 1200 Master Module Interface Device**

### Distinctive Features

- Bus interface circuitry for single master VSB systems

- VSB master chip contains

- Single level arbiter

- Bus requester

- Bus controller

- Vectored interrupt acknowledge cycle logic

- Supports the following performance enhancing options

- Block moves

- Early Bus Busy release

- Drives 48mA VSB bus signals: DS\*, BUSY\*, PAS\*

- Input hysteresis allows device to monitor VSB signals without additional input buffers

- Available in Commercial, Industrial and Military temperature ranges

### Applications

• Bus interface circuitry for VSB master in single master VSB systems

### Packages\_

### VSB 1200 General Information

|                                                     | Commercial                                                            | Industrial                                                            | Military                                                              |

|-----------------------------------------------------|-----------------------------------------------------------------------|-----------------------------------------------------------------------|-----------------------------------------------------------------------|

|                                                     | 0°C to +70°C                                                          | −40°C to +85°C                                                        | −55°C to  + 125°C                                                     |

| Package Type                                        | 24 pin 300 mil DIP                                                    | 24 pln 300 mil DIP                                                    | 24 pin 300 mil DIP                                                    |

|                                                     | 28 pin J-Lead LCC                                                     | 28 pin J-Lead LCC                                                     | 28 pin J-Lead LCC                                                     |

| Package<br>Material                                 | Plastic<br>Ceramic                                                    | Ceramic                                                               | Ceramic                                                               |

| High Drive<br>Current Outputs<br>(I <sub>OL</sub> ) | To VSB bus spec<br>(up to 48mA, Open<br>Collector or Three-<br>state) | To VSB bus spec<br>(up to 48mA, Open<br>Collector or Three-<br>state) | To VSB bus spec<br>(up to 48mA, Open<br>Collector or Three-<br>state) |

### General Description

The VSB 1200 is a CMOS device which incorporates the protocol logic, drivers and buffers required to interface a master, typically a CPU, to the VSB (VME Subsystem Bus). It is packaged in a compact 24 pin, 300 mil wide DIP or 28 pin LCC.

The VSB 1200 contains a VSB bus requester, controller and arbiter. The requester portion of the device asserts a VSB bus request in response to a request from the local master. The controller portion of the VSB 1200 supervises all the handshaking between the local master and the slaves. Because the VSB 1200 is designed to work in a single master VSB system, the arbiter portion of the device always grants the bus to the local master.

The protocols in the VSB 1200 are fully asynchronous.

This device is designed to function with any type of slave device or circuitry which meets the VSB specifications.

### **Pin Descriptions**

| VSB 12         | 200           |           |     |                                                                                                                                                                         |

|----------------|---------------|-----------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 28-Pin<br>LCC  | 24-Pin<br>DIP | Signal    | I/O | Function                                                                                                                                                                |

| 3              | 2             | VSBREQ*   | 1   | Active low; Local master wants the bus.                                                                                                                                 |

| 4              | 3             | AC        | ł   | Active high; Indicates to master when address por-<br>tion of VSB cycle is complete.                                                                                    |

| 5              | 4             | WAIT*     | I   | Active low; VSB cycle should not be terminated until<br>WAIT* is deasserted.                                                                                            |

| 6              | 5             | ACK*      | 1   | Active Low*; Informs local master that data is valid<br>or has been accepted.                                                                                           |

| 7              | 6             | ERR*      | I   | Active Low; Informs local master that there is a bus<br>error or a time-out has occurred.                                                                               |

| 9              | 7             | ASACK0*   | 1   | Active low; informs master of byte size and that slaves acknowledge are ready for the data cycle.                                                                       |

| 10             | 8             | ASACK1*   | 1   | Active low; Informs master of byte size and that slaves acknowledge are ready for the data cycle.                                                                       |

| 11             | 9             | LDS*      | 1   | Active Low; Data strobe from local master.                                                                                                                              |

| 12             | 10            | SYSRESET* | 1   | Active low; System reset Input, Initializes the VSB<br>2000 and should be tied to the VME SYSRESET*<br>line or the local master's reset line.                           |

| 13             | 11            | INTACK*   | -   | Active low; Interrupt Acknowledge input, Indicates that a vectored interrupt acknowledge cycle is be-<br>ing initiated by the local master. If not used, must tie high. |

| 14,<br>21, 24  | 12,<br>18, 20 |           |     | Chip<br>Ground                                                                                                                                                          |

| 16             | 13            | PAS*      | 0   | Active Low; Indicates valid address on bus; 48mA<br>TS.                                                                                                                 |

| 17             | 14            |           | 1   | Tie to Ground                                                                                                                                                           |

| 18             | 15            | BUSY*     | 0   | Active low; Indicates to local master that single or<br>block transfer cycle is complete.                                                                               |

| 19             | 16            | DBEN*     | 1   | Active Low; Data buffer enable.                                                                                                                                         |

| 20             | 17            | LNAR*     | 0   | Active Low; Informs local master that single or block<br>required transfer cycle is complete.                                                                           |

| 23             | 19            | ADDEN*    | 0   | Active Low; Address buffer enable.                                                                                                                                      |

| 25             | 21            | HAVEBUS*  | 0   | Active Low; informs local master that it owns bus<br>and enables address and data strobes.                                                                              |

| 26             | 22            | DS*       | -   | Active Low; Indicates valid data on bus; 48mA TS.                                                                                                                       |

| 27             | 23            | BREQ*     |     | Active low; VSB bus request; 48 mA OC.                                                                                                                                  |

| 2, 28          | 1, 24         | Vcc       | -   | 5V supply.                                                                                                                                                              |

| 1, 8<br>15, 22 |               | NC        | -   | No Connect                                                                                                                                                              |

Note: TS is Tri-state OC is Open Collector

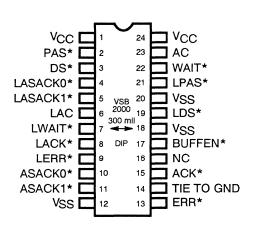

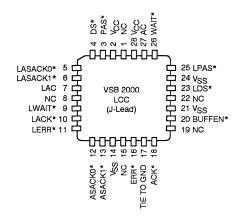

### VSB 2000 Slave Module Interface Device

- Provides logic, high current drive and buffers for slave module to VSB bus interface in slim 24 pin DIP or 28 pin LCC package

- Supports Block Transfers

- Drives 48 mA open collector VSB signals: AC, WAIT\*, ACK\* and ERR\*

- Input hysteresis allows device to monitor VSB signals without additional input buffers

- Available in Commercial, Industrial and Military temperature ranges

### Applications

Bus interface circuitry for VSB slave modules such as memories or I/Os functioning as responding or participating slaves

### Packages

### **VSB 2000 General Information**

|                                         | Commercial                                                            | Industrial                                                            | Military                                                              |

|-----------------------------------------|-----------------------------------------------------------------------|-----------------------------------------------------------------------|-----------------------------------------------------------------------|

|                                         | 0°C to +70°C                                                          | -40°C to +85°C                                                        | -55°C to  + 125°C                                                     |

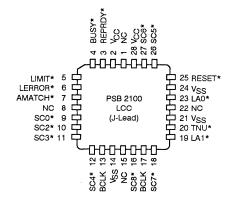

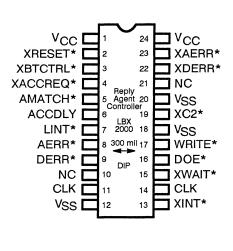

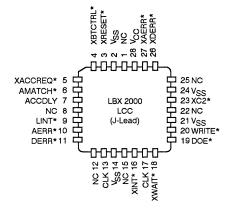

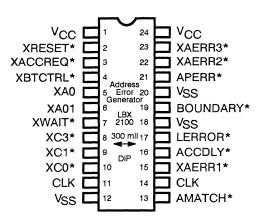

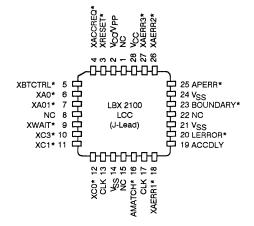

| Package Type                            | 24 pin 300 mil DIP                                                    | 24 pin 300 mil DIP                                                    | 24 pin 300 mil DIP                                                    |