16-bit 80C51XA Microcontrollers (eXtended Architecture)

1997

Data Handbook IC25 CD-ROM included

PHILIPS

Philips Semiconductors

#### QUALITY ASSURED

Our quality system focuses on the continuing high quality of our components and the best possible service for our customers. We have a three-sided quality strategy: we apply a system of total quality control and assurance; we operate customer-oriented dynamic improvement programmes; and we promote a partnering relationship with our customers and suppliers.

#### PRODUCT SAFETY

In striving for state-of-the-art perfection, we continuously improve components and processes with respect to environmental demands. Our components offer no hazard to the environment in normal use when operated or stored within the limits specified in the data sheet.

Some components unavoidably contain substances that, if exposed by accident or misuse, are potentially hazardous to health. Users of these components are informed of the danger by warning notices in the data sheets supporting the components. Where necessary the warning notices also indicate safety precautions to be taken and disposal instructions to be followed. Obviously users of these components, in general the set-making industry, assume responsibility towards the consumer with respect to safety matters and environmental demands.

All used or obsolete components should be disposed of according to the regulations applying at the disposal location. Depending on the location, electronic components are considered to be 'chemical', 'special' or sometimes 'industrial' waste. Disposal as domestic waste is usually not permitted.

# 16-bit 80C51XA (eXtended Architecture) Microcontrollers Data Handbook

## CONTENTS

page

| SECTION 1 | SELECTION GUIDES          | 5   |

|-----------|---------------------------|-----|

| SECTION 2 | GENERAL INFORMATION       | 21  |

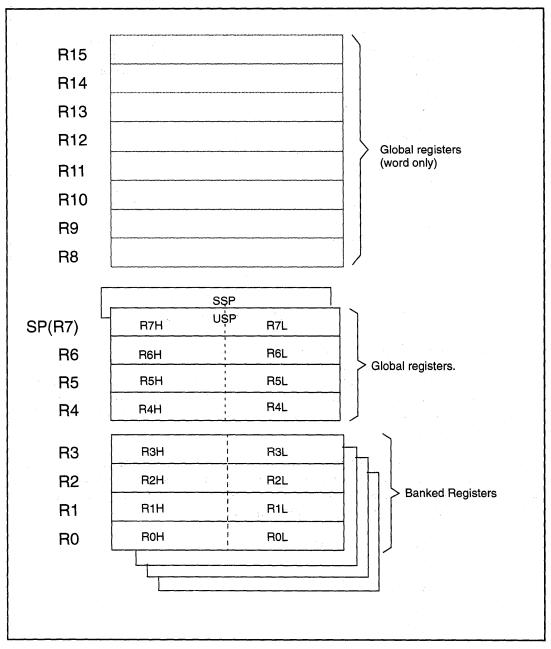

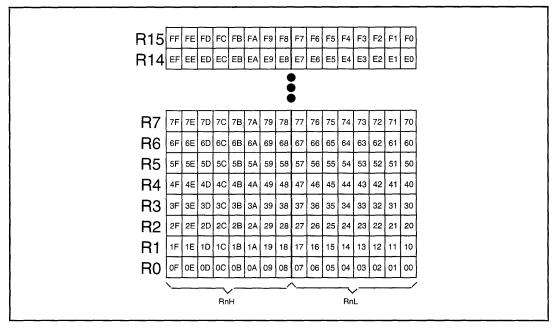

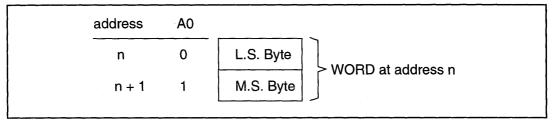

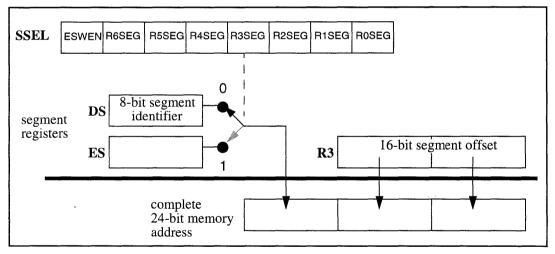

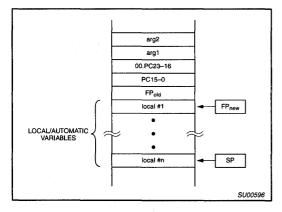

| SECTION 3 | XA USER GUIDE             | 31  |

| SECTION 4 | XA FAMILY DERIVATIVES     | 315 |

| SECTION 5 | FUTURE DERIVATIVES        | 411 |

| SECTION 6 | APPLICATION NOTES         | 423 |

| SECTION 7 | DEVELOPMENT SUPPORT TOOLS | 659 |

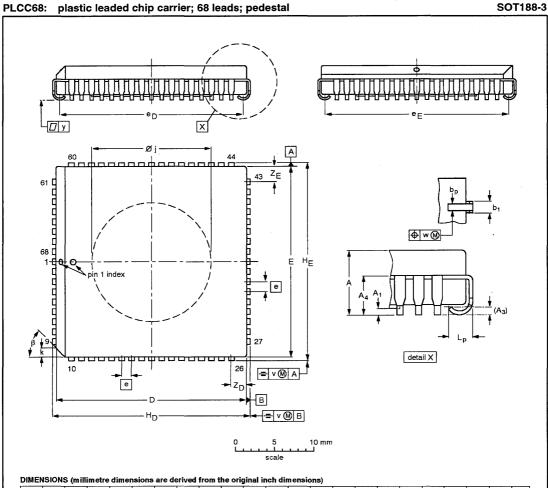

| SECTION 8 | PACKAGE INFORMATION       | 737 |

| SECTION 9 | DATA HANDBOOK SYSTEM      | 749 |

#### DEFINITIONS

| Data Sheet Identification       | Product Status                                                           | Definition (Note)                                                                                                                                                                                                                                                   |

|---------------------------------|--------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>Objective Specification</b>  | Formative or in Design                                                   | This data sheet contains the design target or goal specifications for<br>product development. Specifications may change in any manner<br>without notice.                                                                                                            |

| Preliminary Specification       | Preproduction Product                                                    | This data sheet contains preliminary data, and supplementary data<br>will be published at a later date. Philips Semiconductors reserves the<br>right to make changes at any time without notice in order to improve<br>design and supply the best possible product. |

| Product Specification           | Full Production                                                          | This data sheet contains Final Specifications. Philips Semiconductors<br>reserves the right to make changes at any time without notice, in<br>order to improve design and supply the best possible product.                                                         |

| Short-form specification        |                                                                          | The data in this specification is extracted from a full data sheet with<br>the same type number and title. For detailed information see the<br>relevant data sheet or data handbook.                                                                                |

| Limiting values                 |                                                                          | • • • • • • • • • • • • • • • • • • •                                                                                                                                                                                                                               |

| values may cause permanent dama | age to the device. These are stres<br>Characteristics sections of the sp | Rating System (IEC 134). Stress above one or more of the limiting<br>s ratings only and operation of the device at these or at any other<br>secification is not implied. Exposure to limiting values for extended                                                   |

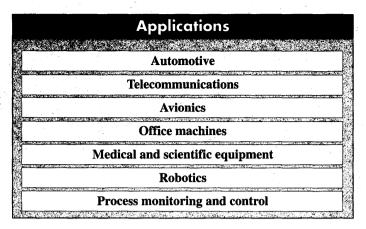

Applications that are described herein for any of these products are for illustrative purposes only. Philips Semiconductors makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification

#### LIFE SUPPORT APPLICATIONS

These products are not designed for use in life support appliances, devices, or systems where malfunction of these products can reasonably be expected to result in personal injury. Philips Semiconductors customers using or selling these products for use in such applications do so at their own risk and agree to fully indemnify Philips Semiconductors for any damages resulting from such improper use or sale.

#### PURCHASE OF PHILIPS I<sup>2</sup>C COMPONENTS

Purchase of Philips I<sup>2</sup>C components conveys a license under the Philips' I<sup>2</sup>C patent to use the components in the I<sup>2</sup>C system provided the system conforms to the I<sup>2</sup>C specifications defined by Philips. This specification can be ordered using the code 9398 393 40011.

#### DISCLAIMER

Philips Semiconductors reserves the right to make changes, without notice, in the products, including circuits, standard cells, and/or software, described or contained herein in order to improve design and/or performance. Philips Semiconductors assumes no responsibility or liability for the use of any of these products, conveys no license or title under any patent, copyright, or mask work right to these products, and makes no representations or warranties that these products are free from patent, copyright, or mask work right infringement, unless otherwise specified.

**NOTE:** Always check with your local Philips Semiconductors Sales Office to be certain that you have the latest data sheet(s) before completing a design.

# Preface

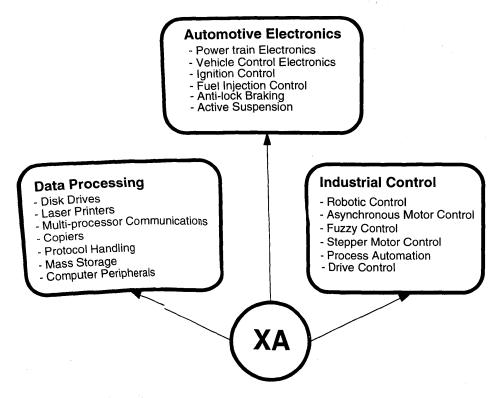

#### XA Microcontrollers from Philips Semiconductors

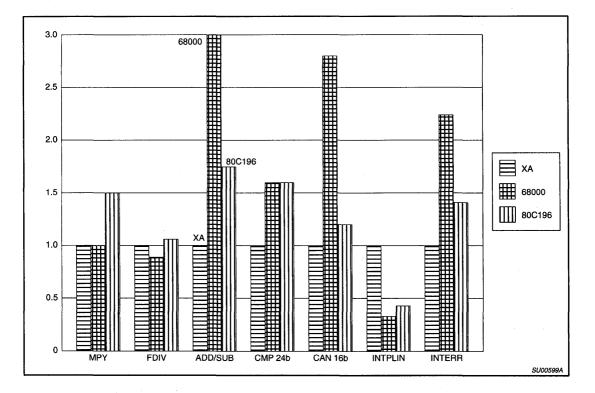

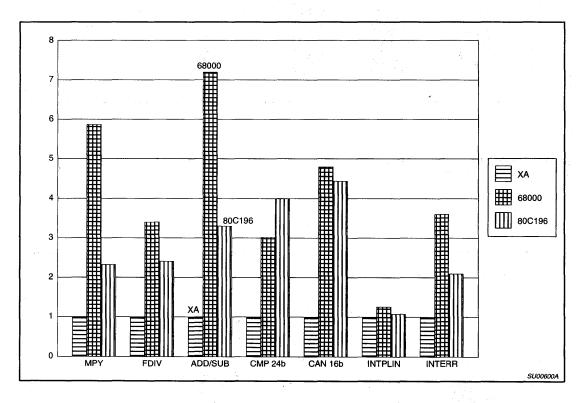

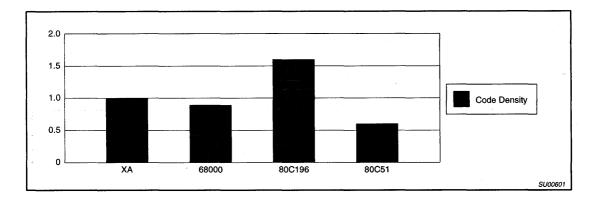

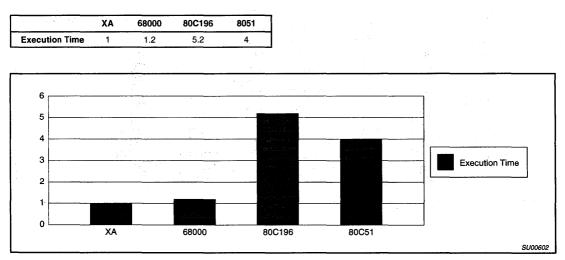

Philips Semiconductors offers a wide range of microcontrollers based on the 8048, 80C51, and now the XA architectures. The XA is a new architecture that was developed by Philips Semiconductors in response to the market need for higher performance than what can be obtained from the 8-bit 80C51 and retained compatibility with the 80C51 designed-in architecture. The XA successfully addresses both of these needs. It is compatible with the 80C51 at the source code level. All of the internal registers and operating modes of the 80C51 are fully supported within the XA, as are all of the 80C51 instructions. Yet compatibility with the 80C51 has in no way hindered the performance is 3 to 4 times faster than that of the most popular 16 bit architectures and 10 to 100 times faster than the 80C51.

If you use or are familiar with the 80C51 and need higher performance, the XA is the architecture for you. You will find it very easy to understand. Rather than having to learn its programmer's model, you will find that you already know it, and, better, are very familiar with it. You will be able to focus on the enhanced features of the XA and quickly move your design to much higher performance. You will also notice that the features on the XA, in many cases, exceed what you need today. We have designed the XA so that it will meet your needs not only today but well into the future; you will not need to look for another architecture for many years to come.

As Philips Semiconductors has done with the 8048 and 80C51, we will develop the XA into a broad family of derivatives. Advance information has been included in this handbook that covers the first two of these. It is our plan to introduce 3 to 4 XA derivatives in 1997 and 5 to 8 per year after that. In addition to this, we will continue to move the XA into Philips Semiconductors' most advanced processes and we have plans to increase the clocking frequency of the architecture to over 100MHz (greater than 30MIPS execution rate).

Philips Semiconductors offers you one of the industry's widest selections of microcontrollers. The XA architecture is an extension of this strategy that gives you the ability to easily upgrade your designs to very high performance with the only 16-bit, 80C51-compatible microcontroller available on the market.

•

# Section 1 Selection Guides

#### CONTENTS

| XA tools linecard                                  | 7  |

|----------------------------------------------------|----|

| Microcontroller internet and bulletin board access | 8  |

| Philips Fax-On-Demand System                       | 10 |

| CMOS and NMOS 8-bit microcontroller family         | 11 |

| CMOS 16-bit microcontroller family                 | 15 |

| 80C51 microcontroller family features guide        | 16 |

5

at a set of the set

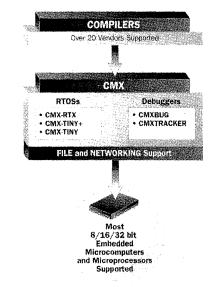

## XA tools linecard

|                             |                     | Product                               |          |                 |                                       |                 |  |  |  |  |  |  |

|-----------------------------|---------------------|---------------------------------------|----------|-----------------|---------------------------------------|-----------------|--|--|--|--|--|--|

|                             | North A             | )e                                    | Product  |                 |                                       |                 |  |  |  |  |  |  |

| C Compilers                 |                     |                                       |          |                 |                                       |                 |  |  |  |  |  |  |

| Archimedes                  | 1-206-822-6300      | Mary Sorensen                         | sw       | 41.61.331.7151  | Claude Vonlanthen                     | C-51XA          |  |  |  |  |  |  |

| CMX Company                 | 15088727675         | Charles Behrmann                      | US       | 1-508-872-7675  | Charles Behrmann                      | Hi-Tech XAC     |  |  |  |  |  |  |

| Hi-Tech                     | 1-207-236-9055      | Avocet - T. Taylor                    | UK       | 44.1.932.829460 | Computer Solutions                    | Hi–Tech C (XA)  |  |  |  |  |  |  |

| Pantasoft                   | 1-314-830-4084      | Roly Schwartzman                      | GE       | 49.6151.27505   | M. Kimron                             | C-XA            |  |  |  |  |  |  |

| Tasking                     | 1-617-320-9400      | Vaughn Orchard                        | US       | 1-617-320-9400  | Vaughn Orchard                        | C-Compiler      |  |  |  |  |  |  |

| Emulators (including        | g Debuggers)        |                                       |          |                 |                                       | •               |  |  |  |  |  |  |

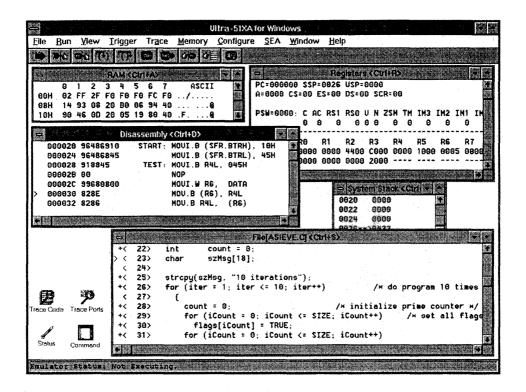

| Ashling                     | 1-508-366-3220      | Bob Labadini                          | IR       | 353.61.334466   | Micheal Healy                         | Ultra2000-XA    |  |  |  |  |  |  |

| Ceibo                       | 1-314-830-4084      | Roly Schwartzman                      | GE       | 49.6151.27505   | M. Kimron                             | DS-XA           |  |  |  |  |  |  |

| Nohau                       | 1-408-866-1820      | Jim Straub                            | SW       | 46.40.922425    | Mikael Johnsson                       | EMUL51XA-PC     |  |  |  |  |  |  |

| Cross Assemblers            |                     |                                       |          |                 |                                       |                 |  |  |  |  |  |  |

| Archimedes                  | 1-206-822-6300      | Mary Sorensen                         | sw       | 41.61.331.7151  | Claude Vonlanthen                     | A51XA           |  |  |  |  |  |  |

| Ashling                     | 1-508-366-3220      | Bob Labadini                          | IR       | 353.61.334466   | Micheal Healy                         | SDS-XA          |  |  |  |  |  |  |

| Pantasoft                   | 1-314-830-4084      | Roly Schwartzman                      | GE       | 49.6151.27505   | M. Kimron                             | ASM-XA          |  |  |  |  |  |  |

| Philips/Macraigor*          | 1-408-991-51XA      | Moti Kama                             | US       | 1.408.991.5192  | Moti Kama                             | Mcgtool         |  |  |  |  |  |  |

| Tasking                     | 1-617-320-9400      | Vaughn Orchard                        | US       | 1-617-320-9400  | Vaughn Orchard                        | C-Compiler      |  |  |  |  |  |  |

| Real-Time Operating         | Systems             | -                                     | <b>.</b> |                 |                                       | ·               |  |  |  |  |  |  |

| CMX Company                 | 1-508-872-7675      | Charles Behrmann                      | US       | 1.508.872.7675  | Charles Behrmann                      | CMX-RTX         |  |  |  |  |  |  |

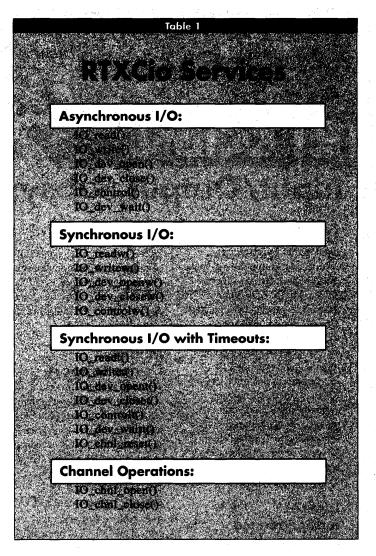

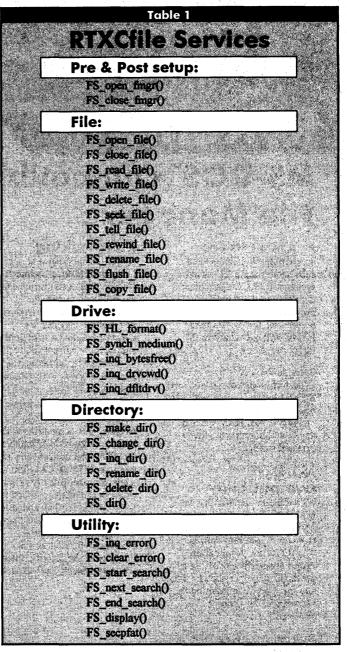

| Embedded<br>System Products | 1-713-561-9990      | Ron Hodge                             | US       | 1.713.516.9990  | Ron Hodge                             | RTXC            |  |  |  |  |  |  |

| R&D Publications            | 1-913-841-1631      | Customer Service                      | US       | 1.913.841.1631  | Customer Service                      | Labrosse MCU/OS |  |  |  |  |  |  |

| Simulators & Softwa         | re Generation Tools |                                       |          |                 |                                       |                 |  |  |  |  |  |  |

| Aisys                       | 1-800-397-7922      | Customer Service                      | IL       | 972.3.9226860   | Oren Katz                             | DriveWay-XA     |  |  |  |  |  |  |

| Archimedes                  | 1-206-822-6300      | Mary Sorensen                         | SW       | 41.61.331.7151  | Claude Vonlanthen                     | SimCASE51XA     |  |  |  |  |  |  |

| Pantasoft                   | 1-314-830-4084      | Roly Schwartzman                      | GE       | 49.6151.27505   | M. Kimron                             | DEBUG-XA        |  |  |  |  |  |  |

| Philips/Macraigor*          | 1-408-991-51XA      | Moti Kama                             | US       | 1.408.991.5192  | Moti Kama                             | Mcgtool         |  |  |  |  |  |  |

| Translators (80C51-         | toXA)               |                                       |          |                 |                                       |                 |  |  |  |  |  |  |

| Philips/Macraigor*          | 1-408-991-51XA      | Mike Thompson                         | US       | 1.408.991.5192  | Mike Thompson                         | Mcgtool         |  |  |  |  |  |  |

| Development Kits            |                     |                                       |          |                 |                                       |                 |  |  |  |  |  |  |

| CMX (Hi–Tech)               | 1-508-872-7675      | Charles Behrmann                      | UK       | 44.1.932.829460 | Charles Behrmann                      | XA DEV          |  |  |  |  |  |  |

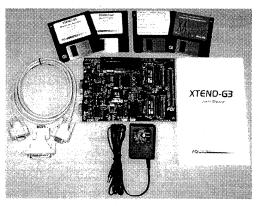

| Future Designs              | 1-205-830-4116      | Mark Hall                             | US       | 1-205-830-4116  | Mark Hall                             | XTEND-G3        |  |  |  |  |  |  |

| Philips/Macraigor           | 1-408-991-51XA      | Moti Kama                             | US       | 1.408.991.5192  | Moti Kama                             | P51XADBE SD     |  |  |  |  |  |  |

| EPROM Programme             | rs                  |                                       | •        |                 | ****                                  | •               |  |  |  |  |  |  |

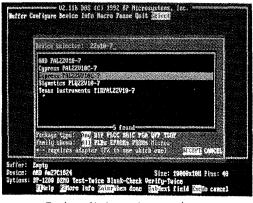

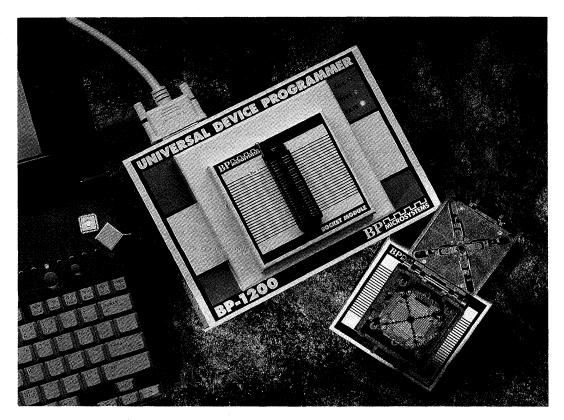

| BP Microsystems             | 1-800-225-2102      | Sales Department                      | US       | 1.713.688.4600  | Sales Department                      | BP-1200         |  |  |  |  |  |  |

| Ceibo                       | 1-314-830-4084      | Roly Schwartzman                      | GE       | 49.6151.27505   | M. Kimron                             | MP-51           |  |  |  |  |  |  |

| Data I/O Corp.              | 1-800-247-5700      | Tech Heip Desk                        | BE       | 32.1.638.0808   | Roland Appeltants                     | UniSite         |  |  |  |  |  |  |

| Adapters & Sockets          |                     |                                       | •        |                 | · · · · · · · · · · · · · · · · · · · |                 |  |  |  |  |  |  |

| EDI Corp                    | 1-702-735-4997      | Milos Krejcik                         | US       | 1.702.735.4997  | Milos Krejcik                         | 44PG/44PL       |  |  |  |  |  |  |

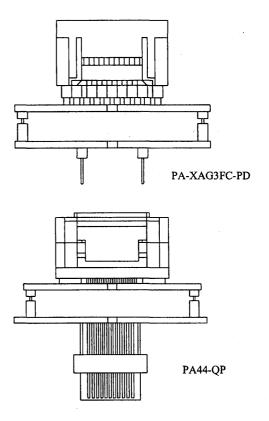

| Logical Systems             | 1-315-478-0722      | Lynn Burko                            | US       | 1.315.478.0722  | Lynn Burko                            | PA-XG3FC-44     |  |  |  |  |  |  |

|                             |                     | · · · · · · · · · · · · · · · · · · · | <u> </u> |                 |                                       | 1               |  |  |  |  |  |  |

\* The Philips cross assembler, simulator, and translator are available on the Philips FTP site at ftp://ftp.philipsMCU.com/pub. File name XA-TOOLS.ZIP

press 1 May 114 - May

# Microcontroller internet and bulletin board access

## **INTERNET ACCESS**

## Philips Semiconductors World Wide Web:

http://www.semiconductors.philips.com

## Internet XA 16-bit 80C51 Support Address:

XA\_help@sv.sc.philips.com

## **Microcontroller FTP Site:**

ftp://ftp.PhilipsMCU.com

### Internet Microcontroller Newsletter:

To subscribe, send email to: News-Request@PhilipsMCU.com

## Internet 80C51 Discussion Forum:

Forum-Request@PhilipsMCU.com

## Internet 80C51 Applications Support Address:

## 80C51\_help@sv.sc.philips.com

Send us your questions and we will respond quickly.

# Microcontroller internet and bulletin board access

## **BULLETIN BOARDS**

To better serve our customers, Philips maintains a microcontroller bulletin board. This computer bulletin board system features microcontroller newsletters, application and demonstration programs for download.

The telephone numbers is:

## European Bulletin Board MAX 14.400 baud Standards V32/V42/V42.bis/HST +31 40 2721102

## Sunnyvale ROMcode Bulletin Board

We also have a ROM code bulletin board through which you can submit ROM codes. This is a closed bulletin board for security reasons. To get an ID, contact your local sales office. The system can be accessed with a 2400, 1200, or 300 baud modem, and is available 24 hours a day.

The telephone number is:

## (408) 991-3459

All code for application notes in this databook are available on the Philips web site.

wa water and the firm

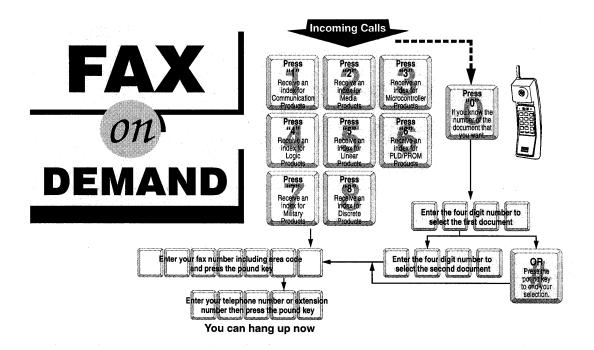

## FAX-on-DEMAND System

#### What is it?

The FAX-on-DEMAND system is a computer facsimile system that allows customers to receive selected documents by fax automatically.

#### How does it work?

To order a document, you simply enter the document number. This number can be obtained by asking for an index of available documents to be faxed to you the first time you call the system.

Our system has a selection of the latest product data sheets from Philips with varying page counts. As you know, it takes approximately one minute to FAX one page. This isn't bad if the number of pages is less than 10. But if the document is 37 pages long, be ready for a long transmission!

Philips Semiconductors also maintains product information on the World-Wide Web. Our home page can be located at:

http://www.semiconductors.philips.com

# Who do I contact if I have a question about FAX-on-DEMAND?

Contact your local Philips sales office.

#### FAX-on-DEMAND phone numbers:

| England<br>(United Kingdom, Ireland) | 44-181-730-5020  |

|--------------------------------------|------------------|

| France                               | 33-1-40-99-60-60 |

| Italy                                | 39-167-295502    |

| North America                        | 1-800-282-2000   |

#### Locations soon to be in operation: Hong Kong Japan The Netherlands

1997 Mar 04

#### 8400 FAMILY CMOS

| TYPE                                                                                                                           | ROM                                                                  | RAM                                                                | SPEED<br>(MHz)                                                 | PACKAGE                                              | FUNCTIONS                                                                                                                 | REMARKS                                                                                                                                                                          | PROBE<br>SDS          | REMARKS                                                                                                   |

|--------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|--------------------------------------------------------------------|----------------------------------------------------------------|------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|-----------------------------------------------------------------------------------------------------------|

| 84C21A<br>84C41A<br>84C81A                                                                                                     | 2k<br>4k<br>8k                                                       | 64<br>128<br>256                                                   | 10<br>10<br>10                                                 | DIL28/SO28<br>DIL28/SO28<br>DIL28/SO28               | 20 I/O lines<br>8-bit timer<br>Byte I <sup>2</sup> C                                                                      |                                                                                                                                                                                  | OM1083                | OM1025<br>(LSDS)                                                                                          |

| 84C22A<br>84C42A<br>84C12A                                                                                                     | 2k<br>4k<br>1k                                                       | 64<br>64<br>64                                                     | 10<br>10<br>16                                                 | DIL20/SO20<br>DIL20/SO20<br>DIL20/SO20<br>DIL20/SO20 | 13 I/O lines<br>8-bit timer                                                                                               |                                                                                                                                                                                  | OM1083 +<br>Adapter_1 | OM1025<br>(LSDS)                                                                                          |

| 84C00B                                                                                                                         | 0                                                                    | 256                                                                | 10                                                             | 28 pins                                              | 20 I/O lines<br>8-bit timer<br>Byte I <sup>2</sup> C                                                                      | Piggyback                                                                                                                                                                        | OM1080                |                                                                                                           |

| 84C00T                                                                                                                         | 0                                                                    | 256                                                                | 10                                                             | VSO-56                                               | -,                                                                                                                        | ROMIess                                                                                                                                                                          | OM1080                |                                                                                                           |

| 84C121                                                                                                                         | 1k                                                                   | 64                                                                 | 10                                                             | DIL20/SO20                                           | 13 I/O lines<br>2 8-bit timers<br>8 bytes                                                                                 |                                                                                                                                                                                  | OM1073                | OM1025(LEDS)                                                                                              |

| 84C121B                                                                                                                        | 0                                                                    | 64                                                                 | 10                                                             |                                                      | EEPROM                                                                                                                    | Piggyback                                                                                                                                                                        |                       | OM1027                                                                                                    |

| 84C122A<br>84C122B                                                                                                             | 1k                                                                   | 32                                                                 | 10                                                             | A: SO20<br>B: SO24                                   | Controller for<br>remote control                                                                                          |                                                                                                                                                                                  | OM4830                |                                                                                                           |

| 84C422A<br>84C422B                                                                                                             | 4K                                                                   | 32                                                                 |                                                                | C: SO28                                              | A: 12 I/O<br>B: 16 I/O                                                                                                    |                                                                                                                                                                                  |                       |                                                                                                           |

| 84C822A<br>84C822B<br>84C822B<br>84C822C                                                                                       | 8К                                                                   | 32                                                                 |                                                                |                                                      | C: 20 1/O                                                                                                                 |                                                                                                                                                                                  |                       |                                                                                                           |

| 84C230                                                                                                                         | 21                                                                   | 64                                                                 | 10                                                             | DIL40/VSO40                                          | 12 I/O lines<br>8-bit timer<br>16*4 LCD drive                                                                             |                                                                                                                                                                                  | OM1072                |                                                                                                           |

| 84C430                                                                                                                         | 4k                                                                   | 128                                                                | 10                                                             | QFP64                                                | 24 I/O lines<br>8-bit timer<br>Byte I <sup>2</sup> C<br>24*4 LCD drive                                                    |                                                                                                                                                                                  | OM1072                |                                                                                                           |

| 84C430BH                                                                                                                       | 0                                                                    | 128                                                                | 10                                                             |                                                      | 5                                                                                                                         | Piggyback for C230<br>and C430                                                                                                                                                   |                       | -                                                                                                         |

| 84C633<br>84C633B                                                                                                              | 6k<br>0                                                              | 256                                                                | 16<br>16                                                       | VSO56                                                | 28 I/O lines<br>8-bit timer<br>16-bit up/down<br>counter<br>16-bit timer<br>with compare<br>and capture<br>16*4 LCD drive |                                                                                                                                                                                  | ОМ1086                |                                                                                                           |

| 84C440<br>84C441<br>84C443<br>84C444<br>84C640<br>84C641<br>84C643<br>84C643<br>84C644<br>84C840<br>84C841<br>84C841<br>84C843 | 4k<br>4k<br>4k<br>6k<br>6k<br>6k<br>6k<br>8k<br>8k<br>8k<br>8k<br>8k | 128<br>128<br>128<br>128<br>128<br>128<br>128<br>128<br>128<br>128 | 10<br>10<br>10<br>10<br>10<br>10<br>10<br>10<br>10<br>10<br>10 | DIP42 shrunk                                         | RC: 29 I/O lines<br>LC: 28 I/O lines<br>8-bit timer<br>1 14-bit PWM<br>3-bit ADC<br>OSD 2L-16                             | 1 <sup>2</sup> C, RC<br>1 <sup>2</sup> C, LC<br>RC<br>LC<br>1 <sup>2</sup> C, RC<br>1 <sup>2</sup> C, LC<br>LC<br>1 <sup>2</sup> C, RC<br>1 <sup>2</sup> C, LC<br>RC<br>LC<br>LC | OM1074                | For emulation of<br>LC versions,<br>use OM1074 +<br>adapter_3 +<br>2 adapter_5<br>Baud for LCDS<br>OM4831 |

### 8400 FAMILY CMOS (Continued)

| TYPE              | ROM      | RAM        | SPEED<br>(MHz) | PACKAGE                    | FUNCTIONS                                                                                                                                                                                                                                                            | REMARKS                                      | PROBE<br>SDS       | REMARKS              |

|-------------------|----------|------------|----------------|----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|--------------------|----------------------|

| 84C646<br>84C846  | 6k<br>8k | 192<br>192 | 10<br>10       | DIP42 shrunk               | 30 I/O lines<br>DOS clock =<br>PLL<br>8 bit timer<br>1-14 bit PWM<br>4-7 bit PWM<br>3-4 bit ADC<br>DOS: 64 disp.<br>RAM<br>62 char, fonts<br>Char, blinking<br>Shadow modes<br>8 foreground<br>colors/char.<br>8 background<br>colors/word<br>DOS: clock:<br>8 20MHz | 1 <sup>2</sup> C, RC<br>1 <sup>2</sup> C, RC | OM4829 +<br>OM4832 | OM4833 for<br>LCD584 |

| 84C85             | 8k       | 256        | 10             | DIL40/VSO40                | 32 I/O lines<br>8-bit timer<br>Byte I <sup>2</sup> C                                                                                                                                                                                                                 |                                              | OM1070             |                      |

| 84C85B            | 0        | 256        | 10             |                            |                                                                                                                                                                                                                                                                      | Piggyback for C85                            |                    |                      |

| 84C853<br>84C853B | 8k<br>0  | 256        | 16             | DIL40/VSO40                | 33 I/O lines<br>8-bit timer<br>16-bit up/down<br>counter<br>16-bit timer with<br>compare and<br>capture                                                                                                                                                              | Piggyback for C853                           | OM1081             |                      |

| 84C270<br>84C470  | 2k<br>4k | 128<br>128 | 10<br>10<br>10 | DIL40/VSO40<br>DIL40/VSO40 | 8 I/O lines<br>16*8 capture<br>keyboard matrix                                                                                                                                                                                                                       | Tiggyback for 0000                           | OM1077             |                      |

| 84C270B           | 0        | 128        | 10             |                            | 8-bit timer                                                                                                                                                                                                                                                          | Piggyback for C270                           |                    |                      |

| 84C470B           | 0        | 128        | 10             |                            | 470 also<br>handles mech.<br>keys                                                                                                                                                                                                                                    | Piggyback for C470                           |                    |                      |

| 84C271            | 2k       | 128        | 10             | DIL40                      | 8 I/O lines<br>16*8 mech.<br>keyboard matrix<br>8-bit timer                                                                                                                                                                                                          |                                              | OM1078             |                      |

#### 8400 FAMILY NMOS

| TYPE                         | ROM                  | RAM                    | SPEED<br>(MHz) | PACKAGE                                                            | FUNCTIONS                                            | REMARKS            | EMULATOR<br>TOOLS | REMARKS                      |

|------------------------------|----------------------|------------------------|----------------|--------------------------------------------------------------------|------------------------------------------------------|--------------------|-------------------|------------------------------|

| 8411<br>8421<br>8441<br>8461 | 1k<br>2k<br>4k<br>6k | 64<br>64<br>128<br>128 | 6<br>6<br>6    | DIL28/SO28<br>DIL28/SO28<br>DIL28/SO28<br>DIL28/SO28<br>DIL28/SO28 | 20 I/O lines<br>8-bit timer<br>Byte I <sup>2</sup> C |                    |                   | OM1025<br>(LCDS) +<br>OM1026 |

| 8422<br>8442                 | 2k<br>4k             | 64<br>128              | 6<br>6         | DIL20<br>DIL20                                                     | 13 I/O lines<br>8-bit timer<br>Bit I <sup>2</sup> C  |                    |                   |                              |

| 8401B                        | 0                    | 128                    | 6              | 28-pin                                                             |                                                      | Piggyback for 84X1 |                   |                              |

#### 3300 FAMILY CMOS

| TYPE  | ROM  | RAM | SPEED<br>(MHz) | PACKAGE    | FUNCTIONS                                                                                          | REMARKS                        | PROBE<br>SDS          | REMARKS                  |

|-------|------|-----|----------------|------------|----------------------------------------------------------------------------------------------------|--------------------------------|-----------------------|--------------------------|

| 3315A | 1.5k | 160 | 10             | DIL28/SO28 | 20 I/O lines<br>8-bit timer<br>V <sub>DD</sub> > 1.8V                                              |                                | OM1083                | OM1025(LCDS)             |

| 3343  | Зk   | 224 | 10             | DIL28/SO28 | 20 I/O lines<br>8-bit timer<br>V <sub>DD</sub> > 1.8V<br>Byte I <sup>2</sup> C                     |                                | OM1083                | OM1025(LCDS)             |

| 3344A | 2k   | 224 | 3.58           | DIL28/SO28 | 20 I/O lines<br>8-bit timer<br>DTMF generator                                                      |                                | OM1071                | OM1025(LCDS)<br>+ OM1028 |

| 3346A | 4k   | 128 | 10             | DIL28/SO28 | 20 I/O lines<br>8-bit timer<br>Byte I <sup>2</sup> C<br>256 bytes EEPROM<br>V <sub>DD</sub> < 1.8V |                                | OM1076                |                          |

| 3347  | 1.5k | 64  | 3.58           | DIL20/SO20 | 12 I/O lines<br>8-bit timer<br>DTMF generator                                                      |                                | OM1071 +<br>Adapter_2 | OM1025(LCDS)<br>+ OM1028 |

| 3348A | 8k   | 256 | 10             | DIL28/SO28 | 20 I/O lines<br>8-bit timer<br>Byte $I^2$ C<br>V <sub>DD</sub> < 1.8V                              |                                | OM1083                | OM1025(LCDS)             |

| 3349A | 4k   | 224 | 3.58           | DIL28/SO28 | 20 I/O lines<br>8-bit timer<br>DTMF generator                                                      |                                | OM1071                | OM1025(LCDS)<br>+ OM1028 |

| 3350A | 8k   | 128 | 3.58           | VSO64      | 30 I/O lines<br>8-bit timer<br>DTMF generator<br>256 bytes EEPROM                                  |                                |                       |                          |

| 3351A | 2k   | 64  | 3.58           | DIL28/SO28 | 20 I/O lines<br>8-bit timer<br>DTMF generator<br>128 bytes EEPROM                                  |                                | OM5000                |                          |

| 3352A | 6k   | 128 | 3.58           | DIL28/SO28 | 20 I/O lines<br>8-bit timer<br>DTMF generator<br>128 byte EEPROM                                   |                                | OM5000                |                          |

| 3353A | 6k   | 128 | 16             | DIL28/SO28 | 20 I/O lines<br>8-bit timer<br>DTMF generator<br>Ringer out<br>128 bytes EEPROM                    | March '92                      | OM5000                |                          |

| 3354A | 8k   | 256 | 16             | QFP64      | 36 I/O lines<br>8-bit timer<br>DTMF generator<br>Ringer out<br>256 bytes EEPROM                    | June '92                       | OM4829 +<br>OM5003    | OM4829: Probe<br>base    |

| 8755A | 0    | 128 | 16             | DIL28/SO28 | 8k OTP<br>20 I/O lines<br>8-bit timer<br>DTMF generator<br>Melody output<br>128 bytes EEPROM       | In Development                 |                       |                          |

| 3301B |      |     |                |            |                                                                                                    | Piggyback for 3315, 3343, 3348 | OM1083                |                          |

| 3344B |      |     |                |            |                                                                                                    | Piggyback for 3344, 3347, 3349 | OM1071                |                          |

| 3346B |      | 1   |                |            |                                                                                                    | Piggyback for 3346             | OM1076                | 1                        |

Bare Bare Law . ....

| 3300 | FAMILY | CMOS | (Continued) |

|------|--------|------|-------------|

|------|--------|------|-------------|

| TYPE  | ROM | RAM | SPEED<br>(MHz) | PACKAGE | FUNCTIONS | REMARKS                                 | PROBE<br>SDS      | REMARKS |

|-------|-----|-----|----------------|---------|-----------|-----------------------------------------|-------------------|---------|

| 3350B |     |     |                |         |           | Piggyback for 3350A                     | OM4829+<br>OM5003 |         |

| 3351B |     |     |                |         |           | Piggyback for<br>3351A, 3352A,<br>3353A | OM5000            |         |

| 3354B |     |     |                |         |           | Piggyback for 3354A                     | OM4829+<br>OM5010 |         |

## CMOS 16-bit microcontroller family

| TYPE  | (EP)ROM | RAM | SPEED<br>(MHz) | FUNCTIONS                      | REMARKS          | DEVELOPMENT TOOLS                    |

|-------|---------|-----|----------------|--------------------------------|------------------|--------------------------------------|

| XA-G1 | 8k      | 512 | 30             | 3 timers, watchdog,<br>2 UARTs | -40 to<br>+125°C | Nohau<br>Ceibo<br>MacCraigor Systems |

| XA-G2 | 16k     | 512 | 30             | 3 timers, watchdog,<br>2 UARTs | -40 to<br>+125°C | Nohau<br>Ceibo<br>MacCraigor Systems |

| XA-G3 | 32k     | 512 | 30             | 3 timers, watchdog,<br>2 UARTs | -40 to<br>+125°C | Nohau<br>Ceibo<br>MacCraigor Systems |

#### 16-BIT CONTROLLERS (XA ARCHITECTURE)

#### 16-BIT CONTROLLERS (68000 ARCHITECTURE)

| TYPE    | (EP)ROM                 | RAM                     | SPEED<br>(MHz) | FUNCTIONS                                                                                                            | REMARKS               | PHILIPS TOOLS                                                                                                                                                                                                          | THIRD-PARTY<br>TOOLS             |

|---------|-------------------------|-------------------------|----------------|----------------------------------------------------------------------------------------------------------------------|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

| 68070   | -                       | -                       | 17.5           | 2 DMA channels,<br>MMU, UART,<br>16-bit timer, I <sup>2</sup> C,<br>68000 bus interface,<br>16Mb address range       |                       | OM4160 Microcore 1<br>OM4160/2 Microcore 2<br>OM4161 (SBE68070)<br>OM4767/2 XRAY68070SBE<br>high level symbolic debugger<br>OM4222 68070DS development<br>system<br>OM4226 XRAY68070DS<br>high level symbolic debugger | TRACE32-ICE68070<br>(Lauterbach) |

| 93C101  | 34k                     | 512                     | 15             | Derivative with low<br>power modes                                                                                   | Not for new<br>design |                                                                                                                                                                                                                        |                                  |

| 90CE201 | 16MB<br>external<br>ROM | 16MB<br>external<br>RAM | 24             | UART, fast I <sup>2</sup> C,<br>3 timers (16 bit),<br>Watchdog timer.<br>68000 software<br>compatible, EMC,<br>QFP64 | –25 to<br>+85°C       | OM4162 Microcore 4                                                                                                                                                                                                     | TRACE32 –<br>(Lauterbach)        |

International Party International

|     | Part Number       |     | Memory |     | Counter              | Counter I/O | Serial                 | External  | Comments/                                                                              |

|-----|-------------------|-----|--------|-----|----------------------|-------------|------------------------|-----------|----------------------------------------------------------------------------------------|

|     | (ROMiess)         | ROM | EPRM   | RAM | Timers               | Port        | Interfaces             | Interrupt | Special Features                                                                       |

| Р   | 83C750            | 1K  | 1.1    | 64  | 1 (16-bit)           | 2-3/8       | · -                    | 2         | 40 MHz, Lowest cost, SSOP                                                              |

| Р   | 87C750            |     | 1K     | 64  | 1 (16-bit)           | 2-3/8       | <b>.</b>               | 2         | 40 MHz, Lowest cost, SSOP                                                              |

| Р   | 83C748            | 2K  |        | 64  | 1 (16-bit)           | 2-3/8       | -                      | 2         | 8XC751 w/o I <sup>2</sup> C, SSOP                                                      |

| Р   | 87C748            |     | 2K     | 64  | 1 (16-bit)           | 2-3/8       | •                      | 2         | 8XC751 w/o I <sup>2</sup> C, SSOP                                                      |

| S   | 83C751            | 2K  |        | 64  | 1 (16-bit)           | 2-3/8       | l <sup>2</sup> C (bit) | 2         | 24-pin Skinny DIP, SSOP                                                                |

| S   | 87C751            |     | 2K     | 64  | 1 (16-bit)           | 2-3/8       | I <sup>2</sup> C (bit) | 2         | 24-pin Skinny DIP, SSOP                                                                |

| Р   | 83C749            | 2K  |        | 64  | 1 (16-bit)           | 2-5/8       | -                      | 2         | 8XC752 w/o I <sup>2</sup> C, SSOP                                                      |

| Р   | 87C749            |     | 2K     | 64  | 1 (16-bit)           | 2-5/8       |                        | 2         | 8XC752 w/o I <sup>2</sup> C, SSOP                                                      |

| S   | 83C752            | 2K  |        | 64  | 1 (16-bit)           | 2-5/8       | I <sup>2</sup> C (bit) | 2         | 5 Channel 8-bit A/D, PWM Output, SSOP                                                  |

| S   | 87C752            |     | 2K     | 64  | 1 (16-bit)           | 2-5/8       | I <sup>2</sup> C (bit) | -2        | 5 Channel 8-bit A/D, PWM Output, SSOP                                                  |

| SC  | 80C51 (80C31)     | 4K  |        | 128 | 2                    | 4           | UART                   | 2         | CMOS (Sunnyvale)                                                                       |

| PCx | 80C51 (80C31)     | 4K  |        | 128 | 2                    | 4           | UART                   | 2         | CMOS (Hamburg)                                                                         |

| SC  | 87C51             |     | 4K     | 128 | 2                    | 4           | UART                   | 2         | CMOS                                                                                   |

| Ρ   | 80CL51 (80CL31)   | 4K  |        | 128 | 2                    | 4           | UART                   | 10        | Low Voltage (1.8V to 6V), Low Power                                                    |

| Р   | 83CL410 (80CL410) | 4K  |        | 128 | 2                    | 4           | I <sup>2</sup> C       | 10        | Low Voltage (1.8V to 6V), Low Power                                                    |

| SC  | 83C451 (80C451)   | 4K  |        | 128 | 2                    | 7           | UART                   | 2         | Extended I/O, Processor Bus Interface                                                  |

| SC  | 87C451            |     | 4K     | 128 | 2                    | 7           | UART                   | 2         | Extended I/O, Processor Bus Interface                                                  |

| Р   | 83C550 (80C550)   | 4K  |        | 128 | 2 + Watchdog         | 4           | UART                   | 2         | 8 Channel 8-bit A/D                                                                    |

| Ρ   | 87C550            |     | 4K     | 128 | 2 + Watchdog         | 4           | UART                   | 2         | 8 Channel 8-bit A/D                                                                    |

| Ρ   | 83C851 (80C851)   | 4K  |        | 128 | 2                    | 4           | UART                   | 2         | 256B EEPROM, 80C51 Pin compatible                                                      |

| Ρ   | 83C852            | 6K  |        | 256 | 2 (16-bit)           | 2/8         | -                      | 1         | Smartcard Controller with 2K EEPROM (Data,<br>Code) Cryptographic Calc Unit            |

| Ρ   | 83CL580 (80CL580) | 6K  |        | 256 | 3 + Watchdog         | 5           | UART, I <sup>2</sup> C | 9         | 4 Channel 8-bit A/D, PWM Output,<br>Low Voltage (2.5V to 6V), Low Power                |

| Ρ   | 80C52 (80C32)     | 8K  |        | 256 | 3                    | 4           | UART                   | 2         | 80C51 Pin Compatible                                                                   |

| Р   | 87C52             |     | 8K     | 256 | 3                    | 4           | UART                   | 2         | (see above)                                                                            |

| P   | 83C652 (80C652)   | 8К  |        | 256 | 2                    | 4           | UART, I <sup>2</sup> C | 2         | 80C51 Pin Compatible                                                                   |

| S   | 87C652            |     | 8K     | 256 | 2                    | 4           | UART, I <sup>2</sup> C | 2         | (see above)                                                                            |

| Ρ   | 83C453 (80C453)   | 8K  |        | 256 | 2                    | 7           | UART                   | 2         | Extended I/O, Processor Bus Interface                                                  |

| р   | 87C453            |     | 8K     | 256 | 2                    | 7           | UART                   | 2         | Extended I/O, Processor Bus Interface                                                  |

| S   | 83C51FA (80C51FA) | 8K  |        | 256 | 3 + PCA              | 4           | UART                   | 2         | Enhanced UART, 3 timers + PCA                                                          |

| S   | 87C51FA           |     | 8K     | 256 | 3 + PCA              | 4           | UART                   | 2         | Enhanced UART, 3 timers + PCA                                                          |

| S   | 83L51FA           | 8K  |        | 256 | 3 + PCA              | 4           | UART                   | 2         | Low Voltage 83C51FA (3V @ 20MHz)                                                       |

| S   | 87L51FA           |     | 8K     | 256 | 3 + PCA              | 4           | UART                   | 2         | Low Voltage OTP 87C51FA (3V @ 20MHz)                                                   |

| Ρ   | 83C575 (80C575)   | 8K  |        | 256 | 3 + PCA+<br>Watchdog | 4           | UART                   | 2         | High Reliability, with Low Voltage Detect,<br>OSC Fail Detect, Analog Comparators, PCA |

| Ρ   | 87C575            |     | 8K     | 256 | (see above)          | 4           | UART                   | 2         | (see above)                                                                            |

| Ρ   | 83C576 (80C576)   | 8K  |        | 256 | 3 + PCA+<br>Watchdog | 4           | UART                   | 2         | Same as 8XC575 plus UPI and 10-bit A/D                                                 |

| Р   | 87C576            |     | 8K     | 256 | (see above)          | 4           | UART                   | 2         | (see above)                                                                            |

| PC  | 83C562 (80C562)   | 8K  |        | 256 | 3 + Watchdog         | 6           | UART                   | 2         | 8 Channel 8-bit A/D, 2 PWM Outputs,<br>Capture/Compare Timer                           |

| PCx | 83C552 (80C552)   | 8K  |        | 256 | 3 + Watchdog         | 6           | UART, I <sup>2</sup> C | 2         | 8 Channel 10-bit A/D, 2 PWM Outputs,<br>Capture/Compare Timer                          |

| s   | 87C552            |     | 8K     | 256 | 3 + Watchdog         | 6           | UART, I <sup>2</sup> C | 2         | (see above)                                                                            |

Notes: Part number prefixes are noted in the first column. All combinations of part type, speed, temperature and package may not be available.

| Part Number       | Program | Clock Freq | Terr        | nperature Ran | iges (°C)  | Package     |                |      |         |      |              |

|-------------------|---------|------------|-------------|---------------|------------|-------------|----------------|------|---------|------|--------------|

| (ROMIess)         |         | Security?  | (MHz)       | 0 to 70       | -40 to +85 | -55 to +125 | PDIP           | CDIP | PLCC    | CLCC | PQFP/SSOP    |

| 83C750            | S       | N          | 3.5 to 40   | X             | X          |             | N24            | F24  | A28     |      | DB24 (0-70F) |

| 87C750            | s       | Y          | 3.5 to 40   | X             | X          |             | N24            | F24  | A28     |      | DB24 (0-70F) |

| 83C748            | S       | N          | 3.5 to16    | Х             | Х          |             | N24            |      | A28     |      | DB24 (0-70F) |

| 87C748            | s       | Y          | 3.5 to16    | х             | x          |             | N24            | F24  | A28 .   |      | DB24 (0-70F) |

| 83C751            | s       | N          | 3.5 to16    | х             | x          |             | N24            |      | A28     |      | DB24 (0-70F) |

| 87C751            | s       | Y          | 3.5 to16    | х             | х          |             | N24            | F24  | A28     |      | DB24 (0-70F) |

| 83C749            | S       | N          | 3.5 to 16   | х             | Х          |             | N28            |      | A28     |      | DB28 (0-70F) |

| 87C749            | s       | Y          | 3.5 to 16   | x             | ×          |             | N28            | F28  | A28     |      | DB28 (0-70F) |

| 83C752            | S       | N          | 3.5 to 16   | х             | Х          | Х           | N28            |      | A28     |      | DB28 (0-70F) |

| 87C752            | S       | Y          | 3.5 to 16   | х             | Х          | ×           | N28            | F28  | A28     |      | DB28 (0-70F) |

| SC80C51 (80C31)   | S       | Y          | 3.5 to 33   | Х             | Х          | ×           | N40            |      | A44     |      | B44 (5)      |

| PCx80C51 (80C31)  | н       | N          | 1.2 to 30   | х             | Х          | x           | P (40)         |      | WP (44) |      | H (44)       |

| 87C51             | s       | Y          | 3.5 to 33   | х             | х          | x           | N40            | F40  | A44     | K44  | B44 (5)      |

| 80CL51 (80CL31)   | Z       | N          | 0 to 16 (1) |               | х          |             | N40 (2)        |      |         |      | B44          |

| 83CL410(80CL410)  | Z       | N          | 0 to 12 (1) |               | х          | 1           | N40 (2)        |      |         |      | B44          |

| 83C451 (80C451)   | s       | N          | 3.5 to 16   | х             | х          | x           | N64 (4)        |      | A68     |      |              |

| 87C451            | s       | Y          | 3.5 to16    | х             | х          | ×           | N64 (4)        |      | A68     |      |              |

| 83C550 (80C550)   | s       | Y          | 3.5 to 16   | Х             | х          |             | N40            |      | A44     |      |              |

| 87C550            | s       | Y          | 3.5 to 16   | х             | X          | -40 to +125 | N40            | F40  | A44     | K44  | 1            |

| 83C851 (80C851)   | н       | Y          | 1.2 to 16   | Х             | х          |             | N40            |      | A44     |      | B44          |

| 83C852            | н       | Y          | 1 to 12     | X             |            |             | SO28<br>or die |      |         |      |              |

| 83CL580 (80CL580) | Z       | N          | 0 to 12 (1) |               | X          |             | (3)            |      |         |      | B64          |

| 80C52 (80C32)     | S       | Y          | 3.5 to 24   | Х             | Х          |             | N40            |      | A44     | ·    | B44 (5)      |

| 87C52             | s       | Y          | 3.5 to 24   | Х             | Х          | ×           | N40            | F40  | A44     | K44  | B44 (5)      |

| 83C652 (80C652)   | н       | Y          | 1.2 to 24   | х             | х          | -40 to +125 | N40            |      | A44     |      | B44          |

| 87C652            | S       | Y          | 1.2 to 20   | х             | х          | x           | N40            | F40  | A44     | K44  |              |

| 83C453 (80C453)   | s       | N          | 3.5 to 16   | х             | Х          |             |                |      | A68     |      |              |

| 87C453            | s       | Y          | 3.5 to16    | х             | X          |             |                |      | A68     |      |              |

| 83C51FA (80C51FA) | s       | Y          | 3.5 to 24   | Х             | Х          |             | N40            |      | A44     |      | B44          |

| 87C51FA           | s       | Y          | 3.5 to 24   | х             | X          |             | N40            | F40  | A44     | K44  | B44          |

| 83L51FA           | s       | Y          | 3.5 to 20   | х             | х          |             | N40            |      | A44     |      | B44          |

| 87L51FA           | s       | Y          | 3.5 to 20   | х             | X          |             | N40            | F40  | A44     | K44  | B44          |

| 83C575 (80C575)   | s       | Ŷ          | 4 to 16     | ×             |            | ×           | N40            |      | A44     |      | B44          |

| 87C575            | s       | Y          | 4 to 16     | х             |            | X           | N40            | F40  | A44     | K44  | B44          |

| 83C576 (80C576)   | s       | Y          | 4 to 16     | x             |            | x           | N40            |      | A44     |      | B44          |

| 87C576            | s       | Y          | 4 to 16     | х             |            | х           | N40            | F40  | A44     | K44  | B44          |

| 83C562 (80C562)   | н       | N          | 1.2 to 16   | x             | x          | -40 to +125 |                |      | A68     |      | B80          |

| 83C552 (80C552)   | н       | N          | 1.2 to 30   | х             | x          | -40 to +125 |                |      | A68     |      | B80          |

| 87C552            | s       | Y          | 1.2 to 16   | x             |            |             | <b> </b>       |      | A68     | K68  |              |

Notes: Production Centers are indicated in the second column: H – Hamburg, S – Sunnyvale, Z – Zurich. All combinations of part type, speed, temperature and package may not be available.

1) Oscillator options start from 32kHz.

2) Also available in VSO40 package.

3) Also available in VSO56 Package.

4) Not recommended for new design.

5) Package available up to 16 MHz only.

No. Pr. Harling. Pr.

| Part Number |                   | Memory |      |      | Counter      | 1/0   | Serial                     | External  | Comments/                                                                       |

|-------------|-------------------|--------|------|------|--------------|-------|----------------------------|-----------|---------------------------------------------------------------------------------|

|             | (ROMless)         | ROM    | EPRM | RAM  | Timers       | Port  | Interfaces                 | Interrupt | Special Features                                                                |

| P           | 83C055            | 16K    |      | 256  | 2 (16-bit)   | 3 1/2 | -                          | 2         | On-Screen Display, 9 PWM Outputs,<br>3 Software A/D Inputs                      |

| Ρ           | 87C055            |        | 16K  | 256  | 2 (16-bit)   | 3 1/2 | -                          | 2         | (see above)                                                                     |

| Ρ           | 80C54             | 16K    |      | 256  | 3            | 4     | UART                       | 2         | Standard; 80C51 compatible                                                      |

| Р           | 87C54             |        | 16K  | 256  | 3            | 4     | UART                       | 2         | Standard; 87C51 compatible                                                      |

| P           | 83C654            | 16K    |      | 256  | 2            | 4     | UART, I <sup>2</sup> C     | 2         | 80C51 Pin Compatible                                                            |

| s           | 87C654            |        | 16K  | 256  | 2            | 4     | UART, I <sup>2</sup> C     | 2         | (see above)                                                                     |

| Ρ           | 83CE654           | 16K    |      | 256  | 2            | 4     | UART, I <sup>2</sup> C     | 2         | 83C654 with Reduced EMI                                                         |

| Ρ           | 83CL781           | 16K    |      | 256  | 3            | 4     | UART, I <sup>2</sup> C     | 10        | Low Voltage (1.8V to 6V), Low Power                                             |

| Ρ           | 83CL782           | 16K    |      | 256  | 3            | 4     | UART, I <sup>2</sup> C     | 10        | 83CL781 Optimized 12MHz @ 3.1V                                                  |

| S           | 83C51FB           | 16K    |      | 256  | 3 + PCA      | 4     | UART                       | 2         | Enhanced UART, 3 timers + PCA                                                   |

| S           | 87C51FB           |        | 16K  | 256  | 3 + PCA      | 4     | UART                       | 2         | Enhanced UART, 3 timers + PCA                                                   |

| S           | 83L51FB           | 16K    |      | 256  | 3 + PCA      | 4     | UART                       | 2         | Low Voltage 83C51FB (3V @ 20MHz)                                                |

| s           | 87L51FB           |        | 16K  | 256  | 3 + PCA      | 4     | UART                       | 2         | Low Voltage OTP 87C51FB (3V @ 20MHz)                                            |

| Ρ           | 83C524            | 16K    |      | 512  | 3 + Watchdog | 4     | UART, I <sup>2</sup> C-bit | 2         | 512 RAM                                                                         |

| Ρ           | 87C524            |        | 16K  | 512  | 3 + Watchdog | 4     | UART, I <sup>2</sup> C-bit | 2         | 512 RAM                                                                         |

| Ρ           | 83C592 (80C592)   | 16K    |      | 512  | 3 + Watchdog | 6     | UART, CAN                  | 6         | CAN Bus Controller with 8 x 10-bit A/D,<br>2 PWM outputs, Capture/Compare Timer |

| Ρ           | 87C592            |        | 16K  | 512  | 3 + Watchdog | 6     | UART, CAN                  | 6         | (see above)                                                                     |

| Ρ           | 80C58             | 32K    |      | 256  | 3            | 4     | UART                       | 2         | Standard; 80C51 compatible                                                      |

| Ρ           | 87C58             |        | 32K  | 256  | 3            | 4     | UART                       | 2         | Standard; 87C51 compatible                                                      |

| s           | 83C51FC           | 32K    |      | 256  | 3 + PCA      | 4     | UART                       | 2         | Enhanced UART, 3 timers + PCA                                                   |

| s           | 87C51FC           |        | 32K  | 256  | 3 + PCA      | 4     | UART                       | 2         | Enhanced UART, 3 timers + PCA                                                   |

| Ρ           | 83C528 (80C528)   | 32K    |      | 512  | 3 + Watchdog | 4     | UART, I <sup>2</sup> C-bit | 2         | Large Memory for High Level Languages                                           |

| Р           | 87C528            |        | 32K  | 512  | 3 + Watchdog | 4     | UART, I <sup>2</sup> C-bit | 2         | Large Memory for High Level Languages                                           |

| Р           | 83CE528 (80CE528) | 32K    |      | 512  | 3 + Watchdog | 4     | UART, I <sup>2</sup> C-bit | 2         | 8XC528 with Reduced EMI                                                         |

| P           | 83CE598 (80CE598) | 32K    |      | 512  | 3 + Watchdog | 6     | UART, CAN                  | 6         | CAN Bus Controller, 8 x 10-bit A/D,<br>2 PWM outputs, WD, T2, Reduced EMI       |

| Ρ           | 87CE598           |        | 32K  | 512  | 3 + Watchdog | 6     | UART, CAN                  | 6         | (see above)                                                                     |

| Ρ           | 83CE558(80CE558)  | 32K    |      | 1024 | 3 + Watchdog | 6     | UART, I <sup>2</sup> C     | 2         | Low EMI, 8 Channel 10-bit A/D,<br>2 PWM Outputs, Capture/Compare Timer          |

| Р           | 89CE558           | 1      | 32K  | 1024 | 3 + Watchdog | 6     | UART, I <sup>2</sup> C     | 2         | 32K FLash EEPROM plus above                                                     |

Notes: Part number prefixes are noted in the first column. All combinations of part type, speed, temperature and package may not be available.

| Part Number       |   | Program   | Clock Freq  | Terr    | perature Ran | ges (°C)    |             |          | Package |      |           |

|-------------------|---|-----------|-------------|---------|--------------|-------------|-------------|----------|---------|------|-----------|

| (ROMless)         |   | Security? | (MHz)       | 0 to 70 | -40 to +85   | -55 to +125 | PDIP        | CDIP     | PLCC    | CLCC | PQFP/SSOF |

| 83C055            | S | N         | 3.5 to 20   | x       |              |             | NB42        |          |         |      |           |

| 87C055            | s | N         | 3.5 to 20   | x       |              |             | NB42        |          | -       | -    |           |

| 80C54             | s | Y         | 3.5 to 24   | Х       | X            |             | N40         |          | A44     |      | B44       |

| 87C54             | s | Y         | 3.5 to 24   | Х       | X            |             | N40         | F40      | A44     | K44  | B44       |

| 83C654 (80C654)   | н | Y         | 1.2 to 24   | x       | x            | -40 to +125 | R42,<br>N40 |          | A44     |      | B44       |

| 87C654            | s | Y         | 1.2 to 20   | X       | X            | x           | N40         | F40      | A44     | K44  | B44       |

| 83CE654           | н | Y         | 1.2 to 16   | х       | X            |             |             |          |         |      | B44       |

| 83CL781           | Ζ | N         | 0 to 12 (1) |         | X            |             | N40         |          |         |      | B44       |

| 83CL782           | Ζ | N         | 0 to 12 (1) |         | -25 to +55   |             | N40         |          |         |      | B44       |

| 83C51FB           | s | Y         | 3.5 to 24   | х       | X            |             | N40         |          | A44     |      | B44       |

| 87C51FB           | s | Y         | 3.5 to 24   | Х       | х            |             | N40         | F40      | A44     | K44  | B44       |

| 83L51FB           | S | Y         | 3.5 to 20   | х       |              |             | N40         |          | A44     |      | B44       |

| 87L51FB           | S | Y         | 3.5 to 20   | х       |              |             | N40         | F40      | A44     | K44  | B44       |

| 83C524            | н | Y         | 1.2 to 16   | х       | Х            |             | N40         |          | A44     |      | B44       |

| 87C524            | s | Y         | 3.5 to 20   | X       | Х            |             | N40         | F40      | A44     | K44  | B44       |

| 83C592 (80C592)   | н | Y         | 1.2 to 16   |         | ×            | -40 to +125 |             |          | A68     | K68  |           |

| 87C592            | н | Y         | 1.2 to 16   | х       |              |             | R42         |          | A68     | K68  |           |

| 80C58             | S | Ŷ         | 3.5 to 16   | Х       | Х            |             | N40         |          | A44     |      | B44       |

| 87C58             | s | Y         | 3.5 to 16   | х       | X            |             | N40         | F40      | A44     | K44  | B44       |

| 83C51FC           | s | Y         | 3.5 to 24   | Х       | Х            |             | N40         |          | A44     | -    | B44       |

| 87C51FC           | s | Y         | 3.5 to 24   | х       | X            |             | N40         | F40      | A44     | K44  | B44       |

| 83C528 (80C528)   | н | Y         | 1.2 to 16   | х       | X            | -40 to +125 | N40         |          | A44     |      | B44       |

| 87C528            | s | Y         | 3.5 to 20   | х       | X            |             | N40         | F40      | A44     | K44  | B44       |

| 83CE528 (80CE528) | н | Y         | 1.2 to 16   | Х       | Х            | -40 to +125 |             | -        | A44     |      | B44       |

| 83CE598 (80CE598) | н | Y         | 1.2 to 16   |         | ×            | -40 to +125 |             |          |         |      | B80       |

| 87CE598           | н | Y         | 3.5 to 16   | x       | x            |             | l           | 1        | 1       |      | B80       |

| 83CE558 80CE558   | н | Y         | 1.2 to 16   | x       | х            | -40 to +125 |             |          | 1       |      | B80       |

| 89CE558           | н | Y         | 1.2 to 16   | x       | x            |             | l           | <u> </u> | +       | Q80  | B80       |

Notes: Production Centers are indicated in the second column: H – Hamburg, S – Sunnyvale, Z – Zurich. All combinations of part type, speed, temperature and package may not be available.

1) Oscillator options start from 32kHz.

2) Also available in VSO40 package.

3) Also available in VSO56 Package.

4) Not recommended for new design.

5) Package available up to 16 MHz only.

Barr Inger Barr In.

## Section 2 General Information

#### CONTENTS

| Contents             | 23 |

|----------------------|----|

| Ordering information | 27 |

| Quality              | 28 |

| Handling MOS devices | 29 |

| Rating systems       | 30 |

un profile per tr

at <sup>gereged for the</sup>

| IC25: 16-bit 80C51XA | (eXtended Architecture | ) Microcontrollers |

|----------------------|------------------------|--------------------|

|----------------------|------------------------|--------------------|

|    | Prefa                         | ace                                                  |                                                                                                                                                                                                                                 |

|----|-------------------------------|------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

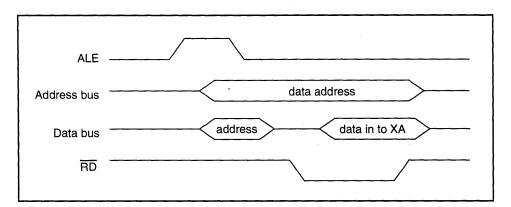

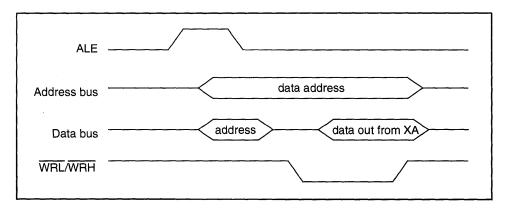

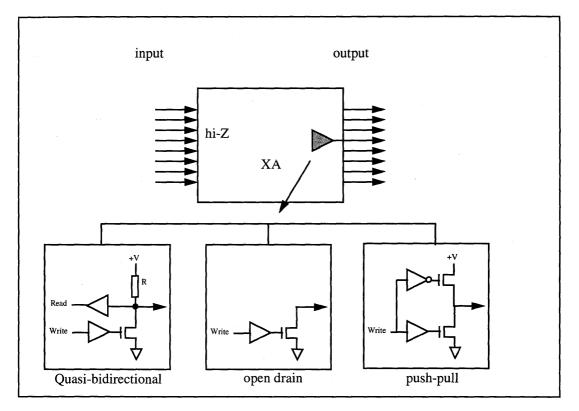

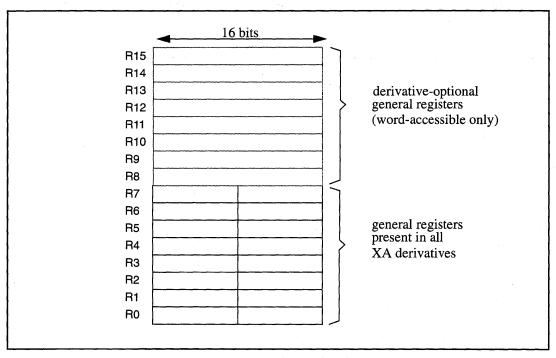

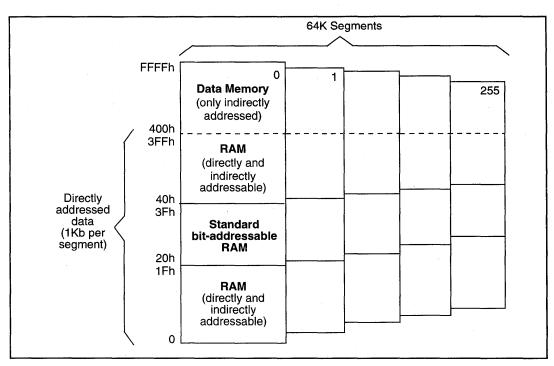

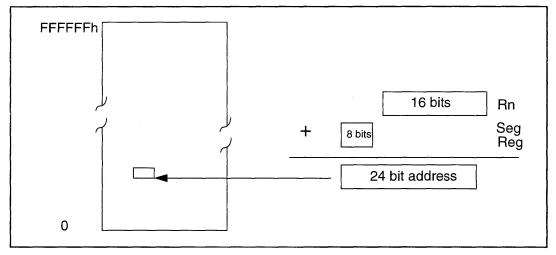

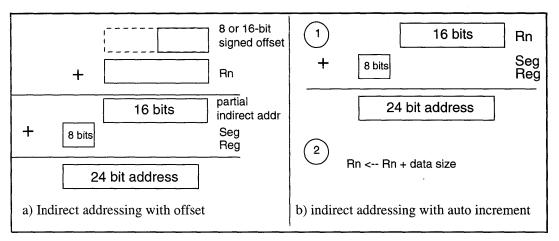

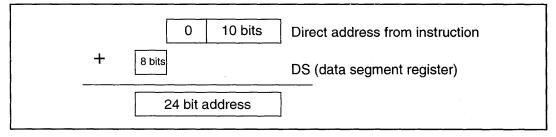

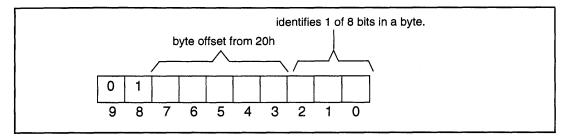

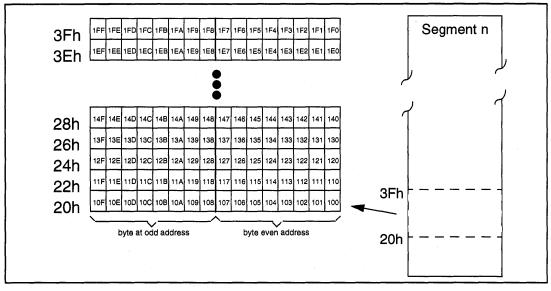

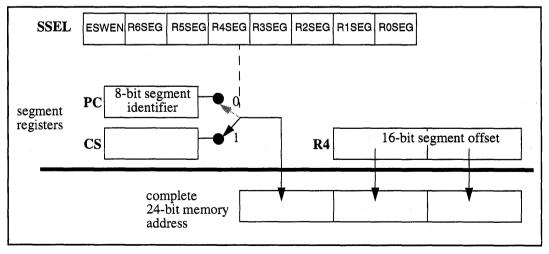

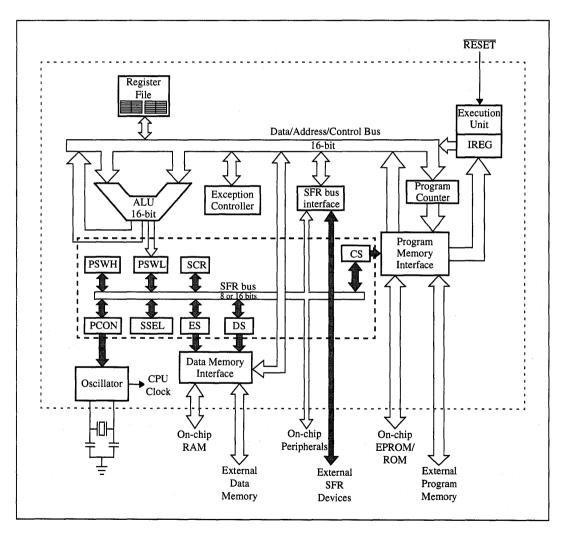

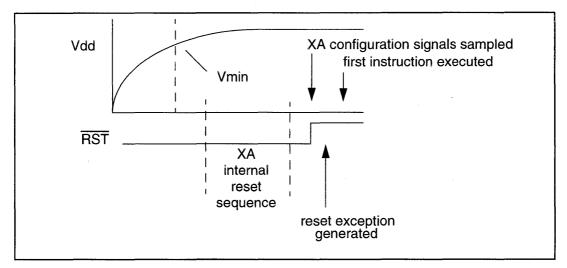

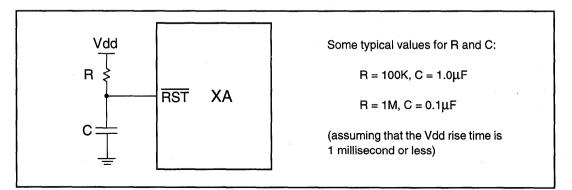

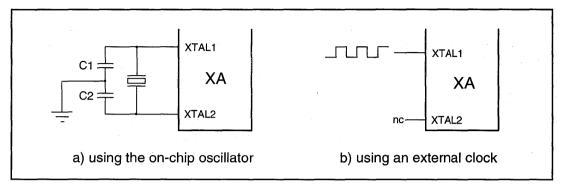

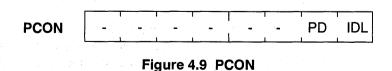

| Se | ctior                         | n 1 – Sel                                            | ection Guides                                                                                                                                                                                                                   |