# INTEGRATED CIRCUITS

# **I<sup>2</sup>C** Peripherals

1997

PHILIPS

1997

Data Handbook IC12

Philips Semiconductors

# I<sup>2</sup>C Peripherals

CONTENTS

|                                       | Page |

|---------------------------------------|------|

| PREFACE                               | 3    |

| INDEX                                 | 5    |

| SELECTION GUIDE                       | 9    |

| GENERAL                               | 33   |

| I <sup>2</sup> C SPECIFIC INFORMATION | 41   |

| DEVICE DATA                           | 91   |

| PACKAGE INFORMATION                   | 699  |

| DATA HANDBOOK SYSTEM                  | 725  |

#### DEFINITIONS

| This data sheet contains target or goal specifications for product development.                                                                                               |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| This data sheet contains preliminary data; supplementary data may be published later.                                                                                         |

| This data sheet contains final product specifications.                                                                                                                        |

| The data in this specification is extracted from a full data sheet with the same type number and title. For detailed information see the relevant data sheet or data handbook |

|                                                                                                                                                                               |

|                                                                                                                                                                               |

Limiting values given are in accordance with the Absolute Maximum Rating System (IEC 134). Stress above one or more of the limiting values may cause permanent damage to the device. These are stress ratings only and operation of the device at these or at any other conditions above those given in the Characteristics sections of the specification is not implied. Exposure to limiting values for extended periods may affect device reliability.

#### **Application information**

Where application information is given, it is advisory and does not form part of the specification.

#### LIFE SUPPORT APPLICATIONS

These products are not designed for use in life support appliances, devices, or systems where malfunction of these products can reasonably be expected to result in personal injury. Philips customers using or selling these products for use in such applications do so at their own risk and agree to fully indemnify Philips for any damages resulting from such improper use or sale.

#### PURCHASE OF PHILIPS I<sup>2</sup>C COMPONENTS

Purchase of Philips I<sup>2</sup>C components conveys a license under the Philips' I<sup>2</sup>C patent to use the components in the I<sup>2</sup>C system provided the system conforms to the I<sup>2</sup>C specification defined by Philips. This specification can be ordered using the code 9398 393 40011.

#### PREFACE

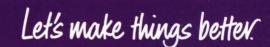

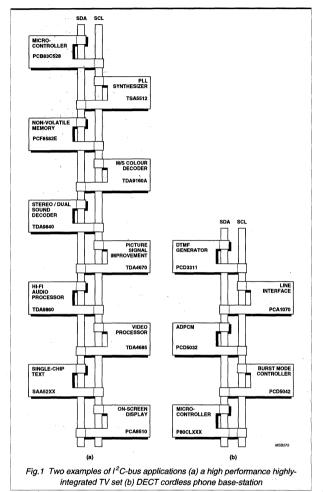

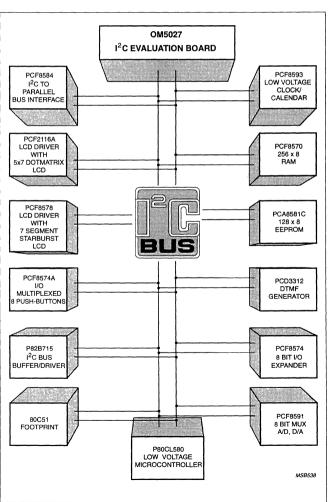

Since Philips first invented it almost 18 years ago, the two-wire I<sup>2</sup>C-bus has grown far beyond our initial expectations. I<sup>2</sup>C it is now firmly established worldwide as the 'King of Serial Buses' for embedded applications.

Since its birth as a serial bus for consumer electronics, the I<sup>2</sup>C-bus is now used extensively in PCs and workstations as a diagnostics and power management bus, in mobile phones it's used to control Synthesizers, LCD and Realtime clocks, in wired phones for access to DTMF and EEPROM ICs. It's also used as a de-facto standard in Plug-in Video cards for PCs due to Philips' extensive range of video processing ICs with I<sup>2</sup>C. And when you see an LCD display in a car dashboard or car radio, odds are it's got I<sup>2</sup>C running behind the glass.

For simple tasks such as monitoring a keypad, driving an LED or LCD, storing crucial non-volatile data, measuring a temperature, driving a reed-relay, tracking the time-of-day, to all sorts of complex functions for video, audio, and closed-loop control applications, I<sup>2</sup>C is the serial bus of choice.

In this 1997 edition of our I<sup>2</sup>C Peripherals Handbook, we have compiled an ever-growing list of Philips' I<sup>2</sup>C Peripheral ICs for general purpose. Specialized I<sup>2</sup>C peripherals for specific applications (i.e. video/audio processors, synthesizers) can be found in Philips application-specific data handbooks.

Philips also provides a large palette of microcontrollers with dedicated I<sup>2</sup>C interface. Contact your local Philips Semiconductors representative for further details about I<sup>2</sup>C-bus microcontrollers, specialized peripherals, demoboards, emulators, evaluation tools, and application notes. They will be happy to assist you with your I<sup>2</sup>C bus designs!

INDEX

# I<sup>2</sup>C Peripherals

Index

Types added to the range since the last issue of data handbook IC12 (1996 issue) are shown in bold print

|                    |                                                                        | PAGE |

|--------------------|------------------------------------------------------------------------|------|

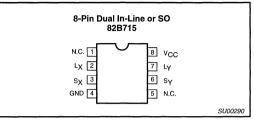

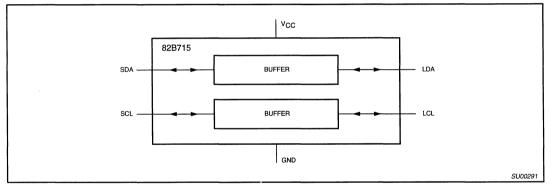

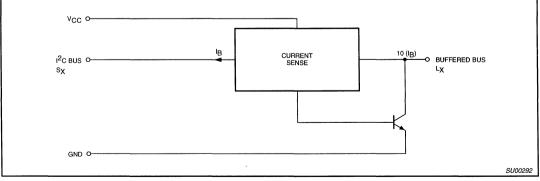

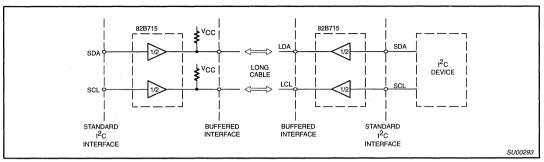

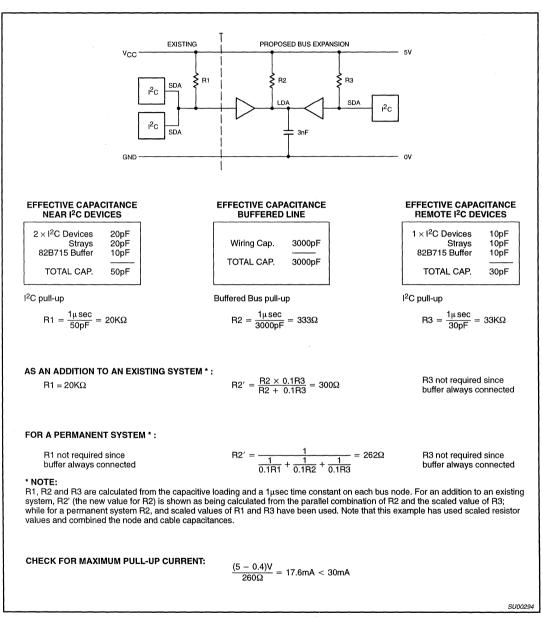

| 82B715             | I <sup>2</sup> C bus extender                                          | 92   |

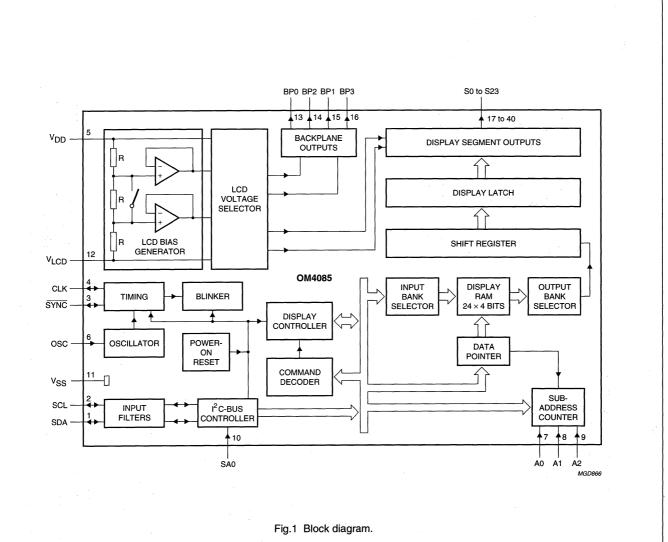

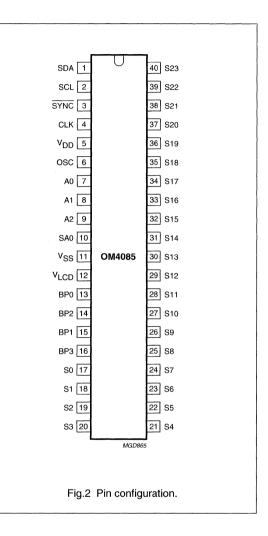

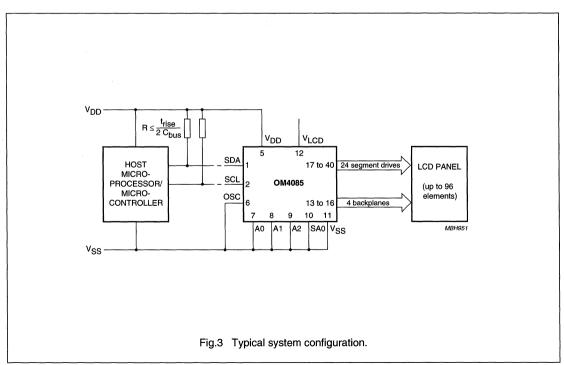

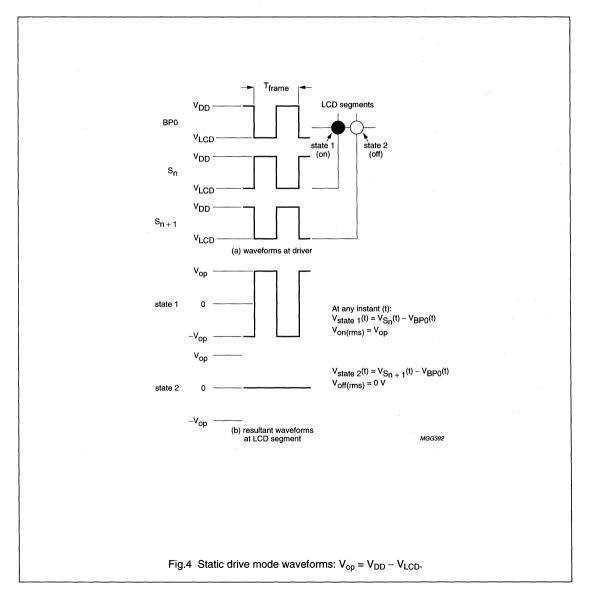

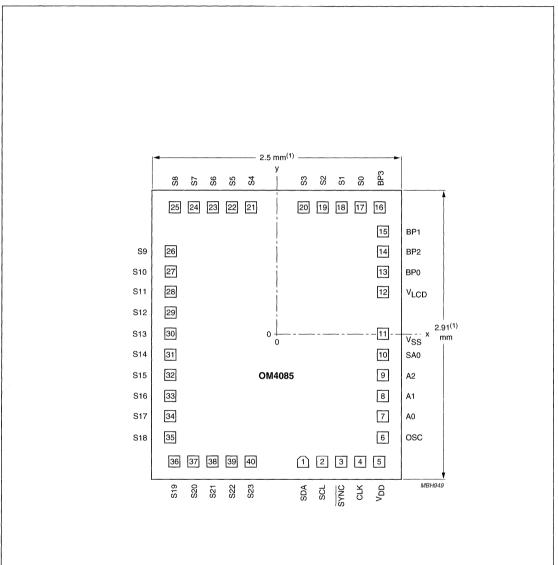

| OM4085             | Universal LCD driver for low multiplex rates                           | 97   |

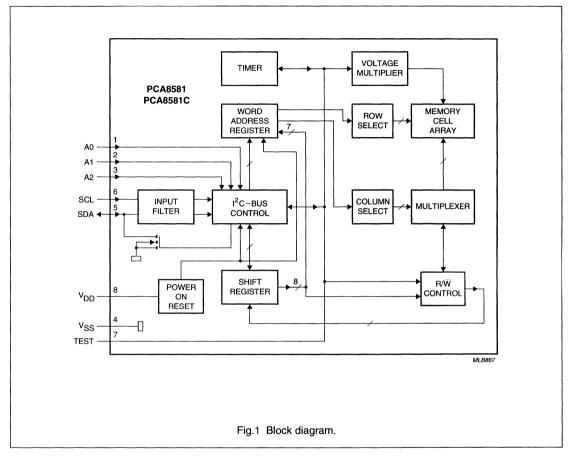

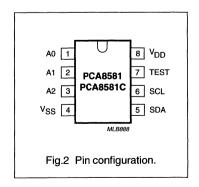

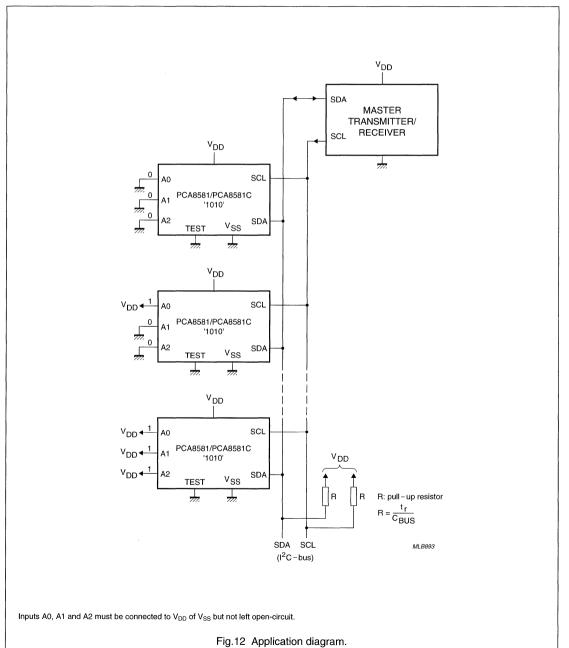

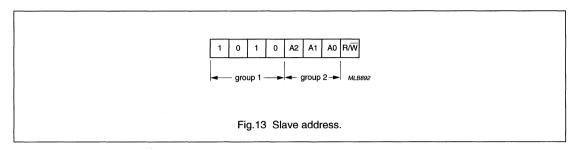

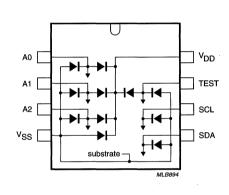

| PCA8581; PCA8581C  | 128 x 8-bit EEPROM with I <sup>2</sup> C-bus interface                 | 127  |

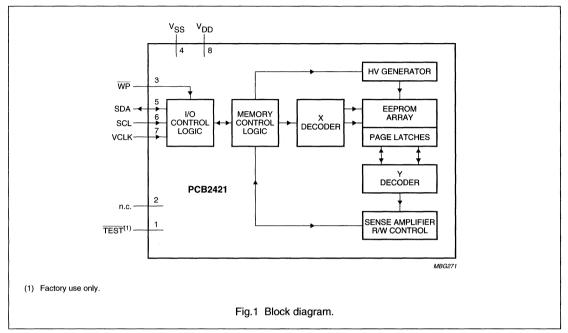

| PCB2421            | 1K dual mode serial EEPROM                                             | 139  |

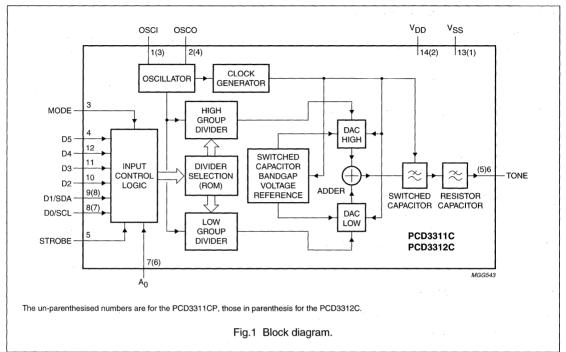

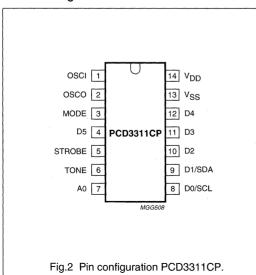

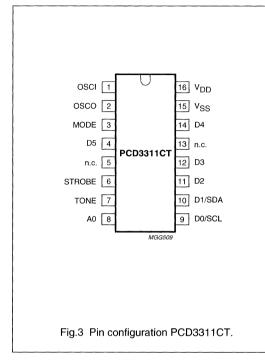

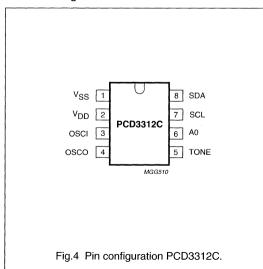

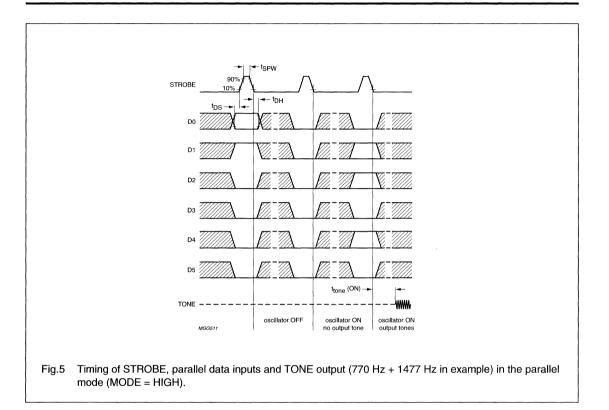

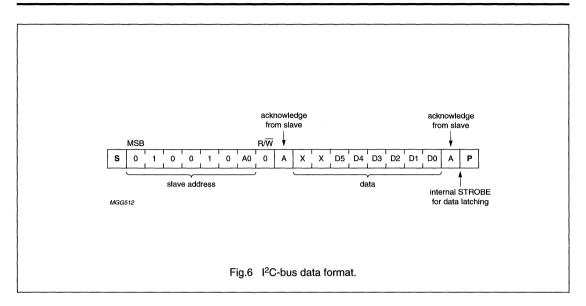

| PCD3311C; PCD3312C | DTMF/modem/musical-tone generators                                     | 154  |

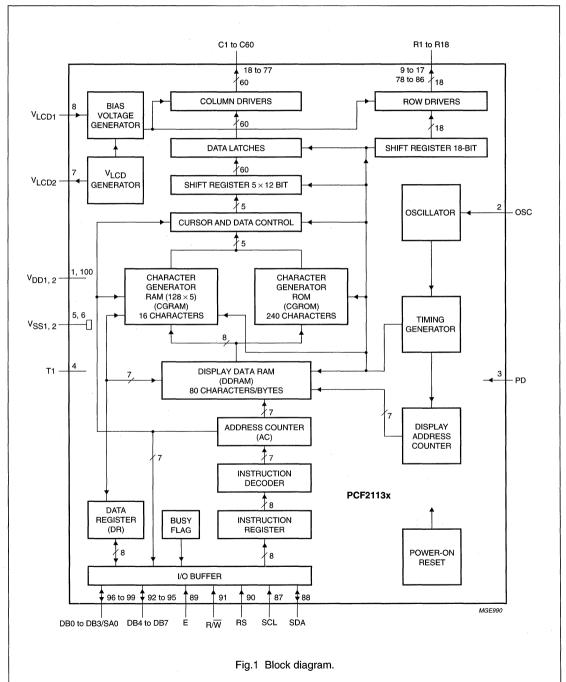

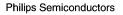

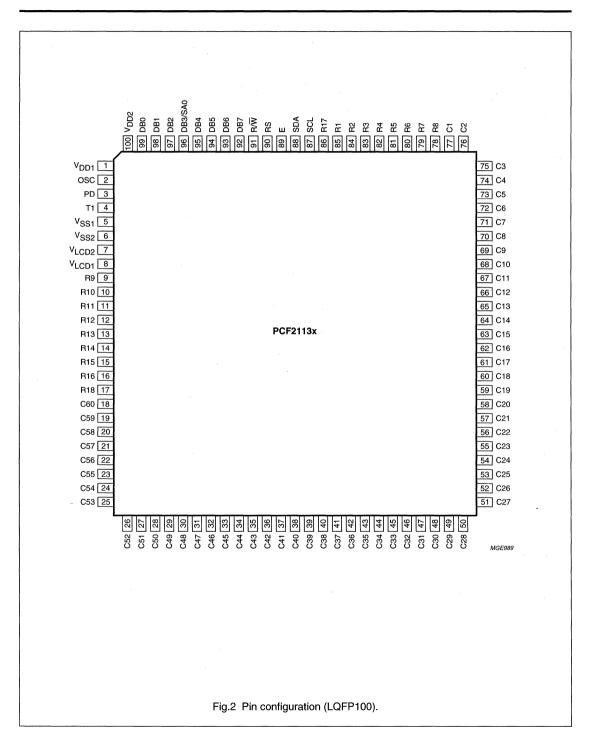

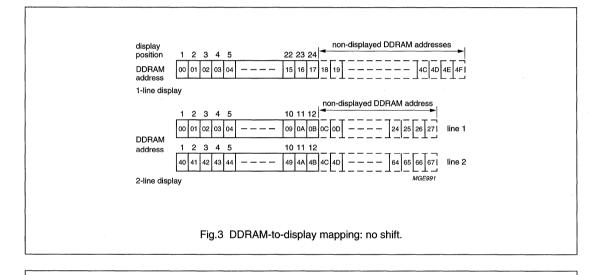

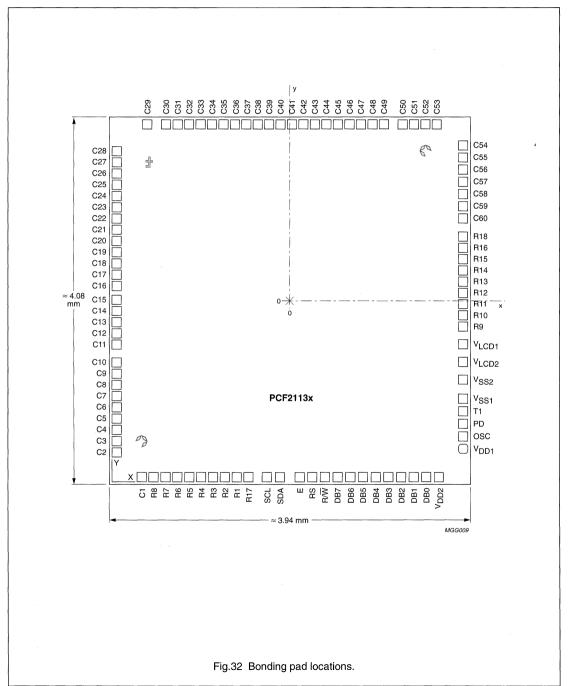

| PCF2113x           | LCD controller/drivers                                                 | 174  |

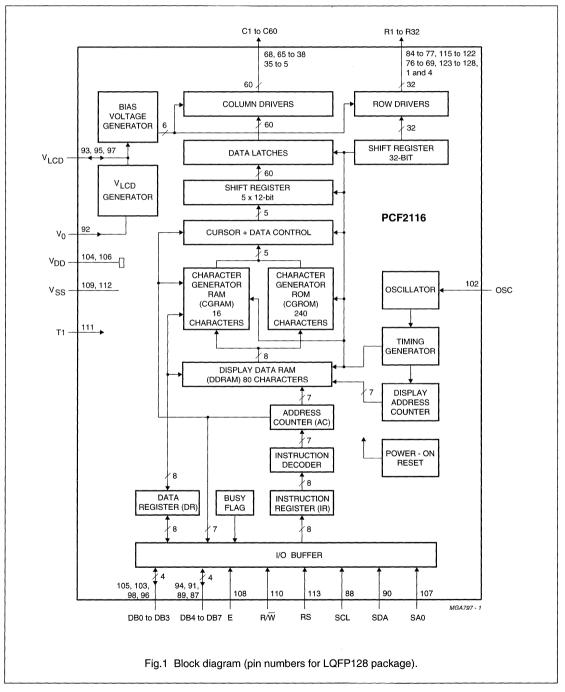

| PCF2116 family     | LCD controller/drivers                                                 | 229  |

| PCF21xxC family    | LCD drivers                                                            | 287  |

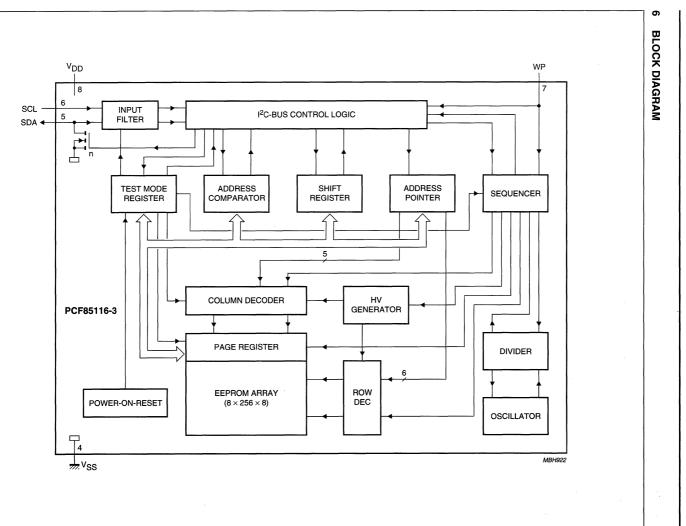

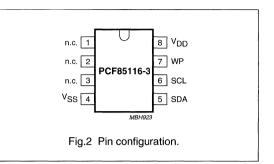

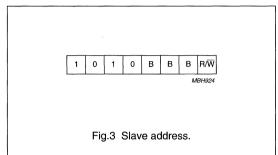

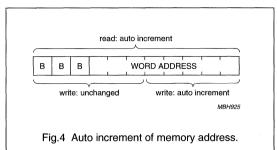

| PCF85116-3 family  | 2048 x 8-bit CMOS EEPROMS with I <sup>2</sup> C-bus interface          | 303  |

| PCF8558            | Universal LCD driver for small graphic panels                          | 315  |

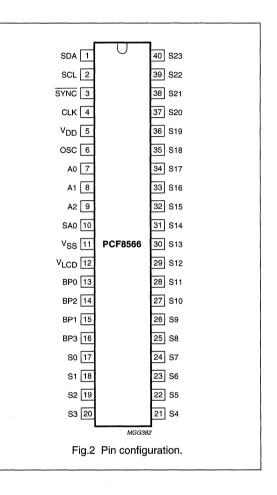

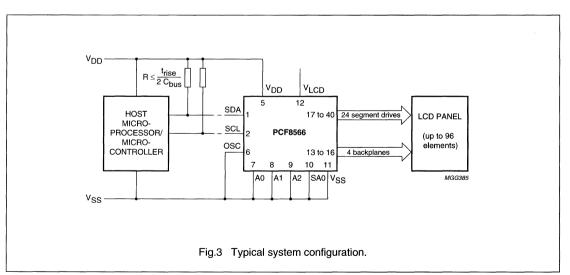

| PCF8566            | Universal LCD driver for low multiplex rates                           | 335  |

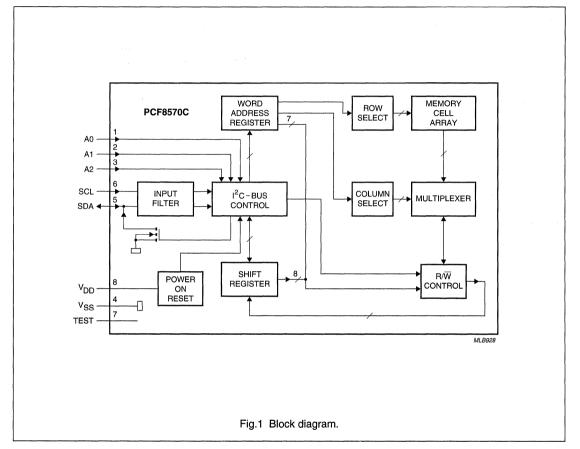

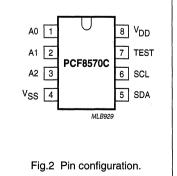

| PCF8570C           | 256 x 8-bit static low-voltage RAM with I <sup>2</sup> C-bus interface | 366  |

| PCF8573            | Clock/calendar with serial I/O                                         | 378  |

| PCF8574            | Remote 8-bit I/O expander for I <sup>2</sup> C-bus                     | 395  |

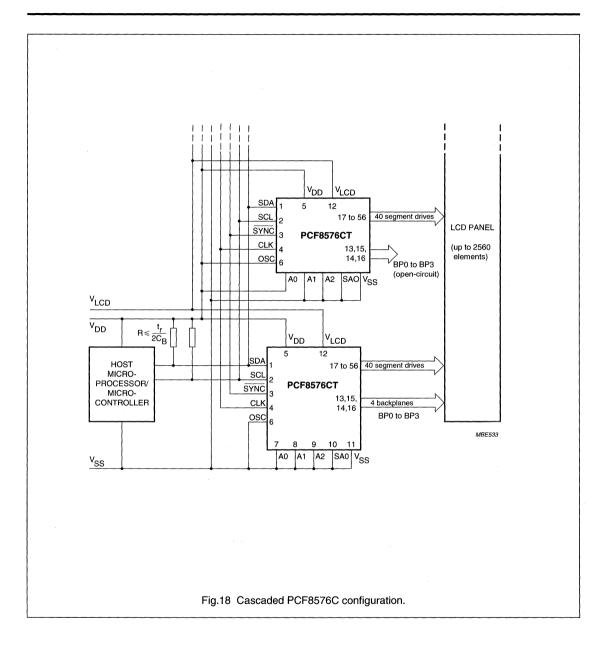

| PCF8576C           | Universal LCD driver for low multiplex rates                           | 409  |

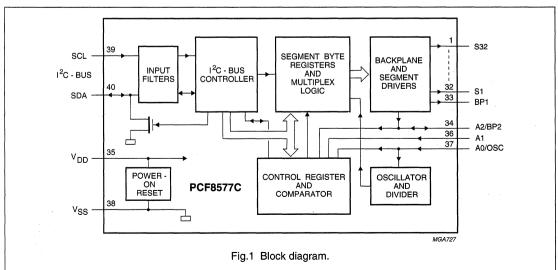

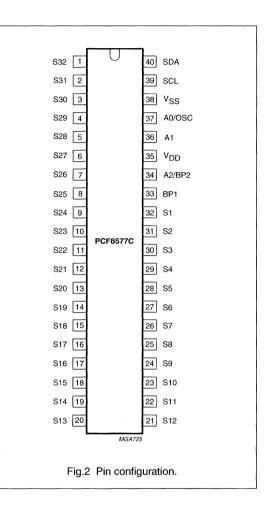

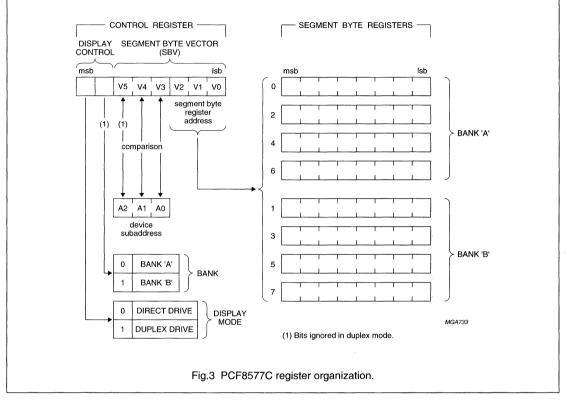

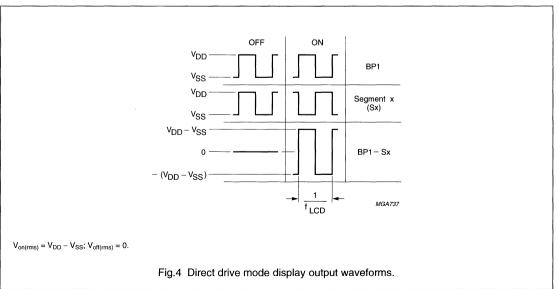

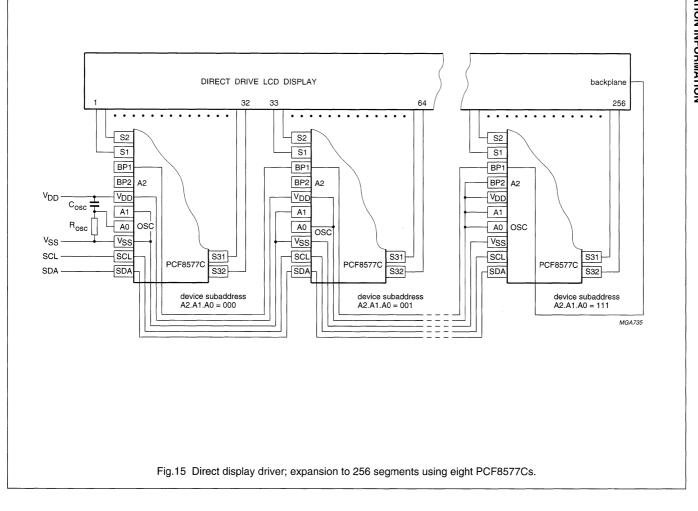

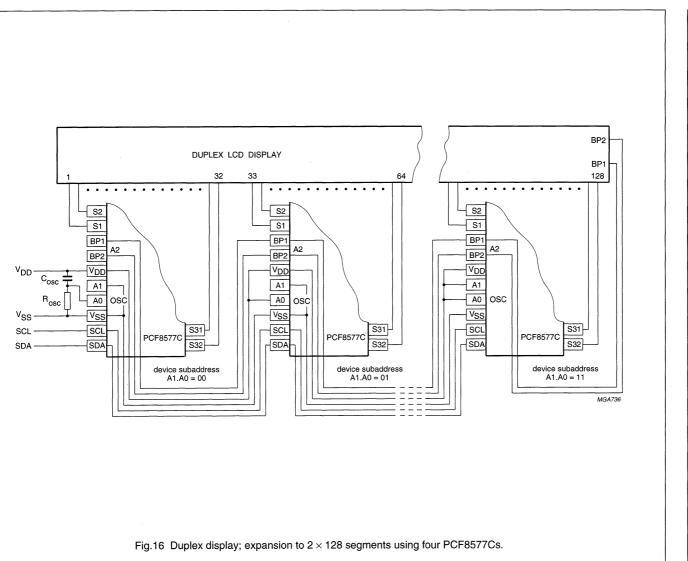

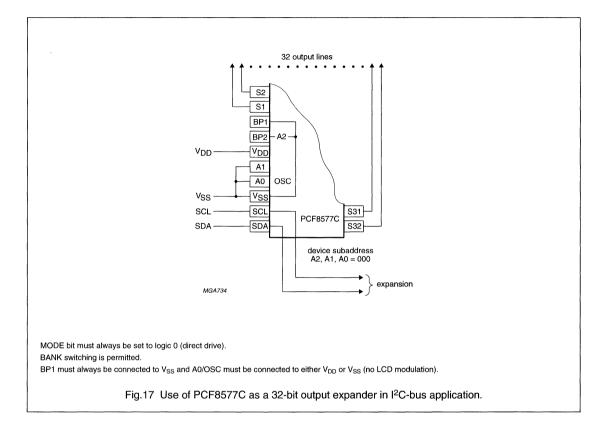

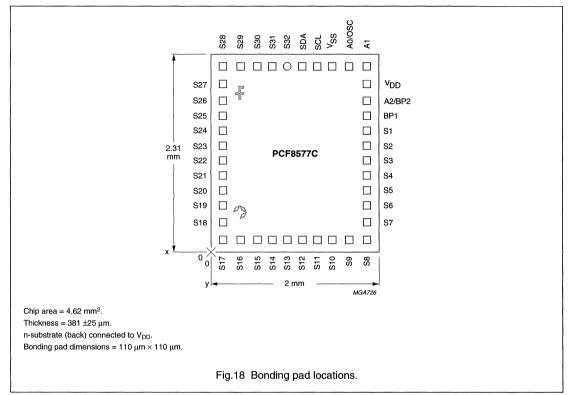

| PCF8577C           | LCD direct/duplex driver with I <sup>2</sup> C-bus interface           | 443  |

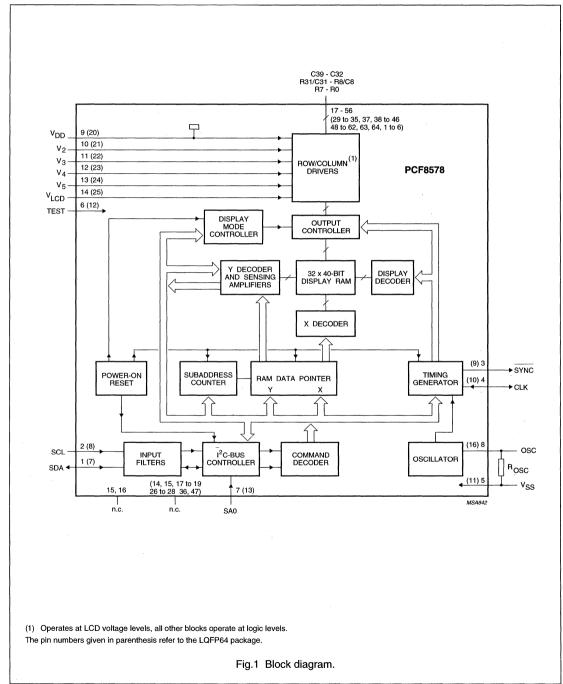

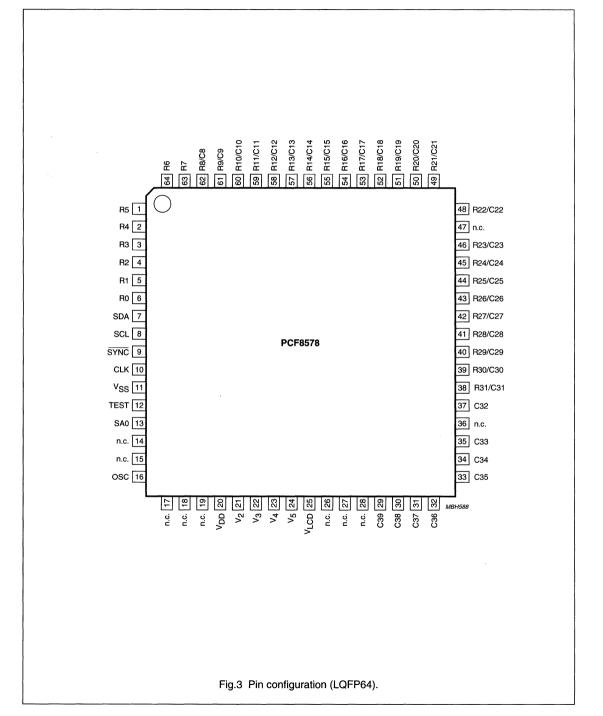

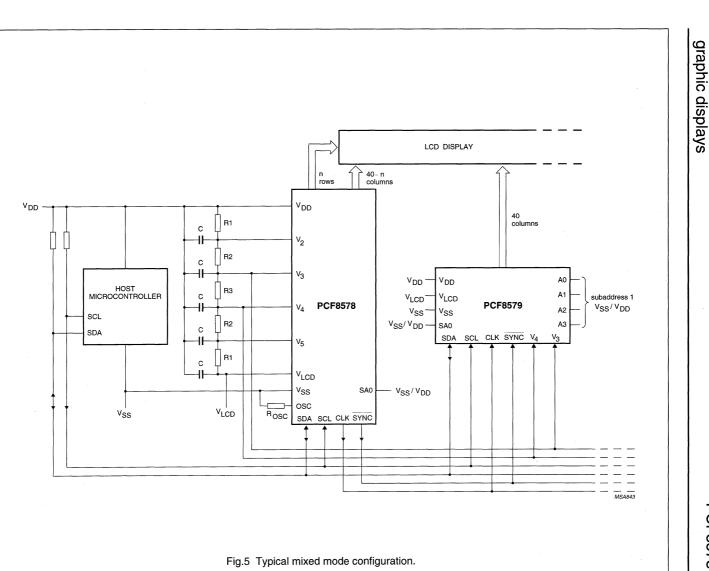

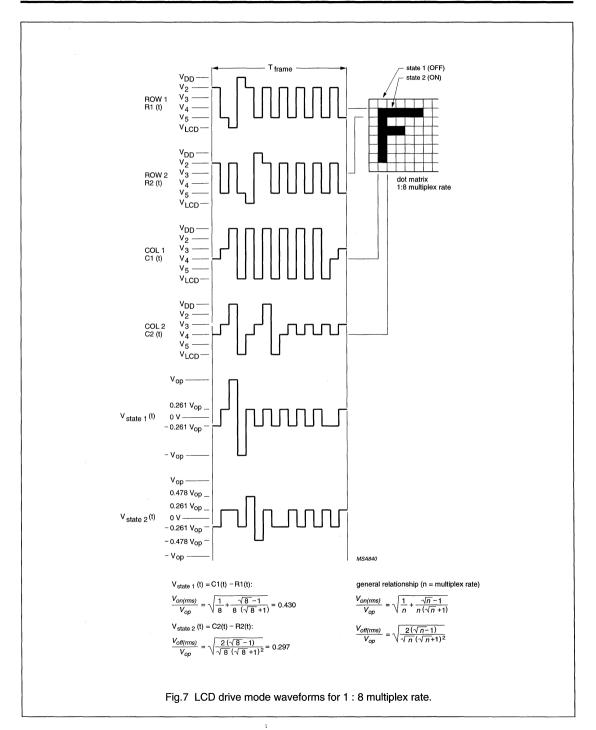

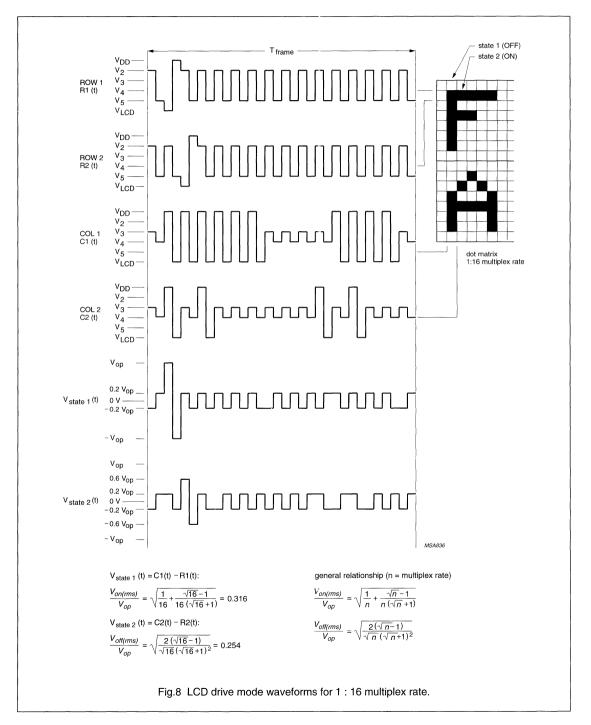

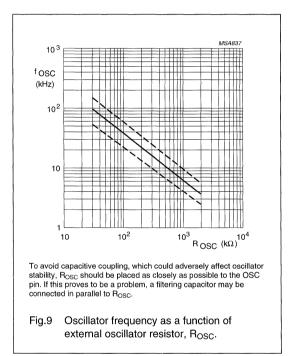

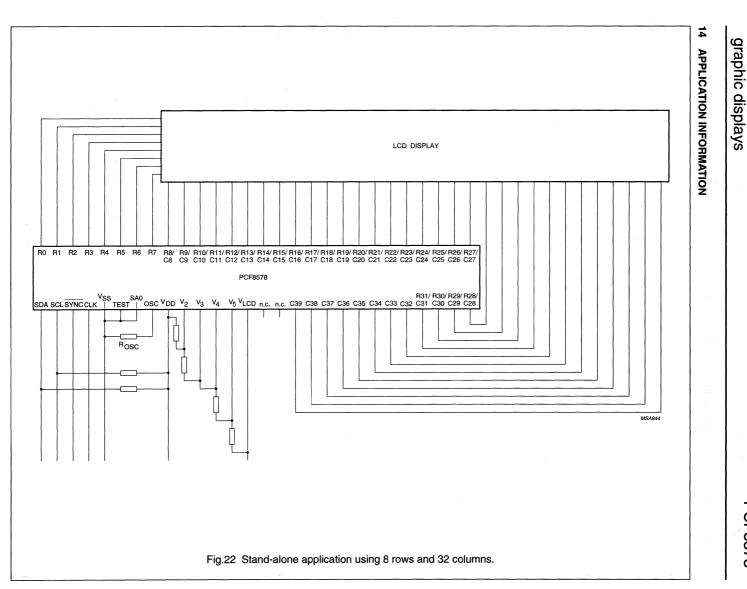

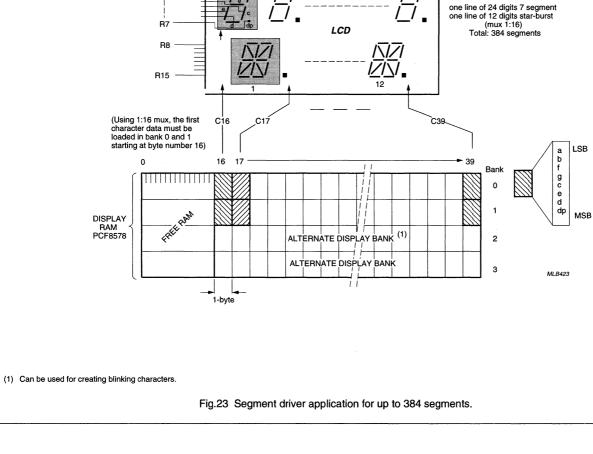

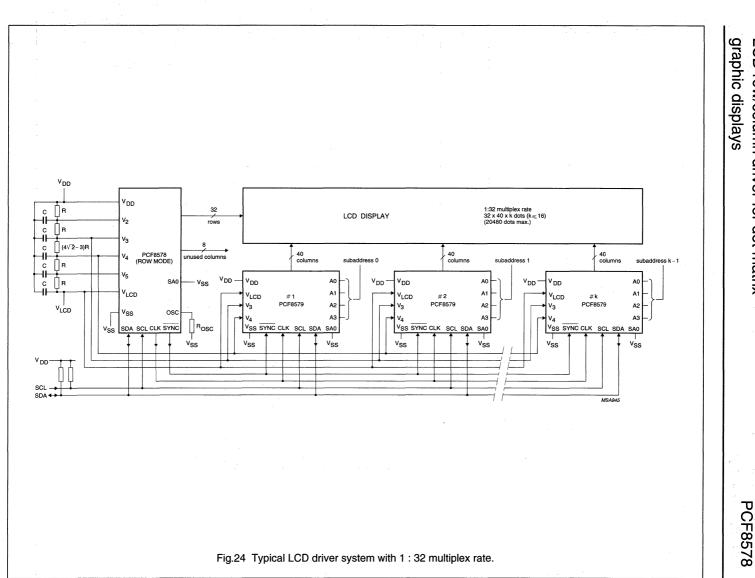

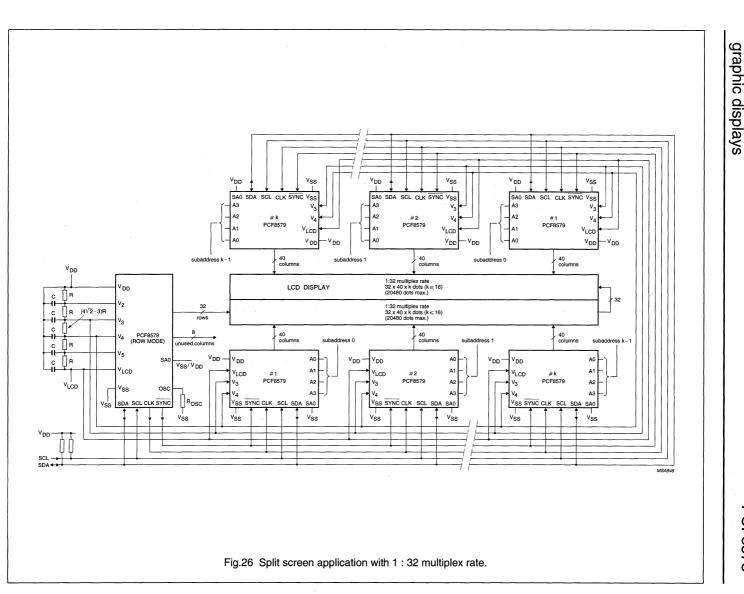

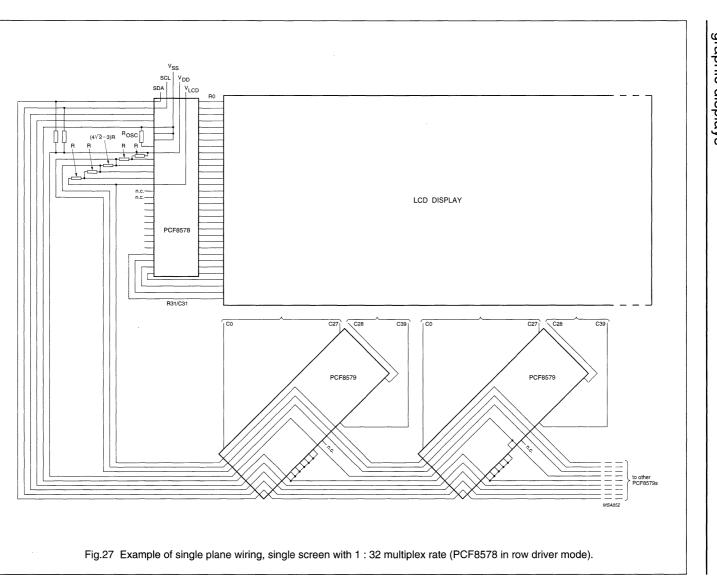

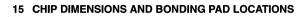

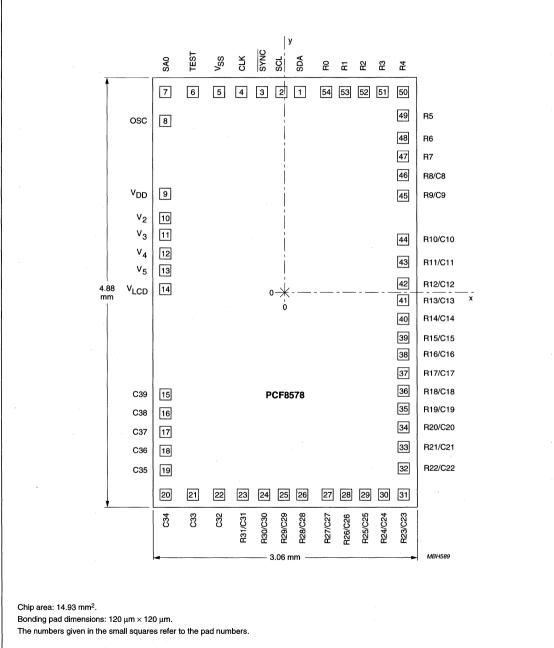

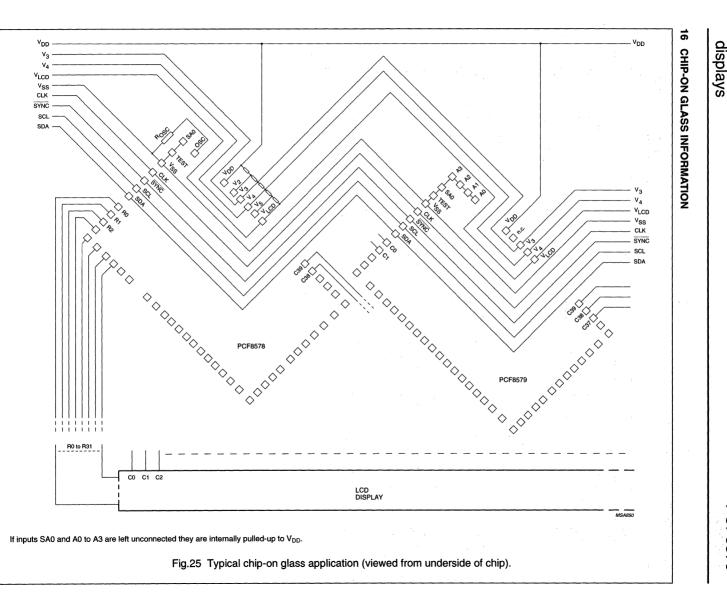

| PCF8578            | LCD row/column driver for dot matrix graphic displays                  | 462  |

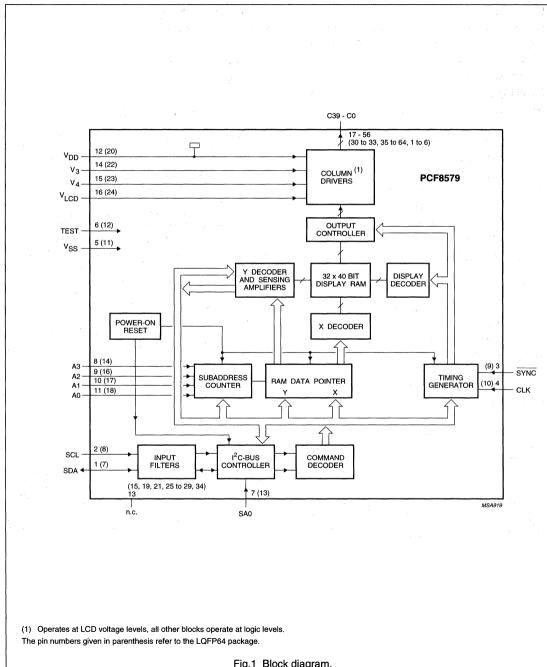

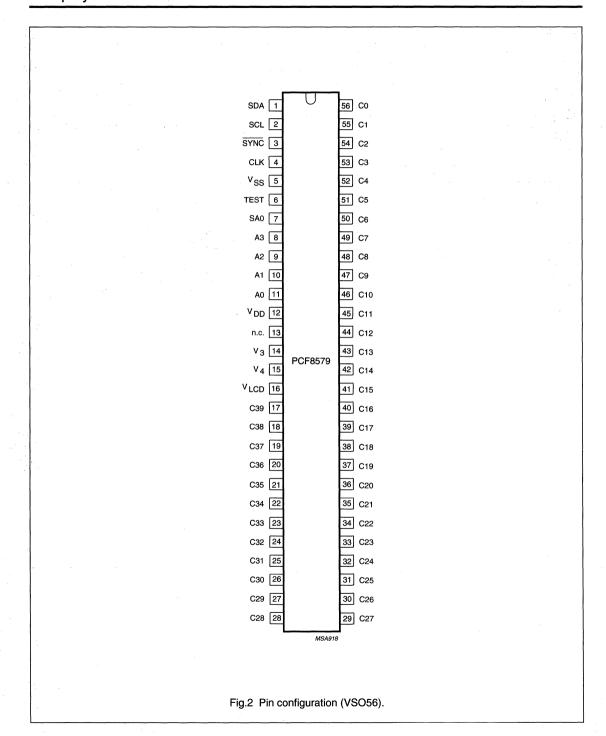

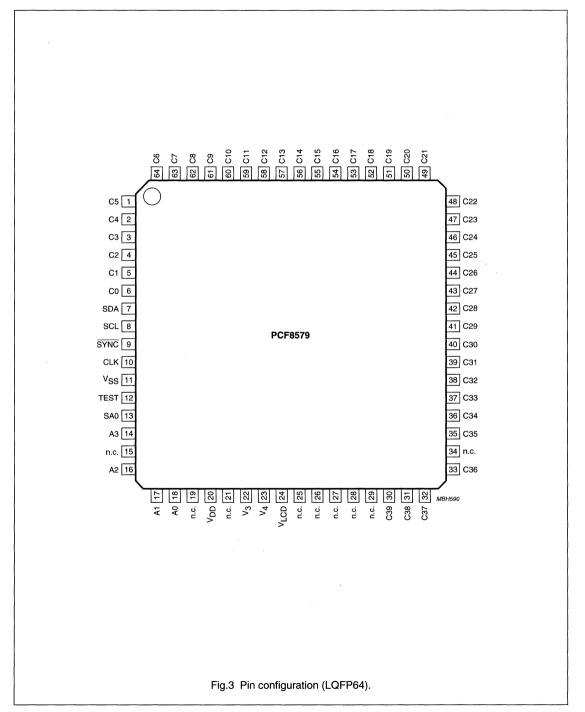

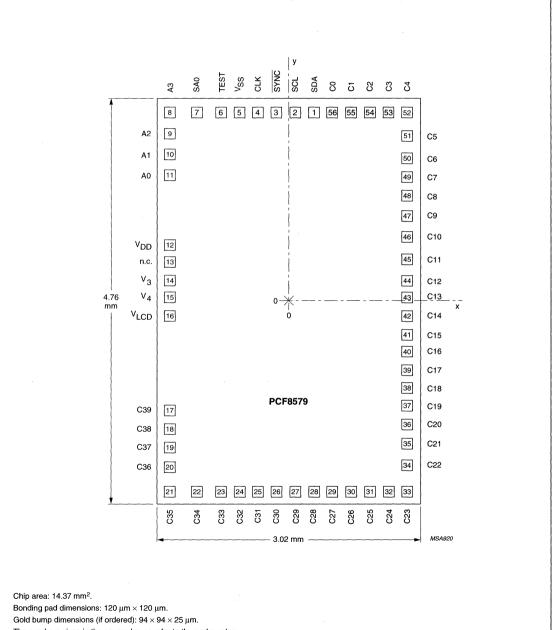

| PCF8579            | LCD column driver for dot matrix graphic displays                      | 500  |

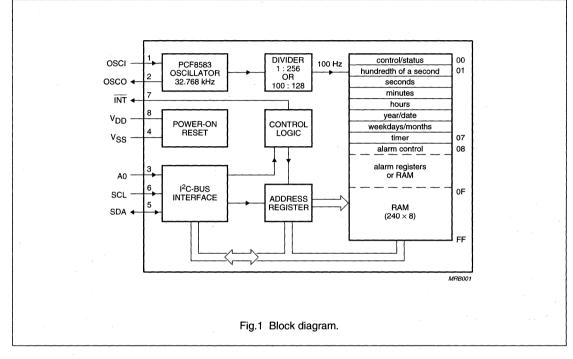

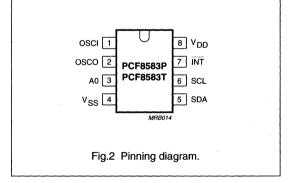

| PCF8583            | Clock calendar with 256 x 8-bit static RAM                             | 533  |

| PCF8584            | I <sup>2</sup> C-bus controller                                        | 554  |

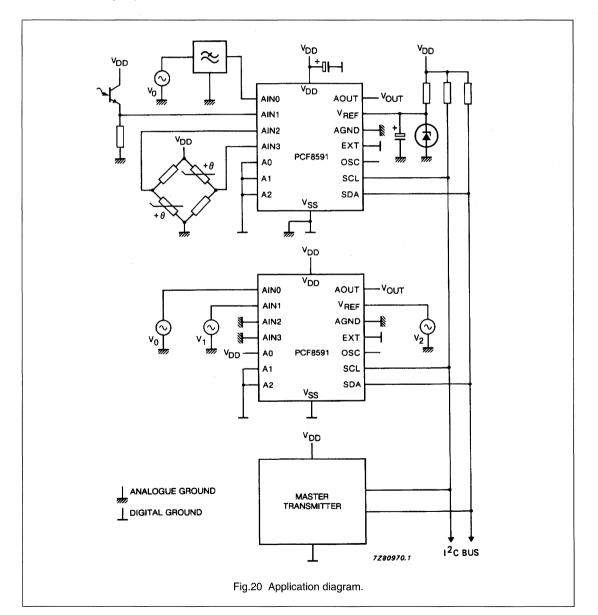

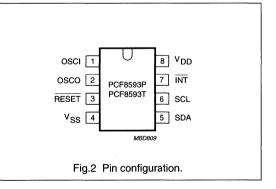

| PCF8591            | 8-bit A/D and D/A converter                                            | 587  |

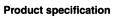

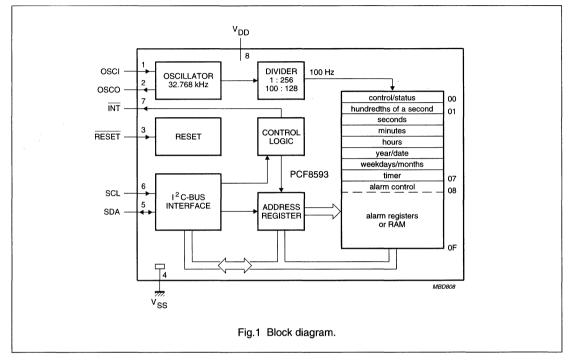

| PCF8593            | Low power clock calendar                                               | 607  |

| PCF85xxC-2 family  | 256 to 1024 x 8-bit CMOS EEPROMS with I <sup>2</sup> C-bus interface   | 629  |

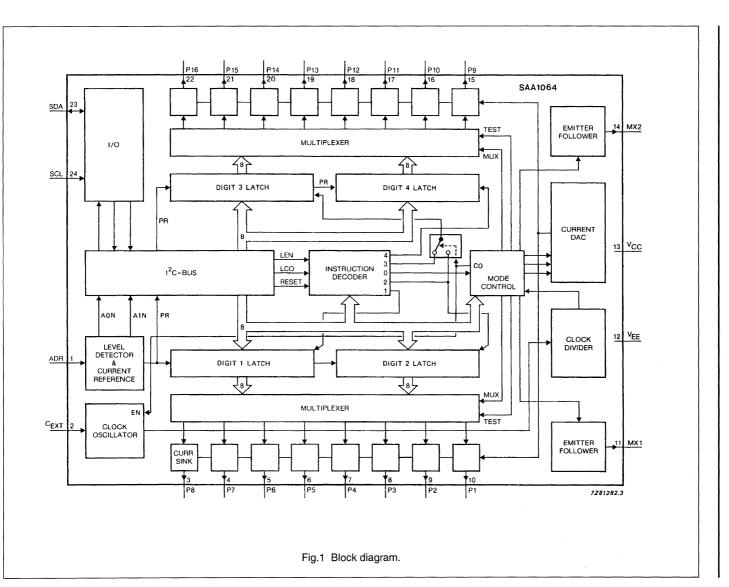

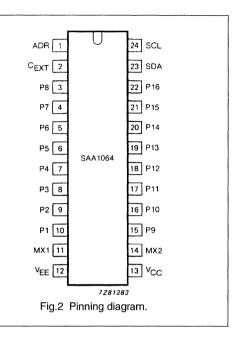

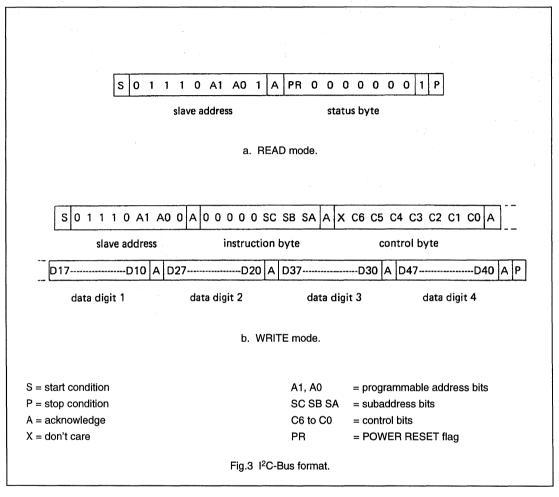

| SAA1064            | 4-digit LED driver with I <sup>2</sup> C-bus interface                 | 643  |

| SAA1300            | Tuner switching circuit                                                | 657  |

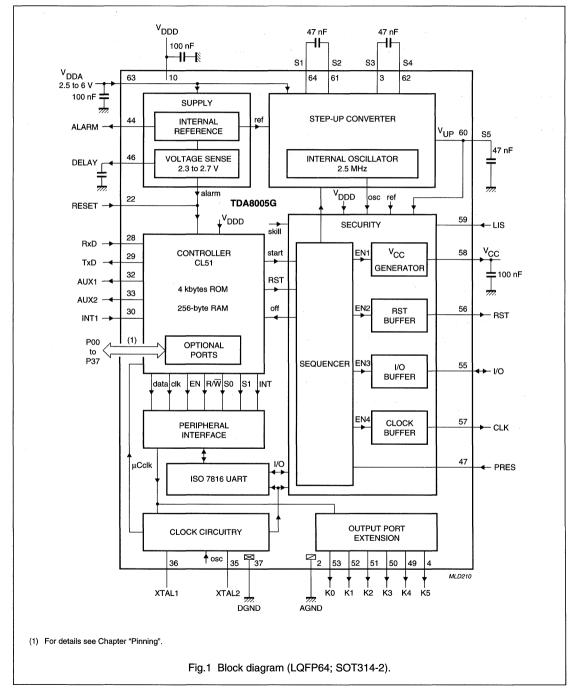

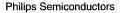

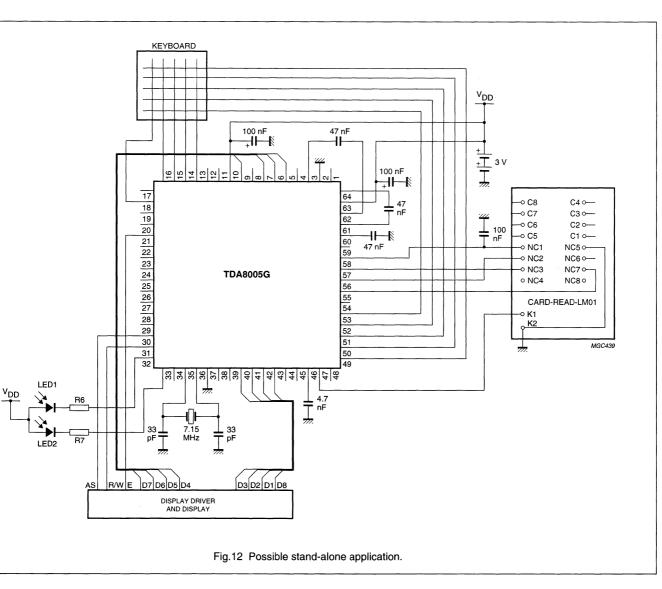

| TDA8005            | Low-power smart card coupler                                           | 660  |

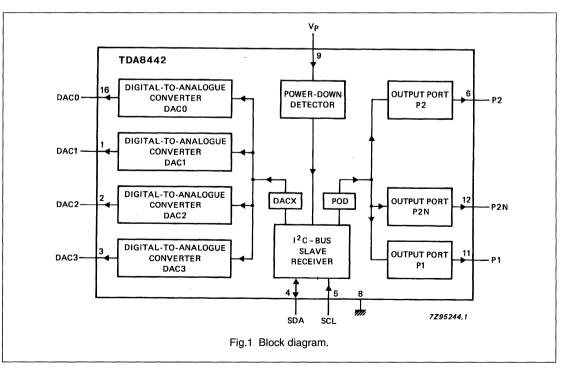

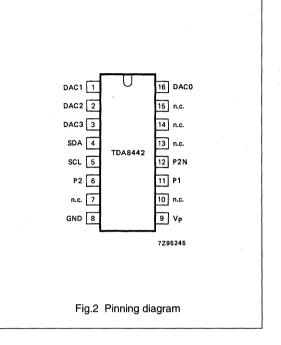

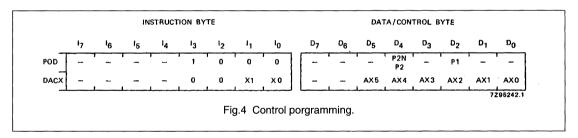

| TDA8442            | I <sup>2</sup> C-bus interface for color decoders                      | 685  |

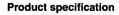

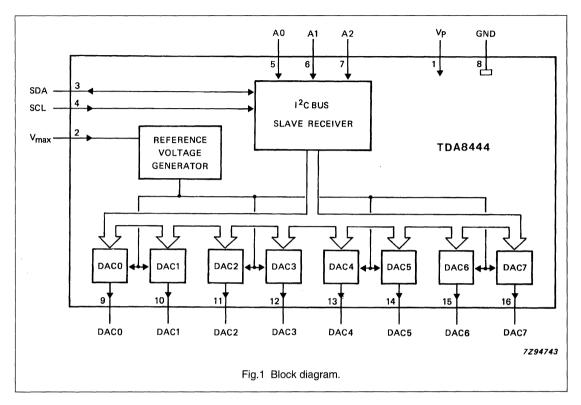

| TDA8444            | Octuple 6-bit DAC with I <sup>2</sup> C-bus                            | 692  |

|                    |                                                                        |      |

# **SELECTION GUIDES**

Page

| Functional index                            | 10 |

|---------------------------------------------|----|

| Assigned I <sup>2</sup> C-bus addresses     | 12 |

| I <sup>2</sup> C address allocation table   | 16 |

| Microcontroller bulletin board              | 20 |

| Philips Fax-on-demand system                | 22 |

| Internet WWW home page                      | 23 |

| 80C51 microcontroller family features guide | 24 |

| CMOS and NMOS 8-bit microcontroller family  | 28 |

| CMOS 16-bit microcontroller family          | 32 |

# I<sup>2</sup>C Peripherals

# **Functional index**

Types added to the range since the last issue of dat handbook IC12 (1996 issue) are shown in bold print

PAGE

#### MEMORIES

|                    | _                                                                      |     |

|--------------------|------------------------------------------------------------------------|-----|

| PCA8581; PCA8581C  | 128 x 8-bit EEPROM with I <sup>2</sup> C-bus interface                 | 127 |

| PCB2421            | 1K dual mode serial EEPROM                                             | 139 |

| PCF8570C           | 256 x 8-bit static low-voltage RAM with I <sup>2</sup> C-bus interface | 366 |

| PCF8583            | Clock calendar with 256 x 8-bit static RAM                             | 533 |

| PCF85xxC-2 family  | 256 to 1024 x 8-bit CMOS EEPROMS with I <sup>2</sup> C-bus interface   | 629 |

| PCF85116-3 family  | 2048 x 8-bit CMOS EEPROMS with I <sup>2</sup> C-bus interface          | 303 |

| DATA CONVERTERS    |                                                                        |     |

| PCF8591            | 8-bit A/D and D/A converter                                            | 587 |

| TDA8442            | I <sup>2</sup> C-bus interface for color decoders                      | 685 |

| TDA8444            | Octuple 6-bit DAC with I <sup>2</sup> C-bus                            | 692 |

| LCD DRIVERS        |                                                                        |     |

| OM4085             | Universal LCD driver for low multiplex rates                           | 97  |

| PCF2113x           | LCD controller/drivers                                                 | 174 |

| PCF2116 family     | LCD controller/drivers                                                 | 229 |

| PCF21xxC family    | LCD drivers                                                            | 287 |

| PCF8558            | Universal LCD driver for small graphic panels                          | 315 |

| PCF8566            | Universal LCD driver for low multiplex rates                           | 335 |

| PCF8576C           | Universal LCD driver for low multiplex rates                           | 409 |

| PCF8577C           | LCD direct/duplex driver with I <sup>2</sup> C-bus interface           | 443 |

| PCF8578            | LCD row/column driver for dot matrix graphic displays                  | 462 |

| PCF8579            | LCD column driver for dot matrix graphic displays                      | 500 |

| INPUT/OUTPUT PORTS |                                                                        |     |

| 82B715             | I <sup>2</sup> C bus extender                                          | 92  |

| PCF8574            | Remote 8-bit I/O expander for I <sup>2</sup> C-bus                     | 395 |

| PCF8584            | l <sup>2</sup> C-bus controller                                        | 554 |

| SAA1064            | 4-digit LED driver with I <sup>2</sup> C-bus interface                 | 643 |

| SAA1300            | Tuner switching circuit                                                | 657 |

|                    |                                                                        |     |

# I<sup>2</sup>C Peripherals

# Functional index

| PAGE |

|------|

|------|

#### CLOCK/CALENDAR CIRCUITS

| PCF8573              | Clock/calendar with serial I/O             | 378 |

|----------------------|--------------------------------------------|-----|

| PCF8583              | Clock calendar with 256 x 8-bit static RAM | 533 |

| PCF8593              | Low power clock calendar                   | 607 |

| DTMF/TONE GENERATORS |                                            |     |

| PCD3311C; PCD3312C   | DTMF/modem/musical-tone generators         | 154 |

|                      |                                            |     |

| MISCELLANEOUS        |                                            |     |

| TDA8005              | Low-power smart card coupler               | 660 |

# Assigned I<sup>2</sup>C-bus addresses

#### ASSIGNED I<sup>2</sup>C-BUS ADDRESSES (IN ALPHANUMERIC ORDER OF TYPE NUMBER)

| ТҮРЕ        |                                                                    | I <sup>2</sup> C SLAVE ADDRESSES <sup>(1)</sup> |    |    |    |    |    |    |  |

|-------------|--------------------------------------------------------------------|-------------------------------------------------|----|----|----|----|----|----|--|

| NUMBER      | DESCRIPTION                                                        | A6                                              | A5 | A4 | A3 | A2 | A1 | A0 |  |

|             | General call address                                               | 0                                               | 0  | 0  | 0  | 0  | 0  | 0  |  |

| -           | Reserved addresses                                                 | 0                                               | 0  | 0  | 0  | X  | X  | X  |  |

|             | Reserved addresses                                                 |                                                 | 1  | 1  | 1  | Х  | X  | X  |  |

| CCR921      | RDS/RBDS decoder                                                   | 0                                               | 0  | 1  | 0  | 0  | A  | Α  |  |

| NE5751      | Audio processor for RF communication                               | 1                                               | 0  | 0  | 0  | 0  | 0  | Α  |  |

| PCA1070     | Programmable speech transmission IC                                | 0                                               | 1  | 0  | 0  | 0  | 0  | A  |  |

| PCA8516     | Stand-alone OSD IC                                                 | 1                                               | 0  | 1  | 1  | 1  | 0  | 1  |  |

| PCA8581/C   | 128 × 8-bit EEPROM                                                 | 1                                               | 0  | 1  | 0  | A  | A  | Α  |  |

| PCB2421     | 1K dual mode serial EEPROM                                         | 1                                               | 0  | 1  | 0  | 0  | 0  | 0  |  |

| PCD3311C    | DTMF/modem/musical tone generator                                  | 0                                               | 1  | 0  | 0  | 1  | 0  | A  |  |

| PCD3312C    | DTMF/modem/musical tone generator                                  | 0                                               | 1  | 0  | 0  | 1  | 0  | Α  |  |

| PCD4440     | Voice scrambler/descrambler for mobile telephones                  | 1                                               | 1  | 0  | 1  | 1  | 1  | Α  |  |

| PCD5002     | Pager decoder                                                      | 0                                               | 1  | 0  | 0  | 1  | 1  | 1  |  |

| PCD5096     | Universal codec                                                    | 0                                               | 0  | 1  | 1  | 0  | Α  | A  |  |

| PCE84C467/8 | 8-bit CMOS auto-sync monitor controller                            | 0                                               | 1  | 1  | 0  | 0  | 1  | 1  |  |

| PCE84C882   |                                                                    |                                                 |    | 1  | 0  | 0  | 1  | 1  |  |

| PCE84C886   | 8-bit microcontroller for monitor applications                     | 0                                               | 1  | 1  | 0  | 0  | 1  | 1  |  |

| PCF2116     | LCD controller/driver                                              | 0                                               | 1  | 1  | 1  | 0  | 1  | A  |  |

| PCF8522/4   | 512 × 8-bit CMOS EEPROM                                            | 1                                               | 0  | 1  | 0  | Α  | A  | A  |  |

| PCF8566     | 96-segment LCD driver 1:1 - 1:4 Mux rates                          | 0                                               | 1  | 1  | 1  | 1  | 1  | A  |  |

| PCF8568     | LCD row driver for dot matrix displays                             | 0                                               | 1  | 1  | 1  | 1  | 0  | A  |  |

| PCF8569     | LCD column driver for dot matrix displays                          | 0                                               | 1  | 1  | 1  | 1  | 0  | Α  |  |

| PCF8570     | $256 \times 8$ -bit static RAM                                     | 1                                               | 0  | 1  | 0  | Α  | A  | A  |  |

| PCF8573     | Clock/calendar                                                     | 1                                               | 1  | 0  | 1  | 0  | A  | A  |  |

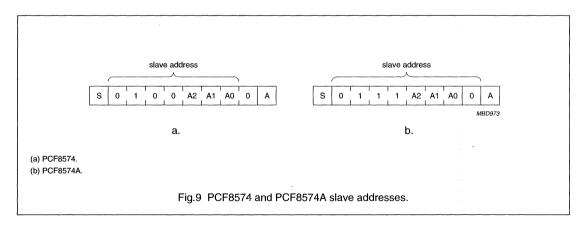

| PCF8574     | 8-bit remote I/O port (I <sup>2</sup> C-bus to parallel converter) | 0                                               | 1  | 0  | 0  | A  | Α  | A  |  |

| PCF8574A    | 8-bit remote I/O port (I <sup>2</sup> C-bus to parallel converter) | 0                                               | 1  | 1  | 1  | A  | A  | A  |  |

| PCF8576C    | 16-segment LCD driver 1:1 - 1:4 Mux rates                          | 0                                               | 1  | 1  | 1  | 0  | 0  | A  |  |

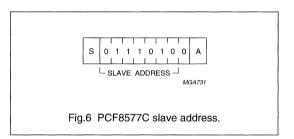

| PCF8577C    | 32/64-segment LCD display driver                                   | 0                                               | 1  | 1  | 1  | 0  | 1  | 0  |  |

| PCF8578/9   | Row/column LCD dot matrix driver/display                           | 0                                               | 1  | 1  | 1  | 1  | 0  | A  |  |

| PCF8582/A   | 256 × 8-bit EEPROM                                                 | 1                                               | 0  | 1  | 0  | A  | A  | A  |  |

| PCF8583     | $256 \times 8$ -bit RAM/clock/calendar                             | 1                                               | 0  | 1  | 0  | 0  | 0  | A  |  |

| PCF8584     | I <sup>2</sup> C-bus controller                                    | X                                               | X  | x  | X  | X  | X  | x  |  |

| PCF8591     | 4-channel, 8-bit Mux ADC and one DAC                               | 1                                               | 0  | 0  | 1  | A  | A  | A  |  |

| PCF8593     | Low-power clock calender                                           | 1                                               | 0  | 1  | 0  | 0  | 0  | 1  |  |

| PCX8594     | 512 × 8-bit CMOS EEPROM                                            | 1                                               | 0  | 1  | 0  | A  | A  | P  |  |

| PCX8598     | 1024 × 8-bit CMOS EEPROM                                           | 1                                               | 0  | 1  | 0  | A  | P  | Р  |  |

| PDIUSB11    | Universal serial bus                                               | 0                                               | 0  | 1  | 1  | 0  | 1  | 1  |  |

| SAA1064     | 4-digit LED driver                                                 | 0                                               | 1  | 1  | 1  | 0  | A  | A  |  |

# Assigned I<sup>2</sup>C-bus addresses

| ТҮРЕ          |                                             |    | I <sup>2</sup> C SLAVE ADDRESSES <sup>(1)</sup> |    |    |    |    |    |  |  |

|---------------|---------------------------------------------|----|-------------------------------------------------|----|----|----|----|----|--|--|

| NUMBER        | DESCRIPTION                                 | A6 | A5                                              | A4 | A3 | A2 | A1 | A0 |  |  |

| SAA1300       | Tuner switch circuit                        | 0  | 1                                               | 0  | 0  | 0  | A  | A  |  |  |

| SAA1770       | D2MAC decoder for satellite and cable TV    | 0  | 0                                               | 1  | 1  | 1  | 1  | A  |  |  |

| SAA2502       | MPEG audio source decoder                   | 0  | 0                                               | 1  | 1  | 1  | 0  | 1  |  |  |

| SAA2510       | Video-CD MPEG-audio/video decoder           | 0  | 0                                               | 1  | 1  | 0  | 1  | Α  |  |  |

| SAA2530       | ADR/DMX digital receiver                    | 0  | 0                                               | 0  | 1  | 1  | A  | A  |  |  |

| SAA4700/T     | VPS dataline processor                      | 0  | 0                                               | 1  | 0  | 0  | 0  | Α  |  |  |

| SAA5233       | Dual standard PDC decoder                   | 0  | 0                                               | 1  | 0  | 0  | 0  | Α  |  |  |

| SAA5243       | Computer controlled teletext circuit        | 0  | 0                                               | 1  | 0  | 0  | 0  | 1  |  |  |

| SAA5244       | Integrated VIP and teletext                 | 0  | 0                                               | 1  | 0  | 0  | 0  | 1  |  |  |

| SAA5245       | 525-line teletext decoder/controller        | 0  | 0                                               | 1  | 0  | 0  | 0  | 1  |  |  |

| SAA5246A      | Integrated VIP and teletext                 | 0  | 0                                               | 1  | 0  | 0  | 0  | 1  |  |  |

| SAA5249       | VIP and teletext controller                 | 0  | 0                                               | 1  | 0  | 0  | 0  | 1  |  |  |

| SAA5252       | Line 21 decoder                             | 0  | 0                                               | 1  | 0  | 1  | 0  | 0  |  |  |

| SAA5301       | MOJI processor for Japan/China              | 0  | 1                                               | 1  | 0  | 0  | 0  | 0  |  |  |

| SAA6750       | MPEG2 encoder for Desk Top Video (=SAA7137) | 0  | 1                                               | 0  | 0  | 0  | 0  | 0  |  |  |

| SAA7110A      |                                             |    | 0                                               | 0  | 1  | 1  | 1  | A  |  |  |

| SAA7140B      | High performance video scaler               | 0  | 1                                               | 1  | 1  | 0  | 0  | A  |  |  |

| SAA7151B      | 8-bit digital multistandard TV decoder      | 1  | 0                                               | 0  | 0  | 1  | A  | 1  |  |  |

| SAA7165       | Video enhancement D/A processor             | 1  | 0                                               | 1  | 1  | 1  | 1  | 1  |  |  |

| SAA7186       | Digital video scaler                        | 1  | 0                                               | 1  | 1  | 1  | Α  | 0  |  |  |

| SAA7191B      | Digital multistandard TV decoder            | 1  | 0                                               | 0  | 0  | 1  | A  | 1  |  |  |

| SAA7192       | Digital colour space-converter              | 1  | 1                                               | 1  | 0  | 0  | 0  | A  |  |  |

| SAA7199B      | Digital multistandard encoder               | 1  | 0                                               | 1  | 1  | 0  | 0  | A  |  |  |

| SAA7370       | CD-decoder plus digital servo processor     | 0  | 0                                               | 1  | 1  | 0  | 0  | A  |  |  |

| SAA9056       | Digital SCAM colour decoder                 | 1  | 0                                               | 0  | 0  | 1  | Α  | 1  |  |  |

| SAA9065       | Video enhancement and D/A processor         | 1  | 0                                               | 1  | 1  | 1  | 1  | 1  |  |  |

| SAB9075H      | PIP controller for NTSC                     | 0  | 0                                               | 1  | 0  | 1  | 1  | A  |  |  |

| SAF1135       | Dataline 16 decoder for VPS (call array)    | 0  | 0                                               | 1  | 0  | 0  | Α  | Α  |  |  |

| TDA1551Q      | $2 \times 22$ W BTL audio power amplifier   | 1  | 1                                               | 0  | 1  | 1  | 0  | 0  |  |  |

| TDA4670/1/2   | Picture signal improvement (PSI) circuit    | 1  | 0                                               | 0  | 0  | 1  | 0  | 0  |  |  |

| TDA4680/5/7/8 | Video processor                             | 1  | 0                                               | 0  | 0  | 1  | 0  | 0  |  |  |

| TDA4780       | Video control with gamma control            | 1  | 0                                               | 0  | 0  | 1  | 0  | 0  |  |  |

| TDA4845       | Vector processor for TV-pictures tubes      | 1  | 1                                               | 0  | 1  | 1  | Α  | A  |  |  |

| TDA4885       | 150 MHz video controller                    | 1  | 0                                               | 0  | 0  | 1  | 0  | 0  |  |  |

| TDA8043       | QPSK demodulator and decoder                | 1  | 1                                               | 0  | 1  | 0  | 0  | Α  |  |  |

| TDA8045       | QAM-64 demodulator                          | 0  | 0                                               | 0  | 1  | 1  | Α  | A  |  |  |

| TDA4853/4     | Autosync deflection processor               | 1  | 0                                               | 0  | 0  | 1  | 1  | 0  |  |  |

| TDA8366       | Multistandard one-chip video processor      | 1  | 0                                               | 0  | 0  | 1  | 0  | 1  |  |  |

| TDA8373       | NTSC one-chip video processor               | 1  | 0                                               | 0  | 0  | 1  | 0  | 1  |  |  |

# Assigned I<sup>2</sup>C-bus addresses

| TYPE        | DESODIDION                                           | I <sup>2</sup> C SLAVE ADDRESSES <sup>(1)</sup> |    |            |    |    |     |    |  |

|-------------|------------------------------------------------------|-------------------------------------------------|----|------------|----|----|-----|----|--|

| NUMBER      | DESCRIPTION                                          | A6                                              | A5 | <b>A</b> 4 | A3 | A2 | A1  | A0 |  |

| TDA8374     | Multistandard one-chip video processor               | 1                                               | 0  | 0          | 0  | 1  | 0   | 1  |  |

| TDA8375/A   | Multistandard one-chip video processor               | 1                                               | 0  | 0          | 0  | 1  | 0   | 1  |  |

| TDA8376/A   | Multistandard one-chip video processor               | 1                                               | 0  | 0          | 0  | 1  | 0   | 1  |  |

| TDA8415     | TV/VCR stereo/dual sound processor                   | 1                                               | 0  | 0          | 0  | 0  | 1   | 0  |  |

| TDA8416     | TV/VCR stereo/dual sound processor                   | 1                                               | 0  | 1          | 1  | 0  | 1 . | 0  |  |

| TDA8417     | TV/VCR stereo/dual sound processor                   | 1                                               | 0  | 0          | 0  | 0  | 1   | 0  |  |

| TDA8421     | Audio processor                                      | 1                                               | 0  | 0          | 0  | 0  | 0   | Α  |  |

| TDA8424/5/6 | Audio processor                                      | 1                                               | 0  | 0          | 0  | 0  | 0   | 1  |  |

| TDA8433     | TV deflection processor                              | 1                                               | 0  | 0          | 0  | 1  | 1   | Α  |  |

| TDA8440     | Video/audio switch                                   | 1                                               | 0  | 0          | 1  | A  | A   | A  |  |

| TDA8442     | Interface for colour decoder                         | 1                                               | 0  | 0          | 0  | 1  | 0   | 0  |  |

| TDA8443A    | YUV/RGB matrix switch                                | 1                                               | 1  | 0          | 1  | A  | A   | A  |  |

| TDA8444     | Octuple 6-bit DAC                                    | 0                                               | 1  | 0          | 0  | A  | A   | A  |  |

| TDA8480T    | RGB gamma-correction processor                       | 1                                               | 0  | 0          | 0  | 0  | 1   | Α  |  |

| TDA8540     | $4 \times 4$ video switch matrix                     | 1                                               | 0  | 0          | 1  | A  | A   | A  |  |

| TDA8722     |                                                      |                                                 | 1  | 0          | 0  | 1  | 0   | 0  |  |

| TDA8735     | 150 MHz PLL frequency synthesiser                    | 1                                               | 1  | 0          | 0  | 0  | 1   | A  |  |

| TDA8745     | Satellite sound decoder                              | 1                                               | 1  | 0          | 1  | 0  | . 1 | A  |  |

| TDA8752     | Triple fast ADC for LCD                              | 1                                               | 0  | 0          | 1  | 1  | A   | A  |  |

| TDA9141/3/4 | Alignment-free multistandard decoder                 | 1                                               | 0  | 0          | 0  | 1  | A   | 1  |  |

| TDA9150B    | Deflection processor                                 | 1                                               | 0  | 0          | 0  | 1  | 1   | 0  |  |

| TDA9151B    | Programmable deflection processor                    | 1                                               | 0  | 0          | 0  | 1  | 1   | 0  |  |

| TDA9160     | Multistandard decoder/sync. processor                | 1                                               | 0  | 0          | 0  | 1  | A   | 1  |  |

| TDA9161A    | Bus-controlled decoder/sync. processor               | 1                                               | 0  | 0          | 0  | 1  | 0   | 1  |  |

| TDA9162     | Multistandard decoder/sync. processor                | 1                                               | 0  | 0          | 0  | 1  | A   | 1  |  |

| TDA9170     | YUV processor with picture improvement               | 1                                               | 1  | 0          | 1  | 0  | 0   | A  |  |

| TDA9177     | 2nd address for LTI (1st is '40')                    | 1                                               | 1  | 1          | 0  | 0  | 0   | 0  |  |

| TDA9177     | YUV transient improvement processor                  | 0                                               | 1  | 0          | 0  | 0  | 0   | 0  |  |

| TDA9178     | 2nd address for LTI (1st is '40')                    | 1                                               | 1  | 1          | 0  | 0  | 0   | 0  |  |

| TDA9178     | YUV transient improvement processor                  | 0                                               | 1  | 0          | 0  | 0  | 0   | 0  |  |

| TDA9610     | Audio FM processor for VHS                           | 1                                               | 0  | 1          | 1  | 1  | 0   | 0  |  |

| TDA9614H    | Audio processor for VHS                              | 1                                               | 0  | 1          | 1  | 1  | 0   | 0  |  |

| TDA9840     | TV stereo/dual sound processor                       | 1                                               | 0  | 0          | 0  | 0  | 1   | 0  |  |

| TDA9850     | BTSC stereo/SAP decoder                              | 1                                               | 0  | 1          | 1  | 0  | 1   | A  |  |

| TDA9852     | BTSC stereo/SAP decoder                              | 1                                               | 0  | 1          | 1  | 0  | 1   | 1  |  |

| TDA9855     | BTSC stereo/SAP decoder                              | 1                                               | 0  | 1          | 1  | 0  | 1   | A  |  |

| TDA9860     | Hi-fi audio processor                                | 1                                               | 0  | 0          | 0  | 0  | 0   | A  |  |

| TEA6100     | FM/IF for computer-controlled radio                  | 1                                               | 1  | 0          | 0  | 0  | 0   | 1  |  |

| TEA6300     | Sound fader control and preamplifier/source selector | 1                                               | 0  | 0          | 0  | 0  | 0   | 0  |  |

# Assigned I<sup>2</sup>C-bus addresses

| TYPE                                           | DESCRIPTION                                 |    | I <sup>2</sup> C SLAVE ADDRESSES <sup>(1)</sup> |            |    |    |    |    |  |  |

|------------------------------------------------|---------------------------------------------|----|-------------------------------------------------|------------|----|----|----|----|--|--|

| NUMBER                                         | DESCRIPTION                                 | A6 | A5                                              | <b>A</b> 4 | A3 | A2 | A1 | A0 |  |  |

| TEA6320/1/2/3                                  | Sound fader control circuit                 | 1  | 0                                               | 0          | 0  | 0  | 0  | 0  |  |  |

| TEA6330                                        | Tone/volume controller                      | 1  | 0                                               | 0          | 0  | 0  | 0  | 0  |  |  |

| TEA6360                                        | 5-band equalizer                            | 1  | 0                                               | 0          | 0  | 1  | 1  | A  |  |  |

| TEA6821/2 Car radio AM                         |                                             | 1  | 1                                               | 0          | 0  | 0  | 1  | 0  |  |  |

| TEA6824T Car radio IF IC                       |                                             | 1  | 1                                               | 0          | 0  | 0  | 1  | 0  |  |  |

| TSA5511/2/4                                    | 1.3 GHz PLL frequency synthesizer for TV    | 1  | 1                                               | 0          | 0  | 0  | Α  | Α  |  |  |

| TSA5522/3M                                     | 1.4 GHz PLL frequency synthesizer for TV    | 1  | 1                                               | 0          | 0  | 0  | Α  | Α  |  |  |

| TSA6057                                        | Radio tuning PLL frequency synthesizer      | 1  | 1                                               | 0          | 0  | 0  | 1  | A  |  |  |

| TSA6060 Radio tuning PLL frequency synthesizer |                                             | 1  | 1                                               | 0          | 0  | 0  | 1  | A  |  |  |

| UMA1000T                                       | Data processor for mobile telephones        | 1  | 1                                               | 0          | 1  | 1  | A  | A  |  |  |

| UMA1014                                        | Frequency synthesizer for mobile telephones | 1  | 1                                               | 0          | 0  | 0  | 1  | A  |  |  |

Note

1. X = Don't care, A = Programmable address bit, P = Page selection bit.

# I<sup>2</sup>C-bus allocation table

#### I<sup>2</sup>C-BUS ALLOCATION TABLE (IN GROUP ORDER)

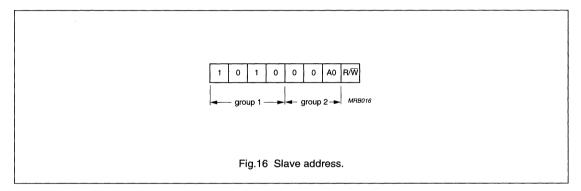

The group number represents the hexadecimal equivalent of the four most significant bits of the slave address (A6-A3).

| (     | GROUP <sup>(1)</sup> |         | TYPE NUMBER                           | DESCRIPTION                                                        |  |  |  |

|-------|----------------------|---------|---------------------------------------|--------------------------------------------------------------------|--|--|--|

| Group | 0 (0000              | )       | · · · · · · · · · · · · · · · · · · · |                                                                    |  |  |  |

| 0     | 0                    | 0       |                                       | General call address                                               |  |  |  |

| Х     | X                    | X       | -                                     | Reserved addresses                                                 |  |  |  |

| Group | 1 (0001              | )       | <b>.</b>                              |                                                                    |  |  |  |

| 1     | A1                   | A0      | SAA2530                               | ADR/DMX digital receiver                                           |  |  |  |

| 1     | A1                   | A0      | TDA8045                               | QAM-64 demodulator                                                 |  |  |  |

| Group | 2 (0010              | )       |                                       |                                                                    |  |  |  |

| 0     | ,<br>O               | ,<br>A0 | SAA4700/T                             | VPS dataline processor                                             |  |  |  |

| 0     | 0                    | A0      | SAA5233                               | Dual standard PDC decoder                                          |  |  |  |

| 0     | 0                    | 1       | SAA5243                               | Computer controlled teletext circuit                               |  |  |  |

| 0     | 0                    | 1       | SAA5244                               | Integrated VIP and teletext                                        |  |  |  |

| 0     | 0                    | 1       | SAA5245                               | 525-line teletext decoder/controller                               |  |  |  |

| 0     | 0                    | 1       | SAA5246A                              | Integrated VIP and teletext                                        |  |  |  |

| 0     | 0                    | 1       | SAA5249                               | VIP and teletext controller                                        |  |  |  |

| 0     | A1                   | A0      | CCR921                                | RDS/RBDS decoder                                                   |  |  |  |

| 0     | A1                   | A0      | SAF1135                               | Dataline 16 decoder for VPS (call array)                           |  |  |  |

| 1     | 0                    | 0       | SAA5252                               | Line 21 decoder                                                    |  |  |  |

| 1     | 1                    | A0      | SAB9075H                              | PIP controller for NTSC                                            |  |  |  |

| Group | 3 (0011              | )       | <b>-</b>                              |                                                                    |  |  |  |

| 0     | 0                    | A0      | SAA7370                               | CD-decoder plus digital servo processor                            |  |  |  |

| 0     | A1                   | A0      | PCD5096                               | Universal codec                                                    |  |  |  |

| 0     | 1                    | A0      | SAA2510                               | Video-CD MPEG-audio/video decoder                                  |  |  |  |

| 0     | 1                    | 1       | PDIUSB11                              | Universal serial bus                                               |  |  |  |

| 1     | 0                    | 1       | SAA2502                               | MPEG audio source decoder                                          |  |  |  |

| 1     | 1                    | A0      | SAA1770                               | D2MAC decoder for satellite and cable TV                           |  |  |  |

| Group | 4 (0100              | )       |                                       |                                                                    |  |  |  |

| 0     | 0                    | 0       | SAA6750                               | MPEG2 encoder for Desk Top Video (=SAA7137)                        |  |  |  |

| 0     | 0                    | 0       | TDA9177                               | YUV transient improvement processor                                |  |  |  |

| 0     | 0                    | 0       | TDA9178                               | YUV transient improvement processor                                |  |  |  |

| 0     | 0                    | A0      | PCA1070                               | Programmable speech transmission IC                                |  |  |  |

| 0     | A1                   | A0      | SAA1300                               | Tuner switch circuit                                               |  |  |  |

| A2    | A1                   | A0      | TDA8444                               | Octuple 6-bit DAC                                                  |  |  |  |

| A2    | A1                   | A0      | PCF8574                               | 8-bit remote I/O port (I <sup>2</sup> C-bus to parallel converter) |  |  |  |

| 1     | 0                    | A0      | PCD3311C                              | DTMF/modem/musical tone generator                                  |  |  |  |

| 1     | 0                    | A0      | PCD3312C                              | DTMF/modem/musical tone generator                                  |  |  |  |

| 1     | 1                    | 1       | PCD5002                               | Pager decoder                                                      |  |  |  |

# I<sup>2</sup>C-bus allocation table

| (     | GROUP(  | 1)    | TYPE NUMBER   | DESCRIPTION                                                        |  |  |  |  |  |  |

|-------|---------|-------|---------------|--------------------------------------------------------------------|--|--|--|--|--|--|

| Group | 6 (0110 | )     |               |                                                                    |  |  |  |  |  |  |

| 0     | 0       | 0     | SAA5301       | MOJI processor for Japan/China                                     |  |  |  |  |  |  |

| 0     | 1       | 1     | PCE84C467/8   | 8-bit CMOS auto-sync monitor controller                            |  |  |  |  |  |  |

| 0     | 1       | 1     | PCE84C882     | 8-bit microcontroller for monitor applications                     |  |  |  |  |  |  |

| 0     | 1       | 1     | PCE84C886     | 8-bit microcontroller for monitor applications                     |  |  |  |  |  |  |

|       | 7 (0111 | )     |               |                                                                    |  |  |  |  |  |  |

| 0     | 0       | ,<br> | SAA7140B      | High performance video scaler                                      |  |  |  |  |  |  |

| 0     | 0       | AO    | PCF8576C      | 16-segment LCD driver 1:1 - 1:4 Mux rates                          |  |  |  |  |  |  |

| 0     | A1      | A0    | SAA1064       | 4-digit LED driver                                                 |  |  |  |  |  |  |

| A2    | A1      | AO    | PCF8574A      | 8-bit remote I/O port (I <sup>2</sup> C-bus to parallel converter) |  |  |  |  |  |  |

| 0     | 1       | 0     | PCF8577C      | 32/64-segment LCD display driver                                   |  |  |  |  |  |  |

| 0     | 1       | AO    | SAA2116       | LCD controller/driver                                              |  |  |  |  |  |  |

| 1     | 0       | A0    | PCF8578/9     | Row/column LCD dot matrix driver/display                           |  |  |  |  |  |  |

| 1     | 0       | A0    | PCF8568       | LCD row driver for dot matrix displays                             |  |  |  |  |  |  |

| 1     | 0       | AO    | PCF8569       | LCD column driver for dot matrix displays                          |  |  |  |  |  |  |

| 1     | 1       | A0    | PCF8566       | 96-segment LCD driver 1:1 - 1:4 Mux rates                          |  |  |  |  |  |  |

|       | 8 (1000 | L     | 1             | <b>J</b>                                                           |  |  |  |  |  |  |

| 0     | 0       | 0     | TEA6300       | Sound fader control and preamplifier/source selector               |  |  |  |  |  |  |

| 0     | 0       | 0     | TEA6320/1/2/3 | Sound fader control circuit                                        |  |  |  |  |  |  |

| 0     | 0       | 0     | TEA6330       | Tone/volume controller                                             |  |  |  |  |  |  |

| 0     | 0       | AO    | NE5751        | Audio processor for RF communication                               |  |  |  |  |  |  |

| 0     | 0       | AO    | TDA8421       | Audio processor                                                    |  |  |  |  |  |  |

| 0     | 0       | AO    | TDA9860       | Hi-fi audio processor                                              |  |  |  |  |  |  |

| 0     | 0       | 1     | TDA8424/5/6   | Audio processor                                                    |  |  |  |  |  |  |

| 0     | 1       | 0     | TDA8415       | TV/VCR stereo/dual sound processor                                 |  |  |  |  |  |  |

| 0     | 1       | 0     | TDA8417       | TV/VCR stereo/dual sound processor                                 |  |  |  |  |  |  |

| 0     | 1       | 0     | TDA9840       | TV stereo/dual sound processor                                     |  |  |  |  |  |  |

| 0     | 1       | AO    | TDA8480T      | RGB gamma-correction processor                                     |  |  |  |  |  |  |

| 1     | 0       | 0     | TDA4670/1/2   | Picture signal improvement (PSI) circuit                           |  |  |  |  |  |  |

| 1     | 0       | 0     | TDA4680/5/7/8 | Video processor                                                    |  |  |  |  |  |  |

| 1     | 0       | 0     | TDA4780       | Video control with gamma control                                   |  |  |  |  |  |  |

| 1     | 0       | 0     | TDA4885       | 150 MHz video controller                                           |  |  |  |  |  |  |

| 1     | 0       | 0     | TDA8442       | Interface for colour decoder                                       |  |  |  |  |  |  |

| 1     | 0       | 1     | TDA8366       | Multistandard one-chip video processor                             |  |  |  |  |  |  |

| 1     | 0       | 1     | TDA8373       | NTSC one-chip video processor                                      |  |  |  |  |  |  |

| 1     | 0       | 1     | TDA8374       | Multistandard one-chip video processor                             |  |  |  |  |  |  |

| 1     | 0       | 1     | TDA8375/A     | Multistandard one-chip video processor                             |  |  |  |  |  |  |

| 1     | 0       | 1     | TDA8376/A     | Multistandard one-chip video processor                             |  |  |  |  |  |  |

| 1     | 0       | 1     | TDA9161A      | Bus-controlled decoder/sync. processor                             |  |  |  |  |  |  |

| 1     | A1      | 1     | SAA7151B      | 8-bit digital multistandard TV decoder                             |  |  |  |  |  |  |

# I<sup>2</sup>C-bus allocation table

| C     | GROUP   | 1) | TYPE NUMBER                             | DESCRIPTION                           |  |  |  |  |  |  |  |

|-------|---------|----|-----------------------------------------|---------------------------------------|--|--|--|--|--|--|--|

| 1     | A1      | 1  | SAA7191B                                | Digital multistandard TV decoder      |  |  |  |  |  |  |  |

| 1     | A1      | 1  | SAA9056                                 | Digital SCAM colour decoder           |  |  |  |  |  |  |  |

| 1     | A1      | 1  | TDA9141/3/4                             | Alignment-free multistandard decoder  |  |  |  |  |  |  |  |

| 1     | A1      | 1  | TDA9160                                 | Multistandard decoder/sync. processor |  |  |  |  |  |  |  |

| 1     | A1      | 1  | TDA9162                                 | Multistandard decoder/sync. processor |  |  |  |  |  |  |  |

| 1     | 1       | 0  | TDA4853/4                               | Autosync deflection processor         |  |  |  |  |  |  |  |

| 1     | 1       | 0  | TDA9150B                                | Deflection processor                  |  |  |  |  |  |  |  |

| 1     | 1       | 0  | TDA9151B                                | Programmable deflection processor     |  |  |  |  |  |  |  |

| 1     | 1       | A0 | TEA6360                                 | 5-band equalizer                      |  |  |  |  |  |  |  |

| 1     | 1       | A0 | TDA8433                                 | TV deflection processor               |  |  |  |  |  |  |  |

| Group | 9 (1001 | )  | • • · · · · · · · · · · · · · · · · · · |                                       |  |  |  |  |  |  |  |

| A2    | A1      | A0 | PCF8591                                 | 4-channel, 8-bit Mux ADC and one DAC  |  |  |  |  |  |  |  |

| A2    | A1      | A0 | TDA8440                                 | Video/audio switch                    |  |  |  |  |  |  |  |

| A2    | A1      | A0 | TDA8540                                 | $4 \times 4$ video switch matrix      |  |  |  |  |  |  |  |

| 1     | A1      | A0 | TDA8752                                 | Triple fast ADC for LCD               |  |  |  |  |  |  |  |

| 1     | 1       | A0 | SAA7110A                                | Digital multistandard decoder         |  |  |  |  |  |  |  |

| Group | A (1010 | )) | · · · · · · · · · · · · · · · · · · ·   |                                       |  |  |  |  |  |  |  |

| 0     | 0       | 0  | PCB2421                                 | 1K dual mode serial EEPROM            |  |  |  |  |  |  |  |

| 0     | 0       | A0 | PCF8583                                 | 256 × 8-bit RAM/clock/calendar        |  |  |  |  |  |  |  |

| 0     | 0       | 1  | PCF8593                                 | Low-power clock calender              |  |  |  |  |  |  |  |

| A2    | A1      | A0 | PCF8570                                 | 256 × 8-bit static RAM                |  |  |  |  |  |  |  |

| A2    | A1      | A0 | PCF8522/4                               | 512 × 8-bit CMOS EEPROM               |  |  |  |  |  |  |  |

| A2    | A1      | A0 | PCA8581/C                               | 128 × 8-bit EEPROM                    |  |  |  |  |  |  |  |

| A2    | A1      | A0 | PCF8582/A                               | 256 × 8-bit EEPROM                    |  |  |  |  |  |  |  |

| A2    | A1      | P0 | PCX8594                                 | 512 × 8-bit CMOS EEPROM               |  |  |  |  |  |  |  |

| A2    | P1      | P0 | PCX8598                                 | 1024 × 8-bit CMOS EEPROM              |  |  |  |  |  |  |  |

| Group | B (1011 | )  |                                         |                                       |  |  |  |  |  |  |  |

| 0     | 0       | A0 | SAA7199B                                | Digital multistandard encoder         |  |  |  |  |  |  |  |

| 0     | 1       | 0  | TDA8416                                 | TV/VCR stereo/dual sound processor    |  |  |  |  |  |  |  |

| 0     | 1       | A0 | TDA9850                                 | BTSC stereo/SAP decoder               |  |  |  |  |  |  |  |

| 0     | 1       | A0 | TDA9855                                 | BTSC stereo/SAP decoder               |  |  |  |  |  |  |  |

| 0     | 1       | 1  | TDA9852                                 | BTSC stereo/SAP decoder               |  |  |  |  |  |  |  |

| 1     | 0       | 0  | TDA9610                                 | Audio FM processor for VHS            |  |  |  |  |  |  |  |

| 1     | 0       | 0  | TDA9614H                                | Audio processor for VHS               |  |  |  |  |  |  |  |

| 1     | A1      | 0  | SAA7186                                 | Digital video scaler                  |  |  |  |  |  |  |  |

| 1     | 0       | 1  | PCA8516                                 | Stand-alone OSD IC                    |  |  |  |  |  |  |  |

| 1     | 1       | 1  | SAA7165                                 | Video enhancement D/A processor       |  |  |  |  |  |  |  |

| 1     | 1       | 1  | SAA9065                                 | Video enhancement and D/A processor   |  |  |  |  |  |  |  |

| Group | C (1100 | )) | - <b>I</b>                              |                                       |  |  |  |  |  |  |  |

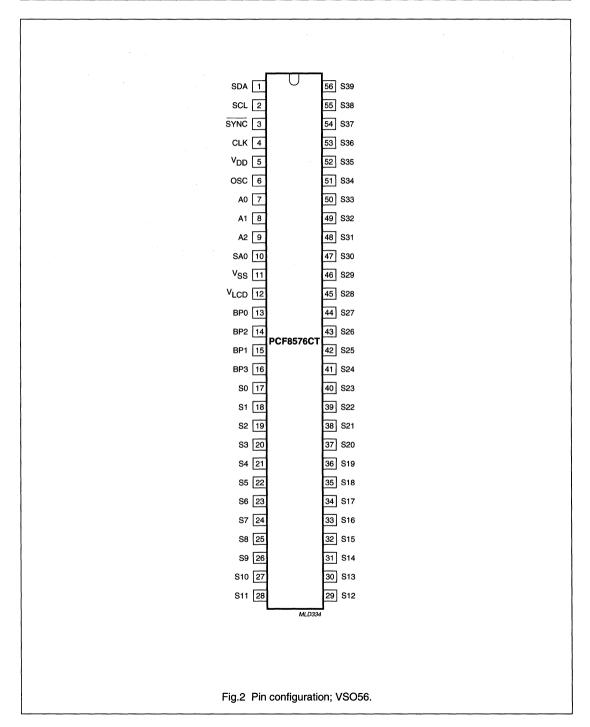

| 0     | 0       | 1  | TEA6100                                 | FM/IF for computer-controlled radio   |  |  |  |  |  |  |  |

# I<sup>2</sup>C-bus allocation table

| C     | GROUP    | 1)      | TYPE NUMBER | DESCRIPTION                                       |  |  |  |  |  |

|-------|----------|---------|-------------|---------------------------------------------------|--|--|--|--|--|

| 0     | 1        | 0       | TEA6821/2   | Car radio AM                                      |  |  |  |  |  |

| 0     | 1        | 0       | TEA6824T    | Car radio IF IC                                   |  |  |  |  |  |

| 0     | A1       | A0      | TSA5511/2/4 | 1.3 GHz PLL frequency synthesizer for TV          |  |  |  |  |  |

| 0     | A1       | A0      | TSA5522/3M  | 1.4 GHz PLL frequency synthesizer for TV          |  |  |  |  |  |

| 0     | 1        | A0      | TDA8735     | 150 MHz PLL frequency synthesizer                 |  |  |  |  |  |

| 0     | 1        | A0      | TSA6057     | Radio tuning PLL frequency synthesizer            |  |  |  |  |  |

| 0     | 1        | A0      | TSA6060     | Radio tuning PLL frequency synthesizer            |  |  |  |  |  |

| 0     | 1        | A0      | UMA1014     | Frequency synthesizer for mobile telephones       |  |  |  |  |  |

| 1     | 0        | 0       | TDA8722     | Negative video modulator with FM sound            |  |  |  |  |  |

| Group | D (1101  | )       |             |                                                   |  |  |  |  |  |

| 0     | 0        | A0      | TDA8043     | QPSK demodulator and decoder                      |  |  |  |  |  |

| 0     | 0        | A0      | TDA9170     | YUV processor with picture improvement            |  |  |  |  |  |

| 0     | A1       | A0      | PCF8573     | Clock/calendar                                    |  |  |  |  |  |

| A2    | A1       | A0      | TDA8443A    | YUV/RGB matrix switch                             |  |  |  |  |  |

| 0     | 1        | A0      | TDA8745     | Satellite sound decoder                           |  |  |  |  |  |

| 1     | 0        | 0       | TDA1551Q    | $2 \times 22$ W BTL audio power amplifier         |  |  |  |  |  |

| 1     | A1       | A0      | TDA4845     | Vector processor for TV-pictures tubes            |  |  |  |  |  |

| 1     | A1       | A0      | UMA1000T    | Data processor for mobile telephones              |  |  |  |  |  |

| 1     | 1        | A0      | PCD4440     | Voice scrambler/descrambler for mobile telephones |  |  |  |  |  |

| Group | E (1110  | )       |             |                                                   |  |  |  |  |  |

| 0     | 0        | 0       | TDA9177     | 2nd address for LTI (1st is '40')                 |  |  |  |  |  |

| 0     | 0        | 0       | TDA9178     | 2nd address for LTI (1st is '40')                 |  |  |  |  |  |

| 0     | 0        | A0      | SAA7192     | Digital colour space-converter                    |  |  |  |  |  |

| Group | F (1111  | )       |             | ·                                                 |  |  |  |  |  |

| Х     | Х        | Х       | -           | Reserved addresses                                |  |  |  |  |  |

| Group | 0 to F ( | 0000 to | 1111)       |                                                   |  |  |  |  |  |

| X     | X        | X       | PCF8584     | I <sup>2</sup> C-bus controller                   |  |  |  |  |  |

Note

1. X = Don't care, A = Programmable address bit, P = Page selection bit

# Microcontroller internet and bulletin board access

## **INTERNET ACCESS**

#### **Philips Semiconductors World Wide Web:**

http://www.semiconductors.philips.com

### Internet 80C51 Applications Support Address:

#### 80C51\_help@scs.philips.com

Send us your questions and we will respond quickly.

#### **Microcontroller FTP Site:**

ftp://ftp.PhilipsMCU.com

## Internet Microcontroller Newsletter:

To subscribe, send email to:

News-Request@PhilipsMCU.com

## Internet 80C51 Discussion Forum:

Forum-Request@PhilipsMCU.com

### Internet XA 16-bit 80C51 Support Address:

XA\_help@scs.philips.com

# Microcontroller internet and bulletin board access

### **BULLETIN BOARDS**

To better serve our customers, Philips maintains two microcontroller bulletin boards. These computer bulletin board systems feature microcontroller newsletters, application and demonstration programs for download, and the ability to send messages to microcontroller application engineers.

The telephone numbers are:

North American Bulletin Board MAX 14.400 baud 8-N-1 (800) 451-6644 (in the U.S.) or (408) 991-2406

European Bulletin Board MAX 14.400 baud Standards V32/V42/V42.bis/HST +31 40 2721102

# Sunnyvale ROMcode Bulletin Board

We also have a ROM code bulletin board through which you can submit ROM codes. This is a closed bulletin board for security reasons. To get an ID, contact your local sales office. The system can be accessed with a 2400, 1200, or 300 baud modem, and is available 24 hours a day.

The telephone number is:

# (408) 991-3459

All code for application notes in this databook are available on the Philips BBS, as well as on the world-wide web.

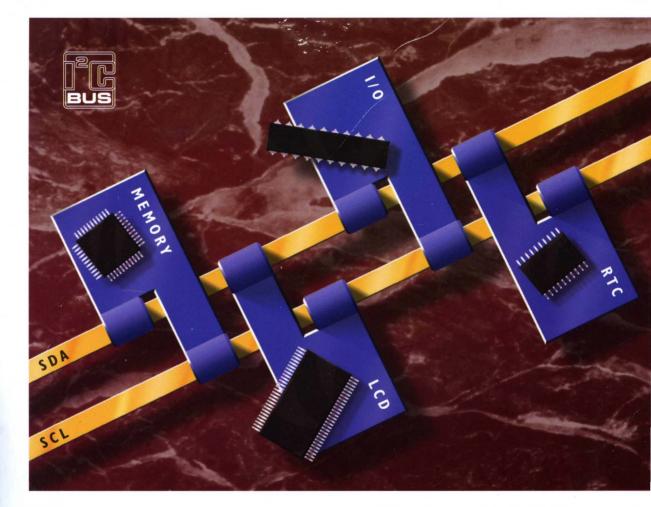

# FAX-on-DEMAND System

#### What is it?

The FAX-on-DEMAND system is a computer facsimile system that allows customers to receive selected documents by fax automatically.

#### How does it work?

To order a document, you simply enter the document number. This number can be obtained by asking for an index of available documents to be faxed to you the first time you call the system.

Our system has a selection of the latest product data sheets from Philips with varying page counts. As you know, it takes approximately one minute to FAX one page. This isn't bad if the number of pages is less than 10. But if the document is 37 pages long, be ready for a long transmission!

Philips Semiconductors also maintains product information on the World-Wide Web. Our home page can be located at:

http://www.semiconductors.philips.com

# Who do I contact if I have a question about FAX-on-DEMAND?

Contact your local Philips sales office.

#### FAX-on-DEMAND phone numbers:

| England<br>(United Kingdom, Ireland) | 44-181-730-5020  |

|--------------------------------------|------------------|

| France                               | 33-1-40-99-60-60 |

| Italy                                | 39-167-295502    |

| North America                        | 1-800-282-2000   |

Locations soon to be in operation: Hong Kong Japan The Netherlands

# Internet World Wide Web Home Page

#### WHAT IS IT?

Welcome to our place in cyberspace.

Explore our Web pages and take a look at our product offering of advance High-performance Applications and Products.

In addition we offer you the latest information on Products, News, Support, Employment and Offices.

#### HOW TO REACH US

For access to the Philips Semiconductors Home Page go to the World Wide Web location:

http://www.semiconductors.philips.com/

|     | Part Number       | T   | Memory |     | Counter              | 1/0   | Serial                 | External  | Comments/                                                                              |

|-----|-------------------|-----|--------|-----|----------------------|-------|------------------------|-----------|----------------------------------------------------------------------------------------|

|     | (ROMless)         | ROM | EPRM   | RAM | Timers               | Port  | Interfaces             | Interrupt | Special Features                                                                       |

| Р   | 83C750            | 1K  |        | 64  | 1 (16-bit)           | 2-3/8 | -                      | 2         | 40 MHz, Lowest cost, SSOP                                                              |

| Р   | 87C750            |     | 1K     | 64  | 1 (16-bit)           | 2-3/8 | -                      | 2         | 40 MHz, Lowest cost, SSOP                                                              |

| Р   | 83C748            | 2K  |        | 64  | 1 (16-bit)           | 2-3/8 | -                      | 2         | 8XC751 w/o I <sup>2</sup> C, SSOP                                                      |

| Р   | 87C748            |     | 2K     | 64  | 1 (16-bit)           | 2-3/8 | -                      | 2         | 8XC751 w/o I <sup>2</sup> C, SSOP                                                      |

| S   | 83C751            | 2K  |        | 64  | 1 (16-bit)           | 2-3/8 | I <sup>2</sup> C (bit) | 2         | 24-pin Skinny DIP, SSOP                                                                |

| S   | 87C751            |     | 2K     | 64  | 1 (16-bit)           | 2-3/8 | I <sup>2</sup> C (bit) | 2         | 24-pin Skinny DIP, SSOP                                                                |

| Р   | 83C749            | 2K  |        | 64  | 1 (16-bit)           | 2-5/8 | -                      | 2         | 8XC752 w/o I <sup>2</sup> C, SSOP                                                      |

| Р   | 87C749            |     | 2K     | 64  | 1 (16-bit)           | 2-5/8 | -                      | 2         | 8XC752 w/o I <sup>2</sup> C, SSOP                                                      |

| S   | 83C752            | 2K  |        | 64  | 1 (16-bit)           | 2-5/8 | I <sup>2</sup> C (bit) | 2         | 5 Channel 8-bit A/D, PWM Output, SSOP                                                  |

| S   | 87C752            |     | 2K     | 64  | 1 (16-bit)           | 2-5/8 | I <sup>2</sup> C (bit) | 2         | 5 Channel 8-bit A/D, PWM Output, SSOP                                                  |

| SC  | 80C51 (80C31)     | 4K  |        | 128 | 2                    | 4     | UART                   | 2         | CMOS (Sunnyvale)                                                                       |

| PCx | 80C51 (80C31)     | 4K  |        | 128 | 2                    | 4     | UART                   | 2         | CMOS (Hamburg)                                                                         |

| SC  | 87C51             |     | 4K     | 128 | 2                    | 4     | UART                   | 2         | CMOS                                                                                   |

| Р   | 80CL51 (80CL31)   | 4K  |        | 128 | 2                    | 4     | UART                   | 10        | Low Voltage (1.8V to 6V), Low Power                                                    |

| Р   | 83CL410 (80CL410) | 4K  |        | 128 | 2                    | 4     | I <sup>2</sup> C       | 10        | Low Voltage (1.8V to 6V), Low Power                                                    |

| SC  | 83C451 (80C451)   | 4K  |        | 128 | 2                    | 7     | UART                   | 2         | Extended I/O, Processor Bus Interface                                                  |

| SC  | 87C451            |     | 4K     | 128 | 2                    | 7     | UART                   | 2         | Extended I/O, Processor Bus Interface                                                  |

| Р   | 83C550 (80C550)   | 4K  |        | 128 | 2 + Watchdog         | 4     | UART                   | 2         | 8 Channel 8-bit A/D                                                                    |

| Р   | 87C550            |     | 4K     | 128 | 2 + Watchdog         | 4     | UART                   | 2         | 8 Channel 8-bit A/D                                                                    |

| Р   | 83C851 (80C851)   | 4K  |        | 128 | 2                    | 4     | UART                   | 2         | 256B EEPROM, 80C51 Pin compatible                                                      |

| Ρ   | 83C852            | 6K  |        | 256 | 2 (16-bit)           | 2/8   | -                      | 1         | Smartcard Controller with 2K EEPROM (Data,<br>Code) Cryptographic Calc Unit            |

| Ρ   | 83CL580 (80CL580) | 6K  |        | 256 | 3 + Watchdog         | 5     | UART, I <sup>2</sup> C | 9         | 4 Channel 8-bit A/D, PWM Output,<br>Low Voltage (2.5V to 6V), Low Power                |

| Ρ   | 80C52 (80C32)     | 8K  |        | 256 | 3                    | 4     | UART                   | 2         | 80C51 Pin Compatible                                                                   |

| Р   | 87C52             |     | 8K     | 256 | 3                    | 4     | UART                   | 2         | (see above)                                                                            |

| Ρ   | 83C652 (80C652)   | 8K  |        | 256 | 2                    | 4     | UART, I <sup>2</sup> C | 2         | 80C51 Pin Compatible                                                                   |

| S   | 87C652            |     | 8K     | 256 | 2                    | 4     | UART, I <sup>2</sup> C | 2         | (see above)                                                                            |

| Р   | 83C453 (80C453)   | 8K  |        | 256 | 2                    | 7     | UART                   | 2         | Extended I/O, Processor Bus Interface                                                  |

| Р   | 87C453            |     | 8K     | 256 | 2                    | 7     | UART                   | 2         | Extended I/O, Processor Bus Interface                                                  |

| S   | 83C51FA (80C51FA) | 8K  |        | 256 | 3 + PCA              | 4     | UART                   | 2         | Enhanced UART, 3 timers + PCA                                                          |

| S   | 87C51FA           |     | 8K     | 256 | 3 + PCA              | 4     | UART                   | 2         | Enhanced UART, 3 timers + PCA                                                          |

| S   | 83L51FA           | 8K  |        | 256 | 3 + PCA              | 4     | UART                   | 2         | Low Voltage 83C51FA (3V @ 20MHz)                                                       |

| S   | 87L51FA           |     | 8K     | 256 | 3 + PCA              | 4     | UART                   | 2         | Low Voltage OTP 87C51FA (3V @ 20MHz)                                                   |

| Ρ   | 83C575 (80C575)   | 8K  |        | 256 | 3 + PCA+<br>Watchdog | 4     | UART                   | 2         | High Reliability, with Low Voltage Detect,<br>OSC Fail Detect, Analog Comparators, PCA |

| Ρ   | 87C575            |     | 8K     | 256 | (see above)          | 4     | UART                   | 2         | (see above)                                                                            |

| Ρ   | 83C576 (80C576)   | 8K  |        | 256 | 3 + PCA+<br>Watchdog | 4     | UART                   | 2         | Same as 8XC575 plus UPI and 10-bit A/D                                                 |

| Р   | 87C576            |     | 8K     | 256 | (see above)          | 4     | UART                   | 2         | (see above)                                                                            |

| PC  | 83C562 (80C562)   | 8K  |        | 256 | 3 + Watchdog         | 6     | UART                   | 2         | 8 Channel 8-bit A/D, 2 PWM Outputs,<br>Capture/Compare Timer                           |

| PCx | 83C552 (80C552)   | 8K  |        | 256 | 3 + Watchdog         | 6     | UART, I <sup>2</sup> C | 2         | 8 Channel 10-bit A/D, 2 PWM Outputs,<br>Capture/Compare Timer                          |

| S   | 87C552            |     | 8K     | 256 | 3 + Watchdog         | 6     | UART, I <sup>2</sup> C | 2         | (see above)                                                                            |

Notes: Part number prefixes are noted in the first column.

All combinations of part type, speed, temperature and package may not be available.

| Part Number         |                | Program   | Clock Freq  | Tem     | perature Ran | ges (°C)    |         |      | Packa   | ge   |              |

|---------------------|----------------|-----------|-------------|---------|--------------|-------------|---------|------|---------|------|--------------|

| (ROMIess)           |                | Security? | (MHz)       | 0 to 70 | -40 to +85   | -55 to +125 | PDIP    | CDIP | PLCC    | CLCC | PQFP/SSOP    |

| 83C750              | S              | N         | 3.5 to 40   | Х       | Х            |             | N24     | F24  | A28     |      | DB24 (0-70F) |

| 87C750              | S              | Y         | 3.5 to 40   | Х       | Х            |             | N24     | F24  | A28     |      | DB24 (0-70F) |

| 83C748              | S              | N         | 3.5 to16    | Х       | Х            |             | N24     |      | A28     |      | DB24 (0-70F) |

| 87C748              | S              | Y         | 3.5 to16    | х       | х            |             | N24     | F24  | A28     |      | DB24 (0-70F) |

| 83C751              | S              | N         | 3.5 to16    | Х       | Х            |             | N24     |      | A28     |      | DB24 (0-70F) |

| 87C751              | S              | Y         | 3.5 to16    | х       | х            |             | N24     | F24  | A28     |      | DB24 (0-70F) |

| 83C749              | S              | N         | 3.5 to 16   | х       | х            |             | N28     |      | A28     |      | DB28 (0-70F) |

| 87C749              | S              | Y         | 3.5 to 16   | х       | Х            |             | N28     | F28  | A28     |      | DB28 (0-70F) |

| 83C752              | S              | N         | 3.5 to 16   | х       | X            | Х           | N28     |      | A28     |      | DB28 (0-70F) |

| 87C752              | S              | Y         | 3.5 to 16   | Х       | X            | х           | N28     | F28  | A28     |      | DB28 (0-70F) |

| SC80C51 (80C31)     | s              | Ý         | 3.5 to 33   | Х       | X            | Х           | N40     |      | A44     |      | B44 (5)      |

| PCx80C51 (80C31)    | н              | N         | 1.2 to 30   | Х       | Х            | Х           | P (40)  |      | WP (44) |      | H (44)       |

| 87C51               | S              | Y         | 3.5 to 33   | Χ.      | х            | Х           | N40     | F40  | A44     | K44  | B44 (5)      |

| 80CL51 (80CL31)     | Ζ              | N         | 0 to 16 (1) |         | Х            |             | N40 (2) |      | 1       |      | B44          |

| 83CL410(80CL410)    | Ζ              | N         | 0 to 12 (1) |         | х            |             | N40 (2) |      |         |      | B44          |

| 83C451 (80C451)     | s              | N         | 3.5 to 16   | Х       | X            | Х           | N64 (4) |      | A68     |      |              |

| 87C451              | s              | Y         | 3.5 to16    | X       | Х            | x           | N64 (4) |      | A68     |      |              |

| 83C550 (80C550)     | S              | Y         | 3.5 to 16   | Х       | х            |             | N40     |      | A44     |      |              |

| 87C550              | S              | Y         | 3.5 to 16   | Х       | Х            | -40 to +125 | N40     | F40  | A44     | K44  |              |

| 83C851 (80C851)     | н              | Y         | 1.2 to 16   | х       | Х            |             | N40     |      | A44     |      | B44          |

| 83C852              | н              | Ŷ         | 1 to 12     | X       |              |             | SO28    |      |         |      |              |

| 0001 500 (0001 500) | z              |           | 01, 10 (1)  |         |              | ·····       | or die  |      |         |      | 504          |

| 83CL580 (80CL580)   | 1 <sup>2</sup> | N         | 0 to 12 (1) |         | ×            |             | (3)     |      |         |      | B64          |

| 80C52 (80C32)       | S              | Y         | 3.5 to 24   | X       | x            |             | N40     |      | A44     |      | B44 (5)      |

| 87C52               | S              | Y         | 3.5 to 24   | х       | х            | Х           | N40     | F40  | A44     | K44  | B44 (5)      |

| 83C652 (80C652)     | н              | Y         | 1.2 to 24   | х       | Х            | -40 to +125 | N40     |      | A44     |      | B44          |

| 87C652              | S              | Y         | 1.2 to 20   | Х       | Х            | ×           | N40     | F40  | A44     | K44  |              |

| 83C453 (80C453)     | s              | N         | 3.5 to 16   | х       | х            |             |         |      | A68     |      | 1            |

| 87C453              | S              | Y         | 3.5 to16    | Х       | Х            |             |         |      | A68     |      |              |

| 83C51FA (80C51FA)   | S              | Y         | 3.5 to 24   | х       | х            |             | N40     |      | A44     |      | B44          |

| 87C51FA             | S              | Y         | 3.5 to 24   | х       | Х            |             | N40     | F40  | A44     | K44  | B44          |

| 83L51FA             | S              | Y         | 3.5 to 20   | х       | X            |             | N40     |      | A44     | 1    | B44          |

| 87L51FA             | S              | Y         | 3.5 to 20   | х       | Х            |             | N40     | F40  | A44     | K44  | B44          |

| 83C575 (80C575)     | S              | Y         | 4 to 16     | x       |              | х           | N40     |      | A44     |      | B44          |

| 87C575              | s              | Y         | 4 to 16     | x       |              | x           | N40     | F40  | A44     | K44  | B44          |

| 83C576 (80C576)     | s              | Y         | 4 to 16     | x       |              | ×           | N40     |      | A44     |      | B44          |

| 87C576              | s              | Y         | 4 to 16     | x       |              | x           | N40     | F40  | A44     | K44  | B44          |

| 83C562 (80C562)     | н              | N         | 1.2 to 16   | x       | x            | -40 to +125 | [       |      | A68     | 1    | B80          |

| 83C552 (80C552)     | н              | N         | 1.2 to 30   | x       | x            | -40 to +125 |         |      | A68     |      | B80          |

| 87C552              | s              | Y         | 1.2 to 16   | X       | t            |             | <b></b> |      | A68     | K68  | <u>†</u>     |

Notes: Production Centers are indicated in the second column: H – Hamburg, S – Sunnyvale, Z – Zurich. All combinations of part type, speed, temperature and package may not be available.

1) Oscillator options start from 32kHz.

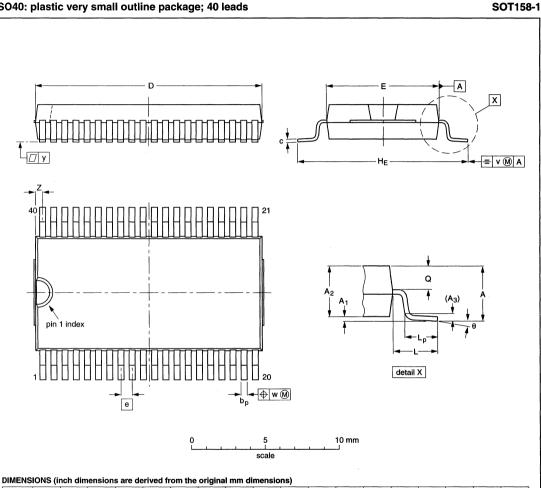

2) Also available in VSO40 package.

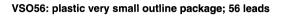

3) Also available in VSO56 Package.

4) Not recommended for new design.

5) Package available up to 16 MHz only.

|   | Part Number       |     | Memory |      | Counter      | 1/0   | Serial                     | External  | Comments/                                                                       |

|---|-------------------|-----|--------|------|--------------|-------|----------------------------|-----------|---------------------------------------------------------------------------------|

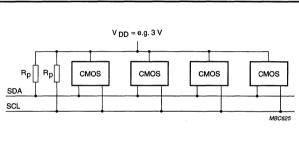

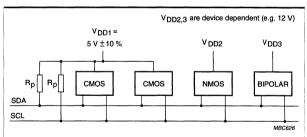

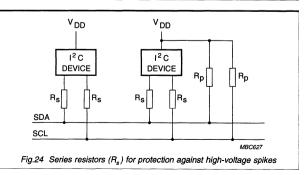

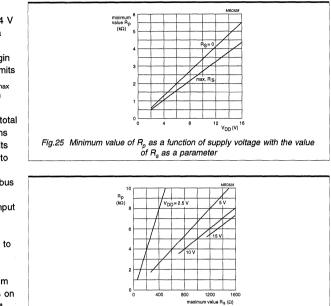

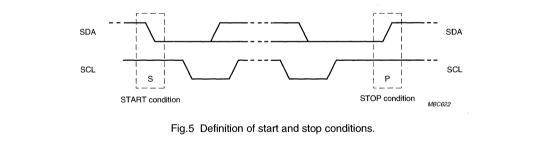

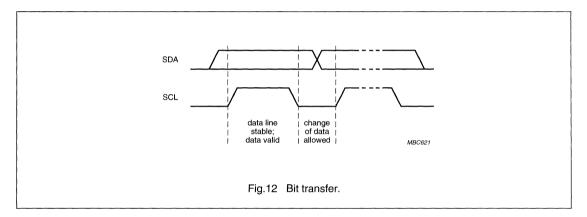

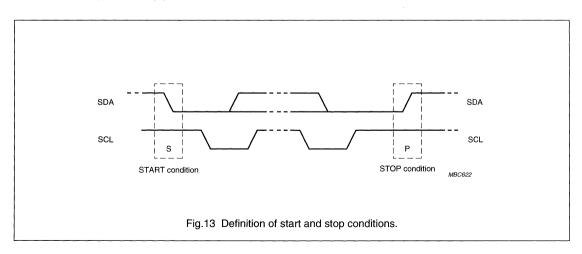

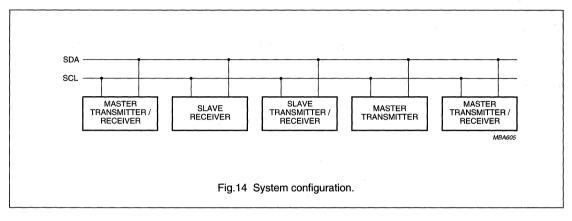

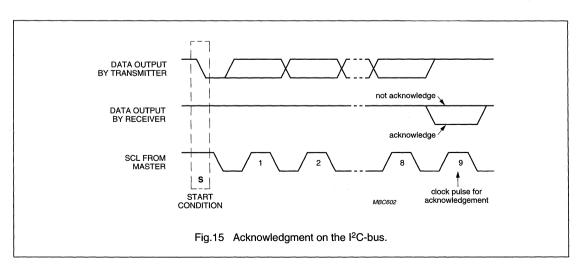

|   | (ROMIess)         | ROM | EPRM   | RAM  | Timers       | Port  | Interfaces                 | Interrupt | Special Features                                                                |