# DATA HANDBOOK

N

6

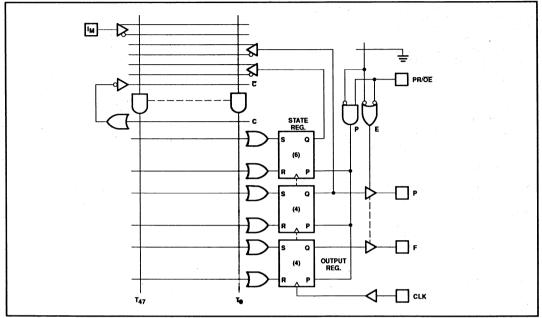

5

3

- C - 1

0 0 K

8

PHILIPS

# Programmable Logic Devices (PLD)

Signetics Philips Semiconductors

**Signetics**

**Philips Semiconductors**

Signetics reserves the right to make changes, without notice, in the products, including circuits, standard cells, and/or software, described or contained herein in order to improve design and/or performance. Signetics assumes no responsibility or liability for the use of any of these products, conveys no license or title under any patent, copyright, or mask work right to these products, and makes no representations or warranties that these products are free from patent, copyright, or mask work right infringement, unless otherwise specified. Applications that are described herein for any of these products are for illustrative purposes only. Signetics makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification.

#### LIFE SUPPORT APPLICATIONS

Signetics Products are not designed for use in life support appliances, devices, or systems where malfunction of a Signetics Product can reasonably be expected to result in a personal injury. Signetics customers using or selling Signetics Products for use in such applications do so at their own risk and agree to fully indemnify Signetics for any damages resulting from such improper use or sale.

Signetics registers eligible circuits under the Semiconductor Chip Protection Act.

© Copyright 1992 Signetics Company.

All rights reserved.

# Preface

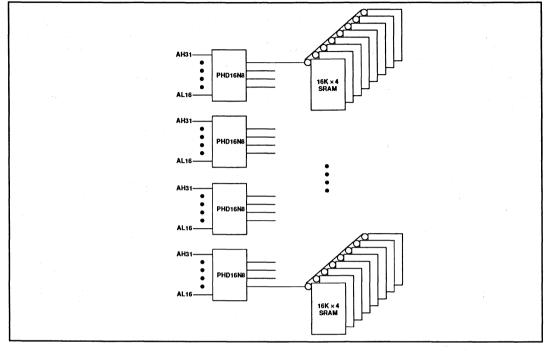

The 1992 Philips Semiconductors–Signetics PLD Data Handbook is loaded with information on new parts. Using the fastest technologies in the most innovative architectures, today's system designer can pick from the largest selection of PLDs in the industry. Featured in 1992 are the ultra high-speed BiCMOS devices designed to be pin, function, and fusemap identical to existing industry standard parts. Some highlights of this handbook include the fastest silicon PLDs available (PHD16N8 and PHD48N22)—at 5 nanoseconds! These devices make ideal decoders to squeeze maximum performance from powerful microprocessors. If that's not fast enough, check out the 10H20EV8 at 4.5 nanoseconds!

Designers using DRAM, VRAM and graphics will appreciate the speed and power of the new line of sequencers which include the PLC415, PLC42VA12, PLUS405 and PLUS105. These sequencers also make innovative bus and LAN controllers for emerging standard protocols.

At last, the logical power of dual programmable arrays comes forth in the PLUS153 and PLUS173 devices—at 10 nanosecond propagation delays.

The PLC18V8Z is the only zero power 20-pin device which can replace 16V8's!

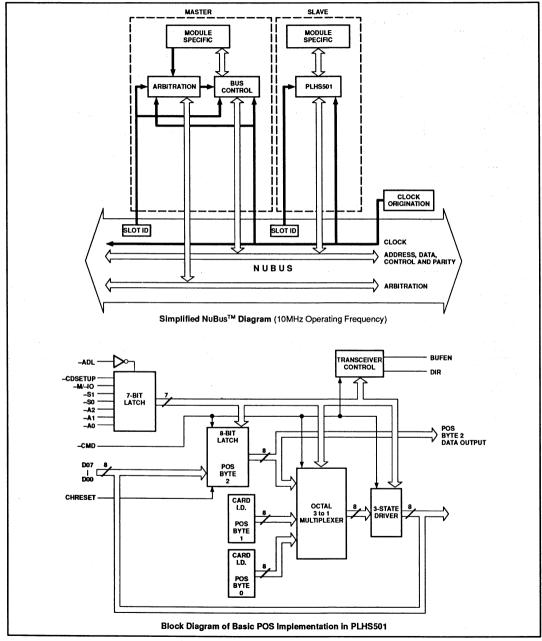

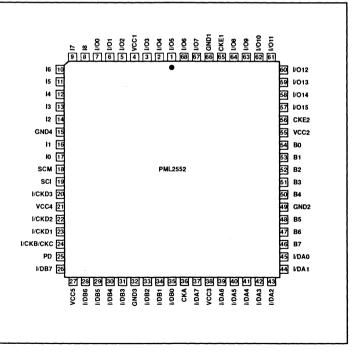

For maximum density in a truly compact system, the Programmable Macro Logic family now boasts three members—the PML2552, the PML2852, and the original PLHS501. The PML2552 is the PLD industry's first dense device to implement SCAN test.

To complement the devices, SLICE design software is offered through our Sales Offices (see Section 11) and SNAP software is available for high level support. Read about them under Product Support.

Expanding customer service has been an ongoing effort. Our Applications staff continues to answer your technical questions on PLD designs and our free computer Bulletin Board, with 24-hour service, is at (800)451-6644.

# Product Status

| DEFINITIONS                  |                        |                                                                                                                                                                                                                                                    |  |  |  |  |  |

|------------------------------|------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Data Sheet<br>Identification | Product Status         | Definition                                                                                                                                                                                                                                         |  |  |  |  |  |

| Objective Specification      | Formative or In Design | This data sheet contains the design target or goa<br>specifications for product development. Specifications may<br>change in any manner without notice.                                                                                            |  |  |  |  |  |

| Preliminary Specification    | Preproduction Product  | This data sheet contains preliminary data ar<br>supplementary data will be published at a later dat<br>Signetics reserves the right to make changes at any tim<br>without notice in order to improve design and supply the be<br>possible product. |  |  |  |  |  |

| Product Specification        | Full Production        | This data sheet contains Final Specifications. Signetics<br>reserves the right to make changes at any time without notice<br>in order to improve design and supply the best possible<br>product.                                                   |  |  |  |  |  |

# Contents

| Preface                                                                               |                                                                                                                                                                                                                                                                                                                               | iii               |

|---------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| Product Status                                                                        |                                                                                                                                                                                                                                                                                                                               | iv                |

| Selection Guide                                                                       | nation                                                                                                                                                                                                                                                                                                                        | 3<br>4<br>6       |

| Section 2 – Introduction                                                              |                                                                                                                                                                                                                                                                                                                               |                   |

| What is Signetics Prog<br>Quality and Reliability                                     | rammable Logic                                                                                                                                                                                                                                                                                                                | 9<br>26<br>38     |

| Section 3 - PAL® Device I                                                             | Data Sheets                                                                                                                                                                                                                                                                                                                   |                   |

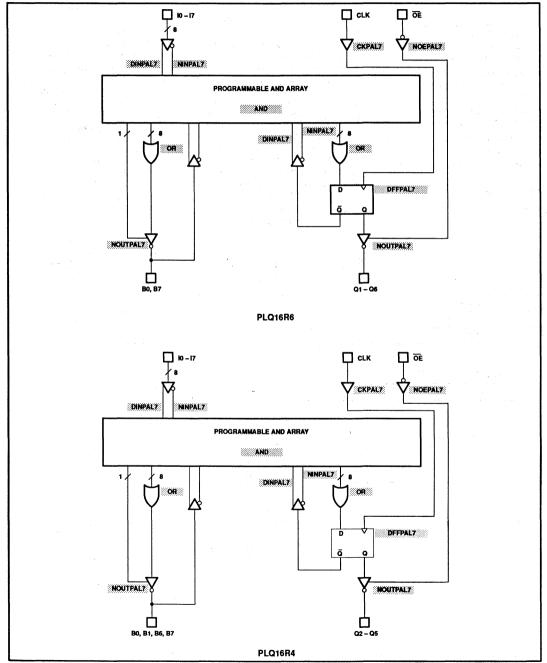

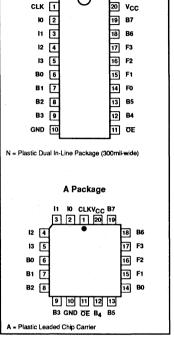

| Series 20<br>PHD16N8-5<br>PLC18V8235/I<br>PLC18V8225/IA<br>PLUS16R8D/-7<br>PLU316R8-5 | Programmable High-Speed Decoder (16 × 16 × 8); 5ns<br>Zero Standby Power CMOS Versatile PAL Devices<br>Zero Standby Power CMOS Versatile PAL Devices<br>PAL Devices (Includes PLUS16L8D/-7, PLUS16R6D/-7, PLUS16R6D/-7, PLUS16R8D/-7); 7.5ns & 10ns<br>PAL Devices (Includes PLQ16L8-5, PLQ16R4-5, PLQ16R6-5, PLQ16R8-5); 5ns | 62<br>75          |

| Series 24                                                                             |                                                                                                                                                                                                                                                                                                                               |                   |

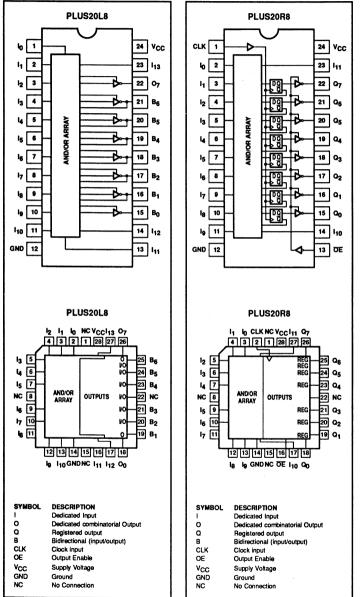

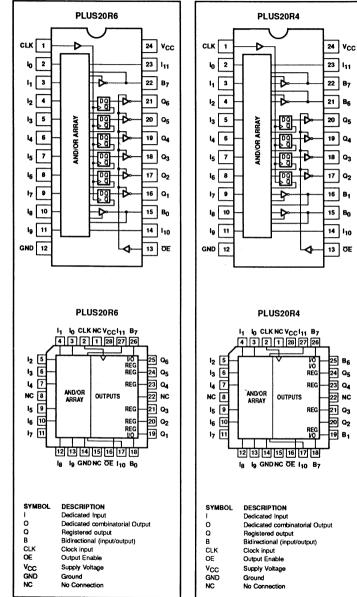

| PLUS20R8D/-7<br>PLQ20R8-5<br>PL22V10-10/-12/-15,                                      | PAL Devices (Includes PLUS20L8D/-7, PLUS20R4D/-7, PLUS20R6D/-7, PLUS20R8D/-7); 7.5ns & 10ns<br>PAL Devices (Includes PLQ20L8-5, PLQ20R4-5, PLQ20R6-5, PLQ20R8-5); 5ns                                                                                                                                                         |                   |

| PL22V10I15<br>PLQ22V10-7                                                              | CMOS Programmable Electrically Erasable Logic Device                                                                                                                                                                                                                                                                          | 152               |

| <b>Series 68</b><br>PHD48N22-7                                                        | Programmable High-Speed Decoder (48 × 73 × 22); 7.5ns                                                                                                                                                                                                                                                                         | 182               |

| Section 4 – Programmable                                                              | e Logic Array Devices Data Sheets                                                                                                                                                                                                                                                                                             |                   |

| <b>Series 20</b><br>PLS153/A<br>PLUS153B/D<br>PLUS153-10                              | Programmable Logic Arrays (18 × 42 × 10); 40/30ns         Programmable Logic Arrays (18 × 42 × 10); 15/12ns         Programmable Logic Array (18 × 42 × 10); 10ns                                                                                                                                                             | 203               |

| <b>Series 24</b><br>PLS173<br>PLUS173B/D                                              | Programmable Logic Array (22 × 42 × 10); 30ns                                                                                                                                                                                                                                                                                 | 219               |

| PLUS173-10<br><b>Series 28</b>                                                        | Programmable Logic Array (22 × 42 × 10); 10ns                                                                                                                                                                                                                                                                                 | 235               |

| PLS100/101                                                                            | Programmable Logic Arrays (16 × 48 × 8); 50ns                                                                                                                                                                                                                                                                                 | 243               |

| Series 20                                                                             | e Logic Sequencer Devices Data Sheets                                                                                                                                                                                                                                                                                         | 050               |

| PLS155<br>PLS157<br>PLS159A                                                           | Programmable Logic Sequencer (16 × 45 × 12); 14MHz         Programmable Logic Sequencer (16 × 45 × 12); 14MHz         Programmable Logic Sequencer (16 × 45 × 12); 18MHz                                                                                                                                                      | 265               |

| Series 24<br>PLS167/A<br>PLS168/A<br>PLS179<br>PLC42VA12<br>PLC42VA121                | Programmable Logic Sequencers (14 × 48 × 6); 14, 20MHz<br>Programmable Logic Sequencers (12 × 48 × 8); 14, 20MHz<br>Programmable Logic Sequencer (20 × 45 × 12); 18MHz<br>CMOS Programmable Multi-function PLD (42 × 105 × 12); 25MHz<br>CMOS Programmable Multi-function PLD (42 × 105 × 12); 25MHz                          | 301<br>313<br>325 |

PAL is a registered trademark of AMD.

## Contents (Continued)

#### Section 5 - Programmable Logic Sequencer Devices Data Sheets (continued)

|     | Series 28               |                                                                      |     |

|-----|-------------------------|----------------------------------------------------------------------|-----|

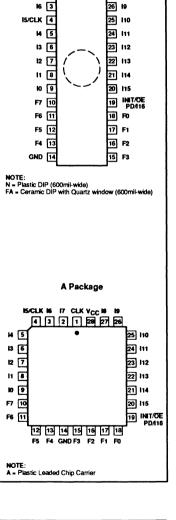

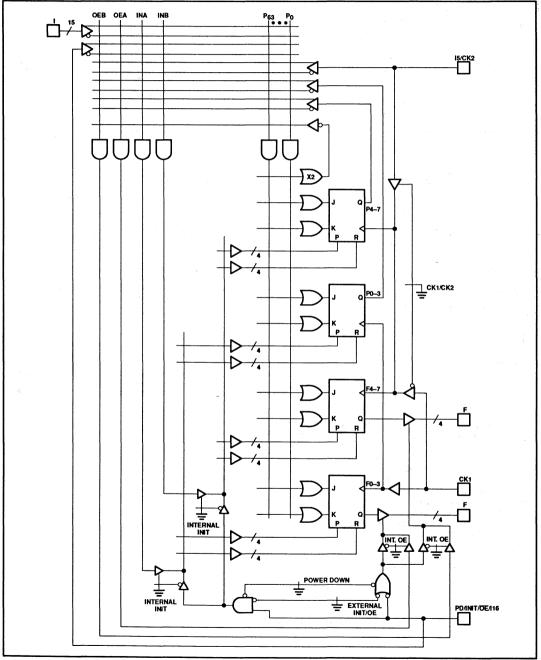

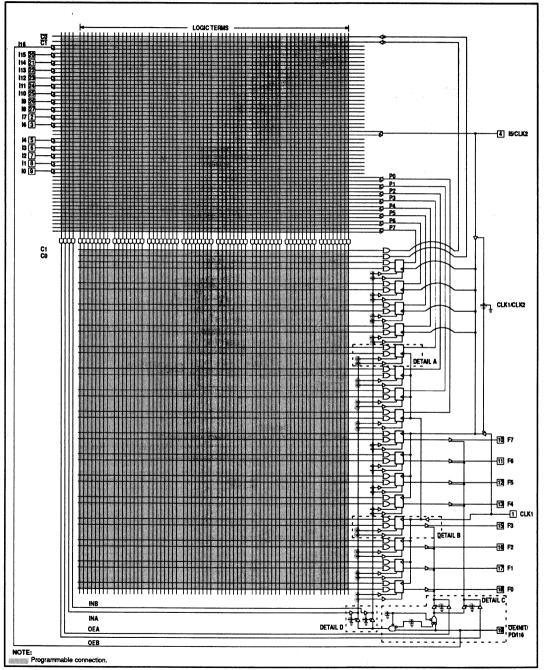

|     | PLC415-16               | CMOS Programmable Logic Sequencer (17 × 68 × 8); 16MHz               | 365 |

|     | PLS105/A                | Programmable Logic Sequencers (16 × 48 × 8); 14, 20MHz               | 384 |

|     | PLUS105-45              | Programmable Logic Sequencer (16 × 48 × 8); 45MHz                    | 396 |

|     | PLUS105-55              | Programmable Logic Sequencer (16 × 48 × 8); 55MHz                    | 409 |

|     | PLUS405-37/-45          | Programmable Logic Sequencers ( $16 \times 64 \times 8$ ); 37, 45MHz |     |

|     | PLUS405-55              | Programmable Logic Sequencer (16 × 64 × 8); 55MHz                    | 438 |

| Sec | tion 6 – Programmable   | e Macro Logic Devices Data Sheets                                    |     |

|     | PLHS501                 | Programmable Macro Logic                                             | 457 |

|     | PML2552                 | CMOS High Density Programmable Macro Logic                           |     |

|     | PML2852                 | CMOS High Density Programmable Macro Logic                           |     |

| Sec | tion 7 – Military Produ | rte                                                                  |     |

|     | •                       | e                                                                    | 511 |

| ~   | -                       |                                                                      |     |

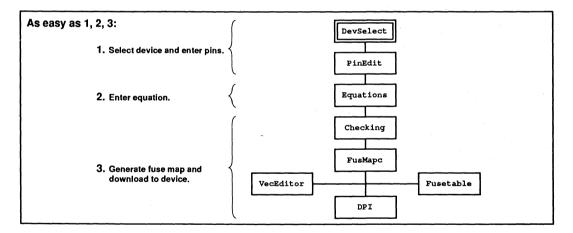

| Sec | tion 8 – Development    |                                                                      | E1E |

|     |                         | ·····                                                                |     |

|     |                         |                                                                      |     |

|     | Interpreting the S      | LICE Fusetable                                                       | 525 |

| Sec | tion 9 – Third-Party Pr | ogrammer/Software Support                                            |     |

|     | PROGRAMMER              |                                                                      |     |

|     |                         | nming Guide                                                          |     |

|     | PLD Programmer Refe     | erence Guide — Data I/O Corporation                                  | 534 |

|     | -                       | erence Guide — Stag Micro Systems, Inc.                              |     |

|     | •                       | dors Contact Guide                                                   | 537 |

|     | SOFTWARE                |                                                                      |     |

|     |                         | ipport                                                               |     |

|     | -                       | Support                                                              |     |

|     |                         |                                                                      |     |

|     |                         |                                                                      |     |

|     | •                       |                                                                      |     |

|     | PLD Sonware vendors     | s Contact Guide                                                      | 543 |

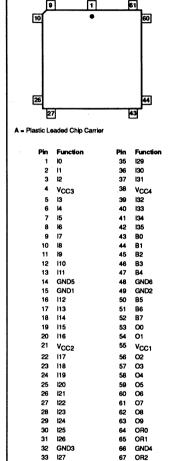

| Sec | tion 10 – Package Out   | lines                                                                |     |

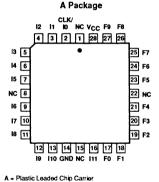

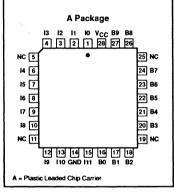

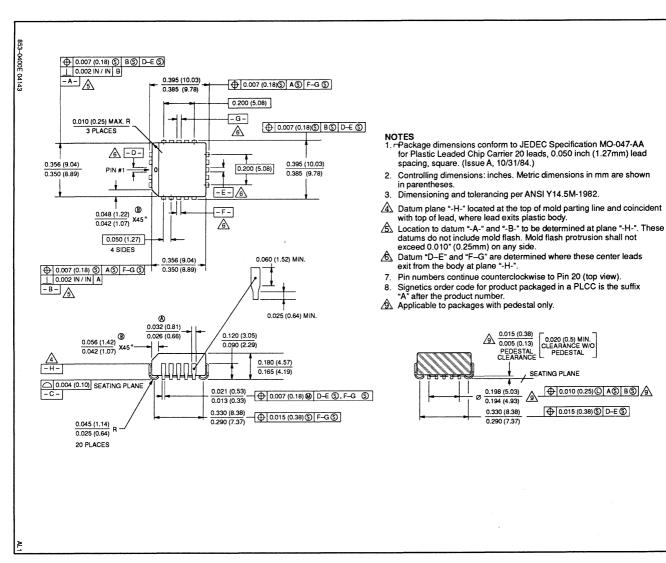

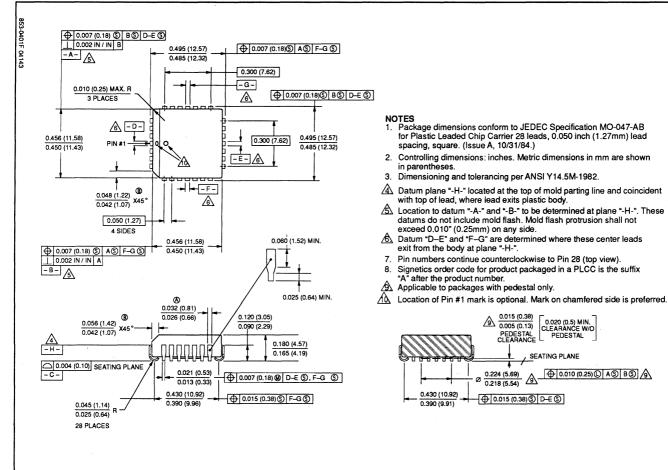

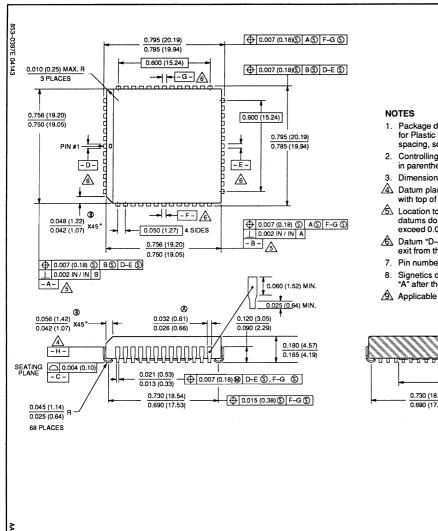

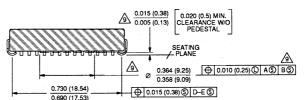

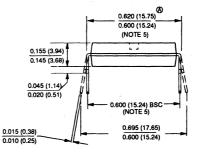

|     | PLCC                    |                                                                      | 547 |

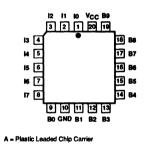

|     | 20-Pin Plastic Le       | aded Chip Carrier (A) Package                                        | 548 |

|     | 28-Pin Plastic Le       | aded Chip Carrier (A) Package                                        | 549 |

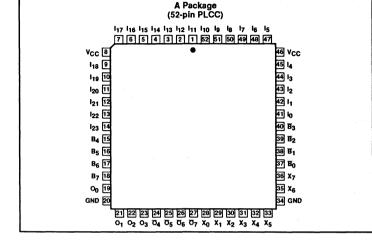

|     | 52-Pin Plastic Le       | aded Chip Carrier (A) Package                                        | 550 |

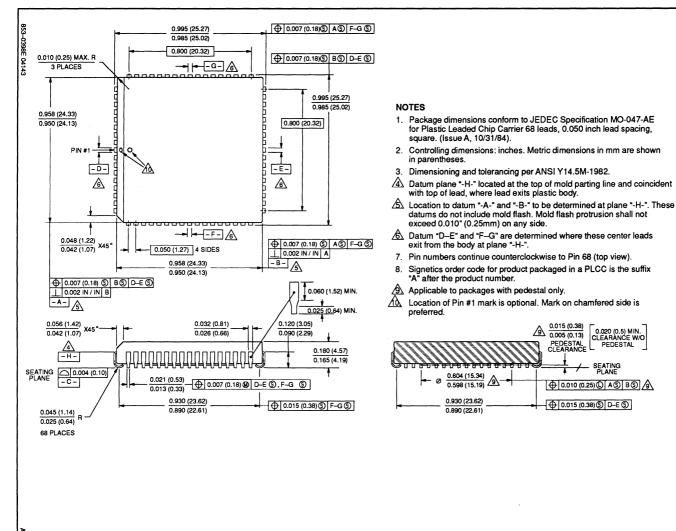

|     |                         | aded Chip Carrier (A) Package                                        |     |

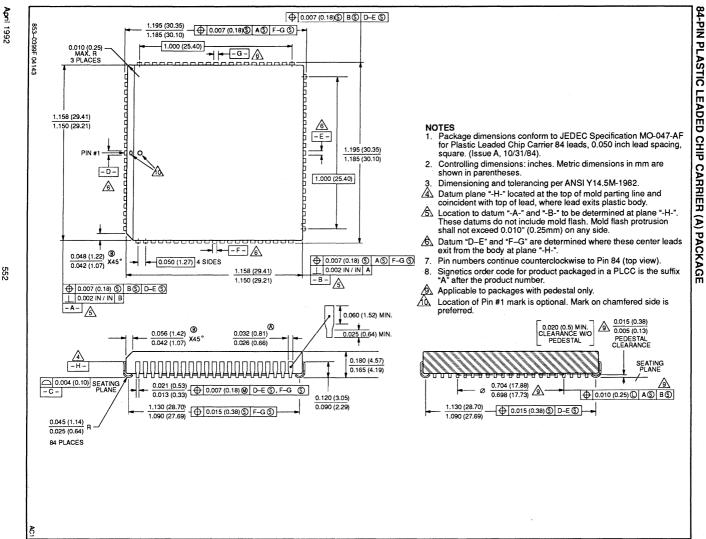

|     |                         | aded Chip Carrier (A) Package                                        |     |

|     |                         |                                                                      |     |

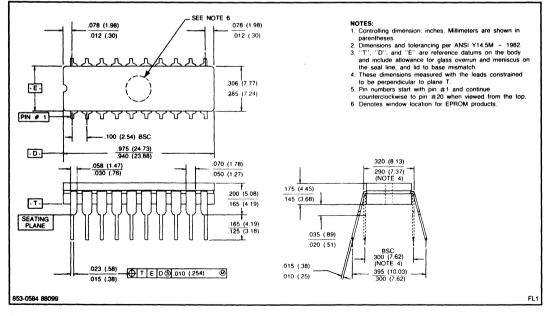

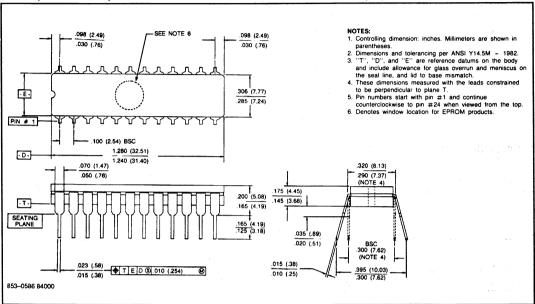

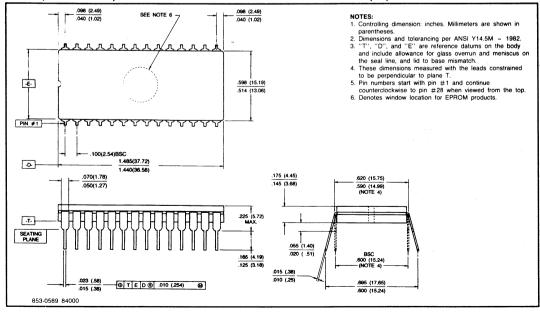

|     | •                       | wide) Ceramic Dual In-Line (F) Package                               |     |

|     |                         | wide) Ceramic Dual In-Line with Quartz Window (FA) Package           |     |

|     |                         | wide) Ceramic Dual In-Line (F) Package                               |     |

|     |                         | wide) Ceramic Dual In-Line with Quartz Window (FA) Package           |     |

|     |                         | wide) Ceramic Dual In-Line (F) Package                               |     |

|     |                         | wide) Ceramic Dual In-Line with Quartz Window (FA) Package           |     |

|     |                         |                                                                      |     |

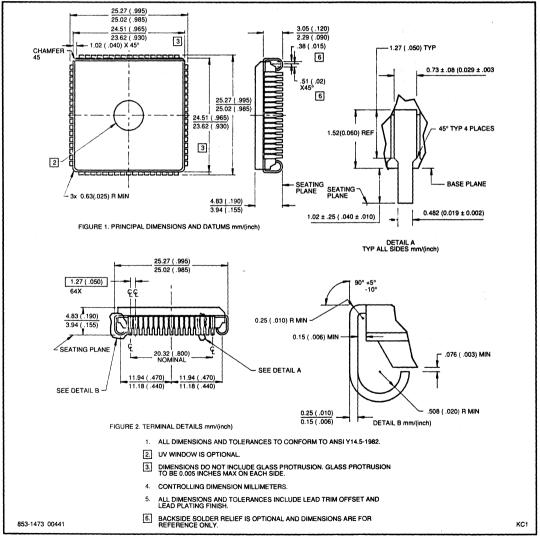

|     |                         | J-Bend with Quartz Window (KA) Package                               |     |

|     |                         | J-Bend with Quartz Window (KA) Package                               |     |

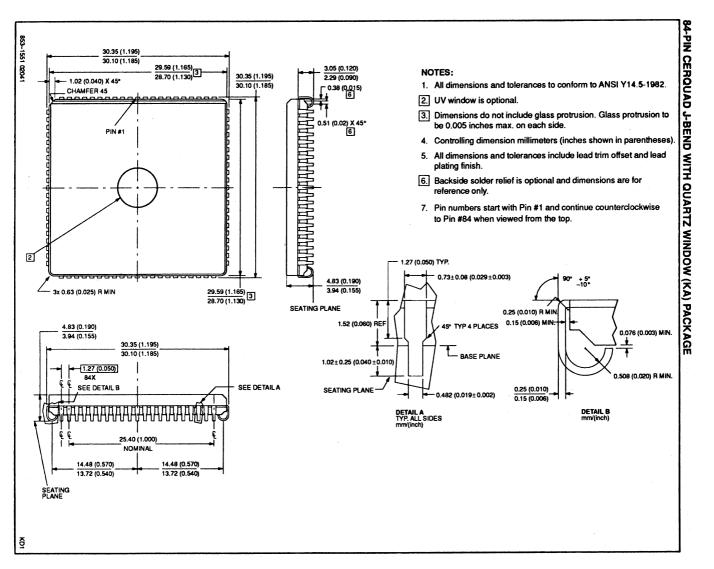

|     |                         |                                                                      |     |

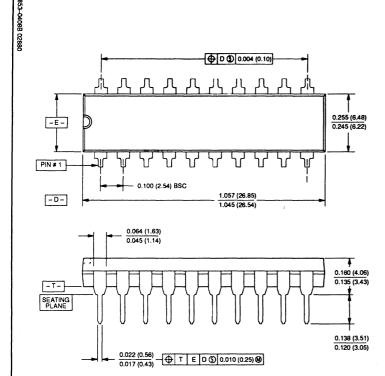

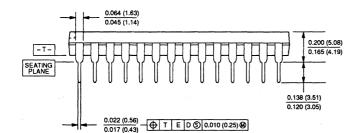

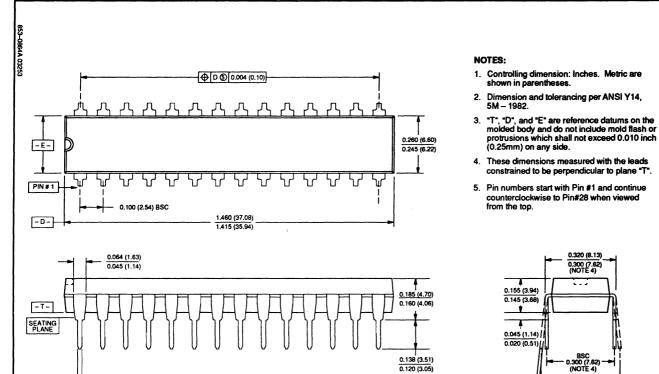

|     |                         | wide) Plastic Dual In-Line (N) Package                               |     |

|     |                         | wide) Plastic Dual In-Line (N) Package                               |     |

|     |                         | wide) Plastic Dual In-Line (N) Package                               |     |

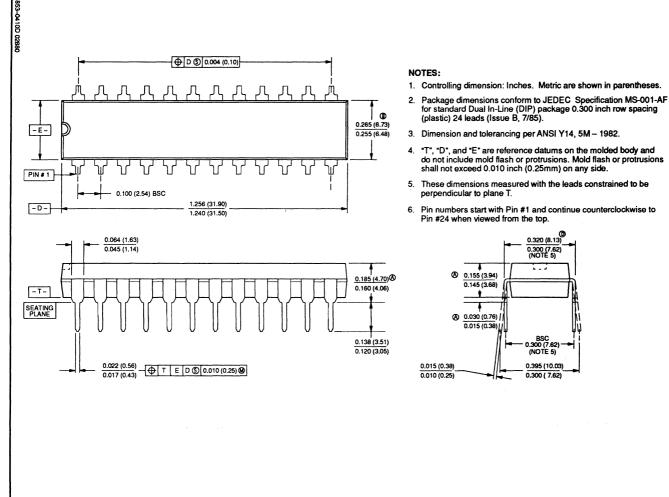

|     | 28-Pin (300 mils        | wide) Plastic Dual In-Line (N3) Package                              | 561 |

| Sec | tion 11 – Sales Offices | s, Representatives and Distributors                                  | 565 |

# Section 1 General Information

#### INDEX

| Alphanumeric Index   | 3 |

|----------------------|---|

| Selection Guide      | 4 |

| Ordering Information | 6 |

## Alphanumeric index

| · · · · · · · · · · · · · · · · · · · |           |                                                             |     |

|---------------------------------------|-----------|-------------------------------------------------------------|-----|

| PHD16N8-5                             | Series 20 | Programmable High-Speed Decoder (16 × 16 × 8); 5ns          |     |

| PHD48N22-7                            | Series 68 | Programmable High-Speed Decoder (48 × 73 × 22); 7.5ns       |     |

| PLC18V8Z25/IA                         | Series 20 | Zero Standby Power CMOS Versatile PAL Devices; 25, 40ns     |     |

| PLC18V8Z35/I                          | Series 20 | Zero Standby Power CMOS Versatile PAL Devices; 35, 40ns     | 49  |

| PLC42VA12                             | Series 24 | CMOS Programmable Multi-function PLD (42 × 105 × 12); 25MHz | 325 |

| PLC42VA12I                            | Series 24 | CMOS Programmable Multi-function PLD (42 × 105 × 12); 25MHz | 345 |

| PLC415-16                             | Series 28 | CMOS Programmable Logic Sequencer (17 × 68 × 8); 16MHz      | 365 |

| PLHS501                               |           | Programmable Macro Logic                                    | 457 |

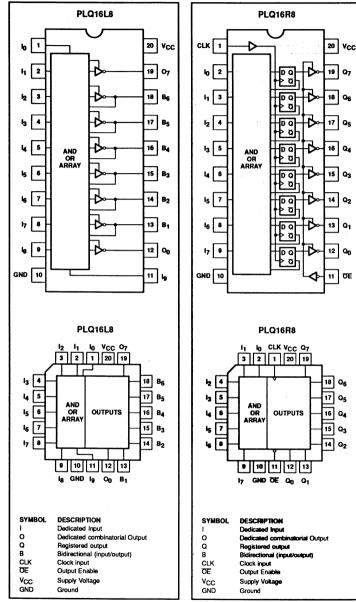

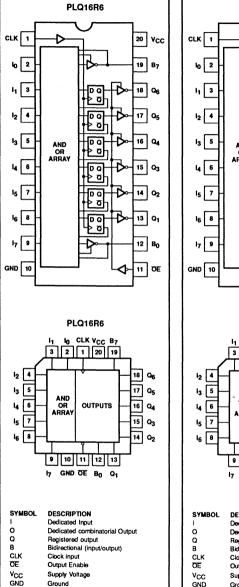

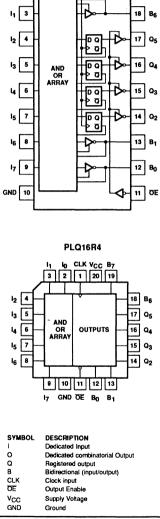

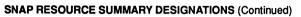

| PLQ16R8-5                             | Series 20 | PAL Devices (16L8, 16R4, 16R6 and 16R8); 5ns                | 90  |

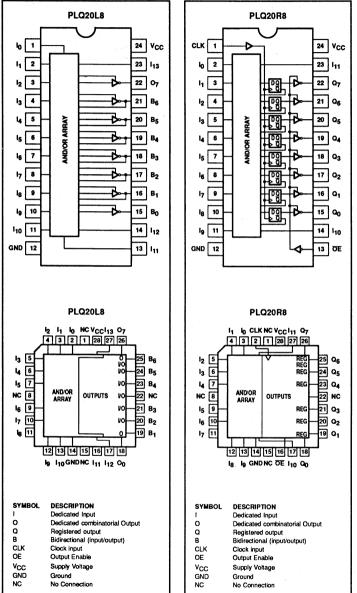

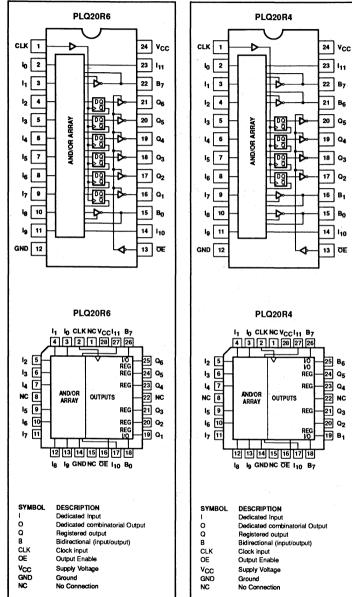

| PLQ20R8-5                             | Series 24 | PAL Devices (20L8, 20R4, 20R6 and 20R8); 5ns                | 121 |

| PLQ22V10-7                            | Series 24 | BiCMOS Versatile PLD Device; 7.5ns                          | 152 |

| PLS100/101                            | Series 28 | Programmable Logic Arrays (16 × 48 × 8); 50ns               | 243 |

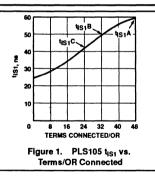

| PLS105/A                              | Series 28 | Programmable Logic Sequencers (16 × 48 × 8); 14, 20MHz      | 384 |

| PLS153/A                              | Series 20 | Programmable Logic Arrays (18 × 42 × 10); 40/30ns           | 195 |

| PLS155                                | Series 20 | Programmable Logic Sequencer (16 × 45 × 12); 14MHz          | 253 |

| PLS157                                | Series 20 | Programmable Logic Sequencer (16 × 45 × 12); 14MHz          | 265 |

| PLS159A                               | Series 20 | Programmable Logic Sequencer (16 × 45 × 12); 18MHz          | 277 |

| PLS167/A                              | Series 24 | Programmable Logic Sequencers (14 × 48 × 6); 14, 20MHz      | 289 |

| PLS168/A                              | Series 24 | Programmable Logic Sequencers (12 × 48 × 8); 14, 20MHz      | 301 |

| PLS173                                | Series 24 | Programmable Logic Array (22 × 42 × 10); 30ns               | 219 |

| PLS179                                | Series 24 | Programmable Logic Sequencer (20 × 45 × 12); 18MHz          | 313 |

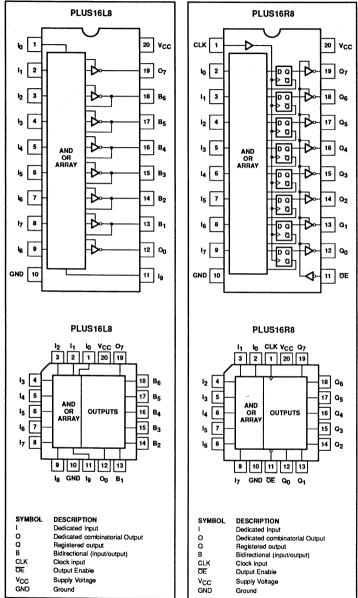

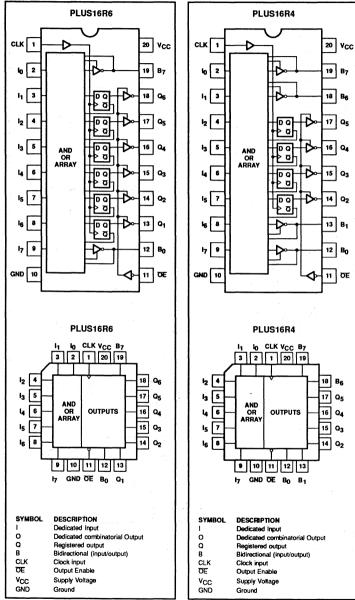

| PLUS16R8D/-7                          | Series 20 | PAL Devices (16L8, 16R4, 16R6 and 16R8); 7.5ns & 10ns       | 75  |

| PLUS20R8D/-7                          | Series 24 | PAL Devices (20L8, 20R4, 20R6 and 20R8); 7.5ns & 10ns       | 106 |

| PLUS105-45                            | Series 28 | Programmable Logic Sequencer (16 × 48 × 8); 45MHz           | 396 |

| PLUS105-55                            | Series 28 | Programmable Logic Sequencer (16 × 48 × 8); 55MHz           | 409 |

| PLUS153B/D                            | Series 20 | Programmable Logic Arrays (18 × 42 × 10); 15/12ns           | 203 |

| PLUS153-10                            | Series 20 | Programmable Logic Array (18 × 42 × 10); 10ns               | 211 |

| PLUS173B/D                            | Series 24 | Programmable Logic Arrays (22 × 42 × 10); 15/12ns           | 227 |

| PLUS173-10                            | Series 24 | Programmable Logic Array (22 × 42 × 10); 10ns               | 235 |

| PLUS405-37/-45                        | Series 28 | Programmable Logic Sequencers (16 × 64 × 8); 37, 45MHz      | 422 |

| PLUS405-55                            | Series 28 | Programmable Logic Sequencer (16 × 64 × 8); 55MHz           | 438 |

| PL22V10-10/-12/-15,                   |           |                                                             |     |

| PL22V10I15                            | Series 24 | CMOS Programmable Electrically Erasable Logic Device        | 137 |

| PML2552                               |           | CMOS High Density Programmable Macro Logic                  | 469 |

| PML2852                               |           | CMOS High Density Programmable Macro Logic                  | 488 |

| 10H20EV8/10020EV8                     | Series 24 | ECL Programmable Array Logic; 4.5ns                         | 165 |

|                                       |           |                                                             |     |

## Selection guide

| SIGNETICS<br>PART NUMBER | ARCHITECTURE<br>(Inputs × Terms*<br>× Outputs) | PACKAGE | TOTAL<br>INPUTS<br>(# Dedicated) | PRODUCT<br>TERMS PER<br>OR GATE | INTERNAL<br>STATE<br>REGISTERS<br>(# Dedicated) | OUTPUTS<br>C, I/O, R, R I/O | t <sub>PD</sub> (Max) | fmax   | I <sub>CC</sub> (Max) |

|--------------------------|------------------------------------------------|---------|----------------------------------|---------------------------------|-------------------------------------------------|-----------------------------|-----------------------|--------|-----------------------|

| PAL DEVICES              |                                                |         |                                  |                                 |                                                 |                             |                       |        |                       |

| 10H20EV8-4/              |                                                |         |                                  |                                 |                                                 |                             |                       | Γ      |                       |

| 10020EV8-4               | 20 × 90 × 8                                    | 24-Pin  | 20 (12)                          | 8 to 12                         | 0                                               | 8 varied                    | 4.5ns                 | 208MHz | -250mA                |

| PHD16N8-5                | 16 × 16 × 8                                    | 20-Pin  | 16 (10)                          | 1+                              | 0                                               | 2 C, 6 I/O                  | 5ns                   |        | 180mA                 |

| PHD48N22-7               | 48 × 73 × 22                                   | 68-Pin  | 48 (36)                          | 7 to 12                         | 0                                               | 10 C, 12 I/O                | 7.5ns                 |        | 420mA                 |

| PLUS16L8-7               | 16 × 64 × 8                                    | 20-Pin  | 16 (10)                          | 7                               | 0                                               | 2 C, 6 I/O                  | 7.5ns                 |        | 180mA                 |

| PLUS16R4-7               | 16 × 64 × 8                                    | 20-Pin  | 16 (8)                           | 7 to 8                          | 4 (0)                                           | 4 I/O, 4 R                  | 7.5ns                 | 74MHz  | 180mA                 |

| PLUS16R6-7               | 16 × 64 × 8                                    | 20-Pin  | 16 (8)                           | 7 to 8                          | 6 (0)                                           | 2 1/O, 6 R                  | 7.5ns                 | 74MHz  | 180mA                 |

| PLUS16R8-7               | 16 × 64 × 8                                    | 20-Pin  | 16 (8)                           | 8                               | 8 (0)                                           | 8 R                         |                       | 74MHz  | 180mA                 |

| PLUS16L8D                | 16 × 64 × 8                                    | 20-Pin  | 16 (10)                          | 7                               | 0                                               | 2 C, 6 I/O                  | 10ns                  |        | 180mA                 |

| PLUS16R4D                | 16 × 64 × 8                                    | 20-Pin  | 16 (8)                           | 7 to 8                          | 4 (0)                                           | 4 VO, 4 R                   | 10ns                  | 60MHz  | 180mA                 |

| PLUS16R6D                | 16 × 64 × 8                                    | 20-Pin  | 16 (8)                           | 7 to 8                          | 6 (0)                                           | 2 I/O, 6R                   | 10ns                  | 60MHz  | 180mA                 |

| PLUS16R8D                | 16 × 64 × 8                                    | 20-Pin  | 16 (8)                           | 8                               | 8 (0)                                           | 8 R                         |                       | 60MHz  | 180mA                 |

| PLUS20L8-7               | 20 × 64 × 8                                    | 24-Pin  | 20 (14)                          | 7                               | 0                                               | 2 C, 6 1/O                  | 7.5ns                 |        | 210mA                 |

| PLUS20R4-7               | 20 × 64 × 8                                    | 24-Pin  | 20 (12)                          | 7 to 8                          | 4 (0)                                           | 4 VO, 4 R                   | 7.5ns                 | 74MHz  | 210mA                 |

| PLUS20R6-7               | $20 \times 64 \times 8$                        | 24-Pin  | 20 (12)                          | 7 to 8                          | 6 (0)                                           | 2 I/O, 6 R                  | 7.5ns                 | 74MHz  | 210mA                 |

| PLUS20R8-7               | 20 × 64 × 8                                    | 24-Pin  | 20 (12)                          | 8                               | 8 (0)                                           | 8 R                         |                       | 74MHz  | 210mA                 |

| PLUS20L8D                | 20 × 64 × 8                                    | 24-Pin  | 20 (14)                          | 7                               | 0                                               | 2 C, 6 1/O                  | 10ns                  |        | 210mA                 |

| PLUS20R4D                | 20 × 64 × 8                                    | 24-Pin  | 20 (12)                          | 7 to 8                          | 4 (0)                                           | 4 VO, 4R                    | 10ns                  | 60MHz  | 210mA                 |

| PLUS20R6D                | $20 \times 64 \times 8$                        | 24-Pin  | 20 (12)                          | 7 to 8                          | 6 (0)                                           | 2 I/O, 6 R                  | 10ns                  | 60MHz  | 210mA                 |

| PLUS20R8D                | 20 × 64 × 8                                    | 24-Pin  | 20 (12)                          | 8                               | 8 (0)                                           | 8 R                         |                       | 60MHz  | 210mA                 |

| PLQ16L8-5                | 16 × 64 × 8                                    | 20-Pin  | 16 (10)                          | 7                               | 0                                               | 2 C, 6 I/O                  | 5ns                   |        | 180mA                 |

| PLQ16R4-5                | 16 × 64 × 8                                    | 20-Pin  | 16 (8)                           | 7 to 8                          | 4 (0)                                           | 4 I/O, 4 R                  | 5ns                   | 118MHz | 180mA                 |

| PLQ16R6-5                | 16 × 64 × 8                                    | 20-Pin  | 16 (8)                           | 7 to 8                          | 6 (0)                                           | 2 VO, 6R                    | 5ns                   | 118MHz | 180mA                 |

| PLQ16R8-5                | 16 × 64 × 8                                    | 20-Pin  | 16 (8)                           | 8                               | 8 (0)                                           | 8 R                         |                       | 118MHz | 180mA                 |

| PLQ20L8D                 | 20 × 64 × 8                                    | 24-Pin  | 20 (14)                          | 7                               | 0                                               | 2 C, 6 I/O                  | 5ns                   |        | 210mA                 |

| PLQ20R4D                 | $20 \times 64 \times 8$                        | 24-Pin  | 20 (12)                          | 7 to 8                          | 4 (0)                                           | 4 I/O, 4R                   | 5ns                   | 118MHz | 210mA                 |

| PLQ20R6D                 | $20 \times 64 \times 8$                        | 24-Pin  | 20 (12)                          | 7 to 8                          | 6 (0)                                           | 2 I/O, 6 R                  | 5ns                   | 118MHz | 210mA                 |

| PLQ20R8D                 | $20 \times 64 \times 8$                        | 24-Pin  | 20 (12)                          | 8                               | 8 (0)                                           | 8 R                         |                       | 118MHz | 210mA                 |

| PLQ22V10-7               | 22 × 130 × 10                                  | 24-Pin  | 22 (12)                          | 8 to 16                         | 10 (0)                                          | 10 varied                   | 7.5ns                 | 87MHz  | 180mA                 |

| PL22V10-15/I15           | 22 × 130 × 10                                  | 24-Pin  | 22 (12)                          | 8 to 16                         | 10 (0)                                          | 10 varied                   | 15ns                  | 53MHz  | 110mA,<br>0.5mA/MHz   |

| PL22V10-12               | 22 × 130 × 10                                  | 24-Pin  | 22 (12)                          | 8 to 16                         | 10 (0)                                          | 10 varied                   | 12ns                  | 67MHz  | 110mA,<br>0.5mA/MHz   |

| PL22V10-10               | 22 × 130 × 10                                  | 24-Pin  | 22 (12)                          | 8 to 16                         | 10 (0)                                          | 10 varied                   | 10ns                  | 77MHz  | 110mA,<br>0.5mA/MHz   |

| PLC18V8Z35<br>PLC18V8ZI  | 18 × 74 × 8                                    | 20-Pin  | 18 (8)                           | 8                               | 8 (0)                                           | 8 varied                    | 35, 40ns              | 21MHz  | 100µA,<br>1.5mA/MHz   |

| PLC18V8Z25<br>PLC18V8ZAI | 18 × 74 × 8                                    | 20-Pin  | 18 (8)                           | 8                               | 8 (0)                                           | 8 varied                    | 25ns                  | 30MHz  | 100µA,<br>1.5mA/MHz   |

| PLA                      |                                                |         |                                  |                                 |                                                 |                             |                       |        |                       |

| PLS100/101               | 16 × 48 × 8                                    | 28-Pin  | 16 (16)                          | Up to 48                        | 0                                               | 8 C                         | 50ns                  |        | 170mA                 |

| PLS153                   | 18 	imes 42 	imes 10                           | 20-Pin  | 18 (8)                           | Up to 32                        | 0                                               | 10 I/O                      | 40ns                  |        | 155mA                 |

| PLS153A                  | 18 × 42 × 10                                   | 20-Pin  | 18 (8)                           | Up to 32                        | 0                                               | 10 I/O                      | 30ns                  |        | 155mA                 |

| PLUS153B                 | 18 	imes 42 	imes 10                           | 20-Pin  | 18 (8)                           | Up to 32                        | 0                                               | 10 I/O                      | 15ns                  |        | 200mA                 |

| PLUS153D                 | 18 	imes 42 	imes 10                           | 20-Pin  | 18 (8)                           | Up to 32                        | 0                                               | 10 I/O                      | 12ns                  |        | 200mA                 |

| PLUS153-10               | 18 × 42 × 10                                   | 20-Pin  | 18 (8)                           | Up to 32                        | 0                                               | 10 I/O                      | 10ns                  |        | 200mA                 |

| PLS173                   | $22 \times 42 \times 10$                       | 24-Pin  | 22 (12)                          | Up to 32                        | 0                                               | 10 I/O                      | 30ns                  |        | 170mA                 |

| PLUS173B                 | $22 \times 42 \times 10$                       | 24-Pin  | 22 (12)                          | Up to 32                        | 0                                               | 10 I/O                      | 15ns                  |        | 200mA                 |

| PLUS173D                 | 22 	imes 42 	imes 10                           | 24-Pin  | 22 (12)                          | Up to 32                        | 0                                               | 10 I/O                      | 12ns                  |        | 200mA                 |

| PLUS17310                | $22 \times 42 \times 10$                       | 24-Pin  | 22 (12)                          | Up to 32                        | 0                                               | 10 I/O                      | 10ns                  |        | 210mA                 |

## Selection guide

| SIGNETICS<br>PART NUMBER | ARCHITECTURE<br>(Inputs × Terms*<br>× Outputs) | PACKAGE | TOTAL<br>INPUTS<br>(# Dedicated) | PRODUCT<br>TERMS PER<br>OR GATE | INTERNAL<br>STATE<br>REGISTERS<br>(# Dedicated) | OUTPUTS<br>C, 1/0, R, R 1/0 | t <sub>PD</sub> (Max) | f <sub>MAX</sub> | I <sub>CC</sub> (Max) |

|--------------------------|------------------------------------------------|---------|----------------------------------|---------------------------------|-------------------------------------------------|-----------------------------|-----------------------|------------------|-----------------------|

| PLS                      | a the set                                      |         |                                  |                                 |                                                 |                             |                       |                  |                       |

| PLS105                   | 22 × 48 × 8                                    | 28-Pin  | 22 (16)                          | Up to 48                        | 6 (6)                                           | 8 R                         |                       | 14MHz            | 180mA                 |

| PLS105A                  | 22 × 48 × 8                                    | 28-Pin  | 22 (16)                          | Up to 48                        | 6 (6)                                           | 8 R                         |                       | 20MHz            | 180mA                 |

| PLUS105-45               | 22 × 48 × 8                                    | 28-Pin  | 22 (16)                          | Up to 48                        | 6 (6)                                           | 8 R                         | Į į                   | 45MHz            | 200mA                 |

| PLUS105-55               | 22 × 48 × 8                                    | 28-Pin  | 22 (16)                          | Up to 48                        | 6 (6)                                           | 8 R                         |                       | 55MHz            | 200mA                 |

| PLUS405-37               | 24 × 64 × 8                                    | 28-Pin  | 24 (16)                          | Up to 64                        | 8 (8)                                           | 8 R                         |                       | 37MHz            | 225mA                 |

| PLUS405-45               | 24 × 64 × 8                                    | 28-Pin  | 24 (16)                          | Up to 64                        | 8 (8)                                           | 8 R                         |                       | 45MHz            | 225mA                 |

| PLUS405-55               | 24 × 64 × 8                                    | 28-Pin  | 24 (16)                          | Up to 64                        | 8 (8)                                           | 8 R                         |                       | 55MHz            | 225mA                 |

| PLS155                   | 16 × 45 × 12                                   | 20-Pin  | 16 (4)                           | Up to 32                        | 4 (0)                                           | 8 I/O, 4 R I/O              | 50ns                  | 14MHz            | 190mA                 |

| PLS157                   | 16 × 45 × 12                                   | 20-Pin  | 16 (4)                           | Up to 32                        | 6 (0)                                           | 6 I/O, 6 R I/O              | 50ns                  | 14MHz            | 190mA                 |

| PLS159A                  | 16 × 45 × 12                                   | 20-Pin  | 16 (4)                           | Up to 32                        | 8 (0)                                           | 4 I/O, 8 R I/O              | 35ns                  | 18MHz            | 190mA                 |

| PLS167                   | 22 × 48 × 6                                    | 24-Pin  | 22 (14)                          | Up to 48                        | 8 (6)                                           | 6 R                         |                       | 14MHz            | 180mA                 |

| PLS167A                  | 22 × 48 × 6                                    | 24-Pin  | 22 (14)                          | Up to 48                        | 8 (6)                                           | 6 R                         |                       | 20MHz            | 180mA                 |

| PLS168                   | 22 × 48 × 8                                    | 24-Pin  | 22 (12)                          | Up to 48                        | 10 (6)                                          | 8 R                         |                       | 14MHz            | 180mA                 |

| PLS168A                  | 22 × 48 × 8                                    | 24-Pin  | 22 (12)                          | Up to 48                        | 10 (6)                                          | 8 R                         |                       | 20MHz            | 180mA                 |

| PLS179                   | 20 × 45 × 12                                   | 24-Pin  | 20 (8)                           | Up to 32                        | 8 (0)                                           | 4 I/O, 8 R I/O              | 35ns                  | 18MHz            | 210mA                 |

| PLC42VA12/I              | 42 × 105 × 12                                  | 24-Pin  | 42 (10)                          | Up to 64                        | 10 (0)                                          | 10 I/O or R I/O,<br>2 I/O   | 35ns                  | 25MHz            | 135mA                 |

| PLC415-16                | 25 × 68 × 8                                    | 28-Pin  | 25 (17)                          | Up to 64                        | 8 (8)                                           | 8 R                         |                       | 16MHz            | 100µА/<br>80mА        |

| PML                      |                                                |         |                                  |                                 |                                                 |                             |                       |                  |                       |

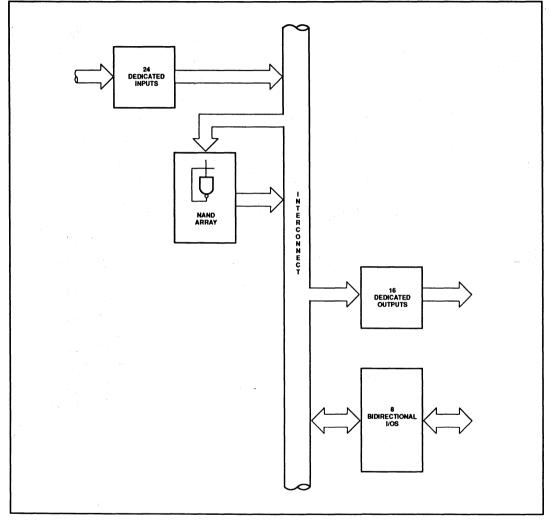

| PLHS501                  | 104 × 116 × 24                                 | 52-Pin  | 32 (24)                          | Up to 136+                      | 0                                               | 16 C, 8 VO                  | 22ns                  |                  | 295mA                 |

| PML2552-35               | 205 × 210 × 24                                 | 68-Pin  | 53 (29)                          | Up to 258 •                     | 36 (20)                                         | 8 I/O, 16 R I/O             | 35ns                  | 50MHz            | 10mA/<br>100mA        |

| PML2552-50               | 205 × 210 × 24                                 | 68-Pin  | 53 (29)                          | Up to 258 •                     | 36 (20)                                         | 8 1/O, 16 R 1/O             | 50ns                  | 35MHz            | 10mA/<br>100mA        |

| PML2852-35               | 205 × 210 × 40                                 | 84-Pin  | 53 (29)                          | Up to 258 •                     | 36 (20)                                         | 16 C, 8 VO,<br>16 R VO      | 35ns                  | 50MHz            | 10mA/<br>100mA        |

| PML2852-50               | 205 × 210 × 40                                 | 84-Pin  | 53 (29)                          | Up to 258•                      | 36 (20)                                         | 16 C, 8 VO,<br>16 R VO      | 50ns                  | 35MHz            | 10mA/<br>100mA        |

PAL Device = Programmable Array Logic (Fixed OR Array)-Type PHD = Programmable High-Speed Decoder PLA = Programmable Logic Array PLS = Programmable Logic Sequencer PML = Programmable Macro Logic

OUTPUTS:

C = Combinatorial outputR = Registered output

I/O = Combinatorial I/O

R I/O = Registered I/O

#### NOTES:

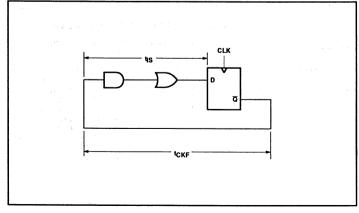

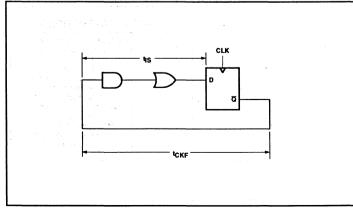

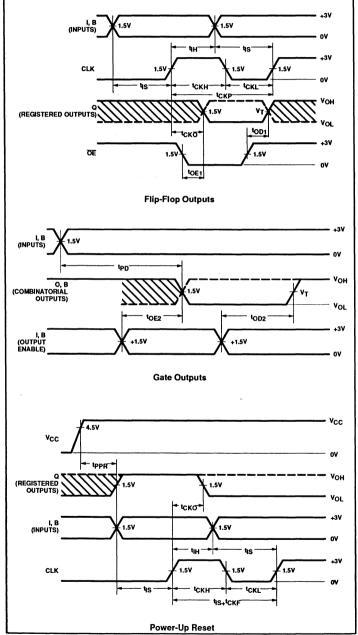

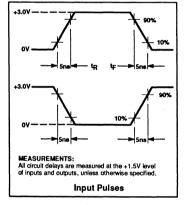

$f_{MAX} = 1/(t_{IS} + t_{CKO})$  worst case \* Includes control product terms Product terms per NAND gate

PAL is a registered trademark of AMD.

PML is a trademark of Signetics.

All packages refer to DIP configurations except PHD48N22, PML2552 and PML2852, which are offered in PLCC only.

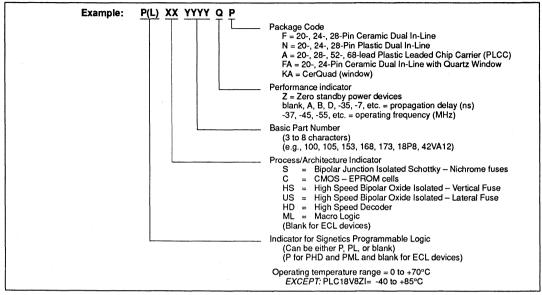

## **Ordering information**

#### PLD PRODUCTS

# Section 2 Introduction

#### INDEX

| What is Programmable Logic? | 9  |

|-----------------------------|----|

| Quality and Reliability     |    |

|                             | 30 |

andrika († 1995) 1990 - Standard Market, 1997 - Standard Market, 1997 1997 - Standard Market, 1997 - Standard Market, 1997 - Standard Market, 1997 - Standard Market, 1997 - Standard 1997 - Standard Market, 1997 - Standard Market, 1997 - Standard Market, 1997 - Standard Market, 1997 - Standard

## Introduction

## WHAT IS PROGRAMMABLE LOGIC?

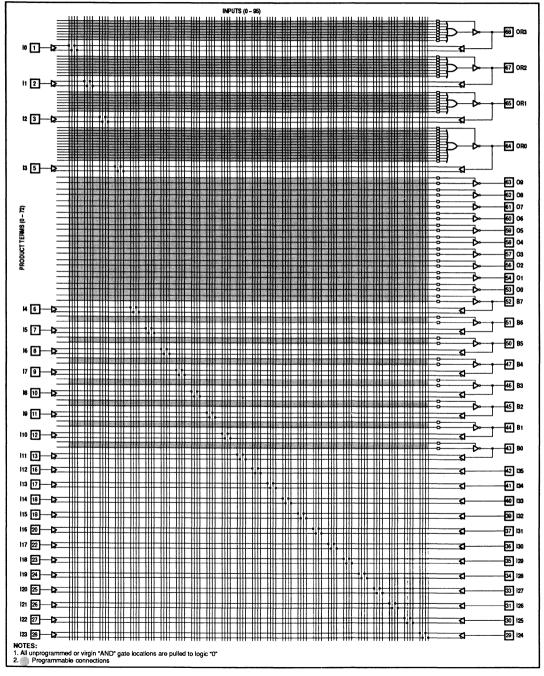

In 1975, Signetics Corporation developed a new product family by combining its expertise in semi-custom gate array products and fuse-link Programmable Read Only Memories (PROMs). Out of this marriage came Signetics Programmable Logic Family. The PLS100 Field-Programmable Logic Array (FPLA) was the first member of this family. The FPLA was an important industry first in two ways. First, the AND/OR/INVERT architecture allowed the custom implementations of Sum of Product logic equations. Second, the three-level fusing allows complete flexibility in the use of this device family. All logic interconnections from input to output are programmable.

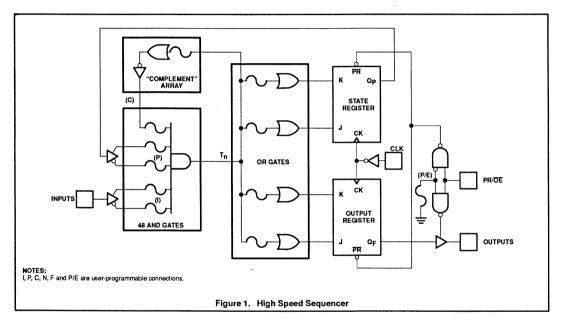

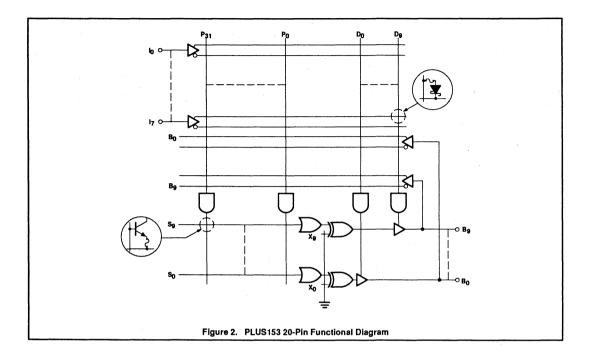

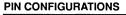

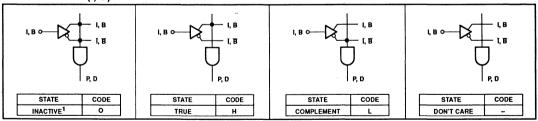

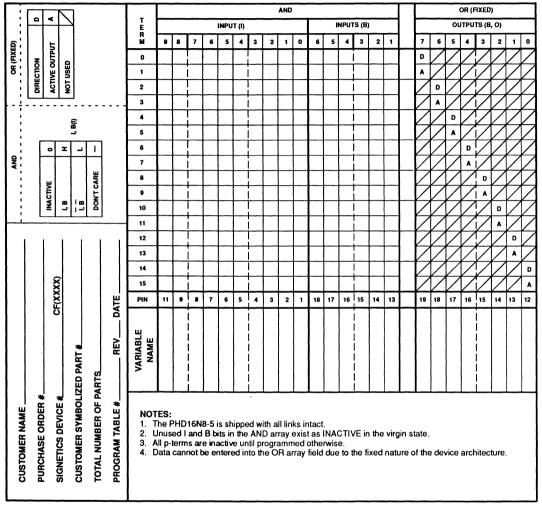

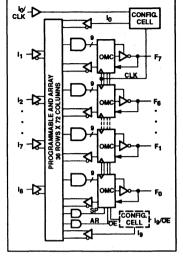

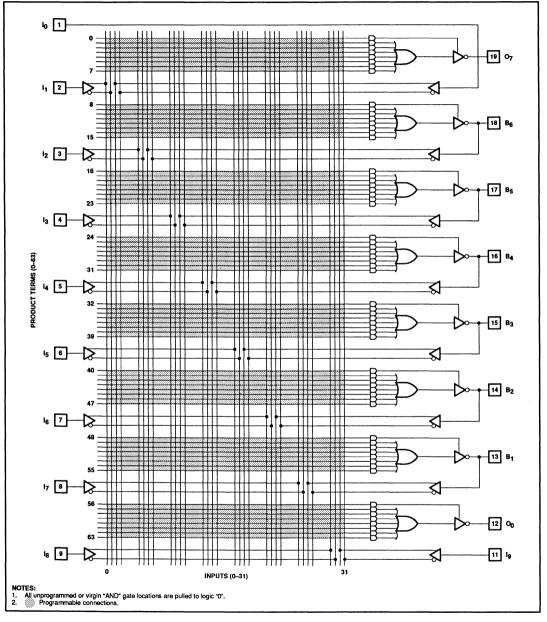

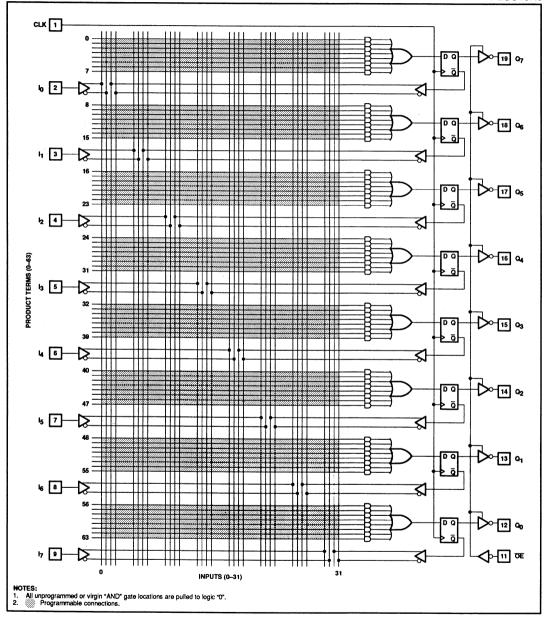

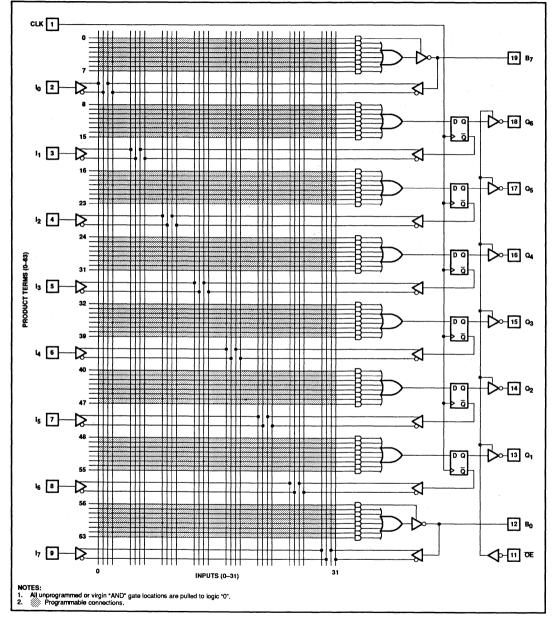

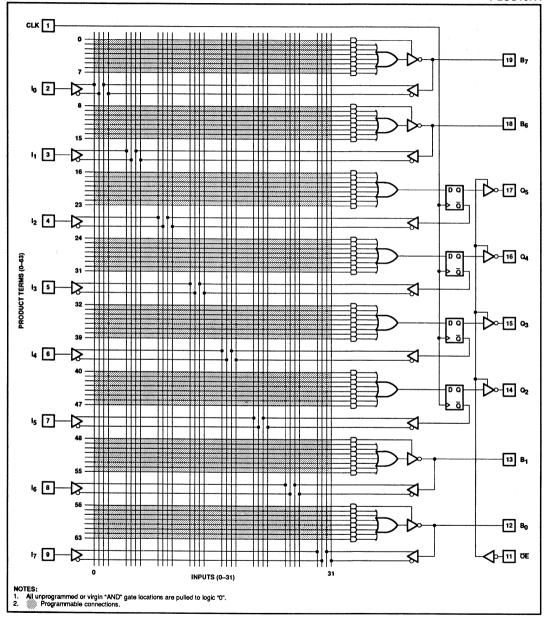

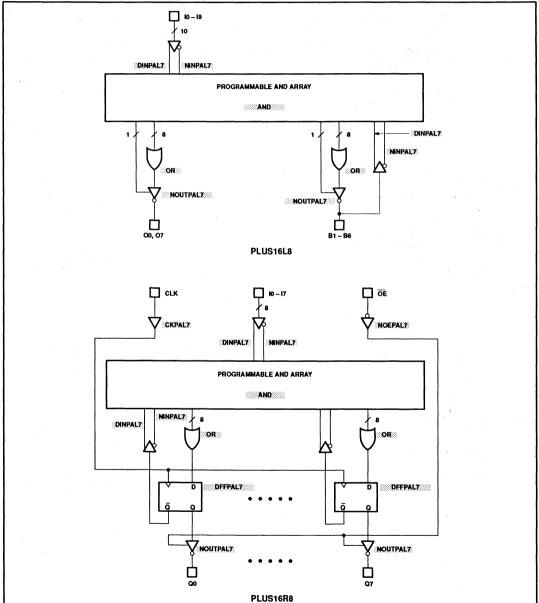

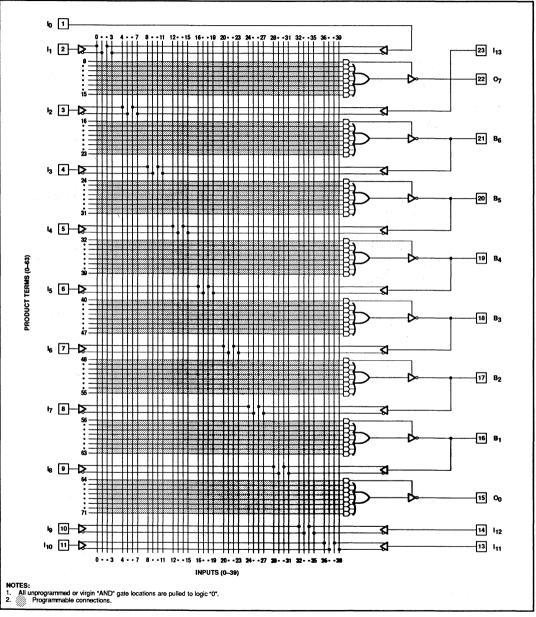

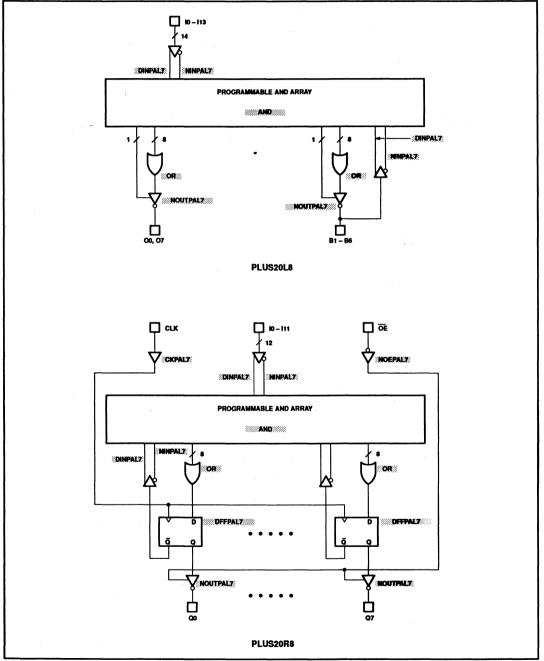

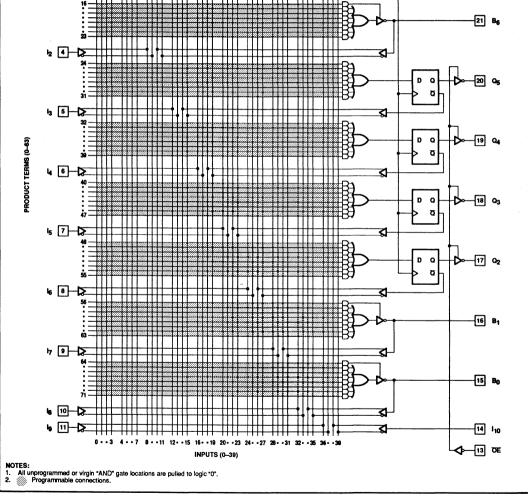

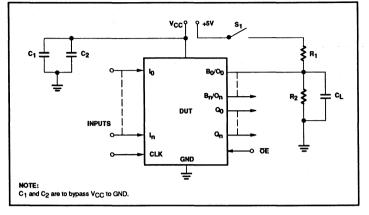

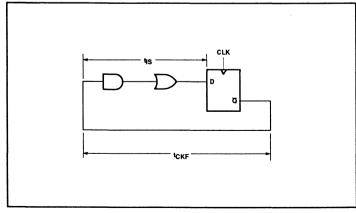

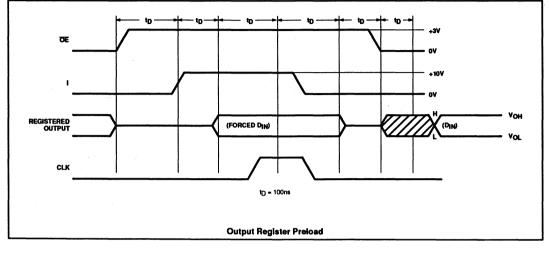

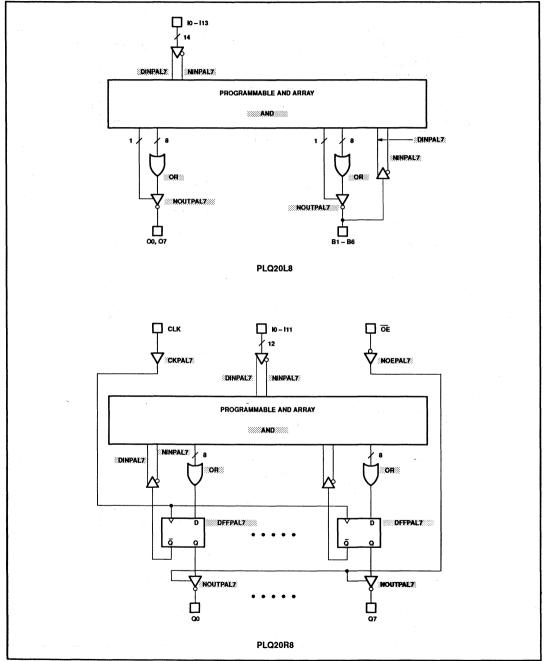

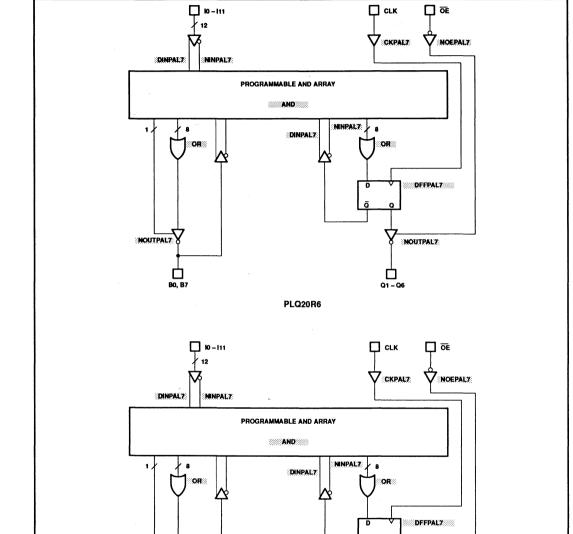

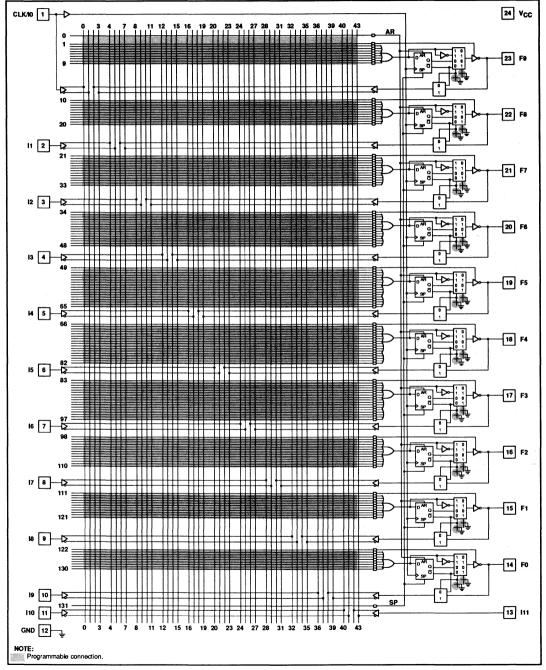

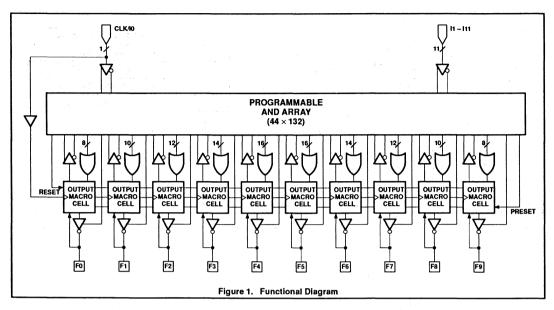

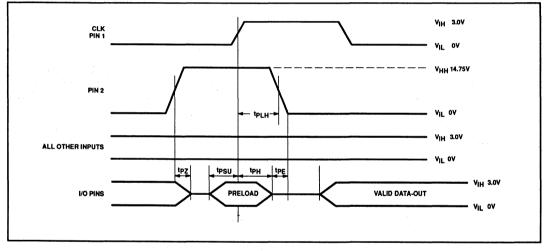

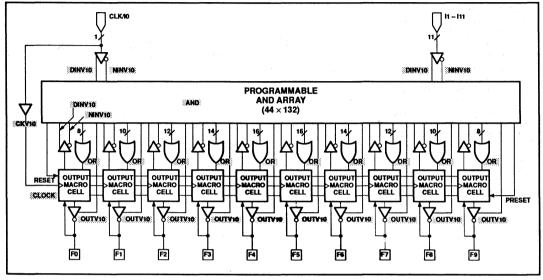

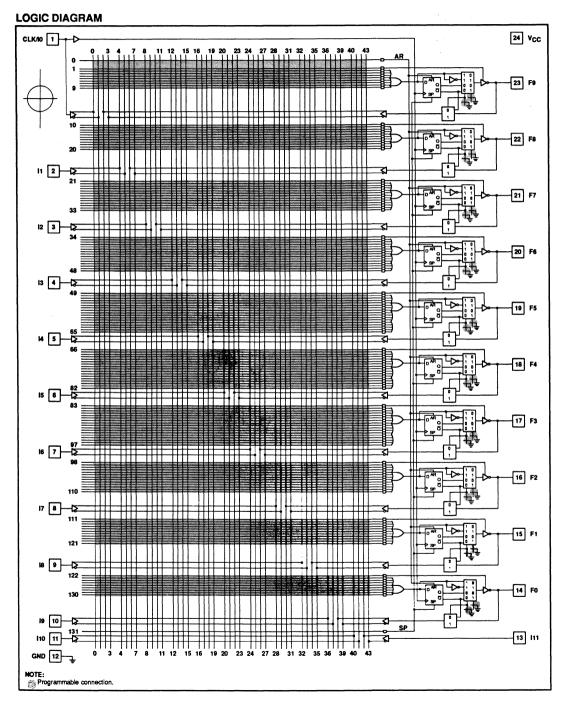

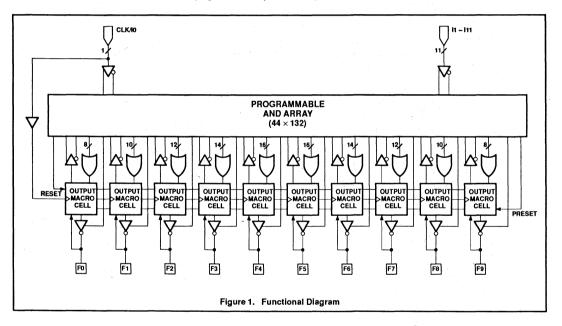

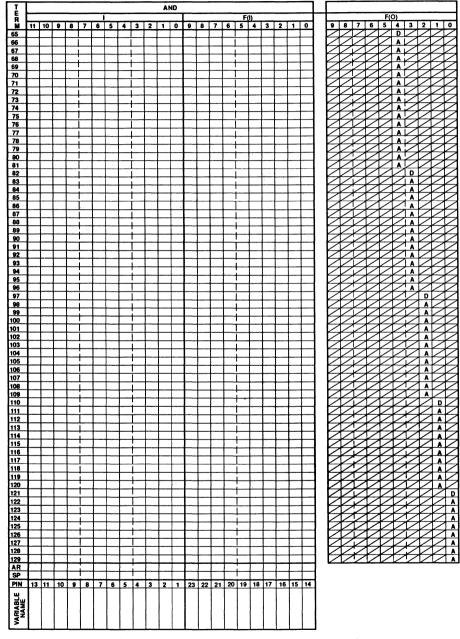

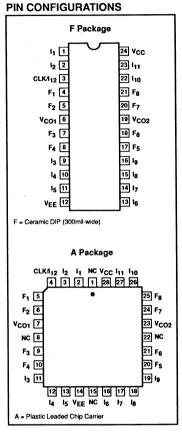

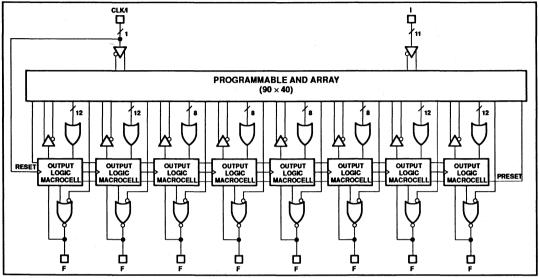

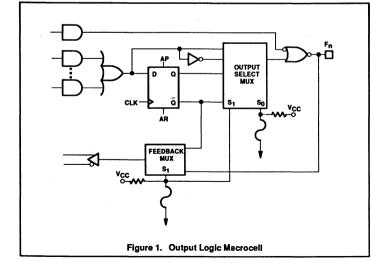

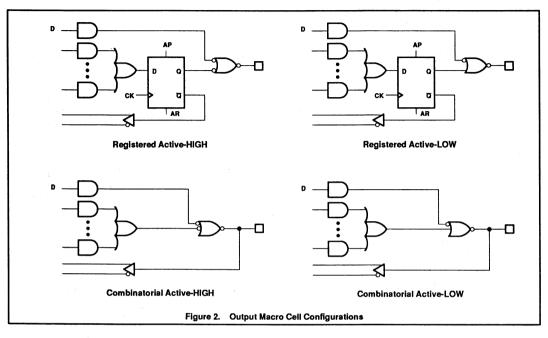

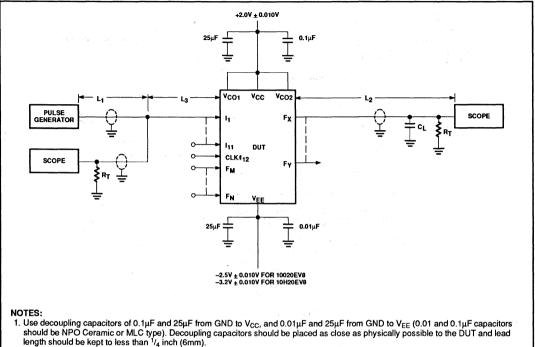

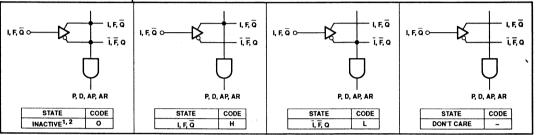

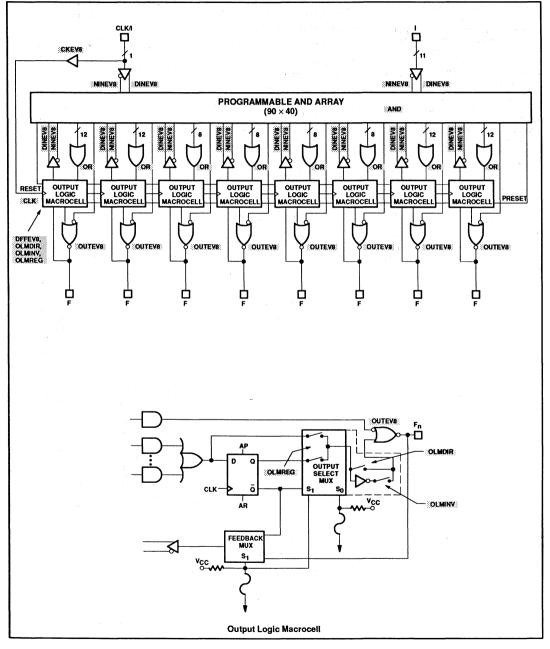

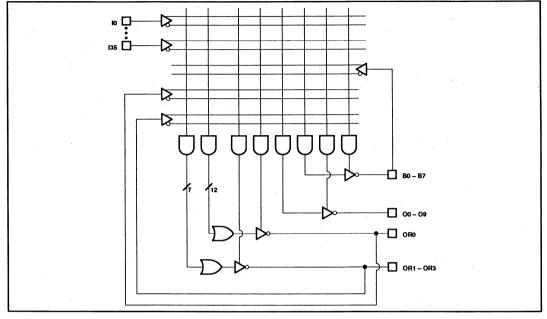

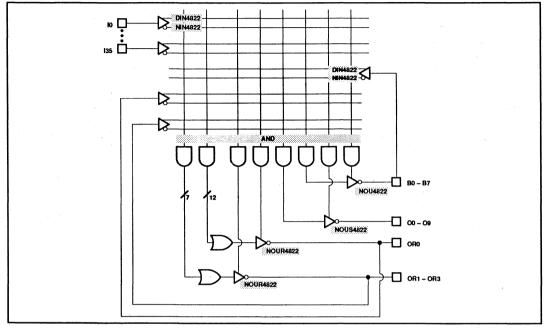

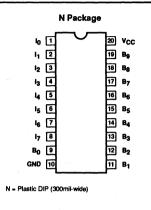

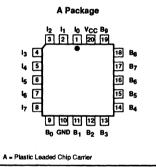

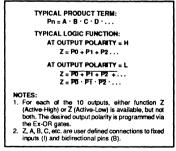

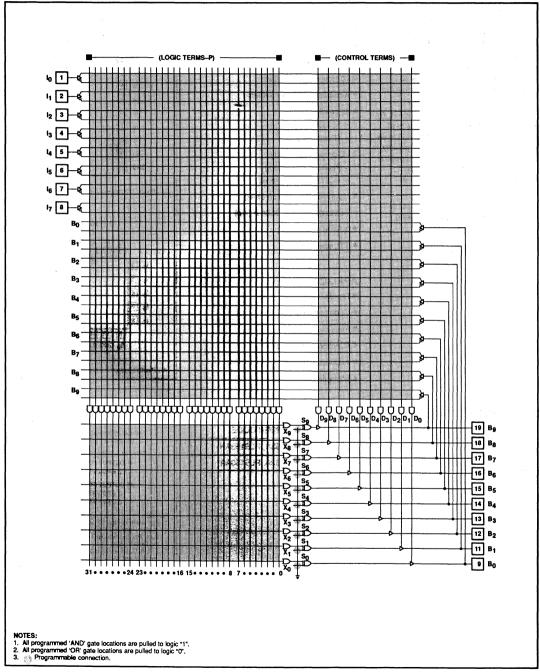

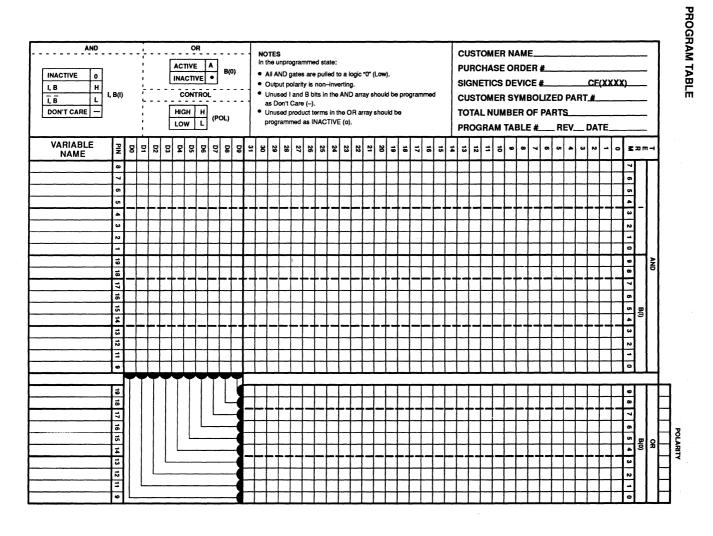

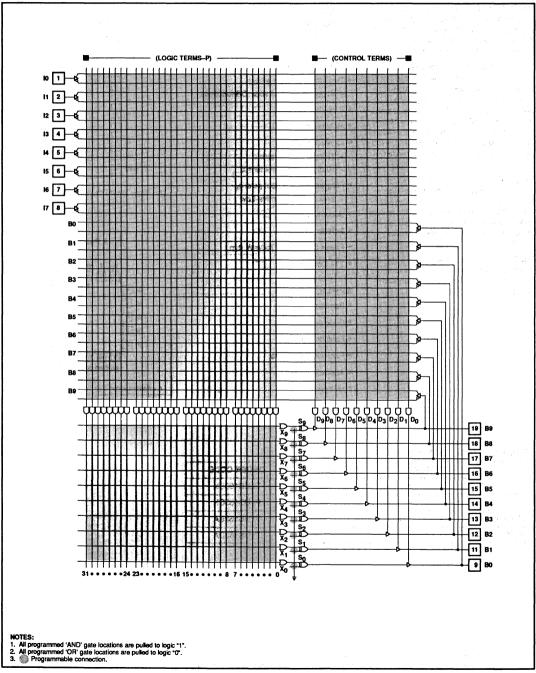

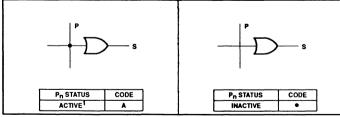

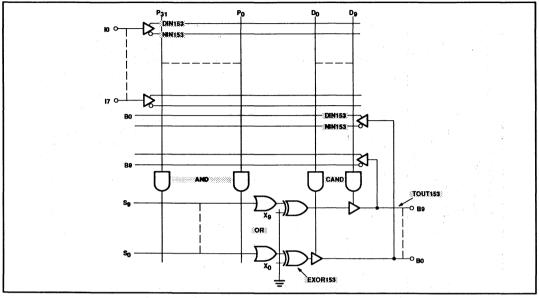

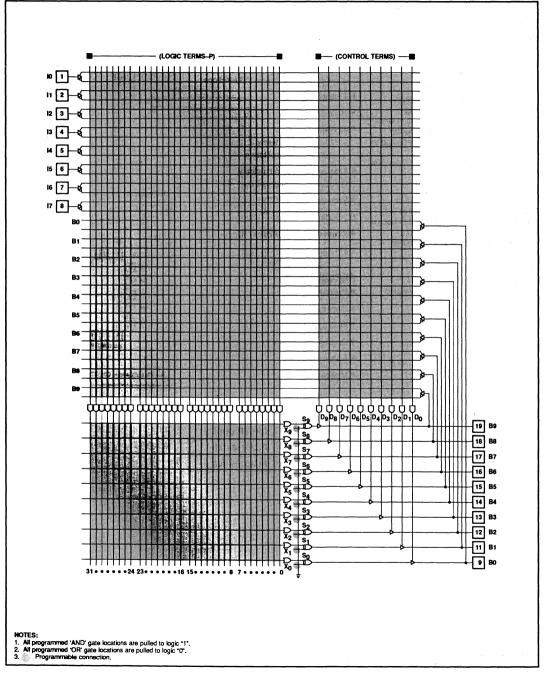

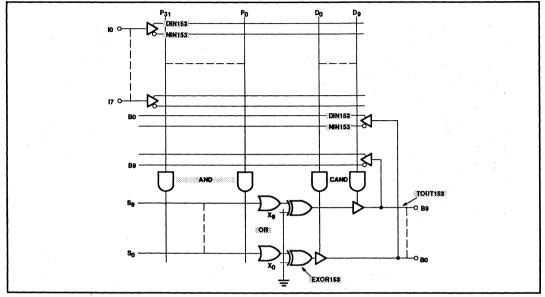

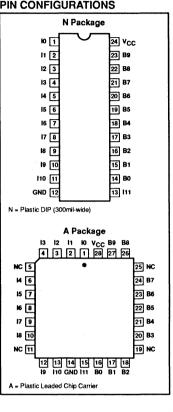

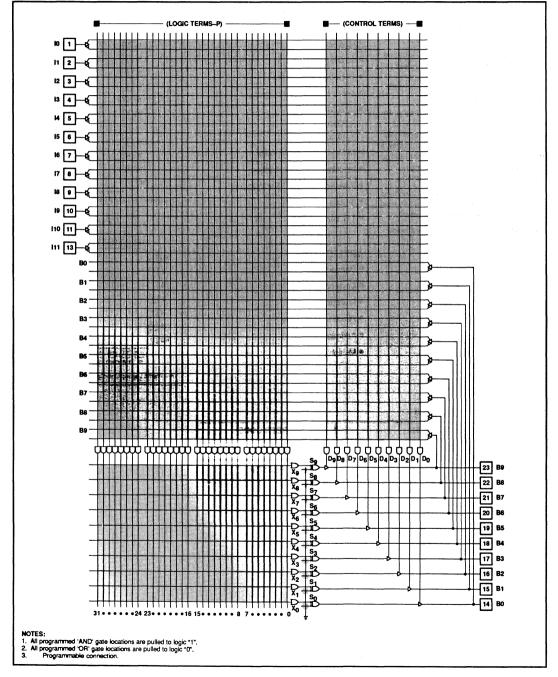

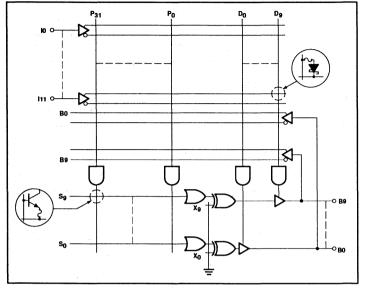

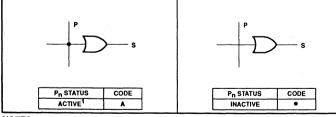

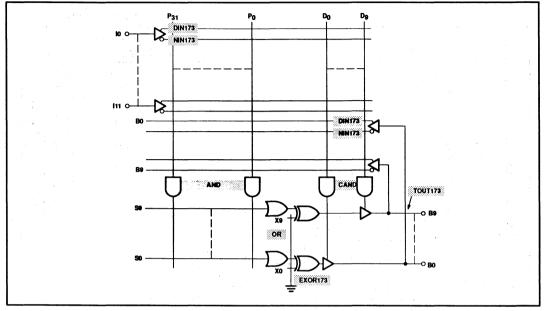

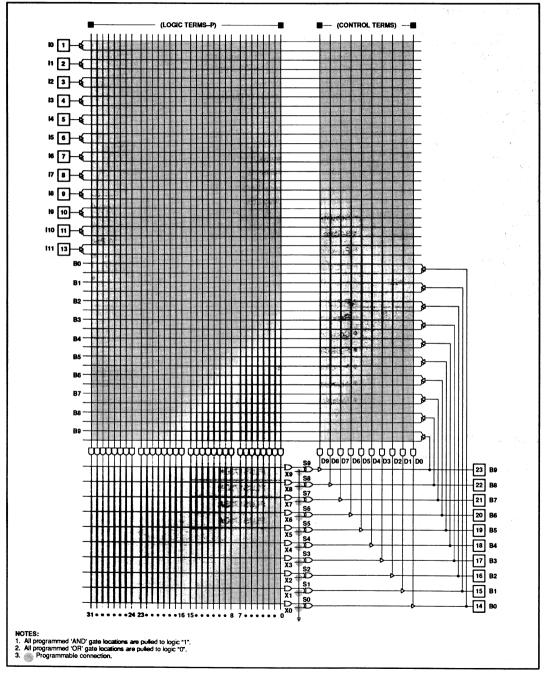

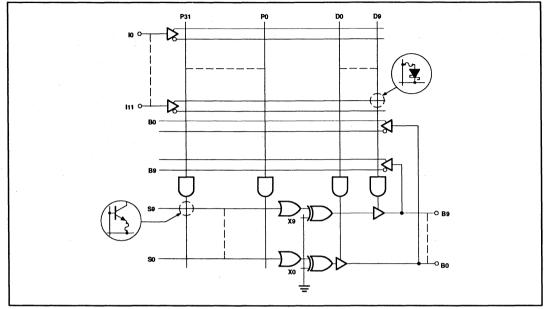

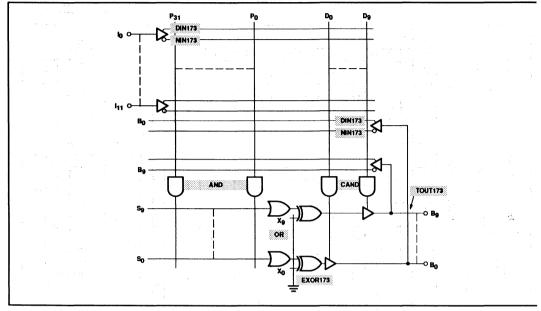

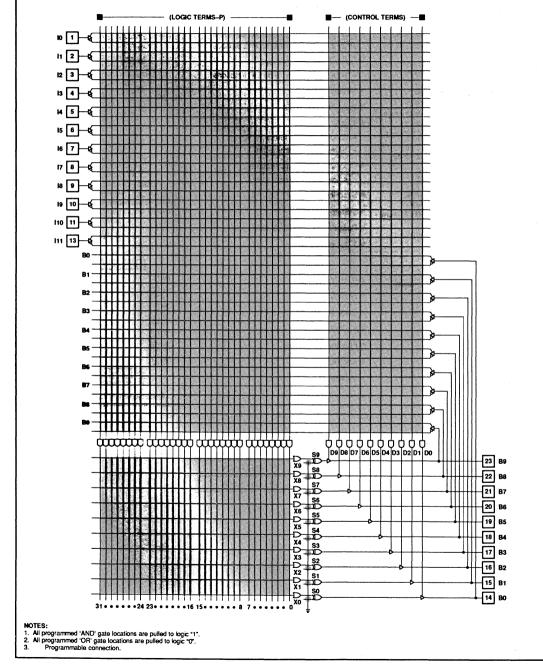

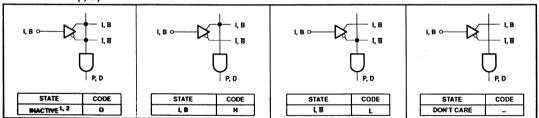

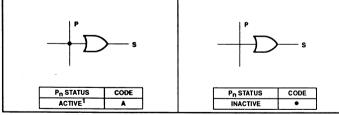

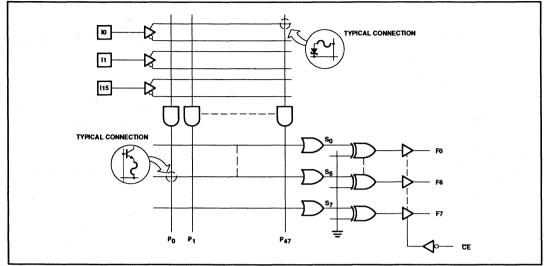

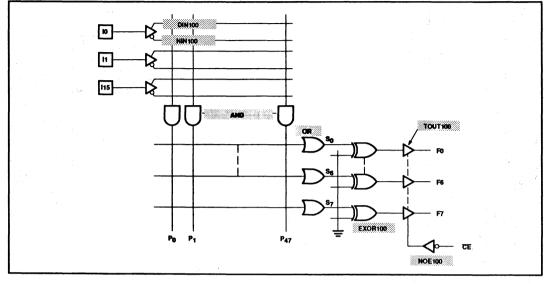

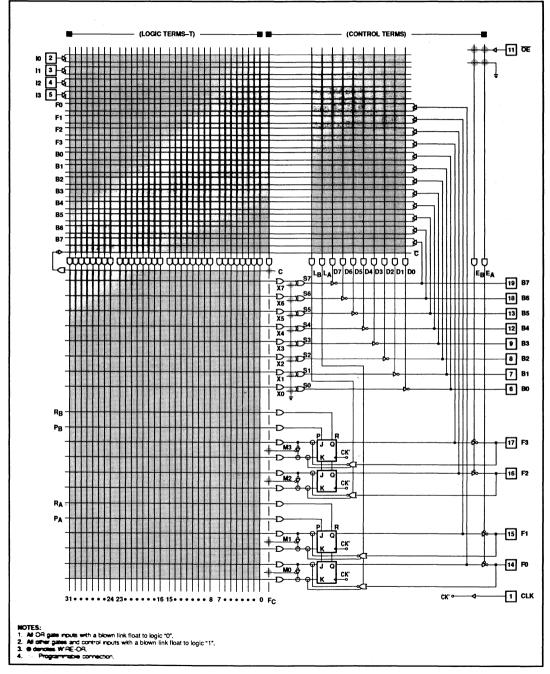

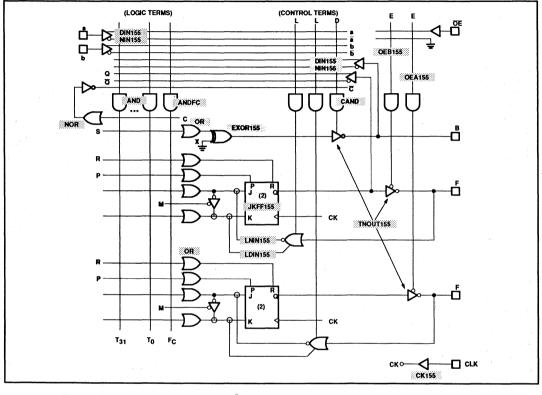

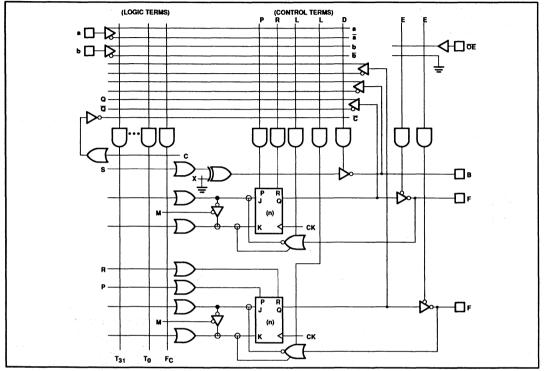

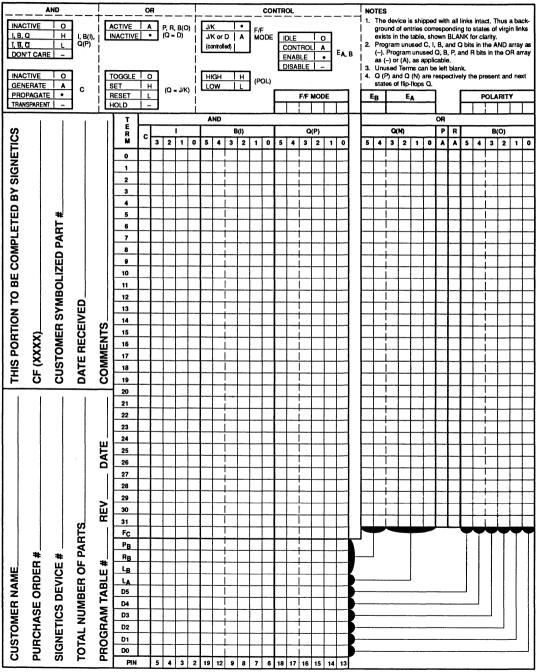

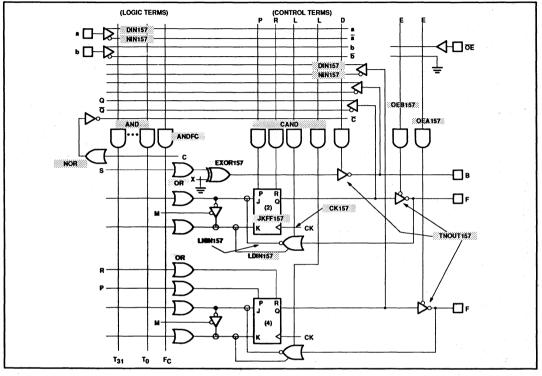

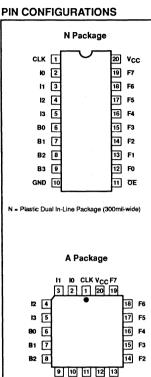

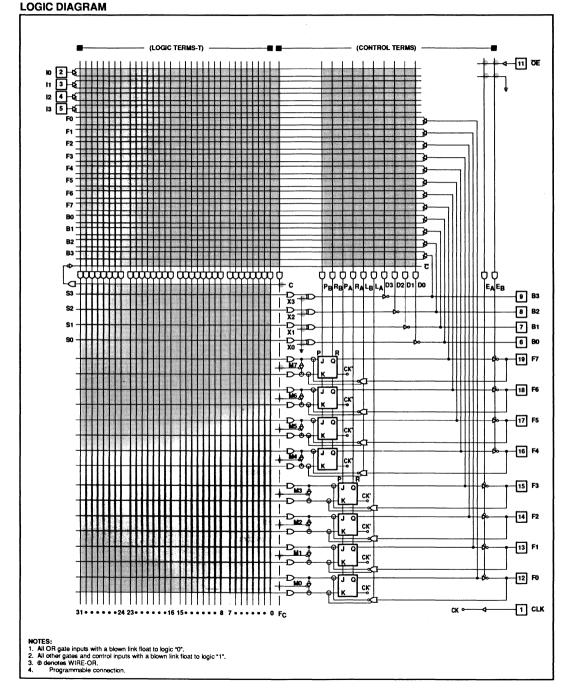

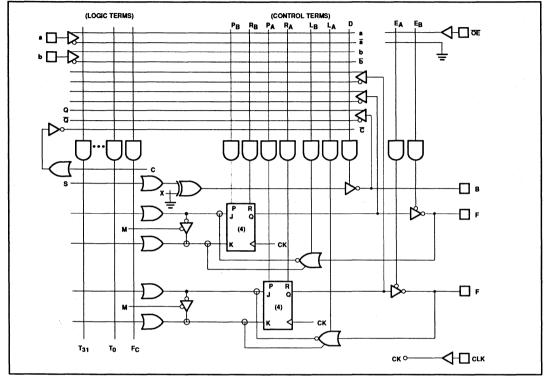

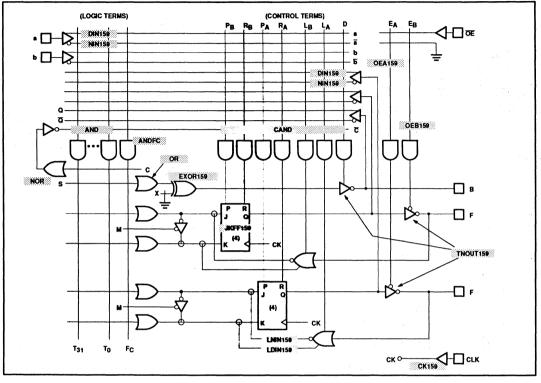

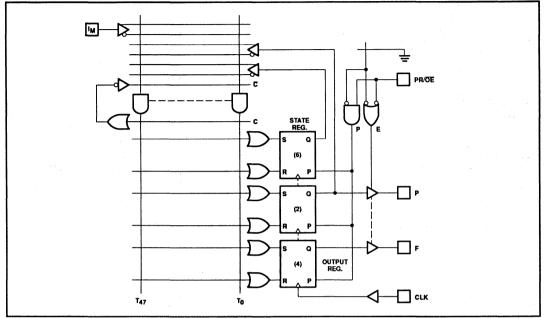

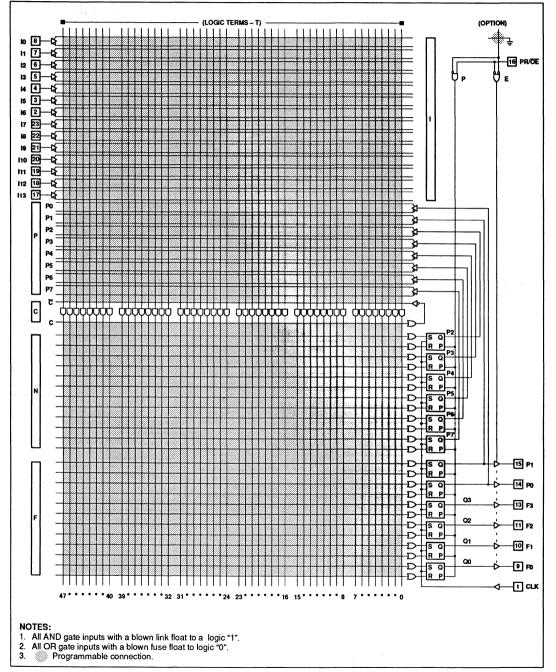

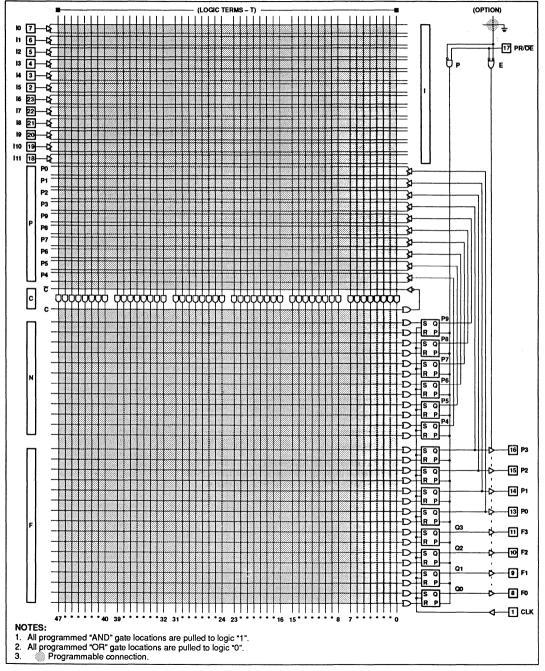

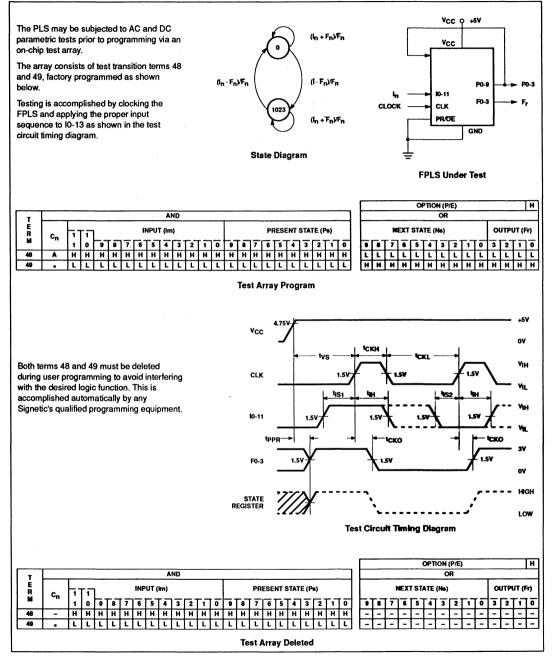

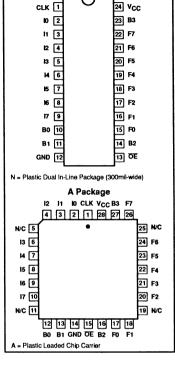

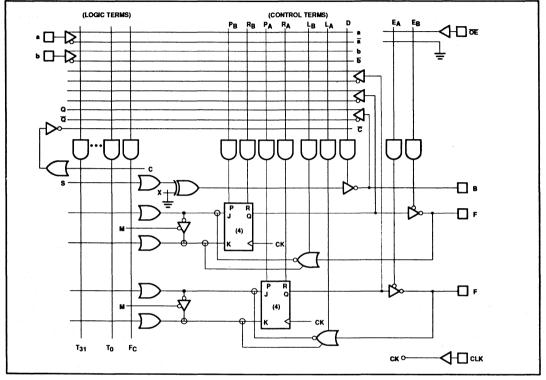

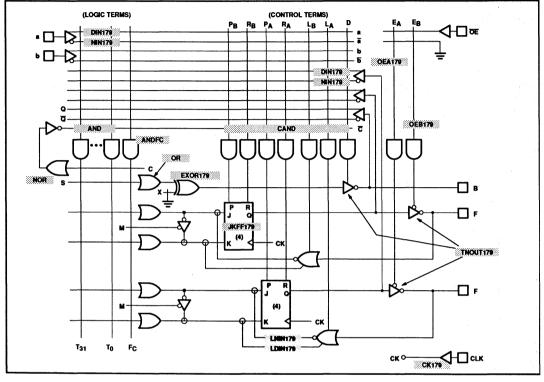

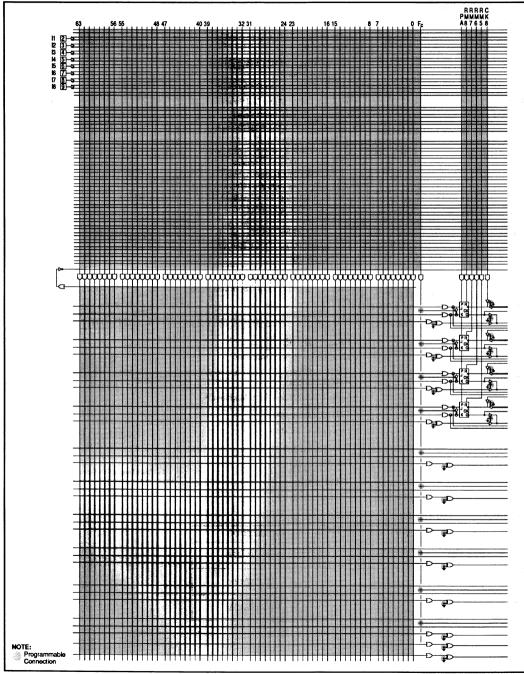

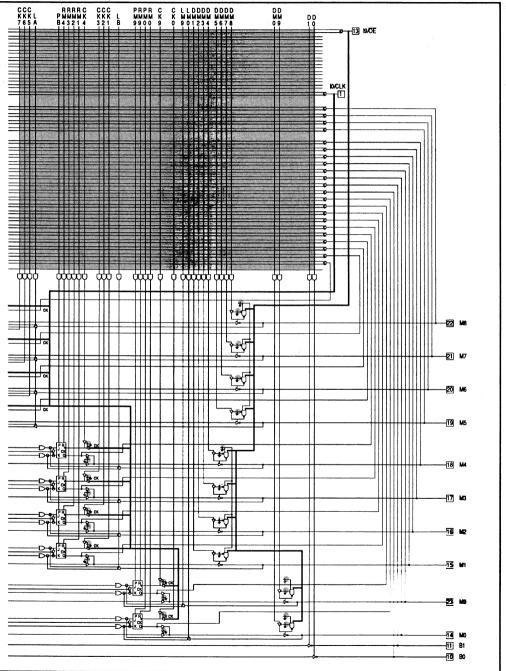

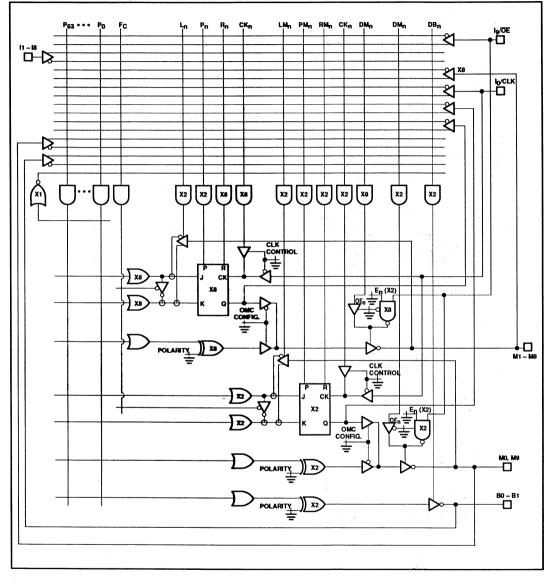

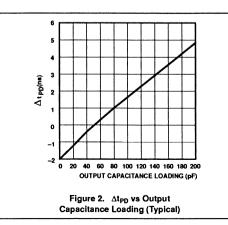

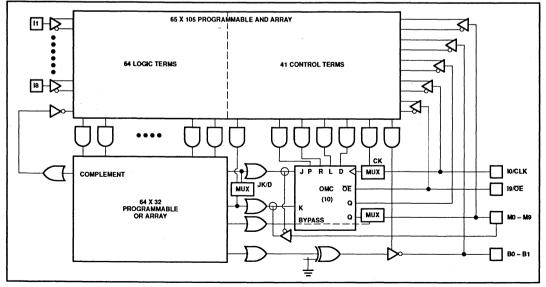

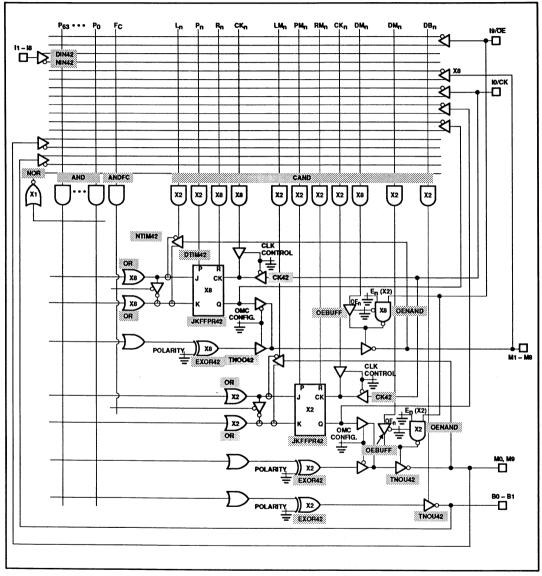

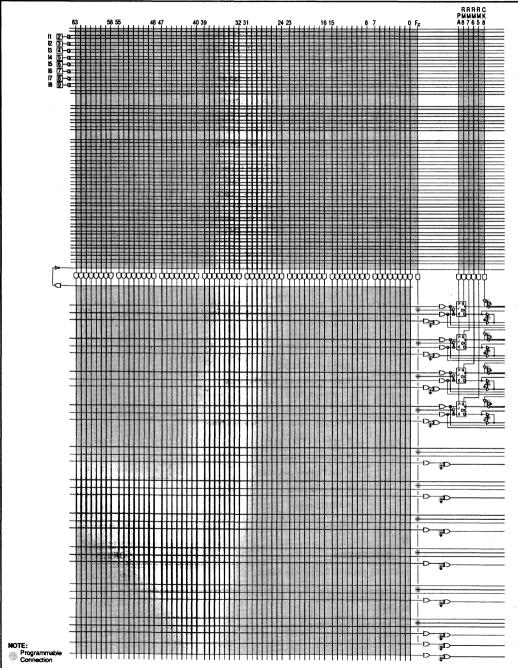

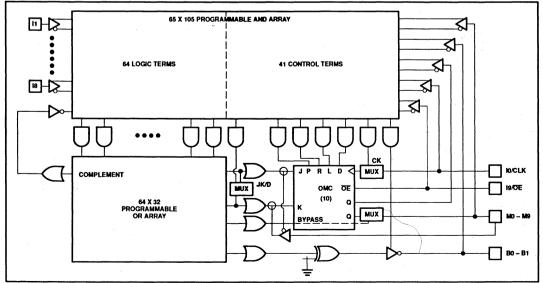

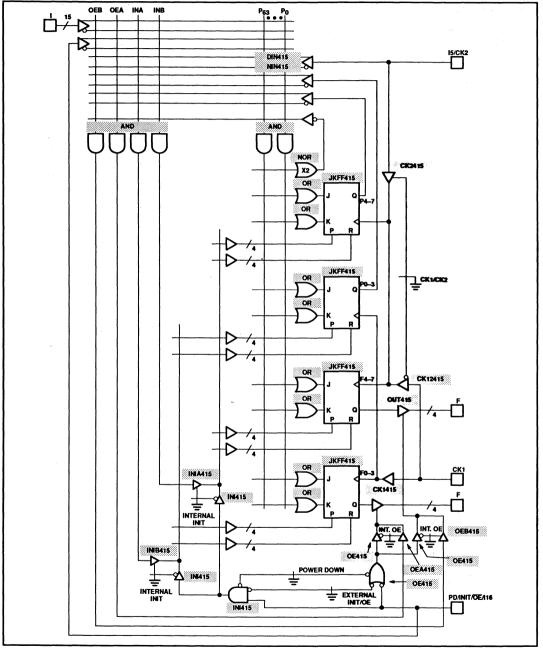

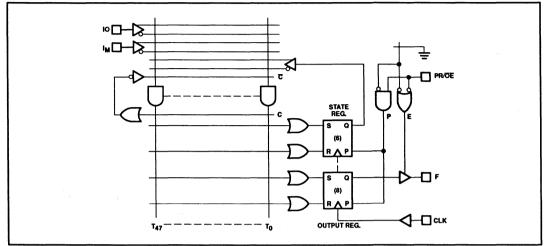

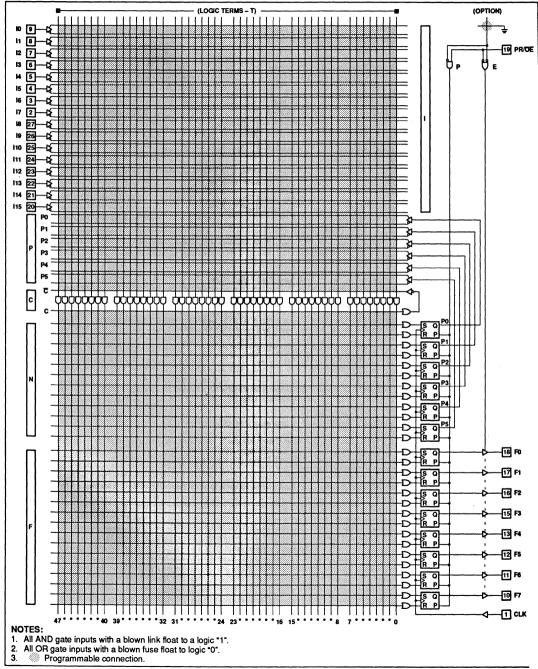

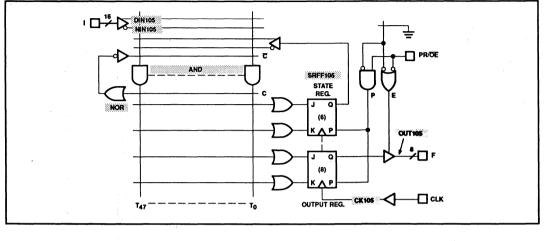

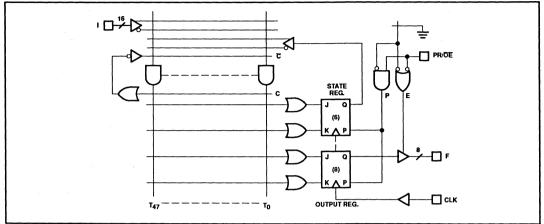

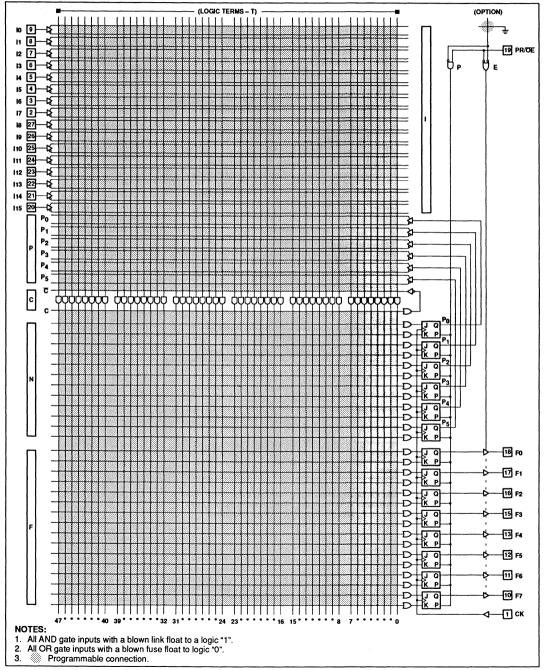

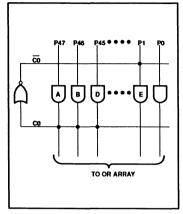

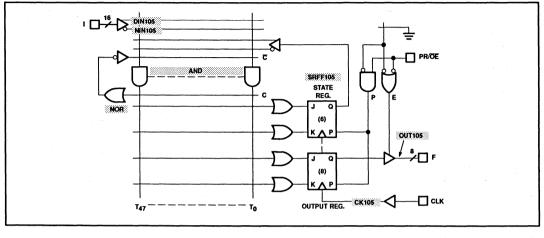

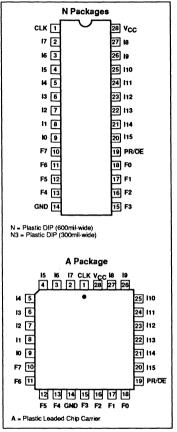

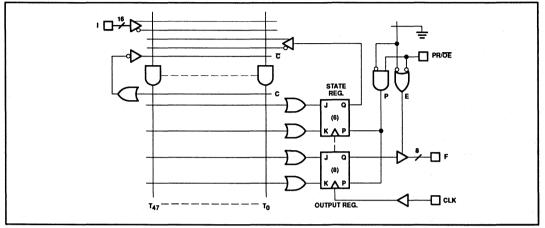

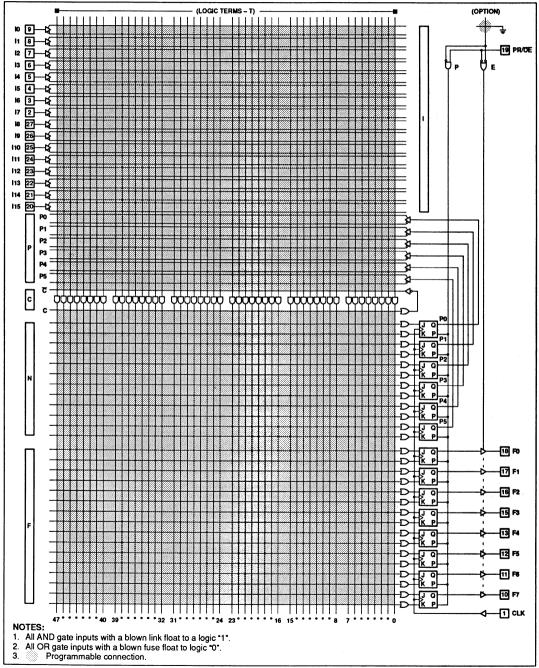

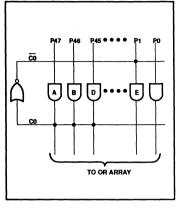

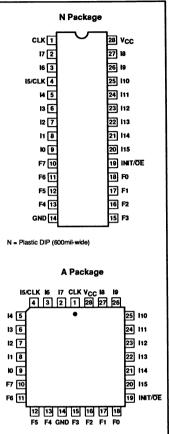

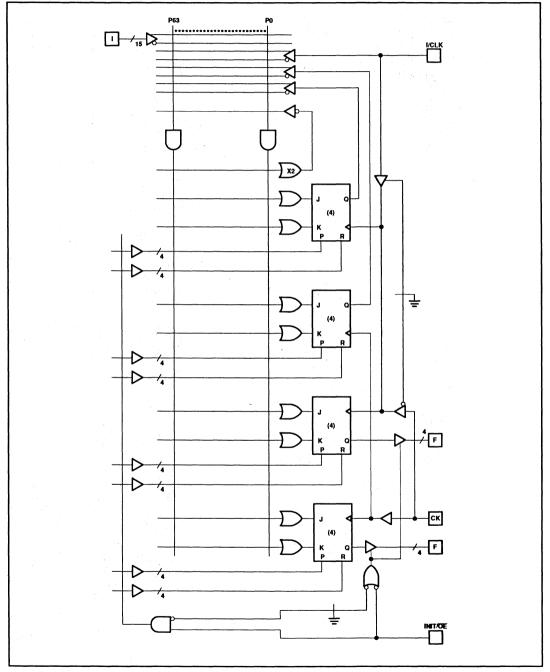

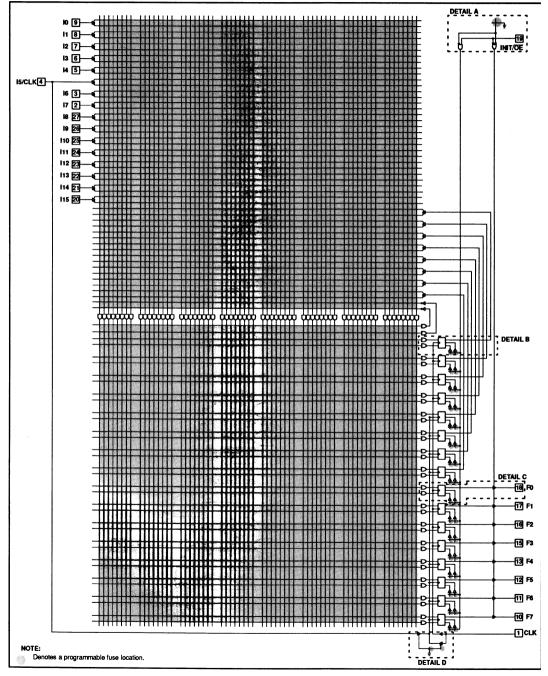

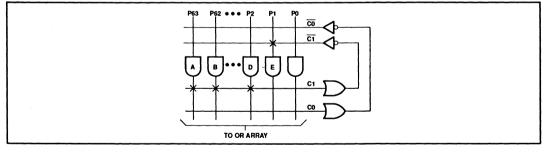

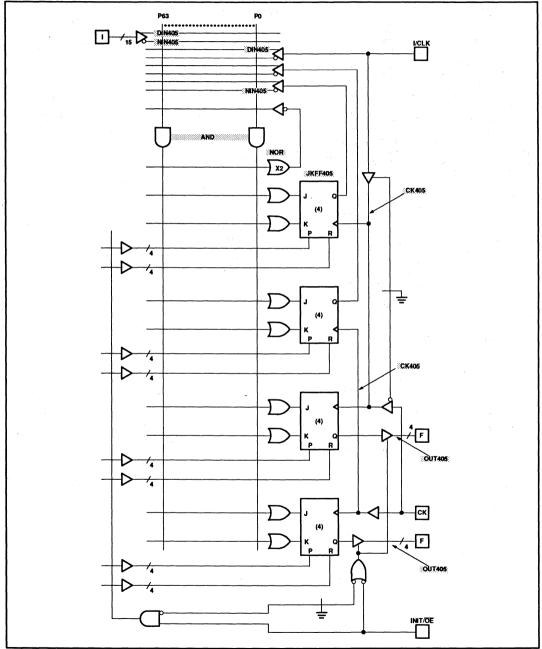

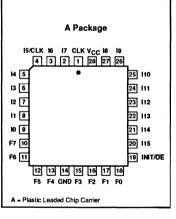

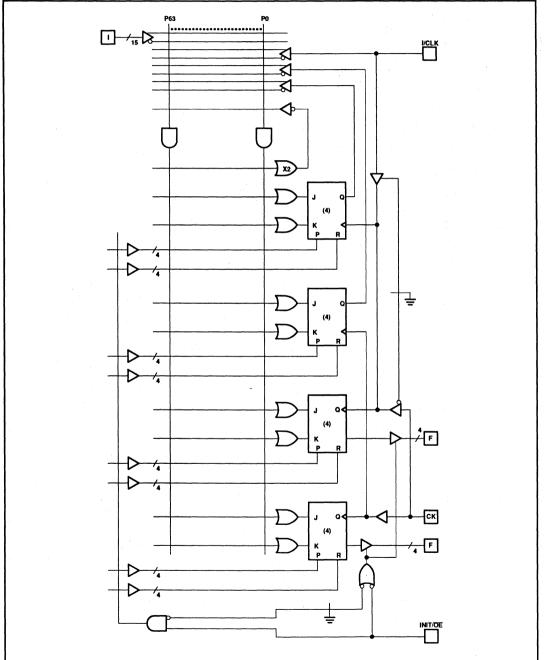

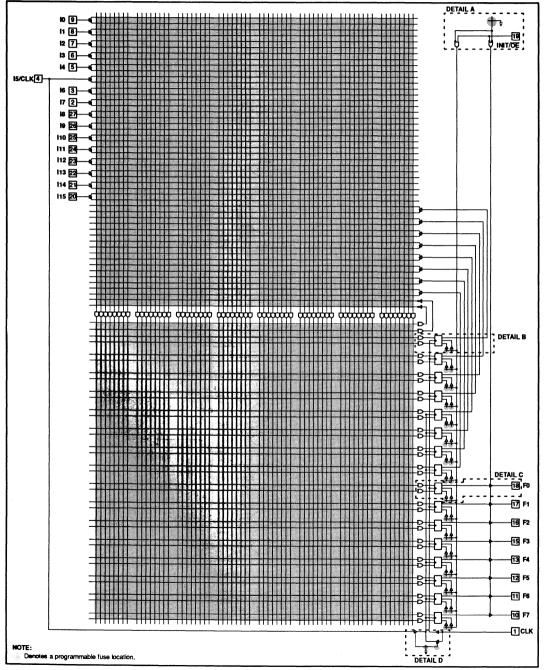

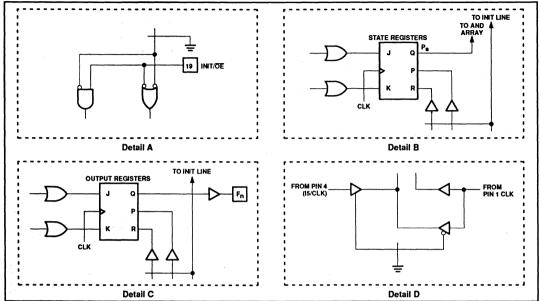

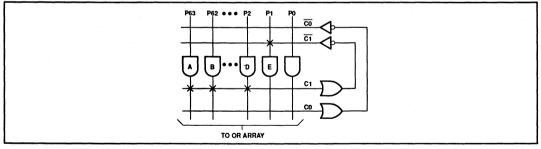

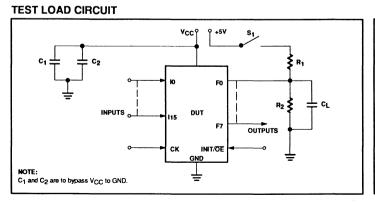

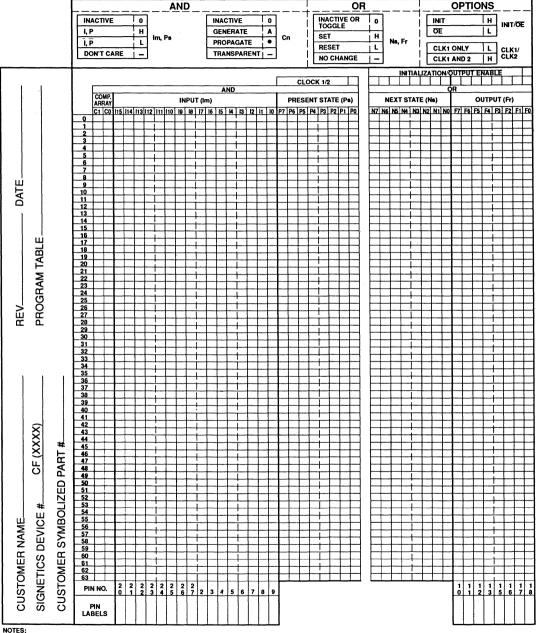

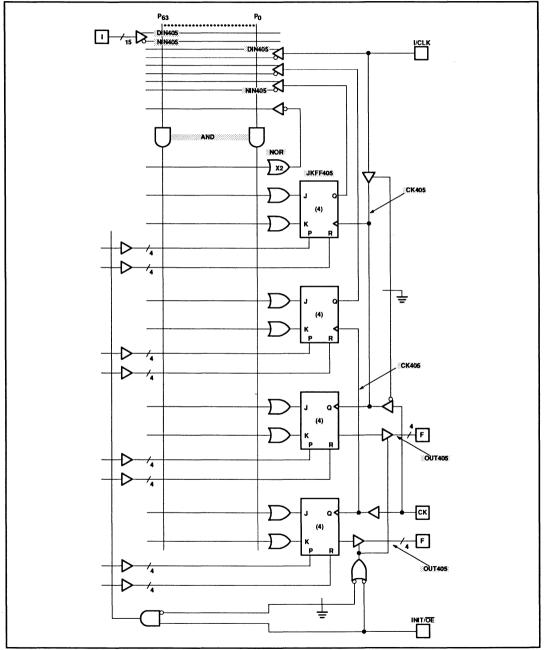

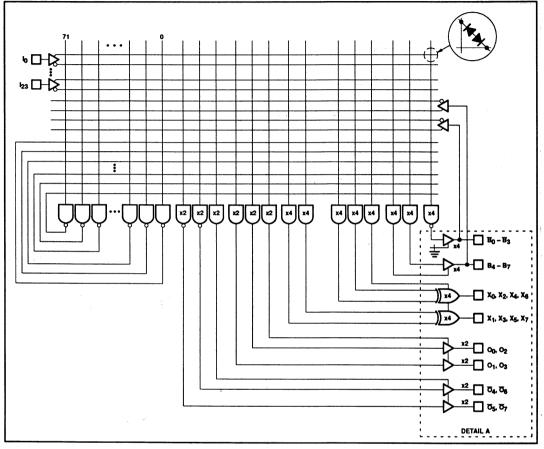

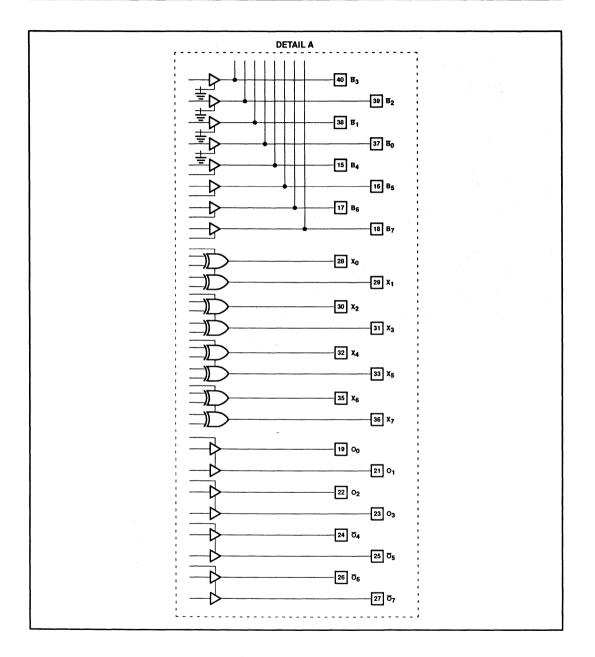

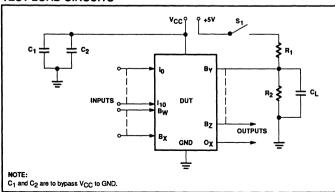

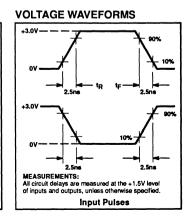

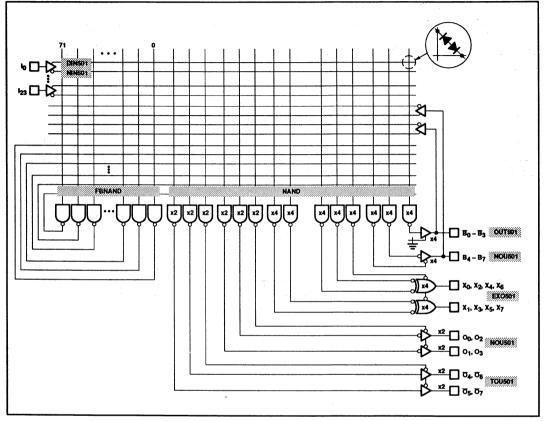

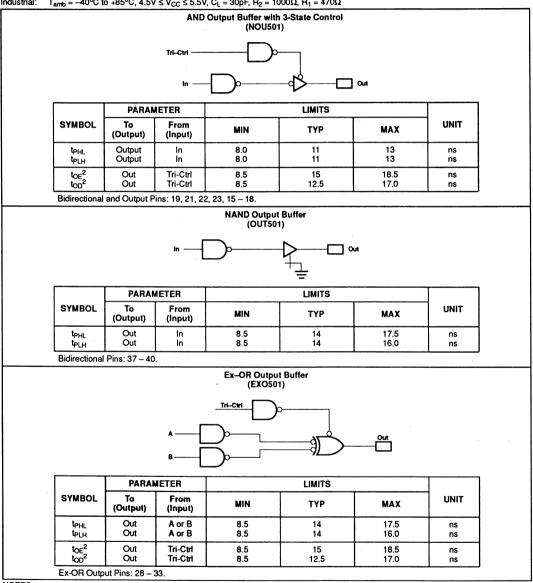

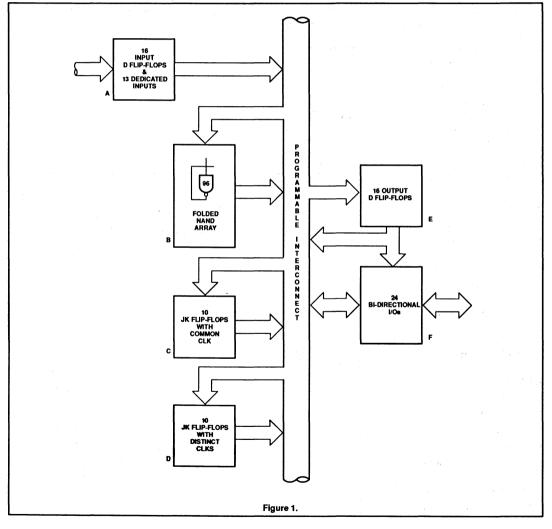

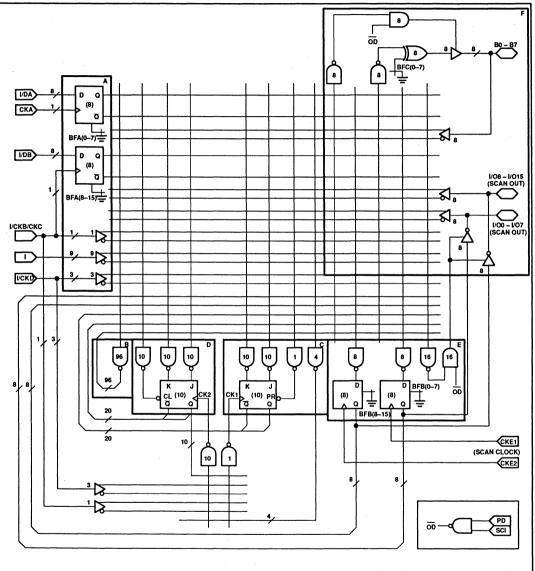

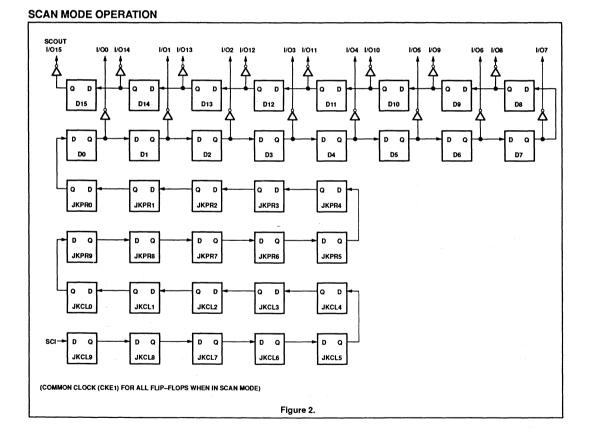

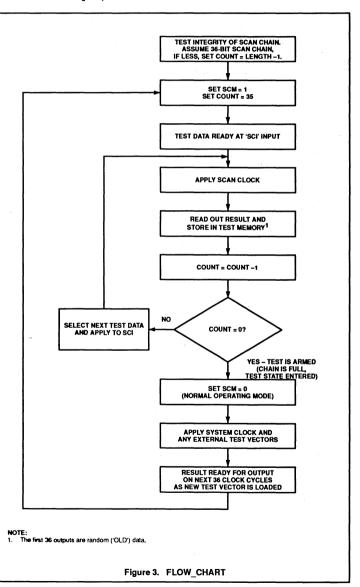

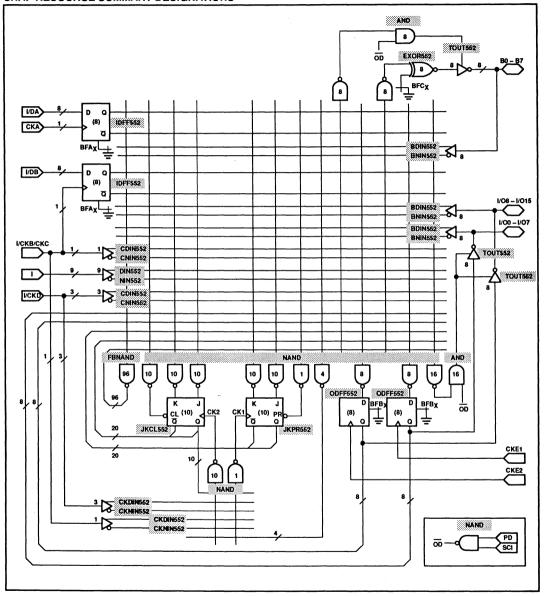

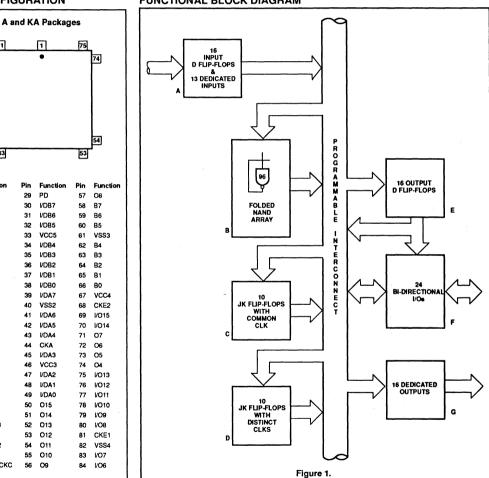

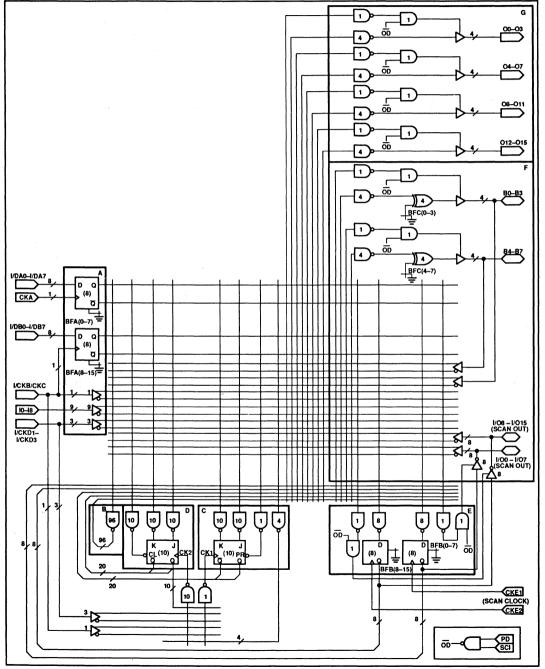

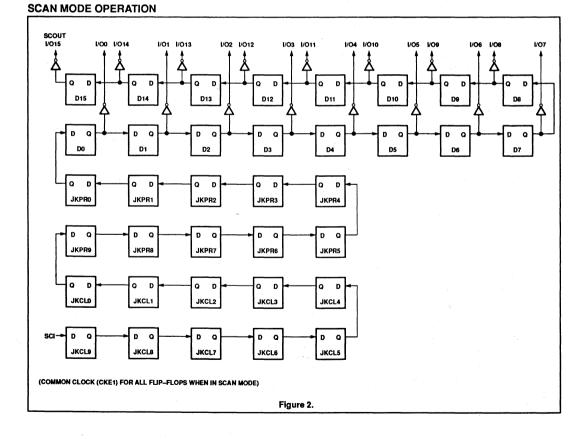

Figure 1 shows the architecture of a high performance sequencer combining a PLA architecture with JK flip-flops. The Selection Guide shown on pages 4 and 5 of this data handbook shows the current spectrum of Philips Semiconductors–Signetics PLDs. Parts for every need are available in nearly every architecture and across at least three technologies. The PLUS and PLHS prefixes describe bipolar parts, the PLC prefix describes EPLD (CMOS) parts and the PLQ prefix refers to the new Signetics QUBiC BiCMOS process. Figure 2 shows a shorthand image of the PLUS153 programmable logic array (PLA), which was derived from the original PLS100.

## Introduction

#### PLD LOGIC SYNTHESIS

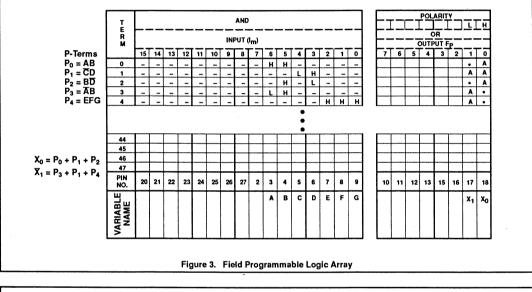

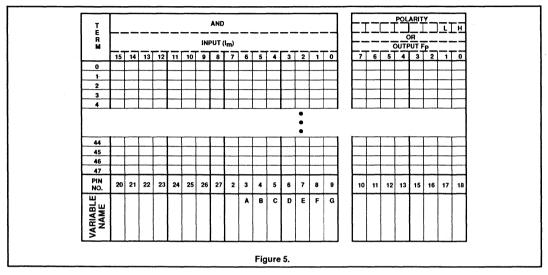

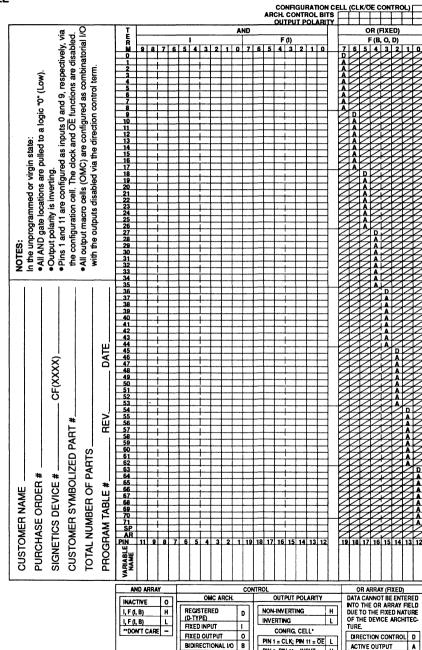

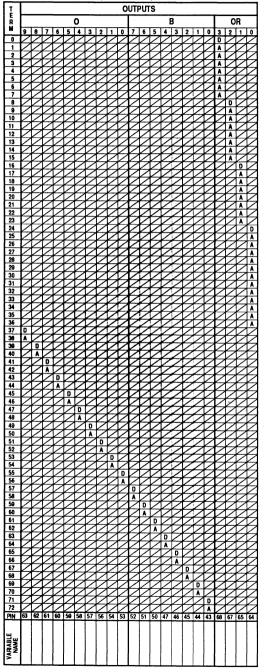

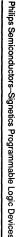

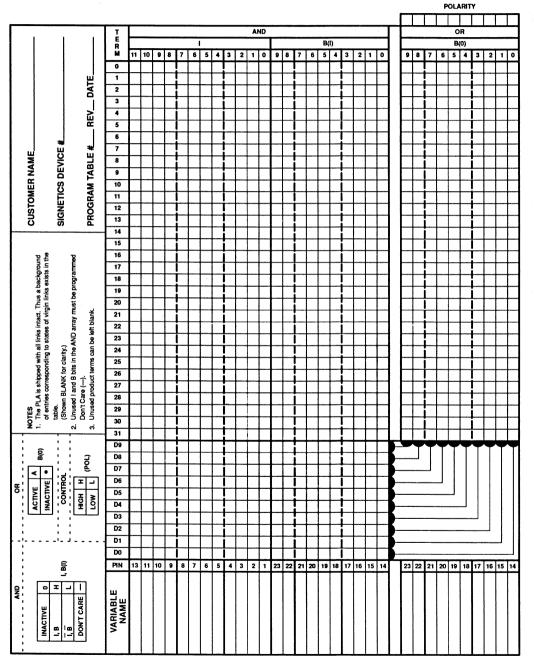

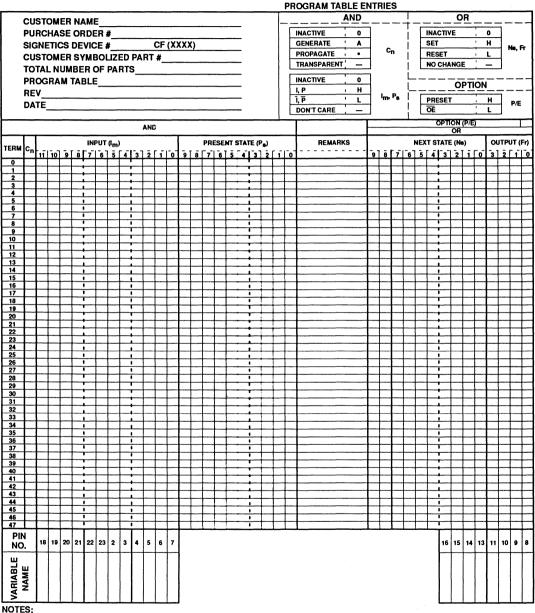

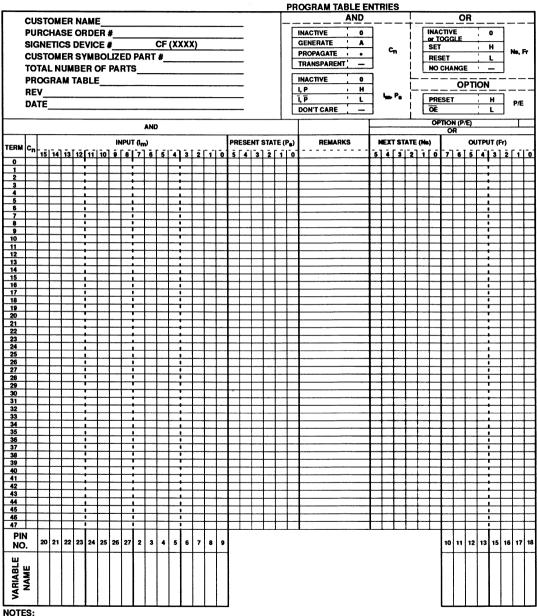

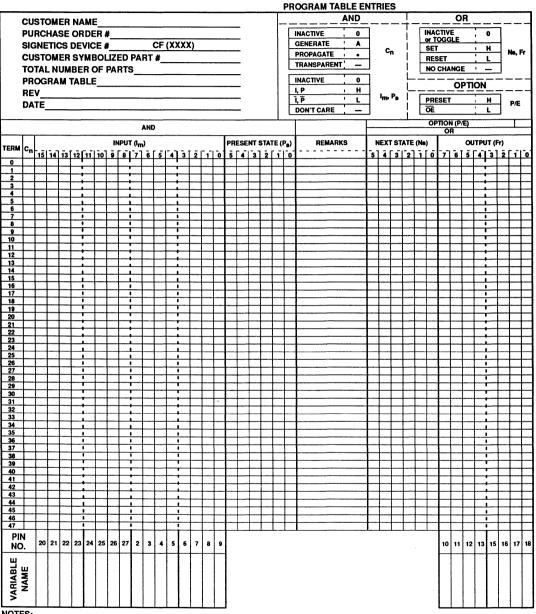

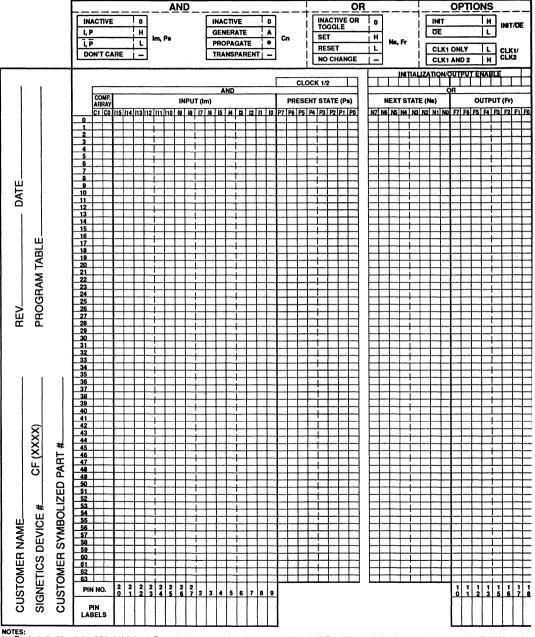

No intermediate step is required to implement Boolean Logic Equations with PLDs. Each term in each equation simply becomes a direct entry into the Logic Program Table. The following example illustrates this straightforward concept:

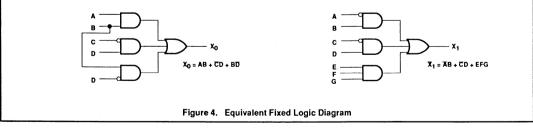

$X_0 = AB + \overline{C}D + B\overline{D}$

$\overline{X}_1 = \overline{A}B + \overline{C}D + EFG$

## Introduction

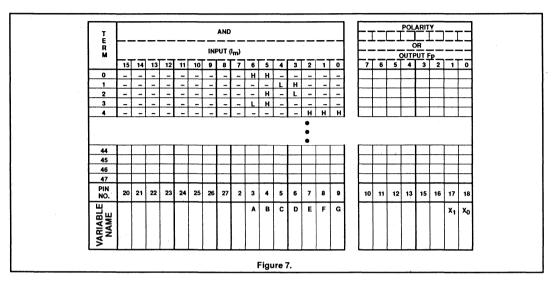

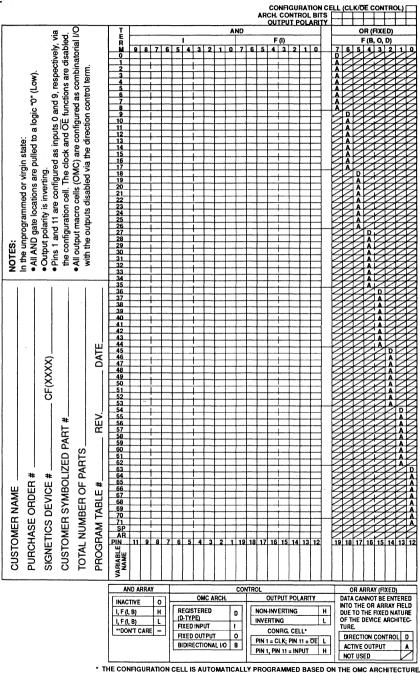

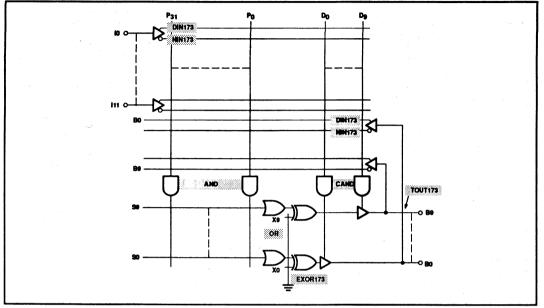

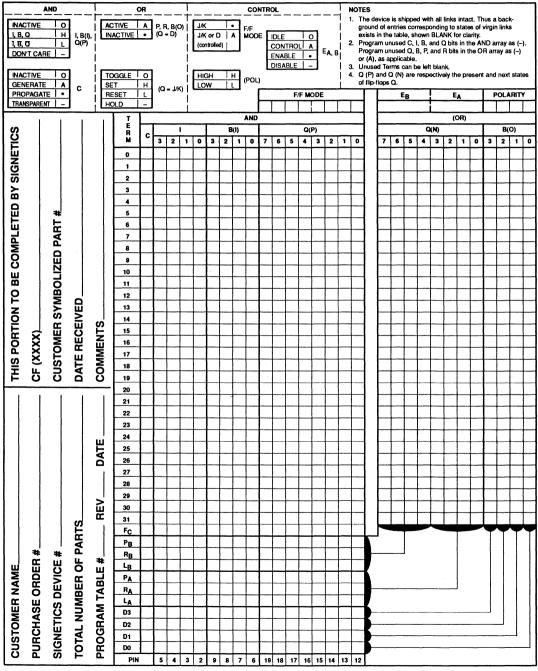

In the previous example, the two Boolean Logic equations were broken into Product terms. Each P-term was then programmed into the P-term section of the PLA Program Table. This was accomplished in the following manner:

#### Step 1

Select which input pins  $I_0 - I_{15}$  will correspond to the input variables. In this case A - G are the input variable names.  $I_6$ through  $I_0$  were selected to accept inputs A - G respectively.

#### Step 2

Transfer the Boolean Terms to the PLA Program Table. This is done simply by defining each term and entering it on the Program Table.

e.g., P<sub>0</sub> = AB

This P-term translates to the Program Table by selecting  $\mathbf{A} = \mathbf{I}_6 = \mathbf{H}$  and  $\mathbf{B} = \mathbf{I}_5 = \mathbf{H}$  and entering the information in the appropriate column.

This term is defined by selecting  $C = I_4 = L$ and  $D = I_3 = H$ , and entering the data into the Program Table. Continue this operation until all P-terms are entered into the Program Table.

Introduction

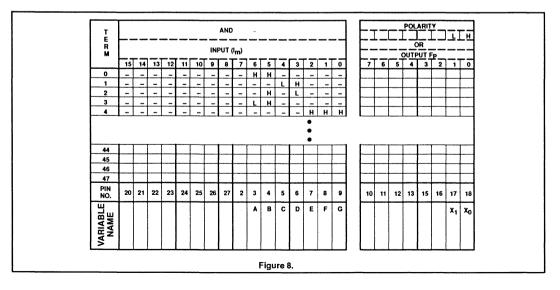

#### Step 3

Select which output pins correspond to each output function. In this case  $F_0 =$ Pin 18 = X<sub>0</sub>, and  $F_1 =$  Pin 17 = X<sub>1</sub>.

#### Step 4

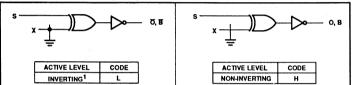

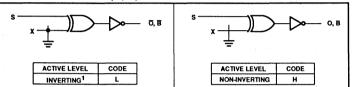

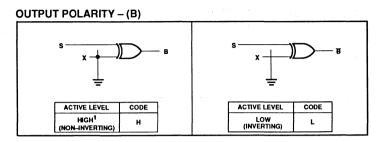

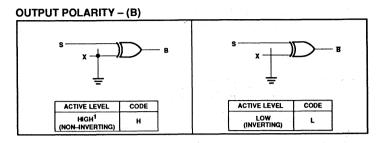

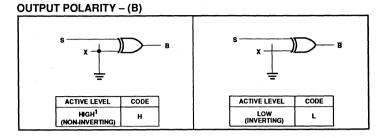

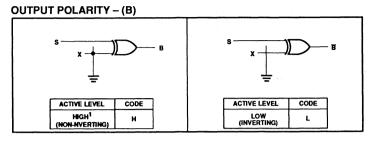

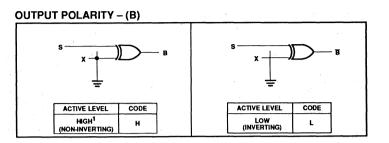

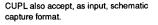

Select the Output Active Level desired for each Output Function. For  $X_0$  the active level is high for a positive logic expression of

this equation. Therefore, it is only necessary to place an (H) in the Active Level box above Output Function 0, (F\_0). Conversely,  $X_1$  can

be expressed as  $\overline{X}_1$  by placing an (L) in the Active Level box above Output Function 1, (F<sub>1</sub>).

## Introduction

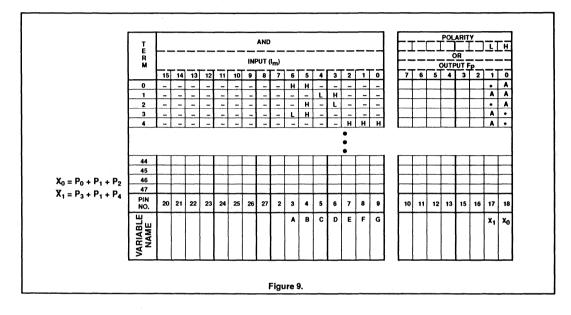

#### Step 5

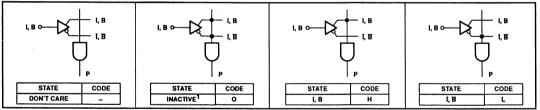

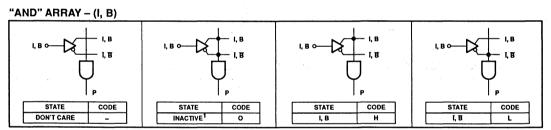

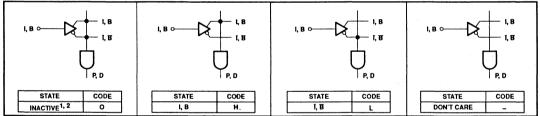

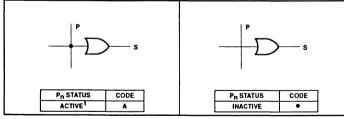

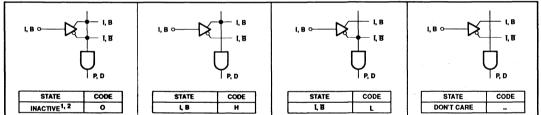

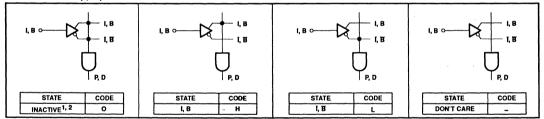

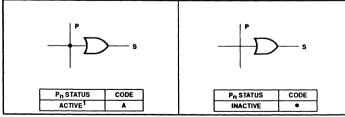

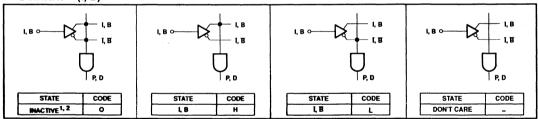

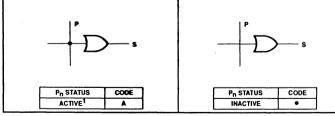

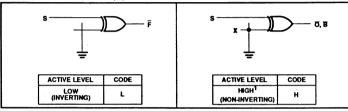

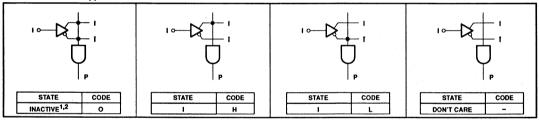

Select the P-Terms you wish to make active for each Output Function. In this case  $X_0 = P_0 + P_1 + P_2$ , so an A has been placed in the intersection box for  $P_0$  and  $X_0$ ,  $P_1$  and  $X_0$  and  $P_2$  and  $X_0$ .

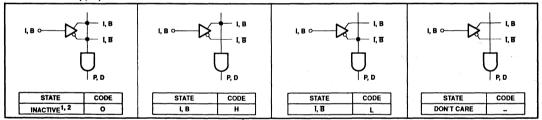

Terms which are not active for a given output are made inactive by placing a (•) in the box under that P-term. Leave all unused P-terms unprogrammed.

Continue this operation until all outputs have been defined in the Program Table.

#### Step 6

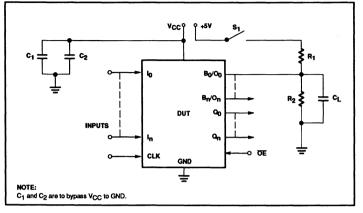

Enter the data into a Signetics approved programmer. The input format is identical to the Signetics Program Table. You specify the P-terms, Output Active Level, and which P-terms are active for each output exactly the way it appears on the Program Table.

## Introduction

#### PLD LOGIC SYNTHESIS (Continued)

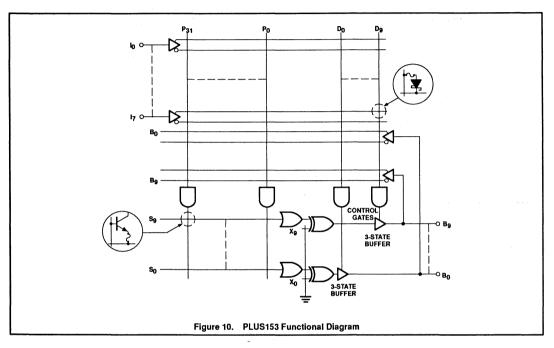

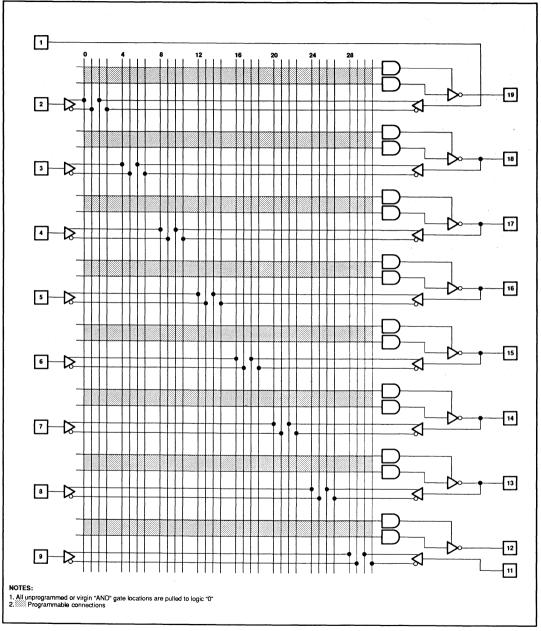

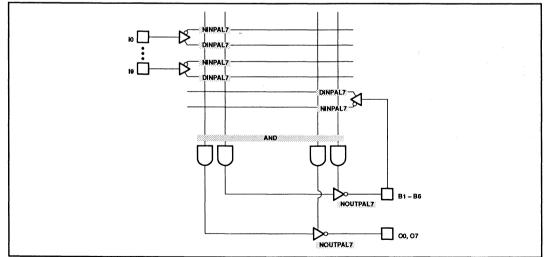

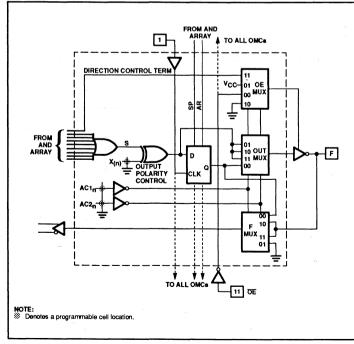

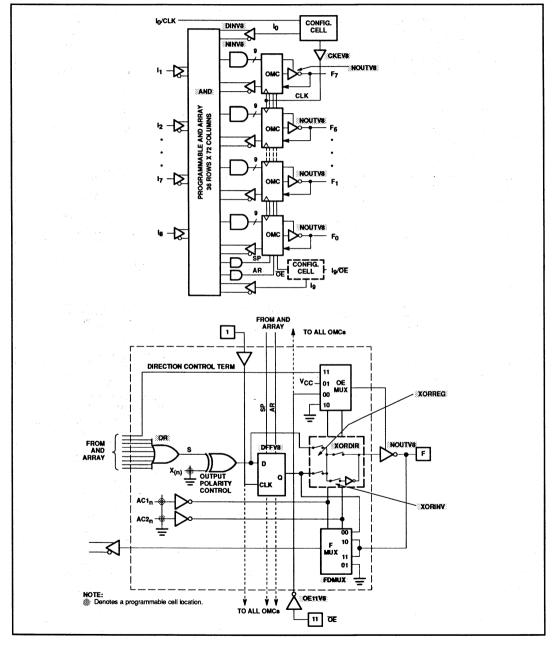

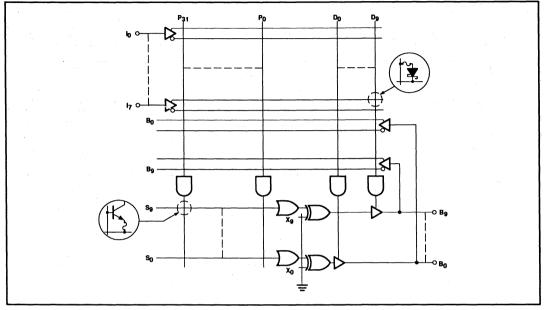

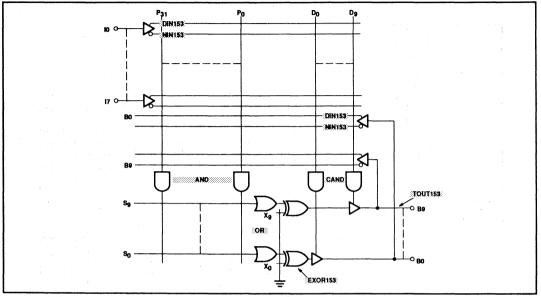

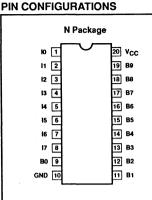

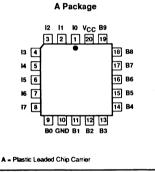

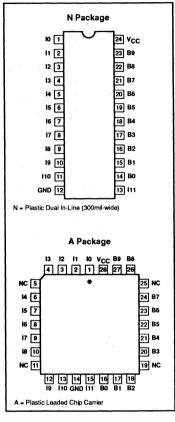

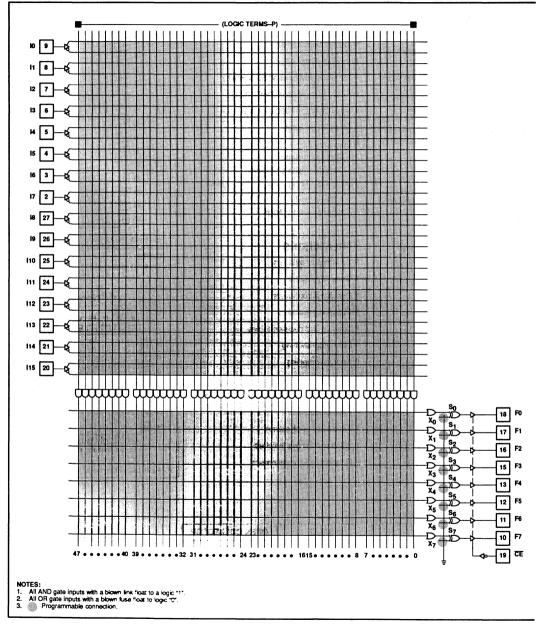

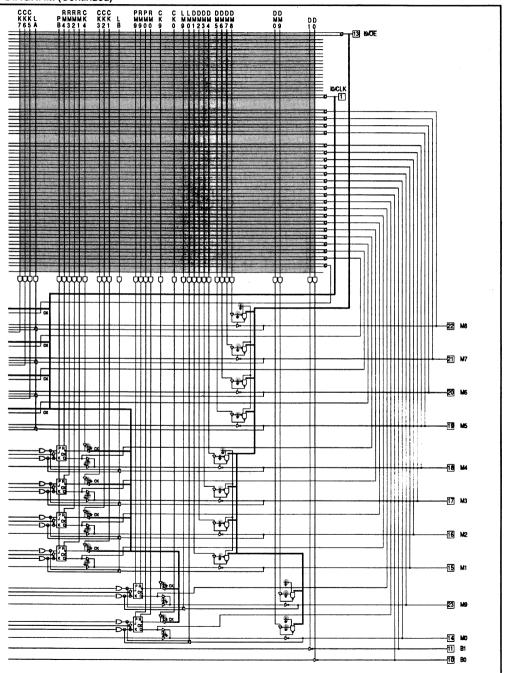

When fewer inputs and outputs are required in a logic design and low cost is most important, the Signetics 20-pin PLD should be considered first choice. The PLUS153 is a PLA with 8 inputs, 10 I/O pins, and 42 product terms. The user can configure the device by defining the direction of the I/O pins. This is easily accomplished by using the direction control terms  $D_0 - D_9$  to establish

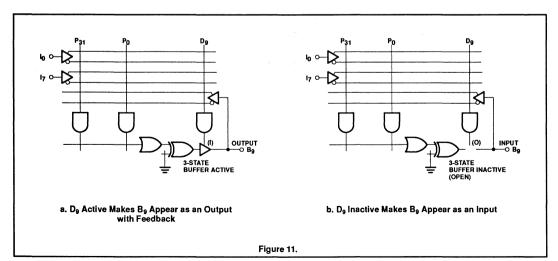

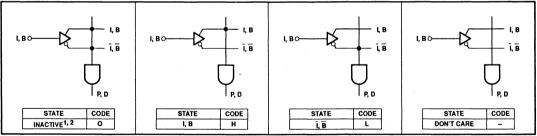

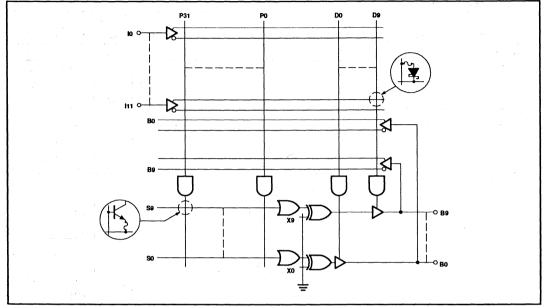

the direction of pins  $B_0-B_9$ . The D-terms control the 3-State buffers found on the outputs of the Ex-OR gates. Figures 10 and 11 show how the D-term configures each  $B_X$  pin.

## Introduction

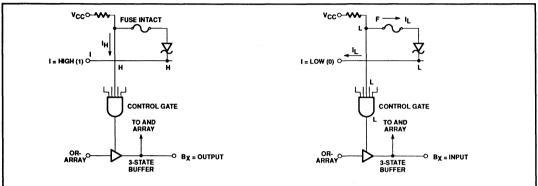

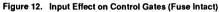

To control each D-term, it is necessary to understand that each control gate is a 36-input AND gate. To make the 3-State buffer active ( $B_x$  pin an output), the output of the control gate must be at logic HIGH (1). This can be accomplished in one of two

ways. A HIGH can be forced on all control gate input nodes, or fuses can be programmed. When a fuse is programmed, that control gate input node is internally pulled up to HIGH (1). See Figure 12 and Figure 13. Programming the fuse permanently places a HIGH (1) on the input to the control gate. The input pin no longer has any effect on that state.

## Introduction

#### **DEDICATING B<sub>X</sub> PIN DIRECTION**

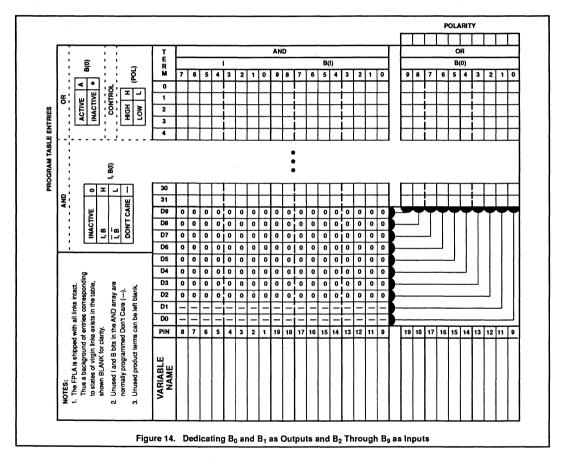

Since each input to the D-terms is true and complement buffered (see Figure 11), when the device is shipped with all fuses intact, all control gates have half of the 36 input lines at logic low (0). The result of this is all Control Gate outputs are low (0) and the 3-State buffers are inactive. This results in all  $B_X$  pins being in the input condition. the resultant device is, therefore, an 18-input, 0-output FPLA. While useful as a bit bucket or Write-Only-Memory (WOM), most applications require at least one output. Clearly, the first task is to determine which of the B<sub>X</sub> pins are to be outputs. The next step is to condition the control gate to make the 3-State buffer for those gates active. To dedicate B<sub>0</sub> and B<sub>1</sub> as outputs, it is necessary to program all fuses to the inputs to Control Gates D<sub>0</sub> and D<sub>1</sub>. This internally pulls all inputs to those gates to HIGH (1) permanently. since all inputs to the Control Gates are HIGH (1), the output is HIGH (1) and the 3-State buffers for  $B_0$  and  $B_1$  are active. This permanently enables  $B_0$  and  $B_1$ as outputs. Note that even though  $B_0$  and  $B_1$ are outputs, the output data is available to the AND array via the internal feedback (see Figure 11a).

To program this data, the PLUS153 Program Table is used as shown in Figure 14.

## Introduction

By placing a (—) Don't Care in each input box you are specifying that the True and Complement fuses are programmed on each Control Gate, thus permanently dedicating the  $B_0$  and  $B_1$  pins as outputs. By placing a (0) in all input boxes for  $B_2 - B_9$ , you are specifying that both True and Complement fuses are intact. This causes a low (0) to be forced on half of the Control Gate inputs, guaranteeing the output of the Control Gate will be low (0). When the Control Gate outputs are low (0), the 3-State buffer is inactive and the  $B_2$  -  $B_9$  pins are enabled as inputs. All  $B_X$  pin directions can be controlled in this manner.

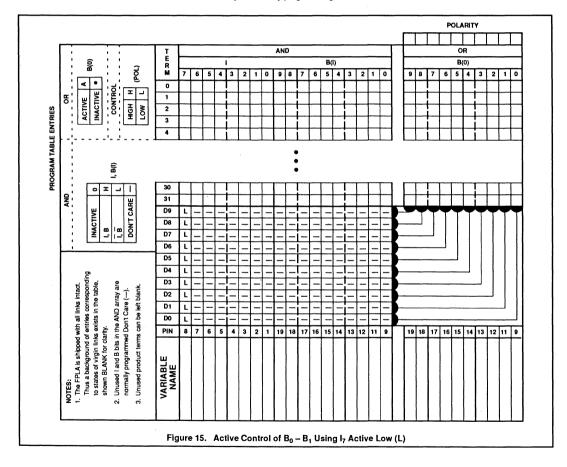

#### ACTIVE DIRECTION CONTROL

Sometimes it is necessary to be able to actively change the direction of the  $B_X$  pins without permanently dedicating them. Some applications which require this include 3-State bus enable, multi-function decoding, etc. This can easily be done by programming the

Control Gate to respond to one or more input pins. It is only necessary to select which  $I_X$  and  $B_X$  pins will control the pin directions and the active level HIGH (H) or LOW (L) that will be used. The PLUS153 Program Table in Figure 15 shows the method of controlling  $B_0 - B_9$  with  $I_7$ . When  $I_7$  is LOW (L), pins  $B_0 - B_9$  are outputs; when  $I_7$  is HIGH (H), pins  $B_0 - B_9$  are inputs. Note that by programming all other  $I_X$  and  $B_X$  pins as DON'T CARE (—), they are permanently disconnected from control of  $B_X$  pin direction.

## Introduction

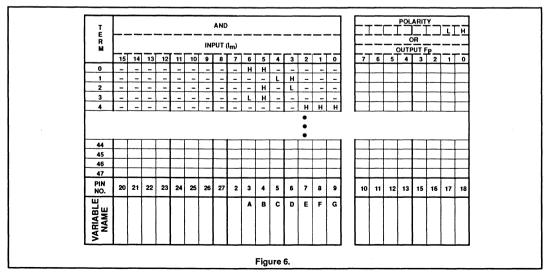

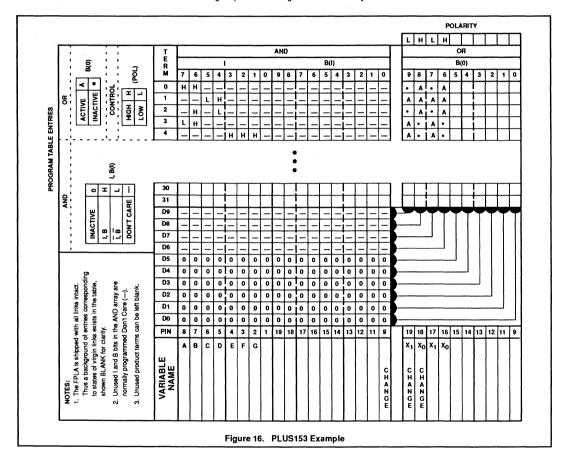

The previous 28-pin logic synthesis example could be done on the PLUS153 as follows:

$$X_0 = AB + \overline{C}D + B\overline{D}$$

$$\overline{X}_1 = \overline{AB} + \overline{CD} + \overline{EFG}$$

Note that  $B_0$  was used as a CHANGE input. When  $B_0$  is HIGH (H) the outputs appear on  $B_8$  and  $B_9$ . When  $B_0$  is LOW (L), the outputs appear on  $B_6$  and  $B_7$ .  $B_1$  through  $B_5$  are not used and therefore left unprogrammed.

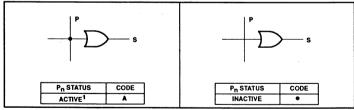

Signetics offers two packages for user-friendly design assistance. The first package, AMAZE, has evolved over 10 years to support Signetics programmable products with logic equation, state equation, and schematic entry. AMAZE can compile designs guite well for Signetics lower density parts. However, to satisfy the needs of Programmable Macro Logic users, Signetics developed an additional software package called SNAP. SNAP expands upon the capabilities of AMAZE in its approach to design implementation, more closely resembling a gate array methodology. Both of these products are described in more depth at a later point in this handbook.

## Introduction

# SEQUENTIAL LOGIC CONSIDERATIONS

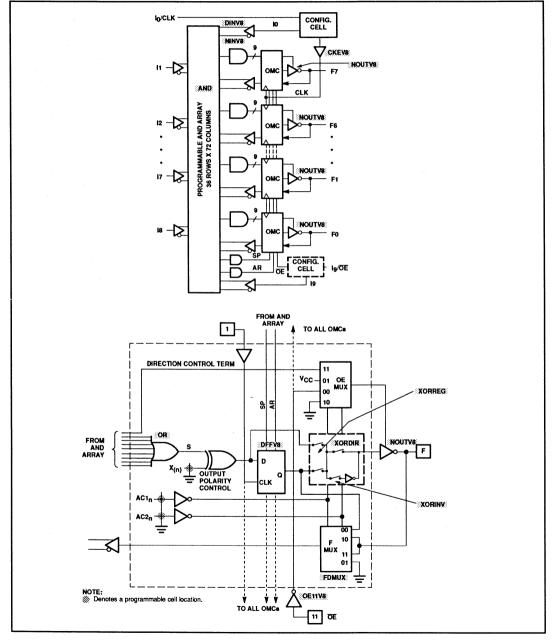

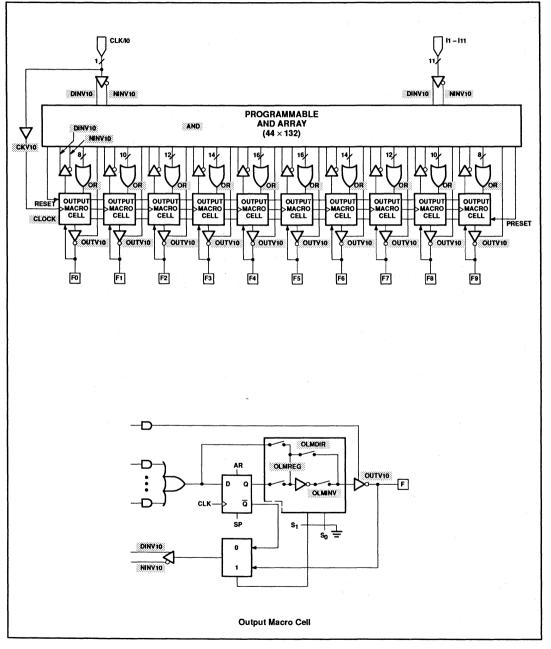

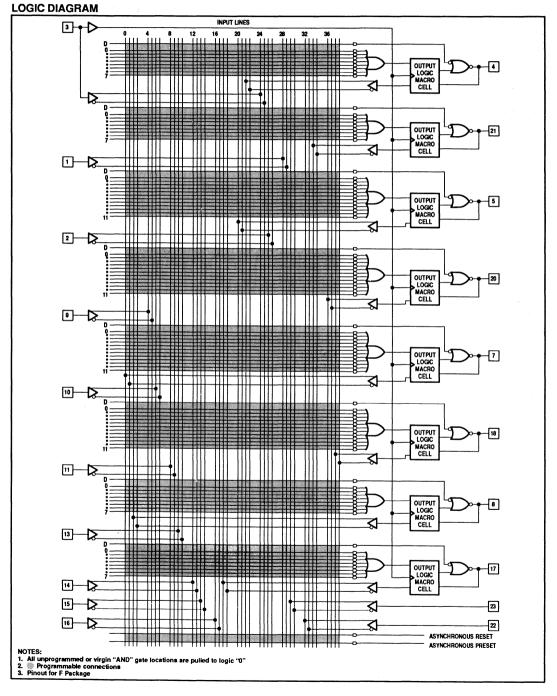

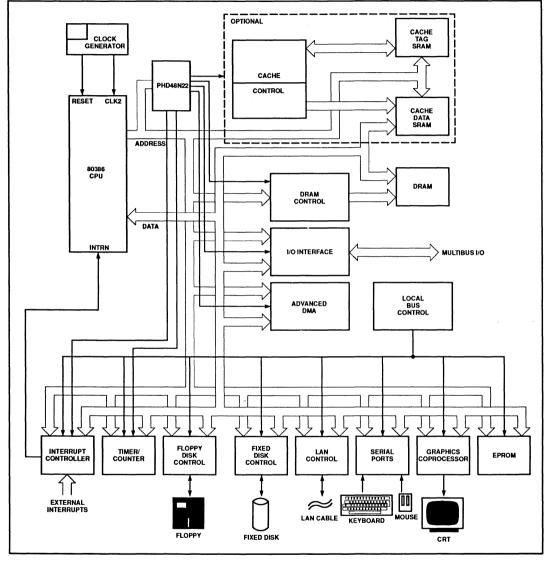

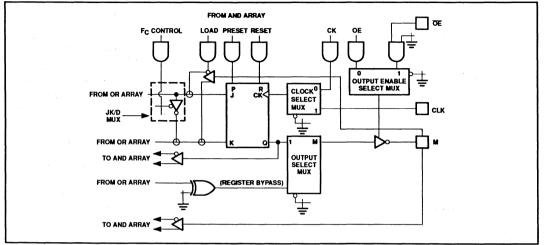

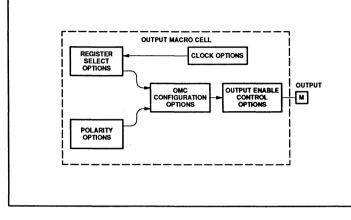

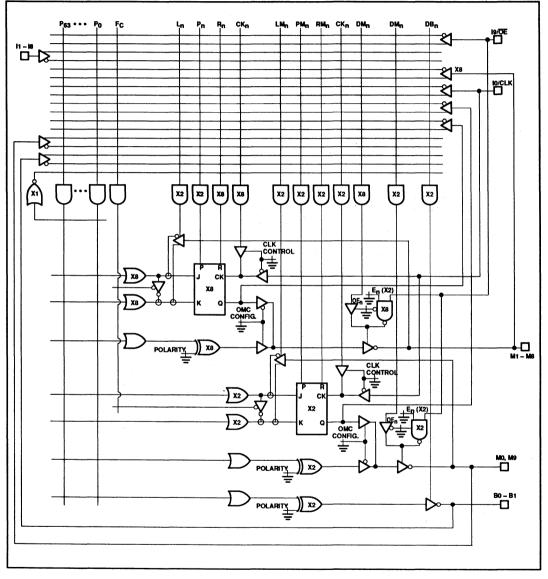

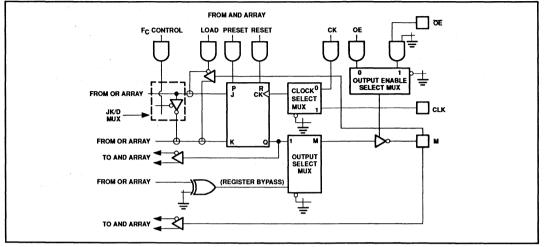

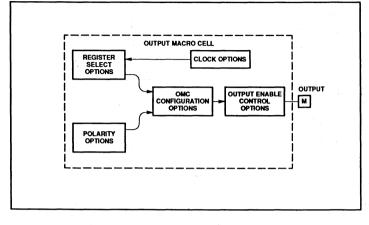

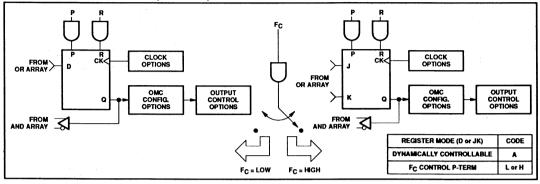

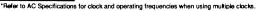

The PLUS405, PLUS105 and PLC42VA12 represent significant increases in complexity when compared to the combinatorial logic devices previously discussed. By combining the AND/OR combinatorial logic with clock output flip-flops and appropriate feedback, Signetics has created the first family of totally flexible sequential logic machines.

The PLUS405 (Programmable Logic Sequencer) is an example of a high-order machine whose applications are many. Application areas for this device include VRAM, DRAM, Bus and LAN control. The PLUS405 is fully capable of performing fast sequential operations in relatively high-speed processor systems. By placing repetitive sequential operations on the PLUS405, processor overhead is reduced.

The following pages summarize the PLUS405 architecture and features.

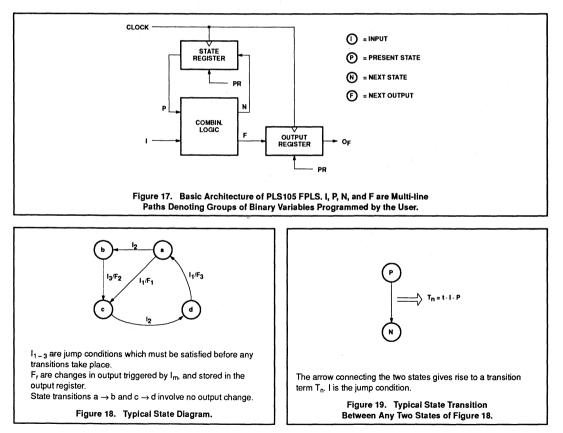

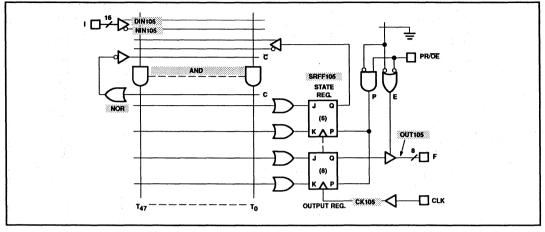

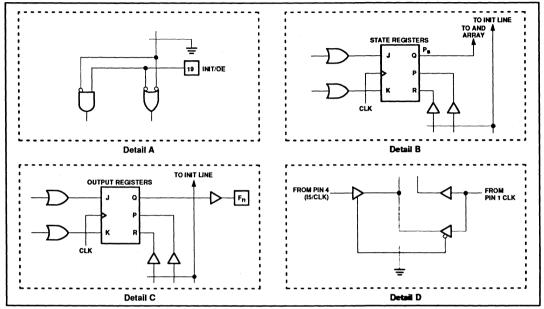

#### Sequencer Architecture

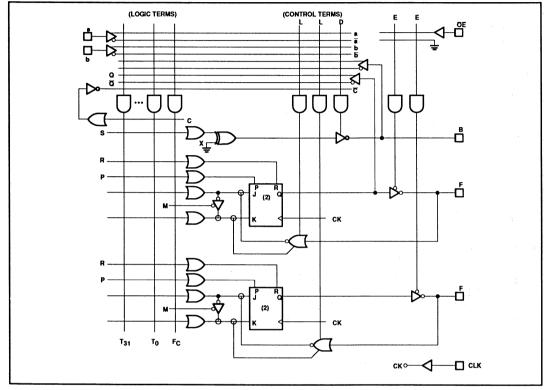

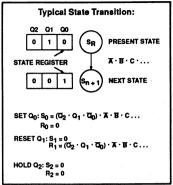

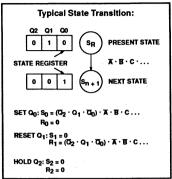

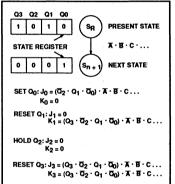

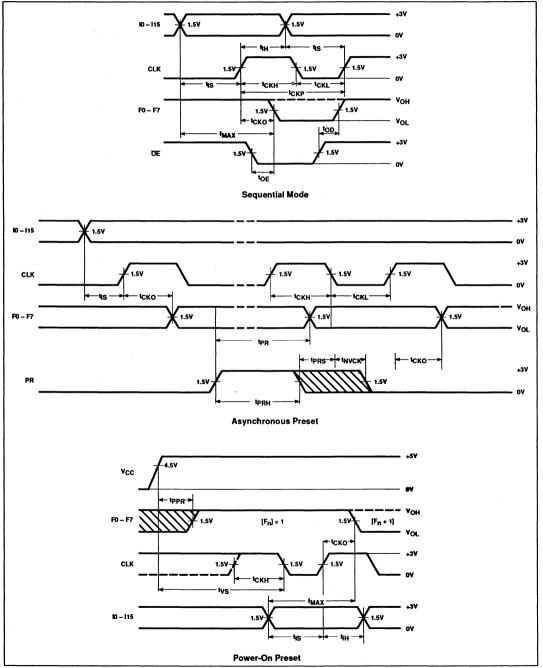

The PLUS405 Logic Sequencer is a programmable state machine, in which the output is a function of the present state and the present input.

With the PLUS405, a user can program any logic sequence expressed as a series of jumps between stable states, triggered by a valid input condition (I) at clock time (t). All stable states are stored in the State Register. The logic output of the machine is also

programmable, and is stored in the Output Register. The PLUS105 is a subset of the PLUS405.

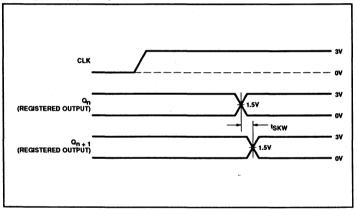

#### **Clocked Sequence**

A synchronous logic sequence can be represented as a group of circles interconnected with arrows. The circles represent stable states, labeled with an arbitrary numerical code (binary, hex, etc.) corresponding to discrete states of a suitable register. The arrows represent state transitions, labeled with symbols denoting the jump condition and the required **change** in output. The number of states in the sequence depends on the length and complexity of the desired algorithm.

## Introduction

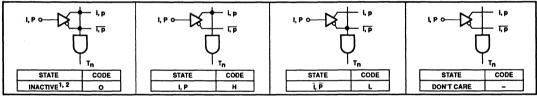

#### State Jumps

The state from which a jump originates is referred to as the Present state (P), and the state to which a jump terminates is defined as the Next state (N). A state jump always causes a change in state, but may or may not cause a change in machine output (F).

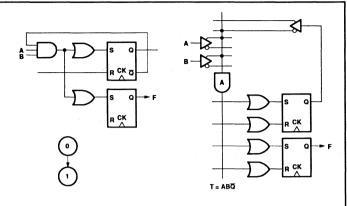

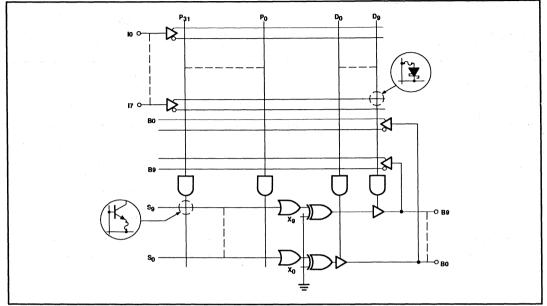

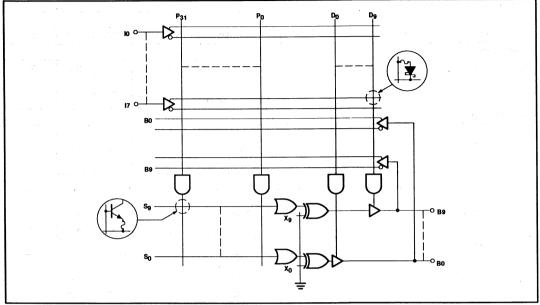

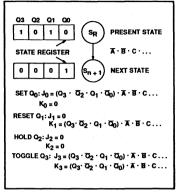

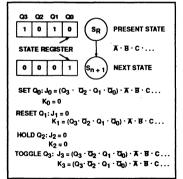

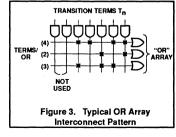

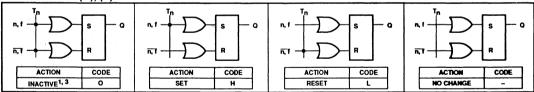

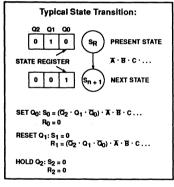

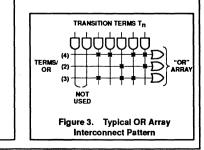

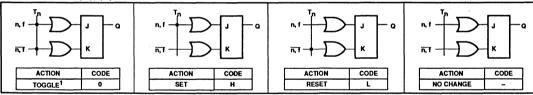

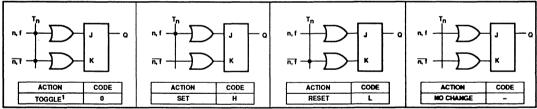

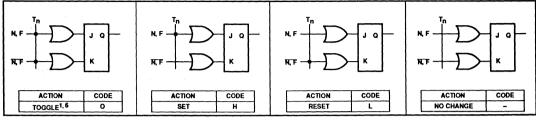

State jumps can occur only via "transition terms"  $T_n$ . These are logical AND functions of the clock (t), the Present state (P), and a valid input (I). Since the clock is actually applied to the State Register,  $T_n = I \cdot P$ . When  $T_n$  is "true", a control signal is generated and used at clock time (t) to force the contents of the State Register from (P) to (N), and to change the contents of the Output Register (if necessary). The simple state jump in Figure 20, involving 2 inputs, 1 state bit, and 1 output bit, illustrates the equivalence of discrete and programmable logic implementations.

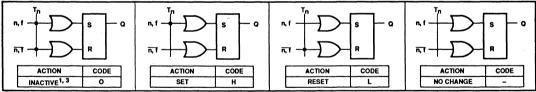

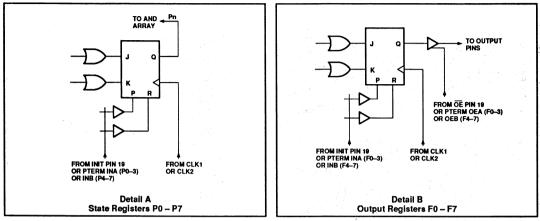

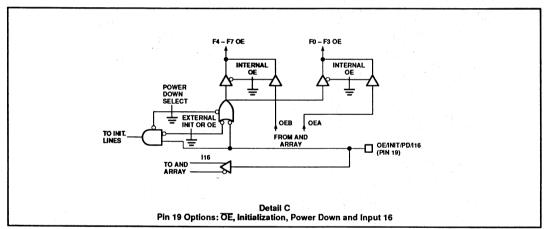

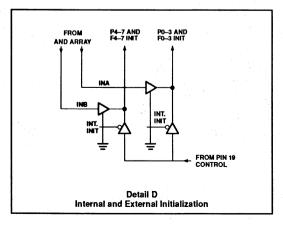

#### Sequencer Logic Structure

The Sequencer consists of programmable AND and OR gate arrays which control the Set and Reset inputs of a State Register, as well as monitor its output via an internal feedback path. The arrays also control an independent Output Register, added to store output commands generated during state transitions, and to hold the output constant during state sequences involving no output changes. If desired, any number of bits of the Output Register can be used to extend the width of the State Register, via external feedback.

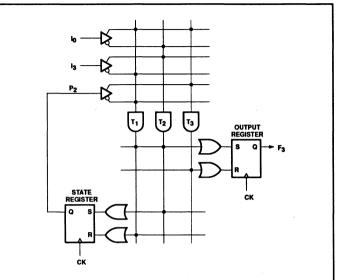

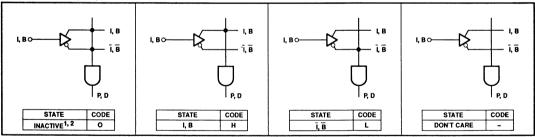

Figure 20. Typical State Jump From State (0) to State (1), if Inputs A = B = "1". The Jump Also Forces F = "1", as Required.

## Introduction

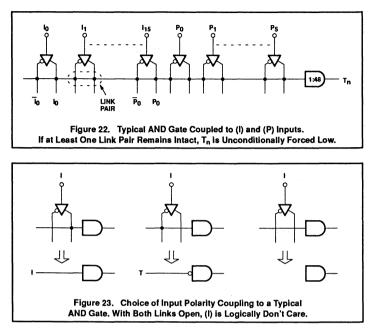

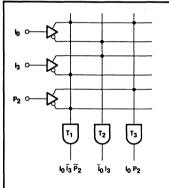

Figure 24. Typical Transition Terms Involving Arbitrary Inputs and State Variables. All Remaining Gate Inputs Are Programmed Don't Care. Note That T<sub>2</sub> Output is State Independent.

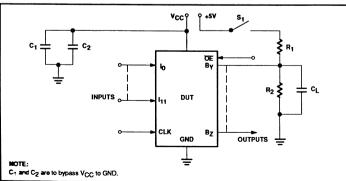

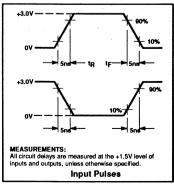

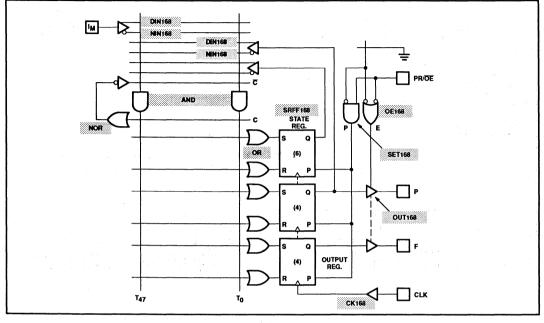

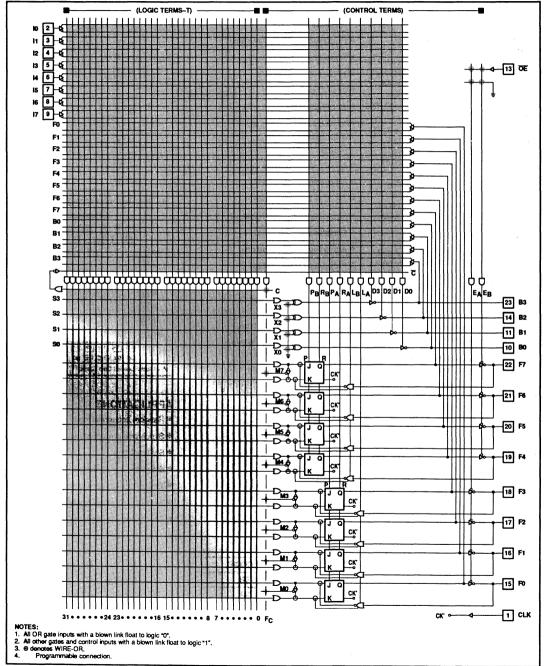

#### Input Buffers

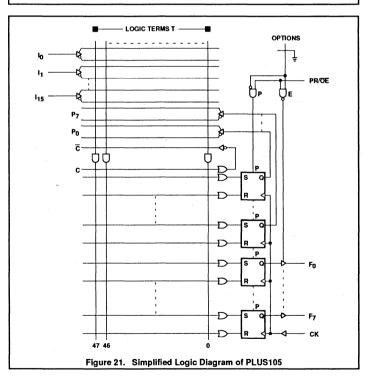

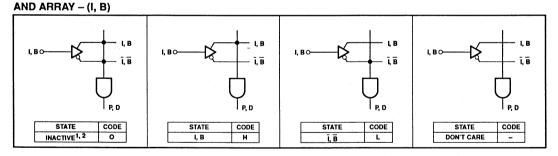

16 external inputs  $(I_m)$  and 6 internal inputs  $(P_s)$ , fed back from the State Register, are combined in the AND array through two sets of True/Complement (T/C) buffers. There are a total of 22 T/C buffers, all connected to multi-input AND gates via fusible links which are initially intact.

Selective fusing of these links allows coupling either True, Complement, or Don't Care values of  $(I_m)$  and  $(P_s)$ .

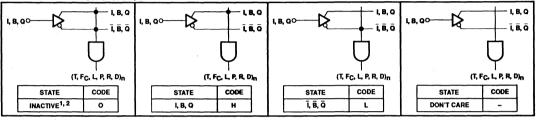

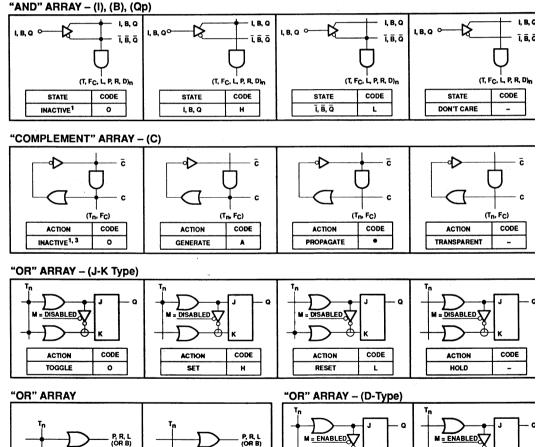

#### "AND" Array

State jumps and output changes are triggered at clock time by valid transition terms  $T_n$ . These are logical AND functions of the present state (P) and the present input (I).

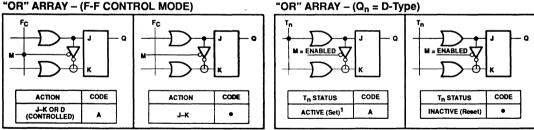

The PLUS105 AND Array contains a total of 48 AND gates. Each gate has 45 inputs – 44 connected to 22 T/C input buffers, and 1 dedicated to the Complement Array. The outputs of all AND gates are propagated through the OR Array, and used at clock time (t) to force the contents of the State Register from (P) to (N). they are also used to control the Output Register, so that the FPLS 8-bit output F<sub>r</sub> is a function of the inputs and the present state. The PLUS405 contains 64 AND gates in its' AND array.

## Introduction

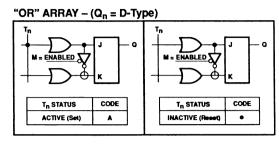

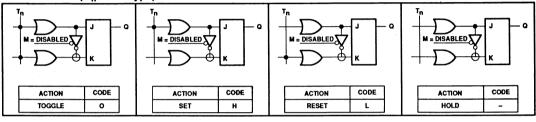

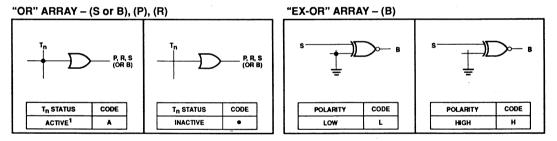

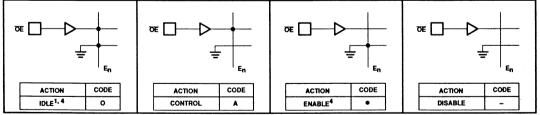

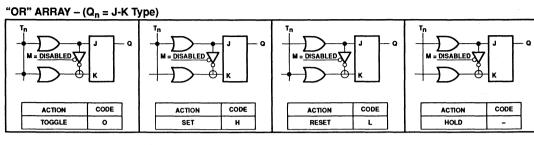

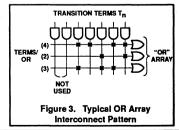

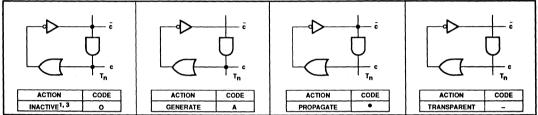

#### "OR" Array

In general, a clocked sequence will consist of several stable states and transitions, as determined by the complexity of the desired algorithm. All state and output changes in the state diagram imply changes in the contents of State and Output Registers.

Thus, each flip-flop in both registers may need to be conditionally set or reset several times with  $T_n$  commands. This is accomplished by selectively ORing through a programmable OR Array all AND gate outputs  $T_n$  necessary to activate the proper flip-flop control inputs.

The PLUS105 OR Array consists of 14 pairs of OR gates, controlling the S/R inputs of 14 State and Output Register stages, and a single NOR gate for the Complement Array. All gates have 48 inputs for connecting to all 48 AND gates. The PLUS405 uses 64 input gates.

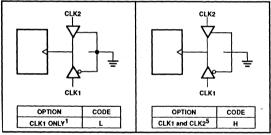

The PLUS405 contains 16 pairs of OR gates controlling state transitions and output stages and two additional NOR gates for dual complement arrays.

## Introduction

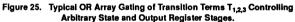

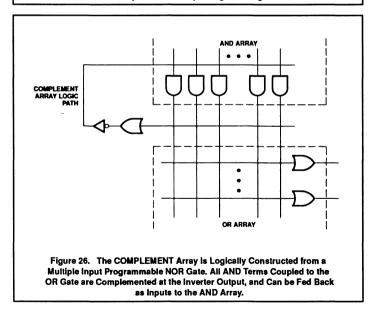

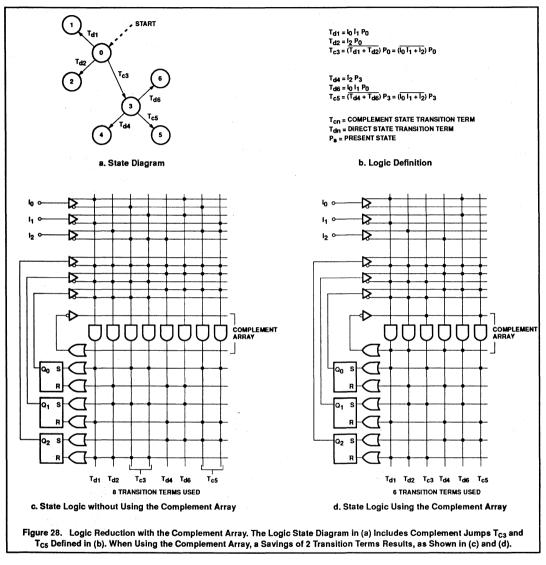

b. Note that the Complementary Logic Expression for  $T_3$ ,  $T_1 + T_2$ , Corresponds Exactly to the Logic Structure of the Complement Array.

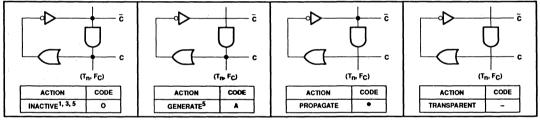

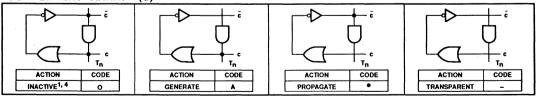

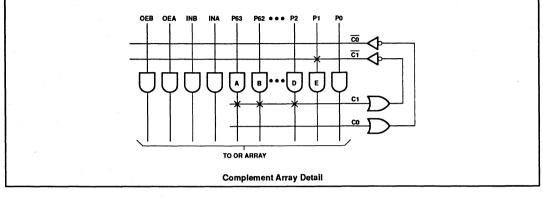

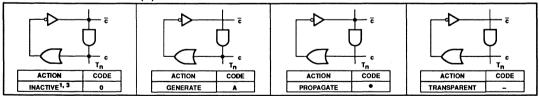

#### **Complement Array**

The COMPLEMENT Array provides an asynchronous feedback path from the OR Array back to the AND Array.

This structure enables the sequencer to perform both direct and complement sequential state jumps with a minimum of transition (AND) terms,

Typically direct jumps, such as  $T_1$  and  $T_2$  in Figure 27 require only a single AND gate each.

But a complement jump such as  $T_3$  generally requires many AND gates if implemented as a direct jump. However, by using the Complement Array, the logic requirements for this type of jump can be handled with just one more gate from the AND Array. Because it can be split into separate machines (2 clocks), the PLUS405 incorporates two COMPLEMENT Arrays. As indicated in Figure 28, the single Complement Array gate may be used for many states of the state diagram. This happens because all transition terms linked to the OR gate include the present state as a part of their conditional logic. In any particular state, only those transition terms which are a function of that state are enabled; all other terms coupled to different states are disabled and do not influence the output of the Complement Array. As a general rule of thumb, the Complement Array can be used as many times as there are states.

## Introduction

Additional features are available depending on a specific part. In particular, the PLC42VA12 has everything mentioned here, and more. More details on PLAs, PAL devices and Sequencers can be found in the application section later in the manual.

Programmable Macro Logic, Signetics very high density logic is fully described in detail in its own section.

#### SUMMARY

The Signetics Company was founded in September, 1961 by a group of scientists and engineers who were among the pioneers in the development of integrated circuits. Signetics, acquired by Philips in 1975, was the first company in the world to be established for the sole purpose of designing, developing, manufacturing, and marketing ICs. Philips celebrated its 100th anniversary in 1991. On 1st January 1991, the Integrated Circuits and Discrete Semiconductor Business Units, formerly part of Philips Components, were merged into an autonomous product division (PD)-Philips Semiconductors as part of a major reorganization to focus Philips' semiconductor activities and to strengthen its standing in selected strategic markets. At the heart of this reorganization comes quality.

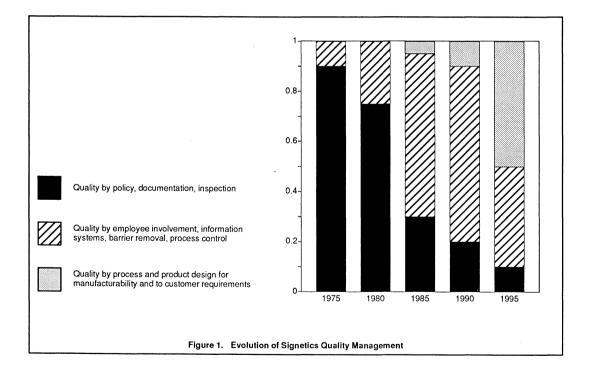

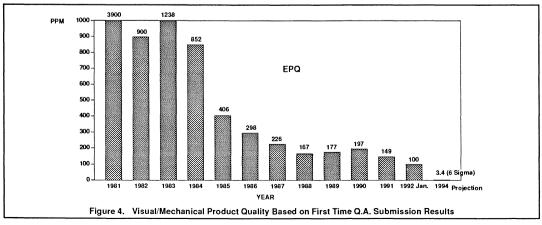

The Signetics approach to Quality Management has evolved with each evolution building upon the foundation laid. The emphasis in the 1960s and 1970s was quality by policy, documentation, and inspection. The emphasis in the 1980s was guality by employee involvement and process control. In the 1990s quality is achieved by emphasizing process and product Design For Manufacturability (DFM) and to customer requirements. (See Figure 1.) To ensure transformation, a formal Design Development Process (DDP) exists which requires the utilization of Cross-Functional Teams (CFTs) to assure that the customer Dimensions of Performance are met.

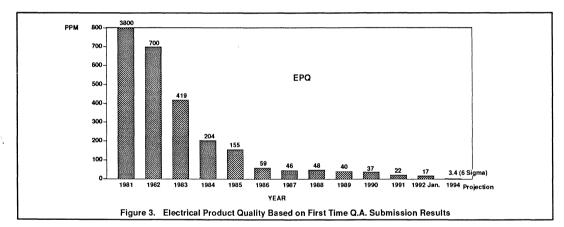

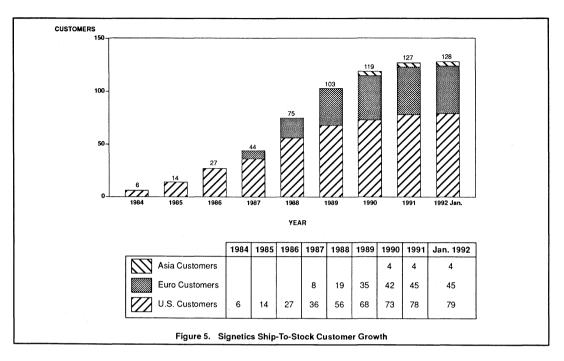

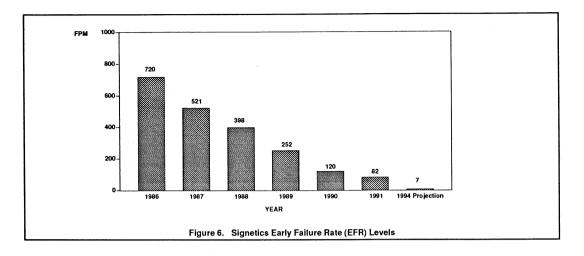

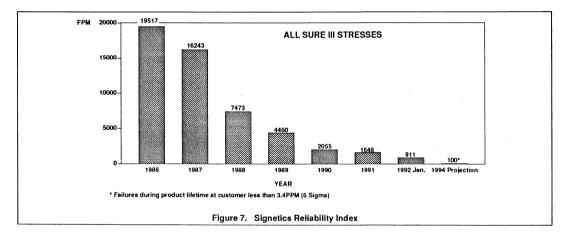

The modern Signetics Quality Journey (see Table 1) began in 1980. During the ensuing decade it achieved a 90-fold improvement in product electrical quality, 30-fold improvement in product visual and mechanical quality and a 20-fold improvement in product reliability. The great reduction in defect levels and a continued commitment to our customers made possible the following industry firsts:

- Ship-To-Stock Program

- Self-Qualification Program

- · Zero Defects Warranty Policy

The Journey never ends—Signetics continues to strive for **EXCELLENCE** in all aspects of our business through company focus and initiatives aimed at achieving three performance level goals in 1994:

- · Industry Leader in Customer Satisfaction

- With Products of Six Sigma Quality and Reliability

- And World Class Responsiveness to Customer Needs and Wants.

#### SIGNETICS' QUALITY IMPROVEMENT PROCESS

In 1979, Signetics recognized that quality was becoming a major competitive issue, not only in the semiconductor business but also in other industries. Increases in the volume of products imported from the Far East (steel, automobiles, and consumer products) sent strong signals that new competitive forces were at work.

An investigation into a variety of quality programs was started. The company realized that quality improvement would require a contribution from all employees. Management commitment and participation, however, was recognized as the primary prerequisite for this program to work successfully. Resources required for the resolution of defects were under management control.

The "Signetics Quality Journey" from 1980 into the decade of the '90s is summarized in Table 1. In 1980 a program was developed which focused on quality management. Rearranging previous quality control philosophies, we developed a decentralized. distributed quality organization and simultaneously installed a Quality Improvement Process (QIP) based on the 14-Step improvement program advocated by Phil Crosby. The process was formally begun company-wide in 1981. Since then substantial progress has been made in every aspect of our operations. From incoming raw material conformance to improvements in clerical errors - every department and individual is involved and striving for Zero Defects. Zero Accept sampling plans and Zero Defects warranties are evidence of our ongoing commitment to and progress in quality. The Crosby 14 steps evolved into 9 elements as the foundation of the QIP. The QIP continued to expand, including more processes and disciplines as Signetics' vision cleared.

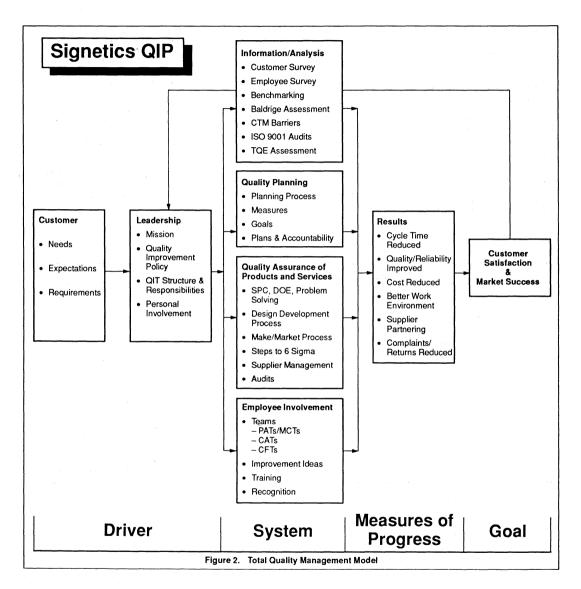

Today the Total Quality Management (TQM) model is applied to the QIP, as illustrated in Figure 2, having a far-reaching impact on all aspects of our business. The customer is at the start (driver) and end (goal) of the TQM model which requires a driver, system, measures and goal. The customer is the primary driver. Leadership is provided by Quality Improvement Teams (QITs) which ensure that customer interaction occurs and that the organization supports the mission, QI policy and customer direction. TQM requires a clear set of management principles which mandate systems and measurements consistent with stated objectives. TQM endorses and utilizes the seven major examination categories of the U.S.A. Malcolm Baldrige National Quality Award. Together, the examination categories address all major components of an integrated, prevention based system built around continuous improvement and customer satisfaction.

#### ZERO DEFECTS WARRANTY

In the '80s, American industry demanded increased product quality of its IC suppliers in order to meet growing international competitive pressure. As a result of this quality focus, it became clear that what once was thought to be unattainable— Zero Defects— is, in fact, achievable.

Signetics offers a Zero Defects Warranty which states that we will take back an entire lot if a single defective part is found. This precedent setting warranty implemented in 1985 effectively ended the IC industry's "war of the AQLs" (Acceptable Quality Levels). The ongoing efforts of IC suppliers to reduce PPM (Parts Per Million) defect levels is now a competitive customer service measure. This intense commitment to quality provides an advantage to today's electronics OEM. That advantage can be summed up in four words: *Reduced Cost of Ownership.*

As IC customers look beyond purchase price to the total cost of doing business with a supplier, it is apparent that a quality-conscious supplier represents a viable cost reduction resource. Consistent high-quality circuits reduce requirements for expensive test equipment and personnel, and allow for smaller inventories, less rework, and fewer field failures. Programs such as Self Qualification and Ship-To-Stock implemented in 1984 and Cycle Time Management (CTM) implemented in 1989 help reduce cost of ownership.

#### STATISTICAL PROCESS CONTROL (SPC)

Although application of statistics in our process development and manufacturing activities goes back to the early 1970's, the corporate-wide emphasis on Statistical Process Control (SPC) did not come until mid-1984.

A natural evolution of our quality improvement process made introduction of SPC and other related programs an inevitable event. SPC was, therefore, introduced under the QIP umbrella. The Crosby definition of Quality, "Conformance To Requirements (Specification)" was expanded to include "Conformance To Specified Targets". The measurement definition of "continuous improvement" was expanded to include "Continuous Reduction of Variability Around the Specified Target".

The objective of SPC is to institutionalize a systematic and scientific approach to business and manufacturing activities. This approach utilizes sound statistical theory. Managers are expected to be able to turn data into information and to make decisions solely on data (not perception).

The most critical and challenging aspect of implementing SPC is the establishment of a discipline within the operating areas so that decision making is fundamentally based on verifiable data and so that actions are documented. The other is the realization that statistical tools merely point out the problems but are not themselves solutions. The burden of action on the process is still on the shoulders of the person that implemented it. In order to implement SPC effectively, three steps are continually followed:

- 1. Documenting and understanding the process and using process flow charts and component diagrams.

- Establishing data collection systems and using SPC tools to identify process problems and opportunities for improvement.

- 3. Acting on the process and establishing guidelines to monitor and maintain process control.

#### Repeating steps 1-3 again.

These fundamentals are the basis of establishing specifications and operating philosophy with respect to SPC. The management of SPC, be it policy, function deployment or ongoing continuous improvement is accomplished in a systematic way by following the four step Plan, Do, Check, Act – PDCA/Shewart/Deming Cycles of Learning.

| F<br>O<br>C<br>U<br>S<br>S<br>S<br>UPPLIER         | Raw Material<br>Quality     Product Quality     Individual<br>Responsibility for<br>Quality     No Waiver Policy     Audits                                             | Supplier<br>Partnerships     Manufacturing<br>Excellence     Recognition                                                                         | Customer<br>Partnerships     In-process Quality<br>Control     Product Reliability     SPC                                                     | Cross Functional<br>Operation     Better<br>Management<br>Practices     Cycle Time<br>Management     Measurement-<br>TORDC                                                                                     | <ul> <li>Customer Driven</li> <li>Design Quality</li> <li>Involve Everyone</li> <li>Competitive &amp;<br/>Functional<br/>Benchmarks</li> <li>Cycle Time<br/>Management</li> </ul>                                                                                              |

|----------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| I                                                  | Certification     Program                                                                                                                                               | • Ship-to-Stock<br>(STS)                                                                                                                         | Implementation                                                                                                                                 | Supplier Teams                                                                                                                                                                                                 | Broaden to<br>Equipment &<br>Service                                                                                                                                                                                                                                           |

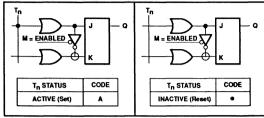

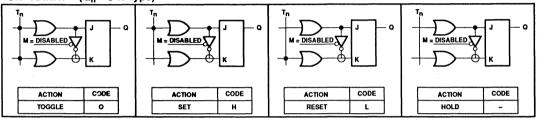

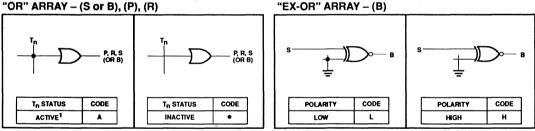

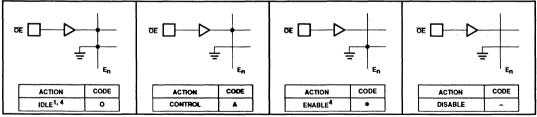

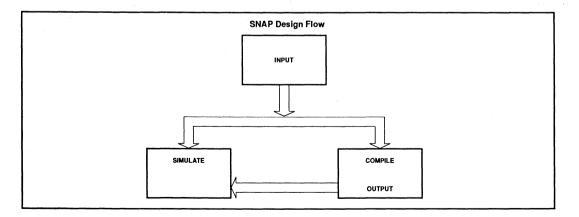

| N<br>I<br>T<br>A INTERNAL<br>T<br>I<br>V<br>E<br>S | <ul> <li>Decentralized Q &amp;<br/>R Function</li> <li>Crosby 14 Steps &amp;<br/>Absolutes</li> <li>33 QITs Formed</li> <li>All Employees<br/>Sign ZD Pledge</li> </ul> | <ul> <li>JIT Manufacturing</li> <li>Zero Accept<br/>Sampling Plans</li> <li>Repeat 14 Steps</li> </ul>                                           | <ul> <li>SPC Introduction</li> <li>Early Failure C/A<br/>Program</li> <li>14 Steps to 9<br/>Elements</li> <li>Customer<br/>Workshop</li> </ul> | <ul> <li>Design<br/>Development<br/>Cycle Time<br/>Reduction</li> <li>Make Market<br/>Cycle Time<br/>Reduction</li> <li>Inventory<br/>Reduction</li> <li>Baldrige<br/>Assessment &amp;<br/>Planning</li> </ul> | <ul> <li>6 Sigma Strategy</li> <li>Responsiveness<br/>Strategy</li> <li>Benchmarking <ul> <li>Design<br/>Methodology</li> <li>Mfg. Excellence</li> <li>Quality &amp; Service</li> </ul> </li> <li>QIP Audits</li> <li>ISO 9001<br/>Certification</li> <li>TQE Award</li> </ul> |