PHILIPS

Microprocessors and peripherals

# PHILIPS

## Data handbook

Electronic components and materials

## Integrated circuits

Book IC18 1987

## Microprocessors and peripherals

### MICROPROCESSORS AND PERIPHERALS

| Contents                                                                                                                | xiii |

|-------------------------------------------------------------------------------------------------------------------------|------|

| Section1 – Quality and Reliability<br>Quality and Reliability                                                           | 1.3  |

| Section 2 Microprocessor Products Index                                                                                 | 2.1  |

| Section 3 – Microcontroller Products<br>Not included in this book; for data see book "Microcontrollers and peripherals" |      |

| Section 4 — Package outlines Index                                                                                      | 4.1  |

| Section 5 – Alphanumeric Index<br>Alphanumeric Index                                                                    | 5.3  |

Signetics reserves the right to make changes, without notice, in the products, including circuits, standard cells, and/or software, described or contained herein in order to improve design and/or performance. Signetics assumes no responsibility or liability for the use of any of these products, conveys no license or title under any patent, copyright, or mask work right to these products, and makes no representations or warranties that these products are free from patent, copyright, or mask work right infringement, unless otherwise specified. Applications that are described herein for any of these products are for illustrative purposes only. Signetics makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification.

#### LIFE SUPPORT APPLICATIONS

Signetics' Products are not designed for use in life support appliances, devices, or systems where malfunction of a Signetics Product can reasonably be expected to result in a personal injury. Signetics' customers using or selling Signetics' Products for use in such applications do so at their own risk and agree to fully indemnify Signetics for any damages resulting in such improper use or sale.

Signetics registers eligible circuits under the Semiconductor Chip Protection Act.

© Copyright 1987 Signetics Corporation

All rights reserved.

### **GENERAL CONTENTS**

Contents Ordering information Product status definitions

## Contents

### **Microprocessor Products**

| Ordering Information                            |                                                                | vii   |

|-------------------------------------------------|----------------------------------------------------------------|-------|

| Product Status                                  |                                                                | viii  |

| Section 1 – QUALITY AN<br>Quality and Reliabili | ID RELIABILITY                                                 | 1-3   |

| Section 2 - MICROPROC                           | ESSOR PRODUCTS                                                 |       |

| SCN2641                                         | Asynchronous Commmunications Interface                         | 2-3   |

| SCN2651                                         | Programmable Communications Interface (PCI)                    | 2-16  |

| SCN2652/68652                                   | Multi-Protocol Communications Controller (MPCC)                | 2-32  |

| SCN2653/68653                                   | Polynomial Generator Checker (PGC)                             | 2-52  |

| SCN2661/68661                                   | Enhanced Programmable Communications Interface (EPCI)          | 2-70  |

| SCN2671                                         | Programmable Keyboard and Communication Controller (PKCC)      | 2-87  |

| SCN2672                                         | Programmable Video Timing Controller (PVTC)                    | 2-109 |

| SCB2673                                         | Video Attributes Controller (VAC)                              | 2-132 |

| SCN2674                                         | Advanced Video Display Controller (AVDC)                       | 2-145 |

| SCB2675                                         | Color/Monochrome Attributes Controller (CMAC)                  | 2-177 |

| SCB2675T                                        | Turbo Color/Monochrome Attributes Controller (Turbo-CMAC)      | 2-188 |

| SCB2677                                         | Video Attributes Controller (VAC)                              | 2-199 |

| SCN2681                                         | Dual Asynchronous Receiver/Transmitter (DUART)                 | 2-211 |

| SCC2691                                         | Universal Asynchronous Receiver/Transmitter (UART)             | 2-230 |

| SCC2692                                         | Dual Asynchronous Receiver/Transmitter (DUART)                 | 2-247 |

| SCC2698                                         | Octal Universal Asynchronous Receiver/Transmitter (Octal UART) | 2-266 |

| SCC63484                                        | Advanced CRT Controller (ACRTC)                                | 2-285 |

| SCN68000                                        | 16-/32-Bit Microprocessor                                      | 2-340 |

| SCN68010                                        | 16-Bit Virtual Memory Microprocessor                           | 2-402 |

| SCB68154                                        | Interrupt Generator                                            | 2-471 |

| SCB68155                                        | Interrupt Handler                                              | 2-482 |

| SCB68171                                        | Very Little Serial Interface Chip (VLSIC)                      | 2-499 |

| SCB68172                                        | VMEbus Controller (BUSCON)                                     | 2-504 |

| SCC68173                                        | VMSbus Controller (VMSCON)                                     | 2-530 |

| SCB68430                                        | Direct Memory Access Interface (DMAI)                          | 2-544 |

| SCN68562                                        | Dual Universal Serial Communications Controller (DUSCC)        | 2-565 |

| SCN68681                                        | Dual Asynchronous Receiver/Transmitter (DUART)                 | 2-612 |

| SCC68692                                        | Dual Asynchronous Receiver/Transmitter (DUART)                 | 2-632 |

| Section 4 – PACKAGE O                           | UTLINES                                                        |       |

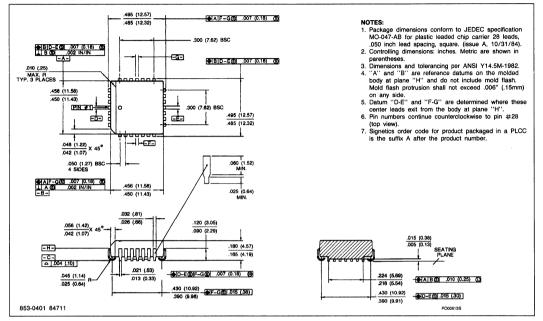

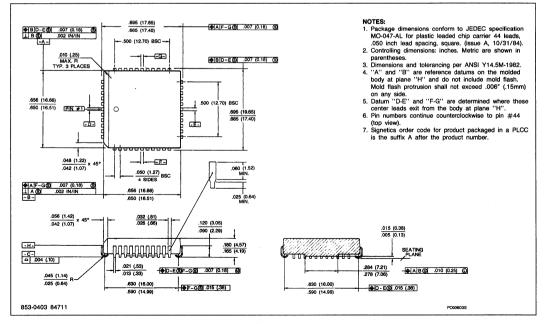

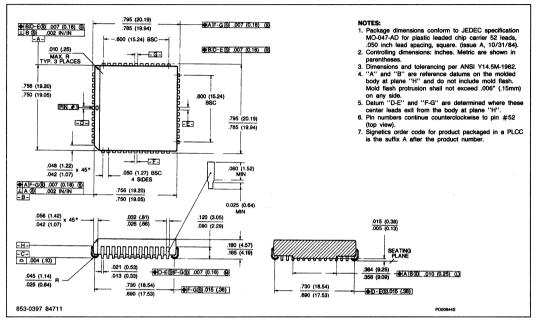

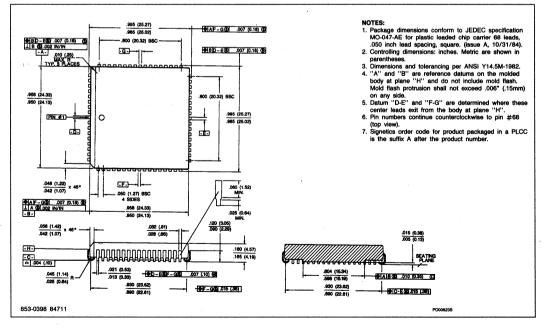

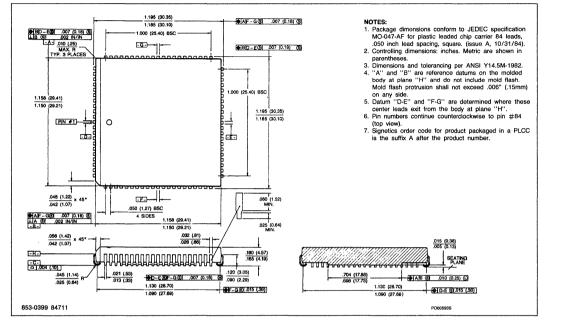

| A                                               | Plastic Leaded Chip Carrier                                    | 4-3   |

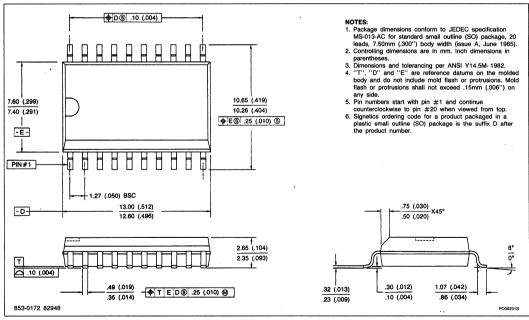

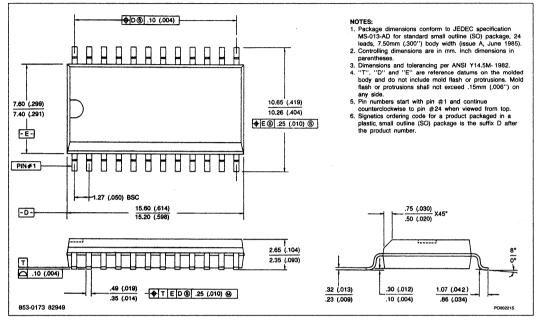

| D                                               | Plastic Small Outline                                          |       |

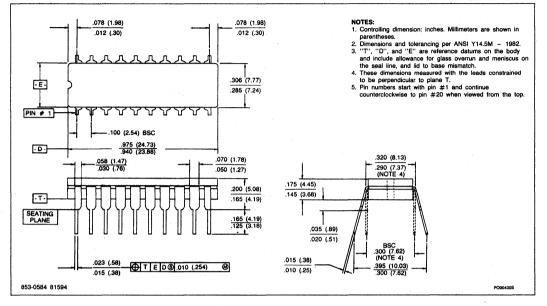

| F                                               | Hermetic CERDIP                                                |       |

| 1                                               | Hermetic SDIP                                                  |       |

| N                                               | Plastic DIP                                                    |       |

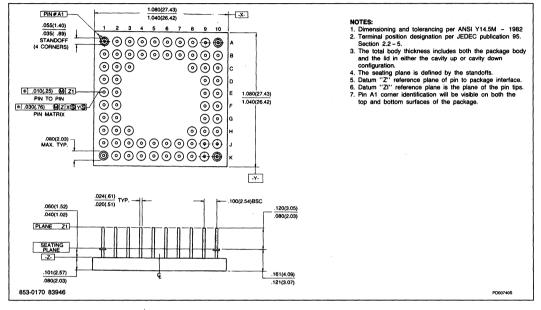

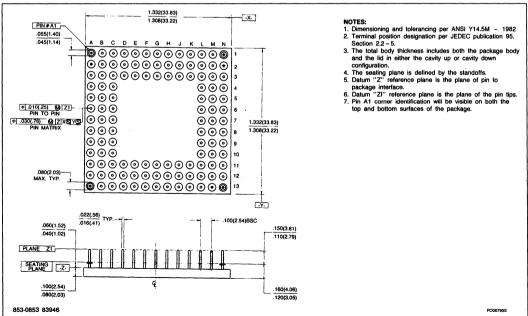

| Р                                               | Grid Array                                                     | 4-18  |

| Section 5 – ALPHANUME<br>Alphanumeric Inde      | ERIC INDEX<br>x                                                | 5-3   |

1

## Ordering Information

**Microprocessor Products**

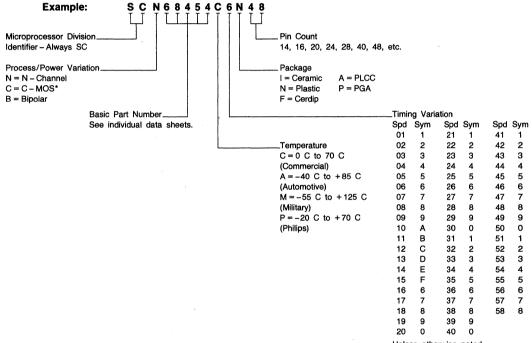

### PART NUMBERING SYSTEM

Unless otherwise noted.

#### \*CMOS designed may be part of basic part type.

Product Status

**Microprocessor Products**

| DEFINITIONS                    |                        |                                                                                                                                                                                                                                                       |  |  |  |  |  |

|--------------------------------|------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Data Sheet<br>Identification   | Product Status         | Definition                                                                                                                                                                                                                                            |  |  |  |  |  |

| <b>Objective Specification</b> | Formative or In Design | This data sheet contains the design target or goal<br>specifications for product development. Specifications may<br>change in any manner without notice.                                                                                              |  |  |  |  |  |

| Preliminary Specification      | Preproduction Product  | This data sheet contains preliminary data and supplementary<br>data will be published at a later date. Signetics reserves the<br>right to make changes at any time without notice in order to<br>improve design and supply the best possible product. |  |  |  |  |  |

| Product Specification          | Full Production        | This data sheet contains Final Specifications. Signetics<br>reserves the right to make changes at any time without<br>notice in order to improve design and supply the best<br>possible product.                                                      |  |  |  |  |  |

## Section 1 Quality and Reliability

**Microprocessor Products**

#### **Microprocessor Products**

### INTRODUCTION

The Microprocessor Division was formed in 1979 when it became apparent that microprocessor circuits and their peripheral devices would become increasingly important system components to the OEM customer base. Because of performance to cost ratios, reduced power requirements and inherent reliability, these components provide the solution to designers' complex system requirements.

NMOS became the dominant technology because of the simplicity of its design and processing and its large historical reliability data base. To date, NMOS has serviced 95% of the division's device requirements. Bipolar devices are used to a limited extent as interface drivers between the NMOS system components and CRT displays.

The Microprocessor Division serves a broad base of customers with its product lines of eight and sixteen bit microprocessors, microcontrollers, and data communication and CRT peripheral circuits. The division's customers range from large mainframe computer manufacturers to small systems users, and the division can generally satisfy all the microprocessor requirements of any customer.

Our goal is to establish ourselves as the preferred alternate source in both the 68000 microprocessor and the 80XX microcontroller product areas and at the same time become the prime supplier of the interface and peripheral circuits required to integrate the parts within a system. Our design philosophy is to give superior performance while minimizing the overall number of parts required for the overall system.

The terms quality and reliability are often misinterpreted. In general, quality refers to the condition of a device when received; reliability covers extent of useful life. Quality is readily measurable; reliability is predictable and verifiable based on historical evidence.

## Quality and Reliability

### MICROPROCESSOR DIVISION RELIABILITY

No amount of stress testing can improve a product's reliability. Stress tests are used to measure and define an end of life which can be expected from a family of products. Reliability as well as quality must be built in through proper design, processing, assembly, testing and handling. For Signetics' Microprocessor Division parts, accelerated life test data show an extremely reliable product line and serve as one input for continuous product reliability improvement.

#### DESIGN

Product quality and reliability begin in design. Strategic questions directly affecting reliability must be answered. How much static protection is required on input leads? Do formal design rules exist? Can they ever be violated? What method is used to anticipate future processes or "shrinks"?

Within Signetics' Microprocessor Division, rigid guidelines are in effect to ensure compliance with our design rules. Design rules, once established, are inviolate.

#### QUALIFICATION TESTING

Signetics' Microprocessor Division verifies device reliability through a series of qualification tests and a continuous reliability monitor program, Sure III (Systematic Uniform Reliability Evaluation).

All new fab processes at Signetics are qualified by stress testing parts from a variety of production lots. This accelerated stress testing is shown in the table.

#### SURE III

Continuous reliability monitoring is performed via our SURE III program. Devices are ran-

domly selected from production lots and subjected to the same environmental stresses noted in the table. The program is administered by the Corporate Reliability Engineering Group, which publishes a summary of results on a quarterly basis.

The SURE III program covers two functions: Monitoring short term and long term reliability performance.

### LONG-TERM AUDIT

One hundred devices from each generic family are subjected to each of the following stresses every other four weeks:

- High Temperature Operating Life T<sub>J</sub> = 150°C, 1000 hours — (Static Biased or Dynamic Operation, as appropriate);

- Temperature-Humidity Biased Life 85°C, 85% RH, 1000 hours, static biased;

- Temperature Cycling (Air-Air) -65°C to +150°C, 1000 cycles.

### SHORT-TERM MONITOR

Every week 20-piece samples from each generic family are run to 96 hours of pressure pot (15 psig, 121°C, 100% saturated steam), 300 cycles of thermal shock (-65°C to +150°C) and 168 hours of high temperature operating life ( $T_J = 150^{\circ}$ C, static or dynamic operation).

In addition, each Signetics assembly plant performs SURE product monitor stresses weekly on each generic family and molded package, by pin count and frame type. Fifty pieces are subjected to 300 cycles of thermal shock (Cond. C) and 100 devices are subjected to pressure pot stress at 20 psig for 72 hours (168 hour equivalent at 15 psig).

### Quality and Reliability

#### Accelerated Life Stress Tests

|      | TEST                             | TEST CONDITION                     | NUMBER OF<br>DEVICES | DURATION   |

|------|----------------------------------|------------------------------------|----------------------|------------|

| DHTL | Dynamic high temperature life    | T <sub>A</sub> @125°C (operating)  | 52                   | 1000 hrs   |

| SHTL | Static high temperature life     | T <sub>A</sub> @125°C (operating)  | 52                   | 1000 hrs   |

| THBS | Biased temperature humidity life | 85°C/85% RH (operating)            | 52                   | 1000 hrs   |

| PPOT | Pressure pot (autoclave)         | 121°C/15 psig (storage)            | 52                   | 96 hrs     |

| TMSK | Thermal shock                    | -55°C/125°C liq. to liq. (storage) | 77                   | 300 cycles |

| TMCL | Temperature cycle (air-to-air)   | -65°C/150°C (storage)              | 77                   | 300 cycles |

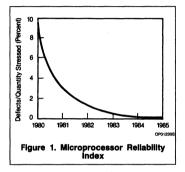

Figure 1 shows the relative improvement in Sure III performance for the Microprocessor Division for the past five years. This curve combines all the stress tests and plots the overall percentage defective by year. Clearly, the reliability of our product line is improving, and more importantly, it is consistent and predictable.

### SIGNETICS' QUALITY IMPROVEMENT PROGRAM

Signetics began its Quality Improvement Program in 1980, and developed it around the concepts outlined in the book, "Quality is Free," by Phil Crosby.

This program, which is actively supported by top management, defines Quality as "Conformance to the Specification." With this definition in mind, our performance standard is "Zero Defects." Tracking charts measuring quality improvement targets are used and displayed throughout the Division.

Microprocessor Division personnel are all actively involved in this program. Our people have taken formal training in Quality College and have pledged to ''Do It Right the First Time, On Time.'' Administrative personnel promise to ''Make Certain'' of their own work.

The program improves quality through education, commitment and feedback.

Internally, there are many signs of the program's success. The SURE III Reliability Assurance Monitor shows improved results in each of the past three years. In-line quality improvements are impressive. All new products are placed on QRA Hold until completion of environmental stress testing; all significant process changes go through qualification prior to release to production; test programs are controlled and released only after extensive engineering correlation; wafers with less than the required minimum number of good die are scrapped to avoid jeopardizing product quality.

These are examples of how the Quality Improvement Program functions internally. However, the real measure of the program is customer belief in and acceptance of our improvement.

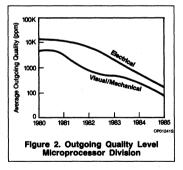

Over the past few years, customers have verified a continuous improvement in the quality and reliability of Microprocessor Division parts. Figure 2 shows the improvement in visual mechanical and electrical outgoing quality levels over the past several years. In addition to the marked improvement in our AOQ (Average Outgoing Quality), we have become a qualified source for the 80XX and the 68000 families, as well as our own proprietary peripheral circuits, for more than 200 customers. We have developed Ship-to-Stock programs for several key accounts, eliminating the need for costly incoming inspection by our customers.

The improved reliability of our parts has allowed several customers to drop their requirements for burn-in for high reliability programs. This, of course, has lowered their costs significantly and has allowed them to improve their over-all system reliability.

Reliability testing is an important monitor of our manufacturing process. Signetics' microprocessor parts not only meet specifications when shipped but continue to operate satisfactorily throughout their lifetime.

## Section 2 Microprocessor Products

**Microprocessor Products**

### INDEX

| SCN2651         Programmable Communications Interface (PCI)         2           SCN2652/68652         Multi-Protocol Communications Controller (MPCC)         2           SCN2653/68653         Polynomial Generator Checker (PGC)         2           SCN2661/68661         Enhanced Programmable Communications         2           Interface (EPCI)         2         2           SCN2661/68661         Enhanced Programmable Communications         2           SCN2671         Programmable Keyboard and Communication         2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 2-3<br>-16<br>-32<br>-52<br>-70<br>-87 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| SCN2652/68652       Multi-Protocol Communications Controller (MPCC)       2-         SCN2653/68653       Polynomial Generator Checker (PGC)       2-         SCN2661/68661       Enhanced Programmable Communications       2-         Interface (EPCI)       2-         SCN2671       Programmable Keyboard and Communication       2-         SCN2673       Video Attributes Controller (PVTC)       2-1         SCN2674       Advanced Video Display Controller (AVDC)       2-1         SCN2675       Color/Monochrome Attributes Controller (CMAC)       2-1         SCB2675       Turbo Color/Monochrome Attributes Controller (CMAC)       2-1         SCB2677       Video Attributes Controller (VAC)       2-1         SCB2675       Color/Monochrome Attributes Controller (CMAC)       2-1         SCB2677       Video Attributes Controller (VAC)       2-1         SCB2677       Video Attributes Controller (VAC)       2-1         SCB2671       Dual Asynchronous Receiver/Transmitter (DUART)       2-2 | -32<br>-52<br>-70<br>-87               |

| SCN2653/68653       Polynomial Generator Checker (PGC)       2         SCN2661/68661       Enhanced Programmable Communications       2         SCN2671       Programmable Keyboard and Communication       2         SCN2672       Programmable Keyboard and Communication       2         SCN2673       Video Attributes Controller (PVTC)       2-1         SCN2674       Advanced Video Display Controller (AVDC)       2-1         SCB2675       Color/Monochrome Attributes Controller (CMAC)       2-1         SCB26757       Video Attributes Controller (VAC)       2-1         SCB2675       Dual Asynchronous Receiver/Transmitter (DUART)       2-2                                                                                                                                                                                                                                                                                                                                                          | -52<br>-70<br>-87                      |

| SCN2661/68661       Enhanced Programmable Communications<br>Interface (EPCI)       2         SCN2671       Programmable Keyboard and Communication<br>Controller (PKCC)       2         SCN2672       Programmable Video Timing Controller (PVTC)       2         SCB2673       Video Attributes Controller (VAC)       2         SCN2674       Advanced Video Display Controller (AVDC)       2         SCB2675       Color/Monochrome Attributes Controller (CMAC)       2         SCB2675       Turbo Color/Monochrome Attributes Controller (Turbo-CMAC)       2         SCB2677       Video Attributes Controller (VAC)       2         SCB2671       Dual Asynchronous Receiver/Transmitter (DUART)       2                                                                                                                                                                                                                                                                                                        | -70                                    |

| Interface (EPCI)       2         SCN2671       Programmable Keyboard and Communication<br>Controller (PKCC)       2         SCN2672       Programmable Video Timing Controller (PVTC)       2-1         SCB2673       Video Attributes Controller (VAC)       2-1         SCN2674       Advanced Video Display Controller (AVDC)       2-1         SCB2675       Color/Monochrome Attributes Controller (CMAC)       2-1         SCB2675       Turbo Color/Monochrome Attributes Controller (CMAC)       2-1         SCB2677       Video Attributes Controller (VAC)       2-1         SCN2681       Dual Asynchronous Receiver/Transmitter (DUART)       2-2                                                                                                                                                                                                                                                                                                                                                            | -87                                    |

| SCN2671         Programmable Keyboard and Communication<br>Controller (PKCC)         2           SCN2672         Programmable Video Timing Controller (PVTC)         2-1           SCB2673         Video Attributes Controller (VAC)         2-1           SCN2674         Advanced Video Display Controller (AVDC)         2-1           SCB2675         Color/Monochrome Attributes Controller (CMAC)         2-1           SCB2675         Turbo Color/Monochrome Attributes Controller (Turbo-CMAC)         2-1           SCB2677         Video Attributes Controller (VAC)         2-1           SCB2671         Dual Asynchronous Receiver/Transmitter (DUART)         2-2                                                                                                                                                                                                                                                                                                                                         | -87                                    |

| Controller (PKCC)         2           SCN2672         Programmable Video Timing Controller (PVTC)         2-1           SCB2673         Video Attributes Controller (VAC)         2-1           SCN2674         Advanced Video Display Controller (AVDC)         2-1           SCB2675         Color/Monochrome Attributes Controller (CMAC)         2-1           SCB2675         Turbo Color/Monochrome Attributes Controller (CMAC)         2-1           SCB2677         Video Attributes Controller (VAC)         2-1           SCB2681         Dual Asynchronous Receiver/Transmitter (DUART)         2-2                                                                                                                                                                                                                                                                                                                                                                                                          |                                        |

| SCN2672         Programmable Video Timing Controller (PVTC)         2-1           SCB2673         Video Attributes Controller (VAC)         2-1           SCN2674         Advanced Video Display Controller (AVDC)         2-1           SCB2675         Color/Monochrome Attributes Controller (CMAC)         2-1           SCB2675T         Turbo Color/Monochrome Attributes Controller (Turbo-CMAC)         2-1           SCB2677         Video Attributes Controller (VAC)         2-1           SCN2681         Dual Asynchronous Receiver/Transmitter (DUART)         2-2                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                        |

| SCB2673       Video Attributes Controller (VAC)       2-1         SCN2674       Advanced Video Display Controller (AVDC)       2-1         SCB2675       Color/Monochrome Attributes Controller (CMAC)       2-1         SCB2675T       Turbo Color/Monochrome Attributes Controller (Turbo-CMAC)       2-1         SCB2677       Video Attributes Controller (VAC)       2-1         SCN2681       Dual Asynchronous Receiver/Transmitter (DUART)       2-2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 100                                    |

| SCB2673       Video Attributes Controller (VAC)       2-1         SCN2674       Advanced Video Display Controller (AVDC)       2-1         SCB2675       Color/Monochrome Attributes Controller (CMAC)       2-1         SCB2675T       Turbo Color/Monochrome Attributes Controller (Turbo-CMAC)       2-1         SCB2677       Video Attributes Controller (VAC)       2-1         SCN2681       Dual Asynchronous Receiver/Transmitter (DUART)       2-2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 108                                    |

| SCB2675         Color/Monochrome Attributes Controller (CMAC)         2-1           SCB2675T         Turbo Color/Monochrome Attributes Controller (Turbo-CMAC)         2-1           SCB2677         Video Attributes Controller (VAC)         2-1           SCN2681         Dual Asynchronous Receiver/Transmitter (DUART)         2-2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                        |

| SCB2675T         Turbo Color/Monochrome Attributes Controller (Turbo-CMAC)2-1           SCB2677         Video Attributes Controller (VAC)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 145                                    |

| SCB2677         Video Attributes Controller (VAC)         2-1           SCN2681         Dual Asynchronous Receiver/Transmitter (DUART)         2-2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 177                                    |

| SCN2681 Dual Asynchronous Receiver/Transmitter (DUART) 2-2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 188                                    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 199                                    |

| SCC2691 Universal Asynchronous Receiver/Transmitter (UART) 2-2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 211                                    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 230                                    |

| SCC2692 Dual Asynchronous Receiver/Transmitter (DUART) 2-2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 247                                    |

| SCC2698 Octal Universal Asynchronous Receiver/Transmitter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                        |

| (Octal UART) 2-2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 266                                    |

| SCC63484 Advanced CRT Controller (ACRTC) 2-2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 285                                    |

| SCN68000 16-/32-Bit Microprocessor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 340                                    |

| SCN68010 16-Bit Virtual Memory Microprocessor 2-4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 102                                    |

| SCB68154 Interrupt Generator 2-4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | \$71                                   |

| SCB68155 Interrupt Handler 2-4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 182                                    |

| SCB68171 Very Little Serial Interface Chip (VLSIC) 2-4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 199                                    |

| SCB68172 VMEbus Controller (BUSCON) 2-5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 504                                    |

| SCC68173 VMSbus Controller (VMSCON) 2-5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 530                                    |

| SCB68430 Direct Memory Access Interface (DMAI) 2-5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 544                                    |

| SCN68562 Dual Universal Serial Communications Controller (DUSCC) 2-5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 565                                    |

| SCN68681 Dual Asynchronous Receiver/Transmitter (DUART) 2-6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 312                                    |

| SCC68692 Dual Asynchronous Receiver/Transmitter (DUART) 2-6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                        |

### **Microprocessor Products**

### DESCRIPTION

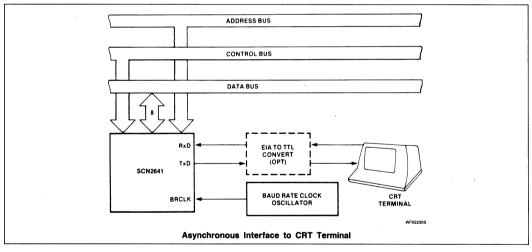

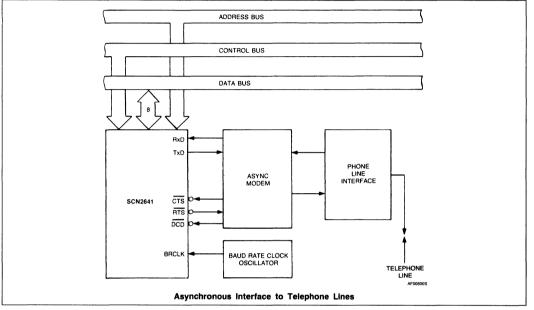

The Signetics SCN2641 is a universal asynchronous data communications controller chip that interfaces directly to most 8-bit microprocessors and may be used in a polled or interrupt-driven system environment. The SCN2641 accepts programmed instructions from the microprocessor while supporting asynchronous serial data communications in full- or half-duplex mode.

The SCN2641 serializes parallel data characters received from the microprocessor for transmission. Simultaneously, it can receive serial data and convert it into parallel data characters for input to the microcomputer.

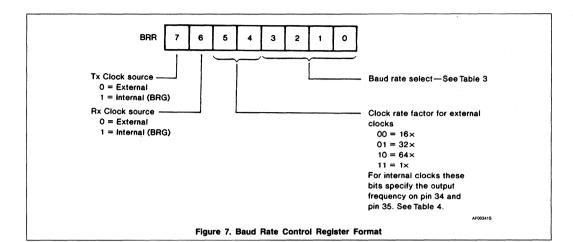

The SCN2641 contains a baud rate generator which can be programmed to either accept an external clock or to generate internal transmit or receive clocks. Sixteen different baud rates can be selected under program control when operating in the internal clock mode.

The SCN2641 is constructed using Signetics n-channel silicon gate depletion load technology and is packaged in a 24-pin DIP.

## SCN2641 Asynchronous Communications Interface

**Product Specification**

### FEATURES

- 5- to 8-bit characters plus parity

- 1, 1<sup>1</sup>/<sub>2</sub> or 2 stop bits transmitted

- · Odd, even or no parity

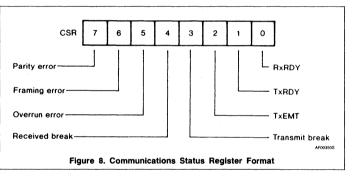

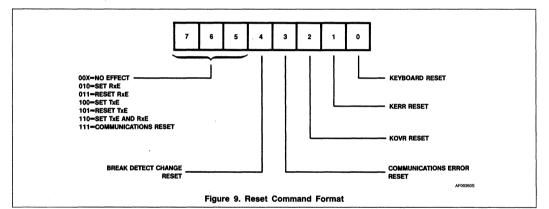

- Parity, overrun and framing error detection

- Line break detection and generation

- False start bit detection

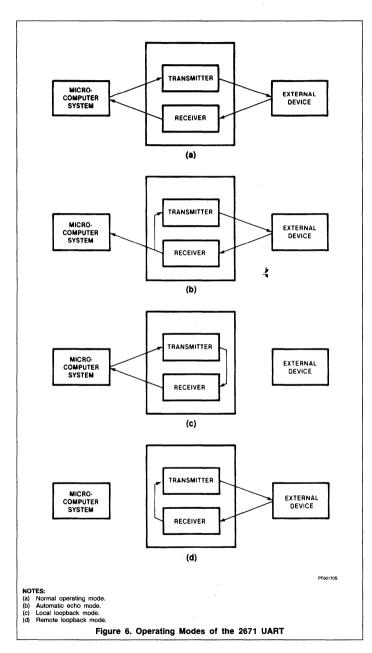

- Automatic serial echo mode (echoplex)

- Local or remote maintenance loopback mode

- Baud rate:

- DC to 1M bps (1X clock)

- DC to 62.5K bps (16X clock)

- DC to 15.625K bps (64X clock)

- Internal or external baud rate clock

- 16 internal rates

- Double-buffered transmitter and receiver

- Single +5V power supply

- 400 mil package width

#### **APPLICATIONS**

- Intelligent terminals

- Network processors

- Front-end processors

- Remote data concentrators

- Serial peripherals

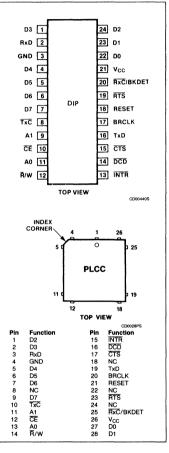

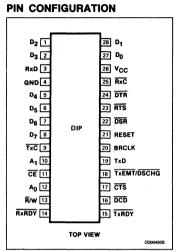

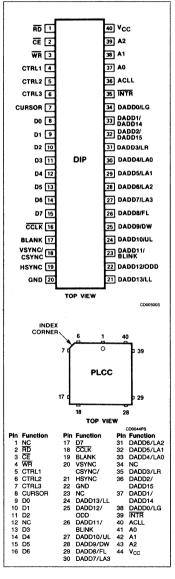

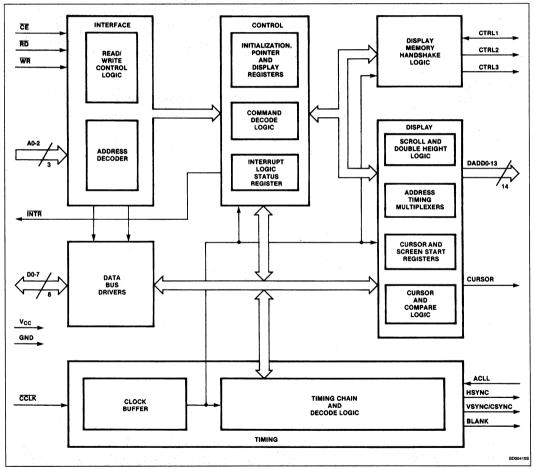

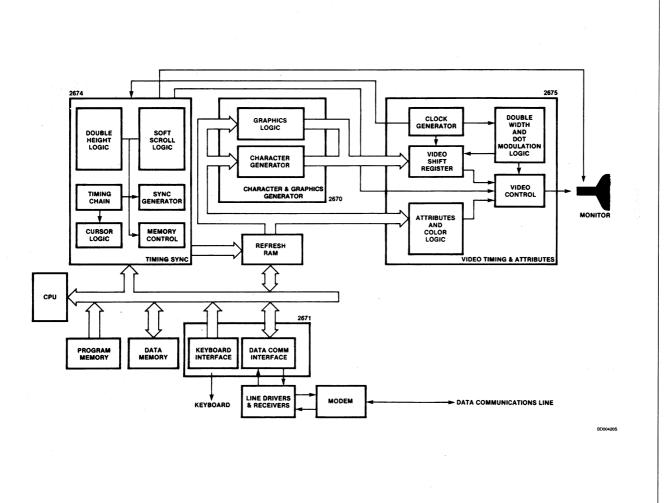

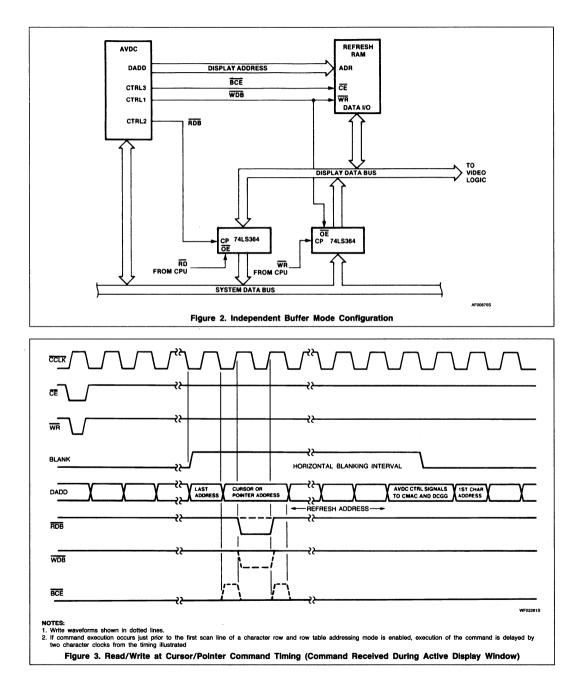

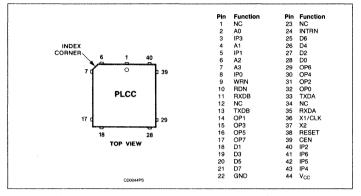

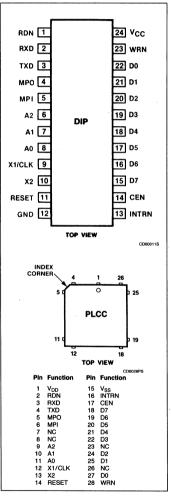

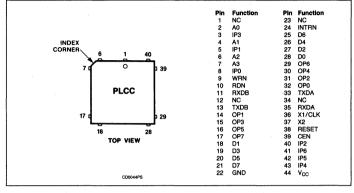

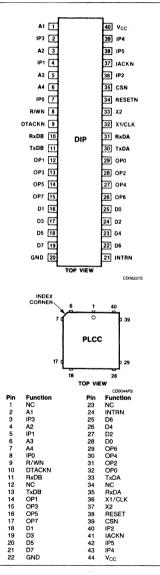

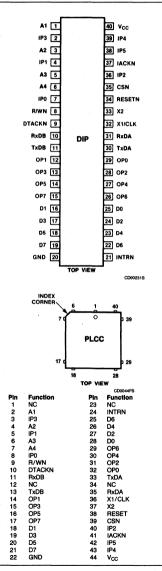

### PIN CONFIGURATIONS

### ORDERING INFORMATION

| PACKAGES    | $V_{CC} = 5V \pm 5\%$ , $T_A = 0^{\circ}C$ to $70^{\circ}C$ |

|-------------|-------------------------------------------------------------|

| Plastic DIP | SCN2641CC1N24                                               |

| Plastic LCC | SCN2641CC1A28                                               |

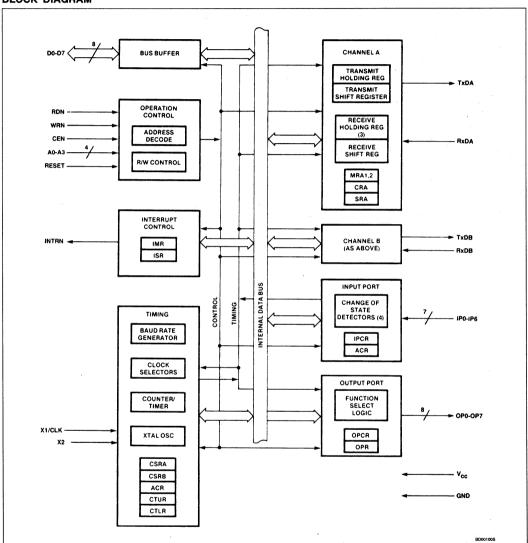

### **BLOCK DIAGRAM**

#### **BLOCK DIAGRAM**

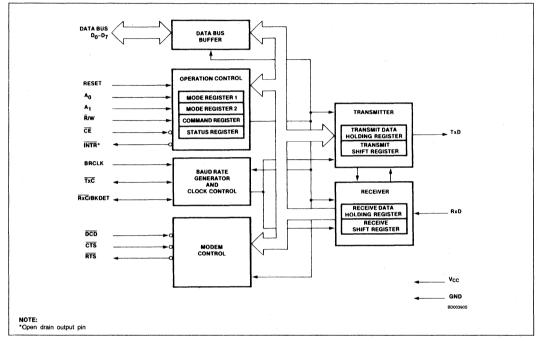

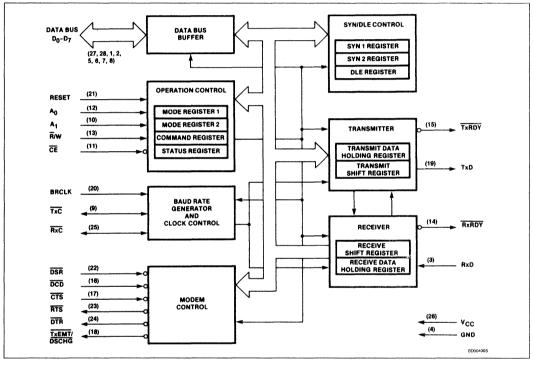

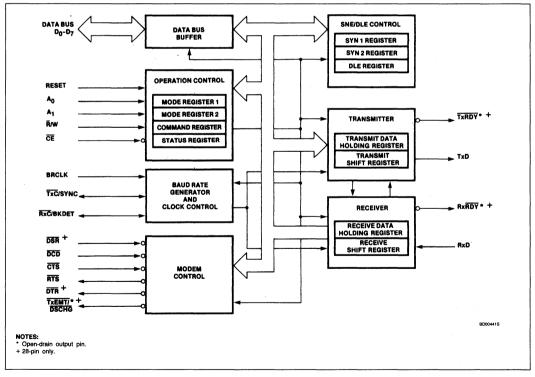

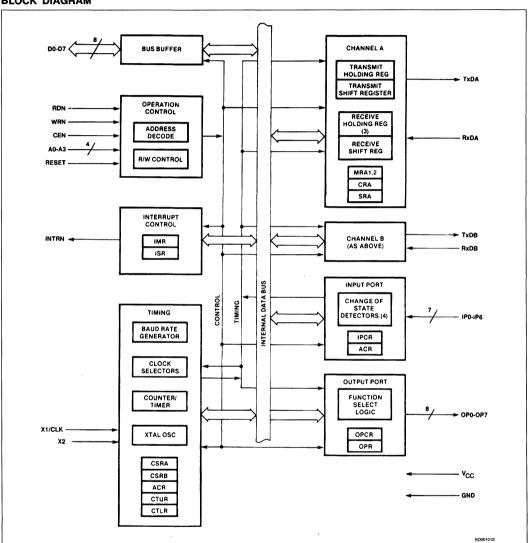

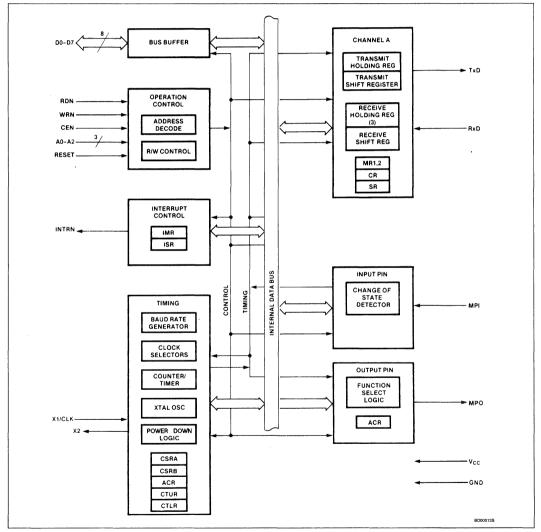

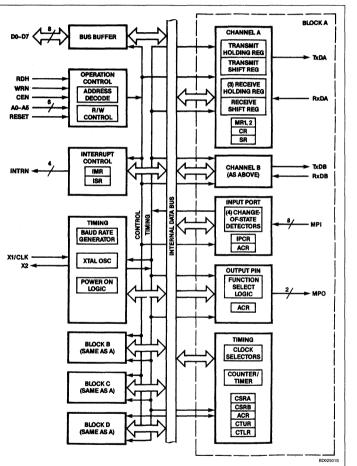

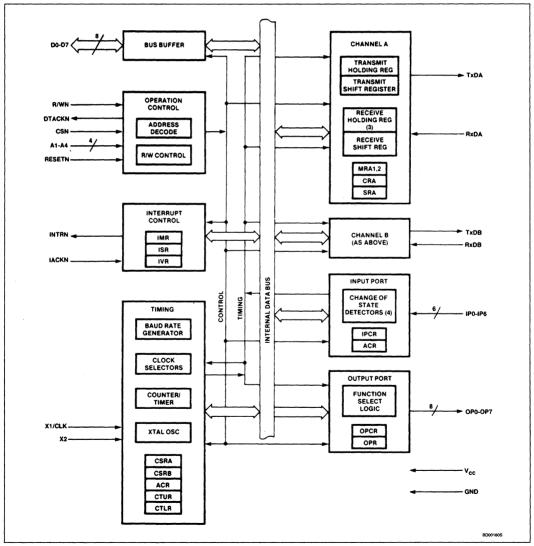

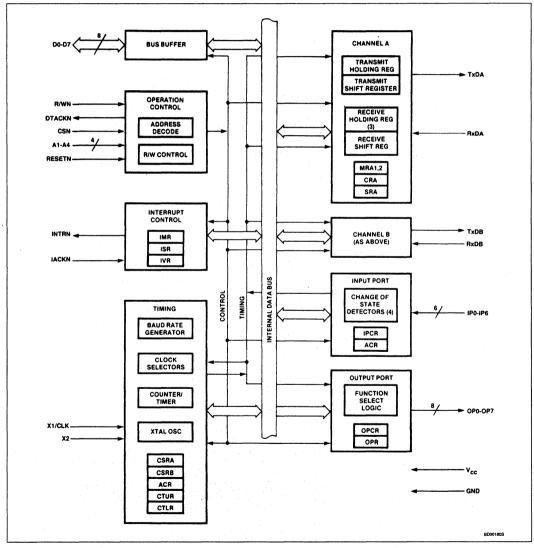

The SCN2641 consists of five major sections: the transmitter, receiver, timing, operation control and modem control. These sections communicate with each other via an internal data bus and an internal control bus. The internal data bus interfaces to the microprocessor data bus via a data bus buffer.

### **Operation Control**

This functional block stores configuration and operation commands from the CPU and generates appropriate signals to various internal sections to control the overall device operation. It contains read and write circuits to permit communications with the microprocessor via the data bus and contains mode registers 1 and 2, the command register, and the status register. Details of register addressing are presented in the SCN2641 programming section of this data sheet.

### Timing

The SCN2641 contains a baud rate generator (BRG) which is programmable to accept external transmit or receive clocks or to divide an external clock to perform data communications. The unit can generate 16 commonly used baud rates, any one of which can be selected for full-duplex operation. See Table 1.

#### Receiver

The receiver accepts serial data on the RxD pin, converts this serial input to parallel format, checks for certain errors and sends an "assembled" character to the CPU.

#### Transmitter

The transmitter accepts parallel data from the CPU, appends start and stop bits, and, optionally, a parity bit, and outputs a composite serial stream of data on the TXD output pin.

#### **Modem Control**

The modem control section provides interfacing for two input signals and one output signal used for "handshaking" and status indication between the CPU and a modem.

### INTERFACE SIGNALS

The SCN2641 interface signals can be grouped into two types: the CPU-related signals (shown in Table 2), which interface the SCN2641 to the microprocessor system and the device-related signals (shown in Table 3), which are used to interface to the communications device or system.

### OPERATION

The functional operation of the SCN2641 is programmed by a set of control words supplied by the CPU. These control words speci-

### SCN2641

SCN2641

| MR23 - 20 | BAUD<br>RATE | ACTUAL FREQUENCY<br>16X CLOCK | PERCENT<br>ERROR | DIVISOR |

|-----------|--------------|-------------------------------|------------------|---------|

| 0000      | 50           | 0.8kHz                        |                  | 4608    |

| 0001      | 75           | 1.2                           | ·                | 3072    |

| 0010      | 110          | 1.7596                        | -0.022           | 2095    |

| 0011      | 134.5        | 2.152                         | _                | 1713    |

| 0100      | 150          | 2.4                           | —                | 1536    |

| 0101      | 300          | 4.8                           |                  | 768     |

| 0110      | 600          | 9.6                           | -                | 384     |

| 0111      | 1200         | 19.2                          | _                | 192     |

| 1000      | 1800         | 28.8                          | _                | 128     |

| 1001      | 2000         | 32.055                        | 0.174            | 115     |

| 1010      | 2400         | 38.4                          |                  | 96      |

| 1011      | 3600         | 57.6                          | _                | 64      |

| 1100      | 4800         | 76.8                          |                  | 48      |

| 1101      | 7200         | 115.2                         |                  | 32      |

| 1110      | 9600         | 153.6                         | -                | 24      |

| 1111      | 19200        | 307.2                         |                  | 12      |

### Table 1. Baud Rate Generator Characteristics (BRCLK = 3.6864MHz)

fy items such as baud rate, number of bits per character, etc. The programming procedure is described in the SCN2641 programming section of this data sheet.

After programming, the SCN2641 is ready to perform the desired communications functions. The receiver performs serial to parallel conversion of data received from a modem or equivalent device. The transmitter converts parallel data received from the CPU to a serial bit stream. These actions are accomplished within the framework specified by the control words.

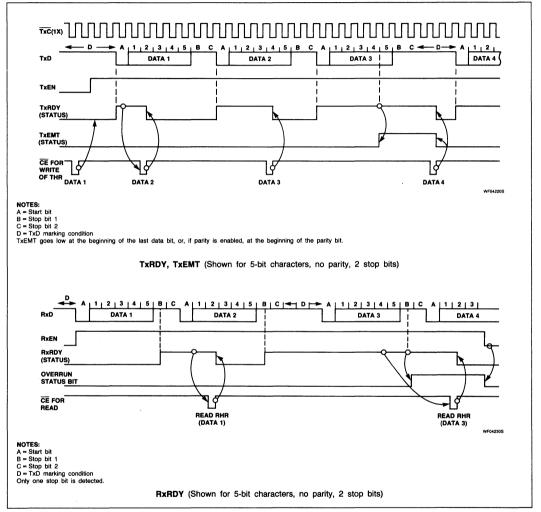

#### Receiver

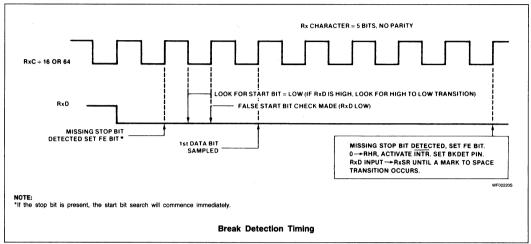

The SCN2641 is conditioned to receive data when the  $\overline{DCD}$  input is low and the RxEN bit in the command register is true. The receiver looks for a high-to-low transition of the start bit on the RxD input line. If a transition is detected, the state of the RxD line is sampled again after a delay of one-half of a bit time. If RxD is now high, the search for a valid start bit is begun again. If RxD is still low, a valid start bit is assumed and the receiver continues to sample the input line at one bit time intervals until the proper number of data bits, the parity bit, and one stop bit have been assembled. The data is then transferred to the receive data holding register, the RxRDY

bit in the status register is set, and the INTR output is asserted. If the character length is less than 8 bits, the high-order unused bits in the holding register are set to zero. The parity error, framing error, and overrun error status bits are strobed into the status register on the positive-going edge of RxC corresponding to the received character boundary. If the stop bit is present, the receiver will immediately begin its search for the next start bit. If the stop bit is absent (framing error), the receiver will interpret a space as a start bit if it persists into the next bit time interval. If a break condition is detected (RxD is low for the entire character as well as the stop bit), only one character consisting of all zeros (with the FE status bit set) will be transferred to the holding register. The RxD input must return to a high condition before a search for the next start bit begins.

Pin 20 can be programmed to be a break detect output by appropriate setting of MR27 – MR24. If so, a detected break will cause that pin to go high. When RxD returns to mark for one RxC time, pin 20 will go low. Refer to the break detection timing diagram.

#### Transmitter

The SCN2641 is conditioned to transmit data when the  $\overline{\text{CTS}}$  input is low and the TxEN

command register bit is set. The SCN2641 indicates to the CPU that it can accept a character for transmission by setting the TxRDY status bit and asserting the INTR output. When the CPU writes a character into the transmit data holding register, these conditions are negated. Data is transferred from the holding register to the transmit shift register when it is idle or has completed transmission of the previous character. The TxRDY conditions are then asserted again. Thus, one full character time of buffering is provided.

The transmitter automatically sends a start bit followed by the programmed number of data bits, the least significant bit being sent first. It then appends an optional odd or even parity bit and the programmed number of stop bits. If, following transmission of the data bits, a new character is not available in the transmit holding register, the TxD output remains in the marking (high) condition and the TxEMT/ DSCHG status bit and the INTR output are asserted. Transmission resumes when the CPU loads a new character into the holding register. The transmitter can be forced to output a continuous low (BREAK) condition by setting the send break command bit (CR3) hiah.

### SCN2641

### Table 2. CPU-Related Signals

| PIN                             | PIN             | NO.                     | INPUT/ |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|---------------------------------|-----------------|-------------------------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME                            | DIP             | PLCC                    | OUTPUT | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| V <sub>CC</sub>                 | 21              | 26                      | I      | +5V supply input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| GND                             | з               | 4                       | 1      | Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

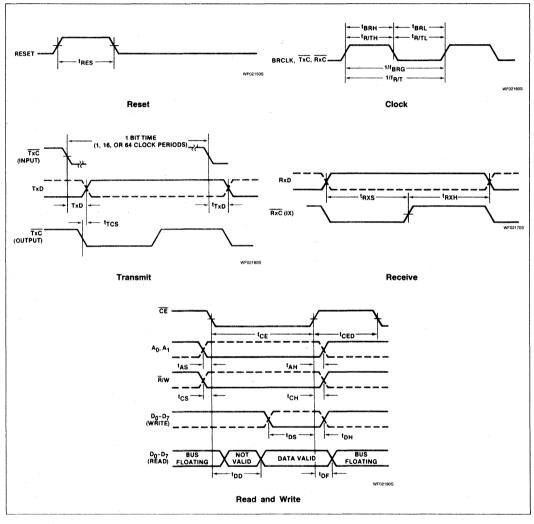

| RESET                           | 18              | 21                      |        | A high on this input performs a master reset on the SCN2641. This signal asynchronously terminates any device activity and clears the mode, command and status registers. The device assumes the idle state and remains there until initialized with appropriate control words.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| A <sub>1</sub> – A <sub>0</sub> | 9, 11           | 11, 13                  | I.     | Address lines used to select internal SCN2641 registers.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| ₹/W                             | 12              | 14                      | I      | Read command when low, write command when high.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| CE                              | 10              | 12                      | l      | Chip enable command. When low, indicates that control and data lines to the SCN2641 are valid and that the operation specified by the $\overline{R}/W$ , $A_1$ and $A_0$ inputs should be performed. When high, places the $D_0 - D_7$ lines in the 3-State condition.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| D <sub>7</sub> – D <sub>0</sub> | 7-4,1,<br>24-22 | 9,7-5,<br>2,1,<br>28,27 | 1/0    | 8-bit, 3-State data bus used to transfer commands, data and status between the SCN2641 and the CPU. $D_0$ is the least significant bit; $D_7$ the most significant bit.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

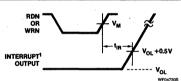

| INTR                            | 13              | 15                      |        | Interrupt request output (open drain). This output is asserted (low) under the following conditions.<br>1. When the transmitter holding register (THR) is ready to accept a data character from the CPU. This corresponds to assertion of status bit SR0. If this is the only condition asserting the output, the output will be negated (high) when the THR is loaded by the CPU, or if the transmitter is disabled via command register bit CR0.<br>2. When the receiver holding register (RHR) has a character ready to be read by the CPU. This corresponds to asserting the output, the output will be negated (high) when the RHR is read by the CPU. This corresponds to asserting the output, the output will be negated (high) when the RHR is read by the CPU, or if the receiver is disabled via command register bit CR2.<br>3. When the transmitter has completed serialization of the last character loaded by the CPU. This corresponds to asserting the output, the output will be negated (high) when the THR is loaded by the CPU.<br>4. When a change of state has occurred at the DCD input while either the receiver or the transmitter are enabled. This corresponds to assertion of status bit SR2. If this is the only condition asserting the output, the output will be negated (high) when the THR is loaded by the CPU. |

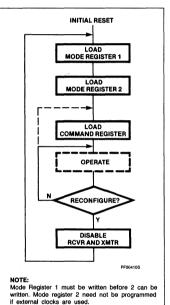

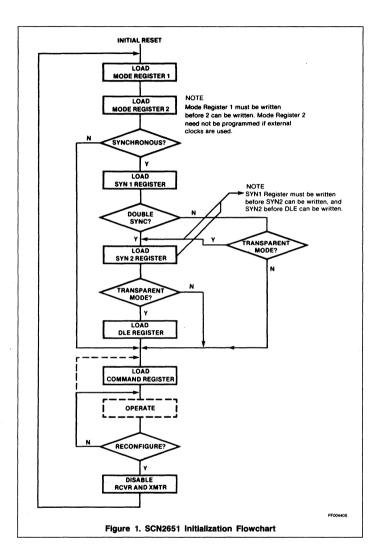

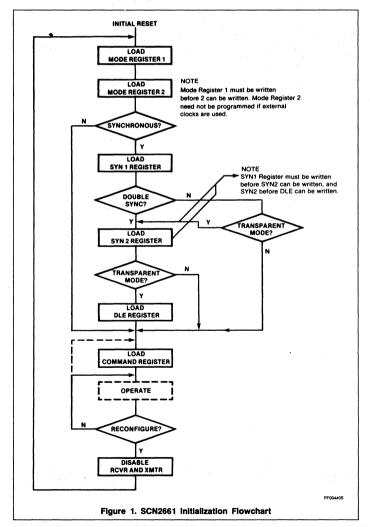

#### PROGRAMMING

Prior to initiating data communications, the SCN2641 operational mode must be programmed by performing write operations to the mode and command registers. The SCN2641 can be reconfigured at any time during program execution. A flowchart of the initialization process appears in Figure 1.

The internal registers of the SCN2641 are accessed by applying specific signals to the  $\overline{CE}$ ,  $\overline{R}/W$ ,  $A_1$  and  $A_0$  inputs. The conditions

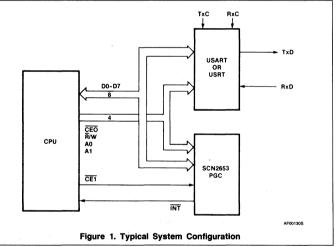

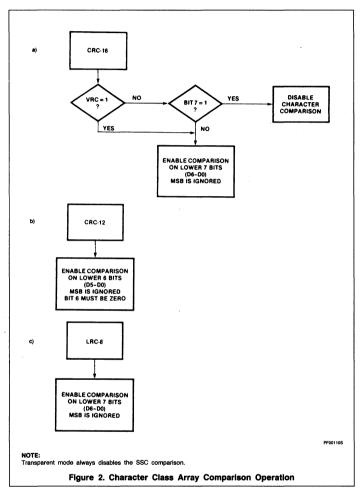

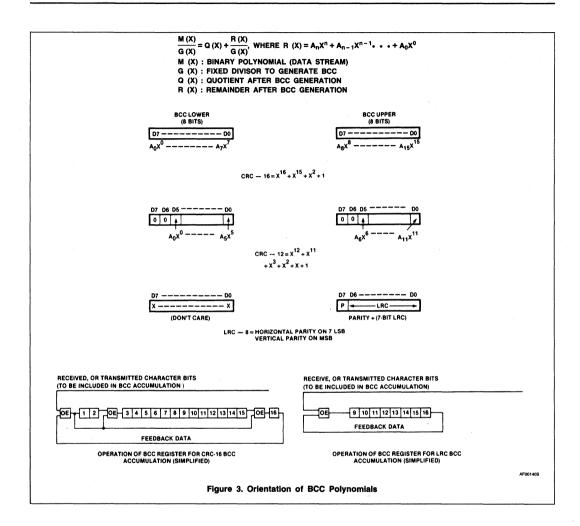

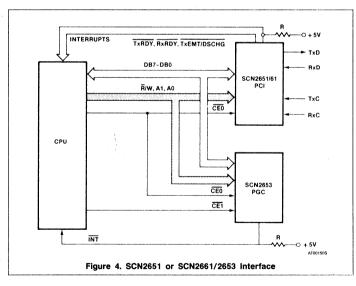

necessary to address each register are shown in Table 4.