Video and associated systems Types MAB8031 AH to TDA1524A

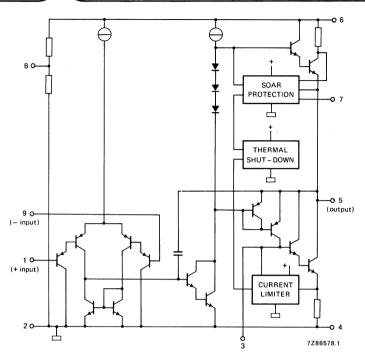

ICO2Na New series 1985

Integrated circuits

Book IC02Na New series 1985

Video and associated systems

Bipolar, MOS

Types MAB8031 AH to TDA1524A

# VIDEO AND ASSOCIATED SYSTEMS BIPOLAR, MOS Types MAB8031AH to TDA1524A

| pa               | ige |

|------------------|-----|

| roduction        | 1   |

| ection guide     |     |

| Functional index | 5   |

| Numerical index  | 12  |

| neral            |     |

| Type designation | 21  |

|                  | 23  |

|                  | 25  |

| vice data        | 29  |

| kage outlines    | 57  |

## DATA HANDBOOK SYSTEM

Our Data Handbook System comprises more than 60 books with specifications on electronic components, subassemblies and materials. It is made up of four series of handbooks:

| ELECTRON TUBES           | BLUE   |

|--------------------------|--------|

| SEMICONDUCTORS           | RED    |

| INTEGRATED CIRCUITS      | PURPLE |

| COMPONENTS AND MATERIALS | GREEN  |

The contents of each series are listed on pages iv to viii.

The data handbooks contain all pertinent data available at the time of publication, and each is revised and reissued periodically.

When ratings or specifications differ from those published in the preceding edition they are indicated with arrows in the page margin. Where application information is given it is advisory and does not form part of the product specification.

Condensed data on the preferred products of Philips Electronic Components and Materials Division is given in our Preferred Type Range catalogue (issued annually).

Information on current Data Handbooks and on how to obtain a subscription for future issues is available from any of the Organizations listed on the back cover.

Product specialists are at your service and enquiries will be answered promptly.

## ELECTRON TUBES (BLUE SERIES)

The blue series of data handbooks comprises:

| T1 Tubes for r.f. hea | eating |

|-----------------------|--------|

|-----------------------|--------|

- T2a Transmitting tubes for communications, glass types

- T2b Transmitting tubes for communications, ceramic types

- T3 Klystrons

- T4 Magnetrons for microwave heating

- T5 Cathode-ray tubes Instrument tubes, monitor and display tubes, C.R. tubes for special applications

- T6 Geiger-Müller tubes

- T7 Gas-filled tubes (will not be reprinted)

- T8 Picture tubes and components

Colour TV picture tubes, black and white TV picture tubes, colour monitor tubes for data graphic display, monochrome monitor tubes for data graphic display, components for colour television, components for black and white television and monochrome data graphic display

- T9 Photo and electron multipliers

- T10 Plumbicon camera tubes and accessories

- T11 Microwave semiconductors and components

- T12 Vidicon and Newvicon camera tubes

- T13 Image intensifiers

T14 Infrared detectors Data collations on these subjects are available now. Data Handbooks will be published in 1985.

- T15 Dry reed switches

- T16 Monochrome tubes and deflection units Black and white TV picture tubes, monochrome data graphic display tubes, deflection units

## SEMICONDUCTORS (RED SERIES)

The red series of data handbooks comprises:

### S1 Diodes Small-signal germanium diodes, small-signal silicon diodes, voltage regulator diodes (< 1,5 W), voltage reference diodes, tuner diodes, rectifier diodes

- S2a Power diodes

- S2b Thyristors and triacs

- S3 Small-signal transistors

- S4a Low-frequency power transistors and hybrid modules

- S4b High-voltage and switching power transistors

- S5 Field-effect transistors

- S6 R.F. power transistors and modules

- S7 Surface mounted semiconductors

### S8 Devices for optoelectronics Photosensitive diodes and transistors, light-emitting diodes, displays, photocouplers, infrared sensitive devices, photoconductive devices.

- S9 Power MOS transistors

- S10 Wideband transistors and wideband hybrid IC modules

- S11 Microwave semiconductors (to be published in this series in 1985) At present available in Handbook T11

- S12 Surface acoustic wave devices

۷

## INTEGRATED CIRCUITS (PURPLE SERIES)

The purple series of data handbooks comprises:

| IC3       ICs for digital systems in radio, audio and video equipment         IC4       Digital integrated circuits<br>CMOS HE4000B family         IC5       Digital integrated circuits ECL<br>ECL10 000 (GX family), ECL100 000 (HX family), dedicated designs         IC6       Professional analogue integrated circuits         IC7       Signetics bipolar memories         IC8       Signetics analogue circuits         IC9       Signetics TTL logic | EXIST | ING SERIES                                                  | Superseded by:  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-------------------------------------------------------------|-----------------|

| IC3       ICs for digital systems in radio, audio and video equipment         IC4       Digital integrated circuits<br>CMOS HE4000B family         IC5       Digital integrated circuits ECL<br>ECL10 000 (GX family), ECL100 000 (HX family), dedicated designs         IC6       Professional analogue integrated circuits         IC7       Signetics bipolar memories         IC8       Signetics analogue circuits         IC9       Signetics TTL logic | IC1   | Bipolar ICs for radio and audio equipment                   |                 |

| IC4       Digital integrated circuits<br>CMOS HE4000B family         IC5       Digital integrated circuits ECL<br>ECL10 000 (GX family), ECL100 000 (HX family), dedicated designs         IC6       Professional analogue integrated circuits         IC7       Signetics bipolar memories         IC8       Signetics analogue circuits         IC9       Signetics TTL logic                                                                               | IC2   | Bipolar ICs for video equipment                             | IC02N           |

| CMOS HE4000B family       IC08N         IC5       Digital integrated circuits ECL<br>ECL10 000 (GX family), ECL100 000 (HX family), dedicated designs       IC08N         IC6       Professional analogue integrated circuits       IC08N         IC7       Signetics bipolar memories       IC11N         IC8       Signetics analogue circuits       IC11N         IC9       Signetics TTL logic       IC09N and IC15N                                      | IC3   | ICs for digital systems in radio, audio and video equipment |                 |

| IC6       Professional analogue integrated circuits         IC7       Signetics bipolar memories         IC8       Signetics analogue circuits         IC9       Signetics TTL logic                                                                                                                                                                                                                                                                          | IC4   |                                                             |                 |

| IC7     Signetics bipolar memories       IC8     Signetics analogue circuits       IC9     Signetics TTL logic                                                                                                                                                                                                                                                                                                                                                | IC5   |                                                             | 1C08N           |

| IC8     Signetics analogue circuits     IC11N       IC9     Signetics TTL logic     IC09N and IC15N                                                                                                                                                                                                                                                                                                                                                           | IC6   | Professional analogue integrated circuits                   |                 |

| IC9 Signetics TTL logic IC09N and IC15N                                                                                                                                                                                                                                                                                                                                                                                                                       | IC7   | Signetics bipolar memories                                  |                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                               | IC8   | Signetics analogue circuits                                 | IC11N           |

| IC10 Signetics Integrated Fuse Logic (IFL) IC13N                                                                                                                                                                                                                                                                                                                                                                                                              | IC9   | Signetics TTL logic                                         | IC09N and IC15N |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                               | IC10  | Signetics Integrated Fuse Logic (IFL)                       | IC13N           |

IC11 Microprocessors, microcomputers and peripheral circuitry

February 1985

### NEW SERIES

| IC01N | Radio, audio and associated systems<br>Bipolar, MOS             |                  |

|-------|-----------------------------------------------------------------|------------------|

| IC02N | Video and associated systems<br>Bipolar, MOS                    | (published 1985) |

| IC03N | Telephony equipment<br>Bipolar, MOS                             |                  |

| ICO4N | HE4000B logic family<br>CMOS                                    |                  |

| IC05N | HE4000B logic family uncased integrated circuits<br>CMOS        | (published 1984) |

| IC06N | High-speed CMOS; PC54/74HC/HCT/HCU<br>Logic family              | (published 1985) |

| IC07N | PC54/74HC/HCU/HCT uncased integrated circuits<br>HCMOS          |                  |

| IC08N | 10K and 100K logic family<br>ECL                                | (published 1984) |

| IC09N | Logic series<br>TTL                                             | (published 1984) |

| IC10N | Memories<br>MOS, TTL, ECL                                       |                  |

| IC11N | Linear LSI                                                      | (published 1985) |

| IC12N | Semi-custom gate arrays & cell libraries<br>ISL, ECL, CMOS      |                  |

| IC13N | Semi-custom<br>Integrated Fuse Logic                            | (published 1985) |

| IC14N | Microprocessors, microcontrollers & peripherals<br>Bipolar, MOS |                  |

| IC15N | Logic series<br>FAST TTL                                        | (published 1984) |

|       |                                                                 |                  |

### Note

Books available in the new series are shown with their date of publication.

Ĵ,

## COMPONENTS AND MATERIALS (GREEN SERIES)

The green series of data handbooks comprises:

- C1 Programmable controller modules PLC modules, PC20 modules

- C2 Television tuners, coaxial aerial input assemblies, surface acoustic wave filters

- C3 Loudspeakers

- C4 Ferroxcube potcores, square cores and cross cores

- C5 Ferroxcube for power, audio/video and accelerators

- C6 Synchronous motors and gearboxes

- C7 Variable capacitors

- C8 Variable mains transformers

- C9 Piezoelectric quartz devices

- C10 Connectors

- C11 Non-linear resistors Voltage dependent resistors (VDR), light dependent resistors (LDR), negative temperature coefficient thermistors (NTC), positive temperature coefficient thermistors (PTC)

- C12 Potentiometers, encoders and switches

- C13 Fixed resistors

- C14 Electrolytic and solid capacitors

- C15 Ceramic capacitors

- C16 Permanent magnet materials

- C17 Stepping motors and associated electronics

- C18 Direct current motors

- C19 Piezoelectric ceramics

- C20 Wire-wound components for TVs and monitors

- C21 Assemblies for industrial use HNIL FZ/30 series, NORbits 60-, 61-, 90-series, input devices

- C22 Film capacitors

## INTRODUCTION

This new edition of the data handbook for video and associated systems has been expanded to include MOS as well as bipolar integrated circuits as the use of MOS circuits in video equipment is becoming more and more widespread (remote control, digital tuning, teletext, etc.).

The expansion of data has made it necessary to produce this handbook in two volumes: IC02Na; IC02Nb. IC02Na contains device data on types MAB8031AH to TDA1524A.

IC02Nb contains device data on types TDA2501 to TEA1002.

Each volume contains an index, associated information and package outlines.

The data handbook now includes dedicated video circuits and general purpose products (microcontrollers, display circuits, etc.) that find application in video systems. Full specifications are provided for the dedicated circuits; in some cases the general purpose circuits have short-form specifications. More detailed information can be found in the relevant data sheets and handbooks.

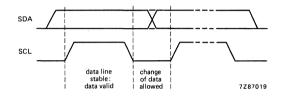

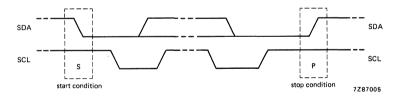

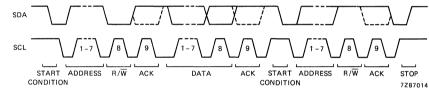

### I<sup>2</sup>C bus compatible ICs

Some of the ICs in this handbook are I<sup>2</sup>C bus compatible (indicated by the logo shown below). The following clause applies:

Purchase of Philips'  $1^2$ C components conveys a license under the Philips'  $1^2$ C patent to use the components in the  $1^2$ C system provided the system conforms to the  $1^2$ C specifications defined by Philips.

FUNCTIONAL AND NUMERICAL INDEX

# SELECTION GUIDE BY FUNCTION

| type number              | description                                                                                 | page           |

|--------------------------|---------------------------------------------------------------------------------------------|----------------|

| Vision I.F. circuits     |                                                                                             |                |

| Economical circuit       | 'S                                                                                          |                |

| TDA2540; Q               | IF amplifier and demodulator; NPN tuners                                                    | b- <b>89</b>   |

| TDA2541; Q               | IF amplifier and demodulator; PNP tuners                                                    | b-97           |

| TDA2542; Q               | IF amplifier and demodulator; for E and L standards; PNP tuners                             | b-105          |

| TDA2544; Q<br>TDA2548; Q | IF amplifier and demodulator; MOS tuners<br>IF amplifier and demodulator; PNP tuners        | b-119<br>b-139 |

| 1DA2546, U               | if amplifier and demodulator, five tuners                                                   | D-139          |

| High-performance         | circuits                                                                                    |                |

| TDA3540; Q               | IF amplifier and demodulator; NPN tuners                                                    | b-343          |

| TDA3541; Q               | IF amplifier and demodulator; PNP tuners                                                    | b-343          |

| Colour decoding ci       | ircuits                                                                                     |                |

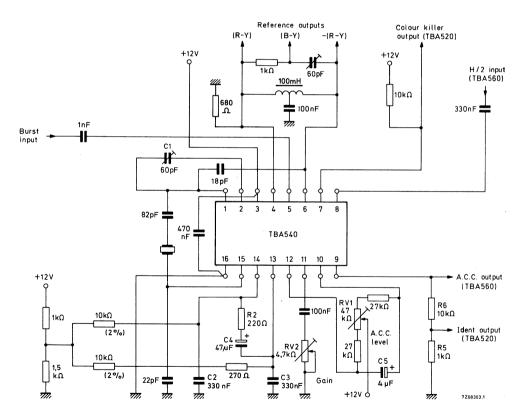

| TBA540                   | reference combination                                                                       | a-549          |

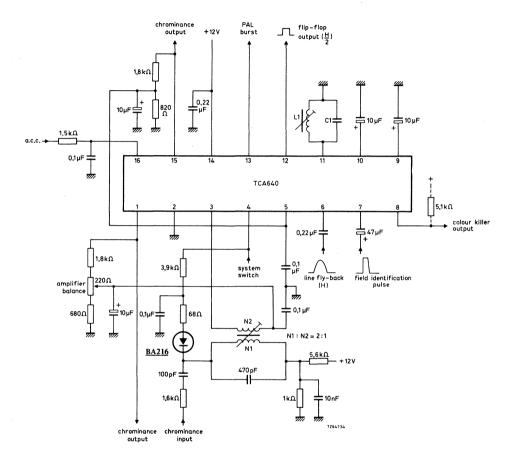

| TCA640                   | chrominance amplifier for SECAM or PAL/SECAM decoders                                       | a-571          |

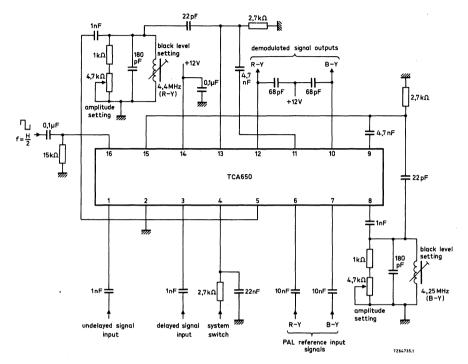

| TCA650                   | chrominance demodulator for SECAM or PAL/SECAM decoders                                     | a-579          |

| TCA660B                  | contrast, saturation and brightness control circuit for colour                              |                |

| <b>TD 40</b> 500         | difference and luminance signals                                                            | a-587          |

| TDA2506                  | SECAM encoder                                                                               | b- <b>69</b>   |

| TDA2507                  | FM modulator controller                                                                     | b-81           |

| TDA3501<br>TDA3505       | video control combination<br>video control combination with automatic cut-off control       | b-323<br>b-331 |

| TDA3505<br>TDA3510       | PAL decoder                                                                                 | b-339          |

| TDA3560                  | PAL decoder                                                                                 | b-353          |

| TDA3561A                 | PAL decoder                                                                                 | ≂ 363          |

| TDA3562A                 | PAL/NTSC decoder                                                                            | b-375          |

| TDA3563                  | NTSC decoder                                                                                | b-391          |

| TDA3564                  | NTSC decoder without R.G.B. inputs                                                          | b-401          |

| TDA3565                  | PAL decoder                                                                                 | b-411          |

| TDA3590                  | SECAM processor circuit                                                                     | b-453          |

| TDA3590A                 | SECAM processor circuit (improved TDA3590)                                                  | b- <b>467</b>  |

| TDA3591                  | SECAM processor circuit                                                                     | b-483          |

| TDA3591A<br>TDA4510      | SECAM processor circuit<br>PAL decoder                                                      | b-497<br>b-675 |

|                          |                                                                                             |                |

| TDA4555<br>TDA4556       | multi-standard decoder for $-(R-Y)$ , $-(B-Y)$ signals                                      | b-681          |

| TDA4556<br>TDA4560       | multi-standard decoder for $+(R-Y)$ , $+(B-Y)$ signals colour transient improvement circuit | b-681<br>b-689 |

| TDA4500                  | l <sup>2</sup> C bus interface for colour decoders                                          | b-689<br>b-699 |

|                          |                                                                                             | 5 000          |

| type number                                                   | description                                                                                                                                                                                                                                                       | page                                      |

|---------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|

| Vertical deflection ci                                        | rcuits                                                                                                                                                                                                                                                            |                                           |

| TDA2653A<br>TDA2654S<br>TDA2655B<br>TDA3650<br>TDA3651        | vertical deflection circuit; PIL-S4; 30AX systems and monitors<br>vertical deflection circuit; monochrome, 110°; tiny-vision colour, 90°<br>vertical deflection circuit; colour and monochrome, 90°<br>vertical deflection circuit<br>vertical deflection circuit | b-257<br>b-265<br>b-273<br>b-507<br>b-515 |

| TDA3651A; AQ<br>TDA3652; Q<br>TDA3653; A                      | vertical deflection circuit<br>vertical deflection circuit<br>vertical deflection circuit with + 60 V and protection                                                                                                                                              | b-523<br>b-531<br>b-537                   |

| Sync processors; hori                                         | zontal; vertical                                                                                                                                                                                                                                                  |                                           |

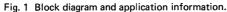

| TBA920S<br>TDA2577A<br>TDA2578A<br>TDA2593<br>TDA2594         | horizontal combination<br>synchronization circuit with vertical oscillator and driver stages<br>synchronization circuit with vertical oscillator and driver stages<br>horizontal combination<br>horizontal combination with transmitter identification            | a-565<br>b-151<br>b-165<br>b-221<br>b-229 |

| TDA2595                                                       | horizontal combination with transmitter identification and                                                                                                                                                                                                        |                                           |

| TDA3571B                                                      | protection circuits<br>sync combination with transmitter identification and vertical<br>divider (625 lines)                                                                                                                                                       | b-237<br>b-419                            |

| TDA3576B                                                      | sync combination with transmitter identification and vertical divider (625 lines)                                                                                                                                                                                 |                                           |

| TDA3586                                                       | horizontal and vertical sync processor                                                                                                                                                                                                                            | b-431<br>b-445                            |

| Sound circuits                                                |                                                                                                                                                                                                                                                                   |                                           |

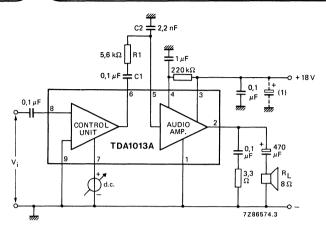

| TBA120U<br>TBA750C; CQ<br>TDA1013A<br>TDA1029<br>TDA1512; Q   | sound i.f. amplifier/demodulator<br>limiter/amplifier<br>4 W audio power amplifier with d.c. volume control<br>signal sources switch (4 x two channels)<br>12 to 20 W hi-fi audio power amplifier                                                                 | a-543<br>a-557<br>a-601<br>a-605<br>a-625 |

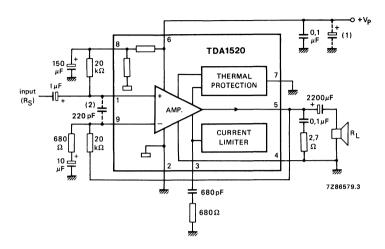

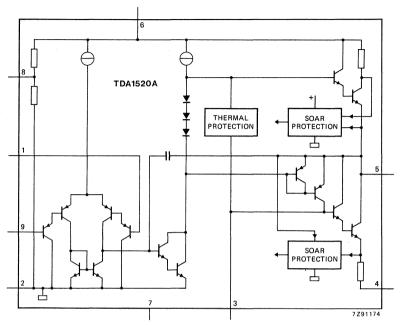

| TDA1520; Q<br>TDA1520A; AQ<br>TDA1524A<br>TDA2543<br>TDA2545A | 20 W hi-fi audio power amplifier<br>20 W hi-fi audio power amplifier<br>stereo-tone/volume control circuit<br>AM sound IF circuit for French standard<br>quasi-split-sound circuit                                                                                | a-631<br>a-637<br>a-643<br>b-113<br>b-127 |

| TDA2546A<br>TDA2555<br>TDA2611A<br>TDA2791<br>TDA2795         | quasi-split-sound circuit; 5,5 MHz demodulation<br>dual TV sound demodulator circuit<br>5 W audio power amplifier<br>TV sound combination; volume, treble, bass<br>TV stereo/dual sound identification decoder                                                    | b-133<br>b-147<br>b-247<br>b-293<br>b-305 |

| TDA3800G<br>TDA3800GS<br>TDA3803A<br>TDA3810                  | stereo/dual TV sound processor (dynamic selection)<br>stereo/dual TV sound processor (static selection)<br>stereo/dual TV sound processor<br>spatial, stereo and pseudo-stereo sound circuit                                                                      | b-615<br>b-615<br>b-623<br>b-631          |

### Selection guide by function

| type number                                                         | description                                                                                                                                                                                                                   | page                                      |

|---------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|

| Video recorder ci                                                   |                                                                                                                                                                                                                               |                                           |

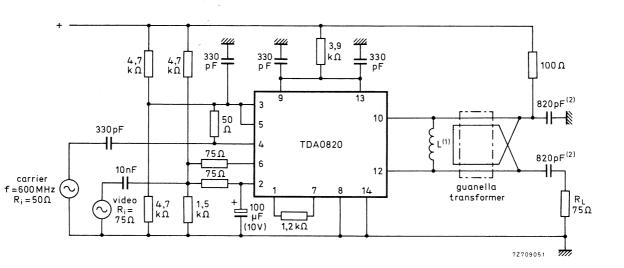

| TDA0820T<br>TDA2501<br>TDA2502<br>TDA2502<br>TDA2503<br>TDA2504P; T | double balanced modulator/demodulator<br>PAL/NTSC encoder<br>tacho motor speed controller<br>track sensing amplifier<br>FM modem for 8 mm video                                                                               | a-597<br>b-29<br>b-35<br>b-45<br>b-51     |

| TDA2730<br>TDA2740<br>TDA3701<br>TDA3710<br>TDA3720                 | FM limiter/demodulator<br>amplifier and drop-out identification circuit<br>PAL synchronization processor for V2000 system<br>chrominance signal/mixer for V2000 system<br>SECAM chrominance signal processor for V2000 system | b-281<br>b-289<br>b-545<br>b-553<br>b-561 |

| TDA3724<br>TDA3730<br>TDA3740<br>TDA3755<br>TDA3760                 | SECAM identification circuit<br>frequency demodulator and drop-out compensator<br>video processor/frequency modulator<br>PAL/NTSC synchronization processor for VHS system<br>PAL chrominance signal processor for VHS system | b-567<br>b-569<br>b-575<br>b-581<br>b-591 |

| TDA3771<br>TDA3780<br>TDA3791                                       | video processor<br>frequency modulator<br>band selector and window detector                                                                                                                                                   | b-599<br>b-605<br>b-609                   |

| Video camera circ                                                   | cuits                                                                                                                                                                                                                         |                                           |

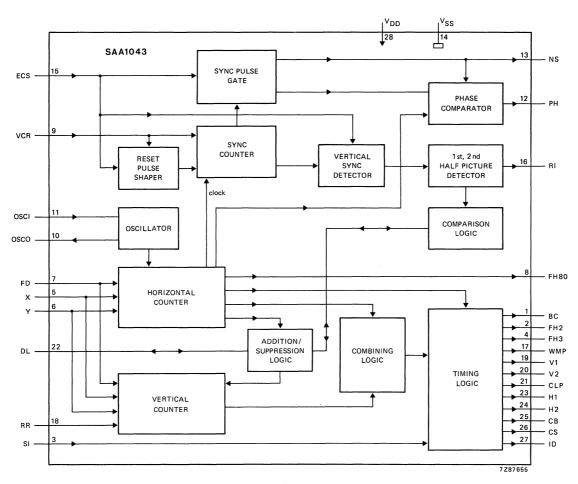

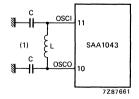

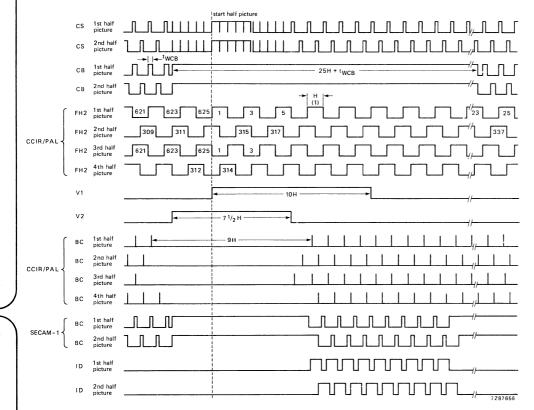

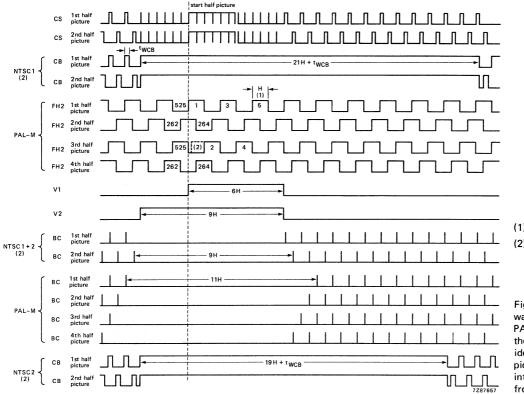

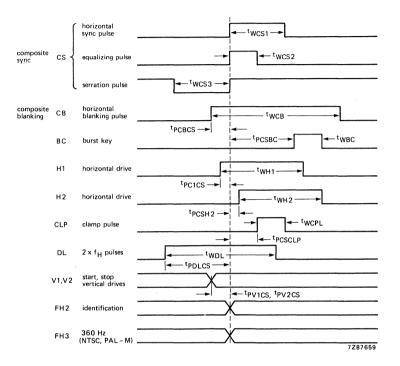

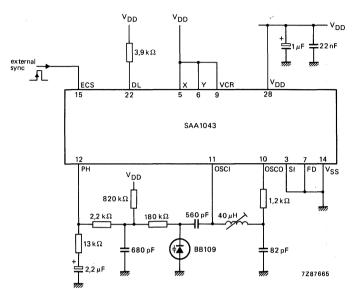

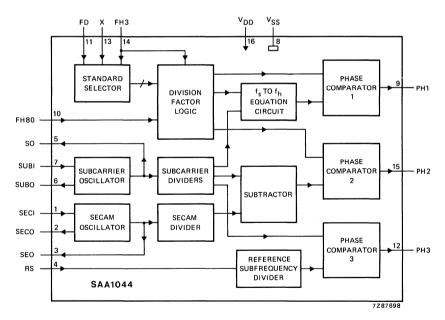

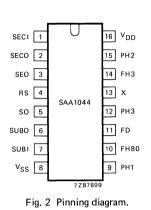

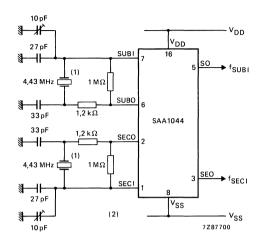

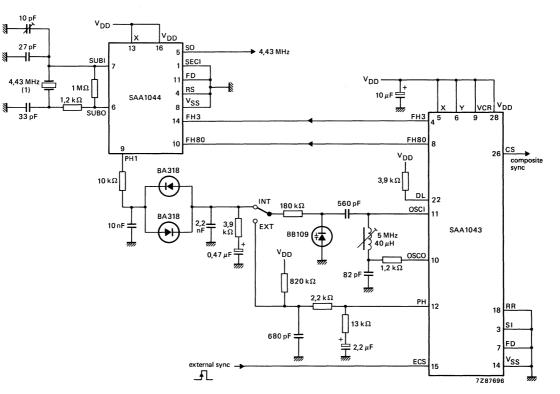

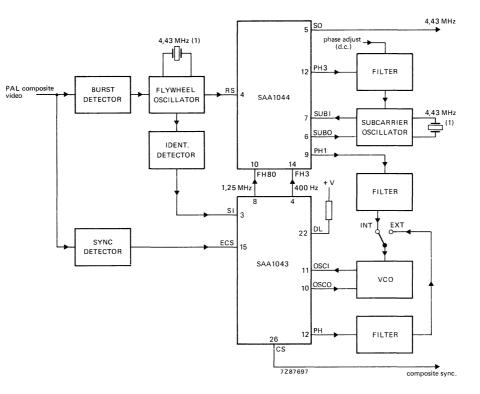

| SAA1043<br>SAA1044                                                  | universal sync generator<br>subcarrier coupling circuit                                                                                                                                                                       | a-113<br>a-129                            |

| Miscellaneous                                                       |                                                                                                                                                                                                                               |                                           |

| TDA1082<br>TDA2579                                                  | east-west correction driver circuit sync circuit with synchronized vertical divider system                                                                                                                                    | a-619                                     |

| TDA2581; Q<br>TDA2582; Q<br>TDA4500                                 | and output stages<br>control circuit for SMPS<br>control circuit for PPS<br>small signal combination IC for monochrome TV                                                                                                     | b-179<br>b-195<br>b-207<br>b-635          |

| TDA4501<br>TDA4503<br>TDA5030<br>TEA1002                            | small signal combination IC for colour TV<br>small signal combination IC for B/W TV<br>mixer/oscillator for VHF tuner<br>PAL colour encoder and video summer                                                                  | b-647<br>b-661<br>b-695<br>b-717          |

| Remote control sy                                                   | ystems                                                                                                                                                                                                                        |                                           |

| For general purpo                                                   |                                                                                                                                                                                                                               |                                           |

| SAA1082P                                                            | remote transmitter                                                                                                                                                                                                            | a-173                                     |

| SAA1082P | remote transmitter                        | a-173 |

|----------|-------------------------------------------|-------|

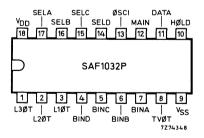

| SAF1032P | receiver/decoder for infrared operation   | a-519 |

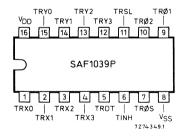

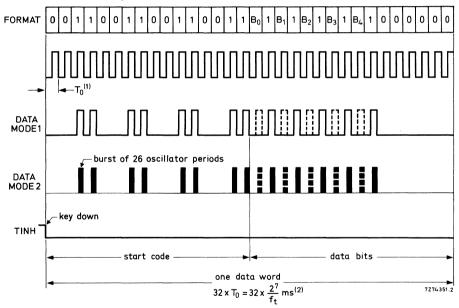

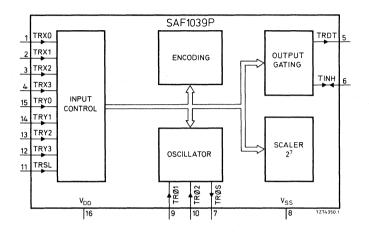

| SAF1039P | remote transmitter for infrared operation | a-519 |

| type number                                                         | description                                                                                                                                                                                                                                                                       | page                                      |

|---------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|

| Remote control syst                                                 | tems (continued)                                                                                                                                                                                                                                                                  |                                           |

| For sophisticated ra                                                | dio and video systems                                                                                                                                                                                                                                                             |                                           |

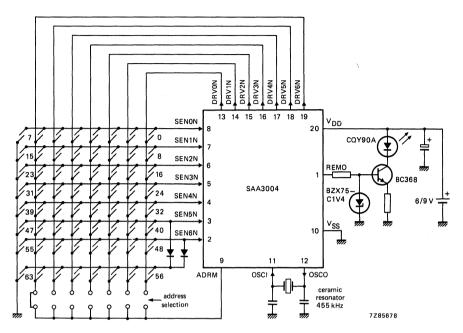

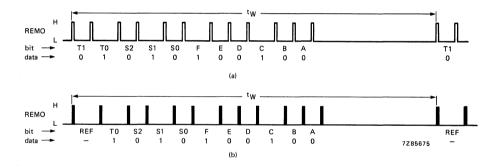

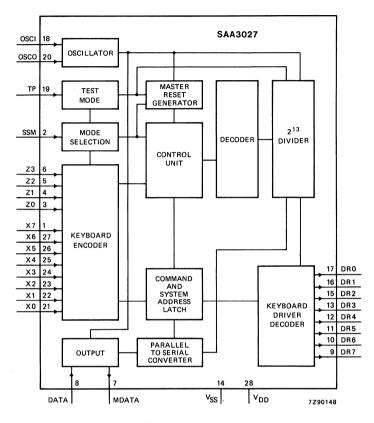

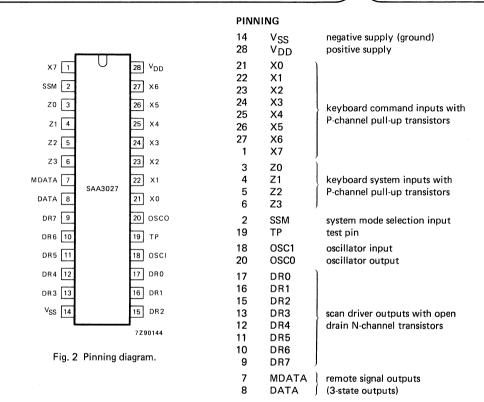

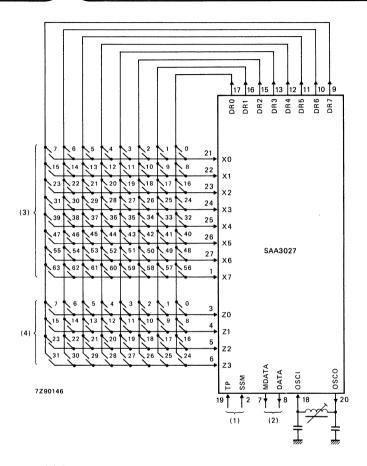

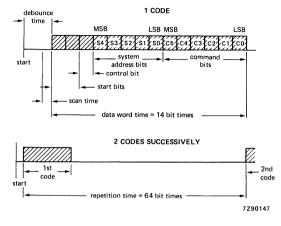

| SAA3004P; T<br>SAA3006<br>SAA3027<br>SAA3028<br>TDA3047             | remote control transmitter for infrared operation<br>low voltage infrared remote control transmitter (RC-5)<br>infrared remote control transmitter (RC-5)<br>infrared remote control transcoder (RC-5); $1^{2}$ C bus compatible<br>infrared receiver circuit; $V_{0}$ = positive | a-205<br>a-215<br>a-229<br>a-243<br>b-311 |

| TDA3048<br>TDB2033                                                  | infrared receiver circuit; V <sub>0</sub> = negative<br>preamplifier for infrared remote control transmission                                                                                                                                                                     | b-317<br>b-707                            |

| Tuning system                                                       |                                                                                                                                                                                                                                                                                   |                                           |

| Display drivers                                                     |                                                                                                                                                                                                                                                                                   |                                           |

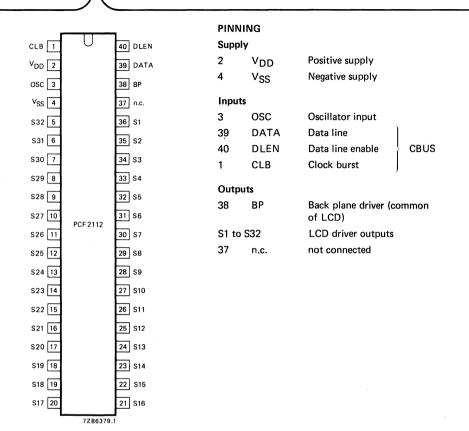

| PCF2100P; T<br>PCF2110P; T<br>PCF2111P; T<br>PCF2112P; T<br>SAA1060 | LCD duplex driver; 40 segments<br>LCD duplex driver; 60 segments and 2 LEDs<br>LCD duplex driver; 64 segments<br>LCD driver; 32 segments<br>LED display/interface circuit                                                                                                         | a-43<br>a-53<br>a-63<br>a-73<br>a-155     |

| SAA1061<br>SAA1062A; AT                                             | LED driver/output port expander<br>LCD display/interface circuit                                                                                                                                                                                                                  | a-161<br>a-167                            |

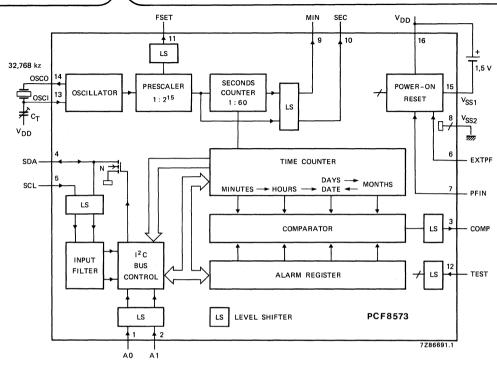

| Clock timers                                                        |                                                                                                                                                                                                                                                                                   |                                           |

| PCF8573P;T<br>SAF3019                                               | clock/calendar with serial I/O; I <sup>2</sup> C bus interface<br>clock/timer with serial I/O; microcontroller controlled                                                                                                                                                         | a-81<br>a-533                             |

| Tuning circuits                                                     |                                                                                                                                                                                                                                                                                   |                                           |

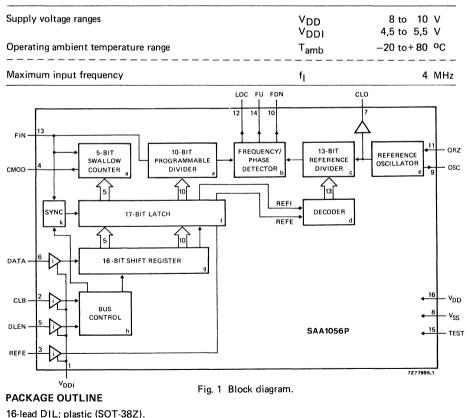

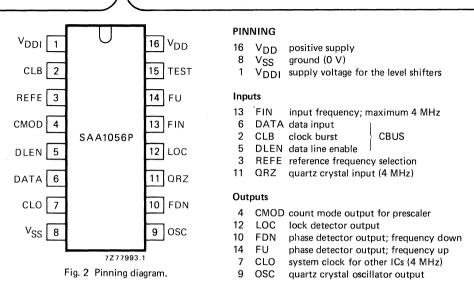

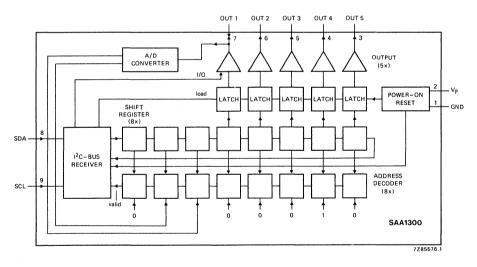

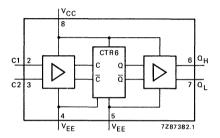

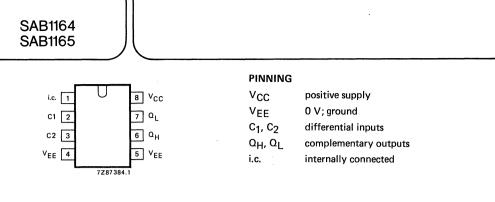

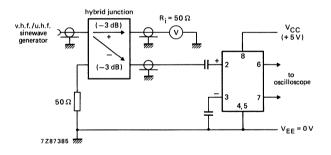

| SAA1056P<br>SAA1057<br>SAA1300<br>SAB1164<br>SAB1165                | PLL frequency synthesizer<br>radio tuning PLL frequency synthesizer (SYMO II)<br>tuner switching unit<br>sensitive 1 GHz divider-by-64; $R_0 = 1 k\Omega$<br>sensitive 1 GHz divider-by-64; $R_0 = 0.5 k\Omega$                                                                   | a-137<br>a-145<br>a-201<br>a-437<br>a-437 |

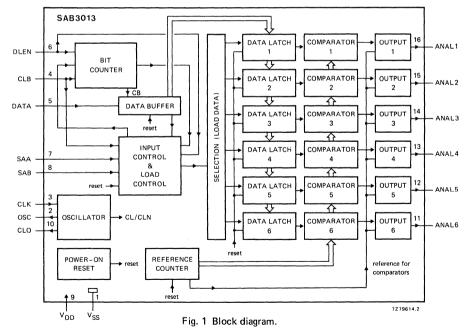

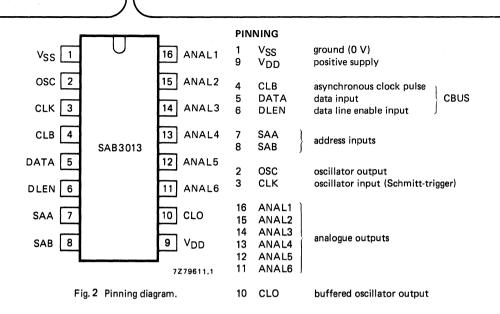

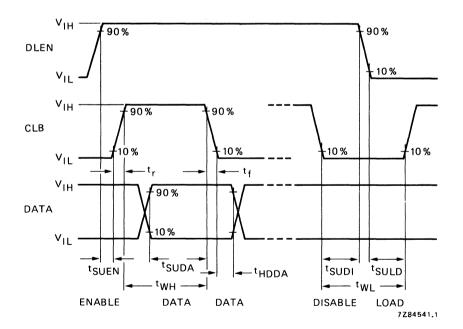

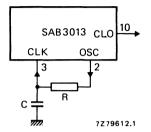

| SAB1256<br>SAB3013<br>SAB3034<br>SAB3035                            | sensitive 1 GHz divider-by-256<br>computer controlled analogue memory providing 6 analogue functions<br>analogue and tuning circuit (A & T)<br>computer interface for tuning and control (CITAC); 8 DACs;<br>I <sup>2</sup> C bus compatible                                      | a-443<br>a-449<br>a-457<br>a-471          |

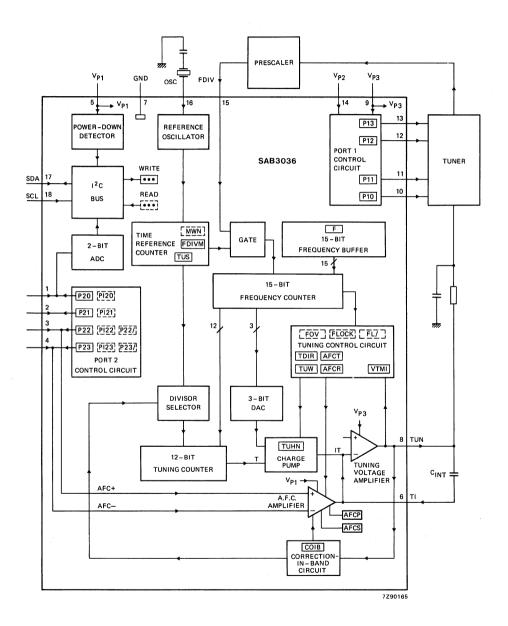

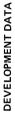

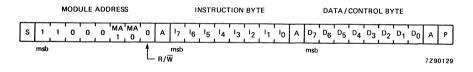

| SAB3036                                                             | computer interface for tuning and control (CITAC); without DACs;<br>I <sup>2</sup> C bus compatible                                                                                                                                                                               | a-487                                     |

| SAB3037                                                             | computer interface for tuning and control (CITAC); 4 DACs;<br>I <sup>2</sup> C bus compatible                                                                                                                                                                                     | a-503                                     |

| type number               | description                                                                                                 | 5000           |

|---------------------------|-------------------------------------------------------------------------------------------------------------|----------------|

|                           |                                                                                                             | page           |

| Text decoder systems      |                                                                                                             |                |

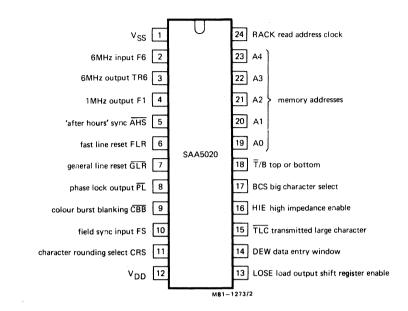

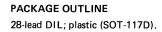

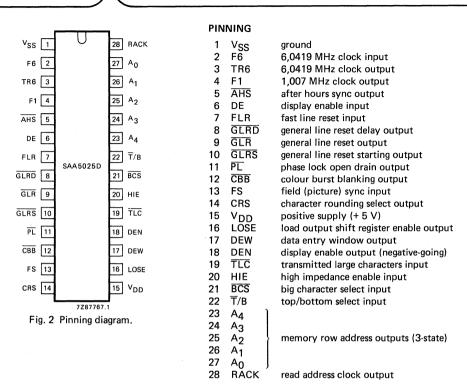

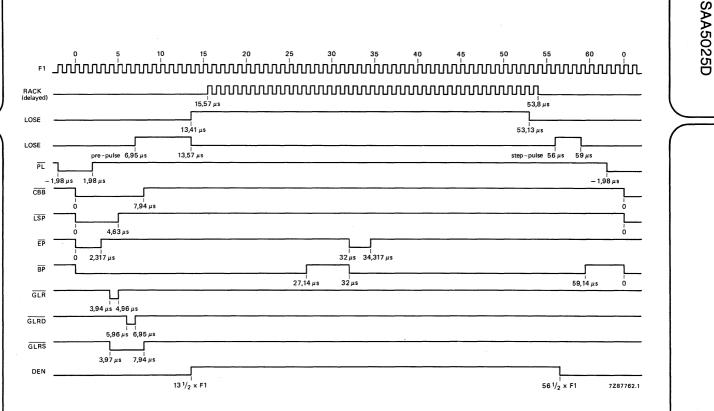

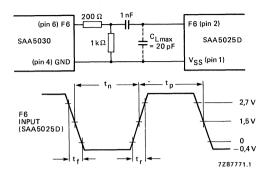

| SAA5020<br>SAA5025D       | teletext timing chain circuit (625 lines)<br>teletext timing chain circuit for USA 525 line system (USTIC); | a-251          |

| C 1 1 5 0 2 0             | 40 characters per row, 24 rows (8 TV-lines per row)                                                         | a-261          |

| SAA5030<br>SAA5040A; B; C | teletext video processor<br>teletext acquisition and control circuit                                        | a-279          |

| SAA5040A, B, C            | teletext acquisition and control circuit                                                                    | a-289<br>a-289 |

| SAA5042                   | teletext acquisition and control circuit                                                                    | a-289          |

| SAA5045                   | gearing address logic array for USA teletext (GALA)                                                         | a-309          |

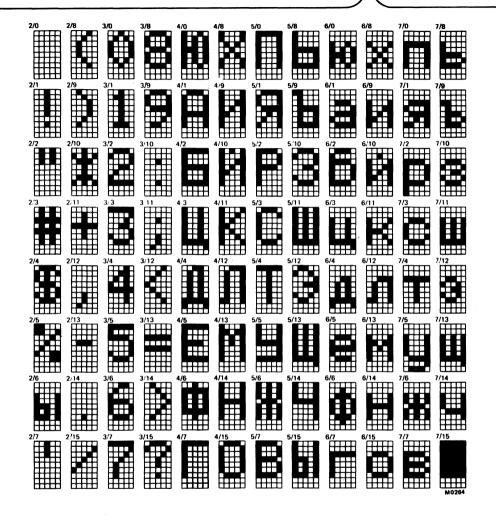

| SAA5050                   | teletext character generator (English)                                                                      | a-317          |

| SAA5051                   | teletext character generator (German)                                                                       | a-317          |

| SAA5052                   | teletext character generator (Swedish)                                                                      | a-317          |

| SAA5053                   | teletext character generator (Italian)                                                                      | a-317          |

| SAA5054                   | teletext character generator (Belgian)                                                                      | a-317          |

| SAA5055                   | teletext character generator (US ASCII)                                                                     | a-317          |

| SAA5056                   | teletext character generator (Hebrew)                                                                       | a-317          |

| SAA5057                   | teletext character generator (Cyrillic)                                                                     | a-317          |

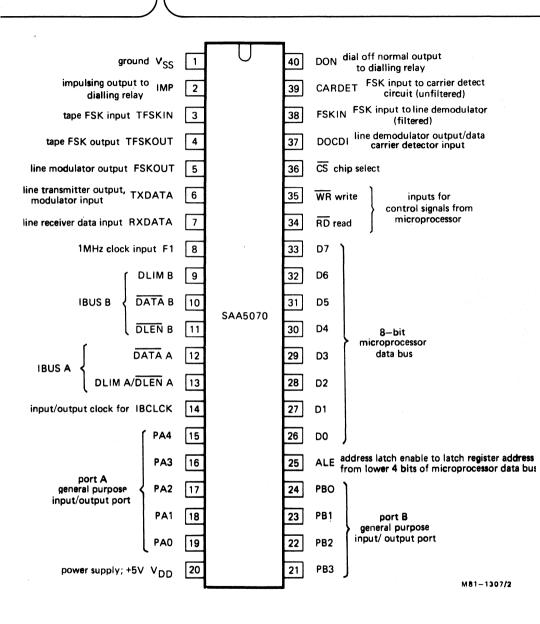

| SAA5070                   | peripheral IC for viewdata (LUCY); µC controlled                                                            | a-341          |

| SAA5230                   | teletext video processor                                                                                    | a-371          |

| SAA5240A                  | computer controlled teletext circuit (CCT);                                                                 |                |

|                           | 625-line system (English, German, Swedish)                                                                  | a-383          |

| SAA5240B                  | computer controlled teletext circuit (CCT);                                                                 |                |

|                           | 625-line system (Italian, German, French)                                                                   | a-383          |

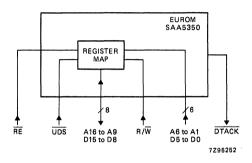

| SAA5350                   | colour CRT controller (EUROM); CEPT standard                                                                | a-409          |

| Microcontrollers          |                                                                                                             |                |

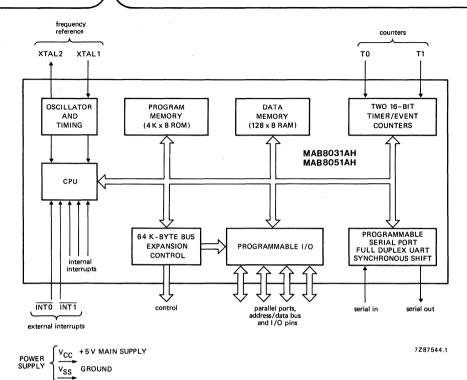

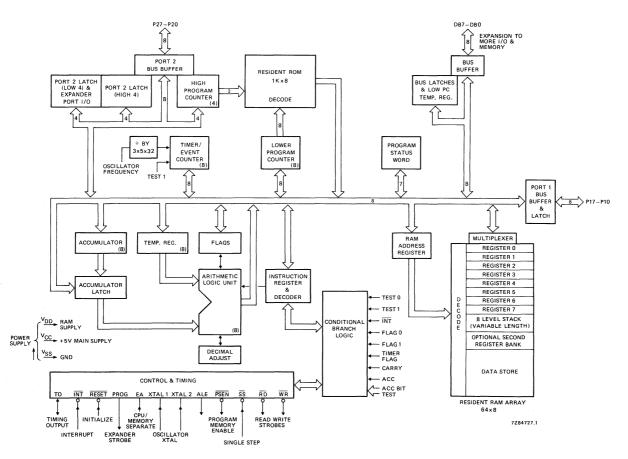

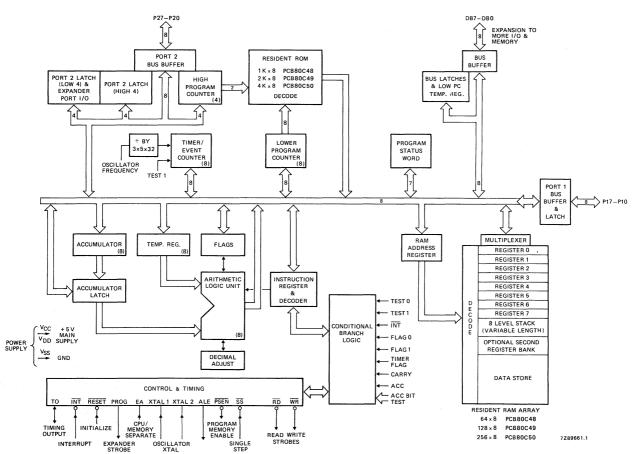

| MAB8031AHP                | single-chip 8-bit µC; ROM-less version of MAB8051AH                                                         | a-29           |

| MAB8031AHWP               | single-chip 8-bit µC; ROM-less version of MAB8051AH                                                         | a-29           |

| MAB8035HLP                | single-chip 8-bit $\mu$ C; ROM-less version of MAB8048H                                                     | a-31           |

| MAB8035HLWP               | single-chip 8-bit $\mu$ C; ROM-less version of MAB8048H                                                     | a-31           |

| MAB8035HLT                | single-chip 8-bit $\mu$ C; ROM-less version of MAB8048H                                                     | a-31           |

| MAB8039HLP                | single-chip 8-bit $\mu$ C; ROM-less version of MAB8049H                                                     | a-33           |

| MAB8039HLWP               | single-chip 8-bit $\mu$ C; ROM-less version of MAB8049H                                                     | a-33           |

| MAB8039HLT                | single-chip 8-bit $\mu$ C; ROM-less version of MAB8049H                                                     | a-33           |

| MAB8040HLP                | single-chip 8-bit $\mu$ C; ROM-less version of MAB8050H                                                     | a-35           |

| MAB8048HP                 | single-chip 8-bit μC; 1Kx8 ROM, 64x8 RAM                                                                    | a-31           |

| MAB8048HWP                | single-chip 8-bit µC; 1Kx8 ROM, 64x8 RAM                                                                    | a-31           |

| MAB8048HT                 | single-chip 8-bit μC; 1Kx8 ROM, 64x8 RAM                                                                    | a-31           |

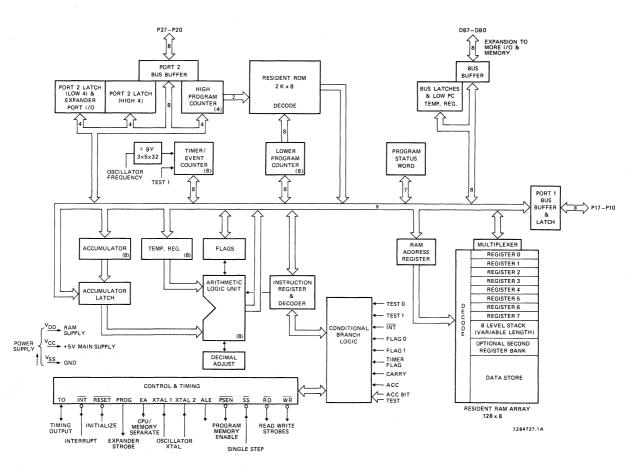

| MAB8049HP                 | single-chip 8-bit $\mu$ C; 2Kx8 ROM, 128x8 RAM                                                              | a-33           |

| MAB8049HWP                | single-chip 8-bit $\mu$ C; 2Kx8 ROM, 128x8 RAM                                                              | a-33           |

| MAB8049HT                 | single-chip 8-bit $\mu$ C; 2Kx8 ROM, 128x8 RAM                                                              | a-33           |

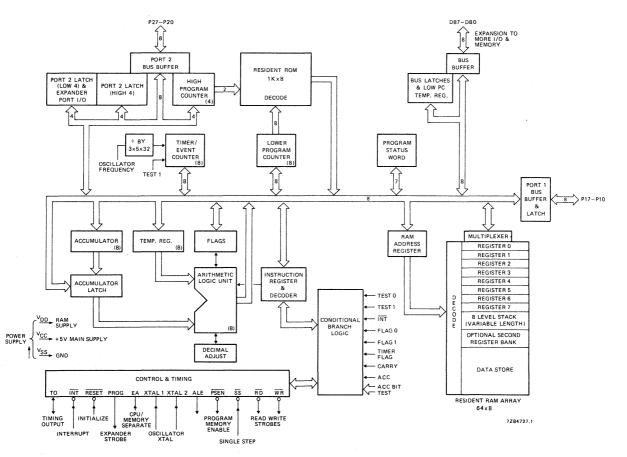

| MAB8050HP                 | single-chip 8-bit μC; 4Kx8 ROM, 256x8 RAM                                                                   | a-35           |

| MAB8051AHP                | single-chip 8-bit μC; 4Kx8 ROM, 128x8 RAM                                                                   | a-29           |

| MAB8051AHWP               | single-chip 8-bit $\mu$ C; 4Kx8 ROM, 128x8 RAM                                                              | a-29           |

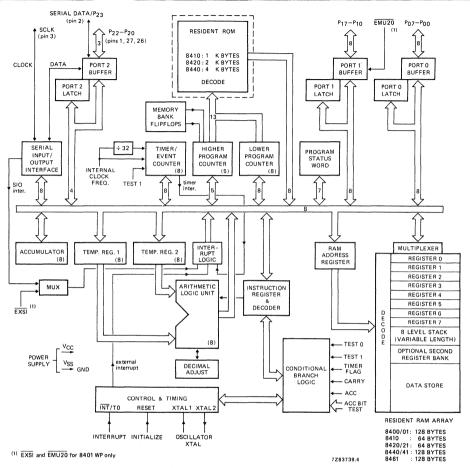

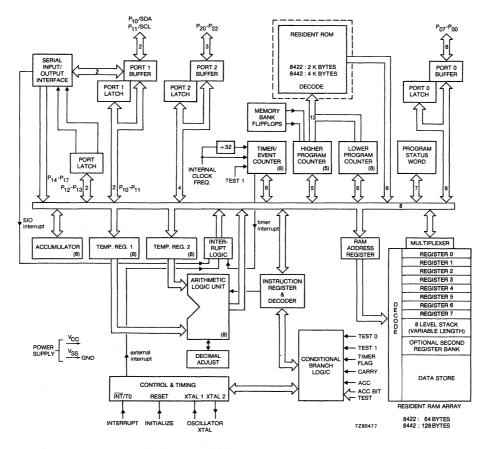

| MAB8400B                  | single-chip 8-bit $\mu$ C; 128 RAM bytes                                                                    | a-37           |

| MAB8400WP                 | single-chip 8-bit $\mu$ C; 128 RAM bytes                                                                    | a-37           |

| ype number            | description                                                                 | page |

|-----------------------|-----------------------------------------------------------------------------|------|

| licrocontrollers (con | tinued)                                                                     |      |

| /IAB8401B             | like MAB8400 but with 8-bit LED-driver                                      | a-37 |

| AB8401WP              | like MAB8400 but with 8-bit LED-driver                                      | a-37 |

| /IAB8410P             | single-chip 8-bit $\mu$ C; 1K ROM/64 RAM bytes                              | a-37 |

| /AB8410T              | single-chip 8-bit $\mu$ C; 1K ROM/64 RAM bytes                              | a-37 |

| /AB8420P              | single-chip 8-bit $\mu$ C; 2K ROM/64 RAM bytes                              | a-37 |

| /IAB8420T             | single-chip 8-bit µC; 2K ROM/64 RAM bytes                                   | a-37 |

| /IAB8421P             | single-chip 8-bit µC; 2K ROM/64 RAM bytes plus 8-bit LED driver             | a-37 |

| /IAB8421T             | single-chip 8-bit $\mu$ C; 2K ROM/64 RAM bytes plus 8-bit LED driver        | a-37 |

| /IAB8422P             | single-chip 8-bit $\mu$ C; 2K ROM/64 RAM bytes                              | a-39 |

| /IAB8440P             | single-chip 8-bit $\mu$ C; 4K ROM/128 RAM bytes                             | a-37 |

| /IAB8440T             | single-chip 8-bit µC; 4K ROM/128 RAM bytes                                  | a-37 |

| /IAB8441P             | single-chip 8-bit $\mu$ C; 4K ROM/128 RAM bytes plus 8-bit LED driver       | a-37 |

| /IAB8441T             | single-chip 8-bit $\mu$ C; 2K ROM/128 RAM bytes plus 8-bit LED driver       | a-37 |

| /IAB8442P             | single-chip 8-bit μC; 4K ROM/128 RAM bytes                                  | a-39 |

| /AB8461P              | single-chip 8-bit $\mu$ C; 6K ROM/128 RAM bytes plus 8-bit LED driver       | a-37 |

| AF8031AHP             | single-chip 8-bit $\mu$ C; ROM-less version of MAB8051AH;                   |      |

|                       | extended temperature                                                        | a-29 |

| AF8031AHWP            | single-chip 8-bit $\mu$ C; ROM-less version of MAB8051AH;                   |      |

|                       | extended temperature                                                        | a-29 |

| /AF8035HLP            | single-chip 8-bit $\mu$ C; ROM-less version of MAB8048H;                    |      |

|                       | extended temperature                                                        | a-31 |

| AF8035HLWP            | single-chip 8-bit $\mu$ C; ROM-less version of MAB8048H;                    |      |

| AF8039HLP             | extended temperature<br>single-chip 8-bit µC; ROM-less version of MAB8049H; | a-31 |

| IAI 803911LF          | extended temperature                                                        | a-33 |

| /AF8039HLWP           | single-chip 8-bit $\mu$ C; ROM-less version of MAB8049H;                    | 4.00 |

| /AF6039HLWF           | extended temperature                                                        | a-33 |

| /AF80A39HLP           | single-chip 8-bit μC; ROM-less version of MAB80A49H;                        | a-30 |

|                       | reduced frequency; extended temperature                                     | a-33 |

| /IAF8048HP            | single-chip 8-bit $\mu$ C; 1Kx8 ROM, 64x8 RAM; extended temperature         | a-31 |

| AF8048HWP             | single-chip 8-bit $\mu$ C; 1Kx8 ROM, 64x8 RAM; extended temperature         | a-31 |

| /AF8049HP             | single-chip 8-bit $\mu$ C; 2Kx8 ROM, 128x8 RAM; extended temperature        | a-33 |

| AF8049HWP             | single-chip 8-bit µC; 2Kx8 ROM, 128x8 RAM; extended temperature             | a-33 |

| AF80A49HP             | single-chip 8-bit $\mu$ C; 2Kx8 ROM, 128x8 RAM; reduced frequency;          | 4 00 |

|                       | extended temperature                                                        | a-33 |

| AF8051AHP             | single-chip 8-bit $\mu$ C; 4Kx8 ROM, 128x8 RAM; extended temperature        | a-29 |

| /AF8051AHWP           | single-chip 8-bit $\mu$ C; 4Kx8 ROM, 128x8 RAM; extended temperature        | a-29 |

| /IAF8410P             | single-chip 8-bit $\mu$ C; 1K ROM/64 RAM bytes                              | a-37 |

| /AF8420P              | single-chip 8-bit µC; 2K ROM/64 RAM bytes                                   | a-37 |

| /AF8421P              | single-chip 8-bit $\mu$ C; 2K ROM/64 RAM bytes plus 8-bit LED driver        | a-37 |

| /AF8422P              | single-chip 8-bit $\mu$ C; 2K ROM/64 RAM bytes; extended temperature        | a-39 |

|                       |                                                                             |      |

| AF84A22P              | single-chip 8-bit $\mu$ C; 2K ROM/64 RAM bytes; reduced frequency;          |      |

| AF84A22P              | extended temperature                                                        | a-39 |

| type number        | description                                                                                   | page         |

|--------------------|-----------------------------------------------------------------------------------------------|--------------|

| Microcontrollers ( | continued)                                                                                    |              |

| MAF8441P           | single-chip 8-bit $\mu$ C; 4K ROM/128 RAM bytes plus 8-bit LED driver                         | a-37         |

| MAF8442P           | single-chip 8-bit $\mu$ C; 4K ROM/128 RAM bytes; extended temperature                         | a-39         |

| MAF84A42P          | single-chip 8-bit μC; 4K ROM/128 RAM bytes; reduced frequency                                 | . 20         |

| MAF8461P           | extended temperature<br>single-chip 8-bit $\mu$ C; 6K ROM/128 RAM bytes plus 8-bit LED driver | a-39<br>a-37 |

| PCB80C35P          | single-chip 8-bit $\mu$ C; ROM-less version of PCB80C48                                       | a-37<br>a-41 |

| PCB80C35WP         | single-chip 8-bit $\mu$ C; ROM-less version of PCB80C48                                       | a-41         |

| PCB80C39P          | single-chip 8-bit µC; ROM-less version of PCB80C49                                            | a-41         |

| PCB80C39WP         | single-chip 8-bit $\mu$ C; ROM-less version of PCB80C49                                       | a-41         |

| PCB80C48P          | single-chip 8-bit µC; 1Kx8 ROM, 64x8 RAM                                                      | a-41         |

| PCB80C48WP         | single-chip 8-bit μC; 1Kx8 ROM, 64x8 RAM                                                      | a-41         |

| PCB80C49P          | single-chip 8-bit $\mu$ C; 2Kx8 ROM, 128x8 RAM                                                | a-41         |

| PCB80C49WP         | single-chip 8-bit µC; 2Kx8 ROM, 128x8 RAM                                                     | a-41         |

| Video games        |                                                                                               |              |

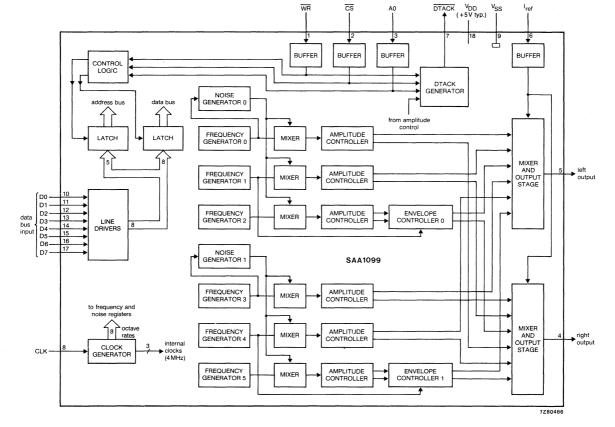

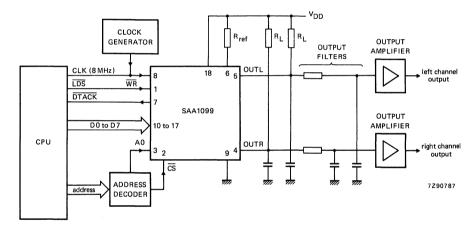

| SAA1099            | stereo sound generator for sound effects and music synthesis;                                 |              |

|                    | μC controlled                                                                                 | a-185        |

| TDA2505            | SECAM encoder                                                                                 | b-61         |

| TEA1002            | PAL colour encoder and video summer                                                           | b-71         |

| A/D and D/A conv   | verters                                                                                       |              |

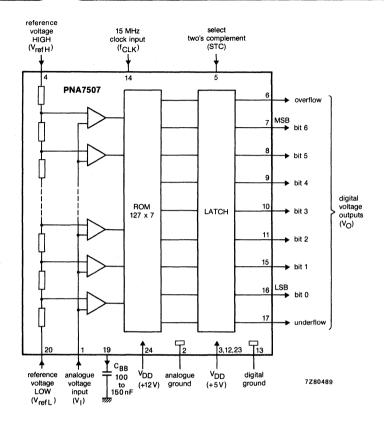

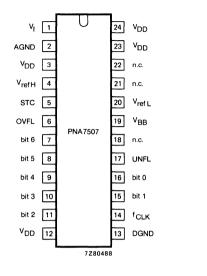

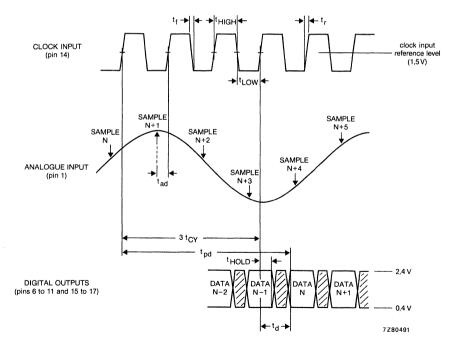

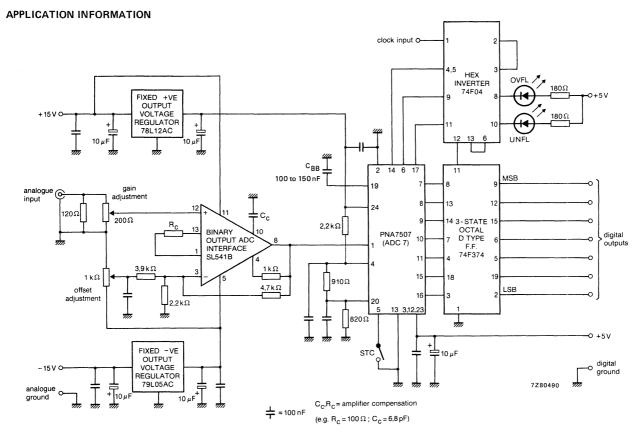

| PNA7507; A         | 7-bit analogue-to-digital converter (ADC 7)                                                   | a- <b>99</b> |

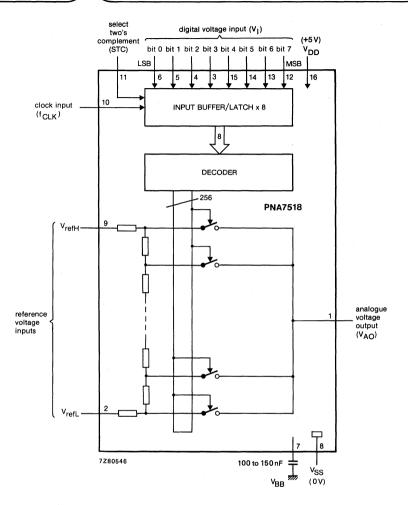

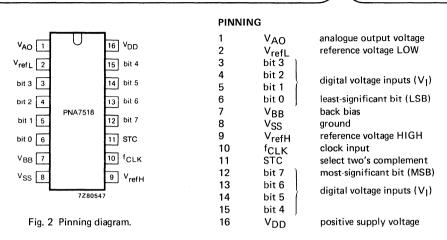

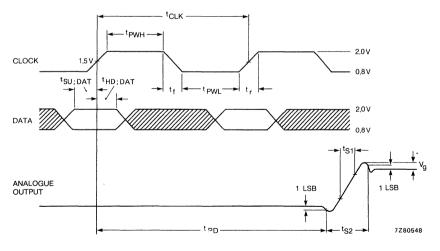

| PNA7518            | 8-bit multiplying DAC                                                                         | a-107        |

# NUMERICAL INDEX

| type number             | description                                                                                      | package code               | page         |

|-------------------------|--------------------------------------------------------------------------------------------------|----------------------------|--------------|

| MAB8031AHP              | single-chip 8-bit $\mu$ C; ROM-less version of                                                   |                            |              |

| MAB8031AHWP             | MAB8051AH single-chip 8-bit $\mu$ C; ROM-less version of                                         | SOT-129                    | a-29         |

|                         | MAB8051AH                                                                                        | 44-PLCC;SOT-187            | a-29         |

| MAB8035HLP              | single-chip 8-bit $\mu$ C; ROM-less version of MAB8048H                                          | SOT-129                    | a-31         |

| MAB8035HLWP             | single-chip 8-bit $\mu$ C; ROM-less version of MAB8048H                                          | 44-PLCC:SOT-187            | a-31         |

| MAB8035HLT              | single-chip 8-bit μC; ROM-less version of                                                        | 44-PLCC;501-187            | a-31         |

|                         | MAB8048H                                                                                         | VSO-40;SOT-158A            | a-31         |

| MAB8039HLP              | single-chip 8-bit µC; ROM-less version of MAB8049H                                               | SOT-129                    | a-33         |

| MAB8039HLWP             | single-chip 8-bit $\mu$ C; ROM-less version of                                                   |                            |              |

| MAB8039HLT              | MAB8049H<br>single-chip 8-bit µC; ROM-less version of                                            | 44-PLCC;SOT-187            | a-33         |

| MAB8040HLP              | MAB8049H                                                                                         | VSO-40; SOT-158A           | a-33         |

| MAB8040HLP              | single-chip 8-bit $\mu$ C; ROM-less version of MAB8050H                                          | SOT129                     | a-35         |

| MAB8048HP               | single-chip 8-bit $\mu$ C; 1Kx8 ROM, 64x8 RAM                                                    | SOT-129                    | a-31         |

| MAB8048HWP              | single-chip 8-bit μC; 1Kx8 ROM, 64x8 RAM                                                         | 44-PLCC;SOT-187            | a-31         |

| MAB8048HT<br>MAB8049HP  | single-chip 8-bit $\mu$ C; 1Kx8 ROM, 64x8 RAM                                                    | VSO-40;SOT-158A            | a-31         |

| MAB8049HP<br>MAB8049HWP | single-chip 8-bit $\mu$ C; 2Kx8 ROM, 128x8 RAM<br>single-chip 8-bit $\mu$ C; 2Kx8 ROM, 128x8 RAM | SOT-129<br>44-PLCC;SOT-187 | a-33<br>a-33 |

| MAB8049HT               | single-chip 8-bit $\mu$ C; 2Kx8 ROM, 128x8 RAM                                                   | VSO-40; SOT-158A           | a-33         |

| MAB8050HP               | single-chip 8-bit µC; 4Kx8 ROM, 256x8 RAM                                                        | SOT-129                    | a-35         |

| MAB8051AHP              | single-chip 8-bit $\mu$ C; 4Kx8 ROM, 128x8 RAM                                                   | SOT-129                    | a-29         |

| MAB8051AHWP             | single-chip 8-bit µC; 4Kx8 ROM, 128x8 RAM                                                        | 44-PLCC; SOT-187           | a-29         |

| MAB8400B                | single-chip 8-bit $\mu$ C; 128 RAM bytes                                                         | 28/28 "Piggy back"         | a-37         |

| MAB8400WP               | single-chip 8-bit µC; 128 RAM bytes                                                              | 68-PLCC; SOT-188A          | a-37         |

| MAB8401B                | like MAB8400 but with 8-bit LED-driver                                                           | 28/28 "Piggy back"         | a-37         |

| MAB8401WP               | like MAB8400 but with 8-bit LED-driver                                                           | 68-PLCC; SOT-188A          | a-37         |

| MAB8410P                | single-chip 8-bit $\mu$ C; 1K ROM/64 RAM bytes                                                   | SOT-117A                   | a-37         |

| MAB8410T<br>MAB8420P    | single-chip 8-bit µC; 1K ROM/64 RAM bytes<br>single-chip 8-bit µC; 2K ROM/64 RAM bytes           | SO-28; SOT-136A            | a-37         |

|                         |                                                                                                  | SOT-117A                   | a-37         |

| MAB8420T<br>MAB8421P    | single-chip 8-bit $\mu$ C; 2K ROM/64 RAM bytes<br>single-chip 8-bit $\mu$ C; 2K ROM/64 RAM bytes | SO-28; SOT-136A            | a-37         |

| MADOAOAT                | plus 8-bit LED driver                                                                            | SOT-117A                   | a-37         |

| MAB8421T                | single-chip 8-bit $\mu$ C; 2K ROM/64 RAM bytes plus 8-bit LED driver                             | CO 20. COT 12C A           | - 27         |

| MAB8422P                | single-chip 8-bit $\mu$ C; 2K ROM/64 RAM bytes                                                   | SO-28;SOT-136A<br>SOT-146  | a-37<br>a-39 |

| MAB8440P                | single-chip 8-bit $\mu$ C; 4K ROM/128 RAM bytes                                                  | SOT117A                    | a-39<br>a-37 |

|                         |                                                                                                  |                            |              |

### Numerical index

| type number                | description                                                                                                                         | package code                | page         |

|----------------------------|-------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|--------------|

| MAB8440T<br>MAB8441P       | single-chip 8-bit $\mu$ C; 4K ROM/128 RAM bytes<br>single-chip 8-bit $\mu$ C; 4K ROM/128 RAM bytes                                  | SO-28;SOT-136A              | a-37         |

| MAB8441T                   | plus 8-bit LED driver<br>single-chip 8-bit μC; 2K ROM/128 RAM bytes                                                                 | SOT-117A                    | a-37         |

| MAB8442P<br>MAB8461P       | plus 8-bit LED driver<br>single-chip 8-bit $\mu$ C; 4K ROM/128 RAM bytes<br>single-chip 8-bit $\mu$ C; 6K ROM/128 RAM bytes         | SO-28; SOT-136A<br>SOT-146  | a-37<br>a-39 |

|                            | plus 8-bit LED driver                                                                                                               | SOT-117A                    | a-37         |

| MAF8031AHP<br>MAF8031AHWP  | single-chip 8-bit $\mu$ C; ROM-less version of<br>MAB8051AH; extended temperature<br>single-chip 8-bit $\mu$ C; ROM-less version of | SOT-129                     | a-29         |

| MAF8035HLP                 | MAB8051AH; extended temperature<br>single-chip 8-bit $\mu$ C; ROM-less version of                                                   | 44-PLCC;SOT-187             | a-29         |

| MAF8035HLWP                | MAB8048H; extended temperature single-chip 8-bit $\mu$ C; ROM-less version of                                                       | SOT-129                     | a-31         |

| MAF8039HLP                 | MAB8048H; extended temperature single-chip 8-bit $\mu$ C; ROM-less version of                                                       | 44-PLCC;SOT-187             | a-31         |

|                            | MAB8049H; extended temperature                                                                                                      | SOT-129                     | a-33         |

| MAF8039HLWP<br>MAF80A39HLP | single-chip 8-bit $\mu$ C; ROM-less version of<br>MAB8049H; extended temperature<br>single-chip 8-bit $\mu$ C; ROM-less version of  | 44-PLCC; SOT-187            | a-33         |

| MAF8048HP                  | MAB80A49H; reduced frequency;<br>extended temperature<br>single-chip 8-bit $\mu$ C; 1Kx8 ROM, 64x8 RAM;                             | SOT-129                     | a-33         |

| MAF8048HWP                 | extended temperature single-chip 8-bit $\mu$ C; 1Kx8 ROM, 64x8 RAM;                                                                 | SOT-129                     | a-31         |

| MAF8049HP                  | extended temperature single-chip 8-bit $\mu$ C; 2Kx8 ROM, 128x8 RAM;                                                                | 44-PLCC;SOT-187             | a-31         |

| MAF8049HWP                 | extended temperature<br>single-chip 8-bit μC; 2Kx8 ROM, 128x8 RAM;                                                                  | SOT-129                     | a-33         |

| MAF80A49HP                 | extended temperature<br>single-chip 8-bit μC; 2Kx8 ROM, 128x8 RAM;                                                                  | 44-PLCC;SOT-187             | a-33         |

| MAF8051AHP                 | reduced frequency; extended temperature single-chip 8-bit $\mu$ C; 4Kx8 ROM, 128x8 RAM;                                             | SOT-129                     | a-33         |

| MAF8051AHWP                | extended temperature single-chip 8-bit $\mu$ C; 4Kx8 ROM, 128x8 RAM;                                                                | SOT-129                     | a-29         |

| MAF8410P                   | extended temperature single-chip 8-bit $\mu$ C; 1K ROM/64 RAM bytes                                                                 | 44-PLCC;SOT-187<br>SOT-117A | a-29<br>a-37 |

| MAF8420P<br>MAF8421P       | single-chip 8-bit $\mu$ C; 2K ROM/64 RAM bytes single-chip 8-bit $\mu$ C; 2K ROM/64 RAM bytes                                       | SOT-117A                    | a-37         |

| MAF8422P                   | plus 8-bit LED driver<br>single-chip 8-bit μC; 2K ROM/64 RAM bytes;                                                                 | SOT-117A                    | a-37         |

| MAF84A22P                  | extended temperature<br>single-chip 8-bit $\mu$ C; 2K ROM/64 RAM bytes;<br>reduced frequency; extended temperature                  | SOT-146<br>SOT-146          | a-39         |

| MAF8440P                   | single-chip 8-bit $\mu$ C; 4K ROM/128 RAM bytes                                                                                     | SOT-117A                    | a-39<br>a-37 |

| type number             | description                                                                            | package code               | page           |

|-------------------------|----------------------------------------------------------------------------------------|----------------------------|----------------|

| MAF8441P                | single-chip 8-bit µC; 4K ROM/128 RAM bytes                                             |                            |                |

|                         | plus 8-bit LED driver                                                                  | SOT-117A                   | a-37           |

| MAF8442P                | single-chip 8-bit $\mu$ C; 4K ROM/128 RAM bytes;                                       |                            | u 07           |

|                         | extended temperature                                                                   | SOT-146                    | a-39           |

| MAF84A42P               | single-chip 8-bit µC; 4K ROM/128 RAM bytes;                                            |                            |                |

|                         | reduced frequency; extended temperature                                                | SOT-146                    | a-39           |

| MAF8461P                | single-chip 8-bit µC; 6K ROM/128 RAM bytes                                             |                            |                |

|                         | plus 8-bit LED driver                                                                  | SOT-117A                   | a-37           |

| PCB80C35P               | single-chip 8-bit $\mu$ C; ROM-less version of                                         |                            |                |

|                         | PCB80C48                                                                               | SOT-129                    | a-41           |

| PCB80C35WP              | single-chip 8-bit µC; ROM-less version of                                              |                            |                |

|                         | PCB80C48                                                                               | 44-PLCC;SOT-187            | a-41           |

| PCB80C39P               | single-chip 8-bit $\mu$ C; ROM-less version of                                         | 00T 100                    |                |

| PCB80C39WP              | PCB80C49<br>single-chip 8-bit μC; ROM-less version of                                  | SOT-129                    | a-41           |

| FCDOUCSSWF              | PCB80C49                                                                               | 44-PLCC;SOT-187            | a-41           |

| PCB80C48P               | single-chip 8-bit µC; 1Kx8 ROM, 64x8 RAM                                               | SOT-129                    | a-41<br>a-41   |

| PCB80C48WP              | single-chip 8-bit $\mu$ C; 1Kx8 ROM, 64x8 RAM                                          | 44-PLCC;SOT-187            | a-41<br>a-41   |

| PCB80C49P               | <b>3</b>                                                                               |                            |                |

| PCB80C49P<br>PCB80C49WP | single-chip 8-bit μC; 2Kx8 ROM, 128x8 RAM<br>single-chip 8-bit μC; 2Kx8 ROM, 128x8 RAM | SOT-129<br>44-PLCC;SOT-187 | a-41<br>a-41   |

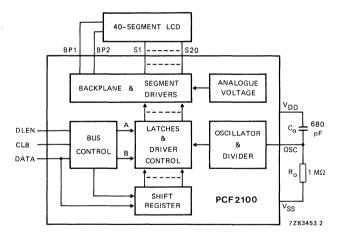

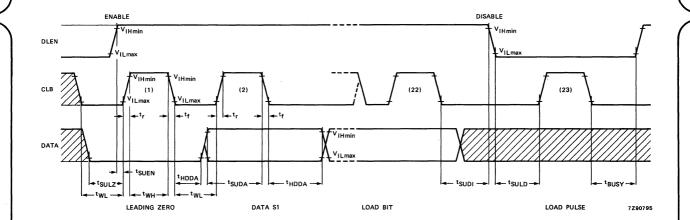

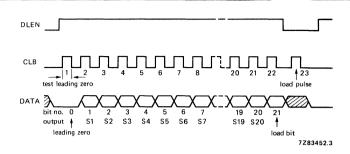

| PCF2100P                | LCD duplex driver; 40 segments                                                         | SOT-117D                   | a-41<br>a-43   |

| PCF2100T                | LCD duplex driver; 40 segments                                                         | SO-28;SOT-136A             | a-43           |

| PCF2110P                | LCD duplex driver; 60 segments and 2 LEDs                                              | SOT-129                    | a-53           |

| PCF2110T                | LCD duplex driver; 60 segments and 2 LEDs                                              | VSO-40; SOT-158A           | a-53           |

| PCF2111P                | LCD duplex driver; 64 segments                                                         | SOT-129                    | a-55<br>a-63   |

| PCF2111T                | LCD duplex driver; 64 segments                                                         | VSO-40; SOT-158A           | a-63           |

| PCF2112P                | LCD driver; 32 segments                                                                | SOT-129                    | a-73           |

| PCF2112T                | LCD driver; 32 segments                                                                | VSO-40; SOT-158A           | a-73           |

| PCF8573P                | clock/calendar with serial I/O (I <sup>2</sup> C bus)                                  | SOT-38                     | a-81           |

| PCF8573T                | clock/calender with serial I/O (I <sup>2</sup> C bus)                                  | SO-16L;SOT-162A            | a-81           |

| PNA7507; A              | 7-bit analogue-to-digital converter (ADC 7)                                            | SOT-101A                   | a-99           |

| PNA7518                 | 8-bit multiplying DAC                                                                  | SOT-38WE-1                 | a-107          |

| SAA1043                 | universal sync generator                                                               | SOT-117                    | a-113          |

| SAA1044                 | subcarrier coupling circuit                                                            | SOT-38                     | a-129          |

| SAA1056P                | PLL frequency synthesizer                                                              | SOT-38Z                    | a-137          |

| SAA1057                 | radio tuning PLL frequency synthesizer (SYMOII)                                        | SOT-102HE                  | a-145          |

| SAA1060                 | LED display/interface circuit                                                          | SOT-101A                   | a-155          |

| SAA1061                 | LED driver/output port expander                                                        | SOT-101A                   | a-161          |

| SAA1062A                | LCD display/interface circuit                                                          | SOT-117                    | a-167          |

| SAA1062AT               | LCD display/interface circuit                                                          | SO-28;SOT-136A             | a-167          |

| SAA1082P                | remote transmitter                                                                     | SOT-117                    | a-173          |

| SAA1099                 | stereo sound generator for sound effects                                               | SOT 10200                  | - 405          |

| SAA1300                 | and music synthesis; µC controlled tuner switching unit                                | SOT-102CS<br>SOT-142B      | a-185<br>a-201 |

| 0441000                 | conse switching unit                                                                   | 301-142D                   | a-201          |

### Numerical index

| type number                                         | description                                                                                                                                                                                                     | package code                                        | page                                               |

|-----------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|----------------------------------------------------|

| SAA3004P<br>SAA3004T<br>SAA3006                     | remote control transmitter for infrared operation<br>remote control transmitter for infrared operation<br>low voltage infrared remote control transmitter                                                       | SOT-146<br>SO-20; SOT-163A                          | a-205<br>a-205                                     |

| SAA3027<br>SAA3028                                  | (RC-5)<br>infrared remote control transmitter (RC-5)<br>infrared remote control transcoder                                                                                                                      | SOT-117<br>SOT-117                                  | a-215<br>a-229                                     |

| SAA5020<br>SAA5025D                                 | (RC-5); I <sup>2</sup> C bus compatible<br>teletext timing chain (625 lines)<br>teletext timing chain for USA 525 line system<br>(USTIC); 40 characters per row,                                                | SOT-38Z<br>SOT-101A                                 | a-243<br>a-251                                     |

| SAA5030<br>SAA5040A, B, C<br>SAA5041                | 24 rows (8 TV lines per row)<br>teletext video processor<br>teletext acquisition and control circuit<br>teletext acquisition and control circuit                                                                | SOT-117D<br>SOT-101A<br>SOT-117<br>SOT-117          | a-261<br>a-279<br>a-289<br>a-289                   |

| SAA5042<br>SAA5045                                  | teletext acquisition and control circuit<br>gearing and address logic array for USA                                                                                                                             | SOT-117                                             | a-289                                              |

| SAA5050<br>SAA5051<br>SAA5052                       | teletext (GALA)<br>teletext character generator (English)<br>teletext character generator (German)<br>teletext character generator (Swedish)                                                                    | SOT-117D<br>SOT-117<br>SOT-117<br>SOT-117           | a-309<br>a-317<br>a-317<br>a-317                   |

| SAA5053<br>SAA5054<br>SAA5055<br>SAA5056<br>SAA5057 | teletext character generator (Italian)<br>teletext character generator (Belgian)<br>teletext character generator (US ASCII)<br>teletext character generator (Hebrew)<br>teletext character generator (Cyrillic) | SOT-117<br>SOT-117<br>SOT-117<br>SOT-117<br>SOT-117 | a-317<br>a-317<br>a-317<br>a-317<br>a-317<br>a-317 |

| SAA5070<br>SAA5230<br>SAA5240A                      | peripheral IC for viewdata (LUCY); $\mu$ C controlled<br>teletext video processor<br>computer controlled teletext circuit (CCT);                                                                                | SOT-129<br>SOT-117                                  | a-341<br>a-371                                     |

| SAA5240B                                            | 625-line system (English, German, Swedish)<br>computer controlled teletext circuit (CCT);<br>625-line system (Italian, German, French)                                                                          | SOT-129<br>SOT-129                                  | a-383<br>a-383                                     |

| SAA5350<br>SAB1164                                  | colour CRT controller (EUROM); CEPT standard sensitive 1 GHz divider by-64; $R_0 = 1 k\Omega$                                                                                                                   | SOT-129<br>SOT-97A                                  | a-409<br>a-437                                     |

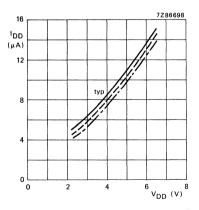

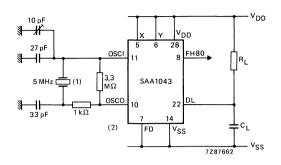

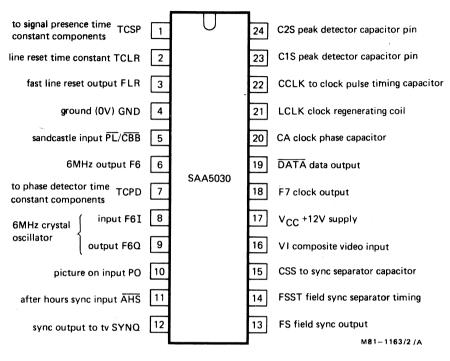

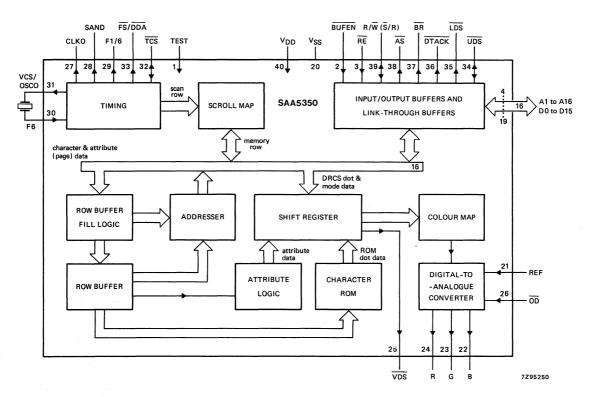

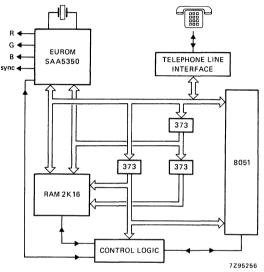

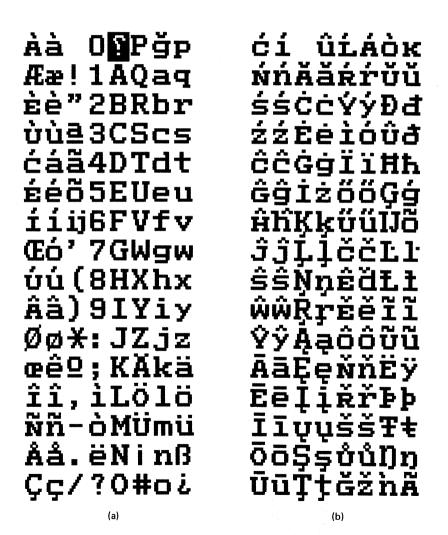

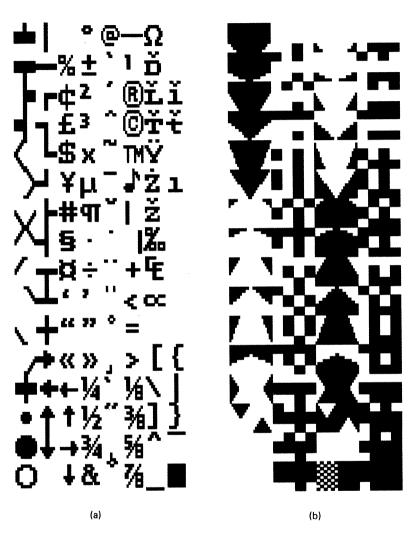

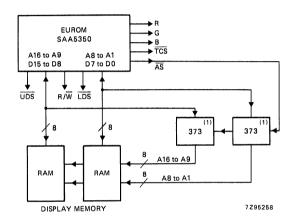

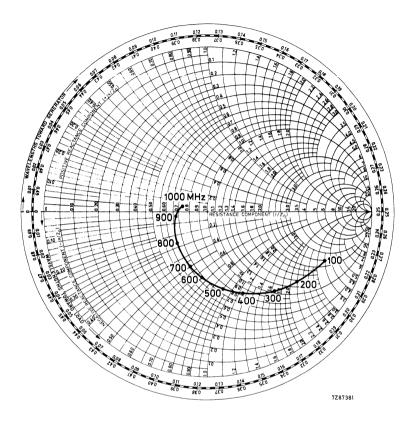

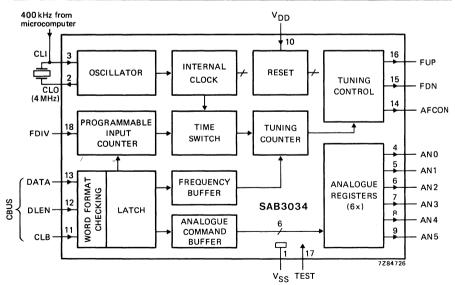

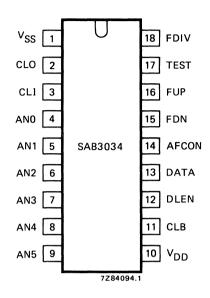

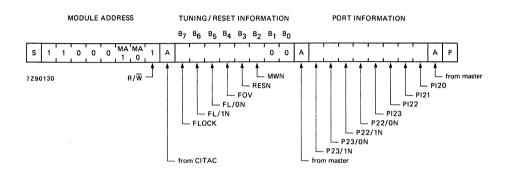

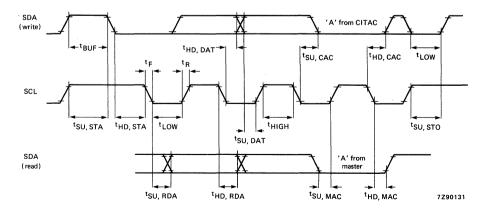

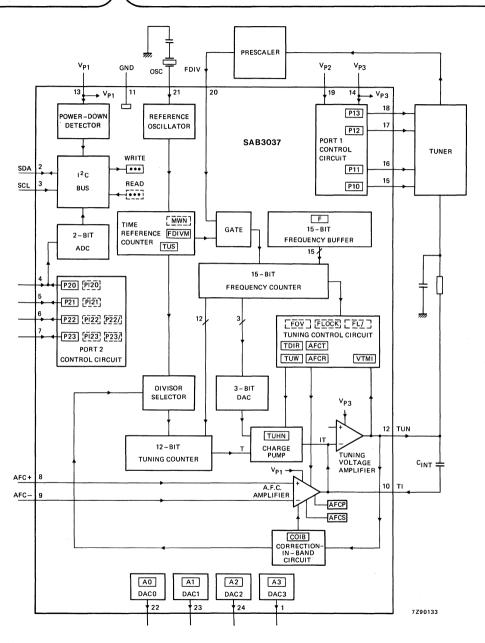

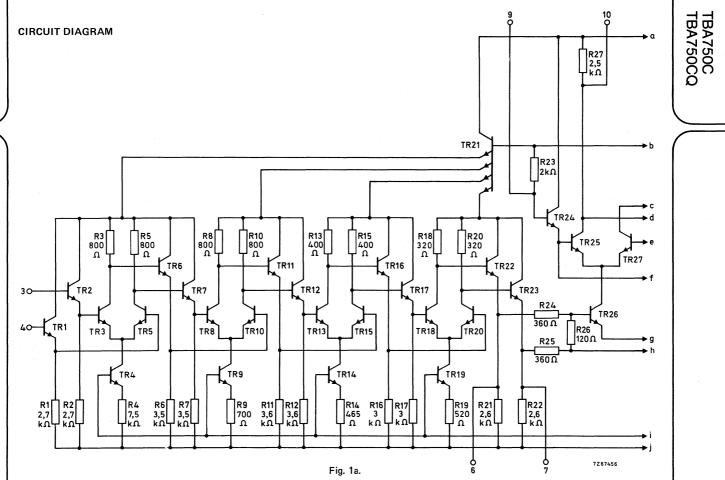

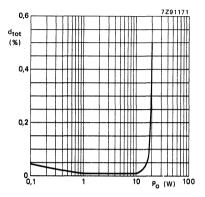

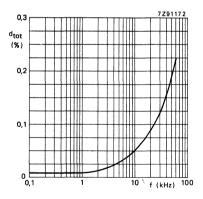

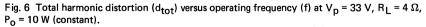

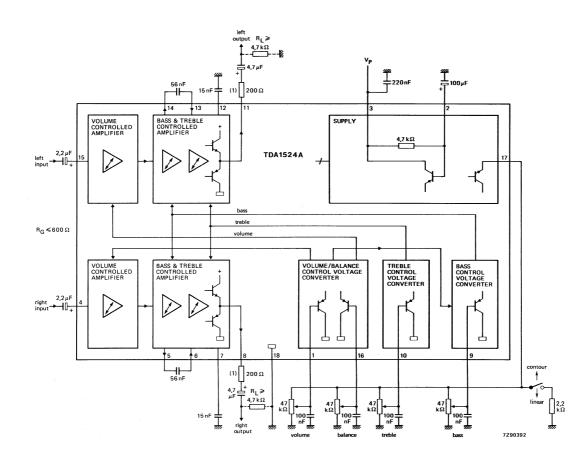

| SAB1165<br>SAB1256<br>SAB3013<br>SAB3034            | sensitive 1 GHz divider-by-64; $R_0 = 0.5 k\Omega$<br>sensitive 1 GHz divider-by-256<br>6 function analogue memory; $\mu$ C controlled<br>analogue and tuning circuit (A & T)                                   | SOT-97A<br>SOT-97A<br>SOT-38<br>SOT-102CS           | a-437<br>a-443<br>a-449                            |