Data handbook

Electronic components and materials

# Components and materials

Part 1

May 1983

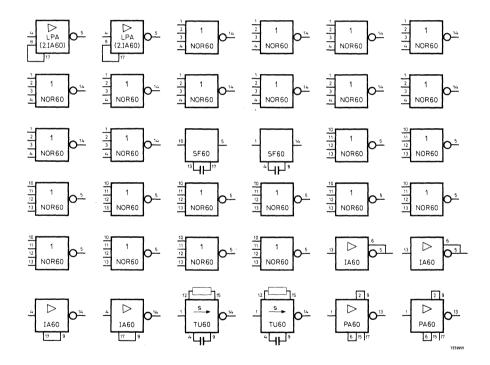

**PLC** modules

PC20 modules

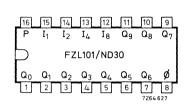

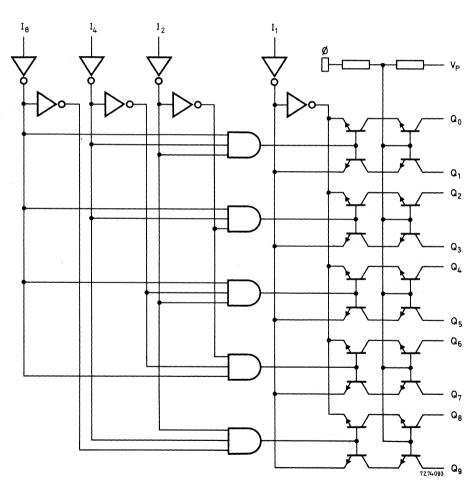

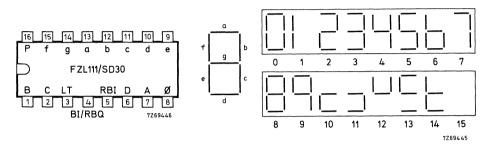

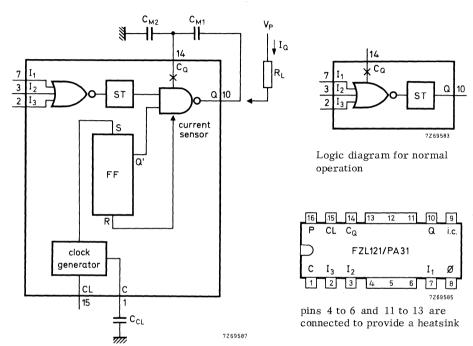

HNIL FZ/30-series

NORbits 60-series, 61-series, 90-series

Input devices

Hybrid integrated circuits

# COMPONENTS AND MATERIALS

PART 1 - MAY 1983 ASSEMBLIES

PLC MODULES

PC20 MODULES

HNIL FZ/30-SERIES

NORBITS 60-SERIES, 61-SERIES, 90-SERIES

INPUT DEVICES

HYBRID INTEGRATED CIRCUITS

CONTENTS

#### DATA HANDBOOK SYSTEM

Our Data Handbook System is a comprehensive source of information on electronic components, sub-assemblies and materials; it is made up of four series of handbooks each comprising several parts.

**ELECTRON TUBES**

**BLUE**

**SEMICONDUCTORS**

RED

INTEGRATED CIRCUITS

PURPLE

COMPONENTS AND MATERIALS

**GREEN**

The several parts contain all pertinent data available at the time of publication, and each is revised and reissued periodically.

Where ratings or specifications differ from those published in the preceding edition they are pointed out by arrows. Where application information is given it is advisory and does not form part of the product specification.

If you need confirmation that the published data about any of our products are the latest available, please contact our representative. He is at your service and will be glad to answer your inquiries.

This information is furnished for guidance, and with no guarantee as to its accuracy or completeness; its publication conveys no licence under any patent or other right, nor does the publisher assume liability for any consequence of its use; specifications and availability of goods mentioned in it are subject to change without notice; it is not to be reproduced in any way, in whole or in part without the written consent of the publisher.

# **ELECTRON TUBES (BLUE SERIES)**

The blue series of data handbooks is comprised of the following parts:

- T1 Tubes for r.f. heating

- T2 Transmitting tubes for communications

- T3 Klystrons, travelling-wave tubes, microwave diodes

- ET3 Special Quality tubes, miscellaneous devices (will not be reprinted)

- T4 Magnetrons

- T5 Cathode-ray tubes

Instrument tubes, monitor and display tubes, C.R. tubes for special applications

- T6 Geiger-Müller tubes

- T7 Gas-filled tubes

Segment indicator tubes, indicator tubes, dry reed contact units, thyratrons, industrial rectifying tubes, ignitrons, high-voltage rectifying tubes, associated accessories

- T8 Picture tubes and components

Colour TV picture tubes, black and white TV picture tubes, colour monitor tubes for data graphic display, monochrome monitor tubes for data graphic display, components for colour television, components for black and white television and monochrome data graphic display

- T9 Photo and electron multipliers

Photomultiplier tubes, phototubes, single channel electron multipliers, channel electron multiplier plates

- T10 Camera tubes and accessories, image intensifiers

- T11 Microwave components and assemblies

# SEMICONDUCTORS (RED SERIES)

The red series of data handbooks is comprised of the following parts:

| <b>S1</b> | Diodes Small-signal germanium diodes, small-signal silicon diodes, voltage regulator diodes(< 1,5 W), voltage reference diodes, tuner diodes, rectifier diodes          |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| S2        | Power diodes, thyristors, triacs Rectifier diodes, voltage regulator diodes (> 1,5 W), rectifier stacks, thyristors, triacs                                             |

| S3        | Small-signal transistors                                                                                                                                                |

| S4        | Low-frequency power transistors and hybrid IC modules                                                                                                                   |

| S5        | Field-effect transistors                                                                                                                                                |

| <b>S6</b> | R.F. power transistors and modules                                                                                                                                      |

| <b>S7</b> | Microminiature semiconductors for hybrid circuits                                                                                                                       |

| <b>S8</b> | Devices for optoelectronics Photosensitive diodes and transistors, light-emitting diodes, displays, photocouplers, infrared sensitive devices, photoconductive devices. |

| <b>S9</b> | Taken into handbook T11 of the blue series                                                                                                                              |

| S10       | Wideband transistors and wideband hybrid IC modules                                                                                                                     |

# INTEGRATED CIRCUITS (PURPLE SERIES)

The purple series of data handbooks is comprised of the following parts:

- IC1 Bipolar ICs for radio and audio equipment

- IC2 Bipolar ICs for video equipment

- IC3 ICs for digital systems in radio, audio and video equipment

- IC4 Digital integrated circuits

LOCMOS HE4000B family

- IC5 Digital integrated circuits ECL ECL10 000 (GX family), ECL100 000 (HX family), dedicated designs

- IC6 Professional analogue integrated circuits

- IC7 Signetics bipolar memories

- IC8 Signetics analogue circuits

- IC9 Signetics TTL logic

- IC10\* Signetics Integrated Fuse Logic (IFL)

- IC11\* Microprocessors, microcomputers and peripheral circuitry

\* This handbook will be available later this year.

# COMPONENTS AND MATERIALS (GREEN SERIES)

The green series of data handbooks is comprised of the following parts:

Piezoelectric ceramics, permanent magnet materials

C16

| CT  | Assemblies for industrial use PLC modules, PC20 modules, HNIL FZ/30 series, NORbits 60-, 61-, 90-series, input devices, hybrid ICs                                                               |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| C2  | Television tuners, video modulators, surface acoustic wave filters                                                                                                                               |

| C3  | Loudspeakers                                                                                                                                                                                     |

| C4  | Ferroxcube potcores, square cores and cross cores                                                                                                                                                |

| C5  | Ferroxcube for power, audio/video and accelerators                                                                                                                                               |

| C6  | Electric motors and accessories Permanent magnet synchronous motors, stepping motors, direct current motors                                                                                      |

| C7  | Variable capacitors                                                                                                                                                                              |

| C8  | Variable mains transformers                                                                                                                                                                      |

| С9  | Piezoelectric quartz devices  Quartz crystal units, temperature compensated crystal oscillators, compact integrated oscillators, quartz crystal cuts for temperature measurements                |

| C10 | Connectors                                                                                                                                                                                       |

| C11 | Non-linear resistors  Voltage dependent resistors (VDR), light dependent resistors (LDR), negative temperature coefficient thermistors (NTC), positive temperature coefficient thermistors (PTC) |

| C12 | Variable resistors and test switches                                                                                                                                                             |

| C13 | Fixed resistors                                                                                                                                                                                  |

| C14 | Electrolytic and solid capacitors                                                                                                                                                                |

| C15 | Film capacitors, ceramic capacitors                                                                                                                                                              |

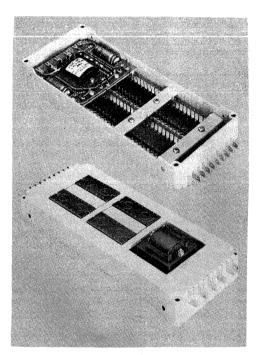

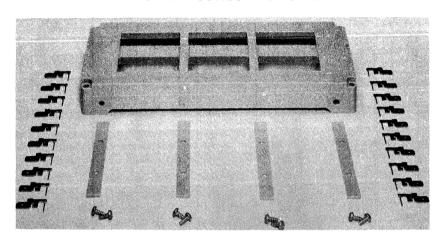

PLC MODULES

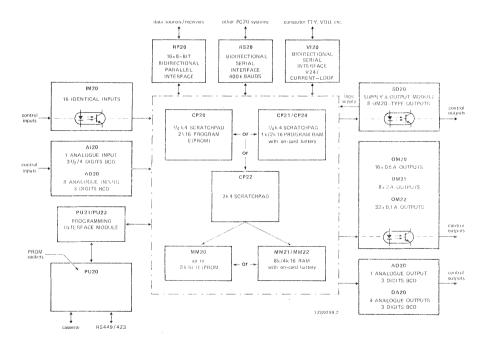

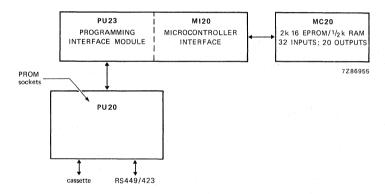

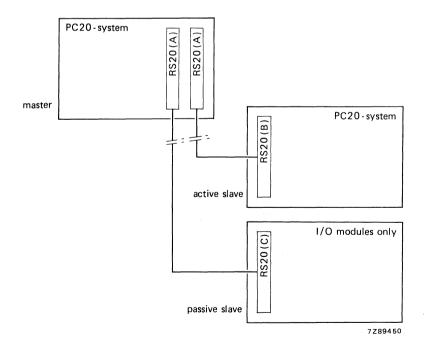

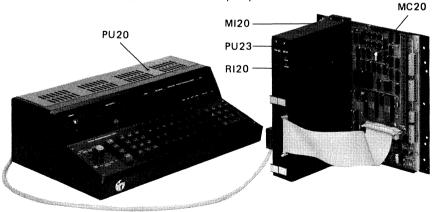

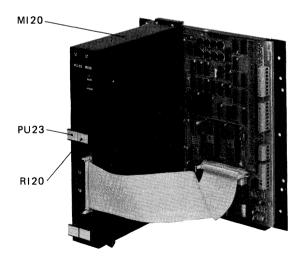

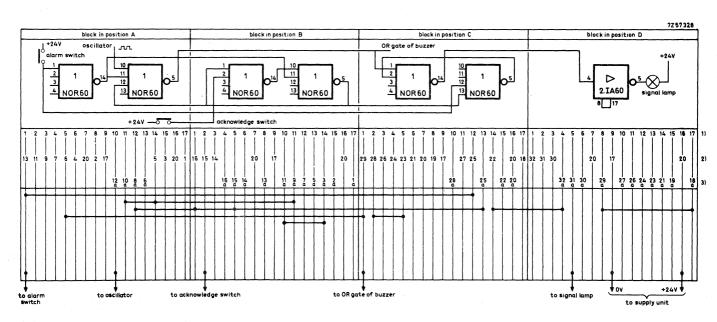

### MODULES FOR PROGRAMMABLE LOGIC CONTROLLERS

#### INTRODUCTION

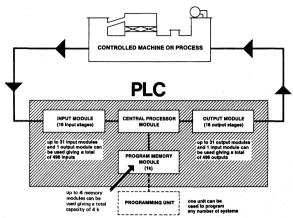

The programmable logic controller (PLC) is used for the controlling of machines or processes. It can be easily programmed and re-programmed as required.

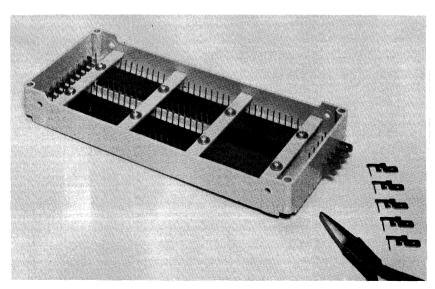

The modular design of the PLC enables a user to build a PLC which is 'tailor-made' for his control task. By specifying the number and the types of PLC modules that he requires, he avoids purchasing more of the expensive electronic capability than he needs.

The PLC modules are formed on standard double Eurocards. Optically coupled interface circuits, specifically designed for an industrial environment, provide excellent noise immunity and a high degree of isolation. The internationally accepted machine signal level of 24 V is used and generous tolerances on operational margins and thresholds ease compatibility headaches.

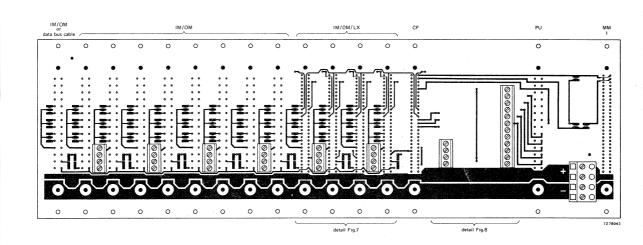

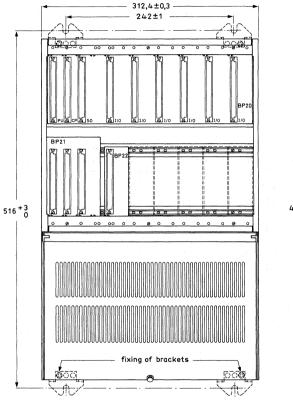

Besides the PLC modules, the PLC comprises back panels, a frame (19 in rack) and a standard power supply. The frame must conform to IEC297 or DIN41494 (for racks) and IEC130-14 or DIN41612 (for connectors). The adoption of these standards means that the frame and the power supply should be easily obtainable.

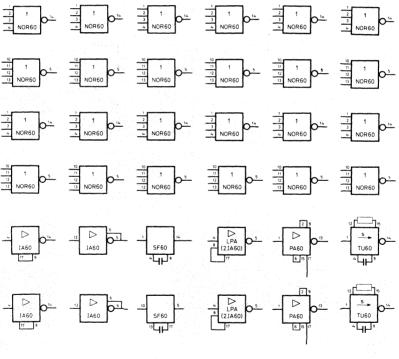

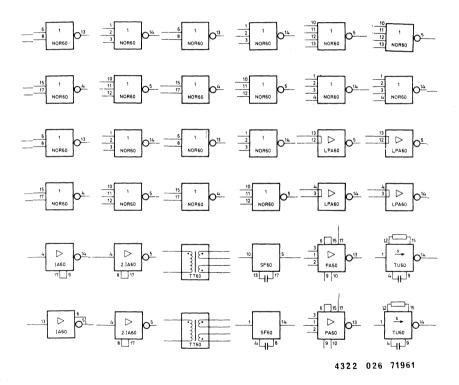

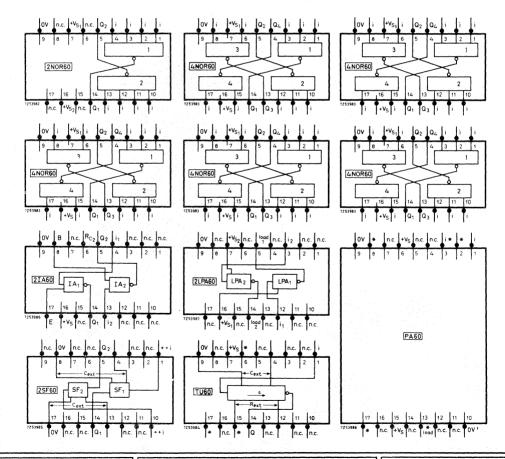

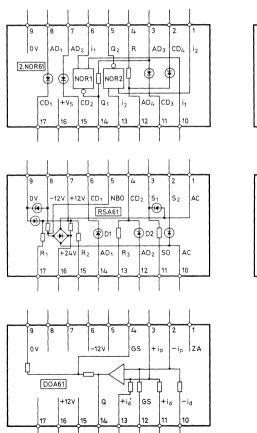

The following PLC modules are available.

| type    | description                                                                                                        | catalogue no.  |

|---------|--------------------------------------------------------------------------------------------------------------------|----------------|

| CP10    | central processor, 32 registers                                                                                    | 4322 027 90420 |

| CP11    | central processor, without registers                                                                               | 4322 027 90390 |

| IM10    | input module, 16 inputs, 24 V d.c.                                                                                 | 4322 027 90434 |

| IM11    | input module, 16 inputs, 24 V a.c.                                                                                 | 4322 027 90403 |

| LX10    | load external interface module                                                                                     | 4322 027 91600 |

| MM10    | program memory module, 1 k, non-volatile core RAM                                                                  | 4322 027 91400 |

| MM11    | program memory module, non-volatile, UV-erasable PROMs, 1 k 13 or 2 k 13 capacity; for program copying or read-out | 4322 027 91630 |

| MM12    | program memory module, non-volatile, UV-erasable PROMs, 1 k 13 or 2 k 13 capacity: for read-out only               | 4322 027 91640 |

| OM10    | output module, 16 outputs, max. 0,1 A each, 24 V d.c.                                                              | 4322 027 90440 |

| OM12    | output module, 8 outputs max. 2 A each, 24 V d.c.                                                                  | 9360 011 50112 |

| PI10*   | punch and teletype interface module                                                                                | 8222 412 41572 |

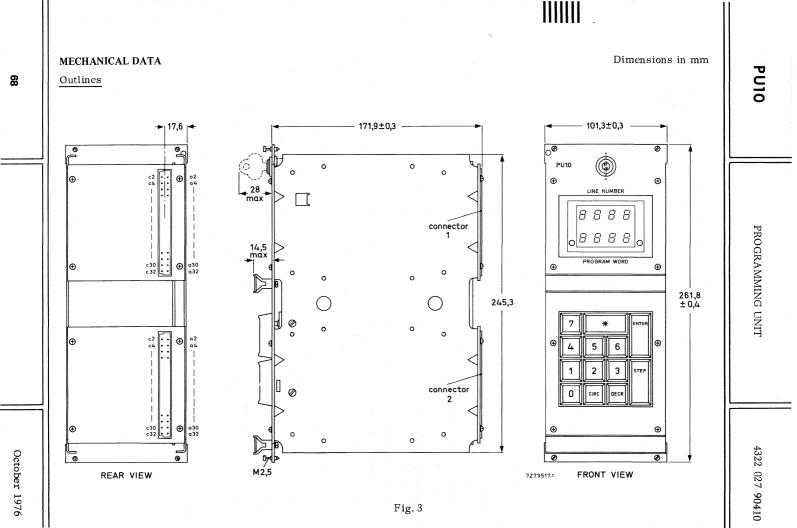

| PU10    | programming unit                                                                                                   | 4322 027 90410 |

| BP11 to | back panels                                                                                                        | 9390 269 .0112 |

<sup>\*</sup> Development type.

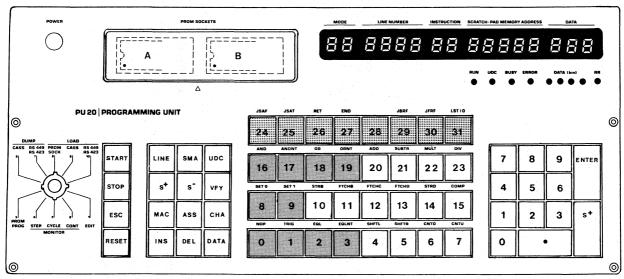

# MODULES FOR PROGRAMMABLE LOGIC CONTROLLERS

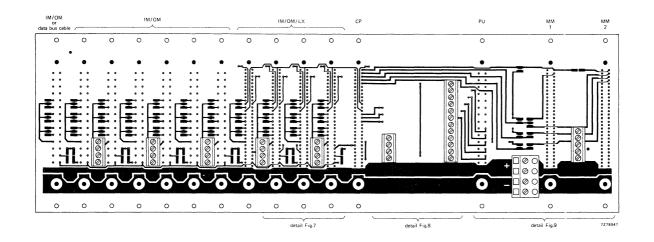

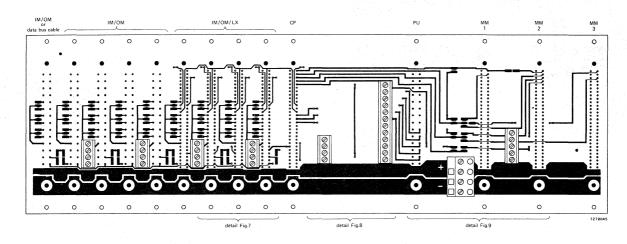

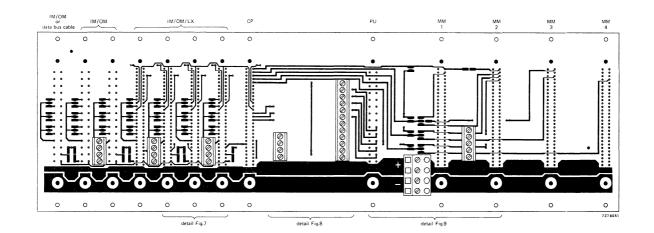

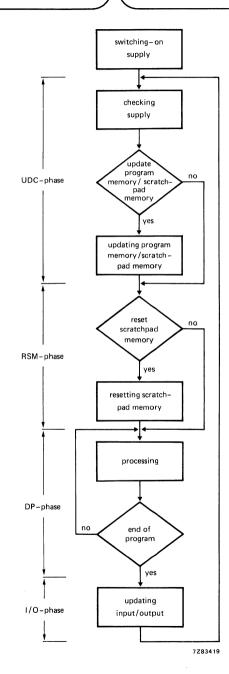

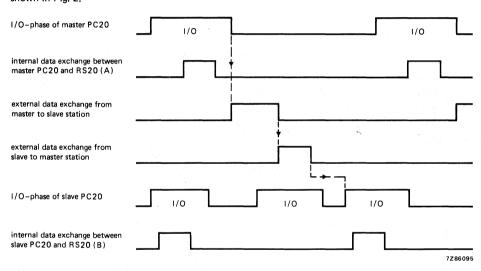

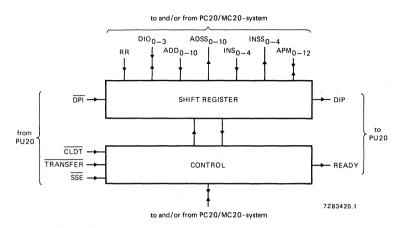

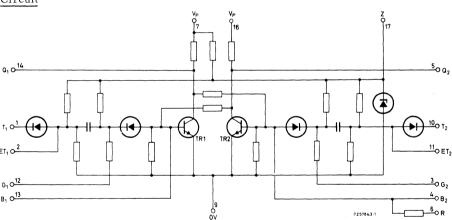

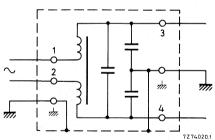

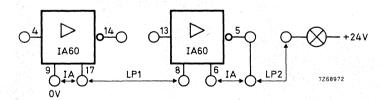

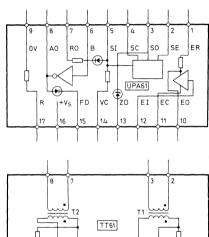

The diagram shows, in a simplified form, the function of each of the PLC modules. In operation the PLC cycles continuously through a data input/output cycle and a data processing cycle.

The input module converts the signals from the plant into a binary form acceptable to the central processor.

The central processor reads the data from the input module, performs logic equations on it in accordance with the program instructions and transfers the results to the output module.

The output module converts the binary data from the central processor to electrical signals suitable for the control of the plant.

The program memory is the store in which the set of instructions that comprise the program are stored. These instructions dictate the actions which must be taken in response to the condition of each input.

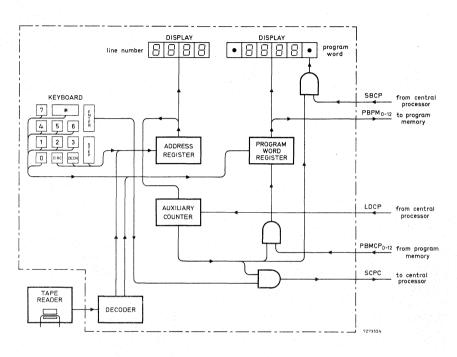

The programming unit is the means by which an operator can write a program, or changes to a program, into the program memory. The unit is portable and thus one may be used to serve any number of PLCs. It is also sufficiently inexpensive to make the permanent location of one in each PLC for monitoring or test purposes, a realistic and useful proposition.

# MODULES FOR

PLC

#### PROGRAMMABLE LOGIC CONTROLLERS

#### GENERAL CHARACTERISTICS

Operating temperature range

0 to +60 °C

Storage temperature range

-40 to +70  $^{\rm O}{\rm C}$

Dimensions

160 mm x 233 mm (double Eurocard)

Supply voltage (d.c.)

according to IEC297 or DIN41494  $V_P = 5 \text{ V } \pm 5\%; \frac{dV_P}{dr} \le 5 \text{ V/ms}$

ry vortage (d. c.)

512

Maximum program length

Maximum number of input + output signals

4 x 1024 words

Cycle time

$0,029 (n_{\text{IM}} + n_{\text{OM}}) + 1,85 n_{\text{MM}} \text{ ms}$

$n_{\text{IM}}$  = number of input modules

$n_{IM}$  = number of input modules  $n_{OM}$  = number of output modules  $n_{MM}$  = number of memory modules

#### TESTS AND REQUIREMENTS

All modules are designed to meet the tests below.

# Vibration test

IEC68-2, test method Fc: 5 to 55 Hz, amplitude 1,5 mm or 5 g (whichever is less).

#### Shock test

IEC68-2, test method Ea: 3 shocks in 6 directions, pulse duration 11 ms, peak acceleration 50 g.

#### Rapid change of temperature test

IEC68-2, test method Na: 5 cycles of 2 h at -40  $^{\circ}$ C and 2 h at +70  $^{\circ}$ C.

#### Damp heat test

IEC68-2, test method Ca: 21 days at 40  $^{\rm o}\text{C}\text{, R.H. }90\text{ to }95\%.$

#### CENTRAL PROCESSORS

#### DESCRIPTION

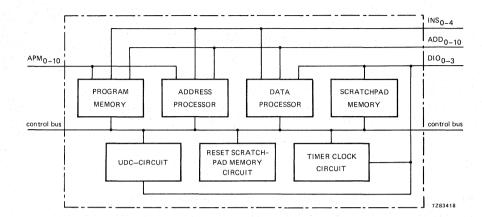

These central processors are modules intended for use in combination with the input module IM10 (or IM11), memory module MM10 (or MM11 or MM12), output module OM10 (or OM12) and programming unit PU10 to assemble a programmable logic controller (PLC). The central processor is the heart of the logic controller; it asks the input modules for data and the program memory for instructions, processes the data according to these instructions, and applies the result to the output modules. It also generates the internal timing of the controller.

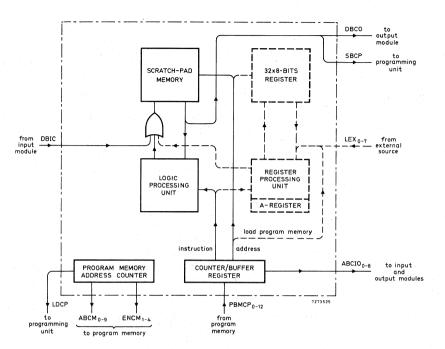

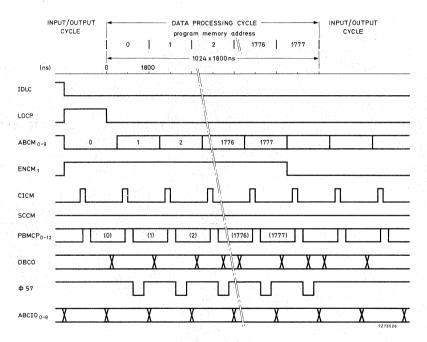

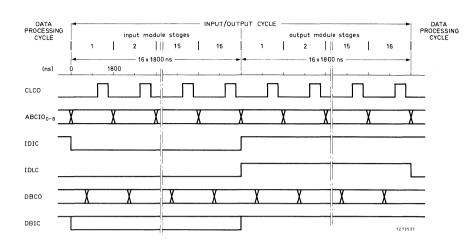

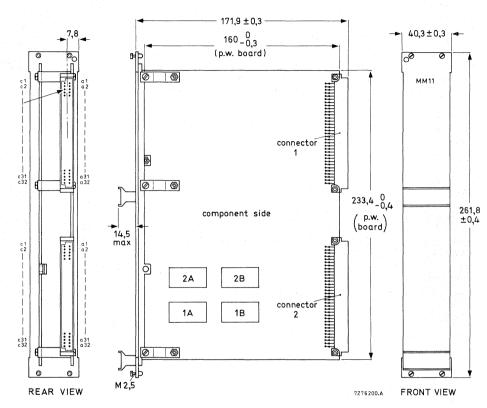

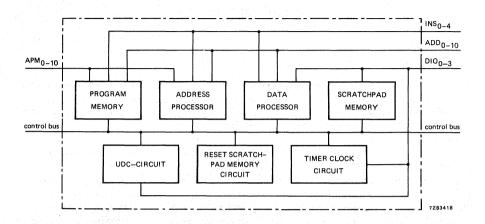

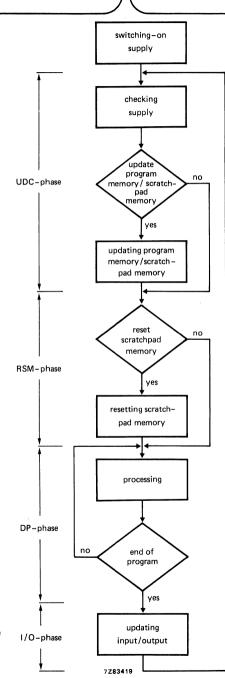

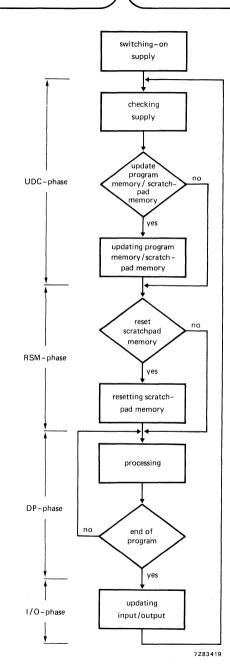

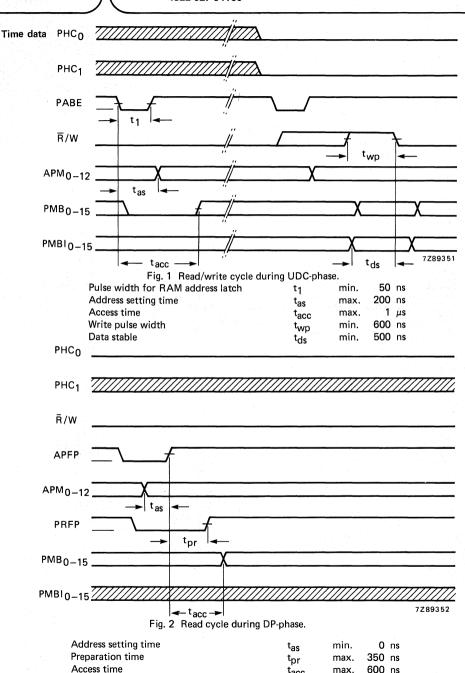

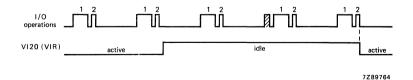

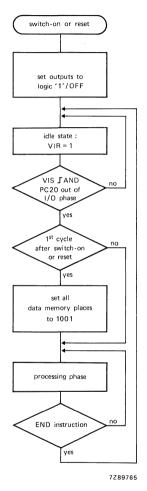

The processor actions take place in two distinct cycles: an input/output cycle and a data processing cycle.

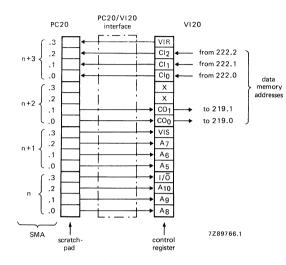

During the input/output cycle the processor addresses each input stage in turn (counter/buffer register) and transfers the present data to the corresponding scratch-pad memory location, see Fig. 1. In the same cycle the processed data of the previous data processing cycle are clocked out from the scratch-pad memory into the latch flip-flops of the output modules. As the scratch-pad memory can hold up 512 bits of data the central processor can handle a maximum combination of 512 inputs, outputs, and intermediate results. Provision is made to prevent loss of information of the scratch-pad memory in the case of power failure.

During the data processing cycle the processor applies an address and a cycle initiate signal to the program memory, which in turn then apply a program word to the processor. The program word contains an instruction and an address, which comprise 13 data bits. An instruction consists of 4 bits of data; these are applied to the logic processing unit and the register processing unit. \(^1\) The other 9 bits of data form the scratch-pad memory address and are used to select the data bit at this memory location, and also one of the 32 8-bit registers. \(^1\) The logic processing unit only processes data from the scratch-pad memory. The register processing unit processes the data stored in one of the 8-bits registers, in conjunction with a working register (A-register). Due to the fact that a register is always selected when a scratch-pad memory address is selected, the results of register processing will be stored in the corresponding scratch-pad memory location (condition register). Data for the registers can be supplied by the program memory or by an external source. These data are stored in the registers during the data processing cycle.

<sup>1)</sup> Only present in the CP10.

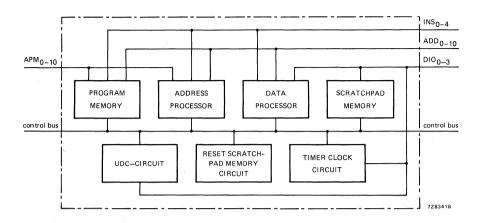

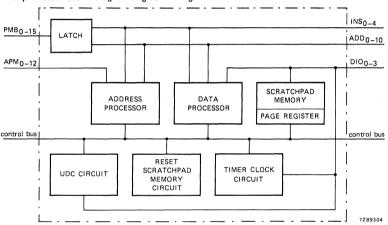

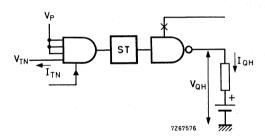

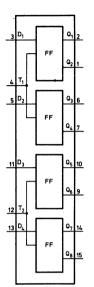

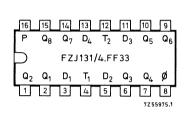

Fig. 1. Simplified block diagram of the central processor. Blocks drawn with broken lines are only extant in the CP10.

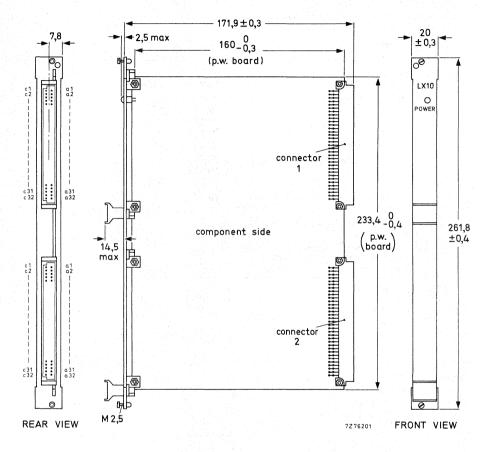

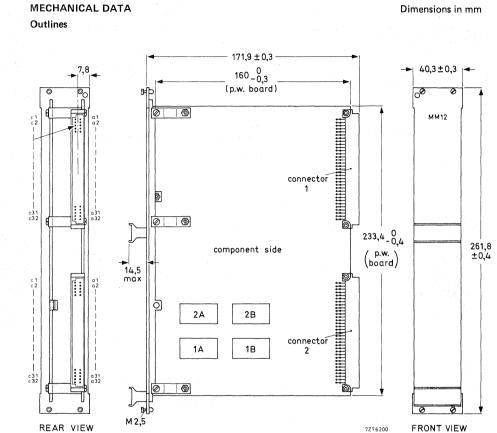

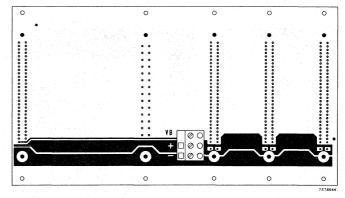

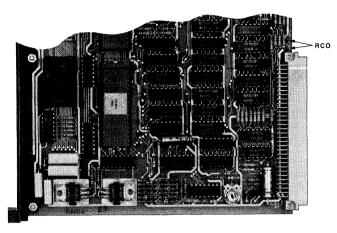

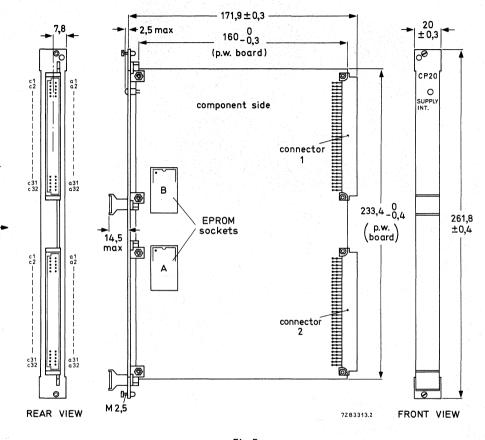

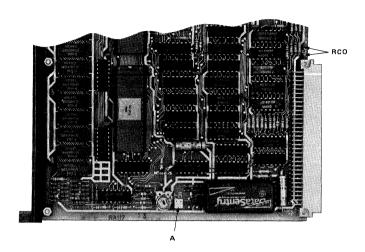

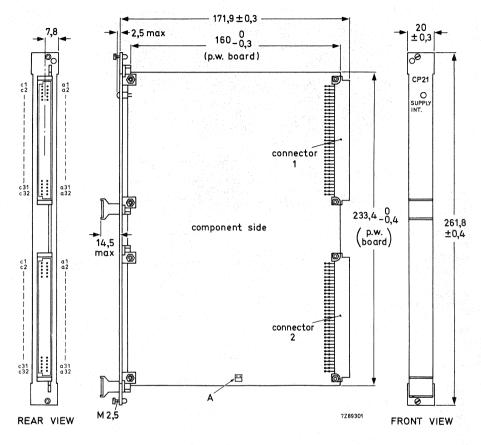

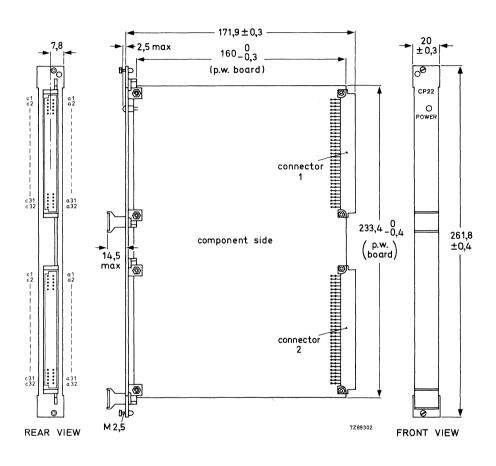

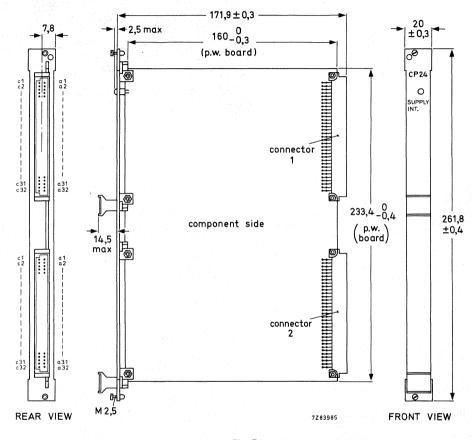

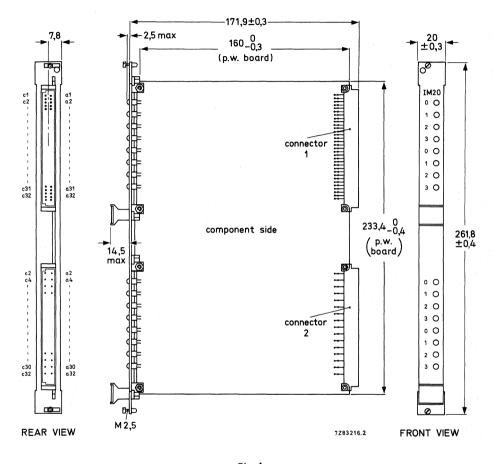

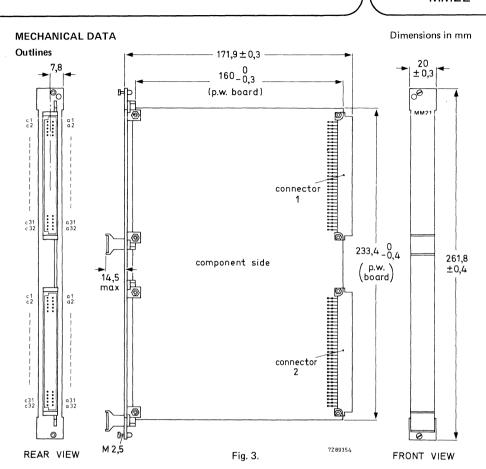

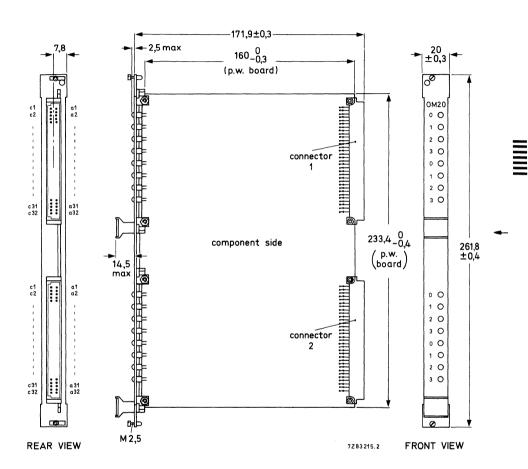

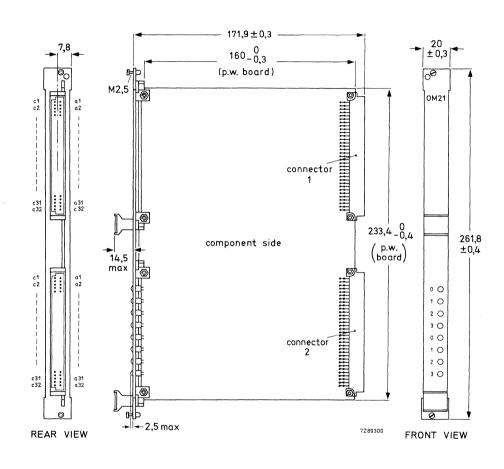

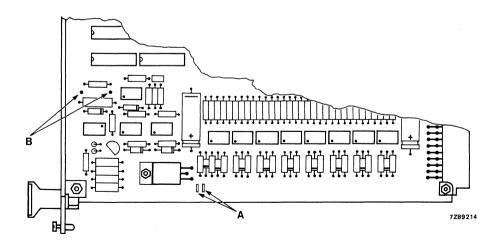

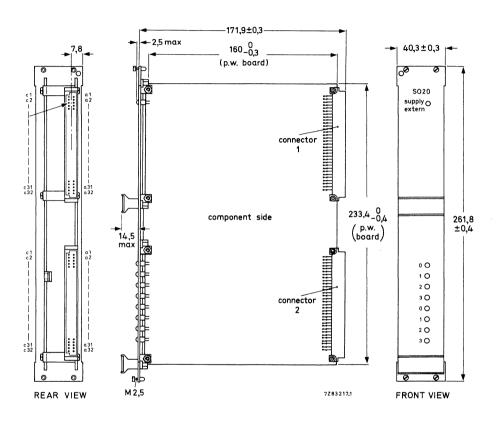

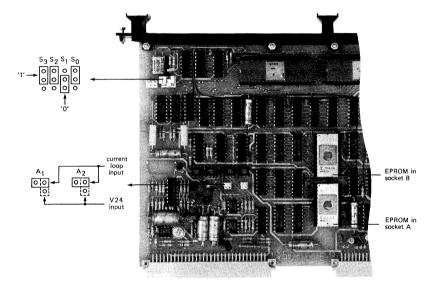

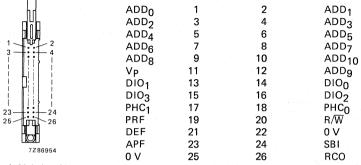

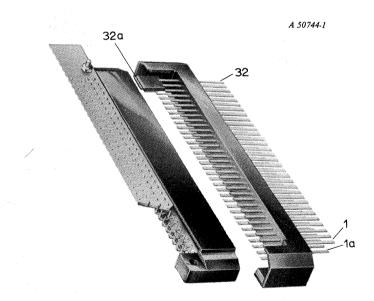

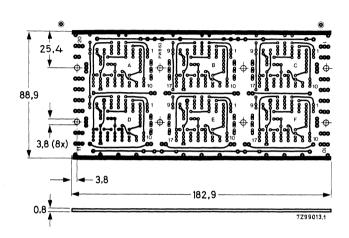

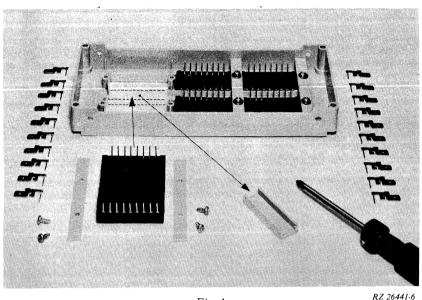

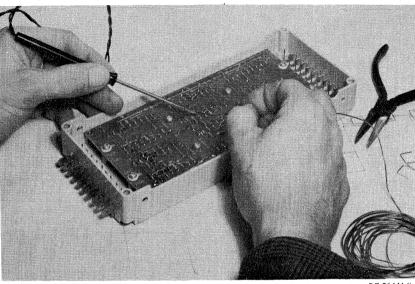

The central processor is built on an epoxy-glass printed-wiring board of 233,4 mm x 160 mm (Euro-card system). The board is provided with two F068-I connectors (board parts); the corresponding panel parts are available under catalogue number 2422 025 89288 (pins for wire wrap), 2422 025 89298 (pins for dip soldering) or 2422 025 89326 (solder tags)  $^1$ ). The board has a metal screen at the components side, which is connected to the 0 V line.

<sup>1)</sup> For a general description of the Euro-card system see IEC 297 or DIN 41494 for 19-in racks and IEC 130-14 or DIN 41612 for connectors.

#### ELECTRICAL DATA

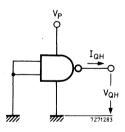

#### Supply

Supply voltage (d.c.) current

V<sub>P</sub> 5 V ± 5% I<sub>P</sub> max. 2, 1 A typ. 1, 9 A

Battery back-up requirements to save contents of the scratch-pad memory in case of power failure.

Battery voltage

Dattery voltage

Battery current (V<sub>P</sub> = 0 V)

Trickle charge current (V<sub>P</sub> = 5 V)

#### Input data

All inputs meet the standard TTL specifications.

| input               | function                                                                                                                                                                                              | load  | terminatio  | ons (Fig. 4) |

|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-------------|--------------|

|                     |                                                                                                                                                                                                       |       | connector 1 | connector 2  |

| РВМСР0              |                                                                                                                                                                                                       | 1 TTL |             | a2, c2       |

| PBMCP <sub>1</sub>  |                                                                                                                                                                                                       | 1 TTL |             | a3, c3       |

| PBMCP <sub>2</sub>  |                                                                                                                                                                                                       | 1 TTL |             | a4, c4       |

| PBMCP3              |                                                                                                                                                                                                       | 1 TTL |             | a5, c5       |

| PBMCP <sub>4</sub>  |                                                                                                                                                                                                       | 1 TTL |             | a6, c6       |

| PBMCP5              |                                                                                                                                                                                                       | 1 TTL |             | а7, с7       |

| PBMCP <sub>6</sub>  | Program word bits from program                                                                                                                                                                        | 1 TTL |             | a8, c8       |

| PBMCP <sub>7</sub>  | memory.                                                                                                                                                                                               | 1 TTL |             | a9, c9       |

| PBMCP <sub>8</sub>  |                                                                                                                                                                                                       | 1 TTL |             | a10, c10     |

| PBMCP9              |                                                                                                                                                                                                       | 1 TTL |             | all, cll     |

| PBMCP <sub>10</sub> |                                                                                                                                                                                                       | 1 TTL |             | a12, c12     |

| PBMCP <sub>11</sub> |                                                                                                                                                                                                       | 1 TTL |             | a13, c13     |

| PBMCP <sub>12</sub> |                                                                                                                                                                                                       | 1 TTL |             | a14, c14     |

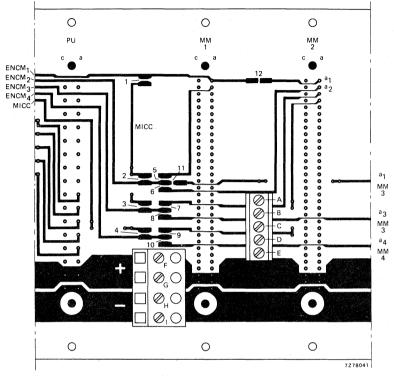

| MICC                | Memory identification signal; this signal is connected to one of the four ENCM-outputs of the central processor.                                                                                      | 2 TTL | a5          |              |

| SCPC                | Store command from programming unit; initiates SCCM (see output data) when the central processor is in a data processing cycle.                                                                       | 2 TTL |             | a15, c15     |

| DBIC                | Data bit from input stage; data is stored in scratch-pad memory during input/output cycle.                                                                                                            | 3 TTL | c20         |              |

| CLCP                | Clear signal from external source. When CLCP is LOW the central processor is kept in the start position of an input/output cycle; when CLCP is HIGH the central processor is running (see also SPCE). | 2 TTL | a20         |              |

| input                                                                                                                                                        | function                                                                                                                                                                                                                                                                                                                                   | load                                                        | terminations (Fig. 4)                            |             |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|--------------------------------------------------|-------------|--|

|                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                            |                                                             | connector 1                                      | connector 2 |  |

| SPCE                                                                                                                                                         | Scratch-pad clear enable line from external source. When SPCE is HIGH and CLCP goes from LOW to HIGH all scratch-pad places (except those which are addressed as an input) are set to zero in the first input/output cycle; when SPCE is LOW and CLCP goes from LOW to HIGH the central processor starts with a normal input/output cycle. | 2 TTL                                                       | a22                                              |             |  |

| IDIC                                                                                                                                                         | Identification signal from input module; prepares central processor for data on DBIC to be written in the scratch-pad memory.                                                                                                                                                                                                              | 3 TTL                                                       | c24                                              |             |  |

| IDLC                                                                                                                                                         | Identification signal from last input or output module; indicates that the last input or output module has been selected.                                                                                                                                                                                                                  | 2 TTL                                                       | c26                                              |             |  |

| LEX <sub>0</sub><br>LEX <sub>1</sub><br>LEX <sub>2</sub><br>LEX <sub>3</sub><br>LEX <sub>4</sub><br>LEX <sub>5</sub><br>LEX <sub>6</sub><br>LEX <sub>7</sub> | Data inputs from an external source; eight data bits from an external source can be loaded into the A-register.                                                                                                                                                                                                                            | 1 TTL<br>1 TTL<br>1 TTL<br>1 TTL<br>1 TTL<br>1 TTL<br>1 TTL | a6<br>a7<br>a8<br>a9<br>a10<br>a11<br>a12<br>a13 |             |  |

#### Output data

All outputs meet the standard  $\ensuremath{\mathsf{TTL}}$  specifications.

| output                                                                                                                                                                                             | function                                                                                                                                                  | loada-                                                                                 | terminatio                                       | ons (Fig. 4) |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|--------------------------------------------------|--------------|

|                                                                                                                                                                                                    |                                                                                                                                                           | bility                                                                                 | connector 1                                      | connector 2  |

| ABCIO <sub>0</sub><br>ABCIO <sub>1</sub><br>ABCIO <sub>2</sub><br>ABCIO <sub>3</sub><br>ABCIO <sub>4</sub><br>ABCIO <sub>5</sub><br>ABCIO <sub>6</sub><br>ABCIO <sub>7</sub><br>ABCIO <sub>8</sub> | Address bits to input and output modules. ABCIO <sub>0-3</sub> select the input or output stage, ABCIO <sub>4-8</sub> select the input or output modules. | 32 TTL<br>32 TTL<br>32 TTL<br>32 TTL<br>32 TTL<br>32 TTL<br>32 TTL<br>32 TTL<br>32 TTL | c2<br>c4<br>c6<br>c8<br>c10<br>c12<br>c14<br>c16 |              |

| output                                                                                                                                                                                                | function                                                                                                                                                                                                          | loada-                                                                                           | terminations (Fig. 4)    |                                                                                                                      |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|--------------------------|----------------------------------------------------------------------------------------------------------------------|--|

|                                                                                                                                                                                                       |                                                                                                                                                                                                                   | bility                                                                                           | connector 1              | connector                                                                                                            |  |

| ABCM <sub>0</sub> ABCM <sub>1</sub> ABCM <sub>2</sub> ABCM <sub>3</sub> ABCM <sub>4</sub> ABCM <sub>5</sub> ABCM <sub>6</sub> ABCM <sub>6</sub> ABCM <sub>7</sub> ABCM <sub>8</sub> ABCM <sub>9</sub> | Address bits to program memory, initiated by program address counter.                                                                                                                                             | 10 TTL<br>10 TTL<br>10 TTL<br>10 TTL<br>10 TTL<br>10 TTL<br>10 TTL<br>10 TTL<br>10 TTL<br>10 TTL |                          | a20, c20<br>a21, c21<br>a22, c22<br>a23, c23<br>a24, c24<br>a25, c25<br>a26, c26<br>a27, c27<br>a28, c28<br>a29, c29 |  |

| ENCM <sub>1</sub><br>ENCM <sub>2</sub><br>ENCM <sub>3</sub><br>ENCM <sub>4</sub>                                                                                                                      | Enable signal to program memory; four lines are necessary when program memory capacity is extended to 4 k                                                                                                         | 8 TTL<br>8 TTL<br>8 TTL<br>8 TTL                                                                 | a1, c1<br>a2<br>a3<br>a4 |                                                                                                                      |  |

| SCCM                                                                                                                                                                                                  | Store command to program memory; level determines whether a program word is read out from program memory to central processor (LOW) or a new program word is written into the program memory (HIGH). SCCM = SCPC. | 10 TTL                                                                                           |                          | a17, c17                                                                                                             |  |

| CICM<br>CICM                                                                                                                                                                                          | Cycle initiate signal to program memory; depending on the level of SCCM, CICM starts read/restore or clear/write cycle (bipolar to reduce noise sensitivity).                                                     | 9 TTL                                                                                            |                          | a19, c19<br>a18, c18                                                                                                 |  |

|                                                                                                                                                                                                       | Inverted clock signal to programming unit.                                                                                                                                                                        | 10 TTL                                                                                           | a 15                     |                                                                                                                      |  |

| CLCO                                                                                                                                                                                                  | Clock signal to output module, stores data on DBCO into output stage during input/output cycle.                                                                                                                   | 32 x<br>OM10                                                                                     | a28                      |                                                                                                                      |  |

| DBCO                                                                                                                                                                                                  | Data bit to output module; data is stored in output stage by CLCO.                                                                                                                                                | 31 TTL                                                                                           | c22                      |                                                                                                                      |  |

| SBCP                                                                                                                                                                                                  | Status bit to programming unit; clocked by $\phi_{57}$ it indicates "1" or "0" at selected scratch-pad memory address.                                                                                            | 1 TŢL                                                                                            | a16                      |                                                                                                                      |  |

| LDCP                                                                                                                                                                                                  | Synchronization signal to programming unit, synchronizes auxiliary address counter in programming unit with address counter in central processor.                                                                 | 10 TTL                                                                                           | a14                      |                                                                                                                      |  |

| <sup>Ф</sup> 57                                                                                                                                                                                       | Clock signal for state indication on programming unit; occurs only during data processing cycle.                                                                                                                  | 10 TTL                                                                                           |                          | a16, c16                                                                                                             |  |

Alarm output (a26 of connector 1): open collector output, which indicates a LOW level when  $\rm V_P<$  4,75 V.  $\rm V_{alarm}$ , LOW level < 0,4 V at  $\rm I_C$  = 3 mA.

#### Time data

Scan time per input or output module Read time per 1 k memory module

Total cycle time

0,029 ms 1,85 ms

$0,029 (n_{IM} + n_{OM}) + 1,85 n_{MM} ms$

$n_{IM}$  = number of input modules

$n_{\mbox{OM}}$  = number of output modules  $n_{\mbox{MM}}$  = number of memory modules

Note - By removing a wire jump, marked "A", on the central processor board the scan time per input or output module is set to  $7,4~\mathrm{ms}$ .

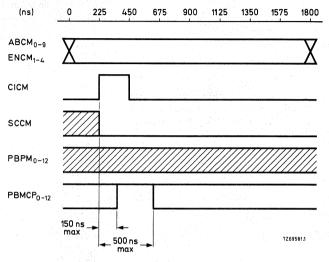

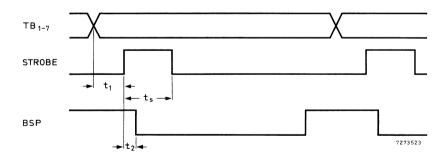

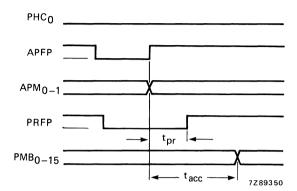

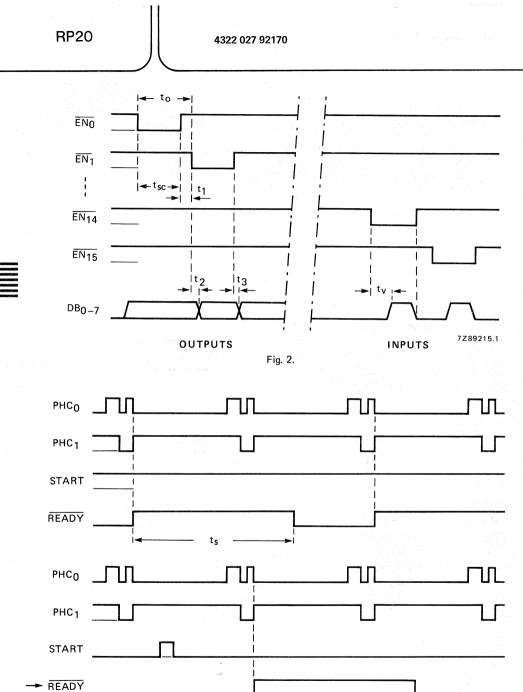

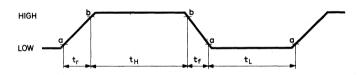

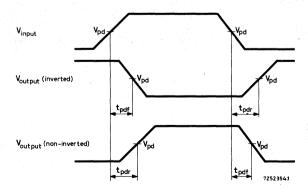

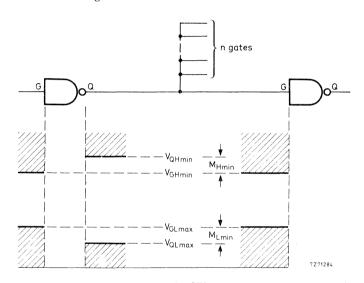

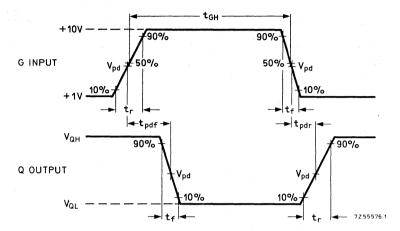

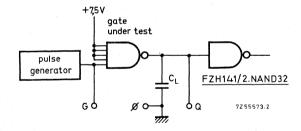

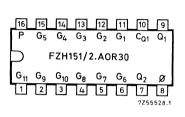

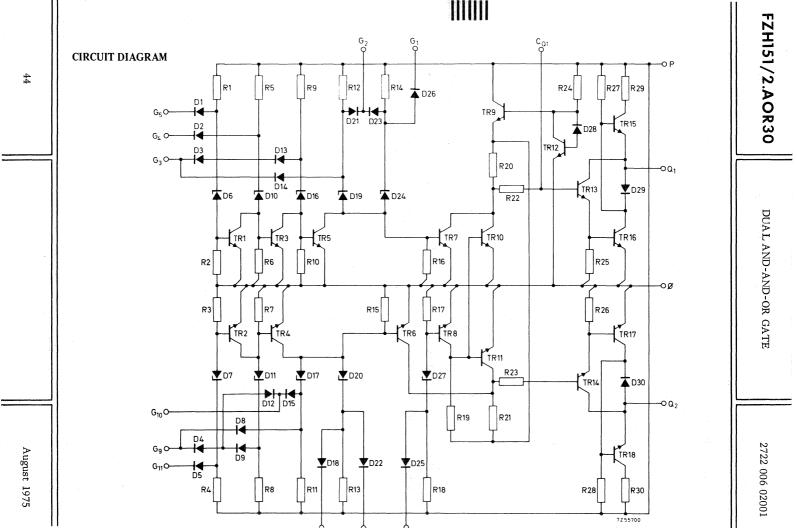

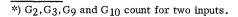

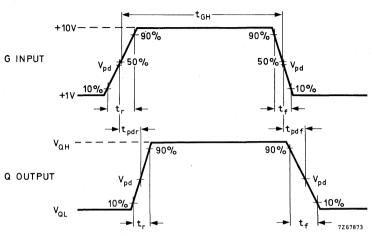

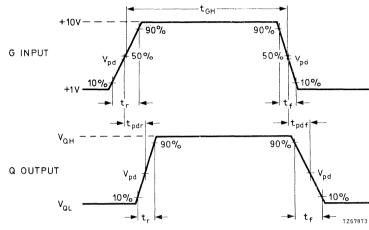

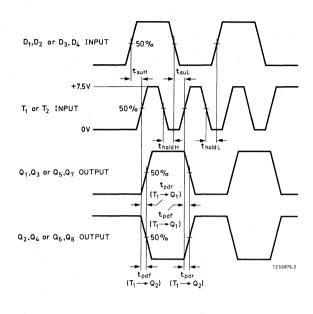

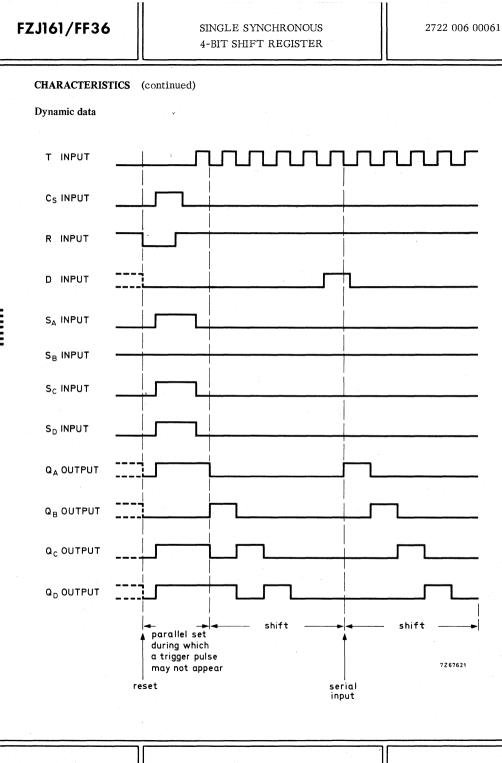

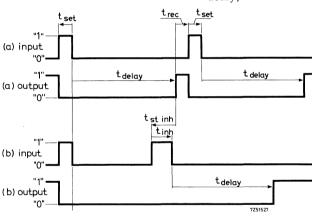

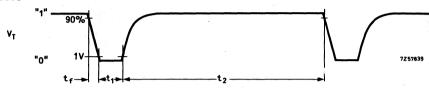

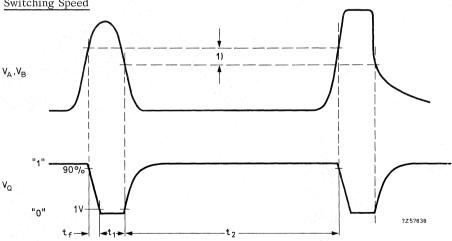

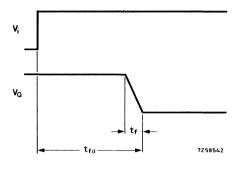

Fig. 2. Timing diagram of data processing cycle.

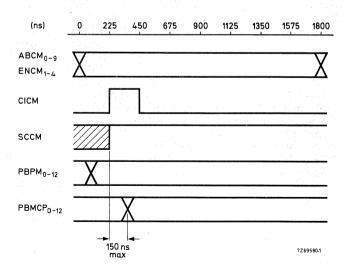

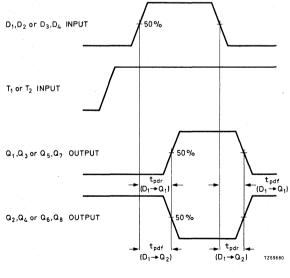

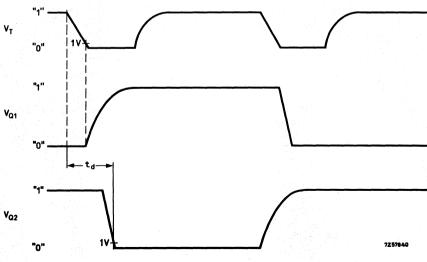

Fig. 3. Timing diagram of input/output cycle.

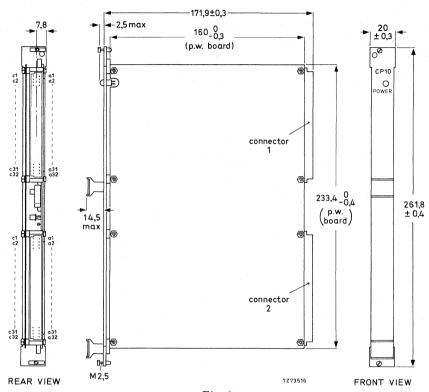

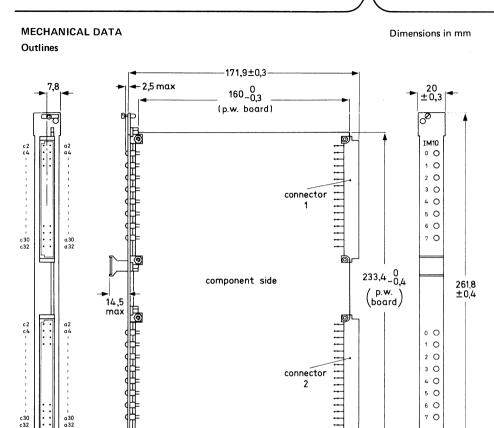

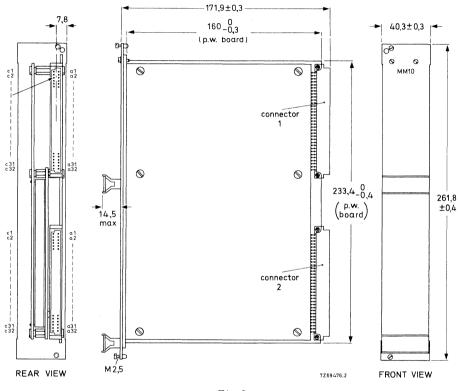

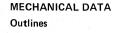

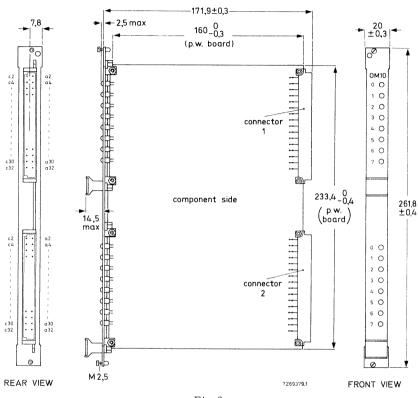

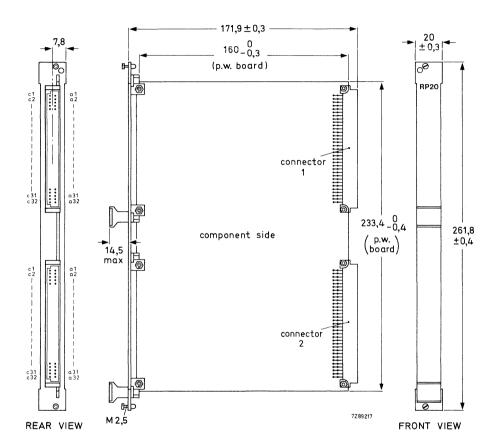

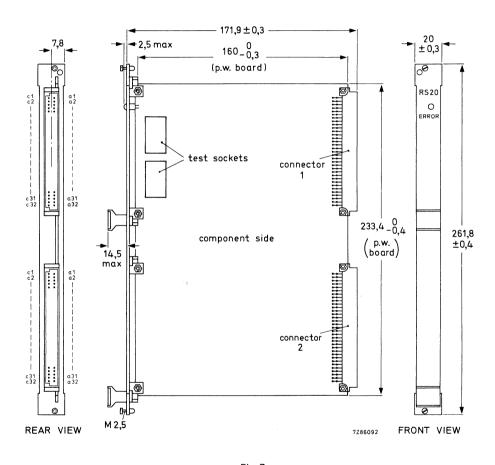

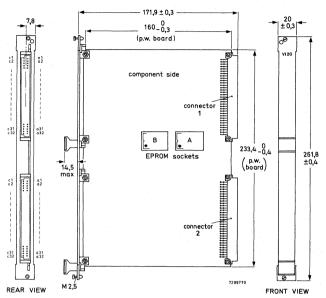

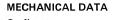

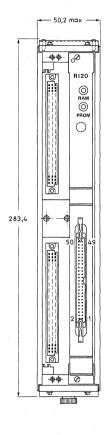

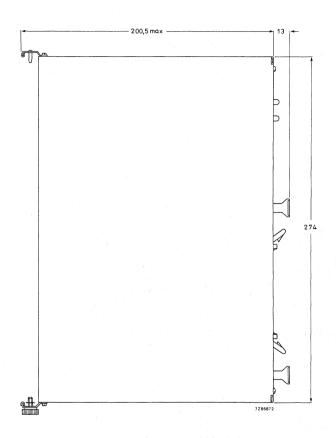

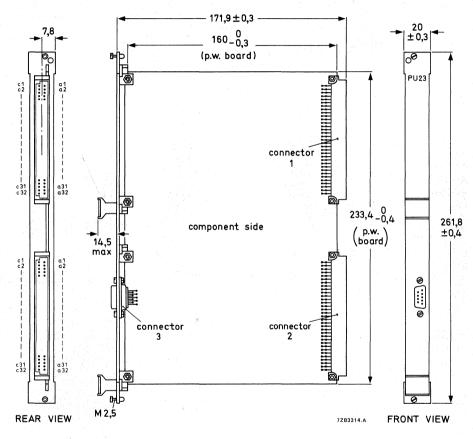

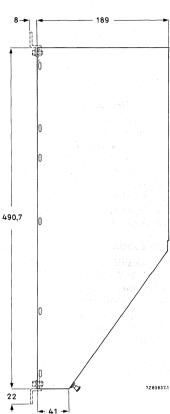

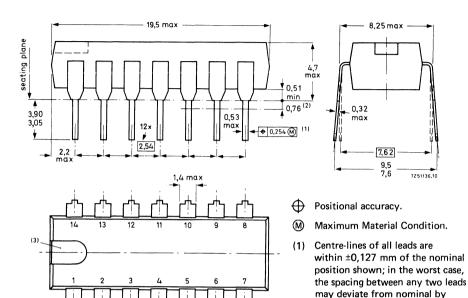

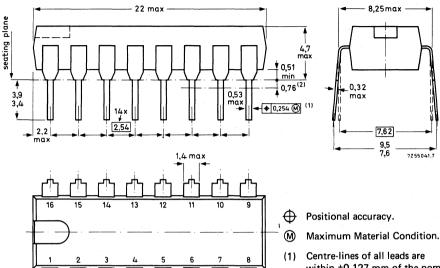

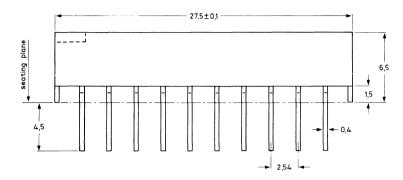

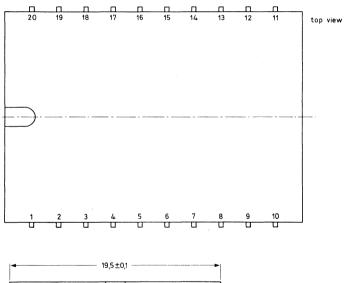

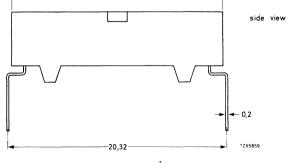

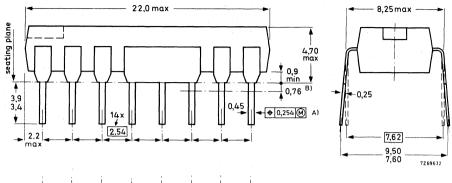

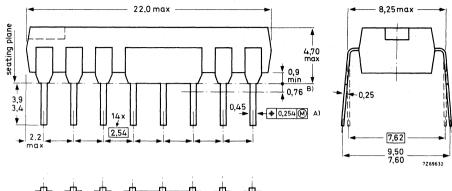

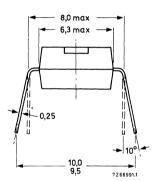

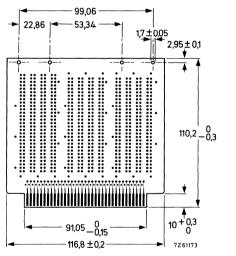

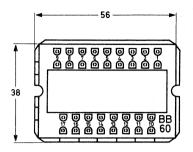

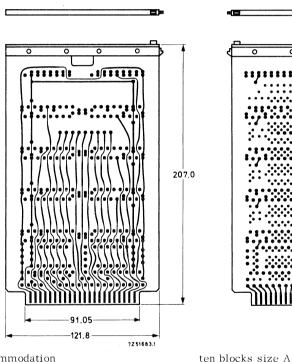

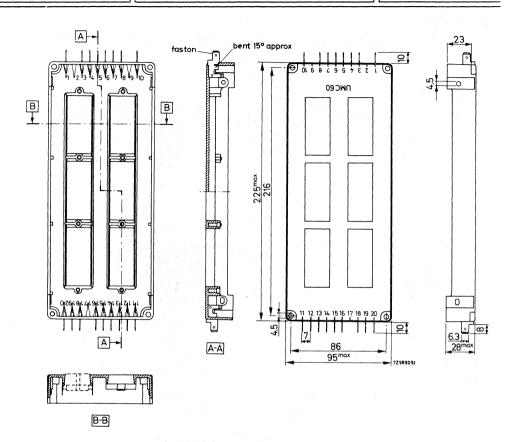

### MECHANICAL DATA

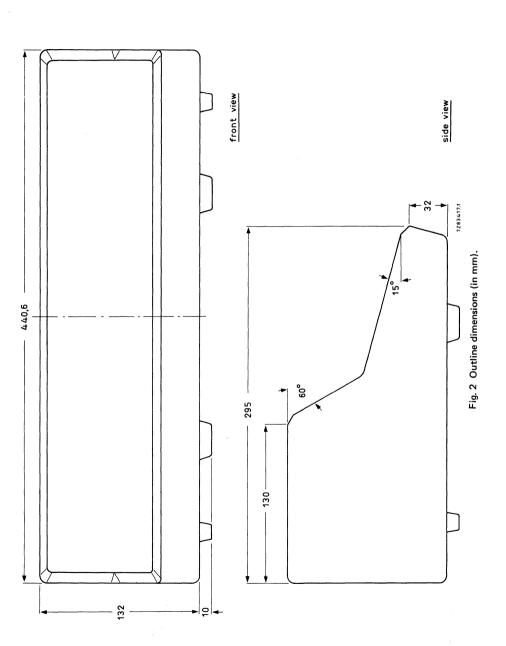

Outlines

Fig. 4

Mass

400 g

#### Terminal location

| co                 | onnector | 1                          | co                        | onnector | 2                    |

|--------------------|----------|----------------------------|---------------------------|----------|----------------------|

| row c              |          | row a                      | row c                     |          | row a                |

| ENCM <sub>1</sub>  | 1        | ENCM <sub>1</sub>          | i.c.                      | 1        | i.c.                 |

| $ABCIO_0$          | 2        | ENCM <sub>2</sub>          | PBMCP <sub>0</sub>        | 2        | $PBMCP_0$            |

| n.c.               | 3        | ENCM3                      | PBMCP <sub>1</sub>        | 3        | $PBMCP_1$            |

| ABCIO 1            | 4        | ${\tt ENCM_4}$             | PBMCP <sub>2</sub>        | 4        | PBMCP <sub>2</sub>   |

| n.c.               | 5        | MICC                       | PBMCP3                    | 5        | PBMCP3               |

| $ABCIO_2$          | 6        | $\text{LEX}_0$             | PBMCP 4                   | 6        | PBMCP <sub>4</sub>   |

| n.c.               | 7        | LEX <sub>1</sub>           | PBMCP5                    | 7        | PBMCP5               |

| ABCIO <sub>3</sub> | 8        | LEX <sub>2</sub>           | PBMCP <sub>6</sub>        | 8        | PBMCP6               |

| n.c.               | 9        | LEX3                       | PBMCP7                    | 9        | PBMCP7               |

| ABCIO 4            | 10       | $LEX_4$                    | PBMCP <sub>8</sub>        | 10       | PBMCP <sub>8</sub>   |

| n.c.               | 11       | LEX <sub>5</sub>           | PBMCP9                    | 11       | PBMCP <sub>9</sub>   |

| ABCIO5             | 12       | LEX <sub>6</sub>           | PBMCP <sub>10</sub>       | 12       | PBMCP <sub>10</sub>  |

| n.c.               | 13       | LEX <sub>7</sub>           | PBMCP <sub>11</sub>       | 13       | PBMCP <sub>11</sub>  |

| ABCIO <sub>6</sub> | 14       | LDCP                       | PBMCP $_{12}$             | 14       | PBMCP <sub>12</sub>  |

| n.c.               | 15       | $\overline{	ext{CL}}_{23}$ | SCPC                      | 15       | SCPC                 |

| ABCIO <sub>7</sub> | 16       | SBCP                       | φ57                       | 16       | $\phi$ 57            |

| n.c.               | 17       | n.c.                       | SCCM                      | 17       | SCCM                 |

| ABCIO8             | 18       | n.c.                       | CICM                      | 18       | CICM                 |

| n.c.               | 19       | n.c.                       | CICM                      | 19       | CICM                 |

| DBIC               | 20       | CLCP                       | $ABCM_0$                  | 20       | $^{\mathrm{ABCM}_0}$ |

| n.c.               | 21       | n.c.                       | ABCM <sub>1</sub>         | 21       | $_{ m ABCM}_{ m 1}$  |

| DBCO               | 22       | SPCE                       | ${\sf ABCM}_2$            | 22       | ${ m ABCM_2}$        |

| n.c.               | 23       | n.c.                       | ABCM3                     | 23       | ABCM3                |

| IDIC               | 24       | n.c.                       | ABCM <sub>4</sub>         | 24       | $ABCM_4$             |

| n.c.               | 25       | n.c.                       | ABCM5                     | 25       | ABCM <sub>5</sub>    |

| IDLC               | 26       | alarm                      | ABCM <sub>6</sub>         | 26       | ABCM <sub>6</sub>    |

| n.c.               | 27       | n.c.                       | ABCM <sub>7</sub>         | 27       | ABCM <sub>7</sub>    |

| 0 V <sup>1</sup> ) | 28       | CLCO                       | ABCM <sub>8</sub>         | 28       | ABCM <sub>8</sub>    |

| n.c.               | 29       | n.c.                       | ABCM9                     | 29       | ABCM9                |

| n.c.               | 30       | n.c.                       | $\mathbf{v}_{\mathbf{B}}$ | 30       | $v_B$                |

| $v_{P}$            | 31       | $v_{\mathbf{P}}$           | $V_{\mathbf{P}}$          | 31       | $v_{P}$              |

| 0 V                | 32       | 0 V                        | 0 V                       | 32       | 0 V                  |

n.c. = not connected.

i.c. = internal connection.

<sup>1)</sup> No supply line; only to be used as a ground connection for CLCO.

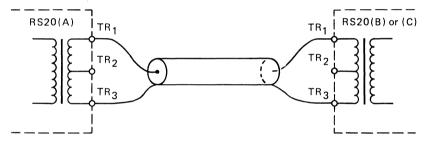

#### INPUT MODULES

#### DESCRIPTION

These input modules are intended for use in combination with the central processor CP10 (or CP11), memory module MM10 (or MM11 or MM12), output module OM10 (or OM12) and programming unit PU10 to assemble a programmable logic controller (PLC).

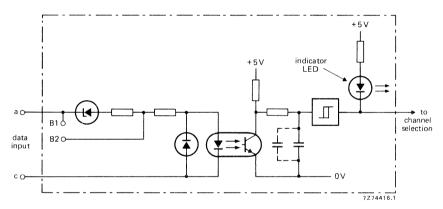

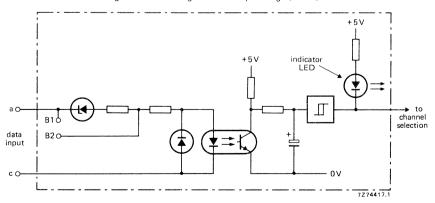

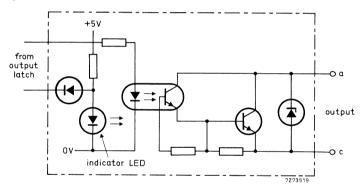

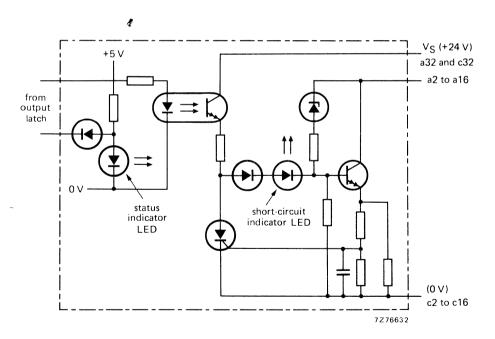

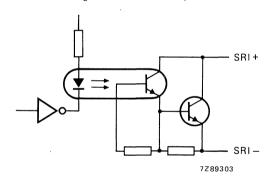

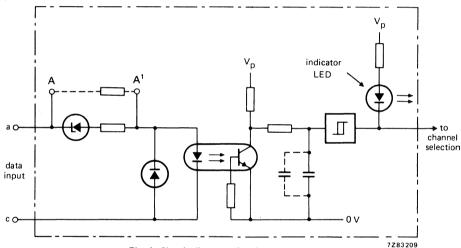

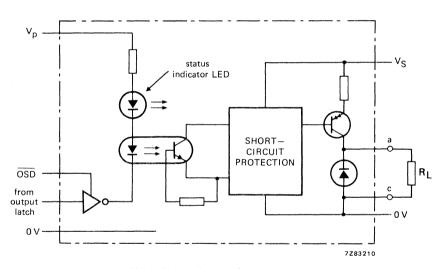

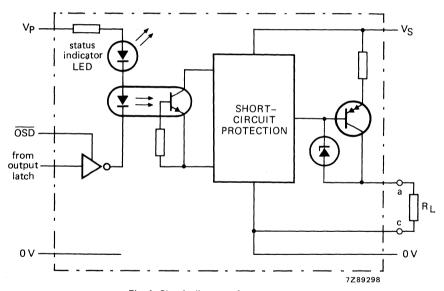

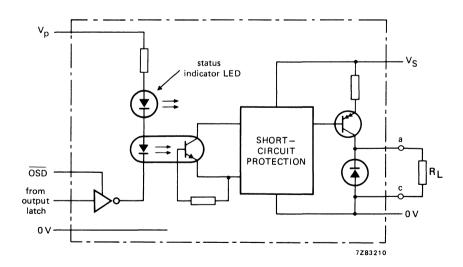

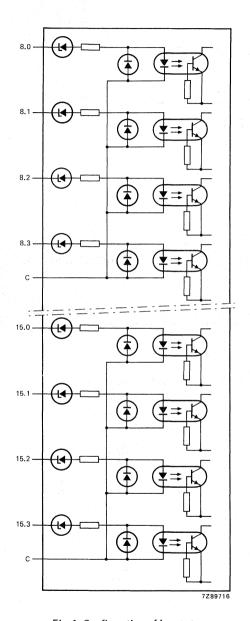

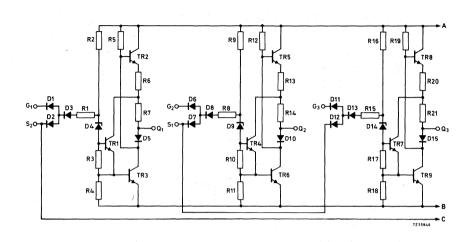

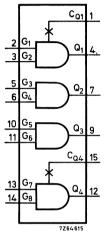

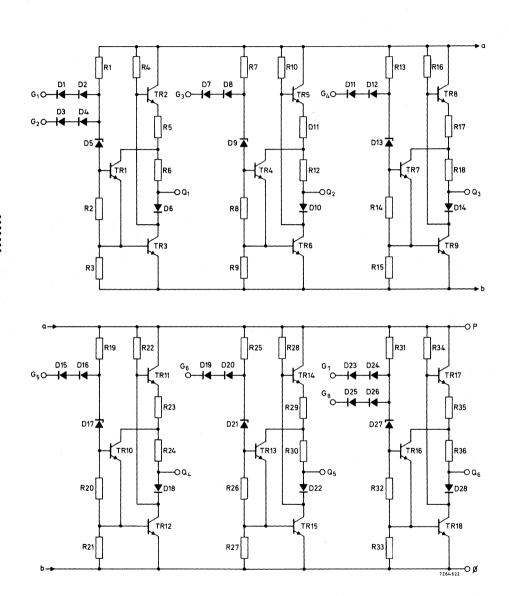

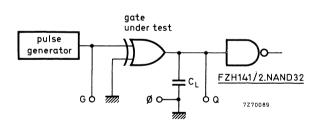

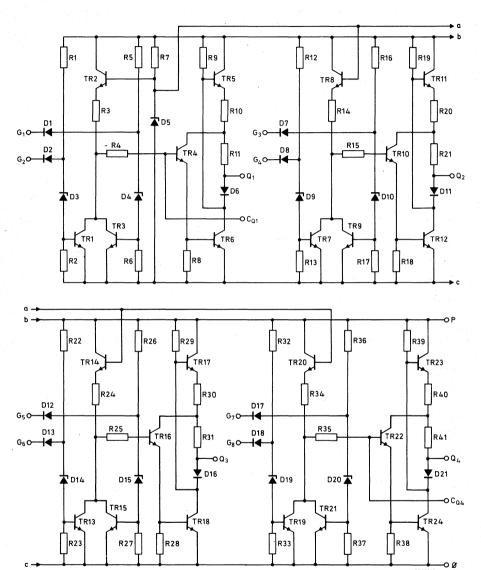

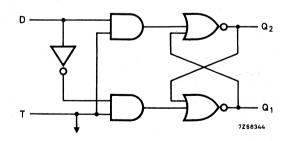

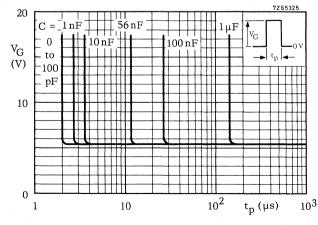

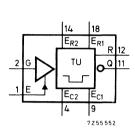

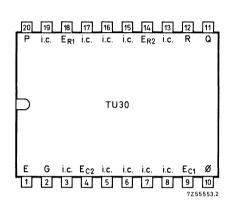

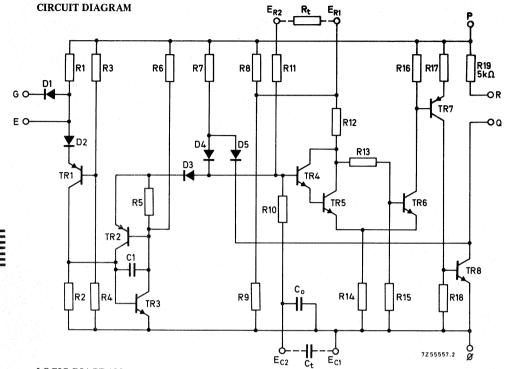

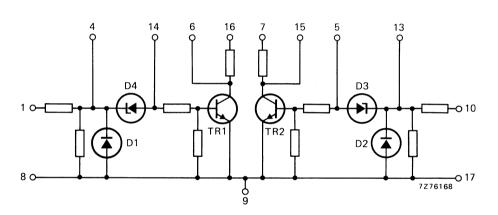

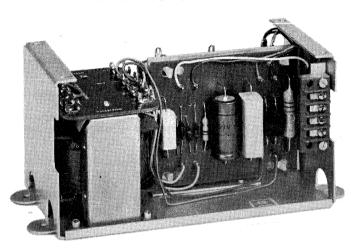

The IM10 and IM11 are identical in many respects, but the IM10 is designed for d.c. inputs, whereas the IM11 is designed for a.c. and unsmoothed rectified inputs. Each input module contains 16 addressable input stages, equipped with photocouplers to obtain electrical isolation between external and internal circuitry (Fig. 1). All inputs are floating with respect to each other. Each input stage has a LED for status indication: it is lit when the input is active. A delay circuit (symmetrical delay time typ. 1 ms) is incorporated in each input stage of the IM10, to increase the noise immunity. The delay time can be increased by adding extra capacitance (approx. 0,068  $\mu$ F/ms). A rectifying and smoothing circuit is incorporated in each input stage of the IM11.

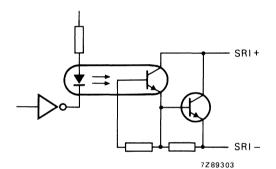

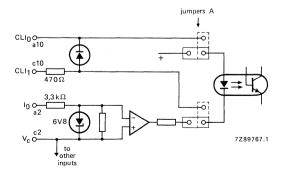

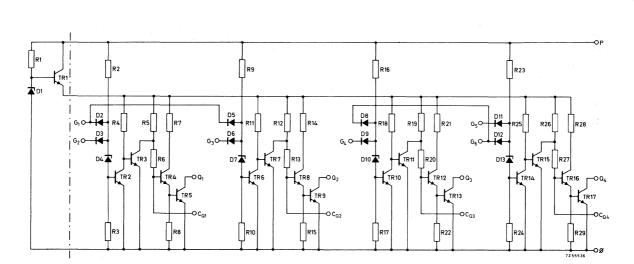

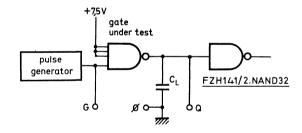

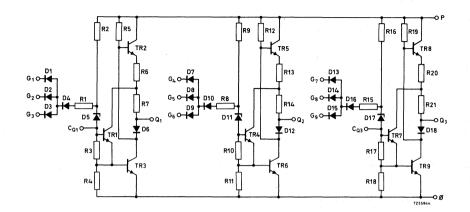

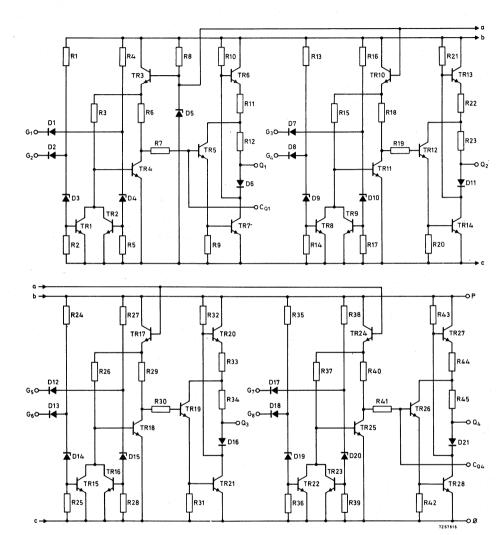

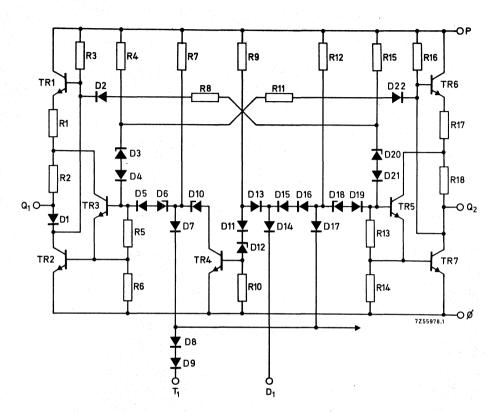

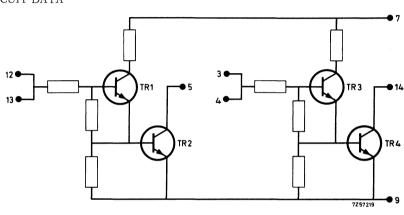

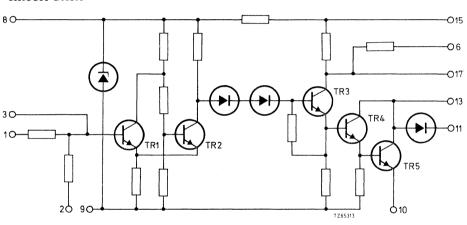

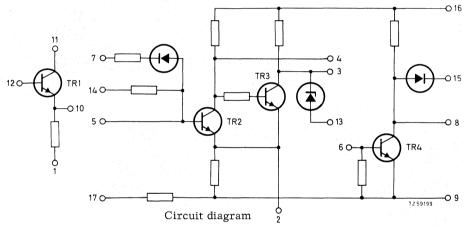

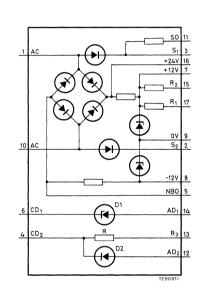

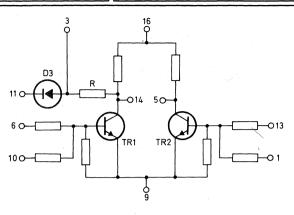

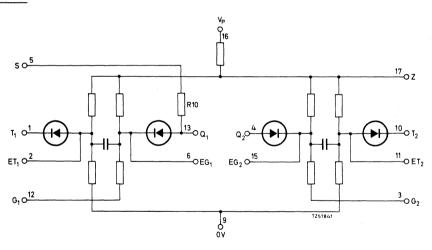

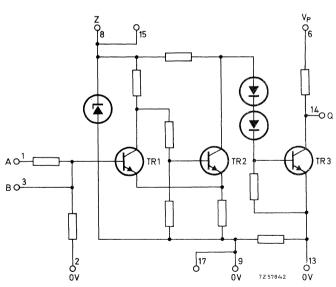

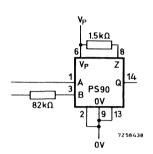

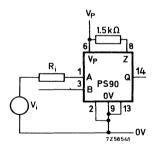

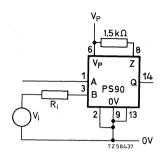

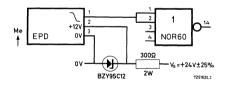

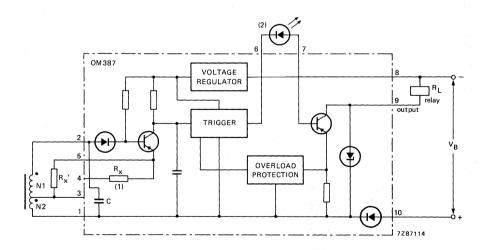

Fig. 1a Circuit diagram of an input stage (IM10).

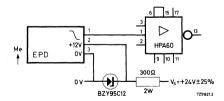

Fig. 1b Circuit diagram of an input stage (IM11).

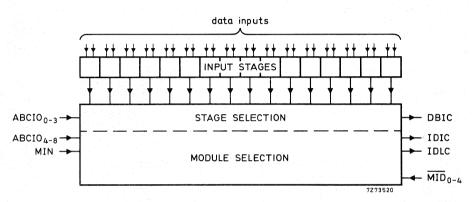

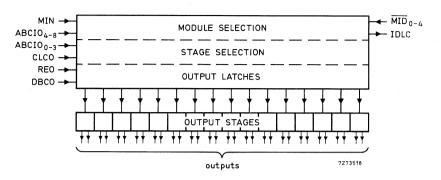

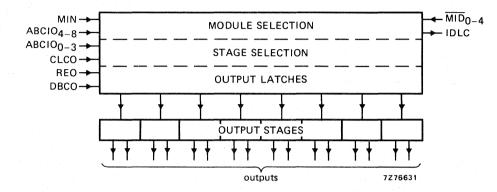

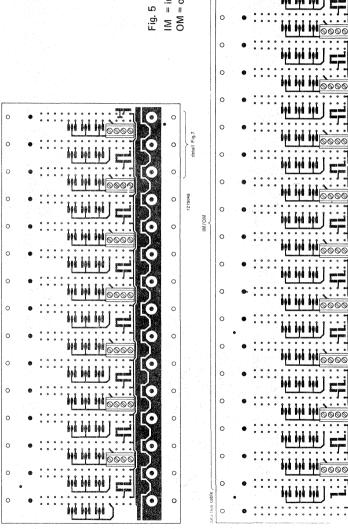

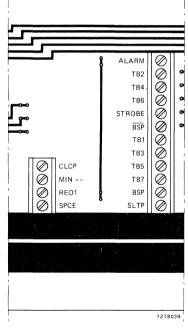

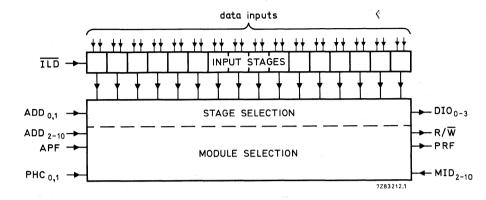

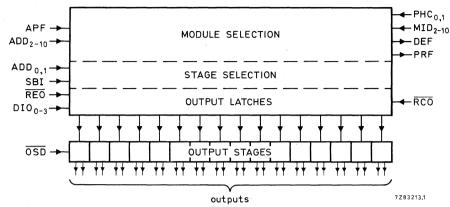

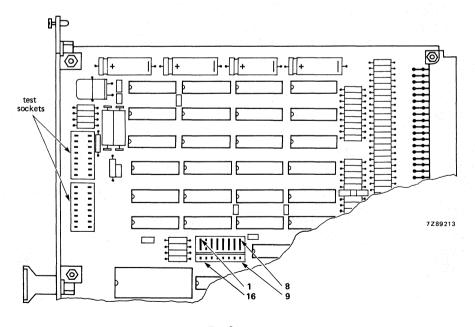

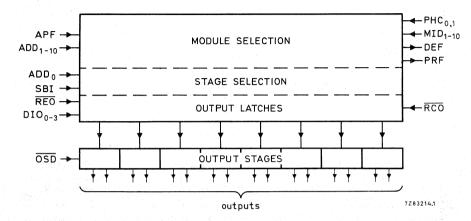

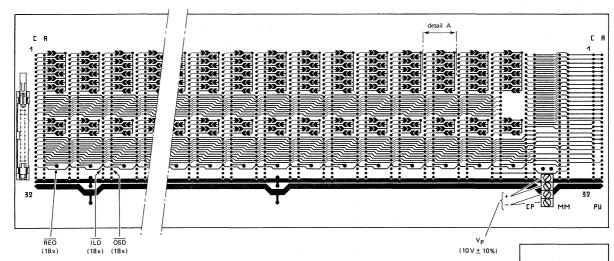

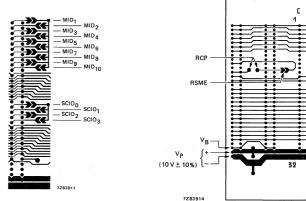

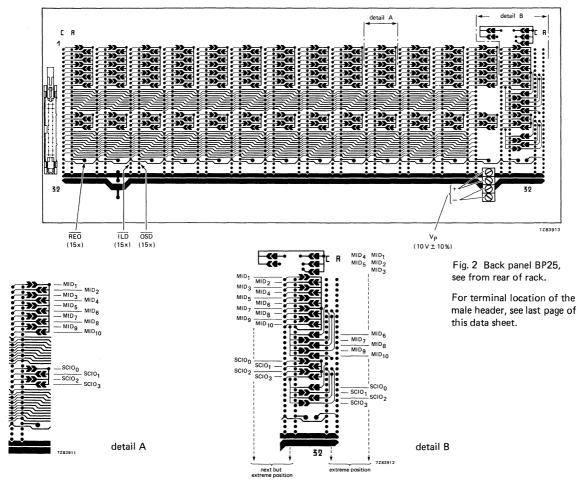

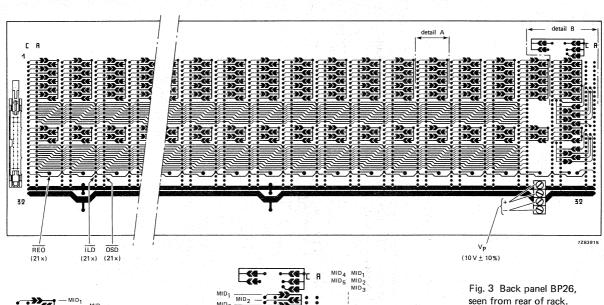

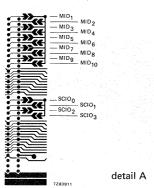

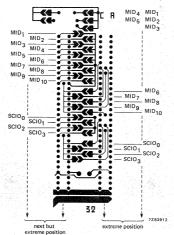

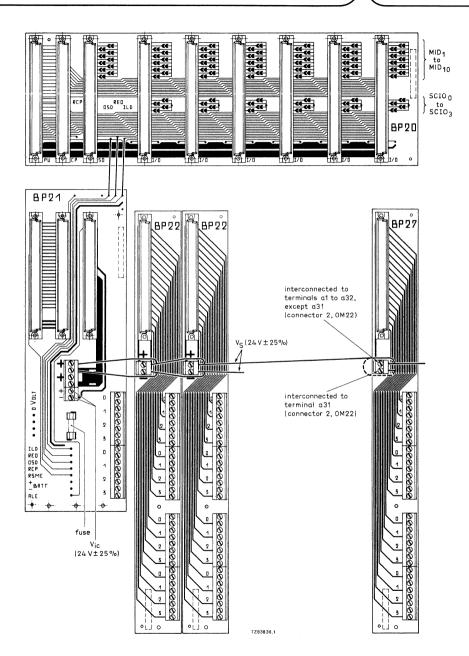

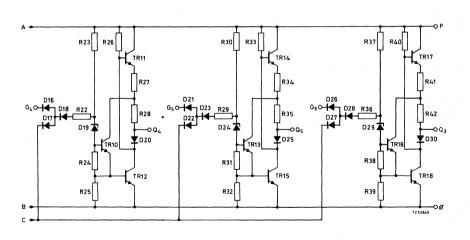

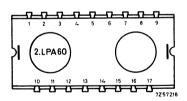

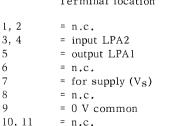

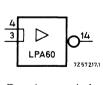

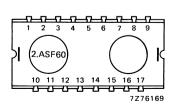

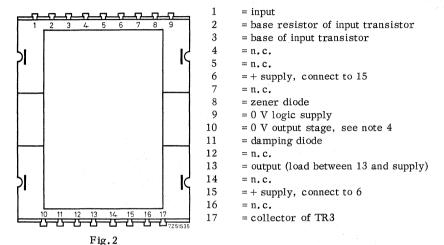

Each input module has nine address inputs (ABCIO<sub>0-8</sub>) and five module identification inputs (MID<sub>0-4</sub>), which are accessible on the connectors at the rear (Fig. 2).

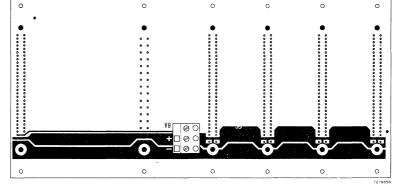

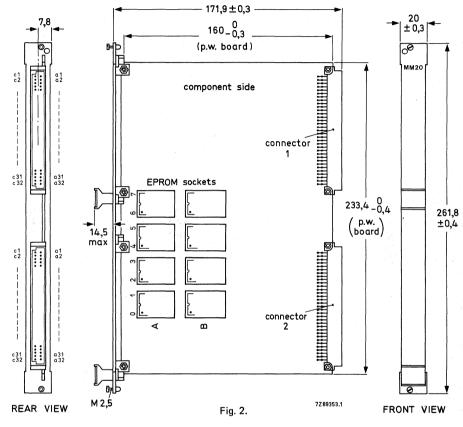

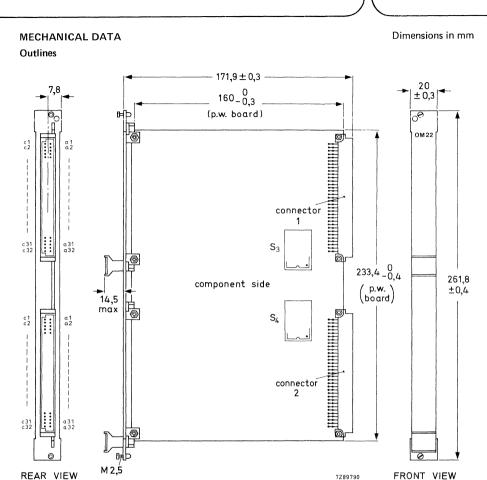

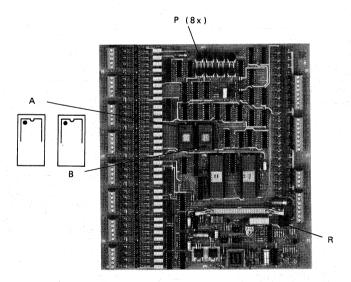

The circuit is built on an epoxy-glass printed-wiring board of 233,4 mm  $\times$  160 mm (Euro-card system). The board is provided with two F068-1 connectors (board parts); the corresponding rack parts are available on the back panels BP11 to BP16 or separately under catalogue number 2422 025 89291 (pins for wire wrapping), 2422 025 89299 (pins for dip soldering) or 2422 025 89327 (solder tags).\*

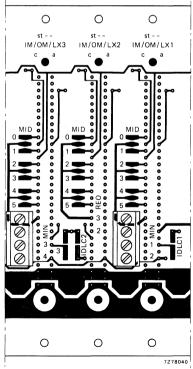

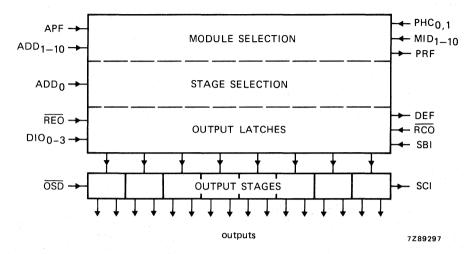

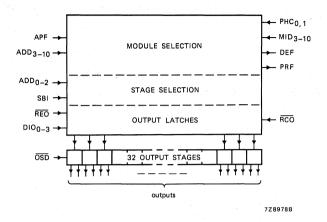

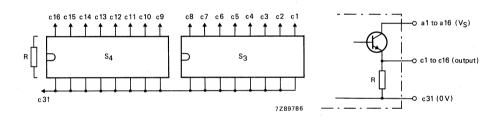

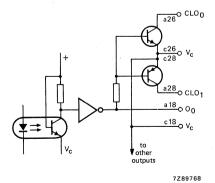

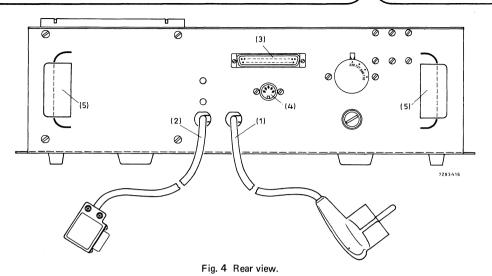

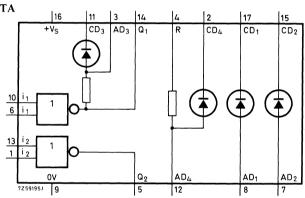

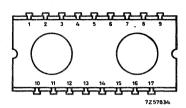

Fig. 2 Block diagram of the input modules.

<sup>\*</sup> For a general description of the Euro-card system see IEC 297 or DIN 41494 for 19-in racks and IEC 130-14 or DIN 41612 for connectors.

#### **ELECTRICAL DATA**

#### Supply

Supply voltage (d.c.)

current

VР lρ

5 V ± 5%

max. 0,5 A typ. 0,45 A

#### Input data

The data inputs are  $DI_{XY0}$  to  $DI_{XY7}$  and  $DI_{XZ0}$  to  $DI_{XZ7}$ . They are accessible on connector 2, see "Terminal location".

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 5 V level**             | 24 V level            |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|-----------------------|

| Active voltage (V <sub>a-c</sub> )*                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 3,5 to 6 V▲             | 17 to 30 V▲           |

| Non-active voltage (V <sub>a-c</sub> )*                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 0 to 0,8 V or floating▲ | 0 to 7 V or floating▲ |

| Input current, active at $V_{a-c} = 5 \text{ V or } 24 \text{ V resp.}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | typ. 10 mA              | typ. 10 mA            |

| THE STATE OF THE S |                         |                       |

The inputs mentioned below meet the standard TTL specifications

| input                                                                                                                                                                      | function                                                                                                                                                             | load                                                                          | terminations of connector 1 (Fig. 3)                                    |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|-------------------------------------------------------------------------|--|

| ABCIO <sub>0</sub> ABCIO <sub>1</sub> ABCIO <sub>2</sub> ABCIO <sub>3</sub> ABCIO <sub>4</sub> ABCIO <sub>5</sub> ABCIO <sub>6</sub> ABCIO <sub>7</sub> ABCIO <sub>8</sub> | Address bits from central processor; ABCIO <sub>0-3</sub> select the input stage, ABCIO <sub>4-8</sub> selection the input module.                                   | 1 TTL<br>1 TTL<br>1 TTL<br>1 TTL<br>1 TTL<br>1 TTL<br>1 TTL<br>1 TTL<br>1 TTL | a2, c2<br>a4, c4<br>a6, c6<br>a8, c8<br>a10<br>a12<br>a14<br>a16<br>a18 |  |

| MIN                                                                                                                                                                        | Module inhibit signal from external source; a low level applied to this input inhibits data on DBIC to be stored in the scratch-pad memory of the central processor. | 2 TTL                                                                         | c26                                                                     |  |

| MID <sub>0</sub> MID <sub>1</sub> MID <sub>2</sub> MID <sub>3</sub> MID <sub>4</sub>                                                                                       | Module identification inputs; provide module with individual identity.                                                                                               | 2 TTL<br>2 TTL<br>2 TTL<br>2 TTL<br>2 TTL<br>2 TTL                            | c10<br>c12<br>c14<br>c16<br>c18                                         |  |

- \* Voltage between terminal of row a and terminal of row c of connector 2.

- \*\* By short-circuiting terminals B1 and B2 (see Figs 1a and 1b).

- ▲ D.C. (for IM10) or a.c. values (for IM11).

#### Output data

All outputs (open collector) meet the standard TTL specifications.

| output | function                                                                                                                                                                                         | loadability | terminations of connector 1 (Fig. 3) |

|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--------------------------------------|

| DBIC   | Data bit to central processor; data is stored in scratch-pad memory of central processor.                                                                                                        | 10 TTL      | a20                                  |

| IDIC   | Identification signal to central processor (active LOW); prepares central processor for data on DBIC to be written in the scratch-pad memory.                                                    | 10 TTL      | c24                                  |

| IDLC   | Identification signal from last input module to central processor (active HIGH); only the IDLC output of the last input module has to be connected with the IDLC input of the central processor. | 2 TTL       | a26                                  |

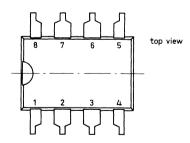

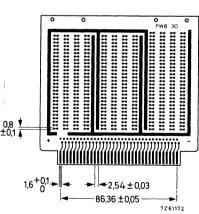

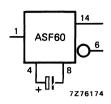

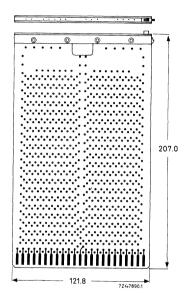

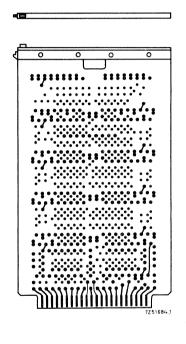

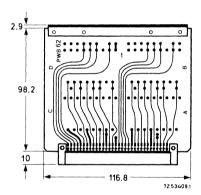

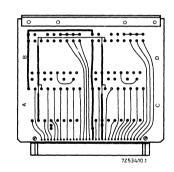

Fig. 3.

**Mass** 250 g

REAR VIEW

M 2,5

FRONT VIEW

7Z69378.1

#### **Terminal location**

| connector 1          |    | C                  | connector 2       |    |       |

|----------------------|----|--------------------|-------------------|----|-------|

| row c                |    | row a              | row c             |    | row a |

| ABCIO <sub>0</sub>   | 2  | ABCIO <sub>0</sub> | DI <sub>XY0</sub> | 2  | DIXY  |

| ABCIO <sub>1</sub>   | 4  | ABCIO <sub>1</sub> | DIXY1             | 4  | DIXY  |

| ABCIO <sub>2</sub>   | 6  | ABCIO <sub>2</sub> | DIXY2             | 6  | DIXY  |

| ABCIO3               | 8  | ABCIO3             | DIXY3             | 8  | DIXY  |

| $\overline{MID}_{0}$ | 10 | ABCIO <sub>4</sub> | DIXY4             | 10 | DIXY  |

| MID <sub>1</sub>     | 12 | ABCIO <sub>5</sub> | DI <sub>XY5</sub> | 12 | DIXY  |

| $\overline{MID}_2$   | 14 | ABCIO <sub>6</sub> | DIXY6             | 14 | DIXY  |

| MID <sub>3</sub>     | 16 | ABCIO <sub>7</sub> | DIXY7             | 16 | DIXY  |

| MID <sub>4</sub>     | 18 | ABCIO <sub>8</sub> | DI <sub>XZ0</sub> | 18 | DIXZ  |

| 0 V*                 | 20 | DBIC               | DIXZ1             | 20 | DIXZ  |

| 0 V*                 | 22 | n.c.               | DI <sub>XZ2</sub> | 22 | DIXZ  |

| IDIC                 | 24 | n.c.               | DI <sub>XZ3</sub> | 24 | DIXZ  |

| MIN                  | 26 | IDLC               | DI <sub>XZ4</sub> | 26 | DIXZ  |

| n.c.                 | 28 | n.c.               | DI <sub>XZ5</sub> | 28 | DIXZ  |

| VP                   | 30 | V <sub>P</sub>     | DIXZ6             | 30 | DIXZ  |

| 0 V                  | 32 | 0 V                | DI <sub>XZ7</sub> | 32 | DIXZ  |

n.c. = not connected.

<sup>\*</sup> No supply line; only to be used for coding of the  $\overline{\text{MID}}_{0\text{-}4}$  lines.

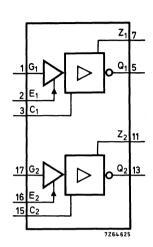

#### LOAD EXTERNAL INTERFACE

#### DESCRIPTION

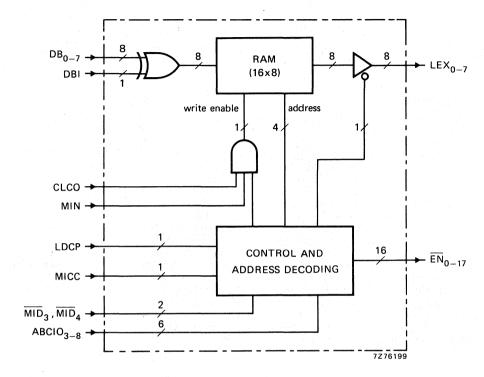

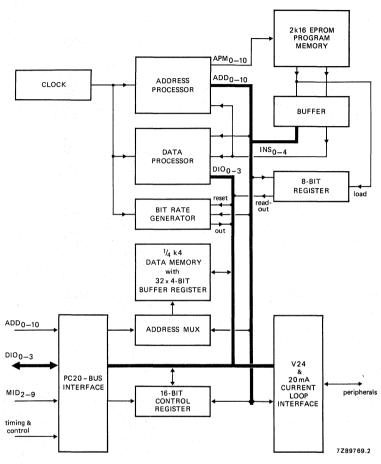

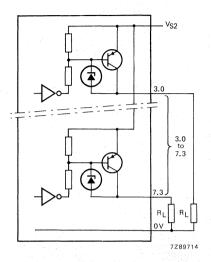

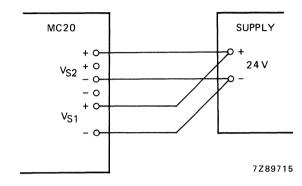

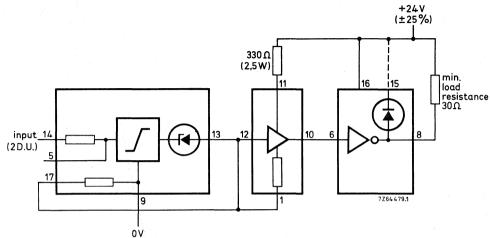

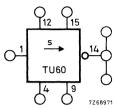

This load external interface is intended for use in combination with the central processor CP10, input module IM10 or IM11, output module OM10 or OM12, memory module MM10, MM11 or MM12 and programming unit PU10 to assemble a programmable logic controller (PLC). The module can be used as an interface between the load external inputs LEX<sub>0</sub> to LEX<sub>7</sub> on the CP10 and a number of 8-bit data sources. The data outputs of the different data sources have to be connected to one 8-bit data bus. The LX10 has 16 enable outputs  $\overline{\text{EN}}_0$  to  $\overline{\text{EN}}_{17}$ , which are to enable the different data sources. The 8-bit data bus has to be connected to the data inputs DB<sub>0</sub> to DB<sub>7</sub>. The data applied to the data inputs can be inverted on the LX10 by activating the data bit invert input DBI (see the truth table on the next page). The applied data can have a 5 V or a 24 V level. A block diagram is given in Fig. 1. The data inputs and enable outputs are electrically isolated from the 5 V logic circuitry by means of photocouplers. All data inputs are floating with respect to each other. Reading data from the data sources will only occur during the input/output cycle. The data are then stored in a 16  $\times$  8 randomaccess memory (RAM) on the LX10. The data can be read out of the RAM during the data processing cycle. Storing data into the RAM can be inhibited by applying a 0 V level to the module inhibit input (MIN). Reading data out of the RAM cannot be inhibited. The module has 6 address inputs ABCIO3 to ABCIOg. This means that a total number of 64 data sources of 8-bits can be connected to the PLC system via 4 LX10 modules. Therefore the module is provided with 2 module identification inputs (MID<sub>3</sub>, MID<sub>4</sub>) which are accessible on the connector. Irrespective of the number of LX10 modules used, a complete input/output cycle of 0,924 ms will occur.

Fig. 1.

| <b>T</b> | .41. | -  |   |   |

|----------|------|----|---|---|

| ı rı     | ıth  | ıа | n | Ω |

| data inputs<br>DB <sub>0</sub> to DB <sub>7</sub> | data input<br>DBI | data ouput<br>LEX <sub>0</sub> to LEX <sub>7</sub> |

|---------------------------------------------------|-------------------|----------------------------------------------------|

| active                                            | active            | 0                                                  |

| non-active                                        | active            | . 1                                                |

| active                                            | non-active        | 1                                                  |

| non-active                                        | non-active        | 0                                                  |

# ELECTRICAL DATA

#### Supply

Logic supply voltage (d.c.)

Logic supply current (d.c.)

Supply voltage (d.c.) to drive enable outputs

Supply current (d.c.) to drive enable outputs

$V_P$  5 V  $\pm$  5%

max. 0,7 A typ. 0,6 A

5 V ± 5%

24 V ± 25%

max. 3 mA tvp. 2.5 mA

#### Input data

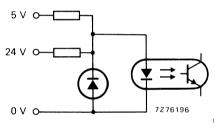

The data inputs are DB<sub>0</sub> to DB<sub>7</sub> and DBI. They are accessible on connector 2 (see "Terminal location" and Fig. 2 for connection).

|                                                                         | 5 V level  | 24 V level |

|-------------------------------------------------------------------------|------------|------------|

| Active voltage (V <sub>a-c</sub> )*                                     | 3,5 to 6 V | 18 to 30 V |

| Non-active voltage (V <sub>a-c</sub> ) *                                | 0 to 0,8 V | 0 to 0,8 V |

| Input current, active at $V_{a-c} = 5 \text{ V or } 24 \text{ V resp.}$ | typ. 10 mA | typ. 10 mA |

#### Connector 2

row a, terminals 1, 3, 5, 7, 9, 11, 13, 15, 17

row a, terminals 2, 4, 6, 8, 10, 12, 14, 16, 18

row c, terminals (1,2), (3,4), (5,6), (7,8), (9,10), (11,12), (13,14), (15,16), (17,18)

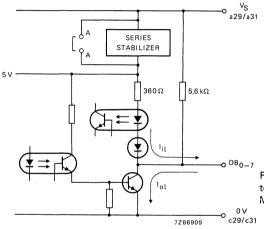

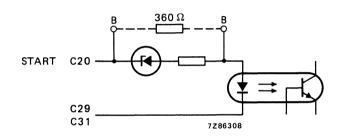

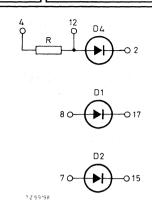

Fig. 2 Input circuit  $DB_0$  to  $DB_7$  and DBI.

All other inputs are connected to the CP10 and meet the standard TTL specification except the CLCO-input.

<sup>\*</sup> Voltage between terminal of row a and terminal of row c of connector 2.

| input                                                    | function                                                                                                                                                               | load                                               | terminations (Fig. 4)                 |             |  |

|----------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|---------------------------------------|-------------|--|

|                                                          |                                                                                                                                                                        |                                                    | connector 1                           | connector 2 |  |

| ABCIO3<br>ABCIO4<br>ABCIO5<br>ABCIO6<br>ABCIO7<br>ABCIO8 | Address bits from central processor.                                                                                                                                   | 1 TTL<br>1 TTL<br>1 TTL<br>1 TTL<br>1 TTL<br>1 TTL | a8<br>a10<br>a12<br>a14<br>a16<br>a18 |             |  |

| LDCP                                                     | Signal from central processor indicating the beginning of data processing cycle.                                                                                       | 2 TTL                                              | c15                                   |             |  |

| місс                                                     | Signal from central processor;<br>trailing edge indicates the end of<br>the data processing cycle.                                                                     | 1 TTL                                              | c5                                    |             |  |

| MIN                                                      | Module inhibit signal from external source; a LOW level applied to this input inhibits data on DB <sub>0</sub> to DB <sub>7</sub> to be stored in the RAM on the LX10. | 2 TTL                                              | c26                                   |             |  |

| MID <sub>3</sub><br>MID <sub>4</sub>                     | Module identification inputs.                                                                                                                                          | 2 TTL<br>2 TTL                                     | c16<br>c18                            |             |  |

| CLCO *                                                   | Clock signal from central processor.                                                                                                                                   | *                                                  | a28                                   |             |  |

<sup>\*</sup> Input with relatively high input resistance (typ. 40 k $\Omega$ ). CLCO-input, LOW level: max. 1 V; HIGH level: min. 2,4 V.

#### Output data

The enable outputs are  $\overline{EN}_0$  to  $\overline{EN}_{17}$ ; they are open-collector outputs.

Output voltage LOW, with respect to COMMON

at  $\overline{EN} = 80 \text{ mA}$ Output voltage HIGH

≤ 0,5 V

≤30 V

| output                                                       | function                                                                                                                                                     | loada-<br>bility                                                             | terminations (Fig. 4)       |             |  |

|--------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|-----------------------------|-------------|--|

|                                                              |                                                                                                                                                              |                                                                              | connector 1                 | connector 2 |  |

| LEX0<br>LEX1<br>LEX2<br>LEX3<br>LEX4<br>LEX5<br>LEX6<br>LEX7 | Data outputs to be connected to LEX <sub>0</sub> to LEX <sub>7</sub> inputs of CP10.                                                                         | 10 TTL<br>10 TTL<br>10 TTL<br>10 TTL<br>10 TTL<br>10 TTL<br>10 TTL<br>10 TTL | a7 c7 a9 c9 a11 c11 a13 c13 |             |  |

| IDLC                                                         | Identification signal from the LX10 to the CP10. This connection forces a complete input/output cycle. This terminal is direct connected to 0 V on the LX10. |                                                                              | a25                         |             |  |

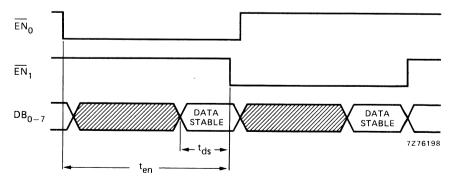

#### Time data

Time that a data source is enabled

when CP10 is used with non-extended input/output cycle

when CP10 is used with extended

input/output cycle

t<sub>en</sub> 58 μs

t<sub>en</sub> 14,8 ms

Time that data have to be present on DB<sub>0</sub> to DB<sub>7</sub>

before end of enable signal

with non-extended input/output cycle

with extended input/output cycle

$t_{ds}$  12  $\mu$ s  $t_{ds}$  2 ms

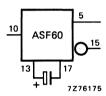

Fig. 3.

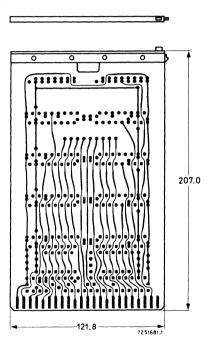

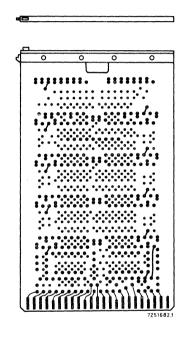

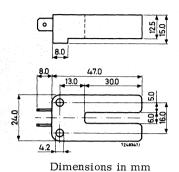

MECHANICAL DATA

Outlines

Dimensions in mm

Fig. 4.

Mass

270 g

**Terminal location**

|          | connector 1              |          |                                                                 | connector 2 |                                     |          |                                                 |

|----------|--------------------------|----------|-----------------------------------------------------------------|-------------|-------------------------------------|----------|-------------------------------------------------|

|          | row c                    |          | row a                                                           | row c       |                                     |          | row a                                           |

|          | n.c.<br>n.c.             | 1 2      | n.c.                                                            | (note 4)    | DB <sub>0</sub>                     | 1<br>2   | DB <sub>0</sub> (5 V)<br>DB <sub>0</sub> (24 V) |

|          | n.c.<br>n.c.             | 3<br>4   | n.c.<br>n.c.                                                    | (note 4) {  | DB <sub>1</sub>                     | 3<br>4   | DB <sub>1</sub>                                 |

|          | MICC<br>n.c.             | 5<br>6   | n.c.<br>n.c.                                                    | (note 4)    | DB <sub>2</sub><br>DB <sub>2</sub>  | 5<br>6   | DB <sub>2</sub><br>DB <sub>2</sub>              |

|          | LEX <sub>1</sub><br>n.c. | 7<br>8   | LEX <sub>0</sub><br>ABCIO <sub>3</sub>                          | (note 4)    | DB <sub>3</sub><br>DB <sub>3</sub>  | 7<br>8   | DB <sub>3</sub>                                 |

|          | LEX <sub>3</sub><br>n.c. | 9<br>10  | LEX <sub>2</sub><br>ABCIO <sub>4</sub>                          | (note 4)    | DB <sub>4</sub><br>DB <sub>4</sub>  | 9<br>10  | DB <sub>4</sub>                                 |

|          | LEX <sub>5</sub><br>n.c. | 11<br>12 | LEX <sub>4</sub><br>ABCIO <sub>5</sub>                          | (note 4) {  | DB <sub>5</sub><br>DB <sub>5</sub>  | 11<br>12 | DB <sub>5</sub>                                 |

|          | LEX <sub>7</sub><br>n.c. | 13<br>14 | LEX <sub>6</sub><br>ABCIO <sub>6</sub>                          |             | DB <sub>6</sub>                     | 13<br>14 | DB <sub>6</sub>                                 |

|          | LDCP<br>MID <sub>3</sub> | 15<br>16 | n.c.<br>ABCIO <sub>7</sub>                                      | (note 4)    | DB <sub>7</sub><br>DB <sub>7</sub>  | 15<br>16 | DB <sub>7</sub>                                 |

|          | n.c.<br>MID <sub>4</sub> | 17<br>18 | n.c.<br>ABCIO <sub>8</sub>                                      | (note 4)    | DBI<br>DBI                          | 17<br>18 | DBI (5 V)<br>DBI (24 V)                         |

|          | n.c.<br>0 V (note 1)     | 19<br>20 | n.c.<br>n.c.                                                    |             | n.c.<br>EN <sub>0</sub>             | 19<br>20 | n.c.<br>EN1                                     |

|          | n.c.<br>0 V (note 1)     | 21<br>22 | n.c.<br>n.c.                                                    |             | EN <sub>2</sub><br>EN <sub>4</sub>  | 21<br>22 | EN <sub>3</sub><br>EN <sub>5</sub>              |

|          | n.c.<br>n.c.             | 23<br>24 | n.c.                                                            |             | EN <sub>6</sub><br>EN <sub>10</sub> | 23<br>24 | EN <sub>7</sub><br>EN <sub>11</sub>             |

|          | n.c.<br>MIN              | 25<br>26 | IDLC<br>n.c.                                                    |             | EN 12<br>EN 14                      | 25<br>26 | EN <sub>13</sub><br>EN <sub>15</sub>            |

|          | n.c.<br>0 V (note 2)     | 27<br>28 | n.c.<br>CLCO                                                    |             | EN <sub>16</sub><br>n.c.            | 27<br>28 | EN <sub>17</sub><br>n.c.                        |

|          | n.c.                     | 29<br>30 | n.c.                                                            |             | n.c.<br>24 V                        | 29<br>30 | n.c.<br>24 V                                    |

| (note 3) | 5 V<br>0 V               | 31<br>32 | $\begin{cases} 5 \text{ V} \\ 0 \text{ V} \end{cases}$ (note 3) | (note 5) {  | 5 V<br>COMMON                       | 31<br>32 | 5 V (note 5)                                    |

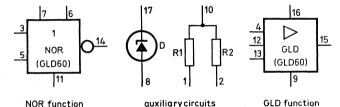

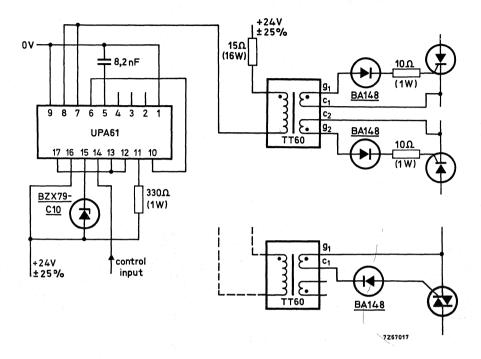

n.c. = not connected