# PYTHON CHIPSET FOR PENTIUM<sup>™</sup> PROCESSORS

82C546 & 82C547 Data Book Version 1.0

# Disclaimer

The information contained within this document is subject to change without notice.

OPTi Inc. reserves the right to make changes in this manual at any time as well as in the products it describes, at any time without notice or obligation.

OPTi Inc. assumes no responsibility for any errors contained within.

In no event will OPTi Inc. be liable for any damages, direct, indirect, incidental or consequential resulting from any error, defect, or omission in this manual.

Copyright © 1994 by OPTi Inc. All rights reserved.

#### **OPTi Inc.**

2525 Walsh Avenue Santa Clara, CA 95051 Tel: (408) 980-8178 Fax: (408) 980-8860

OPTi is a trademark of OPTi Incorporated. Pentium is a trademark of Intel Corporation. All other brand and product names are trademarks or copyrights of their respective owners.

# **Table of Contents**

| 1.0 | Feat  | ures      | ••••••      |                                     | 1    |

|-----|-------|-----------|-------------|-------------------------------------|------|

| 2.0 | Over  | view      |             |                                     | 2    |

|     | 2.1   | 82C546 (  | (ATC) AT    | Bus Controller                      | 2    |

|     | 2.2   | 82C547    | (SYSC) Sy   | stem Controller                     | 2    |

|     | 2.3   | 82C206    | (IPC) Integ | grated Peripheral Controller        | 3    |

|     | 2.4   | Support   | Chips       |                                     | 3    |

| 3.0 | Signa | al Defini | itions      |                                     | 5    |

|     | 3.1   | Signal D  | escription  | 5                                   | . 17 |

|     |       | 3.1.1     | -           | TC Signal Descriptions              |      |

|     |       | 5.1.1     | 3.1.1.1     | Clock and Reset Interface Signals   |      |

|     |       |           | 3.1.1.2     | Data Bus Interface Signals          |      |

|     |       |           | 3.1.1.3     | Local Bus Interface Signals         |      |

|     |       |           | 3.1.1.4     | Buffer Control Interface Signals    |      |

|     |       |           | 3.1.1.5     | Bus Arbitration Interface Signals   |      |

|     |       |           | 3.1.1.6     | AT Bus Interface Signals            |      |

|     |       |           | 3.1.1.7     | Miscellaneous Interface Signals     |      |

|     |       |           | 3.1.1.8     | Power and Ground Pins               |      |

|     |       | 3.1.2     | 82C547 S    | YSC Signal Descriptions             |      |

|     |       | J.1.2     | 3.1.2.1     | Clock and Reset Interface Signals   |      |

|     |       |           | 3.1.2.2     | Data Bus Interface Signals          |      |

|     |       |           | 3.1.2.3     | VL Bus Interface Signals            |      |

|     |       |           | 3.1.2.4     | Cache Interface Signals             |      |

|     |       |           | 3.1.2.5     | System DRAM Interface Signals       |      |

|     |       |           | 3.1.2.6     | Bus Arbitration Interface Signals   |      |

|     |       |           | 3.1.2.7     | Data Buffer Interface Signals       |      |

|     |       |           | 3.1.2.8     | Miscellaneous Interface Signals     |      |

|     |       |           | 3.1.2.9     | Ground and Power Pins               |      |

|     |       | 3.1.3     |             | Signal Descriptions                 |      |

|     |       |           | 3.1.3.1     | CPU Interface Signals               |      |

|     |       |           | 3.1.3.2     | ISA/VL/Memory Bus Interface Signals |      |

|     |       |           | 3.1.3.3     | Buffer Control Interface Signals    |      |

|     |       |           | 3.1.3.4     | Ground and Power Pins               |      |

|     |       | 3.1.4     | 82C606B     | Signal Definitions                  | 30   |

|     |       |           | 3.1.4.1     | CPU/Cache Interface Signals         |      |

|     |       |           | 3.1.4.2     | ISA/VL Bus Interface Signals        |      |

|     |       |           |             | 5                                   |      |

2

# 82C546/82C547

|     |      |                     | 3.1.4.3            | Buffer Control Interface Signals                                                  |    |

|-----|------|---------------------|--------------------|-----------------------------------------------------------------------------------|----|

|     |      |                     | 3.1.4.4            | Miscellaneous Interface Signals                                                   |    |

|     |      |                     | 3.1.4.5            | Ground and Power Pins                                                             |    |

| 4.0 | Fune | ctional I           | Descripti          | on                                                                                |    |

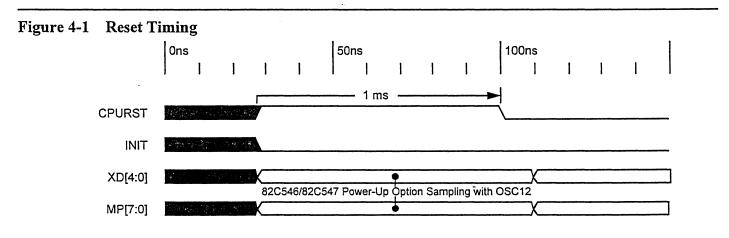

|     | 4.1  | Reset L             | -<br>ogic          | ,<br>                                                                             |    |

|     |      |                     | 0                  |                                                                                   |    |

|     | 4.2  | <b>System</b> 4.2.1 |                    | SYSC Clocks                                                                       |    |

|     | ч,   |                     |                    |                                                                                   |    |

|     |      | 4.2.2               |                    | Clocks                                                                            |    |

|     |      | 4.2.3               | AT Bus (           | Clocks                                                                            |    |

|     | 4.3  | Cache S             | ubsystem.          |                                                                                   |    |

|     |      | 4.3.1               | CPU Bur            | st Mode Control                                                                   |    |

|     |      | 4.3.2               | Cache Cy           | /cle Types                                                                        |    |

|     |      | 4.3.3               | Cache Op           | peration                                                                          |    |

|     |      |                     | 4.3.3.1            | L2 Cache Read-Hit                                                                 |    |

|     |      |                     | 4.3.3.2            | L2 Cache Write-Hit Cycle                                                          |    |

|     |      |                     | 4.3.3.3            | L2 Cache Read-Miss                                                                |    |

|     |      |                     | 4.3.3.4            | L2 Cache Write-Miss                                                               |    |

|     |      |                     | 4.3.3.5            | Tag Compare Table                                                                 |    |

|     |      |                     | 4.3.3.6            | Cache Critical Paths                                                              |    |

|     |      |                     | 4.3.3.7            | Single Bank Cache Verses Double Bank Cache                                        |    |

|     |      |                     | 4.3.3.8<br>4.3.3.9 | Cache Initialization<br>Write-Back Cache with DMA/ISA Master/VL Master Operations |    |

|     |      |                     | 4.3.3.9            | DMA/Master Write Cycle                                                            |    |

|     |      |                     | 4.3.3.10           | Cacheability and Write Protection                                                 |    |

|     |      |                     | 4.3.3.12           | SRAM Requirements                                                                 |    |

|     | 4.4  | DDAM                |                    | *                                                                                 |    |

|     | 4.4  |                     |                    | ·                                                                                 |    |

|     |      | 4.4.1               |                    | Read Cycle                                                                        |    |

|     |      | 4.4.2               | DRAM V             | Vrite Cycle                                                                       |    |

|     |      | 4.4.3               | DRAM P             | arity Generation/Detection Logic                                                  |    |

|     |      | 4.4.4               | DRAM F             | Refresh Logic                                                                     | 55 |

|     |      | 4.4.5               | DRAM A             | Address Muxing                                                                    | 55 |

|     |      | 4.4.6               | DRAM I             | DMA/Master Cycles                                                                 | 56 |

|     | 4.5  | AT Bus              | Interface          |                                                                                   |    |

|     | 4.6  | Bus Arl             | bitration L        | .ogic                                                                             |    |

|     | 4.7  | VL Bus              | Interface          | ······································                                            |    |

|     |      | 4.7.1               | VL Bus S           | Slave                                                                             | 59 |

|     |      | 4.7.2               | VL Bus I           | Master                                                                            | 60 |

~

|     | 4.8  | Data Bus Conversion/Data Path Control Logic                                                   |

|-----|------|-----------------------------------------------------------------------------------------------|

|     | 4.9  | Deturbo/Slow Mode Operations                                                                  |

|     | 4.10 | Fast GATEA20 and RESET Emulation 61                                                           |

|     | 4.11 | Special Cycles                                                                                |

|     |      | 4.11.1 Shadow RAM                                                                             |

|     |      | 4.11.2 System ROM BIOS Cycles                                                                 |

|     |      | 4.11.3 System Shutdown/Halt Cycles                                                            |

| 5.0 | Conf | iguration Registers63                                                                         |

|     | 5.1  | Keyboard I/O Control Registers: Ports 60h and 64h 63                                          |

| 6.0 | Maxi | imum Ratings75                                                                                |

|     | 6.1  | Absolute Maximum Ratings                                                                      |

|     | 6.2  | DC Characteristics: 5.0 Volt (Vcc = $5.0V \pm 5\%$ , Ta = $-25^{\circ}C$ to $+70^{\circ}C$ )  |

|     | 6.3  | DC Characteristics: 3.3 Volt (Vcc = $3.3V \pm 5\%$ , Ta = $-25^{\circ}$ C to $+70^{\circ}$ C) |

|     | 6.4  | 82C546 AC Characteristics (60MHz - Preliminary)76                                             |

|     | 6.5  | 82C547 AC Characteristics (60MHz - Preliminary)77                                             |

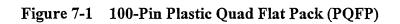

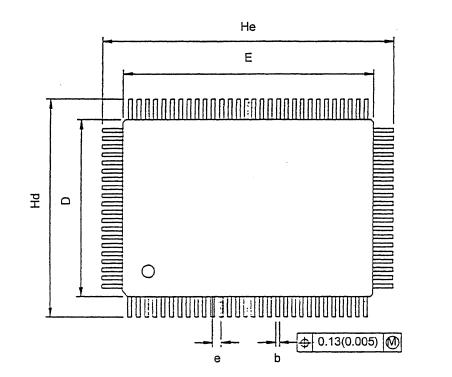

| 7.0 | Mecł | 1anical Package Outlines81                                                                    |

.

~

-

.

# List of Figures

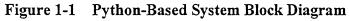

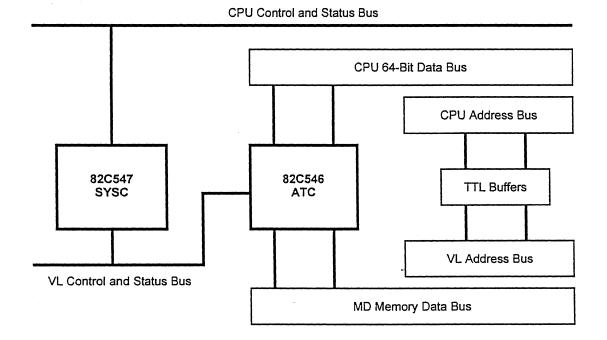

| Figure 1-1  | Python-Based System Block Diagram                           | . 1 |

|-------------|-------------------------------------------------------------|-----|

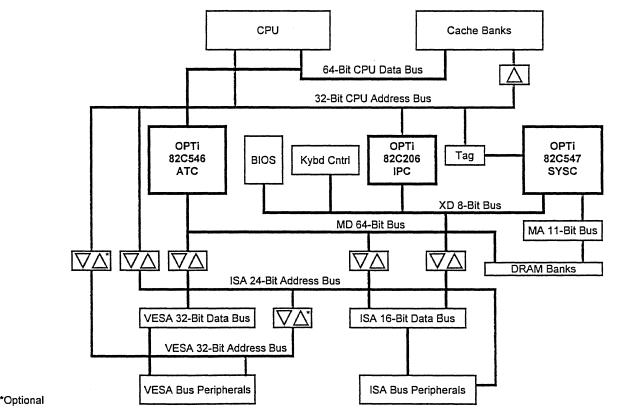

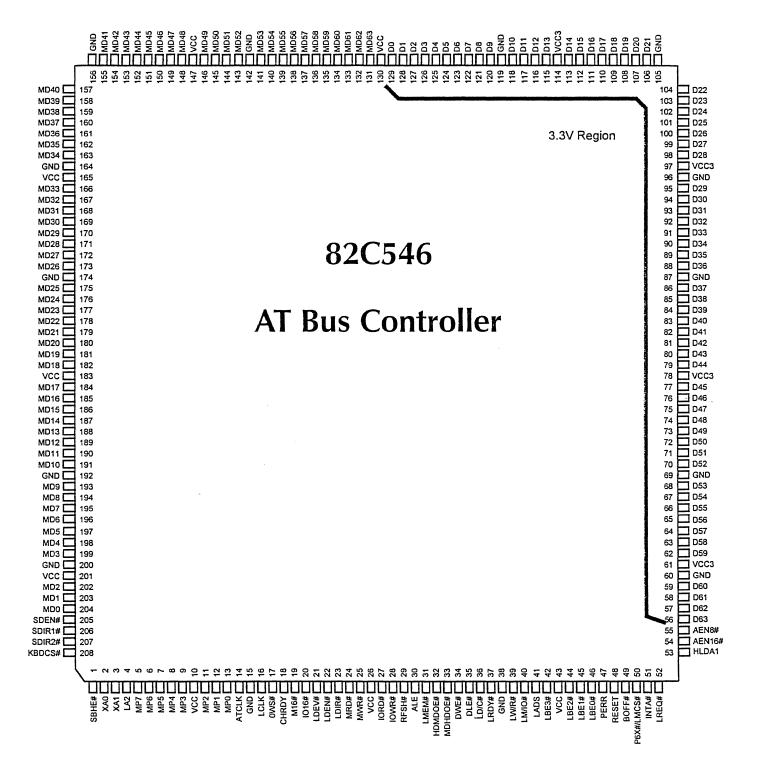

| Figure 3-1  | 82C546 ATC Pin Diagram                                      | . 5 |

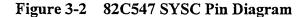

| Figure 3-2  | 82C547 SYSC Pin Diagram                                     | . 8 |

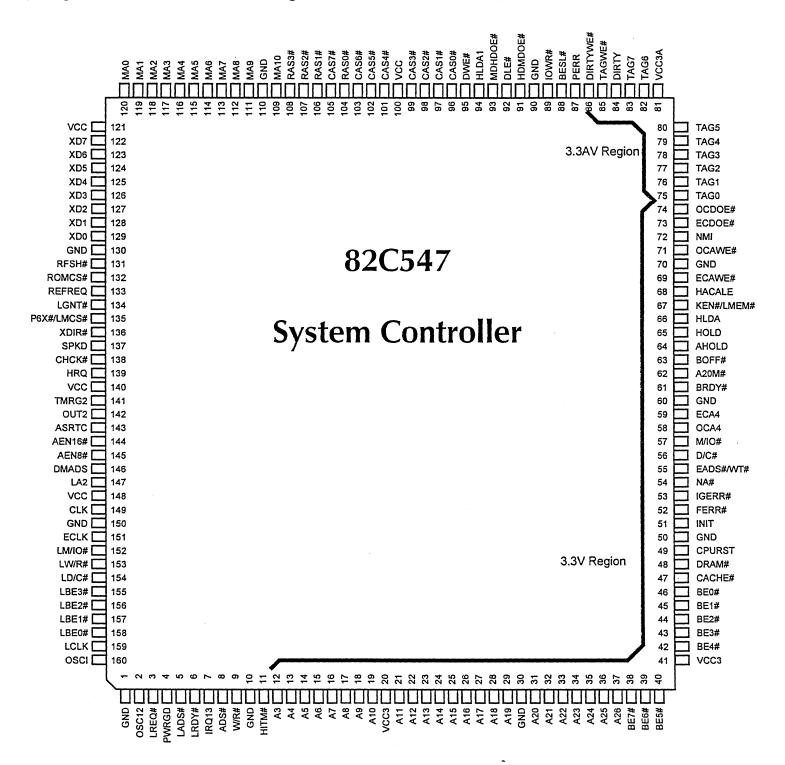

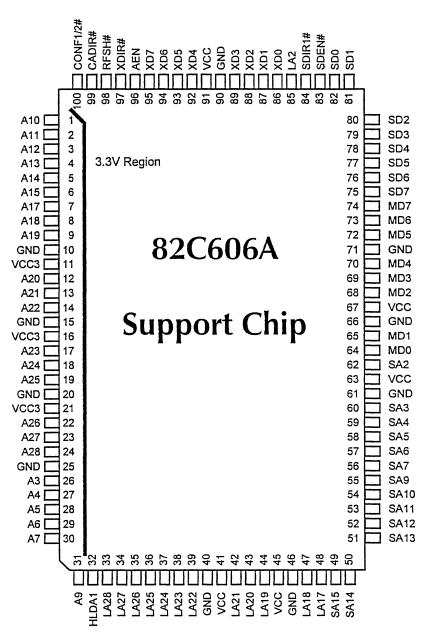

| Figure 3-3  | 82C606A Pin Diagram                                         | 11  |

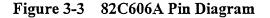

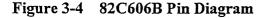

| Figure 3-4  | 82C606B Pin Diagram                                         | 14  |

| Figure 4-1  | Reset Timing                                                | 33  |

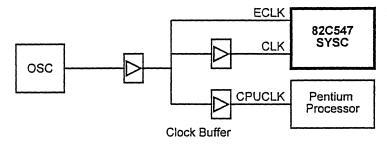

| Figure 4-2  | CPU and SYSC Clock Distribution                             | 34  |

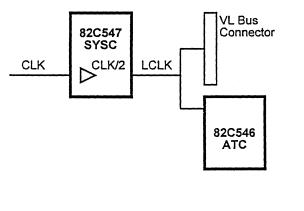

| Figure 4-3  | Clock Distribution Method for Single VL Bus Connector       | 34  |

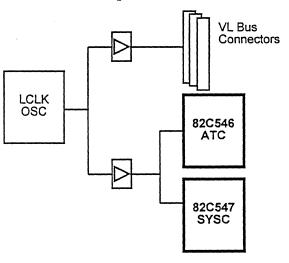

| Figure 4-4  | Clock Distribution Method for Multiple VL Bus Connectors    | 34  |

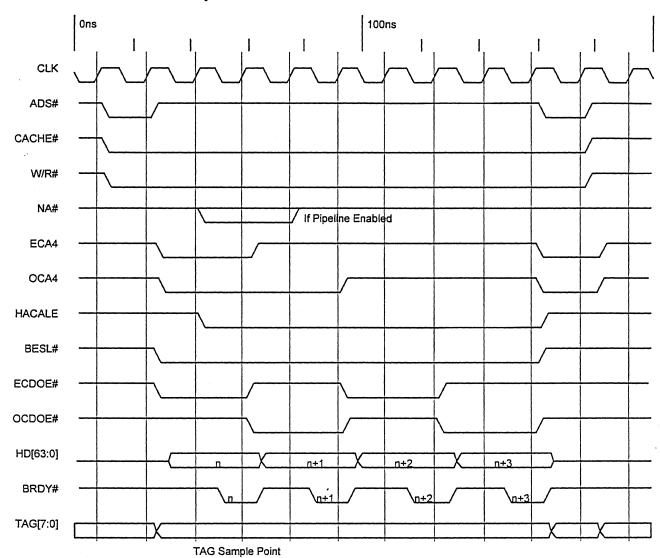

| Figure 4-5  | L2 Cache Read-Hit Cycle                                     | 38  |

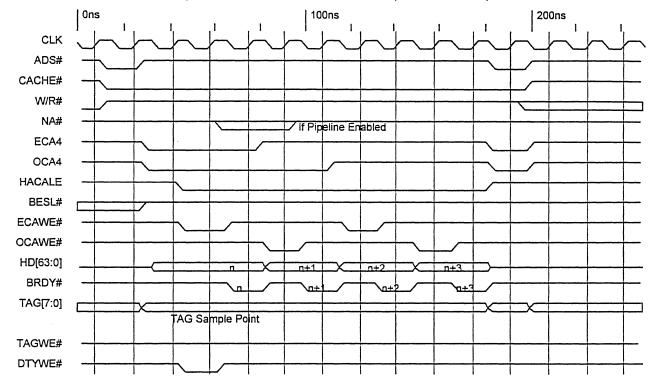

| Figure 4-6  | Write-Hit Burst Cycle for the Write-Back Mode (Double Bank) | 39  |

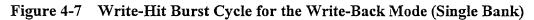

| Figure 4-7  | Write-Hit Burst Cycle for the Write-Back Mode (Single Bank) | 39  |

| Figure 4-8  | L2 Cache Read-Miss Clean Burst of 8-3-3-3 (Linefill Cycle)  | 41  |

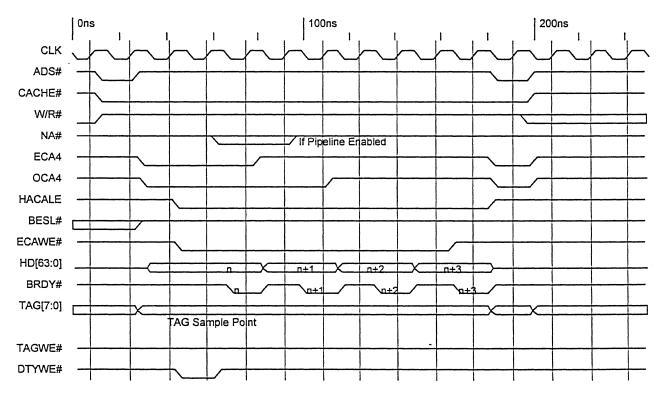

| Figure 4-9  | L2 Cache Read-Miss Dirty Cycle                              | 42  |

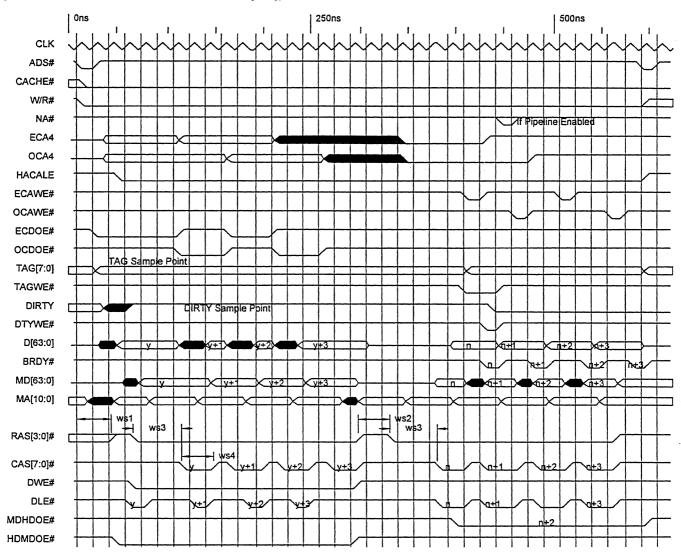

| Figure 4-10 | L2 Cache Write-Miss Burst (4-3-3-3)                         | 43  |

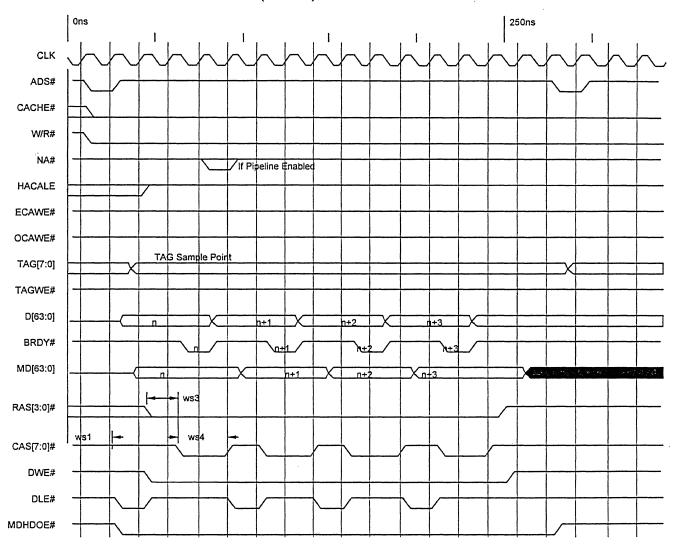

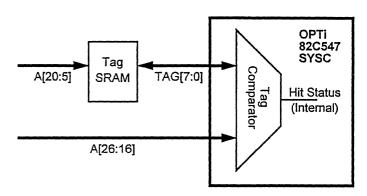

| Figure 4-11 | L2 Cache Structure Block Diagram                            | 44  |

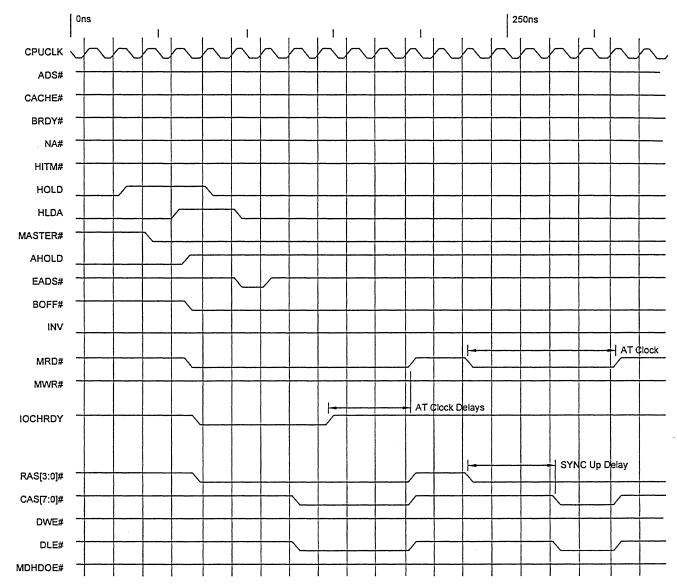

| Figure 4-12 | AT DMA/Master Read (L1 Cache Line Clean)                    | 47  |

| Figure 4-13 | AT DMA/Master Read (L1 Cache Line Modified)                 | 48  |

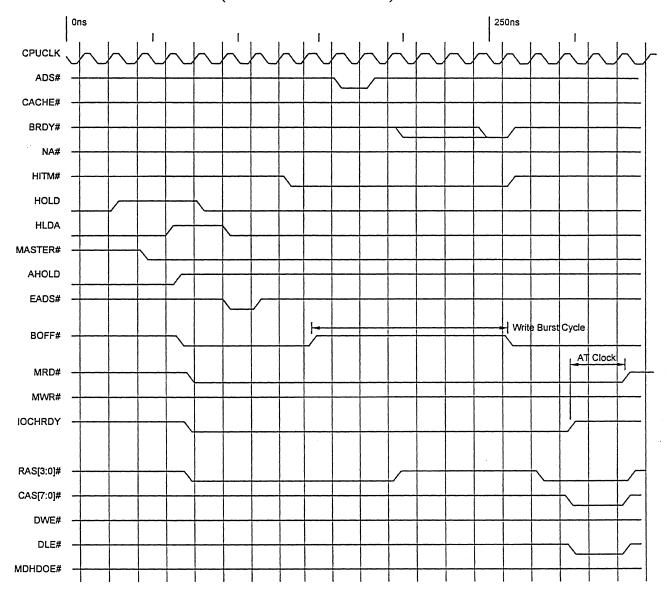

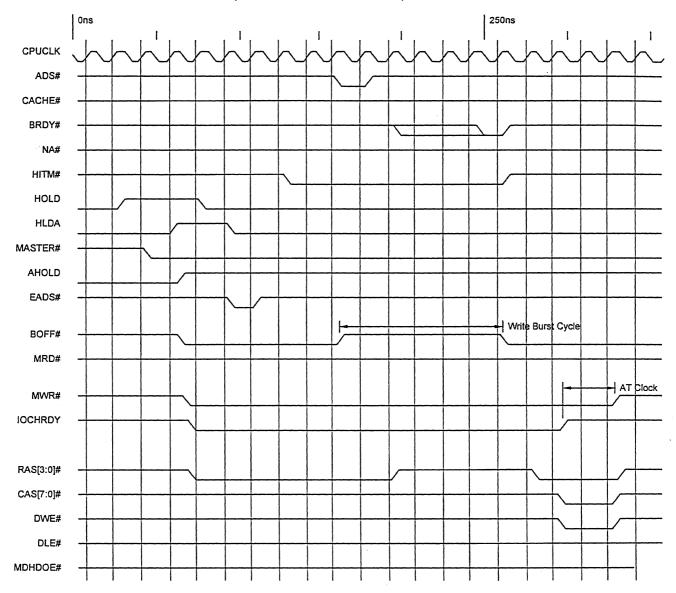

| Figure 4-14 | AT DMA Master Write (L1 Cache Line Modified)                | 50  |

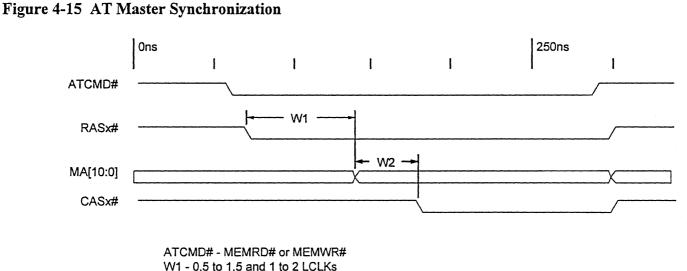

| Figure 4-15 | AT Master Synchronization                                   | 56  |

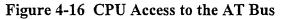

| Figure 4-16 | CPU Access to the AT Bus                                    | 57  |

| Figure 4-17 | CPU to VL Bus Interface Block Diagram                       | 58  |

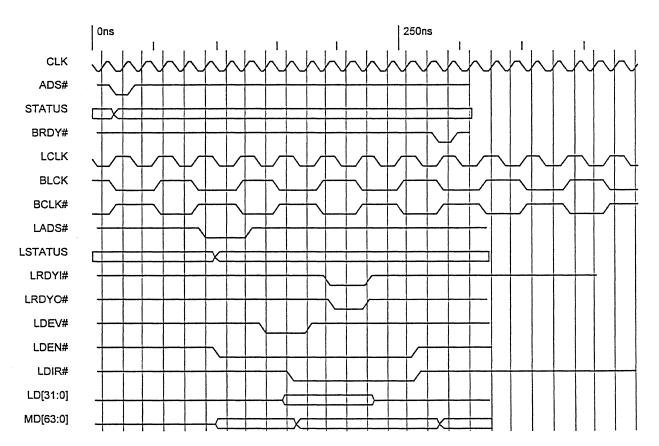

| Figure 4-18 | CPU Read from VESA Slave                                    | 59  |

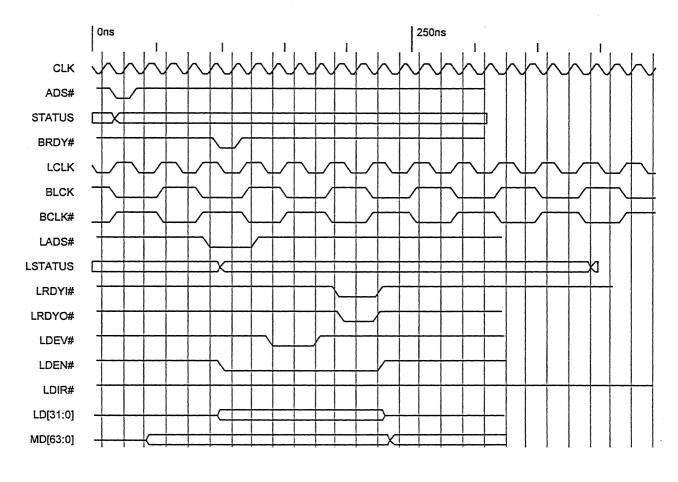

| Figure 4-19 | CPU Write to VESA Slave                                     | 60  |

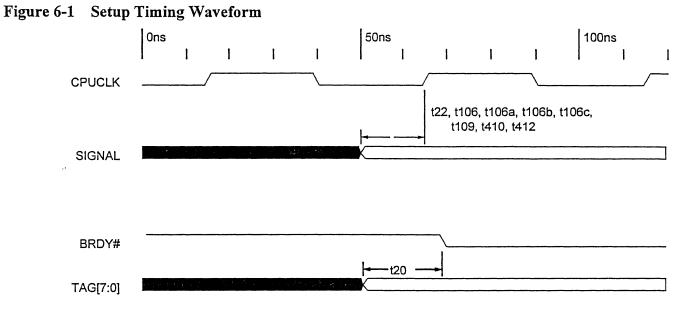

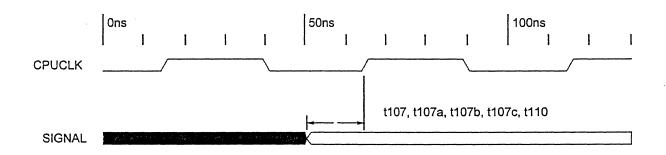

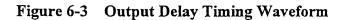

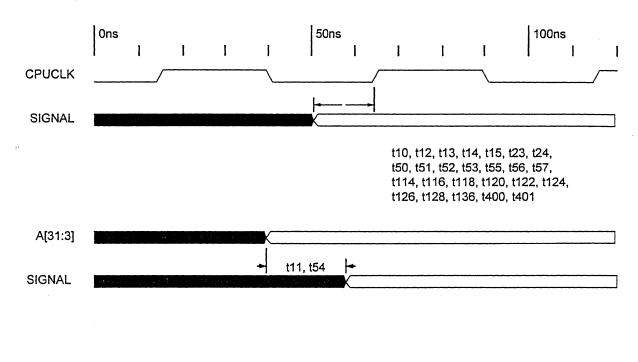

| Figure 6-1  | Setup Timing Waveform                                       | 79  |

| Figure 6-2  | Hold Timing Waveform                                        | 79  |

| Figure 6-3  | Output Delay Timing Waveform                                | 80  |

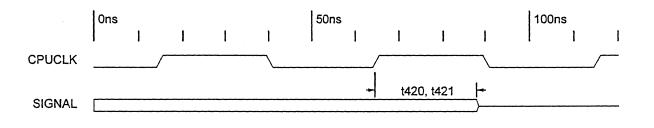

| Figure 6-4  | Float Delay Timing Waveform                                 | 80  |

| Figure 7-1  | 100-Pin Plastic Quad Flat Pack (PQFP)                       | 81  |

| Figure 7-2  | 160-Pin Plastic Quad Flat Pack (PQFP)                       | 82  |

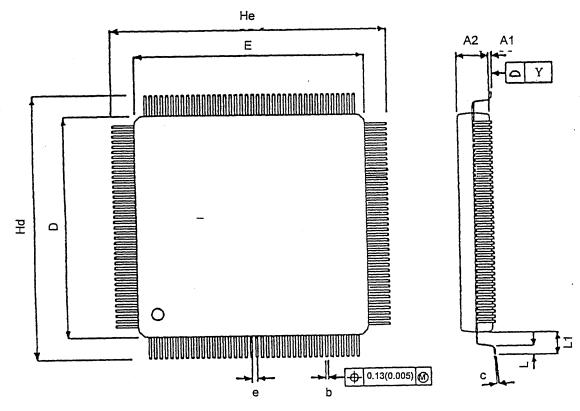

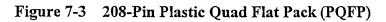

| Figure 7-3  | 208-Pin Plastic Quad Flat Pack (PQFP)                       | 83  |

•

DBS-01-CS002-1.0

.

# List of Tables

| Table 3-1  | 82C546 ATC Numerical Pin Cross-Reference List    | 6    |

|------------|--------------------------------------------------|------|

| Table 3-2  | 82C546 ATC Alphabetical Pin Cross-Reference List | 7    |

| Table 3-3  | 82C547 SYSC Numerical Pin Cross-Reference List   | 9    |

| Table 3-4  | 82C547 SYSC Alphabetical Pin Cross-Reference     | . 10 |

| Table 3-5  | 82C606A Numerical Pin Cross-Reference            | . 12 |

| Table 3-6  | 82C606A Alphabetical Pin Cross-Reference         | . 13 |

| Table 3-7  | 82C606B Numerical Pin Cross-Reference            | . 15 |

| Table 3-8  | 82C606B Alphabetical Pin Cross-Reference         | . 16 |

| Table 4-1  | Power-On Reset and LCK Relationship              | . 34 |

| Table 4-2  | Power-On Reset and LCLK to ATCLK Relationship    | . 35 |

| Table 4-3  | Power-On Reset and I/O Buffer Select             | . 36 |

| Table 4-4  | Tag Compare                                      | . 44 |

| Table 4-5  | DMA/Master Read Cycle Summary                    | . 46 |

| Table 4-6  | DMA/Master Write Cycle Summary                   | . 49 |

| Table 4-7  | Write Protection Control Methods                 | . 51 |

| Table 4-8  | Data SRAM Configurations                         | . 52 |

| Table 4-9  | Data and Tag SRAM Speed Requirements             | . 52 |

| Table 4-10 | DRAM Programmable Control                        | . 53 |

| Table 4-11 | DRAM Timing Mode - Read Cycle                    | . 53 |

| Table 4-12 | DRAM Timing Mode - Write Cycle                   | . 53 |

| Table 4-13 | POR and MDHDOE#                                  | . 54 |

| Table 4-14 | DRAM Row/Column MA to Address Bit Map            | . 55 |

| Table 4-15 | POR and AT Back-to-Back I/O Cycles               | . 57 |

| Table 4-16 | VL Bus POR Signal Strapping                      | . 59 |

| Table 5-1  | Port B Register: Index 61h                       | . 63 |

| Table 5-2  | DRAM Configuration Register 1: Index 00h         | . 64 |

| Table 5-3  | DRAM Control Register 1: Index 01h               | . 65 |

| Table 5-4  | Cache Control Register 1: Index 02h              | . 65 |

| Table 5-5  | Cache Control Register 2: Index 03h              | . 66 |

| Table 5-6  | Shadow RAM Control Register 1: Index 04h         |      |

| Table 5-7  | Shadow RAM Control Register 2: Index 05h         | . 68 |

| Table 5-8  | Shadow RAM Control Register 3: Index 06h         | . 68 |

-

# 82C546/82C547

| <b>CO</b>   |

|-------------|

| . 69        |

| . 69        |

| . 70        |

| . 70        |

| . 70        |

| . 70        |

| . 71        |

| .71         |

| . 72        |

| . 72        |

| . 73        |

| . 73        |

| -<br>-<br>- |

# **PYTHON CHIPSET**

#### 1.0 Features

- 100% PC/AT<sup>®</sup> compatible

- Fully supports the 3.3V/5.0V Pentium<sup>™</sup> processors

- Three chip solution:

- 82C547 System Controller (SYSC) (160-pin PQFP)

- 82C546 AT<sup>TM</sup> Bus Controller (ATC) (208-pin PQFP)

- 82C206 Integrated Peripherals Controller (IPC) (84-pin PLCC or 100-pin PQFP)

- Two buffer/translator support chips:

- 82C606A (100-pin PQFP)

- 82C606B (100 pin PQFP)

- Supports Pentium CPU address pipelining

- 1X clock source, supporting systems running Pentium processor bus clocks up to 60MHz

- Write-back, direct-mapped cache with size selections: 64KB, 128KB, 256KB, 512KB, 1MB, and 2MB

- Programmable cache write policy: write-back or writethrough

- Fully programmable cache and DRAM read/write cycles

- Supports 3-2-2-2 cache burst read cycles at 60MHz

- Built-in tag auto-invalidation circuitry

- Support for two programmable non-cacheable memory regions

- Options for cacheable, write-protected, system and video BIOS

- Supports two banks of 64-bit wide DRAMs with 256KB, 512KB, 1MB, 2MB, 4MB and 8MBx36 Page Mode DRAMs

- Supports DRAM configurations up to 128MB

- Supports 3-3-3-3 pipeline DRAM burst cycles

- DRAM post write buffer

- Support for flash ROM

- Shadow RAM option

#### Features (Cont.)

- Hidden refresh with CAS-before-RAS refresh supported

- High-performance 32-bit local bus support

- Performance-oriented snoop-line comparator for VL/ISA bus masters

- Extended DMA page register

- Turbo/slow speed selection

- Asynchronous CPU and VL bus interface

- AT bus clock speed programmability

- Transparent 8042 emulation for Fast CPU Reset and GATEA20 generation

- Supports Port 92h, Gate A20, and Fast Reset

- Mixed voltage (3.3V and 5.0V), low-power, high-speed, 0.8-micron CMOS technology

#### 2.0 Overview

The OPTi Python Chipset provides a highly integrated solution for fully compatible, high-performance PC/AT platforms. Together, with OPTi's 82C206 Integrated Peripheral Controller (IPC), this chipset will support the Pentium processor in the most cost effective and feature-rich designs available today. This highly integrated approach provides the foundation for a cost effective platform without compromising performance. The OPTi Python Chipset supplies a powerful solution positioned to deliver value without neglecting quality, compatibility, or reliability.

The Python Chipset is comprised of two chips, the 82C547 System Controller (SYSC) and the 82C546 AT Bus Controller (ATC). A complete Pentium processor solution consists of the Python Chipset and the 82C206 Integrated Peripheral Controller (IPC).

#### 2.1 82C546 (ATC) AT Bus Controller

The 82C546 ATC integrates the AT bus interface and data buffers for transfers between the CPU data bus, local data bus and the DRAM data bus. It also provides the ISA to local bus command translation.

- 208-pin PQFP

- Data bus buffer (host data to memory data)

- Data bus buffer control (ISA to memory)

- Parity generation and detection circuitry

- Keyboard controller chip select

- Local bus interface (ISA to local bus command translation)

#### 2.2 82C547 (SYSC) System Controller

The 82C547 SYSC provides the control functions for the host CPU interface, the 32-bit local bus interface, the 64-bit Level 2 (L2) cache and the 64-bit DRAM bus. The SYSC also controls the data flow between the CPU bus, the DRAM bus, the local bus, and the 8/16-bit ISA bus.

- 160-pin PQFP

- Pentium CPU interface

- DRAM controller

- L2 cache controller

- L1 cache controller

- Local bus interface

- Reset generation

- Arbitration logic

- Data bus buffer control (memory data to/from host data)

- Extended DMA page register

- Keyboard emulation of A20M# and CPU warm reset

- Port B and Port 92h Register

#### 2.3 82C206 (IPC) Integrated Peripherals Controller

The 82C206 IPC provides two DMA controllers, two interrupt controllers, one timer/counter, and a real-time clock in an industry standard single-chip solution for the peripherals attached to the PC/AT peripheral bus.

- 84-pin PLCC or 100-pin PQFP

- Supports four DMA transfer modes

- Special Commands provided for ease of programming

#### 2.4 Support Chips

The 82C606A and 82C606B are two buffer/translation devices used to translate 3.3V signals to 5.0V signal levels in Python motherboard solutions. These devices buffer the CPU address bus to the ISA and VL address buses, the 82C546 ATC's memory data bus to the ISA data bus, the peripheral XD bus to the ISA SA and SD buses. The 82C606A and 82C606B integrate a number of glue logic TTL devices (approximately eleven), hence reducing the amount of TTL on the motherboard.

The 82C606A and 82C606B devices are actually the same device with two strapping options. Pulling the CONF1/2# pin high causes the device to function in the 82C606A Mode. Pulling the CONF1/2# pin low configures the device to function in the 82C606B Mode of operation.

- 100-pin PQFP

- Mixed voltage to support 3.3V to 5.0V signal translation

- Two devices replace approximately eleven TTL devices

.

#### 3.0 Signal Definitions

| Pin# | Pin Name   | Pin # | Pin Name | Pin # | Pin Name | Pin # | Pin Name     |

|------|------------|-------|----------|-------|----------|-------|--------------|

| 1    | SBHE#      | 53    | HLDAI    | 105   | GND      | 157   | MD40         |

| 2    | XA0        | 54    | AEN16#   | 106   | D21      | 158   | MD39         |

| 3    | XAI        | 55    | AEN8#    | 107   | D20      | 159   | MD38         |

| 4    | LA2        | 56    | D63      | 108   | D19      | 160   | MD37         |

| 5    | MP7        | 57    | D62      | 109   | D18      | 161   | MD36         |

| 6    | MP6        | 58    | D61      | 110   | D17      | 162   | MD35         |

| 7    | MP5        | 59    | D60      | 111   | D16      | 163   | MD34         |

| 8    | MP4        | 60    | GND      | 112   | D15      | 164   | GND          |

| 9    | MP3        | 61    | VCC3     | 113   | D14      | 165   | VCC          |

| 10   | VCC        | 62    | D59      | 114   | VCC3     | 166   | MD33         |

| 11   | MP2        | 63    | D58      | 115   | D13      | 167   | MD32         |

| 12   | MP1        | 64    | D57      | 116   | D12      | 168   | MD31         |

| 13   | MP0        | 65    | D56      | 117   | D11      | 169   | MD30         |

| 14   | ATCLK      | 66    | D55      | 118   | D10      | 170   | MD29         |

| 15   | GND        | 67    | D54      | 119   | GND      | 171   | MD28         |

| 16   | LCLK       | 68    | D53      | 120   | D9       | 172   | MD27         |

| 17   | 0WS#       | 69    | GND      | 120   | D8       | 172   | MD26         |

| 18   | CHRDY      | 70    | D52      | 121   | D7       | 174   | GND          |

| 19   | M16#       | 71    | D51      | 122   | D6       | 174   | MD25         |

| 20   | IO16#      | 72    | D50      | 123   | D5       | 175   | MD24         |

| 20   | LDEV#      | 73    | D30      | 124   | D3       | 170   | MD24<br>MD23 |

| 22   | LDEV#      | 74    | D49      | 125   | D3       | 178   | MD22         |

| 23   | LDIR#      | 75    | D48      | 120   | D2       | 179   | MD22<br>MD21 |

| 23   | MRD#       | 76    | D47      | 127   | D1       | 180   | MD21<br>MD20 |

| 25   | MWR#       | 77    | D40      | 128   | D0       | 180   | MD19         |

| 26   | VCC        | 78    | VCC3     | 129   | VCC      | 181   | MD19<br>MD18 |

| 20   | IORD#      | 79    | D44      |       | MD63     | 182   | VCC          |

| 28   | IOWR#      | 80    | D44      | 131   |          |       |              |

|      |            |       |          | 132   | MD62     | 184   | MD17         |

| 29   | RFSH#      | 81    | D42      | 133   | MD61     | 185   | MD16         |

| 30   | ALE        | 82    | D41      | 134   | MD60     | 186   | MD15         |

| 31   | LMEM#      | 83    | D40      | 135   | MD59     | 187   | MD14         |

| 32   | HDMDOE#    | 84    | D39      | 136   | MD58     | 188   | MD13         |

| 33   | MDHDOE#    | 85    | D38      | 137   | MD57     | 189   | MD12         |

| 34   | DWE#       | 86    | D37      | 138   | MD56     | 190   | MD11         |

| 35   | DLE#       | 87    | GND      | 139   | MD55     | 191   | MD10         |

| 36   | LD/C#      | 88    | D36      | 140   | MD54     | 192   | GND          |

| 37   | LRDY#      | 89    | D35      | 141   | MD53     | 193   | MD9          |

| 38   | GND        | 90    | D34      | 142   | GND      | 194   | MD8          |

| 39   | LW/R#      | 91    | D33      | 143   | MD52     | 195   | MD7          |

| 40   | LM/IO#     | 92    | D32      | 144   | MD51     | 196   | MD6          |

| 41   | LADS#      | 93    | D31      | 145   | MD50     | 197   | MD5          |

| 42   | LBE3#      | 94    | D30      | 146   | MD49     | 198   | MD4          |

| 43   | VCC        | 95    | D29      | 147   | VCC      | 199   | MD3          |

|      | LBE2#      | 96    | GND      | 148   | MD48     | 200   | GND          |

| 45   | LBE1#      | 97    | VCC3     | 149   | MD47     | 201   | VCC          |

| 46   | LBE0#      | 98    | D28      | 150   | MD46     | 202   | MD2          |

| 47   | PERR       | 99    | D27      | 151   | MD45     | 203   | MD1          |

| 48   | RESET      | 100   | D26      | 152   | MD44     | 204   | MD0          |

| 49   | BOFF#      | 101   | D25      | 153   | MD43 -   | 205   | SDEN#        |

| 50   | P6X#/LMCS# | 102   | D24      | 154   | MD42     | 206   | SDIR1#       |

| 51   | INTA#      | 103   | D23      | 155   | MD41     | 207   | SDIR2#       |

| 52   | LREQ#      | 104   | D22      | 156   | GND      | 208   | KBDCS#       |

Table 3-1

82C546 ATC Numerical Pin Cross-Reference List

| Pin Name | Pin No. | Pin Name | Pin No. | Pin Name     | Pin No. | Pin Name   | Pin No. |

|----------|---------|----------|---------|--------------|---------|------------|---------|

| 0WS#     | 17      | D45      | 77      | LDEV#        | 21      | MD45       | 151     |

| AEN16#   | 54      | D46      | 76      | LDIR#        | 23      | MD46       | 150     |

| AEN8#    | 55      | D47      | 75      | LM/IO#       | 40      | MD47       | 149     |

| ALE      | 30      | D48      | 74      | LRDY#        | 37      | MD48       | 148     |

| ATCLK    | 14      | D49      | 73      | LREQ#        | 52      | MD49       | 146     |

| BOFF#    | 49      | D50      | 72      | LW/R#        | 39      | MD50       | 145     |

| CHRDY    | 18      | D51      | 71      | M16#         | 19      | MD51       | 144     |

| D0       | 129     | D52      | 70      | MD0          | 204     | MD52       | 143     |

| D1       | 128     | D53      | 68      | MD1          | 203     | MD53       | 141     |

| D2       | 127     | D54      | 67      | MD2          | 202     | MD54       | 140     |

| D3       | 126     | D55      | 66      | MD3          | 199     | MD55       | 139     |

| D4       | 125     | D56      | 65      | MD4          | 198     | MD56       | 138     |

| D5       | 124     | D57      | 64      | MD5          | 197     | MD57       | 137     |

| D6       | 123     | D58      | 63      | MD6          | 196     | MD58       | 136     |

| D7       | 122     | D59      | 62      | MD7          | 195     | MD59       | 135     |

| D8       | 121     | D60      | 59      | MD8          | 194     | MD60       | 134     |

| D9       | 120     | D61      | 58      | MD9          | 193     | MD61       | 133     |

| D10      | 118     | D62      | 57      | MD10         | 191     | MD62       | 132     |

| D11      | 117     | D63      | 56      | MD11         | 190     | MD63       | 131     |

| D12      | 116     | DLE#     | 35      | MD12         | 189     | MDHD0E#    | 33      |

| D13      | 115     | DWE#     | 34      | MD13         | 188     | MP0        | 13      |

| D14      | 113     | GND      | 15      | MD14         | 187     | MP1        | 12      |

| D15      | 112     | GND      | 38      | MD15         | 186     | MP2        | 11      |

| D16      | 111     | GND      | 60      | MD16         | 185     | MP3        | 9       |

| D17      | 110     | GND      | 69      | MD17         | 184     | MP4        | 8       |

| D18      | 109     | GND      | 87      | MD18         | 182     | MP5        | 7       |

| D19      | 108     | GND      | 96      | MD19         | 181     | MP6        | 6       |

| D20      | 107     | GND      | 105     | MD20         | 180     | MP7        | 5       |

| D21      | 106     | GND      | 119     | MD21         | 179     | MRD#       | 24      |

| D22      | 104     | GND      | 142     | MD22         | 178     | MWR#       | 25      |

| D23      | 103     | GND      | 156     | MD23         | 177     | P6X#/LMCS# | 50      |

| D24      | 102     | GND      | 164     | MD24         | 176     | PERR       | 47      |

| D25      | 101     | GND      | 174     | MD25         | 175     | RESET      | 48      |

| D26      | 100     | GND      | 192     | MD26         | 173     | RFSH#      | 29      |

| D27      | 99      | GND      | 200     | MD27         | 172     | SBHE#      | 1       |

| D28      | 98      | HDMDOE#  | 32      | MD28         | 171     | SDEN#      | 205     |

| D29      | 95      | HLDA1    | 53      | MD29         | 170     | SDIR1#     | 206     |

| D30      | 94      | INTA#    | 51      | MD30         | 169     | SDIR2#     | 207     |

| D31      | 93      | IO16#    | 20      | MD31         | 168     | VCC        | 10      |

| D32      | 92      | IORD#    | 27      | MD32         | 167     | VCC        | 26      |

| D33      | 91      | IOWR#    | 28      | MD33         | 166     | VCC        | 43      |

| D34      | 90      | KBDCS#   | 208     | MD34         | 163     | VCC        | 130     |

| D35      | 89      | LMEM#    | 31      | MD35         | 162     | VCC        | 147     |

| D36      | 88      | LA2      | 4       | MD36         | 161     | VCC        | 165     |

| D37      | 86      | LADS#    | 41      | MD37         | 160     | VCC        | 183     |

| D38      | 85      | LBE0#    | 46      | MD38         | 159     | VCC        | 201     |

| D39      | 84      | LBE1#    | 45      | MD39         | 158     | VCC3       | 61      |

| D40      | 83      | LBE2#    | 44      | MD40         | 150     | VCC3       | 78      |

| D41      | 82      | LBE3#    | 42      | MD40<br>MD41 | - 155   | VCC3       | 97      |

| D42      | 81      | LCLK     | 16      | MD41<br>MD42 | 154     | VCC3       | 114     |

| D42      | 80      | LD/C#    | 36      | MD42<br>MD43 | 154     | XA0        | 2       |

| D44      | 79      | LDEN#    | 22      | MD43<br>MD44 | 153     | XAU        | 3       |

## Table 3-2 82C546 ATC Alphabetical Pin Cross-Reference List

u

## 82C546/82C547

. . . . . .

**OPAR** Page 8

| Pin No. | Pin Name | Pin No. | Pin Name   | Pin No. | Pin Name | Pin No. | Pin Name   |

|---------|----------|---------|------------|---------|----------|---------|------------|

| 1       | GND      | 41      | VCC3       | 81      | VCC3A    | 121     | VCC        |

| 2       | OSC12    | 42      | BE4#       | 82      | TAG6     | 122     | XD7        |

| 3       | LREQ#    | 43      | BE3#       | 83      | TAG7     | 123     | XD6        |

| 4       | PWRGD    | 44      | BE2#       | 84      | DIRTY    | 124     | XD5        |

| 5       | LADS#    | 45      | BE1#       | 85      | TAGWE#   | 125     | XD4        |

| 6       | LRDY#    | 46      | BE0#       | 86      | DIRTYWE# | 126     | XD3        |

| 7       | IRQ13    | 47      | CACHE#     | 87      | PERR     | 127     | XD2        |

| 8       | ADS#     | 48      | DRAM#      | 88      | BESL#    | 128     | XD1        |

| 9       | W/R#     | 49      | CPURST     | 89      | IOWR#    | 129     | XD0        |

| 10      | GND      | 50      | GND        | 90      | GND      | 130     | GND        |

| 11      | HITM#    | 51      | INIT       | 91      | HDMDOE#  | 131     | RFSH#      |

| 12      | A3       | 52      | FERR#      | 92      | DLE#     | 132     | ROMCS#     |

| 13      | A4       | 53      | IGERR#     | 93      | MDHDOE#  | 133     | REFREQ     |

| 14      | A5       | 54      | NA#        | 94      | HLDA1    | 134     | LGNT#      |

| 15      | A6       | 55      | EADS#/WT#  | 95      | DWE#     | 135     | P6X#/LMCS# |

| 16      | A7       | 56      | D/C#       | 96      | CAS0#    | 136     | XDIR#      |

| 17      | A8       | 57      | M/IO#      | 97      | CAS1#    | 137     | SPKD       |

| 18      | A9       | 58      | OCA4       | 98      | CAS2#    | 138     | CHCK#      |

| 19      | A10      | 59      | ECA4       | 99      | CAS3#    | 139     | HRQ        |

| 20      | VCC3     | 60      | GND        | 100     | VCC      | 140     | VCC        |

| 21      | A11      | 61      | BRDY#      | 101     | CAS4#    | 141     | TMRG2      |

| 22      | A12      | 62      | A20M#      | 102     | CAS5#    | 142     | OUT2       |

| 23      | A13      | 63      | BOFF#      | 103     | CAS6#    | 143     | ASRTC      |

| 24      | A14      | 64      | AHOLD      | 104     | RAS0#    | 144     | AEN16#     |

| 25      | A15      | 65      | HOLD       | 105     | CAS7#    | 145     | AEN8#      |

| 26      | A16      | 66      | HLDA       | 106     | RAS1#    | 146     | DMADS      |

| 27      | A17      | 67      | KEN#/LMEM# | 107     | RAS2#    | 147     | LA2        |

| 28      | A18      | 68      | HACALE     | 108     | RAS3#    | 148     | VCC        |

| 29      | A19      | 69      | ECAWE#     | 109     | MA10     | 149     | CLK        |

| 30      | GND      | 70      | GND        | 110     | GND      | 150     | GND        |

| 31      | A20      | 71      | OCAWE#     | 111     | MA9      | 151     | ECLK       |

| 32      | A21 ·    | 72      | NMI        | 112     | MA8      | 152     | LM/IO#     |

| 33      | A22      | 73      | ECDOE#     | 113     | MA7      | 153     | LW/R#      |

| 34      | A23      | 74      | OCDOE#     | 114     | MA6      | 154     | LD/C#      |

| 35      | A24      | 75      | TAG0       | 115     | MA5      | 155     | LBE3#      |

| 36      | A25      | 76      | TAG1       | 116     | MA4      | 156     | LBE2#      |

| 37      | A26      | 77      | TAG2       | 117     | MA3 -    | 157     | LBE1#      |

| 38      | BE7#     | 78      | TAG3       | 118     | MA2      | 158     | LBE0#      |

| 39      | BE6#     | 79      | TAG4       | 119     | MA1      | 159     | LCLK       |

| 40      | BE5#     | 80      | TAG5       | 120     | MA0      | 160     | OSCI       |

#### Table 3-3 82C547 SYSC Numerical Pin Cross-Reference List

••

| Pin Name | Pin No. | Pin Name  | Pin No. | Pin Name   | Pin No. | Pin Name   | Pin No. |

|----------|---------|-----------|---------|------------|---------|------------|---------|

| A3       | 12      | BRDY#     | 61      | HLDA1      | 94      | OSCI       | 160     |

| A4       | 13      | CACHE#    | 47      | HOLD       | 65      | OUT2       | 142     |

| A5       | 14      | CAS0#     | 96      | HRQ        | 139     | P6X#/LMCS# | 135     |

| A6       | 15      | CAS1#     | 97      | IGERR#     | 53      | PERR       | 87      |

| A7       | 16      | CAS2#     | 98      | INIT       | 51      | PWRGD      | 4       |

| A8       | 17      | CAS3#     | 99      | IOWR#      | 89      | RAS0#      | 104     |

| A9       | 18      | CAS4#     | 101     | IRQ13      | 7       | RAS1#      | 106     |

| A10      | 19      | CAS5#     | 102     | KEN#/LMEM# | 67      | RAS2#      | 107     |

| A11      | 21      | CAS6#     | 103     | LA2        | 147     | RAS3#      | 108     |

| A12      | 22      | CAS7#     | 105     | LADS#      | 5       | REFREQ     | 133     |

| A13      | 23      | CHCK#     | 138     | LBE0#      | 158     | RFSH#      | 131     |

| A14      | 24      | CLK       | 149     | LBE1#      | 157     | ROMCS#     | 132     |

| A15      | 25      | CPURST    | 49      | LBE2#      | 156     | SPKD       | 137     |

| A16      | 26      | D/C#      | 56      | LBE3#      | 155     | TAG0       | 75      |

| A17      | 27      | DIRTY     | 84      | LCLK       | 159     | TAG1       | 76      |

| A18      | 28      | DIRTYWE   | 86      | LD/C#      | 154     | TAG2       | 77      |

| A19      | 29      | DLE#      | 92      | LGNT#      | 134     | TAG3       | 78      |

| A20      | 31      | DMADS     | 146     | LM/IO#     | 152     | TAG4       | 79      |

| A20M#    | 62      | DRAM#     | 48      | LRDY#      | 6       | TAG5       | 80      |

| A21      | 32      | DWE#      | 95      | LREQ#      | 3       | TAG6       | 82      |

| A22      | 33      | EADS#/WT# | 55      | LW/R#      | 153     | TAG7       | 83      |

| A23      | 34      | ECA4      | 59      | M/IO#      | 57      | TAGWE#     | 85      |

| A24      | 35      | ECAWE#    | 69      | MA0        | 120     | TMRG2      | 141     |

| A25      | 36      | ECDOE#    | 73      | MA1        | 119     | VCC        | 100     |

| A26      | 37      | ECLK      | 151     | MA2        | 118     | VCC        | 121     |

| ADS#     | 8       | FERR#     | 52      | MA3        | 117     | VCC        | 140     |

| AEN8#    | 145     | GND       | 1       | MA4        | 116     | VCC        | 148     |

| AEN16#   | 144     | GND       | 10      | MA5        | 115     | VCC3       | 20      |

| AHOLD    | 64      | GND       | 30      | MA6        | 114     | VCC3       | 41      |

| ASRTC    | 143     | GND       | 50      | MA7        | 113     | VCC3A      | 81      |

| BE0#     | 46      | GND       | 60      | MA8        | 112     | W/R#       | 9       |

| BE1#     | 45      | GND       | 70      | MA9        | 111     | XD0        | 129     |

| BE2#     | 44      | GND       | 90      | MA10       | 109     | XD1        | 128     |

| BE3#     | 43      | GND       | 110     | MDHDOE#    | 93      | XD2        | 127     |

| BE4#     | 42      | GND       | 130     | NA#        | 54      | XD3        | 126     |

| BE5#     | 40      | GND       | 150     | NMI        | 72      | XD4        | 125     |

| BE6#     | 39      | HACALE    | 68      | OCA4       | - 58    | XD5        | 124     |

| BE7#     | 38      | HDMDOE#   | 91      | OCAWE#     | 71      | XD6        | 123     |

| BESL#    | 88      | HITM#     | 11      | OCDOE#     | 74      | XD7        | 122     |

| BOFF#    | 63      | HLDA      | 66      | OSC12      | 2       | XDIR#      | 136     |

#### Table 3-482C547 SYSC Alphabetical Pin Cross-Reference

Python Chipset

| Pin No. | Pin Name |

|---------|----------|---------|----------|---------|----------|---------|----------|

| 1       | A10      | 26      | A3       | 51      | SA13     | 76      | SD6      |

| 2       | A11      | 27      | A4       | 52      | SA12     | 77      | SD5      |

| 3       | A12      | 28      | A5       | 53      | SA11     | 78      | SD4      |

| 4       | A13      | 29      | A6       | 54      | SA10     | 79      | SD3      |

| 5       | A14      | 30      | A7       | 55      | SA9      | 80      | SD2      |

| 6 🕫     | A15      | 31      | A9       | 56      | SA7      | 81      | SD1      |

| 7       | A17      | 32      | HLDA1    | 57      | SA6      | 82      | SD0      |

| 8       | A18      | 33      | LA28     | 58      | SA5      | 83      | SDEN#    |

| 9       | A19      | 34      | LA27     | 59      | SA4      | 84      | SDIR1#   |

| 10      | GND      | 35      | LA26     | 60      | SA3      | 85      | LA2      |

| 11      | VCC3     | 36      | LA25     | 61      | GND      | 86      | XD0      |

| 12      | A20      | 37      | LA24     | 62      | VCC      | 87      | XD1      |

| 13      | A21      | 38      | LA23     | 63      | SA2      | 88      | XD2      |

| 14      | A22      | 39      | LA22     | 64      | MD0      | 89      | XD3      |

| 15      | GND      | 40      | GND      | 65      | MD1      | 90      | GND      |

| 16      | VCC3     | 41      | VCC      | 66      | GND      | 91      | VCC      |

| 17      | A23      | 42      | LA21     | 67      | VCC      | 92      | XD4      |

| 18      | A24      | 43      | LA20     | 68      | MD2      | 93      | XD5      |

| 19      | A25      | 44      | LA19     | 69      | MD3      | 94      | XD6      |

| 20      | GND      | 45      | VCC      | 70      | MD4      | 95      | XD7      |

| 21      | VCC3     | 46      | GND      | 71      | GND      | 96      | AEN      |

| 22      | A26      | 47      | LA18     | 72      | MD5      | 97      | XDIR#    |

| 23      | A27      | 48      | LA17     | 73      | MD6      | 98      | RFSH#    |

| 24      | A28      | 49      | SA15     | 74      | MD7      | 99      | CADIR#   |

| 25      | GND      | 50      | SA14     | 75      | SD7      | 100     | CONF1/2# |

Table 3-582C606A Numerical Pin Cross-Reference

| Pin Name | Pin No. |

|----------|---------|----------|---------|----------|---------|----------|---------|

| A3       | 26      | CADIR#   | 99      | LA28     | 33      | SD2      | 80      |

| A4       | 27      | CONF1/2# | 100     | MD0      | 64      | SD3      | 79      |

| A5       | 28      | GND      | 10      | MD1      | 65      | SD4      | 78      |

| A6       | 29      | GND      | 15      | MD2      | 68      | SD5      | 77      |

| A7       | 30      | GND      | 20      | MD3      | 69      | SD6      | 76      |

| A9 8     | 31      | GND      | 25      | MD4      | 70      | SD7      | 75      |

| A10      | 1       | GND      | 40      | MD5      | 72      | SDEN#    | 83      |

| A11      | 2       | GND      | 46      | MD6      | 73      | SDIR1#   | 84      |

| A12      | 3       | GND      | 61      | MD7      | 74      | VCC      | 41      |

| A13      | 4       | GND      | 66      | RFSH#    | 98      | VCC      | 45      |

| A14      | 5       | GND      | 71      | SA2      | 63      | VCC      | 62      |

| A15      | 6       | GND      | 90      | SA3      | 60      | VCC      | 67      |

| A17      | 7       | HLDA1    | 32      | SA4      | 59      | VCC      | 91      |

| A18      | 8       | LA2      | 85      | SA5      | 58      | VCC3     | 11      |

| A19      | 9       | LA17     | 48      | SA6      | 57      | VCC3     | 16      |

| A20      | 12      | LA18     | 47      | SA7      | 56      | VCC3     | 21      |

| A21      | 13      | LA19     | 44      | SA9      | 55      | XD0      | 86      |

| A22      | 14      | LA20     | 43      | SA10     | 54      | XD1      | 87      |

| A23      | 17      | LA21     | 42      | SA11     | 53      | XD2      | 88      |

| A24      | 18      | LA22     | 39      | SA12     | 52      | XD3      | 89      |

| A25      | 19      | LA23     | 38      | SA13     | 51      | XD4      | 92      |

| A26      | 22      | LA24     | 37      | SA14     | 50      | XD5      | 93      |

| A27      | 23      | LA25     | 36      | SA15     | 49      | XD6      | 94      |

| A28      | 24      | LA26     | 35      | SD0      | 82      | XD7      | 95      |

| AEN      | 96      | LA27     | 34      | SD1      | 81      | XDIR#    | 97      |

Table 3-682C606A Alphabetical Pin Cross-Reference

•

| Pin No. | Pin Name |

|---------|----------|---------|----------|---------|----------|---------|----------|

| 1       | A31      | 26      | DIRTYO   | 51      | SA3      | 76      | SD14     |

| 2       | BE0#     | 27      | INTROUT  | 52      | XA7      | 77      | SD13     |

| 3       | BE1#     | 28      | A8       | 53      | XA6      | 78      | SD12     |

| 4       | BE2#     | 29      | A16      | 54      | MEMR#    | 79      | SD11     |

| 5       | BE3#     | 30      | A29      | 55      | LA31     | 80      | SD10     |

| 6       | BE4#     | 31      | A30      | 56      | LA30     | 81      | SD9      |

| 7       | BE5#     | 32      | HLDA1    | 57      | LA29     | 82      | SD8      |

| 8       | BE6#     | 33      | LREQ#    | 58      | SA16     | 83      | SDEN#    |

| 9       | BE7#     | 34      | BESL#    | 59      | SA8      | 84      | SDIR2#   |

| 10      | GND      | 35      | W/R#     | 60      | AEN8#    | 85      | CADIR#   |

| 11      | VCC3     | 36      | LW/R#    | 61      | GND      | 86      | XA8      |

| 12      | CACS0#   | 37      | AEN      | 62      | VCC      | 87      | XA16     |

| 13      | CACS1#   | 38      | MASTER#  | 63      | AEN16#   | 88      | ACK#     |

| 14      | CACS2#   | 39      | DMADS    | 64      | MD8      | 89      | AEN#     |

| 15      | GND      | 40      | GND      | 65      | MD9      | 90      | GND      |

| 16      | VCC3     | 41      | VCC      | 66      | GND      | 91      | VCC      |

| 17      | CACS3#   | 42      | ADSTB8   | 67      | VCC      | 92      | MRD#     |

| 18      | CACS4#   | 43      | ADSTB16  | 68      | MD10     | 93      | XA3      |

| 19      | CACS5#   | 44      | DIRTY05V | 69      | MD11     | 94      | XA4      |

| 20      | GND      | 45      | VCC      | 70      | MD12     | 95      | XA5      |

| 21      | VCC3     | 46      | GND      | 71      | GND      | 96      | INTRIN   |

| 22      | CACS6#   | 47      | SA7      | 72      | MD13     | 97      | LRQATC#  |

| 23      | CACS7#   | 48      | SA6      | 73      | MD14     | 98      | RFSH#    |

| 24      | HACALE   | 49      | SA5      | 74      | MD15     | 99      | LGNT#    |

| 25      | GND      | 50      | SA4      | 75      | SD15     | 100     | CONF1/2# |

Table 3-782C606B Numerical Pin Cross-Reference

~

.

| Pin Name | Pin No. |

|----------|---------|----------|---------|----------|---------|----------|---------|

| A8       | 28      | CACS4#   | 18      | LA31     | 55      | SD9      | 81      |

| A16      | 29      | CACS5#   | 19      | LGNT#    | 99      | SD10     | 80      |

| A29      | 30      | CACS6#   | 22      | LREQ#    | 33      | SD11     | 79      |

| A30      | 31      | CACS7#   | 23      | LRQATC#  | 97      | SD12     | 78      |

| A31      | 1       | CADIR#   | 85      | LW/R#    | 36      | SD13     | 77      |

| ACK#     | 88      | CONF1/2# | 100     | MASTER#  | 38      | SD14     | 76      |

| ADSTB8   | 42      | DIRTYO   | 26      | MD8      | 64      | SD15     | 75      |

| ADSTB16  | 43      | DIRTYO5V | 44      | MD9      | 65      | SDEN#    | 83      |

| AEN      | 37      | DMADS    | 39      | MD10     | 68      | SDIR2#   | 84      |

| AEN#     | 89      | GND      | 10      | MD11     | 69      | VCC      | 45      |

| AEN8#    | 60      | GND      | 15      | MD12     | 70      | VCC      | 62      |

| AEN16#   | 63      | GND      | 20      | MD13     | 72      | VCC      | 67      |

| BE0#     | 2       | GND      | 25      | MD14     | 73      | VCC      | 83      |

| BE1#     | 3       | GND      | 40      | MD15     | 74      | VCC      | 91      |

| BE2#     | 4       | GND      | 46      | MEMR#    | 54      | VCC3     | 11      |

| BE3#     | 5       | GND      | 61      | MRD#     | 92      | VCC3     | 16      |

| BE4#     | 6       | GND      | 66      | RFSH#    | 98      | VCC3     | 21      |

| BE5#     | 7       | GND      | 71      | SA3      | 51      | W/R#     | 35      |

| BE6#     | 8       | GND      | 90      | SA4      | 50      | XA3      | 93      |

| BE7#     | 9       | HACALE   | 24      | SA5      | 49      | XA4      | 94      |

| BESL#    | 34      | HLDA1    | 32      | SA6      | 48      | XA5      | 95      |

| CACS0#   | 12      | INTRIN   | 96      | SA7      | 47      | XA6      | 53      |

| CACS1#   | 13      | INTROUT  | 27      | SA8      | 59      | XA7      | 52      |

| CACS2    | 14      | LA29     | 57      | SA16     | 58      | XA8      | 86      |

| CACS3#   | 17      | LA30     | 56      | SD8      | 82      | XA16     | 87      |

Table 3-882C606B Alphabetical Pin Cross-Reference

-

#### 3.1 Signal Descriptions

•

,

| Signal Name        | Pin<br>No.                                                                                              | Signal<br>Type | Signal Description                                                                                                                                   |

|--------------------|---------------------------------------------------------------------------------------------------------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3.1.1.1 Clock      | and Reset Inte                                                                                          | erface Sign    | nals                                                                                                                                                 |

| LCLK               | 16                                                                                                      | I              | Local Bus Clock: This clock is used by local bus devices and to derive the AT clock signal.                                                          |

| ATCLK              | 14                                                                                                      | 0              | AT Bus Clock: Derived from an internal division of LCLK. ATCLK = LCLK/ 2,3,4,5.                                                                      |

| RESET              | 48                                                                                                      | I              | System Reset: Output by the 82C547 (CPURST) in response to a PWRGD input.                                                                            |

| 3.1.1.2 Data B     | us Interface S                                                                                          | lignals        |                                                                                                                                                      |

| D[63:0]<br>(3.3 V) | 56:59,<br>62:68,<br>70:77,<br>79:86,<br>88:95,<br>98:104,<br>106:113,<br>115:118,<br>120:129            | I/O            | CPU Data Bus: These pins are connected directly to the CPU's data bus.                                                                               |

| MD[63:0]           | 131:141,<br>143:146,<br>148:155,<br>157:163,<br>166:173,<br>175:182,<br>184:191,<br>193:199,<br>202:204 | I/O            | Memory Data Bus: These pins are connected directly to the system DRAM and are<br>buffered to generate the ISA SD data bus and the local LD data bus. |

| PERR               | 47                                                                                                      | 0              | <b>Parity Error:</b> Indicates that parity check detected a parity error during a read from the DRAM.                                                |

#### 3.1.1 82C546 ATC Signal Descriptions

Python Chipset

#### 82C546 ATC Signal Descriptions (Cont.)

| Signal Name   | Pin<br>No.    | Signal<br>Type | Signal Description                                                                                                                                                                                   |

|---------------|---------------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MP[7:0]       | 5:9, 11:13    | I/O            | <b>Memory Parity:</b> As outputs, these lines are only driven when DWE# is active. As inputs, they are used as strapping pins that are sampled at reset time to configure the 82C546 ATC as follows: |

| μ.            |               |                | AT Clock SelectionMP1MP0001LCLK/50110LCLK/3111LCLK/2                                                                                                                                                 |

|               |               |                | Back-to-Back AT I/O Cycle SelectMP2Function0Slow - add 12 AT clocks to back-to-back I/O cycles1Fast - add 2 AT clocks to back-to-back I/O cycles                                                     |

|               |               |                | LDEV# Sample SelectMP3Function0Sample LDEV# at the end of the second T21Sample LDEV# at the end of the first T2                                                                                      |

|               |               |                | Local Bus Disable SelectMP4Function0VL bus disabled1VL bus enabled                                                                                                                                   |

|               |               |                | Internal Test Mode SelectMP5Function0Reserved1Normal Operation                                                                                                                                       |

|               |               |                | 82C546 Power Plane SelectMP6Function0D[63:0] on 3.3V power plane for operation with 3.3V Pentium processor1D[63:0] on 5.0V power plane for operation with Pentium processor                          |

|               |               |                | 82C822 Select         MP7       Function         0       82C822 is installed         1       82C822 is not installed                                                                                 |

| 3.1.1.3 Local | Bus Interface | Signals        |                                                                                                                                                                                                      |

| LA2           | 4             | I              | Local Bus Address Line 2: This address line is used for address decoding and to distinguish high bytes[7:4] from low bytes[3:0] on the 64-bit address bus.                                           |

| LBE[3:0]#     | 42, 44:46     | I/O            | Local Byte Enable Bits 3 through 0: Normally inputs, these signals become outputs during AT DMA or bus master cycles.                                                                                |

| LADS#         | 41            | I/O            | Local Bus Address Strobe: Normally an input, this signal becomes an output dur-<br>ing AT DMA or bus master cycles.                                                                                  |

| LRDY#         | 37            | I/O            | Local Ready: Normally an input, this signal will be driven when CPU, DMA, or AT masters are accessing AT slaves.                                                                                     |

## 82C546 ATC Signal Descriptions (Cont.)

\*

.

| Signal Name    | Pin<br>No.    | Signal<br>Type | Signal Description                                                                                                                                                                                                                                                                       |

|----------------|---------------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LM/IO#         | 40            | I/O            | Local Memory/IO: Normally an input, but becomes an output during AT DMA or bus master cycles.                                                                                                                                                                                            |

| LD/C#          | 36            | I/O            | Local Data/Control: Normally an input, becomes an output during AT DMA or bus master cycles.                                                                                                                                                                                             |

| LW/R#          | 39            | I/O            | Local Write/Read: Normally an input, becomes an output during AT DMA or bus master cycles.                                                                                                                                                                                               |

| LDEV#          | 21            | I              | Local Device Indication: Sampled if the cycle is not in the system memory area.                                                                                                                                                                                                          |

| LDEN#          | 22            | 0              | <ul> <li>Local Bus Data Buffer Enable: Activated when:</li> <li>1) CPU local bus write cycle</li> <li>2) CPU local bus read from local device</li> <li>3) AT DMA or master write cycle</li> <li>4) AT DMA or master read from local device</li> <li>5) Local bus master cycle</li> </ul> |

| LDIR#          | 23            | 0              | <ul> <li>Local Bus Data Buffer Direction Control: Activated when:</li> <li>1) CPU local bus read from local device</li> <li>2) AT DMA or master read from local device</li> <li>3) Normally is low for local bus master and becomes high for local bus master read cycle</li> </ul>      |

| 3.1.1.4 Buffer | Control Inter | face Signa     | ls                                                                                                                                                                                                                                                                                       |

| MDHDOE#        | 33            | I              | <ul> <li>Memory Data to Host Data Output Enable: This is used by the 82C546 ATC to distinguish:</li> <li>1) Reads from DRAM</li> <li>2) Reads from local slave or local bus slave</li> <li>3) INTA# cycles</li> <li>4) Non-CPU cycles and secondary cache write-hits</li> </ul>          |

| HDMDOE#        | 32            | I              | <ul> <li>Host Data to Memory Data Output Enable: This is used by the 82C546 ATC to distinguish:</li> <li>1) Writes to DRAM</li> <li>2) Non CPU cycles and secondary cache read-hits</li> </ul>                                                                                           |

| DLE#           | 35            |                | <ul> <li>Data Latch Enable: This is used by the 82C546 ATC to distinguish:</li> <li>1) Writes to DRAM</li> <li>2) Reads from DRAM</li> <li>3) Read DRAM parity data</li> </ul>                                                                                                           |

| SDEN#          | 205           | 0              | System Data Bus Output Enable: Output enable signal for the buffers between the MD and SD data buses.                                                                                                                                                                                    |

| SDIR1#         | 206           | 0              | <b>Direction Control #1:</b> Direction control for the buffer between the MD[7:0] and SD[7:0] data buses.                                                                                                                                                                                |

| Signal Name    | Pin<br>No.    | Signal<br>Type | Signal Description                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|----------------|---------------|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SDIR2#         | 207           | 0              | <b>Direction Control #2:</b> Direction control for the buffer between the MD[15:8] and SD[15:8] data buses.                                                                                                                                                                                                                                                                                                                                                                      |

| 3.1.1.5 Bus Ar | bitration Int | erface Sign    | als                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| AEN8#          | 55            | I              | Address Enable 8-Bit: The 82C547 SYSC monitors this signal to decode 8-bit DMA cycles.                                                                                                                                                                                                                                                                                                                                                                                           |

| AEN16#         | 54            | I              | Address Enable 16-Bit: The 82C547 SYSC monitors this signal to decode 16-bit DMA cycles.                                                                                                                                                                                                                                                                                                                                                                                         |

| RFSH#          | 29            | Ι              | <b>Refresh:</b> This signal is used by the ATC to distinguish AT refresh cycles and DMA or master cycles.                                                                                                                                                                                                                                                                                                                                                                        |

| BOFF#          | 49            | I              | Back-off: This signal indicates that an inquire cycle is in progress.                                                                                                                                                                                                                                                                                                                                                                                                            |

| LREQ#          | 52            | I              | Local Bus Master Request: Local bus master cycle request from a bus master on the local bus.                                                                                                                                                                                                                                                                                                                                                                                     |

| HLDA1          | 53            | I              | <b>AT DMA or Master Hold Acknowledge:</b> Indicates a hold acknowledge in response to a DMA or master hold request.                                                                                                                                                                                                                                                                                                                                                              |

| 3.1.1.6 AT Bu  | s Interface S | ignals         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| XA0            | 2             | I/O            | System Address XA0: This signal is an output except during master or 8-bit DMA cycles when it serves as an input.                                                                                                                                                                                                                                                                                                                                                                |

| XA1            | 3             | I/O            | System Address XA1: This signal is an output except during master or DMA cycles when it serves as an input.                                                                                                                                                                                                                                                                                                                                                                      |

| CHRDY          | 18            | I/O            | <b>Channel Ready:</b> This is normally an input from the AT bus which is pulled low (not ready) by a slow memory or I/O device to lengthen memory or I/O cycles. Any slow device using this line should drive it low immediately upon detecting its valid address and a read/write command. This pin becomes an output when AT DMA or a master accesses local memory or a local I/O device, and will be driven low until LRDY# is received. This is a Schmitt-trigger input pin. |

| 0WS#           | . 17          | I              | Zero Wait State: This input is from the AT bus and is a Schmitt-trigger input pin.                                                                                                                                                                                                                                                                                                                                                                                               |

| IO16#          | 20            | I/O            | <b>16-bit I/O Slave:</b> AT bus signal to indicate a 16-bit I/O slave is responding. This is a Schmitt-trigger input pin.                                                                                                                                                                                                                                                                                                                                                        |

| M16#           | 19            | I/O            | 16-bit Memory Slave: An AT bus signal which indicates that a 16-bit memory slave is responding. M16# is normally an input, however, it becomes an output when a master accesses local memory. This is a Schmitt-trigger input pin.                                                                                                                                                                                                                                               |

| IORD#          | 27            | I/O            | AT I/O Read: Normally an output, this pin becomes an input during master and DMA cycles.                                                                                                                                                                                                                                                                                                                                                                                         |

| IOWR#          | 28            | I/O            | AT I/O Write: Normally an output, this pin becomes an input during master and DMA cycles.                                                                                                                                                                                                                                                                                                                                                                                        |

| MRD#           | 24            | I/O            | AT Memory Read: Normally an output, this pin becomes an input during master and DMA cycles.                                                                                                                                                                                                                                                                                                                                                                                      |

## 82C546 ATC Signal Descriptions (Cont.)

-

## S82C546 ATC Signal Descriptions (Cont.)

••

.

| Signal Name     | Pin<br>No.                                                                    | Signal<br>Type | Signal Description                                                                                                                                                                                                   |

|-----------------|-------------------------------------------------------------------------------|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MWR#            | 25                                                                            | I/O            | AT Memory Write: Normally an output, this pin becomes an input during master and DMA cycles.                                                                                                                         |

| ALE             | 30                                                                            | 0              | Address Latch Enable: ALE indicates the start of an AT cycle and is externally buffered before connection to the AT bus. It is high during non-CPU cycles.                                                           |

| SBHE#           | 1                                                                             | I/O            | System Byte High Enable: Indicates a transfer on the upper bytes of the AT data bus SD[15:8]. Normally an output, this pin becomes an input during master cycles.                                                    |

| 3.1.1.7 Miscell | laneous Interf                                                                | ace Signal     | S                                                                                                                                                                                                                    |

| KBDCS#          | 208                                                                           | 0              | Keyboard Controller Chip Select: The 82C547 SYSC decodes accesses to the keyboard controller and issues this chip select signal when necessary.                                                                      |

| INTA#           | 51                                                                            | 0              | Interrupt Acknowledge: This signal goes to the 82C206 IPC to indicate that the processor is executing an interrupt acknowledge cycle.                                                                                |

| DWE#            | 34                                                                            | I              | DRAM Write Enable: Used to enable the memory parity bits, MP[7:0].                                                                                                                                                   |

| LMEM#           | 31                                                                            | Ι              | Local Memory Accessed Indication: This signal is used for two purposes. The first is for generating M16# during AT master cycles. Secondly, this serves as a local device indication during local bus master cycles. |

| P6X#/LMCS#      | 50                                                                            | I              | <b>Port 6Xh Address Decode:</b> This signal is asserted on all memory accesses below 1MB.                                                                                                                            |

|                 |                                                                               |                | Port 6Xh is decoded as follows:                                                                                                                                                                                      |

|                 |                                                                               |                | A[15:7] = 0<br>A[6:5] = 1<br>A[4:3] = 0<br>Others bits = don't care.                                                                                                                                                 |

| 3.1.1.8 Power   | and Ground I                                                                  | Pins           |                                                                                                                                                                                                                      |

| GND             | 15, 38, 60,<br>69, 87, 96,<br>105, 119,<br>142, 156,<br>164, 174,<br>192, 200 | I              | Ground Connection                                                                                                                                                                                                    |