### TELECOM LSI DATA BOOK

# TELECOM LSI DATA BOOK 1987

PRODUCT LINE-UP

PACKAGING

DATA SHEET

#### Π

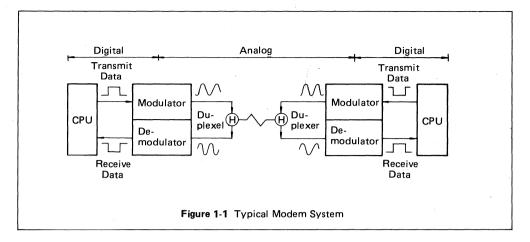

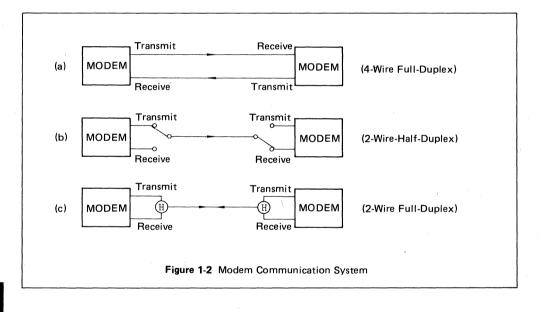

#### **APPLICATION NOTE** I FOR SINGLE CHIP MODEM

#### © Copyright 1986, OKI ELECTRIC INDUSTRY COMPANY, LTD.

OKI makes no warranty for the use of its products and assumes no responsibility for any errors which may appear in this document nor does it make a commitment to update the information contained herein.

OKI retains the right to make changes to these specifications at any time, without notice.

#### CONTENTS

#### I PRODUCT LINE-UP

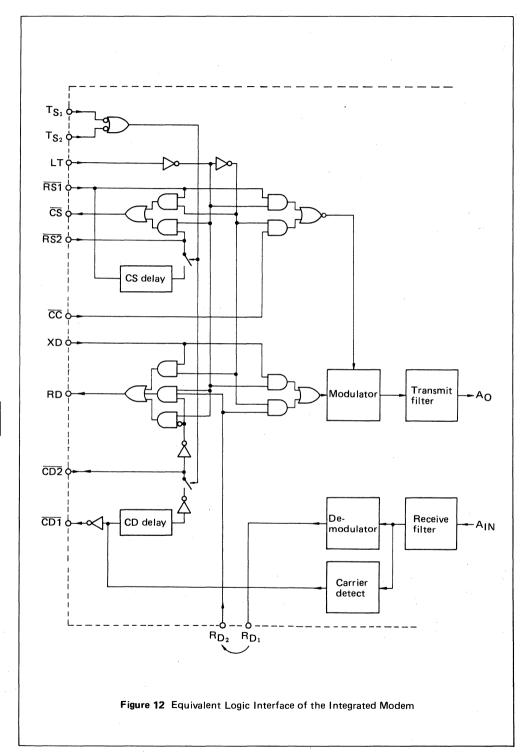

MSM6052-05

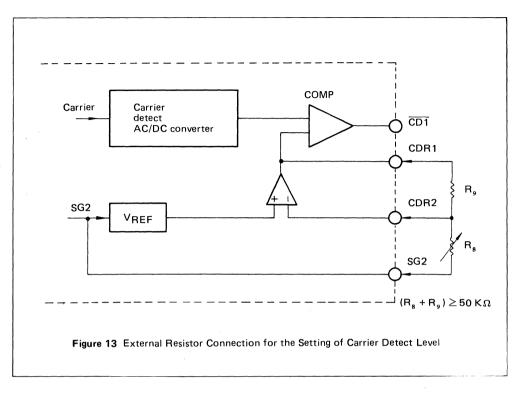

| 11 P/  | ACKAGING       |                                                                  |

|--------|----------------|------------------------------------------------------------------|

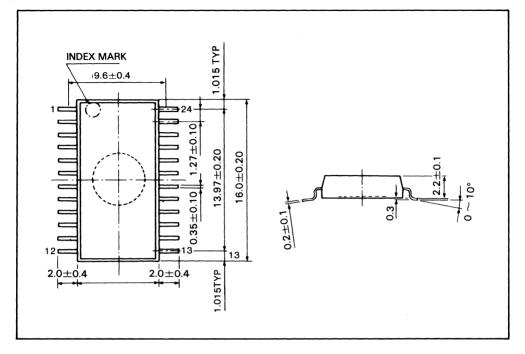

| •      | 16 PIN PLASTIC | CDIP II-5                                                        |

| •      | 18 PIN PLASTIC | CDIP II-5                                                        |

| •      | 22 PIN PLASTIC | CDIP II-6                                                        |

| •      | 24 PIN PLASTIC | CDIP II-6                                                        |

| •      | 28 PIN PLASTIC | CDIP II-7                                                        |

| •      | 40 PIN PLASTIC | CDIP II-7                                                        |

| •      | 42 PIN PLASTIC | CDIP II-8                                                        |

| •      | 16 PIN CERAMI  | C DIP (CERDIP) II-8                                              |

| •      | 22 PIN CERAMI  | C DIP (CERDIP) II-9                                              |

| •      | 28 PIN CERAMI  | C DIP (CERDIP) II-9                                              |

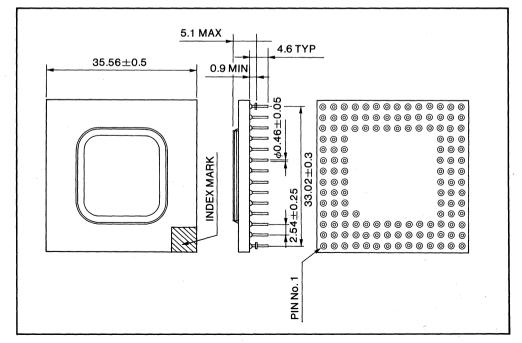

| •      | 120 PIN CERAN  | IIC PGA II-10                                                    |

| •      | 132 PIN CERAM  | IIC PGA II-10                                                    |

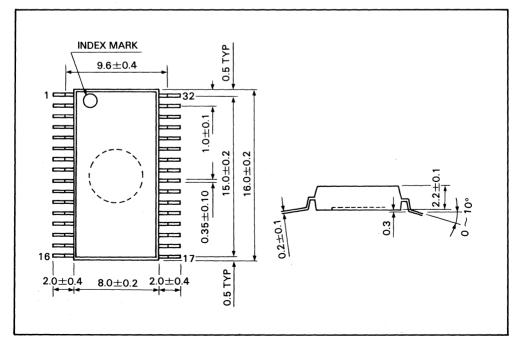

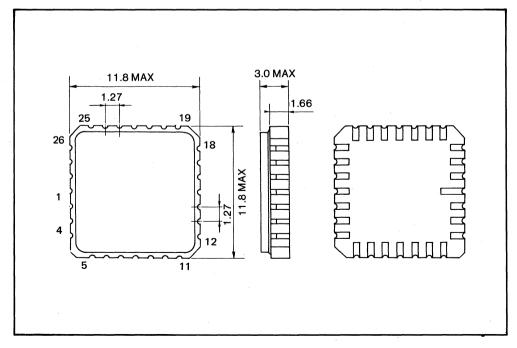

| •      | 24 PIN PLASTIC | ; FLAT II-11                                                     |

| •      | 32 PIN PLASTIC | ; FLAT II-11                                                     |

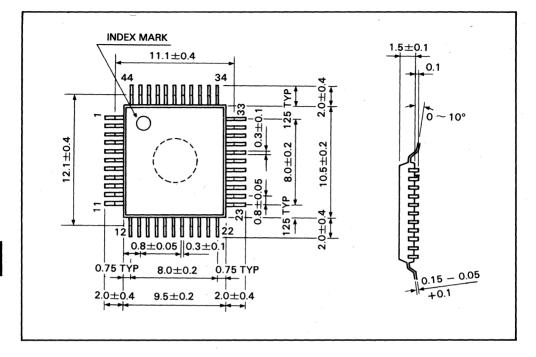

| •      | 44 PIN PLASTIC | FLAT II-12                                                       |

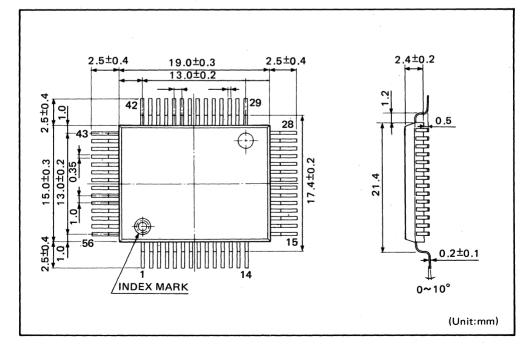

| •      | 56 PIN PLASTIC | FLAT II-12                                                       |

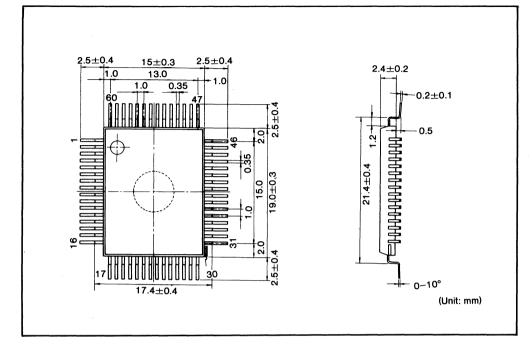

| •      | 60 PIN PLASTIC | CFLAT II-13                                                      |

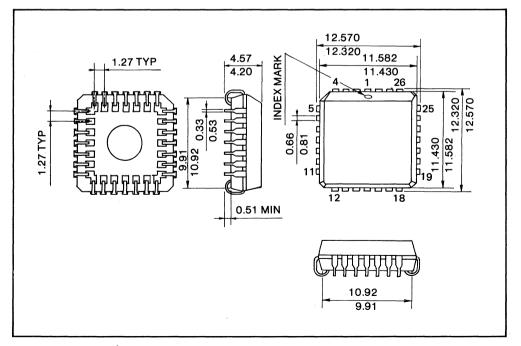

| •      | 28 PIN PLCC    | II-13                                                            |

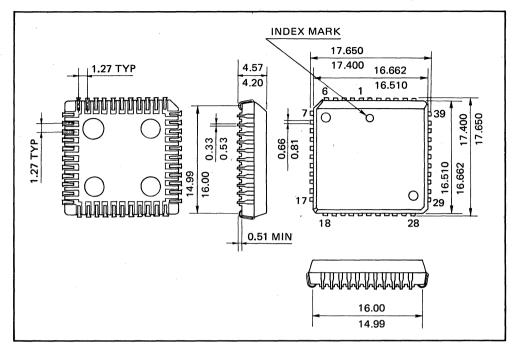

| •      | 44 PIN PLCC    | II-14                                                            |

|        |                | C CC II-14                                                       |

|        |                | E PLASTIC DIP II-15                                              |

| III D/ | ATA SHEET      |                                                                  |

| Α.     | MODEM APPL     |                                                                  |

|        | MSM6926        | SINGLE CHIP FSK MODEM, 300 BPS FULL DUPLEX, CCITT V.21 III-A-5   |

|        | MSM6946        | SINGLE CHIP FSK MODEM, 300 BPS FULL DUPLEX, BELL 103 III-A-5     |

|        | MSM6927        | SINGLE CHIP FSK MODEM, 1200 BPS HALF DUPLEX,                     |

|        |                | CCITT V.23 III-A-28                                              |

|        | MSM6947        | SINGLE CHIP FSK MODEM, 1200 BPS HALF DUPLEX, BELL 202 . III-A-28 |

|        | MSM6948        | SINGLE CHIP MSK MODEM, 1200 BPS III-A-56                         |

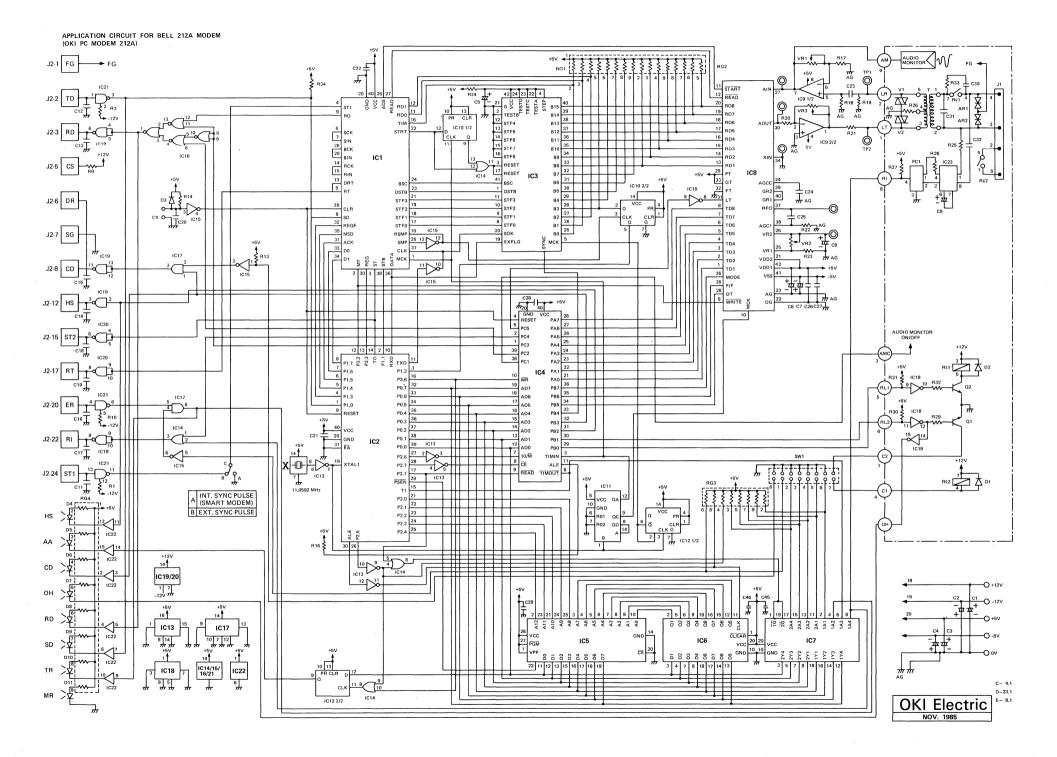

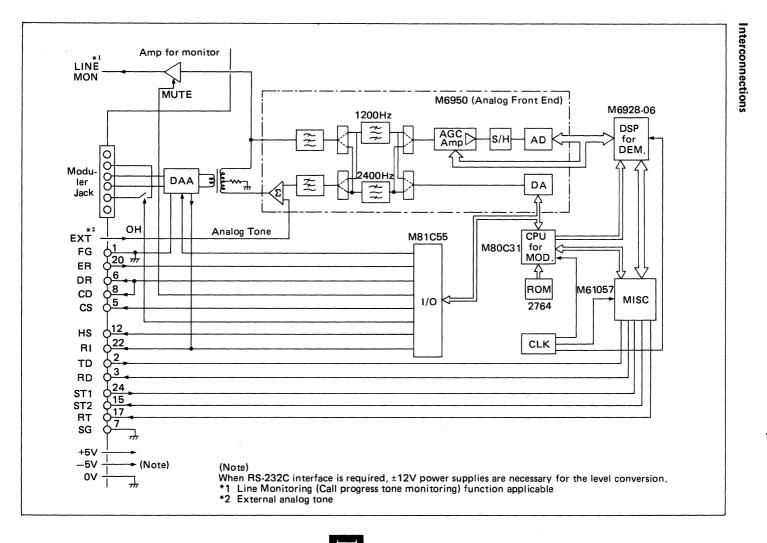

|        |                | CHIP SET FOR BELL 212A MODEM III-A-67                            |

|        |                | CHIP SET FOR 2400 BPS FULL DUPLEX MODEM III-A-81                 |

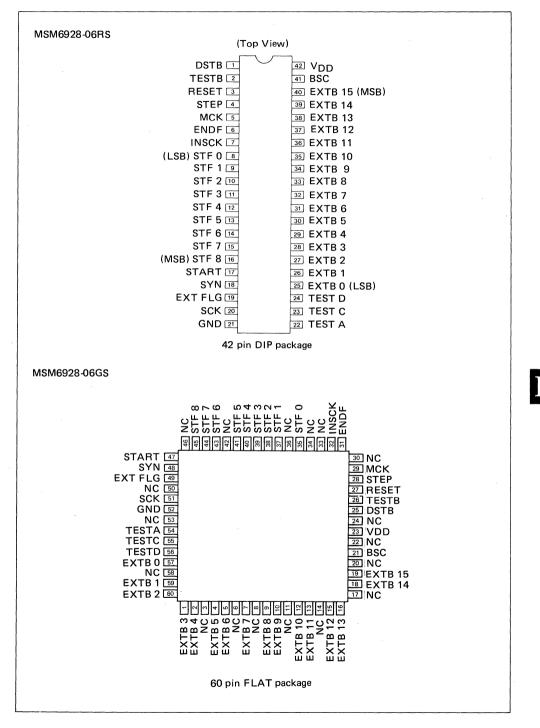

|        | MSM6928-06     | DSP FOR OKI'S 1200 BPS FDX MODEM CHIP SET III-A-138              |

|        | MSM61057       | GATE ARRAY FOR OKI'S 1200 BPS FDX MODEM CHIP SET III-A-152       |

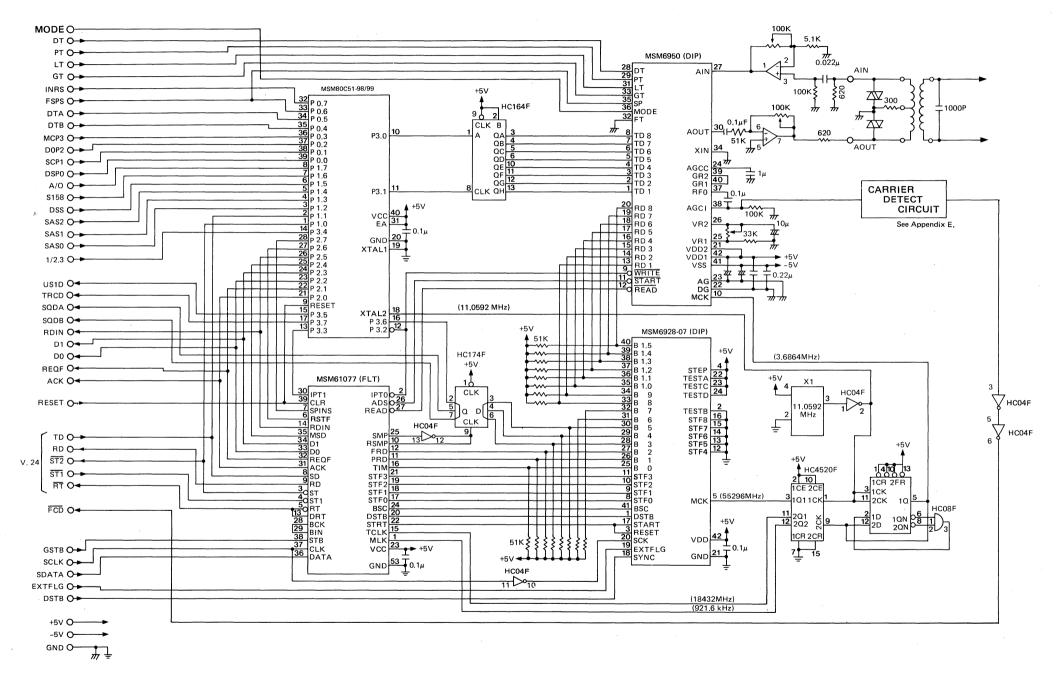

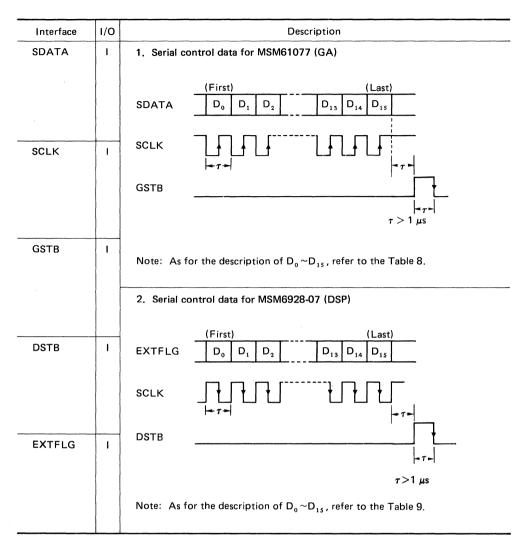

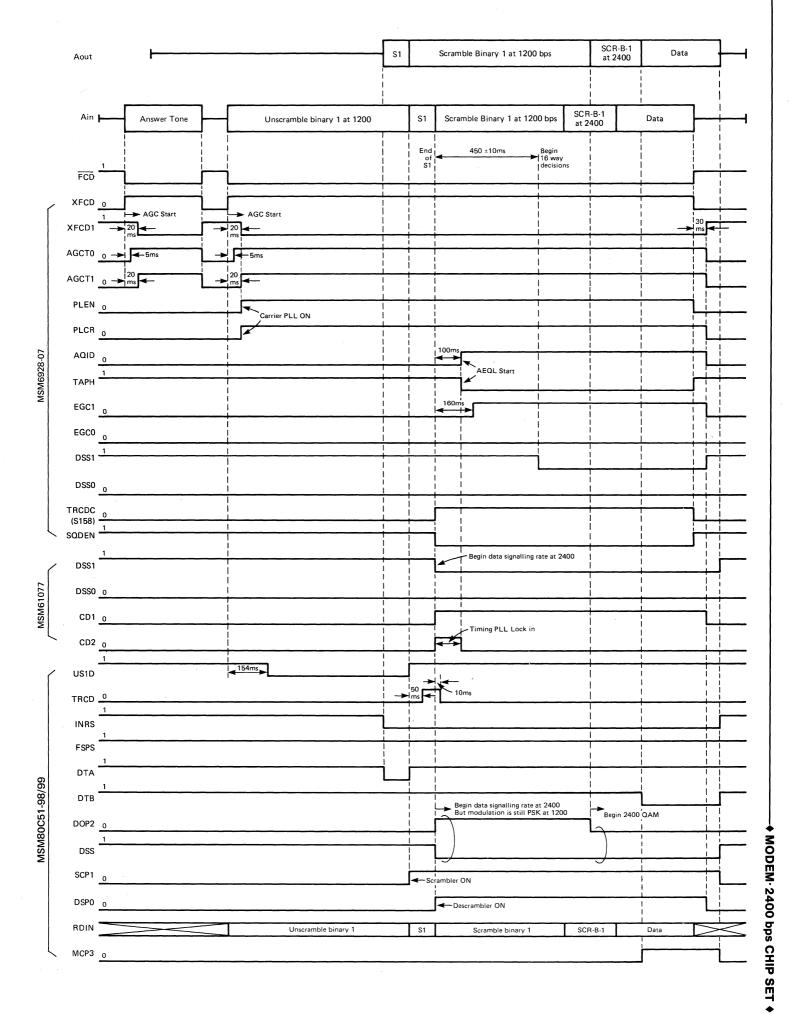

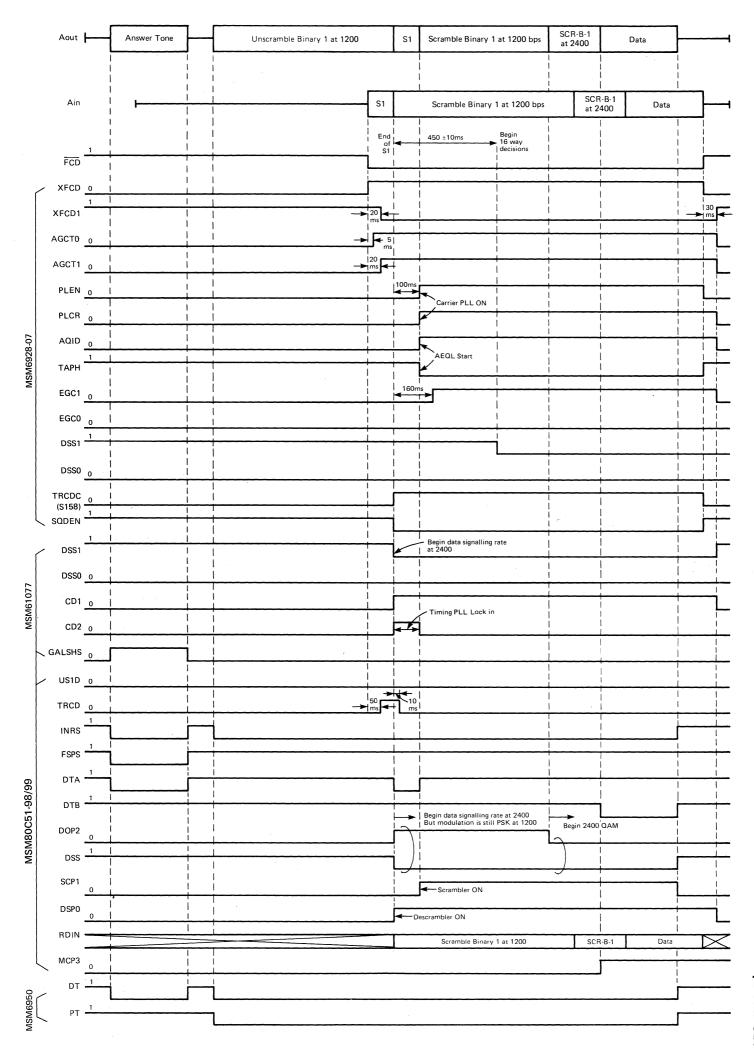

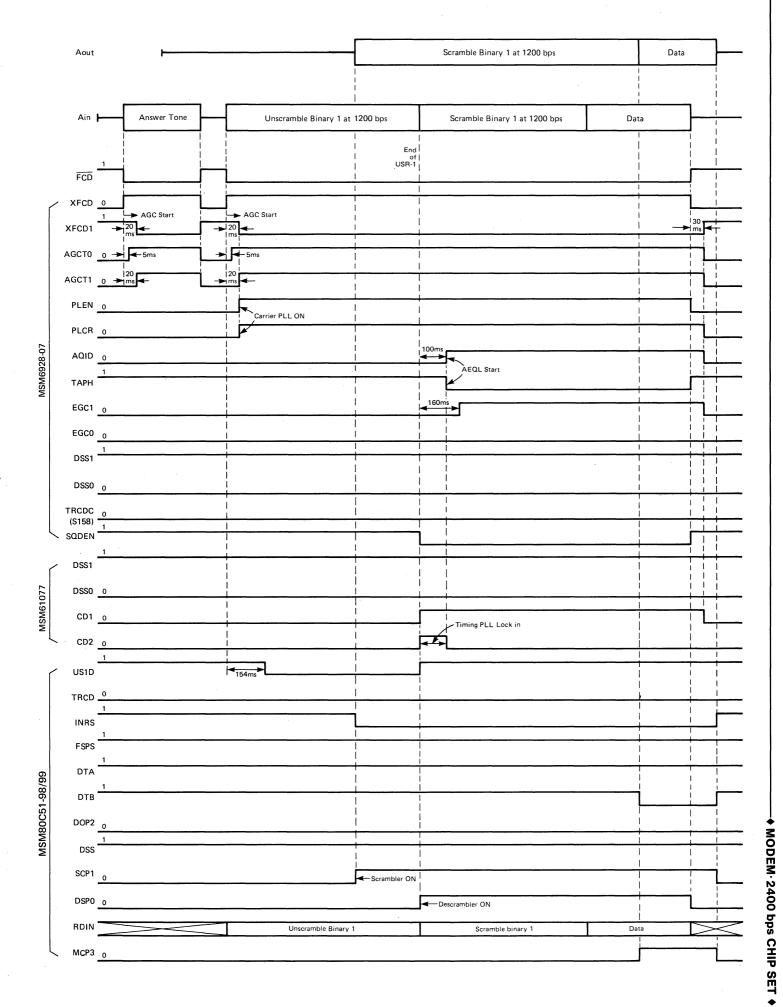

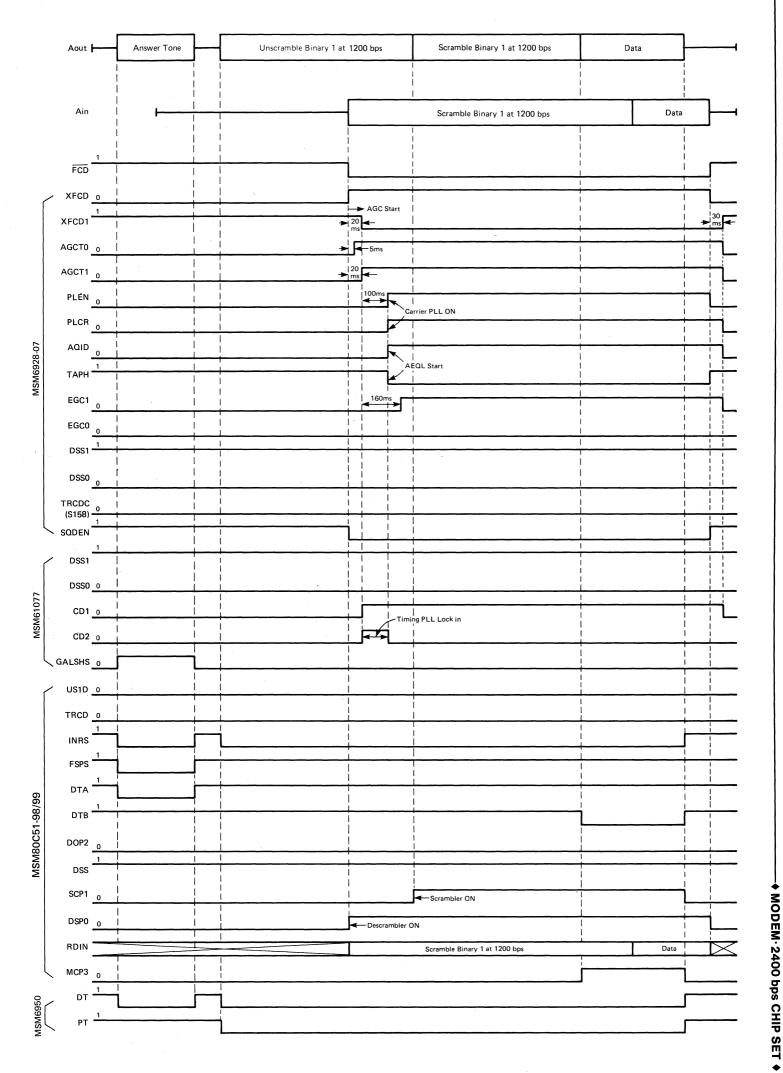

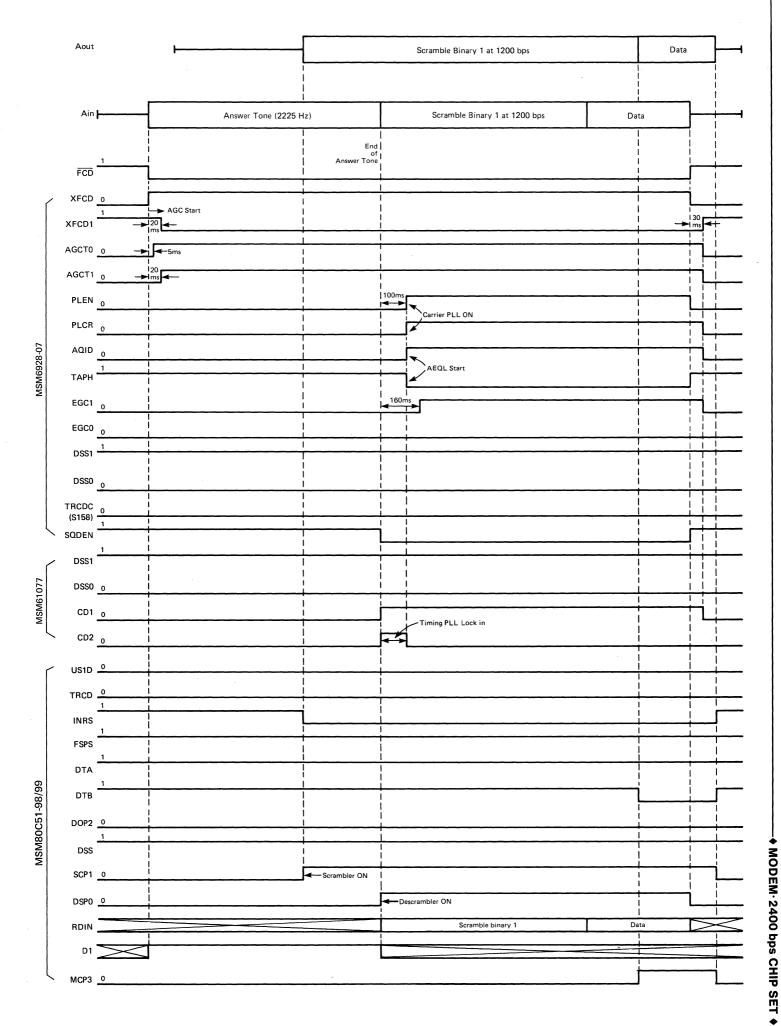

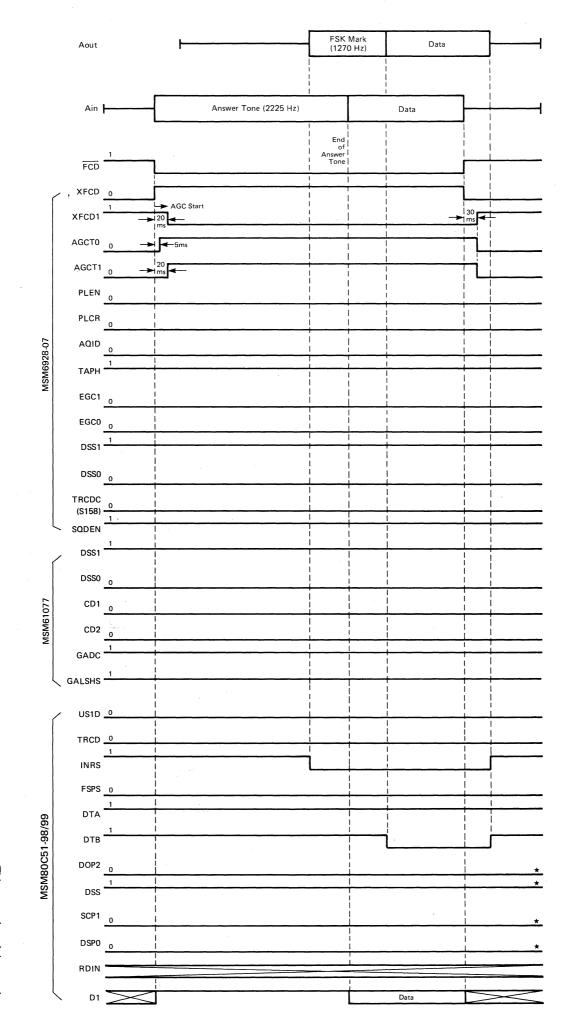

|        | MSM6928-07     | DSP FOR OKI'S 2400 BPS FDX MODEM CHIP SET III-A-164              |

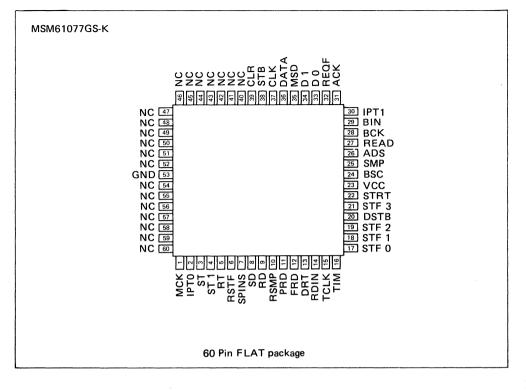

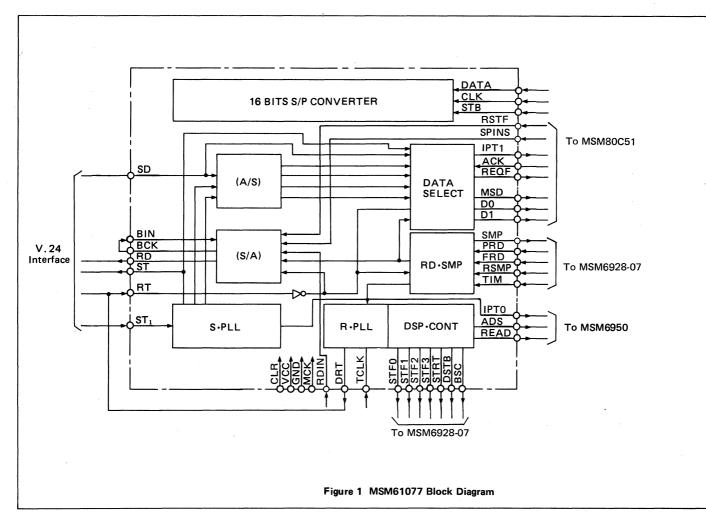

|        | MSM61077       | GATE ARRAY FOR OKI'S 2400 BPS FDX MODEM CHIP SET III-A-178       |

|        | MSM6950        | ANALOG FRONT END FOR 1200 BPS/2400 BPS FDX MODEM III-A-187       |

| _      | MSM6949        | ANALOG FRONT END FOR 4800 BPS/9600 BPS HDX MODEM III-A-220       |

| В.     | TELEPHONE A    |                                                                  |

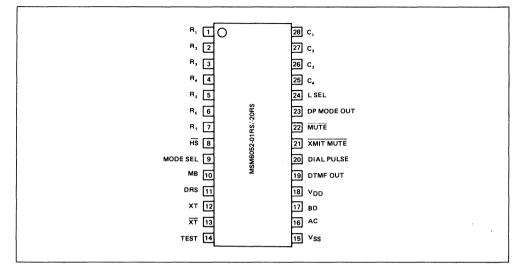

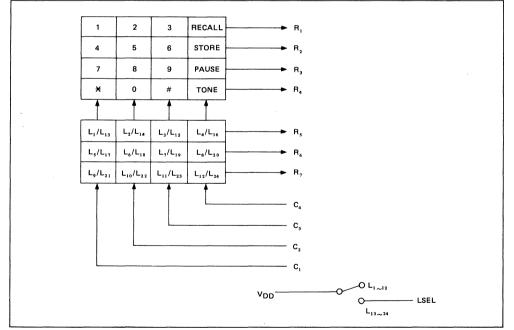

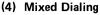

|        | MSM6052        | 4-BIT MCU WITH ON-CHIP DTMF GENERATOR III-B-3                    |

|        | MSM6052-01     | TONE/PULSE REPERTORY DIALER III-B-14                             |

|        | MSM6052-20     | TONE/PULSE REPERTORY DIALER III-B-14                             |

TONE/PULSE REPERTORY DIALER ..... III-B-28

ί

|    |    | MSM6052-10    | TONE/PULSE REPERTORY DIALER III-B-28                        |

|----|----|---------------|-------------------------------------------------------------|

|    |    | MSM6052-11    | TONE/PULSE REPERTORY DIALER III-B-28                        |

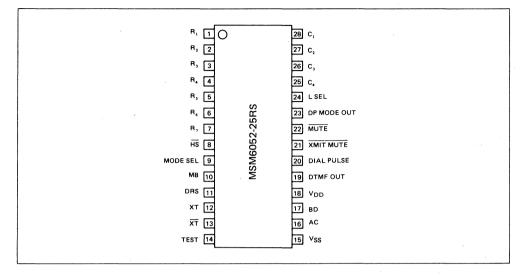

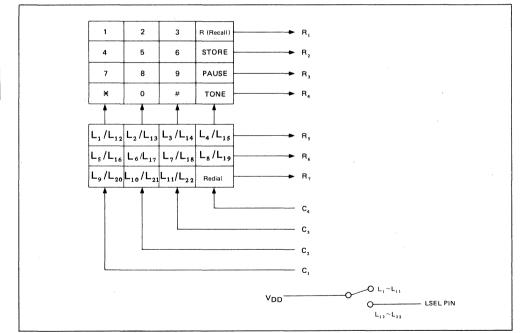

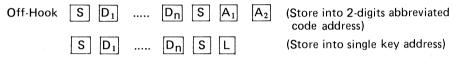

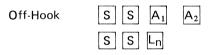

|    |    | MSM6052-25    | TONE/PULSE REPERTORY DIALER III-B-49                        |

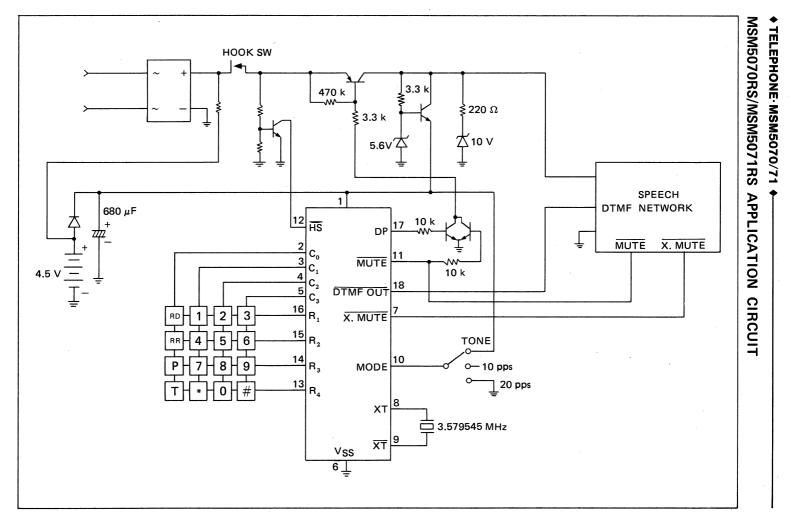

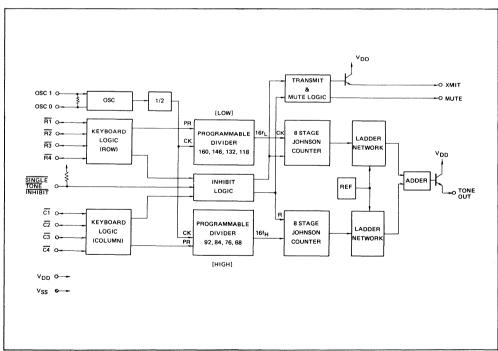

|    |    | MSM5070       | TONE/PULSE DIALER WITH REDIAL III-B-63                      |

|    |    | MSM5071       | TONE/PULSE DIALER WITH REDIAL III-B-63                      |

|    |    | MSM6224       | TONE DIALER III-B-73                                        |

|    |    | MSM6234       | TONE DIALER III-B-81                                        |

|    | C. | COMBO CODE    | C                                                           |

|    |    | MSM6932       | μ-LAW COMBO CODEC III-C-3                                   |

|    |    | MSM6933       | A-LAW COMBO CODEC III-C-3                                   |

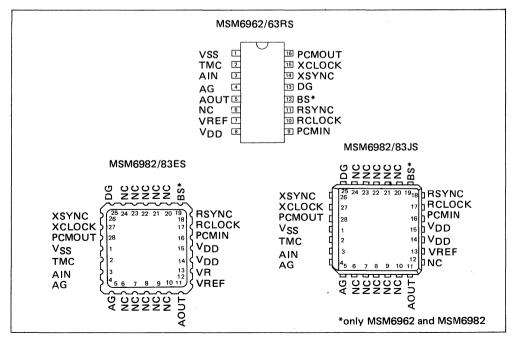

|    |    | MSM6962       | μ-LAW COMBO CODEC III-C-14                                  |

|    |    | MSM6963       | A-LAW COMBO CODEC III-C-14                                  |

|    |    | MSM6982       | μ-LAW COMBO CODEC III-C-14                                  |

|    |    | MSM6983       | A-LAW COMBO CODEC III-C-14                                  |

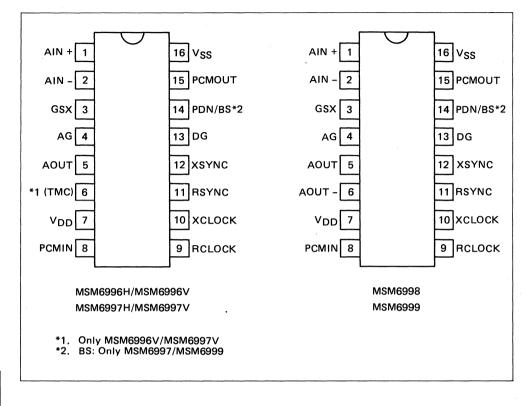

|    |    | MSM6996H      | A-LAW COMBO CODEC III-C-28                                  |

|    |    | MSM6997H      | μ-LAW COMBO CODEC III-C-28                                  |

|    |    | MSM6996V      | A-LAW COMBO CODEC III-C-28                                  |

|    |    | MSM6997V      | <i>μ</i> -LAW COMBO CODEC III-C-28                          |

|    |    | MSM6998       | A-LAW COMBO CODEC III-C-28                                  |

|    |    | MSM6999       | μ-LAW COMBO CODEC III-C-28                                  |

|    |    | MSM6814       | μ-LAW COMBO TA CODEC III-C-44                               |

|    |    | MSM6815       | A-LAW COMBO TA CODEC III-C-44                               |

|    | D. | PABX APPLICA  |                                                             |

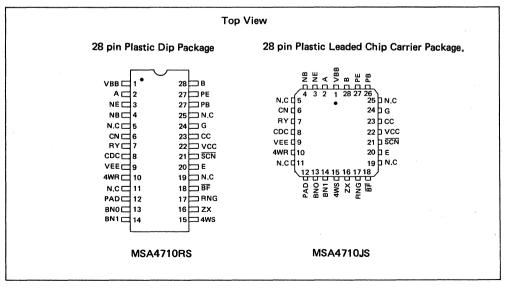

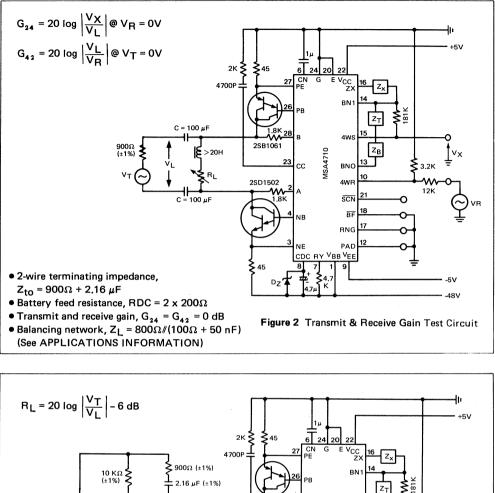

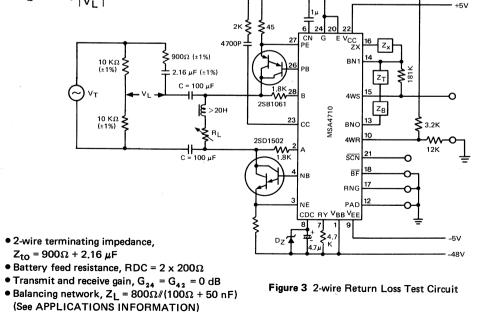

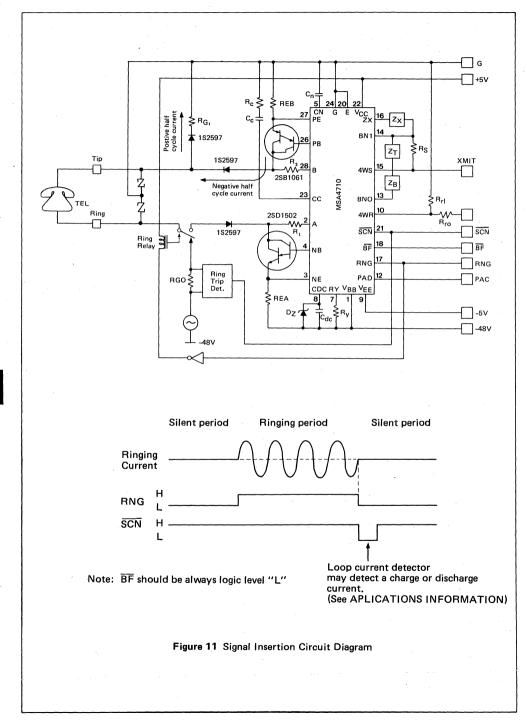

|    |    | MSA4710       | BSH LSI FOR SLIC III-D-3                                    |

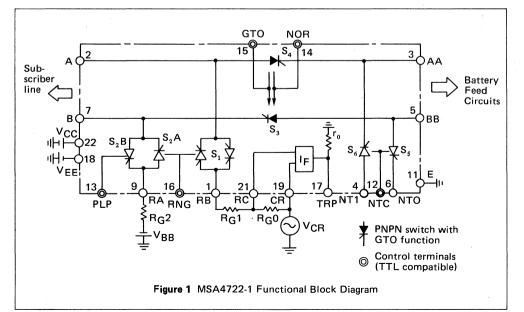

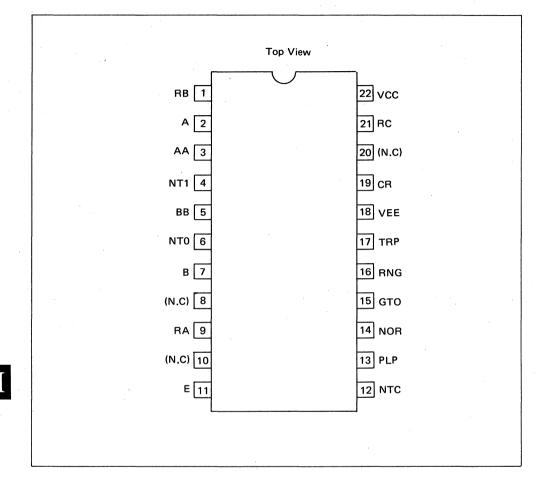

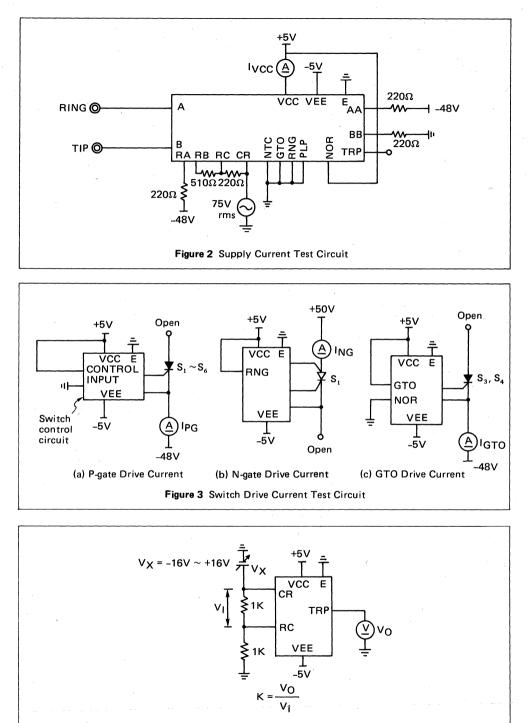

|    |    | MSA4722-1     | RINGING SWITCHES FOR CODEC III-D-19                         |

|    |    | MSM6912       | PCM VOICE CHANNEL FILTER III-D-30                           |

|    |    | MSM6913       | 8-BIT SERIAL-PARALLEL CONVERTER III-D-39                    |

|    |    | MSM6914       | HIGHWAY SWITCH MATRIX III-D-46                              |

|    | Ε. | DIGITAL SIGNA | AL PROCESSOR                                                |

|    |    | MSM77C20      | DIGITAL SIGNAL PROCESSOR III-E-3                            |

|    |    | MSM6992       | HIGH-SPEED FLOATING POINT DIGITAL SIGNAL PROCESSOR III-E-19 |

|    | F. | CELLULAR MC   | BILE PHONE                                                  |

|    |    | MSM6807       | BASEBAND FILTER FOR AMPS CELLULAR PHONE III-F-3             |

|    |    | MSM6817       | BASEBAND FILTER FOR TACS CELLULAR PHONE III-F-3             |

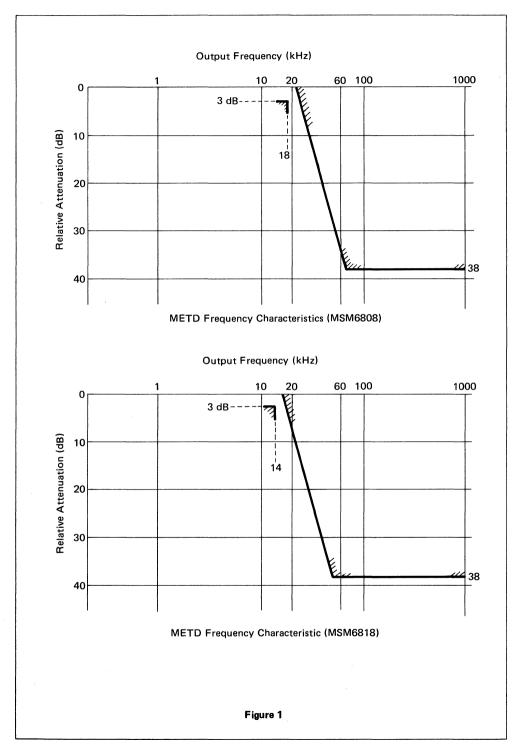

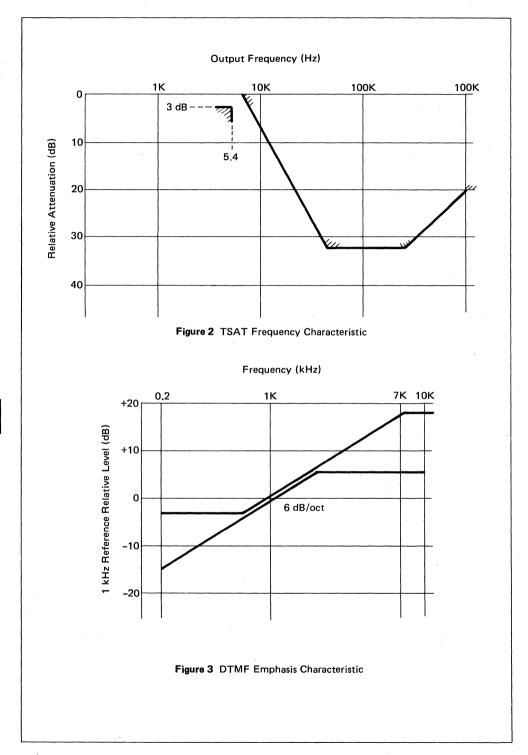

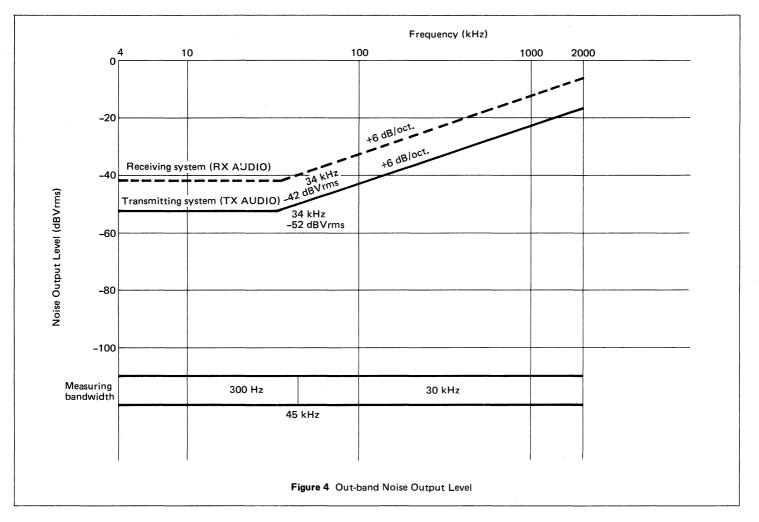

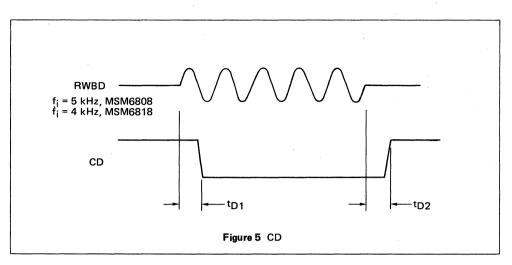

|    |    | MSM6808       | SPLIT FILTER FOR AMPS CELLULAR PHONE III-F-20               |

|    |    | MSM6818       | SPLIT FILTER FOR TACS CELLULAR PHONE III-F-20               |

|    |    | MSM74017      | MODEM FOR CELLULAR MOBILE PHONE III-F-39                    |

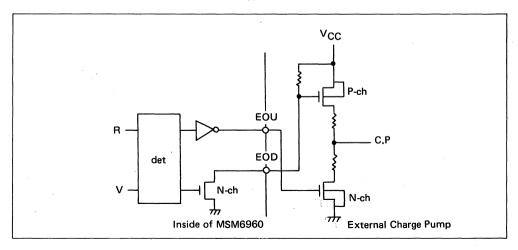

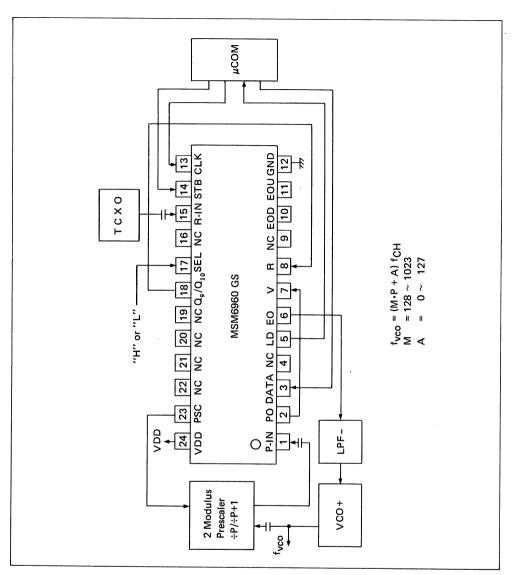

|    |    | MSM6960       | PLL FREQUENCY SYNTHESIZER III-F-51                          |

|    | G. | OTHERS        |                                                             |

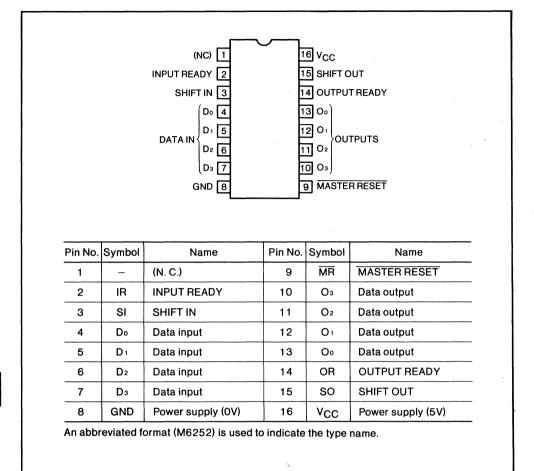

|    |    | MSM6252       | FIFO MEMORY III-G-3                                         |

|    |    | MSM6920       | SINGLE CHIP DTMF DECODER FOR PABX III-G-12                  |

|    |    | MSM6945       | SINGLE CHIP DTMF DECODER FOR TERMINAL III-G-12              |

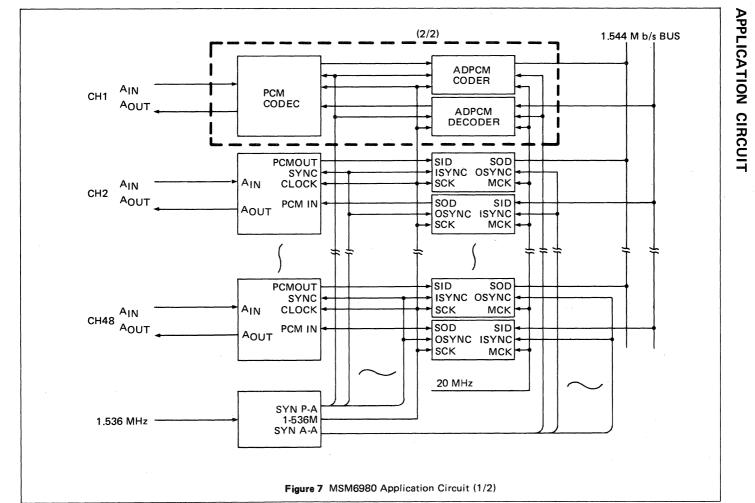

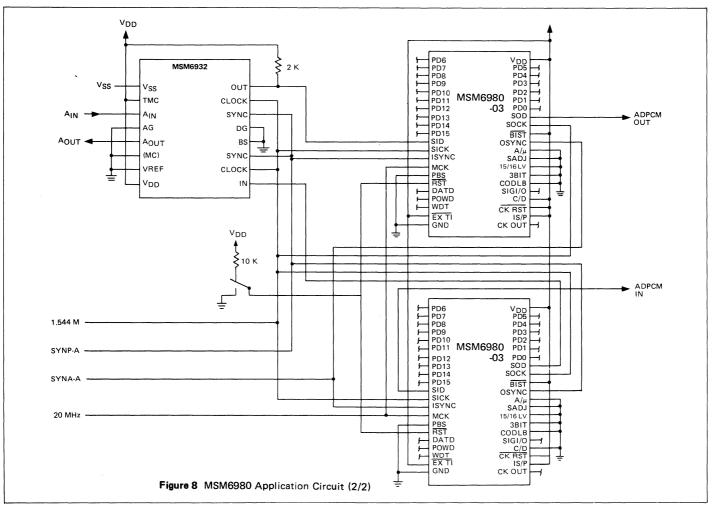

|    | _  | MSM6980-03    | 32K-BIT/SEC ADPCM CODEC III-G-26                            |

| ĪV | AP | PLICATION NO  | TE FOR SINGLE CHIP MODEM IV-3                               |

#

#### PRODUCT LINE-UP

|                |                                                           |                                                                                                                                                                           | Power         |                               |                           |         |                                                                                                                      |  |

|----------------|-----------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|-------------------------------|---------------------------|---------|----------------------------------------------------------------------------------------------------------------------|--|

| Type No.       | Function                                                  | Features                                                                                                                                                                  | Supply<br>(V) | Con-<br>sump-<br>tion<br>(mW) | Package                   | Process | Applications                                                                                                         |  |

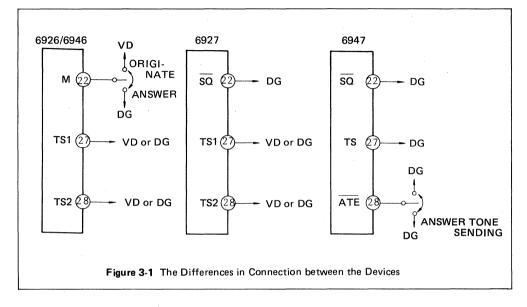

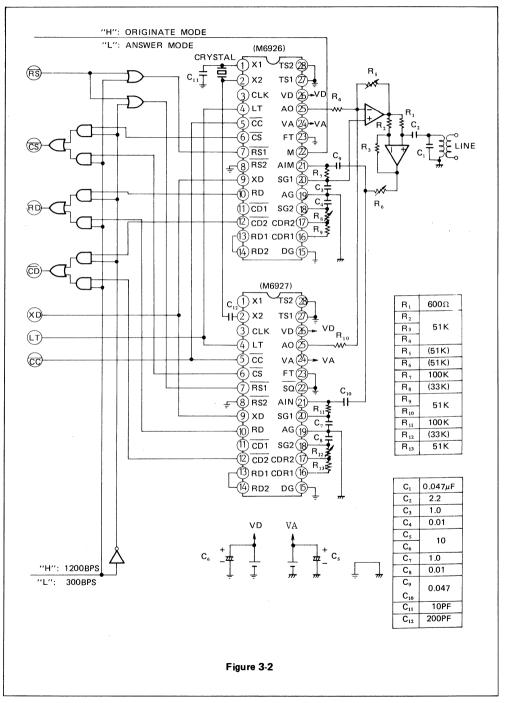

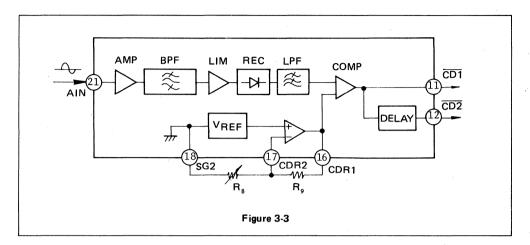

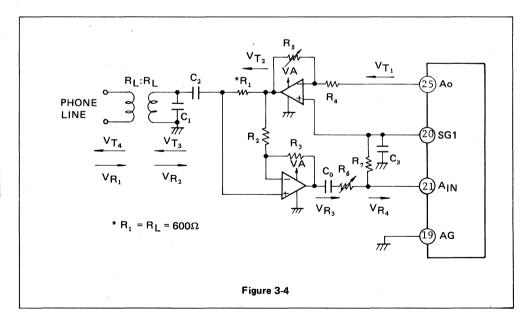

| MSM6926        | Single Chip FSK<br>Modem, 300 bps<br>Full Duplex          | CCITT V. 21     Modulator, Demodula-<br>tor, Filters and Carrier<br>Detect                                                                                                | +5,+12        | 90                            | 28 Pin DIP<br>44 Pin FLAT | CMOS    | <ul> <li>POS terminal</li> <li>CAT system</li> <li>Handy data<br/>terminal</li> <li>Medam phone</li> </ul>           |  |

| MSM6946        | Single Chip FSK<br>Modem, 300 bps<br>Full Duplex          | <ul> <li>Bell 103</li> <li>Modulator, Demodula-<br/>tor, Filter and Carrier<br/>Detect</li> </ul>                                                                         | +5,+12        | 90                            | 28 Pin DIP<br>44 Pin FLAT | смоз    | <ul> <li>Modem phone</li> <li>Tele-writing<br/>system</li> <li>Vending ma-<br/>chine</li> <li>Tele-sector</li> </ul> |  |

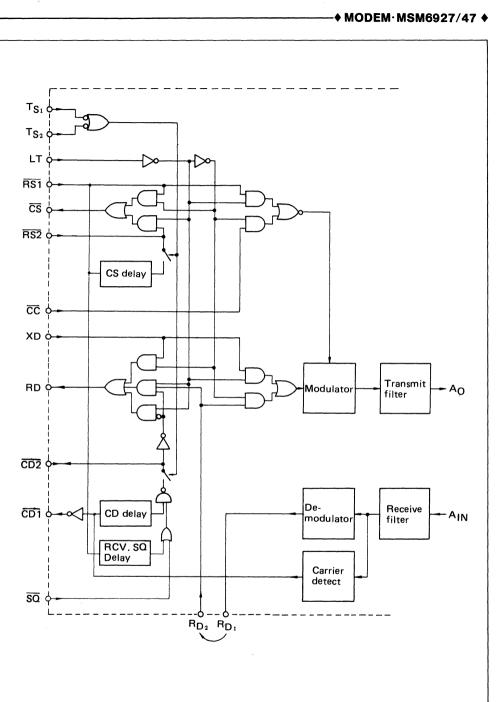

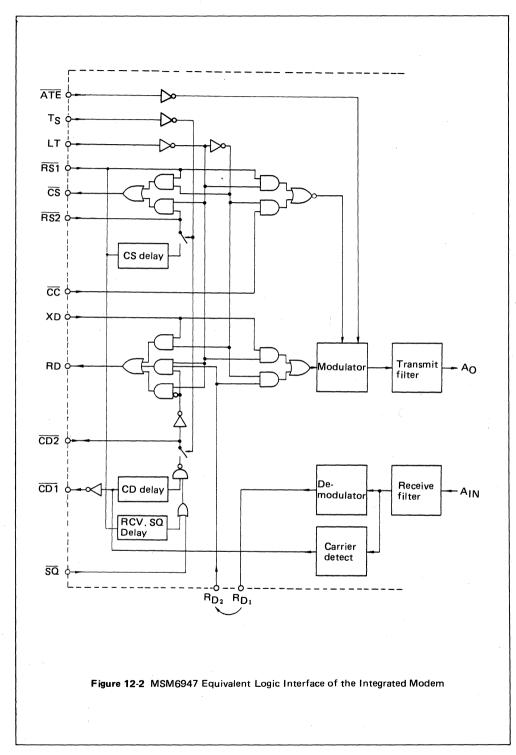

| MSM6927        | Single Chip FSK<br>Modem, 1200 bps<br>Half Duplex         | <ul> <li>CCITT V. 23</li> <li>Modulator, Demodulator, Filters and Carrier Detect</li> </ul>                                                                               | +5,+12        | 90                            | 28 Pin DIP<br>44 Pin FLAT | смоз    | <ul> <li>Tele-meter</li> <li>system</li> <li>Coin telephone</li> </ul>                                               |  |

| MSM6947        | Single Chip FSK<br>Modem, 1200 bps<br>Half Duplex         | <ul> <li>Bell 202</li> <li>Modulator, Demodula-<br/>tor, Filters and Carrier<br/>Detect</li> </ul>                                                                        | +5,+12        | 90                            | 28 Pin DIP<br>44 Pin FLAT | смоз    |                                                                                                                      |  |

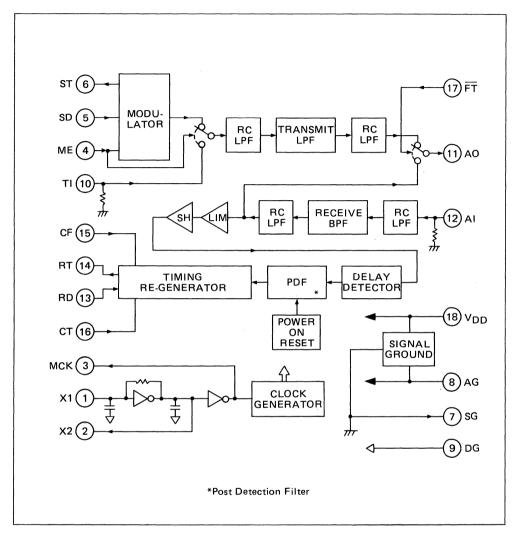

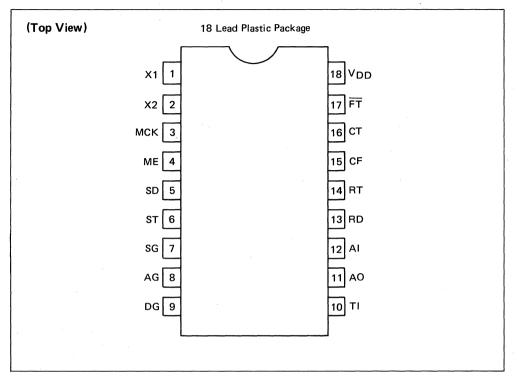

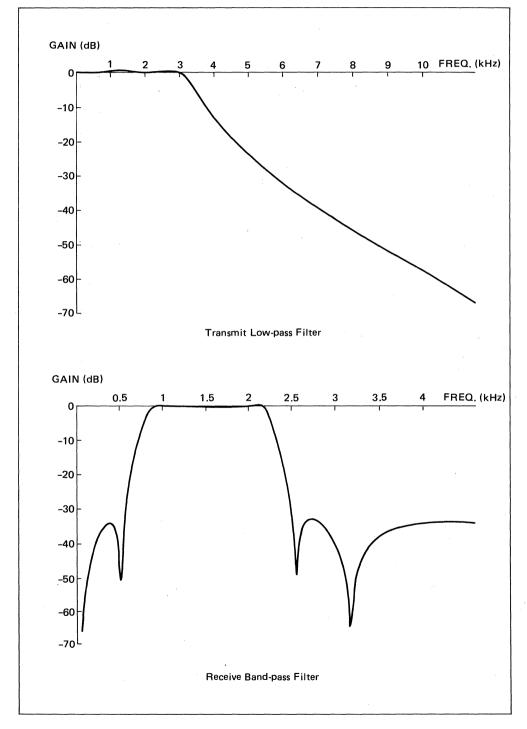

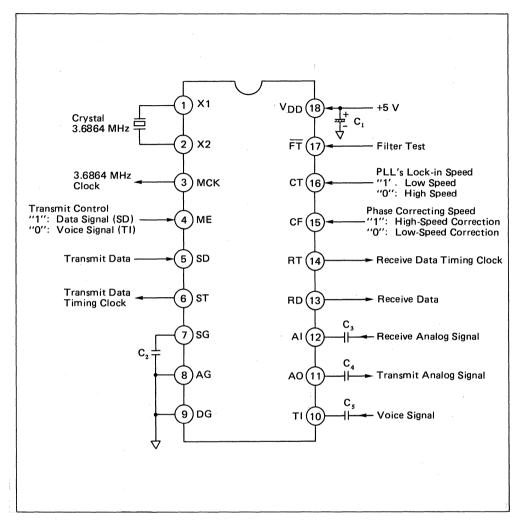

| MSM6948        | Single Chip MSK<br>Modem, 1200 bps                        | <ul> <li>Modulator, Demodulator, Filters and Digital</li> <li>PLL</li> <li>Carrier Frequency:<br/>1500±300 Hz</li> </ul>                                                  | +5            | 15                            | 18 Pin DIP<br>24 Pin FLAT | смоз    | <ul> <li>Wireless com -<br/>munication</li> <li>Cordless tele-<br/>phone</li> <li>Pager</li> </ul>                   |  |

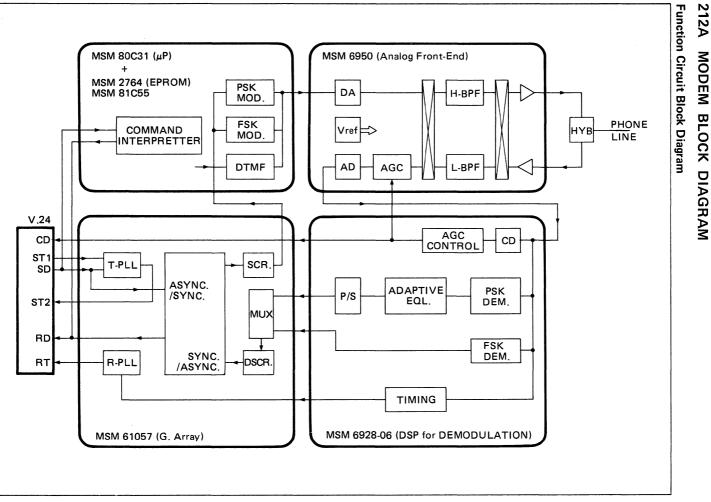

| CHIP SET       | 1200 bps Full<br>Duplex Modem                             | Bell 212A     Hayes Compatible     Adaptive Equalizing Function     MSM6928-06     MSM6950     MSM61057     MSM61057     MSM80C31     MSM80C31     MSM27C64     MSM81C55A | ±5.0          | 600                           | _                         | смоз    | <ul> <li>Stand alone<br/>modem</li> <li>Modem card</li> </ul>                                                        |  |

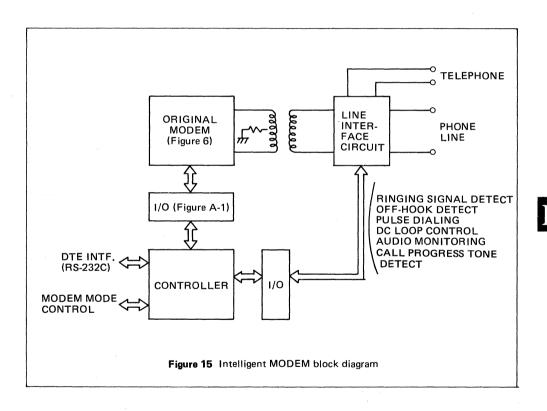

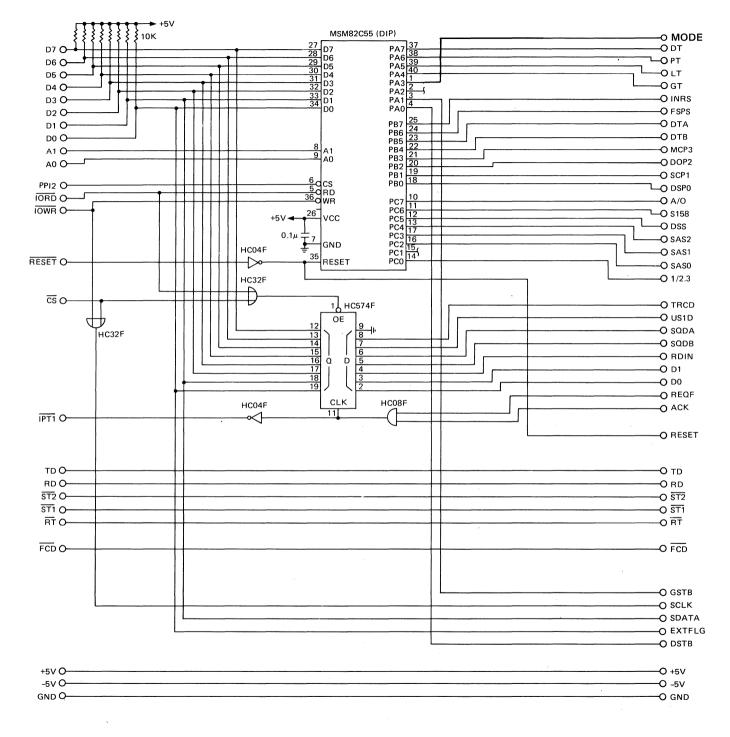

| CHIP SET       | 2400 bps Full<br>Duplex Modem                             | CCITT V. 22 bis<br>Bell 212A     Adaptive Equalizing<br>Function     MSM6928-07     MSM6950     MSM61077     SMSM80C51-98/99                                              | ±5.0          | 400                           | _                         | смоз    | Stand alone<br>modem •<br>Modem card                                                                                 |  |

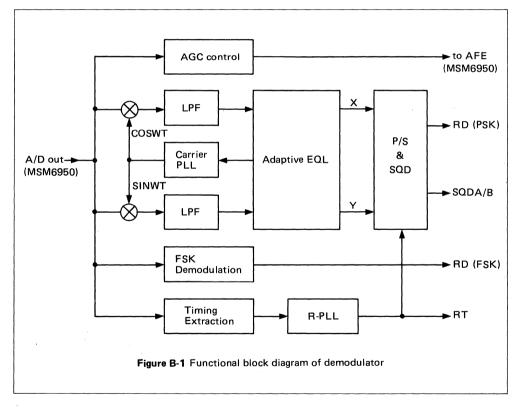

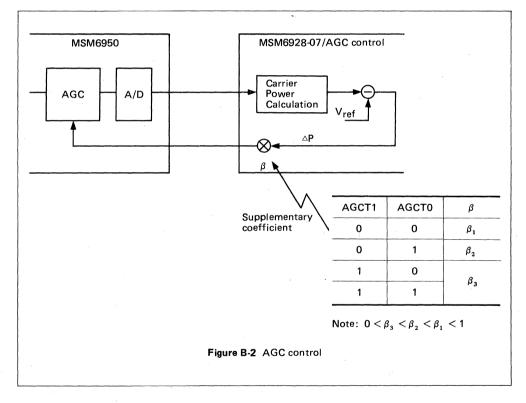

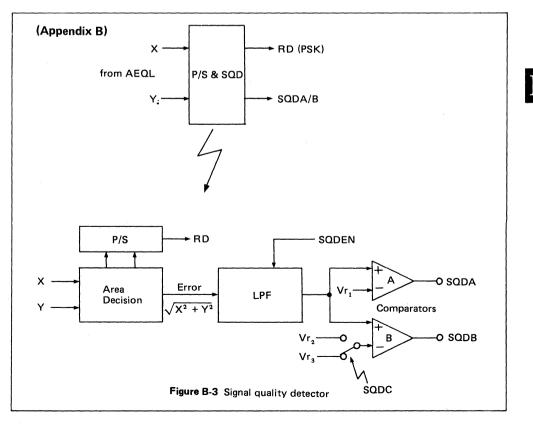

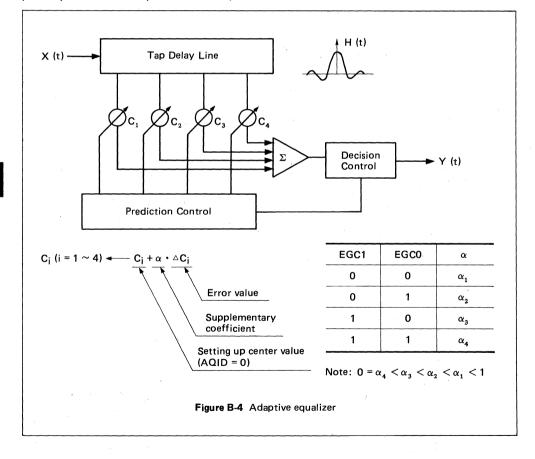

| MSM6928-<br>06 | DSP for OKI's<br>1200 bps FDX<br>Modem Chip Set           | - Demodulator<br>- Carrier P <sub>LL</sub> , Timing<br>P <sub>LL</sub><br>- Adaptive EQL<br>- Carrier Detect                                                              | +5.0          | 150                           | 42 Pin DIP<br>60 Pin FLAT | смоѕ    | OKI's 1200 bps<br>FDX Modem<br>Chip Set                                                                              |  |

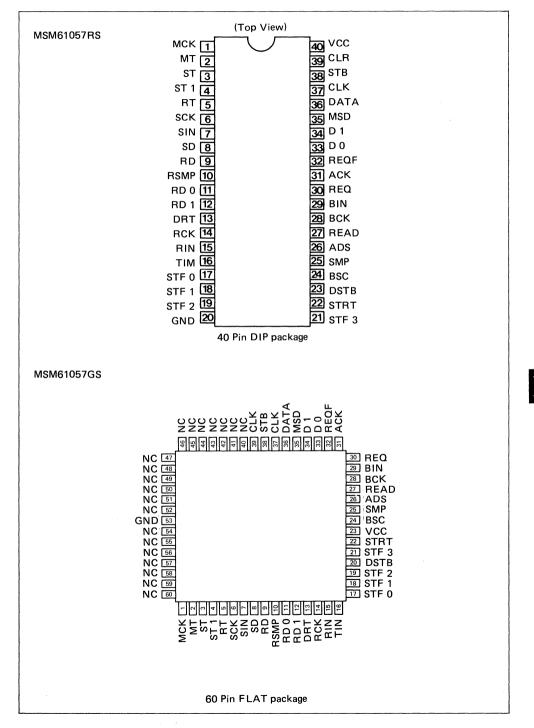

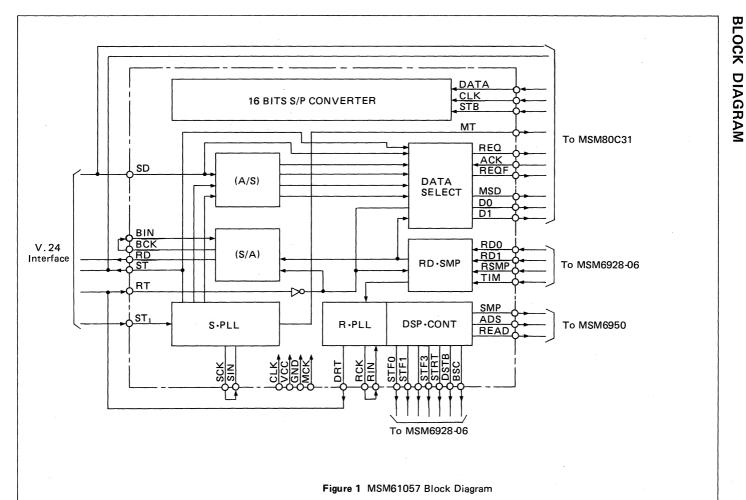

| MSM61057       | Gate Array for<br>OKI's 1200 bps<br>FDX Modem<br>Chip Set | - Asynchronous/Syn-<br>chronous and Syn-<br>chronous/Asynchronous<br>Converters<br>- PLL                                                                                  | +5.0          | 50                            | 40 Pin DIP<br>60 Pin FLAT | смоѕ    |                                                                                                                      |  |

| MSM6928-<br>07 | DSP for OKI's<br>2400 bps FDX<br>Modem Chip Set           | <ul> <li>Demodulator</li> <li>Adaptive EQL</li> </ul>                                                                                                                     | +5.0          | 150                           | 42 Pin DIP<br>60 Pin FLAT | смоѕ    | OKI's 2400 bps<br>FDX Modem<br>Chip Set                                                                              |  |

| MSM61077       | Gate Array for<br>OKI's 2400 bps<br>FDX Modem<br>Chip Set | Gate Array for - Asynchronous/Syn-<br>DKI's 2400 bps - chronous and Syn-<br>DX Modem - chronous/Asynchro-                                                                 |               | 50                            | 60 Pin FLAT               | смоѕ    |                                                                                                                      |  |

#### ♦ PRODUCT LINE-UP ♦

|                                  |                                                        |                                                                                                                                                                                                                         | Pov           | ver                           |                                                |         |                                                                                                                     |  |

|----------------------------------|--------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|-------------------------------|------------------------------------------------|---------|---------------------------------------------------------------------------------------------------------------------|--|

| Type No.                         | Function                                               | Features                                                                                                                                                                                                                | Supply<br>(V) | Con-<br>sump-<br>tion<br>(mW) | Package                                        | Process | Applications                                                                                                        |  |

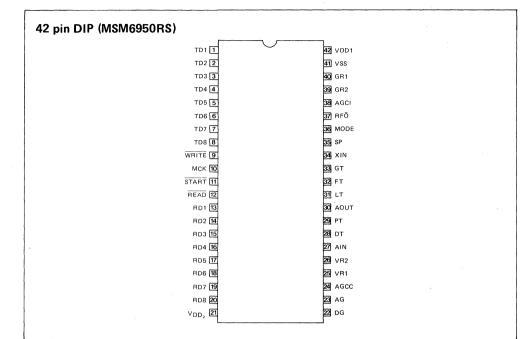

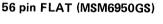

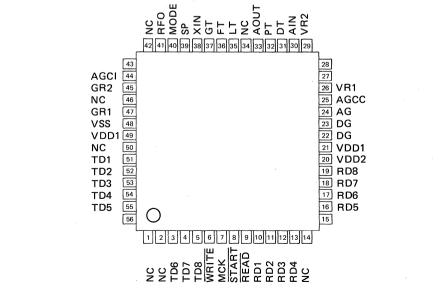

| MSM6950                          | Analog Front End<br>for 1200 bps/2400<br>bps FDX Modem | <ul> <li>Analog Functions for<br/>CCITT V.22, V.22 bis<br/>and Bell 212A</li> <li>8-bit D/A and A/D<br/>Converter</li> </ul>                                                                                            | ±5.0          | 100                           | 42 Pin DIP<br>56 Pin FLAT                      | смоз    | <ul> <li>V.22 modem</li> <li>V.22 bis modem</li> <li>Bell 212A<br/>modem</li> </ul>                                 |  |

| MSM6949                          | Analog Front End<br>for 4800 bps/9600<br>bps HDX Modem | Analog Functions for<br>CCITT V.26, V.27 and<br>V.29     8-bit D/A and A/D<br>Converter     Band Limiting Filter,<br>AGC                                                                                                | ±5.0          | 140                           | 64 Pin Mini<br>DIP                             | смоз    | · V.26 modem<br>· V.27 modem<br>· V.29 modem                                                                        |  |

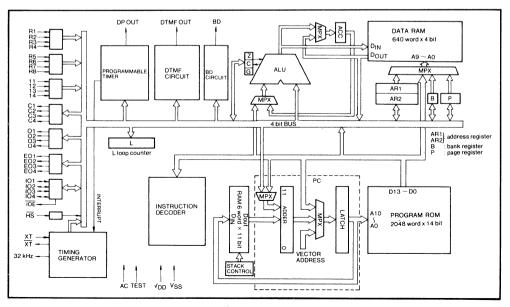

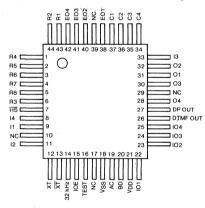

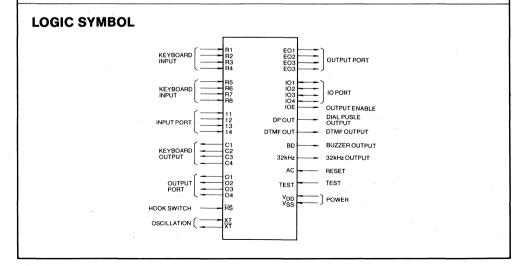

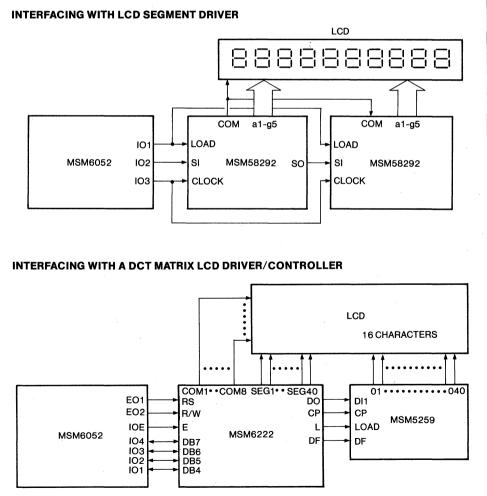

| MSM6052                          | 4-bit MCU with<br>On-Chip DTMF<br>Generator            | <ul> <li>2,048x14-bit ROM</li> <li>640x4-bit RAM</li> <li>3x4 Input Port</li> <li>3x4 Output Port</li> <li>1x4 Input/Output Port</li> </ul>                                                                             | +2.5~<br>+6.0 | 3.6<br>(3V)<br>20<br>(6V)     | 28 Pin DIP<br>40 Pin DIP<br>44 Pin FLAT<br>DIE | смоз    | <ul> <li>Telephone</li> <li>Answering<br/>machine</li> <li>Security</li> <li>system</li> <li>Modem phone</li> </ul> |  |

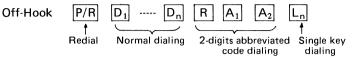

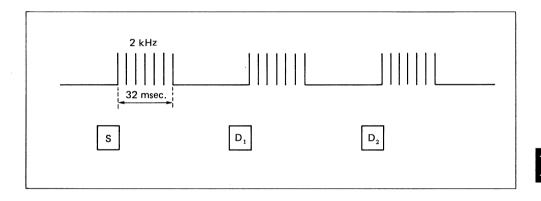

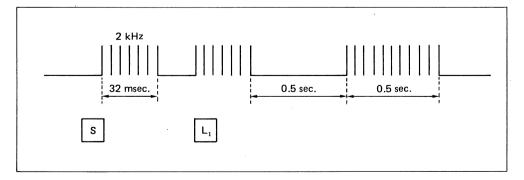

| MSM6052-<br>01<br>MSM6052-<br>20 | Tone/Pulse Re-<br>pertory Dialer                       | <ul> <li>500 Digit Memory<br/>(54 Numbers)</li> <li>Last Number Redial:<br/>32 Digit</li> <li>Make/Break Ratio<br/>Selectable</li> <li>Dial Pulse Ratio<br/>Selectable</li> <li>Off-hook Memory</li> </ul>              | +2.5~<br>+6.0 | 3.6<br>(3V)<br>20<br>(6V)     | 28 Pin DIP                                     | смоз    | · Feature phone                                                                                                     |  |

|                                  |                                                        | Storing                                                                                                                                                                                                                 |               |                               |                                                |         |                                                                                                                     |  |

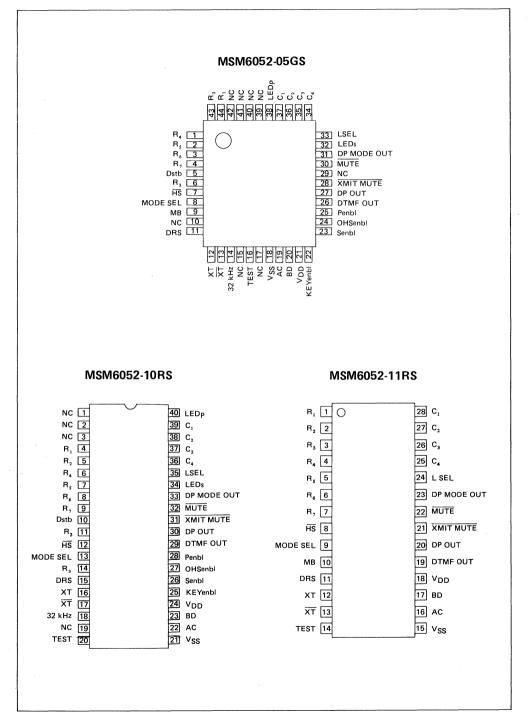

| MSM6052-<br>05                   | Tone/Pulse<br>Repertory Dialer                         | <ul> <li>500 Digit Memory<br/>(54 Numbers)</li> <li>Last Number Redial:<br/>32 Digit<br/>Make/Break Ratio<br/>Selectable</li> </ul>                                                                                     | +2.5~<br>+6.0 | 3.6<br>(3∨)<br>20             | 44 Pin FLAT                                    | смоз    |                                                                                                                     |  |

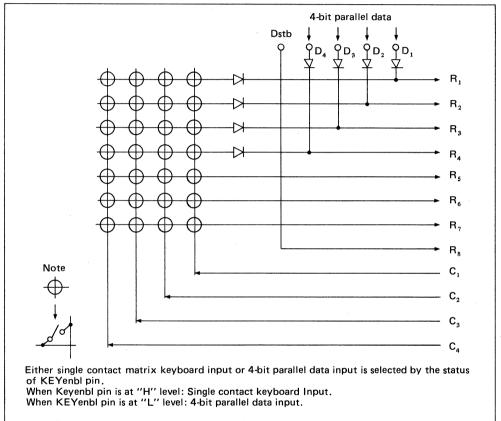

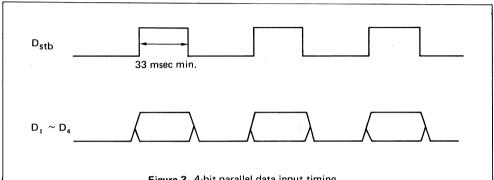

| MSM6052-<br>10                   |                                                        | <ul> <li>Dial Pulse Ratio<br/>Selectable</li> <li>On-hook/Off-hook<br/>Memory Storing</li> <li>4-bit Parallel Data<br/>Input</li> </ul>                                                                                 |               | (6V)                          | 40 Pin DIP                                     |         |                                                                                                                     |  |

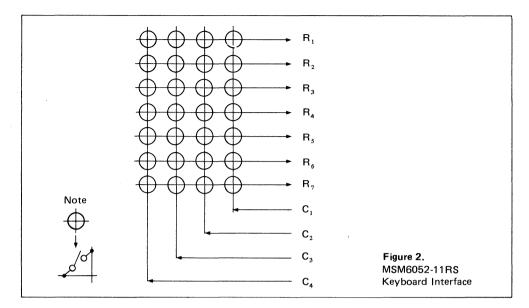

| MSM6052-<br>11                   | Tone/Pulse<br>Repertory Dialer                         | <ul> <li>500 Digit Memory<br/>(54 Numbers)</li> <li>Last Number Redial:<br/>32 Digit</li> <li>Make/Break Ratio<br/>Selectable</li> <li>Dial Pulse Ratio<br/>Selectable</li> <li>On-hook Memory<br/>Storing</li> </ul>   | +2.5~<br>+6.0 | 3.6<br>(3V)<br>20<br>(6V)     | 28 Pin DIP                                     | смоз    |                                                                                                                     |  |

| MSM6052-<br>25                   | Tone/Pulse<br>Repertory Dialer                         | <ul> <li>505 Digits Memory<br/>(52 Numbers)</li> <li>Last Number Redial:<br/>32 Digit</li> <li>Make/Break Ratio<br/>Selectable</li> <li>Dial Pulse Ratio<br/>Selectable</li> <li>Off-hook Memory<br/>Storing</li> </ul> | +2.5~<br>+6.0 | 3.6<br>(3V)<br>20<br>(6V)     | 28 Pin DIP                                     | CMOS    |                                                                                                                     |  |

Π

#### -+ PRODUCT LINE-UP +

| Type No.           |                                  |                                                                                                                                                                            | Power                        |             | 1                         | 1       |                                                                                       |  |

|--------------------|----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|-------------|---------------------------|---------|---------------------------------------------------------------------------------------|--|

|                    | Function                         | Features                                                                                                                                                                   | Supply<br>(V)<br>(W)<br>(mW) |             | Package                   | Process | Applications                                                                          |  |

| MSM5070            | Tone/Pulse Dialer<br>with Redial | <ul> <li>Last Number Redial:</li> <li>31 Digits</li> <li>Make/Break: 33/67</li> </ul>                                                                                      | +3.5~<br>+6.0                | 55          | 18 Pin DIP                | смоѕ    | <ul> <li>Telephone</li> <li>Answering<br/>machine</li> <li>Sogurity system</li> </ul> |  |

| MSM5071            | Tone/Pulse Dialer<br>with Redial | <ul> <li>Last Number Redial:</li> <li>31 Digits</li> <li>Make/Break: 40/60</li> </ul>                                                                                      | +3.5~<br>+6.0                | 55          | 18 Pin DIP                | смоѕ    | Security system     Modem phone     Feature phone                                     |  |

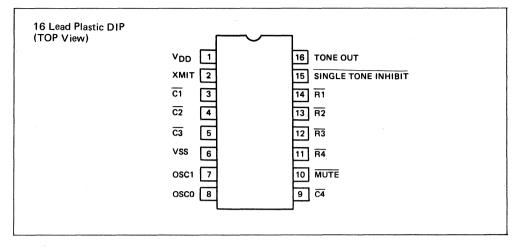

| MSM6224            | Tone Dialer                      | • MK5087 Compatible                                                                                                                                                        | +2.5~<br>+8.5                | 25<br>(MAX) | 16 Pin DIP                | смоз    |                                                                                       |  |

| MSM6234            | Tone Dialer                      | MK5089 Compatible     Easy Interface with     MCU                                                                                                                          | +2.5~<br>+8.5                | 25<br>(MAX) | 16 Pin DIP                | смоз    |                                                                                       |  |

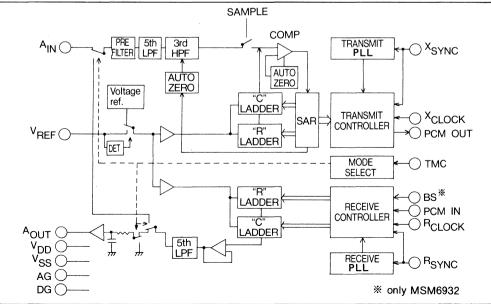

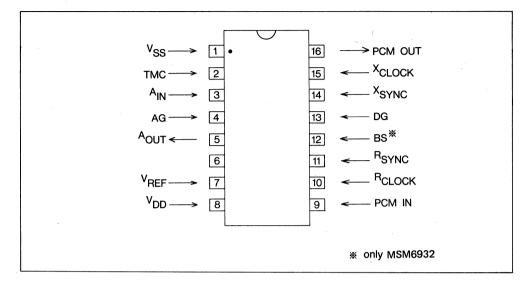

| MSM6932            |                                  | - MSM6932: μ-Law<br>- MSM6933: Α-Law                                                                                                                                       |                              |             |                           |         | · PABX<br>· Key system                                                                |  |

| MSM6933            | COMBO CODEC                      | Serial Data Rate:<br>64K bps~2048K bps                                                                                                                                     | ±5.0                         | 65          | 16 Pin DIP                | CMOS    | SLIC     PCM system                                                                   |  |

| MSM6962            |                                  | • MSM6962, MSM6982:                                                                                                                                                        |                              |             |                           |         | <ul> <li>ADPCM system</li> <li>Digital telephone</li> </ul>                           |  |

| MSM6963            |                                  | μ-Law<br>• MSM6963, MSM6983:                                                                                                                                               |                              |             | 16 Pin DIP                |         | - Voice recogni-<br>tion<br>- Digital voice<br>recorder                               |  |

| MSM6982            | COMBO CODEC                      | A-Law<br>Serial Data Rate:                                                                                                                                                 | ±5.0                         | 55          | 28 Pin PLCC               | CMOS    |                                                                                       |  |

| MSM6983            |                                  | 512/1024/1536/1544 /<br>2048 K bps                                                                                                                                         |                              |             |                           |         |                                                                                       |  |

| MSM6996-           |                                  | - MSM6996H: A-Law<br>- MSM6997H: <i>μ</i> -Law                                                                                                                             |                              | 65          | 16 Pin DIP                | смоз    |                                                                                       |  |

| H<br>MSM6997-<br>H | COMBO CODEC                      | <ul> <li>Serial Data Rate:</li> <li>64K bps~2048K bps</li> <li>600Ω Drive Capability</li> </ul>                                                                            | ±5.0                         |             |                           |         |                                                                                       |  |

| MSM6996-<br>V      | 001100 00050                     | <ul> <li>MSM6996V: A-Law</li> <li>MSM6997V: μ-Law</li> <li>Serial Data Rate:</li> <li>64k bps~2048k bps</li> <li>600Ω Drive and Analog<br/>Loop Test Capability</li> </ul> | ±5.0                         | 65          | 16 Pin DIP                | смоѕ    |                                                                                       |  |

| MSM6997-<br>V      | COMBO CODEC                      |                                                                                                                                                                            |                              | 05          |                           |         |                                                                                       |  |

| MSM6998            | COMBO CODEC                      | • MSM6998: A-Law<br>• MSM6999: μ-Law<br>• Serial Data Rate:                                                                                                                | ±5.0                         | 70          | 16 Pip DIP                | смоз    |                                                                                       |  |

| MSM6999            | COMBO CODEC                      | 64k bps ~ 2048k bps<br>600Ω Push-pull Drive<br>and Analog Loop Test<br>Capability                                                                                          |                              | 70          | 16 Pin DIP                | CIMOS   |                                                                                       |  |

| MSM6814            | COMBO CODEC<br>with Time Slot    | <ul> <li>MSM6814: μ-Law</li> <li>MSM6815: A-Law</li> <li>Time Slot Assignment:<br/>32 Time/Frame Maxi-</li> </ul>                                                          | ±5.0                         | 70          | 22 Pin DIP<br>28 Pin PLCC | CMOS    |                                                                                       |  |

| MSM6815            | Assignment                       | mum<br>· Serial Data Rate:<br>512/1024/1536/1544/<br>2048k bps                                                                                                             |                              |             |                           |         |                                                                                       |  |

| MSA4710            | BSH LSI for<br>SLIC              | <ul> <li>Battery Feed, Super-<br/>vision and Hybrid<br/>Function</li> <li>Loop Current<br/>Capability: 20~80 mA</li> <li>Longitudinal Balance:<br/>53 dB</li> </ul>        | 48,<br>±5.0                  | 120         | 28 Pin DIP                | Bipolar | · PABX<br>· SLIC                                                                      |  |

| MSA4722-<br>1      | RINGING<br>SWITCHES for<br>SLIC  | <ul> <li>Ringing, Line Test<br/>Function</li> <li>Breakdown Voltage:<br/>350V</li> <li>ON Resistance: 6Ω</li> <li>DC Current Capability:<br/>250mA</li> </ul>              | ±5.0                         | 40          | 22 Pin DIP                | Bipolar |                                                                                       |  |

Ι

I-5

#### ♦ PRODUCT LINE-UP ♦

|                    |                                                            |                                                                                                                                                                                                                                                                                                                                            | Power         |                               |                           |         |                                                                                             |  |

|--------------------|------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|-------------------------------|---------------------------|---------|---------------------------------------------------------------------------------------------|--|

| Type No.           | Function                                                   | Features                                                                                                                                                                                                                                                                                                                                   | Supply<br>(V) | Con-<br>sump-<br>tion<br>(mW) | Package                   | Process | Applications                                                                                |  |

| MSM6912            | PCM Voice<br>Channel Filter                                | • Transmit BPF:<br>0.3~3.4 kHz<br>• Receive LPF:0~3.4kHz                                                                                                                                                                                                                                                                                   | ±5.0          | 50                            | 16 Pin Cera-<br>mic DIP   | смоѕ    | <ul> <li>PABX</li> <li>Digital switching<br/>system</li> <li>Multiplexer</li> </ul>         |  |

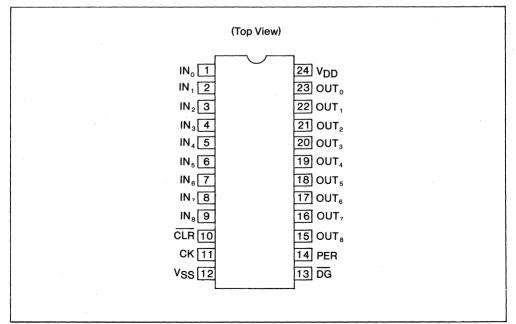

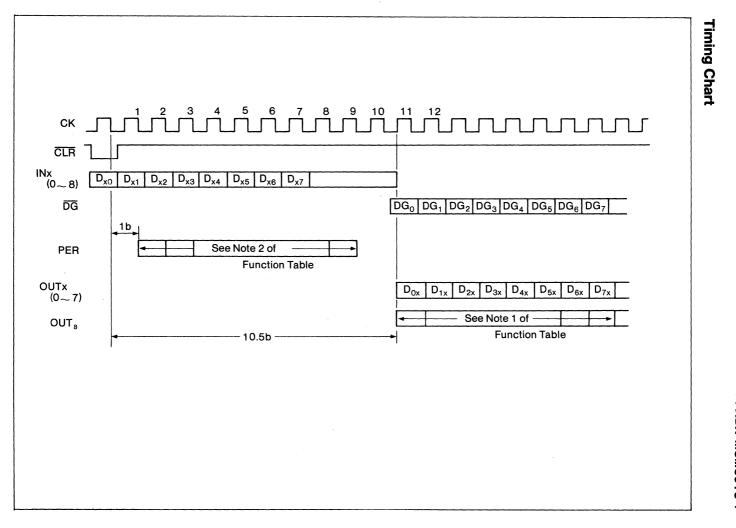

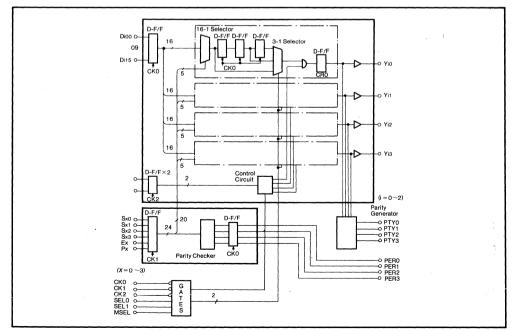

| MSM6913            | 8-bit Serial-<br>parallel Converter                        | <ul> <li>8-bit Serial-parallel/<br/>Parallel-serial Con-<br/>version</li> <li>Maximum Operating<br/>Frequency: 9 MHz</li> </ul>                                                                                                                                                                                                            | +5.0          | 250<br>(MAX)                  | 24 Pin DIP                | смоѕ    |                                                                                             |  |

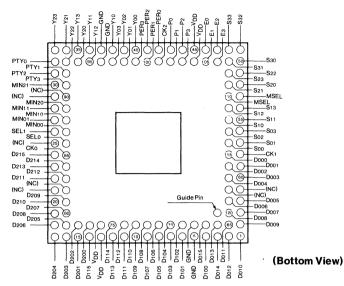

| MSM6914            | Highway Switch<br>Matrix                                   | • Matrix Size: 16-bit x<br>4-bit x 3-layers<br>• Maximum Operating<br>Frequency: 9 MHz                                                                                                                                                                                                                                                     | +5.0          | 650<br>(MAX)                  | 120 Pin Cera-<br>mic PGA  | смоз    |                                                                                             |  |

| MSM77C-<br>20      | Digital Signal<br>Processor                                | <ul> <li>Instruction Cycle:<br/>250 ns</li> <li>Instruction ROM:<br/>512 x 23-bit</li> <li>Data ROM: 512 x<br/>13-bit</li> <li>Data RAM: 128 x<br/>16-bit</li> <li>Multiplexer: 16 x 16 =<br/>31 bits</li> </ul>                                                                                                                           | +5.0          | 120                           | 28 Pin DIP<br>44 Pin PLCC | смоѕ    | <ul> <li>Modem</li> <li>Voice synthe-<br/>sizer</li> <li>Voice recogni-<br/>tion</li> </ul> |  |

| MSM6992            | High Speed Float-<br>ing Point Digital<br>Signal Processor | <ul> <li>Data Form: Floating<br/>Point<br/>16E6x16E6→16E6</li> <li>Fixed Point<br/>16 x 16 → 31</li> <li>Instruction Cycle:<br/>100 ns/125 ns</li> <li>ROM: Internal<br/>1k x 32-bit<br/>External<br/>64k x 32-bit x2<br/>External<br/>64k x 22-bit x2</li> <li>External<br/>64k x 22-bit</li> <li>Data Word Length:<br/>22 bit</li> </ul> | +5.0          | 400                           | 132 Pin PGA               | CMOS    | <ul> <li>Modem</li> <li>Voice Recognition</li> <li>Echo canceller</li> <li>ADPCM</li> </ul> |  |

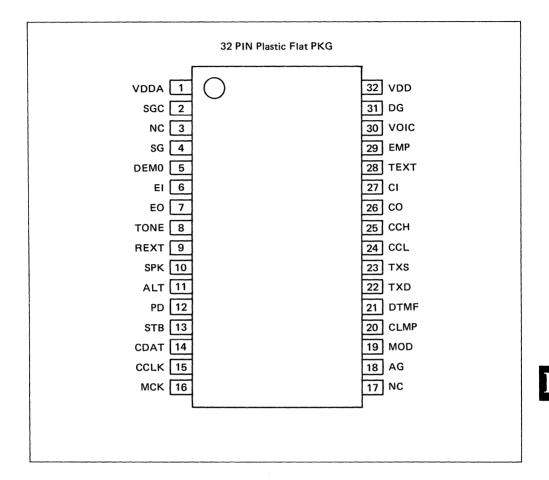

| MSM6807<br>MSM6817 | Baseband Filter<br>for Cellular<br>Mobile Phone            | Voice BPF, Pre-<br>emphasis, De-emphasis<br>and Smoothing Filter                                                                                                                                                                                                                                                                           | +5.0          | 30                            | 32 Pin FLAT               | CMOS    | <ul> <li>Wireless Com-<br/>munication</li> <li>Cellular phone</li> </ul>                    |  |

|                    |                                                            | <sup>-</sup> MSM6807 : AMPS<br>MSM6817 : TACS                                                                                                                                                                                                                                                                                              |               |                               |                           |         |                                                                                             |  |

| MSM6808            | Split Filter for<br>Cellular Mobile<br>Phone               | • 10k bps/8k bps SPL<br>Modem Timing<br>Extractor                                                                                                                                                                                                                                                                                          | +5.0          | 40                            | 44 Pin FLAT               | смоз    |                                                                                             |  |

| MSM6818            |                                                            | <ul> <li>Filters for SAT and<br/>SPL modem</li> <li>DTMF Tone Generator<br/>MSM6808 : AMPS<br/>MSM6818 : TACS</li> </ul>                                                                                                                                                                                                                   |               | -                             |                           |         |                                                                                             |  |

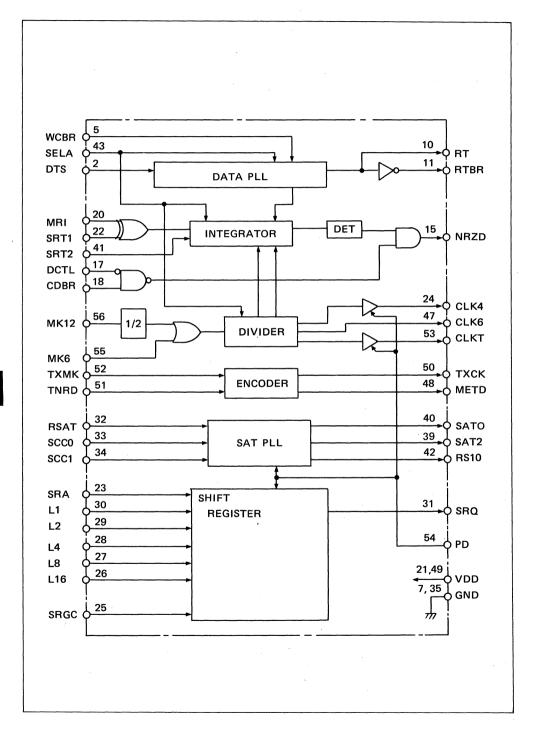

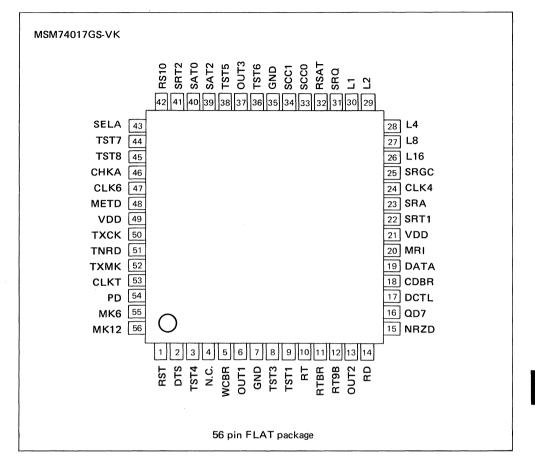

| MSM74017           | Modem for<br>Cellular Mobile<br>Phone                      | · SPL Modem     · Built in Data PLL     · Built in SAT PLL                                                                                                                                                                                                                                                                                 | +5.0          | 20                            | 56 Pin FLAT               | смоз    |                                                                                             |  |

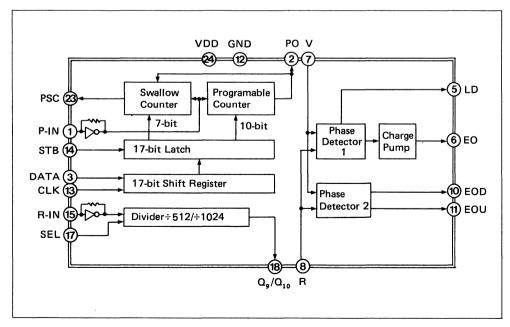

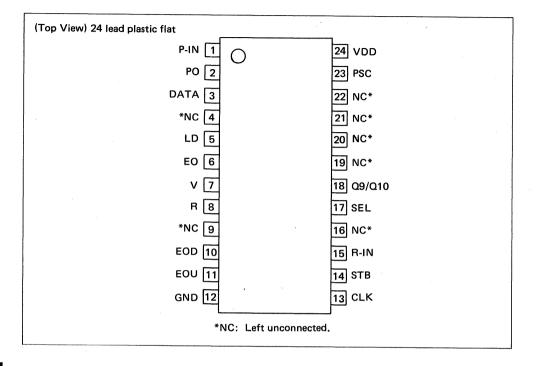

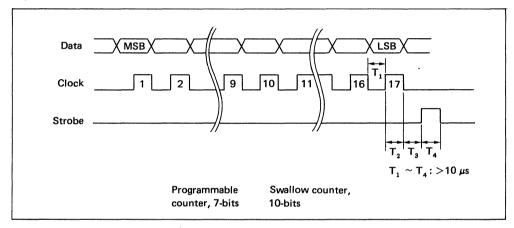

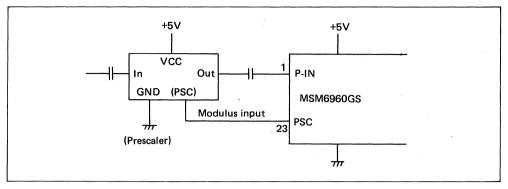

| MSM6960            | P <sub>LL</sub> Frequency<br>Synthesizer                   | <ul> <li>10 bits Programmable<br/>and 7 bits Swallow<br/>Counter</li> <li>Selectable Reference<br/>Divider: 2<sup>9</sup> or 2<sup>10</sup></li> </ul>                                                                                                                                                                                     | +5.0          | 20                            | 24 Pin FLAT               | смоѕ    | • Wireless Com-<br>munication                                                               |  |

#### + PRODUCT LINE-UP +

|          |                                                     |                                                                                                                                                     | Power          |                               |            |                                                                    |                                                                                                                               |  |

|----------|-----------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|----------------|-------------------------------|------------|--------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|--|

| Туре No. | Function                                            | Features                                                                                                                                            | Supply<br>(V)  | Con-<br>sump-<br>tion<br>(mW) | Package    | Process                                                            | Applications                                                                                                                  |  |

| MSM6252  | FIFO Memory                                         | ory -64 Words x 4-bit<br>First-in First-out<br>Memory +5.0 80<br>-F3341 (Fairchild)<br>Compatible                                                   |                | 16 Pin DIP                    | смоѕ       | <ul> <li>Digital trans-<br/>mission system</li> <li>LAN</li> </ul> |                                                                                                                               |  |

| MSM6920  | Single Chip DTMF<br>Decoder for<br>PAB <sub>X</sub> | <ul> <li>Receive Signal Level:<br/>-5~-32 dBm</li> <li>Voice Hit Protection<br/>Filter</li> </ul>                                                   | +5.0,<br>+12.0 | 80                            | 28 Pin DIP | смоз                                                               | <ul> <li>PAB<sub>x</sub></li> <li>Key system</li> <li>Dial-in equip-<br/>ment</li> </ul>                                      |  |

| MSM6945  | Single Chip DTMF<br>Decoder for<br>Terminal         | <ul> <li>Receive Signal Level:<br/>-5~-48 dBm</li> <li>Echo Control Circuit:</li> </ul>                                                             | +5.0,<br>+12.0 | 80                            | 28 Pin DIP | смоѕ                                                               | <ul> <li>Security system</li> <li>Answering<br/>machine</li> <li>Telecontrol<br/>system</li> <li>Dial-in equipment</li> </ul> |  |

| MSM6980  | 32k-bit/sec<br>ADPCM CODEC                          | OKI's Original 24k bps<br>and 32k bps ADPCM<br>Algorithm<br>9600 bps Data Trans-<br>mission Capability<br>Selectable Coder and<br>Decoder Functions | +5.0           | 70                            | 42 Pin DIP | смоѕ                                                               | • Digital trans-<br>mission system                                                                                            |  |

• .

#### PACKAGING

|            |            | PACKAGE        |                |                                                                                                                 |                 |                                                               |               |                             |  |  |  |  |

|------------|------------|----------------|----------------|-----------------------------------------------------------------------------------------------------------------|-----------------|---------------------------------------------------------------|---------------|-----------------------------|--|--|--|--|

| Product    | No.        | RS AS AS       |                |                                                                                                                 | GS              | SS                                                            |               |                             |  |  |  |  |

| Name       | of<br>Pins | PLASTIC<br>DIP | CERAMIC<br>DIP | PGA                                                                                                             | PLASTIC<br>FLAT | PLASTIC<br>LCC                                                | CERAMIC<br>CC | MINI-SIZE<br>PLASTIC<br>DIP |  |  |  |  |

| MSM6926    | 28         | 0              |                |                                                                                                                 |                 |                                                               |               |                             |  |  |  |  |

|            | 44         |                |                |                                                                                                                 | 0               |                                                               |               |                             |  |  |  |  |

| MSM6946    | 28<br>44   | 0              | · ·            |                                                                                                                 | 0               |                                                               |               |                             |  |  |  |  |

|            | 28         | 0              |                |                                                                                                                 |                 |                                                               |               |                             |  |  |  |  |

| MSM6927    | 44         |                |                |                                                                                                                 | 0               |                                                               |               |                             |  |  |  |  |

|            | 28         | 0              | 1              |                                                                                                                 |                 |                                                               |               |                             |  |  |  |  |

| MSM6947    | 44         |                |                |                                                                                                                 | 0               |                                                               |               |                             |  |  |  |  |

|            | 18         | 0              |                |                                                                                                                 |                 |                                                               |               |                             |  |  |  |  |

| MSM6948    | 24         |                |                |                                                                                                                 | 0               |                                                               |               |                             |  |  |  |  |

|            | 42         | 0              |                |                                                                                                                 |                 | ·····                                                         |               |                             |  |  |  |  |

| MSM6928-06 | 60         |                |                |                                                                                                                 | 0               |                                                               |               |                             |  |  |  |  |

|            | 40         | 0              |                |                                                                                                                 | -               |                                                               |               |                             |  |  |  |  |

| MSM61057   | 60         |                |                |                                                                                                                 | 0               |                                                               | []            |                             |  |  |  |  |

|            | 42         | 0              |                |                                                                                                                 |                 |                                                               |               |                             |  |  |  |  |

| MSM6928-07 | 60         |                |                |                                                                                                                 | 0               |                                                               |               |                             |  |  |  |  |

| MSM61077   | 60         |                |                |                                                                                                                 | 0               |                                                               |               |                             |  |  |  |  |

| <b></b>    | 42         | 0              |                |                                                                                                                 |                 |                                                               |               |                             |  |  |  |  |

| MSM6950    | 56         |                |                |                                                                                                                 | 0               |                                                               |               |                             |  |  |  |  |

| MSM6949    | 64         |                |                |                                                                                                                 |                 |                                                               |               | 0                           |  |  |  |  |

|            | 28         | 0              |                |                                                                                                                 |                 |                                                               |               |                             |  |  |  |  |

| MSM6052    | 40         | 0              |                |                                                                                                                 |                 |                                                               |               |                             |  |  |  |  |

|            | 44         |                |                |                                                                                                                 | 0               |                                                               |               |                             |  |  |  |  |

| MSM6052-01 | 28         | 0              |                |                                                                                                                 |                 | ar an russialaidh ann a' <sub>bhail</sub> na an an an Arbaran |               |                             |  |  |  |  |

| MSM6052-05 | 44         | T              |                |                                                                                                                 | 0               |                                                               |               |                             |  |  |  |  |

| MSM6052-10 | 40         | 0              |                |                                                                                                                 |                 |                                                               |               |                             |  |  |  |  |

| MSM6052-11 | 28         | 0              |                |                                                                                                                 |                 |                                                               |               |                             |  |  |  |  |

| MSM6052-20 | 28         | 0              |                | and and the second of the second s |                 |                                                               |               |                             |  |  |  |  |

| MSM6052-25 | 28         | 0              |                |                                                                                                                 |                 |                                                               |               |                             |  |  |  |  |

| MSM5070    | 18         | 0              |                |                                                                                                                 |                 |                                                               |               |                             |  |  |  |  |

| MSM5071    | 18         | 0              |                |                                                                                                                 |                 |                                                               |               |                             |  |  |  |  |

| MSM6224    | 16         | 0              |                |                                                                                                                 |                 |                                                               |               |                             |  |  |  |  |

| MSM6234    | 16         | 0              |                |                                                                                                                 |                 |                                                               |               | ······                      |  |  |  |  |

| MSM6932    | 16         | 0              | 0              |                                                                                                                 |                 |                                                               |               |                             |  |  |  |  |

| MSM6933    | 16         | 0              | 0              |                                                                                                                 |                 |                                                               |               |                             |  |  |  |  |

| MSM6962    | 16         | 0              | 0              |                                                                                                                 |                 |                                                               |               |                             |  |  |  |  |

| MSM6963    | 16         | 0              | 0              |                                                                                                                 |                 |                                                               |               |                             |  |  |  |  |

| MSM6982    | 28         |                |                | an - C. C. Salara an an Anna Anna Anna                                                                          |                 | 0                                                             | 0             |                             |  |  |  |  |

| MSM6983    | 28         |                |                |                                                                                                                 |                 | 0                                                             | 0             |                             |  |  |  |  |

| MSM6996H   | 16         | 0              | 0              | · · · · · · · · · · · · · · · · · · ·                                                                           |                 |                                                               |               |                             |  |  |  |  |

| MSM6997H   | 16         | 0              | 0              |                                                                                                                 |                 |                                                               |               |                             |  |  |  |  |

| MSM6996V   | 16         | 0              | 0              |                                                                                                                 |                 |                                                               |               |                             |  |  |  |  |

| MSM6997V   | 16         | 0              | 0              |                                                                                                                 |                 |                                                               |               |                             |  |  |  |  |

| MSM6998    | 16         | 0              | 0              |                                                                                                                 |                 |                                                               |               |                             |  |  |  |  |

| MSM6999    | 16         | 0              | 0.             |                                                                                                                 |                 |                                                               |               |                             |  |  |  |  |

#### PACKAGING

|              |            | PACKAGE        |                |     |                 |                |               |                             |  |  |  |

|--------------|------------|----------------|----------------|-----|-----------------|----------------|---------------|-----------------------------|--|--|--|

| Product      | No.        | RS             | AS             | AS  | GS              | JS             | ES            | SS                          |  |  |  |

| Name         | of<br>Pins | PLASTIC<br>DIP | CERAMIC<br>DIP | PGA | PLASTIC<br>FLAT | PLASTIC<br>LCC | CERAMIC<br>CC | MINI-SIZE<br>PLASTIC<br>DIP |  |  |  |

| MSM6814      | 22         | 0              | 0              |     |                 |                |               |                             |  |  |  |

| 10131010814  | 28         |                |                |     |                 | 0              |               |                             |  |  |  |

| MSM6815      | 22         | 0              | 0              |     |                 |                |               |                             |  |  |  |

| 101010010    | 28         |                |                |     |                 | 0              |               |                             |  |  |  |

| MSA4710      | 28         | 0              |                |     |                 |                |               |                             |  |  |  |

| MSA4722-1    | 22         | 0              |                |     |                 |                |               |                             |  |  |  |

| MSM6912      | 16         |                | 0              |     |                 |                |               | -                           |  |  |  |

| MSM6913      | 24         | 0              |                |     |                 |                |               |                             |  |  |  |

| MSM6914      | 120        |                |                | 0   |                 |                |               |                             |  |  |  |

| MSM77C20     | 28         | 0              | 0              |     |                 |                |               |                             |  |  |  |

| 101310177620 | 44         |                |                |     |                 | 0              |               |                             |  |  |  |

| MSM6992      | 132        |                |                | 0   |                 |                |               |                             |  |  |  |

| MSM6807      | 32         |                |                |     | 0               |                |               |                             |  |  |  |

| MSM6817      | 32         |                |                |     | 0               |                |               |                             |  |  |  |

| MSM6808      | 44         |                |                |     | 0               |                |               |                             |  |  |  |

| MSM6818      | 44         |                |                |     | 0               |                |               |                             |  |  |  |

| MSM74017     | 56         |                |                |     | 0               |                |               |                             |  |  |  |

| MSM6960      | 24         |                |                |     | 0               |                |               |                             |  |  |  |

| MSM6252      | 16         | 0              |                |     |                 |                |               |                             |  |  |  |

| MSM6920      | 28         | 0              |                |     |                 |                |               |                             |  |  |  |

| MSM6945      | 28         | 0              |                |     |                 |                |               |                             |  |  |  |

| MSM6980-03   | 42         | 0              |                |     |                 |                |               |                             |  |  |  |

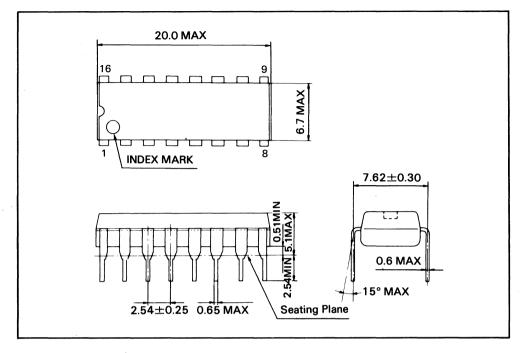

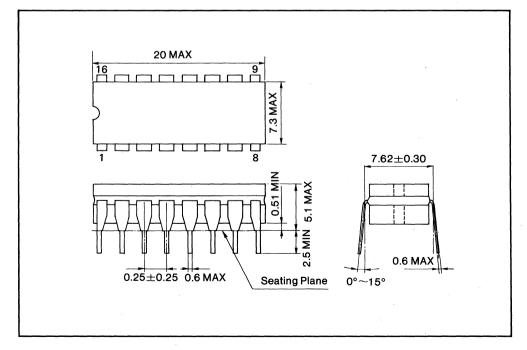

#### • 16 PIN PLASTIC DIP

#### • 18 PIN PLASTIC DIP

#### PACKAGING +-

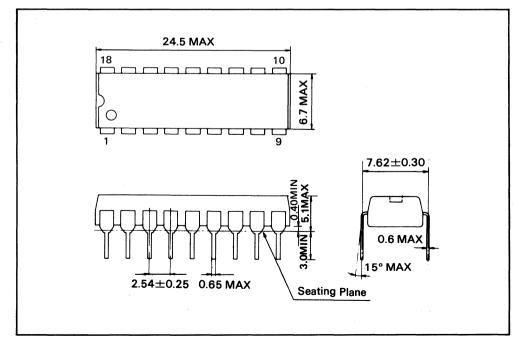

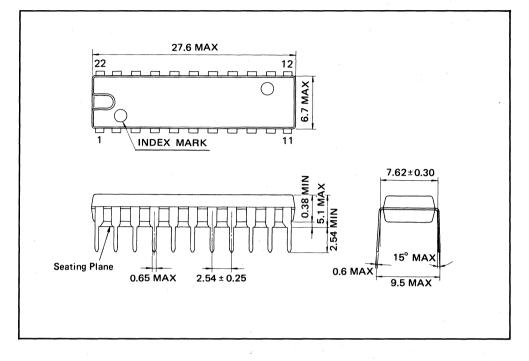

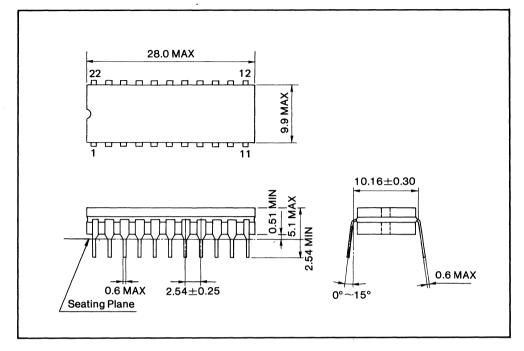

#### • 22 PIN PLASTIC

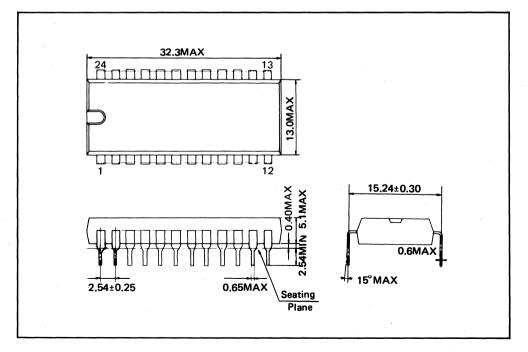

#### • 24 PIN PLASTIC DIP

II-6

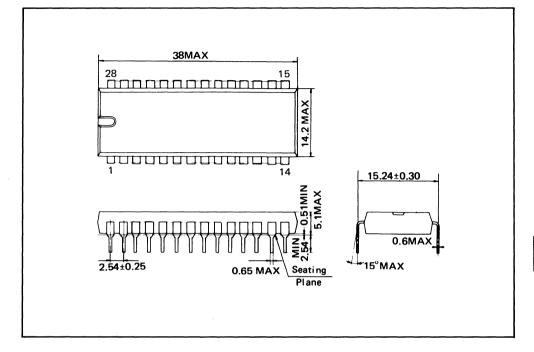

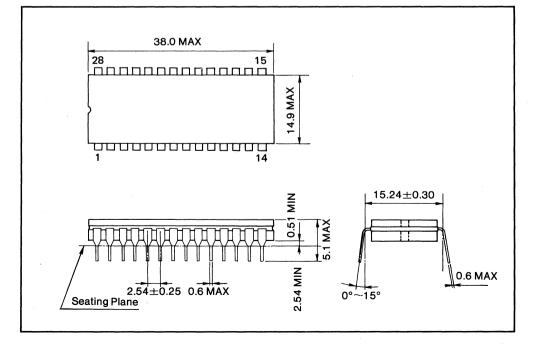

#### • 28 PIN PLASTIC DIP

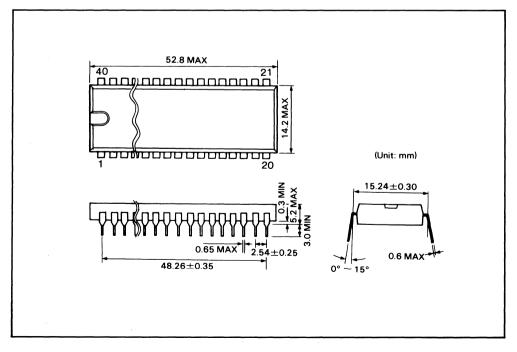

#### • 40 PIN PLASTIC DIP

II-7

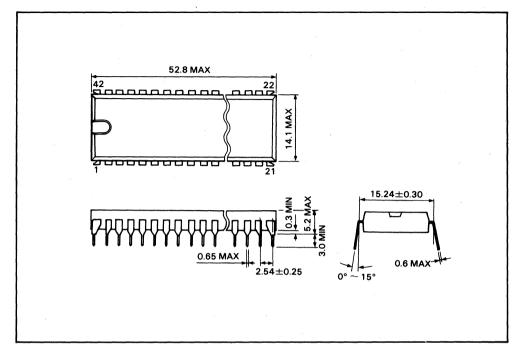

♦ PACKAGING ♦-

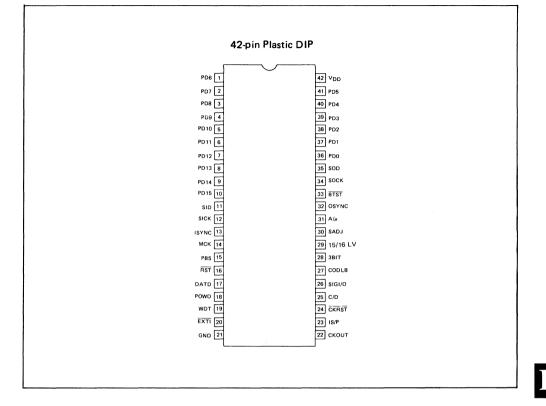

#### • 42 PIN PLASTIC DIP

#### • 16 PIN CERAMIC DIP (CERDIP)

I**I-8**

#### • 22 PIN CERAMIC DIP (CERDIP)

#### • 28 PIN CERAMIC DIP (CERDIP)

II-9

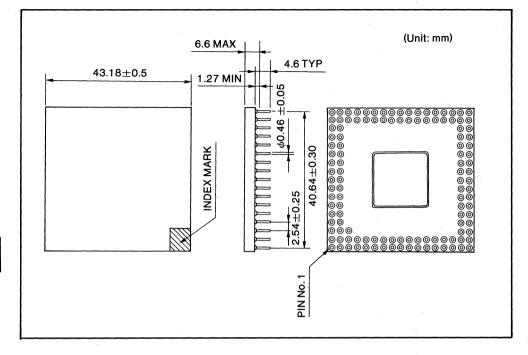

#### ♦ PACKAGING ♦

#### 120 PIN CERAMIC PGA

#### 132 PIN CERAMIC PGA

II-10

Ι

#### • 24 PIN PLASTIC FLAT

#### • 32 PIN PLASTIC FLAT

#### PACKAGING +--

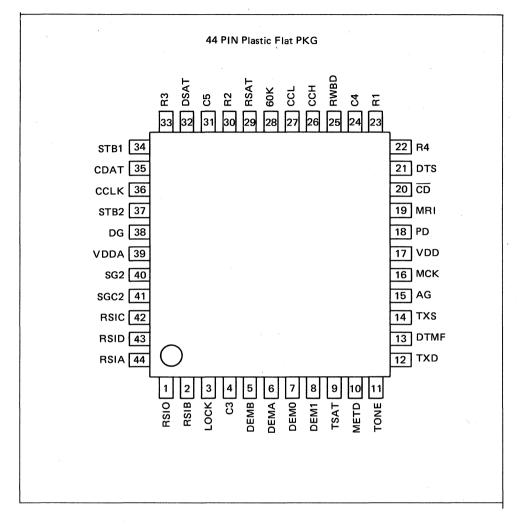

#### • 44 PIN PLASTIC FLAT

#### • 56 PIN PLASTIC FLAT (L)

II-12

#### • 60 PIN PLASTIC FLAT

#### • 28 PIN PLCC

#### **+ PACKAGING +**-

#### • 44 PIN PLCC

#### • 28 PIN CERAMIC CC

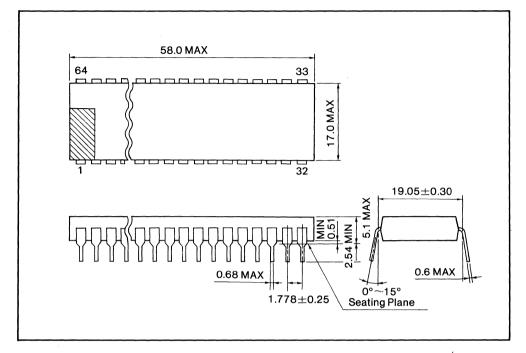

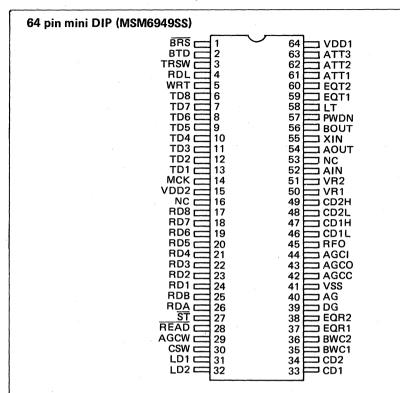

#### • 64 PIN MINI SIZE PLASTIC DIP

## III I DATA SHEE1

## A. MODEM

#### **OKI** semiconductor MSM6926 CCITT V.21/ MSM6946 BEL 103

300 BPS SINGLE CHIP MODEM

#### **GENERAL DESCRIPTION**

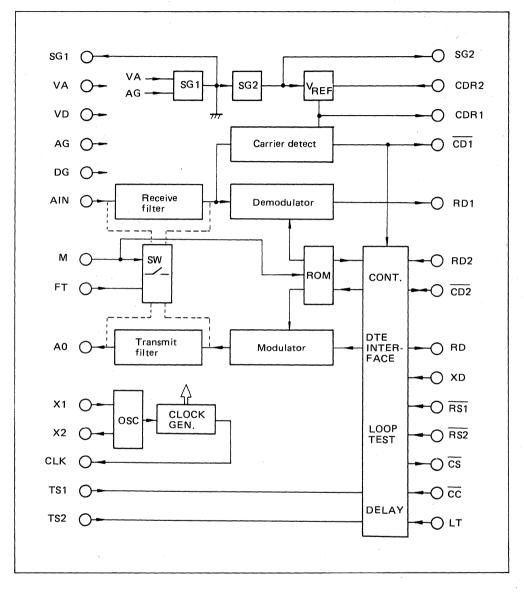

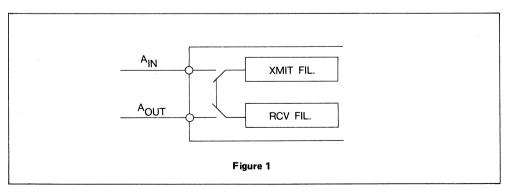

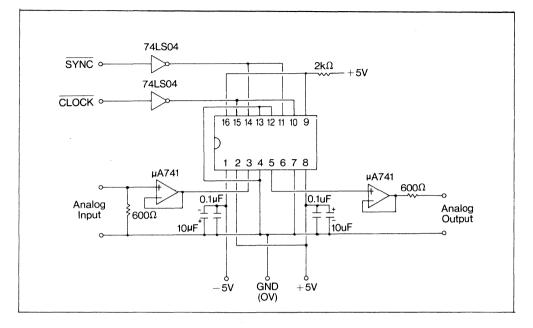

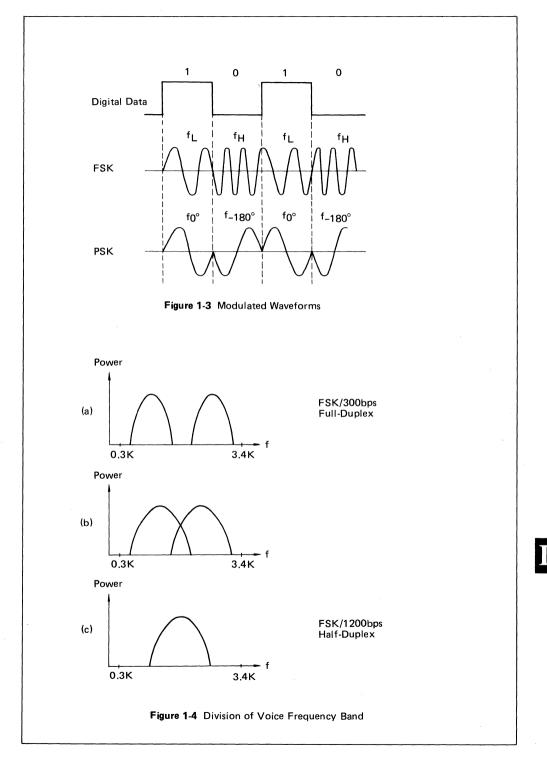

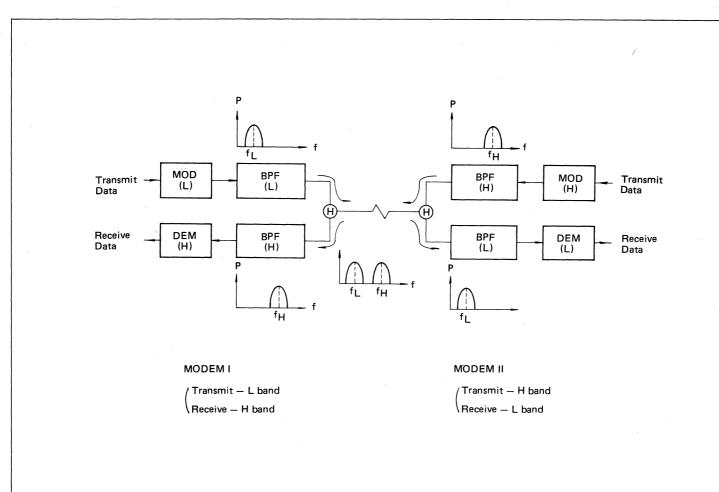

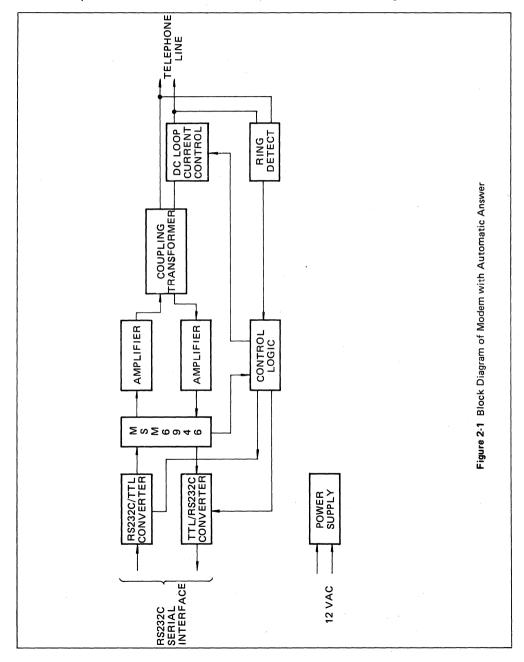

The MSM6926 and the MSM6946 are OKI's 300 bps single chip modem series that transmit and receive serial, binary data over a switched telephone network using frequency shift keyed (FSK) modulation.

The MSM6926 is compatible with CCITT V.21 series data sets, while the MSM6946 is compatible with Bell 103 series data sets.

These devices provide all the necessary modulation, demodulation, and filtering required to implement a serial, asynchronous communication link.

OKI's single chip modem series are designed for users who are not telecommunication experts and are easy to use cost effective alternative to standard discrete modem design.

CMOS LSI technology provides the advantages of small size, low power, and increased reliability.

The design of the integrated circuit assures compatibility with a broad base of installed low speed modems and acoustic couplers. Applications include interactive terminals, desk top computers, point of sale equipment, and credit verification systems.

#### **FEATURES**

- Compatible with CCITT V.21 (MSM-6926)

- Compatible with BELL 103 (MSM6946)

- CMOS silicon gate process

- Switched capacitor and advanced CMOS analog technology

- Data rate from zero to 300 bps

- Full duplex (2-wire)

- Originate and Answer modes

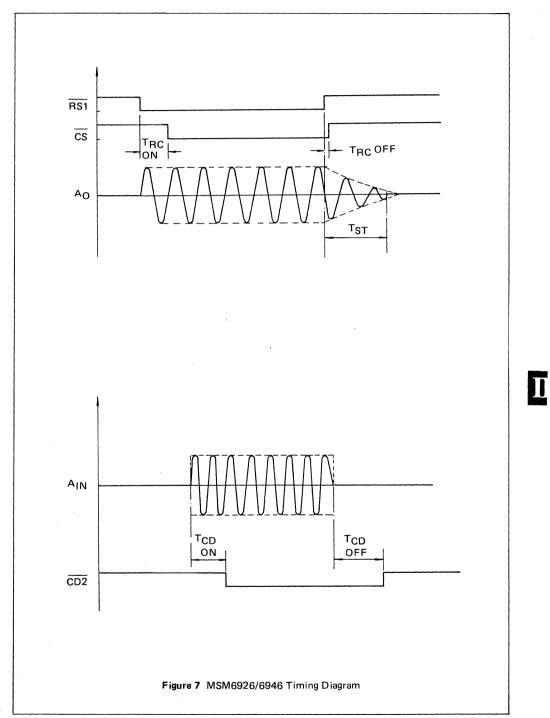

- Selectable built-in timers and external delay timers possible

- All filtering, modulation, demodulation, and DTE interface on chip

- TTL compatible digital interface

- Low power dissipation 90 mW

- 28 pin plastic DIP package

- 44 pin plastic FLAT package

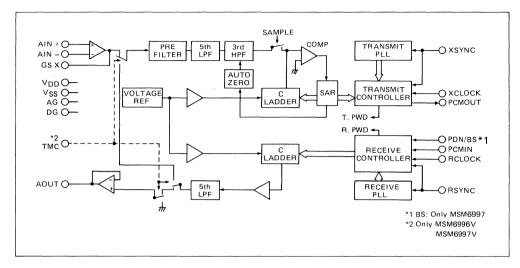

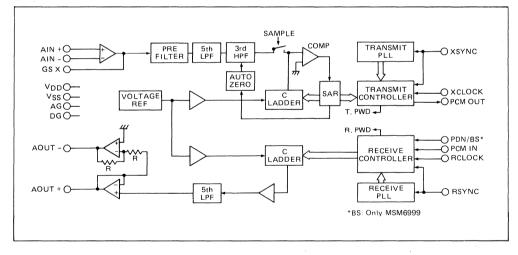

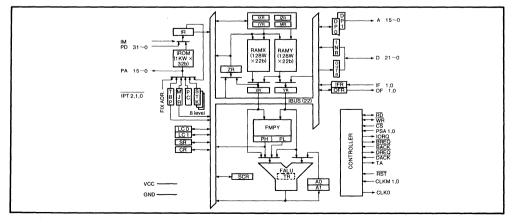

#### **BLOCK DIAGRAM**

**Ⅲ-**A-6

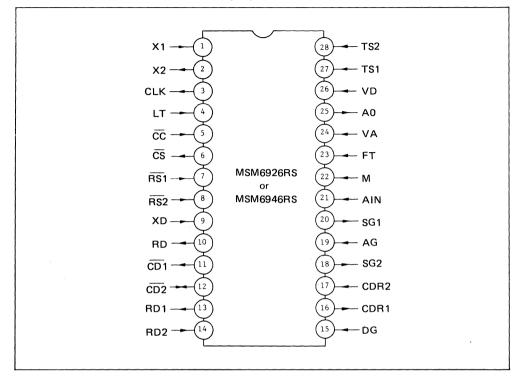

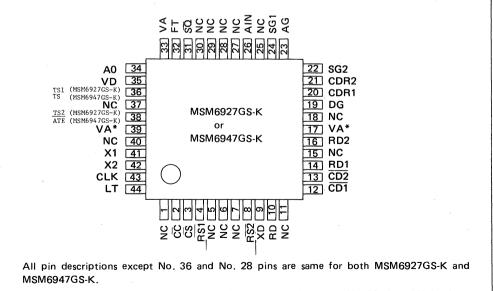

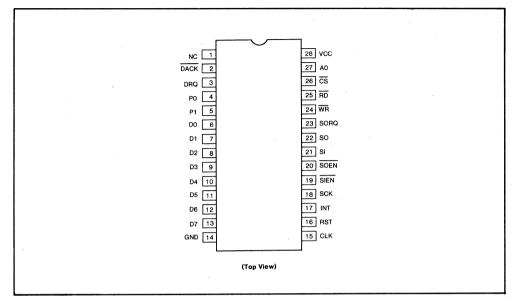

#### PIN CONFIGURATION (TOP VIEW) 28 LEAD PLASTIC DIP PACKAGE (RS)

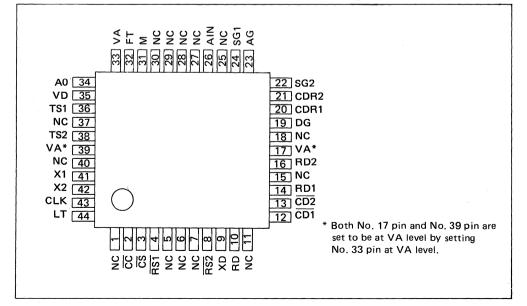

44 LEAD PLASTIC FLAT PACKAGE (GS-K)

# ABSOLUTE MAXIMUM RATINGS

| Parameter                              | Symbol | Condition                                            | Ratings         | Unit |  |

|----------------------------------------|--------|------------------------------------------------------|-----------------|------|--|

| Power supply                           | VA     |                                                      | -0.3 ~ 15       |      |  |

| voltage                                | VD     | 1                                                    | -0.3 ~ 7        |      |  |

| Analog * <sub>1</sub><br>input voltage | VIA    | T <sub>a</sub> = 25°C<br>With respect<br>to AG or DG | -0.3 ~ VA + 0.3 | v    |  |

| Digital *2<br>input voltage            | VID    |                                                      | -0.3 ~ VD + 0.3 | -    |  |

| Operating<br>temperature               | Тор    | _                                                    | 0~ 70           | °C   |  |

| Storage<br>temperature                 | TSTG   | _                                                    | -55 ~ 150       | C    |  |

\*1 CDR2, AIN

\*2 X1, LT, CC, RS1, RS2, XD, CD2, RD2, M, FT, TS1, TS2

\*3: CD2 is I/O terminal.

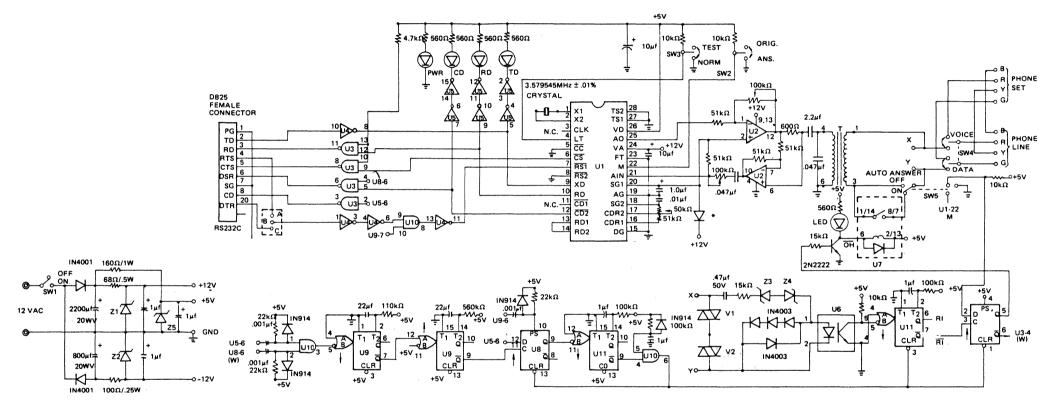

# **RECOMMENDED OPERATING CONDITIONS**

| Parameter                       | Symbol          | Condition                           | Min  | Тур      | Max  | Unit |

|---------------------------------|-----------------|-------------------------------------|------|----------|------|------|

|                                 | VA              | With respect to AG                  | 10.8 | 12.0     | 13.2 |      |

| Power supply voltage            | VD              | With respect to DG                  | 4.75 | 5.00     | 5.25 | v    |

|                                 | AG, DG          |                                     |      | 0        |      |      |

| Operating<br>temperature        | Т <sub>ОР</sub> |                                     | 0    |          | 70   | °C   |

| CRYSTAL                         |                 |                                     |      | 3.579545 |      | MHz  |

| R <sub>1</sub>                  |                 | Transformer impedance = $600\Omega$ |      | 600      |      | Ω    |

| R <sub>2</sub>                  |                 |                                     |      | 51       |      |      |

| R <sub>3</sub>                  |                 |                                     |      | 51       |      |      |

| R <sub>4</sub>                  |                 |                                     |      | 51       |      |      |

| R <sub>s</sub>                  |                 |                                     |      | 51       |      | kΩ   |

| R <sub>6</sub>                  |                 |                                     |      | 51       |      | K32  |

| R <sub>7</sub>                  |                 |                                     |      | 51       |      |      |

| R <sub>8</sub>                  |                 |                                     |      | 33       |      |      |

| R,                              |                 |                                     |      | 51       |      |      |

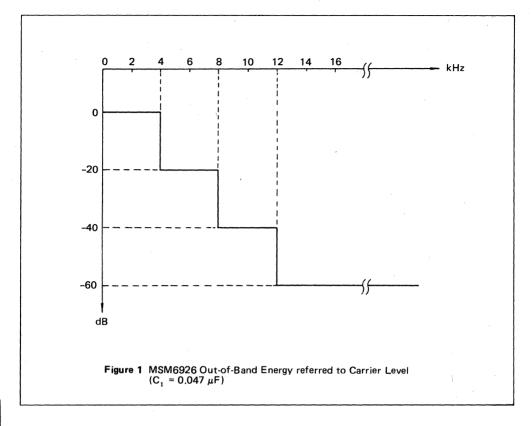

| C <sub>0</sub> , C <sub>1</sub> |                 |                                     |      | 0.047    |      |      |

| C <sub>2</sub>                  |                 | 1                                   |      | 2.2      |      |      |

| C <sub>3</sub>                  |                 |                                     | 1.0  |          |      |      |

| C <sub>4</sub>                  |                 |                                     | 0.01 |          |      | μF   |

| C <sub>5</sub>                  |                 | 1                                   |      | 10       |      |      |

| C <sub>6</sub>                  |                 | ]                                   |      | 10       |      |      |

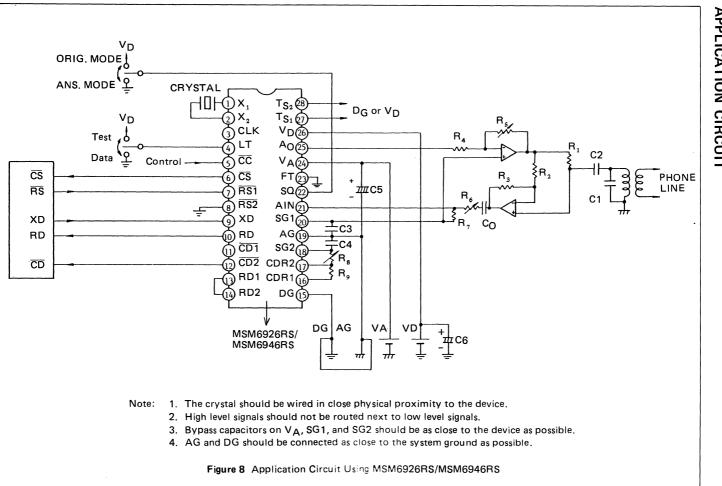

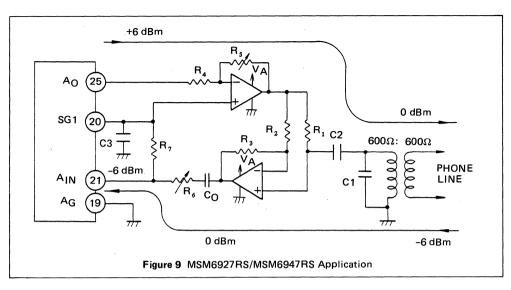

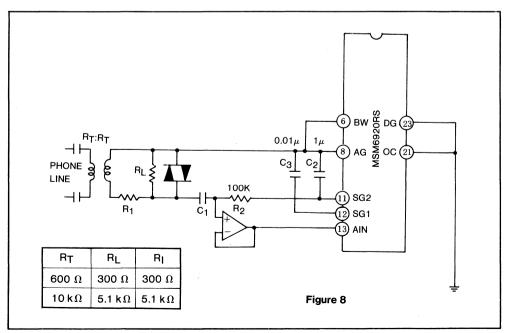

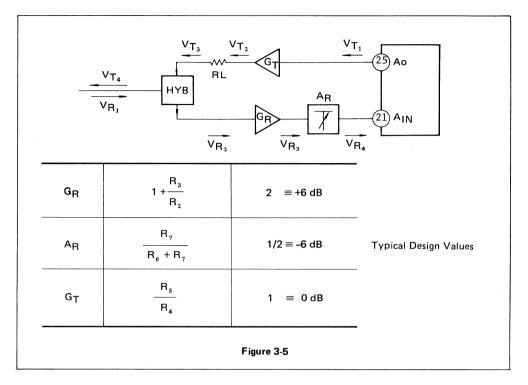

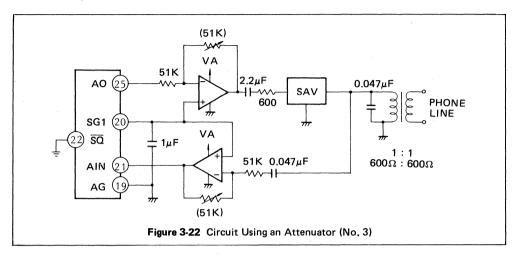

Application circuits using above conditions are proviced in Figure 8.

# DC AND DIGITAL INTERFACE CHARACTERISTICS

$(VA = 12 V \pm 10\%, VD = 5 V \pm 5\%, T_a = 0 \sim 70^{\circ}C)$

| Parameter                   | Symbol          | Condition                       | Min      | Тур | Max  | Unit       |

|-----------------------------|-----------------|---------------------------------|----------|-----|------|------------|

| Power supply                | IA              | Ordinary                        |          | 7.5 | 15.0 |            |

| current                     | ID              | operation                       |          | 1.0 | 2.0  | - mA       |

| Input<br>leakage current *1 | Ι <sub>ΙL</sub> | VI = OV                         | -10      |     | 10   |            |

|                             | Чн              | V <sub>I</sub> = V <sub>D</sub> | -10      |     | 10   | μΑ         |

| Inmutuelteen *1             | VIL.            |                                 | 0        |     | 0.8  |            |

| Input voltage *1            | VIH             |                                 | 2.2      |     | VD   |            |

| Output voltage *2           | VOL             | I <sub>OL</sub> = 1.6 mA        | 0        |     | 0.4  | ] <b>`</b> |

|                             | Voн             | l <sub>OH</sub> = 400 μA        | 0.8 • VD |     | VD   | 1          |

\*1 LT,  $\overrightarrow{CC}$ ,  $\overrightarrow{RS1}$ ,  $\overrightarrow{RS2}$ , XD,  $\overrightarrow{CD2}$ , RD2, M, FT, T<sub>S1</sub>, T<sub>S2</sub> \*2 CLK,  $\overrightarrow{CS}$ , RD,  $\overrightarrow{CD1}$ ,  $\overrightarrow{CD2}$ , RD1

CD2 is I/O terminal. \*3

# ANALOG INTERFACE CHARACTERISTICS

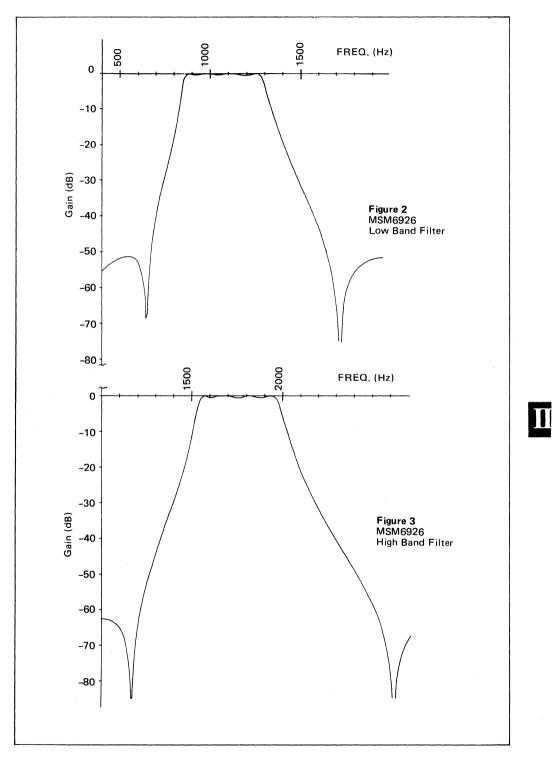

## 1. MSM6926

| Parameter | Symbol | Condition | Min | Тур | Max | Unit |

|-----------|--------|-----------|-----|-----|-----|------|

| C         |        |           |     |     | L   |      |

#### Transmit Carrier Out (A<sub>0</sub>)

| ORIGINATE<br>MODE                                    | Mark<br>1  | <sup>f</sup> ом  |                                     | 974                | 980            | 986                |        |

|------------------------------------------------------|------------|------------------|-------------------------------------|--------------------|----------------|--------------------|--------|

| Carrier<br>frequency 0                               |            | fos              |                                     | 1174               | 1180           | 1186               |        |

| MODE                                                 | Mark<br>1  | <sup>f</sup> AM  | <sup>f</sup> CRYSTAL = 3.579545 MHz | 1644               | 1650           | 1656               | Hz     |

|                                                      | Space<br>O | fAS              |                                     | 1844               | 1850           | 1856               |        |

| Output resistar                                      | nce        | R <sub>OXA</sub> |                                     |                    | 200            |                    | Ω      |

| Load resistance                                      | e          | R <sub>LXA</sub> |                                     | 50                 |                |                    | kΩ     |

| Load capacitar                                       | nce        | C <sub>LXA</sub> |                                     |                    |                | 100                | PF     |

| Transmit level                                       |            | VOXA             |                                     | 4                  | 6              | 8                  | *1 dBm |

| Output offset<br>voltage                             |            | V <sub>OSX</sub> |                                     | $\frac{VA}{2}$ - 1 | <u>VA</u><br>2 | $\frac{VA}{2}$ + 1 | v      |

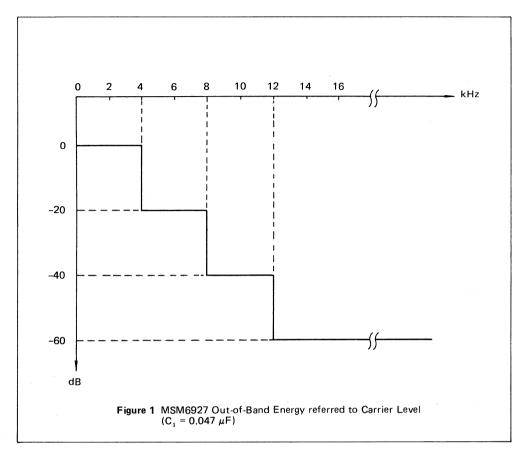

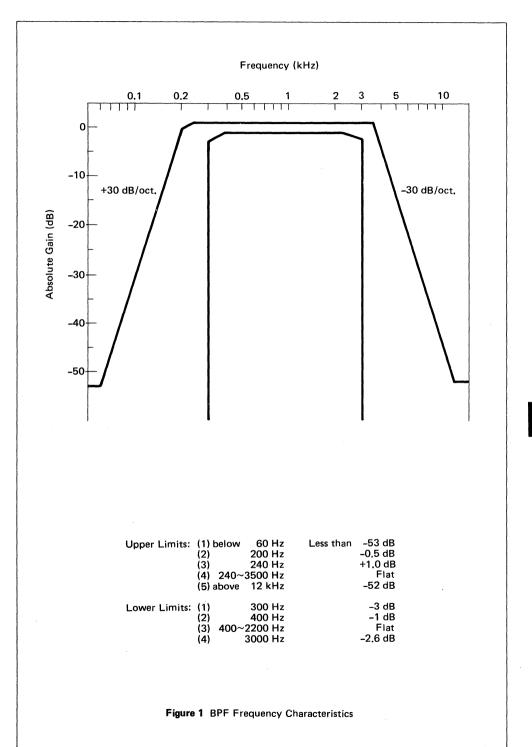

| Out-of-band energy<br>(referred to carrier<br>level) |            | EOX              | C <sub>1</sub> = 0.047 μF           | Refe               | er to Fig      | ure 1              | dB     |

#### Receive Carrier Input (AIN)

| Input resistar                | ice | RIRA                |                                          | 100 |     | kΩ    |

|-------------------------------|-----|---------------------|------------------------------------------|-----|-----|-------|

| Receive signal<br>level range |     | VIRA                |                                          | -48 | -6  |       |

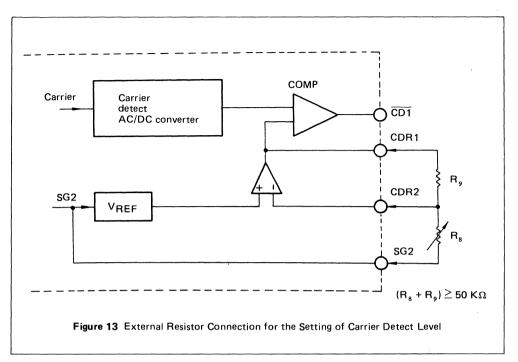

| detect level                  | ON  | V <sub>CD</sub> ON  | $R_8 = 33 k Ω^{*2}$<br>$R_9 = 51 k Ω$    |     | -43 | *1dBm |

|                               | OFF | V <sub>CD</sub> OFF | $R_9 = 51 \text{ k}\Omega$               | -48 |     |       |

| Carrier detect<br>hysteresis  | [   | H <sub>YS</sub>     | V <sub>CD</sub> ON – V <sub>CD</sub> OFF | 2   |     | dB    |

**Receive Filter**

| Group delay<br>distortion  | Det | ORIG.<br>MODE | 1600 ~1900 Hz       |  | 800 | e    |

|----------------------------|-----|---------------|---------------------|--|-----|------|

|                            | DDL | ANS.<br>MODE  | 930 ~ 1230 Hz       |  | 850 | - μS |

| Adjacent channel rejection | LAC | v             | $V_{AIN} = -6  dBm$ |  |     | dB   |

Note: \*1 0 dBm = 0.775 Vrms

\*2 The resistor values are typical.

## ◆ MODEM· MSM6926/46 ◆

## ◆ MODEM· MSM6926/46 ◆-

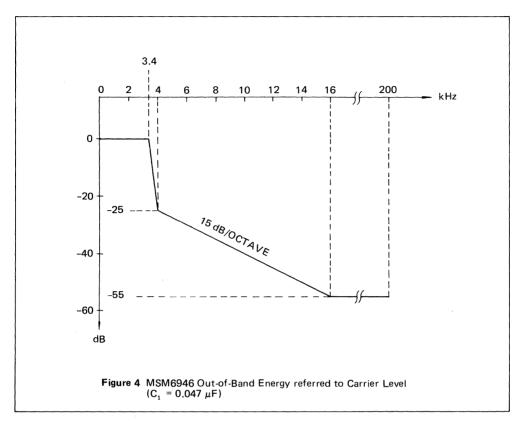

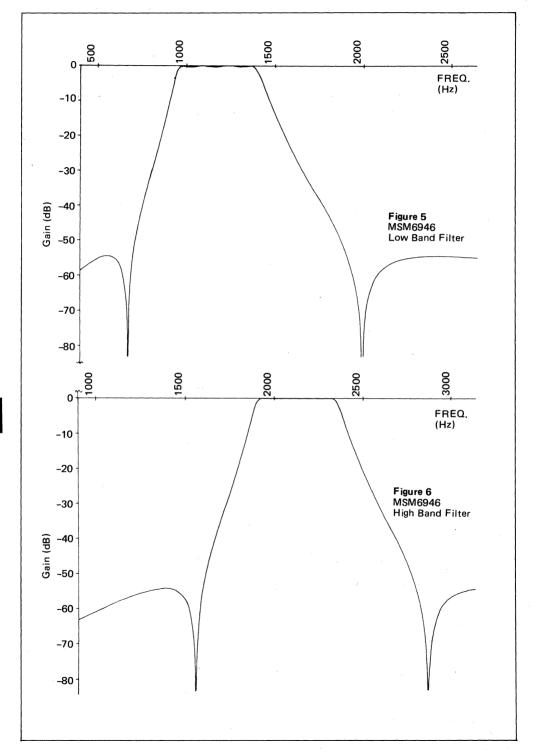

#### 2. MSM6946

| (VA = 12 V ±10%, VD = 5 V ±5%, T <sub>a</sub> = |        |           |     |     |     |      |  |

|-------------------------------------------------|--------|-----------|-----|-----|-----|------|--|

| Parameter                                       | Symbol | Condition | Min | Тур | Max | Unit |  |

#### Transmit Carrier Out (A<sub>0</sub>)

|                                        |                                                          | U.               |                                     |                   |                |                    |        |

|----------------------------------------|----------------------------------------------------------|------------------|-------------------------------------|-------------------|----------------|--------------------|--------|

| ORIGINATE<br>MODE                      | Mark<br>1                                                | fom              |                                     | 1264              | 1270           | 1276               |        |

| Carrier<br>frequency                   | Space<br>0                                               | fos              |                                     | 1064              | 1070           | 1076               |        |

| ANSWER<br>MODE<br>Carrier<br>frequency | Mark<br>1                                                | <sup>f</sup> AM  | <sup>f</sup> CRYSTAL = 3.579545 MHz | 2219              | 2225           | 2231               | Hz     |

|                                        | Space<br>O                                               | fAS              |                                     | 2019              | 2025           | 2031               |        |

| Output resista                         | nce                                                      | R <sub>OXA</sub> |                                     |                   | 200 Ω          |                    | Ω      |

| Load resistanc                         | e                                                        | R <sub>LXA</sub> |                                     | 50                | )              |                    | kΩ     |

| Load capacitar                         | nce                                                      | C <sub>LXA</sub> |                                     |                   |                | 100                | PF     |

| Transmit level                         |                                                          | Voxa             |                                     | 4                 | 6              | 8                  | *1 dBm |

| Output offset<br>voltage               |                                                          | V <sub>OSX</sub> |                                     | $\frac{VA}{2}$ -1 | $\frac{VA}{2}$ | $\frac{VA}{2}$ + 1 | v      |

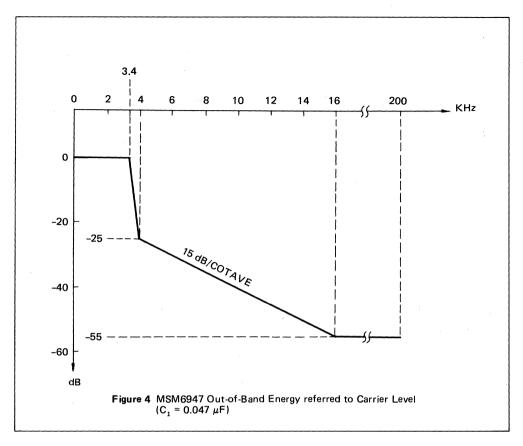

|                                        | Out-of-band energy<br>(referred to carrier EOX<br>level) |                  | $C_1 = 0.047 \ \mu F$               | Refer to Figure 4 |                | dB                 |        |

## Receive Carrier Input (AIN)

| Input resistar                | ice | R <sub>IRA</sub>    | A |                                                       | 100 |     | kΩ     |

|-------------------------------|-----|---------------------|---|-------------------------------------------------------|-----|-----|--------|

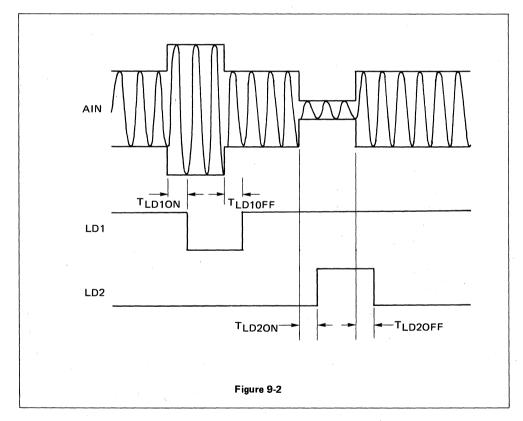

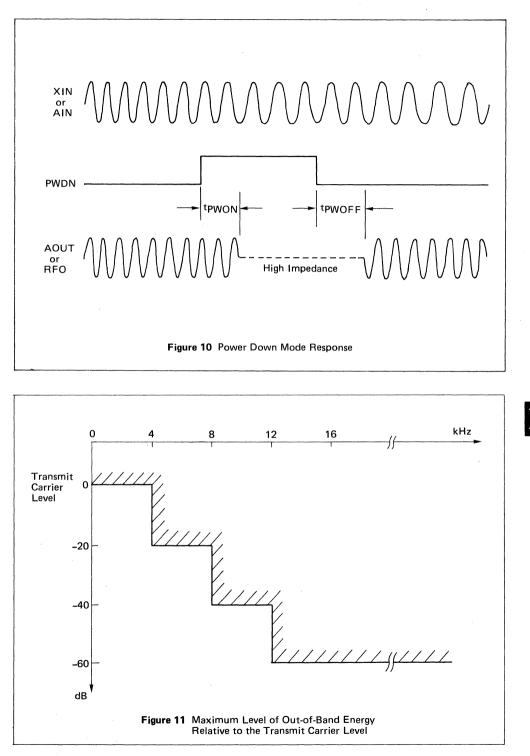

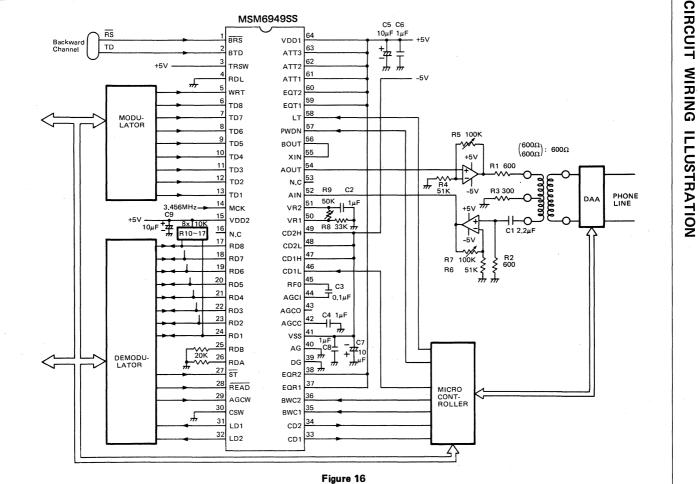

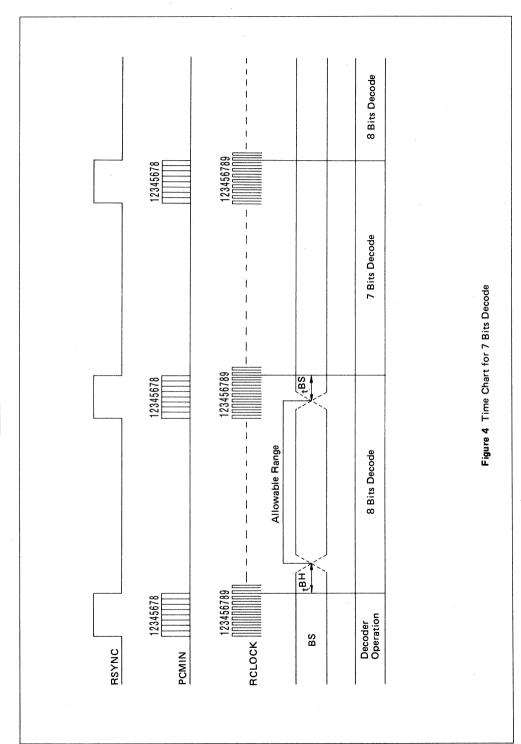

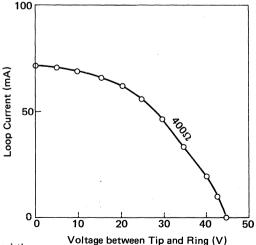

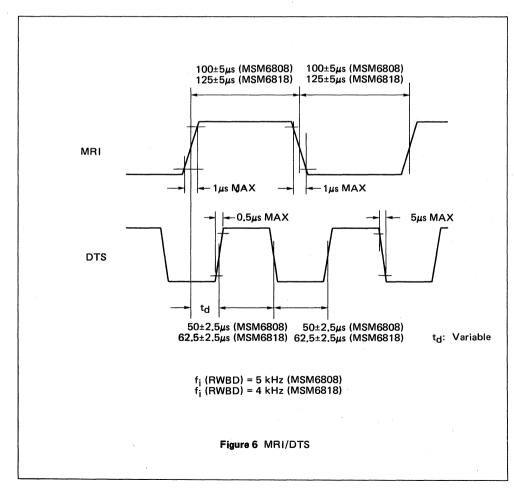

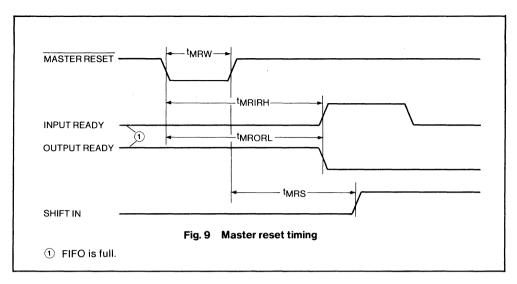

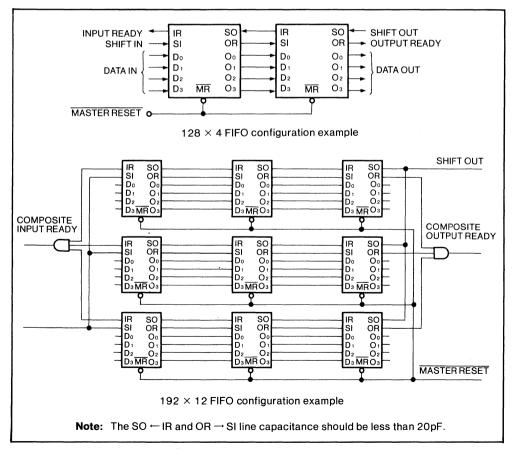

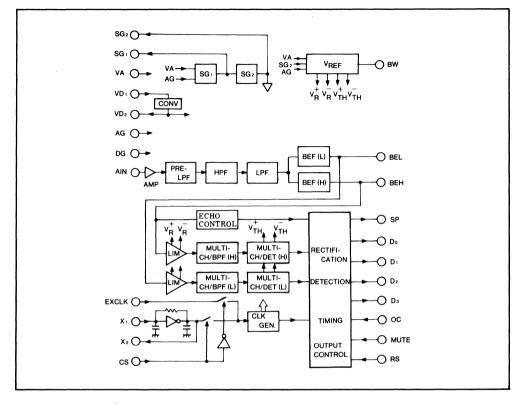

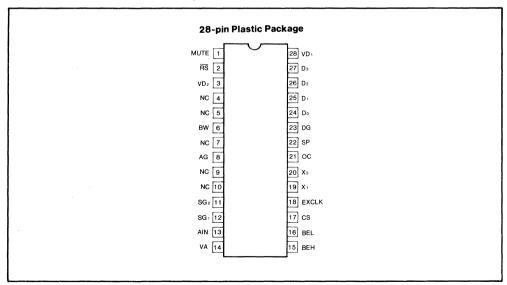

| Receive signal<br>level range |     | VIRA                |   |                                                       | -48 | -6  |        |