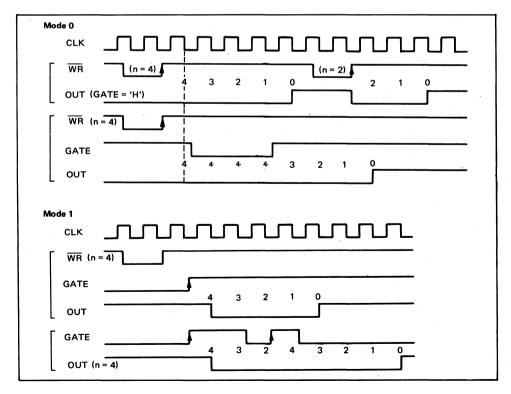

# MICROPROCESSOR DATA BOOK

SECOND EDITION ISSUE DATE : DEC 1986

## **MICROPROCESSOR**<sup>-</sup> DATA BOOK 1987

CMOS MICROPROCESSOR LINE-UP

SYSTEM CONFIGURATION 2

RELIABILITY INFORMATION

DATA SHEETS

#### © Copyright 1986, OKI ELECTRIC INDUSTRY COMPANY, LTD.

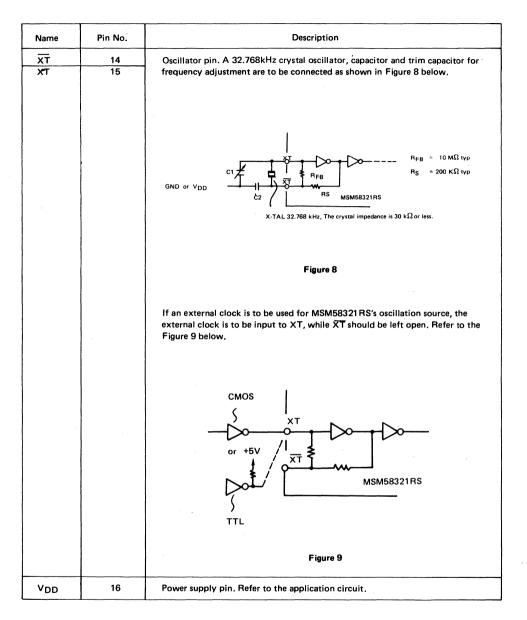

OKI makes no warranty for the use of its products and assumes no responsibility for any errors which may appear in this document nor does it make a commitment to update the information contained herein.

OKI retains the right to make changes to these specifications at any time, without notice.

#### CONTENTS

| 1 | CMOS MICROPROCESSOR LINE-UP 1                             |                            |                      |                                                                        |     |  |  |  |  |

|---|-----------------------------------------------------------|----------------------------|----------------------|------------------------------------------------------------------------|-----|--|--|--|--|

| 2 | 2 SYSTEM CONFIGURATION (PERSONAL COMPUTER/WORD PROCESSOR) |                            |                      |                                                                        |     |  |  |  |  |

| 3 | PACK                                                      | AGING                      |                      |                                                                        | 9   |  |  |  |  |

| 4 | RELIA                                                     | BILITY INFORM              | IATION               |                                                                        | 21  |  |  |  |  |

| 5 | DATA                                                      | SHEETS                     |                      |                                                                        | 31  |  |  |  |  |

|   | •                                                         | CPUs                       |                      |                                                                        | 33  |  |  |  |  |

|   |                                                           | MSM80C85A                  | RS/GS/JS             | 8-BIT MICROPROCESSOR                                                   | 35  |  |  |  |  |

|   |                                                           | MSM80C85A-2                | RS/GS/JS             | 8-BIT MICROPROCESSOR                                                   | 52  |  |  |  |  |

|   |                                                           | MSM80C86<br>MSM80C86-2     | RS/GS/JS<br>RS/GS/JS | 16-BIT MICROPROCESSOR<br>16-BIT MICROPROCESSOR                         | 71  |  |  |  |  |

|   |                                                           | MSM80C86A                  | RS/GS/JS             | 16-BIT MICROPROCESSOR                                                  |     |  |  |  |  |

|   |                                                           | MSM80C86A-2                |                      |                                                                        | 96  |  |  |  |  |

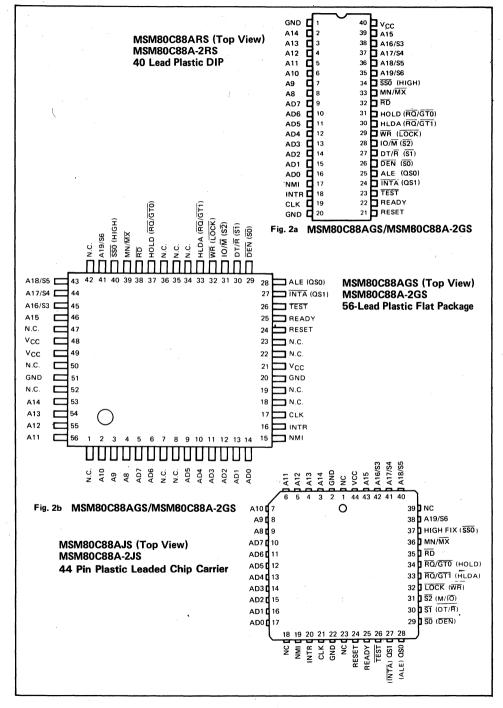

|   |                                                           | MSM80C88<br>MSM80C88-2     | RS/GS/JS<br>RS/GS/JS | 8-BIT MICROPROCESSOR<br>8-BIT MICROPROCESSOR                           | 123 |  |  |  |  |

|   |                                                           | MSM80C88A<br>MSM80C88A-2   | RS/GS/JS             | 8-BIT MICROPROCESSOR<br>8-BIT MICROPROCESSOR                           | 147 |  |  |  |  |

|   | •                                                         |                            |                      | о-bit microprocessor                                                   |     |  |  |  |  |

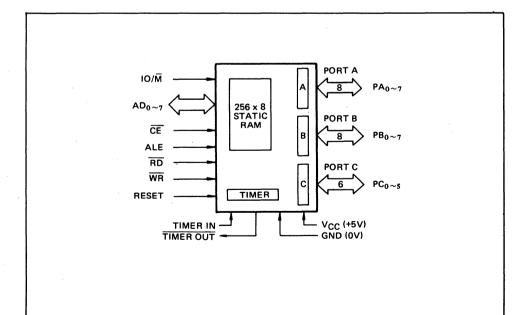

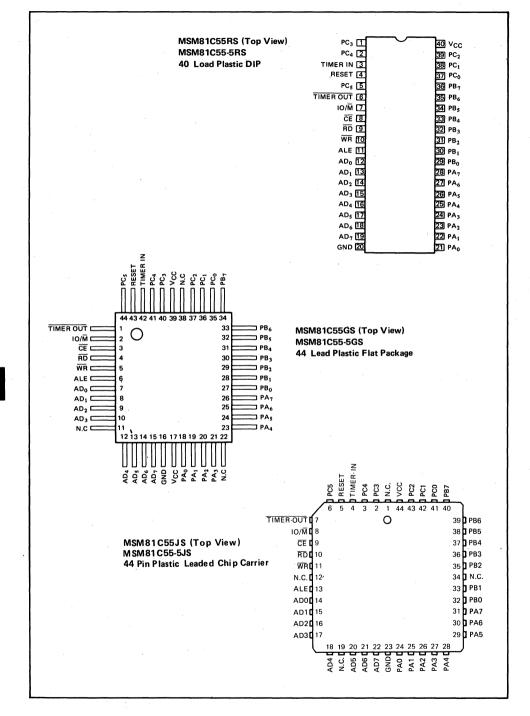

|   | •                                                         | I/O<br>MSM81C55            | RS/GS/JS             | 2048 BIT SRAM WITH I/O, TIMER                                          | 173 |  |  |  |  |

|   |                                                           | MSM81C55-5                 | RS/GS/JS             | 2048 BIT SRAM WITH I/O, TIMER                                          | 175 |  |  |  |  |

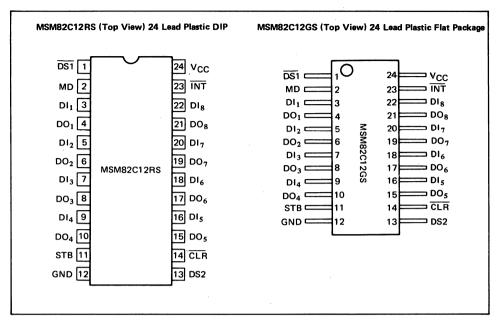

|   |                                                           | MSM82C12                   | RS/GS                | 8-BIT INPUT/OUTPUT PORT                                                |     |  |  |  |  |

|   |                                                           | MSM82C37A                  | RS/GS/JS             | PROGRAMMABLE DMA CONTROLLER                                            | 196 |  |  |  |  |

|   |                                                           | MSM82C37A-5                | 5 RS/GS/JS           | PROGRAMMABLE DMA CONTROLLER                                            | 220 |  |  |  |  |

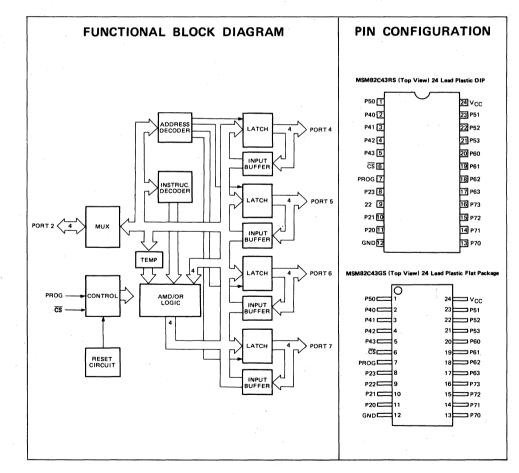

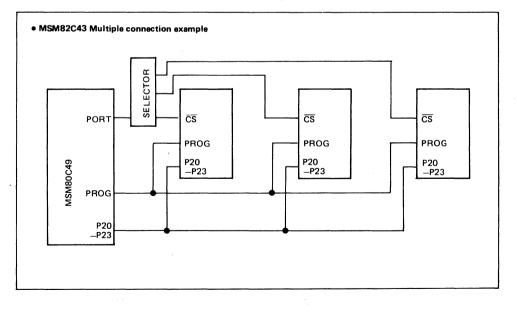

|   |                                                           | MSM82C43                   | RS/GS                | INPUT/OUTPUT PORT EXPANDER                                             | 244 |  |  |  |  |

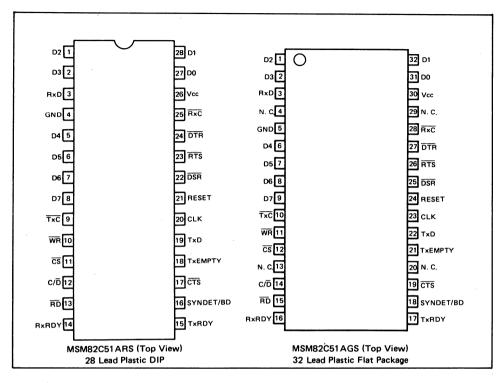

|   |                                                           | MSM82C51A                  | RS/GS                | PROGRAMMABLE COMMUNICATIONS                                            | 250 |  |  |  |  |

|   |                                                           | MSM82C51A-2                | RS/GS/JS             | PROGRAMMABLE COMMUNICATIONS                                            | 266 |  |  |  |  |

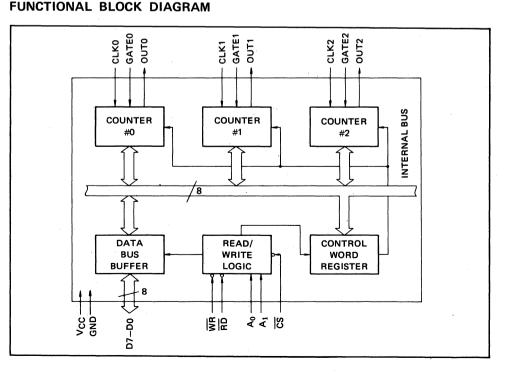

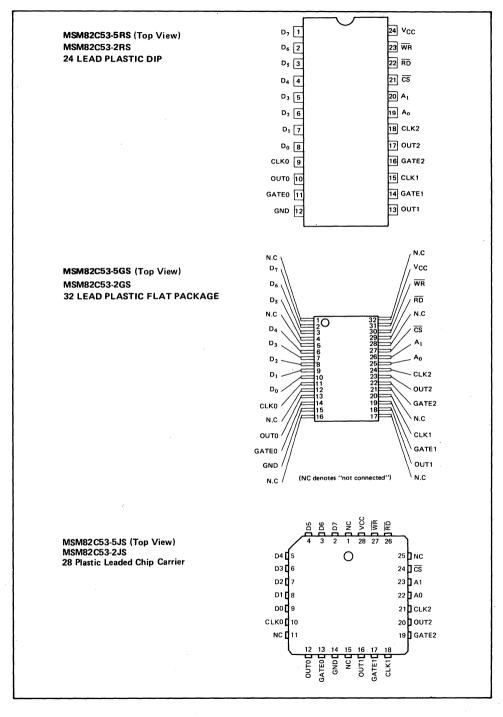

|   |                                                           | MSM82C53-5<br>MSM82C53-2   |                      | PROGRAMMABLE INTERVAL TIMER PROGRAMMABLE INTERVAL TIMER                | 282 |  |  |  |  |

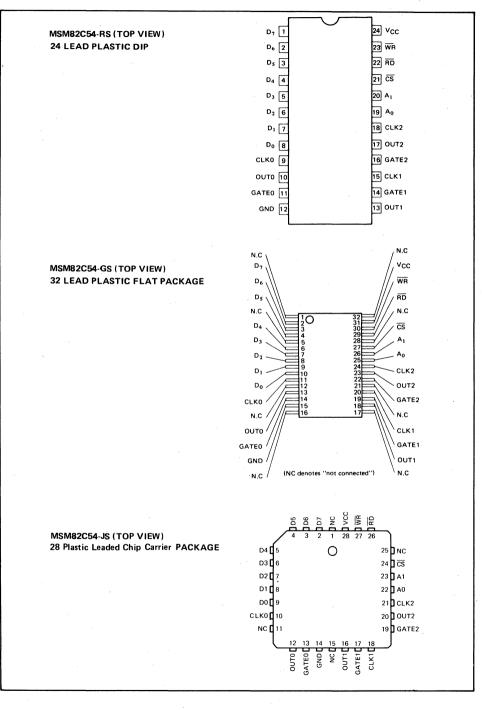

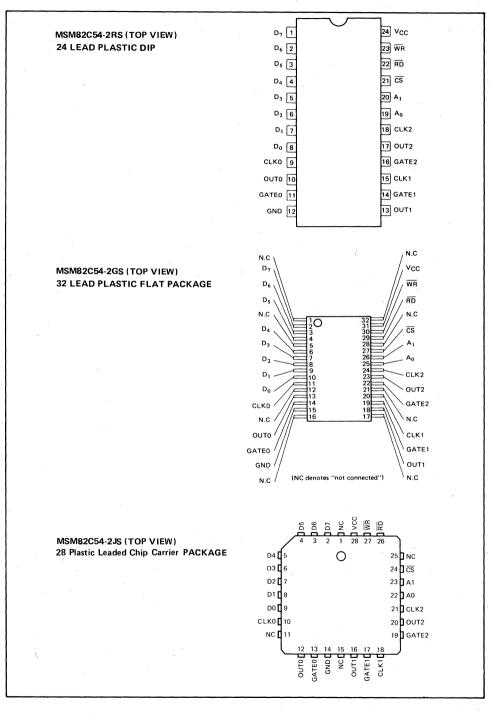

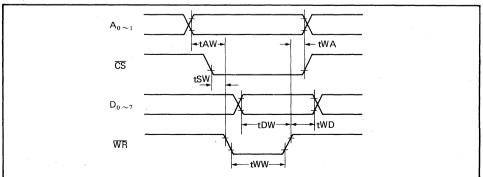

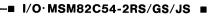

|   |                                                           | MSM82C54                   | RS/GS/JS             | PROGRAMMABLE INTERVAL TIMER                                            | 293 |  |  |  |  |

|   |                                                           | MSM82C54-2                 | RS/GS/JS             | PROGRAMMABLE INTERVAL TIMER                                            | 307 |  |  |  |  |

|   |                                                           | MSM82C55A-5<br>MSM82C55A-2 |                      | PROGRAMMABLE PERIPHERAL INTERFACE<br>PROGRAMMABLE PERIPHERAL INTERFACE | 321 |  |  |  |  |

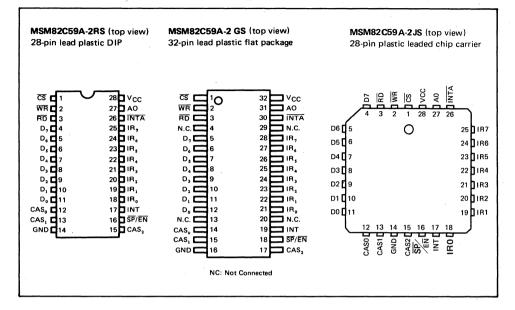

|   |                                                           | MSM82C59A-2                | RS/GS/JS             | PROGRAMMABLE INTERRUPT CONTROLLER                                      | 337 |  |  |  |  |

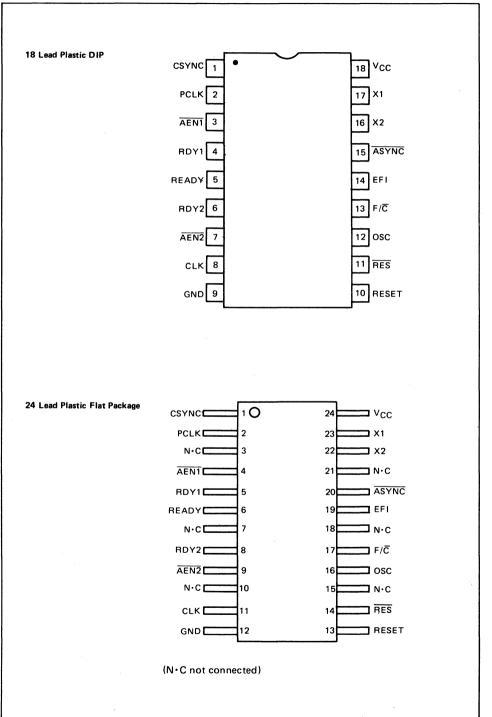

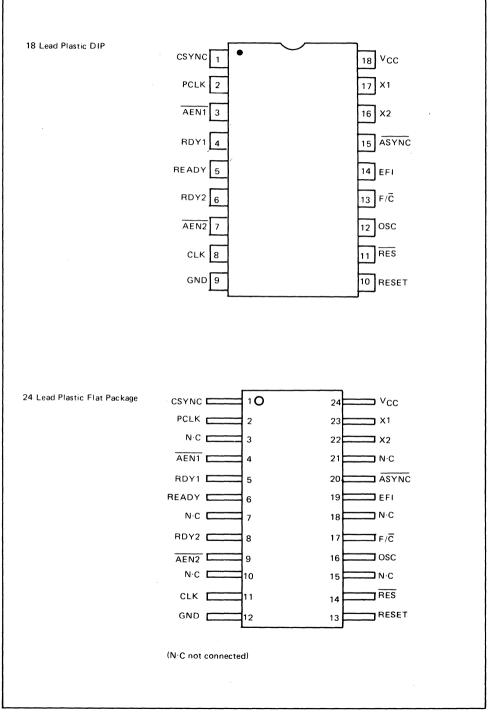

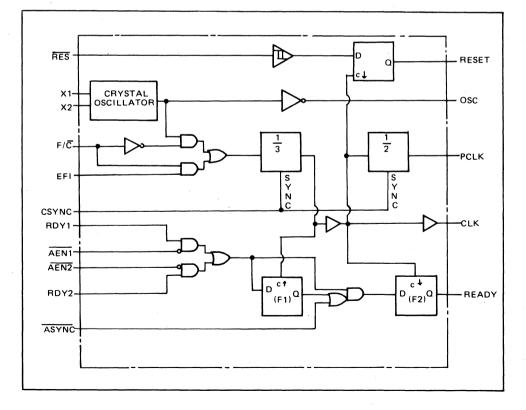

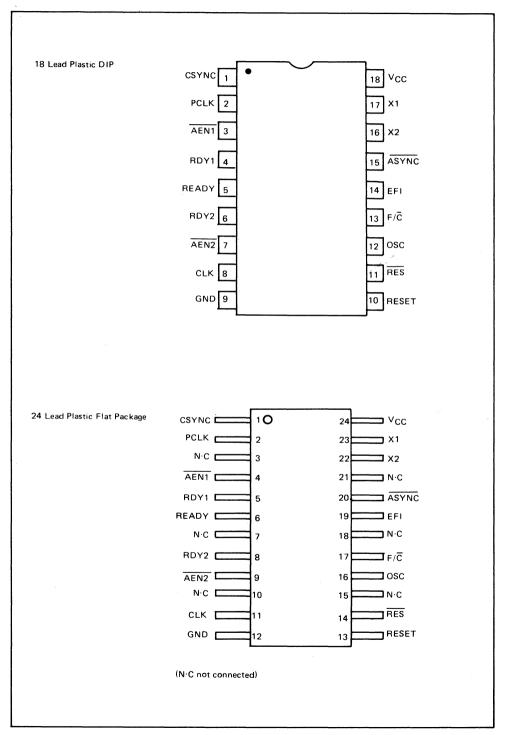

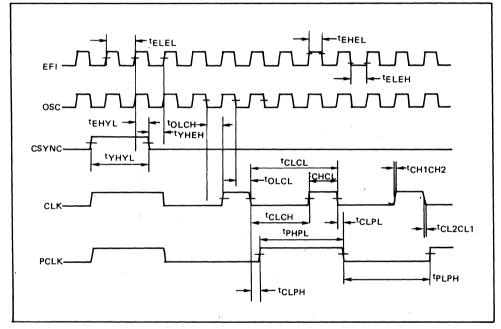

|   |                                                           | MSM82C84A                  | RS/GS                | CLOCK GENERATOR AND DRIVER                                             | 354 |  |  |  |  |

|   |                                                           | MSM82C84A-5                | 5RS/GS               | CLOCK GENERATOR AND DRIVER                                             | 364 |  |  |  |  |

|   |                                                           | MSM82C84A-2                | RS/GS                | CLOCK GENERATOR AND DRIVER                                             | 374 |  |  |  |  |

|   |                                                           | MSM82C88                   | AS/GS                | BUS CONTROLLER                                                         | 384 |  |  |  |  |

|   |                                                           | MSM82C88-2                 | RS/GS                | BUS CONTROLLER                                                         | 393 |  |  |  |  |

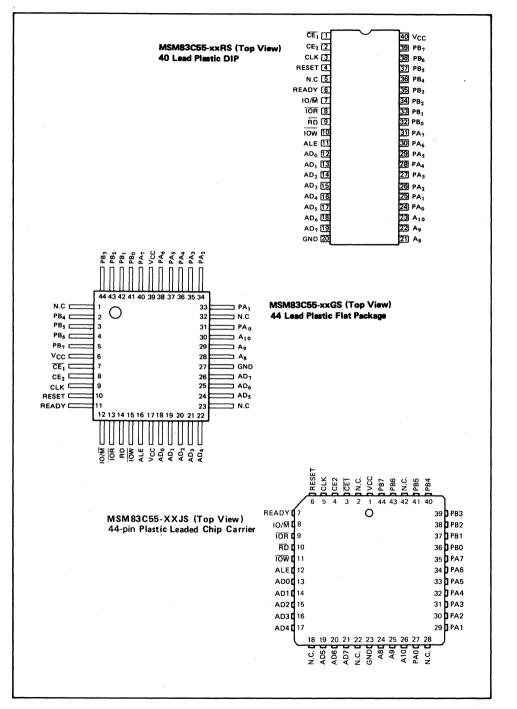

|   |                                                           | MSM83C55-XX                | (RS/GS/JS            | 16384 BIT ROM WITH I/O                                                 | 402 |  |  |  |  |

|   | •                                                         | PERIPHERALS                |                      | ····                                                                   | 409 |  |  |  |  |

|   |                                                           | MSM5832                    | RS                   | REAL TIME CLOCK/CALENDAR                                               | 411 |  |  |  |  |

|   |                                                           | MSM58321                   | RS                   | REAL TIME CLOCK/CALENDAR                                               | 421 |  |  |  |  |

|   |                                                           | MSM6242                    | RS/GS                | REAL TIME CLOCK/CALANDAR<br>(BUS INTERFACE)                            | 437 |  |  |  |  |

i

# CMOS MICROPROCESSOR LINE - UP

## CMOS MICROPROCESSOR LINE - UP

|                  |                            | POWER   | SUPPLY           |                                           | I                                          | COMPAT   | BILITY  |

|------------------|----------------------------|---------|------------------|-------------------------------------------|--------------------------------------------|----------|---------|

| PRODUCTS         | PART NAME                  | VOLTAGE | CURRENT<br>(MAX) | PACKAGE                                   | REMARKS                                    | SUPPLIER | TYPE    |

| 8 BIT CPU        | MSM80C85A                  | 5V      | 22mA             | 40 DIP<br>44 FLAT<br>44 PLCC              | 8 BIT MICROPROCESSOR<br>3 MHz              | Intel    | 8085A   |

| 8 BTT CPU        | MSM80C85A-2                | 5V      | 20mA             | 40 DIP<br>44 FLAT<br>44 PLCC              | 8 BIT MICROPROCESSOR<br>5 MHz              | Intel    | 8085A-2 |

| 8 BIT CPU        | MSM80C86<br>MSM80C86A      | 5V      | 55mA             | 40 DIP<br>56 FLAT                         | 16 BIT MICROPROCESSOR<br>5 MHz             | Intel    | 8086    |

| 16 BIT CPU       | MSM80C86-2<br>MSM80C86A-2  | 50      | 80mA             | 44 PLCC                                   | 8 MHz                                      | Intel    | 8086-2  |

| 8 BIT CPU        | MSM80C88<br>MSM80C88A      | 5V      | 55mA             | 40 DIP<br>56 FLAT                         | 8 BIT MICROPROCESSOR<br>5 MHz              | Intel    | 8088    |

|                  | MSM80C88-2<br>MSM80C88A-2  |         | 80m A            | 40 PLCC                                   | 8 MHz                                      | Intel    | 8088-2  |

|                  | MSM81C55<br>MSM81C55-5     | 5V      | 5mA              | 40 DIP<br>44 FLAT<br>44 PLCC              | 2048 BIT STRAM with I/O<br>and TIMER       | Intel    | 8355    |

|                  | MSM82C12                   | 5V      | 1mA              | 24 DIP<br>24 FLAT 8 BIT INPUT/OUTPUT PORT |                                            | Intel    | 8212    |

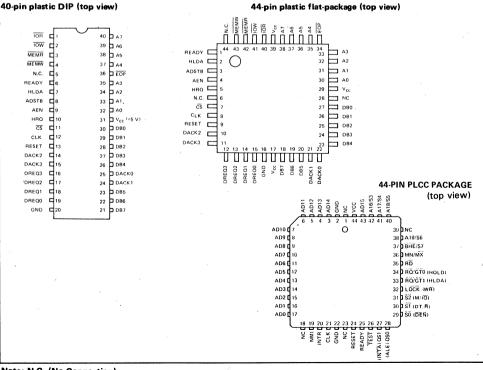

|                  | MSM82C37A<br>MSM82C37A-5   | 5V      | 10mA             | 40 DIP<br>44 FLAT<br>44 PLCC              | PROGRAMMABLE DMA                           | Intel    | 8237A   |

|                  | MSM82C43                   | 5V      | 1mA              | 24 DIP<br>24 FLAT                         | INPUT/OUTPUT PORT EXPANDER                 |          |         |

|                  | MSM82C51A<br>MSM82C51A-2   | 5V      | 5mA              | 28 DIP<br>32 FLAT<br>28 PLCC              | PROGRAMMABLE COMMUNICA-<br>TIONS INTERFACE | Intel    | 8251A   |

|                  | MSM82C53-5<br>MSM82C53-2   | 5V      | 5mA<br>8mA       | 24 DIP<br>32 FLAT<br>28 PLCC              | PROGRAMMABLE INTERVAL<br>TIMER             | Intel    | 8253    |

|                  | MSM82C54<br>MSM82C54-2     | 5V      | 10mA             | 24 DIP<br>32 FLAT<br>28 PLCC              | PROGRAMMABLE<br>COUNTER                    | Intel    | 8254    |

| 1/0              | MSM82C55A-5<br>MSM82C55A-2 | - 5V    | 5mA<br>8mA       | 40 DIP<br>44 FLAT<br>44 PLCC *1           | PROGRAMMABLE PERIPHERAL<br>INTERFACE       | Intel    | 8255    |

|                  | MSM82C59A-2                | 5V      | 5mA              | 28 DIP<br>32 FLAT<br>28 PLCC              | PROGRAMMABLE INTERRUPT<br>CONTROLLER       | Intel    | 8259A-2 |

|                  | MSM82C84A                  | 5V      | 10mA             | 18 DIP<br>24 FLAT                         | CLOCK GENERATOR and DRIVER                 | Intel    | 8284A   |

|                  | MSM82C84A-5                | - 5V    | 10mA             | 18 DIP                                    | CLOCK GENERATOR and DRIVER<br>(5 MHz)      | Intel    | 8284A   |

|                  | MSM82C84A-2                |         | 16mA             | 24 FLAT                                   | CLOCK GENERATOR and DRIVER<br>(5 MHz)      |          |         |

|                  | MSM82C88<br>MSM82C88-2     | 5V      | 10mA             | 20 DIP<br>24 FLAT                         | BUS CONTROLLER                             | Intel    | 8288    |

|                  | MSM83C55                   | 5V      | 5mA              | 40 DIP<br>44 FLAT<br>44 PLCC              | 16384 BIT ROM with I/O                     | Intel    | 8355    |

|                  | MSM5832                    | 5V      | 0.1mA            | 18 DIP                                    | REAL TIME CLOCK                            | ļ        |         |

| PERI-<br>PHERALS | MSM58321                   | 5V      | 0.1mA            | 16 DIP                                    | REAL TIME CLOCK                            |          |         |

|                  | MSM6242                    | 5∨      | 10µA             | 18 DIP<br>24 FLAT                         | REAL TIME CLOCK<br>DIRECT BUS CONNECTED    |          |         |

\*1 44PLCC is only available for 82C55A-2.

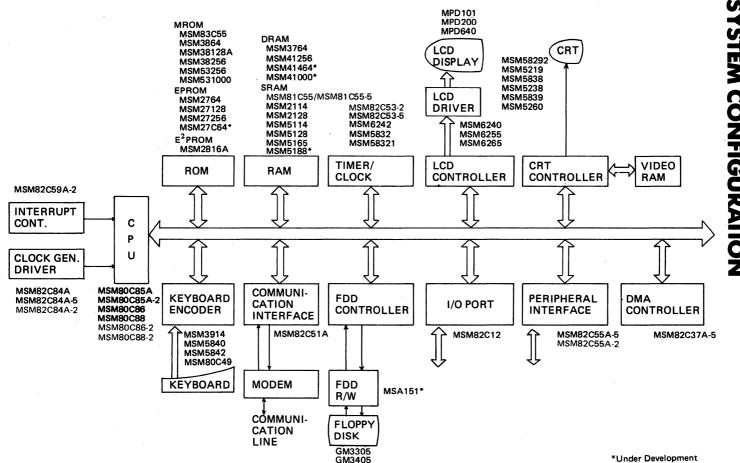

# SYSTEM CONFIGURATION

τ 11 Ζ S n MPU R Ĵ π OCESSOR

\*

### PACKAGING

| PRO-  |                    | PACK | AGE/PIN C | OUNT |

|-------|--------------------|------|-----------|------|

| DUCTS | PART NAME          | DIP  | FLAT      | PLCC |

|       | M80C85A (Note: 1)  | 40   | 44        | 44   |

|       | M80C85A-2          | 40   | 44        | 44   |

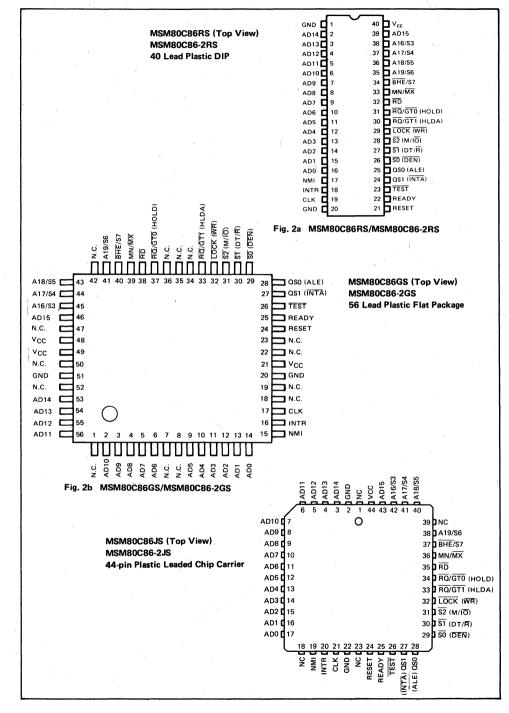

|       | M80C86             | 40   | 56        | 44   |

|       | M80C86-2           | 40   | 56        | 44   |

|       | M80C86A            | 40   | 56        | 44   |

| MPU   | M80C86A-2          | 40   | 56        | 44   |

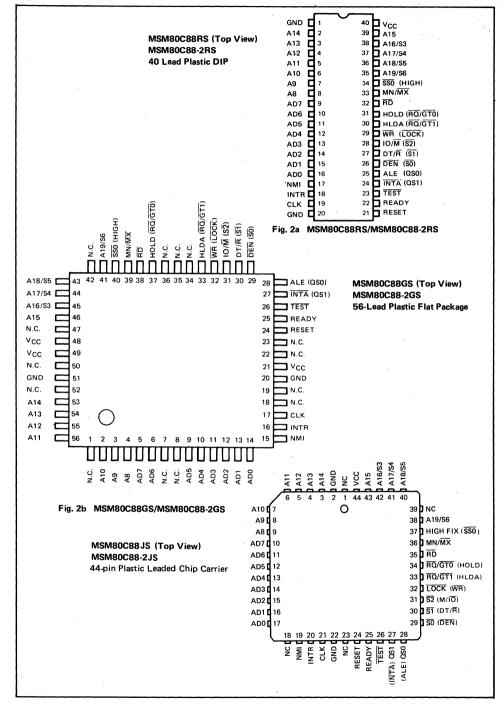

|       | M80C88             | 40   | 56        | 44   |

|       | M80C88-2           | 40   | 56        | 44   |

|       | M80C88A            | 40   | 56        | 44   |

|       | M80C88A-2          | 40   | 56        | 44   |

|       | M81C55/81C55-5     | 40   | 44        | 44   |

|       | M82C12             | 24   | 24        | -    |

|       | M82C37A            | 40   | 44        | 44   |

|       | M82C37A-5          | 40   | 44        | 44   |

|       | M82C43             | 24   | 24        | -    |

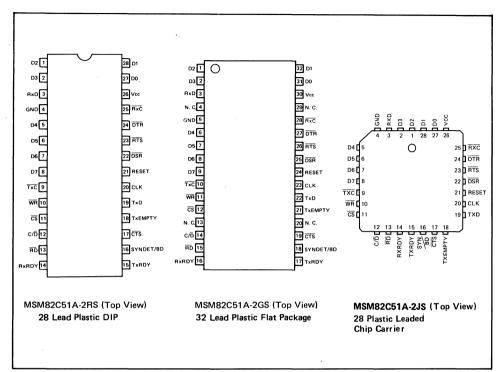

| 1/0   | M82C51A            | 28   | 32        | _    |

|       | M82C51A-2          | 28   | 32        | 28   |

|       | M82C53-5/82C53-2   | 24   | 32        | 28   |

|       | M82C54             | 24   | 32        | 28   |

|       | M82C54-2           | 24   | 32        | 28   |

|       | M82C55A-5/82C55A-2 | 40   | 44        | 44   |

|       | M82C59A-2          | 28   | 32        | 28   |

|       | M82C84A            | 18   | 24        | _    |

|       | M82C84A-5/84A-2    | 18   | 24        | -    |

|       | M82C88             | 20   | 24        | -    |

|       | M82C88-2           | 20   | 24        | -    |

|       | M83C55             | 40   | 44        | 44   |

| PERI- | M5832              | 18   |           |      |

| PHER- | M58321             | 16   | _         | _    |

| ALS   | M6242              | 18   | 24        | -    |

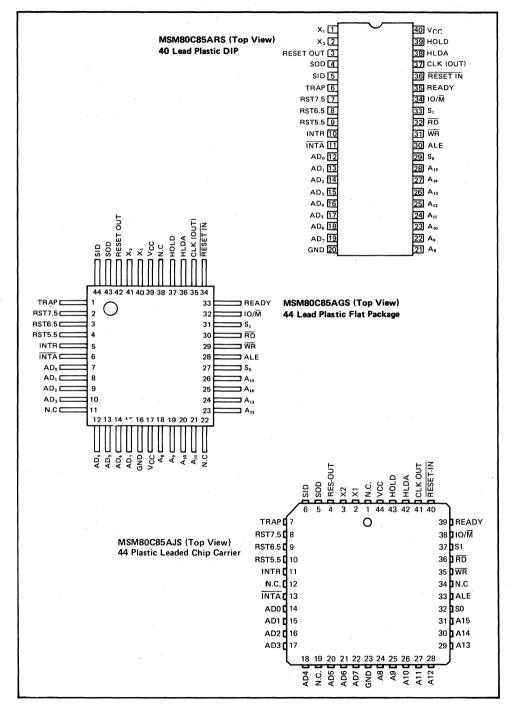

Note: 1. Model numbers suffixed by RS denote plastic DIP, while GS denotes plastic FLAT. MSM80C85ARS . . . . . . plastic DIP MSM80C85AGS . . . . . . plastic FLAT Ex.

#### PACKAGING =

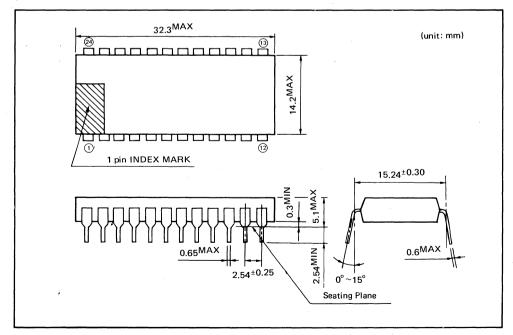

#### • 20 PIN PLASTIC SKINNY DIP

#### • 16 PIN PLASTIC DIP

.

#### 18 PIN PLASTIC DIP

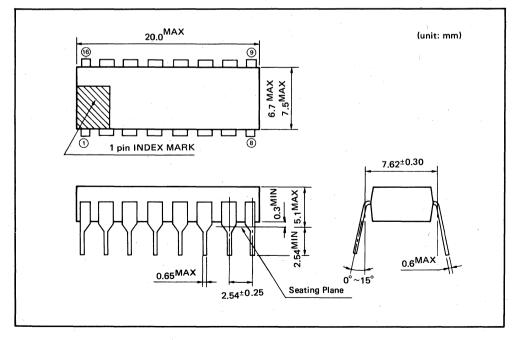

#### • 24 PIN PLASTIC DIP

PACKAGING =-

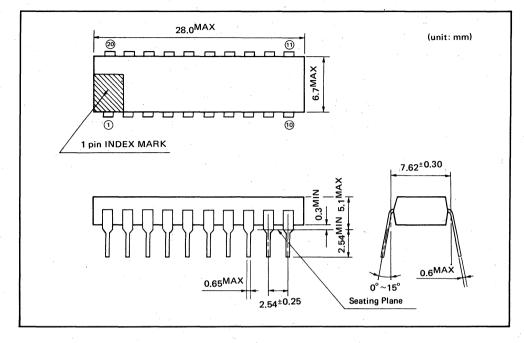

#### • 28 PIN PLASTIC DIP

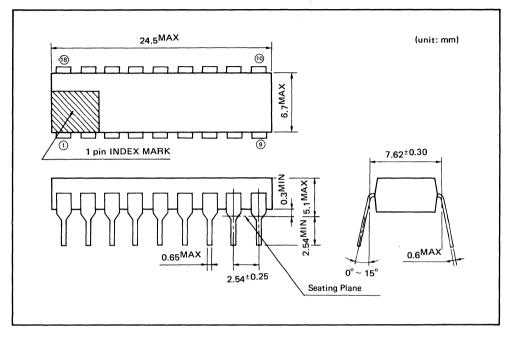

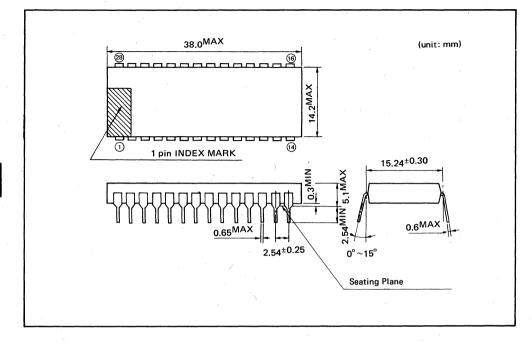

• 40 PIN PLASTIC DIP

#### ---- PACKAGING

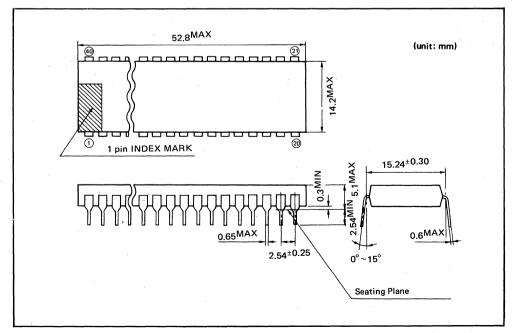

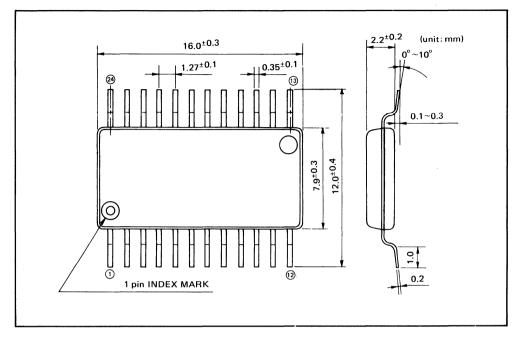

#### • 24 PIN PLASTIC FLAT

#### • 32 PIN PLASTIC FLAT

- PACKAGING

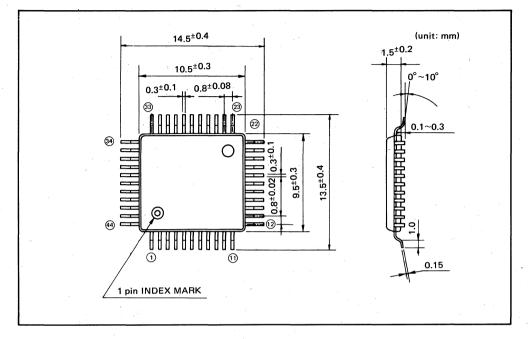

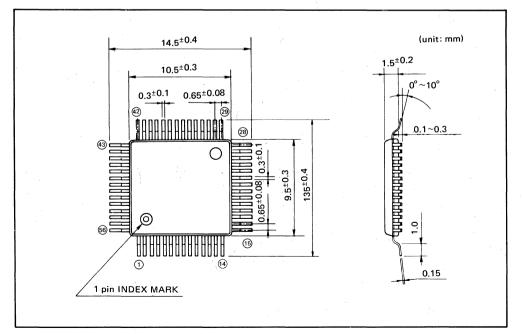

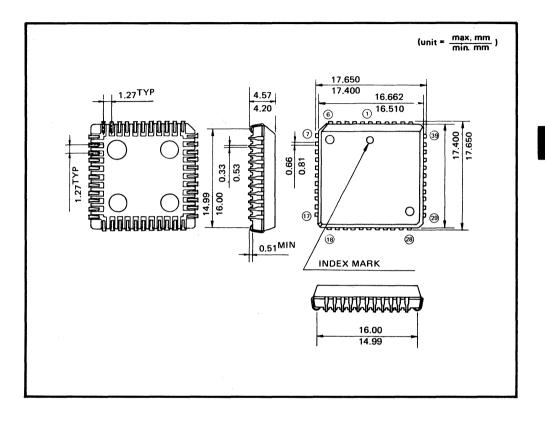

- 44 PIN PLASTIC FLAT

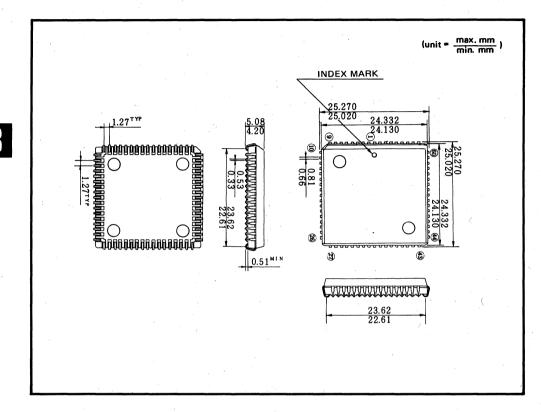

#### • 56 PIN PLASTIC FLAT

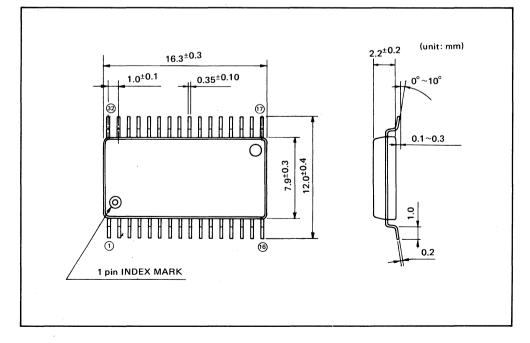

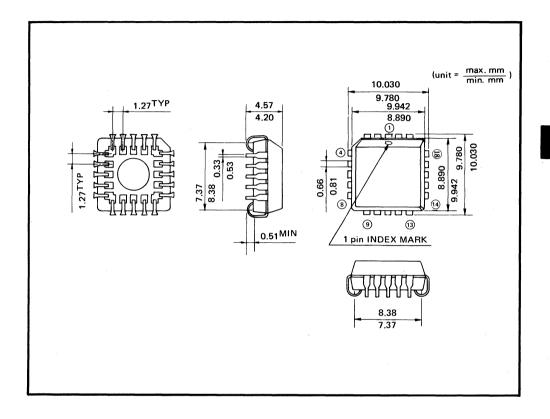

#### • 20 PIN SQUARE PLCC

PACKAGING =

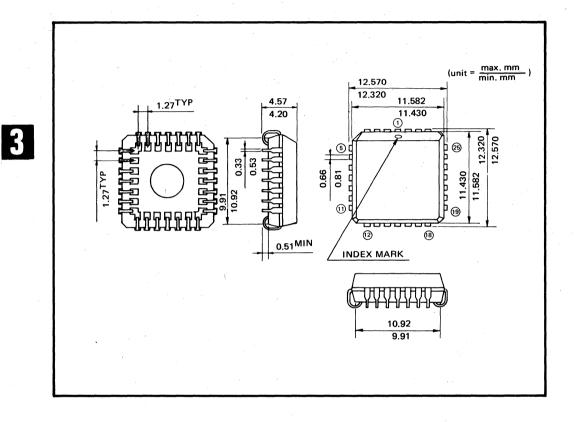

28 PIN SQUARE PLCC

#### • 44 PIN QUAD PLCC

PACKAGING =

#### 68 PIN SQUARE PLCC

3

# **RELIABILITY**

## RELIABILITY INFORMATION

#### **1. INTRODUCTION**

Semiconductor devices play a leading role in the explosive progress of semiconductor technology. They use some of the most advanced design and manufacturing technology developed to date. With greater integration, diversity and reliability, their applications have expanded enormously. Their use in large scale computers, control equipment, calculators, electronic games and in many other fields has increased at a fast rate.

A failure in electronic banking or telephone switching equipment, for example, could have far reaching effects and can cause incalculable losses. So, the demand, for stable high quality memory devices is strong.

We, at Oki are fully aware of this demand. So we have adopted a comprehensive quality assurance system based on the concept of consistency in development, manufacturing and sales.

With the increasing demand for improvement in function, capability and reliability, we will expand our efforts in the future. Our quality assurance system and the underlying concepts are outlined briefy below.

#### 2. QUALITY ASSURANCE SYSTEM AND UNDERLYING CONCEPTS

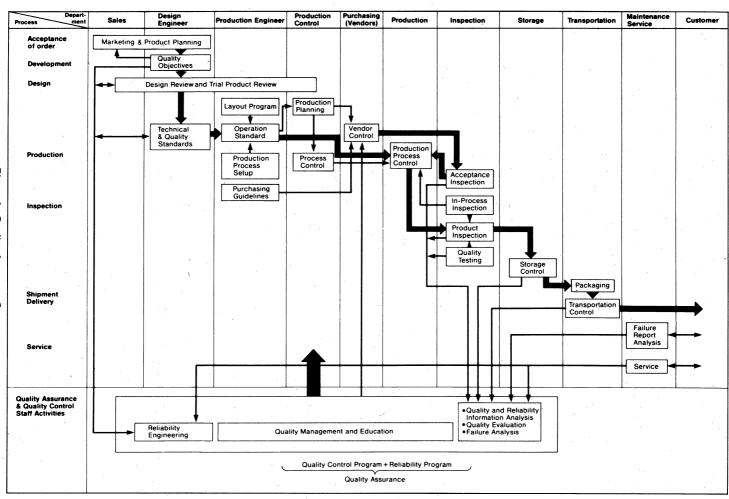

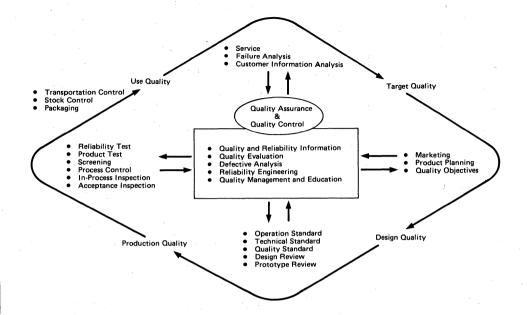

The quality assurance system employed by Oki can be divided into four major stages: device planning, developmental prototype, production prototype, and mass production. This system is outlined in the following block diagram (Fig. 1).

#### 1) Device planning stage

To manufacture devices that meet market demands and satisfy customer needs, we carefully consider functional and failure rate requirements, utilization form, environment and other conditions. Once we determine the proper type, material and structure, we check the design and manufacturing techniques, and the line processing capacity. Then we prepare the development planning and time schedule.

#### 2) Developmental prototype stage

We determine circuits, pattern design, process settings, assembly techniques and structural requirements during this stage. At the same time, we carry out actual prototype reliability testing. Since device quality is largely determined during the designing stage, Oki pays careful attention to quality confirmation during this stage.

This is how we do it:

(1) After completion of circuit design (or pattern design), personnel from the design, process technology, production technology, installation technology and reliability departments get together for a thorough review to ensure design quality and to anticipate problems that may occur during mass production. Past experience and know-how guide these discussions.

- (2) Since many semiconductor memories involve new concepts and employ high level manufacturing technology, the TEG evaluation test is often used during this stage.

- Note: TEG (Test Element Group) refers to the device group designed for stability evaluation of MOS transistors, diodes, resistors, capacitors and other circuit component element used in LSI memories.

- (3) Prototypes are subjected to repeated reliability and other special evaluation tests. In addition, the stability and capacity of the manufacturing process are checked.

#### 3) Production prototype stage

During this stage, various tests check the reliability and other special features of the production prototype at the mass production factory level. After confirming the quality of a device, we prepare the various standards required for mass production, and then start production. Although reliability and other special tests performed on the production prototype are much the same as those performed on the developmental prototype, the personnel, facilities and production site differ for the two prototypes, necessitating repeated confirmation tests.

#### 4) Mass production

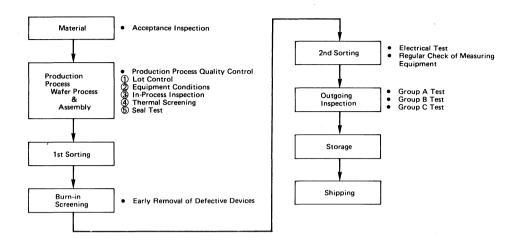

During the mass production stage, careful management of purchased materials, parts and facilities used during the manufacturing process, measuring equipment, manufacturing conditions and environment is necessary to ensure device quality first stipulated during the designing stages. The manufacturing process (including inspection of the completed device) is followed by a lot guarantee inspection to check that the specified quality is maintained under conditions identical to those under which a customer would actually use the device. This lot guarantee inspection is performed in three different forms as shown below.

- (1) Group A tests: appearance, labels, dimensions and electrical characteristics inspection

- (2) Group B tests: check of durability under thermal and mechanical environmental stresses, and operating life characteristics

- (3) Group C tests: performed periodically to check operational life, etc., on a long term basis.

- Note: Like the reliability tests, the group B tests conform to the following standards. MIL-STD-883B, JIS C 7022, EIAJ-IC-121

24

Figure **Quality Assurance System**

Figure 2 Manufacturing Process

Devices which pass these lot guarantee inspections are stored in a warehouse awaiting shipment to customers. Standards are also set up for handling, storage and transportation during this period, thereby ensuring quality prior to delivery. Figure 2 shows the manufacturing flow of the completed device. 5) At Oki, all devices are subjected to thorough quality checks. If, by chance, a failure does occur after delivery to the customer, defective devices are processed and the problem rectified immediately to minimize the inconvenience to the customer in accordance with the following flowchart.

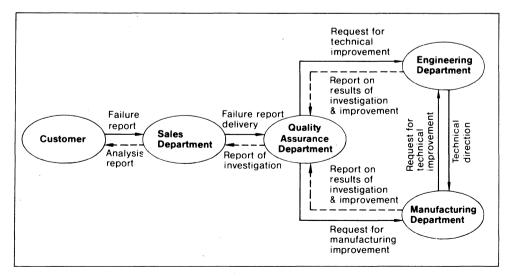

Figure 3 Failure report process

#### **RELIABILITY INFORMATION**

#### 3. EXAMPLE OF RELIABILITY TEST RESULTS

We have outlined the quality assurance system and the underlying concepts employed by Oki. Now, we will give a few examples of the reliability tests performed during the developmental and production prototype stages. All reliability tests performed by Oki conform to the following standards.

#### MIL-STD-883B, JIS C 7022, EIAJ-IC-121

Since these reliability tests must determine performance under actual working conditions in a short period of time, they are performed under severe test conditions. For example, the  $125^{\circ}$ C high temperature continuous operation test performed for 1000 hours is equivalent to testing device life from 2 to 300 years of use at Ta =  $40^{\circ}$ C.

By repeating these accelerated reliability tests, device quality is checked and defects analyzed. The resulting information is extremely useful in improving the manufacturing processes. Some of the more common defects in LSI elements and their analysis are described on next page.

|                              | Part name                                                  | MSM                     | 80C85/                        | A-2RS    | MS                                                    | M81C5                        | 5RS | MSM                                     | 82C59/                       | A-2RS    | -                                  |

|------------------------------|------------------------------------------------------------|-------------------------|-------------------------------|----------|-------------------------------------------------------|------------------------------|-----|-----------------------------------------|------------------------------|----------|------------------------------------|

|                              | Function                                                   | 8 BIT<br>MICROPROCESSOR |                               |          | 2048 BIT CMOS<br>STATIC RAM WITH<br>I/O PORTS & TIMER |                              |     | PROGRAMMABLE<br>INTERRUPT<br>CONTROLLER |                              |          | Referred<br>standard               |

| Test<br>item                 | Test<br>condition                                          | Sample<br>size<br>(pcs) | Test<br>hours<br>or<br>cycles | Failures | size<br>(pcs)                                         | Test<br>hours<br>&<br>cycles |     | Sample<br>size<br>(pcs)                 | Test<br>hours<br>&<br>cycles | Failures |                                    |

| Operating<br>life test       | Ta = 125°C<br>Vcc = 6V                                     | 88                      | 2000<br>(H)                   | 0        | 22                                                    | 2000<br>(H)                  | 0   | 88                                      | 2000<br>(H)                  | 0        | MIL-<br>STD-883C<br>METHOD<br>1006 |

| Temperature<br>humidity test |                                                            | 100                     | 2000<br>(H)                   | 0        | 25                                                    | 2000<br>(H)                  | 0   | 100                                     | 2000<br>(H)                  | 0        |                                    |

| Temperature<br>cycling test  | − 55°C <b>≓RT</b> ≓150°C<br>(30 min) ↑ (30 min)<br>(5 min) | 100                     | 500<br>(cy)                   | 0        | 50                                                    | 300<br>(cy)                  | 0   | 100                                     | 500<br>(cy)                  | 0        | MIL-STD-<br>883C<br>METHOD<br>1010 |

| Pressure<br>cooker test      | Ta = 121°C<br>RH = 100%<br>2 atm                           | 50                      | 200<br>(H)                    | 0        | 50                                                    | 200<br>(H)                   | 0   | 50                                      | 200<br>(H)                   | 0        |                                    |

#### MICROPROCESSOR LIFE TEST RESULTS

|                              | Part name                                         | MSM                     | 80C86                        | /88JS            | MSM8                    |                              |          |                                    |

|------------------------------|---------------------------------------------------|-------------------------|------------------------------|------------------|-------------------------|------------------------------|----------|------------------------------------|

|                              | Function                                          |                         |                              | ESSOR<br>:RSION) | MICRO<br>(STAT          | Referred<br>standard         |          |                                    |

| Test<br>item                 | Test<br>condition                                 | Sample<br>size<br>(pcs) | Test<br>hours<br>&<br>cycles |                  | Sample<br>size<br>(pcs) | Test<br>hours<br>&<br>cycles | Failures |                                    |

| Operating<br>life test       | Ta = 125°C<br>Vcc = 6V                            | 88                      | 2000<br>(H)                  | 0                | 88                      | 1000<br>(H)                  | 0        | MIL-<br>STD-883C<br>METHOD<br>1005 |

| Temperature<br>humidity test | Ta = 85°C<br>RH = 85%<br>Vcc = 6V                 | 100                     | 2000<br>(H)                  | 0                | 100                     | 1000<br>(H)                  | 0        |                                    |

| Temperature<br>cycling test  | – 55°C≓RT≓150°C<br>(30 min) ↑ (30 min)<br>(5 min) | 100                     | 500<br>(cy)                  | 0                | 100                     | 500<br>(cy)                  | 0        | MIL-STD-<br>883C<br>METHOD<br>1010 |

| Pressure<br>cooker test      | Ta = 121°C<br>RH = 100%<br>2 atm                  | 50                      | 200<br>(H)                   | 0                | 50                      | 200<br>(H)                   | 0        |                                    |

|        | _                                |         | <b>D</b>                                                |                         |          |                                                       |          |                                         |          | /                                  |

|--------|----------------------------------|---------|---------------------------------------------------------|-------------------------|----------|-------------------------------------------------------|----------|-----------------------------------------|----------|------------------------------------|

| $\sim$ |                                  |         | Part name                                               | MSM80C                  | 86A-2HS  | MSM81                                                 | C55HS    | MSM82C                                  | 59A-2RS  |                                    |

|        | Test<br>item                     |         | Function                                                | 8 BIT<br>MICROPROCESSOR |          | 2048 BIT CMOS<br>STATIC RAM WITH<br>I/O PORTS & TIMER |          | PROGRAMMABLE<br>INTERRUPT<br>CONTROLLER |          | Referred<br>standard               |

|        |                                  |         | Test<br>condition                                       | Sample<br>size (pcs)    | Failures | Sample<br>size (pcs)                                  | Failures | Sample<br>size (pcs)                    | Failures |                                    |

|        | PRE-I                            | Bake    | Bake<br>(125°C, 6 hrs)                                  | 22                      | 0        | 22                                                    | 0        | 22                                      | 0        |                                    |

|        | Soldering<br>Heat Test           |         | 260°C<br>10 SEC                                         | 22                      | 0        | 22                                                    | 0        | 22                                      | 0        | MIL-<br>STD-883C<br>METHOD<br>2003 |

|        | ▼<br>Temperature<br>Cycling Test |         | – 55°C≓RT≓ 150°C<br>(30min) (5min) (30min)<br>20 cycles | 22                      | 0        | 22                                                    | 0        | 22                                      | 0        | MIL-<br>STD-883C<br>METHOD<br>1010 |

|        | Thermal<br>Shock<br>Test         |         | 100°C≓0°C<br>(5min) (5min)<br>10 cycles                 | 22                      | 0        | 22                                                    | 0        | 22                                      | 0        | MIL-<br>STD-8830<br>METHOD<br>1011 |

|        | Lead<br>Integrity                | Tensile | 500 g 10SEC                                             | 11                      | 0        | 11                                                    | 0        | 11                                      | 0        | MIL-<br>STD883C                    |

|        |                                  | Bending | 250 g 90° BEND<br>3 TIMES                               | • 1                     |          |                                                       |          |                                         | r        | METHOD<br>2004                     |

|        | Solderability                    |         | 230°C 5 SEC                                             | 22                      | 0        | 22                                                    | 0        | 22                                      | 0        | MIL<br>STD8830<br>METHOD<br>2003   |

#### MICROPROCESSOR ENVIRONMENTAL TEST RESULTS

| $\square$       |                             | Part name                                                                                                                   | MSM800               | C86/88JS                   | MSM80C8              | 35A/88AJS                  |                                    |

|-----------------|-----------------------------|-----------------------------------------------------------------------------------------------------------------------------|----------------------|----------------------------|----------------------|----------------------------|------------------------------------|

|                 |                             | Function                                                                                                                    | MICROPR              | BIT<br>OCESSOR<br>VERSION) | MICROPR              | BIT<br>OCESSOR<br>VERSION) | Referred<br>standard               |

|                 | Test<br>item                | Test<br>condition                                                                                                           | Sample<br>size (pcs) | Failures                   | Sample<br>size (pcs) | Failures                   |                                    |

| Test            | PRE-Bake                    | Bake<br>(125°C, 6 hrs)                                                                                                      |                      |                            | 4                    |                            |                                    |

| Environmental 1 | Soldering<br>Heat Test      | Vapor Phase Reflow<br>(215±2°C,90+10,-0sec)<br>2 times                                                                      |                      |                            |                      |                            |                                    |

| Thermal Envir   | Temperature<br>Cycling Test | - 55°C≓RT≓150°C<br>(30min) (5min) (30min)<br>20 cycles                                                                      | 22                   | 0                          | 22                   | 0                          | MIL-<br>STD-883C<br>METHOD<br>1010 |

|                 | Thermal<br>Shock<br>Test    | 100°C <b>≓0°C</b><br>(5min) (5min)<br>10 cycles                                                                             |                      |                            |                      |                            | MIL-<br>STD-883C<br>METHOD<br>1011 |

| Other Test      | Solderability               | <ul> <li>⊖ Bake (125°C, 24hrs)</li> <li>⊖ Immerse into Flux</li> <li>○ Immerse into Solder<br/>(215±2°C 10±1sec)</li> </ul> | 22                   | 0                          | 22                   | 0                          |                                    |

4

#### 4. SEMICONDUCTOR MEMORY FAILURES

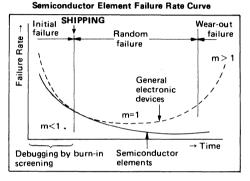

The life-span characteristics of semiconductor elements in general (not only semiconductor IC devices) is described by the curve shown in the diagram below. Although semiconductor memory failures are similar to those of ordinary integrated circuits, the degree of integration (miniaturization), manufacturing complexity and other circuit element factors influence their incidence.

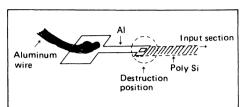

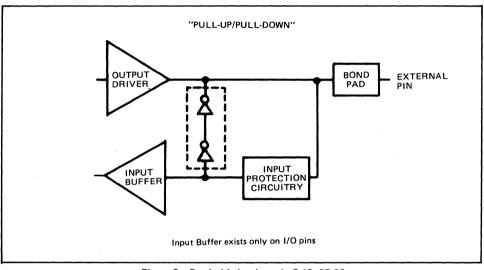

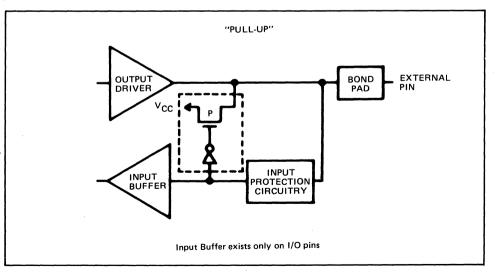

#### 1) Surge Destruction

This is destruction of the input/output stage circuits by external surge currents or static electricity. The accompanying photograph shows a point of contact between aluminum and polysilicon that has been dissolved by a surge current. A hole has formed in the substrate silicon, leading to a short circuit. This kind of failure is traceable in about 30% of defective devices returned to the manufacturer. Despite miniaturization of semiconductor memory component elements (which means the elements themselves are less resistant), these failures usually occur during assembly and other handling operations. At Oki, all devices are subjected to static electricity intensity tests (under simulated operation

Example of surge destruction

al conditions) in the development stage to reduce this type of failure. In addition to checking endurance against surge currents, special protective circuits are incorporated in the input and output sections.

#### 2) Oxide Film Insulation Destruction (Pin Holes)

Unlike surge destruction, this kind of failure is caused by manufacturing defects. Local weakened sections are ruptured when subjected to external electrical stress. Although this problem is accentuated by the miniaturization of circuit elements, it can be resolved by maintaining an ultra-clean manufacturing environment and through 100% burn-in screening.

3) Surface Deterioration due to lonic Impurities Under some temperature and electric field conditions, charged ionic impurities moving within the oxide film previously resulted in occasional deterioration of silicon surfaces. This problem has been eliminated by new surface stabilization techniques.

#### 4) Photolithographic Defects

Integrated circuits are formed by repeated photographic etching processes. Dust and scratches on the mask (which corresponds to a photographic negative) can cause catastrophic defects. At present, component elements have been reduced in size to the order of 10 cm through miniaturization. However, the size of dust and scratches stays the same. At Oki, a high degree of automation, minimizing human intervention in the process, and unparalleled cleanliness, solves this problem.

Photolithographic Defect

#### RELIABILITY INFORMATION =

#### 5) Aluminum Corrosion

Aluminum corrosion is due to electrolytic reactions caused by the presence of water and minute impurities. When aluminum dissolves, lines break. This problem is unique to the plastic capsules now used widely to reduce costs. Oki has carefully studied the possible cause and effect relationship between structure and manufacturing conditions on the one hand, and the generation of aluminum corrosion on the other. Refinements incorporated in Oki LSIs permit superior endurance to even the most severe high humidity conditions.

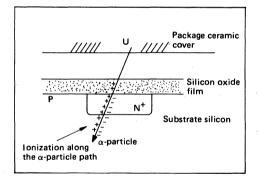

#### 6) Alpha-Particle Soft Failure

This problem occurs when devices are highly miniaturized, such as in 1 megabit RAMs. The inversion of memory cell data by alpha-particle generated by radio-active elements like uranium and thorium (present in minute quantities, measured in ppb) in the ceramic package material causes defects. Since failure is only temporary and normal operation restored quickly, this is referred to as a "soft" failure. At Oki we have eliminated the problem by coating the chip surface of 1 megabit RAMs with a resin which effectively screens out these alpha-particles.

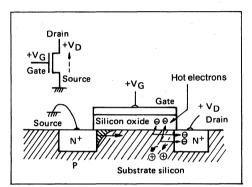

#### 7) Degradation in Performance Characteristics Due to Hot Electrons

With increased miniaturization of circuit elements, internal electric field strength in the channels increases since the applied voltage remains the same at 5V. As a result, electrons flowing in the channels, as shown in the accompanying diagram, tend to enter into the oxide film near the drain, leading to degradation of performance. Although previous low-temperature operation tests have indicated an increase of this failure, we have confirmed by our low-temperature acceleration tests, including checks on test element groups, that no such problem exists in Oki LSIs.

With further progress in the miniaturization of circuit components, failures related to pin hole oxide film destruction and photolithography have increased. To eliminate these defects during manufacturing, Oki has been continually improving its production processes based on reliability tests and information gained from the field. And we subject all devices to high-temperature burnin screening for 48 to 96 hours to ensure even greater reliability.

# **OKI** semiconductor MSM80C85A RS/GS/JS

8-BIT CMOS MICROPROCESSOR

## **GENERAL DESCRIPTION**

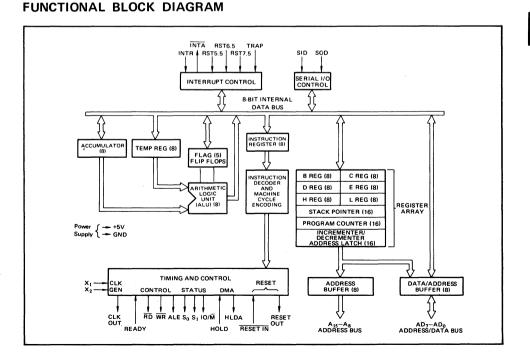

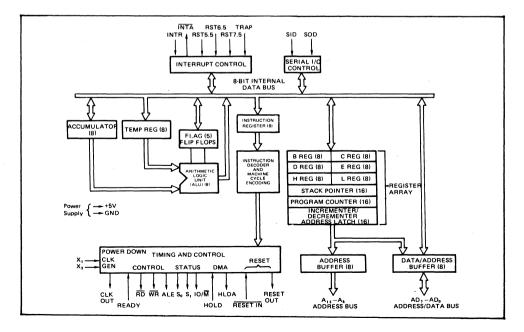

The MSM80C85A is a complete 8-bit parallel central processor implemented in silicon gate C-MOS technology. It is designed with the same processing speed and lower power consumption compared with MSM8085A, thereby offering a high level of system integration.

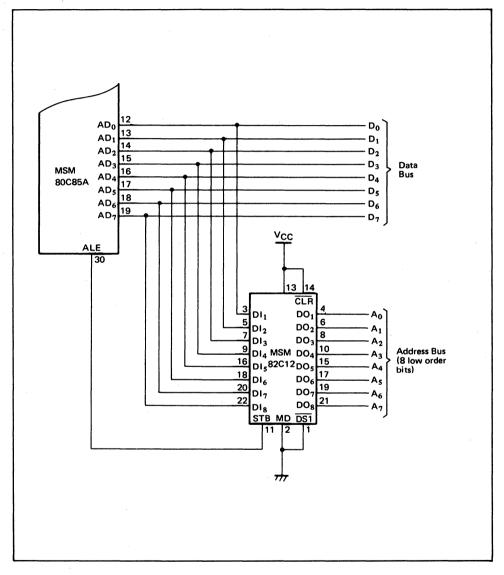

The MSM80C85A uses a multiplexed address/data bus. The address is split between the 8-bit address bus and the 8-bit data bus. The on-chip address latches of MSM81C55/MSM83C55 memory products allow a direct interface with the MSM80C85A.

## FEATURES

- Low Power Dissipation: 50 mW Typ

- Single +4 to +6 V Power Supply

- --40 to +85°C, Operating Temperature

- 1.3µ Instruction Cycle

- On-Chip Clock Generator (with External Crystal)

- On-Chip System Controller; Advanced Cycle Status Information Available for Large System Control

- TTL Compatible

- Four Vectored Interrupt Inputs (One is non-maskable) Plus the 8080A-compatible interrupt.

- Serial In/Serial Out Port

- Decimal, Binary and Double Precision Arithmetic

- Addressing Capability to 64K Bytes of Memory

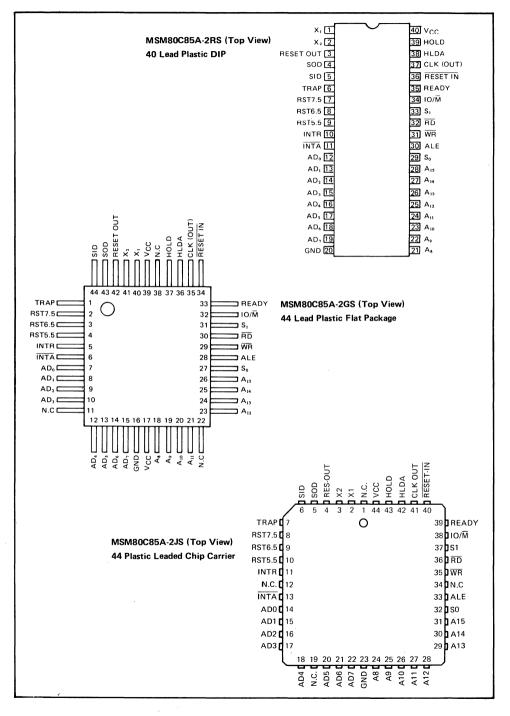

- 40-pin Plastic DIP (MSM80C85ARS)

- 44-pin Plastic Flat Package (MSM80C85AGS)

- 44-pin PLCC Package (MSM80C85AJS)

### ■ CPU·MSM80C85ARS/GS/JS ■

### PIN CONFIGURATION

## MSM80C85A FUNCTIONAL PIN DEFINITION

The following describes the function of each pin:

| Symbol                                               | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |

|------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| A <sub>8</sub> -A <sub>15</sub><br>(Output, 3-state) | Address Bus: The most significant 8-bits of the memory address or the 8-bits of the I/O address, 3-stated during Hold and Halt modes and during RESET.                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |

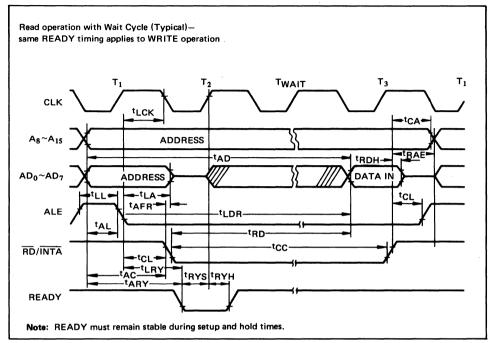

| AD <sub>0</sub> -AD7<br>(Input/Output)<br>3-state    | Multiplexed Address/Data Bus: Lower 8-bits of the memory address (or I/O address) appear on the bus during the first clock cycle (T state) of a machine cycle. It then becomes the data bus during the second and third clock cycles.                                                                                                                                                                                                                                                                              |  |  |  |  |  |

| ALE<br>(Output)                                      | Address Latch Enable: It occurs during the first clock state of a machine cycle and enables<br>the address to get latched into the on-chip latch of peripherals. The falling edge of ALE<br>is set to guarantee setup and hold times for the address information. The falling edge<br>of ALE can also be used to strobe the status information. ALE is never 3-stated.                                                                                                                                             |  |  |  |  |  |

| S₀, S₁, IO/M<br>(Output)                             | $\begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |

| RD<br>(Output, 3-state)                              | READ control: A low level on $\overline{RD}$ indicates the selected memory or I/O device is to be read and that the Data Bus is available for the data transfer, 3-stated during Hold and Halt modes and during RESET.                                                                                                                                                                                                                                                                                             |  |  |  |  |  |

| WR<br>(Output, 3-state)                              | WRITE control: A low level on $\overline{WR}$ indicates the data on the Data Bus is to be written into the selected memory or I/O location. Data is set up at the trailing edge of WR, 3-stated during Hold and Halt modes and during RESET.                                                                                                                                                                                                                                                                       |  |  |  |  |  |

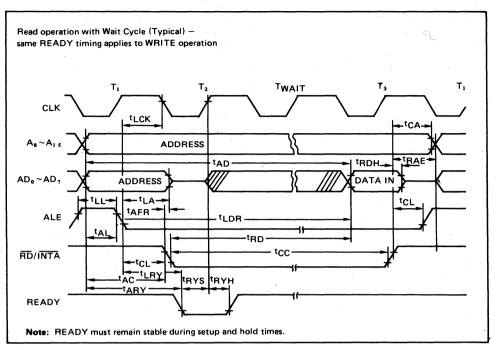

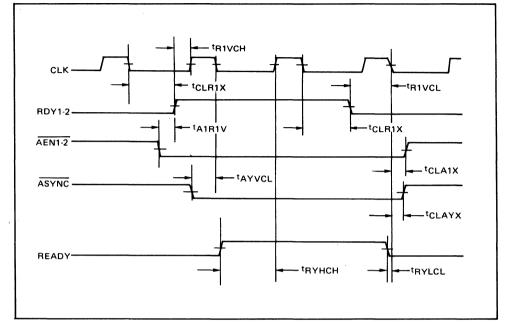

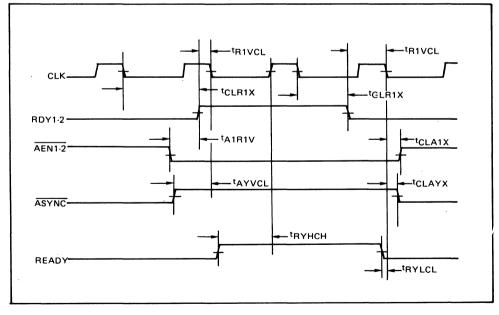

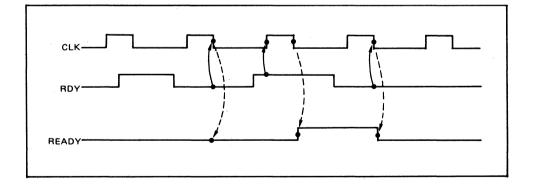

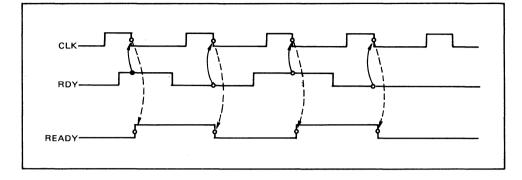

| READY<br>(Input)                                     | If READY is high during a read or write cycle, it indicates that the memory or peripheral<br>is ready to send or receive data. If READY is low, the cpu will wait an integral number<br>of clock cycles for READY to go high before completing the read or write cycle. READY<br>must conform to specified setup and hold times.                                                                                                                                                                                   |  |  |  |  |  |

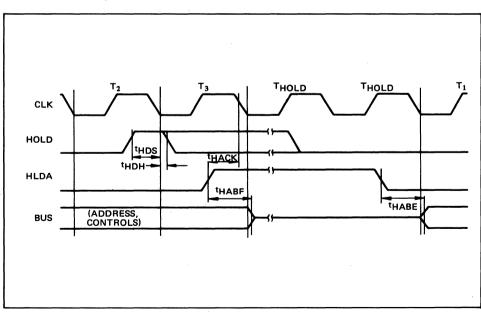

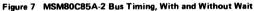

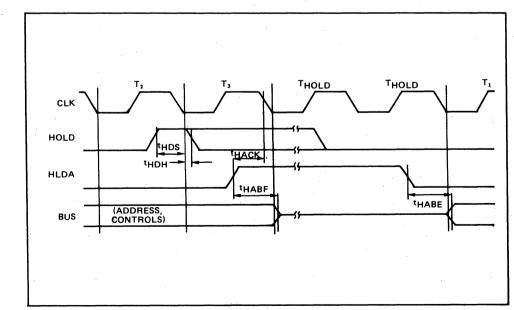

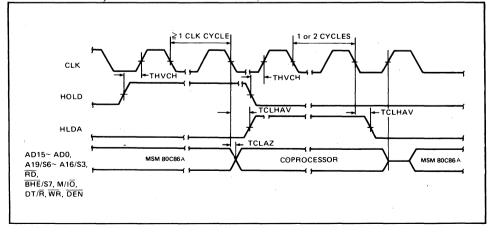

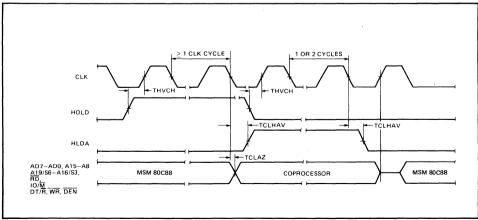

| HOLD<br>(Input)                                      | HOLD indicates that another master is requesting the use of the address and data buses.<br>The cpu, upon receiving the hold request, will relinquish the use of the bus as soon as the<br>completion of the current bus transfer. Internal processing can continue. The processor<br>can regain the bus only after the HOLD is removed. When the HOLD is acknowledged,<br>the Address, Data, RD, WR, and IO/M lines are 3-stated.                                                                                  |  |  |  |  |  |

| HLDA<br>(Output)                                     | HOLD ACKNOWLEDGE: Indicates that the cpu has received the HOLD request and that it will relinquish the bus in the next clock cycle. HLDA goes low after the Hold request is removed. The cpu takes the bus one half clock cycle after HLDA goes low.                                                                                                                                                                                                                                                               |  |  |  |  |  |

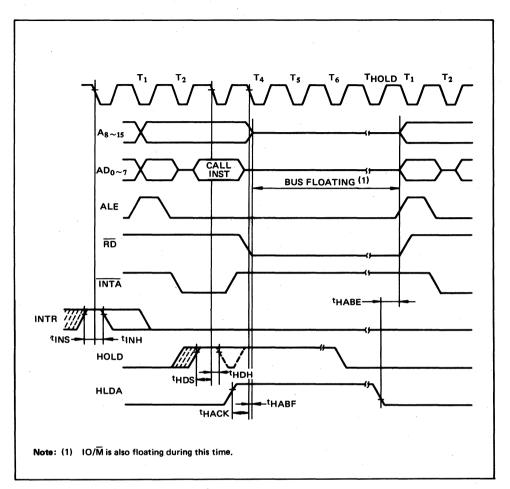

| INTR<br>(Input)                                      | INTERRUPT REQUEST: Is used as a general purpose interrupt. It is sampled only during the next to the last clock cycle of an instruction and during Hold and Halt states. If it is active, the Program Counter (PC) will be inhibited from incrementing and an INTA will be issued. During this cycle a RESTART or CALL instruction can be inserted to jump to the interrupt service routine. The INTR is enabled and disabled by software. It is disabled by Reset and immediately after an interrupt is accepted. |  |  |  |  |  |

| INTA<br>(Output)                                     | INTERRUPT ACKNOWLEDGE: Is used instead of (and has the same timing as) $\overline{\text{RD}}$ during the instruction cycle after an INTR is accepted.                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |

| RST 5.5<br>RST 6.5<br>RST 7.5<br>(Input)             | RESTART INTERRUPTS: These three inputs have the same timing as INTR except they cause an internal RESTART to be automatically inserted.<br>The priority of these interrupts is ordered as shown in Table 1. These interrupts have a higher priority than INTR. In addition, they may be individually masked out using the SIM instruction.                                                                                                                                                                         |  |  |  |  |  |

| TRAP<br>(Input)                                      | Trap interrupt is a nonmaskable RESTART interrupt. It is recognized at the same timing<br>as INTR or RST 5.5–7.5. It is unaffected by any mask or Interrupt Disable. It has the<br>highest priority of any interrupt. (See Table 1.)                                                                                                                                                                                                                                                                               |  |  |  |  |  |

#### CPU·MSM80C85ARS/GS/JS

| Symbol                                     | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|--------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

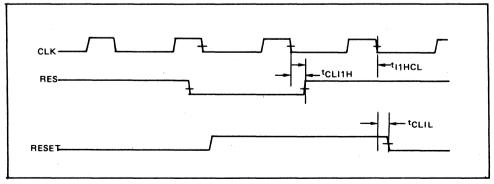

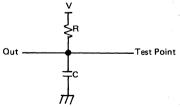

| RESET IN<br>(Input)                        | Sets the Program Counter to zero and resets the Interrupt Enable and HLDA flip-flops.<br>The data and address buses and the control lines are 3-stated during RESET and because<br>of the asynchronous nature of RESET, the processor's internal registers and flags may be<br>altered by RESET with unpredictable results. RESET IN is a Schmitt-triggered input,<br>allowing connection to an R-C network for power-on RESET delay. The cpu is held in<br>the reset condition as long as RESET IN is applied. |

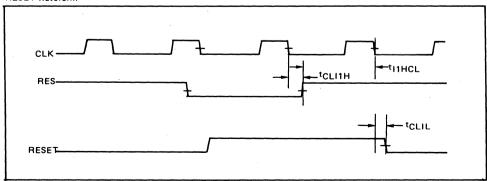

| RESET OUT<br>(Output)                      | Indicates cpu is being reset. Can be used as a system reset. The signal is synchronized to the processor clock and lasts an integral number of clock periods.                                                                                                                                                                                                                                                                                                                                                   |

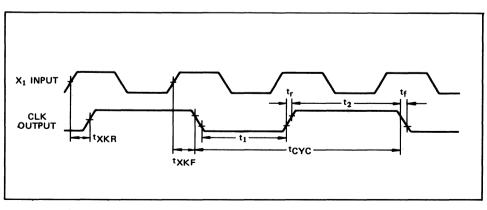

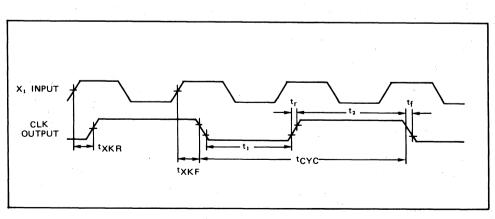

| X <sub>1</sub> , X <sub>2</sub><br>(Input) | $X_1$ and $X_2$ are connected to a crystal to drive the internal clock generator. $X_1$ can also be an external clock input from a logic gate. The input frequency is divided by 2 to give the processor's internal operating frequency.                                                                                                                                                                                                                                                                        |

| CLK<br>(Output)                            | Clock Output for use as a system clock. The period of CLK is twice the $X_1, X_2$ input period.                                                                                                                                                                                                                                                                                                                                                                                                                 |

| SID<br>(Input)                             | Serial input data line. The data on this line is loaded into accumulator bit 7 whenever<br>a RIM instruction is executed.                                                                                                                                                                                                                                                                                                                                                                                       |

| SOD<br>(Output)                            | Serial output data line. The output SOD is set or reset as specified by the SIM instruction.                                                                                                                                                                                                                                                                                                                                                                                                                    |

| V <sub>CC</sub>                            | +5 volt supply.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| GND                                        | Ground Reference.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

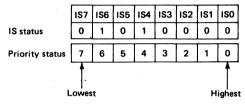

### Table 1 Interrupt Priority, Restart Address, and Sensitivity

| Name    | Priority | Address Branched To (1)<br>When Interrupt Occurs | Type Trigger                                 |

|---------|----------|--------------------------------------------------|----------------------------------------------|

| TRAP    | 1        | 24H                                              | Rising edge and high level until<br>sampled. |

| RST 7.5 | 2        | 3CH                                              | Rising edge (latched).                       |

| RST 6.5 | 3        | 34H                                              | High level until sampled.                    |

| RST 5.5 | 4        | 2CH                                              | High level until sampled.                    |

| INTR    | 5        | (2)                                              | High level until sampled.                    |

Notes: (1)

The processor pushes the PC on the stack before branching to the indicated address. The address branched to depends on the instruction provided to the cpu when the interrupt is ac-(2) knowledged.

### FUNCTIONAL DESCRIPTION

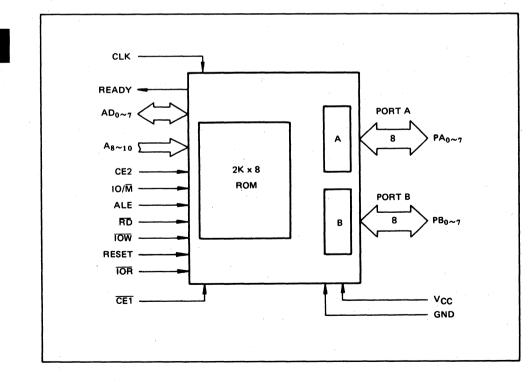

The MSM80C85A is a complete 8-bit parallel central processor. It is designed with silicon gate C-MOS technology and requires a single +5 volt supply. Its basic clock speed is 3MHz, thus improving on the present 8080A's performance with higher system speed. Also it is designed to fit into a minimum system of three IC's: The cpu (MSM80C85A), a RAM/IO (MSM81C55), and a ROM/IO chip (MSM83C55).

The MSM80C85A, has twelve addressable 8-bit registers. Four of them can function only as two 16-bit register pairs. Six others can be used interchangeably as 8-bit registers or a 16-bit register pairs. The MSM-80C85A register set is as follows:

| Mnemonic   | Register          | Contents              |

|------------|-------------------|-----------------------|

| ACC or A   | Accumulator       | 8-bits                |

| PC         | Program Counter   | 16-bit address        |

| BC, DE, HL | General-Purpose   | 8-bit x 6 or          |

|            | Registers;        | 16-bits x 3           |

|            | data pointer (HL) |                       |

| SP         | Stack Pointer     | 16-bit address        |

| Flags or F | Flag Register     | 5 flags (8-bit space) |

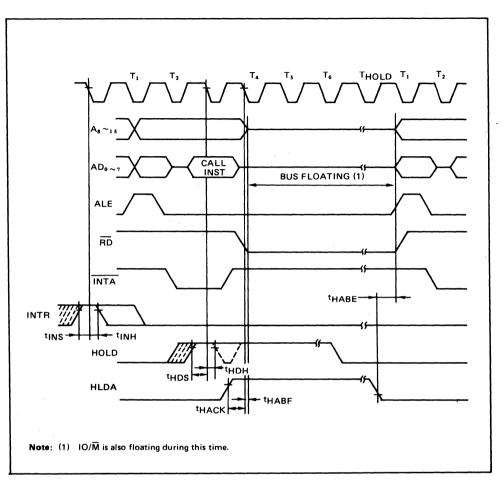

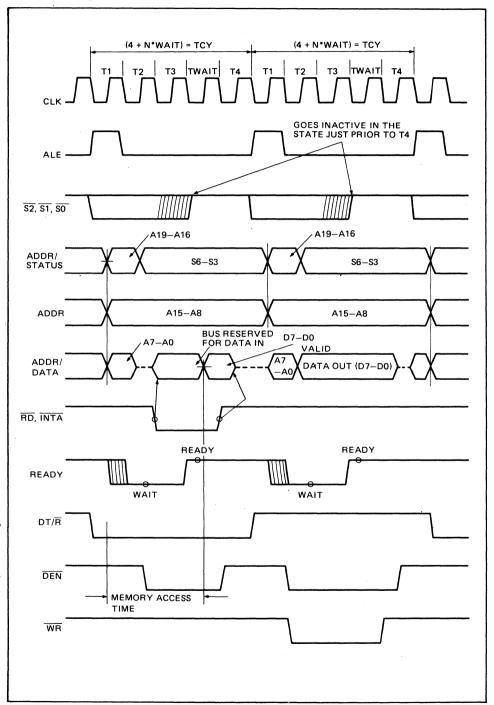

The MSM80C85A uses a multiplexed Data Bus. The address is split between the higher 8-bit Address Bus and the lower 8-bit Address/Data Bus. During the first T state (clock cycle) of a machine cycle the low order address is sent out on the Address/Data Bus. These lower 8-bits may be latched externally by the Address Latch Enable signal (ALE). During the rest of the machine cycle the data bus is used for memory or I/O data.

The MSM80C85A provides  $\overline{\text{RD}}$ ,  $\overline{\text{WR}}$ ,  $S_0$ ,  $S_1$  and  $IO/\overline{\text{M}}$  signals for bus control. An Interrupt Acknowledge signal ( $\overline{\text{INTA}}$ ) is also provided. Hold and all Interrupts are synchronized with the processor's internal clock. The MSM80C85A also provides Serial Input Data (SID) and Serial Output Data (SOD) lines for a simple serial interface.

In addition to these features, the MSM80C85A has three maskable, vector interrupt pins and one nonmaskable TRAP interrupt.

### **INTERRUPT AND SERIAL I/O**

The MSM80C85A has 5 interrupt inputs: INTR, RST 5.5, RST 6.5, RST 7.5, and TRAP, INTR is identical in function to the 8080A INT. Each of the three RESTART inputs, 5.5, 6.5, and 7.5, has a programmable mask. TRAP is also a RESTART interrupt but it is nonmaskable.

The three maskable interrupts cause the internal

execution of RESTART (saving the program counter in the stack and branching to the RESTART address) if the interrupts are enabled and if the interrupt mask is not set. The nonmaskable TRAP causes the internal execution of a RESTART vector independent of the state of the interrupt enable or masks. (See Table 1.)

There are two different types of inputs in the restart interrupts. RST 5.5 and RST 6.5 are high level-sensitive like INTR (and INT on the 8080A) and are recognized with the same timing as INTR. RST 7.5 is rising edge-sensitive.

For RST 7.5, only a pulse is required to set an internal flip-flop which generates the internal interrupt request. The RST 7.5 request flip-flop remains set until the request is serviced. Then it is reset automatically. This flip-flop may also be reset by using the SIM instruction or by issuing a RESET IN to the MSM80C85A. The RST 7.5 internal flip-flop will be set by a pulse on the RST 7.5 pin even when the RST 7.5 interrupt is masked out.

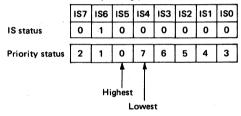

The interrupts are arranged in a fixed priority that determines which interrupt is to be recognized if more than one is pending as follows: TRAP-highest priority, RST 7.5, RST 6.5, RST 5.5, INTR-lowest priority. This priority scheme does not take into account the priority of a routine that was started by a higher priority interrupt. RST 5.5 can interrupt an RST 7.5 routine if the interrupts are re-enabled before the end of the RST 7.5 routine.

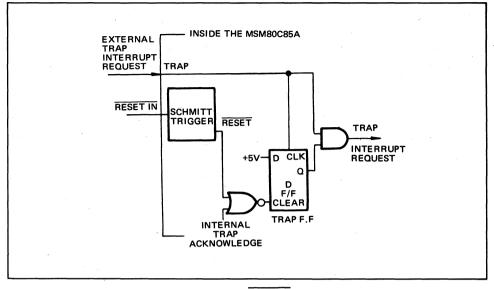

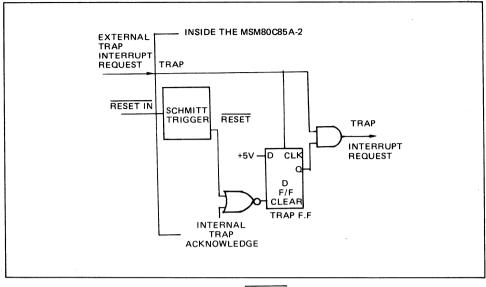

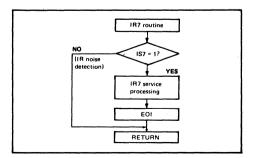

The TRAP interrupt is useful for catastrophic events such as power failure or bus error. The TRAP input is recognized just as any other interrupt but has the highest priority. It is not affected by any flag or mask. The TRAP input is both edge and level sensitive. The TRAP input must go high and remain high until it is acknowledged. It will not be recognized again until it goes low, then high again. This avoids any false triggering due to noise or logic glitches. Figure 3 illustrates the TRAP interrupt request circuitry within the MSM80C85A. Note that the servicing of any interrupt (TRAP, RST 7.5, RST 6.5, RST 5.5, INTR) disables all future interrupts (except TRAPs) until an El instruction is executed.

The TRAP interrupt is special in that it disables interrupts, but preserves the previous interrupt enable status. Performing the first RIM instruction following a TRAP interrupt allows you to determine whether interrupts were enabled or disabled prior to the TRAP. All subsequent RIM instructions provide current interrupt enable status. Performing a RIM instruction following INTR or RST 5.5–7.5 will provide current interrupt Enable status, revealing that interrupts are disabled.

The serial I/O system is also controlled by the RIM and SIM instructions. SID is read by RIM, and SIM sets the SOD data.

Figure 3 Trap and RESET IN Circuit

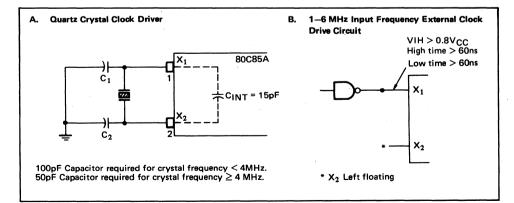

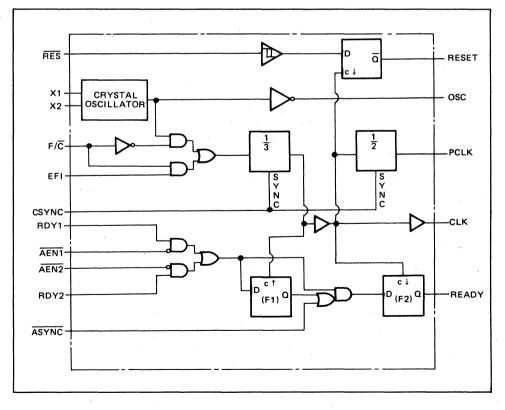

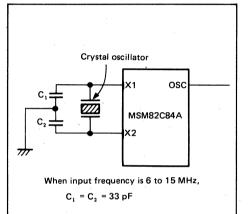

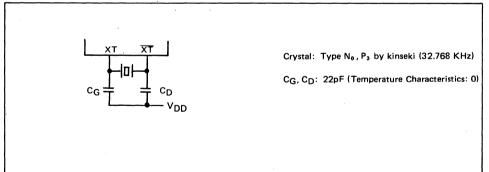

### DRIVING THE X<sub>1</sub> and X<sub>2</sub> INPUTS

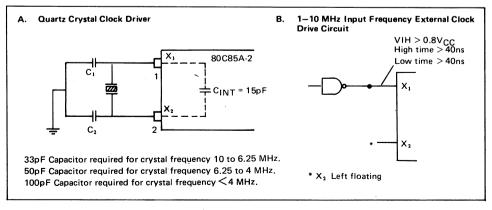

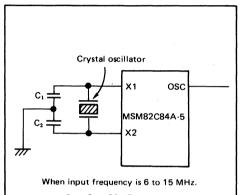

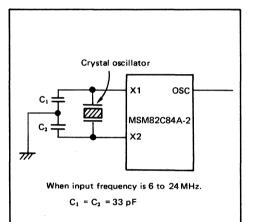

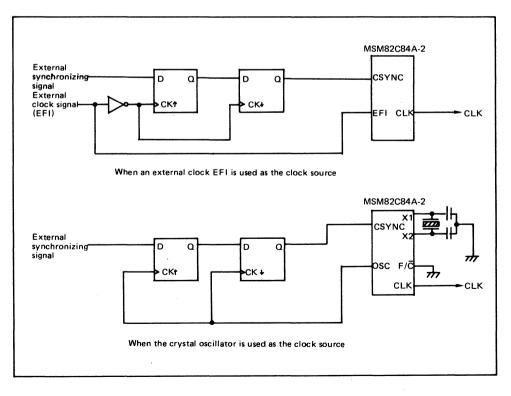

You may drive the clock inputs of the MSM80C-85A with a crystal, or an external clock source. The driving frequency must be at least 1 MHz, and must be twice the desired internal clock frequency; hence, the MSM80C85A is operated with a 6 MHz cyrstal (for 3 MHz clock). If a crystal is used, it must have the following characteristics:

- Parallel resonance at twice the clock frequency desired

- $C_L$  (load capacitance)  $\leq$  30 pF

- $C_S$  (shunt capacitance)  $\leq$  7 pF

$R_{S}$  (equivalent shunt resistance)  $\leq$  75 ohms

Drive level: 10 mW

Frequency tolerance: ±.005% (suggested)

Note the use of the capacitors between  $X_1$ ,  $X_2$  and ground. These capacitors are required to assure oscillator startup at the correct frequency.

Figure 4 shows the recommended clock driver circuits. Note in B that a pullup resistor is required to assure that the high level voltage of the input is at least 4V.

For driving frequencies up to and including 6 MHz you may supply the driving signal to  $X_1$  and leave  $X_2$  open-circuited (Figure 4B). To prevent self-oscillation of the MSM80C85A, be sure that  $X_2$  is not coupled back to  $X_1$  through the driving circuit.

Figure 4 Clock Driver Circuits

### ■ CPU·MSM80C85ARS/GS/JS ■

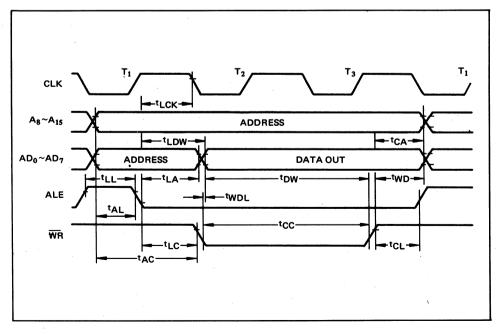

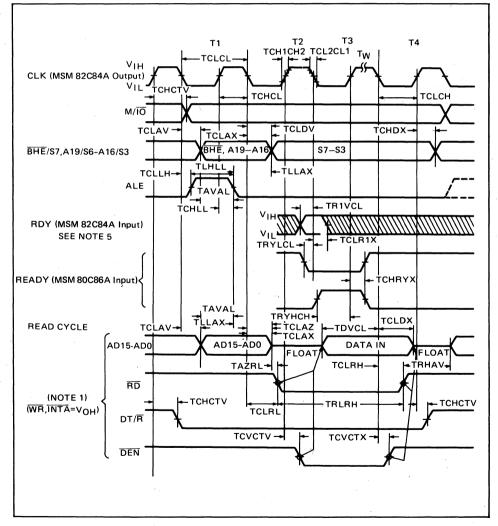

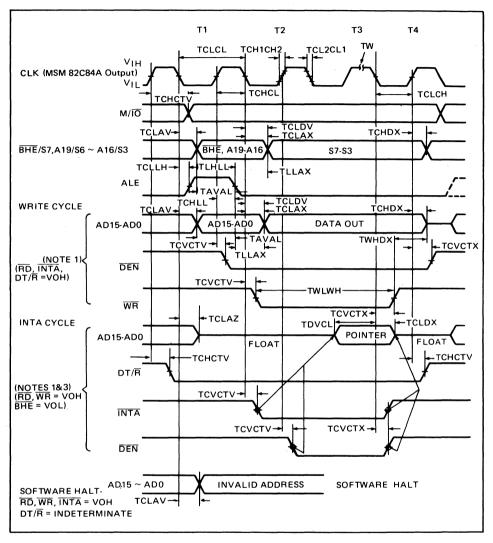

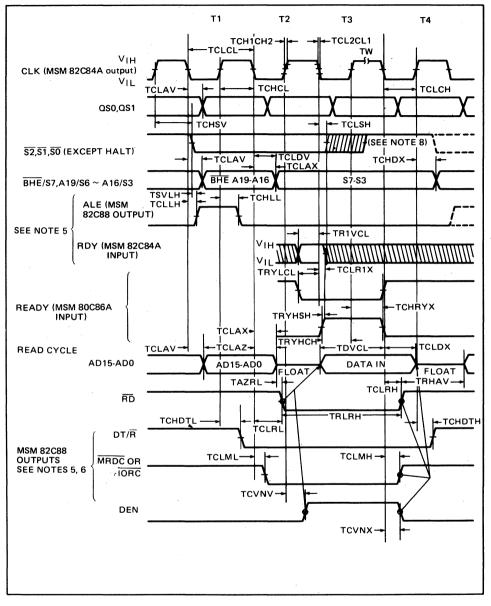

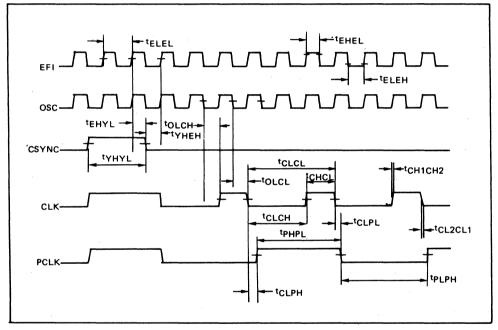

### **BASIC SYSTEM TIMING**

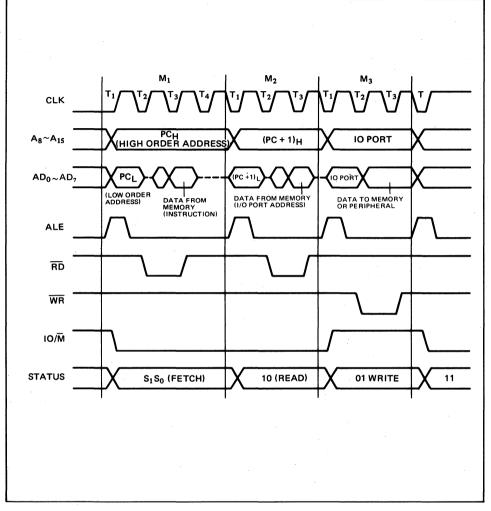

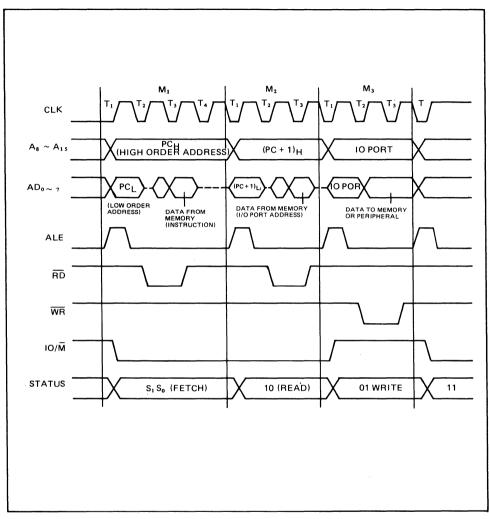

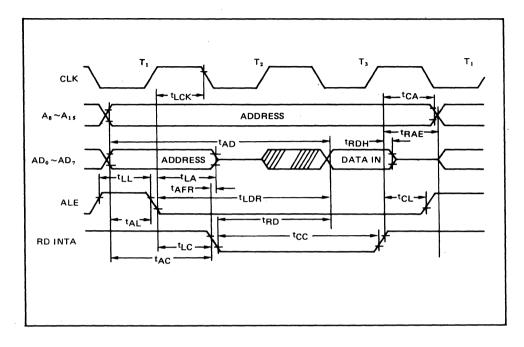

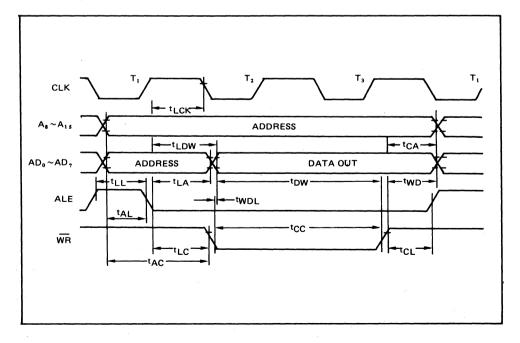

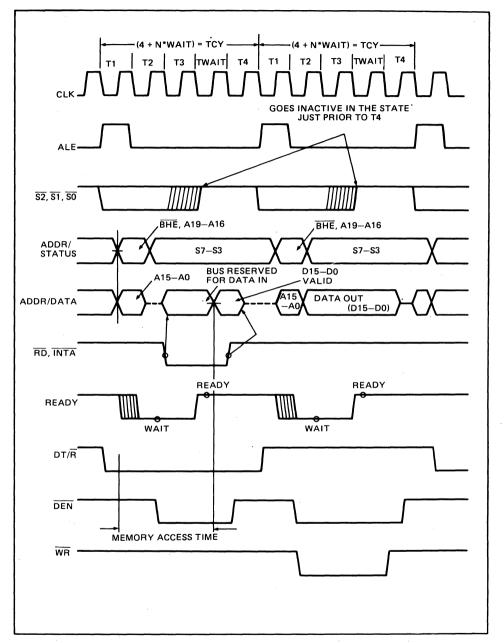

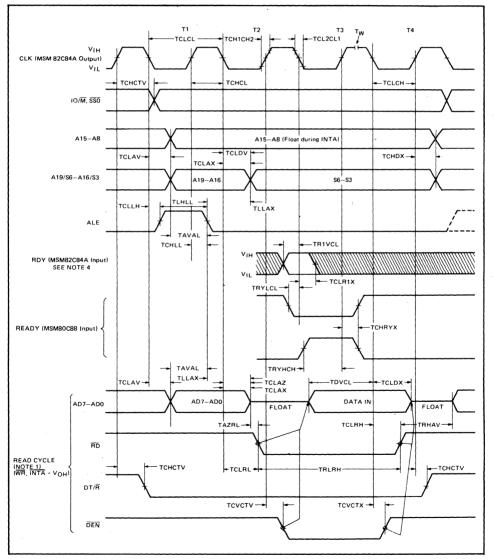

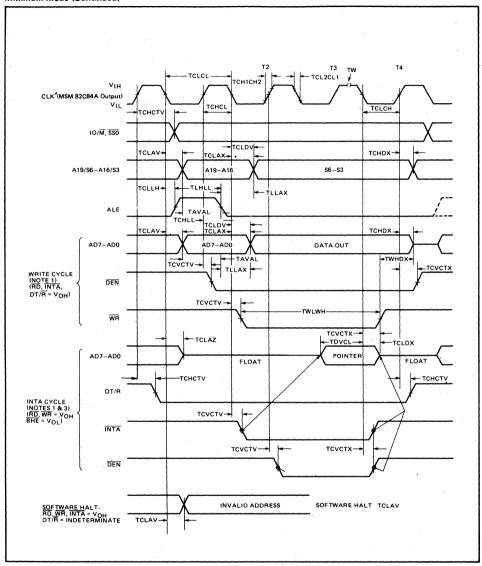

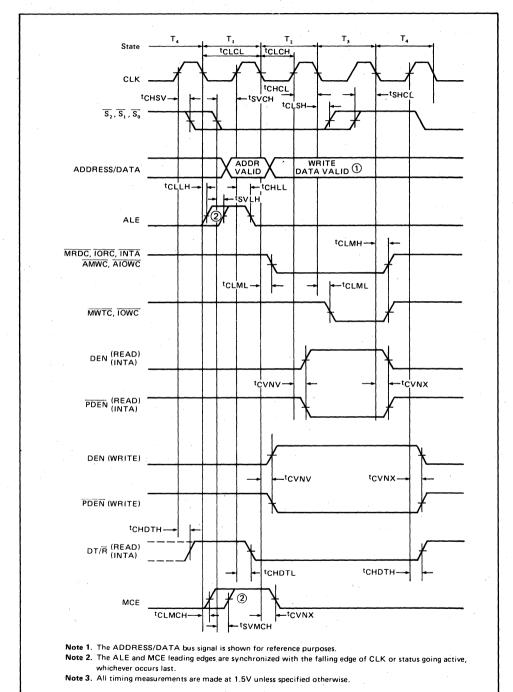

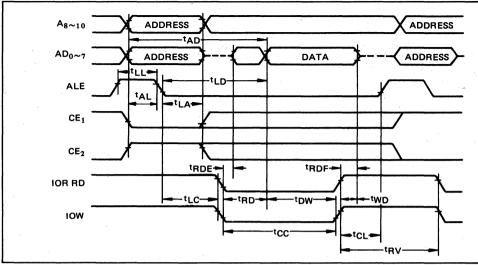

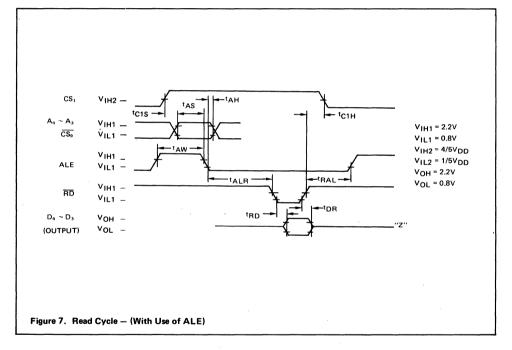

The MSM80C85A has a multiplexed Data Bus. ALE is used as a strobe to sample the lower 8-bits of address on the Data Bus. Figure 5 shows an instruction fetch, memory read and I/O write cycle (as would occur during processing of the OUT instruction). Note that during the I/O write and read cycle that the I/O port address is copied on both the upper and lower half of the address.

There are seven possible types of machine cycles. Which of these seven takes place is defined by the status of the three status lines  $(10/M, S_1, S_0)$  and the

three control signals ( $\overline{RD}$ ,  $\overline{WR}$ , and  $\overline{INTA}$ ). (See Table 2.) The status line can be used as advanced controls (for device selection, for example), since they become active at the T<sub>1</sub> state, at the outset of each machine cycle. Control lines  $\overline{RD}$  and  $\overline{WR}$  become active later, at the time when the transfer of data is to take place, so are used as command lines.

A machine cycle normally consists of three T states, with the exception of OPCODE FETCH, which normally has either four or six T states (unless WAIT or HOLD states are forced by the receipt of READY or HOLD inputs). Any T state must be one of ten possible states, shown in Table 3.

|                     |                     | Status |   |   | Control |    |      |

|---------------------|---------------------|--------|---|---|---------|----|------|

| Machine C           | ycie                | 10/M   |   |   | RD      | WR | INTA |

| Opcode Fetch        | (OF)                | 0      | 1 | 1 | 0       | 1  | 1    |

| Memory Read         | (MR)                | 0      | 1 | 0 | 0       | 1  | 1    |

| Memory Write        | (MW)                | 0      | 0 | 1 | 1       | 0  | 1    |

| I/O Read            | (IOR)               | 1      | 1 | 0 | 0       | 1  | 1    |

| I/O Write           | (IOW)               | 1      | 0 | 1 | 1       | 0  | 1    |

| Acknowledge of INTR | (INA)               | 1      | 1 | 1 | 1       | 1  | 0    |

| Bus Idle            | (BI):DAD<br>ACK. OF | 0      | 1 | 0 | 1       | 1  | 1    |

|                     | RST, TRAP           | 1      | 1 | 1 | 1       | 1  | 1    |

|                     | HALT                | тs     | 0 | 0 | TS      | TS | 1    |

### Table 2 MSM80C85A Machine Cycle Chart

|  | Table 3 | MSM80C85A | Machine | State | Chart |

|--|---------|-----------|---------|-------|-------|

|--|---------|-----------|---------|-------|-------|

| M 11 0         |                                 | Status | & Buses                         |         |        | Control |       |

|----------------|---------------------------------|--------|---------------------------------|---------|--------|---------|-------|

| Machine State  | S <sub>1</sub> , S <sub>0</sub> | 10/M   | A <sub>8</sub> -A <sub>15</sub> | AD0-AD7 | RD, WR | INTA    | ALE   |

| Т1             | х                               | x      | x                               | X       | 1      | 1       | 1 (1) |

| T <sub>2</sub> | х                               | x      | x                               | ×       | x      | x       | 0     |

| TWAIT          | х                               | x      | x                               | x       | x      | x       | 0     |

| T <sub>3</sub> | X                               | x      | x                               | ×       | x      | x       | 0     |

| Т4             | 1                               | 0 (2)  | x                               | TS      | 1      | 1       | 0     |

| T <sub>5</sub> | 1                               | 0 (2)  | ×                               | TS      | 1      | 1       | 0     |

| т <sub>6</sub> | 1                               | 0 (2)  | ×                               | TS      | 1      | 1       | 0     |

| TRESET         | х                               | TS     | TS                              | TS      | тs     | 1       | 0     |

| THALT          | 0                               | TS     | TS                              | TS      | TS     | 1       | 0     |

| THOLD          | х                               | тѕ     | TS                              | TS      | TS     | 1       | 0     |

0 = Logic "0"

1 = Logic "1"

TS = High Impedance

X = Unspecified

Notes: (1) ALE not generated during 2nd and 3rd machine cycles of DAD instruction. (2)  $IO/\overline{M} = 1$  during  $T_4 \sim T_6$  of INA machine cycle. Ð

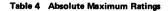

| Ambient Temperature under Bias   | -40°C to + 85°C  |

|----------------------------------|------------------|

| Storage Température              | –55°C to + 150°C |

| Supply Voltage Respect to Ground | -0.3V to + 7.0V  |

| Input Voltage Respect to Ground  |                  |

| Power Dissipation                | 1.0 Watt (DIP)   |

|                                  | 0.7 Watt (FLAT)  |

|                                  | 1.0 Watt (PLCC)  |

Note: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

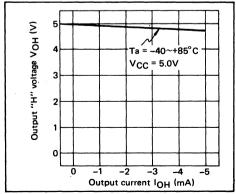

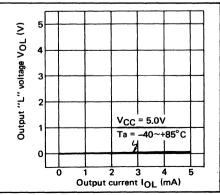

## **D.C. CHARACTERISTICS**

(T<sub>A</sub> = -40°C to + 85°C; V<sub>CC</sub> = 5V  $\pm$ 10%; unless otherwise specified)

| Parameter               | Symbol | Min. | Тур. | Max.                  | Units | Test Conditions                                                                   | l.                        |

|-------------------------|--------|------|------|-----------------------|-------|-----------------------------------------------------------------------------------|---------------------------|

| Input Low Voltage       | VIL    | -0.3 |      | +0.8                  | v     |                                                                                   |                           |

| Input High Voltage      | ∨ін    | 2.2  |      | V <sub>CC</sub> + 0.3 | v     |                                                                                   |                           |

| Output Low Voltage      | VOL    |      |      | 0.45                  | v     | IOL = 2mA                                                                         |                           |

| Output High Voltage     | Val    | 2.4  |      |                       | v     | I <sub>OH</sub> =400μA                                                            |                           |

|                         | VOH    | 4.2  |      |                       | v     | I <sub>OH</sub> = -40μA                                                           |                           |

| Input Leak              | 1LI    | -10  |      | 10                    | μA    | $0V \le V_{IN} \le V_{CC}$                                                        |                           |

| Output Leak             | ILO    | -10  |      | 10                    | μA    | $0V \le V_{OUT} \le V_{CC}$                                                       |                           |

| Input Low Level, RESET  | VILR   | -0.3 |      | +0.8                  | v     |                                                                                   |                           |

| Input High Level, RESET | VIHR   | 3.0  |      | V <sub>CC</sub> + 0.3 | v     |                                                                                   |                           |

| Hysteresis, RESET       | VHY    | 0.25 |      |                       | v     |                                                                                   |                           |

| Baura Suralu Currant    |        |      | 10   | 22                    | mA    | $V_{CC} = 4.5V \text{ to } 5.5V$<br>$T_A = -40^{\circ}C \text{ to } +85^{\circ}C$ | tCYC =<br>320ns           |

| Power Supply Current    | ICC    |      | 10   | 17                    | mA    | $V_{CC} = 4.75V \text{ to } 5.25V$<br>$T_A = 0^{\circ}C \text{ to } +85^{\circ}C$ | Reset<br>Active<br>CL=0pF |

| Power Supply Voltage    | Vcc    | 4    | 5    | 6                     | v     |                                                                                   |                           |

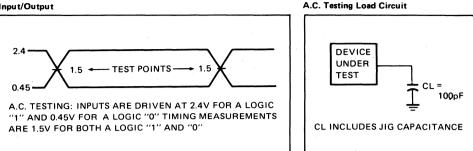

## A.C. CHARACTERISTICS

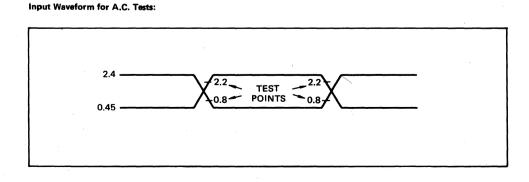

$(T_A = -40^{\circ}C \text{ to } 85^{\circ}C; V_{CC} = 5V \pm 10\%)$

| Parameter                                                       | Cumbal                          | 800  | 85A  | Units |

|-----------------------------------------------------------------|---------------------------------|------|------|-------|

| rarameter                                                       | Symbol                          | Min. | Max. |       |

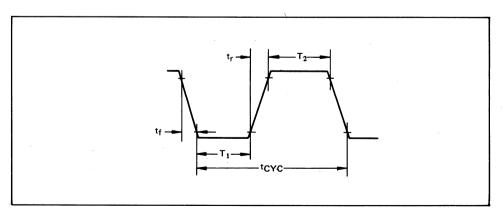

| CLK Cýcle Period                                                | tCYC                            | 320  | 2000 | ns    |

| CLK Low Time                                                    | t <sub>1</sub>                  | 80   |      | ns    |

| CLK High Time                                                   | t <sub>2</sub>                  | 120  |      | ns    |

| CLK Rise and Fall Time                                          | t <sub>r</sub> , t <sub>f</sub> |      | 30   | ns    |

| X <sub>1</sub> Rising to CLK Rising                             | <sup>t</sup> XKR                | 30   | 120  | ns    |

| X <sub>1</sub> Rising to CLK Falling                            | <sup>t</sup> XKF                | 30   | 150  | ns    |

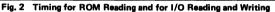

| $A_{8\sim15}$ Valid to Leading Edge of Control (1)              | tAC                             | 270  |      | ns    |

| $A_{0\sim7}$ Valid to Leading Edge of Control                   | tACL                            | 240  |      | ns    |

| A <sub>0~15</sub> Valid to Valid Data In                        | tAD                             |      | 575  | ns    |

| Address Float After Leading Edge of RD (INTA)                   | tAFR                            |      | 0    | ns    |

| $A_{8\sim 15}$ Valid Before Trailing Edge of ALE <sup>(1)</sup> | tAL                             | 115  |      | ns    |

| $A_{0\sim7}$ Valid Before Trailing Edge of ALE                  | tALL                            | 90   |      | ns .  |

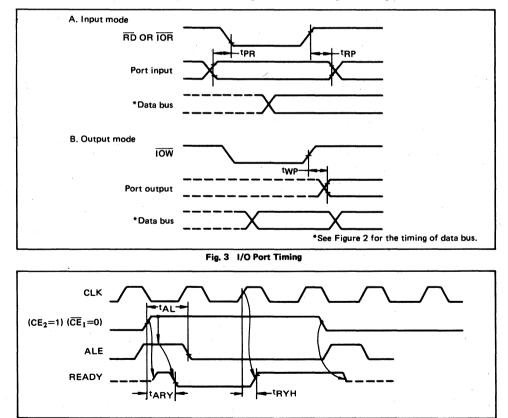

| READY Valid from Address Valid                                  | <sup>t</sup> ARY                |      | 220  | ns    |

| Address (A8-A15) Valid After Control                            | <sup>t</sup> CA                 | 120  |      | ns    |

| Width of Control Low (RD, WR, INTA)                             | tcc                             | 400  |      | ns    |

| Trailing Edge of Control to Leading Edge of ALE                 | tCL                             | 50   |      | ns    |

| Data Valid to Trailing Edge of WR                               | tDW                             | 420  |      | ns    |

| HLDA to Bus Enable                                              | tHABE                           |      | 210  | ns    |

| Bus Float After HLDA                                            | tHABF                           |      | 210  | ns    |

### CPU·MSM80C85ARS/GS/JS

### A.C. CHARACTERISTICS (cont'd)

| Parameter                                                | Symbol           | 800  | 85A  | 11-1-1- |

|----------------------------------------------------------|------------------|------|------|---------|

| rarameter                                                | Symbol           | Min. | Max. | Units   |

| HLDA Valid to Trailing Edge of CLK                       | <b>tHACK</b>     | 110  |      | ns      |

| HOLD Hold Time                                           | tHDH             | 0    |      | ns      |

| HOLD Setup Time to Trailing Edge of CLK                  | tHDS             | 170  |      | ns      |

| INTR Hold Time                                           | ЧNН              | 0    |      | ns      |

| INTR, RST, and TRAP Setup Time to Falling Edge<br>of CLK | tINS             | 160  |      | ns      |

| Address Hold Time After ALE                              | <sup>t</sup> LA  | 100  | ×    | ns      |

| Trailing Edge of ALE to Leading Edge of Control          | tLC              | 130  |      | ns      |

| ALE Low During CLK High                                  | <sup>t</sup> LCK | 100  |      | ns      |

| ALE to Valid Data During Read                            | <sup>t</sup> LDR |      | 460  | ns      |

| ALE to Valid Data During Write                           | tLDW             |      | 200  | ns      |

| ALE Width                                                | <sup>t</sup> LL  | 140  |      | ns      |

| ALE to READY Stable                                      | <sup>‡</sup> LRY |      | 110  | ns      |

| Trailing Edge of RD to Re-Enabling of Address            | <sup>t</sup> RAE | 150  |      | ns      |

| RD (or INTA) to Valid Data                               | tRD              |      | 300  | ns      |

| Control Trailing Edge to Leading Edge of Next Control    | <sup>t</sup> RV  | 400  |      | ns      |

| Data Hold Time After RD INTA (7)                         | tRDH             | 0    |      | ns      |

| READY Hold Time                                          | <sup>t</sup> RYH | 0    |      | ns      |

| READY Setup Time to Leading Edge of CLK                  | tRYS             | 110  |      | ns      |

| Data Valid After Trailing Edge of WR                     | tWD              | 100  |      | ns      |

| LEADING Edge of WR to Data Valid                         | tWDL             |      | 40   | ns      |

Notes: (1)  $A_8 - A_{15}$  address Specs apply to  $IO/\overline{M}$ ,  $S_0$ , and  $S_1$  except  $A_8 - A_{15}$  are undefined during  $T_4 - T_6$  of OF cycle whereas  $IO/\overline{M}$ , S<sub>0</sub>, and S<sub>1</sub> are stable.

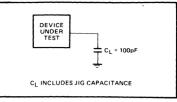

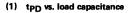

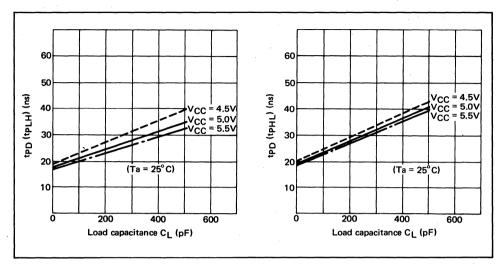

(2) Test conditions:  $t_{CYC} = 320$ ns  $C_L = 150$ pF (3) For all output timing where  $C_L = 150$ pF use the following correction factors:

$25pF \leq C_{L} < 150pF$ : -0.10ns/pF  $150 pF < C_L \le 300 pF: +0.30 ns/pF$

(4) Output timings are measured with purely capacitive load.

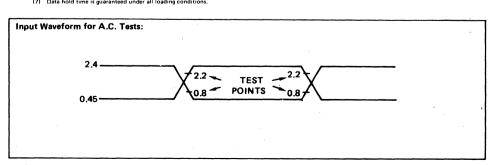

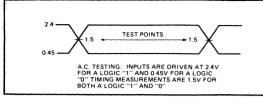

- (5) All timings are measured at output voltage  $V_L = 0.8V$ ,  $V_H = 2.2V$ , and 1.5V with 10ns rise and fall time on inputs.

- (6) To calculate timing specifications at other values of tCYC use Table 7.

- (7) Data hold time is guaranteed under all loading conditions.

|                   | MSM80C85A |                  |     |  |  |  |  |

|-------------------|-----------|------------------|-----|--|--|--|--|

| <sup>t</sup> AL   | -         | (1/2)T — 45      | MIN |  |  |  |  |

| <sup>t</sup> LA   | -         | (1/2)T — 60      | MIN |  |  |  |  |

| tLL               | -         | (1/2)T — 20      | MIN |  |  |  |  |

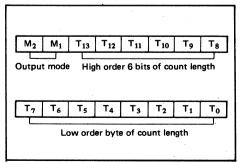

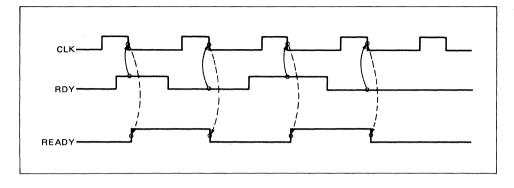

| <sup>t</sup> LCK  | -         | (1/2)T — 60      | MIN |  |  |  |  |