# NxVL<sup>™</sup> System Controller Databook

PRELIMINARY March 4, 1994

PROPRIETARY and CONFIDENTIAL COPYING is FORBIDDEN

**NexGen™** Microproducts, Inc. 1623 Buckeye Drive Milpitas, CA 95035

Order # NxDOC-DB002-01-W

#### Copyright © 1993, 1994 by NexGen Microproducts, Inc.

The goal of this databook is to enable our customers to make informed purchase decisions and to design systems around our described products. Every effort is made to provide accurate information in support of these goals. However, representations made by this databook are not intended to describe the internal logic and physical design. Wherever product internals are discussed, the information should be construed as conceptual in nature. No presumptions should be made about the internal design based on this document. Information about the internal design of NexGen products is provided via nondisclosure agreement ("NDA") on a need to know basis.

The material in this document is for information only and is subject to change without notice. NexGen reserves the right to make changes in the product specification and design without reservation and without notice to its users. THIS DOCUMENT DOES NOT CONSTITUTE A WARRANTY OF ANY KIND WITH RESPECT TO THE NEXGEN INC. PRODUCTS, AND NEXGEN INC. SHALL NOT BE LIABLE FOR ANY ERRORS THAT APPEAR IN THIS DOCUMENT.

All purchases of NexGen products shall be subject to NexGen's standard terms and conditions of sale. THE WARRANTIES AND REMEDIES EXPRESSLY SET FORTH IN SUCH TERMS AND CONDITIONS SHALL BE THE SOLE WARRANTIES AND THE BUYER'S SOLE AND EXCLUSIVE REMEDIES, AND NEXGEN INC. SPECIFICALLY DISCLAIMS ANY AND ALL OTHER WARRANTIES, WHETHER EXPRESS, IMPLIED OR STATUTORY, INCLUDING THE IMPLIED WARRANTIES OF FITNESS FOR A PARTICULAR PURPOSE, AGAINST INFRINGEMENT AND OF MERCHANTABILITY. No person is authorized to make any other warranty or representation concerning the performance of the NexGen products. In particular, NexGen's products are not specifically designed, manufactured or intended for sale as components for the planning, design, construction, maintenance, operation or use of any nuclear facility or other ultra-hazardous activity, and neither NexGen nor its suppliers shall have any liability with respect to such use

#### Trademark Acknowledgments

NexGen, Nx586, Nx587, RISC86, NexBus, NxPCI, and NxVL are trademarks of NexGen Microproducts, Inc..

IBM, AT, and PS/2 are registered trademarks of International Business Machines, Inc. Intel is a registered trademark of Intel Corporation. i386, i387, i486 and Pentium are trademarks of Intel Corporation. Tri-state is a registered trademark of National Semiconductor Corporation. VL-Bus is a trademark of Video Electronics Standards Association.

#### Restricted Rights and Limitations

Use, duplication, or disclosure by the Government is subject to restrictions set forth in subparagraph (c)(1)(ii) of the Rights in technical Data and Computer Software clause at 252.2777-7013

NexGen, Nx586, Nx587, RISC86, NexBus, NxPCI, and NxVL are trademarks of NexGen Microproducts, Inc. NOTICE: THESE MATERIALS ARE PROPRIETARY TO NEXGEN AND ARE PROVIDED PURSUANT TO A CONFIDENTIALITY AGREEMENT FOR YOUR EVALUATION ONLY. ANY VIOLATION IS SUBJECT TO LEGAL ACTION.

# Contents

| Preface                                        | vi |

|------------------------------------------------|----|

| Notation                                       | vi |

| Related Publications                           | iz |

| NxVL Features and Signals                      | 1  |

| NxVL Pinouts by Signal Names                   |    |

| NxVL Pinouts by Pin Numbers                    |    |

| NexBus Signals                                 | 10 |

| NexBus Arbitration                             | 10 |

| NexBus Cycle Control                           | 11 |

| NexBus Cache Control                           | 12 |

| NexBus Transceiver Control                     | 13 |

| NexBus Address and Data Bus                    | 13 |

| VL-Bus Signals                                 | 14 |

| VL-Bus Arbitration                             | 14 |

| VL-Bus Cycle Control                           | 14 |

| VL-Bus Address                                 | 16 |

| VL-Bus Data                                    | 16 |

| ISA Bus Signals                                | 17 |

| ISA-Bus Cycle Control                          | 17 |

| ISA-Bus Transceiver Control                    | 19 |

| ISA-Bus Address, Refresh, and Clock            | 20 |

| Memory-Bus Signals                             | 21 |

| Integrated Peripheral Controller (IPC) Signals | 22 |

| NxVL System Signals                            | 23 |

| NxVL Alphabetical Signal Summary               | 25 |

| Hardware Architecture                          | 29 |

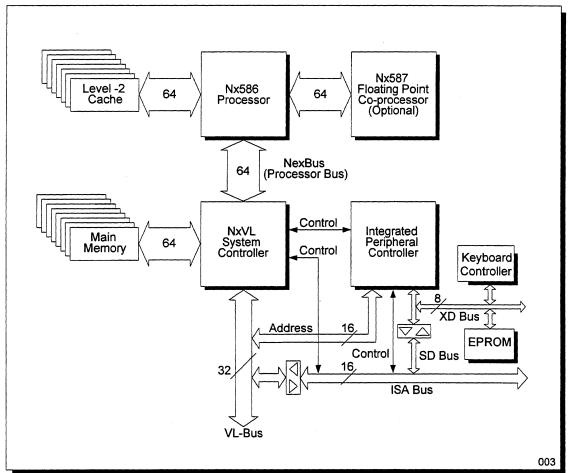

| System Overview                                | 29 |

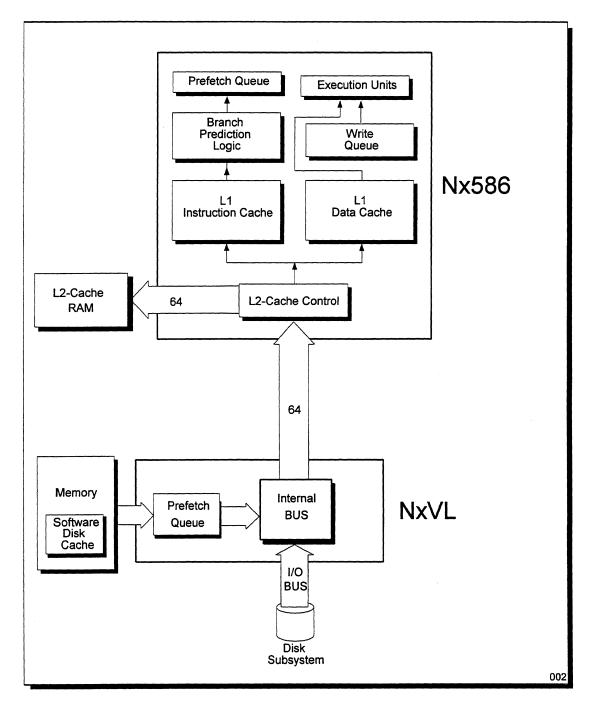

| Internal Architecture                          |    |

| Main-Memory Write Queue                        |    |

| Bus Structure                                  |    |

|                                                |    |

**PRELIMINARY**

NxVL™ Systems Logic

III

| NexBus                                         | . 37 |

|------------------------------------------------|------|

| VL-Bus                                         | 40   |

| ISA-bus                                        | 41   |

| Bus Arbitration                                | 47   |

| Bus-Crossing Operations                        |      |

| Memory                                         | 49   |

| Organization                                   | 49   |

| Read/Write Reordering                          | 50   |

| DMA Transfers                                  | 50   |

| Bus Snooping and Cache Coherency               | 51   |

| Design Example                                 |      |

|                                                |      |

| Bus Operations                                 |      |

| Arbitration Protocols                          |      |

| Bus-Arbitration Protocol                       |      |

| Main-Memory Arbitration Protocol               |      |

| Nx586 Processor Operations                     |      |

| Bus Arbitration, Address Phase, and Data Phase | 59   |

| Processor Write to Main Memory                 |      |

| Processor Read from Main Memory                | 65   |

| Processor Write to VL Slave                    | 68   |

| Processor Read from VL Slave                   | 71   |

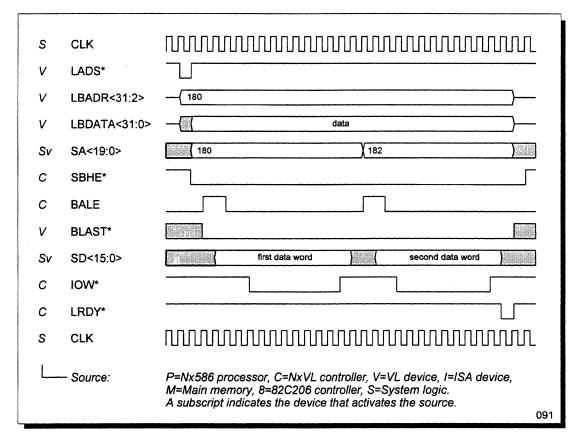

| Processor Write to ISA Slave                   | 72   |

| Processor Read from ISA Slave                  | 75   |

| Snooping and Processor Intervention            |      |

| VL-Bus Master Operations                       | 78   |

| Bus Arbitration                                | 78   |

| VL Write to Main Memory                        | 79   |

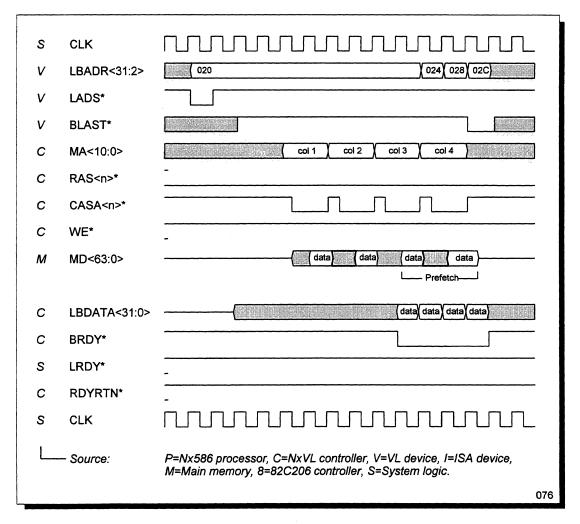

| VL Read from Main Memory                       | 80   |

| VL Write to ISA Slave                          | 83   |

| VL Read from ISA Slave                         | 84   |

| ISA-Bus Master Operations                      | 85   |

| Bus Arbitration                                | 86   |

| ISA Write to Main Memory                       | 87   |

| ISA Read from Main Memory                      | . 88 |

| ISA Write to VL Slave                          | 88   |

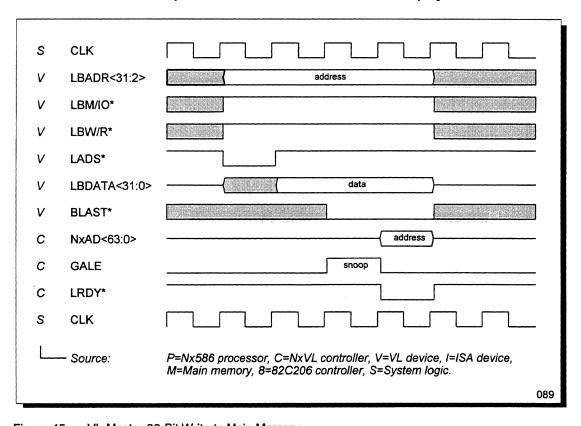

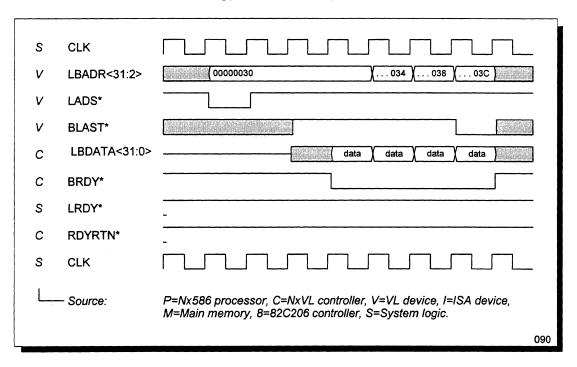

| ISA Read from VL Slave                         | 90   |

| ISA-Bus Memory Refresh                         | 91   |

| DMA Operations                                 |      |

| ISA I/O to VL Memory                           |      |

| Main Memory to ISA I/O                         |      |

| Main-Memory Operations                         |      |

| Slow Main-Memory Cycles                        |      |

| Fast Main-Memory Cycles                        |      |

NxVL™ Systems Logic

| Reset and Configuration Registers   |     |

|-------------------------------------|-----|

| Reset and Initialization            | 101 |

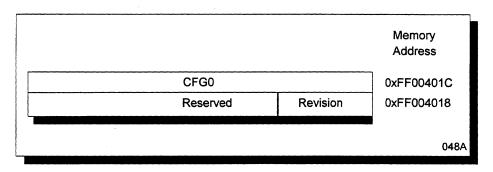

| Configuration and Mapping Registers | 102 |

| Configuration Register (CFG0)       |     |

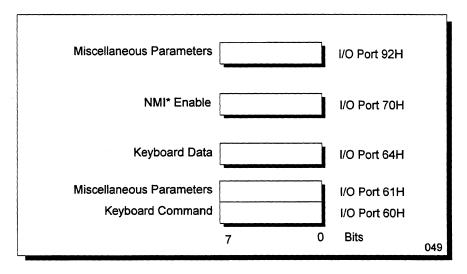

| Port 61                             | 106 |

| Port 70 (NMI*)                      | 107 |

| Port 92                             | 107 |

| Port 60 and Port 64 (Keyboard)      | 108 |

| Electrical Data                     | 109 |

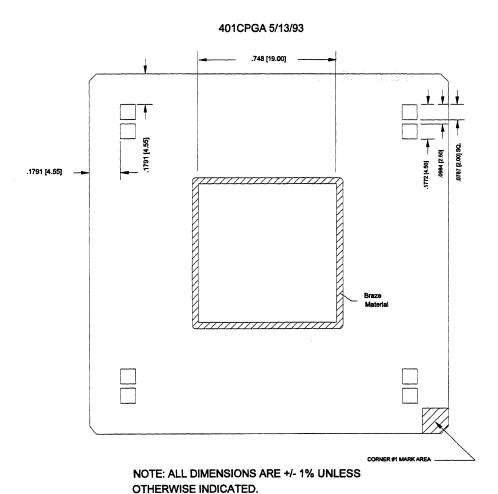

| Mechanical Data                     | 111 |

| Glossary                            | 115 |

| Index                               | 121 |

|   |  |   | Ī |  |  |

|---|--|---|---|--|--|

|   |  |   |   |  |  |

|   |  |   |   |  |  |

|   |  |   |   |  |  |

|   |  |   |   |  |  |

|   |  |   |   |  |  |

|   |  |   |   |  |  |

|   |  |   |   |  |  |

|   |  |   |   |  |  |

|   |  |   |   |  |  |

|   |  |   |   |  |  |

|   |  |   |   |  |  |

|   |  |   |   |  |  |

|   |  | · |   |  |  |

|   |  |   |   |  |  |

|   |  |   |   |  |  |

|   |  |   |   |  |  |

|   |  |   |   |  |  |

|   |  |   |   |  |  |

|   |  |   |   |  |  |

|   |  |   |   |  |  |

|   |  |   |   |  |  |

|   |  |   |   |  |  |

|   |  |   |   |  |  |

|   |  |   | ! |  |  |

|   |  |   |   |  |  |

| , |  |   |   |  |  |

|   |  |   |   |  |  |

# **Figures**

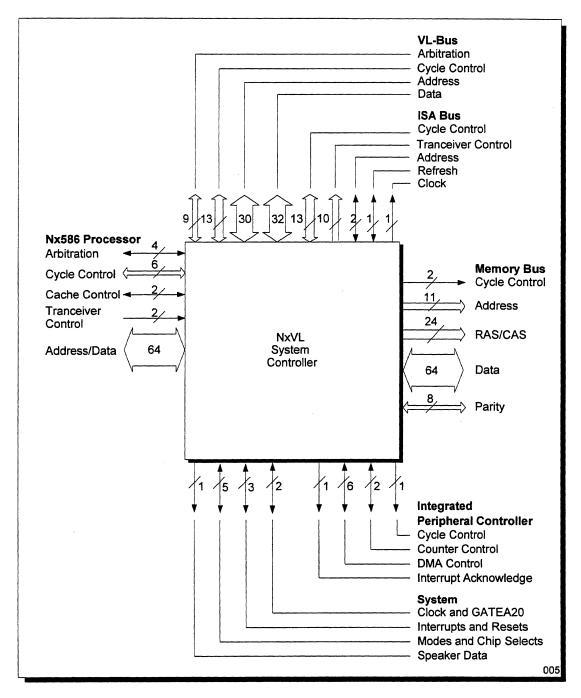

| Figure 1  | NxVL Signal Organization                         | 3  |

|-----------|--------------------------------------------------|----|

| Figure 2  | NxVL Pin List, By Signal Name                    | 4  |

| Figure 3  | NxVL Pin List, By Signal Name (continued)        | 5  |

| Figure 4  | NxVL Pin List, By Pin Number                     | 6  |

| Figure 5  | NxVL Pin List, By Pin Number (continued)         | 7  |

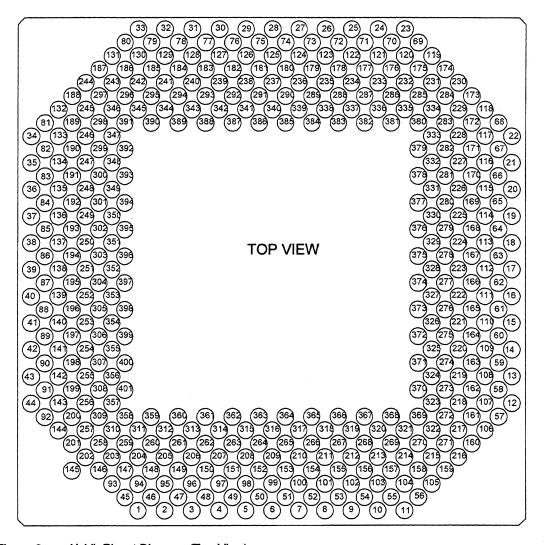

| Figure 6  | Pinout Diagram (Top View)                        | 8  |

| Figure 7  | Pinout Diagram (Bottom View)                     | 9  |

| Figure 8  | NxVL Alphabetical Signal Summary                 |    |

| Figure 8  | NxVL Alphabetical Signal Summary (Continued)     | 26 |

| Figure 8  | NxVL Alphabetical Signal Summary (Continued)     | 27 |

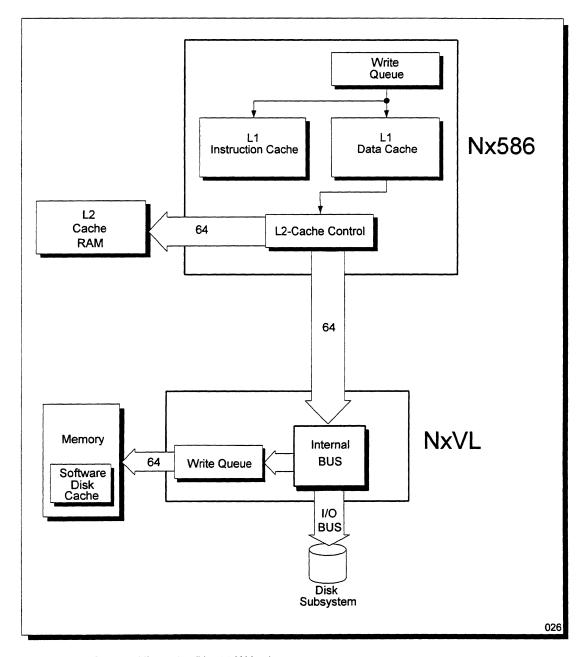

| Figure 9  | System Block Diagram                             | 30 |

| Figure 10 | Storage Hierarchy (Nx586 Reads)                  | 32 |

| Figure 11 | Storage Hierarchy (Nx586 Writes)                 | 33 |

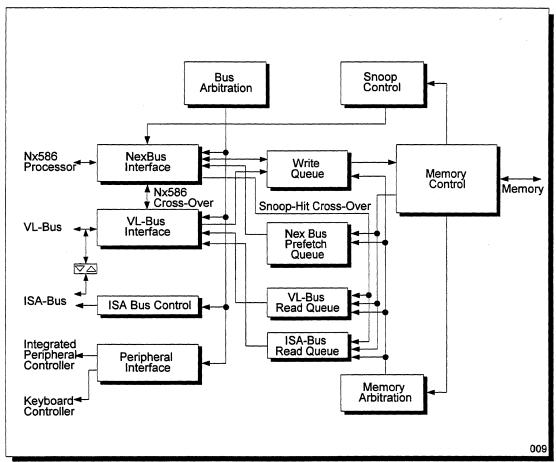

| Figure 12 | Internal Architecture                            |    |

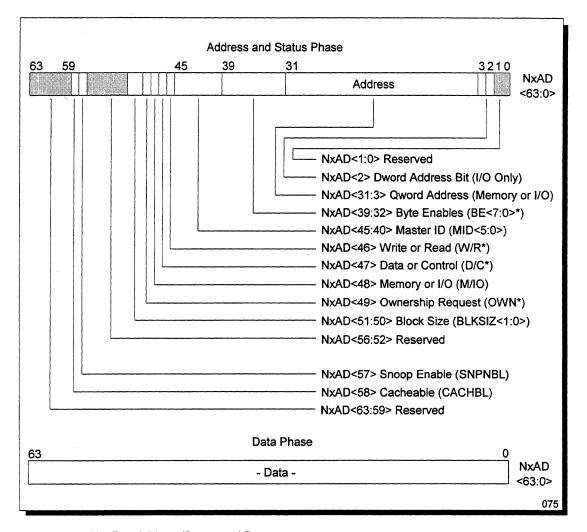

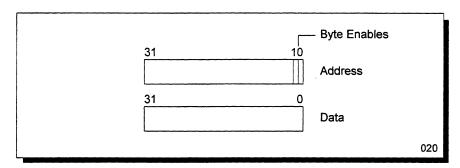

| Figure 13 | NexBus Address/Status and Data                   | 38 |

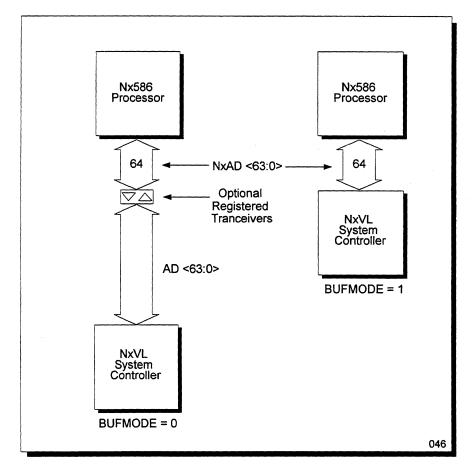

| Figure 14 | NexBus Connection Alternatives                   | 40 |

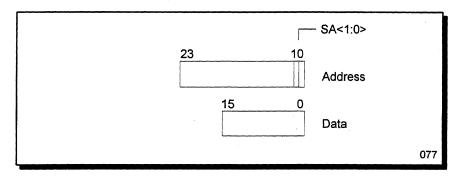

| Figure 15 | VL-Bus Address and Data                          | 41 |

| Figure 16 | ISA-Bus Address and Data                         | 42 |

| Figure 17 | VL-Bus Signals                                   | 43 |

| Figure 18 | ISA-Bus Signals                                  | 44 |

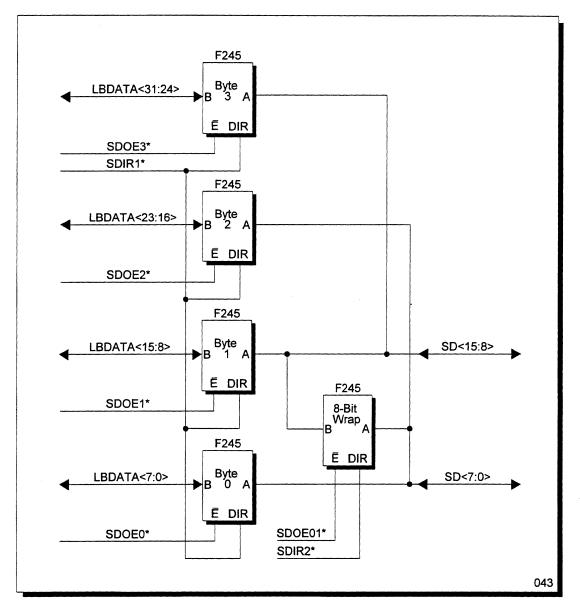

| Figure 19 | VL-Bus to ISA-Bus Data Transceivers              |    |

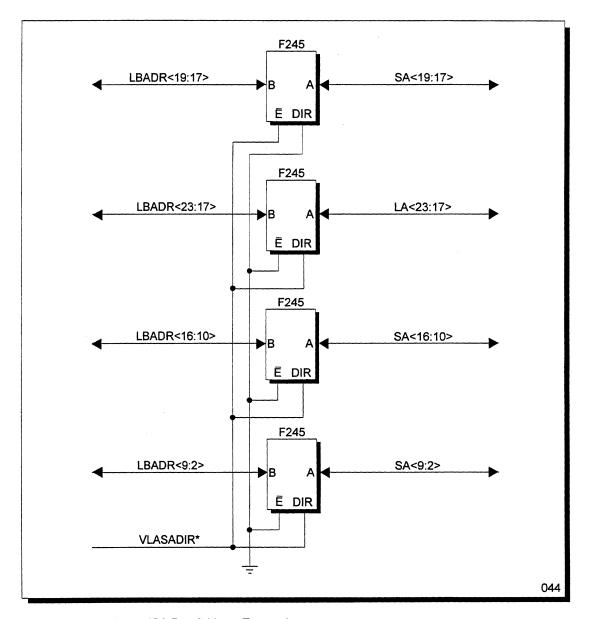

| Figure 20 | VL-Bus to ISA-Bus Address Transceivers           | 46 |

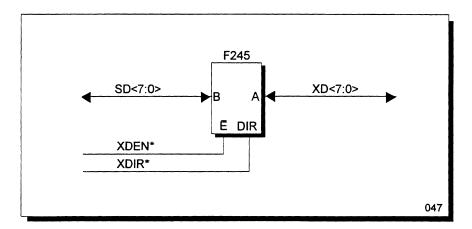

| Figure 21 | 82C206 SA-Bus to XA-Bus Data Transceiver         | 47 |

| Figure 22 | Memory Banks—4 32-bit memory modules             | 49 |

| Figure 23 | Memory Banks—4 32-bit interleaved memory modules | 49 |

| Figure 24 | Memory Banks—8 32-bit memory modules             | 49 |

| Figure 25 | Memory Banks—8 32-bit interleaved memory modules | 50 |

| Figure 26 | SIMM Configurations                              | 50 |

| Figure 27 | Active Components in Design Example              | 52 |

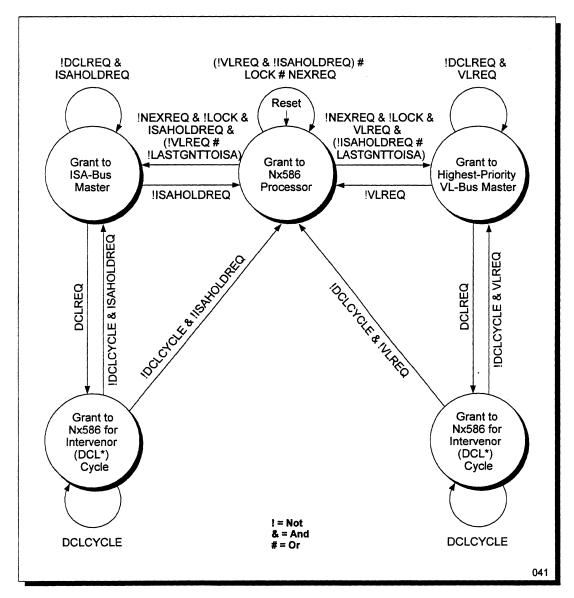

| Figure 28 | Global Bus Arbitration Protocol                  | 55 |

| Figure 29 | Bus-Arbitration State Transition Times           |    |

| Figure 30 | Main-Memory Access Priorities                    | 57 |

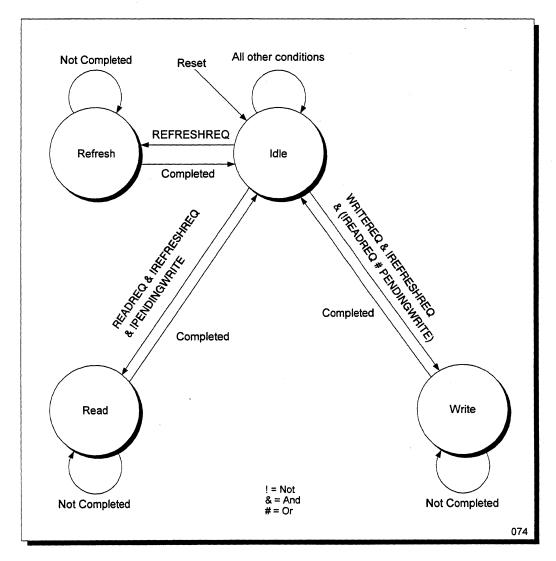

| Figure 31 | Main-Memory Arbitration State Diagram            | 58 |

|           |                                                  |    |

**PRELIMINARY**

NxVL<sup>™</sup> Systems Logic

vii

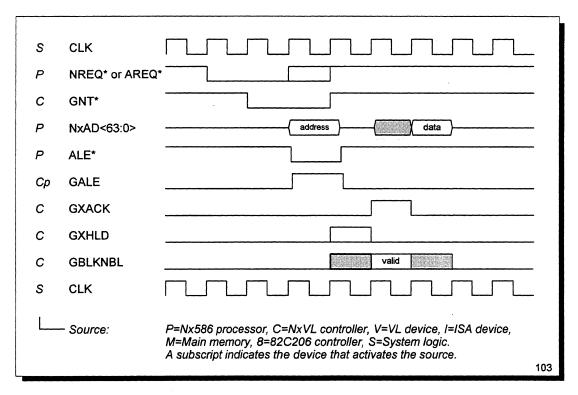

| Figure 32 | Bus Arbitration, Address, and Data Phase (BUFMODE = $0$ ) | 62      |

|-----------|-----------------------------------------------------------|---------|

| Figure 33 | Bus Arbitration, Address, and Data Phase (BUFMODE = 1)    | 63      |

| Figure 34 | Processor 64-Bit Write to Main Memory (Queue Hit)         | 64      |

| Figure 35 | Processor 64-Bit Read from Main Memory (Queue Hit)        | 65      |

| Figure 36 | Processor 64-Bit Read from Main Memory (DRAM-Page Mi      | iss) 67 |

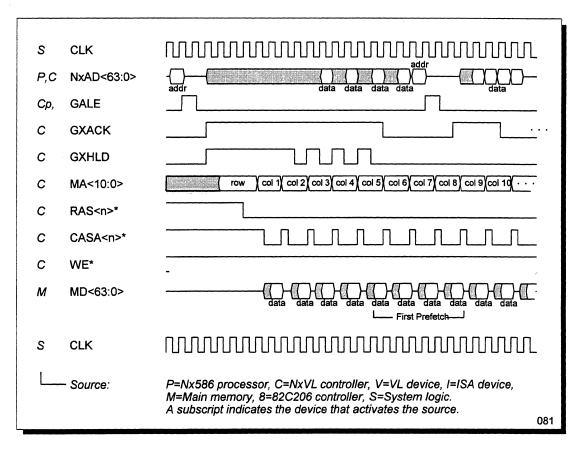

| Figure 37 | Processor 32-Byte Block Read from Main Memory             | 68      |

| Figure 38 | Processor 64-Bit Write to VL-Bus 16-Bit Memory Slave      | 70      |

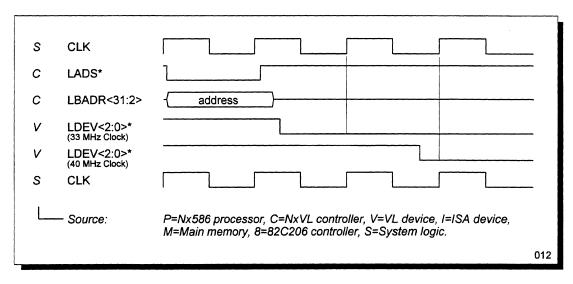

| Figure 39 | Response by a VL-Bus Device to Address Strobe             | 71      |

| Figure 40 | Processor 64-Bit Read from VL-Bus 32-Bit Memory Slave     | 72      |

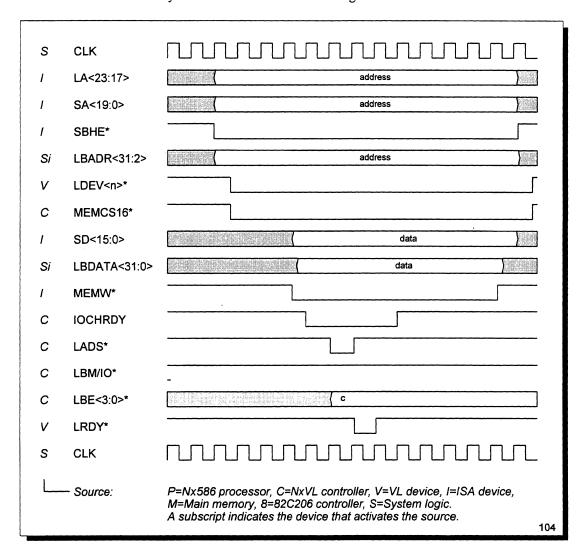

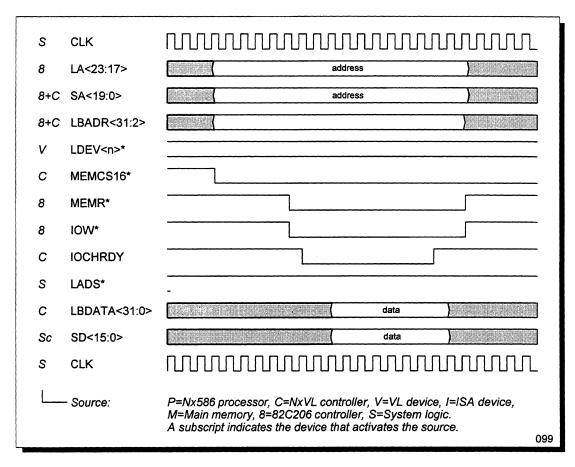

| Figure 41 | Processor 16-Bit Write to ISA-Bus 16-Bit Memory           | 74      |

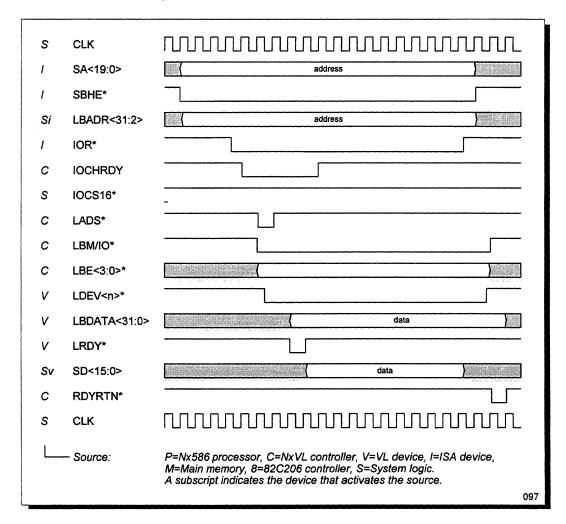

| Figure 42 | Processor 64-Bit Read from ISA-Bus 16-Bit Memory          | 75      |

| Figure 43 | Snoop Hit During VL-Master Read from Main Memory          | 77      |

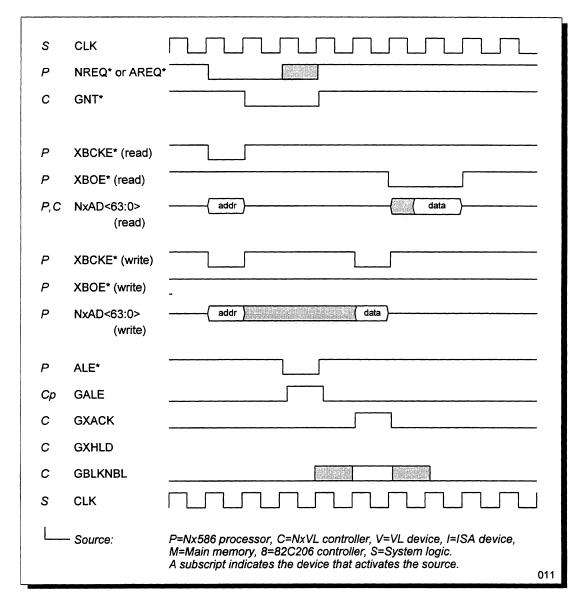

| Figure 44 | Bus Arbitration by VL-Bus Master                          | 79      |

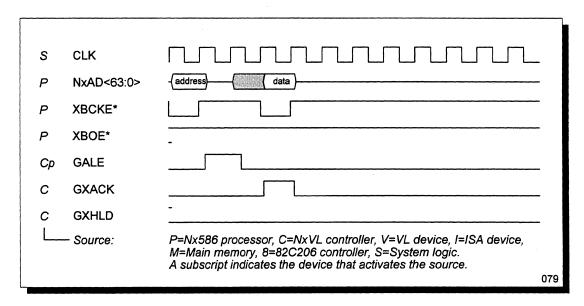

| Figure 45 | VL-Master 32-Bit Write to Main Memory                     | 80      |

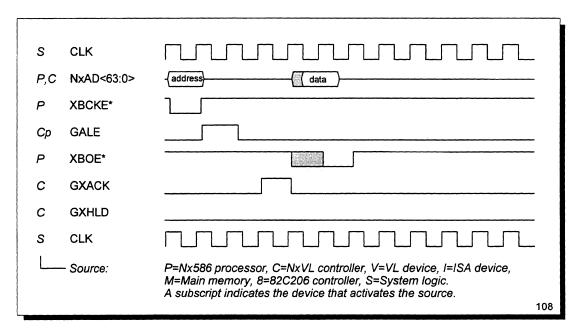

| Figure 46 | VL-Master 16-Byte Burst Read from Main Memory (Queue      | Hit)81  |

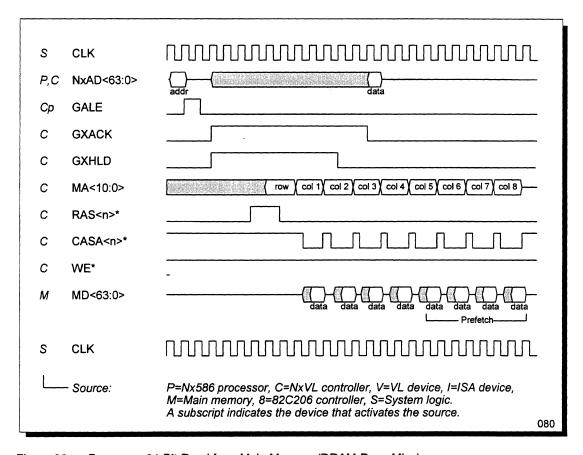

| Figure 47 | VL-Master 16-Byte Burst Read from Main Memory             | 82      |

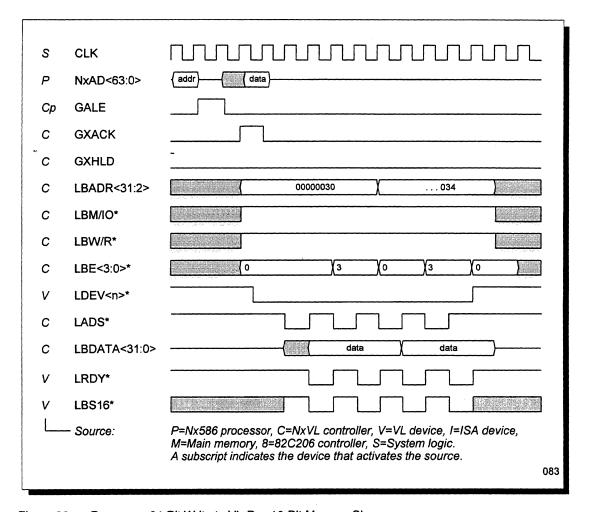

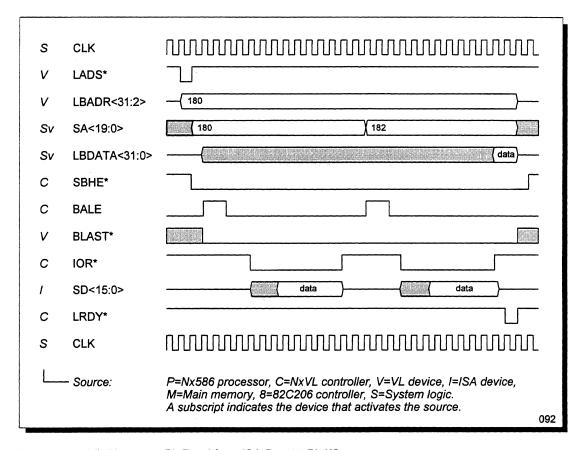

| Figure 48 | VL-Master 32-Bit Write to ISA-Bus 16-Bit I/O              | 83      |

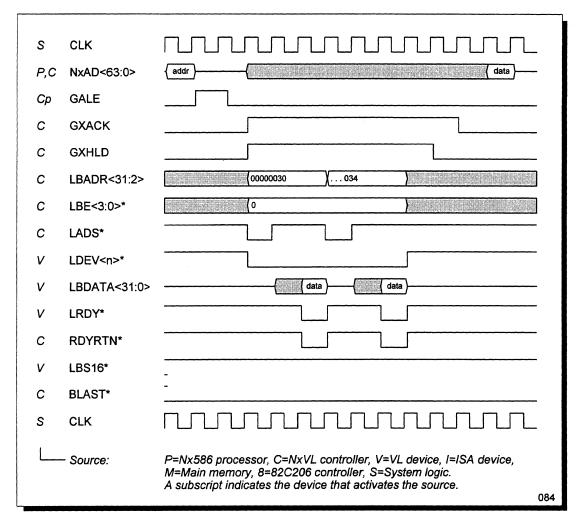

| Figure 49 | VL-Master 32-Bit Read from ISA-Bus 16-Bit I/O             | 84      |

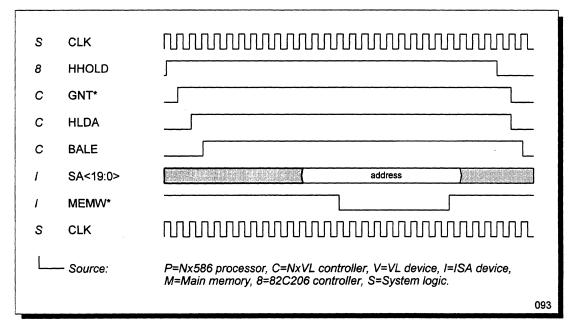

| Figure 50 | Bus Arbitration by ISA-Bus Master                         | 86      |

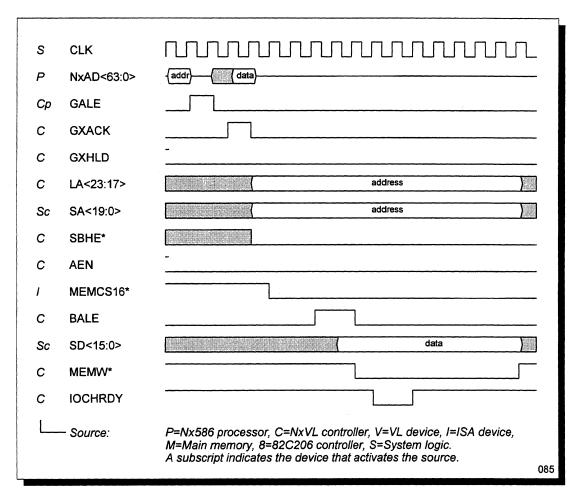

| Figure 51 | ISA-Master 16-Bit Write to Main Memory                    | 87      |

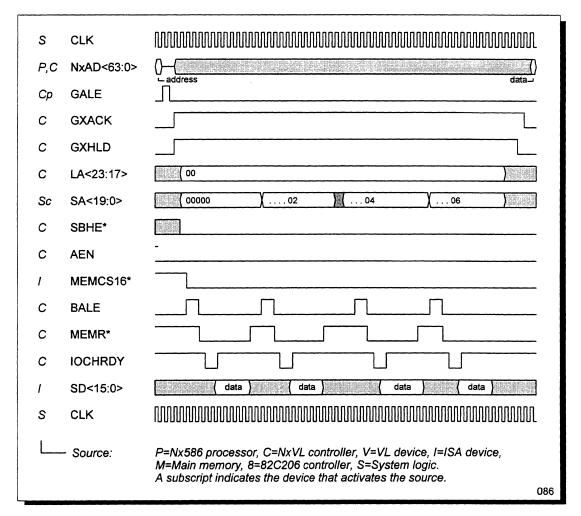

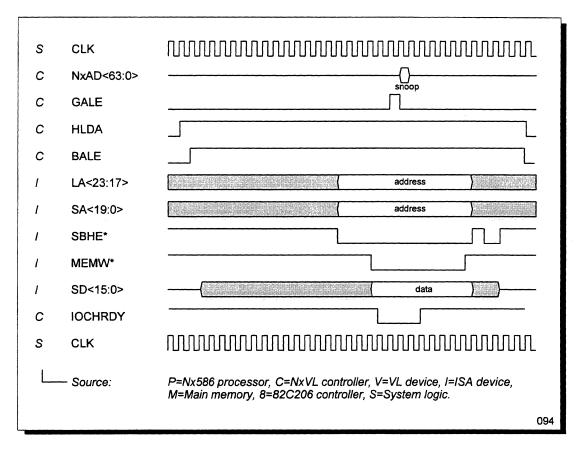

| Figure 52 | ISA-Master 16-Bit Read from Main Memory                   | 88      |

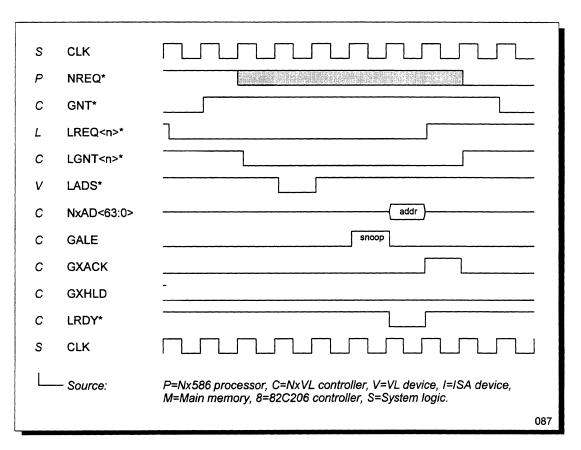

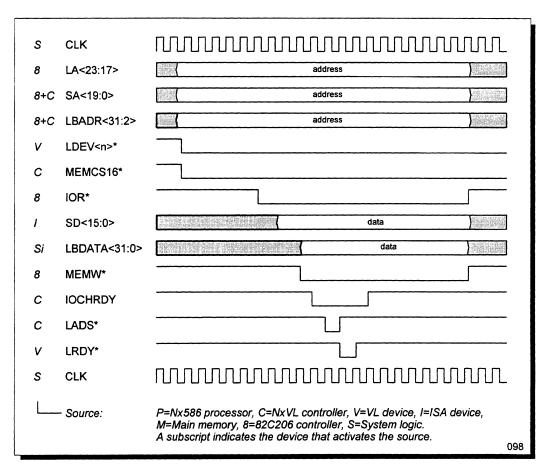

| Figure 53 | ISA-Master 16-Bit Write to VL-Bus Memory                  | 89      |

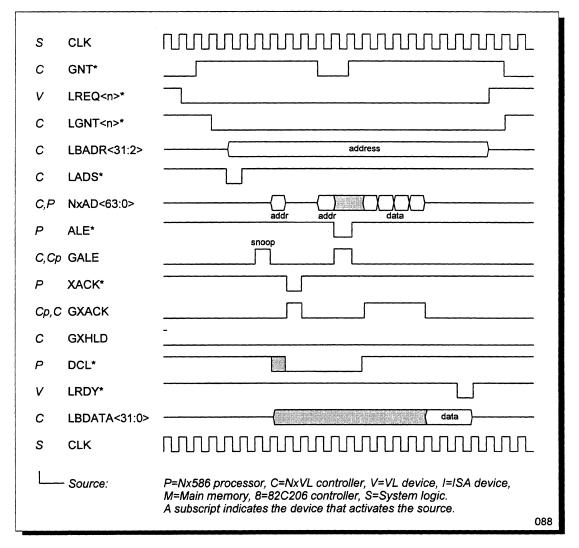

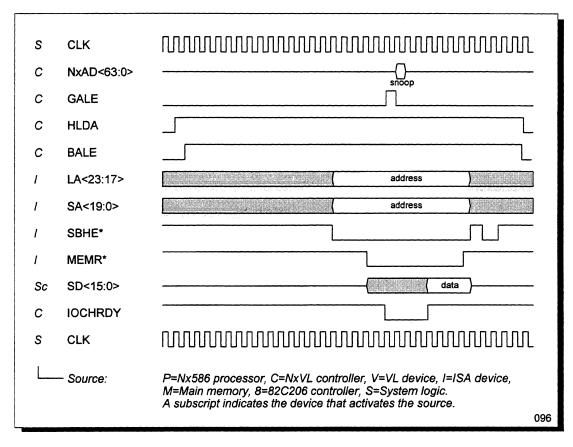

| Figure 54 | ISA-Master 16-Bit Read from VL-Bus I/O                    | 90      |

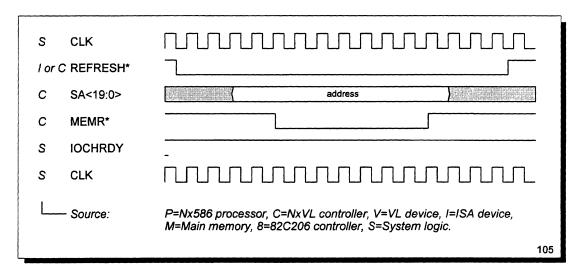

| Figure 55 | ISA-Bus Memory Refresh Cycle                              | 91      |

| Figure 56 | DMA Transfer from ISA-Bus 8-Bit I/O to VL-Bus Memory.     | 93      |

| Figure 57 | DMA Transfer from Main Memory to ISA-Bus 8-Bit I/O        | 94      |

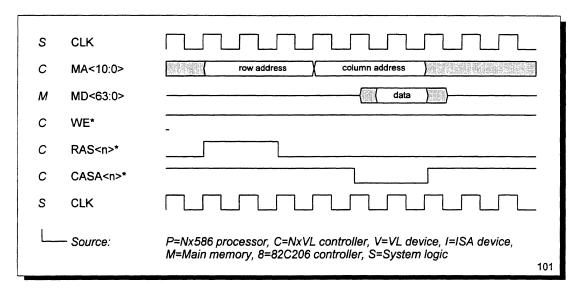

| Figure 58 | Slow Write to Main Memory (No Precharge)                  | 96      |

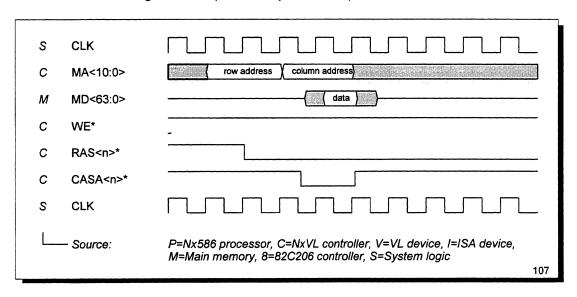

| Figure 59 | Slow Read from Main Memory (Precharge)                    |         |

| Figure 60 | Slow Read from Main Memory (Overlapping Precharge)        | 98      |

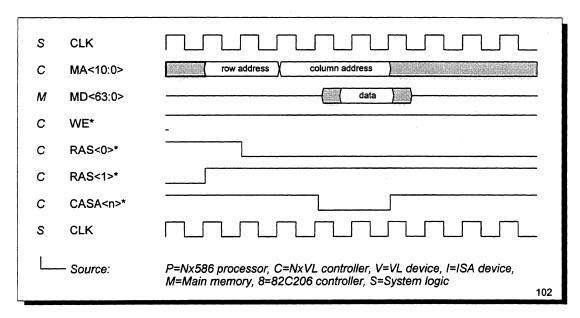

| Figure 61 | Fast Write to Main Memory (No Precharge)                  |         |

| Figure 62 | Fast Read from Main Memory (No Precharge)                 |         |

| Figure 63 | Configuration Registers                                   | 102     |

| Figure 64 | Configuration Registers (I/O-Mapped)                      | 102     |

| Figure 65 | CFG0 Bit-12 Minimum Times                                 |         |

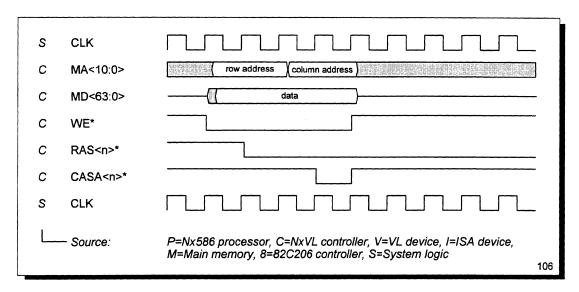

| Figure 66 | CFG0 Bit-22 CAS Timing for Memory Reads                   | 105     |

| Figure 67 | CFG0 Bit-23 CAS Timing for Memory Writes                  |         |

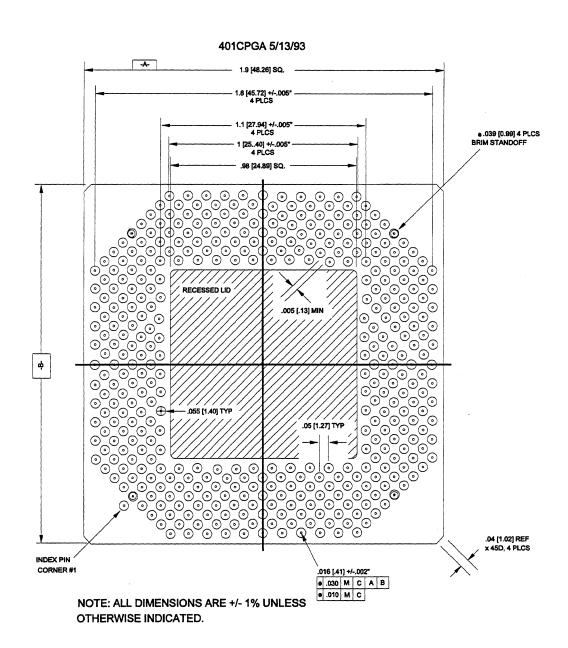

| Figure 68 | NxVL Package Diagram (top)                                |         |

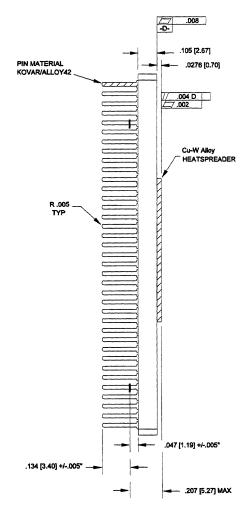

| Figure 69 | NxVL Package Diagram (side)                               | 113     |

| Figure 70 | NvVI Package Diagram (hottom)                             | 114     |

NxVL™ Systems Logic

# **Preface**

This databook covers the NxVL<sup>TM</sup> systems logic, the systems controller for the Nx586<sup>TM</sup> and Nx587<sup>TM</sup> processors. This book is written for system designers considering the use of NexGen<sup>TM</sup> products in their designs. We assume an experienced audience, familiar not only with system design conventions but also with the x86 architecture. The *Glossary* at the end of the book defines NexGen's terminology, and the *Index* gives quick access to the subject matter.

#### **Notation**

The following notation and conventions are used in this book:

#### Chip and Bus Names

- NxVL—The NxVL system controller chip described in this book.

- Processor or CPU—The Nx586 processor chip described in the Nx586 Processor and Nx587 Floating Point Coprocessor Databook.

- Floating Point Coprocessor or NP—The Nx587 floating-point unit chip described in the Nx586 Processor and Nx587 Floating Point Coprocessor Databook.

- NexBus<sup>TM</sup>System Bus—The Nx586 processor bus, including its multiplexed address/status and data bus (NxAD<63:0>) and related control signals.

#### Signals and Timing Diagrams

- Active-Low Signals—Signal names that are followed by an asterisk, such as ALE\*, indicate active-low signals. They are said to be "asserted" in their low-voltage state and "negated" in their high-voltage state.

- Bus Signals—In signal names, the notation <n:m> represents bits n through m of a bus.

- Reserved Bits and Signals—Signals or bus bits marked "reserved" must be driven inactive or left unconnected, as indicated in the signal descriptions. These bits and signals are reserved by NexGen for future implementations. When software reads registers with reserved bits, the reserved bits must be

**PRELIMINARY**

NxVL™ Systems Logic

ix

- masked. When software writes such registers, it must first read the register and change only the non-reserved bits before writing back to the register.

- Source—In timing diagrams, the left-hand column indicates the "Source" of each signal. This is the device or logic that generates the signal. When signals are driven by multiple sources, all sources are shown, in the order in which they drive the signal. In some timing diagrams, bus signals take on different names as outputs cross buses through transceivers or are ORed in group-signal logic. In these cases, the signal source is shown with a subscript, where the subscript indicates the device or logic that originally caused the change in the signal.

- Tri-state®—In timing diagrams, signal ranges that are high impedance are shown as a straight horizontal line half-way between the high and low level.

- Invalid and Don't Care—In timing diagrams, signal ranges that are invalid or don't care are filled with a screen pattern.

#### Data

- Quantities—A word is two bytes (16 bits), a dword or doubleword is four bytes (32 bits), and a qword or quadword is eight bytes (64 bits).

- Addressing—Memory is addressed as a series of bytes on eight-byte (64-bit) boundaries, in which each byte can be separately enabled.

- Abbreviations—The following notation is used for bits and bytes:

```

Bits b as in "64b/qword"

Bytes B as in "32B/block"

kilo k as in "4kB/page"

Mega M as in "1Mb/sec"

Giga G as in "4GB of memory space"

```

- Little Endian Convention—The byte with the address xx...xx00 is in the least-significant byte position (little end). In byte diagrams, bit positions are numbered from right to left: the little end is on the right and the big end is on the left. Data structure diagrams in memory show small addresses at the bottom and high addresses at the top. When data items are "aligned," bit notation on a 64-bit data bus maps directly to bit notation in 64-bit-wide memory. Because byte addresses increase from right to left, strings appear in reverse order when illustrated.

- Bit Ranges—In a range of bits, the highest and lowest bit numbers are separated by a colon, as in <63:0>.

- Bit Values—Bits can either be set to 1 or cleared to 0.

- Hexadecimal and Binary Numbers—Unless the context makes interpretation clear, hexadecimal numbers are followed by an h, binary numbers are followed by a b, and decimal numbers are followed by a d.

NxVL™ Systems Logic

1

#### **Related Publications**

The following books discuss various aspects of computer architecture, that may be useful for your understanding of NexGen products:

#### NexGen Products

Nx586 Processor and Nx587 Coprocessor Databook, NexGen, Milpitas, CA, Tel: (408) 435-0202.

#### VL-Bus Architecture

VL-Bus<sup>™</sup> Proposal, Video Electronics Standards Association (VESA), San Jose, CA, 1992. Tel: (408) 435-0333.

#### ISA-Bus Architecture

Edward Solari, AT Bus Design, IEEE P996 Compatible, Annabooks, San Diego, CA, 1990.

#### Other Products and Architecture

82C206 Integrated Peripheral Controller Data Sheet, OPTi, Tel: (408)

980-8178; Chips and Technologies, Tel: (408) 434-0600; UMC; and others.

|   |  |  | The second measures and the second se |  |  |  |  |   |

|---|--|--|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|---|

|   |  |  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  | i |

|   |  |  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |   |

|   |  |  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |   |

|   |  |  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |   |

|   |  |  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |   |

|   |  |  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |   |

|   |  |  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |   |

|   |  |  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |   |

|   |  |  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |   |

|   |  |  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |   |

|   |  |  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |   |

|   |  |  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |   |

|   |  |  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |   |

|   |  |  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |   |

|   |  |  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |   |

|   |  |  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |   |

|   |  |  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |   |

|   |  |  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |   |

|   |  |  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  | 1 |

|   |  |  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |   |

|   |  |  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |   |

|   |  |  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |   |

|   |  |  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |   |

|   |  |  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |   |

|   |  |  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |   |

|   |  |  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |   |

|   |  |  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |   |