February 1991

IPD

# µPD72611 SCSI-2 Controller

Preliminary User's Manual

The information contained in this document is being issued in advance of the production cycle for the device. The parameters for the device may change before final production or NEC Electronics Inc., at its own discretion, may withdraw the device prior to production.

The information in this document is subject to change without notice. NEC Electronics Inc. assumes no responsibility for any errors or omissions that may appear in this document. Devices sold by NEC Electronics Inc. are covered by the warranty and patent indemnification provisions appearing in NEC Electronics Inc. Terms and Conditions of Sale only. NEC Electronics Inc. makes no warranty, express, statutory, implied, or by description, regarding the information set forth herein or regarding the freedom of the described devices from patent infringement. NEC Electronics Inc. makes no warranty of merchantability or fitness for any purpose. NEC Electronics Inc. makes no commitment to update or to keep current the information contained in this document. No part of this document may be copied or reproduced in any form or by any means without the prior written consent of NEC Electronics Inc.

uPD72611

SCSI-2 CONTROLLER

PRELIMINARY USER'S MANUAL

Document Pro.

Microcomputer & Memory Engineering Dept.

Semiconductor Application Engineering Div.

NEC Corporation

February 28, 1991

IEU-773 February 1991P Total 209 pages

© NEC Corporation 1991

The information in this document is subject to change without notice.

No part of this document may be copied or reproduced in any form or by any means without the prior written consent of NEC Corporation. NEC Corporation assumes no responsibility for any errors which may appear in this document.

NEC Corporation does not assume any liability for infringement of patents, copyrights or other intellectual property rights of third parties by or arising from use of a device described herein or any other liability arising from use of such device. No license, either express, implied or otherwise, is granted under any patents, copyrights or other intellectual property rights of NEC Corporation or others.

The devices listed in this document are not suitable for use in the field where very high reliability is required including, but not limited to, aerospace equipment, submarine cables, nuclear reactor control systems and life support systems. If customers intend to use NEC devices for above applications or those intend to use "Standard", or "Special" quality grade NEC devices for the applications not intended by NEC, please contact our sales people in advance.

Application examples recommended by NEC Corporation

| Standard: | Communication equipment (terminal, mobile),<br>Test and Measurement equipment, Audio and Video                                                                                                                                                                        |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Special : | equipment, Other consumer products, etc.<br>Automotive and Transportation equipment, Com-<br>munication equipment (trunk line), Train and<br>Traffic control devices, Industrial robots,<br>Burning control systems, antidisaster systems,<br>anticrime systems, etc. |

#### PREFACE

Intended

- Readership : This manual is intended for users' engineers who require an understanding of the functions of uPD72611 and wish to design application systems using this device.

- Purpose : The purpose of this manual is to give users an understanding of the hardware functions of the uPD72611 listed below.

- Organization : This manual is broadly organized as follows:

- . General Description

- . Pin Functions

- . Internal Block Functions

- . Commands

- . Control

- . System Configuration

- Using this

- Manual : Readers require a general understanding of electrical and logic circuits and microcomputers.

For users with previous experience of a different SCSI controller:

+ Check the differences between the uPD72611 and the other SCSI controller in 1.4 "Features", and focus on the relevant descriptions.

To check the function of a command:

+ Check the contents to find the description of that command.

|         |   | command name is no<br>generally understo<br>+ Find the command | t k<br>od:<br>na | of a command when the<br>nown but the function is<br>me in 1.3 "Commands", then<br>d Functions" for the |

|---------|---|----------------------------------------------------------------|------------------|---------------------------------------------------------------------------------------------------------|

|         |   | uPD72611:                                                      |                  | the functions of the with the contents.                                                                 |

|         | - | Circlificance in                                               |                  |                                                                                                         |

| Legend  | ÷ | Significance in<br>data notation                               | -                | Wich option digits on last                                                                              |

|         |   | data notation                                                  | ÷                | High-order digit on left,                                                                               |

|         |   | - · · · · · · · · · · · · · · · · · · ·                        |                  | low-order digit on right                                                                                |

|         |   | Active-low notatio                                             | n:               | XXX (Line above pin or                                                                                  |

|         |   |                                                                |                  | signal name)                                                                                            |

|         |   | *                                                              | :                | Explanation of item marked                                                                              |

|         |   |                                                                |                  | with an asterisk in the                                                                                 |

|         | • |                                                                |                  | text                                                                                                    |

|         |   | NOTE                                                           | :                | Item to be especially noted                                                                             |

|         |   | Remarks                                                        | :                | Supplementary information                                                                               |

|         |   | Numeric notations                                              |                  | Binary xxxx or                                                                                          |

|         |   |                                                                |                  | xxxxB                                                                                                   |

|         |   |                                                                |                  | Decimal xxxx                                                                                            |

|         |   |                                                                |                  | Hexadecimal xxxxH                                                                                       |

| Related |   |                                                                |                  |                                                                                                         |

Related

Documentation: o Documentation on the uPD72611:

- . Brochure (IF-6070A)

- . Preliminary Data Sheet (ID-8343)

- . Preliminary User's Manual (This manual)

## CONTENTS

| CHAPTER | 1. GENERAL DESCRIPTION                       | 1-1 |

|---------|----------------------------------------------|-----|

| 1.1     | System Outline                               | 1-1 |

| 1.2     | Outline of System Operation                  | 1-3 |

| 1.3     | Commands                                     | 1-4 |

| 1.4     | Features                                     | 1-5 |

| 1.5     | Ordering Information                         | 1-6 |

| 1.6     | Pin Configuration (Top View)                 | 1-7 |

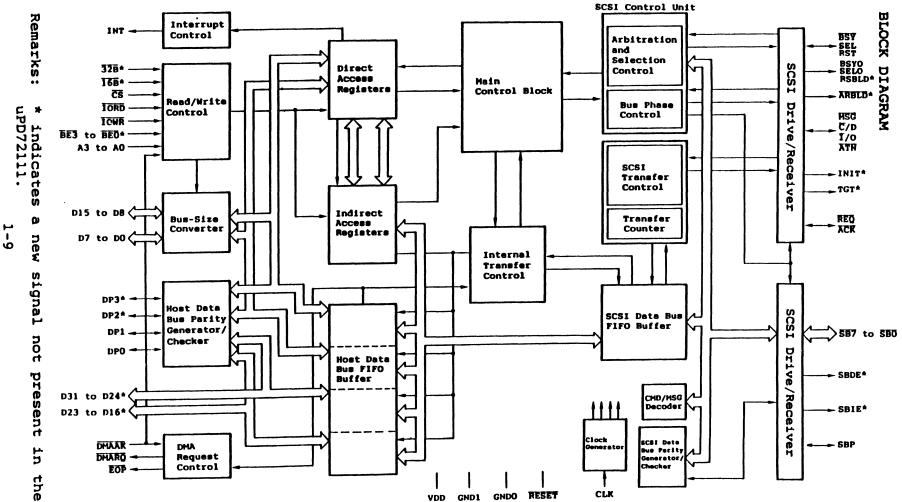

| 1.7     | Block Diagram                                | 1-9 |

| CHAPTER | 2. PIN FUNCTIONS                             | 2-1 |

| 2.1     | CPU Interface Pins                           | 2-1 |

| 2.2     | SCSI Interface Pins                          | 2-4 |

| 2.3     | Other Pins                                   | 2-7 |

| 2.4     | Status of Output and Input/Output Pins After |     |

|         | Reset                                        | 2-8 |

| CHAPTER | 3. INTERNAL BLOCK FUNCTIONS                  | 3-1 |

| 3.1     | SCSI Driver/Receiver                         | 3-1 |

| 3.2     | Arbitration and Selection Control            | 3-1 |

| 3.3     | BUS Phase Control                            | 3-1 |

| 3.4     | SCSI Transfer Control                        | 3-2 |

| 3.5     | SCSI Data Bus FIFO Buffer (SCSI FIFO Buffer) | 3-2 |

| 3.6     | CMD/MSG Decoder                              | 3-2 |

| 3.7     | SCSI Data Bus Parity Generator/Checker       | 3-3 |

| 3.8     | Main Control Block                           | 3-3 |

| 3.9     | Internal Transfer Control                    | 3-3 |

| 3.10    | Direct Access Registers                      | 3-3 |

| 3.11    | Indirect Access Registers                    | 3-3 |

| 3.12    | Host Data Bus FIFO Buffer (Host FIFO Buffer) | 3-4 |

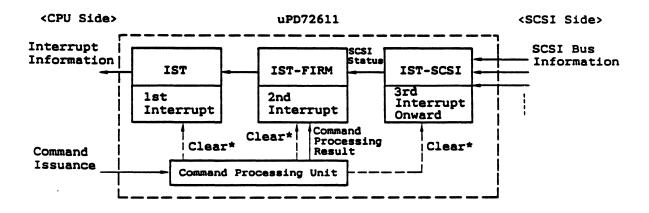

| 3.13    | Interrupt Control                            | 3-4 |

| 3.14    | Read/Write Control                           | 3-4 |

| 3.15    | Bus-Size Generator                           | 3-4 |

| 3.16    | Host Data Bus Parity Generator/Checker       | 3-4 |

.

| 3.17    | DMA Request Control 3                       | -5   |

|---------|---------------------------------------------|------|

| 3.18    | Clock Generator 3                           | -5   |

| CHAPTER | 4. INTERNAL REGISTER CONFIGURATION 4        | -1   |

| 4.1     | Direct Access Registers 4                   | -1   |

| 4.2     | Indirect Access Registers 4                 | -27  |

| CHAPTER | 5. COMMANDS 5                               | -1   |

| 5.1     | Outline of Commands 5                       | -1   |

| 5.2     | Command Functions 5                         | -4   |

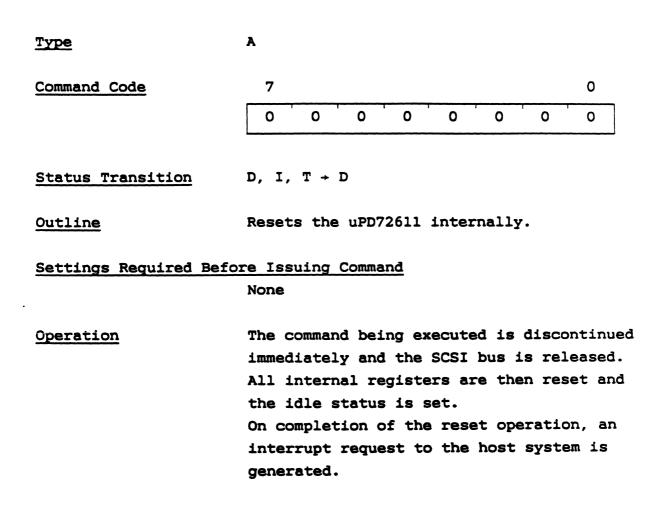

|         | CHIP RESET                                  | -6   |

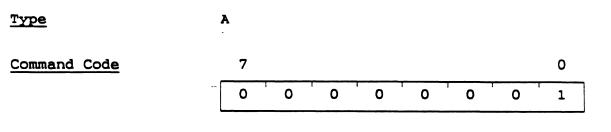

|         | BREAK                                       | -7   |

|         | DISCONNECT                                  | -8   |

|         | CLEAR FIFO                                  | -9   |

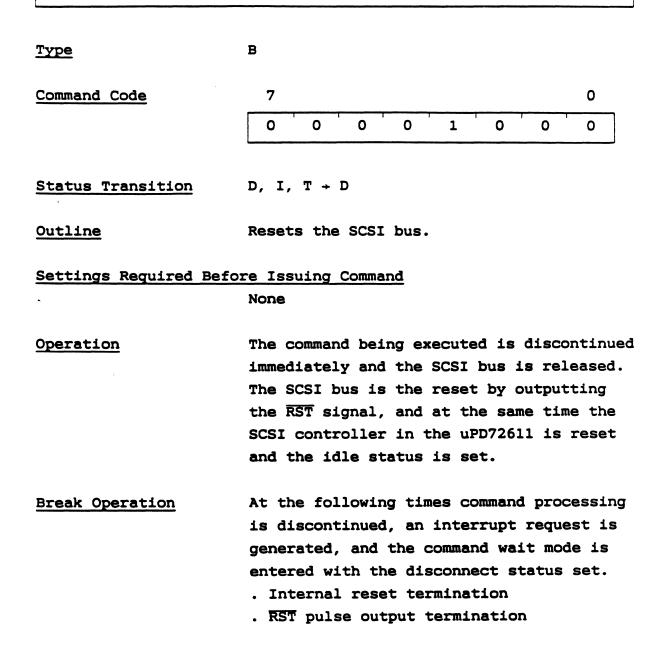

|         | SCSI RESET                                  | -10  |

| •       | SET ATN                                     | -12  |

|         | RESET ACK                                   | -13  |

|         | SELECT                                      | -14  |

|         | TRANSFER                                    | -22  |

|         | AUTO INITIATOR                              | -30  |

|         | <b>AUTO INITIATOR 2 5</b>                   | -44  |

|         | <b>RESELECT</b>                             | -51  |

|         | RECEIVE                                     | -57  |

|         | SEND                                        | -63  |

|         | AUTO TARGET 5                               | -69  |

|         | AUTO TARGET 2 5                             | -78  |

|         | <b>RE-RECEIVE</b>                           | -82  |

|         | <b>RE-SEND</b>                              | -91  |

| 5.3     | Command Codes 5                             | -101 |

| CHAPTER | 6. CONTROL                                  | -1   |

| 6.1     | uPD72611 Operations 6                       | 5-1  |

| 6.2     | Outline of Host CPU Processing Operations 6 | 5-3  |

| 6.2.1   | Command Issuance Processing                 | 5-3  |

| 6.2.2   | 2 Caution on uPD72611 Initialization        | 5-6  |

| 6.2.3 | Interrupt Servicing    | 6-7  |

|-------|------------------------|------|

| 6.3   | Control Sequence       | 6-9  |

| 6.3.1 | Host Adapter Control   | 6-9  |

| 6.3.2 | Device Adapter Control | 6-19 |

| CHAPTER 7. | System | CONFIGURATION | ••••• | 7-1 |

|------------|--------|---------------|-------|-----|

|            |        |               |       |     |

•

.

# List of Figures

| 1-1       System Configuration Example       1         1-2       SCSI Bus Phase Transitions       1         4-1       DF0 Format       4         4-2       DF1 Format       4         4-3       DF2 Format       4         4-4       CST Format       4         4-5       ADR Format       4         4-6       WIN1 & WIN2 Format       4         4-7       TP Format       4         4-8       DID Format       4         4-9       IST Format       4         4-10       Registers for Holding Interrupt Sources and<br>Register Configuration       4         4-11       CMD Format       4         4-12       EXST Format       4         4-13       TST Format       4         4-14       SBST Format       4         4-15       SID Format       4         4-16       MSG Format       4         4-17       CDB Format       4         4-18       TMOD Format       4         4-19       CTCL/CTCM/CTCH Format       4         4-20       BTCL/BTCM/BTCH Format       4         4-21       MSG2 Format       4         4-22       <                                               | Figure<br>No. | Title                                       | Page |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|---------------------------------------------|------|

| 4-1       DFO Format       4         4-2       DF1 Format       4         4-3       DF2 Format       4         4-4       CST Format       4         4-5       ADR Format       4         4-6       WIN1 & WIN2 Format       4         4-7       TP Format       4         4-8       DID Format       4         4-9       IST Format       4         4-10       Registers for Holding Interrupt Sources and<br>Register Configuration       4         4-11       CMD Format       4         4-12       EXST Format       4         4-13       TST Format       4         4-14       SBST Format       4         4-15       SID Format       4         4-16       MSG Format       4         4-17       CDB Format       4         4-18       TMOD Format       4         4-19       CTCL/CTCM/CTCH Format       4         4-20       BTCL/BTCM/BTCH Format       4         4-21       MSG2 Format       4         4-22       MSG3 Format       4         4-23       EXMOD Format       4         4-24       BFTOUT Format       <                                                        | 1-1           | System Configuration Example                | 1-2  |

| 4-2       DF1 Format       4         4-3       DF2 Format       4         4-3       DF2 Format       4         4-4       CST Format       4         4-5       ADR Format       4         4-5       MDR Format       4         4-6       WIN1 & WIN2 Format       4         4-7       TP Format       4         4-8       DID Format       4         4-9       IST Format       4         4-9       IST Format       4         4-10       Registers for Holding Interrupt Sources and<br>Register Configuration       4         4-11       CMD Format       4         4-12       EXST Format       4         4-13       TST Format       4         4-14       SBST Format       4         4-15       SID Format       4         4-16       MSG Format       4         4-17       CDB Format       4         4-18       TMOD Format       4         4-19       CTCL/CTCM/CTCH Format       4         4-20       BTCL/BTCM/BTCH Format       4         4-21       MSG2 Format       4         4-22       MSG3 Format       4 <td>1-2</td> <td>SCSI Bus Phase Transitions</td> <td>1-3</td> | 1-2           | SCSI Bus Phase Transitions                  | 1-3  |

| 4-3       DF2 Format       4         4-4       CST Format       4         4-5       ADR Format       4         4-6       WIN1 & WIN2 Format       4         4-7       TP Format       4         4-8       DID Format       4         4-9       IST Format       4         4-10       Registers for Holding Interrupt Sources and<br>Register Configuration       4         4-11       CMD Format       4         4-12       EXST Format       4         4-13       TST Format       4         4-14       SBST Format       4         4-15       SID Format       4         4-16       MSG Format       4         4-17       CDB Format       4         4-18       TMOD Format       4         4-19       CTCL/CTCM/CTCH Format       4         4-20       BTCL/BTCM/BTCH Format       4         4-21       MSG2 Format       4         4-22       MSG3 Format       4         4-23       EXMOD Format       4         4-24       BFTOUT Format       4         4-25       SRTOUT Format       4         4-26       RATOUT Format                                                        | 4-1           | DFO Format                                  | 4-3  |

| 4-4       CST Format                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 4-2           | DF1 Format                                  | 4-4  |

| 4-5       ADR Format       4         4-6       WIN1 & WIN2 Format       4         4-7       TP Format       4         4-8       DID Format       4         4-9       IST Format       4         4-10       Registers for Holding Interrupt Sources and<br>Register Configuration       4         4-11       CMD Format       4         4-12       EXST Format       4         4-13       TST Format       4         4-14       SBST Format       4         4-15       SID Format       4         4-16       MSG Format       4         4-17       CDB Format       4         4-18       TMOD Format       4         4-17       CDB Format       4         4-18       TMOD Format       4         4-19       CTCL/CTCM/CTCH Format       4         4-19       CTCL/CTCM/BTCH Format       4         4-20       BTCL/BTCM/BTCH Format       4         4-21       MSG2 Format       4         4-22       MSG3 Format       4         4-23       EXMOD Format       4         4-24       BFTOUT Format       4         4-25       SRTOUT                                                    | 4-3           | DF2 Format                                  | 4-4  |

| 4-6       WIN1 & WIN2 Format       4         4-7       TP Format       4         4-8       DID Format       4         4-9       IST Format       4         4-10       Registers for Holding Interrupt Sources and<br>Register Configuration       4         4-11       CMD Format       4         4-12       EXST Format       4         4-13       TST Format       4         4-14       SBST Format       4         4-15       SID Format       4         4-16       MSG Format       4         4-17       CDB Format       4         4-18       TMOD Format       4         4-17       CDB Format       4         4-18       TMOD Format       4         4-19       CTCL/CTCM/CTCH Format       4         4-20       BTCL/BTCM/BTCH Format       4         4-21       MSG2 Format       4         4-22       MSG3 Format       4         4-23       EXMOD Format       4         4-24       BFTOUT Format       4         4-25       SRTOUT Format       4         4-26       RATOUT Format       4         4-28       MOD Format<                                                   | 4-4           | CST Format                                  | 4-5  |

| 4-7       TP Format       4         4-8       DID Format       4         4-9       IST Format       4         4-10       Registers for Holding Interrupt Sources and<br>Register Configuration       4         4-11       CMD Format       4         4-12       EXST Format       4         4-13       TST Format       4         4-14       SBST Format       4         4-15       SID Format       4         4-16       MSG Format       4         4-17       CDB Format       4         4-18       TMOD Format       4         4-19       CTCL/CTCM/CTCH Format       4         4-20       BTCL/BTCM/BTCH Format       4         4-21       MSG2 Format       4         4-22       MSG3 Format       4         4-23       EXMOD Format       4         4-24       BFTOUT Format       4         4-25       SRTOUT Format       4         4-26       RATOUT Format       4         4-27       CDBL Format       4         4-28       MOD Format       4         4-29       FID Format       4 <td>4-5</td> <td>ADR Format</td> <td>4-7</td>                                           | 4-5           | ADR Format                                  | 4-7  |

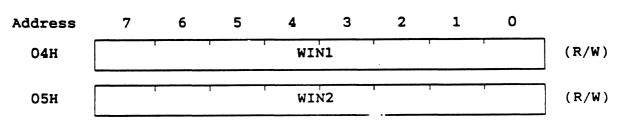

| 4-8       DID Format       4         4-9       IST Format       4         4-10       Registers for Holding Interrupt Sources and       4         4-11       CMD Format       4         4-12       EXST Format       4         4-13       TST Format       4         4-14       SBST Format       4         4-15       SID Format       4         4-16       MSG Format       4         4-17       CDB Format       4         4-18       TMOD Format       4         4-19       CTCL/CTCM/CTCH Format       4         4-20       BTCL/BTCM/BTCH Format       4         4-21       MSG2 Format       4         4-22       MSG3 Format       4         4-23       EXMOD Format       4         4-24       BFTOUT Format       4         4-25       SRTOUT Format       4         4-26       RATOUT Format       4         4-27       CDBL Format       4         4-28       MOD Format       4         4-29       PID Format       4                                                                                                                                                       | 4-6           | WIN1 & WIN2 Format                          | 4-7  |

| 4-9       IST Format       4         4-10       Registers for Holding Interrupt Sources and<br>Register Configuration       4         4-11       CMD Format       4         4-12       EXST Format       4         4-13       TST Format       4         4-14       SBST Format       4         4-15       SID Format       4         4-16       MSG Format       4         4-17       CDB Format       4         4-18       TMOD Format       4         4-19       CTCL/CTCM/CTCH Format       4         4-20       BTCL/BTCM/BTCH Format       4         4-21       MSG2 Format       4         4-22       MSG3 Format       4         4-23       EXMOD Format       4         4-24       BFTOUT Format       4         4-25       SRTOUT Format       4         4-26       RATOUT Format       4         4-27       CDBL Format       4         4-28       MOD Format       4         4-29       FID Format       4                                                                                                                                                                  | 4-7           | TP Format                                   | 4-8  |

| 4-10       Registers for Holding Interrupt Sources and         Register Configuration       4         4-11       CMD Format       4         4-12       EXST Format       4         4-13       TST Format       4         4-14       SBST Format       4         4-15       SID Format       4         4-16       MSG Format       4         4-17       CDB Format       4         4-18       TMOD Format       4         4-19       CTCL/CTCM/CTCH Format       4         4-20       BTCL/BTCM/BTCH Format       4         4-21       MSG2 Format       4         4-22       MSG3 Format       4         4-23       EXMOD Format       4         4-24       BFTOUT Format       4         4-25       SRTOUT Format       4         4-26       RATOUT Format       4         4-27       CDBL Format       4         4-28       MOD Format       4         4-29       PID Format       4                                                                                                                                                                                                  | 4-8           | DID Format                                  | 4-11 |

| Register Configuration       4         4-11       CMD Format       4         4-12       EXST Format       4         4-13       TST Format       4         4-14       SBST Format       4         4-15       SID Format       4         4-16       MSG Format       4         4-17       CDB Format       4         4-18       TMOD Format       4         4-19       CTCL/CTCM/CTCH Format       4         4-20       BTCL/BTCM/BTCH Format       4         4-21       MSG2 Format       4         4-22       MSG3 Format       4         4-23       EXMOD Format       4         4-24       BFTOUT Format       4         4-25       SRTOUT Format       4         4-26       RATOUT Format       4         4-27       CDBL Format       4         4-28       MOD Format       4         4-29       PID Format       4                                                                                                                                                                                                                                                                 | 4-9           | IST Format                                  | 4-12 |

| 4-11       CMD Format       4         4-12       EXST Format       4         4-13       TST Format       4         4-14       SBST Format       4         4-15       SID Format       4         4-16       MSG Format       4         4-17       CDB Format       4         4-18       TMOD Format       4         4-19       CTCL/CTCM/CTCH Format       4         4-20       BTCL/BTCM/BTCH Format       4         4-21       MSG2 Format       4         4-21       MSG3 Format       4         4-22       SG3 Format       4         4-23       EXMOD Format       4         4-24       BFTOUT Format       4         4-25       SRTOUT Format       4         4-26       RATOUT Format       4         4-27       CDBL Format       4         4-28       MOD Format       4         4-29       PID Format       4                                                                                                                                                                                                                                                                  | 4-10          | Registers for Holding Interrupt Sources and |      |

| 4-12       EXST Format       4         4-13       TST Format       4         4-14       SBST Format       4         4-15       SID Format       4         4-16       MSG Format       4         4-17       CDB Format       4         4-18       TMOD Format       4         4-19       CTCL/CTCM/CTCH Format       4         4-20       BTCL/BTCM/BTCH Format       4         4-21       MSG2 Format       4         4-22       MSG3 Format       4         4-23       EXMOD Format       4         4-24       BFTOUT Format       4         4-25       SRTOUT Format       4         4-26       RATOUT Format       4         4-27       CDBL Format       4         4-28       MOD Format       4         4-29       PID Format       4                                                                                                                                                                                                                                                                                                                                              |               | Register Configuration                      | 4-19 |

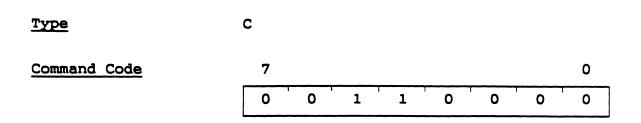

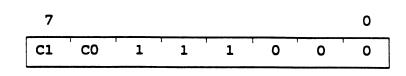

| 4-13       TST Format       4         4-14       SBST Format       4         4-15       SID Format       4         4-16       MSG Format       4         4-17       CDB Format       4         4-18       TMOD Format       4         4-19       CTCL/CTCM/CTCH Format       4         4-20       BTCL/BTCM/BTCH Format       4         4-21       MSG2 Format       4         4-22       MSG3 Format       4         4-23       EXMOD Format       4         4-24       BFTOUT Format       4         4-25       SRTOUT Format       4         4-26       RATOUT Format       4         4-27       CDBL Format       4         4-28       MOD Format       4         4-29       PID Format       4                                                                                                                                                                                                                                                                                                                                                                                     | 4-11          | CMD Format                                  | 4-24 |

| 4-14       SBST Format       4         4-15       SID Format       4         4-16       MSG Format       4         4-17       CDB Format       4         4-18       TMOD Format       4         4-19       CTCL/CTCM/CTCH Format       4         4-20       BTCL/BTCM/BTCH Format       4         4-21       MSG2 Format       4         4-22       MSG3 Format       4         4-23       EXMOD Format       4         4-24       BFTOUT Format       4         4-25       SRTOUT Format       4         4-26       RATOUT Format       4         4-27       CDBL Format       4         4-28       MOD Format       4         4-29       PID Format       4                                                                                                                                                                                                                                                                                                                                                                                                                           | 4-12          | EXST Format                                 | 4-26 |

| 4-15       SID Format       4         4-16       MSG Format       4         4-17       CDB Format       4         4-18       TMOD Format       4         4-19       CTCL/CTCM/CTCH Format       4         4-20       BTCL/BTCM/BTCH Format       4         4-21       MSG2 Format       4         4-22       MSG3 Format       4         4-23       EXMOD Format       4         4-24       BFTOUT Format       4         4-25       SRTOUT Format       4         4-26       RATOUT Format       4         4-27       CDBL Format       4         4-28       MOD Format       4         4-29       PID Format       4                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 4-13          | TST Format                                  | 4-28 |

| 4-16       MSG Format       4         4-17       CDB Format       4         4-18       TMOD Format       4         4-19       CTCL/CTCM/CTCH Format       4         4-20       BTCL/BTCM/BTCH Format       4         4-21       MSG2 Format       4         4-21       MSG2 Format       4         4-22       MSG3 Format       4         4-23       EXMOD Format       4         4-24       BFTOUT Format       4         4-25       SRTOUT Format       4         4-26       RATOUT Format       4         4-27       CDBL Format       4         4-28       MOD Format       4         4-29       PID Format       4                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 4-14          | SBST Format                                 | 4-29 |

| 4-17       CDB Format       4         4-18       TMOD Format       4         4-19       CTCL/CTCM/CTCH Format       4         4-20       BTCL/BTCM/BTCH Format       4         4-21       MSG2 Format       4         4-22       MSG3 Format       4         4-23       EXMOD Format       4         4-24       BFTOUT Format       4         4-25       SRTOUT Format       4         4-26       RATOUT Format       4         4-27       CDBL Format       4         4-28       MOD Format       4         4-29       PID Format       4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 4-15          | SID Format                                  | 4-29 |

| 4-18       TMOD Format       4         4-19       CTCL/CTCM/CTCH Format       4         4-20       BTCL/BTCM/BTCH Format       4         4-21       MSG2 Format       4         4-21       MSG2 Format       4         4-22       MSG3 Format       4         4-23       EXMOD Format       4         4-24       BFTOUT Format       4         4-25       SRTOUT Format       4         4-26       RATOUT Format       4         4-27       CDBL Format       4         4-28       MOD Format       4         4-29       PID Format       4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 4-16          | MSG Format                                  | 4-31 |

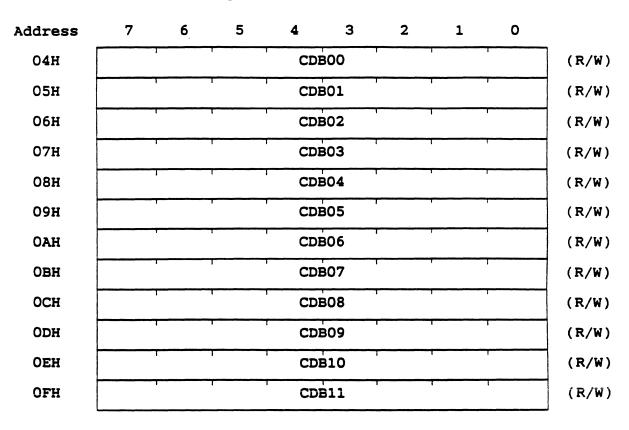

| 4-19CTCL/CTCM/CTCH Format44-20BTCL/BTCM/BTCH Format44-21MSG2 Format44-22MSG3 Format44-23EXMOD Format44-24BFTOUT Format44-25SRTOUT Format44-26RATOUT Format44-27CDBL Format44-28MOD Format44-29PID Format4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 4-17          | CDB Format                                  | 4-32 |

| 4-20       BTCL/BTCM/BTCH Format       4         4-21       MSG2 Format       4         4-22       MSG3 Format       4         4-23       EXMOD Format       4         4-24       BFTOUT Format       4         4-25       SRTOUT Format       4         4-26       RATOUT Format       4         4-27       CDBL Format       4         4-28       MOD Format       4         4-29       PID Format       4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 4-18          | TMOD Format                                 | 4-32 |

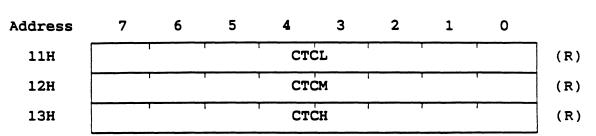

| 4-21       MSG2 Format       4         4-22       MSG3 Format       4         4-23       EXMOD Format       4         4-24       BFTOUT Format       4         4-25       SRTOUT Format       4         4-26       RATOUT Format       4         4-27       CDBL Format       4         4-28       MOD Format       4         4-29       PID Format       4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 4-19          | CTCL/CTCM/CTCH Format                       | 4-35 |

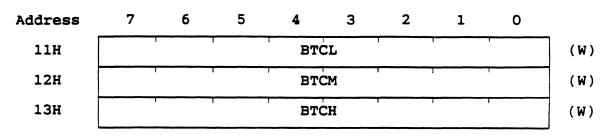

| 4-22       MSG3 Format       4         4-23       EXMOD Format       4         4-24       BFTOUT Format       4         4-25       SRTOUT Format       4         4-26       RATOUT Format       4         4-27       CDBL Format       4         4-28       MOD Format       4         4-29       PID Format       4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 4-20          | BTCL/BTCM/BTCH Format                       | 4-36 |

| 4-23       EXMOD Format       4         4-24       BFTOUT Format       4         4-25       SRTOUT Format       4         4-26       RATOUT Format       4         4-27       CDBL Format       4         4-28       MOD Format       4         4-29       PID Format       4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 4-21          | MSG2 Format                                 | 4-37 |

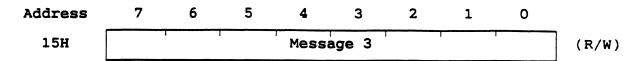

| 4-24       BFTOUT Format       4         4-25       SRTOUT Format       4         4-26       RATOUT Format       4         4-27       CDBL Format       4         4-28       MOD Format       4         4-29       PID Format       4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 4-22          | MSG3 Format                                 | 4-38 |

| 4-25       SRTOUT Format       4         4-26       RATOUT Format       4         4-27       CDBL Format       4         4-28       MOD Format       4         4-29       PID Format       4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 4-23          | EXMOD Format                                | 4-38 |

| 4-26       RATOUT Format       4         4-27       CDBL Format       4         4-28       MOD Format       4         4-29       PID Format       4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 4-24          | BFTOUT Format                               | 4-39 |

| 4-27         CDBL Format         4           4-28         MOD Format         4           4-29         PID Format         4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 4-25          | SRTOUT Format                               | 4-40 |

| 4-28 MOD Format                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 4-26          | RATOUT Format                               | 4-4] |

| 4-29 PID Forme                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 4-27          | CDBL Format                                 | 4-42 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 4-28          | MOD Format                                  | 4-43 |

| 6-1 Command Issuance Processing Operation Flow 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 4-29          | PID Forme                                   | 4-44 |

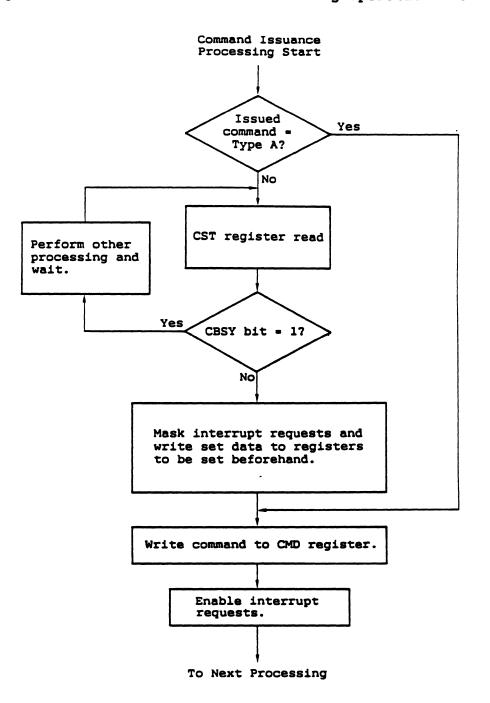

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 6-1           | Command Issuance Processing Operation Flow  | 6-5  |

| Figure<br>No. | Title                                   | Page |

|---------------|-----------------------------------------|------|

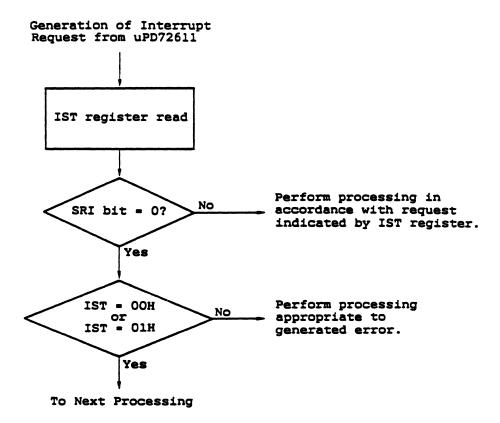

| 6-2           | Interrupt Service Operation Flow        | 6-8  |

| 7-1           | System Configuration Example            | 7-1  |

| 7-2           | Example of External Differential Driver |      |

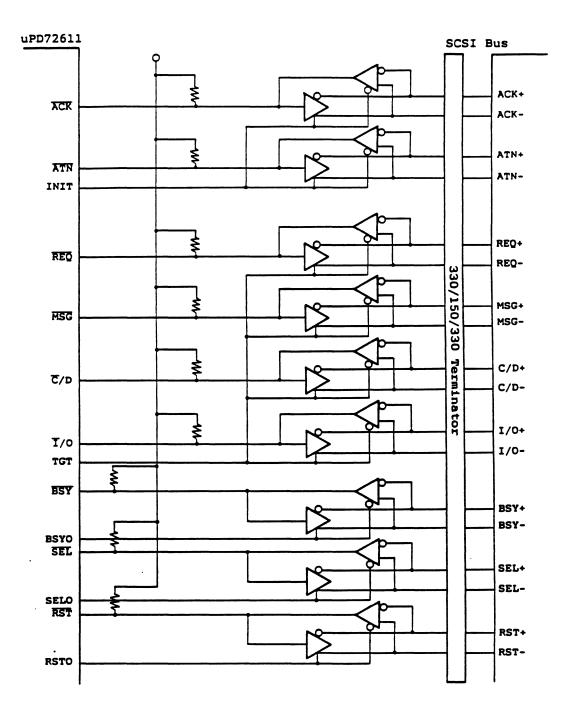

|               | Configuration (SCSI Control Bus)        | 7-2  |

| 7-3           | Example of External Differential Driver |      |

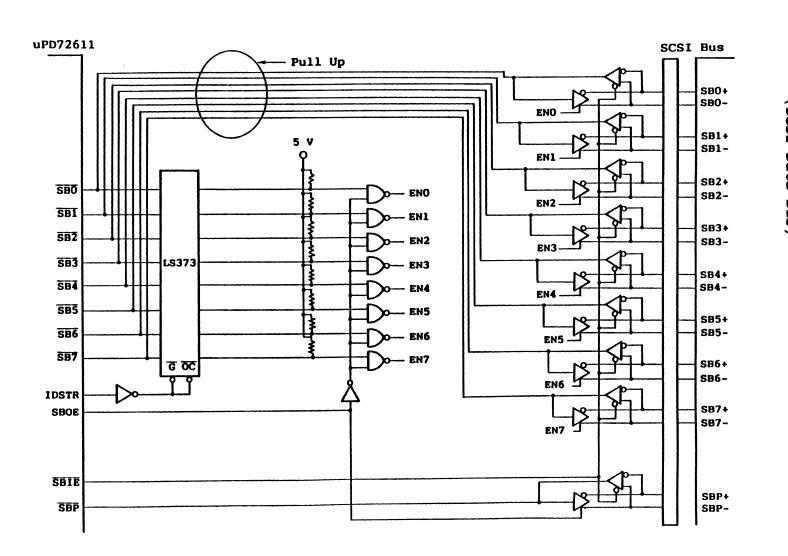

|               | Configuration (SCSI Data Bus)           | 7-3  |

.

## List of Tables

| Table<br>No. | Title                                             | Page |

|--------------|---------------------------------------------------|------|

| 1-1          | Commands                                          | 1-4  |

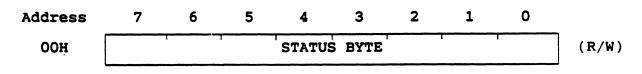

| 4-1          | Direct Registers                                  | 4-2  |

| 4-2          | IST Format and INT Status                         | 4-13 |

| 4-3          | Interrupt Sources                                 | 4-15 |

| 4-4          | IST Contents After Normal Command Termination     | 4-17 |

| 4-5          | Commands Which Clear Interrupt Source             | 4-20 |

| 4-6          | Conditions for Holding Multiple Interrupt Sources |      |

|              | (IST-FIRM)                                        | 4-23 |

| 4-7          | Outline of Command Code                           | 4-24 |

| 4-8          | Indirect Access Registers                         | 4-27 |

| 5-1          | Command Functions                                 | 5-2  |

| 5-2          | Command Codes                                     | 5-10 |

•

•

#### CHAPTER 1. GENERAL DESCRIPTION

The uPD72611 is an SCSI-2 (Small System Interface-2) controller compliant with ANSI X3T9.2/86-109 Rev.10c.

It incorporates bus phase sequence control functions, allowing the load on the host processor to be reduced. It is compatible with a 32-, 16- or 8-bit CPU data bus.

A single-end type driver/receiver is incorporated at the SCSI bus side, allowing direct connection with a SCSI bus. In addition, an external differential driver/receiver is supported.

#### 1.1 SYSTEM OUTLINE

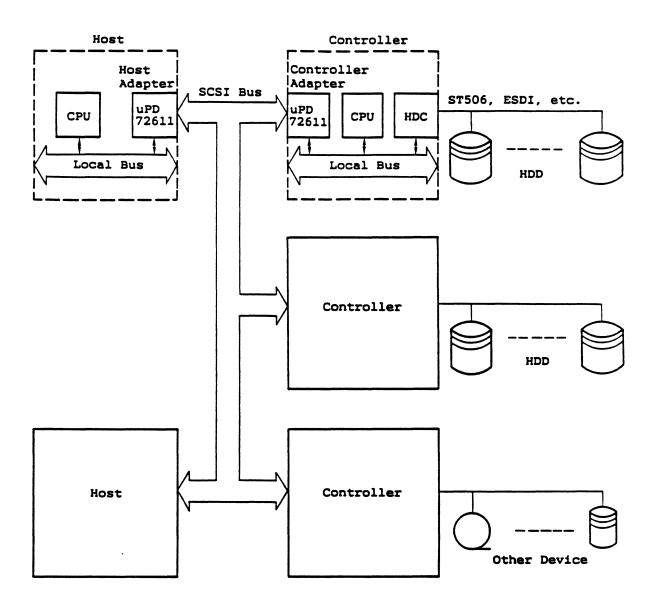

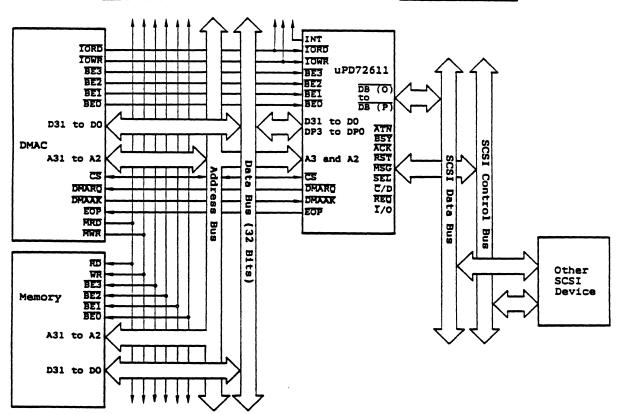

The position of uPD72611s in the configuration of an SCSI system is shown in Figure 1-1. Up to eight SCSI devices, including both hosts and controllers, can be connected to the SCSI bus. The uPD72611 functions as a host adapter/ controller adapter which interfaces with the SCSI bus. Each SCSI device is assigned a fixed ID number between 0 and 7.

On the SCSI bus, communication is carried out between two SCSI devices, specified as the initiator and the target.

1-1

Figure 1-1 System Configuration Example

1.2 OUTLINE OF SYSTEM OPERATION

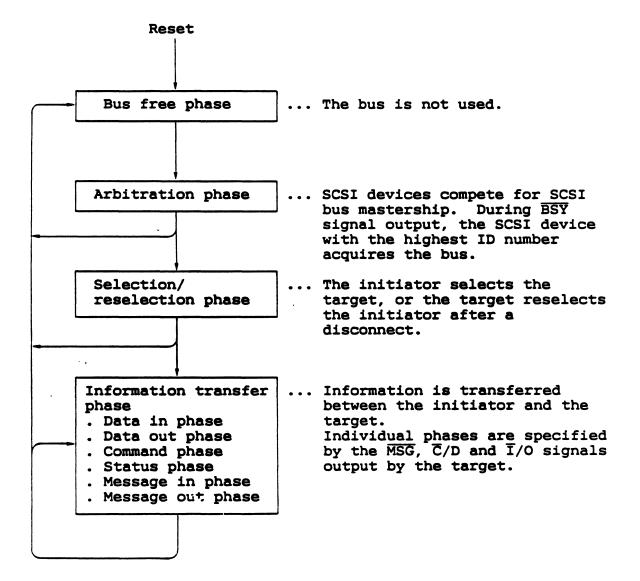

In an SCSI system, communication is performed between an SCSI device specified as the initiator and an SCSI device specified as the target.

SCSI bus phase transitions are shown in the figure below. Bus phase control in the information transfer phase is performed by the target.

Figure 1-2 SCSI Bus Phase Transitions

## 1.3 COMMANDS

The uPD72611 incorporates the 18 commands shown below.

| Туре         | Command Name     | Mnemonic | Outline of Operation                                                  |

|--------------|------------------|----------|-----------------------------------------------------------------------|

| Group        | CHIP RESET       | CRST     | Internal uPD72611 reset                                               |

|              | BREAK            | BRK      | Suspension of command execution                                       |

|              | DISCONNECT       | DIS      | SCSI bus release                                                      |

|              | CLEAR FIFO       | CLRF     | FIFO buffer clearance                                                 |

|              | SCSI RESET       | SRST     | SCSI bus reset                                                        |

| Group<br>II  | SET ATN          | SETAT    | ATN signal setting (0)                                                |

|              | RESET ACK        | RSTAK    | ACK signal reset (1)                                                  |

|              | SELECT           | SEL      | Target selection                                                      |

|              | TRANSFER         | TFR      | Information transmission/reception (initiator)                        |

|              | AUTO INITIATOR   | AINI     | Automatic execution of initiator standard operation                   |

|              | AUTO INITIATOR 2 | AINI2    | Automatic execution of initiator standard operation after reselection |

| Group<br>III | RESELECT         | RSEL     | Initiator reselection                                                 |

|              | RECEIVE          | REC      | Information reception (target)                                        |

|              | SEND             | SND      | Information transmission (target)                                     |

|              | AUTO TARGET      | ATGT     | Automatic execution of target standard operation                      |

|              | AUTO TARGET 2    | ATGT2    | Automatic execution of target standard termination operation          |

|              | RE-RECEIVE       | RREC     | Reselection + data reception consecutive execution (target)           |

|              | RE-SEND          | RSND     | Reselection - data transmission<br>consecutive execution (target)     |

## Table 1-1 Commands

Remarks: A group is a set of commands classified by use. This is different from the SCSI command group.

#### 1.4 FEATURES

- o Conforms to ANSI X3T9.2/86-109 Rev.10c (SCSI-2 standard)

- o System clock: Max. 20 MHz

- o Data transfer rate

- . Asynchronous (5.0M bytes/sec or above)

- . Synchronous (Max. 5.0M bytes/sec: Programmable in 7 steps)

- . High-speed synchronous (Max. 10.0M bytes/sec: Programmable in 7 steps)

- o Operable as initiator or target

- o CPU-side bus width selectable (32/16/8 bits)

- o On-chip single-end type SCSI bus driver and Schmitt type receiver

- o Supports external differential driver and receiver.

- o Supports 6 compound commands which alleviate the host CPU interrupt handling load.

- o Command queuing function

3-byte message transfer supported for each compound command

- o Parity through supported

- o Synchronization offset value specifiable (1 to 8)

- o On-chip 24-bit transfer counter

## 1.5 ORDERING INFORMATION

| Product Name   | Package           | Quality Grade |

|----------------|-------------------|---------------|

| uPD72611GF-3BA | 100-pin plastic Q | FP Standard   |

Please refer to "Quality grade on NEC Semiconductor Devices" (Document number IEI-1209) published by NEC Corporation to know the specification of quality grade on the devices and its recommended applications.

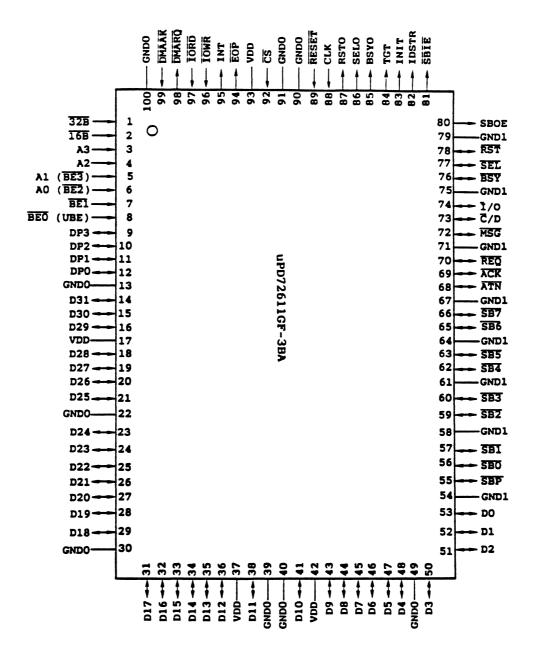

## 100-pin plastic QFP

1-7

| $\overline{SB0}$ to $\overline{SB7}$ : | : | SCSI Buses 0 to 7               |

|----------------------------------------|---|---------------------------------|

| SBP :                                  | : | SCSI Bus Parity                 |

| ANT :                                  | : | Attention                       |

| ACK :                                  | : | Acknowledge                     |

| REQ :                                  | : | Request                         |

| MSG :                                  | : | Message                         |

| <u>c</u> /d :                          | : | Command/Data                    |

| Ī/0 :                                  | : | Input/Output                    |

| BSY :                                  | : | Busy                            |

| SEL :                                  | : | Select                          |

| RST :                                  | : | Reset                           |

| RSTO :                                 | : | Reset Out                       |

| BSYO :                                 | : | Busy Out                        |

| SELO :                                 | : | Select Out                      |

| IDSTR :                                | : | ID Strobe                       |

| INIT :                                 | : | Initiator                       |

| TGT :                                  | : | Target                          |

| SBOE :                                 | : | SCSI Bus Out Enable             |

| SBIE :                                 | : | SCSI Bus In Enable              |

| INT :                                  | : | Interrupt Request               |

| IORD :                                 | : | I/O Read                        |

| IOWR :                                 | : | I/O Write                       |

| A2 & A3 :                              | : | Addresses 2 & 3                 |

| AO/BE2 & A1/BE3:                       | : | Address 0 & 1/Byte Enable 2 & 3 |

| BEO/UBE :                              | : | Byte Enable O/Upper Byte Enable |

| BE1 :                                  | : | Byte Enable 1                   |

| <u>CS</u> :                            | : | Chip Select                     |

| D0 to D31 :                            | : | Data Buses 0 to 31              |

| DPO to DP3 :                           | : | Data Parity 0 to 3              |

| DMARQ :                                | • | DMA Request                     |

| DMAAK :                                | : | DMA Acknowledge                 |

| EOP :                                  | : | End of Process                  |

| RESET :                                | : | Reset                           |

| 16B :                                  | : | 16-bit Bus                      |

| 32B :                                  | : | 32-bit Bus                      |

.

1.7

## CHAPTER 2. PIN FUNCTIONS

uPD72611 pins are divided into those on the CPU interface side and those on the SCSI interface side.

## 2.1 CPU INTERFACE PINS

.

| Name                                                                | Input/<br>Output | Pin No. | Function                                                                                                                                                                                                                                                                                        |

|---------------------------------------------------------------------|------------------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| INT<br>(Interrupt<br>Request)                                       | Output           | 95      | Pin which outputs interrupt request signal to<br>the CPU<br>Activated when an internal interrupt source is<br>generated.                                                                                                                                                                        |

| IROD<br>(I/O Read)                                                  | Input            | 97      | Read signal input pin for reading from<br>uPD72611 internal registers by the CPU                                                                                                                                                                                                                |

| IOWR<br>(I/O Write)                                                 | Input            | 96      | Write signal input pin for writing to<br>uPD72611 internal registers by the CPU                                                                                                                                                                                                                 |

| A2 & A3<br>(Addresses<br>2 & 3)                                     | Input            | 4.3     | Input pins for high-order 2 bits of address<br>Specify the direct access register to be<br>accessed.                                                                                                                                                                                            |

| AO/BE2 &<br>A1/BE3<br>(Addresses<br>0 & 1/<br>Byte Enable<br>2 & 3) | Input            | 6, 5    | <ul> <li>In 32-bit bus mode Input pins for signals indicating valid bus in a data access together with BEI &amp; BEO signals In 16-/8-bit bus mode Input pins for low-order 2 bits of address </li> </ul>                                                                                       |

| BE1<br>(Byte<br>Enable 1)                                           | Input            | 7       | . In 32-bit bus mode<br>Input pin for signal indicating valid bus in<br>a data access together with BE3, BE2 & BEO<br>signals                                                                                                                                                                   |

| BEO/UBE<br>(Byte<br>Enable O/<br>Upper Byte<br>Enable)              | Input            | 8       | <ul> <li>In 32-bit bus mode<br/>Input pin for signal indicating valid bus in<br/>a data access together with BE3, BE2 &amp; BE1<br/>signals</li> <li>In 16-bit bus mode<br/>Input pin for upper byte data input/output<br/>enable signal</li> <li>Only valid in 32-/16-bit bus mode.</li> </ul> |

(to be continued)

# (cont'd)

| Name                                                               | Input/<br>Output | Pin No.                                                                                                                                                          | Function                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

|--------------------------------------------------------------------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| BEO/UBE<br>(Byte<br>Enable O/<br>Upper Byte<br>Enable)<br>(cont'd) | Input            | 8                                                                                                                                                                | A0UBEInternal Register AccessLLInternal register D15 to D0<br>(16 bits)LHInternal register D7to D0 (8 bits)HLInternal register D15 to D8<br>(8 bits)HHUse prohibited                                                                                                                                                                                                                                                               |  |  |  |

| CS<br>(Chip<br>Select)                                             | Input            | 92                                                                                                                                                               | Chip select signal input pin. Enables access to internal register.                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

| D0 to D31<br>(Data 0 to<br>31)                                     | Input/<br>output | 53. 52.<br>51. 50.<br>48. 47.<br>46. 45.<br>44. 43.<br>36. 35.<br>34. 33.<br>32. 31.<br>29. 28.<br>27. 26.<br>25. 24.<br>23. 21.<br>20. 19.<br>18. 16.<br>15. 14 | These pins function as follows according to<br>the bus mode specification:<br>. In 32-bit bus mode<br>D0 to D7 : Input/output pins for lower<br>byte of low-order 16 bits of<br>32-bit data<br>D8 to D15 : Input/output pins for upper<br>byte of low-order 16 bits of<br>32-bit data<br>D16 to D31: Input/output pins for high-<br>order 16 bits of 32-bit data<br>. In 16-bit bus mode<br>D0 to D7 : Input/output pins for lower |  |  |  |

| DPO to DP3<br>(Data<br>Parity O to<br>3)                           | Input/<br>output | 12, 11,<br>10, 9                                                                                                                                                 | <pre>Input/output pins for parity signals added to data bus . In 32-bit bus mode D0 to D7 : DP0 D8 to D15 : DP1 D16 to D23: DP2 D24 to D31: DP3</pre>                                                                                                                                                                                                                                                                              |  |  |  |

(to be continued)

(cont'd)

.

|                                                      |                  |                  | (cont d)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|------------------------------------------------------|------------------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Name                                                 | Input/<br>Output | Pin No.          | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| DPO to DP3<br>(Data<br>Parity O to<br>3)<br>(cont'd) | Input/<br>output | 12, 11,<br>10, 9 | <ul> <li>In 16-bit bus mode D0 to D7 : DP0 D8 to D15 : DP1 The DP2 &amp; DP3 pins are in the high-impedance (input) state and should be fixed high or low.</li> <li>In 8-bit data mode D0 to D7 : DP0 The DP1, DP2 &amp; DP3 pins are in the high- impedance (input) state and should be fixed high or low.</li> </ul>                                                                                                                                                                                                                                                                |

| DMARQ<br>(DMA<br>Request)                            | Output           | 98               | DMA service request signal output pin. In the<br>data in/data out phase when DMA mode has been<br>specified, outputs a low-level signal when the<br>FIFO buffer is in the following state:<br>Write to FIFO buffer : When there are only 6<br>or fewer levels of<br>data in the FIFO<br>buffer.<br>Read from FIFO buffer: When there are 2 or<br>more levels of data in<br>the FIFO buffer.<br>However, when the last<br>transfer data is left<br>in the FIFO buffer,<br>this pin also outputs<br>a low-level signal<br>when only one level of<br>data is left in the<br>FIFO buffer. |

| DMAAK<br>(DMA Ac-<br>knowledge)                      | Input            | 99               | DMA service enable signal input pin. When<br>this pin is activated, the data FIFO register<br>is specified as the object of the access<br>irrespective of the status of the CS and AO to<br>A2 signals. When DMA mode is not specified,<br>this pin should be fixed high.                                                                                                                                                                                                                                                                                                             |

| EOP<br>(End of<br>Process)                           | Output           | 94               | Output pin for signal indicating end of data<br>transfer. Activated in case of uPD72611<br>abnormal termination or break operation.<br>Open-drain output.                                                                                                                                                                                                                                                                                                                                                                                                                             |

## 2.2 SCSI INTERFACE PINS

| Name                                       | Input/<br>Output | Pin No.                                 | Function                                                                                                                                                              |

|--------------------------------------------|------------------|-----------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SBO to SB7<br>*1<br>(SCSI Buses<br>0 to 7) | Input/<br>output | 56. 57.<br>59. 60.<br>62. 63.<br>65. 66 | SCSI data bus input/output pins                                                                                                                                       |

| SBP *1<br>(SCSI Bus<br>Parity)             | Input/<br>output | 55                                      | Input/output pins for parity signals added to<br>SCSI data bus                                                                                                        |

| BSY *1<br>(Busy)                           | Input/<br>output | 76                                      | Input/output pin connected to SCSI control bus<br>BSY signal. Indicates the another SCSI device<br>is using the SCSI bus.                                             |

| SEL *1<br>(Select)                         | Input/<br>output | 77                                      | Input/output pin connected to SCSI control bus<br>SEL signal. Indicates that a select/reselect<br>operation is being executed in the selection/<br>reselection phase. |

| REQ *1<br>(Request)                        | Input/<br>output | 70                                      | Input/output pin connected to SCSI control bus<br>REQ signal. Indicates a target information<br>transfer request.                                                     |

| ACK *1<br>(Acknowl-<br>edge)               | Input/<br>output | 69                                      | Input/output pin connected to SCSI control bus<br>ACK signal. Indicates initiator has accepted<br>a target information transfer request.                              |

| ATN *1<br>(Attention)                      | Input/<br>output | 68                                      | Input/output pin connected to SCSI control bus<br>ATN signal. Indicates initiator is requesting<br>message out phase.                                                 |

| MSG *1<br>(Message)                        | Input/<br>output | 72                                      | Input/output pins connected to SCSI control<br>bus MSG, C/D & I/O signals. The SCSI bus<br>phase is indicated by a combination of these                               |

| C/D *1<br>(Command/<br>Data)               | Input/<br>output | 73                                      | signals as shown below.                                                                                                                                               |

| I/0 *1(Input/<br>Output)                   | Input/<br>output | 74                                      |                                                                                                                                                                       |

(to be continued)

(cont'd)