# **PRODUCT DESCRIPTION**

# μPD7201/7201A μPD72001 μPD7210 μPD72105

# PRODUCT DESCRIPTION

μΡD7201/7201A μΡD72001 μΡD7210 μΡD72105

# COMMUNICATIONS CONTROLLERS

μPD7201/7201AMULTIPROTOCOL SERIAL COMMUNICATION CONTROLLERμPD72001ADVANCED MULTIPROTOCOL SERIAL CONTROLLERμPD7210GPIB CONTROLLERμPD72105LOCAL AREA NETWORK CONTROLLER

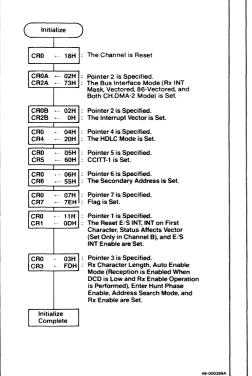

Table of Contents - uPD7201/7201A Product Decsription

| S | ec | ti | on |

|---|----|----|----|

|   |    |    |    |

| 1 | Introduction                                                |

|---|-------------------------------------------------------------|

| 2 | Pin Description1-2                                          |

|   | CPU Interface Signals1-3                                    |

|   | Channel Interface Signals1-4                                |

|   | Modem Interface Signals1-5                                  |

| 3 | Functional Description1-7                                   |

|   | Receiver Section1-7                                         |

|   | Transmitter Section1-8                                      |

|   | CPU Interface Section1-8                                    |

| 4 | Registers                                                   |

|   | Control Register 0 (CR0)1-13                                |

|   | Control Register 1 (CR1)1-15                                |

|   | Control Register 2, Channel A (CR2A)1-16                    |

|   | Control Register 2, Channel B (CR2B)1-18                    |

|   | Control Register 3 (CR3)1-18                                |

|   | Control Register 4 (CR4)1-19                                |

|   | Control Register 5 (CR5)1-20                                |

|   | Control Registers 6 and 7 (CR6 and CR7)1-21                 |

|   | Status Register 0 (SRO)1-22                                 |

|   | Status Register 1 (SR1)1-24                                 |

|   | Status Register Channel B (SR2B)                            |

|   | Status Registers 3 and 4 (SR3 and SR4) $\ldots \ldots 1-26$ |

|   | Tx Length Register, High Byte and Low Byte                  |

|   | (TxLR-H and TxLR-L)1-26                                     |

| 5 | Operating Modes1-27                                         |

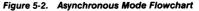

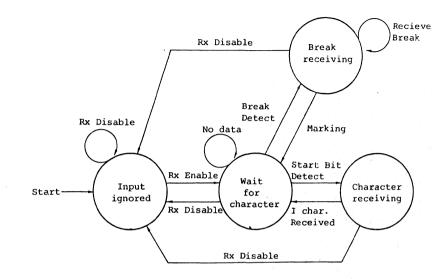

|   | Asynchronous Mode1-27                                       |

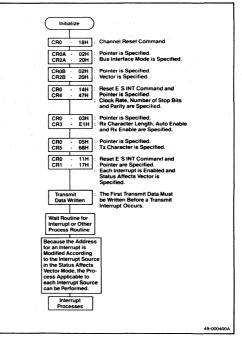

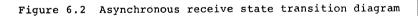

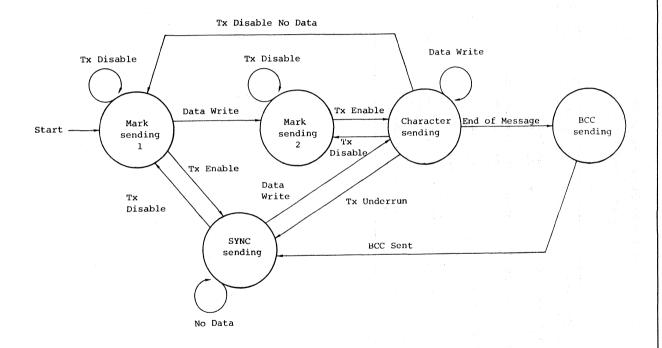

|   | Synchronous Mode1-30                                        |

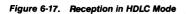

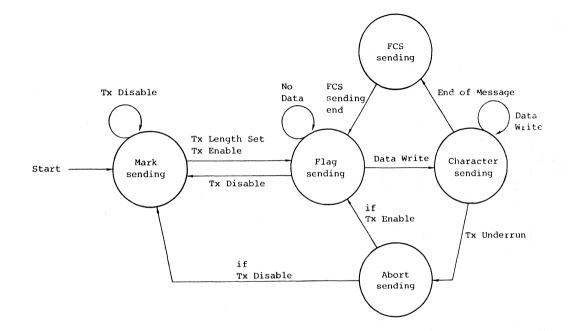

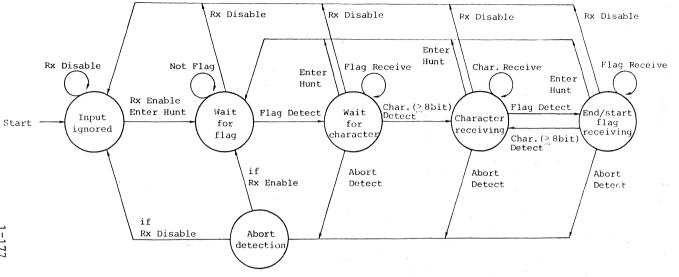

|   | HDLC (SDLC) Mode1-36                                        |

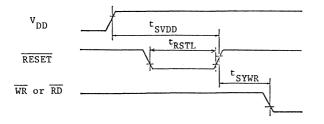

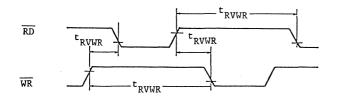

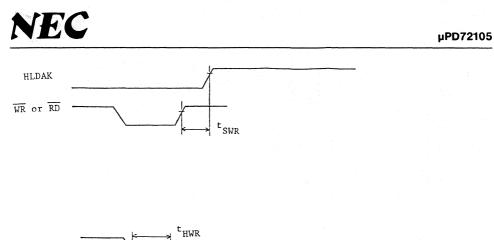

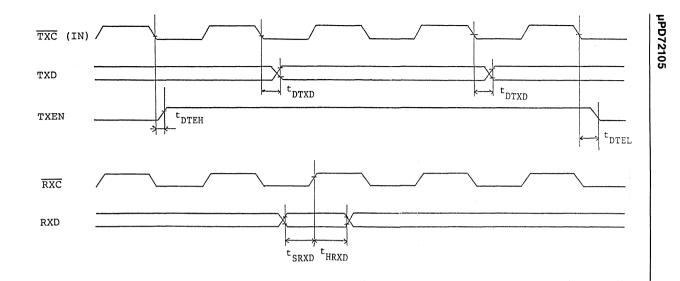

| 6 | Timing1-45                                                  |

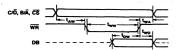

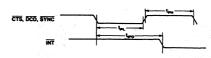

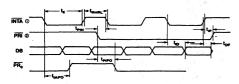

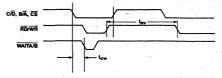

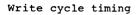

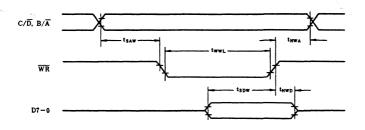

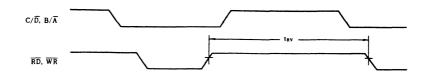

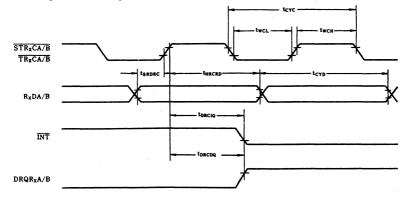

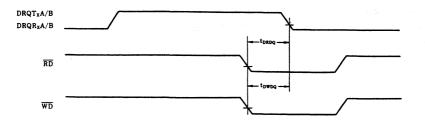

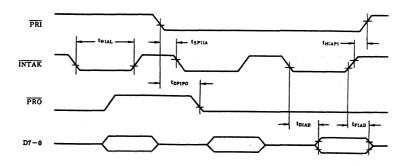

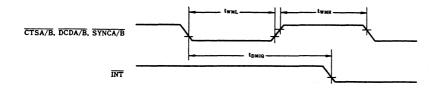

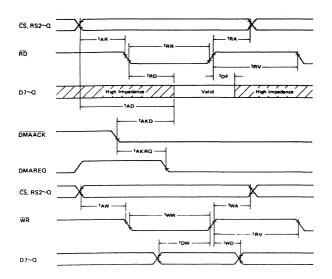

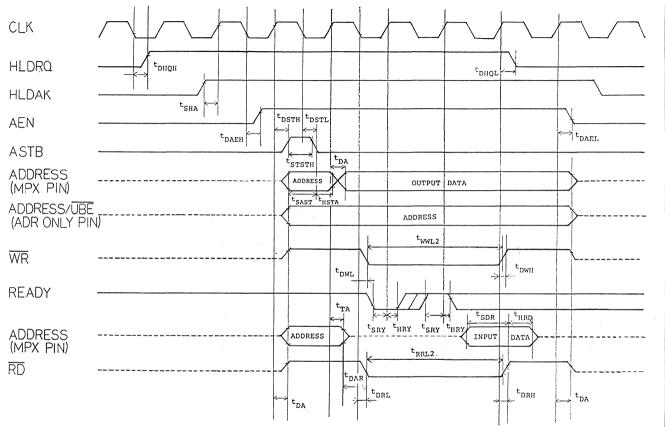

|   | CPU Interface Timing1-45                                    |

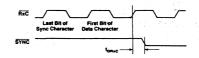

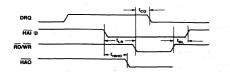

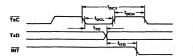

|   | Transmission/Reception Timing                               |

Table of Contents - uPD7201/7201A Product Decsription

| Section | Page                                                                             |

|---------|----------------------------------------------------------------------------------|

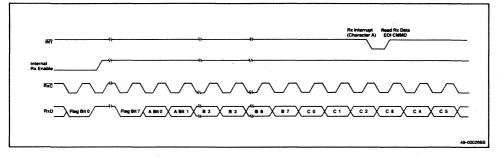

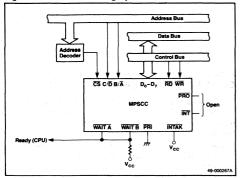

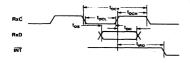

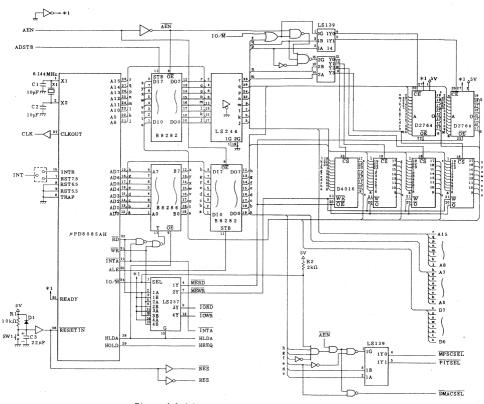

| 7       | System Configurations                                                            |

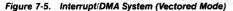

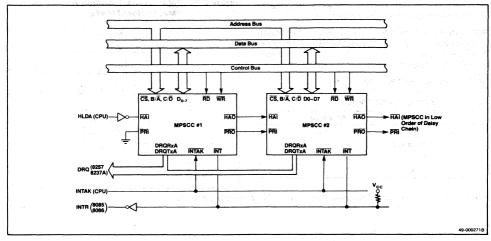

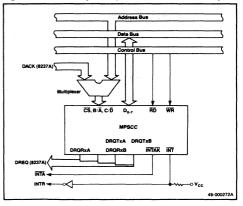

|         | Channels A and B in Interrupt Mode1-55<br>Channel A in DMA Mode and Channel B in |

|         | Interrupt Mode1-56<br>Channels A and B in DMA Mode1-57                           |

| 8       | Electrical Specification1-59                                                     |

| 9       | Appendix (uPD7201A and uPD7201 Comparison)1-61                                   |

| 10      | Application Note1-65                                                             |

II

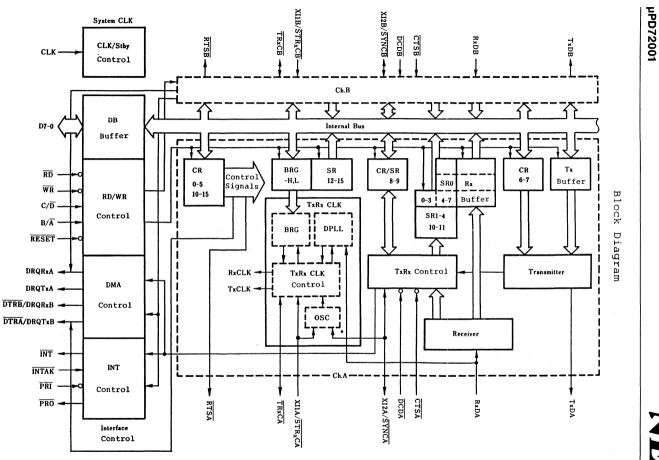

Table of Contents - uPD72001 Product Description Section

Page

|     | Introduction                          |

|-----|---------------------------------------|

|     | Features                              |

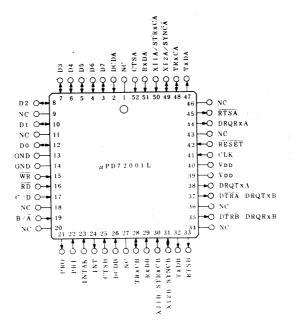

|     | Pin Configuration2-3                  |

|     | Block Diagram                         |

|     |                                       |

| 1.  | Pin Functions2-5                      |

| 1.1 | System Interface Pins2-5              |

| 1.2 | Send/Receive Operation Pins2-11       |

|     |                                       |

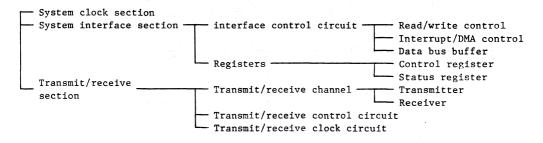

| 2.  | Configuration                         |

| 2.1 | System Clock Section2-15              |

| 2.2 | System Interface Section2-15          |

|     | 2.2.1 Interface control circuit2-16   |

|     | 2.2.2 Registers                       |

| 2.3 | Transmitter/Receiver Section2-17      |

|     |                                       |

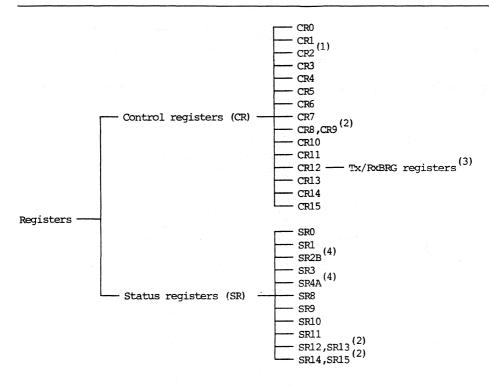

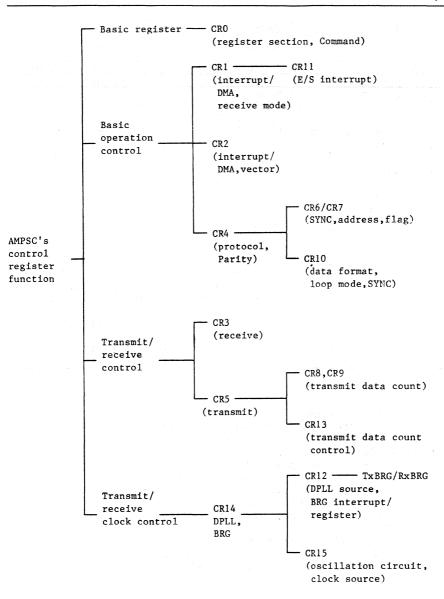

| з.  | Register Configuration2-18            |

| 3.1 | Outline of Registers2-18              |

| 3.2 | Control Registers (CR)2-28            |

|     | 3.2.1 Control Register 0 (CR0)2-30    |

|     | 3.2.2 Control Register 1 (CR1)2-34    |

|     | 3.2.3 Control Register 2A (CR2A)2-39  |

|     | 3.2.4 Control Register 2B (CR2B)2-42  |

|     | 3.2.5 Control Register 3 (CR3)2-43    |

|     | 3.2.6 Control Register 4 (CR4)2-48    |

|     | 3.2.7 Control Register 5 (CR5)2-50    |

|     | 3.2.8 Control Register 6 (CR6)2-54    |

|     | 3.2.9 Control Register 7 (CR7)2-55    |

|     | 3.2.10 Control Register 8 (CR8)2~56   |

|     | 3.2.11 Control Register 9 (CR9)2-56   |

|     | 3.2.12 Control Register 10 (CR10)2-57 |

|     | 3.2.13 Control Register 11 (CR11)2-62 |

|     | 3.2.14 Control Register 12 (CR12)2-65 |

|     | 3.2.15 Control Register 13 (CR13)2-68 |

|     | 3.2.16 Control Register 14 (CR14)2-71 |

|     | 3.2.17 Control Register 15 (CR15)     |

Table of Contents - uPD72001 Product Description

Section

| 3.3 | Status | Registers (SR)2-77            |

|-----|--------|-------------------------------|

|     | 3.3.1  | Status Register 0 (SR0)2-77   |

|     | 3.3.2  | Status Register 1 (SR1)2-82   |

|     | 3.3.3  | Status Register 2B (SR2B)2-88 |

|     | 3.3.4  | Status Register 3 (SR3)2-89   |

|     | 3.3.5  | Status Register 4A (SR4A)2-92 |

|     | 3.3.6  | Status Register 8 (SR8)2-94   |

|     | 3.3.7  | Status Register 9 (SR9)2-95   |

|     | 3.3.8  | Status Register 10 (SR10)2-95 |

|     | 3.3.9  | Status Register 11 (SR11)2-98 |

|     | 3.3.10 | Status Register 12 (SR12)2-98 |

|     | 3.3.11 | Status Register 13 (SR13)2-98 |

|     | 3.3.12 | Status Register 14 (SR14)2-99 |

|     | 3.3.13 | Status Register 15 (SR15)2-99 |

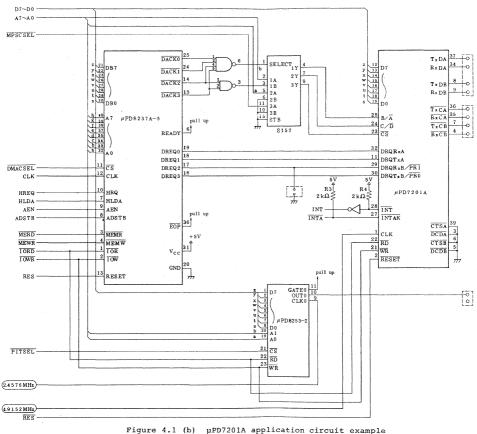

| 4.  | System | Configuration Example         |

|     |        |                               |

| 5.  | Target | Specs                         |

Table of Contents - uPD7210 Product Description

|  |  | on |

|--|--|----|

|  |  |    |

|  |  |    |

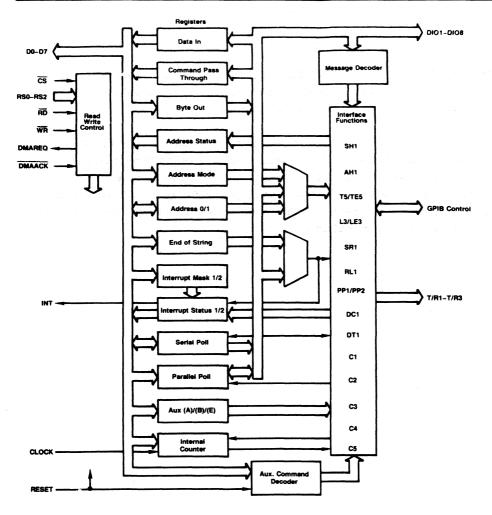

| 1.  | Introduction                               |

|-----|--------------------------------------------|

| 1.1 | General Description                        |

| 1.2 | IEEE STD-448-1978                          |

|     |                                            |

| 2.  | Functional Description                     |

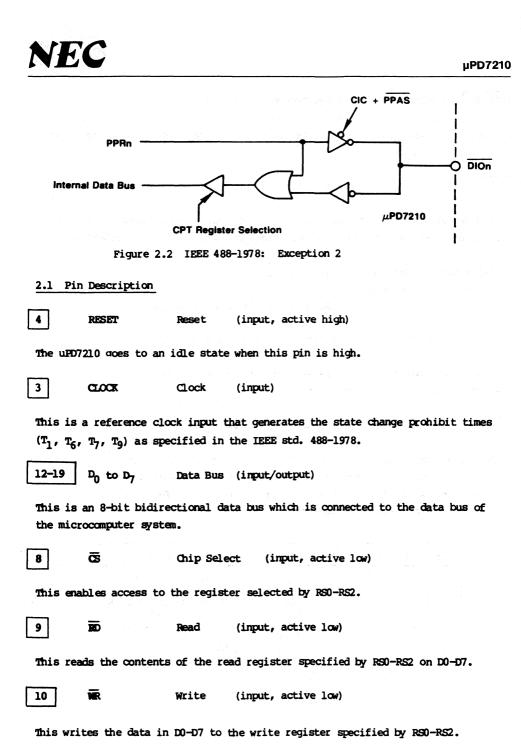

| 2.1 | Pin Description                            |

|     |                                            |

| 3.  | Internal Registers                         |

| 3.1 | Data Registers                             |

| 3.2 | Interrupt Registers                        |

|     | 3.2.1 Interrupt Bits                       |

|     | 3.2.2 Non-Interrupt Bits                   |

| 3.3 | Serial Poll Registers                      |

| 3.4 | Address Mode Status Registers              |

|     | 3.4.1 Selecting T/R2 and T/R3 Pin Function |

|     | 3.4.2 Selecting Address Mode               |

| 3.5 | Address Registers                          |

| 3.6 | Command Pass Through Registers             |

| 3.7 | End of String (EOS) Register               |

| 3.8 | Auxiliary Mode Register                    |

|     | 3.8.1 Auxiliary Commands                   |

|     | 3.8.2 Internal Counter                     |

|     | 3.8.3 Auxiliary Register A                 |

|     | 3.8.4 Auxiliary Register B                 |

|     | 3.8.5 Auxuliary Register E                 |

|     | 3.8.6 Parralel Poll Register               |

## Table of Contents - uPD7210 Product Description

Section

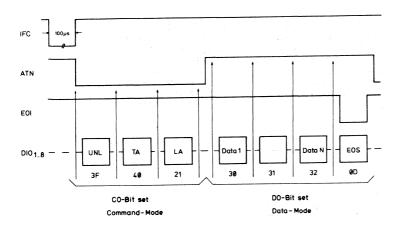

| 4.   | Using the uPD7210                                                |

|------|------------------------------------------------------------------|

| 4.1  | Transmitting Commands                                            |

| 4.2  | Processing the Undefined Commands                                |

| 4.3  | Processing Address Pass Through                                  |

| 4.4  | Beginning Data Transfer                                          |

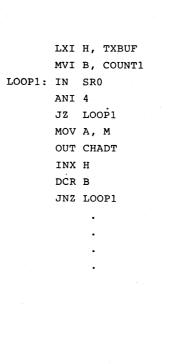

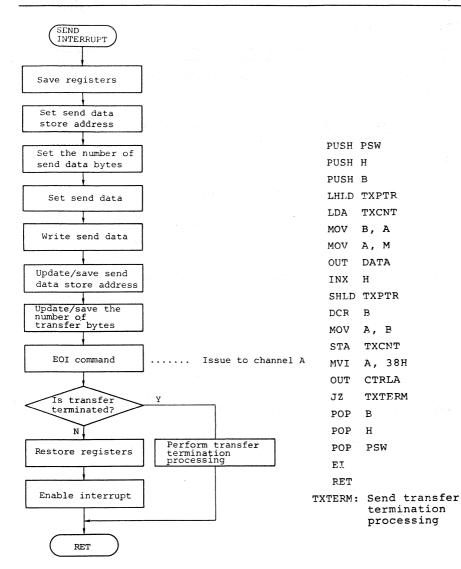

| 4.5  | Transmitting Data                                                |

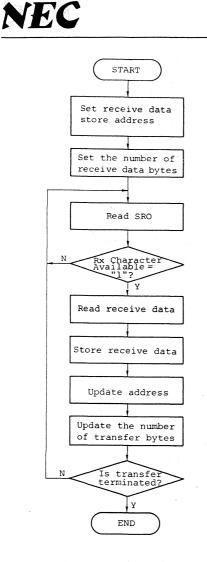

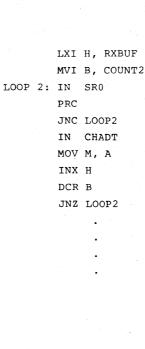

| 4.6  | Receiving Data                                                   |

|      | 4.6.1 Normal Handshake Mode (A0=A1=0)                            |

|      | 4.6.2 RFD Holdoff on All Data Mode (A0=1, A1=0)3-34              |

|      | 4.6.3 RFD Holdoff on End Mode (A0=0, A1=1) $\ldots 3-34$         |

|      | 4.6.4 Continous Mode (A0=A1=1)                                   |

| 4.7  | Completing Data Block Transfer                                   |

|      | 4.7.1 Placing EOS Byte After Data Block                          |

|      | 4.7.2 Using the EOI Line                                         |

|      | 4.7.3 Transmission of the EOS Message                            |

|      | 4.7.4 Transmission of the END Message                            |

|      | 4.7.5 Detecting the EOS Message                                  |

|      | 4.7.6 Detecting the END Message                                  |

| 4.8  | Discouting Data Transfer3-36                                     |

|      | 4.8.1 Using the Take Control Asynchronously Command $\dots$ 3-36 |

|      | 4.8.2 Using the Take Control Synchronously Command3-37           |

|      | 4.8.3 Using the Take Control Synchronously on End                |

|      | Command                                                          |

| 4.9  | Serial Polling                                                   |

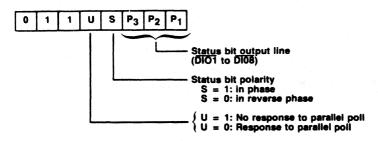

| 4.10 | Parallel Polling                                                 |

| 4.11 | Parallel Poll Protocol                                           |

Table of Contents - uPD7210 Product Description

| Sect | tion                         | Page |

|------|------------------------------|------|

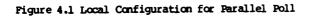

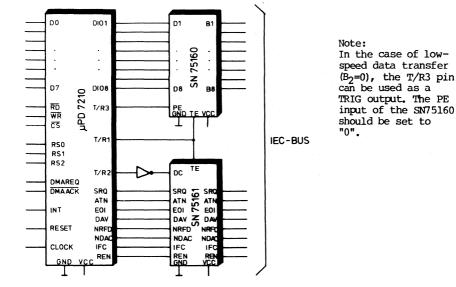

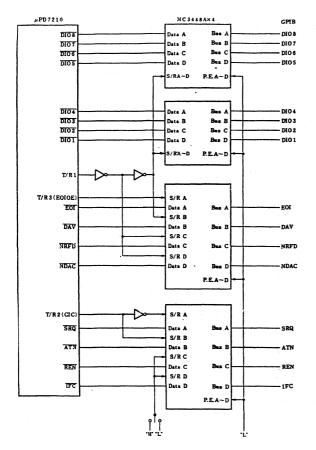

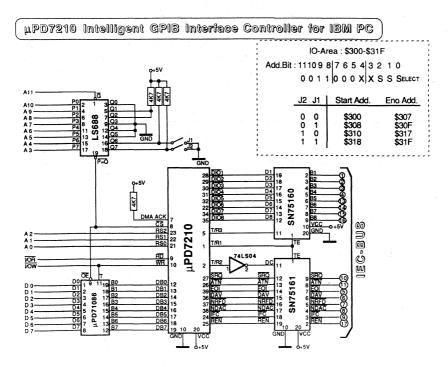

| 5    | GPIB-Interface using uPD7210 |      |

|      | Hardware                     |      |

| 5.2  | Software                     | 3-43 |

|      |                              |      |

| 6.   | Electrical Specification     |      |

| 7.   | Appendix                     |      |

| 8.   | Application Note             |      |

Table of Contents - uPD72105 Product Description

| Sect | cion Page                        |

|------|----------------------------------|

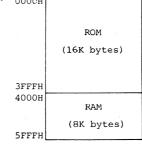

|      | Introduction4-1                  |

|      | Features                         |

|      | Pin Connection                   |

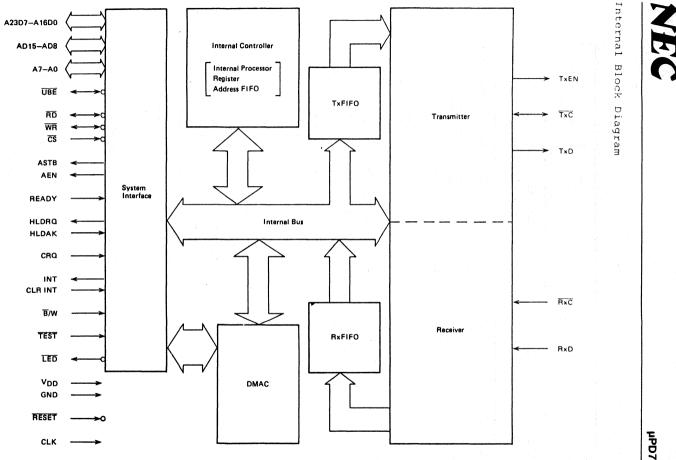

|      | Block Diagram4-3                 |

| 1.   | Pin Functions                    |

| _    |                                  |

| 2.   | Internal Configuration4-9        |

| 2.1  | Internal Controller4-9           |

| 2.2  | System Interface4-9              |

| 2.3  | DMA Controller4-9                |

| 2.4  | RxFIFO                           |

| 2.5  | TxFIFO                           |

| 2.6  | Receiver                         |

| 2.7  | Transmitter4-10                  |

| з.   | Interfacing with Host System4-11 |

| 3.1  | Control Register                 |

| 3.2  | Status Register                  |

| 3.3  | Address FIFO                     |

Table of Contents - uPD72105 Product Description

Section

| 4.  | Commands       |             |               |             |         | ••••••              |      |

|-----|----------------|-------------|---------------|-------------|---------|---------------------|------|

| 4.1 | Types of Comma | nds         |               |             |         | •••••••             |      |

| 4.2 | Command Functi | o <b>ns</b> |               |             | ••••••• |                     |      |

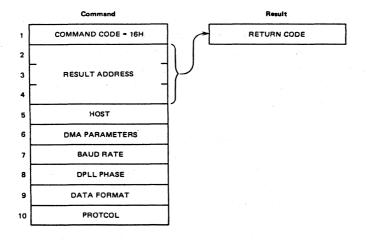

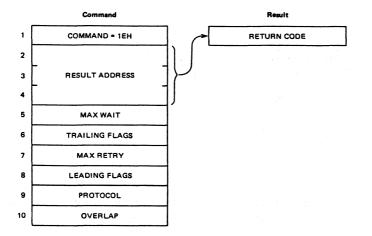

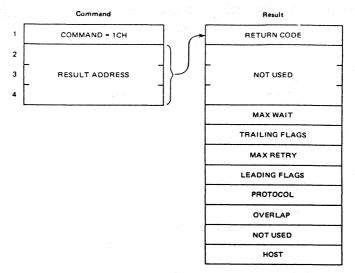

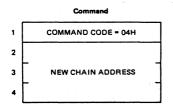

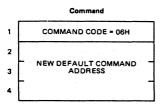

|     | 4.2.1 INIT     |             |               |             |         |                     |      |

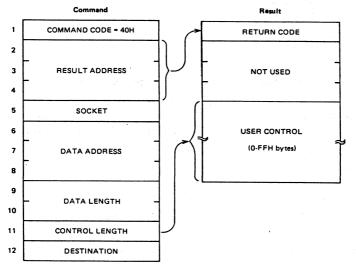

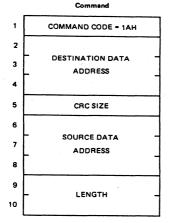

|     | 4.2.2 SEND     |             |               |             |         | · · · · · · · · · · | 4-18 |

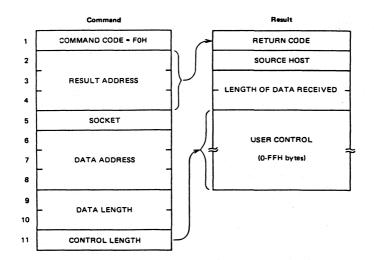

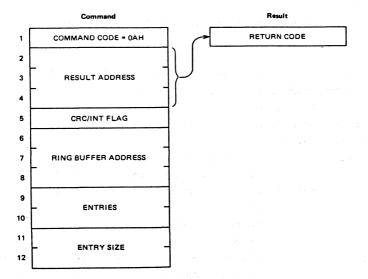

|     | 4.2.3 SETUP R  | cv          |               |             |         | •••••               |      |

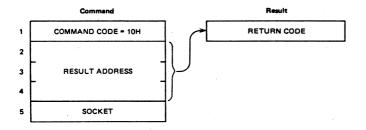

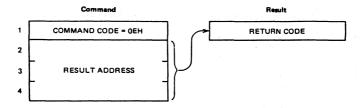

|     | 4.2.4 END RCV  |             |               |             |         |                     | 4-22 |

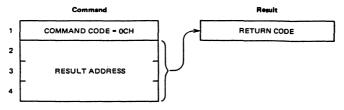

|     | 4.2.5 WAIT RC  | v           |               |             |         | •••••               |      |

|     | 4.2.6 RCV LIS  | ST          |               |             |         |                     |      |

|     | 4.2.7 ECHO     |             |               |             |         |                     |      |

|     | 4.2.8 LOOP BA  | CK          |               |             |         |                     |      |

|     | 4.2.9 INIT MC  | DNIT        |               |             |         |                     |      |

|     | 4.2.10 MONIT C | )FF         |               |             |         |                     |      |

|     | 4.2.11 MONIT C | )N          |               |             |         |                     |      |

|     | 4.2.12 SET PAR | ιм          |               |             |         |                     |      |

|     | 4.2.13 GET PAR | αм          |               |             |         |                     |      |

|     | 4.2.14 NEW CH2 | AIN         |               |             |         |                     |      |

|     | 4.2.15 NEW DEE | LT ADDR     |               | • • • • • • |         |                     |      |

|     | 4.2.16 CLR STA | \т          |               |             |         |                     |      |

|     | 4.2.17 GET ST  | АТ          | • • • • • • • |             | •••••   |                     |      |

|     |                |             |               |             |         |                     |      |

| 5.  | Control        |             |               |             |         |                     |      |

|     |                |             |               |             |         |                     |      |

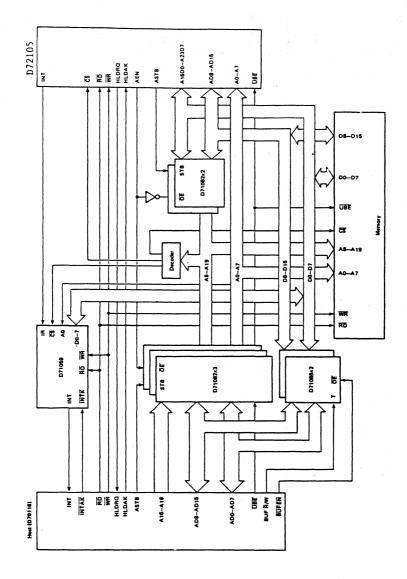

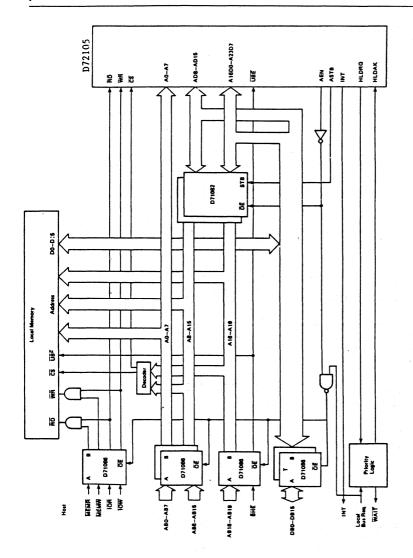

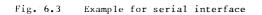

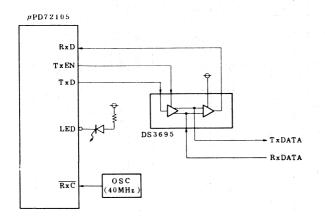

| 6.  | System Configu | iration 1   | Example       | es          | •••••   |                     |      |

|     |                |             |               |             |         |                     |      |

| 7.  | Target Specs   |             |               |             |         |                     |      |

µPD7201/7201A MULTIPROTOCOL SERIAL COMMUNICATION CONTROLLER

#### µPD7201/7201A

#### Description

The  $\mu$ PD7201 and  $\mu$ PD7201A Multiprotocol Serial Communication Controllers (MPSCC) are microcomputer peripherals that serve as multi-function peripheral devices capable of supporting a variety of serial data communications. The basic function of the MPSCC is to interface a microcomputer system (CPU) with serial data processing devices such as modems. The  $\mu$ PD7201A is an improved version of the  $\mu$ PD7201. Added features are described in the text, and listed in Appendix A.

The MPSCC controls three protocols:

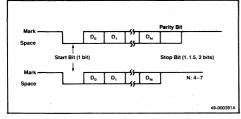

- Asynchronous (start-stop synchronous)

- Bit-oriented synchronous

- Byte-oriented synchronous

Asynchronous operation provides stop bit lengths of 1,  $1/_2$ , or 2 bits. It also provides transmit and receive clock rates programmable to 1, 16, 32, and 64 times the input frequency.

Bit-oriented synchronous operations such as HDLC (see note 1) and SDLC (see note 2) include the following features:

- Zero insertion/deletion

- · Flag transmission and removal detection

- Fractional character processing

- Secondary address/global address

- End of frame

- Abort transmission detection

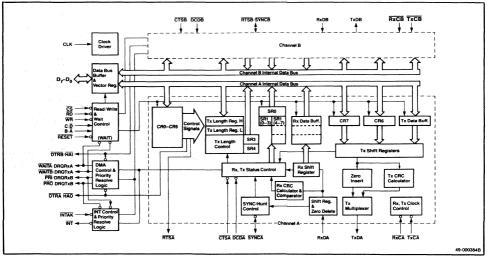

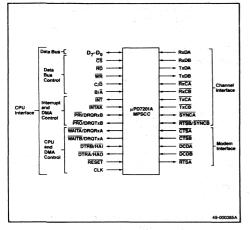

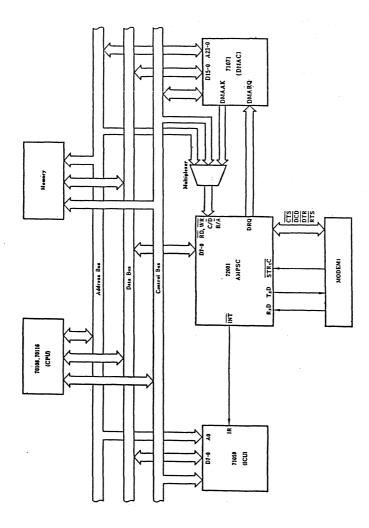

#### Figure 1-1. MPSCC Block Diagram

Bit-oriented synchronous operation also has a 16-bit transmit length counter and register to control the number of transmit characters (7201A only).

Byte-oriented synchronous operation such as Monosync, External Sync, and Bisync (see note 3) operation includes program-selectable SYNC characters and SYNC character transmission/removal detection.

- NOTES: 1. High-level Data Link Control (ISO)

- 2. Synchronous Data Link Control (IBM)

- 3. Binary Synchronous Communication (IBM)

#### Features

- □ µPD8085/8086 bus compatible

- High-speed transmit/receive operations of 1. 1 Mb/s at5 MHZ system clock (7201A) or 880 kb/s at 4 MHz (7201)

- Data buffering

- 5- to 8-bit character length

- Add/checking for odd, even, or no parity

- Cyclic Redundancy Check (CRC) generation/ checking (CCITT-0)

- Error checking (parity, framing, Rx overrun, CRC)

- Modem control (two channels, four signals)

- □ 21/29 control, data, and status registers (7201/7201A)

- Various interrupt functions

- + 5 V single power supply

- N-channel MOS

- 40-pin plastic DIP (μPD7201AC, μPD7201C)

- 40-pin ceramic DIP (μPD7201AD, μPD7201D)

Figure 1-1 shows the MPSCC functional block diagram.

#### **Pin Identification**

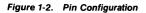

Figure 1-2 shows the pin configuration of the MPSCC. Table 1-1 gives the pin number, signal name, direction, and definition for each signal. The signal names and definitions of pins with two functions are separated by a slash (/).

|                | 1  | $\sim$        | 40 - Vcc        |

|----------------|----|---------------|-----------------|

| RESET          | 2  |               | 39 CTSA         |

| DCDA           | 3  |               | 38 RTSA         |

| RxCB [         | 4  |               | 37 TXDA         |

| DCDB           | 5  |               |                 |

| CTSB C         | 6  |               | 35 RXCA         |

| TxCB           | 7  |               | 34 RxDA         |

| TxDB           |    | ٩             | 33 SYNCA        |

| R×DB [         | 9  | 201           | 32 WAITA/DRQRXA |

| RTSB/SYNCB     | 10 | 5             | 31 DTRA/HAO     |

| WAITB/DRQTXA   | 11 | µPD7201/7201A | 30 PRO/DRQTxB   |

| 07 🗆           |    | - La          | 29 PRI/DRQRxB   |

| D6 🗆           | 13 |               | 28 🖵 INT        |

| Ds 🗆           | 14 |               | 27 📮 INTAK      |

| D4 🗆           | 15 |               | 26 DTRAB/HAI    |

| D3 🗆           |    |               | 25 🖓 B/Ā        |

| D2 🗆           |    |               | 24 🟳 C/D        |

| D1             |    |               | 23 2 23         |

| D <sub>0</sub> |    |               | 22 🛛 RD         |

| GND 🗆          | 20 |               | 21 🗆 WR         |

|                |    |               | 49-000383A      |

| No.   | Symbol       | Direction | Function                                                  |

|-------|--------------|-----------|-----------------------------------------------------------|

| 1     | CLK          | In        | System clock                                              |

| 2     | RESET        | In        | Reset                                                     |

| 3     | DCDA         | In        | Data carrier detect, channel A                            |

| 4     | RxCB         | In        | Receive clock, channel B                                  |

| 5     | DCDB         | In        | Data carrier detect, channel B                            |

| 6     | CTSB         | in        | Clear to send, channel B                                  |

| 7     | TxCB         | In        | Transmit clock, channel B                                 |

| 8     | TxDB         | Out       | Transmit data, channel B                                  |

| 9     | RxDB         | In        | Receive data, channel B                                   |

| 10    | RTSB/SYNCB   | In/Out    | Request to send, channel<br>B/Synchronization, channel B  |

| 11    | WAITB/DRQTxA | Out       | Wait, channel B/DMA request<br>transmit, channel A        |

| 12-19 | D7-D0        | In/Out    | Data bus                                                  |

| 20    | GND          |           | Ground potential                                          |

| 21    | WR           | in        | Write                                                     |

| 22    | RD           | In        | Read                                                      |

| 23    | <u>CS</u>    | in        | Chip select                                               |

| 24    | C/D          | In        | Control/data                                              |

| 25    | B/A          | In        | Channel B/Channel A                                       |

| 26    | DTRB/HAI     | In/Out    | Data terminal ready, channe<br>B/Hold acknowledge input   |

| 27    | INTAK        | In        | Interrupt acknowledge                                     |

| 28    | INT          | Out       | Interrupt request                                         |

| 29    | PRI/DRQRxB   | In/Out    | Priority input/DMA request, receive, channel B            |

| 30    | PRO/DRQTxB   | Out       | Priority output/DMA request, transmit, channel B          |

| 31    | DTRA/HAO     | Out       | Data terminal ready, channel<br>A/Hold acknowledge output |

| 32    | WAITA/DRQRxA | Out       | Wait, channel A/DMA request, receive, channel A           |

| 33    | SYNCA        | In/Out    | Synchronization, channel A                                |

| 34    | RxDA         | in .      | Receive data, channel A                                   |

| 35    | RxCA         | In        | Receive clock, channel A                                  |

| 36    | TxCA         | In        | Transmit clock, channel A                                 |

| 37    | TxDA         | Out       | Transmit data, channel A                                  |

| 38    | RTSA         | Out       | Request to send, channel A                                |

| 39    | CTSA         | In        | Clear to send, channel A                                  |

| 40    | VCC          |           | Power supply                                              |

NEC

NEC

The pins of the MPSCC function in three interface categories: CPU, channel, and modern. This section describes the pin functions of each interface category.

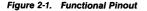

Figure 2-1 shows pinouts of the MPSCC by each interface category.

#### **CPU INTERFACE SIGNALS**

The following signals function as the CPU interface:

#### **RESET** (Reset)

A low-level input to this pin for at least one clock cycle causes the MPSCC to perform a system reset. Since a system reset may cause data loss to control registers, write or rewrite data to the control registers before data transmission or reception.

The state of the MPSCC when the system is reset is:

| Transmitter/receiver | Disabled   |

|----------------------|------------|

| Interrupt/DMA        | Disabled   |

| TxDA/TxDB output     | Marking 1s |

| Modem control output | <b>1</b>   |

See Section 4,  $D_5$ - $D_3$  (Command Bits) for a comparison of the states of each register and pin when the system is reset and when the channel reset command is issued.

#### CLK (System Clock)

Inputs a single-phase, system clock that is TTL-compatible. The system clock rate must be 4.5 times faster than the data rate.

#### D7 - D0 (Data Bus)

$D_7-D_0$  is an 8-bit bidirectional data bus. These tri-state pins connect the MPSCC to a standard CPU such as the  $\mu$ PD8080AF,  $\mu$ PD8085A, or  $\mu$ PD8086. The data bus transmits data, commands, or status signals between the MPSCC and CPU.

#### **CS** (Chip Select)

Provides access to the Tx or Rx buffer or the status or control register specified by the register pointer, B/A, or  $C/\overline{D}$  pins.

#### WR (Write)

Host sends a low-level signal when data or commands are transmitted from the CPU or memory to the MPSCC.

#### **RD** (Read)

Host sends a low-level signal when data or commands are transmitted from the CPU or memory to the MPSCC.

#### C/D (Control/Data)

Indicates the type of data on the data bus when a write or read operation is performed. A high level indicates that commands or status data is on the data bus. A low level indicates that transmit or receive data is on the data bus.

#### B/A (Channel B/Channel A)

Indicates the channel to or from which data on the data bus is written or read, when a write or read operation is performed. A high level specifies channel B. A low level specifies channel A.

Table 2-1 shows the different states and functions of the  $C/\overline{D}$ ,  $\overline{WR}$ ,  $\overline{RD}$ ,  $\overline{CS}$ , and  $B/\overline{A}$  signals.

#### Table 2-1. Signal Functions

| C D | WR  | RD               | <u>CS</u> | B/A   | Channel | Function                                                      |

|-----|-----|------------------|-----------|-------|---------|---------------------------------------------------------------|

| 0   |     |                  |           | 0     | А       | Writes transmit data                                          |

| U   | U   | - 1 <sup>-</sup> | U         | 1 5.2 | В       | to the Tx buffer                                              |

| 0   |     |                  |           | 0     | A       | Reads receive data                                            |

| 0   | 1   | U                | U         | 1     | В       | from the Rx buffer                                            |

|     |     | · .              |           | 0     | A       | Writes data to the                                            |

| - 1 | 0   | 1 0              |           | 1,    | В       | <ul> <li>command parameter<br/>(CR7-CR0) registers</li> </ul> |

|     |     |                  |           | 0     | ~       | Reads data from the                                           |

| 1   | I U | 0                | 0         | 1     | В       | <ul> <li>status vector (SR4-<br/>SR0) registers.</li> </ul>   |

#### **INT** (Interrupt Request)

Outputs an interrupt request signal. A low-level signal indicates an interrupt within the MPSCC. INT is an open-drain output.

#### **INTAK** (Interrupt Acknowledge)

Inputs an interrupt acknowledge signal in response to an interrupt request signal. When several MPSCCs simultaneously request an interrupt, the one with the top priority accepts this signal. The MPSCC may also output an interrupt vector to the data bus, depending on the specified mode. If this pin is not used, it must be held high with a pullup resistor.

#### PRI/DRQRxB (Priority Input/DMA Request RxB)

Transmits or receives the  $\overrightarrow{PRI}$  and  $\overrightarrow{DRQRxB}$  signals. The state of the INT/DMA mode bits ( $D_1$  and  $D_0$ ) of the CR2A register specify the function of this pin.

$\overline{\text{PRI}}$  is used when two or more interrupt devices are used to fom a daisy chain. A low level indicates that an interrupt device assigned a higher priority is not receiving service by the CPU's interrupt routine. When only one MPSCC is used, this pin must be held low (except when using a  $\mu\text{PD7201A}$  in 85-3 Vectored Mode).

DRQRxB is used as a DMA request signal to the DMA controller. The signal is active when data is input to the receive buffer of channel B (Rx Character Available).

#### PRO/DRQTxB (Priority Output/DMA Request TxB)

The state of the INT/DMA mode bits ( $D_1$  and  $D_0$ ) of the CR2A register specify the function of this pin.

PRO is paired with the PRI signal to control interrupt priority by using a daisy chain. When PRI is high, PRO outputs a high-level signal. When PRI is low, the PRO signal goes high when the MPSCC requests an interrupt from the CPU. If the interrupt signal is not ouput to the CPU, PRO remains low even if PRI is high.

DRQTxB outputs a DMA request signal to the DMA controller and becomes active when the Tx buffer of channel B becomes empty.

#### WAITA/DRQRxA (Wait A/DMA Request RxA)

The state of the INT/DMA bits ( $D_1$  and  $D_0$ ) of the CR2A register specify the function of this pin.

WAITA requests the CPU to enter the WAIT state via the CPU's READY pin. Used as an open-drain output.

DRQRxA outputs a DMA request signal to the DMA controller. This signal becomes active when a character is input to the Rx buffer of channel A.

#### WAITB/DRQTxA (Wait B/DMA Request TxA)

The state of the INT/DMA mode bits  $(D_1 \text{ and } D_0)$  of the CR2A register specify the function of this pin.

WAITE requests the CPU to enter the WAIT state via the CPU's READY pin. Used as an open-drain output when the WAIT function is used.

DRQTxA outputs a DMA request signal to the DMA controller and becomes active when the Tx buffer of channel A becomes empty.

#### DTRB/HAI (Data Terminal Ready B/Hold Acknowledge Input)

The state of INT/DMA mode bits ( $D_1$  and  $D_0$ ) of the CR2A register specify the function of this pin.

The level of  $\overline{\text{DTRB}}$  changes according to the state of the DTR bit (D<sub>7</sub> of the CR5 register) of channel B. When the DTR bit is 1,  $\overline{\text{DTRB}}$  becomes 0. When the DTR bit is 0, the DTRB signal becomes 1.

HAI is used to control the DMA priority with a daisy chain. Normally, HLDA is input to the HAI pin of the MPSCC with the highest DMA priority. A low-level input to this pin indicates that this particular MPSCC is selected for the DMA operation.

#### DTRA/HAO (Data Terminal Ready A/Hold Acknowledge Output)

The state of the INT/DMA mode bits ( $D_1$  and  $D_0$ ) of the CR2A register specify the function of this pin.

The level of  $\overline{\text{DTRA}}$  changes according to the state of the DTR bit of channel A (D<sub>7</sub> of the CR5 register). When the DTR bit is 1,  $\overline{\text{DTRA}}$  is 0. When the DTR bit is 0,  $\overline{\text{DTRA}}$  is 1.

HAO is paired with HAI to control the DMA daisy chain. When HAI is at a high level, HAO outputs a high. When HAI is at a low level, HAO outputs a high when the MPSCC requests a DMA operation. This inhibits another MPSCC daisy chained in the lower order from performing the DMA operation. If the DMA request signal is not output from the MPSCC, a low-level signal is output and DMA operations by the lower-order MPSCCs in the daisy chain are enabled.

#### **CHANNEL INTERFACE SIGNALS**

The following signals function as the channel interface.

#### RxDA, RxDB (Receive Data A/B)

Inputs receive data.

#### TxDA, TxDB (Transmit Data A/B)

Outputs transmit data.

#### RxCA, RxCB (Receive Clock A/B)

Inputs clocks for sampling receive data. Sampling is performed on the leading edge of the RxC signal.

When the asynchronous mode is specified, the clock rate of the  $\overline{TxC}$  signal must be a 1, 16, 32, or 64 multiple of the data rate.

### TxCA, TxCB (Transmit Clock A/B)

Inputs clocks for transmit data. Data is output at the leading edge of the  $\overline{TxC}$  signal. When the asynchronous mode is specified, the clock rate of the  $\overline{TxC}$  signal must be a 1, 16, 32, or 64 multiple of the data rate.

#### SYNCA (Synchronization A)

The function of this pin depends on the operating protocol of the MPSCC.

Asynchronous Mode (Input). If external/synchronous (E/S) interrupts are enabled, an interrupt occurs at the leading or trailing edge of the SYNC signal (or according to the state of the E/S bit). Inverted data from the  $\overline{SYNCA}$  pin is latched at the SYNC/Hunt bit (D<sub>4</sub> of the SR0 register).

**External Asynchronous Mode (External/Sync) (Input).** The E/S interrupt operation and function of the E/S bit in this mode is similar to the asynchronous mode.

If the MPSCC is in the hunt phase (Section 4, D<sub>4</sub> (Enter Hunt Phase)) when the program specifies the external/ sync mode, the MPSCC goes out of the hunt phase at the leading edge of an input SYNC signal. The MPSCC then starts assembling characters, beginning from the character sampled at the leading edge of the RxC signal input before the SYNC signal.

When the SYNC character has been detected, the external synchronization circuit resets the SYNC signal to a low level after two cycles of the  $\overline{\text{RxC}}$  signal. The SYNC signal must be held low until the character synchronization is lost or a new message starts.

Internal Synchronous Mode (Monosync) (Output). Outputs a low-level signal each time the SYNC character is detected in received data.

Internal Synchronous Mode (Bisync) (Output). Outputs a low-level signal only when the first SYNC character is received after the MPSCC has entered the hunt phase.

#### **RTSB/SYNCB** (Request to Send B/ Synchronization B)

Transmits or receives the RTSB and SYNCB signals, respectively. The state of the RTSB/SYNCB select bit ( $D_7$  of the CR2A register) specifies which function the pin performs.

When the RTSB/SYNCB select bit is 0, the RTSB signal is selected. When the RTSB/SYNCB select bit is 1, the SYNCB signal is selected.

The functions of the  $\overrightarrow{\text{RTSB}}$  and  $\overrightarrow{\text{SYNCB}}$  signals are the same as those of the  $\overrightarrow{\text{RTSA}}$  and  $\overrightarrow{\text{SYNCA}}$  signals, except that the  $\overrightarrow{\text{RTSB}}$  and  $\overrightarrow{\text{SYNCB}}$  signals are applied to channel B.

#### **MODEM INTERFACE SIGNALS**

The following signals function as the modern interface.

#### CTSA, CTSB (Clear to Send A/B) DCDA, DCDB (Data Carrier Detect A/B)

The  $\overline{\text{CTS}}$  and  $\overline{\text{DCD}}$  pins have similar functions. The E/S interrupt is generated (when interrupts are enabled) at the leading or trailing edge of these signals and latched at the E/S bits (D<sub>5</sub> and D<sub>3</sub>) of the SR0 register. The CTS and DCD pins can also be used as a trigger input in the auto enable mode. In this case, when bit D<sub>3</sub> of the CR3 is 1, either the transmitter ( $\overline{\text{CTS}}$ ) or receiver ( $\overline{\text{DCD}}$ ) is enabled by the presence of a low-level signal. When the MPSCC is not in auto enable mode, these two pins are used as general purpose input pins.

#### **RTSA** (Request to Send A)

The state of the RTS bit (D<sub>1</sub> of the CR5 register) controls this pin. If the RTS bit is reset in the asynchronous mode, a high level will not be output on the RTS pin until all transmit characters are written and the all sent bit (D<sub>0</sub> of the SR1 register) is set.

In the synchronous mode, the state of the RTS bit is used as is. That is, when the RTS bit is 0, the  $\overline{\text{RTS}}$  pin is 1. When the RTS bit is 1, the  $\overline{\text{RTS}}$  pin is 0.

(a) The second s second seco second sec

(4) Let us and the second state of the seco

#### an an an Albertaine

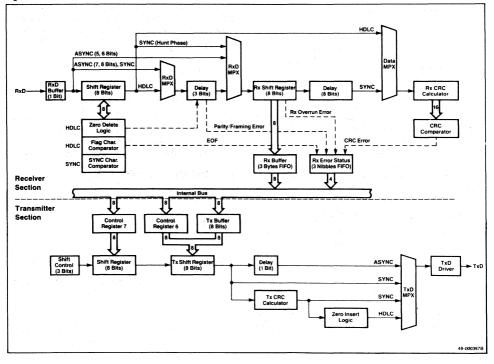

The MPSCC consists of a transmitter/receiver and CPU interface section. The transmitter/receiver section has two full-duplex channels (A and B) and control circuits for communication with other serial data processing devices via a modem. Both channels A and B have a receiver and transmitter and identical structure. Figure 3-1 shows the flow of transmit/receive data in each channel.

The CPU interface section has status and control registers, interrupt and DMA control circuitry, and a data bus buffer.

#### **RECEIVER SECTION**

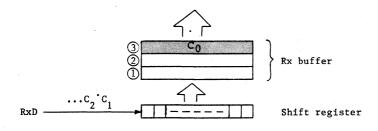

Receive (Rx) data input from the RxD terminal is converted into 8-bit data by the Rx shift register and transferred to the Rx data buffer. The operation mode and character length of the data determines the path along which data flows.

#### Serial Data Path

In the asynchronous mode, serial data received by the MPSCC is transmitted to the Rx shift register by two methods. If the character of the received data consists of 7 or 8

bits, it is transferred via a 3-bit buffer. If it consists of 5 or 6 bits, the data is directly input to the Rx shift register.

In the synchronous mode, the serial data is compared with the SYNC character which was input in the 8-bit shift register while the MPSCC is in the hunt phase. If the MPSCC goes out of the hunt phase, or if it is set in the external synchronous mode, serial data is transferred to the 3-bit buffer, bypassing the 8-bit shift register. When the MPSCC is in the hunt phase, input data is compared at the 8-bit shift register with the contents of the CR6 or CR7 register by the Rx SYNC register.

In the monosync mode (8-bit SYNC character), data is compared with the contents of the CR7 register.

In the bisync mode (16-bit SYNC character), the first 8 bits of the input data are compared with the contents of the CR6 register and the last 8 bits with the contents of the CR7 register. If the input data is matched with the contents of the above registers, the MPSCC goes out of the hunt phase. Input data then bypasses the 8-bit shift register as long as this synchronization is maintained. Note that the syn-

#### µPD7201/7201A

chronization may not be properly established when xxH SYNC characters (for example 55H or 33H) are used in the monosync or bisync mode.

In the HDLC mode, input data follows the same data path regardless of whether the MPSCC is in the hunt phase or synchronization is established. Input data is first transferred to the 8-bit shift register and the zeros of the input data are deleted if necessary. The MPSCC then also determines whether the input data contains a flag or abort sequence. The input data is subsequently transferred to the 3-bit buffer, then to the Rx shift register. If the register finds that the first five consecutive bits of the input data are 1s, the MPSCC then performs a function according to the state of the next (6th or 7th) bit(s) as follows:

| Rx Shift Register Data Bits<br>1 2 3 4 5 6 7 | Function                |  |

|----------------------------------------------|-------------------------|--|

| 111110                                       | Deletes 0               |  |

| 1111110                                      | Receives flag sequence  |  |

| 1111111                                      | Receives abort sequence |  |

In the 7201A, an abort sequence is only reported after a flag sequence has been detected.

#### Cyclic Redundancy Check (CRC)

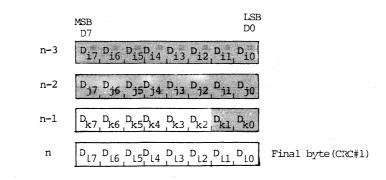

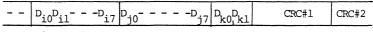

The CRC calculation operation is performed by the Rx CRC calculator and the CRC comparator. Receive data is transferred to the Rx CRC calculator from the Rx shift register via the CRC delay register in the synchronous mode. In the HDLC mode, the receive data is directly transferred to the Rx CRC calculator from the 8-bit shift register.

In the bisync mode, the program must make a decision whether to include each receive character in the CRC calculation. The CRC delay register holds the receive data for 8 bits to compensate for the process. It then transfers the data to the Rx CRC calculator.

In the HDLC mode, flag patterns are not included in the CRC calculation and the calculation is performed on data other than flag patterns. The MPSCC determines whether the CRC calculation is performed on a given character.

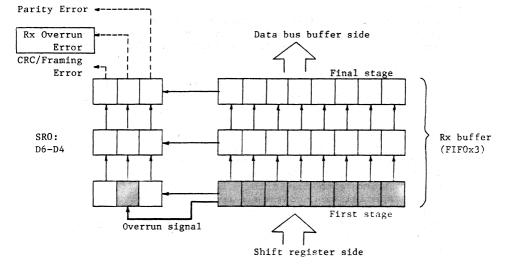

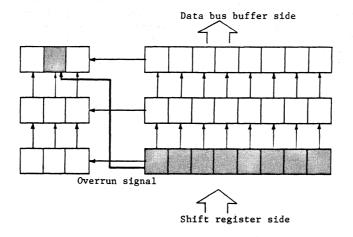

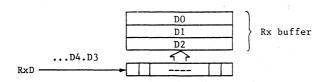

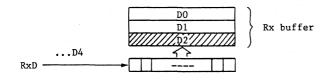

#### Parallel Data Path and Error Display

Serial data is transferred to the Rx buffer (three 8-bit buffers) after it is converted into 8-bit parallel data by the Rx shift register. The Rx buffer has a capacity of three bytes, sufficient capacity for data processing to transfer parallelconverted Rx data into the CPU.

Error data concerning receive data is stored in three 4-bit error registers. Each register indicates parity, overrun, CRC/framing, and end of frame errors. Each 4-bit error register has error data that corresponds to each byte of the 3-byte Rx buffer. The contents of the error registers can be read from bits D<sub>7</sub> to D<sub>4</sub> of the SR1 register.

#### TRANSMITTER SECTION

The 8-bit transmit data sent to the MPSCC is transferred to the Tx buffer via the internal data bus. At the same time, the SYNC character in the synchronous mode or a secondary address and a flag in the HDLC mode are loaded into control register 6 (CR6) and control register 7 (CR7). The contents of the Tx buffer and the CR6 and CR7 registers are then sent to the Tx shift register (3-bit shift control, two 8-bit shift registers and 1-bit delay) and converted to serial data.

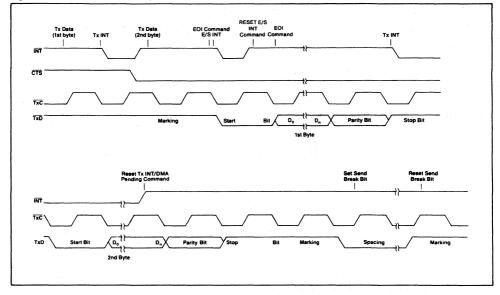

#### Asynchronous Mode

In this mode, asynchronous data in the Tx buffer is transferred to the Tx shift register and converted to serial data. Then parity, start, and stop bits are appended to the serialconverted data. The data is then subsequently transferred to the Tx multiplexer at a specified clock rate for transmittal from the TxD pin.

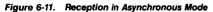

#### Synchronous Mode

As in the asynchronous mode, transmit data is sent to the Tx shift register from the Tx buffer. The contents of the CR6 or CR7 registers are sent to the Tx shift register as the SYNC characters, or as a time-fill character for a starting message or when a Tx underrun error occurs. Data output from the Tx shift register is also sent to the Tx multiplexer and to the Tx CRC calculator.

#### **HDLC Mode**

The Tx data is sent to the Tx shift register from the Tx buffer, and a flag pattern is sent to the Tx shift register from the Tx buffer when a message starts and ends. The output data from the Tx shift register is sent to the zero insert logic circuit and to the Tx CRC calculator. In the zero insert logic circuit, a zero is inserted after any five consecutive 1s in all fields other than the flags (address, control, frame check).

#### **CPU INTERFACE SECTION**

The CPU interface consists of a register section and a control section.

#### **Register Section**

The register section consists of eight control registers (CR7-CR0) and five status registers (SR4-SR0) for the 7201A, or three status registers (SR0-SR2) for the 7201. The control registers control the operation mode of the MPSCC, the internal data flow, and retain SYNC characters or flag patterns. The status registers hold status information.

Note that the CR2 register performs different functions depending on the channel to which the register belongs. The CR2 register of channel A (CR2A) is used to determine the system configuration. The CR2 register of channel B

(CR2B) receives an interrupt vector. The interrupt vector written to the CR2B register can be read from the SR2B register. In addition to the CR0-CR7 registers, each channel of the 7201A has a 2-byte transmit length register. Section 4 gives detailed descriptions of the functions of each register.

#### **Control Section**

The control section provides an interface between the MPSCC and the main system, and controls data transmission/reception. Data communication between the MPSCC and CPU is performed via an 8-bit data bus consisting of the  $D_7-D_0$  pins. The type of data transmitted and data transmission directions are controlled by input control signals. Table 3-1 shows how to:

- · Select channels using control signals

- · Specify a read or write operation

- Select control or status registers

Table 3-1. MPSCC Control Signals

Three data transmission methods exist for communication between the MPSCC and CPU: polling, interrupt, and DMA modes. Each channel (A or B) is set in one of these modes by the contents of the CR2A register. However, each channel's CR1 register determines whether to enable or disable either the interrupt or DMA mode.

The CR2A register also determines the priority of an MPSCC interrupt or DMA request. Table 3-2 shows how the CR2A register specifies the mode (interrupt or DMA), pin function, or priority. Table 3-3 shows the interrupt mode's selection by the CR2A register and the contents of the data bus (interrupt vector) in the interrupt acknowledge cycle.

| CÖ | 1   | ĊŜ |     | RD | 5    | WR | INTA  | ik  | PRI           | HAI | BĀ | Channel | Function                                                   |

|----|-----|----|-----|----|------|----|-------|-----|---------------|-----|----|---------|------------------------------------------------------------|

| 0  |     | 0  |     | 0  | ÷.,, | 1  | 1     | , · | x             | 1   | 0  | A       | Reads receive data from Rx buffer and reads data           |

|    | ÷., |    | 1.1 |    | -    |    | <br>  |     |               |     | 1  | В       | received by DMA operation in<br>DMA-2 mode (7201A only)    |

| 0  |     | 0  |     | 1  |      | 0  | 1     |     | x             | 1   | 0  | A       | Writes transmit data to Tx<br>buffer and writes data       |

|    |     |    |     |    |      |    |       |     |               |     | 1  | В       | transmitted by DMA operation<br>in DMA-2 mode (7201A only) |

| 1  |     | 0  |     | 0  |      | 1  | 1     |     | x             | 1   | 0  | A       | Reads data from                                            |

|    |     |    |     |    |      |    |       |     |               |     | 1  | В       | status vector registers<br>(SR0-SR4).                      |

| 1  |     | 0  |     | 1  |      | 0  | 1     |     | x             | - 1 | 0  | A       | Writes data to                                             |

|    |     |    |     |    |      |    |       |     |               |     | 1  | В       | command parameter registers<br>(CR0-CR7).                  |

| x  |     | 0  |     |    |      |    |       |     | ination othe  |     |    |         | Prohibited                                                 |

| x  |     | 1  |     | х  |      | x  | 0     |     | 1             | x   | x  |         | Reads CALL command and                                     |

|    |     |    |     |    |      |    |       |     |               |     |    |         | interrupt vector in<br>interrupt acknowledge cycle.        |

| x  |     | 1  |     | 0  |      | 1  | <br>1 |     | x             | 0   | x  |         | Reads receive data by DMA operation in DMA-1 mode.         |

| X  |     | 1  |     | 1  |      | 0  | 1     |     | x             | 0   | x  |         | Writes transmit data by DMA operation in DMA-1 mode.       |

| x  |     | 1  |     |    |      |    |       |     | ination other |     |    |         | No read or write operation is performed.                   |

Notes: 1. x = Don't care

2. If the HAI pin is not used for a hold acknowledge input, it will be treated as a don't care pin.

#### Table 3-2. CR2A Register Control

|                | CR2/           | A  | INT/DI         | A            |                                          |        | Pin Fund | tion   |      | 2 <u>- 1</u> - 1 - 1 |      |         | P   | riority |      | ÷                                                       |

|----------------|----------------|----|----------------|--------------|------------------------------------------|--------|----------|--------|------|----------------------|------|---------|-----|---------|------|---------------------------------------------------------|

| 0 <sub>2</sub> | D <sub>1</sub> | Do | Channel<br>A   | Channel<br>B | 32                                       | 11     | 29       | 30     | 26   | 31                   | High | 3       |     |         |      | Low                                                     |

| 0              | 0              | 0  | INT            | INT          | WAITA                                    | WAITB  | PRI      | PRO    | DTRB | DTRA                 | RxA  | TxA     | RxB | TxB     | E/SA | E/SB                                                    |

| 1              | 0              | 0  | INT            | INT          | -                                        |        |          |        |      |                      | RxA  | RxB     | TxA | TxB     | E/SA | E/SB                                                    |

|                |                |    | DMA            |              | DRQRxA                                   | DRQTxA | PRI      | PRO    | HAI  | HAO                  | RxA  | TxA     |     |         |      |                                                         |

| х              | 0              | 1  | 1. 1. 1. North | INT          | -                                        |        |          |        |      |                      | RxA  |         | RxB | TxB     | E/SA | E/SB                                                    |

|                |                |    | DMA            | DMA          | DRQRxA                                   | DRQTxA | DRQRxB   | DRQTxB | HAI  | HAO                  | RxA  | TxA     | RxB | TxB     |      |                                                         |

| 0              | 1              | 0  |                |              | n an |        |          |        |      |                      | RxA  |         | RxB |         | E/SA | E/SB                                                    |

|                |                |    | DMA            | DMA          | -                                        |        |          |        |      |                      | RxA  | RxB     | TxA | TxB     |      | 1997 - 1997<br>1997 - 1997 - 1997<br>1997 - 1997 - 1997 |

| 1              | 1              | 0  |                |              | -                                        |        |          |        |      |                      | RxA  | RxB     |     |         | E/SA | E/SB                                                    |

| x              | 1              | 1  | DMA            | DMA          | -                                        |        |          |        | DTRB | DTRA                 | No p | riority |     |         |      |                                                         |

|                | 7201<br>only   |    |                |              | -                                        |        |          |        |      |                      | RxA  | RxB     |     |         | E/SA | E/SB                                                    |

Notes: x = Don't care

\* These priorities are for the special receive and external status interrupts which can occur when using dual channel DMA operation.

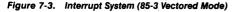

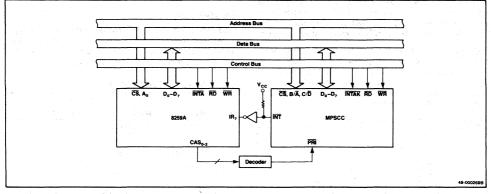

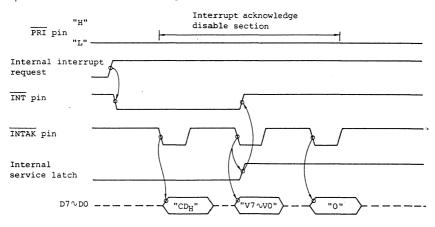

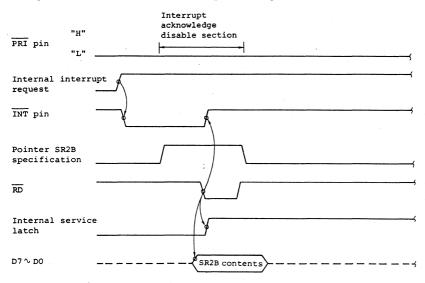

Table 3-3. Vectored Interrupt Control

|    | CR2A |    | INTA CYCLE               |     |                  |        |      |  |  |  |  |

|----|------|----|--------------------------|-----|------------------|--------|------|--|--|--|--|

| D5 | D4   | D3 | interrupt Mode<br>Select | PRI | 1                | 2      | 3    |  |  |  |  |

|    |      |    | 05.4                     | 0   | CD HEX (CALL OP) | VECTOR | 0    |  |  |  |  |

| 1  | 0    | 0  | 85-1                     | 1   | CD HEX (CALL OP) | HI-Z   | HI-Z |  |  |  |  |

|    |      |    |                          | 0   | HI-Z             | VECTOR | 0    |  |  |  |  |

| 1  | 0    | 1  | 85-2                     | 1   | HI-Z             | HI-Z   | HI-Z |  |  |  |  |

|    |      | ·  |                          | 0   | HI-Z             | VECTOR | 0    |  |  |  |  |

| 1  | 1    | 1  | 85-3 Note 1              | 1   | HI-Z             | HI-Z   | HI-Z |  |  |  |  |

|    |      | -  | 00 14 10                 | 0   | HI-Z             | VECTOR |      |  |  |  |  |

| 1  | 1    | 0  | 86 Note 2                | 1   | HI-Z             | HI-Z   |      |  |  |  |  |

Notes: 1. 85-3 mode activates the  $\overline{INT}$  line if an internal interrupt exists whether or not the  $\overline{PRI}$  line is high. Therefore, a daisy chain using the  $\overline{PRI}$  and  $\overline{PRO}$  pins cannot be performed. (This mode is available on the  $\mu$ PD7201A only.)

2. 8086 mode issues two INTAK pulses instead of three.

When operating in the 8080/5 modes, the MPSCC issues an 8080-type CALL CD vv (hex) instruction where vv is the contents of control register 2B. Register 2B is modified by the cause of the interrupt if the status affects vector feature is enabled. An MPSCC programmed for 8085 master mode always places the CALL opcode on the data bus whether or not that MPSCC has a pending interrupt request. To avoid problems caused by momentary bus contention, never program more than one device to operate in this mode.

#### **Data Transmission Between MPSCC and CPU**

Data transmission between the CPU and MPSCC (or memory and the MPSCC) is performed in either polling, interrupt, or DMA mode.

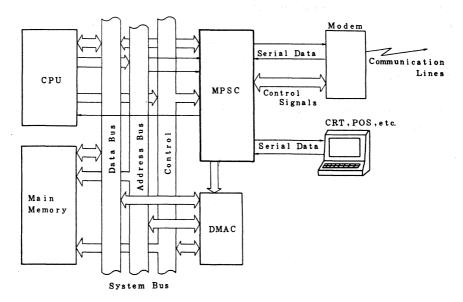

Polling Mode. When data transmission is performed in the polling mode, the CPU must monitor the status of the MPSCC to learn the timing of the data transmission. The CPU reads status information from the MPSCC's SR0 and SR1 registers and determines whether:

- a Tx data transmit (MPSCC to CPU) request exists,

- an Rx data receive (CPU to MPSCC) request exists, or

- an error occured in the MPSCC.

If an Rx character available bit ( $D_0$  of the SR0 register) is set, for example, valid Rx data exists in the Rx buffer of the MPSCC, then the CPU must immediately read the data.

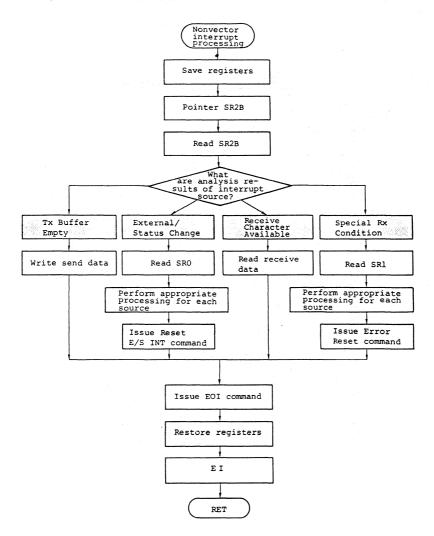

Also, the interrupt vector may be used in the SR2B register (vector bits V<sub>4</sub>-V<sub>2</sub> or V<sub>2</sub>-V<sub>0</sub>) for checking the status of the MPSCC. In this case, channels A and B must be set in the interrupt mode by bits D<sub>0</sub> and D<sub>1</sub> of the CR2A register, or in a nonvectored mode. The 85 mode is set when bits D<sub>5</sub>-D<sub>3</sub> of the CR2A register are 000, 001, or 011. The 86 mode is set when bits D<sub>5</sub>-D<sub>3</sub> of the CR2A register are 010. The status affects vector bit (D<sub>2</sub> of the CR1B register) must also be set, vector bits V<sub>4</sub>-V<sub>2</sub> of the interrupt vector are modified in the nonvectored 85 mode and V<sub>2</sub>-V<sub>0</sub> in the nonvectored 86 mode.

NEC

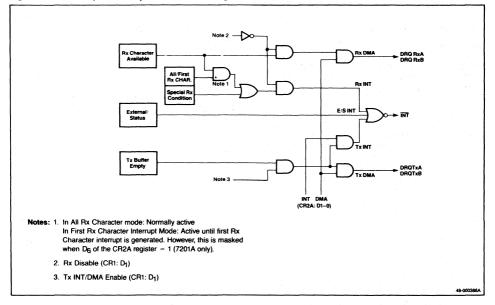

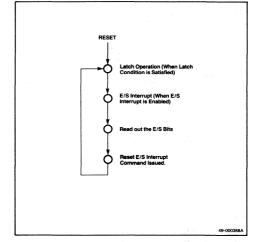

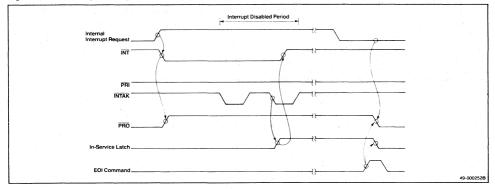

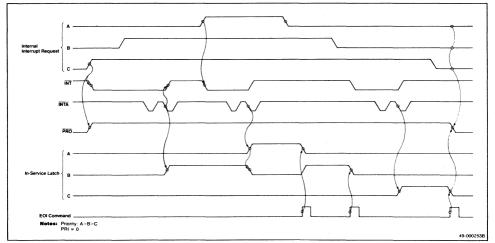

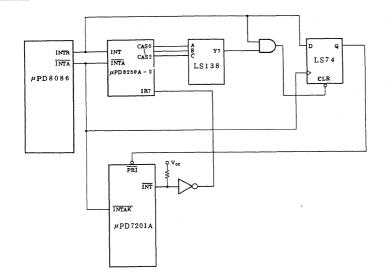

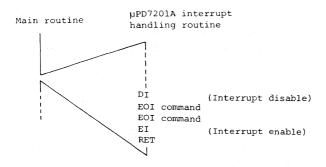

**Interrupt Mode.** The MPSCC has one interrupt request terminal ( $\overline{INT}$ ). When an interrupt source occurs inside the MPSCC, the  $\overline{INT}$  signal becomes active and informs the CPU or interrupt controller of an interrupt request.

In a system using more than one MPSCC, the interrupt process can be performed through a daisy chain using the  $\overline{PRI}$  and  $\overline{PRO}$  pins. If an interrupt source occurs inside the MPSCC, the interrupt vector corresponding to the interrupt source can be generated when the vector mode is specified and the status affects vector bit is set.

Eight types of interrupt vectors, each corresponding to a given interrupt source inside the MPSCC, can be generated by setting the status affects vector bit (D<sub>2</sub> of the CR1B register). These interrupt vectors allow direct branching to the process routine for each interrupt source. The MPSCC also has nonvectored modes for CPU's that cannot read vectors in an interrupt source is issuing the request by reading the contents of the status or vector registers of the MPSCC. The CPU will then execute the appropriate process routine.

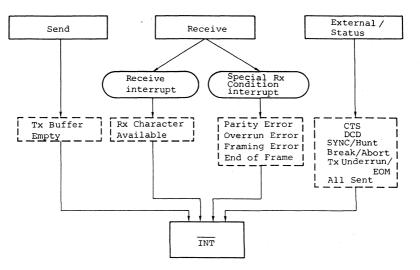

Three interrupt sources can occur in the MPSCC.

- Receive (Rx)

- Transmit (Tx)

- External/Status (E/S)

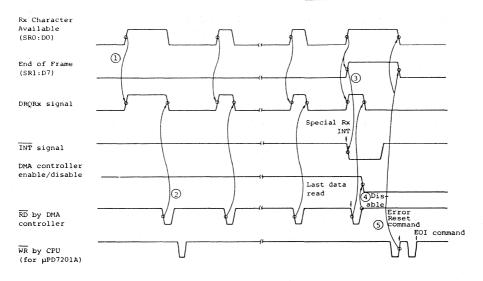

The Rx interrupt occurs when the following conditions exist: the MPSCC receives data; the valid (character) data for the read operation to be performed by the CPU is loaded to the Rx buffer; and Rx interrupts are enabled. There are three modes of Rx interrupts.

First Rx Character. In this mode an interrupt occurs only when the first character is received by the MPSCC. In other words, an interrupt is caused by the first character loaded to the Rx buffer after this mode is set. Once an interrupt occurs, subsequent interrupts in this mode can be enabled by issuing the enable interrupt on next Rx character command.

This mode is generally used for data transmission controlled by the software. It is also used for DMA data transmission. This interrupt can be masked by setting bit  $D_6$  or the CR2A register to 1 (7201A only).

All Rx Characters. This mode is used for data transmission by using an interrupt each time a character is loaded to the Rx buffer.

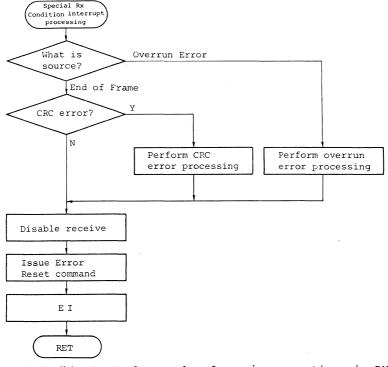

**Special Rx Conditions.** This interrupt is a special case of Rx interrupt and occurs when either the first Rx character interrupt or all Rx character interrupt is specified. Special

Rx conditions refer to parity, overrun, framing, or end of frame errors. When the first Rx character interrupt mode is specified, parity errors are not treated as a special Rx condition. When all Rx character interrupt mode is specified, specify whether or not parity errors are included in the special Rx conditions.

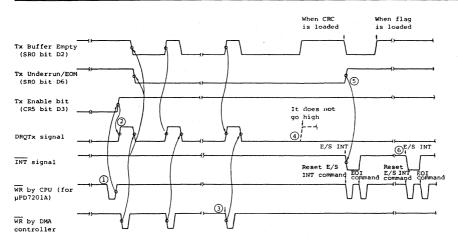

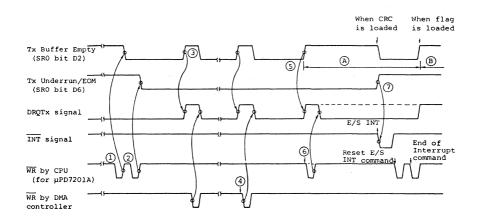

The Tx interrupt occurs when the Tx buffer is empty and Tx interrupts are enabled. This interrupt indicates that the MPSCC is requesting transmit data. The interrupt is satisfied when data is written to the Tx buffer or when the reset Tx INT/DMA pending command is issued. The Tx interrupt also occurs when transmission of CRC characters has been completed in the synchronous or HDLC mode. However, immediately after the MPSCC has been reset (RESET signal or channel reset command), the Tx buffer is empty and the Tx interrupt does not occur even if enabled. Note: If bit D<sub>6</sub> of the CR1 register is set to 1 (7201A only) in the HLDC mode, the Tx interrupt will occur if the first data is written to the Tx buffer.

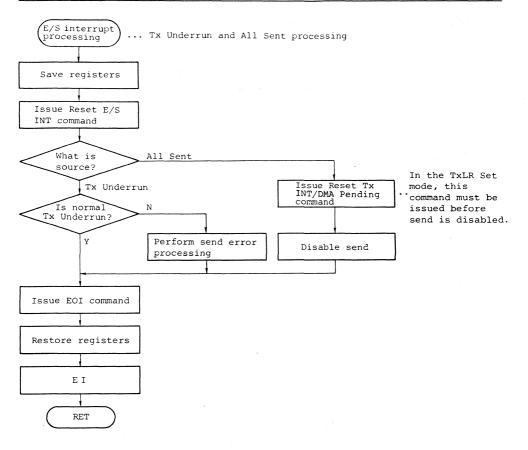

The E/S interrupt checks whether the state of the  $\overline{\text{CTS}}$ ,  $\overline{\text{DCD}}$ , or SYNC pin has changed. This interrupt is also used to detect the Tx underrun error, break state (asynchronous mode), abort sequence, or completion of data transmission (HDLC mode).

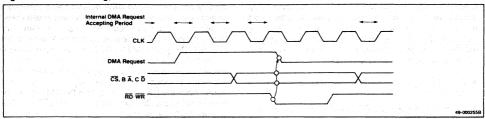

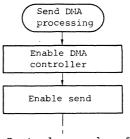

**DMA.** The MPSCC has four DMA request pins. When DMA is enabled by  $D_1$ ,  $D_3$ , and  $D_4$  of the CR1 register, a DMA request occurs as follows:

DRQTxA, DRQTxB: When the Tx buffer becomes empty. However, the DMA request does not occur if the Tx buffer is empty immediately after it has been reset. This does not apply when bit  $D_6$  of the CR1 register is 1 (HDLC mode, 7201A only).

DRQRxA, DRQRxB: When a character exists in the Rx buffer.

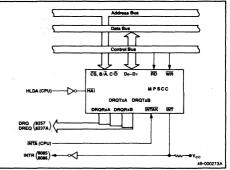

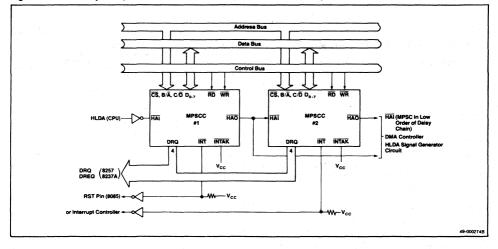

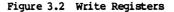

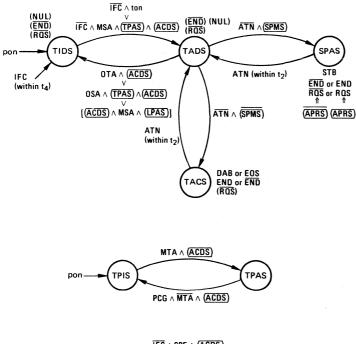

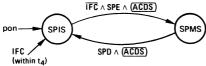

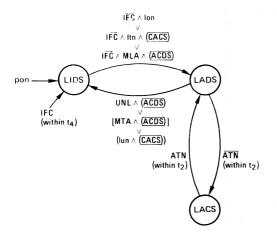

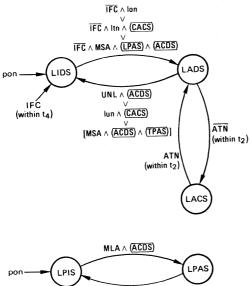

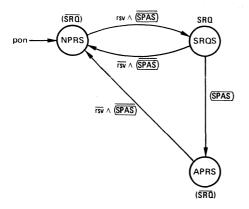

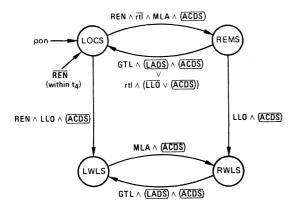

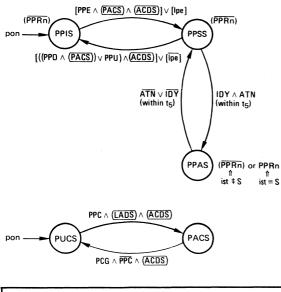

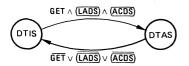

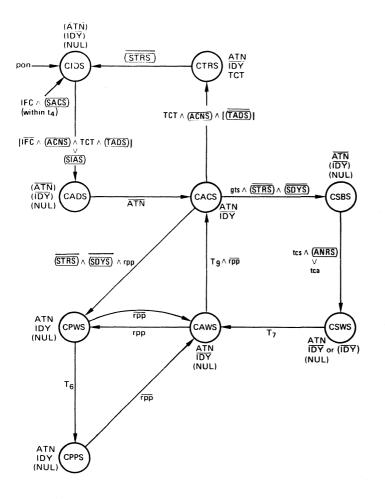

Interrupt and DMA. Bits  $D_1$  and  $D_0$  of the CR2A register specify whether data transmission is performed by means of an interrupt or DMA. An interrupt or DMA is enabled or disabled by bit  $D_1$  (Tx interrupt/DMA) and  $D_4$ ,  $D_3$  (Rx interrupt/DMA) of the CR1 register. When DMA is specified to a channel, the Tx interrupt of that channel is inhibited. However, the Rx, special Rx condition, and E/S interrupts can still occur when interrupts are enabled. Normally, the first Rx character interrupt is specified as the Rx interrupt mode of the channel that has been specified for DMA operation. This first Rx character interrupt can be masked by setting bit  $D_6$  of the CR2A register to 1 (7201A only). See table 3-2 for details on specifying interrupts or DMA. Figure 3-2 shows interrupt/DMA request generation logic.

## µPD7201/7201A

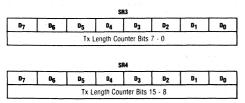

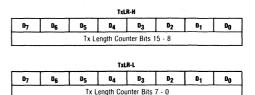

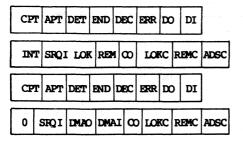

Both channels A and B of the MPSCC have eight control registers (CR0-CR7), two transmit length registers (TxLR: 7201A only), and two or four status registers (SR0 and SR1: 7201; and SR0, SR1, SR3, and SR4: 7201A). Channel B also has an additional status register (SR2B).

The control registers select the required functions for the MPSCC's particular application system. These functions include selecting the following:

- CPU Interface mode

- Serial transmit/receive protocol (asynchronous, bisync, or HDLC)

- MPSCC operation mode used with the selected protocol

- Various parameters

- SYNC character codes

The status registers indicate the internal state of the MPSCC, interrupt status or vectors, and the contents of the transmit length counter (7201A only).

This section describes the function of each register; table 4-1 summarizes the function of each register for both channels.

#### Table 4-1. Register Functions

| Register | Channel | Function                                                                                                      |  |  |  |

|----------|---------|---------------------------------------------------------------------------------------------------------------|--|--|--|

| CR0      | A. B    | Selects a status or control register and resets CRC logic<br>and sets commands (reset of the MPSCC interrupt) |  |  |  |

| CR1      | A. B    | Selects the bus interface mode (data transfer mode between CPU and MPSCC)                                     |  |  |  |

| CR2A     | Α       | Specifies system configuration                                                                                |  |  |  |

| CR2B     | В       | Sets the interrupt vectors                                                                                    |  |  |  |

| CR3      | A. B    | Controls data reception operation                                                                             |  |  |  |

| CR4      | A. B    | Controls common operation of data transmission and reception                                                  |  |  |  |

| CR5      | A. B    | Controls data transmission operation                                                                          |  |  |  |

| CR6      | A. B    | Specifies SYNC character, flags, and secondary address                                                        |  |  |  |

| CR7      | A. B    | (HDLC mode)                                                                                                   |  |  |  |

| TxLR-L   | A. B    | Specifies the length of transmit data                                                                         |  |  |  |

| TxLR-H   | A, B    | up to 16 bits (7201A only)                                                                                    |  |  |  |

| SR0      | A. B    | Specifies the states of E/S bits, interrupts, or buffers                                                      |  |  |  |

| SR1      | A. B    | Sets the special Rx condition or residue codes                                                                |  |  |  |

| SR2      | В       | Indicates interrupt vectors                                                                                   |  |  |  |

| SR3      | A. B    | Indicates contents of a 16-bit Tx                                                                             |  |  |  |

| SR4      | A. B    | length counter (7201A only)                                                                                   |  |  |  |

Note: The function CR2 performs is determined by its channel. The CR2 register of channel A (CR2A) defines the system configuration, and the CR2 register of channel B (CR2B) specifies the interrupt vector to be transmitted in the interrupt acknowledge cycle. The contents of the CR2B register can also be read from the SR2B register. Channel A does not have the SR2 register.

#### **CONTROL REGISTER 0 (CR0)**

The functions of the CR0 register bits are summarized in table 4-2.

| Table 4-2. | CR0 Bit | Functions |

|------------|---------|-----------|

|------------|---------|-----------|

| Bit            | Name | Definition         | Function                                                        |  |  |  |

|----------------|------|--------------------|-----------------------------------------------------------------|--|--|--|

| D7             | CRC1 | CRC initialization | Initializes CRC logic                                           |  |  |  |

| D <sub>6</sub> | CRCO | code               |                                                                 |  |  |  |

| D5             | CMD2 | Command bits       | Sets commands used to reset the MPSCC enables, interrupts, etc. |  |  |  |

| D4             | CMD1 |                    |                                                                 |  |  |  |

| D3             | CMD0 |                    |                                                                 |  |  |  |

| D <sub>2</sub> | PTR2 | Pointer bits       | Selects a status or control register                            |  |  |  |

| D1             | PTR1 |                    |                                                                 |  |  |  |

| Do             | PTR0 |                    |                                                                 |  |  |  |

#### D7 and D6 (CRC Initialization Code)

Table 4-3 shows the bit pattern and related function for the CRC bits.

#### Table 4-3. CRC Bit Functions

| CRC1 | CRCO |                                  | Function                                        |

|------|------|----------------------------------|-------------------------------------------------|

| 0    | 0    | No operation                     |                                                 |

| 0    | 1    | Initializes Rx<br>CRC calculator | In Synchronous mode: all 0s<br>(CCITT-0 CRC-16) |

| 1    | 0    | Initializes Tx<br>CRC calculator | in HDLC mode: all 1s<br>(CCITT-1)               |

| 1    | 1    | Resets Tx underrun               | EOM bit (D6 of the SR0 register) (See Note      |

Note: Effective when one character is written and Tx is enabled.

#### D<sub>5</sub>-D<sub>3</sub> (Command Bits)

| D <sub>5</sub> | D4 | D <sub>3</sub> |                |

|----------------|----|----------------|----------------|

| 0              | 0  | 0              | (No operation) |

No operation is performed. Specified when the CR0 register is used for purposes other than issuing commands.

HDLC abort bits (8 bits, all 1s) are transmitted followed by a flag that causes the CRC circuit of the receiver to reset. 8 to 13 bits are transmitted depending on the number of bits (1s) preceding the abort bits. The contents of the Tx (transmit) buffer are lost when this command is issued.

#### D<sub>5</sub> D<sub>4</sub> D<sub>3</sub> 0 1 0 (Reset External/Status Interrupt)

External/status (E/S) interrupt is re-enabled, and status latch operations to E/S bits ( $D_7$ - $D_3$  of the SR0 register and  $D_0$  of SR1 register) can be performed. Once an E/S interrupt occurs, issue this command to allow other E/S inter-

#### µPD7201/7201A

rupts. Also, issue this command to allow status latch operations to the E/S bits.

Performs almost the same operation on channel A or B as the external reset. When executed to reset a channel, part of the register contents of the channel is lost. Therefore, it is necessary to rewrite data to the register whose contents have been lost. Issue a new command after the lapse of four system clock cycles when this command has been executed.

Tables 4-4 and 4-5 show the states of the registers and pins after a system reset and after execution of the channel reset command.

| Register                 | Bits          | At System                                                                                                       | Reset    | At Channel Reset |

|--------------------------|---------------|-----------------------------------------------------------------------------------------------------------------|----------|------------------|

| CR2A                     | 0-5, 7        | 0                                                                                                               |          | See table 4-5    |

| CR0                      | 0-2           | 0                                                                                                               |          | 0                |

| CR1                      | 0, 1, 3, 4, 7 | 0                                                                                                               |          | 0                |

| CR3                      | 0-7           | 0                                                                                                               |          | 0                |

| CR5                      | 1-4, 7        | 0                                                                                                               |          | 0                |

|                          | 0-1           | 0                                                                                                               |          | 5.e O            |

| SR0                      | 2, 6          | 1                                                                                                               |          | - 1              |

|                          | 3-5, 7        |                                                                                                                 | Undefine | d                |

| SR1                      | 4-7           | 0                                                                                                               | . 1      | 0                |

|                          | 0-3           | a secondaria de la composición de la co | Undefine | d                |

| SR3, SR4<br>(7201A only) | 0-7           | 0                                                                                                               | · ·      | 0                |

Table 4-4. Register State at Reset

| Table 4-5. | Pin State | at Reset |

|------------|-----------|----------|

|------------|-----------|----------|

|                  |                 | CR2A, D <sub>2</sub> -D <sub>0</sub> |                            |                              |  |  |  |  |  |

|------------------|-----------------|--------------------------------------|----------------------------|------------------------------|--|--|--|--|--|

|                  | -               | 000 001<br>or or<br>100 101          | 010<br>or<br>110           | 011<br>or<br>111             |  |  |  |  |  |

| Pin              | At System Reset | At Cha                               | nnel Reset                 |                              |  |  |  |  |  |

| WAITA/<br>DRQRxA | WAITA = Hi-Z    | DRQRxA = 0                           | 1                          | e' .                         |  |  |  |  |  |

| WAITB/<br>DRQRxA | WAITB = Hi-Z    | DRQTxA = 0                           | )                          |                              |  |  |  |  |  |

| PRI/DRQRxB       | PRI = input     | . : "                                | DRQRxB = 0                 |                              |  |  |  |  |  |

| PRO/DRQTxB       | PRO = by PRI    |                                      | DRQTxB = 0                 |                              |  |  |  |  |  |

| DTRB/HAI         | DTRB = 1        | HAI = input                          |                            | $\overline{\text{DTRB}} = 1$ |  |  |  |  |  |

| DTRA/HAO         | DTRA = 1        | HAO = HAI                            | 3                          | $\overline{\text{DTRA}} = 1$ |  |  |  |  |  |

| INT              | Hi⊢Z            |                                      |                            |                              |  |  |  |  |  |

| RTSA, RTSB       | 1 6.            |                                      |                            |                              |  |  |  |  |  |

| SYNCA,<br>Syncb  | Input state     | 2                                    | na ang ang<br>Tang ang ang |                              |  |  |  |  |  |

$D_5 D_4 D_3 1 0 0$

(Enable Interrupt on Next Receive Character)

If an interrupt occurs in the first Rx character mode (first character has been received), this command causes another interrupt with the first character after the command is issued. Prepares for new messages after receiving a series of messages.

D<sub>5</sub> D<sub>4</sub> D<sub>3</sub> 1 0 1 (Reset Transmitter Interrupt/DMA Pending)

When the Tx buffer becomes empty, a Tx interrupt/DMA request is generated to request that new data be written to the Tx buffer. In some instances (when a message ends) this request may not be acknowledged. Issue this command to clear the interrupt/DMA request inside the MPSCC.

$D_5$   $D_4$   $D_3$ 1 1 0 (Error Reset)

Resets an error bit and the EOF bits ( $D_4$ - $D_7$  of the SR1 register). If the special Rx condition interrupt occurs in the first Rx character interrupt mode, the characters loaded to the Rx buffer following the character that caused the interrupt will not be assembled until this command is issued.

$$D_5$$

$D_4$   $D_3$

1 1 1 (End of Interrupt)

Resets the in service latch that has the higher priority among the in service latches which are set. Set on channel A only. If there is an interrupt request in service whose process currently is terminated, interrupt request processing will be resumed unless INTAK is generated to request an interrupt assigned a higher priority than the interrupt in service. In this manner, the end of interrupt command enables an interrupt with lower priority in the daisy chain. Priority status will be reanalyzed to determine which interrupt takes precedence, if an INTAK sequence occurs from the interrupt with a priority higher than the one in service.

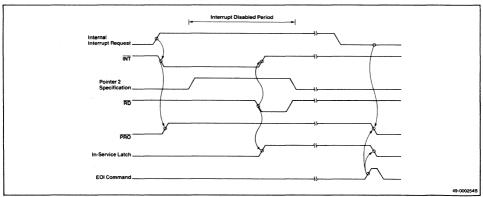

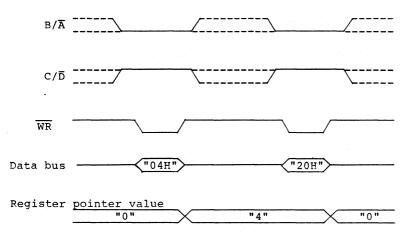

#### D<sub>2</sub> - D<sub>0</sub> (Pointer Bits)

These bits specify the register to be used for the next read or write operation. Generally, each register is accessed by the MPSCC according to this procedure. The pointer indicates 000 after an external reset or a channel reset command.

**Pointer Specification.** The pointer bits specify a binary register number used to perform a read or write operation.

**Read/Write Operation.** The register specified as a pointer will be accessed if the read or write operation is performed when  $C/\overline{D}$  is 1.

**Pointer Restoration.** The pointer bits return to 000 after the read or write operation has been performed. Therefore, do not respecify the pointer bits when the CR0 or SR0 register is accessed.

**Example 1 (Setting CR2A).** The pointer bits of the CR0A register specify 2 ( $D_2 - D_0 = 010$ ). The CR2A register inputs data written during the next write to the MPSCC, for instance,  $\overline{CS} = 0$ ,  $C/\overline{D} = 1$ .

**Example 2 (Reading SR3B).** The pointer bits of the CR0B register specify 3 ( $D_2 - D_0 = 011$ ). The SR3B register outputs the contents of the Tx length register.

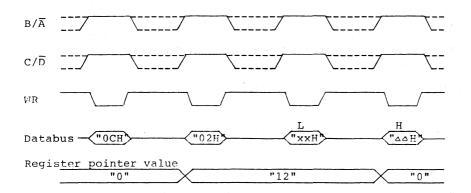

The Tx length registers (TxLR-L, TxLR-H; 7501A only) use a special data setting method. The values of these registers are set (without specifying the pointer) by a series of two write cycles that follow writing a 1 to bit  $D_6$  of the CR1 register.

**Example 3 (Setting TxLR of Channel A).** The pointer bits of the CR0A register specify 1 ( $D_2 - D_0 = 001$ ). Bit  $D_6$  of the CR1A register is set to 1 and other necessary specifications in this register are then performed. The number of transmit data characters is set in TxLR-L and TxLR-H by the successive write cycles of CRxA.

#### **CONTROL REGISTER 1 (CR1)**

The functions of the CR1 register bits are summarized in table 4-6.

#### Table 4-6. CR1 Bit Functions

| Bit            | Name                   | Function                                                   |

|----------------|------------------------|------------------------------------------------------------|

| D7             | Wait Enable            | Controls operation of WAIT pin                             |

| D <sub>6</sub> | Tx Length Register Set | Instructs data setting of Tx length registers (7201A only) |

| D5             | Wait on Rx/Tx          | Controls operation of WAIT pin                             |

| D4             | Rx INT Mode 1          | Selects the mode for Rx interrupts                         |

| D3             | Rx INT Mode 0          |                                                            |

| D <sub>2</sub> | Status Affects Vector  | Modifies the interrupt vector caused by an interrupt       |

| D1             | Tx INT/DMA Enable      | Enables the Tx interrupt/DMA                               |

| Do             | E/S Interrupt Enable   | Enables the E/S interrupt                                  |

#### D7 (Wait Enable) and D5 (Wait on Rx/Tx)

These bits are meaningful only when both channels A and B are set in the interrupt mode ( $D_0$  and  $D_2$  of the CR2A register = 0). When  $D_5$  is 1, WAIT becomes active (goes low) when an attempt is made to read receive (Rx) data when the MPSCC is not in the Rx character available state; that is, when the MPSCC has not received data. WAIT becomes inactive (high impedance) when the MPSCC enters the Rx character available state. When  $D_5$  is 0, WAIT becomes active when data is written to the MPSCC when the Tx buffer is full. When the Tx buffer becomes

empty, WAIT becomes inactive. Table 4-7 shows the state of bits  $\mathsf{D}_7$  and  $\mathsf{D}_5$  during receive and transmit operations.

Table 4-7. Bits D7 and D5 of CR1

| 07 | D5 | Rx/Tx Operation | Condition                                                    | WAIT Output |

|----|----|-----------------|--------------------------------------------------------------|-------------|

| 0  | x  |                 |                                                              | Hi-Z        |

| 1  | 0  | Tx buffer       | When data is written<br>to the Tx buffer while<br>it is full | Low         |

|    |    |                 | When the Tx buffer is<br>or becomes empty                    | Hi-Z        |