μPD372

# FLOPPY DISK CONTROLLER USERS' MANUAL

Five Militia Drive/Lexington, Massachusetts 02173

Telephone (617) 862-6410

March 11, 1977

.

# USERS' MANUAL

# LSI FLOPPY DISK CONTROLLER CHIP

NEC MICROCOMPUTERS, INC.

uPD372D

The NEC uPD372D is a high performance N-channel LSI floppy disk controller designed to interface between most minicomputers or microprocessors and most floppy disk drives.

The uPD372D is the most versatile floppy disk controller chip available.

FEATURES - Compatible with IBM3740 format

- Compatible with Shugart Minifloppy format

- Compatible with many other formats

- Generates and checks Cyclic Redundancy Characters

- Initiates operations at address marks or physical index

- Formats clear disks

- Handles up to four floppy disk drives

- Can read or write on one drive while simultaneously track seeking on another

- Track stepping rate and step pulse width are programmable

- Sector size programmable from one byte to one sector per track

- Data transfer rate easily changed

- Standard power supply voltages +12V, +5V, -5V

The uPD372D is compatible with most floppy disk drives including:

| Calcomp 140 | Pertec FD400  |

|-------------|---------------|

| CDC BR8Ø3   | Potter DD4740 |

| GSI Ø5Ø     | Remex RFS7400 |

| GSI 110     | Shugart SA400 |

| Innovex 210 | Shugart SA9ØØ |

| Orbis 74    | Sycor 145     |

| Persci 75   |               |

# TABLE OF CONTENTS

| INTRODUCTION                   | 4  |

|--------------------------------|----|

| INPUT/OUTPUT SIGNALS           | 6  |

| INTRODUCTION                   | 6  |

| PROCESSOR INTERFACE            | 6  |

| DISK DRIVE INTERFACE           | 9  |

| ADDRESSABLE INTERNAL REGISTERS | 12 |

| INTRODUCTION                   | 12 |

| WRITE REGISTERS                | 14 |

| READ REGISTERS                 | 22 |

| DATA CONDITIONER               | 26 |

| INTRODUCTION                   | 26 |

| DATA CONDITIONER EXAMPLE       | 30 |

| FLOPPY DISK CONTROLLER EXAMPLE | 32 |

| HARDWARE                       | 32 |

| SOFTWARE                       | 35 |

| uPD372 SPECIFICATIONS          | 65 |

#### INTRODUCTION

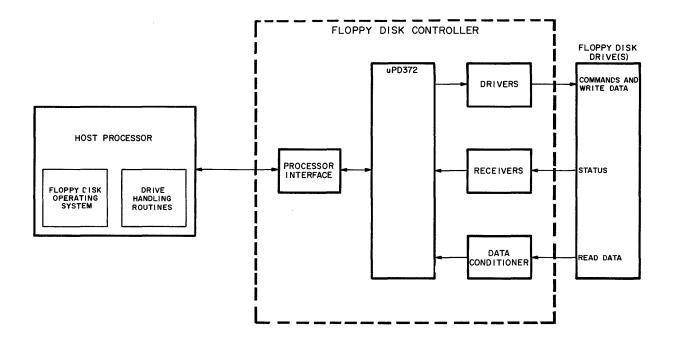

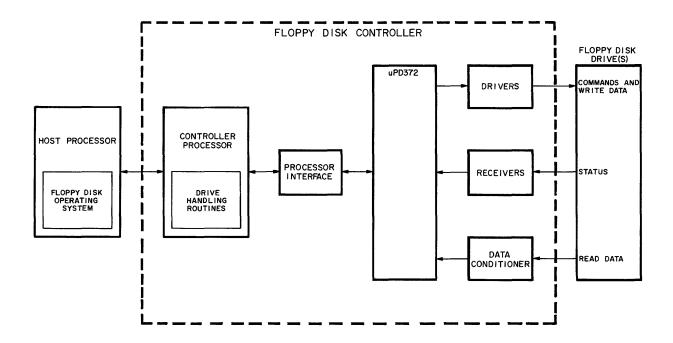

The uPD372 may be interfaced directly to a host processor as shown in Figure 1 or it may be interfaced to a controller processor which in turn is interfaced to the host processor as shown in Figure 2. Most processors interfaced to the uPD372 must, when reading from or writing a record on the disk, be completely dedicated to the task of controlling the disk drive(s). These periods may last several milliseconds. If the nature of the other tasks performed by the host processor allows them to be neglected for this length of time, then the uPD372 may be interfaced directly to the host processor. Otherwise, a controller processor is required.

Whichever approach is chosen, the floppy disk drive control workload is shared between the uPD372 hardware and the processor(s) software.

The uPD372 converts information, which the software transmits to uPD372 internal registers, into commands and serial data which are transmitted to the disk drive(s). The uPD372 converts status signals and serial data from the drives into register information which is read by the software. The uPD372 also controls the timing of most disk operations and performs many other tasks such as Cyclic Redundancy Character generation and checking.

The software tasks are usually divided into two groups as shown in Figures 1 and 2. The Drive Handling Routines control sector reading and writing and track seeking. The Floppy Disk Operating System contains the executive programs which instruct the Drive Handling Routines to read or write a particular sector on a particular track. The Floppy Disk Operating System programs also decide from what area of memory write data should be taken and into what area of memory read data should be stored.

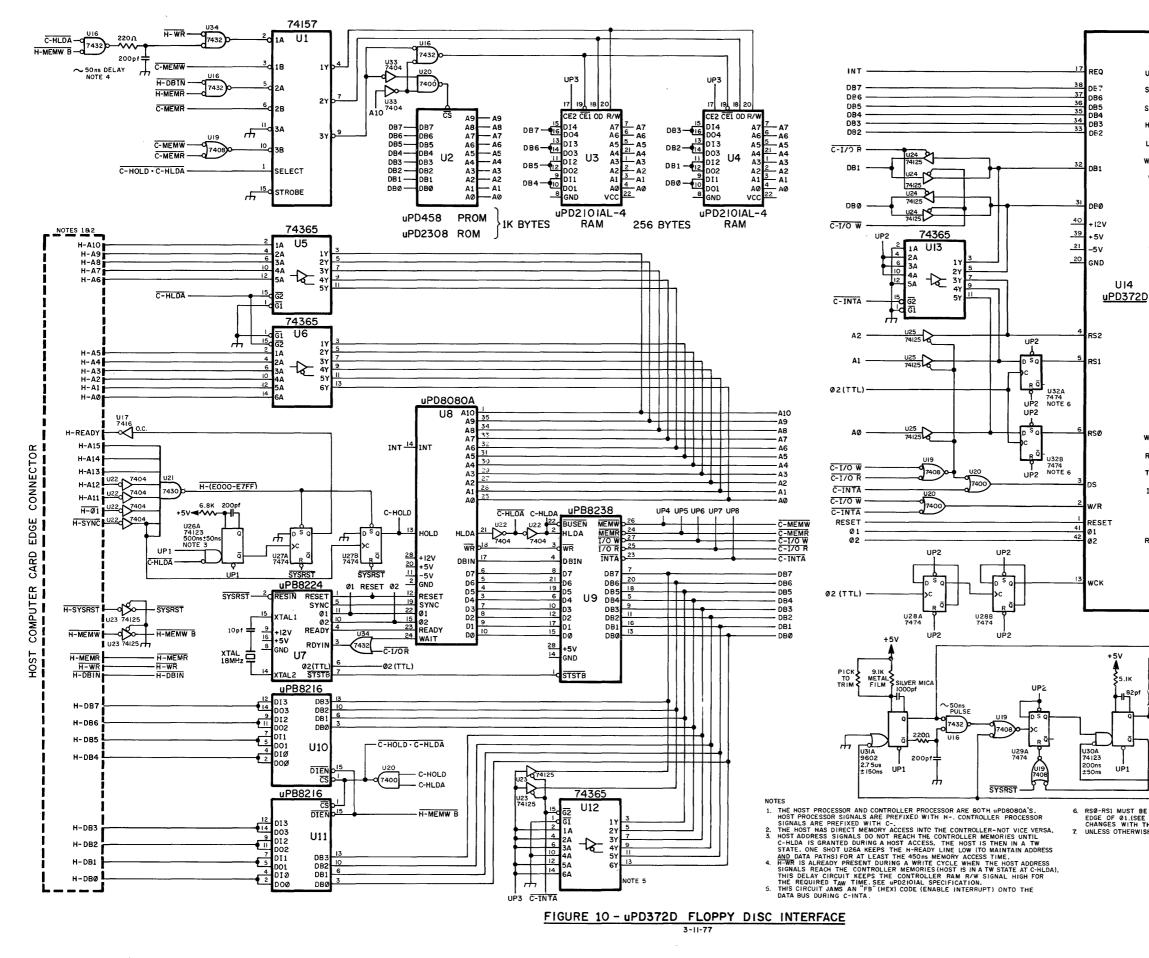

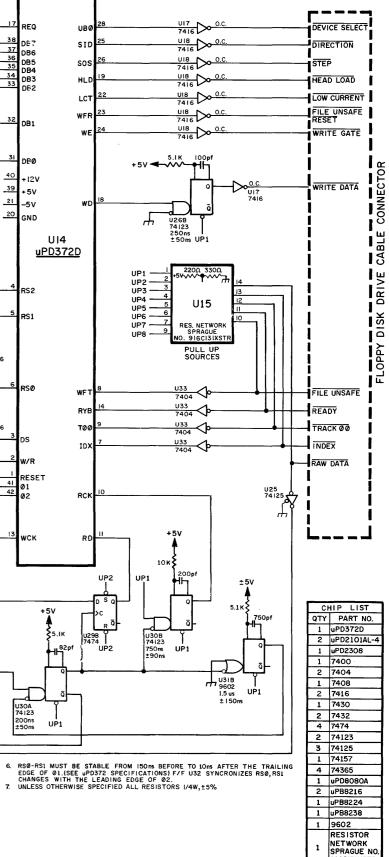

A uPD372 interface between a uPD8080A microprocessor and an IBM3740 compatible drive is shown in the right hand side of Figure 10 in the FLOPPY DISK CONTROLLER EXAMPLE section. This circuit may be interfaced directly to a uPD8080A host processor or to a uPD8080A controller processor similar to the example shown in the left hand side of Figure 10.

Since the disk drive(s) operate under program control, complete uPD8080A assembly listings of the Drive Handling Routines with extensive comments are included in the FLOPPY DISK CONTROLLER EXAMPLE section. The listings describe the sequence of events of each disk operation. Although the sequences are specific to IBM3740 format and to a uPD8080A microprocessor, sequences for other formats are very similar in most respects and the uPD8080A instructions used are largely limited to simple INPUTS, OUTPUTS, CONDITIONAL JUMPS, etc., which are similar to those of other processors.

FIGURE 1 uPD372 INTERFACED DIRECTLY TO HOST PROCESSOR (15-20 CHIPS)

FIGURE 2 uPD372 INTERFACED TO HOST PROCESSOR THROUGH CONTROLLER PROCESSOR (34-40 CHIPS)

#### INTRODUCTION

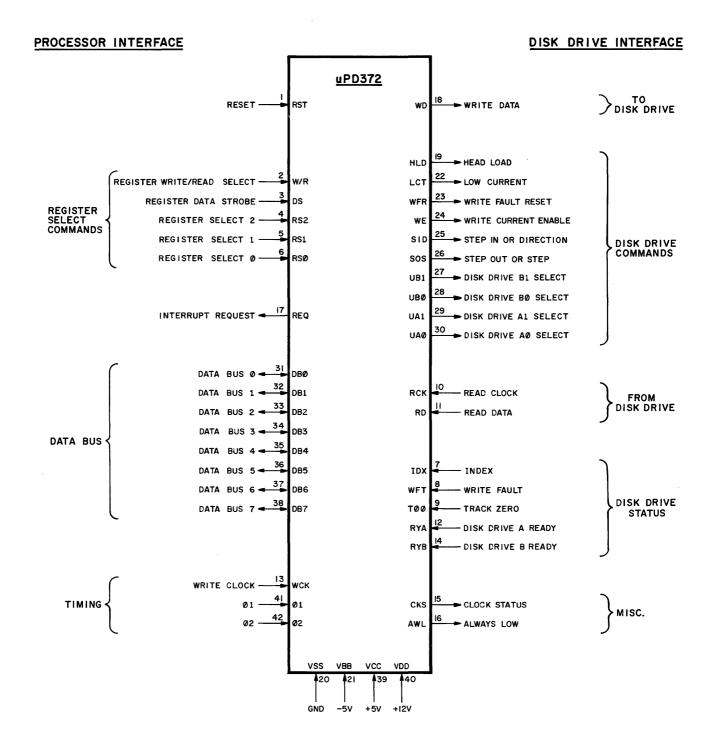

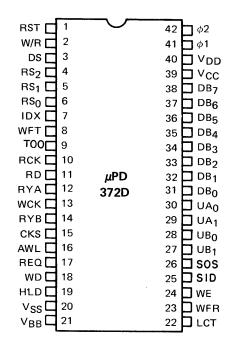

Figure 3 shows the input/output signals of the uPD372 grouped into 10 categories.

RESET REGISTER SELECT COMMANDS INTERRUPT REQUEST DATA BUS TIMING WRITE DATA DISK DRIVE COMMANDS READ DATA DISK DRIVE STATUS MISCELLANEOUS

The REGISTER SELECT COMMANDS control Data Transfers from the DATA BUS to the 6 uPD372 write registers. The contents of the write registers are translated by the uPD372 into WRITE DATA and DISK DRIVE COMMANDS. The REGISTER SELECT COMMANDS also control Data Transfers from the 3 uPD372 read registers to the data bus. The processor may then read the DISK DRIVE STATUS and READ DATA from the data bus.

The processor generates DISK DRIVE COMMANDS by manipulating bits in the uPD372 write registers and the DISK DRIVE STATUS signals control the state of bits in the read registers. To avoid repetition the signals in these two categories are described in the ADDRESSABLE INTERNAL REGISTERS section only. All other input/output signals are described below.

#### Processor Interface

#### Reset

Pin 1 RST (Reset)

A logic one at pin l causes a general reset of the uPD372. For a list of signals and registers affected, see RST-bit 7 of Write Register  $\emptyset$  (WR $\emptyset$ ) in the ADDRESSABLE INTERNAL REGISTERS section.

FIGURE 3 INPUT/OUTPUT SIGNALS

#### Register Select Commands and Data Bus

| Pin 2      | W/R     | (Register Write/Read Select) |

|------------|---------|------------------------------|

| Pin 3      | DS      | (Register Data Strobe)       |

| Pins 4-6   | RSØ-RS2 | (Register Address)           |

| Pins 31-38 | DBØ-DB7 | (Data Bus)                   |

W/R, DS and RSØ-RS2 control Data Bus transfers between the uPD372 and the processor as follows:

Writing into a uPD372 register

When W/R is a logic one, information the processor places on DBØ-DB7 is written into the uPD372 Write Register selected by RSØ-RS2. The information is written at the time of the trailing edge of each  $\emptyset$ 2 which occurs while DS is a logic one.

Reading from a uPD372 register

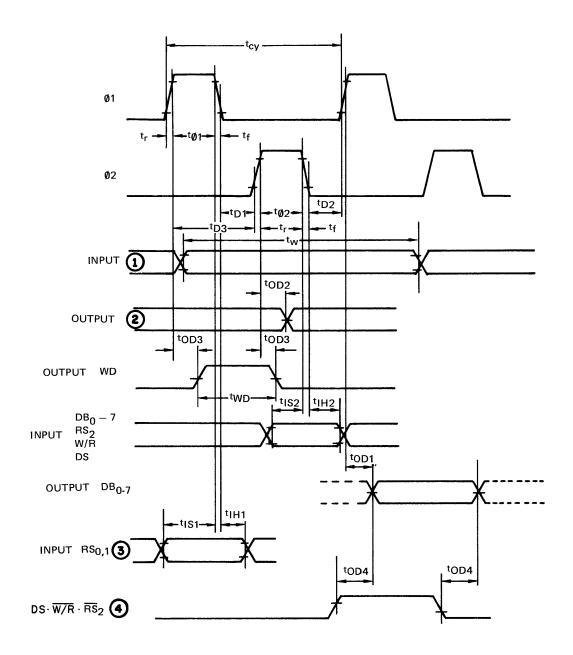

When W/R is a logic zero, information from the uPD372 Read Register selected by  $RS\emptyset-RS2$  is placed on  $DB\emptyset-DB7$ to be read by the processor. The information remains on  $DB\emptyset-DB7$  as long as DS is a logic one. See uPD372 SIGNAL TIMING DIAGRAM, Figure 12 for exact timing.

- NOTE: The logic condition which places uPD372 READ Register information on the Data Bus is DS.W/R.RS2. If these three signals are allowed to change asynchronously with respect to each other, care must be taken to insure that this condition does not become true inadvertantly. The simplest method is to require that W/R and RS2 must not change state while DS is a logic one.

- NOTE: RSØ and RS1 must not change state during the period from 150ns before until 10ns after the trailing edge of 01 or else register contents and DISK DRIVE COMMANDS may be modified. A simple method to accomplish this is to use a dual flip-flop to synchronize changes in RS0 and RS1 with the leading edge of 02(TTL) as shown in Figure 10.

#### Interrupt Request

Pin 17 REQ (Interrupt Request)

Interrupt requests are generated by the uPD372 only while STT (Start-bit 5 of WR3) is true. Two types of interrupt requests occur -- Index Requests and Data Requests.

Index Requests occur once per disk revolution when the physical index hole passes a photodetector. See IRQ-bit l of Read Register Ø (RRØ) in the ADDRESSABLE INTERNAL REGISTERS section.

Data Requests begin during disk reading after an address mark is read and then occur each time an eight-bit byte, assembled from disk serial data, is available to be read by the processor program. Data requests occur during disk writing or formatting each time an eight-bit byte is required from the processor program. See DRQ-bit Ø of Read Register Ø (RRØ) in the ADDRESSABLE INTERNAL REGISTERS section.

Timing Signals

Pin 41 Ø1

Pin 42 Ø2

The uPD372 requires two MOS level clock signals, Øl and Ø2. A uPD8224 generates both Øl and Ø2 as well as a TTL level Ø2. If the uPD372 is interfaced to a uPD8080A microprocessor and if both devices are in the same proximity, they may share a uPD8224 as shown in Figure 10.

Pin 13 WCK (Write Clock)

WCK determines the bit transfer rate to the selected disk drive while writing. IBM standard drives require a 500KHz WCK. The Shugart Minifloppy requires a 250KHz WCK. Other standards may require different WCK frequencies. In each case the WCK frequency should be twice the bit transfer rate.

DISK DRIVE INTERFACE

#### Write Data

Pin 18 WD (Write Data)

Serial Frequency Modulated (FM) code to be written on a floppy disk leaves the uPD372 at pin 18. Pin 18 should be connected to the WRITE DATA input of the selected disk drive.

# Disk Drive Commands

The following commands to the disk drive(s) are generated under program control by modifying the contents of uPD372 Write Registers. The description of each command may be found in the ADDRESSABLE INTERNAL REGISTERS section under the appropriate write register and register bit.

| Pin 19 | HLD (Head Load)            | See Write Register Ø (WRØ)<br>bit 3 |

|--------|----------------------------|-------------------------------------|

| Pin 22 | LCT (Low Current)          | See WRØ bit 2                       |

| Pin 23 | WFR (Write Fault Reset)    | See WRØ bit l                       |

| Pin 24 | WE (Write Current Enable)  | See WR3 bits 2 and 4                |

| Pin 25 | SOS (Step Out or Step)     | See WR4 bit 5                       |

| Pin 26 | SID (Step In or Direction) | See WR4 bit 6                       |

| Pin 27 | UBl (Disk Drive Bl Select) | See WR4 bit 1                       |

| Pin 28 | UBØ (Disk Drive BØ Select) | See WR4 bit Ø                       |

| Pin 29 | UAl (Disk Drive Al Select) | See WRl bit l                       |

| Pin 30 | UAØ (Disk Drive AØ Select) | See WRl bit Ø                       |

#### Read Data

Pin 10 RCK (Read Clock)

Pin 11 RD (Read Data)

RD is a changing logic level updated by each data and clock pulse in the raw data read from the selected disk drive. RCK is a clock the positive transition of which strobes RD into the uPD372. Both signals are derived from the raw data by the DATA CONDITIONER circuit. See the DATA CONDITIONER section for a complete description of RCK and RD.

# Disk Drive Status Signals

The following status signals from the disk drive(s) each control the logic level of a bit in uPD372 Read Registers Ø and 1 (RRØ and RR1). By reading the contents of these registers the processor program senses the disk drive status signals. A description of each status signal may be found in the ADDRESSABLE INTERNAL REGISTERS section under the appropriate read register and bit.

| Pin | 7  | IDX | (Index)              | See | Read Register Ø (RRØ)<br>bit l |

|-----|----|-----|----------------------|-----|--------------------------------|

| Pin | 8  | WFT | (Write Fault)        | See | RR1 bit 2                      |

| Pin | 9  | тØØ | (Track Zero)         | See | RRl bit 6                      |

| Pin | 12 | RYA | (Disk Drive A Ready) | See | RR1 bit 3                      |

| Pin | 14 | RYB | (Disk Drive B Ready) | See | RRØ bit 6                      |

# Miscellaneous

Pin 15 CKS (Clock Status)

A logic one at CKS indicates that the uPD372 has been commanded (by WCS, bit 6-WR3) to operate with timing signals from the Write Clock (WCK, pin 13). A logic zero at CKS indicates that the uPD372 has been commanded (by RCS, bit 7-WR3) to operate with timing signals from the Read Clock (RCK, pin 10).

Pin 16 AWL (Always Low)

AWL is a logic zero output under all normal operating conditions.

## INTRODUCTION

Data transfers to and from the uPD372 addressable internal registers are controlled by signals W/R, DS and RSØ-RS2 at pins 2-6. These signals are discussed in the INPUT/OUTPUT SIGNALS section.

The address of each register and a mnemonic abbreviation for each register bit are shown in Figure 4. The function initiated, controlled or signalled by each register bit is described in this section.

An important internal timing signal, the Bit Ring Pulse (BRP), affects the functions of more than one third of the register bits. The BRP is a pulse that occurs each time 8-bits (one byte) of data have been read from or written on the disk.

While reading:

the first BRP occurs when the first I.D. address mark, Data address mark or Deleted Data address mark is read after STT (bit 5 of WR3) has been set. BRP's continue to occur each time 8 bits (1 byte) have been read until STT is reset.

While writing:

BRP's occur each time 8 bits (1 byte) have been written until STT is reset.

While formating:

the first BRP occurs when the physical index hole passes the floppy disk drive photodetector after IXS and STT (bits 3 and 5 of WR3) have been set. BRP's continue to occur each time 8 bits (1 byte) have been written until STT is reset.

| REGISTER ADDRESS |     |     | ss  | REGISTER |   | BIT NUMBERS |   |   |   |   |   |   |  |

|------------------|-----|-----|-----|----------|---|-------------|---|---|---|---|---|---|--|

| W/R              | RS2 | RS1 | RSØ | NAME     | 7 | 6           | 5 | 4 | 3 | 2 | 1 | 0 |  |

# WRITE REGISTERS

| 1 | Ø | Ø | Ø | WRØ     | RST   | MBL | x   | x   | HLD                                   | LCT | WFR | x                          |

|---|---|---|---|---------|-------|-----|-----|-----|---------------------------------------|-----|-----|----------------------------|

|   |   |   |   |         |       |     |     |     | L                                     | I   | l   |                            |

| 1 | 0 | 0 | 1 | WR1     | CBS   | x   | CB5 | CB4 | СВЗ                                   | UAS | UA1 | UAØ                        |

|   |   |   |   |         |       |     |     |     | · · · · · · · · · · · · · · · · · · · |     |     |                            |

| 1 | Ø | 1 | Ø | WR2     | WD7   | WD6 | WD5 | WD4 | WD3                                   | WD2 | WD1 | WDØ                        |

|   |   |   |   |         |       |     |     |     |                                       |     |     |                            |

| 1 | Ø | 1 | 1 | WR3     | RCS   | wcs | STT | WES | IXS                                   | WER | CCG | ccw                        |

|   |   |   |   |         |       |     |     |     |                                       |     |     |                            |

| 1 | 1 | Ø | Ø | WR4     | STS   | SID | SOS | x   | x                                     | UBS | UB1 | UBØ                        |

|   |   |   |   | ٢       |       |     |     |     |                                       |     |     |                            |

|   |   |   |   |         |       |     |     |     |                                       |     |     |                            |

| 1 | 1 | 1 | 0 | WR6     | x     | x   | ×   | x   | x                                     | TRR | IRR | DRR                        |

|   |   |   |   |         |       |     |     |     |                                       |     |     |                            |

|   |   |   |   | READ RE | GISTE | RS  |     |     |                                       |     |     |                            |

|   |   |   |   | I       |       |     |     |     |                                       |     |     |                            |

| 0 | Ø | Ø | 0 | RRØ     | ALH   | RYB | UB1 | UBØ | ERR                                   | TRQ | IRQ | DRQ                        |

|   |   |   |   |         |       |     |     |     |                                       |     |     |                            |

| 0 | Ø | 0 | 1 | RR1     | WRT   | TØØ | DER | COR | RYA                                   | WFT | UA1 | UAØ                        |

|   |   |   |   |         |       |     |     |     |                                       |     |     | •••••••••••••••••••••••••• |

RR2

RD7

RD6

RD5

RD4

RD3

RD2

RD1

RDØ

X = NOT

USED

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

FIGURE 4 ADDRESSABLE INTERNAL REGISTERS

0

0 1 0

#### WRITE REGISTERS

Write Register Ø (WRØ)

WRØ-Bit Ø Not Used.

WRØ-Bit 1 WFR (Write Fault Reset)

A logic one transmitted to bit 1 sets the output of WFR pin 23 to a logic one. The one logic level remains at pin 23 until a logic zero is transmitted to bit 1. The signal at pin 23 may be used for any command purpose, but normally is used to reset a Write Fault condition.

To reset Write Fault, a logic one is transmitted to bit 1 and about løus later a logic zero is transmitted to bit 1. This forms an approximately løus wide pulse at pin 23 - the width specified by most disk drive manufacturers.

A Write Fault is signaled by a drive whenever an attempt is made to turn on the write current illegally (viz. when the head is not loaded). The Write Fault condition is sensed by the processor in bit 2 of RR1.

The status of LCT and HLD, bits 2 and 3 of WRØ should be preserved during Write Fault Reset commands. See note after bit 7 of WRØ.

WRØ-Bit 2 LCT (Low Current)

IBM floppy disk specifications define two values of write current. The higher value is to be used when writing on the outer tracks ( $\emptyset\emptyset$ -43) and the lower value is to be used on the inner (higher density) tracks (44-76).

Pin 22, LCT, of the uPD372 should be connected to the floppy disk drive's Low Current input control line. A logic zero in bit 2 sets a flip-flop to the high current state; a logic one sets the flip-flop to the low current state. The output of the flip-flop is connected to pin 22.

During the SEEK routine LCT should be set to a one when the software track counter becomes greater than 43. It should be set to zero when the counter becomes less than or equal to 43.

The state of HLD, bit 3, WRØ should be preserved during Low Current commands. See note after bit 7 of WRØ.

WRØ-Bit 3 HLD (Head Load)

A logic one at the HLD bit sets the Head Load flip-flop. A logic zero resets the flip-flop. The Q output of the Head Load flip-flop is internally connected to pin 19, HLD. Pin 19 should be connected to the floppy disk drive HEAD LOAD input control line.

The head requires a settling time (approx. 40ms -- see drive specifications) after loading the head and before reading or writing begins.

The state of LCT, bit 2, WRØ should be preserved during Head Load commands. See the note after bit 7 of WRØ.

WRØ-Bit 4 Not Used.

WRØ-Bit 5 Not used.

WRØ-Bit 6 MBL (Must Be Low)

This bit must be a logic zero during each command to WRØ.

WRØ-Bit 7 RST (Reset)

A logic one transmitted to bit 7 resets the uPD372. The effect is exactly the same as that of a pulse on pin 1.

All bits in all write registers; all bits in the read data register, RR2; all disk drive command signals; and Write Data (pin 18) are set to a logic zero.

NOTE: Commands are made to individual bits in WRØ. However, every WRØ bit is affected by any data transfer to WRØ. For instance, to load the head of the selected drive, HLD is set to a one, but what should the other bits of the command be? RST, MBL and WFR should be zero. Bits  $\emptyset$ , 4 and 5 may be anything but the LCT status of the selected drive should be left unchanged. Consequently, a software image of HLD and LCT must be maintained for Whenever HLD, LCT or WFR is addressed, the each drive. selected drive HLD and LCT status must be recalled and incorporated in the command data transfer. This is accomplished by the WRØ MANAGER subroutine in the software listing for the FLOPPY DISK CONTROLLER EXAMPLE given in this manual.

Write Register 1 (WR1)

WR1-Bit Ø UAØ (Unit AØ Set)

# WR1-Bit 1 UA1 (Unit Al Set)

WR1-Bit 2 UAS (Unit A Strobe)

Bit Ø (UAØ) and bit 1 (UA1) control the logic levels of output pins 3Ø (UAØ) and 29 (UA1) respectively. These logic levels may be used for any command function. The logic levels at pins 3Ø and 29, along with these at pins 28 and 27 (see WR4 bits Ø, 1 and 2 -- UBØ, UB1 and UB5) could simply be the select signals for four disk drives. Or, in a more sophisticated system, UAØ and UA1 can select one of up to four drives for a read or write operation and UBØ and UB1 can select another of the drives for a simultaneous track seek operation.

If bit 2, UAS is a logic zero when addressing WR1, the logic levels at pins 30 and 29 remain unchanged regardless of the content of bits 0 and 1. If bit 2 is a logic one when addressing WR1, the logic levels at pins 30 and 29 are set to the logic levels of bits 0 and 1. This allows the write clock bits (bits 3, 4, 5 and 7 of WR1) to be addressed independently from the Unit A select bits.

WR1-Bit 3 CB3 (Write Clock Bit 3)

WR1-Bit 4 CB4 (Write Clock Bit 4)

WR1-Bit 5 CB5 (Write Clock Bit 5)

WR1-Bit 6 (Not Used)

WR1-Bit 7 CBS (Write Clock Bit Strobe)

IBM specifications include definitions of four special byte code patterns termed "address marks". See the INTRODUCTION of the DATA CONDITIONER section for a discussion of code patterns and address marks. What distinguishes the address marks from other bytes sent to or read from the disk is that some of the "clock" pulses are missing.

The clock pattern for ID address marks, Data address marks and Deleted Data address marks is a C7 (hex). The clock pattern for the Index address mark is D7 (hex). Since all clock pulses are present for every other byte (gap or data byte) the clock pattern is FF (hex).

For all three clock patterns bits  $\emptyset$ , 1, 2, 6 and 7 must be logic ones. Only bits 3, 4 and 5 may be zeros. During writing the uPD372 allows the state of clock bits 3, 4 and 5 to be

controlled by CB3, CB4 and CB5. The other clock bits are always logic ones.

In order to change the state of CB3, CB4 or CB5, CBS must be a logic one. If CBS is a zero, CB3, CB4 and CB5 are unaffected by data transfers into WR1.

To set an FF (hex) clock pattern for data and gap bytes, B8 (hex) should be written into WR1. To set a C7 (hex) clock pattern for ID, Data or Deleted Data address marks, 80 (hex) should be written into WR1. To set a D7 (hex) clock pattern for Index address marks, 90 (hex) should be written into WR1.

Write Register 2 (WR2)

WR2-Bits Ø-7 WDØ-WD7 (Write Data Register)

When the uPD372 is writing on the disk, the data from WR2 and the clock pattern from WR1 are transferred to a 16-bit shift register once every 16 Write Clock (WCK) cycles. The data and clock bits are frequency modulation encoded and serially transmitted from the shift register through pin 18, WD (Write Data) to the selected floppy disk drive read/write head.

If the processor does not transfer new data to WR2, the write data pattern in WR2 remains constant and is repeatedly written on the disk.

Write Register 3 (WR3)

WR3-Bit Ø CCW (Cyclic Check Words)

CCW must be set to a one while the floppy disk drive read/write head is either reading or writing the last data byte of an ID or data record. It must be reset to a zero while the head is reading or writing the second CRC byte. See program listings for READ ID, READ DATA and WRITE DATA for exact sequence.

In the Read Mode, the Bit Ring Pulse (BRP) which follows the setting of CCW begins a bit-by-bit serial comparison between the CRC bytes read from the disk and the CRC bytes generated and stored in the uPD372 CRC register. The comparison ends at the time of the BRP which follows the resetting of CCW. The same BRP sets bit 5 of RR1 (DER-Data Error) to a one if an error was detected. DER is set to a zero if no error was detected. The DER information remains valid for one byte time (while the head is reading the first gap byte following the record).

In the Write mode, CCW is used to write the two CRC bytes. The BRP which follows the setting of CCW causes write data to be taken from the CRC register rather than the write data register, WR2. The writing of the CRC bytes ends at the time of the BRP following the resetting of CCW. See program listing for WRITE DATA.

WR3-Bit 1 CCG (Write Cyclic Check Generator Start)

CCG is used only in the write mode to start the calculation of the CRC. (CRC calculation begins automatically at the address mark in the read mode.) CCG must be set to a one while the head is writing the last gap byte before writing an ID or Data record. CRC calculation begins at the time of any BRP which occurs while CCG is a one. Consequently, CCG must be reset to a zero while the head is writing the first byte (address mark) of the record or the next BRP would start the CRC calculation again. See the program listing for WRITE DATA for the exact sequence.

WR3-Bit 2 WER (Write Enable Reset)

See Bit 4 of WR3 (Write Enable Set--WES)

WR3-Bit 3 IXS (Index Start)

IXS is used in conjunction with STT to start the formatting routine at the physical index. See STT, bit 5 of WR3.

WR3-Bit 4 WES (Write Enable Set)

A logic one at WES sets and a logic one at WER resets a flip-flop. The Q output of this flip-flop is synchronized with the BRP to set the Write Enable flip-flop. The Q output of the Write Enable flip-flop is connected to pin 24, WE. The signal on this pin should be used to enable the write current of the selected floppy disk drive.

WR3-Bit 5 STT (Start)

STT starts and ends every read, write and format operation.

Reading:

An AØ (hex) is transmitted to WR3 (STT and RCS=1). The next ID address mark, Data address mark or Deleted Data address mark read by the disk drive causes an interrupt request and a BRP. Interrupts continue to occur as each byte is read and at each physical index until STT is reset. Writing:

Each write operation is preceded by a READ ID routine (which STT starts). STT remains a logic one during READ ID, during the gap between the ID record and the data record and while writing a new data record. STT is not reset until the data record has been written.

The clock source is switched to the Write Clock and write current is enabled 11 bytes (in IBM format) after the ID record. Writing begins at the next BRP. Six new gap bytes are written, the data record is written and one new byte in the following gap is written before STT is reset. After STT is reset, the next (and last) BRP resets the write current.

BRP's and interrupt requests occur at each byte from the start of READ ID until STT is reset at the end of WRITE DATA. See listing of WRITE DATA.

Formatting:

A 78 (hex) is transmitted to WR3 (STT, WCS, WES and IXS = 1). The next physical index signal (IDS pin 7) enables the write current and starts a series of BRP's and interrupt requests. These continue for one entire disk revolution while the track is being formatted with data bytes, gap bytes and address marks provided by the processor. STT is reset at the next index request flag (IRQ bit 1 of RRØ) ending the BRP's and interrupt requests and turning off the write current. See the listing of the FORMAT routine.

Resetting STT automatically resets Write Enable, sets WCS (Write Clock Set) and prevents further data requests (DRQ) and index requests (IRQ). See program listings of READ ID, READ DATA and WRITE DATA for examples of the use of STT.

WR3-Bit 6 WCS (Write Clock Set)

WR3-Bit 7 RCS (Read Clock Set)

WCS and RCS do not enable write current nor do they determine whether the uPD372 is in the write mode or the read mode; they simply select one of two sources of clock signals for the internal timing of the uPD372. The two clock sources are WCK (Write Clock-pin 13) and RCK (Read Clock-pin 10). Both signals have a frequency of 500KHz (2usec period) for IBM format. WCK should be derived from a crystal controlled oscillator. RCK must be derived from and synchronized with data and clock pulses read from a disk. This is accomplished by the DATA CONDITIONER circuit. See DATA CONDITIONER section. The Read Clock is used only when STT is set and data is being read from the disk. The Write Clock is the normal clock source. The timing source is switched from the Read Clock to the Write Clock by any of the following.

1. By the BRP following the setting of WCS.

2. By resetting STT

3. By RST

The logic level of CKS (Clock Status) pin 15 is set high by any of the above.

The source of timing signals is switched from WCK to RCK by setting RCS. The logic level of CKS is set low by RCS.

Write Register 4 (WR4)

WR4-Bit Ø UBØ (Unit BØ Select)

WR4-Bit 1 UB1 (Unit Bl Select)

WR4-Bit 2 UBS (Unit B Strobe)

Bit Ø (UBØ) and bit 1 (UB1) control the logic levels of output pins 28 (UBØ) and 27 (UB1) respectively. These logic levels may be used for any command function. The logic levels at pins 28 and 27, along with those at pins 30 and 29 (see WR1 bits  $\emptyset$ , 1 and 2--UAØ, UA1 and UAS) could simply be the select signals for four disk drives. Or, in a more sophisticated system, UAØ and UA1 can select one of up to four drives for a read or write operation and UBØ and UB1 can select another of the drives for a simultaneous track seek operation.

If bit 2, UBS is a logic zero when addressing WR4, the logic levels at pins 28 and 27 remain unchanged regardless of the content of bits  $\emptyset$  and 1. If bit 2 is a logic one when addressing WR4, the logic levels at pins 28 and 27 are set to the logic levels of bits  $\emptyset$  and 1. This allows the step bits (bits 5, 6 and 7 of WR4) to be addressed independently from the unit B select bits.

WR4-Bit 3 Not used

WR4-Bit 4 Not used

WR4-Bit 5 SOS (Step Out or Step)

WR4-Bit 6 SID (Step In or Direction)

WR4-Bit 7 STS (Step Strobe)

Bits 5 (SOS) and 6 (SID) control the logic levels of output pins 26 (SOS) and 25 (SID) respectively. These logic levels may be used for any command function but are normally used to form stepping pulses to move the read/write head of the selected drive.

The step pulse width, repetition rate and the direction control scheme vary from one drive to another. The uPD372 can adapt to any drive with software changes only. For instance, many drives require a DIRECTION logic level to determine which direction (in or out) the read/write head is to move and a STEP pulse to trigger the actual movement. For these drives uPD372 pin 25 is connected to the drive DIRECTION input and pin 26 to the STEP input. To move the read/write head, DIRECTION is set with bit 6 and STEP is set to a one with bit 5. One pulse width later (usually about løusec) STEP is set to a zero with bit 5. One repetition period later (usually about 10msec) STEP is again set to a one with bit 5. One pulse width later STEP is set to a zero again. This process continues until the read/write head arrives at the correct track.

The timing of the repetition rate is facilitated by the 1.024msec timer provided by the uPD372. See RRØ-Bit 2, TRQ (Timer Request).

Other drives require STEP IN pulses on one input line and STEP OUT pulses on another. For these drives uPD372 pin 25 is connected to the drive STEP IN input and pin 26 is connected to the drive STEP OUT input. STEP IN or STEP OUT pulses are formed under program control in a manner similar to that described above.

If bit 7, STS (Step Strobe) is a logic zero when addressing WR4, the logic levels at pins 26 and 25 remain unchanged regardless of the content of bits 5 and 6. If bit 7 is a logic one when addressing WR4, the logic levels of pins 26 and 25 are set to the logic levels of bits 5 and 6. This allows the unit select bits (bits  $\emptyset$ , 1 and 2 of WR4) to be addressed independently from the step bits.

Write Register 5 (WR5) Not used.

Write Register 6 (WR6)

WR6-Bit Ø DRR (Data Request Reset)

A logic one transmitted to DRR resets the Data Request, DRQ. See DRQ bit Ø of RRØ.

WR6-Bit 1 IRR (Index Request Reset)

A logic one transmitted to IRR resets the Index Request (IRQ). See IRQ bit 1 of RRØ.

WR6-Bit 2 TRR (Timer Request Reset)

A logic one transmitted to TRR resets the Timer Request (TRQ). See TRQ bit 2 of RRØ.

WR6-Bit 3-Bit 7 Not Used.

# READ REGISTERS

Read Register Ø (RRØ)

RRØ-Bit Ø DRQ (Data Request)

When DRQ is true, the processor controlling the uPD372 should read a data byte from RR2 during the read mode or transmit a data byte to WR2 during the write mode.

DRQ causes an Interrupt Request (REQ) at pin 17.

DRQ's are generated as follows:

- 1. During the read mode the first ID address mark, Data address mark or Deleted Data address mark (but not Index address mark) which is read following the setting of STT (bit 5-WR3) sets DRQ. From this point on, DRQ is set again by every BRP (i.e., after every byte--data byte, gap byte or address mark--is read) until STT is reset. DRQ must be reset, by DRR (Data Request Reset--bit Ø, WR6) each time that it is set. If DRQ is still true at the time of the following BRP, a Command Overrun Error results (signaled by COR--bit 4, RR1). DRQ is automatically reset when STT is reset.

- During the write mode Data Requests occur at each BRP (i.e., after each byte--data byte, gap byte or address mark--is written). As in (1) above, DRQ must be reset each time that it is set or a Command Overrun Error results.

3. During formatting a series of DRQ's begins when the physical index hole is detected after setting STT and IXS (bits 3 and 5 of WR3). The DRQ's continue to occur at every BRP until STT is reset. (STT and IXS should be reset at the end of one complete revolution--when IRQ, Index Request, bit 2, RR6 becomes true.)

## RRØ-Bit 1 IRQ (Index Request)

IRQ is set true by the leading edge of the physical index pulse. The physical index pulse is generated when the index hole of the floppy disk passes a photo detector in the disk drive. STT must be set to enable IRQ.

IRQ causes an Interrupt Request (REQ--pin 17).

IRQ is reset by transmitting a logic one to IRR (Index Request Reset--bit 1, WR6), by resetting STT and by RST.

RRØ-Bit 2 TRQ (Timer Request)

TRQ is the Q output of a flip-flop which is set by every 512th Write Clock (WCK, pin 13) pulse. The Write Clock period for IBM compatible controllers is 2us causing TRQ to be set every 1.024msec. TRQ is set every 2.048msec when using Shugart Minifloppy format.

TRQ does not cause an Interrupt Request (REQ, pin 17).

TRQ is reset by transmitting a logic one to TRR (Timer Request Reset--bit 2, WR6) and by RST.

# RRØ-Bit 3 ERR (Error)

ERR indicates a condition that must be corrected before issuing a command to the disk drive. ERR is the logical OR of three status signals:

$ERR = WFT + \overline{RYA} + COR$

where: WFT is Write Fault--bit 2, RR1

RYA is Disk Drive A Ready--bit 3, RR1

COR is Command Overrun--bit 4, RR1

RYB is not involved in the calculation of ERR.

RRØ-Bit 4 UBØ (Drive BØ Selected)

RRØ-Bit 5 UB1 (Drive Bl Selected)

UBØ and UB1 are two of the four status bits (the other being bits  $\emptyset$  and 1 of RR1) that indicate which disk drive has been selected. See descriptions of bits  $\emptyset$ , 1 and 2 of WR4 and pins 27 and 28.

RRØ-Bit 6 RYB (Drive B Ready)

This status bit indicates the logic level of RYB at pin 14. Pin 14 is usually connected to the READY output of the drive selected by UBØ and UB1 (bits  $\emptyset$  and 1 of WR4).

RRØ-Bit 7 ALH (Always High)

This bit is a logic one as long as power is supplied to the uPD372.

Read Register 1 (RR1)

RR1-Bit Ø UAØ (Drive AØ Selected)

RR1-Bit 1 UA1 (Drive Al Selected)

UAØ and UAl are two of the four status bits (the other being bits 4 and 5 of RRØ) that indicate which disk drive has been selected. See descriptions of bits 0, 1 and 2 of WRl and pins 29 and 30.

RR1-Bit 2 WFT (Write Fault)

This status bit indicates the logic level of WFT, pin 8. Pin 8 is usually connected to the WRITE FAULT output of the selected drive. A write fault condition occurs when a floppy disk drive detects an illegal command during a write operation. All commands to that drive are ignored as long as the write fault condition exists. The write fault is reset by WFR, bit 1, WRØ.

RR1-Bit 3 RYA (Drive A Ready)

This status bit indicates the logic level of RYA at input pin 12. Pin 12 is usually connected to the READY output of the drive selected by UAØ and UA1 (bits Ø and 1 of WR1). RR1-Bit 4 COR (Command Overrun)

COR indicates that the processor did not respond in time to a Data Request (DRQ) during either a read or a write operation. See DRQ, bit Ø of RRØ.

RR1-Bit 5 DER (Data Error)

DER indicates that a CRC error occurred during a read operation. DER is explained in detail in the description of CCW (Cyclic Check Words) bit Ø of WR3.

RR1-Bit 6 TØØ (Track Zero)

This status bit indicates the logic level of TØØ at input pin 9. Pin 9 is usually connected to the TRACK ØØ output of the selected disk drive. The disk drive places a high logic level on TRACK ØØ when and only when the read/write head is at track zero.

RR1-Bit 7 WRT (Write Mode)

WRT indicates which clock signals the uPD372 is using for internal timing--Write Clock (WCK, pin 13) or Read Clock (RCK, pin 10). The selection is made by WCS (Write Clock Select) or RCS (Read Clock Select) bits 6 and 7 of WR3.

The logic level of WRT is identical to the logic level of CKS, output pin 15.

Read Register 2 (RR2)

RR2-Bits Ø-7 RDØ-RD7 (Read Data Register)

Data, serially read from the selected disk drive, is assembled into 8-bit parallel bytes in an internal shift register and is then transferred to RR2 at each BRP. See READ ID and READ RECORD routines for examples of the use of the Read Data Register.

## DATA CONDITIONER

#### INTRODUCTION

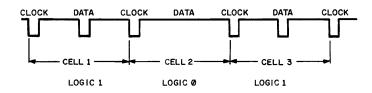

Frequency modulation encoded data as transmitted to or received from a floppy disk drive consists of a series of timing or "clock" pulses interleaved with a series of data pulses (see Figure 5). The period between successive clock pulses is termed a "data cell". The presence of a data pulse within a data cell represents a logic one data bit. The absence of a data pulse within a data cell represents a logic zero data bit.

The clock pulses also contain information. Just as with the data pulses the presence of a clock pulse within a data cell represents a logic one clock bit. And, the absence of a clock pulse within a data cell represents a logic zero clock bit. Each byte is made up of eight data bits and eight clock bits for a total of sixteen.

Since the data read from a floppy disk is in serial format, the controller must have some means of distinguishing between clock bits and data bits and must also be able to determine the beginning of each byte. To provide this synchronization, soft-sectored floppy disks are written with a special byte, an address mark, at the beginning of every record.

All bytes, except address marks, contain the full complement of eight clock pulses for a clock pattern of FF (hex). In IBM format the address marks written at the beginning of records (ID Address Mark, Data Address Mark and Deleted Data Address Mark) each have a C7 (hex) or 11000111 (binary) clock pattern.

The data pattern for an ID address mark is FE (hex) or 11111110 (binary), for a Data address mark is FB (hex) or 11111011 (binary) and for a Deleted Data address mark is F8 (hex) or 11111000 (binary).

The generalized sixteen bit (interleaved clock and data) pattern for these address marks takes the form:

# llll0l0l0llAlBlC (binary)

where at least one of the numbers, A, B or C is a zero.

This pattern cannot be generated by any sixteen bit sequence read from a floppy disk except those of an address mark. All other sixteen bit sequences must have a logic one in alternate locations to represent an FF (hex) clock pattern.

FIGURE 5 FLOPPY DISK DRIVE SERIAL DATA FORMAT

Tcy = Ø1 CYCLE TIME

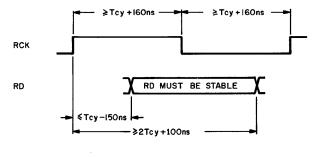

FIGURE 6 READ CLOCK (RCK) AND READ DATA (RD) REQUIRED BY uPD372

FIGURE 8 SAME DATA READ BACK (TRACK 76)

Each bit (clock and data) received by the uPD372 from a floppy disk drive is clocked into a sixteen bit shift register. Once STT (bit 5 of register WR3) is set to a one, the uPD372 begins looking for the address mark pattern in the shift register. When the address mark pattern is found, a BRP (Bit Ring Pulse) is formed, the eight data bits in the shift register are transferred into the Read Register (RR2) and the Data Request flag is raised. From that point until STT is reset, every sixteenth bit clocked into the shift register causes a BRP and a Data Request and transfers the data bits to the Read Register.

# Signals Required by the uPD372

In order to clock a bit into the uPD372 shift register, the desired logic level, zero or one, must be maintained at the READ DATA input (RD, pin 11) and a positive going transition must be made at the READ CLOCK input (RCK, pin 10).

The uPD372 samples RCK with the trailing edge of  $\emptyset 2$ . Since RCK is asynchronous with  $\emptyset 2$ , there is an uncertainty of one  $\emptyset 2$ clock cycle, Tcy, in the time when the uPD372 senses the positive going edge of RCK. Furthermore, RCK is not sampled instantaneously -- a setup time and hold time are required. Consequently, after RCK goes high, it must remain high for at least Tcy + 160ns to guarantee that the positive transition is sensed. For the same reason, after RCK returns to the low state, it must remain low for Tcy + 160ns before the next positive transition.

Once a positive transition of RCK is sensed by Ø2, the following Ø2 clocks the logic level at RD into the shift register. So, the earliest time that RD can be clocked is nearly Tcy after the positive transition of RCK and the latest time is about 2 Tcy after the positive transition of RCK. RD must be stable during this period and for a short time before and after.

The timing requirements of RCK and RD are summarized in Figure 6.

Most floppy disk controllers require that the data pulses read from a drive be separated from the clock pulses by an external "DATA SEPARATOR" circuit. The uPD372, on the other hand, reads the combined clock and data information and separates the data internally. So, it does not require an external DATA SEPARATOR.

The uPD372 does, however, require some modification of the raw data read from the disk. The modification is accomplished by a circuit termed a "DATA CONDITIONER".

# Data Conditioner Algorithm

The function of the DATA CONDITIONER is to translate the pulses of the raw data, read from a disk, into the RD and RCK signals required by the uPD372. Except for an amendment, which for the sake of clarity is introduced later, the DATA CONDITIONER performs the translation by using the following algorithm:

- 1. Each time a raw data pulse (clock or data) is received from a floppy disk drive, the DATA CONDITIONER sets the uPD372 RD input to a logic one and sends a positive pulse to the RCK input. The RD and RCK signals must meet the requirements of Figure 6. In addition, the receipt of a raw data pulse starts an interval timer with a period of 1.4T--where T is the average time between adjacent clock and data pulses. In other words, T is the approximate time before the next raw data pulse will arrive, if it is present. GO TO 2. or 3.

- If the next raw data pulse arrives before 1.4T, the DATA CONDITIONER continues to maintain a logic one at RD, generates another RCK pulse and restarts the interval timer. GO TO 2. or 3.

- 3. If no raw data pulse has arrived by 1.4T, the pulse is declared absent. The DATA CONDITIONER sets the RD input to a logic zero and generates another RCK pulse. The interval timer is not reset until the next raw data pulse is received. GO TO 1.

An amendment must be made to the above algorithm in order to guarantee that the requirements of Figure 6 are always satisfied. Once RCK goes high, it must remain high for a least Tcy + 160ns before going low. Once low, it must remain low for at least Tcy + 160ns before going high. The minimum RCK cycle time is, therefore, 2Tcy + 320ns. For the normal Tcy of 500ns the minimum RCK cycle time is 1320ns. This presents no problem in the long run because the average time between adjacent raw data pulses (in IBM format) is 2us, but it does present a problem between any two closely spaced pulses.

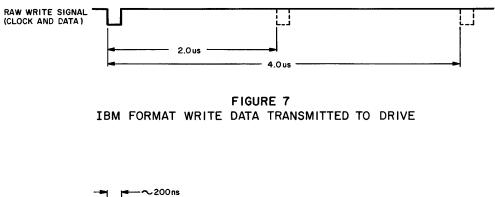

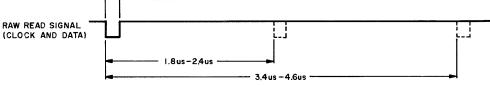

Figure 7 shows the regularly spaced raw write data sent to a floppy disk drive and Figure 8 shows the timing variations in the same data read back from the drive. A decision that the second pulse is missing in Figure 8 cannot be made until 2.8us after the first pulse (T = 2us in IBM format). If a RCK cycle is begun at 2.8us, it cannot be completed for another 1320ns or not until 4.12us after the first pulse; but, the third pulse may occur as early as 3.4us. Obviously, in order to meet the requirements of Figure 6, the DATA CONDITIONER must be capable of storing the information about one raw data pulse while completing the RCK cycle of another. To meet this requirement the first sentence of the algorithm must be amended as follows:

Each time a raw data pulse (clock or data) is received from a floppy disk drive, the DATA CONDITIONER waits until the previous <u>RCK</u> cycle is completed and then sets the uPD372 RD input to a logic one and sends a positive pulse to the RCK input.

# DATA CONDITIONER EXAMPLE

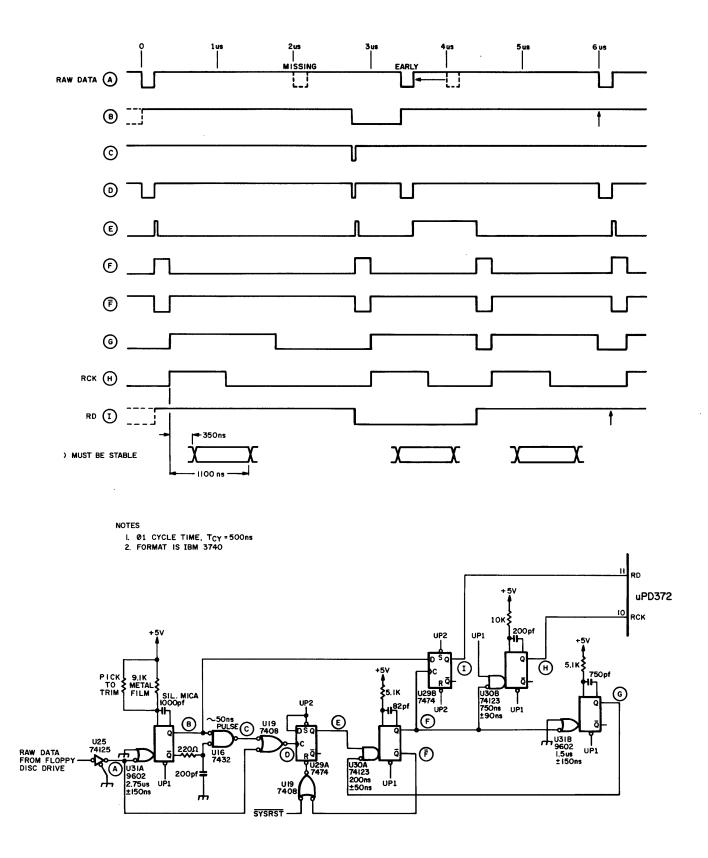

A DATA CONDITIONER which uses the above algorithm and with one-shot times set for IBM format is shown in Figure 9 along with a timing diagram. Tcy, the 02 cycle time, is assumed to be 500ns.

Raw data consisting of clock and data pulses is shown in the top line of the timing diagram. The first pulse occurs at time zero. The second pulse is missing indicating a logic zero. The third pulse is early by 600ns. The fourth pulse occurs at the expected time. This pattern is the worst case because of the short time interval between the decision that the second pulse is missing and the early third pulse.

One-shot U31A generates the 1.4T time interval. Flip-flop U29A stores the information that a RCK cycle should begin when possible. One-shot U31B prevents the start of a RCK cycle until the previous cycle is completed. Flip-flop U29B double buffers the raw data. One-shot U30B forms RCK.

# Other Formats and Other Ø2 Cycle Times

The same DATA CONDITIONER will operate with formats other than IBM and with 02 cycle times other than 500ns.

When using other formats the only parameter which affects the DATA CONDITIONER is the read data transfer rate and the only one-shot affected is the 1.4T time interval one-shot, U31A. The period of U31A should be 1.4T for all T. For example: T=2us in IBM Format so the period of U31A should be 2.8us and T=4us for the Shugart Minifloppy so the period of U31A should be 5.6us.

When using other  $\emptyset$ 2 cycle times, the two one-shots which define RCK are affected. If the  $\emptyset$ 2 cycle time is Tcy, then the period of U3 $\emptyset$ B should be Tcy + 25 $\emptyset$  ns and the period of U31B should be 2 Tcy + 5 $\emptyset$  $\emptyset$  ns in order to keep RCK consistent with Figure 6.

FIGURE 9 DATA CONDITIONER EXAMPLE AND TIMING DIAGRAM

## FLOPPY DISK CONTROLLER EXAMPLE

#### HARDWARE

Figure 10 is divided into two sections. The section on the right shows a floppy disk controller which may be interfaced either directly to a host processor or indirectly through a controller processor. The section on the left shows a controller microprocessor system. Both the host and the controller processors are uPD8080A's in this example and the single floppy disk drive is IBM3740 compatible.

The controller and host processors share a common memory. 1K bytes of ROM is accessed by the controller processor between  $\emptyset 0 \emptyset 0 - \emptyset 3$ FF of its address space. The same ROM is accessed by the host processor between  $E \emptyset 0 \emptyset - E 3$ FF of its address space. 256 bytes of RAM is accessed by the controller processor between  $\emptyset 4 \emptyset \emptyset - \emptyset 4$ FF of its address space. The same RAM is accessed by the host processor between  $E 4 \emptyset \emptyset - E 4$ FF of its address space. The ROM stores the Disk Handling Routines and the RAM provides temporary storage for data, commands, status, etc.

The controller processor system configuration shown in Figure 10 is a testbed for software and hardware changes in the floppy disk interface. The intent is to give the host processor (which is assumed to have an editor and a console) the ability to monitor the performance of the controller processor and the rest of the floppy disk interface. Consequently, the direction of Direct Memory Access is from the host into the controller rather than vice versa and no provision is made to allow the controller to interrupt the host.

An interrupt feature would require the addition of only two chips. The resulting controller would be satisfactory for many applications although the host would have to transfer data between the common RAM and the desired storage locations. A circuit which allows Direct Memory Access from the controller into the host would require several logic changes resulting in a net gain of a few chips.

# Circuit Description

The circuitry to the right of the uPD372 in Figure 10 contains the line drivers and receivers for the floppy disk drive. One shot U26B "stretches" the 60-100ns wide Write Data (WD) pulses into the width specified by the drive manufacturer.

The logic below the uPD372 is the Data Conditioner which is described in the DATA CONDITIONER section.

914CI31XSTF 34 TOTAL Flip-flops U28A and U28B generate a 500KHz Write Clock for IBM formats. The Shugart Minifloppy format requires an additional flip-flop to generate a 250KHz clock. Other formats may require other clock frequencies. In each case the period of the clock is equal to the period between adjacent clock and data pulses in the Frequency Modulated data stream.

U13, U24 and 3 gates of U25 force a Øl (hex) into WR6 during interrupt acknowledge. This causes a hardware reset of the Data Request (but not of the Index Request). See bits Ø and l of WR6.

The remaining chips in the right hand section of Figure 10, give a uPD8080A processor data transfer control over the uPD372 addressable internal registers.

The Direct Memory Access control logic is shown at the left of the uPD8080A in Figure 10. Flip-flops U27A and U27B are both set at the beginning of each host machine cycle in which the host addresses the common memory. Flip-flop U27B makes a HOLD request of the controller uPD8080A. Flip-flop U27A places the host uPD8080A in the WAIT state by lowering the host's READY input. When the controller uPD8080A grants the HOLD request, signified by C-HLDA, the host uPD8080A is given control over:

- 1) the Chip Enable, Output Disable and Read/Write inputs of the common memory by Ul;

- 2) the common memory address lines by U5 and U6;

- 3) the common memory data bus by UlØ and Ull.

After one-shot U26A causes a delay equal to the memory access time, flip-flop U27A releases the host uPD8080A from the WAIT state. When the host uPD8080A has completed the machine cycle in which it addressed common memory, it issues a SYNC pulse which causes U27B to release the controller uPD8080A from the HOLD state. When C-HLDA goes low the controller processor is free to continue execution of its own programs.

There is sufficient delay before C-HLDA goes low to prevent this design from allowing two successive host machine cycles to be addressed to the common memory. The main effect is to prevent the host processor from executing programs in common memory, which is not a requirement of this design.

OR-gate U34, between the uPD8080A and the uPD8224, causes one wait state to occur in each machine cycle during which data is read from the uPD372; but does not cause a wait state in any other machine cycle. The uPD372 places read register information on the data bus 90ns (max.) after 01 - which is too late to remain within uPD8080A specifications without a wait state. A wait state is not required at any other time. In fact a wait state in <u>every</u> machine cycle is not allowed since it would make a uPD8080A system too slow to handle disk data transfers.

#### SOFTWARE

The software for the controller processor may be divided into catagories as follows:

Executive Routines

INITIALIZE RETURN FROM COMMAND IDLE LOOP EXECUTE COMMAND

Main Routines

READ ID READ DATA WRITE DATA FORMAT SEEK

Subroutines

STEP IN STEP OUT HEAD LOAD HEAD UNLOAD WRØ MANAGER UNIT SELECT DELAY

The Executive Routines initialize the floppy disk drive system after startup, interpret commands from the host processor and transfer control to the appropriate Main Routine. The Main Routines perform the actual disk drive operations. At the completion of a Main Routine, control is transferred back to the Executive Routines which inform the host processor of the result and then wait for the next processor command.

All of the software, including FORMAT, for a single disk drive controller may be stored in one 1K x 8 ROM. Nearly 1/4 of this area is available for program expansion to allow control of up to four disk drives and for other purposes. This area is made available by storing most of FORMAT on a disk rather than in ROM. When formatting is required, the major portion of FORMAT is recalled from a disk and stored in the controller RAM with only a minor portion permanently stored in ROM.

An introduction is given below to READ ID, READ DATA and WRITE DATA. The comments in the uPD8080A assembler listing which follows this section should be sufficient to understand the rest of the controller software.

#### Read Sector M on Track N

Before the read operation begins, the host processor writes the desired sector address in SECTR (location 403 in the listing) the desired track address in TRACK, the desired disk drive in UNIT and the sector size in SCTS2. If no sector size is transmitted from the host, the controller program assumes a size of 128 (decimal) bytes.

The host processor initiates the read operation by writing an  $\emptyset$ l in CMND (location  $4\emptyset\emptyset$ ). The controller program interprets the  $\emptyset$ l as a read command and if the sector address, track address, drive address and sector size are within acceptable limits, control of the controller processor is transferred to READ DATA (See READ DATA in listing).

READ DATA starts by calling READ ID to find the correct sector and track.

## READ ID

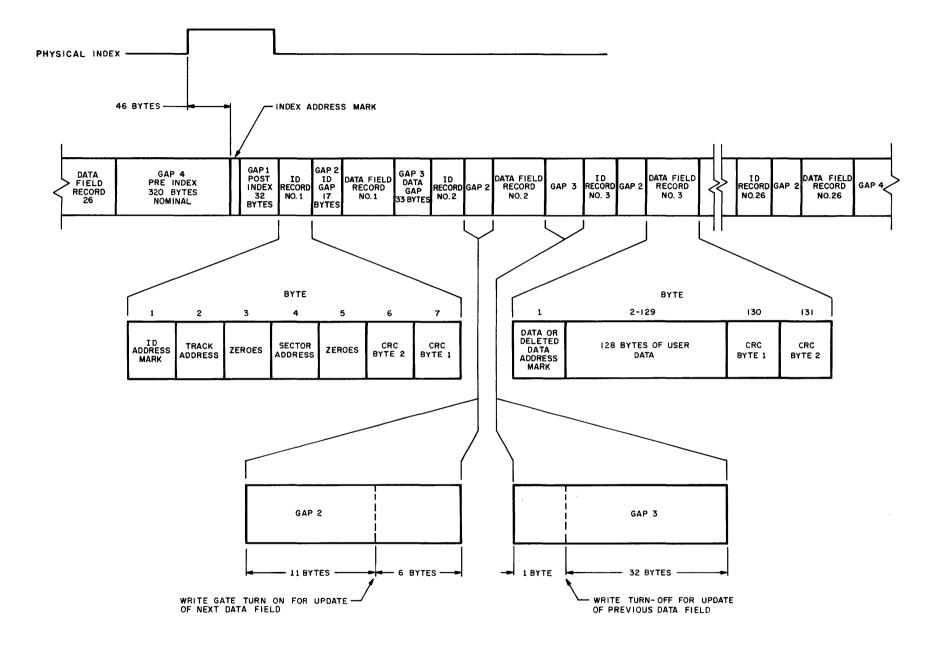

READ ID starts by calling the SEEK routine which positions the read/write head at the requested track. Next the read/write head is loaded (if it is not already loaded because of a previous operation). The read/write head then begins reading somewhere on the requested track. See IBM TRACK FORMAT Figure II. A limit is placed on the number of index holes (4) that may be counted without successfully reading the specified ID record before giving up.

The H, L registers are initialized to point to TRACK, the location containing the desired track number and the first location in the group of parameters.

The D, E registers are initialized to point to WTRK (Wrong Track) the first location in a group of error flags. uPD8080A register B is cleared and a 00 is transmitted to uPD372 write register WR3. The effect is to insure that one particular bit, bit 5, STT (Start) is at a logic zero. All the other bits of WR3 are known to be at a logic zero at this time.

An AØ is then transmitted to WR3. The effect of this command is to set STT, bit 5, and RCS (Read Clock Set) bit 7. RCS instructs the uPD372 to use read clock pulses from the disk for its internal timing control. STT instructs the uPD372 to cause an interrupt request when the next address mark passes the read/write head.

Interrupts are then enabled and the processor is halted while waiting for the interrupt.

FIGURE 11 IBM TRACK FORMAT

## Halt -- Interrupt Technique

The transfer rate of IBM standard floppy disks is one byte every 32us which is too fast for the usual technique of "jamming" a RST (Restart) instruction on the data bus during INTA (Interrupt Acknowledge) followed by a JMP to a service routine which ends with a RET (Return) instruction.

Instead, as shown in the READ ID routine, the processor is halted before an expected interrupt to keep the Program Counter from advancing.

When an address mark is read, an interrupt request is generated and CRC calculation automatically begins.

During INTA an EI (Enable Interrupts) instruction is jammed onto the data bus (by Ul2 and U23 shown in the bottom center of Figure 10) and is executed by the processor. The Program Counter is not incremented by an instruction which occurs during INTA so the next instruction executed is the one following the HLT.

Another event which occurs during each INTA is the clearing of the data request flag by Ul3, U24 and U25 (near the center of Figure 10) which write a 01 into WR6 (DRR-Data Request Reset).

After the address mark interrupt and the EI instruction, the READ ID routine inputs the data byte read from the disk. The data is compared with FE (hex) to determine whether or not the address mark which caused the interrupt was an ID address mark. If it was not an ID address mark, a JMP is made to the RIM subroutine which makes sure the revolution limit has not been exceeded, and then returns the Program Counter to RIA to wait for the next address mark. If it was an ID address mark, the processor is halted to wait for the next interrupt.

The next interrupt occurs when the uPD372 has read the first data byte of the ID record -- the track address. The processor is then halted again.

Using the halt-interrupt technique the READ ID routine reads the first zero byte, the sector address, the second zero byte and the two CRC bytes, storing appropriate error messages if required. If the sector address is incorrect, the Program Counter is returned to RIA and READ ID waits for the next address mark.

The sector number of the ID record just read provides enough information for a READ ID program to compute what the delay will be before the desired ID record will come around to the read/write head. This time could be spent by the controllerprocessor to perform other tasks such as track seeking on another drive. Eventually, an ID record is read with the correct sector address. If no read errors occur, READ ID returns control to READ DATA having found Sector M and Track N.

READ ID exited having read three of the 17 gap bytes between the ID record and the data record (See Figure 11). Between gap bytes 11 and 12, there may be noise on the disk resulting from the turning on of write current each time the data record was updated in the past. To avoid encountering the noise, READ DATA switches the uPD372 internal timing to the Write Clock. Using the Write Clock which has the same frequency as the Read Clock (although the two are not in sync) READ DATA times out past the noisy area.

After the 13th byte (approximately) STT is reset. Several "housekeeping" functions are then performed in preparation for reading the data record.

Near the center of the 6 "clean" bytes adjacent to the data record, STT is set and the controller processor is halted to wait for the data address mark.

When the address mark is read, an interrupt occurs and the CRC calculation begins. If the address mark was a Deleted Data mark or an illegal address mark, appropriate error flags are set. If the address mark was a Data mark, then the data record is read and stored in the data buffer in the common RAM (locations 480-4FF in the controller processor address space).

If no CRC error is found, READ DATA returns control to the Executive Routines which signal the host processor that the requested data is in the common RAM.

### Write Sector M on Track N

Before the write operation begins, the host processor fills the data buffer in common RAM and writes the desired sector, track and drive addresses and sector size in the parameter area.

The host processor initiates the write operation by writing Ø2 in CMND. The controller processor Executive Routines then transfer control to WRITE DATA (See WRITE DATA in listing).

WRITE DATA begins in exactly the same way as READ DATA by calling READ ID to find the correct sector and track. READ ID returns control to WRITE DATA after reading three gap bytes.

WRITE DATA continues reading the gap bytes until gap byte 11 is read. At the end of gap byte 11, an attempt is made to turn on the write current. If the disk drive indicates a Write Fault condition, the write current is not turned on and WRITE DATA is aborted.

If no Write Fault is indicated, 6 gap bytes, all the data

bytes, the two CRC bytes and one gap byte are written. The Write current is then turned off, STT is reset and control is returned to the Executive Routines which signal the host processor that the data buffer has been written in the requested sector of the requested track.

|              | •                                                          | LOPPY DIS<br>NG SEQUEN | SK DRIVE CONTROLLER PROGRAM Ø3-Ø9-77 11ØØ (GCY)<br>NCE |  |  |

|--------------|------------------------------------------------------------|------------------------|--------------------------------------------------------|--|--|

|              | ; SET                                                      | UNIT (Î-NU             | J), TRACK(Ø-NTRKS), SECTR(1-NSCTR)                     |  |  |

|              | ; OPTIONAL: SET SCTSZ(4-NBSCT)<br>; SET CMND(1-NCMDS) LAST |                        |                                                        |  |  |

|              | ;                                                          | WAIT FOR               |                                                        |  |  |

|              |                                                            |                        | SE WITH UPD372                                         |  |  |

|              | ; EQUAT                                                    | LS FUR U               | SE WIIH OPDS/2                                         |  |  |

| 0000         | WØ                                                         |                        | ;WRITE REGISTER ZERO                                   |  |  |

| ØØ8Ø<br>ØØ4Ø |                                                            | EQU 80H                | ;RESET<br>;MUST BE LOW                                 |  |  |

| 0000         |                                                            |                        | ;HEAD LOAD                                             |  |  |

| 0004         | WØLCT                                                      | EQU Ø4H                | ;LOW CURRENT                                           |  |  |

| 0002         |                                                            | EQU Ø2H                | ;WRITE FAULT RESET                                     |  |  |

| 0001         | ;<br>Wl                                                    | EQU l                  | ;WRITE REGISTER ONE                                    |  |  |

| 0080         | WICBS                                                      |                        | ;CLOCK BIT STROBE                                      |  |  |

| ØØ38<br>ØØ1Ø | WlCBN<br>WlCBI                                             |                        | CLOCK BITS FOR NORMAL DATA                             |  |  |

| 0000         | WICBI                                                      |                        | CLOCK BITS FOR ID, DATA,                               |  |  |

|              | 12000                                                      |                        | OR DELETED DATA ADDRESS MARK                           |  |  |

| 0004         |                                                            | ~                      | ;UNIT A STROBE                                         |  |  |

| 0003         | WlUAA<br>;                                                 | EQU Ø3H                | ;UNIT A ADDRESS MASK                                   |  |  |

| 0002         | W2                                                         | EQU 2                  | ;WRITE DATA REGISTER                                   |  |  |

| 0003         | ;<br>W3                                                    | EOU 3                  | WRITE REGISTER THREE                                   |  |  |

| 0080         | W3RCS                                                      |                        | ;READ CLOCK SET                                        |  |  |

| ØØ4Ø         | W3WCS                                                      |                        | ;WRITE CLOCK SET                                       |  |  |

| ØØ2Ø         | W3STT                                                      |                        | START READ/WRITE OPERATION                             |  |  |

| ØØ1Ø<br>ØØØ8 | W3WES<br>W3IXS                                             |                        | ;WRITE ENABLE SET<br>;INDEX START                      |  |  |

| 0004         |                                                            |                        | WRITE ENABLE RESET                                     |  |  |

| 0002         |                                                            |                        | ;CYCLIC CHECK GENERATE                                 |  |  |

| 0001         | W3CCW                                                      | EQU Ø1H                | ;CYCLIC CHECK WORDS                                    |  |  |

| 0004         | w4                                                         | EQU 4                  | ;WRITE REGISTER FOUR                                   |  |  |

| 0080         | W4STS                                                      |                        | ;STEP STROBE                                           |  |  |

| ØØ4Ø<br>ØØ2Ø | W4SID<br>W4SOS                                             |                        | ;STEP IN OR DIRECTION<br>;STEP OUT OR STEP             |  |  |

| 0020<br>0004 |                                                            |                        | ;UNIT B STROBE                                         |  |  |

| 0003         | W4UBA                                                      |                        | ;UNIT B ADDRESS MASK                                   |  |  |

| 0006         | w6                                                         | EQU 6                  | ;WRITE REGISTER SIX                                    |  |  |

| 0004         | W6TRR                                                      |                        | ;TIMER REQUEST RESET                                   |  |  |

| 0002<br>0001 | W6IRR<br>W6DRR                                             |                        | ;INDEX REQUEST RESET<br>;DATA REQUEST RESET            |  |  |

|              | ;                                                          | -                      | · ~                                                    |  |  |

| 0000         | RØ                                                         |                        | ;READ REGISTER ZERO                                    |  |  |

| ØØ8Ø<br>ØØ4Ø | RØALH<br>RØRYB                                             |                        | ;ALWAYS HIGH<br>;READY B                               |  |  |

| 0030         | RØUBA                                                      |                        | ;UNIT B ADDRESS MASK                                   |  |  |

|              |                                                            |                        |                                                        |  |  |

|   | ~ ~ ~ ~     |                |            | <i></i>                    |                                    |

|---|-------------|----------------|------------|----------------------------|------------------------------------|

|   | 0008        | RØERR          |            | Ø8H ;ERI                   |                                    |

|   | 0004        | RØTRQ          |            |                            | MER REQUEST                        |

|   | 0002        | RØIRQ          |            |                            | IDEX REQUEST                       |

|   | 0001        | RØDRQ          | EQU        | ØlH ;DA                    | ATA REQUEST                        |

|   |             | ;              |            | _                          |                                    |

|   | 0001        | Rl             | -          | •                          | CAD REGISTER ONE                   |

|   | 0080        | RIWRT          | EQU        | 80H ;WR]                   | RITE MODE                          |

|   | 0040        | RITØØ          | EQU        | 40H ;TRA                   | RACK ØØ                            |

|   | 0020        | RIDER          | EQU        | 20H ;DAT                   | TA ERROR (CRC)                     |

|   | 0010        | RICOR          |            |                            | MMAND OVERRUN                      |

| · | 0008        | RIRYA          |            | Ø8H ;REA                   |                                    |

|   | 0004        | RIWFT          |            | •                          | RITE FAULT                         |

|   | 0003        | RIUAA          |            | •                          | IIT A ADDRESS MASK                 |

|   | 0000        | ;              | 770        | <b>0</b> 511 <b>,</b> 011. |                                    |

|   | 0002        | ,<br>R2        | EQU        | 2 • REA                    | CAD DATA REGISTER                  |

|   | 5552        | ;              | 120        | 2 , 1(1)                   |                                    |

|   | 0000        | MU             | EQU        | Ø                          | ;MULTIPLE UNITS (Ø=NO, ØFFFFH=YES) |

|   | 0001        | NU             | EQU        |                            | ;NUMBER OF FDD UNITS               |

|   | ØØ4D        | NTRKS          |            | 1<br>77                    | ;NUMBER OF TRACKS                  |

|   | 001A        |                | . –        |                            | ;NUMBER OF SECTORS                 |

|   | ØØ8Ø        | NSCTR<br>NBSCT | EQU<br>EQU |                            | ;NUMBER OF BYTES IN A SECTOR       |

|   |             |                |            |                            | •                                  |

|   | 0003        | NTRYS          | EQU        |                            | ;NUMBER OF READ RETRYS             |

|   | ØØ2B        | LHCTK          |            | 43                         | ;LAST HIGH CURRENT TRACK           |

|   | 0004        | RVLIM          | EQU        |                            | ;REVOLUTION LIMIT IN IDLE LOOP     |

|   | 0470        | STACK          | EQU        | Ø47ØH                      |                                    |

|   |             | ;              |            |                            |                                    |

|   |             | ;              | 0.00       | a                          |                                    |

|   | 0000        | Dama           | ORG        | Ø                          |                                    |

|   | 0000 F3     | RSTØ:          | DI         |                            | ;RESET                             |

|   | ØØØ1 3E8Ø   |                |            | A,WØRST                    |                                    |

|   | ØØØ3 D3ØØ   |                | OUT        |                            | ;RESET 372                         |

|   | 0005 317004 |                |            | SP, STACI                  |                                    |

|   |             | •              |            |                            | REA TO ZERO                        |

|   | 0008 210004 | RSØ2Ø:         |            | H,CMND                     |                                    |

|   | ØØØB Ø617   |                |            | B,NB                       | ;B=NO. OF BYTES                    |

|   | ØØØD AF     |                | XRA        |                            |                                    |

|   | ØØØE 77     | RSØ3Ø:         | MOV        | •                          | ; M=Ø                              |

|   | ØØØF 23     |                | INX        |                            |                                    |

|   | ØØ1Ø Ø5     |                | DCR        |                            | ; DONE?                            |

|   | ØØ11 C2ØEØØ |                |            | RSØ3Ø                      | ;NO                                |

|   |             | ; INITIA       |            | E SECTOR                   |                                    |

|   | ØØ14 3E8Ø   |                |            | A,NBSCT                    |                                    |

|   | ØØ16 32Ø4Ø4 |                |            | SCTSZ                      |                                    |

|   |             | ; INITIA       |            | E ALL UNI                  | IITS                               |

|   |             |                | IF N       |                            |                                    |

|   |             |                |            | A,1                        | ;START WITH UNIT #1                |

|   |             | RSØ1Ø:         |            | UNIT                       | ;SET UNIT #                        |

|   |             |                | ENDI       |                            |                                    |

|   | ØØ19 CD1FØØ |                |            | L INIT                     |                                    |

|   |             |                | IF M       |                            |                                    |

|   |             |                |            | UNIT                       |                                    |

|   |             |                | CPI        |                            | ;LAST UNIT?                        |

|   |             |                |            | RTØlØ                      | ;YES                               |

|   |             |                | INR        | A                          | ;NO                                |

|   |             |                |            |                            |                                    |

|                |                |         | JMP RSØ1Ø<br>ENDIF            | ;GO DO NEXT UNIT                      |

|----------------|----------------|---------|-------------------------------|---------------------------------------|

| ØØ1C           | C346ØØ         | ;       | JMP RTØlØ                     |                                       |

|                |                | ;       |                               |                                       |

| ØØlf           |                | •       | LIZE DISK UNIT SU             |                                       |

| זבממ           |                | INIT    | EQU \$<br>IF MU               | ;INITIALIZE WRØ                       |

|                |                |         | LXI D,WRØ                     |                                       |

|                |                |         | CALL INDXA                    |                                       |

|                |                |         | ENDIF                         |                                       |

| 001F           | 2113Ø4         |         | IF NOT MU<br>LXI H,WRØ        |                                       |

| 0011           | 211304         |         | ENDIF                         |                                       |

| ØØ22           |                |         | XRA A                         |                                       |