K-SERIES MICROCONTROLLERS DATA BOOK

MICRO controllers

**DATA BOOK**

1994

8- and 16-Bit Microcontrollers

**Development Tools**

1994

AHO

NEC

# 1994 K-SERIES MICROCONTROLLERS DATA BOOK

Document No. 50053-1

©1994 NEC Electronics Inc. All rights reserved.

Printed in the United States of America.

No part of this document may be copied or reproduced in any form or by any means without the prior written consent of NEC Electronics Inc. (NECEL). The information in this document is subject to change without notice. Devices sold by NECEL are covered by the warranty and patent indemnification provisions appearing in NECEL Terms and Conditions of Sale only. NECEL makes no warranty, express, statutory, implied, or by description, regarding the information set forth herein or regarding the freedom of the described devices from patent infringement. NECEL makes no warranty of merchantability or fitness for any purpose. NECEL assumes no responsibility for any errors that may appear in this document. NECEL makes no commitment to update or to keep current information contained in this document. The devices listed in this document are not suitable for use in applications such as, but not limited to, aircraft, aerospace equipment, submarine cables, nuclear reactor control systems and life support systems. If customers intend to use NEC devices in these applications or they intend to use "standard" quality grade NEC devices in applications not intended by NECEL, please contact our sales people in advance. "Standard" quality grade devices are recommended for computers, office equipment, communication equipment, test and measurement equipment, machine tools, industrial robots, audio and visual equipment, and other consumer products. "Special" quality grade devices are recommended for automotive and transportation equipment, traffic control systems, anti-disaster and anti-crime systems, etc.

| Reliability and Quality Control |  |

|---------------------------------|--|

| μ <b>PD</b> 78 <b>C</b> 00      |  |

| μ <b>PD78K</b> 0                |  |

| μ <b>PD</b> 78 <b>K</b> 2       |  |

| μPD78K3                         |  |

| Development Tools               |  |

| Soldering                       |  |

Package Drawings

8

# NEC

# NEC

| Section 1 Reliability and Quality Control                                                                                                                           |     | Section 3 (cont)<br>µPD78K0 Product Line<br>8-Bit, K-Series Microcontrollers                                              |     |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|---------------------------------------------------------------------------------------------------------------------------|-----|

| Section 2<br>μPD78C00 Product Line<br>8-Bit, Single-Chip Microcontrollers                                                                                           |     | μPD78064 Family (μPD78062/063/064/P064) 8-Bit, K-Series Microcontrollers With LCD Controller/Driver, UART, and A/D        | 3-g |

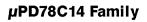

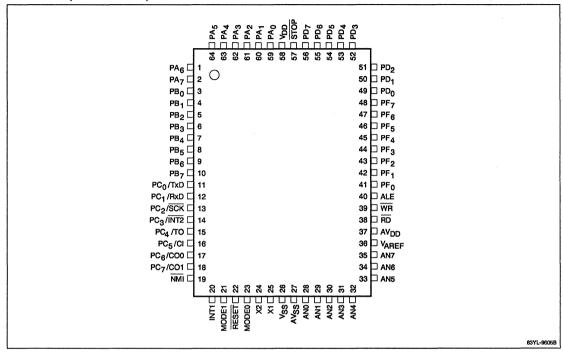

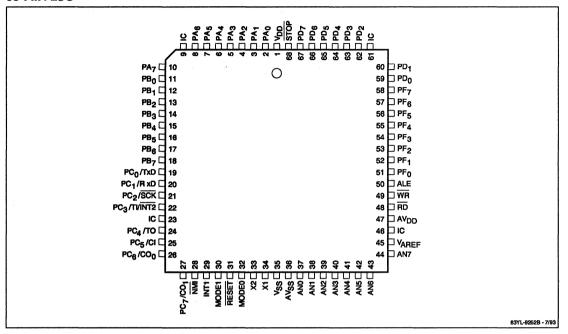

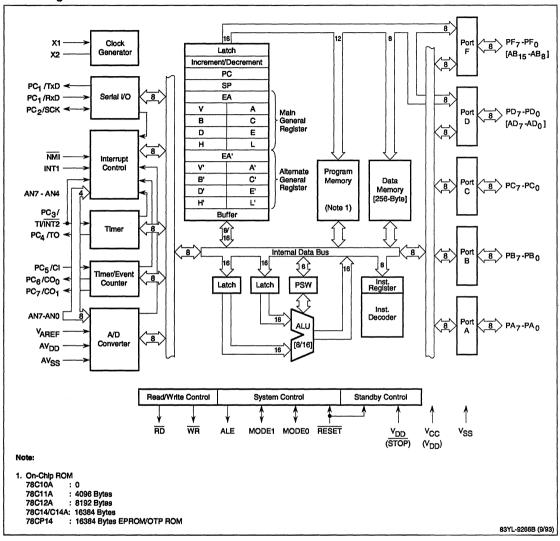

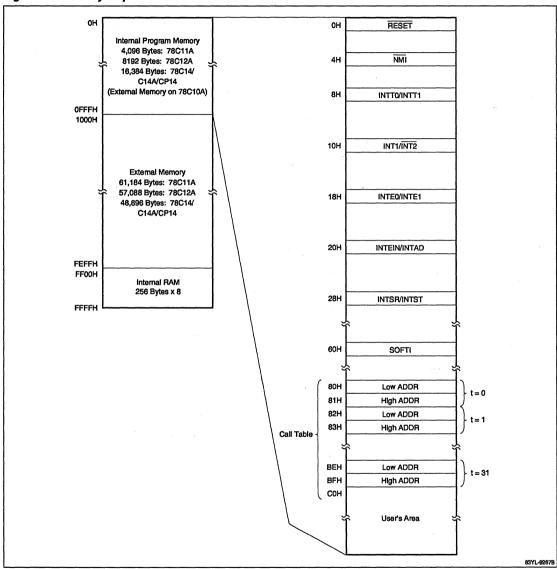

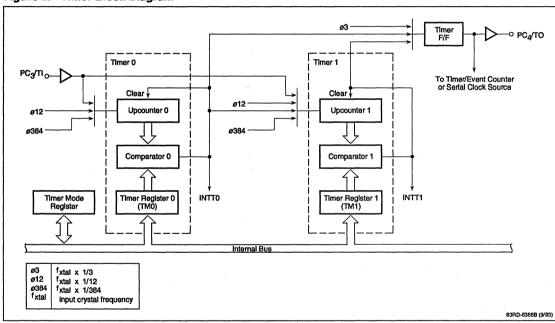

| μPD78C14 Family (μPD78C10A/C11A/C12A/C14/C14A/CP14) 8-Bit, Single-Chip Microcontrollers With A/D Converter                                                          | 2-a | Converter  µPD78K0 Product Line  Programming Reference                                                                    | 3-h |

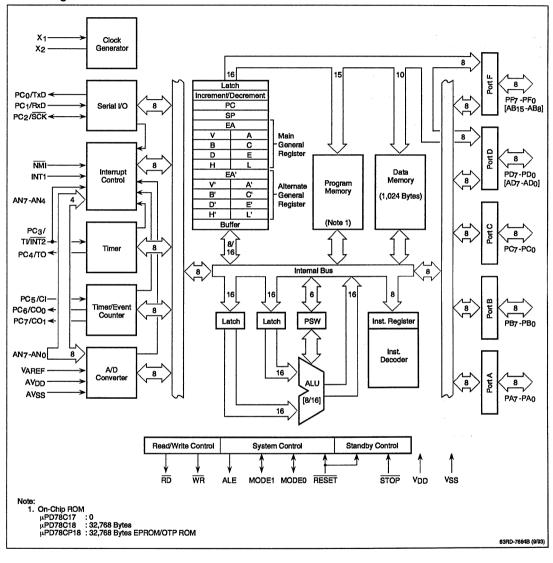

| μPD78C18 Family (μPD78C17/C18/CP18) 8-Bit, Single-Chip Microcontrollers With A/D Converter                                                                          | 2-b | Section 4<br>μPD78K2 Product Line<br>8-Bit, K-Series Microcontrollers                                                     |     |

| μPD78C00 Product Line Programming Reference                                                                                                                         | 2-c | μPD78214 Family (μPD78212/213/214/P214) 8-Bit, K-Series Microcontrollers With A/D Converter, Real-Time Output Ports       | 4-a |

| Section 3<br>μPD78K0 Product Line<br>8-Bit, K-Series Microcontrollers                                                                                               |     | μPD78218A Family<br>(μPD78217A/218A/P218A)<br>8-Bit, K-Series Microcontrollers                                            | 4-b |

| μPD78002 Family<br>(μPD78001B/002B/P014)<br>8-Bit, K-Series Microcontrollers<br>General Purpose                                                                     | 3-a | With A/D Converter, Real-Time Output Ports  μPD78224 Family (μPD78220/224/P224) 8-Bit, K-Series Microcontrollers          | 4-0 |

| μPD78002Y Family (μPD78001BY/002BY/P014Y) 8-Bit, K-Series Microcontrollers General Purpose with I <sup>2</sup> C Bus                                                | 3-b | With Analog Comparators, Real-Time Output Ports  μPD78238 Family                                                          | 4-d |

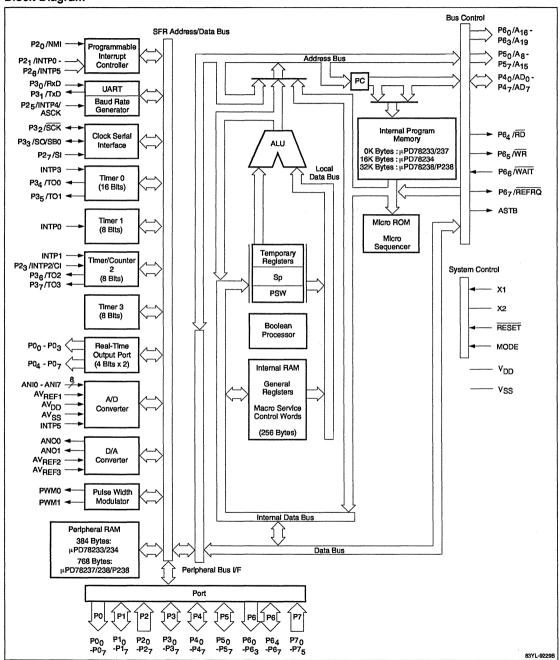

| μ <b>PD78014 Family</b><br>(μ <b>PD78011B</b> /012B/013/014/P014)<br>8-Bit, K-Series Microcontrollers                                                               | 3-c | (μPD78233/234/237/238/P238)<br>8-Bit, K-Series Microcontrollers<br>With A/D and D/A Converters, Real-Time<br>Output Ports |     |

| General Purpose with A/D Converter  #PD78014Y Family (#PD78011BY/012BY/013Y/014Y/P014Y) 8-Bit, K-Series Microcontrollers General Purpose with A/D Converter and I2C | 3-d | μPD78244 Family (μPD78243/244) 8-Bit, K-Series Microcontrollers With A/D Converter, EEPROM, Real-Time Output Ports        | 4-е |

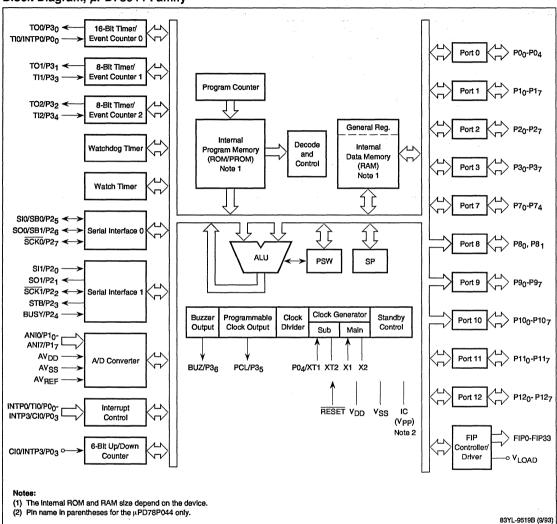

| Bus  µPD78044 Family (µPD78042/043/044/P044) 8-Bit, K-Series Microcontrollers With FIP (VP) Controller/Driver and A/D Converter                                     | 3-e | μPD78K2 Product Line Programming Reference                                                                                | 4-1 |

| μPD78054 Family (μPD78052/053/054/P054) 8-Bit, K-Series Microcontrollers With UART, A/D and D/A Converters                                                          | 3-f |                                                                                                                           |     |

| Section 5<br>μPD78K3 Product Line<br>16-/8-Bit, K-Series Microcontrollers                                                          |     |

|------------------------------------------------------------------------------------------------------------------------------------|-----|

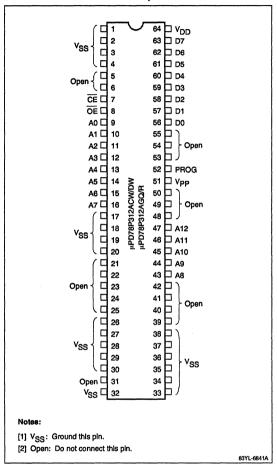

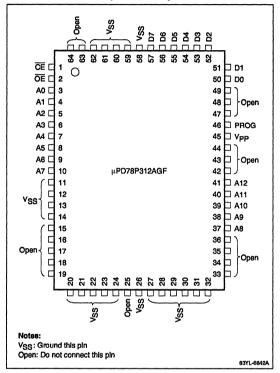

| μPD78312A Family<br>(μPD78310A/312A/P312A)<br>16-/8-Bit, K-Series Microcontrollers<br>With Real-Time Output Ports                  | 5-a |

| μPD78322 Family<br>(μPD78320/322/P322)<br>16-/8-Bit, K-Series Microcontrollers<br>With A/D Converter, Real-Time Output Ports       | 5-b |

| μPD78352 Family<br>(μPD78350/352A/P352)<br>16-/8-Bit, K-Series Microcontrollers<br>With Real-Time Output Ports                     | 5-c |

| μPD78356 Family<br>(μPD78355/356/P356)<br>16-/8-Bit, K-Series Microcontrollers<br>With A/D Converter and Convolution<br>Capability | 5-d |

| Section 6 Development Tools                                                                                                        |     |

| Development Tools Selection Guide                                                                                                  | 6-a |

| ROM Code Submission Guide                                                                                                          | 6-b |

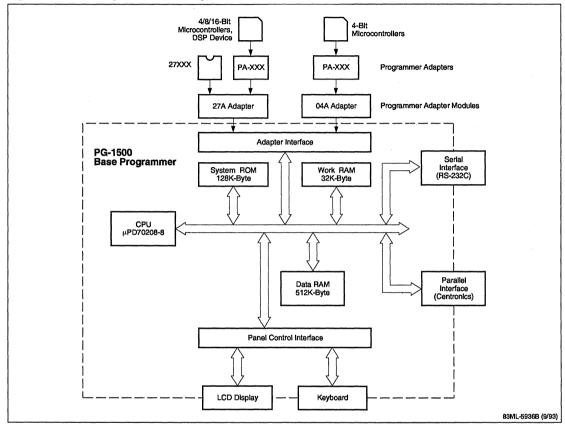

| PG-1500 Series<br>PROM Programmer                                                                                                  | 6-c |

| μPD78C00 Product Line: 8-Bit Microcontroller                                                                                       | s   |

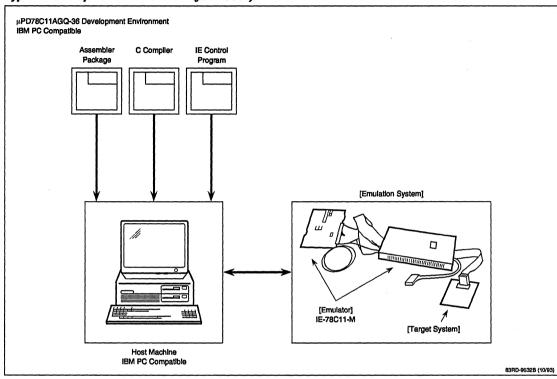

| IE-78C11-M<br>In-Circuit Emulator for the μPD78C00 Product<br>Line                                                                 | 6-d |

| CC87 Micro-Series C Compiler Package for the μPD78C00 Product Line                                                                 | 6-е |

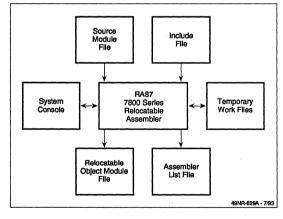

| <b>RA87</b> Relocatable Assembler Package for the $\mu$ PD78C00 Product line                                                       | 6-f |

| μΡD78K0 Product Line: 8-Bit Microcontrollers                                                                                       |     |

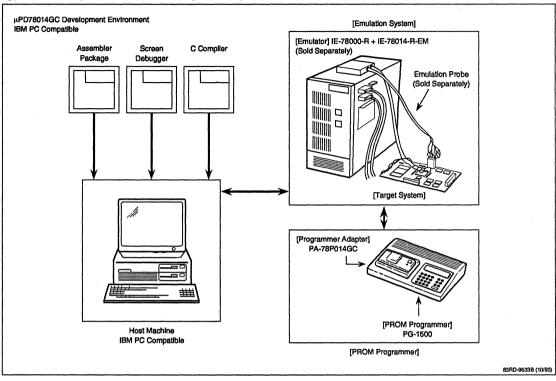

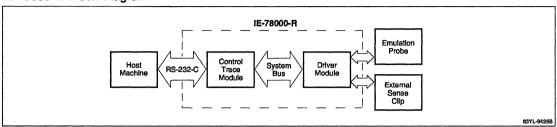

| <b>IE-78000-R</b> In-Circuit Emulator for the $\mu$ PD78K0 Product Line                                                            | 6-g |

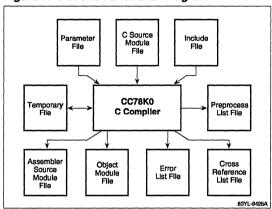

| CC78K0<br>C Compiler for the µPD78K0 Product Line                                                                                  | 6-h |

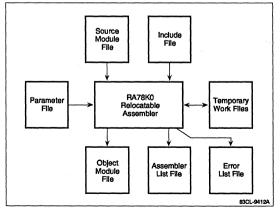

| <b>RA78K0</b> Relocatable Assembler Package for the $\mu$ PD78K0 Product Line                                                      | 6-i |

| Section 6 (cont)<br>Development Tools                                         |      |

|-------------------------------------------------------------------------------|------|

| SD78K0<br>Screen Debugger for the μPD78K0 Product<br>Line                     | 6-j  |

| μPD78K2 Product Line: 8-Bit Microcontrollers                                  | ;    |

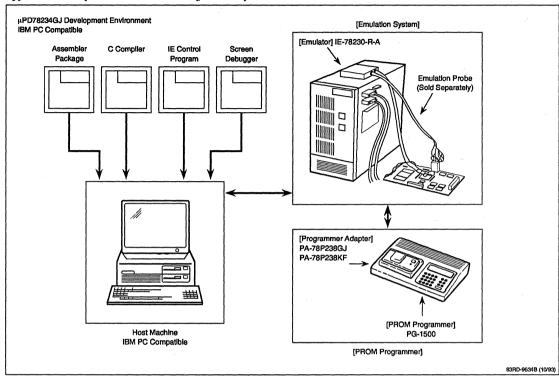

| IE-78230-R<br>In-Circuit Emulator for the μPD78224/238<br>Families            | 6-k  |

| <b>IE-78240-R</b> In-Circuit Emulator for the $\mu$ PD78214/218A/244 Families | 6-I  |

| DDB-78K2<br>Evaluation Board for the μPD78K2 Product<br>Line                  | 6-m  |

| EB-78230-PC<br>Evaluation Board for the μPD78238 Family                       | 6-n  |

| <b>EB-78240-PC</b> Evaluation Board for the $\mu$ PD78214/218A/244 Families   | 6-0  |

| CC78K2<br>C Compiler for the µPD78K2 Product Line                             | 6-p  |

| RA78K2<br>Relocatable Assembler Package for the<br>μPD78K2 Product Line       | 6-q  |

| μPD78K3 Product Line: 16-/8-Bit Microcontrol                                  | lers |

| IE-78310A-R<br>In-Circuit Emulator for the μPD78312A Family                   | 6-r  |

| IE-78327-R<br>In-Circuit Emulator for the µPD78322 Family                     | 6-s  |

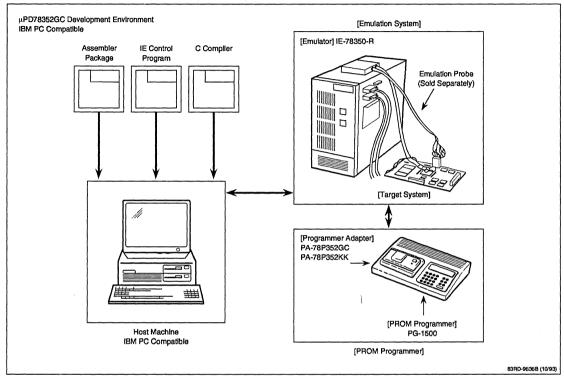

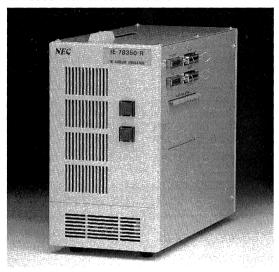

| IE-78350-R In-Circuit Emulator for the $\mu$ PD78352/356 Families             | 6-t  |

| <b>EB-78320-PC</b> Evaluation Board for the μPD78322 Family                   | 6-u  |

| <b>EB-78350-PC</b> Evaluation Board for the μPD78352 Family                   | 6-v  |

| CC78K3<br>C Compiler for the µPD78K3 Product Line                             | 6-w  |

| RA78K3 Relocatable Assembler Package for the $\mu$ PD78K3 Product Line        | 6-x  |

| Section 7<br>Soldering                                       |            |

|--------------------------------------------------------------|------------|

| μPD78C00 Product Line;                                       | 7-1        |

| Soldering and Packaging Information                          |            |

| μPD78K0 Product Line;                                        | 7-3        |

| Soldering and Packaging Information                          |            |

| μPD78K2 Product Line;                                        | 7-5        |

| Soldering and Packaging Information                          |            |

| μPD78K3 Product Line;                                        | 7-7        |

| Soldering and Packaging Information                          |            |

| Soldering Conditions                                         | 7-9        |

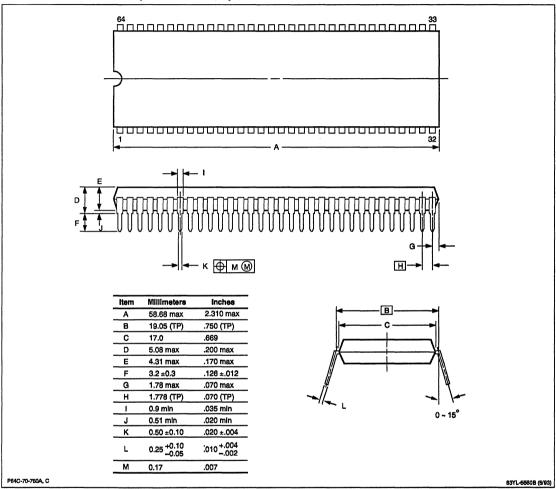

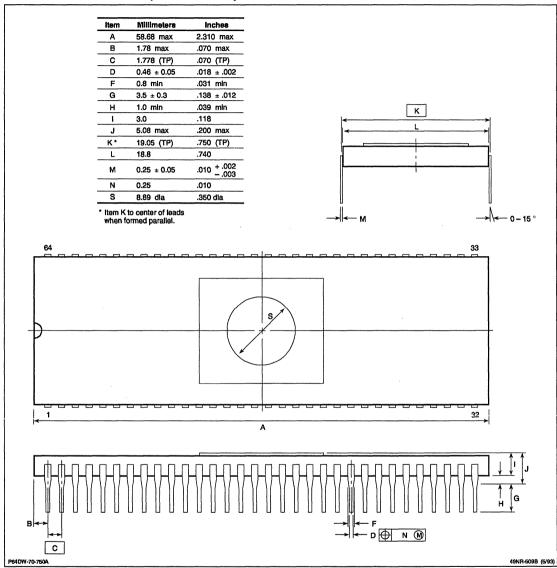

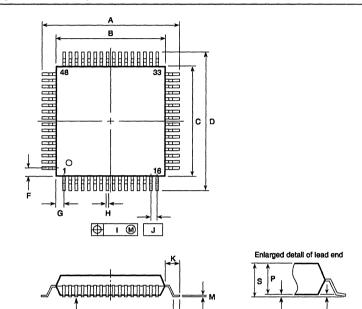

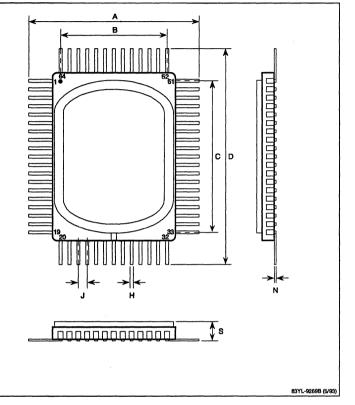

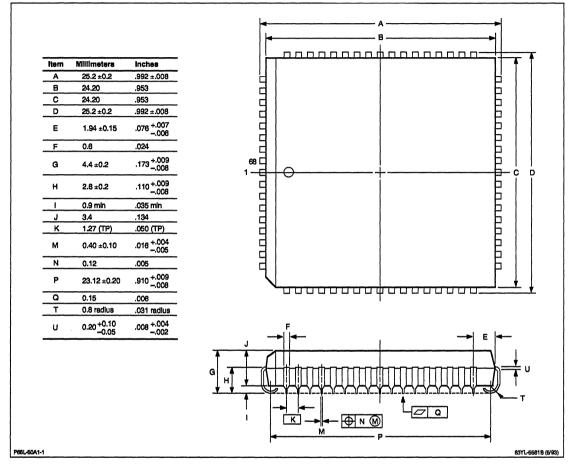

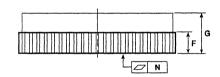

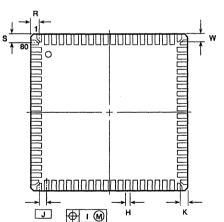

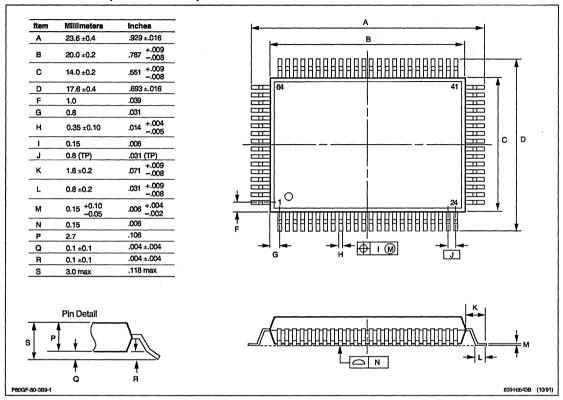

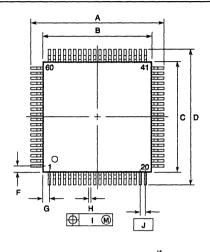

| Package Drawings 64-Pin Plastic Shrink DIP (P64C-70-750A, C) | 8-1        |

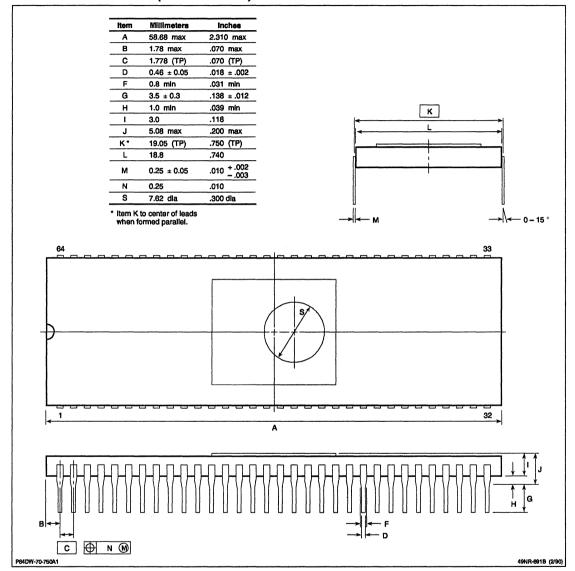

| 64-Pin Ceramic Shrink DIP (P64DW-70-750A)                    | 8-2        |

| 64-Pin Ceramic Shrink DIP (P64DW-70-750A1)                   | 8-3        |

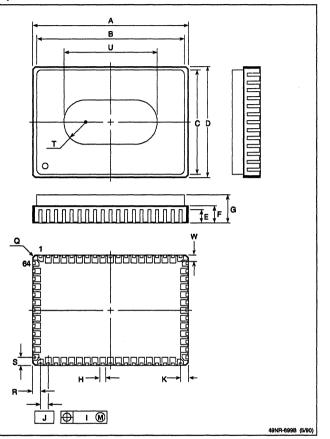

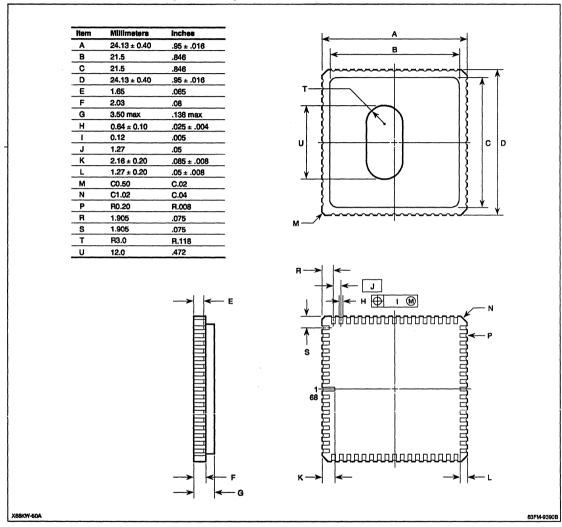

| 64-Pin Ceramic LCC w/window (X80KW-80B)                      | 8-4        |

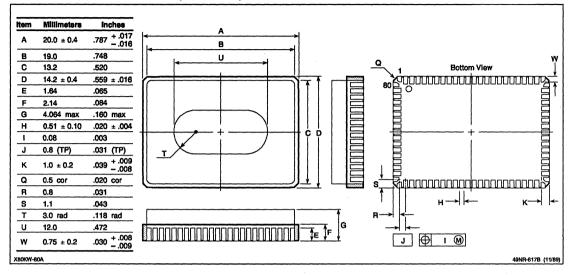

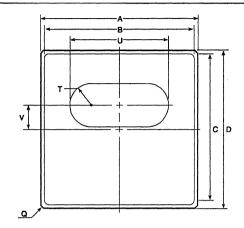

| 64-Pin Ceramic LCC w/window (X64KW-100A-1)                   | 8-5        |

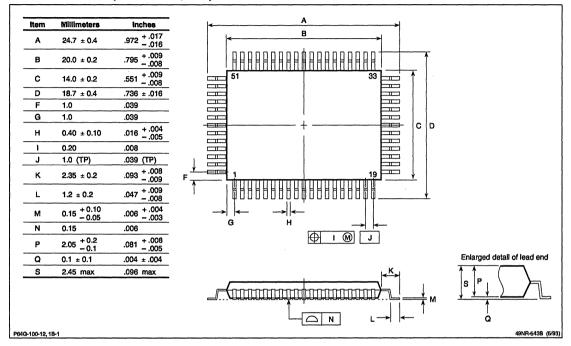

| 64-Pin Plastic QFP (P64G-100-12, 1B-1)                       |            |

| 64-Pin Plastic QFP (P64GC-80-AB8-2)                          | 8-6        |

| 64 Dia Plantia OFD (D04OF 400 ODD ODF 4)                     | 8-6<br>8-7 |

| 64-Pin Plastic QFP (P64GF-100-3B8, 3BE-1)                    |            |

| Section 8 (cont) Package Drawings                    |      |

|------------------------------------------------------|------|

| 64-Pin Plastic QFP (1.7-mm height)<br>(P64G-80-22-1) | 8-10 |

| 64-Pin Ceramic QFP for Engineering Samples           | 8-11 |

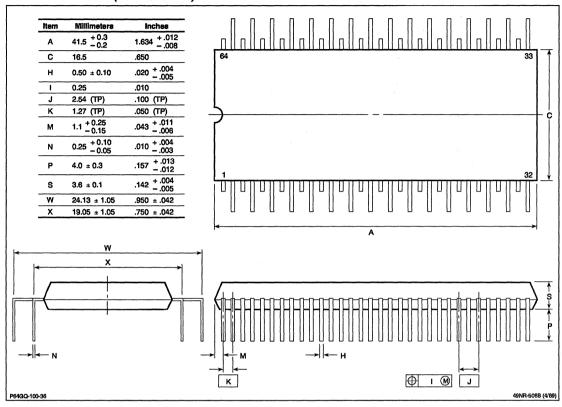

| 64-Pin Plastic QUIP (P64GQ-100-36)                   | 8-12 |

| 64-Pin Plastic QUIP (P64GQ-100-37)                   | 8-13 |

| 64-Pin Ceramic QUIP w/window (P64RQ-100-A)           | 8-14 |

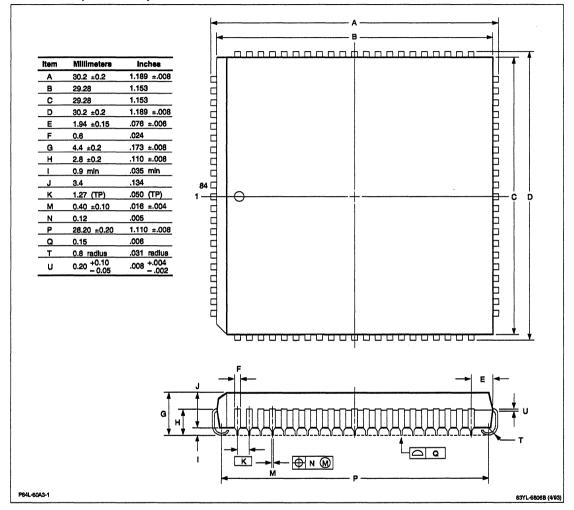

| 68-Pin PLCC (P68L-50A1-1)                            | 8-15 |

| 68-Pin Ceramic LCC w/window (X68KW-50A)              | 8-16 |

| 74-Pin Plastic QFP(S74GJ-100-5BJ-1)                  | 8-17 |

| 80-Pin Ceramic LCC w/window (X80KW-80A)              | 8-18 |

| 80-Pin Ceramic LCC w/window (X80KW-65A)              | 8-19 |

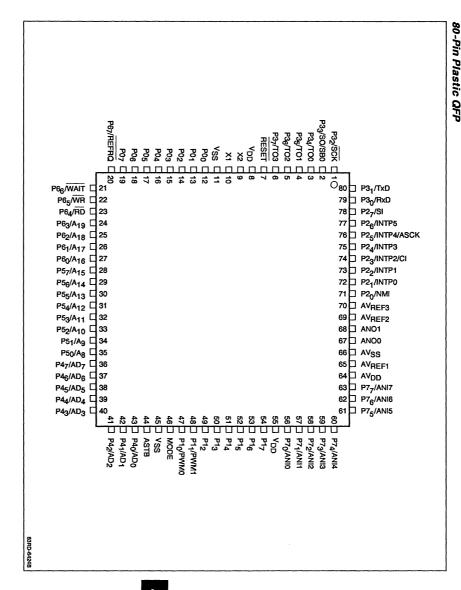

| 80-Pin Plastic QFP (P80GF-80-3B9-1)                  | 8-20 |

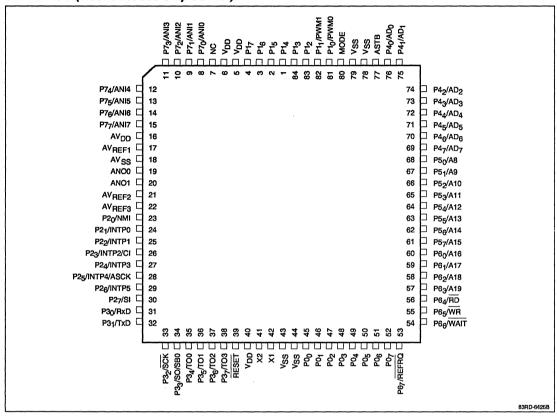

| 80-Pin Plastic QFP (S80GC-65-3B9-1)                  | 8-21 |

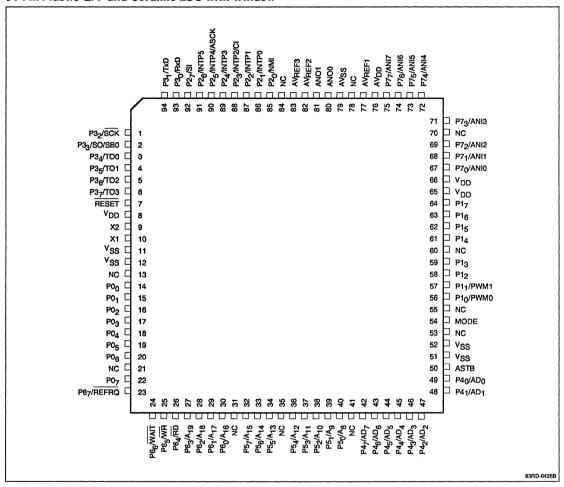

| 80-Pin Plastic TQFP (P80GK-50-BE9-1)                 | 8-22 |

| 84-Pin PLCC (P84L-50A3-1)                            | 8-23 |

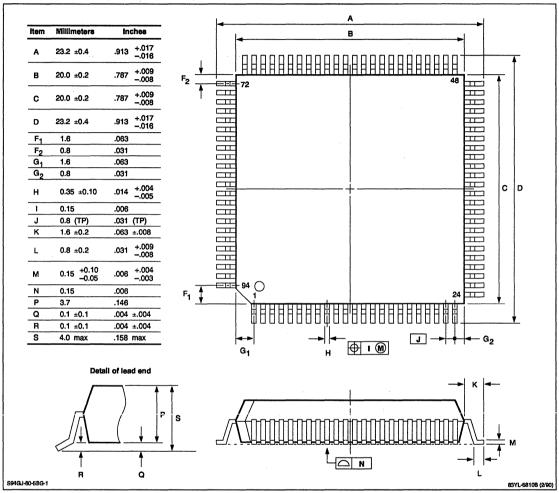

| 94-Pin Plastic QFP (S94GJ-80-5BG-1)                  | 8-24 |

| 94-Pin Ceramic LCC (X94KW-80A)                       | 8-25 |

| 100-Pin Plastic QFP (P100GC-50-7EA)                  | 8-26 |

| 100-Pin Plastic QFP (P100GF-65-3BA)                  | 8-27 |

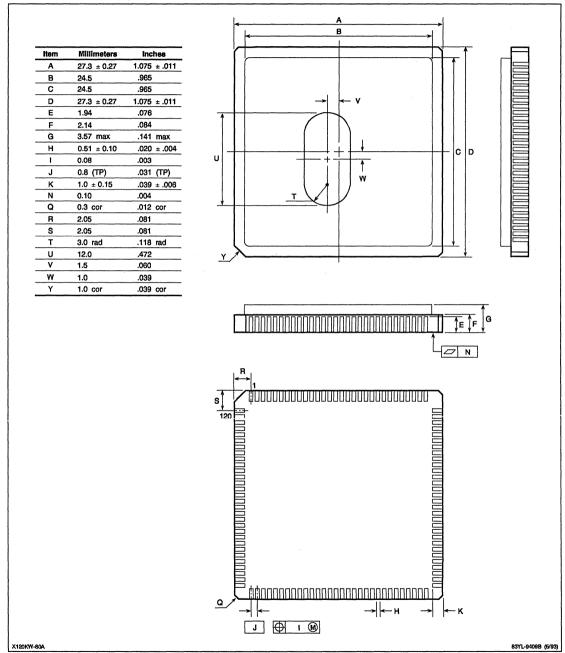

| 120-Pin Ceramic LCC (X120KW-80A)                     | 8-28 |

| Numerical Index                                   |            |

|---------------------------------------------------|------------|

| Device, μPD                                       | Page       |

| 78C10A<br>78C11A<br>78C12A<br>78C14<br>78C14A     | <b>2-a</b> |

| 78CP14<br>78C17<br>78C18<br>78CP18                | 2-b        |

| 78001B<br>78002B                                  | 3-a        |

| 78001BY<br>78002BY                                | 3-b        |

| 78011B<br>78012B<br>78013<br>78014<br>78P014      | 3-с        |

| 78011BY<br>78012BY<br>78013Y<br>78014Y<br>78P014Y | 3-d        |

| 78042<br>78043<br>78044<br>78P044                 | 3-е        |

| 78052<br>78053<br>78054<br>78P054                 | 3-f        |

| 78062<br>78063<br>78064<br>78P064                 | 3-g        |

| Device, μPD                                | Page |

|--------------------------------------------|------|

| 78212<br>78213<br>78214<br>78P214          | 4-a  |

| 78217A<br>78218A<br>78P218A                | 4-b  |

| 78220<br>78224<br>78P224                   | 4-c  |

| 78233<br>78234<br>78237<br>78238<br>78P238 | 4-d  |

| 78243<br>78244                             | 4-e  |

| 78310A<br>78312A<br>78P312A                | 5-a  |

| 78320<br>78322<br>78P322                   | 5-b  |

| 78350<br>78352A<br>78P352                  | 5-с  |

| 78355<br>78356<br>78P356                   | 5-d  |

uPD78C00

2

uPD78K0

Ĵ

uPD78K2

4

µPD78K3

Development Tools

Soldering

Package Drawings

8

# Reliability and Quality Control

| Section 1   |     |         |         |

|-------------|-----|---------|---------|

| Reliability | and | Quality | Control |

| nonability and duality control      |      |

|-------------------------------------|------|

| Introduction                        | 1-1  |

| Built-In TQC                        | 1-2  |

| Approaches to TQC                   | 1-2  |

| Zero Defects Program                | 1-2  |

| Statistical Approach                | 1-3  |

| Implementation of Quality Control   | 1-3  |

| Product Development                 | 1-4  |

| Incoming Material Inspection        | 1-4  |

| In-Process Quality Inspection       | 1-4  |

| Electrical Testing and Screening    | 1-4  |

| Outgoing Inspection                 | 1-4  |

| Reliability Assurance Test          | 1-5  |

| Process/Product Changes             | 1-5  |

| Reliability Theory                  | 1-5  |

| Life Distribution                   | 1-5  |

| Failure Distribution at NECEL       | 1-6  |

| Infant Mortality Failure Screening  | 1-6  |

| Accelerated Reliability Testing     | 1-7  |

| Reliability Assurance Tests         | 1-7  |

| Failure Rate Calculation/Prediction | 1-8  |

| Failure Rate Calculation Example    | 1-9  |

| Failure Rate Goals                  | 1-9  |

| Failure Analysis                    | 1-10 |

| Summary                             | 1-10 |

NECEL Electronics Inc. is dedicated to the QCD principle of providing the highest *quality* product at the lowest possible *cost* with on-time *delivery* to our customers.

As large-scale integrated (LSI) circuits increase in density, the reliability of individual devices imposes a more profound impact on system reliability. As a result, great emphasis has been placed by LSI circuit manufacturers on assuring device reliability.

Conventionally, performing reliability tests and using feedback from the field have been the only methods of monitoring and measuring reliability. As LSI density increases, however, internal device circuit elements have become more difficult to activate from external terminals and to detect their degradation. Testing and feedback alone cannot provide enough information to ensure today's demanding reliability requirements.

To guarantee and improve the reliability of LSI circuits, a new philosophy and methodology are needed for reliability assurance. Quality and reliability must not only be monitored and measured but, most importantly, must be built into the product.

#### **BUILT-IN TQC**

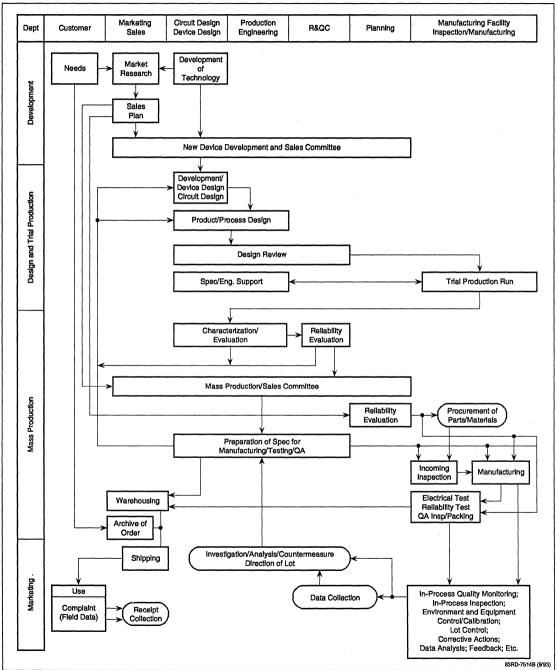

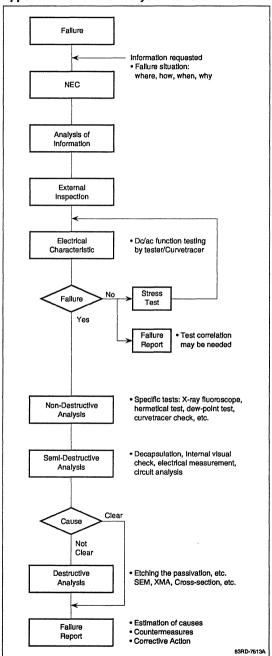

NECEL introduced the concept of total quality control (TQC) across its entire semiconductor product line to implement this philosophy. Quality control is now an integral part of each process step and requires production, engineering, quality control staffs, and all management personnel to participate in TQC activities. Figure 1 is a flowchart that shows how these activities form a comprehensive quality control system at NECEL.

In addition to TQC, NECEL introduced a pre-screening method into the production line that eliminates potentially defective units. This combination of building in quality and screening out projected early failures has resulted in superior quality and reliability.

Most LSI circuits use high-density MOS technology. Their state-of-the-art high performance improved fine-line generation techniques. When physical parameters are reduced, circuit density and performance increase and active circuit power dissipation decreases. The information presented here will show that this ad-

vanced technology combined with the practice of TQC yields products as reliable as those from previous technologies.

#### APPROACHES TO TQC

TQC activities are geared toward total customer satisfaction. The success of these activities depends on management's commitment to enhancing employee development, maintaining a customer-first attitude, and fulfilling community responsibilities.

TQC is implemented in the following steps. First, quality control is embedded into each process, allowing early detection of possible failure mechanisms and immediate feedback. Second, the reliability and quality assurance policy is upheld through company-wide quality control activities. Third, emphasis is placed on research and development efforts to achieve even higher standards of device quality and reliability. Fourth, extensive failure analysis is performed periodically, and appropriate corrective actions are taken as preventative measures.

Process control limits are based on statistical data gathered from this analysis and used to determine the effectiveness of the in-process quality control steps.

New standards are continuously upgraded, and the iterative process continues. The goal is to maintain the superior product quality and reliability that has become synonymous with the NEC name.

#### Zero Defects Program

One of the quality control activities that involves every staff level is the "Zero Defects" (ZD) program. The purpose of the ZD program is to minimize, if not prevent, defects due to controllable causes. These activities are organized by groups of workers around these four premises.

- A group must have a target or purpose to pursue.

- Several groups can be organized to pursue a common target.

- · Each group must have a responsible leader.

- Each group is well supported by management.

Figure 1. NECEL's Quality Control System

The group's target is selected from items relating to specifications, inspections, operation standards, etc. When past data is available, a Pareto diagram is created and reviewed to select an item most in need of quality improvement. Target defects related to this item are clearly defined. Records are analyzed to compute numerical equivalents of the defects. Then, action is taken to control these defects.

#### Statistical Approach

Another approach to quality control is statistical analysis. NECEL uses statistical analysis at each stage of LSI product development, trial runs, and mass production. These are some implementations of this statistical approach:

- · Process comparisons

- Control charts

- Data analysis

- Correlation, regression, multivariance, etc.

- Cp/Cpk studies

- Variables and attributes data (performed monthly)

Process control sheets and other QC tools are used to monitor important parameters such as Cp, Cpk, X, X-R, electrical parameters, pattern dimensions, bond strength, test percentage defects, etc. The results of these studies are monitored by the production staff, QC engineers, and other associated engineers. If any out-of-control or out-of-specification limit is observed, corrective procedures are quickly taken.

#### IMPLEMENTATION OF QUALITY CONTROL

Building quality into a product requires early detection of possible failure mechanisms and immediate feedback to remove such problems. A fixed quality inspection station often cannot provide prompt and accurate feedback about the process steps prior to the inspection. Quality control functions have therefore been distributed into each process step including the conceptual stage. These are the most significant areas where quality control has been placed:

- Product development

- Incoming material inspection

- Wafer processing

- Chip mounting and packaging

- Electrical testing and infant mortality screening

- Outgoing material inspection

- Reliability assurance tests

- Process/product changes

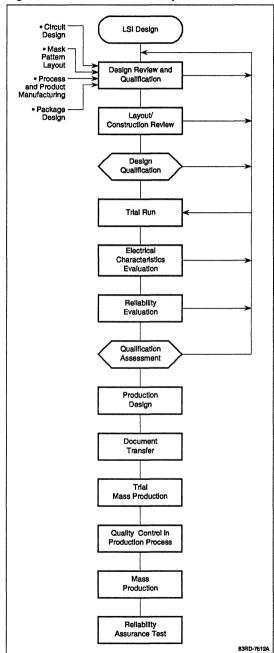

Figure 2. New Product Development

## **Reliability and Quality Control**

#### **Product Development**

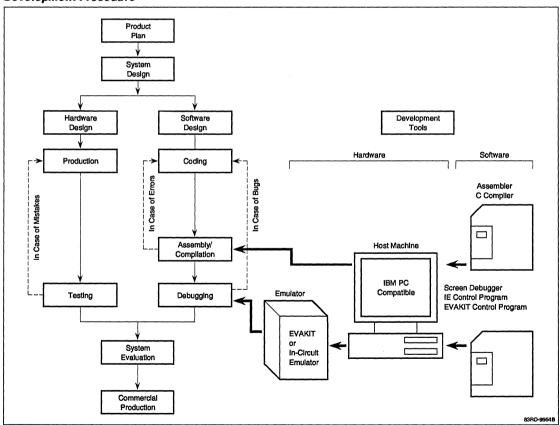

New product development includes the product concept, device proposal review, physical element design and organization, engineering evaluation, and, finally, product transfer to manufacturing. Quality and reliability are considered at every step. The new product development flow at NECEL is shown in figure 2.

Design is the first and most important step in new product development. NECEL believes that the foundation of device quality is determined at the design stage. The four steps involved are circuit design, mask pattern layout, package design, and the setting of process and product manufacturing conditions. Design standards have been established at NECEL to maximize quality and reliability.

After completion of the design, a design review is performed to check for conformity to design standards and to consider other factors influencing reliability and quality. At this stage, modification or re-design may be necessary. NECEL believes that design reviews are essential for product modifications as well as for newly designed products.

Once a design successfully passes its review, a trial run takes place in which the product's electrical and mechanical characteristics, quality, and reliability are evaluated.

Additional runs are performed in which process conditions are varied deliberately, causing characteristic factors to change in mass production. These samples are evaluated to determine the best combination of process conditions. Reliability tests are then conducted to check the new product's electrical and mechanical stress resistance. If no problems are found at this stage, the product is approved for mass production.

Mass production begins after the product design department prepares a schedule that includes reliability and quality control steps. The standards for production and control steps are continuously re-examined for possible improvement, even after mass production has started.

#### Incoming Material Inspection

NECEL has the following programs to control incoming materials:

- · Vendor/material qualification system

- · Purchasing specifications for materials

- · Incoming materials inspection

- Inspection data feedback

- · Meetings with vendors concerning quality

- Vendor audits

If any parts or materials are rejected at incoming inspection, they are returned to the vendor with a rejection notification form specifying the failure items and modes. The results of these inspections are used to rate the vendors for future purchasing.

#### In-Process Quality Inspection

Typical in-process quality inspections performed at wafer fabrication, chip mounting and packaging, and device testing stages are listed in appendix 1A and appendix 1B.

#### **Electrical Testing and Screening**

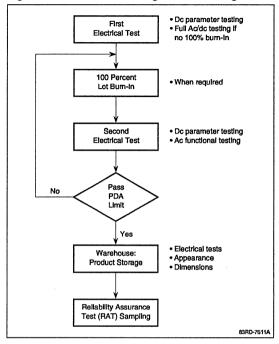

At the first electrical test, dc parameters are tested according to electrical specifications on 100% of each lot. This is a prescreening prior to any infant mortality test. At the second electrical test, ac functional tests as well as dc parameter tests are performed on 100% of each lot. If the percentage of defective units in a lot is unacceptably high in this test, the lot is subjected to an infant mortality rescreen. During this time, any defective units undergo extensive failure analysis. The results of these analyses are fed back into the process through corrective actions.

Figure 3 is a flowchart of the typical infant mortality screening and electrical testing.

#### Outgoing Inspection

Prior to warehouse storage or shipment, lots are subjected to an outgoing inspection according to the following sampling plan:

- Electrical

- Dc parameters, lot tolerance parts defective (LTPD) 3%

- Ac functional LTPD 3%

- Appearance

- Major LTPD 3%

- Minor LTPD 7%

Figure 3. Electrical Testing and Screening

#### Reliability Assurance Tests

Prior to shipment, representative samples from each process family are taken on a regular basis and subjected to monitoring reliability tests. This testing is performed to confirm that NECEL's products continually meet their field reliability targets.

#### **Process/Product Changes**

As mentioned previously, a design review occurs for product changes as well as for new products. Once a design is approved and processes are altered for maximum quality, qualification testing is performed to check reliability. If the test results are acceptable, the product is internally qualified for mass production.

The typical reliability qualification tests performed at NECEL are listed in appendix 3.

#### RELIABILITY THEORY

Reliability is defined as a characteristic of an item expressed by the probability that it will perform a required function, under specific conditions, for a cer-

tain period of time. The concept of probability, the definition of required function, and the knowledge of how time affects the item of concern are therefore necessary tools for the study of reliability.

Definition of a required function, by implication, treats the definition of a failure. Failure of a device is defined as the termination of a device's ability to perform its required function. A device has failed if it is unable to meet guaranteed values given in its electrical specifications.

Failures are categorized by the period of time in which they occur. The critical times used in the discussion of device reliability and failure are the periods of early, random, and wearout failures. Probability is used to quantitatively estimate reliability levels during these periods as well as overall reliability. The relevant theories and methods of calculation will be discussed later.

Regarding individual devices, specific failure mechanisms seen in life tests and in infant mortality screening tests are the parameters of concern in the determination of overall device failure rates, thus reliability levels.

Regarding systems, the sum of individual device failure rates is the expected failure rate of the system hardware.

#### Life Distribution

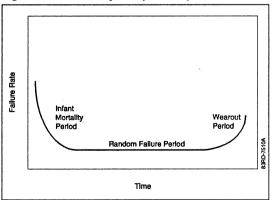

The fundamental principles of reliability engineering predict that the failure rate of a group of devices will follow the well-known bathtub curve in figure 4.

Figure 4. Reliability Life (Bathtub) Curve

The curve is divided into three regions: infant mortality, random failures, and wearout failures.

The infant mortality section of the curve, where the failure rate is declining rapidly, represents the early-life device failures. These failures are usually associated with one or more manufacturing defects.

After a period of time, the failure rate reaches a low value. This random failure area of the curve represents the useful portion of a device's life. During this random failure period, a slight decline is observed due to the depletion of potential random failures from the general population.

Wearout failures occur at the end of useful device life. These failures are observed in the rapidly rising failure rate portion of the curve; devices are wearing out both physically and electrically.

Therefore, for a device that has a very long life expectancy compared to the system that contains it, the areas of concern will be the infant mortality and random failure portions of the bathtub curve.

#### Failure Distribution at NECEL

To eliminate infant mortality failures, NECEL subjects its products to production burn-in whenever necessary. This burn-in is performed at an elevated temperature on 100% of the devices involved and is designed to remove potentially defective units.

After elimination of early device failures, a system will be left to the random failures of its components. To make proper projections of the failure rate of a system in the operating environment, random failure rates must be predicted for the system's components.

To qualitatively study random failures, integrated circuits returned from the field, as well as in-house life testing failures, undergo extensive failure analyses at respective NEC manufacturing divisions. Failure mechanisms are identified and resulting data is fed back to appropriate production and engineering groups. Longterm failure rates are determined from this data to quantitatively study this random failure population.

#### Infant Mortality Failure Screening

Establishing infant mortality screening requires knowledge of likely failure mechanisms and their associated activation energies.

Typical problems associated with infant mortality failures are manufacturing defects and process anomalies, which consist of contamination, cracked chips, wire bond shorts, or bad wire bonds. Since these problems can result from a number of possible failure mechanisms, the activation energy for infant mortality can vary considerably. Correspondingly, the effectiveness of an infant mortality screening condition (preferably at some stress level to shorten the screening time) varies greatly with the failure mechanism.

For example, failures due to ionic contamination have an activation energy of approximately 1.0 eV. Therefore, a 15-hour stress at 125°C junction temperature would be the equivalent of approximately 314 days of operation at a junction temperature of 55°C. On the other hand, failures due to oxide defects have an activation energy of approximately 0.3 eV. A 15-hour stress at 125°C junction temperature in this case would be the equivalent of approximately 4 days of operation at 55°C junction temperature. The condition and duration of infant mortality screening is determined by the economic factors involved in the screening and by the allowable rate of component failure. A component failure causes a system failure.

Empirical data gathered at NECEL indicates that any early failures generally occur after less than 4 hours of stress at 125°C ambient temperature. This fact is supported by the bathtub curve created from actual life test results. The failure rate after 4 hours of such stress testing shows random distribution as opposed to the rapidly decreasing failure rate observed in the early life portion of the curve.

Whenever necessary, NECEL has adopted this infant mortality burn-in at 125°C as a standard production screening procedure. NECEL believes it is imperative that failure modes associated with such infant mortality screens be understood and fixed at the manufacturing level. Failure analysis is performed on all infant mortality failures for this purpose. This in-line data coupled with data accumulated from the field is used to introduce corrective actions and quality improvement measures. If the early-life failures of a device can be minimized or eliminated and countermeasures appropriately monitored, then such screens can be eliminated. The result of such practices is that field reliability of NECEL devices is an order of magnitude higher than NECEL's long-term failure rate goals.

Table 1. Typical Reliability Test Results

| Name              | Туре                | HTB (1000H)          | T/H (1000H) | PCT (192H) | T/C (300) |

|-------------------|---------------------|----------------------|-------------|------------|-----------|

| Micro<br>(Note 1) | NMOS                | 9/26169<br>(13 FIT)  | 3/15977     | 0/16928    | 0/3542    |

|                   | CMOS                | 7/29829<br>(4.3 FIT) | 7/23123     | 0/23275    | 0/12238   |

| Memory<br>(HTOL)  | 1 Meg DRAM (Note 2) | 44/38217<br>(43 FIT) | 0/18210     | 0/6320     | 0/11300   |

|                   | 4 Meg DRAM (Note 3) | 12/8085<br>(2.2 FIT) | 1/2866      | 0/2100     | 0/2020    |

|                   | 256K SRAM (Note 4)  | 1/2812<br>(22 FIT)   | 1/2562      | 0/1900     | 0/3232    |

|                   | 1 Meg SRAM (Note 4) | 0/2136<br>(1.25 FIT) | 2/1959      | 0/1080     | 0/1375    |

| ASIC<br>(Note 5)  | смоѕ                | 7/8787<br>(21 FIT)   | 0/3577      | 5/13971    | 6/9693    |

|                   | BiCMOS              | 3/2801<br>(29 FIT)   | 0/3601      | 0/4535     | 0/5825    |

#### Note:

Information in the table above has been extracted from NECEL report numbers:

(1) IRQ-3Q-24163

(4) TRQ-93-07-0165 (5) TRQ-93-07-0163

(2) TRQ-93-01-0142

(3) TRQ-93-01-0141

#### Accelerated Reliability Testing

NECEL performs extensive reliability testing at both pre-production and post-production levels to ensure that all products meet NECEL's minimum expectations and those of the field.

Assume an electronic system contains 1000 integrated circuits and that 1% system failures per month can be tolerated by this system. The allowable failure rate per component is then calculated as follows:

The rate of 14 FITs corresponds to one failure in 85 devices during an operating test of approximately 10,000 hours. To demonstrate this reliability level in a reasonable amount of time, a test condition is apparently required to accelerate the time-to-failure in a predictable and understandable way.

The most common method for decreasing time-tofailure is the use of high temperature to accelerate physiochemical reactions that can lead to device failure. Other stressful environmental conditions are voltage, current, humidity, vibration, or some combination of these. Appendix 2 lists typical accelerated reliability assurance tests performed at NECEL on molded integrated circuits. Table 1 shows the results of some of these tests for various process types.

#### Reliability Assurance Tests

NECEL's life tests consist of the high-temperature operating/bias life (HTOL/HTB), the high-humidity storage life (HHSL), the high-temperature, high-humidity (T/H = HHSL + bias), and the high-temperature storage life (HTSL). Additionally, NECEL performs various environmental and mechanical tests.

HTOL/HTB Test. These tests are used to accelerate failure mechanisms by operating devices in a dynamic (operating life) or static (bias) condition at an elevated temperature of 125°C. The data obtained is translated to a lower temperature to estimate device life expectancy using the Arrhenius relationship explained later.

HHSL and T/H Tests. Integrated circuits are extremely sensitive to the effects of humidity such as electrolytic corrosion between biased lines. The high-temperature and high-humidity tests are performed to detect failure mechanisms accelerated by temperature and humidity, such as leakage related problems and drifts in device parameters due to process instability.

HTSL Test. Another common test is the high-temperature storage life test in which devices are subjected to elevated temperatures with no applied bias. This test is used to detect process instability and stress migration problems.

**Environmental Tests.** Other environmental tests such as the pressure cooker test (PCT) or the temperature cycling test (T/C) detect problems related to the package and/or interactions between materials as well as the degradation of environmentally sensitive device characteristics.

#### Failure Rate Calculation/Prediction

To predict the device failure rate from accelerated life test data, the activation energies of the failure mechanisms involved should be considered. In some cases, an average activation energy is assumed to accomplish a quick first-order approximation. NECEL assumes an average activation energy of 0.7 eV or 0.45 eV for most products (0.3 eV for high-density memory devices). These values have been assessed from extensive reliability test results and yield conservative failure rates.

Since most semiconductor failures are temperature dependent, the Arrhenius relationship is used to normalize failure rate predictions at a system operation temperature of 55°C. It assumes that temperature dependence is an exponential function that defines the probability of failure occurrence, and that degradation of a performance parameter is linear with time. The Arrhenius model includes the effects of temperature and activation energies of the failure mechanisms in the following Arrhenius equation:

$$A = \exp \frac{-E_A(T_{J1}-T_{J2})}{k(T_{J1})(T_{J2})}$$

Where:

A(T) = Acceleration factor

$E_A$  = Activation energy

$T_{J1}$  = Junction temperature (in K) at  $T_{A1}$  = 55°C

$T_{J2}$  = Junction temperature (in K) at  $T_{A2}$  = 125°C

$k = Boltzmann's constant = 8.62 \times 10^{-5} eV/K$

Because the thermal resistance and power dissipation of a particular device type cannot be ignored, junction temperatures ( $T_{J1}$  and  $T_{J2}$ ) are used instead of ambient temperatures ( $T_{A1}$  and  $T_{A2}$ ). We calculate junction temperatures using the following formula:

$T_J = T_A + \text{(thermal resistance)(power diss. at } T_A)$

With this information, a temperature acceleration factor can be calculated.

In some cases, the effect of voltage acceleration on failure rate must also be considered. Voltage acceleration can be characterized by the following equation:  $A(V) = \exp \left[-\beta(Vd - Vs)\right]$

Where:

Vd = Operating voltage (5.5 V)

Vs = Life test stress voltage (7 V)

β = Empirically determined constant (dependent on electric field constant and oxide thickness)

The constant  $\beta$  has been given the value  $\approx$  1, which is a conservative figure. Therefore, the overall acceleration factor will be determined as the product:

$$A(T,V) = A(T) * A(V)$$

To estimate long-term failure rate, the acceleration factor must be multiplied by the actual time to determine the simulated test time. From the high-temperature operating or bias life test results, failure rates can then be predicted at a 60% confidence level using the following equation:

$$L = \frac{(X^2)10^5}{2T}$$

Where:

L = Failure rate in %/1000 hours

X² = The tabular value of chi-squared distribution at a given confidence level and calculated degrees of freedom (2f + 2, where f = number of failures) See note below.

T = # of equivalent device hours = (# of devices) x (# of test hours) x (acceleration factor)

Note: Since the failures of concern here are the long-term failures, not the infant mortality failures (that is, the end of the downward slope and the middle constant section of the bathtub curve in figure 4), X<sup>2</sup> is determined by assuming a one-sided, fixed time test.

Another method of expressing failures is in FITs (failures in time). One FIT is equal to one failure in  $10^9$  hours. Since L is already expressed as %/1000 hours ( $10^{-5}$  failure/hr), an easy conversion from %/1000 hours to FIT would be to multiply the value of L by  $10^4$ .

To accurately determine this failure rate, a statistically large sample size must be accumulated. Depending on the accuracy needed, the following conditions should be imposed:

- A minimum of 1.2 million device hours (equal to sample size multiplied by test period) at 125°C should be accumulated to accurately predict a failure rate of 0.02% per 1000 hours at 55°C, with a 60% confidence level.

- A minimum of 3 million device hours at 125°C should be accumulated to accurately predict a failure rate of 0.01% per 1000 hours at 55°C, with a 60% confidence level.

Failure Rate Calculation Example. As an example of how this failure rate is calculated, assume a sample of 960 pieces was subjected to 1000 hours at 125°C burnin. One reject was observed. Given that the acceleration factor was calculated to be 34.6 using the Arrhenius equation, what is the failure rate normalized to 55°C using a confidence level of 60%. Express the failure rate in FITs.

Solution:

For

$$n = 2f + 2 = 2(1) + 2 = 4$$

,  $X^2 = 4.046$

Then L =

$$\frac{(X^2)10^5}{2T}$$

(%/1000 hours)

=  $\frac{(X^2)10^5}{2(\text{# devices})(\text{# test hours})(\text{accel. factor})}$

$$= \frac{(4.046)10^5}{2(960)(1000)(34.6)} = 0.0061 \text{ (\%/1000 hours)}$$

Therefore,  $FIT = (0.0061)(10^4) = 61$

#### Failure Rate Goals

Outgoing electrical and mechanical quality levels, as well as mortality and long-term failure rates, are monitored and checked against quality and reliability targets. Long-term failure rate goals are based on mask and process designs. NECEL's quality and reliability targets are listed in tables 2 and 3.

Table 2. NECEL Quality Targets

|      |        |       | Outgoing I      | Electrical   | (PPM) |            |               |        | Outgoing Mechanical |                 |              |       | I (PPM)    |               |  |

|------|--------|-------|-----------------|--------------|-------|------------|---------------|--------|---------------------|-----------------|--------------|-------|------------|---------------|--|

| ,    |        |       |                 | BiPolar      |       |            |               |        |                     |                 |              | BiPol | ar         |               |  |

| Year | Memory | Micro | System<br>Micro | CMOS<br>ASIC | RAM   | ECL<br>G/A | BICMOS<br>G/A | Memory | Micro               | System<br>Micro | CMOS<br>ASIC | RAM   | ECL<br>G/A | BiCMOS<br>G/A |  |

| 1993 | 10     | 60    | 50              | 50           | 80    | 300        | 80            | 10     | 60                  | 50              | 50           | 80    | 300        | 80            |  |

| 1994 | 3.4    | 40    | 40              | 10           | 80    | 300        | 80            | 3.4    | 40                  | 40              | 10           | 80    | 300        | 80            |  |

| 1995 | 3.4    | 40    | 30              | 5            | 80    | 150        | 50            | 3.4    | 40                  | 30              | 5            | 80    | 150        | 50            |  |

Table 3. NECEL Reliability Targets

|      |        | Infant Mortality (FIT) |                 |              |     |            |               |        | Long-Term Reliability (FIT) |                 |              |         |            |               |

|------|--------|------------------------|-----------------|--------------|-----|------------|---------------|--------|-----------------------------|-----------------|--------------|---------|------------|---------------|

|      |        |                        |                 |              |     | BiPol      | ar            |        |                             |                 |              | BiPolar |            |               |

| Year | Memory | Micro                  | System<br>Micro | CMOS<br>ASIC | RAM | ECL<br>G/A | BICMOS<br>G/A | Memory | Micro                       | System<br>Micro | CMOS<br>ASIC | RAM     | ECL<br>G/A | BICMOS<br>G/A |

| 1993 | 10     | 40                     | 50              | 100          | 50  | 300        | 80            | 10     | 30                          | 100             | 50           | 30      | 300        | 80            |

| 1994 | 3.4    | 30                     | 40              | 50           | 50  | 300        | 80            | 3.4    | 20                          | 100             | 10           | 30      | 300        | 80            |

| 1995 | 3.4    | 30                     | 30              | 10           | 50  | 150        | 50            | 3.4    | 20                          | 100             | 5            | 30      | 150        | 50            |

#### **FAILURE ANALYSIS**

At NECEL, failure analysis is performed not only on reliability testing and field failures, but also on products that exhibit defects during production. This data is closely checked for correlation process quality information, inspection results, and reliability test data. Information derived from these failure analyses is fed back into the process.

Since many failure mechanisms can be exhibited by LSI devices, highly advanced analytical tools and methodologies are required to investigate such LSI failures in detail. The standard failure analysis flow-chart relating to the returned products from customers is shown in appendix 4.

#### **Special Grade Devices**

Some applications require a wider temperature range and/or higher reliability than most, such as medical or safety equipment, transportation control systems, etc. For these requirements, NEC offers special grade devices based on a mutual quality agreement. The typical differences between special and standard grade devices are shown in table 4. NEC's quality and reliability targets for grade (A) microprocessor/controller products are shown in table 5.

#### SUMMARY

Building quality and reliability into products by forming a total quality control system is the most efficient way to ensure product success.

The combination of building quality into products, effective prescreening of potential failures, and monitoring of reliability through extensive testing has established a singularly high standard for NECEL's large-scale integrated circuits.

The company's quality control program supports research and development activities, failure analyses, and process improvements. With this extensive program, NECEL continuously sets and maintains higher standards of quality and reliability.

Table 4. Standard Grade and Special Grade Differences

| Item                  | Standard Grade                 | Special Grade                                                         |

|-----------------------|--------------------------------|-----------------------------------------------------------------------|

| Reliability Ev        | aluation                       |                                                                       |

| HTB, T/H<br>HTS       | > 1000 hours                   | > 2000 hours                                                          |

| T/C                   | > 100 cy                       | > 300 cy                                                              |

| PCT                   | > 96 hours                     | > 192 hous                                                            |

| Quality               | Standard quality control steps | Special control when necessary                                        |

| Screening             | Standard burn-in               | Increased burn-in time                                                |

| Electrical<br>testing | Standard                       | Addition of high<br>temperature testing (if<br>not performed already) |

| Storage<br>life       | 3 years                        | 5 years                                                               |

Table 5. Grade (A) Micro Reliability and Quality

Targets

| Quality/Rel. Item         | 1993 | 1994 | 1995 |

|---------------------------|------|------|------|

| Outgoing electrical (PPM) | 10   | 3.4  | 3.4  |

| Outgoing mechanical (PPM) | 10   | 3.4  | 3.4  |

| Infant mortality (FIT)    | 10   | 5    | 5    |

| Long term rel. (FIT)      | 10   | 5    | 5    |

## Appendix 1A. Typical QC Flow for CMOS Fabrication

|               | Wafer Fabrication Proce                   | OC Flow (CMOS)                                                                                                                                                 |            |

|---------------|-------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

|               | Waler Fabrication Proces                  | SS GC FIOW (CNICS)                                                                                                                                             |            |

| Flow          | Process Material                          | In-process Inspection/quality Monitor                                                                                                                          |            |

| $\triangle$   | Silicon Wafer                             |                                                                                                                                                                |            |

|               | Incoming<br>Inspection                    | Resistivity (sampling by lot) Dimension (sampling by lot) Visual (sampling by lot)                                                                             |            |

|               | Well<br>Formation                         |                                                                                                                                                                |            |

| T             | Oxidation<br>Photo Lithography            | Oxide thickness (sampling by lot) Alignment and etching accuracy (sampling by lot)                                                                             |            |

|               | ion implantation Field Formation          | Layer resistance (sampling by lot)                                                                                                                             |            |

|               | Deposition<br>Photo Lithography           | Deposit thickness (sampling by lot) Alignment and etching accuracy (sampling by lot)                                                                           |            |

|               | Oxidation  Channel Stopper  Formation     | Oxide thickness (sampling by lot)                                                                                                                              |            |

| $\mathcal{L}$ | Photo Lithography                         | Alignment and etching accuracy (sampling by lot)                                                                                                               |            |

|               | lon Implantation<br>Oxidation             | Layer resistance (sampling by lot) Oxide thickness (sampling by lot)                                                                                           |            |

| $\bigcirc$    | Gate<br>Formation                         |                                                                                                                                                                |            |

|               | Deposition<br>Doping<br>Photo Lithography | Deposit thickness (sampling by lot) Layer resistance (sampling by lot) Alignment and etching accuracy (sampling by lot) Gate electrode width (sampling by lot) |            |

|               | p/n SD Formation                          | ,                                                                                                                                                              |            |

|               | Photo Lithography                         | Alignment and etching accuracy (sampling by lot)                                                                                                               |            |

|               | Ion Implantation<br>Anneal                | Layer resistance (sampling by lot)                                                                                                                             |            |

|               | Contact<br>Hole                           |                                                                                                                                                                |            |

|               | Deposition<br>Photo Lithography           | Deposit thickness (sampling by lot) Alignment and etching accuracy (sampling by lot)                                                                           |            |

|               | Metallization                             |                                                                                                                                                                |            |

|               | Metal Deposition<br>Photo Lithography     | Metal thickness (sampling by lot) Alignment and etching accuracy (sampling by lot)                                                                             |            |

|               | Alloy                                     | Parametric test (sampling by lot)                                                                                                                              |            |

| $\bigcirc$    | Passivation                               |                                                                                                                                                                |            |

|               | Deposition<br>Photo Lithography           | Deposit thickness (sampling by lot) Alignment and etching accuracy (sampling by lot)                                                                           |            |

|               | Wafer Sort                                | Electrical test                                                                                                                                                |            |

|               | Contact hole and metallization st         | eps are repeated twice.                                                                                                                                        | 83RD-7509B |

# **Reliability and Quality Control**

Appendix 1B. Typical QC Flow for PLCC Assembly/Test

| ProcessMaterials   Inspection   | ·       |                       | Inspection of Manufacturing Conditions |                |                                |                 | Inspection of Manufacturing Qualities |                                    |                  |                 |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|-----------------------|----------------------------------------|----------------|--------------------------------|-----------------|---------------------------------------|------------------------------------|------------------|-----------------|--|

| Variety Sorted Warfers   Variety Sorted Warfer Visual   Variety Sorted Warfer Visual   Variety Sorted Warfer Visual   Variety Sorted Warfer Press   Conditions Sorted Warfer Visual Visual Warfer Visual Warfer Visual Warfer Visual Warfer Visual Visual Warfer Visual Warfer Visual Warfer Visual Visual Visual Warfer Visual Visu   | Proc    | cess/Materials        | Inspection<br>Item                     | Frequency      | Instrument                     | Inspected<br>by | Inspection<br>Item                    | Frequency                          | Instrument       | Inspected<br>by |  |

| Table Speed Di Water Blade Height Shift Gauges P.C. Sawing Dimensions Running With Electronic Shift Gauges Dimensions Running With Electronic Shift Gauges Dimensions Running With Electronic Shift Gauges Dimensions Running With Electronic Shift Canal Running With Electronic Shift Ca | 4       | Sorted Wafers         |                                        |                | 13                             |                 |                                       |                                    |                  |                 |  |

| Soliding   Di Water Break   Elade Height   Elade    | 2       | Wafer Visual          |                                        |                |                                |                 | Wafer Visual                          | 100%                               | Naked Eye        | Operator        |  |

| Break and Expand   Wafer Expand   Conditions   Wafer Expand   Conditions   Water Expand    | 3       | Dicing                | DI Water                               | Every<br>Shift | Indicators<br>Gauges           | P.C.            | Sawing<br>Dimensions                  |                                    | With Filter      | Operator        |  |

| Die Visual Inspection  Die Attached Severy Conditions Shift Die Attached Conditions Shift Die Attached Severy Shift Die Attached Product)  Beginnen Severy Core (Not Done for Gold (Not Done for Gold Die Attached product)  Pre-Seal Visual Severy Conditions Shift Die Attached product)  Wire Bonding Severy Conditions Shift Indicators P.C. Visual Severy Magazine Every Shift Dynamometer Operator Shift Die Attached product)  Pre-Seal Visual Severy Magazine Shift Dynamometer Operator Shift Die Attached product)  Pre-Seal Visual Severy Magazine Shift Dynamometer Operator Shift Die Attached product)  Pre-Seal Visual Severy Microscope Operator Shift Die Severy Sh | 4       | Break and Expand      | Conditions Wafer Expand                | Every<br>Shift |                                | P.C.            | Wafer Visual                          | 100%                               | Naked Eye        | Operator        |  |

| Die Attached   Temperature   Potentiometer   Coverage   Coverage   Magazine   Every Shift   Microscope   Coverage   Every Shift   Every Magazine   Coverage   Microscope   Coverage   Coverage   Coverage   Coverage   Coverage   Every Shift   Every Magazine   Coverage   Co   | 5       | Die Visual Inspection |                                        |                |                                |                 |                                       | Every Lot<br>Sampling<br>(Or 100%) | Microscope       | Operator        |  |

| Temperature   Every Shift   Microscope                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |         | Lead Frames           |                                        | Every<br>Shift | Thermocouple,                  | P.C.            | Epoxy                                 | Every<br>Magazine                  | Naked Eye        | Operator        |  |

| Second Contention   Contentio   | 7       | Die Attached          | Temperature                            |                | Potentiometer                  |                 | Coverage                              | Every Shift                        | Microscope       |                 |  |

| Temperature Every Week Potentiometer P.C. Wire Pull Test Shift Tension Gauge Coperator Week Potentiometer P.C. Wire Pull Test Shift Tension Gauge Coperator Shift Tensection  Temperature of Pellet, Expiration Date Every Shift Expiration Date Profile of Die Set Temperature Pressure Cure Time  Molding Temperature Every Shift Indicator P.C. Visual 100% Naked Eye Operator Potentiometer P.C. Visual Every Lot Naked Eye Operator Potentiometer Pressure Cure Time  Mold Aging Temperature Every Shift Indicator P.C. Visual Every Lot Naked Eye Operator Pendent Temperature Pressure Cure Time Every Shift Indicators P.C. Visual Every Lot Naked Eye Operator Tensely Every Week Every Week Every Week Every Week Every Day Pitating Conditions P.C. Visual Every Lot Naked Eye Operator Pendent Tensely Every Week Every Day Pitating Conditions P.C. Visual Every Lot Naked Eye Operator Pendent Tensely Every Day Pitating Conditions P.C. Visual Every Lot Naked Eye Operator Pendent Tensely Every Day Pitating Conditions P.C. P.C. Visual Every Lot Naked Eye Operator Pendent Tensely Every Day Pitating Conditions P.C. P.C. Visual Every Lot Naked Eye Operator Pitating Every Day Pitating Conditions P.C. P.C. Potentiometer P.C. P.C. Physical Every Lot Naked Eye Operator Pressure Pressure Every Day Indicators P.C. P.C. P.C. Potentiometer P.C. P.C. Physical Every Lot Naked Eye Operator P.C. P.C. Potentiometer P.C. P.C. P.C. P.C. P.C. P.C. P.C. P.C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | •       | (Not Done for Gold    | Temperature                            | Every<br>Shift |                                | P.C.            |                                       |                                    | Dynamometer      | Operator        |  |

| Test   Shift   Gauge                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | <u></u> | Fine Wire             | Bonding<br>Conditions                  | Every<br>Shift | Indicators                     | P.C.            | Visual                                | Every<br>Magazine                  | Microscope       | Operator        |  |

| 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 10      | Wire Bonding          | Temperature                            | Every<br>Week  | and                            | P.C.            |                                       | Every<br>Shift                     | Tension<br>Gauge | Operator        |  |

| Molding Compound of Pellet, Expiration Date Profile of Die Set Preheat Temperature Pressure Cure Time  14 Mold Aging Temperature Every Shift Indicator P.C.  Deflashing Conditions Concentration Density Water Jet Pressure Every Day Plating Conditions Conditions Plating Conditions Every Day Plating Conditions P.C.  Preheat Temperature Every Shift Indicator P.C.  Deflashing Conditions Concentration Density Every Week Density Meter Tech.  Every Day Indicators P.C.  Plating Conditions P.C.  Plating Every Day Indicators P.C.  Plating Every Day Indicators P.C.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 11      |                       |                                        |                |                                |                 |                                       | Sampling                           | Microscope       | Inspector       |  |

| Profile of Die Set Preheat Temperature Pressure Cure Time  Temperature Pressure Cure Time  Temperature Pressure Cure Time  Deflashing Conditions Concentration Density Water Jet Pressure Every Day Gauge Tech. Potentiometer Potentiometer Potentiometer Pressure Pressure Pressure Pres | 12      | Molding Compound      | of Pellet,                             | Every<br>Shift | Thermocouple                   | P.C.            |                                       |                                    |                  |                 |  |

| Temperature Pressure Cure Time  Temperature Pressure Cure Time  Temperature Every Shift Indicator P.C.  Deflashing Conditions Concentration Every Week Titration Tech. Density Every Week Density Meter Tech. Water Jet Pressure  Plating Conditions Every Day Indicators P.C.  Indicators P.C. Visual Every Lot Naked Eye Operator  O | 13      | Molding               | Profile of                             | Every Shift    | Thermocouple,<br>Potentiometer | P.C.            | Visual                                | 100%                               | Naked Eye        | Operator        |  |

| Temperature Every Shift Indicator P.C.  Deflashing Conditions Concentration Density Every Week Density Meter Tech. Plating Conditions Every Day Gauge Tech.  P.C. Visual Every Lot Naked Eye Operator  Temperature Every Week Density Meter Tech. Plating Conditions Every Day Indicators P.C.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |         |                       | Temperature                            |                |                                |                 |                                       |                                    |                  |                 |  |

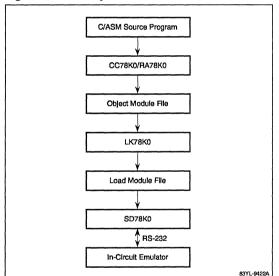

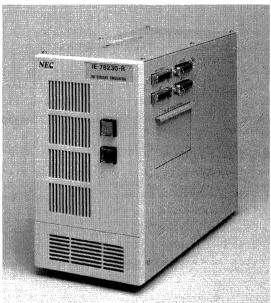

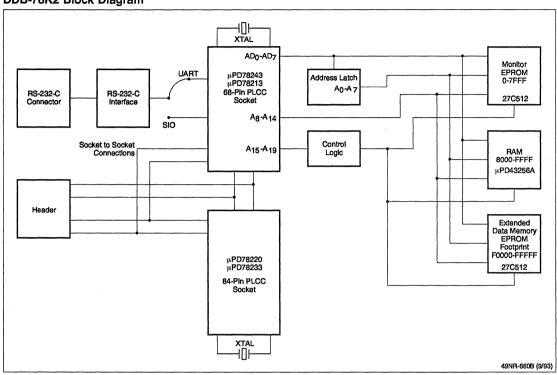

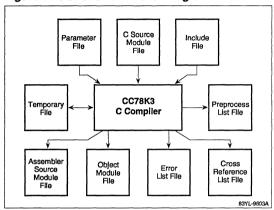

| Deflashing Conditions Concentration Density Every Week Pressure  Tech.  Plating Conditions  Every Day Plating Conditions  Every Day Concentration Density Every Day Conditions  Every Day Conditions  Every Day Conditions  Every Day Conditions  P.C. Visual Every Lot Naked Eye Operator  Tech.  Tech.  Plating Conditions  Every Day Indicators  P.C.  Visual Every Lot Naked Eye Operator  Operator  Operator  Operator  Operator  Petery Day Indicators  P.C.  Visual Every Lot Naked Eye Operator  Operato |         |                       | Cure Time                              |                |                                | 5               |                                       |                                    |                  |                 |  |