MEMORY PRODUCTS DATA BOOK Volume 2 of 2 SRAMs, ASMs, EEPROMs

## 1993 MEMORY PRODUCTS DATA BOOK

Volume 2 of 2 SRAMs, ASMs, EEPROMs

Document No. 60105-1-V2 ©1993 NEC Electronics Inc. All rights reserved. Printed in the United States of America.

No part of this document may be copied or reproduced in any form or by any means without the prior written consent of NEC Electronics Inc. (NECEL). The information in this document is subject to change without notice. Devices sold by NECEL are covered by the warranty and patent indemnification provisions appearing in NECEL Terms and Conditions of Sale only. NECEL makes no warranty, express, statutory, implied, or by description, regarding the information set forth herein or regarding the freedom of the described devices from patent infringement. NECEL makes no warranty of merchantability or fitness for any purpose. NECEL assumes no responsibility for any errors that may appear in this document. NECEL makes no commitment to update or to keep current information contained in this document. The devices listed in this document are not suitable for use in aircraft, aerospace equipment, submarine cables, nuclear reactor control systems and life support systems. If customers intended by NEC, please contact our sales people in advance.

takis takista takista shirista takita shirista

> an an the Araba The State St

الم الكلم ويعينها متحدة محميل المعني معامل معامل معامل محمد محمد محمد المعامل معامل معامل المعامل المعامل المحم التي ي طبق من محمد محميل المعامل معامل معامل معامل ويعامل معامل محمد المحمد المعامل معامل معامل محمد ويعام التي المحمد ويعامل ويعامل والمعامل ويعامل المعامل معامل معامل معامل معامل معامل المعامل المعامل محمد محمد ويعام المعام ويعامل ويعامل معامل معامل ويعامل محمد المعامل محمد المعامل المعامل معامل معامل المعامل محمد المعامل ويعام المعام المعامل ويعامل ويعامل ويعامل معامل ويعامل المعامل محمد ويعامل المعامل معامل معامل معامل ويعامل المعام المعام ويعامل ويعامل ويعامل ويعامل ويعامل المعامل ويعامل المعامل المعامل ويعامل المعامل ويعامل المعامل ويعامل ا المعامل المعامل ويعامل ويعامل ويعامل ويعامل ويعامل المعامل ويعامل المعامل ويعامل المعامل ويعامل ويعامل ويعامل المعامل ويعامل ويعامل ويعامل ويعامل ويعامل ويعامل و ويعامل ويعامل

General

## Volume 1

| Section 1. General Information                      |    |

|-----------------------------------------------------|----|

| Upcoming Products                                   | 1  |

| Manufacturing in Roseville, California              | 3  |

| Device Numbering Guide                              | 4  |

| Quick Reference Guide                               | 5  |

| Section 2. Reliability and Quality Control          |    |

| Built-in Total Quality Control (TQC)                | 1  |

| Approaches to TQC                                   | 1  |

| Implementation of Quality Control                   | 3  |

| Reliability Theory                                  | 5  |

| Failure Analysis                                    | 9  |

| Summary                                             | 9  |

| Figure 1. NEC's Quality Control System              | 2  |

| Figure 2. New Product Development                   | 3  |

| Figure 3. Electrical Testing and Screening          | 5  |

| Figure 4. Reliability Life (Bathtub) Curve          | 5  |

| Appendix 1A. Typical QC Flow for CMOS Fabrication   | 10 |

| Appendix 1B. Typical QC Flow for PLCC Assembly/Test | 11 |

| Appendix 2. Typical Reliability Assurance Tests     | 13 |

| Appendix 3. New Product/Process Change Tests        | 13 |

| Appendix 4. Failure Analysis Flowchart              | 14 |

|                                                     |    |

### Section 3. 256K DRAMs

| μPD   | Organization | Features   |    |

|-------|--------------|------------|----|

| 41256 | 256K x 1     | Page; NMOS | За |

| 41464 | 64K x 4      | Page; NMOS | 3b |

7

## Volume 1 (cont)

| μPD           | Organization      | Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | i na sta             |

|---------------|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| 421000        | 1M x 1            | Fast-page (See App Note 53.)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 4a                   |

| 424256        | 256K x 4          | Fast-page                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 4b                   |

| Section 5. 4M | DRAMs (4M x 1 and | J 1M x 4)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                      |

| μPD           | Organization      | Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | and the second       |

| 424100        | 4M x 1            | Fast-page                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 5a                   |

| 424100A       | 4M x 1            | Fast-page                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                      |

| 424100L       | 4M x 1            | Fast-page; 3.3-volt                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | ng ta shine ta shine |

| 42\$4100A     | 4M x 1            | Fast-page; self-refresh                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                      |

| 42\$4100L     | 4M x 1            | Fast-page; self-refresh; 3.3-volt                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | e te suthat          |

| 424101        | 4M x 1            | Nibble                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 5b                   |

| 424102        | 4M x 1            | Static-column                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 5c                   |

| 424400        | 1M x 4            | Fast-page                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 5d                   |

| 424400A       | 1M x 4            | Fast-page                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | t ja kara s          |

| 424400L       | 1M x 4            | Fast-page; 3.3-volt                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Carlo I.,            |

| 42\$4400A     | 1M x 4            | Fast-page; self-refresh                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                      |

| 42\$4400L     | 1M x 4            | Fast-page; self-refresh; 3.3-volt                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                      |

| 424402        | 1M x 4            | Static-column means the second state of the se | 5e                   |

| 424410        | 1M x 4            | Fast-page; write-per-bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 5f                   |

| 424412        | 1M x 4            | Static-column; write-per-bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 5g                   |

| 424440        | 1M x 4            | Fast-page; 4 CAS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 5h                   |

| 424440L       | 1M x 4            | Fast-page; 4 CAS; 3.3-volt                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                      |

| 42\$4440      | 1M x 4            | Fast-page; 4 CAS: self-refresh                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                      |

| 42S4440L      | 1M x 4            | Fast-page; 4 CAS; self-refresh; 3.3-volt                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                      |

# NEC

## Volume 1 (cont)

### Section 6. 4M DRAMs (512K x 8/9)

| μPD      | Organization | Features                                         |       |

|----------|--------------|--------------------------------------------------|-------|

| 424800A  | 512K x 8     | Fast-page                                        | 6a    |

| 424800L  | 512K x 8     | Fast-page; 3.3-volt                              | · .   |

| 42S4800A | 512K x 8     | Fast-page; self-refresh                          |       |

| 42S4800L | 512K x 8     | Fast-page; self-refresh; 3.3-volt                |       |

| 424810A  | 512K x 8     | Fast-page; write-per-bit                         | 6b    |

| 424810L  | 512K x 8     | Fast-page; write-per-bit; 3.3-volt               |       |

| 42S4810A | 512K x 8     | Fast-page; write-per-bit; self-refresh           |       |

| 42S4810L | 512K x 8     | Fast-page; write-per-bit; self-refresh; 3.3-volt |       |

| 424900A  | 512K x 9     | Fast-page                                        | 60    |

| 424900L  | 512K x 9     | Fast-page; 3.3-volt                              |       |

| 42S4900A | 512K x 9     | Fast-page; self-refresh                          |       |

| 42S4900L | 512K x 9     | Fast-page; self-refresh; 3.3-volt                | ····· |

### Section 7. 4M DRAMs (256K x 16/18)

| μPD      | Organization | Features                                                                 | 10.00 |

|----------|--------------|--------------------------------------------------------------------------|-------|

| 424170A  | 256K x 16    | Fast-page; 2 WE; 1K refresh                                              | 7a    |

| 424170L  | 256K x 16    | Fast-page; 2 WE; 1K refresh; 3.3-volt                                    |       |

| 42S4170A | 256K x 16    | Fast-page; 2 WE; 1K refresh; self-refresh                                |       |

| 42S4170L | 256K x 16    | Fast-page; 2 WE; 1K refresh; self-refresh; 3.3-volt                      |       |

| 424190A  | 256K x 18    | Fast-page; 2 WE; 1K refresh                                              | 7b    |

| 424190L  | 256K x 18    | Fast-page; 2 WE; 1K refresh; 3.3-volt                                    |       |

| 42S4190A | 256K x 18    | Fast-page; 2 WE; 1K refresh; self-refresh                                |       |

| 42S4190L | 256K x 18    | Fast-page; 2 WE; 1K refresh; self-refresh; 3.3-volt                      |       |

| 424260A  | 256K x 16    | Fast-page; 2 CAS; 512 refresh                                            | 7c    |

| 424260L  | 256K x 16    | Fast-page; 2 CAS; 512 refresh; 3.3-volt                                  |       |

| 42S4260A | 256K x 16    | Fast-page; 2 CAS; 512 refresh; self-refresh                              |       |

| 42S4260L | 256K x 16    | Fast-page; 2 CAS; 512 refresh; self-refresh; 3.3-volt                    |       |

| 424263A  | 256K x 16    | Fast-page; 2 CAS; 512 refresh; write-per-bit                             | 7d    |

| 424263L  | 256K x 16    | Fast-page; 2 CAS; 512 refresh; write-per-bit; 3.3-<br>volt               |       |

| 42S4263A | 256K x 16    | Fast-page; 2 CAS; 512 refresh; write-per-bit; self-<br>refresh           |       |

| 42S4263L | 256K x 16    | Fast-page; 2 CAS; 512 refresh; write-per-bit; self-<br>refresh; 3.3-volt |       |

### Section 7. 4M DRAMs (256K x 16/18) (cont)

| μPD      | Organization | Features                                              |    |

|----------|--------------|-------------------------------------------------------|----|

| 424280A  | 256K x 18    | Fast-page; 2 CAS; 512 refresh                         | 7e |

| 424280L  | 256K x 18    | Fast-page; 2 CAS; 512 refresh; 3.3-volt               |    |

| 42S4280A | 256K x 18    | Fast-page; 2 CAS; 512 refresh; self-refresh           |    |

| 42S4280L | 256K x 18    | Fast-page; 2 CAS; 512 refresh; self-refresh; 3.3-volt |    |

### Section 8. 16M DRAMs

| μPD       | Organization | Features                                      |    |

|-----------|--------------|-----------------------------------------------|----|

| 4216100   | 16M x 1      | Fast-page; 4K refresh                         | 8a |

| 4217100   | 16M x 1      | Fast-page; 2K refresh                         |    |

| 4216101   | 16M x 1      | Nibble; 4K refresh                            | 8b |

| 4217101   | 16M x 1      | Nibble; 2K refresh                            |    |

| 4216102   | 16M x 1      | Static-column; 4K refresh                     | 8c |

| 4217102   | 16M x 1      | Static-column; 2K refresh                     |    |

| 4216400   | 4M x 4       | Fast-page; 4K refresh                         | 8d |

| 4217400   | 4M x 4       | Fast-page; 2K refresh                         |    |

| 4216402   | 4M x 4       | Static-column; 4K refresh                     | 8e |

| 4217402   | 4M x 4       | Static-column; 2K refresh                     |    |

| 4216410   | 4M x 4       | Fast-page; 4K refresh; write-per-bit          | 8f |

| 4217410   | 4M x 4       | Fast-page; 2K refresh; write-per-bit          |    |

| 4216412   | 4M x 4       | Static-column; 4K refresh; write-per-bit      | 8g |

| 4217412   | 4M x 4       | Static-column; 2K refresh; write-per-bit      |    |

| 4216800   | 2M x 8       | Fast-page; 4K refresh                         | 8h |

| 4216800L  | 2M x 8       | Fast-page; 4K refresh; 3.3-volt               |    |

| 42S16800  | 2M x 8       | Fast-page; 4K refresh; self-refresh           |    |

| 42S16800L | 2M x 8       | Fast-page; 4K refresh; self-refresh; 3.3-volt |    |

| 4217800   | 2M x 8       | Fast-page; 2K refresh                         |    |

| 4217800L  | 2M x 8       | Fast-page; 2K refresh; 3.3-volt               |    |

| 42S17800  | 2M x 8       | Fast-page; 2K refresh; self-refresh           |    |

| 42S17800L | 2M x 8       | Fast-page; 2K refresh; self-refresh; 3.3-volt |    |

| 4216802   | 2M x 8       | Static-column                                 | 8i |

| tion 8. 16M DRAMs (cont) |                                               |     |

|--------------------------|-----------------------------------------------|-----|

| Organization             | Features                                      |     |

| 900 2M x 9               | Fast-page; 4K refresh                         | 8j  |

| 900L 2M x 9              | Fast-page; 4K refresh; 3.3-volt               |     |

| 6900 2M x 9              | Fast-page; 4K refresh; self-refresh           | · · |

| 6900L 2M x 9             | Fast-page; 4K refresh; self-refresh; 3.3-volt |     |

| 2900 2M x 9              | Fast-page; 2K refresh                         |     |

| 900L 2M x 9              | Fast-page; 2K refresh; 3.3-volt               |     |

| 7900 2M x 9              | Fast-page; 2K refresh; self-refresh           |     |

| 7900L 2M x 9             | Fast-page; 2K refresh; self-refresh; 3.3-volt | 1   |

| 902 2M x 9               | Static-column                                 | 8k  |

| 160 1M x 16              | Fast-page; 4K refresh                         | 81  |

| 160L 1M x 16             | Fast-page; 4K refresh; 3.3-volt               |     |

| 6160 1M x 16             | Fast-page; 4K refresh; self-refresh           |     |

| 6160L 1M x 16            | Fast-page; 4K refresh; self-refresh; 3.3-volt |     |

| '160 1M x 16             | Fast-page; 2K refresh                         |     |

| 160L 1M x 16             | Fast-page; 2K refresh; 3.3-volt               |     |

| 7160 1M x 16             | Fast-page; 2K refresh; self-refresh           |     |

| 7160L 1M x 16            | Fast-page; 2K refresh; self-refresh; 3.3-volt | ,   |

| 160 1M x 16              | Fast-page; 1K refresh                         |     |

| 160L 1M x 16             | Fast-page; 1K refresh; 3.3-volt               |     |

| 8160 1M x 16             | Fast-page; 1K refresh; self-refresh           |     |

| 8160L 1M x 16            | Fast-page; 1K refresh; self-refresh; 3.3-volt |     |

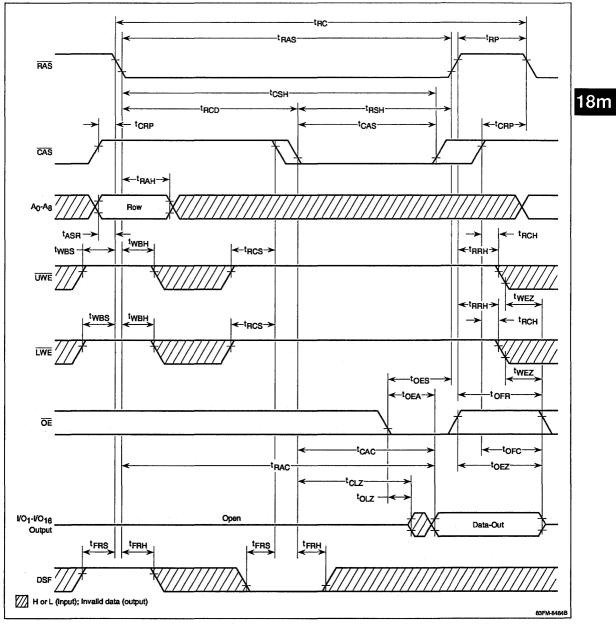

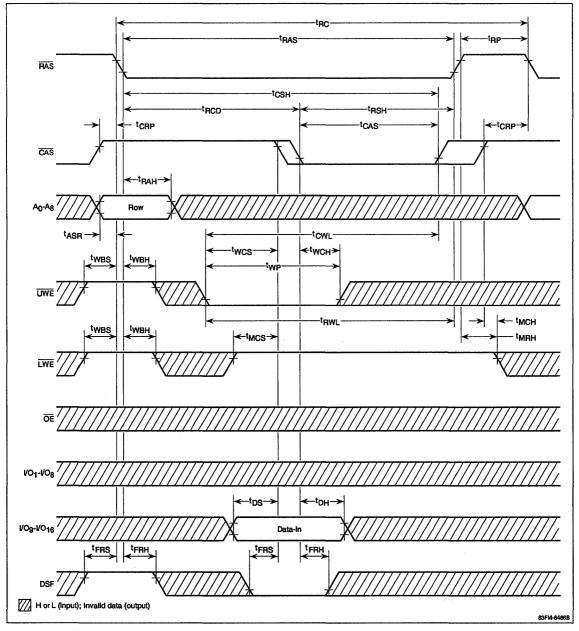

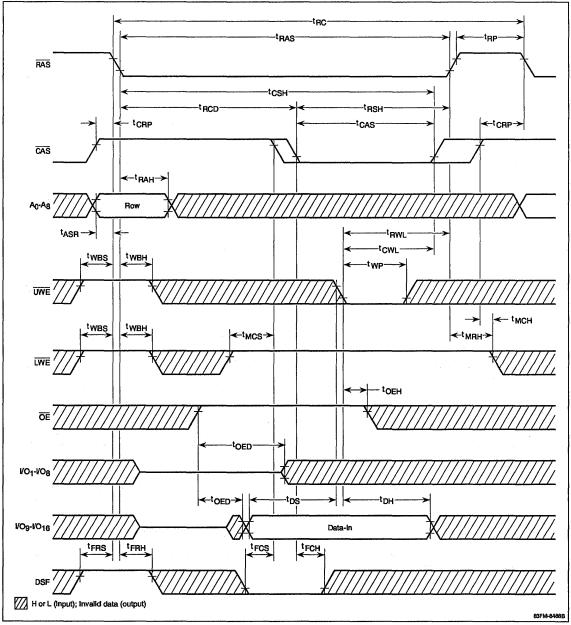

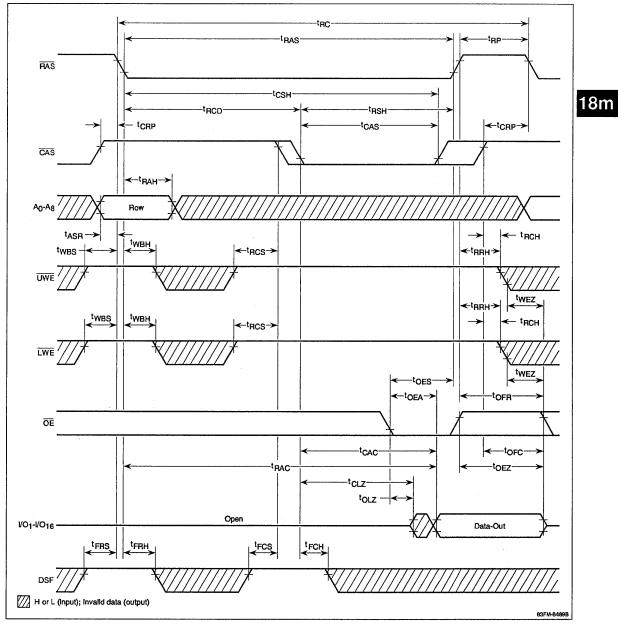

| 180 1 M x 18             | Fast-page; 4K refresh                         | 8m  |

| 180L 1M x 18             | Fast-page; 4K refresh; 3.3-volt               |     |

| 6180 1 M x 18            | Fast-page; 4K refresh; self-refresh           |     |

| 6180L 1M x 18            | Fast-page; 4K refresh; self-refresh; 3.3-volt |     |

| 180 1 M x 18             | Fast-page; 2K refresh                         |     |

| 180L 1M x 18             | Fast-page; 2K refresh; 3.3-volt               |     |

| 7180 1M x 18             | Fast-page; 2K refresh; self-refresh           |     |

| 7180L 1M x 18            | Fast-page; 2K refresh; self-refresh; 3.3-volt |     |

| 180 1M x 18              | Fast-page; 1K refresh                         |     |

| 180L 1M x 18             | Fast-page; 1K refresh; 3.3-volt               |     |

| 8180 1M x 18             | Fast-page; 1K refresh; self-refresh           |     |

| 8180L 1M x 18            | Fast-page; 1K refresh; self-refresh; 3.3-volt |     |

| Section 9. DRA            | Section 9. DRAM Modules (256K/512K x n) |           |          |         |  |    |

|---------------------------|-----------------------------------------|-----------|----------|---------|--|----|

| МС                        | Organization                            | Features  | a 11 - 1 | - · · · |  |    |

| -42256AB8                 | 256K x 8                                | Fast-page |          | ۹.      |  | 9a |

| -42256AB9                 | 256K x 9                                | Fast-page |          | τ.      |  | 9b |

| -42256A32                 | 256K x 32                               | Fast-page |          |         |  | 90 |

| -42256A36                 | 256K x 36                               | Fast-page |          | · ·     |  | 9d |

| -42256AA40                | 256K x 40                               | Fast-page |          |         |  | 9e |

| -42512A32                 | 512K x 32                               | Fast-page |          |         |  | 9f |

| -42512A36                 | 512K x 36                               | Fast-page |          |         |  | 9g |

| -42512AA40,<br>-42512AB40 | 512K x 40                               | Fast-page |          | , .     |  | 9h |

### Section 10. DRAM Modules (1M/2M x n)

| MC                          | Organization | Features  |     |

|-----------------------------|--------------|-----------|-----|

| -421000A8                   | 1M x 8       | Fast-page | 10a |

| -421000A9                   | 1M x 9       | Fast-page | 10b |

| -421000A32                  | 1M x 32      | Fast-page | 10c |

| -421000A36                  | 1M x 36      | Fast-page | 10d |

| -421000AA40,<br>-421000AB40 | 1M x 40      | Fast-page | 10e |

| -422000A32                  | 2M x 32      | Fast-page | 10f |

| -422000A36                  | 2M x 36      | Fast-page | 10g |

| -422000AA40                 | 2M x 40      | Fast-page | 10h |

#### Section 11. DRAM Modules (4M/8M x n)

| МС         | Organization | Features      |

|------------|--------------|---------------|

| -424000A8  | 4M x 8       | Fast-page 11a |

| -424000A9  | 4M x 9       | Fast-page 11b |

| -424000A32 | 4M x 32      | Fast-page 11c |

| -424000A36 | 4M x 36      | Fast-page 11d |

| -428000A32 | 8M x 32      | Fast-page 11e |

| -428000A36 | 8M x 36      | Fast-page 11f |

|            |              |               |

### Section 12. Video RAMs (See App Notes 89-15, 89-16, 90-01.)

| μPD      | Organization | Features                       |     |

|----------|--------------|--------------------------------|-----|

| 41264    | 64K x 4      | Page; NMOS                     | 12a |

| 42264    | 64K x 4      | Page; CMOS                     | 12b |

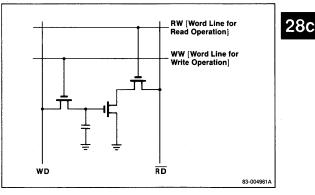

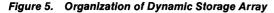

| 42273    | 256K x 4     |                                | 12c |

| 42274    | 256K x 4     | Flash-write                    | 12d |

| 42274-80 | 256K x 4     | Flash-write; high-performance  | 12e |

| 42275    | 128K x 8     |                                | 12f |

| 482234   | 256K x 8     | Fast-page                      | 12g |

| 482235   | 256K x 8     | Hyper-page (extended data out) |     |

### Section 13. Synchronous DRAM

| μPD      | Organization | Features |           |

|----------|--------------|----------|-----------|

| 42116420 | 4M x 4       | 3.3-volt | 13a       |

| 42116820 | 2M x 8       | 3.3-volt |           |

| 42116920 | 2M x 9       | 3.3-volt |           |

| 42116162 | 1M x 16      | 3.3-volt |           |

| 42116182 | 1 M x 18     | 3.3-volt | ,,,,,,,,, |

### Section 14. Rambus DRAM

| μPD    | Organization | Features |     |

|--------|--------------|----------|-----|

| 488130 | 2M x 8       | 3.3-volt | 14a |

| 488170 | 2M x 9       | 3.3-volt |     |

### Section 15. Application Notes

| App Note 53    |                              | 15a |

|----------------|------------------------------|-----|

| App Note 89-15 | Computer Graphics Overview   | 15b |

| App Note 89-16 | Frame Buffer Architecture    | 15c |

| App Note 90-01 | Realism in Computer Graphics | 15d |

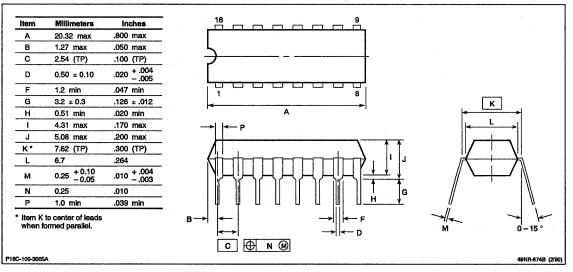

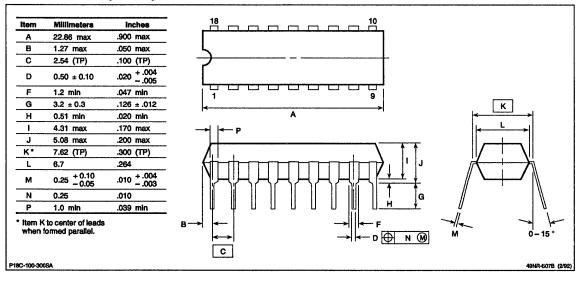

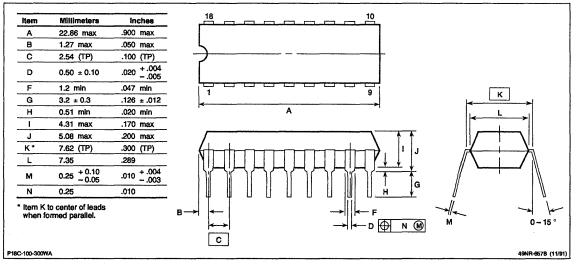

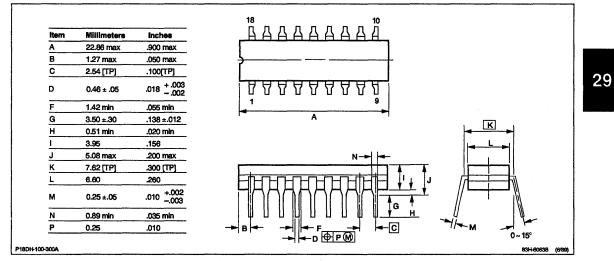

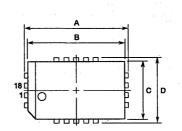

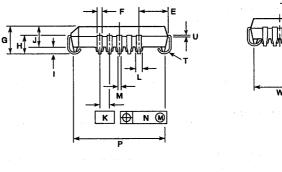

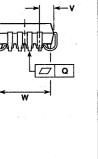

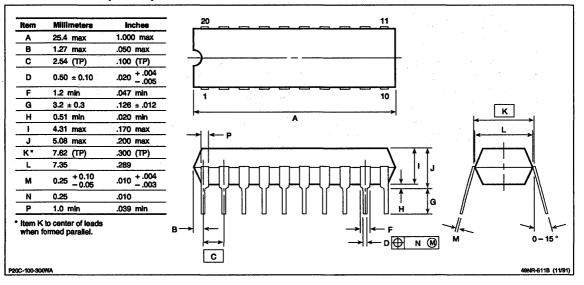

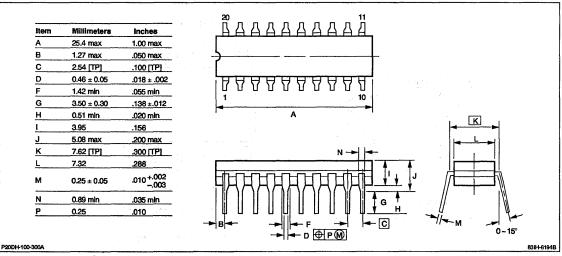

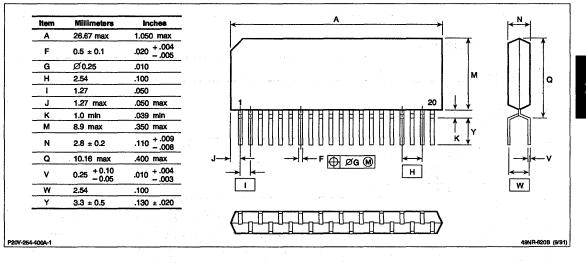

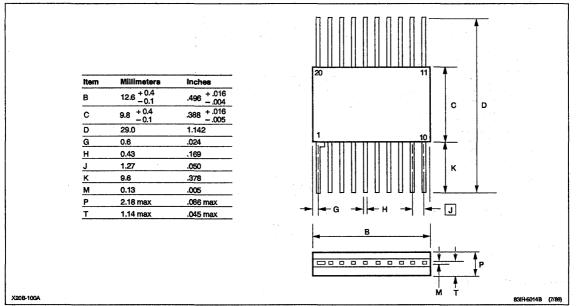

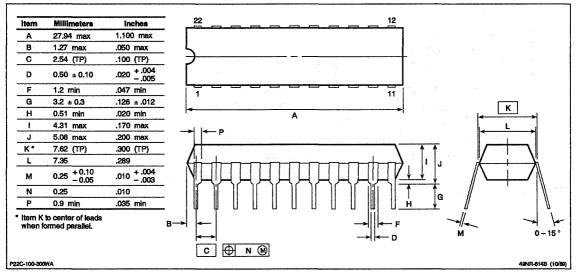

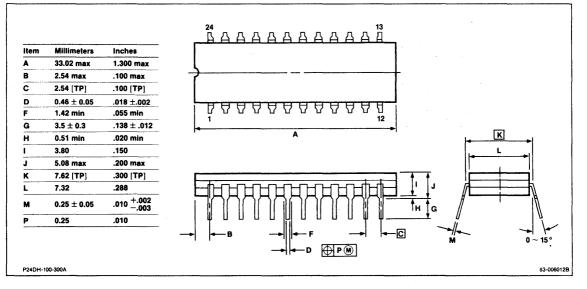

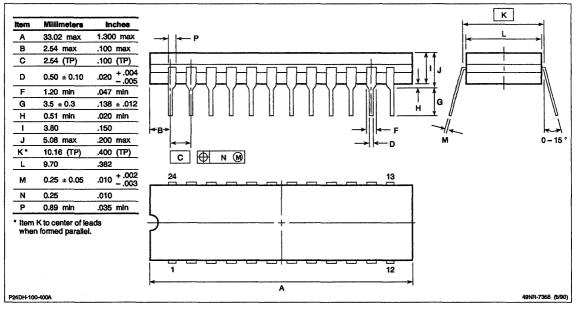

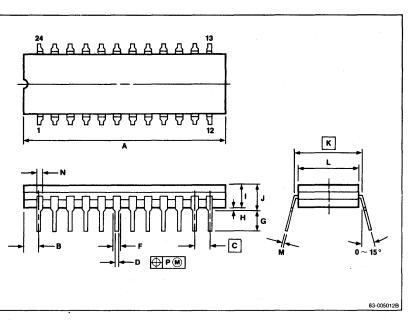

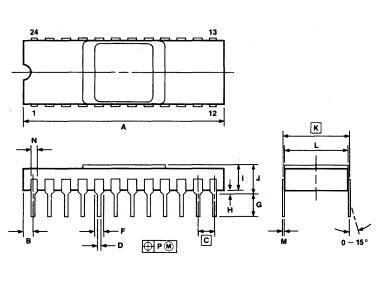

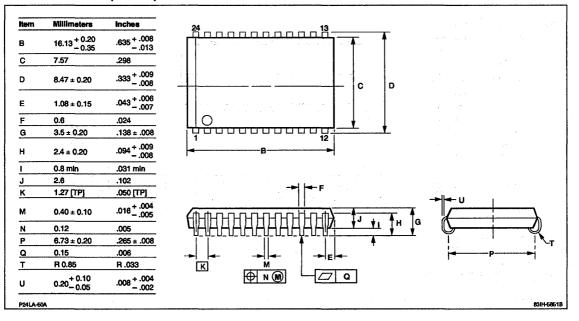

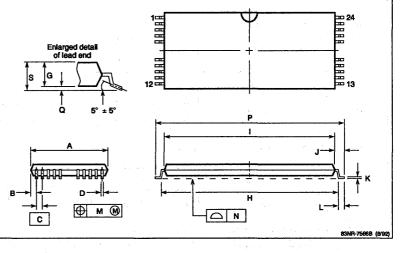

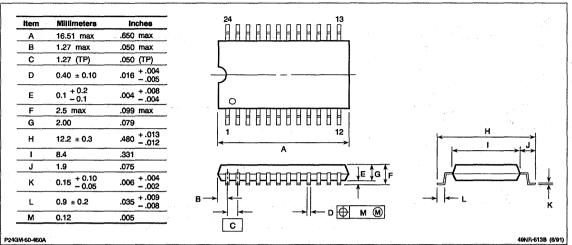

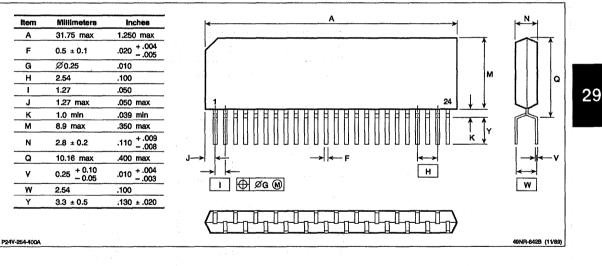

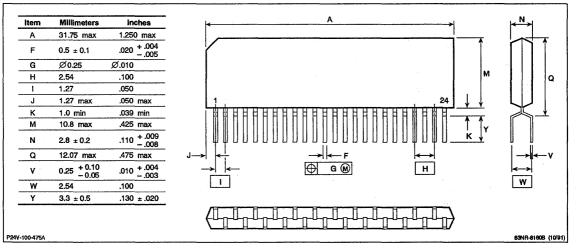

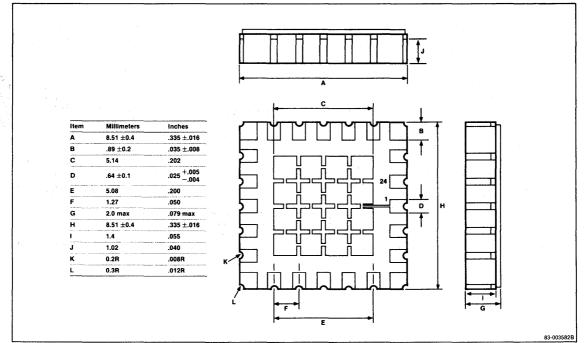

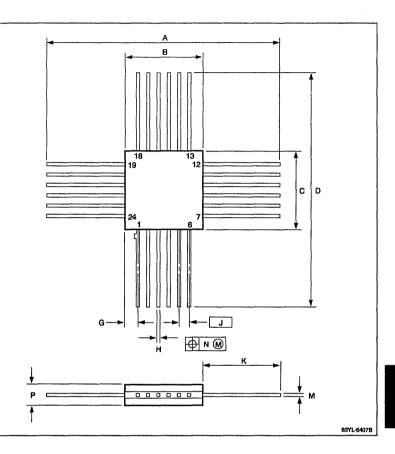

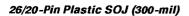

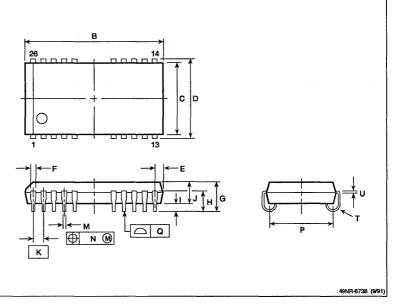

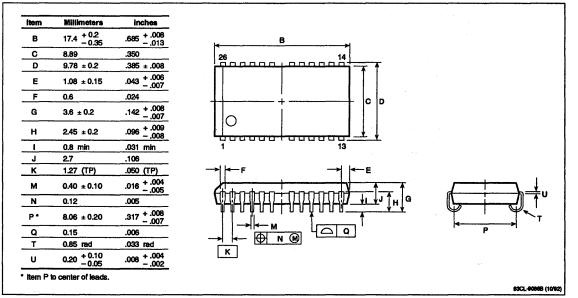

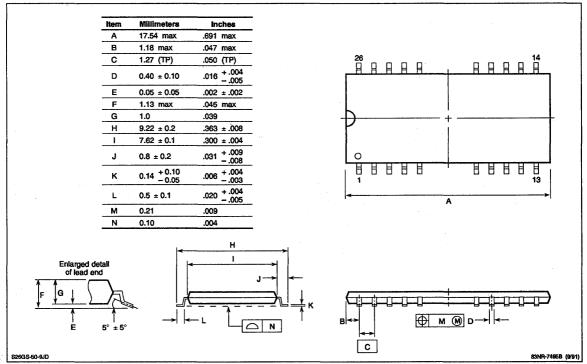

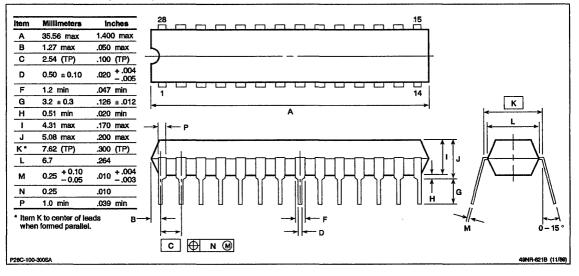

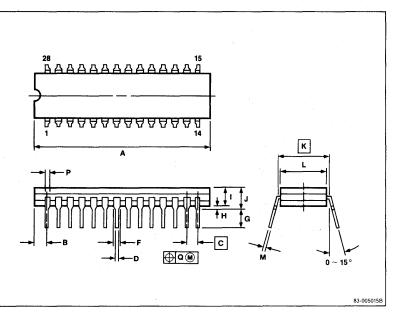

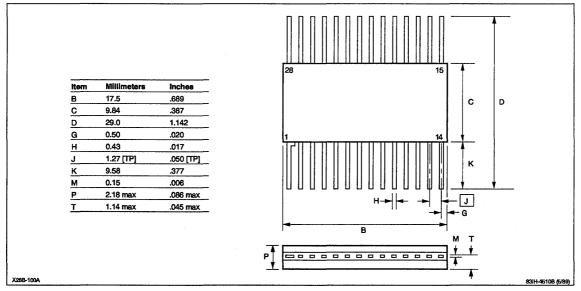

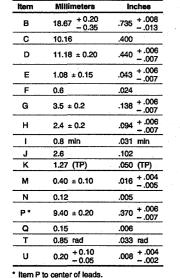

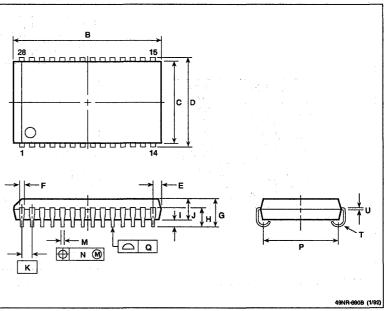

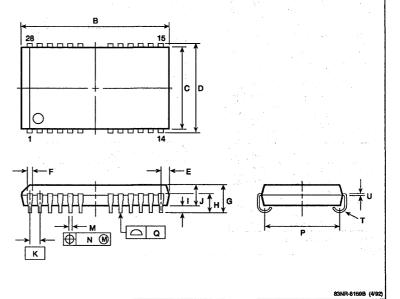

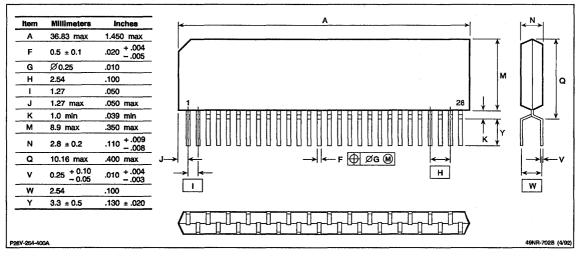

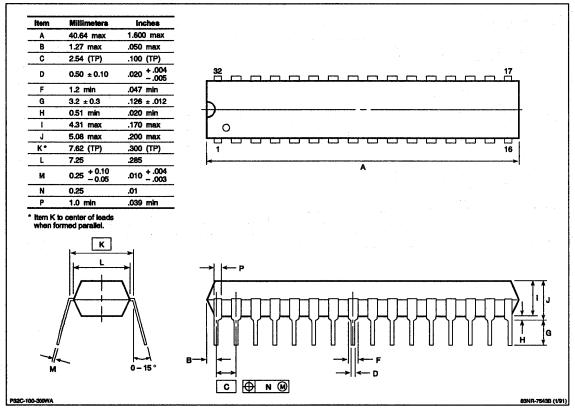

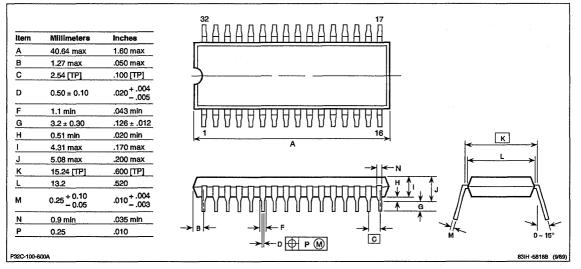

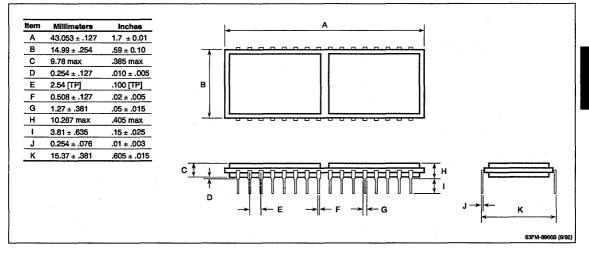

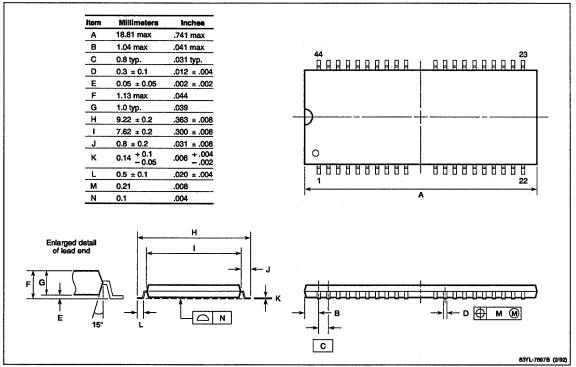

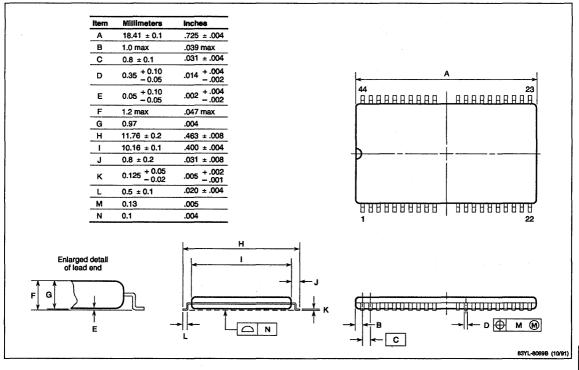

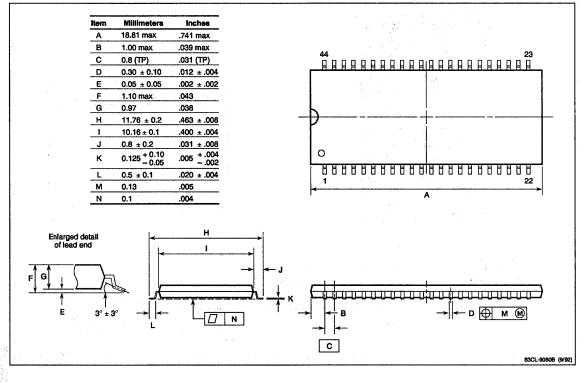

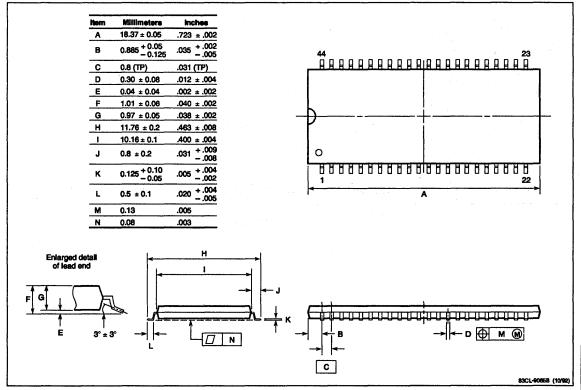

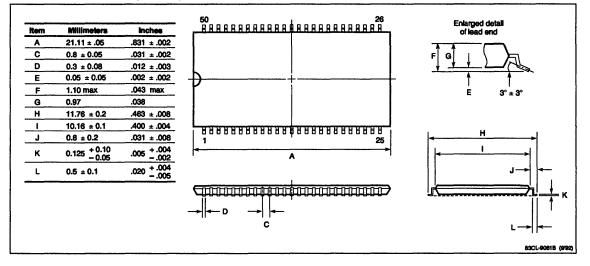

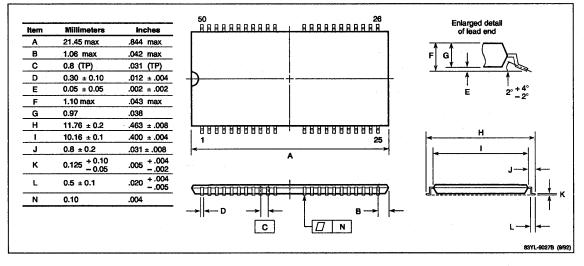

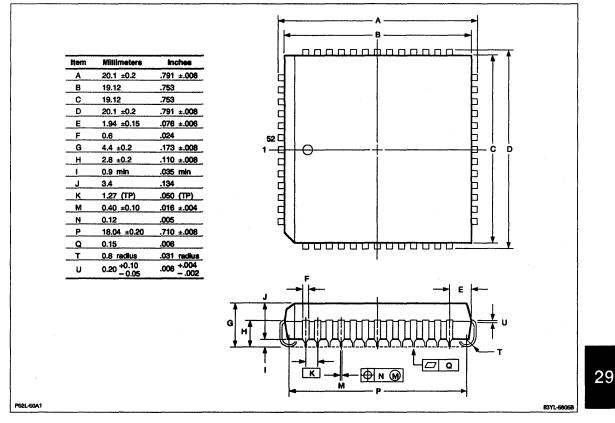

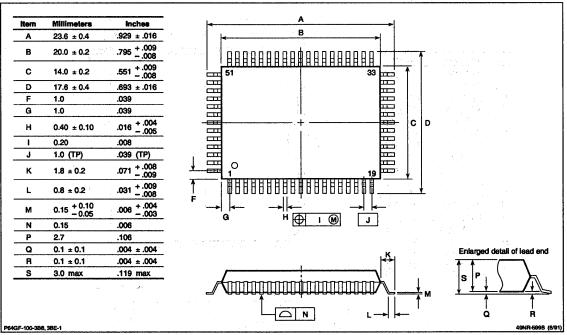

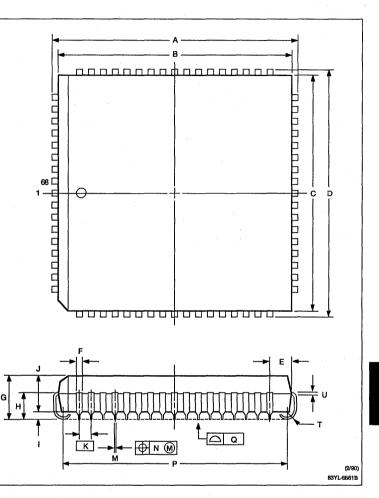

### Section 16. Package Drawings

| Device/Package Cross-Reference                | 1  |

|-----------------------------------------------|----|

| Package Drawings (in order by number of pins) | 16 |

## Volume 2

| Section 17. General Information        | 1 | · · · · · · · · · · · · · · · · · · · |

|----------------------------------------|---|---------------------------------------|

| Upcoming Products                      |   | 1                                     |

| Manufacturing in Roseville, California |   | 3                                     |

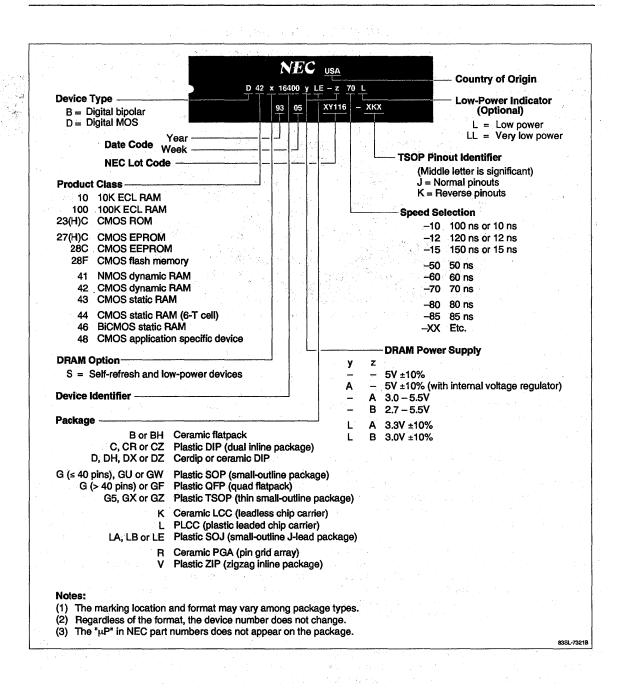

| Device Numbering Guide                 |   | 4                                     |

| Quick Reference Guide                  |   | 5                                     |

| Annullandian One soldie Devis | es (See App Notes 54 thru 58 | 00 00 00 00 V    |

|-------------------------------|------------------------------|------------------|

| ADDUCATION SPACIFIC LIAVICA   |                              | un_ne un_ne i    |

| ADDIICATION ODECTTIC DEVICE   |                              | . 30-00, 30-00,1 |

|                               |                              |                  |

| μPD    | Description                                         |     |

|--------|-----------------------------------------------------|-----|

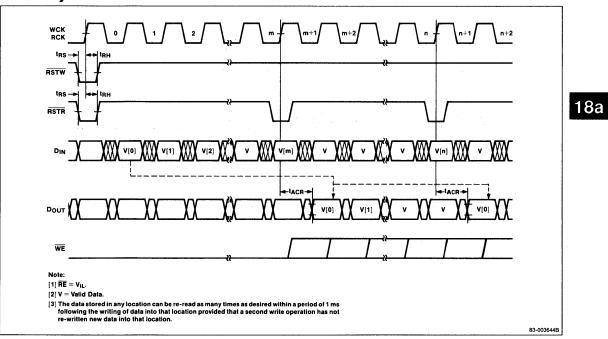

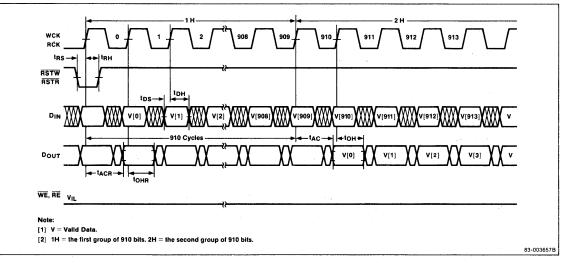

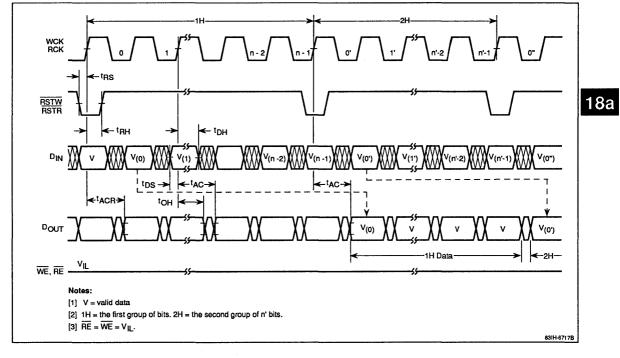

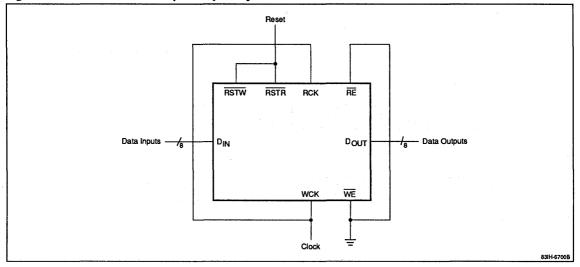

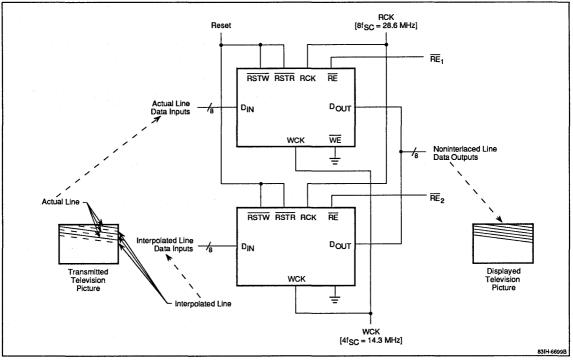

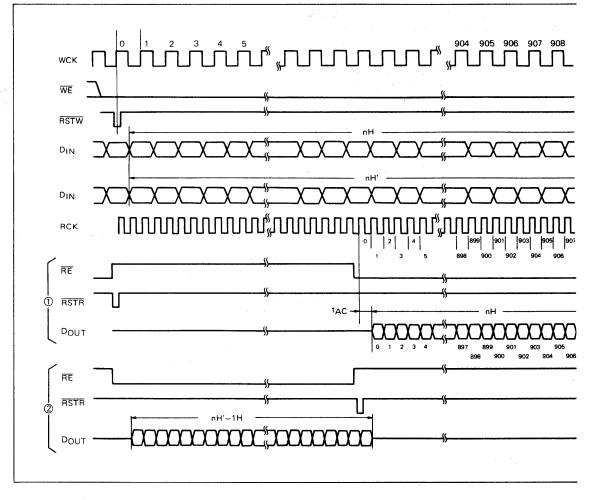

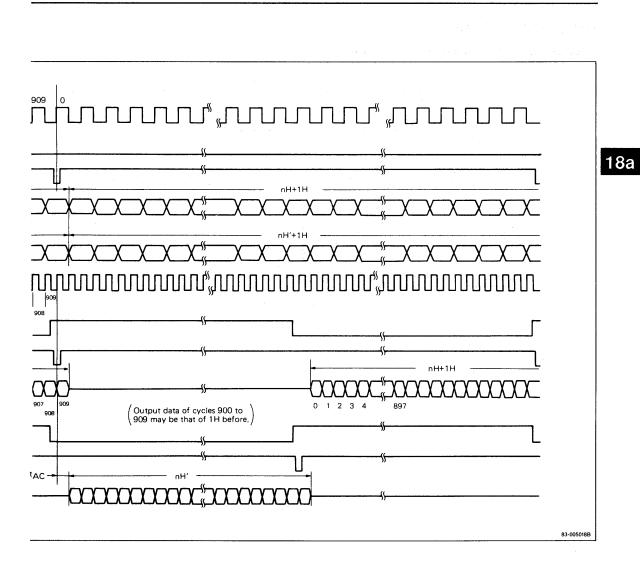

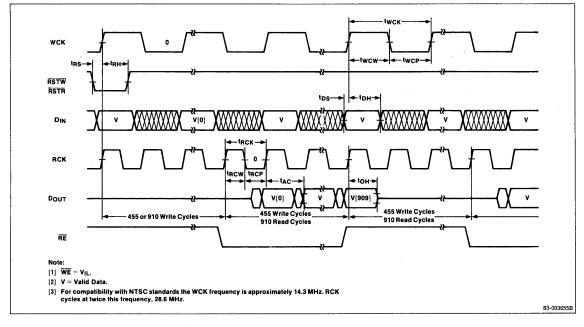

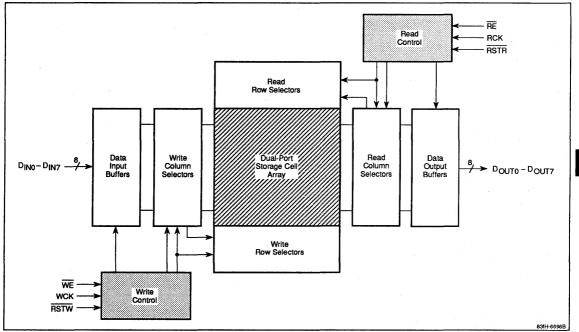

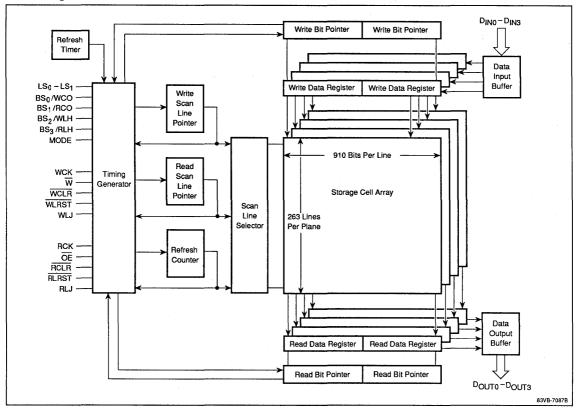

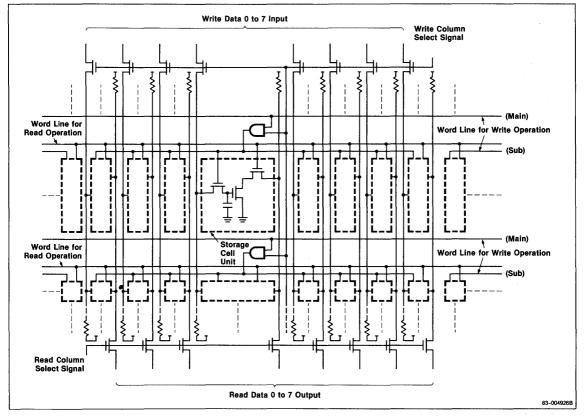

| 42101  | 910 x 8-bit line buffer for NTSC TV                 | 18a |

| 42102  | 1134 x 8-bit line buffer for PAL TV                 | 18b |

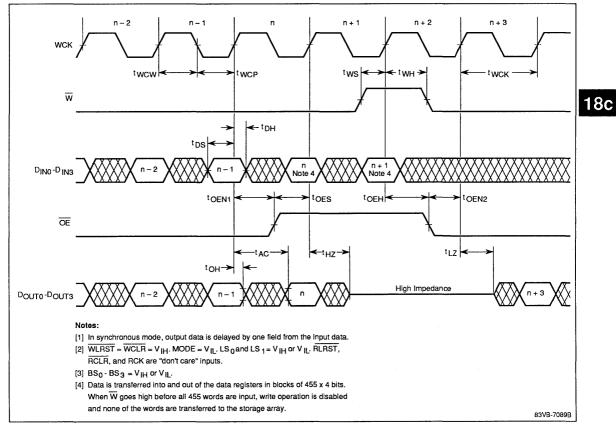

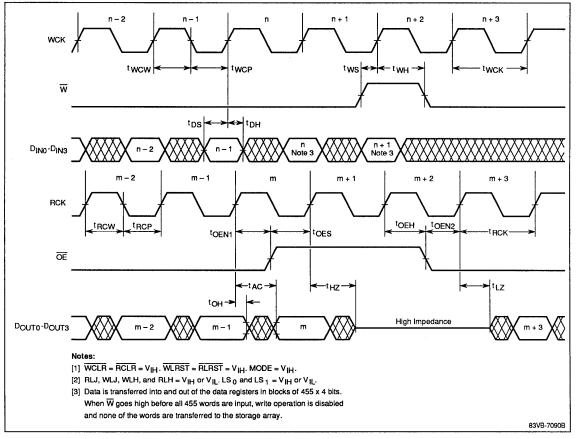

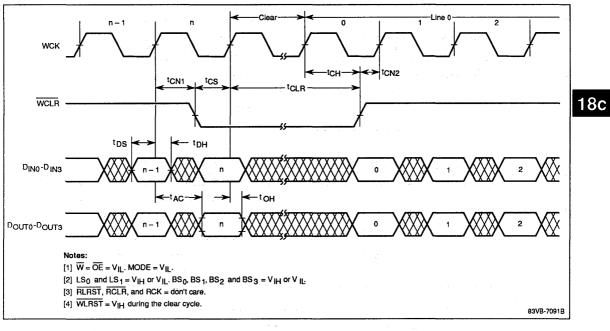

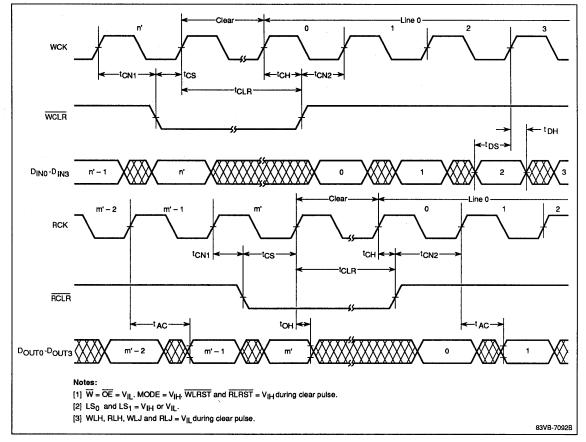

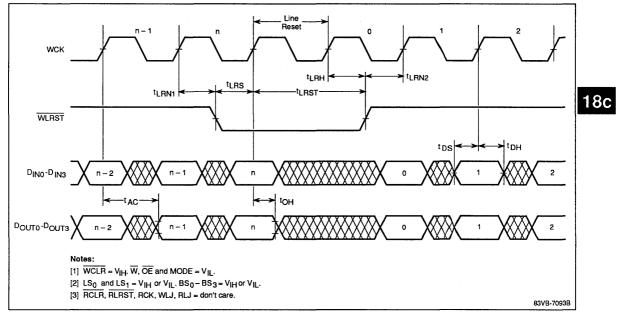

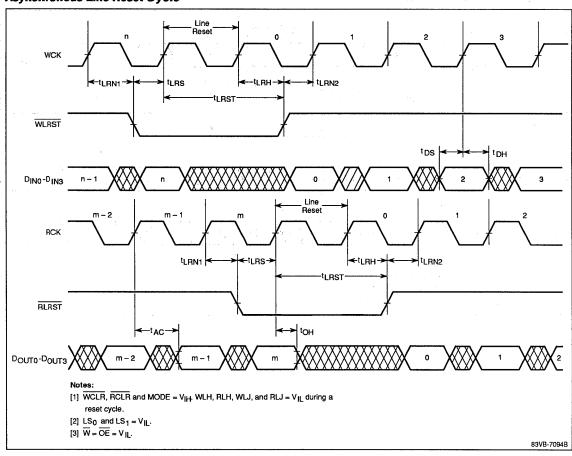

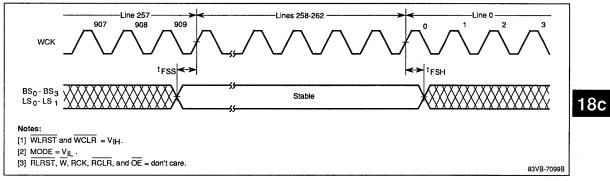

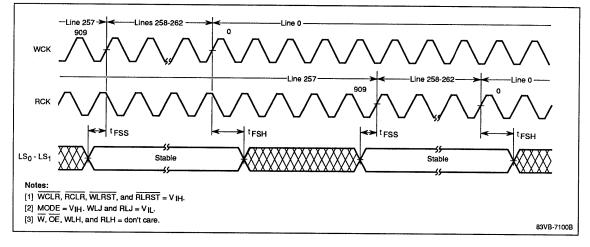

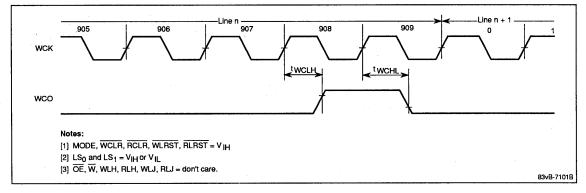

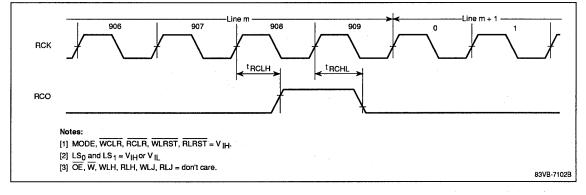

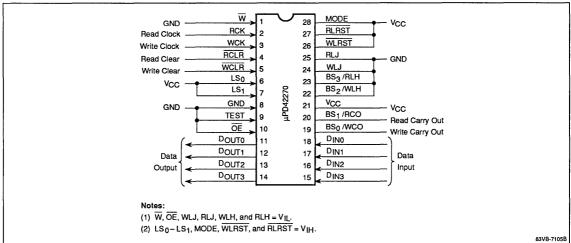

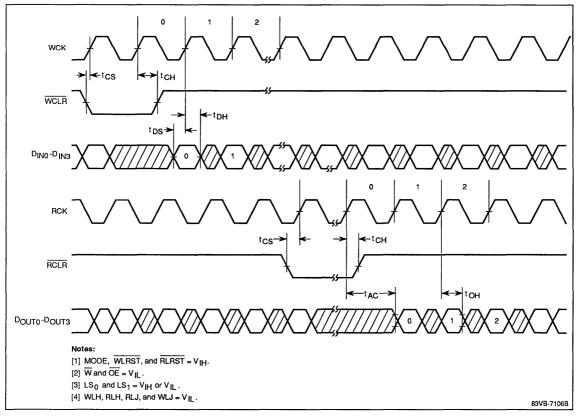

| 42270  | 263 lines of 910 x 4 bits NTSC field buffer         | 18c |

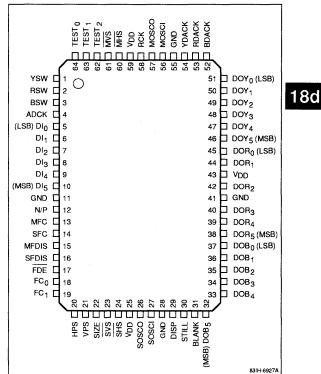

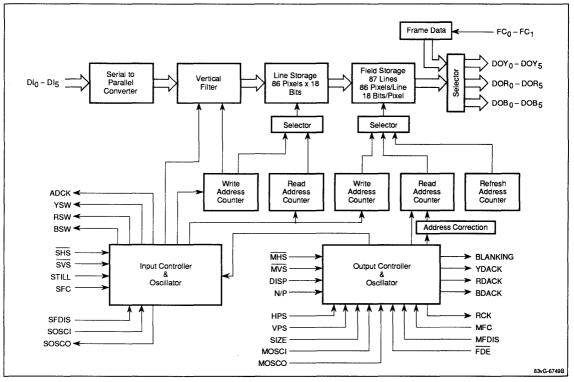

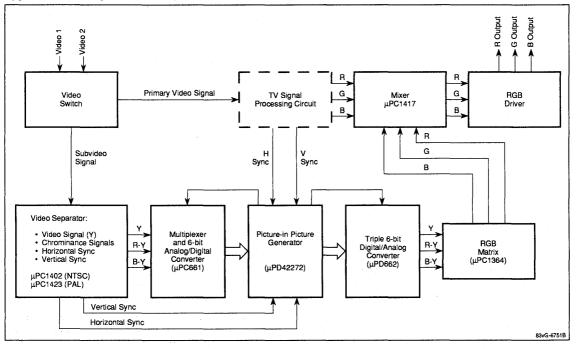

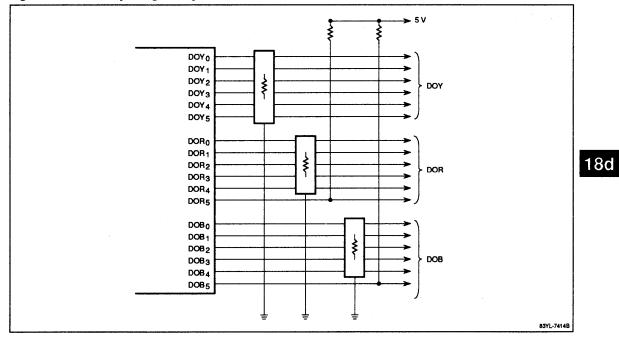

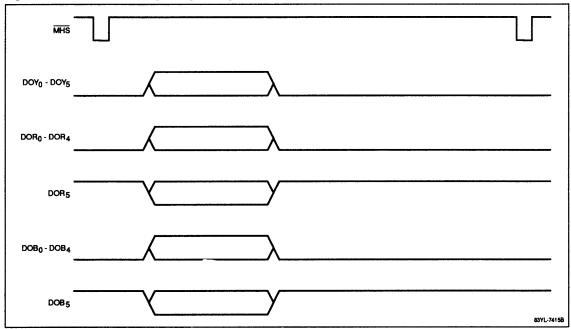

| 42271  | Picture-in-picture generator                        | 18d |

| 42272  | Picture-in-picture generator with color border      |     |

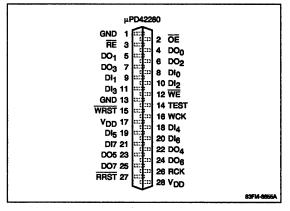

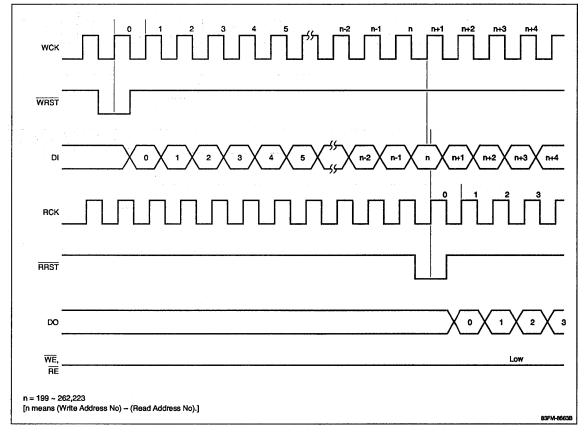

| 42280  | 256K x 8-bit field buffer                           | 18e |

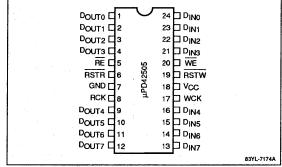

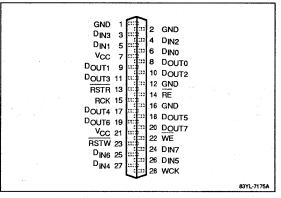

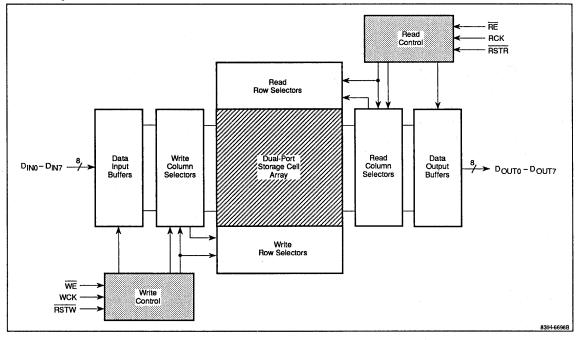

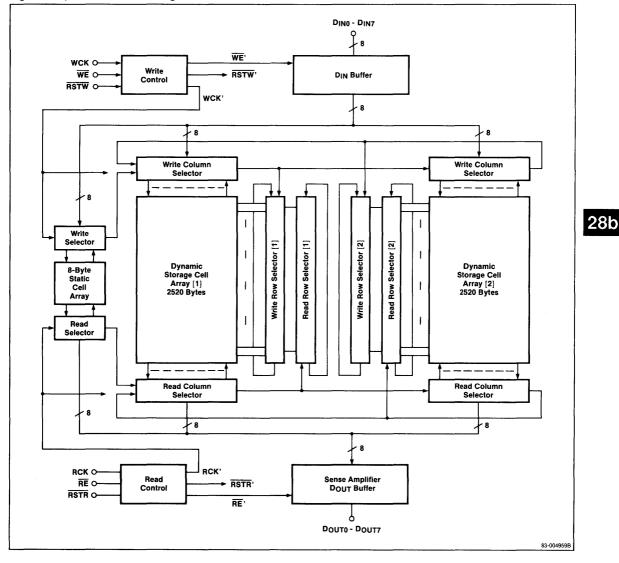

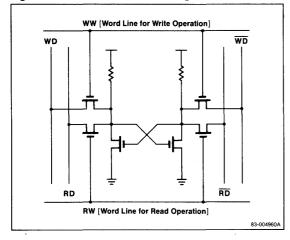

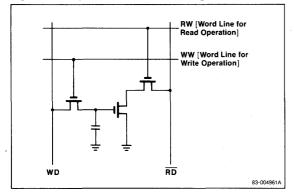

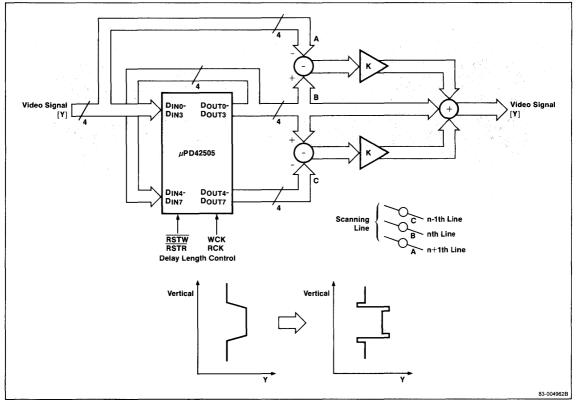

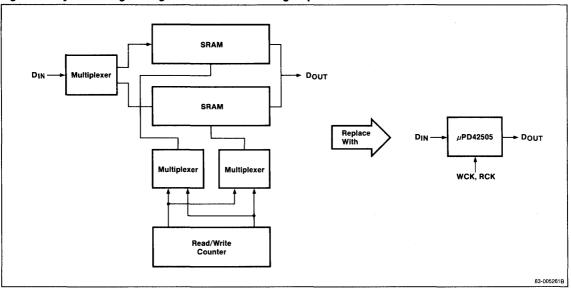

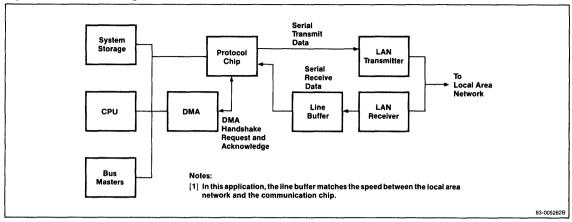

| 42505  | 5048 x 8-bit line buffer for communications systems |     |

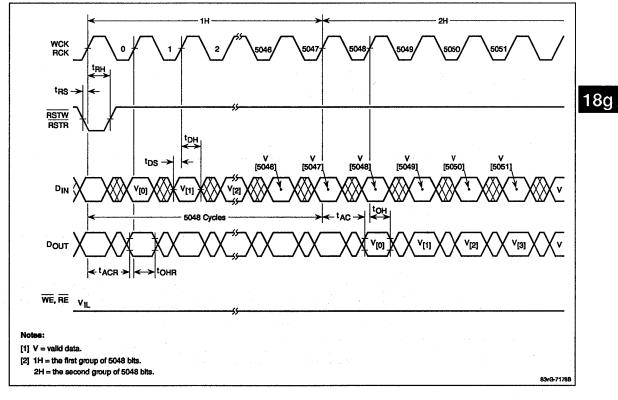

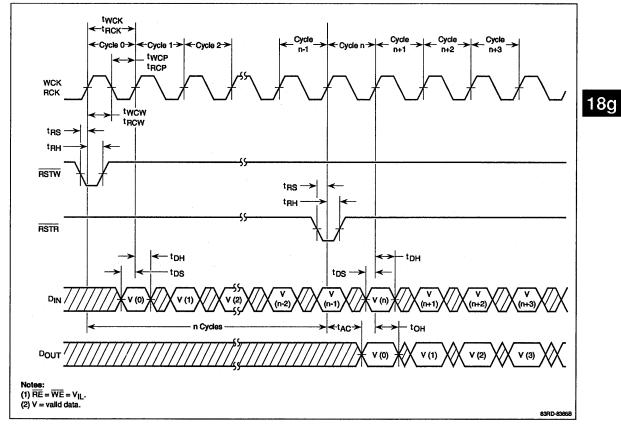

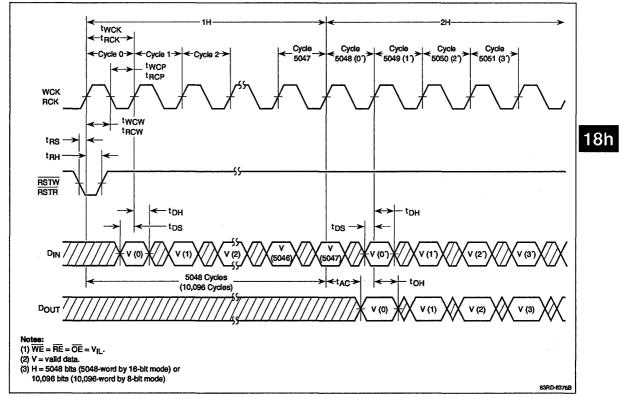

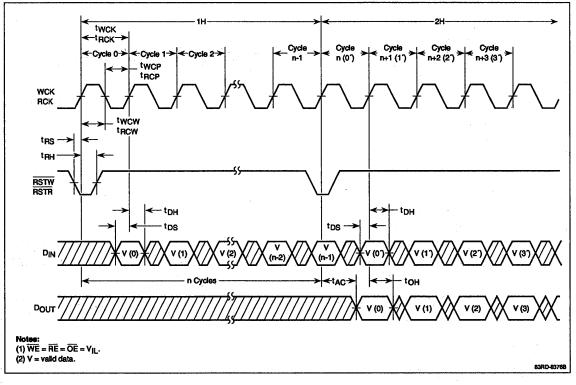

| 485505 | 5048 x 8-bit line buffer                            | 18g |

| 485506 | 5048 x 16 line buffer                               | 18h |

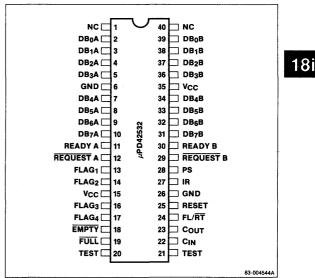

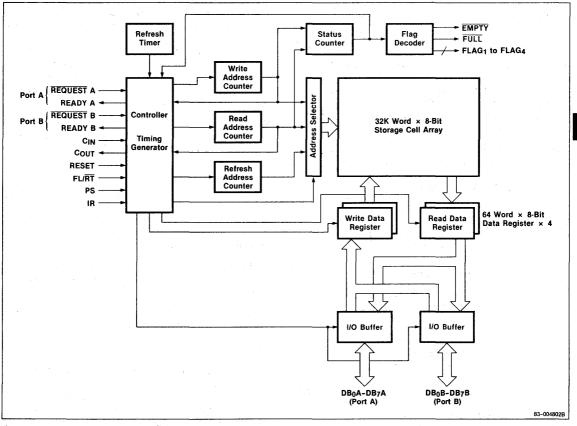

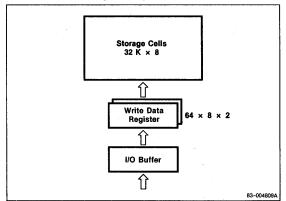

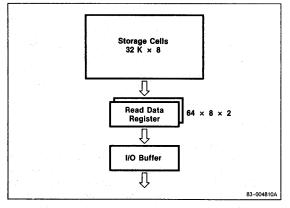

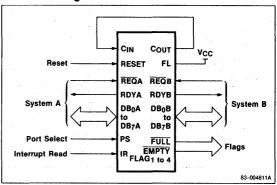

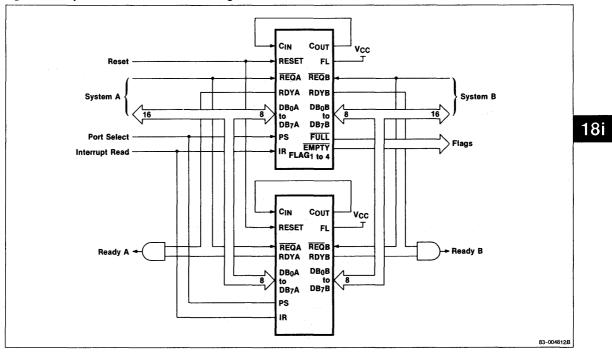

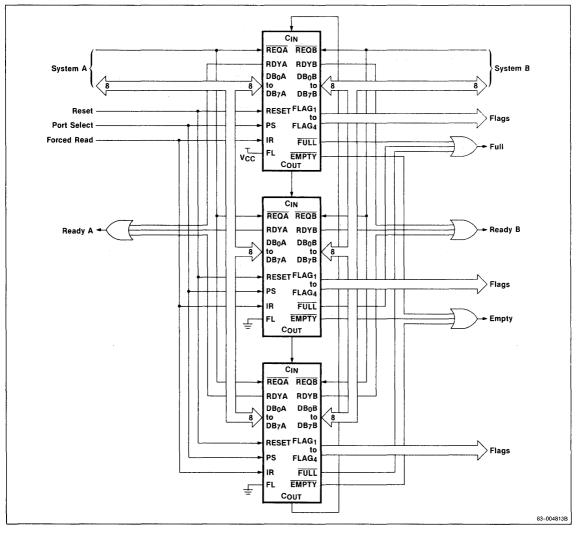

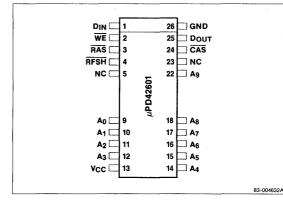

| 42532  | 32K x 8 bidirectional data buffer                   | 18i |

| 42601  | 1M x 1 silicon file                                 | 18j |

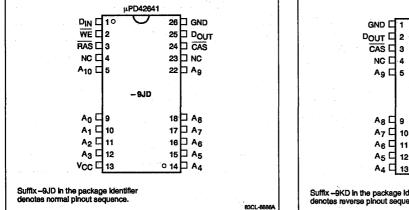

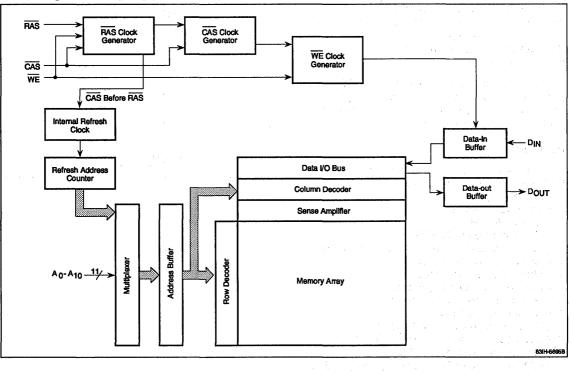

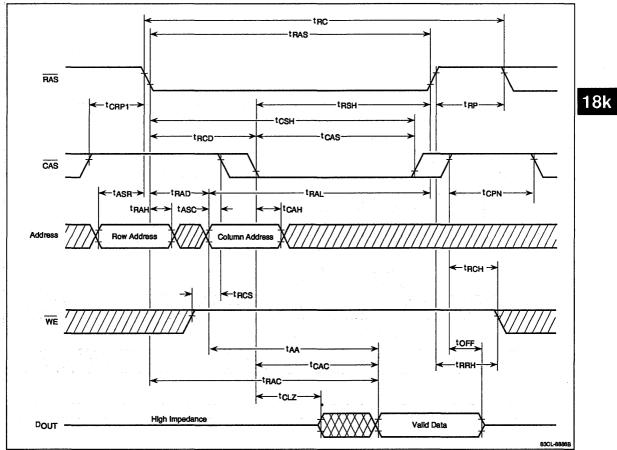

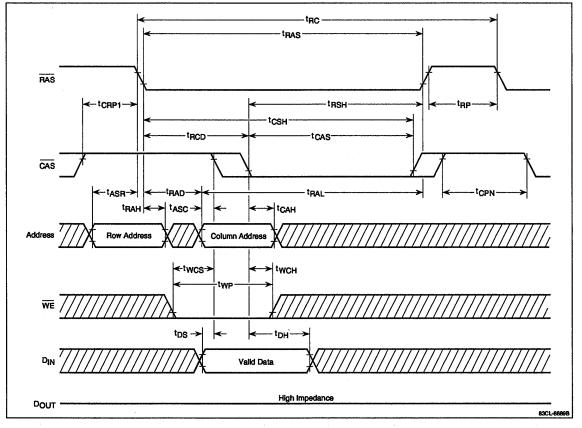

| 42641  | 4M x 1 silicon file                                 | 18k |

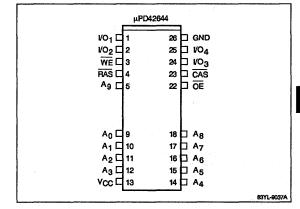

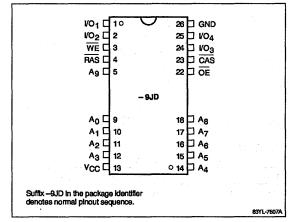

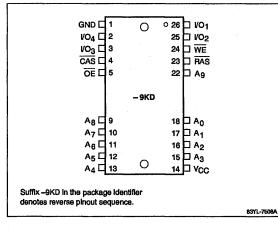

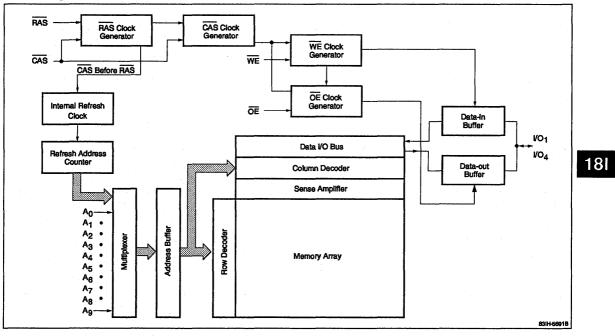

| 42644  | 1M x 4 silicon file                                 | 181 |

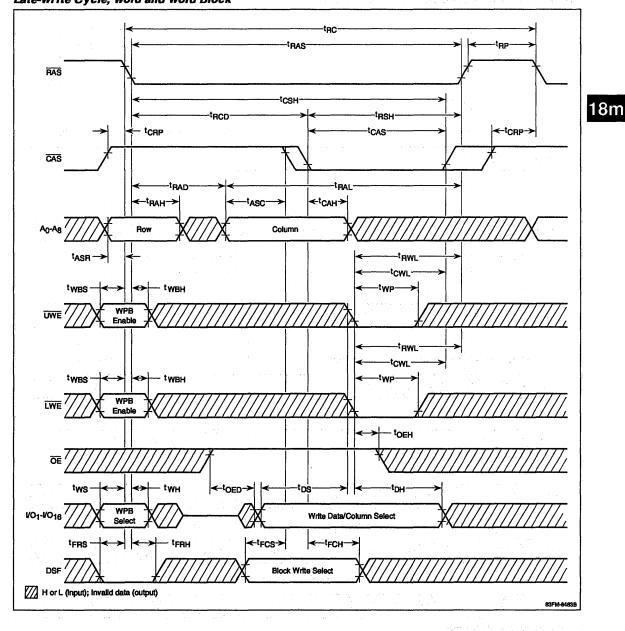

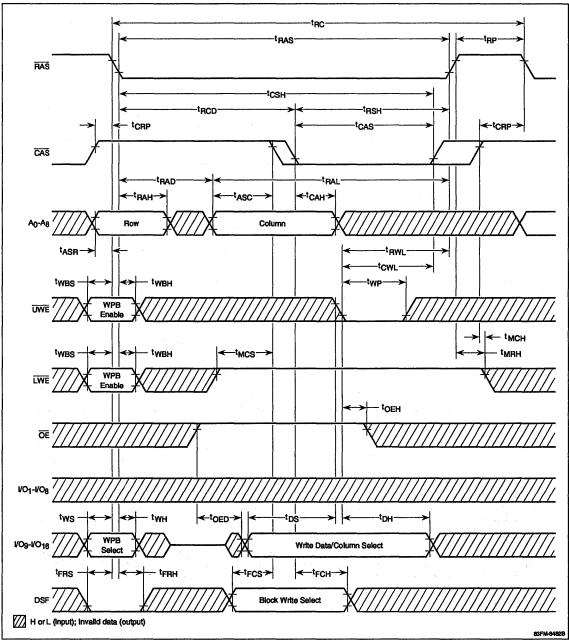

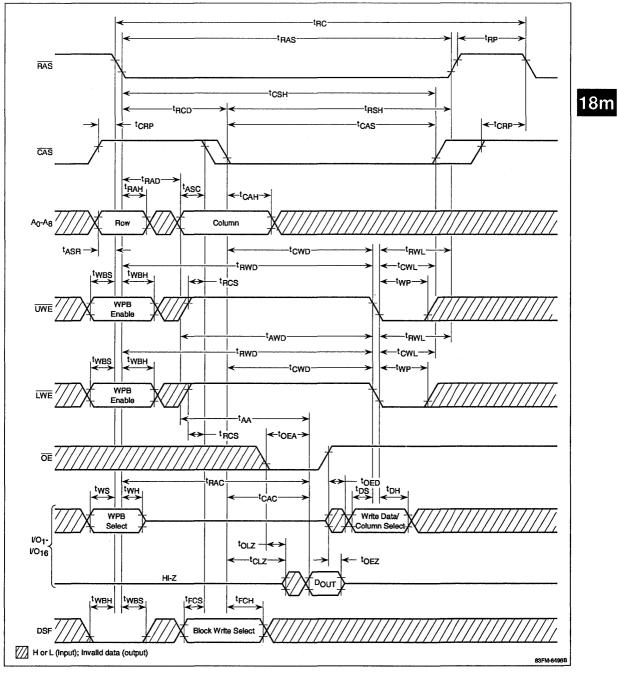

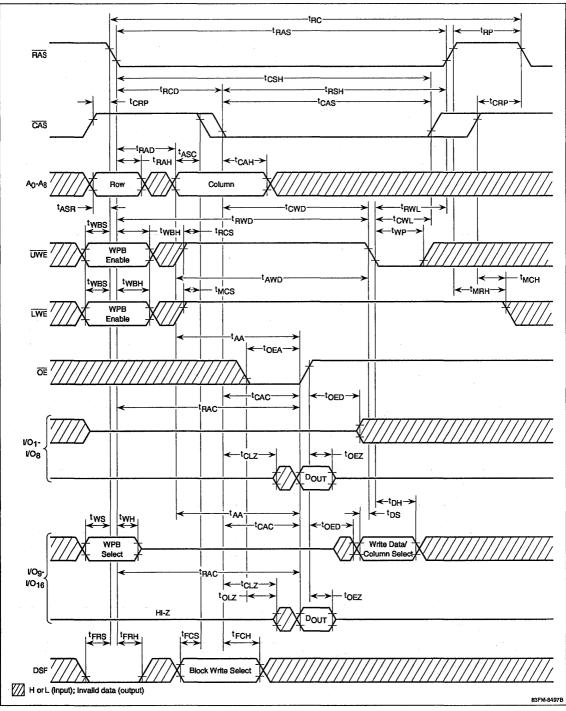

| 481440 | 256K x 16 graphics DRAM; hyper-page                 | 18m |

23b

## Volume 2 (cont)

| μPD                               | Organization                                 | Features                               | 1.54       |

|-----------------------------------|----------------------------------------------|----------------------------------------|------------|

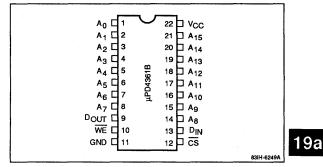

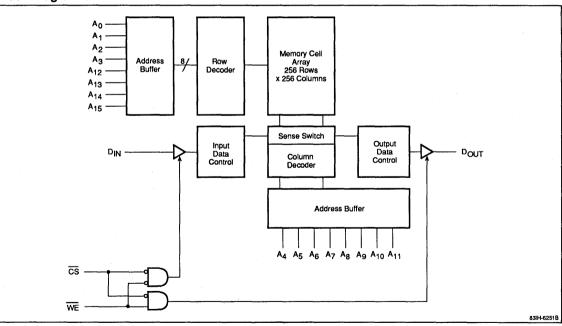

| 4361B                             | 64K x 1                                      | 12-ns entrance and the second second   | 19a        |

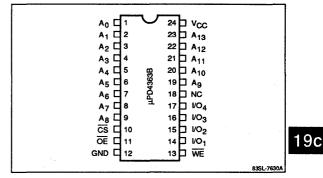

| 4362B                             | 16K x 4                                      | 12-ns all the regime to the            | 19b        |

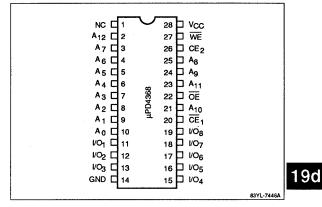

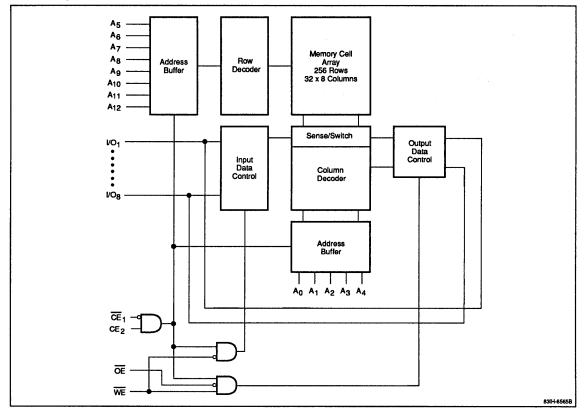

| 4363B                             | 16K x 4                                      | 12-ns; Output enable                   | 190        |

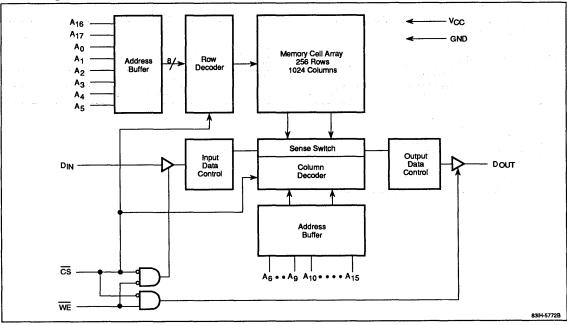

| 4368                              | 8K x 8                                       | 15-ns; Output enable, two chip enables | 190        |

| 4369                              | 8K x 9                                       | 15-ns; Output enable, two chip enables | 19e        |

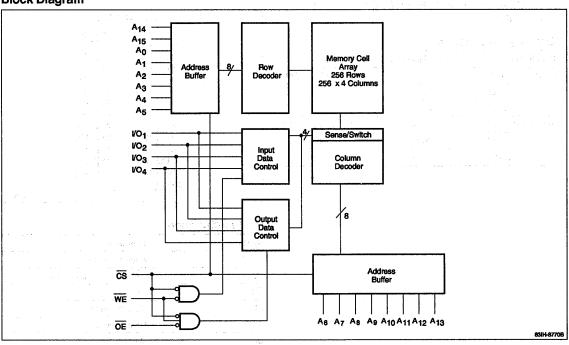

| Section 20.                       | Fast Static RAMs (256K)                      |                                        | 1          |

| μPD                               | Organization                                 | Features                               |            |

| 43251B                            | 256K x 1                                     | 15-ns                                  | 20a        |

| 43253B                            | 64K x 4                                      | 15-ns; Output enable                   | 20b        |

| 43254B                            | 64K x 4                                      | 15-ns                                  | 200        |

| 43258A                            | 32K x 8                                      | 15-ns; Output enable                   | 200        |

| 43259A                            | 32K x 9                                      | 15-ns; Output enable                   | 206        |

| Section 21.                       | Fast Static RAMs (1M)                        |                                        |            |

| μPD                               | Organization                                 |                                        |            |

| 431001                            | 1M x 1                                       | 20-ns                                  | 21a        |

| 431004                            | 256K x 4                                     | 20-ns                                  | 21b        |

| 431008                            | 128K x 8                                     | 15-ns; Output enable                   | 210        |

| 431009                            | 128K x 9                                     | 15-ns; Output enable                   | 210        |

| 431016                            | 64K x 16                                     | 15-ns; Output enable                   | 216        |

| 431018                            | 64K x 18                                     | 15-ns; Output enable                   | 21         |

|                                   | Fast Static RAMs (4M)                        |                                        |            |

| Section 22.                       |                                              |                                        |            |

|                                   | Organization                                 |                                        |            |

|                                   |                                              | 20-ns                                  | 228        |

| μ <b>PD</b><br>434001             | Organization                                 | 20-ns<br>20-ns; Output enable          | 22a<br>22t |

| μPD                               | Organization<br>4M x 1                       |                                        |            |

| μPD<br>434001<br>434004<br>434008 | Organization<br>4M x 1<br>1M x 4             | 20-ns; Output enable                   | 22t        |

| μPD<br>434001<br>434004<br>434008 | Organization<br>4M x 1<br>1M x 4<br>512K x 8 | 20-ns; Output enable                   | 22t        |

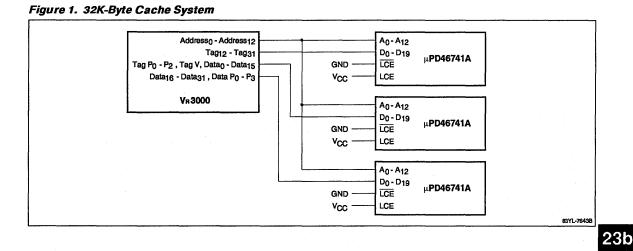

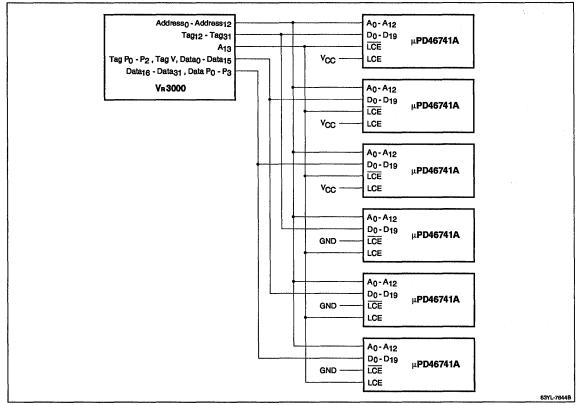

Cache data; 12-ns

46741A

8K x 20 bit x 2

| Section 24. Standard Static RAMs (S | See App Notes 50, 90-04.) |

|-------------------------------------|---------------------------|

|-------------------------------------|---------------------------|

| μPD       | Organization | $\mathbb{P}^{(1,1)} = \mathbb{P}^{(1,1)}$ | - 1 g |

|-----------|--------------|-------------------------------------------|-------|

| 43256A    | 32K x 8      | 85-ns; Output enable                      | 24a   |

| 43256B    | 32K x 8      | 55-ns; Output enable                      | 24b   |

| 431000A   | 128K x 8     | 70-ns; Output enable, two chip enables    |       |

| 434000    | 512K x 8     | 55-ns; Output enable                      |       |

| MC-434000 | 512K x 8     | Module; 85-ns; Output enable              | 24e   |

|           |              |                                           |       |

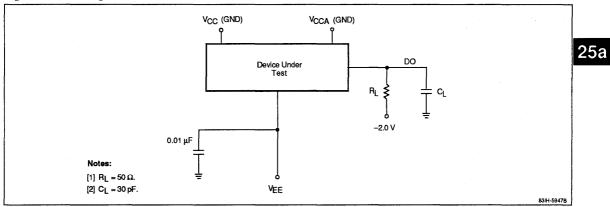

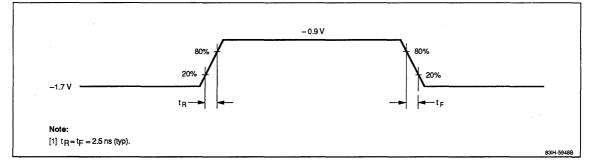

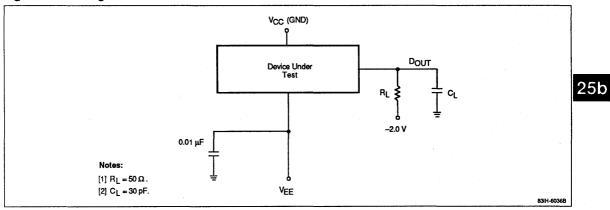

## Section 25. ECL RAMs (10K Interface)

| μPB               | Organization         | Features      | 9. a.e. |

|-------------------|----------------------|---------------|---------|

| 10422             | 256 x 4              | 7-ns          | 25a     |

| 10470             | 4K x 1               | 10-ns         | 25b     |

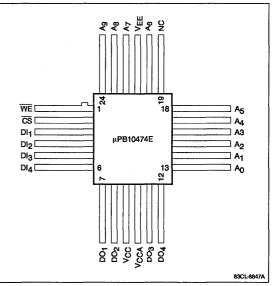

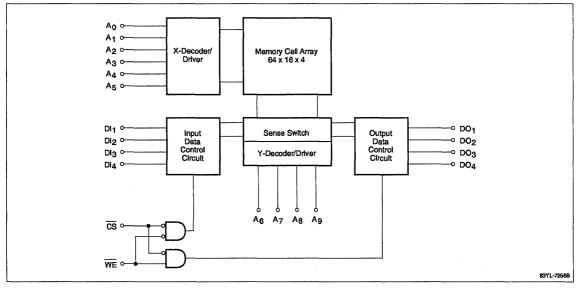

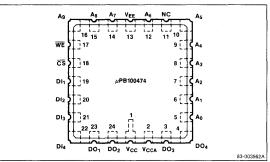

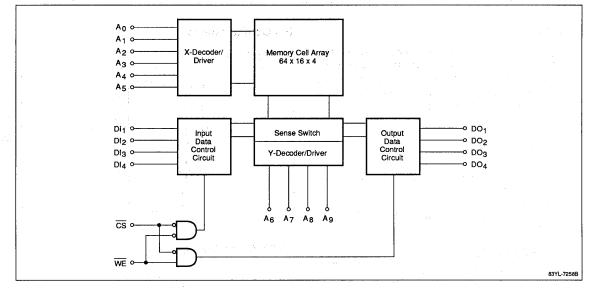

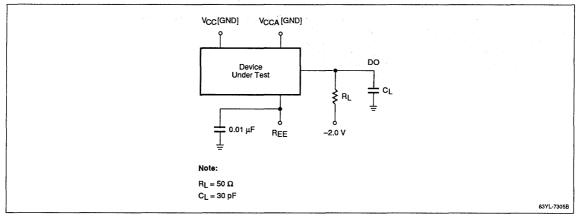

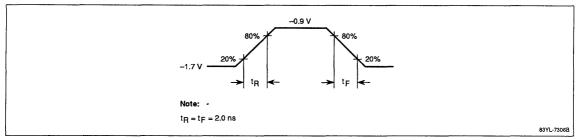

| 10474             | 1K x 4               | 8-ns          | 250     |

| 10474A            | 1K x 4               | 5-ns          | 25d     |

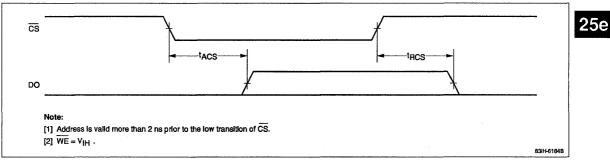

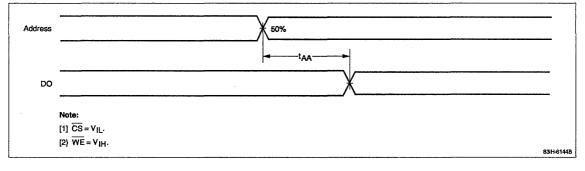

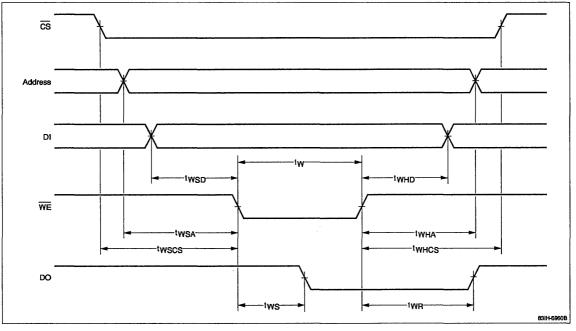

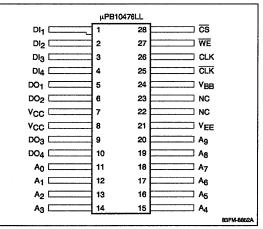

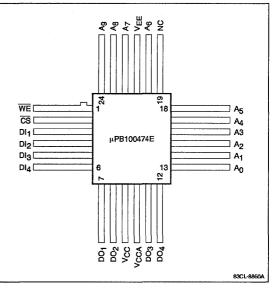

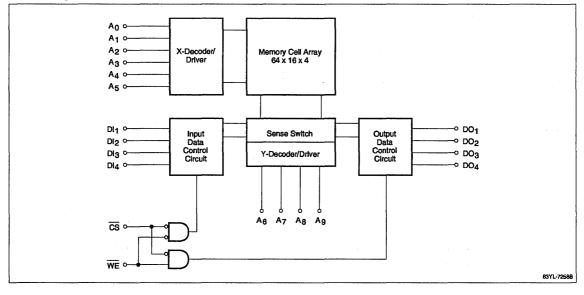

| 10474E            | 1K x 4               | 3-ns          | 25e     |

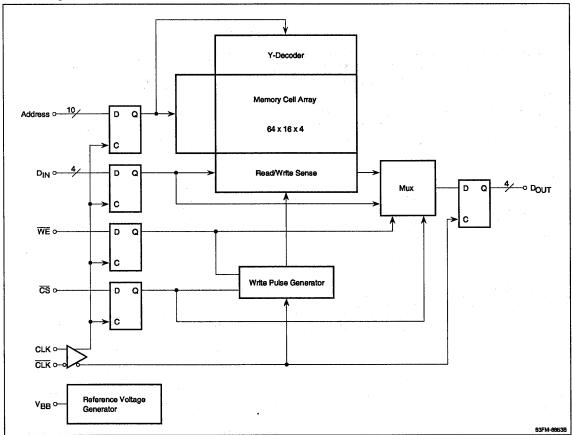

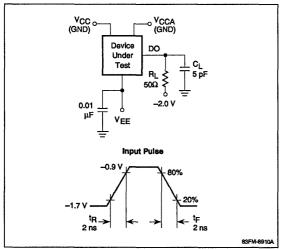

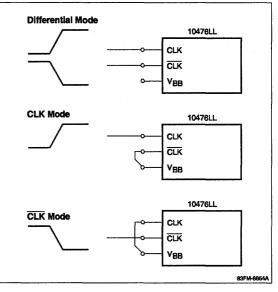

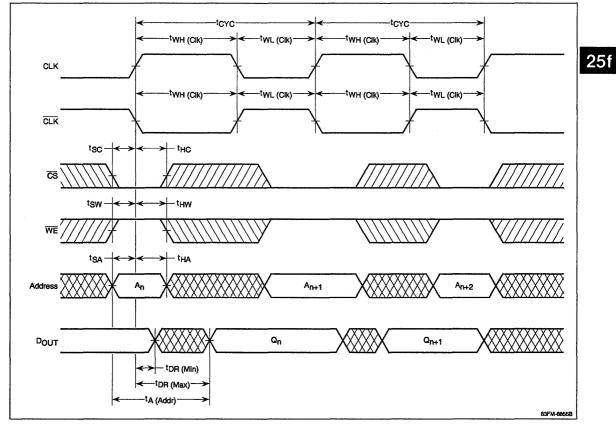

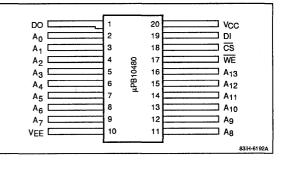

| 10476LL           | 1K x 4               | 6-ns          | 25f     |

| 10480             | 16K x 1              | 10-ns         | 25g     |

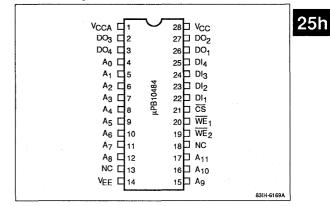

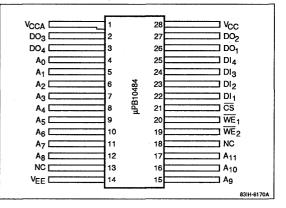

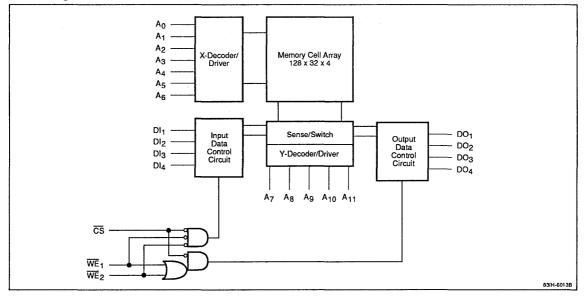

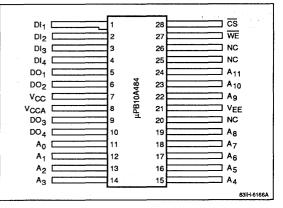

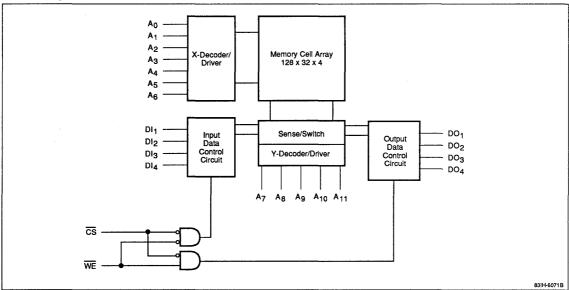

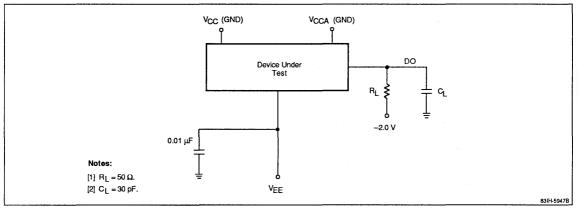

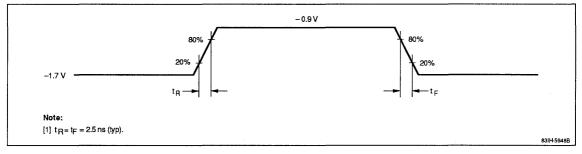

| 10484             | 4K x 4               | 10-ns         | 25h     |

| 10484A            | 4K x 4               | 5-ns          | 25i     |

| 10A484            | 4K x 4               | 5-ns          | 25j     |

| µPD10500          | 256K x 1             | 15-ns; BiCMOS | 25k     |

| Section 26. ECL R | AMs (100K Interface) |               |         |

### Section 26. ECL RAMs (100K Interface)

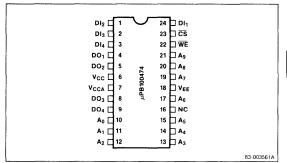

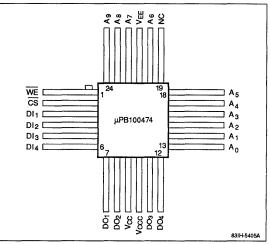

| μPB       | Organization | Features      |     |

|-----------|--------------|---------------|-----|

| 100422    | 256 x 4      | 7-ns          | 26a |

| 100470    | 4K x 1       | 10-ns         | 26b |

| 100474    | 1K x 4       | 4.5-ns        | 26c |

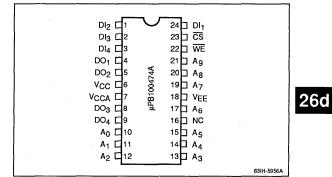

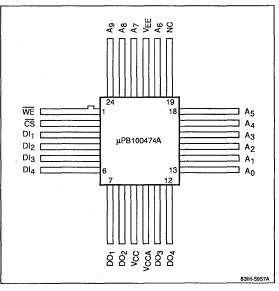

| 100474A   | 1K x 4       | 5-ns          | 26d |

| 100474E   | 1K x 4       | 3-ns          | 26e |

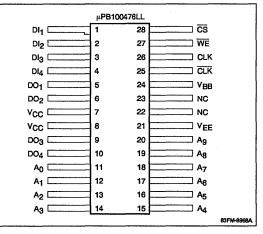

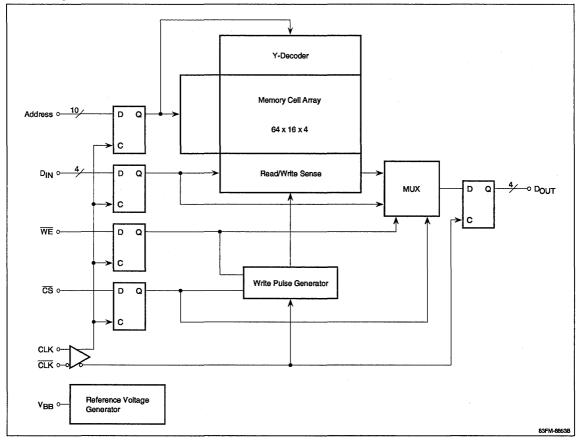

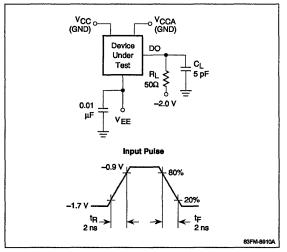

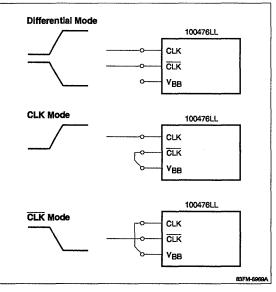

| 100476LL  | 1K x 4       | 6-ns          | 26f |

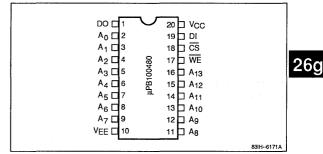

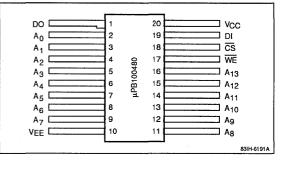

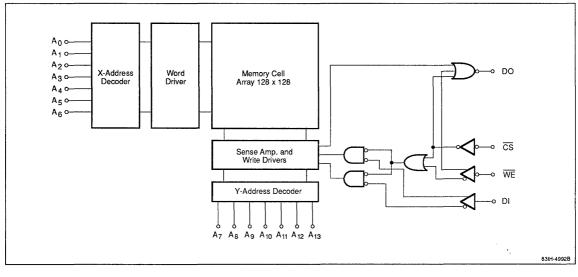

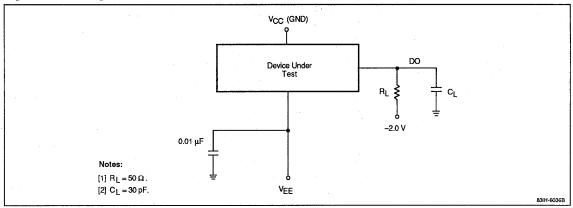

| 100480    | 16K x 1      | 10-ns         | 26g |

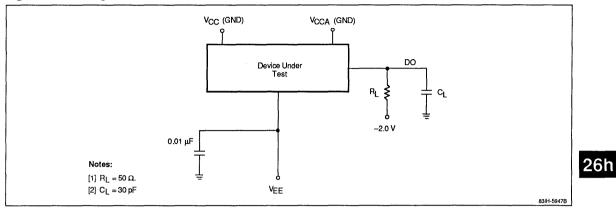

| 100484    | 4K x 4       | 10-ns         | 26h |

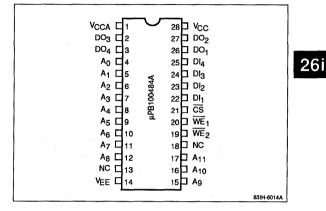

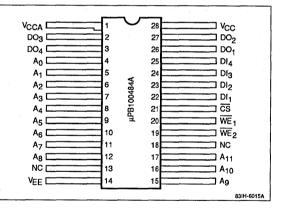

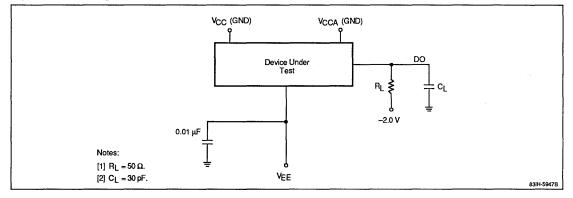

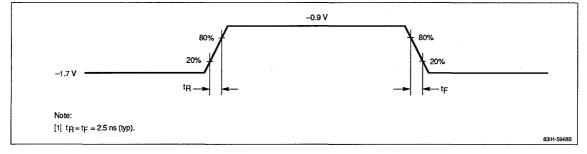

| 100484A   | 4K x 4       | 5-ns          | 26i |

| 100A484   | 4K x 4       | 5-ns          | 26j |

| μPD100500 | 256K x 1     | 15-ns; BiCMOS | 26k |

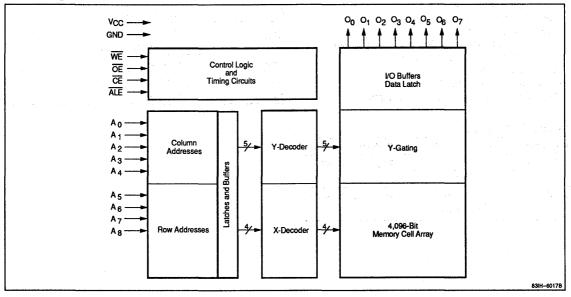

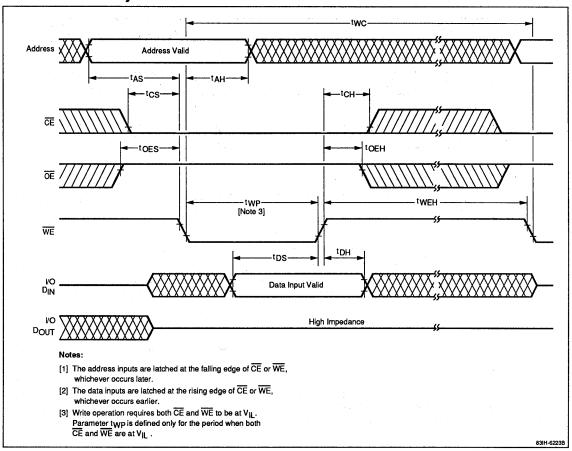

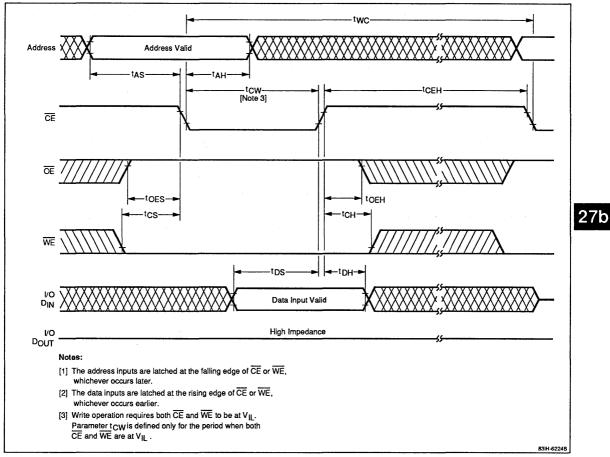

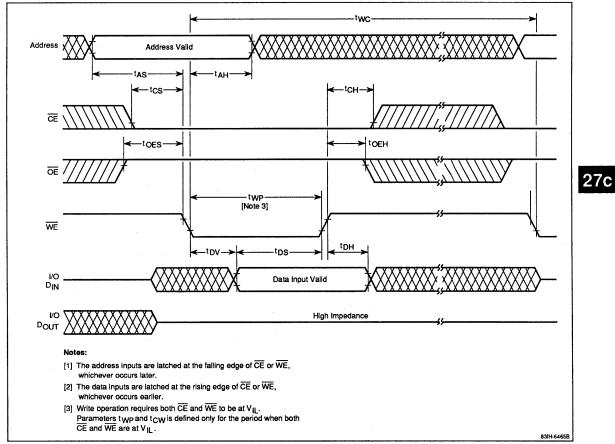

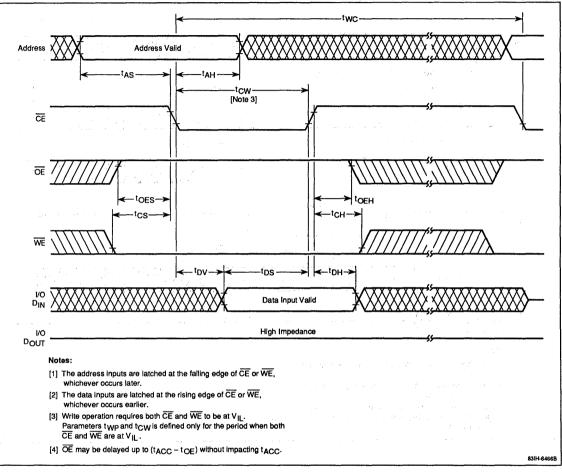

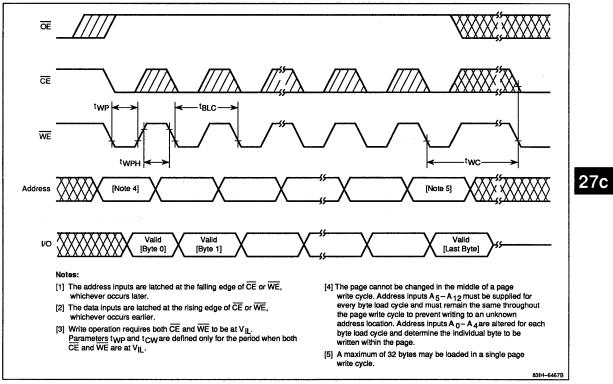

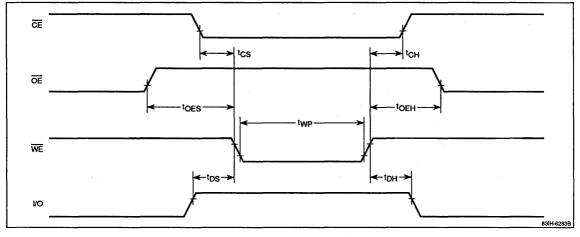

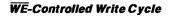

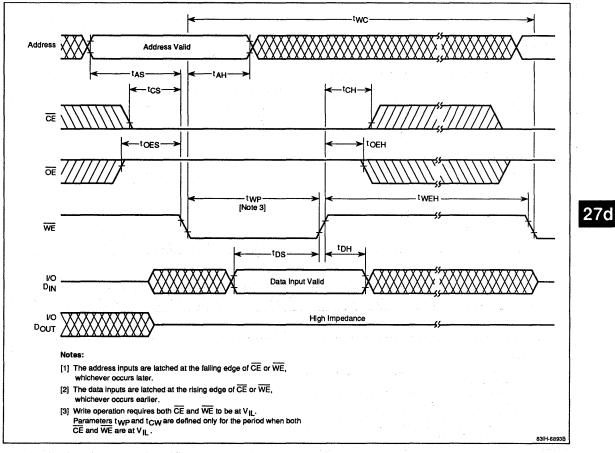

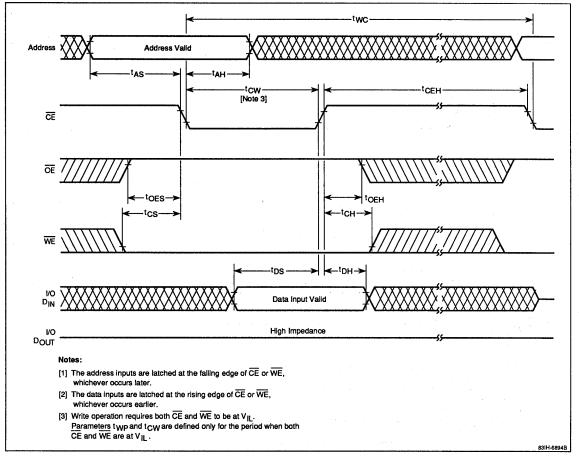

### Section 27. EEPROMs

| μPD    | Organization | · · |

|--------|--------------|-----|

| 28C04  | 512 x 8      | 27a |

| 28C05  | 512 x 8      | 27b |

| 28C64  | 8K x 8       | 27c |

| 28C256 | 32K x 8      | 27d |

### Section 28. Application Notes

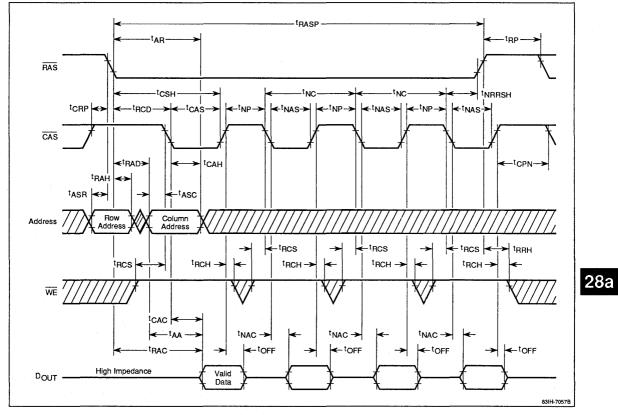

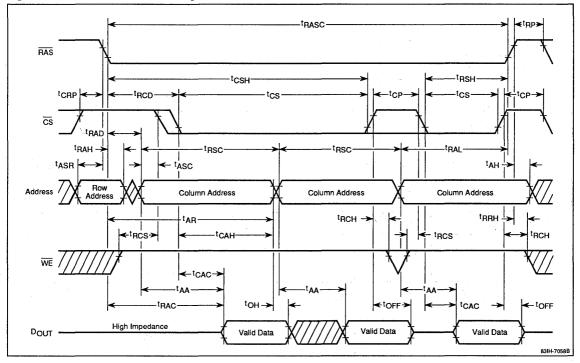

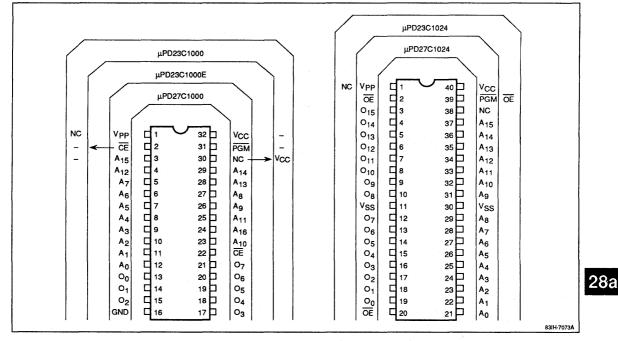

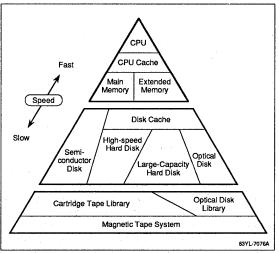

| App Note 90-03 | Memory Systems Overview                                                                    | 28a |

|----------------|--------------------------------------------------------------------------------------------|-----|

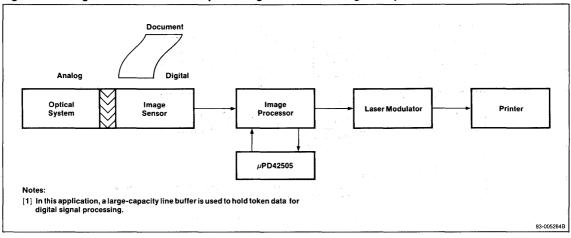

| App Note 54    | µPD42505 Line Buffer for Communications Systems                                            |     |

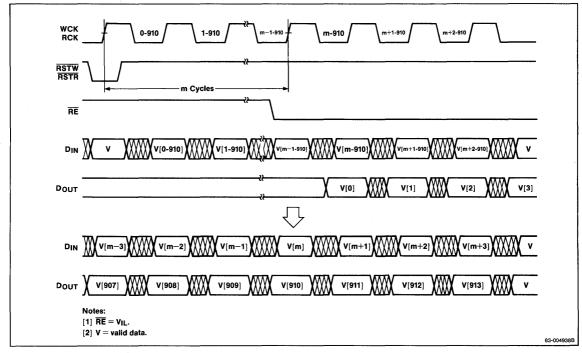

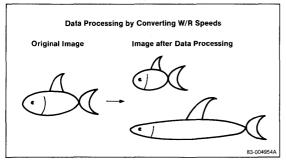

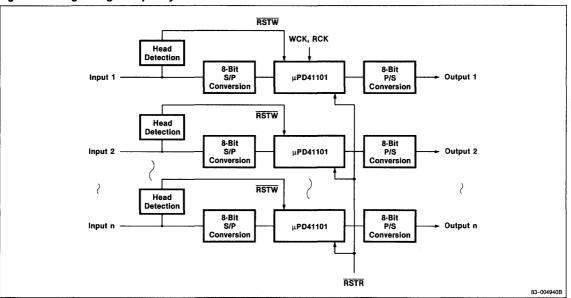

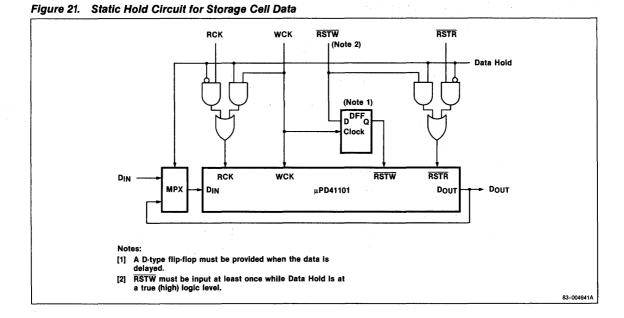

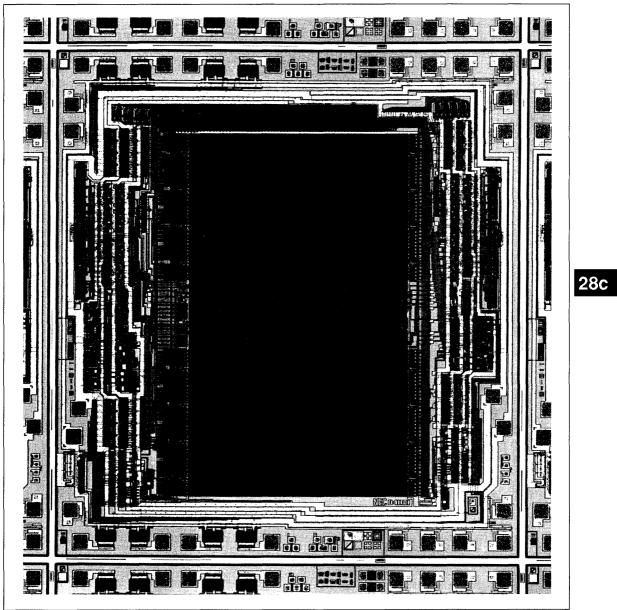

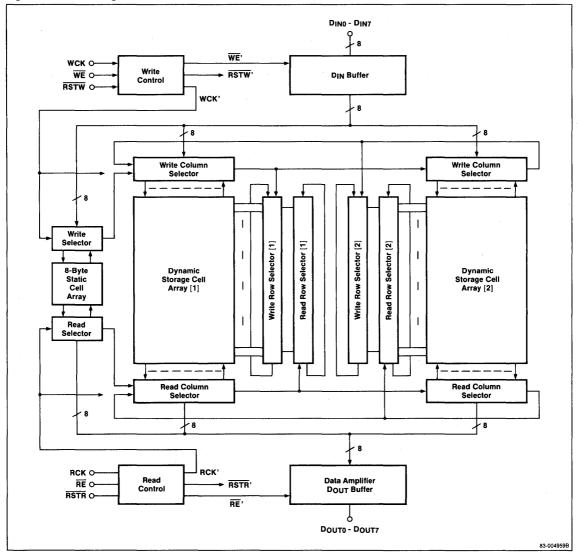

| App Note 55    | µPD42101/42102 High-Speed Line Buffers                                                     | 28c |

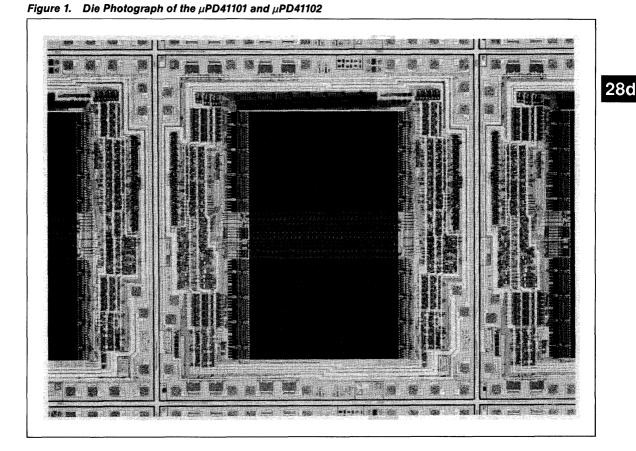

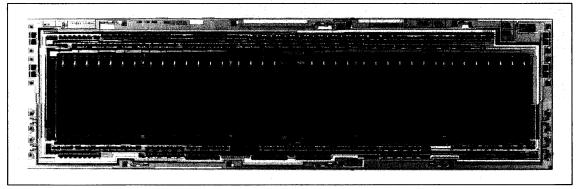

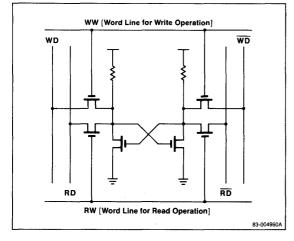

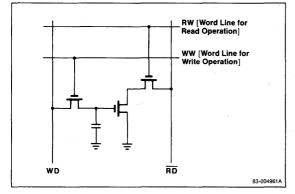

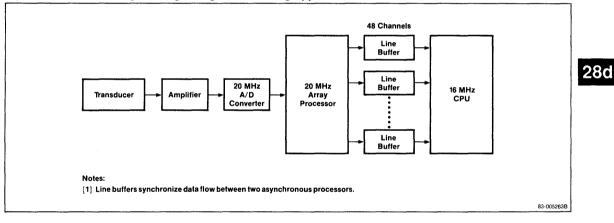

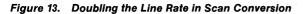

| App Note 57    | μPD42101/42102/42505 High-Speed Line Buffers                                               | 28d |

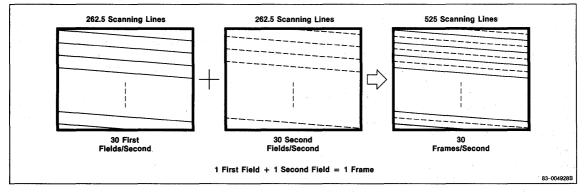

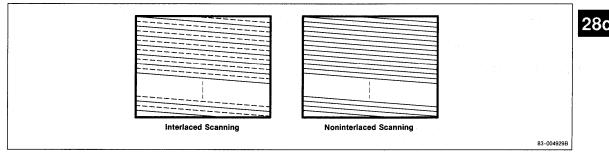

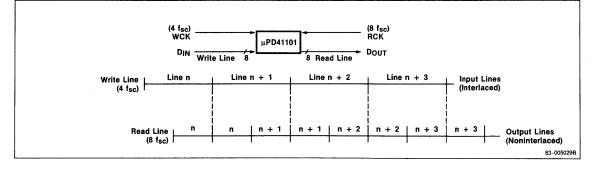

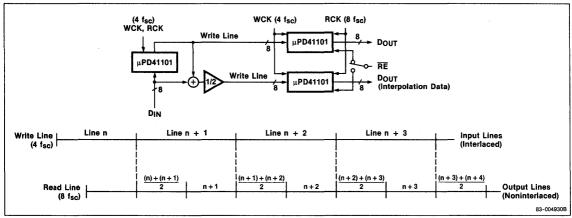

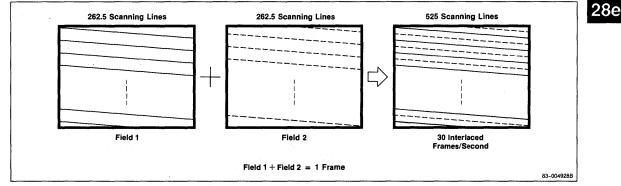

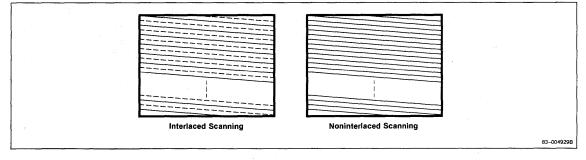

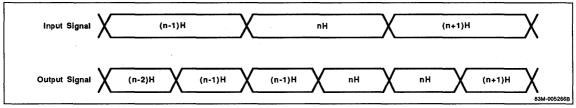

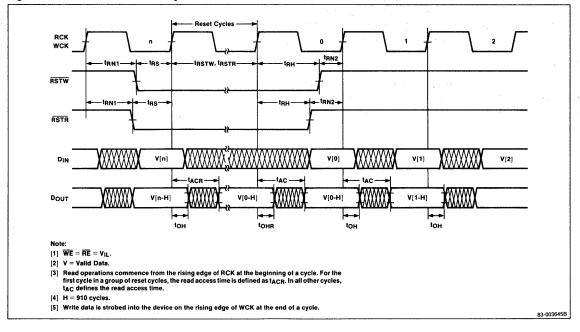

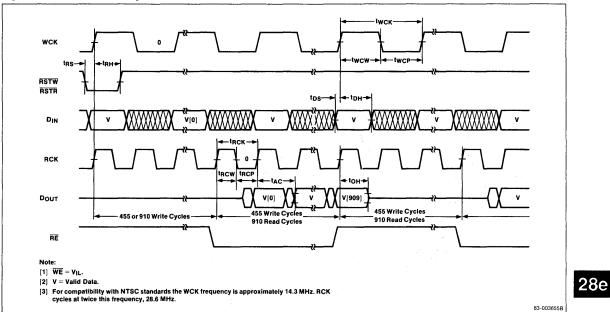

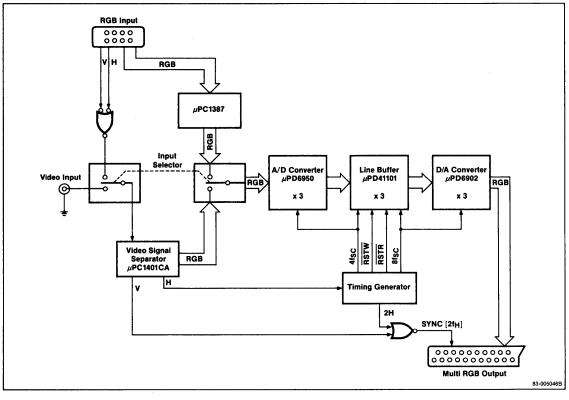

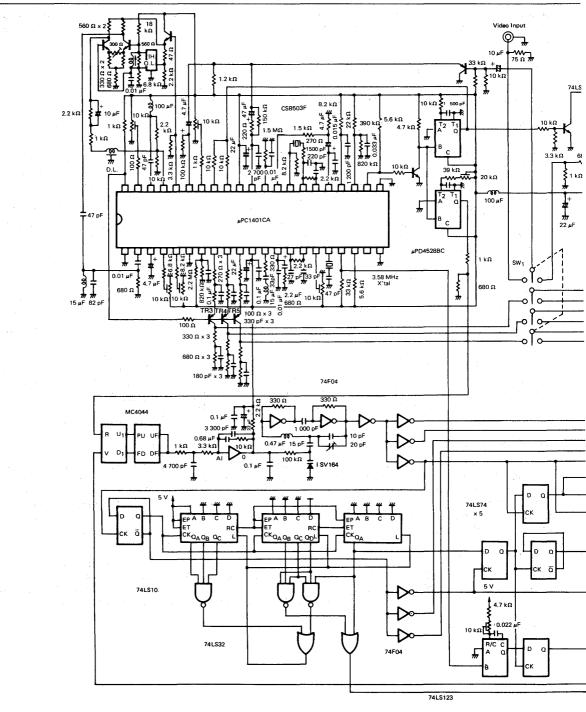

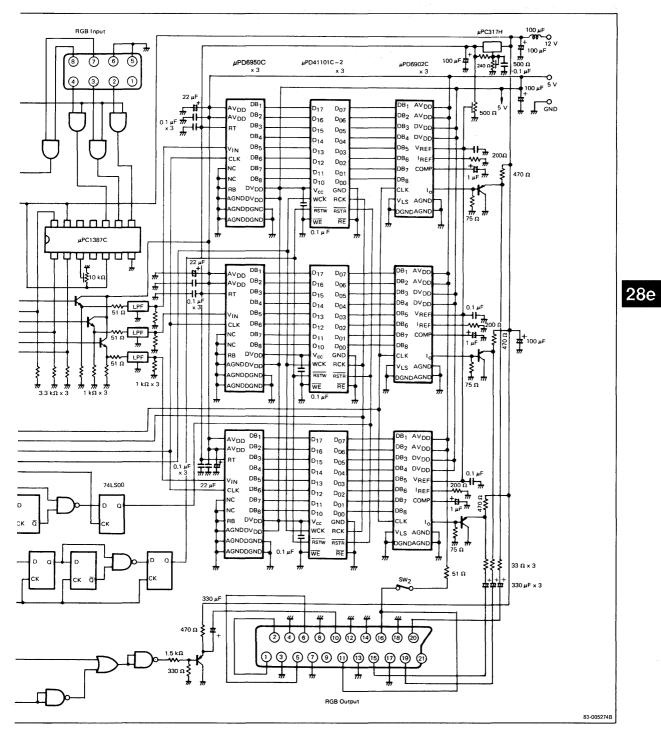

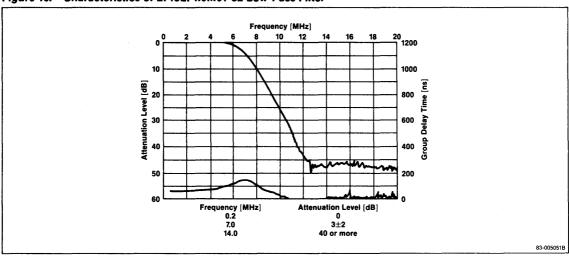

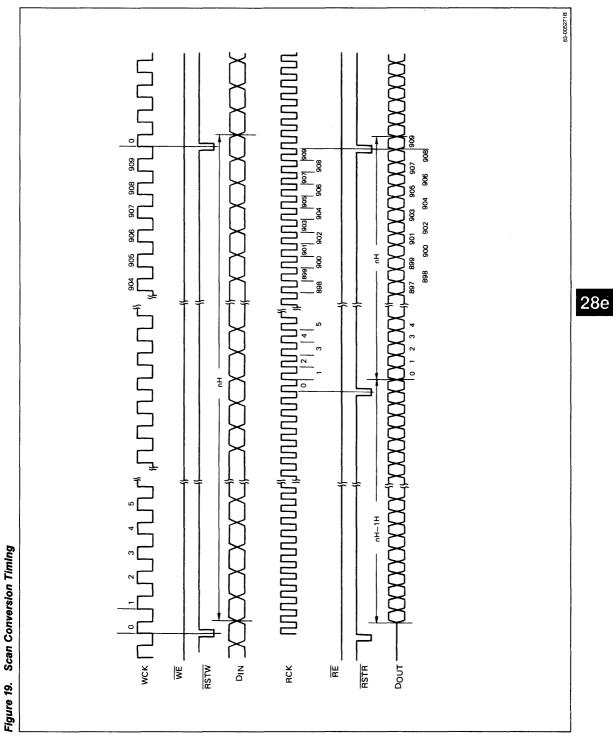

| App Note 58    | Interlaced to Noninterlaced Scan Conversion Using the $\mu$ PD42101 High-Speed Line Buffer | 28e |

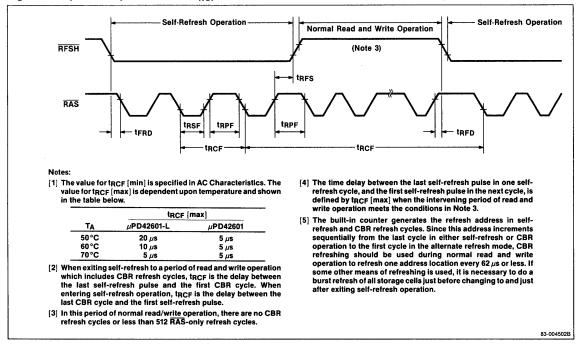

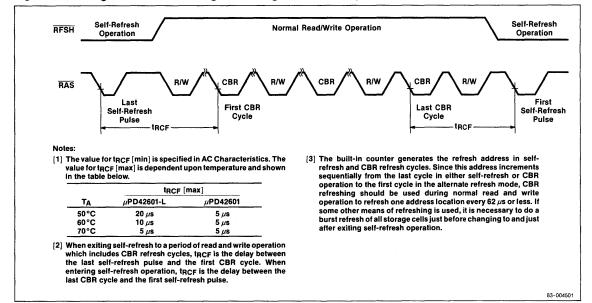

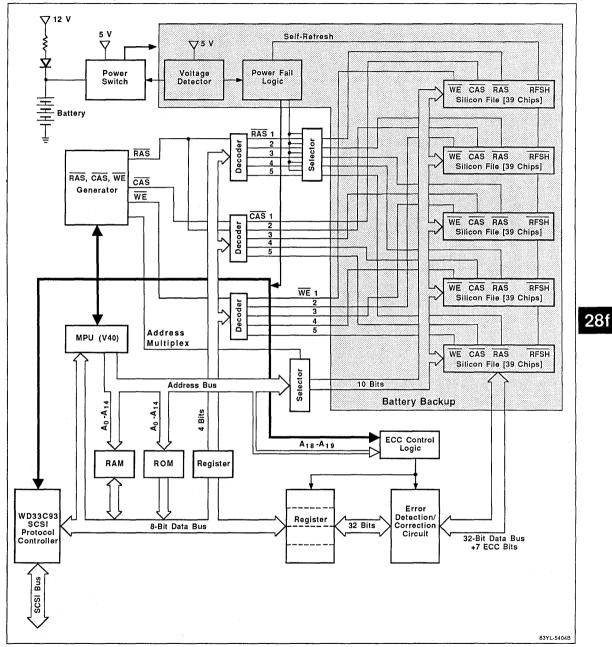

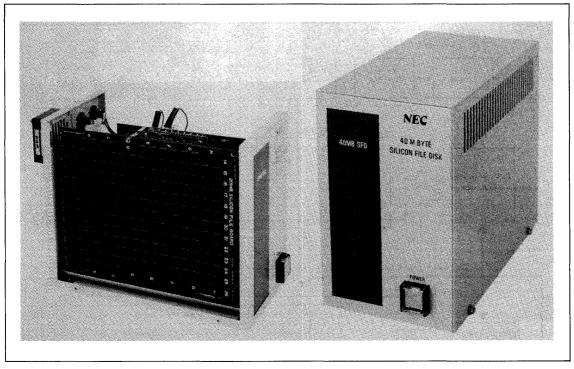

| App Note 56    | μPD42601 Silicon File                                                                      | 28f |

| App Note 90-06 | Silicon File System Architecture                                                           | 28g |