16-BIT V-SERIES MICROPROCESSOR DATA BOOK

# 1990 16-Bit V-Series Microprocessor Data Book

May 1990

Document No. 50054

© 1990 NEC Electronics Inc./Printed in U.S.A.

No part of this document may be copied or reproduced in any form or by any means without the prior written consent of NEC Electronics Inc. The information in this document is subject to change without notice. Devices sold by NEC Electronics Inc. are covered by the warranty and patent indemnification provisions appearing in NEC Electronics Inc. Terms and Conditions of Sale only. NEC Electronics Inc. makes no warranty, express, statutory, implied, or by description, regarding the information set forth herein or regarding the freedom of the described devices from patent infringement. NEC Electronics Inc. makes no warranty of merchantability or fitness for any purpose. NEC Electronics Inc. assumes no responsibility for any errors that may appear in this document. NEC Electronics Inc. makes no commitment to update or to keep current the information contained in this document.

| Reliability and Quality Control |

|---------------------------------|

| 16-Bit CPUs                     |

| 16-Bit Microcomputers           |

| Peripherals for CPUs            |

| Development Tools               |

| Package Drawings                |

**Selection Guides**

6

| Section 1<br>Selection Guides                |      | Section 2 Reliability and Quality Control (cont)          |      |

|----------------------------------------------|------|-----------------------------------------------------------|------|

| Single-Chip Microcomputers                   | 1-3  | Figure 6. NEC Quality and Reliability Targets             | 2-10 |

| μPD75XX Series Development Tools             | 1-7  | Appendix 1. Typical QC Flow                               | 2-12 |

| μPD75XXX Series Development Tools            | 1-9  | Appendix 2. Typical Reliability Assurance Tests           | 2-15 |

| μPD78XX Series Development Tools             | 1-11 | Appendix 3. New Product/Process Change                    | 2-16 |

| μPD782XX Series Development Tools            | 1-13 | Tests                                                     |      |

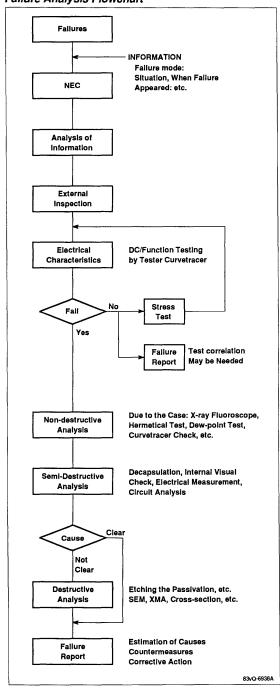

| μPD783XX Series Development Tools            | 1-15 | Appendix 4. Failure Analysis Flowchart                    | 2-17 |

| PG-1500 Programming Adapters                 | 1-17 |                                                           |      |

| V-Series Microprocessors and Peripherals     | 1-19 | Section 3                                                 |      |

| Intelligent Peripheral Devices (IPD)         | 1-23 | 16-Bit CPUs                                               |      |

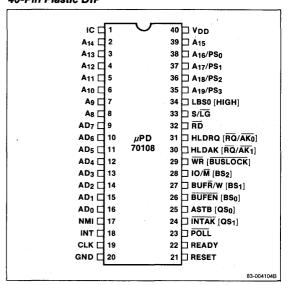

| DSP and Speech Products                      | 1-25 | μPD70108 (V20)<br>8/16-Bit Microprocessor:                | 3a   |

| V-Series Development Tools                   | 1-27 | High-Performance, CMOS                                    |      |

| DSP and Speech Development Tools             | 1-31 | μPD70116 (V30)                                            | 3b   |

|                                              |      | 16-Bit Microprocessor:<br>High-Performance, CMOS          |      |

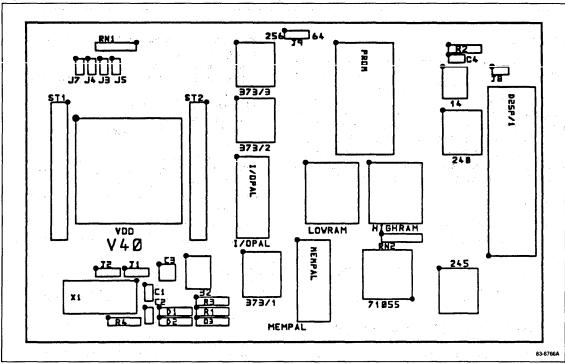

| Section 2<br>Reliability and Quality Control |      | μPD70208 (V40)<br>8/16-Bit Microprocessor:                | 30   |

| Introduction                                 | 2-3  | High-Integration, CMOS                                    |      |

| Built-In Quality and Reliability             | 2-3  | μPD70216 (V50)                                            | 3d   |

| Technology Description                       | 2-3  | 16-Bit Microprocessor:<br>High-Integration, CMOS          |      |

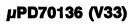

| Approaches to Total Quality Control          | 2-3  | μPD70136 (V33)                                            | 3e   |

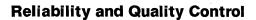

| Implementation of Quality Control            | 2-5  | 16-Bit Microprocessor:                                    | 00   |

| Reliability Testing                          | 2-7  | High-Speed, CMOS                                          |      |

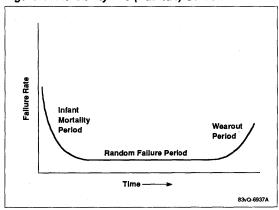

| Life Distribution                            | 2-7  | μPD70236 (V53)                                            | 3f   |

| Failure Distribution at NEC                  | 2-7  | 16-Bit Microprocessor: High-Speed, High-Integration, CMOS |      |

| Infant Mortality Failure Screening           | 2-8  |                                                           |      |

| Long-Term Failure Rate                       | 2-8  | Section 4                                                 |      |

| Accelerated Reliability Testing              | 2-8  | 16-Bit Microcomputers                                     |      |

| Failure Rate Calculation/Prediction          | 2-9  | μPD70320/70322 (V25)                                      | 4a   |

| Product/Process Changes                      | 2-10 | 16-Bit Microcomputers:<br>Single-Chip, CMOS               |      |

| Failure Analysis                             | 2-10 | μPD70330/70332 (V35)                                      | 4b   |

| NEC's Goals on Failure Rates                 | 2-10 | 16-Bit Microcomputers:                                    | 45   |

| Summary and Conclusion                       | 2-10 | Advanced, Single-Chip, CMOS                               |      |

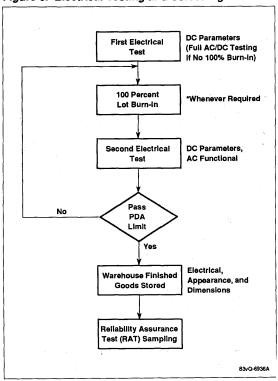

| Figure 1. Quality Control System Flowchart   | 2-5  | μPD70P322                                                 | 4c   |

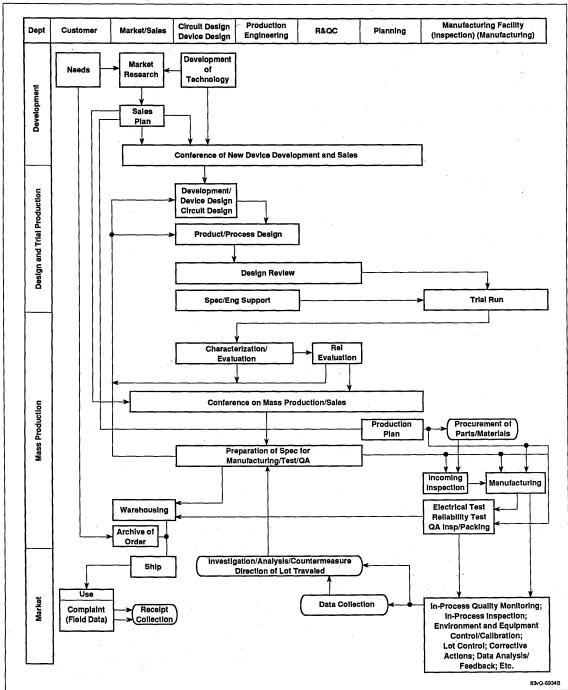

| Figure 2. New Product Development Flow       | 2-6  | 16-Bit Microcomputer:<br>Single-Chip, CMOS,               |      |

| Figure 3. Electrical Testing and Screening   | 2-6  | With EPROM for V25/V35 Modes                              |      |

| Figure 4. Reliability Life (Bathtub) Curve   | 2-7  |                                                           |      |

| Figure 5. Typical Reliability Test Results   | 2-9  |                                                           |      |

# **Contents**

| Section 4<br>16-Bit Microcomputers (cont)                                                            |    | Section 5 Peripherals for CPUs (cont)                                       |    |

|------------------------------------------------------------------------------------------------------|----|-----------------------------------------------------------------------------|----|

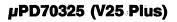

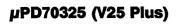

| μPD70325 (V25 Plus) 16-Bit Microcomputer:                                                            | 4d | μ <b>PD71086, 71087</b><br>8-Bit Bus Buffer/Drivers                         | 5j |

| High-Speed DMA, Single-Chip, CMOS<br>μPD70335 (V35 Plus)                                             | 4e | μ <b>PD71088</b><br>System Bus Controller                                   | 5k |

| 16-Bit Microcomputer:<br>Advanced, High-Speed DMA,<br>Single-Chip, CMOS                              |    | μPD71641<br>Cache Memory Controller                                         | 51 |

| μ <b>PD70327 (V25 Software Guard)</b><br>16-Bit Microcomputer:<br>Software-Secure, Single-Chip, CMOS | 4f | Section 6 Development Tools                                                 |    |

| µPD70337 (V35 Software Guard)<br>16-Bit Microcomputer:<br>Software-Secure, Single-Chip, CMOS         | 4g | CC70116<br>V-Series C Compiler                                              | 6a |

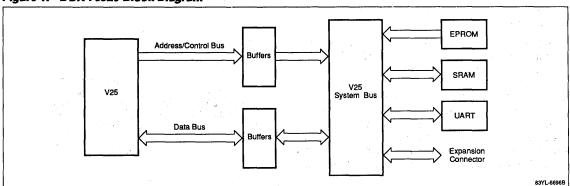

| μPD79011                                                                                             | 4h | DDK-70320 Evaluation Board for V25 Microcomputer                            | 6b |

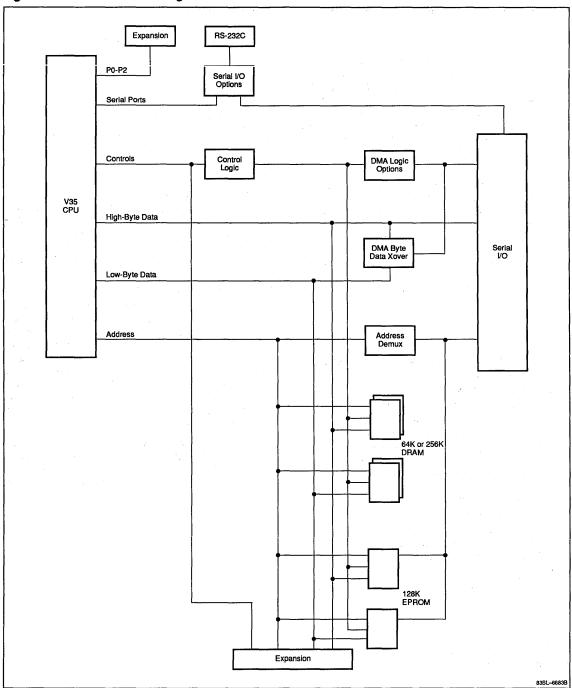

| 16-Bit Microcomputer:<br>Single-Chip, CMOS, With Built-In RTOS                                       |    | DDK-70330<br>Evaluation Board for V35 Microcomputer                         | 6c |

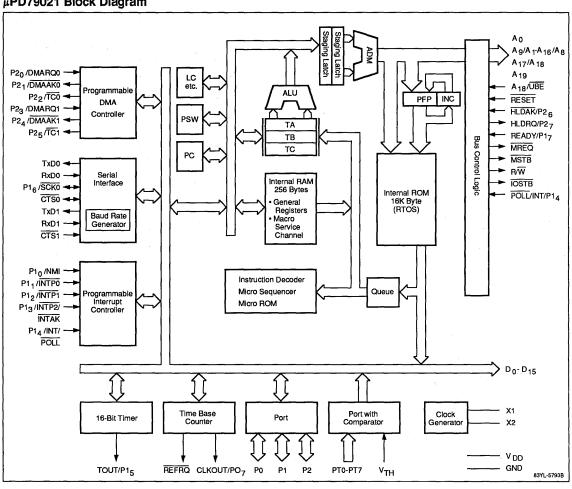

| μ <b>PD79021</b><br>16-Bit Microcomputer:<br>Single-Chip, CMOS, With Built-In RTOS                   | 4i | IE-70136 In-Circuit Emulator for μPD70136 (V33) Microprocessor              | 6d |

| Section 5<br>Peripherals for CPUs                                                                    |    | IE-70136-PC<br>In-Circuit Emulator for μPD70136 (V33)<br>Microprocessor     | 6e |

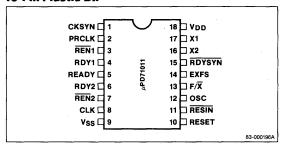

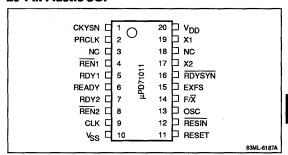

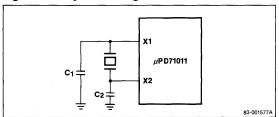

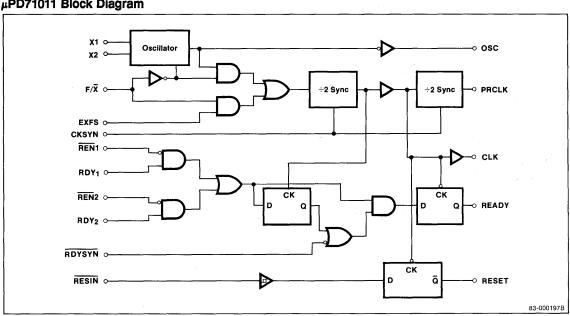

| μ <b>PD71011</b><br>Clock Pulse Generator/Driver                                                     | 5a | IE-70208, IE-70216<br>In-Circuit Emulators for $\mu$ PD70208 (V40) and      | 6f |

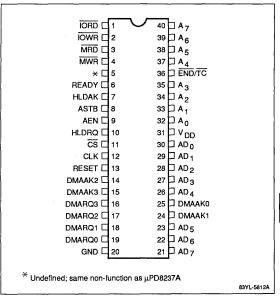

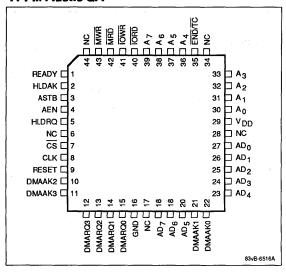

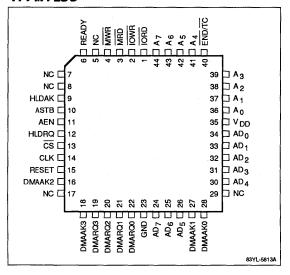

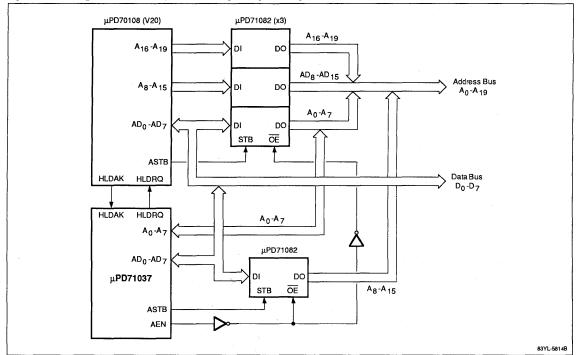

| μPD71037 Direct Memory Access (DMA) Controller                                                       | 5b | μPD70216 (V50) Microprocessors IE-70320                                     | 6g |

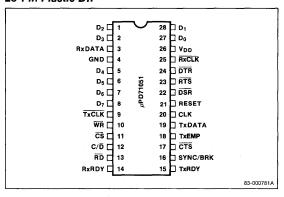

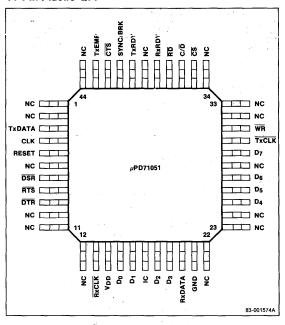

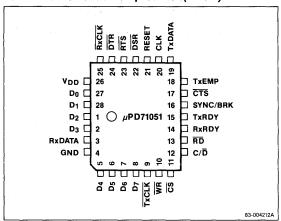

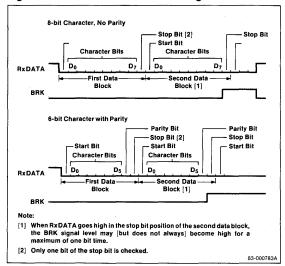

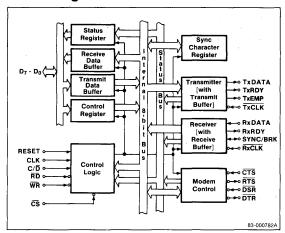

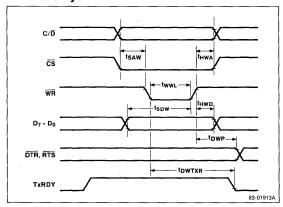

| μ <b>PD71051</b><br>Serial Control Unit                                                              | 5c | In-Circuit Emulator for $\mu$ PD70320/70322 (V25)<br>Microcomputers         |    |

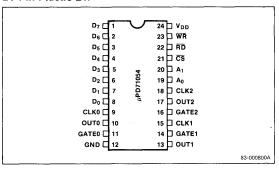

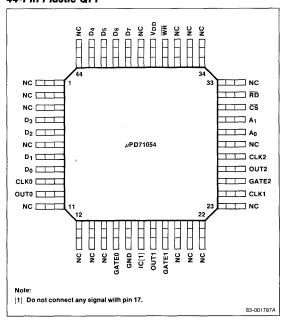

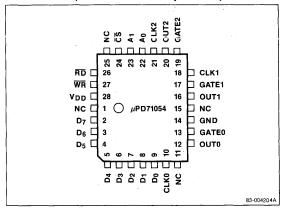

| μ <b>PD71054</b><br>Programmable Timer/Counter                                                       | 5d | <b>IE-70330</b> In-Circuit Emulator for μPD70330/70332 (V35) Microcomputers | 6h |

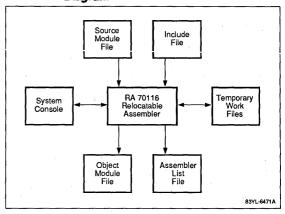

| μ <b>PD71055</b><br>Parallel Interface Unit                                                          | 5e | RA70116 Relocatable Assembler Package for V20-V50                           | 6i |

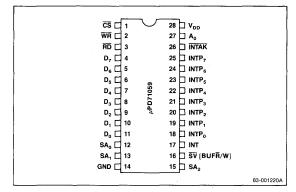

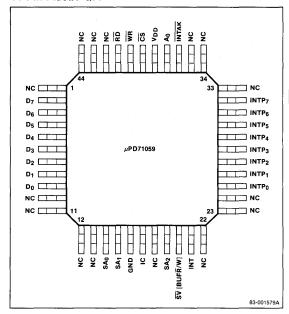

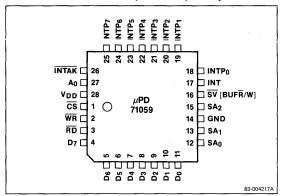

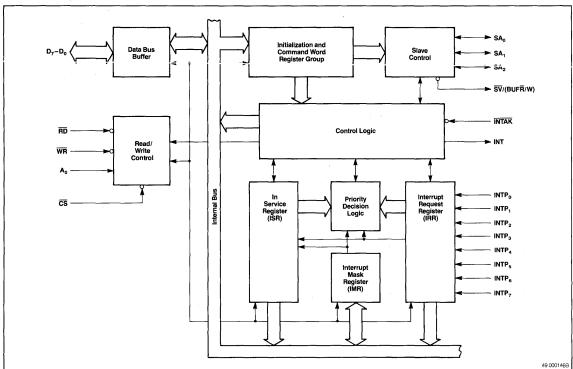

| μ <b>PD71059</b><br>Interrupt Control Unit                                                           | 5f | Microprocessors RA70136                                                     | ei |

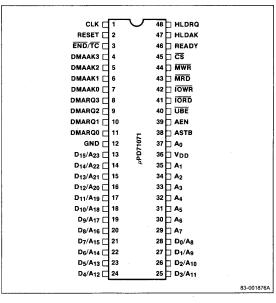

| μ <b>PD71071</b><br>DMA Controller                                                                   | 5g | Relocatable Assembler Package for V33<br>Microprocessor                     | 6j |

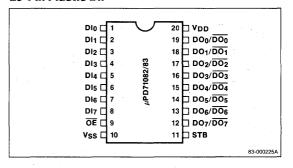

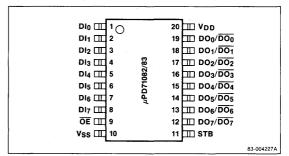

| μ <b>PD71082, 71083</b><br>8-Bit Latches                                                             | 5h | RA70320 Relocatable Assembler Package for V25/V35                           | 6k |

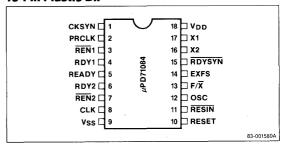

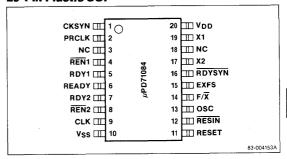

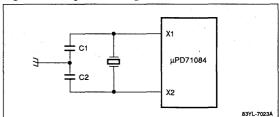

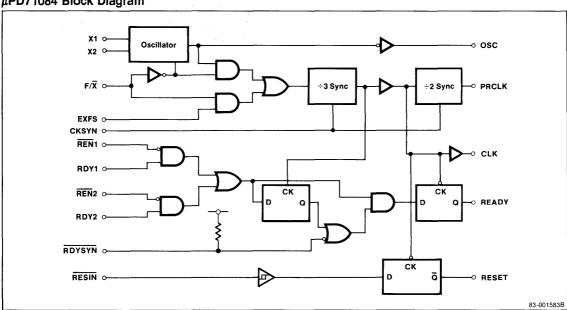

| μ <b>PD71084</b><br>Clock Pulse Generator/Driver                                                     | 5i | Microcomputers  V25/V35 MINI-IE Plus In-Circuit Emulator                    | 61 |

|                                                                                                      |    | V40/V50 MINI-IE<br>In-Circuit Emulator                                      | 6m |

## **Contents**

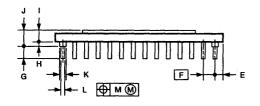

## Section 7 Package Drawings

| Package Drawings                  |      |

|-----------------------------------|------|

| Package/Device Cross-Reference    | 7-3  |

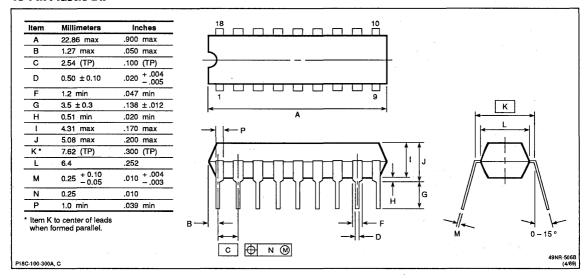

| 18-Pin Plastic DIP                | 7-5  |

| 20-Pin Plastic DIP (300 mil)      | 7-5  |

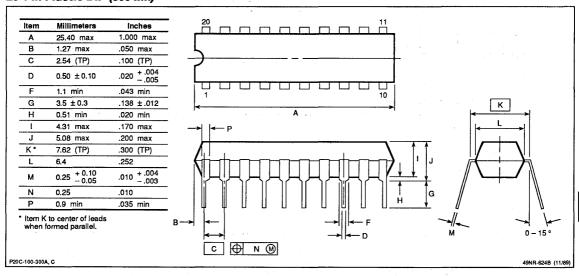

| 20-Pin Plastic SOP (300 mil)      | 7-6  |

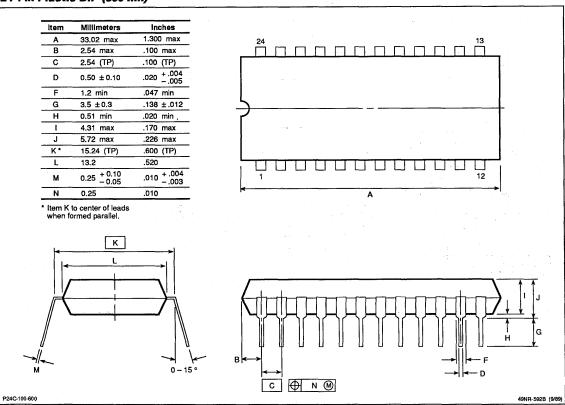

| 24-Pin Plastic DIP (600 mil)      | 7-6  |

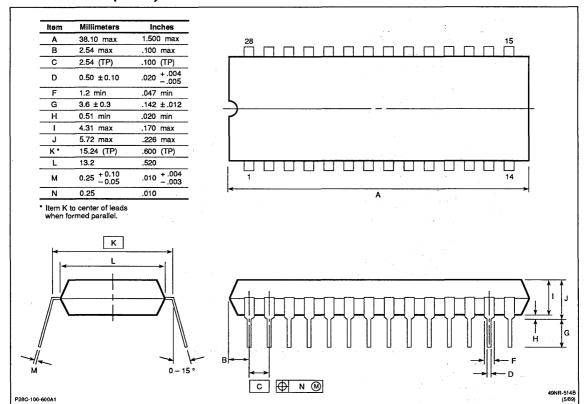

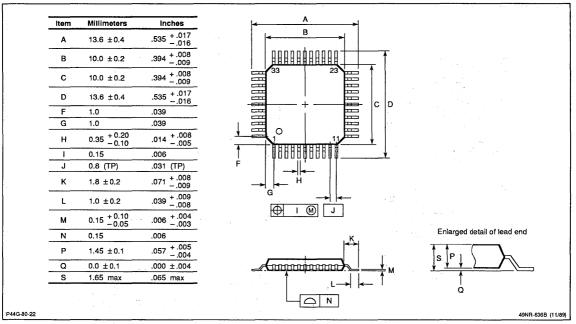

| 28-Pin Plastic DIP (600 mil)      | 7-7  |

| 28-Pin PLCC                       | 7-8  |

| 40-Pin Plastic DIP (600 mil)      | 7-8  |

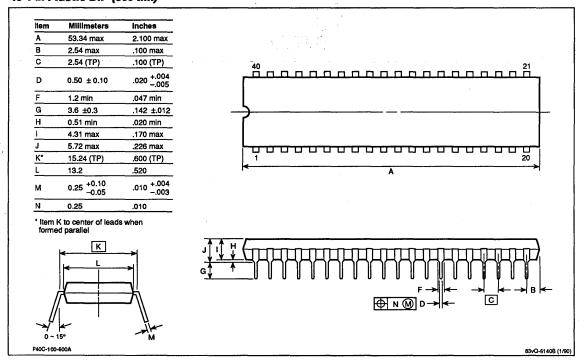

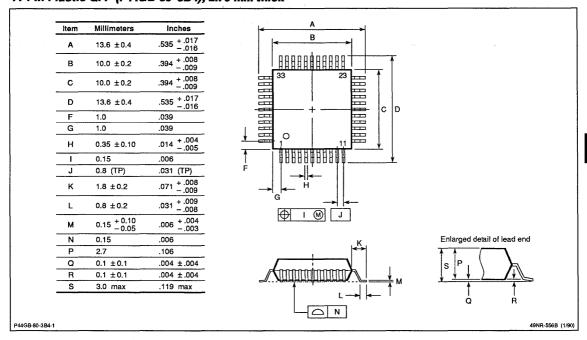

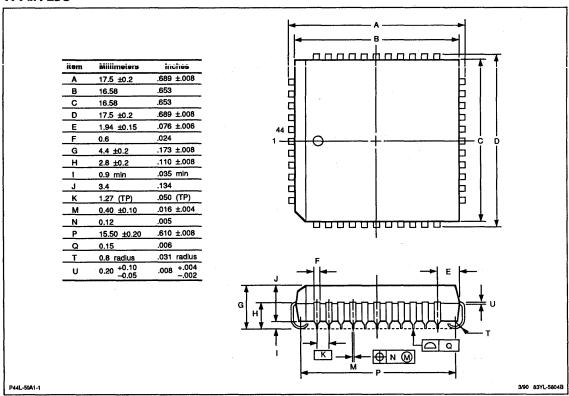

| 44-Pin Plastic QFP (P44G-80-22)   | 7-9  |

| 44-Pin Plastic QFP (P44GB-80-3B4) | 7-9  |

| 44-Pin PLCC                       | 7-10 |

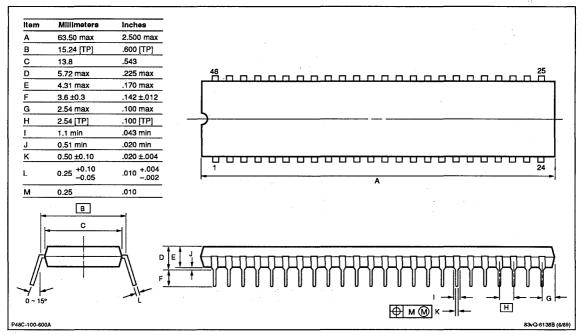

| 48-Pin Plastic DIP                | 7-11 |

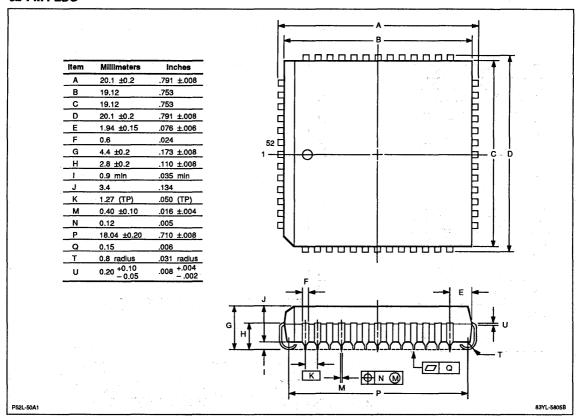

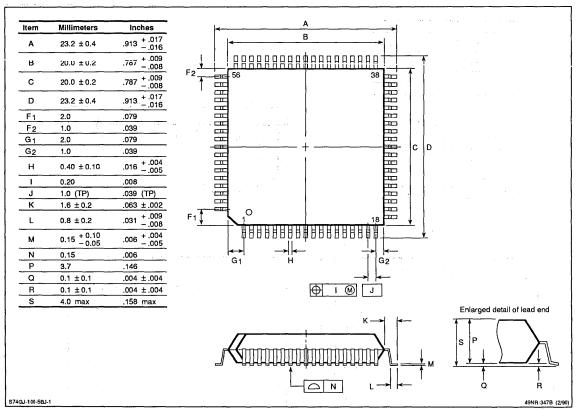

| 52-Pin Plastic QFP                | 7-12 |

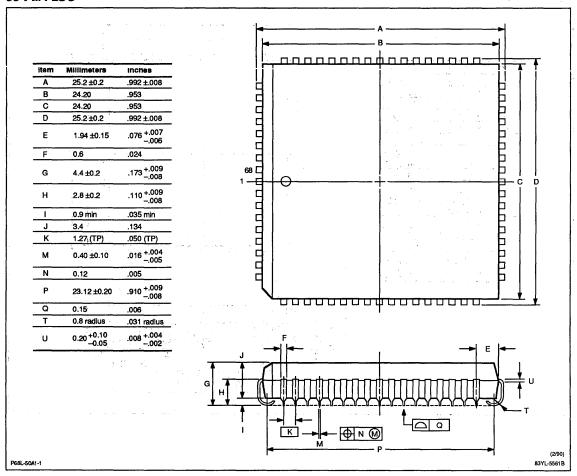

| 52-Pin PLCC                       | 7-13 |

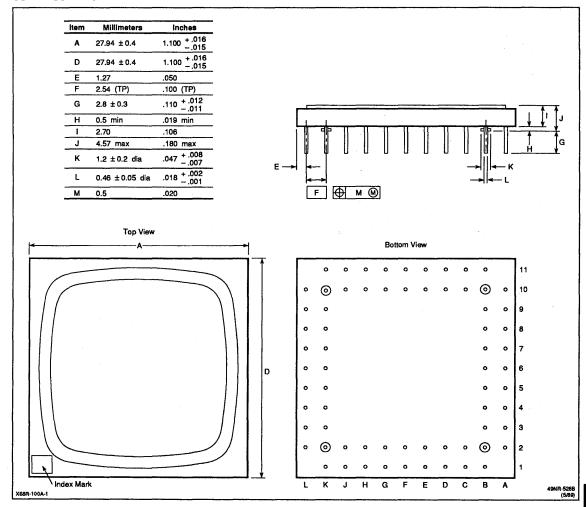

| 68-Pin PLCC                       | 7-14 |

| 68-Pin Ceramic PGA                | 7-15 |

| 74-Pin Plastic QFP                | 7-16 |

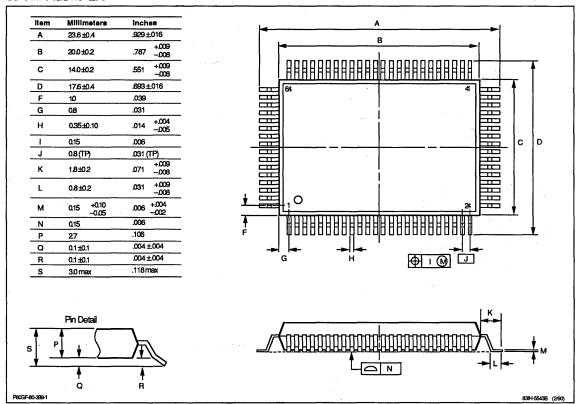

| 80-Pin Plastic QFP                | 7-17 |

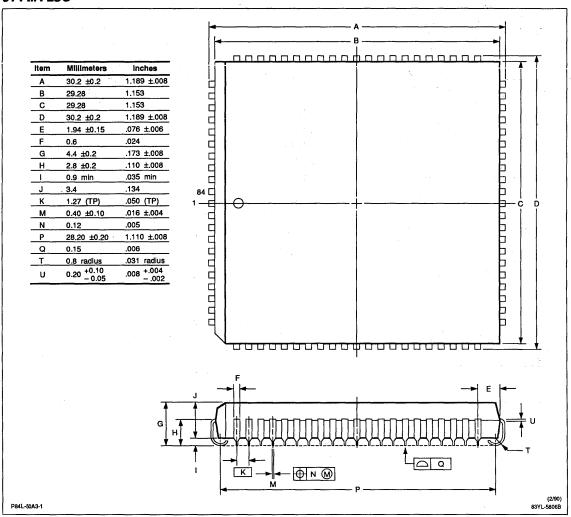

| 84-Pin PLCC                       | 7-18 |

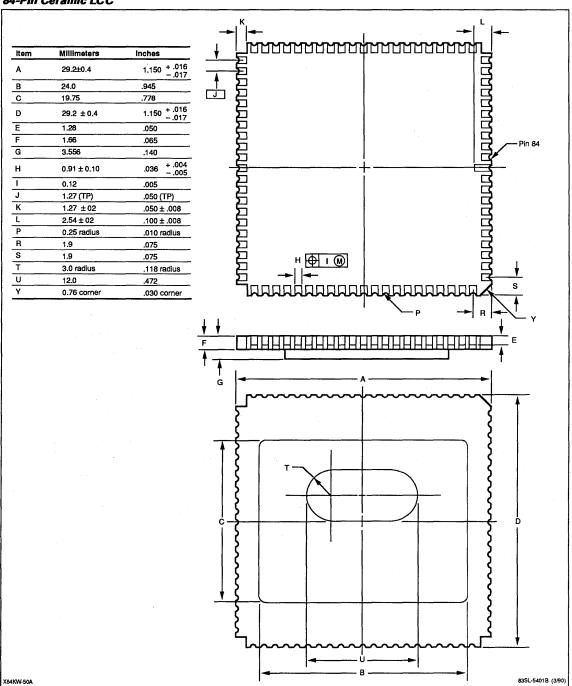

| 84-Pin Ceramic LCC                | 7-19 |

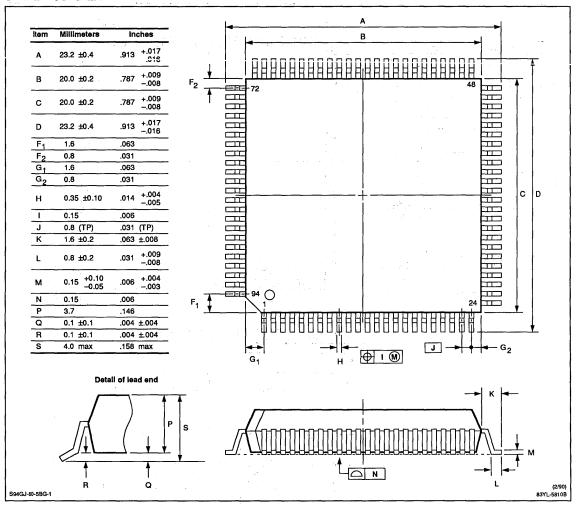

| 94-Pin Plastic QFP                | 7-20 |

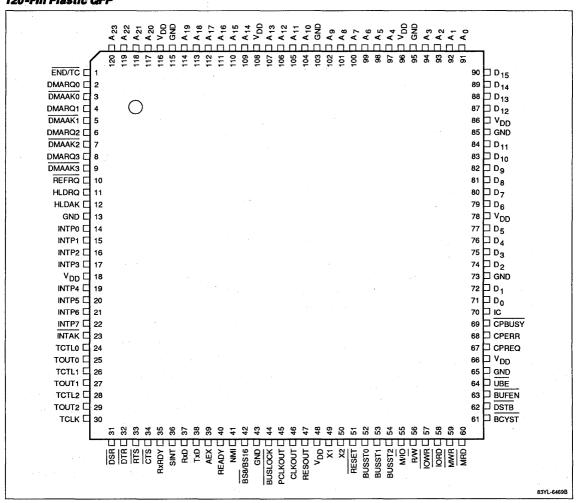

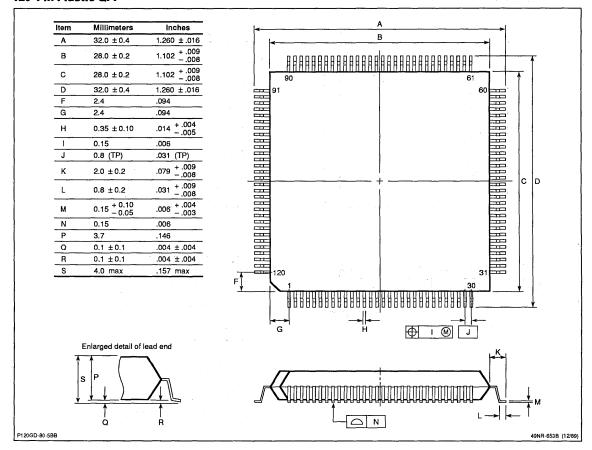

| 120-Pin Plastic QFP               | 7-21 |

| 132-Pin Ceramic PGA               | 7-22 |

|                                   |      |

## Numerical Index

| Device, μPD        | Section    |

|--------------------|------------|

| 70108              | 3a         |

| 70116              | 3b         |

| 70136              | 3e         |

| 70208              | 3c         |

| 70216              | 3d         |

| 70236              | 3f         |

| 70320              | 4a         |

| 70322              | 4a         |

| 70325              | 4d         |

| 70327              | 4f         |

| 70330              | 4b         |

| 70332              | 4b         |

| 70335              | 4e         |

| 70337              | 4g         |

| 70P322             | 4c         |

| 71011              | 5a         |

| 71037              | 5b         |

| 71051              | 5c         |

| 71054              | 5d         |

| 71055<br>71059     | 5e<br>5f   |

|                    |            |

| 71071<br>71082     | 5g<br>5h   |

| 71083              | 5h         |

| 71084              | 5i         |

| 71084              | 5j         |

| 71087              | 5 <u>j</u> |

| 71088              | 5k         |

| 71641              | 51         |

| 79011              | 4h         |

| 79021              | 4i         |

| V20                |            |

| V25                | 4a         |

| V25 Plus           | 4d         |

| V25 Software Guard | 4f         |

| V30                | 3b         |

| V33                | 3e         |

| V35                | 4b         |

| V35 Plus           | 4e         |

| V35 Software Guard | 4g         |

| V40                | 30         |

| V50                | 3d         |

| V53                | 3f         |

|                    |            |

|             |     | Se    | lect | tion | Gui    | des  |

|-------------|-----|-------|------|------|--------|------|

| Reliability | an  | (d. ( | )ua  | ity  | Gon    | troi |

|             |     |       |      |      | it C   | PUS  |

| g O a       |     |       | CYO  | 601  | ngu    | ters |

| <b>S</b>    | eri | ph    | era  | ls f | or C   | PUs  |

|             | De  | :Ve   | iop: | mei  | rt T ( | ois  |

it Microcomputers

**Selection Guides**

Package Drawings

## **Selection Guides**

## Section 1 Selection Guides

| Selection Guides                         |      |

|------------------------------------------|------|

| Single-Chip Microcomputers               | 1-3  |

| μPD75XX Series Development Tools         | 1-7  |

| μPD75XXX Series Development Tools        | 1-9  |

| μPD78XX Series Development Tools         | 1-11 |

| μPD782XX Series Development Tools        | 1-13 |

| μPD783XX Series Development Tools        | 1-15 |

| PG-1500 Programming Adapters             | 1-17 |

| V-Series Microprocessors and Peripherals | 1-19 |

| Intelligent Peripheral Devices (IPD)     | 1-23 |

| DSP and Speech Products                  | 1-25 |

| V-Series Development Tools               | 1-27 |

| DSP and Speech Development Tools         | 1-31 |

|                                          |      |

## **Part Numbering System**

| μPD72001L | Typical microdevice part number           |

|-----------|-------------------------------------------|

| μP        | NEC monolithic silicon integrated circuit |

| D         | Device type (D = digital MOS)             |

| 72001     | Device identifier (alphanumeric)          |

| L         | Package type (L = PLCC)                   |

A part number may include an alphanumeric suffix that identifies special device characteristics; for example,  $\mu\text{PD72001L-11}$  has an 11-MHz data clock rating.

| 4-Bit, S | ingle-Chi <sub>l</sub> | o CMOS | Microcompute | rs |

|----------|------------------------|--------|--------------|----|

|----------|------------------------|--------|--------------|----|

| Device,<br>μPD | Features                                       | Clock<br>(MHz) | Supply<br>Voltage (V) | ROM<br>(X8)  | RAM<br>(X4) | 1/0 | # Package   | Pins     |

|----------------|------------------------------------------------|----------------|-----------------------|--------------|-------------|-----|-------------|----------|

| 7502           | LCD controller/driver                          | 0.41           | 2.5 to 6.0            | 2K           | 128         | 23  | QFP         | 64       |

| 7503           | LCD controller/driver                          | 0.41           | 2.5 to 6.0            | 4K           | 224         | 23  | QFP         | 64       |

| 7507           | General-purpose                                | 0.41           | 2.5 to 6.0            | 2K           | 128         | 32  | DIP         | 40       |

|                | -                                              |                |                       |              |             |     | SDIP<br>QFP | 40<br>52 |

| 7507H          | General-purpose                                | 4.19           | 2.7 to 6.0            | 2K           | 128         | 32  | DIP         | 40       |

| 100711         | deneral-purpose                                | 4.13           | 2.7 10 0.0            | ZN           | 120         | 32  | SDIP        | 40       |

|                |                                                |                |                       |              |             |     | QFP         | 52       |

| 7508           | General-purpose                                | 0.41           | 2.5 to 6.0            | 4K           | 224         | 32  | DIP         | 40       |

|                |                                                |                |                       |              |             |     | SDIP<br>QFP | 40<br>52 |

| 7508H          | General-purpose                                | 4.19           | 2.7 to 6.0            | 4K           | 224         | 32  | DIP         | 40       |

|                | denotal purpose                                | 4.10           | 2.7 10 0.0            | 711          | 227         |     | SDIP        | 40       |

|                |                                                |                |                       |              |             |     | QFP         | 52       |

| 75CG08         | Piggyback EPROM                                | 0.41           | 4.5 to 5.5            | 2K or 4K     | 224         | 32  | Ceramic DIP | 40       |

| 75CG08H        | Piggyback EPROM                                | 4.19           | 4.5 to 5.5            | 2K or 4K     | 224         | 32  | Ceramic DIP | 40       |

| 7527A          | FIP controller/driver                          | 0.61           | 2.7 to 6.0            | 2K           | 128         | 35  | DIP<br>SDIP | 42<br>42 |

| 7528A          | FIP controller/driver                          | 0.61           | 2.7 to 6.0            | 4K           | 160         | 35  | DIP         | 42       |

| 7520A          | TIF CONTIONED CONVE                            | 0.01           | 2.7 10 0.0            | 40           | 100         | 33  | SDIP        | 42       |

| 75CG28         | Piggyback EPROM;<br>FIP controller/driver      | 0.5            | 4.5 to 5.5            | 4K           | 160         | 35  | Ceramic DIP | 42       |

| 7533           | A/D converter                                  | 0.5            | 2.7 to 6.0            | 4K           | 160         | 30  | DIP         | 42       |

|                | 72.0 001101101                                 | . 0.0          | 2.7 10 0.0            |              | 100         |     | SDIP        | 42       |

|                |                                                |                |                       |              |             |     | QFP         | 44       |

| 750G33         | Piggyback EPROM;<br>A/D converter              | 0.5            | 4.5 to 5.5            | 4K           | 160         | 30  | Ceramic DIP | 42       |

| 7537A          | FIP controller/driver                          | 0.61           | 2.7 to 6.0            | 2K           | 128         | 35  | DIP<br>SDIP | 42<br>42 |

| 7538A          | FIP controller/driver                          | 0.61           | 2.7 to 6.0            | 4K           | 160         | 35  | DIP<br>SDIP | 42<br>42 |

| 75CG38         | Piggyback EPROM;<br>FIP controller/driver      | 0.61           | 4.5 to 5.5            | 4K           | 160         | 35  | Ceramic DIP | 42       |

| 7554           | Serial I/O; external clock<br>or RC oscillator | 0.71           | 2.5 to 6.0            | 1K           | 64          | 16  | SDIP<br>SOP | 20<br>20 |

| 7554A          | Serial I/O; external clock<br>or RC oscillator | 0.71           | 2.0 to 6.0            | 1K           | 64          | 16  | SDIP<br>SOP | 20<br>20 |

| 75P54          | Serial I/O; external clock<br>or RC oscillator | 0.71           | 4.5 to 6.0            | 1K<br>OTPROM | 64          | 16  | SDIP<br>SOP | 20<br>20 |

| 7564/7564A     | Serial I/O; ceramic oscillator                 | 0.71           | 2.7 to 6.0            | 1K           | 64          | 15  | SDIP<br>SOP | 20<br>20 |

| 75P64          | Serial I/O; ceramic oscillator                 | 0.71           | 4.5 to 6.0            | 1K<br>OTPROM | 64          | 15  | SDIP<br>SOP | 20<br>20 |

| 7556           | Comparator; external clock or RC oscillator    | 0.71           | 2.5 to 6.0            | 1K           | 64          | 20  | SDIP<br>SOP | 24<br>24 |

| 7556A          | Comparator; external clock or RC oscillator    | 0.71           | 2.0 to 6.0            | 1K           | 64          | 20  | SDIP<br>SOP | 24<br>24 |

| 75P56          | Comparator; external clock or RC oscillator    | 0.71           | 4.5 to 6.0            | 1K<br>OTPROM | 64          | 20  | SDIP<br>SOP | 24<br>24 |

| 7566/7566A     | Comparator; ceramic oscillator                 | 0.71           | 2.7 to 6.0            | 1K           | 64          | 19  | SDIP<br>SOP | 24<br>24 |

| 75P66          | Comparator; ceramic oscillator                 | 0.71           | 4.5 to 6.0            | 1K<br>OTPROM | 64          | 19  | SDIP<br>SOP | 24<br>24 |

| 75004          | General-purpose                                | 4.19           | 2.7 to 6.0            | 4K           | 512         | 34  | SDIP<br>QFP | 42<br>44 |

|                |                                                |                |                       |              |             |     |             |          |

<sup>#</sup> Plastic unless ceramic (or cerdip) is specified.

<sup>\*</sup> Under development; consult Microcontroller Marketing for availability.

4-Bit, Single-Chip CMOS Microcomputers (cont)

| Device,<br>μPD | Features                                                   | Clock<br>(MHz) | Supply<br>Voltage (V) | ROM<br>(X8)   | RAM<br>(X4) | 1/0 | # Package                    | Pins           |

|----------------|------------------------------------------------------------|----------------|-----------------------|---------------|-------------|-----|------------------------------|----------------|

| 75006          | General-purpose                                            | 4.19           | 2.7 to 6.0            | 6K            | 512         | 34  | SDIP<br>QFP                  | 42<br>44       |

| 75008          | General-purpose                                            | 4.19           | 2.7 to 6.0            | 8K            | 512         | 34  | SDIP<br>QFP                  | 42<br>44       |

| 75P008         | General-purpose                                            | 4.19           | 4.5 to 5.5            | 8K<br>OTPROM  | 512         | 34  | SDIP<br>QFP                  | 42<br>44       |

| 75028 *        | A/D converter                                              | 4.19           | 2.7 to 6.0            | 8K            | 512         | 48  | SDIP<br>QFP                  | 64<br>64       |

| 75P036 *       | A/D converter                                              | 4.19           | 2.7 to 6.0            | 16K           | 1024        | 48  | SDIP<br>QFP                  | 64<br>64       |

| 75048 *        | A/D converter; 1K x 4 EEPROM                               | 4.19           | 2.7 to 6.0            | 8K            | 512         | 48  | SDIP<br>QFP                  | 64<br>64       |

| 75P056 *       | A/D converter; 1K x 4 EEPROM                               | 4.19           | 2.7 to 6.0            | 16K           | 512         | 48  | SDIP<br>QFP                  | 64<br>64       |

| 75104          | High-end with 8-bit instruction                            | 4.19           | 2.7 to 6.0            | 4K            | 320         | 58  | SDIP<br>QFP                  | 64<br>64       |

| 75104A         | High-end with 8-bit instruction                            | 4.19           | 2.7 to 6.0            | 4K            | 320         | 58  | QFP                          | 64             |

| 75106          | High-end with 8-bit instruction                            | 4.19           | 2.7 to 6.0            | 6K            | 320         | 58  | SDIP<br>QFP                  | 64<br>64       |

| 75108          | High-end with 8-bit instruction                            | 4.19           | 2.7 to 6.0            | 8K            | 512         | 58  | SDIP<br>QFP                  | 64<br>64       |

| 75108A         | High-end with 8-bit instruction                            | 4.19           | 2.7 to 6.0            | 8K            | 512         | 58  | QFP<br>QFP                   | 64<br>64       |

| 75P108         | High-end with 8-bit instruction; on-chip OTPROM or UVEPROM | 4.19           | 4.5 to 5.5            | 8K            | 512         | 58  | SDIP<br>QFP<br>Shrink cerdip | 64<br>64<br>64 |

| 75P108B        | High-end with 8-bit instruction; on-chip OTPROM            | 4.19           | 2.7 to 6.0            | 8K            | 512         | 58  | SDIP<br>QFP                  | 64<br>64       |

| 75112          | High-end with 8-bit instruction                            | 4.19           | 2.7 to 6.0            | 12K           | 512         | 58  | SDIP<br>QFP                  | 64<br>64       |

| 75116          | High-end with 8-bit instruction                            | 4.19           | 2.7 to 6.0            | 16K           | 512         | 58  | SDIP<br>QFP                  | 64<br>64       |

| 75P116         | High-end with 8-bit instruction on-chip OTPROM             | 4.19           | 4.5 to 5.5            | 16K<br>OTPROM | 512         | 58  | SDIP<br>QFP                  | 64<br>64       |

| 75206          | FIP controller/driver                                      | 4.19           | 2.7 to 6.0            | 6K            | 369         | 33  | SDIP<br>QFP                  | 64<br>64       |

| 75208          | FIP controller/driver                                      | 4.19           | 2.7 to 6.0            | 8K            | 497         | 33  | SDIP<br>QFP                  | 64<br>64       |

| 75CG208        | FIP controller/driver;<br>piggyback EPROM                  | 4.19           | 4.5 to 5.5            | 8K            | 512         | 33  | Ceramic SDIP<br>Ceramic QFP  | 64<br>64       |

| 75212A         | FIP controller/driver                                      | 4.19           | 2.7 to 6.0            | 12K           | 512         | 33  | SDIP<br>QFP                  | 64<br>64       |

| 75216A         | FIP controller/driver                                      | 4.19           | 2.7 to 6.0            | 16K           | 512         | 33  | SDIP<br>QFP                  | 64<br>64       |

| 75CG216A       | FIP controller/driver;                                     | 4.19           | 4.5 to 5.5            | 16K           | 512         | 33  | Ceramic SDIP<br>Ceramic QFP  | 64<br>64       |

| 75P216A        | FIP controller/driver                                      | 4.19           | 4.5 to 5.5            | 16K<br>OTPROM | 512         | 33  | SDIP                         | 64             |

| 75268          | FIP controller/driver                                      | 4.19           | 2.7 to 6.0            | 8K            | 512         | 32  | SDIP<br>QFP                  | 64<br>64       |

| 75304          | LCD controller/driver                                      | 4.19           | 2.7 to 6.0            | 4K            | 512         | 40  | QFP                          | 80             |

| 75306          | LCD controller/driver                                      | 4.19           | 2.7 to 6.0            | 6K            | 512         | 40  | QFP                          | 80             |

| 75308          | LCD controller/driver                                      | 4.19           | 2.7 to 6.0            | . 8K          | 512         | 40  | QFP                          | 80             |

| 75P308         | LCD controller/driver;<br>on-chip OTPROM or UVEPROM        | 4.19           | 4.75 to 5.25          | 8K            | 512         | 40  | QFP<br>Ceramic LCC           | 80<br>80       |

## 4-Bit, Single-Chip CMOS Microcomputers (cont)

| Device,<br>μPD | Features                                            | Clock<br>(MHz) | Supply<br>Voltage (V) | ROM<br>(X8)   | RAM<br>(X4) | 1/0 | # Package          | Pins           |

|----------------|-----------------------------------------------------|----------------|-----------------------|---------------|-------------|-----|--------------------|----------------|

| 75312          | LCD controller/driver                               | 4.19           | 2.7 to 6.0            | 12K           | 512         | 40  | QFP                | 80             |

| 75316          | LCD controller/driver                               | 4.19           | 2.7 to 6.0            | 16K           | 512         | 40  | QFP                | 80             |

| 75P316         | LCD controller/driver;<br>on-chip OTPROM            | 4.19           | 4.75 to 5.25          | 16K<br>OTPROM | 512         | 40  | QFP                | 80             |

| 75P316A *      | LCD controller/driver;<br>on-chip OTPROM or UVEPROM | 4.19           | 2.7 to 6.0            | 16K<br>OTPROM | 512         | 40  | QFP<br>Ceramic LCC | 80<br>80       |

| 75328          | LCD controller/driver;<br>A/D converter             | 4.19           | 2.7 to 6.0            | 8K            | 512         | 44  | QFP                | 80             |

| 75P328         | LCD controller/driver;<br>A/D converter             | 4.19           | 4.5 to 5.5            | 8K<br>OTPROM  | 512         | 44  | QFP                | 80             |

| 75402A         | Low-end                                             | 4.19           | 2.7 to 6.0            | 2K            | 64          | 22  | DIP<br>SDIP<br>QFP | 28<br>28<br>44 |

| 75P402         | Low-end                                             | 4.19           | 4.5 to 5.5            | 2K<br>OTPROM  | 64          | 22  | DIP<br>SDIP<br>QFP | 28<br>28<br>44 |

| 75512          | High-end; A/D converter                             | 4.19           | 2.7 to 6.0            | 12K           | 512         | 64  | QFP                | 80             |

| 75516          | High-end; A/D converter                             | 4.19           | 2.7 to 6.0            | 16K           | 512         | 64  | QFP                | 80             |

| 75P516         | High-end; A/D converter                             | 4.19           | 4.75 to 5.5           | 16K<br>OTPROM | 512         | 64  | QFP<br>Ceramic LCC | 80<br>80       |

## 8-Bit, Single-Chip CMOS Microcomputers

| Device,<br>μPD | Features                                     | Clock<br>(MHz) | Supply<br>Voltage (V) | ROM<br>(X8)      | RAM<br>(X8) | 1/0 | # Package                     | Pins                 |

|----------------|----------------------------------------------|----------------|-----------------------|------------------|-------------|-----|-------------------------------|----------------------|

| 78C10/78C10A   | CMOS; A/D converter                          | 15             | 4.5 to 5.5            | External         | 256         | 32  | QUIP<br>SDIP                  | 64<br>64             |

|                |                                              |                |                       |                  |             |     | QFP<br>PLCC                   | 64<br>68             |

| 78C11/78C11A   | CMOS; A/D converter                          | 15             | 4.5 to 5.5            | 4K               | 256         | 44  | QUIP<br>SDIP<br>QFP<br>PLCC   | 64<br>64<br>64<br>68 |

| 78C12A         | CMOS; A/D converter                          | 15             | 4.5 to 5.5            | 8K               | 256         | 44  | QUIP<br>SDIP<br>QFP<br>PLCC   | 64<br>64<br>64<br>68 |

| 78C14/78C14A   | CMOS; A/D converter                          | 15             | 4.5 to 5.5            | 16K              | 256         | 44  | QUIP<br>SDIP<br>QFP<br>PLCC   | 64<br>64<br>64<br>68 |

| 78CP14         | CMOS; A/D converter                          | 15             | 4.75 to 5.25          | 16K<br>OTPROM    | 256         | 44  | QUIP<br>SDIP<br>QFP<br>PLCC   | 64<br>64<br>64<br>68 |

|                |                                              |                | •                     | 16K<br>UVEPROM   | 256         | 44  | Ceramic QUIP<br>Shrink cerdip | 64<br>64             |

| 78CG14         | CMOS; A/D converter;<br>piggyback EPROM      | 15             | 4.5 to 5.5            | 4K, 8K or<br>16K | 256         | 44  | Ceramic QUIP                  | 64                   |

| 78213          | CMOS; A/D converter;<br>advanced peripherals | 12             | 4.5 to 5.5            | External         | 512         | 54  | SDIP<br>QUIP<br>QFP<br>PLCC   | 64<br>64<br>74<br>68 |

| 78214          | CMOS; A/D converter;<br>advanced peripherals | 12             | 4.5 to 5.5            | 16K              | 512         | 54  | SDIP<br>QUIP<br>QFP<br>PLCC   | 64<br>64<br>74<br>68 |

# 8-Bit, Single-Chip NMOS/CMOS Microcomputers (cont)

| Device,<br>μPD | Features                                           | Clock<br>(MHz) | Supply<br>Voltage (V) | ROM<br>(X8)    | RAM<br>(X8) | 1/0 | # Package                   | Pins                 |

|----------------|----------------------------------------------------|----------------|-----------------------|----------------|-------------|-----|-----------------------------|----------------------|

| 78P214         | CMOS; A/D converter;<br>advanced peripherals       | 12             | 4.5 to 5.5            | 16K<br>OTPROM  | 512         | 54  | SDIP<br>QUIP<br>QFP<br>PLCC | 64<br>64<br>74<br>68 |

|                |                                                    |                |                       | 16K<br>UVEPROM | 512         | 54  | Shrink cerdip               | 64                   |

| 78220          | CMOS; analog comparator; large I/O                 | 12             | 4.5 to 5.5            | External       | 640         | 71  | PLCC<br>QFP                 | 84<br>94             |

| 78224          | CMOS; analog comparator;<br>large I/O              | 12             | 4.5 to 5.5            | 16K            | 640         | 71  | PLCC<br>QFP                 | 84<br>94             |

| 78P224         | CMOS; analog comparator;<br>large I/O              | 12             | 4.5 to 5.5            | 16K<br>OTPROM  | 640         | 71  | PLCC<br>QFP                 | 84<br>94             |

| 78233          | CMOS; real-time outputs;<br>A/D and D/A converters | 12             | 4.5 to 5.5            | External       | 640         | 64  | QFP<br>QFP<br>PLCC          | 80<br>94<br>84       |

| 78234          | CMOS; real-time outputs;<br>A/D and D/A converters | 12             | 4.5 to 5.5            | 16K            | 640         | 64  | QFP<br>QFP<br>PLCC          | 80<br>94<br>84       |

| 78P238         | CMOS; real-time outputs;<br>A/D and D/A converters | 12             | 4.5 to 5.5            | 32K<br>OTPROM  | 640         | 64  | QFP<br>QFP<br>PLCC          | 80<br>94<br>84       |

|                |                                                    |                |                       | 32K<br>UVEPROM | 640         | 64  | Ceramic LCC                 | 94                   |

## 8/16-Bit, Single-Chip CMOS Microcomputers

| Device,<br>μPD | Features                      | Clock<br>(MHz) | Supply<br>Voltage (V) | ROM<br>(X8) | RAM<br>(X8) | 1/0 | # Package     | Pins |

|----------------|-------------------------------|----------------|-----------------------|-------------|-------------|-----|---------------|------|

| 78310A         | Real-time motor control       | 12             | 4.5 to 5.5            | External    | 256         | 48  | SDIP          | 64   |

|                |                               |                |                       |             |             |     | QUIP          | 64   |

|                |                               |                |                       |             |             |     | QFP           | 64   |

|                | <u></u>                       |                |                       |             |             |     | PLCC          | 68   |

| 78312A         | Real-time motor control       | 12             | 4.5 to 5.5            | 8K          | 256         | 48  | SDIP          | 64   |

|                | 4.                            |                |                       |             |             |     | QUIP          | 64   |

|                |                               |                |                       |             |             |     | QFP           | 64   |

|                |                               |                |                       |             |             |     | PLCC          | 68   |

| 78P312A        | Real-time motor control       | 12             | 4.5 to 5.5            | 8K          | 256         | 48  | Shrink cerdip | 64   |

|                |                               |                | •                     | UVEPROM     |             |     | Ceramic QUIP  | 64   |

|                |                               |                | •                     | 8K          | 256         | 48  | SDIP          | 64   |

|                |                               |                |                       | OTPROM      |             |     | QUIP          | 64   |

|                |                               |                | *                     |             |             |     | QFP           | 64   |

|                |                               |                |                       |             |             |     | PLCC          | 68   |

| 78320          | High-end; advanced analog     | 16             | 4.5 to 5.5            | External    | 640         | 55  | QFP           | 64   |

|                | and digital peripherals       |                |                       |             |             |     | PLCC          | 68   |

| 78322          | High-end; advanced analog     | 16             | 4.5 to 5.5            | 16K         | 640         | 55  | QFP           | 64   |

|                | and digital peripherals       |                |                       |             |             |     | PLCC          | 68_  |

| 78P322         | High-end; advanced analog     | 16             | 4.5 to 5.5            | 16K         | 640         | 55  | PLCC          | 68   |

|                | and digital peripherals       |                |                       | OTPROM      |             |     | QFP           | 74   |

|                |                               |                |                       | 16K         | 640         | 55  | Ceramic LCC   | 68   |

|                |                               |                |                       | UVEPROM     | - • •       |     | Ceramic LCC   | 74   |

| 71P301         | Port and memory extender      |                | 4.5 to 5.5            | 16K         | 1K          | 16  | PLCC          | 44   |

|                | used with 7832X microcomputer |                | 4.5 10 0.0            | OTPROM      | •••         |     | QFP           | 64   |

|                | family; UVEPROM or OTPROM     |                |                       | 5tom        |             |     | QUIP          | 64   |

|                | ,,                            |                | •                     | 16K         | 1K          | 16  | Ceramic LCC   | 44   |

|                |                               |                |                       | UVEPROM     | •••         |     | Ceramic LCC   | 64   |

|                |                               |                |                       | 012.110.01  |             |     | Ceramic QUIP  | 64   |

## $\mu\text{PD75XX}$ Series Development Tools Selection Guide

| Part Number<br>(Note 1) | Emulator*    | Add-on<br>Board*   | System<br>Evaluation<br>Board | EPROM/OTP<br>Device | PG-1500<br>Adapter<br>(Note 2) | Absolute<br>Assembler<br>(Note 3) |

|-------------------------|--------------|--------------------|-------------------------------|---------------------|--------------------------------|-----------------------------------|

| μPD7502G-12             | EVAKIT-7500B | EV7514             | SE-7514A                      | _                   | _                              | ASM75                             |

| μPD7503G-12             | EVAKIT-7500B | EV7514             | SE-7514A                      |                     |                                | ASM75                             |

| μPD7507C                | EVAKIT-7500B |                    | -                             | μPD78CG08E          |                                | ASM75                             |

| μPD7507CU               | EVAKIT-7500B | _                  | _                             | <del></del>         |                                | ASM75                             |

| μPD7507G-00             | EVAKIT-7500B | _                  | _                             |                     |                                | ASM75                             |

| μPD7507HC               | EVAKIT-7500B | EV7508H            |                               | μPD75CG08HE         |                                | ASM75                             |

| μPD7507HCU              | EVAKIT-7500B | EV7508H            |                               |                     | <del>-</del>                   | ASM75                             |

| μPD7507HG-22            | EVAKIT-7500B | EV7508H            | _                             |                     | _                              | ASM75                             |

| μPD7508C                | EVAKIT-7500B | _                  |                               | μPD78CG08E          |                                | ASM75                             |

| μPD7508CU               | EVAKIT-7500B | _                  | <del>_</del>                  |                     |                                | ASM75                             |

| μPD7508G-00             | EVAKIT-7500B |                    |                               |                     |                                | ASM75                             |

| μPD75CG08E              | EVAKIT-7500B | <del></del>        |                               |                     | _                              | ASM75                             |

| μPD7508HC               | EVAKIT-7500B | EV7508H            |                               | иPD78CG08HE         |                                | ASM75                             |

| μPD7508HCU              | EVAKIT-7500B | EV7508H            |                               |                     |                                | ASM75                             |

| μPD7508HG-22            | EVAKIT-7500B | EV7508H            |                               |                     | <del></del>                    | ASM75                             |

| μPD75CG08HE             | EVAKIT-7500B | EV7508H            | _                             |                     |                                | ASM75                             |

| μPD7527AC               | EVAKIT-7500B | EV7528             |                               | μPD78CG28E          |                                | ASM75                             |

| μPD7527ACU              | EVAKIT-7500B | EV7528             |                               | <u> </u>            |                                | ASM75                             |

| μPD7528AC               | EVAKIT-7500B | EV7528             |                               | μPD78CG28E          |                                | ASM75                             |

| μPD7528ACU              | EVAKIT-7500B | EV7528             |                               |                     |                                | ASM75                             |

| μPD75CG28E              | EVAKIT-7500B | EV7528             |                               |                     | <u>-</u>                       | ASM75                             |

| μPD7533C                | EVAKIT-7500B | EV7533             | ·                             | иPD75CG33E          |                                | ASM75                             |

| µРD7533CU               | EVAKIT-7500B | EV7533             |                               | μ-υ/30α33Ε          |                                | ASM75                             |

| μPD7533G-22             | EVAKIT-7500B | EV7533             |                               |                     |                                | ASM75                             |

| μPD75CG33E              | EVAKIT-7500B | EV7533             |                               |                     |                                | ASM75                             |

| μPD7537AC               | EVAKIT-7500B | EV7528             |                               | µРD75CG38E          |                                | ASM75                             |

| μPD7537ACU              | EVAKIT-7500B | EV7528             |                               | ш втоосос           |                                | ASM75                             |

| μPD7538AC               | EVAKIT-7500B | EV7528             |                               | µРD75CG38E          |                                | ASM75                             |

| μPD7538ACU              | EVAKIT-7500B | EV7528             |                               | <u>ш втоссов.</u>   |                                | ASM75                             |

| μPD75CG38E              | EVAKIT-7500B | EV7528             |                               |                     |                                | ASM75                             |

| μPD7554CS               | EVAKIT-7500B | EV7554A            | SE-7554A                      | μPD75P54CS          | PA-75P54CS                     | ASM75                             |

| μPD7554G                | EVAKIT-7500B | EV7554A            | SE-7554A                      | µРD75Р54G           | PA-75P54CS                     | ASM75                             |

| μPD7554ACS              | EVAKIT-7500B | EV7554A            | SE-7554A                      | µРD75Р54CS          | PA-75P54CS                     | ASM75                             |

| µРD7554AG               | EVAKIT-7500B | EV7554A<br>EV7554A | SE-7554A                      | µРD75Р54G           | PA-75P540S                     | ASM75                             |

| μPD75P54CS              | EVAKIT-7500B | EV7554A            | —                             | μευτοιοία           |                                | ASM75                             |

| µРD75Р54G               | EVAKIT-7500B | EV7554A            |                               |                     |                                | ASM75                             |

| μPD7556CS               | EVAKIT-7500B | EV7554A            | SE-7554A                      | μPD75P56CS          | PA-75P56CS                     | ASM75                             |

| μPD7556G                | EVAKIT-7500B | EV7554A            | SE-7554A                      | µРD75Р56G           | PA-75P56CS                     | ASM75                             |

| μPD7556ACS              | EVAKIT-7500B | EV7554A            | SE-7554A                      | μPD75P56CS          | PA-75P56CS                     | ASM75                             |

| μPD7556AG               | EVAKIT-7500B | EV7554A<br>EV7554A | SE-7554A                      | µРD75P56G           | PA-75P56CS                     | ASM75                             |

| μPD75P56CS              |              |                    | 5E-7554A                      | μευτονουα           | FA-75F3003                     | ASM75                             |

| <del></del>             | EVAKIT-7500B | EV7554A            |                               |                     |                                | ASM75                             |

| μPD75P56G<br>μPD7564CS  | EVAKIT-7500B | EV7554A<br>EV7554A | SE-7554A                      | шPD75P64CS          | PA-75P54CS                     | ASM75                             |

|                         | EVAKIT-7500B |                    |                               |                     |                                | ASM75                             |

| μPD7564G                | EVAKIT-7500B | EV7554A            | SE-7554A                      | μPD75P64G           | PA-75P54CS<br>PA-75P54CS       | ASM75                             |

| μPD7564ACS              | EVAKIT-7500B | EV7554A            | SE-7554A                      | μPD75P64CS          |                                |                                   |

| μPD7564AG               | EVAKIT-7500B | EV7554A            | SE-7554A                      | μPD75P64G           | PA-75P54CS                     | ASM75                             |

| μPD75P64CS              | EVAKIT-7500B | EV7554A            |                               | _                   |                                | ASM75                             |

| μPD75P64G               | EVAKIT-7500B | EV7554A            |                               |                     |                                | ASM75                             |

| μPD7566CS               | EVAKIT-7500B | EV7554A            | SE-7554A                      | μPD75P66CS          | PA-75P56CS                     | ASM75                             |

| μPD7566G                | EVAKIT-7500B | EV7554A            | SE-7554A                      | μPD75P66G           | PA-75P56CS                     | ASM75                             |

<sup>\*</sup> Required Tools

## $\mu \text{PD75XX Series Development Tools Selection Guide (cont)}$

| Part Number<br>(Note 1) | Emulator*    | Add-on<br>Board* | System<br>Evaluation<br>Board | EPROM/OTP<br>Device | PG-1500<br>Adapter<br>(Note 2) | Absolute<br>Assembler<br>(Note 3) |

|-------------------------|--------------|------------------|-------------------------------|---------------------|--------------------------------|-----------------------------------|

| μPD7566ACS              | EVAKIT-7500B | EV7554A          | SE-7554A                      | μPD75P66CS          | PA-75P56CS                     | ASM75                             |

| μPD7566AG               | EVAKIT-7500B | EV7554A          | SE-7554A                      | μPD75P66G           | PA-75P56CS                     | ASM75                             |

| μPD75P66CS              | EVAKIT-7500B | EV7554A          | <del>-</del>                  | _                   | _                              | ASM75                             |

| μPD75P66G               | EVAKIT-7500B | EV7554A          | -                             | <del></del>         | _                              | ASM75                             |

<sup>\*</sup> Required Tools

#### Notes:

(1) Packages:

### Package Description

| _    | and the state of t |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| C    | 40-pin plastic DIP (μPD7507/07H/08/08H)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|      | 42-pin plastic DIP (μPD7527A/28A/33/37A/38A)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| CS   | 20-pin plastic shrink DIP (µPD7554/54A/P54/64/64A/P64)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|      | 24-pin plastic shrink DIP (µPD7556/56A/P56/66/66A/P66)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| CU   | 40-pin plastic shrink DIP (μPD7507/07H/08/08H)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|      | 42-pin plastic shrink DIP (µPD7527A/28A/33/37A/38A)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| E    | 40-pin ceramic piggy-back DIP (μPD75CG08/08H)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|      | 42-pin ceramic piggy-back DIP (μPD75CG28/33/38)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| G    | 20-pin plastic SO (μPD7554/54A/P54/64/64A/P64)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|      | 24-pin plastic SO (μPD7556/56A/P56/66/66A/P66)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| G-00 | 52-pin plastic QFP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |