**NEC Electronics Inc.**

# MEMORY PRODUCTS

## 1986 MEMORY DATA BOOK

April 1986 NECEL-000154 Stock No. 600100 ©1986 NEC Electronics Inc./Printed in U.S.A.

No part of this document may be copied or reproduced in any form or by any means without the prior written consent of NEC Electronics Inc. The information in this document is subject to change without notice. Devices sold by NEC Electronics Inc. are covered by the warranty and patent indemnification provisions appearing in NEC Electronics Inc. Terms and Conditions of Sale only. NEC Electronics Inc. makes no warranty, express, statutory, implied, or by description, regarding the information set forth herein or regarding the freedom of the described devices from patent infringement. NEC Electronics Inc. makes no warranty of merchantability or fitness for any purpose. NEC Electronics Inc. assumes no responsibility for any errors that may appear in this document. NEC Electronics Inc. makes no commitment to update or to keep current the information contained in this document.

# NEC

#### **GENERAL INFORMATION**

#### **QUALITY AND RELIABILITY**

#### **APPLICATION-SPECIFIC MEMORIES**

#### **DYNAMIC RAM MODULES**

**DYNAMIC RAMs**

XRAMs

1

2

3

4

5

6

7

8

9

10

11

12

**MOS STATIC RAMs**

ECL RAMs

**UV and OTP EPROMs**

**MASK-PROGRAMMABLE ROMs**

**BIPOLAR TTL PROMs**

#### **PACKAGING INFORMATION**

#### **TABLE OF CONTENTS**

#### Section 1 — General Information

#### Page

| Introduction                | 1-1  |

|-----------------------------|------|

| Memory Product Overview     | 1-1  |

| Alphanumeric Index          | 1-2  |

| Memory Part Number Guide    | 1-4  |

| Advanced Memory Products    | 1-5  |

| Selection Guides            | 1-6  |

| Application-Specific Memory | 1-6  |

| Dynamic RAM Modules         |      |

| Dynamic RAM                 | 1-7  |

| ХŔАМ                        | 1-7  |

| MOS Static RAM              | 1-8  |

| ECL RAM                     |      |

| EPROM                       |      |

| Mask-Programmable ROM       | 1-11 |

| Bipolar PROM                | 1-11 |

#### Section 2 — Quality and Reliability

| troduction                                       |

|--------------------------------------------------|

| proaches to Total Quality Control 2-1            |

| plementations of Distributed Quality Control 2-1 |

| oduct Development                                |

| afer Fabrication Process Flow                    |

| sembly Process Flow of Plastic Memories          |

| ectricial Testing and Screening                  |

| e-Inventory Inspection                           |

| liability Assurance Test                         |

| ımmary 2-3                                       |

#### Section 3 — Application-Specific Memories

| μPD41101     | 910 x 8-Bit FIFO Memory                                  | . 3-1 |

|--------------|----------------------------------------------------------|-------|

| μPD41102     | 1135 x 8-Bit FIFO Memory                                 |       |

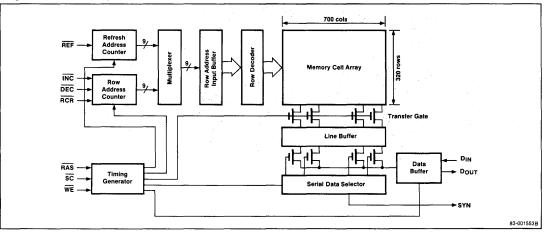

| μPD41221     | 224,000-Bit Serial-Access NMOS RAM                       | 3-25  |

| µPD41264     | 262,144-Bit Dual Port Dynamic NMOS RAM                   | 3-33  |

| App. Note 32 | µPD41221 Serial Access Memory with Customized Array Size | 3-43  |

| App. Note 33 | μPD41264 VRAM and μPD7220A System Implementation         | 3-53  |

| App. Note 34 | μPD41264 262,144-Bit Dual-Port Dynamic NMOS RAM          | 3-59  |

#### Section 4 — Dynamic RAM Modules

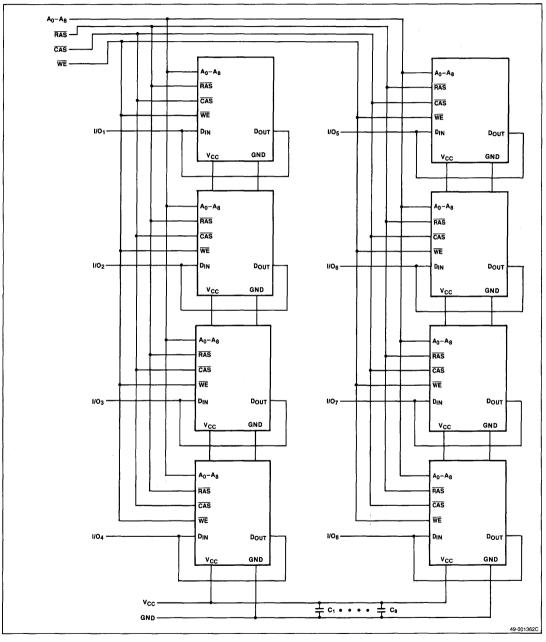

| MC-41256A4  | 262,144 x 4-Bit Dynamic NMOS RAM Module   | 4-1  |

|-------------|-------------------------------------------|------|

| MC-41256A5  | 262,144 x 5-Bit Dynamic NMOS RAM Module   | 4-9  |

| MC-41256A8  | 262,144 x 8-Bit Dynamic NMOS RAM Module   | 4-17 |

| MC-41256A9  | 262,144 x 9-Bit Dynamic NMOS RAM Module   | 4-27 |

| MC-411000A1 | 1,048,576 x 1-Bit Dynamic NMOS RAM Module | 4-37 |

#### Section 5 — Dynamic RAMs

| µPD4164  | 65,536 x 1-Bit Dynamic NMOS RAM  | 5-1  |

|----------|----------------------------------|------|

| µPD4265  | 65,536 x 1-Bit Dynamic CMOS RAM  | 5-5  |

| µPD41256 | 262,144 x 1-Bit Dynamic NMOS RAM | 5-11 |

| µPD41257 | 262,144 x 1-Bit Dynamic NMOS RAM | 5-21 |

| µPD41416 | 16,384 x 4-Bit Dynamic NMOS RAM  | 5-29 |

| μPD41464 | 65,536 x 4-Bit Dynamic NMOS RAM  | 5-35 |

Page

#### Section 5 — Dynamic RAMs (cont)

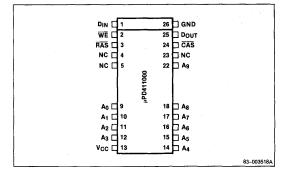

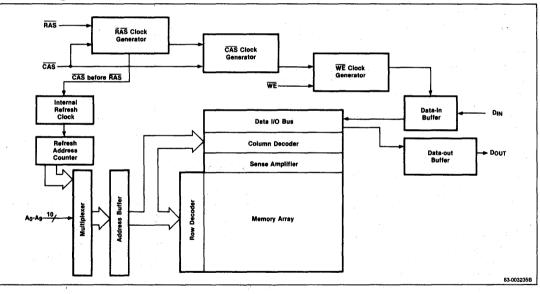

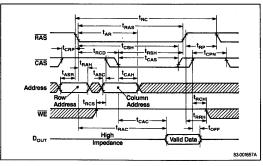

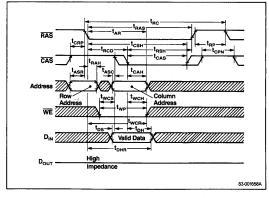

| μPD411000 | 1,048,576 x 1-Bit Dynamic NMOS RAM 5-43 |

|-----------|-----------------------------------------|

| µPD411001 | 1,048,576 x 1-Bit Dynamic NMOS RAM 5-51 |

| μPD414256 | 262,144 x 4-Bit Dynamic NMOS RAM 5-61   |

#### Section 6 – XRAMS

| μPD4168  | 8,192 x 8-Bit NMOS XRAM  | 6-1 |

|----------|--------------------------|-----|

| µPD42832 | 32,768 x 8-Bit CMOS XRAM | 6-9 |

#### Section 7 — MOS Static RAMs

| μPD446   | 2,048 x 8-Bit Static CMOS RAM     | 7-1  |

|----------|-----------------------------------|------|

| μPD449   | 2,048 x 8-Bit Static CMOS RAM     | 7-5  |

| μPD2147A | 4,096 x 1-Bit Static NMOS RAM     | 7-9  |

| μPD2149  | 1,024 x 4-Bit Static NMOS RAM     | 7-13 |

| μPD4016  | 2,048 x 8-Bit Static NMOS RAM     | 7-17 |

| μPD4311  | 16,384 x 1-Bit Static MIX-MOS RAM | 7-21 |

| μPD4314  | 4,096 x 4-Bit Static MIX-MOS RAM  | 7-25 |

| μPD4361  | 65,536 x 1-Bit Static MIX-MOS RAM | 7-29 |

| μPD4362  | 16,384 x 4-Bit Static MIX-MOS RAM | 7-35 |

| μPD4364  | 8,192 x 8-Bit Static MIX-MOS RAM  | 7-39 |

| μPD4464  | 8,192 x 8-Bit Static CMOS RAM     | 7-45 |

| μPD43256 | 32,768 x 8-Bit Static MIX-MOS RAM | 7-51 |

#### Section 8 — ECL RAMs

| µPB10422  | 256 x 4-Bit 10K ECL RAM      | 8-1  |

|-----------|------------------------------|------|

| μPB10470  | 4,096 x 1-Bit 10K ECL RAM    | 8-5  |

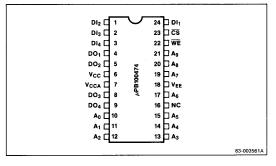

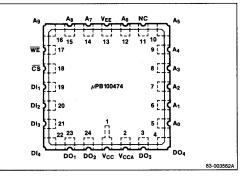

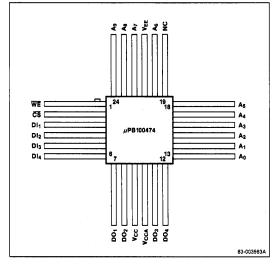

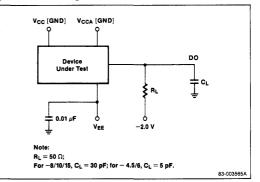

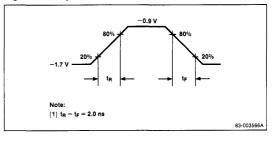

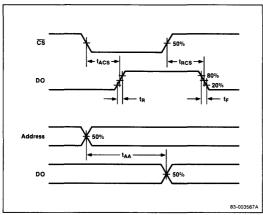

| μPB10474  | 1,024 x 4-Bit 10K ECL RAM    | 8-9  |

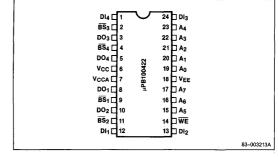

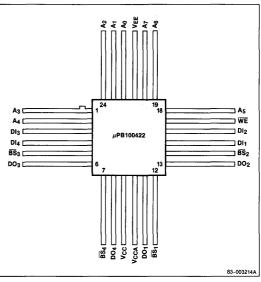

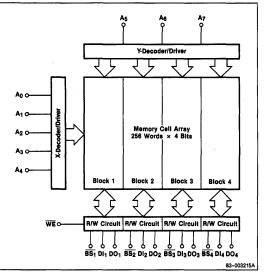

| µPB100422 | 256 x 4-Bit 100K ECL RAM 8   | 8-13 |

| μPB100470 | 4,096 x 1-Bit 100K ECL RAM   | 8-17 |

| μPB100474 | 1,024 x 4-Bit 100K ECL RAM 8 | 3-21 |

#### Section 9 — UV and OTP EPROMs

| μPD2764    | 8,192 x 8-Bit NMOS UV/OTP EPROM  | 9-1  |

|------------|----------------------------------|------|

| μPD27128   | 16,384 x 8-Bit NMOS UV/OTP EPROM | 9-5  |

| μPD27256   | 32,768 x 8-Bit NMOS UV EPROM     | 9-9  |

| μPD27C64   | 8,192 x 8-Bit CMOS UV/OTP EPROM  | 9-13 |

| µPD27C256  | 32,768 x 8-Bit CMOS UV/OTP EPROM | 9-19 |

| µPD27C256A | 32,768 x 8-Bit CMOS UV/OTP EPROM | 9-23 |

| µPD27C512  | 65,536 x 8-Bit CMOS UV EPROM     | 9-29 |

| µPD27C1024 | 65,536 x 16-Bit CMOS UV EPROM    | 9-35 |

#### Section 10 — Mask-Programmable ROMs

| μPD2364A   | 8,192 x 8-Bit Mask-Programmable NMOS ROM 10-1    |

|------------|--------------------------------------------------|

| µPD2364E   | 8,192 x 8-Bit Mask-Programmable NMOS ROM 10-3    |

| µPD23128E  | 16,384 x 8-Bit Mask-Programmable NMOS ROM 10-5   |

| μPD23C64E  | 8,192 x 8-Bit Mask-Programmable CMOS ROM 10-7    |

| µPD23C128E | 16,384 x 8-Bit Mask-Programmable CMOS ROM 10-11  |

| µPD23C256E | 32,768 x 8-Bit Mask-Programmable CMOS ROM 10-13  |

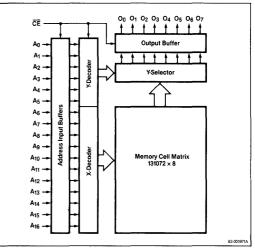

| µPD23C1000 | 131,072 x 8-Bit Mask-Programmable CMOS ROM 10-17 |

| µPD23C2000 | 2,097,152-Bit Mask-Programmable CMOS ROM 10-19   |

#### TABLE OF CONTENTS

Page

#### Section 11 — Bipolar TTL PROMs

| μPB426 | 1,024 x 4-Bit Bipolar TTL PROM | 11-1 |

|--------|--------------------------------|------|

| μPB429 | 2,048 x 8-Bit Bipolar TTL PROM | 11-5 |

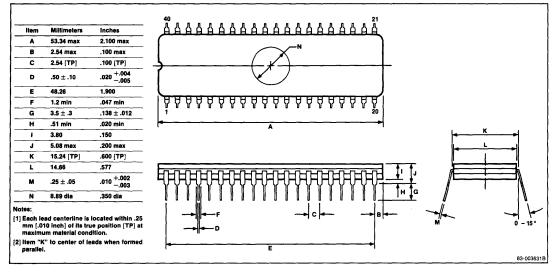

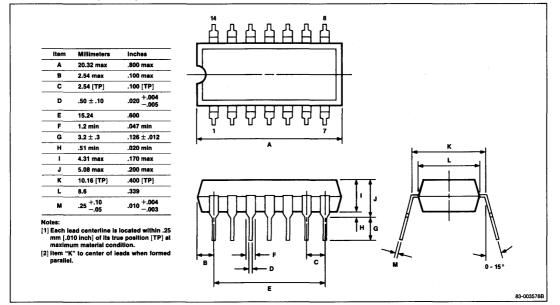

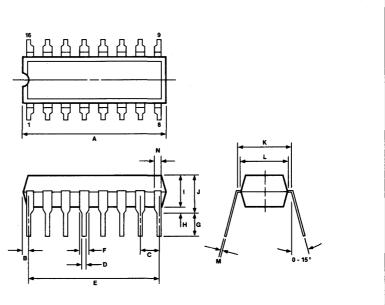

#### Section 12 – Packaging Information

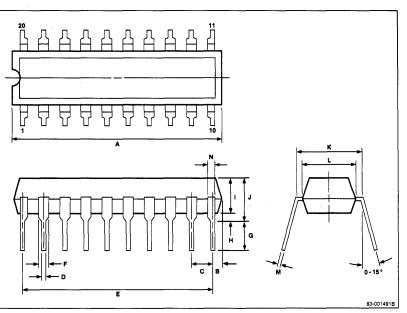

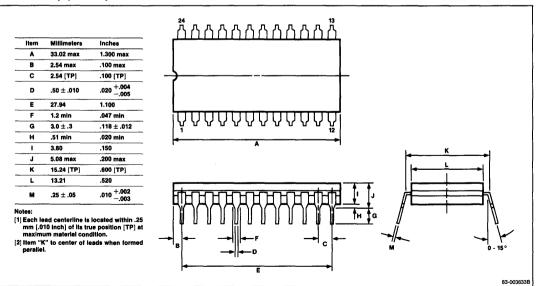

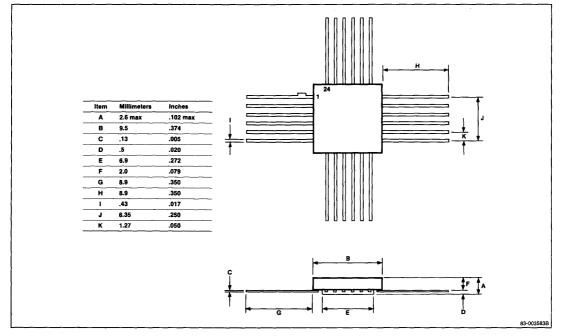

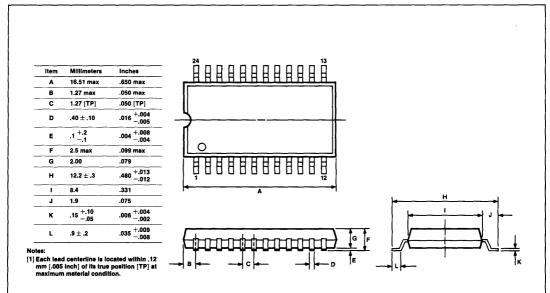

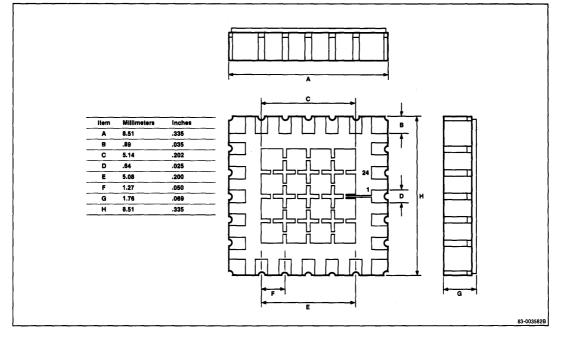

| Package/Device ( | Cross Reference                                | -1 |

|------------------|------------------------------------------------|----|

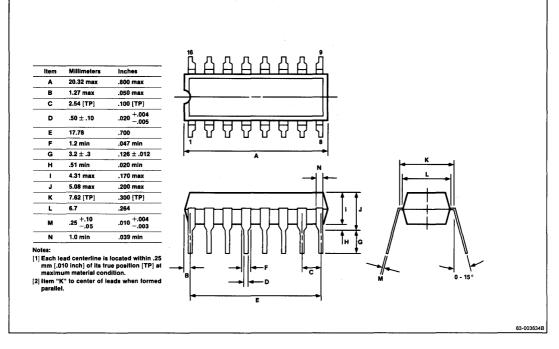

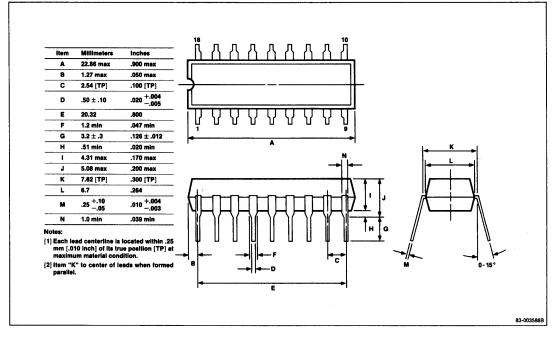

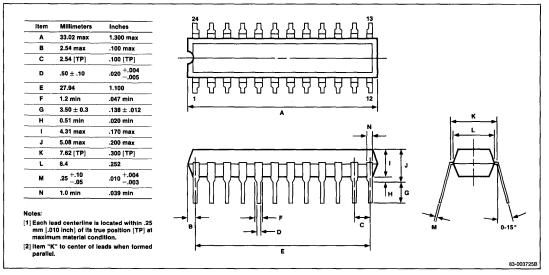

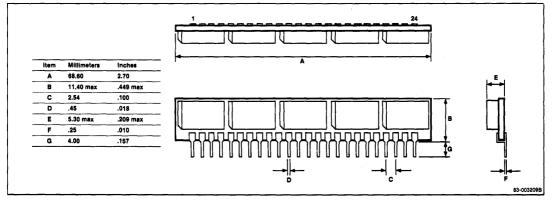

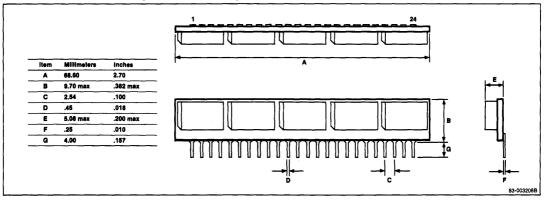

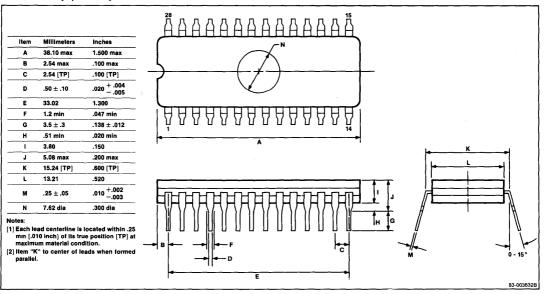

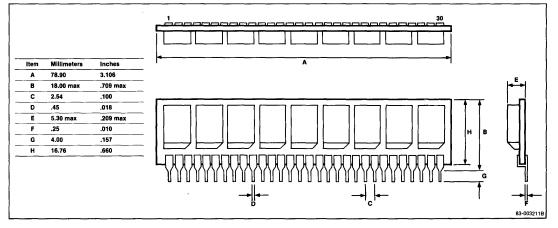

| 14 Pin           | Plastic DIP (400 mil) 12-                      | -3 |

| 16 Pin           | Plastic DIP (300 mil) 12-                      |    |

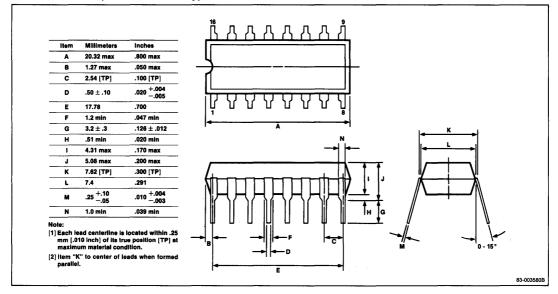

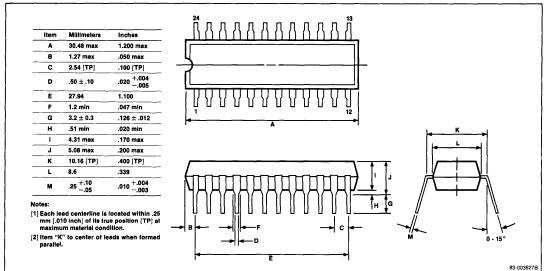

| 16 Pin           | Plastic DIP (300 mil, Semiwide Body) 12-       | -4 |

| 16 Pin           | Plastic DIP (300 mil, Wide Body) 12-           | -4 |

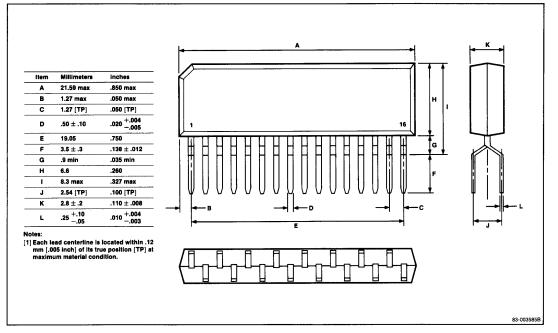

| 16 Pin           | Plastic ZIP 12-                                | -5 |

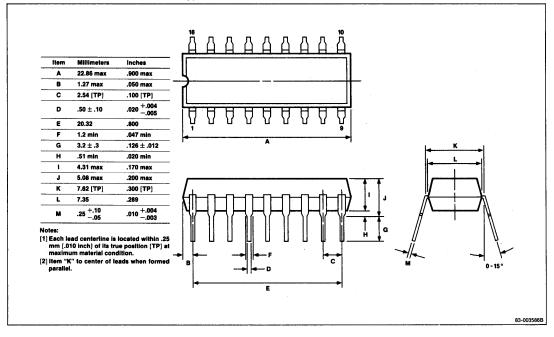

| 18 Pin           | Plastic DIP (300 mil) 12-                      | -5 |

| 18 Pin           | Plastic DIP (300 mil, Semiwide Body) 12-       | -6 |

| 18 Pin           | Plastic DIP (300 mil, Wide Body) 12-           | -6 |

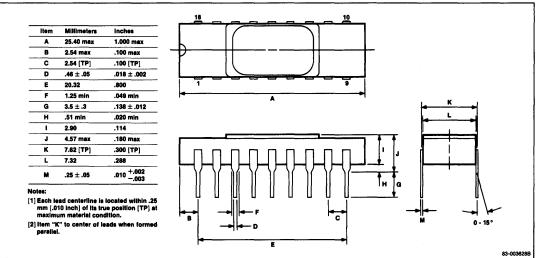

| 18 Pin           | Plastic Leadless Chip Carrier 12-              | -7 |

| 18 Pin           | Ceramic DIP (300 mil) 12-                      | -7 |

| 18 Pin           | Cerdip (300 mil) 12-                           | -8 |

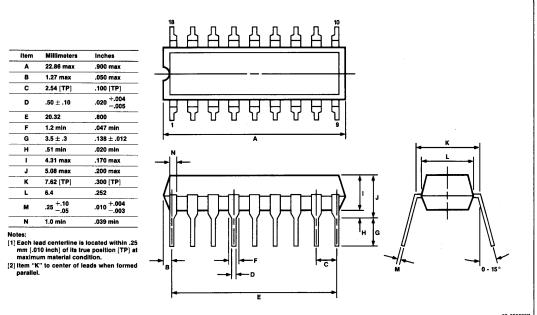

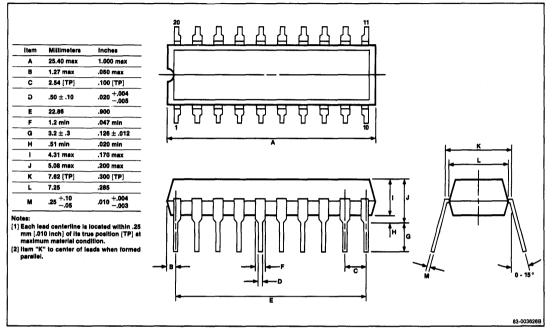

| 20 Pin           | Plastic DIP (300 mil) 12-                      | -8 |

| 20 Pin           | Plastic DIP (300 mil, Wide Body) 12-           | -9 |

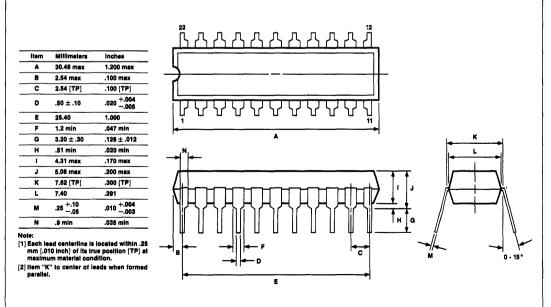

| 22 Pin           | Plastic DIP (300 mil, Wide Body) 12-           | -9 |

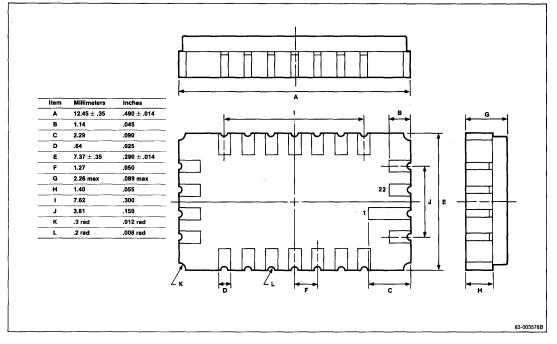

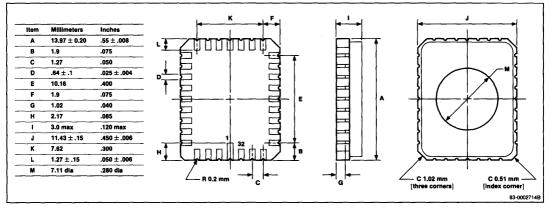

| 22 Pin           | Ceramic Leadless Chip Carrier 12-              | 10 |

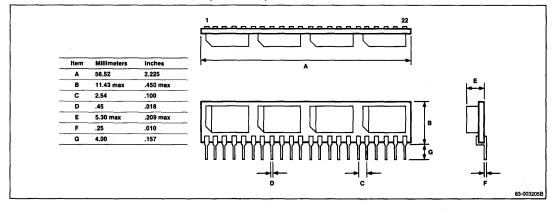

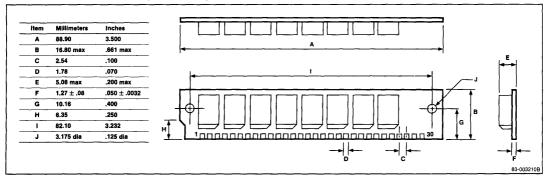

| 22 Pin           | SIMM, MC-41256A4A (Glass-epoxy Substrate) 12-  | 10 |

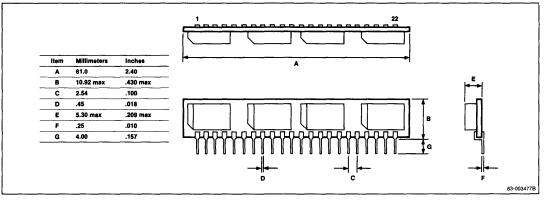

| 22 Pin           | SIMM, MC-411000A1A (Glass-epoxy Substrate) 12- | 11 |

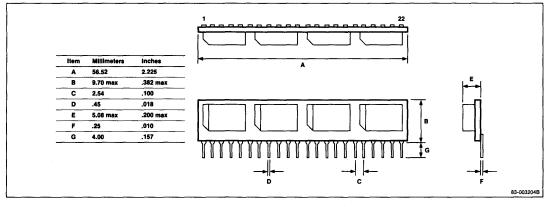

| 22 Pin           | SIMM, MC-41256A4C (Ceramic Substrate) 12-      | 11 |

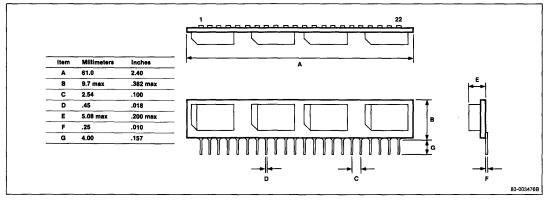

| 22 Pin           | SIMM, MC-411000A1C (Ceramic Substrate) 12-     | 12 |

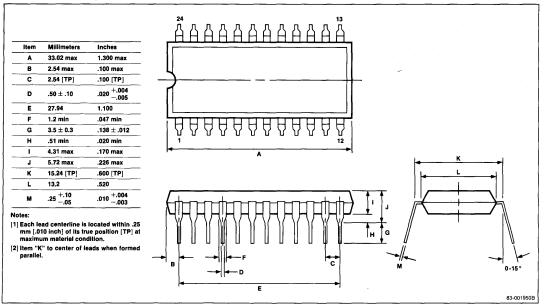

| 24 Pin           | Plastic DIP (300 mil) 12-                      | 12 |

| 24 Pin           | Plastic DIP (400 mil) 12-                      | 13 |

| 24 Pin           | Plastic DIP (600 mil) 12                       | 13 |

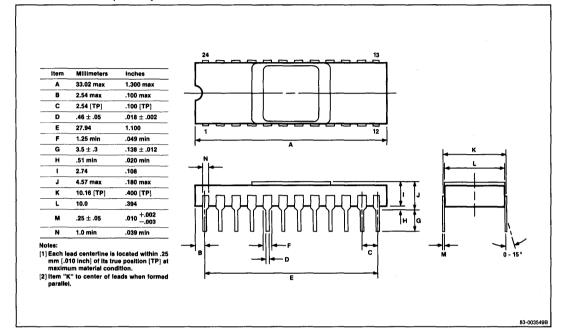

| 24 Pin           | Ceramic DIP (400 mil) 12-                      | 14 |

| 24 Pin           | Cerdip (600 mil) 12-                           | 14 |

| 24 Pin           | Ceramic Flatpack 12-1                          | 15 |

| 24 Pin           | Plastic Miniflat 12-                           | 15 |

| 24 Pin           | Ceramic Leadless Chip Carrier 12-              | 16 |

| 24 Pin           | SIMM, MC-41256A5A (Glass-epoxy Substrate)12-   | 16 |

| 24 Pin           | SIMM, MC-41256A5C (Ceramic Substrate) 12-      | 17 |

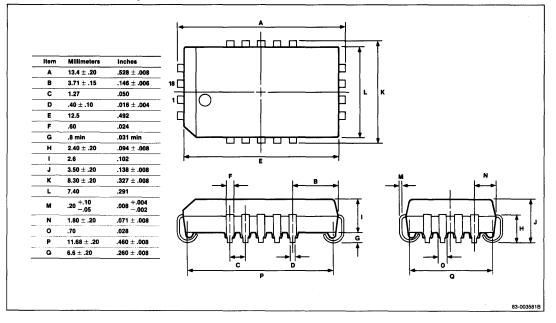

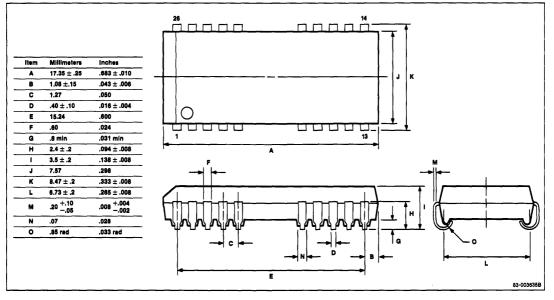

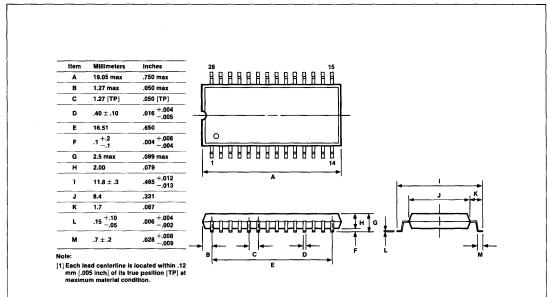

| 26/20 Pin        | Plastic SOJ 12-                                |    |

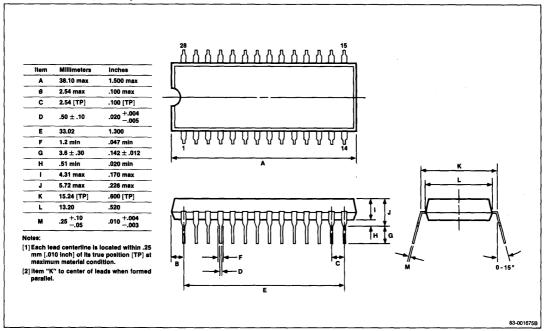

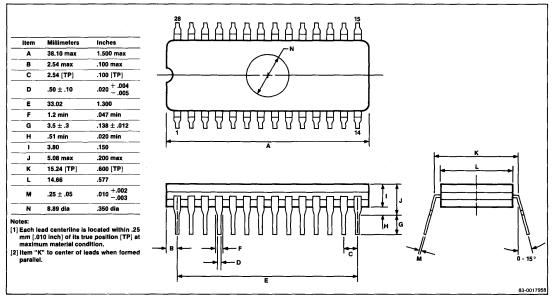

| 28 Pin           | Plastic DIP (600 mil) 12-                      | 18 |

| 28 Pin           | Cerdip (600 mil) 12-                           | 18 |

| 28 Pin           | Cerdip (600 mil, Wide Body) 12-                | 19 |

| 28 Pin           | Plastic Miniflat 12-                           | 19 |

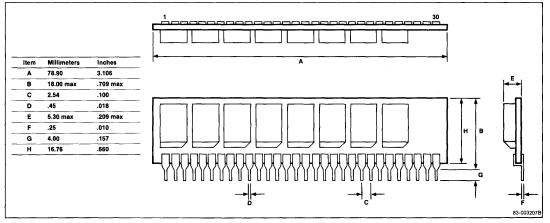

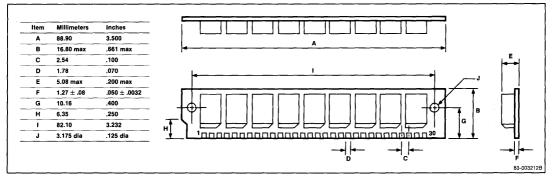

| 30 Pin           | SIMM, MC-41256A8A (Glass-epoxy Substrate) 12-2 | 20 |

| 30 Pin           | SIMM, MC-41256A9A (Glass-epoxy Substrate) 12-2 | 20 |

| 30 Pin           | SIMM, MC-41256A8B (Glass-epoxy Substrate) 12-2 | 21 |

| 30 Pin           | SIMM, MC-41256A9B (Glass-epoxy Substrate) 12-2 |    |

| 32 Pin           | Ceramic Leadless Chip Carrier 12-2             | 22 |

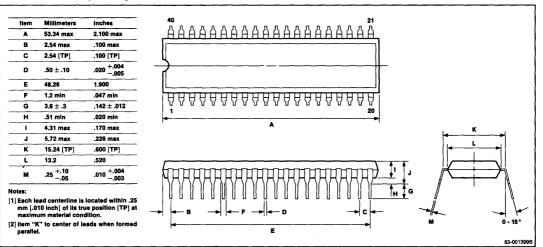

| 40 Pin           | Plastic DIP (600 mil) 12-2                     |    |

| 40 Pin           | Cerdip (600 mil, Wide Body) 12-2               | 23 |

#### **GENERAL INFORMATION**

#### **GENERAL INFORMATION**

Page

#### Section 1 — General Information

# Introduction1-1Memory Product Overview1-1Alphanumeric Index1-2Memory Part Number Guide1-4Advanced Memory Products1-5Selection Guides1-6Application-Specific Memory1-6Dynamic RAM Modules1-6Dynamic RAM1-7XRAM1-7MOS Static RAM1-8ECL RAM1-9EPROM1-11Bipolar PROM1-11

#### Introduction

This catalog provides you with details about NEC's total memory product line, which is the broadest in the industry today. NEC memories not only give you a wider selection of device types, they also allow you to choose from various configurations and process technologies within a specific type of device. The variety of NEC memories gives you greater design alternatives and the ability to choose the part that truly fits your product.

The catalog is divided into sections for each of our major memory groups: ASMs, DRAM Modules, DRAMs, XRAMs, MOS SRAMs, ECL RAMs, EPROMs, Masked ROMs, Bipolar PROMs, and Packaging Information. The selection guides include detailed specifications and packaging information. In Section 2 of this catalog, you will find a description of the quality and reliability procedures that have enabled NEC to reach the highest quality standard currently available.

#### **Memory Product Overview**

|         | Application                           |                                         |                                     | RAM      |                                          | EPF                                            | ROM                                 |                                        | Bipolar                           |        |

|---------|---------------------------------------|-----------------------------------------|-------------------------------------|----------|------------------------------------------|------------------------------------------------|-------------------------------------|----------------------------------------|-----------------------------------|--------|

| Density | Specific                              | Module                                  | Dynamic                             | XRAM     | MOS Static                               | ECL                                            | UV                                  | OTP                                    | RGM                               | PROM   |

| 1K      |                                       |                                         |                                     |          |                                          | μPB10422<br>μPB100422                          |                                     |                                        |                                   |        |

| 4K      |                                       |                                         |                                     |          | μPD2147A<br>μPD2149                      | μPB10470<br>μPB10474<br>μPB100470<br>μPB100474 |                                     | -                                      |                                   | μPB426 |

| 8K      | μPD41101<br>μPD41102                  |                                         |                                     |          |                                          |                                                |                                     |                                        |                                   |        |

| 16K     | · · · · · · · · · · · · · · · · · · · |                                         |                                     |          | μPD446<br>μPD449<br>μPD4016<br>μPD4311   |                                                |                                     |                                        |                                   | μPB429 |

|         |                                       |                                         |                                     |          | µPD4314                                  |                                                |                                     |                                        |                                   |        |

| 64K     |                                       |                                         | μPD4164<br>μPD4265<br>μPD41416      | μPD4168  | μPD4361<br>μPD4362<br>μPD4364<br>μPD4364 |                                                | μPD2764<br>μPD27C64                 | μPD2764<br>μPD27C64                    | μPD2364A<br>μPD2364E<br>μPD23C64E |        |

| 128K    |                                       |                                         |                                     | <u></u>  |                                          |                                                | µPD27128                            | µPD27128                               | μPD23128E<br>μPD23C128E           |        |

| 256K    | μPD41221<br>μPD41264                  |                                         | μPD41256<br>μPD41257<br>μPD41464    | µPD42832 | µPD43256                                 |                                                | μPD27256<br>μPD27C256<br>μPD27C256A | μPD27C256<br>μPD27C256A                | μPD23C256E                        |        |

| 512K    |                                       |                                         |                                     |          |                                          |                                                | µPD27C512                           | ······································ |                                   |        |

| 1M      |                                       | MC-41256A4<br>MC-41256A5<br>MC-411000A1 | μPD411000<br>μPD411001<br>μPD414256 |          |                                          |                                                | µPD27C1024                          |                                        | µPD23C1000                        |        |

| 2M      |                                       | MC-41256A8<br>MC-41256A9                |                                     |          |                                          |                                                |                                     |                                        | µPD23C2000                        |        |

#### **GENERAL INFORMATION**

#### Alphanumeric Index

| Page |

|------|

|------|

| MC-41256A4<br>MC-41256A5<br>MC-41256A8<br>MC-41256A9<br>MC-411000A1  | 262,144 x 4-Bit Dynamic NMOS RAM Module       4-1         262,144 x 5-Bit Dynamic NMOS RAM Module       4-9         262,144 x 8-Bit Dynamic NMOS RAM Module       4-17         262,144 x 9-Bit Dynamic NMOS RAM Module       4-17         262,144 x 9-Bit Dynamic NMOS RAM Module       4-27         1,048,576 x 1-Bit Dynamic NMOS RAM Module       4-37 |

|----------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| μΡΒ426<br>μΡΒ429<br>μΡΒ10422<br>μΡΒ10470<br>μΡΒ10474                 | 1,024 x 4-Bit Bipolar TTL PROM       11-1         2,048 x 8-Bit Bipolar TTL PROM       11-5         256 x 4-Bit 10K ECL RAM       8-1         4,096 x 1-Bit 10K ECL RAM       8-5         1,024 x 4-Bit 10K ECL RAM       8-9                                                                                                                             |

| μΡΒ100422<br>μΡΒ100470<br>μΡΒ100474<br>μΡD446<br>μΡD449              | 256 x 4-Bit 100K ECL RAM       8-13         4,096 x 1-Bit 100K ECL RAM       8-17         1,024 x 4-Bit 100K ECL RAM       8-21         2,048 x 8-Bit Static CMOS RAM       7-1         2,048 x 8-Bit Static CMOS RAM       7-5                                                                                                                           |

| μΡD2147A<br>μPD2149<br>μPD2364A<br>μPD2364E<br>μPD2364E<br>μPD23C64E | 4,096 x 1-Bit Static NMOS RAM       7-9         1,024 x 4-Bit Static NMOS RAM       7-13         8,192 x 8-Bit Mask-Programmable NMOS ROM       10-1         8,192 x 8-Bit Mask-Programmable NMOS ROM       10-3         8,192 x 8-Bit Mask-Programmable CMOS ROM       10-3         8,192 x 8-Bit Mask-Programmable CMOS ROM       10-7                  |

| μPD2764<br>μPD27C64<br>μPD4016<br>μPD4164<br>μPD4168                 | 8,192 x 8-Bit NMOS UV/OTP EPROM       9-1         8,192 x 8-Bit CMOS UV/OTP EPROM       9-13         2,048 x 8-Bit Static NMOS RAM       7-17         65,536 x 1-Bit Dynamic NMOS RAM       5-1         8,192 x 8-Bit NMOS XRAM       6-1                                                                                                                 |

| μPD4265<br>μPD4311<br>μPD4314<br>μPD4361<br>μPD4362                  | 65,536 x 1-Bit Dynamic CMOS RAM       5-5         16,384 x 1-Bit Static MIX-MOS RAM       7-21         4,096 x 4-Bit Static MIX-MOS RAM       7-25         65,536 x 1-Bit Static MIX-MOS RAM       7-29         16,384 x 4-Bit Static MIX-MOS RAM       7-35                                                                                              |

| μΡD4364<br>μΡD4464<br>μΡD23128E<br>μΡD23C128E<br>μΡD23C256E          | 8, 192 x 8-Bit Static MIX-MOS RAM       7-39         8, 192 x 8-Bit Static CMOS RAM       7-45         16,384 x 8-Bit Mask-Programmable NMOS ROM       10-5         16,384 x 8-Bit Mask-Programmable CMOS ROM       10-11         32,768 x 8-Bit Mask-Programmable CMOS ROM       10-13                                                                   |

#### Alphanumeric Index (cont)

| μPD27128   | 16,384 x 8-Bit NMOS UV/OTP EPROM                 |

|------------|--------------------------------------------------|

| µPD27256   | 32,768 x 8-Bit NMOS UV EPROM                     |

| μPD27C256  | 32,768 x 8-Bit CMOS UV/OTP EPROM                 |

| µPD27C256A | 32,768 x 8-Bit CMOS UV/OTP EPROM                 |

| μPD27C512  | 65,536 x 8-Bit CMOS UV EPROM                     |

| µPD41101   | 910 x 8-Bit FIFO Memory                          |

| µPD41102   | 1135 x 8-Bit FIFO Memory                         |

| µPD41221   | 224.000-Bit Serial-Access NMOS RAM               |

| µPD41256   | 262,144 x 1-Bit Dynamic NMOS RAM 5-11            |

| µPD41257   | 262,144 x 1-Bit Dynamic NMOS RAM 5-21            |

| µPD41264   | 262,144-Bit Dual Port Dynamic NMOS RAM 3-33      |

| μPD41416   | 16,384 x 4-Bit Dynamic NMOS RAM                  |

| μPD41464   | 65,536 x 4-Bit Dynamic NMOS RAM                  |

| μPD42832   | 32,768 x 8-Bit CMOS XRAM                         |

| μPD43256   | 32,768 x 8-Bit Static MIX-MOS RAM                |

| µPD23C1000 | 131,072 x 8-Bit Mask-Programmable CMOS ROM 10-17 |

| μPD23C2000 | 2,097,152-Bit Mask-Programmable CMOS ROM 10-19   |

| μPD27C1024 | 65,536 x 16-Bit CMOS UV EPROM 9-35               |

| μPD411000  | 1,048,576 x 1-Bit Dynamic NMOS RAM 5-43          |

| μPD411001  | 1,048,576 x 1-Bit Dynamic NMOS RAM 5-51          |

| μPD414256  | 262,144 x 4-Bit Dynamic NMOS RAM 5-61            |

Page

#### **GENERAL INFORMATION**

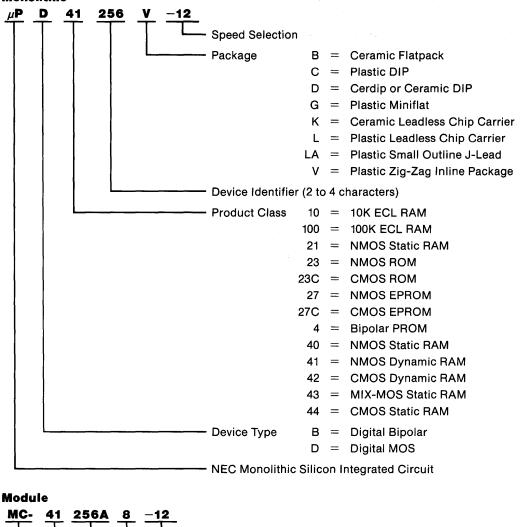

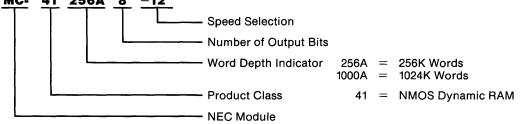

#### **MEMORY PART NUMBER GUIDE**

#### **Advanced Memory Products**

Several products were in development but not yet announced at the time of printing this Data Book. In order to help the customers of NEC Electronics with their product planning and to extend the useful life of this Data Book, some of these new products are outlined below.

#### **Application-Specific Memories**

The industry-leading Video RAM is the  $\mu$ PD41264. In 1986 the focus for this device will be on new higherperformance versions and also denser packaging options and lower power consumption.

Other application specific memories in development are targeted for graphics, data communications, and other specialized memory requirements.

#### **Dynamic RAM Modules**

More module-based products will be announced in 1986 based on dynamic RAM and other memory technologies.

#### **Dynamic RAMs**

NEC Electronics will continue to build on its leadership position in this product category with new devices (1 M DRAMs) and enhanced performance versions of previously announced devices. Key product developments are centered around higher density, lower power, and faster access times. There are also product development trends toward higher density packaging and alternate memory organizations (x 4, x 8).

#### XRAMs

Higher-density products are in development in this unique product family. These products will be CMOS for low power and ease of use.

#### Static RAMs

1986 will be a year of many new announcements in this product family. There will be an emphasis on faster speed and lower power for the industry leader in density, the  $\mu$ PD43256, a 32K x 8 Mix-MOS Static RAM. In both the MOS and the ECL product families from NEC Electronics, several new high-speed products will be announced in 1986, including a 256K Mix-Mos Static RAM and a 16K ECL RAM; and there will be new speed options available on existing devices, such as the  $\mu$ PD4364,  $\mu$ PD4464, and  $\mu$ PD43256. In addition, NEC Electronics will continue to focus on the other needs of its customers, particularly in the areas of high-density surface mount packaging and wide memory organization (x 4, x 8).

#### **Non-volatile Memories**

In this product family, too, the emphasis will be on advanced packaging, such as for the  $\mu$ PD27C256AK/G (32K x 8 CMOS EPROM), and advanced products such as the  $\mu$ PD28C64 (8K x 8 EEPROM), OTP EPROMs, the  $\mu$ PD27C1024 (64K x 16 CMOS EPROM), and the  $\mu$ PD23C2000 (128K x 16 or 256K x 8 CMOS ROM).

#### **Application-Specific Memory Selection Guide**

| Device                                 |                 |         | Access                  | Cycle                   | Supply  | Maximum Power<br>Dissipation (mW) |        |         |      |

|----------------------------------------|-----------------|---------|-------------------------|-------------------------|---------|-----------------------------------|--------|---------|------|

|                                        | Organization    | Process | Time (ns)               | Time (ns)               | Voltage | Standby                           | Active | Package | Pins |

| μPD41101-3<br>μPD41101-2<br>μPD41101-1 | 910 x 8         | NMOS    | 27<br>27<br>49          | 34<br>34(R)/69(W)<br>69 | +5      | _                                 | 495    | C       | 24   |

| μPD41102-3<br>μPD41102-2<br>μPD41102-1 | 1135 x 8        | NMOS    | 21<br>21<br>40          | 28<br>28(R)/56(W)<br>56 | +5      |                                   | 495    | C       | 24   |

| μPD41221-70<br>μPD41221-90             | 224K x 1        | NMOS    | 55<br>75                | 70<br>90                | +5      | 83                                | 385    | C       | 14   |

| µPD41264-12                            | 64K x 4<br>with | NMOS    | 120 Port A<br>40 Port B | 220 Port A<br>40 Port B | +5      | 66                                | 853    | С       | 24   |

| µPD41264-15                            | dual<br>ports   |         | 150 Port A<br>60 Port B | 270 Port A<br>60 Port B |         |                                   | 715    |         |      |

Note:

Package: C = Plastic DIP

#### **Dynamic RAM Module Selection Guide**

| Device                           |              |         | Access     | Cycle<br>Time (ns) | Supply<br>Voltage | Maximum Power<br>Dissipation (mW) |              |         |      |

|----------------------------------|--------------|---------|------------|--------------------|-------------------|-----------------------------------|--------------|---------|------|

|                                  | Organization | Process | Time (ns)  |                    |                   | Standby                           | Active       | Package | Pins |

| MC-41256A4-12<br>MC-41256A4-15   | 256K x 4     | NMOS    | 120<br>150 | 220<br>260         | +5                | 110                               | 1826<br>1540 | A/C     | 22   |

| MC-41256A5-12<br>MC-41256A5-15   | 256K x 5     | NMOS    | 120<br>150 | 220<br>260         | +5                | 138                               | 2283<br>1925 | A/C     | 24   |

| MC-41256A8-12<br>MC-41256A8-15   | 256K x 8     | NMOS    | 120<br>150 | 220<br>260         | +5                | 220                               | 3652<br>3080 | A/B     | 30   |

| MC-41256A9-12<br>MC-41256A9-15   | 256K x 9     | NMOS    | 120<br>150 | 220<br>260         | +5                | 248                               | 4109<br>3465 | A/B     | 30   |

| MC-411000A1-12<br>MC-411000A1-15 | 1M x 1       | NMOS    | 120<br>150 | 220<br>260         | +5                | 110                               | 539<br>468   | A/C     | 22   |

Note:

Package: A = Single Inline Memory Module (SIMM), Leaded, Glass-Epoxy Substrate; B = SIMM, Socket Mounted; C = SIMM, Leaded, Ceramic Substrate

#### **Dynamic RAM Selection Guide**

|                                                      |                |         | Access                   | Cycle                    | Supply  | Maximu<br>Dissipati |                          |              |                        |

|------------------------------------------------------|----------------|---------|--------------------------|--------------------------|---------|---------------------|--------------------------|--------------|------------------------|

| Device                                               | Organization   | Process | Time (ns)                | Time (ns)                | Voltage | Standby             | Active                   | -<br>Package | Pins                   |

| μPD4164-10<br>μPD4164-12<br>μPD4164-15<br>μPD4164-20 | 64K x 1        | NMOS    | 100<br>120<br>150<br>200 | 200<br>230<br>260<br>330 | +5      | 28                  | 330<br>303<br>275<br>248 | С            | 16                     |

| μPD4265-20<br>μPD4265-25                             | 64K x 1        | CMOS    | 200<br>250               | 335<br>410               | +5      | 2.8                 | 193<br>165               | С            | 16                     |

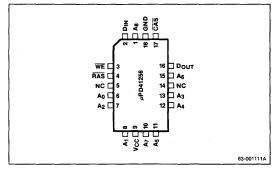

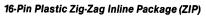

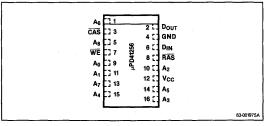

| μPD41256-12<br>μPD41256-15<br>μPD41256-20            | 256K x 1       | NMOS    | 120<br>150<br>200        | 220<br>260<br>330        | +5      | 28                  | 457<br>385<br>330        | C/L/V        | C = 16, L = 18, V = 16 |

| μPD41257-15<br>μPD41257-20                           | 256K x 1       | NMOS    | 150<br>200               | 270<br>335               | +5      | 28                  | 385<br>330               | C/L          | C = 16,<br>L = 18      |

| μPD41416-12<br>μPD41416-15<br>μPD41416-20            | 26K x 4        | NMOS    | 120<br>150<br>200        | 220<br>260<br>330        | +5      | 28                  | 303<br>275<br>248        | C            | 18                     |

| μPD41464-10<br>μPD41464-12<br>μPD41464-15            | 64K x 4        | NMOS    | 100<br>120<br>150        | 200<br>220<br>260        | +5      | 28                  | 440<br>413<br>385        | C/L          | 18                     |

| μPD411000-10<br>μPD411000-12<br>μPD411000-15         | 1 <b>M</b> x 1 | MNOS    | 100<br>120<br>150        | 200<br>220<br>260        | +5      | 28                  | 550<br>495<br>440        | C/LA         | C = 18,<br>LA = 26/20  |

| μPD411001-10<br>μPD411001-12<br>μPD411001-15         | 1M x 1         | NMOS    | 100<br>120<br>150        | 200<br>220<br>260        | +5      | 28                  | 550<br>495<br>440        | C/LA         | C = 18,<br>LA = 26/20  |

| μPD414256-10<br>μPD414256-12<br>μPD414256-15         | 256K x 4       | NMOS    | 100<br>120<br>150        | 200<br>220<br>260        | +5      | 28                  | 550<br>495<br>440        | C/LA         | C = 20,<br>LA = 26/20  |

#### Note:

Package: C = Plastic DIP; L = Plastic Leaded Chip Carrier; V = Zig-zag Inline Package; LA = Small Outline J-Lead Package

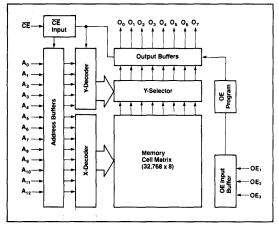

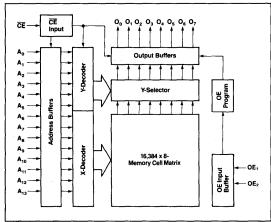

#### **XRAM Selection Guide**

| Device                                    | Organization |         | Access            | Cycle             | Supply  | Maximuı<br>Dissipati |                   | _       |      |

|-------------------------------------------|--------------|---------|-------------------|-------------------|---------|----------------------|-------------------|---------|------|

|                                           |              | Process | Time (ns)         | Time (ns)         | Voltage | Standby              | Active            | Package | Pins |

| μPD4168-12<br>μPD4168-15<br>μPD4168-20    | 8K x 8       | NMOS    | 120<br>150<br>200 | 220<br>260<br>330 | +5      | 28                   | 358<br>330<br>303 | С       | 28   |

| μPD42832-10<br>μPD42832-12<br>μPD42832-15 | 32K x 8      | CMOS    | 100<br>120<br>150 | 160<br>190<br>235 | +5      | 2.8                  | 330<br>275<br>220 | C/G     | 28   |

Note:

Package: C = Plastic DIP; G = Plastic Miniflat Package

#### **MOS Static RAM Selection Guide**

|                                                      |              |         | Access                   | Cycle                    | Supply  | Maximum Power<br>Dissipation (mW) |                         |                      |      |

|------------------------------------------------------|--------------|---------|--------------------------|--------------------------|---------|-----------------------------------|-------------------------|----------------------|------|

| Device                                               | Organization | Process | Time (ns)                | Time (ns)                | Voltage | Standby                           | Active                  | -<br>Package         | Pins |

| μΡD446-3<br>μΡD446-2<br>μΡD446-1<br>μΡD446           | 2K x 8       | CMOS    | 150<br>200<br>250<br>450 | 150<br>200<br>250<br>450 | +5      | 0.055*                            | 209<br>165<br>143<br>99 | C/G                  | 24   |

| μPD449-3<br>μPD449-2<br>μPD449-1<br>μPD449           | 2K x 8       | CMOS    | 150<br>200<br>250<br>450 | 150<br>200<br>250<br>450 | +5      | 0.055*                            | 209<br>165<br>143<br>99 | C                    | 24   |

| μPD2147A-25<br>μPD2147A-35<br>μPD2147A-45            | 4K x 1       | NMOS    | 25<br>35<br>45           | 25<br>35<br>45           | +5      | 110                               | 880                     | D                    | 18   |

| μPD2149-2<br>μPD2149-1<br>μPD2149                    | 1K x 4       | NMOS    | 35<br>45<br>55           | 35<br>45<br>55           | +5      |                                   | 990                     | D                    | 18   |

| μPD4016-5<br>μPD4016-3<br>μPD4016-2<br>μPD4016-1     | 2K x 8       | NMOS    | 120<br>150<br>200<br>250 | 120<br>150<br>200<br>250 | +5      | 83                                | 330                     | C                    | 24   |

| μPD4311-35<br>μPD4311-45<br>μPD4311-55               | 16K x 1      | Mix-MOS | 35<br>45<br>55           | 35<br>45<br>55           | +5      | 11                                | 440                     | С                    | 20   |

| μPD4314-35<br>μPD4314-45<br>μPD4314-55               | 4K x 4       | Mix-MOS | 35<br>45<br>55           | 35<br>45<br>55           | +5      | 11                                | 440                     | С                    | 20   |

| μPD4361-40<br>μPD4361-45<br>μPD4361-55<br>μPD4361-70 | 64K x 1      | Mix-MOS | 40<br>45<br>55<br>70     | 40<br>45<br>55<br>70     | +5      | 11                                | 660                     | К<br>С/К<br>С/К<br>С | 22   |

| μPD4362-45<br>μPD4362-55<br>μPD4362-70               | 16K x 4      | Mix-MOS | 45<br>55<br>70           | 45<br>55<br>70           | +5      | 11                                | 495                     | C                    | 22   |

| μPD4364-12<br>μPD4364-15<br>μPD4364-20               | 8K x 8       | Mix-MOS | 120<br>150<br>200        | 120<br>150<br>200        | +5      | 11/0.55/0.055                     | 220<br>220<br>193       | C/G                  | 28   |

| μPD4464-15<br>μPD4464-20                             | 8K x 8       | CMOS    | 150<br>200               | 150<br>200               | +5      | 0.055/0.0055                      | 220<br>193              | C/G                  | 28   |

| μPD43256-10<br>μPD43256-12<br>μPD43256-15            | 32K x 8      | Mix-MOS | 100<br>120<br>150        | 100<br>120<br>150        | +5      | 11/0.55                           | 385                     | C/G                  | 28   |

Note:

Package: C = Plastic DIP; G = Plastic Miniflat Package; D = Cerdip; K = Ceramic Leadless Chip Carrier (LCC)

\* Lower power version available; refer to the data sheet for more detail.

#### **ECL RAM Selection Guide**

| Device                                                                      | Organization | Process | Address<br>Access<br>Time (ns) | Chip Select<br>Access<br>Time (ns) | Supply<br>Voltage | Maximum Power<br>Dissipation (mW) | Package                       | Pins |

|-----------------------------------------------------------------------------|--------------|---------|--------------------------------|------------------------------------|-------------------|-----------------------------------|-------------------------------|------|

| μPB10422-7<br>μPB10422-10                                                   | 256 x 4      | 10K     | 7<br>10                        | 5*<br>5*                           | 5.2               | 1144                              | D                             | 24   |

| μPB10470-10<br>μPB10470-15                                                  | 4K x 1       | 10K     | 10<br>15                       | 6<br>8                             | 5.2               | 1144                              | D                             | 18   |

| μΡΒ10474-8<br>μΡΒ10474-10<br>μΡΒ10474-15                                    | 1K x 4       | 10K     | 8<br>10<br>15                  | 5<br>6<br>8                        | 5.2               | 1144                              | D                             | 24   |

| μPB100422-7<br>μPB100422-10                                                 | 256 x 4      | 100K    | 7<br>10                        | 5*<br>5*                           | -4.5              | 990                               | B/D                           | 24   |

| μPB100470-10<br>μPB100470-15                                                | 4K x 1       | 100K    | 10<br>15                       | 6<br>8                             | -4.5              | 990                               | D                             | 18   |

| μPB100474-4.5<br>μPB100474-6<br>μPB100474-8<br>μPB100474-10<br>μPB100474-15 | 1K x 4       | 100K    | 4.5<br>6<br>8<br>10<br>15      | 4<br>4<br>5<br>6<br>8              | -4.5              | 2025<br>2025<br>990<br>990<br>990 | K<br>B/K<br>B/D<br>B/D<br>B/D | 24   |

#### Note:

Package: D = Ceramic DIP; B = Ceramic Flat Package; K = Ceramic Leadless Chip Carrier (LCC)

\* Block Select Access Time (ns).

#### **GENERAL INFORMATION**

#### **EPROM Selection Guide**

|                                                    |              |         | Access                   | Programming<br>Option            | Supply  | Maximu<br>Dissipat | m Power<br>ion (mW) |                           |                       |

|----------------------------------------------------|--------------|---------|--------------------------|----------------------------------|---------|--------------------|---------------------|---------------------------|-----------------------|

| Device 🐳                                           | Organization | Process | Time (ns)                |                                  | Voltage | Standby            | Active              | Package                   | Pins                  |

| μPD2764-2<br>μPD2764<br>μPD2764-3<br>μPD2764-3     | 8K x 8       | NMOS    | 200<br>250<br>300<br>450 | UV<br>UV/OTP<br>UV/OTP<br>UV/OTP | +5      | 210                | 499                 | D<br>C/D<br>C/D<br>C/D    | 28                    |

| μPD27128-2<br>μPD27128<br>μPD27128-3<br>μPD27128-4 | 16K x 8      | NMOS    | 200<br>250<br>300<br>450 | UV<br>UV/OTP<br>UV/OTP<br>UV/OTP | +5      | 210                | 604                 | D<br>C/D<br>C/D<br>C/D    | 28                    |

| μPD27256<br>μPD27256-3                             | 32K x 8      | NMOS    | 250<br>300               | UV                               | +5      | 210                | 604                 | D                         | 28                    |

| μPD27C64-20<br>μPD27C64-25<br>μPD27C64-30          | 8K x 8       | CMOS    | 200<br>250<br>300        | UV<br>UV/OTP<br>UV/OTP           | +5      | 0.55               | 165                 | D<br>C/D<br>C/D           | 28                    |

| μPD27C256-15<br>μPD27C256-20<br>μPD27C256-25       | 32K x 8      | CMOS    | 150<br>200<br>250        | UV<br>UV/OTP<br>UV/OTP           | +5      | 0.55               | 165                 | D<br>C/D<br>C/D           | 28                    |

| μPD27C256A-12<br>μPD27C256A-15<br>μPD27C256A-20    | 32K x 8      | CMOS    | 120<br>150<br>200        | UV<br>UV/OTP<br>UV/OTP           | +5*     | 0.55               | 165                 | D/K<br>C/D/G/K<br>C/D/G/K | 28<br>(except K = 32) |

| μPD27C512-15<br>μPD27C512-20<br>μPD27C512-25       | 64K x 8      | CMOS    | 150<br>200<br>250        | UV                               | +5*     | 0.55               | 165                 | D                         | 28                    |

| μPD27C1024-15<br>μPD27C1024-20<br>μPD27C1024-25    | 64K x 16     | CMOS    | 150<br>200<br>250        | UV                               | +5*     | 0.55               | 275                 | D                         | 40                    |

#### Note:

Package: C = Plastic DIP for OTP (One Time Programmable) EPROMs; G = Plastic Miniflat Package for OTP; D = Ceramic DIP with quartz window; K = Ceramic Leadless Chip Carrier with quartz window

\*Programming voltage =  $12.5 \pm 0.3 \text{ V}$

#### **Mask-Programmable ROM Selection Guide**

|                            |                          |         | Access     | Cycle      |           | Maximum<br>Dissipation |            |         |                                                                                                                                                     |

|----------------------------|--------------------------|---------|------------|------------|-----------|------------------------|------------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| Device                     | Organization             | Process | Time (ns)  | Time (ns)  | Operation | Standby                | Active     | Package | Pins           24           28           28           28           28           28           28           28           28           28           28 |

| μPD2364A-1<br>μPD2364A     | 8K x 8                   | NMOS    | 150<br>200 | 150<br>200 | Static    | 83                     | 385        | С       | 24                                                                                                                                                  |

| μPD2364E-1<br>μPD2364E     | 8K x 8                   | NMOS    | 200<br>250 | 200<br>250 | Static    | 105                    | 420        | С       | 28                                                                                                                                                  |

| µPD23128E                  | 16K x 8                  | NMOS    | 250        | 250        | Static    | 138                    | 495        | C       | 28                                                                                                                                                  |

| μPD23C64E-1<br>μPD23C64E   | 8K x 8                   | CMOS    | 150<br>200 | 150<br>200 | Static    | 0.165                  | 165<br>138 | С       | 28                                                                                                                                                  |

| μPD23C128E-1<br>μPD23C128E | 16K x 8                  | CMOS    | 150<br>200 | 150<br>200 | Static    | 0.165                  | 165<br>138 | С       | 28                                                                                                                                                  |

| μPD23C256E-1<br>μPD23C256E | 32K x 8                  | CMOS    | 150<br>200 | 150<br>200 | Static    | 0.165                  | 165<br>138 | C/G     | 28                                                                                                                                                  |

| μPD23C1000-1<br>μPD23C1000 | 128K x 8                 | CMOS    | 200<br>250 | 200<br>250 | Static    | 0.55                   | 220        | С       | 28                                                                                                                                                  |

| µPD23C2000                 | 128K x 16 or<br>256K x 8 | CMOS    | 250        | 250        | Static    | 0.55                   | 220        | С       | 40                                                                                                                                                  |

#### Note:

Package: C = Plastic DIP; G = Plastic Miniflat Package

\* Supply voltage = +5 V for all ROMs.

#### **Bipolar PROM Selection Guide**

| Device                                     | Organization | Process | Address<br>Access<br>Time (ns) | Chip Select<br>Access<br>Time (ns) | Supply<br>Voltage | Maximum Power<br>Dissipation (mW) | Package | Pins |

|--------------------------------------------|--------------|---------|--------------------------------|------------------------------------|-------------------|-----------------------------------|---------|------|

| μPB426-3<br>μPB426-2<br>μPB426-1<br>μPB426 | 1K x 4       | TTL     | 35<br>50<br>60<br>70           | 25<br>30<br>40<br>45               | +5                | 826                               | C/D     | 18   |

| μPB429-3<br>μPB429-2<br>μPB429-1<br>μPB429 | 2K x 8       | TTL     | 45<br>50<br>60<br>70           | 30<br>30<br>40<br>50               | +5                | 880                               | C/D     | 24   |

Note:

Package: C = Plastic DIP; D = Ceramic DIP

#### **GENERAL INFORMATION**

### QUALITY AND RELIABILITY

#### **QUALITY AND RELIABILITY**

Page

#### Section 2 — Quality and Reliability

# Introduction 2-1 Approaches to Total Quality Control 2-1 Implementations of Distributed Quality Control 2-1 Product Development 2-1 Wafer Fabrication Process Flow 2-1 Assembly Process Flow of Plastic Memories 2-2 Electricial Testing and Screening 2-2 Pre-Inventory Inspection 2-2 Reliability Assurance Test 2-3 Summary 2-3

#### Introduction

NEC has adopted Total Quality Control (TQC) to ensure the highest quality and reliability of its state-ofthe-art memory products. With TQC, excellence is built into the product at every phase of production.

As large-scale integration reaches higher density levels, simple quality inspections cannot ensure adequate levels of excellence. Only with TQC during every stage of production, can NEC maintain its total product superiority in the semiconductor industry.

#### **Approaches to Total Quality Control**

Total Quality Control enables early detection of possible failures in memory products, so that problems in design may be prevented. Immediate action can then be taken before a problem occurs.

At NEC, all employees are involved with the concept and methodology of TQC. This quality insurance policy is an integral part of the entire organization.

NEC's research and development constantly strives to achieve higher standards. This ongoing process reduces extensive failure analysis and corrective actions taken as preventative measures.

Our goals are to upgrade quality standards and to further improve the superior product that has become synonymous with the NEC name.

#### Implementations of Distributed Quality Control

Building excellence into a product requires the earliest possible detection of failure in each phase. Immediate action is taken to remove the cause of failure. Because fixed-station quality inspection often precludes the ability to take immediate action, it is necessary to perform quality control functions at each step especially at the conceptual stage.

Here are the significant stages

- Product development

- □ Wafer processing

- Assembly

- Electrical testing and screening

- Pre-inventory inspection

- Reliability assurance test

#### **Product Development**

The product development phase includes product conception, review of the device proposal, organization and physical element design, engineering evaluations, and transfer of the product to manufacturing.

In every step of the product development phase, quality and reliability requirements **must** be satisfied. Utilizing the TQC approach has shortened the product development cycles by two to three months. Building superiority into the product cannot be sacrificed — TQC is a way of life at NEC.

#### **Wafer Fabrication Process Flow**

The in-process quality inspections (frequency) that occurs at the wafer fabrication stage are as follows:

| Flow         | Process                   | Typical Item               | Frequency  |

|--------------|---------------------------|----------------------------|------------|

| Ŷ            | (Wafers)                  |                            |            |

| 1            |                           | Dimension                  | Every lot  |

| ф            | Incoming inspection       | Resistivity                | Every lot  |

|              |                           | Appearance                 | Every lot  |

| 7            | (Masks)                   |                            |            |

|              | Incoming inspection       |                            |            |

| ð            | Photo lithography         | Alignment accuracy         | Every lot  |

|              |                           | Etching accuracy           | Every lot  |

| ¢            | <b>Difuse and oxidize</b> | Oxide thickness            | Every lot  |

|              |                           | Sheet resistivity          | Every lot  |

| ¢            | Metalize                  | Aluminum thickness         | Every run  |

|              |                           | Electrical parameters      | Every lot  |

| ¢            | Passivation               | CVD thickness              | Every run  |

| Ŷ            | Wafer sort                | Electrical characteristics | 100% chips |

| ģ            | Dicing                    |                            |            |

| ф            | Chip visual               | Appearance                 | 100% chip: |

| $\downarrow$ | To assembly               |                            |            |

Note: The wafer fabrication steps repeated in the actual flow, which complies with our manufacturing specification, are eliminated in this diagram.

#### **Assembly Process Flow of Plastic Memories**

The in-process quality inspections (frequency) that are done during the assembly process are as follows:

| Flow         | Process              | Typical item       | Frequency   |

|--------------|----------------------|--------------------|-------------|

| Y            | Chip                 |                    |             |

| γ            | (Lead frame, solder) |                    |             |

| 힌            | Incoming inspection  |                    |             |

| ¢            | Chip mounting        | Appearance         | Every lot   |

| $\nabla$     | (Fine Wire)          |                    |             |

| 민            | Incoming inspection  |                    |             |

| ¢            | Wire bonding         | Bond strength      | Every shift |

| ¢            | Pre-seal visual      | Appearance         | 100% IC's   |

| $\nabla$     | (Molding compound)   |                    |             |

|              | Incoming inspection  |                    |             |

| ¢            | Molding              | Appearance         | 100% IC's   |

| ¢            | Thermal aging        |                    |             |

| þ            | Plating              |                    |             |

| ф            | Plating inspection   | Appearance         | Every lot   |

|              |                      | Solderability      | Every day   |

|              |                      | Thickness          | Every day   |

| þ            | Lead cut and bending |                    |             |

| ģ            | Marking              | Marking permanency | Every run   |

| $\downarrow$ | To test              |                    |             |

#### **Electrical Testing and Screening**

Electrical testing and infant mortality screening are performed at this stage. The flow chart below depicts the process.

| flow | Process                    | Frequency                   |

|------|----------------------------|-----------------------------|

| 7    | Assembly                   |                             |

| Ş    | 1st electrical test        | 1 <b>00</b> %               |

| )    | Burn-in                    | 100%                        |

| 5    | 2nd electrical test        | 100%                        |

| \$   | PDA                        |                             |

| 5    | Pre-inventory inspection   | Every lot                   |

|      | Reliability assurance test | Every lot or<br>every month |

| φ.   | Warehouse/finished goods   |                             |

| Ą    | Customer                   |                             |

In the first electrical test, DC parameters are tested, in accordance with electrical specifications, on 100% of each lot. This prescreen performance is completed prior to the infant mortality testing. 100% burn-in, as an integral part of the standard production process, is the most significant preventative measure NEC has implemented.

In the second electrical test, AC functional as well as DC parameter tests are performed. If the percentage of defective units exceeds a set limit, the lot is subject to an additional burn-in. During this second burn-in, the defective units undergo a failure analysis. The results of this analysis are then fed back into the process for corrective action.

#### **Pre-Inventory Inspection**

Prior to warehouse storage, lots are subject to an incoming inspection according to the following sampling plan:

- Electrical Test DC parameters LTPD 3% Function test LTPD 3%

- Appearance LTPD 3%

#### **Reliability Assurance Test**

The reliability assurance tests performed by NEC consist of high temperature operating life (HTOL), high temperature humidity life (HTSL), high humidity storage life (HHSL), and high humidity operating life (HHOL). In addition, various environmental and mechanical tests are also performed. Table 1 shows test conditions of various life tests, environmental tests, and mechanical tests performed on samples taken from similar process families on a monthly basis. **Table 1**.

| Test Item                          | Symbol | MIL-STD 883B<br>Method, Condition                               | Remarks                                                      |

|------------------------------------|--------|-----------------------------------------------------------------|--------------------------------------------------------------|

| High temperature<br>operating life | HTOL   | 1005D (T <sub>A</sub> = 125 °C)<br>V <sub>DD</sub> as specified | Note 1                                                       |

| High temperature<br>storage life   | HTSL   | 1008 (T <sub>A</sub> = 150 °C)                                  | Note 1                                                       |

| High humidity<br>operating life    | HHOL   | $T_A=85^\circ\text{C}$ at 85% RH $V_{DD}$ as specified          | Note 1                                                       |

| High humidity<br>storage life      | HHSL   | T <sub>A</sub> = 85 °C at 85% RH                                | Note 1                                                       |

| Pressure cooker test               | PCT    | 125 °C (2.5 atm)                                                | Note 1                                                       |

| Lead Fatigue                       | C3     | 2004B2                                                          | Broken lead is<br>considered to be<br>a reject               |

| Solderability                      | C4     | T <sub>A</sub> = 230 °C, 5 sec<br>Use resin base flux           | Less than 95%<br>coverage is<br>considered to be<br>a reject |

| Soldering heat                     | C6     | 260 °C, 10 sec w/out<br>flux — Note 2                           | Note 1                                                       |

| Temperature cycle                  | C6     | 1010C; 10 cycles;<br>—65 °C to 150 °C                           | Note 1                                                       |

| Thermal shock                      | C6     | 1011A; 15 cycles<br>0 °C to 100 °C                              | Note 1                                                       |

Notes: 1. Electrical test per data sheet is performed. Devices that exceed these data sheet limits are considered to be rejects.

2. MIL-STD-750A Method 2031.

#### Summary

Building quality and reliability into products is the most efficient way to ensure product excellence. NEC's TQC process steps form a consolidated quality control system and guarantees a superior product.

The introduction of 100% burn-in and the performance of monthly reliability assurance tests, have established a singularly high standard of excellence for NEC's large-scale integrated circuits.

With total commitment to Total Quality Control, NEC is committed to producing superior products. Through continuous research and development, extensive failure analysis and process improvements, NEC continues to set and maintain the highest standards of quality and reliability.

#### **QUALITY AND RELIABILITY**

2-4

#### **APPLICATION-SPECIFIC MEMORIES**

#### Section 3 — Application-Specific Memories

#### Page

| μPD41101     | 910 x 8-Bit FIFO Memory 3-1                                   |

|--------------|---------------------------------------------------------------|

| μPD41102     | 1135 x 8-Bit FIFO Memory 3-13                                 |

| μPD41221     | 224,000-Bit Serial-Access NMOS RAM 3-25                       |

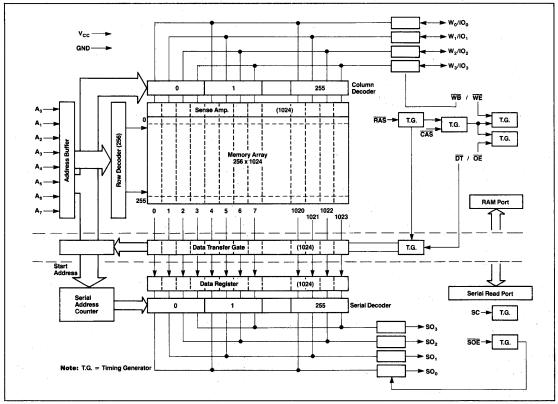

| μPD41264     | 262,144-Bit Dual Port Dynamic NMOS RAM 3-33                   |

| App. Note 32 | µPD41221 Serial Access Memory with Customized Array Size 3-43 |

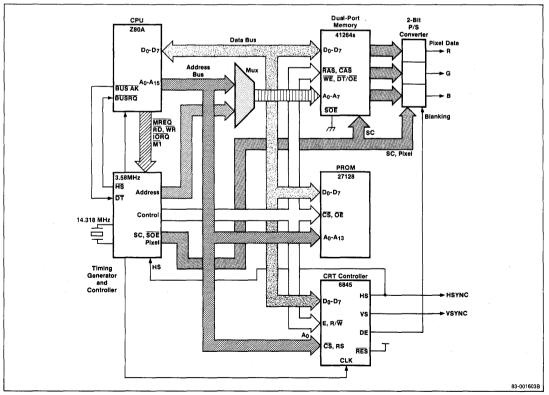

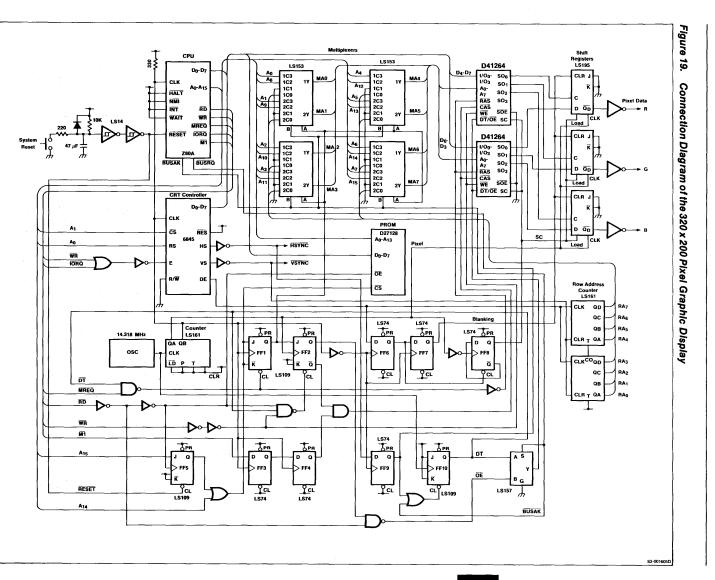

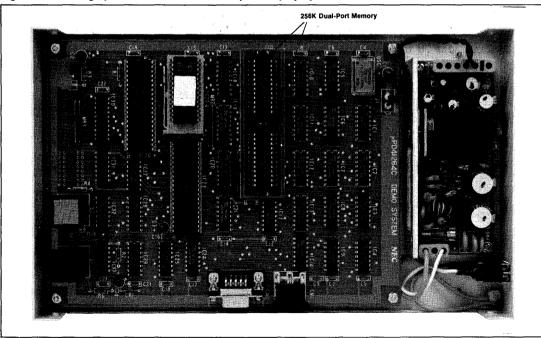

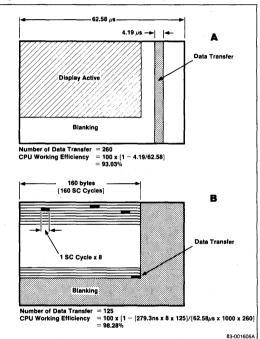

| App. Note 33 | µPD41264 VRAM and µPD7220A System Implementation              |

| App. Note 34 | μPD41264 262,144-Bit Dual-Port Dynamic NMOS RAM               |

#### PRELIMINARY INFORMATION

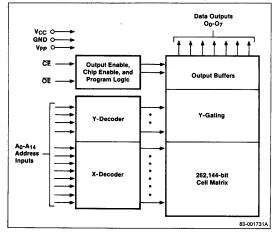

#### Description

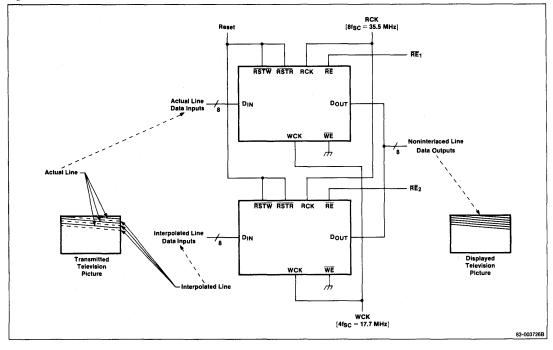

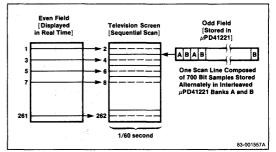

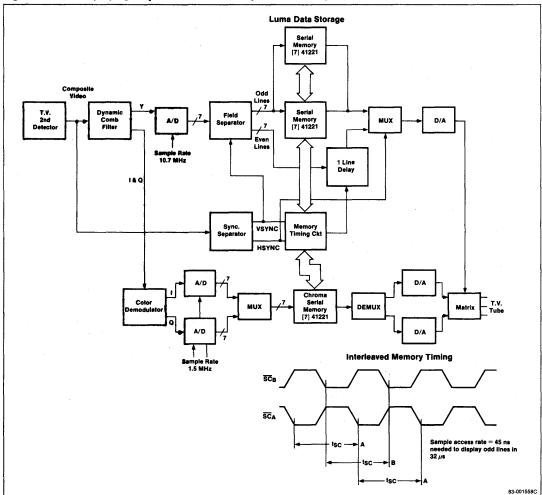

This device is a 910-word by 8-bit first-in first-out biport memory fabricated with the N-channel silicon gate process. The device helps to create an NTSC flicker-free television picture (noninterlace conversion) by providing intermediate storage and very high speed read and write operations.

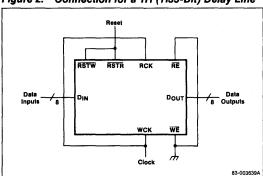

The  $\mu$ PD41101 can also be used as a digital delay line. The delay length is variable from 10 to 910 bits.

#### Features

- 910-word x 8-bit organization

- FIFO (first-in first-out) biport memory

- □ Suitable for NTSC, 4f<sub>SC</sub> digital television systems

- Asynchronous and simultaneous read/write operations

- Can be used as a 1H (910-bit) delay line

- TTL compatible

- □ Three-state outputs

- $\Box$  Single 5 V  $\pm$  10% power supply

- 24-pin, 300 mil DIP package

#### **Performance Ranges**

| Device     | Read<br>Cycle<br>Time (Min) | Read<br>Access<br>Time (Max) | Write<br>Cycle<br>Time (Min) |

|------------|-----------------------------|------------------------------|------------------------------|

| μPD41101-3 | 34 ns                       | 27 ns                        | 34 ns                        |

| μPD41101-2 | 34 ns                       | 27 ns                        | 69 ns                        |

| μPD41101-1 | 69 ns                       | 49 ns                        | 69 ns                        |

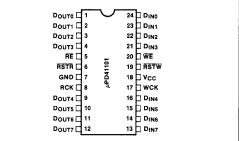

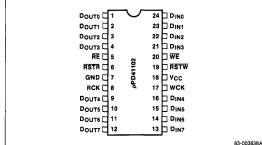

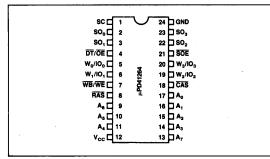

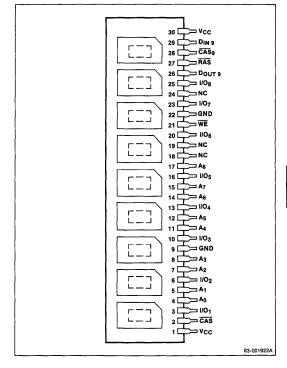

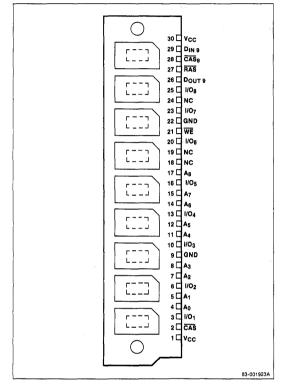

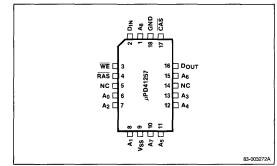

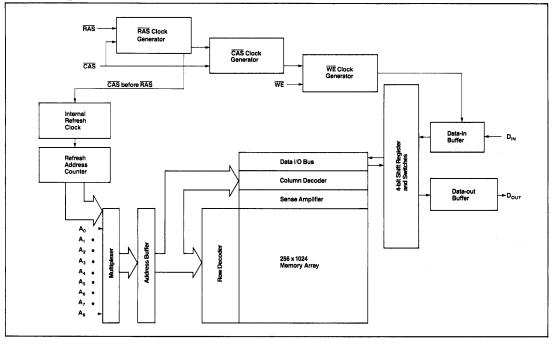

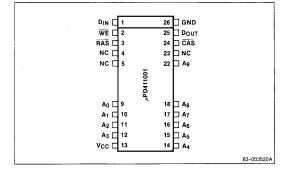

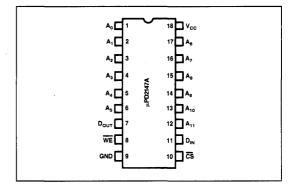

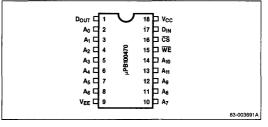

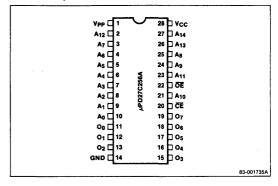

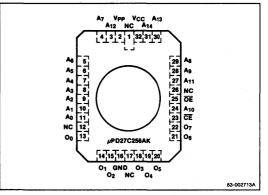

#### **Pin Identification**

| No.                | Symbol                               | Function                 |  |  |

|--------------------|--------------------------------------|--------------------------|--|--|

| 1-4, 9-12          | D <sub>OUTO</sub> -D <sub>OUT7</sub> | Read data outputs        |  |  |

| 5                  | RE                                   | Read enable input        |  |  |

| 6                  | RSTR                                 | Read address reset input |  |  |

| 7                  | GND                                  | Ground                   |  |  |

| 8 RCK              |                                      | Read clock input         |  |  |

| 13-16, 21-24       | DINO-DIN7                            | Write data inputs        |  |  |

| 17                 | WCK                                  | Write clock input        |  |  |

| 18 V <sub>CC</sub> |                                      | 5 V power supply         |  |  |

| 19 RSTW            |                                      | Write address reset inpu |  |  |

| 20 WE              |                                      | Write enable input       |  |  |

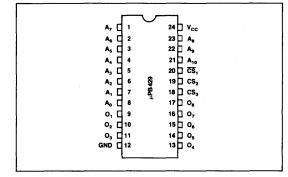

#### **Pin Configuration**

#### **Pin Functions**

#### DINO-DIN7 [Data Inputs]

In a digital television application, the digital composite signal, luminance, chrominance, etc., information is written into these inputs.

#### DOUT0-DOUT7 [Data Outputs]

These tri-state outputs are used to access the stored information. In a simple digital delay line application, a minimum delay of 10 clock cycles is required to move data from the data inputs to the data outputs.

#### **RSTW** [Write Address Reset Input]

Bringing this signal to a low level resets the internal write address to 0. The state of this input is strobed by the rising edge of WCK.

#### **RSTR** [Read Address Reset Input]

Strobed by the rising edge of RCK, this signal resets the internal read address to 0.

#### WE [Write Enable Input]

This input controls write operations. If  $\overline{WE}$  is at a low level, all write operations proceed. If  $\overline{WE}$  is at a high level, no data is written to storage cells and the write address stops increasing. The state of  $\overline{WE}$  is strobed by the rising edge of WCK.

#### RE [Read Enable Input]

This signal is similar to  $\overline{WE}$  but controls read operations. If  $\overline{RE}$  is at a high level, the data outputs become high impedance and the internal read address stops increasing. The state of  $\overline{RE}$  is strobed by the rising edge of RCK.

#### WCK [Write Clock Input]

All write operations are performed synchronously with WCK. The states of both RSTW and WE are strobed by the rising edge of WCK at the beginning of a cycle, and the data inputs are strobed by the rising edge of WCK at the end of a cycle. The internal write address increases with each WCK cycle unless WE is at a high level to hold the write address constant. Unless inhibited by WE, the internal write address will automatically wrap around from 909 to 0 and begin increasing again.

#### **RCK** [Read Clock Input]

All read operations are performed synchronously with RCK. The states of both  $\overline{\text{RSTR}}$  and  $\overline{\text{RE}}$  are strobed by the rising edge of RCK at the beginning of a cycle. This same edge of RCK starts the internal read operation, and access time is referenced to this edge. The internal read address increases with each RCK cycle unless  $\overline{\text{RE}}$  is at a high level to hold the read address constant. Unless inhibited by  $\overline{\text{RE}}$ , the internal read address will automatically wrap around from 909 to 0 and begin increasing again.

#### **Absolute Maximum Ratings**

| Supply voltage, V <sub>CC</sub>               | -1.5 to +7.0 V |

|-----------------------------------------------|----------------|

| Voltage on any input pin, Vi                  | -1.5 to +7.0 V |

| Voltage on any output pin, V <sub>0</sub>     | -1.5 to +7.0 V |

| Short circuit output current, I <sub>OS</sub> | 20 mA          |

| Operating temperature, T <sub>OPR</sub>       | -20 to +70 °C  |

| Storage temperature, T <sub>STG</sub>         | -55 to +125°C  |

**Comment:** Exposing the device to stresses above those listed in Absolute Maximum Ratings could cause permanent damage. The device is not meant to be operated under conditions outside the limits described in the operational sections of this specification. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

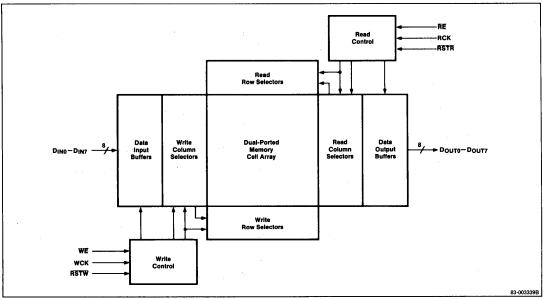

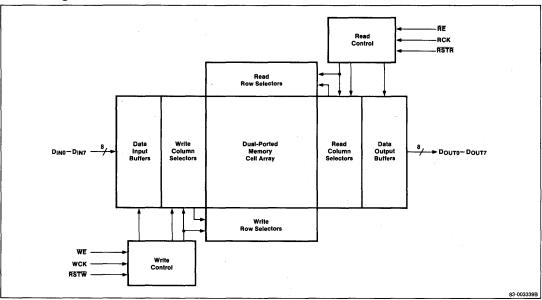

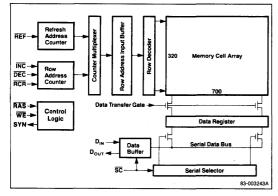

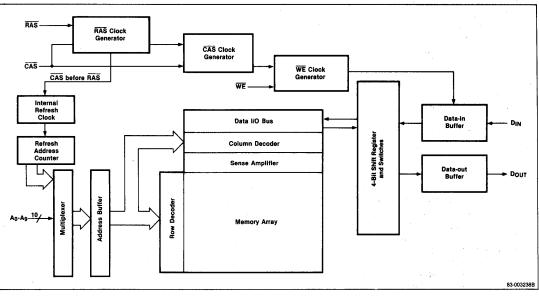

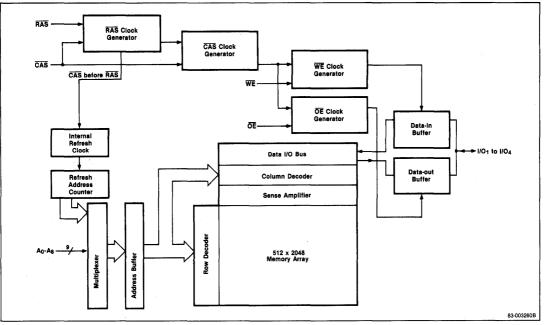

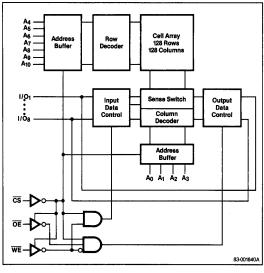

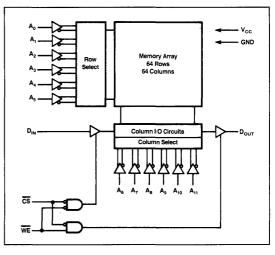

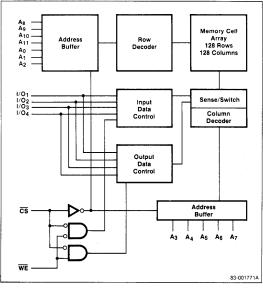

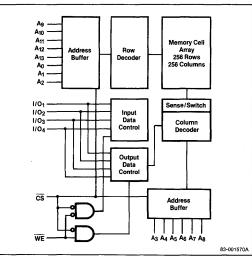

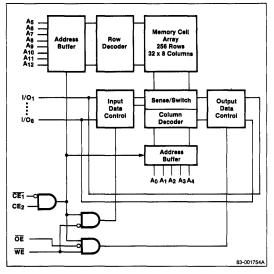

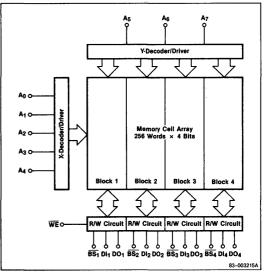

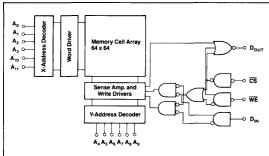

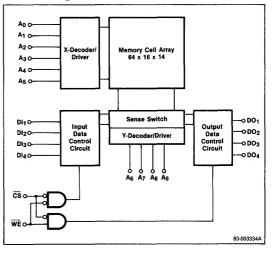

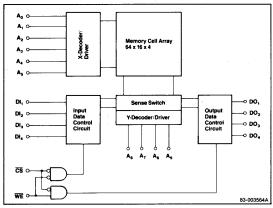

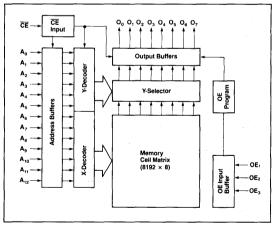

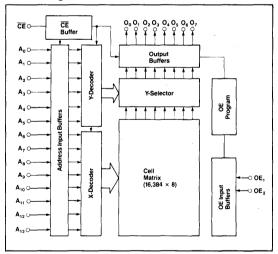

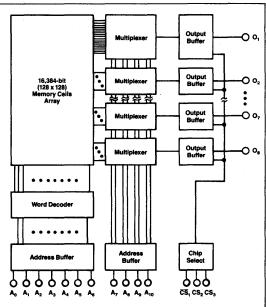

#### **Block Diagram**

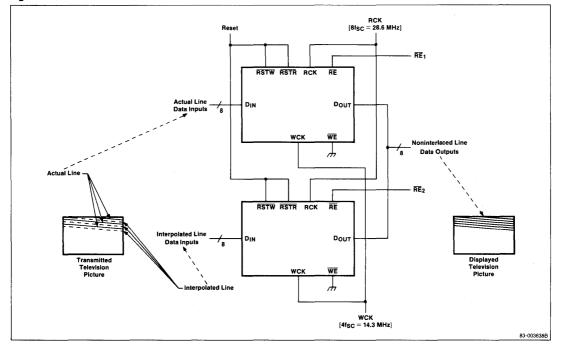

Figure 1. Connection for Noninterlace Conversion

#### **Recommended DC Operating Conditions**

$T_A = -20 \text{ to } +70 \text{ }^\circ\text{C}$

|                       |                 |      | Limits |     |      | Test       |  |

|-----------------------|-----------------|------|--------|-----|------|------------|--|

| Parameter             | Symbol          | Min  | Тур    | Max | Unit | Conditions |  |

| Supply<br>voltage     | V <sub>CC</sub> | 4.5  | 5.0    | 5.5 | V    |            |  |

| Ground                | GND             | 0    | 0      | 0   | ٧    |            |  |

| Input voltage<br>high | VIH             | 2.4  |        | 5.5 | v    | -          |  |

| Input voltage<br>low  | VIL             | -1.5 |        | 0.8 | v    |            |  |

#### Capacitance

$T_A = -20 \text{ to } +70 \text{ }^{\circ}\text{C}; V_{CC} = 5.0 \text{ V} \pm 10\%; \text{ } \text{f} = 1 \text{ MHz}$

|                       |                | Limits |     |     |      | Test                                          |  |

|-----------------------|----------------|--------|-----|-----|------|-----------------------------------------------|--|

| Parameter             | Symbol         | Min    | Тур | Max | Unit | Conditions                                    |  |

| Input<br>capacitance  | CI             |        |     | 5   | pF   | WE, RE, WCK,<br>RCK, RSTW,<br>RSTR, DINO-DIN7 |  |

| Output<br>capacitance | C <sub>0</sub> |        |     | 7   | ρF   | D <sub>OUT0</sub> -D <sub>OUT7</sub>          |  |

#### Note:

(1) These parameters are sampled and not 100% tested.

#### **DC Characteristics**

$T_{A}=-20$  to +70 °C;  $V_{CC}=5.0$  V  $\pm10\%$

|                                          |                 |     | Limits |     |      | Test                                                        |  |

|------------------------------------------|-----------------|-----|--------|-----|------|-------------------------------------------------------------|--|

| Parameter                                | Symbol          | Min | Тур    | Max | Unit | Conditions                                                  |  |

| Write/Read<br>cycle operating<br>current | Icc             |     |        | 90  | mA   |                                                             |  |

| Input leakage<br>current                 | lţ              | -10 |        | 10  | μA   | $V_I = 0$ to $V_{CC}$ ; all other pins not under test = 0 V |  |

| Output leakage<br>current                | I <sub>0</sub>  | -10 |        | 10  | μA   | $D_{0UT}$ is disabled;<br>$V_0 = 0$ to 5.5 V                |  |

| Output voltage<br>high                   | V <sub>OH</sub> | 2.4 |        |     | ۷    | $I_{OH} = -1 \text{ mA}$                                    |  |

| Output voltage<br>low                    | V <sub>OL</sub> |     |        | 0.4 | ۷    | $I_{OL} = 2 \text{ mA}$                                     |  |

#### Note:

(1) All voltages are referenced to ground.

#### **AC Characteristics**

$T_{A}$  = -20 to +70 °C;  $V_{CC}$  = 5.0 V  $\pm$  10%

| Symbol            |                                      | Limits              |          |            |          |            |          |      |            |

|-------------------|--------------------------------------|---------------------|----------|------------|----------|------------|----------|------|------------|

|                   |                                      | μ <b>PD4</b> 1101-3 |          | µPD41101-2 |          | µPD41101-1 |          |      | Test       |

|                   | Parameter                            | Min                 | Max      | Min        | Max      | Min        | Max      | Unit | Conditions |

| twck              | Write clock cycle time               | 34                  | 1090     | 69         | 1090     | 69         | 1090     | ns   |            |

| twcw              | WCK pulse width                      | 14                  |          | 25         |          | 25         |          | ns   |            |

| twcp              | WCK precharge time                   | 14                  |          | 25         |          | 25         |          | ns   |            |

| t <sub>rck</sub>  | Read clock cycle time                | 34                  | 1090     | 34         | 1090     | 69         | 1090     | ns   |            |

| tRCW              | RCK pulse width                      | 14                  |          | 14         |          | 25         |          | ns   |            |

| t <sub>rcp</sub>  | RCK precharge time                   | 14                  |          | 14         |          | 25         |          | ns   |            |

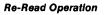

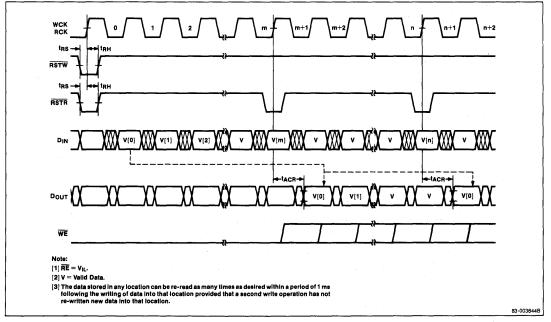

| t <sub>AC</sub>   | Access time                          |                     | 27       |            | 27       |            | 49       | ns   | -          |

| t <sub>ACR</sub>  | Access time after a reset cycle      |                     | 49       |            | 49       |            | 49       | ns   |            |

| toH               | Output hold time                     | 5                   |          | 5          |          | 5          |          | ns   |            |

| tohr              | Output hold time after a reset cycle | 5                   |          | 5          |          | 5          |          | ns   | (Note 7)   |

| t <sub>LZ</sub>   | Output active time                   | 5                   | 27       | 5          | 27       | 5          | 49       | ns   | (Note 4)   |

| t <sub>HZ</sub>   | Output disable time                  | 5                   | 27       | 5          | 27       | 5          | 49       | ns   | (Note 4)   |

| t <sub>DS</sub>   | Data-in set-up time                  | 14                  |          | 18         |          | 18         |          | ns   |            |

| t <sub>DH</sub>   | Data-in hold time                    | 5                   |          | 5          |          | 5          |          | ns   |            |

| t <sub>RS</sub>   | Reset active set-up time             | 14                  |          | 14         |          | 20         |          | ns   | (Note 8)   |

| t <sub>RH</sub>   | Reset active hold time               | 5                   |          | 5          |          | 5          |          | ns   | (Note 8)   |

| t <sub>RN1</sub>  | Reset inactive hold time             | 5                   |          | 5          |          | 5          |          | ns   | (Note 9)   |

| t <sub>RN2</sub>  | Reset inactive set-up time           | 14                  |          | 14         |          | 20         |          | ns   | (Note 9)   |

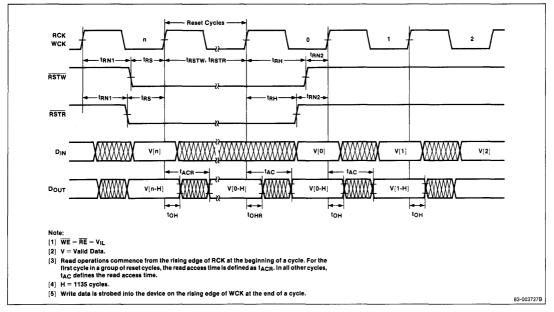

| twes              | Write enable set-up time             | 14                  |          | 20         |          | 20         |          | ns   | (Note 10)  |

| tweh              | Write enable hold time               | 5                   |          | 5          |          | 5          |          | ns   | (Note 10)  |

| twen1             | Write enable high delay from WCK     | 5                   |          | 5          |          | 5          |          | ns   | (Note 11)  |

| t <sub>WEN2</sub> | Write enable low delay to WCK        | 14                  |          | 20         |          | 20         |          | ns   | (Note 11)  |

| tRES              | Read enable set-up time              | 14                  |          | 14         | -        | 20         |          | ns   | (Note 10)  |

| tREH              | Read enable hold time                | 5                   |          | 5          |          | 5          |          | ns   | (Note 10)  |

| t <sub>REN1</sub> | Read enable high delay from RCK      | 5                   |          | 5          |          | 5          |          | ns   | (Note 11)  |

| t <sub>REN2</sub> | Read enable low delay to RCK         | 14                  |          | 14         |          | 20         |          | ns   | (Note 11)  |

| twew              | Write disable pulse width            | 0                   | (Note 6) | 0          | (Note 6) | 0          | (Note 6) | ms   |            |

| tREW              | Read disable pulse width             | 0                   | (Note 6) | 0          | (Note 6) | 0          | (Note 6) | ms   |            |

| trstw             | Write reset time                     | 0                   | (Note 6) | 0          | (Note 6) | 0          | (Note 6) | ms   |            |

| t <sub>rstr</sub> | Read reset time                      | 0                   | (Note 6) | 0          | (Note 6) | 0          | (Note 6) | ms   |            |

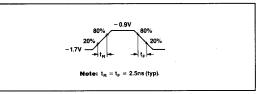

| tŢ                | Transition time                      | 3                   | 35       | 3          | 35       | 3          | 35       | ns   |            |

Note:

(1) All voltages are referenced to ground.

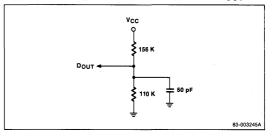

(2) Input pulse rise and fall times assume  $t_T = 5$  ns.

(3) Input pulse levels = GND to 3 V. Transition times are measured between 3 V and 0 V.

(4) This delay is measured at  $\pm$  200 mv from the steady state voltage with the load specified in figure 4. Under any conditions,  $t_{LZ} \ge t_{HZ}$ .

(5) Input timing reference levels = 1.5 V.

#### **AC Characteristics (cont)**

#### Note [cont]:

- (6) t<sub>WEW</sub> (max) and t<sub>REW</sub> (max) must be satisfied by the next equations in 1 line cycle operation: t<sub>WEW</sub> + t<sub>RSTW</sub> + 910t<sub>WCK</sub> ≤ 1 ms t<sub>REW</sub> + t<sub>RSTR</sub> + 910t<sub>RCK</sub> ≤ 1 ms

- (7) This parameter has meaning when  $t_{RCK} \ge t_{ACR}$  (max).

- (8) If either t<sub>RS</sub> or t<sub>RH</sub> is less than the specified value, reset operations are not guaranteed.

- (9) If either t<sub>RN1</sub> or t<sub>RN2</sub> is less than the specified value, internal reset operations may extend to cycles immediately preceding or following the period of desired reset operations.

- (10) If either tWES or tWEH (tRES or tREH) is less than the specified value, write (read) disable operations are not guaranteed.

- (11) If either t<sub>WEN1</sub> or t<sub>WEN2</sub> (t<sub>REN1</sub> or t<sub>REN2</sub>) is less than the specified value, internal write (read) disable operations may extend to cycles immediately preceding or following the period of desired disable operations.

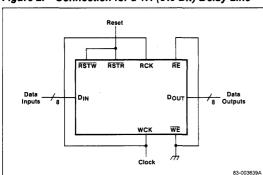

Figure 2. Connection for a 1H (910 Bit) Delay Line

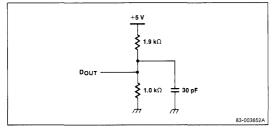

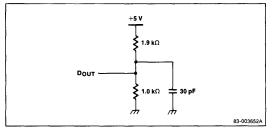

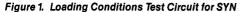

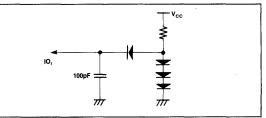

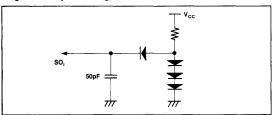

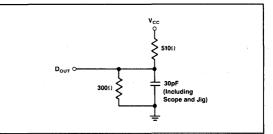

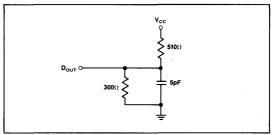

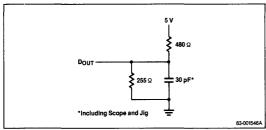

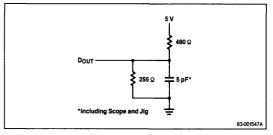

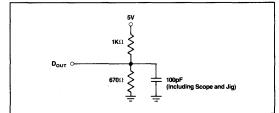

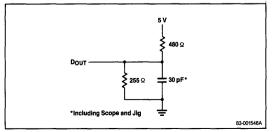

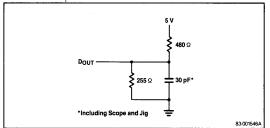

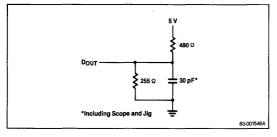

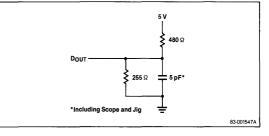

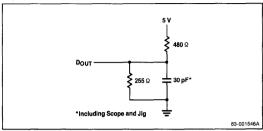

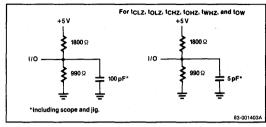

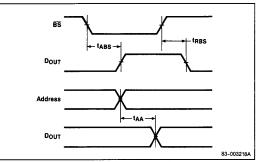

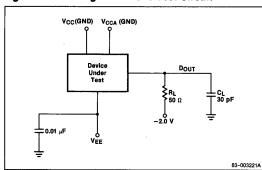

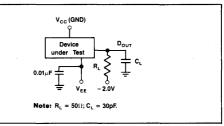

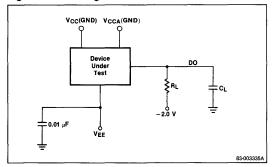

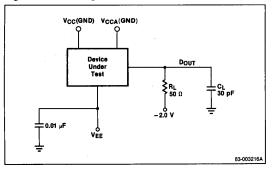

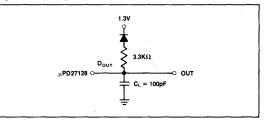

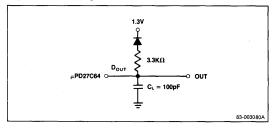

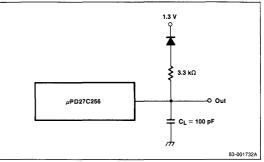

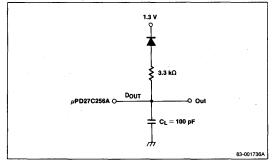

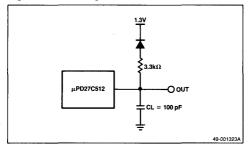

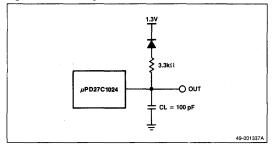

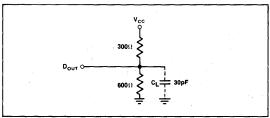

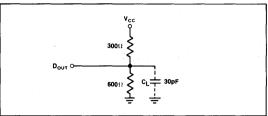

#### Figure 3. Output Load for t<sub>AC</sub>, t<sub>ACR</sub>, t<sub>OH</sub>, and t<sub>OHR</sub>

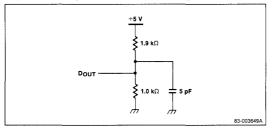

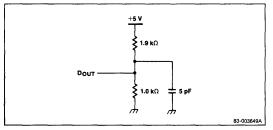

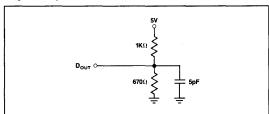

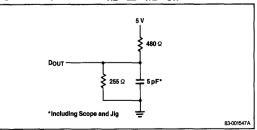

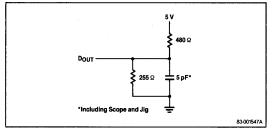

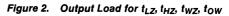

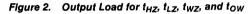

#### Figure 4. Output Load for t<sub>LZ</sub> and t<sub>HZ</sub>

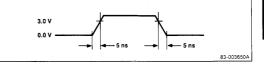

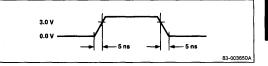

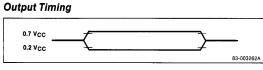

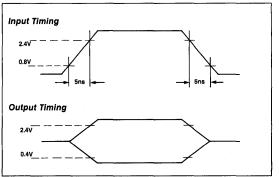

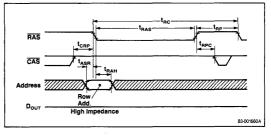

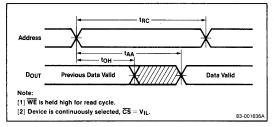

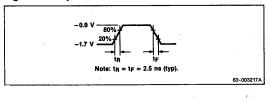

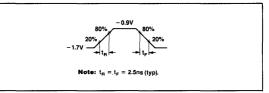

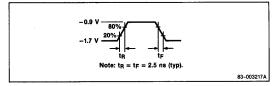

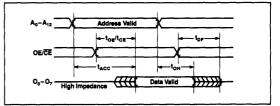

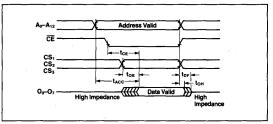

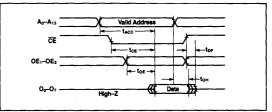

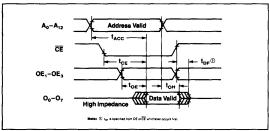

#### AC Input Timing Reference Waveform

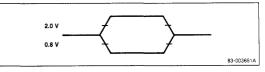

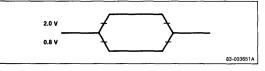

#### AC Output Timing Reference Waveform

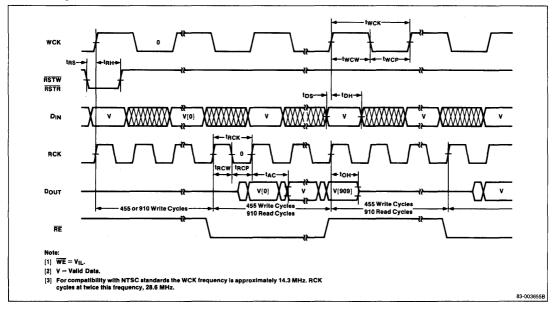

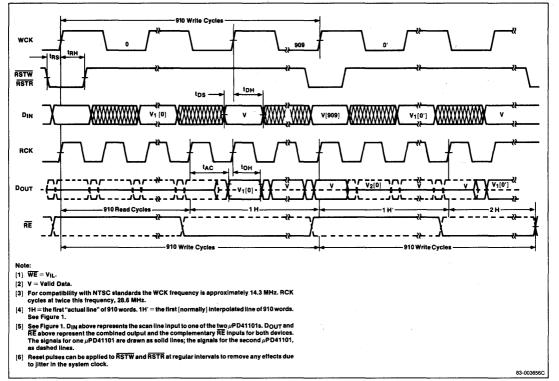

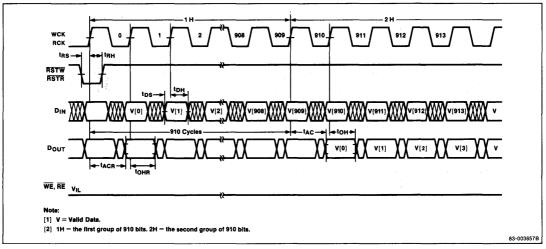

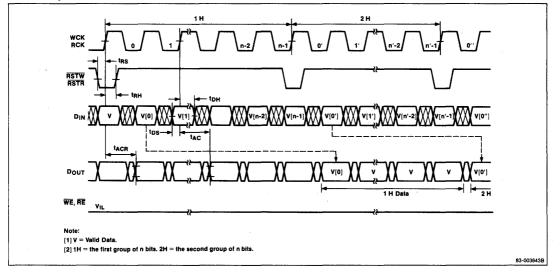

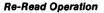

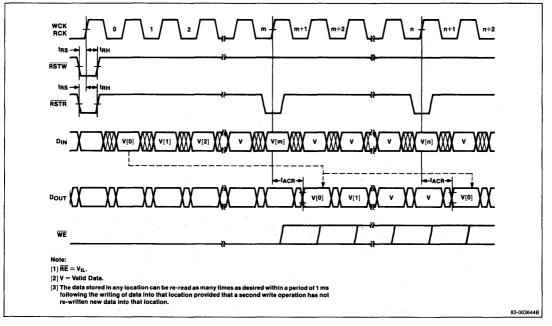

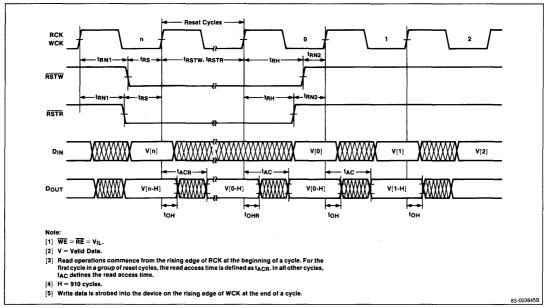

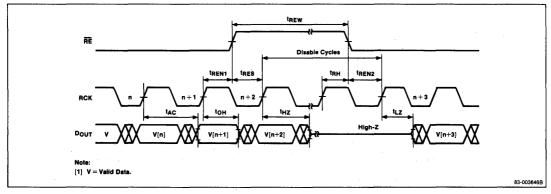

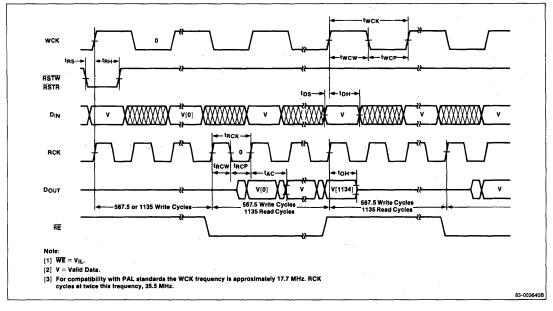

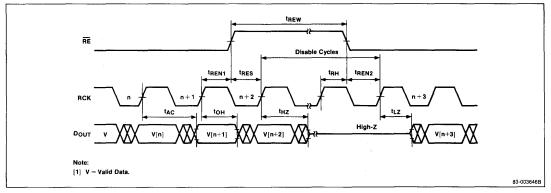

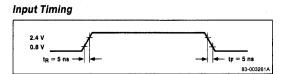

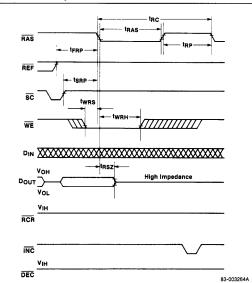

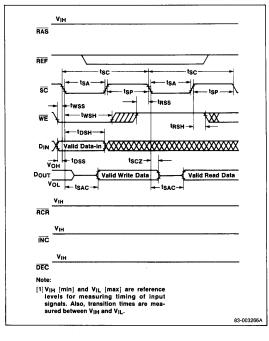

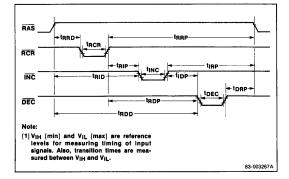

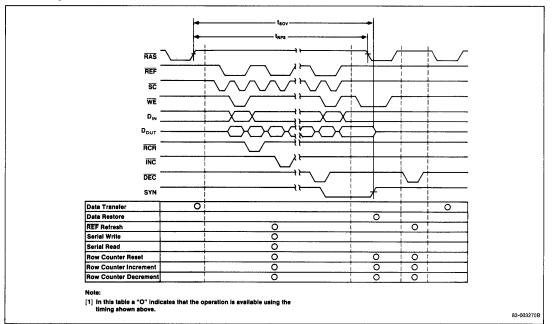

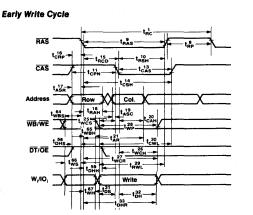

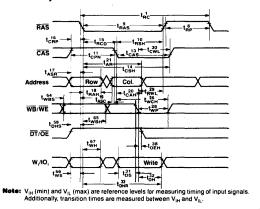

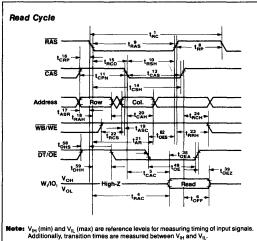

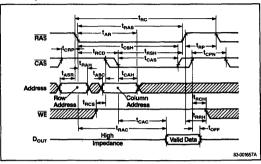

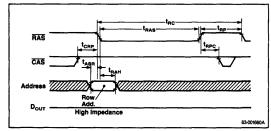

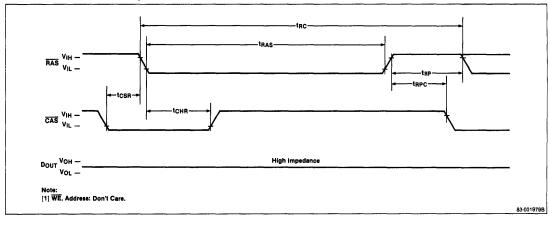

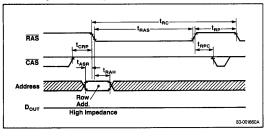

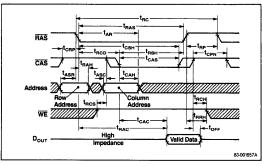

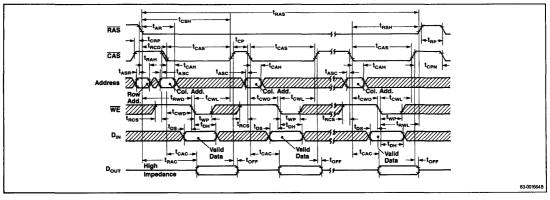

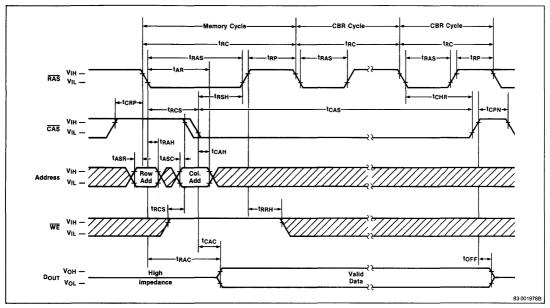

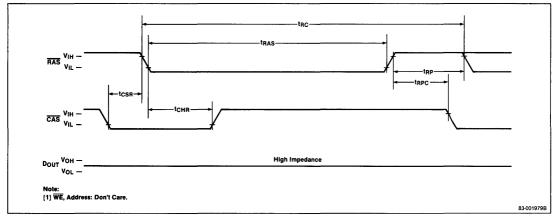

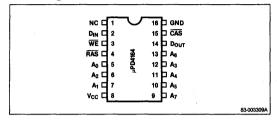

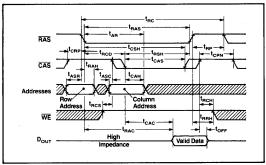

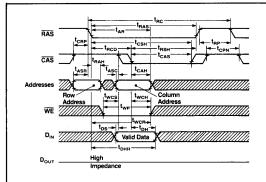

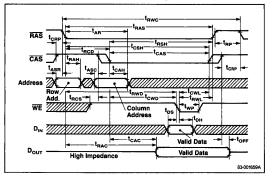

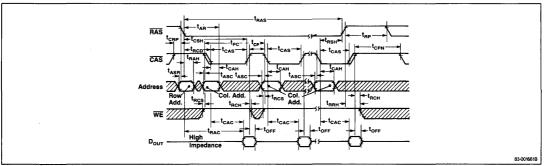

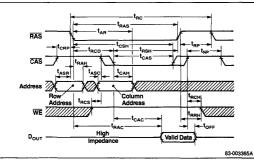

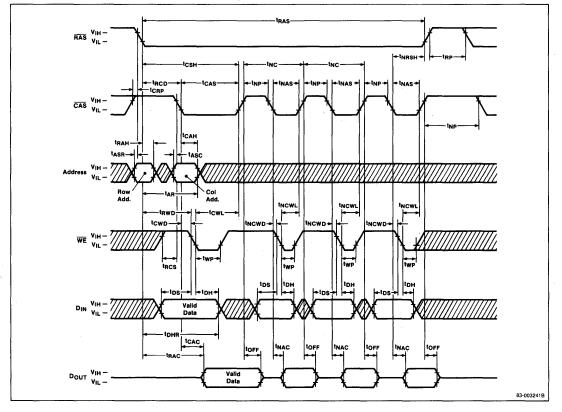

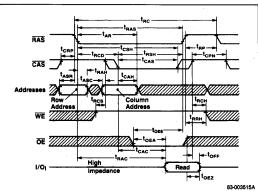

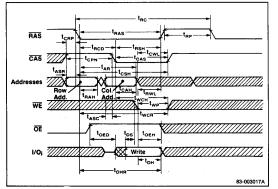

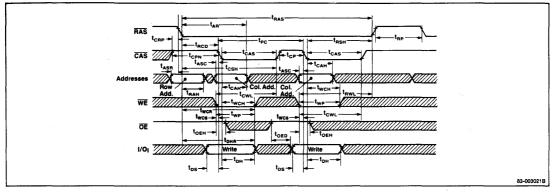

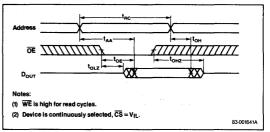

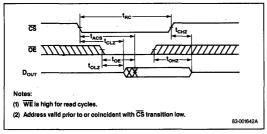

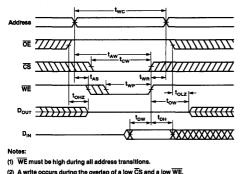

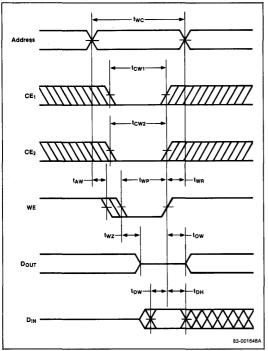

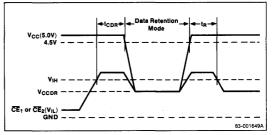

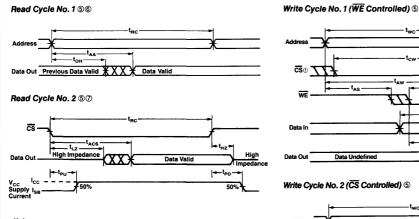

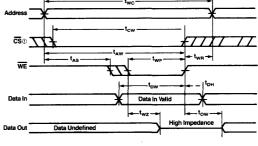

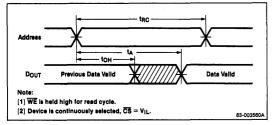

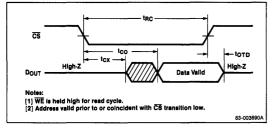

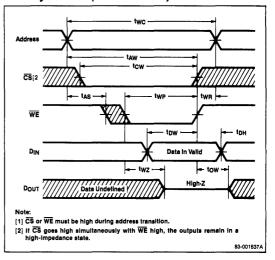

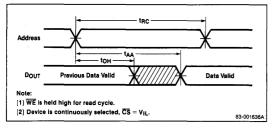

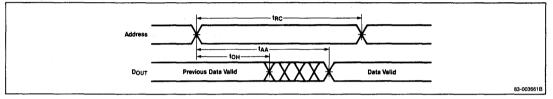

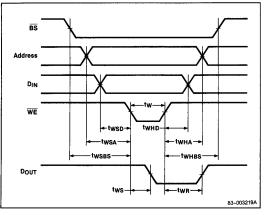

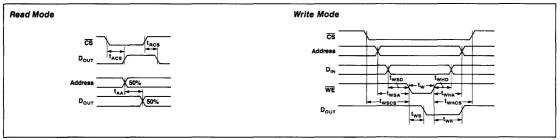

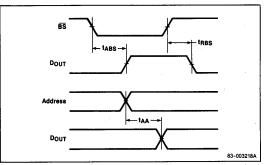

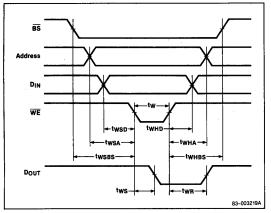

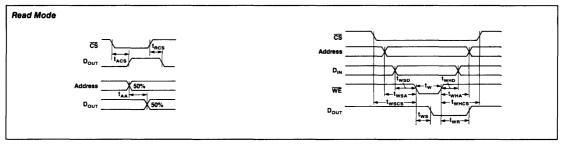

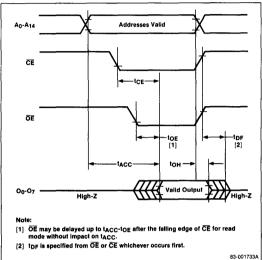

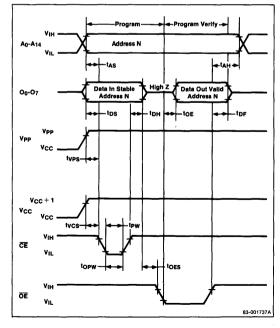

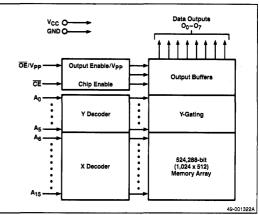

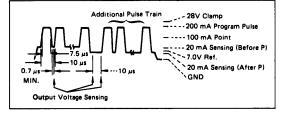

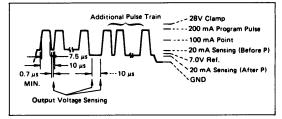

#### **Timing Waveforms**

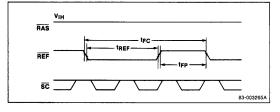

#### **Basic Timing for Noninterlace Conversion**

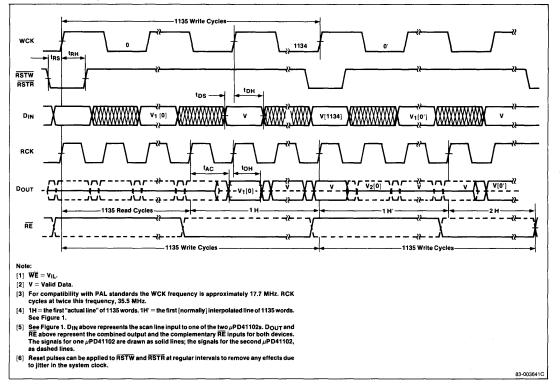

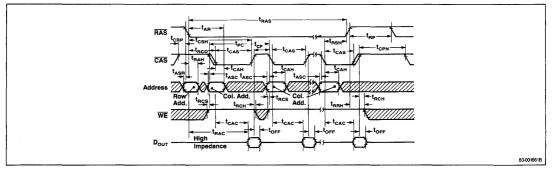

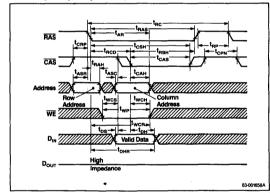

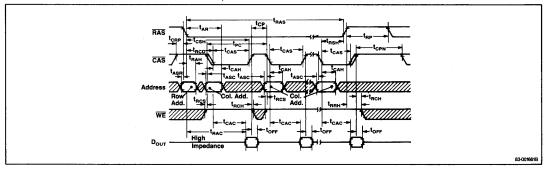

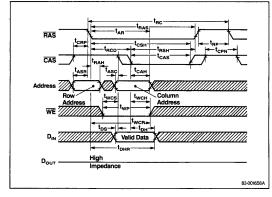

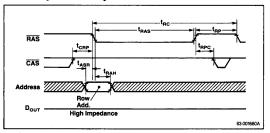

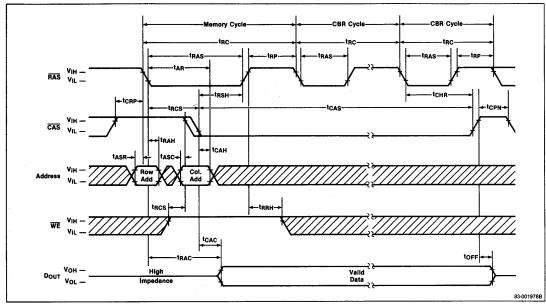

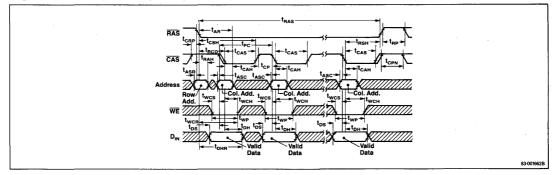

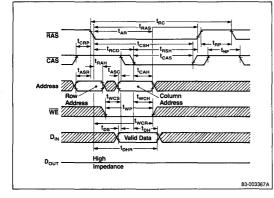

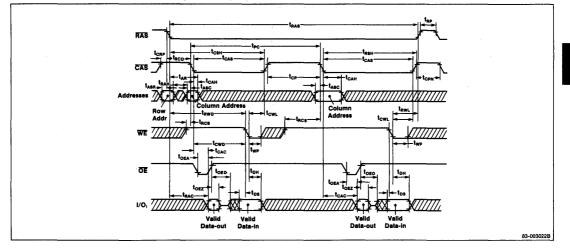

#### **Timing Waveforms (cont)**

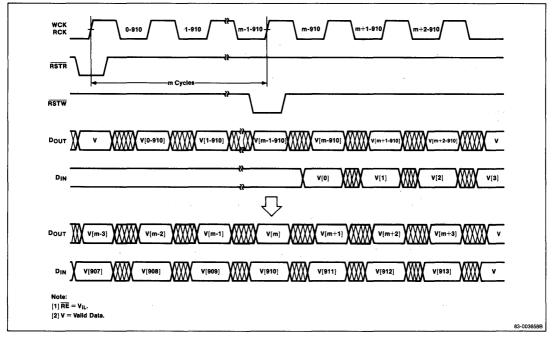

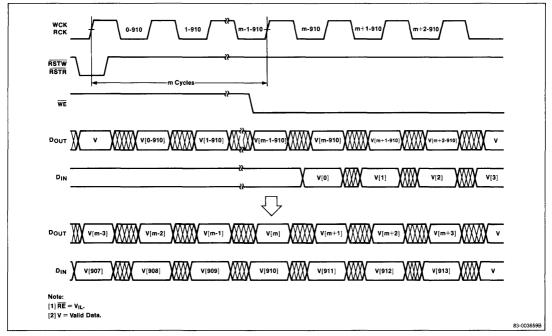

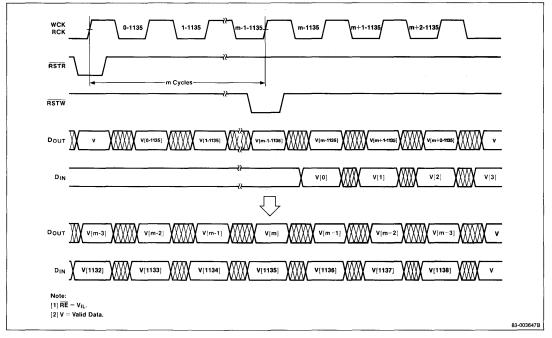

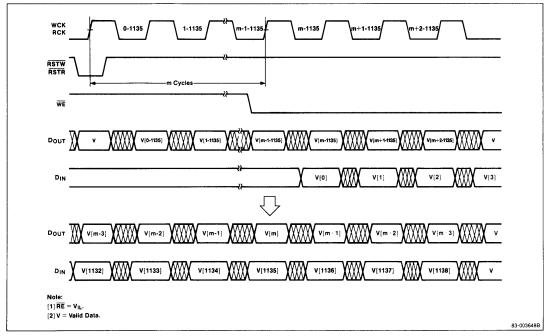

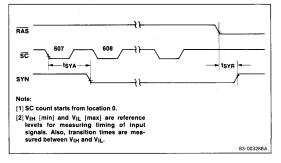

#### Application Timing for Noninterlace Conversion

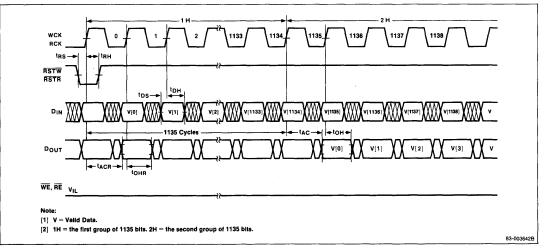

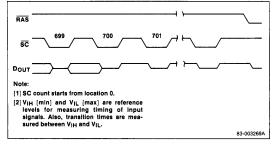

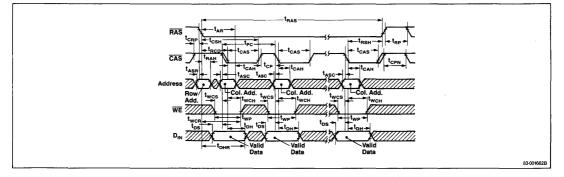

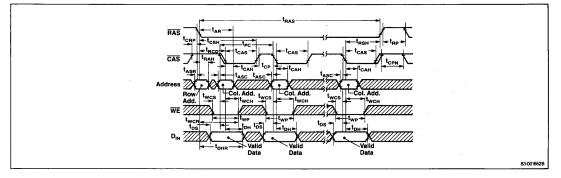

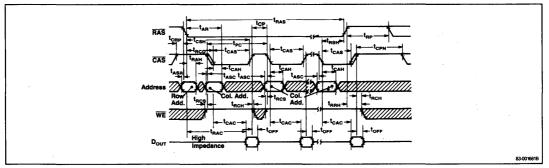

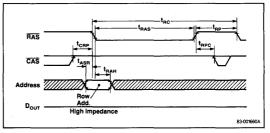

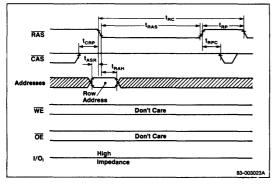

#### 910-Bit Delay Line

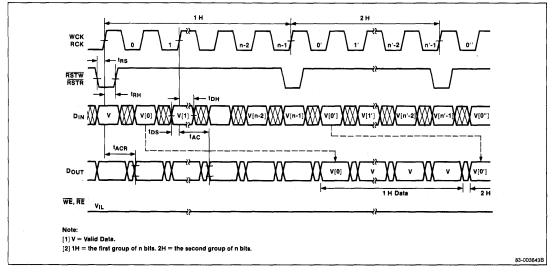

## n-Bit Delay Line

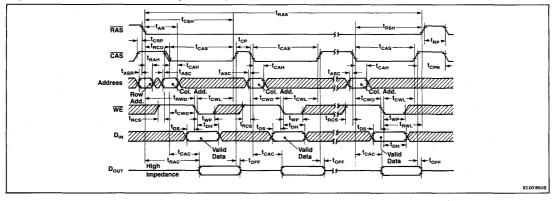

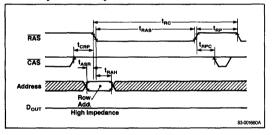

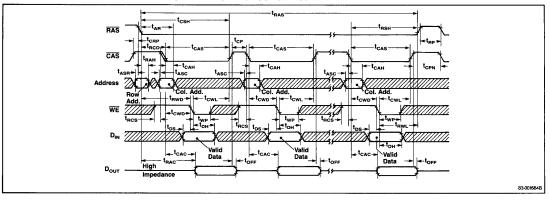

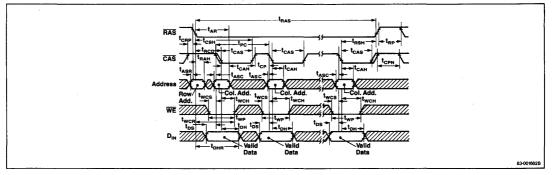

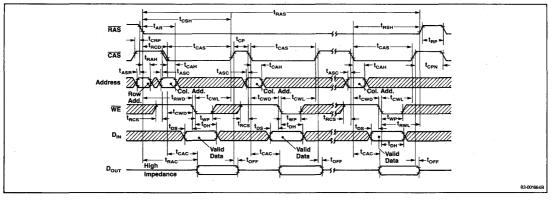

## **Read or Write Reset**

## μ**PD41101**

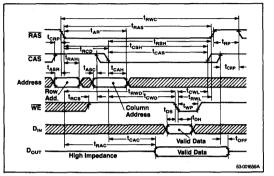

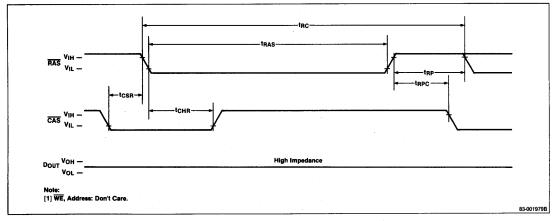

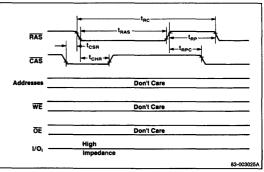

## **Timing Waveforms (cont)**

## **Read Disable**

## (910-m)-Bit Delay Line, No. 1

## (910-m)-Bit Delay Line, No. 2

3-11

## PRELIMINARY INFORMATION

## Description

This device is a 1135-word by 8-bit first-in first-out biport memory fabricated with the N-channel silicon gate process. The device helps to create a PAL flickerfree television picture (noninterlace conversion) by providing intermediate storage and very high speed read and write operations.

The  $\mu$ PD41102 can also be used as a digital delay line. The delay length is variable from 12 to 1135 bits.

## Features

- □ 1135-word x 8-bit organization

- □ FIFO (first-in first-out) biport memory

- □ Suitable for PAL, 4f<sub>SC</sub> digital television systems

- □ Asynchronous and simultaneous read/write

- operations

- □ Can be used as a 1H (1135-bit) delay line

- □ TTL compatible

- □ Three-state outputs

- $\Box$  Single 5 V  $\pm$  10% power supply

- □ 24-pin, 300 mil DIP package

## **Performance Ranges**

| Device     | Read<br>Cycle<br>Time (Min) | Read<br>Access<br>Time (Max) | Write<br>Cycle<br>Time (Min) |

|------------|-----------------------------|------------------------------|------------------------------|

| μPD41102-3 | 28 ns                       | 21 ns                        | 28 ns                        |

| μPD41102-2 | 28 ns                       | 21 ns                        | 56 ns                        |

| µPD41102-1 | 56 ns                       | 40 ns                        | 56 ns                        |

## **Pin Identification**