# **MICROCOMPUTER PRODUCTS**

DATA BOOK

1983/1984 MICROCOMPUTER CATALOG

The information in this document is subject to change without notice. NEC Electronics Inc. makes no warranty of any kind with regard to this material, including, but not limited to, the implied warranties of merchantability and fitness for a particular purpose. NEC Electronics Inc. assumes no responsibilities for any errors that may appear in this document. NEC Electronics Inc. makes no commitment to update nor to keep current the information contained in this document.

No part of this document may be copied or reproduced in any form or by any means without the prior written consent of NEC Electronics Inc.

© 1983 by NEC Electronics Inc. Printed in the United States of America

| 1 | CONTENTS                                     |

|---|----------------------------------------------|

| 2 | GENERAL INFORMATION                          |

| 3 | SINGLE CHIP 4-BIT MICROCOMPUTERS             |

| 4 | SINGLE CHIP 8-BIT MICROCOMPUTERS             |

| 5 | MICROPROCESSORS                              |

| 6 | PERIPHERALS                                  |

| 7 | PACKAGE OUTLINES                             |

| 8 | QUALITY & RELIABILITY OF NEC MICROPROCESSORS |

| 9 | REPRESENTATIVES & DISTRIBUTORS               |

### **FUNCTIONAL INDEX**

# NEC

| SINGLE CHIP                                                                                                                                                                                                                                                                                                                                                      |                                                                                                       |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|

| 4-BIT MICROCOMPUTERS                                                                                                                                                                                                                                                                                                                                             |                                                                                                       |

| Selection Guide                                                                                                                                                                                                                                                                                                                                                  | 2-1                                                                                                   |

| Alternate Source Guide                                                                                                                                                                                                                                                                                                                                           | 2-4                                                                                                   |

| ROM-Based Products Ordering                                                                                                                                                                                                                                                                                                                                      |                                                                                                       |

| Procedure                                                                                                                                                                                                                                                                                                                                                        | 2-6                                                                                                   |

| μ <b>COM-4</b>                                                                                                                                                                                                                                                                                                                                                   | 3-1                                                                                                   |

| μ <b>PD557L</b>                                                                                                                                                                                                                                                                                                                                                  | 3-13                                                                                                  |

| μ <b>PD552/553</b>                                                                                                                                                                                                                                                                                                                                               | 3-15                                                                                                  |

| μ <b>PD550/554</b>                                                                                                                                                                                                                                                                                                                                               | 3-17                                                                                                  |

| μ <b>PD550L/554L</b>                                                                                                                                                                                                                                                                                                                                             | 3-19                                                                                                  |

| μPD556B Evaluation Chip                                                                                                                                                                                                                                                                                                                                          | 3-21                                                                                                  |

| μPD7500 Series Introduction                                                                                                                                                                                                                                                                                                                                      | 3-25                                                                                                  |

| μ <b>PD7501</b>                                                                                                                                                                                                                                                                                                                                                  | 3-35                                                                                                  |

| μ <b>PD7502/7503</b>                                                                                                                                                                                                                                                                                                                                             | 3-41                                                                                                  |

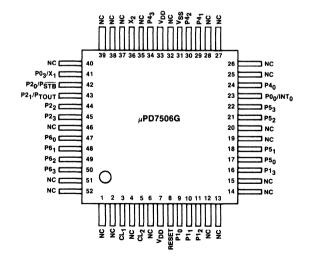

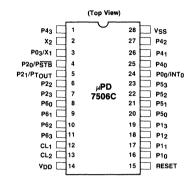

| μ <b>PD7506</b>                                                                                                                                                                                                                                                                                                                                                  | 3-47                                                                                                  |

| μ <b>PD7507/7508</b>                                                                                                                                                                                                                                                                                                                                             | 3-53                                                                                                  |

| μPD7507S                                                                                                                                                                                                                                                                                                                                                         | 3-61                                                                                                  |

| μ <b>PD7508A</b>                                                                                                                                                                                                                                                                                                                                                 | 3-67                                                                                                  |

| μ <b>PD7508H</b>                                                                                                                                                                                                                                                                                                                                                 | 3-75                                                                                                  |

| μ <b>PD</b> 7514                                                                                                                                                                                                                                                                                                                                                 | 3-81                                                                                                  |

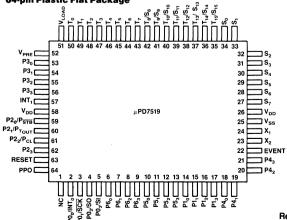

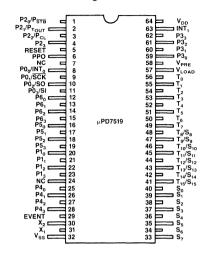

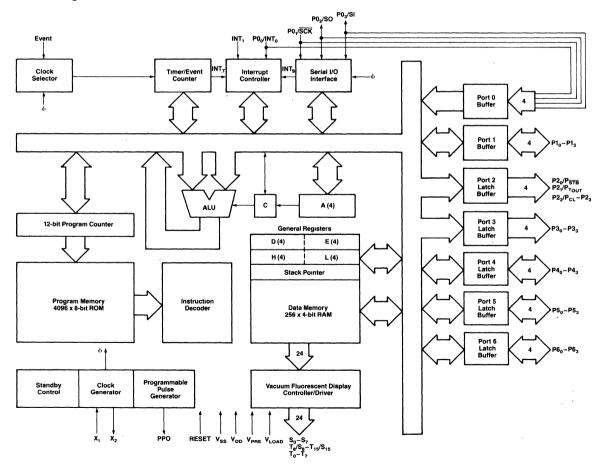

| μPD7519/75CG19E                                                                                                                                                                                                                                                                                                                                                  | 3-89                                                                                                  |

| μ <b>PD7520</b>                                                                                                                                                                                                                                                                                                                                                  | 3-97                                                                                                  |

| μPD7527/7528/7537/7538                                                                                                                                                                                                                                                                                                                                           | 3-103                                                                                                 |

| μPD7500 Evaluation Chip                                                                                                                                                                                                                                                                                                                                          | 3-105                                                                                                 |

| MC-430P                                                                                                                                                                                                                                                                                                                                                          | 3-113                                                                                                 |

| SINGLE CHIP                                                                                                                                                                                                                                                                                                                                                      |                                                                                                       |

| SINGLE CHIP 8-BIT MICROCOMPUTERS                                                                                                                                                                                                                                                                                                                                 |                                                                                                       |

| 8-BIT MICROCOMPUTERS Selection Guide                                                                                                                                                                                                                                                                                                                             | 2-2                                                                                                   |

| 8-BIT MICROCOMPUTERS Selection Guide Alternate Source Guide                                                                                                                                                                                                                                                                                                      | 2-2<br>2-4                                                                                            |

| 8-BIT MICROCOMPUTERS Selection Guide                                                                                                                                                                                                                                                                                                                             | 2-4                                                                                                   |

| 8-BIT MICROCOMPUTERS Selection Guide                                                                                                                                                                                                                                                                                                                             | 2-4<br>2-6                                                                                            |

| 8-BIT MICROCOMPUTERS Selection Guide                                                                                                                                                                                                                                                                                                                             | 2-4<br>2-6<br>4-1                                                                                     |

| 8-BIT MICROCOMPUTERS Selection Guide                                                                                                                                                                                                                                                                                                                             | 2-4<br>2-6<br>4-1<br>4-11                                                                             |

| 8-BIT MICROCOMPUTERS Selection Guide                                                                                                                                                                                                                                                                                                                             | 2-4<br>2-6<br>4-1<br>4-11<br>4-35                                                                     |

| 8-BIT MICROCOMPUTERS Selection Guide                                                                                                                                                                                                                                                                                                                             | 2-4<br>2-6<br>4-1<br>4-11<br>4-35<br>4-45                                                             |

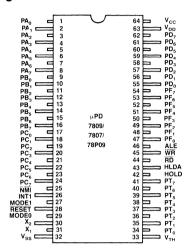

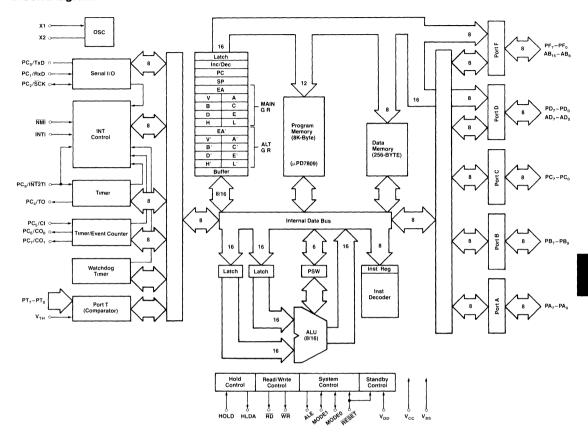

| 8-BIT MICROCOMPUTERS Selection Guide Alternate Source Guide ROM-Based Products Ordering Procedure  µPD7800  µPD7801/7802  µPD7806/78C05  µPD7809/7807/78P09  µPD7810/7811                                                                                                                                                                                        | 2-4<br>2-6<br>4-1<br>4-11<br>4-35<br>4-45<br>4-51                                                     |

| 8-BIT MICROCOMPUTERS Selection Guide                                                                                                                                                                                                                                                                                                                             | 2-4<br>2-6<br>4-1<br>4-11<br>4-35<br>4-45<br>4-51<br>4-65                                             |

| 8-BIT MICROCOMPUTERS Selection Guide Alternate Source Guide ROM-Based Products Ordering Procedure                                                                                                                                                                                                                                                                | 2-4<br>2-6<br>4-1<br>4-11<br>4-35<br>4-45<br>4-51<br>4-65<br>4-71                                     |

| 8-BIT MICROCOMPUTERS Selection Guide Alternate Source Guide ROM-Based Products Ordering Procedure                                                                                                                                                                                                                                                                | 2-4<br>2-6<br>4-1<br>4-11<br>4-35<br>4-45<br>4-51<br>4-65<br>4-71<br>4-83                             |

| 8-BIT MICROCOMPUTERS Selection Guide Alternate Source Guide ROM-Based Products Ordering Procedure                                                                                                                                                                                                                                                                | 2-4<br>2-6<br>4-1<br>4-11<br>4-35<br>4-45<br>4-51<br>4-65<br>4-71<br>4-83<br>4-91                     |

| 8-BIT MICROCOMPUTERS Selection Guide Alternate Source Guide ROM-Based Products Ordering Procedure                                                                                                                                                                                                                                                                | 2-4<br>2-6<br>4-1<br>4-11<br>4-35<br>4-45<br>4-51<br>4-65<br>4-71<br>4-83<br>4-91<br>4-103            |

| 8-BIT MICROCOMPUTERS Selection Guide Alternate Source Guide ROM-Bassed Products Ordering Procedure                                                                                                                                                                                                                                                               | 2-4<br>2-6<br>4-1<br>4-11<br>4-35<br>4-45<br>4-51<br>4-65<br>4-71<br>4-83<br>4-91<br>4-103<br>4-119   |

| 8-BIT MICROCOMPUTERS Selection Guide Alternate Source Guide ROM-Based Products Ordering Procedure                                                                                                                                                                                                                                                                | 2-4<br>2-6<br>4-1<br>4-11<br>4-35<br>4-45<br>4-51<br>4-65<br>4-71<br>4-83<br>4-91<br>4-103            |

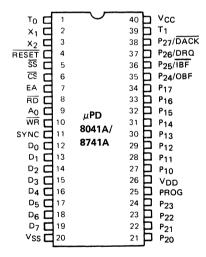

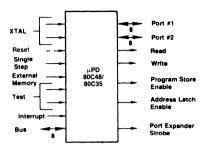

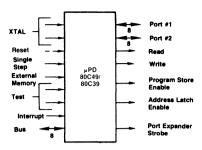

| 8-BIT MICROCOMPUTERS Selection Guide Alternate Source Guide ROM-Based Products Ordering Procedure μPD7800 μPD7801/7802 μPD7809/780778P09 μPD7810/7811 μPD8021 μPD8021 μPD8041A/8741A μPD8048H/8035HL μPD8748 μPD80C48/80C35 μPD80C49/80C39                                                                                                                       | 2-4<br>2-6<br>4-11<br>4-35<br>4-45<br>4-51<br>4-65<br>4-71<br>4-83<br>4-91<br>4-103<br>4-119<br>4-127 |

| 8-BIT MICROCOMPUTERS Selection Guide Alternate Source Guide ROM-Based Products Ordering Procedure                                                                                                                                                                                                                                                                | 2-4<br>2-6<br>4-11<br>4-35<br>4-45<br>4-51<br>4-65<br>4-71<br>4-83<br>4-91<br>4-103<br>4-119<br>4-127 |

| 8-BIT MICROCOMPUTERS Selection Guide Alternate Source Guide ROM-Bassed Products Ordering Procedure  μPD7800  μPD7801/7802  μPD7806/78C05  μPD7809/7807/78P09  μPD7810/7811  μPD8021  μPD8021  μPD8041A/8741A  μPD8048H/8035HL  μPD80748/80C35  μPD80C49/80C39  MICROPROCESSORS Selection Guide Alternate Source Guide                                            | 2-4<br>2-6<br>4-11<br>4-35<br>4-45<br>4-51<br>4-65<br>4-71<br>4-83<br>4-91<br>4-103<br>4-119<br>4-127 |

| 8-BIT MICROCOMPUTERS Selection Guide Alternate Source Guide ROM-Based Products Ordering Procedure  μPD7800  μPD7801/7802  μPD7809/7807/78P09  μPD7810/7811  μPD8021  μPD8021  μPD8041A/8741A  μPD8048H/8035HL  μPD8748  μPD8749/80C35  μPD8049/80C39  MICROPROCESSORS Selection Guide  μPD780                                                                    | 2-4 2-6 4-11 4-35 4-45 4-51 4-65 4-71 4-83 4-91 4-103 4-127 2-2 2-4 5-1                               |

| 8-BIT MICROCOMPUTERS Selection Guide Alternate Source Guide ROM-Based Products Ordering Procedure μPD7800 μPD7801/7802 μPD7809/7807/78P09 μPD7809/7807/78P09 μPD7810/7811 μPD8021 μPD8041A/8741A μPD8048H/8035HL μPD8748 μPD80C48/80C35 μPD8049H/8749H/8039HL μPD80C49/80C39  MICROPROCESSORS Selection Guide Alternate Source Guide μPD780 μPD8085AH/μPD8085A-2 | 2-4 2-6 4-11 4-35 4-45 4-51 4-65 4-71 4-83 4-91 4-103 4-119 4-127 2-2 2-4 5-1 5-15                    |

| 8-BIT MICROCOMPUTERS Selection Guide Alternate Source Guide ROM-Based Products Ordering Procedure  μPD7800  μPD7801/7802  μPD7809/7807/78P09  μPD7810/7811  μPD8021  μPD8021  μPD8041A/8741A  μPD8048H/8035HL  μPD8748  μPD8749/80C35  μPD8049/80C39  MICROPROCESSORS Selection Guide  μPD780                                                                    | 2-4 2-6 4-11 4-35 4-45 4-51 4-65 4-71 4-83 4-91 4-103 4-127 2-2 2-4 5-1                               |

| PERIPHERALS                                  |                |

|----------------------------------------------|----------------|

| Selection Guide                              | 2-3            |

| Alternate Source Guide                       | 2-4            |

| ROM-Based Products Ordering                  |                |

| Procedure                                    | 2-6            |

| μ <b>PD765A/7265</b>                         | 6-1            |

| μ <b>PD7201A</b>                             | 6-15           |

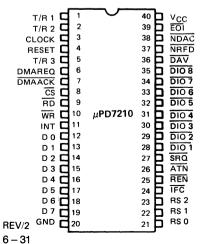

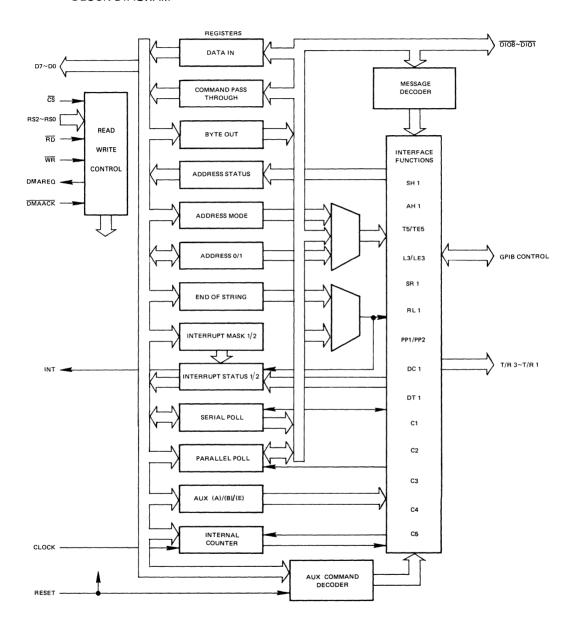

| μ <b>PD7210</b>                              | 6-31           |

| μ <b>PD7220</b>                              | 6-47           |

| μ <b>PD7225</b>                              | 6-71           |

| μ <b>PD7227</b>                              | 6-79           |

| μ <b>PD7228</b>                              |                |

| μ <b>PD7261</b>                              |                |

| μ <b>PD7720</b>                              | 6-115          |

| μ <b>PD77P20</b>                             | 6-123          |

| μ <b>PD7751</b>                              | 6-131          |

| μ <b>PD7752</b>                              | 6-133          |

| μPD7761/7762//MC-4760                        | 6-135          |

| μ <b>PD8155/8156</b>                         | 6-137          |

| μPD8155H/μPD8156H                            | 6-145          |

| μΡΒ8212                                      | 6-153          |

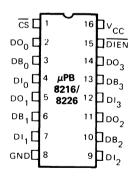

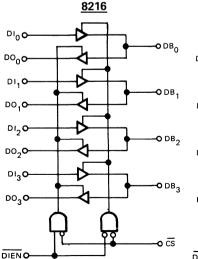

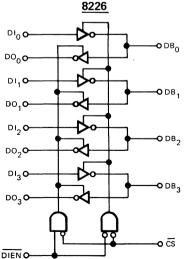

| μΡΒ8216/8226                                 | 6-159          |

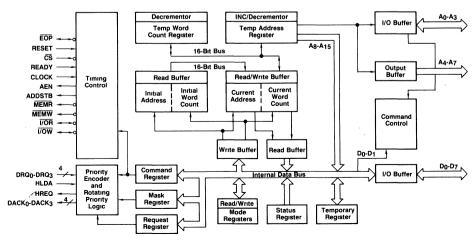

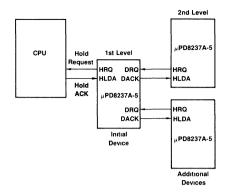

| μPD8237A-5                                   | 6-163<br>6-179 |

| μ <b>PD8243</b>                              | 6-18           |

| μPD8251A/8251AF                              | 6-18           |

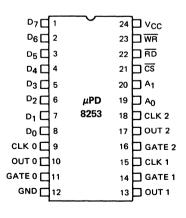

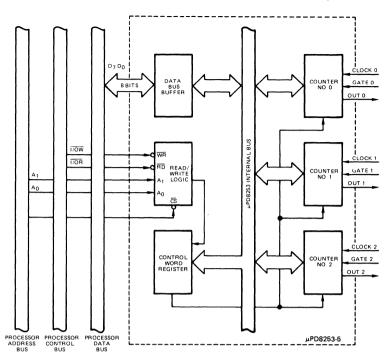

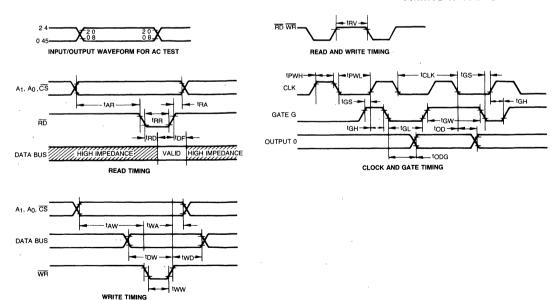

| μPD8253-2/μPD8253-5                          | 6-20           |

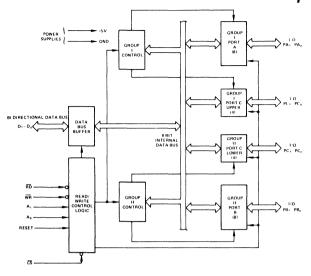

| μPD8255A-2/μPD8255A-5                        | 6-213          |

| μPD8257-2/μPD8257-5                          | 6-22           |

| μΡD8259Α/μΡD8259Α-2                          | 6-23           |

| μPD8279-2/μPD8279-5                          | 6-249          |

| μ <b>PB8282/8283</b>                         | 6-259          |

| μ <b>PB8284A</b>                             | 6-263          |

| μ <b>PB8286/8287</b>                         | 6-269          |

| μ <b>PB8288</b>                              | 6-27           |

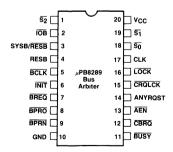

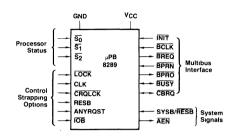

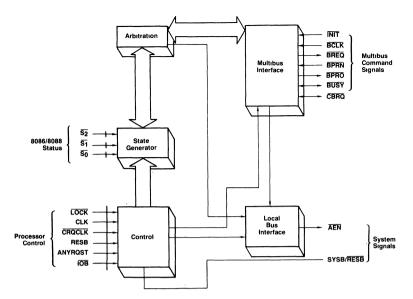

| μ <b>PB8289</b>                              | 6-283          |

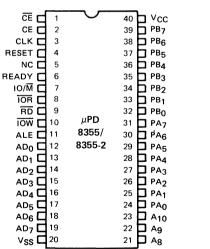

| μPD8355/μPD8355-2/                           |                |

| μ <b>PD8755A</b>                             | 6-293          |

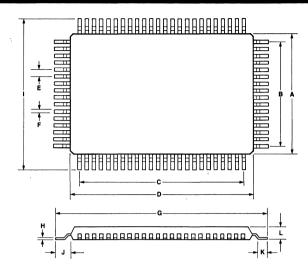

| PACKAGE OUTLINES                             | . 7-           |

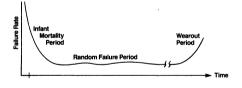

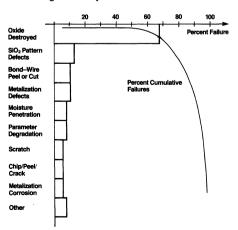

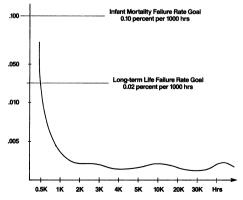

| QUALITY & RELIABILITY OF NEC MICROPROCESSORS | 8-             |

| MICROPROCESSORS                              | 0-             |

| REPRESENTATIVES & DISTRIBUTORS               | . 9–           |

1-2

| PRODUCT                     | PAGE  | PRODUCT            | PAGE  |

|-----------------------------|-------|--------------------|-------|

| μ <b>COM-4</b>              | 3-1   | μ <b>PD7810</b>    | 4-51  |

| MC-430P                     | 3-113 | μ <b>PD7811</b>    | 4-51  |

| MC-4760                     | 6-135 | μ <b>PD8021</b>    | 4-65  |

| μ <b>PD550</b>              | 3-17  | μ <b>PD8035HL</b>  | 4-83  |

| μ <b>PD550L</b>             | 3-19  | μ <b>PD80C35</b>   | 4-103 |

| μ <b>PD552</b>              | 3-15  | µРD8039HL          | 4-119 |

| μPD553                      | 3-15  | μ <b>PD80C39</b>   | 4-127 |

| μ <b>PD</b> 554             | 3-17  | μ <b>PD8041A</b>   | 4-71  |

| μ <b>PD554L</b>             | 3-19  | μ <b>PD8048H</b>   | 4-83  |

| μ <b>PD</b> 556B            | 3-21  | μPD80C48           | 4-103 |

| μ <b>PD557L</b>             | 3-13  | μ <b>PD8049H</b>   | 4-119 |

| μ <b>PD765A</b>             | 6-1   | μ <b>PD80C49</b>   | 4-127 |

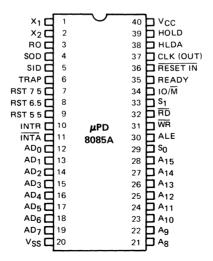

| μ <b>PD780</b>              | 5–1   | μ <b>PD8085AH</b>  | 5-15  |

| μ <b>PD7201A</b>            | 6-15  | μ <b>PD8085A-2</b> | 5-15  |

| μ <b>PD7210</b>             | 6-31  | μ <b>PD8086</b>    | 5-27  |

| μ <b>PD7220</b>             | 6-47  | μΡD8088            | 5-39  |

| μ <b>PD7225</b>             | 6-71  | μΡD8155            | 6-137 |

| μ <b>PD7227</b>             | 6-79  | μ <b>PD8155H</b>   |       |

| μ <b>PD7228</b>             |       | μΡD8156            | 6-137 |

| μPD7261                     |       | μ <b>PD8156H</b>   | 6-145 |

| μ <b>PD7265</b>             | 6-1   | μΡΒ8212            | 6-153 |

| μPD7500 Evaluation Chip     | 3-105 | •                  | -     |

| μPD7500 Series Introduction | 3-105 | μΡΒ8216            |       |

| μPD7501                     | 3-35  | μΡΒ8226            |       |

| μPD7502                     | 3-41  | μΡD8237A-5         |       |

| μPD7503                     | 3-41  | μΡD8243            |       |

| μΡD7506                     | 3-47  | μΡD82C43           |       |

| •                           |       | μ <b>PD8251A</b>   | 6-187 |

| μΡD7507                     | 3-53  | μ <b>PD8251AF</b>  |       |

| μΡD7507S                    | 3-61  | μΡD8253-2          | 6-205 |

| μΡD7508                     | 3-53  | μΡD8253-5          |       |

| μΡD7508A                    | 3-67  | μ <b>PD8255A-2</b> |       |

| μΡD7508Η                    | 3-75  | μ <b>PD8255A-5</b> |       |

| μΡD7514                     | 3-81  | μ <b>PD8257-2</b>  |       |

| μΡD7519                     | 3-89  | μΡD8257-5          |       |

| μΡD7520                     | 3-97  | μ <b>PD8259A</b>   |       |

| μΡD7527                     |       | μ <b>PD8259A-2</b> |       |

| μΡD7528                     | 3-103 | μ <b>PD8279-2</b>  |       |

| μΡD7537                     | 3-103 | μ <b>PD8279-5</b>  |       |

| μΡD7538                     | 3-103 | μ <b>PD8282</b>    | 6-259 |

| μΡD7720                     | ,     | μ <b>PD8283</b>    | 6-259 |

| μ <b>PD77P20</b>            | 4     | μ <b>PD8284A</b>   | 6-263 |

| μΡD7751                     |       | μ <b>PD8286</b>    | 6-269 |

| μΡD7752                     |       | μ <b>PD8287</b>    | 6-269 |

| μ <b>PD7761</b>             |       | μ <b>PD</b> 8288   | 6-275 |

| μ <b>PD7762</b>             |       | μ <b>PD8289</b>    | 6-283 |

| μ <b>PD7800</b>             | 4-1   | μ <b>PD8355</b>    | 6-293 |

| μ <b>PD7801</b>             | 4–11  | μ <b>PD8355-2</b>  | 6-293 |

| μΡD7802                     | 4–11  | μ <b>PD8355A</b>   | 6-293 |

| μ <b>PD78C05</b>            | 4-35  | μ <b>PD8741A</b>   | 4-71  |

| μ <b>PD78C06</b>            | 4-35  | μ <b>PD8748</b>    | 4-91  |

| μ <b>PD7807</b>             | 4-45  | μ <b>PD8749H</b>   | 4-119 |

| μ <b>PD7809</b>             | 4-45  | μ <b>PD8755A</b>   | 6-293 |

| μ <b>PD78P09</b>            | 4-45  | 4 0                |       |

2

GENERAL INFORMATION

## **MICROCOMPUTER SELECTION GUIDE**

## SINGLE CHIP 4-BIT MICROCOMPUTERS

| DEVICE     | FAMILY         | ROM      | RAM     | I/O | PROCESS | OUTPUT | FEATURES | SUPPLY<br>VOLTAGE | PINS  |

|------------|----------------|----------|---------|-----|---------|--------|----------|-------------------|-------|

| μPD553     | μCOM-43H       | 2000 × 8 | 96 × 4  | 35  | PMOS    | O.D.   | Α        | -10               | 42    |

| μPD557L    | μCOM-43SL      | 2000 × 8 | 96 × 4  | 21  | PMOS    | O.D.   | Α        | -8                | 28    |

| μPD552     | μCOM-44H       | 1000 × 8 | 64 × 4  | 35  | PMOS    | O.D.   | Α        | -10               | 42    |

| μPD550     | μCOM-45        | 640 × 8  | 32 × 4  | 21  | PMOS    | O.D.   | Α        | -10               | 28    |

| μPD550L    | μCOM-45L       | 640 × 8  | 32 × 4  | 21  | PMOS    | O.D.   | Α        | -8                | 28    |

| μPD554     | μCOM-45        | 1000 × 8 | 32 × 4  | 21  | PMOS    | O.D.   | Α        | -10               | 28    |

| μPD554L    | μCOM-45L       | 1000 × 8 | 32 × 4  | 21  | PMOS    | O.D.   | Α        | -8                | 28    |

| μPD556B    | μCOM-43        | External | 96 × 4  | 35  | PMOS    | O.D.   | В        | -10               | 64    |

| MC-430P    | μCOM-43        | 2000 × 8 | 96 × 4  | 35  | PMOS    | O.D.   | G        | -10               | 42    |

|            |                | UV EPROM |         |     |         |        |          |                   |       |

| μPD7500    | μPD7500 Series | External | 256 × 4 | 46  | CMOS    | O.D.   | С        | + 2.7 to 5.5      | 64    |

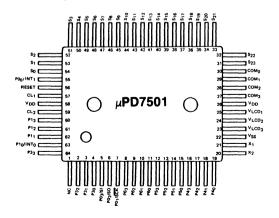

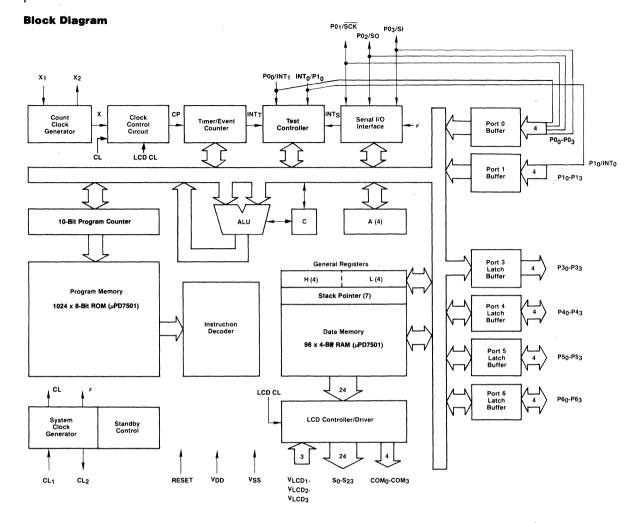

| μPD7501    | μPD7500 Series | 1024 × 8 | 96 × 4  | 24  | CMOS    | O.D.   | D        | +2.7 to 5.5       | 64    |

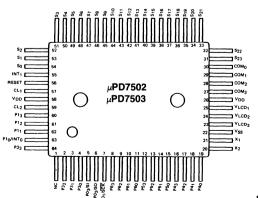

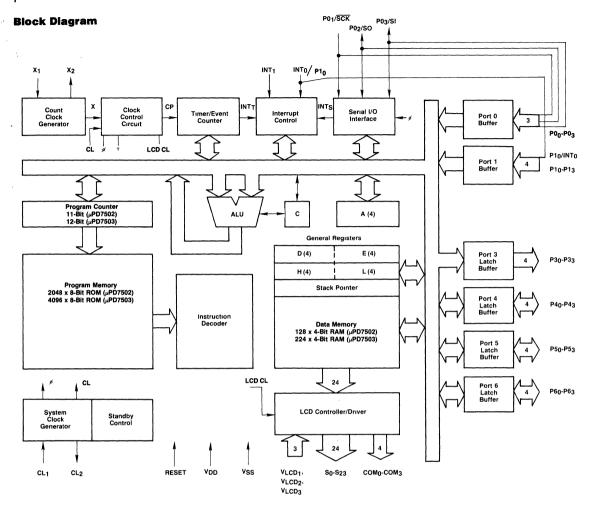

| μPD7502    | μPD7500 Series | 2048 × 8 | 128 × 4 | 23  | CMOS    | O.D.   | D        | +2.7 to 5.5       | 64    |

| μPD7503    | μPD7500 Series | 4096 × 8 | 224 × 4 | 23  | CMOS    | O.D.   | D        | + 2.7 to 5.5      | 64    |

| μPD7506    | μPD7500 Series | 1024 × 8 | 64 × 4  | 22  | CMOS    | O.D.   |          | + 2.7 to 5.5      | 28    |

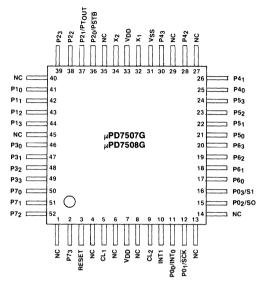

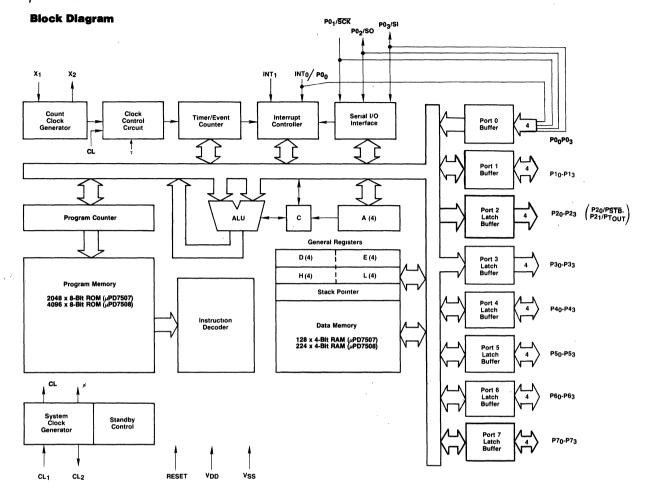

| μPD7507    | μPD7500 Series | 2048 × 8 | 128 × 4 | 32  | CMOS    | O.D.   |          | + 2.7 to 5.5      | 40/52 |

| μPD7507S   | μPD7500 Series | 2048 × 8 | 128 × 4 | 20  | CMOS    | O.D.   |          | + 2.7 to 5.5      | 28    |

| μPD7508    | μPD7500 Series | 4096 × 8 | 224 × 4 | 32  | CMOS    | O.D.   |          | + 2.7 to 5.5      | 40/52 |

| μPD7508H   | μPD7500 Series | 4096 × 8 | 224 × 4 | 32  | CMOS    | O.D.   |          | + 2.7 to 5.5      | 40/52 |

| μPD7508A   | μPD7500 Series | 4096 × 8 | 208 × 4 | 32  | CMOS    | O.D.   | Α        | + 2.7 to 5.5      | 40    |

| μPD7519    | μPD7500 Series | 4096 × 8 | 256 × 4 | 28  | CMOS    | O.D.   | F        | + 2.7 to 5.5      | 64    |

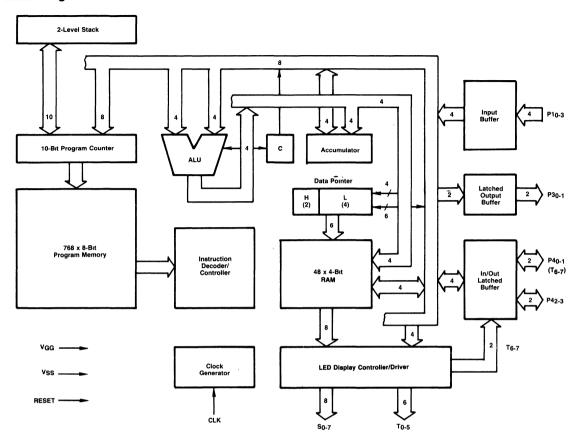

| μPD7520    | μPD7500 Series | 768 × 8  | 48 × 4  | 24  | PMOS    | O.D.   | E        | -6 to -10         | 28    |

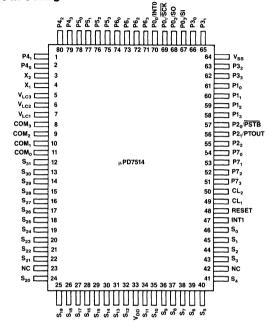

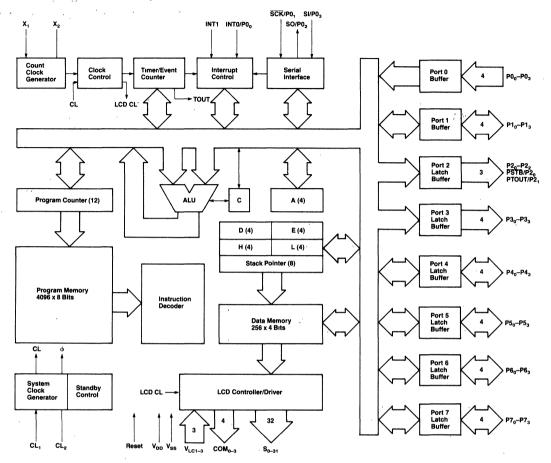

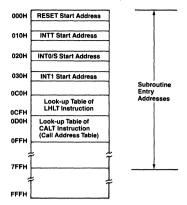

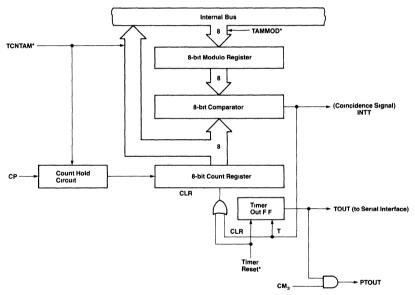

| μPD7514    | μPD7500 Series | 4096 × 8 | 256 × 4 | 31  | CMOS    | O.D.   | D        | + 2.7 to 5.5      | 80    |

| μPD7528/38 | μPD7500 Series | 4096 × 8 | 160 × 4 | 35  | CMOS    | O.D.   | Α        | + 2.7 to 5.5      | 42    |

| μPD7527/37 | μPD7500 Series | 2048 × 8 | 160 × 4 | 35  | смоѕ    | O.D.   | Α        | + 2.7 to 5.5      | 42    |

Notes. A = -35V VF Display Drive B  $= \mu COM-4$  Evaluation Chip

C = μPD750X Evaluation Chip

D = LCD Controller/Driver

E = LED Display Controller/Driver

F = VF Display Controller/Driver

$G = Pin-Compatible with \, \mu PD546$  O.D. = Open Drain

# MICROCOMPUTER SELECTION GUIDE

## SINGLE CHIP 8-BIT MICROCOMPUTERS

| DEVICE    | SPECIAL FEATURES                 | ROM      | RAM     | 1/0 | PROCESS | ОUТРUТ | CYCLE   | SUPPLY<br>VOLTAGE | PINS |

|-----------|----------------------------------|----------|---------|-----|---------|--------|---------|-------------------|------|

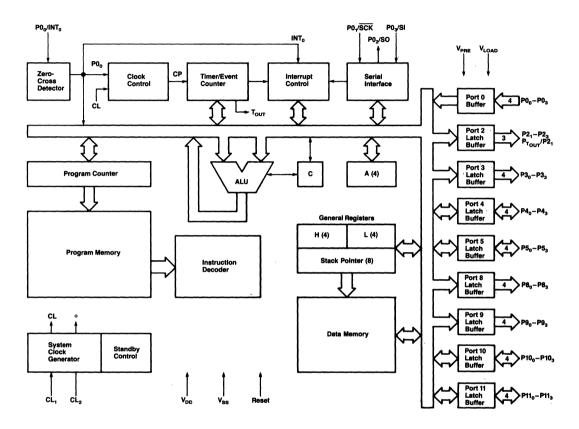

| μPD8021   | Zero-Cross Detector              | 1024 × 8 | 64 × 8  | 21  | NMOS    | BD     | 3.6 MHz | +5                | 28   |

| μPD8035HL | μPD8048 w/External Memory        | External | 64 × 8  | 27  | HMOS    | TS, BD | 6 MHz   | +5                | 40   |

| μPD8039HL | μPD8049 w/External Memory        | External | 128 × 8 | 27  | HMOS    | TS, BD | 11 MHz  | +5                | 40   |

| μPD8041   | Peripheral Interface w/Slave Bus | 1024 × 8 | 64 × 8  | 18  | NMOS    | TS, BD | 6 MHz   | +5                | 40   |

| μPD8041A  | Enhanced μPD8041                 | 1024 × 8 | 64 × 8  | 18  | NMOS    | TS, BD | 6 MHz   | + 5               | 40   |

| μPD8048H  | Expansion Bus                    | 1024 × 8 | 64 × 8  | 27  | HMOS    | TS, BD | 6 MHz   | +5                | 40   |

| μPD8049H  | High Speed μPD8048               | 2048 × 8 | 128 × 8 | 27  | HMOS    | TS, BD | 11 MHz  | +5                | 40   |

| μPD8741A  | UV-EPROM μPD8041A                | 1024 × 8 | 64 × 8  | 18  | NMOS    | TS, BD | 6 MHz   | + 5               | 40   |

| μPD8748   | UV-EPROM µPD8048                 | 1024 × 8 | 64 × 8  | 27  | NMOS    | TS, BD | 6 MHz   | +5                | 40   |

| μPD8749H  | UV-EPROM μPD8049                 | 2048 × 8 | 128 × 8 | 27  | HMOS    | TS, BD | 11 MHz  | +5                | 40   |

| μPD80C35  | CMOS 8035                        | External | 64 × 8  | 27  | CMOS    | TS, BD | 6 MHz   | + 2.7 to 5.5      | 40   |

| μPD80C48  | CMOS 8048                        | 1024 × 8 | 64 × 8  | 27  | CMOS    | TS, BD | 6 MHz   | + 2.7 to 5.5      | 40   |

| μPD80C39  | CMOS 8039                        | External | 128 × 8 | 27  | CMOS    | TS, BD | 8 MHz   | + 2.7 to 5.5      | 40   |

| μPD80C39H | CMOS 8039H                       | External | 128°× 8 | 27  | CMOS    | TS, BD | 12 MHz  | + 2.7 to 5.5      | 40   |

| μPD80C49  | CMOS 8049                        | 2048 × 8 | 128 × 8 | 27  | CMOS    | TS, BD | 8 MHz   | + 2.7 to 5.5      | 40   |

| μPD80C49H | CMOS 8049H                       | 2048 × 8 | 128 × 8 | 27  | CMOS    | TS, BD | 12 MHz  | + 2.7 to 5.5      | 40   |

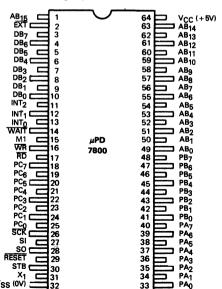

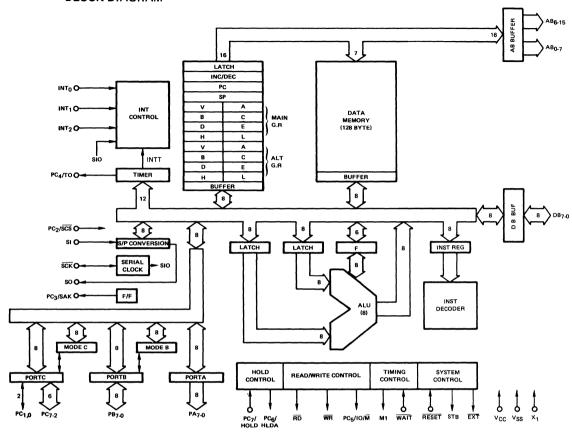

| μPD7800   | Development Chip                 | External | 128 × 8 | 48  | NMOS    | TS, BD | 4 MHz   | +5                | 64   |

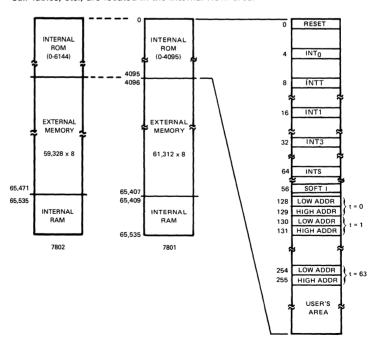

| μPD7801   | 8080 Expansion Bus               | 4096 × 8 | 128 × 8 | 48  | NMOS    | TS, BD | 4 MHz   | +5                | 64   |

|           | 64K Memory Address Space         |          |         |     |         |        |         |                   |      |

| μPD7802   | Expanded μPD7801                 | 6144 × 8 | 64 × 8  | 48  | NMOS    | TS, BD | 4 MHz   | +5                | 64   |

| μPD78C05  | CMOS Microprocessor              | External | 128 × 8 | 46  | CMOS    | TS, BD | 4 MHz   | +5                | 64   |

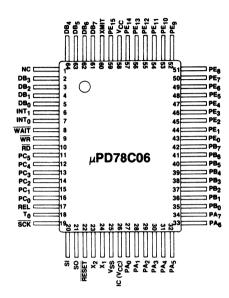

| μPD78C06  | CMOS Microcomputer               | 4096 × 8 | 128 × 8 | 46  | нсмоѕ   | TS, BD | 4 MHz   | +5                | 64   |

| μPD7807   | 7809 w/Ext. Memory               | External | 256 × 8 | 40  | HMOS    | TS, BD | 12 MHz  | +5                | 64   |

| μPD7809   | 8/16 Bit Microcomputer           | 8192 × 8 | 256 × 8 | 40  | HMOS    | TS, BD | 12 MHz  | ++5               | 64   |

| μPD7810   | Romless µPD7811                  | External | 256 × 8 | 44  | NMOS    | TS, BD | 12 MHz  | +5                | 64   |

| μPD7811   | 8 Channel A/D/8-16 Bit Micro     | 4096 × 8 | 128 × 8 | 44  | NMOS    | TS, BD | 12 MHz  | +5                | 64   |

### **MICROPROCESSORS**

| DEVICE     | PRODUCT        | SIZE   | PROCESS | OUTPUT  | CYCLE   | SUPPLY<br>VOLTAGES | PINS |

|------------|----------------|--------|---------|---------|---------|--------------------|------|

| μPD780     | Microprocessor | 8-bit  | NMOS    | 3-State | 2.5 MHz | +5                 | 40   |

| μPD780-1   | Microprocessor | 8-bit  | NMOS    | 3-State | 4.0 MHz | +5                 | 40   |

| μPD780-2   | Microprocessor | 8-bit  | NMOS    | 3-State | 6.0 MHz | +5                 | 40   |

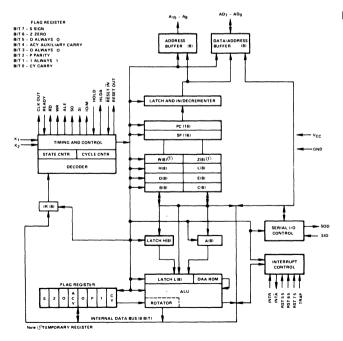

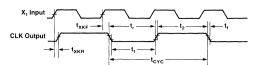

| μPD8085A   | Microprocessor | 8-bit  | NMOS    | 3-State | 3.0 MHz | +5                 | 40   |

| μPD8085A-2 | Microprocessor | 8-bit  | NMOS    | 3-State | 5.0 MHz | +5                 | 40   |

| μPD8085AH  | Microprocessor | 8-bit  | NMOS    | 3-State | 3.0 MHz | +5                 | 40   |

| μPD8086    | Microprocessor | 16-bit | NMOS    | 3-State | 5.0 MHz | +5                 | 40   |

| μPD8086-2  | Microprocessor | 16-bit | NMOS    | 3-State | 8.0 MHz | +5                 | 40   |

| μPD8088 ·  | Microprocessor | 8-bit  | NMOS    | 3-State | 5.0 MHz | +5                 | 40   |

# **MICROCOMPUTER SELECTION GUIDE**

#### SYSTEM SUPPORT

| DEVICE                         | PRODUCT                                               | SIZE                 | PROCESS                | ОИТРИТ                        | CYCLE                     | SUPPLY<br>VOLTAGES  | PINS           |

|--------------------------------|-------------------------------------------------------|----------------------|------------------------|-------------------------------|---------------------------|---------------------|----------------|

| μPD765A                        | Double Sided/Double Density<br>Floppy Disk Controller | 8-bit                | NMOS                   | 3-State                       | 8 MHz                     | +5                  | 40             |

| μPD7201A                       | Multi-Protocol Serial Controller                      | 8-bit                | NMOS                   | 3-State                       | 4 MHz                     | +5                  | 40             |

| μPD7210                        | IEEE Controller (Talker, Listener,<br>Controller)     | 8-bit                | NMOS                   | 3-State                       | 8 MHz                     | +5                  | 40             |

| μPD7220                        | Color Graphic Display Controller                      | 8-bit                | NMOS                   | 3-State                       | 5 MHz                     | +5                  | 40             |

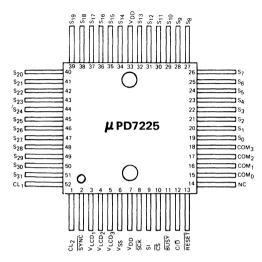

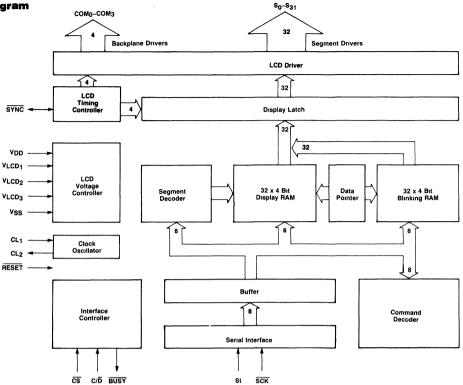

| μPD7225                        | Alpha Numeric LCD<br>Controller/Driver                | 8-bit                | CMOS                   | -                             | -                         | 2.7 to 5.5          | 52             |

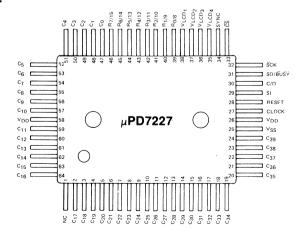

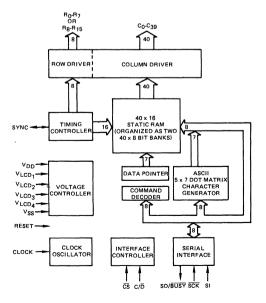

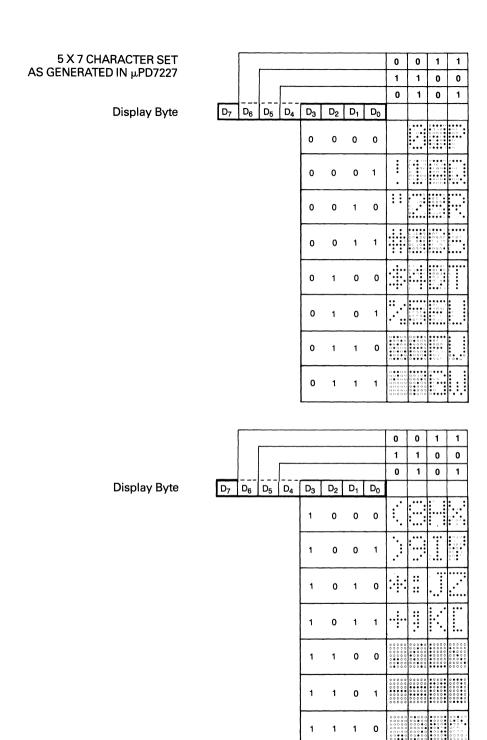

| μPD7227                        | Dot Matrix LCD Controller/Driver                      | 8-bit                | CMOS                   | -                             | -                         | 2.7 to 5.5          | 64             |

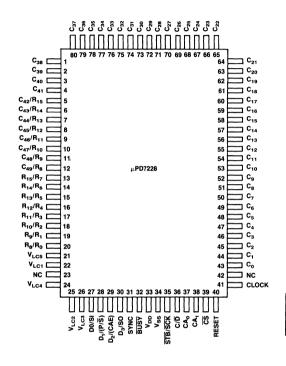

| μPD7228                        | Dot Matrix LCD Controller/Driver                      | 8-bit                | CMOS                   | -                             | -                         | 2.7 to 5.5          | 80             |

| μPD7720                        | Signal Processor                                      | 16-bit               | NMOS                   | 3-State                       | 8 MHz                     | +5                  | 28             |

| μPD77P20                       | EPROM Version of μPD7720                              | 16-bit               | NMOS                   | 3-State                       | 8 MHz                     | +5                  | 28             |

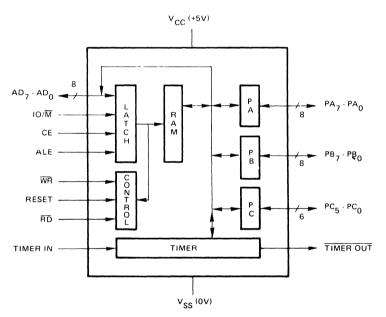

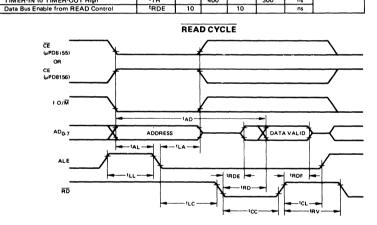

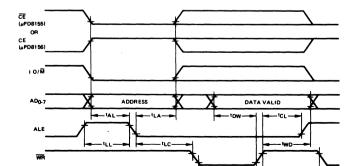

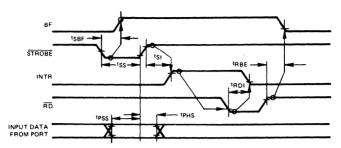

| μPD8155H                       | 256 x 8 RAM with I/O Ports<br>and Timer               | 8-bit                | HMOS                   | 3-State                       | -                         | +5                  | 40             |

| μPD8155-2                      | 256 x 8 RAM with I/O Ports<br>and Timer               | 8-bit                | NMOS                   | 3-State                       | -                         | +5                  | 40             |

| μPD8156H                       | 256 x 8 RAM with I/O Ports<br>and Timer               | 8-bit                | HMOS                   | 3-State                       | -                         | +5                  | 40             |

| μPD8156-2                      | 256 x 8 RAM with I/O Ports<br>and Timer               | 8-bit                | NMOS                   | 3-State                       | -                         | +5                  | 40             |

| μPB8212                        | I/O Port                                              | 8-bit                | Bipolar                | 3-State                       | -                         | +5                  | 24             |

| μPB8216                        | Bus Driver Non-Inverting                              | 4-bit                | Bipolar                | 3-State                       | -                         | + 5                 | 16             |

| µРВ8226                        | Bus Driver Inverting                                  | 4-bit                | Bipolar                | 3-State                       | -                         | + 5                 | 16             |

| μPD8243                        | I/O Expander                                          | 4 x 4 bits           | NMOS                   | 3-State                       | -                         | +5                  | 24             |

| μPD82C43                       | I/O Expander                                          | 4 x 4 bits           | CMOS                   | 3-State                       | -                         | +5                  | 24             |

| μPD8251A/AF                    | Programmable Communications Interface (Async/Sync)    | 8-bit                | NMOS                   | 3-State                       | A-9.6K baud<br>S-64K baud | +5                  | 28             |

| μPD8253-2/-5                   | Programmable Timer                                    | 8-bit                | NMOS                   | 3-State                       | 4.0 MHz                   | + 5                 | 24             |

| μPD8255A-2/-5                  | Peripheral Interface                                  | 8-bit                | NMOS                   | 3-State                       | -                         | +5                  | 40             |

| μPD8257-2/-5                   | Programmable DMA Controller                           | 8-bit                | NMOS                   | 3-State                       | 4 MHz                     | +5                  | 40             |

| μPD8259-2/-5                   | Programmable Keyboard/Display<br>Interface            | 8-bit                | NMOS                   | 3-State                       | -                         | +5                  | 40             |

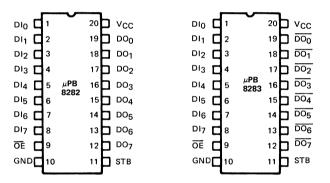

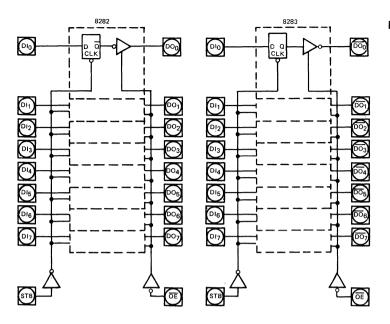

| μPB8282/8283                   | 8-Bit Latches                                         |                      | Bipolar                | 3-State                       | 5 MHz                     | +5                  | 20             |

| µPB8284A                       | Clock Driver                                          |                      | Bipolar                | 3-State                       | 5 MHz                     | +5                  | 18             |

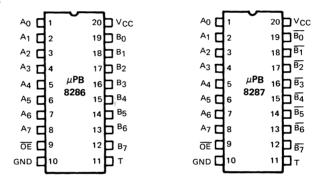

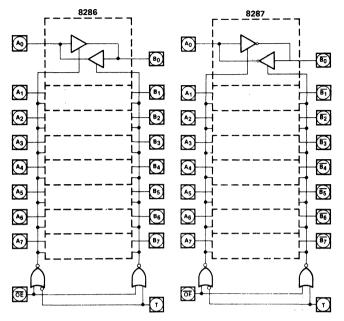

| uPB8286/8287                   | 8-Bit Bus Transceivers                                |                      | Bipolar                | 3-State                       | 5 MHz                     | +5                  | 20             |

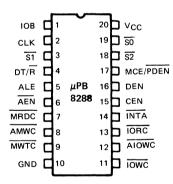

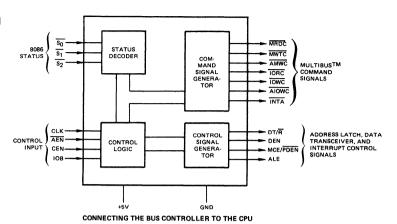

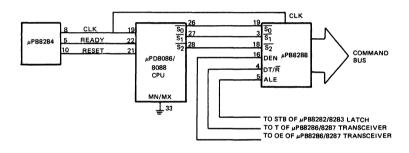

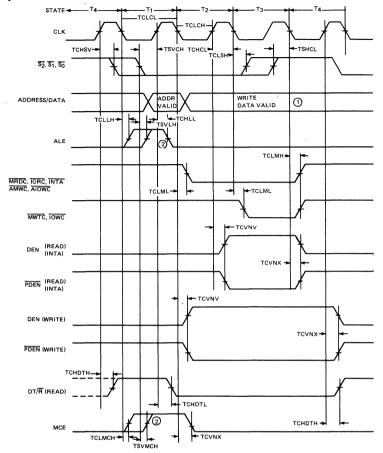

| µPB8288                        | Bus Controller                                        |                      | Bipolar                | 3-State                       | 5 MHz                     | +5                  | 20             |

| μPB8289                        | Bus Arbiter                                           |                      | Bipolar                | 3-State                       | 5 MHz                     | +5                  | 20             |

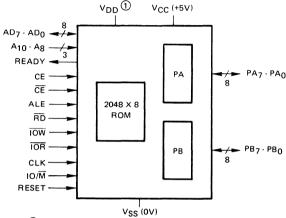

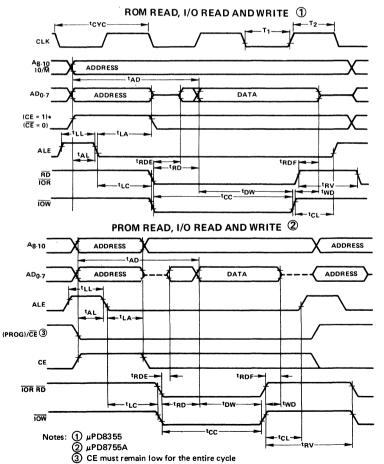

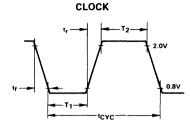

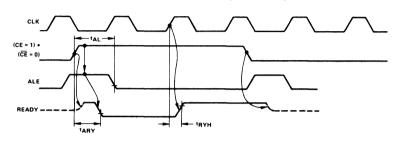

| μPD8355/-2/A                   | 2048 x 8 ROM with I/O Ports                           | 8-bit                | NMOS                   | 3-State                       | -                         | +5                  | 40             |

| иPD8755A                       | 2048 x 8 EPROM with I/O Ports                         | 8-bit                | NMOS                   | 3-State                       | _                         | +5                  | 40             |

| μPD8759A/A-2                   | Programmable Interrupt Controller                     | 8-bit                | HMOS                   | 3-State                       | 5/8 MHz                   | +5                  | 28             |

| SPEECH<br>PRODUCTS             | ,                                                     |                      |                        |                               |                           |                     |                |

| μPD7751                        | ADPCM Speech Synthesizer                              | 8-bit                | NMOS                   | 3-State                       | 6 MHz                     | +5                  | 40             |

| μPD7752                        | Formant Speech Synthesizer                            | 8-bit                | CMOS                   | 3-State                       | 3 6 MHz                   | +5                  | 28             |

| μPD7761<br>μPD7762<br>μMC-4760 | K 3 Chip-SR Speech Recognition<br>Chip Set            | 16-bit<br>8-bit<br>– | NMOS<br>NMOS<br>Hybrid | 3-State<br>3-State<br>3-State | 8 MHz<br>4 MHz<br>2 MHz   | +5<br>+5<br>+5, ±12 | 28<br>64<br>24 |

# MICROCOMPUTER ALTERNATE SOURCE GUIDE

| MANUFACTURER | PART NUMBER | DESCRIPTION                                            | NEC REPLACEMENT |

|--------------|-------------|--------------------------------------------------------|-----------------|

| AMD          | AM8085A     | Microprocessor (3.0 MHz)                               | μPD8085A        |

|              | AM8155      | Programmable Peripheral Interface<br>with 256 x 8 RAM  | μPD8155         |

|              | AM8156      | Programmable Peripheral Interface<br>with 256 x 8 RAM  | μPD8156         |

|              | AM8212      | I/O Port (8-Bit)                                       | μPB8212         |

|              | AM8214      | Priority Interrupt Controller                          | μPB8214         |

|              | AM8216      | Bus Driver, Inverting                                  | μPB8216         |

|              | AM8226      | Bus Driver, Non-Inverting                              | μPB8226         |

|              | AM8251      | Programmable Communications Interface                  | μPD8251         |

|              | AM8255      | Programmable Peripheral Interface                      | μPD8255         |

|              | AM8257      | Programmable DMA Controller                            | μPD8257         |

|              | AM8355      | Programmable Peripheral Interface<br>with 2048 x 8 ROM | μPD8355         |

|              | AM8048      | Single Chip Microcomputer                              | μPD8048         |

| AMI          | 7500 Family | 4-Bit CMOS Microcomputer                               | μPD750X         |

| ,            | 78C06/78C05 | 8-Bit CMOS Microcomputer                               | μPD78C06/78C05  |

|              | 7810/7811   | 16-Bit High-Performance<br>Microcomputer               | μPD7810/7811    |

|              | 7807/7809   | 16-Bit High-Performance<br>Microcomputer               | μPD7807/7809    |

|              | 7720        | Signal Processor                                       | μPD7720         |

| INTEL        | 8021        | Microcomputer with ROM                                 | μPD8021         |

|              | 8035HL      | Microprocessor                                         | μPD8035HL       |

|              | 8039HL      | Microprocessor                                         | μPD8039HL       |

|              | 8041A       | Programmable Peripheral Controller with ROM            | μPD8041A        |

|              | 8048H       | Microcomputer with ROM                                 | μPD8048H        |

|              | 8049H       | Microcomputer with ROM                                 | μPD8049H        |

|              | 8085A       | Microprocessor (3.0 MHz)                               | μPD8085A        |

|              | 8085A-2     | Microprocessor (5.0 MHz)                               | μPD8085A-2      |

|              | 8086        | Microprocessor (16-Bit)                                | μPD8086         |

|              | 8155/8155-2 | Programmable Peripheral Interface<br>with 256 x 8 RAM  | μPD8155/8155-2  |

|              | 8156/8156-2 | Programmable Peripheral Interface<br>with 256 x 8 RAM  | μPD8156/8156-2  |

|              | 8212        | I/O Port (8-Bit)                                       | μPB8212         |

|              | 8214        | Priority Interrupt Controller                          | μPB8214         |

|              | 8216        | Bus Driver, Non-Inverting                              | μPB8216         |

|              | 8226        | Bus Driver, Inverting                                  | μPB8226         |

|              | 8243        | I/O Expander                                           | μPD8243         |

# MICROCOMPUTER ALTERNATE SOURCE GUIDE

| MANUFACTURER  | PART NUMBER | DESCRIPTION                                            | NEC REPLACEMENT |

|---------------|-------------|--------------------------------------------------------|-----------------|

| INTEL (CONT.) | 8251A       | Programmable Communications Interface (Async/Sync)     | μPD8251A        |

|               | 8253-5      | Programmable Timer                                     | μPD8253-5       |

|               | 8255A-5     | Programmable Peripheral Interface                      | μPD8255A-5      |

|               | 8257-5      | Programmable DMA Controller                            | μPD8257-5       |

|               | 8259A       | Programmable Interrupt Controller                      | μPD8259A        |

|               | 8272        | Double Sided/Double Density<br>Floppy Disk Controller  | μPD765          |

|               | 8279-5      | Programmable Keyboard/Display<br>Interface             | μPD8279-5       |

|               | 8282/8283   | 8-Bit Latches                                          | μPB8282/8283    |

|               | 8284        | Clock Driver                                           | μPB8284         |

|               | 8286/8287   | 8-Bit Transceivers                                     | μPB8286/8287    |

|               | 8288        | Bus Controller                                         | μPB8288         |

|               | 8355        | Programmable Peripheral Interface<br>with 2048 x 8 ROM | μPD8355         |

|               | 8741A       | Programmable Peripheral Controller with EPROM          | μPD8741A        |

|               | 8748        | Microcomputer with EPROM                               | μPD8748         |

|               | 8749H       | Microcomputer with EPROM                               | μPD8749H        |

|               | 8755A       | Programmable Peripheral Interface<br>with 2K x 8 EPROM | μPD8755A        |

|               | 8274        | Multiprotocol Serial Controller                        | μPD7201         |

| NATIONAL      | INS8048     | Microcomputer with ROM                                 | μPD8048         |

|               | INS8049     | Microcomputer with ROM                                 | μPD8049         |

|               | 8212        | I/O Port (8-Bit)                                       | μPB8212         |

|               | 8214        | Priority Interrupt Controller                          | μPB8214         |

|               | 8216        | Bus Driver, Non-Inverting                              | μPB8216         |

|               | 8226        | Bus Driver, Inverting                                  | μ <b>PB8226</b> |

|               | INS8251     | Programmable Communications Interface                  | μPD8251A        |

|               | INS8253     | Programmable Timer                                     | μPD8253-5       |

|               | INS8255     | Programmable Peripheral Interface                      | μPD8255A-5      |

|               | INS8257     | Programmable DMA Controller                            | μPD8257-5       |

|               | INS8259     | Programmable Interrupt Controller                      | μPD8259A        |

| т.і.          | SN74S412    | I/O Port (8-Bit)                                       | μPB8212         |

#### ROM-BASED PRODUCTS ORDERING PROCEDURE

The following NEC products fall under the guidelines set by the ROM-based Products Ordering Procedure:

| µPD7801<br>µPD7802<br>µPD78C06<br>µPD7807<br>µPD7808<br>µPD7811<br>µPD8021 | µPD80C48<br>µPD8049H<br>µPD80C49<br>µPD8355<br>µPD550<br>µPD550L<br>µPD552 | µPD554L<br>µPD557L<br>µPD7501<br>µPD7502<br>µPD7503<br>µPD7506<br>µPD7507 | µPD7508A<br>µPD7508H<br>µPD7514<br>µPD7519<br>µPD7520<br>µPD7527<br>µPD7528 | μPD2308A<br>μPD2316E<br>μPD2332<br>μPD2364<br>μPD2380<br>μPD23128<br>μPD23256 |

|----------------------------------------------------------------------------|----------------------------------------------------------------------------|---------------------------------------------------------------------------|-----------------------------------------------------------------------------|-------------------------------------------------------------------------------|

|                                                                            |                                                                            |                                                                           |                                                                             |                                                                               |

| •                                                                          | P                                                                          | · ·                                                                       | ,                                                                           |                                                                               |

| μPD8041AH                                                                  | μPD553                                                                     | μPD7507S                                                                  | μPD7537                                                                     | μPD231000                                                                     |

| μPD8048H                                                                   | μPD554                                                                     | μPD7508                                                                   | μPD7538                                                                     | μPD23C128                                                                     |

|                                                                            |                                                                            |                                                                           | μPD7720                                                                     | μPD73128G<br>μPD23C256                                                        |

|                                                                            |                                                                            |                                                                           |                                                                             | uPD731000                                                                     |

NEC Electronics Inc. is able to accept mask patterns in a variety of formats to facilitate the transferral of ROM mask information. These are intended to suit various customer needs and minimize turnaround time. Always enclose a listing of the code and a complete "ROM Code Submission" form. The following is a list of acceptable media for code transferral.

- PROM/EPROM equivalents to ROM devices

- Sample ROMs or ROM-based microcomputers

- ISIS-II compatible 8" floppy disks

- CP/M (® Digital Research Corp.) compatible 8" single-density floppy disk

Thoroughly tested verification procedures protect against unnecessary delays or costly mistakes. NEC Electronics Inc. will return the ROM code patterns to the customer in the most convenient format. Unprogrammed EPROMs, if sent with the ROM code, can be programmed and returned for verification. Earth satellites and the world-wide GE Mark III timesharing systems provide reliable and instant communication of ROM patterns to the factory.

The following is an example of a ROM code transferral procedure. The  $\mu$ PD8048H is used here; however, the process is the same for all other ROM-based products.

- The customer contacts his local NEC Electronics Inc. Sales Representative, concerning a ROM pattern for the μPD8048H that he would like to send.

- Since an EPROM version of that part is available, the μPD8748 is proposed as a code transferral medium. Alternatively, a μPD2716 or a floppy disk may be used.

- 3. Two programmed µPD8748s are sent to NEC Electronics Inc., along with a listing and the "ROM Code Submission" form. A floppy disk may also be sent as back-up.

- 4. NEC Electronics Inc. compares the media provided and enters the code into GE-TSS. The GE-TSS file is accessed at the NEC factory and a copy of the code is returned to NEC Electronics Inc. for verification. One of the μPD8748s is erased and reprogrammed with the customer's code as the NEC factory has it. The μPD8748s, a listing, and a "ROM Code Verification" form are returned to the customer for final verification.

- 5. Once the customer has notified NEC Electronics Inc. *in writing* that the code is verified, and has provided both the mask charge payment and a hard-copy purchase order, work begins immediately on production of his μPD8048Hs.

Please contact your local Sales Representative for assistance with all ROM-based product orders.

# **ROM Code Submission**

| To <sup>.</sup> | NEC Electronics Inc.<br>252 Humboldt Court<br>Sunnyvale, CA 94086 |                       |                                                                               | D           | ate·                 | - <del> </del>     |

|-----------------|-------------------------------------------------------------------|-----------------------|-------------------------------------------------------------------------------|-------------|----------------------|--------------------|

| Attn            | ROM-Based Product                                                 | Administrator         |                                                                               |             |                      |                    |

| We a            | re ready to place our po                                          | urchase order for ou  | Customer Part Number                                                          | your        | NEC Part Number      | , and are          |

| subm            | itting Two copies of the                                          | e ROM Code on the     | following medium/media (Pl                                                    | lease chec  | k all applicable bo  | oxes) <sup>.</sup> |

|                 | □ µPD2716                                                         | □ µPD8741A            | ☐ CP/M® compatible 8″                                                         | ' sıngle-de | nsity floppy disk    |                    |

|                 | ☐ µPD2732                                                         | μPD8748               | ☐ Intel ISIS-II compatible                                                    | 8" single-  | density floppy disl  | k                  |

|                 | ☐ µPD2764                                                         | □ µPD8749H            | ☐ Intel ISIS-II compatible                                                    | 8" double   | e-density floppy dis | sk                 |

|                 | ☐ μPD27128                                                        | □ μPD8755A            |                                                                               |             |                      |                    |

| and n           | ot available on all othe                                          | r NEC ROM-Based       | IPD7528, µPD7537, µPD753: Products) selected on the basting are also enclosed | ick of this |                      |                    |

|                 |                                                                   | Name                  | ,                                                                             |             |                      |                    |

|                 |                                                                   | Company               |                                                                               |             |                      |                    |

|                 |                                                                   | Division              |                                                                               |             |                      |                    |

|                 |                                                                   | Shipping Address (not | a P O Box please)                                                             |             |                      |                    |

|                 |                                                                   | City                  | State                                                                         | Zıp         |                      |                    |

|                 |                                                                   | Telephone Number      |                                                                               |             |                      |                    |

|                 |                                                                   |                       | and the mask charge paymen<br>-Based Product Administrato                     |             |                      | d with "ROM        |

CP/M is a registered trademark of Digital Research Corp

| Device   | Port                              | I/O Port Loading Option                       |                                                             |  |  |  |  |  |  |  |

|----------|-----------------------------------|-----------------------------------------------|-------------------------------------------------------------|--|--|--|--|--|--|--|

| μPD7519  | SO                                | open drain                                    | ☐ pull-down resistor to V LOAD                              |  |  |  |  |  |  |  |

| F        | S1                                | open drain                                    | ☐ pull-down resistor to V LOAD                              |  |  |  |  |  |  |  |

|          | S2                                | open drain                                    | □ pull-down resistor to V LOAD                              |  |  |  |  |  |  |  |

|          | S3                                | open drain                                    | ☐ pull-down resistor to V LOAD                              |  |  |  |  |  |  |  |

|          | S4                                | open drain                                    | D pull down resister to V                                   |  |  |  |  |  |  |  |

|          | S5                                | open drain                                    | □ pull-down resistor to V LOAD                              |  |  |  |  |  |  |  |

|          | S6                                |                                               | □ pull-down resistor to V LOAD                              |  |  |  |  |  |  |  |

|          | S7                                | open drain                                    | ☐ pull-down resistor to V <sub>LOAD</sub>                   |  |  |  |  |  |  |  |

|          |                                   | open drain                                    | ☐ pull-down resistor to V LOAD                              |  |  |  |  |  |  |  |

|          | T8/S8                             | open drain                                    | ☐ pull-down resistor to V LOAD                              |  |  |  |  |  |  |  |

|          | T9/S9                             | open drain                                    | ☐ pull-down resistor to V LOAD                              |  |  |  |  |  |  |  |

|          | T10/S10                           | open drain                                    | ☐ pull-down resistor to V LOAD                              |  |  |  |  |  |  |  |

|          | T11/S11                           | open drain                                    | ☐ pull-down resistor to V <sub>LOAD</sub>                   |  |  |  |  |  |  |  |

|          | T12/S12                           | popen drain                                   | ☐ pull-down resistor to V LOAD                              |  |  |  |  |  |  |  |

|          | T13/S13                           | popen drain                                   | pull-down resistor to V LOAD                                |  |  |  |  |  |  |  |

|          | T14/S14                           | pen drain                                     | pull-down resistor to V LOAD                                |  |  |  |  |  |  |  |

|          | T15/S15                           | open drain                                    | pull-down resistor to V LOAD                                |  |  |  |  |  |  |  |

|          | T0                                | open drain                                    | pull-down resistor to V LOAD                                |  |  |  |  |  |  |  |

|          | T1                                | open drain                                    | pull-down resistor to V LOAD                                |  |  |  |  |  |  |  |

|          | T2                                | open drain                                    | □ pull-down resistor to V LOAD                              |  |  |  |  |  |  |  |

|          | T3                                | open drain                                    | pull-down resistor to V LOAD                                |  |  |  |  |  |  |  |

|          | T4                                | pen drain                                     | pull-down resistor to V LOAD                                |  |  |  |  |  |  |  |

|          | T5                                | pen drain                                     | ☐ pull-down resistor to V LOAD                              |  |  |  |  |  |  |  |

|          | T6                                | open drain                                    | ☐ pull-down resistor to V LOAD                              |  |  |  |  |  |  |  |

|          | T7                                | open drain                                    | □ pull-down resistor to V LOAD                              |  |  |  |  |  |  |  |

|          | PO <sub>o</sub> /INT <sub>o</sub> | direct connection (no zero-crossing detector) | zero-crossing detector                                      |  |  |  |  |  |  |  |

|          | P2 <sub>3</sub> -P2 <sub>1</sub>  | ☐ open drain                                  | □ pull-down resistor to V LOAD                              |  |  |  |  |  |  |  |

|          | P3 <sub>3</sub> -P3 <sub>0</sub>  | open drain                                    | pull-down resistor to V LOAD                                |  |  |  |  |  |  |  |

|          | P4 <sub>3</sub> -P4 <sub>0</sub>  | open drain                                    | □ pull-down resistor to V LOAD                              |  |  |  |  |  |  |  |

|          | P5 <sub>3</sub> -P5 <sub>0</sub>  | ☐ open drain                                  | □ pull-down resistor to V LOAD                              |  |  |  |  |  |  |  |

|          | P8₀                               | open drain                                    | □ pull-down resistor to V LOAD                              |  |  |  |  |  |  |  |

|          | P8 <sub>1</sub>                   | ☐ open drain                                  | □ pull-down resistor to V LOAD                              |  |  |  |  |  |  |  |

|          | P8 <sub>2</sub>                   | ☐ open drain                                  | ☐ pull-down resistor to V LOAD                              |  |  |  |  |  |  |  |

|          | P8 <sub>3</sub>                   | pen drain                                     | ☐ pull-down resistor to V LOAD                              |  |  |  |  |  |  |  |

| µPD7527  | P9₀                               | ☐ open drain                                  | □ pull-down resistor to V <sub>LOAD</sub>                   |  |  |  |  |  |  |  |

| µPD7528  | P9 <sub>1</sub>                   | open drain                                    | □ pull-down resistor to V <sub>LOAD</sub>                   |  |  |  |  |  |  |  |

| µPD7537  | P9 <sub>2</sub>                   | open drain                                    | ☐ pull-down resistor to V LOAD                              |  |  |  |  |  |  |  |

| μPD7538  | P9 <sub>3</sub>                   | open drain                                    | ☐ pull-down resistor to V LOAD                              |  |  |  |  |  |  |  |

| •        | P10 <sub>0</sub>                  | ☐ open drain                                  | ☐ pull-down resistor to V LOAD                              |  |  |  |  |  |  |  |

|          | P10 <sub>1</sub>                  | ☐ open drain                                  | ☐ pull-down resistor to V LOAD                              |  |  |  |  |  |  |  |

|          | P10 <sub>2</sub>                  | open drain                                    | ☐ pull-down resistor to V LOAD                              |  |  |  |  |  |  |  |

|          | P10 <sub>3</sub>                  | open drain                                    | ☐ pull-down resistor to V LOAD                              |  |  |  |  |  |  |  |

|          | P11 <sub>0</sub>                  | open drain                                    | ☐ pull-down resistor to V LOAD                              |  |  |  |  |  |  |  |

|          | P11 <sub>1</sub>                  | open drain                                    | □ pull-down resistor to V LOAD                              |  |  |  |  |  |  |  |

|          | P11 <sub>2</sub>                  | open drain                                    | □ pull-down resistor to V LOAD                              |  |  |  |  |  |  |  |

|          | P11 <sub>3</sub>                  | open drain                                    | ☐ pull-down resistor to V LOAD                              |  |  |  |  |  |  |  |

|          |                                   |                                               |                                                             |  |  |  |  |  |  |  |

| μPD8021  | T1<br>P00-P07                     | ☐ zero-crossing detector<br>☐ open drain      | <ul><li>☐ TTL-compatible</li><li>☐ TTL-compatible</li></ul> |  |  |  |  |  |  |  |

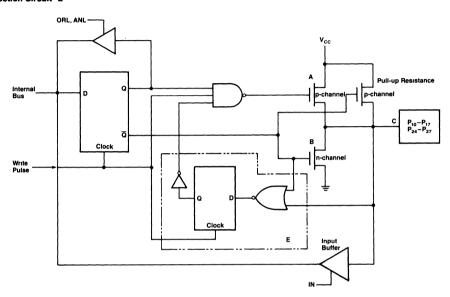

| μPD80C48 | P10-P17                           | ☐ CMOS (-5µA)                                 | ☐ TTL-compatible ( – 50µA)                                  |  |  |  |  |  |  |  |

| µPD80C49 | P20-P23                           | ☐ CMOS (-5µA)                                 | ☐ TTL-compatible ( – 50µA)                                  |  |  |  |  |  |  |  |

|          | P24-P27                           | ☐ CMOS (-5µA)                                 | ☐ TTL-compatible ( – 50µA)                                  |  |  |  |  |  |  |  |

|          |                                   |                                               |                                                             |  |  |  |  |  |  |  |

**SINGLE CHIP 4-BIT MICROCOMPUTERS**

#### 4-BIT SINGLE CHIP MICROCOMPUTER FAMILY

#### DESCRIPTION

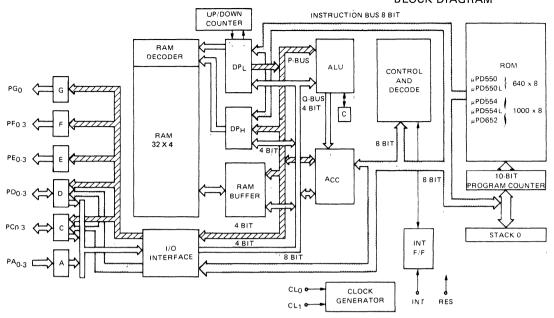

The µCOM-4 4-bit Microcomputer Family is a broad product line of 14 individual devices designed to fulfill a wide variety of design criteria. The product line shares a compatible architecture and instruction set. The architecture includes all functional blocks necessary for a single chip controller, including an ALU, Accumulator, Bytewide ROM, RAM, and Stack. The instruction set maximizes the efficient utilization of the fixed ROM space, and includes a variety of Single Bit Manipulation, Table Look-Up, BCD arithemetic, and Skip instructions.

The µCOM-4 Microcomputer Family includes seven different products capable of directly driving 35V Vacuum Fluorescent Displays. Four products are manufactured with a CMOS process technology, µCOM-4 Microcomputers are ideal for low-cost general purpose controller applications such as industrial controls, instruments, appliance controls, intelligent VF display drivers, and games.

- FEATURES Choice of ROM size: 2000 x 8, 1000 x 8, or 640 x 8

- Choice of RAM size: 96 x 4, 64 x 4, or 32 x 4

- Six 4-Bit Working Registers Available

- One 4-Bit Flag Register Available

- Powerful Instruction Set

- Choice of 80 or 58 Instructions

- Table Look-Up Capability with CZP and JPA Instructions

- Single Bit Manipulation of RAM or I/O Ports

- BCD Arithmetic Capability

- Choice of 3-Level, 2-Level, or 1-Level Subroutine Stack

- Extensive I/O Capability

- Choice of 35 or 21 I/O Lines

|                                        | 42/52-Pin Packages | 28-Pin Package |

|----------------------------------------|--------------------|----------------|

| <ul> <li>4-Bit Input Ports</li> </ul>  | 2                  | 1              |