# 1980 Catalog

Price \$2.50

NEC

# CONTENTS

FUNCTIONAL AND NUMERICAL INDEXES ROM ORDERING PROCEDURE

> MEMORY SELECTION GUIDE AND ALTERNATE SOURCE GUIDE

> > **RANDOM ACCESS MEMORIES**

4

5

6

8

9

2

READ ONLY MEMORIES

MICROCOMPUTER SELECTION GUIDE AND ALTERNATE SOURCE GUIDE

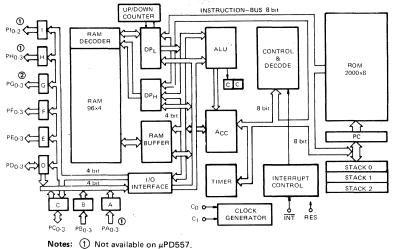

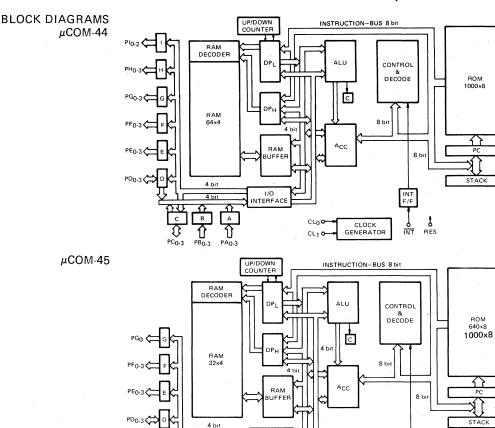

> μCOM-4 SINGLE CHIP 4-BIT MICROCOMPUTERS

μCOM-8 MICROPROCESSORS

μCOM-8 SINGLE CHIP 8-BIT MICROCOMPUTERS

μCOM-8 PERIPHERALS

**NEC Microcomputers, Inc.** 1980 Product Catalog

REFERENCE SECTION Quality Assurance Chart Representatives & Distributors

### **FUNCTIONAL INDEX**

### RANDOM ACCESS MEMORIES

| Selection Guide 8        |

|--------------------------|

| Alternate Source Guide 9 |

| Dynamic NMOS RAMs        |

| μPD411                   |

| μΡD411Α                  |

| μPD416                   |

| μPD2118                  |

| μPD4164                  |

| Static NMOS RAMs         |

| μPD41043                 |

| μPD4104                  |

| μPD2114L                 |

| μPD2147                  |

| μPD421 63                |

| μPD2167                  |

| CMOS RAMs                |

| μPD5101L 69              |

| μPD444/6514 . <b></b>    |

| µPD445L                  |

### **READ ONLY MEMORIES**

| Selection Guide 8        |

|--------------------------|

| Alternate Source Guide 9 |

| ROM Ordering Procedure 6 |

| Mask Programmable ROMs   |

| μPD2308A                 |

| μPD2316E                 |

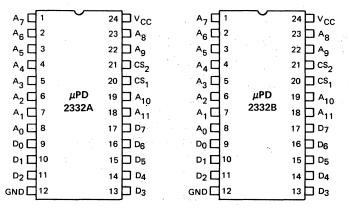

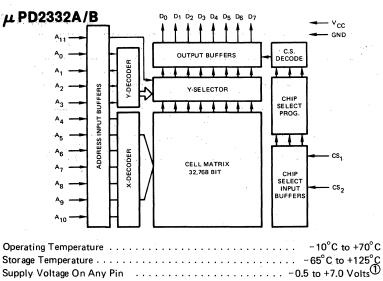

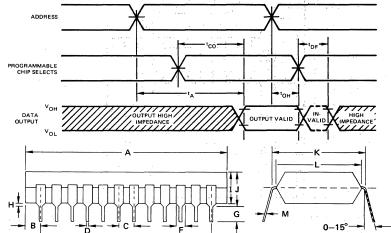

| μPD2332A/B               |

| μPD236497                |

| Field Programmable ROMs  |

| (U.V. Erasable)          |

| μPD2716                  |

| uPD2732 102              |

### μCOM-4 SINGLE CHIP 4-BIT MICROCOMPUTERS

| Selection Guide ,      | 104 |

|------------------------|-----|

| ROM Ordering Procedure | 6   |

| μCOM-42                | 109 |

| μPD548                 | 113 |

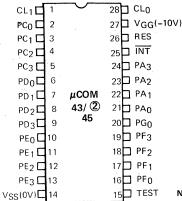

| μCOM-43/44/45          | 115 |

| μPD546                 | 121 |

| μPD553                 | 123 |

| μPD557L                | 125 |

| μPD650                 | 127 |

| μPD547                 | 129 |

| μPD547L                | 131 |

| μPD552                 | 133 |

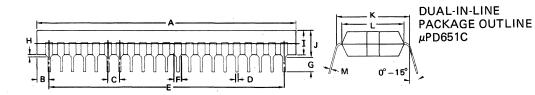

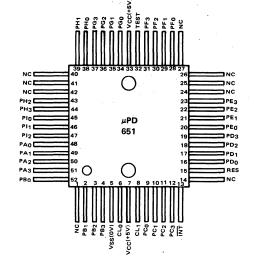

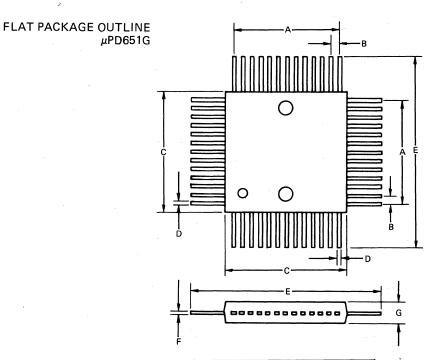

| μPD651                 | 135 |

| μΡD550                 | 139 |

| μPD550L                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| μPD554L 145<br>μPD652                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

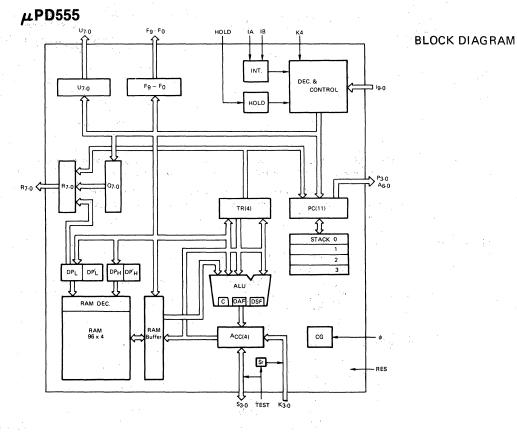

| μPD555 149                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

| uCOM-75                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

| uCOM-8 MICROPROCESSORS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

| Selection Guide 104                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |

| Alternate Source Guide 106                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

| μPD8080AF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

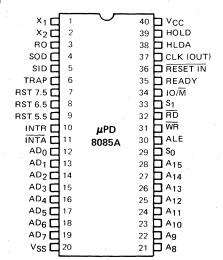

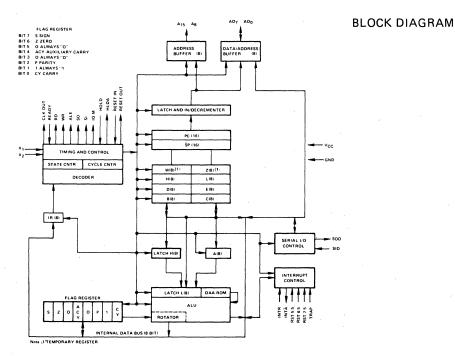

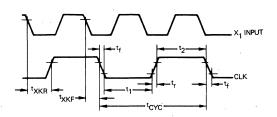

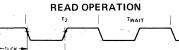

| μPD8085A 179                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

| Selection Guide 104                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |

| Alternate Source Guide 106                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

| ROM Ordering Procedure 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

| $\mu$ PD8021                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

| μPD8041/8741Α                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

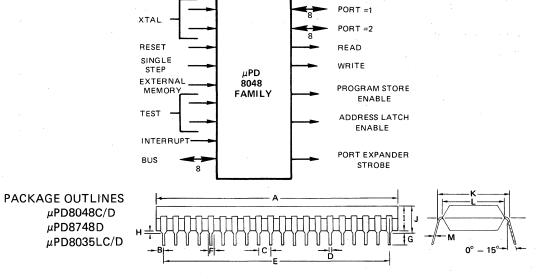

| µPD8048/8748/8035L 219                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

| uPD8049/80391 231                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

| μ. Βοστο,σοσσε                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

| uCOM-8 PERIPHERALS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

| COM-8 PERIPHERALS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

| COM-8 PERIPHERALS<br>Selection Guide 105<br>Alternate Source Guide 106                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

| u <b>COM-8 PERIPHERALS</b><br>Selection Guide 105<br>Alternate Source Guide 106<br>μPD765                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

| μ <b>COM-8 PERIPHERALS</b><br>Selection Guide                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

| μ <b>COM-8 PERIPHERALS</b><br>Selection Guide                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

| μ         COM-8 PERIPHERALS           Selection Guide         105           Alternate Source Guide         106           μPD765         241           μPD781         259           μPD782         271           μPD3301         283                                                                                                                                                                                                                                                                                                                                     |  |  |

| μ       COM-8 PERIPHERALS         Selection Guide       105         Alternate Source Guide       106         μPD765       241         μPD781       259         μPD782       271         μPD3301       283         μPD7001       291                                                                                                                                                                                                                                                                                                                                     |  |  |

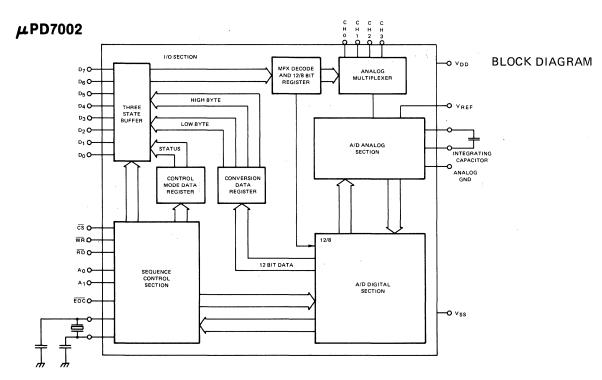

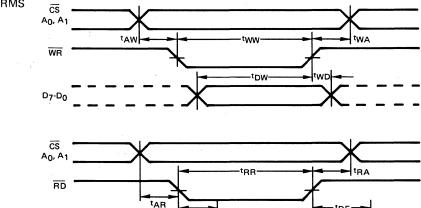

| μ       COM-8 PERIPHERALS         Selection Guide       105         Alternate Source Guide       106         μPD765       241         μPD781       259         μPD782       271         μPD3301       283         μPD7001       291         μPD7002       295                                                                                                                                                                                                                                                                                                           |  |  |

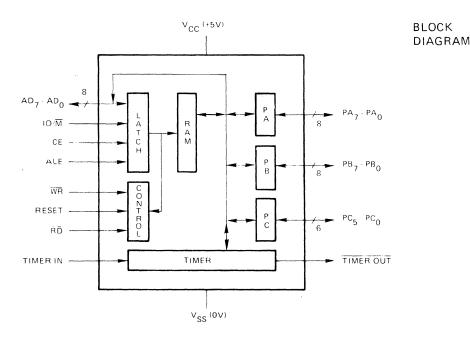

| μ       COM-8 PERIPHERALS         Selection Guide       105         Alternate Source Guide       106         μPD765       241         μPD781       259         μPD782       271         μPD3301       283         μPD7001       291         μPD7002       295         μPD8155/8156       299                                                                                                                                                                                                                                                                            |  |  |

| μCOM-8 PERIPHERALS         Selection Guide       105         Alternate Source Guide       106         μPD765       241         μPD781       259         μPD782       271         μPD3301       283         μPD7001       291         μPD7002       295         μPD8155/8156       299         μPB8212       307                                                                                                                                                                                                                                                         |  |  |

| $\mu$ COM-8 PERIPHERALS         Selection Guide       105         Alternate Source Guide       106 $\mu$ PD765       241 $\mu$ PD781       259 $\mu$ PD782       271 $\mu$ PD3301       283 $\mu$ PD7001       291 $\mu$ PD7002       295 $\mu$ PD8155/8156       299 $\mu$ PB8212       307 $\mu$ PB8214       313                                                                                                                                                                                                                                                     |  |  |

| $\mu$ COM-8 PERIPHERALS         Selection Guide       105         Alternate Source Guide       106 $\mu$ PD765       241 $\mu$ PD781       259 $\mu$ PD782       271 $\mu$ PD3301       283 $\mu$ PD7002       291 $\mu$ PD7002       295 $\mu$ PB8155/8156       299 $\mu$ PB8214       313 $\mu$ PB8216       319                                                                                                                                                                                                                                                     |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

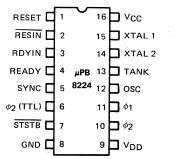

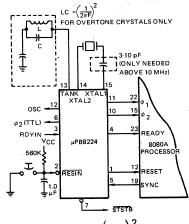

| $\mu$ COM-8 PERIPHERALS         Selection Guide       105         Alternate Source Guide       106 $\mu$ PD765       241 $\mu$ PD781       259 $\mu$ PD782       271 $\mu$ PD3301       283 $\mu$ PD7002       291 $\mu$ PD7002       295 $\mu$ PB8155/8156       299 $\mu$ PB8214       313 $\mu$ PB8224       323 $\mu$ PB8228       329                                                                                                                                                                                                                              |  |  |

| $\mu$ COM-8 PERIPHERALS         Selection Guide       105         Alternate Source Guide       106 $\mu$ PD765       241 $\mu$ PD781       259 $\mu$ PD782       271 $\mu$ PD3301       283 $\mu$ PD7002       291 $\mu$ PD7002       295 $\mu$ PD8155/8156       299 $\mu$ PB8214       313 $\mu$ PB8226       319 $\mu$ PB8228       323 $\mu$ PB8243       335                                                                                                                                                                                                       |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

| $\mu$ COM-8 PERIPHERALSSelection Guide105Alternate Source Guide106 $\mu$ PD765241 $\mu$ PD781259 $\mu$ PD782271 $\mu$ PD3301283 $\mu$ PD7002291 $\mu$ PD7002295 $\mu$ PD8155/8156299 $\mu$ PB8212307 $\mu$ PB8226319 $\mu$ PB8228323 $\mu$ PB8214335 $\mu$ PB8251/8251359                                                                                                                                                                                                                                                                                               |  |  |

| $\mu$ COM-8 PERIPHERALS         Selection Guide       105         Alternate Source Guide       106 $\mu$ PD765       241 $\mu$ PD781       259 $\mu$ PD782       271 $\mu$ PD3301       283 $\mu$ PD7002       291 $\mu$ PD7002       295 $\mu$ PB3155/8156       299 $\mu$ PB8214       313 $\mu$ PB8216/8226       319 $\mu$ PB8228       323 $\mu$ PB8224       335 $\mu$ PD8251/8251A       341 $\mu$ PD8255/8255A-5       367                                                                                                                                      |  |  |

| $\mu$ COM-8 PERIPHERALS         Selection Guide       105         Alternate Source Guide       106 $\mu$ PD765       241 $\mu$ PD781       259 $\mu$ PD782       271 $\mu$ PD3301       283 $\mu$ PD7002       291 $\mu$ PD7002       295 $\mu$ PB8155/8156       299 $\mu$ PB8214       313 $\mu$ PB8216/8226       319 $\mu$ PB8228       323 $\mu$ PB8228       329 $\mu$ PD8251/8251A       341 $\mu$ PD8255/8255A-5       367 $\mu$ PD8257       375                                                                                                               |  |  |

| $\mu$ PD555149 $\mu$ PD556153COM-75157 $\mu$ PD7520157 <b>COM-8 MICROPROCESSORS</b> election Guide104Iternate Source Guide106 $\mu$ PD8080AF165 $\mu$ PD8085A179 <b>COM-8 SINGLE CHIPBIT MICROCOMPUTERS</b> election Guide104Iternate Source Guide106OM Ordering Procedure6 $\mu$ PD7801193 $\mu$ PD8022205 $\mu$ PD8041/8741A211 $\mu$ PD8049/8039L231 <b>COM-8 PERIPHERALS</b> 219election Guide106 $\mu$ PD765241 $\mu$ PD781259 $\mu$ PD782271 $\mu$ PD301283 $\mu$ PD7001291 $\mu$ PD8243307 $\mu$ PB8214313 $\mu$ PB8214335 $\mu$ PD8243335 $\mu$ PD8251/8251A367 |  |  |

| $\mu$ COM-8 PERIPHERALSSelection Guide105Alternate Source Guide106 $\mu$ PD765241 $\mu$ PD781259 $\mu$ PD782271 $\mu$ PD3301283 $\mu$ PD7002291 $\mu$ PD7002295 $\mu$ PB8155/8156299 $\mu$ PB8212307 $\mu$ PB8226319 $\mu$ PB8228329 $\mu$ PB8243335 $\mu$ PD8251/8251A341 $\mu$ PB8255/8255A-5367 $\mu$ PD8259383 $\mu$ PD8259383 $\mu$ PD8259383                                                                                                                                                                                                                      |  |  |

NOTES

NEC

## NUMERICAL INDEX

### PRODUCT

### PAGE

PRODUCT

| P | 1 | 1 | G | l |  |

|---|---|---|---|---|--|

|   |   |   |   |   |  |

| μPD410         |       |      |      | • • | 43   |

|----------------|-------|------|------|-----|------|

| μPD411         |       |      |      | ••• | 11   |

| μPD411A        |       | •••  |      |     | 19   |

| μPD416         |       |      |      |     | 27   |

| μPD421         |       |      |      | ••  | 63   |

| μPD444/6514    |       | :.   |      |     | 75   |

| μPD445L        |       |      |      |     | 79   |

| μPD546         |       |      |      |     | 121  |

| μPD547         |       |      | •••• |     | 1,29 |

| μPD547L        |       |      |      |     | 131  |

| μPD548         |       |      | •••  |     | 113  |

| μPD550         | • • • |      |      |     | 139  |

| μPD550L        |       |      |      | • • | 141  |

| μPD552         |       |      |      |     | 133  |

| μPD553         |       |      |      | • • | 123  |

| μPD554         | • • • | •••  |      | • • | 143  |

| μPD554L        |       |      | •••  |     | 145  |

| μPD555         | •••   | ••   | • •  | ••• | 149  |

| μPD556         |       |      | •••  |     | 153  |

| μPD557L        | •••   |      | •••  | • • | 125  |

| μPD650         |       | •••  | •••  | • • | 127  |

| μPD651         |       | •••  | •••  | ••• | 135  |

| μPD652         | • • • |      | • •  | • • | 147  |

| μPD <b>765</b> | • • • | •••• | •••  |     | 241  |

| μPD781         |       |      | • •  | ••  | 259  |

| μPD782         | • • • | •••  | • •  | ••• | 271  |

| μPD2114L       | • • • | •••  | ••   |     | 53   |

| μPD2118        |       | • •  | • •  | ••  | 36   |

| μPD2147        | • • • | • •  | •••  | ••  | 59   |

| μPD2167        | •••   | • •  | • •  | ••  | 67   |

| μPD2308A       | • • • |      | ••   | • • | 85   |

| μPD2316E       |       | •••  | •••  | • • | 89   |

| μPD2332A/B     |       | ••   | •••  | ••• | 93   |

| μPD2364        |       | • .  | •••  | ••• | 97   |

| μPD2716        | • • • | ••   | •••  | ••  | 101  |

| μPD2732        | • • • |      | •••  |     | 102  |

| μPD3301        |       |      |      |     | 283  |

| μPD4104   | •  | • | • | •   | •  | •   |     |   |    | •   |    | •  |    |     |   | 47  |

|-----------|----|---|---|-----|----|-----|-----|---|----|-----|----|----|----|-----|---|-----|

| μPD4164   | •  | • | • | •   |    | •   | •   | • | •  | •   | ۰. | •  | •  | •   | • | 37  |

| μPD5101L  | •  |   | • | •   | •  |     |     | • |    | •   | •  | •  | •  | •   | • | 69  |

| µPD7001   |    |   |   | •   | •  |     | •   |   |    | •   | •  | •  |    |     | • | 291 |

| µPD7002   |    |   | • | •   | •  |     | •   |   |    | •   |    | •  | •  |     |   | 295 |

| μPD7520   |    |   | • | •   |    | •   | ·   | • |    | •   |    |    |    | •   |   | 157 |

| μPD7801   |    |   | • | •   |    | •   | •   | • |    | •   | •  | •  | •  |     | • | 193 |

| µPD8021   | •  |   | • |     | •  |     |     | • |    | •   |    |    |    |     |   | 199 |

| µPD8022   |    |   | • |     |    |     |     |   |    |     |    |    |    |     | • | 205 |

| µPD8035L  |    |   | • | ÷   | •  | • . |     | • |    | •   | •  | •  | •  |     | • | 219 |

| µPD8039L  |    |   | • |     | •  | •   |     | • | ·  | •   |    |    | •  | •,  |   | 231 |

| µPD8041   | •  |   | • |     | •  |     | •   |   | ۰. | •   | •  |    | •  |     |   | 211 |

| µPD8048   |    |   |   | •   | •  |     |     | • |    |     |    | •  | •  |     |   | 219 |

| µPD8049   | •  | • |   |     | •  | •   |     | • | .• |     | •  |    |    | • • |   | 231 |

| µPD8080A  | F  |   | • | •   |    | ÷   |     | • | •  | •   | •  |    |    |     |   | 165 |

| µPD8085A  |    |   | • | •   | •  | •   |     | • | •  |     | •  | •  | •  |     |   | 179 |

| µPD8155   | •  |   | • | • . |    |     |     |   | •  | • , | •  | •  | ۰. |     |   | 299 |

| µPD8156   | •  | • | • | •   | •  | •   | •   | • | •. |     | •  | •  | •  | •   | • | 299 |

| µPB8212   | •  |   | • | •   | •  | •   | •   | • | •  | •   | •  | •  | •  |     |   | 307 |

| μPB8214   | •  |   | • | •   | •  | ٠   | •   | • | ·  | •   | •  | •  | •  | •   | • | 313 |

| μPB8216   | •  | • | • |     | •  | •   | •   | • |    | •   | •  | •  | •  | •   | • | 319 |

| μPB8224   | •  |   | • | •   | •  | •   |     |   | •  | •   | •  |    | •  | •   | • | 323 |

| µPB8226   | •  | • | • |     | •  | •   |     | • |    | •   | •  | •  | •  | •   | • | 319 |

| µPB8228   | •  | • | • | •   | •  |     |     | • |    | •   | •  | •  | •  |     | • | 329 |

| µPD8243   | •  | • | • | •   | •  |     | •   | • |    | •   | •  |    | •  | •   |   | 335 |

| µPD8251   | •  | • | • | •   | •  |     | • ' | • | •  | •   | •  | •  | •  |     | • | 341 |

| µPD8251A  |    |   | • | •   | •  | •   | •   | • |    | •   | •  | •  | •  | ,   | • | 341 |

| µPD8253   |    | • | • | •   | •  | •   | •   | • |    | • . | •  | ÷  | •  | •   | • | 359 |

| µPD8255   |    | • | • | ·   | •  | •   | •   | • |    | •   | •  | •  | •  |     | • | 367 |

| µPD8255A  | -5 |   | • | •   | •  | •   | •   |   | •  |     | •  | •  | •  | •   | • | 367 |

| µPD8257   |    | • | • |     | ۰. |     | •   | • | •  | •   |    |    | •  |     |   | 375 |

| µPD8259   | •  | • | • | •   | •  | •   | •   | • | •  | •   | •  | •  | •  | •   |   | 383 |

| μPD8279-5 | i  |   | • | •   | •  | •   |     | • | •  | •   | •  |    |    |     |   | 399 |

| µPD8355   | •  | • | • | •   |    | •   |     | • | •  |     |    |    | •  |     |   | 409 |

| μPD8741A  |    |   |   | •   | •  |     |     |   |    | •   |    | •. |    |     |   | 211 |

| µPD8748   |    |   | • |     | •  | •   | •   | • |    |     | •  |    |    |     |   | 219 |

| μPD8755A  |    |   |   |     | •  |     |     |   |    |     |    |    |    |     |   | 409 |

### **ROM ORDERING PROCEDURE — MEMORIES AND MICROCOMPUTERS**

The following NEC products fall under the guidelines set by the ROM Ordering Procedure:

| μPD2308A   | μPD8049 | μPD553   |

|------------|---------|----------|

| μPD2316E   | μPD8355 | μPD554   |

| μPD2332A/B | μPD546  | µPD554L  |

| μPD2364    | μPD547  | μPD557 L |

| μPD7801    | μPD547L | μPD650   |

| μPD8021    | μPD548  | μPD651   |

| μPD8022    | μPD550  | μPD652   |

| μPD8041    | μPD552  | μPD7520  |

| UPD8048    |         |          |

In order to facilitate the transferal of ROM mask information, NEC Microcomputers, Inc., is able to accept mask patterns in a variety of formats. These are intended to suit various customer needs and minimize the turnaround time. A listing of the code must always be enclosed. The following is a list of valid media for code transferal.

- Sample ROMs or ROM-based microcomputers

- PROM/EPROM equivalent to ROM parts

- NEC μPD458 EEPROM

- BNPF Paper Tapes

- Hex Paper Tapes

- Timesharing Files

- Other (Contact NEC Microcomputers, Inc., for arrangements.)

Thoroughly tested verification procedures protect against unnecessary delays or costly mistakes. NEC Microcomputers, Inc., will return the ROM mask patterns to the customer in the most convenient format. Unprogrammed EPROMs, if sent with the ROM code can be programmed and returned for verification.

Earth satellites and the world-wide GE Mark III timesharing systems provide reliable and instant communication of ROM patterns to the factory. Customers with access to GE-TSS may further reduce the turnaround time by transferring files directly to NEC Microcomputers, Inc.

The following is an example of a ROM mask transferal procedure. The  $\mu$ PD8048 is used here, however the process is the same for the other ROM-based products.

- 1. The customer contacts NEC Microcomputers, Inc., concerning a ROM pattern for the  $\mu$ PD8048 that he would like to send.

- 2. Since an EPROM version of that part is available, the 8748 is proposed as a code transferal medium, or alternatively, a paper tape and listing.

- 3. Two programmed 8748's are sent to NEC Microcomputers, Inc., with a listing and a paper tape as back-up.

- 4. NEC Microcomputers, Inc., compares the media provided and enters the code into GE-TSS. The GE-TSS file is accessed at the NEC factory and a copy of the code is returned to NEC Microcomputers for verification purposes. One of the 8748's is erased and reprogrammed with the customer's code as the NEC factory has it. Both 8748's along with a new papertape and listing are returned to the customer for his final verification.

MEMORIES

### **MEMORY SELECTION GUIDE**

| 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - |      |         | ACCESS |       | SUPPLY   | PACKAG   | BE   |

|-----------------------------------------------------------------------------------------------------------------|------|---------|--------|-------|----------|----------|------|

| DEVICE                                                                                                          | SIZE | PROCESS | TIME   | CYCLE | VOLTAGES | MATERIAL | PINS |

|                                                                                                                 |      |         |        |       |          |          |      |

### DYNAMIC RANDOM ACCESS MEMORIES

| μPD411   | 4K x 1 TS  | NMOS | 150 ns | 380 ns | +12, +5, -5 | D   | 22 |

|----------|------------|------|--------|--------|-------------|-----|----|

| μPD411-4 | 4K x 1 TS  | NMOS | 135 ns | 320 ns | +15, +5, -5 | D   | 22 |

| μPD411A  | 4K x 1 TS  | NMOS | 200 ns | 400 ns | +12, +5, -5 | с   | 22 |

| μPD416   | 16K x 1 TS | NMOS | 120 ns | 320 ns | +12, +5, -5 | C/D | 16 |

| μPD2118  | 16K x 1 TS | NMOS | 100 ns | 235 ns | +5          | D   | 16 |

| μPD4164  | 64K x 1 TS | NMOS | 200 ns | 375 ns | +5          | D   | 16 |

### STATIC RANDOM ACCESS MEMORIES

| μPD5101L    | 256 x 4 TS | CMOS | 450 ns | 450 ns | +5          | С   | 22 |

|-------------|------------|------|--------|--------|-------------|-----|----|

| μPD444/6514 | 1K x 4 TS  | CMOS | 200 ns | 200 ns | +5          | C C | 18 |

| μPD445L     | 1K x 4 TS  | CMOS | 450 ns | 450 ns | +5          | с   | 20 |

| μPD2167     | 16K x 1 TS | NMOS | 35 ns  | 55 ns  | +5          | D,  | 20 |

| μPD2114L    | 1K x 4 TS  | NMOS | 150 ns | 150 ns | +5          | C/D | 18 |

| μPD2147     | 4K x 1 TS  | NMOS | 55 ns  | 55 ns  | +5          | D   | 18 |

| μPD410      | 4K x 1 TS  | NMOS | 90 ns  | 220 ns | +12, +5, -5 | C/D | 22 |

| μPD421      | 1K × 8 TS  | NMOS | 150 ns | 150 ns | +5          | Ď   | 22 |

| μPD4104     | 4K x 1 TS  | NMOS | 150 ns | 260 ns | +5          | C/D | 18 |

### MASK PROGRAMMED READ ONLY MEMORIES

| μPD2308A     | 1K x 8 TS | NMOS | 450 ns | 450 ns | +5 | C/D | 24 |

|--------------|-----------|------|--------|--------|----|-----|----|

| μPD2316E     | 2K x 8 TS | NMOS | 450 ns | 450 ns | +5 | C   | 24 |

| μPD2332A/B   | 4K x 8 TS | NMOS | 450 ns | 450 ns | +5 | С   | 24 |

| µPD2332A/B-1 | 4K x 8 TS | NMOS | 350 ns | 350 ns | +5 | , c | 24 |

| μPD2364      | 8K x 8 TS | NMOS | 450 ns | 450 ns | +5 | C   | 24 |

### FIELD PROGRAMMABLE READ ONLY MEMORIES (U.V. ERASABLE)

| μPD2716 | 2K x 8 TS | NMOS | 450 ns | 450 ns | +5 | D | 24 |

|---------|-----------|------|--------|--------|----|---|----|

| μPD2732 | 4K x 8 TS | NMOS | 450 ns | 450 ns | +5 | D | 24 |

Notes: (F) - Future Product

- \* Read Mode

- C Plastic Package

- D Hermetic Package

TS - 3-State

| MANUFACTURER                                                                                                                                                                                                                        | PART NUMBER | DESCRIPTION  | NEC REPLACEMENT           |  |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--------------|---------------------------|--|--|--|

| AMD                                                                                                                                                                                                                                 | 2716        | 2K x 8 EPROM | μPD2716                   |  |  |  |

|                                                                                                                                                                                                                                     | 8308        | 1K x 8 ROM   | μPD2308A                  |  |  |  |

|                                                                                                                                                                                                                                     | 9016        | 16K x 1 DRAM | μPD416                    |  |  |  |

|                                                                                                                                                                                                                                     | 9060        | 4K x 1 DRAM  | μPD411/μPD411A            |  |  |  |

|                                                                                                                                                                                                                                     | 9107        | 4K x 1 DRAM  | μPD411/μPD411A            |  |  |  |

| and an and a second                                                                                                                      | 9114        | 1K x 4 SRAM  | μPD2114L                  |  |  |  |

|                                                                                                                                                                                                                                     | 9124        | 1K x 4 SRAM  | μPD2114L                  |  |  |  |

|                                                                                                                                                                                                                                     | 9147        | 4K x 1 SRAM  | μPD2147                   |  |  |  |

| and the second second                                                                                                                                                                                                               | 9216        | 2K x 8 ROM   | μPD2316E                  |  |  |  |

| EM & M                                                                                                                                                                                                                              | 2114        | 1K x 4 SRAM  | μPD2114L                  |  |  |  |

|                                                                                                                                                                                                                                     | 4200        | 4K x 1 SRAM  | μPD410                    |  |  |  |

|                                                                                                                                                                                                                                     | 4300        | 4K x 1 SRAM  | μPD410<br>μPD410          |  |  |  |

|                                                                                                                                                                                                                                     | 4402        | 4K x 1 SRAM  | μΡD410                    |  |  |  |

|                                                                                                                                                                                                                                     | 8108        | 1K x 8 SRAM  | μPD421                    |  |  |  |

|                                                                                                                                                                                                                                     |             |              | MI DTLI                   |  |  |  |

| AIRCHILD                                                                                                                                                                                                                            | F2114       | 1K x 4 SRAM  | μPD2114L                  |  |  |  |

|                                                                                                                                                                                                                                     | F2716       | 2K x 8 EPROM | μPD2716                   |  |  |  |

| × .                                                                                                                                                                                                                                 | F16K        | 16K x 1 DRAM | μPD416                    |  |  |  |

|                                                                                                                                                                                                                                     |             |              |                           |  |  |  |

| UJITSU                                                                                                                                                                                                                              | MBM2147     | 4K x 1 SRAM  | μPD2147                   |  |  |  |

|                                                                                                                                                                                                                                     | MBM2716     | 2K x 8 EPROM | μPD2716                   |  |  |  |

| en de Sateria                                                                                                                                                                                                                       | MBM2732     | 4K x 8 EPROM | μPD2732                   |  |  |  |

| a de la companya de l<br>La companya de la comp | MB8107      | 4K x 1 DRAM  | μPD411/μPD411A            |  |  |  |

|                                                                                                                                                                                                                                     | MB8114      | 1K x 4 SRAM  | μPD2114L                  |  |  |  |

|                                                                                                                                                                                                                                     | MB8116      | 16K x 1 DRAM | μPD416                    |  |  |  |

| 2 - 1                                                                                                                                                                                                                               | MB8216      | 16K x 1 DRAM | μPD416                    |  |  |  |

|                                                                                                                                                                                                                                     | MB8308      | 1K x 1 ROM   | μPD2308A                  |  |  |  |

|                                                                                                                                                                                                                                     | MB8414      | 1K x 4 SRAM  | μPD444/6514               |  |  |  |

| · · · ·                                                                                                                                                                                                                             |             |              | DD51011                   |  |  |  |

| IARRIS                                                                                                                                                                                                                              | HM6501      | 256 x 4 SRAM | μPD5101L                  |  |  |  |

|                                                                                                                                                                                                                                     | HM6514      | 1K x 4 SRAM  | μPD444/6514               |  |  |  |

| НТАСНІ                                                                                                                                                                                                                              | HM435101    | 256 x 4 SRAM | μPD5101L                  |  |  |  |

|                                                                                                                                                                                                                                     | HM4716A     | 16K x 1 DRAM | μPD416                    |  |  |  |

|                                                                                                                                                                                                                                     | HM4816      | 16K x 1 DRAM | μPD2118                   |  |  |  |

|                                                                                                                                                                                                                                     | HM4864      | 16K x 1 DRAM | μPD4164                   |  |  |  |

|                                                                                                                                                                                                                                     | HM6147      | 4K x 1 SRAM  | μPD2147                   |  |  |  |

|                                                                                                                                                                                                                                     |             |              |                           |  |  |  |

| NTEL                                                                                                                                                                                                                                | 2107        | 4K x 1 DRAM  | $\mu$ PD411/ $\mu$ PD411A |  |  |  |

| 1                                                                                                                                                                                                                                   | 2114        | 1K x 4 SRAM  | μPD2114L                  |  |  |  |

|                                                                                                                                                                                                                                     | 2117        | 16K x 1 DRAM | μPD416                    |  |  |  |

|                                                                                                                                                                                                                                     | 2118        | 16K x 1 DRAM | μPD2118                   |  |  |  |

|                                                                                                                                                                                                                                     | 2147        | 4K x 1 SRAM  | μPD2147                   |  |  |  |

|                                                                                                                                                                                                                                     | 2308A       | 1K x 8 ROM   | μPD2308A                  |  |  |  |

| ÷.                                                                                                                                                                                                                                  | 2316E       | 2K x 8 ROM   | μPD2316E                  |  |  |  |

|                                                                                                                                                                                                                                     | 2332        | 4K x 8 ROM   | µPD2332A/B                |  |  |  |

|                                                                                                                                                                                                                                     |             | 8K x 8 ROM   | μPD2364                   |  |  |  |

|                                                                                                                                                                                                                                     | 2364        |              |                           |  |  |  |

|                                                                                                                                                                                                                                     | 2364 2716   | 2K x 8 EPROM | μPD2716                   |  |  |  |

|                                                                                                                                                                                                                                     |             |              | μPD2716<br>μPD2732        |  |  |  |

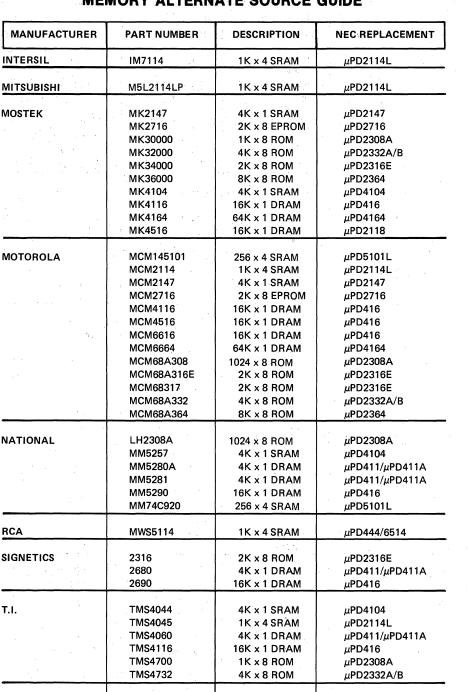

## MEMORY ALTERNATE SOURCE GUIDE

NEC

1K x 4 SRAM

µPD445L

### **MEMORY ALTERNATE SOURCE GUIDE**

NH K

TOSHIBA

TC5047

### FULLY DECODED RANDOM ACCESS MEMORY

#### DESCRIPTION

The  $\mu$ PD411 Family consists of six 4096 words by 1 bit dynamic N-channel MOS RAMs. They are designed for memory applications where very low cost and large bit storage are important design objectives. The  $\mu$ PD411 Family is designed using dynamic circuitry which reduces the standby power dissipation.

Reading information from the memory is a non-destructive. Refreshing is easily accomplished by performing one read cycle on each of the 64 row addresses. Each row address must be refreshed every two milliseconds. The memory is refreshed whether Chip Select is a logic high on a logic low.

### FEATURES

All of these products are guaranteed for operation over the 0 to 70°C temperature range.

Important features of the µPD411 family are:

- Low Standby Power

- 4096 words x 1 bit Organization

- A single low-capacitance high level clock input with solid ±1 volt margins.

- Inactive Power/0.3 mW (Typ.)

- Power Supply: +12, +5, -5V

- Easy System Interface

- TTL Compatible (Except CE)

- · Address Registers on the Chip

- Simple Memory Expansion by Chip Select

- Three State Output and TTL Compatible

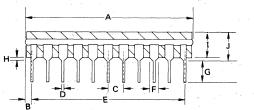

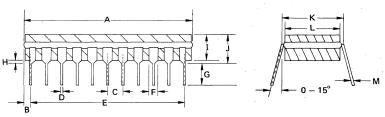

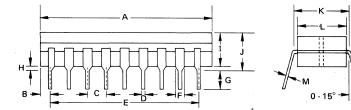

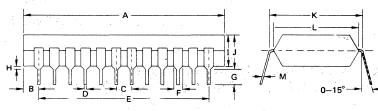

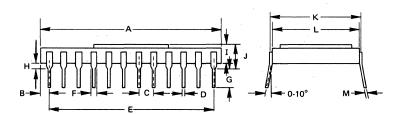

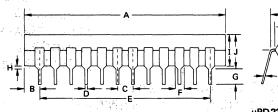

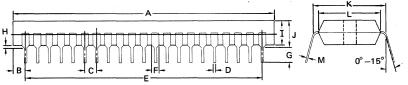

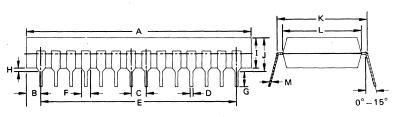

- 22 pin Ceramic Dual-in-Line Package

- Replacement for INTEL'S 2107B, TI'S 4060 and Equivalent Devices.

- 5 Performance Ranges:

|          | ACCESS TIME | R/W CYCLE | RMW CYCLE | REFRESH TIME |

|----------|-------------|-----------|-----------|--------------|

| μPD411   | 300 ns      | 470 ns    | 650 ns    | 2 ms         |

| μPD411-1 | 250 ns      | 470 ns    | 640 ns    | 2 ms         |

| μPD411-2 | 200 ns      | 400 ns    | 520 ns    | 2 ms         |

| μPD411-3 | 150 ns      | 380 ns    | 470 ns    | 2 ms         |

| μPD411-4 | 135 ns      | 320 ns    | 320 ns*   | 2 ms         |

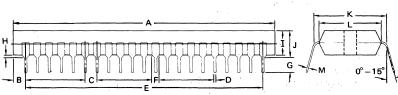

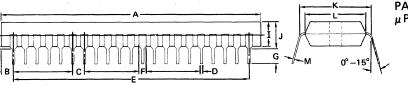

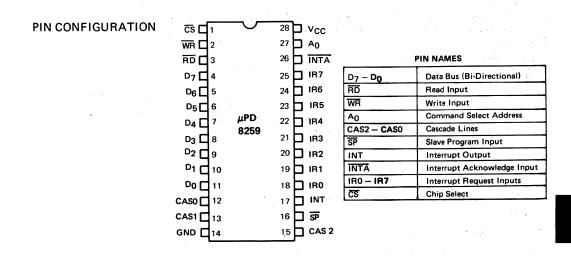

#### **PIN CONFIGURATION**

| ∨ввС  | 1  | 0   | 22 🗖 V <sub>SS</sub> |

|-------|----|-----|----------------------|

| ^9 🗖  | 2  |     | 21 🗖 A8              |

| A10 🗖 | 3  |     | 20 🗖 A7              |

| A11 🗖 | 4  |     | 19 🗖 🗛               |

| cs 🗖  | 5  | μPD |                      |

| DIN 🗖 | 6  | 411 | 17 CE                |

|       | 7  |     | 16 0 NC              |

| A0 🗖  | 8  |     | 15 A5                |

| A1 🗖  | 9  |     |                      |

| A2 🗖  | 10 |     | 13 🗖 A3              |

| Vcc 🗖 | 11 |     | 12 WE                |

|       |    |     |                      |

#### **PIN NAMES**

| TINNAMES          |  |  |  |  |  |  |

|-------------------|--|--|--|--|--|--|

| Address Inputs    |  |  |  |  |  |  |

| Refresh Addresses |  |  |  |  |  |  |

| Chip Enable       |  |  |  |  |  |  |

| Chip Select       |  |  |  |  |  |  |

| Data Input        |  |  |  |  |  |  |

| Data Output       |  |  |  |  |  |  |

| Write Enable      |  |  |  |  |  |  |

| Power (+12V)      |  |  |  |  |  |  |

| Power (+5V)       |  |  |  |  |  |  |

| Ground            |  |  |  |  |  |  |

| Power             |  |  |  |  |  |  |

| No Connection     |  |  |  |  |  |  |

|                   |  |  |  |  |  |  |

#### **CE Chip Enable**

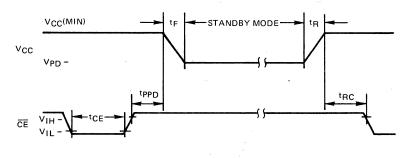

A single external clock input is required. All read, write, refresh and read-modify-write operations take place when chip enable input is high. When the chip enable is low, the memory is in the low power standby mode. No read/write operations can take place because the chip is automatically precharging.

### CS Chip Select

The chip select terminal affects the data in, data out and read/write inputs. The data input and data output terminals are enabled when chip select is low. The chip select input must be low on or before the rising edge of the chip enable and can be driven from standard TTL circuits. A register for the chip select input is provided on the chip to reduce overhead and simplify system design.

### WE Write Enable

The read or write mode is selected through the write enable input. A logic high on the  $\overline{WE}$  input selects the read mode and a logic low selects the write mode. The  $\overline{WE}$  terminal can be driven from standard TTL circuits. The data input is disabled when the read mode is selected.

#### A0-A11 Addresses

All addresses must be stable on or before the rising edge of the chip enable pulse. All address inputs can be driven from standard TTL circuits. Address registers are provided on the chip to reduce overhead and simplify system design.

#### **DIN Data Input**

Data is written during a write or read-modify-write cycle while the chip enable is high. The data in terminal can be driven from standard TTL circuits. There is no register on the data in terminal.

#### DOUT Data Output

The three state output buffer provides direct TTL compatibility with a fan-out of two TTL gates. The output is in the high-impedance (floating) state when the chip enable is low or when the Chip Select input is high. Data output is inverted from data in.

#### Refresh

Refresh must be performed every two milliseconds by cycling through the 64 addresses of the lower-order-address inputs  $A_0$  through  $A_5$  or by addressing every row within any 2-millisecond period. Addressing any row refreshes all 64 bits in that row.

The chip does not need to be selected during the refresh. If the chip is refreshed during a write mode, the chip select must be high.

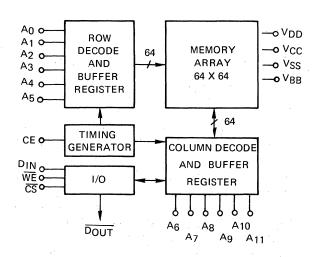

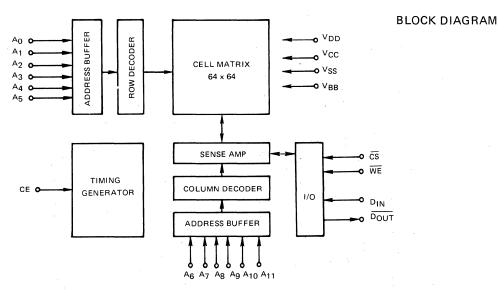

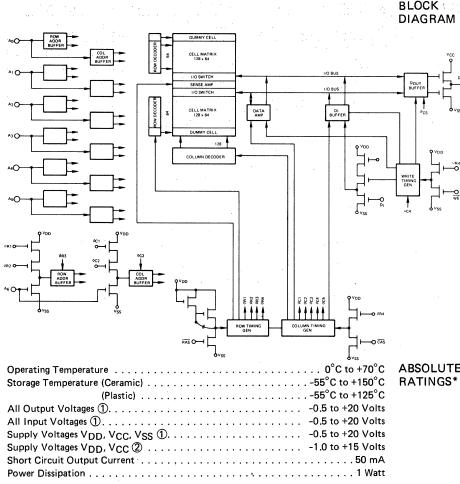

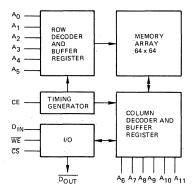

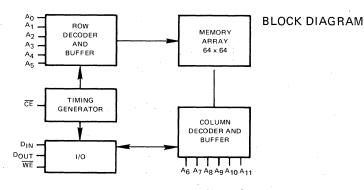

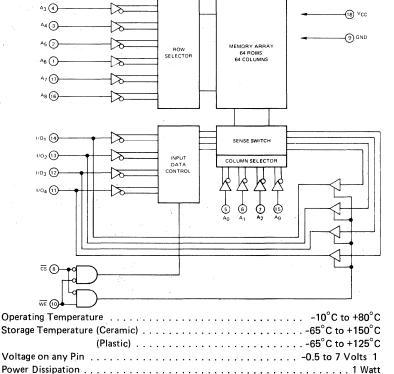

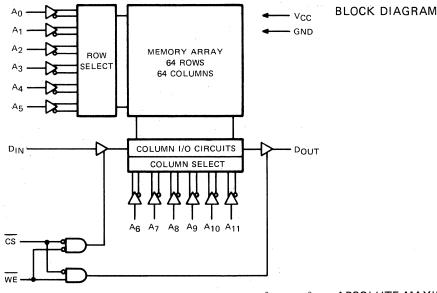

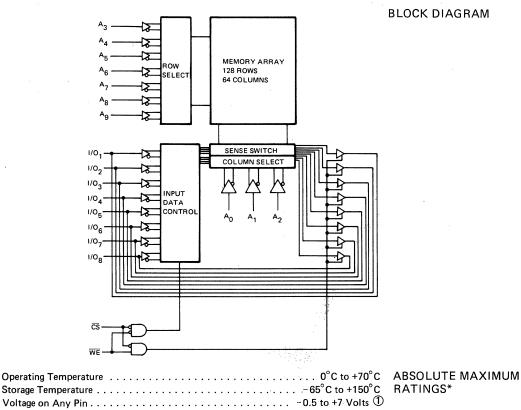

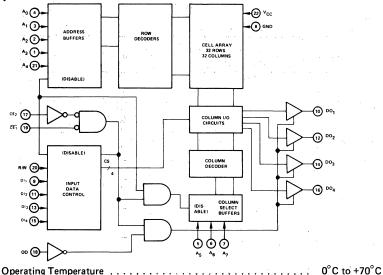

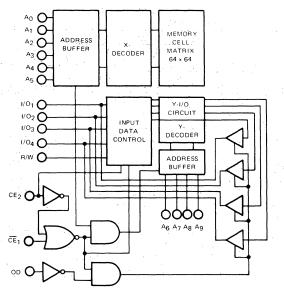

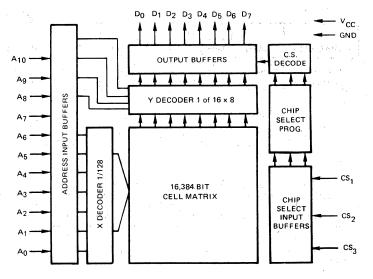

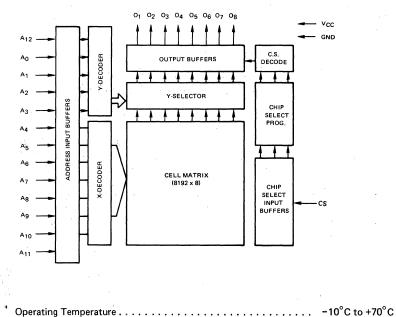

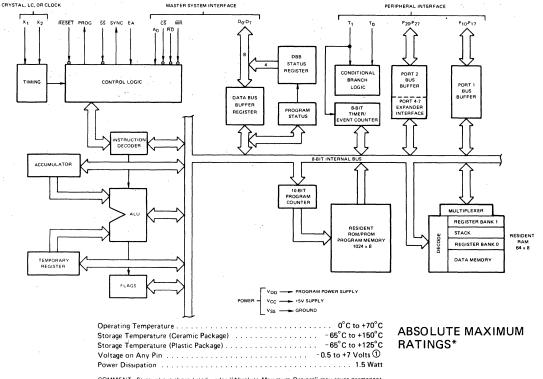

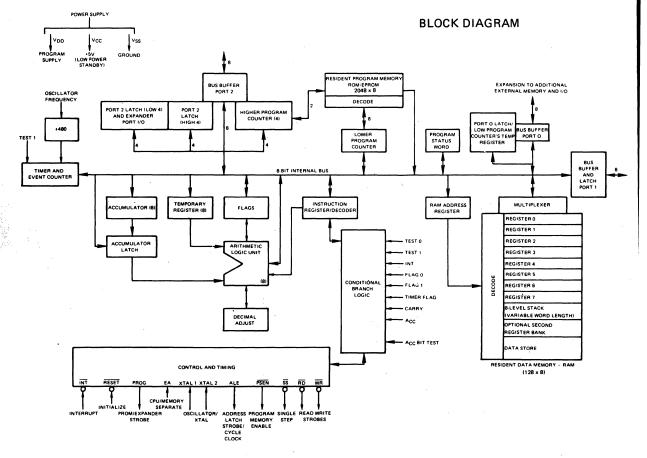

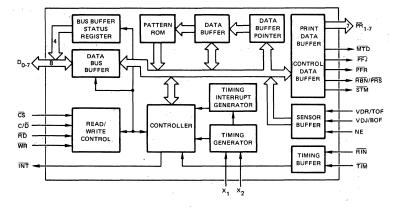

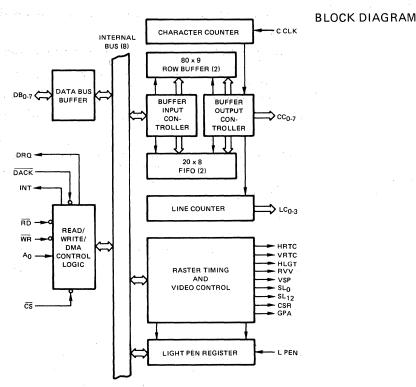

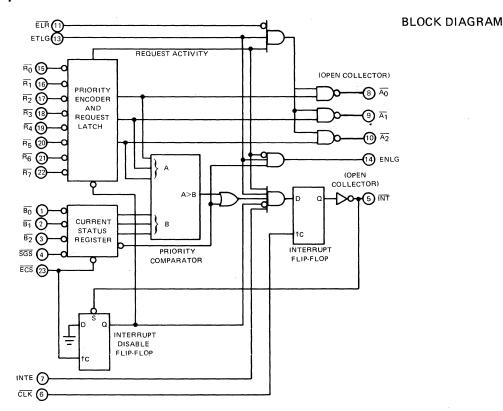

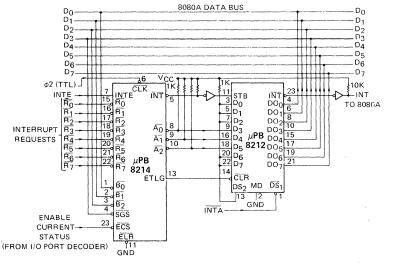

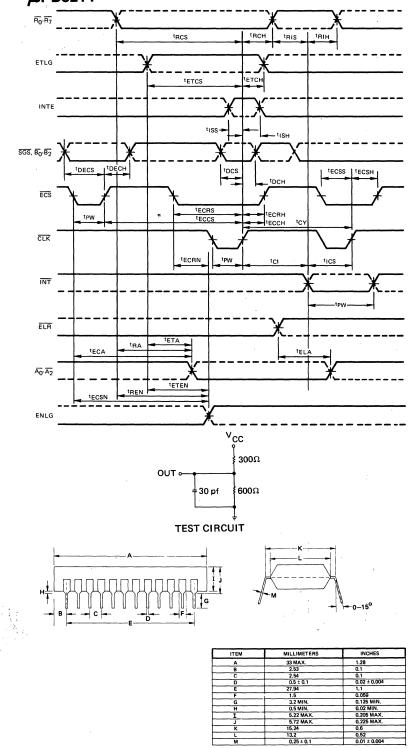

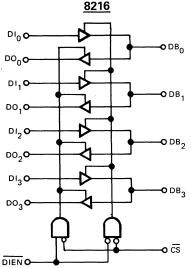

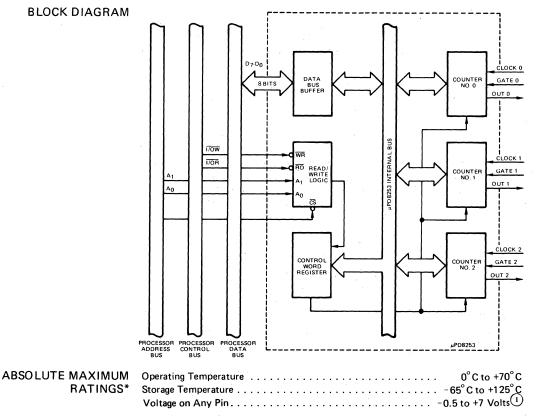

### BLOCK DIAGRAM

### FUNCTIONAL DESCRIPTION

### μPD411-4

### μPD411 FAMILY (EXCEPT 411-4)

| Operating Temperature | $ 0^{\circ}$ C to +70°C $ +10^{\circ}$ C to +55°C                       |

|-----------------------|-------------------------------------------------------------------------|

| Storage Temperature   | $-55^{\circ}$ C to $+150^{\circ}$ C $-55^{\circ}$ C to $+150^{\circ}$ C |

| All Output Voltages   | -0.3 to +20 Volts0.3 to +25 Volts ①                                     |

| All Input Voltages    | -0.3 to +20 Volts0.3 to +25 Volts 1                                     |

| Supply Voltage VDD    | -0.3 to +20 Volts0.3 to +25 Volts ①                                     |

| Supply Voltage VCC    | -0.3 to +20 Volts0.3 to +25 Volts 1                                     |

| Power Dissipation     | 1.0W 1.5W                                                               |

### Note: 1 Relative to VBB

COMMENT: Stress above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### DC CHARACTERISTICS

ABSOLUTE MAXIMUM

**RATINGS\***

$\label{eq:tau} T_a=0^{\circ}C\ to\ 70^{\circ}C,\ V_{DD}=+12V\ \pm5\%,\ V_{CC}=+5V\ \pm5\%,\ V_{BB}=-5V\ \pm5\%,\ V_{SS}=0V,\\ Except\ V_{DD}=+15V\ \pm5\%\ for\ 4114.$

|                                                                                           | LIMITS                                                                                                     |                    |                            |                      |                      |                                                                                                                                    |

|-------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|--------------------|----------------------------|----------------------|----------------------|------------------------------------------------------------------------------------------------------------------------------------|

| PARAMETER                                                                                 | SYMBOL                                                                                                     | MIN                | TYP ①                      | MAX                  | UNIT                 | TEST CONDITIONS                                                                                                                    |

| Input Load Current                                                                        | I <sub>LI</sub>                                                                                            | -<br>-             | 0.01                       | 10                   | μA                   | VIN = VIL MIN to VIH MAX                                                                                                           |

| CE Input Load Current                                                                     | LC                                                                                                         |                    | 0.01                       | 10                   | μA                   | VIN = VILC MIN to VIHC MAX                                                                                                         |

| Output Leakage Current<br>for High Impedance State                                        | ILO .                                                                                                      |                    | 0.01                       | 10                   | μA                   | CE = V <sub>ILC</sub> or <del>CS</del> ≫VIH<br>V <sub>0</sub> = 0V to 5.25V <u>}</u>                                               |

| VDD Supply Current<br>during CE off                                                       | IDD OFF                                                                                                    |                    | 20                         | 200                  | μA                   | CE = 1.0V to 0.6V                                                                                                                  |

| VDD Supply Current<br>during CE on                                                        | DD ON                                                                                                      |                    | 35 (5)                     | 60 ④                 | mA                   | CE = V <sub>IHC</sub> , T <sub>a</sub> = 25°C                                                                                      |

| Average V <sub>DD</sub> Current<br>µPD411<br>µPD411-1<br>µPD411-2<br>µPD411-3<br>µPD411-4 | I <sub>DD</sub> AV<br>I <sub>DD</sub> AV<br>I <sub>DD</sub> AV<br>I <sub>DD</sub> AV<br>I <sub>DD</sub> AV |                    | 37<br>37<br>37<br>41<br>55 | 60<br>60<br>65<br>80 | mA<br>mA<br>mA<br>mA | $T_a = 25^\circ C$ Cycle Time = 470 ns<br>Cycle Time = 470 ns<br>Cycle Time = 400 ns<br>Cycle Time = 380 ns<br>Cycle Time = 320 ns |

| VBB Supply Current (2)                                                                    | IBB                                                                                                        |                    | 5                          | 100                  | μA                   |                                                                                                                                    |

| V <sub>CC</sub> Supply Current<br>during CE off ③                                         | ICC OFF                                                                                                    |                    | 0.01                       | 10                   | μА                   | CE = VILC or CS = VIH                                                                                                              |

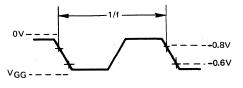

| Input Low Voltage                                                                         | VIL                                                                                                        | 1.0                |                            | 0.6                  | v                    |                                                                                                                                    |

| Input High Voltage                                                                        | VIH                                                                                                        | 2.4                |                            | Vcc+1                | v                    |                                                                                                                                    |

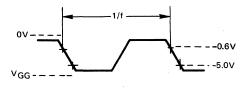

| CE Input Low Voltage                                                                      | VILC                                                                                                       | 1.0                |                            | 0.6                  | v                    |                                                                                                                                    |

| CE Input High Voltage                                                                     | VIHC                                                                                                       | V <sub>DD</sub> -1 | VDD                        | V <sub>DD</sub> +1   | v                    |                                                                                                                                    |

| Output Low Voltage                                                                        | VOL                                                                                                        | 0                  |                            | 0.40                 | V                    | I <sub>OL</sub> = 3.2 mA                                                                                                           |

| Output High Voltage                                                                       | VOH                                                                                                        | 2.4                |                            | Vcc                  | v                    | I <sub>OH</sub> = 2.0 mA                                                                                                           |

Notes: (1) Typical values are for  $T_a = 25^{\circ}C$  and nominal power supply voltages.

2 The IBB current is the sum of all leakage current.

- (3) During CE on  $V_{CC}$  supply current is dependent on output loading.

- $V_{CC}$  is connected to output buffer only.

- ④ 65 mA for µPD411-3

- 80 mA for µPD411-4

- (5) 41 mA for μPD411-3 55 mA for μPD411-4

### CAPACITANCE

#### $T_a = 0^\circ - 70^\circ C$

|                         |        |     | LIMIT | S   |      | TEST       |  |

|-------------------------|--------|-----|-------|-----|------|------------|--|

| PARAMETER               | SYMBOL | MIN | түр   | MAX | UNIT | CONDITIONS |  |

| Address Capacitance, CS | CAD    |     | 4     | 6   | рF   | VIN = VSS  |  |

| CE Capacitance          | CCE    |     | 18    | 27  | pF   | VIN = VSS  |  |

| Data Output Capacitance | COUT   |     | 5     | 7   | рF   | VOUT = 0V  |  |

| DIN and WE Capacitance  | CIN    |     | 8     | 10  | pF   | VIN = VSS  |  |

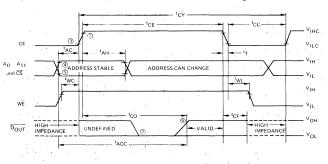

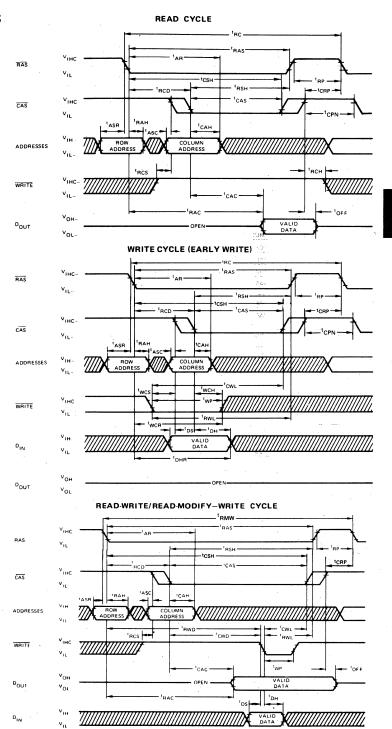

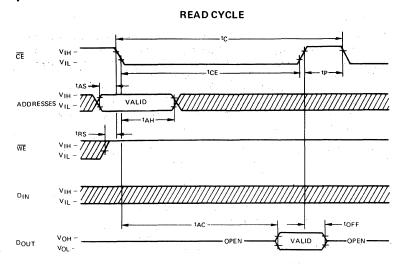

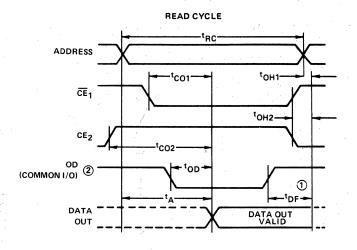

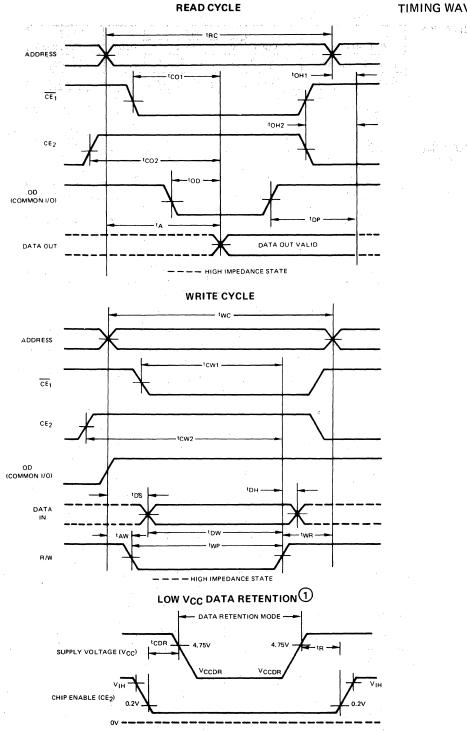

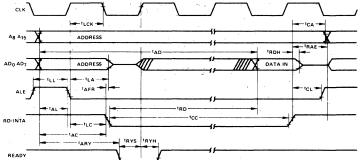

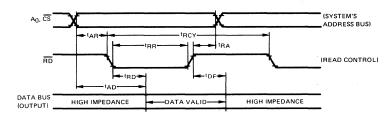

### READ CYCLE

$T_a = 0^{\circ}C$  to  $70^{\circ}C$ ,  $V_{DD} = 12V \pm 5\%$ ,  $V_{CC} = 5V \pm 5\%$ ,  $V_{BB} = -5V \pm 5\%$ ,  $V_{SS} = 0V$ , unless otherwise noted, Except V<sub>DD</sub> = +15V ± 5% for 411-4

#### LIMITS PARAMETER SYMBOL µPD411 µPD411-1 µPD411-2 µPD411-3 μPD411-4 UNIT MIN MAX MIN MAX MIN MAX MIN MAX MIN MAX Time Between Refresh 2 ms <sup>t</sup>REF 2 2 2 2 Address to CE Set Up Time 0 0 0 0 0 <sup>t</sup>AC ns Address Hold Time 150 150 150 150 100 ns <sup>t</sup>AH CE Off Time 130 170 130 130 80 tCC ns **CE Transition Time** 0 40 0 40 0 40 0 40 0 40 t٣ ns CE Off to Output High <sup>t</sup>CF 0 130 0 130 0 130 0 130 0 130 ns Impedance State Cycle Time 470 470 400 380 tCY 320 ns CE on Time 300 3000 260 3000 230 3000 210 3000 200 <sup>t</sup>CE 3000 ns CE Output Delay 280 180 tco 230 130 115 ns Access Time 300 200 135 250 150 <sup>t</sup>ACC ns CE to WE 40 40 40 twL 40 40 ns WE to CE on 0 0 0 0 0 twc ns

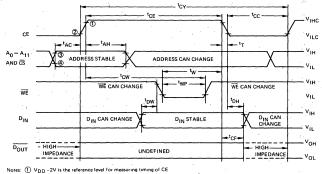

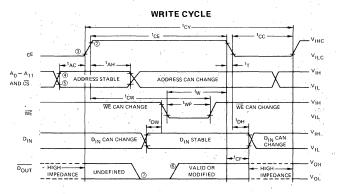

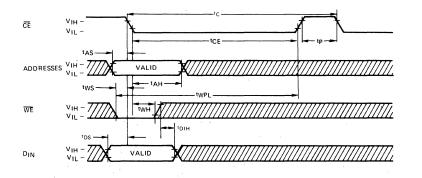

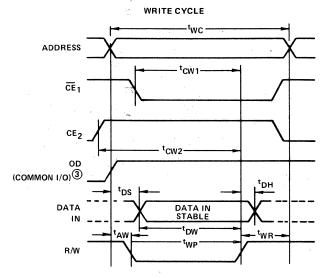

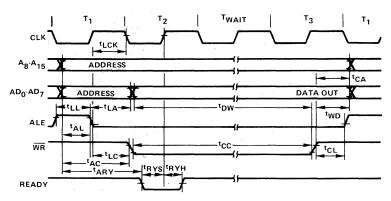

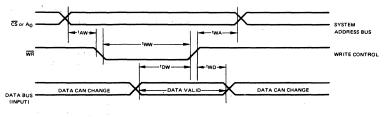

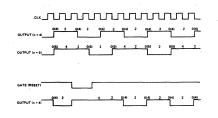

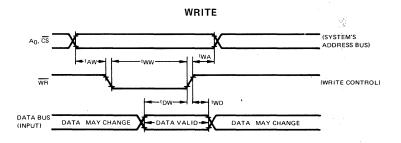

#### WRITE CYCLE

Ta = 0°C to 70°C, V\_DD = 12V  $\pm$  5%, V\_CC = 5V  $\pm$  5%, V\_BB = -5V  $\pm$  5%, V\_SS = 0V, unless otherwise noted, Except V\_DD = +15V  $\pm$  5% for 411-4

|                                          |                  | LIMITS |      |          |      |          |      |          |      |          |      |      |

|------------------------------------------|------------------|--------|------|----------|------|----------|------|----------|------|----------|------|------|

| PARAMETER                                | SYMBOL           | μPD411 |      | μPD411-1 |      | µPD411-2 |      | μPD411-3 |      | µPD411-4 |      | UNIT |

|                                          |                  | MIN    | MAX  | MIN      | MAX  | MIN      | MAX  | MIN      | MAX  | MIN      | MAX  |      |

| Cycle Time                               | tCY              | 470    |      | 470      |      | 400      |      | 380      |      | 320      |      | ns   |

| Time Between Refresh                     | <sup>t</sup> REF |        | 2    |          | 2    |          | 2    |          | 2    |          | 2    | ms   |

| Address to CE Set Up Time                | <sup>t</sup> AC  | 0      |      | 0        |      | 0        |      | 0        |      | 0        |      | ns   |

| Address Hold Time                        | <sup>t</sup> AH  | 150    |      | 150      |      | 150      |      | 150      |      | 100      |      | ns   |

| CE Off Time                              | tCC              | 130    |      | 170      |      | 130      |      | 130      |      | 80       |      | ns   |

| CE Transition Time                       | tT               | 0      | 40   | 0        | 40   | 0        | 40   | 0        | 40   | 0        | 40   | ns   |

| CE Off to Output High<br>Impedance State | <sup>t</sup> CF  | 0      | 130  | 0        | 130  | 0        | 130  | 0        | 130  | 0        | 130  | ns   |

| CE on Time                               | <sup>t</sup> CE  | 300    | 3000 | 260      | 3000 | 230      | 3000 | 210      | 3000 | 200      | 3000 | ns   |

| WE to CE off                             | tw               | 180    |      | 180      |      | 150      |      | 150      |      | 65       |      | ns   |

| CE to WE                                 | tCW              | 300    |      | 260      |      | 230      |      | 210      |      | 200      |      | ns   |

| DIN to WE Set Up (1)                     | tDW              | . 0    |      | 0        |      | 0        |      | 0        |      | 0        |      | ns   |

| D <sub>IN</sub> Hold Time                | <sup>t</sup> DH  | , 40   |      | 40       |      | 40       |      | 40       |      | 40       |      | ns   |

| WE Pulse Width                           | tWP              | 180    |      | 180      |      | 150      |      | 100      |      | 65       |      | ns   |

Note: (1) If  $\overline{\text{WE}}$  is low before CE goes high then D<sub>IN</sub> must be valid when CE goes high.

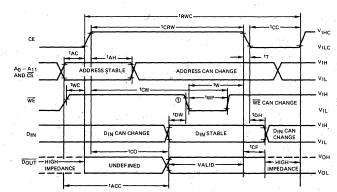

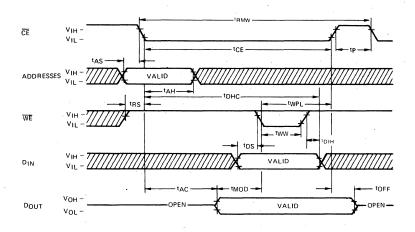

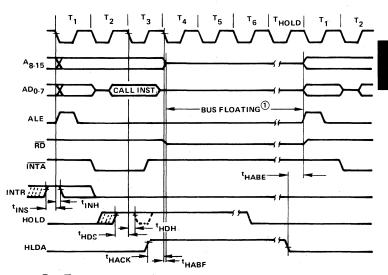

#### **READ - MODIFY - WRITE CYCLE**

$T_a = 0^{\circ} C \text{ to } 70^{\circ} C, V_{DD} = 12V \pm 5\%, V_{CC} = 5V \pm 5\%, V_{BB} = 5V \pm 5\%, V_{SS} = 0V, \text{ unless otherwise noted}, Except V_{DD} = +15V \pm 5\% \text{ for } 411-4$

|                                          |                  | LIMITS |      |          |      |          |      |          |      |          |      |      |

|------------------------------------------|------------------|--------|------|----------|------|----------|------|----------|------|----------|------|------|

| PARAMETER                                | SYMBOL           | μPD411 |      | µPD411-1 |      | μPD411-2 |      | μPD411-3 |      | μPD411-4 |      | UNIT |

|                                          |                  | MIN    | MAX  | MIN      | MAX  | MIN      | MAX  | MIN      | MAX  | MIN      | MAX  |      |

| Read—Modify—Write<br>(RMW) Cycle Time    | tRWC             | 650    |      | 640      |      | 520      |      | 470      |      | 320      |      | ns   |

| Time Between Refresh                     | <sup>t</sup> REF |        | 2    |          | 2    |          | 2    |          | 2    |          | 2    | ms   |

| Address to CE Set Up Time                | tAC ·            | 0      |      | 0        |      | 0        |      | Q        |      | 0        | 1    | ns   |

| Address Hold Time                        | <sup>t</sup> AH  | 150    |      | 150      |      | 150      |      | 150      |      | 100      |      | ns   |

| CE Off Time                              | tcc              | 130    |      | 170      |      | 130      |      | 130      |      | 80       |      | ns   |

| CE Transition Time                       | ۲Ţ               | 0      | 40   | 0        | 40   | 0        | 40   | 0        | 40   | 0        | 40   | ns   |

| CE Off to Output High<br>Impedance State | tCF              | 0      | 130  | 0        | 130  | 0        | 130  | . 0      | 130  | 0        | 130  | ns   |

| CE Width During RMW                      | <sup>t</sup> CRW | 480    | 3000 | 430      | 3000 | 350      | 3000 | 300      | 3000 | 200      | 3000 | ns   |

| WE to CE on                              | twc              | 0      |      | 0        |      | 0        |      | 0        |      | 0        |      | ns   |

| WE to CE off                             | tw               | 180    |      | 180      |      | 150      |      | 150      |      | 65       |      | ns   |

| WE Pulse Width                           | tWP              | 180    |      | 180      |      | 150      |      | 100      |      | 65       |      | ns   |

| DIN to WE Set Up                         | tDW              | . 0    | . /  | 0        |      | 0        | ÷.,  | 0        |      | 0        |      | ns   |

| DIN Hold Time                            | <sup>t</sup> DH  | 40     |      | 40       |      | 40       |      | 40       |      | 40       |      | ns   |

| CE to Output Display                     | tco              |        | 280  |          | 230  | 14       | 180  |          | 130  |          | 115  | ns   |

| Access Time                              | tACC             |        | 300  |          | 250  |          | 200  |          | 150  |          | 1,35 | ns   |

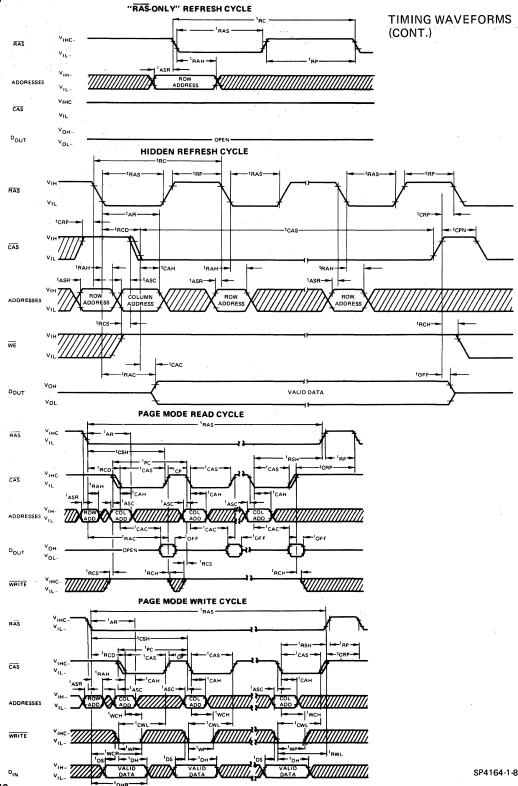

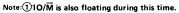

### AC CHARACTERISTICS

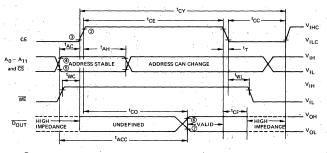

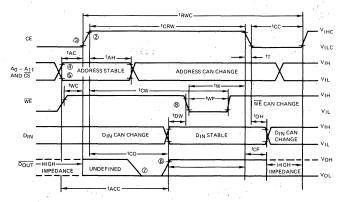

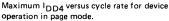

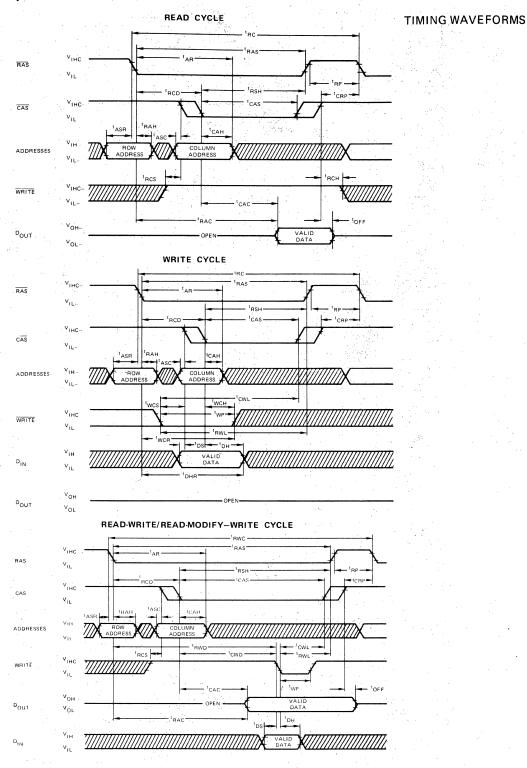

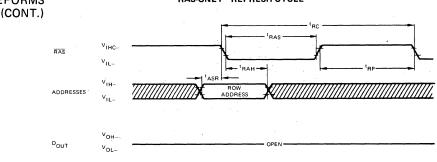

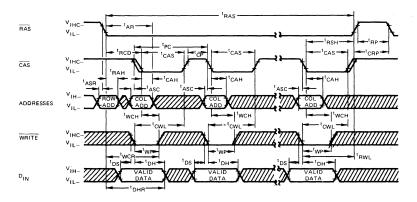

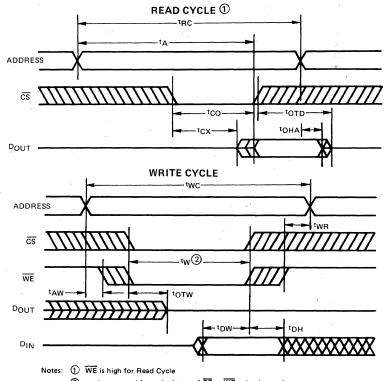

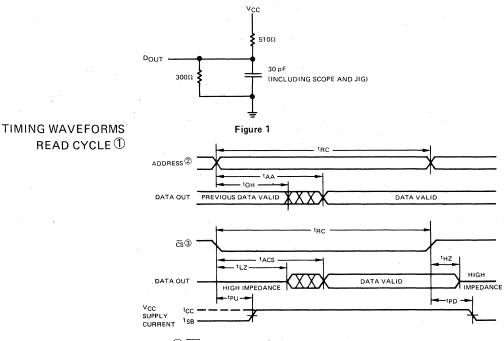

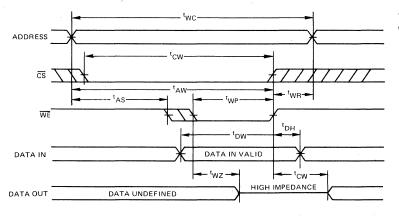

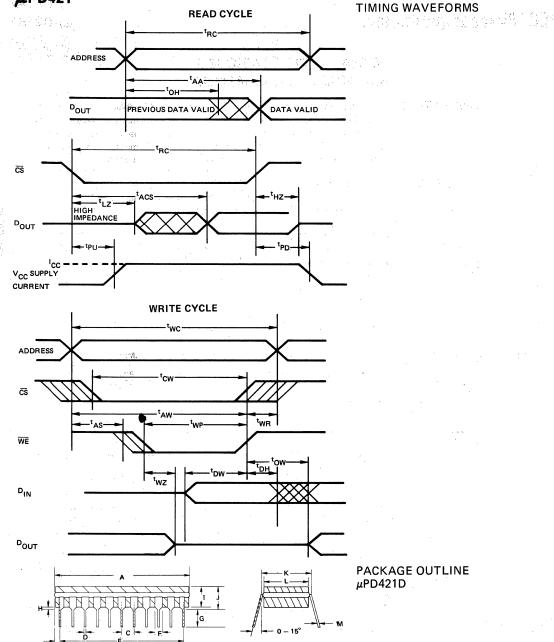

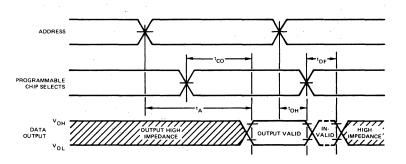

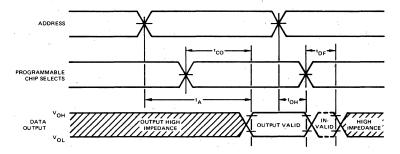

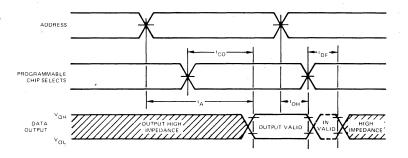

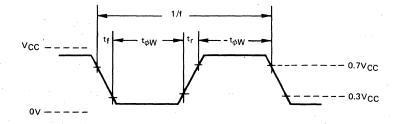

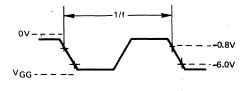

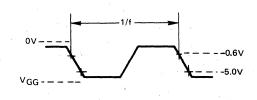

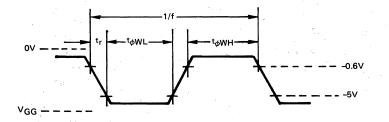

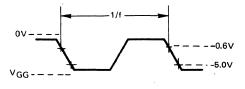

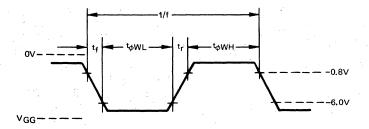

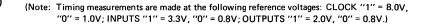

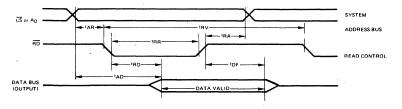

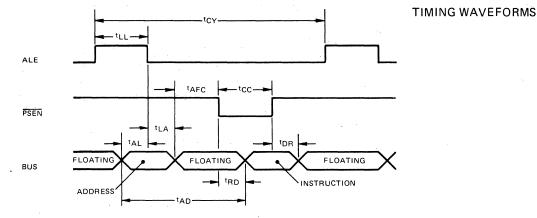

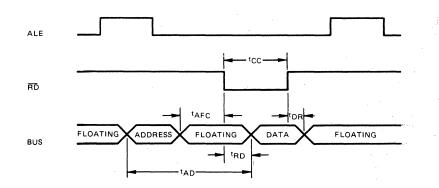

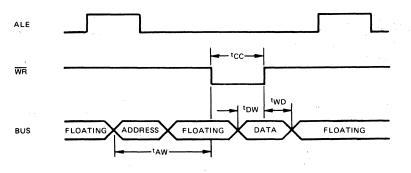

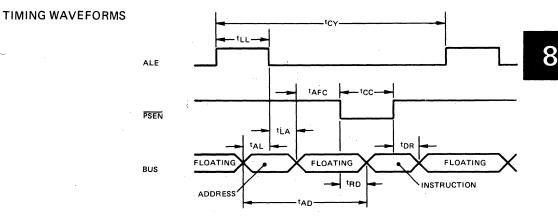

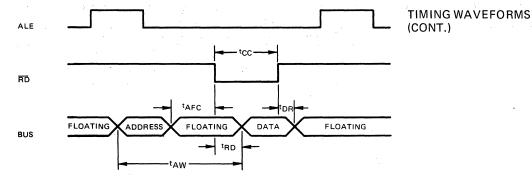

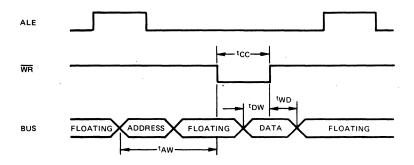

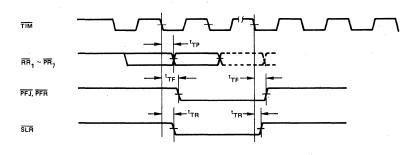

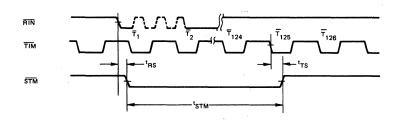

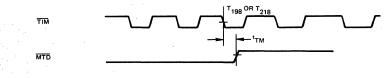

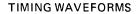

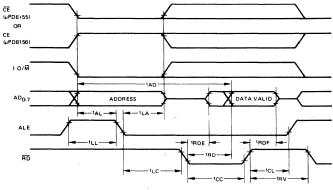

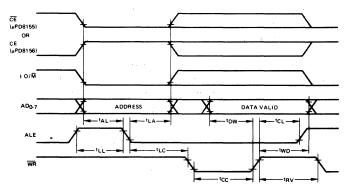

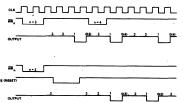

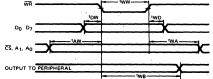

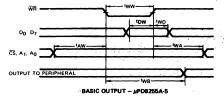

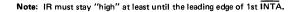

### TIMING WAVEFORMS

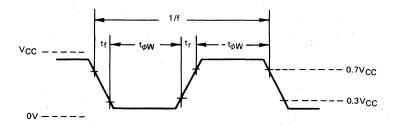

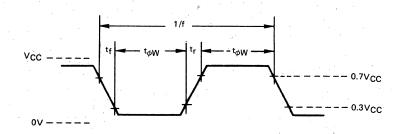

### READ CYCLE ①

#### Notes: (1) For refresh cycle row and column stable tac and remain stable for entire tAH period.

- (2) V<sub>DD</sub> 2V is the reference level for measuring timing of CE.

- ③ V<sub>SS</sub>+2V is the reference level for measuring timing of CE.

- VI<sub>IHMIN</sub> is the reference level for measuring timing of the addresses, CS, WE and DIN.

- (5) V<sub>1LMAX</sub> is the reference level for measuring timing of the addresses,  $\overline{CS}$ ,  $\overline{WE}$  and D<sub>1N</sub>.

- (6)  $V_{SS}$  +2.0V is the reference level for measuring timing of  $\overline{D_{OUT}}$ .

- (7) VSS +0.8V is the reference level for measuring timing of  $\overline{\text{D}_{\text{OUT}}}$

OD 20 V<sub>S</sub> + 2V is the reference level for measuring timing of CE.

(3) V<sub>IHMIN</sub> is the reference level for measuring timing of the addresses, CS, WE and D<sub>IN</sub>.

(4) V<sub>ILMAX</sub> is the WE and D<sub>IN</sub>. reference level for measuring timing of the addresses,  $\overline{\text{CS}}$ ,

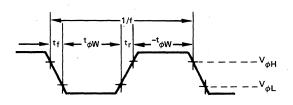

#### **READ-MODIFY-WRITE CYCLE**

Note: (1)  $\overline{\text{WE}}$  must be at VIH until end of tCO.

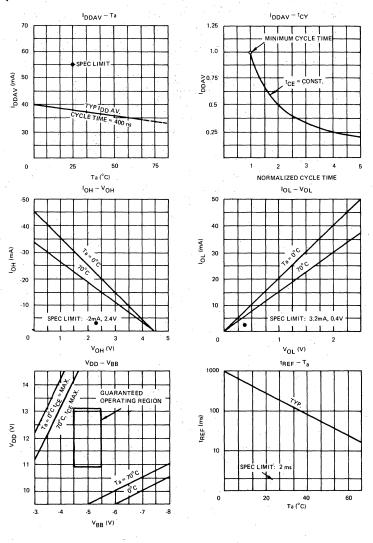

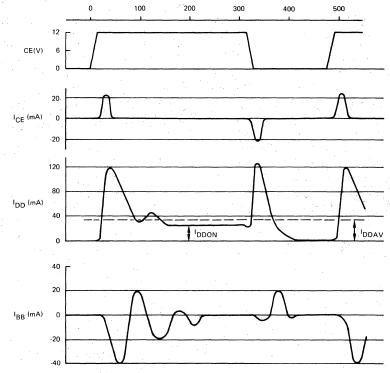

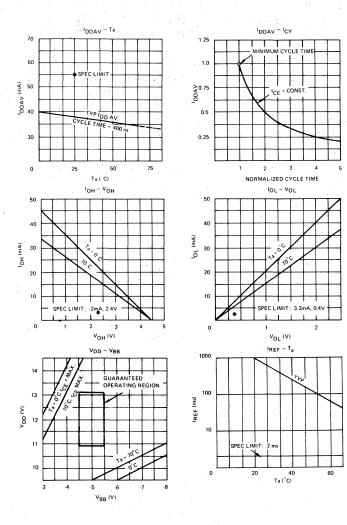

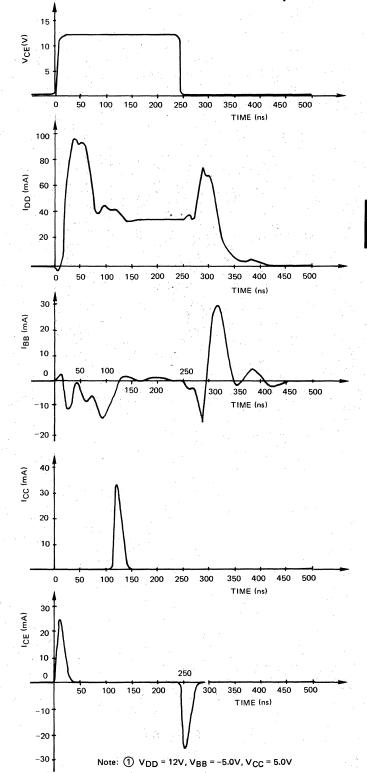

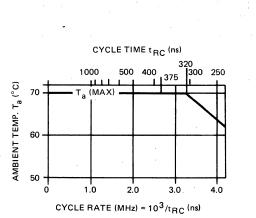

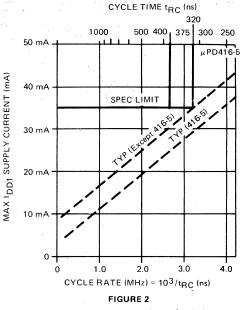

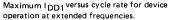

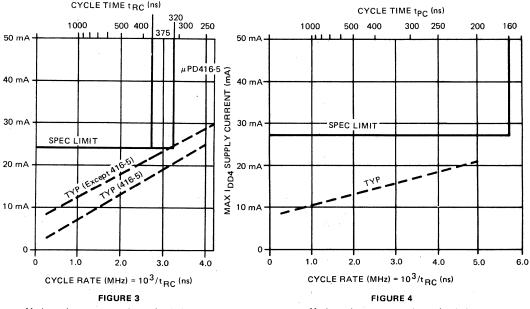

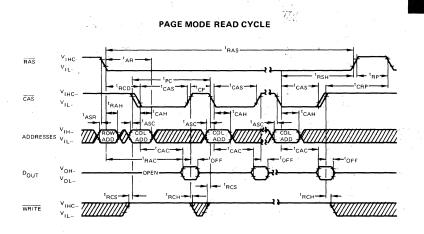

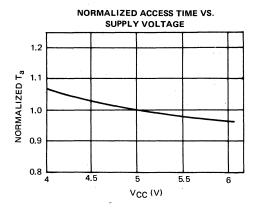

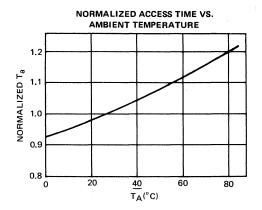

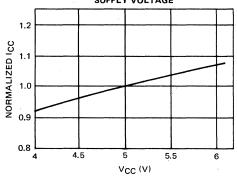

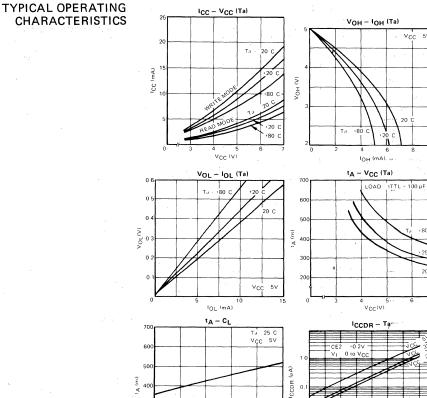

### TYPICAL OPERATING CHARACTERISTICS (Except 411-4)

Power consumption =  $V_{DD} \times I_{DDAV} + V_{BB} \times I_{BB}$ .

Typical power dissiption for each product is shown below.

|          | mW (TYP.) | CONDITIONS                                                   |