# **Table of Contents**

| Section 1<br>Applications Support                                                                                                                                                                                         | 1-1                               |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|

| Section 2<br>Introduction                                                                                                                                                                                                 | 2-1                               |

| Section 3<br>DP8390 Evaluation Board<br>Cable Installation                                                                                                                                                                | 3-2<br>3-11                       |

| Section 4 - Software Reference<br>Software Update<br>Computer Conferencing<br>Demostration Network Software<br>NIA Access Software<br>Network Load Simulator<br>Network Evaluation Software<br>Writing Drivers for DP8390 | 4-5<br>4-7<br>4-9<br>4-17<br>4-21 |

| Section 5 - Hardware Reference<br>DP8390 Introductory Guide<br>Hardware Design Guide<br>Guide to Loopback<br>StarLAN with the DP8390                                                                                      | 5-1<br>5-9<br>5-17<br>5-26        |

| Section 6<br>Tranceiver Evaluation Kit                                                                                                                                                                                    | 6-1                               |

# SECTION 1

# APPLICATION CONTACTS

Objectives Preliminary July 1986

### OBJECTIVE OF DP839EB CHEAPER/ETHER DEMONSTRATION KIT

The Cheaper/Ether demonstration kit is intended to provide designers with tools for evaluations and development of networking products using the DP839X chip set. The kit supports Ethernet, Cheapernet and Starlan networks as described in the IEEE 802.3 standard. All required documentation has been provided inside this binder, including the circuit diagram. PAL equations and option settings. Software tools are also provided as guides to developing drivers for the DP8390 Network Interface Controller. It is important to read all hardware and software manuals prior to installing the demonstration kit.

### IN CASE OF PROBLEMS...

If you encounter problems not addressed in the documentation, contact your local National Semiconductor Field Engineer or Field Sales Office. They will provide you with any additional support you may require.

If you have further technical inquiries regarding operation of the DP839X chip set contact National Semiconductor at (408) 721 4247 (for the DP8390) or (408) 721 3857 (DP8392 and DP8391).

# SECTION 2

# INTRODUCTION

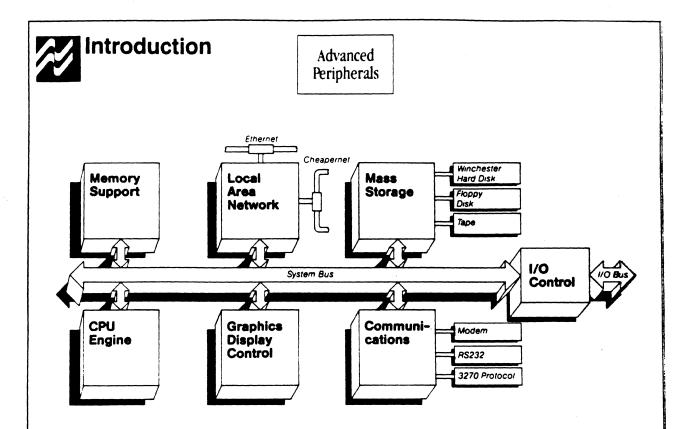

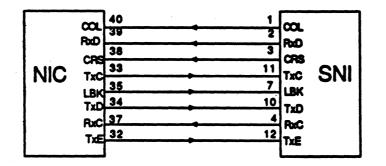

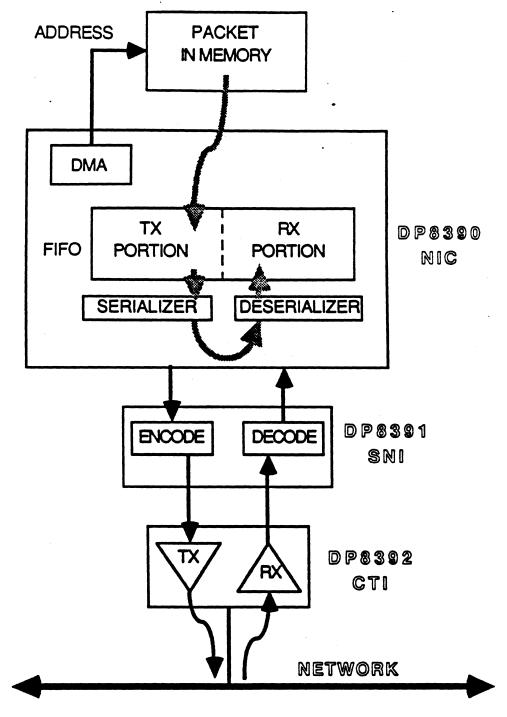

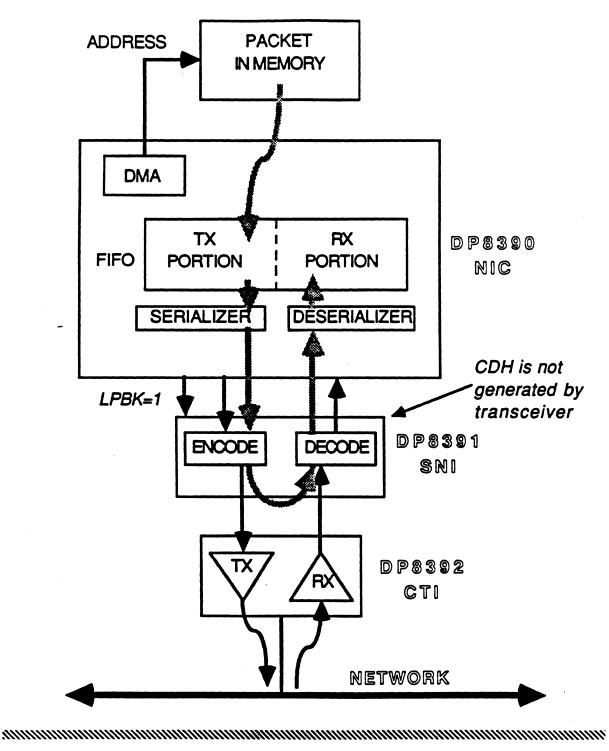

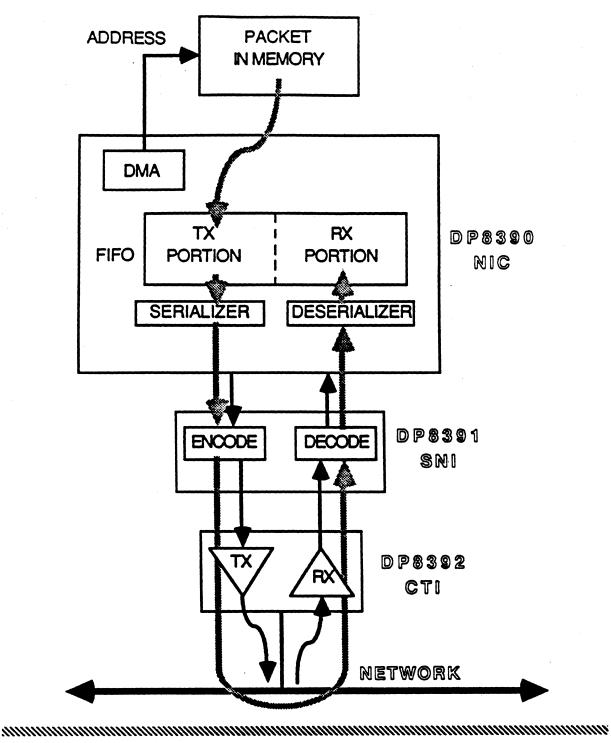

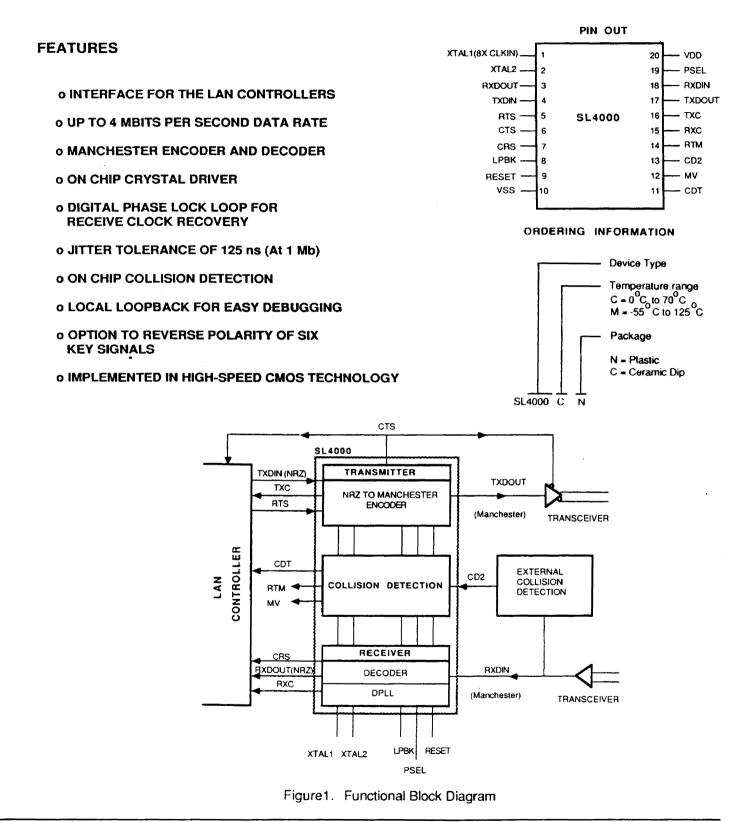

Today's computer systems and information processing needs have created a huge demand for Local Area Networks (LANs). The IEEE 802.3 Standard for Ethernet/Cheapernet and Starlan has become the most popular networking solution. National Semiconductor provides a complete three chip solution for an entire 802.3 design as well as supplying a broad range of products to fill the needs of network design engineers. The chipset consists of the DP8390 Network Interface Controller (NIC), the DP8391 Serial Network Interface (SNI) and the DP8392 Coaxial Transceiver Interface (CTI).

To place your name on the mailing list for design information updates and to receive further information on National's Advanced Peripherals please return the enclosed card or contact your local National Semiconductor Sales Office.

### THE CHIPSET FEATURES INCLUDE

### DP8390

- Interfaces with 8-, 16-, and 32-bit microprocessor systems

- Implements simple, versatile

buffer management

- Utilizes low power microCMOS

process

- Includes

- -Two 16-bit DMA channels -16-byte internal FIFO with programmable threshold -Network statistics storage

### DP8391

- 10 Mbit/sec Manchester encoding/decoding with receive clock recovery

- Patented digital phase locked loop decoder requires no precision external components

- Decodes Manchester data with up to ± 20 ns of jitter

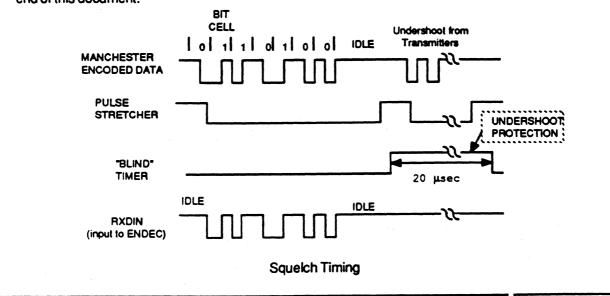

- Squelch circuits at the receive and collision inputs reject noise

- Connects directly to the AUI cable

### DP8392

- Integrates all transceiver electronics except signal and power isolation

- Innovative design minimizes external

component count

- Externally selectable CD heartbeat allows operation with IEEE 802.3 compatible repeaters

- Designed for rigorous reliability requirements of IEEE 802.3

- Squelch circuitry at all inputs rejects noise

# SECTION 3

# NETWORK EVALUATION BOARD

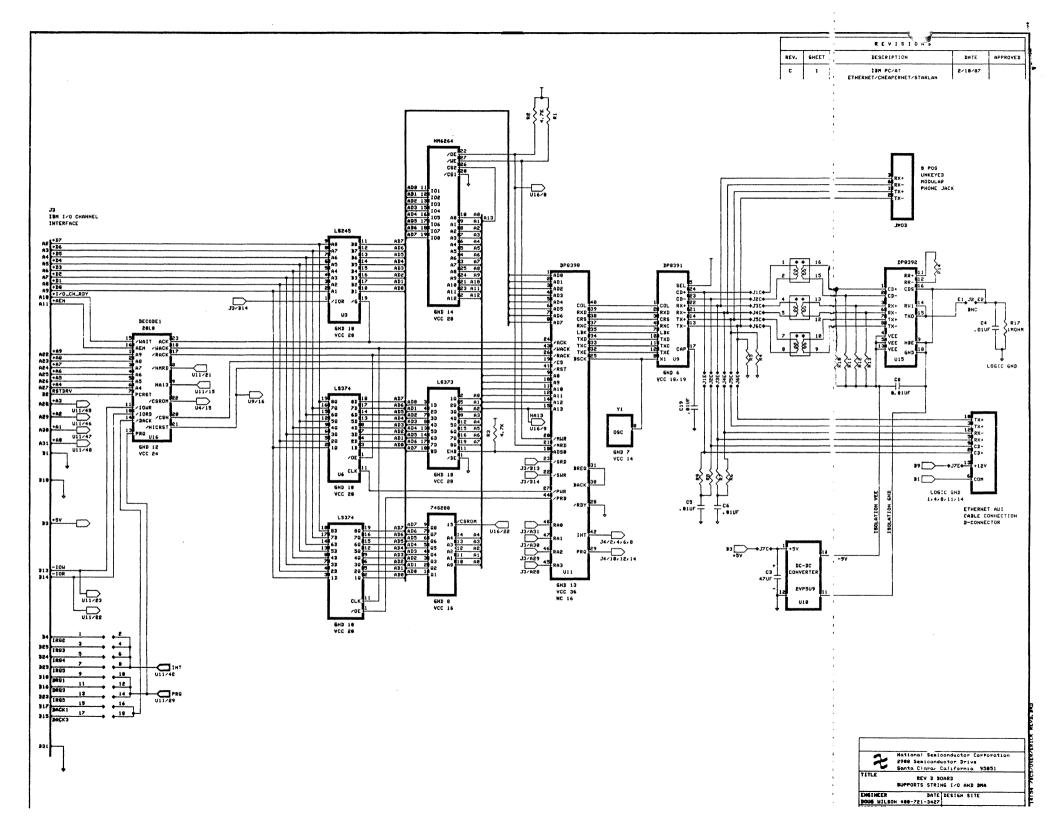

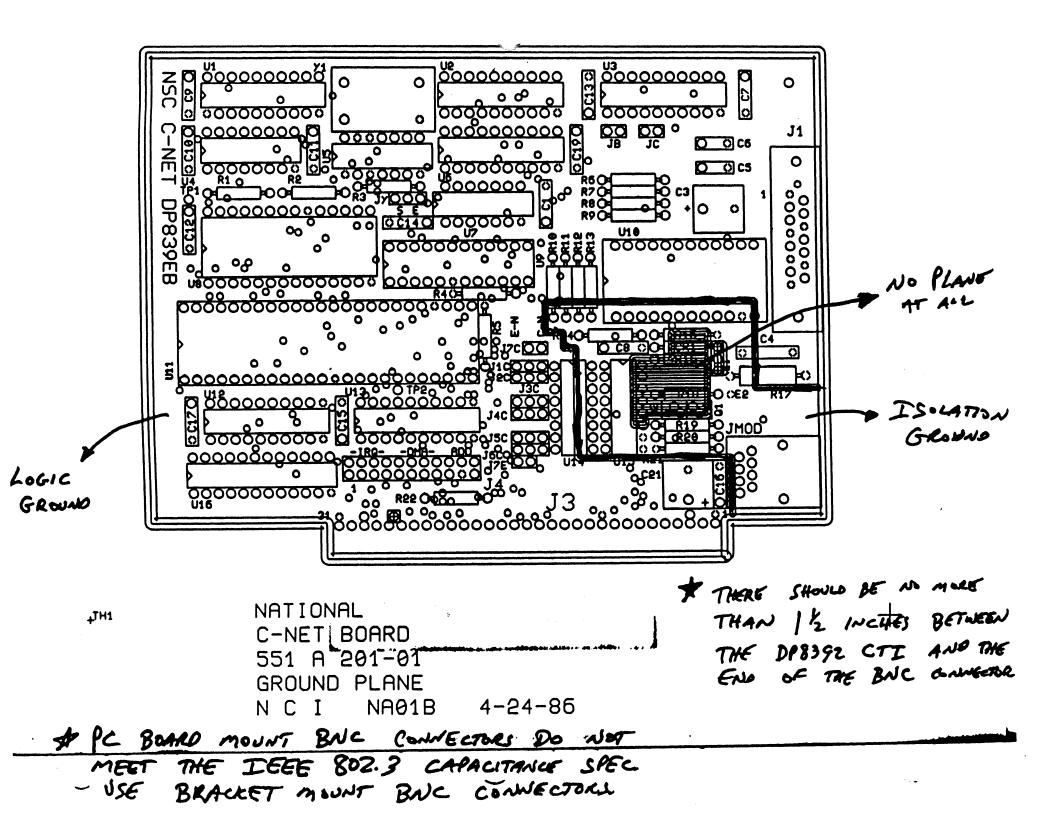

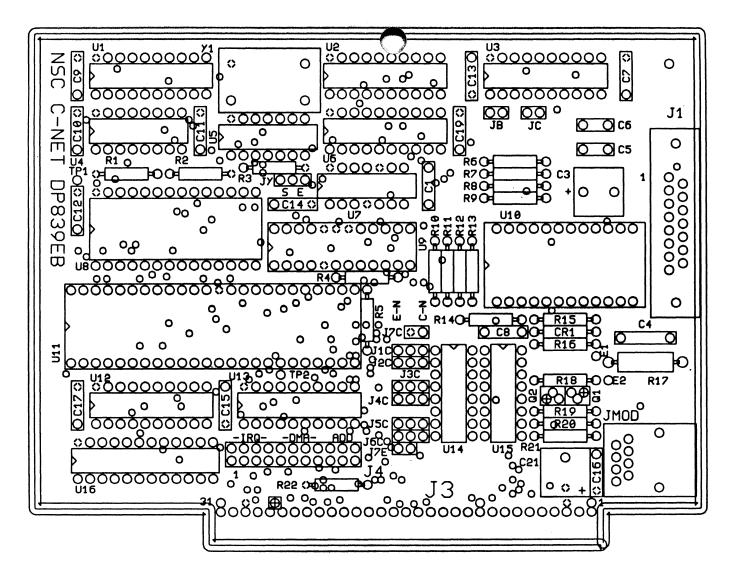

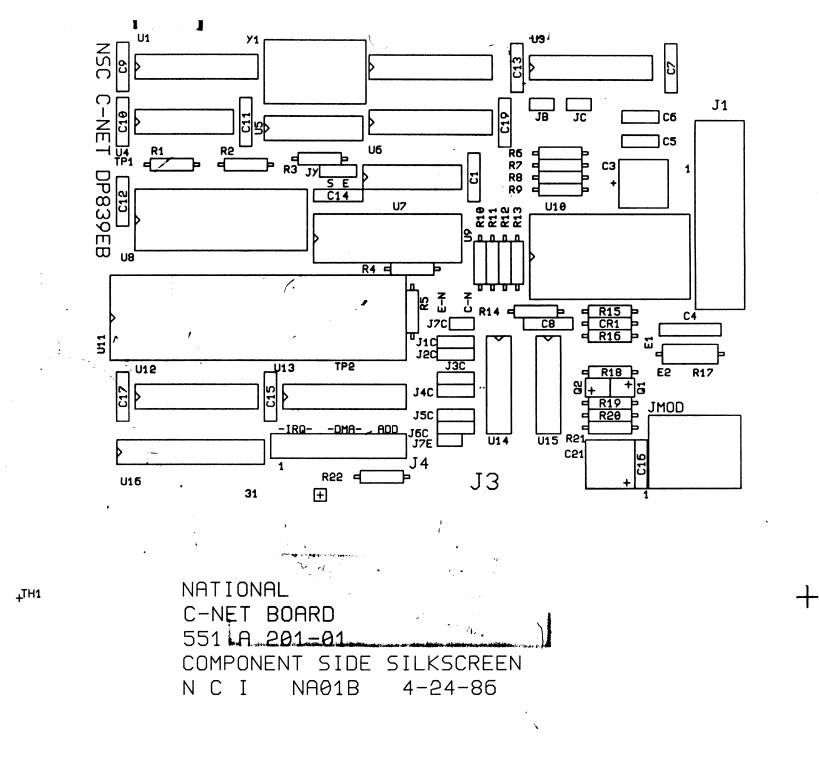

# DP839EB Network Evaluation Board Rev C

### OVERVIEW

The National Semiconductor DP839EB Evaluation Board provides IBM PCs and PC Compatibles with Ethernet, Cheapemet and STARLAN<sup>®</sup> connections. The evaluation board is compatible with the PC-bus and requires only a <sup>1</sup>/<sub>2</sub> Size Slot for installation. The evaluation board utilizes National Semiconductor's Ethernet/Cheapernet chipset consisting of the DP8390 Network Interface Controller, the DP8391 Serial Network Interface and the DP8392 Coaxial Transceiver Interface. The DMA capabilities of the DP8390, coupled with 8 kbytes of buffer RAM, allow the Network Interface Adapter to appear as a standard I/O port to the system.

### HARDWARE FEATURES

- Half-Size IBM PC I/O Card Form Factor

- DP8390 Network Interface Controller with DMA

- 8 kbyte on-board Multipacket Buffer

- Clean DMA Interface to IBM-PC

- Ethernet Interface via 15-Pin D Connector

- Cheapernet Interface via BNC Connector

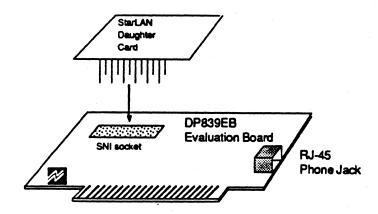

- Starlan Support with Optional Daughter Card and 8-Pin Modular Phone Jack

- DP8391 Serial Network Interface

- DP8392 Coaxial Transceiver Interface (For Cheapernet)

- Low Power Requirement

### SOFTWARE FEATURES

- No Software changes for conversion between Ethernet/ Cheapernet and STARLAN

- Demonstration and diagnostic software available

### **NETWORK INTERFACE OPTIONS**

National Semiconductor Corp.

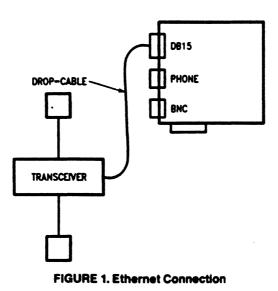

The evaluation board supports three physical layer options: Ethernet, Cheapernet and STARLAN. When using Ethernet, a drop cable is connected to an external transceiver which is connected to a standard Ethernet network. (See *Figure* 1). When using Cheapernet, a low cost version of Ethernet, a transceiver is available on-board allowing direct connection to the network via the evaluation board. (See *Figure* 2). When using a STARLAN network, an optional daughter card replaces the SNI function and implements the required electronics to interface the DP8390 NIC to STARLAN. This configuration is illustrated in *Figure* 3. No software changes are needed for conversion between any of the described configurations.

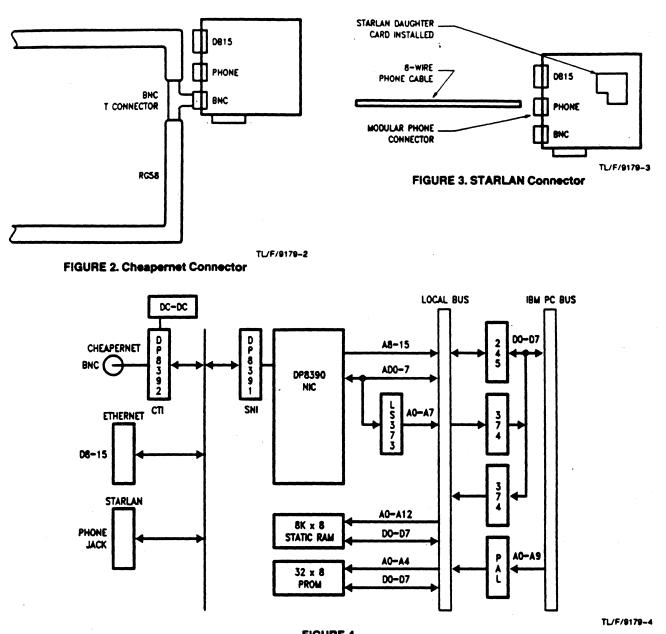

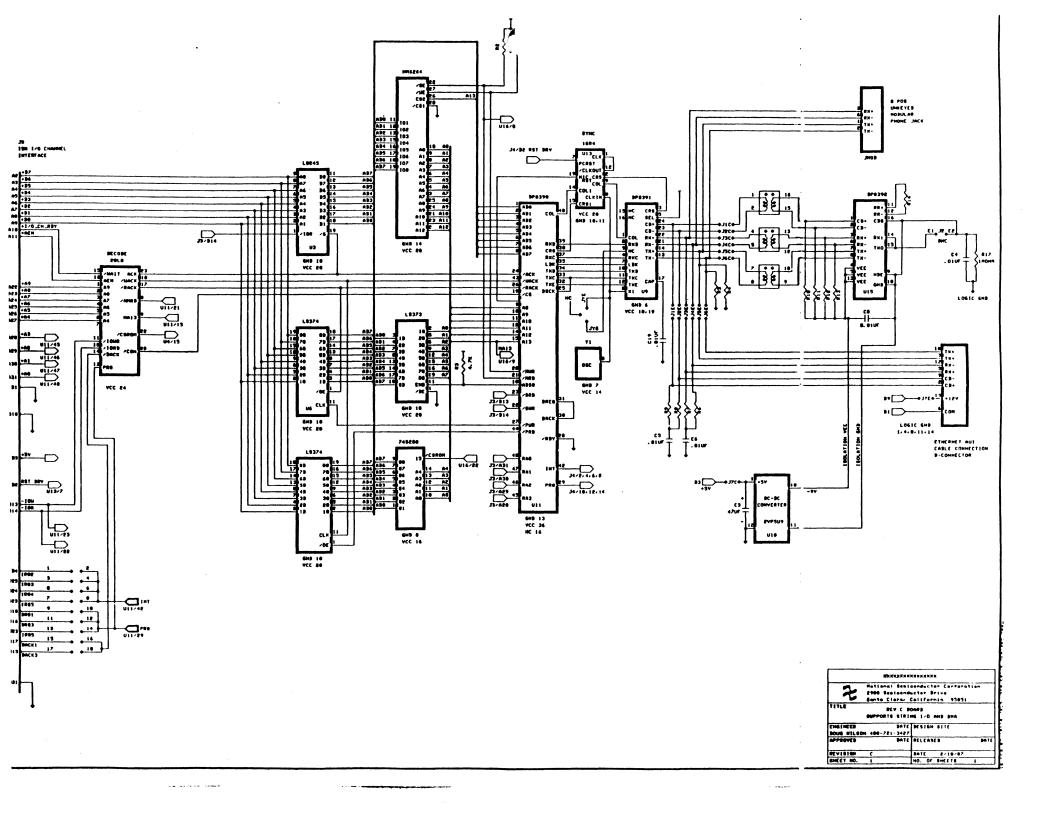

### HARDWARE DESCRIPTION

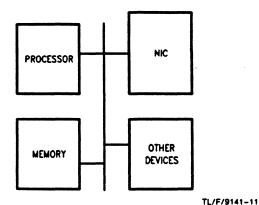

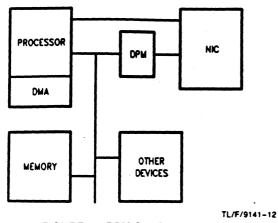

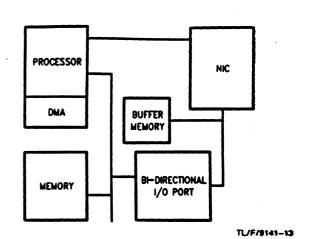

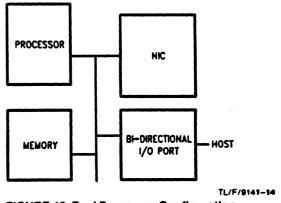

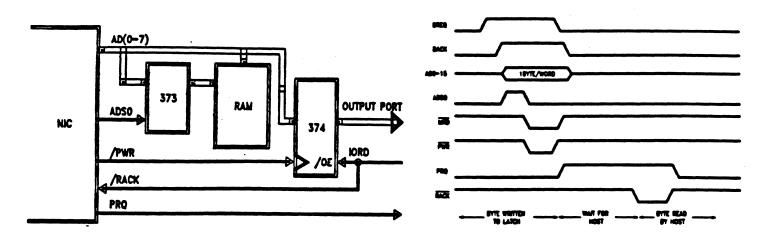

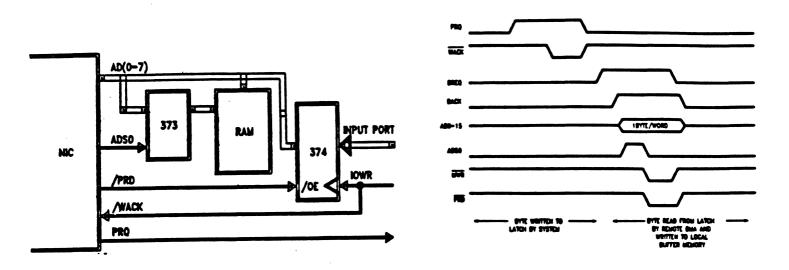

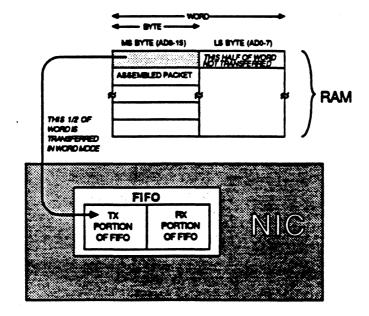

The block diagram shown in Figure 4 illustrates the architecture of the Network Interface Adapter. The system/network interface is partitioned at the DP8390 Network Interface Controller (NIC). The NIC acts as both a master and a slave on the local bus. During reception or transmission of packets, the NIC is a master. When accessed by the PC, the NIC becomes a slave. The NIC utilizes a local 8-bit data bus connected to an 8k x 8 Static RAM for packet storage. The 8k x 8 RAM is partitioned into a transmit buffer and a receive buffer. All outgoing packets are first assembled in the packet buffer and then transmitted by the NIC. All incoming packets are placed in the packet buffer by the NIC and then transferred to the PC's memory. The transfer of data between the evaluation board and the PC is accomplished using the PC's DMA in conjunction with the NIC's Remote DMA. Two LS374 latches implement a bidirectional I/O port with the PC bus. The 8-bit transceiver (LS245) allows the PC

TL/F/9179-1

# P839EB Network Evaluation Board

AN-479

**FIGURE 4**

to access to the NIC's internal registers for programming. A 32 x 8 PROM located on the evaluation board contains the unique Physical Address assigned to each board.

Since the NIC is accessing 8-bit memory, only a single demultiplexing latch is required for the lower 8-bits of address. An LS373 is provided for this purpose.

A 20L8 PAL provides the address decoding and support for DMA handshaking and wait state generation.

### SOFTWARE SUPPORT

The evaluation board provides a simple programming interface for development of software. Several software packages are provided for evaluation and development of networks using the DP8390 Chip set. SDEMO is a demonstration program that provides a low level interface to the DP8390 NIC for transmission and reception of packets. SDEMO supports register dumps and simple register modification. CONF is a conferencing program which supports simple message transfer. WORKSTAT and SERVER support file transfer betw sen two nodes, one configured as a server and a second configured as a workstation. NLS, Network Load Simulator, is a program that simulates network loads based on statistical distributions of packet sizes, bursts and intervals. NLS is useful for performance measurement and debug of software drivers. NES, Network Evaluation Software, consists of sample software drivers implementing a low level interface to the evaluation board.

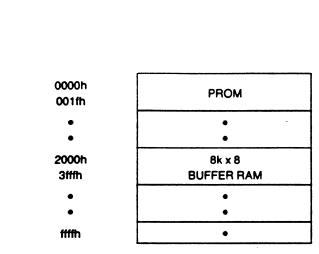

### LOCAL MEMORY MAP

The DP8390 NIC accesses an 8k x 8 buffer RAM located in its 64 kbyte memory space. This buffer RAM is used for temporary storage of receive and transmit packets. Data from this RAM is transferred between the host (the PC) and the evaluation board using the DP8390 NIC's remote DMA channel. An ID address PROM, containing the physical address of the evaluation board is also mapped into the memory space of the NIC.

Note: Partial decoding is performed on the PROM and RAM which will result in these devices appearing at other locations in the 64k memory space. The first occurrance of the PROM and RAM are used for programming purposes.

### **PROM FORMAT**

Each evaluation board is assigned a unique network (physical) address. This address is stored in a 74S288 32 x 8 PROM. The physical address is followed by a checksum. The checksum is calculated by exclusive OR-ing the 6 address bytes with each other. At initialization the software reads the PROM, verifies the checksum and loads the NIC's physical address registers. The following format is used in the PROM:

| Address | Contents                                                  |

|---------|-----------------------------------------------------------|

| 00h     | ADDRESS 0<br>(Physical Address Most<br>Significant Byte)  |

| 01h     | ADDRESS 1                                                 |

| 02h     | ADDRESS 2                                                 |

| 03h     | ADDRESS 3                                                 |

| 04h     | ADDRESS 4                                                 |

| 05h     | ADDRESS 5<br>(Physical Address Least<br>Significant Byte) |

| 06h     | CHECKSUM<br>(XOR OF ADDRESS 0-5)<br>OPTIONAL              |

| 07h     | REV. NUMBER                                               |

| 08h     | MANUFACTURE LOT #                                         |

| 09h     | MANUFACTURE<br>DATE (MONTH)                               |

| 10h     | MANUFACTURE<br>DATE (YEAR)                                |

| 11h-1fh | RESERVED                                                  |

### I/O SPACE

The I/O space and Ethernet/Cheapernet configurations are selected using the various I/O jumpers. There are 4 sets of jumpers that should be programmed prior to installation of the evaluation board into the PC environment. There are:

- J4 I/O address, interrupt selection, DMA channel assignment

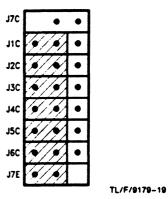

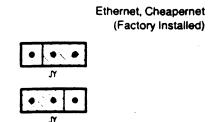

- J1C-J7C, J7E Select Ethernet or Cheapernet

- JY Selects Ethernet/Cheapernet or STARLAN clocking

- JB, JC Selects B3 or C stepping silicon

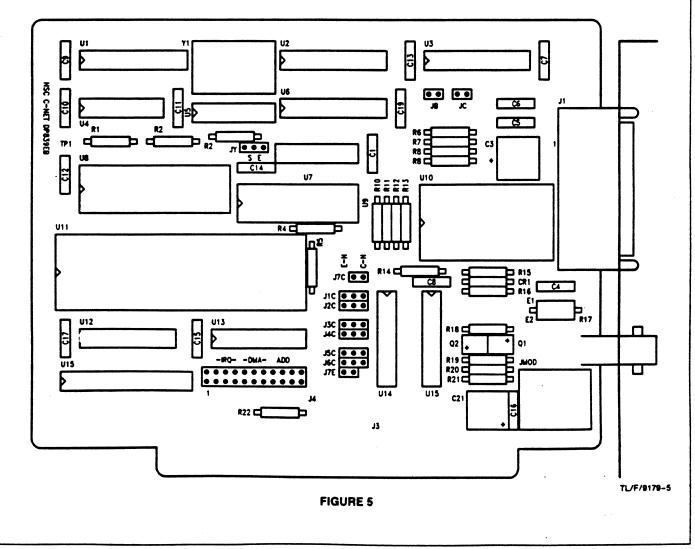

Figure 5 depicts the location of the jumpers on the evaluation board.

The Factory Installed Configuration Is:

I/O base = **30**0h Interrupt = IRO3

DMA = DREQ1, DACK1

J1C-J7C, J7E Cheapernet selected

- JY Ethernet/Cheapernet clock selected

- JB, JC JB shorted selects revision B silicon, JC selects REV C

### I/O SPACE

J4

The evaluation board uses 32 I/O locations in the PC's I/O space. The base address *is fixed AT* 300H AND *is NOT SELECTABLE* using jumpers. (See Switch settings section.) The I/O map is shown below:

| BASE + 00h | COMMAND REGISTER |

|------------|------------------|

| 01h        | NIC REGISTER     |

| 02h        | SPACE            |

| 03h        | •                |

| 04h        | •                |

| 05h        | •                |

| 06h        | •                |

| 07h        | •                |

| •          | •                |

| Ofh        | •                |

| 10h        | I/O PORTS        |

| •          | •                |

| 1¥Fh       | •                |

### NOTES:

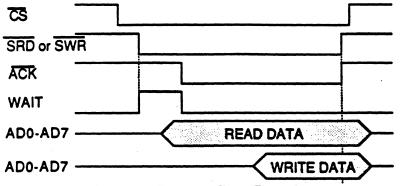

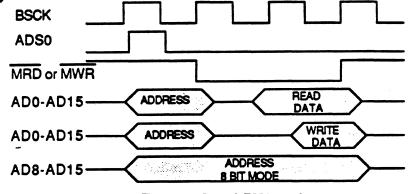

The NIC's Command Register is always mapped at Base + 0. The NIC registers are Base + 01 to Base + 0f will contain different registers depending on the value of bits PS0 and PS1 in the Command Register. These two bits select one of four register pages. For additional information consult the DP8390 data sheet. The NIC uses a DMA channel to read/write data from/to the 8k x 8 Buffer RAM on the evaluation board. Typically a DMA channel on the PC is used in conjunction with the NIC's remote DMA. The I/O ports are then serviced by the DMA channel. If a DMA channel on the PC is not available, the NIC's DMA can still be used by accessing the I/O ports using programmed I/O. Reading the I/O port address will result in a RACK strobe to the NIC while writing the I/O port address will result in a WACK strobe to the NIC.

### SWITCH SETTINGS

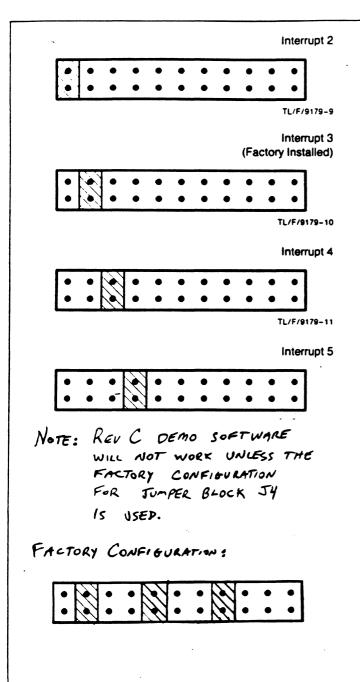

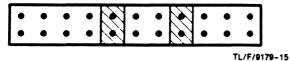

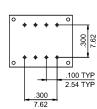

Jumper J4 allows assignment of DMA channel assignments and Interrupt Request assignments. The jumper configuration is shown below and described in the following sections.

| ٠ | ٠ | ٠ | ٠ | ٠ | ٠ | ٠ | ٠ | ٠ | ٠ | ٠ |

|---|---|---|---|---|---|---|---|---|---|---|

| • | ٠ | ٠ | ٠ | ٠ | ٠ | ٠ | ٠ | ٠ | ٠ | ٠ |

| 1 | 1 | 1 | 1 | D | D | 1 | D | D |   |   |

| R | R | R | R | R | R | R | A | A | • |   |

| Q | Q | Q | Q |   | ε | Q | С | С |   |   |

| 2 | 3 | 4 | 5 | Q | Q | 5 | K | K |   |   |

|   |   |   |   | 1 | 3 |   | 1 | 3 |   |   |

TL/F/9179-6

### **I/O BASE ADDRESS**

THE I/O BASE FOR REAC BOARDS IS FIXED AT 300H AND IS NOT SELECTABLE.

### INTERRUPTS

The NIC will generate interrupts based on received and transmitted packets, completion of DMA and other internal events. The interrupt can be connected to Interrupts 2, 3, 4 or 5 (IRQ 2, 3, 4, 5) via Jumper J4. Interrupt 5 is also provided as a software driven DMA Channel. If Interrupt 5 is being used as a DMA channel Interrupt 5 cannot be chosen for the NIC interrupt. The figures below illustrate the jumper positions for the various interrupt levels.

ł

### DMA

The evaluation board requires 1 DMA channel on the PC expansion bus, DMA channel 1 or 3 can be selected. The corresponding DACK line must also be installed on Jumper J4. If your PC contains an SDLC card then DMA channel 3 must be selected.

DMA Channel 1 (Factory Installed)

DMA Channel 3

If a DMA channel is not available an interrupt driven routine can be used to move data between the PC and the buffer memory on the evaluation board. Interrupt 5 is used for this function.

IRQ 5 for DMA

### SELECTING ETHERNET OR CHEAPERNET

Two 10Mbit/sec Interface option are available, a connection to an external transceiver via the DB-15 connector, or a direct interface to a BNC T-connector. Seven jumpers are used to select the appropriate option. These jumpers are labeled J1C-J7C and J7E.

For Cheapernet the following jumpers should be shorted:

TL/F/9179-18

(Factory Installed)

For Ethernet the following jumpers should be shorted.

Double check the jumper positions prior to powering up the board.

### SILICON VERSIONS

The evaluation board supports two revisions of silicon. JB selects REV B3 silicon. J selects REV C silicon.

(JC Factory Installed)

TL/F/9179-20

### OSCILLATOR

For future STARLAN daughter board applications, a divide by 10 scaler is provided to allow switching of the bus clock on the DP8390 to 2 MHz. The jumper, labeled JY should be configured as shown.

TL/F/9179-16

TL/F/9179-21

### APPENDICES

•

The remainder of this document contains the evaluation board parts list, schematic and PAL descriptions.

### PARTS LIST

| Part No.                          | Description                                | Quantity |

|-----------------------------------|--------------------------------------------|----------|

| U1                                | 74LS373N                                   | 1        |

| U2,U6                             | 74LS374N                                   | 2        |

| U3                                | 74LS245N                                   | 1        |

| U4                                | 74S288                                     | 1        |

| U5                                | 74LS290N                                   | 1        |

| U7                                | 74HC74                                     | 1        |

| U8                                | HM6264-100 or Eqv.                         | 1        |

| U9                                | DP8391                                     | 1        |

| U10                               | 2VP5U9                                     | 1        |

| U11                               | DP8390                                     | 1        |

| U12                               |                                            |          |

| U13                               | PAL16R4                                    | 1        |

| U14                               | PE64103                                    | 1        |

| U15                               | DP8392                                     | 1        |

| U16                               | PAL20L8                                    | 1        |

| Y1                                | Crystal Oscillator Module<br>20 MHz + /01% | 1        |

| Q1,Q2                             | PN200-T0-92 pkg.                           | 2        |

| CR1                               | 1N914 diode                                | 1        |

| R1,R2,R3,R22                      | 4.7K 5% carbon                             | 4        |

| R6,R7,R8,R9                       | 39Ω 1%                                     | 4        |

| R4,R5                             | 510Ω 5% carbon                             | 2        |

| R10,R11,R12,R13                   | 1.5K 5% carbon                             | 4        |

| R14                               | 1.0k 1%                                    | 1        |

| R17                               | 1 MΩ 1/2W carbon                           | 1        |

| R19                               | 1.2k 5% carbon                             | 1        |

| R20                               | 3.6k 5% carbon                             | 1        |

| R21                               | 430Ω 5% carbon                             | 1        |

| R15                               | Shorted                                    | 1        |

| R18                               | RRX1-TDB Open                              | 1        |

| R16                               | RRX2-TBD Shorted                           | 1        |

| C1, C7-C17<br>(C10, C19 optional) | 0.47 μF                                    | 13       |

| C3, C21                           | 47 μF ELECTROLYTIC                         | 1        |

Note: Q1, Q2, R21, R20, R19 not required for DP8392-4 parts or later. R15, R18, R16 provided as an option to drive  $93\Omega$  coax.

| Part No.                    | Description            | Quantity |

|-----------------------------|------------------------|----------|

| C5, C6                      | 0.01 µF Ceramic        | 2        |

| C4                          | 0.01 µF Ceramic (600V) | 1        |

| JUMPERS                     | 0.03 sp clips          | 16/board |

| J2                          | PANEL MT. BNC          | 1        |

| J1                          | DB15                   | 1        |

| 48-PIN SOLDERTAIL<br>SOCKET | for U11                | 1        |

| 24-PIN SOLDERTAIL<br>SOCKET | for U16                | 1        |

| 24-PIN AUGAT<br>SOCKET      | for U9                 | 1        |

| 20-PIN SOLDERTAIL<br>SOCKET | for U12, U13           | 2        |

| 14-PIN SOLDERTAIL<br>SOCKET | for U7                 | 1        |

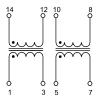

National Sémiconductor PAL2UL8 I/O Address Decode Plus for NIA January 14, 1986 Doug Wilson DECODE 8A A7 A6 NC /NMRD NA13 /IORD /IOWR GND A5 A4 PRO /DACK /WAIT AEN /RACK /WACK /CSX /CSN NC /CSROM /ACK VCC CSN = /AEN\* A9\* A8\* /A7\* /A6\* /A5\* /A4\* IOWR \* /AEN\* A9\* A8\* /A7\* /A6\* /A5\* /A4\* IORD RACK = /AEN\* A9\* A8\* /A7\* /A6\* /A5\* A4\* PRO\* IORD + DACK\* IORD WACK = /AEN\* A9\* A8\* /A7\* /A6\* /A5\* A4\* PRQ\* IOWR + DACK\* IOWR CSX = CSN + /AEN\* A9\* A8\* /A7\* /A6\* /A5\* A4\* IORD + /AEN\* A9\* A8\* /A7\* /A6\* /A5\* A4\* IOWR IF (CSX) WAIT = /ACK + CSN + /PRQ \* /CSN CSROM = /NA13 \* NMRD

Description

This pal performs the I/O decodes for selecting the NIC, and the handshake a hals for NIC's remote dma. The pal supports the dma channels of the PC for remote DMA transfers with the NIC and also allows the use of string I/O between 80286 PC's and NIC's remote DMA.

Using DECODE fixes the I/O BASE of the card at 300h. NIC registers fall in the space 300h - 30fh. To use the string I/O port, reads and writes are done to port 310h.

Wait states are inserted (WAIT) to the PC bus when register accesses are given and the NIC is busy performing other operations (such as local bursts). When the NIC is ready, /ACK is given and no (more) wait states are inserted.

Wait states may also be inserted during remote DMA operations and 80286 machines using string I/O's. WAIT occurs during a remote read if the PC AT's /IORD goes low before the DP8390's PRQ goes high. Similarly, WAIT occurs during a remote write if the PC AT's /IOWR goes low before the NIC's PRQ goes high.

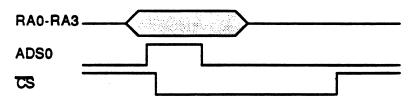

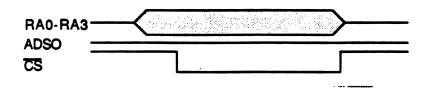

NIC registers are accessed when CSN (Chip Select NIC) is asserted. The IORD and IOWR terms are included to ensure that the address lines are valid when CSN is given.

The RACK and WACK signals are used by the NIC's remote DMA channel to acknowledge the end of a single read or write operation through the remote DMA I/O ports. These port are addressable by the PC DMA channel with DACK and I or IOWR, or by addressing the I/O location 310h (with string I/O's).

CSX is used to enable the TRI-STATE output of WAIT during a register access (CSN), and during string I/O to the remote DMA's I/O port (CSX).

CSROM provides address decode for the card's address PROM. The card's unique Ethernet address is transferred to the system using the NIC's remote DMA. FilleR4 Sinite Transmit Defer Fix SYNC National Semiconductor January 14, 1987 Doug Wilson

CLK CRS NC /MWRIN NC NC PCRST CLKIN COL GND /ENABLE /CLKOUT /MWROUT COL1 CRS1 CRS2 NC NC /NICRST VCC

CLKOUT = CLKIN

/CRS1 := /CRS

- /CRS2 := /CRS1 + /CRS

- /COL1 := /COL

NICRST = PCRST

MWROUT = MWRIN

Description

This pal synchronizes CRS and COL signals from the SNI to ensure that NIC never sees half-level voltages on CRS or COL. This is achieved by sampling them with an inverted 20 Mhz clock (CLKOUT) and giving the COL1 and CRS1 nals to the NIC.

NICRST is a power-on reset signal given to the NIC, generated by inverting the PC signal RST DRV.

NWROUT just passes MWRIN thru. This exists to provided a jumper for the MWR signal that was needed for the SCAP4 pal (Rev B boards).

Cable Installation and Ordering Guide Preliminary July 1986

### Cable Installation and Ordering Guide

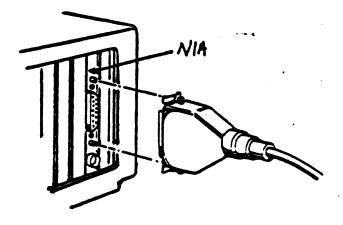

Once the NIAs have been installed into the PCs (see the NIA Hardware Reference Manual for installing NIAs) they are ready to be cabled together.

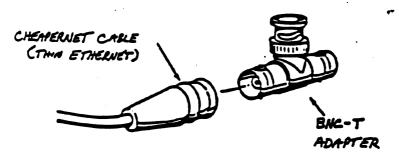

### CHEAPERNET

(

. . . .

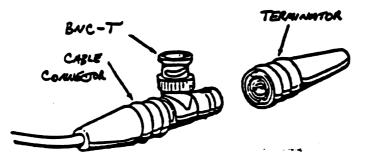

The connection scheme shown below is for Cheapernet (thin Ethernet) networks.

The network is constructed by first connecting two lengths of cable together with a BNC-T adapter as shown below.

At each end of the network a BNC-T adapter and terminator are connected as depicted below.

### Cable Installation and Ordering Guide

### Preliminary

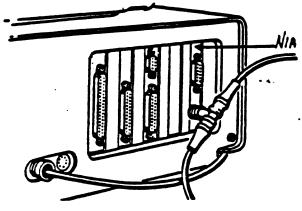

Finally the connection to the NIA board is made with the BNC-T as shown below.

## ETHERNET

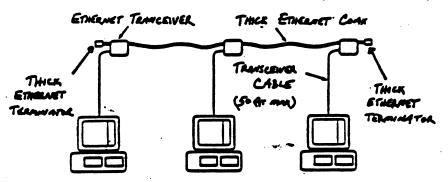

The connection scheme shown below is for Ethernet (thick Ethernet) networks.

The network is constructed by first connecting two lengths of thick Ethernet coax together with an Ethernet transceiver box. Transceiver boxes are also added at each end of the coax. A terminator must be added to the ends of the thick Ethernet segment as depicted below.

### Cable Installation and Ordering Guide

Preliminary

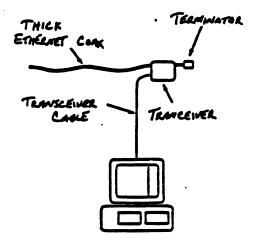

Finally the connection to the NIA board is made with the transceiver cable as shown below.

CONNECTING A TRANCEIVER CABLE AND NIA

### CABLE PROCUREMENT

Both Cheapernet (thin Ethernet) and thick Ethernet cableing and accessories may be ordered through INMAC. Included is a copy of the LAN products offered by INMAC in the June 1986 INMAC catalog. Also included is INMAC ordering information.

# SECTION 4

# SOFTWARE AND SAMPLE DRIVER EXAMPLES

# Software Reference Manual

- \* Computer Conferencing Program

- \* Demonstration Network Software

- \* NIA Access Software

- \* Network Load Simulator

11 ... (

- \* Network Evaluation Software

- \* Writing Drivers for the DP8390

### Software Disclaimer Preliminary July 1986

# SOFTWARE DISCLAIMER

The enclosed software is not a supported product. It was developed and supplied solely for demonstration purposes. Although the demonstration software has been thoroughly tested, National Semiconductor does not assume responsibility for any defects or anomalies found in the software. Source code has been provided to allow modification or troubleshooting by the customer if necessary. Any modification of the software is the sole responsibility of the customer.

### SOFTWARE UPDATE FOR THE DP8390

The enclosed diskette contains software upgrades for using DP8390 Revision C silicon. All of the programs provided in the original DP839EB evaluation kit have been upgraded. The operation of all the upgraded software is the same as in the original DP839EB software.

The program name changes from the original DP839EB versions are listed below:

5-7

| <u>Rev. B3+</u> | <u> </u> | <u>Rev. C</u> |  |

|-----------------|----------|---------------|--|

|                 |          |               |  |

| <b>~</b> 1      |          | <b>C</b> 1    |  |

•

| > | Sdemoc          |

|---|-----------------|

| > | Confc           |

| > | Workstatc       |

| > | Serverc         |

| > | <b>Nesc</b> 300 |

| > | NLSFF           |

|   | ><br>><br>>     |

### Computer Conferencing Program CONF.EXE, Preliminary July 1986

### OVERVIEW

The Computer Conferencing Program (CONF) provides an introduction to local area networks (LAN). Using National Semiconductor's Network Interface Adapter (NIA), CONF sets up a real-time interactive networking environment. Messages entered at one terminal propagate throughout the network and are displayed at the companion NIA equipped terminal running CONF. The NIA is an IBK PC-compatible LAN demonstration board designed to evaluate National's IEEE 802.3-compatible DP8390 network chip set. The DP8390 chip set is one of the latest of National's Advanced Peripheral Processing Solutions (APPS:) family of VLSI circuits for microprocessor peripheral interface applications. The board plugs into any PC-compatible machine and incorporates all of the components required to provide a LAN interface to Ethernet or Cheapernet networks. An optional daughter card allows LAN interface with low cost STARLAN networks.

### FEATURES

- SIMPLE SETUP/CONFIGURATION

- MESSAGES TRANSFERRED AND DISPLAYED ON EACH TERMINAL

- SPLIT SCREEN DISPLAY WITH WINDOWS FOR TRANSMIT AND RECEIVE

### REQUIREMENTS

CONF requires a network of at least two NIA equipped nodes. Each NIA must be previously configured as outlined in the Installation manual. The PC must be operating on DOS 3.0 or greater.

### LOADING AND RUNNING

Boot the node using DOS 3.0 or greater. Insert the EXECUTABLE CODE disk into the active drive. Invoke CONF from the keyboard by typing CONF [return]. Note the status window which indicates the condition of the NIA (see figure 1). If an error message is present follow these troubleshooting procedures:

- 1) Powerdown and re-boot.

- 2) If an error occurs during I/O or DMA testing then check the jumper blocks on the NIA board (see the Network Interface Adapter Hardware Reference Manual).

- 3) If any other error please check the network cable connections and terminators.

If no errors are indicated, press any key to exit the status window.

4-5

Computer Conferencing Program

Preliminary

÷\_ -

| Figure 1 | 100 parts etc.<br>Stild to SNC is complete.<br>Stild to DNI is complete.<br>Stild to complete.<br>Stild through SPESSO RIC<br>Touting implete through SPESSO RIC<br>Touting implete through SPESSO GTI<br>Tuting implete through SPESSO GTI<br>From ony my to combine.                                                                                                                                                                                                                                  |

|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 2 | Matternal Semileconductor       CONF       Computer         External / Cheepernat       Ver 1.3       Contenancing         Message Entry       Contenancing       Program         CONF is a program designed to demonstrate the facebility of node to node communication using Hadronel Semicanductor's Network Interface Adapter (NA).       Press F1 to cond the message         Message Display       Message Clapsery       Message Clapsery         Message Clapsery       Press Control C to guit |

At this point CONF is ready to send and receive messages through the network (provided there is at least one other CONF equipped node on the network). To initiate communication enter a message from the keyboard. The message will appear on your terminal in the Message Entry window as depicted above (figure 2). To send the message simply press F1 (function key 1). The message will propagate through the network and appear in the Message Display window of any other node operating with CONF. The message is automatically sent when the Message Entry window fills to capacity while typing a message.

Messages from other nodes running CONF will appear in the Message Display compartment on your terminal (figure 3). These messages will be replaced by any subsequent transmissions from other nodes. To exit CONF press [control] C.

|          | Heland Samleanducter<br>Ethernet / Chaspernet<br>S-JUD-SS | CONF<br>Ver 1.8                               | Caniputer<br>Canifornating<br>Program                   |     |

|----------|-----------------------------------------------------------|-----------------------------------------------|---------------------------------------------------------|-----|

|          | Manago Entry                                              |                                               |                                                         |     |

| Figure 3 | thereas Gravity                                           | vers F1 to cand the m                         |                                                         |     |

|          | CONF to a program designed                                | to demonstrate the le<br>al Somlaundurter's H | activity of nada to nada<br>struct interface Adapter (M | KAL |

|          |                                                           | Press Control C to                            | çuli                                                    |     |

July 1986

Demonstration Network Software SERVER.EXE. WRKSTAT.EXE, Preliminary July 1988

### OVERVIEW

The Demonstration Network Software package (D-NET) demonstrates file transfer operations within local area networks (LAN). The D-NET software package contains two programs which together emulate the networking relationship between a workstation and a file server. SERVER is the file server emulator and shares its disk drive capabilities with workstations on the network. WRKSTAT is the workstation emulator which may access the file server's disk. Using National Semiconductor's Network Interface Adapter (NIA), D-NET sets up a real-time interactive networking environment in which the workstation can read directories, type and transfer files to and from the file server. The NIA is an IBM PC-compatible LAN demonstration board designed to evaluate National's IEEE 802.3-compatible DP6390 network chip set. The DP6390 chip set is one of the latest of National's Advanced Peripheral Processing Solutions (APPS:) family of VLSI circuits for microprocessor peripheral interface applications. The board plugs into any PC-compatible machine and incorporates all of the components required to provide a LAN interface to Ethernet or Cheapernet networks. An optional daughter card allows LAN interface with low cost STARLAN networks.

### FEATURES

- SIMPLE SETUP/CONFIGURATION

- FILES TRANSFERRED BETWEEN EACH TERMINAL

- A COMPLETE MENU DRIVEN SOFTWARE PACKAGE

### REQUIREMENTS

D-NET requires a network of at least two NIA equipped nodes. Each NIA must be previously configured as outlined in the Installation manual. Additionally. COMMAND.COM must reside in the root directory of the active disk drive. The PC must be operating on DOS 3.0 or greater.

### LOADING AND RUNNING

Boot each node using DOS 3.0 or greater. Insert the EXECUTABLE CODE disks into the active drive of each PC. Invoke SERVER from one keyboard by typing SERVER [return]. Type WRKSTAT [return] on the other. Note the status window on each terminal which indicate the conditions of each NIA (see figure 1). If an error message is present follow these troubleshooting procedures:

- 1) Powerdown and re-boot.

- If an error occurs during 1/0 or DMA testing then check the jumper blocks on the NIA board (see the Network Interface Adapter Hardware Reference Manual).

- 3) If any other error please check the network cable connections and terminators.

4 -7

If no errors are indicated, press any key to exit the status window.

Demonstration Network Software

Preliminary

•• .

|            | ol.<br>GC b constate |          |             |   |   |  |

|------------|----------------------|----------|-------------|---|---|--|

| JAKA ID E  | and is compared      | b<br>b   |             |   |   |  |

| Testing in | appeal through       |          | • <b>t.</b> |   |   |  |

| Taning in  | opteel Upread        | DPENI BI | 1           |   |   |  |

| Tasting in | sphere through       | Drews CT | 1           |   | • |  |

| Press any  | boy to essaie        |          |             |   |   |  |

|            |                      | •        |             |   |   |  |

|            |                      |          |             | • |   |  |

|            |                      |          |             |   | • |  |

|            |                      |          |             |   |   |  |

|            |                      |          |             |   |   |  |

|            |                      |          |             |   |   |  |

|            |                      |          |             |   |   |  |

### THE FILE SERVER

Figure 1

The file server must have a non write-protected disk inserted in its active drive (or a fixed disk as an active drive). The system will not work properly if the file server cannot read and write onto a disk. The file server is now ready to interact with the workstation.

### THE WORKSTATION

A menu of WRKSTAT's main functions is displayed on the terminal as shown in figure 2. The items on the menu are accessed using the cursor control keys of the PC's numeric keypad. Pressing the [24] key moves the cursor down the menu, and the  $[8\tau]$  key moves it up. If the cursor control keys are not performing these functions press the [NumLock] key. The [return] key is used to select the desired function.

Files must be 20Kbytes or less when typing or copying.

When typing a file use [control][S] to stop/start scrolling or [control][C] to abort typing.

| National Somiconductor<br>Ethernet / Cheapernet<br>6-Jun-66                                                                                                                                                                | D-NET<br>NORKSTATION<br>Ver 1.0                                                                                                           | DP639EB<br>Network<br>Program |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|

| MAIN FUNCTIONS<br>List the directory of this<br>List the directory of the<br>Type a file from this work<br>Type a file from this work<br>Copy a file from this work<br>Copy a file from the file<br>Out and return to DOS. | workstation's disk.<br>fileserver's disk.<br>station's disk.<br>station's disk.<br>station to the fileserver<br>erver to this workstation |                               |

|                                                                                                                                                                                                                            |                                                                                                                                           |                               |

Figure 2

NIA Access Software SDEMO.EXE Preliminary June 1986

### OVERVIEW

The Network Interface Adapter Access Software package (henceforth referred to as SDEMO) is a demonstration/learning tool which provides the means to investigate the NIA's capabilities. Using National Semiconductor's Network Interface Adapter (NIA), SDEMO sets up a real-time interactive networking environment. The NIA is an IBM PC-compatible LAN demonstration board designed to evaluate National's IEEE 802.3-compatible DP8390 network chip set. The DP8390 chip set is one of the latest of National's Advanced Peripheral Processing Solutions (APPS:) family of VLSI circuits for microprocessor peripheral interface applications. The board plugs into any PC-compatible machine and incorporates all of the components required to provide a LAN interface to Ethernet or Cheapernet networks. An optional daughter card allows LAN interface with low cost STARLAN networks.

### FEATURES

- SIMPLE SETUP/CONFIGURATION

- COMPLETE NIC ACCESS AND CONTROL

- A COMPLETE MENU DRIVEN SOFTWARE PACKAGE

### REQUIREMENTS

SDEMO requires an NIA equipped PC operating with DOS 3.0 or greater. The NIA must be previously configured as outlined in the NIA Hardware Reference Manual. Additionally, the program storage disk should be conditioned using the Installation Utility.

### LOADING AND RUNNING

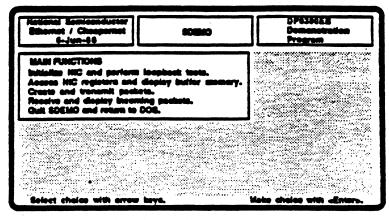

Boot the PC with DOS 3.0 or greater. Invoke SDEMO from the keyboard by typing SDEMO [return]. The terminal will now display the Main Functions selection screen as shown in figure 1.

### ACCESSING THE MENUS

The items on the menu are accessed using the cursor control keys of the PC's numeric keypad. Pressing the [24] key moves the cursor down the menu, [87] moves it up. If the cursor control keys are not performing these functions press the [NumLock] key. The [return] key is used to select the desired function. The Escape key [esc] is used by SDEMO to exit the current window.

Throughout this document the various windows will be numerically referred to by their corresponding section headings. It should be noted that these numbers exist only in this document and are not displayed on the terminal by SDEMO.

4 -

### Preliminary

### **Main Functions**

The Main Functions window is your viewport into SDEMO's four main functions of initialization, register and memory access, packet transmission and packet reception.

SDEMO does not initialize the NIA when it is invoked. This feature is useful for determining the state that the NIA has been left in by another process (a system crash, perhaps). To use SDEMO for anything other than determining the current state of the NIA it is necessary to select the initialization option (window 1.1).

Main Functions

### 1. Initialize NIC and perform loopback tests.

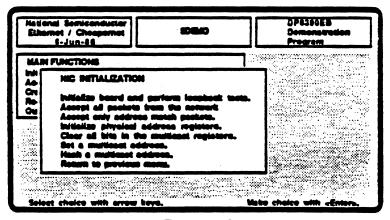

This window (figure 1.0) becomes incumbent when the initialize option is selected from the Main Functions window. The options in this window are for power on initialization and for receive filter initialization.

Figure 1.0

### 1.1. Initialize board and perform loopback tests.

This is the power on initialization option and must be selected before any other options can be executed. This option need only be selected once for each SDEMO session. After selecting this option, note the status window which indicates the condition of the NIA (see figure x). If an error message is present follow these troubleshooting procedures:

National Semiconductor

· • • •

- 1) Powerdown and re-boot.

- 2) If an error occurs during I/O or DMA testing then check the jumper blocks on the NIA board (see the Network Interface Adapter Hardware Reference Manual).

- 3) If any other error please check network cable connections.

Press any key to exit the status window.

### 1.2. Accept all packets from the network.

This selection puts the NIC into promiscuous mode. The NIC's Receive Configuration Register is programmed to 1Fh and all multicast bits are set. Any packet on the network will be accepted.

### 1.3. Accept only address match packets.

In this mode only packets which have a destination address that matches the address residing in the Physical Address Registers and packets that have a multicast address that hashes to a bit set in the Multicast Address Registers will be accepted. The Physical Address Registers must be initialized using window 1.4 before the address match filter will work.

### 1.4. Initialize physical address registers.

This option opens a window (figure 1.4) which prompts for the physical address that is to be programmed into the Physical Address Registers. Twelve hex digits are required. Valid hex digits are  $0 \rightarrow 9$ , and  $A \rightarrow F$ . The registers are automatically programmed with the entered address.

| Nevenel Se<br>Ethernet /<br>G-Jy | Charapernet<br>n-16                          | D DP8350EB<br>Domenstration<br>Program |

|----------------------------------|----------------------------------------------|----------------------------------------|

| MADI FUN<br>bill<br>And          | NC SITTALIZATION                             |                                        |

| 4828                             | PHYSICAL REGISTERS                           |                                        |

|                                  | Brar in ins eit byins (<br>(tusive digita) → | d physical eddress.                    |

Figure 1.4

### 1.5. Clear all bits in the multicast registers.

This option clears all the Multicast Address Register bits to zero so that no multicast address packets will be recognized. This option should be used before any multicast addresses are set to insure that only the desired multicast addresses are recognized.

### Preliminary

### 1.6. Set a multicast address.

This option opens a window which prompts for twelve hex digits of the multicast address. Valid hex digits are  $0 \rightarrow 9$ , and  $A \rightarrow F$ . Once entered, the multicast address is hashed by a routine similar to CRC generation (see PD8390 Data Sheet for more information on multicast address hashing). After the multicast address filter bit number is found by the hashing routine it is displayed and the bit is set in the Multicast Address Registers. The desired multicast address packet will now be recognized by the receive filters.

### 1.7. Hash a multicast address.

Similar to 1.6 except the Multicast Address Register bit is not set. The option only determines which bit a multicast address hashes to. The multicast address will not be recognized by the receive filters unless it has been set using window 1.6.

### 1.8. Return to previous menu.

Returns SDEMO to the Main Functions window (pressing [esc] does the same).

### 2. Access NIC registers and display buffer memory.

This menu (figure 2.0) allows read/write/display access to NIC registers and buffer memory.

| Hetleri<br>Etheri | ni Semicanductor<br>ni / Charpenni<br>S-Jun-48                                                                                          | DFRIBRES<br>Demonstration<br>Program |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|

|                   | Rengtions                                                                                                                               |                                      |

|                   | NC RECIPTER AND DMA ACCESS                                                                                                              |                                      |

| 446               | Read a NIC register.<br>Write to a NIC register.<br>Display butter memory.<br>Display NIC otatus registere.<br>Return to province menu. |                                      |

| Soloc             | 1 chaice with errow boys.                                                                                                               | liate choice with -Entern.           |

Figure 2.0

### 2.1. Read a NIC register.

This option allows you to display the contents of any register without altering the contents. The window prompts for a port number in hex. Enter the desired address and press [return]. The contents of that port will be displayed within the window. Allowed addresses are 0000h  $\rightarrow$  FFFFh.

### 2.2. Write to a NIC register

Using this option you can write a byte of data into any register. The window first prompts for the port number in hex and then for the data byte (in hex) to be written.

### 2.3. Display buffer memory

This selection is used to display a portion of the buffer memory. You will be prompted to first enter in hex the starting address and next for how many bytes you would like to display. Allowed addresses are  $0000h \rightarrow FFFFh$ . NIA ROM starts

National Semicondu stor

at 0000h and ends at 0020h. NIA RAM starts at 2000h and ends at 4000h. SDEMO will indicate that a DMA is in process and then display the specified buffer memory space in hex. Pressing any key during display will terminate the display.

### 2.4. Display NIC status registers.

This option opens a window (figure 2.4) which displays the contents of the NIC's status registers. Each of the eight rows contain the register's name followed by it's value in hex. Also displayed are the register's bit names and numbers, with the numbers of the set bits in each register highlighted by inverse video. Press any key to continue.

| Servicent Registers       | 23H  | POI      | 780   | RCR     |          |               | 779         | STA        | STP           |

|---------------------------|------|----------|-------|---------|----------|---------------|-------------|------------|---------------|

| Transmit Status Registers | 0114 | ajc      | - di  | N       | -        | AUT           | <u> </u>    | 278        | O<br>PTX<br>O |

|                           | 001  | 07<br>7  | 08    | -       | D4<br>4  | 8             | 22          | 01         | Bo            |

| ernat Status Registers    | 804  | PET<br>7 | ICC.  | ON I    | CMV<br>4 | DE            | <b>RE</b> 2 | PTX        | Mik<br>0      |

| ceive Status Pagisters    | 01H  | 7        | 08    | MY<br>S | 4        | RD 3          | FHE 2       | <b>C</b> C | MK O          |

| cake Cardqueatan Reg      | 114  | 7        | ī     |         |          | <b>M</b><br>3 | 2           | AR 1       |               |

| ment Confermion Reg.o     | 00H  | 7        |       |         | -        | ATD           |             | 1          | œ             |

| un Contquesion Augus      |      | 7        | . FTI | FTD     | 4        | 3             | 146         | 1          | WIS<br>0      |

## 2.5. Return to previous menu

Returns SDEMO to the Main Functions window (pressing [esc] does the same).

### 3. Create and transmit packets.

This menu (figure 3.0) accesses SDEMO's packet management and transmission routines.

| Matien<br>Silver | wi Somicondumer<br>Not / Chargemet<br>S-Jun-88                                | DPLINCES<br>Domonstrution<br>Program |

|------------------|-------------------------------------------------------------------------------|--------------------------------------|

|                  | Raicmont                                                                      |                                      |

|                  | TRANSMIT                                                                      |                                      |

|                  | Bot the destination address.                                                  |                                      |

| 2                | Greate a packet from the texploard.<br>Transmit the texploard packet.         |                                      |

|                  | flave the boyboard postet on dat.<br>Transmit a seved postet on the dat.      |                                      |

|                  | Continuously transmit the hayboard packet.<br>Display the MC aster registers. |                                      |

|                  | Arturn to the provides stinders.                                              |                                      |

|                  |                                                                               |                                      |

| Select           | choice with arrow keys.                                                       | e cheles with dimen.                 |

Figure 3.0

4-13

### 3.1. Set the destination address.

This selection prompts for a twelve digit destination address (in hex) for the packet.

### 3.2. Create a packet from the keyboard.

Use this option to create a packet. The packet must not exceed 4096 characters. The [return] key enters the packet into memory and terminates the window. The previous keyboard packet will be overwritten in the process.

### **3.3.** Transmit the keyboard packet.

Selecting this option transmits a single keyboard packet onto the network.

### 3.4. Save the keyboard packet on disk.

This option allows you to save the keyboard packet onto the disk for future use. Enter a valid DOS filename and press [return].

### 3.5. Transmit a saved packet on the disk.

Select this option to transmit a packet which has been previously stored on a disk. Enter the filename and press [return]. At this point pressing any key will transmit the packet and return to the transmit window.

### 3.6. Continuously transmit the keyboard packet.

In this mode the keyboard packet is continuously transmitted. The window prompts for a delay factor between transmissions. The delay is linear (a delay of eight is twice as long as four) and may be between zero and 32000 inclusive. Each transmitted packet is indicated by a dot printed on the screen. Pressing any key terminates transmission and returns to the previous window.

### 3.7. Display the NIC status registers.

This selection is equivalent to window 2.4 described previously.

### 3.8. Return to the previous window.

Returns SDEMO to the Main Functions window (pressing [esc] does the same).

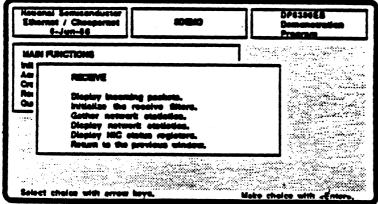

### 4. Receive and display incoming packets.

This menu (figure 4.0) accesses SDEMO's packet display and statistics gathering routines.

Figure 4.0

### 4.1. Display incoming packets.

Selecting this option displays incoming packets which pass through the receive filters. The left column displays the packet in hex while the right column displays it's ASCII equivalent. Pressing any key terminates the display and returns to the previous window.

### 4.2. Initialize the receive filters.

This selection is equivalent to window 1.0 described previously.

### 4.3. Gather network statistics.

This option allows for monitoring network traffic. Each accepted packet is indicated by a dot printed on the screen. The number of accepted packets while in this mode is stored in the number of packets counter which rolls over at 32000. Errored packets are also tallyed and these counters roll over at 192. Pressing any key ends statistic gathering and returns to the receive window.

### 4.4. Display network statistics.

This selection opens a window which displays the network statistics. It indicates how many packets were received and how many were lost due to frame alignment errors, CRC errors and buffer overflow. Press any key to exit this window.

### 4.5. Display NIC status registers.

This selection is equivalent to window 2.4 described previously.

### 4.6. Return to the previous window.

Returns SDEMO to the Main Functions window (pressing [esc] does the same).

### 5. Quit SDEMO and return to DOS.

Terminate the current SDEMO session and reenter the DOS environment (pressing [esc] does the same).

4-15

### Network Load Simulator NLS.EXE Preliminary July 1986

### OVERVIEW

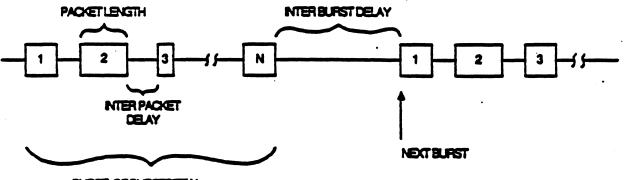

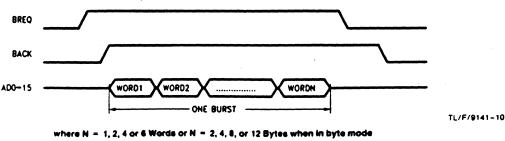

The Network Load Simulator program (NLS) is a useful Local Area Network (LAN) development tool for evaluating and testing driver level software. Packets are transmitted in bursts with menu selected packet sizes, interpacket delays, burst sizes and interburst delays as depicted in figure 1. All parameters can be set to fixed values or may be set to vary linearly or bimodally within a selected range. By using varying delays and packet sizes, traffic on an active LAN can be emulated, and driver software can be tested and evaluated in a typical environment. Packets sent out contain a MOD 15 counting pattern which can be conveniently verified by the receiving nodes (NES supports checking of this pattern).

The NIA is an IBM PC-compatible LAN demonstration board designed to evaluate National's IEEE 802.3-compatible DP8390 network chip set. The DP8390 chip set is one of the latest of National's Advanced Peripheral Processing Solutions (APPS:) family of VLSI circuits for microprocessor peripheral interface applications. The board plugs into any PC-compatible machine and incorporates all of the components required to provide a LAN interface to Ethernet or Cheapernet networks. An optional daughter card allows LAN interface with low cost STARLAN networks.

### FEATURES

- GENERATES NETWORK TRAFFIC

- FLEXIBLE PACKET GENERATOR

- A DRIVER DEVELOPMENT TOOL

- MENU DRIVEN

### REQUIREMENTS

NLS requires an NIA equipped PC. The NIA board jumpers must be configured to use 1/O space 2EO (serial port 2) as described in the 1/O Base Address section of the Network Interface Adapter Hardware Reference Manual.

BURST OF BURSTSIZEN

4- 17

### Network Load Simulator

### Preliminary

### LOADING AND RUNNING

Boot the PC with DOS 2.0 or greater. Insert the DEMO disk into the active disk drive. Invoke NLS from the keyboard by typing NLS [return]. The terminal will display the NLS menu as depicted below in figure 2.

| National Semiconductor APPS<br>Ethernet/Chaspernet/Starlan<br>Notwork Load Simulator (NLS)<br>for the<br>Notwork Interface Adaptar (NLA) |                      |                             |  |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------|----------------------|-----------------------------|--|--|--|

| Pasket Longth                                                                                                                            | constant             | 109                         |  |  |  |

| Packets per Burst                                                                                                                        | constant             | 3                           |  |  |  |

| Selay between Surets<br>Selay between Peekets<br>Surets                                                                                  | constant             | •                           |  |  |  |

| Dolay between Peckets                                                                                                                    | constant             | ٠                           |  |  |  |

| Sureta                                                                                                                                   | single               |                             |  |  |  |

| Peeket Type                                                                                                                              | tano pasiest         |                             |  |  |  |

| Trensmission Status                                                                                                                      | · not transmitting   | Pashet count 0              |  |  |  |

| Hit q to exit ESC befor                                                                                                                  | re entering values f | irree keys to change fields |  |  |  |

Figure 2

### Noving the Cursor

The items on the menu are accessed using the cursor control keys of the PC's numeric keypad. Pressing the [2.] key moves the cursor down the menu,  $[3^+]$  moves it up,  $[4 \leftarrow ]$  to the left and  $[6 \rightarrow ]$  to the right. In the vertical direction the menu wraps around itself. Note: If the cursor control keys are not performing these functions press the [NumLock] key.

### Special Keys

There are five special keys used in NLS. These are [t], [r], [SpaceBar], [esc] and [q] and their functions are as follows:

- [t]: This key brings the cursor from anywhere on the menu to the last row and enters the transmit mode.

- [r]: Reset packet count. The packet count is the number of packets sent out on the network since the count was last reset.

[SpaceBar]:

The [SpaceBar] key is used to toggle the possible selections in the second column.

- [esc] The escape key must be depressed before entering values (see Selecting Value on the following page).

- [q]: Use this option to exit NLS and re-enter the DOS environment.

Note: Pressing any key while continuously transmitting terminates transmission.

## Network Load Simulator

## Preliminary

## Distribution of Packet Lengths, Packets per Burst and Delays

The distribution of packet lengths, packets per burst, delays between bursts and delays between packets have three possibilities: constant, linear and bimodal. To select between these three possibilities simply move the cursor to the second column and the desired row and press the [SpaceBar] as mentioned previously.

Constant: Displayed value used constantly.

- Linear: A psuedo-random linear distribution between the two values displayed.

- Bimodal: A psuedo-random distribution with 65% of first value and 35% of the second value.

Note: Delays increase with the square of the number, with zero being the smallest delay.

#### Selecting Values

Values are entered by moving the cursor to the appropriate position on the menu and then pressing the escape [esc] key. The desired value may now be typed in and entered by pressing [return]. For a linear distribution the left number must be less than the right number.

Bursts may be selected as occurring singularly or continuously.

There are two options for packet type; same packet or different packets. NLS initially loads the transmit buffer with a series of 256 byte pages starting at page 20h. When the Same Packet option is selected the NIC transmits the packet beginning at page 20h and consists of the pattern shown in figure 3. Different packets mode transmits the packets in locations 21h through 21+f (the beginning of 21h is shown below).

| 2000 | 88         | 77         | 66  | 55         | 44 | 33        | 00 | 01         | 02 | 03 | 04  | 05 | 06  | 07        | 08          | 09         |        |      |      |

|------|------------|------------|-----|------------|----|-----------|----|------------|----|----|-----|----|-----|-----------|-------------|------------|--------|------|------|

| 2010 | 0 <b>A</b> | 0B         | 0C  | 0D         | 0E | 00        | 01 | 02         | 03 | 04 | 05  | 06 | 07  | 08        | 09          | <b>0A</b>  |        |      |      |

| 2020 | 0B         | 0C         | 0D  | 0E         | 00 | 01        | 02 | 03         | 04 | 05 | 06  | 07 | 08  | 09        | 0A          | 0 <b>B</b> |        |      |      |

| 2030 | 0C         | OD         | OE. | 00         | 01 | 02        | 03 | 04         | 05 | 06 | 07  | 08 | 09  | 0A        | 0B          | 0C         |        |      |      |

| 2040 | OD         | ΟE         | 00  | 01         | 02 | 03        | 04 | 05         | 06 | 07 | 80  | 09 | 0A  | 0B        | 0C          | 0D         |        |      |      |

| 2050 | ΟE         | 00         | 01  | 02         | 03 | 04        | 05 | 06         | 07 | 08 | 09  | 0A | 0B  | <b>0C</b> | 0D          | 0E         |        |      |      |

| 2060 | 00         | 01         | 02  | 03         | 04 | 05        | 06 | 07         | 08 | 09 | 0A  | 0B | 0C  | OD        | 0E          | 00         |        |      |      |

| 2070 | 01         | 02         | 03  | 04         | 05 | 06        | 07 | <b>8</b> 0 | 09 | 0A | 0B  | 0C | OD  | ΟE        | 00          | 01         |        |      |      |

| 2080 | 02         | 03         | 04  | 05         | 06 | 07        | 80 | 09         | 0A | 0B | 0C  | OD | 0E  | 00        | 01          | 02         |        |      |      |

| 2090 | 03         | 04         | 05  | 06         | 07 | 08        | 09 | 0A         | 0B | 0C | 0D  | ΟE | 00  | 01        | 02          | 03         |        |      |      |

| 20A0 | 04         | 05         | 06  | 07         | 08 | 09        | 0A | 03         | 0C | 0D | 0E  | 00 | 01  | 02        | 03          | 04         |        |      |      |

| 20B0 | 05         | 0 <b>6</b> | 07  | <b>8</b> 0 | 09 | <b>0A</b> | 0B | 0C         | 0D | 0E | 00  | 01 | 02  | 03        | 04          | 05         |        |      |      |

| 20C0 | 06         | 07         | 08  | 09         | 0A | 0B        | 0C | 0D         | 0E | 00 | 01  | 02 | 03  | 04        | 05          | 06         |        |      |      |

| 20D0 | 07         | 08         | 09  | 0A         | 0B | 0C        | 0D | 0E         | 00 | 01 | 02  | 03 | 04  | 05        | 06          | 07         |        |      |      |

| 20E0 | 08         | 09         | 0A  | 0B         | 0C | 0D        | 0E | 00         | 01 | 02 | 03  | 04 | 05  | 06        | 07          | 08         |        |      |      |

| 20F0 | 09         | 0Ą         | 0B  | 0C         | 0D | 0E        | 00 | 01         | 02 | 03 | 04  | 05 | 06  | 07        | 80          | 09         |        | •    |      |

| 2100 | 0A         | 0B         | 0C  | 0D         | 0E | 00        | 01 | 02         | 03 | 04 | 05  | 06 | 07  | 80        | 09          | 0A         | ←Begin | new  | page |

| 2110 | 0B         | 0C         | 0D  | 0E         | 00 | 01        | 02 | 03         | 04 | 05 | 06  | 07 | 80  | 09        | 0A          | 03         | (page  | 21h) | I    |

| 2120 | 0C         | 0D         | ΟE  | 00         | 01 | 02        | 03 | 04         | 05 | 06 | 07  | 80 | 09  | 0A        | 0B          | 0C         |        |      |      |

| 2130 | OD         | ΟE         | 00  | 01         | 02 | 03        | 04 | 05         | 06 | 07 | • • | e  | tce | tera      | <b>a.</b> . |            |        |      |      |

Figure 3

4-19.

National Semiconductor

Network Evaluation Software NES.EXE Preliminary July 1988

## OVERVIEW

NES is an assembly language program used to evaluated the NIC in a real-life network environment. NES is composed of two object modules, nes.obj and isrb3a.obj. The main program module is nes.obj which simulates an operating system shell. The isrb3a.obj module contains the interrupt service routine which handles low-level receive and transmit processing. NES also serves as an example of a driver for upper-level network software.

٠,

#### FEATURES

• EVALUATES DP8390 IN A NETWORK ENVIRONMENT

• TRANSMIT AND RECEIVE ERROR DETECTION

DISPLAYS NETWORK STATISTICS

## REQUIREMENTS

NES requires the NIA to be configured using Serial Port 2, DMA Channel 1 and interrupt request 3 (the factory installed configuration). Refer to the switch settings section of the NIA Hardware reference Manual.

If needed, the address base, interrupt request number and the DMA request number can be changed from their default values of:

address base = 2E0h interrupt request number = IREQ3 DMA request number = DRQ1

In the equate section at the beginning of each object module there are "comment lines" provided to facilitate changing to the other NIA board hardware options (address base = 260h, IREQ5 andDRQ3). The comment lines are as follows:

| Option 1<br>COMMAND<br>; COMMAND                                     | edn<br>edn               | 2E01<br>2601               | ;"coment     | line" | → address    | base | 260h |

|----------------------------------------------------------------------|--------------------------|----------------------------|--------------|-------|--------------|------|------|

| Option 2<br>IRQ3<br>CODE_IRQ3<br>; IRQ5<br>; CODE_IRQ5               | edn<br>edn<br>edn<br>edn | OF7h<br>2Ch<br>ODFh<br>44h |              |       |              |      |      |

| Option 3<br>ENB_DRQ1<br>DISABLE_DRQ1<br>: ENB_DRQ3<br>: DISABLE_DRQ3 | edn<br>edn<br>edn<br>edn | 1<br>5<br>3<br>7           |              |       | •            |      |      |

| To change the MIA hander                                             |                          |                            | and the same |       | an fan tha a |      |      |

To change the NIA hardware options exchange the commented lines for the commented lines. For example, to change the address base to 260h change option 1 to:

| COMMAND   | equ | 260h |

|-----------|-----|------|

| : COMMAND | equ | 2E0h |

## Preliminary

## Network Evaluation Software

## LOADING AND RUNNING

To execute this program, type "nes [options]" on the DOS command line. The options allow you to reconfigure the NIC with different network parameters. The options are as follows: C, T, I, and H, and may be selected in upper or lower case. Examples of invoking the program are shown below.

| A>nes     | no options selected            |

|-----------|--------------------------------|

| A>nes c   | the "c" option selected        |

| A>nes c t | the "c" and "t" option select, |

|           | the order does not matter      |

## PROGRAM OPTIONS

The "C" option allows you to check all incoming packets with a chosen destination address (first 6 bytes) and the following data pattern -0123456789 a b c d e 0 1 2 etc. (the pattern generated by NLS). The chosen address is prompted by the program when the "C" option is selected. If an error occurs, it will be indicated on the screen.

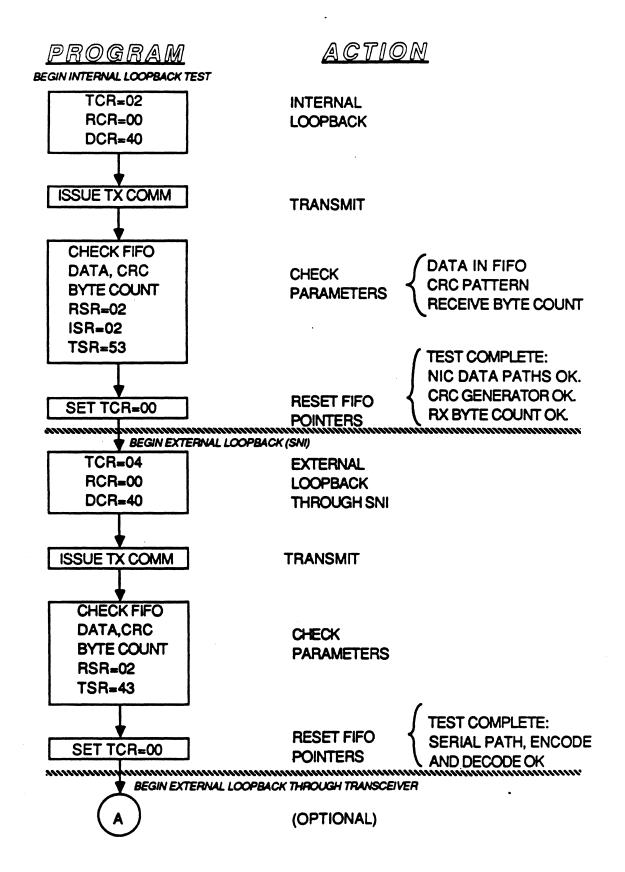

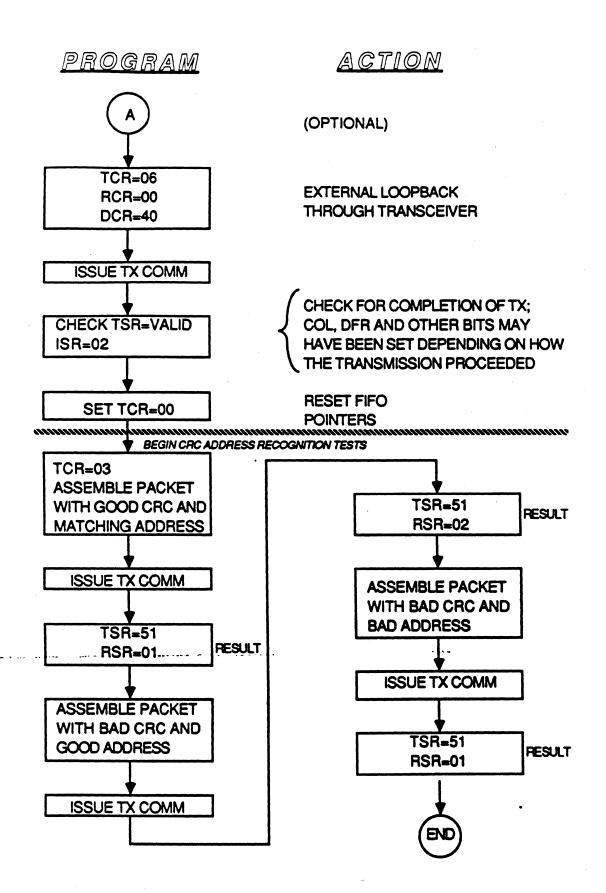

The "T" options allows you to change the NIC configuration registers and interrupt mask register. When this option is selected, you will be prompted to change the Data Configuration Register (DCR), the Transmit Configuration Register (TCR), the Receive Configuration Register (RCR), and Interrupt Mask Register (IMR). The default values are indicated in brackets ([xx]). To change these registers, enter the appropriate hex value; otherwise hit <return> to leave the register unchanged. Note that if this option is not selected, the NIC is configured with the default values shown in the brackets.

The "H" option displays all good packets received.

The "T" option allows you to continuously transmit packets with a destination address prompted by the program.

These options may be-selected singly or together and may be in any order.

## SCREEN DISPLAY

When the program is executing, various messages and characters are displayed to indicate good and bad reception and transmissions. The meanings of the characters are as follows:

good packet received.

- n a packet receive interrupt was set but there was nothing in the Receive Buffer Ring. Action taken: exit the interrupt service routine.

- b packet received but with bad receive status (anything other than 01h or 21h) in NIC header. Action taken: ignore the packet and move on to the next one, if any.

- d packet received but the DMA did not complete. Action taken: reattempt to DMA the packet again.

- r packet received but the Next Page Pointer in the NIC header was outside the limits of the Receive Buffer Ring. Action taken: reset the BOUNDARY and CURRENT registers to their initial conditions.

- 1 packet received but too long (>1500). Action taken: ignore packet and move on to the next packet, if any.

- t good packet transmitted.

- NOTE: There are other messages to indicate transmission errors such as Excessive Collisions, Carrier Sense Lost, and FIFO Underrun.

## Network Evaluation Software

Preliminary

X exiting from the interrupt service routine.

### Messager:

- •••• Bad address in packet ••• [address of packet] This message occurs if there is a mismatch between the address of the incoming packet and the expected address that was entered with the "C" option.

- Bad data in packet \*\*\* [location where error occurred] This message occurs if the incoming packet deviated for the pattern 0,1,2,...,E,0,1,2,...,etc. and the "C" option was selected.

The program has two keyboard commands,  $\sim E$  and any other key. When  $\sim E$  is typed the program displays network statistics (as shown below) then exits and returns to DOS. The program does not exit until the interrupt service routine has exited (i.e. after an "X" has been displayed). Hitting any other key will transmit a packet.

## NETWORK STATISTICS COUNT (hex)

| Number | of | good transmissions: 0000  | 0000 |

|--------|----|---------------------------|------|

| Number | of | bad transmissions:        | 0000 |

| Number | 10 | good receptions: 0000     | 0000 |

|        |    | bad receptions:           | 0000 |

|        |    | Next Page Pointer errors: | 0000 |

Writing Drivers for the DP8390 Preliminary July 1986

## INTRODUCTION

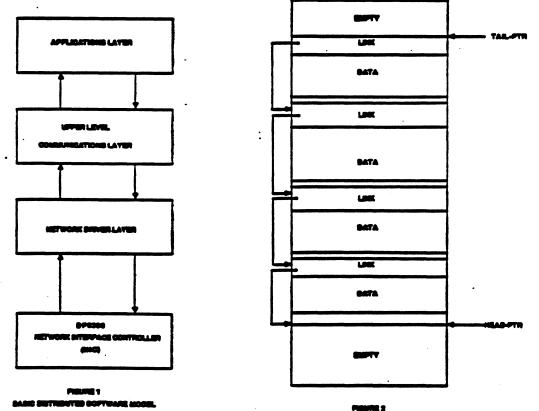

To reduce the complexity of networking software, it is organized as a series of layers. The number of layers, the name of each layer, and the function of each layer varies from network to network. However, in all networks, the purpose of each layer is to offer certain services to its adjacent layers and to shield those layers from how the offered services are actually implemented. Figure 1 illustrates a distributed software model consisting of (1) an applications layer, (2) an upper level communications layer, (3) a driver layer, and (4) the DP8390.

The two upper layers form the bulk of the software model and are beyond the scope of this document. This document is intended to provide the information necessary to write a network communication driver to provide certain services for upper layer software.

#### CUSTOM DRIVER PROCEDURES

The drivers consist of several custom-written procedures which will provide the following services:

- Hardware initialization

- Packet transmission

- Packet reception

- Detecting error conditions

The drivers should be able to run in an interrupt-driven environment which responds to the various interrupts produced by the DP8390. To achieve the highest performance the drivers should have as little overhead as possible.

## INITIALIZATION

The initialization procedure configures the DP8390 to conform to the present network. This involves initializing the proper configuration and address registers of the DP8390. A summary of the network parameters involved are shown below.

- the size of the data bus (8 or 16 bits)

- the physical and multicast addresses

- the types of interrupts used

- the size of the Receive Buffer Ring

- the size of the transmit buffer

- the FIFO threshold

An example of an initialization routine for a typical network system is provided at the end of this document (DriverInitialize).

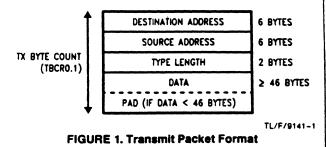

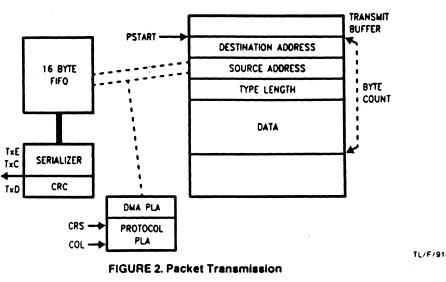

#### PACKET TRANSHISSION

The transmit driver is responsible for making a "best effort" delivery to the destination node. By "best effort" we mean that the drivers ensure that a packet will be delivered with a high probability of success. This is not to say that the driver must make a 100% delivery; this is the responsibility of the upper layer software. Since the DP8390 implements a binary backoff algorithm which retransmits up to 15 times in the event of collisions, some "best effort" delivery is already built into the hardware.

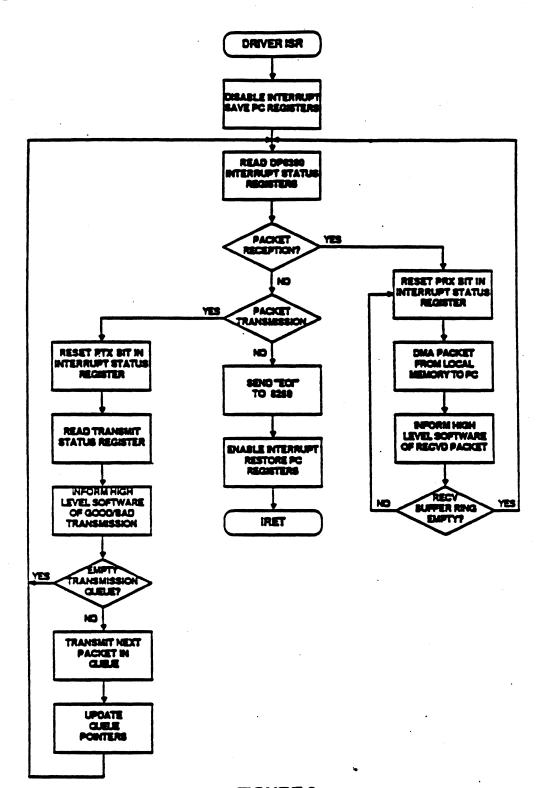

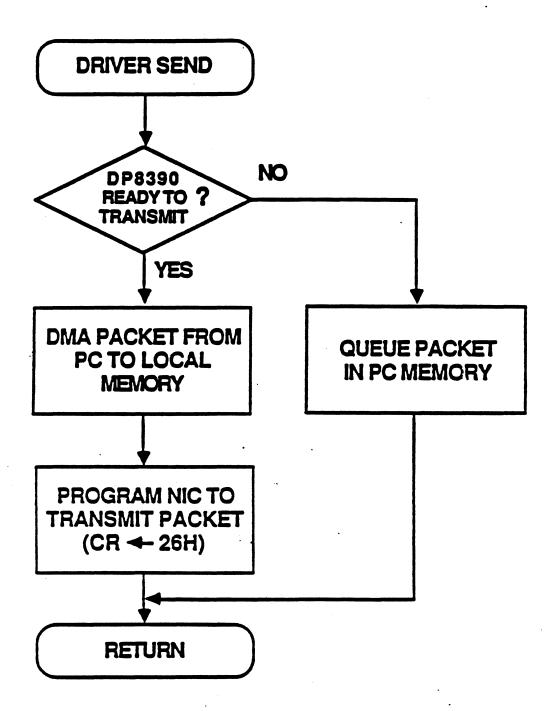

The transmit drivers are generally partitioned into two parts. The first-part (DriverSend) initiates a transmission whenever the upper level software desires to send a packet. If the transmitter is not ready, however, the supplied packet should be queued in a transmit-pending buffer. After transmit initiation or queueing, DriverSend returns.

DriverSend operates in conjunction with an interrupt service routine (Driver-ISR). After completing the transmission, the DP8390 interrupts the CPU to signal the end of the transmission and to indicate status information. Since the transmit drivers can not assure delivery, they must inform the upper level software of successful or errored transmissions. The DP8390 reports this status information in its TRANSMIT STATUS REGISTER.

#### The Transmit Queue

In many instances, a queue for transmitted packets is not required. A queue will be required if the rate at which packets can be generated by the upper level communications routine is higher than the rate at which they can be delivered on the network.

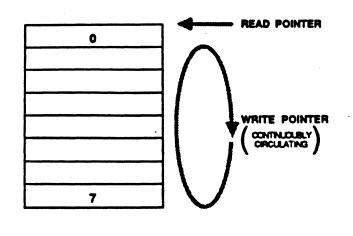

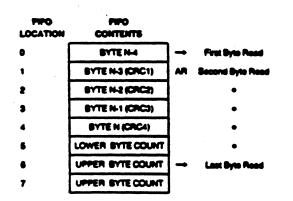

The recommended method for implementing a queue is a linked list as shown in figure 2. The queue consists of two pointers, head\_ptr and tail\_ptr, which respectively point to the next buffer space available and next buffer to be read. At the beginning of each buffer containing a packet, a pointer field points to the next packet in the queue, and the last buffer points to head\_ptr. Each time a packet is added or removed, either the head\_ptr or tail\_ptr is incremented. The queue should be circular where pointers "wrap around" when the boundaries of the queue have been reached.

The most efficient manner to remove packets from the transmit-pending queue is to use DriverSend to initiale transmission of the very first packet in the queue; then upon completion, use the DriverISR to transmit the remaining packets. Using this method, the DriverISR examines the queue, transmits the next available packet, then exits. The DriverISR transmits the next packet after the DP8390 issues the next transmit interrupt.

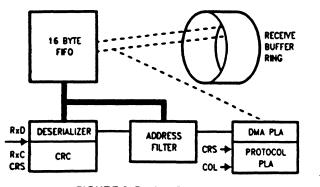

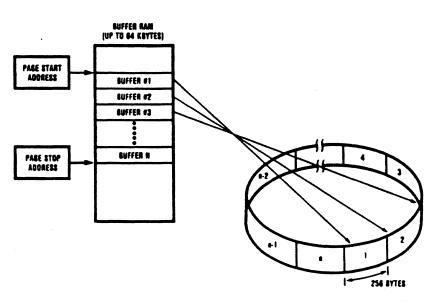

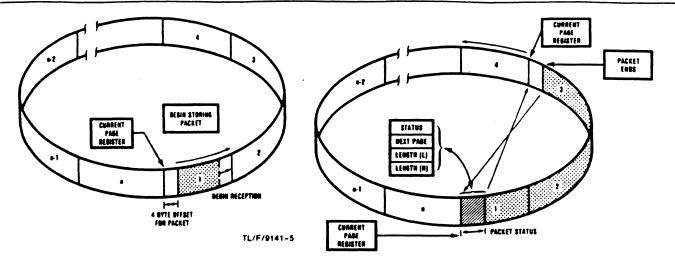

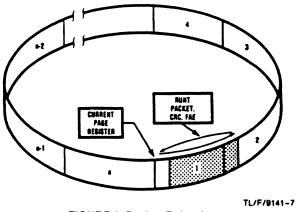

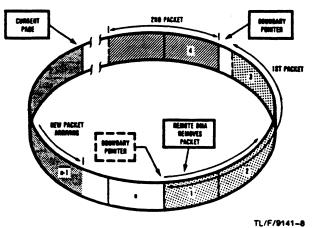

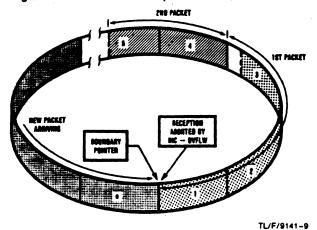

#### RECEIVE PROCESSING

The responsibility of the receive drivers is to buffer incoming packets from the network, and then to transfer them to the host. In most systems, the receive drivers will be operating with two different memory banks. One is the local memory which the DP8390 uses to buffer packets from the network: the other is the host memory. Depending upon which architecture is used, local memory can be dual ported or shared by the host CPU. In shared memory configurations, the host CPU intervenes directly with local memory. In dual ported systems, local memory is shielded from the host and data is transferred through a DVA channel.