DP8496/DP8497 SCSI-2 Disk Data Controller

# DP8496/DP8497 SCSI-2 Disk Data Controller

# **General Description**

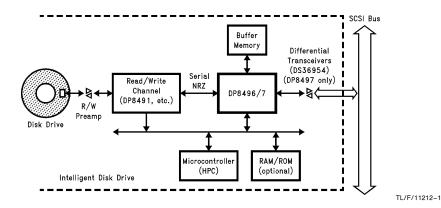

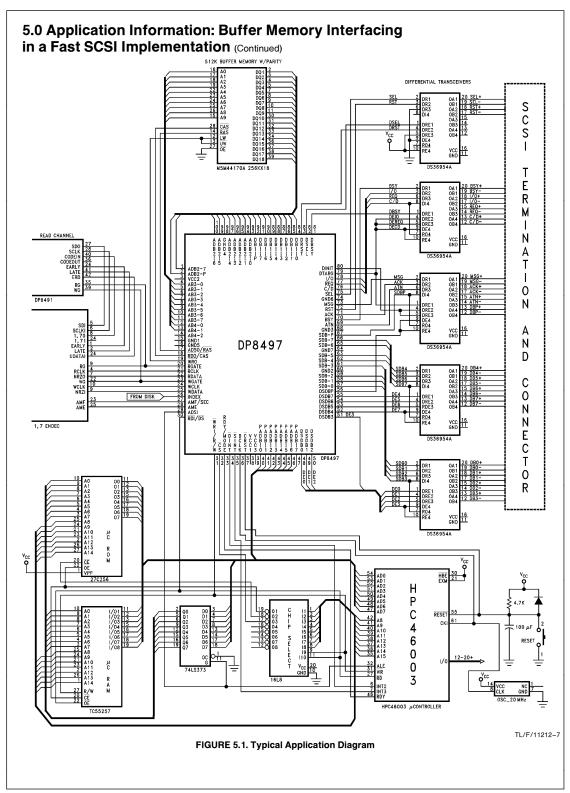

The DP8496/7 is a highly integrated, high-performance CMOS SCSI disk data controller. It is designed for use inside intelligent hard disk drives that utilize the Small Computer System Interface (SCSI) standard. It can also be used in ESDI, SMD and ST506 bridging controller applications. The DP8496/7 includes most of the data path functions needed to implement a complete hard disk controller. It includes a full featured SCSI Bus Controller, Buffer Memory Interface with pipelined pointers, fast Disk Data Controller, and a Processor Interface.

With the addition of National Semiconductor read-channel chips such as a PLL Synchronizer, and Encoder/Decoder, a pulse detector, and a head amplifier, complete data-path electronics of a SCSI drive can be implemented. A microcontroller, such as National's HPCTM, may be used to manage the SCSI commands and the drive specific control signals. The high level of intelligence implemented on the DP8496/7 means lower overhead for the disk-drive's embedded microcontroller, making possible a high-performance design employing only one micro-controller.

The DP8496 provides on-chip single-ended transceivers for driving the SCSI bus. The DP8497 provides all control signals necessary for direct interfacing with differential transceivers recommended for Fast SCSI option of SCSI-2.

# Features

- High disk data rates:

- DP8496/7-33 33 Mbit/sec

- DP8496/7-50 50 Mbit/sec

- Synchronous SCSI-2 transfer rates up to 10 MByte/sec with offset up to 16 (Fast option)

- Asynchronous SCSI transfer rates up to 5 MByte/sec

- Support for Fast Page Mode and Static Column Decode type DRAMs

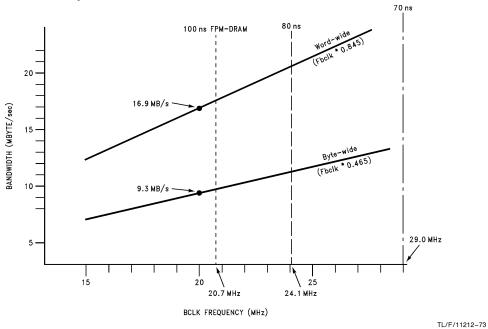

- Attains sustained buffer bandwidths above 9 MByte/sec with byte-wide memory configuration

- Word-wide buffer memory port allows sustained bandwidths of 17 MByte/sec

- Buffer memory up to 4 MBytes DRAM or 1 MByte SRAM

- On-chip DMA with buffered pointer addresses

- Multi-phase type SCSI commands

- Parity error checking on SCSI, buffer memory, and all internal data paths

- Programmable format and sectoring modes including soft, pseudo-hard, and hard

- 32, 48 or 56-bit computer generated ECC with on-chip correction

- On-chip single-ended transceivers on DP8496. DP8497 interfaces directly with differential transceivers for Fast SCSI

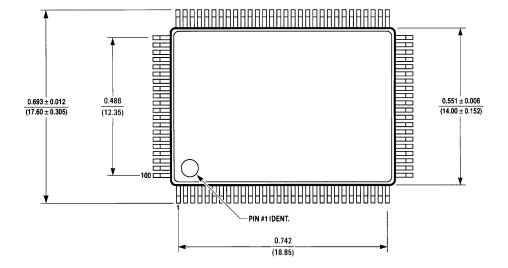

- Available in 100-pin PQFP package

# **System Diagram**

TRI-STATE® is a registered trademark of National Semiconductor Corporation HPC™ is a trademark of National Semiconductor Corporation.

HPC™ is a trademark of National Semiconductor Corporation.

© 1995 National Semiconductor Corporation TL/F/11212

# **Table of Contents**

# 1.0 OVERVIEW

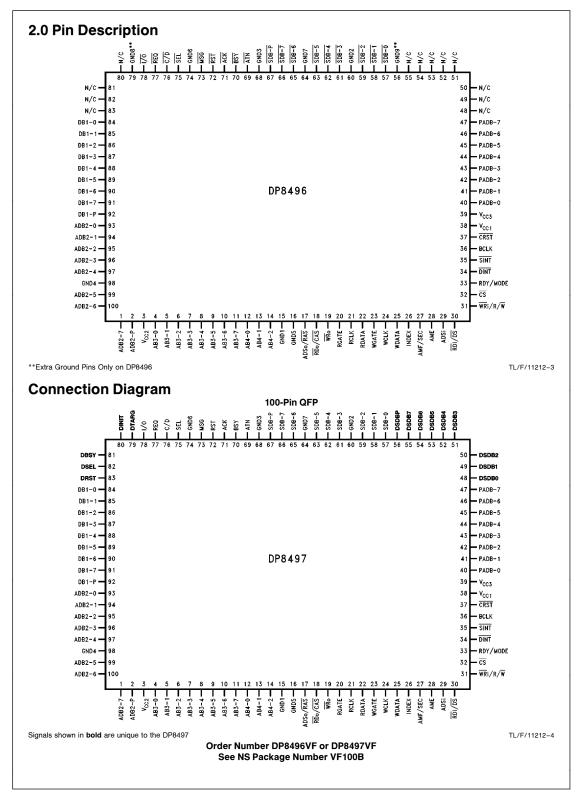

#### 2.0 PIN DESCRIPTION

#### 3.0 REGISTER LIST

- 3.1 Reset Summary

- 3.2 Initialization Registers

#### 4.0 FUNCTIONAL DESCRIPTION

- 4.1 Processor Interface

- 4.1.1 Access by Different Type Processors

- 4.2 Buffer Memory Interface

- 4.2.1 Static RAM

- 4.2.2 Dynamic RAM

- 4.2.3 Data Transfer Timing

- 4.2.4 Pointers

- 4.2.5 Buffer Management

- 4.2.6 Processor Access to Buffer Memory

- 4.2.7 16-Bit Wide Access

- 4.2.8 Sequential Accesses of Buffer Memory

- 4.2.9 Parity

- 4.2.10 Register Description

- 4.3 Disk Data Controller

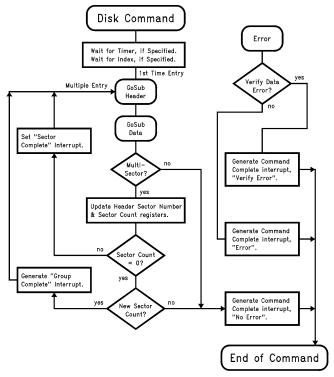

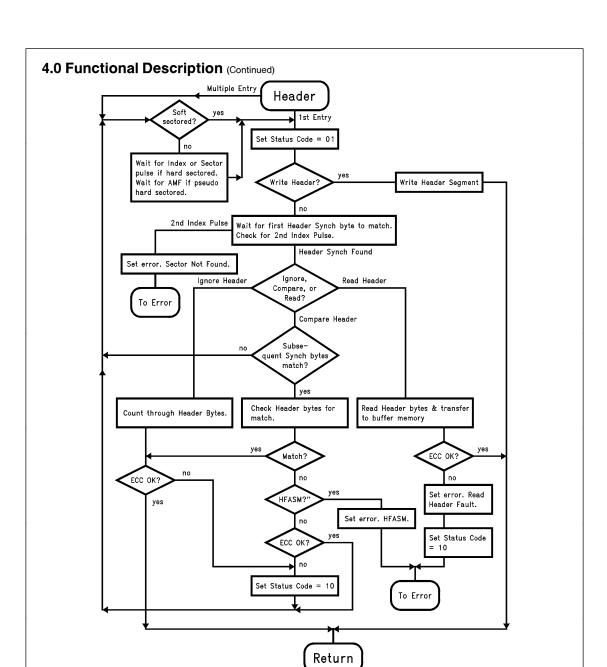

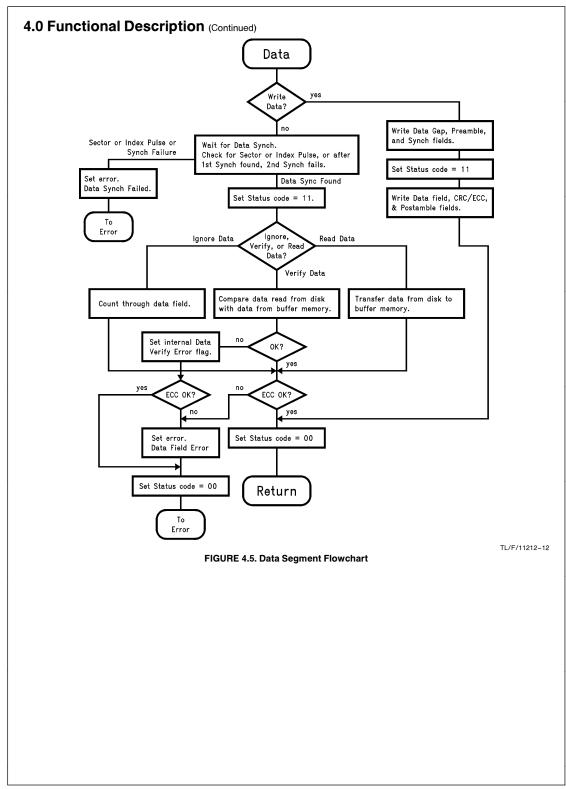

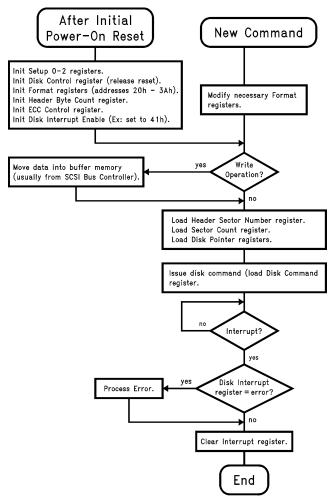

- 4.3.1 Command Operation

- 4.3.2 Disk Command and Control Registers

- 4.3.3 Format Registers

- 4.3.4 Disk Operations

- 4.4 SCSI Interface

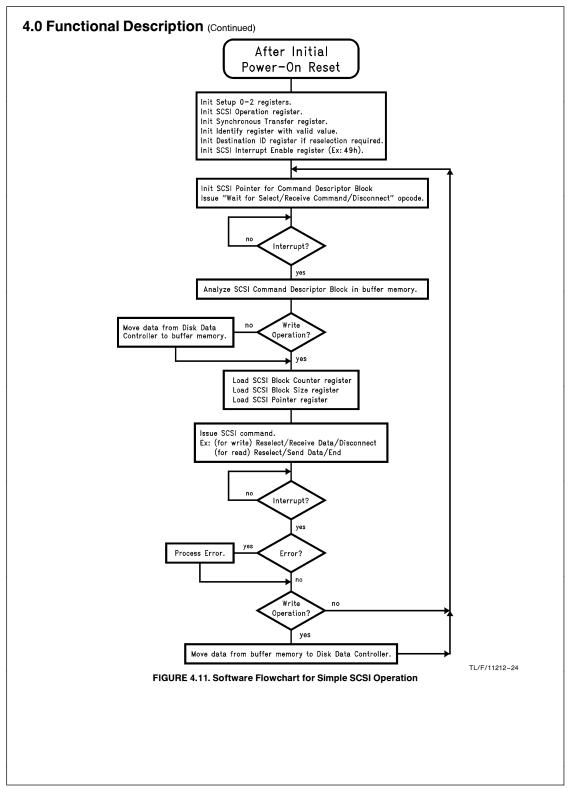

- 4.4.1 Simple SCSI Operations

- 4.4.2 SCSI Registers

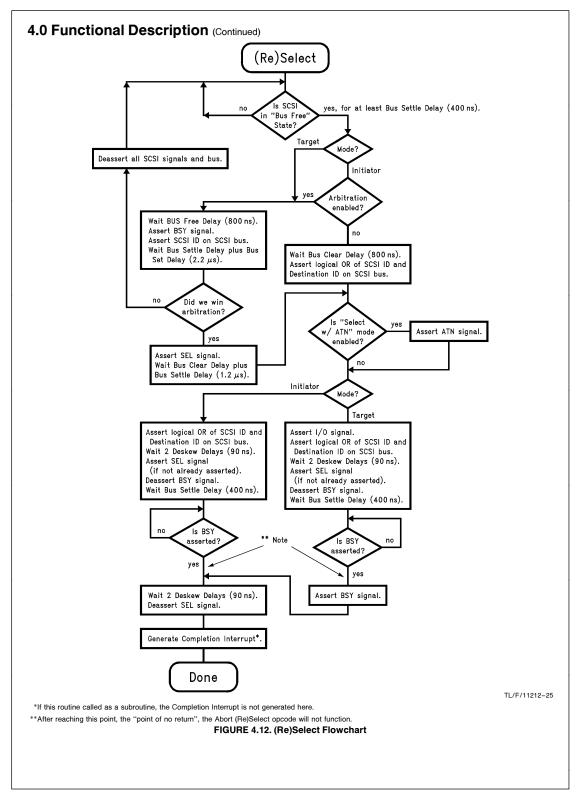

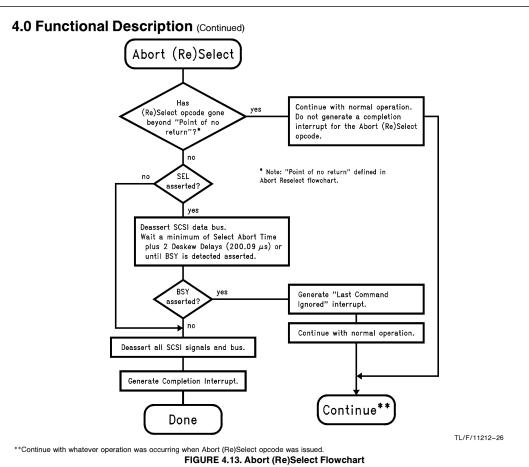

- 4.4.3 SCSI Operations

- 4.5 Timer

- 4.5.1 Timer Register Descriptions

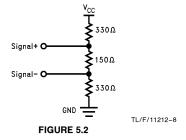

# 5.0 APPLICATION INFORMATION: BUFFER MEMORY INTERFACING IN A FAST SCSI IMPLEMENTATION

#### 6.0 D.C. SPECIFICATIONS

## 7.0 A.C. SPECIFICATIONS

- 7.1 Clock Timing

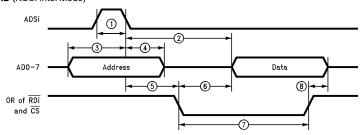

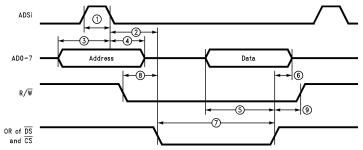

- 7.2 Register Read (Intel)

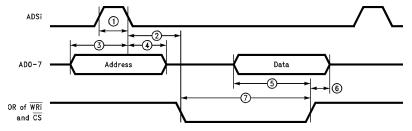

- 7.3 Register Write (Intel)

#### 7.0 A.C. SPECIFICATIONS (Continued)

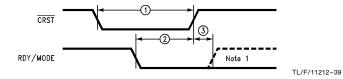

- 7.4 Ready Pin

- 7.5 Mode Pin (Mot.)

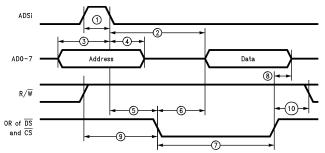

- 7.6 Register Read (Mot.)

- 7.7 Register Write (Mot.)

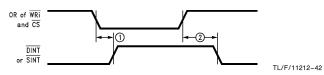

- 7.8 Interrupts

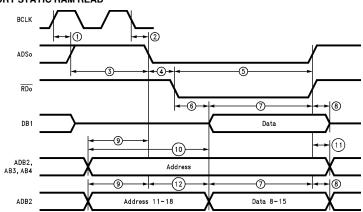

- 7.9 Buffer Memory Static Read

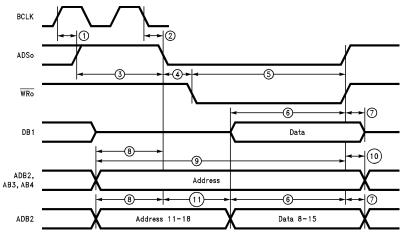

- 7.10 Buffer Memory Static Write

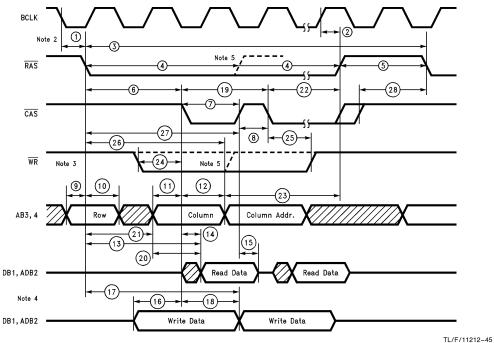

- 7.11 Buffer Memory Dynamic RAM Read/Write

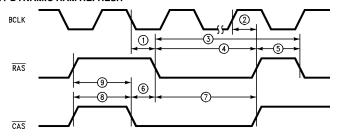

- 7.12 Buffer Memory DRAM Refresh

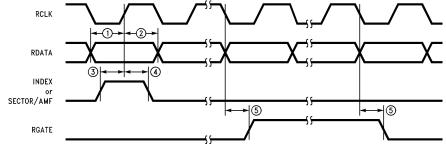

- 7.13 Disk Read Data Timing

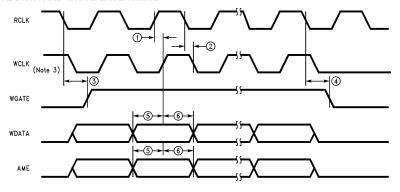

- 7.14 Disk Write Data Timing

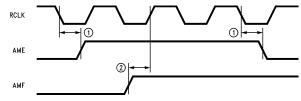

- 7.15 Disk Address Mark

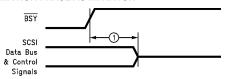

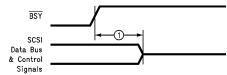

- 7.16 SCSI Reset

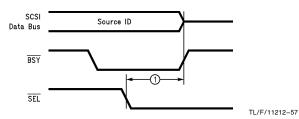

- 7.17 SCSI Arbitration

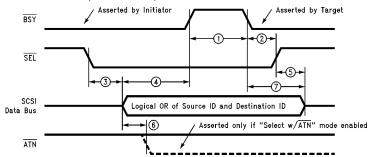

- 7.18 SCSI Selection as Init (w/o Arb.)

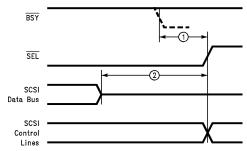

- 7.19 SCSI Selection as Init (with Arb.)

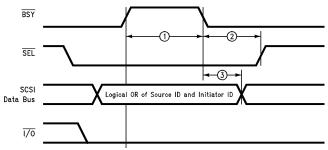

- 7.20 SCSI Reselection as Init

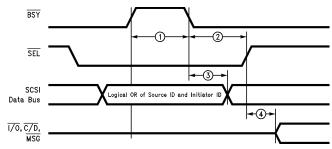

- 7.21 SCSI Selection (Targ)

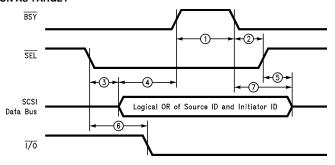

- 7.22 SCSI Reselection (Targ)

- 7.23 SCSI Lost Arbitration

- 7.24 SCSI Abort (Re)Selection

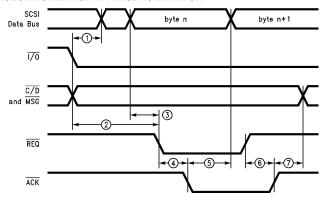

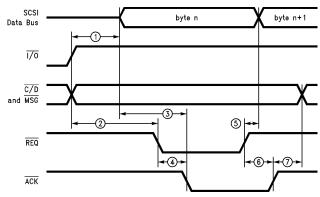

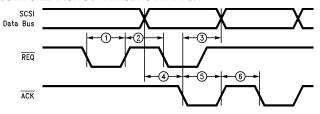

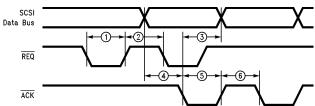

- 7.25 SCSI Async Info In (Init)

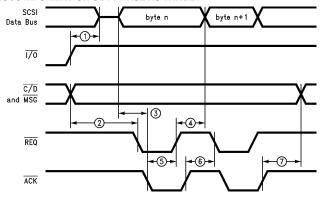

- 7.26 SCSI Async Info In (Targ)

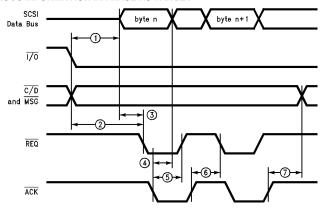

- 7.27 SCSI Async Info Out (Init)

- 7.28 SCSI Async Info Out (Targ)

- 7.20 3031 Asylic lillo Out (18

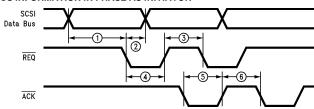

- 7.29 SCSI Sync Info In (Init)

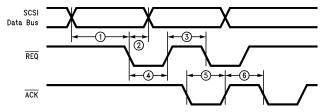

- 7.30 SCSI Sync Info In (Targ)7.31 SCSI Sync Info Out (Init)

- 7.32 SCSI Sync Info Out (Targ)

- 7.33 SCSI Bus Free (Init)

- 7.34 SCSI Bus Free (Targ)

- 7.35 Differential Transceiver Direction Control

- 7.36 Direction Control for Target and Initiator

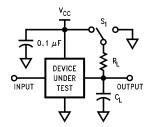

### 8.0 A.C TEST CONDITIONS

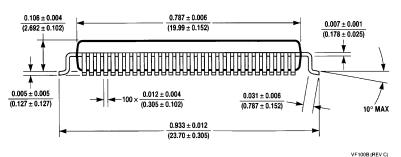

# 9.0 PHYSICAL DIMENSIONS

### 1.0 Overview

The DP8496/7 contains four major sections. Each section is listed below along with the major functions performed within that section.

1. Processor Interface

Processor Interface for chip control

2. Buffer Memory Interface

SRAM/DRAM control timing

Memory access arbitration

Memory access prioritization

3. Disk Data Controller

Serializer/Deserializer (SERDES)

Read/Write/Format Control

CRC/ECC generation/checking/correcting

4. SCSI Bus Controller

SCSI Data Transfer Control

SCSI Bus Control-phase changes

Parity generation/checking

On-chip bus transceivers

The Processor Interface section allows the drive's processor access to all programmable features of the chip. This interface is used to initiate and control any function or operation on both disk and SCSI data. All DP8496/7 registers are accessed through this section.

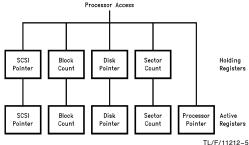

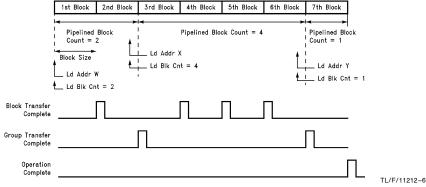

Buffer RAM is needed for all disk or SCSI data transfers. This RAM is connected to the Buffer Memory Interface section. The DP8496/7 assumes exclusive access to this buffer RAM. This enables the chip to utilize the full bandwidth of the RAM to streamline any combination of disk, SCSI or processor transfers. All transfer of data is done with on-chip DMA. Address pointers may be pipelined which will allow different groups of data to be placed in non-consecutive locations in buffer memory.

The Disk Data Controller section transfers NRZ data to the serial disk data path. Sector size, gaps, synch bytes, etc. are programmable. It can work with hard or soft sectored drives. ESDI soft sectored (pseudo-hard) AMF/AME handshaking is programmable. Fixed 32/48/56-bit ECC polynomial hardware automatically generates and checks error correction fields. Correction calculation is done on chip which will relieve the processor of the time and code space overhead of this function.

The SCSI Bus Controller section saves the user board area by integrating the 48 mA open drain drivers. The controller was designed to minimize the number of interrupts generated due to phase changes, parity errors and the like. Groups of often used phase sequences can be invoked with a single command.

An internal timer is also available on the DP8496/7 which may be used to accurately control the execution of certain commands for the disk or SCSI sections.

# **Block Diagram**

TL/F/11212-2

| Symbol        | Pin      | Туре     | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|---------------|----------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DISK DATA     | CONTRO   | LLER PIN | S                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| RGATE         | 20       | 0        | <b>READ GATE:</b> This active high output is asserted while the Disk Data Controller is reading data from the disk. It commands an external data separator to acquire lock and enables the RDATA pin.                                                                                                                                                                                                                                                                                                                                                                                   |

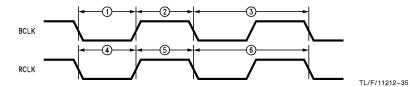

| RCLK          | 21       | ı        | READ CLOCK: This input is the disk data rate clock. When RGATE is deasserted low, this pin will receive the crystal or servo derived clock. When RGATE is asserted high, this pin will receive the recovered NRZ clock from the decoder. Each rising edge of the clock at this input is used to strobe RDATA into the Disk Data Controller. The AC timing characteristics should not be violated, even during the time of transition between clock sources.                                                                                                                             |

| RDATA         | 22       | I        | READ DATA: This active high input accepts NRZ disk data from the data synchronizer/decoder.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| WGATE         | 23       | 0        | WRITE GATE: This active high output is asserted while writing data to the disk.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| WCLK          | 24       | 0        | WRITE CLOCK: This output is derived from RCLK and is used to clock NRZ WDATA out from the DP8496/7. The rising edge indicates vaild WDATA.                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| WDATA         | 25       | 0        | WRITE DATA: This active high output is the NRZ data to be written to the disk. It is synchronized to WCLK. It is held deasserted any time WGATE is deasserted.                                                                                                                                                                                                                                                                                                                                                                                                                          |

| INDEX         | 26       | I        | INDEX: This active high input from the disk drive signifies the start of a track. Disk Data Controller commands may be synchronized to it.                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| AMF/SEC       | 27       | I        | ADDRESS MARK FOUND/SECTOR: This active high input denotes the start of a sector in hard and pseudo-hard sectored drives. Soft sectored drives use AMF to denote the start of header and data fields.                                                                                                                                                                                                                                                                                                                                                                                    |

| AME           | 28       | 0        | ADDRESS MARK ENABLE: This active high output forces the read-channel encoder to generate an Address Mark. It is also used to enable Address Mark detection for pseudo-hard sectored drives.                                                                                                                                                                                                                                                                                                                                                                                             |

| PROCESSO      | R INTERF | ACE PINS | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| CRST          | 37       | I        | <b>RESET:</b> This active low Schmitt input will reset the DP8496/7 immediately without regard to data transfers which may be in progress. Registers affected are listed in Table 3.1.                                                                                                                                                                                                                                                                                                                                                                                                  |

| PADB0:7       | 40-47    | 1/0      | PROCESSOR/ADDRESS/DATA BUS 0-7: These eight active high, bi-directional lines transfer information between the DP8496/7 and the processor.                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| ADSi          | 29       | I        | ADDRESS STROBE IN: This active high input latches the address from PADB0-7 on the falling edge. The latched address is used to select internal registers.                                                                                                                                                                                                                                                                                                                                                                                                                               |

| RDi or DS     | 30       | ı        | The function of this pin is determined by the processor mode initialized by the $\overline{RDY}/MODE$ pin. READ STROBE (IN): NSC/Intel mode: This active low input combined with a low level on $\overline{CS}$ will assert data from the addressed register onto the PADB0–7 bus.  DATA STROBE: Zilog/Motorola Mode: This active low input combined with a low level on $\overline{CS}$ will either assert data from the addressed register onto the PADB0–7 bus, or it will write data present on the PADB0–7 bus into the register. The data direction is determined by the W/R pin. |

| WRi or<br>R/W | 31       | 1        | The function of this pin is determined by the processor mode initialized by the RDY/MODE pin.  WRITE STROBE (IN)—NSC/Intel Mode: This active low input combined with a low level on $\overline{CS}$ will write data present on the PADB0-7 bus into the addressed register.  READ/WRITE—Zilog/Motorola Mode: This pin determines the direction of data transfer on the PADB0-7 bus while the $\overline{CS}$ and $\overline{DS}$ pins are both asserted. High = Read, Low = Write.                                                                                                      |

| CS            | 32       | 1        | CHIP SELECT: This active low input must be asserted to access any of the registers.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Symbol          | Pin                     | Туре     | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

|-----------------|-------------------------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| PROCESS         | OR INTER                | RFACE PI | NS (Continued)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| RDY or<br>MODE  | 33                      | 1/0      | The function of this pin is determined by the state of the $\overline{\text{CRST}}$ pin. <b>READY</b> ( $\overline{\text{CRST}}$ Pin Deasserted): When low, this output indicates that the Buffer Memory Data register access must be extended by the processor. This pin can be connected to the processor's wait-state input. Refer to Section 4.2.8 for a more complete description of this option. This pin is only active while in the NSC/Intel mode. This pin will be driven low internally while in the Zilog/Motorola mode. <b>MODE</b> ( $\overline{\text{CRST}}$ Pin Asserted): This input will determine the processor access mode of the DP8496/7. If this pin is left floating or pulled or driven high while $\overline{\text{CRST}}$ is asserted, the National/Intel mode will be enabled. If this pin is pulled or driven low while $\overline{\text{CRST}}$ is asserted, the Zilog/Motorola mode will be enabled.  While $\overline{\text{CRST}}$ is asserted, an internal pull-up resister is active. See the DC specifications for characteristics. |  |

| DINT            | 34                      | 0        | <b>DISK INTERRUPT:</b> This active low output will be asserted on any Disk Data Controller condition enabled by the Disk Interrupt Enable register. If the CI (Combine Interrupts) bit in the Setup 3 register is set to "1", this pin will become asserted if either a Disk Data Controller or a SCSI Bu Controller interrupt occurs.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

| SINT            | 35                      | 0        | SCSI INTERRUPT: This active low output will be asserted on any SCSI Bus Controller condition enabled by the SCSI Interrupt Enable register.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

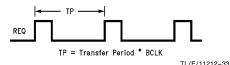

| BCLK            | 36                      | I        | BUS CLOCK: This input is used by the Buffer Memory Interface for access timing and DMA arbitration. It is also used by the SCSI Bus Controller for timing.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

| SCSI BUS        | CONTRO                  | LLER PIN | S (All SCSI Signals are Active High on the DP8497)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

| SDB0:7,<br>SDBP | 57-59<br>61-63<br>65-67 | 1/0      | SCSI DATA, PARITY BUS: These nine active low, open drain, bi-directional lines should be connected directly to the SCSI data bus.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

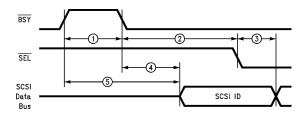

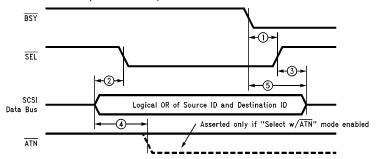

| BSY             | 70                      | 1/0      | BUSY: Same as above. Should be connected to SCSI control bus.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

| SEL             | 75                      | 1/0      | SELECT: Same as above.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

| C/D             | 76                      | 1/0      | COMMAND/DATA: Same as above.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

| Ī/O             | 78                      | 1/0      | INPUT/OUTPUT: Same as above.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

| REQ             | 77                      | 1/0      | REQUEST: Same as above.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

| ĀCK             | 71                      | I/O      | ACKNOWLEDGE: Same as above.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

| ĀTN             | 69                      | 1/0      | ATTENTION: Same as above.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

| MSG             | 73                      | 1/0      | MESSAGE: Same as above.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

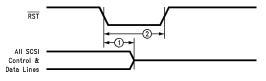

| RST             | 72                      | 1/0      | SCSI RESET: If CRST is asserted during power-up, the RST pin will not produce a glitch. See AC Specifications for input de-glitch description.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| Symbol                       | Pin                    | Type    | Function                                                                                                                                                                                                                                                                                                                                          |

|------------------------------|------------------------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SCSI BUS TI                  | RANSCEIVE              | R DIREC | TION CONTROL PINS (DP8497 Only)                                                                                                                                                                                                                                                                                                                   |

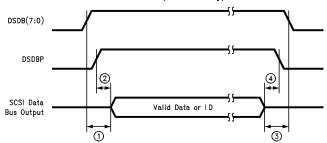

| DSDB0:7,<br>DSDBP            | 48-56                  | 0       | <b>DIRECTION CONTROL FOR SCSI DATA, PARITY BUS:</b> Each of these signals connects to the appropriate enable pin of the differential transceivers used for a Fast SCSI implementation and controls the direction of its corresponding SCSI data bus signal. A high level on these pins enables the driver while a low level enables the receiver. |

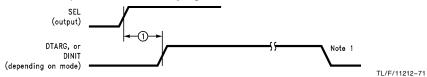

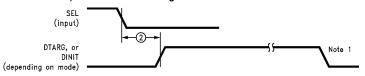

| DTARG                        | 79                     | 0       | DIRECTION CONTROL FOR TARGET SIGNALS: Same as above. Controls the direction of $\overline{C/D}$ , $\overline{I/O}$ , $\overline{REQ}$ and $\overline{MSG}$ signals.                                                                                                                                                                               |

| DINIT                        | 80                     | 0       | <b>DIRECTION CONTROL FOR INITIATOR SIGNALS:</b> Same as above. Controls the direction of $\overline{ACK}$ and $\overline{ATN}$ signals.                                                                                                                                                                                                           |

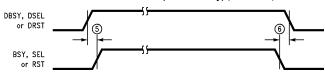

| DBSY                         | 81                     | 0       | <b>DIRECTION CONTROL FOR </b> BSY: Same as above. Controls the direction of BSY signal.                                                                                                                                                                                                                                                           |

| DSEL                         | 82                     | 0       | DIRECTION CONTROL FOR SEL: Same as above. Controls the direction of SEL signal.                                                                                                                                                                                                                                                                   |

| DRST                         | 83                     | 0       | <b>DIRECTION CONTROL FOR RST:</b> Same as above. Controls the direction of RST signal.                                                                                                                                                                                                                                                            |

| BUFFER MEMORY INTERFACE PINS |                        |         |                                                                                                                                                                                                                                                                                                                                                   |

| DB1-0:7,<br>DB1-P            | 84-92                  | 1/0     | <b>DATA BUS 1:</b> These nine active high, bi-directional lines transfer data between the DP8496/7 and the least significant 8-bits plus parity of buffer memory.                                                                                                                                                                                 |

| ADB2-0:7,<br>ADB2-P          | 93–97<br>99–100<br>1–2 | 1/0     | ADDRESS DATA BUS 2: These nine active high, bi-directional lines transfer data between the DP8496/7 and the most significant 8-bits plus parity of buffer memory if word mode is enabled. These pins also contain address information for static RAM. See Tables 4.2 and 4.3.                                                                     |

| AB3-0:7                      | 4–11                   | 0       | ADDRESS BUS 3: These eight active high outputs represent address information for both SRAM and DRAM. See Tables 4.2 to 4.5.                                                                                                                                                                                                                       |

| AB4-0:2                      | 12-14                  | 0       | ADDRESS BUS 4: These three active high outputs represent address information for both SRAM and DRAM. See Tables 4.2 to 4.5.                                                                                                                                                                                                                       |

| RDo or<br>CAS                | 18                     | 0       | The function of this pin is determined by the use of SRAM or DRAM.  READ STROBE (OUT): SRAM.  COLUMN ADDRESS STROBE: DRAM.                                                                                                                                                                                                                        |

| WRo                          | 19                     | 0       | WRITE STROBE (OUT): Always.                                                                                                                                                                                                                                                                                                                       |

| ADSo or<br>RAS               | 17                     | 0       | The function of this pin is determined by the use of SRAM or DRAM.  ADDRESS STROBE (OUT): SRAM. In word mode, controls address latch for ADB2 bus.  High level on this signal should be used by an external latch to accept address inputs— latching them on the falling edge.  ROW ADDRESS STROBE: DRAM.                                         |

# 2.0 Pin Description (Continued)

| Pin                                                | Symbol                                                                       | Function                                                                                                                                                |

|----------------------------------------------------|------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                                                  | ADB2-7<br>ADB2-P                                                             | Buffer Memory<br>Address/Data Bus 2                                                                                                                     |

| 3                                                  | V <sub>CC2</sub>                                                             | +5 V <sub>DC</sub>                                                                                                                                      |

| 4<br>5<br>6<br>7<br>8<br>9<br>10                   | AB3-0<br>AB3-1<br>AB3-2<br>AB3-3<br>AB3-4<br>AB3-5<br>AB3-6<br>AB3-7         | Buffer Memory<br>Address Bus 3                                                                                                                          |

| 12<br>13<br>14                                     | AB4-0<br>AB4-1<br>AB4-2                                                      | Buffer Memory<br>Address Bus 4                                                                                                                          |

| 15<br>16                                           | GND1<br>GND5                                                                 | GND<br>GND                                                                                                                                              |

| 17<br>18<br>19                                     | ADSo/RAS<br>RDo/CAS<br>WRo                                                   | Buffer Memory<br>Strobes                                                                                                                                |

| 20<br>21<br>22<br>23<br>24<br>25<br>26<br>27       | RGATE<br>RCLK<br>RDATA<br>WGATE<br>WCLK<br>WDATA<br>INDEX<br>AMF/SEC         | Disk Read Gate Disk Read Clock Disk Read Data Disk Write Gate Disk Write Clock Disk Write Data Disk Index Input Disk Address Mark Found or Sector Input |

| 28                                                 | AME                                                                          | Address Mark Enable                                                                                                                                     |

| 29<br>30<br>31<br>32<br>33<br>34<br>35<br>36<br>37 | ADSI RDI/DS WRI/R/W CS RDY/MODE DINT SINT BCLK CRST                          | Processor Port<br>Strobes  Ready/Mode Disk Interrupt SCSI Interrupt Bus Clock Chip Reset                                                                |

| 38<br>39                                           | V <sub>CC1</sub><br>V <sub>CC3</sub>                                         | +5 V <sub>DC</sub><br>+5 V <sub>DC</sub>                                                                                                                |

| 40<br>41<br>42<br>43<br>44<br>45<br>46<br>47       | PADB-0<br>PADB-1<br>PADB-2<br>PADB-3<br>PADB-4<br>PADB-5<br>PADB-6<br>PADB-7 | Processor Address/<br>Data Bus                                                                                                                          |

| 48<br>49<br>50<br>51                               | DSDB0<br>DSDB1<br>DSDB2<br>DSDB3                                             | Transceiver Direction<br>Control for DP8497<br>(N/C on DP8496)                                                                                          |

| Pin                                          | Symbol                                                                        | Function                                                                                       |

|----------------------------------------------|-------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|

| 52<br>53<br>54<br>55<br>56                   | DSDB4<br>DSDB5<br>DSDB6<br>DSDB7<br>DSDBP(DP8497)<br>GND9 (DP8496)            | Direction Control (Continued)  GND on DP8496 Only                                              |

| 57<br>58<br>59                               | SDB-0<br>SDB-1<br>SDB-2                                                       | SCSI Data Bus                                                                                  |

| 60                                           | GND2                                                                          | GND                                                                                            |

| 61<br>62<br>63                               | SDB-3<br>SDB-4<br>SDB-5                                                       | SCSI Data Bus                                                                                  |

| 64                                           | GND7                                                                          | GND                                                                                            |

| 65<br>66<br>67                               | SDB-6<br>SDB-7<br>SDB-P                                                       | SCSI Data Bus SCSI Parity                                                                      |

| 68                                           | GND3                                                                          | GND                                                                                            |

| 69<br>70<br>71<br>72<br>73                   | ATN BSY ACK RST MSG                                                           | SCSI Attention SCSI Busy SCSI Acknowledge SCSI Reset SCSI Message                              |

| 74                                           | GND6                                                                          | GND                                                                                            |

| 75<br>76<br>77<br>78                         | SEL<br>C/D<br>REQ<br>I/O                                                      | SCSI Select<br>SCSI Cmd/Data<br>SCSI Request<br>SCSI Input/Output                              |

| 79<br>80<br>81<br>82<br>83                   | GND8 (DP8496) DTARG ('97) DINIT DBSY DSEL DRST                                | Additional GND on DP8496<br>Transceiver Direction<br>Control on DP8497 only<br>(N/C on DP8496) |

| 84<br>85<br>86<br>87<br>88<br>89<br>90<br>91 | DB1-0<br>DB1-1<br>DB1-2<br>DB1-3<br>DB1-4<br>DB1-5<br>DB1-6<br>DB1-7<br>DB1-P | Buffer Memory Data<br>Bus 1                                                                    |

| 93<br>94<br>95<br>96<br>97                   | ADB2-0<br>ADB2-1<br>ADB2-2<br>ADB2-3<br>ADB2-4<br>GND4                        | Buffer Memory<br>Address/Data Bus 2<br>GND                                                     |

| 99                                           | ADB2-5                                                                        | Buffer Memory                                                                                  |

| 100                                          | ADB2-6                                                                        | Address/Data Bus 2                                                                             |

# 3.0 Register List

# DISK DATA CONTROLLER REGISTERS

| Addr. | Name                        | Label | R/W | Pg. |

|-------|-----------------------------|-------|-----|-----|

| 00-06 | ECC Shift Registers 0-6     | ESRx  | R   | 29  |

| 07    | ECC Control                 | EC    | R/W | 28  |

| 08-0F | Reserved                    |       |     |     |

| 10    | Disk Command                | DCMD  | W   | 23  |

| 11    | Disk Control                | DCTL  | R/W | 25  |

| 12    | Disk Interrupt              | DINT  | R/W | 27  |

| 13    | Disk Interrupt Enable       | DINTE | R/W | 27  |

| 14    | Disk Status                 | DSTAT | R   | 26  |

| 15    | Sector Number               | SN    | R/W | 28  |

| 16    | Header Byte Count/Interlock | HBC   | R/W | 28  |

| 17    | Sector Count                | SC    | R/W | 28  |

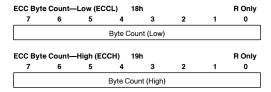

| 18    | ECC Byte Count (Low)        | ECCL  | R   | 29  |

| 19    | ECC Byte Count (High)       | ECCH  | R   | 29  |

| 1A-1F | Reserved                    |       |     |     |

# DISK FORMAT REGISTERS

| Addr. | Name                       | Label | R/W | Pg. |

|-------|----------------------------|-------|-----|-----|

| 20    | Post Sector/Index Count    | PSIG  | R/W | 29  |

| 21    | Header Preamble Count      | HPC   | R/W | 29  |

| 22    | Preamble Pattern           | PREP  | R/W | 30  |

| 23    | Header Synch #1, #2 Counts | HSC   | R/W | 30  |

| 24    | Header Synch #1 Pattern    | HSP1  | R/W | 30  |

| 25    | Header Synch #2 Pattern    | HSP2  | R/W | 30  |

| 26    | Header Byte 0, 1 Control   | HC01  | R/W | 30  |

| 27    | Header Byte 0 Pattern      | HP0   | R/W | 31  |

| 28    | Header Byte 1 Pattern      | HP1   | R/W | 31  |

| 29    | Header Byte 2, 3 Control   | HC23  | R/W | 31  |

| 2A    | Header Byte 2 Pattern      | HP2   | R/W | 31  |

| 2B    | Header Byte 3 Pattern      | HP3   | R/W | 31  |

| 2C    | Header Byte 4, 5 Control   | HC45  | R/W | 31  |

| 2D    | Header Byte 4 Pattern      | HP4   | R/W | 31  |

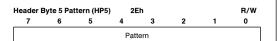

| 2E    | Header Byte 5 Pattern      | HP5   | R/W | 31  |

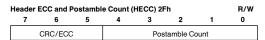

| 2F    | Header ECC & Postamble     | HECC  | R/W | 31  |

|       | Count                      |       |     |     |

| 30    | Postamble Pattern          | POSTP | R/W | 31  |

| 31    | Data Preamble Count        | DPC   | R/W | 31  |

| 32    | Data Synch #1, #2 Count    | DSC   | R/W | 31  |

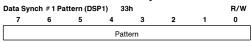

| 33    | Data Synch #1 Pattern      | DSP1  | R/W | 32  |

| 34    | Data Synch #2 Pattern      | DSP2  | R/W | 32  |

| 35    | Sector Byte Count (Low)    | SBCL  | R/W | 32  |

| 36    | Sector Byte Count (High)   | SBCH  | R/W | 32  |

| 37    | Data Format Pattern        | DFP   | R/W | 32  |

| 38    | Data ECC & Postamble       | DECC  | R/W | 32  |

|       | Count                      |       |     |     |

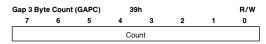

| 39    | Gap 3 Byte Count           | GAPC  | R/W | 32  |

| ЗА    | Gap 3 & PSIG Pattern       | GAPP  | R/W | 32  |

| 3B-3F | Reserved                   |       |     |     |

# SCSI REGISTERS

| Addr. | Name                  | Label | R/W | Pg. |

|-------|-----------------------|-------|-----|-----|

| 40    | SCSI Command          | SCMD  | W   | 39  |

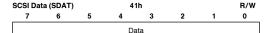

| 41    | SCSI Data             | SDAT  | R/W | 53  |

| 42    | SCSI Control          | SCTL  | R/W | 53  |

| 43    | SCSI Operation        | SOP   | R/W | 53  |

| 44    | Synchronous Transfer  | SYNC  | R/W | 54  |

| 45    | Identify              | IDENT | R/W | 55  |

| 46    | Destination ID        | DID   | R/W | 56  |

| 47    | Source ID             | SID   | R/W | 56  |

| 48    | SCSI Status           | SSTAT | R   | 56  |

| 49    | SCSI Interrupt        | SINT  | R   | 57  |

| 4A    | SCSI Interrupt Enable | SINTE | R/W | 60  |

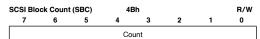

| 4B    | SCSI Block Count      | SBC   | R/W | 60  |

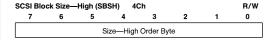

| 4C    | SCSI Block Size (MSB) | SBSH  | R/W | 60  |

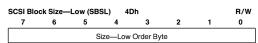

| 4D    | SCSI Block Size (LSB) | SBSL  | R/W | 60  |

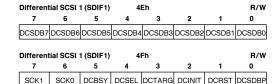

| 4E    | Differential SCSI 1   | SDIF1 | R/W | 60  |

| 4F    | Differential SCSI 2   | SDIF2 | R/W | 60  |

| 50-5F | Reserved              |       |     |     |

# SETUP AND TIMER REGISTERS

| Addr. | Name           | Label | R/W | Pg. |

|-------|----------------|-------|-----|-----|

| 60    | Setup 1        | SUP1  | R/W | 10  |

| 61    | Setup 2        | SUP2  | R/W | 11  |

| 62    | Setup 3        | SUP3  | R/W | 12  |

| 63    | Timer Prescale | TPRE  | R/W | 64  |

| 64    | Timer Count    | TCNT  | R/W | 64  |

# **BUFFER MEMORY REGISTERS**

| Addr. | Name                    | Label | R/W | Pg. |

|-------|-------------------------|-------|-----|-----|

| 65    | Disk Pointer (MSB)      | DP2   | R/W | 19  |

| 66    | Disk Pointer            | DP1   | R/W | 19  |

| 67    | Disk Pointer (LSB)      | DP0   | R/W | 19  |

| 68    | SCSI Pointer (MSB)      | SP2   | R/W | 19  |

| 69    | SCSI Pointer            | SP1   | R/W | 19  |

| 6A    | SCSI Pointer (LSB)      | SP0   | R/W | 19  |

| 6B    | Processor Pointer (MSB) | PP2   | R/W | 19  |

| 6C    | Processor Pointer       | PP1   | R/W | 19  |

| 6D    | Processor Pointer (LSB) | PP0   | R/W | 19  |

| 6E    | Buffer Memory Data      | BMD   | R/W | 19  |

| 6F-7F | Reserved                |       |     |     |

# 3.0 Register List (Continued)

# 3.1 RESET SUMMARY

There are four different types of resets that may be issued. Each reset has its own function and purpose. These are summarized in Table 3.1.

#### **3.2 INITIALIZATION REGISTERS**

The three basic Setup Registers, that must be initialized before proper chip operation can begin, are described in this section. All other registers are described in their respective sections in the Functional Description chapter; i.e., in the Disk Data Controller, SCSI Bus Controller, Processor Interface, Buffer Memory Interface, and Timer sections.

Setup 1 register is typically written only once after a reset to establish the physical path between the DP8496/7 and its buffer memory.

Setup 2 register contains control bits which may be modified by the processor for power-up tests, error recovery or normal operations.

Setup 3 register is typically written only once after a reset to establish pin configuration.

| Setup 1 | (SUP1) |     | 60  | Dh  |     |      | R/W  |  |

|---------|--------|-----|-----|-----|-----|------|------|--|

| 7       | 6      | 5   | 4   | 3   | 2   | 1    | 0    |  |

| CLK1    | CLK0   | sws | DFP | DD1 | DD0 | RSEL | RWID |  |

The contents of this register will be invalid after asserting the  $\overline{\text{CRST}}$  pin. It must be initialized before proper chip operation

#### CLK(1:0): BCLK Frequency

The Bus Clock (BCLK) is used for many functions within the DP8496/7. It is used in the SCSI Bus Controller, Buffer Memory Interface, and Timer sections. Therefore, the choice of Bus Clock frequency is very important. Table 3.2 lists the frequency range allowable for each bit combination of this field to guarantee timing specifications within the SCSI standard.

The minimum BCLK frequency allowed is 10 MHz. Choosing a clock frequency nearest the upper limit in a range results in the optimal and fastest execution fo SCSI operations.

#### **TABLE 3.1. Summary of Resets**

| Reset Type                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Purpose                       | Result                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Assert RST Bit in<br>Disk Control<br>Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Reset Disk<br>Data Controller | Clears and terminates current Disk command and any pipelined command. Clears Disk Status register. Clears bits 0–5 and 7 of the Disk Interrupt register. Deasserts RGATE, WGATE, and AME pins.                                                                                                                                                                                                                                                                   |

| Issue SCSI<br>Reset Command                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Reset SCSI<br>Bus Controller  | Clears all SCSI Bus signals.  Clears and terminates current SCSI command and any pipelined command.  Clears the following registers: SCSI Data, SCSI Control, SCSI Operation except the PEP (Parity Error to Processor) bit, Identify, Destination ID except the ID field, SCSI Status except the DBR (Data Buffer Ready) bit.  Generates an "Operation Complete" interrupt.                                                                                     |

| SCSI Bus Reset Reset All SCSI Devices on SCSI Bus                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                               | Clears all SCSI Bus signals except the RST signal. Clears and terminates current command and any pipelined command. Generates a "SCSI Bus Reset" interrupt.                                                                                                                                                                                                                                                                                                      |

| Assert CRST Pin  Power-Up Reset or Reset All Hardware  Sets RST bit in Disk Control register (see RST bit in Disk Control register)  Same result as issuing a SCSI Reset command (see above) of interrupt.  Clears the SCSI Operation register.  Clears the SCSI Interrupt and SCSI Interrupt Enable registers  The contents of the Setup 1 register becomes invalid.  The contents of the Setup 2 register becomes invalid except bit which is set to a "1" and the SPE bit which is reset to "0".  Resets Timer Prescale and Timer Count registers.  Clears Buffer Memory Data register. (This register will not reflimemory until the Processor Pointer registers are initialized.) |                               | Clears the SCSI Operation register. Clears the SCSI Interrupt and SCSI Interrupt Enable registers. The contents of the Setup 1 register becomes invalid. The contents of the Setup 2 register becomes invalid except the SPP (SCSI Parity Polarity) bit which is set to a "1" and the SPE bit which is reset to "0". Resets Timer Prescale and Timer Count registers. Clears Buffer Memory Data register. (This register will not reflect the contents of buffer |

# 3.0 Register List (Continued)

**TABLE 3.2. BCLK Frequency Range**

|      | K Freq.<br>ode | BCLK Range               |

|------|----------------|--------------------------|

| CLK1 | CLK0           |                          |

| 0    | 0              | 10.00 ≤ BCLK ≤ 15.00 MHz |

| 1    | 0              | 15.00 ≤ BCLK ≤ 17.50 MHz |

| 0    | 1              | 17.50 ≤ BCLK ≤ 20.00 MHz |

| 1    | 1              | 20.00 ≤ BCLK ≤ 25.00 MHz |

Note: Though not in binary order, this table is correct.

#### SWS: SRAM Wait State

This bit allows the user to extend SRAM wait states so that slower SRAMs may be used.

- Normal wait states. Single byte burst takes 5 cycles, 4 word bursts take 12 cycles, and 6 byte bursts take 17 BCLK cycles.

- Extended wait states. Single byte burst is extended to 6 cycles; the 4 word burst transfer is extended to 16 cycles; and the 6 byte burst transfer is extended to 23 cycles.

#### **DFP: Disable Fast Page**

- Fast Page DRAM access mode will be disabled. This

way normal DRAMs can be used. If SRAMs are being

used, then SRAM "Fast mode" will also be disabled;

thus SRAM transfers will occur in single byte/word

bursts.

- 0: Fast Page DRAM access mode will be enabled.

#### DD(1:0): DRAM Size

If DRAM is used, the DP8496/7 needs to know the organization, e.g.,  $64k \times n$ ,  $256k \times n$ , etc. This field controls the row and column address so that the least significant address bits are always on the column address. This will guarantee proper refresh timing during Buffer Memory transfers. The proper bit settings are shown in Table 3.3.

If SRAM is used, these bits are "don't care".

**TABLE 3.3. Organization of DRAM**

| DRAM | Depth | Organization of DRAM            |

|------|-------|---------------------------------|

| RSZ1 | RSZ0  |                                 |

| 0    | 0     | 64k x n, (64k x 1, 64k x 4 )    |

| 0    | 1     | 256k x n, (256k x 1, 256k x 4 ) |

| 1    | 0     | 1M x n, (1M x 1, 1M x 4 )       |

| 1    | 1     | 4M x n, (4M x 1, 4M x 4 )       |

#### **RSEL: DRAM/SRAM Select**

The DRAM/SRAM switch. This bit changes the memory access timing to control static or dynamic RAM memory. This bit must be set before any accesses are attempted to buffer memory. If DRAM is selected, the proper refresh timing to initiate  $\overline{\text{CAS}}$  before  $\overline{\text{RAS}}$  automatic refreshing is provided without any further intervention through the Processor Interface.

- 1 DRAM

- 0 SRAM

#### RWID: RAM Data Path Width

The value of this bit is used by the SDDC to determine whether to provide addresses for a byte-wide memory configuration or word-wide configuration—when disk or SCSI data accesses are made. The state of this bit has no effect on the processor address pointer, which always increments by one.

- Byte Mode. 8-bit wide buffer memory is being used. All address pointers will increment by one.

- Word Mode. 16-bit wide buffer memory is being used. Disk and SCSI address pointers will increment by two.

| Setup 2 | (SUP2) |     | 6   | 1h  |      |      | R/W  |   |

|---------|--------|-----|-----|-----|------|------|------|---|

| 7       | 6      | 5   | 4   | 3   | 2    | 1    | 0    |   |

| Al      | BPP    | BPE | SPP | SPE | SID2 | SID1 | SID0 | l |

The contents of this register will be invalid after assertion of the  $\overline{\text{CRST}}$  pin. This register must be initialized before proper chip operation.

#### Al: Auto Increment

- 1 The Processor Pointer will increment after each access, read or write, of the Buffer Memory Data register.

- No incrementing will occur. The Processor Pointer will remain unchanged unless it is loaded with a new value.

#### **BPP: Buffer Parity Polarity**

- Even parity is checked or generated at the buffer memory port if enabled by the BPE bit.

- Odd parity is checked or generated at the buffer memory port if enabled by the BPE bit.

#### **BPE: Buffer Parity Enable**

1 Enables the checking or generation of parity at the buffer memory port for various types of transfers:

When Writing to Buffer:

Parity is generated for the data exiting at the buffer port; except in the case of SCSI to Buffer transfer, when, the parity is generated only if SCSI Parity is not enabled (SPE = 0). If SPE = 1, then the parity accompanying SCSI Bus Data is checked upon exiting the chip at buffer port.

When Reading from Buffer:

Parity is checked at the port where the data exits the chip; except in the case of Buffer to SCSI transfer with the SCSI Parity disabled: here the parity is checked on the incoming data at the buffer port. Also, in the case of processor reads of buffer memory, the parity is checked on the incoming data at the buffer port.

O Parity is not generated or checked at the buffer memory port. Parity may still be employed at the SCSI port by using the SPE bit of this register.

# 3.0 Register List (Continued)

#### **SPP: SCSI Parity Polarity**

Set to "1" when  $\overline{\text{CRST}}$  is asserted or a SCSI Reset command is issued. This is to prevent the parity bit from driving the bus immediately after a reset while in Manual Mode. (Manual Mode described in Section 4.4.3.)

- 1 Even parity is checked or generated on the SCSI bus if enabled by the SPE bit.

- Odd parity is checked or generated on the SCSI bus if enabled by the SPE bit.

#### **SPE: SCSI Parity Enable**

Set to "0" when  $\overline{\text{CRST}}$  is asserted or a SCSI Reset command is issued. Other than in Arbitration phase, parity is always provided when writing to the SCSI bus; parity is checked if buffer parity is being used (BPE = 1), or generated if buffer parity is not being used (BPE = 0). Parity verification while reading the SCSI bus is dependent upon this bit and some other variables as desribed below.

- 1 SCSI Parity is verified on read data conditional to A/M bit of the SCSI Operation Register (43h) and HE bit of the Synchronous Transfer Register (44h)—as specified in Table 3.4.

- 0 SCSI Parity is never verified.

**TABLE 3.4. SCSI Parity**

|               | 1,7,5,5             | L 0.4. 00011 anty                                                                                                                                                               |

|---------------|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Auto/<br>Man. | Handshake<br>Enable | When is parity checked during a read from the SCSI bus?                                                                                                                         |

| 1             | X                   | Target: Parity checked when<br>ACK asserted.<br>Initiator: Parity checked when<br>REQ asserted.<br>(Re)Select: Parity Checked while<br>SCSI ID matches, SEL true, BSY<br>false. |

| 0             | 1                   | Target: Parity checked when ACK asserted. Initiator: Parity checked when REQ asserted.                                                                                          |

| 0             | 0                   | Parity not checked.                                                                                                                                                             |

Refer to Table 4.10 in Section 4.2.9 for more detail on parity.

#### SID(2:0): SCSI ID

The unique binary address which identifies the SCSI device is loaded here. This number is usually obtained by the processor after a Chip Reset from a PROM or from switches or jumpers. This is not to be confused with the LUN (Logical Unit Number) of which each SCSI device can have eight.

This field will be internally translated to the one-of-eight form required for the SCSI bus.

| Setup 3 | (SUP3) |   |   | 62h  |      |      | R/W  |

|---------|--------|---|---|------|------|------|------|

| 7       | 6      | 5 | 4 | 3    | 2    | 1    | 0    |

| CI      | х      | х | х | REV3 | REV2 | REV1 | REV0 |

Asserting the CRST pin will not effect this register. This register must be initialized before proper interrupt operation.

### CI: Combine Interrupts

- 1 Enabled Disk and SCSI interrupts appear on the DINT pin. The SINT pin is never asserted.

- 0 Enabled Disk interrupts appear on the DINT pin. Enabled SCSI interrupts appear on the SINT pin.

### REV(3:0): Revision Number

These four bits reflect the functional version number of the chip. If a modification is made to the DP8496/7 that may require software or hardware modifications in a system, this value will be modified as well. The Revision Number corresponding to this data sheet is 3h.

The Revision Number will not be affected by a write to this register.

# 4.0 Functional Description

#### **4.1 PROCESSOR INTERFACE**

The processor port of the DP8496/7 can interface with equal ease with NSC/Intel-type and Motorola/Zilog-type processors. An 8-bit multiplexed Address/Data port is provided, and through it the processor can randomly access all SDDC registers. The chip also provides two interrupt lines to allow separate disk and SCSI interrupts.

To the processor, the DP8496/7 appears as a slave peripheral at all times and can be accessed with programmed I/O in memory mapped or I/O mapped systems. All control registers are eight bits wide. Some functions are programmed through more than one register. For example, address pointers are accessed through three different registers because the address may be up to 22 bits wide. The buffer memory data is accessed through one register called the Buffer Memory Data register (6Eh). There are two interrupt registers in the DP8496/7, the SCSI Interrupt register (49h) and the Disk Interrupt register (12h). Each of these interrupt registers has an associated mask and status register.

TABLE 4.1. DP8496/DP8497 Address Map

| Address | DP8496/7 Section             |

|---------|------------------------------|

| 00-1F   | Disk Data Controller         |

| 20-3F   | Disk Format Registers        |

| 40-5F   | SCSI Bus Controller          |

| 60-7F   | Buffer Memory, Setup & Timer |