# Local Area Network Databook

# LOCAL AREA NETWORK DATABOOK

**1992 Edition**

Integrated Ethernet Network Interface Controller Products

**Ethernet Physical Layer Transceivers**

Ethernet Repeater Interface Controller Products Hardware and Software Support Products

**FDDI Products**

i.

Glossary

**Appendix/Physical Dimensions**

#### TRADEMARKS

Following is the most current list of National Semiconductor Corporation's trademarks and registered trademarks. ABICTM FACT Quiet SeriesTM MICROWIRE/PLUSTM Script/Chr

Abuseable™ Anadig™ ANS-R-TRAN™ **APPSTM ASPECT™** Auto-Chem Deflasher™ ВСРТМ BI-FET™ BI-FET II™ BI-LINE™ BIPLANTM **BLCTM BLXTM** ВМАСТМ Brite-Lite™ BSITM CDDTM CheckTrack™ СІМ™ **CIMBUS™ CLASIC™** COMBO® COMBO ITM COMBO IITM COPS™ microcontrollers **CRD™** DA4TM Datachecker® **DENSPAK™** DIBTM **DISCERN™** DISTILL™ DNR® **DPVMTM** E<sup>2</sup>CMOS™ **ELSTAR™** Embedded System ProcessorTM E-Z-LINK™ **FACT™**

FACT Quiet Series™ **FAIRCADTM** Fairtech™ FAST® FASTr™ 5-Star Service™ **FlashTM** GENIX™ GNX™ **GTO™** HAMR™ HandiScan™ HEX 3000™ НРС™ l3Γ® **СМ**ТМ **INFOCHEXTM** Integral ISE™ Intelisplay™ ISETM ISE/06™ ISE/08™ ISE/16™ ISE32™ **ISOPLANAR™ ISOPLANAR-Z™** KeyScan™ LERIC™ LMCMOSTM M<sup>2</sup>CMOS™ Macrobus™ Macrocomponent<sup>™</sup> MAPL™ MAXI-ROM® Meat Chek™ MenuMaster™ Microbus™ data bus MICRO-DAC™ µtalker™ Microtalker™ **MICROWIRE™**

MICROWIRE/PLUS™ MOLETM МРА™ **MSTTM** Naked-8™ National® National Semiconductor® National Semiconductor Corp.® NAX 800™ Nitride Plus™ Nitride Plus Oxide™ NMLTM **NOBUSTM** NSC800™ **NSCISE™** NSX-16™ NS-XC-16™ NTERCOMTM . **NURAM™ OPALTM** OXISS™ P2CMOS™ PC Master™ Perfect Watch™ Pharmar/Chek™ **PLANTM PLANAR™ PLAYER™** Plus-2™ Polycraft™ POSilink™ POSitalker™ Power + Control™ POWERplanar™ QUAD3000TM **QUIKLOOKTM RAT™ RICTM** RTX16™

Script/Chek™ SCXTM SERIES/800™ Series 900™ Series 3000™ Series 32000® Shelf ChekTM Simple Switcher™ SofChek™ SONICTM **SPIRE™** Staggered Refresh™ **STĂR™** Starlink™ **STARPLEX™** ST-NIC™ Super-Block™ SuperChip™ SuperScript™ SYS32™ TapePak® TDSTM. TeleGate™ The National Anthem® Timer Chek™ TINATM TLC™ Trapezoidal™ TRI-CODE™ TRI-POLY™ TRI-SAFE™ TRI-STATE® **TURBOTRANSCEIVER™** VIРтм VR32™ **WATCHDOG™** XMOS™ **XPUTM** Z STAR™ 883B/RETS™ 883S/RETS™

abel™ is a trademark of Data I/O Corporation.

Apple®, Appletalk® and Macintosh® are registered trademarks of Apple Corporation.

COMPAQ® is a registered trademark of COMPAQ Corporation.

CP/M® is a registered trademark of Digital Research Corporation.

Dataphone<sup>®</sup> is a registered trademark of Dataphone Digital Service Corporation.

DECNETTM and VAXTM are trademarks of Digital Equipment Corporation.

General Motors® is a registered trademark of General Motors Corporation.

IBM®, MICROCHANNEL®, NETVIEW®, OS/2®, OS/2 Standard Edition®, PC-AT®, PS/2®, SNA® and System/2® are registered trademarks of International Business Machines Corporation.

**SABR™**

Intel® is a registered trademark of Intel Corporation.

Microsoft®, MS® and MS-DOS® are registered trademarks of Microsoft Corporation.

NetWare™ is a trademark of Novell Inc.

PAL® is a registered trademark of and used under license from Advanced Micro Devices, Inc.

PC/TCP® is a registered trademark of FTP Software Inc.

Tandy® is a registered trademark of Tandy Corporation.

UNIX® is a registered trademark of AT&T Bell Laboratories Corporation.

3Com® is a registered trademark of 3Com Corporation.

#### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

- Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform, when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

National Semiconductor Corporation 2900 Semiconductor Drive, P.O. Box 58090, Santa Clara, California 95052-8090 1-800-272-9959 TWX (910) 339-9240

National does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied, and National reserves the right, at any time without notice, to change said circuitry or specifications.

# **Product Status Definitions**

# **Definition of Terms**

| Data Sheet Identification     | Product Status            | Definition                                                                                                                                                                                                                                                                      |  |  |

|-------------------------------|---------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Advance Information           | Formative or<br>In Design | This data sheet contains the design specifications for product development. Specifications may change in any manner without notice.                                                                                                                                             |  |  |

| Preliminary                   | First<br>Production       | This data sheet contains preliminary data, and supplementary data will<br>be published at a later date. National Semiconductor Corporation<br>reserves the right to make changes at any time without notice in order<br>to improve design and supply the best possible product. |  |  |

| No<br>Identification<br>Noted | Full<br>Production        | This data sheet contains final specifications. National Semiconductor<br>Corporation reserves the right to make changes at any time without<br>notice in order to improve design and supply the best possible product.                                                          |  |  |

National Semiconductor Corporation reserves the right to make changes without further notice to any products herein to improve reliability, function or design. National does not assume any liability arising out of the application or use of any product or circuit described herein; neither does it convey any license under its patent rights, nor the rights of others.

| Table of Contents                                                                                                                   | •<br>•         |     |

|-------------------------------------------------------------------------------------------------------------------------------------|----------------|-----|

| Alphanumeric Index                                                                                                                  | vi             | . A |

| Introduction to Local Area Network Standards and Products                                                                           | vii            |     |

| Section 1 Integrated Ethernet Network Interface Controller Products<br>Network Interface Controllers and ENDECs                     |                |     |

| DP83902 Serial Network Interface Controller for Twisted-Pair (ST-NIC)                                                               | 1-3            |     |

| DP83901A Serial Network Interface Controller (SNIC)                                                                                 | 1-69           |     |

| DP8390D/NS32490D Network Interface Controller                                                                                       | 1-131          |     |

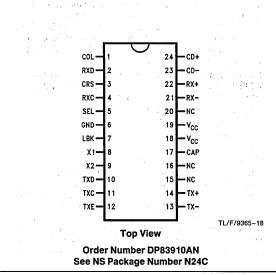

| DP83910A CMOS Serial Network Interface                                                                                              | 1-186          |     |

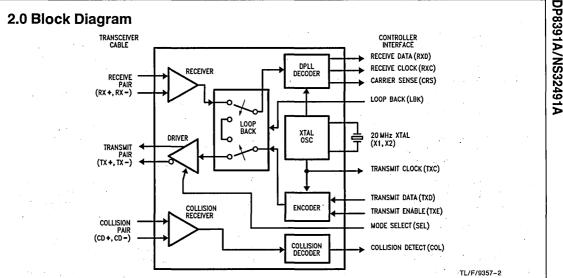

| DP8391A/NS32491A Serial Network Interface                                                                                           | 1-196          |     |

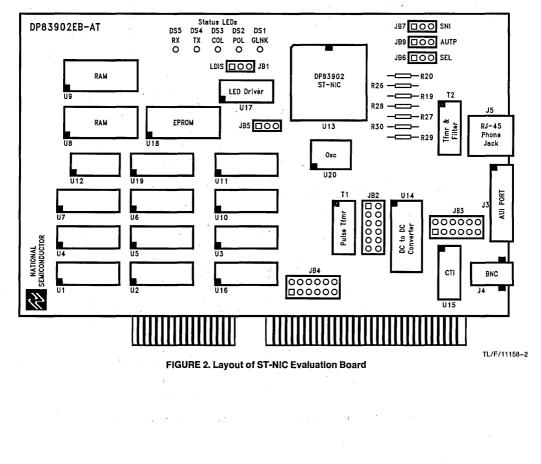

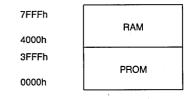

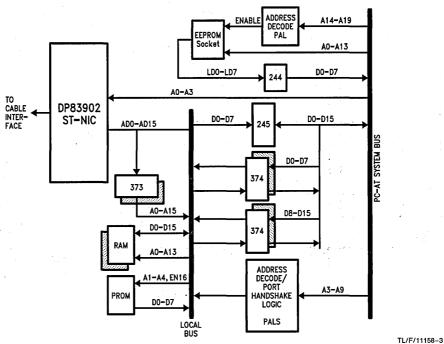

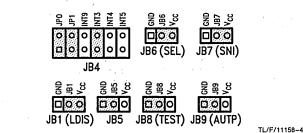

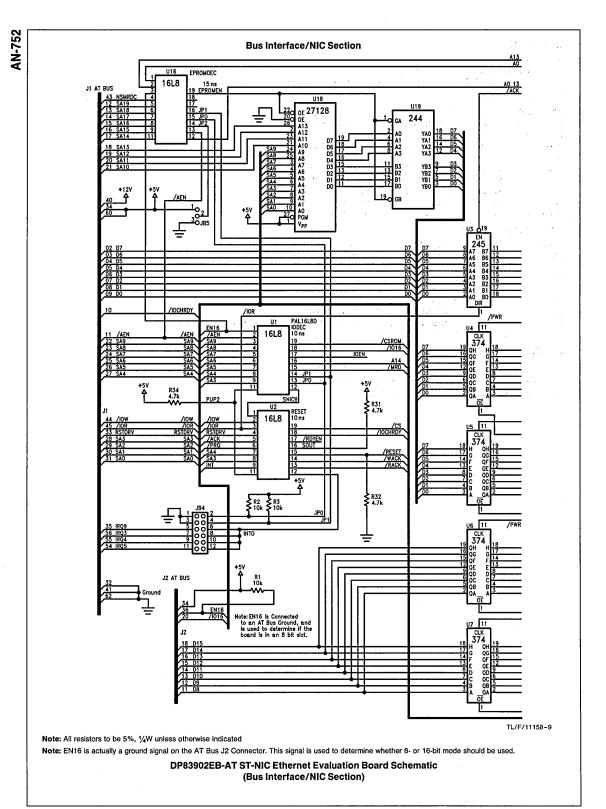

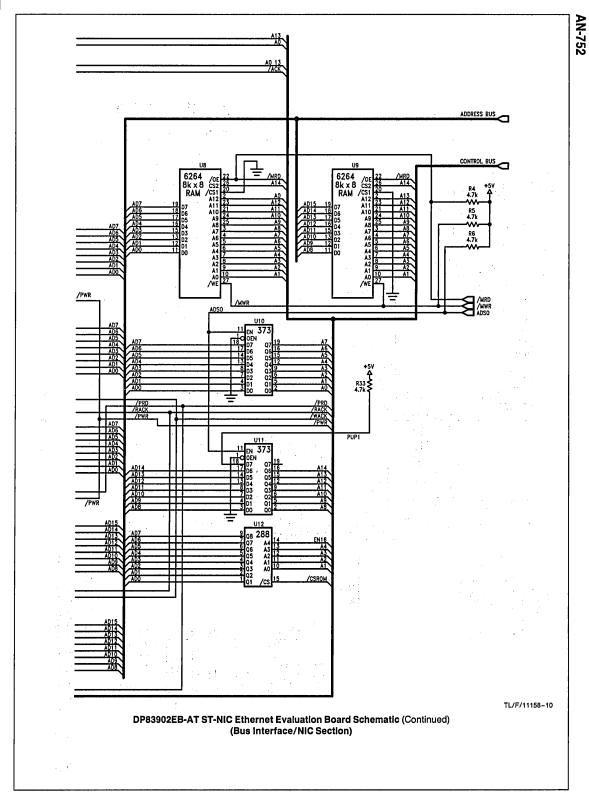

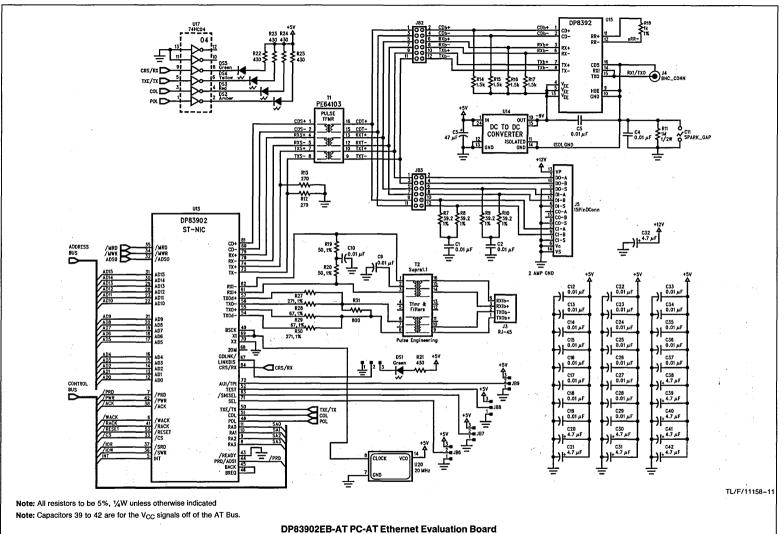

| AN-475 DP8390 Network Interface Controller: An Introductory GuideAN-752 PC-AT Compatible DP83902 ST-NIC Ethernet Evaluation Board   | 1-206          |     |

| (DP83902EB-AT)                                                                                                                      | 1-214          |     |

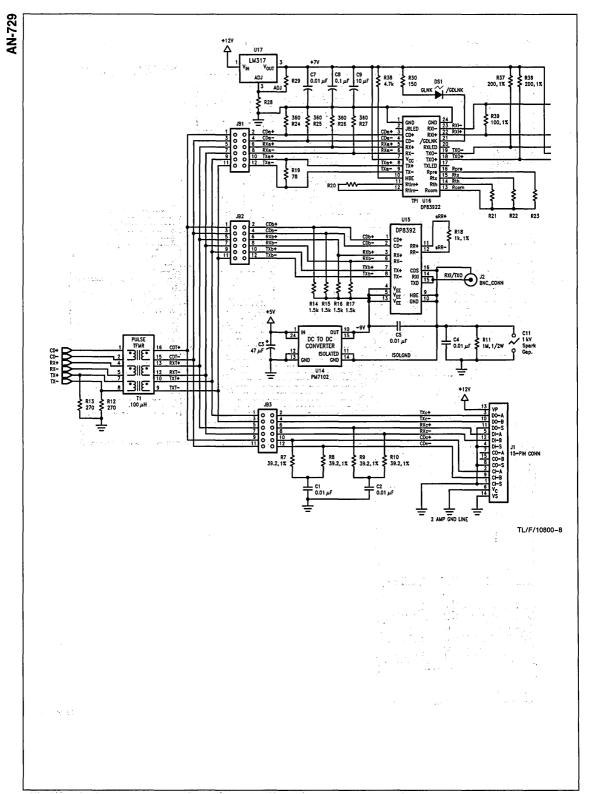

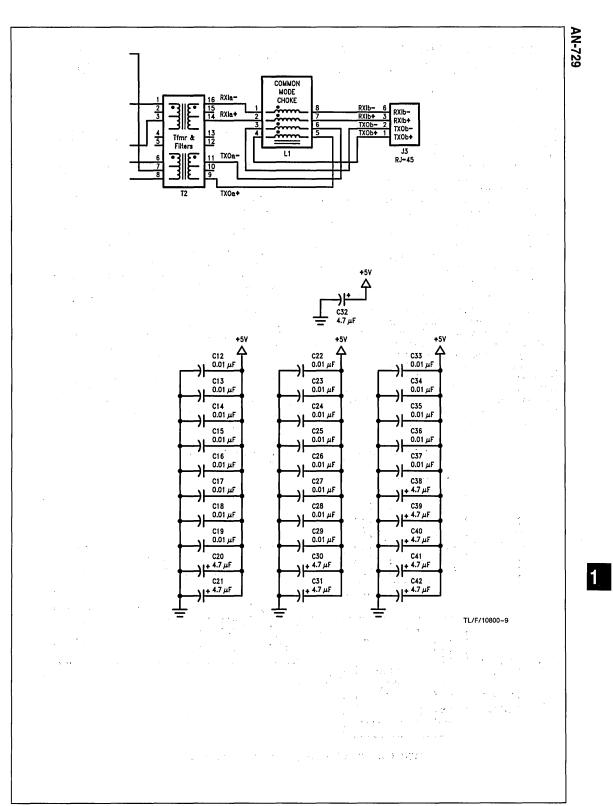

| AN-729 DP839EB-ATN IBM PC-AT Compatible DP83901 Serial Network Interface                                                            |                |     |

| Controller (SNIC) Evaluation Board                                                                                                  | 1-229          |     |

| AN-622 Low Power Ethernet with the CMOS DP83910 Serial Network Interface                                                            | 1-242          |     |

| AN-686 Ethernet Network Interface Adapter for the Apple Macintosh II NuBus                                                          | 1-249          |     |

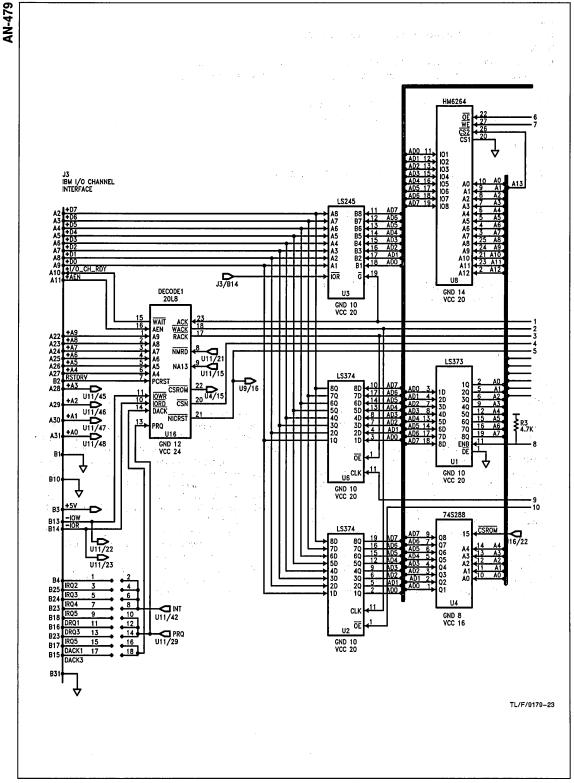

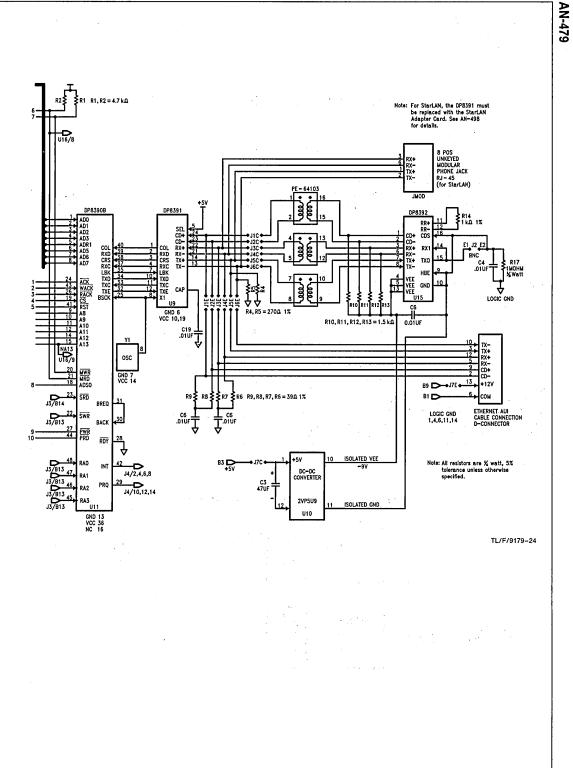

| AN-479 DP839EB Network Evaluation Board Systems-Oriented Network Interface Controller Products                                      | 1-279          |     |

| DP83932B Systems-Oriented Network Interface Controller                                                                              | 1-288          |     |

| AN-745 DP83932 SONIC Bus Operations Guide                                                                                           | 1-384          |     |

| AN-746 Software Driver Programmer's Guide for the DP83932 SONICAN-747 Determining Arbitration and Threshold Levels in a SONIC Based | 1-396          |     |

| MICROCHANNEL Adapter<br>AN-691 32-Bit Bus Master Ethernet Interface for the 68030 (Using the Macintosh                              | 1-426          |     |

| SE/30)                                                                                                                              | 1-433          |     |

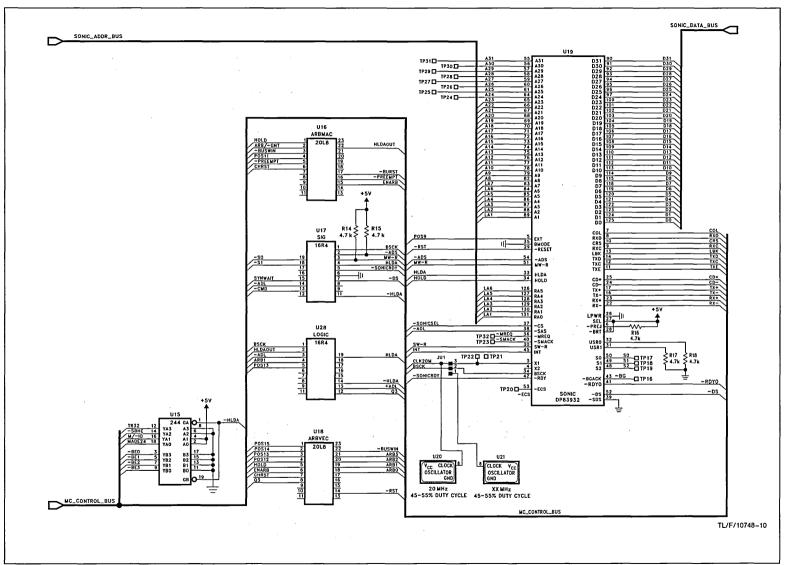

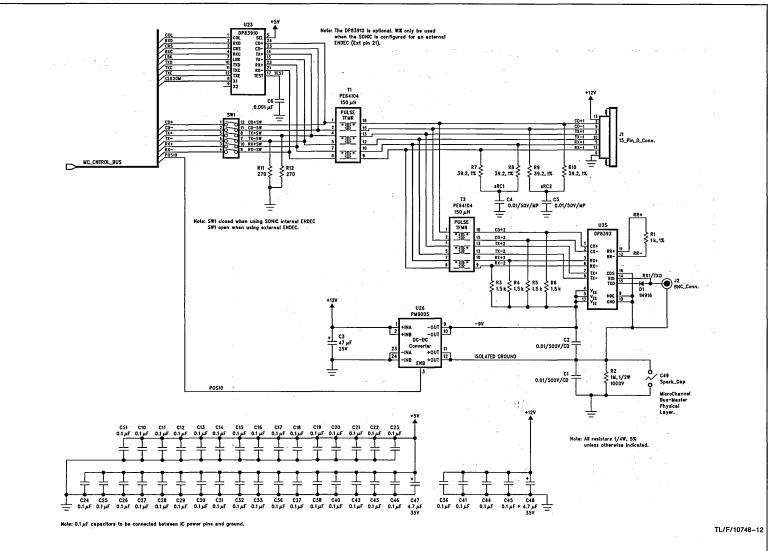

| AN-732 DP839EB-MCS SONIC MICROCHANNEL Ethernet Adapter                                                                              | 1-442          |     |

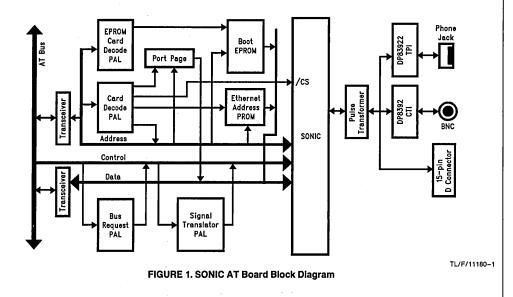

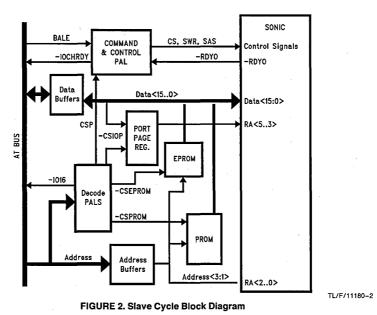

| AN-760 High Performance AT Compatible Bus Master Ethernet Adapter AN-748 DP839EB-ATS SONIC Packet Driver for PC/TCP by FTP Software | 1-467<br>1-498 |     |

| Section 2 Ethernet Physical Layer Transceivers                                                                                      |                |     |

| Coaxial Transceivers                                                                                                                |                |     |

| DP8392C/DP8392C-1 Coaxial Transceiver Interface                                                                                     | 2-3            |     |

| Reliability Data Summary for DP8392                                                                                                 | 2-13           |     |

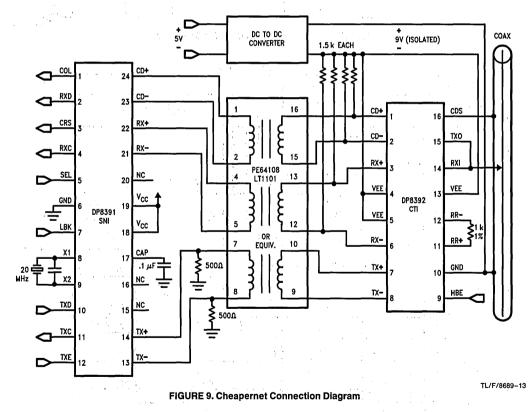

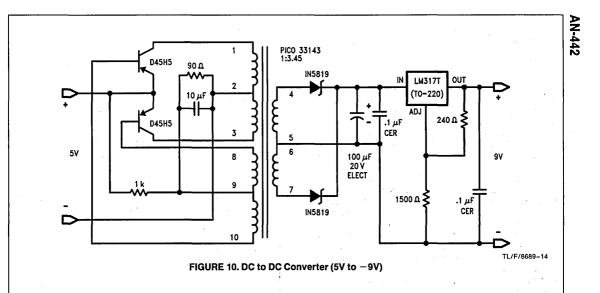

| AN-442 Ethernet/Cheapernet Physical Layer Made Easy with DP8391/92                                                                  | 2-15           |     |

| AN-757 Measuring Ethernet Tap Capacitance                                                                                           | 2-24           |     |

| AN-620 Interfacing the DP8392 to 93 $\Omega$ and 75 $\Omega$ Cable $\ldots$                                                         | 2-27           |     |

| AN-621 Designing the DP8392 for Longer Cable Applications                                                                           | 2-30           |     |

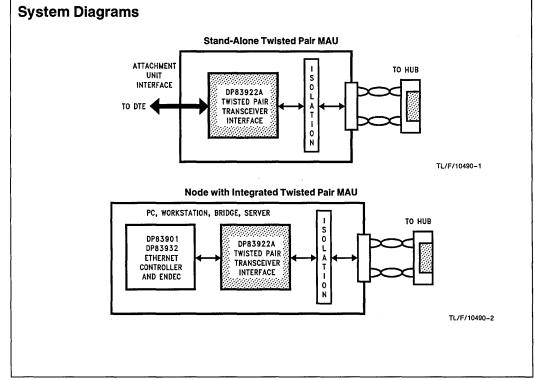

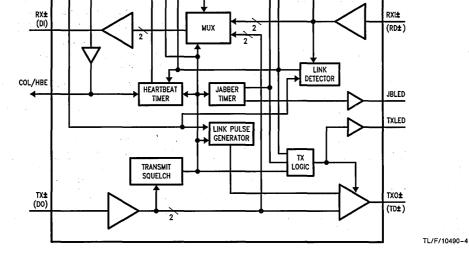

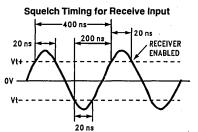

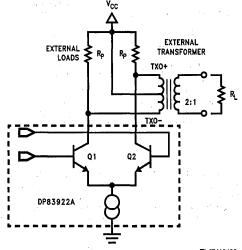

| DP83922A Twisted-Pair Transceiver Interface (TPI)                                                                                   | 2-34           |     |

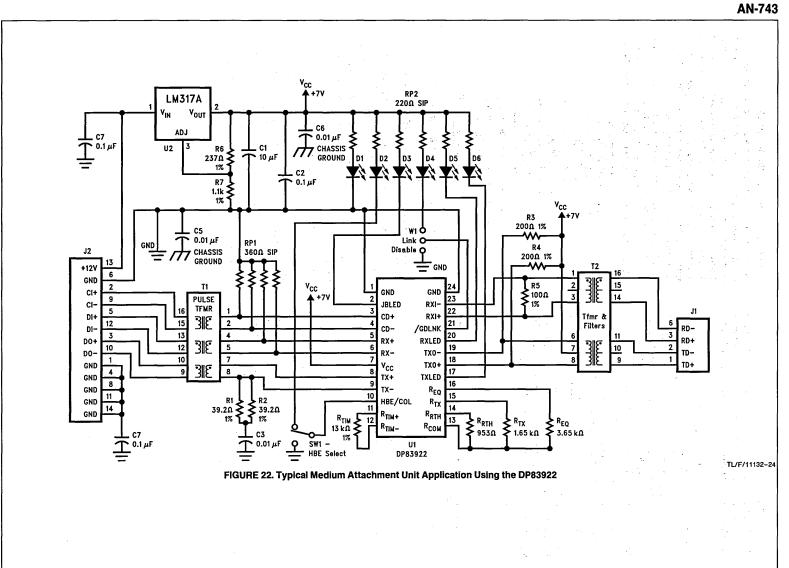

| AN-743 10Base-T Transceiver Design Using the DP83922 Section 3 Ethernet Repeater Interface Controller Products                      | 2-46           |     |

| DP83950A Repeater Interface Controller (RIC)                                                                                        | 3-3            |     |

| LERIC Low End Repeater Interface Controller                                                                                         | 3-74           |     |

| AN-781 DP83950EB-AT IEEE 802.3 Multi-Port Repeater Evaluation Kit                                                                   | 3-75           |     |

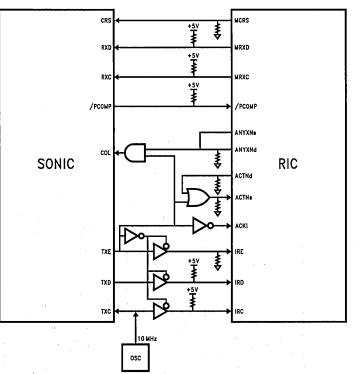

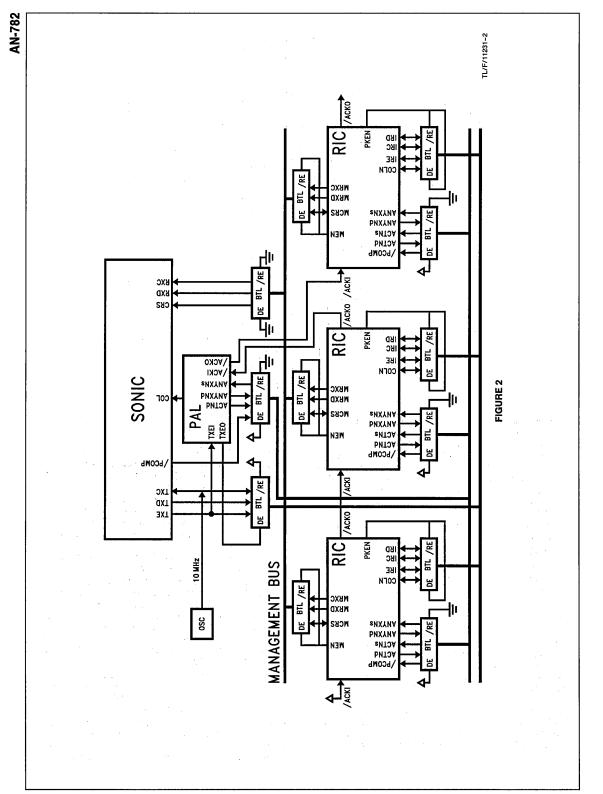

| AN-782 RIC-SONIC Interface                                                                                                          | 3-88           |     |

| AN-783 DP83950 Twisted Pair Parametric Evaluation                                                                                   | 3-92           |     |

| Support Tools and 3rd Party Vendors                                                                                                 |                |     |

| Ethernet Evaluation Hardware and Software Products, and 3rd Party Driver                                                            |                |     |

| Developers                                                                                                                          | 4-3            |     |

| Ethernet Magnetics Vendors for 10BASE-T, 10BASE2 and 10BASE5                                                                        | 4-7            |     |

# Table of Contents (Continued)

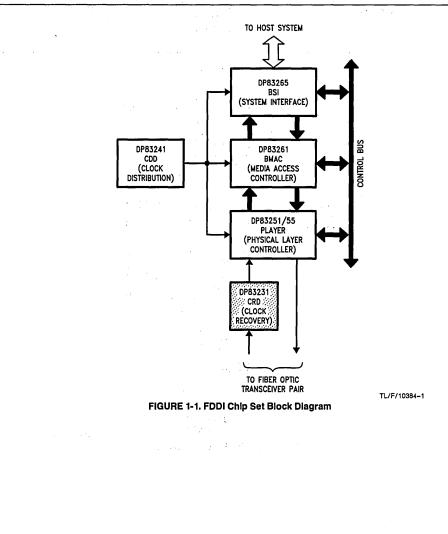

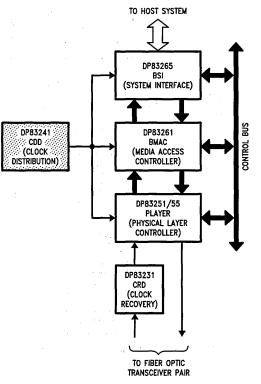

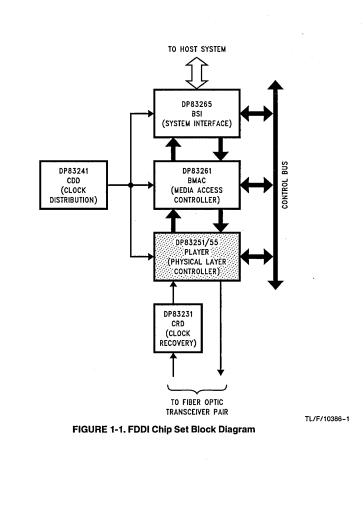

| Section 5 FDDI Products                                         |     |

|-----------------------------------------------------------------|-----|

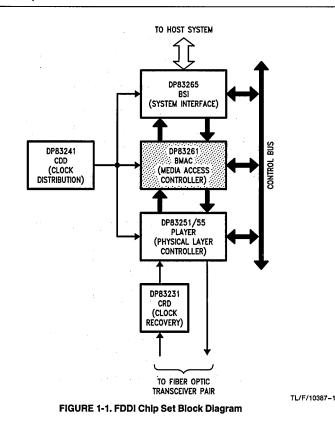

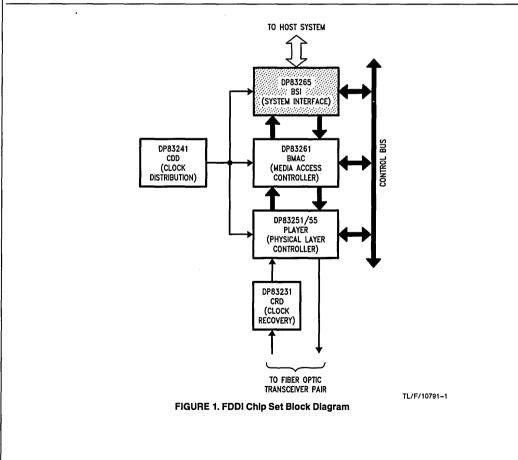

| DP83231 CRD Device (FDDI Clock Recovery Device)                 | 5-3 |

| DP83241 CDD Device (FDDI Clock Distribution Device)             | 5-4 |

| DP83251/DP83255 PLAYER Device (FDDI Physical Layer Controller)  | 5-5 |

| DP83261 BMAC Device (FDDI Media Access Controller)              | 5-6 |

| DP83265 BSI Device (FDDI System Interface)                      | 5-7 |

| Section 6 Glossary                                              |     |

| Ethernet and Networking Acronyms                                | 6-3 |

| Glossary of Local Area Networking and Data Communications Terms | 6-4 |

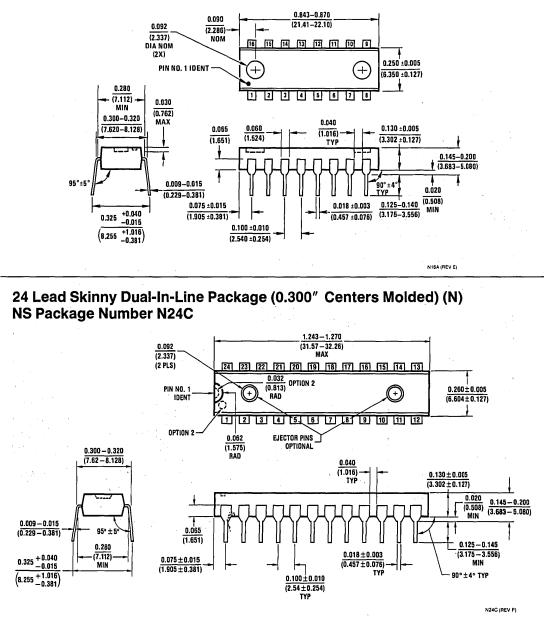

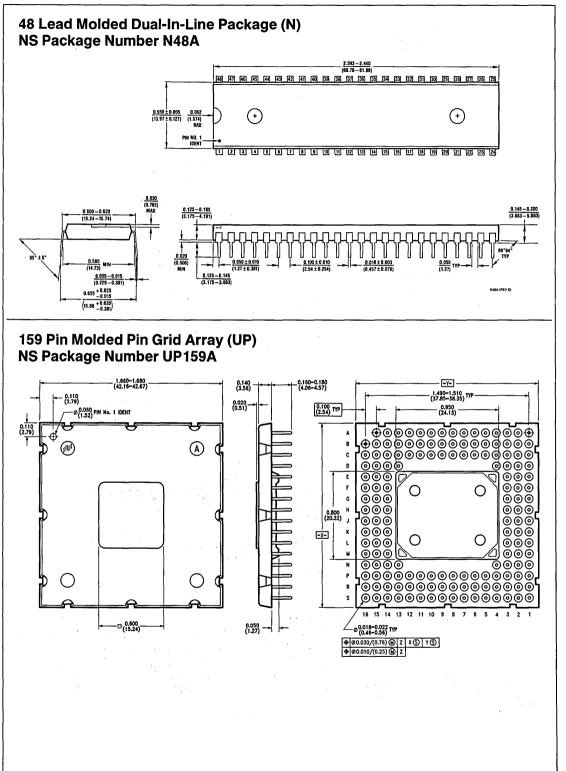

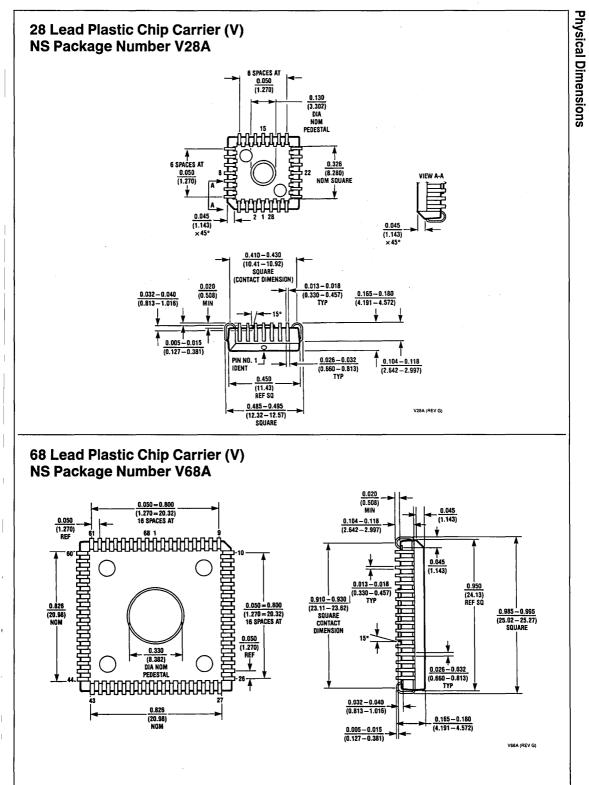

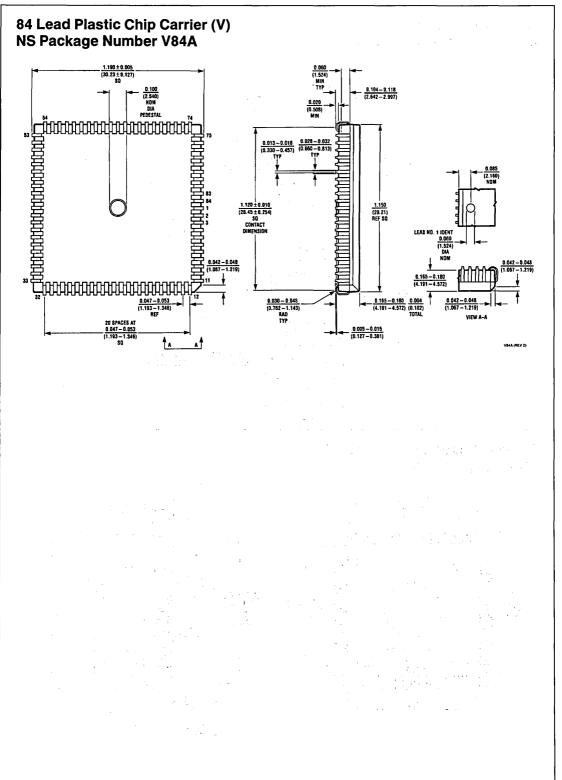

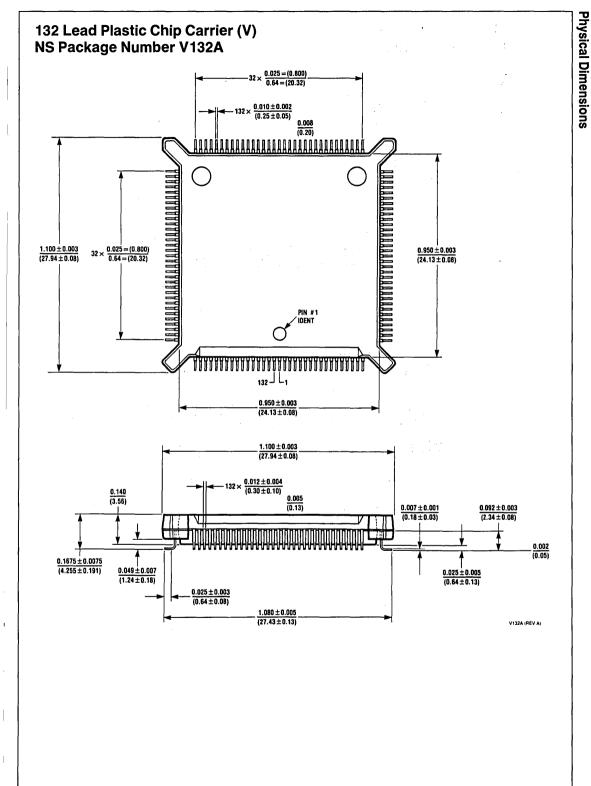

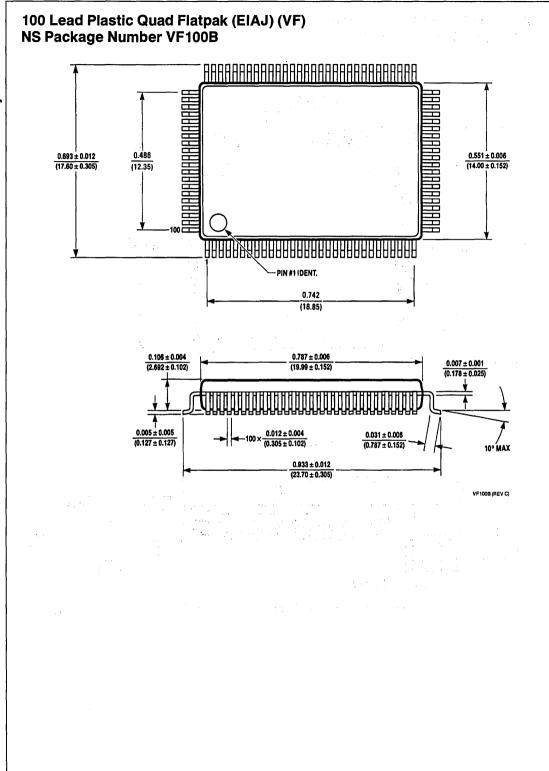

| Section 7 Appendix/Physical Dimensions                          |     |

| Physical Dimensions                                             | 7-3 |

| Bookshelf                                                       |     |

| Distributors                                                    |     |

# Alpha-Numeric Index

| AN-442 Ethernet/Cheapernet Physical Layer Made Easy with DP8391/92                          |

|---------------------------------------------------------------------------------------------|

| AN-475 DP8390 Network Interface Controller: An Introductory Guide                           |

| AN-479 DP839EB Network Evaluation Board1-279                                                |

| AN-620 Interfacing the DP8392 to $93\Omega$ and $75\Omega$ Cable                            |

| AN-621 Designing the DP8392 for Longer Cable Applications                                   |

| AN-622 Low Power Ethernet with the CMOS DP83910 Serial Network Interface                    |

| AN-686 Ethernet Network Interface Adapter for the Apple Macintosh II NuBus                  |

| AN-691 32-Bit Bus Master Ethernet Interface for the 68030 (Using the Macintosh SE/30) 1-433 |

| AN-729 DP839EB-ATN IBM PC-AT Compatible DP83901 Serial Network Interface Controller         |

| (SNIC) Evaluation Board                                                                     |

| AN-732 DP839EB-MCS SONIC MICROCHANNEL Ethernet Adapter                                      |

| AN-743 10Base-T Transceiver Design Using the DP83922                                        |

| AN-745 DP83932 SONIC Bus Operations Guide                                                   |

| AN-746 Software Driver Programmer's Guide for the DP83932 SONIC                             |

| AN-747 Determining Arbitration and Threshold Levels in a SONIC Based MICROCHANNEL           |

| Adapter 1-426                                                                               |

| AN-748 DP839EB-ATS SONIC Packet Driver for PC/TCP by FTP Software                           |

| AN-752 PC-AT Compatible DP83902 ST-NIC Ethernet Evaluation Board (DP83902EB-AT) 1-214       |

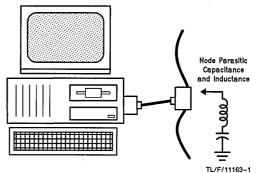

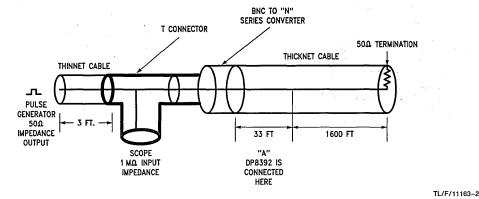

| AN-757 Measuring Ethernet Tap Capacitance                                                   |

| AN-760 High Performance AT Compatible Bus Master Ethernet Adapter                           |

| AN-781 DP83950EB-AT IEEE 802.3 Multi-Port Repeater Evaluation Kit                           |

| AN-782 RIC-SONIC Interface                                                                  |

| AN-783 DP83950 Twisted Pair Parametric Evaluation                                           |

| DP8390D Network Interface Controller                                                        |

| DP8391A Serial Network Interface                                                            |

| DP8392C/DP8392C-1 Coaxial Transceiver Interface                                             |

| DP83231 CRD Device (FDDI Clock Recovery Device)                                             |

| DP83241 CDD Device (FDDI Clock Distribution Device)                                         |

| DP83251 PLAYER Device (FDDI Physical Layer Controller)5-5                                   |

| DP83255 PLAYER Device (FDDI Physical Layer Controller)                                      |

| DP83261 BMAC Device (FDDI Media Access Controller) 5-6                                      |

| DP83265 BSI Device (FDDI System Interface)                                                  |

| DP83901A Serial Network Interface Controller (SNIC) 1-69                                    |

| DP83902 Serial Network Interface Controller for Twisted-Pair (ST-NIC)                       |

| DP83910A CMOS Serial Network Interface                                                      |

| DP83922A Twisted-Pair Transceiver Interface (TPI)                                           |

| DP83932B Systems-Oriented Network Interface Controller                                      |

| DP83950A Repeater Interface Controller (RIC)                                                |

| Ethernet and Networking Acronyms                                                            |

| Ethernet Evaluation Hardware and Software Products, and 3rd Party Driver Developers         |

| Ethernet Magnetics Vendors for 10BASE-T, 10BASE2 and 10BASE5                                |

| Glossary of Local Area Networking and Data Communications Terms                             |

| LERIC Low End Repeater Interface Controller                                                 |

| NS32490D Network Interface Controller 1-131                                                 |

| NS32491A Serial Network Interface                                                           |

| Reliability Data Summary for DP8392 2-13                                                    |

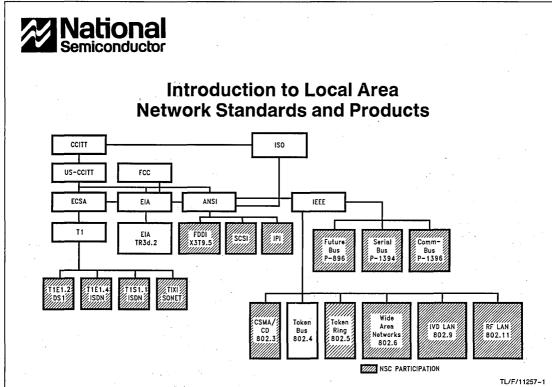

#### PRO-ACTIVE COMMUNICATIONS STANDARDS INVOLVEMENT

Standards are crucial to the development and explosive growth of the communications industry. Several international committees and organizations develop and promote standards to ensure interoperability and interconnectivity. National Semiconductor Corporation takes an active part in the development and definition of these standards and produces a wide range of products that meet the requirements of these standards. Complete silicon solutions for IEEE 802.3 CSMA/CD Ethernet and FDDI are a part of National's communications portfolio, one of the broadest in the semiconductor industry.

#### FDDI (Fiber Distributed Data Interface)

The Fiber Distributed Data Interface is a 100 Mbit/sec. Local Area Network that uses a token passing access method and uses optical fiber as the medium with twisted pair wiring medium specifications to come in the future. Like Ethernet, FDDI has maximized the value of standardization and conformed to the Open Systems Interconnect (OSI) model and is specified by the ANSI X3T9.5 committee. The rich functionality that has been integrated into FDDI to meet the needs of a number of market segments means that it can be the one standard satisfying the requirements of broad, highspeed LANs. FDDI offers a low-cost means for bridging Ethernet to a high-speed fiber optic link, connecting local islands of Ethernet workgroups to similar islands located in another part of a company or office.

For FDDI to grow into a successful LAN, network equipment manufacturers need a practical and cost-effective standard chip set. National, already the leading supplier of IEEE 802.3 network silicon solutions, has developed a highperformance, cost-effective solution, the DP83200 FDDI Introduction to Local Area Network Standards and Products

#### ETHERNET: IEEE 802.3

chip set.

The IEEE 802.3 CSMA/CD Ethernet Protocol has become the most widely accepted standard for Local Area Networks connecting personal computers and workstations with information resources, servers and other peripherals.

The CSMA/CD (Carrier Sense Multiple Access with Collision Detection) protocol defines how a node will gain access to transmit over the cable. The node first monitors the cable to ensure no transmissions are in progress (Carrier Sense). Any node may then decide to transmit (Multiple Access). If more than one node decides to transmit then all nodes must be able to detect this condition (Collision Detection), stop their transmissions and retry.

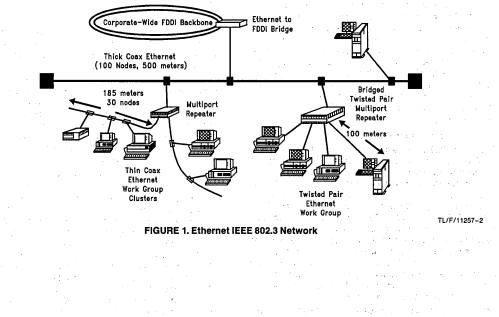

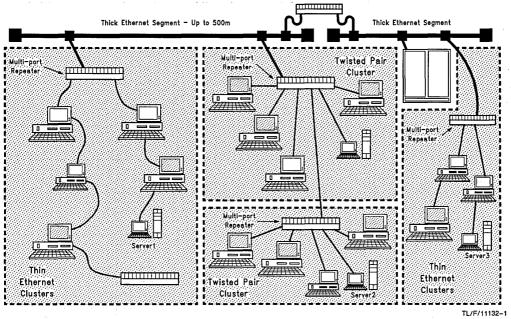

#### PHYSICAL LAYER SPECIFICATIONS

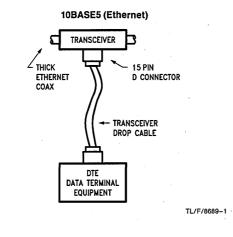

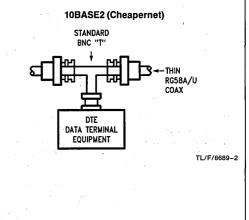

The four IEEE 802.3 Physical Layer Specifications, summarized in Table I, differ primarily in the cable schemes, including media and topology. 10Base5 (Thick Coax Ethernet) uses a thick double-shielded coaxial cable at 10 Mbit/sec. data rate in a bus configuration. 10Base2 (Thin Coax Ethernet) maintains the same 10 Mbit/sec. data rate and bus topology, but uses single-shielded coaxial cable. 1Base5 (StarLAN) uses inexpensive twisted pair cabling in a star topology at only 1 Mbit/sec. data rate. The newest IEEE 802.3 Physical Layer Specification, 10Base-T for Twisted Pair Ethernet, combines the installation convenience of inexpensive twisted pair cable and star topology of 1Base5 at the 10 Mbit/sec. data rate for performance compatibility with 10Base5 and 10Base2 Ethernet networks.

| Icts                                        |                                           |       |

|---------------------------------------------|-------------------------------------------|-------|

| and Product                                 | Parameter                                 |       |

| ٩                                           | Designator                                |       |

|                                             | Data Rate                                 |       |

| ŝ                                           | Segment Length                            |       |

| ard                                         | Topology                                  |       |

| Ê                                           | Cable Type                                |       |

| Sta                                         |                                           |       |

| ntroduction to Local Area Network Standards | Connection                                |       |

| <u>§</u>                                    |                                           |       |

| et                                          | COMPREHENSIV                              | E ET  |

| Z                                           | The demands for h                         |       |

| ĕ                                           | increased functior<br>the selection of Et |       |

| A                                           | wide variety of Eth                       |       |

| S                                           | opment evaluation                         | ı too |

| 2                                           | work product desig                        | -     |

| 2                                           | Integrated Networ<br>ucts for 8-bit and   |       |

| 5                                           | DP83902 Serial N                          |       |

| i <del>či</del>                             | Pair (ST-NIC™),                           |       |

| ā                                           | Controller (SNIC),                        | the   |

| ē                                           | (NIC), and the DI<br>(CSNI). 16-bit and   |       |

| <u>I</u>                                    | interconnectivity                         |       |

## TABLE I. IEEE 802.3 Physical Layer Specifications

| Parameter      | 10Base5                                         | 10Base2                                         | 1Base5                                 | 10Base-T                       |  |

|----------------|-------------------------------------------------|-------------------------------------------------|----------------------------------------|--------------------------------|--|

| Designator     | Thick Coax                                      | Thin Coax                                       | StarLAN                                | Twisted Pair                   |  |

| Data Rate      | 10 Mbit/sec.                                    | 10 Mbit/sec.                                    | 1 Mbit/sec.                            | 10 Mbit/sec.                   |  |

| Segment Length | 500 Meters                                      | 185 Meters                                      | 500 Meters                             | 100 Meters Nominal             |  |

| Topology       | Bus (Multi-Point)                               | Bus (Multi-Point)                               | Star (Point-to-Point)                  | Star (Point-to-Point)          |  |

| Cable Type     | 0.4" Diam. 50Ω,<br>Double Shield Coax<br>(RG11) | 0.2″ Diam. 50Ω,<br>Single Shield Coax<br>(RG58) | 24 Gauge, 100 $\Omega$<br>Twisted Pair | 24 Gauge, 100Ω<br>Twisted Pair |  |

| Connection     | Precision TAP                                   | BNC "T"                                         | 8-Pin, RJ-45                           | 8-Pin, RJ-45                   |  |

#### **COMPREHENSIVE ETHERNET SOLUTIONS**

The demands for high performance, smaller chip count, and increased functionality have become significant factors in the selection of Ethernet silicon solutions. National offers a wide variety of Ethernet industry-standard silicon and development evaluation tools to meet the diverse needs of network product designers and manufacturers.

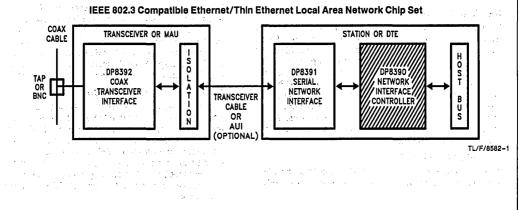

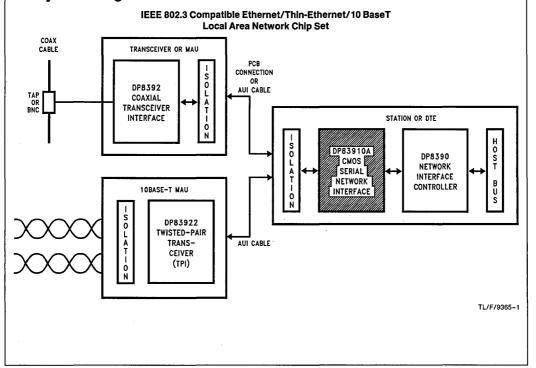

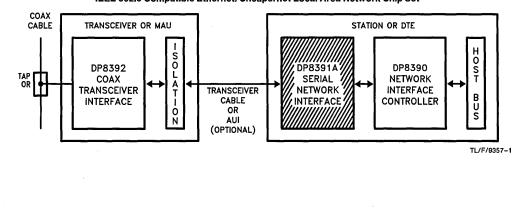

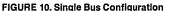

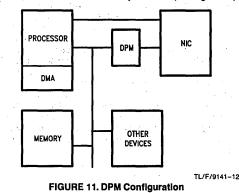

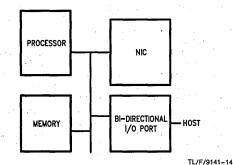

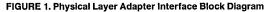

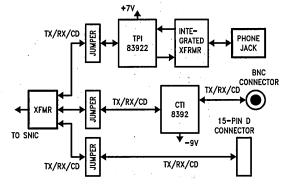

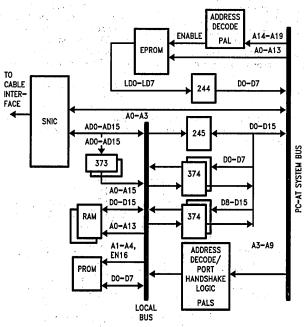

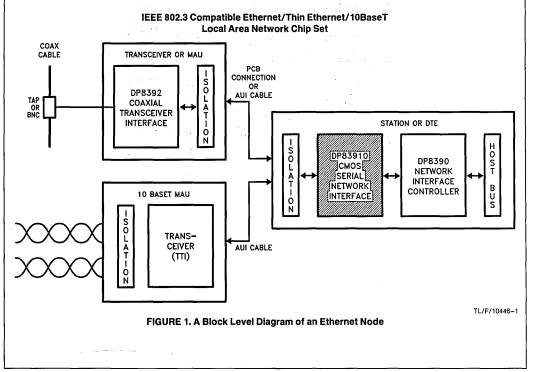

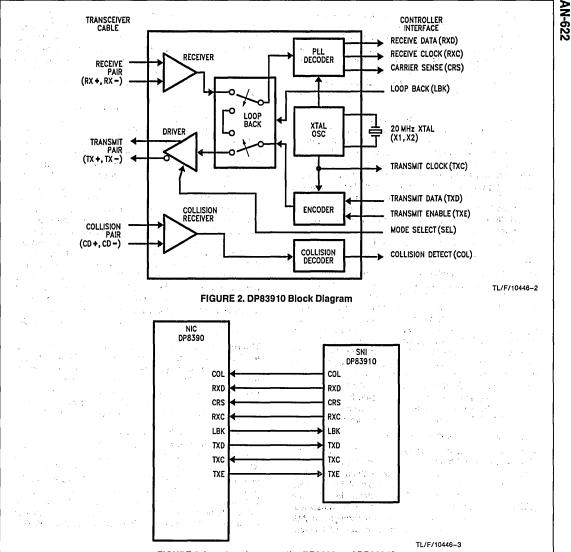

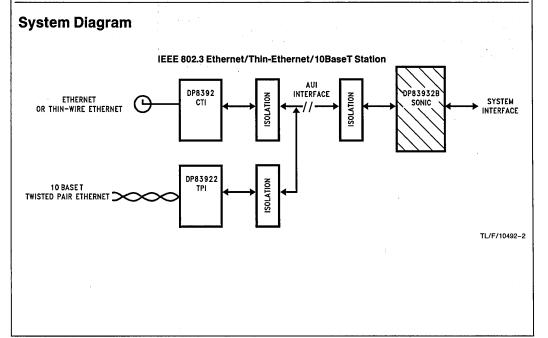

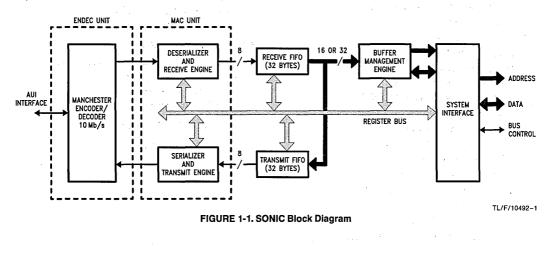

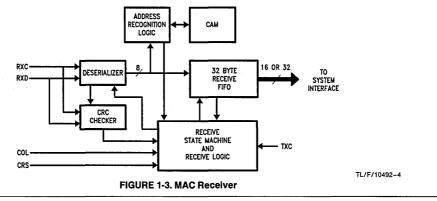

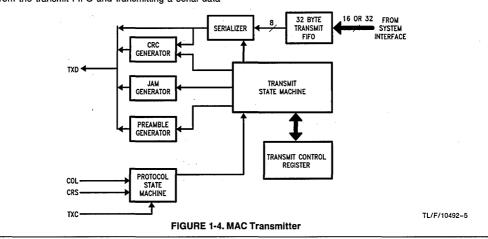

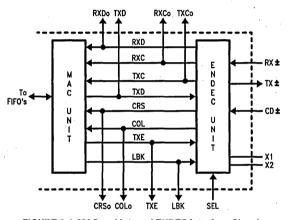

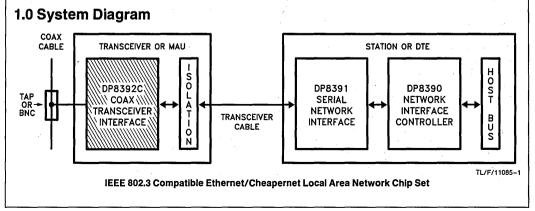

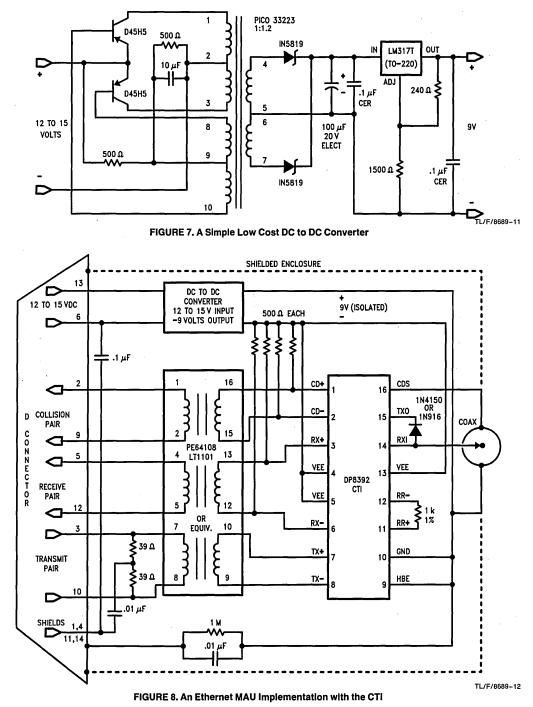

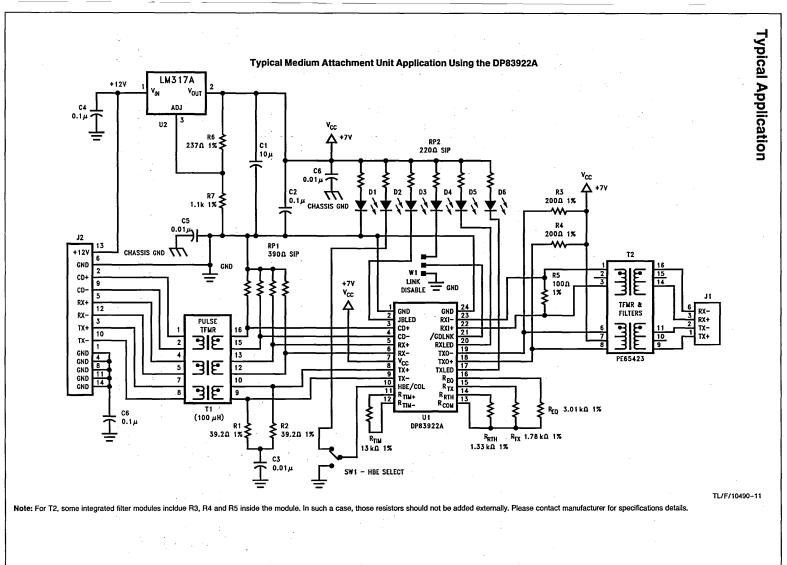

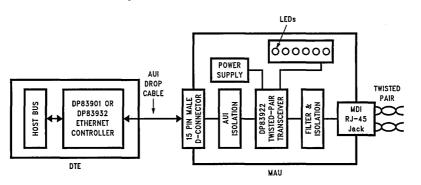

Integrated Network Interface Controller and ENDEC products for 8-bit and 16-bit designs include the single-chip DP83902 Serial Network Interface Controller for Twisted Pair (ST-NICTM), the DP83901 Serial Network Interface Controller (SNIC), the DP8390 Network Interface Controller (NIC), and the DP83910 CMOS Serial Network Interface (CSNI). 16-bit and 32-bit network interface controller and interconnectivity requirements are addressed by the DP83932 Systems Oriented Network Interface Controller (SONICTM). SONIC provides exceptional 16-bit or 32-bit Host-to-Ethernet interface management and performance with all of the major state-of-the-art CISC and RISC microprocessor architectures. IEEE 802.3 Physical Layer Tansceiver products include the industry-standard DP8392 Coaxial Transceiver Interface (CTI) for 10Base5 and 10Base2; and the DP83922 Twisted Pair Transceiver Interface (TPI) for 10Base-T.

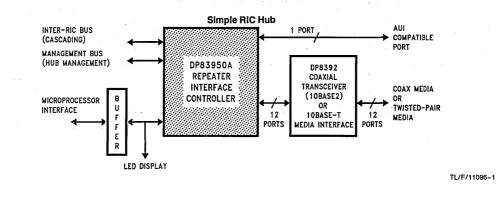

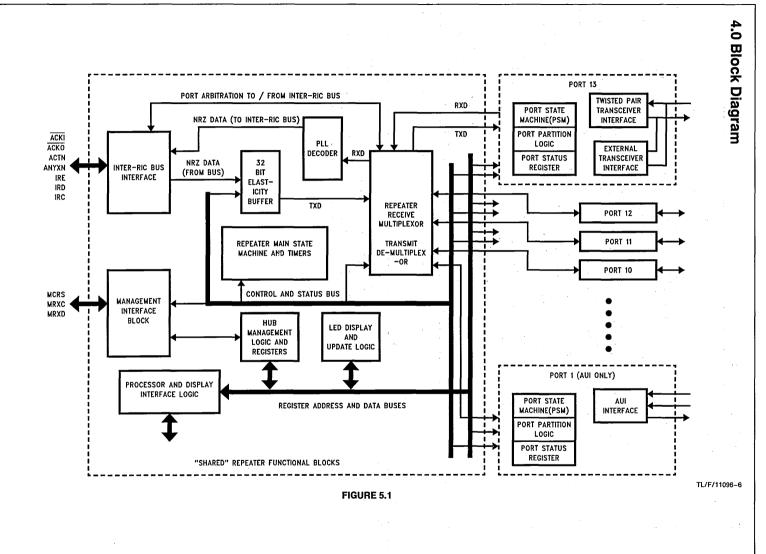

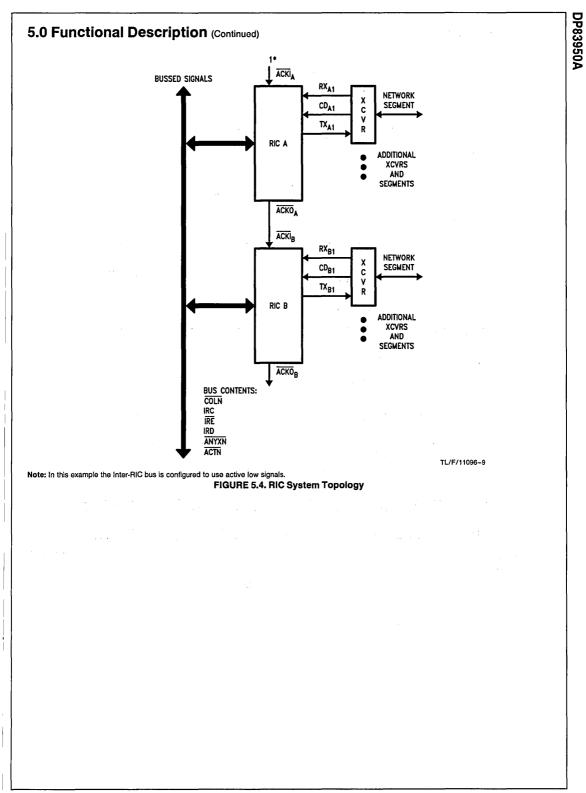

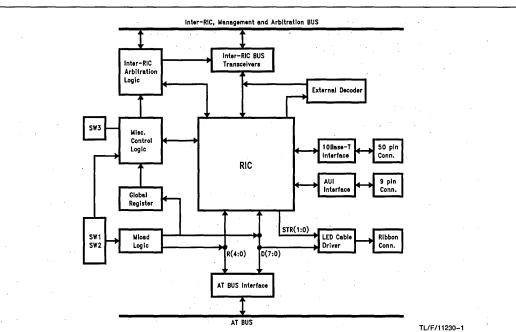

Repeater Interface Controller products are designed to meet the needs of intelligent Multi-Port Repeater or Hub designs. The DP83950 Repeater Interface Controller (RICTM) implements the IEEE 802.3 Repeater Specification, the 10Base-T Specification, and the Hub Management Draft Specification. Designs incorporating both RIC and SONIC provide the necessary hardware platform for Managed Hubs which support Simple Network Management Protocol (SNMP), Common Management Information Protocol (CMIP) and other network management protocols. Simple, unmanaged Multi-Port Repeater or Hub design requirements are met by the Low End Repeater Interface Controller (LERICTM).

National offers an extensive selection of Evaluation Platforms, Demonstration Software, Application Notes, and System Briefs to assist network product designers and manufacturers both in silicon selection and product development.

N

# Section 1 Integrated Ethernet Network Interface Controller Products

. .

···. .

# Section 1 Contents

| Network Interface Controllers and ENDECs                                                                                                                                                                                                                                                                                                                                                                                             |                                                    |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|

| DP83902 Serial Network Interface Controller for Twisted-Pair (ST-NIC)                                                                                                                                                                                                                                                                                                                                                                | 1-3                                                |

| DP83901A Serial Network Interface Controller (SNIC)                                                                                                                                                                                                                                                                                                                                                                                  | 1-69                                               |

| DP8390D/NS32490D Network Interface Controller                                                                                                                                                                                                                                                                                                                                                                                        | 1-131                                              |

| DP83910A CMOS Serial Network Interface                                                                                                                                                                                                                                                                                                                                                                                               | 1-186                                              |

| DP8391A/NS32491A Serial Network Interface                                                                                                                                                                                                                                                                                                                                                                                            | 1-196                                              |

| AN-475 DP8390 Network Interface Controller: An Introductory Guide                                                                                                                                                                                                                                                                                                                                                                    | 1-206                                              |

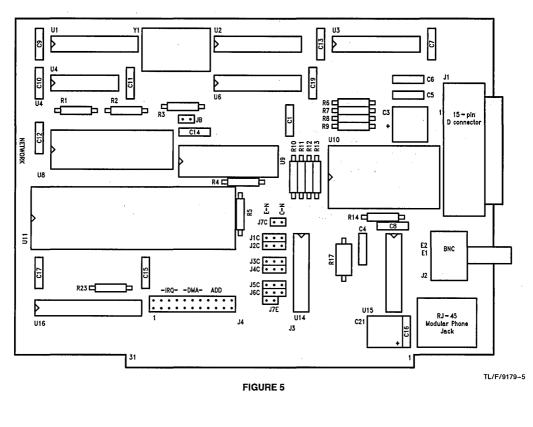

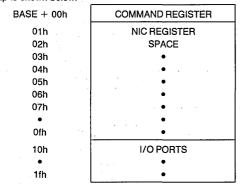

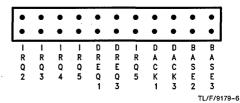

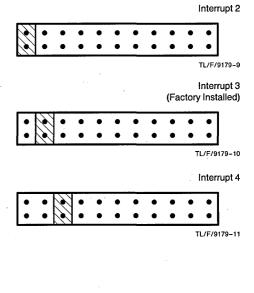

| AN-752 PC-AT Compatible DP83902 ST-NIC Ethernet Evaluation Board (DP83902EB-AT)                                                                                                                                                                                                                                                                                                                                                      | 1-214                                              |

| AN-729 DP839EB-ATN IBM PC-AT Compatible DP83901 Serial Network Interface Controller                                                                                                                                                                                                                                                                                                                                                  |                                                    |

| (SNIC) Evaluation Board                                                                                                                                                                                                                                                                                                                                                                                                              | 1-229                                              |

| AN-622 Low Power Ethernet with the CMOS DP83910 Serial Network Interface                                                                                                                                                                                                                                                                                                                                                             | 1-242                                              |

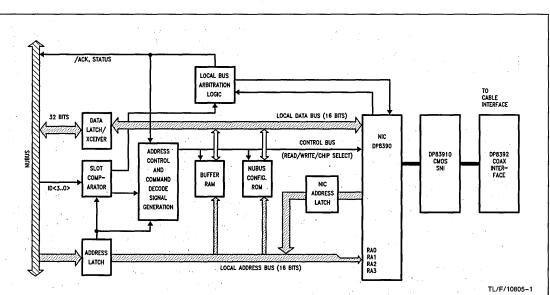

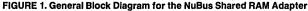

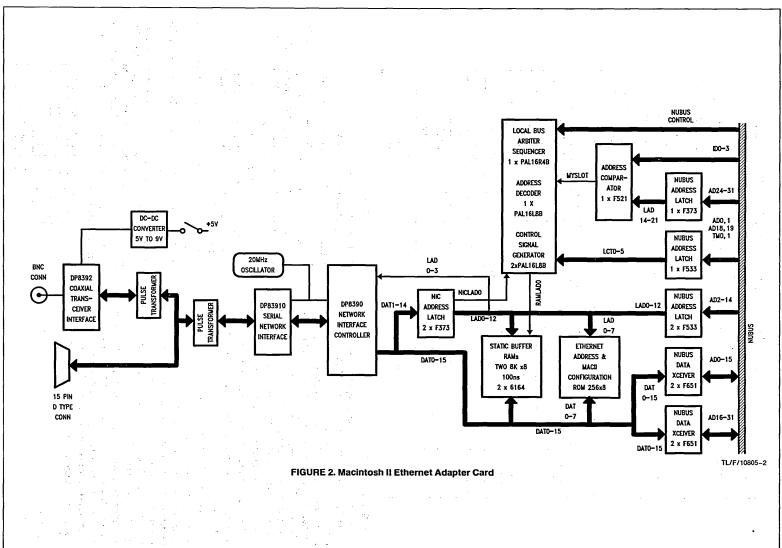

| AN-686 Ethernet Network Interface Adapter for the Apple Macintosh II NuBus                                                                                                                                                                                                                                                                                                                                                           | 1-249                                              |

| AN-479 DP839EB Network Evaluation Board                                                                                                                                                                                                                                                                                                                                                                                              | 1-279                                              |

| Systems-Oriented Network Interface Controller Products                                                                                                                                                                                                                                                                                                                                                                               |                                                    |

| DP83932B Systems-Oriented Network Interface Controller                                                                                                                                                                                                                                                                                                                                                                               | 1-288                                              |

| AN-745 DP83932 SONIC Bus Operations Guide                                                                                                                                                                                                                                                                                                                                                                                            | 1-384                                              |

| AN-746 Software Driver Programmer's Guide for the DP83932 SONIC                                                                                                                                                                                                                                                                                                                                                                      | 1-396                                              |

| AN-747 Determining Arbitration and Threshold Levels in a SONIC Based MICROCHANNEL                                                                                                                                                                                                                                                                                                                                                    |                                                    |

| Adapter                                                                                                                                                                                                                                                                                                                                                                                                                              | 1-426                                              |

| AN-691 32-Bit Bus Master Ethernet Interface for the 68030 (Using the Macintosh SE/30)                                                                                                                                                                                                                                                                                                                                                | 1-433                                              |

| AN-732 DP839EB-MCS SONIC MICROCHANNEL Ethernet Adapter                                                                                                                                                                                                                                                                                                                                                                               | 1-442                                              |

| AN-760 High Performance AT Compatible Bus Master Ethernet Adapter                                                                                                                                                                                                                                                                                                                                                                    | 1-467                                              |

| AN-748 DP839EB-ATS SONIC Packet Driver for PC/TCP by FTP Software                                                                                                                                                                                                                                                                                                                                                                    | 1-498                                              |

| AN-745 DP83932 SONIC Bus Operations Guide<br>AN-746 Software Driver Programmer's Guide for the DP83932 SONIC<br>AN-747 Determining Arbitration and Threshold Levels in a SONIC Based MICROCHANNEL<br>Adapter<br>AN-691 32-Bit Bus Master Ethernet Interface for the 68030 (Using the Macintosh SE/30)<br>AN-732 DP839EB-MCS SONIC MICROCHANNEL Ethernet Adapter<br>AN-760 High Performance AT Compatible Bus Master Ethernet Adapter | 1-384<br>1-396<br>1-426<br>1-433<br>1-442<br>1-467 |

# PRELIMINARY

# DP83902 Serial Network Interface Controller for Twisted Pair (ST-NIC<sup>™</sup>)

# **General Description**

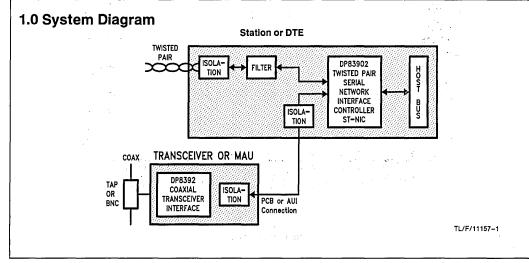

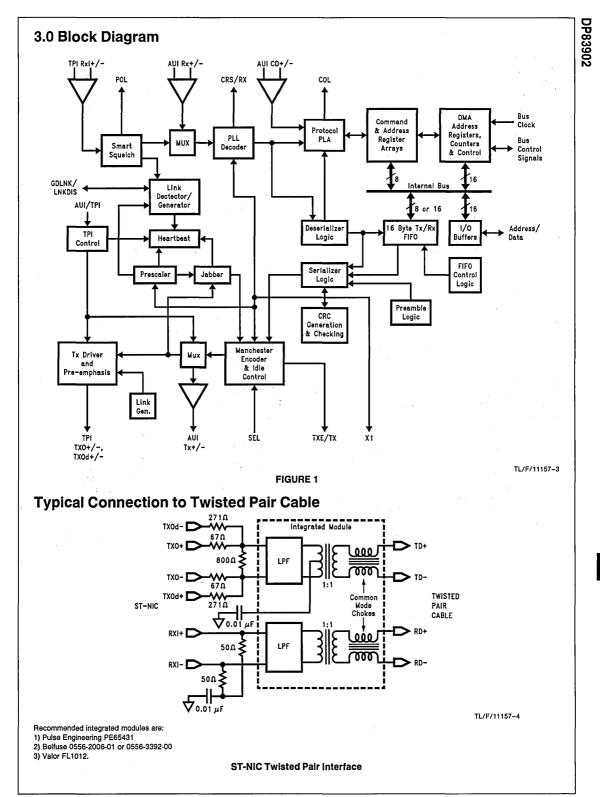

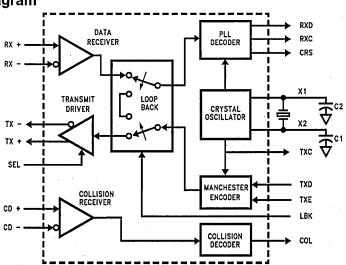

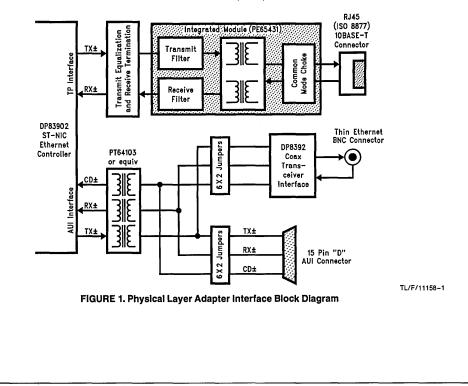

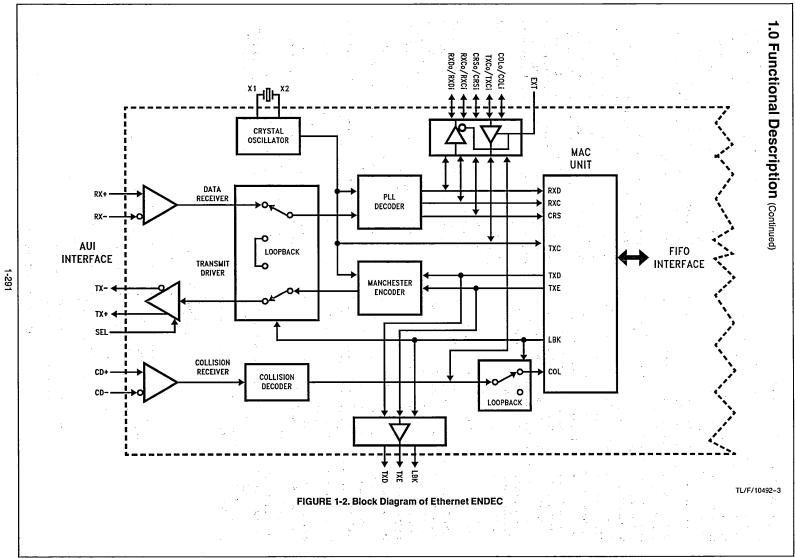

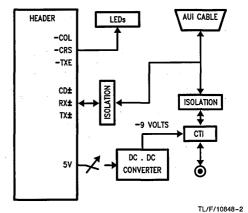

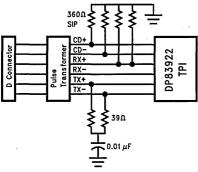

The DP83902 Serial Network Interface Controller for Twisted Pair (ST-NIC) is a microCMOS VLSI device designed for easy implementation of CSMA/CD local area networks. These include Ethernet (10BASE5), Thin Ethernet (10BASE2) and Twisted-pair Ethernet (10BASE-T). The overall ST-NIC solution provides the Media Access Control (MAC) and Encode-Decode (ENDEC) with an AUI interface, and 10BASE-T transceiver functions in accordance with the IEEE 802.3 standards.

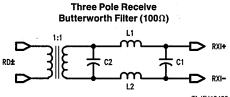

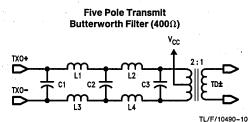

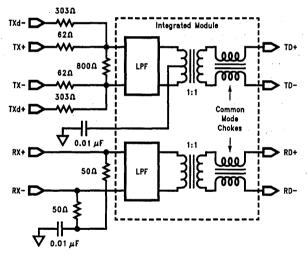

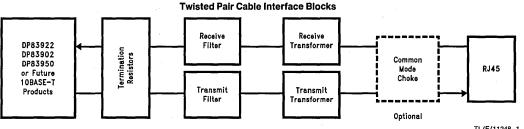

The DP83902's 10BASE-T transceiver fully complies with the IEEE standard. This functional block incorporates the receiver, transmitter, collision, heartbeat, loopback, jabber, and link integrity blocks as defined in the standard. The transceiver when combined with equalization resistors, transmit/receive filters, and pulse transformers provides a complete physical interface from the DP83902's ENDEC module and the twisted pair medium.

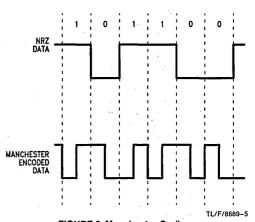

The integrated ENDEC module allows Manchester encoding and decoding via a differential transceiver and phase lock loop decoder at 10 Mbit/sec. Also included are collision detect translator and diagnostic loopback capability. The ENDEC module interfaces directly to the transceiver module, and also provides a fully IEEE compliant AUI (Attachment Unit Interface) for connection to other media transceivers. (Continued)

### Features

- Single chip solution for IEEE 802.3, 10BASE-T

- Integrated controller, ENDEC, and transceiver

- Full AUI interface

- No external precision components required

- 3 levels of loopback supported

#### Transceiver Module

- Integrates transceiver electronics, including:

- Transmitter and receiver

- Collision detect, heartbeat and jabber timer - Link integrity test

- Link disable for use with pre-standard twisted pair implementations

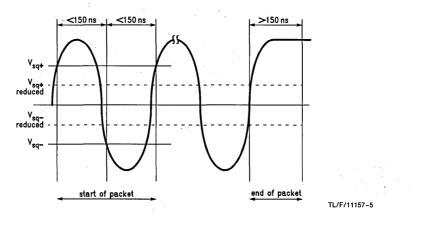

- Integrated smart receive squelch

- Polarity detection/correction

#### **ENDEC Module**

- 10 Mb/s Manchester encoding/decoding, plus clock recovery

- Transmitter half or full step mode

- Squelch on receive and collision pairs

- Lock time 5 bits typical

- Decodes Manchester data with up to ±18 ns jitter

#### **MAC/Controller Module**

- 100% DP8390 software/hardware compatible

- Dual 16-bit DMA channels

- 16-byte internal FIFO

- Efficient buffer management implementation

- Independent system and network clocks

- Supports physical, multicast and broadcast address filtering

- Network statistics storage

### General Description (Continued)

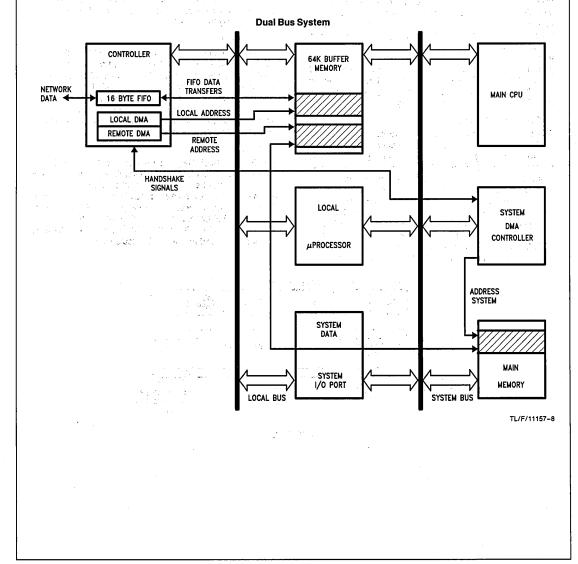

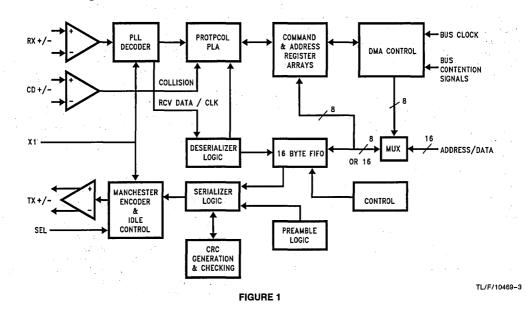

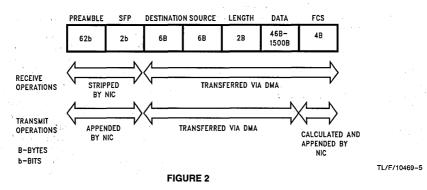

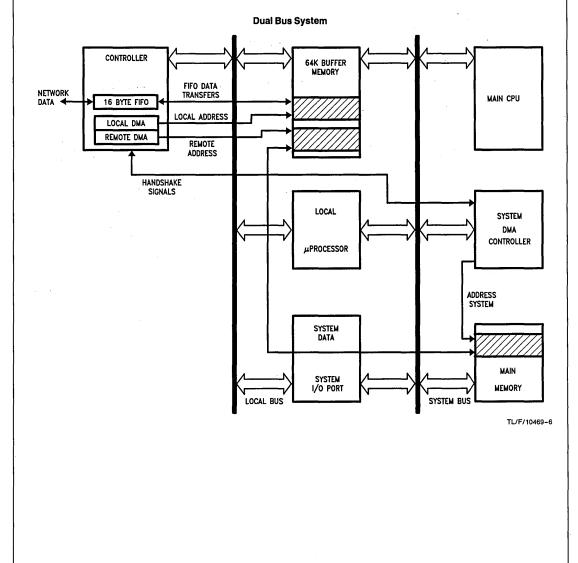

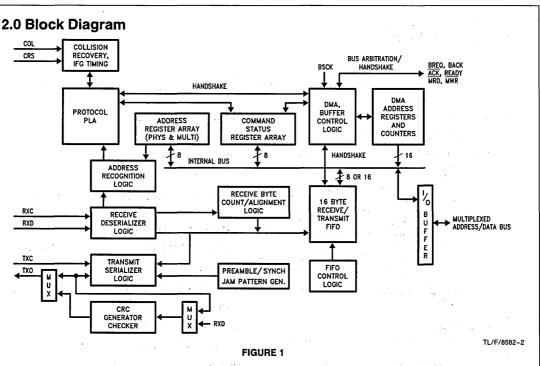

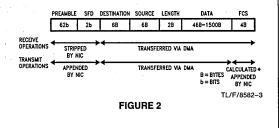

The Media Access Control function which is provided by the Network Interface Control module (NIC) provides simple and efficient packet transmission and reception control by means of unique dual DMA channels and an internal FIFO. Bus arbitration and memory control logic are integrated to reduce board cost and area overheads.

DP83902 provides a comprehensive single chip solution for 10BASE-T IEEE 802.3 networks and is designed for easy interface to other transceivers via the AUI interface.

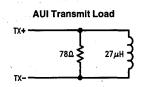

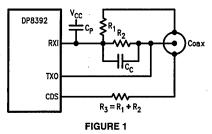

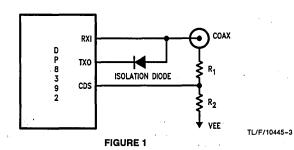

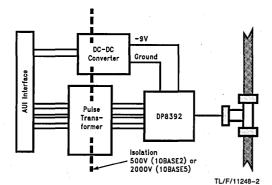

Due to the inherent constraints of CMOS processing, isolation is required at the AUI differential signal interface for 10BASE5 and 10BASE2 applications. Capacitive or inductive isolation may be used.

## **Table Of Contents**

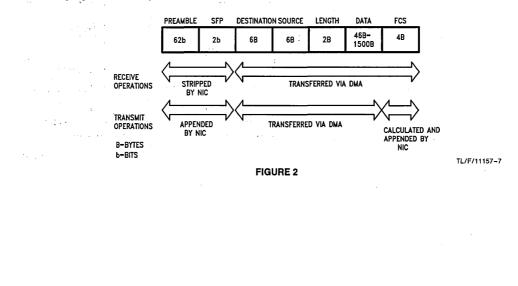

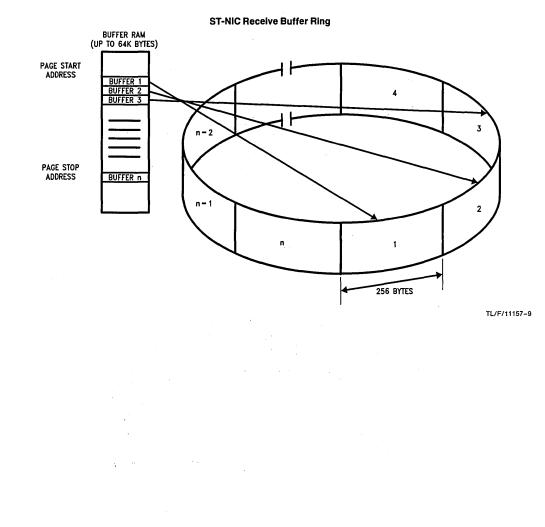

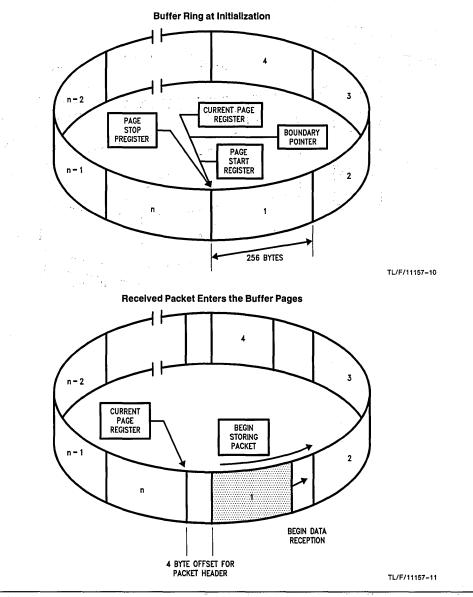

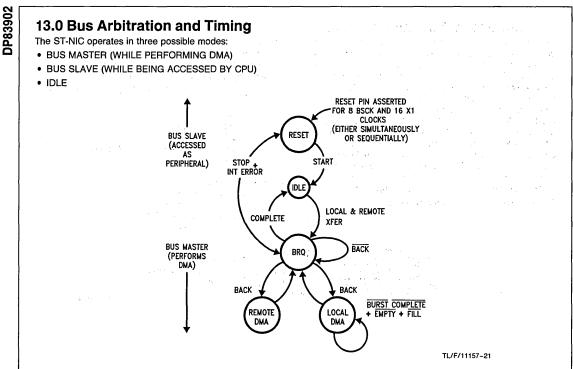

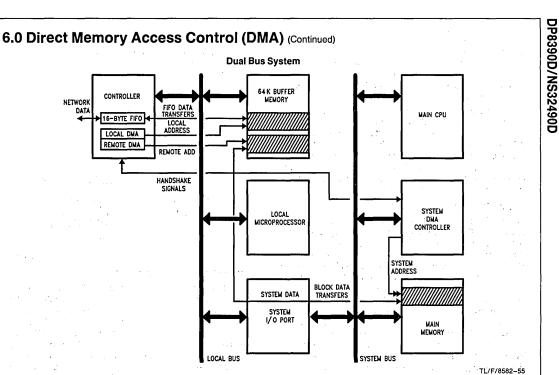

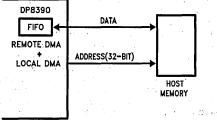

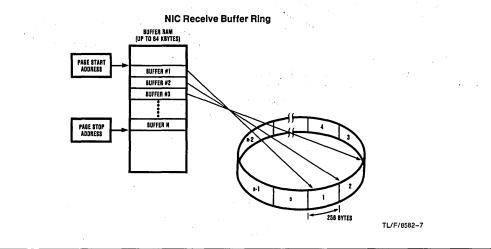

**1.0 SYSTEM DIAGRAM** 2.0 PIN DESCRIPTION 3.0 BLOCK DIAGRAM **4.0 FUNCTIONAL DESCRIPTION** 5.0 TRANSMIT/RECEIVE PACKET **ENCAPSULATION/DECAPSULATION** 6.0 DIRECT MEMORY ACCESS CONTROL (DMA) **7.0 PACKET RECEPTION** 8.0 PACKET TRANSMISSION 9.0 REMOTE DMA **10.0 INTERNAL REGISTERS 11.0 INITIALIZATION PROCEDURES** 12.0 LOOPBACK DIAGNOSTICS **13.0 BUS ARBITRATION AND TIMING** 14.0 PRELIMINARY ELECTRICAL CHARACTERISTICS **15.0 SWITCHING CHARACTERISTICS 16.0 AC TIMING TEST CONDITIONS 17.0 PHYSICAL DIMENSIONS**

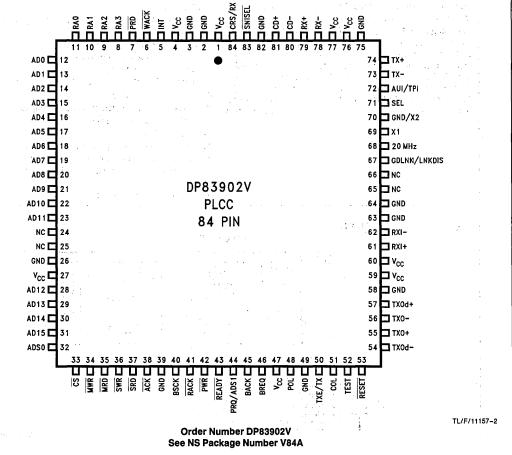

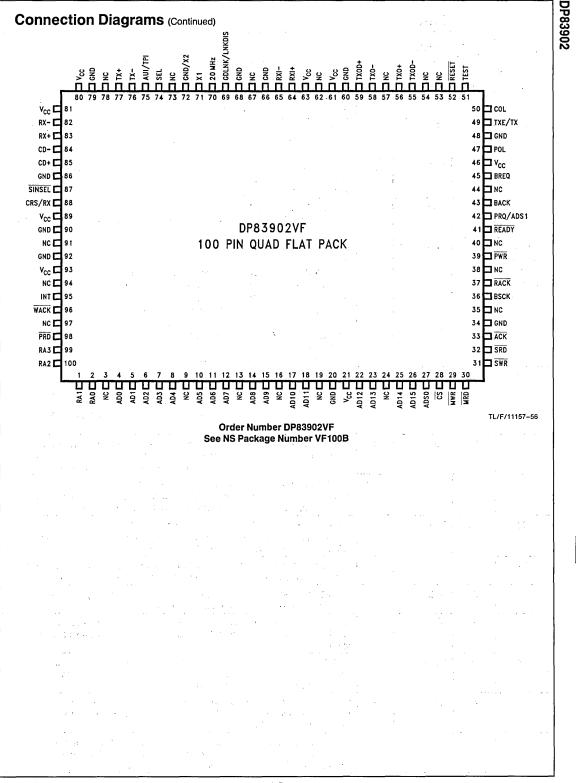

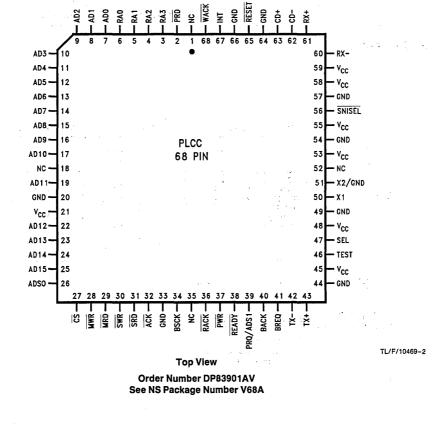

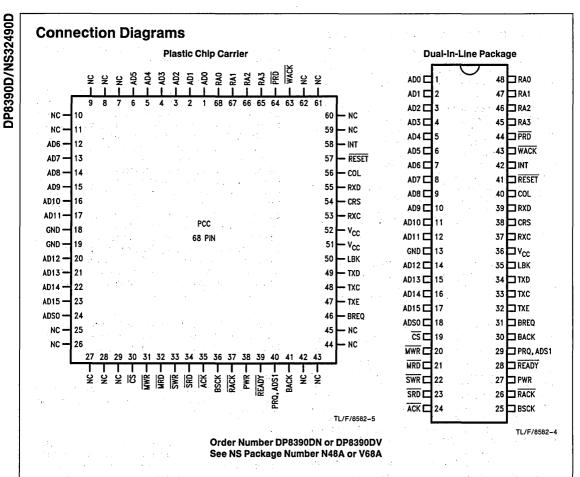

# **Connection Diagrams**

| PQFP<br>Pin No.                                        | PLCC<br>Pin No. | Pin Name | 1/0    | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

|--------------------------------------------------------|-----------------|----------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| BUS INTERI                                             | ACE PINS        | 3        |        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

| 95                                                     | 5               | INT      | 0      | <b>INTERRUPT:</b> Indicates that the DP83902 requires CPU attention after reception transmission or completion of DMA transfers. The interrupt is cleared by writing to the ISR (Interrupt Status Register). All interrupts are maskable.                                                                                                                                                                                                                                                                                                                                                                                         |  |

| 96                                                     | 6               | WACK     | Ι      | WRITE ACKNOWLEDGE: Issued from system to DP83902 to indicate that data has been written to the external latch. The DP83902 will begin a write cycle to place the data in local memory.                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

| 98                                                     | 7               | PRD      | 0      | <b>PORT READ:</b> Enables data from external latch on to local bus during a memory write cycle to local memory (remote write operation). This allows asynchronous transfer of data from the system memory to local memory.                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| 99, 100,<br>1, 2                                       | 8–11            | RA3-RA0  | 1      | <b>REGISTER ADDRESS:</b> These four pins are used to select a register to be read or written. The state of these inputs is ignored when the DP83902 is not in slave mode (CS high).                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

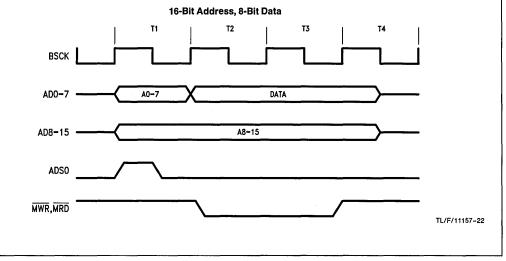

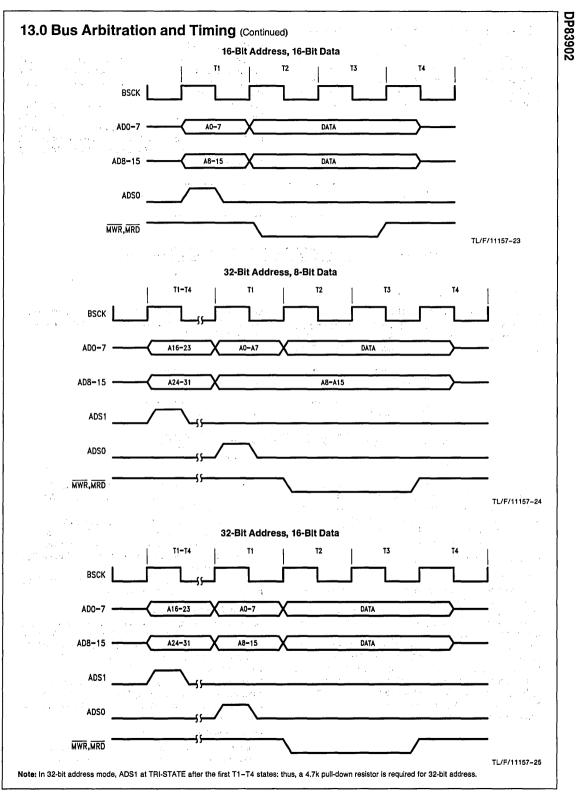

| 4–8,<br>10–12,<br>14, 15, 17,<br>18, 22, 23,<br>25, 26 | 12–23,<br>28–31 | AD0-AD15 | 1/O, Z | <ul> <li>MULTIPLEXED ADDRESS/DATA BUS:</li> <li>Register Access, with DMA inactive, CS low and ACK returned from DP83902, pins AD0-AD7 are used to read and write register data. AD8-AD15 float during I/ O transfers, SRD, SWR pins are used to select direction of transfer.</li> <li>Bus Master with BACK input asserted.<br/>During t1 of memory cycle AD0-AD15 contain address.<br/>During t2, t3, t4 AD0-AD15 contain data (word transfer mode).<br/>During t2, t3, t4 AD0-AD7 contain data, AD8-AD15 contain address (byte transfer mode).<br/>Direction of transfer is indicated by DP83902 on MWR, MRD lines.</li> </ul> |  |

| 27                                                     | 32              | ADS0     | 1/0, Z | <ul> <li>ADDRESS STROBE 0:</li> <li>Input: with DMA inactive and CS low, latches RA0–RA3 inputs on falling edg high, data present on RA0–RA3 will flow through latch.</li> <li>Output: When Bus Master, latches address bits (AD0–AD15) to external mer during DMA transfers.</li> </ul>                                                                                                                                                                                                                                                                                                                                          |  |

| 28                                                     | 33              | टड       | 1      | <b>CHIP SELECT:</b> Chip Select places controller in slave mode for $\mu$ P access to internal registers. Must be valid through data portion of bus cycle. RA0–RA3 ar used to select the internal register. SWR and SRD select direction of data trans                                                                                                                                                                                                                                                                                                                                                                            |  |

| 29                                                     | 34              | MWR      | 0, Z   | MASTER WRITE STROBE: (Strobe for DMA transfers)<br>Active low during write cycles (t2, t3, tw) to buffer memory. Rising edge coincid<br>with the presence of valid output data. TRI-STATE® until BACK asserted.                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

| 30                                                     | 35              | MRD      | 0, Z   | MASTER READ STROBE: (Strobe for DMA transfers)<br>Active during read cycles (t2, t3, tw) to buffer memory. Input data must be valid on<br>rising edge of MRD. TRI-STATE until BACK asserted.                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

| 31                                                     | 36              | SWR      | 1      | SLAVE WRITE STROBE: Strobe from CPU to write an internal register selected by RAO-RA3. Data is latched into the DP83902 on the rising edge of this input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

| 32                                                     | 37              | SRD      | I      | SLAVE READ STROBE: Strobe from CPU to read an internal register selected by RA0–RA3. The register data is output when SRD goes low.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

| 33                                                     | 38              | ACK      | 0      | ACKNOWLEDGE: Active low when DP83902 grants access to CPU. Used to in WAIT states to CPU until DP83902 is synchronized for a register read or write operation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

| 36                                                     | 40              | BSCK     | 1      | BUS CLOCK: This clock is used to establish the period of the DMA memory cycle.<br>Four clock cycles (t1, t2, t3, t4) are used per DMA cycle. DMA transfers can be<br>extended by one BSCK increment using the READY input.                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| 37                                                     | 41              | RACK     | I      | <b>READ ACKNOWLEDGE:</b> Indicates that the system DMA or host CPU has read the data placed in the external latch by the DP83902. The DP83902 will begin a read cycle to update the latch.                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| 39                                                     | 42              | PWR      | 0      | <b>PORT WRITE:</b> Strobe used to latch data from the DP83902 into external latch for transfer to host memory during Remote Read transfers. The rising edge of PWR coincides with the presence of valid data on the local bus.                                                                                                                                                                                                                                                                                                                                                                                                    |  |

| PQFP<br>Pin No.   | PLCC<br>Pin No.   | Pin Name                    | 1/0            | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-------------------|-------------------|-----------------------------|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BUS INTE          | RFACE P           | INS (Continued)             | ·              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 41                | 43                | READY                       | I              | <b>READY:</b> This pin is set high to insert wait states during a DMA transfer. The DP83902 will sample this signal at t3 during DMA transfers.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 42 ,              | 44                | 44 PRQ/ADS1 0, 2            |                | <ul> <li>PORT REQUEST/ADDRESS STROBE 1</li> <li>32-BIT MODE: If LAS is set in the Data Configuration Register, this line is programmed as ADS1. It is used to strobe addresses A16-A31 into external latches. (A16-A31 are the fixed addresses stored in RSAR0, RSAR1). ADS1 will remain at TRI-STATE until BACK is received.</li> <li>16-BIT MODE: If LAS is not set in the Data Configuration Register, this line is programmed as PRQ and is used for Remote DMA Transfers. The DP83902 initiates a single remote DMA read or write operation by asserting this pin. In this mode PRQ will be a standard logic output.</li> <li>Note: This line will power up as TRI-STATE until the Data Configuration Register is programmed.</li> </ul>                                                                                                                                                                                                           |

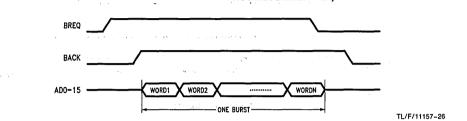

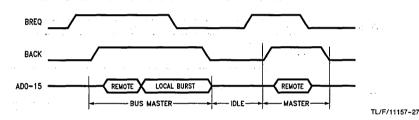

| 43                | 45                | BACK                        | 1              | BUS ACKNOWLEDGE: Bus Acknowledge is an active high signal indicating that the CPU has granted the bus to the DP83902. If immediate bus access is desired, BREQ should be tied to BACK. Tying BACK to V <sub>CC</sub> will result in a deadlock.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 45                | 46                | BREQ                        | 0              | BUS REQUEST: Bus Request is an active high signal used to request the bus for DMA transfers. This signal is automatically generated when the FIFO needs servicing.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 52                | 53                | RESET                       | 1              | <b>RESET:</b> Reset is active low and places the DP83902 in a reset mode immediately.<br>No packets are transmitted or received by the DP83902 until STA bit is set. Affects<br>Command Register, Interrupt Mask Register, Data Configuration Register and<br>Transmit Configuration Register. The DP83902 will execute reset within 10 BSCK<br>cycles.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| NETWOR            | K INTERF          | ACE PINS                    |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

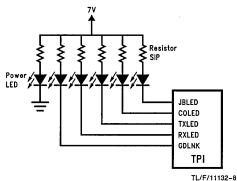

| 47                | .48               | POL                         | O <sup>1</sup> | <b>POLARITY:</b> A TTL/MOS active high output. This signal is normally in the low state.<br>When the TPI module detects seven consecutive link pulses or three consecutive<br>received packets with reversed polarity POL, is asserted.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 49                | 50                | TXE/TX                      | 0              | TRANSMIT ENABLE/TRANSMIT: A TTL/MOS active high output. It is asserted for<br>approximately 50 ms whenever the DP83902 transmits data in either AUI or TPI<br>modes.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 50                | 51                | COL                         | 0              | <b>COLLISION:</b> A TTL/MOS active high output. It is asserted for approximately 50 ms whenever the DP83902 detects a collision in either the AUI or TPI modes.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 51                | 52                | TEST                        | 1              | FACTORY TEST INPUT: Used to check the chip's internal functions. This should be tied low during normal operation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

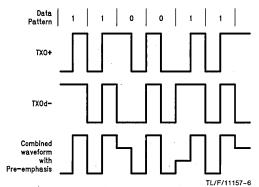

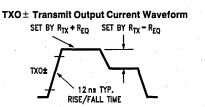

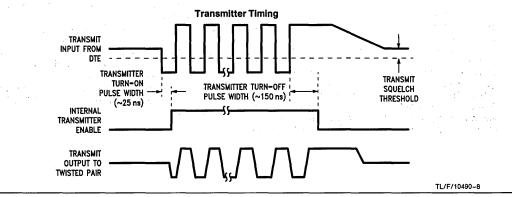

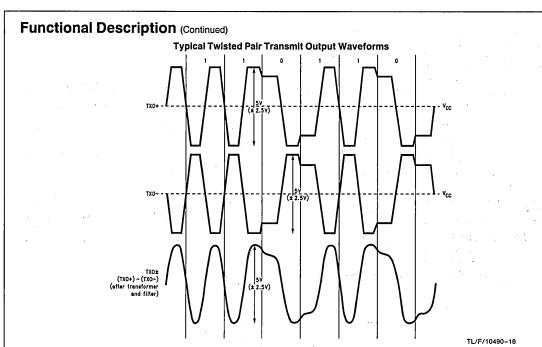

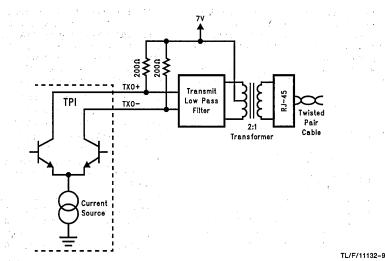

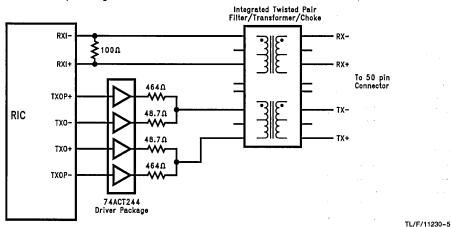

| 55, 56,<br>58, 59 | 54, 55,<br>56, 57 | TXOd-, TXO+,<br>TXO-, TXOd+ | 0              | TWISTED PAIR TRANSMIT OUTPUTS: These high drive CMOS level outputs are resistively combined external to the chip to produce a differential output signal with equalization to compensate for Intersymbol Interference (ISI) on the twisted pair medium.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 64, 65            | 61, 62            | RXI+, RXI-                  |                | TWISTED PAIR RECEIVE INPUTS: These inputs feed a differential amplifier which passes valid data to the ENDEC module.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| . 69              | 67                | GDLNK/LNKDIS                | 1/0            | <b>GOOD LINK/LINK DISABLE:</b> This pin has a dual function both input and output.<br>The function is latched by the DP83902 on the rising edge of the Reset signal i.e.:<br>on the chip returning to normal operation after reset.<br>As an output this pin is configured as an open drain N-channel device and is suitable<br>for driving a LED. It will be latched as output on removal of chip reset if connected to<br>a LED or left open circuit. Under normal conditions (the twisted pair link is not<br>broken) the output will be low, and the LED will be lit. The open drain output will be<br>switched off if the twisted pair link has been detected to be broken. It is<br>recommended that the color of the LED be green. This output will be pulled high in<br>AUI mode, by an internal resistor of approximately 15 k $\Omega$ .<br>When this pin, which has an internal pull-up resistor to V <sub>DD</sub> , is tied low it becomes |

1

| 5  |

|----|

| 0  |

| S. |

| က  |

| œ  |

| Δ. |

| Δ  |

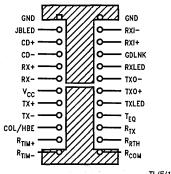

| PQFP<br>Pin No.                              | PLCC<br>Pin No.      | Pin Name        | 1/0           | Description                                                                                                                                                                                                                                                                            |  |

|----------------------------------------------|----------------------|-----------------|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| IETWORK INT                                  | ERFACE PI            | NS (Continued)  |               | n an                                                                                                                                                                                                                                               |  |

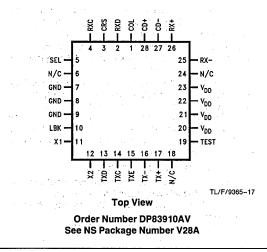

| 70                                           | 68                   | 20 MHz          | 0             | <b>20 MHz:</b> This is a TTL/MOS level signal. It is a buffered version of the oscillator X2. It is suitable to drive external logic.                                                                                                                                                  |  |

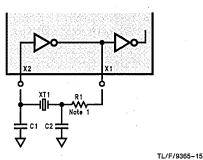

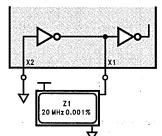

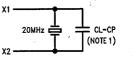

| 71                                           | 69                   | X1 .            | 1             | EXTERNAL OSCILLATOR INPUT                                                                                                                                                                                                                                                              |  |

| 72                                           | 70                   | GND/X2          | <b> </b><br>* | <b>GROUND/X2:</b> This pin should normally be connected to ground. It is possible to use a crystal oscillator using X1 and GND/X2 if certain precautions are taken. Contact National Semiconductor for more information.                                                               |  |

| 74                                           | 71                   | SEL             |               | <b>MODE SELECT:</b> When high, $TX +$ and $TX -$ are the same voltage in the idle state. When low, Transmit + is positive with respect to Transmit - in the idle state, at the transformer's primary.                                                                                  |  |

| 75                                           | 72                   | AUI/TPI         |               | AUI/TPI SELECT: A TTL level active high input that selects either the AUI interface or the TPI module for interface with the ENDEC module. When high the AUI is selected, when low the TPI is selected.                                                                                |  |

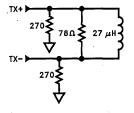

| 76, 77                                       | 73, 74               | TX-, TX+        | 0             | AUI TRANSMIT OUTPUT: Differential driver which sends the encoded data to the transceiver. The outputs are source followers which require $270\Omega$ pulldown resistors.                                                                                                               |  |

| 82, 83                                       | 78, 79               | RX-, RX+        | <u> </u>      | AUI RECEIVE INPUT: Differential receive input pair from the transceiver.                                                                                                                                                                                                               |  |

| 84, 85                                       | 80, 81               | CD-, CD+        | 1             | AUI COLLISION INPUT: Differential collision pair input from the transceiver.                                                                                                                                                                                                           |  |

| 87                                           | 83                   | SNISEL          |               | FACTORY TEST INPUT: For normal operation tied to V <sub>CC</sub> . When low enables the ENDEC module to be tested independently of the DP83902 module.                                                                                                                                 |  |