# Programmable Logic Devices Databook and Design Guide

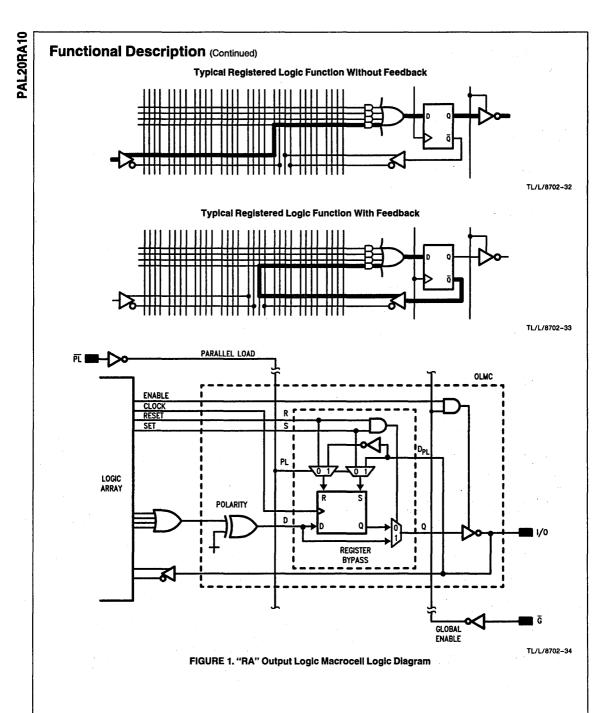

### A Corporate Dedication to Quality and Reliability

National Semiconductor is an industry leader in the manufacture of high quality, high reliability integrated circuits. We have been the leading proponent of driving down IC defects and extending product lifetimes. From raw material through product design, manufacturing and shipping, our quality and reliability is second to none.

We are proud of our success . . . it sets a standard for others to achieve. Yet, our quest for perfection is ongoing so that you, our customer, can continue to rely on National Semiconductor Corporation to produce high quality products for your design systems.

Charles E. Sporck President, Chief Executive Officer National Semiconductor Corporation

#### Wir fühlen uns zu Qualität und Zuverlässigkeit verpflichtet

National Semiconductor Corporation ist führend bei der Herstellung von integrierten Schaltungen hoher Qualität und hoher Zuverlässigkeit. National Semiconductor war schon immer Vorreiter, wenn es galt, die Zahl von IC Ausfällen zu verringern und die Lebensdauern von Produkten zu verbessern. Vom Rohmaterial über Entwurf und Herstellung bis zur Auslieferung, die Qualität und die Zuverlässigkeit der Produkte von National Semiconductor sind unübertroffen.

Wir sind stolz auf unseren Erfolg, der Standards setzt, die für andere erstrebenswert sind. Auch ihre Ansprüche steigen ständig. Sie als unser Kunde können sich auch weiterhin auf National Semiconductor verlassen.

#### La Qualité et La Fiabilité:

Une Vocation Commune Chez National Semiconductor Corporation

National Semiconductor Corporation est un des leaders industriels qui fabrique des circuits intégrés d'une très grande qualité et d'une fiabilité exceptionelle. National a été le premier à vouloir faire chuter le nombre de circuits intégrés défectueux et a augmenter la durée de vie des produits. Depuis les matières premières, en passant par la conception du produit sa fabrication et son expédition, partout la qualité et la fiabilité chez National sont sans équivalents.

Nous sommes fiers de notre succès et le standard ainsi défini devrait devenir l'objectif à atteindre par les autres sociétés. Et nous continuons à vouloir faire progresser notre recherche de la perfection; il en résulte que vous, qui êtes notre client, pouvez toujours faire confiance à National Semiconductor Corporation, en produisànt des systèmes d'une très grande qualité standard.

#### Un Impegno Societario di Qualità e Affidabilità

National Semiconductor Corporation è un'industria al vertice nella costruzione di circuiti integrati di altà qualità ed affidabilità. National è stata il principale promotore per l'abbattimento della difettosità dei circuiti integrati e per l'allungamento della vita dei prodotti. Dal materiale grezzo attraverso tutte le fasi di progettazione, costruzione e spedizione, la qualità e affidabilità National non è seconda a nessuno.

Noi siamo orgogliosi del nostro successo che fissa per gli altri un traguardo da raggiungere. Il nostro desiderio di perfezione è d'altra parte illimitato e pertanto tu, nostro cliente, puoi continuare ad affidarti a National Semiconductor Corporation per la produzione dei tuoi sistemi con elevati livelli di qualità.

Charlie Spork

Charles E. Sporck President, Chief Executive Officer National Semiconductor Corporation

# Programmable Logic Devices DATABOOK AND DESIGN GUIDE

**1990 Edition**

#### PART I — DATA BOOK

PART II — DESIGN GUIDE

**Product Line Overview**

**Data Sheets**

**Designing with PLDs**

**PLD Design Methodology**

PLD Design Development Tools

**Fabrication of Programmable Logic**

**Application Examples**

**Appendices/Physical Dimensions**

#### TRADEMARKS

Following is the most current list of National Semiconductor Corporation's trademarks and registered trademarks.

Abuseable™ Anadia™ ANS-R-TRAN™ **APPSTM ASPECT™** Auto-Chem Deflasher™ **ВСРТМ** BI-FET™ BI-FET II™ BI-LINE™ **BIPLANTM** BI CTM **BLXTM** ВМАС™ Brite-Lite™ **BSITM** BTL™ CDDTM CheckTrack™ СІМ™ **CIMBUS™ CLASIC™** COMBO® COMBO ITM COMBO IITM COPS™ microcontrollers CRD™ Datachecker® **DENSPAKTM** DIB™ Digitalker® **DISCERNTM** DISTILL™ DNR® **DPVMTM** E<sup>2</sup>CMOS™ ELSTAR™ Embedded System Processor<sup>™</sup>

E-Z-LINK™ **FACTTM** FACT Quiet Series™ FAIRCAD™ Fairtech™ **FAST®** 5-Star Service™ Flash™ **GENIX™ GNX™ GTO™** HAMR™ HandiScan™ HEX 3000™ НРС™ |3L® **ICM™ INFOCHEXTM** Integral ISE™ Intelisplay<sup>TM</sup> ISETM ISE/06™ ISE/08™ ISE/16™ ISE32TM **ISOPLANAR™ ISOPLANAR-Z™** KevScan™ LMCMOS™ M<sup>2</sup>CMOS™ Macrobus™ Macrocomponent<sup>™</sup> MAXI-ROM® Meat⊮Chek™ MenuMaster™ Microbus™ data bus MICRO-DAC™ µtalker™ Microtalker™ **MICROWIRE™**

MICROWIRE/PLUS™ **MOLE™** МРА™ MST™ Naked-8™ National® National Semiconductor® National Semiconductor Corp.® NAX 800™ Nitride Plus™ Nitride Plus Oxide™ **NMLTM NOBUS™** NSC800™ NSCISE™ NSX-16™ NS-XC-16™ **NTERCOM™** NURAM™ OXISS™ P<sup>2</sup>CMOS™ PC Master™ Perfect Watch™ Pharmar/Chek™ **PLANTM** PI ANARTM **PLAYERTM** Plus-2™ Polycraft™ POSilink™ POSitalker™ Power + Control™ POWERplanar™ QUAD3000™ **QUIKLOOK™ RATTM** RTX16™ SABR™ Script/Chek™

**SCX™** SERIES/800™ Series 900™ Series 3000™ Series 32000® Shelf**⊮**Chek™ Simple Switcher™ SofChek™ **SONIC™ SPIRE™** Staggered Refresh™ **STARTM** Starlink™ **STARPLEXTM** Super-Block™ SuperChip™ SuperScript™ SYS32™ TapePak® TDSTM TeleGate™ The National Anthem® Time⊮Chek™ TINATM TLC™ Trapezoidal™ TRI-CODE™ TRI-POLY™ TRI-SAFE™ **TRI-STATE® TURBOTRANSCEIVER™** VIPTM VR32™ **WATCHDOG™** XMOS™ **XPUTM** Z STAR™ 883B/RETS™ 883S/RETS™

ABEL<sup>™</sup> is a trademark of Data I/O Corporation.

CUPL® is a registered trademark of Logical Devices.

GAL®, Latch-Lock™ and UltraMOS® are trademarks of Lattice Semiconductor.

IBM® is a registered trademark of International Business Machines Corporation.

IFL™ is a trademark of Signetics Semiconductor.

PAL®, PALASM™ and PALASM2™ are trademarks of and used under license from Advanced Micro Devices, Inc. VAX™ is a trademark of Digital Equipment Corporation.

#### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

- Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform, when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

National Semiconductor Corporation 2900 Semiconductor Drive, P.O. Box 58090, Santa Clara, California 95052-8090 (408) 721-5000 TWX (910) 339-9240

National does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied, and National reserves the right, at any time without notice, to change said circuitry or specifications.

iv

#### Introduction

#### HOW TO USE THIS BOOK

This Data Book and Design Guide is intended for use by system designers and manufacturers who wish to take advantage of the opportunities created with National's Programmable Logic Devices (PLDs). The book goes beyond a collection of available data sheets by adding selected application examples and background information on design techniques and benefits of programmable logic products.

The book is laid out to permit users of varying familiarity with PLDs to find the information they need. It should be used as a reference work at all levels and as an introductory tutorial for those areas which require review. While PLDs provide a level of simplicity, flexibility and compactness beyond that offered by other off-the-shelf parts, their optimal use requires the designer to be familiar with design methodologies, development tools and design testing as well as the details of the products themselves.

Experienced users will find reference information in Part I (Data Book). Part I contains two sections which will aid the designer during actual system design and development process. Section 1 provides an overview of the entire programmable logic product line available from National to aid in device selection. Section 2 presents complete data sheets for all listed devices.

For the user new to PLD design, it is recommended that the introductory Section 3 is read first, followed by careful study of Section 4 on design methodology, with reference to PLD Tools in Section 5 and PLD Fabrication (technology and quality) in Section 6 as required. Following this, a review of available products in Section 1 and examination of a few data sheets of interest in Section 2 will provide background for a study of concrete design examples enumerated in Section 7.

# National Semiconductor

## **Product Status Definitions**

### **Definition of Terms**

| Data Sheet Identification     | Product Status            | Definition                                                                                                                                                                                                                                                                      |  |  |  |

|-------------------------------|---------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Advance Information           | Formative or<br>In Design | This data sheet contains the design specifications for product development. Specifications may change in any manner without notice.                                                                                                                                             |  |  |  |

| Preliminary                   | First<br>Production       | This data sheet contains preliminary data, and supplementary data will<br>be published at a later date. National Semiconductor Corporation<br>reserves the right to make changes at any time without notice in order<br>to improve design and supply the best possible product. |  |  |  |

| No<br>Identification<br>Noted | Full<br>Production        | This data sheet contains final specifications. National Semiconductor<br>Corporation reserves the right to make changes at any time without<br>notice in order to improve design and supply the best possible product.                                                          |  |  |  |

National Semiconductor Corporation reserves the right to make changes without further notice to any products herein to improve reliability, function or design. National does not assume any liability arising out of the application or use of any product or circuit described herein; neither does it convey any license under its patent rights, nor the rights of others.

# **Table of Contents**

| Alphanumeric Index                                           | x     |

|--------------------------------------------------------------|-------|

| PART I-DATA BOOK                                             |       |

| Section 1 Product Line Overview                              |       |

| 1.1 Selection Tables                                         | 1-3   |

| 1.2 Ordering Information                                     | 1-7   |

| 1.3 Block Diagrams                                           | 1-8   |

| Section 2 Data Sheets                                        |       |

| 20-Pin Small PAL Family                                      | 2-3   |

| 20-Pin Medium PAL Family                                     | 2-23  |

| 24-Pin Small PAL Family                                      | 2-48  |

| 24-Pin Exclusive-OR PAL Family                               | 2-62  |

| 24-Pin Medium PAL Family                                     | 2-77  |

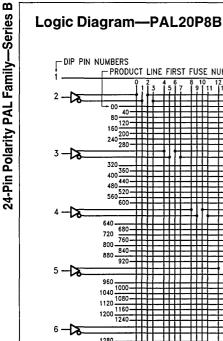

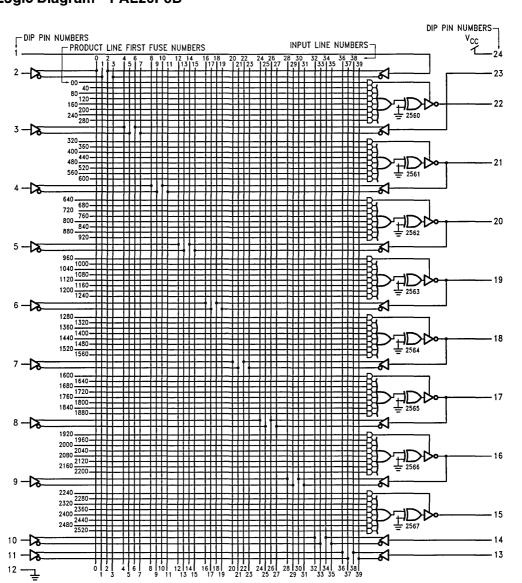

| 24-Pin Polarity PAL Family                                   | 2-95  |

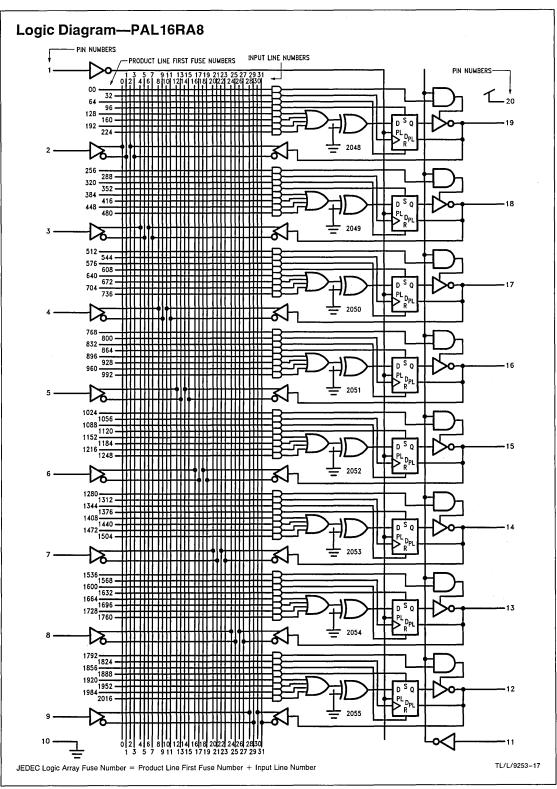

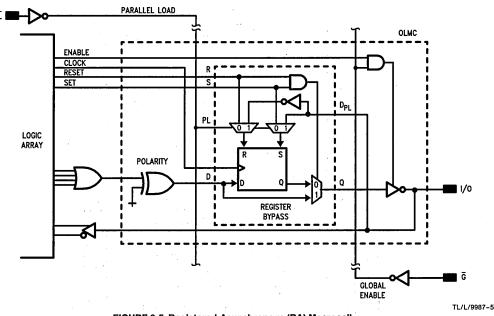

| PAL16RA8 20-Pin Registered Asynchronous PAL                  | 2-108 |

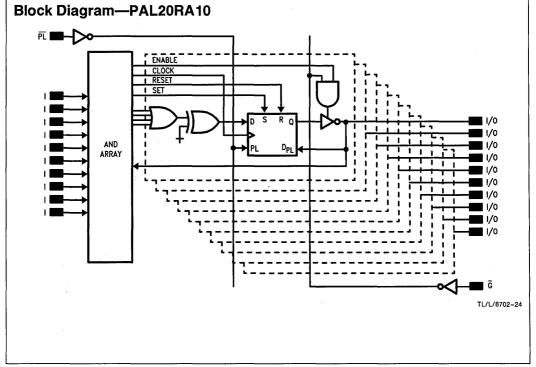

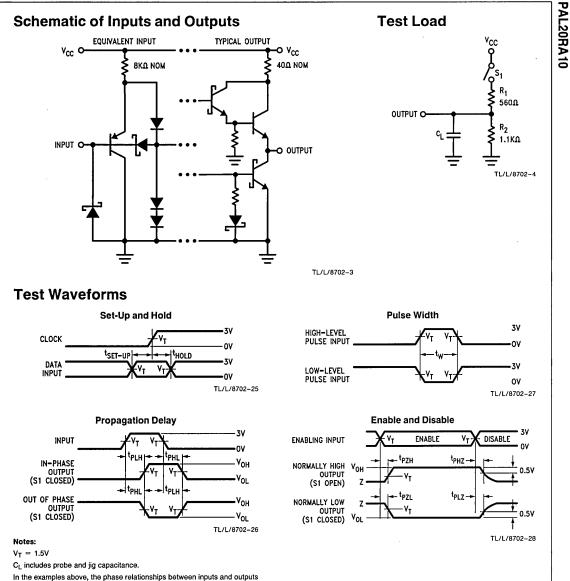

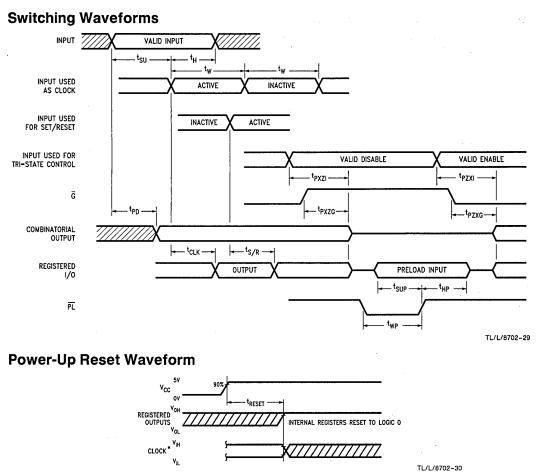

| PAL20RA10 24-Pin Registered Asynchronous PAL                 | 2-118 |

| GAL16V8 Generic Array Logic                                  | 2-129 |

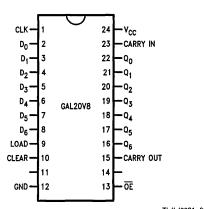

| GAL20V8 Generic Array Logic                                  | 2-145 |

| GAL16V8A Generic Array Logic                                 | 2-162 |

| GAL20V8A Generic Array Logic                                 | 2-177 |

| GAL22V10-15, -20, -25, -30 Generic Array Logic (Preliminary) | 2-193 |

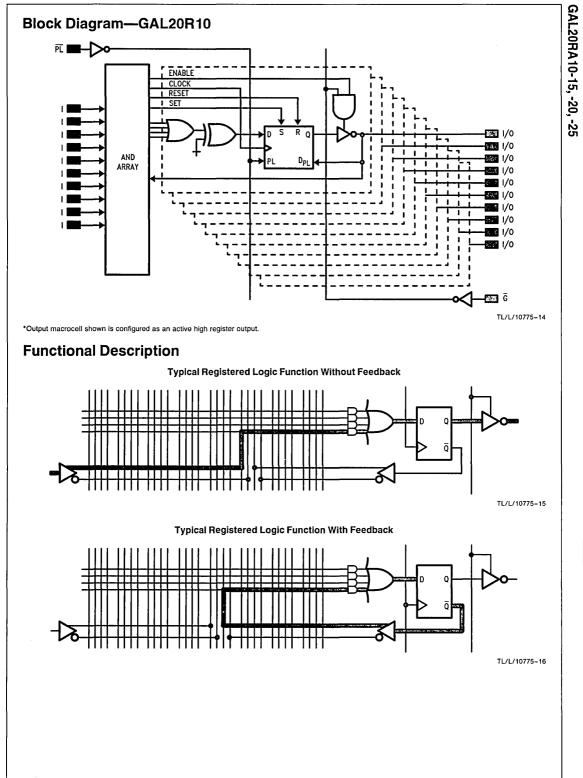

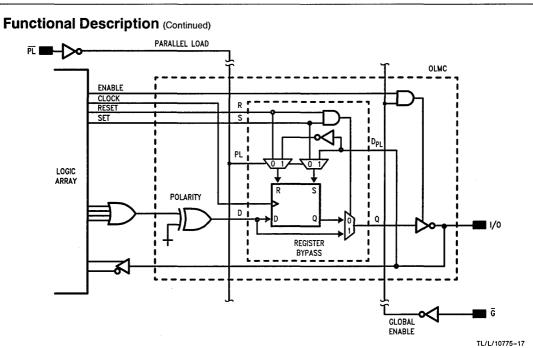

| GAL20RA10-15, -20, -25 Generic Array Logic (Preliminary)     | 2-206 |

| GAL6001 Generic Array Logic (Preliminary)                    | 2-217 |

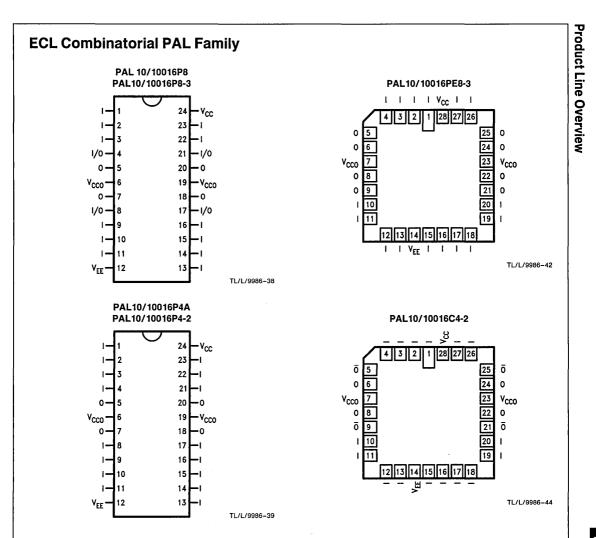

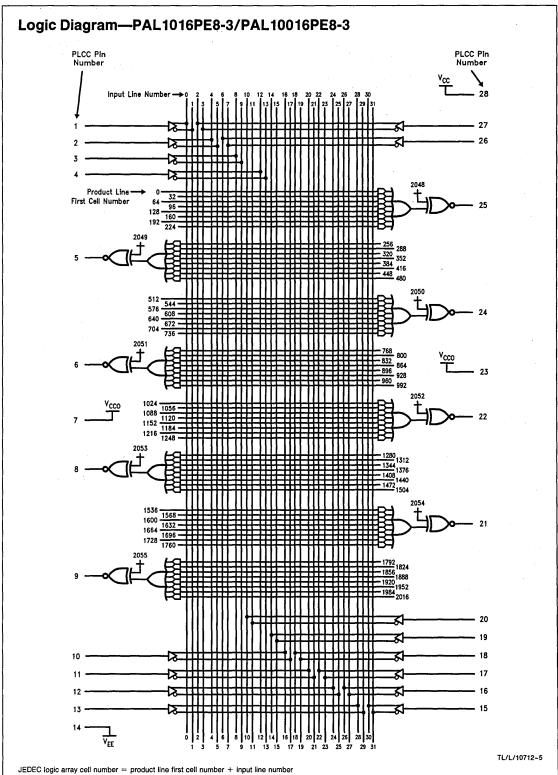

| ECL PAL10/10016P8 Combinatorial PAL                          | 2-227 |

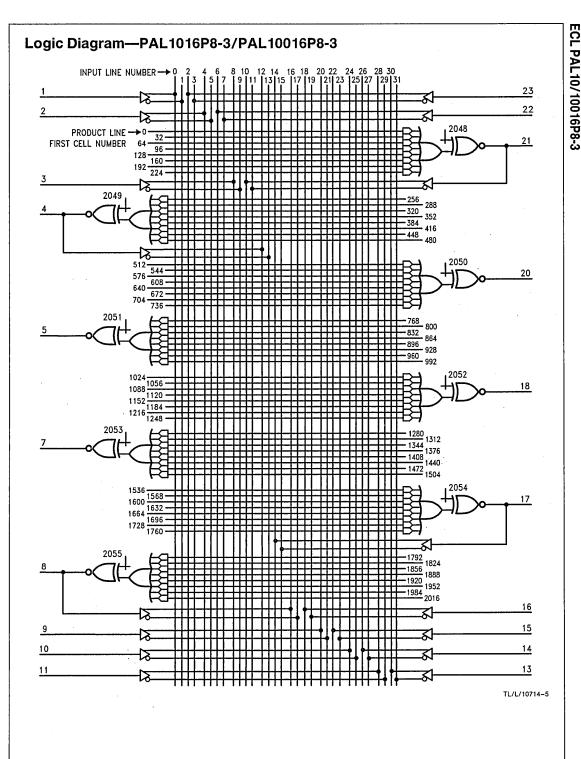

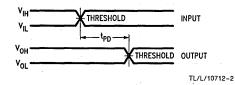

| ECL PAL10/10016P8-3 3 ns Combinatorial PAL (Preliminary)     | 2-236 |

| ECL PAL10/10016PE8-3 3 ns Combinatorial PAL (Preliminary)    | 2-242 |

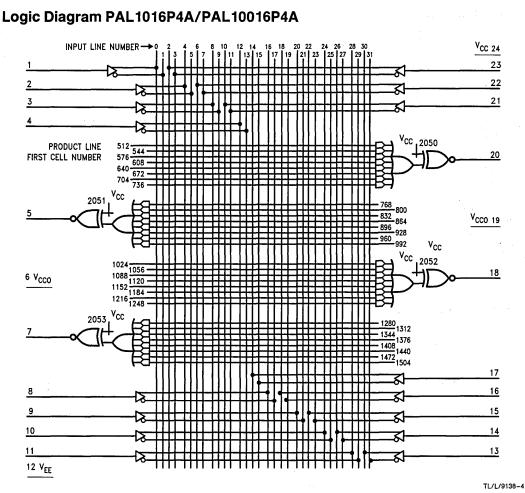

| ECL PAL10/10016P4A Combinatorial PAL                         | 2-247 |

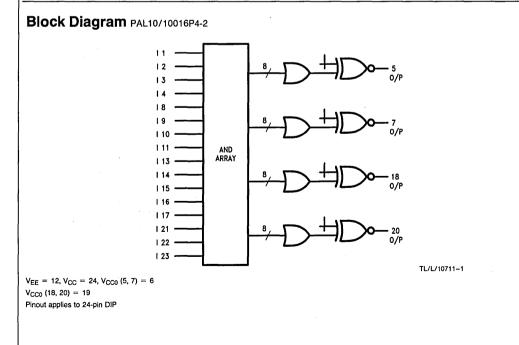

| ECL PAL10/10016P4-2 2 ns Combinatorial PAL (Preliminary)     | 2-251 |

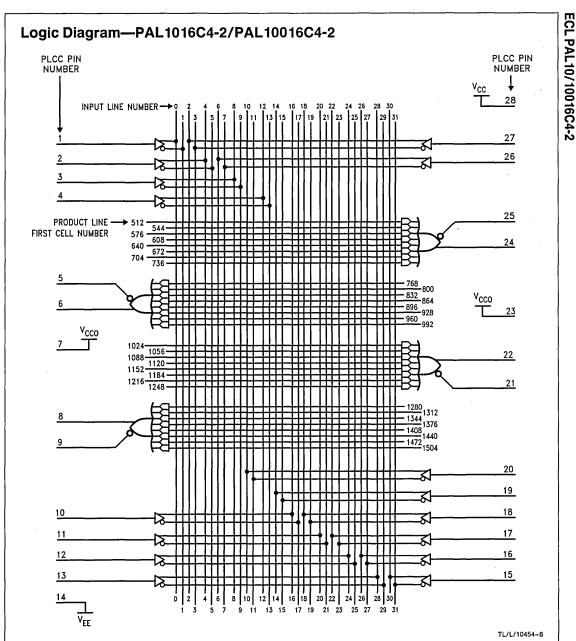

| ECL PAL10/10016C4-2 2 ns Combinatorial PAL (Preliminary)     | 2-257 |

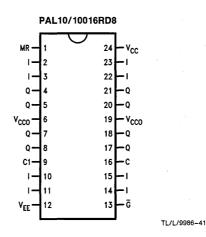

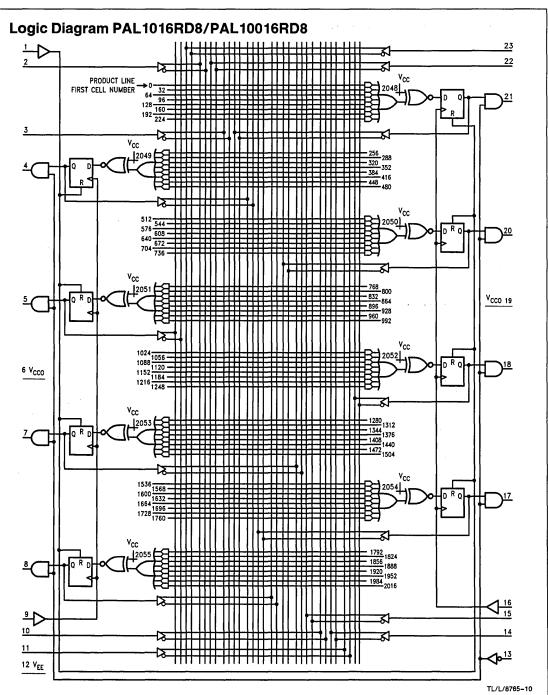

| ECL PAL10/10016RD8 Registered PAL                            | 2-262 |

| ECL PAL10/10016RM4A Registered PAL                           | 2-268 |

| PART II—DESIGN GUIDE                                         |       |

| Section 3 Designing with Programmable Logic                  |       |

| 3.1 Background to PLDs                                       | 3-3   |

| PROM devices                                                 |       |

| FPLA devices                                                 |       |

| PAL devices                                                  |       |

| GAL devices                                                  |       |

| 3.2 Design Advantages                                        | 3-3   |

| Simplified system design                                     |       |

| Increased functional density                                 |       |

| 3.3 Manufacturing Advantages                                 | 3-5   |

| Cost of inventory                                            |       |

| Cost of ownership                                            |       |

| Cost of upgrades and modifications                           |       |

| Higher reliability                                           |       |

| 3.4 Alternative Methodologies                                | 3-6   |

| Standard LSI                                                 |       |

| Standard SSI/MSI                                             |       |

| Full custom                                                  |       |

| Semi-custom ASICs                                            |       |

| Table of Contents (Continued)                           |      |

|---------------------------------------------------------|------|

| Section 3 Designing with Programmable Logic (Continued) |      |

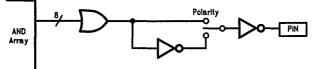

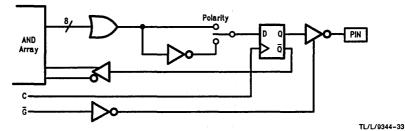

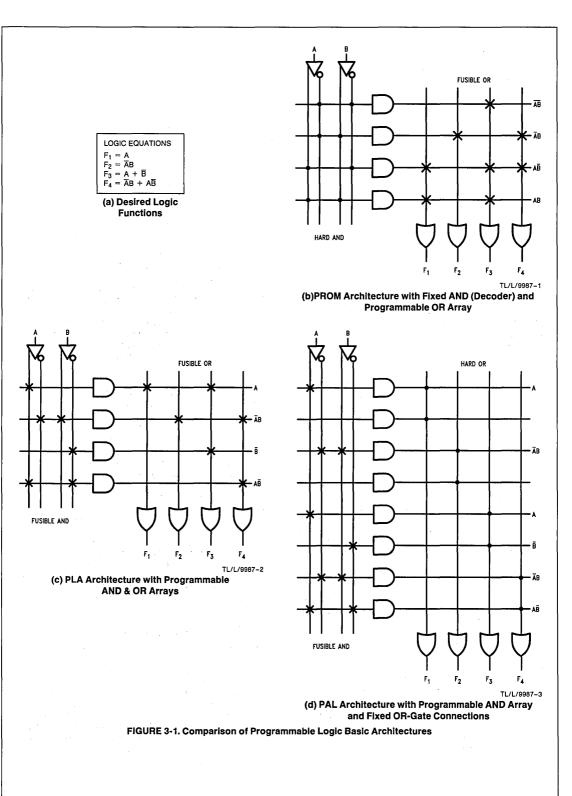

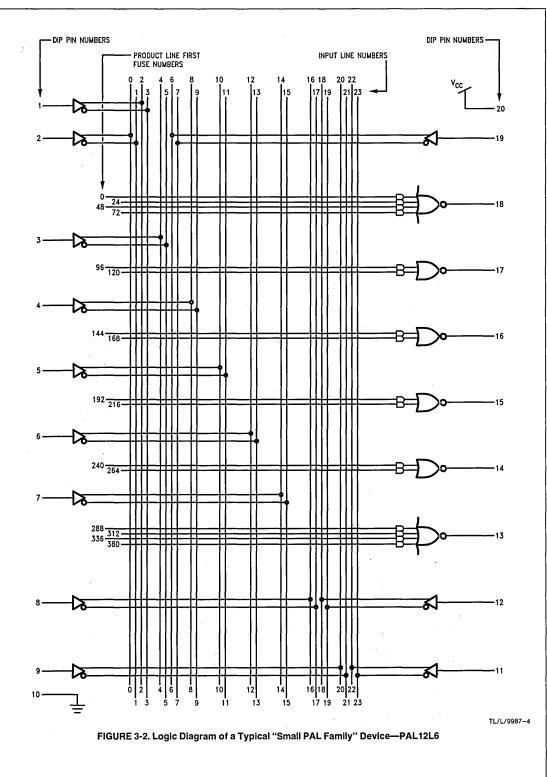

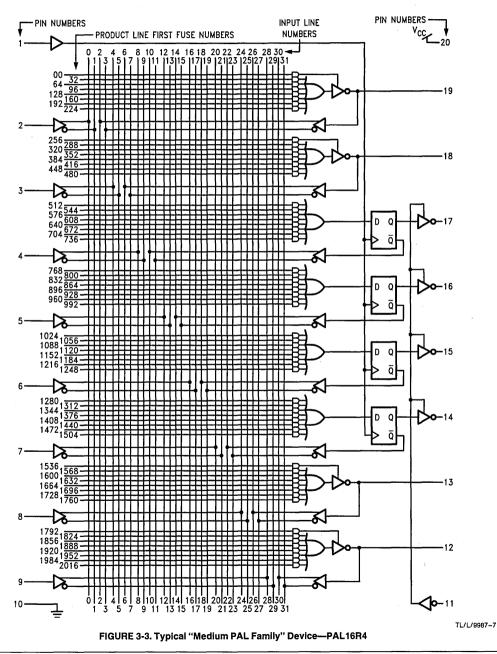

| 3.5 PLD Architecture Overview                           | 3-6  |

| Logic array structure                                   |      |

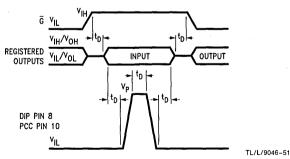

| Registered outputs                                      |      |

| Exclusive-OR gates                                      |      |

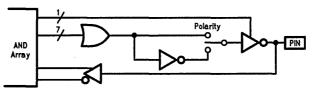

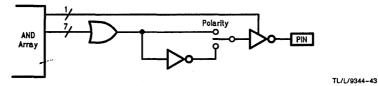

| Programmable output polarity                            |      |

| Advanced product features                               |      |

| 3.6 Programmable Logic from National                    | 3-11 |

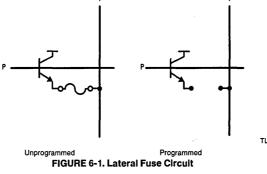

| Lateral fuse TTL PAL products                           |      |

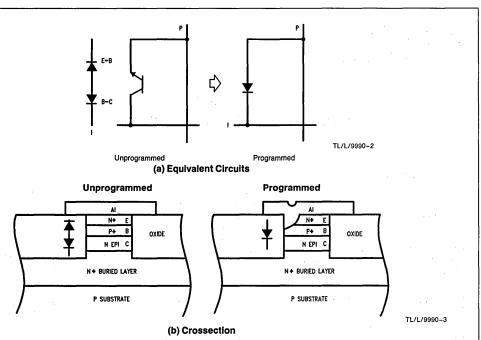

| Vertical fuse TTL PAL products                          |      |

| ECL PAL products                                        |      |

| E <sup>2</sup> CMOS GAL products                        |      |

| Pre-programmed and mask-programmed products             |      |

| 3.7 Design Development Tools                            | 3-12 |

| Programming hardware                                    |      |

| Development software                                    |      |

| NSC PLAN software                                       |      |

| Other assemblers/compilers                              |      |

| Section 4 Programmable Logic Design Methodology         |      |

| 4.1 Design Development Process                          | 4-3  |

| 4.2 Logic Design                                        | 4-3  |

| Defining the problem                                    |      |

| Designing the logic                                     |      |

| Deriving Boolean equations                              |      |

| Logic minimization                                      |      |

| 4.3 Design Implementation                               | 4-6  |

| Selecting a device                                      |      |

| Design/equation entry                                   |      |

| Compilation—creating the JEDEC file                     |      |

| Programming hardware preparation                        |      |

| Device programming                                      |      |

| 4.4 Logic Verification                                  | 4-9  |

| Pattern verfication                                     |      |

| Test vector generation                                  |      |

| Design simulation                                       |      |

| Device functional testing                               |      |

| Section 5 PLD Design Development Tools                  |      |

| 5.1 Selecting Development Tools                         | 5-3  |

| Programming hardware selection                          |      |

| Selecting the development software                      |      |

| 5.2 PLD Programmers                                     | 5-3  |

| Types of programmers                                    |      |

| Programmer certification                                |      |

| 5.3 National PLAN Software                              | 5-5  |

| Eastures of PLAN software                               |      |

| 5.4 Other Assemblers/Compilers                          | 5-7  |

| ABEL software                                           |      |

| CUPL software                                           | •    |

| LOG/IC software                                         |      |

# Table of Contents (Continued)

| Section 6 Fabrication of Programmable Logic                                     |      |

|---------------------------------------------------------------------------------|------|

| 6.1 PLD Technologies                                                            | 6-3  |

| Standard, "Series-A" and "Series-B" TTL PAL devices                             |      |

| ECL PAL devices                                                                 |      |

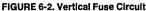

| "Series-D/-7" TTL PAL devices with vertical fuses                               |      |

| E <sup>2</sup> CMOS GAL devices                                                 |      |

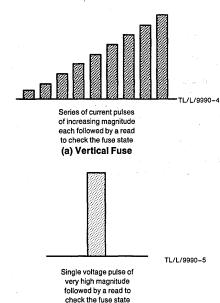

| 6.2 Quality and Factory Testing                                                 | 6-5  |

| Product reliability                                                             |      |

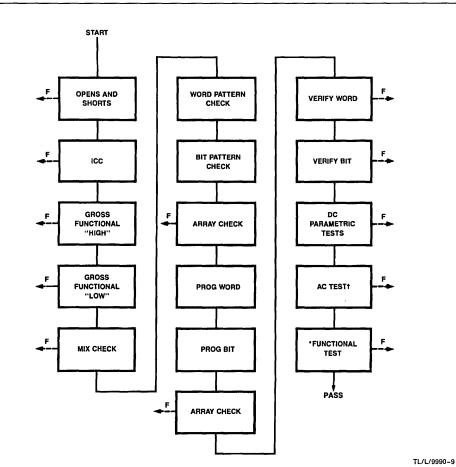

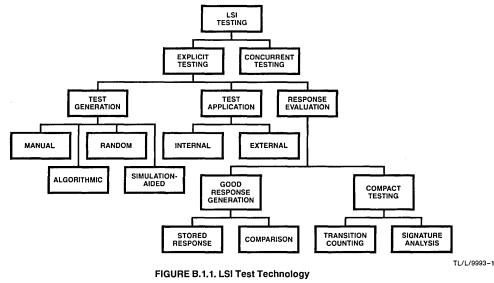

| Test circuitry                                                                  |      |

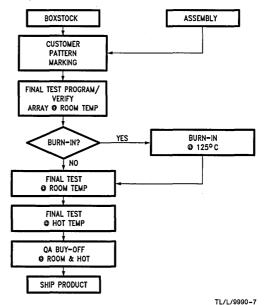

| Normal PLD factory test                                                         |      |

| Pre-programmed PLD factory test                                                 |      |

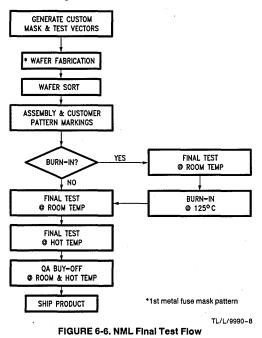

| NML factory test                                                                |      |

| Customer handling and test                                                      | · .  |

| -                                                                               |      |

| Section 7 Application Examples                                                  |      |

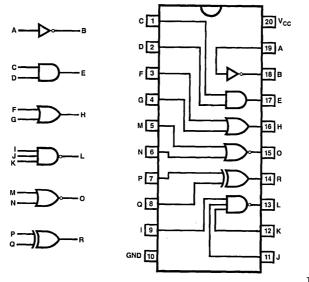

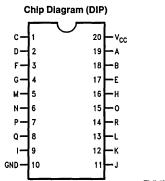

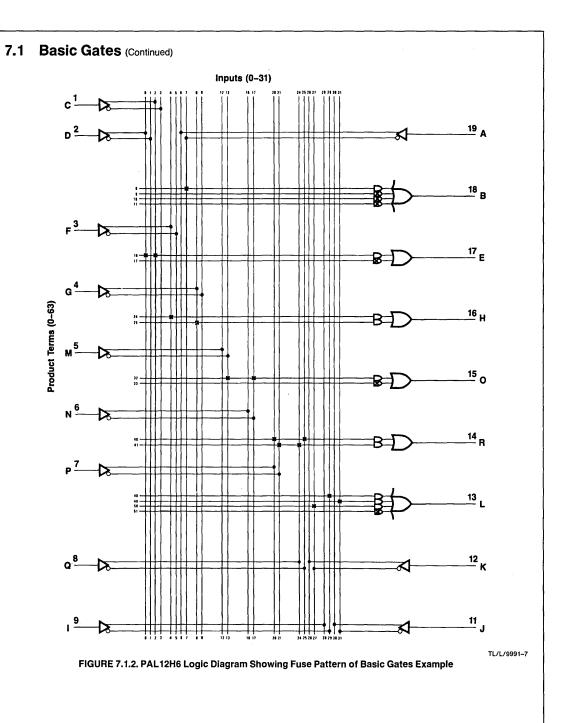

| 7.1 Basic Gates (PAL12H6)                                                       | 7-3  |

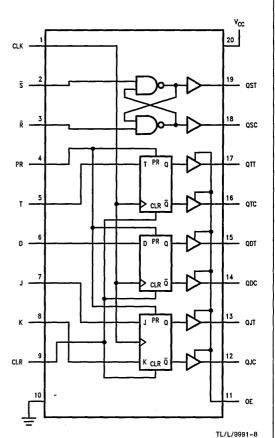

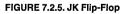

| 7.2 Basic Flip-Flops (GAL16V8)                                                  | 7-7  |

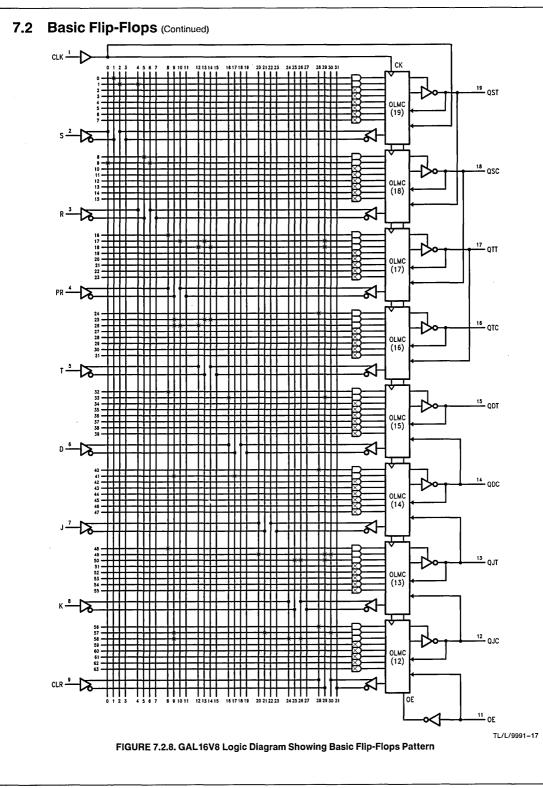

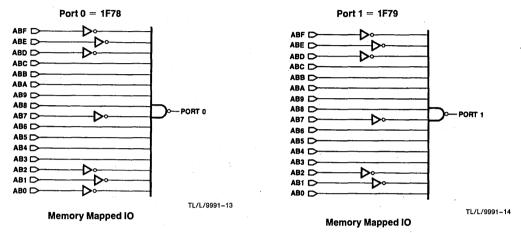

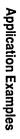

| 7.3 Memory-Mapped I/O Address Decoder (PAL16L2)                                 | 7-12 |

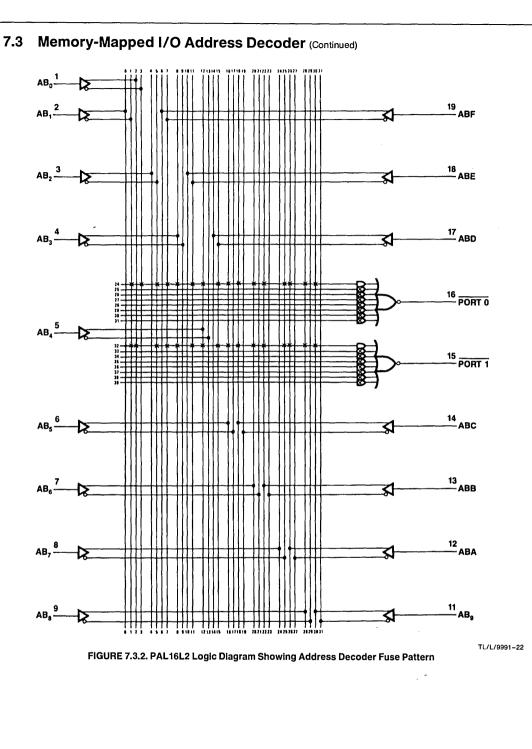

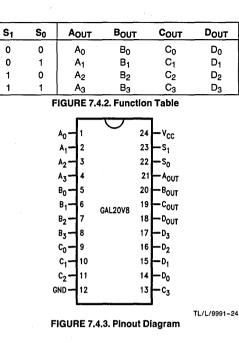

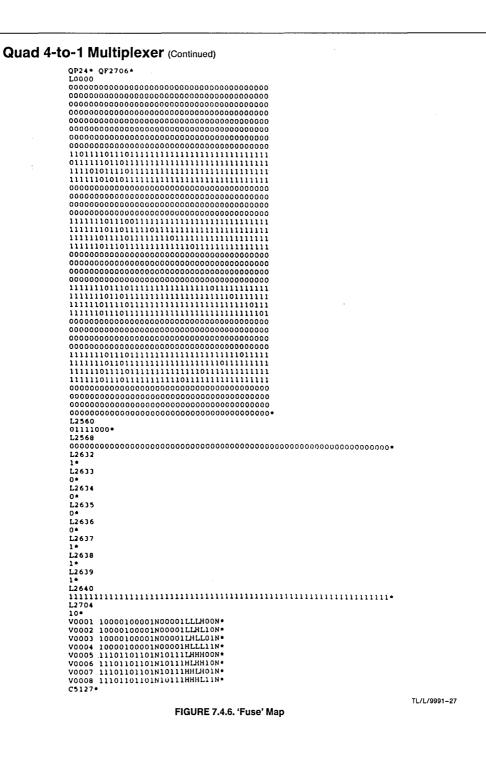

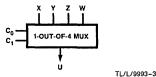

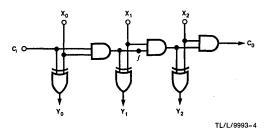

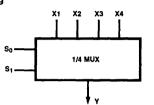

| 7.4 Quad 4-to-1 Multiplexer (GAL20V8)                                           | 7-16 |

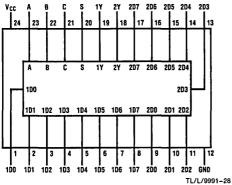

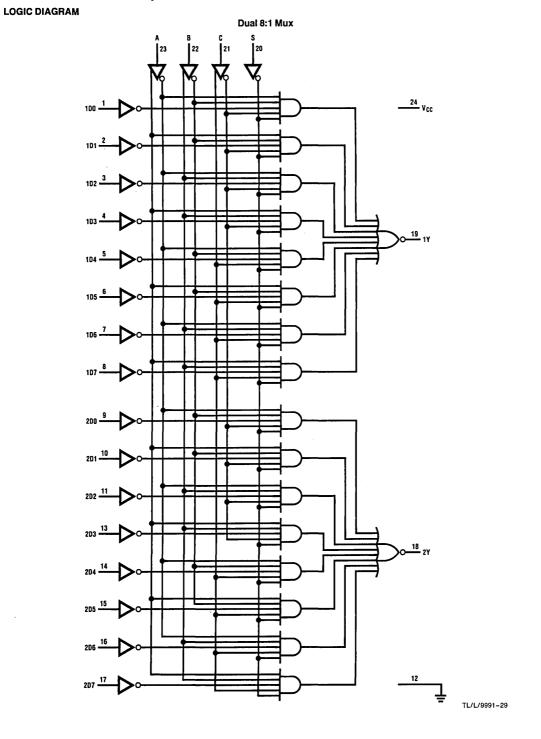

| 7.5 Dual 8-to-1 Multiplexer (PAL20L2)                                           | 7-20 |

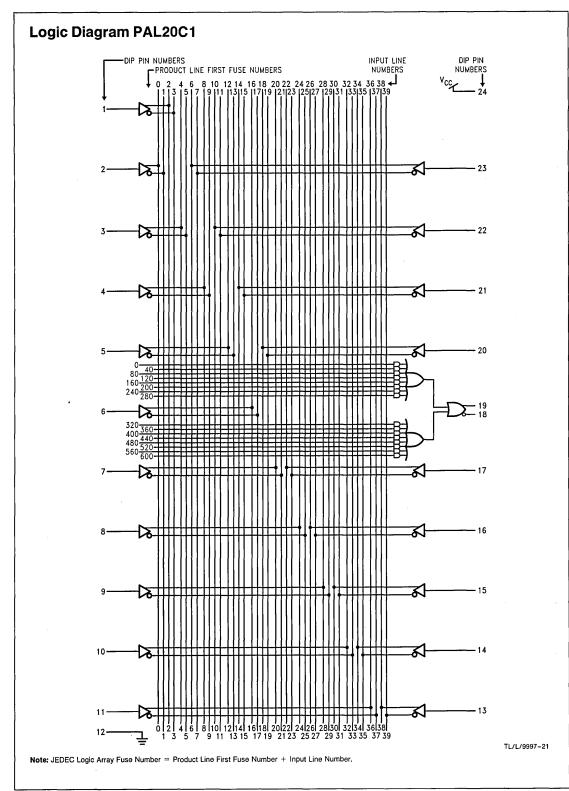

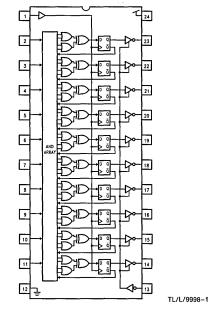

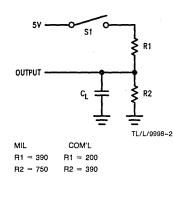

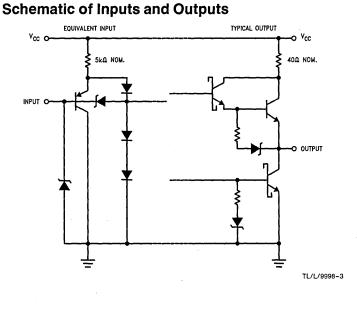

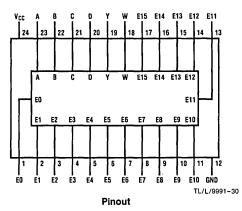

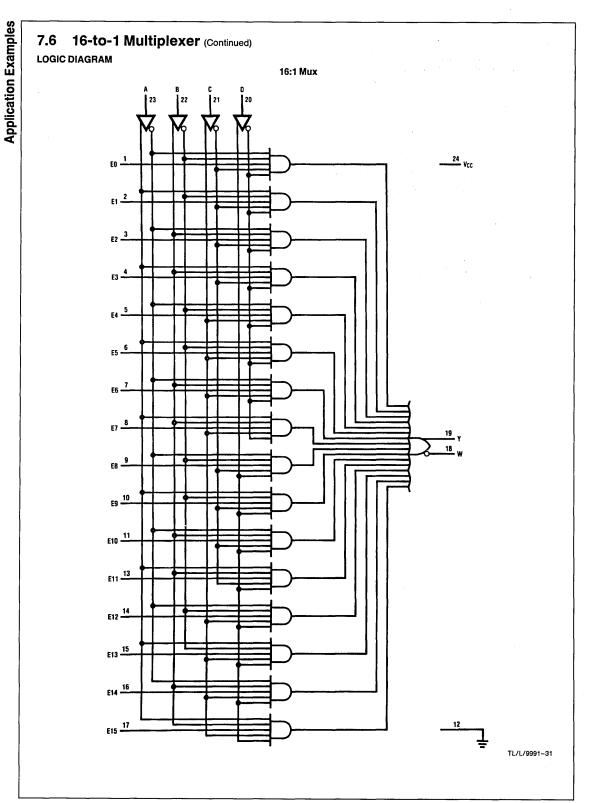

| 7.6 16-to-1 Multiplexer (PAL20C1)                                               | 7-25 |

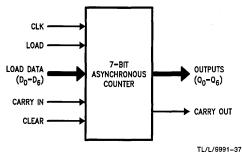

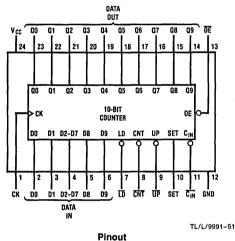

| 7.7 7-Bit Counter with Parallel-Load (GAL20V8)                                  | 7-30 |

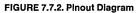

| 7.8 10-Bit Up/Down Counter (PAL20X10)                                           | 7-34 |

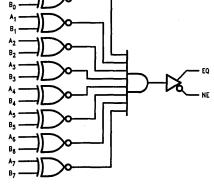

| 7.9 8-Bit Equality Comparator (PAL16C1)                                         | 7-39 |

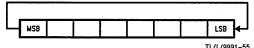

| 7.10 8-Bit Barrel Shifter (GAL20V8)                                             | 7-42 |

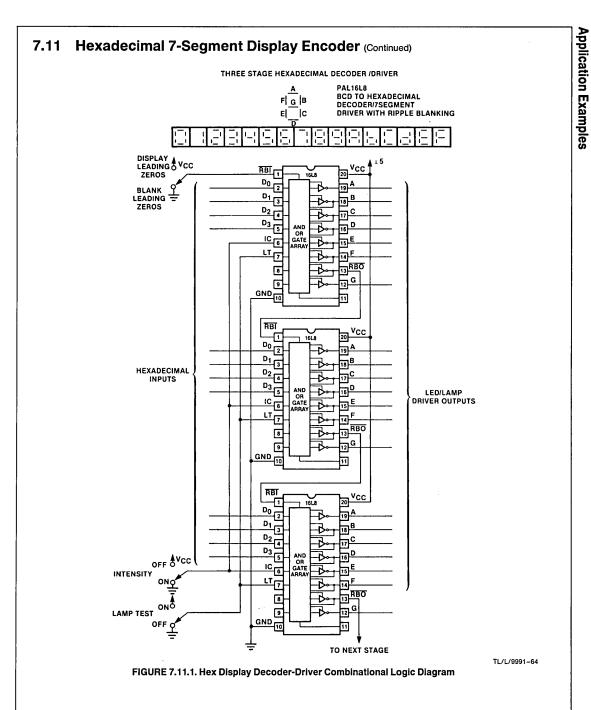

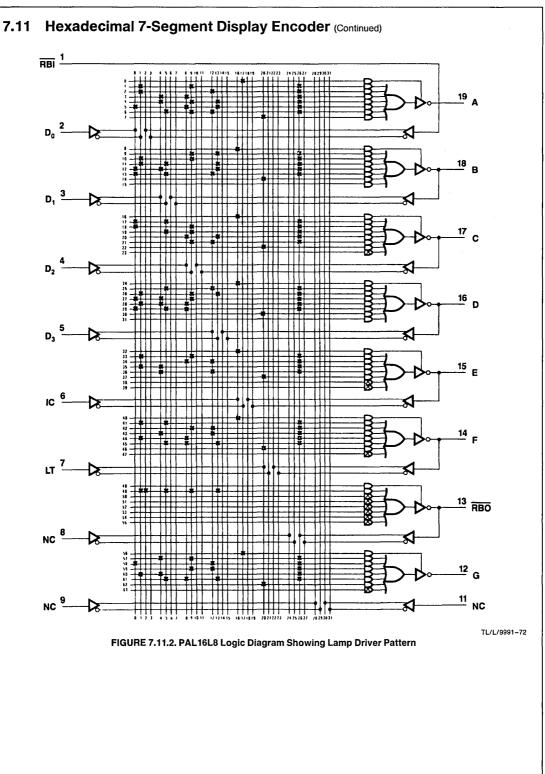

| 7.11 Hexadecimal 7-Segment Display Encoder (PAL16L8)                            | 7-46 |

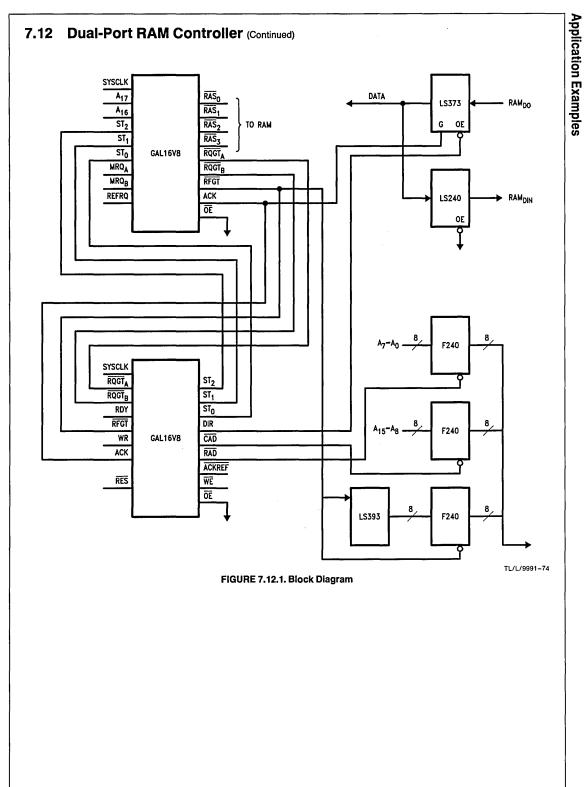

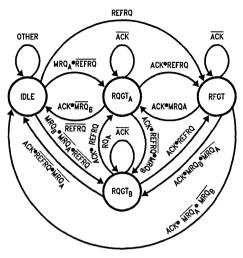

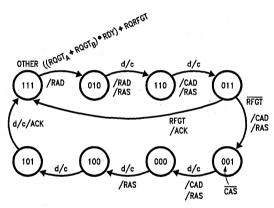

| 7.12 Dual-Port RAM Controller (GAL16V8)                                         | 7-52 |

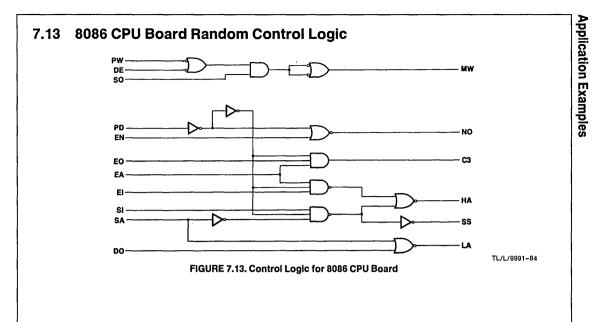

| 7.13 8086 CPU Board Random Control Logic (PAL12H6)                              | 7-61 |

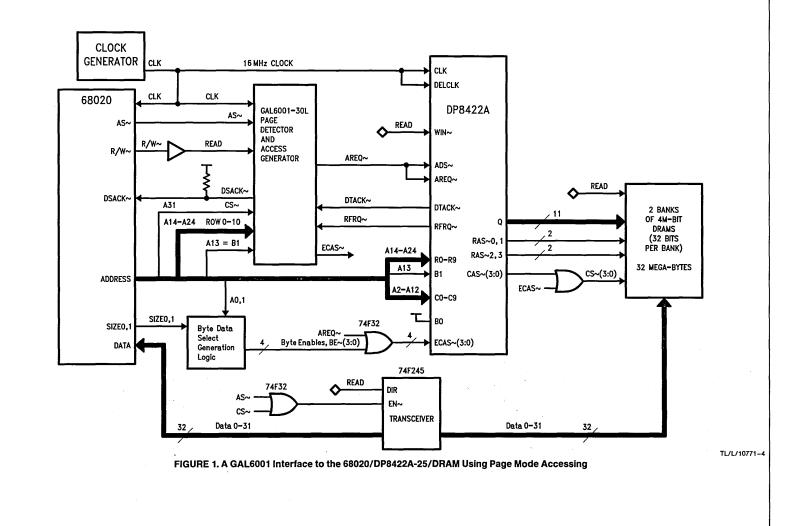

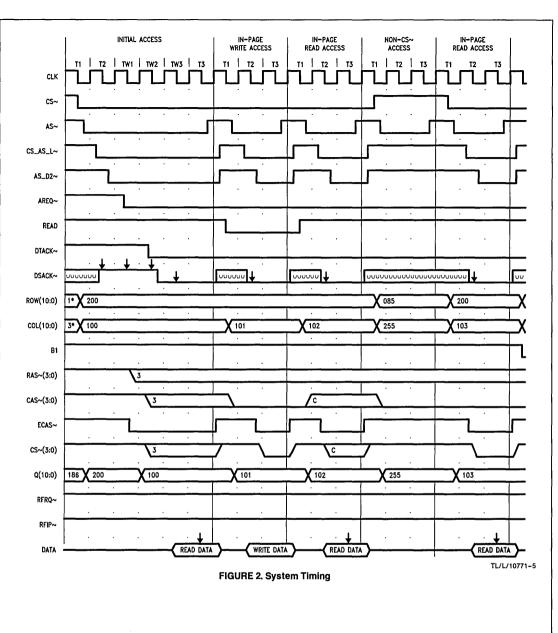

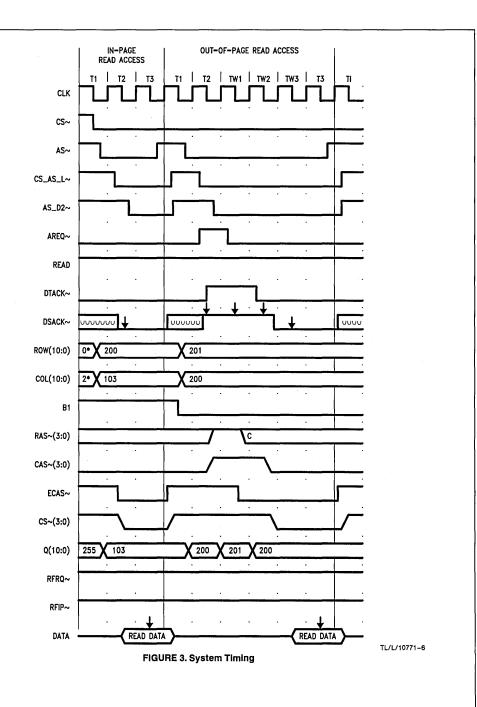

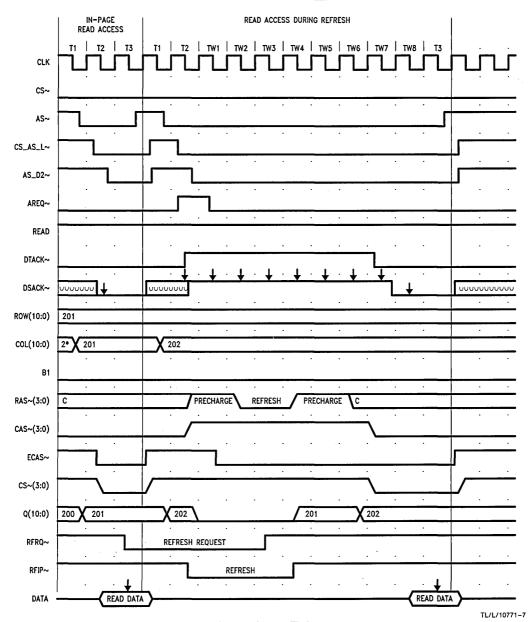

| AN-667 A GAL6001-30L Zero Wait State Page Mode Memory System Interface          | 7-64 |

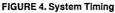

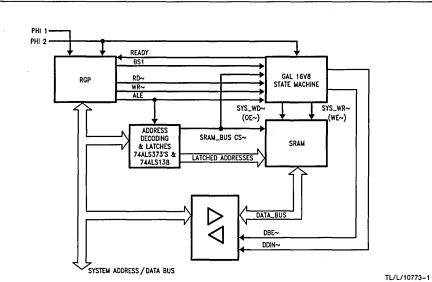

| AN-669 A PAL Interface Between Static Random Access Memory (SRAM) and a         |      |

| Raster Graphics Processor                                                       | 7-74 |

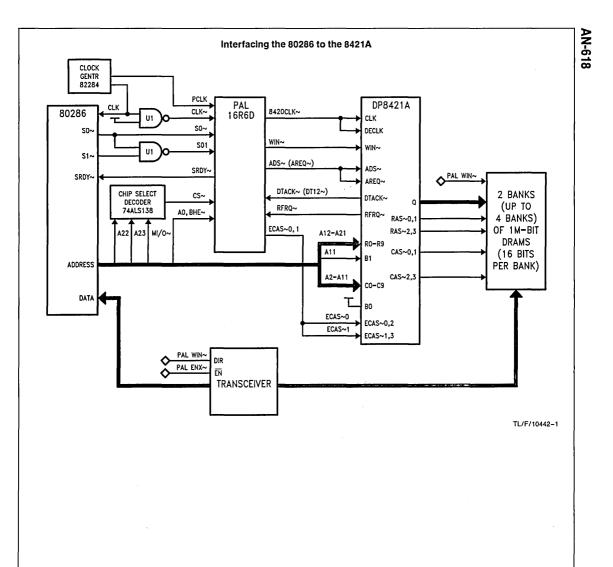

| AN-618 A PAL Interface for a 25 MHz and above No-Wait State DP8422A/80286 Burst |      |

| Mode DRAM Memory System                                                         | 7-81 |

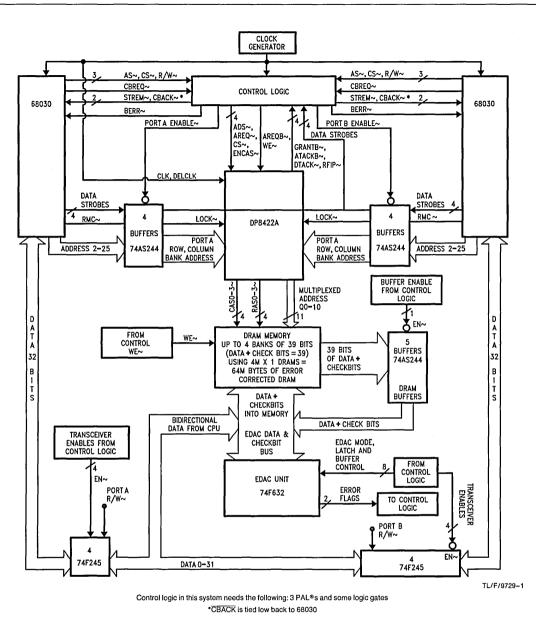

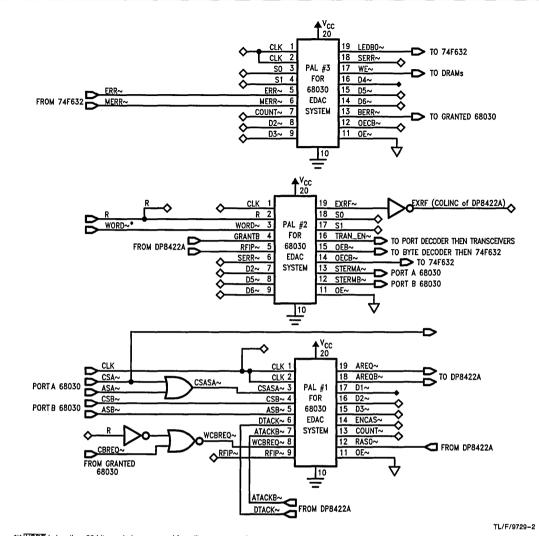

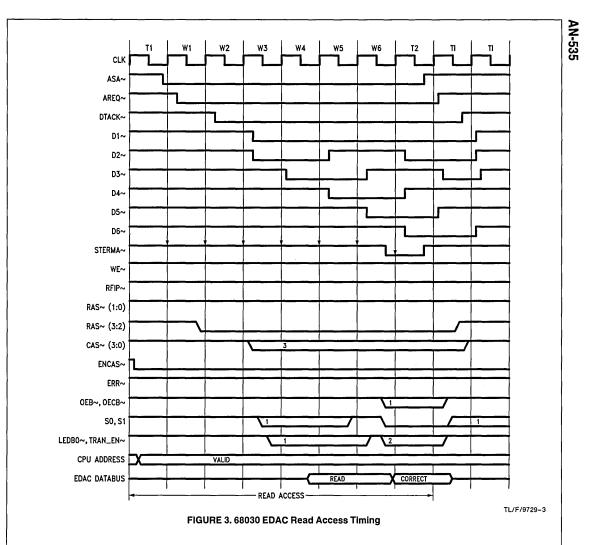

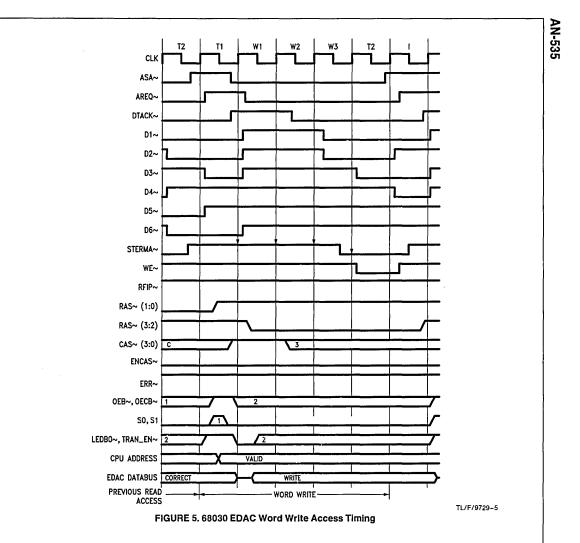

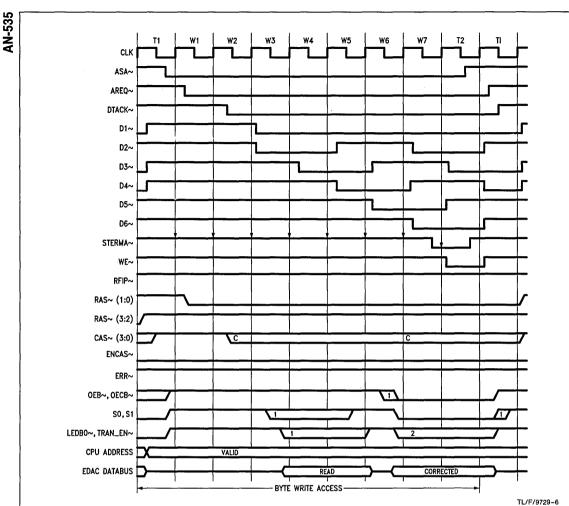

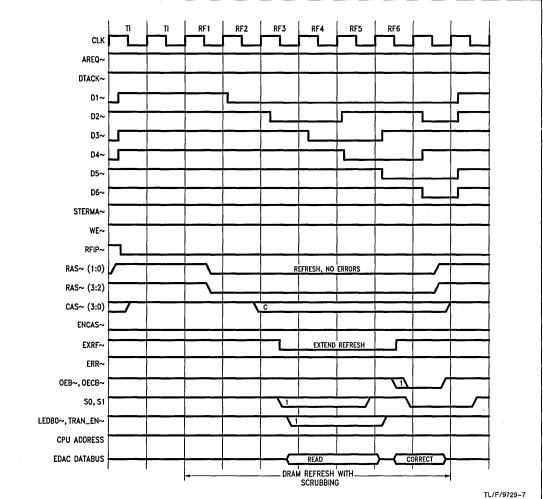

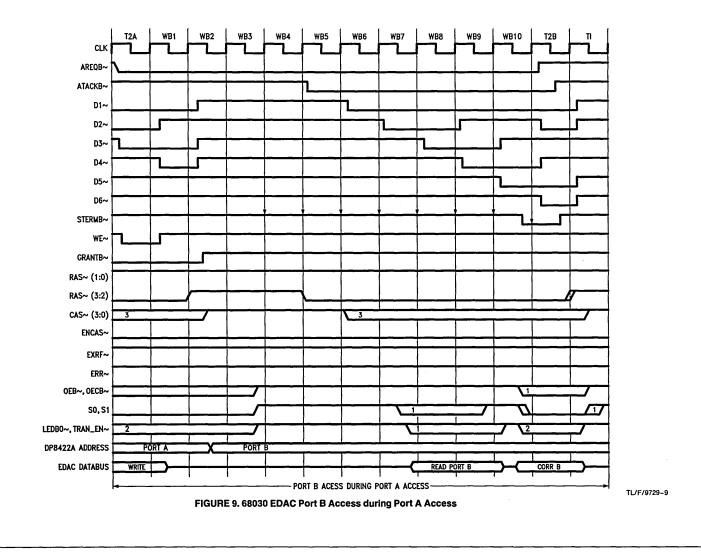

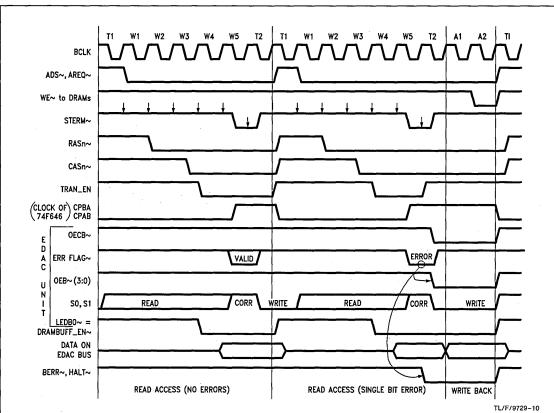

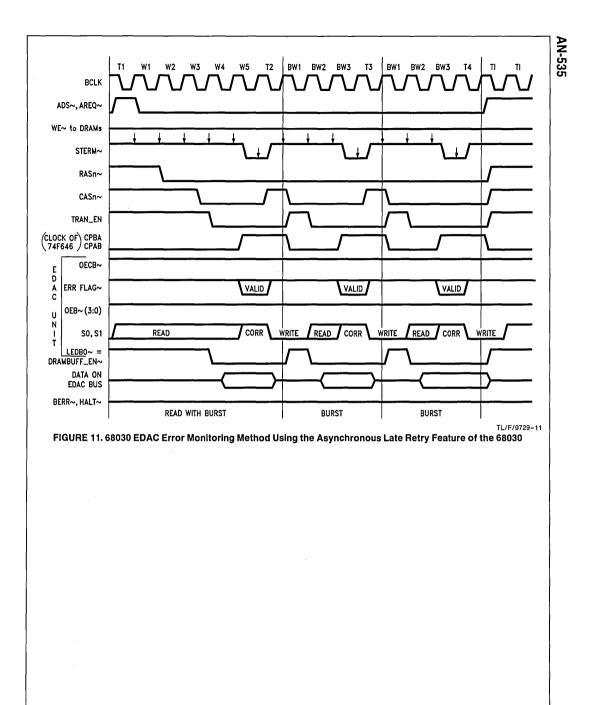

| AN-535 A PAL Interface for a Dual Access DP8422A/68030/74F632 Error Detecting   |      |

| and Correcting Memory System                                                    | 7-90 |

|                                                                                 |      |

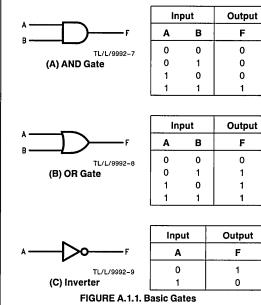

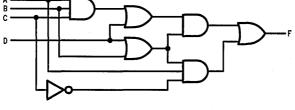

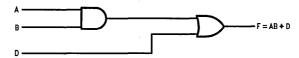

| Section 8 Appendices/Physical Dimensions Appendix A—Boolean Logic Review        | 8-3  |

|                                                                                 | 8-3  |

| A.1 Basic Operators and Theorems                                                |      |

| A.2 Derivation of a Boolean Expression                                          | 8-4  |

| A.3 Minimization                                                                | 8-6  |

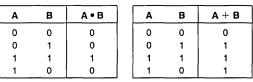

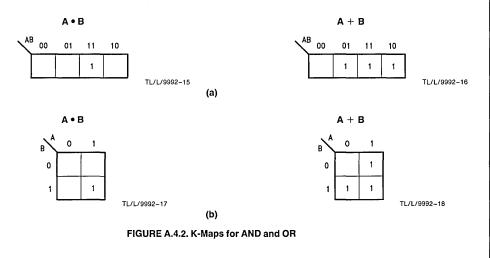

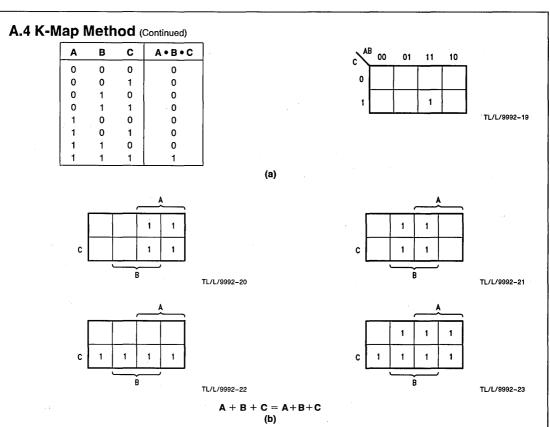

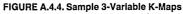

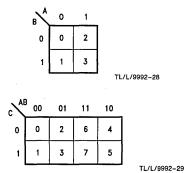

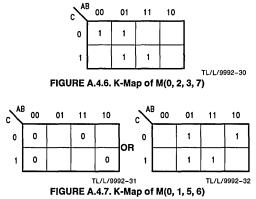

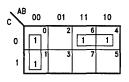

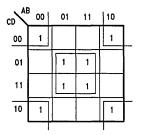

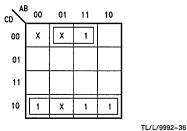

| A.4 K-Map Method                                                                | 8-7  |

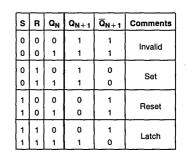

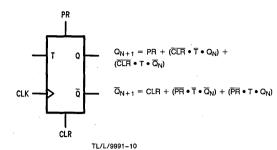

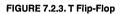

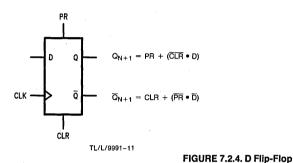

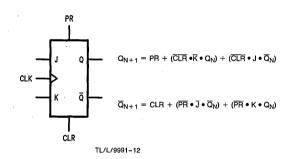

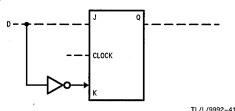

| A.5 Sequential Circuit Elements                                                 | 8-11 |

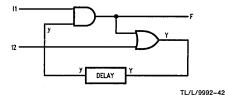

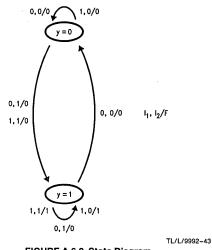

| A.6 State Machine Fundamentals                                                  | 8-12 |

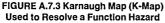

| A.7 Avoiding Logic Hazards                                                      | 8-14 |

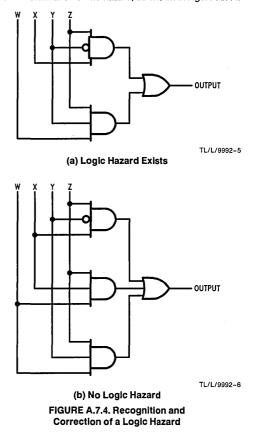

| Appendix B—Theory of PLD Testing                                                | 8-16 |

| B.1 Testing Methods                                                             | 8-16 |

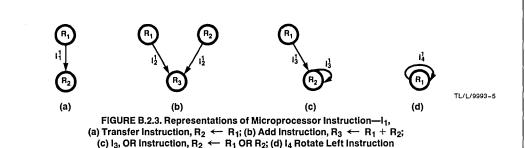

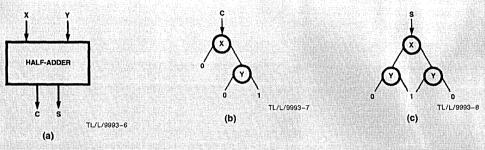

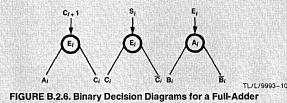

| B.2 Test Generation Techniques                                                  | 8-17 |

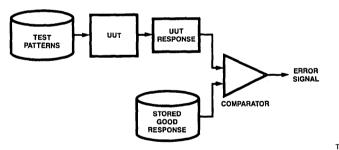

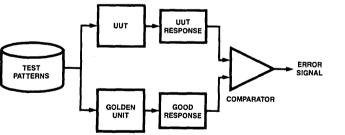

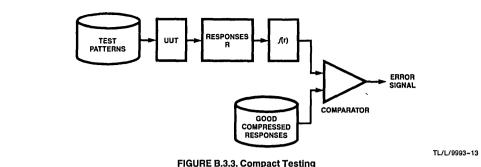

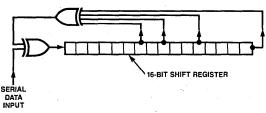

| B.3 Response Evaluation Techniques                                              | 8-27 |

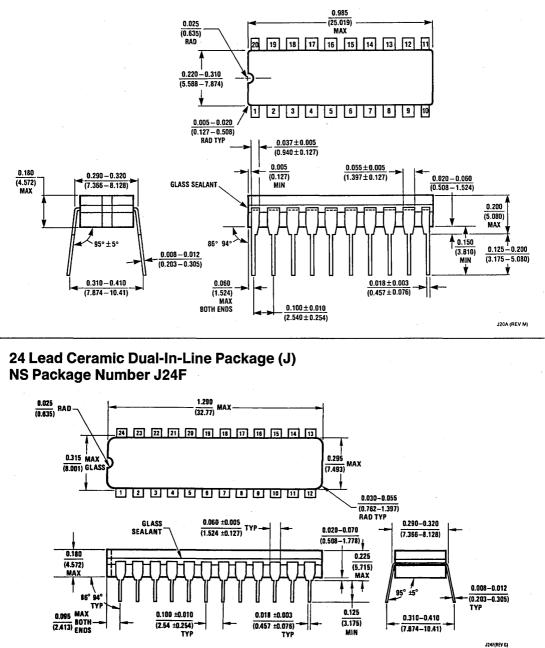

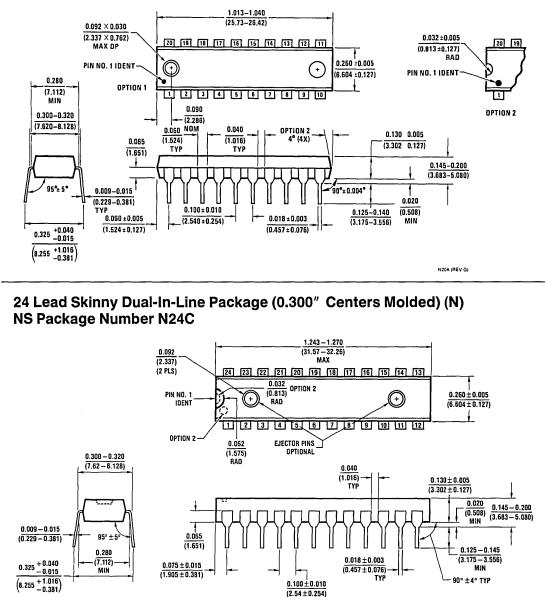

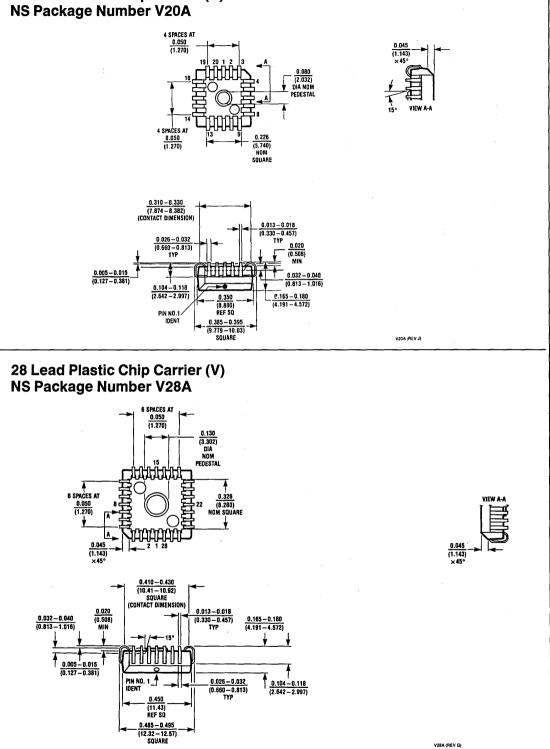

| Physical Dimensions                                                             | 8-32 |

| Bookshelf                                                                       |      |

| Distributors                                                                    |      |

# Alpha-Numeric Index

| AN-535 A PAL Interface for a Dual Access DP8422A/68030/74F632 Error Detecting and Correcting |

|----------------------------------------------------------------------------------------------|

| Memory System                                                                                |

| Memory System                                                                                |

| AN-667 A GAL6001-30L Zero Wait State Page Mode Memory System Interface                       |

| AN-669 A PAL Interface Between Static Random Access Memory (SRAM) and a Raster Graphics      |

| Processor                                                                                    |

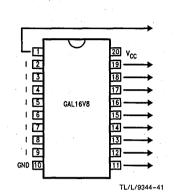

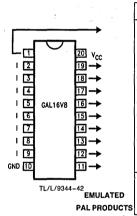

| GAL16V8-20L 20-Pin Generic Array Logic                                                       |

| GAL16V8-25L 20-Pin Generic Array Logic                                                       |

| GAL16V8-25Q 20-Pin Generic Array Logic                                                       |

| GAL16V8-35Q 20-Pin Generic Array Logic                                                       |

| GAL16V8A-10 20-Pin Generic Array Logic                                                       |

| GAL16V8A-12 20-Pin Generic Array Logic                                                       |

| GAL16V8A-15 20-Pin Generic Array Logic                                                       |

| GAL16V8A-20 20-Pin Generic Array Logic                                                       |

| GAL20RA10-15 Generic Array Logic (Preliminary)                                               |

| GAL20RA10-20 Generic Array Logic (Preliminary)                                               |

| GAL20RA10-25 Generic Array Logic (Preliminary)                                               |

| GAL20V8-20L 24-Pin Generic Array Logic                                                       |

| GAL20V8-25L 24-Pin Generic Array Logic                                                       |

| GAL20V8-25Q 24-Pin Generic Array Logic                                                       |

| GAL20V8-35Q 24-Pin Generic Array Logic                                                       |

| GAL20V8A-10 24-Pin Generic Array Logic                                                       |

| GAL20V8A-12 24-Pin Generic Array Logic                                                       |

| GAL20V8A-15 24-Pin Generic Array Logic                                                       |

| GAL20V8A-20 24-Pin Generic Array Logic                                                       |

| GAL22V10-15 Generic Array Logic (Preliminary)                                                |

| GAL22V10-20 Generic Array Logic (Preliminary)                                                |

| GAL22V10-25 Generic Array Logic (Preliminary)                                                |

| GAL22V10-30 Generic Array Logic (Preliminary)                                                |

| GAL6001 Generic Array Logic (Preliminary)                                                    |

| PAL10H8 20-Pin Small PAL                                                                     |

| PAL10H8A 20-Pin Small PAL                                                                    |

| PAL10H8A2 20-Pin Small PAL                                                                   |

| PAL10L8 20-Pin Small PAL                                                                     |

| PAL10L8A 20-Pin Small PAL                                                                    |

| PAL10L8A2 20-Pin Small PAL                                                                   |

| PAL10P4-2 ECL 2 ns Combinatorial PAL (Preliminary) 2-251                                     |

| PAL10PE8-3 ECL 3 ns Combinatorial PAL (Preliminary)2-242                                     |

| PAL10RD8 ECL Registered PAL                                                                  |

| PAL12H6 20-Pin Small PAL                                                                     |

| PAL12H6A 20-Pin Small PAL                                                                    |

| PAL12H6A2 20-Pin Small PAL                                                                   |

| PAL12L6 20-Pin Small PAL                                                                     |

| PAL12L6A 20-Pin Small PAL                                                                    |

| PAL12L6A2 20-Pin Small PAL                                                                   |

| PAL12L10 24-Pin Small PAL                                                                    |

| PAL12L10A 24-Pin Small PAL                                                                   |

| PAL14H4 20-Pin Small PAL                                                                     |

| PAL14H4A 20-Pin Small PAL                                                                    |

| PAL14H4A2 20-Pin Small PAL                                                                   |

# Alpha-Numeric Index (Continued)

| PAL14L4 20-Pin Small PAL                    |

|---------------------------------------------|

| PAL14L4A 20-Pin Small PAL                   |

| PAL14L4A2 20-Pin Small PAL                  |

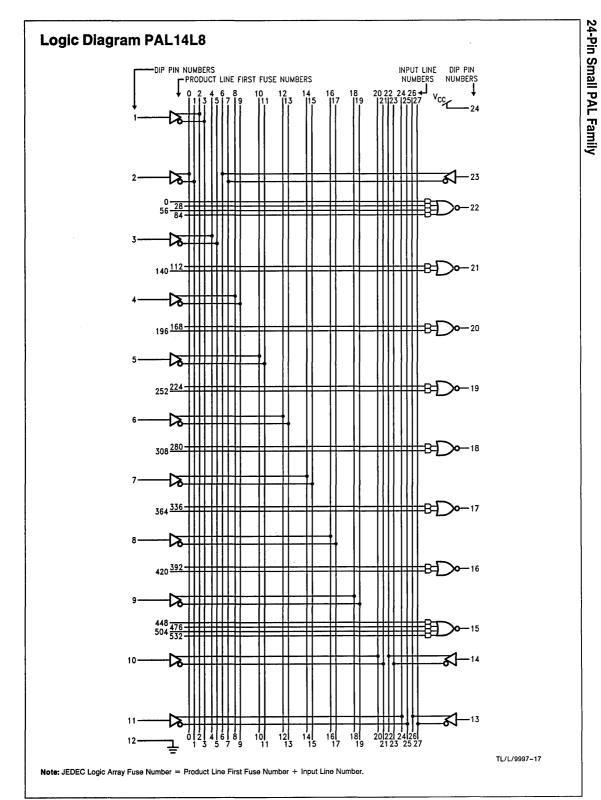

| PAL14L8 24-Pin Small PAL                    |

| PAL14L8A 24-Pin Small PAL                   |

| PAL16C1 20-Pin Small PAL                    |

| PAL16C1A 20-Pin Small PAL                   |

| PAL16C1A2 20-Pin Small PAL                  |

| PAL16H2 20-Pin Small PAL                    |

| PAL16H2A 20-Pin Small PAL                   |

| PAL16H2A2 20-Pin Small PAL                  |

| PAL16L2 20-Pin Small PAL                    |

| PAL16L2A 20-Pin Small PAL                   |

| PAL16L2A2 20-Pin Small PAL                  |

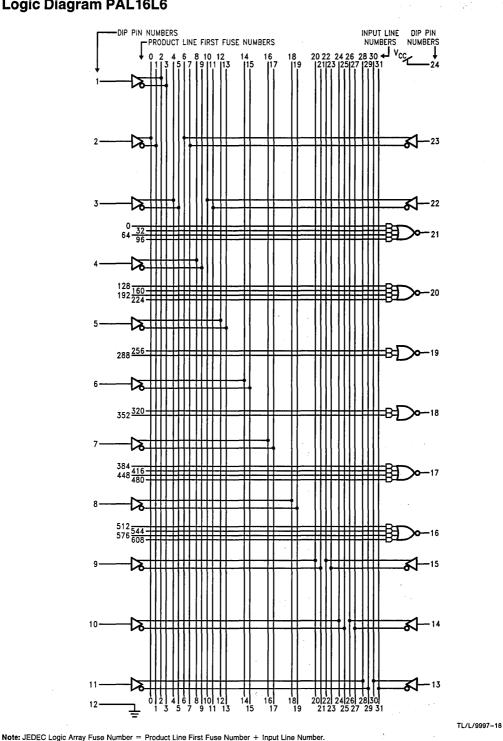

| PAL16L6 24-Pin Small PAL                    |

| PAL16L6A 24-Pin Small PAL                   |

| PAL16L8 20-Pin Medium PAL                   |

| PAL16L8-7 20-Pin Medium PAL                 |

| PAL16L8A 20-Pin Medium PAL                  |

| PALI6L8A2 20-Pin Medium PAL                 |

| PALI6L8B 20-Pin Medium PAL                  |

| PAL10L08 20-Pin Medium PAL                  |

| PAL16L8D 20-Pin Medium PAL                  |

| PAL16E0 20-Pin Medium PAL                   |

| PAL16R4-7 20-Pin Medium PAL                 |

| PAL16R4A 20-Pin Medium PAL                  |

| PAL16R4A2 20-Pin Medium PAL                 |

| PAL 16R4B 20-Pin Medium PAL                 |

| PAL16R4B2 20-Pin Medium PAL                 |

| PAL16R4D 20-Pin Medium PAL                  |

| PAL16R6 20-Pin Medium PAL                   |

|                                             |

| PAL16R6-7 20-Pin Medium PAL                 |

| PAL16R6A 20-Pin Medium PAL                  |

| PAL16R6A2 20-Pin Medium PAL                 |

| PAL16R6B 20-Pin Medium PAL                  |

| PAL16R6B2 20-Pin Medium PAL                 |

| PAL16R6D 20-Pin Medium PAL                  |

| PAL16R8 20-Pin Medium PAL                   |

| PAL16R8-7 20-Pin Medium PAL                 |

| PAL16R8A 20-Pin Medium PAL                  |

| PAL16R8B 20-Pin Medium PAL                  |

|                                             |

| PAL16R8B2 20-Pin Medium PAL                 |

| PAL16R8D 20-Pin Medium PAL                  |

| PAL16RA8 20-Pin Registered Asynchronous PAL |

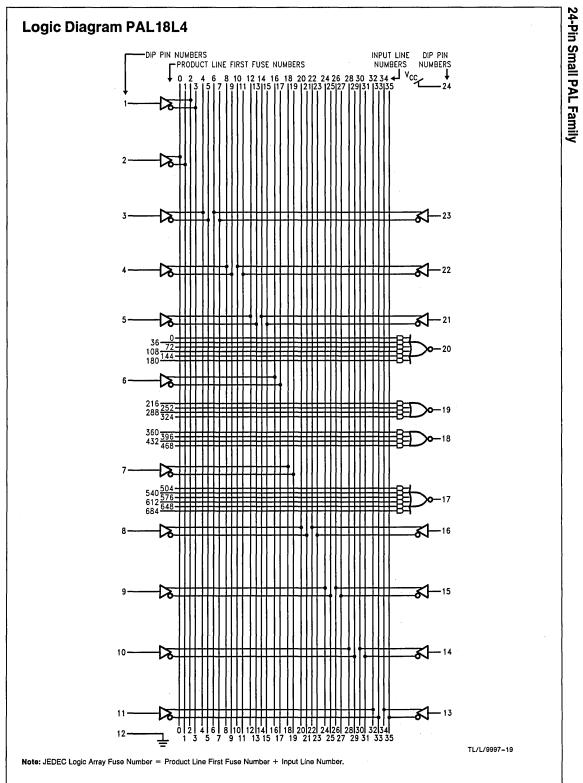

| PAL18L4 24-Pin Small PAL                    |

| PAL18L4A 24-Pin Small PAL                   |

| PAL20C1 24-Pin Small PAL                    |

| PAL20C1A 24-Pin Small PAL                   |

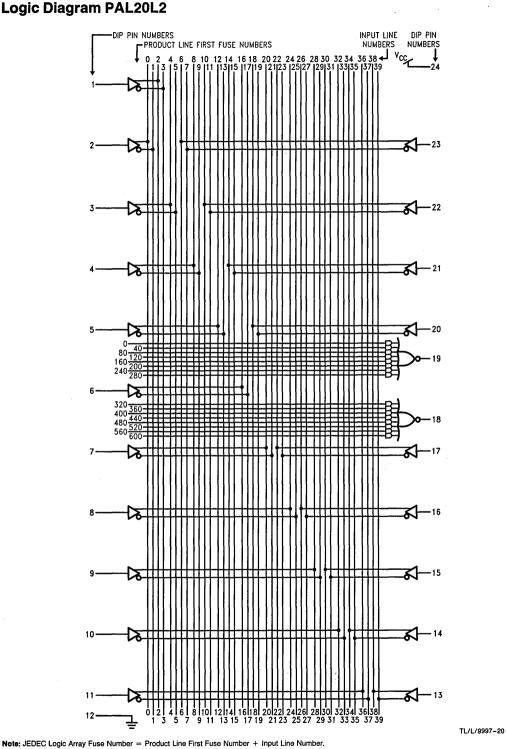

| PAL20L2 24-Pin Small PAL                    |

| PAL20L2A 24-Pin Small PAL                   |

# Alpha-Numeric Index (Continued)

| PAL20L8A 24-Pin Medium PAL                                  |

|-------------------------------------------------------------|

| PAL20L8A 24-Pin Medium PAL                                  |

| PAL20L8B 24-Pin Medium PAL                                  |

| PAL20L8D 24-Pin Medium PAL (Preininary)                     |

| PAL20E10 24-Pin XOR PAL                                     |

| PAL20E10A 24-PII AOH PAL                                    |

| PAL20P8B 24-Pin Polanty PAL                                 |

| PAL20R4B 24-Pin Medium PAL                                  |

| PAL20R4B 24-Pin Medium PAL                                  |

| PAL20H4D 24-Pin Medium PAL (Preliminary)                    |

|                                                             |

| PAL20R6B 24-Pin Medium PAL                                  |

| PAL20R6D 24-Pin Medium PAL (Preliminary)                    |

| PAL20R8A 24-Pin Medium PAL                                  |

| PAL20R8B 24-Pin Medium PAL                                  |

| PAL20R8D 24-Pin Medium PAL (Preliminary)                    |

| PAL20RA10 24-Pin Registered Asynchronous PAL                |

| PAL20RP4B 24-Pin Polarity PAL.                              |

| PAL20RP6B 24-Pin Polarity PAL.                              |

| PAL20RP8B 24-Pin Polarity PAL                               |

| PAL20X4 24-Pin XOR PAL                                      |

| PAL20X4A 24-Pin XOR PAL                                     |

| PAL20X8 24-Pin XOR PAL                                      |

| PAL20X8A 24-Pin XOR PAL                                     |

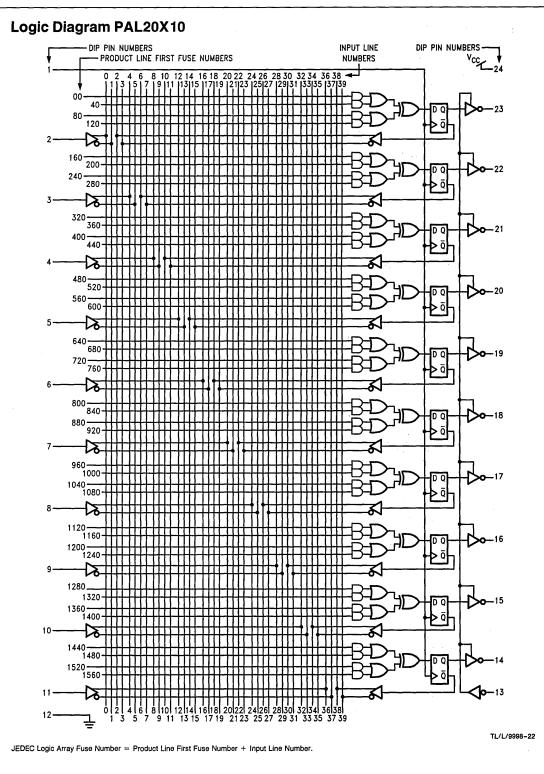

| PAL20X10 24-Pin XOR PAL                                     |

| PAL20X10A 24-Pin XOR PAL                                    |

| PAL100P4-2 ECL 2 ns Combinatorial PAL (Preliminary)         |

| PAL100PE8-3 ECL 3 ns Combinatorial PAL (Preliminary)        |

| PAL100RD8 ECL Registered PAL                                |

| PAL1016C4-2 ECL 2 ns Combinatorial PAL (Preliminary) 2-257  |

| PAL1016P4A ECL 4 ns Combinatorial PAL2-247                  |

| PAL1016P8 ECL Combinatorial PAL                             |

| PAL1016P8-3 ECL 3 ns Combinatorial PAL (Preliminary)2-236   |

| PAL1016RM4A ECL Registered PAL 2-268                        |

| PAL10016C4-2 ECL 2 ns Combinatorial PAL (Preliminary) 2-257 |

| PAL10016P4A ECL 4 ns Combinatorial PAL 2-247                |

| PAL10016P8 ECL Combinatorial PAL                            |

| PAL10016P8-3 ECL 3 ns Combinatorial PAL (Preliminary) 2-236 |

| PAL10016RM4A ECL Registered PAL 2-268                       |

### PART I DATA BOOK

**Product Line Overview**

**Data Sheets**

**v** -1

ſ

# Section 1 Product Line Overview

#### **Section 1 Contents**

| 1.1 | Selection Tables     | 1-3 |

|-----|----------------------|-----|

| 1.2 | Ordering Information | 1-7 |

| 1.3 | Block Diagrams       | 1-8 |

#### and the second second

#### and the second states and the

## National Semiconductor

### Section 1 Product Line Overview

Section 1 is provided as a reference guide to National Semiconductor's programmable logic product line. The product selection tables in Section 1.1 and the collection of product block diagrams in Section 1.3 can be used to compare the features and architectures of the various PLD families and to aid in the selection of the appropriate devices which best suit the designer's application.

#### **1.1 Selection Tables**

The product selection tables which follow are organized by technology group (TTL, E<sup>2</sup>CMOS and ECL), then by "family", then by "series" within each family. The term "family" refers to a set of one or more "device types" which are variations on the same basic architecture. The term "device type" refers to a specific device architecture (regardless of performance characteristics). The term "series" refers to a particular speed/power version in which the devices of a PLD family are available. Thus as technology advancements provide for improved speed/power performance, a new series is added to selected product families.

| Family and<br>Series                  | Part<br>Numbers | <sup>t</sup> PD<br>(max)<br>(Note 1) | I <sub>CC</sub><br>(max) | Outputs       |            | Page |

|---------------------------------------|-----------------|--------------------------------------|--------------------------|---------------|------------|------|

|                                       |                 |                                      |                          | Combinatorial | Registered |      |

| TTL                                   |                 |                                      |                          |               |            |      |

| 20-Pin                                | PAL10H8         | 35                                   | 90                       | 8             | -          | 2-3  |

| Small                                 | PAL10L8         | 35                                   | 90                       | 8             | -          | 2-3  |

| PAL®                                  | PAL12H6         | 35                                   | 90                       | 6             | -          | 2-3  |

| (Standard                             | PAL12L6         | 35                                   | 90                       | 6             | -          | 2-3  |

| Speed)                                | PAL14H4         | 35                                   | 90                       | 4             | -          | 2-3  |

|                                       | PAL14L4         | 35                                   | 90                       | 4             | -          | 2-3  |

| 1                                     | PAL16H2         | 35                                   | 90                       | 2<br>2        | -          | 2-3  |

|                                       | PAL16L2         | 35                                   | 90                       |               | -          | 2-3  |

|                                       | PAL16C1         | 35                                   | 90                       | 1             | _          | 2-3  |

| 20-Pin                                | PAL10H8A        | 25                                   | 90                       | 8             | -          | 2-3  |

| Small                                 | PAL10L8A        | 25                                   | 90                       | 8             | -          | 2-3  |

| PAL                                   | PAL12H6A        | 25                                   | 90                       | 6             | -          | 2-3  |

| Series-A                              | PAL12L6A        | 25                                   | 90                       | 6             | -          | 2-3  |

| . 1                                   | PAL14H4A        | 25                                   | 90                       | 4             | · —        | 2-3  |

|                                       | PAL14L4A        | 25                                   | 90                       | 4             | -          | 2-3  |

|                                       | PAL16H2A        | 25                                   | 90                       | 2<br>2        | -          | 2-3  |

|                                       | PAL16L2A        | 25                                   | 90                       |               | -          | 2-3  |

| · · · · · · · · · · · · · · · · · · · | PAL16C1A        | 30                                   | 90                       | 1             | —          | 2-3  |

| 20-Pin                                | PAL10H8A2       | 35                                   | 45                       | 8             | — .        | 2-3  |

| Small                                 | PAL10L8A2       | 35                                   | 45                       | 8             | · · ·      | 2-3  |

| PAL                                   | PAL12H6A2       | 35                                   | 45                       | 6             | -          | 2-3  |

| Series-A2                             | PAL12L6A2       | 35                                   | 45                       | 6             | -          | 2-3  |

|                                       | PAL14H4A2       | 35                                   | 45                       | 4             | · <u> </u> | 2-3  |

|                                       | PAL14L4A2       | 35                                   | 45                       | 4             | -          | 2-3  |

|                                       | PAL16H2A2       | 35                                   | 45                       | 2             |            | 2-3  |

|                                       | PAL16L2A2       | 35                                   | 45                       | 2             |            | 2-3  |

|                                       | PAL16C1A2       | 40                                   | 45                       | 1             | -          | 2-3  |

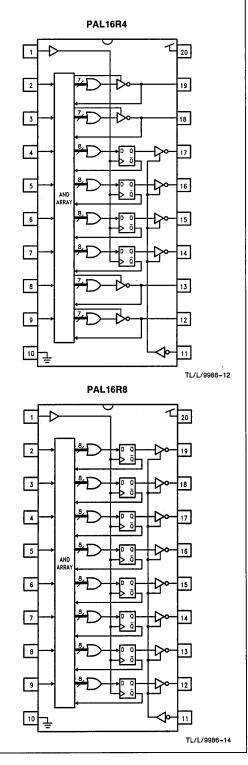

| 20-Pin                                | PAL16L8         | 35                                   | 180                      | 8             | -          | 2-23 |

| Medium                                | PAL16R4         | 35                                   | 180                      | 4             | 4          | 2-23 |

| PAL                                   | PAL16R6         | 35                                   | 180                      | 2             | 6          | 2-23 |

| (Standard)                            | PAL16R8         | 35                                   | 180                      |               | 8          | 2-23 |

#### **TABLE 1-1.** Programmable Logic Product Selection Guide

| Family and          | Part                   | t <sub>PD</sub><br>(max) | lcc        | Outp          | uts         | Page         |

|---------------------|------------------------|--------------------------|------------|---------------|-------------|--------------|

| Series              | Numbers                | (Note 1)                 | (max)      | Combinatorial | Registered  |              |

| TTL (Continued      | )                      |                          |            |               |             |              |

| 20-Pin              | PAL16L8A               | 25                       | 180        | 8             | _           | 2-23         |

| Medium              | PAL16R4A               | 25                       | 180        | 4             | 4           | 2-23         |

| PAL                 | PAL16R6A               | 25                       | 180        | 2             | 6           | 2-23         |

| Series-A            | PAL16R8A               | 25                       | 180        |               | 8           | 2-23         |

| 20-Pin              | PAL16L8A2              | 35                       | 90         | 8             | -           | 2-23         |

| Medium              | PAL16R4A2              | 35                       | 90         | 4             | 4           | 2-23         |

| PAL                 | PAL16R6A2              | 35                       | 90         | 2             | 6           | 2-23         |

| Series-A2           | PAL16R8A2              | 35                       | 90         |               | 8           | 2-23         |

| 20-Pin              | PAL16L8B               | 15                       | 180        | 8             |             | 2-23         |

| Medium<br>PAL       | PAL16R4B<br>PAL16R6B   | 15<br>15                 | 180        | 4<br>2        | 4           | 2-23         |

| Series-B            | PAL16R8B               | 15                       | 180<br>180 | 2             | 8           | 2-23         |

| 20-Pin              | PAL16L8B2              | 25                       | 90         | 8             |             | 2-23         |

| 20-Pin<br>Medium    | PAL16L882<br>PAL16R4B2 | 25                       | 100        | 4             | 4           | 2-23         |

| PAL                 | PAL16R6B2              | 25                       | 100        | 2             | 6           | 2-23         |

| Series-B2           | PAL16R8B2              | 25                       | 100        | <u> </u>      | 8           | 2-23         |

| 20-Pin              | PAL16L8D               | 10                       | 180        | 8             | _           | 2-23         |

| Medium              | PAL16R4D               | 10                       | 180        | 4             | 4           | 2-23         |

| PAL                 | PAL16R6D               | 10                       | 180        | 2             | 6           | 2-23         |

| Series-D            | PAL16R8D               | 10                       | 180        | , <b>—</b>    | 8           | 2-23         |

| 20-Pin              | PAL16L8-7              | 7.0                      | 180        | . 8           |             | 2-23         |

| Medium              | PAL16R4-7              | 7.0                      | 180        | 4             | 4           | 2-23         |

| PAL                 | PAL16R6-7              | 7.0                      | 180        | 2             | 6           | 2-23         |

| Series-7            | PAL16R8-7              | 7.0                      | 180        | _             | 8           | 2-23         |

| 24-Pin              | PAL12L10               | 40                       | 100        | 10            | · · · · · · | 2-48         |

| Small               | PAL14L8                | 40                       | 100        | 8             | ·           | 2-48         |

| PAL<br>(Standard    | PAL16L6                | 40<br>40                 | 100        | 6             | ·           | 2-48         |

| (Standard<br>Speed) | PAL18L4<br>PAL20L2     | 40<br>40                 | 100<br>100 | 4             |             | 2-48<br>2-48 |

| opeeu)              | PAL20C1                | 40                       | 100        | 1             |             | 2-48         |

| 24-Pin              | PAL12L10A              | 25                       | 100        | 10            |             | 2-48         |

| Small               | PAL14L8A               | 25                       | 100        | 8             |             | 2-48         |

| PAL                 | PAL16L6A               | 25                       | 100        | ő             | _           | 2-48         |

| Series-A            | PAL18L4A               | 25                       | 100        | 4             | -           | 2-48         |

|                     | PAL20L2A               | 25                       | 100        | 2             | —           | 2-48         |

|                     | PAL20C1A               | 30                       | 100        | 1             |             | 2-48         |

| 24-Pin              | PAL20L10               | 50                       | 165        | 10            | - 1         | 2-62         |

| XOR                 | PAL20X4                | 50                       | 180        | 6             | 4           | 2-62         |

| PAL<br>(Standard)   | PAL20X8<br>PAL20X10    | 50<br>50                 | 180<br>180 | 2             | 8<br>10     | 2-62         |

| ·                   |                        |                          |            | <u> </u>      | 1. 10       | 2-62         |

| 24-Pin<br>XOR       | PAL20L10A              | 30                       | 165        | 10            |             | 2-62         |

| PAL                 | PAL20X4A<br>PAL20X8A   | 30<br>30                 | 180<br>180 | 6<br>2        | 4<br>8      | 2-62<br>2-62 |

| Series-A            | PAL20X8A<br>PAL20X10A  | 30                       | 180        | <u> </u>      | 10          | 2-62         |

| 24-Pin              | PAL20L8A               | 25                       | 210        | 8             |             | 2-77         |

| Z4-Pin<br>Medium    | PAL20L8A<br>PAL20R4A   | 25<br>25                 | 210        | 8             | 4           | 2-77         |

| PAL                 | PAL20R6A               | 25                       | 210        | 2             | 6           | 2-77         |

| Series-A            | PAL20R8A               | 25                       | 210        | -             | 8           | 2-77         |

| 24-Pin              | PAL20L8B               | 15                       | 210        | 8             | _           | 2-77         |

| Medium              | PAL20R4B               | / 15                     | 210        | 4             | 4           | 2-77         |

| PAL                 | PAL20R6B               | 15                       | 210        | 2             | 6           | 2-77         |

| Series-B            | PAL20R8B               | 15                       | 210        | 1             | 8           | 2-77         |

Note 1: Maximum tpD for combinatorial outputs (commercial operating range). Denotes characteristic speed of family where product has all non-registered outputs.

| Family and<br>Series               | Part                          | t <sub>PD</sub><br>(max)<br>(Note 1) | lcc                | Outputs                         |                           | Page         |

|------------------------------------|-------------------------------|--------------------------------------|--------------------|---------------------------------|---------------------------|--------------|

| Series                             | Numbers                       |                                      | (max)              | Combinatorial                   | Registered                |              |

| TTL (Continued)                    |                               | _                                    | -                  |                                 |                           |              |

| 24-Pin                             | PAL20L8D                      | 10                                   | 210                | 8                               |                           | 2-77         |

| Medium                             | PAL20R4D                      | 10                                   | 210                | 4                               | 4                         | 2-77         |

| PAL                                | PAL20R6D                      | 10                                   | 210                | 2                               | 6                         | 2-77         |

| Series-D                           | PAL20R8D                      | 10                                   | 210                | <b>—</b>                        | 8                         | 2-77         |

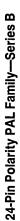

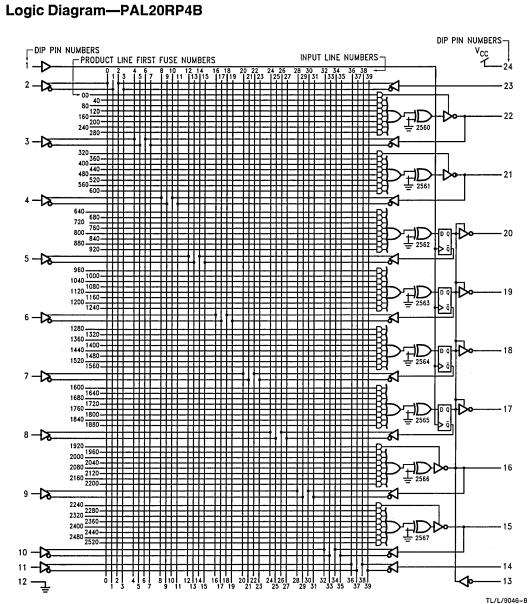

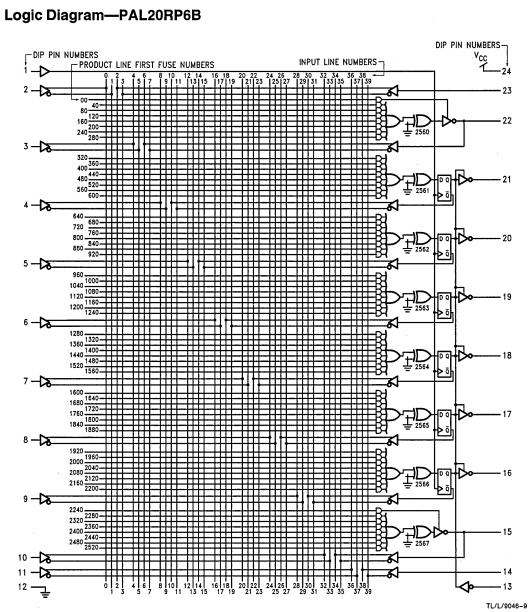

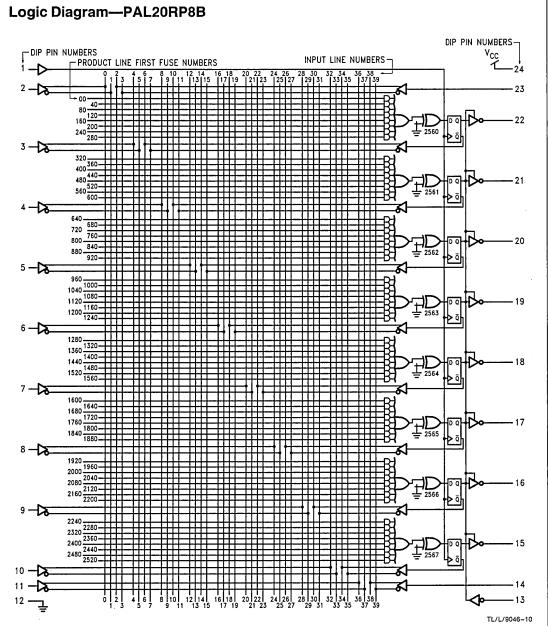

| 24-Pin                             | PAL20P8B                      | 15                                   | 210                | 8                               | _                         | 2-95         |

| Polarity                           | PAL20RP4B                     | 15                                   | 210                | 4                               | 4                         | 2-95         |

| PAL                                | PAL20RP6B                     | 15                                   | 210                | 2                               | 6                         | 2-95         |

| Series-B                           | PAL20RP8B                     | 15                                   | 210                | <u> </u>                        | 8                         | 2-95         |

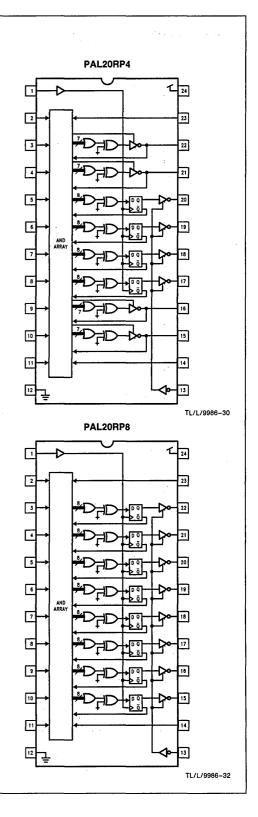

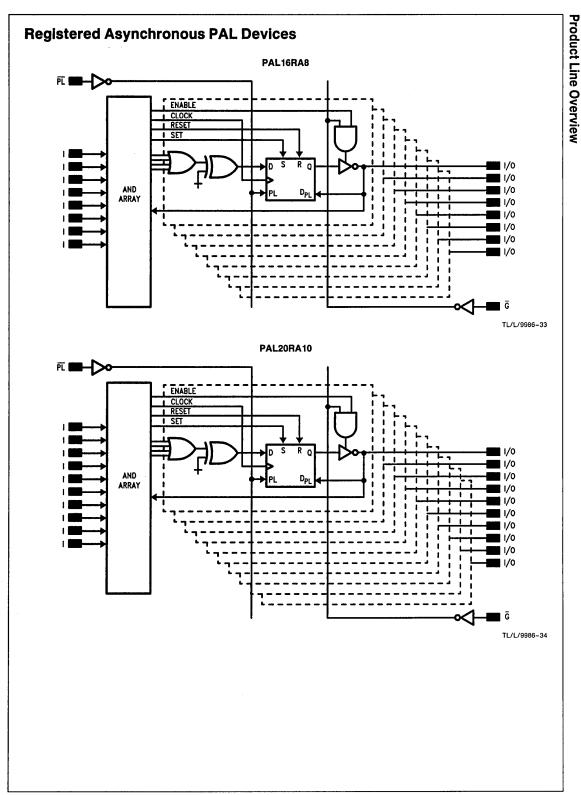

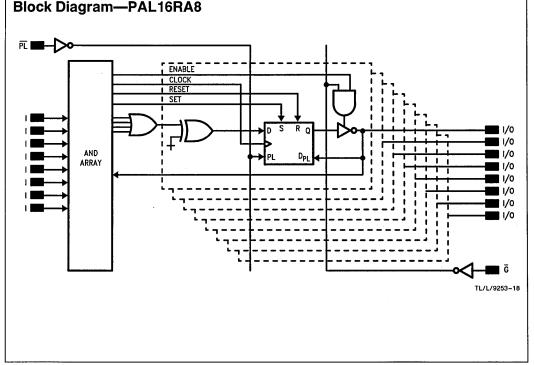

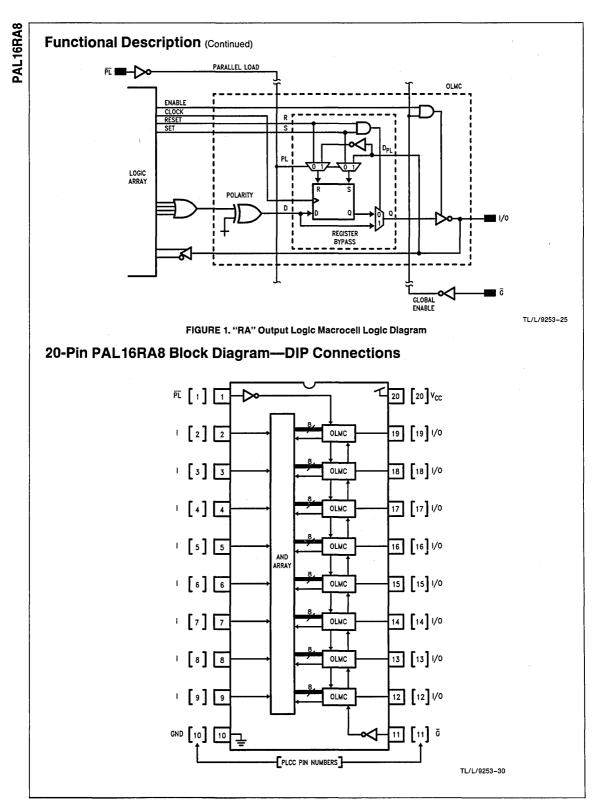

| Registered                         | PAL16RA8                      | 30                                   | 170                | _                               | 8                         | 2-108        |

| Asynchronous                       | PAL20RA10                     | 30                                   | 200                |                                 | 10                        | 2-118        |

| E <sup>2</sup> CMOS                |                               |                                      |                    | · · · · ·                       |                           |              |

| 20-Pin                             | GAL16V8-20L                   | 20                                   | 90                 | _                               | 8                         | 2-129        |

| Generic                            | GAL16V8-25Q                   | 25                                   | 45                 | — · · ·                         | 8                         | 2-129        |

| Array                              | GAL16V8-25L                   | 25                                   | 90                 | ·                               | 8                         | 2-129        |

| Logic                              | GAL16V8-35Q                   | 35                                   | 45                 | —                               | 8                         | 2-129        |

| 20-Pin                             | GAL16V8A-10L                  | 10                                   | 115                | _                               | 8                         | 2-162        |

| Generic                            | GAL16V8A-12L                  | 12                                   | 115                | —                               | 8                         | 2-162        |

| Array                              | GAL16V8A-15L                  | 15                                   | 115                | _                               | 8                         | 2-162        |

| Logic                              | GAL16V8A-20L                  | 20                                   | 115                | -                               | 8                         | 2-162        |

| Series-A                           |                               |                                      |                    |                                 |                           |              |

| 24-Pin                             | GAL20V8-20L                   | 20                                   | 90                 | -                               | 8                         | 2-145        |

| Generic                            | GAL20V8-25Q                   | 25                                   | 45                 | -                               | 8                         | 2-145        |

| Array                              | GAL20V8-25L                   | 25                                   | 90                 | _                               | 8                         | 2-145        |

| Logic                              | GAL20V8-35Q                   | 35                                   | 45                 |                                 | 8                         | 2-145        |

| 24-Pin                             | GAL20V8A-10L                  | 10                                   | 115                | —                               | 8                         | 2-177        |

| Generic                            | GAL20V8A-12L                  | 12                                   | 115                | -                               | 8                         | 2-177        |

| Array                              | GAL20V8A-15L                  | 15                                   | 115                |                                 | 8                         | 2-177        |

| Logic                              | GAL20V8A-20L                  | 20                                   | 115                | -                               | 8                         | 2-177        |

| Series-A                           | GAL22V10-15                   | 15                                   | 130                |                                 | 10                        | 2-193        |

|                                    | GAL22V10-20                   | 20                                   | 130                | -                               | 10                        | 2-193        |

|                                    | GAL22V10-25                   | 25                                   | 130                | -                               | 10                        | 2-193        |

|                                    | GAL20RA10-15                  | 15                                   | 150                | -                               | 10                        | 2-206        |

|                                    | GAL20RA10-20                  | 20                                   | 150                | -                               | 10                        | 2-206        |

|                                    | GAL20RA10-25                  | 25                                   | 150                | -                               | 10                        | 2-206        |

|                                    | GAL6001-30L                   | 30                                   | 150                | -                               | 10                        | 2-217        |

|                                    | GAL6001-35L                   | 35                                   | 150                |                                 | 10                        | 2-217        |

| ote 1: Maximum t <sub>PD</sub> for | r combinatorial outputs (comm | ercial operating range               | e). Denotes charac | cteristic speed of family where | product has all non-regis | tered output |

**Product Line Overview**

| Family and<br>Series | Part<br>Numbers | t <sub>PD</sub><br>(max)<br>(Note 1) | I <sub>CC</sub><br>(max) | Outputs       |            | Page  |

|----------------------|-----------------|--------------------------------------|--------------------------|---------------|------------|-------|

|                      |                 |                                      |                          | Combinatorial | Registered |       |

| ECL                  |                 |                                      |                          |               |            |       |

| Combinatorial        | PAL1016P8       | 6                                    | -240                     | 8             | _          | 2-183 |

|                      | PAL10016P8      | 6                                    | -240                     | 8             |            | 2-18  |

|                      | PAL1016P8-3     | 3                                    | -220                     | 8             | _          |       |

|                      | PAL10016P8-3    | 3                                    | -220                     | 8             | —          |       |

|                      | PAL1016PE8-3    | 3                                    | -220                     | 8             |            |       |

|                      | PAL10016PE8-3   | 3                                    | -220                     | 8             | _          |       |

|                      | PAL1016P4A      | 4                                    | -220                     | 4             | . —        | 2-207 |

|                      | PAL10016P4A     | 4                                    | -220                     | 4             | <u> </u>   | 2-207 |

|                      | PAL1016P4-2     | 2.5                                  | -220                     | 4             | · · · -    |       |

|                      | PAL10016P4-2    | 2.5                                  | -220                     | 4             | _          |       |

|                      | PAL1016C4-2     | 2                                    | -220                     | 4             |            |       |

|                      | PAL10016C4-2    | 2                                    | -220                     | 4             |            |       |

| Registered           | PAL1016RD8      | 6                                    | -280                     | _             | 8          | 2-193 |

|                      | PAL10016RD8     | 6                                    | -280                     | -             | 8          | 2-193 |

|                      | PAL1016RM4A     | 4                                    | -220                     |               | 4          | 2-217 |

|                      | PAL10016RM4A    | 4                                    | -220                     |               | 4          | 2-217 |

Note 1: Maximum tPD for combinatorial outputs (commercial operating range). Denotes characteristic speed of family where product has all non-registered outputs.

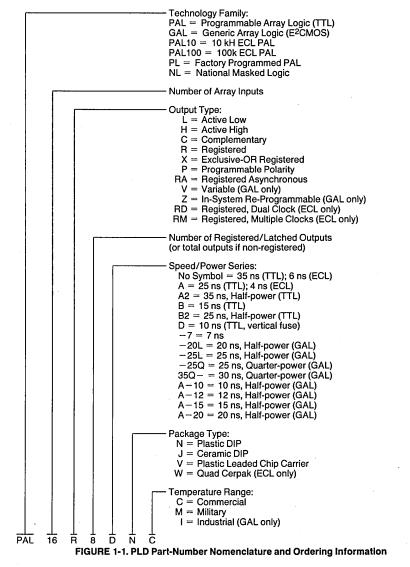

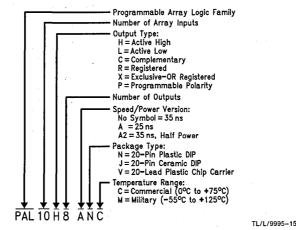

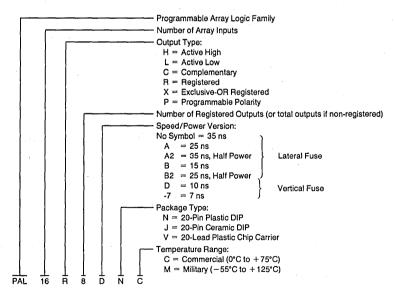

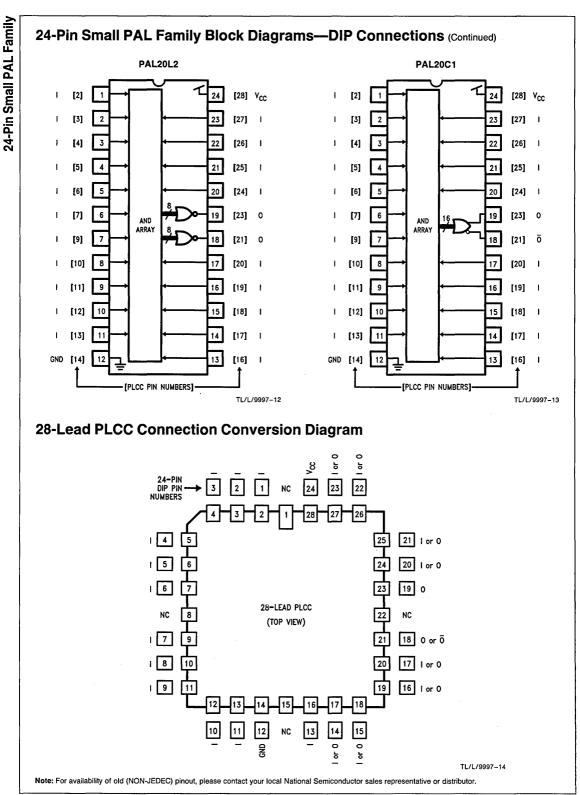

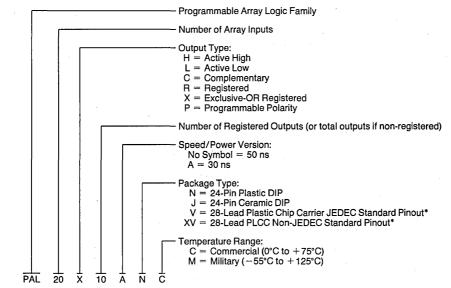

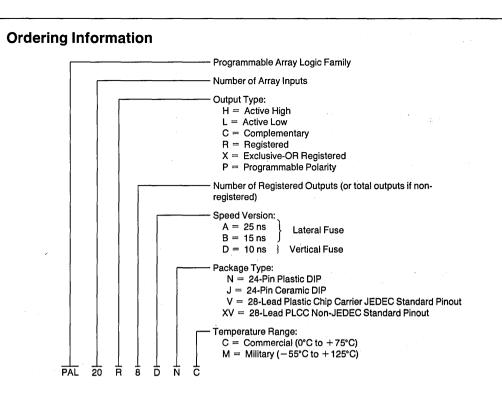

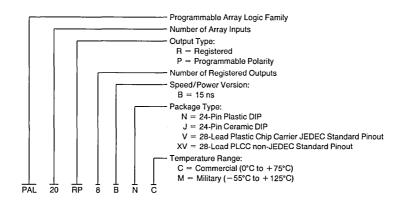

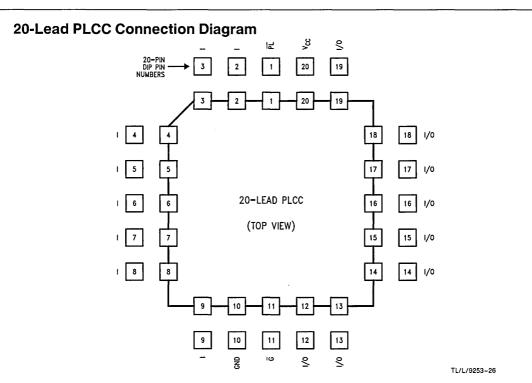

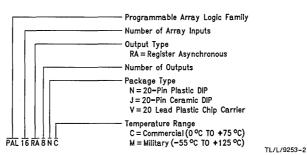

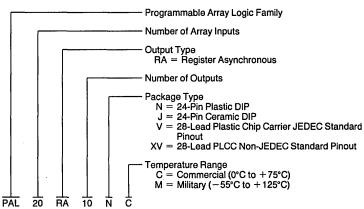

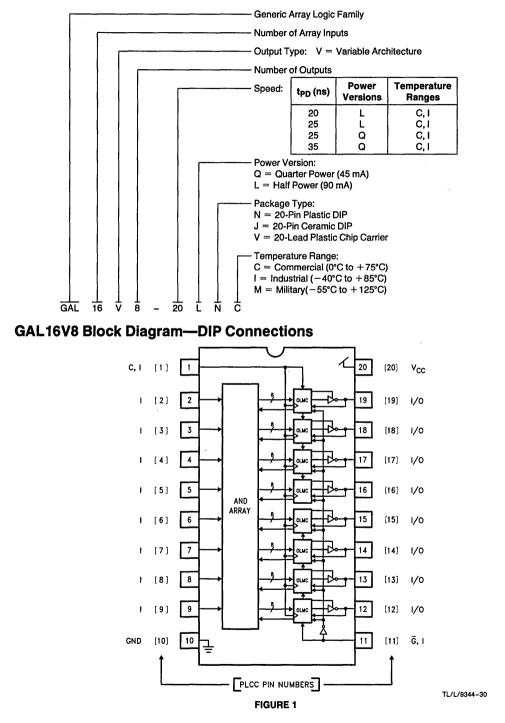

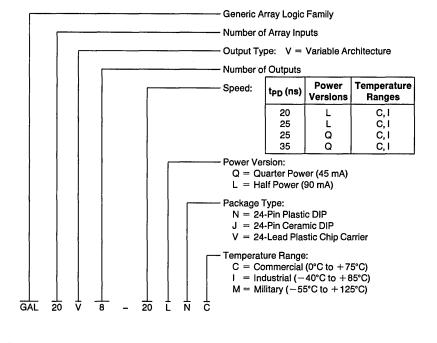

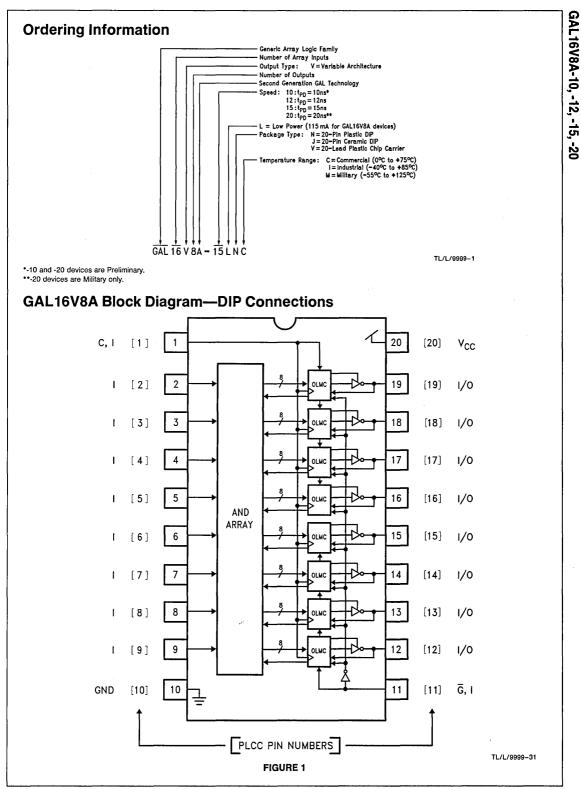

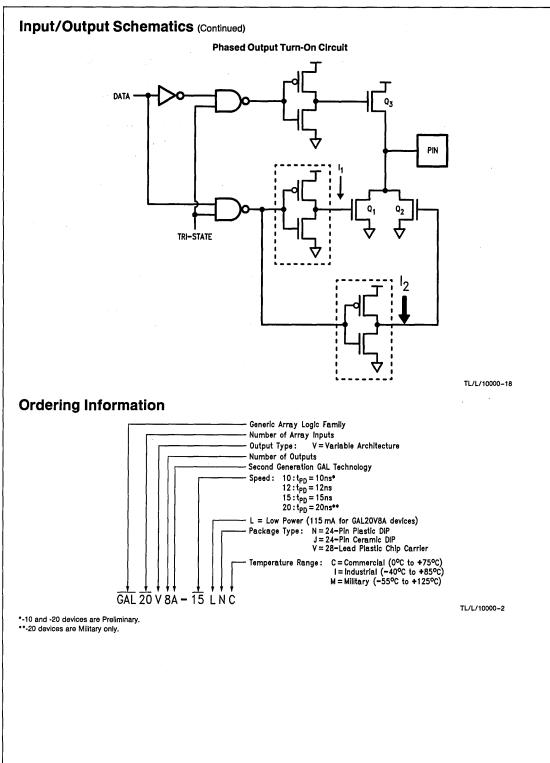

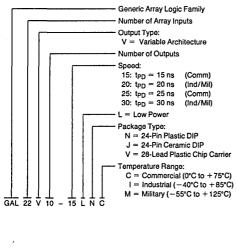

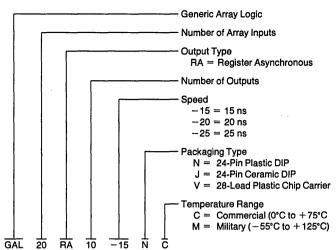

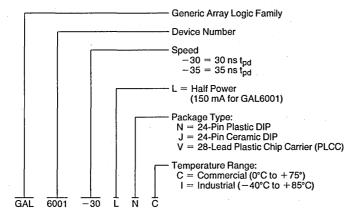

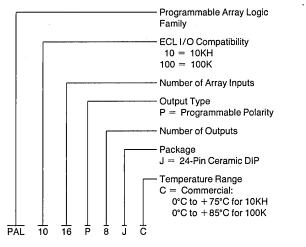

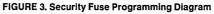

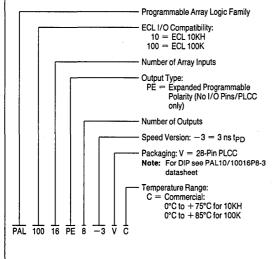

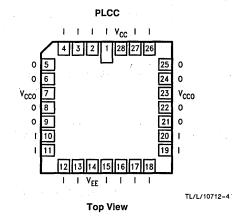

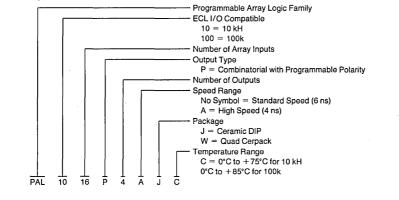

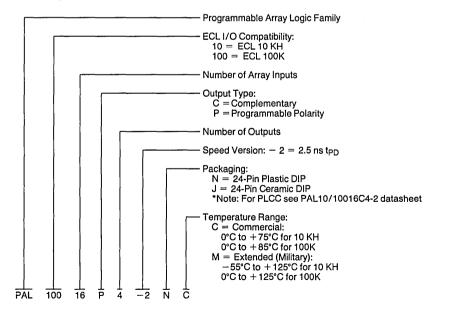

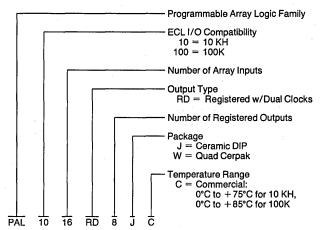

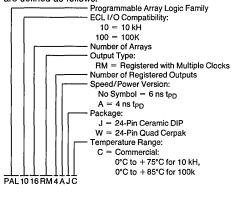

#### **1.2 Ordering Information**

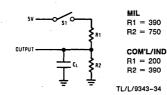

The ordering information diagram below defines the product-number nomenclature used throughout National's programmable logic product line. This nomenclature is based on that used by the original industry-standard PAL products, and are therefore very similar to the product numbers used by other PLD manufacturers. Refer to the corresponding "Ordering Information" diagrams in the individual product datasheets to determine the valid combinations of attributes describing actual PLD products.

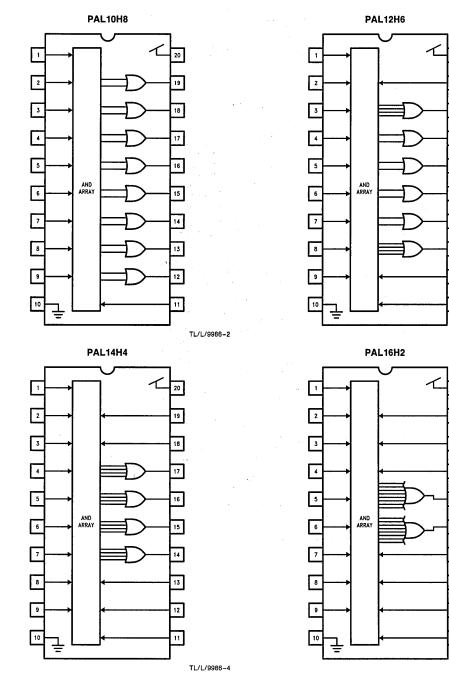

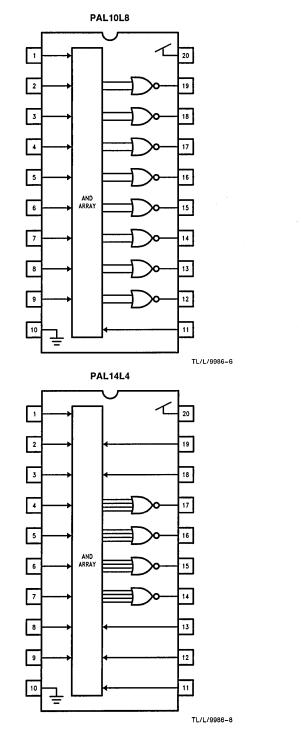

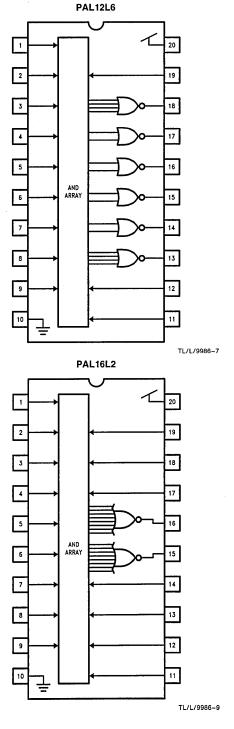

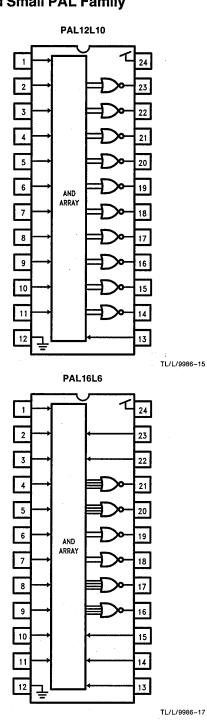

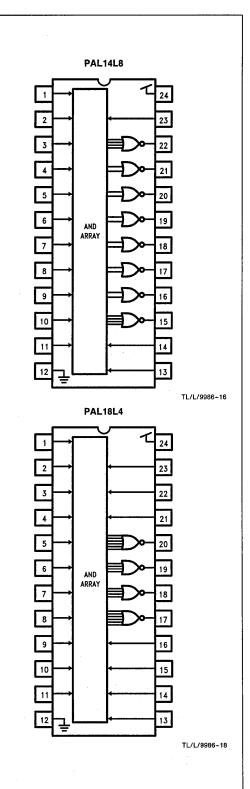

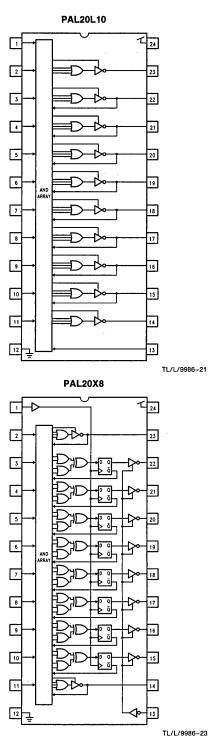

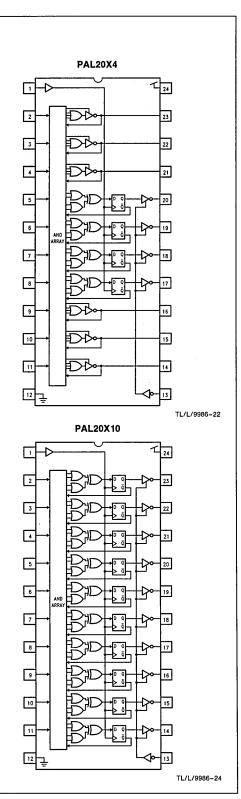

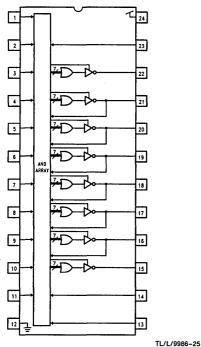

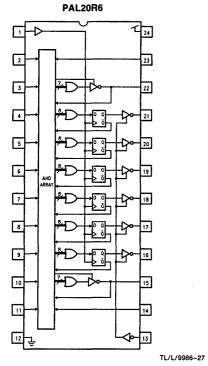

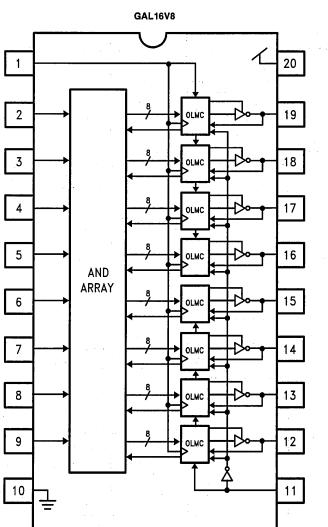

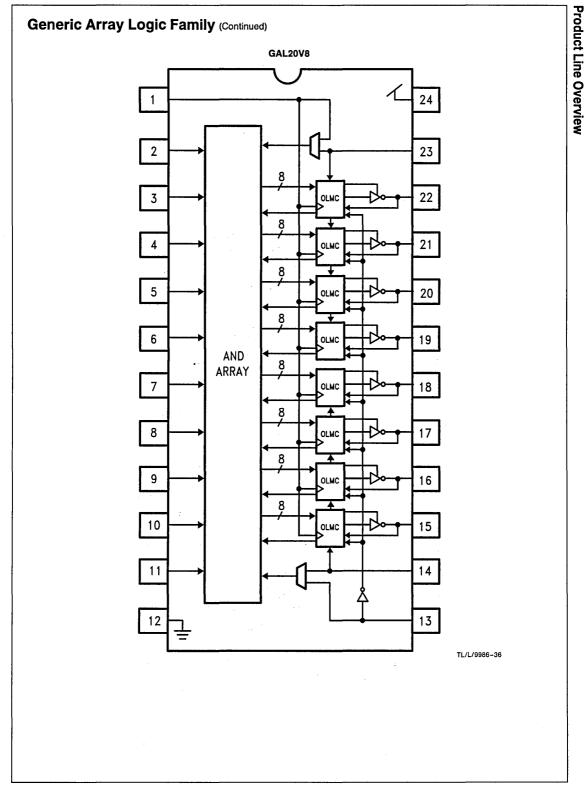

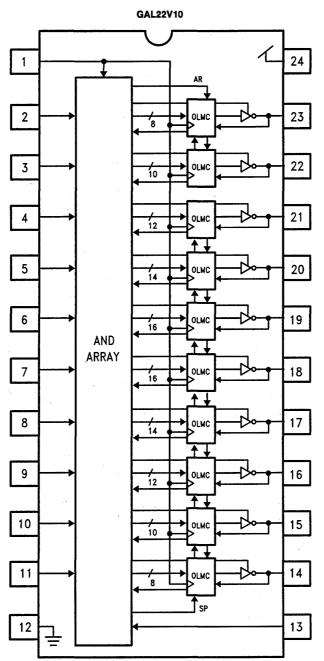

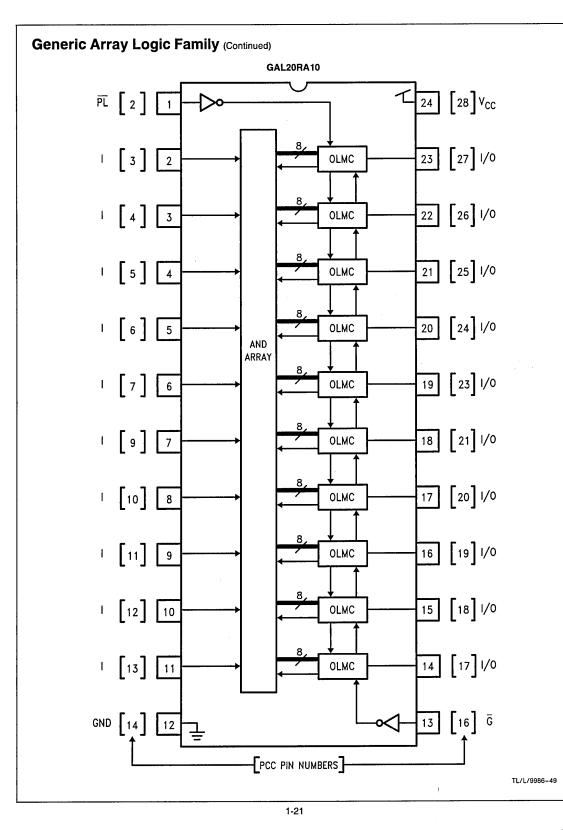

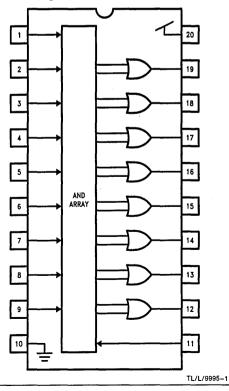

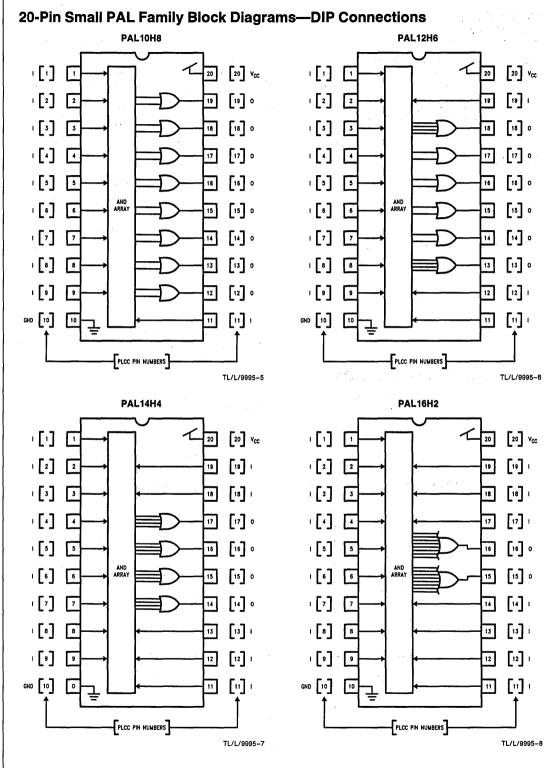

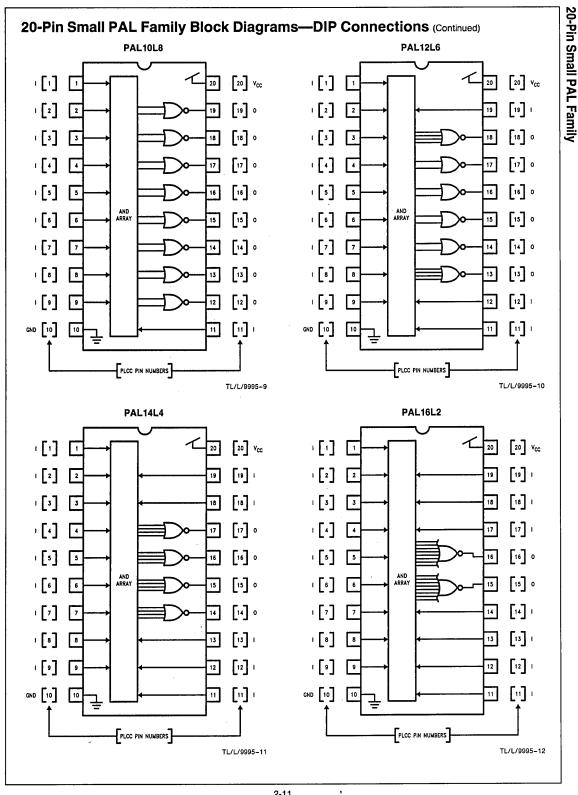

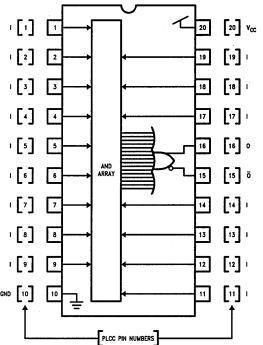

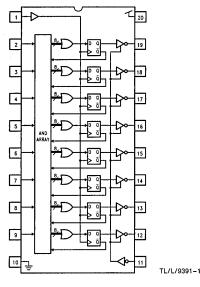

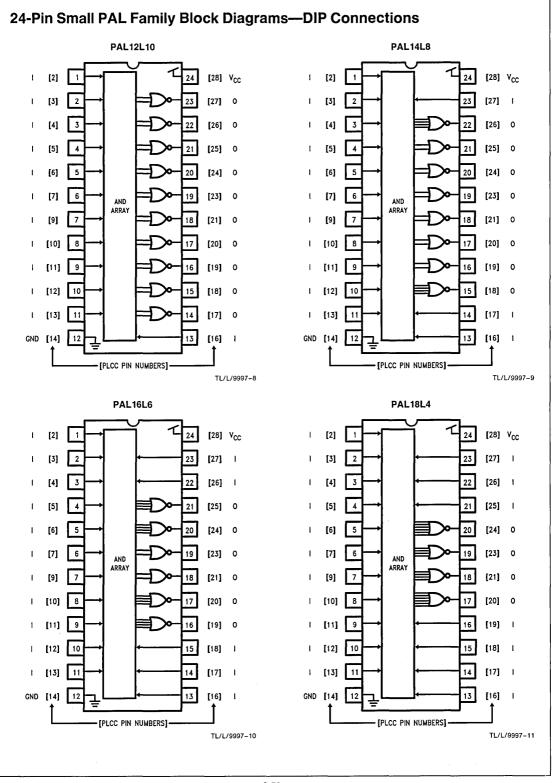

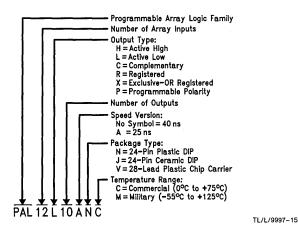

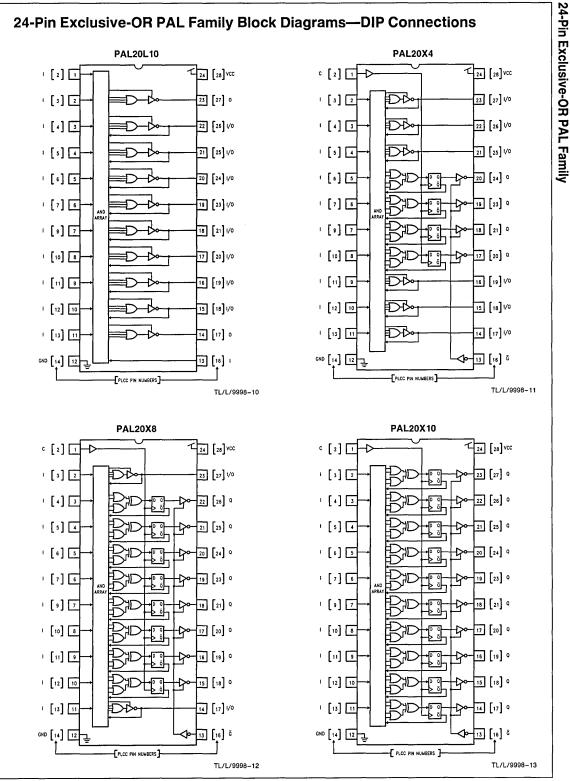

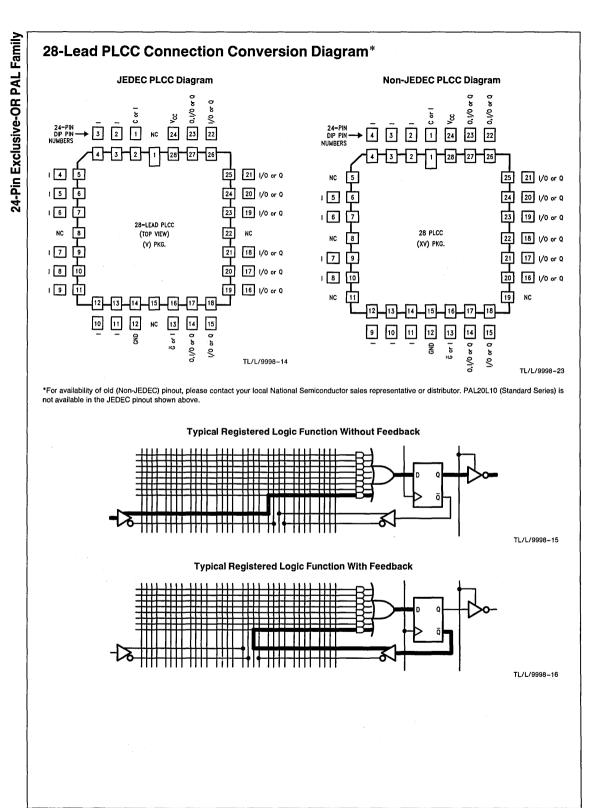

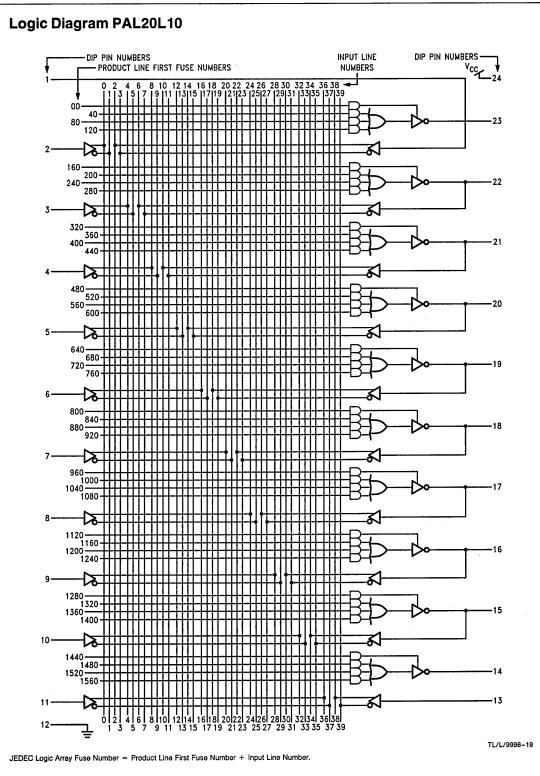

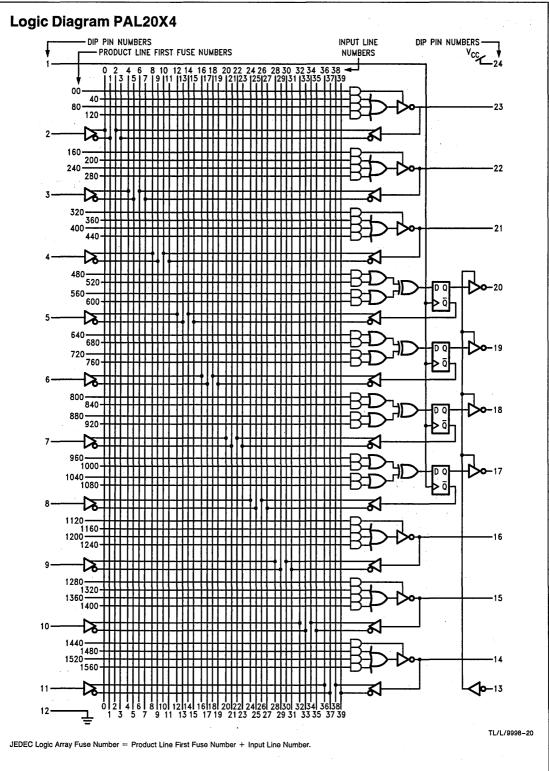

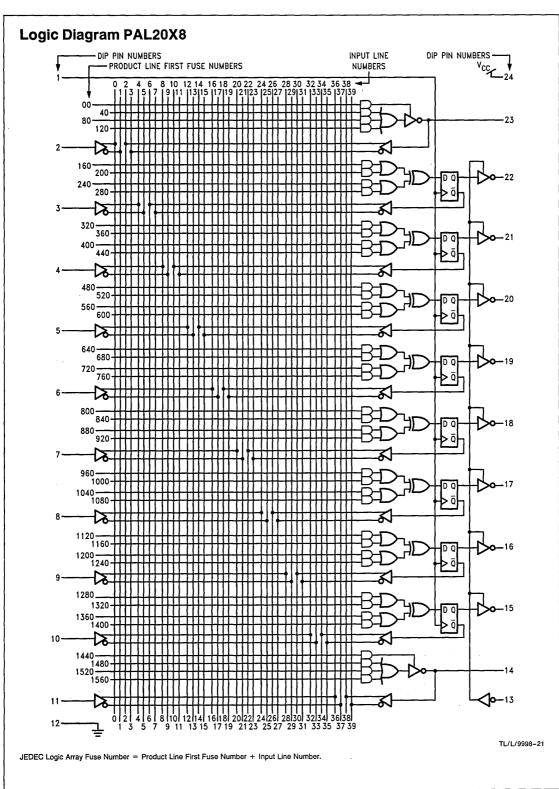

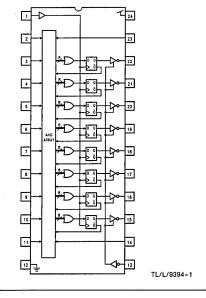

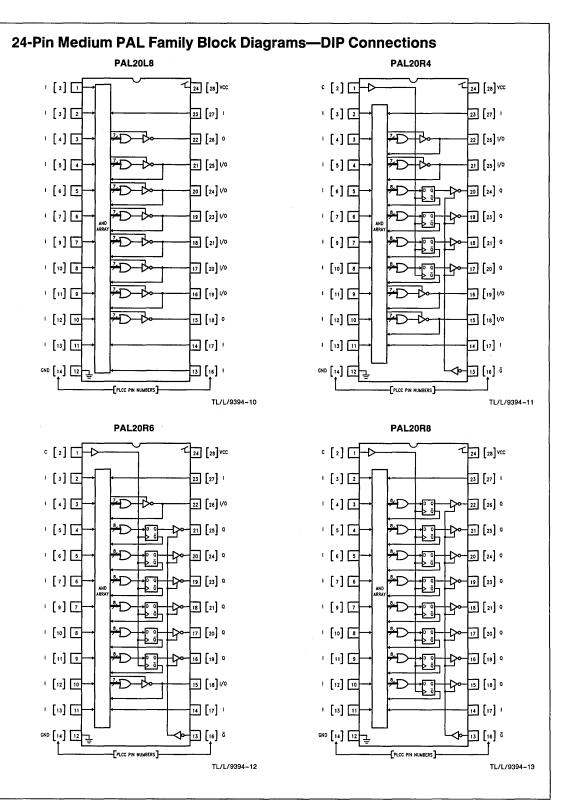

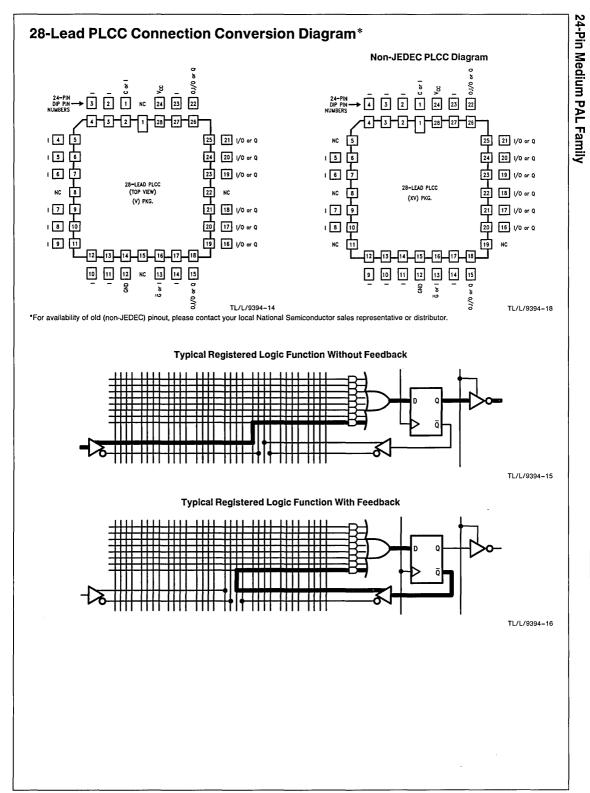

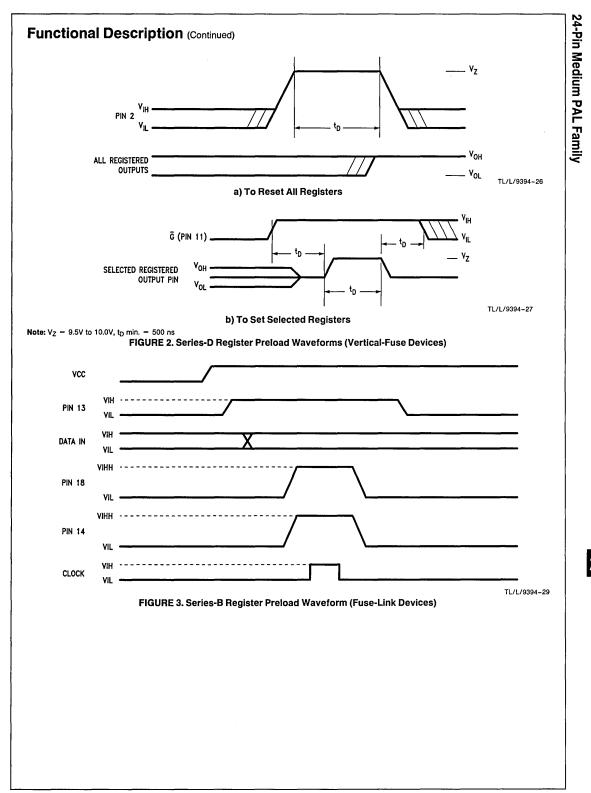

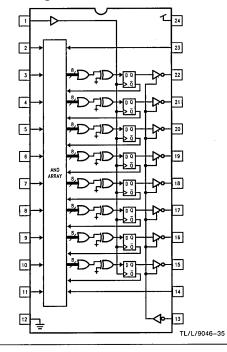

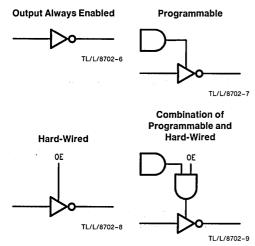

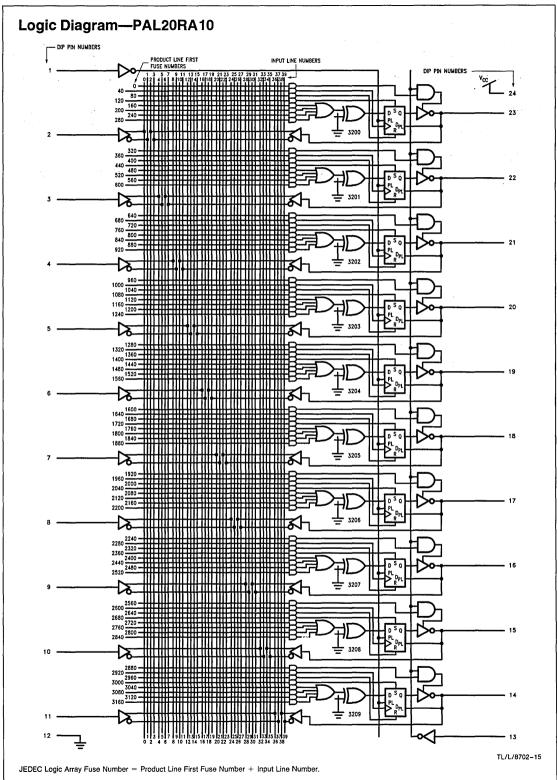

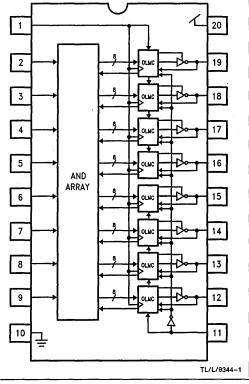

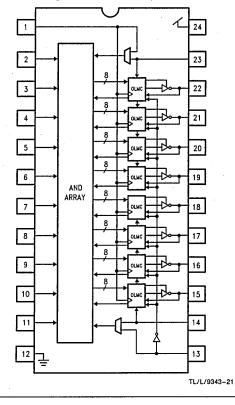

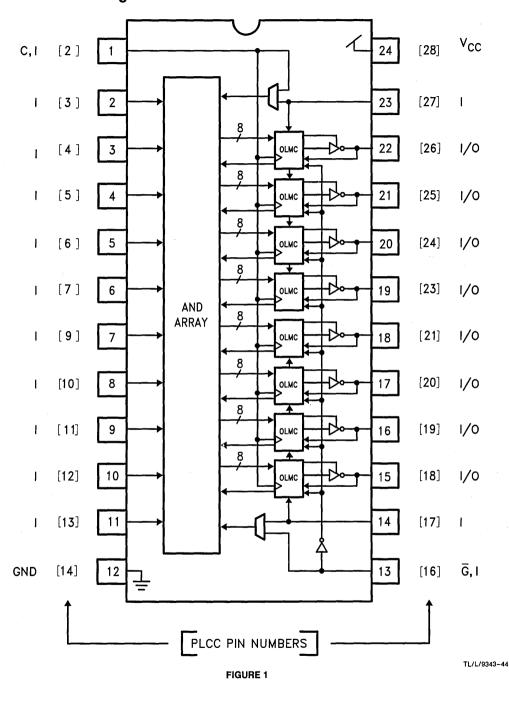

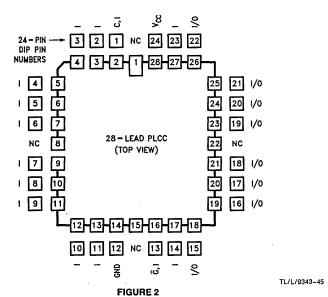

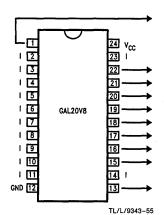

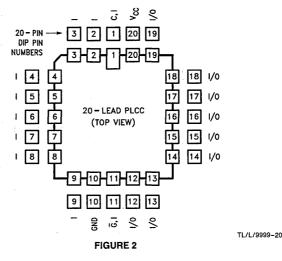

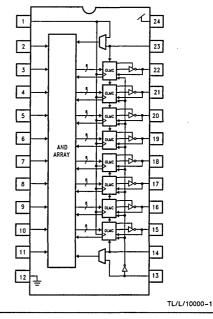

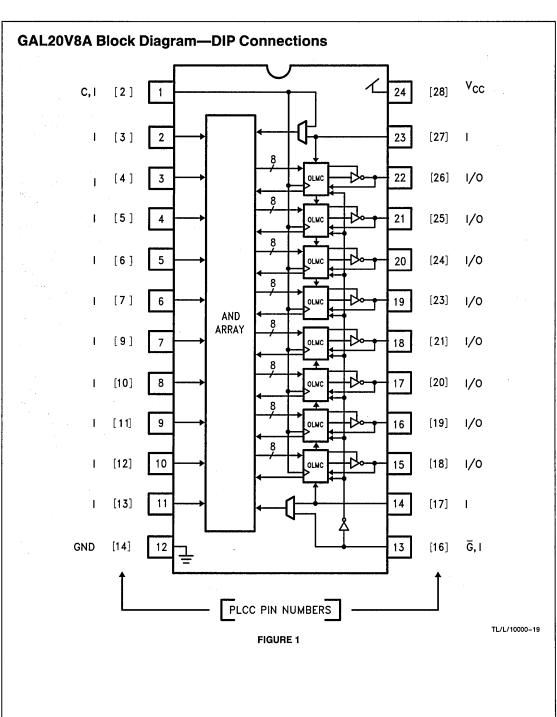

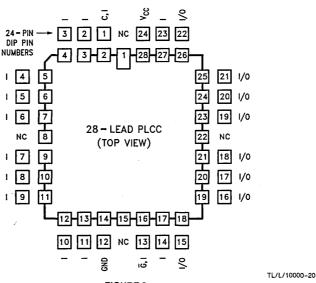

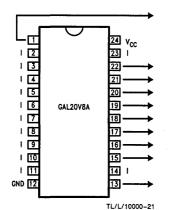

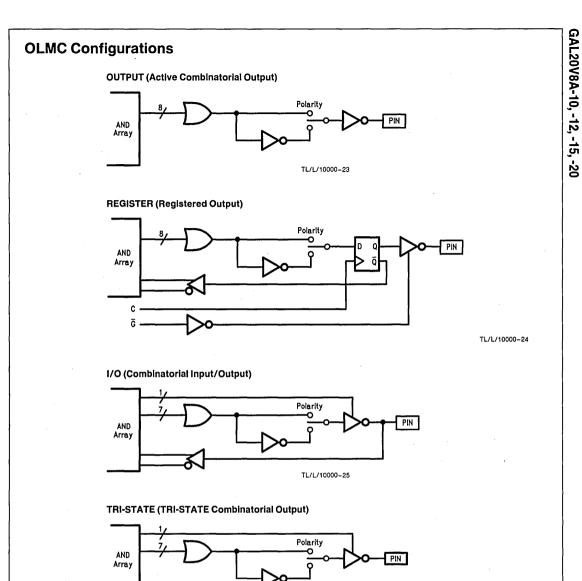

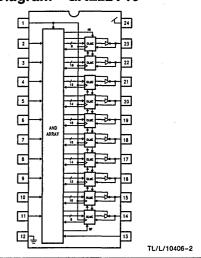

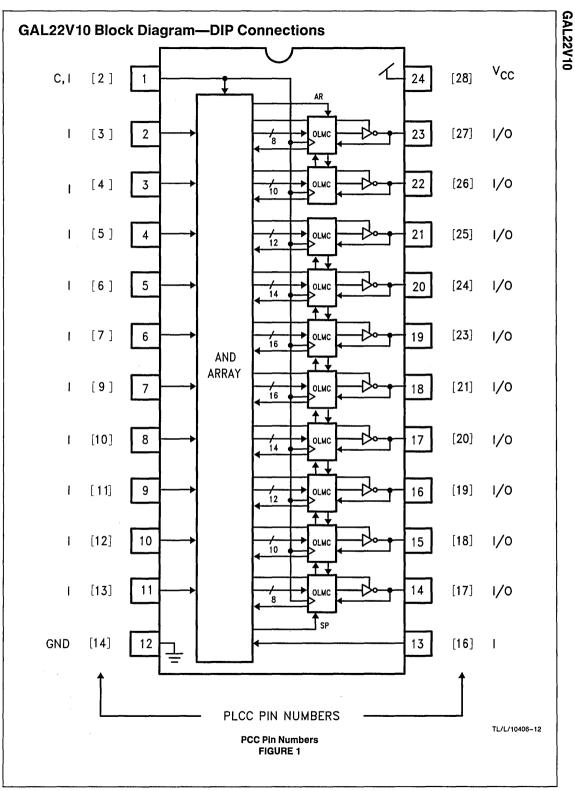

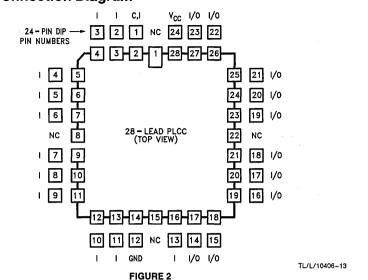

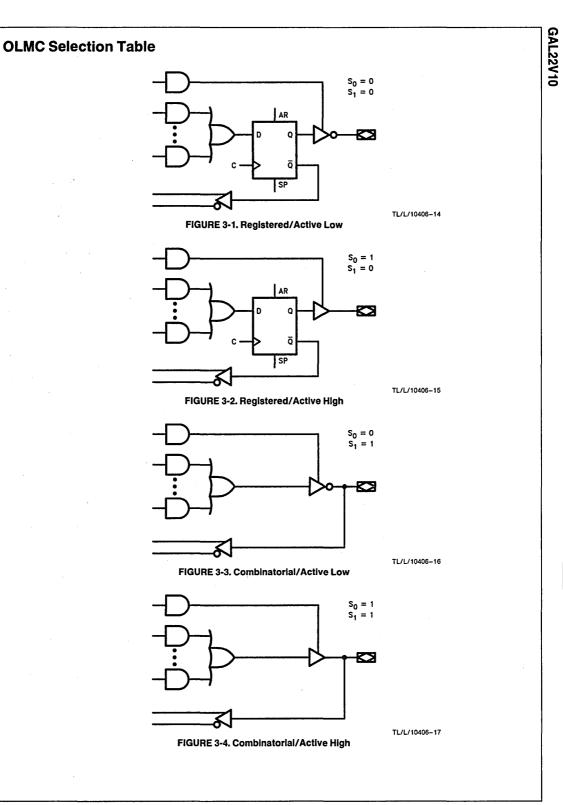

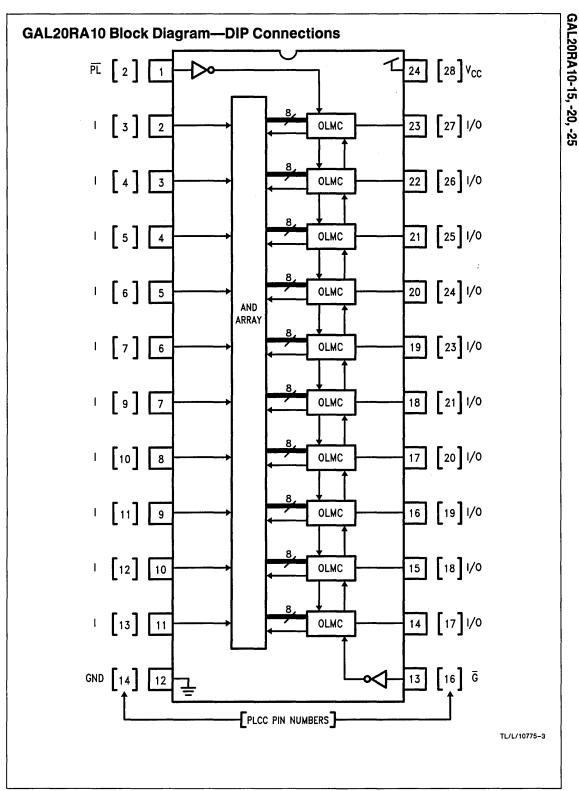

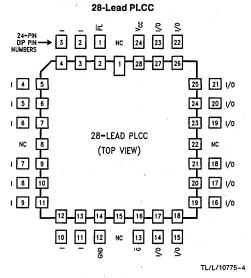

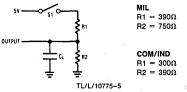

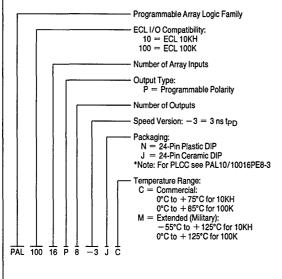

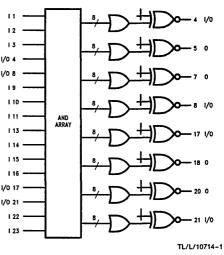

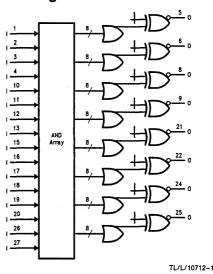

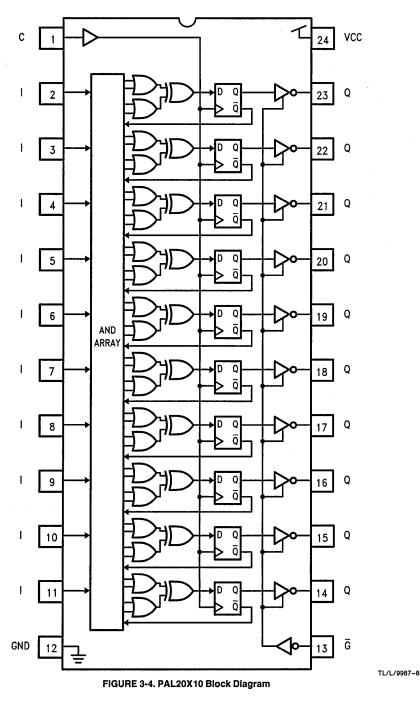

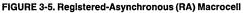

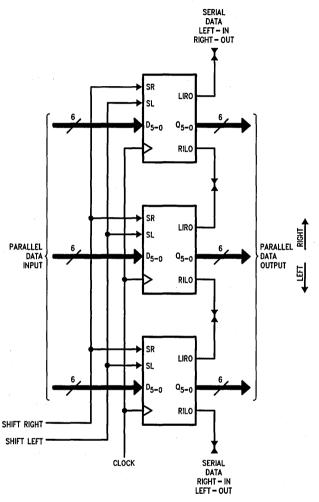

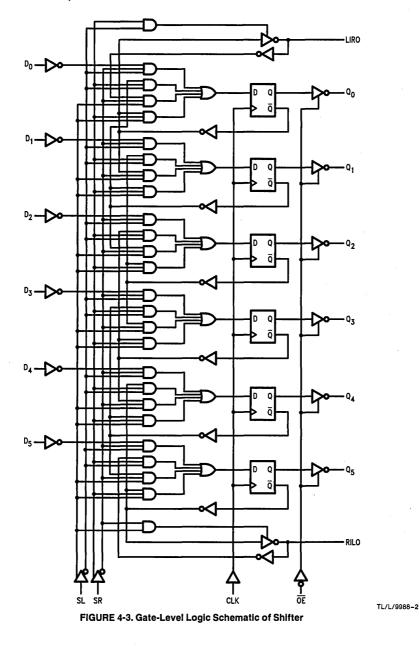

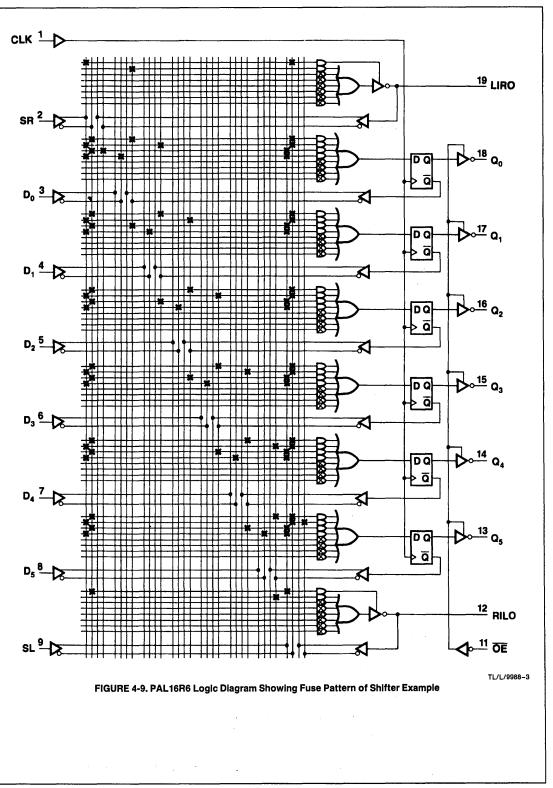

#### 1.3 Block Diagrams

The following collection of block diagrams provides a graphic representation of all product architectures ("device types") in National's programmable logic product line. The block diagrams may be used in conjunction with the selection tables in Section 1.1 to identify the most appropriate PLD products to suit the system's application requirements.

TL/L/9986-5

TL/L/9986-3

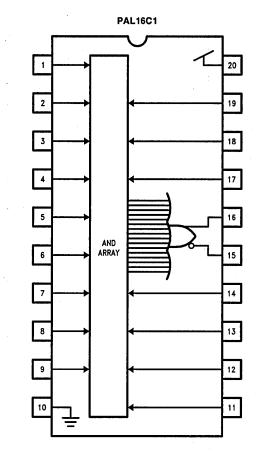

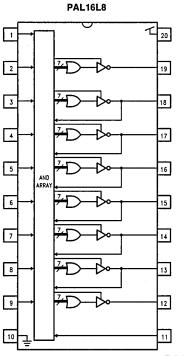

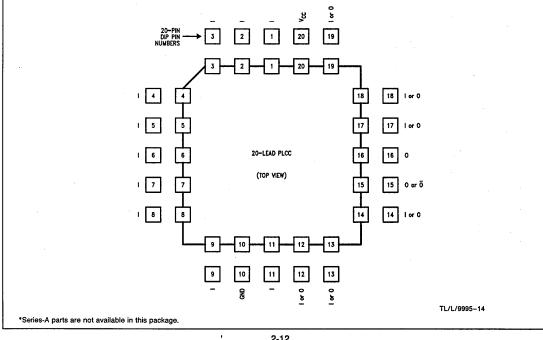

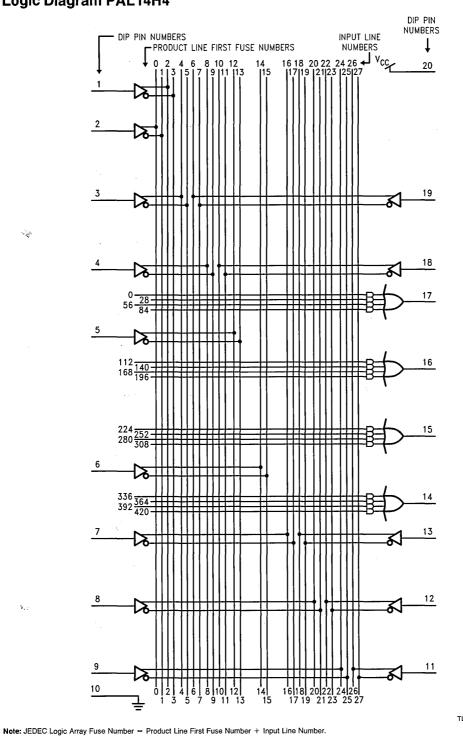

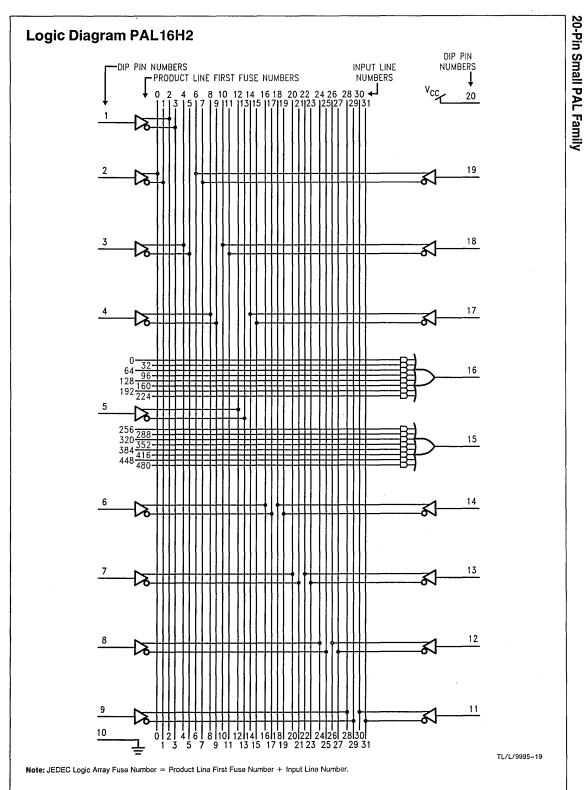

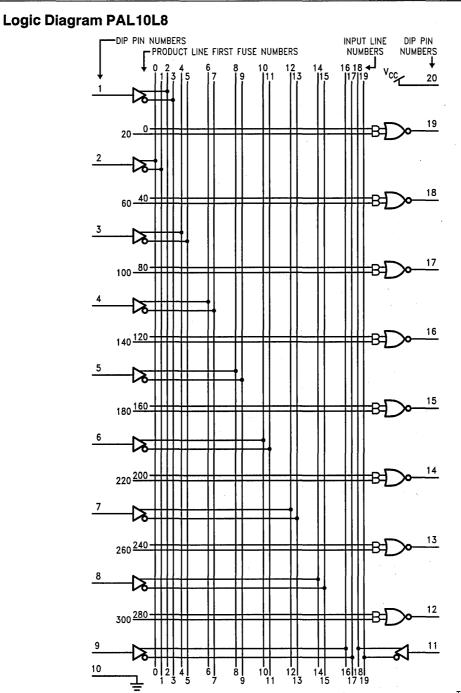

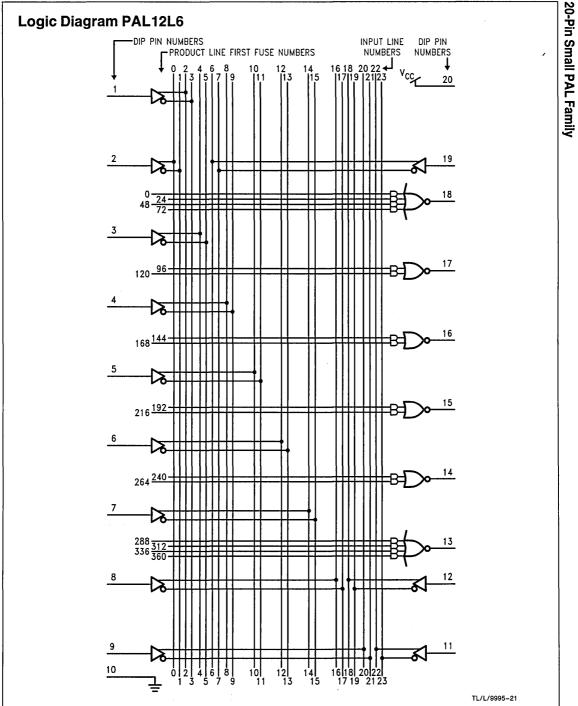

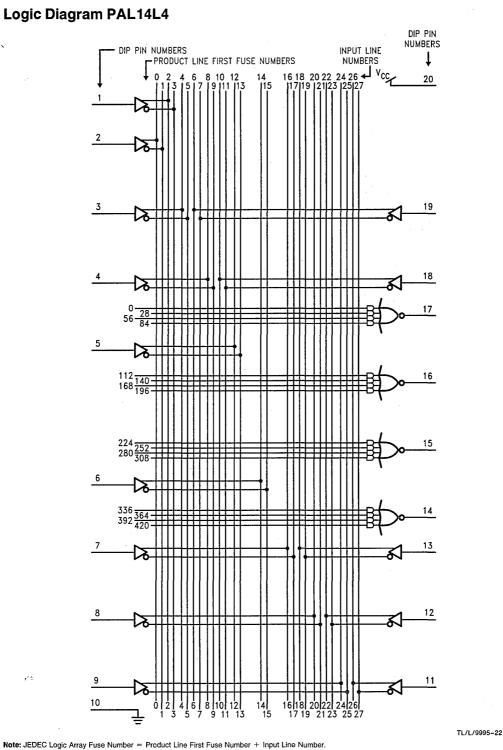

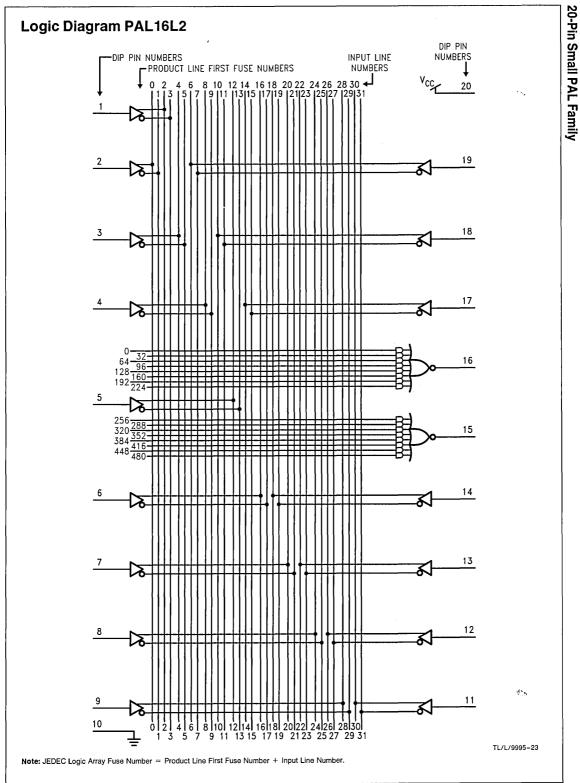

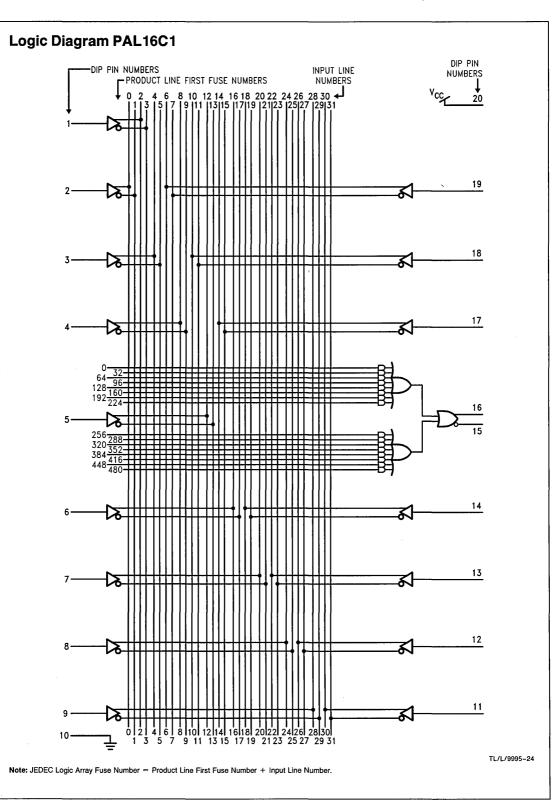

### 20-Pin Small PAL Family

#### 20-Pin Small PAL Family (Continued)

### 20-Pin Small PAL Family (Continued)

TL/L/9986-10

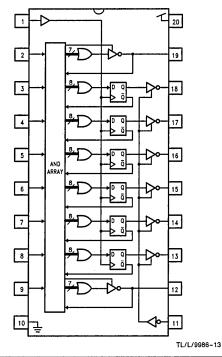

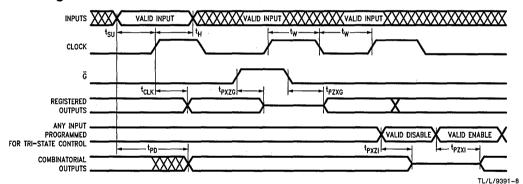

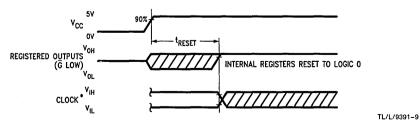

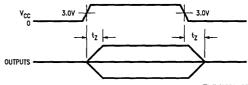

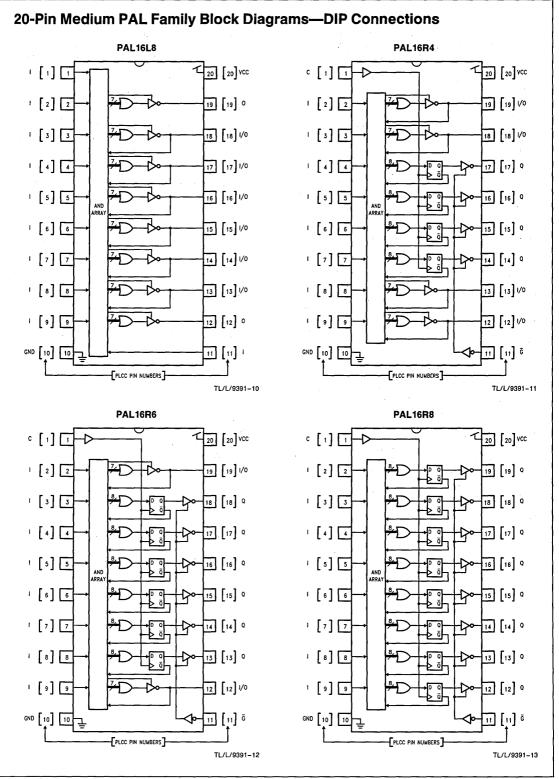

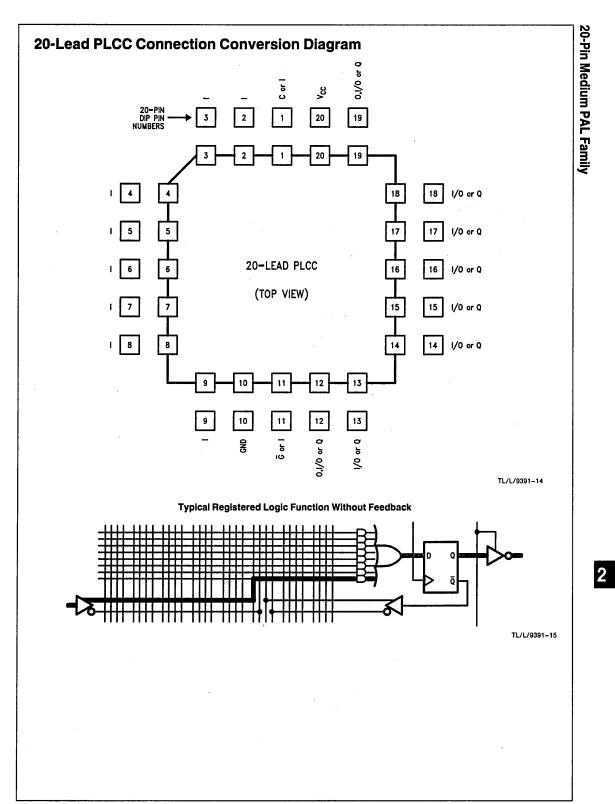

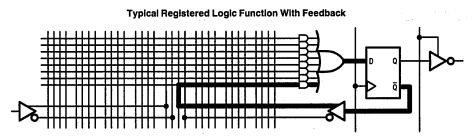

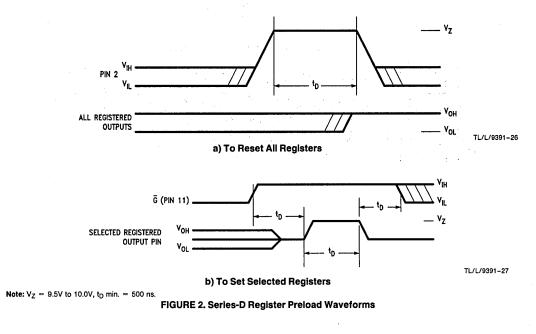

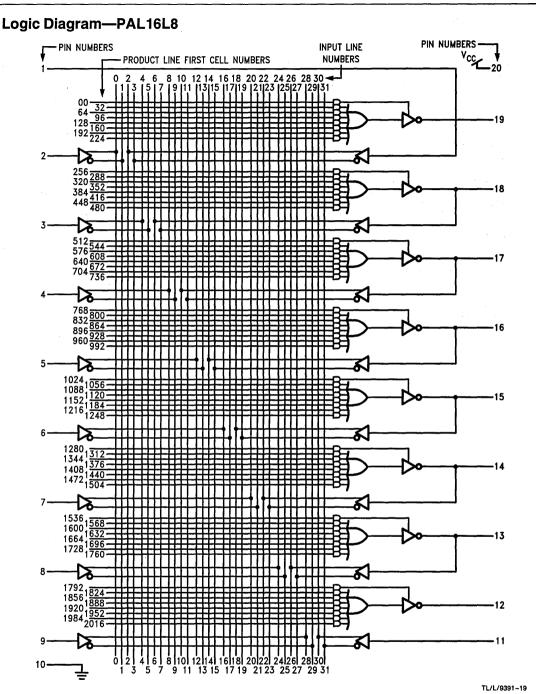

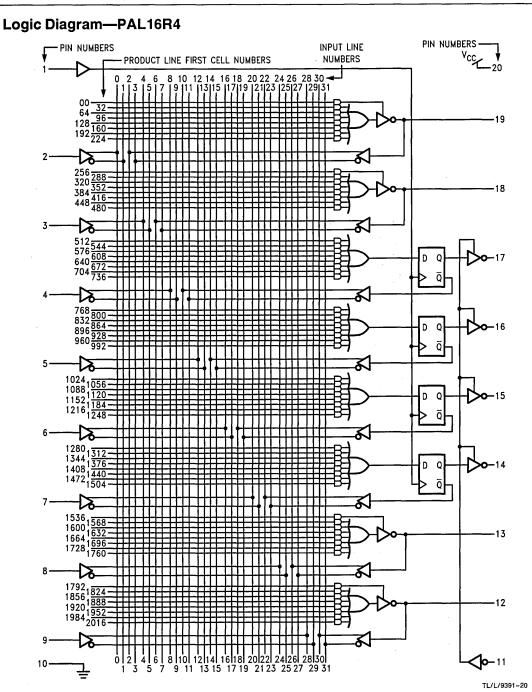

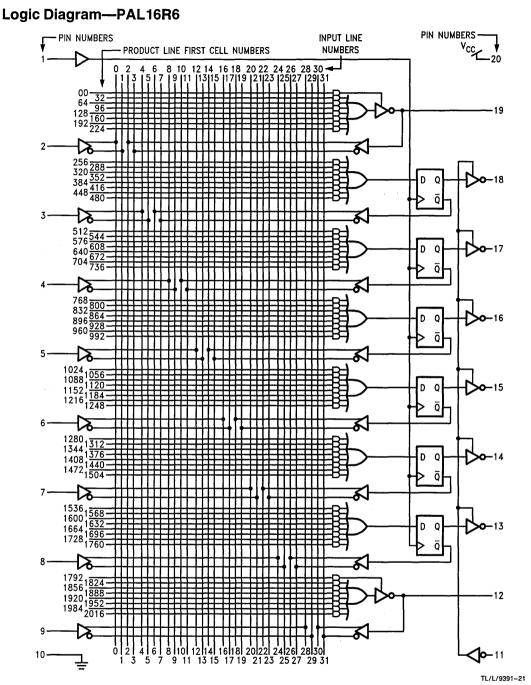

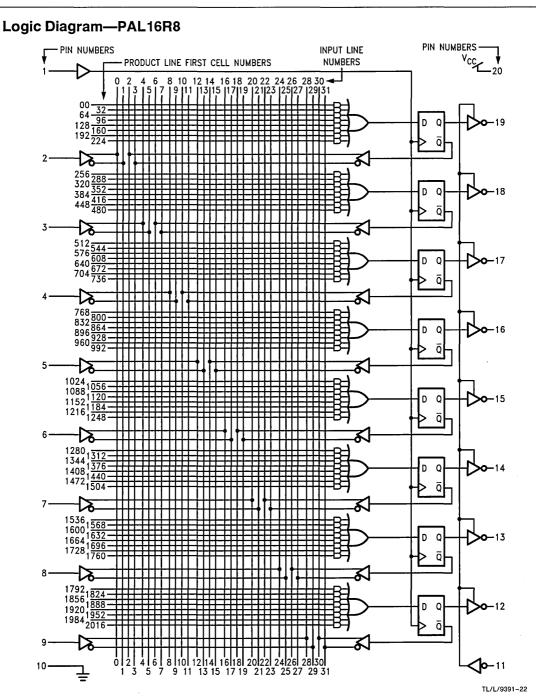

#### 20-Pin Medium PAL Family

TL/L/9986-11

1

### 24-Pin Small PAL Family

**Product Line Overview**

### 24-Pin Exclusive-OR PAL Family

1-14

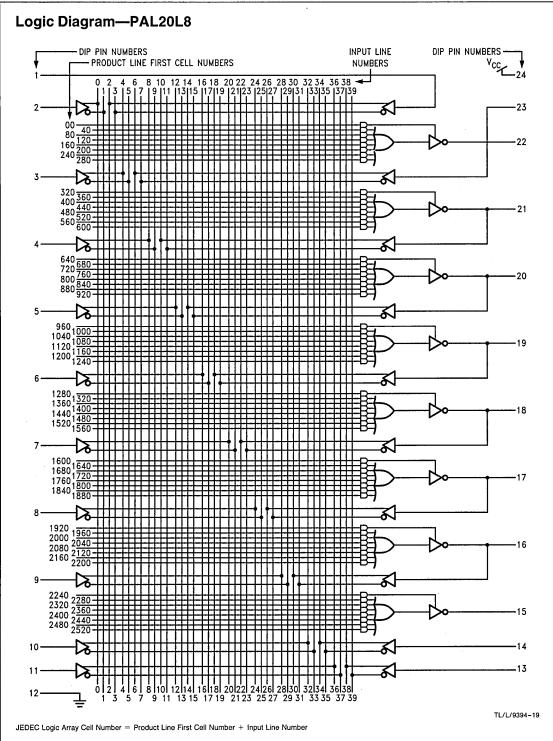

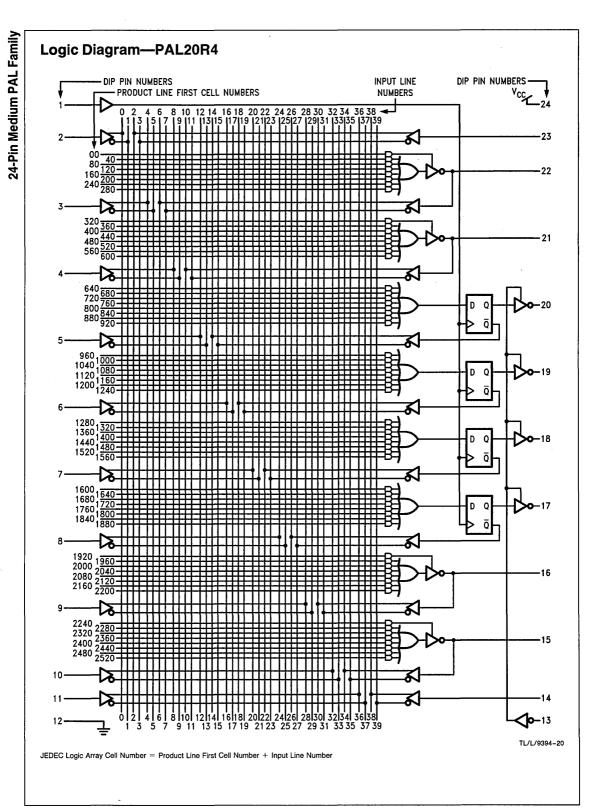

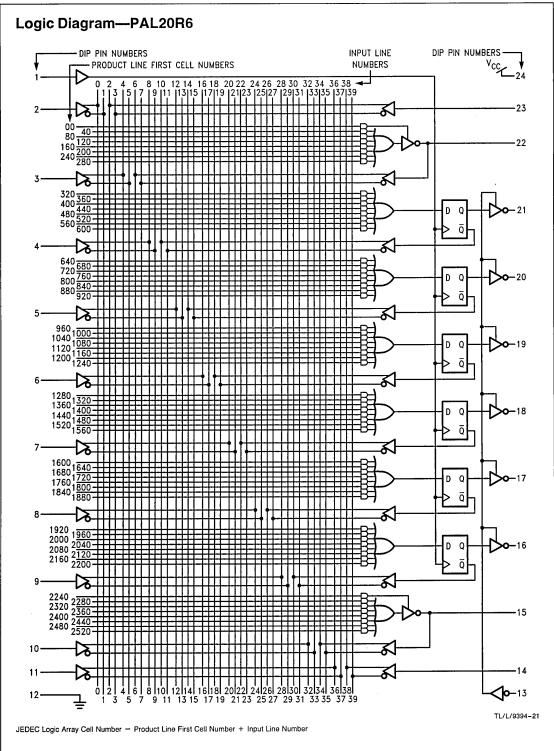

#### 24-Pin Medium PAL Family

PAL20L8

**Product Line Overview**

1

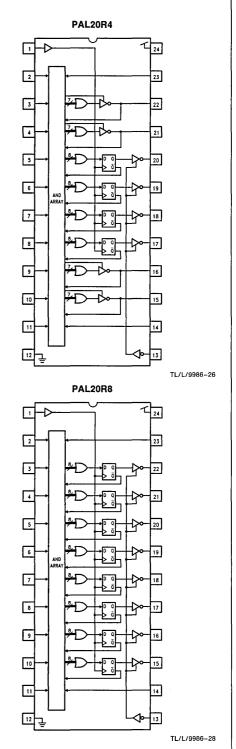

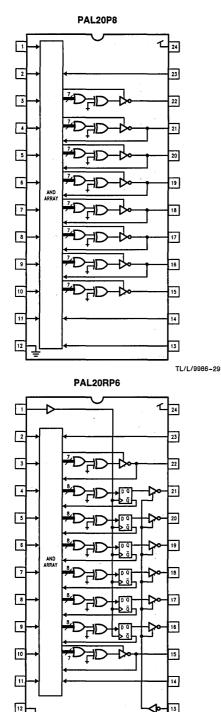

#### 24-Pin Polarity PAL Family

TL/L/9986-31

1-17

Ľ

### **Generic Array Logic Family**

TL/L/9986-35

### Generic Array Logic Family (Continued)

TL/L/9986-48

**Product Line Overview**

# Generic Array Logic Family (Continued)

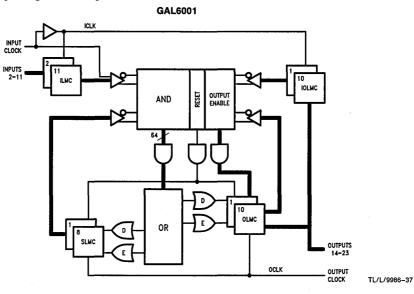

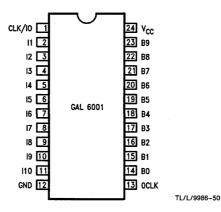

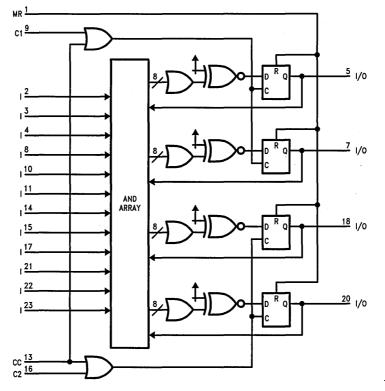

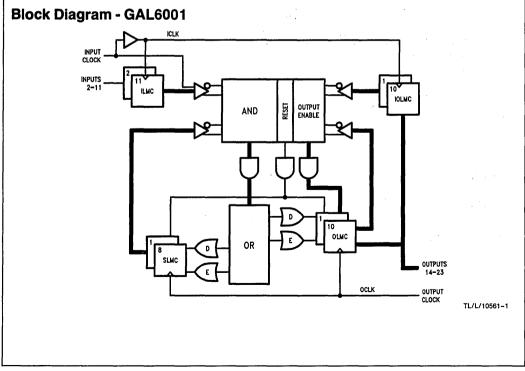

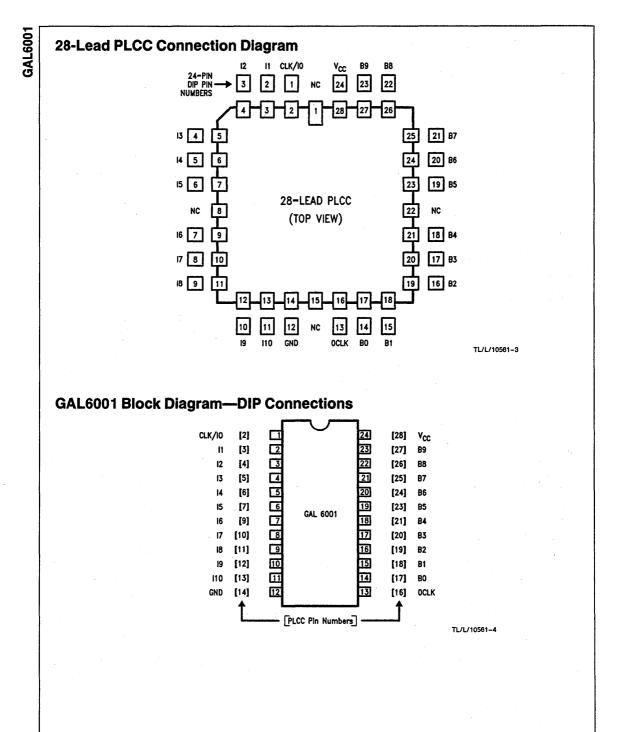

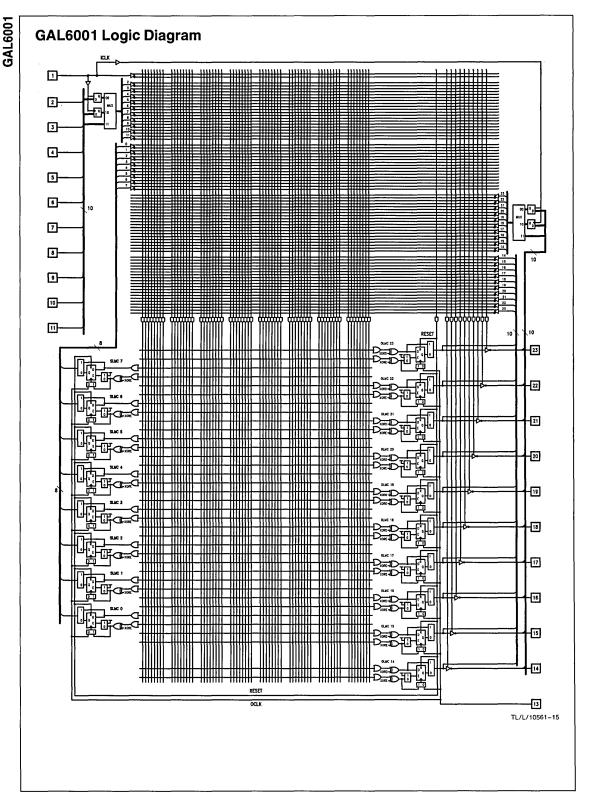

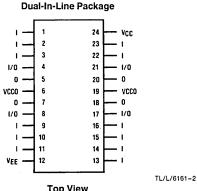

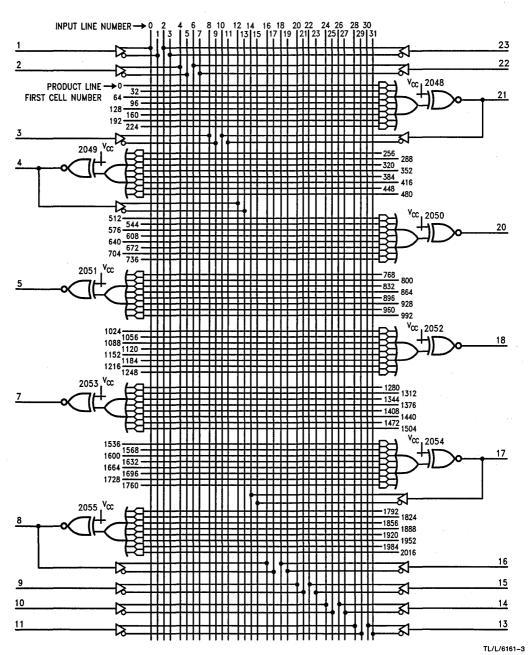

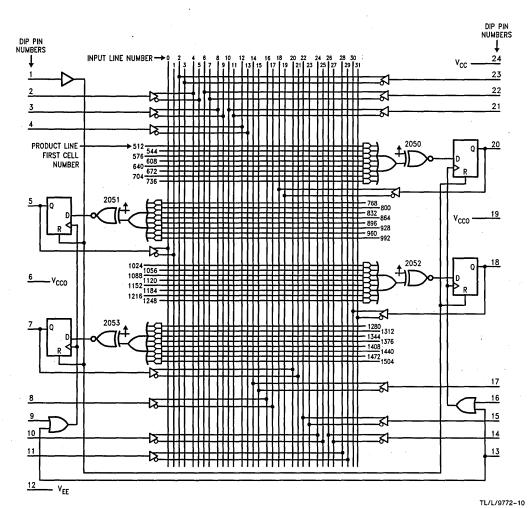

# GAL6001 Block Diagram—DIP Connections

# ECL Registered PAL Family

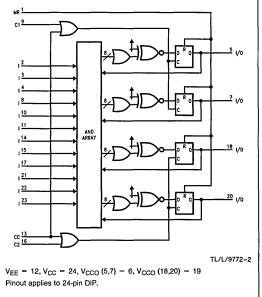

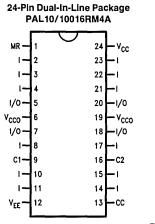

PAL10/10016RM4A

TL/L/9986-47

# Section 2 Data Sheets

# **Section 2 Contents**

| 20-Pin Small PAL Family                                      | 2-3   |

|--------------------------------------------------------------|-------|

| 20-Pin Medium PAL Family                                     | 2-23  |

| 24-Pin Small PAL Family                                      | 2-48  |

| 24-Pin Exclusive-OR PAL Family                               | 2-62  |

| 24-Pin Medium PAL Family                                     | 2-77  |

| 24-Pin Polarity PAL Family                                   | 2-95  |

| PAL16RA8 20-Pin Registered Asynchronous PAL                  | 2-108 |

| PAL20RA10 24-Pin Registered Asynchronous PAL                 | 2-118 |

| GAL16V8 Generic Array Logic                                  | 2-129 |

| GAL20V8 Generic Array Logic                                  | 2-145 |

| GAL16V8A Generic Array Logic                                 | 2-162 |

| GAL20V8A Generic Array Logic                                 | 2-177 |

| GAL22V10-15, -20, -25, -30 Generic Array Logic (Preliminary) | 2-193 |

| GAL20RA10-15, -20, -25 Generic Array Logic (Preliminary)     | 2-206 |

| GAL6001 Generic Array Logic (Preliminary)                    | 2-217 |

| ECL PAL10/10016P8 Combinatorial PAL                          | 2-227 |

| ECL PAL10/10016P8-3 3 ns Combinatorial PAL (Preliminary)     | 2-236 |

| ECL PAL10/10016PE8-3 3 ns Combinatorial PAL (Preliminary)    | 2-242 |

| ECL PAL10/10016P4A Combinatorial PAL                         | 2-247 |

| ECL PAL10/10016P4-2 2 ns Combinatorial PAL (Preliminary)     | 2-251 |

| ECL PAL10/10016C4-2 2 ns Combinatorial PAL (Preliminary)     | 2-257 |

| ECL PAL10/10016RD8 Registered PAL                            | 2-262 |

| ECL PAL10/10016RM4A Registered PAL                           | 2-268 |

# National Semiconductor

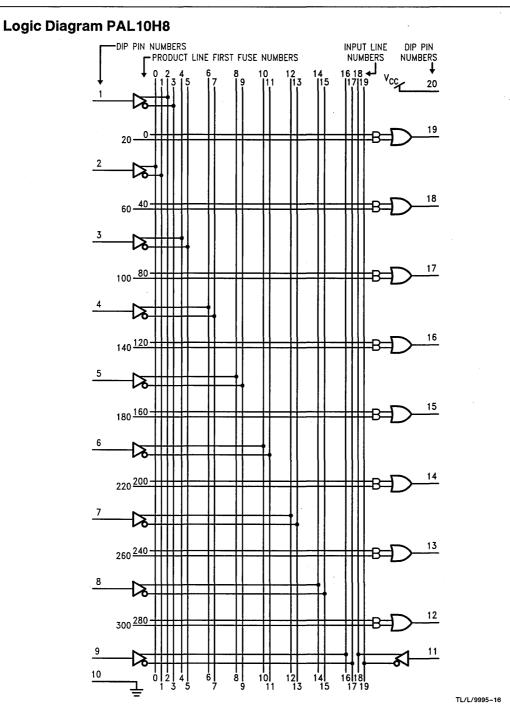

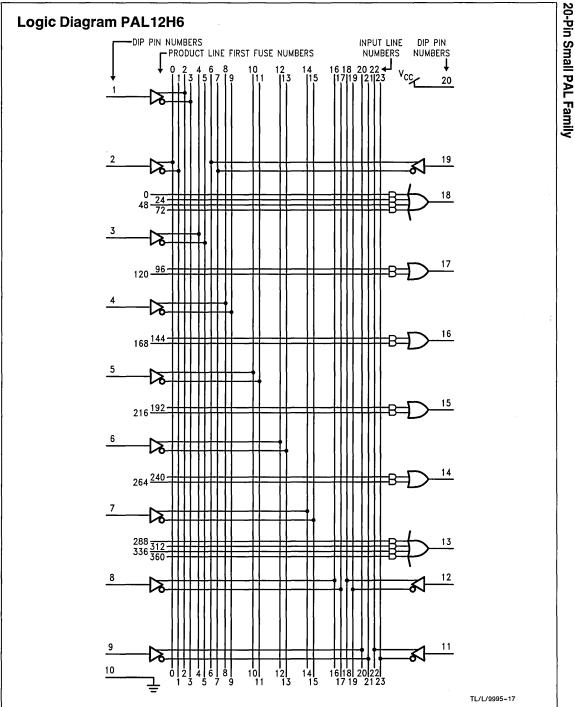

# Programmable Array Logic (PAL®) 20-Pin Small PAL Family

# **General Description**

The 20-pin Small PAL family contains nine popular PAL architectures. The devices in the Small PAL family draw only 90 mA maximum supply current for standard power versions, and as little as 45 mA for Series A2 as compared to 180 mA in the 20-pin Medium PAL devices. These devices offer speeds as fast as 25 ns maximum propagation delay. National Semiconductor's Schottky TTL process with titanium tungsten fusible links provides high-speed user-programmable replacements for conventional SSI/MSI logic with significant chip-count reduction.

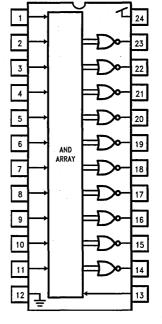

Programmable logic devices provide convenient solutions for a wide variety of application-specific functions, including random logic, custom decoders, state machines, etc. By programming fusible links to configure AND/OR gate connections, the system designer can implement custom logic as convenient sum-of-products Boolean functions. System prototyping and design iterations can be performed quickly using these off-the-shelf products. A large variety of programming units and software makes design development and functional testing of PAL devices quick and easy. The Small PAL logic array has between 10 and 16 complementary input pairs and up to 8 combinatorial outputs generated by a single programmable AND-gate array with fixed OR-gate connections. The Small PAL family offers a variety of input/output combinations as shown in the Device Types table below. Security fuses can be programmed to prevent direct copying of proprietary logic patterns.

#### Features

- As fast as 25 ns maximum propagation delay

- User-programmable replacement for TTL logic

- Large variety of JEDEC-compatible programming equipment available

- Fully supported by National PLAN™ development software

- Security fuse prevents direct copying of logic patterns

# **Device Types**

| Device<br>Type  | Dedicated<br>Inputs | Combinatorial<br>Outputs |

|-----------------|---------------------|--------------------------|

| PAL10H8/PAL10L8 | 10                  | 8                        |

| PAL12H6/PAL12L6 | 12                  | 6                        |

| PAL14H4/PAL14L4 | 14                  | 4                        |

| PAL16H2/PAL16L2 | 16                  | 2                        |

| PAL16C1         | 16                  | 1 Pair                   |

## **Speed/Power Versions**

| Series Example |           | Example Commercial |       |                 | Military |  |  |

|----------------|-----------|--------------------|-------|-----------------|----------|--|--|

|                |           | t <sub>PD</sub>    | Icc   | t <sub>PD</sub> | Icc      |  |  |

| Standard       | PAL10H8   | 35 ns              | 90 mA | 45 ns           | 90 mA    |  |  |

| A              | PAL10H8A  | 25 ns*             | 90 mA | 30 ns*          | 90 mA    |  |  |

| A2             | PAL10H8A2 | 35 ns*             | 45 mA | 45 ns           | 45 mA    |  |  |

\*Except PAL16C1A t\_{PD} = 30 ns Commerciat, 35 ns Military. PAL16C1A2 t\_{PD} = 40 ns Commercial.

#### Block Diagram—PAL10H8

#### Standard Series (PAL10H8, PAL12H6, PAL14H4, PAL16H2, PAL10L8, PAL12L6, PAL14L4, PAL16L2, PAL16C1)

#### Absolute Maximum Ratings (Note 1)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/Distributors for availability and specifications.

| Supply Voltage (V <sub>CC</sub> ) (Note 2) | -0.5 to +7.0V       |

|--------------------------------------------|---------------------|

| Input Voltage (Notes 2 and 3)              | -1.5 to +5.5V       |

| Off-State Output Voltage (Note 2)          | -1.5 to +5.5V       |

| Input Current (Note 2)                     | -30.0 mA to +5.0 mA |

| Output Current (IOL) |

|----------------------|

| Storage Temperature  |

| Ambient Temperature  |

| with Power Applied   |

| Junction Temperature |

+ 100 mA --65°C to + 150°C

#### **Recommended Operating Conditions**

| Symbol          | Parameter                      | Military |     |     |      | Units |      |       |

|-----------------|--------------------------------|----------|-----|-----|------|-------|------|-------|

|                 |                                | Min      | Nom | Max | Min  | Nom   | Max  | Units |

| V <sub>CC</sub> | Supply Voltage                 | 4.5      | 5   | 5.5 | 4.75 | .5    | 5.25 | v     |

| T <sub>A</sub>  | Operating Free-Air Temperature | -55      |     |     | 0    |       | 75   | °C    |

| т <sub>с</sub>  | Operating Care Temperature     |          |     | 125 |      |       |      | °C    |

#### Electrical Characteristics Over Recommended Operating Conditions (Note 4)

| Symbol          | Parameter                                | Test Conditions                   |                            |     | Min     | Тур   | Max   | Units |

|-----------------|------------------------------------------|-----------------------------------|----------------------------|-----|---------|-------|-------|-------|

| V <sub>IL</sub> | Low Level Input Voltage (Note 5)         |                                   |                            |     |         |       | 0.8   | v     |

| ViH             | High Level Input Voltage (Note 5)        |                                   |                            |     | 2       |       |       | v     |

| VIC             | Input Clamp Voltage                      | $V_{CC} = Min, I = -18 mA$        |                            |     |         | -0.8  | - 1.5 | v     |

| ۱ <sub>IL</sub> | Low Level Input Current                  | $V_{CC} = Max, V_I = 0.4V$        |                            |     |         | -0.02 | -0.25 | mA    |

| l <sub>IH</sub> | High Level Input Current                 | $V_{CC} = Max, V_I = 2.4V$        |                            |     |         |       | 25    | μA    |

| 4               | Maximum Input Current                    | $V_{CC} = Max, V_{I} = 5.5V$      |                            |     |         |       | 1     | mA    |

| VOL             | Low Level Output Voltage                 | V <sub>CC</sub> = Min             | $l_{OL} = 8 \text{ mA}$    |     |         | 0.3   | 0.5   | v     |

| VOH             | High Level Output Voltage                | V <sub>CC</sub> = Min             | $I_{OH} = -2 \text{ mA}$   | MIL | 2.4     | 2.9   |       | v     |

|                 |                                          |                                   | $I_{OH} = -3.2  \text{mA}$ | СОМ | 2.4 2.9 |       |       |       |

| los             | Output Short-Circuit Current<br>(Note 6) | $V_{\rm CC} = 5V, V_{\rm O} = 0V$ |                            |     | -30     | -70   | - 130 | mA    |

| Icc             | Supply Current                           | V <sub>CC</sub> = Max, O          | utputs Open                |     |         | 55    | 90    | mA    |

Note 1: Absolute maximum ratings are those values beyond which the device may be permanently damaged. Proper operation is not guaranteed outside the specified recommended operating conditions.

Note 2: Some device pins may be raised above these limits during programming operations according to the applicable specification.

Note 3: It is recommended that precautions be taken to minimize electrostatic discharge when handling and testing this product. Pins 1 and 11 are connected directly to the security fuses, and the security fuses may be damaged preventing subsequent programming and verification operations.

Note 4: All typical values are for V<sub>CC</sub> = 5.0V and T<sub>A</sub> = 25°C.

Note 5: These are absolute voltages with respect to the ground pin on the device and include all overshoots due to system and/or tester noise. Do not attempt to test these values without suitable equipment.

Note 6: To avoid Invalid readings in other parameter tests, it is preferable to conduct the I<sub>OS</sub> test last. To minimize internal heating, only one output should be shorted at a time with a maximum duration of 1.0 second each. Prolonged shorting of a high output may raise the chip temperature above normal and permanent damage may result.

# Standard Series (PAL10H8, PAL12H6, PAL14H4, PAL16H2, PAL10L8, PAL12L6, PAL14L4, PAL16L2, PAL16C1) (Continued)

| Symbol          | Parameter         | Test Conditions          |      | Military                               |                 |                                 | Commerci                                | al           | Unit                               |

|-----------------|-------------------|--------------------------|------|----------------------------------------|-----------------|---------------------------------|-----------------------------------------|--------------|------------------------------------|

|                 |                   |                          | Min  | Тур                                    | Max             | Min                             | Тур                                     | Max          |                                    |

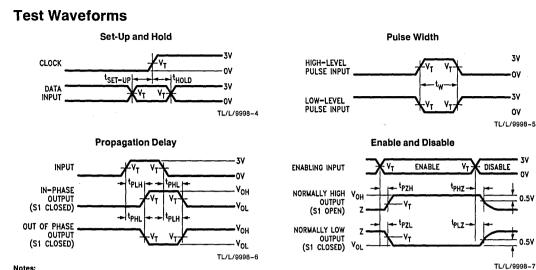

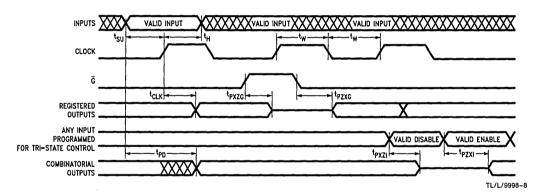

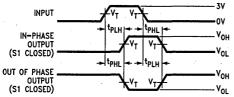

| PD              | Input to Output   | C <sub>L</sub> = 50 pF   |      | 25                                     | 45              |                                 | 25                                      | 35           | ns                                 |

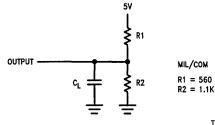

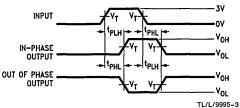

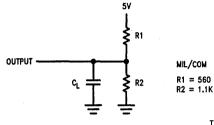

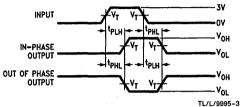

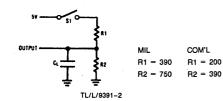

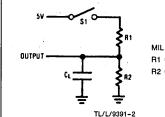

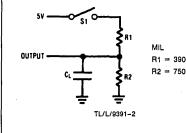

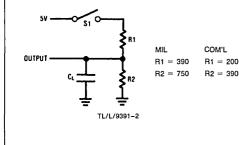

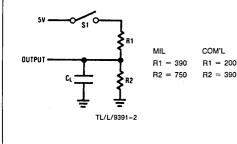

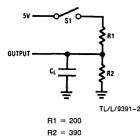

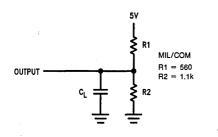

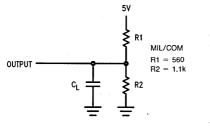

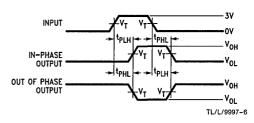

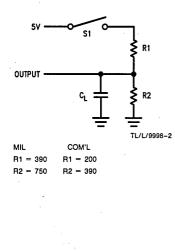

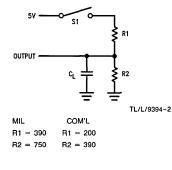

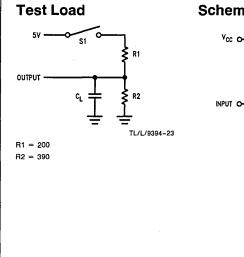

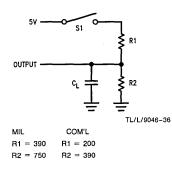

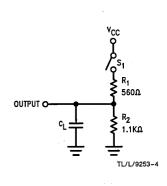

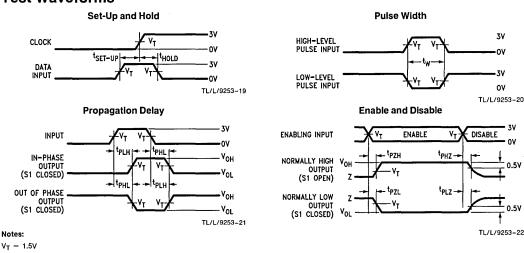

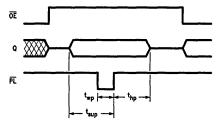

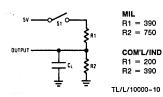

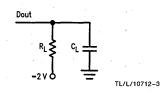

| <b>Fest L</b> o | oad               |                          |      | Test '                                 | Wavef           | orm                             |                                         |              |                                    |

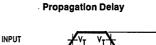

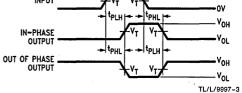

|                 | 57                |                          |      |                                        |                 | Propagat                        | ion Delav                               |              |                                    |

|                 | ļ                 |                          |      |                                        | INPUT           |                                 |                                         |              | 3V                                 |

|                 | _<br>۲            | R1                       |      |                                        |                 | t,                              | T. TT<br>LH}←→  <sup>t</sup> PHI        | . +          | 0V                                 |

| ОЛТРОТ —        |                   | MIL/COM                  |      |                                        |                 |                                 |                                         | ¥            | V <sub>он</sub>                    |

|                 | ◦∟ ┿╴ ≱ਾ          | R2 R1 = 560<br>R2 = 1.1K |      | OUT OF                                 |                 | tp                              | <sub>⊣L</sub>   ← →   t <sub>PL</sub> , | -            |                                    |

|                 | <u> </u>          |                          |      | (                                      | OUTPUT          |                                 | $\frac{1}{\sqrt{1-\lambda^2}}$          | <u>/</u>     | ∨ <sub>он</sub><br>∨ <sub>о∟</sub> |

|                 |                   | TL/L/99                  | 95-2 | Natas                                  |                 |                                 |                                         | т            | L/L/9995-                          |

|                 |                   |                          |      | Notes:<br>V <sub>T</sub> = 1.5V        | •               |                                 |                                         |              |                                    |

|                 |                   |                          |      |                                        |                 | g capacitance<br>the phase rela |                                         | tween inputs | and outpu                          |

|                 |                   |                          |      |                                        | chosen arbitr   |                                 | ·                                       |              |                                    |

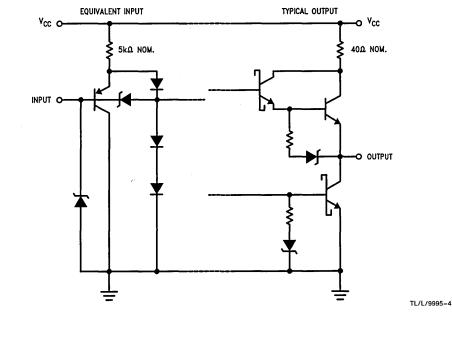

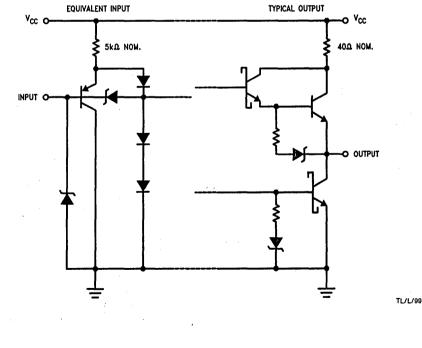

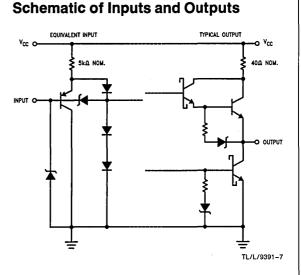

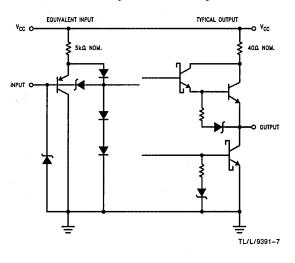

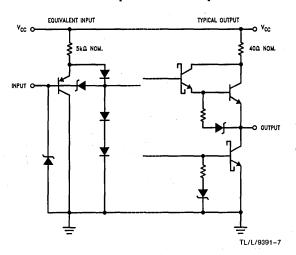

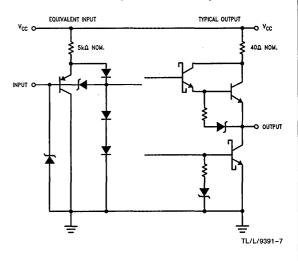

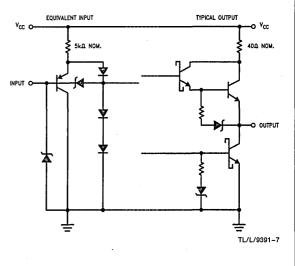

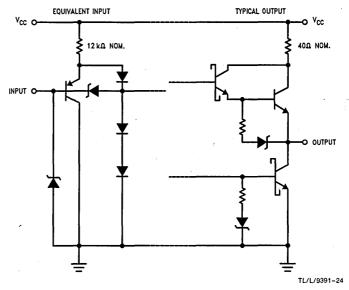

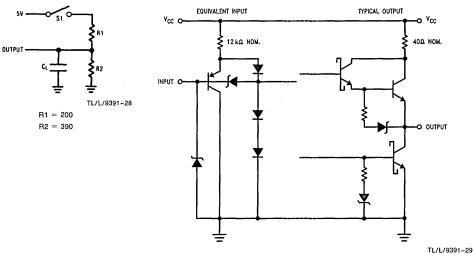

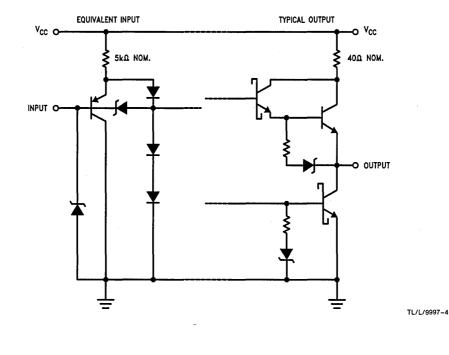

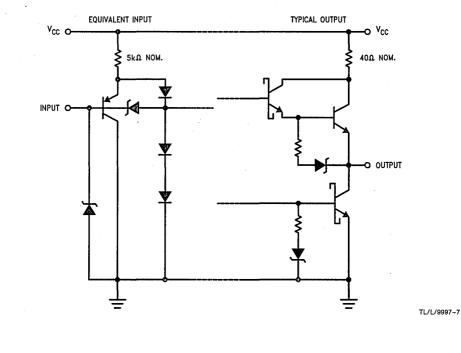

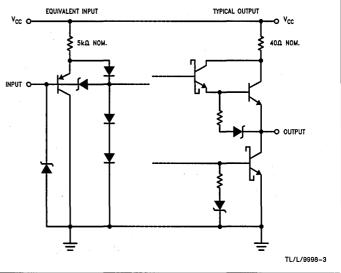

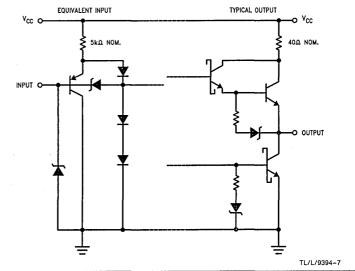

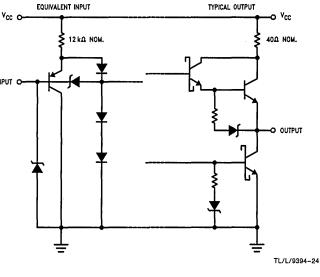

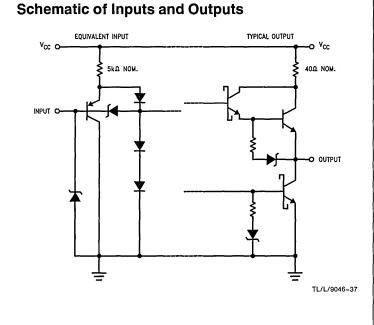

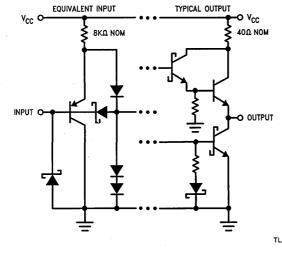

| Schem           | atic of Input     | s and Outputs            |      |                                        |                 |                                 |                                         |              |                                    |

|                 | V <sub>CC</sub> O | EQUIVALENT INPUT         |      |                                        | TYPICAL         | . OUTPUT                        | –o v <sub>cc</sub>                      |              |                                    |

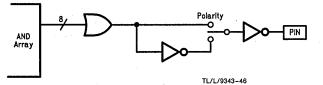

|                 | ·cc 0             |                          |      | ······································ |                 | Ī                               | - <b>O</b> <sup>v</sup> cc              |              |                                    |