Section 3

Rigid Disk Data

Controller

3

# **Section 3 Contents**

| DP8466A Disk Data Controller                                                     | 3-3  |

|----------------------------------------------------------------------------------|------|

| AN-500 Designing an ESDI Disk Controller System with the National DP8466A        | 3-59 |

| AN-501 Interfacing National's DP8466A to the SMD Storage Module Device Interface |      |

| Standard (Hard Sectored Drive)                                                   | 3-74 |

# National Semiconductor

# **DP8466A Disk Data Controller**

## **General Description**

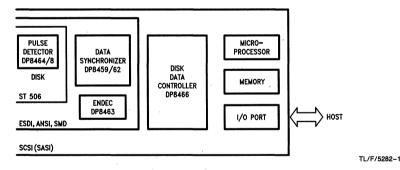

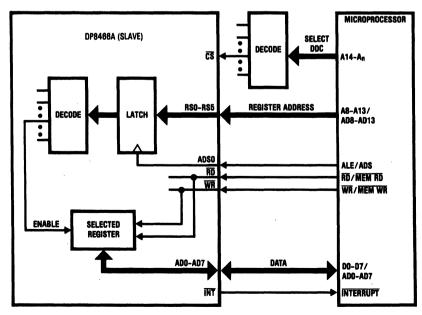

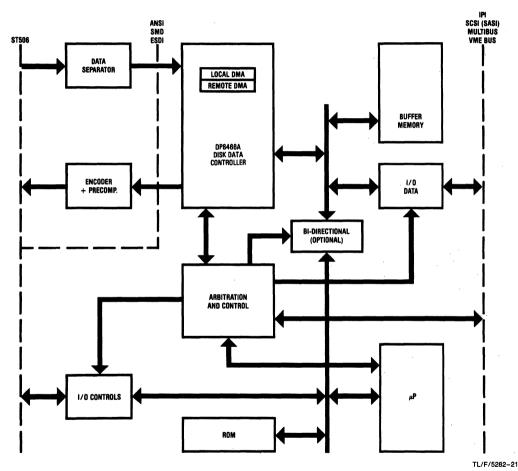

The DP8466A Disk Data Controller (DDC) is an intelligent peripheral which interfaces Winchester or Floppy disk drives to microprocessor based systems. It transfers data between a buffer memory or host system and the serial bit data stream with disk rates up to 25M-bits per second. High speed system data transfer is possible with full on-chip DMA control of buffer or main memory. The 16-bit system I/O interface allows use with any popular 8-bit, 16-bit or 32-bit microprocessor. Programmable track format enables reconfiguration of the DDC for different drive types in a multiple drive environment. Using other National DP8460 series disk data path chips, the DP8466A conforms to ST506, SMD and ESDI standard drive interfaces, as well as to intelligent standard interfaces such as SCSI (SASI) and IPI.

The DP8466A is available in three performance versions DP8466AN-12, DP8466AN-20 and DP8466AN-25.

| Part<br>Number | Max Disk<br>Data Rate | Max DMA<br>Transfer Rate |

|----------------|-----------------------|--------------------------|

| DP8466AN-25    | 25 Mbit/sec           | 10 Mbyte/sec             |

| DP8466AN-20    | 20 Mbit/sec           | 8 Mbyte/sec              |

| DP8466AN-12    | 12 Mbit/sec           | 6 Mbyte/sec              |

#### **Features**

- Easily conforms to any standard drive interface

- Compatible with floppy, hard and optical disk drives

- Compatible with 8, 16 or 32-bit microprocessor systems

- Programmable disk format

- Sector lengths up to 64k bytes, with up to 255 sectors per track

- Programmable 32 or 48-bit ECC polynomial

- Internal ECC correction in less than a sector time

- Disk data rate to 25M bits per second

- Multiple sector transfer capability

- 32 byte internal FIFO data buffer with interleavable burst capability

- 8 or 16-bit wide data transfers

- Single 32-bit or dual 16-bit DMA channel addresses

- Up to 10M bytes per second DMA transfer rate

- +5V supply, 48 pin DIP, microCMOS process

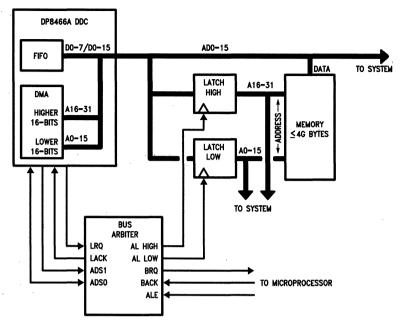

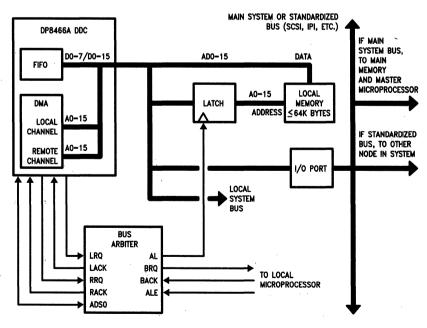

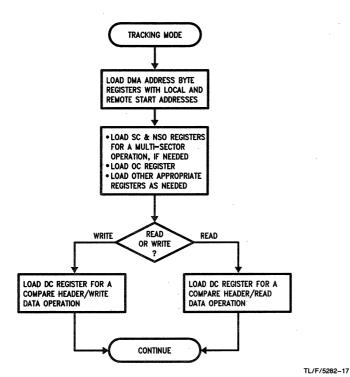

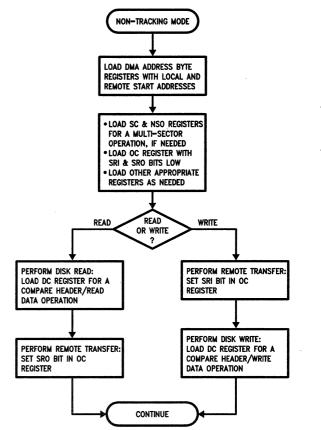

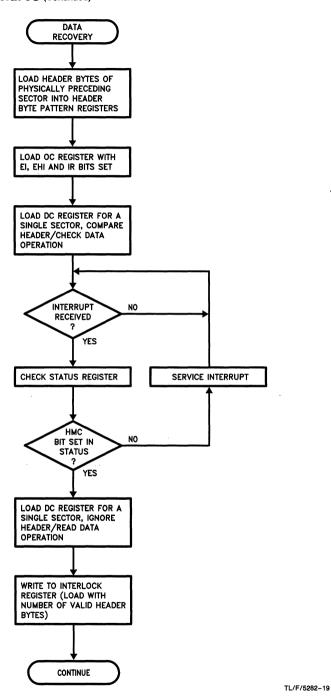

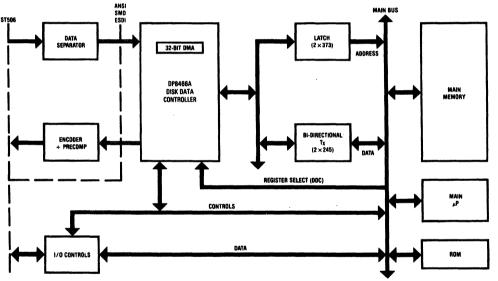

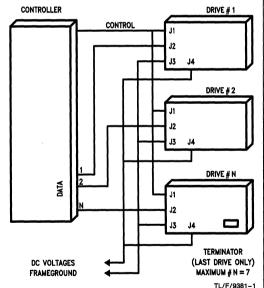

FIGURE 1. Typical System Configuration

#### **Table of Contents**

- 1.0 INTRODUCTION

- 2.0 PIN DESCRIPTION

- 3.0 INTERNAL REGISTERS OF THE DDC

- 4.0 DDC OPERATION

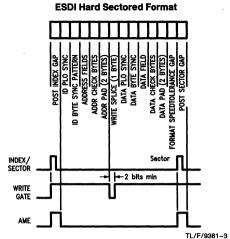

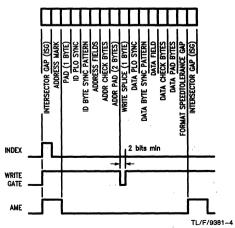

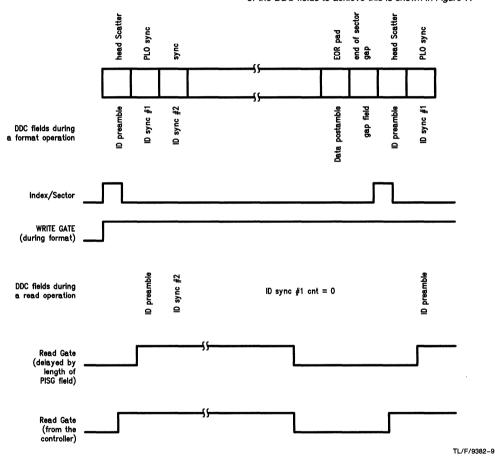

- 5.0 FORMAT, READ AND WRITE

- 6.0 CRC/ECC

- 7.0 DATA TRANSFERS

- **8.0 INTERRUPTS**

- 9.0 ADDITIONAL FEATURES

- 10.0 SYSTEM CONFIGURATIONS

- 11.0 ABSOLUTE MAXIMUM RATINGS

- 12.0 DC ELECTRICAL CHARACTERISTICS

- 13.0 AC ELECTRICAL CHARACTERISTICS AND TIMING DIAGRAMS

- 14.0 AC TEST CONDITIONS

- 15.0 MISCELLANEOUS TIMING INFORMATION

- **16.0 FUNCTIONAL STATUS**

- 17.0 HELPFUL HINTS

- 18.0 APPENDIX

## 1.0 Introduction

National's DP8466A Disk Data Controller (DDC) chip is designed to concentrate only on the data aspects of a disk system, leaving the control signals to either a low cost single chip controller or an I/O port from a microprocessor. For this reason, the DDC will work with any standard drive interface

The DP8466A is an advanced VLSI chip, fabricated in National's latest 2  $\mu$  CMOS technology, that allows for operation with disk data rates from the slowest floppy to the fast Winchester and Optical data rates of 25 megabits per second.

The CMOS design significantly helps the system designer because of reduced power consumption. The chip typically consumes 100 mW.

The DDC is designed for maximum programmability that not only allows the user to select any drive type he wishes, but also allows for different types of drives to be used on the same system. The chip contains 64 registers that can be loaded at any time by a microprocessor connected to the chip's bus. These registers determine the number of bytes in each field of the format, and the byte pattern that each of these fields will repeat. The number of data bytes per sector is selectable from 1 byte to 64k bytes. Finally, both the header field and the data field can each be appended with either a Cyclic Redundancy Check (CRC) field (the 16-bit code used on floppies) or a programmable Error Check and Correct (ECC) field.

The DDC allows the user to load in any 32 or 48-bit ECC polynomial from the microprocessor along with the format

parameters. Once an error has been detected, the microprocessor decides whether to re-read the sector during the next revolution of the disk, or to attempt a correction. The DDC can correct errors in a time shorter than that required to read the next sector.

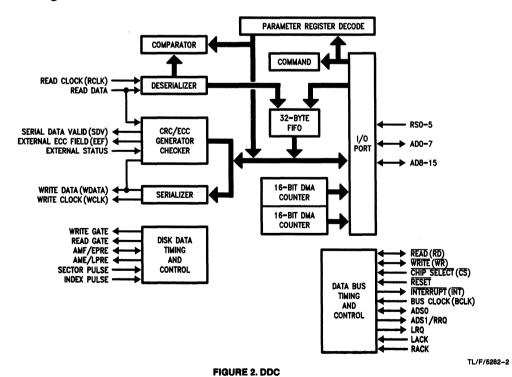

Key blocks in the DDC include a 32-byte FIFO and two 16bit DMA channels that give the chip a 10 megabyte per second memory transfer capability. This high system data throughout is needed for the high speed drives now becomming available. The small FIFO allows for bursts of data to take place on the bus, thereby leaving the bus free for useful periods of time. The threshold for FIFO data storage is selectable to allow for some degree of system latency. The DDC allows for bursts of 2, 8, 16 or 24 bytes of data to be transferred between the FIFO and memory. The width of the data bus is selectable for either 8 or 16-bit transfers. The system designer selects the threshold so that when the FIFO contains the selected amount of data, the DDC will issue a request. The CPU can continue its operation and then stop to acknowledge the DDC, which then bursts the data between FIFO and memory, before the FIFO has time to overflow or underflow. With a 10 megabit per second disk data rate and a 10 megabyte per second memory transfer cycle, the bus will only be occupied for one-eighth of the time transferring data between FIFO and memory. This leaves the bus free for microprocessor usage for over 80% of the time.

# **Block Diagram**

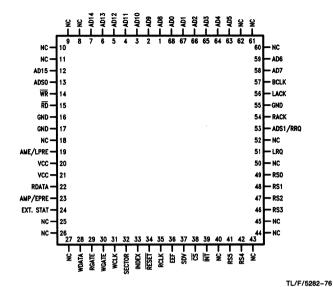

# **Connection Diagrams**

\*This pin must be grounded if not used.

**Top View**

Order Number DP8466AN See NS Package Number N48A

Order Number DP8466AV See NS Package Number V68A

FIGURE 3

# 2.0 Pin Descriptions

#### 2.1 BUS INTERFACE PINS

| Symbol | DIP Pin No. | PCC Pin No. | Туре | Function                                                                                                                                                                                                                                                                                                                                                              |  |

|--------|-------------|-------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| CS     | 28          | 38          | ı    | CHIP SELECT: Sets DDC as a standard I/O port for reading and writing registers. Configures RD and WR pins as inputs when DMA is inactive. This pin is ignored if on-chip DMA is enabled and performing a transfer.                                                                                                                                                    |  |

| INT    | 29          | 39          | 0    | INTERRUPT: An interrupt can be generated on any error, or after completion of a command, a correction cycle or any header operation.                                                                                                                                                                                                                                  |  |

| RESET  | 24          | 34          | ı    | RESET: Clears FIFO, Status and Error registers. Halts DMA immediately Halts disk read and write immediately. Does not affect parameter and most count and command registers. On power-up, must be held low for least 32 RCLK cycles and 4 BCLK cycles. Note that both RCLK and BCl must be active for the reset cycle to complete.                                    |  |

| RD     | 11          | 15          | 1/0  | READ:  MICROPROCESSOR ACCESS MODE, with CS pin low and DMA inactive (RACK AND LACK low): Places data from FIFO or register as selected by pins RS0-5 onto the AD0-7 bus.  SLAVE MODE, with LACK pin high: Places data from FIFO onto the AD0-7/AD0-15 bus.  MASTER MODE: When DMA is active, RD pin enables data from the addressed device onto the address/data bus. |  |

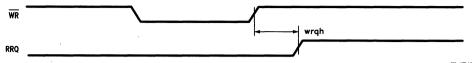

| WR     | 10          | 14          | 1/0  | WRITE:  MICROPROCESSOR ACCESS MODE, with CS low and DMA inactive (RACK and LACK low): Latches data from AD0-7 bus to internal registers selected by RS0-5.  SLAVE MODE, with LACK pin high: Latches data from AD0-7/AD0-15 bus to FIFO.  MASTER MODE: When DMA is active, WR pin enables data from the address/data bus to the addressed device.                      |  |

# 2.0 Pin Descriptions (Continued)

# 2.1 BUS INTERFACE PINS (Continued)

| Symbol   | DIP Pin No. | PCC Pin No.     | Туре | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|----------|-------------|-----------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

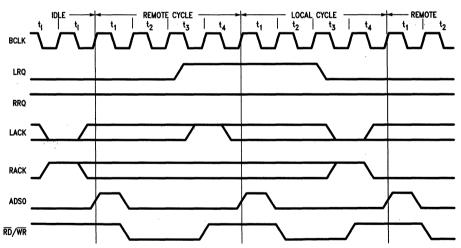

| BCLK     | 40          | 57              | I    | BUS CLOCK: Used as a reference clock when DDC is bus master. Used only during reset and DMA operations. Maximum ratio of RCLK/BCLK is 4 for Word Mode, and 2 for Byte Mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| RACK     | 38          | 54              | ł    | REMOTE DMA ACKNOWLEDGE: System input granting use of the bus for a remote DMA bus cycle. If RACK is de-asserted during a transfer, the current transfer cycle will complete.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| LACK     | 39          | 56              | I    | LOCAL DMA ACKNOWLEDGE: System input granting use of bus for a local DMA bus cycle. If LACK is deasserted during a transfer, the current transfer cycle will complete. LACK has priority over RACK.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| RS0-5    | 35-30       | 41, 42<br>46-49 | l    | <b>REGISTER SELECT:</b> Used as address inputs to select internal registers when $\overline{\text{CS}}$ pin is low.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| AD0-7    | 48-41       | 58, 59<br>63-68 | 1/0  | <ul> <li>ADDRESS/DATA 0-7: These pins float if  on = 1 and DMA is inactive.</li> <li>STANDARD I/O PORT, With DMA inactive and  on incident incident</li></ul> |

| LRQ      | 36          | 51              | 0    | LOCAL DMA REQUEST: Requests are automatically generated when the FIFO needs to have data transferred.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| AD8-15   | 1-8         | 1-7<br>12       | 1/0  | ADDRESS/DATA 8-15:  STANDARD I/O PORT, with DMA inactive and CS pin low: These pins are driven high.  SLAVE MODE, with external DMA active and LACK pin high: D8-15 are transferred between FIFO and memory.  MASTER MODE, with internal DMA active and LACK pin high: A24-31, A8-15 and D8-15 are transferred, depending on DMA mode and bus phase.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| ADS0     | 9           | 13              | 1/0  | ADDRESS STROBE 0:  INPUT with DMA inactive: ADS0 latches RS0-5 inputs when low. When high, data present on RS0-5 will flow through to internal register decoder.  OUTPUT: ADS0 latches low order address bits (A0-15) to external memory during DMA transfers.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| ADS1/RRQ | 37          | 53              | 0    | ADDRESS STROBE 1/REMOTE REQUEST: In 32-bit DMA Mode, ADS1 latches high order address bits (A16–31) to external memory. For remote DMA modes, RRQ pin is active high when SRI or SRO bits in the OC register are set in non-tracking mode, or during a remote transfer in tracking mode. (See RT register description in DMA REGISTERS Section.)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

# 2.2 DISK INTERFACE PINS

| Symbol | DIP Pin No. | PCC Pin No. | Туре | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

|--------|-------------|-------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

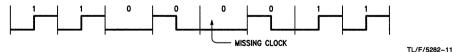

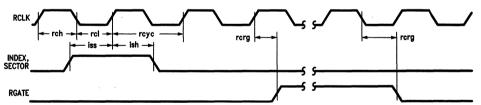

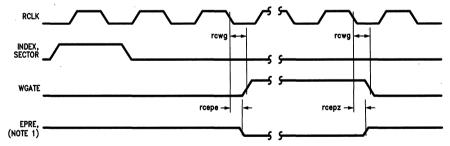

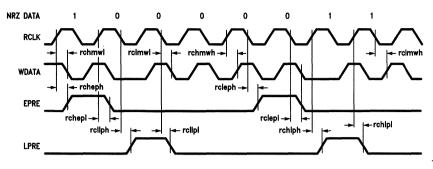

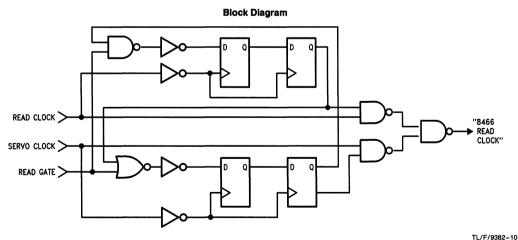

| RCLK   | 25          | 35          |      | READ CLOCK: Disk data rate clock. When RGATE is high, RCLK input will be the recovered/separated clock from the recorded data and is used to strobe data into the DDC. When RGATE is low, this input should become the referenced clock which will be delayed and is used as WCLK to strobe data to the drive. The transition between the recovered/separated clock and reference clock must be made with no short pulses. Short pulses are pulses that are less than the specified minimum RCLK pulse widths which are specified in the AC timing section as rcl and rch. In the event of any short pulses on RCLK or if RCLK is inactive for greater than 10 µs, then the DDC could go into an indeterminant state. If this happens, then the DDC needs to be reset and the format parameters must be updated to ensure normal operation. Maximum ratio of RCLK/BCLK is 4 for word mode, and 2 for byte mode. |  |

# 2.0 Pin Descriptions (Continued)

# 2.2 DISK INTERFACE PINS (Continued)

| Symbol                 | DIP Pin No. | PCC Pin No.      | Туре | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

|------------------------|-------------|------------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

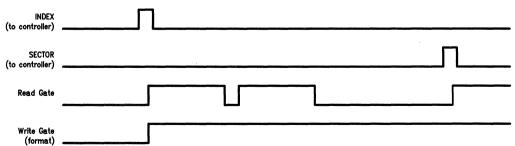

| RGATE                  | 19          | 29               | 0    | READ GATE: Set active high during any disk read operation. This pin commands data separator to acquire lock. Enables RDATA input pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

| RDATA                  | 15          | 22               | 1    | READ DATA: Accepts NRZ disk data from the data separator/decoder.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

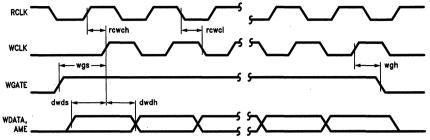

| WCLK                   | 21          | 31               | 0    | WRITE CLOCK: Used when NRZ data is on WDATA pin. Also active when MFM data is used, but normally not utilized. WCLK frequency follows RCLK pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

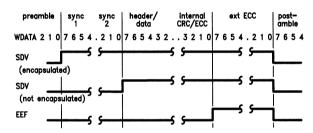

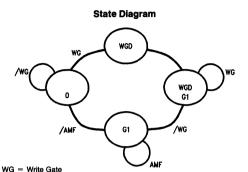

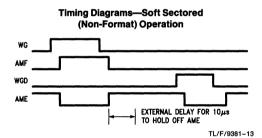

| WGATE                  | 20          | 30               | 0    | WRITE GATE: When writing data onto a disk, WGATE is asserted high with the first bit of data and deasserted low after the last bit of data. WGATE is also de-asserted on reset or on detection of an error.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

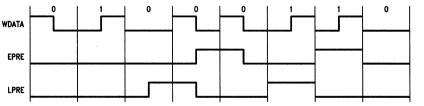

| WDATA                  | 18          | 28               | 0    | WRITE DATA: During any write operation, MFM or NRZ encoded data is output to disk, dependent upon MFM bit status in the DF register. This pin is inactive low when WGATE is low.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

| AMF/EPRE               | 16          | 23               | 1/0  | ADDRESS MARK FOUND/EARLY PRECOMPENSATION: Address mark input is monitored if the HSS bit in the DF register is low (for soft sectoring). If the MFM bit in the DF register and the EP bit in the OC register are both set, then this pin becomes the EPRE control. If both functions are used, WGATE pin determines the function as follows:  • WGATE asserted: EPRE output.  • WGATE de-asserted: AMF input.                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

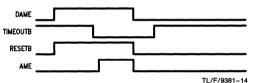

| AME/LPRE               | 13          | 19               | 0    | ADDRESS MARK ENABLE/LATE PRECOMPENSATION: If the MFM in the DF register is low, AME will indicate that an address mark byte(s) being output on WDATA pin. If the MFM bit in the DF register and the E bit in the OC register are both set, LPRE control is output (if internal MF encoding is used).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

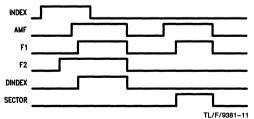

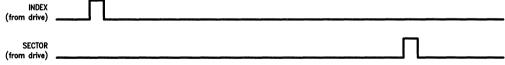

| SECTOR                 | 22          | 32               |      | SECTOR PULSE: In hard sectored drives, this signal comes from the start of a sector. In a soft sectored drive this pin must be tied low.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

| INDEX                  | 23          | 33               | l l  | INDEX PULSE: This signal comes from the disk drive, indicating the start of a track.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

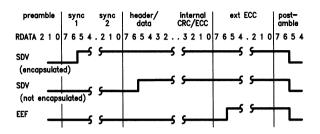

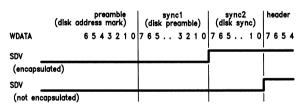

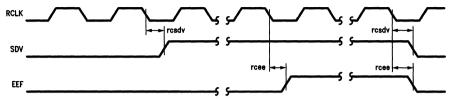

| SDV                    | 27          | 37               | 0    | SERIAL DATA VALID: Asserted when the DDC is either issuing or receiving header field, internal header CRC/ECC, data field, or internal data CRC/ECC information. Mainly used for external ECC and diagnostics.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| EEF                    | 26          | 36               | 0    | EXTERNAL ECC FIELD: Only used if the External ECC Byte Count register(s) are non-zero. Asserted when external ECC check bits are being generated (WGATE high) and checked (RGATE high).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

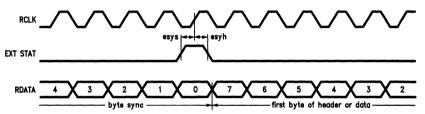

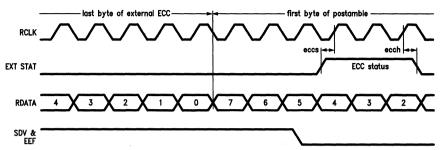

| EXT STAT               | 17          | 24               | I    | EXTERNAL STATUS: IMPORTANT NOTE: This pin MUST be tied low if it is not to be used. This pin has three functions:  1: If EEW bit in the RT register is set, the read and write strobes are extended for both remote and local transfers as long as this pin is high. This is the External Wait State function.  2: If the EEW bit in the RT register is low, this pin will accept a pulse granting valid byte alignment on the last bit of the synch byte before header or data bytes. This is an OR function with the internal synch detect.  3: External ECC Check. Only used if External ECC Byte Count register(s) are non-zero, and EEW bit in the RT register is low. After the last byte of external ECC, this pin will accept a pulse confirming that there has been no error. A CRC/ECC error will be flagged if this pulse is not received. |  |

| V <sub>CC</sub><br>GND | 14,<br>12   | 20, 21<br>16, 17 |      | POWER, GROUND: +5V DC is required. It is suggested that a decoupling capacitor be connected between these pins. It is essential to provide a path to ground for the GND pin with the lowest possible impedance. Otherwise any voltage spikes resulting from transient switching currents will be reflected in the logic levels of the output pins.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

# 3.0 Internal Registers of the DDC

The numerous registers within the DDC are presented below, grouped according to their function. A key is given as an aid for the use of each register. The key data is only suggested for common operation, and should not be considered as an absolute requirement. Following this listing is a description of each register, in the order of which they are listed below. The HA column at the left of this listing gives the Hex Address of each register.

#### KEY

- D May be updated when a different drive type is selected

- C May be updated before each command

- R May be read at any idle time

- F Used during formatting

- I Used during initialization

- NO Operation is not possible

#### COMMAND

| НΑ | Register                                     | Bits | Write | Read |

|----|----------------------------------------------|------|-------|------|

| 10 | Drive Command Register (DC)                  | 8    | C     | NO   |

| 11 | Operation Command Register (OC)              | 8    | C     | NO   |

| 35 | Disk Format Register (DF)                    | 8    | D     | NO   |

| 00 | Status Register (S)                          | 8    | NO    | R    |

| 01 | Error Register (E)                           | 8    | NO    | R    |

| 12 | Sector Counter (SC)                          | 8    | С     | R    |

| 13 | Number of Sector Operations<br>Counter (NSO) | 8    | С     | R    |

| 0F | Header Byte Count (HBC)/Interlock            | 3    | F     | R    |

| 36 | Header Diagnostic Readback (HDR)             | 8    | NO    | R    |

#### DMA

| HA | Register                      | Bits | Write | Read |

|----|-------------------------------|------|-------|------|

| 37 | DMA Sector Counter (DSC)      | 8    | Ю     | R    |

| 37 | Remote Transfer Register (RT) | 8    | ı     | NO   |

| 36 | Local Transfer Register (LT)  | 8    | 1     | NO   |

| 1A | Remote Data Byte Count (L)    | 8    | С     | R    |

| 1B | Remote Data Byte Count (H)    | 8    | С     | R    |

| 1C | DMA Address Byte 0            | 8    | С     | R    |

| 1D | DMA Address Byte 1            | 8    | С     | R    |

| 1E | DMA Address Byte 2            | 8    | С     | R    |

| 1F | DMA Address Byte 3            | 8    | С     | R    |

## FORMAT (See Note)

| HA | Register                             | Bits | Write | Read |

|----|--------------------------------------|------|-------|------|

| 21 | ID Preamble Byte Count               | 5    | D     | R    |

| 31 | ID Preamble Pattern                  | 8    | D     | R    |

| 22 | ID Synch #1 (AM) Byte Count          | 5    | D     | R    |

| 32 | ID Synch #1 (AM) Pattern             | 8    | D     | R    |

| 23 | ID Synch #2 Byte Count               | 5    | D     | R    |

| 33 | ID Synch #2 Pattern                  | 8    | D     | R    |

| 24 | Header Byte 0 Control Register (HC0) | 5    | D     | . R  |

| 14 | Header Byte 0 Pattern                | 8    | D     | R    |

| 25 | Header Byte 1 Control Register (HC1) | 5    | D     | R    |

| 15 | Header Byte 1 Pattern                | 8    | D     | R    |

#### FORMAT (Continued)

| НА | Register                             | Bits | Write | Read |

|----|--------------------------------------|------|-------|------|

| 26 | Header Byte 2 Control Register (HC2) | 5    | D     | R    |

| 16 | Header Byte 2 Pattern                | 8    | D     | R    |

| 27 | Header Byte 3 Control Register (HC3) | 5    | D     | R    |

| 17 | Header Byte 3 Pattern                | 8    | D     | R    |

| 28 | Header Byte 4 Control Register (HC4) | 5    | D     | R    |

| 18 | Header Byte 4 Pattern                | 8    | D     | R    |

| 29 | Header Byte 5 Control Register (HC5) | 5    | D     | R    |

| 19 | Header Byte 5 Pattern                | 8    | D     | R    |

| 2B | ID External ECC Byte Count           | 5    | D     | R    |

| 2C | ID Postamble Byte Count              | 5    | D     | R    |

| зС | ID Postamble Pattern                 | 8    | D     | R    |

| 2D | Data Preamble Byte Count             | 5    | D     | R    |

| 3D | Data Preamble Pattern                | 8    | D     | R    |

| 2E | Data Synch #1 (AM) Byte Count        | 5    | D     | R    |

| 3E | Data Synch #1 (AM) Pattern           | 8    | D     | R    |

| 2F | Data Synch #2 Byte Count             | 5    | D     | R    |

| 3F | Data Synch #2 Pattern                | 8    | D     | R    |

| зв | Data Format Pattern                  | 8    | F     | R    |

| 38 | Sector Byte Count L                  | 8    | D     | R    |

| 39 | Sector Byte Count H                  | 8    | D     | R    |

| 2A | Data External ECC Byte Count         | 5    | D     | R    |

| 20 | Data Postamble Byte Count            | 5    | D     | R    |

| 30 | Data Postamble Pattern               | 8    | D     | R    |

| 34 | Gap Byte Count                       | 8    | F     | R    |

| ЗА | Gap Pattern                          | 8    | F     | R    |

#### CRC/ECC

| НА | Register                        | Bits | Write | Read |

|----|---------------------------------|------|-------|------|

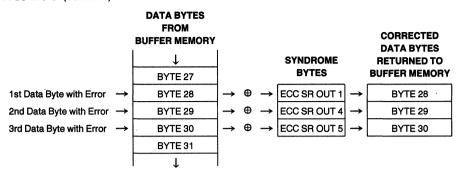

| 02 | ECC SR Out 0                    | 8    | NO    | R    |

| 03 | ECC SR Out 1                    | 8    | NO    | R    |

| 04 | ECC SR Out 2                    | 8    | NO    | R    |

| 05 | ECC SR Out 3                    | 8    | NO    | R    |

| 06 | ECC SR Out 4                    | 8    | NO    | R    |

| 07 | ECC SR Out 5                    | 8    | NO    | R    |

| 02 | Polynomial Preset Byte 0 (PPB0) | 8    | D     | NO   |

| 03 | Polynomial Preset Byte 1 (PPB1) | 8    | D     | NO   |

| 04 | Polynomial Preset Byte 2 (PPB2) | 8    | D     | NO   |

| 05 | Polynomial Preset Byte 3 (PPB3) | 8    | D     | NO   |

| 06 | Polynomial Preset Byte 4 (PPB4) | 8    | D     | NO   |

| 07 | Polynomial Preset Byte 5 (PPB5) | 8    | D     | NO   |

| 08 | Polynomial Tap Byte 0 (PTB0)    | 8    | D     | NO   |

| 09 | Polynomial Tap Byte 1 (PTB1)    | 8    | D     | NO   |

| 0A | Polynomial Tap Byte 2 (PTB2)    | 8    | D     | NO   |

| 0В | Polynomial Tap Byte 3 (PTB3)    | 8    | D     | NO   |

| 0C | Polynomial Tap Byte 4 (PTB4)    | 8    | D     | NO   |

| 0D | Polynomial Tap Byte 5 (PTB5)    | 8    | D     | NO   |

| 0E | ECC/CRC Control (EC)            | 8    | D     | NO   |

| 08 | Data Byte Count L               | 8    | NO    | R    |

| 09 | Data Byte Count H               | 8    | NO    | R    |

# 3.0 Internal Registers of the DDC (Continued)

#### **DUAL-PURPOSE REGISTERS**

Some of the above listed registers have dual functions depending on whether they are being written to or read from. These registers are repeated below to help clarify their operation.

| НА | Register                         | Bits | Write | Read |

|----|----------------------------------|------|-------|------|

| 02 | ECC SR Out 0                     | 8    | NO    | R    |

| 02 | Polynomial Preset Byte 0 (PPB0)  | 8    | D     | NO   |

| 03 | ECC SR Out 1                     | 8    | 8     | R    |

| 03 | Polynomial Preset Byte 1 (PPB1)  | 8    | ם     | NO   |

| 04 | ECC SR Out 2                     | 8    | NO    | R    |

| 04 | Polynomial Preset Byte 2 (PPB2)  | 8    | ם     | NO   |

| 05 | ECC SR Out 3                     | 8    | NO    | R    |

| 05 | Polynomial Preset Byte 3 (PPB3)  | 8    | ۵     | NO   |

| 06 | ECC SR Out 4                     | 8    | NO    | R    |

| 06 | Polynomial Preset Byte 4 (PPB4)  | 8    | ם     | NO   |

| 07 | ECC SR Out 5                     | 8    | 8     | R    |

| 07 | Polynomial Preset Byte 5 (PPB5)  | 8    | ם     | NO   |

| 08 | Polynomial Tap Byte 0 (PTB0)     | 8    | D     | NO   |

| 08 | Data Byte Count (0)              | 8    | 9     | R    |

| 09 | Polynomial Tap Byte 1 (PTB1)     | 8    | ۵     | NO   |

| 09 | Data Byte Count (1)              | 8    | NO    | R    |

| 36 | Header Diagnostic Readback (HDR) | 8    | 9     | R    |

| 36 | Local Transfer Register (LT)     | 8    | 1     | NO   |

| 37 | DMA Sector Counter (DSC)         | 8    | Ю     | R    |

| 37 | Remote Transfer Register (RT)    | 8    | ı     | NO   |

Format Note: It is recommended that the Format Registers be reloaded after the following events:

- 1. A hardware or software reset of the chip

- 2. A Sector Not Found error

- 3. A Sector Overrun error

- 4. A Data Sync Error

#### 3.1 COMMAND REGISTERS

#### DRIVE COMMAND (DC) Hex Address (10) Write Only

The locations within this register, when written to, initiate disk commands and chip functions. For a disk operation, after the DDC has been configured, this register is loaded to initiate command execution.

Loading the DC register constitutes the initiation of a disk operation and will hence generate an operation complete interrupt.

| DO2 | DO1 | H02 | H01 | FMT | MSO | SAIS | RED |

|-----|-----|-----|-----|-----|-----|------|-----|

| 7   | 6   | 5   | 4   | 3   | 2   | 1    | 0   |

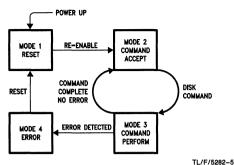

#### **RED: Re-enable DDC**

A 1 should be written into this location during the power up initialization process (see POWER UP AND INITIALIZATION Section), or after an error has been encountered in order to re-enable the DDC to accept commands. (NOTE: If the RES bit in the OC register has been set, a 0 should be written to that location before this operation is performed.) If no error has been encountered, and a command is being issued, a zero should be written to this bit. The Re-enable is an operation by itself and hence an interrupt will be generated on completion of the operation.

#### SAIS: Start at Index or Sector

- Operation begins only upon receipt of an index pulse.

- Operation begins on either an index pulse or sector pulse for hard sector drives or immediately for soft sector drives.

#### MSO: Multi-sector Operation

- 0 Single-sector operation.

- Multi-sector operation using NSO register.

#### **FMT: Format Mode**

- 0 No Format Operation.

- When set, along with other DC register bits, will initiate disk formatting upon receipt of an index pulse.

#### HO1, 2: Header Operation Bits:

#### H<sub>02</sub> H<sub>01</sub>

- 0 0 IGNORE HEADER: associated data transfer operation will take place with any valid sector encountered.

- 0 1 COMPARE HEADER: Normal mode used to find a specific sector. The Header Pattern registers contain the comparison pattern.

- 1 0 WRITE HEADER (Write ID): Normally used only during Format mode to write ID patterns to disk.

- 1 READ HEADER (Read ID): Reads header information from disk for diagnostic purposes.

#### DO1, 2: Data Operation Bits:

#### D02 D01

- 0 0 NO OPERATION: Can be used only with an Ignore Header command. No disk operation is performed with this combination, and it can be used along with the RED command to re-enable the DDC (see OPERATING MODES).

- 1 CHECK DATA: No DMA action and no data movement between disk and FIFO. CRC/ECC checks are calculated and interrupts, if enabled, are asserted on proper conditions. DFE bit in Error register will be set if a data CRC/ECC error occurs unless in Interlock Mode.

- 0 WRITE DATA: Initiates local DMA action to fill the FIFO. Writes data to disk with the proper pre and post appendages in the data field. FIFO is replenished by local DMA.

- 1 1 READ DATA: Data enters FIFO from disk, and local DMA transfer is initiated when the FIFO contains the number of bytes specified by the Burst Length in the LT register.

The following table shows a list of valid commands combining the H01, H02, D01, D02, FMT bits from the DC register and the FTF bit in the DF register. No other DC register combinations are allowed.

# 3.0 Internal Registers of the DDC (Continued)

#### Valid DDC Commands

| <b>D</b> 00 |     | C Regist |     |     | DF Reg | Operation                                           |

|-------------|-----|----------|-----|-----|--------|-----------------------------------------------------|

| D02         | D01 | H02      | H01 | FMT | FTF    |                                                     |

| 0           | 0   | 0        | 0   | 0   | X      | No Operation                                        |

| 0           | 1   | 0        | 1   | 0   | Х      | Check Data, Compare Header                          |

| 0           | 1   | 1        | 0   | 0   | Х      | Check Data, Write Header                            |

| 0           | 1   | 1        | 1   | 0   | х      | Check Data, Read Header                             |

| 1           | 0   | 0        | 0   | 0   | Х      | Write Data, Ignore Header                           |

| 1           | 0   | 0        | 1   | 0   | X      | Write Data, Compare Header, (normal write)          |

| 1           | 0   | 1        | 0   | 0   | Х      | Write Data, Write Header                            |

| 1           | 0   | 1        | 0   | 1   | 0      | Write Data, Write Header, Format with No FIFO Table |

| 1           | 0   | 1        | 0   | 1   | 1      | Write Data, Write Header, FIFO Table Format         |

| 1           | 1   | 0        | 0   | 0   | Х      | Read Data, Ignore Header, (recover data)            |

| 1           | 1   | 0        | 1   | 0   | Х      | Read Data, Compare Header, (normal read)            |

| 1           | 1   | 1        | 1   | 0   | Х      | Read Data, Read Header                              |

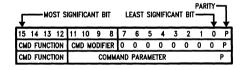

# OPERATION COMMAND (OC)

Hex Address (11)

#### Write Only

The fields within this register enable on-chip operations. In non-tracking mode, a remote DMA operation will be initiated by loading the SRO or SRI bits in this register.

| IR | SCC | EP | SRO | SRI | EHI | EI | RES |

|----|-----|----|-----|-----|-----|----|-----|

| 7  | 6   | 5  | 4   | 3   | 2   | 1  | 0   |

#### **RES: Reset DDC**

- O Clears a previously set RES function. Allows normal operation.

- DDC immediately enters a stand-by mode. The FIFO is reset, Status and Error registers are cleared and all operations in progress are stopped. DDC is placed in the Reset mode (see OPERATING MODES). RGATE and WGATE pins are de-asserted if active. All DMA counters are cleared. Format Parameter, DMA Address and ECC registers are unaffected.

#### El: Enable Interrupts

- 0 Disabled, INT pin remains inactive high.

- 1 Enables interrupts generated by the following:

- Correction cycle complete.

- · Error which sets ED bit in Status register.

- Command successfully completed (including independent remote DMA transfer).

#### EHI: Enable Header Interrupt

El bit must be set if this bit is set.

- 0 Disabled.

- Interrupt issued at start of ID postamble field when:

- Header matches in Compare Header operation.

- Header finished in Read, Write or Ignore Header operation.

#### SRI, SRO: Start Remote Input, Start Remote Output

These bits are only operational in non-tracking mode. The Remote Start Address and Remote Data Byte Count registers must be loaded first.

#### SRI SRO

- 0 0 Remote DMA operation unchanged.

- 0 1 START REMOTE OUTPUT: Asserts RRQ pin and RCB flag in Status register, to begin a remote DMA operation from memory to I/O Port.

- START REMOTE INPUT: Asserts RRQ pin and RCB flag in Status register, to begin a remote DMA operation from I/O Port to local memory.

- STOP CURRENT REMOTE OPERATION: RRQ pin is de-asserted and RCB flag is reset in Status register.

#### **EP: Enable Precompensation**

- Early and late precompensation signals are forced low during a disk write operation.

- Permits precompensation signals to be output to external precompensation circuitry (see MFM ENCODED DATA). This bit is only valid if the MFM bit is set in the DF register.

#### **SCC: Start Correction Cycle**

- No correction is attempted.

- Setting this command will begin the internal correction cycle. The CCA flag in the Status register is set and drive commands should not be issued during this time. At the completion of the cycle, an interrupt is issued.

#### IR: Interlock Required (Interlock Mode)

- 0 No interlock function.

- The interlock (HBC) register must be written to after the header operation has completed and before the DDC encounters the data postamble field. This allows updating of header bytes during a Format operation or changing of drive commands during a multi-sector operation. Normally used with the header interrupt enabled.

# 3

# 3.0 Internal Registers of the DDC (Continued)

| DISK FORMAT (DF) |     |     | He  | x Addr | Write Only |     |     |

|------------------|-----|-----|-----|--------|------------|-----|-----|

| ID2              | 1D1 | IH2 | 1H1 | FTF    | HSS        | SAM | MFM |

| 7                | 6   | 5   | 4   | 3      | 2          | 1   | 0   |

#### MFM: MFM Encode

(See MFM Encoded Data section.)

- NRZ data is output on the WDATA pin when WGATE is active.

- MFM data is output on the WDATA pin when WGATE is active. Also configures AMF/EPRE and AME/LPRE pins as EPRE and LPRE outputs when Write Gate is active. Precompensated outputs are enabled by the EP bit in the OC register.

#### SAM: Start with Address Mark

(See Formatting section)

- O Address Marks will be generated in the synch #1 fields if MFM bit = 1, or AME will be generated if MFM bit = 0.

- 1 Address Mark Enable will be generated in ID preamble if MFM bit = 0.

#### **HSS: Hard or Soft Sectored**

(See Hard Sector vs. Soft Sector Operation).

- 0 Sets DDC for soft sectored operation.

- 1 Sets DDC for hard sectored operation.

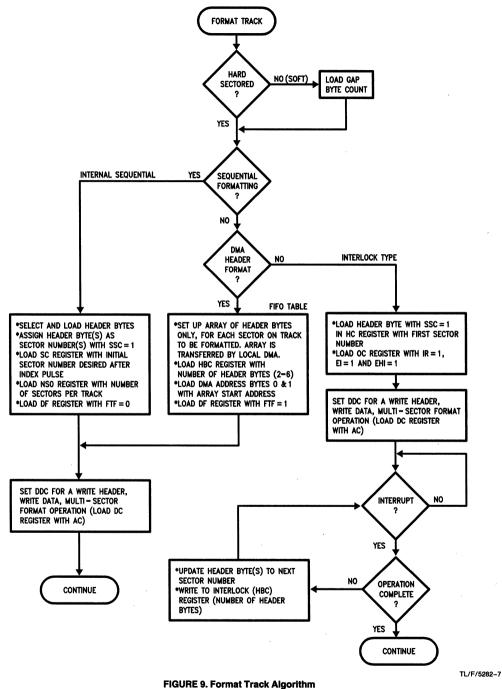

#### FTF: FIFO Table Format

- 0 Formatting is done without the use of DMA.

- The local DMA channel loads the correct number of header bytes (HBC register) per sector into the FIFO from local memory. This data is then substituted for the header bytes during a format operation.

### IH1, 2: Internal Header Appendage

IH2 IH1

- 0 No CRC/ECC is internally appended, but external ECC must be attached.

- 0 1 16-bit CRC CCITT polynomial is appended.

- 1 0 32-bit programmable ECC code is appended.

- 1 1 48-bit programmable ECC code is appended.

External ECC may be used with any internal CRC/ECC selection. 1 to 31 bytes of external ECC may be added.

#### ID1, 2: Internal Data Appendage

ID2, ID1

- 0 0 No CRC/ECC internally appended.

- 0 1 16-bit CRC CCITT polynomial is appended.

- 1 0 32-bit programmable ECC code is appended.

- 48-bit programmable ECC code is appended.

External ECC can be appended to any of the four cases dependent upon the Data External ECC Byte Count register.

#### STATUS (S)

Hex Address (00)

Read Only

The RESET pin and the RES bit in the OC register reset all of the bits in this register.

| ED | CCA | LCB | RCB | LRQ | НМС | NDC | HF |

|----|-----|-----|-----|-----|-----|-----|----|

| 7  | 6   | 5   | 4   | 3   | 2   | 1   | 0  |

#### **HF: Header Fault**

This bit is valid after a Compare Header or Read

Header operation.

CRC/ECC error detected in a header field.

SET RESET

This bit is reset when the DDC begins the next disk operation after a new disk command has been issued.

All ID fields entering the DDC during the operation are checked. The HF bit will be set if an error is detected in any header field encountered. However, if the header being sought is found and has no CRC/ECC error, the HF bit is reset. This bit does not produce an error that will stop operation, assert an interrupt, or set the ED bit in the Status register in a compare header operation, but will in a read header operation.

This bit could provide useful diagnostic information if a Sector Not Found error occurs (see Error Register in this section).

#### **NDC: Next Disk Command**

SET DDC will accept a new command into the DC

register. The header operation is completing the last sector being operated on.

RESET On receipt of a new disk command.

#### **HMC: Header Match Completed**

For each of the following, this bit is set and the interrupt is generated at the start of the header postamble field.

Compare Header Operation:

SET Header field correctly matched with no CRC/

ECC error.

RESET At beginning of subsequent header operation.

Read Header Operation:

SET Header field has been read with no CRC/ECC error.

At beginning of subsequent header operation.

Ignore Header or Write Header Operation:

SET Always set at end of header field.

RESET At beginning of subsequent header operation.

#### LRQ: Local Request

RESET

This bit follows the LRQ pin, and allows application of the DDC in a polled mode.

SET LRQ pin is asserted.

RESET LRQ pin is not asserted.

#### **RCB: Remote Command Busy**

Non-Tracking Mode:

SET When OC register is loaded with a DMA instruction.

RESET Upon completion of the instruction or upon internal or external reset.

## 3.0 Internal Registers of the DDC (Continued)

Trackina Mode:

SET

When RRQ pin is first asserted in a disk write mode, or when the Drive Command register is loaded in a disk read mode.

RESET

Upon completion of the instruction or upon internal or external reset.

#### **LCB: Local Command Busy**

SET

When command requiring local DMA is loaded.

RESET

Upon completion of the last local or remote DMA transfer (in tracking mode) or upon internal or external reset.

## **CCA: Correction Cycle Active**

SET

On asserting SCC bit in the OC register.

RESET

At the end of the correction cycle, simultaneously with the INT pin, if enabled.

#### **ED: Error Detected**

SET

On assertion of one or more bits in the Error reaister.

RESET

Upon internal or external reset.

ERROR(E)

Hex Address (01) **Read Only**

Any bit set in this register generates an interrupt (if EI bit in the OC register is set) and stops the current operation. The RESET pin and the RES bit in the OC register reset all of the bits in this register.

| LI | CF | FDL | NDS | so | SNF | DFE | HFASM |

|----|----|-----|-----|----|-----|-----|-------|

| 7  | 6  | 5   | 4   | 3  | 2   | 1   | 0     |

# Matched

HFASM: Header Failed Although Sector Number

(See HFASM description in ADDITIONAL FEA-TURES)

SET

The header bytes(s) marked with the EHF bit in the corresponding HC register(s) matched correctly, but other header bytes were in error.

RESET Upon internal or external reset.

**DFE: Data Field Error**

SET

On detection of a data field CRC/ECC error in a Read Data or Check Data operation. This bit may be set when another error occurs; especially an error occurring during a Write operation. These errors would be Sector Overrun or FIFO Data Lost.

RESET

Upon internal or external reset.

The RED command must be loaded into the DC register if error correction is to be attempted.

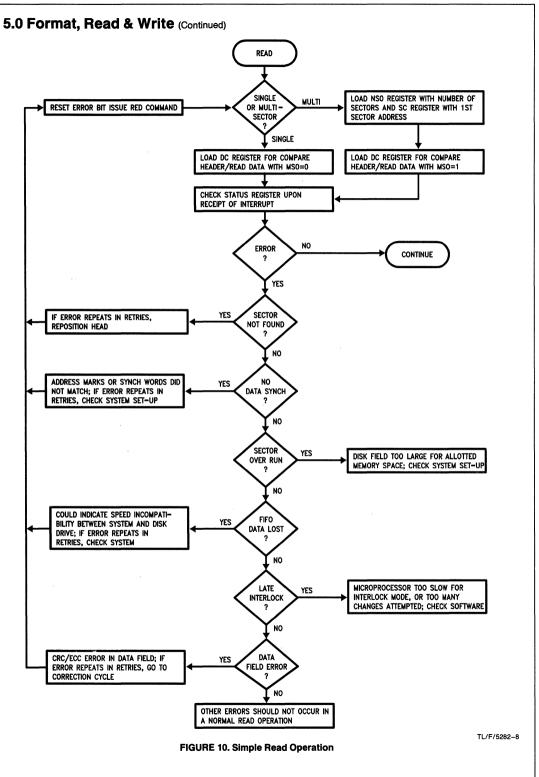

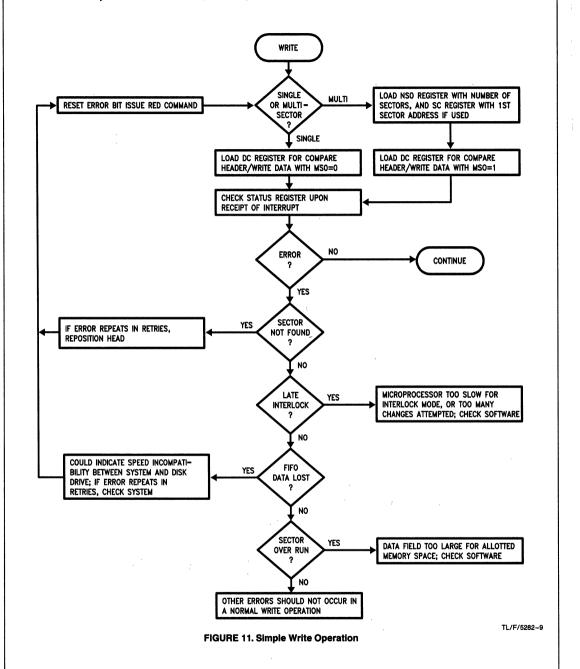

#### SNF: Sector Not Found

SET

When header cannot be matched for two consecutive index pulses in any Compare Header operation.

RESET

Upon internal or external reset.

SO: Sector Overrun

SET

If RGATE is active and FIFO is being written to when a sector or index pulse is received. If WGATE is active, this bit is set when a sector or index pulse is received.

RESET

Upon internal or external reset.

An SO error will not occur during a Format oper-

ation.

#### NDS: No Data Synch

SET

If a sector or index pulse occurs while the DDC is waiting to byte align on the first data synch field (synch #1 or synch #2), or if the DDC byte aligns to the first synch word of the data field but does not match to subsequent bytes (synch #1 or synch #2).

RESET Upon internal or external reset.

#### FDL: FIFO Data Lost

SET

During a disk read operation if the FIFO overflows, or during a disk write operation if the FIFO is read when it is empty.

RESET Upon internal or external reset.

#### **CF: Correction Failed**

SET

If correction is attempted (SCC bit set in OC reg-

ister) and correction failed.

RESET Upon internal or external reset.

#### LI: Late Interlock

Will only occur if IR bit in OC register is set.

SET

Controlling logic has failed to write to the Interlock (HBC) register before the end of the data field of the present sector.

RESET Upon internal or external reset.

#### SECTOR COUNTER (SC)

Allowable Value 0-255 Hex Address (12) Read/Write In a multi-sector operation, the SC register is first loaded with the starting sector number. It is incremented after each header operation is completed. The contents of the SC register will replice any header Byte if the SSC bit is set in the corresponding HC register.

#### NUMBER OF SECTOR OPERATIONS COUNTER (NSO)

Allowable Value 0-255 Hex Address (13) Read/Write In a multisector operation, the NSO register is loaded with the number of sectors to be operated on. It is decremented after every header operation. When zero, the command is finished. This counter must be reloaded after a reset of the DDC.

#### HEADER BYTE COUNT (HBC)/INTERLOCK

Allowable Value 2-6 Hex Address (0F) Read/Write

This register loads the DMA with the number of header bytes to expect in a Read Header, or a Format operation where FIFO table formatting is used. This register is also used in interlock mode to signal completion of update. The upper five bits of this register are pulled low when read.

#### **HEADER DIAGNOSTIC READBACK (HDR)**

#### Hex Address (36)

If a Compare Header/Check Data operation is performed and an HFASM error occurs, the header bytes for that sector will have been loaded into the FIFO. By consecutively reading this address, the header bytes are read from the FIFO to the microprocessor. Data will be valid for only the number of header bytes specified in the parameter RAM. (NOTE: This is a dual function register, sharing operation with the Local Transfer register, see DMA REGISTER.)

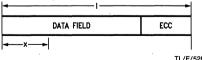

#### SECTOR BYTE COUNT REGISTER (L, H)

Allowable Value 1-64k Hex Address (38, 39) Read/Write

The two bytes (most and least significant) that comprise this register are loaded during initialization, and define the data

# 3

## 3.0 Internal Registers of the DDC (Continued)

field size for each sector. The number of bytes transferred with local DMA is always equal to what has been loaded into this register. Loading *both* with zero is not allowed.

#### **3.2 DMA REGISTERS**

#### LOCAL TRANSFER (LT) Hex Address (36) Write Only

This is a dual function register, sharing operation with the Header Diagnostic Readback (HDR) register (see COMMAND REGISTERS). IMPORTANT NOTE: If any internal DMA is being used, or if the Remote Data Byte Count registers will be read by the processor, the LT (and RT) register must be loaded before the Sector Byte Count and Remote Data Byte Count register pairs.

| LBL2 | LBL1 | LTEB | LA | LSRW | RBO | LWDT | SLD |

|------|------|------|----|------|-----|------|-----|

| 7    | 6    | 5    | 4  | 3    | 2   | 1    | 0   |

#### **SLD: Select Local DMA Mode**

- 0 SLAVE MODE: External DMA must be used in place of on-chip DMA.

- NON-TRACKING MODE: Local DMA is enabled.

Whenever local transfers are needed, the DDC becomes the bus master.

TRACKING MODE: Local and remote DMA are enabled. DMA transfers are interleaved (see DMA in DATA TRANSFER section).

#### **LWDT: Local Word Data Transfer**

- 0 Address increments by 1, 8 bit wide transfers.

- Address increments by 2, 16 bit wide transfers. Address, A0, remains unchanged as it was set by the DMA address.

#### **RBO: Reverse Byte Order**

Valid if LWDT bit is set.

- First byte to/from FIFO is mapped onto the AD0-7 bus.

- 1 First byte to/from FIFO is mapped onto AD8-15 bus (e.g. 68000).

#### LSRW: Local Slow Read And Write

- 0 DMA cycles are four clock periods.

- 1 DMA cycles are five clock periods. RD and WR strobes are widened by one clock period.

#### LA: Long Address

Valid only if SLD = 1, and SRD = 0 in Remote Transfer register.

- 16 address bits are issued and strobed by the ADS0 pin. ADS1/RRQ is available for use by the remote DMA.

- 32 address bits are issued, the lower 16 are strobed by ADS0 pin. The most significant 16 address lines are only issued when a rollover from the least significant 16 address lines occurs, or after loading the upper half of the 32-bit address. When the upper 16 address lines are issued, that DMA cycle is five clock cycles long if no internal or external wait states are used.

#### LTEB: Local Transfer Exact Burst

When DMA tranfer is needed, the FIFO will be filled when writing to disk or emptied when reading from disk. When DMA tranfer is needed, the FIFO will receive (when writing) or deliver (when reading) an exact burst of data.

#### LBL1, 2: Local Burst Length

#### LBL2 LBL1

1

0 0 1 word (2 byte)

0 1 4 word (8 byte)

1 0 8 word (16 byte)

1 1 12 word (24 byte)

When reading from disk, these bits select the number of bytes needed in the FIFO in order to generate an LRQ signal. When writing, these bits select the number of bytes that need to be removed from a full FIFO in order to generate an LRQ. In either case, if the LTEB bit is set, this bit pair indicate how many data transfers will be allowed before LRQ is removed.

Note: Please refer to Section 17, Helpful Hints #29.

#### REMOTE TRANSFER (RT) Hex Address (37) Write Only

This is a dual function register, sharing operation with the DMA Sector Counter (DSC) (see DSC at the end of this section). If any internal DMA is being used, or if Remote Data Byte Count registers will be read by the processor, the RT (and LT) register must be loaded before the Sector Byte Count and Remote Data Byte Count register pairs.

| RBL2 | RBL1 | RTEB | TM | RSRW | EEW | RWDT | SRD |

|------|------|------|----|------|-----|------|-----|

| 7    | 6    | 5    | 4  | 3    | 2   | 1    | 0   |

#### **SRD: Select Remote DMA**

- Remote DMA inhibited, ADS1/RRQ pin is configured as ADS1.

- Remote DMA enabled. This is necessary but not sufficient to start remote transfer.

#### **RWDT: Remote Word Data Transfer**

- Remote address increments by 1.

- Remote address increments by 2. Address A0 remains unchanged as it was set by the starting DMA address.

#### **EEW: Enable External Wait**

- No external wait states acknowledged. Functions 2 and 3 of EXT STAT pin are enabled (see PIN DESCRIPTIONS).

- 1 The EXT STAT pin will lengthen RD and WR strobes during DMA transfers as long as it is maintained at a high level.

#### **RSRW: Remote Slow READ/WRITE**

- 0 Remote DMA cycles are four clock periods long.

- 1 Remote DMA cycles are five clock periods long, if external wait states are not asserted.

#### TM: Tracking Mode

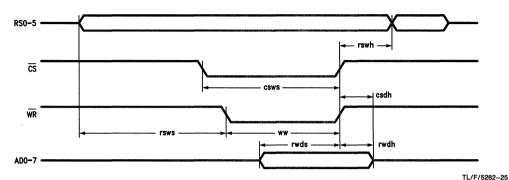

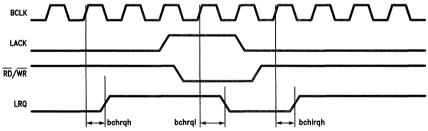

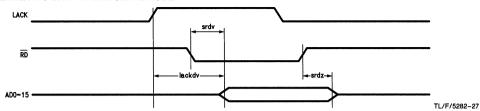

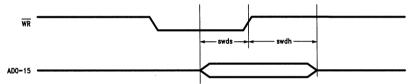

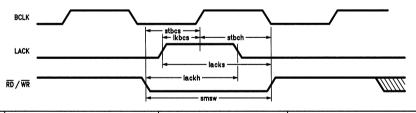

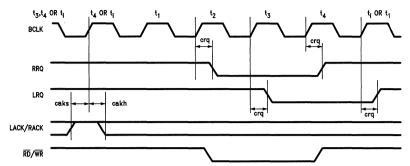

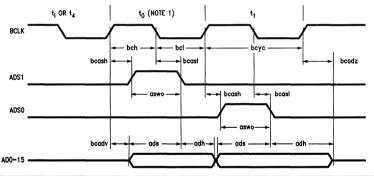

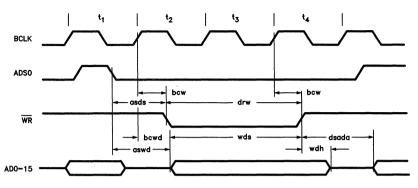

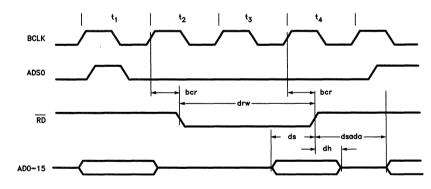

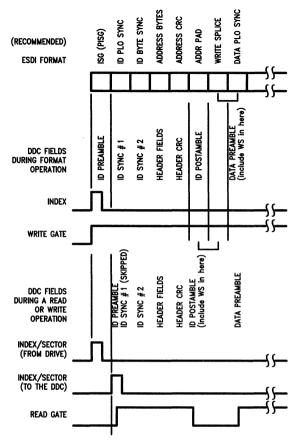

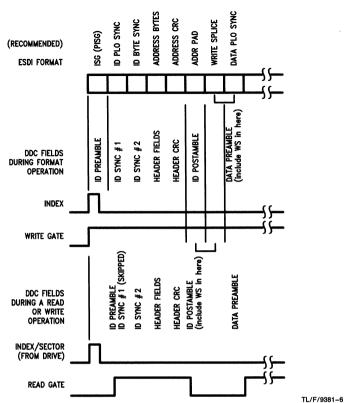

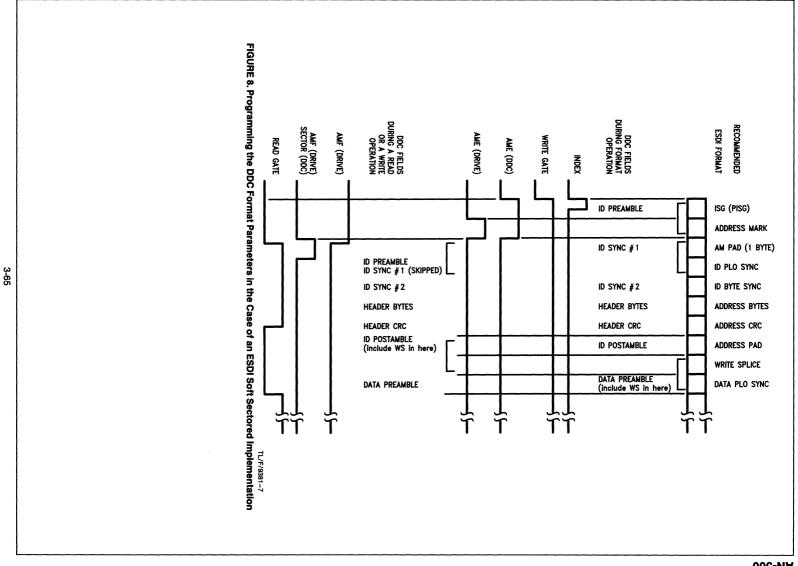

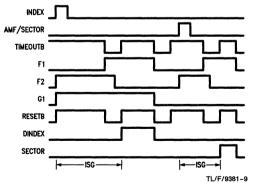

See Tracking Mode description in DATA TRANSFER Section.